Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

616results about "Time-to-digital converters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

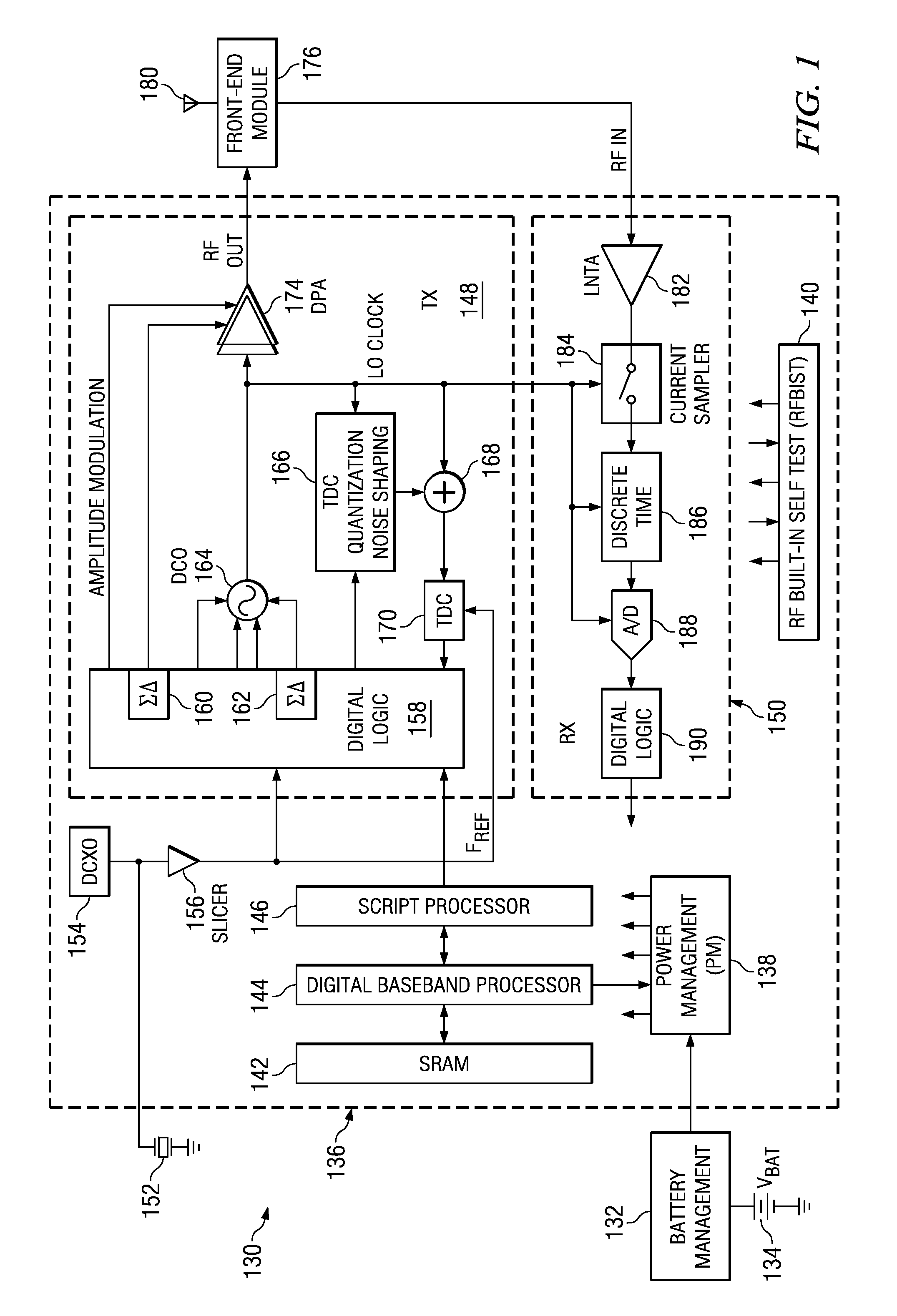

Digital Phase Locked Loop with Integer Channel Mitigation

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal with a plurality of phases. A switch is coupled to receive the RF clock, and is operative to select one of the plurality of phases. A phase detection circuit is coupled to the switch and is operable to receive a selected phase and to provide digital phase error samples indicative of a time difference between the reference clock and the selected phase.

Owner:TEXAS INSTR INC

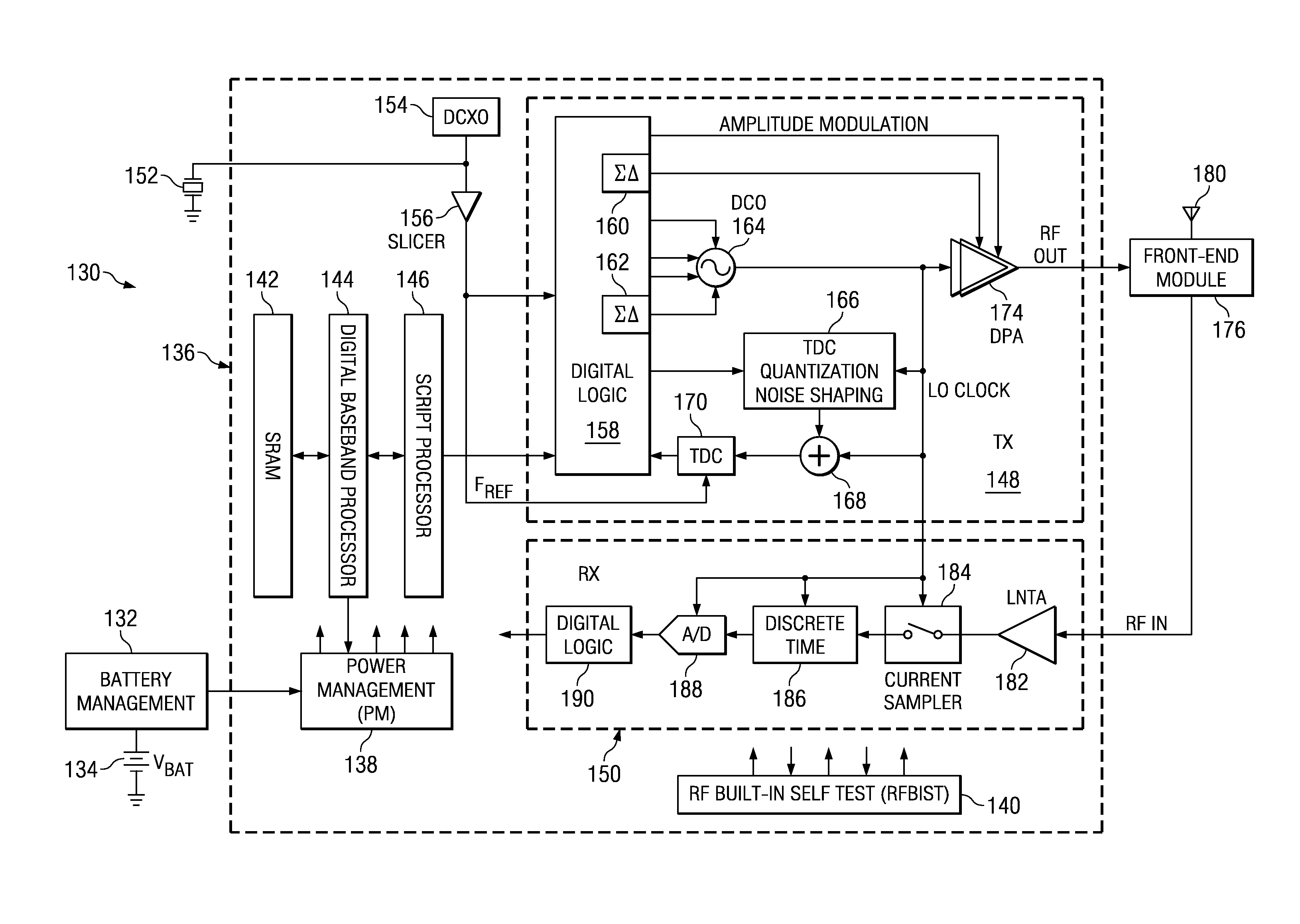

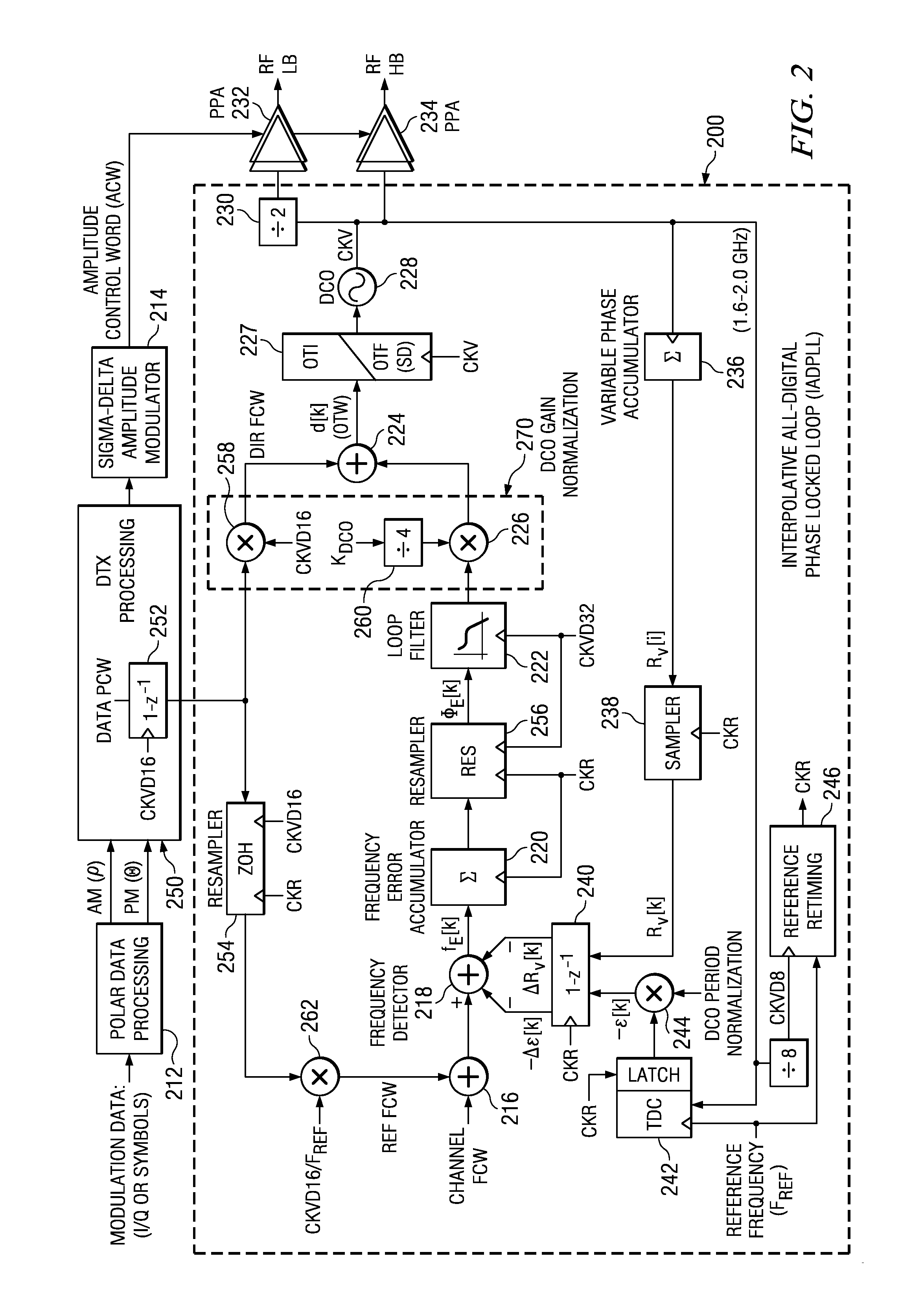

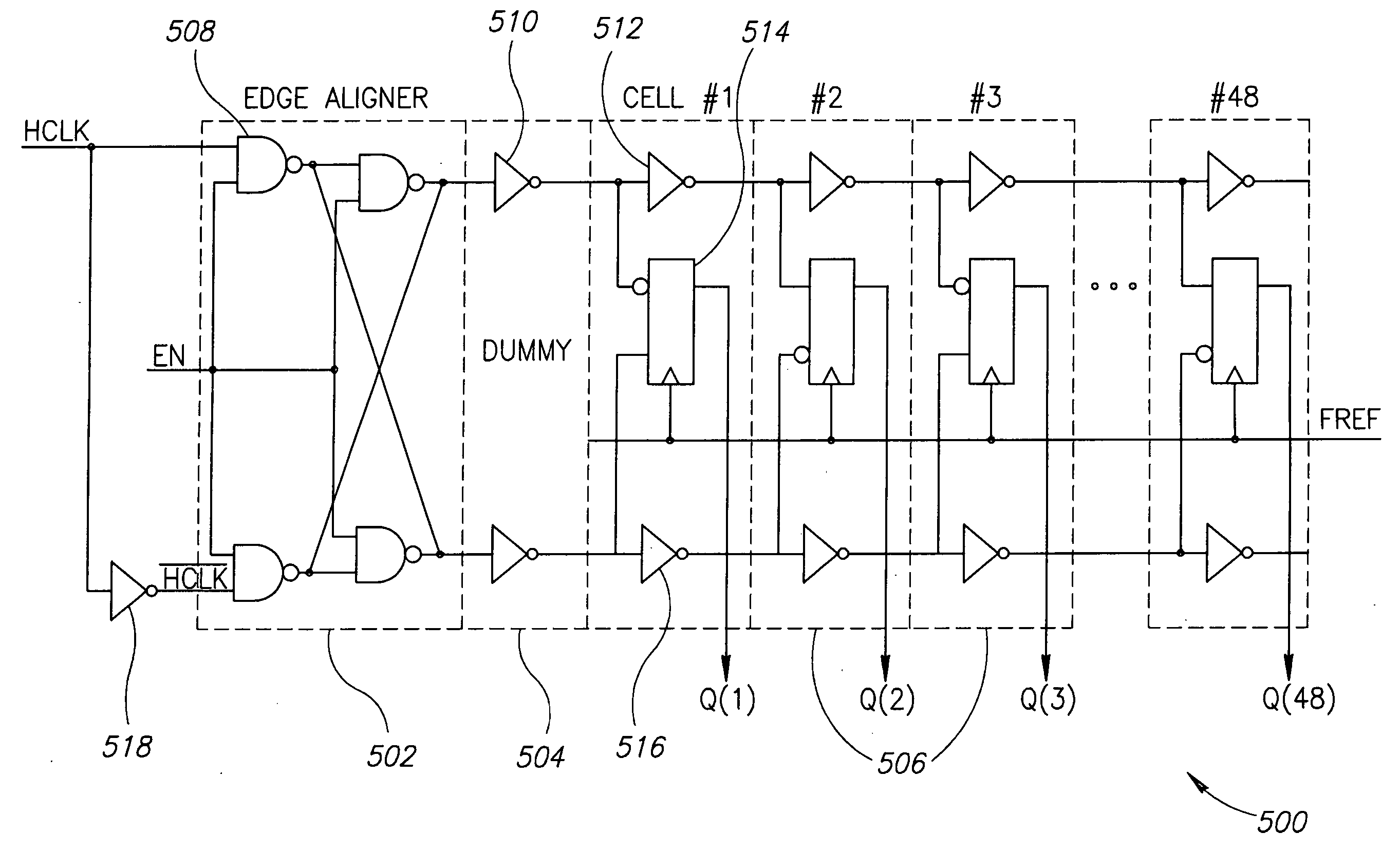

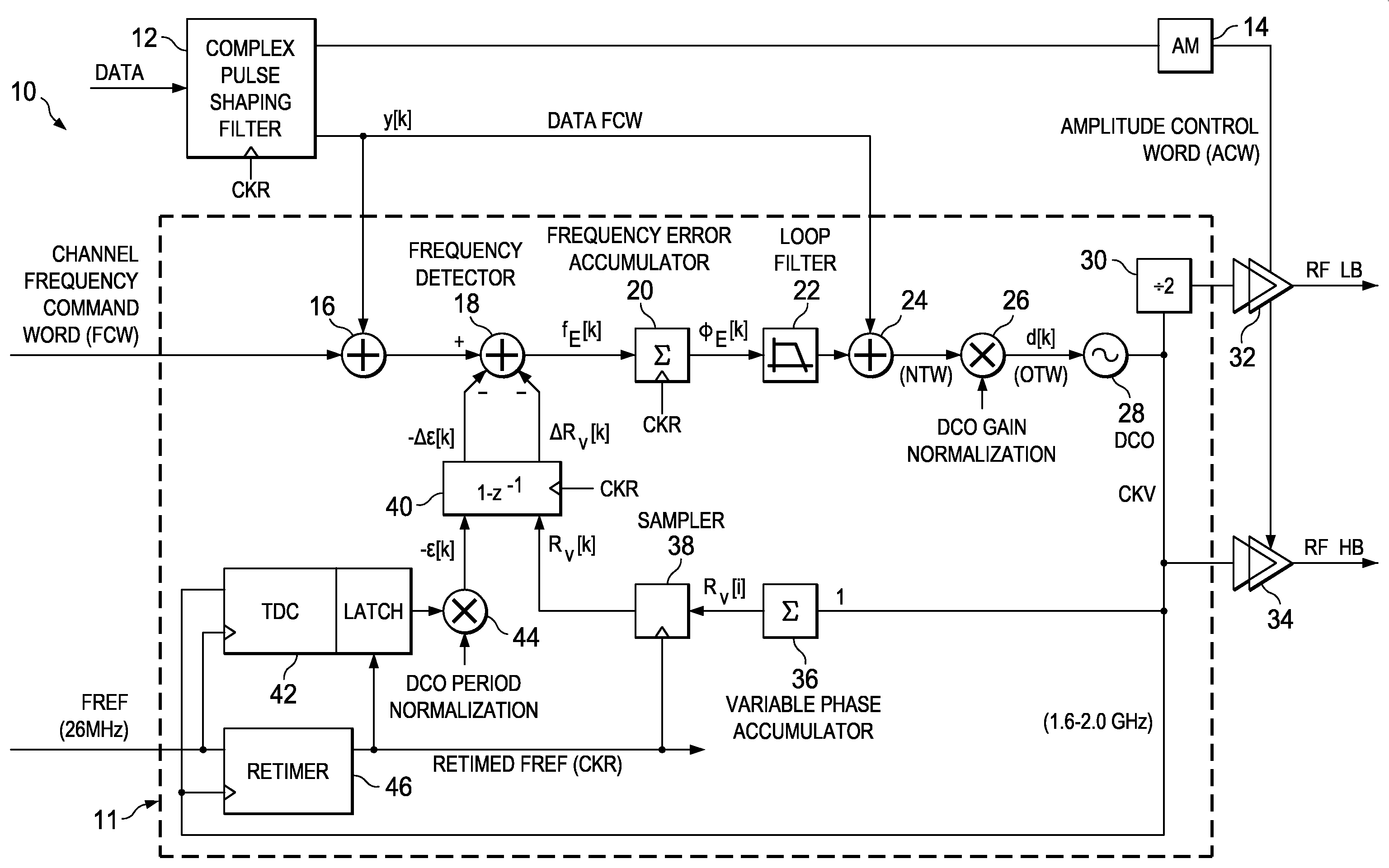

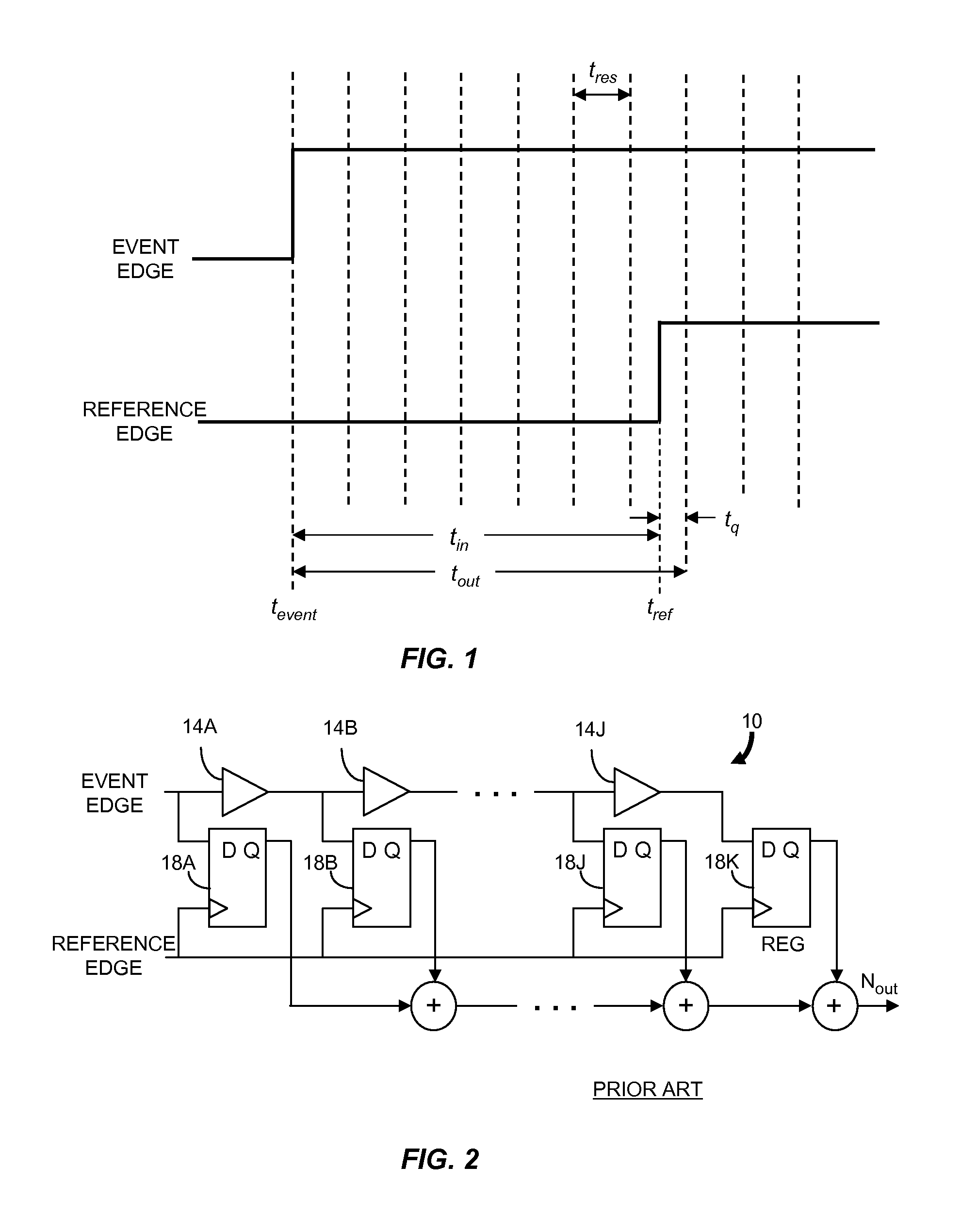

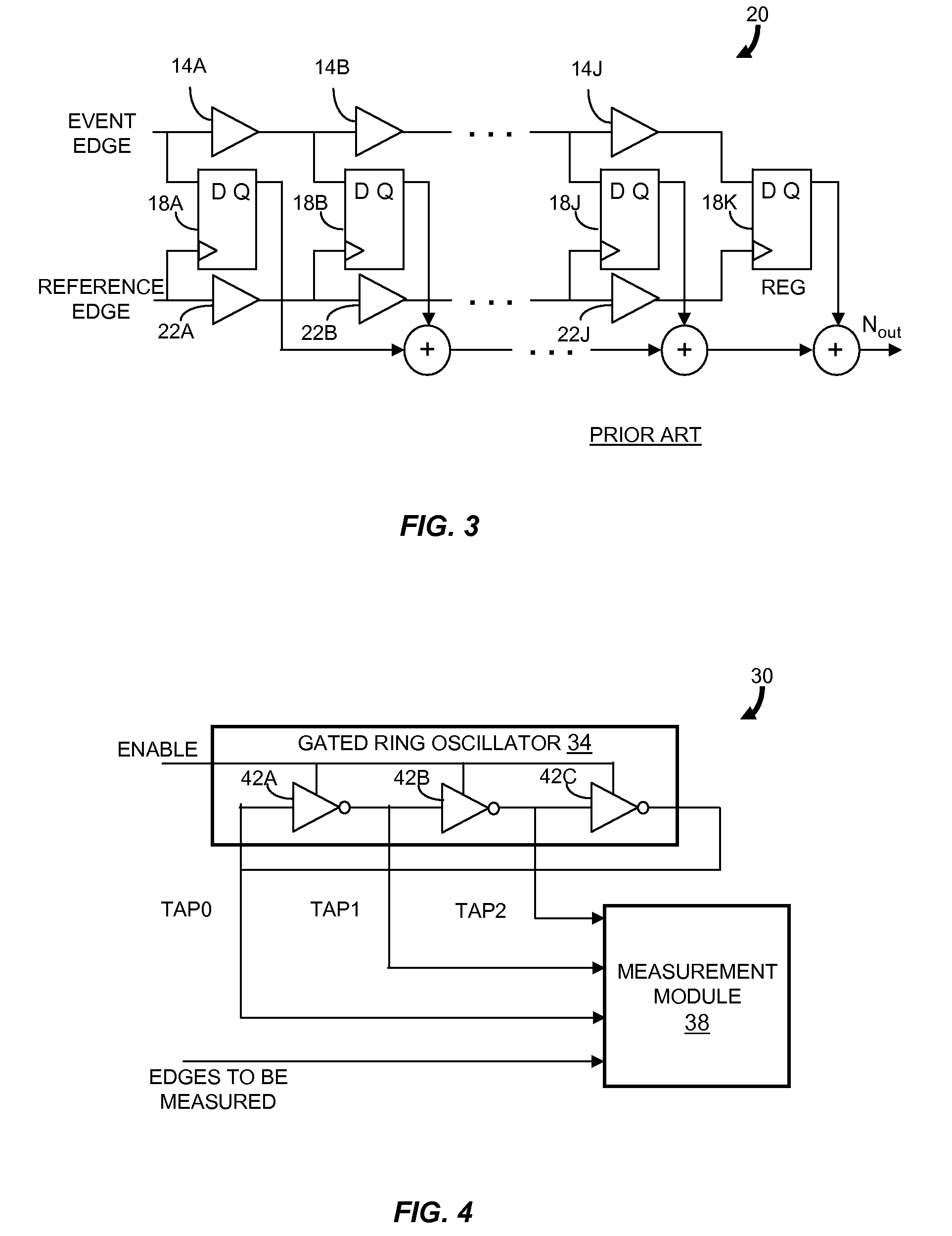

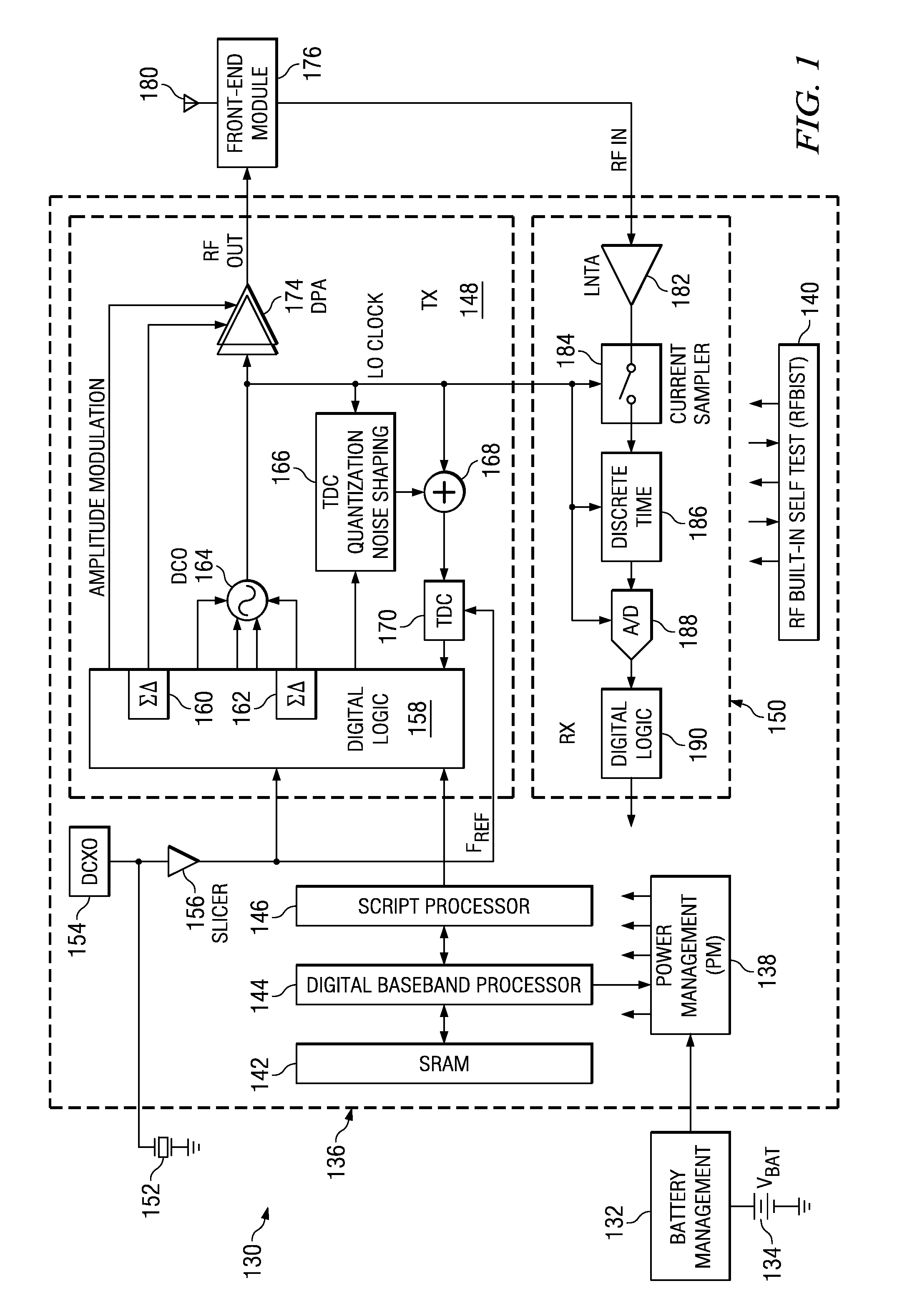

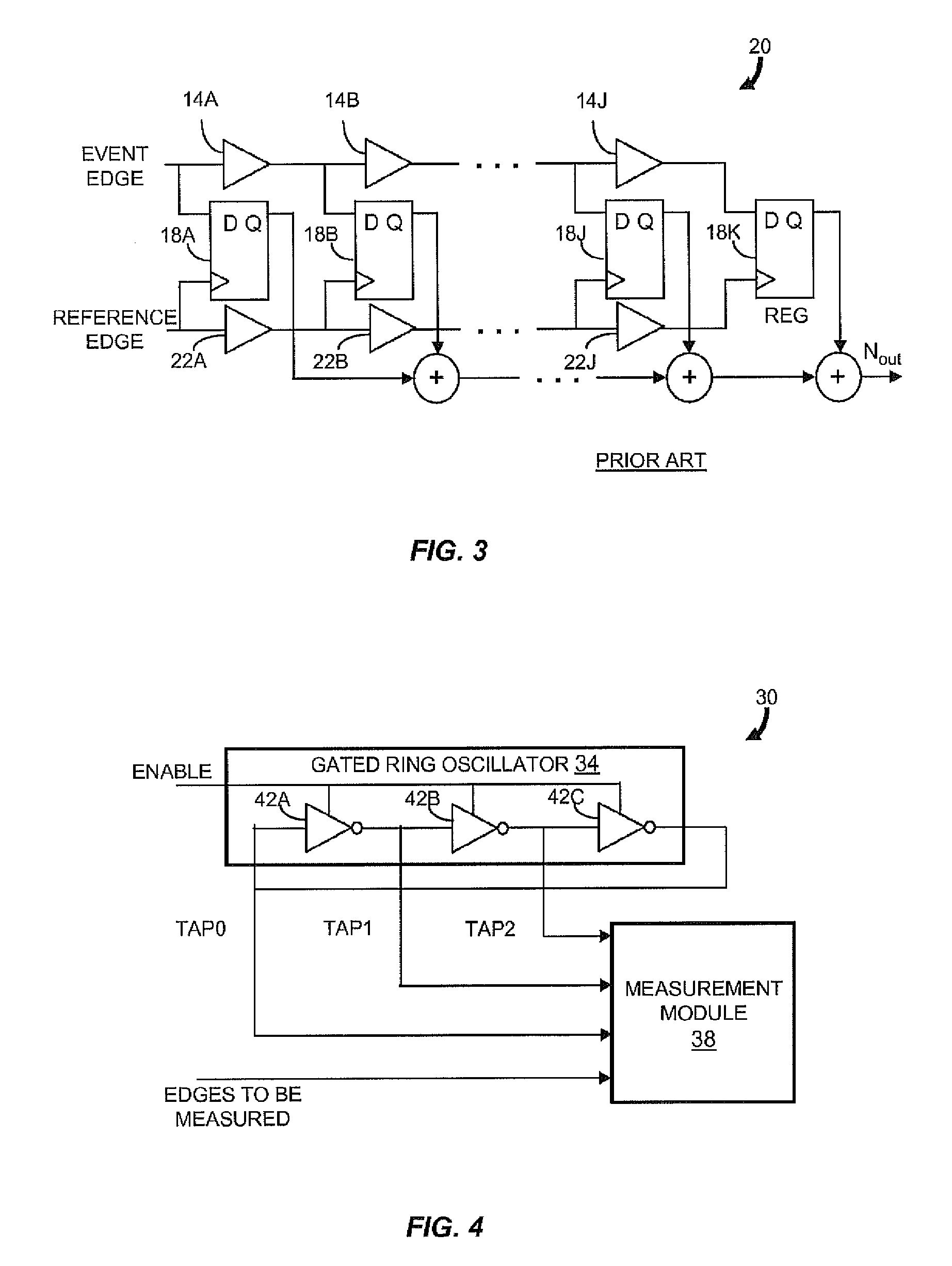

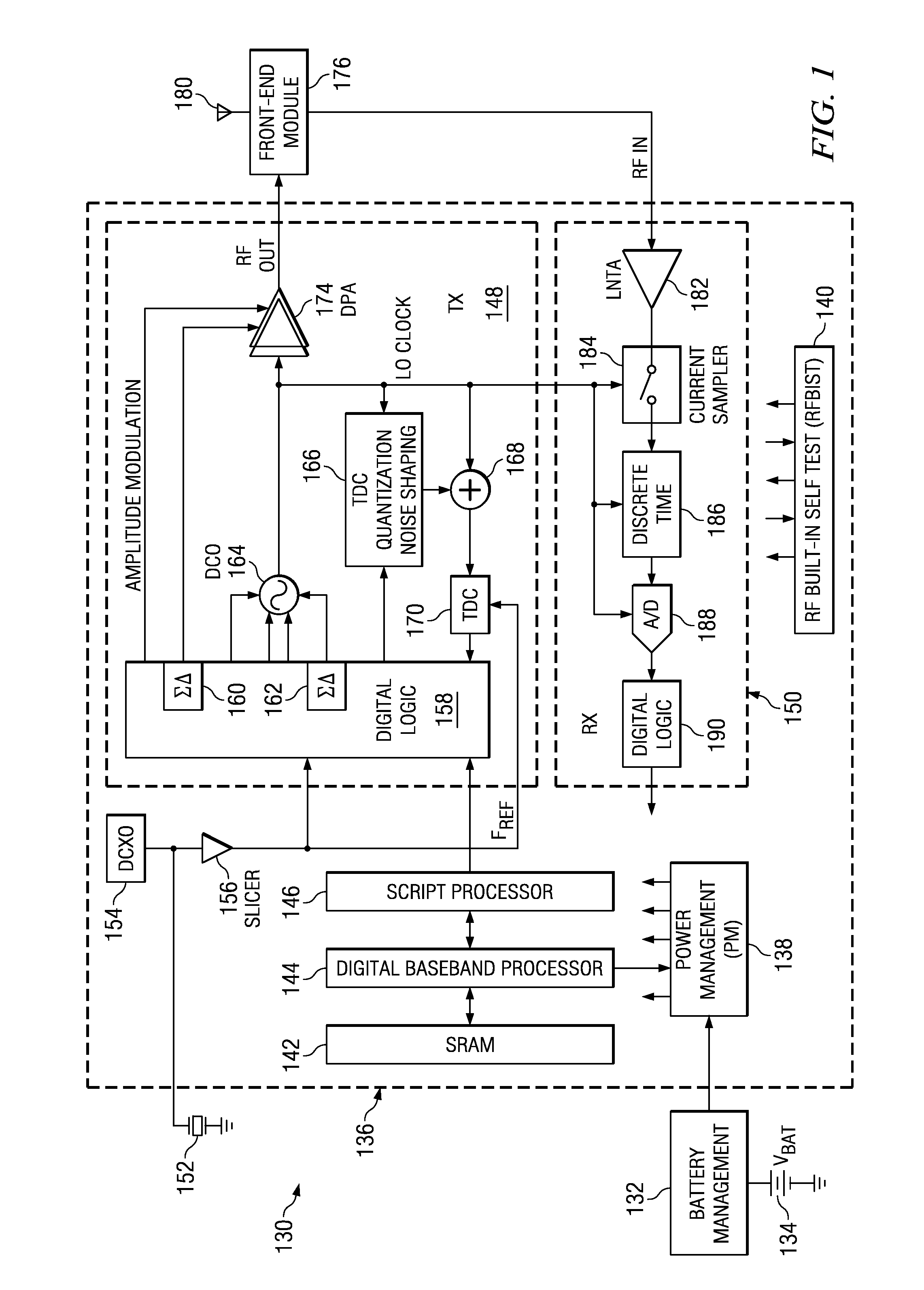

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS20060103566A1Less sensitiveReduce power consumptionElectric signal transmission systemsPulse automatic controlEngineeringDigital converter

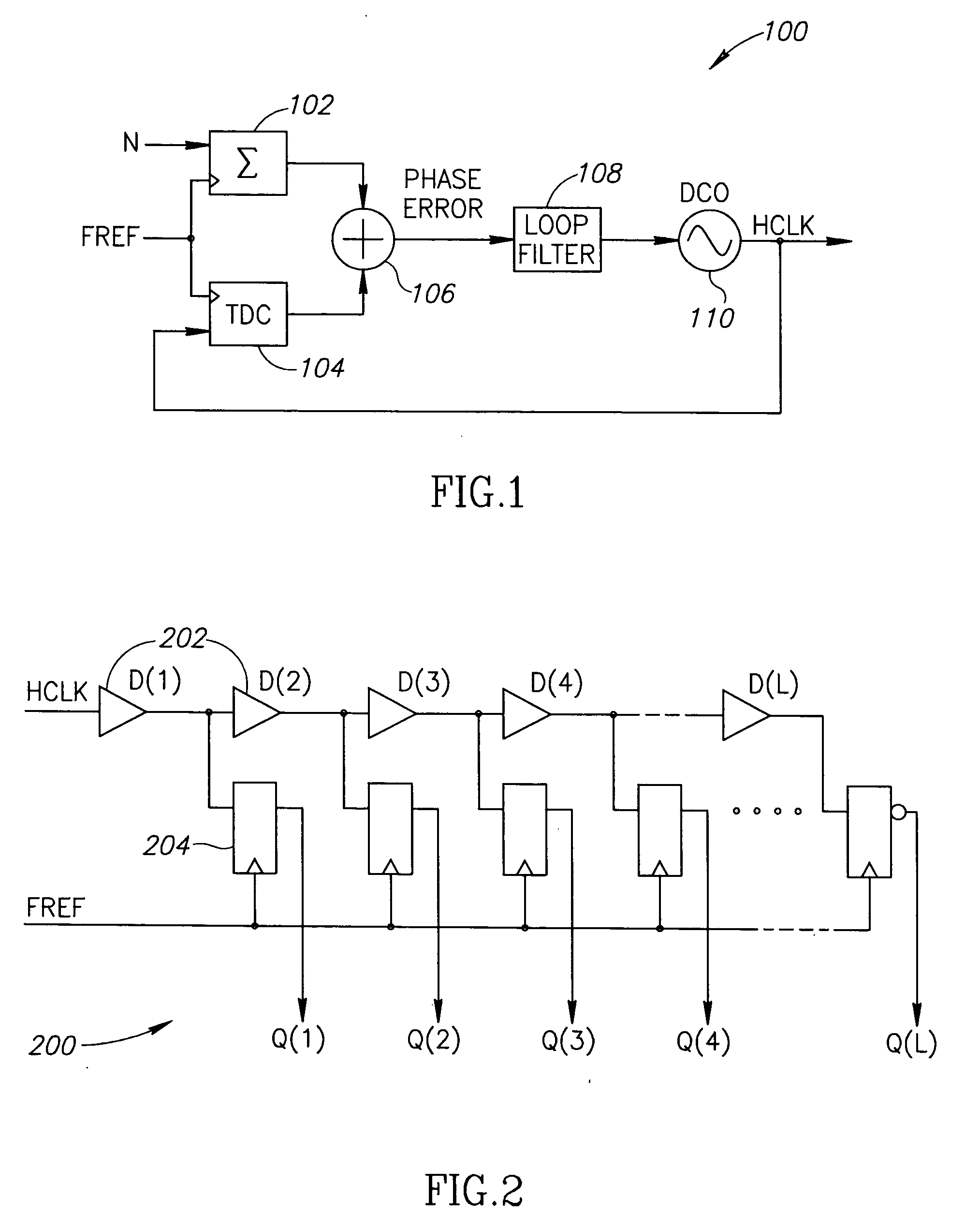

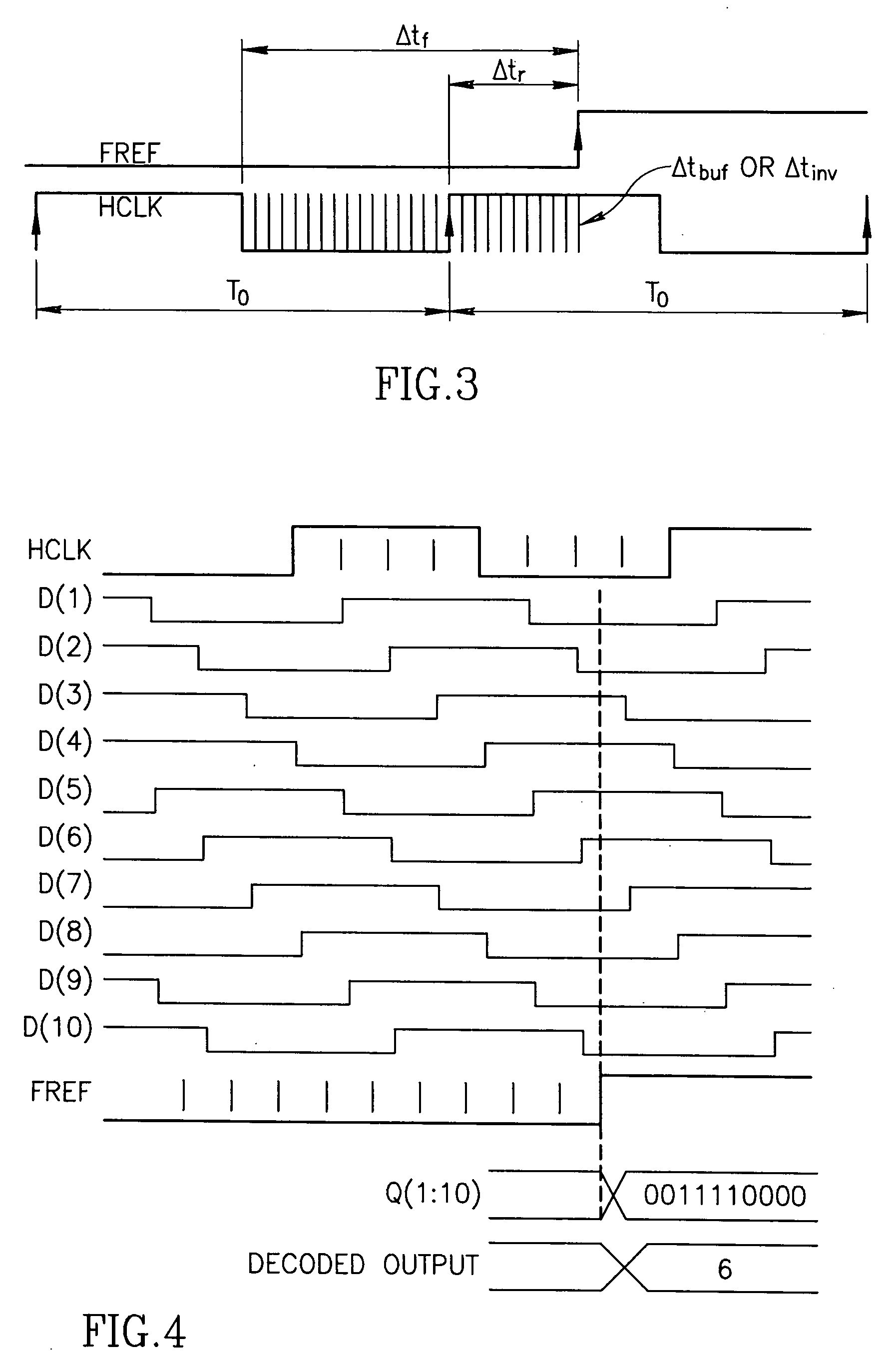

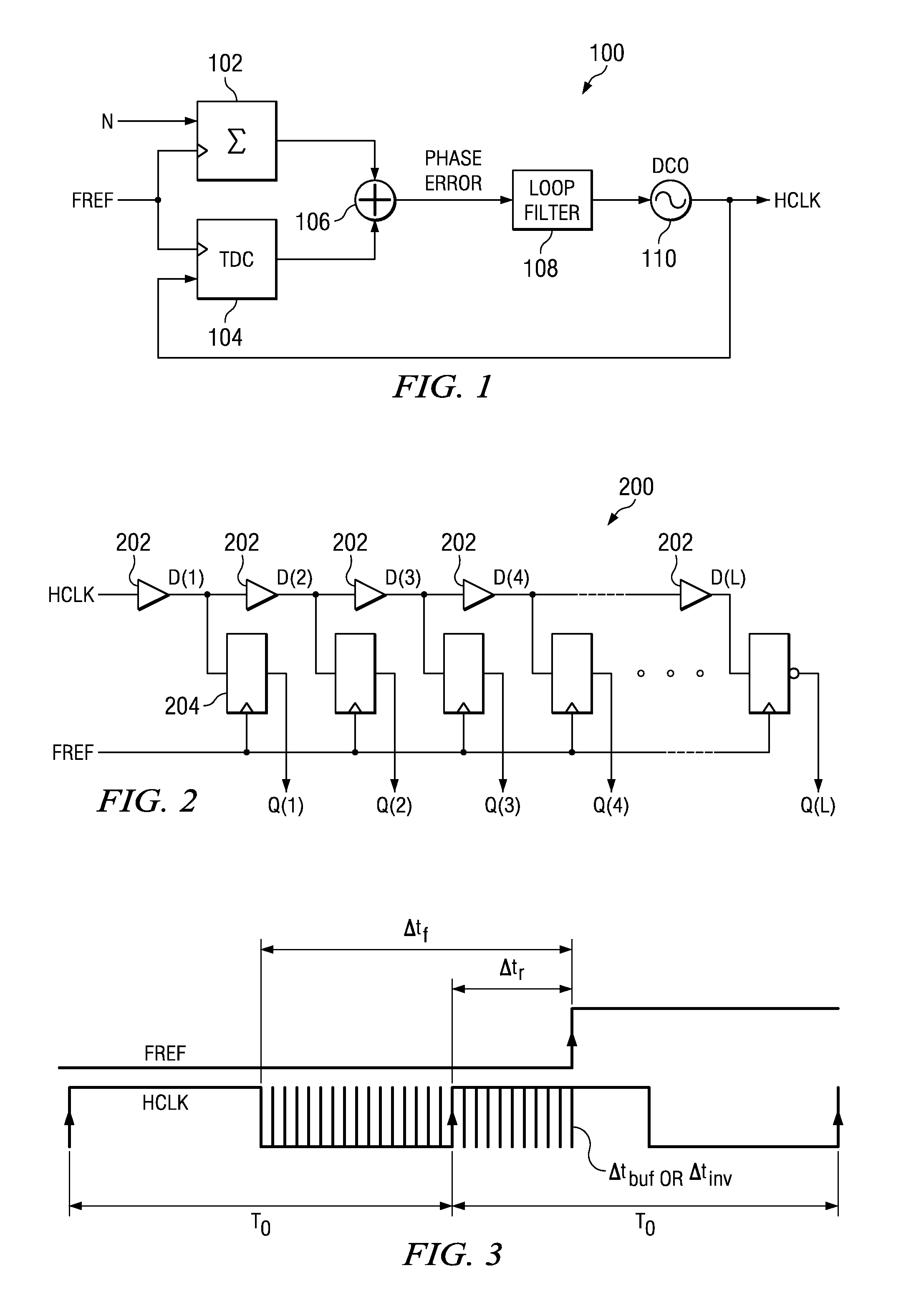

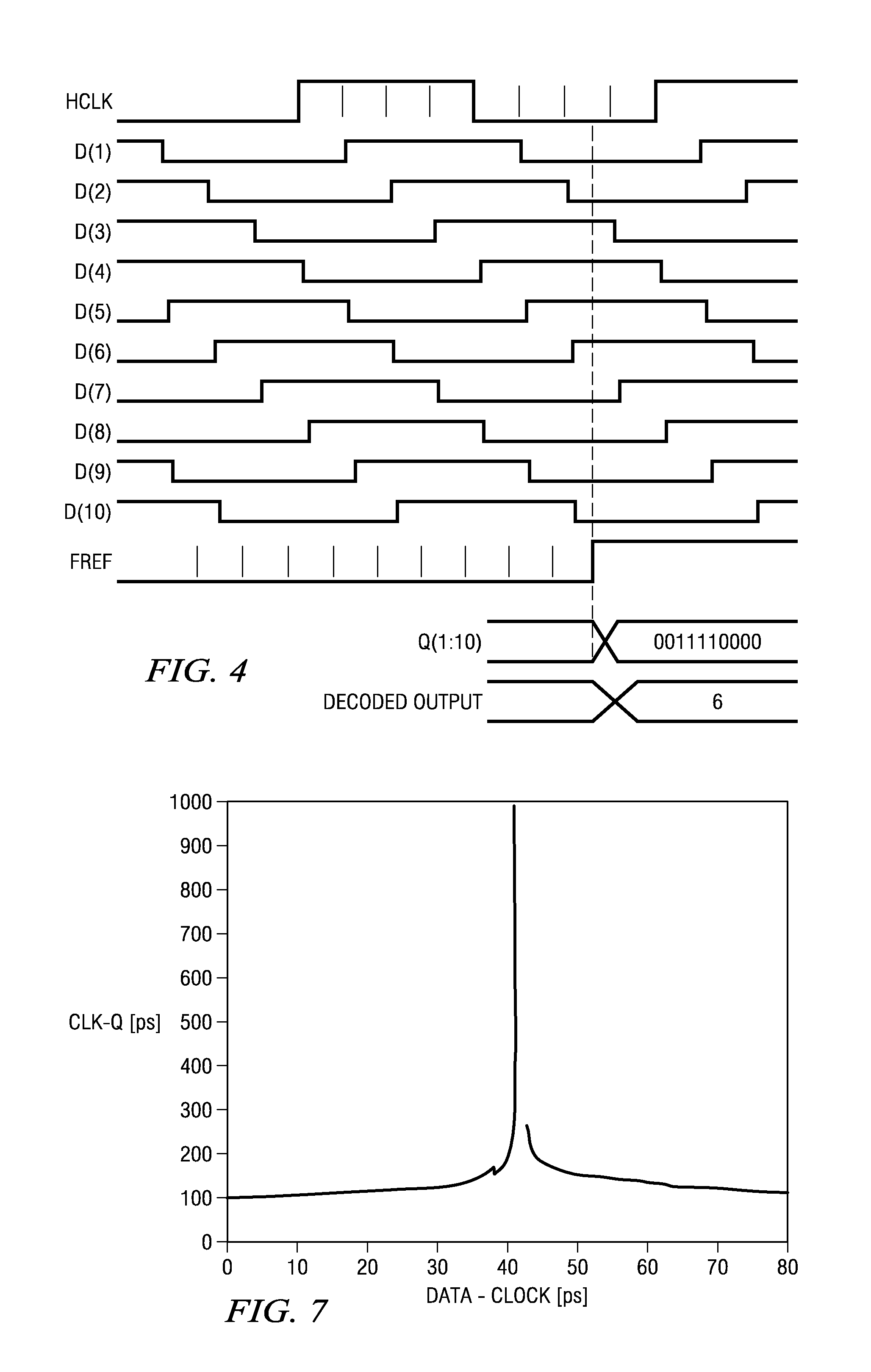

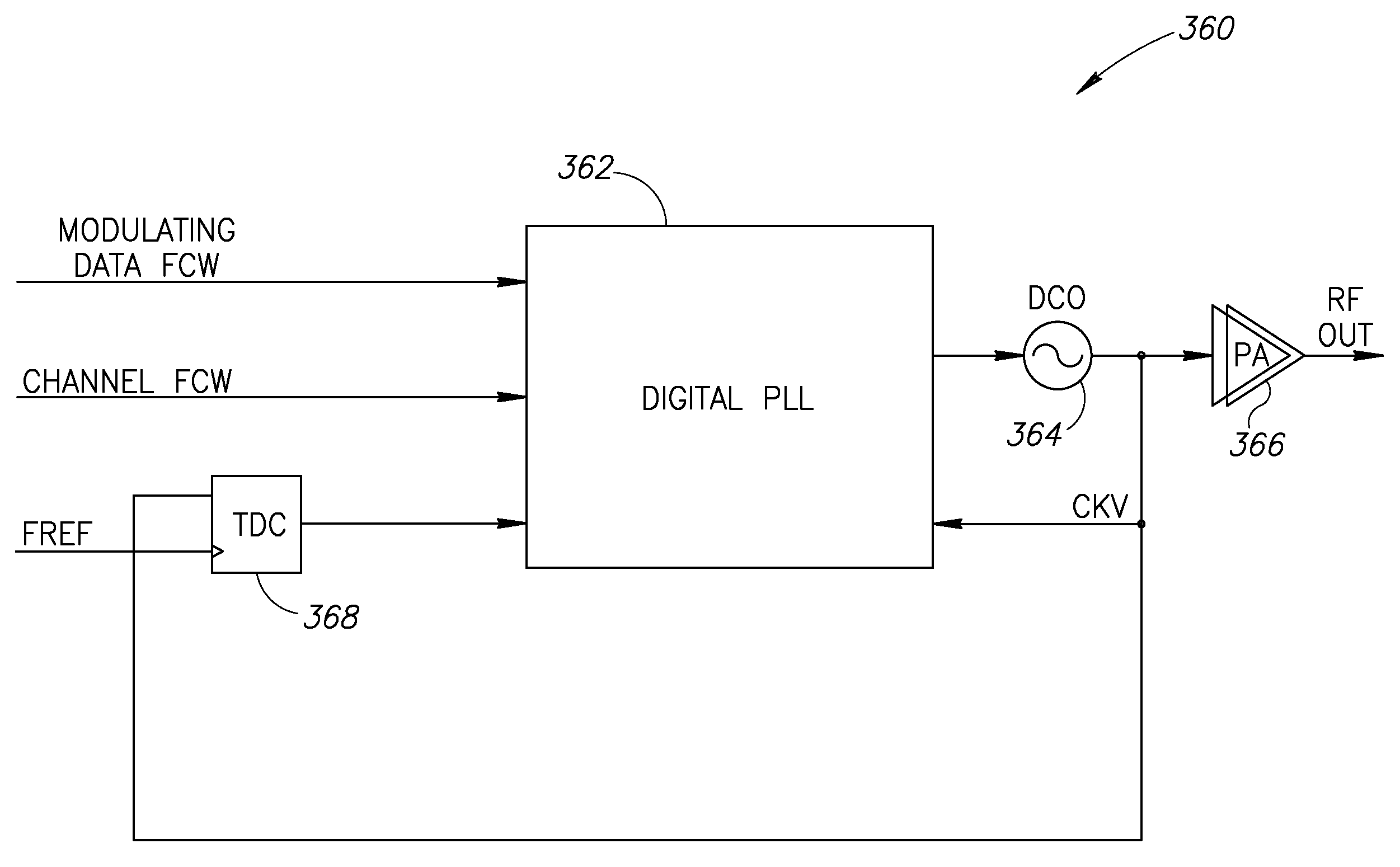

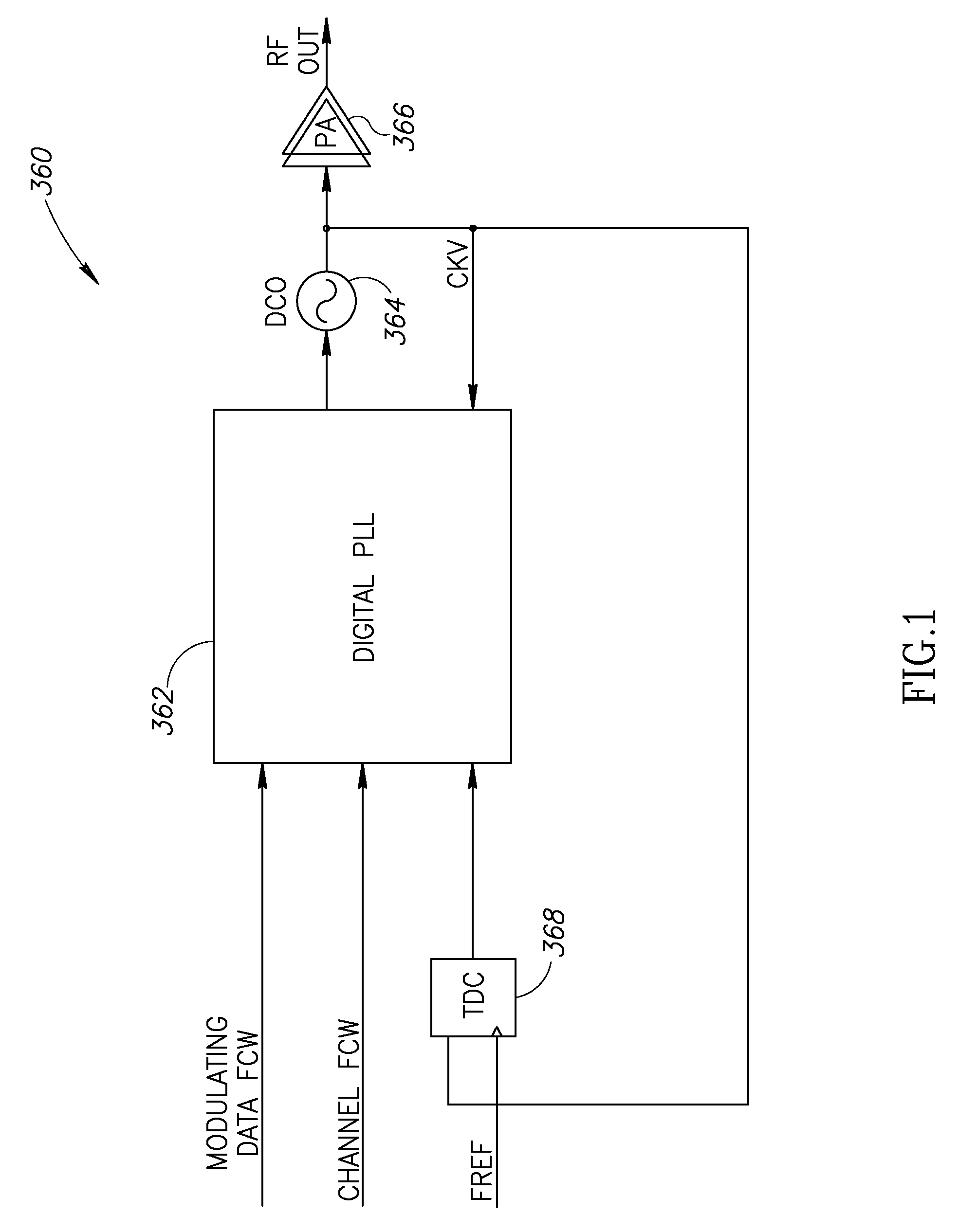

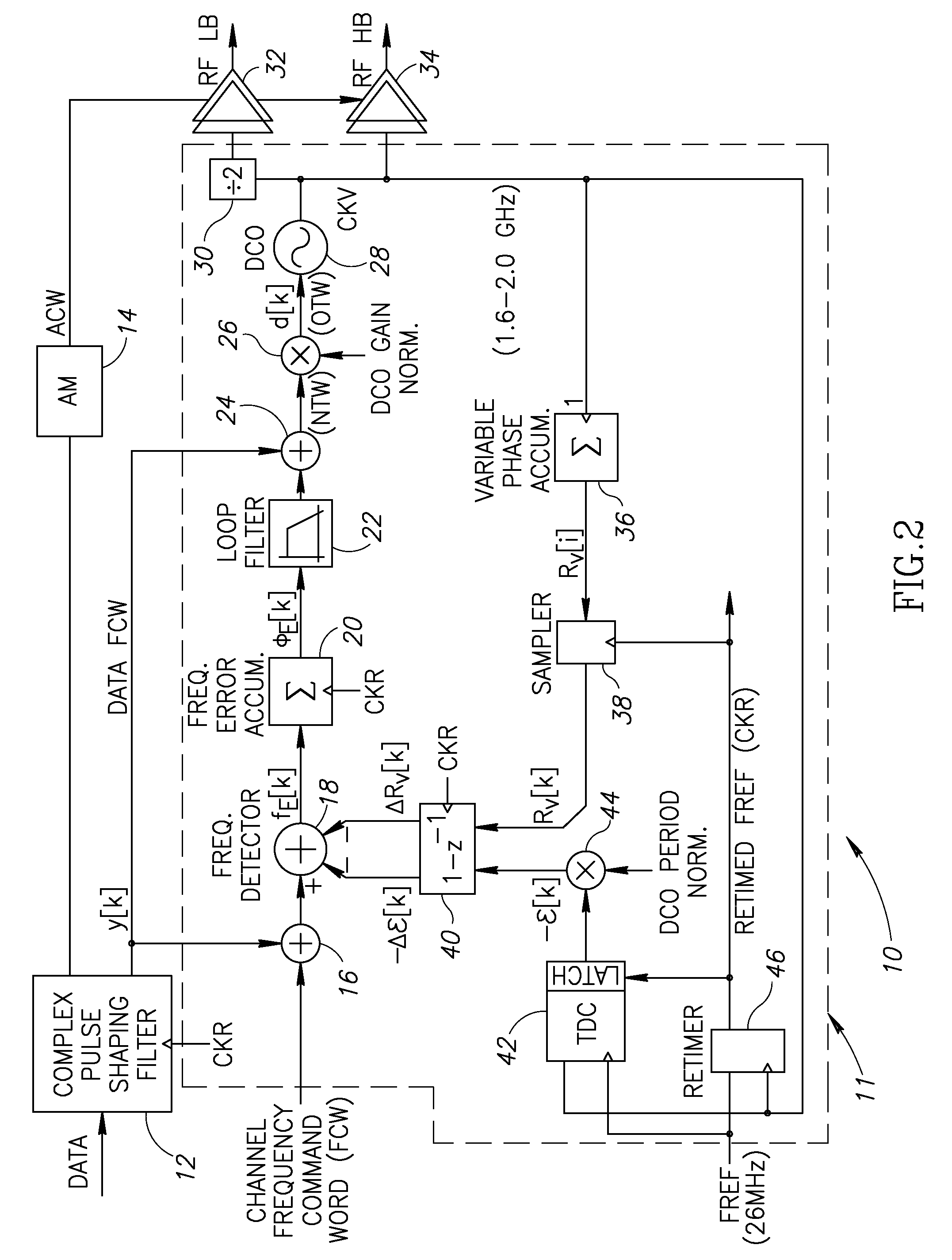

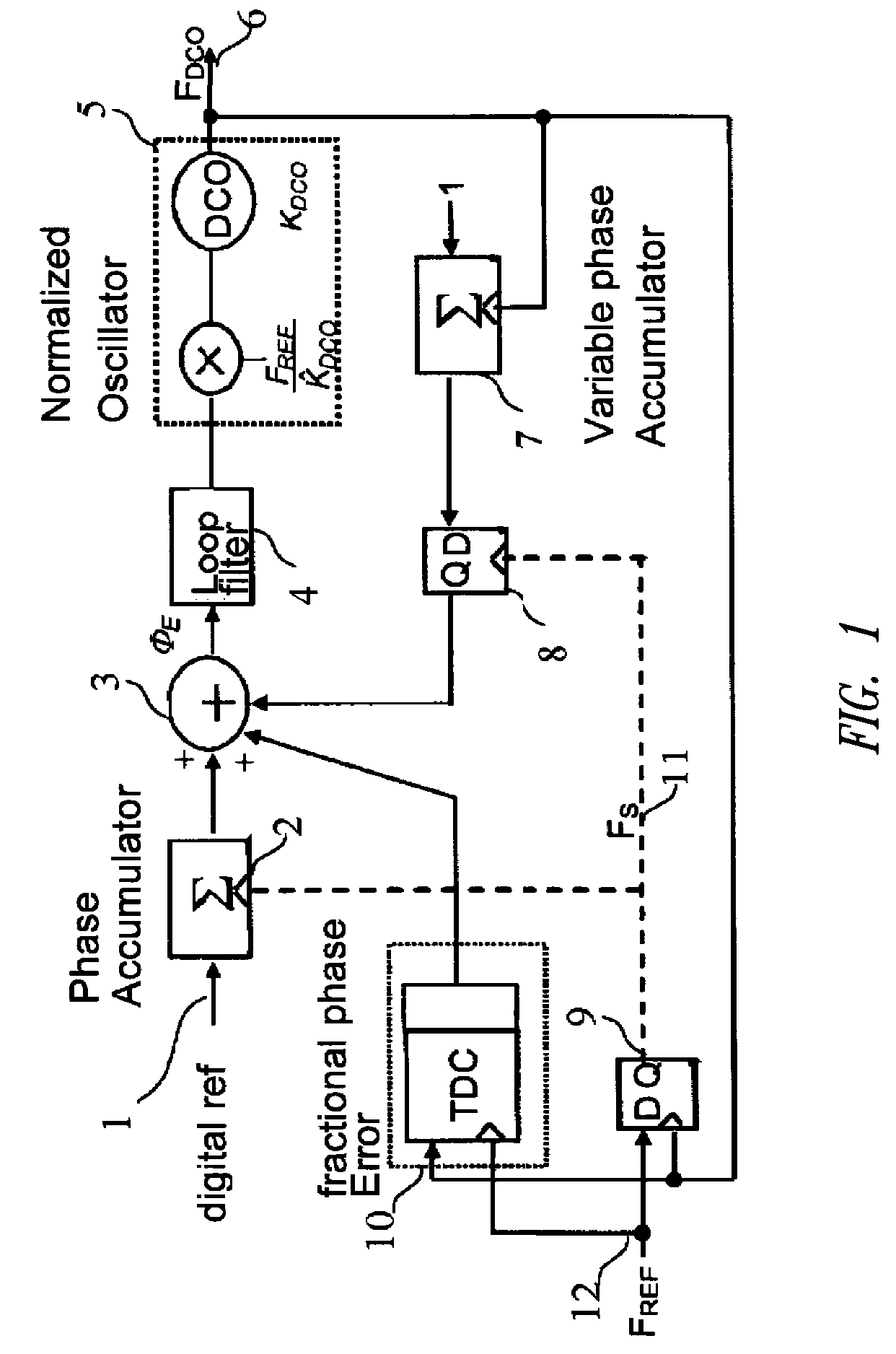

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS7205924B2Less sensitiveReduce power consumptionElectric signal transmission systemsModulated-carrier systemsDigital converterCmos process

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

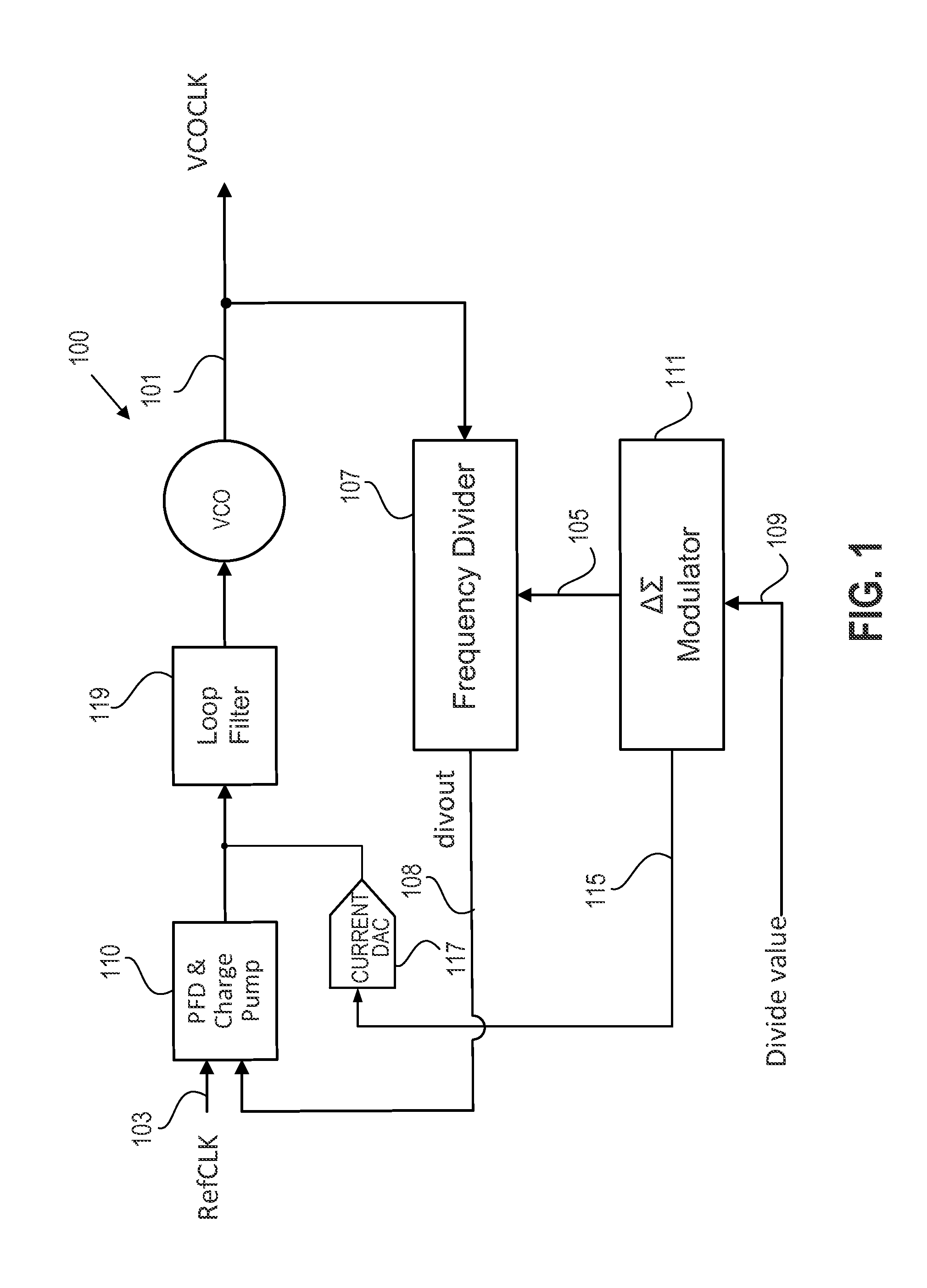

Adaptive spectral noise shaping to improve time to digital converter quantization resolution using dithering

ActiveUS20080068236A1High resolutionHigh frequency noiseElectric signal transmission systemsAnalogue conversionFrequency spectrumNoise shaping

A novel and useful apparatus for and method of improving the quantization resolution of a time to digital converter in a digital PLL using noise shaping. The TDC quantization noise shaping scheme is effective to reduce the TDC quantization noise to acceptable levels especially in the case of integer-N channel operation. The mechanism monitors the output of the TDC circuit and adaptively generates a dither (i.e. delay) sequence based on the output. The dither sequence is applied to the frequency reference clock used in the TDC which adjusts the timing alignment between the edges of the frequency reference clock and the RF oscillator clock. The dynamic alignment changes effectively shape the quantization noise of the TDC. By shaping the quantization noise, a much finer in-band TDC resolution is achieved resulting in the quantization noise being pushed out to high frequencies where the PLL low pass characteristic effectively filters it out.

Owner:TEXAS INSTR INC

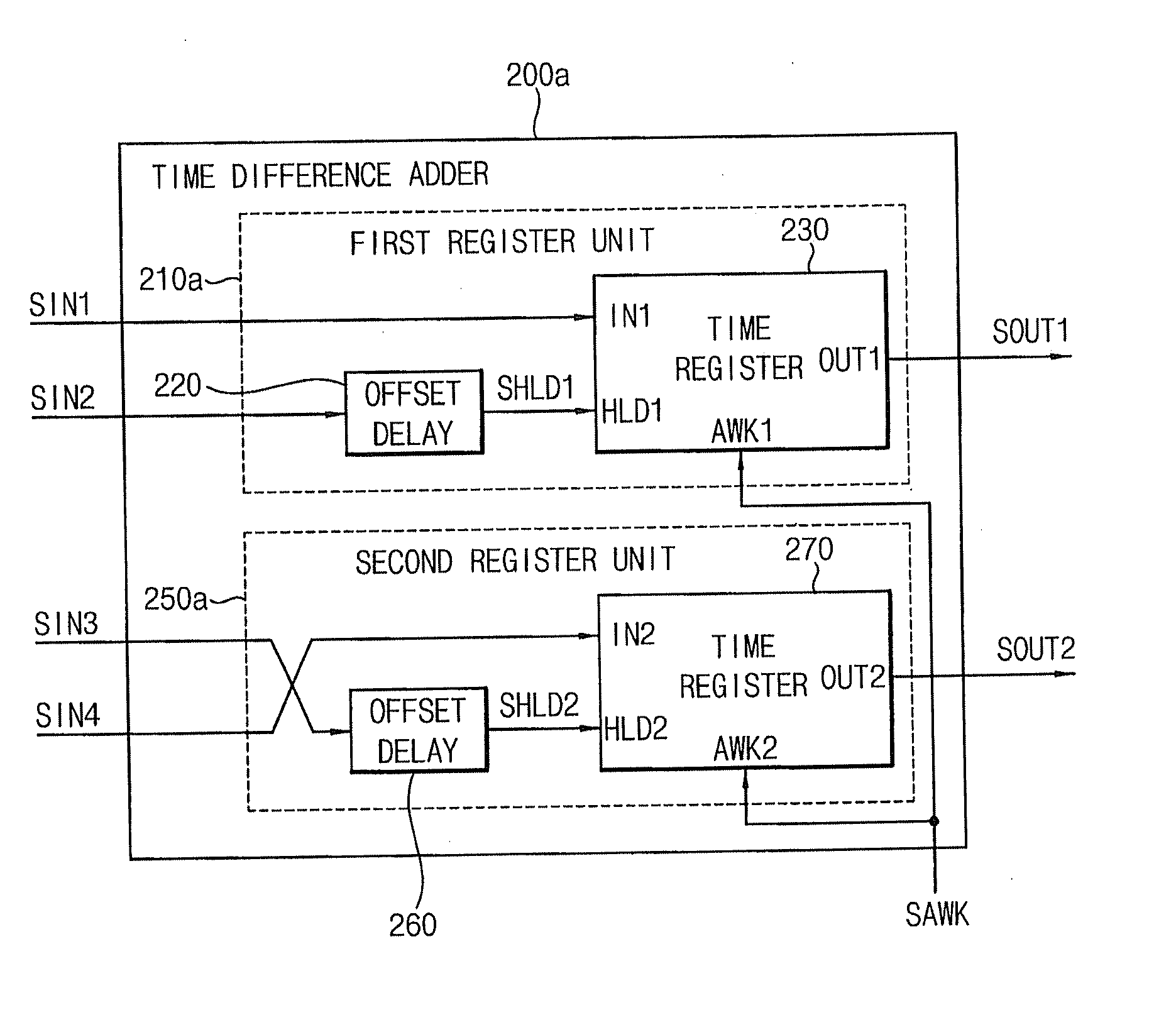

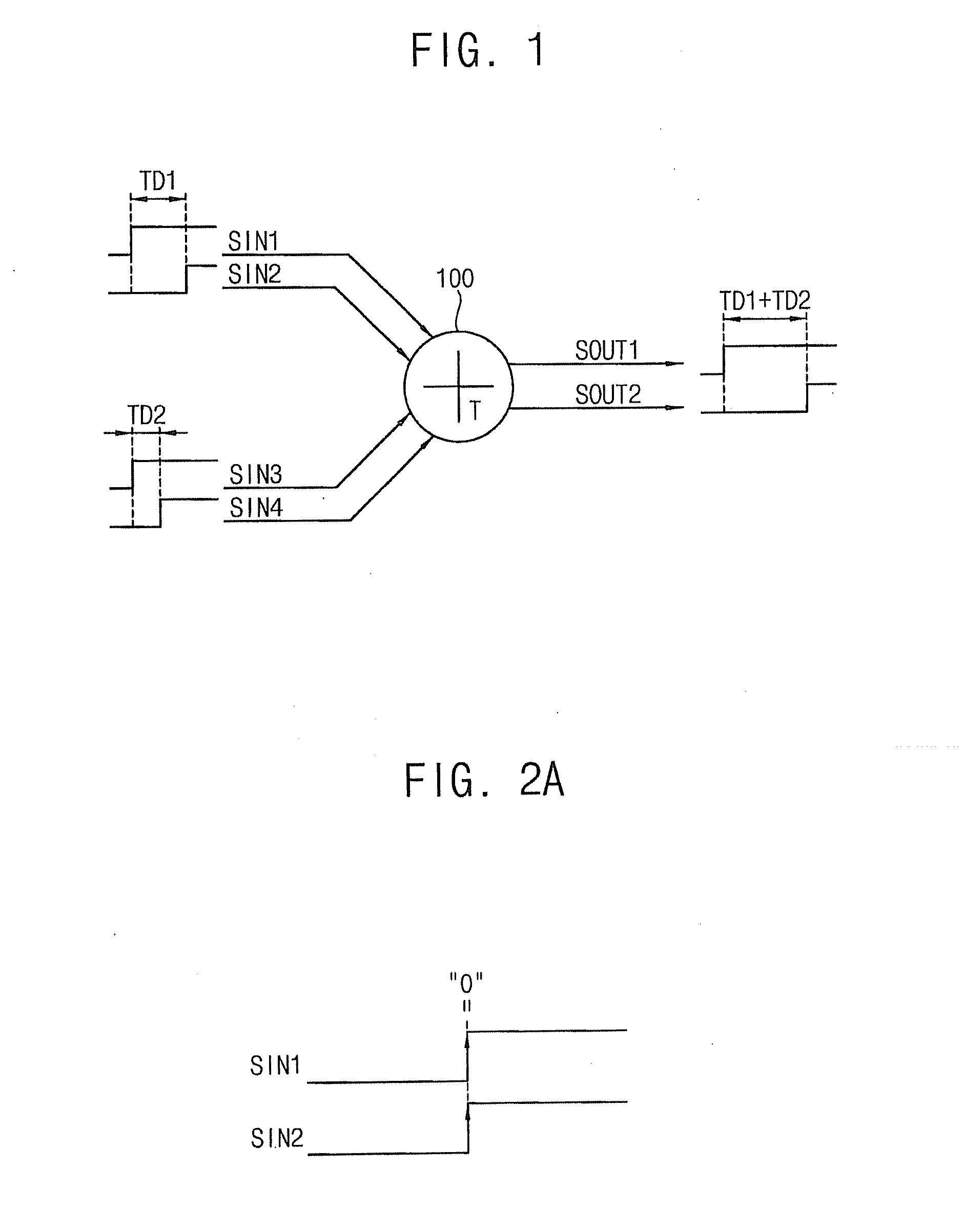

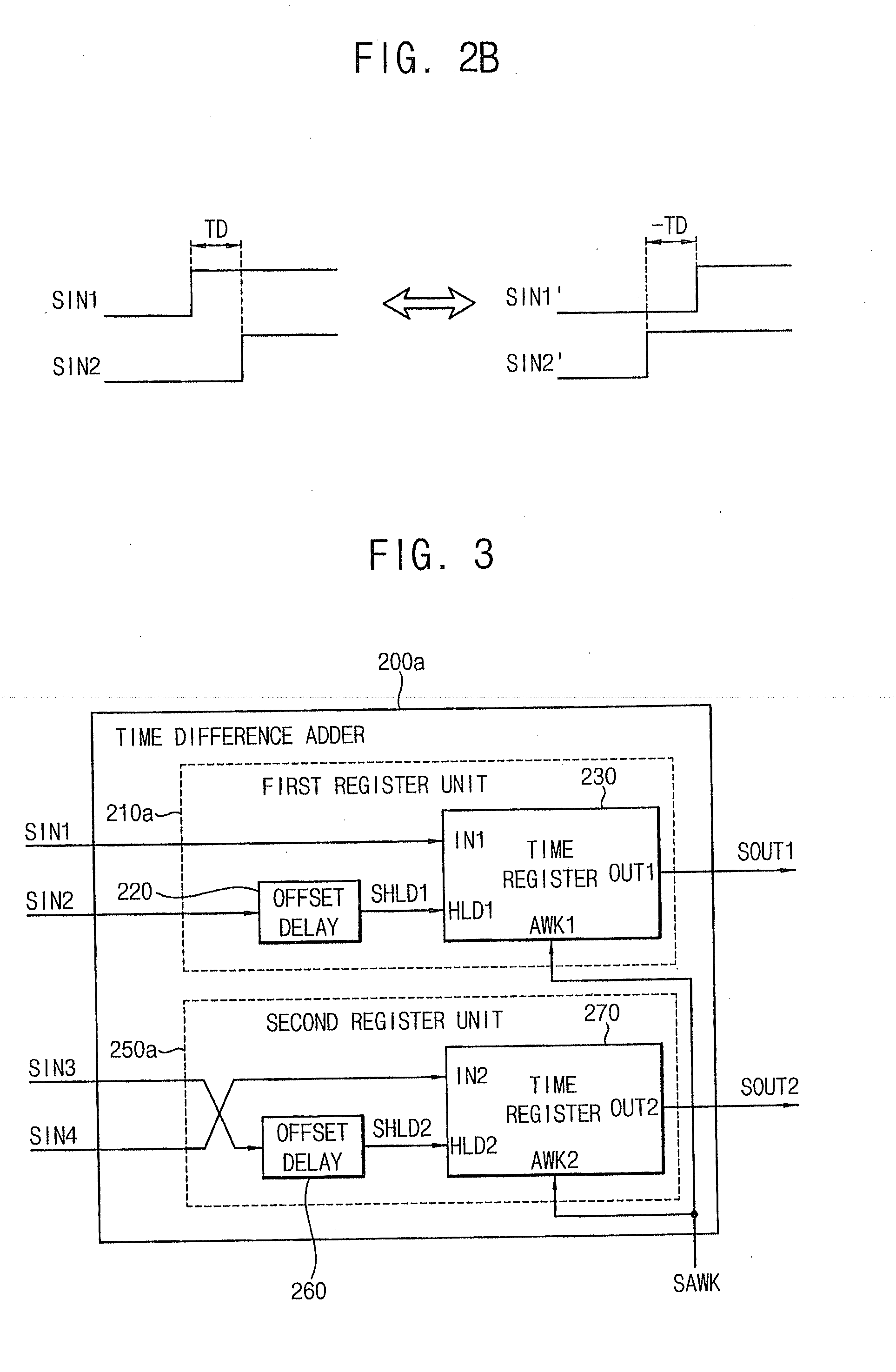

Time difference adders, time difference accumulators, sigma-delta time-to-digital converters, digital phase locked loops and temperature sensors

ActiveUS20120306553A1Computations using contact-making devicesPulse automatic controlDigital down converterProcessor register

A time difference adder included in a system-on-chip (SOC) includes a first register unit and a second register unit. The first register unit is configured to receive first and second input signals having a first time difference, and generate a first output signal in response to a first signal. The second register unit is configured to receive third and fourth input signals having a second time difference, and generate a second output signal having a third time difference with respect to the first output signal in response to the first signal. The third time difference corresponds to a sum of the first time difference and the second time difference.

Owner:SAMSUNG ELECTRONICS CO LTD

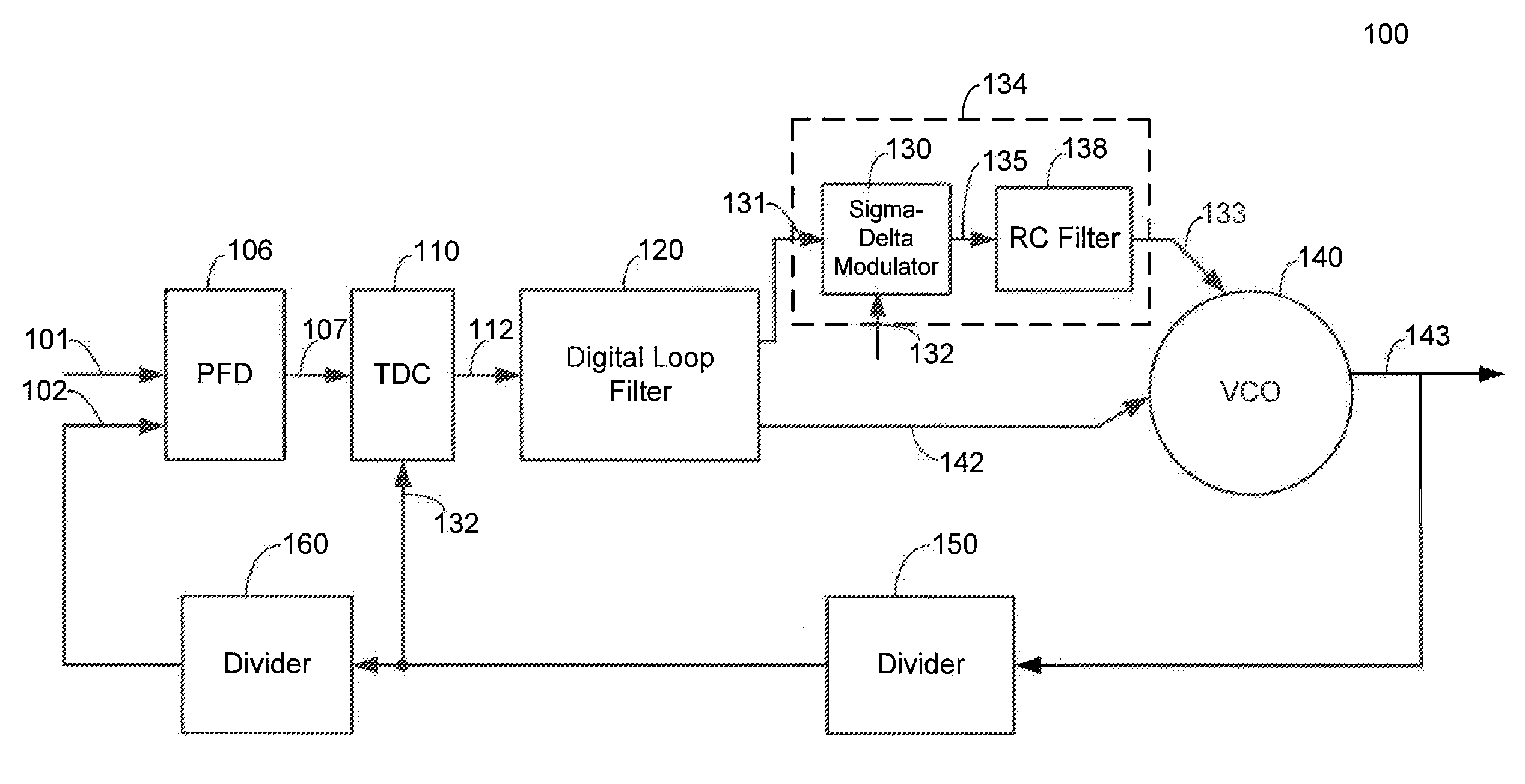

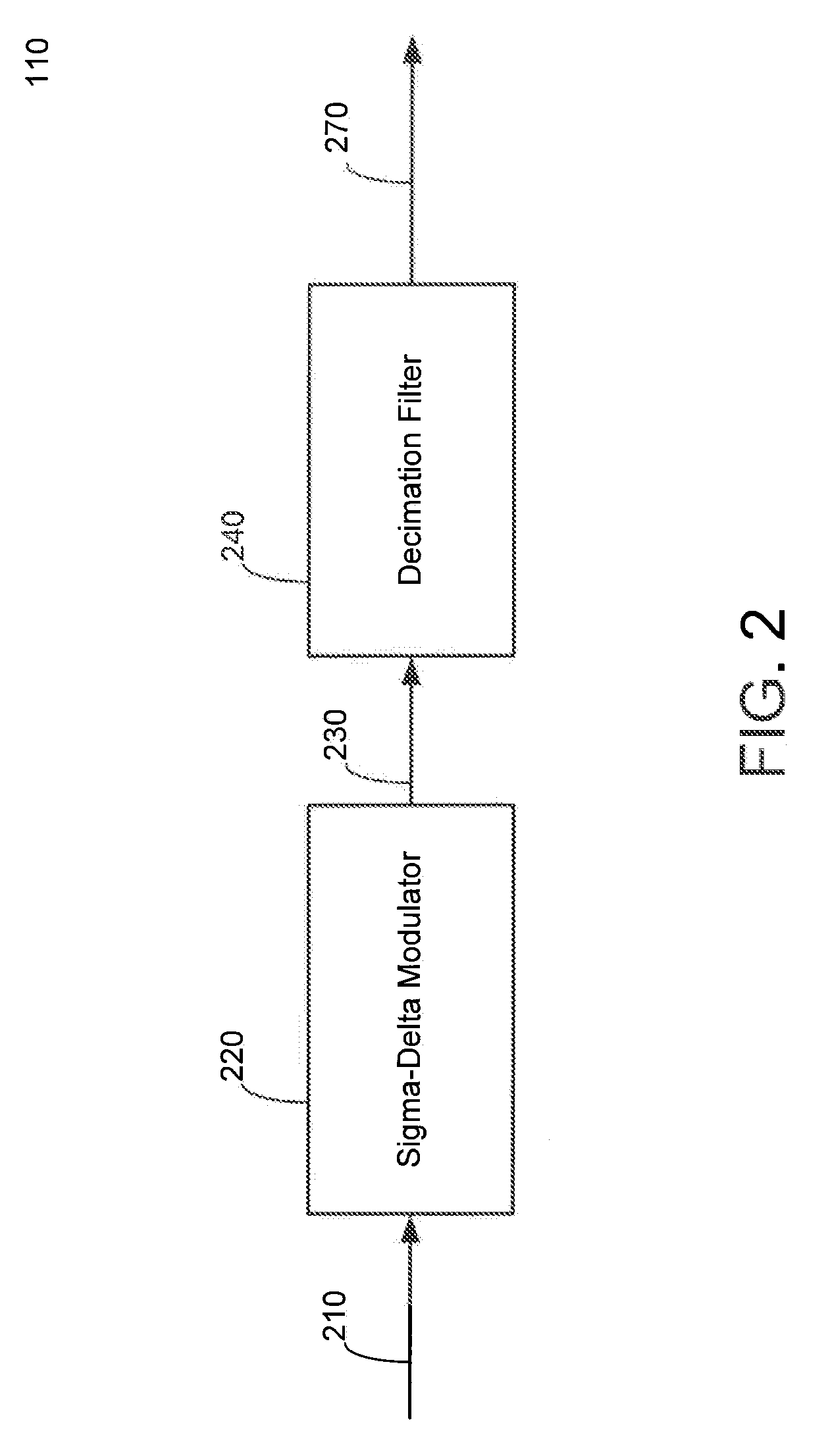

Systems, Circuits, and Methods for a Sigma-Delta Based Time to Digital Converter

ActiveUS20130257494A1Electric signal transmission systemsPulse automatic controlIntegratorEngineering

Systems, methods, and circuits provide a time to digital converter comprising a sigma-delta modulator. The sigma-delta based time to digital converter may receive an analog signal representing a phase error between a reference clock signal and a feedback clock signal and generate a digital signal representing the phase error. The sigma-delta modulator may comprise a subtractor, an integrator, a feedback path, and a quantizer. The subtractor may receive the analog signal and subtract a feedback signal from the analog signal and the integrator may integrate the output of the subtractor. The sigma-delta modulator may accumulate a voltage or a charge over a capacitor as pulses are received from the analog signal and after a number of clock cycles, the capacitor may be discharged to generate a pulse in an output signal.

Owner:AVAGO TECH INT SALES PTE LTD

Adaptive spectral noise shaping to improve time to digital converter quantization resolution using dithering

ActiveUS7570182B2Quantization noise resolutionReduce noiseElectric signal transmission systemsAnalogue conversionFrequency spectrumNoise shaping

Owner:TEXAS INSTR INC

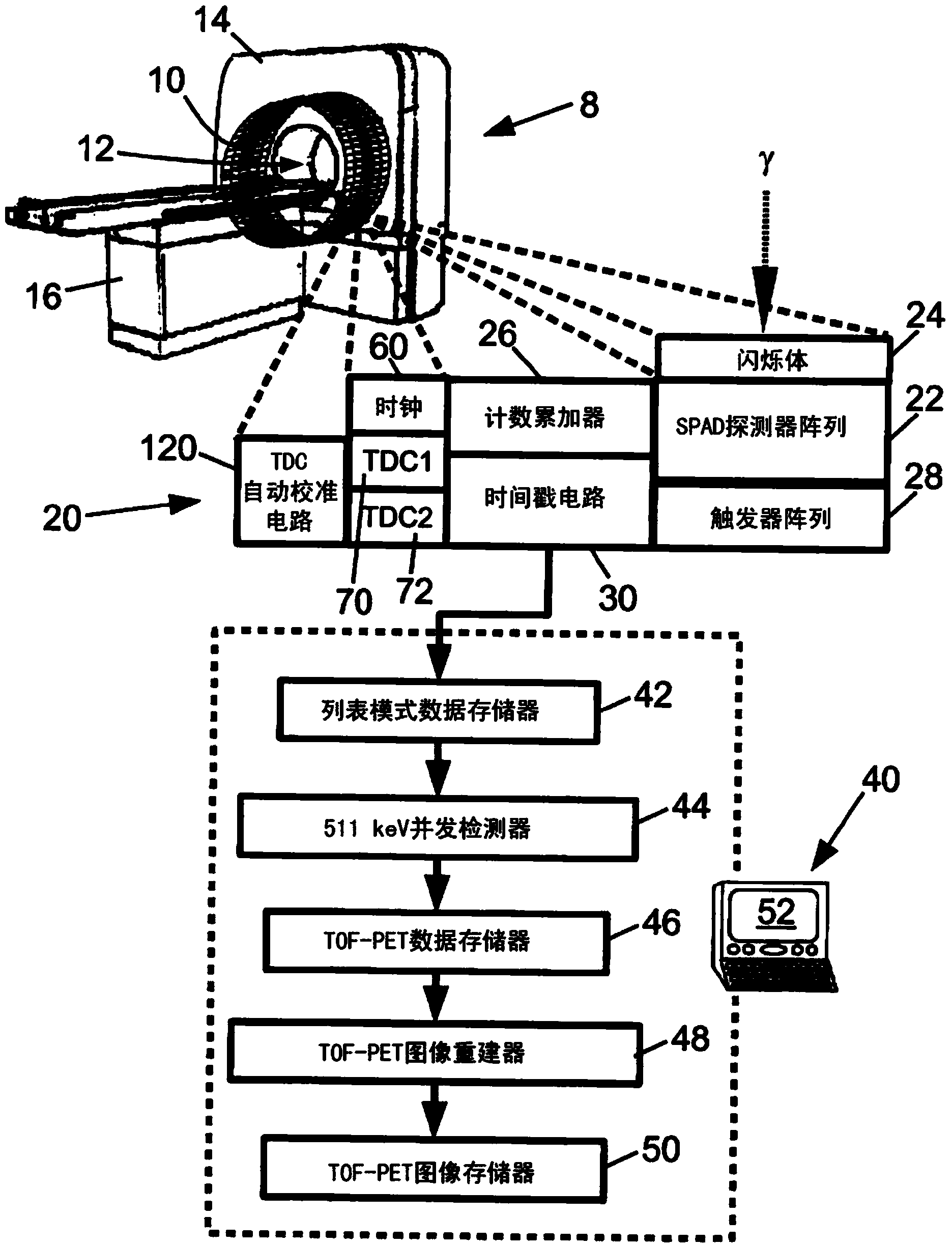

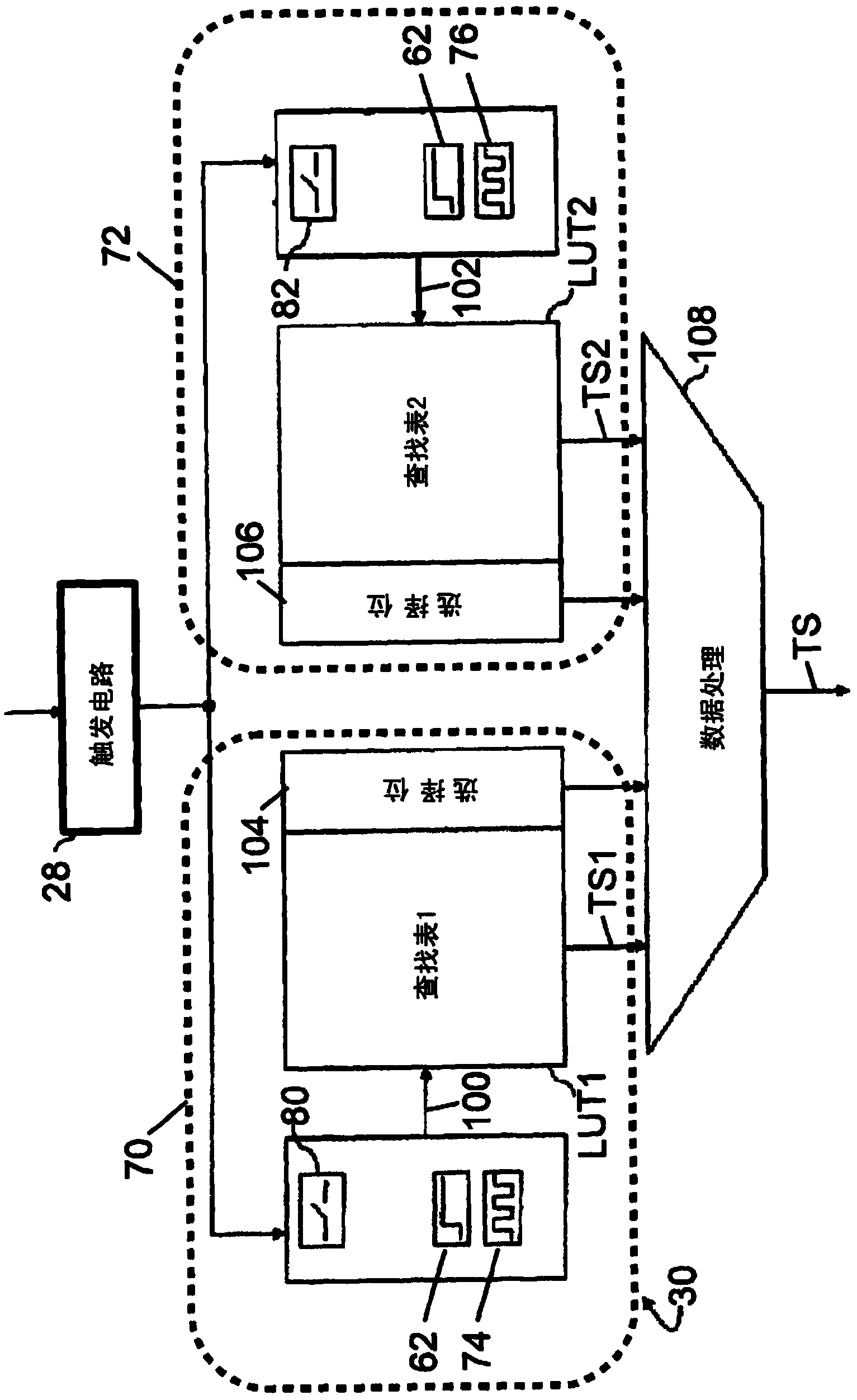

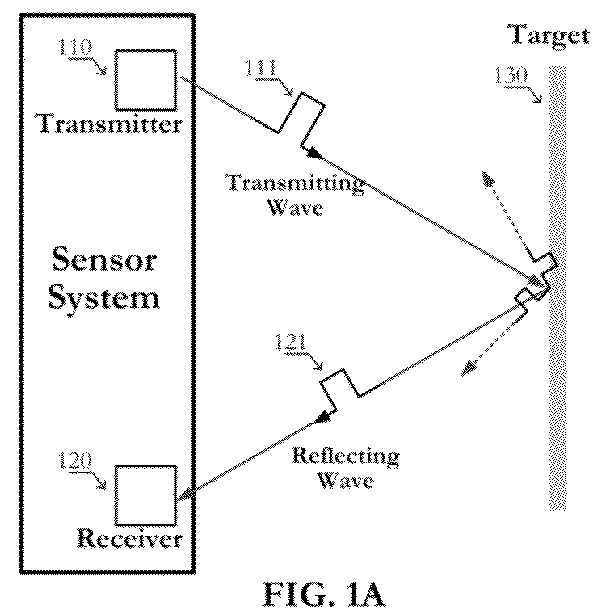

Detector array with time-to-digital conversion having improved temporal accuracy

ActiveCN103460072AImprove time resolutionAccurate time-of-flight PET imagingTomographyX/gamma/cosmic radiation measurmentDetector arrayDigital converter

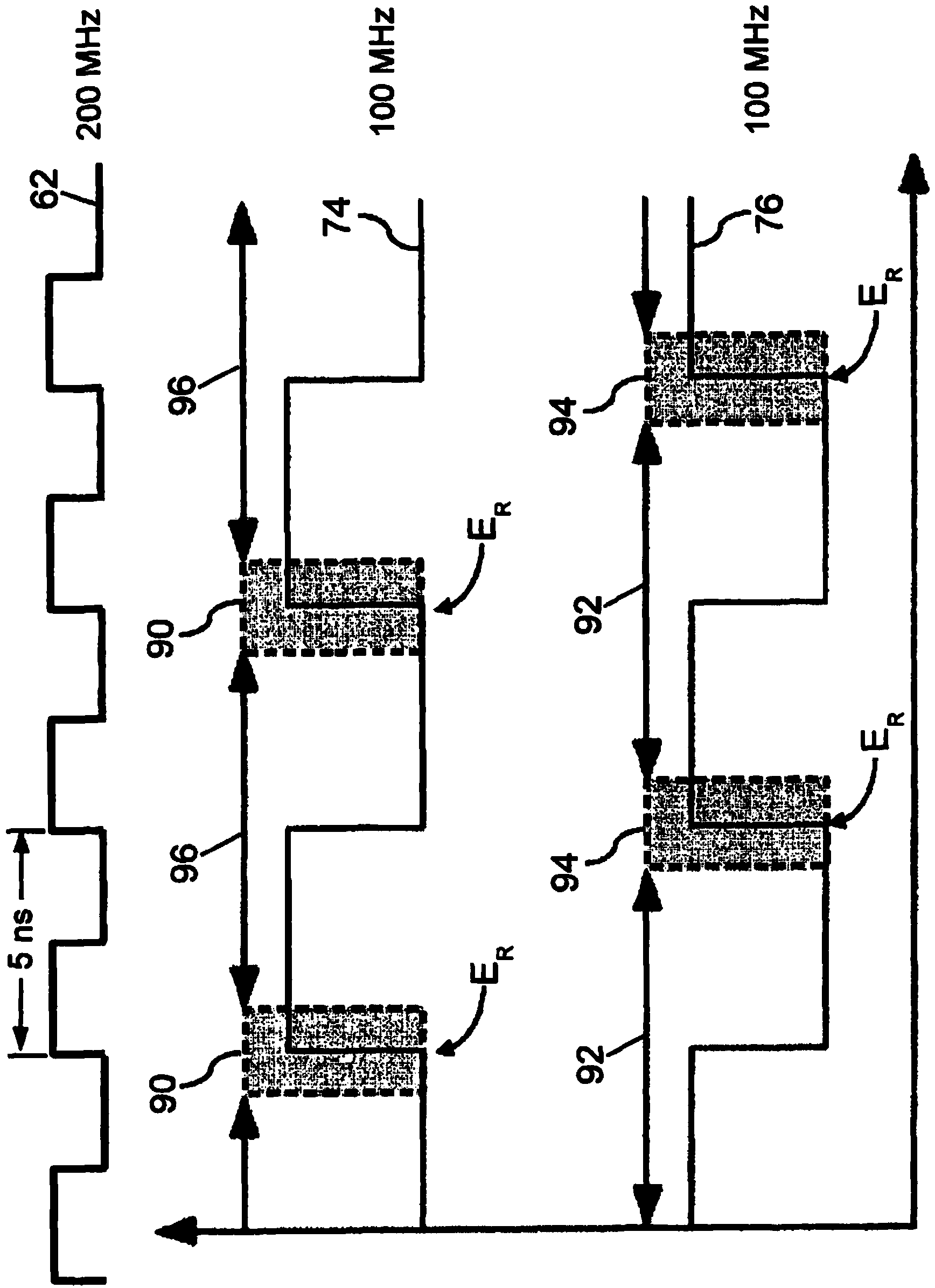

A detector (22) detects an event. First and second time-to-digital converters(TDCs) (70, 72) generate first and second time stamps (TS1, TS2) for the detection of the event. The first TDC and the second TDC are both synchronized with a common clock signal (62) that defines a fixed time offset between the second TDC and the first TDC. An autocalibration circuit (120) adjusts the first TDC and the second TDC to keep the time difference between the second time stamp and the first time stamp equal to the fixed time offset between the second TDC and the first TDC. The detector may be a detector array, and trigger circuitry (28) propagates a trigger signal from a triggering detector of the array of detectors to the first and second TDC's. Skew correction circuitry (132, 134, 136, 142, 60, 162) adjusts a timestamp (TS) based on which detector is the triggering detector.

Owner:KONINKLJIJKE PHILIPS NV

Digital Phase Locked Loop with Gear Shifting

ActiveUS20080315960A1Pulse automatic controlTransmission path divisionProportional controlPhase difference

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal. A phase detection circuit operates on the reference clock to provide digital phase error samples indicative of a phase difference between the reference clock and the RF clock. A programmable filter is connected to receive the phase error samples and connected to provide a filtered output having a gain and a phase margin to the controllable oscillator. The programmable filter includes a proportional loop gain control having a programmable loop gain coefficient (alpha-α) and an integral loop gain control having a programmable loop gain coefficient (rho-ρ). Alpha and rho are configured to be programmatically changed simultaneously and are selected such that the gain is changed and the phase margin remains substantially unchanged

Owner:TEXAS INSTR INC

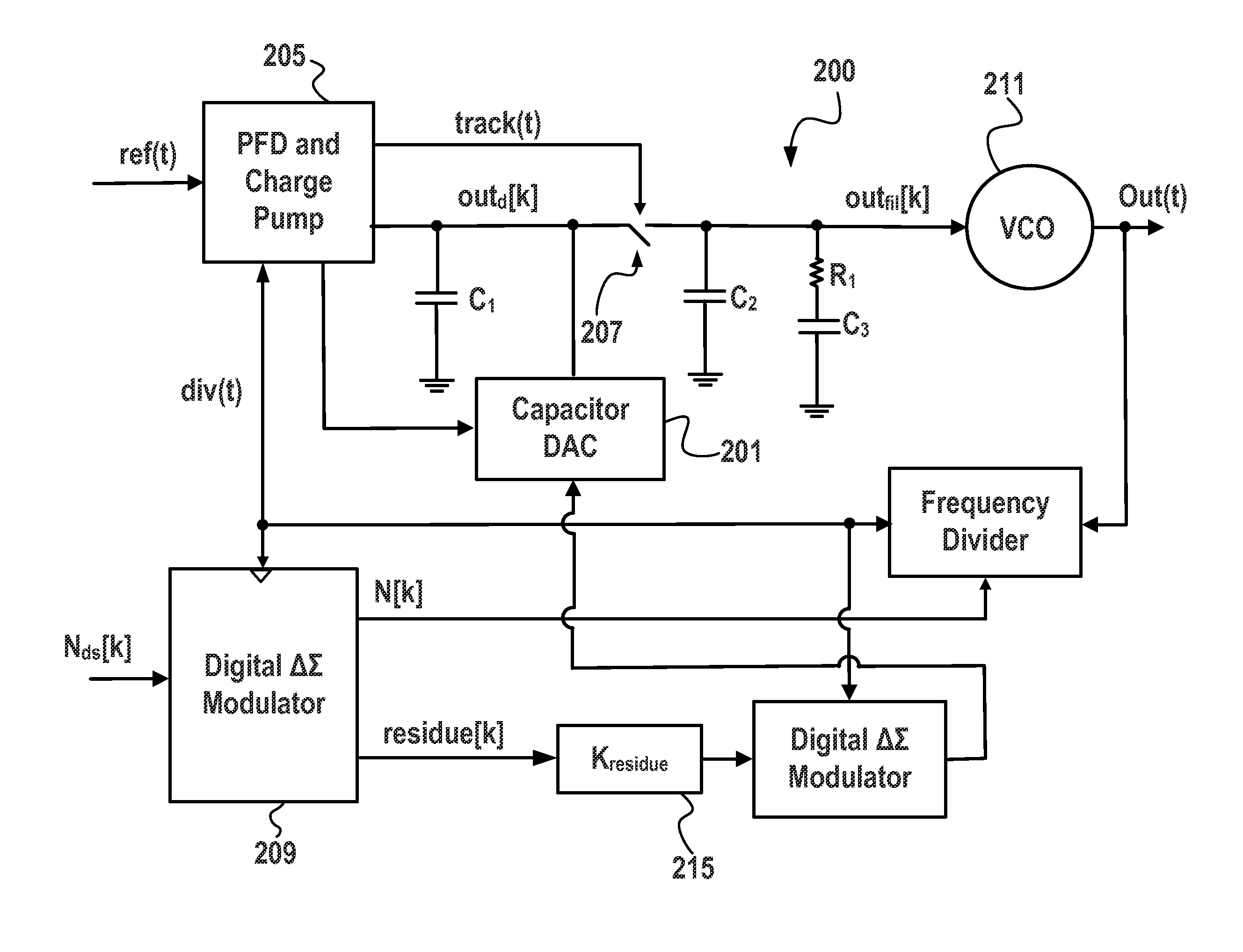

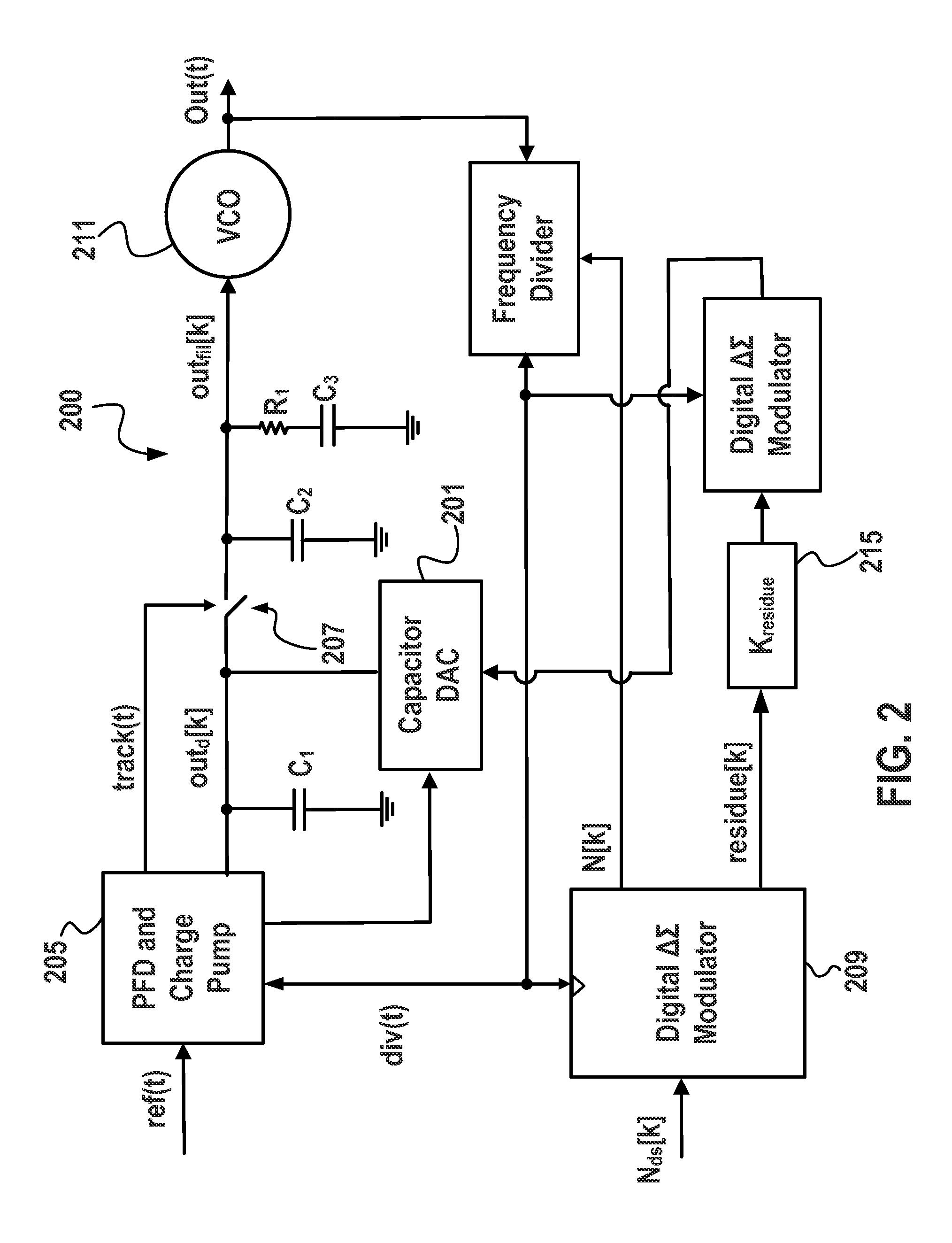

Cancellation of delta-sigma quantization noise within a fractional-n PLL with a nonlinear time-to-digital converter

ActiveUS20150145571A1Reduce quantization noisePulse automatic controlAnalogue conversionEngineeringGreek letter sigma

A fractional-N phase-locked loop (PLL) includes a nonlinear time to digital converter that generates a digital representation of a phase error corresponding to a time difference between a feedback signal of the fractional-N PLL and a reference signal. A nonlinear quantization noise cancellation circuit supplies a correction signal to ensure that the generated digital representation has reduced quantization noise. The correctional signal may be applied in the analog or digital domain.

Owner:SKYWORKS SOLUTIONS INC

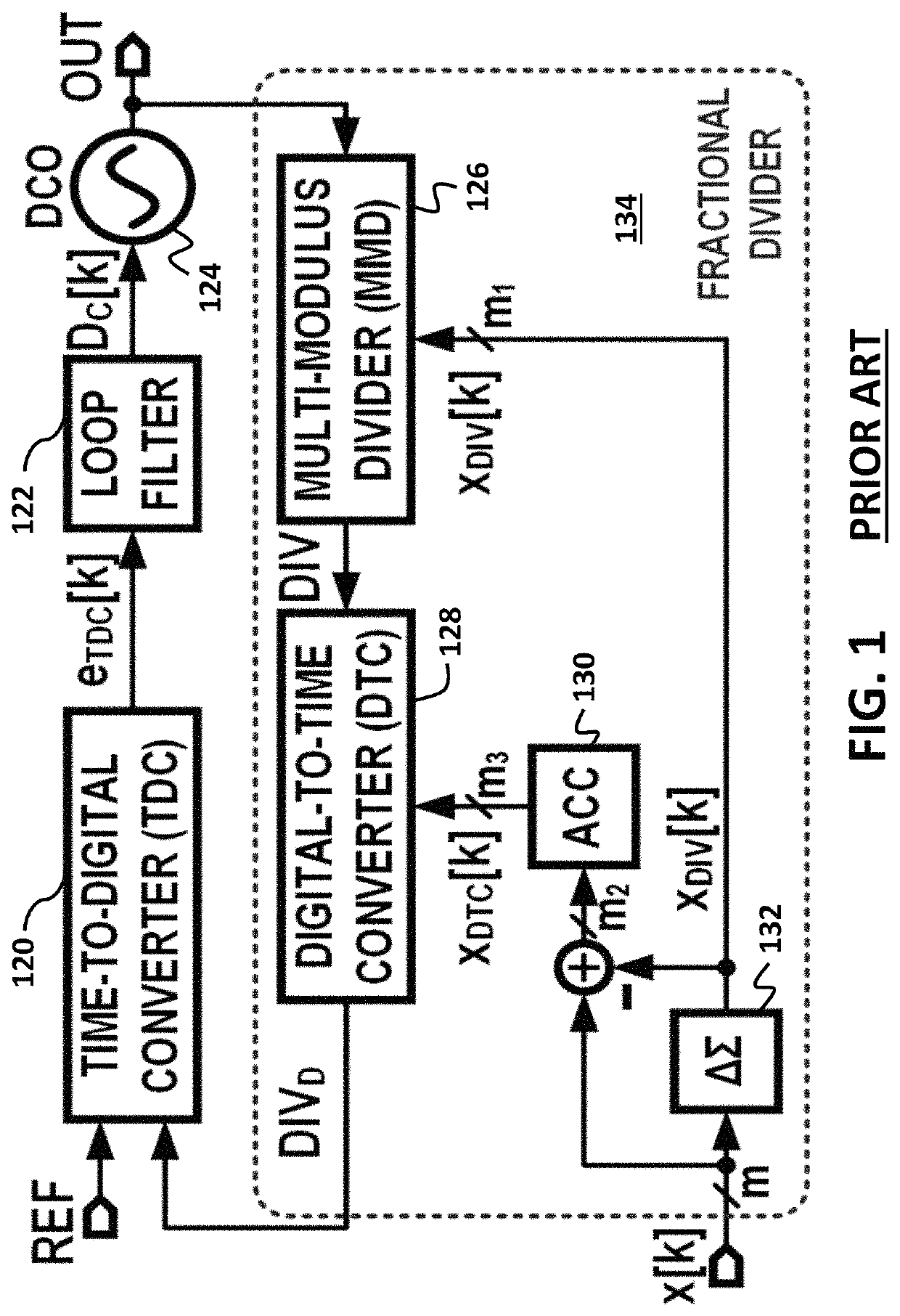

Fractional-N Frequency Synthesizer Incorporating Cyclic Digital-To-Time And Time-To-Digital Circuit Pair

ActiveUS20160056827A1Low spuriousReduce power consumptionPower saving provisionsElectric signal transmission systemsFrequency spectrumFrequency synthesizer

A novel and useful look-ahead time to digital converter (TDC) that is applied to an all digital phase locked loop (ADPLL) as the fractional phase error detector. The deterministic nature of the phase error during frequency / phase lock is exploited to achieve a reduction in power consumption of the TDC. The look-ahead TDC circuit is used to construct a cyclic DTC-TDC pair which functions to reduce fractional spurs of the output spectrum in near-integer channels by randomly rotating the cyclic DTC-TDC structure so that it starts from a different point every reference clock thereby averaging out the mismatch of the elements. Associated rotation and dithering methods are also presented. The ADPLL is achieved using the look-ahead TDC and / or cyclic DTC-TDC pair circuit.

Owner:SHORT CIRCUIT TECH LLC

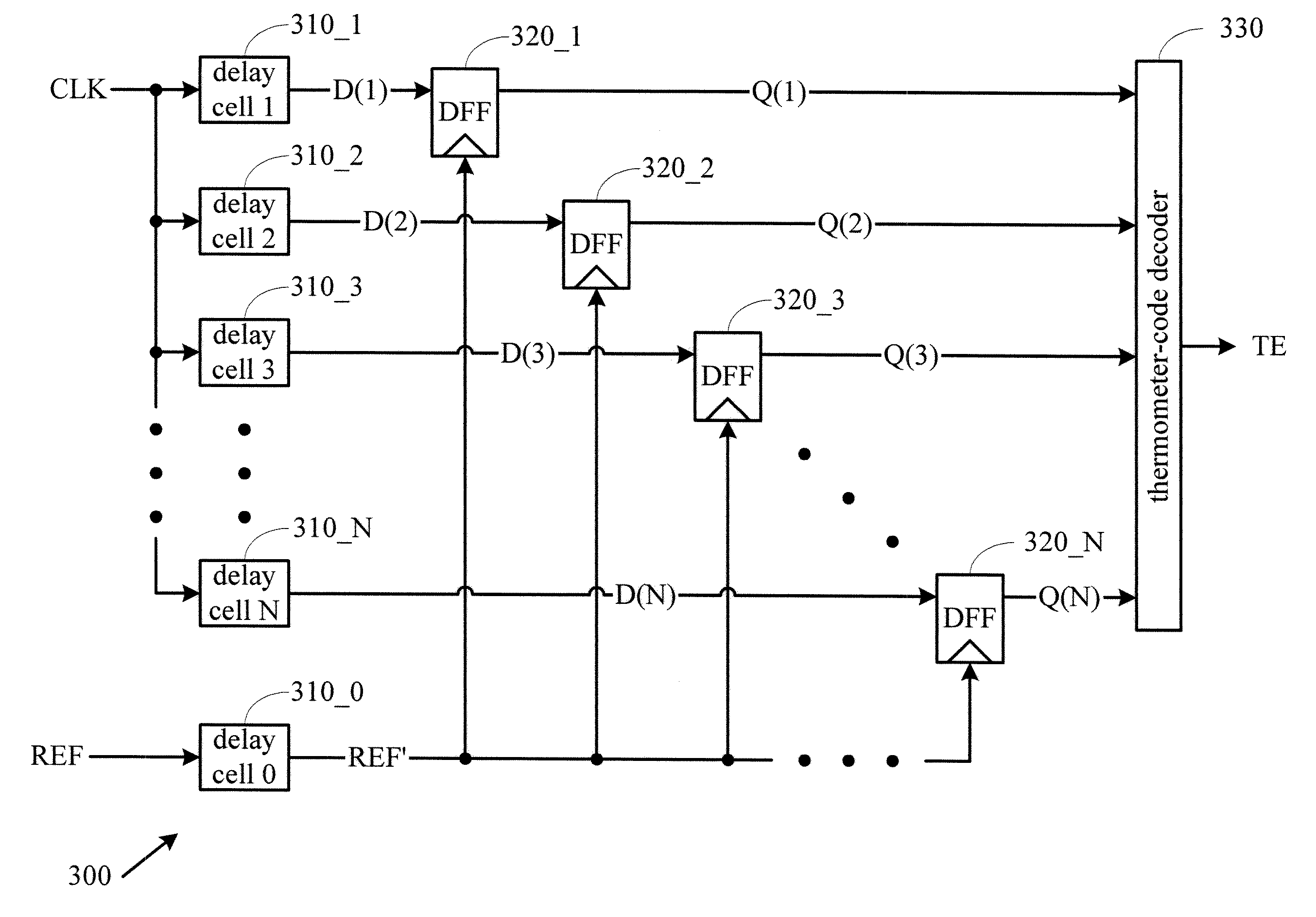

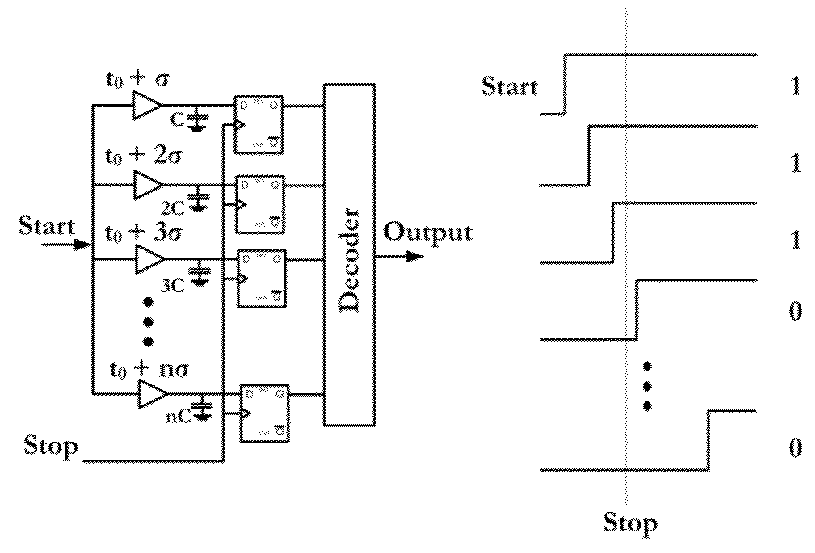

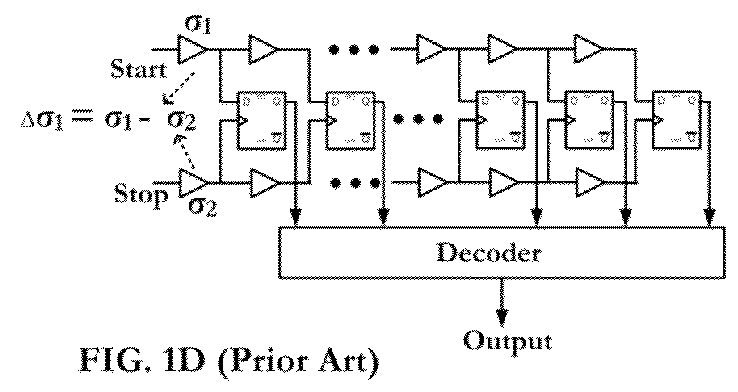

High resolution time-to-digital converter and method thereof

ActiveUS20070273569A1High resolutionElectric signal transmission systemsAnalogue-digital convertersDigital converterTime-to-digital converter

A time-to-digital converter (TDC) is disclosed, the TDC comprising: a plurality of parallel circuits for receiving a common first clock and for generating a plurality of delayed clocks; a plurality of sampling circuits for receiving and sampling said delayed clocks at an edge of a second clock to generate a plurality of decisions, respectively; and a decoder for receiving said decisions and for generating a digital output accordingly.

Owner:REALTEK SEMICON CORP

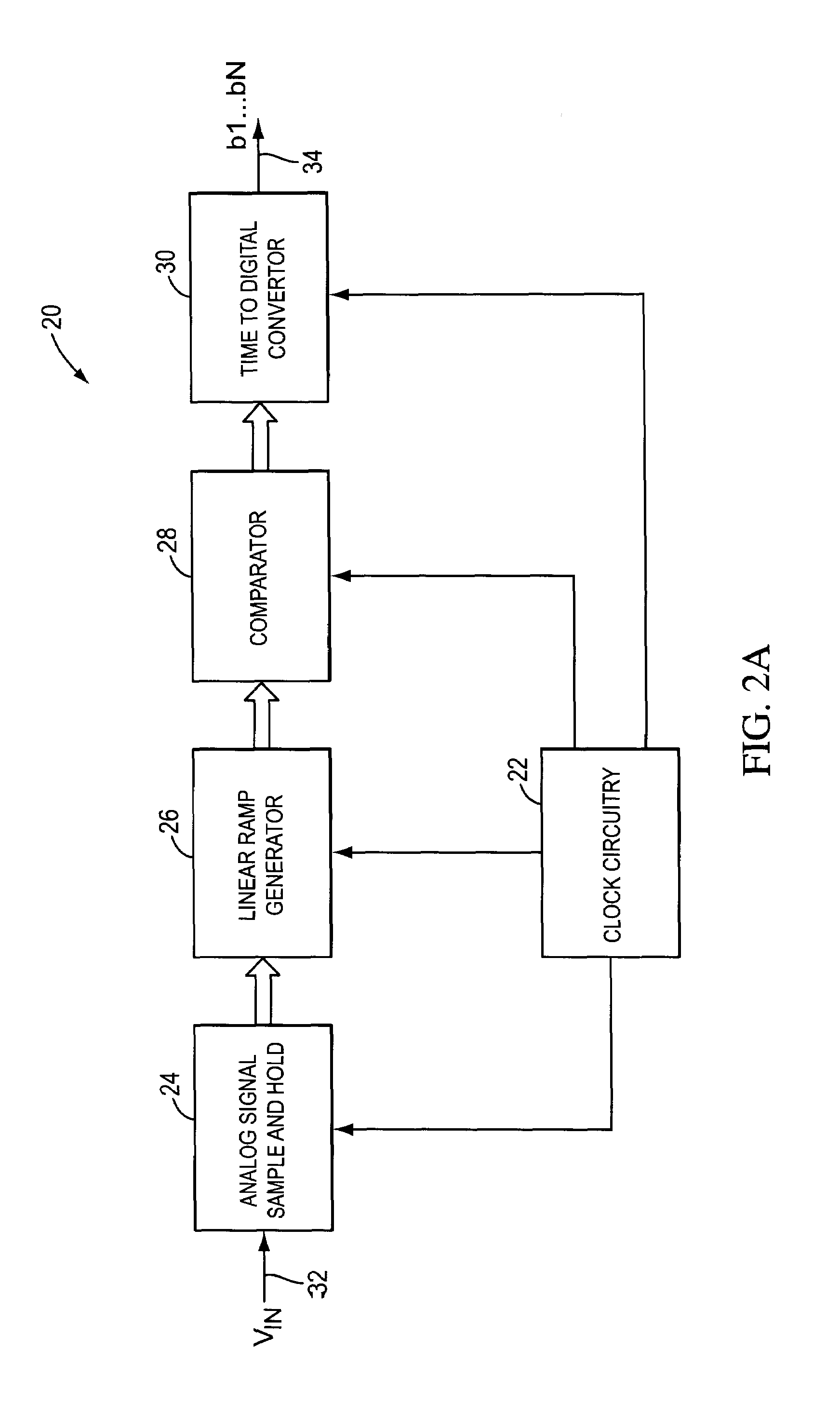

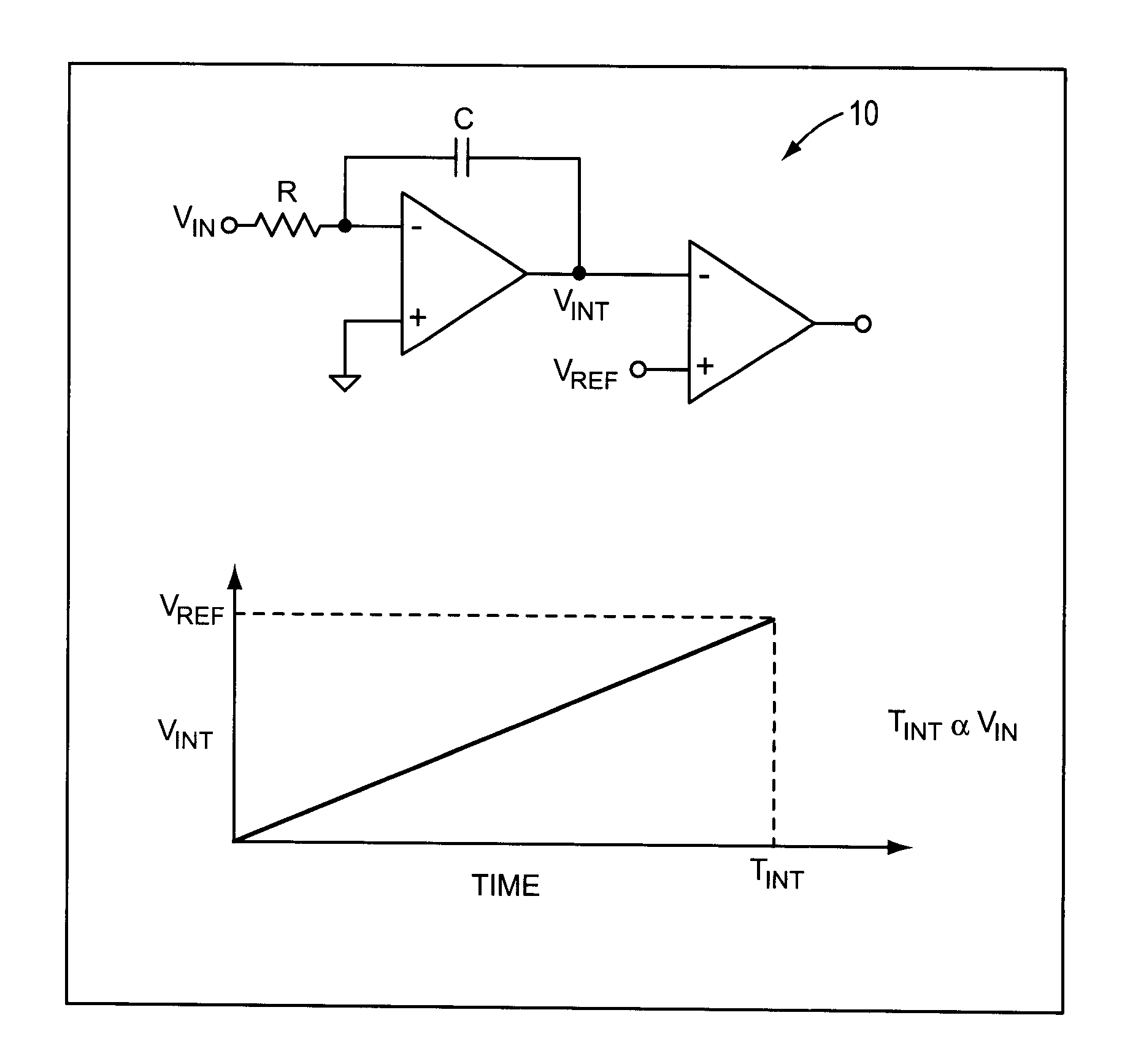

Rotary clock flash analog to digital converter system and method

ActiveUS7609756B2Electric signal transmission systemsPulse automatic controlDigital down converterEngineering

System and method for converting an analog voltage to a digital signal. The system includes an input voltage sampler, a ramp generator, a comparator, a time-to-digital converter (TDC), and a multiphase oscillator, preferably a rotary traveling wave oscillator, that provides the critical system timing. The phases of the multiphase oscillator define a sampling interval during which the input voltage is sampled and held and a conversion interval during which the ramp generator, comparator, and TDC operate to convert the sampled voltage to the digital signal. The TDC samples at times provided by the phases of the multiphase oscillator to form the bits of the digital signal. The sampler, ramp generator, and comparator can be constructed from multiple fragments, one of which is selectable for calibration while the rest of the fragments are joined for normal operation. Multiple converters can be interleaved to increase the sampling rate.

Owner:ANALOG DEVICES INC

Rotary clock flash analog to digital converter system and method

ActiveUS20080272952A1Electric signal transmission systemsPulse automatic controlDigital down converterEngineering

System and method for converting an analog voltage to a digital signal. The system includes an input voltage sampler, a ramp generator, a comparator, a time-to-digital converter (TDC), and a multiphase oscillator, preferably a rotary traveling wave oscillator, that provides the critical system timing. The phases of the multiphase oscillator define a sampling interval during which the input voltage is sampled and held and a conversion interval during which the ramp generator, comparator, and TDC operate to convert the sampled voltage to the digital signal. The TDC samples at times provided by the phases of the multiphase oscillator to form the bits of the digital signal. The sampler, ramp generator, and comparator can be constructed from multiple fragments, one of which is selectable for calibration while the rest of the fragments are joined for normal operation. Multiple converters can be interleaved to increase the sampling rate.

Owner:ANALOG DEVICES INC

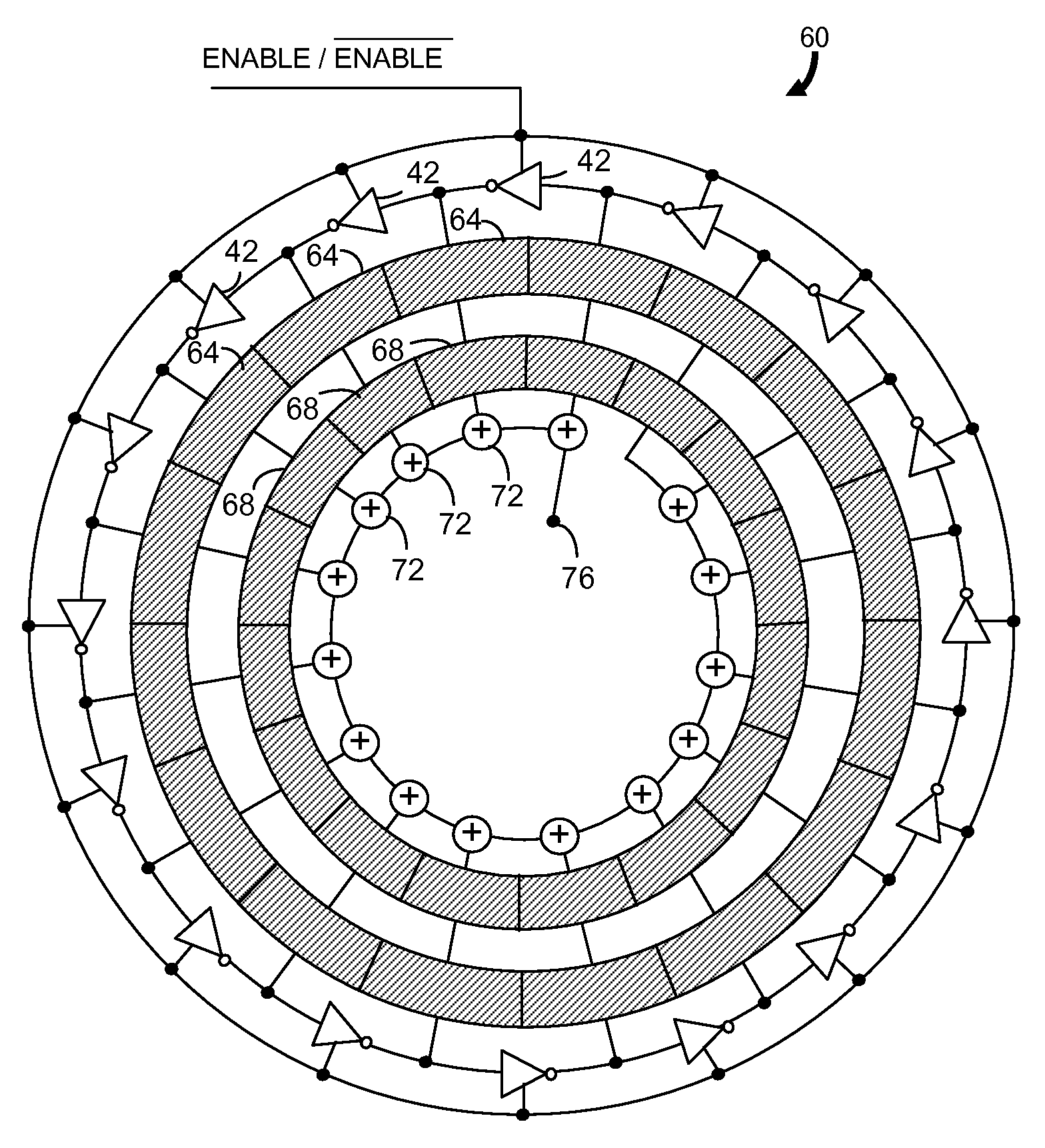

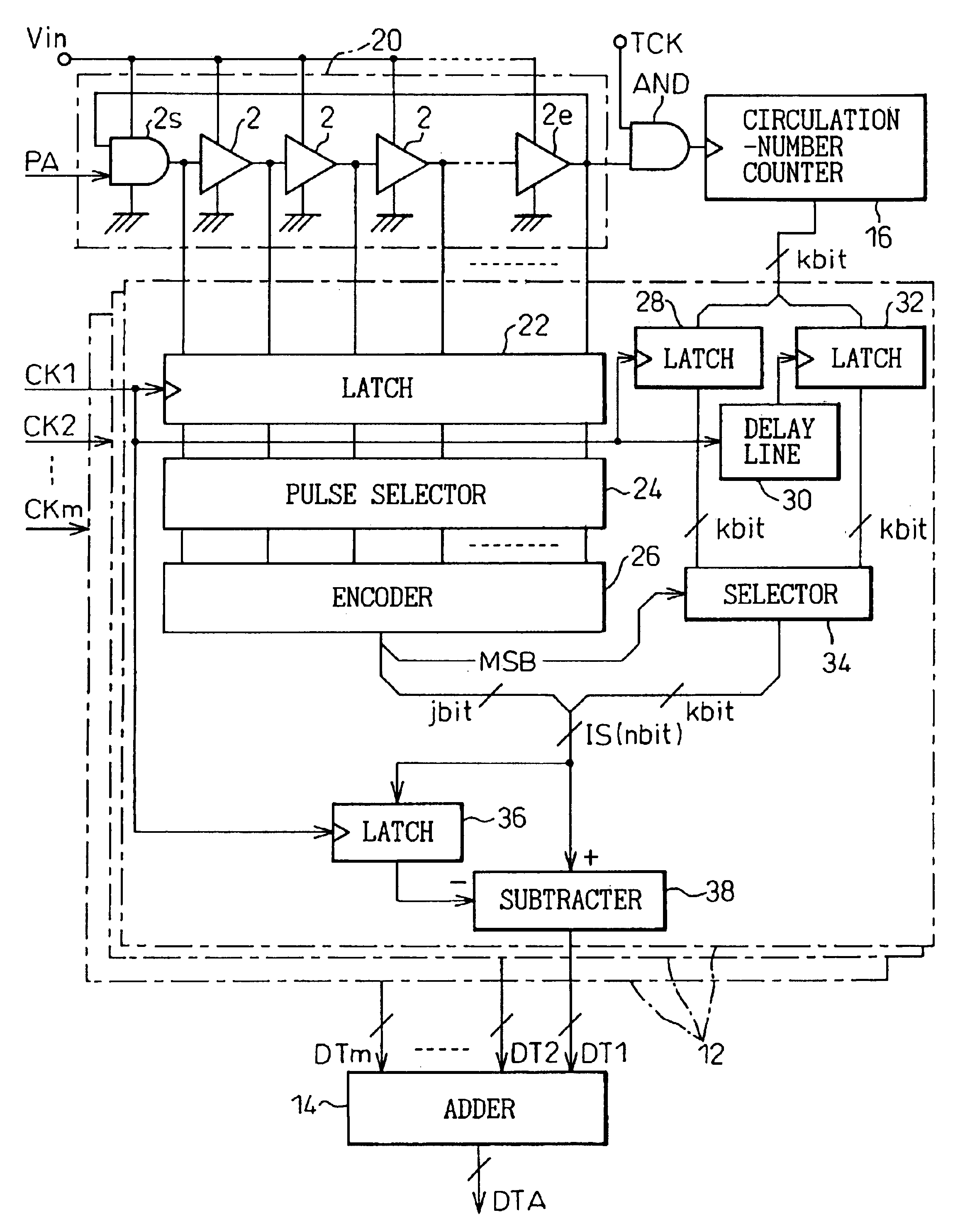

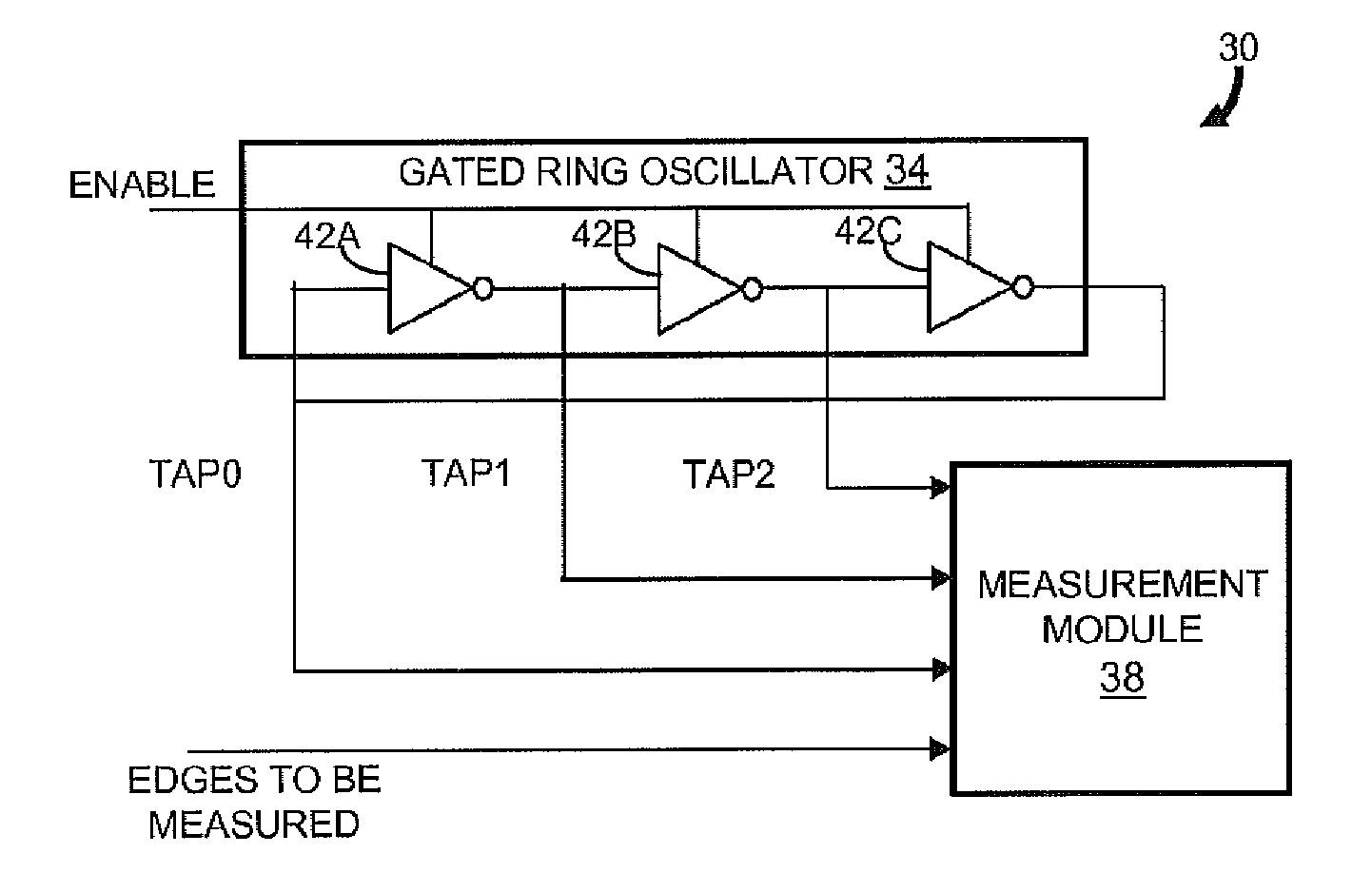

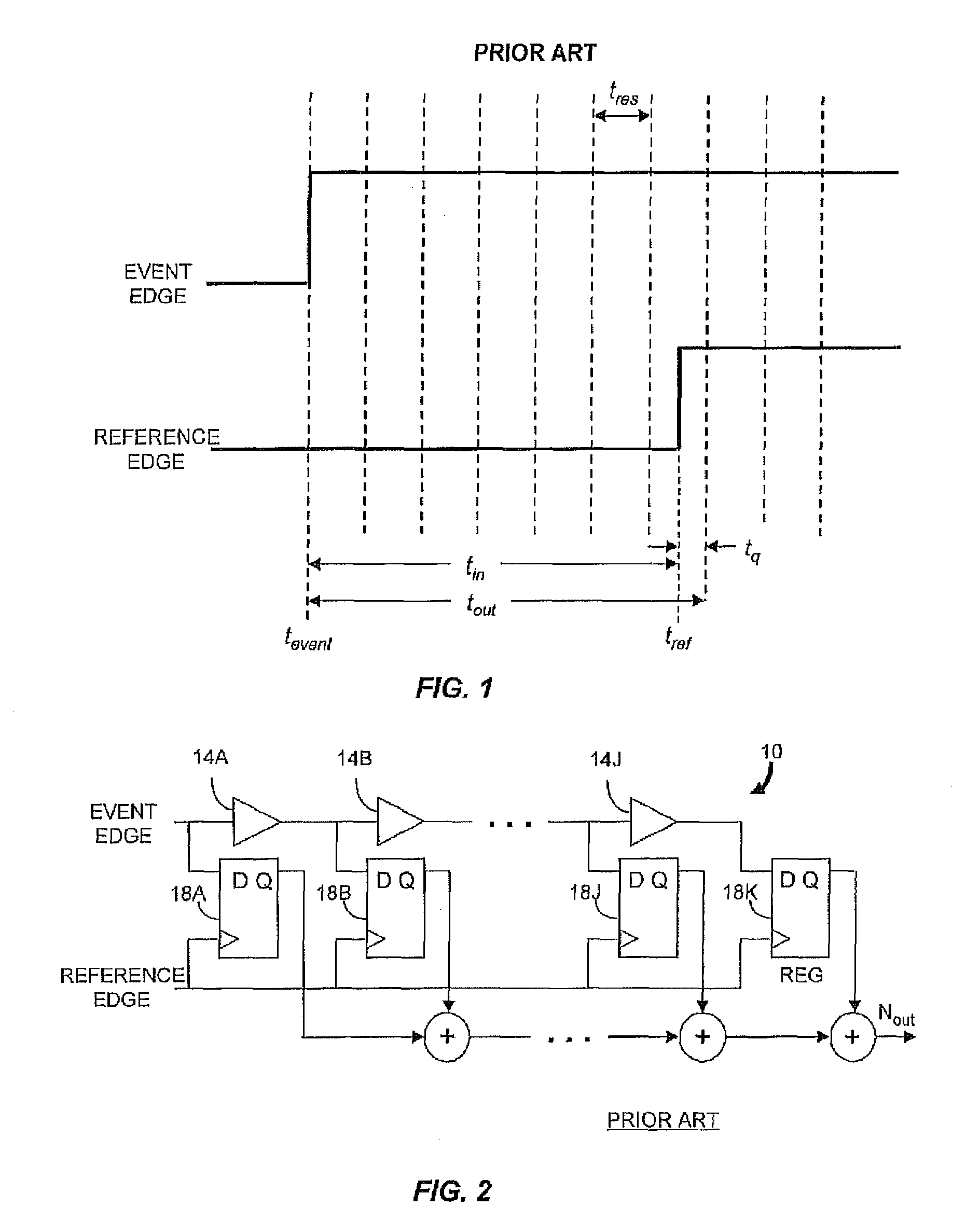

Gated ring oscillator for a time-to-digital converter with shaped quantization noise

ActiveUS20080069292A1Resolution timeContinuously circulated pulse countersCounting chain synchronous pulse countersImage resolutionNoise shaping

Described is a compact, lower power gated ring oscillator time-to-digital converter that achieves first order noise shaping of quantization noise using a digital implementation. The gated ring oscillator time-to-digital converter includes a plurality of delay stages configured to enable propagation of a transitioning signal through the delay stages during an enabled state and configured to inhibit propagation of the transitioning signal through the delay stages during a disabled state. Delay stages are interconnected to allow sustained transitions to propagate through the delay stages during the enabled state and to preserve a state of the gated ring oscillator time-to-digital converter during the disabled state. The state represents a time resolution that is finer than the delay of at least one of the delay stages. A measurement module determines the number of transitions of the delay stages.

Owner:MASSACHUSETTS INST OF TECH

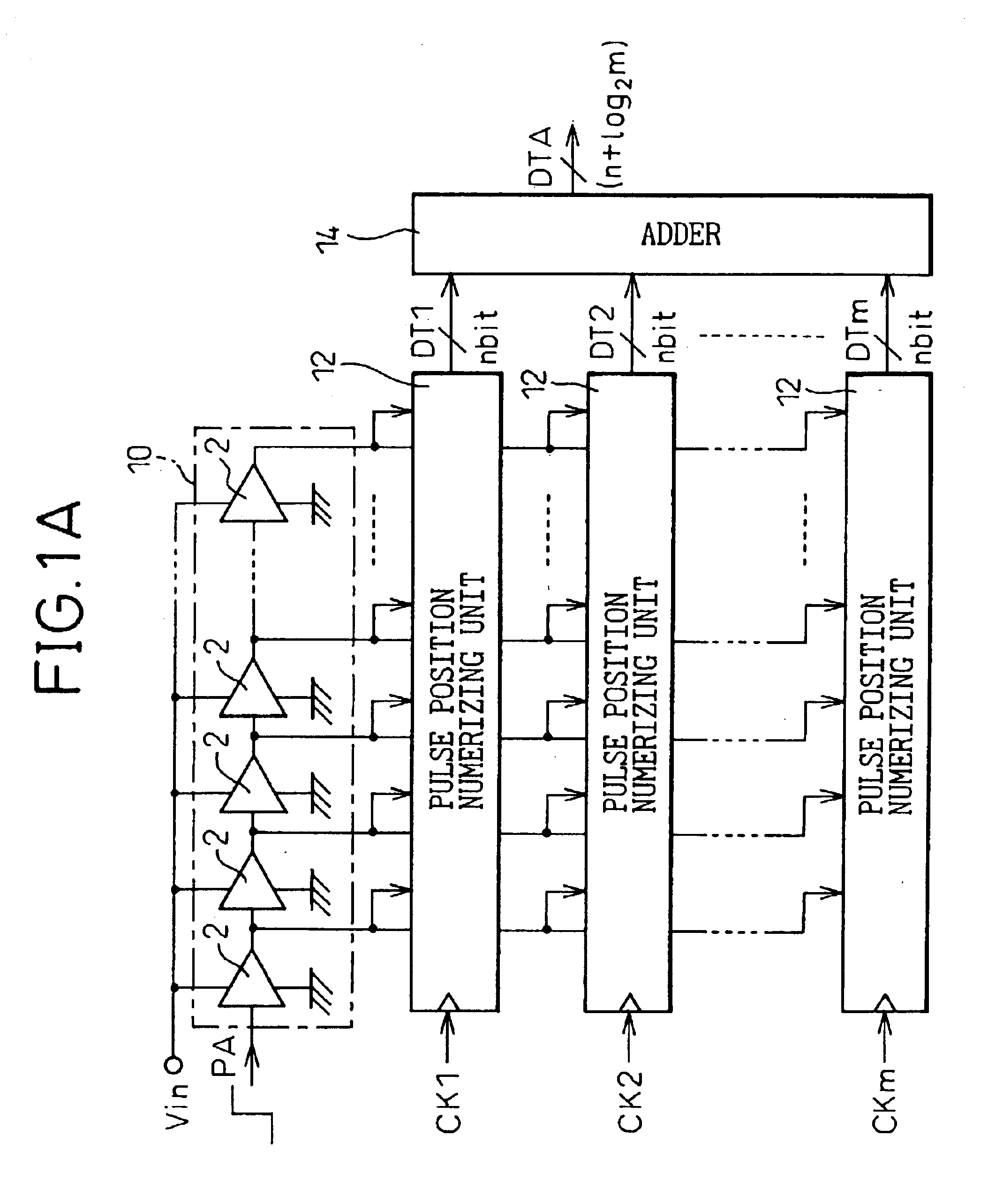

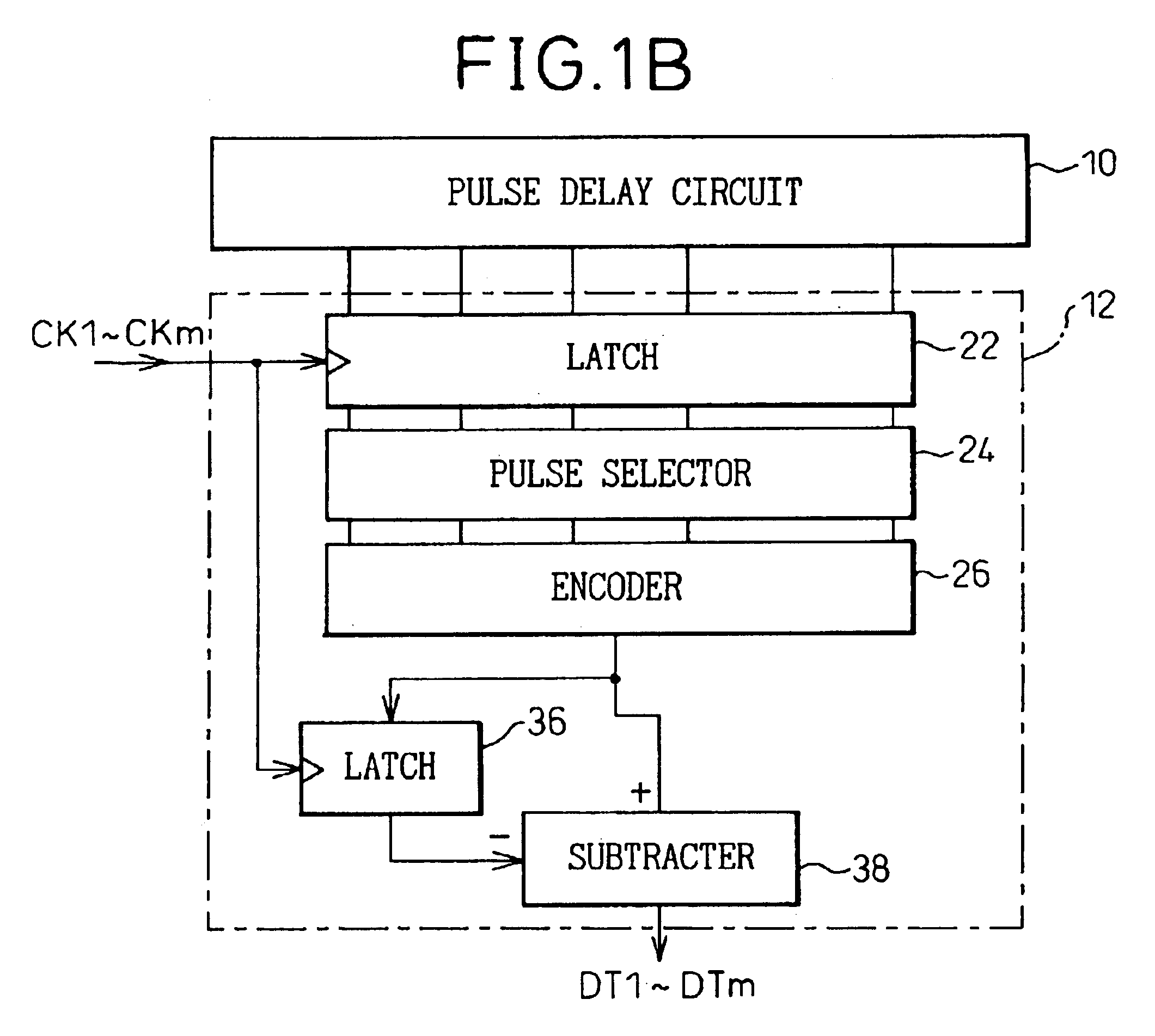

Analog-to-digital conversion method and device

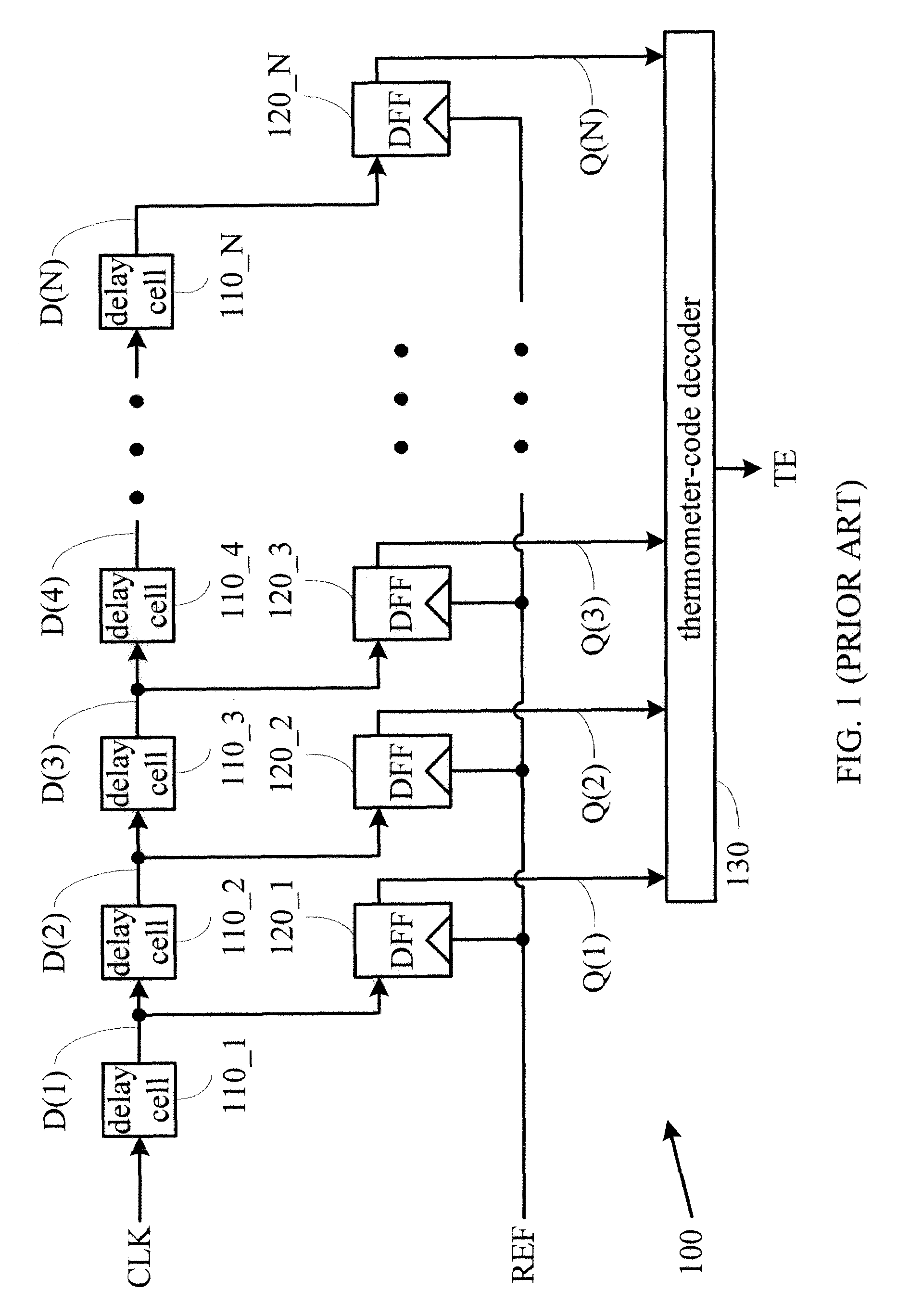

InactiveUS6771202B2Improve accuracyShorten the timeElectric signal transmission systemsPulse generation by logic circuitsDelayed timeEngineering

Owner:DENSO CORP

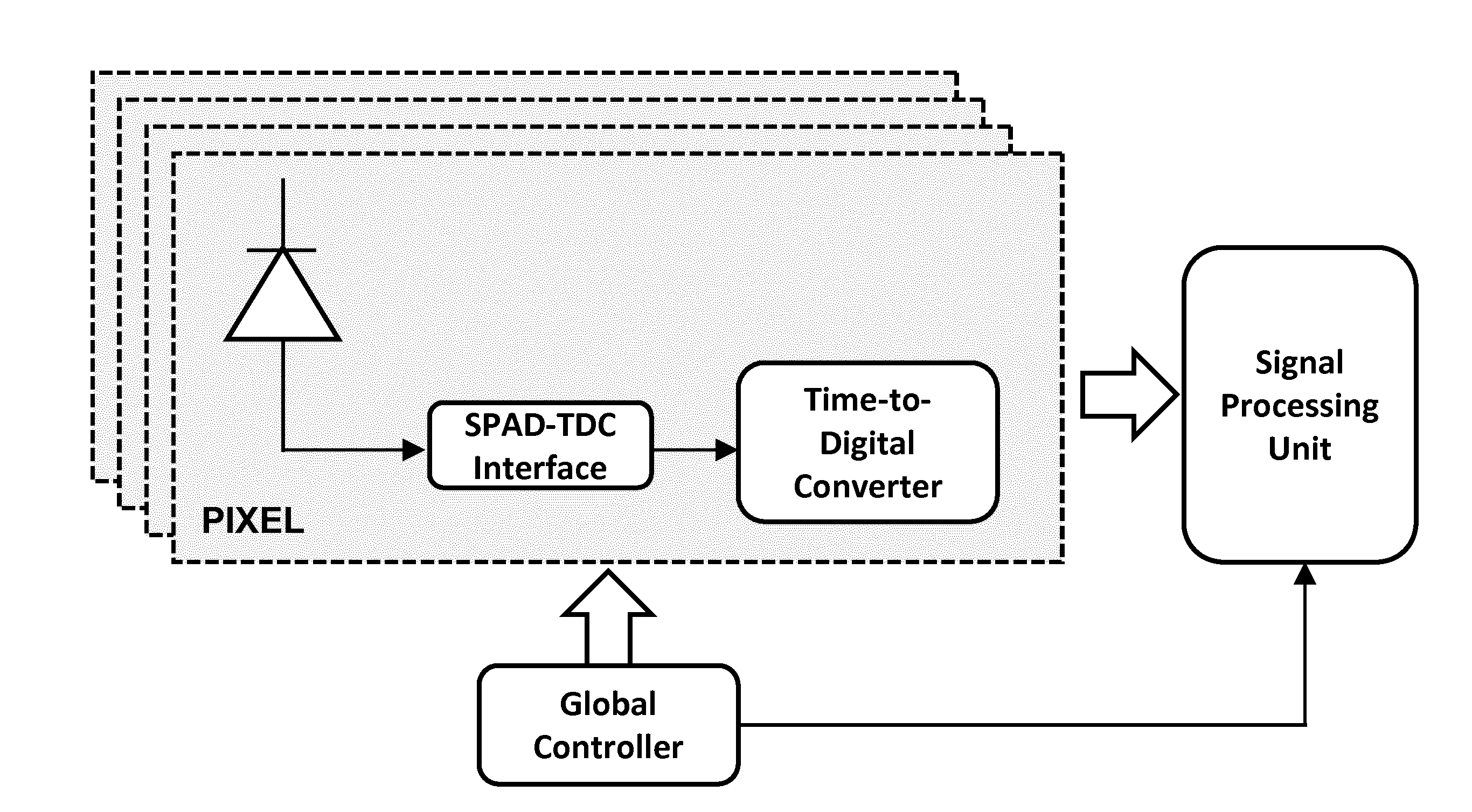

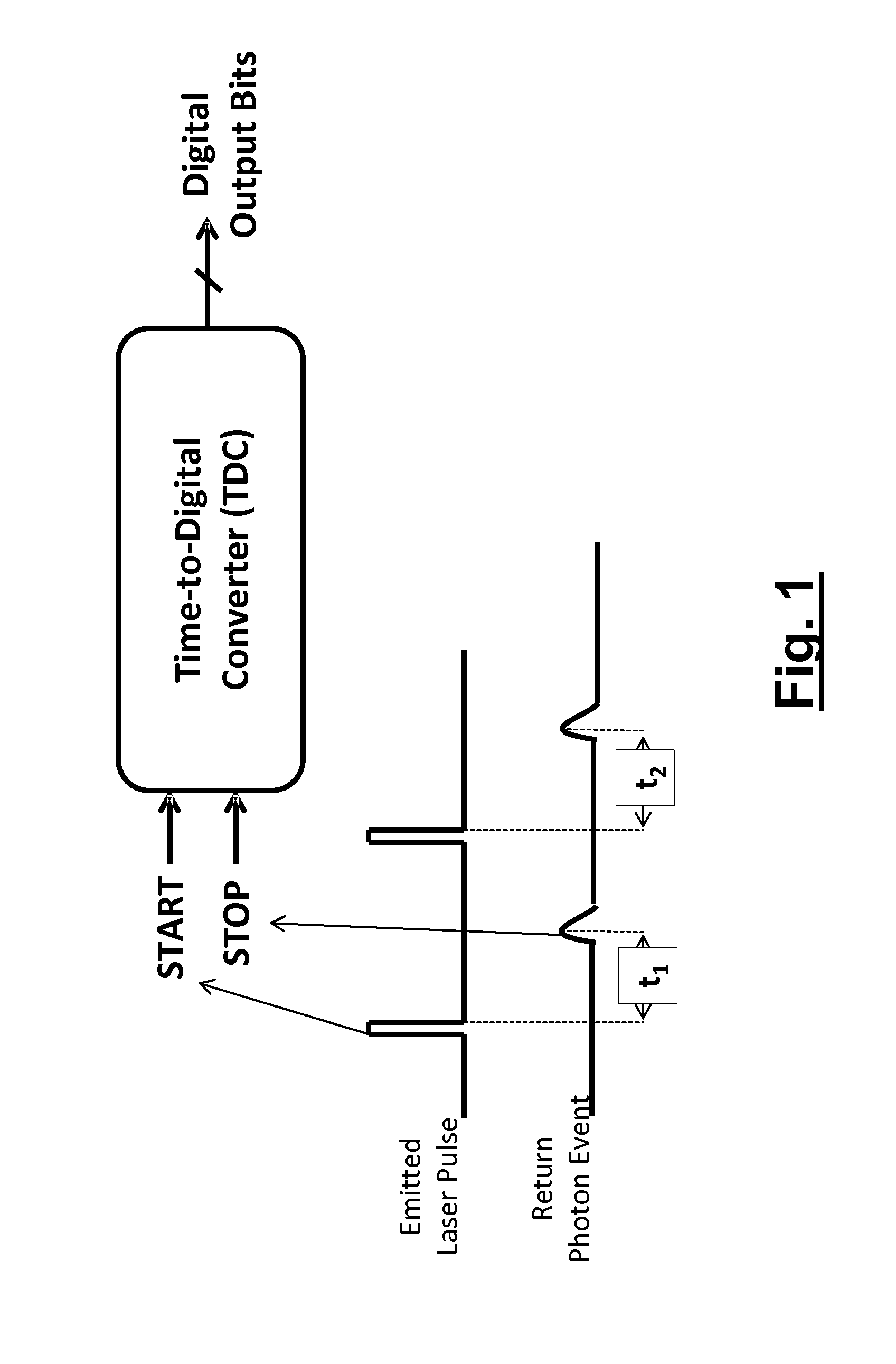

Time-to-digital converter and method therefor

ActiveUS20140232827A1Reduce power consumptionTelevision system detailsPower saving provisionsDigital down converterDigital converter

Time-to-digital converter system including: an event detector configured for detecting an event and generating an event detection signal upon detection of the event; and a time-to-digital converter coupled or connectable to the event detector and including a fine resolution part configured for counting fine time intervals, organized such that the fine resolution part is activated in response to the event detection signal and deactivated in response to a reference clock. 3D imager including an array of pixels, with in each pixel such a time-to-digital converter system, and further including a reference clock generator.

Owner:FASTREE 3D BV

Analog-to-digital conversion method and device

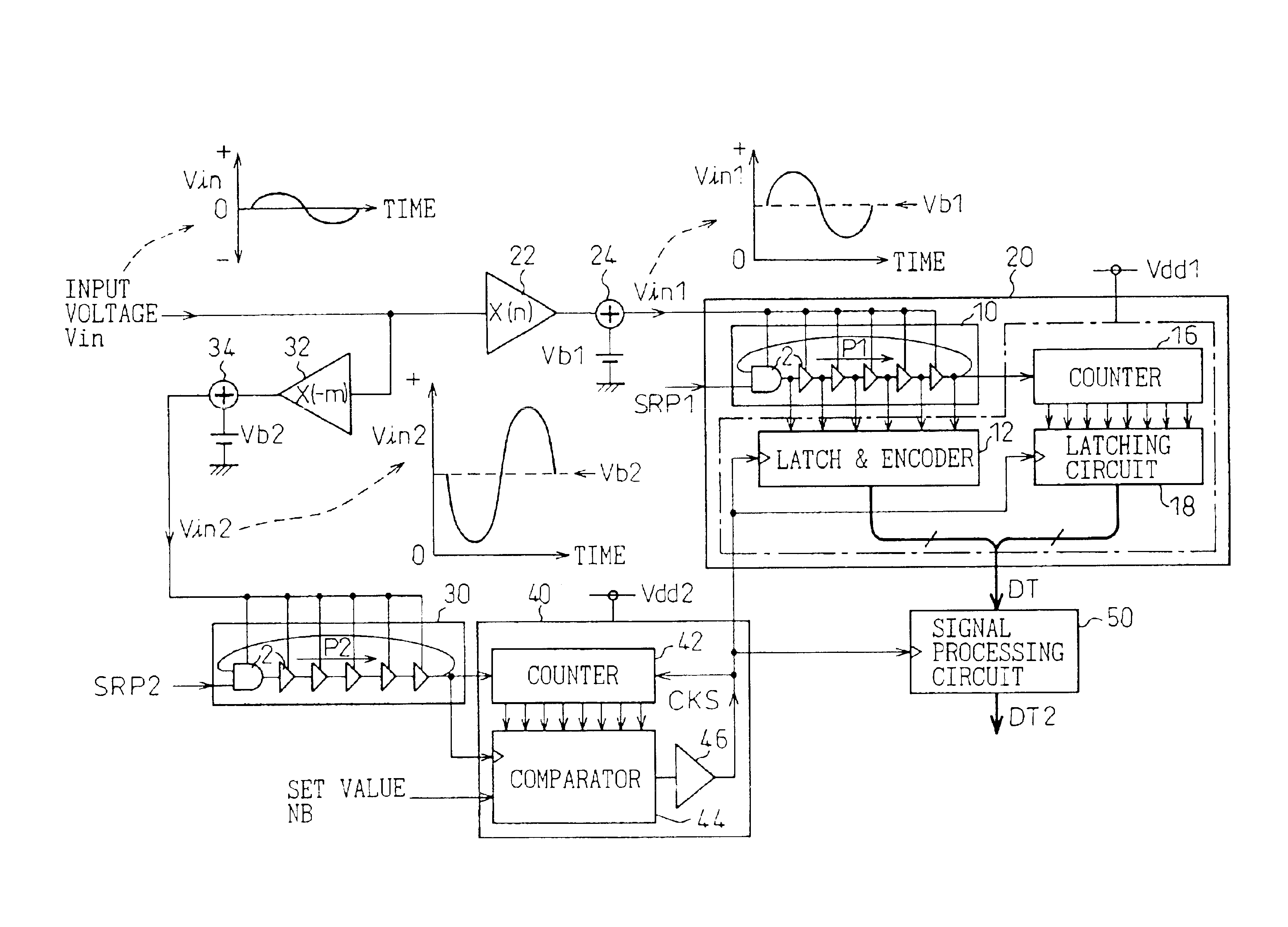

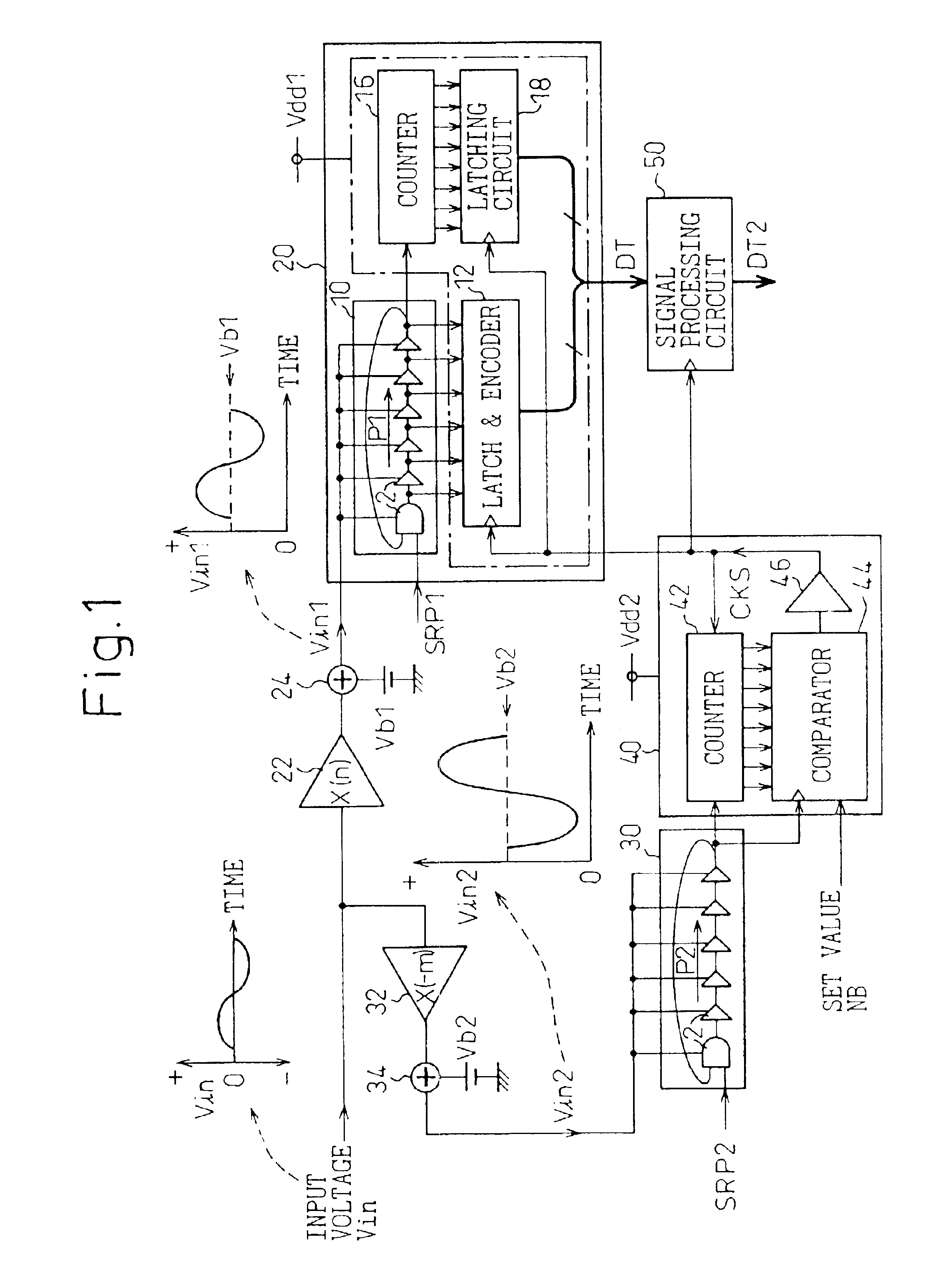

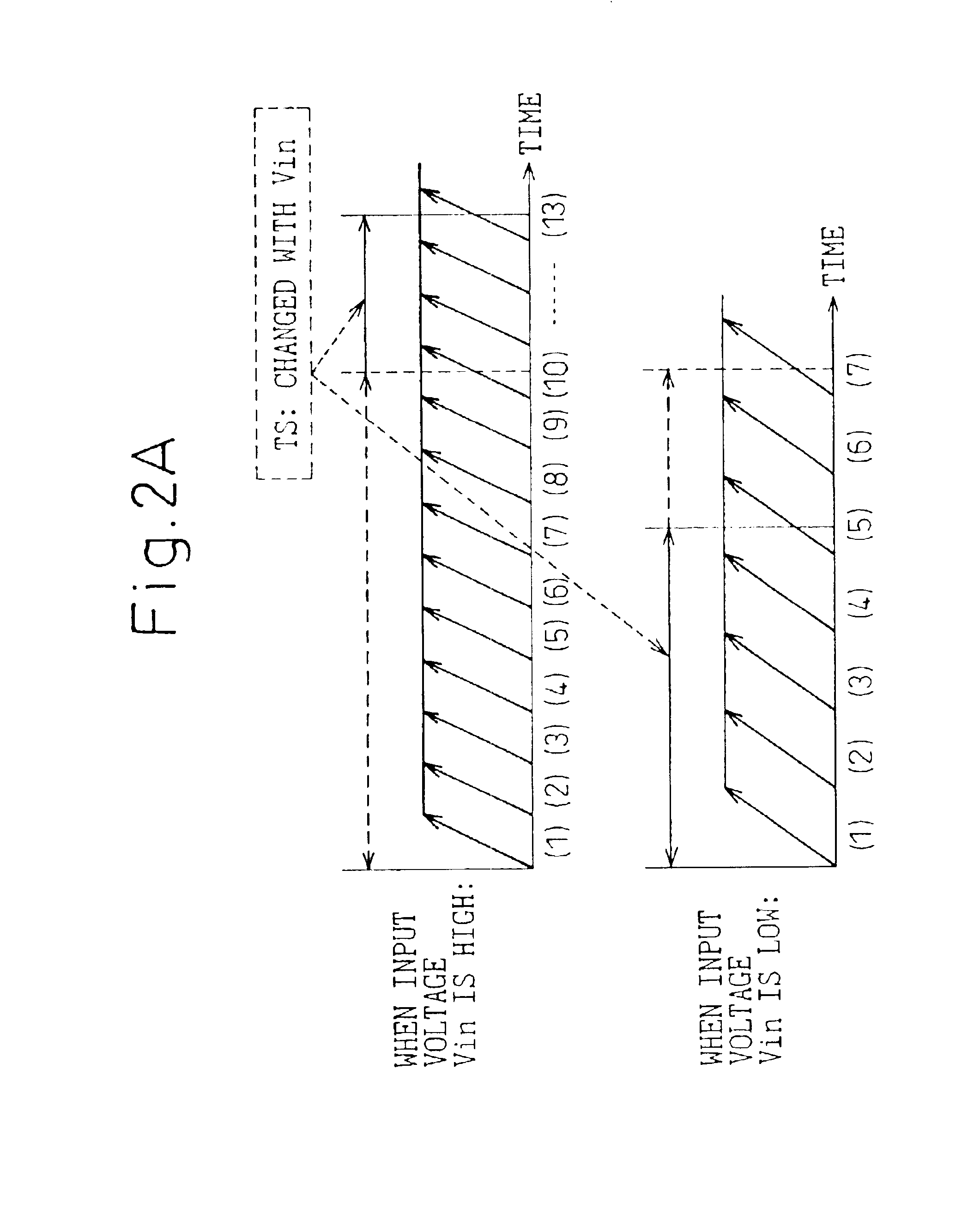

InactiveUS6850178B2High resolutionLarge driving voltageElectric signal transmission systemsAnalogue-digital convertersDigital dataEngineering

An analog-to-digital conversion device is provided that uses pulse delay circuits to convert an input voltage into numerical data and offers a high resolution in analog-to-digital conversion or a high analog-to-digital conversion rate. The analog-to-digital conversion device includes an analog-to-digital conversion unit having a pulse delay circuit composed of a plurality of delay units. The delay units are driven with a voltage produced by amplifying or shifting an input voltage. The number of delay units through which a pulse signal has passed during a predetermined sampling cycle is adopted as a digitized value of the input voltage. Herein, delay units constituting another pulse delay circuit are driven with a voltage produced by inversely amplifying or shifting the input voltage. Every time the number of delay units through which a pulse signal has passed within the pulse delay circuit reaches a predetermined value determined with a set value, a sampling signal is transferred to the analog-to-digital conversion unit.

Owner:DENSO CORP

System and method for a/d conversion

ActiveUS20100134083A1Electric signal transmission systemsElectric pulse generatorEngineeringElectrical and Electronics engineering

In one embodiment, a method of performing an A / D conversion includes comparing a reference signal to a ramp signal, comparing an input signal to the ramp signal and causing a signal to propagate through a delay line when the ramp signal crosses a first of the reference signal or the input signal. The state of the delay line is stored when the ramp signal crosses a second of the reference signal or the input signal after the ramp signal crosses the first of the reference signal or the input signal.

Owner:INFINEON TECH AG

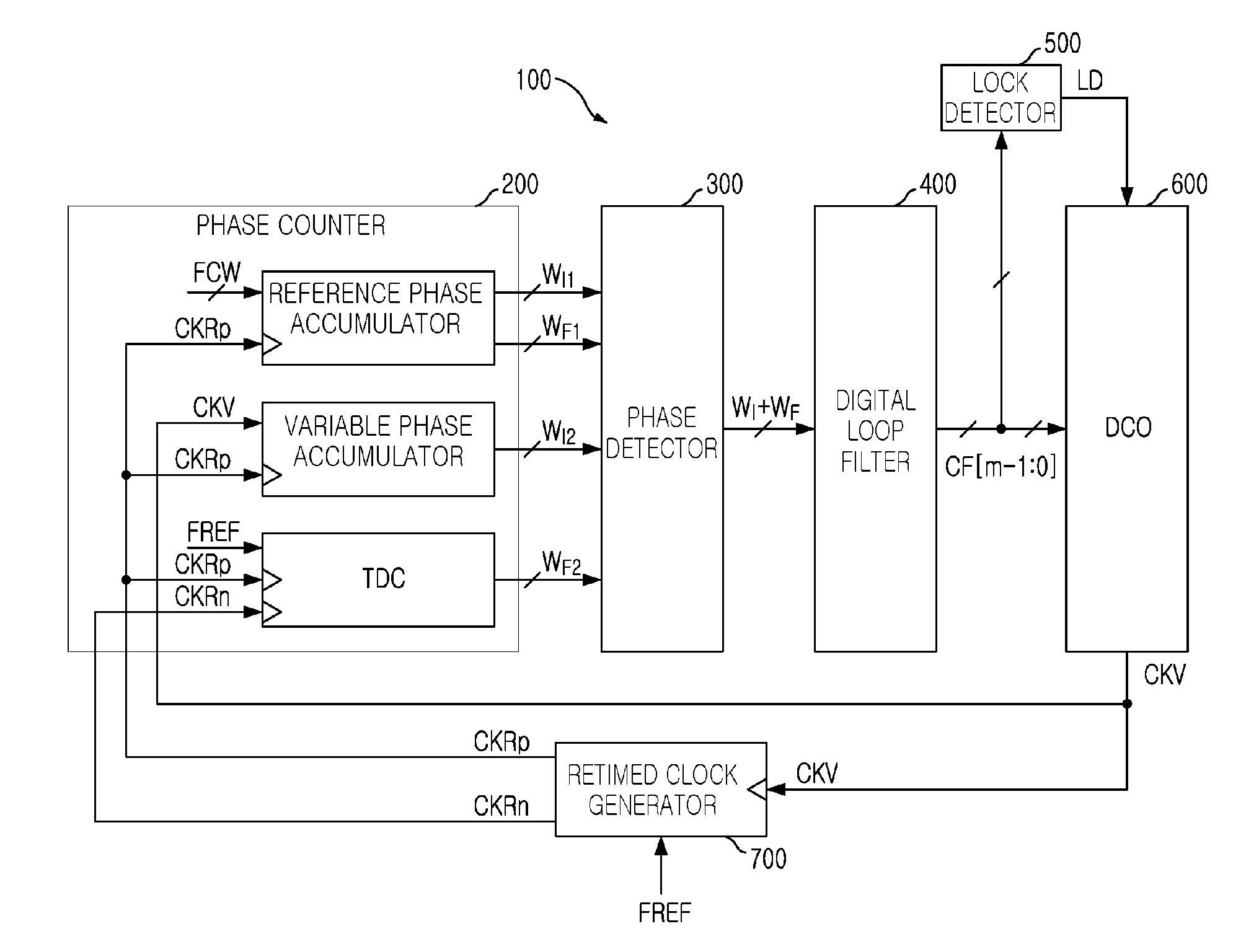

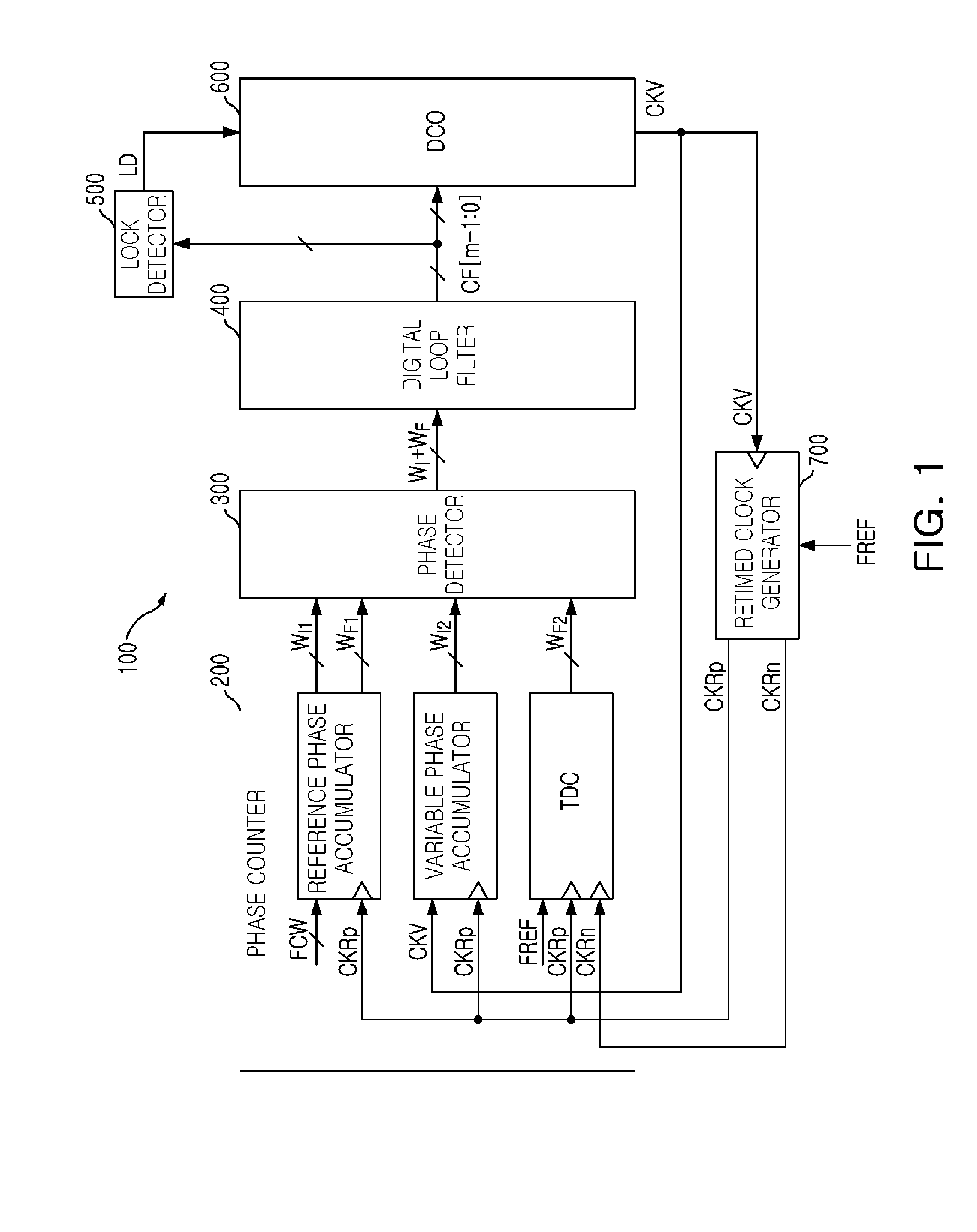

Time-to-digital converter and all digital phase-locked loop including the same

ActiveUS20110148490A1Reduce areaReduce noiseAnalogue/digital conversionElectric signal transmission systemsLoop filterPhase detector

An all digital phase-locked loop (ADPLL) includes: a phase counter accumulating a frequency setting word value and the phase of a digitally controlled oscillator (DCO) clock and detecting a fine phase difference between a reference clock and a retimed clock; a phase detector detecting a digital phase error value compensating for a phase difference between the frequency setting word value and the DCO clock according to the fine phase difference to detect a digital phase error value; a digital loop filter filtering the digital phase error value and controlling PLL operational characteristics; a lock detector generating a lock indication signal according an output of the digital loop filter; a digitally controlled oscillator varying the frequency of the DCO clock according to the output from the digital loop filter; and a retimed clock generator generating the retimed clock by retiming the DCO clock at a low frequency.

Owner:ELECTRONICS & TELECOMM RES INST

Digital phase locked loop with gear shifting

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal. A phase detection circuit operates on the reference clock to provide digital phase error samples indicative of a phase difference between the reference clock and the RF clock. A programmable filter is connected to receive the phase error samples and connected to provide a filtered output having a gain and a phase margin to the controllable oscillator. The programmable filter includes a proportional loop gain control having a programmable loop gain coefficient (alpha—α) and an integral loop gain control having a programmable loop gain coefficient (rho—ρ). Alpha and rho are configured to be programmatically changed simultaneously and are selected such that the gain is changed and the phase margin remains substantially unchanged.

Owner:TEXAS INSTR INC

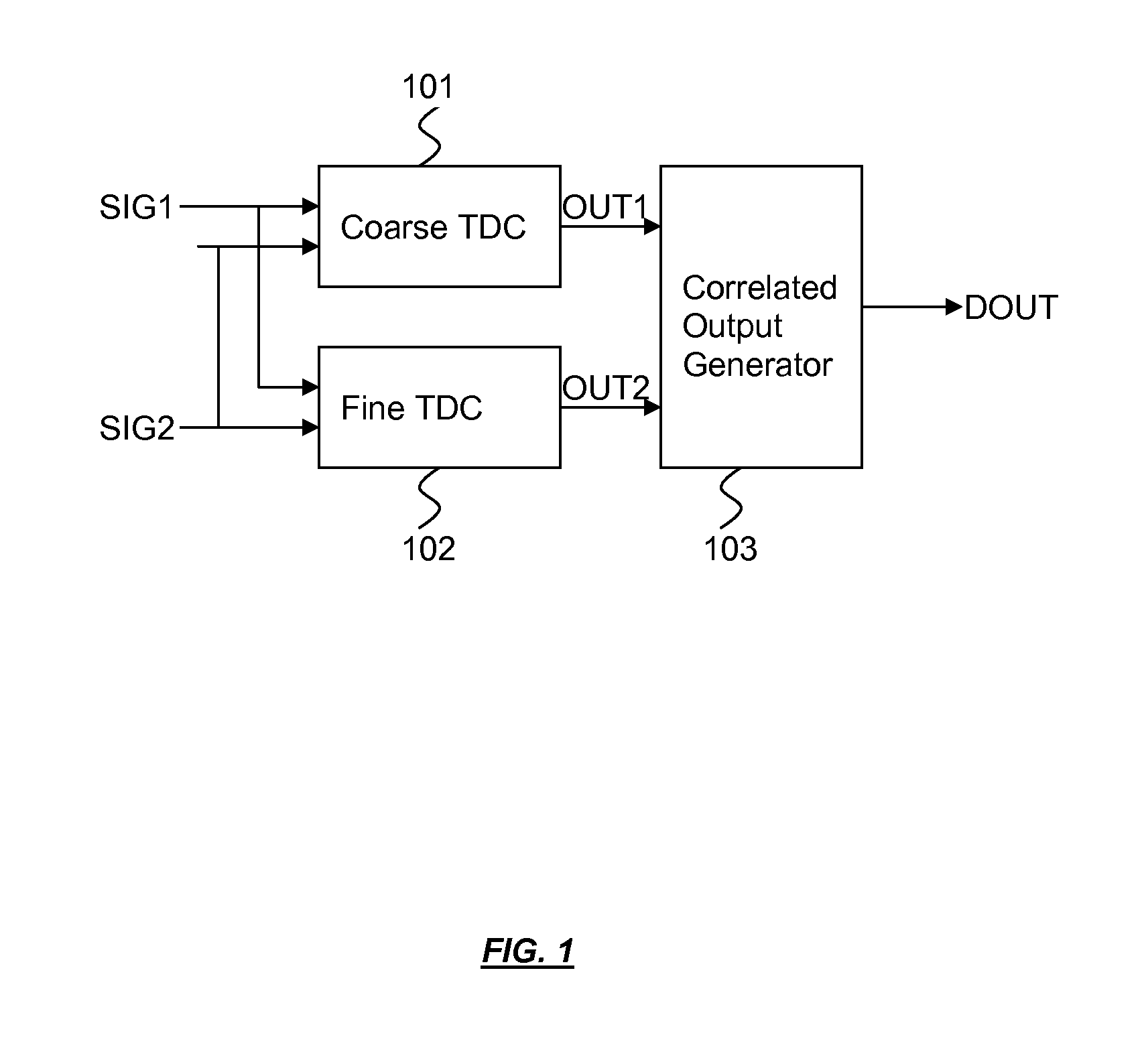

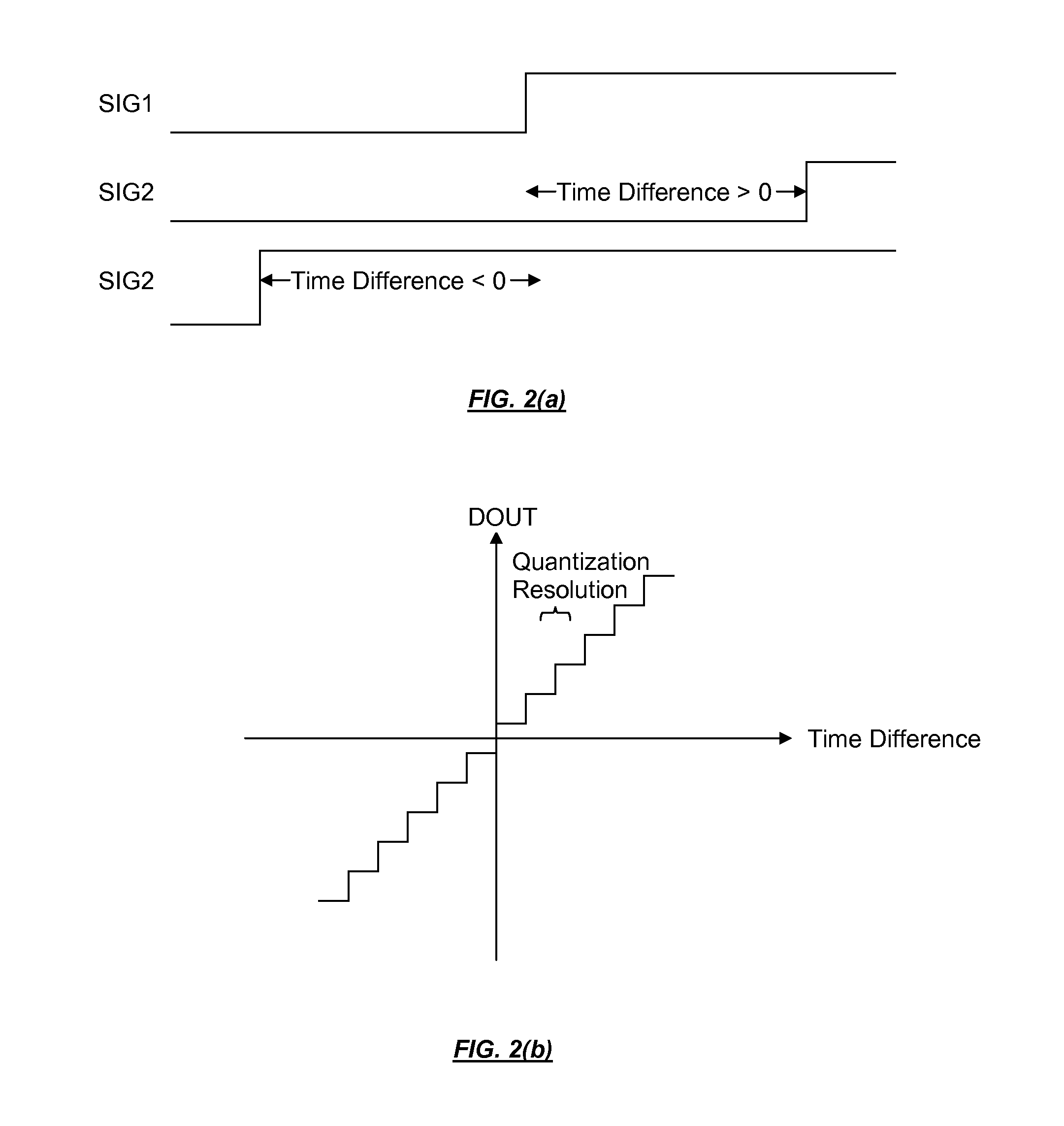

Hybrid coarse-fine time-to-digital converter

ActiveUS7932847B1Low offset outputImprove linearityElectric signal transmission systemsAnalogue-digital convertersDigital down converterEngineering

A hybrid coarse-fine time-to-digital converter is disclosed. The hybrid coarse-fine time-to-digital converter is configured to receive a first input signal and a second input signal and to generate a digital output that corresponds to the time difference of between a rising edge of the first input signal and a rising edge of the second input signal. The hybrid coarse-fine time-to-digital converter comprises a coarse time-to-digital converter, a fine time-to-digital converter, and a correlated output generator.

Owner:REALTEK SEMICON CORP

Gated ring oscillator for a time-to-digital converter with shaped quantization noise

ActiveUS8138843B2Continuously circulated pulse countersCounting chain synchronous pulse countersDigital down converterImage resolution

Described is a compact, lower power gated ring oscillator time-to-digital converter that achieves first order noise shaping of quantization noise using a digital implementation. The gated ring oscillator time-to-digital converter includes a plurality of delay stages configured to enable propagation of a transitioning signal through the delay stages during an enabled state and configured to inhibit propagation of the transitioning signal through the delay stages during a disabled state. Delay stages are interconnected to allow sustained transitions to propagate through the delay stages during the enabled state and to preserve a state of the gated ring oscillator time-to-digital converter during the disabled state. The state represents a time resolution that is finer than the delay of at least one of the delay stages. A measurement module determines the number of transitions of the delay stages.

Owner:MASSACHUSETTS INST OF TECH

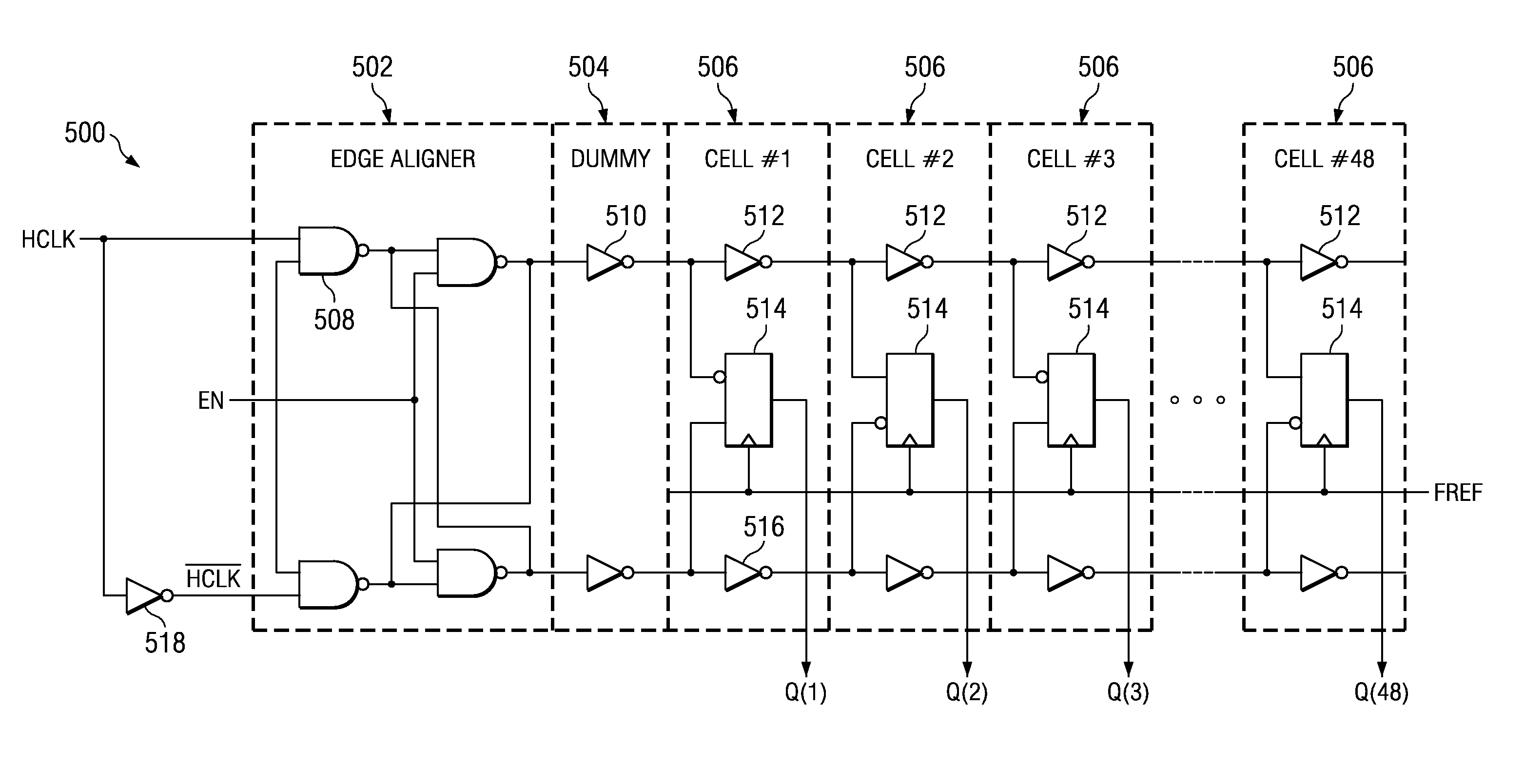

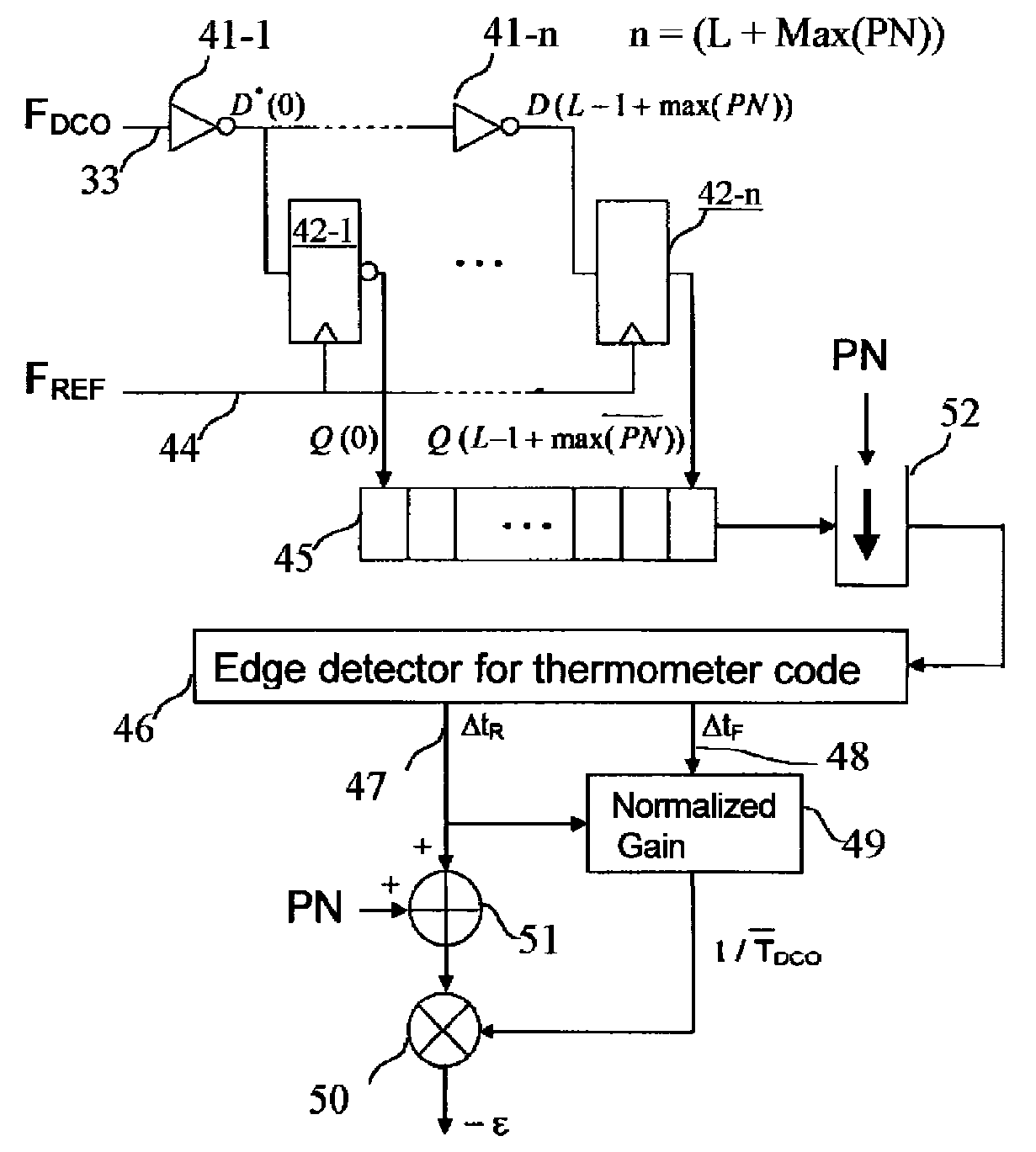

Process for dithering a time to digital converter and circuits for performing said process

ActiveUS20080297208A1Easy to implementLow costElectric signal transmission systemsPulse automatic controlDigital down converterFall time

A process inserts a random noise in a Time to Digital Converter (TDC) designed for calculating the phase error between a first high frequency signal FDCO with respect to a second reference signal, switching at a lower frequency. The process involves: processing of the first signal FDCO by using a chain of delays having a set of n elementary delays which number is chosen so as to extend over a full period of the first signal; storing the outputs of the chain of delays in a set of latches and generation of a thermometer code presenting a stream of “1” separated from a stream of “0” by a border corresponding to the transition of the first signal with respect to the second reference signal; reducing the thermometer code by a random number PN of bits; processing of the result in an edge detecting and thermometer code decoding so as to generate two variables Δtr and Δtf which are representative of the difference between the rise and fall time of the first signal with respect to the second reference signal; computing the normalized gain so as to generate an average value of 1 / TDCO; adding to the value Δtr a binary value corresponding to the number of bits PN; multiplying the preceding result by the average value of 1 / TDCO and computing the phase error between the signals. The delay chain may be arranged with inverters. The process is particularly but not exclusively useful for carrying out a TDC convertor for the purpose of synthesizing of frequencies.

Owner:STMICROELECTRONICS SRL

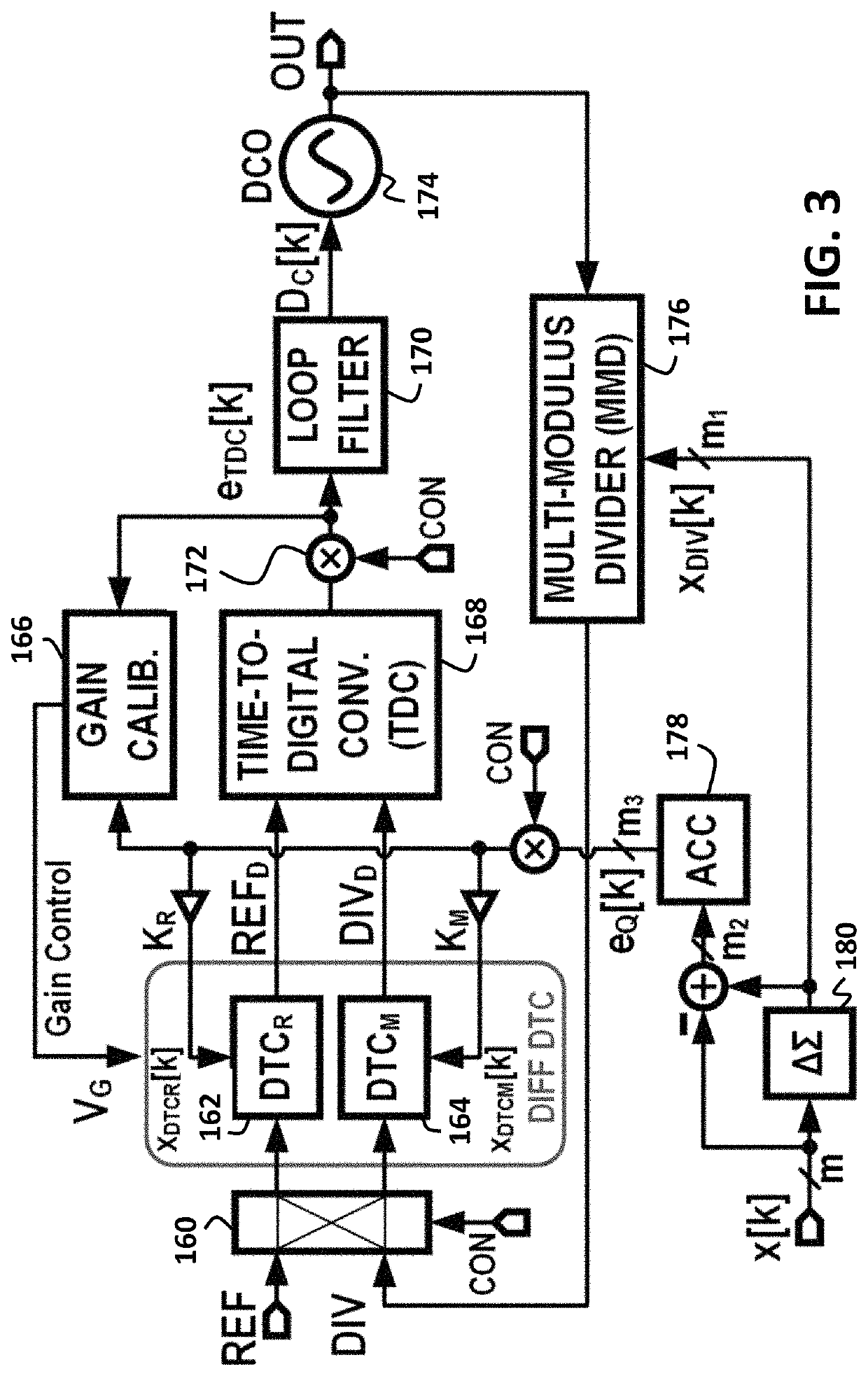

Mixed-domain circuit with differential domain-converters

ActiveUS10895850B1Analogue/digital conversionElectric signal transmission systemsConvertersHemt circuits

A mixed-domain circuit has a differential pair of Digital-to-Time Converters (DTCs), one receiving a reference clock and the other receiving a feedback clock. A Time-to-Digital Converter (TDC) compares outputs from the differential pair of DTCs and generates a digital error value that controls a digital loop filter that controls a Digitally-Controlled Oscillator (DCO) that generates an output clock. A Multi-Modulus Divider (MMD) generates the feedback clock. An accumulated modulation from a delta-sigma modulator is compared to the digital error value by a Least-Mean Square (LMS) correlator to adjust supply voltage or current sources in the pair of DTCs to compensate for errors. A capacitor in each DTC has a charging time adjusted by the accumulated modulation. The DTC can be reduced to a Time-to-Voltage Converter (TVC) and the analog voltages on the capacitors input to an Analog-to-Digital Converter (ADC) to generate the digital error value.

Owner:SI WARE SYST S AE

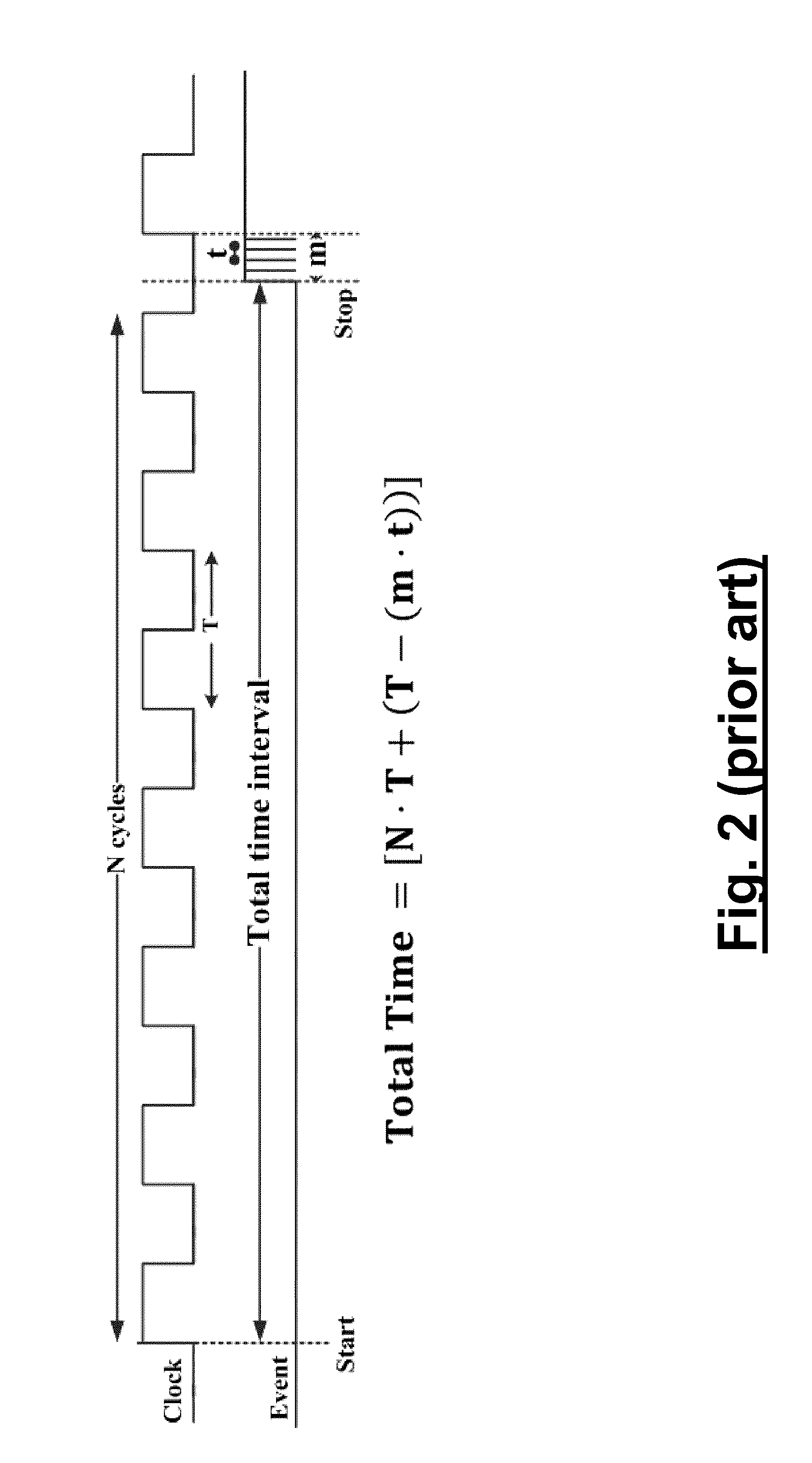

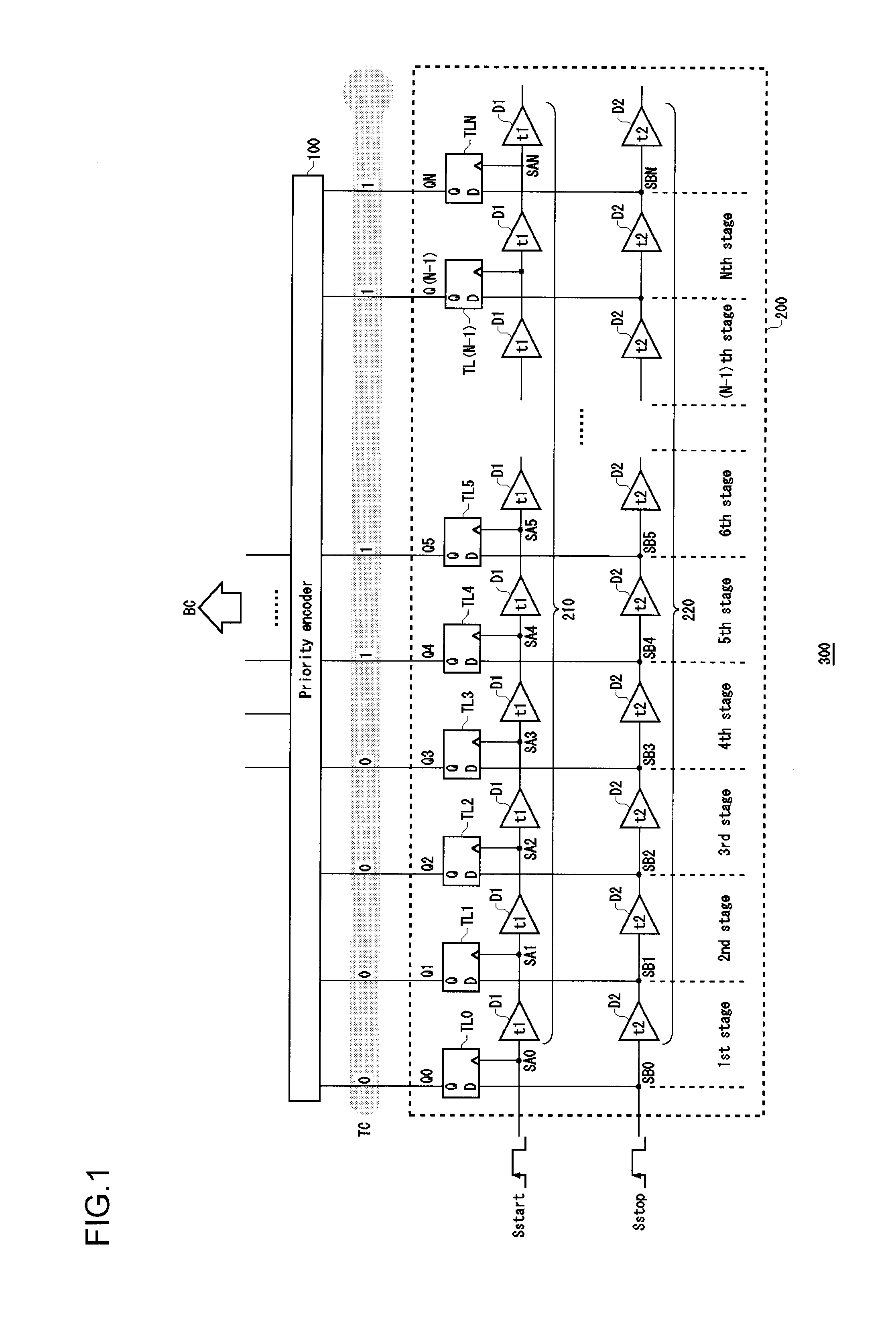

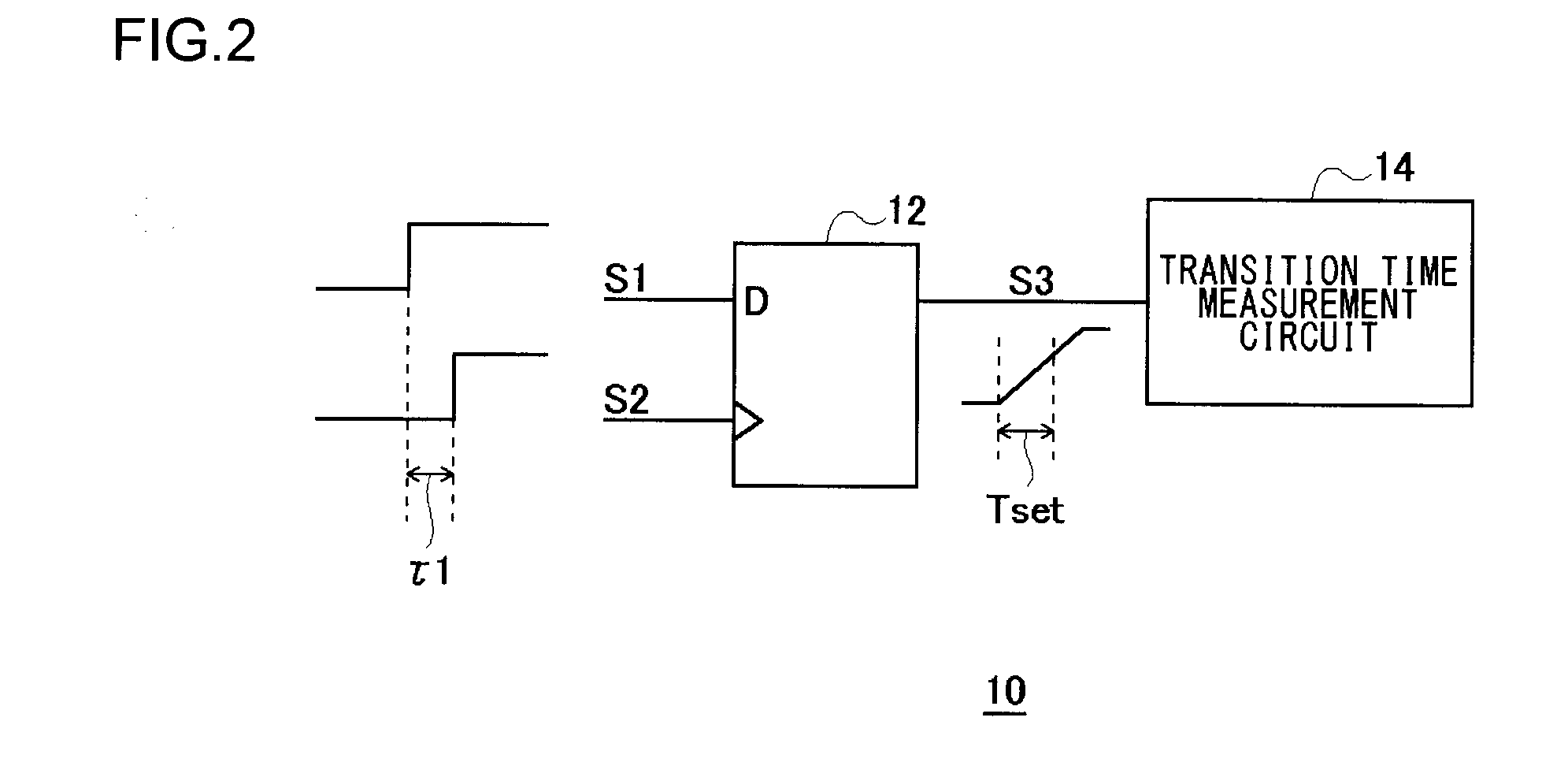

Time measurement circuit

InactiveUS20110133973A1Reduce resolutionMaintain resolutionElectric signal transmission systemsElectrical testingTime differenceTransition time

A time measurement circuit measures the time difference between edges of a first signal and a second signal. A sampling circuit acquires the logical level of the first signal at a timing of the edge of the second signal. When a sampling circuit enters a metastable state, an output signal thereof transits with a long time scale. A transition time measurement circuit measures a transition time (settling time) of the output signal of the sampling circuit in the metastable state.

Owner:ADVANTEST CORP

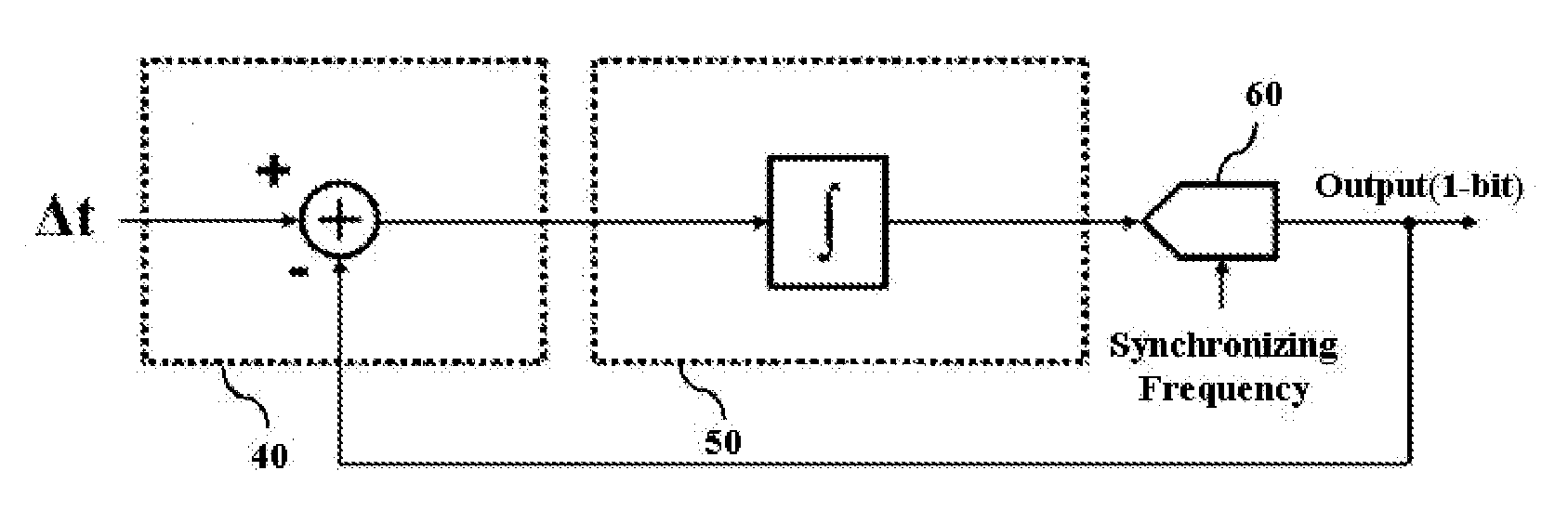

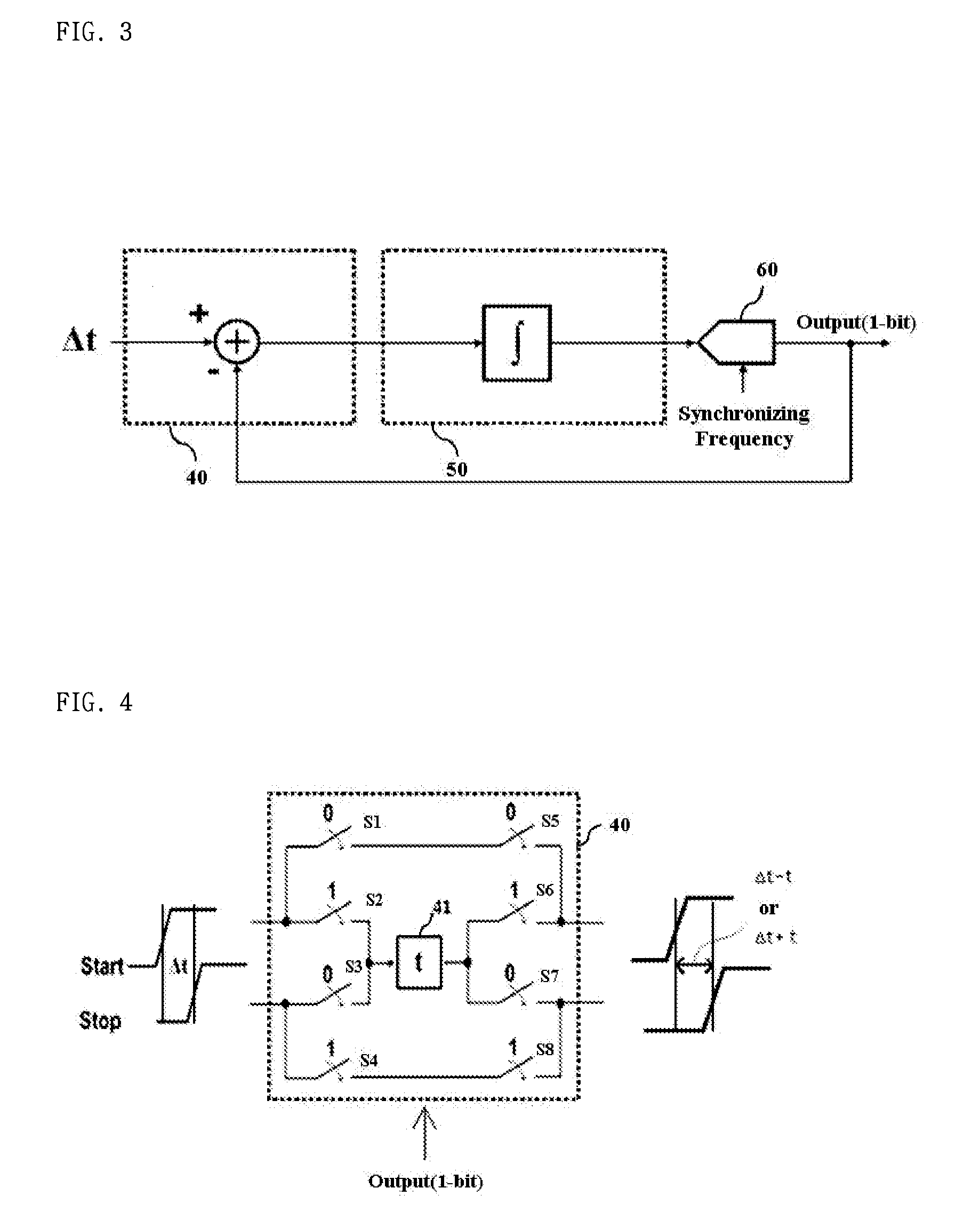

Noise-shaping time to digital converter (TDC) using delta-sigma modulation method

InactiveUS8421661B1Electric signal transmission systemsDelta modulationDigital down converterDelayed time

The present invention relates to a time digital converter, and more particularly, to a noise-shaping time to digital converter (TDC) that has a 1-bit output and uses a delta-sigma modulation method. The noise-shaping time to digital converter (TDC) that has the 1-bit output and uses the delta-sigma modulation method in accordance with the present invention eliminates the need for a large number of D flip-flops or counters and a plurality of delay units connected in series to one another because the time to digital converter is fabricated such that a delay element has a resolution of the effective delay time in a semiconductor process, unlike the conventional time to digital converter. Therefore, the time to digital converter of the present invention has an advantage in that an extremely high resolution and high linearity can be achieved with an efficient circuit configuration and low power consumption.

Owner:POSTECH ACAD IND FOUND

Circuits and methods of TAF-DPS vernier caliper for time-of-flight measurement

ActiveUS9379714B1High resolutionPowerful frequency generation capabilityPulse automatic controlCounting chain synchronous pulse countersPhase detectorFrequency synthesizer

Circuits for measuring TOF between two electrical signals comprises 1) a slow TAF-DPS clock signal generator for generating a slow clock signal, a fast TAF-DPS clock signal generator for generating a fast clock signal, said slow TAF-DPS clock signal generator comprises a gated ring oscillator and a TAF-DPS frequency synthesizer, said fast TAF-DPS clock signal generator comprises a gated ring oscillator and a TAF-DPS frequency synthesizer; 2) a phase detector for receiving said slow and fast clock signals and detecting point-of-coincidence between said slow and fast clock signals; 3) a first digital counter driven by said slow clock signal for storing the number of slow clock cycles and a second digital counter driven by said fast clock signal for storing the number of fast clock cycles; 4) a calibrator for calibrating said gate ring oscillators; 5) a calculation block for calculating TOF measurement result. Methods of using a slow TAF-DPS clock generator and a fast TAF-DPS clock generator for measuring TOF between two electrical signals are also disclosed.

Owner:XIU LIMING

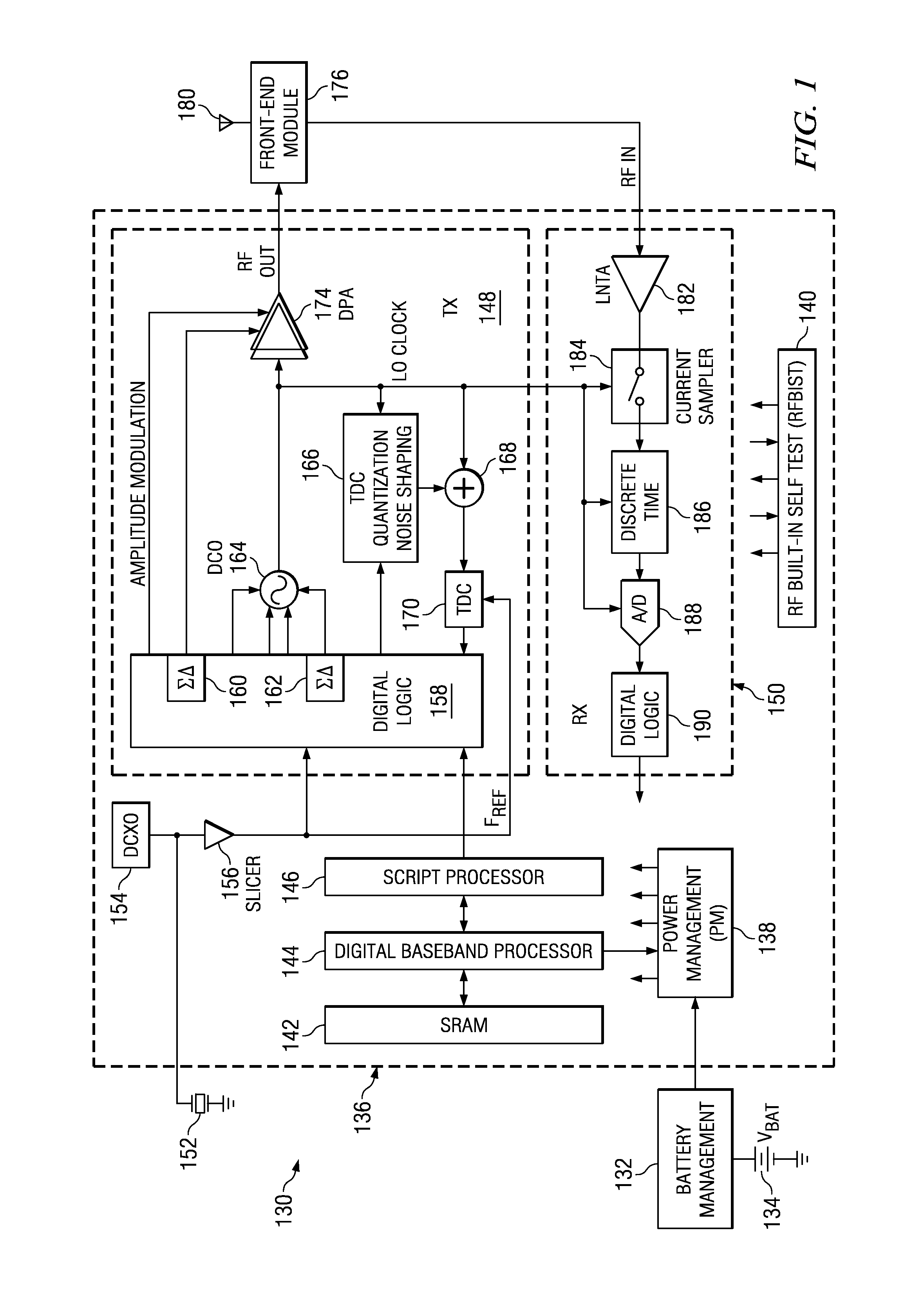

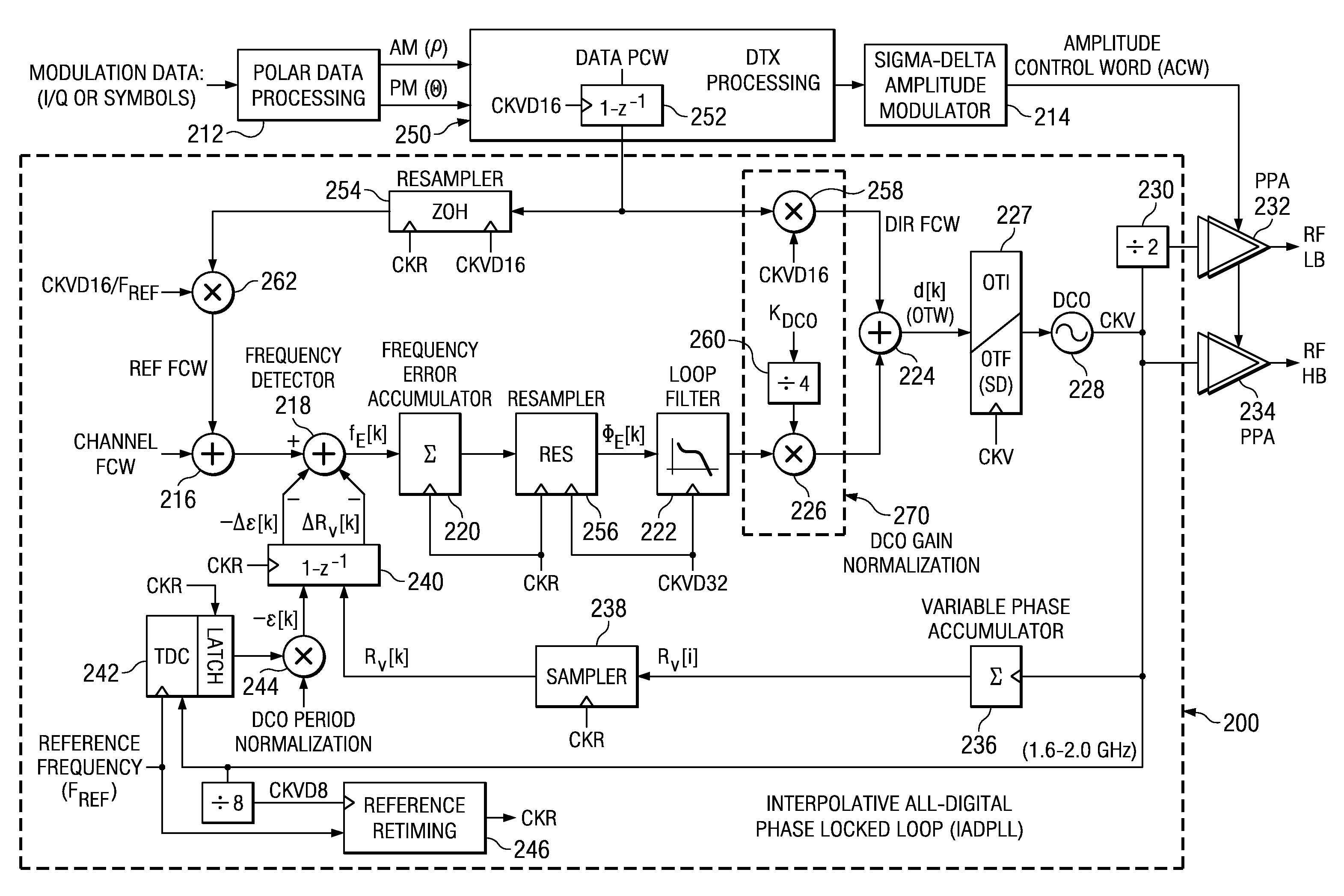

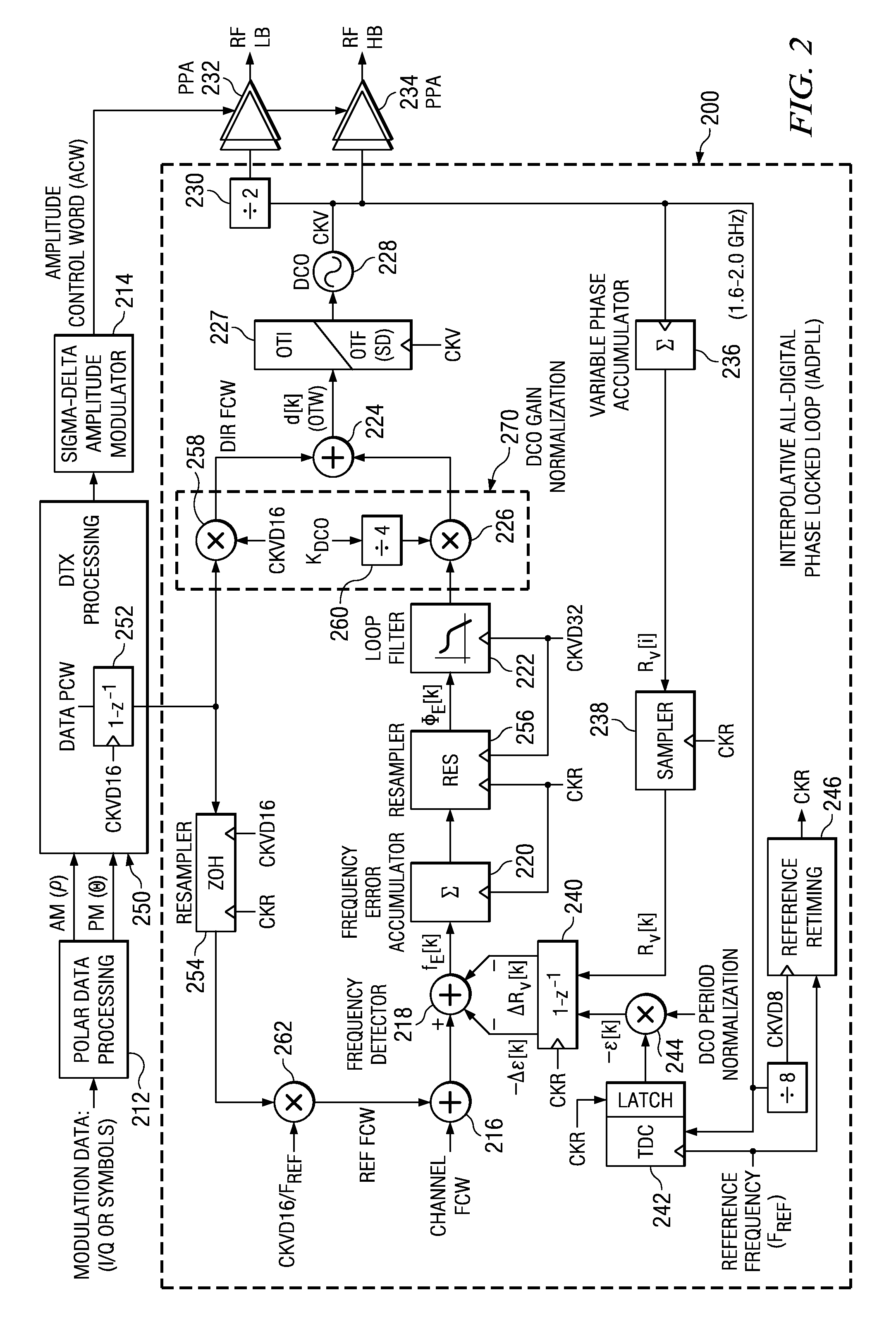

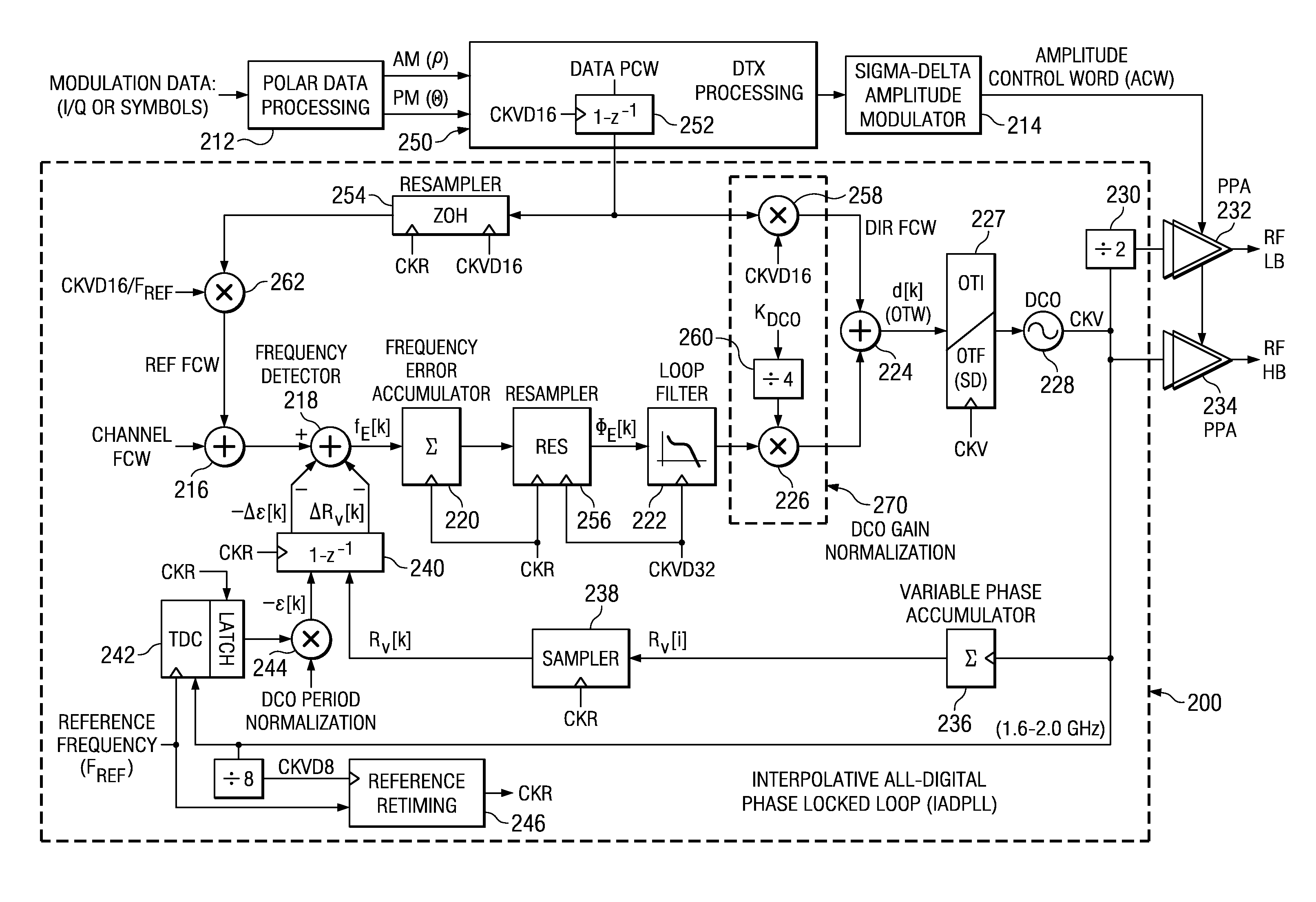

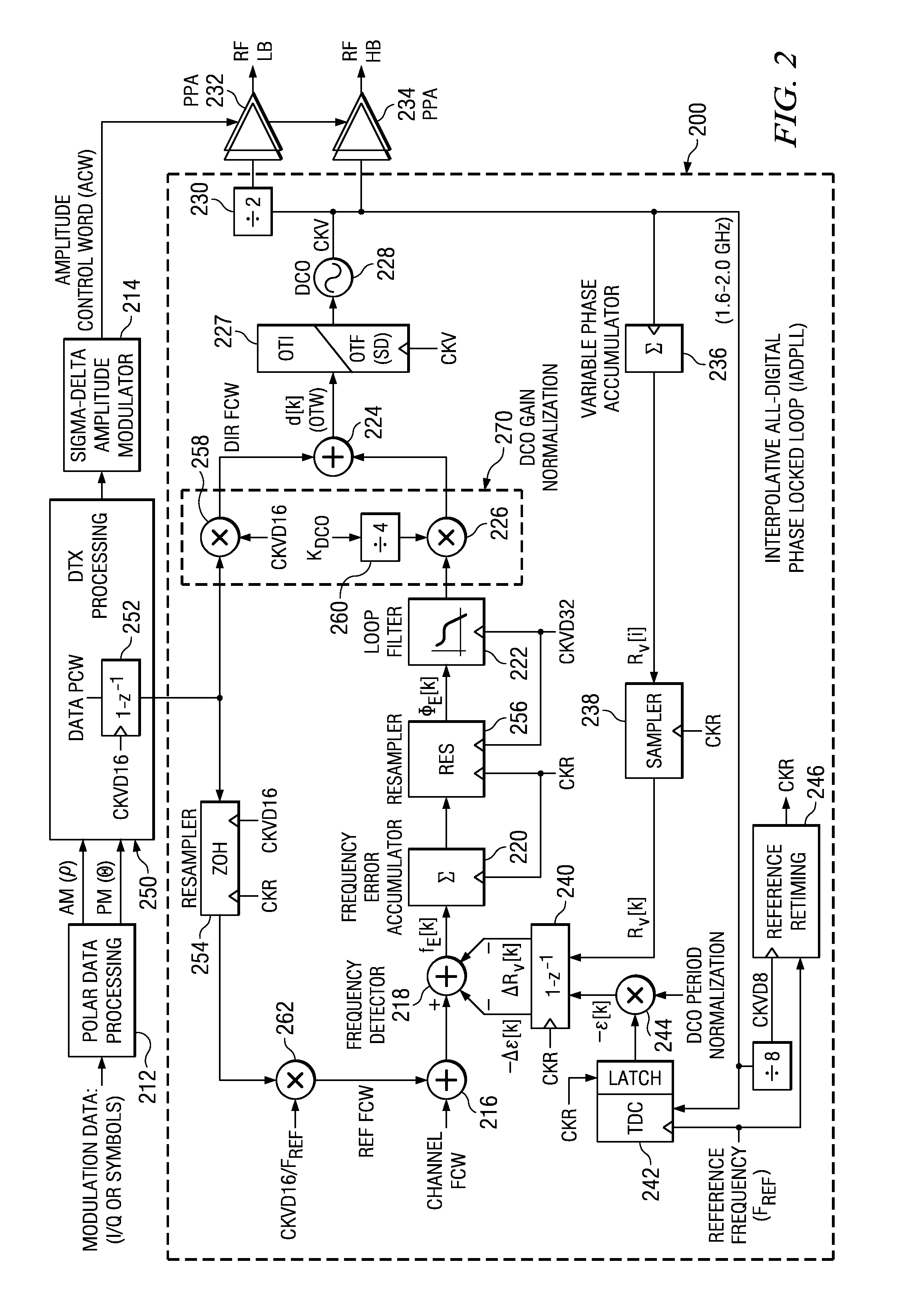

Interpolative All-Digital Phase Locked Loop

ActiveUS20080317187A1Pulse automatic controlTransmission path divisionSample rate conversionPhase difference

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal. A phase detection circuit operates on the reference clock to provide digital phase error samples indicative of a phase difference between the reference clock and the RF clock. An interpolator is coupled to the phase detection circuit for performing a sample rate conversion between the reference clock and the clock derived from the RF clock signal.

Owner:TEXAS INSTR INC

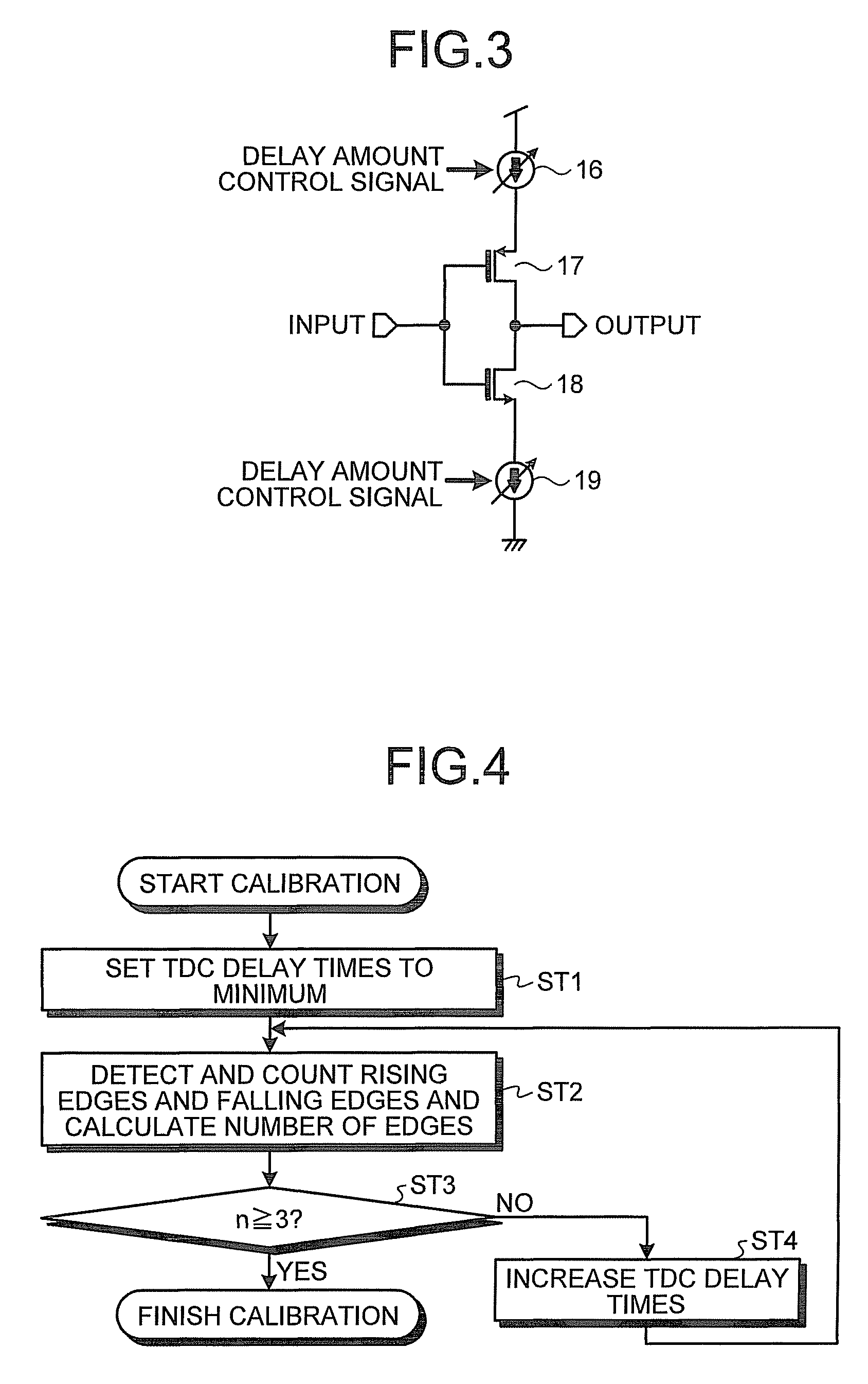

Time to digital converter

InactiveUS8174293B2Multiple input and output pulse circuitsPulse automatic controlDigital down converterEngineering

A time to digital converter includes: a delay circuit having a plurality of delay stages that delay an input clock signal in multiple stages, at least one of the delay stages being a variable delay stage; a plurality of flip flops that capture outputs of the delay stages corresponding thereto in a one-to-one relation in response to input of a reference signal; an edge detecting circuit that detects changing edges of respective outputs of the flip flops; a counter circuit that counts a number of edges detected by the edge detecting circuit; and a control circuit that controls a delay amount of the variable delay stage according to the number of edges counted by the counter circuit.

Owner:KK TOSHIBA

Popular searches

Carrier regulation Angle demodulation by phase difference detection Synchronising arrangement Time-to-digital converters Physical parameters compensation/prevention Thermometers using electric/magnetic elements Using electrical means Computing operations for addition/subtraction Time-delay networks Radio transmission

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com