Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

78results about How to "Guaranteed Signal Integrity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

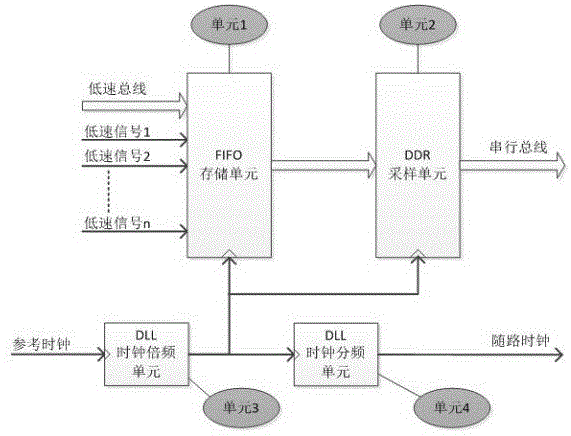

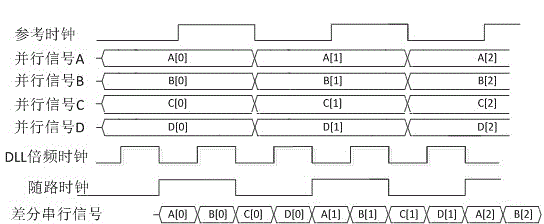

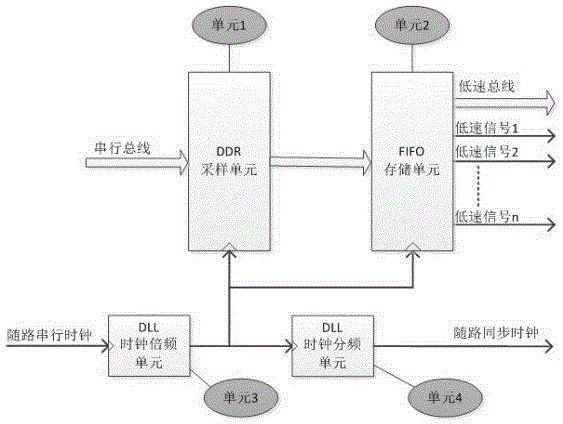

Method for reducing number of cables through interconversion between parallel bus and serial bus

ActiveCN104881390ALower performance requirementsReduce in quantityElectric digital data processingDouble data rateDelay-locked loop

The invention designs a method for reducing the number of cables through interconversion between a parallel bus and a serial bus. A CPLD or FPGA programmable logic chip is adopted, and the CPLD or FPGA programmable logic chip has a delay-locked loop (DLL) function and a double data rate (DDR) function, the base pin rate if the chip and the frequency of a system clock are at least more than two times of frequencies all the low speed signals. Various low speed bus signals and various low speed signals are sent into the programmable logic chip, channel associated synchronized clocks or other clocks are sent into the programmable logic chip, too. An FIFO memory cell is used for caching data during serial-to-parallel convention. A DDR sampling unit is used for synchronously sampling when the low speed signals are in the rising edge and the falling edge of clocks, so that the frequency of the system clock in the programmable logic chip can be reduced by two times, so requirement of the frequency of the system clock in the chip can be reduced.

Owner:杭州紫来测控技术有限公司

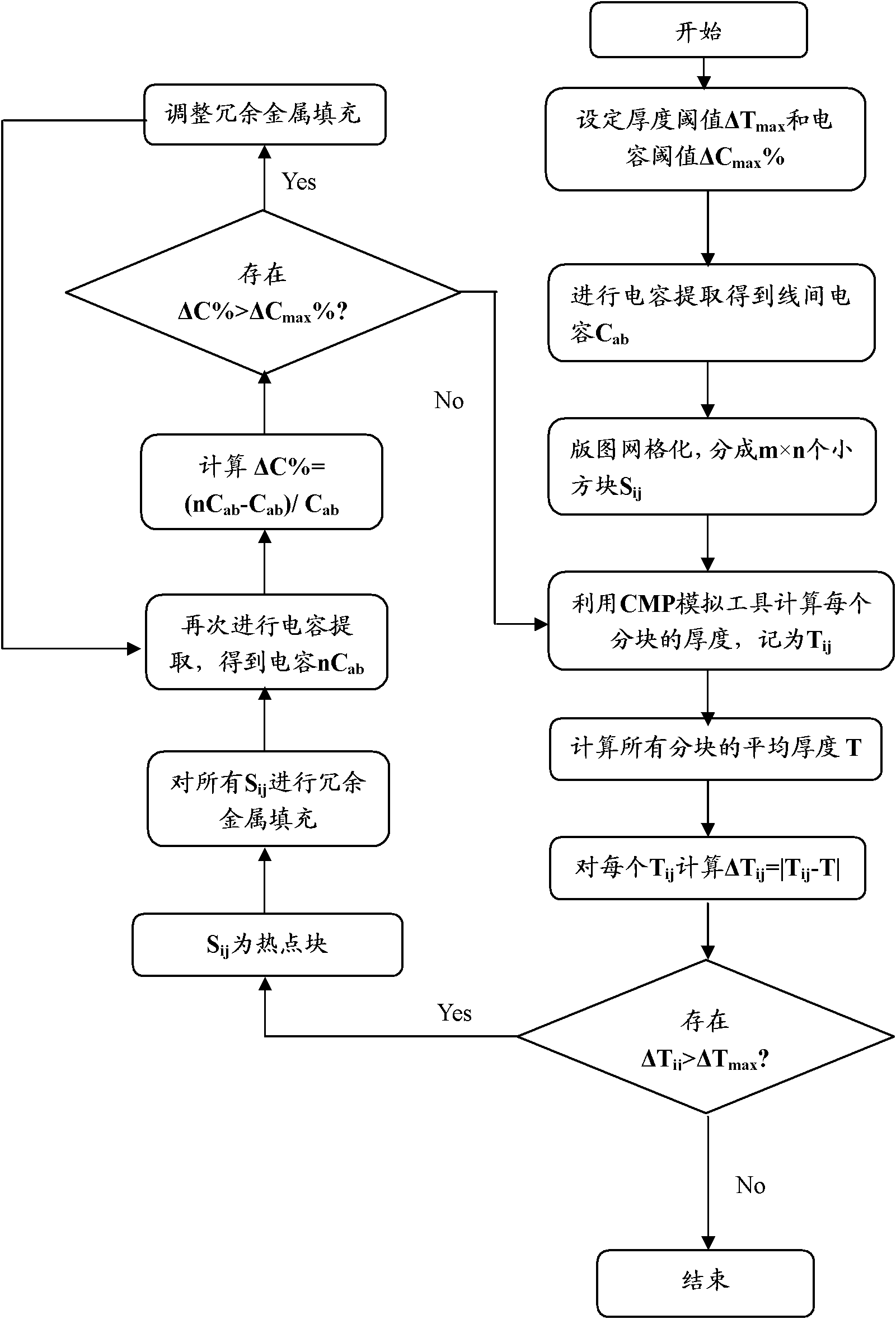

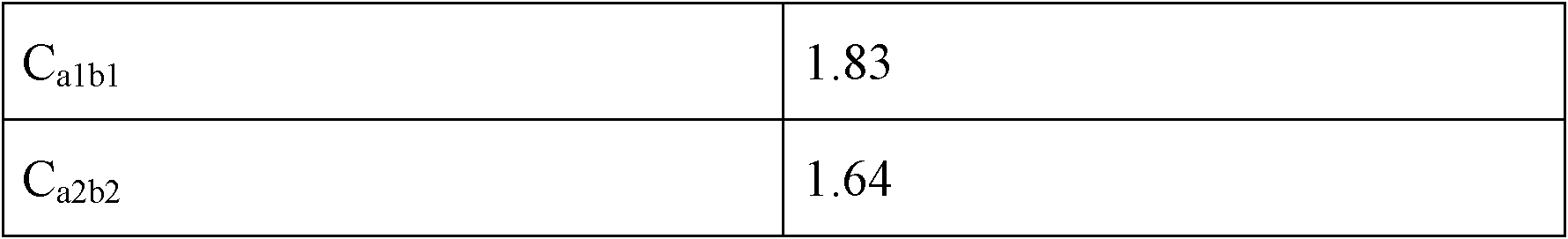

Method for filling redundancy metal

ActiveCN102130043AGuaranteed Signal IntegrityEnsure consistencySemiconductor/solid-state device manufacturingSpecial data processing applicationsCapacitanceEngineering

The invention discloses a method for filling a redundancy metal in a semiconductor manufacturing process. In the method, redundancy metal filling is evaluated and adjusted by combining analogue flatness and extracting the capacitance between metal wires; and all flatness hotspots and capacitance hotspots of a circuit layout are eliminated by a plurality of iteration processes; therefore, not onlythe consistency of the circuit layout thickness after performing chemical mechanical polishing (CMP) can be ensured to improve the yield of chips, but also the damage to functions of the chips causedby the introduction of the redundancy metal can be prevented to ensure the signal completeness of the metal wires in the circuit layout.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

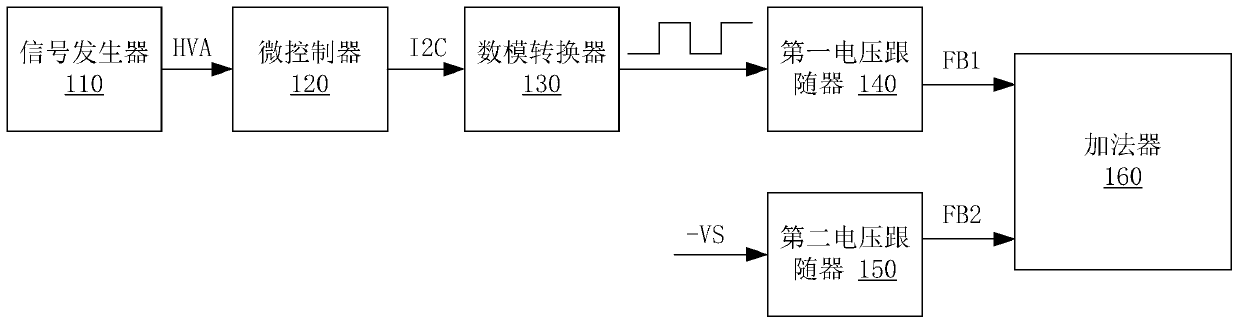

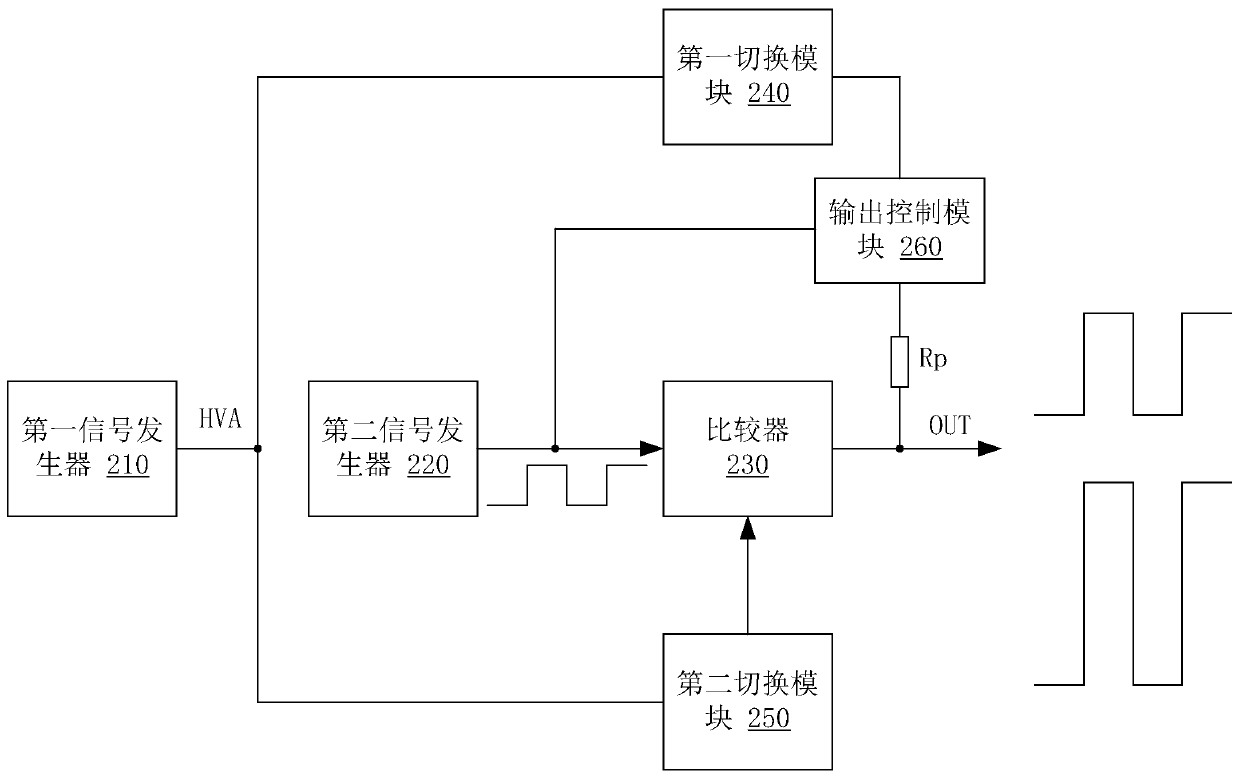

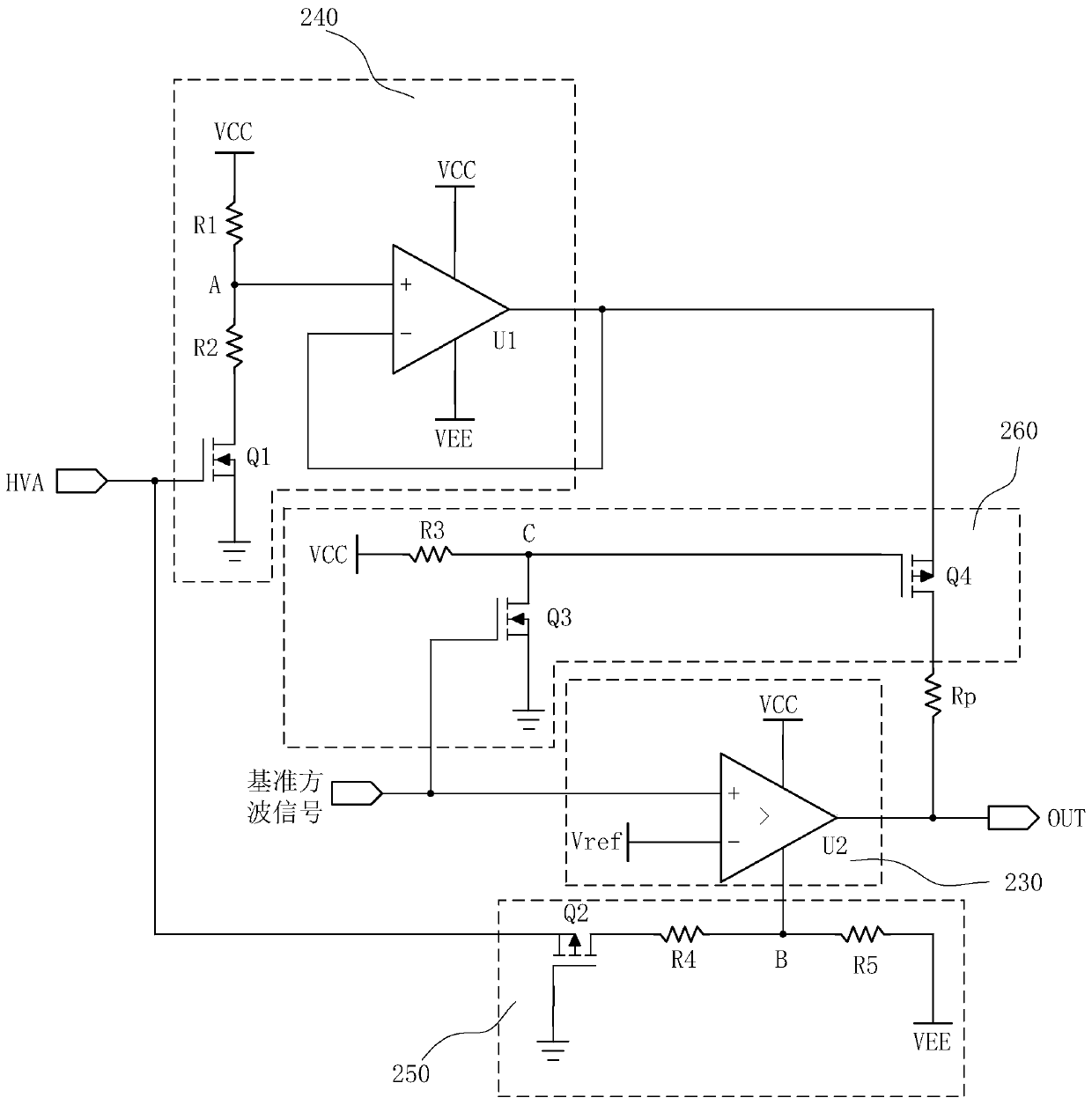

Common voltage generation circuit and method, and display device

ActiveCN111243537AReduce volumeSimple structureStatic indicating devicesControl signalDisplay device

The invention discloses a common voltage generating circuit and method, and a display device. The common voltage generating circuit comprises: a first signal generator which provides a visual angle control signal; a second signal generator providing a reference square wave signal; a first switching module outputting one of a first pull-up signal and a second pull-up signal according to the visualangle control signal; a second switching module outputting one of a first power supply signal and a second power supply signal according to the visual angle control signal; and a comparator used for receiving a reference voltage signal and outputting a first common voltage according to the reference voltage signal, the reference square wave signal, the first pull-up signal and the first power supply signal or outputting a second common voltage according to the reference voltage signal, the reference square wave signal, the second pull-up signal and the second power supply signal. The first common voltage and the second common voltage with different amplitudes can be provided for the display device, and meanwhile the circuit is small in size, simple in structure and low in cost.

Owner:KUSN INFOVISION OPTOELECTRONICS

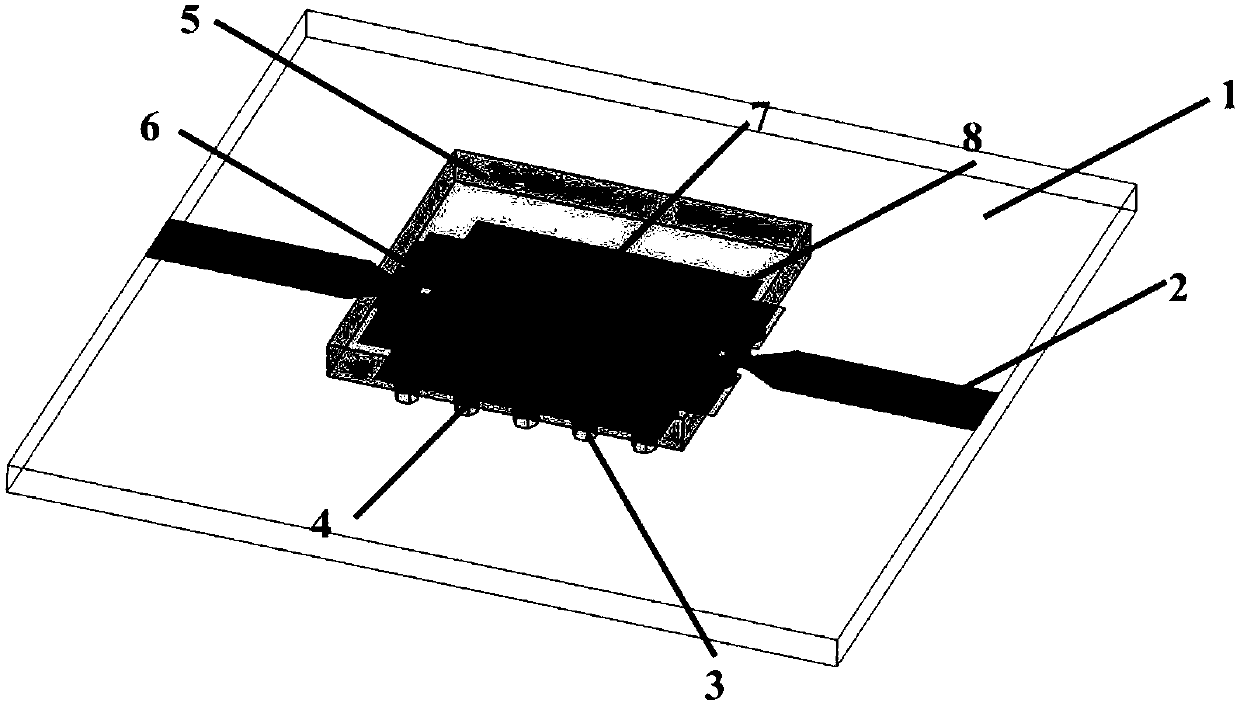

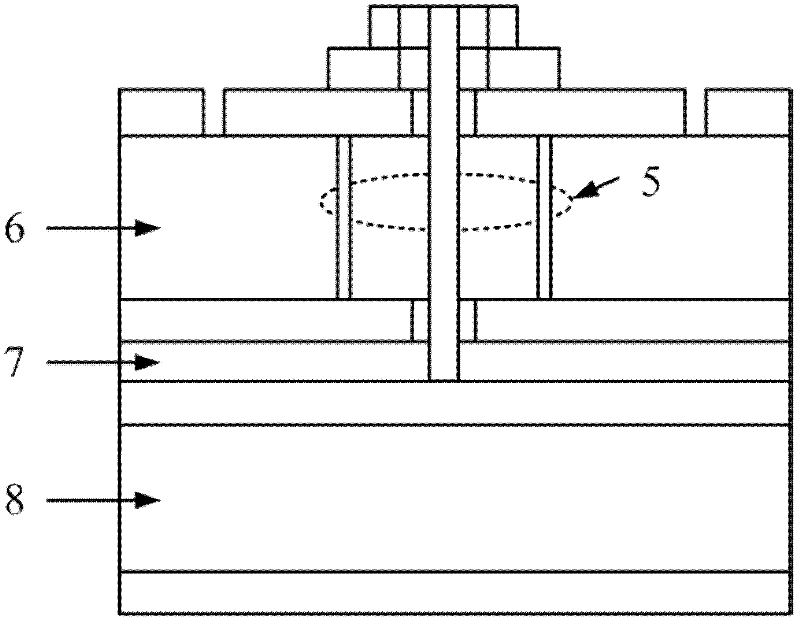

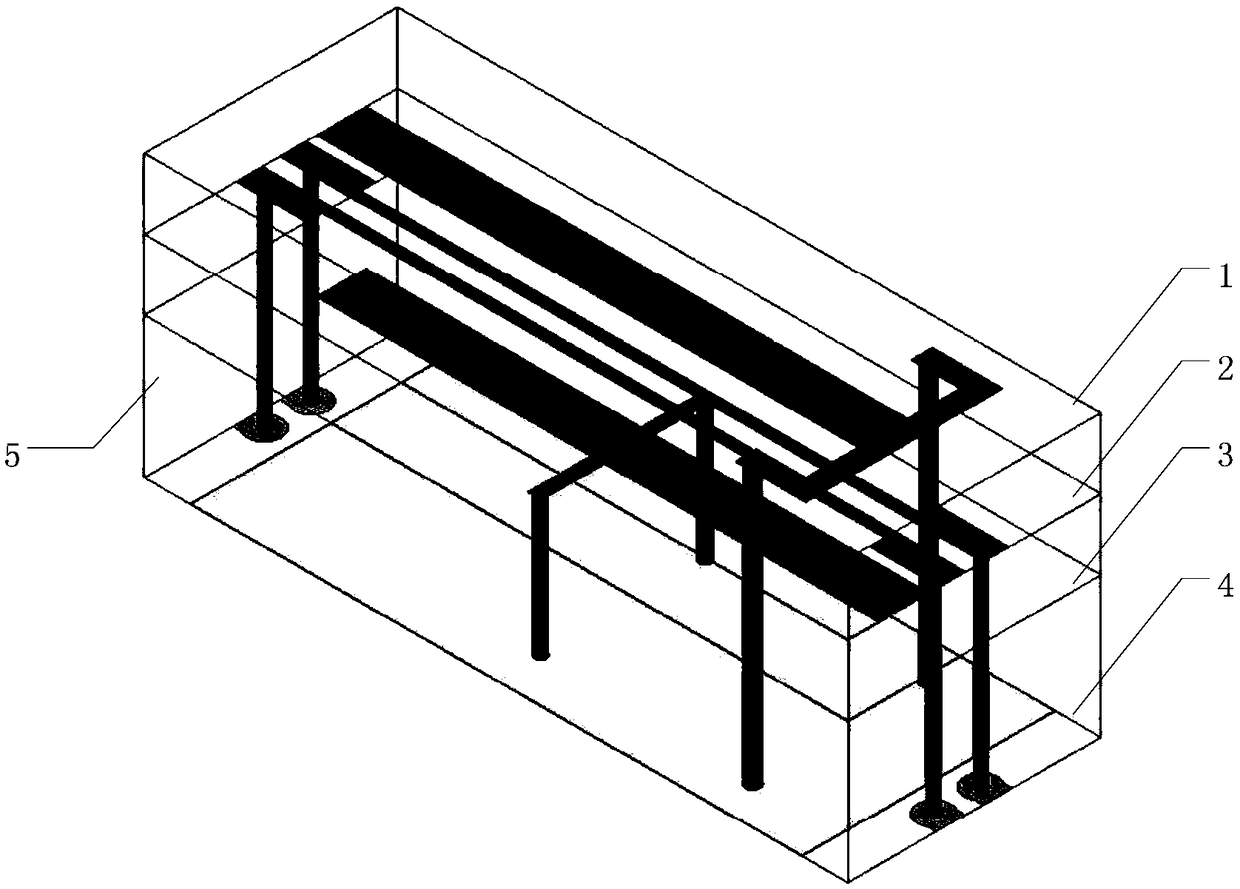

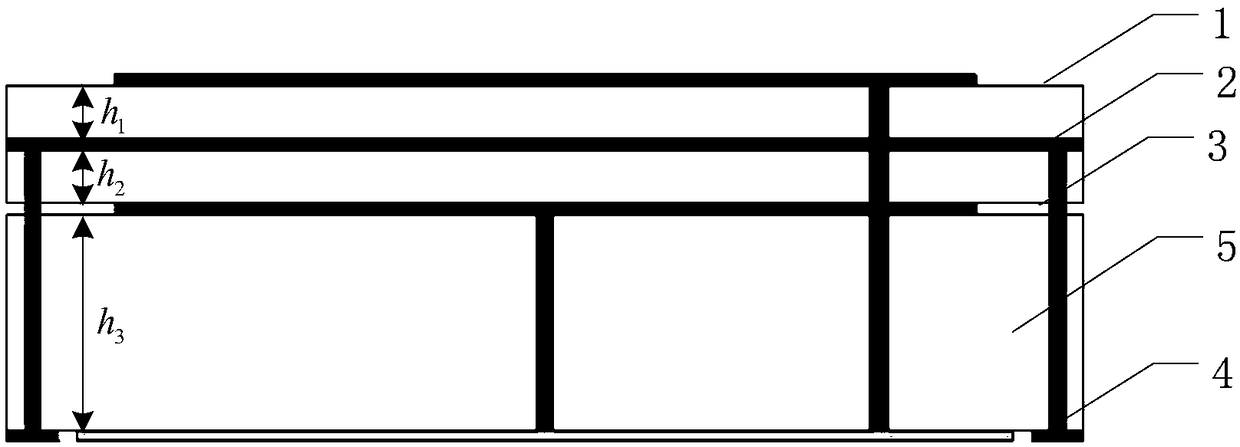

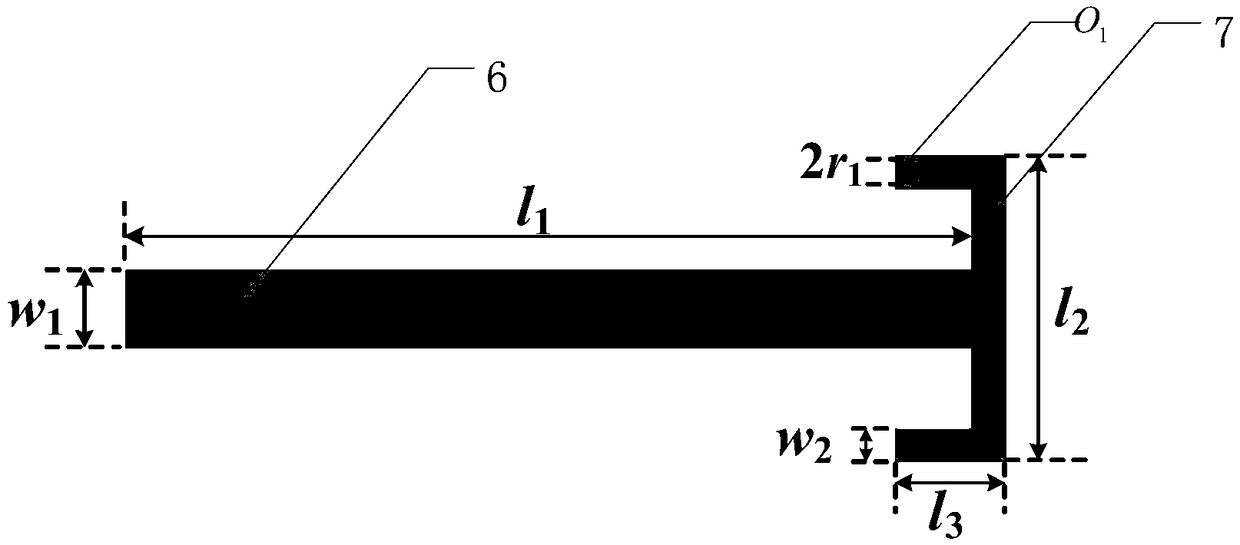

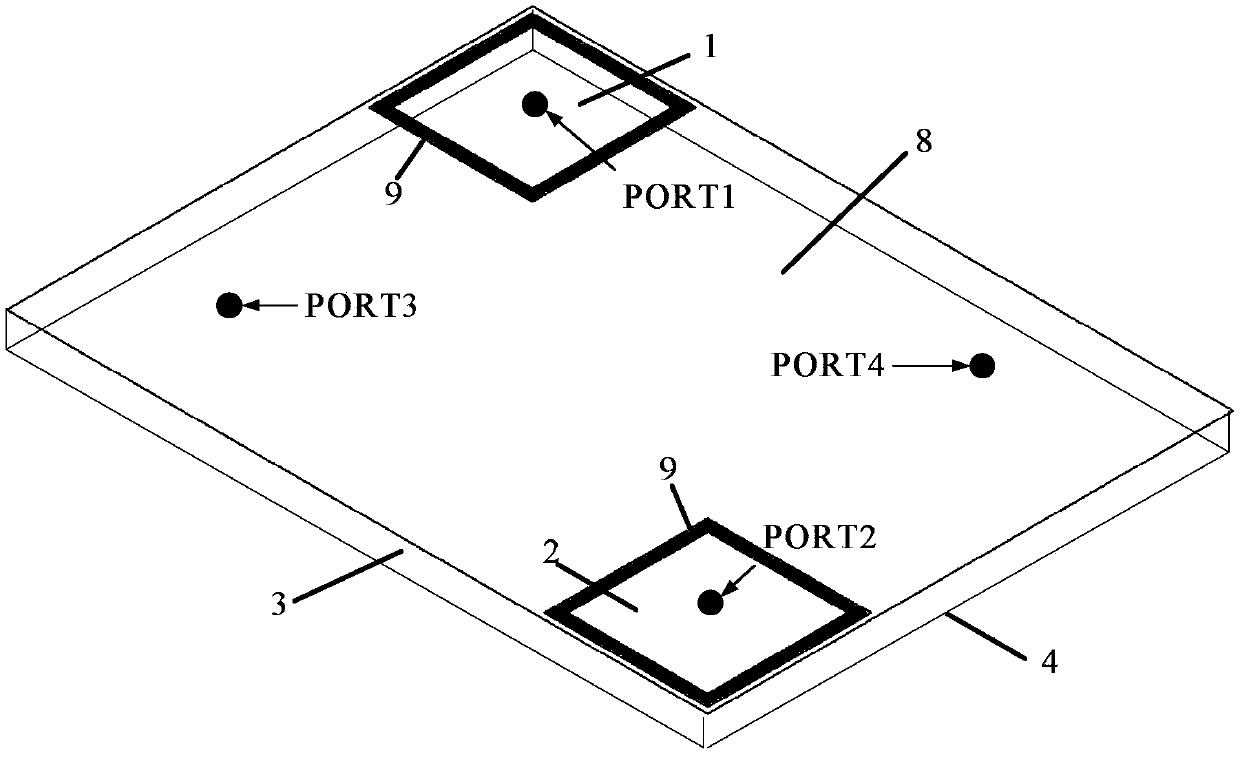

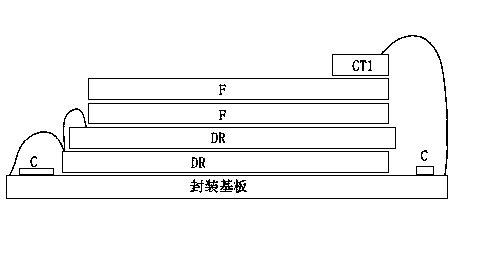

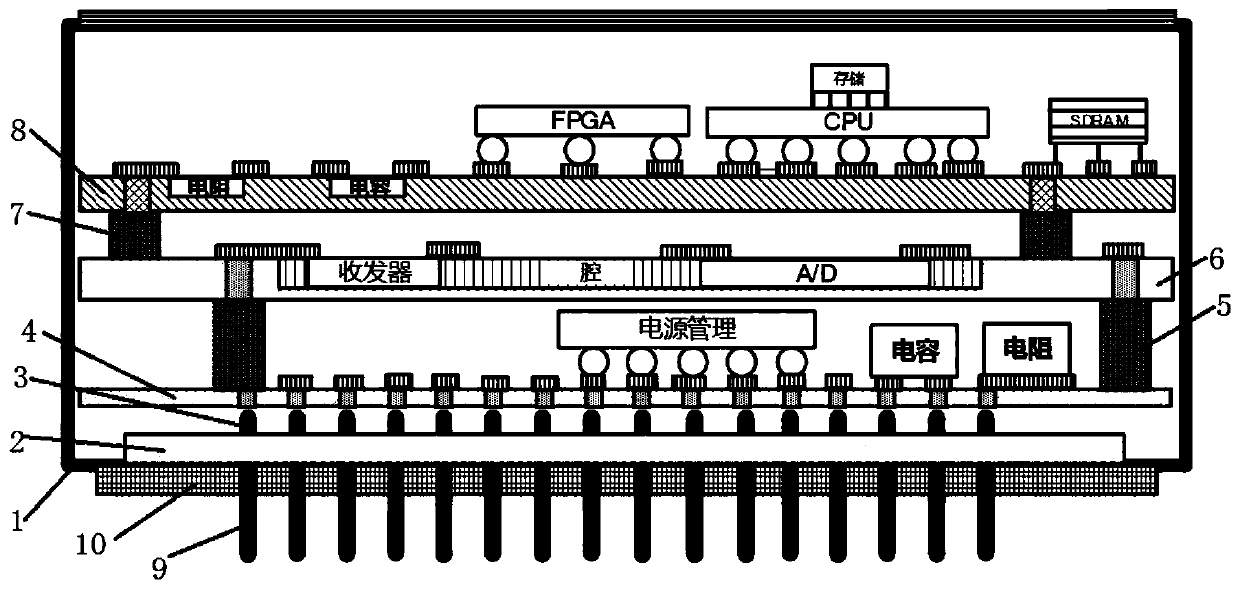

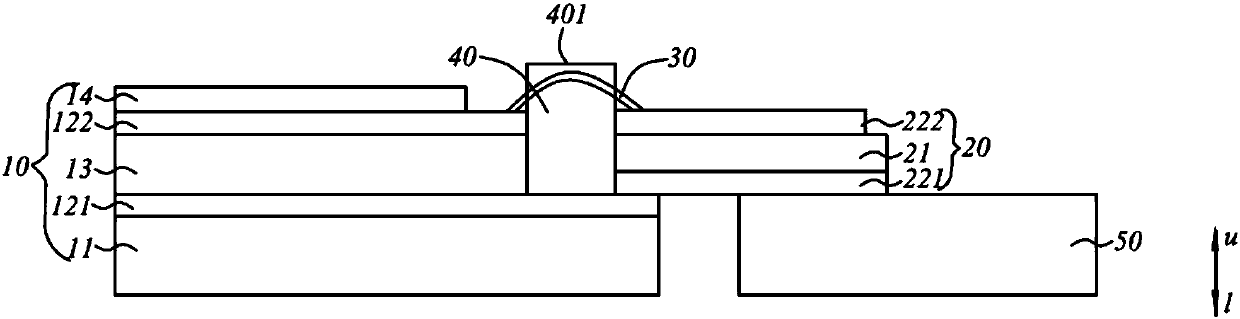

Novel microwave three-dimensional integrated system-in-package interconnection structure

ActiveCN107742622AHighly integratedEasy to achieve 3D integrationSemiconductor/solid-state device detailsSolid-state devicesInterconnectionSystem in package

The invention discloses a novel microwave three-dimensional integrated system-in-package interconnection structure. The microwave three-dimensional integrated system-in-package interconnection structure comprises a substratum medium substrate, a microstrip line, a grounded metallization hole array, a millimeter wave monolithic integrated circuit and a silicon substrate, and the grounded metallization hole array, the millimeter wave monolithic integrated circuit and the silicon substrate are arranged on substratum medium substrate; grounded planar metal is arranged on the grounded metallizationhole array, and the millimeter wave monolithic integrated circuit is arranged between a silicon substrate and grounded planar metal; a cavity is formed in the silicon substrate above a sensitive position of the millimeter wave monolithic integrated circuit; the microstrip line is connected with the millimeter wave monolithic integrated circuit through a planar transmission line. Compared with traditional golden wire bonding, the interconnection size among chips is obviously reduced, which is beneficial to maintenance of signal integrity during transmission of radio frequency and high-speed digital signals.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

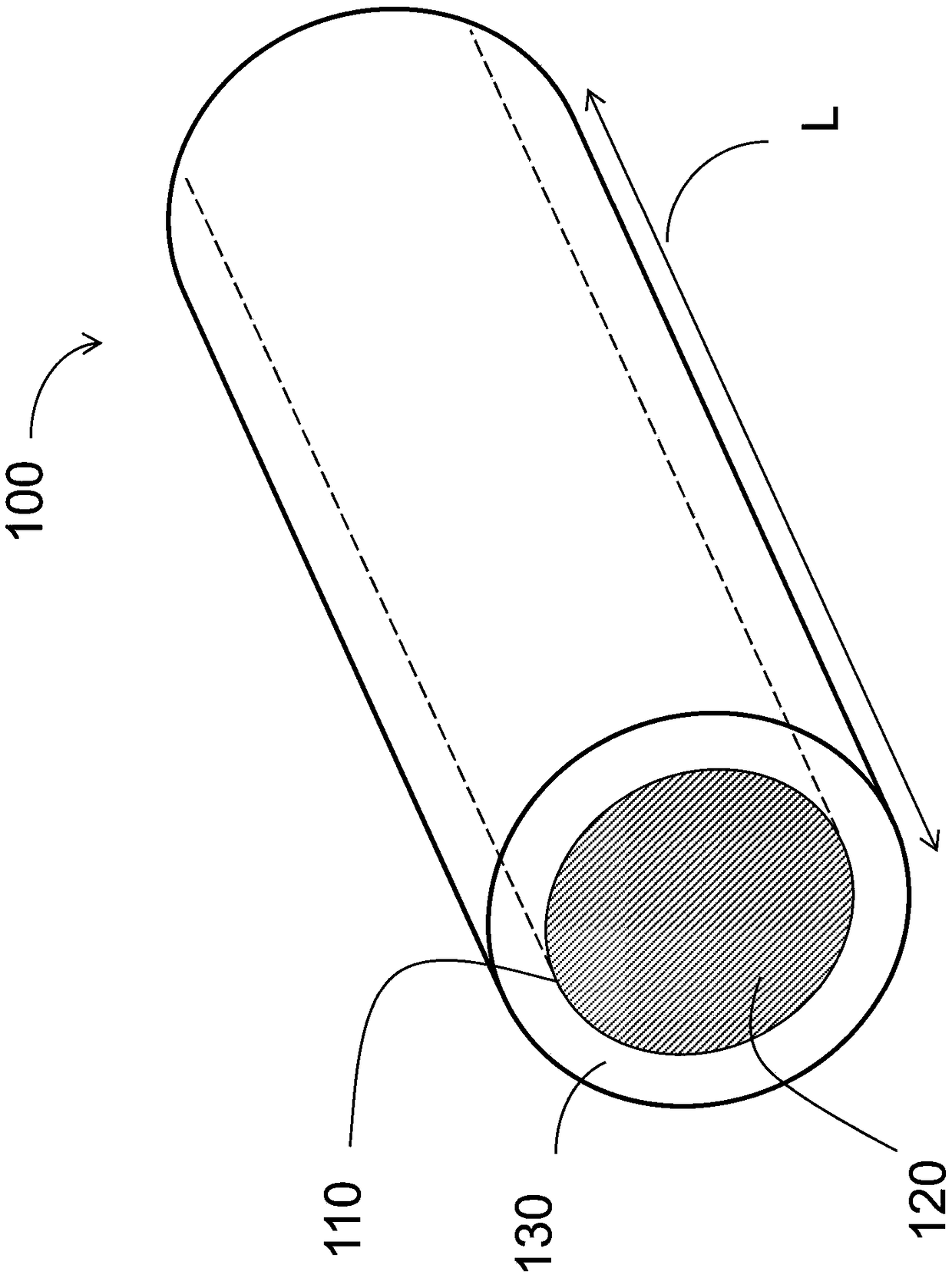

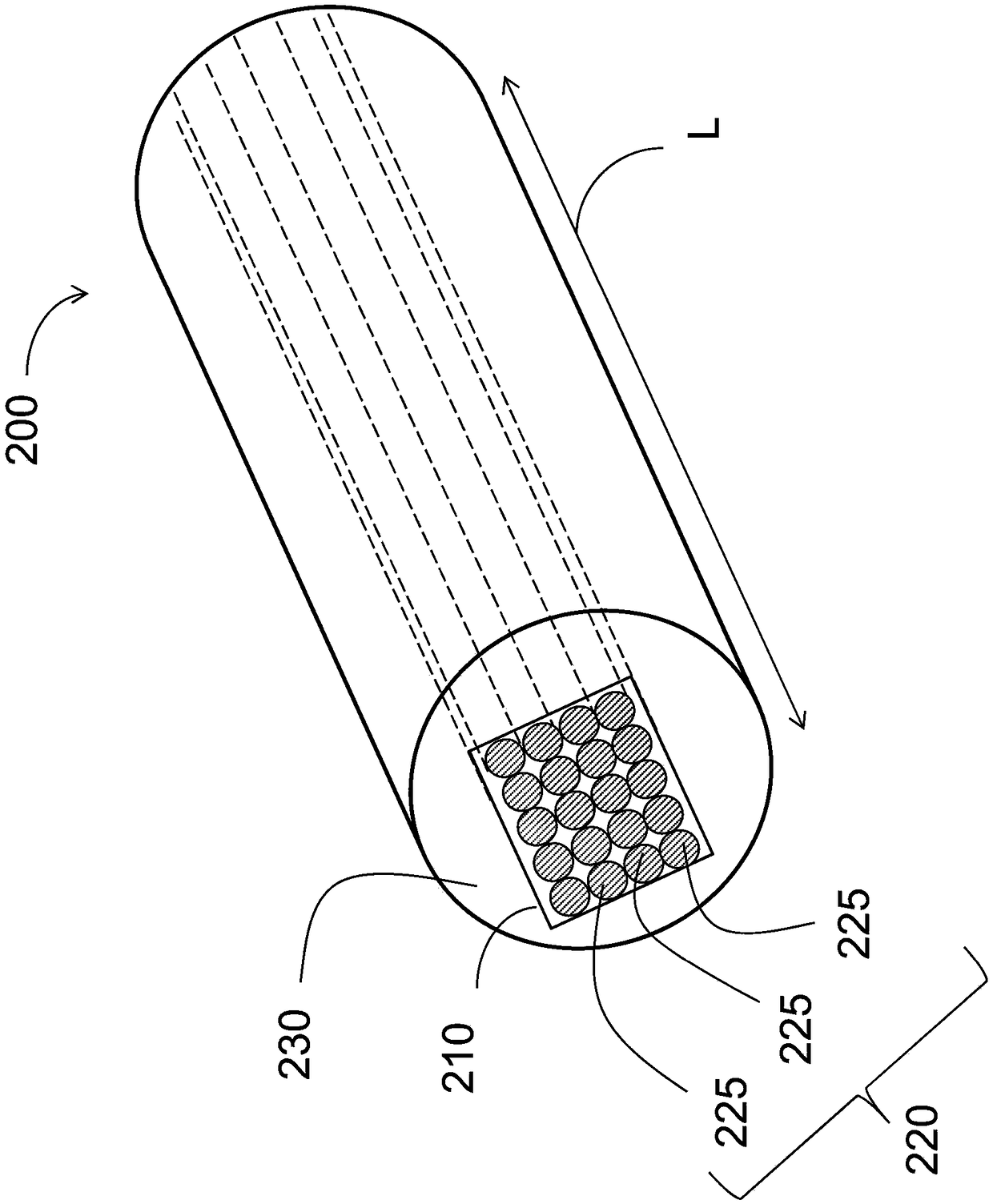

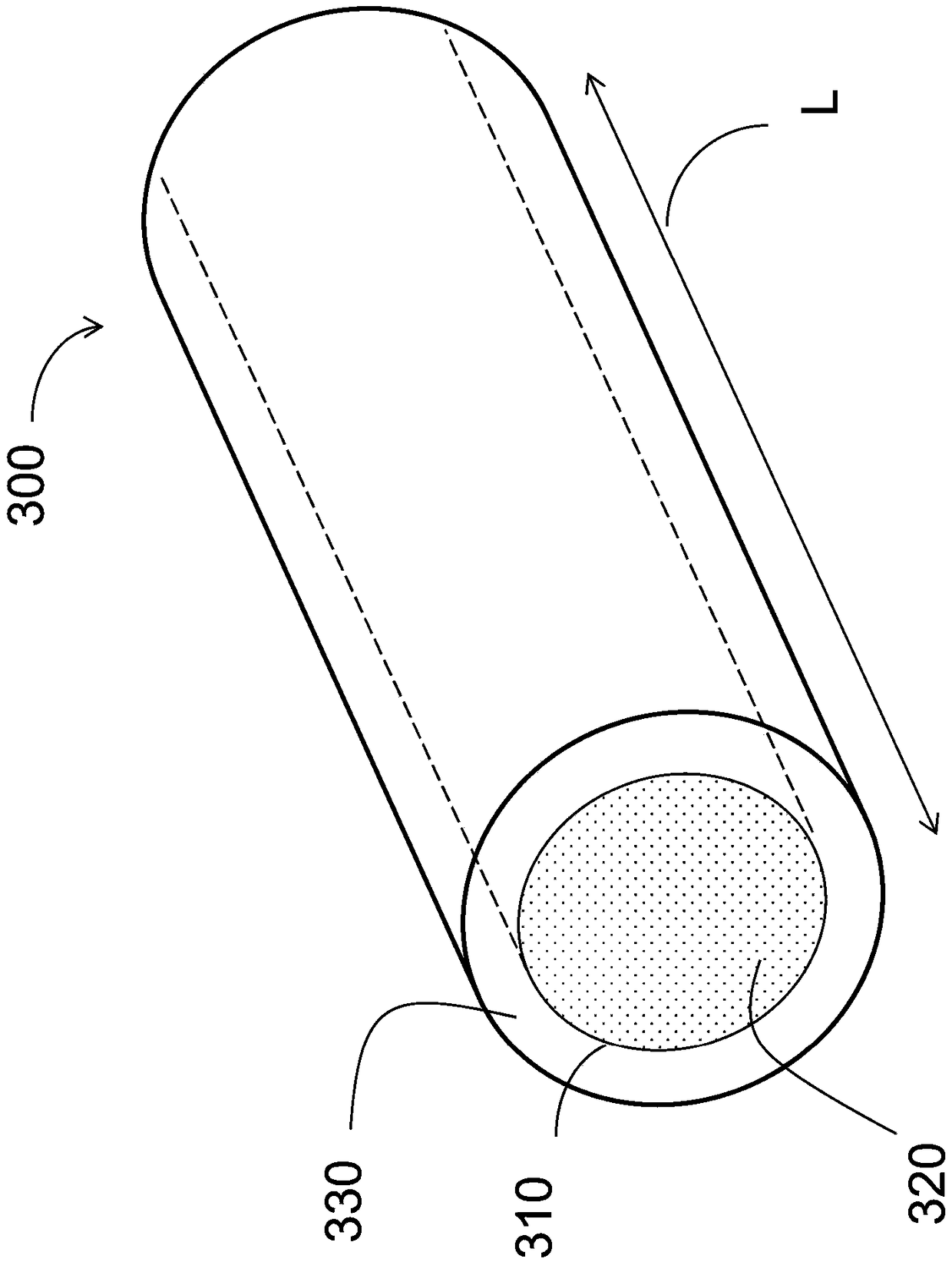

Low-loss dielectric waveguide for transmission of millimeter-wave signals and cable comprising the same

ActiveCN108780938AReduce transmission lossReduce manufacturing costOptical light guidesWaveguidesDielectricEngineering

The present invention provides a dielectric waveguide for transmission of millimeter-wave signals and a cable comprising the same, the dielectric waveguide comprising: an inner core having a dielectric medium adapted to transmit a millimeter- wave signal by carrying an electromagnetic field along the dielectric waveguide, the dielectric medium comprising a dielectric material having dielectric properties adapted to confine the propagating electromagnetic field to the inner core while adding low transmission loss at signal frequencies in a millimeter-wave frequency range. The dielectric mediummay be provided as a core of solid dielectric material, one or more bundles of fibers that extend along the length of the inner core, or as granulate of dielectric material that fills the volume of the inner core. The dielectric material may be quartz or alumina.

Owner:TE CONNECTIVITY GERMANY GMBH

Substrate based bumped flip chip CSP (Chip Scale Package) package part, substrate and manufacturing method

InactiveCN104201156ALower resistanceReduce capacitanceSemiconductor/solid-state device detailsSolid-state devicesThermal dilatationLead bonding

The invention discloses a substrate based bumped flip chip CSP (Chip Scale Package) package part, a substrate and a manufacturing method. The package part comprises the substrate and an IC (Integrated Circuit) chip which is inversely installed on the substrate; padding is filled between the substrate and the IC chip; the substrate comprises a substrate middle layer with an upper surface and a lower surface provided with printing lines; the substrate middle layer is provided with a plurality of cylindrical lateral walls which are connected with the printing lines; the upper face and the lower face of the substrate middle layer are provided with substrate bonding pads which are connected with the printing lines. The substrate is manufactured by procedures such as drilling, electrofacing, paving a dry film, exposing and developing with an FR-4 copper-clad plate or a BT substrate serving as substrate raw materials. The CSP package part is obtained by passivating a wafer; forming a UBM layer on the chip bonding pad; coating photoresist; duplicating patterns on a photoresist layer; forming into a stannum / plumbum metal layer; obtaining welding bumped points through backflow; inversely install the chip; melting the welding bumped points; downward filling and obtaining a CSP package part. The package part solves the problems that lead bonding package high-frequency electrical performance is poor and thermal expansion between the ceramic substrate and the PCB is large in mismatch during the existing IC package circuit connection.

Owner:TIANSHUI HUATIAN TECH

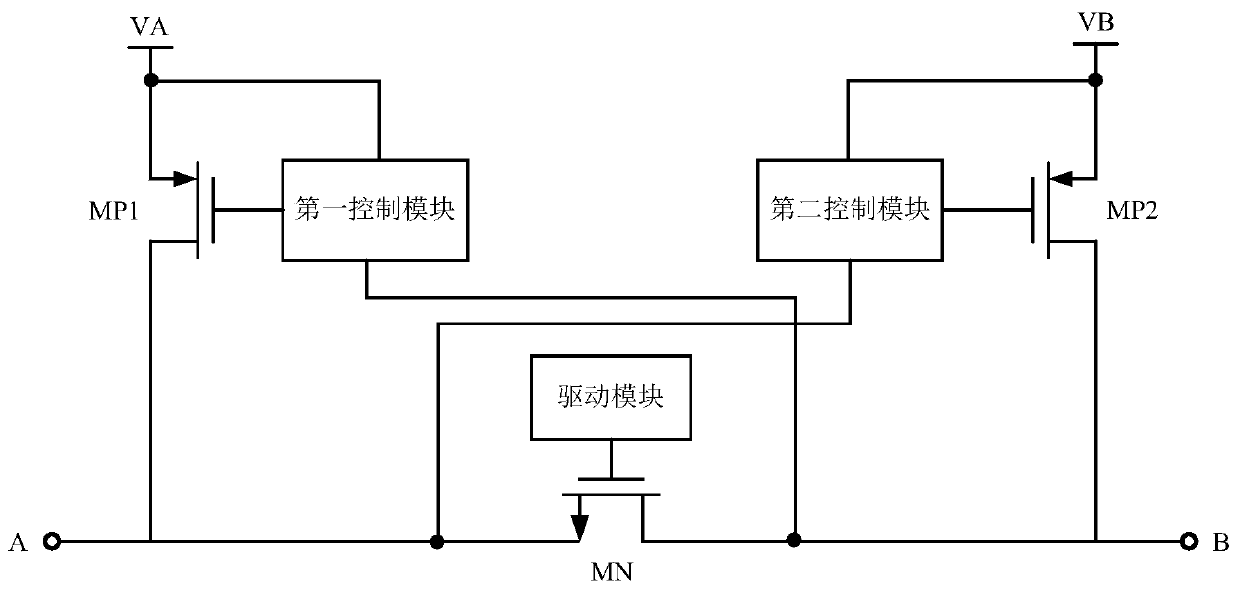

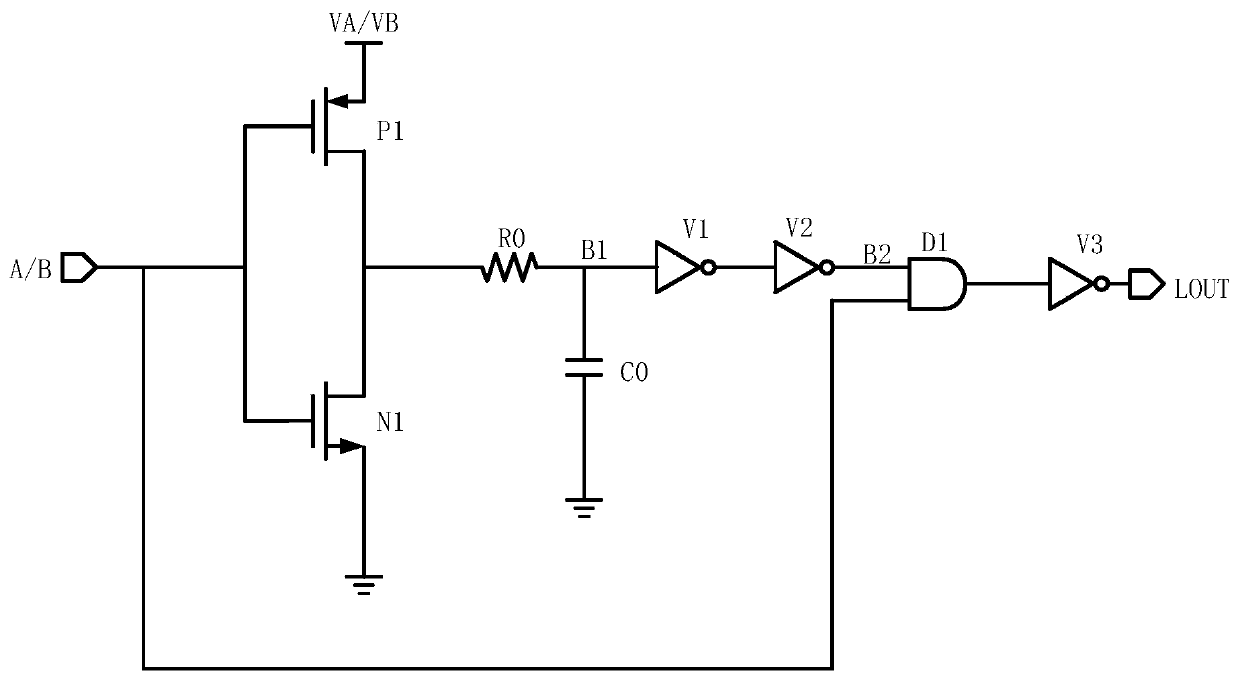

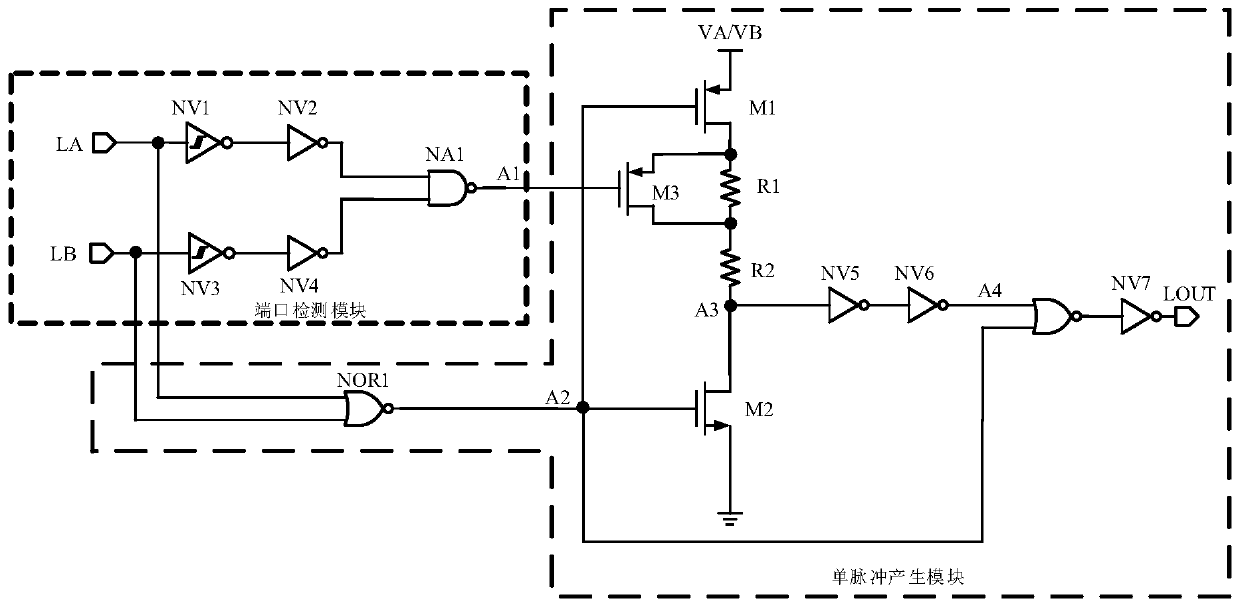

A single pulse generation circuit and a bidirectional level conversion circuit

PendingCN109787614AFast signal transmissionReduce power consumptionLogic circuits coupling/interface using field-effect transistorsVIT signalsElectricity

The invention provides a single pulse generation circuit and a bidirectional level conversion circuit. The single pulse generation circuit comprises a first signal input end, a second signal input end, a port detection module and a single pulse generation module, The port detection module is used for outputting a high level when at least one of the first signal input end and the second signal input end is at a low level, and outputting a low level when both the first signal input end and the second signal input end are at a high level, so that the output of the single pulse generation module is accelerated to turn to a high level; The single pulse generation module is used for generating a single pulse when any one of the first signal input end and the second signal input end is overturnedfrom a low level to a high level; When the first signal input end and the second signal input end are both turned over to high levels, transmission power consumption is reduced, and impedance matching performance and signal integrity of the output port are guaranteed at the same time.

Owner:SHANGHAI AWINIC TECH CO LTD

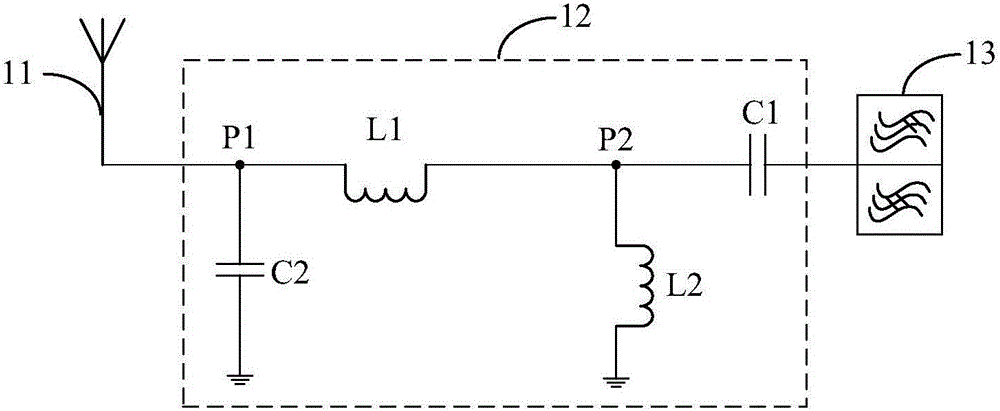

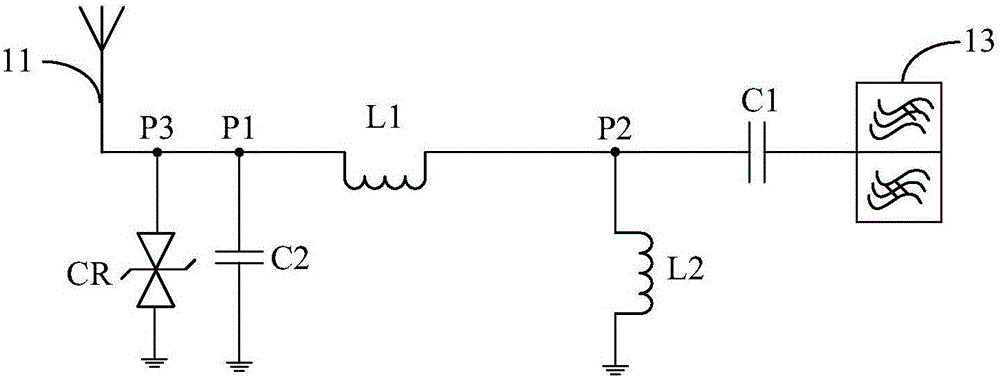

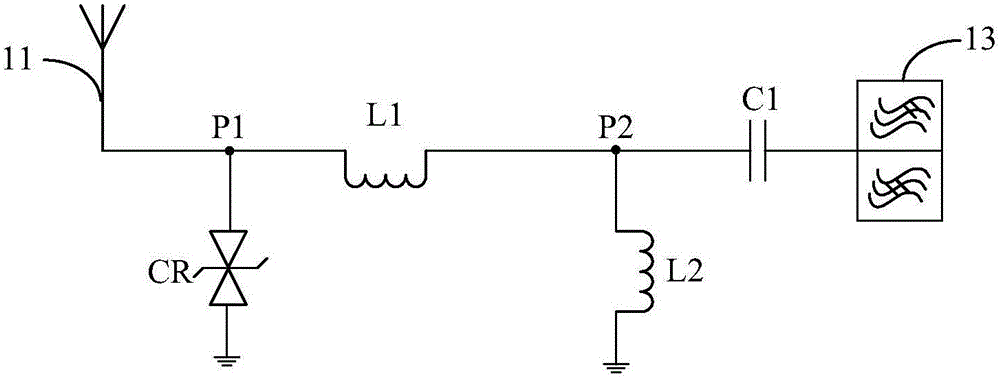

Classifying antenna and mobile terminal

InactiveCN106058433AImprove reliabilityReduce areaAntenna supports/mountingsAntennas earthing switches associationCapacitanceSuppressor

This invention provides a classifying antenna and a mobile terminal. The classifying antenna comprises a classifying antenna main body, a matching circuit, a filter and a static protection circuit, wherein the classifying antenna main body is used for receiving and sending electromagnetic waves; the matching circuit is matched with the classifying antenna main body to receive the electromagnetic waves and send the electromagnetic waves to the filter; the filter is used for filtering radio frequency signals of at least two frequency bands; the matching circuit at least comprises a first inductor (L1) and a first capacitor (C) connected between the classifying antenna main body and the filter in series; the static protection circuit is a static suppressor (CR) connected onto the feeder line of the classifying antenna main body; and, one end of the static suppressor (CR) is connected with the feeder line of the classifying antenna main body, and the other end is connected with the ground. By adoption of the classifying antenna, the static protection performance of the mobile terminal is effectively improved; and the reliability of the mobile terminal is improved.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

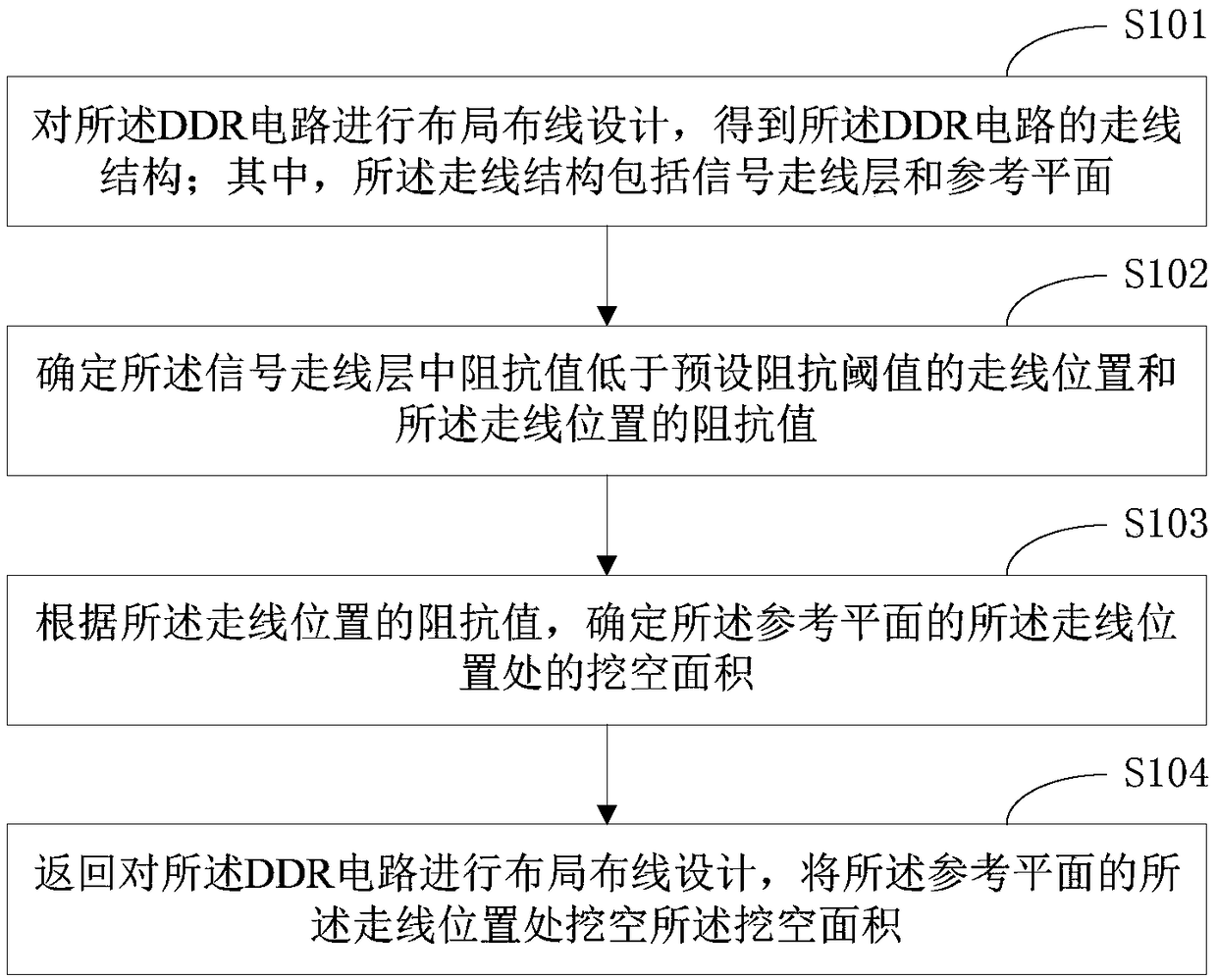

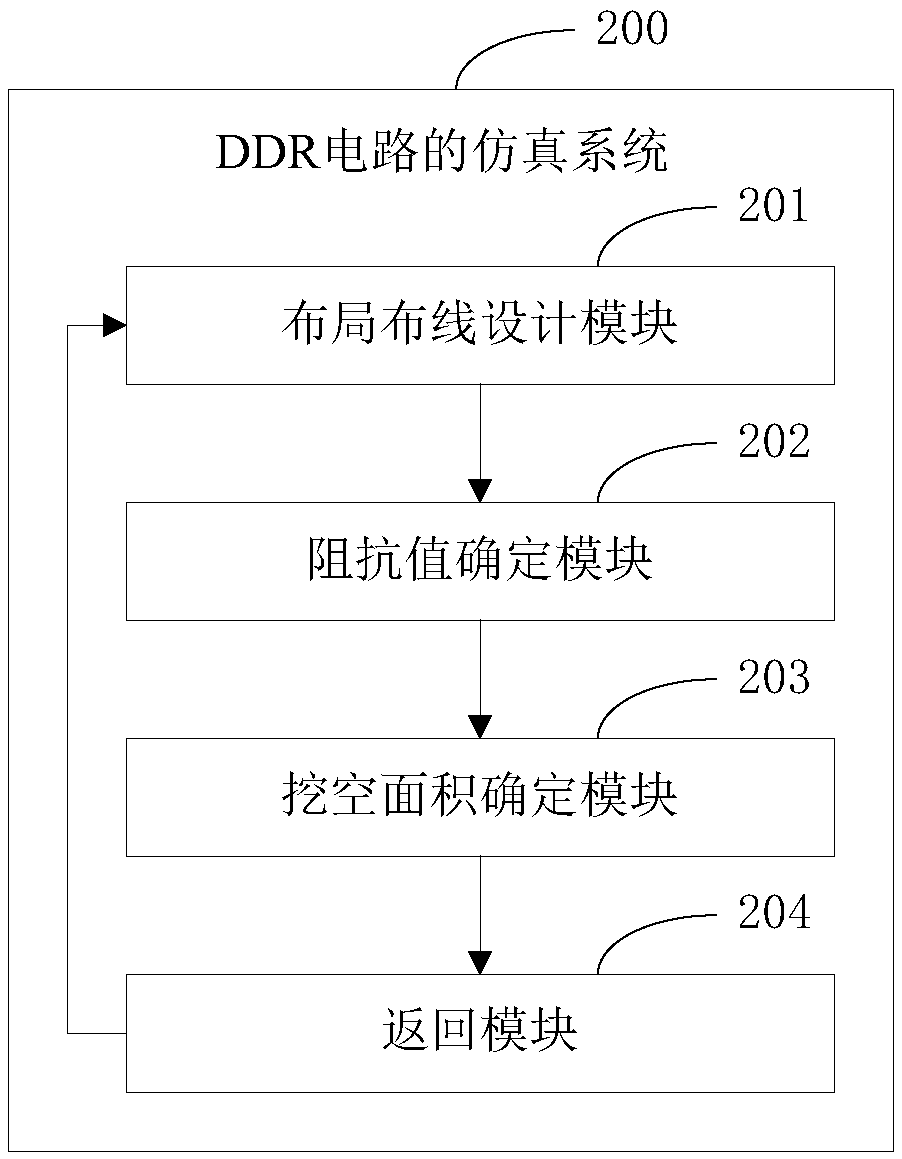

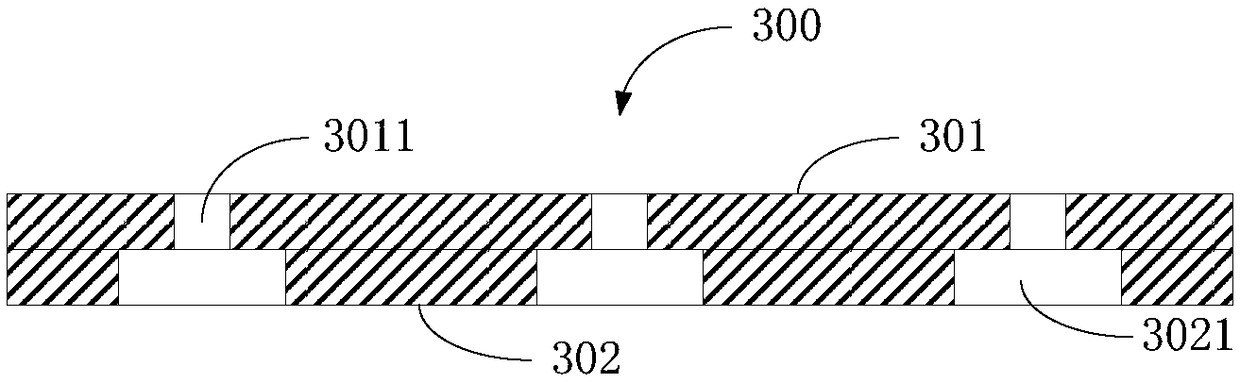

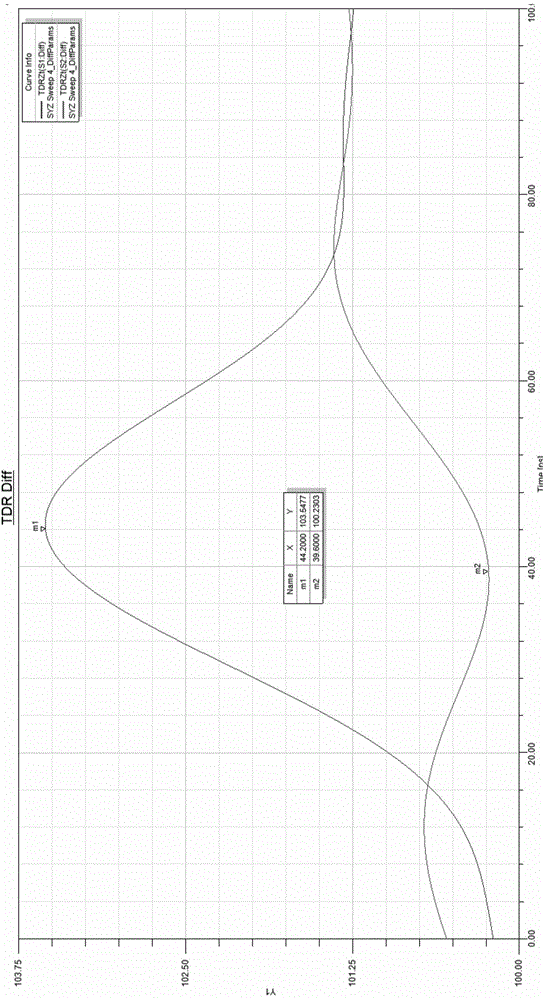

Simulation method and system and wiring structure of DDR circuit

PendingCN108804809AImpedance continuousGuaranteed Signal IntegritySpecial data processing applicationsSignal integritySignal quality

The invention is applicable to the field of DDR SDRAM technology and provides a simulation method and system and a wiring structure of a DDR circuit. The simulation method comprises the steps that layout wiring design is performed on the DDR circuit to obtain the wiring structure of the DDR circuit, wherein the wiring structure comprises a signal wiring layer and a reference plane; a wiring location with an impedance value lower than a preset impedance threshold in the signal wiring layer and the impedance value of the wiring location are determined; according to the impedance value of the wiring location, a hollow-out area at the wiring location of the reference plane is determined; and layout wiring design is performed on the DDR circuit again, and the wiring location of the reference plane is hollowed out according to the hollow-out area. Through the embodiment, target impedance of a signal link on the signal wiring layer can be continuous, so that the signal integrity of the DDR circuit is guaranteed, and the signal quality of the DDR circuit is improved.

Owner:OPPO CHONGQING INTELLIGENT TECH CO LTD

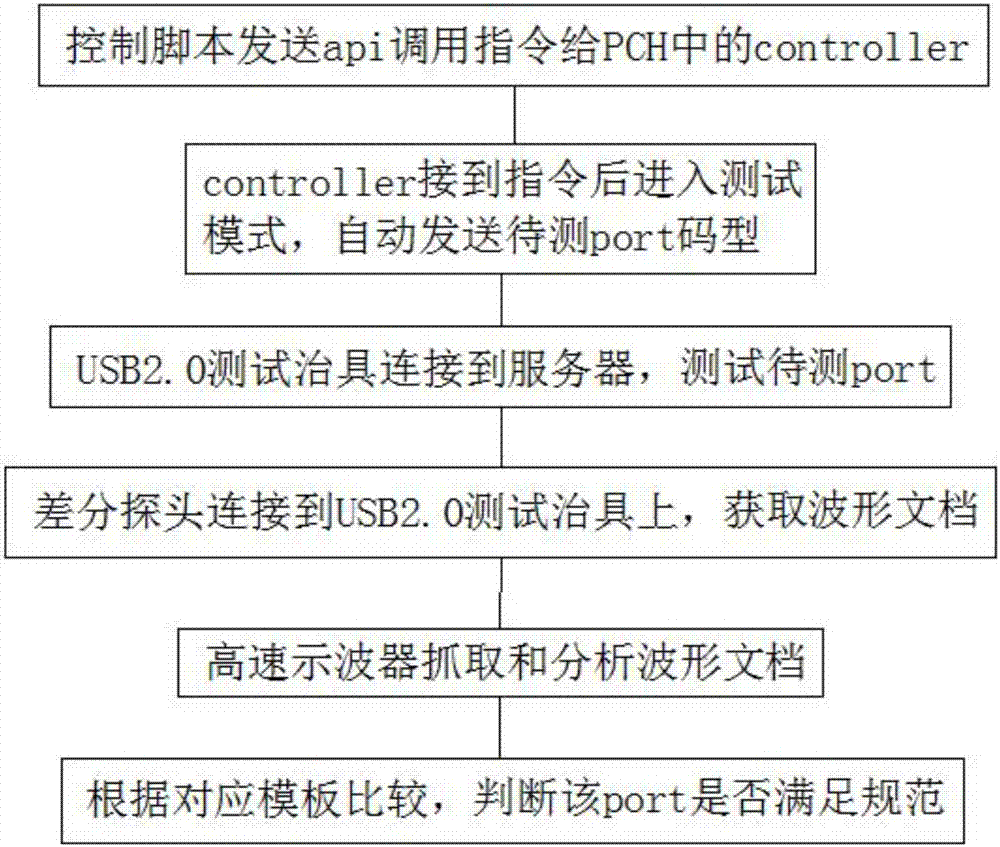

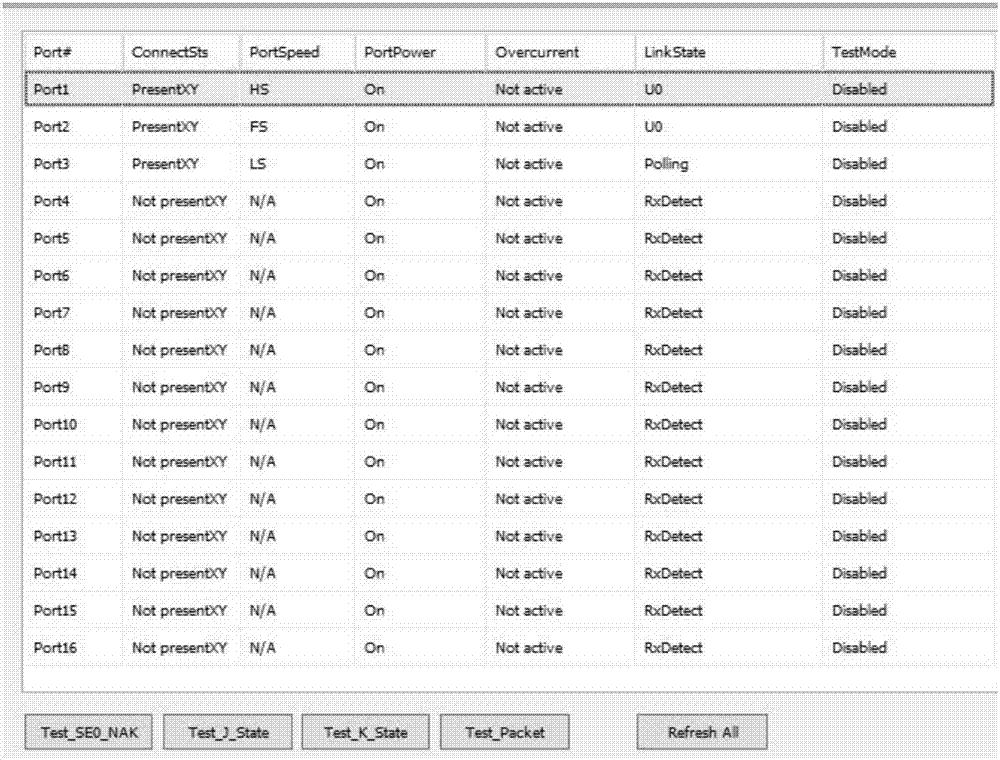

Test method achieving USB 2.0 High Speed controlled packet sending

InactiveCN107239375ASave human effortSave resourcesFaulty hardware testing methodsTest efficiencyHigh speed control

The invention discloses a test method achieving USB 2.0 High Speed controlled packet sending. The method comprises the following steps that 1, a control script sends an api call instruction to a controller in PCH; 2, the controller enters a test mode after receiving the instruction, and a to-be-tested port code pattern is sent automatically; 3, an USB2.0 test fixture is connected to a server to test a to-be-tested port; 4, a differential probe is connected to the USB 2.0 test texture, and a waveform document is obtained; 5, a high-speed oscilloscope captures and analyzes the waveform document; 6, according to corresponding template comparison, whether the port meets the standard or not is judged. Accordingly, the process that a server motherboard is connected with a network card, and the system is controlled remotely through a computer to send a packet is omitted, the labor, resources and time are saved, and the test efficiency is improved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

Power distribution network in high-speed circuit system

InactiveCN102522962AReduce radiation lossBreak continuityDigital technique networkCapacitanceReturn current

The invention discloses a power distribution network in a high-speed circuit system. The metal surface at one side of a buried capacitor is locally etched with a complementary split ring resonator, and the metal surface at the other side of the buried capacitor keeps complete; and simultaneously, the upper side and the lower side of the buried capacitor are respectively added with a layer of FR-4 medium, and SMA (shape memory alloy) coaxial joints are used for connecting a circuit board to a vector network analyzer to test a noise suppression transmission coefficient among ports. According to the power distribution network, the problems that the noise suppression band of a synchronous switch in the high-speed circuit system is not wide and the suppression degree is not deep are effectively solved, and simultaneously the damage for a return current path of a circuit is less. The mixed high-speed circuit system based on the power distribution network has good power integrity, and is convenient for standard technical processing of printed circuit boards.

Owner:SHANGHAI JIAO TONG UNIV

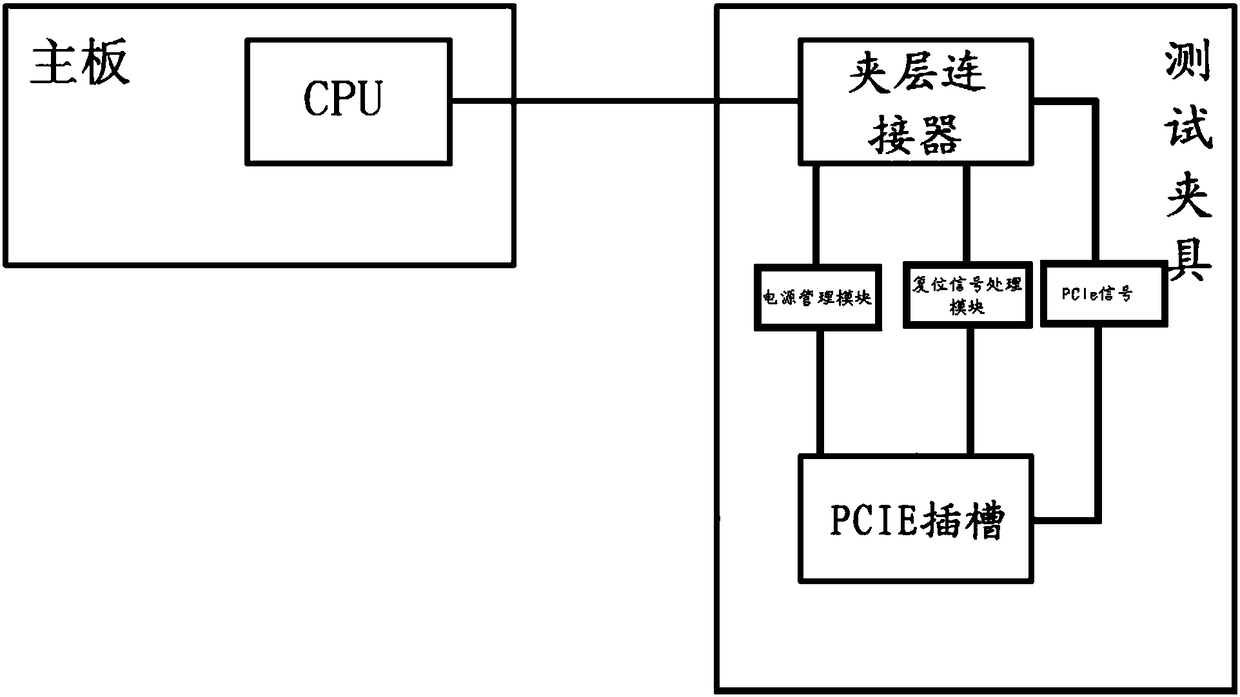

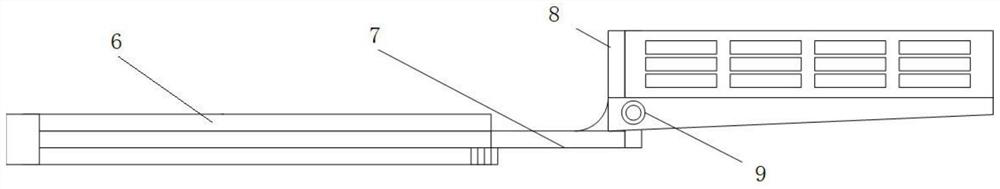

Signal testing device

ActiveCN108255652AGuaranteed Signal IntegrityFaulty hardware testing methodsDesign testingCommunication link

The invention discloses a signal testing device. The device comprises a main board and a testing clamp, wherein the testing clamp is connected with the main board; the testing clamp comprises an interlayer connector and a PCIE slot, the interlayer connector is connected with the main board, and the interlayer connector is further connected with the PCIE slot. According to the device, the interlayer connector is connected with the PCIE slot so that various testing of non-standard PCIE interface signals of the interlayer connector can be achieved through the designed testing clamp, and the signal integrity of a communication link can be effectively ensured.

Owner:中科曙光信息产业成都有限公司 +1

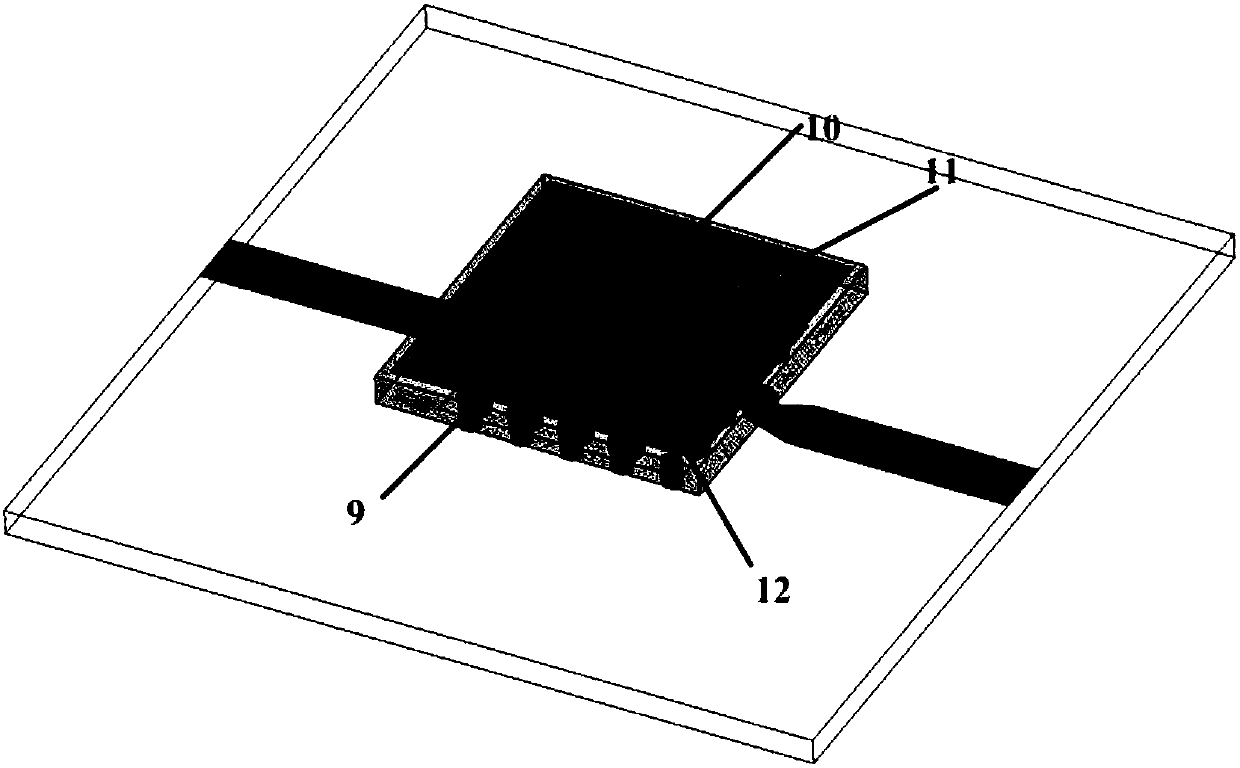

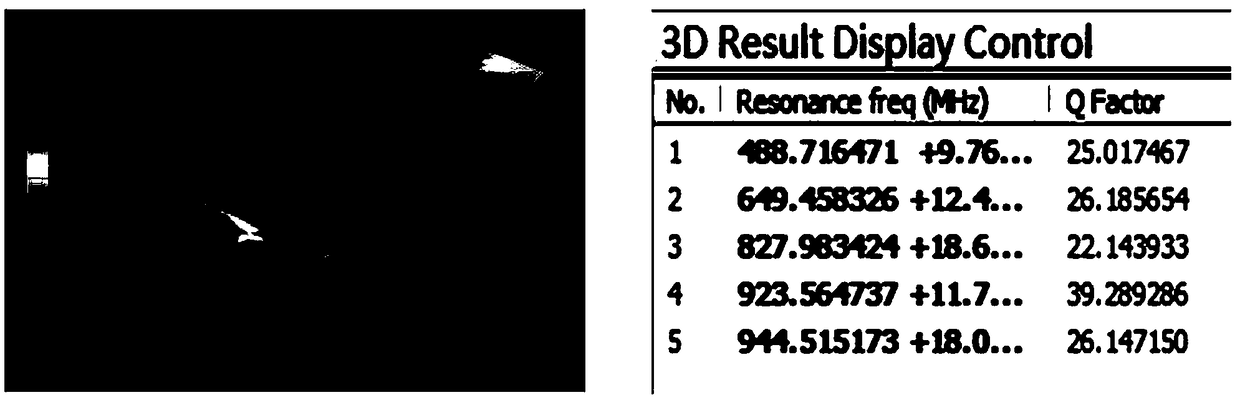

Miniature ultra-wideband common mode noise suppression circuit

ActiveCN108666720AGuaranteed Signal IntegrityWaveguide type devicesUltra-widebandDielectric substrate

The invention discloses a miniature ultra-wideband common mode noise suppression circuit which comprises a quarter-wavelength stepped impedance resonator layer, an embedded differential coupling microstrip line layer, a half-wavelength resonator layer and a reference ground layer, wherein the layers are separated by dielectric substrates. The quarter-wavelength stepped impedance resonator layer comprises a quarter-wavelength stepped impedance resonator, wherein one end of the quarter-wavelength stepped impedance resonator is open circuit, and the other end of the quarter-wavelength stepped impedance resonator is connected with a first branch in parallel. The tail end of the first branch is connected with the reference ground layer through a metal via. The embedded differential coupling microstrip line layer comprises an embedded differential coupling microstrip line. The half-wavelength resonator layer comprises a half-wavelength resonator, and both ends of the half-wavelength resonator are open circuit. The circuit is applicable to the GHz frequency band, and the signal integrity of differential signal transmission can be ensured while common mode noise suppression is realized.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

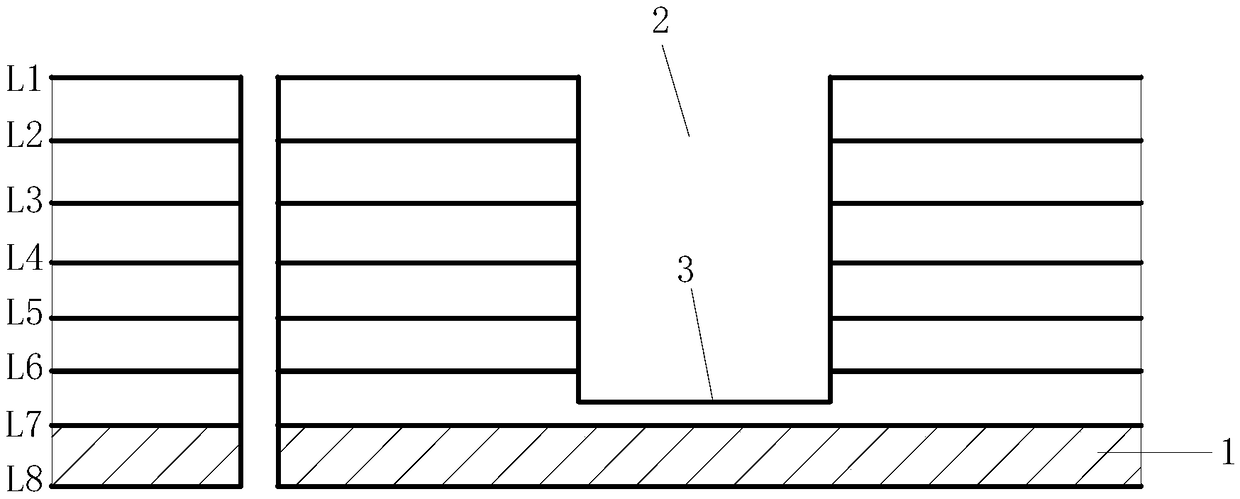

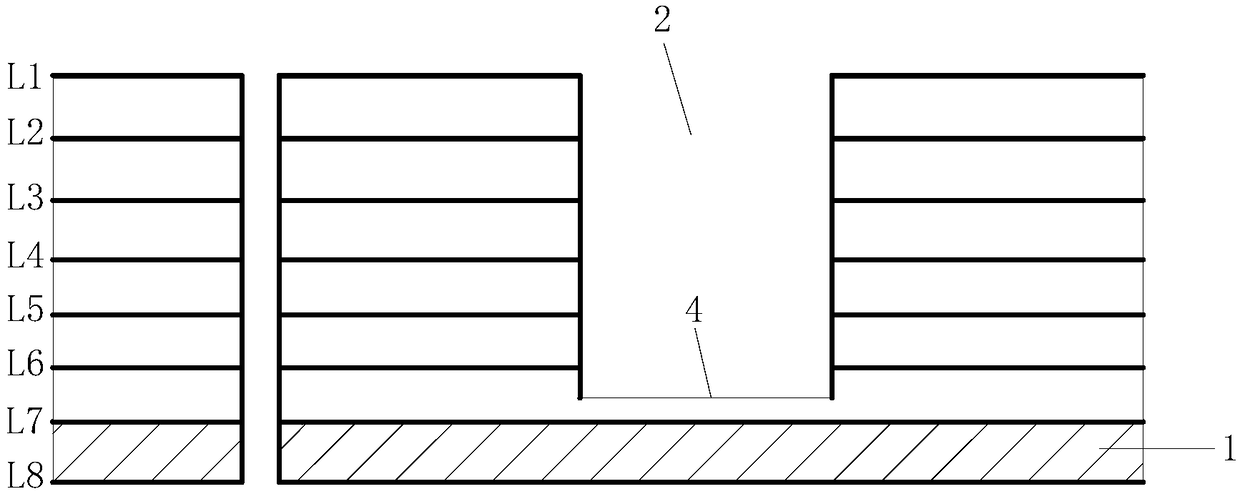

Precise depth-controlled groove milling-based manufacture method of microwave printed circuit board

InactiveCN109121300AAchieve zero damageGuaranteed Signal IntegrityPrinted circuit manufactureMicrowaveCopper plating

The invention discloses a precise depth-controlled groove milling-based manufacture method of a microwave printed circuit board. The method includes the following steps that: a stepped groove is formed in a production board by means of depth-controlled groove milling, and the groove bottom of the stepped groove is located in a dielectric layer at the upper part of a copper layer at the inner sideof a Rogers high-frequency board; electroless copper plating and full-board electroplating treatment are performed on the production board, so that the groove bottom and groove wall of the stepped groove are plated with a copper layer; the production board is coated with a film, and an outer layer pattern is formed on the production board by means of explosion and development, pattern plating is performed on the production board; a plated layer at the bottom of the stepped groove is removed by means of milling, so that the dielectric layer at the bottom of the stepped groove is exposed; the dielectric layer at the bottom of the stepped groove is burned through laser, so that the copper layer at the inner side of the Rogers high-frequency board is exposed; and adhesive removing treatment isperformed on the production board, and the copper layer exposed at the bottom of the stepped groove is removed by means of alkaline etching. With the method of the invention adopted, the zero damageof the Rogers high-frequency board is realized, and the signal integrity of a high-frequency and high-speed printed circuit board during signal transmission can be ensured.

Owner:SHENZHEN SUNTAK MULTILAYER PCB

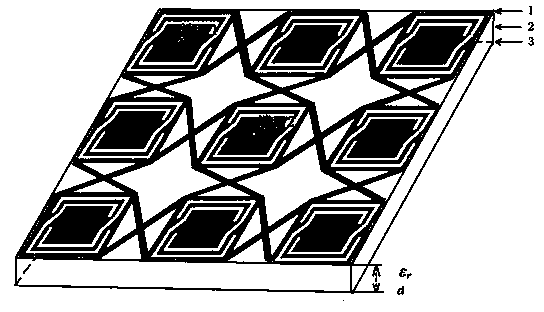

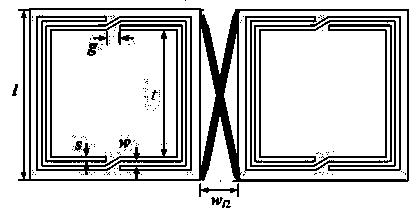

Power supply EBG structure based on open-loop resonator and X-shaped bridge

InactiveCN105517318AReduce the number of layersLow costPrinted circuit detailsPrinted electric component incorporationBroadbandOpen loop resonator

The invention provides a power supply EBG structure based on open-loop resonators and an X-shaped bridge. The power supply EBG structure comprises two metal layers and one dielectric layer, wherein the dielectric layer is arranged between the two metal layers; the upper metal layer is a power supply layer; the lower metal layer is a ground layer; the upper metal layer, namely the power supply layer, utilizes etching open-loop resonators as periodical units of an EBG structure; the open-loop resonators are connected through an X-shaped bridge; the lower metal layer utilizes a complete metal plane; and the open-loop resonators are adjusted by means of adjusting of the size of the open-loop resonators. For the power supply EBG structure based on open-loop resonators and an X-shaped bridge, two metal layers are utilized to design the EBG structure and the periodical units of the structure utilize complementary open-loop resonators and uses the X-shaped bridge to connect the periodical units so as to increase the bandwidth of a stop band and restrain the depth, so that effective suppression of electromagnetic noise can be realized in a broadband range.

Owner:CHANGSHU KAIXI ELECTRONICS & ELECTRICAL CO LTD

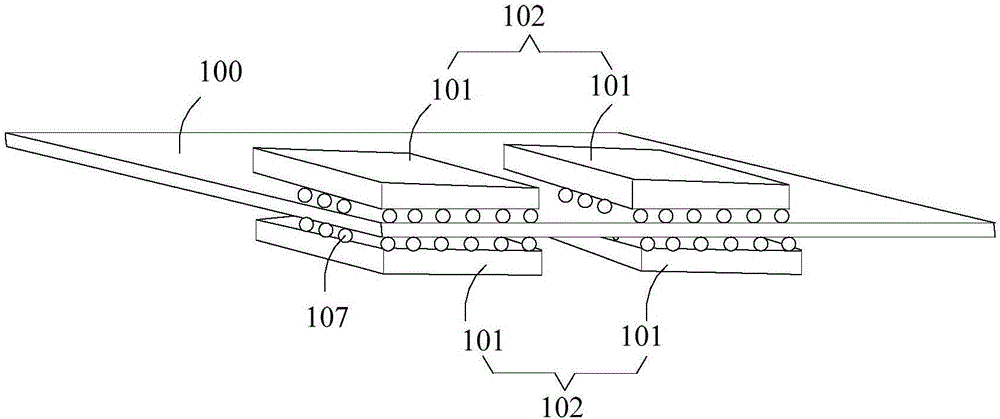

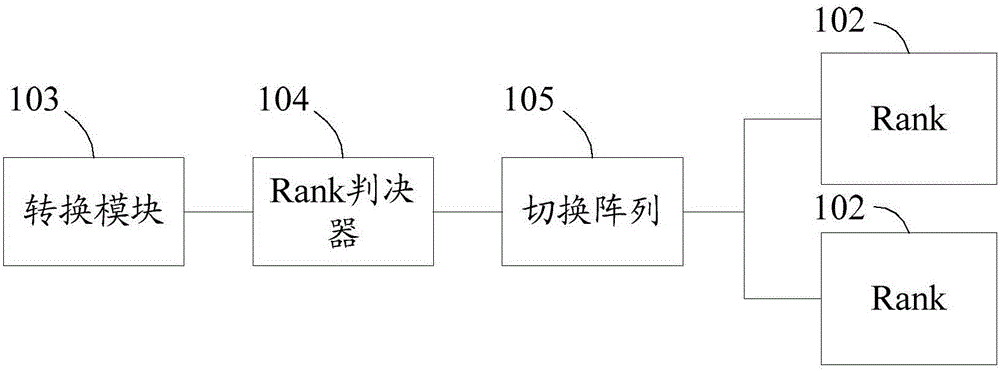

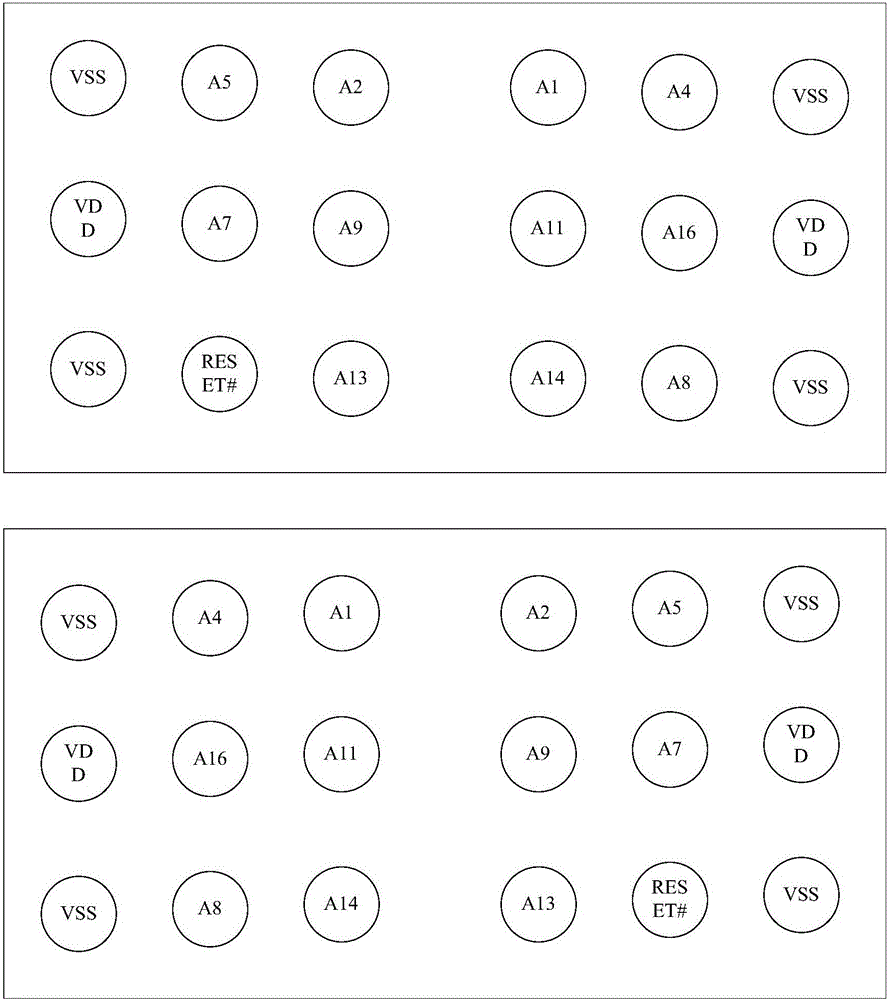

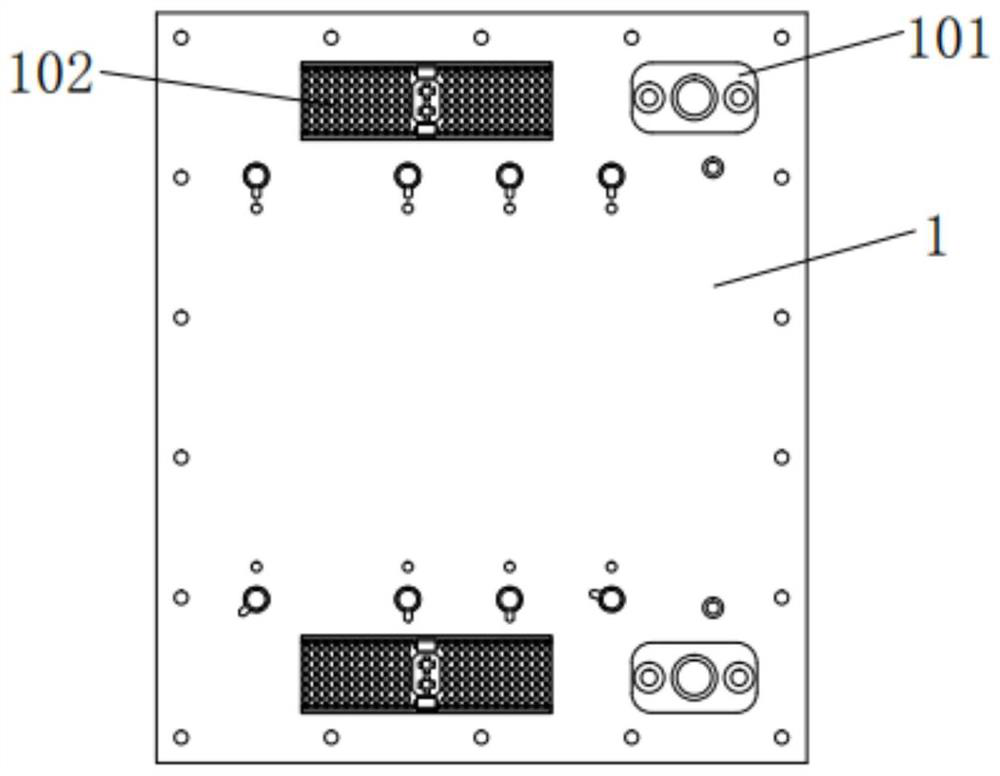

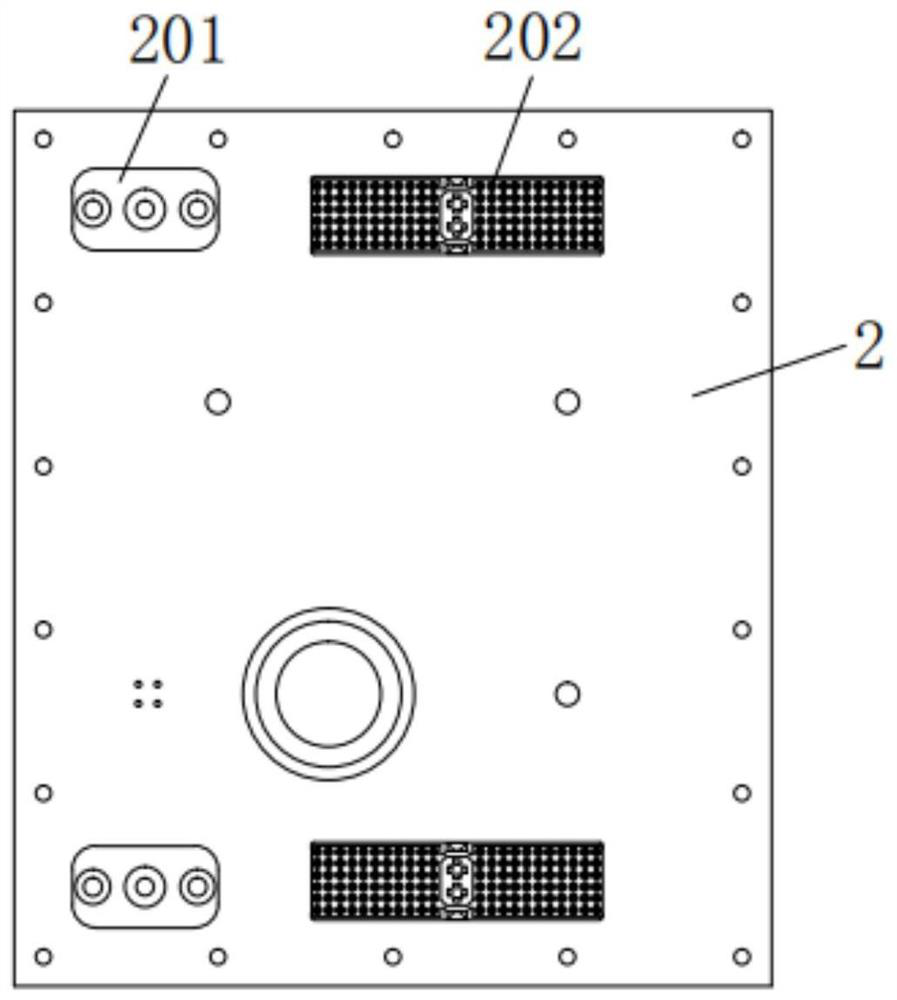

Storage apparatus and data access method

ActiveCN107180000AGuaranteed Signal IntegrityAvoid multiple layersDigital storageElectric digital data processingAccess methodData access

The invention discloses a storage apparatus and a data access method, and belongs to the technical field of storage. The apparatus comprises a PCB (Printed Circuit Board) and a plurality of storage particles symmetrically arranged on two side surfaces of the PCB; the storage particles on one side surface of the PCB form a Rank; the storage particles on the other side surface of the PCB form a Rank; the storage particles comprise a plurality of PINs; a plurality of routes are arranged in the PCB; one of the routes is connected with the two PINs located in the same positions of two sides of the PCB; and the apparatus further comprises a conversion module used for obtaining a system bus signal sent by a system bus and converting the system bus signal into a Rank selection signal and storage particle bus signals, a Rank judger used for determining the selected Rank according to the Rank selection signal, and a switching array used for outputting the storage particle bus signals corresponding to the PINs of the storage particles in the selected Rank to the routes according to corresponding relationships between the PINs of the storage particles in the selected Rank and the routes.

Owner:HUAWEI TECH CO LTD

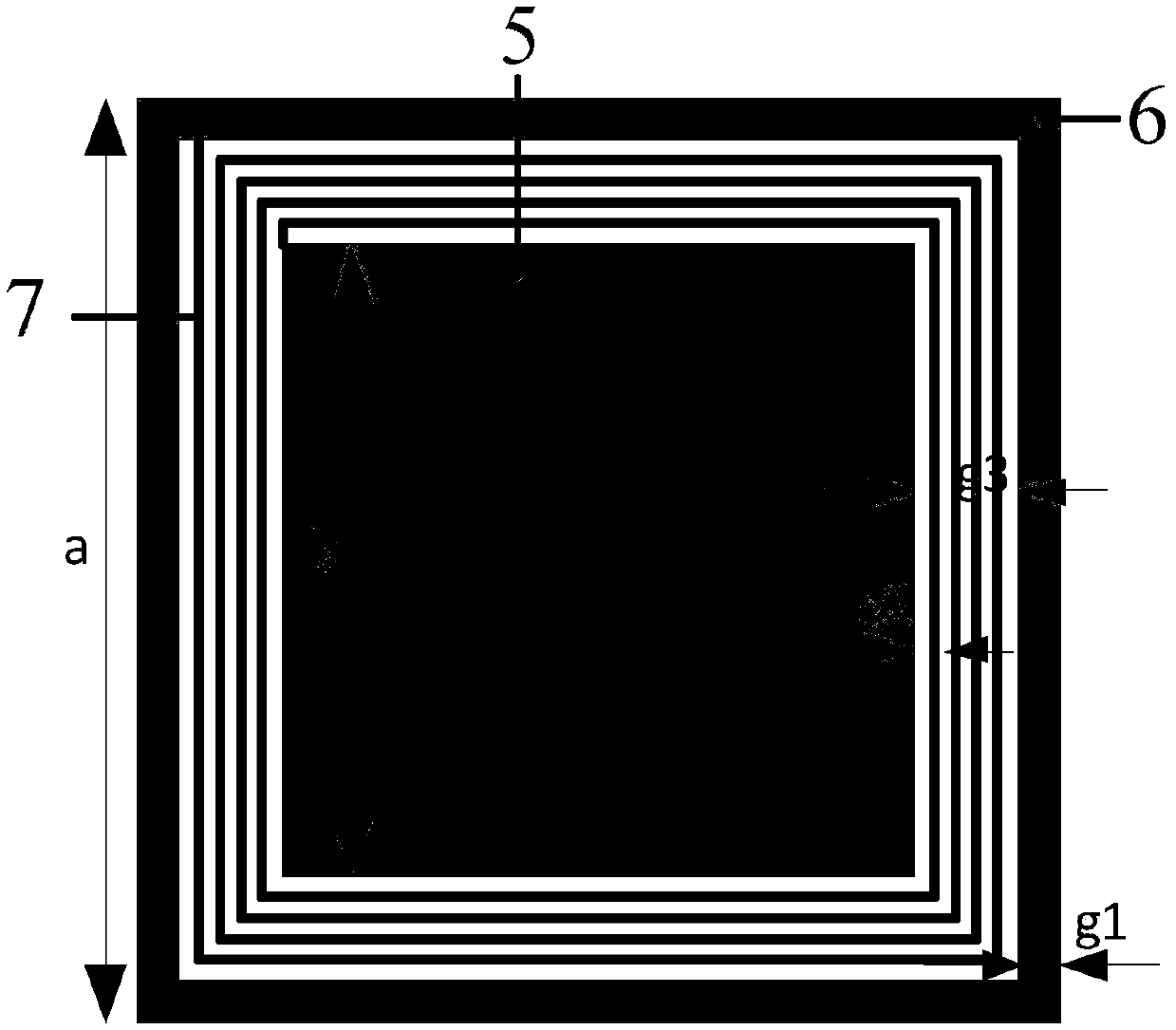

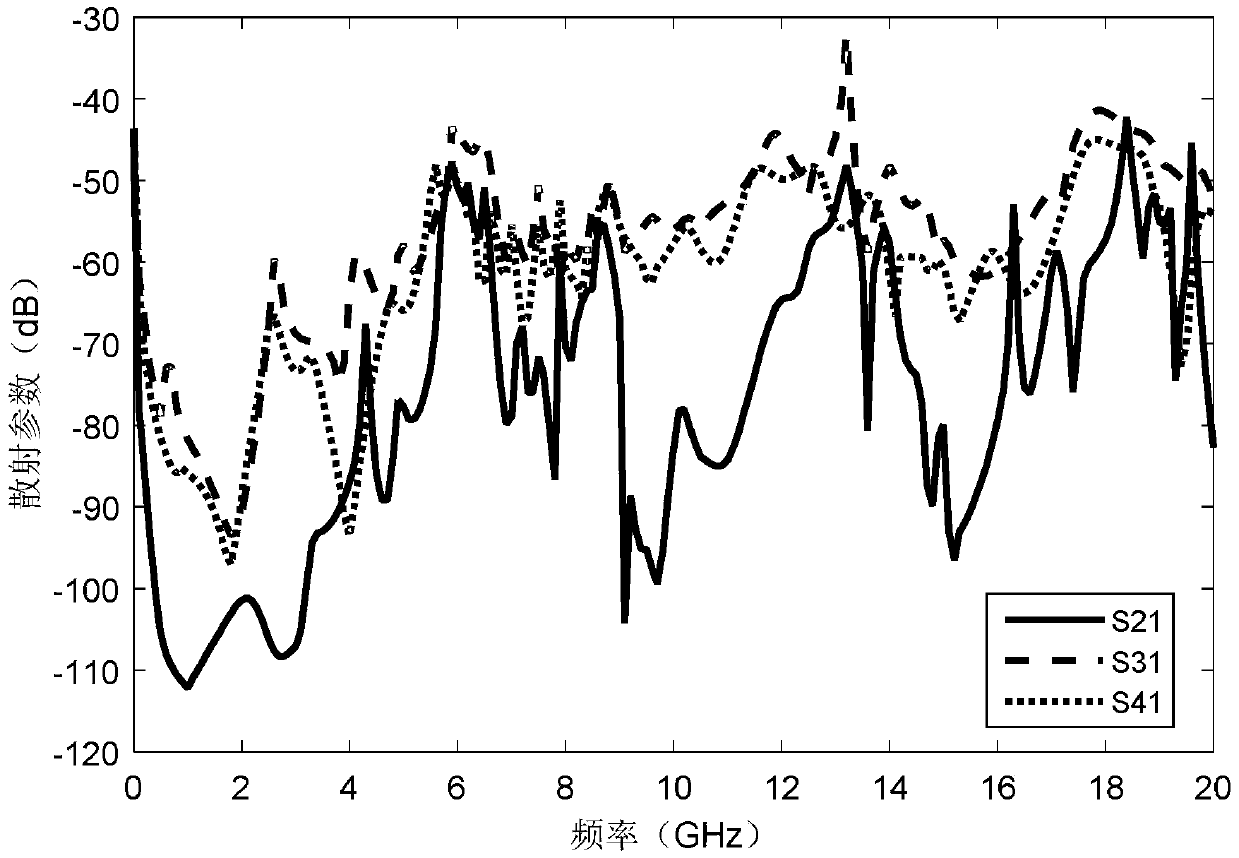

Spiral resonant ring ultra-wideband simultaneous switching noise suppression power distribution network

InactiveCN105515564AImprove practicalitySimple structureVoltage/current interference eliminationUltra-widebandRealizability

The invention discloses a spiral resonant ring ultra-wideband simultaneous switching noise suppression power distribution network, and aims to provide a power distribution network having the advantages of simple structure, high engineering realizability, no need of slotting a power supply plane, no need of any periodical electromagnetic band gap structure and large simultaneous switching noise suppression depth. The technical scheme for realizing the power distribution network is characterized in that a printed circuit board (PCB) structure is adopted for the power distribution network; local isolating structures are positioned in areas where a noise source input circuit and a noise sensitive circuit on a power supply plane structure are positioned respectively, and etched with spiral resonant rings; the spiral resonant rings are etched on the power supply plane according to a power supply plane distribution structure in order to isolate simultaneous switching noise between a power supply and a ground plane; and an attenuation band is formed in a band frequency band through the resonant effects of the spiral resonant rings in conjunction with coupling resonance among the power supply plane, a ground plane metal layer and a dielectric layer, so that a transmission path of the simultaneous switching noise is blocked; surface waves are suppressed; and the simultaneous switching noise is suppressed.

Owner:10TH RES INST OF CETC

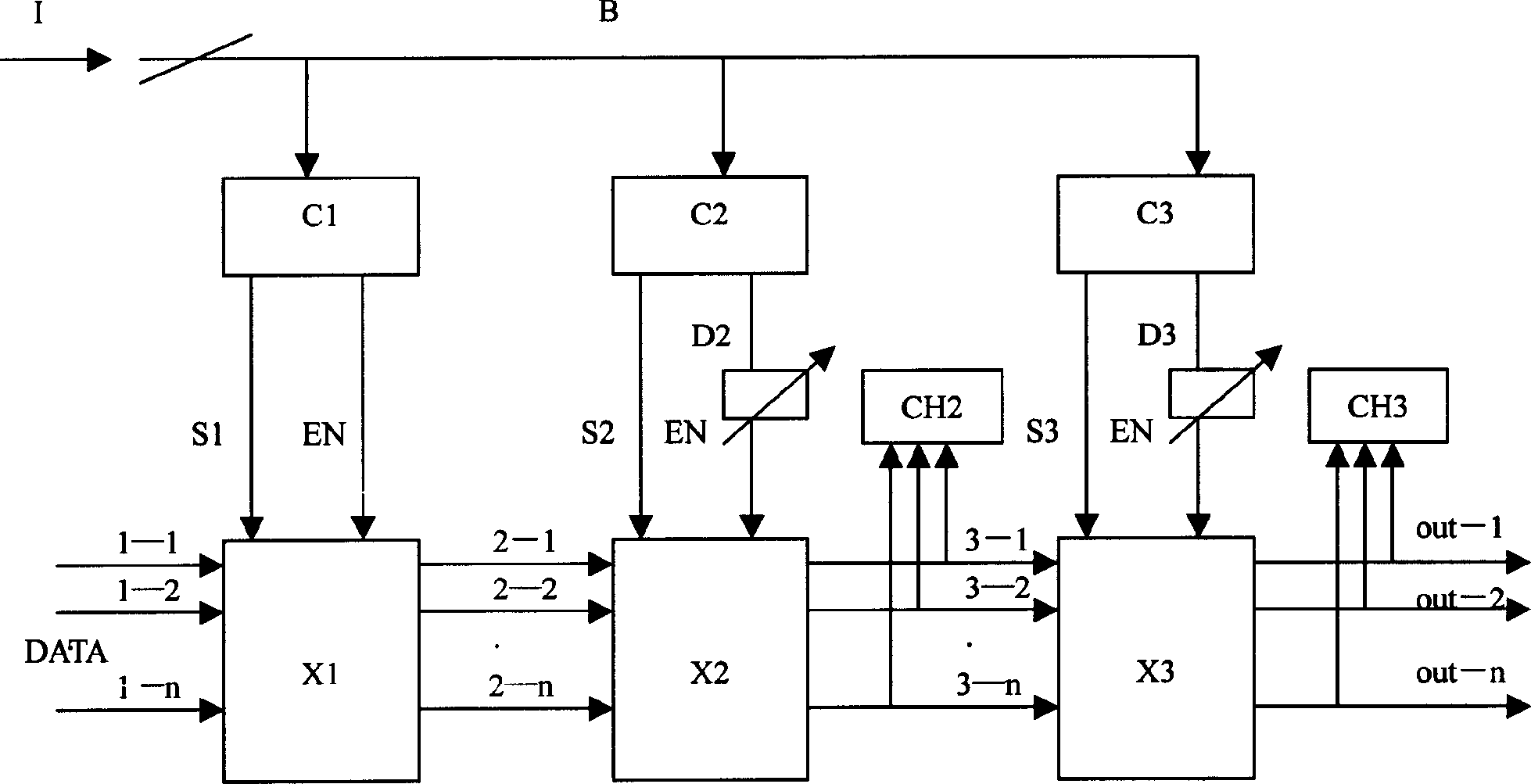

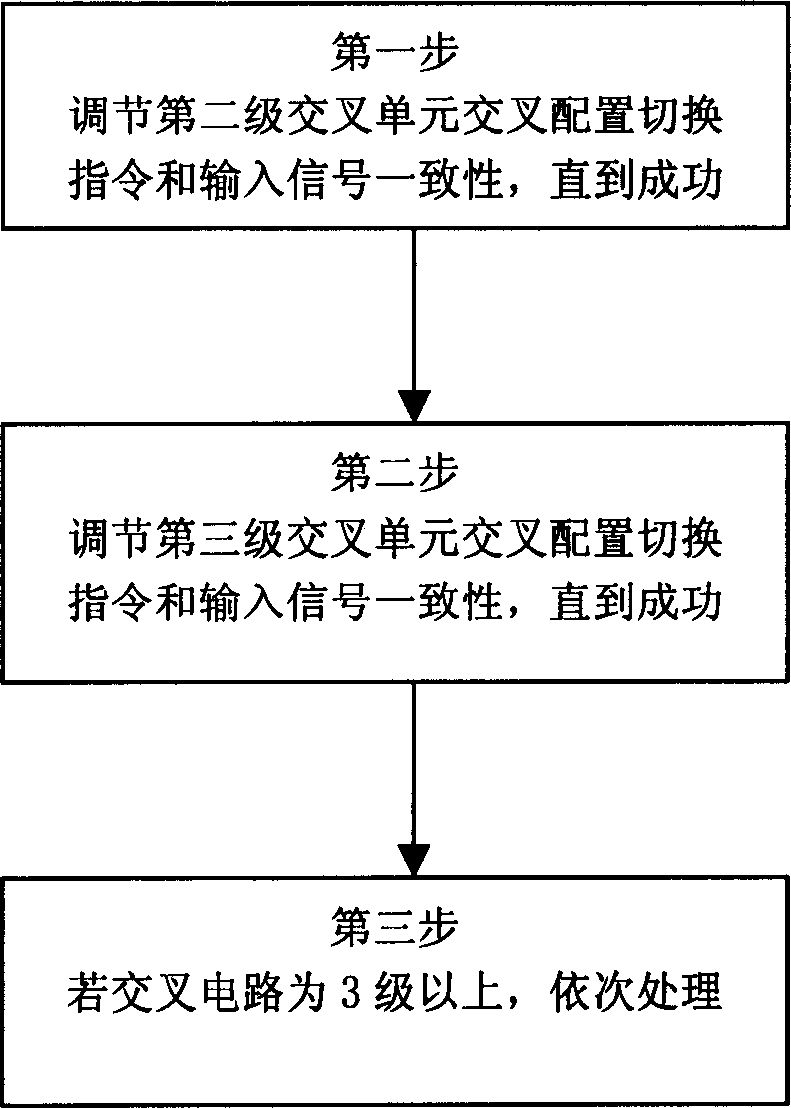

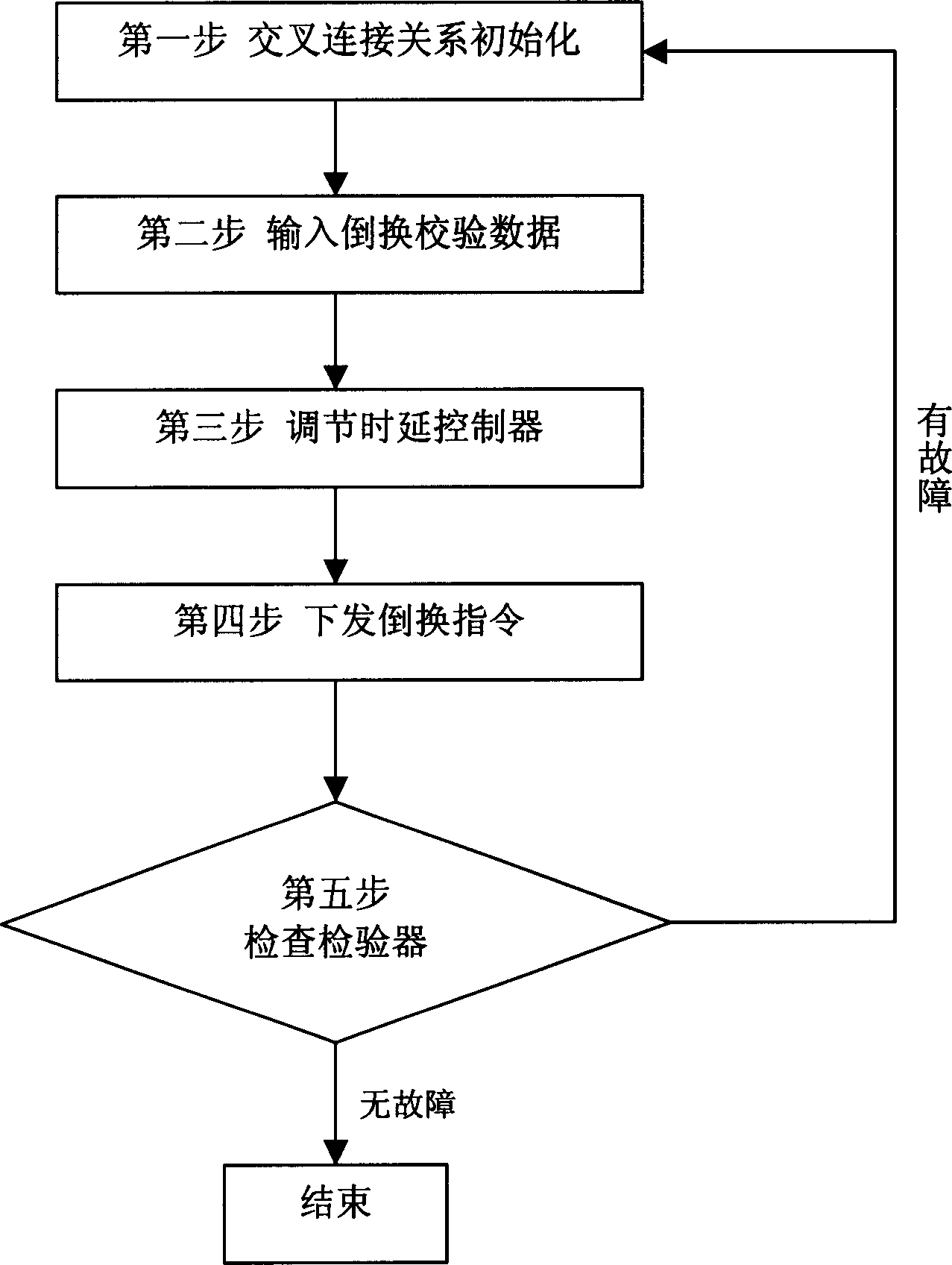

Multi-stage cross cascade circuit and coordination controlling method

InactiveCN1862812AGuaranteed Signal IntegrityNot lostSolid-state devicesSemiconductor/solid-state device manufacturingCross connectionTime delays

This invention relates to multi grades crossing series circuit and its synergetic control method. The circuit includes multi grade crossing units and its corresponding control device. Each grade checker is set on the connecting line between the second and third crossing units, and adjustable time delay control device is set between each grade crossing unit and the corresponding control device. Exchanging connecting of the multiplex transmission signal is realized through each grade crossing unit. Control is done by each control device and the corresponding grades enable and crossing connecting configuration relation signal line that connected to each crossing unit, and the adjustable time delay controller. The time of each adjustable delay controller delay enable signal to the corresponding crossing unit is accurately adjusted by the check result to the crossing configuration switching. The signal integrity before and after the crossing chip action is ensured by using the device and method in this invention, so error code will not occur.

Owner:GLOBAL INNOVATION AGGREGATORS LLC

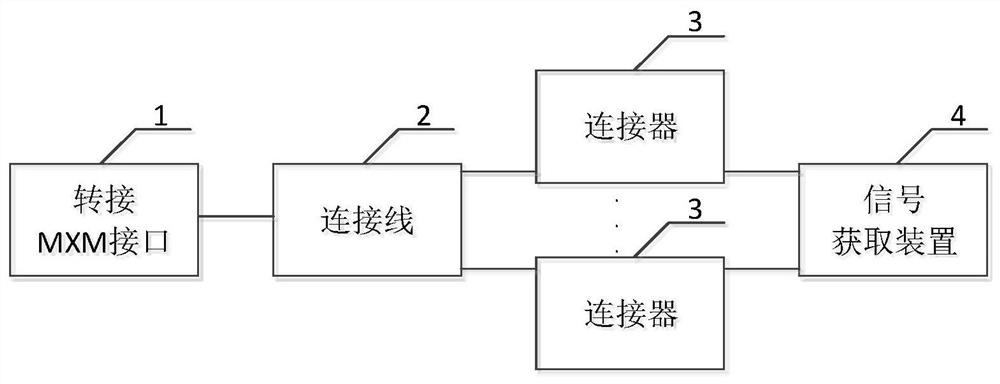

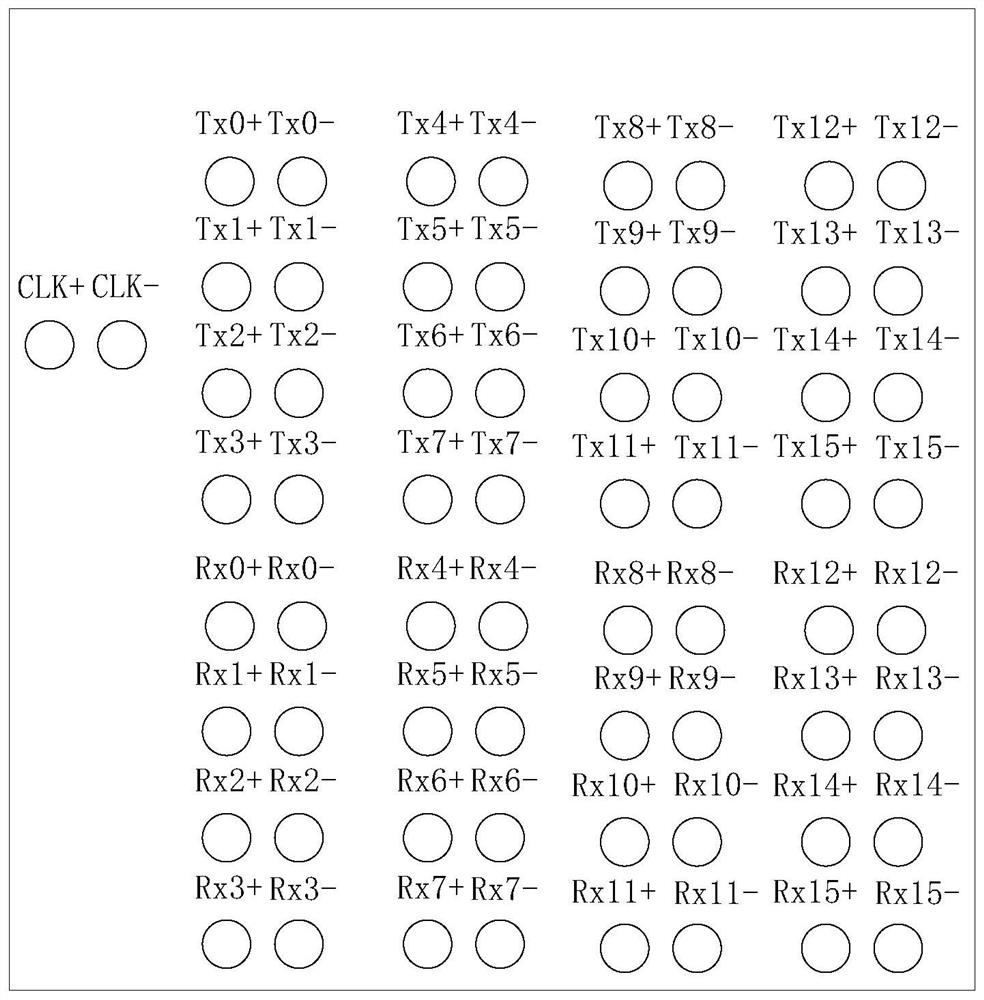

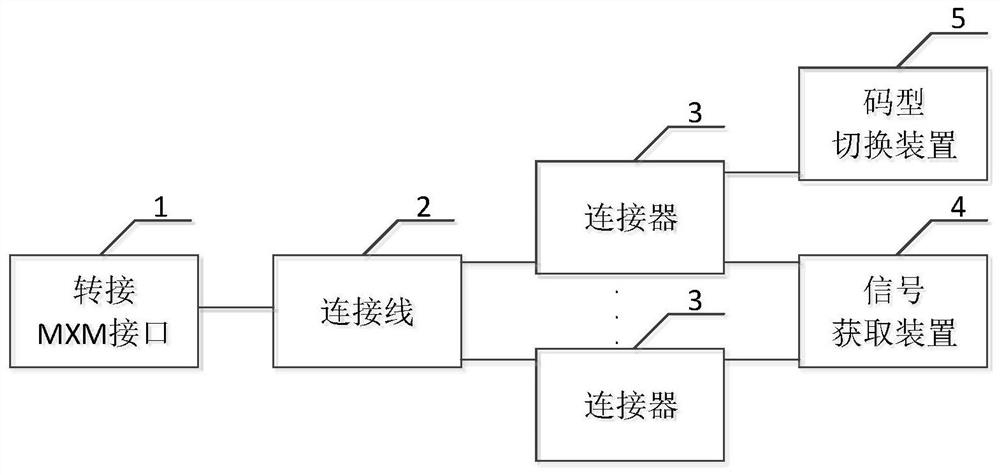

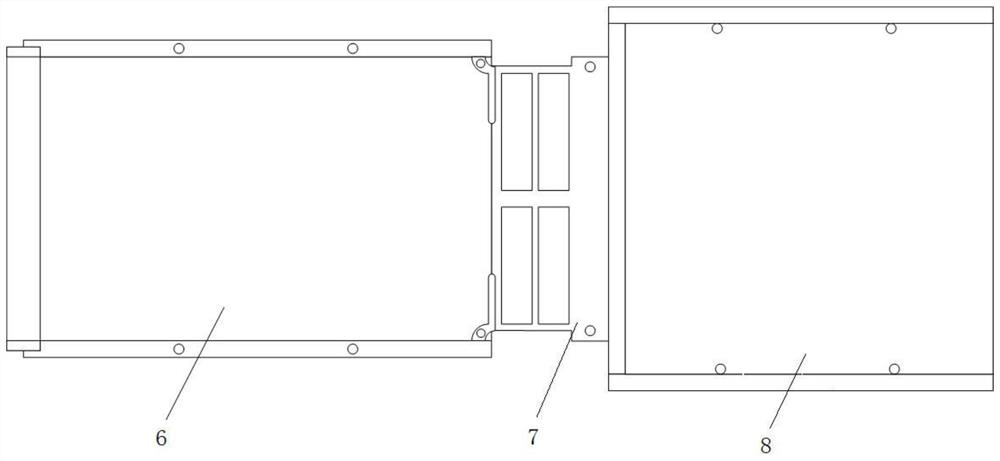

Signal testing system

PendingCN112162187AGuaranteed Signal IntegrityGuarantee normal usePrinted circuit testingMeasurement instrument housingSignal integritySignal quality

The invention discloses a signal testing system. According to the system, all signals in a to-be-tested MXM interface can be smoothly connected to a connector in a one-to-one correspondence manner through a switching MXM interface and a connecting line, and a signal obtaining device can obtain a to-be-tested PCIe signal outputted by the to-be-tested MXM interface through the connector through theconnection with the connector, so that the signal quality of the PCIe signal to be tested can be tested, the signal quality problem of the PCIe signal can be discovered in time, the signal integrity of a PCIe link of a system to be tested is ensured, and the normal use of a graphics processor is ensured.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

Multi-chip package structure

InactiveCN104078436AReduce the number of stacked layersGuaranteed Signal IntegritySemiconductor/solid-state device detailsSolid-state devicesDram chipElectrical and Electronics engineering

The invention provides a multi-chip package structure which comprises a substrate, at least two DRAM chips, a first bonding wire, a second chip, a second bonding wire and a package body. The substrate is provided with a first surface, a second surface, a plurality of wires and at least two windows, wherein the first surface and the second surface are opposite, the wires are arranged on the first surface and the second surface, and the windows penetrate through the first surface and the second surface. The at least two DRAM chips are arranged on the first surface of the substrate and cover one ends of the windows respectively. The first bonding wire penetrates through the windows and is electrically connected with the DRMA chips and the wires on the second surface of the substrate. The second chip is stacked on the DRMA chips, the second bonding wire is electrically connected to the second chip and the wires on the first surface of the substrate, and the package body is packaged on the periphery of the DRAM chips and the second chip and the periphery of the windows of the substrate and covers the first bonding wire and the second bonding wire.

Owner:GERAD TECH SUZHOU

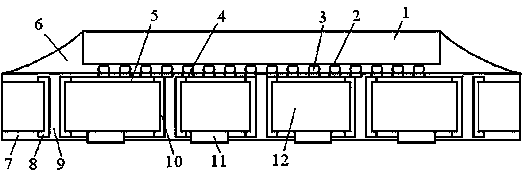

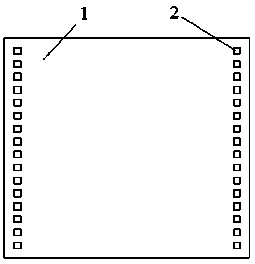

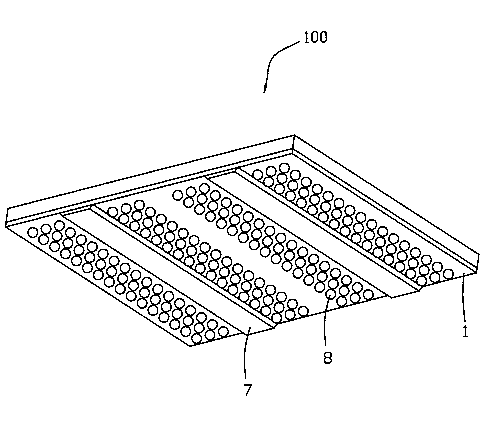

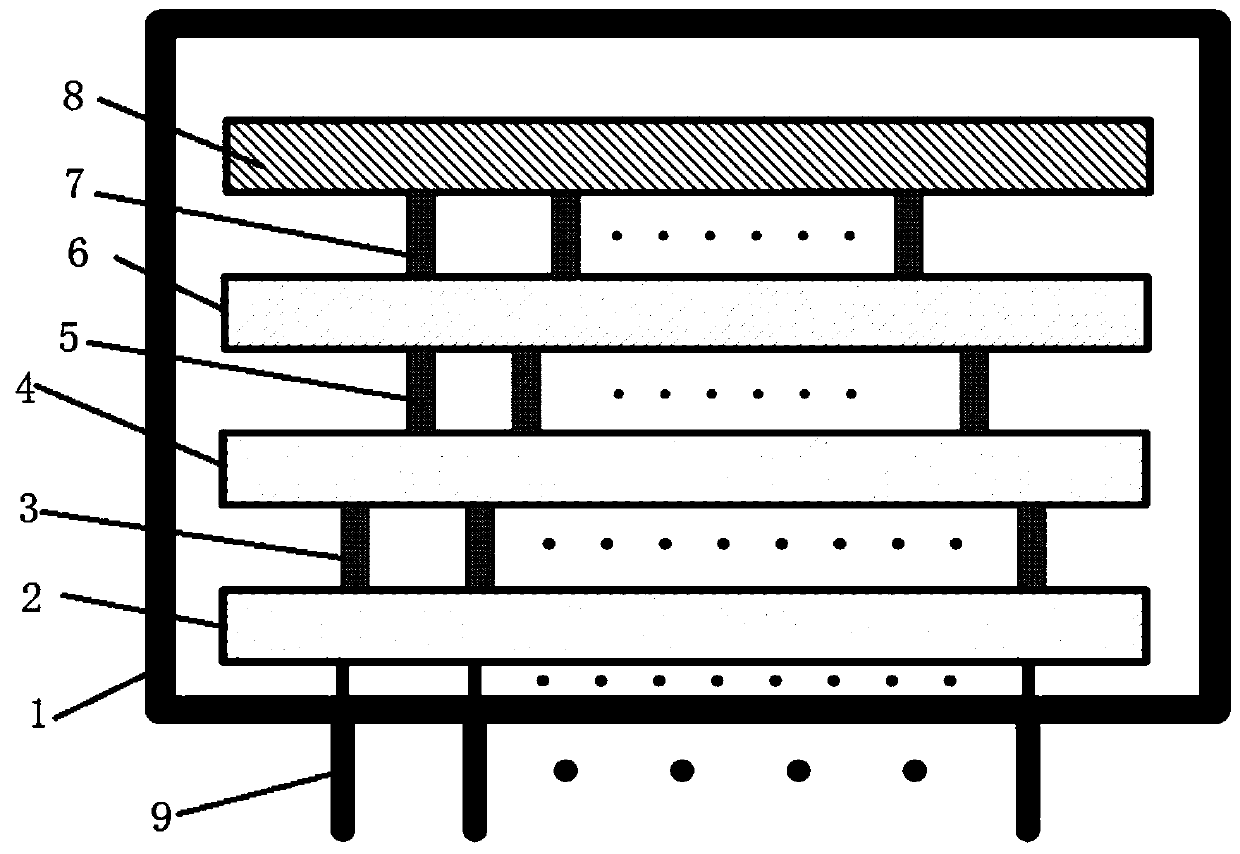

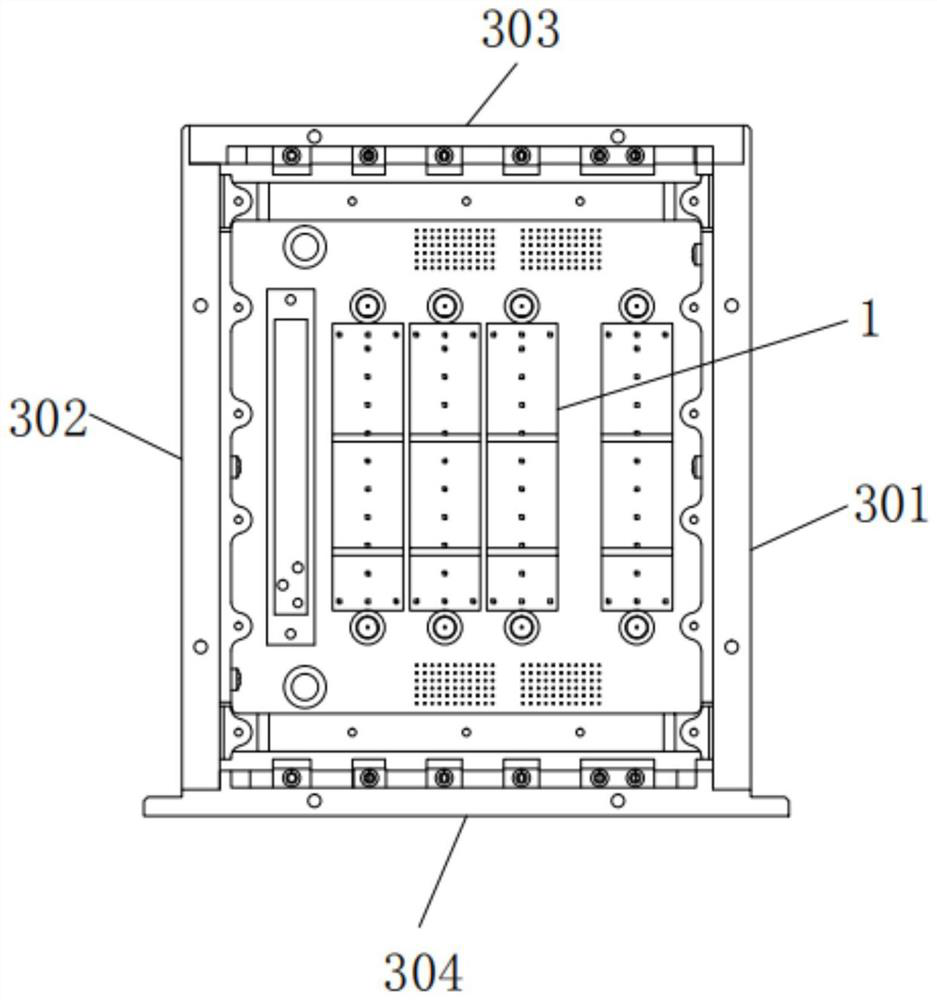

Multi-level fused three-dimensional system integrated structure

ActiveCN110544673AReduce interconnect sizeIntegrity guaranteedSemiconductor/solid-state device detailsSolid-state devicesEngineeringSilicon

The invention relates to a multi-level fusion three-dimensional system integrated structure, and the structure comprises a tube shell, wherein a plurality of pins are arranged on the bottom surface ofthe tube shell, n substrate modules which are sequentially stacked are arranged in the tube shell, convex points are arranged between the n substrate modules, and every two adjacent substrate modulesare separated through the corresponding convex point. A silicon adapter plate module is further arranged above the n substrate modules, and convex points are also arranged between the substrate modules and the silicon adapter plate module, and the substrate modules and the silicon adapter plate module are separated through the convex points. Compared with an existing single-layer TSV technology-based structure, the integrated structure of the multi-layer fused three-dimensional system has the advantages that excessive dependence on the process of the existing single-layer TSV technology-basedstructure is avoided, the three-dimensional integrated process method is simplified, the product yield is improved, and the cost is saved.

Owner:XIDIAN UNIV

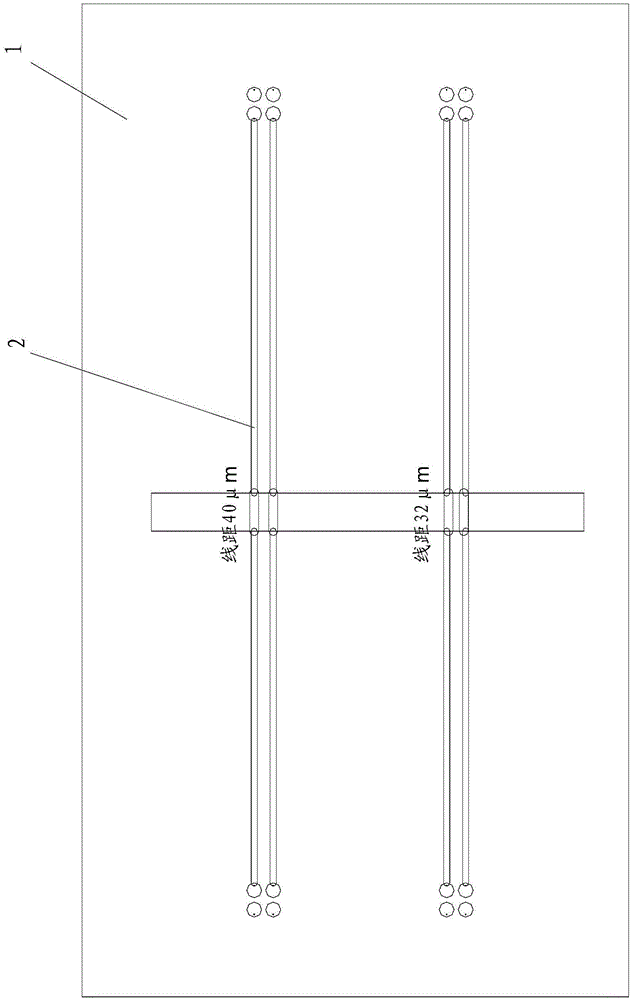

Method for reducing impedance mismatching degree under condition of discontinuous returning path

InactiveCN104797078AGuaranteed impedance continuityGuaranteed Signal IntegrityPrinted circuit detailsPrinted circuit aspectsLine widthMicrometer

The invention provides a method for reducing an impedance mismatching degree under the condition of a discontinuous returning path. A grooving line is arranged on a reference plane of a bottom layer; a top layer is a signal layer with transmission lines; distances among the transmission lines on a portion above the grooving line are smaller than distances among the transmission lines of the rest portion; distances among differential signal lines of which the widths are 40 micrometers and the distances are 40 micrometers on a portion above the grooving line are changed into 32 micrometers from 40 micrometers; and specific numerical values of the distances among the transmission lines on the portion above the grooving line are handled through simulating software so as to obtain data in which impedance performance is improved optimally. The distances among the transmission lines on the portion above the grooving line, namely the transmission lines with discontinuous impedance, are reduced, so that differential mode impedance of the portion can be reduced and is close to differential mode impedance of lines at a position without the grooving line as much as possible. Specific reduced numerical values of the specific distances among the transmission lines need to be determined through simulation. Suitable parameters are selected through simulation so as to guarantee impedance continuity of the transmission lines, and signal integrity is guaranteed.

Owner:FUZHOU ROCKCHIP SEMICON

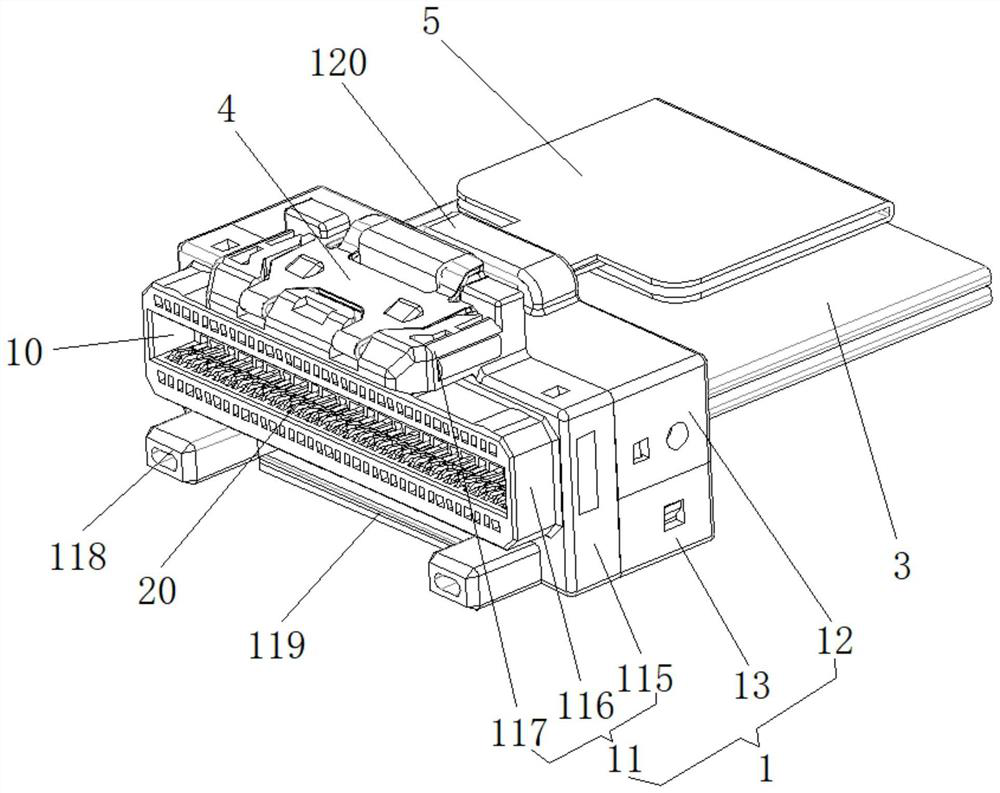

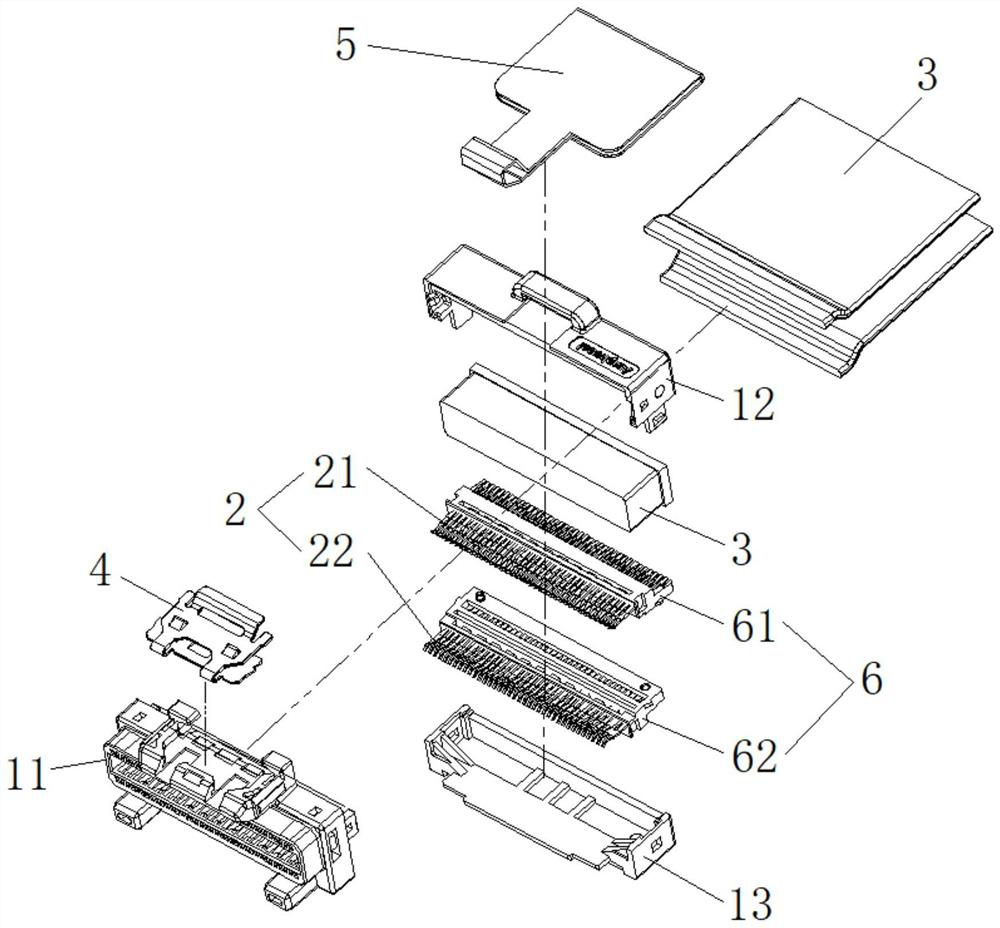

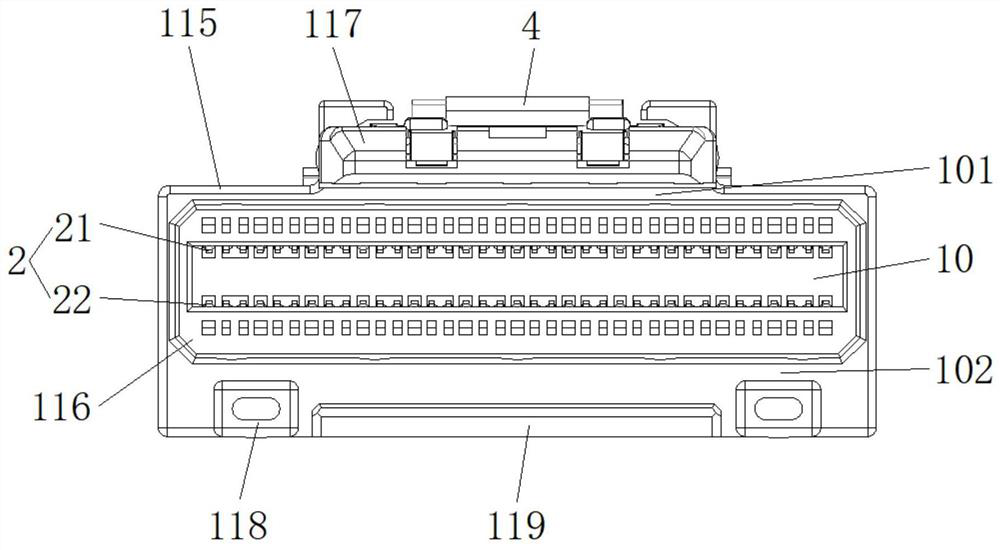

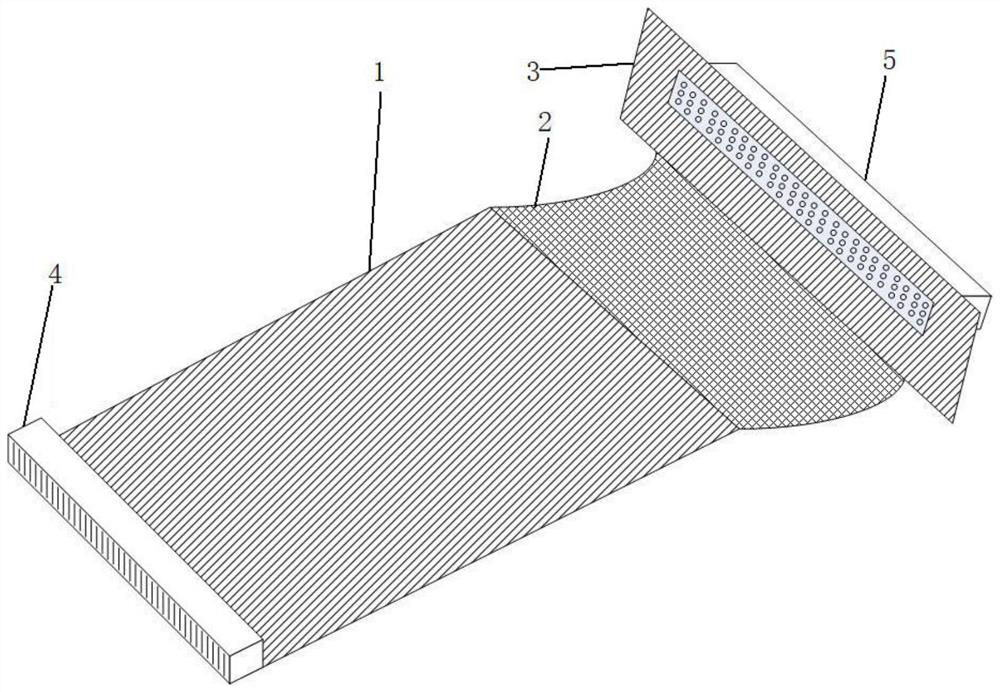

Cable connector and connector assembly

PendingCN114142286ASave spaceAvoid signal interferenceCoupling device detailsFixed connectionsElectrical connectionStructural engineering

The invention discloses a cable connector. The cable connector comprises a shell, a conductive terminal set arranged in the shell and a cable electrically connected with the conductive terminal set. The front end of the shell is provided with a plug-in groove, the conductive terminal group comprises a first terminal strip and a second terminal strip which are symmetrically arranged on the upper side and the lower side of the plug-in groove, and the first terminal strip and the second terminal strip are both composed of a plurality of conductive terminals. Each conductive terminal comprises a main body part, a contact part formed by bending from the front end of the main body part, and a welding part formed by extending backwards from the rear end of the main body part; and the welding part of the first terminal row and the welding part of the second terminal row are arranged in parallel. And the distance between the welding part of the first terminal strip and the welding part of the second terminal strip is 1-2.5 times of the minimum distance between the contact part of the first terminal strip and the contact part of the second terminal strip. The cable connector provided by the invention can avoid signal interference between the terminal strips to the greatest extent while meeting the requirement of low size, thereby ensuring the signal integrity of a product.

Owner:AMPHENOL ELECTRONICS ASSEMBLY XIAMEN CO LTD

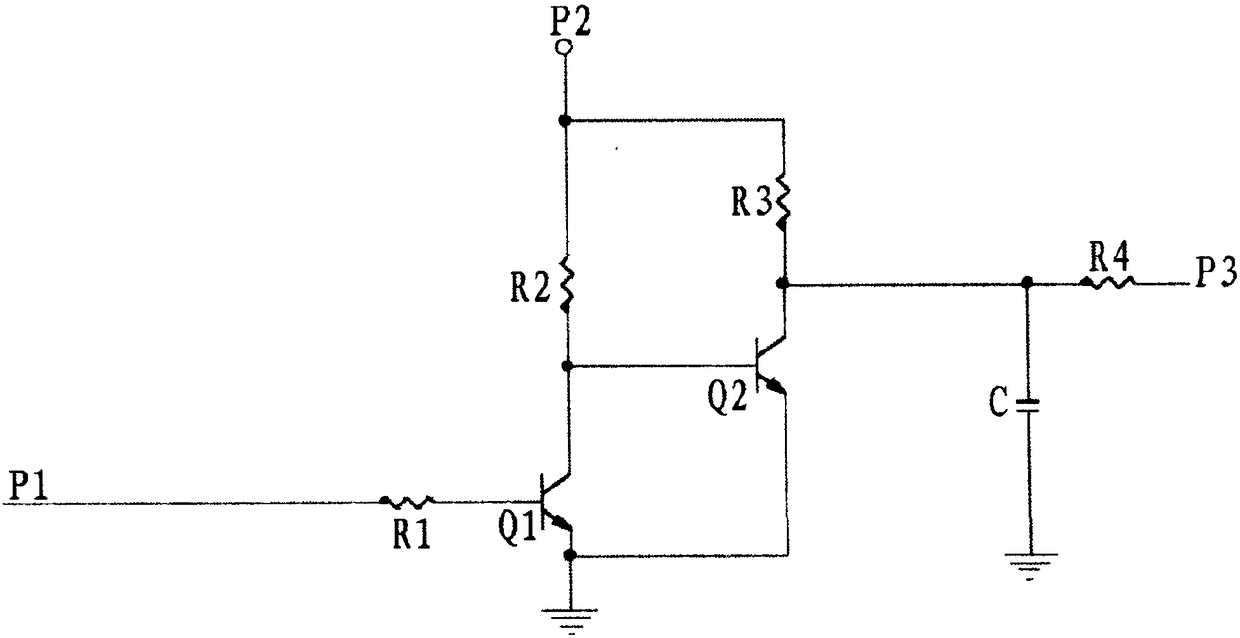

Embedded fault injection module and method and high-speed digital circuit system

ActiveCN111722095AAchieve interventionImplement fault injectionWave based measurement systemsDigital circuit testingHemt circuitsControl circuit

The invention belongs to the technical field of digital circuit testability verification, and discloses an embedded fault injection module, a high-speed digital circuit system and an embedded fault injection method. The embedded fault injection module comprises a signal path circuit which is used for ensuring that a high-speed digital circuit system has the same signal characteristics as before access after the embedded fault injection module is accessed and can intervene in a signal path during fault injection, a fault injection control circuit which is used for controlling the signal path circuit and controlling implementation of fault injection, a fault mode sub-module circuit that is used for storing a fault injection sequence according to a fault mode library of the high-speed digitalcircuit module and generating fault injection data of a low-speed signal, and a data communication circuit which is used for receiving and analyzing the fault mode simulation instruction of an uppercomputer and transmitting information to the fault injection control circuit. Therefore, a problem of high-speed signal fault injection of the high-speed digital circuit module can be solved.

Owner:CHINA ELECTRONICS TECH GRP CORP NO 14 RES INST

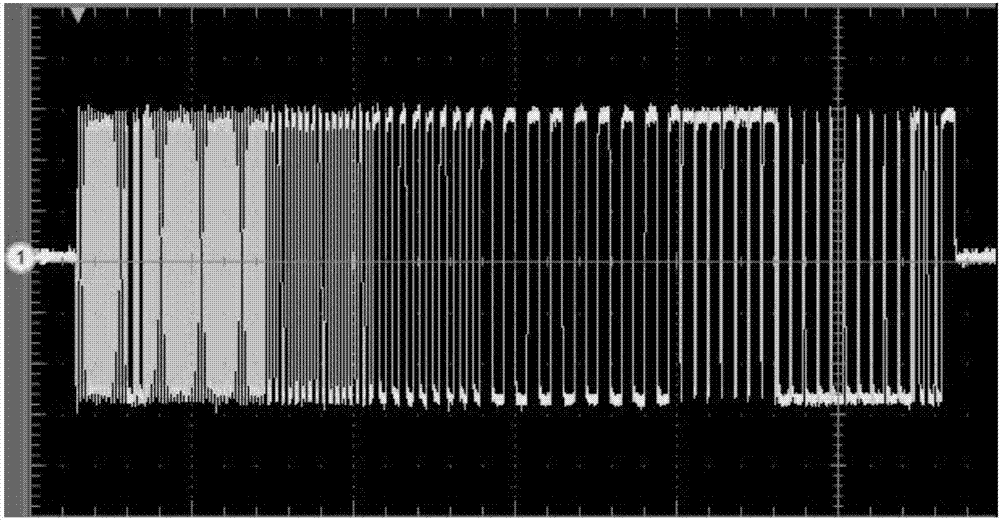

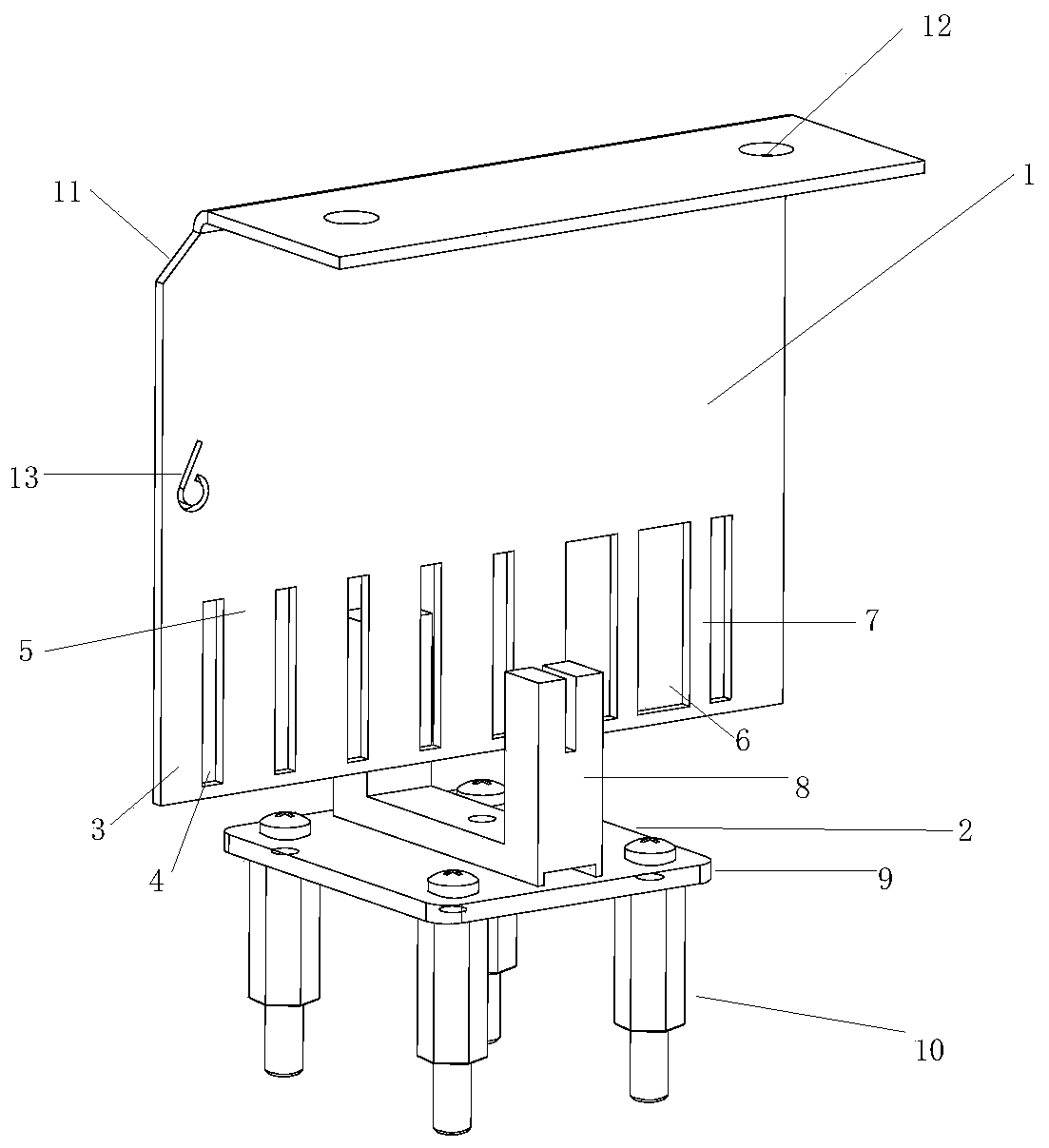

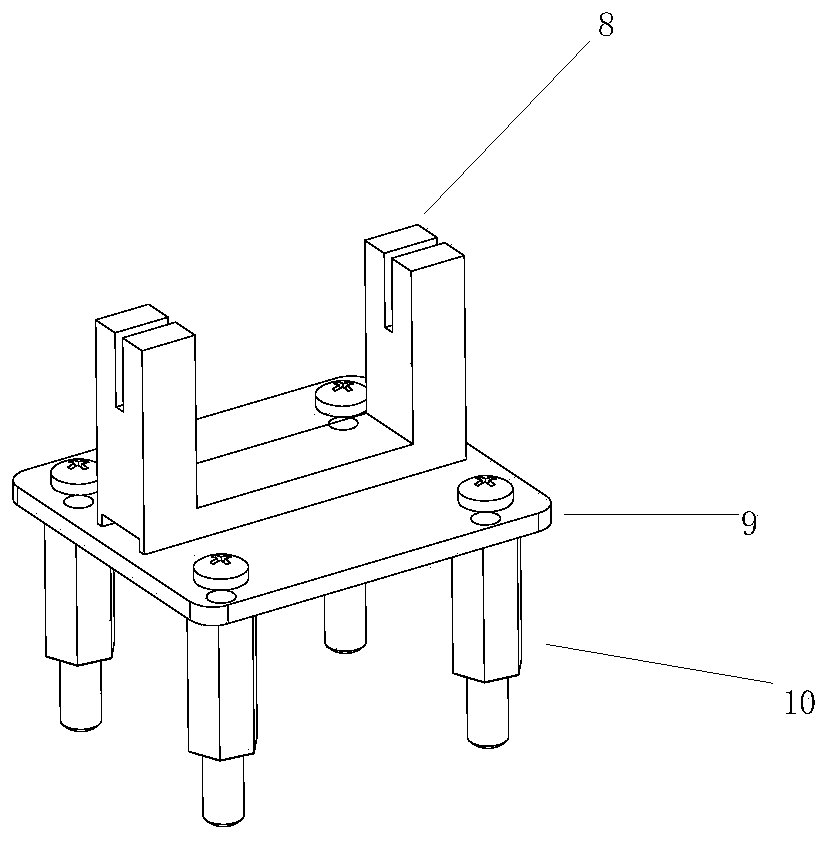

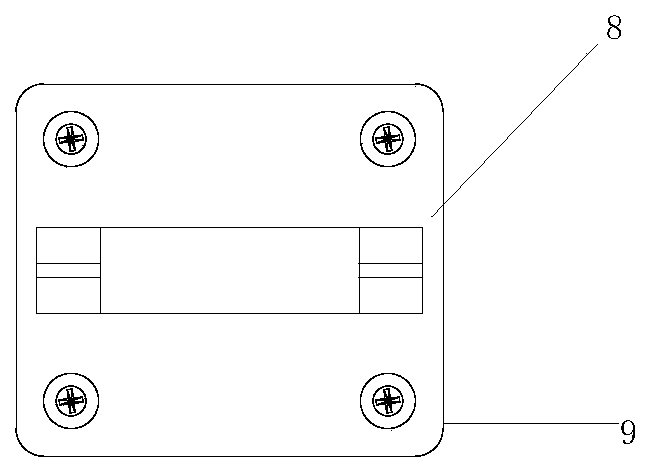

Unique identification device for object carrying trolley of logistics sorting machine and identification method thereof

PendingCN111112096AGuaranteed Signal IntegrityReduce the increase in failure rateSortingComputer visionEngineering

The invention discloses an unique identification device for an object carrying trolley of a logistics sorting machine and an identification method thereof. The device comprises an object carrying trolley unique identity ID device, an object carrying trolley unique identity ID detection device and a signal identification device; the object carrying trolley unique identity ID device is installed onthe object carrying trolley, and a plurality of long strip-shaped through holes are formed in the lower portion of the rectangular flat plate structure, the object carrying trolley unique identity IDdetection device is installed at a sorting port position of the sorting machine, the object carrying trolley unique identity ID detection device comprises an optical coupling infrared transceiving sensor, and when the object carrying trolley unique identity ID device passes from the optical coupling infrared transceiving sensor, an infrared receiver can receive infrared light signals emitted by the infrared transmitter at intervals; the signal identification device judges the unique identity ID of the object carrying trolley by identifying a plurality of time data of a plurality of different intervals of signals of the optical coupling infrared transceiving sensor, any electric device does not need to be installed on the object carrying trolley, and namely, whether the object carrying trolley needs to be sorted or not can be judged by actively identifying and detecting the unique identity of the object carrying trolley through the sorting port.

Owner:辽宁黑北健科技有限公司

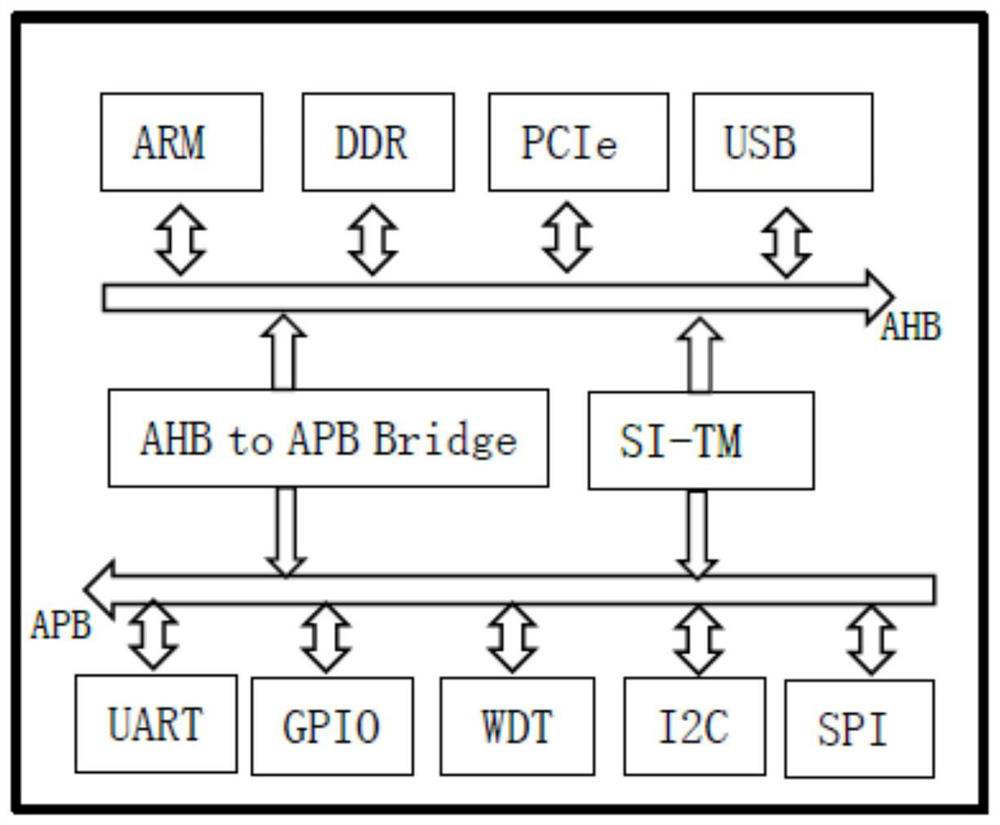

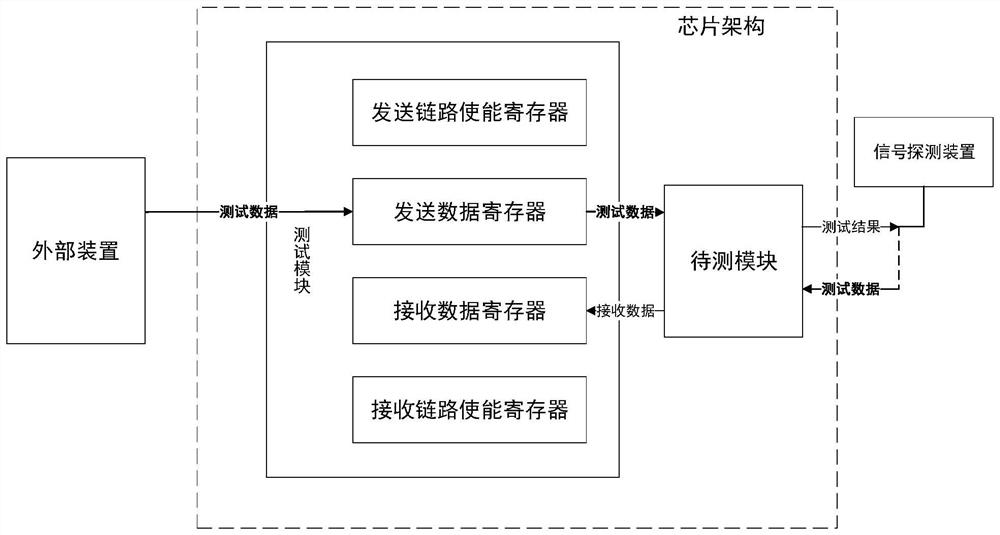

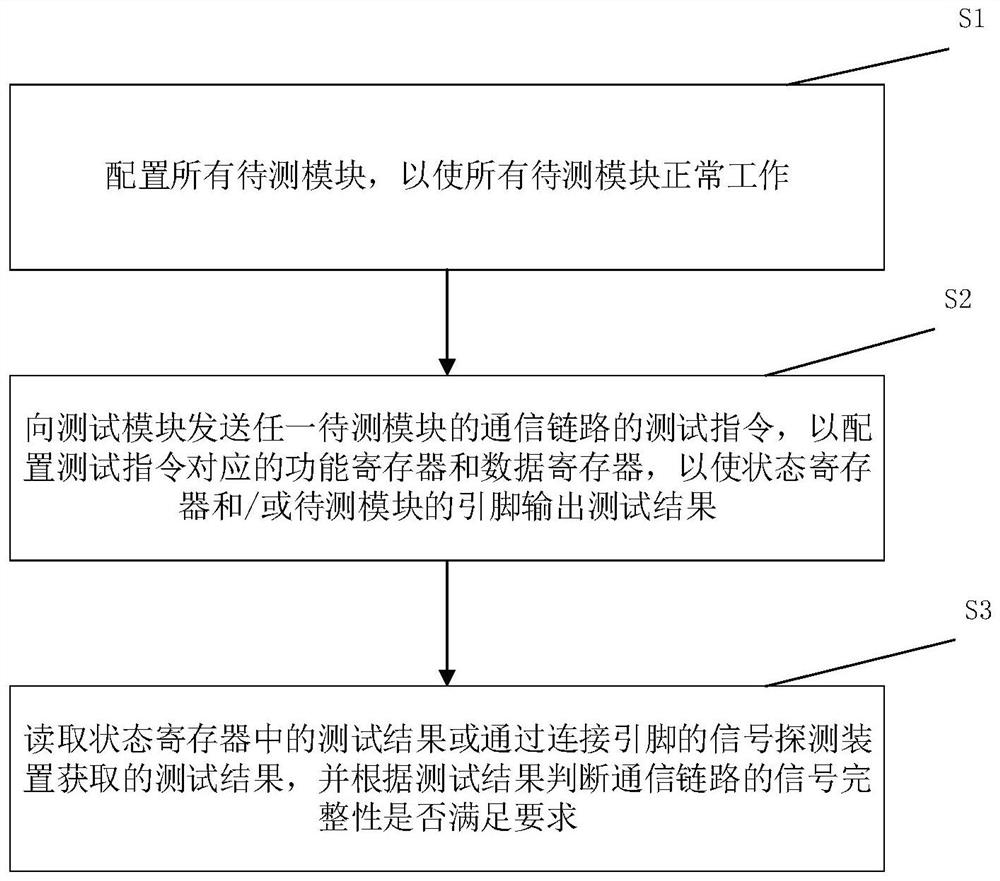

Chip architecture and signal integrity test method

PendingCN114297134AGuaranteed Signal IntegrityAccurately determineDigital circuit testingArchitecture with single central processing unitChip architectureTelecommunications link

The invention discloses a chip architecture and a signal integrity test method.The chip architecture comprises a plurality of modules to be tested and a test module, the test module comprises a function register, a data register and a state register, and when the test module receives a test instruction of a communication link of any one module to be tested, the function register is connected with the data register; and configuring the function register and the data register corresponding to the test instruction according to the test instruction, so that the state register and / or the pin of the to-be-tested module output a test result. The chip does not need to be installed on a mainboard, the signal test result of the communication link of each to-be-tested module can be obtained directly according to the test module in the chip architecture, the process is simple and rapid, the test cost is low, the test range is clear, the test effects of different to-be-tested modules can be accurately and rapidly determined, and the test efficiency is improved. And the signal integrity of the chip is ensured.

Owner:山东云海国创云计算装备产业创新中心有限公司

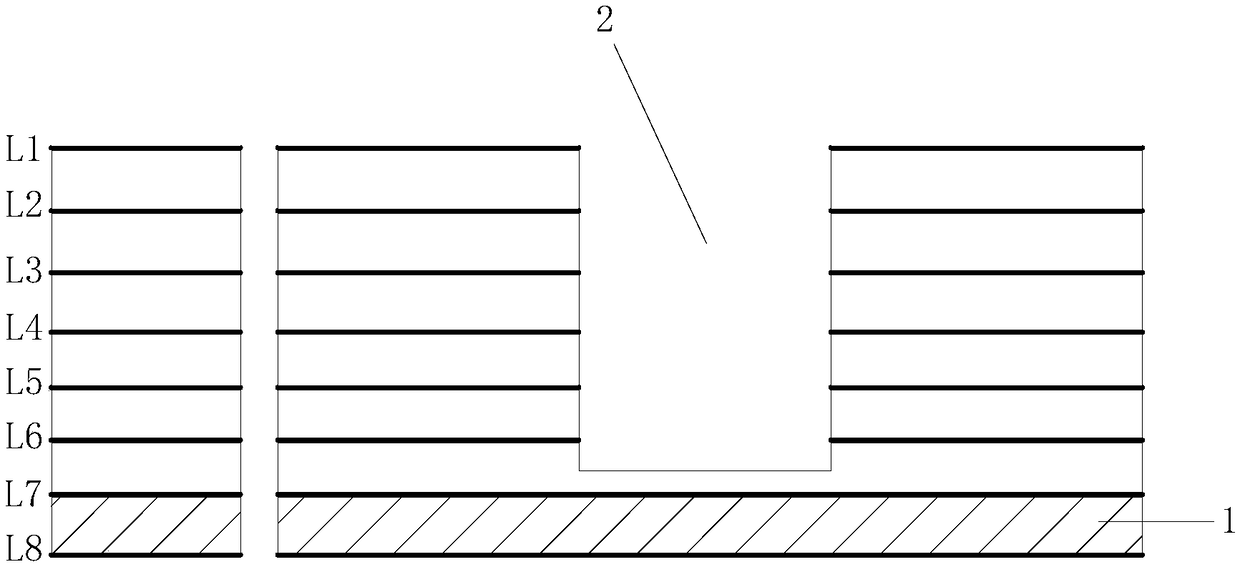

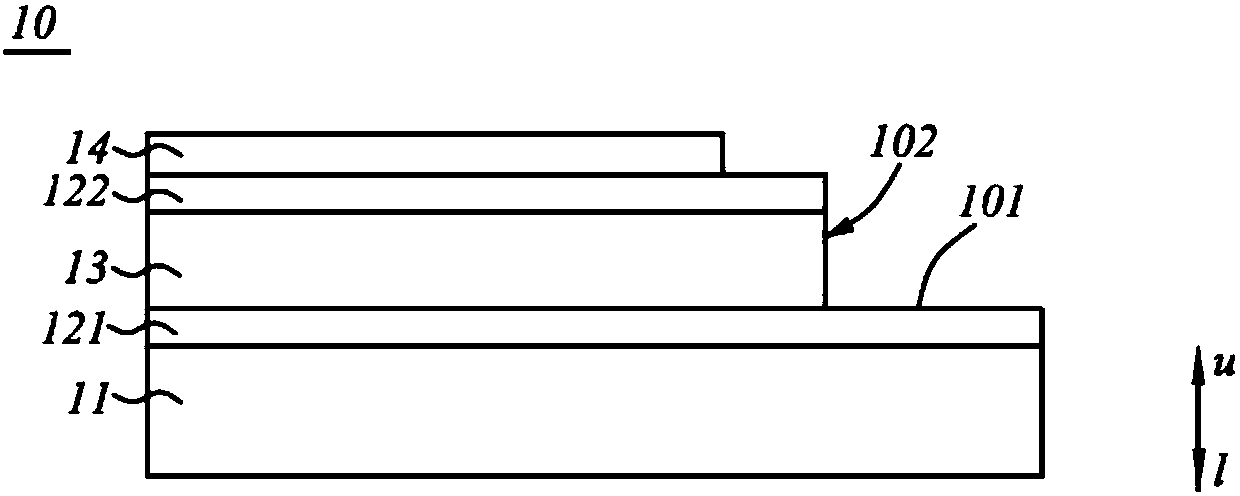

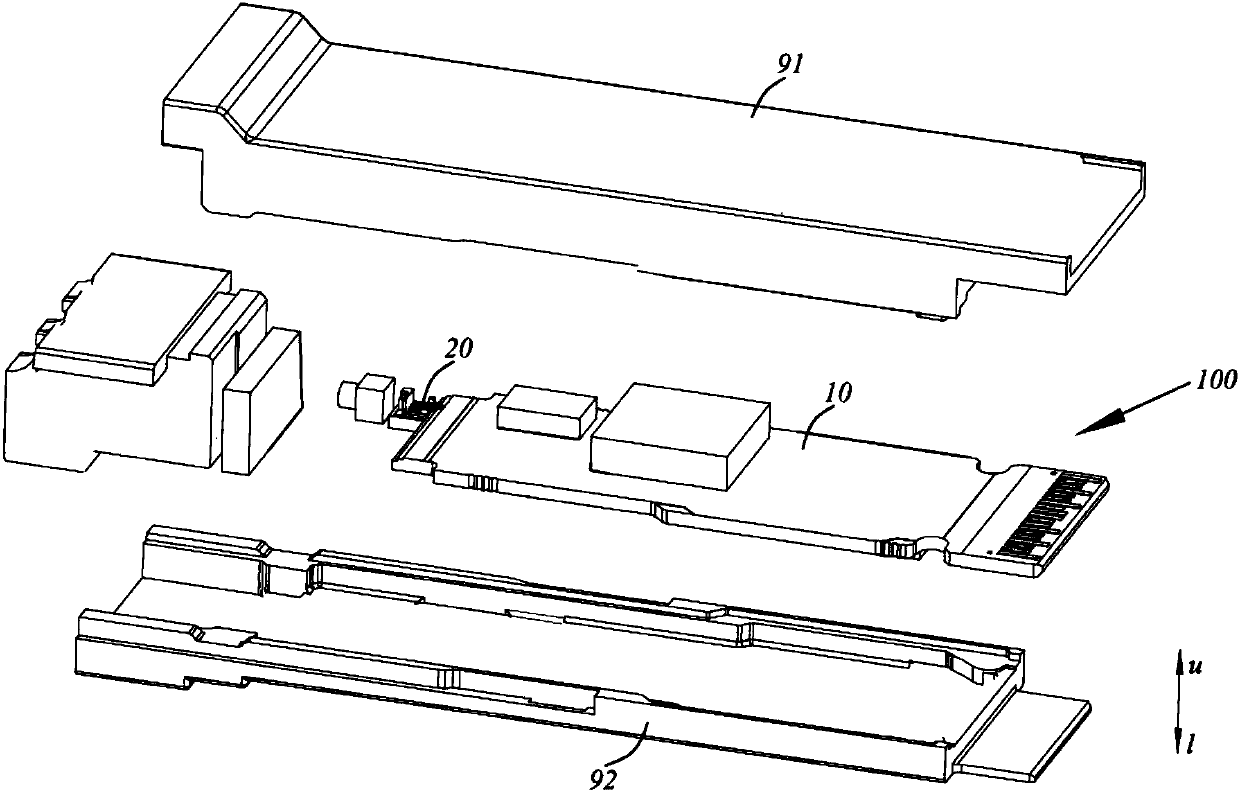

Optical module

ActiveCN109905958ASimple structureGuaranteed tightnessCoupling light guidesPrinted circuits structural associationsOptical ModuleComputer module

The invention discloses an optical module. The optical module includes a shell, and a semiconductor optical element, a first circuit board and a second circuit board arranged in the shell, the first circuit board comprises a first substrate, a first transmission metal layer and a second transmission metal layer successively formed at on the upper surface of the first substrate, and a dielectric layer formed between the first transmission metal layer and the second transmission metal layer. The first transmission metal layer is provided with a signal transmission window, the second circuit board comprises a second substrate, a third transmission metal layer formed on the lower surface of the second substrate, and a fourth transmission metal layer formed on the upper surface of the second substrate, one end of the second circuit board is electrically connected with the semiconductor optical element, the third transmission metal layer at the other end of the second circuit board is arranged on the signal transmission window and electrically connected with the first transmission metal layer through the signal transmission window, and the fourth transmission metal layer and the second transmission metal layer are electrically connected.

Owner:INNOLIGHT TECHNOLOGY (SUZHOU) LTD

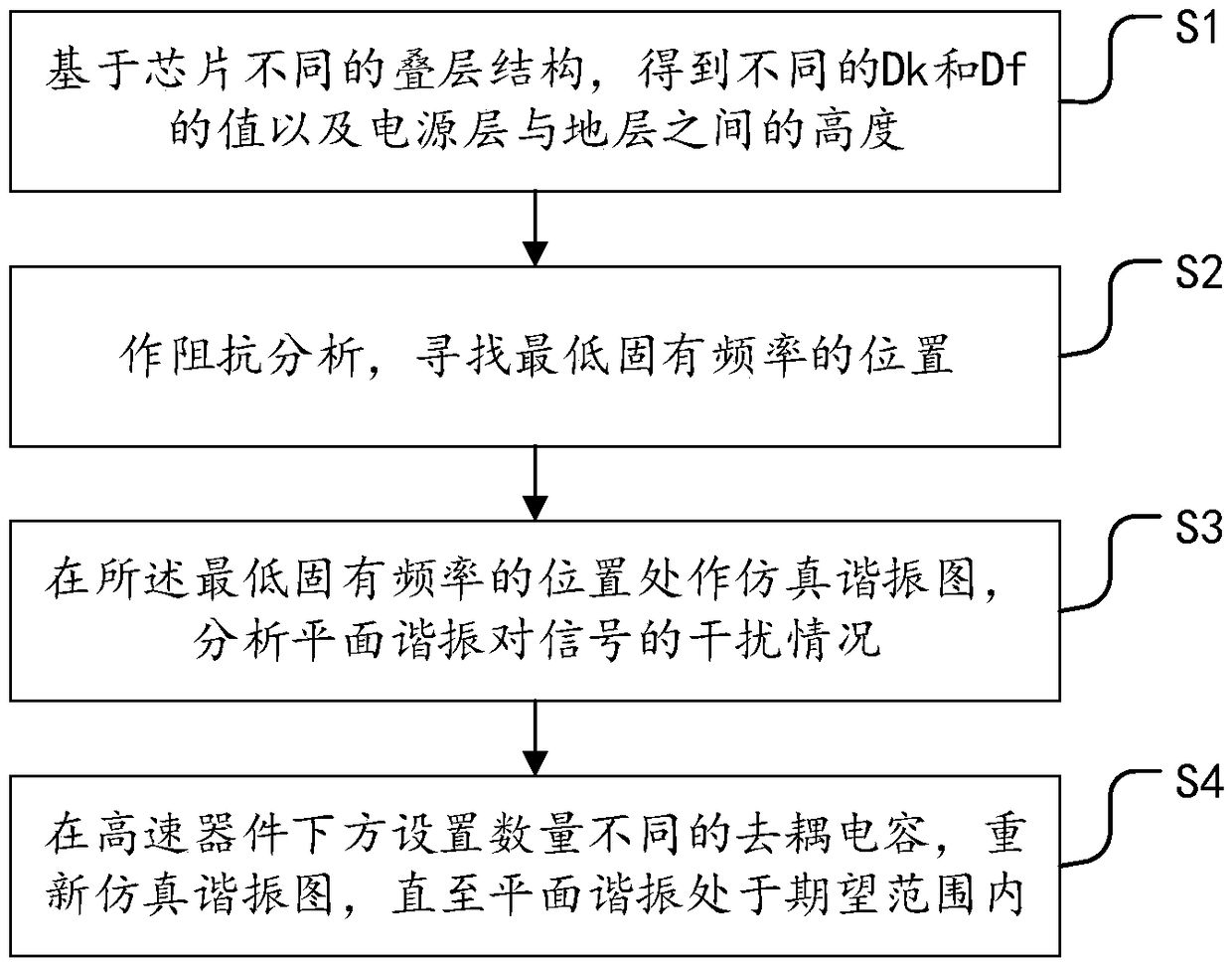

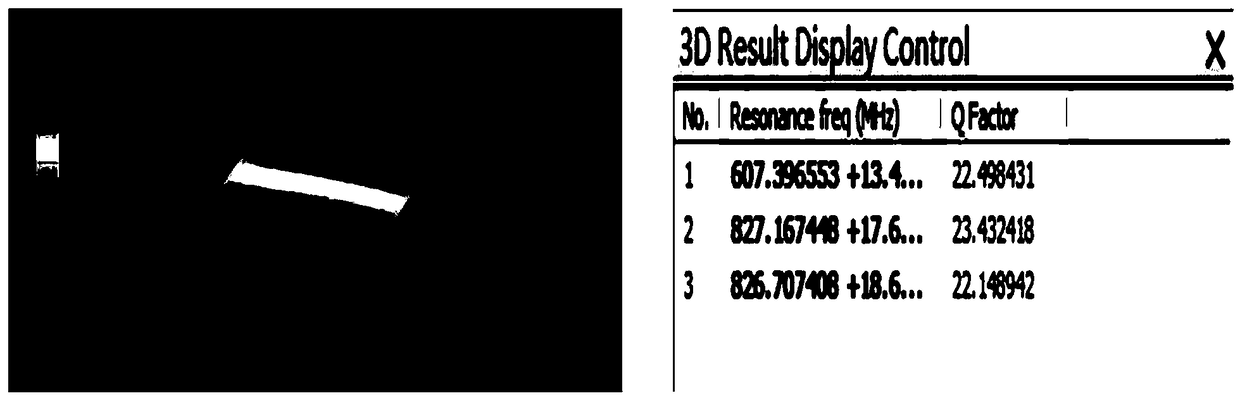

A method and system for suppressing planar resonance by placing capacitor position

ActiveCN109041408ARaise the resonanceReduce ground bounceCross-talk/noise/interference reductionCapacitanceElectromagnetic interference

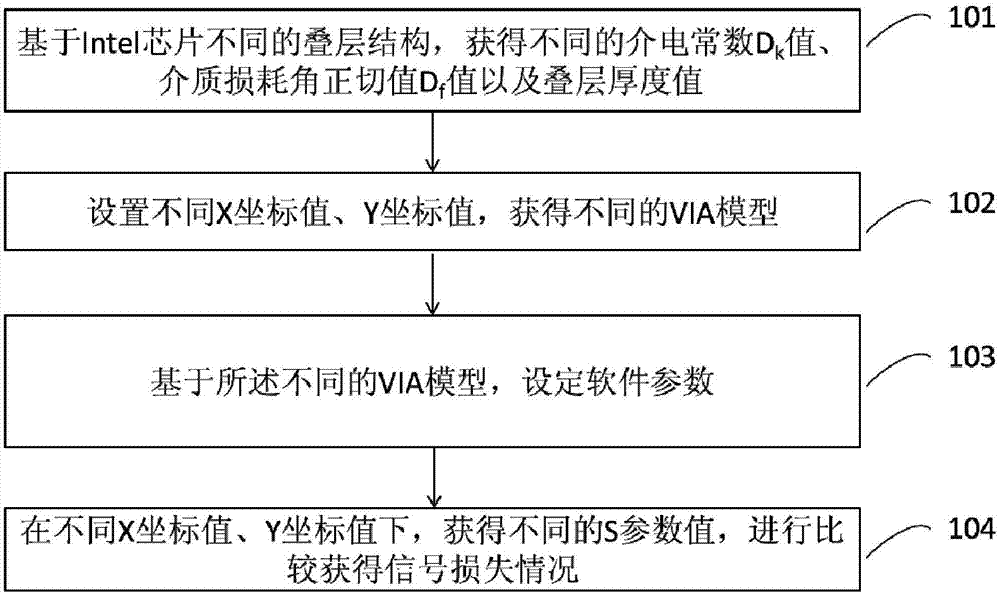

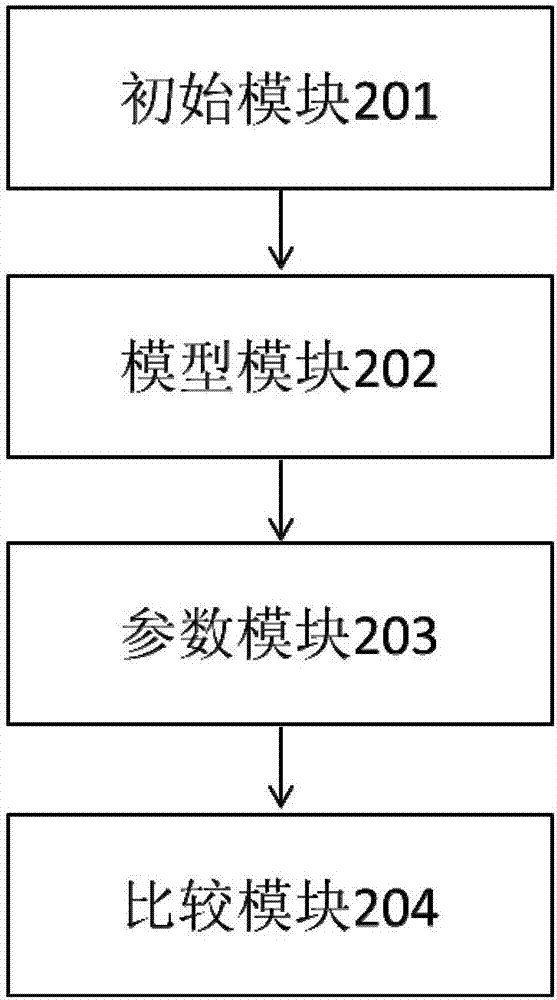

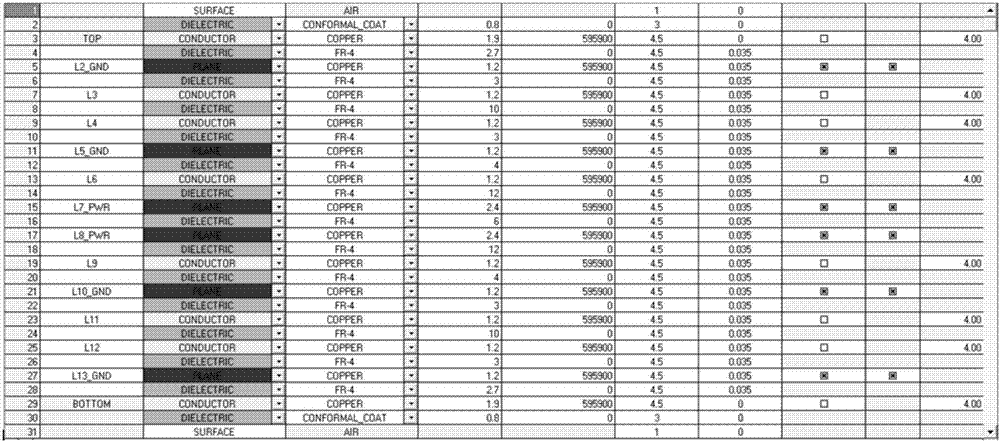

The invention provides a method and a system for suppressing plane resonance by placing a capacitor position, comprising the following steps: S1, obtaining different values of Dk and Df and a height between a power supply layer and a ground layer based on different stack structures of chips; S2, impedance analysis is performed to find the position of the lowest natural frequency; S3, simulating the resonance diagram at the position of the lowest natural frequency, and analyzing the interference of the plane resonance to the signal; S4, set a different number of decoupling capacitors beneath the high speed device and re-simulate the resonance pattern until the planar resonance is within the desired range. The purpose of improving the resonance of the frequency band is realized by changing the cavity formed between the power supply layer and the ground layer. The ground elastic effect caused by cavity resonance can be reduced, and the electromagnetic interference caused by the ground elastic effect can be reduced. The effect of de-resonance on signals caused by the fact the decoupling capacitor is placed in different positions is expressed.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

Double-backboard structure and ATR case thereof

PendingCN111712097ASolve complexitySolve the costSupport structure mountingEngineeringStructural engineering

The invention discloses a double-backboard structure, which comprises a backboard A and a backboard B, wherein a daughter board connector is embedded in the backboard A, a positioning pin seat is further fixedly installed on one side face of the backboard A, a mother board connector is embedded in the backboard B, a positioning pin is fixedly mounted on one side surface of the backboard B, the positioning pin is inserted into the positioning pin seat, the backboard B is connected with the backboard A through matching of the positioning pin and the positioning pin seat, the backboard B is parallel to the backboard A, the mother board connector is connected with the daughter board connector in an inserted mode, the mother board connector is electrically connected with the daughter board connector, the mother board connector and the daughter board connector can be detached independently or along with a back panel, the structure is firm, and maintenance is convenient. The invention furtherdiscloses an ATR case, which comprises a case bottom plate, a case panel, a case back plate, a case right plate, a case left plate, a case top plate, a case internal board, a backboard A and a backboard B, wherein rigid connection can guarantee stability of signals and a system.

Owner:国科北方电子科技(北京)有限公司

Method and apparatus for analyzing influence on signal based on different distances between ground holes and signal holes

InactiveCN107577835AEnsure safetyImprove signal integritySpecial data processing applicationsEngineeringAnalysis method

The invention provides a method and an apparatus for analyzing an influence on a signal based on different distances between ground holes and signal holes. By comparing different ground hole distancesfrom the signal holes, different S parameters are obtained, and a specific signal loss condition can be obtained. The different distance signal holes are researched to obtain the different S parameters for specific data analysis of signal loss; and when the signal integrity of a board card is not ideal, other sub-cards can ensure the signal integrity, so that the running security of a whole server is ensured and the signal integrity and reliability of the RACK server are enhanced.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com