Embedded fault injection module and method and high-speed digital circuit system

A fault injection, digital circuit technology, applied in the direction of digital circuit testing, radio wave measurement system, electronic circuit testing, etc., can solve the lack of reliable basis for the test design evaluation of high-speed digital circuit modules, can not solve the high-speed bus fault injection, difficult to implement Test verification methods, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0041] An embodiment of the present invention introduces an embedded fault injection module and method, which are used for fault simulation and fault injection for radar high-speed digital circuit modules, and provide reliable basis for testing verification and evaluation of radar high-speed digital circuits.

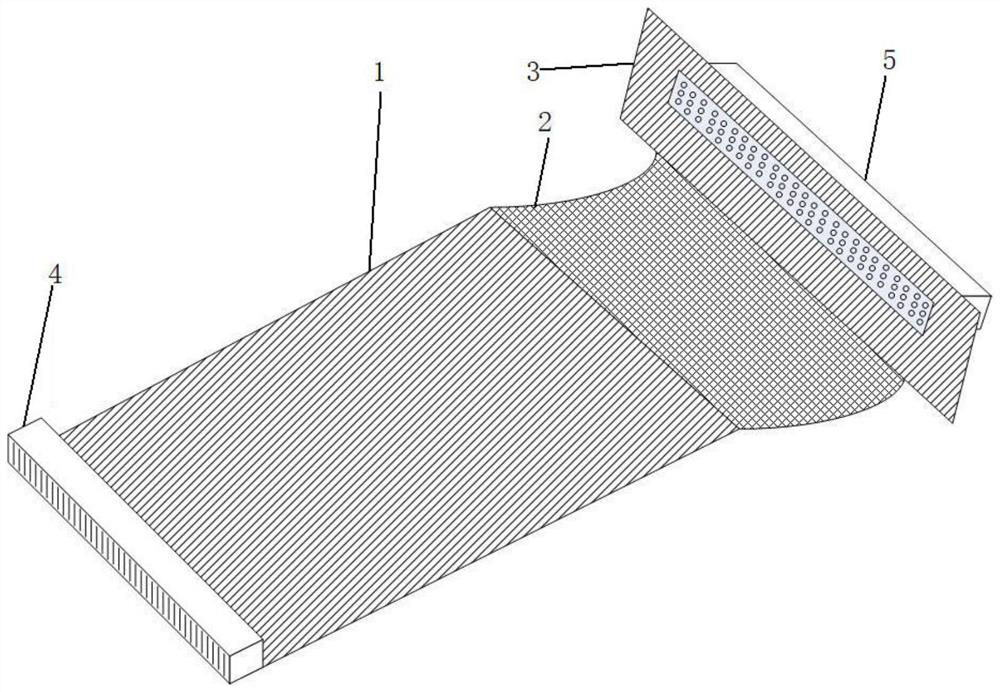

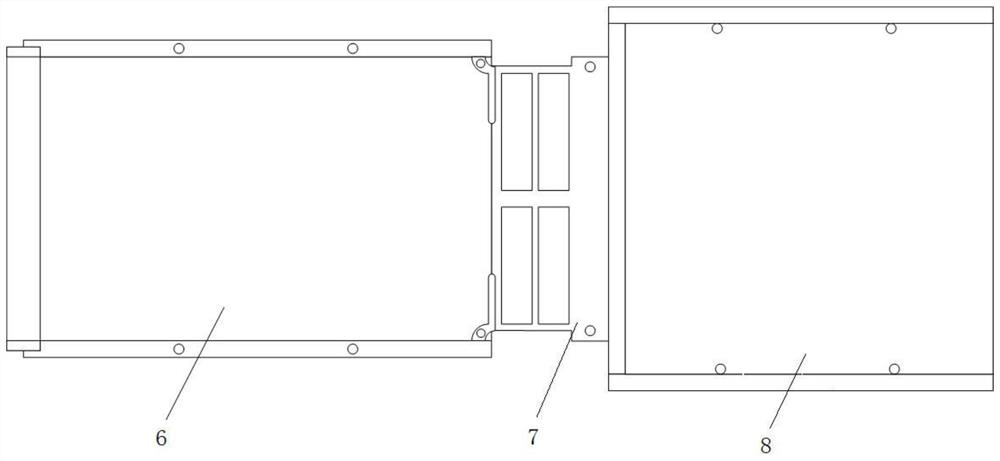

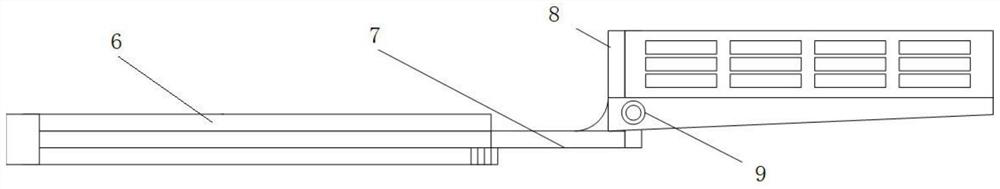

[0042] Such as figure 1 As shown, the embedded fault injection module of the high-speed digital circuit adopts a rigid-flexible PCB board, and the two ends of the PCB board are respectively provided with a first rigid PCB board 1 and a second rigid PCB board 3, and the first rigid PCB board 1 and the second rigid PCB board The middle of the rigid PCB 3 is provided with a flexible PCB 2 that is electrically connected to the first rigid PCB 1 and the second rigid PCB 3 . The free end of the first rigid PCB board 1 is provided with a first connector 4, which is used to connect the backplane of the radar digital circuit system working sub-box; one end of the second rigid PC...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com