Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

944 results about "Semiconductor production" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

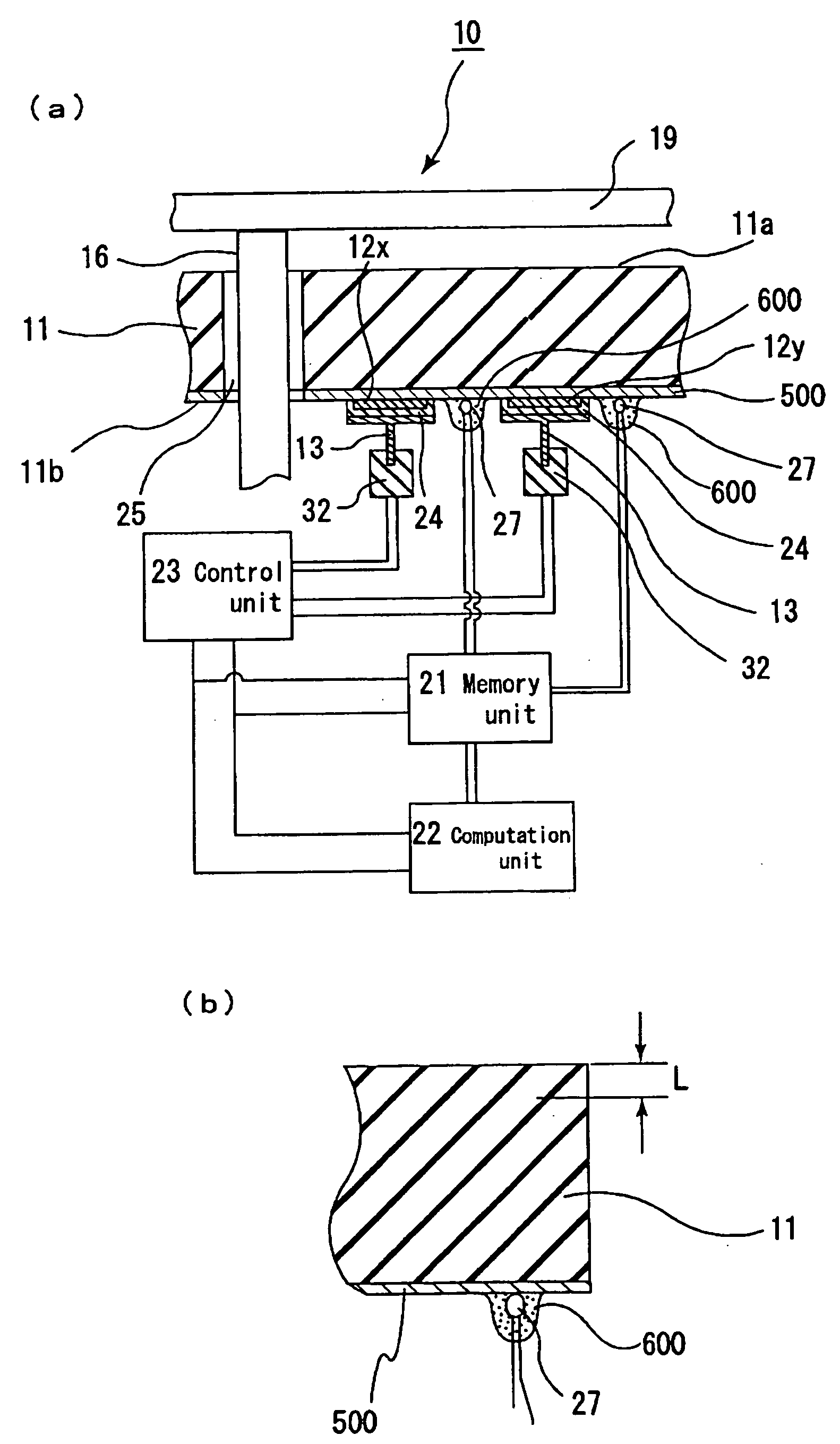

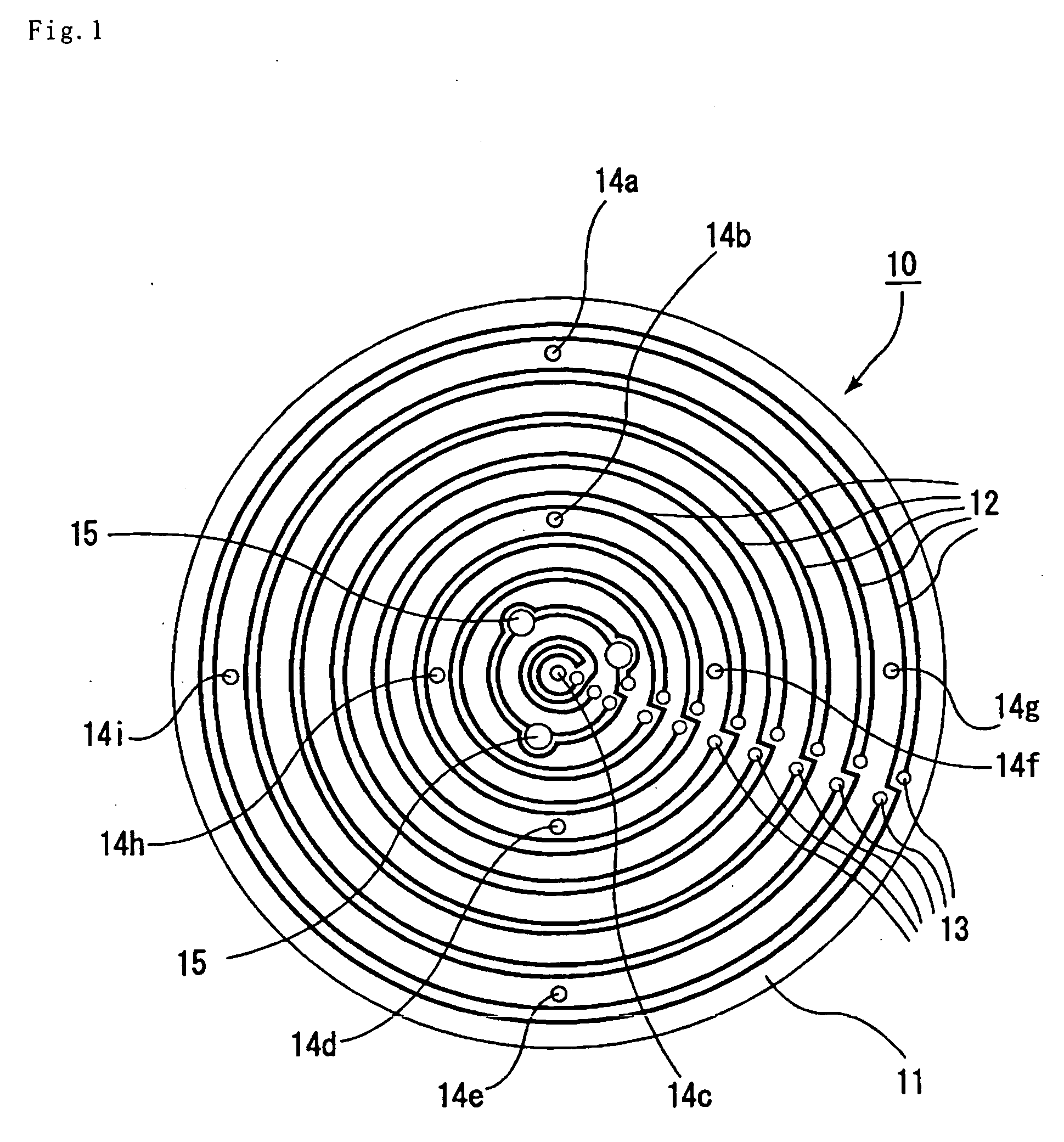

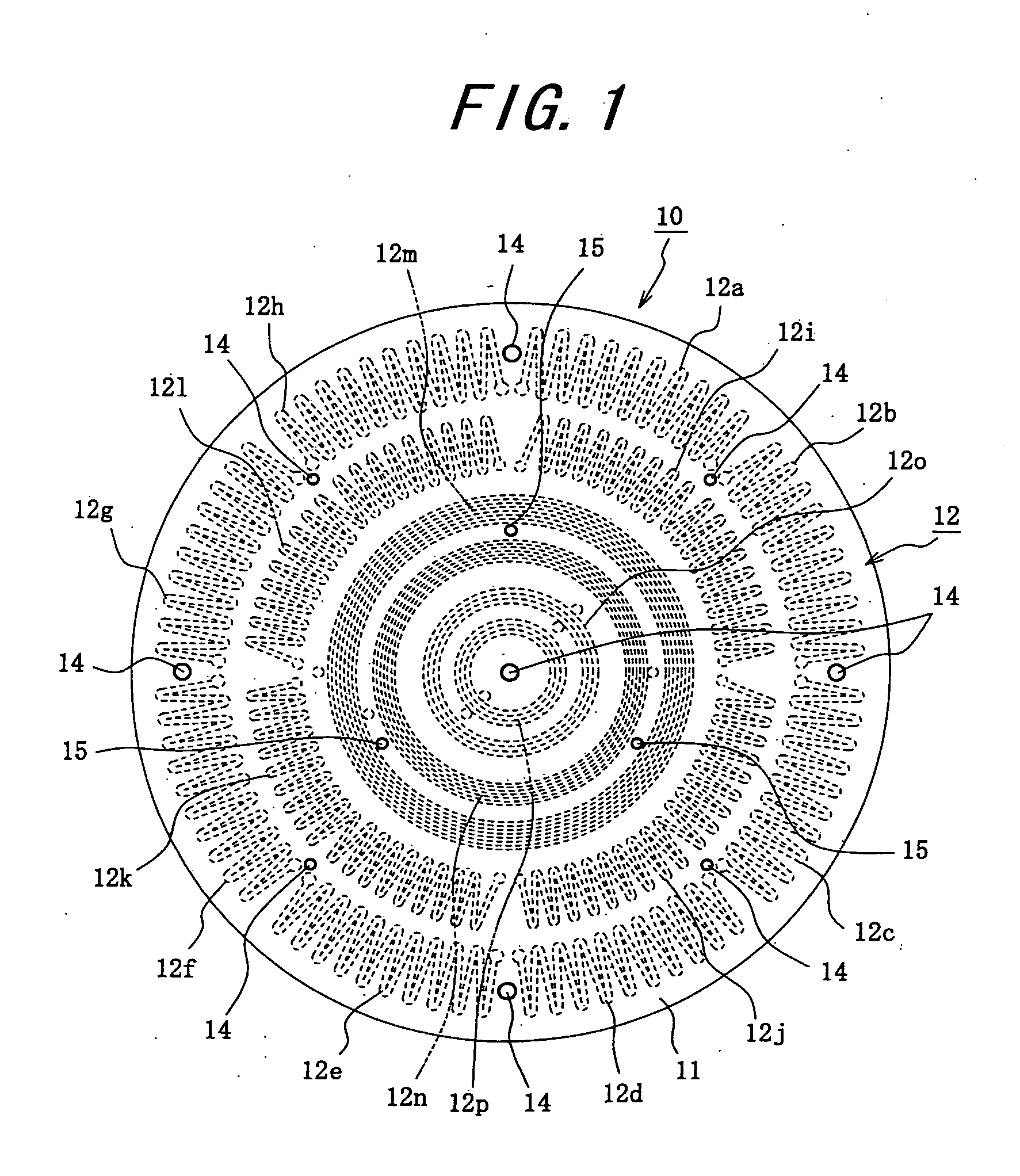

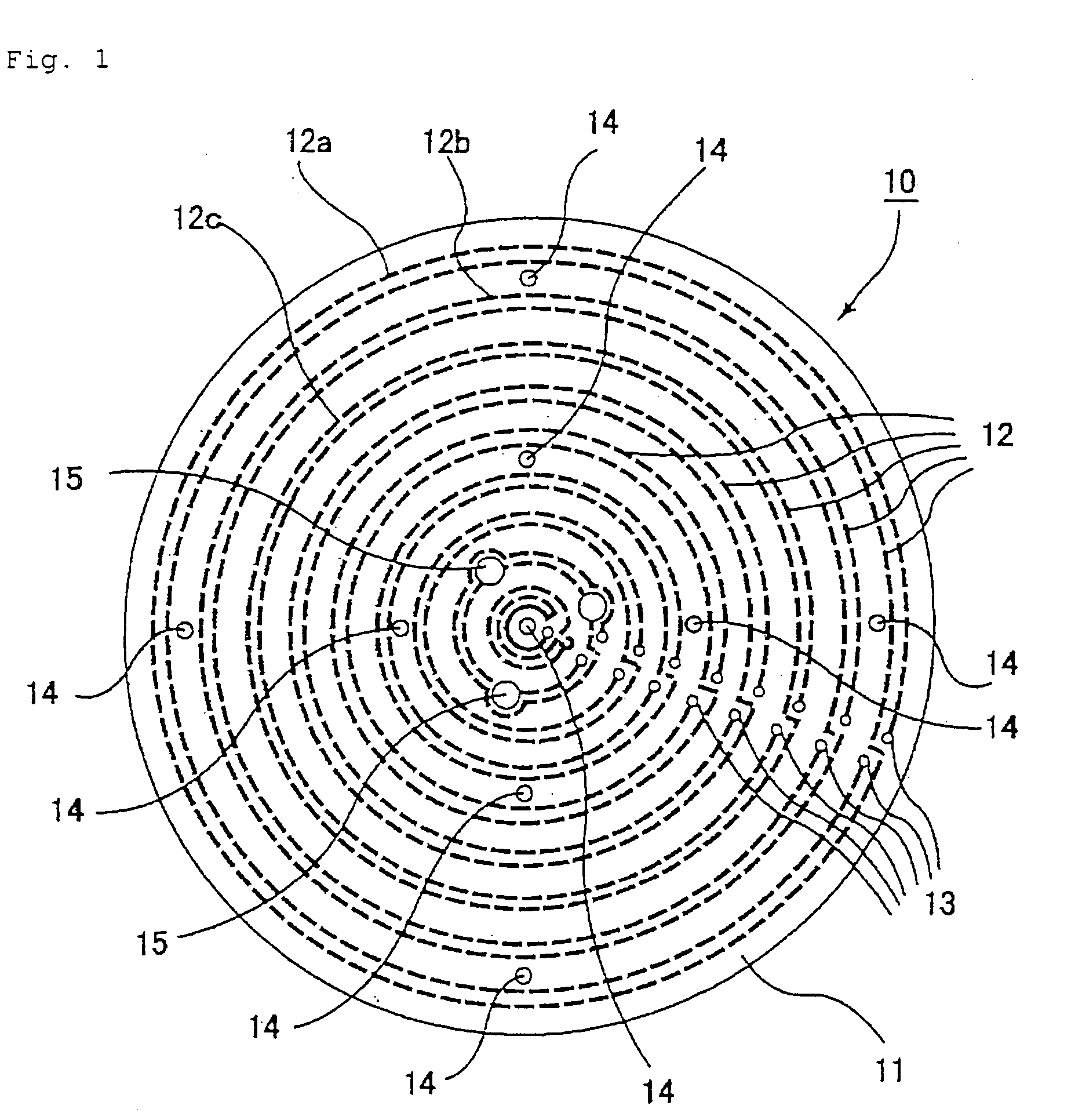

Ceramic heater for semiconductor manufacturing and inspecting equipment

InactiveUS20050092733A1Improve responseCausing temperature distributionMuffle furnacesSemiconductor/solid-state device manufacturingMetallurgySemiconductor

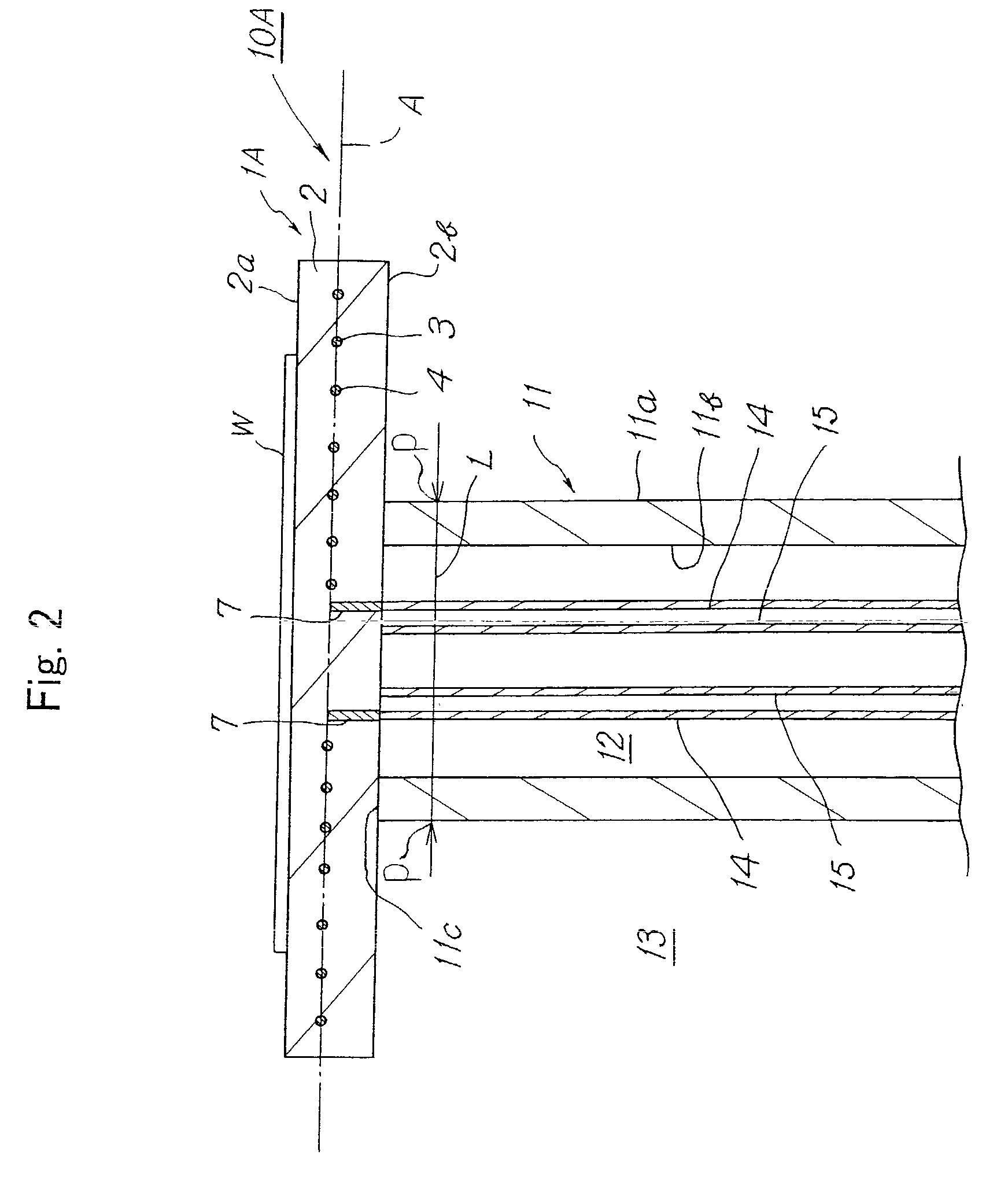

A ceramic heater for a semiconductor producing / examining device including a ceramic substrate having a heating surface for receiving a semiconductor wafer, a heating device for generating heat sufficient for producing / examining the semiconductor wafer and formed on the heating surface or inside the ceramic substrate, and a temperature measuring device for measuring a temperature of the heating surface and pressed against the ceramic substrate.

Owner:IBIDEN CO LTD

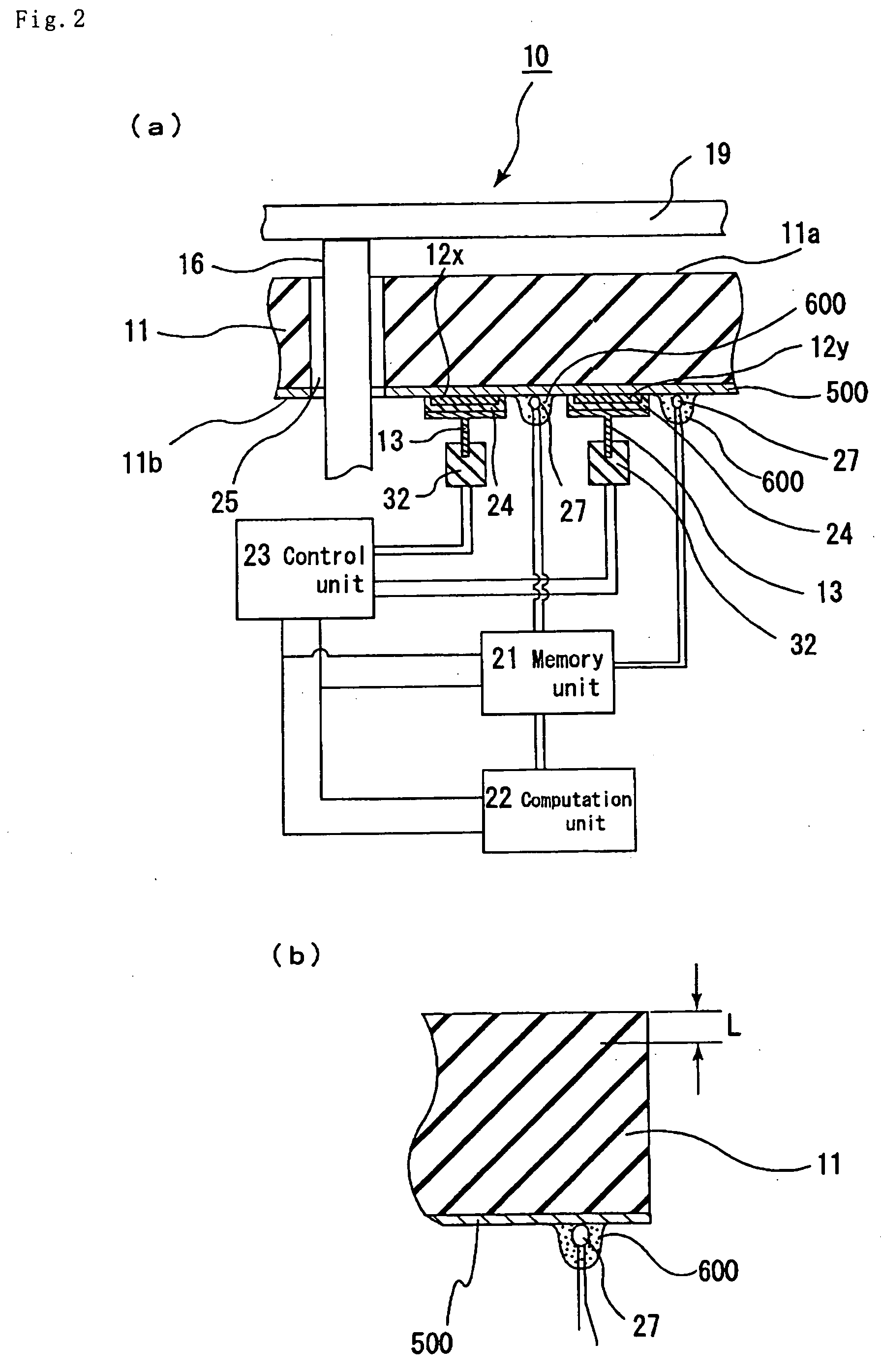

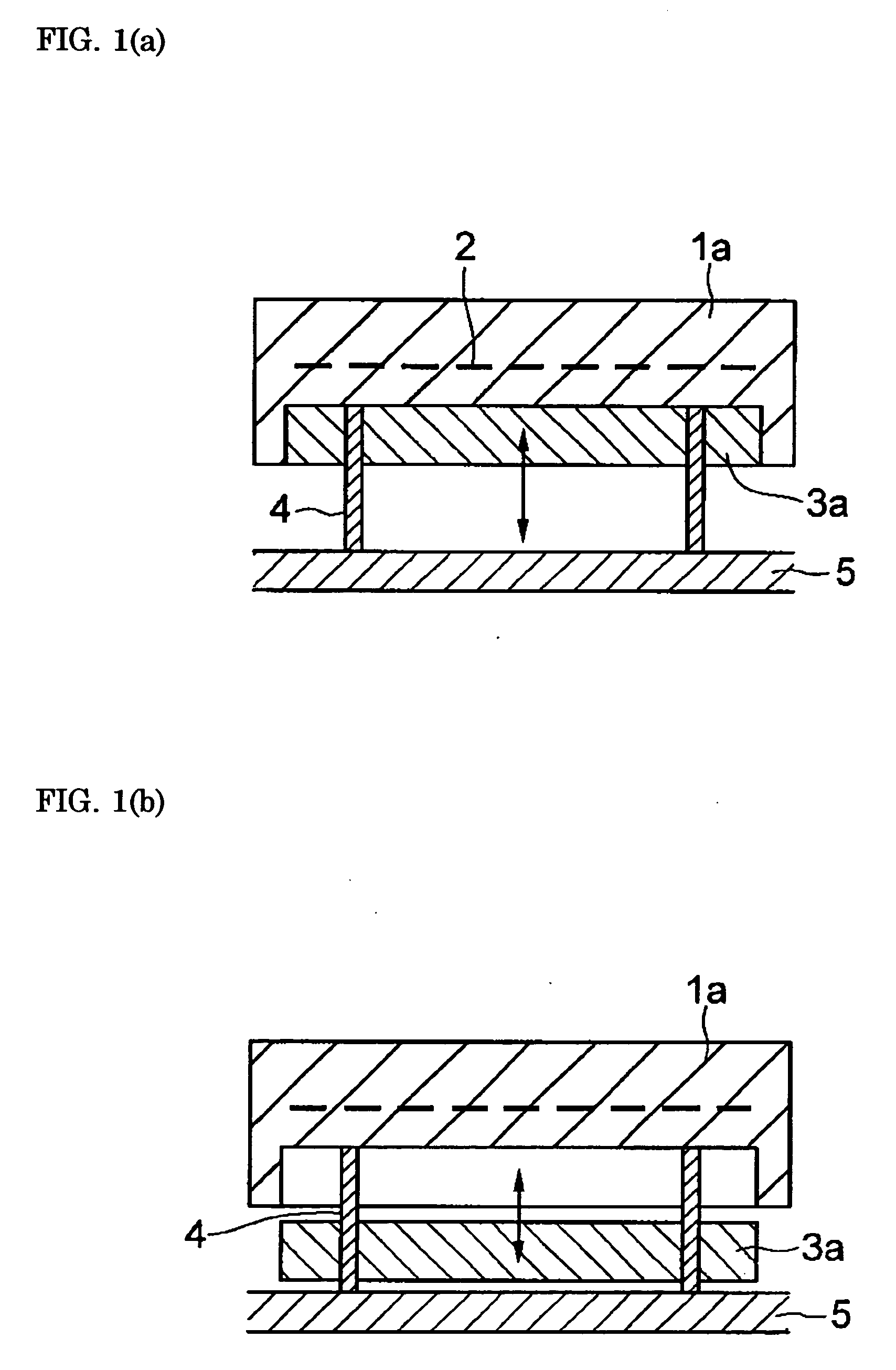

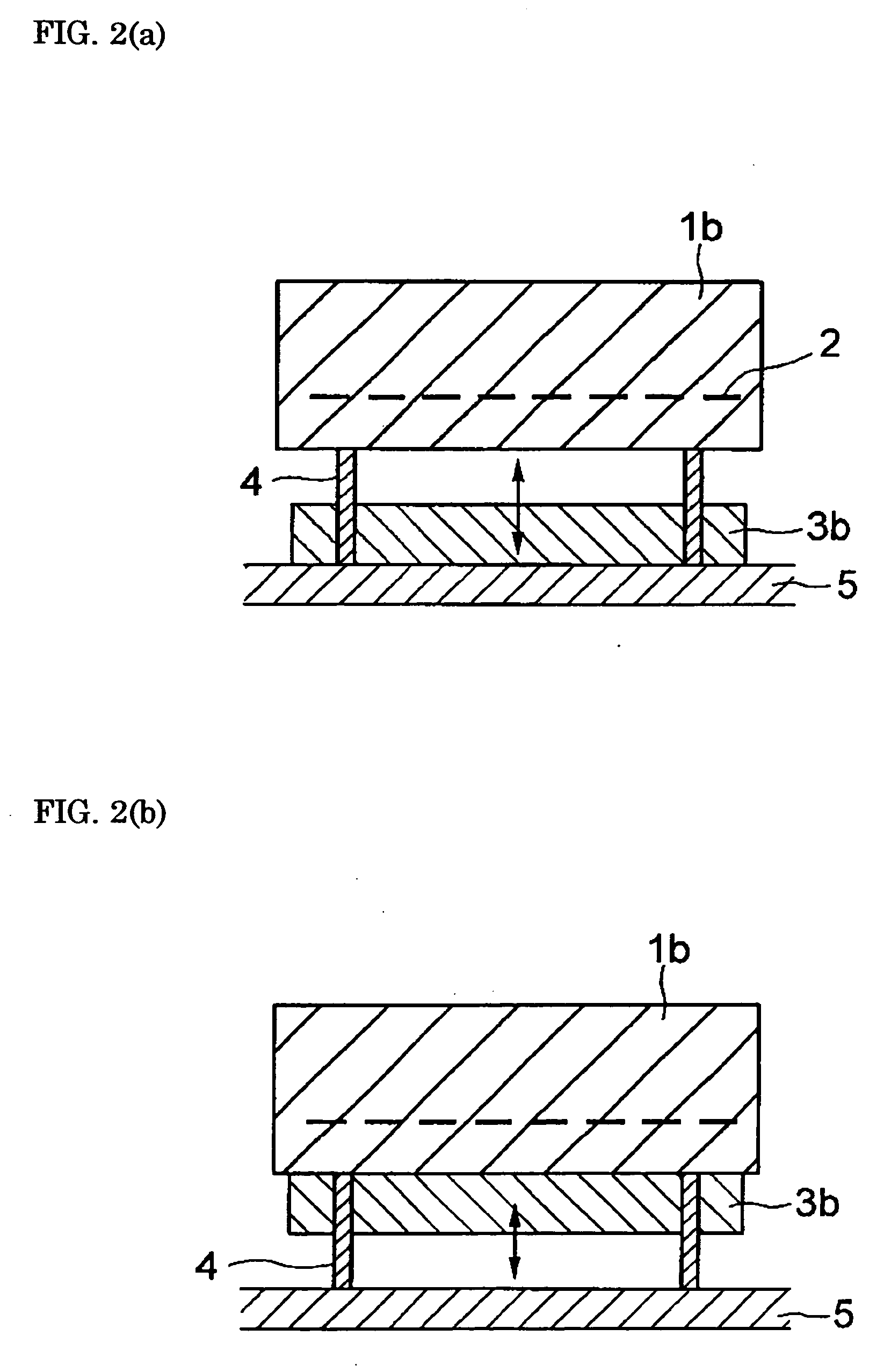

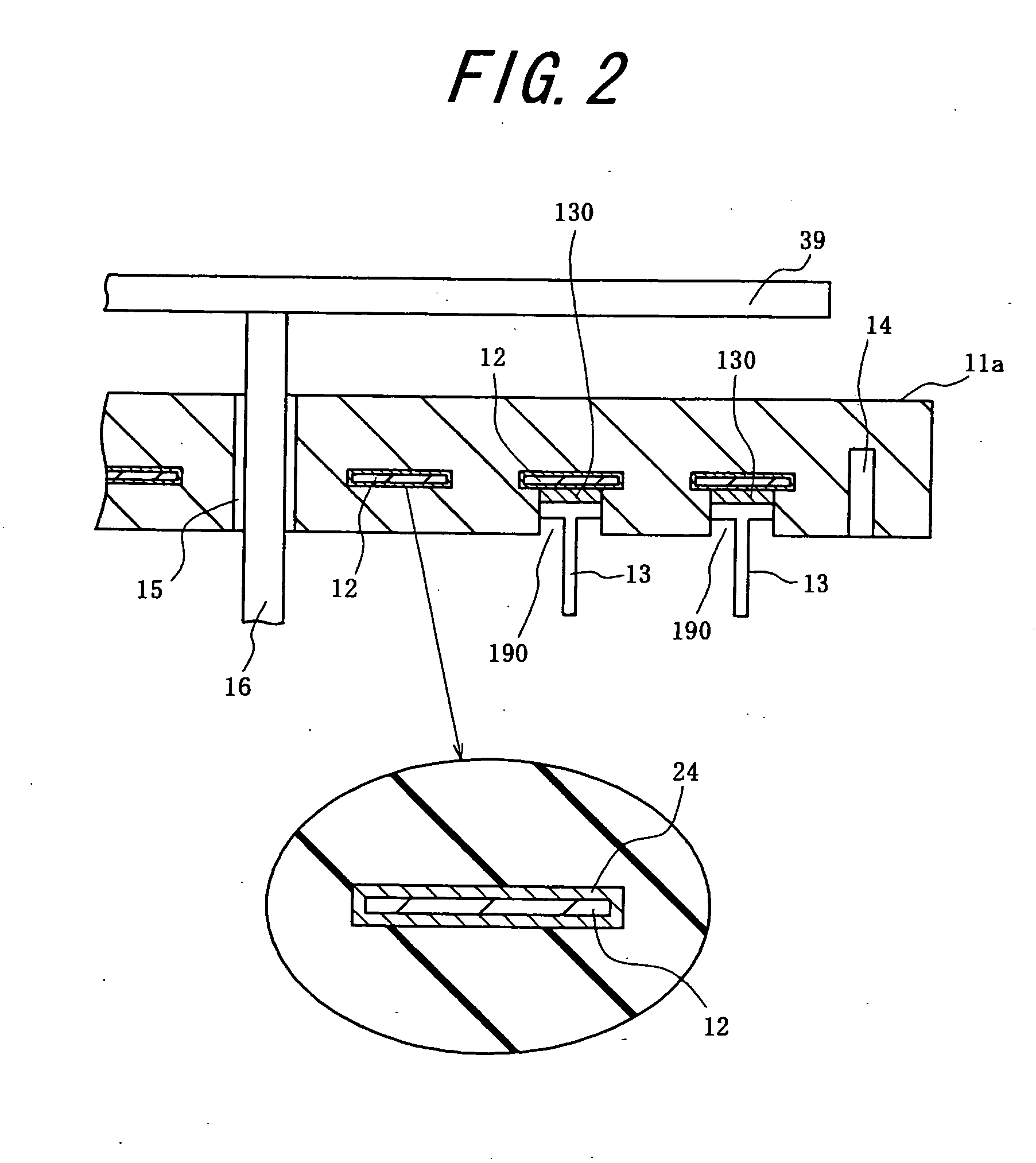

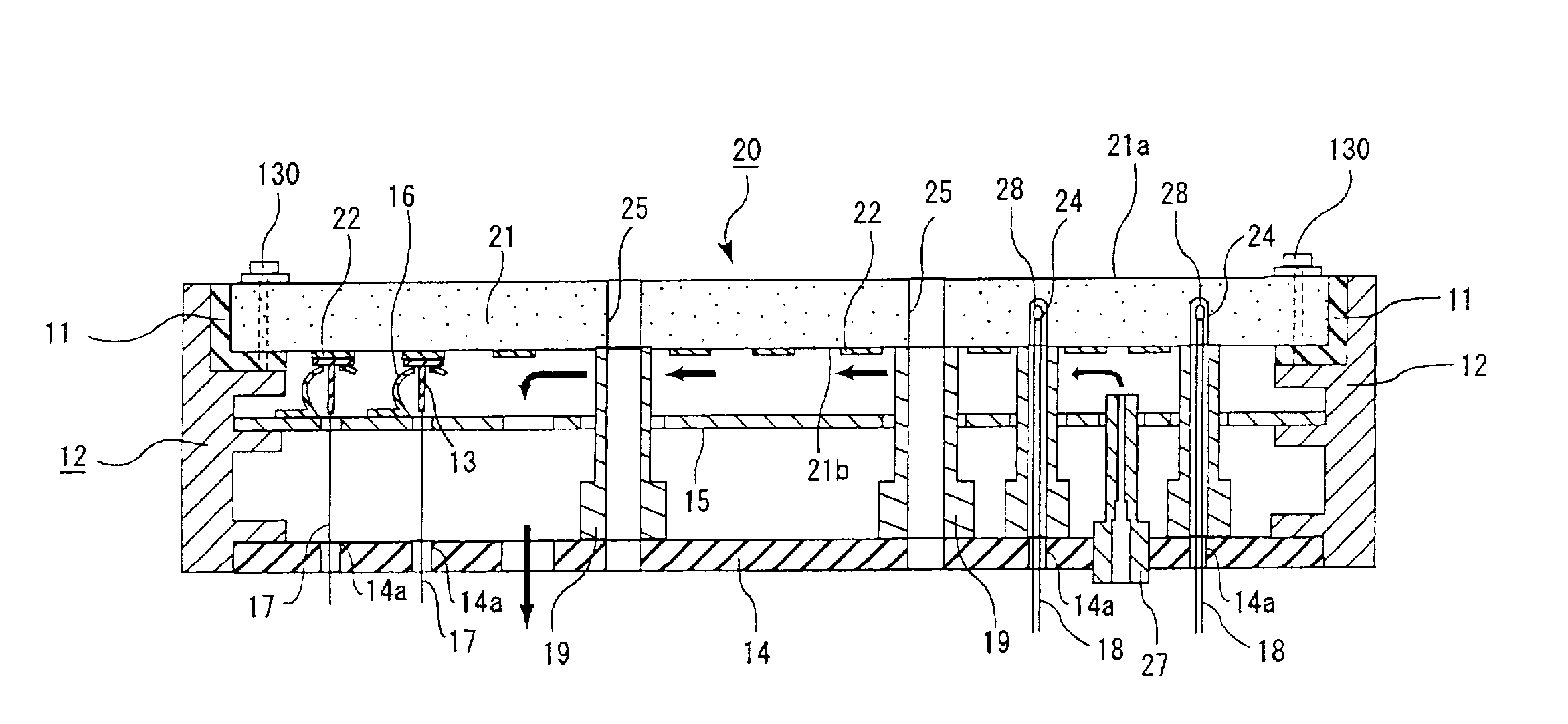

Heater module for semiconductor production system

InactiveUS20040238523A1Speed up coolingHigh bonding strengthSemiconductor/solid-state device manufacturingHot plates heating arrangementsProduction rateComputer module

Heater module, and semiconductor manufacturing equipment in which the heater module is utilized, for raising the cooling speed of a post-heating heater markedly more than conventional, and that can contribute toward bettering and improving productivity, without accompanying scaling-up of and cost increases in the semiconductor manufacturing equipment. The heater module is furnished with heater part 1a for controlled heating of a wafer placed on its top face, and block part 3a provided to be shiftable relative to said heater part, for varying heat capacity in total with heater part 1a by abutting on or separating from the reverse surface of heater part 1a. By having the heat capacity of block part 3a be 20% or more of the total heat capacity of heater part 1a and block part 3a, the heater cooling speed can be made 10° C. / min or more.

Owner:SUMITOMO ELECTRIC IND LTD

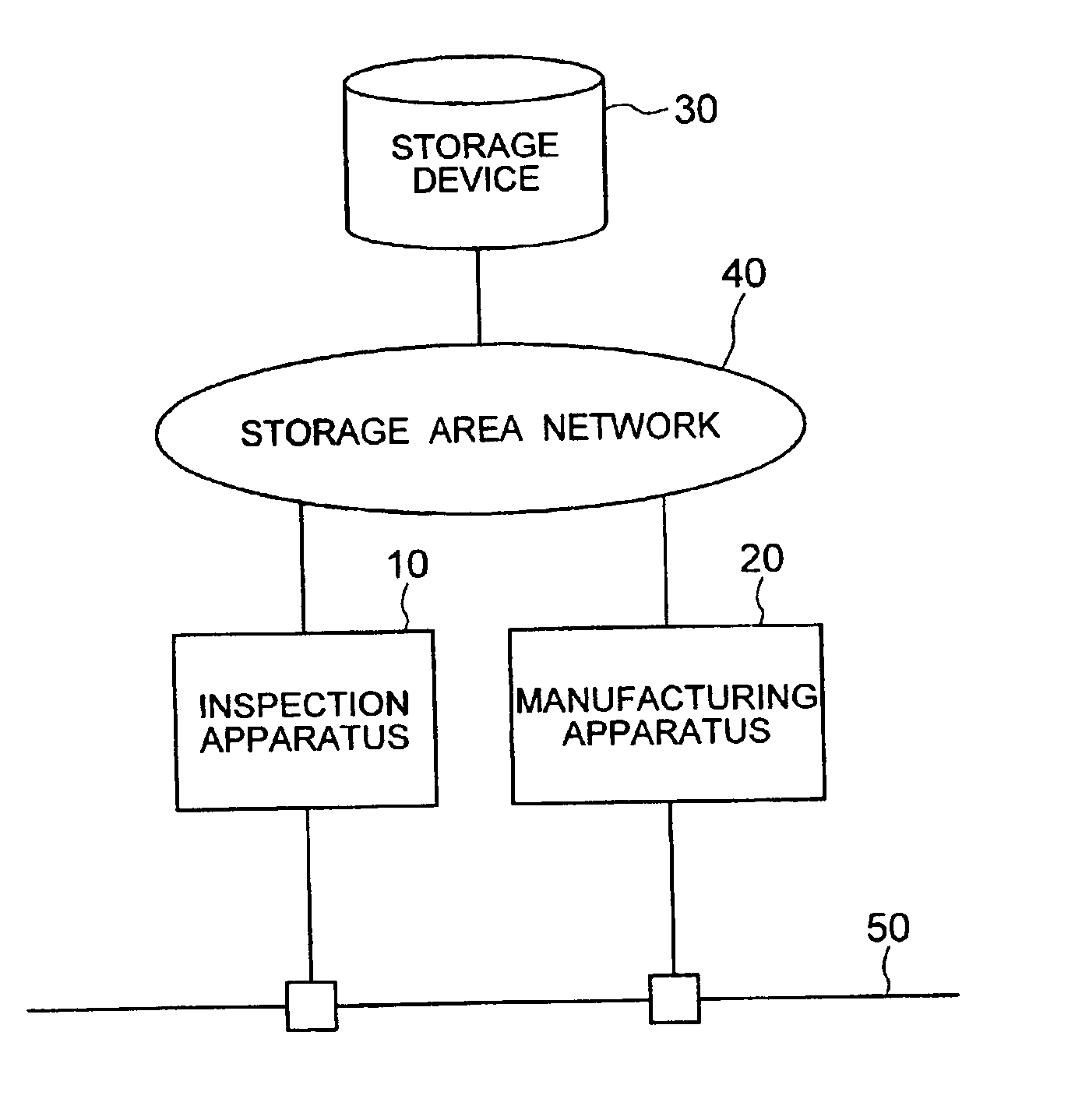

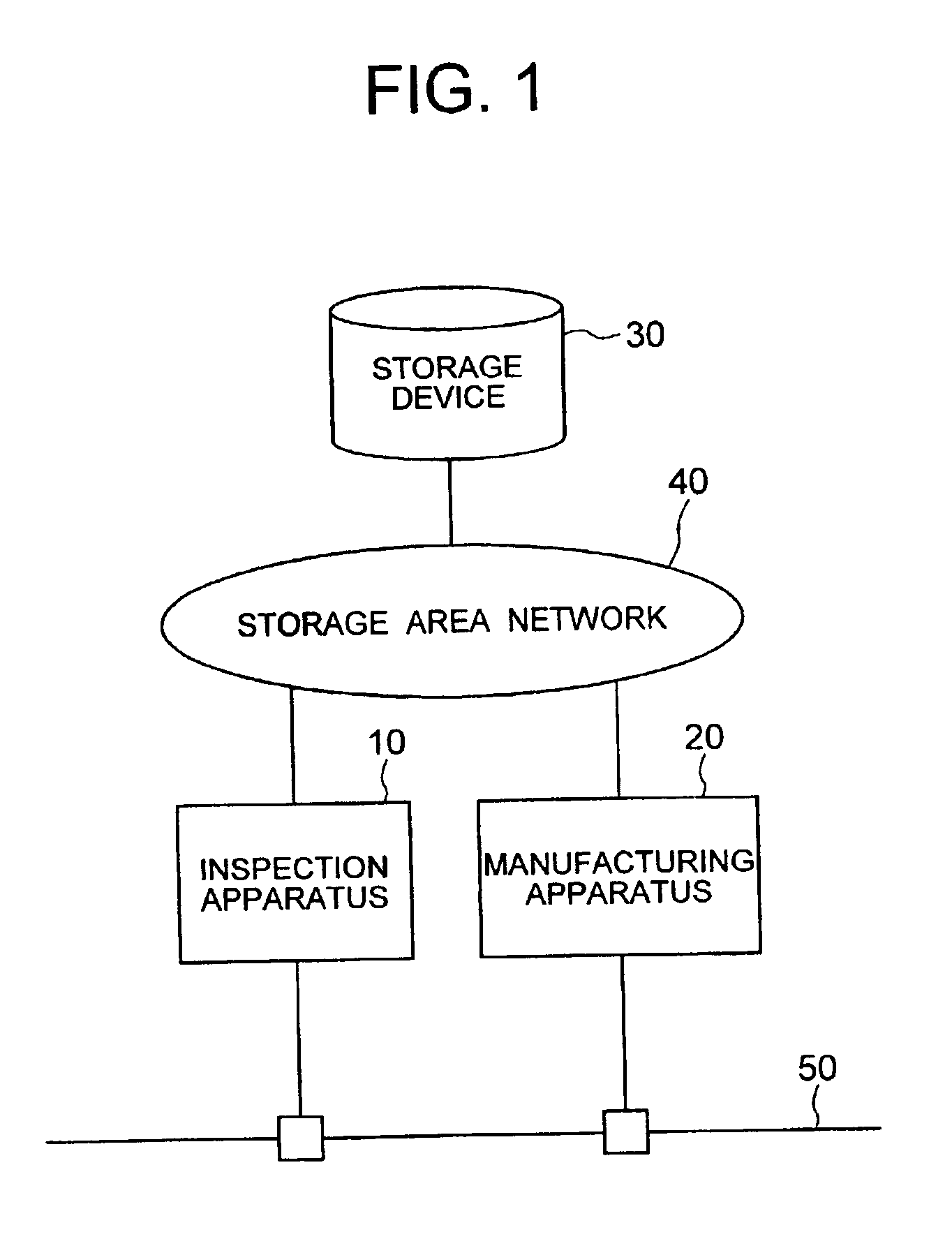

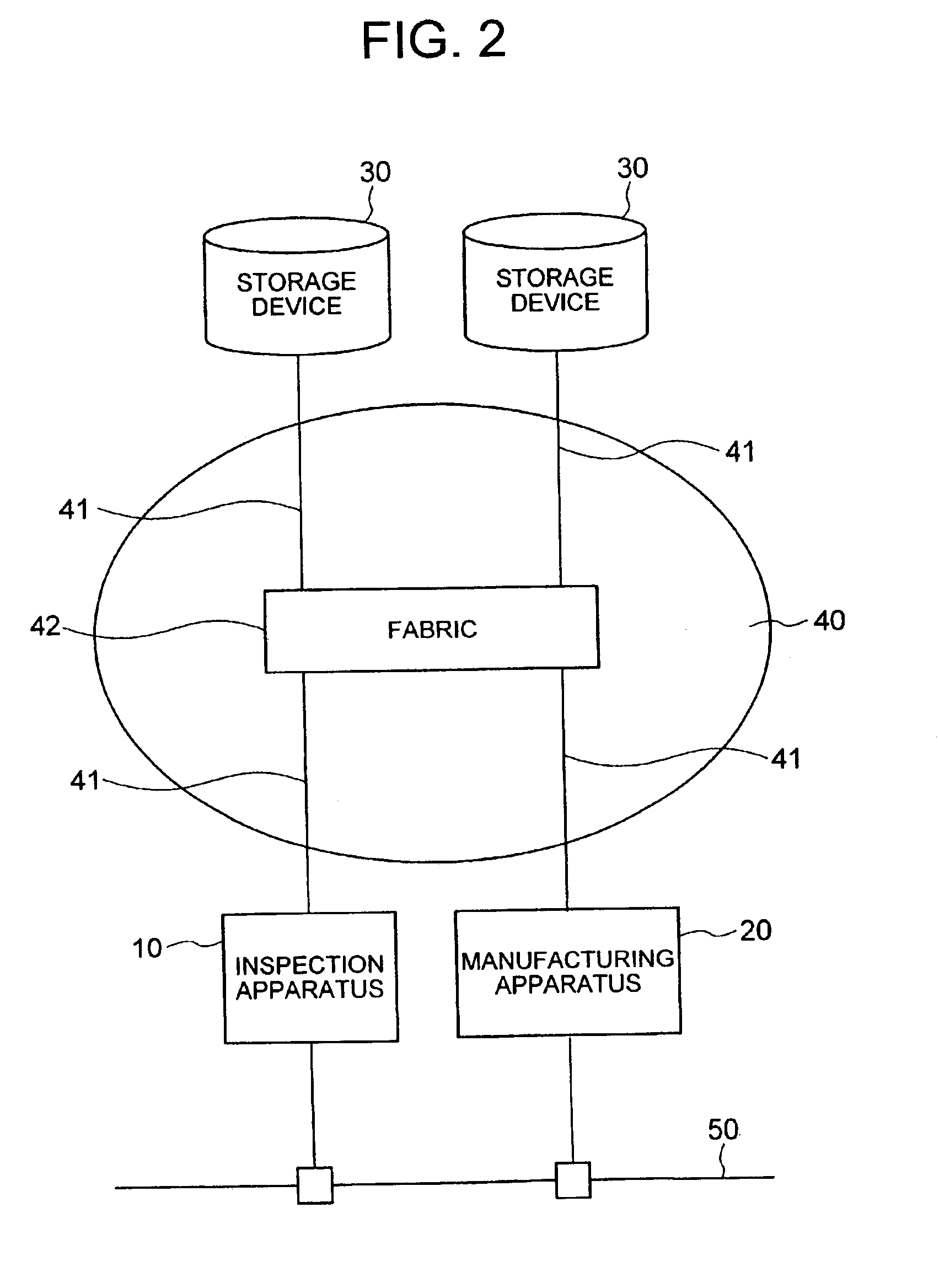

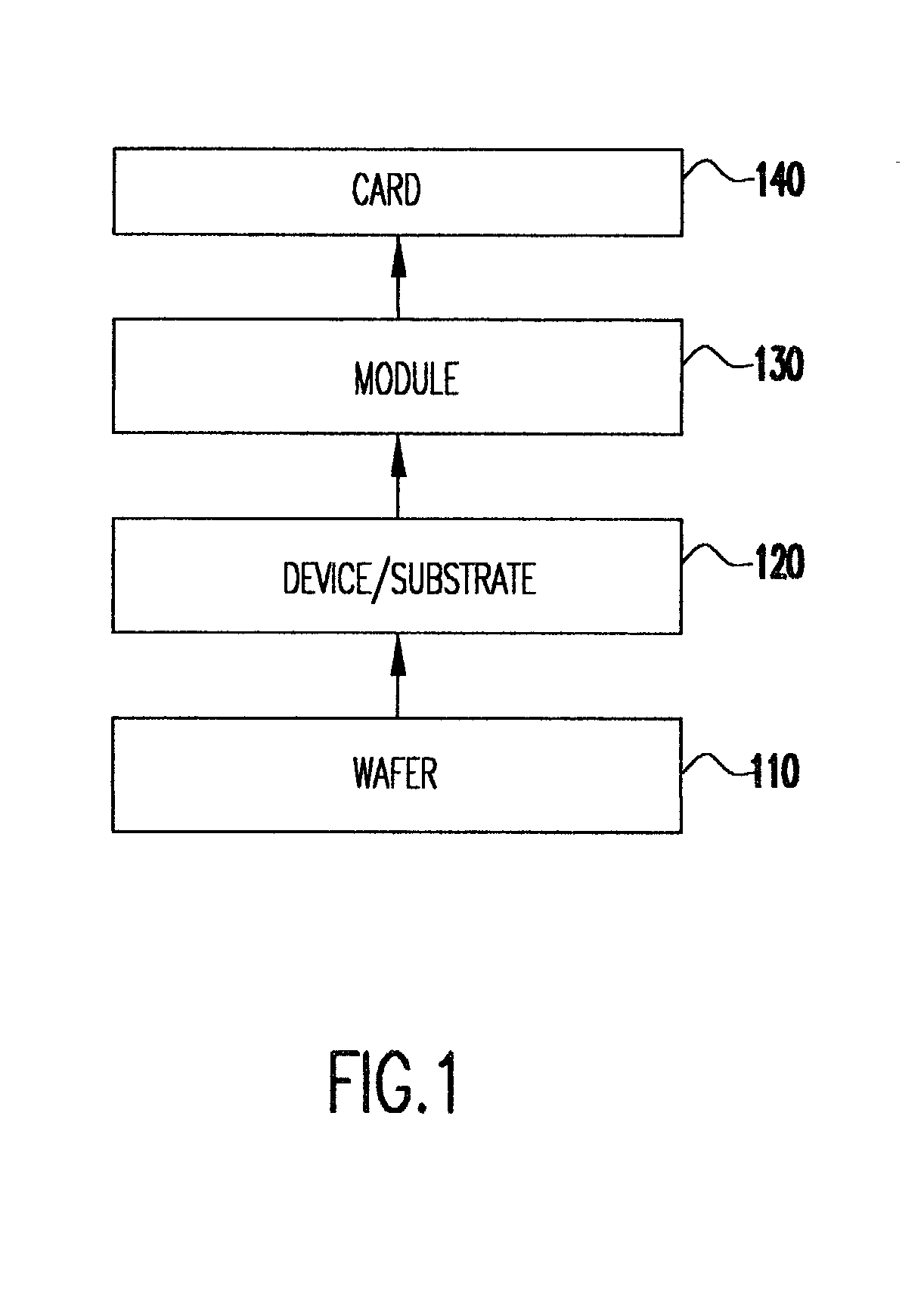

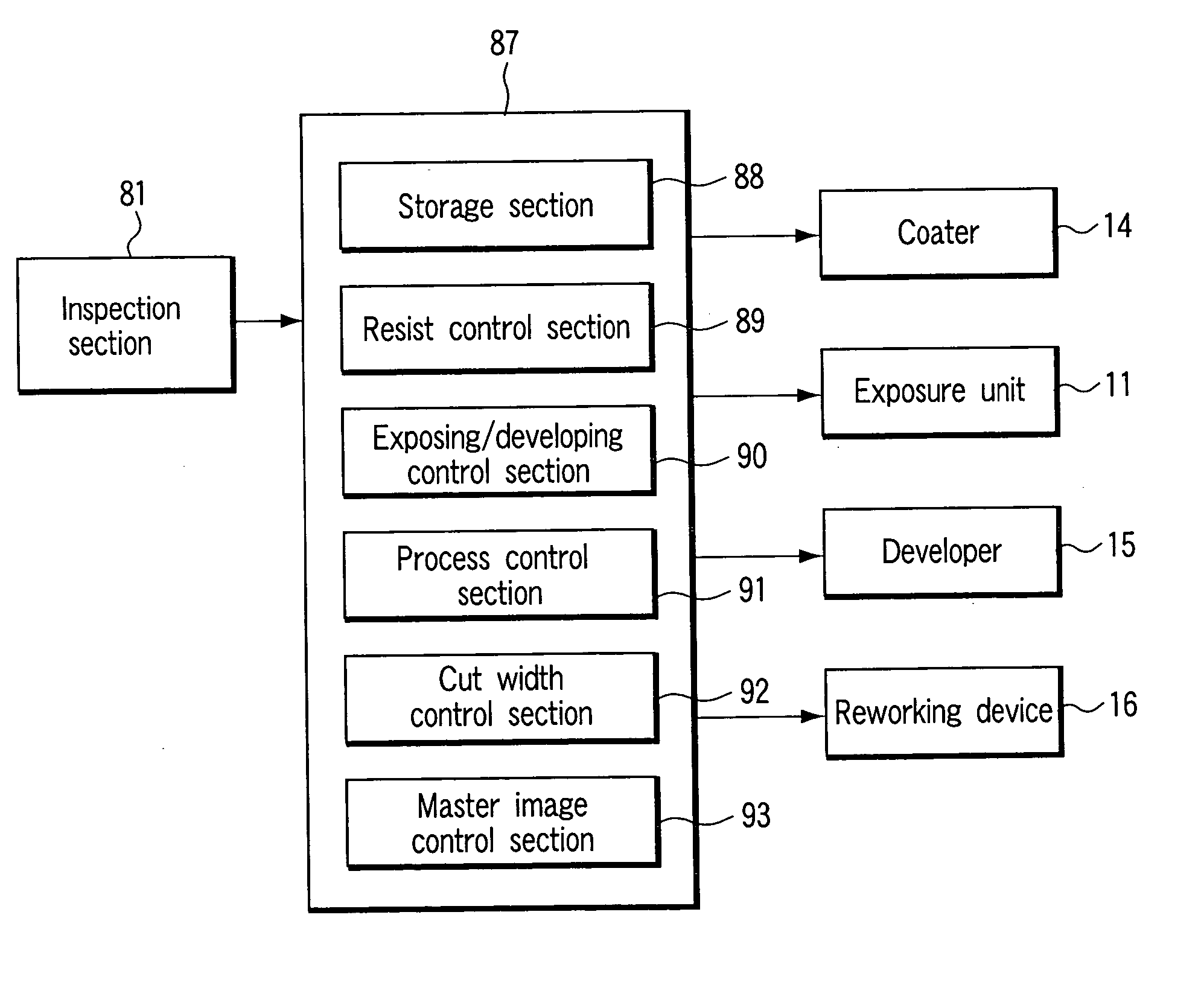

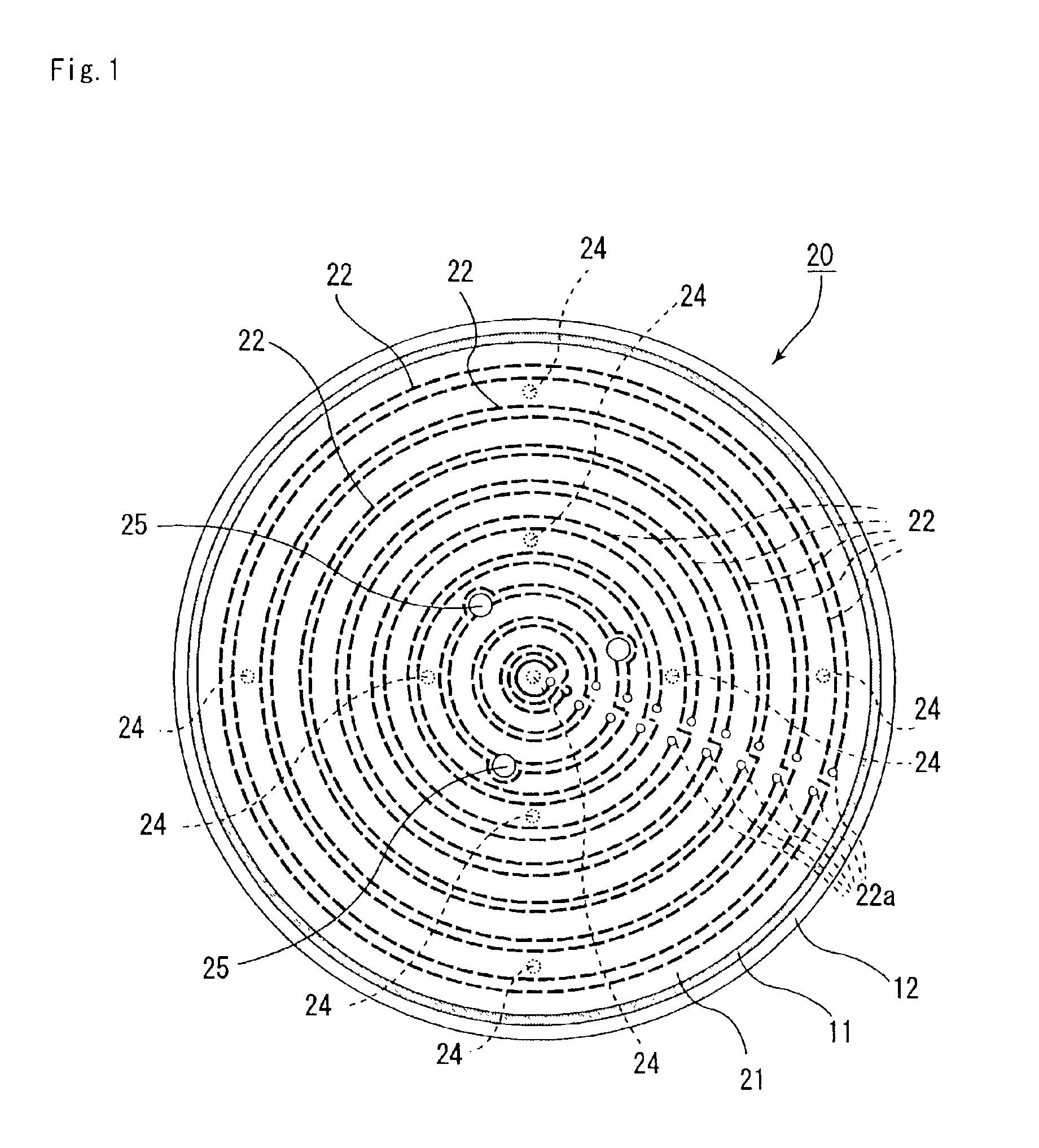

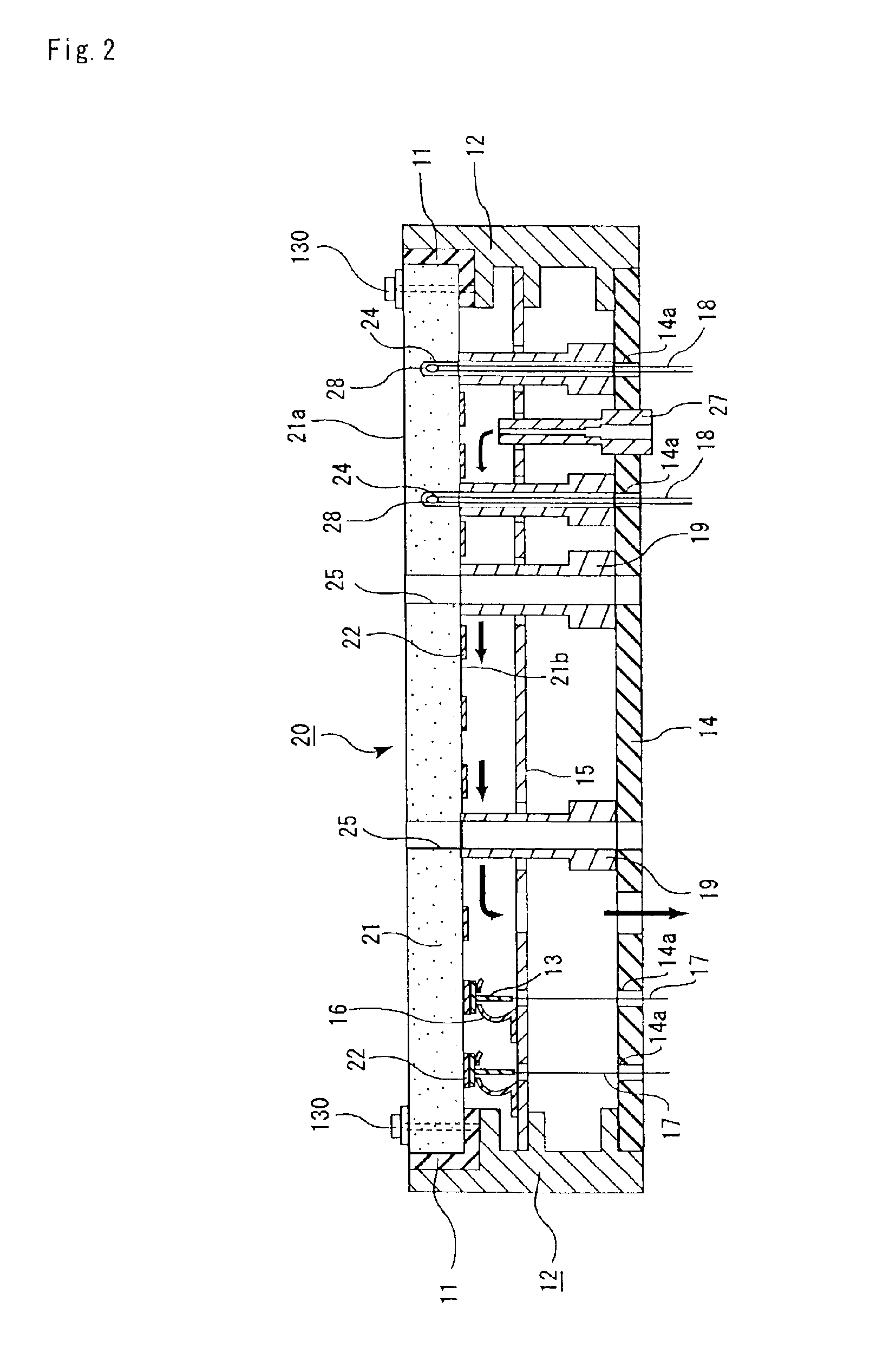

Semiconductor production system

InactiveUS6850854B2Improve system throughputIncrease in sizeSemiconductor/solid-state device testing/measurementElectronic circuit testingStorage area networkObservation unit

A semiconductor production system has a semiconductor manufacturing apparatus having an exposure unit, a control unit for controlling the exposure unit and a storage device; a semiconductor inspection apparatus having an observation unit, a control unit for controlling the observation unit and a storage device; and a storage device commonly used by the semiconductor manufacturing apparatus and the semiconductor inspection apparatus. The manufacturing apparatus, the inspection apparatus and the commonly used storage device are interconnected via a storage area network. With the semiconductor manufacturing apparatus and the storage device linked together via the storage area network, a large volume of image data or design data can be communicated at high speed, thus improving the system throughput.

Owner:HITACHI LTD

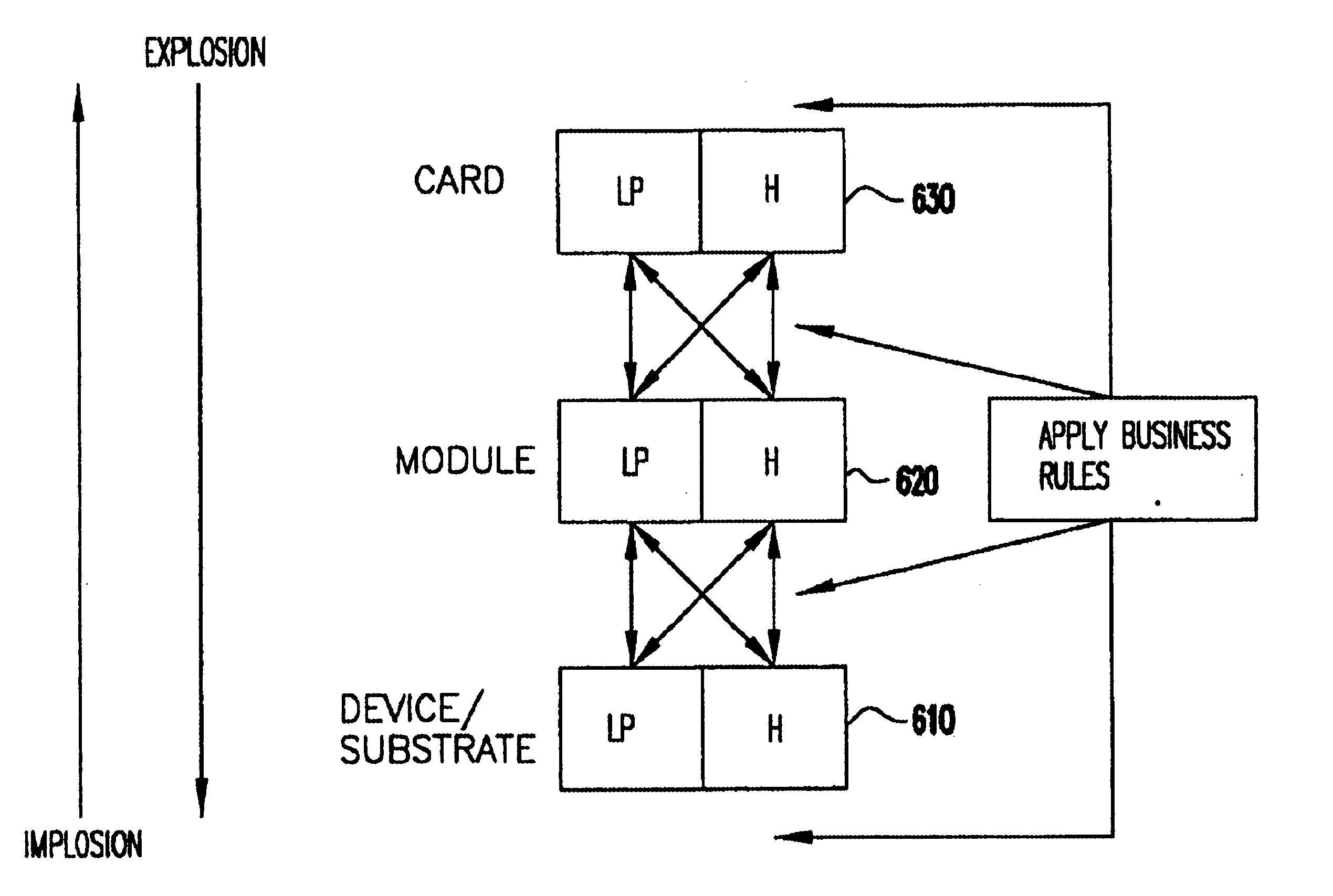

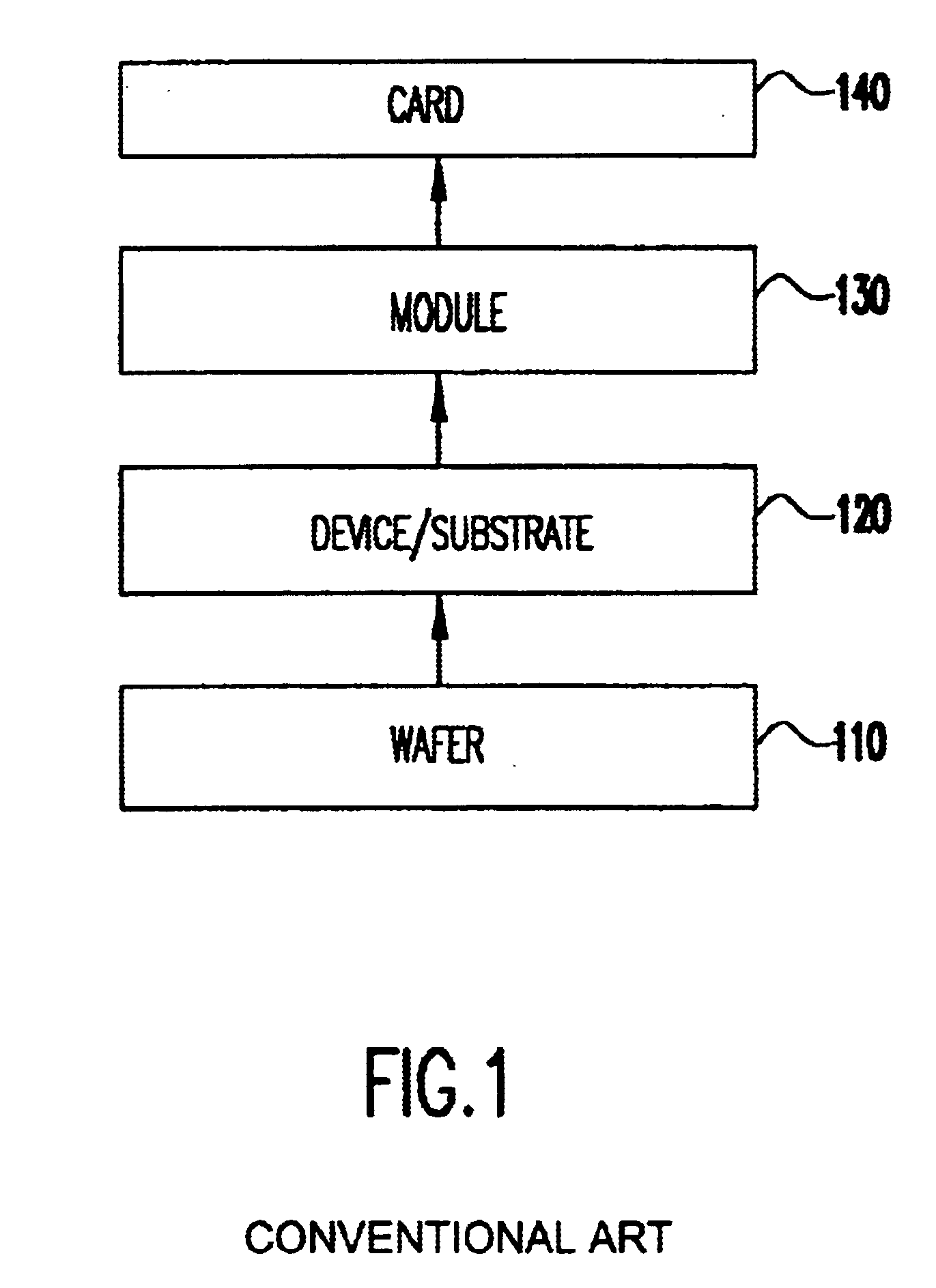

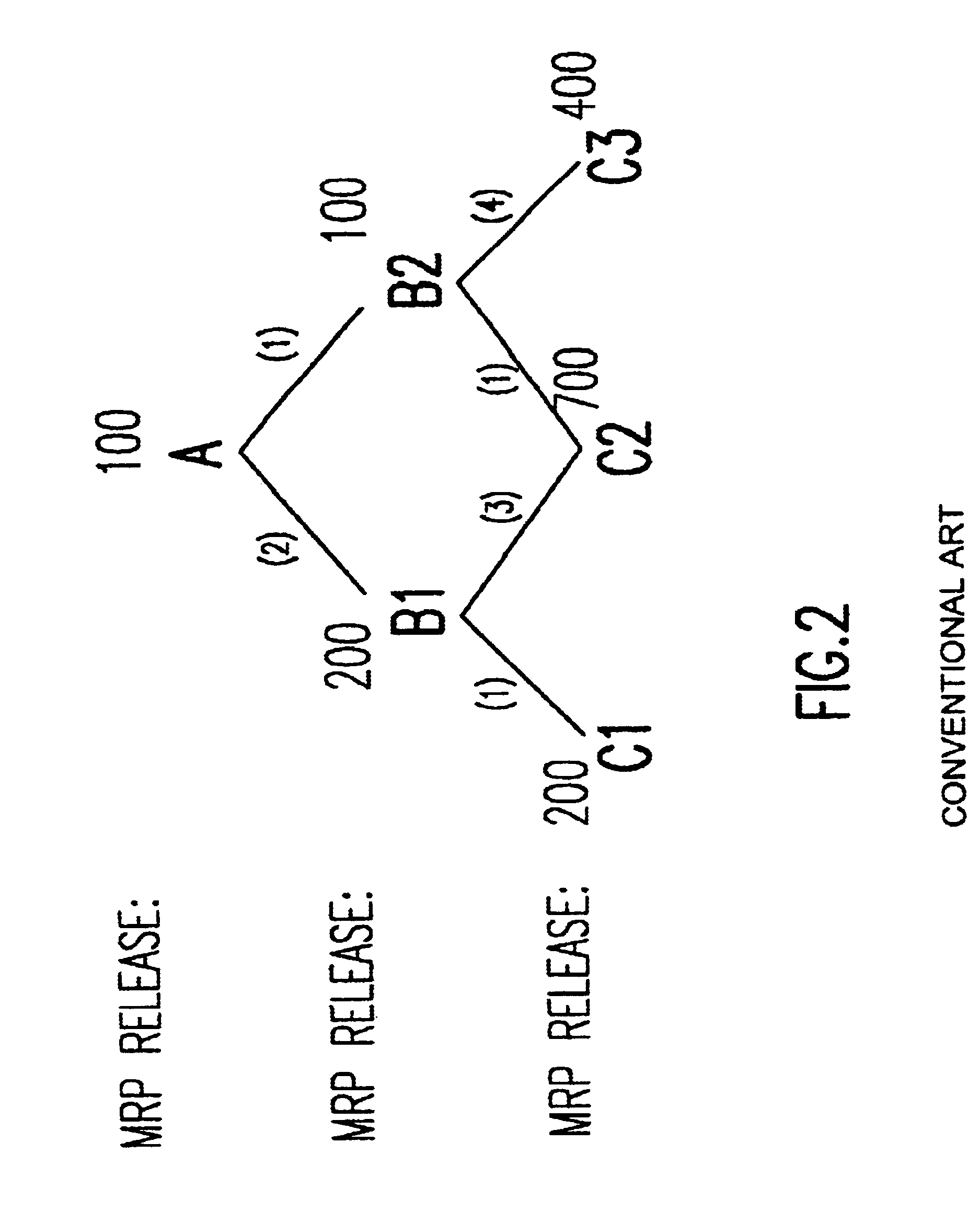

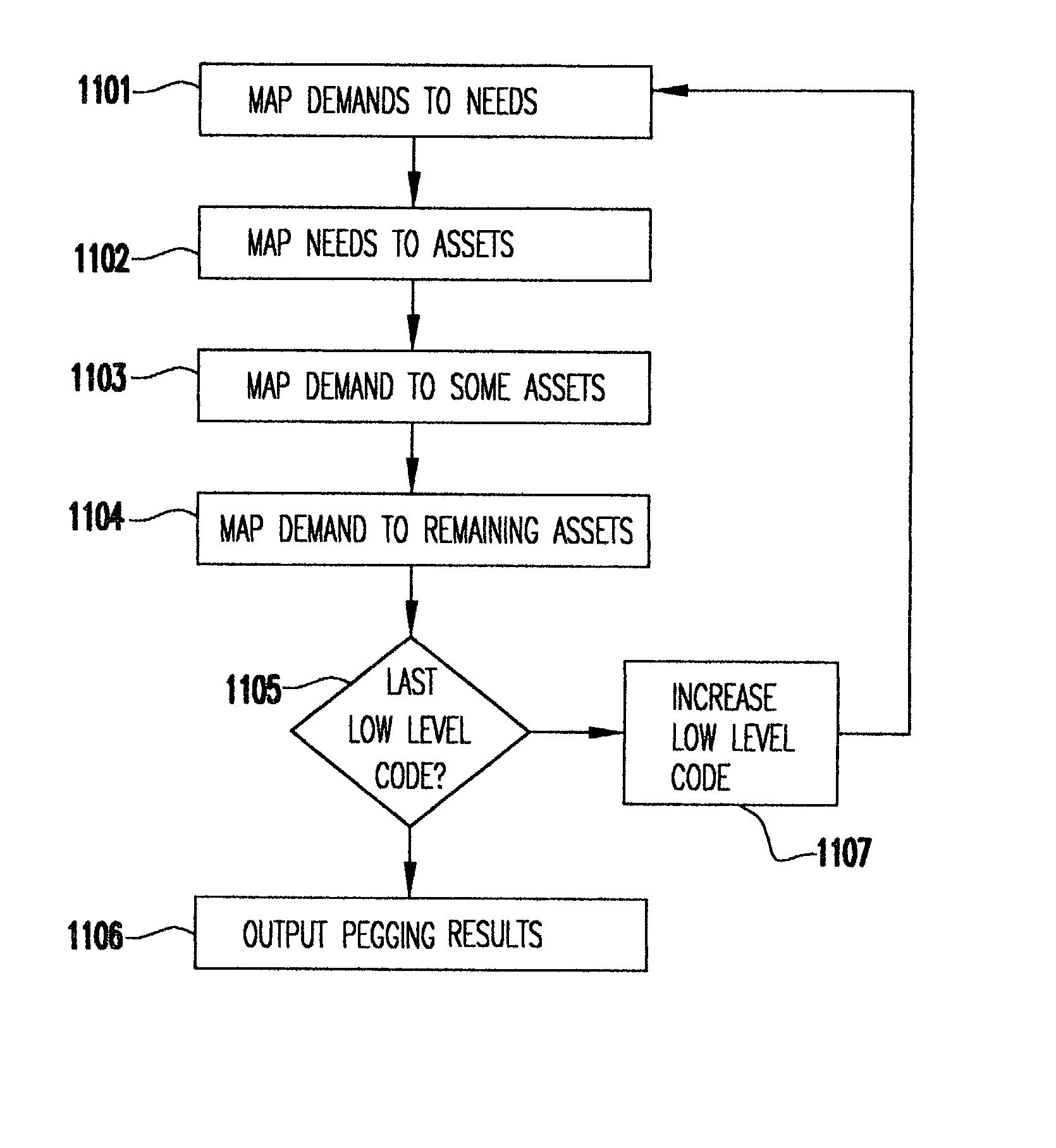

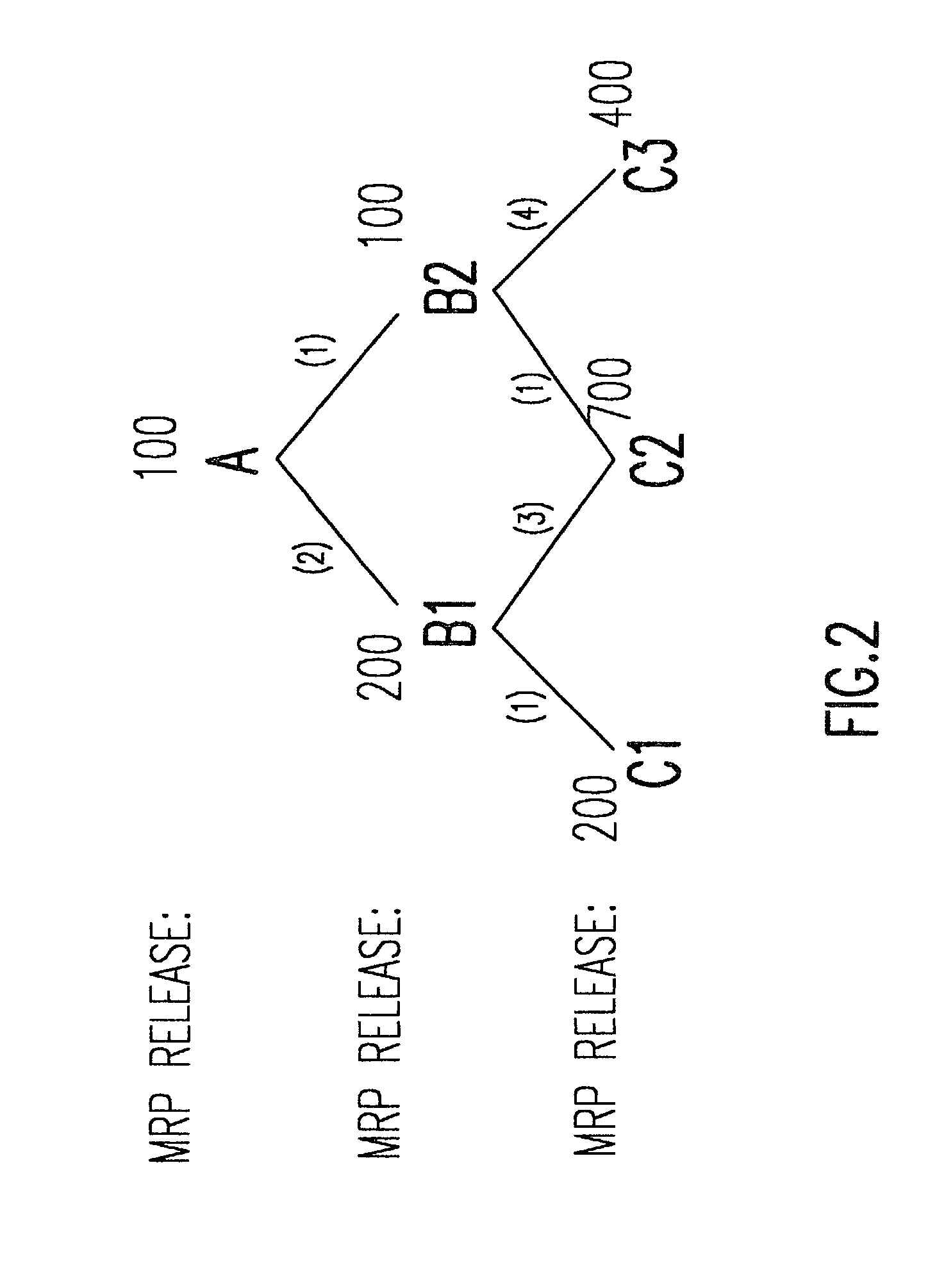

Decomposition system and method for solving a large-scale semiconductor production planning problem

Owner:INT BUSINESS MASCH CORP

Decomposition system and method for solving a large-scale semiconductor production Planning problem

A method and system for efficient allocation of limited manufacturing resources over time to meet customer demand. At the enterprise planning level this typically requires determination of a feasible production schedule for an extended supply chain. The method and system utilizes a new and unique type of systematic decomposition based on both product and process considerations. This approach simultaneously reduces the model size (and therefore computation time) and increases modeling flexibility from strictly linear programming based decision making to include more general nonlinear programming characteristics.

Owner:IBM CORP

Ceramic substrate for a semiconductor production/inspection device

InactiveUS6891263B2Increase the number ofLower volume resistivitySemiconductor/solid-state device detailsSolid-state devicesNon oxide ceramicsElectrical conductor

The present invention provides a ceramic substrate which can keep a sufficiently large breakdown voltage even if the pore diameter of its maximum pore is 50 μm or less to be larger than that of conventional ceramic substrates, can give a large fracture toughness value because of the presence of pores, can resist thermal impact, and can give a small warp amount at high temperature. The ceramic substrate of the present invention is a ceramic substrate for a semiconductor-producing / examining device having a conductor formed on a surface of the ceramic substrate or inside the ceramic substrate, wherein: the substrate is made of a non-oxide ceramic containing oxygen; and the pore diameter of the maximum pore thereof is 50 μm or less.

Owner:IBIDEN CO LTD

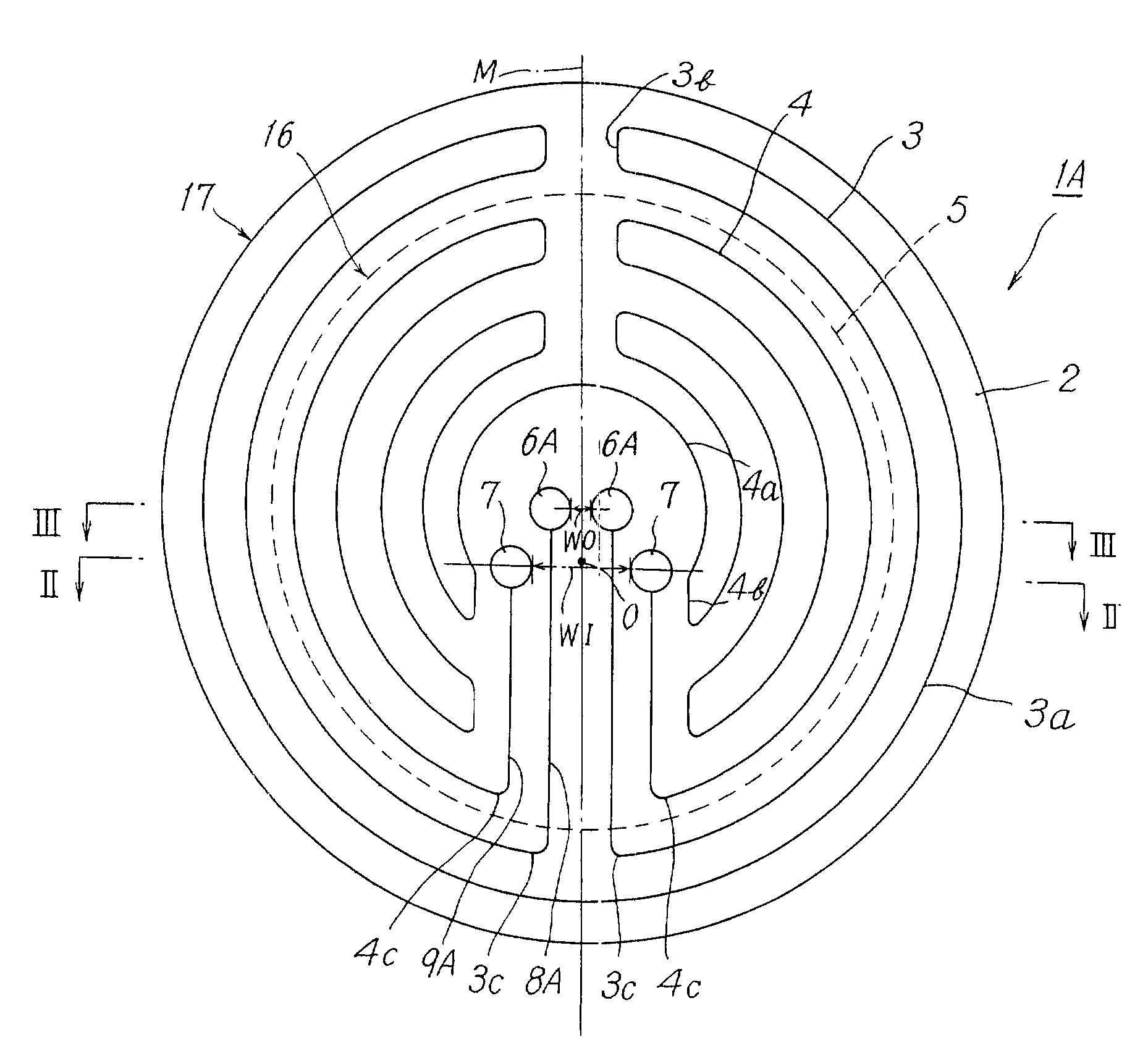

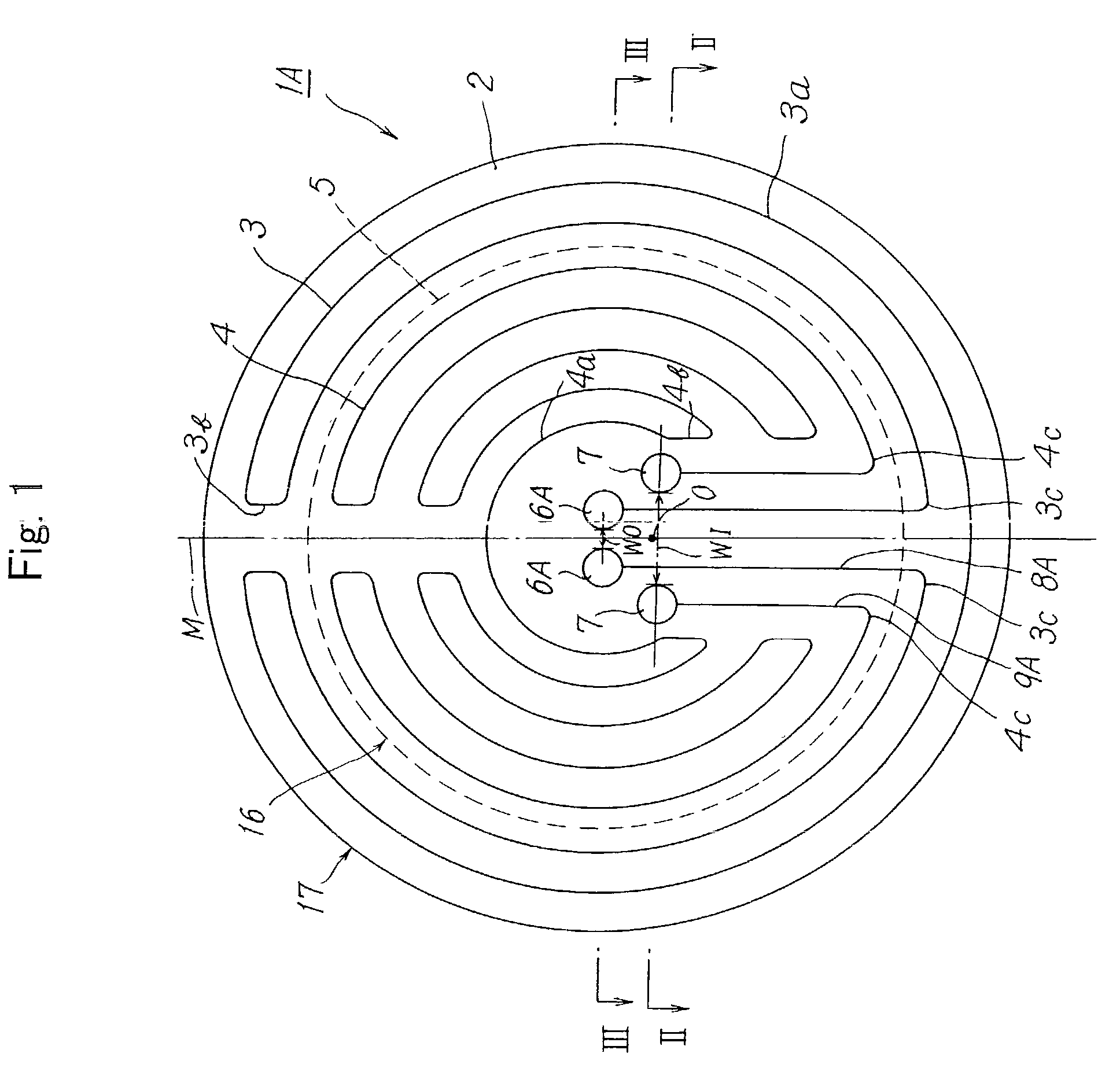

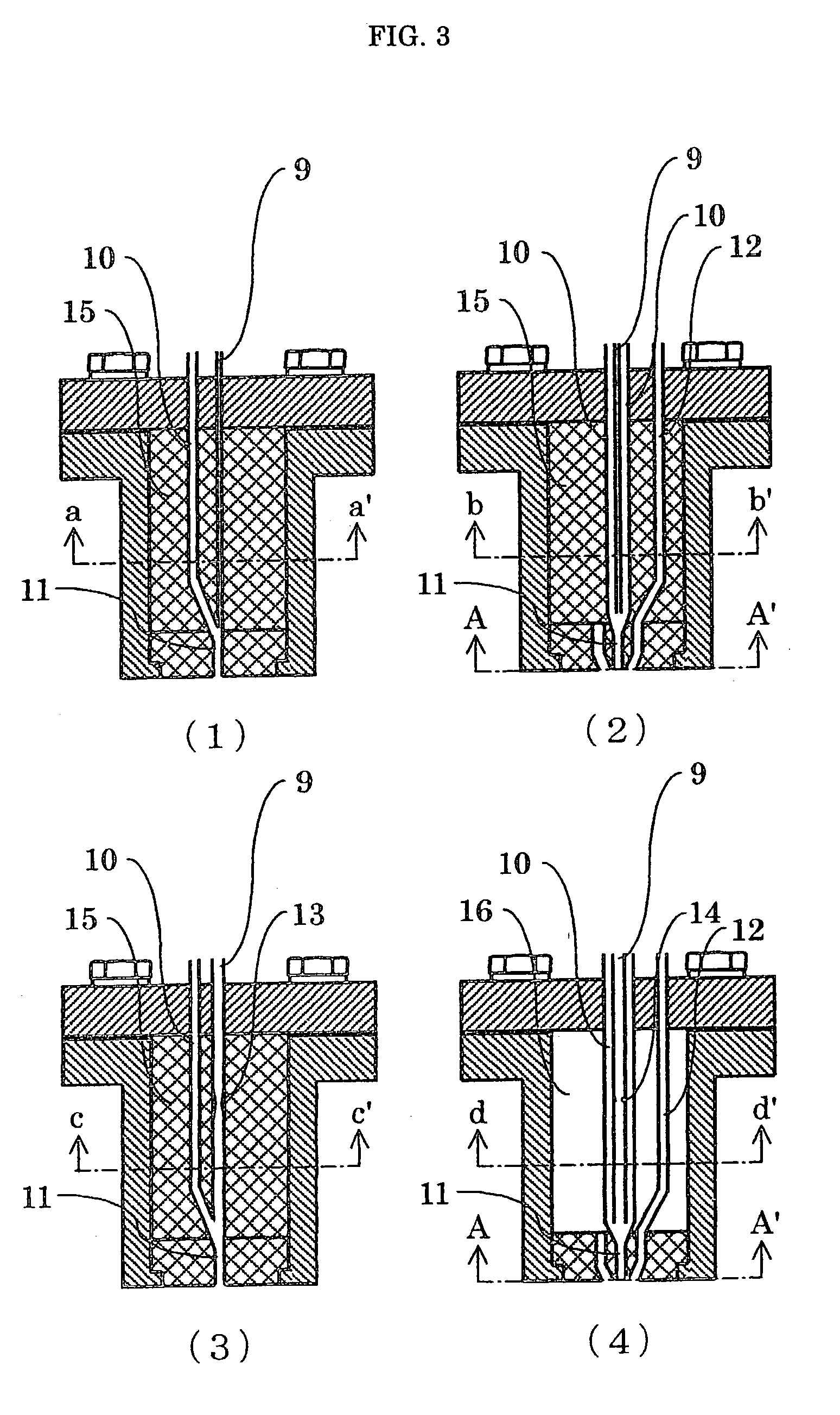

Heating apparatus

InactiveUS7279661B2Prevent increase in heat capacity of heatingEasy to fixOhmic-resistance electrodesHeater elementsEngineeringSemiconductor

A heating apparatus for a semiconductor producing system is provided, including a heater having a mounting face, an opposed back face, a first resistance heating element, a second resistance heating element provided along substantially the same plane as the first heating element, a first terminal connected with the first heating element and a second terminal connected with the second heating element. A supporting member is fixed to the back face of the heater. First and second power supply means are respectively connected with the first and second terminals and contained in an inner space of the supporting member. A conductive connector connects the first heating element and the first terminal but not the second heating element. The first heating element is provided in a first zone, the second heating element is provided in a second zone, and the conductive connector is provided in the plane and the second zone.

Owner:NGK INSULATORS LTD

Semiconductor production method

InactiveUS20050029662A1Inhibit deteriorationImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopper interconnectDevice material

It is an object of the present invention to provide a semiconductor device production method in which an electroconductive capping (metal) layer is formed on a copper interconnect surface, wherein the capping (metal) layer is selectively formed to produce the semiconductor device of high reliability. In the semiconductor device production method, a capping (metal) layer is formed on a copper interconnect in a semiconductor integrated circuit, a first capping (metal) layer is formed by electroless plating with a plating solution containing a reducing agent active on a copper interconnect surface, and then a second capping (metal) layer is formed by another electroless plating.

Owner:HITACHI LTD

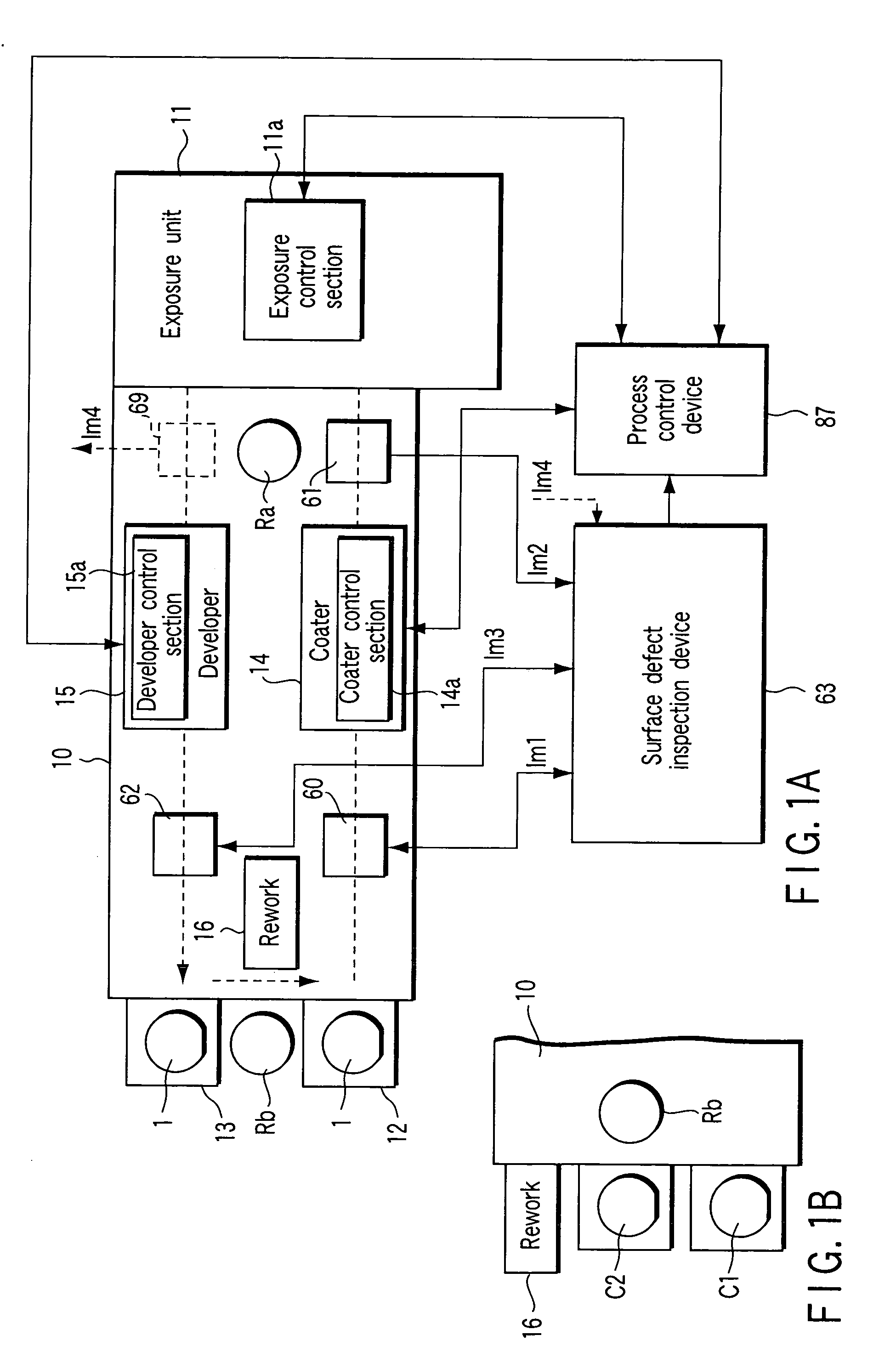

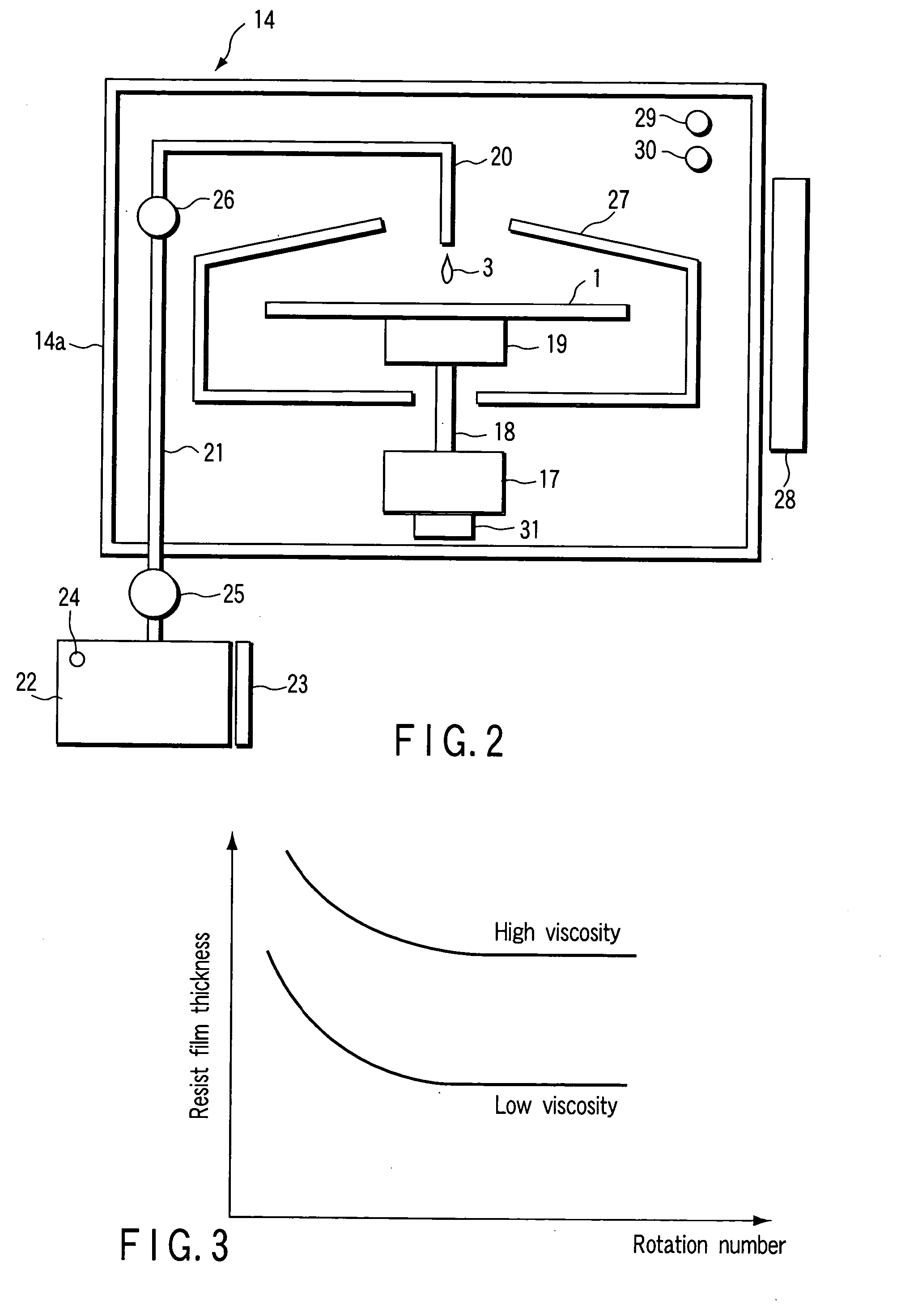

Method and apparatus for manufacturing semiconductor

InactiveUS20050037272A1Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusManufactured apparatusSemiconductor

In a method of manufacturing a semiconductor, in which a semiconductor substrate is worked / treated in each manufacturing step of a semiconductor manufacturing line, image data is acquired before and after working / treating the semiconductor substrate transported into a manufacturing apparatus disposed in each manufacturing step, respectively, defects attributed to treatment conditions of the manufacturing apparatus are detected from the image data before the working / treating, or non-defective master image data, and the image data after the working / treating, and the treatment conditions of the manufacturing apparatus are changed / controlled based on the detection result to work / treat the semiconductor substrate.

Owner:OLYMPUS CORP

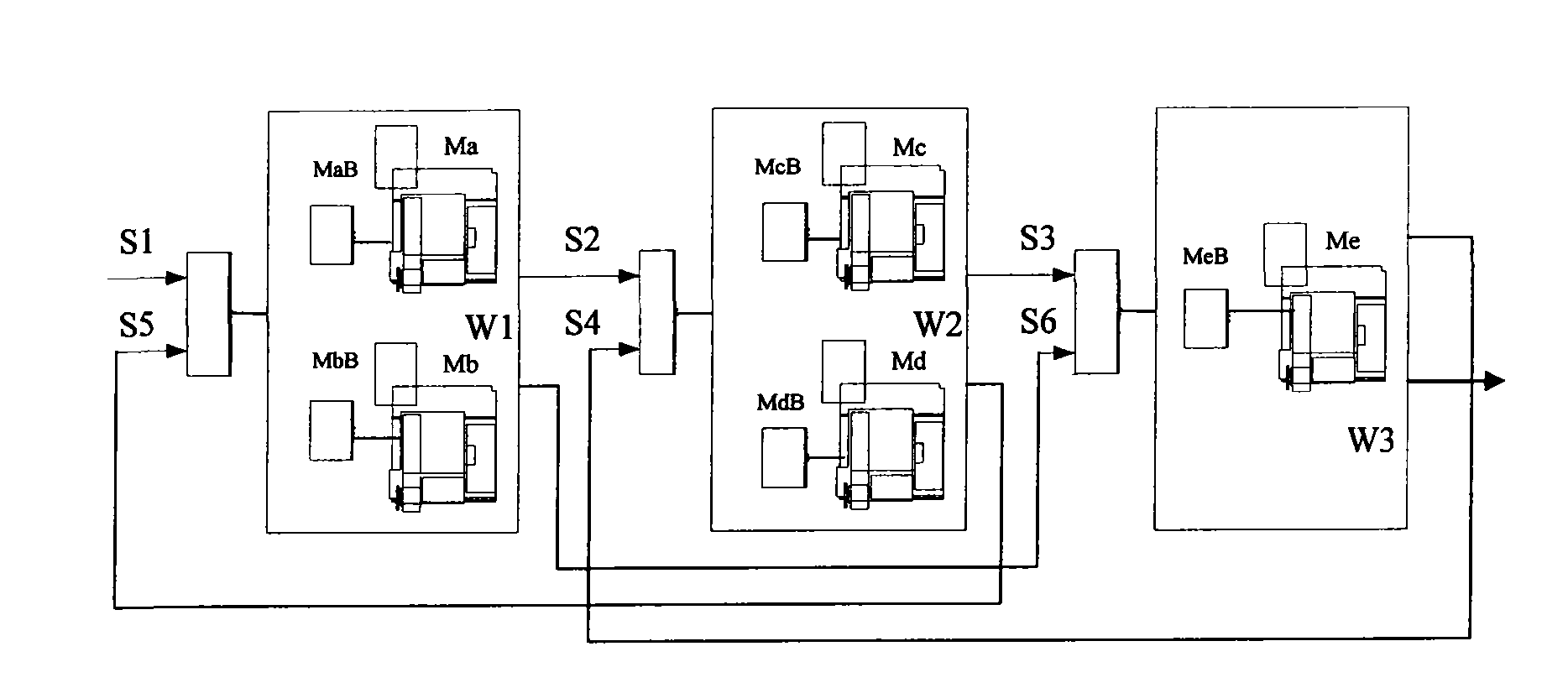

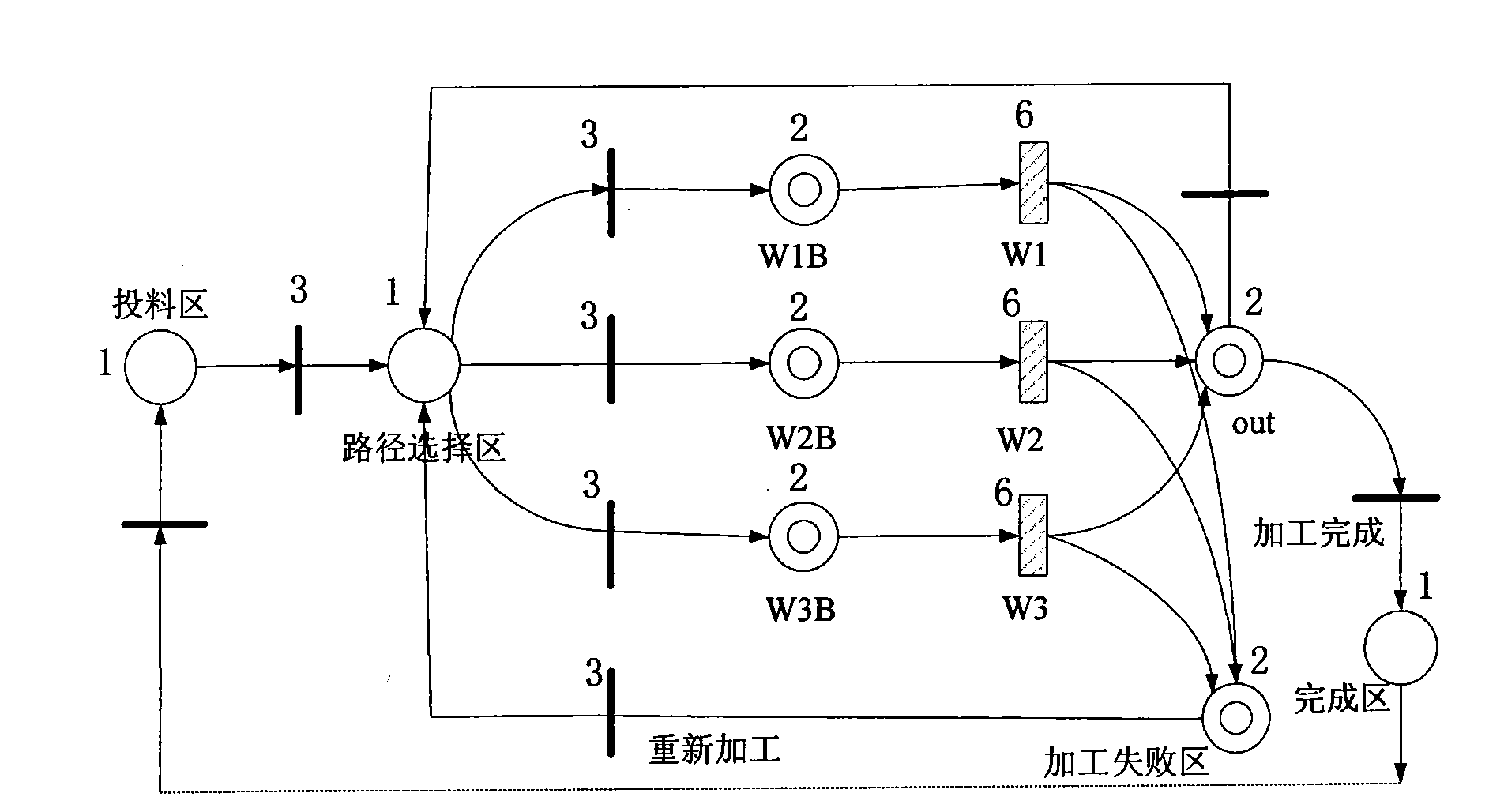

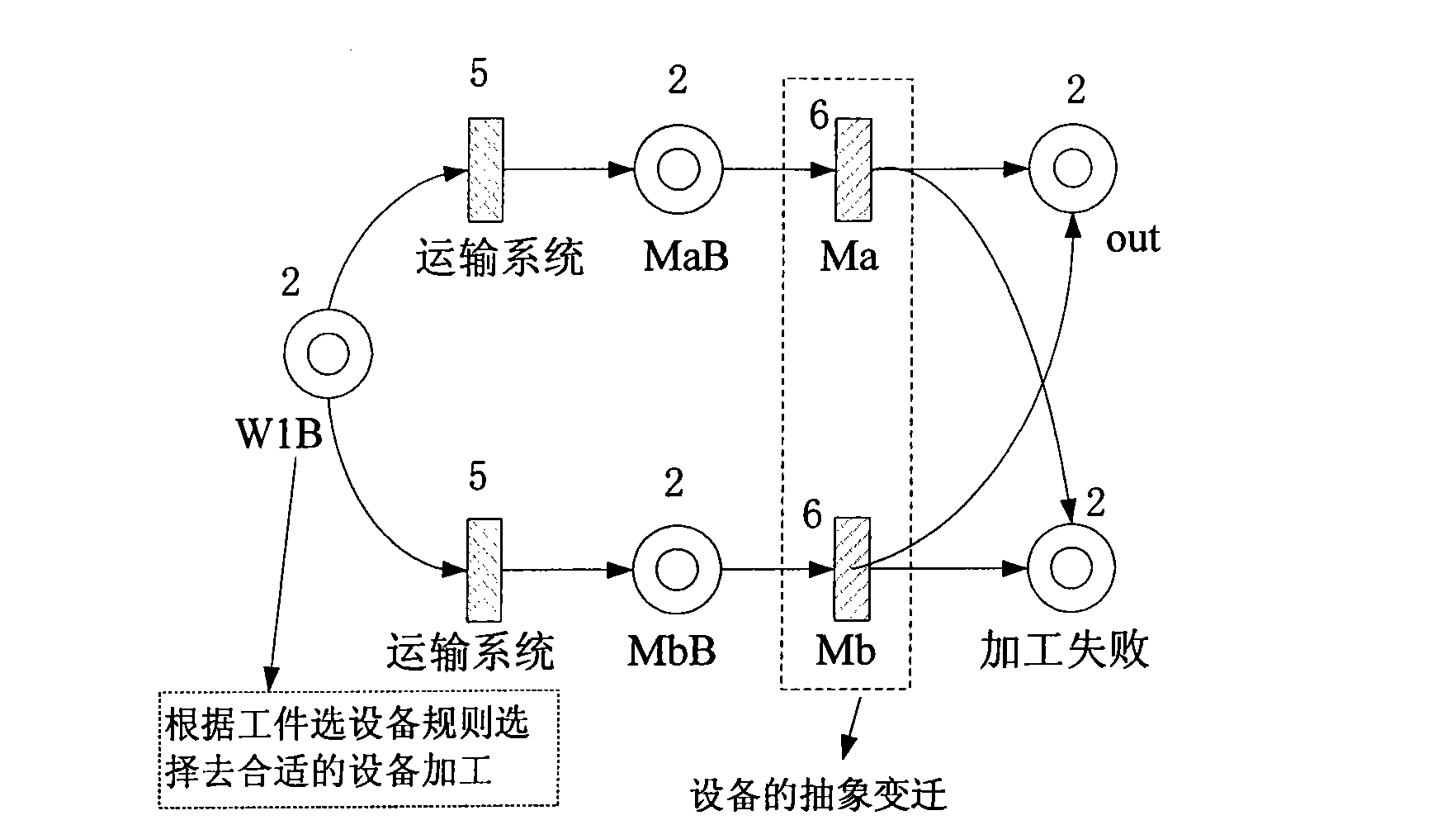

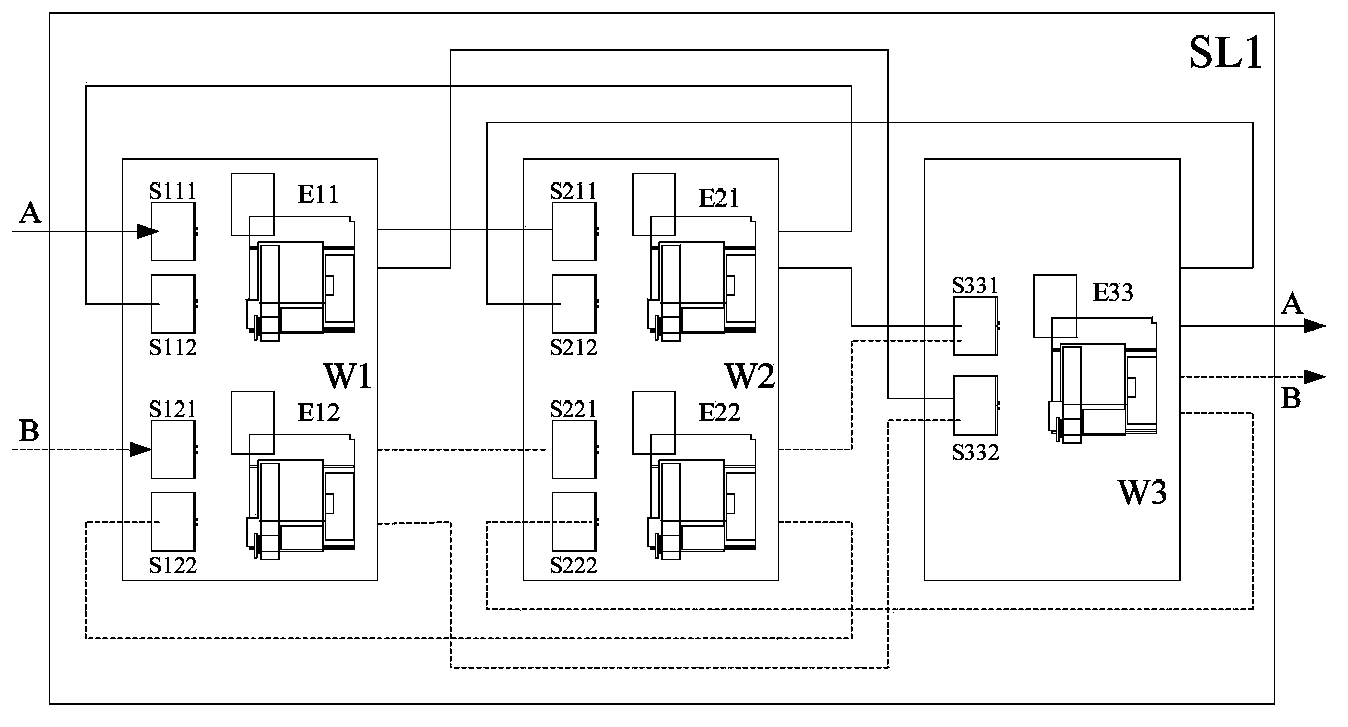

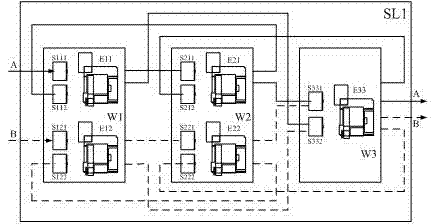

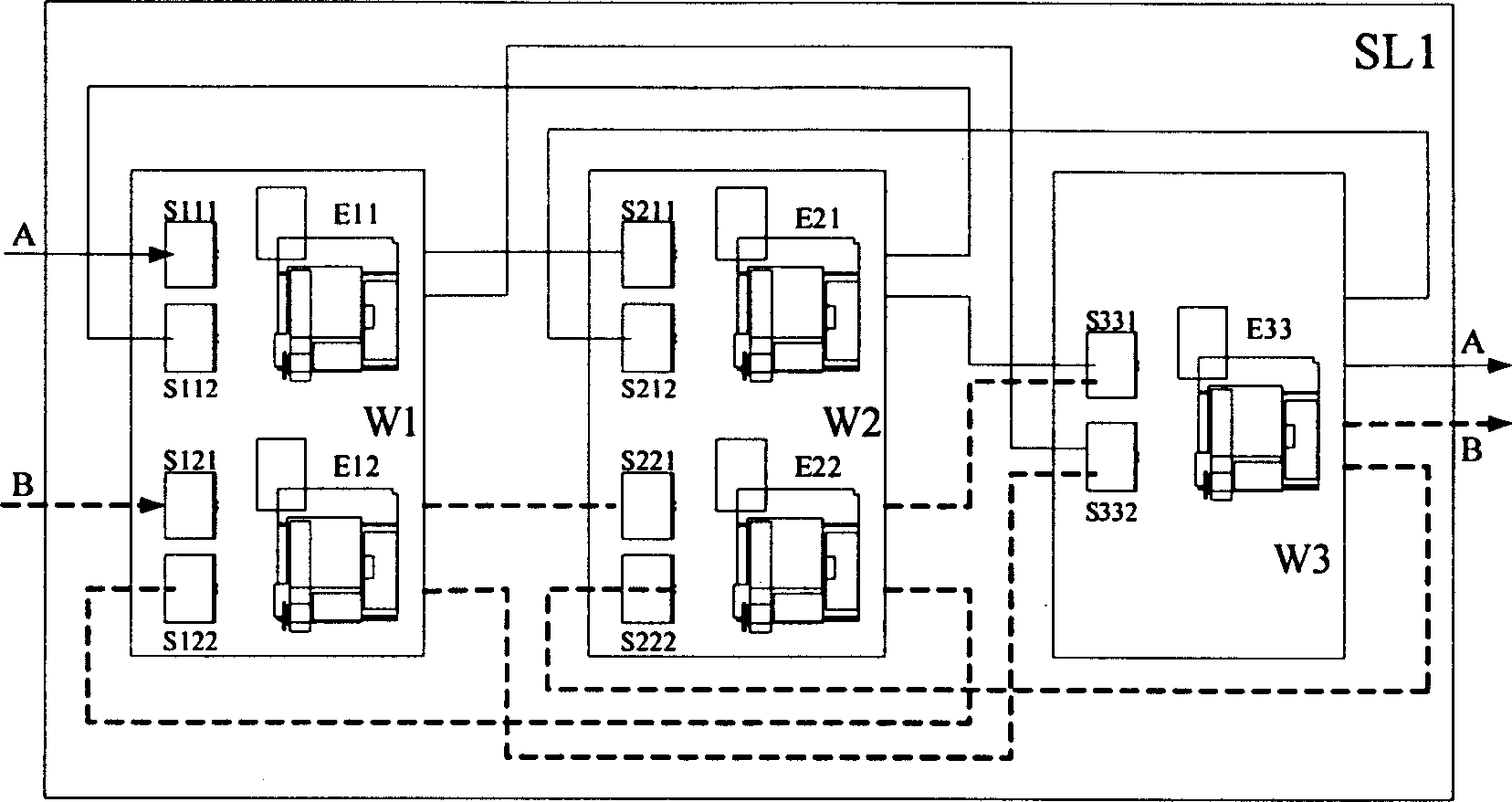

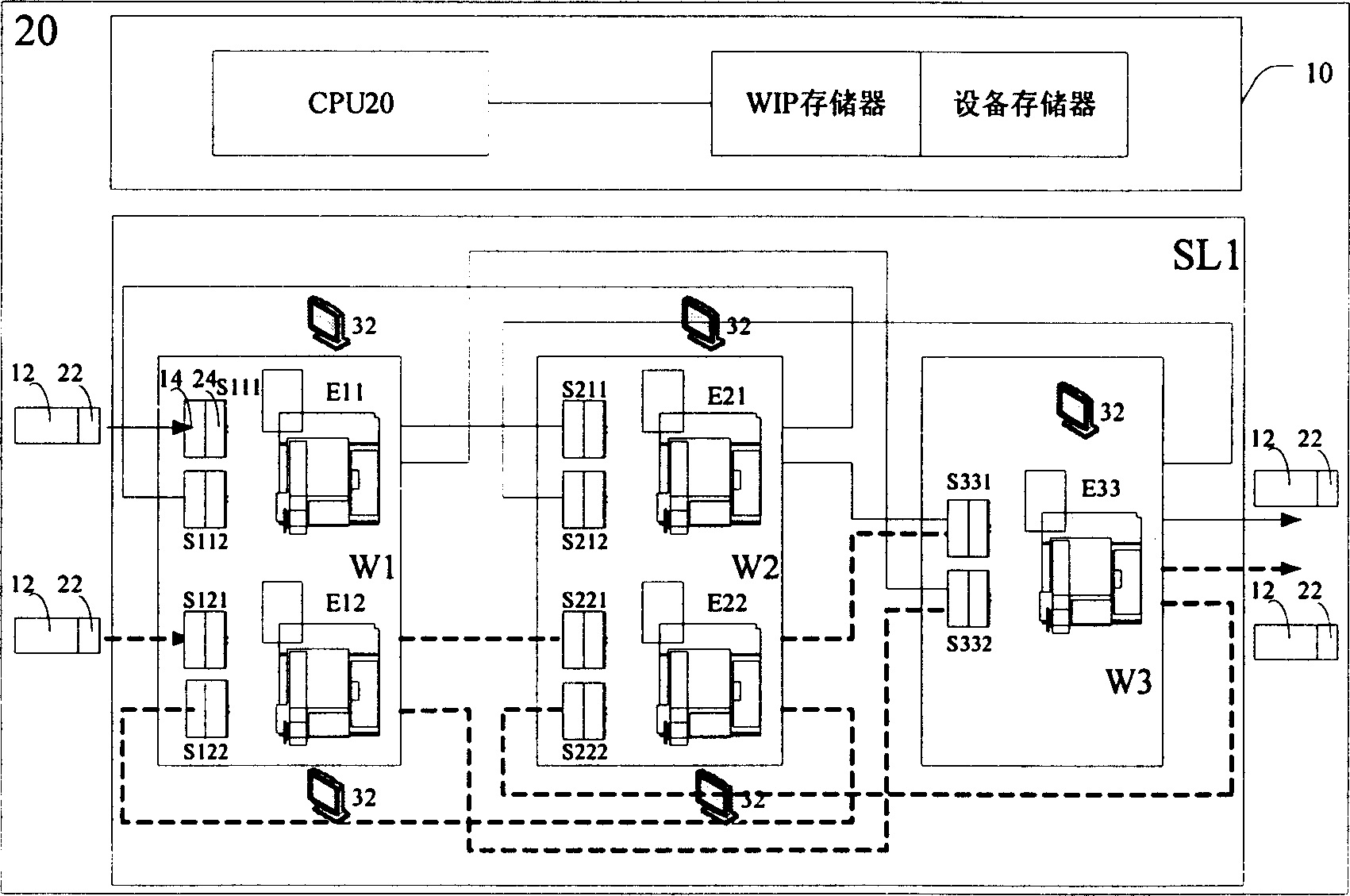

Semiconductor production line model building, optimizing and scheduling method based on petri net and immune arithmetic

InactiveCN101493857AReduce complexityImprove reusabilityGenetic modelsTotal factory controlBatch processingGroup scheduling

The invention provides an optimized scheduling method of a semiconductor production line based on a Petri net and immune algorithm. The method utilizes the Petri net for carrying out modeling to the semiconductor production line, comprising a path scheduling model, an equipment group scheduling model and an equipment scheduling model; and the immune algorithm is embedded in the Petri net model as the scheduling strategy. By the Petri net model, all possible acts of the semiconductor manufacturing system can be described, such as work-piece processing, equipment failure, batch processing, defected wafer rework and the like. The chromosome of the immune algorithm can be directly structured out of search nodes of the Petri net model, and each gene of each chromosome records the scheduling strategy of each equipment group. A better chromosome is obtained by the simulation of the Petri net model, and therefore a sub-optimal scheduling strategy is generated. The optimized scheduling method has the advantages of reducing the complexity of the model and improving the reusability of the model and the scheduling algorithm.

Owner:TONGJI UNIV

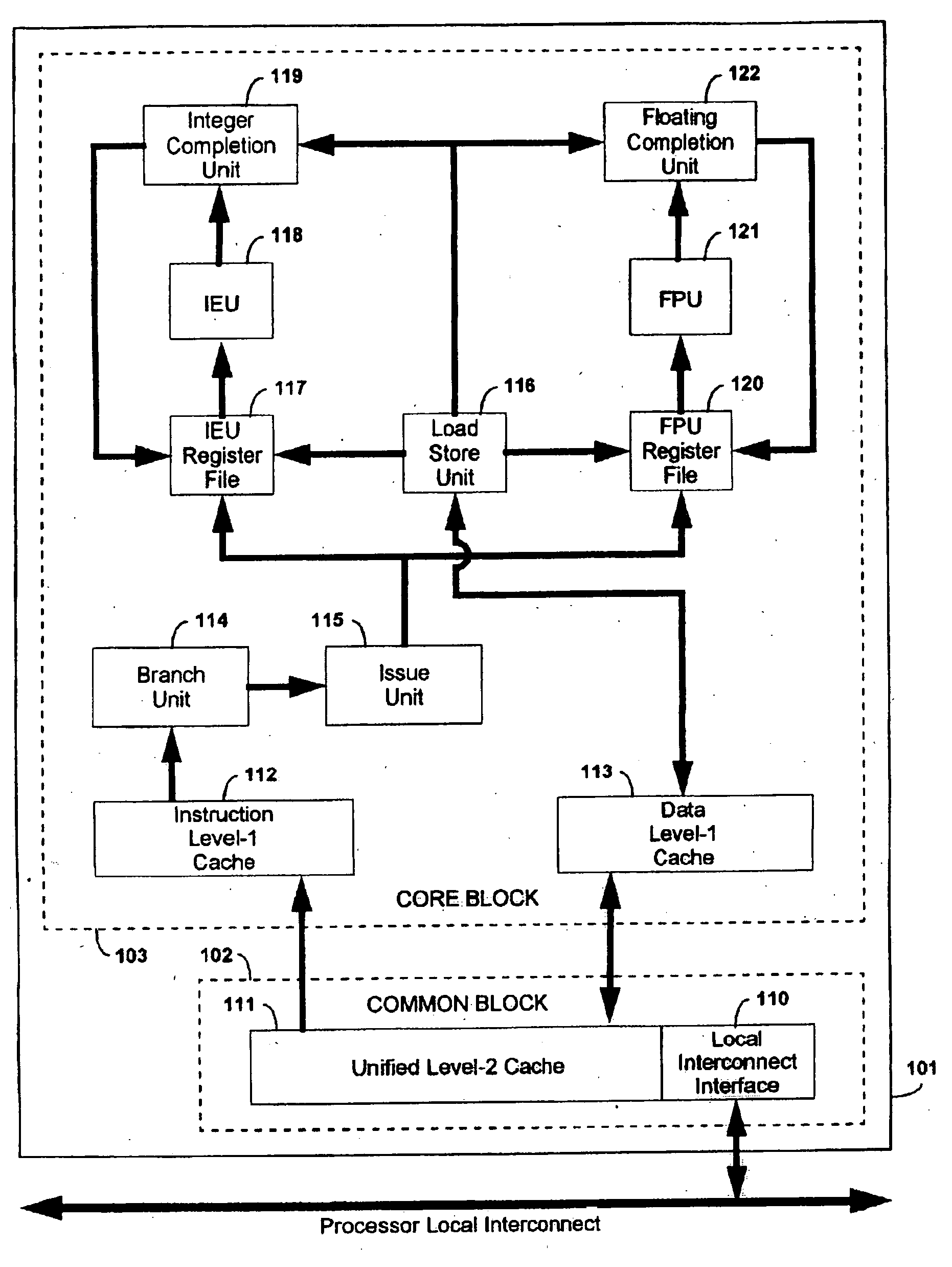

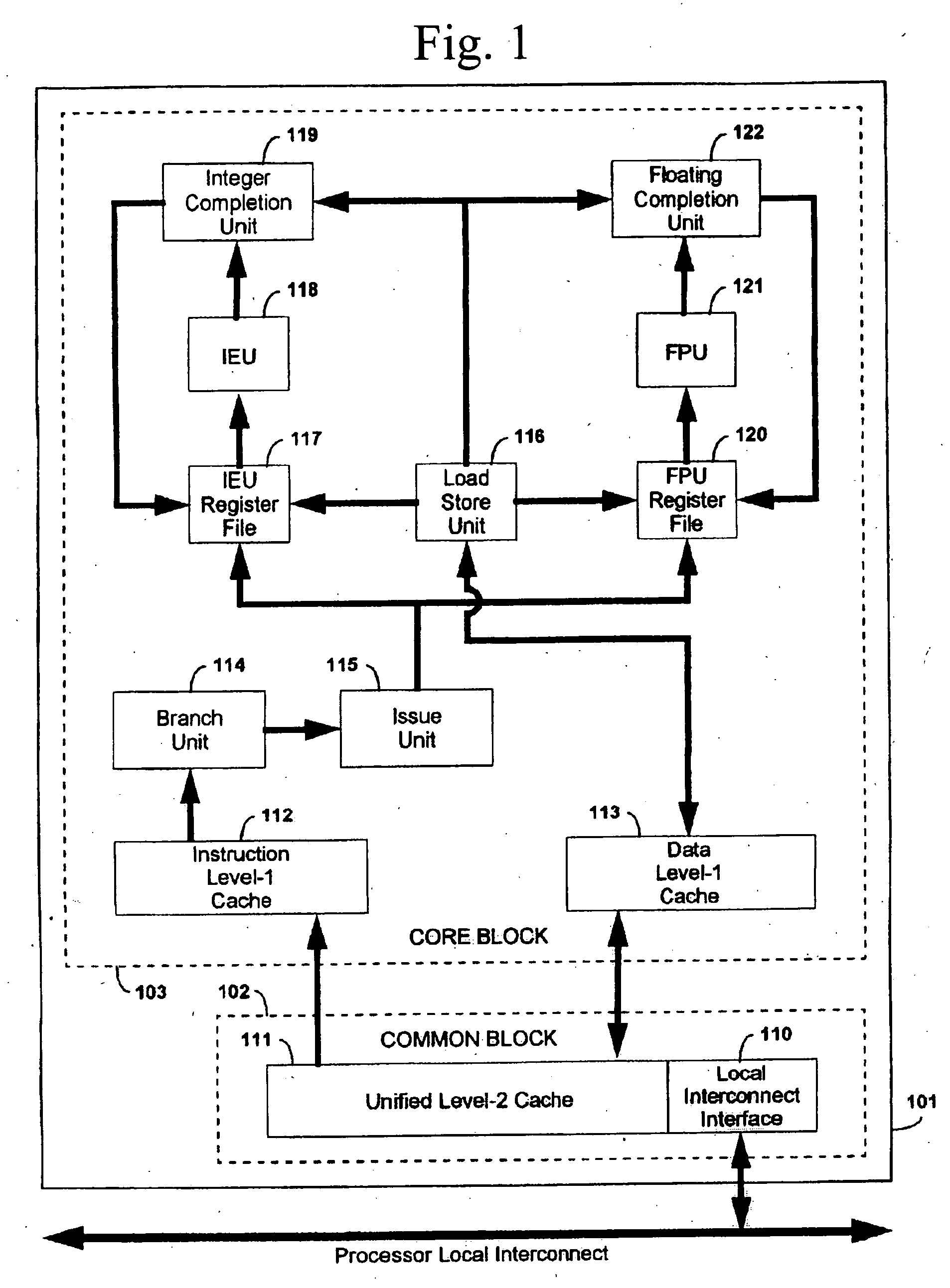

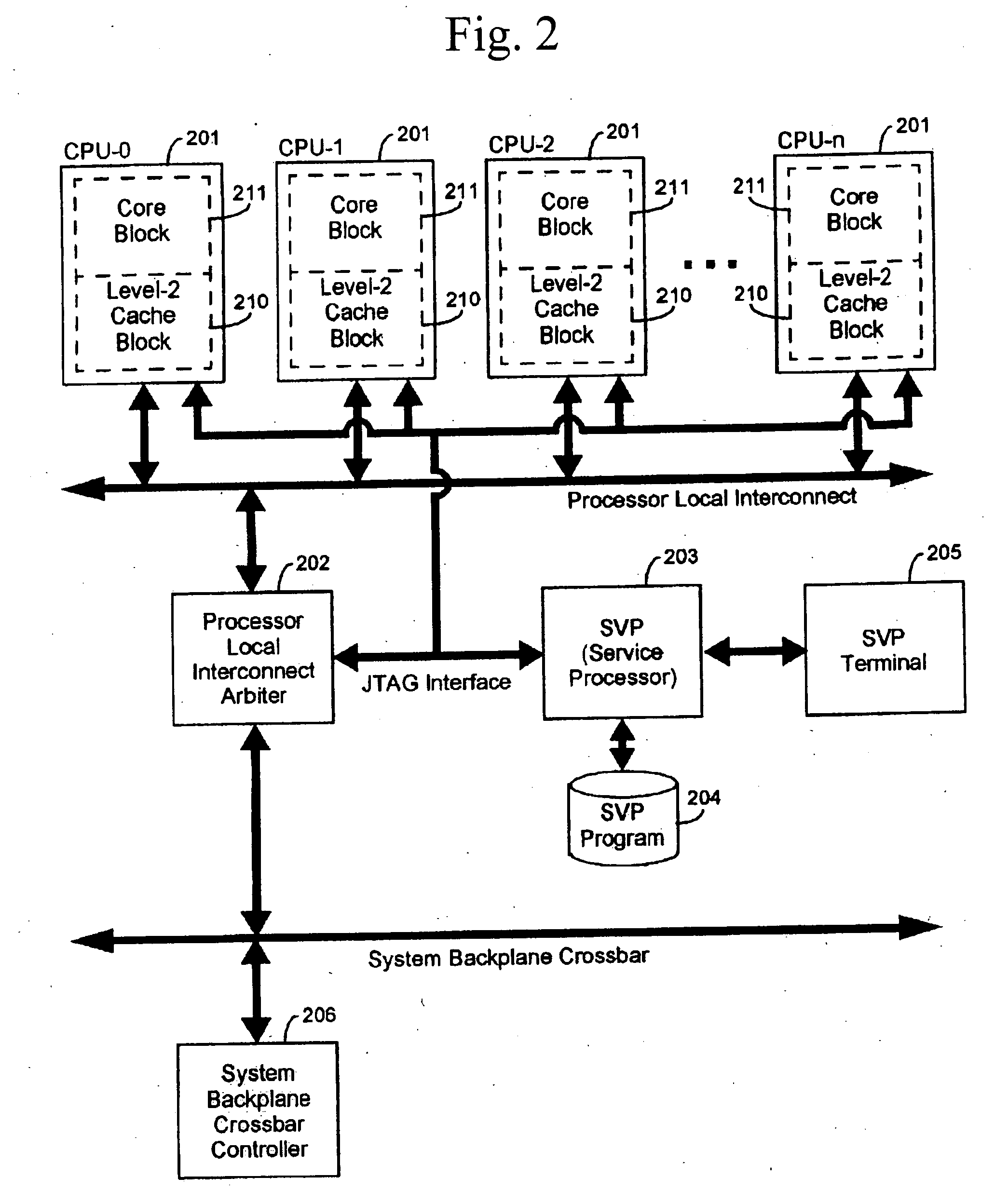

Multi-core processor control method

InactiveUS20050289286A1Shortening of system boot timeIncrease productionError detection/correctionMemory adressing/allocation/relocationMulti-core processorFLAGS register

The load / sense control of the setting value that corresponds to the processor core for CMP, etc. processors that have multi-cores realize, for such processors with multi-core structures, the shortening of system boot time during multi-core operation, flexible debugging methods, and improvement of yield with the aid of partial core quality product chips at time of semiconductor production, by equipping a core selection flag register that maintains the status of each core, and controlling the output to the core block from the processor common block through that core selection flag register status.

Owner:FUJITSU LTD

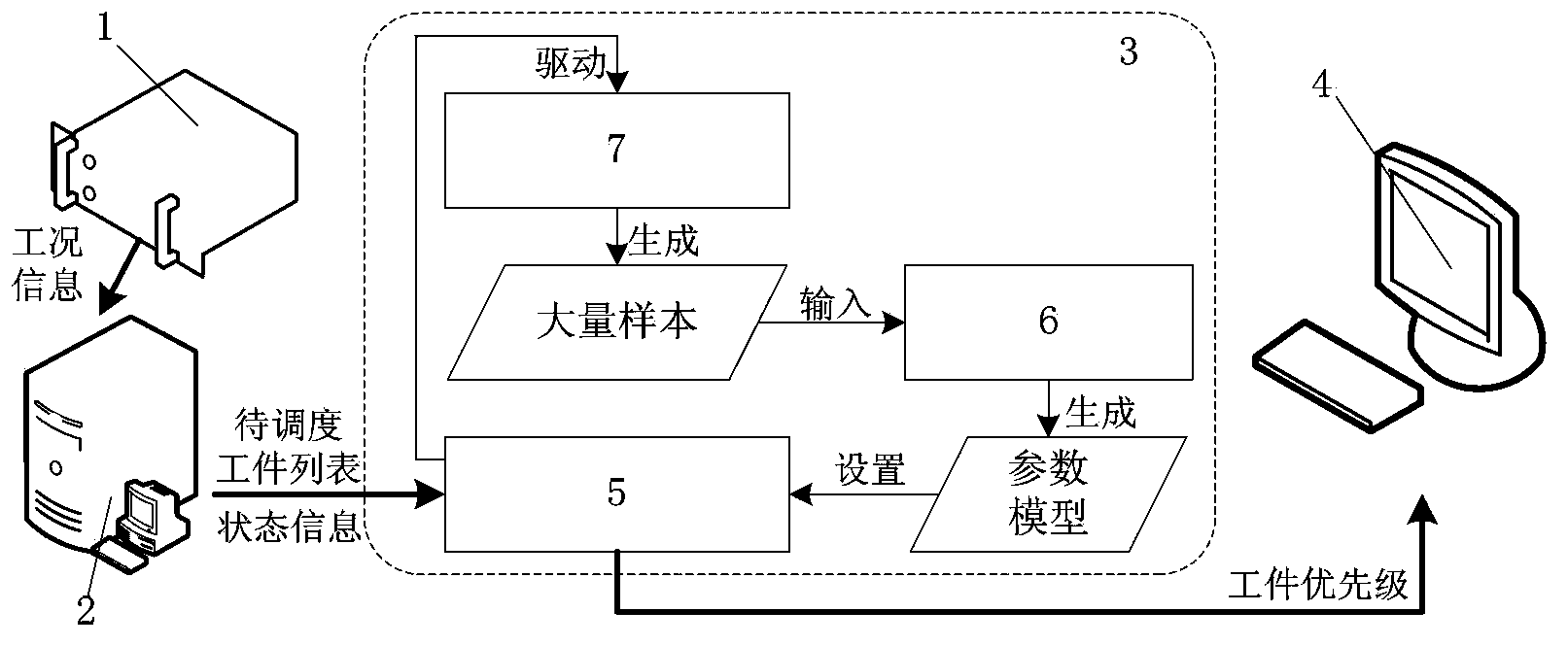

Semiconductor production line self-adaptation dynamic dispatching device

InactiveCN103439886AIncrease profitOn-Time Delivery ImprovementAdaptive controlDisplay deviceManufacturing execution system

The invention relates to a semiconductor production line self-adaptation dynamic dispatching device which is connected with a manufacturing execution system. The dispatching device comprises a dispatching management device, a learning device and a display device. The dispatching management device is connected with the manufacturing execution system, and the dispatching management device, the learning device and the display device are connected in sequence. The dispatching management device acquires a list of current workpieces to be dispatched through the manufacturing execution system and transmits the list of the current workpieces to be dispatched to the learning device, the learning device calculates machining priorities of the current workpieces to be dispatched according to a dispatching rule stored in the learning device and transmits the priorities of the current workpieces to be dispatched to the display device, and the display device displays the priorities of the current workpieces to be dispatched. Compared with the prior art, the semiconductor production line self-adaptation dynamic dispatching device has the advantages of being capable of improving workpiece machining efficiency and bottleneck equipment use ratios, good in dynamic regulation performance, and the like.

Owner:TONGJI UNIV

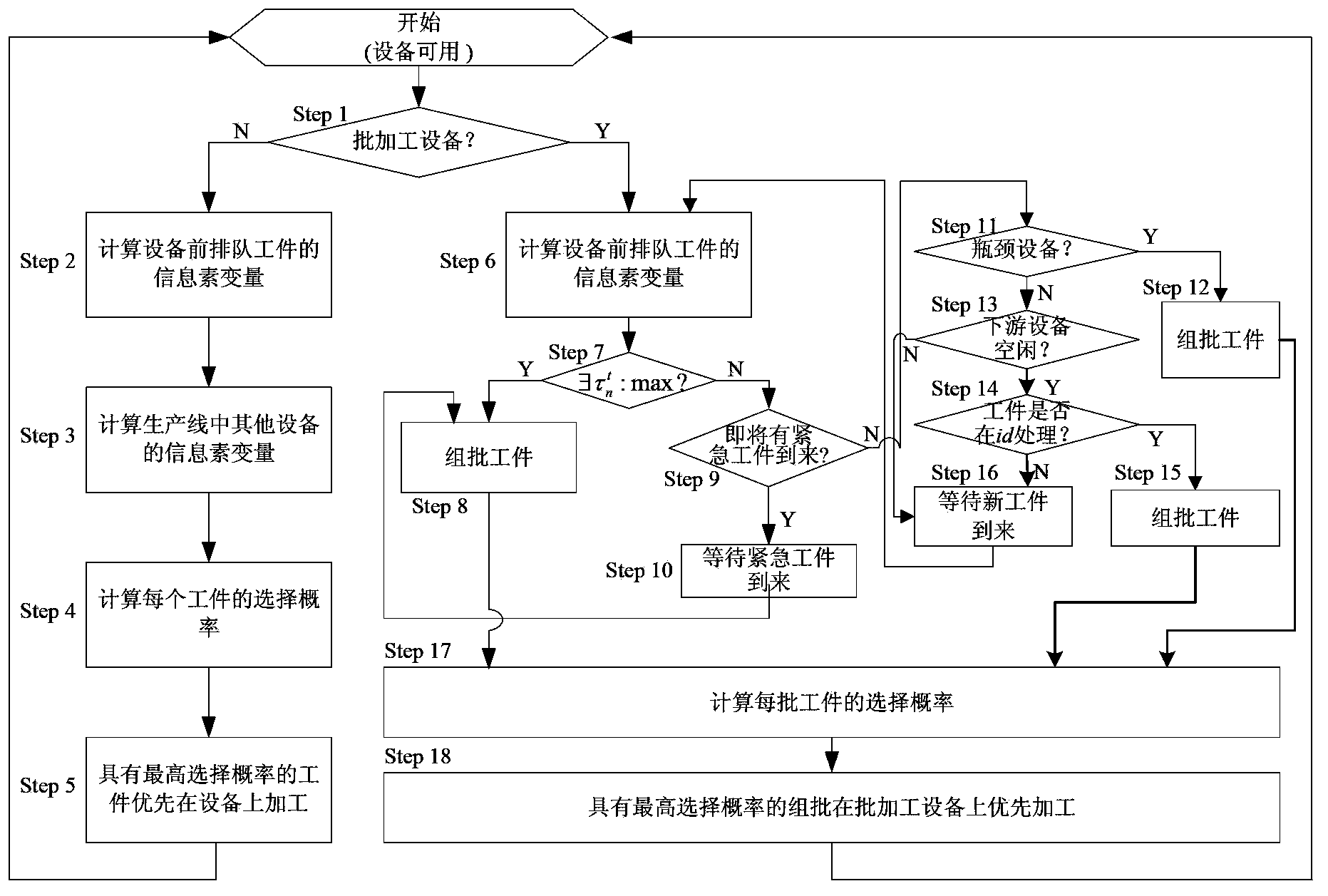

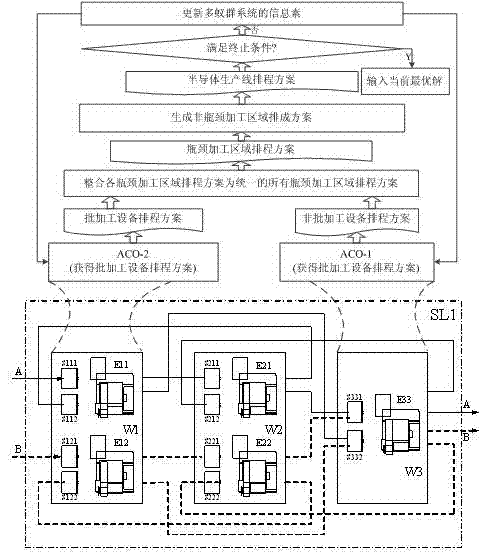

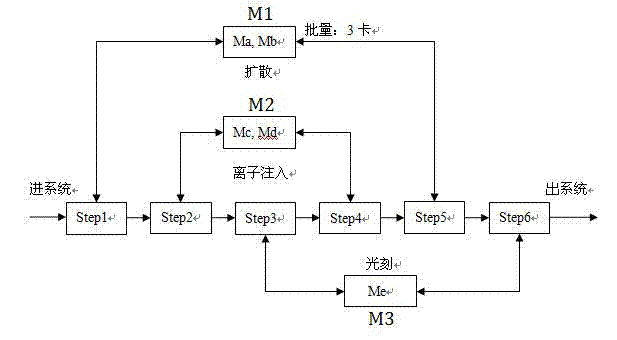

Scheduling method for semiconductor production line based on multi-ant-colony optimization

InactiveCN102253662AThe scheduling method is stableRobust and stableTotal factory controlProgramme total factory controlProduction lineBottleneck

The invention relates to a scheduling method for a semiconductor production line based on multi-ant-colony optimization. The method comprises the following steps of: determining bottleneck processing areas of the semiconductor production line, wherein processing areas, of which average utilization rate exceeds 70 percent, of equipment are regarded as the bottleneck processing areas; setting the number of ant colonies as the number of the bottleneck processing areas, and initializing a multi-ant-colony system; parallelly searching scheduling schemes of all bottleneck processing areas by all ant colony systems; restraining and integrating the scheduling schemes of all bottleneck processing areas into one scheduling scheme for all bottleneck processing areas according to a procedure processing sequence, and deducing the scheduling schemes of other non-bottleneck processing areas by using the scheduling scheme and the procedure processing sequence as restraint to obtain the scheduling scheme of the whole semiconductor production line; and judging whether program ending conditions are met, if so, inputting the scheduling scheme which is optimal in performance, otherwise, updating pheromones of the ant colonies by using the scheduling scheme which is current optimal in performance, and guiding a new round of searching process. The method has the advantages that: an important practical value is provided for solving the optimal dispatching problem of the semiconductor production line; and important instructional significance is provided for improving the production management level of semiconductor enterprises of China.

Owner:TONGJI UNIV

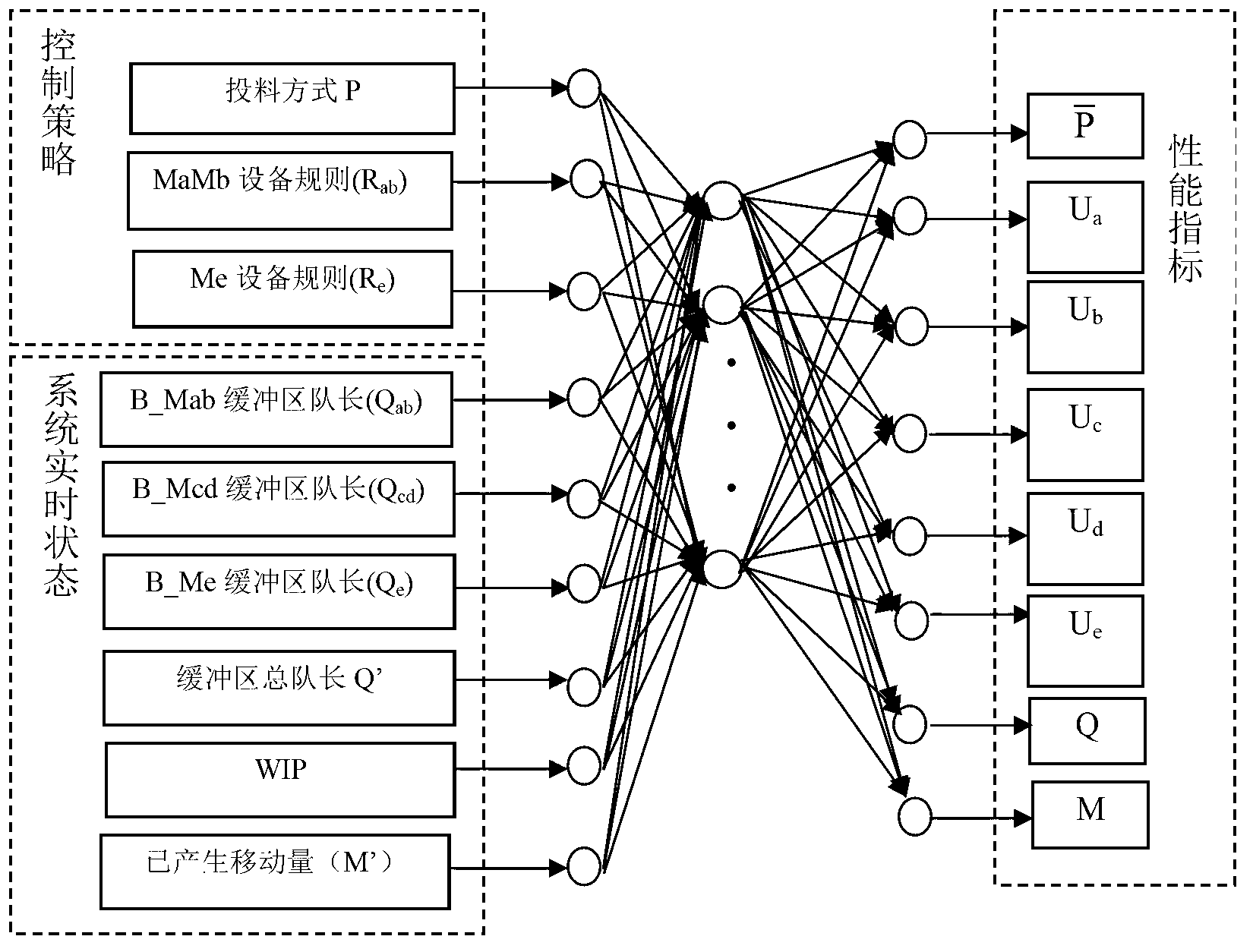

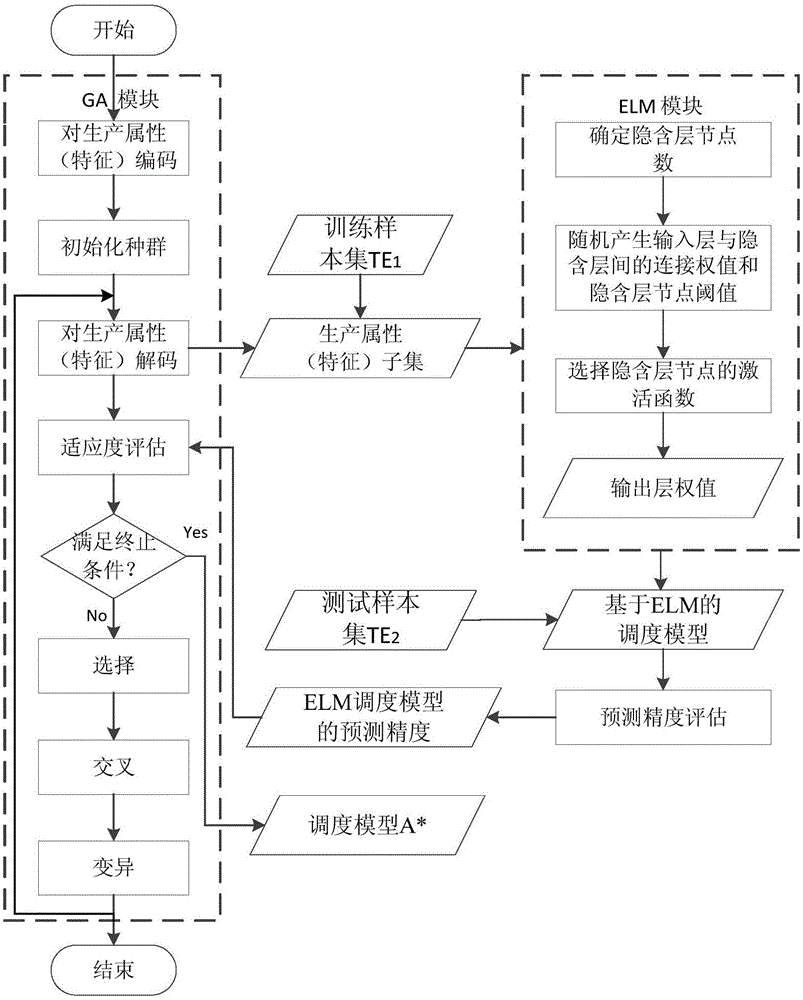

Performance prediction method applicable to dynamic scheduling for semiconductor production line

InactiveCN103310285AReduce the need for reschedulingRealize real-time online optimization controlForecastingLearning machineOptimal control

The invention discloses a performance prediction method applicable to dynamic scheduling for a semiconductor production line. An extreme learning machine (ELM) is applied to prediction and modeling in the performance prediction method. Feeding control and scheduling rules are considered in a unified manner in the method, short-term scheduling key performance indexes such as an equipment utilization rate and a movement step number are predicted on the basis of a real-time state of a system, and a foundation is provided for dynamic real-time scheduling. A novel feed-forward neural network of the ELM is introduced into the semiconductor manufacturing system, and a prediction model is built by the aid of available data of the production line. As shown by test results, ideal prediction results can be quickly acquired by the method implemented by the aid of the ELM, the method has obvious advantages and an obvious application prospect in the aspects of parameter selection and learning speed as compared with the traditional neural network modeling method, and a new idea is provided for online optimal control.

Owner:TONGJI UNIV

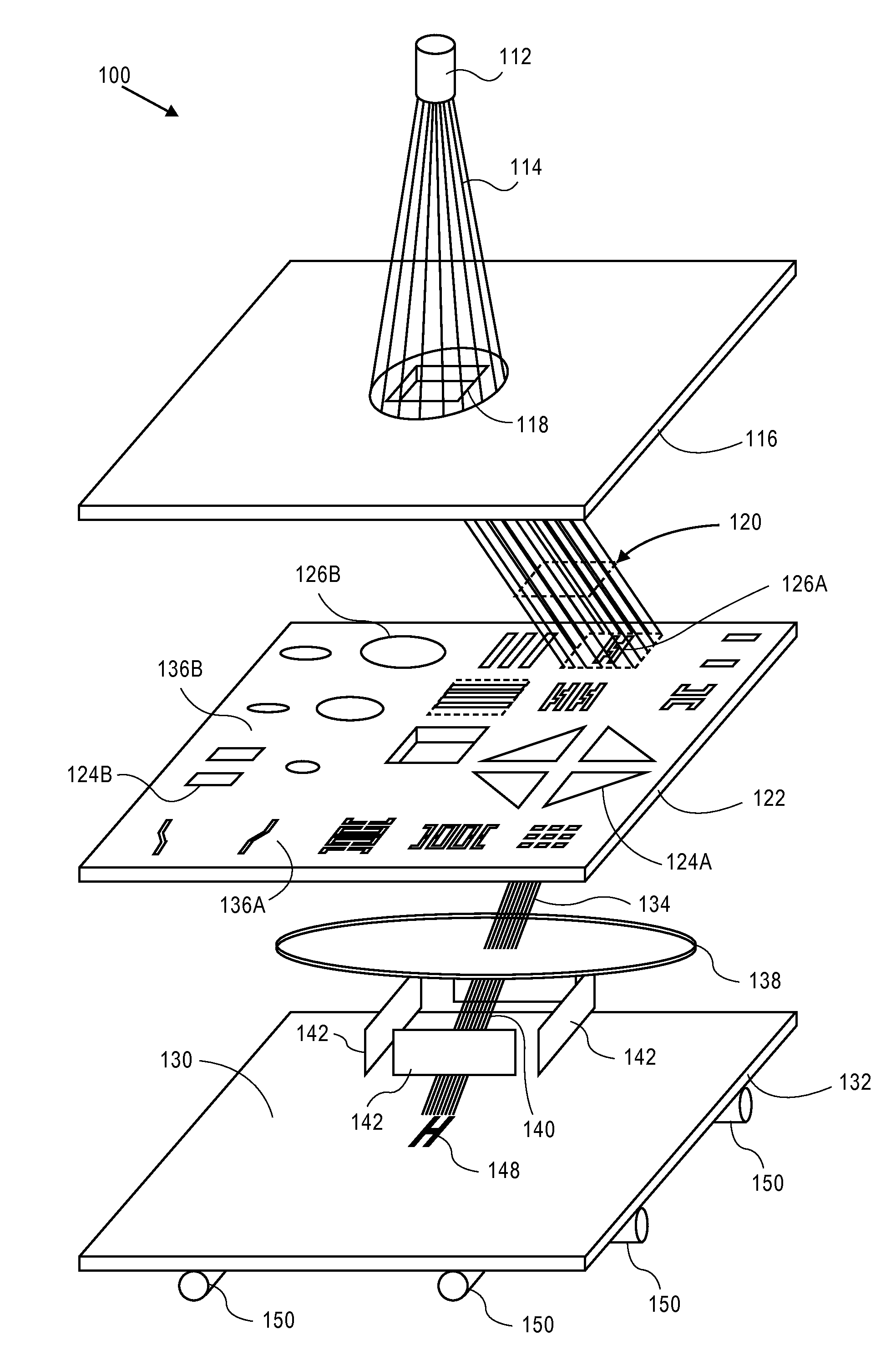

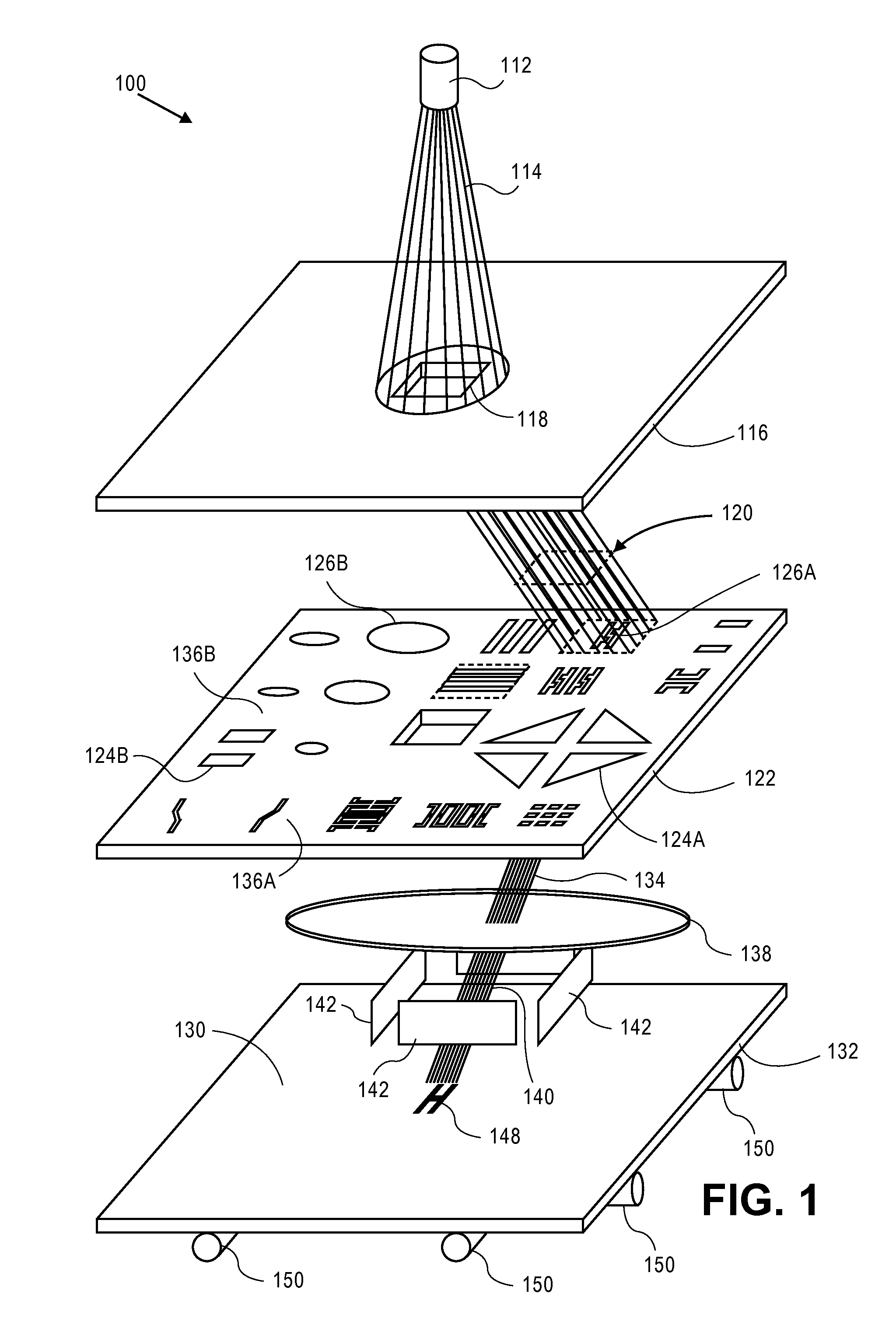

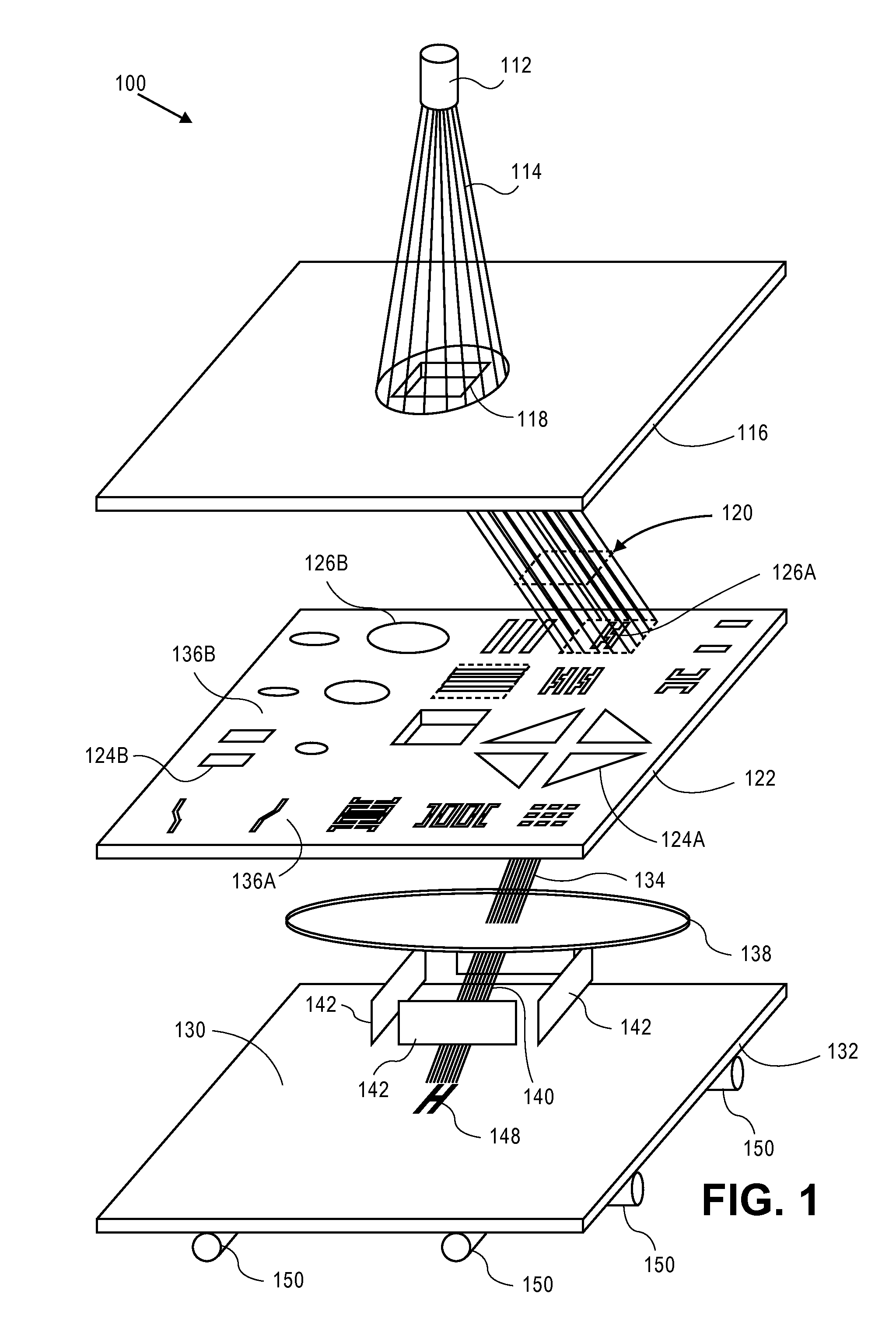

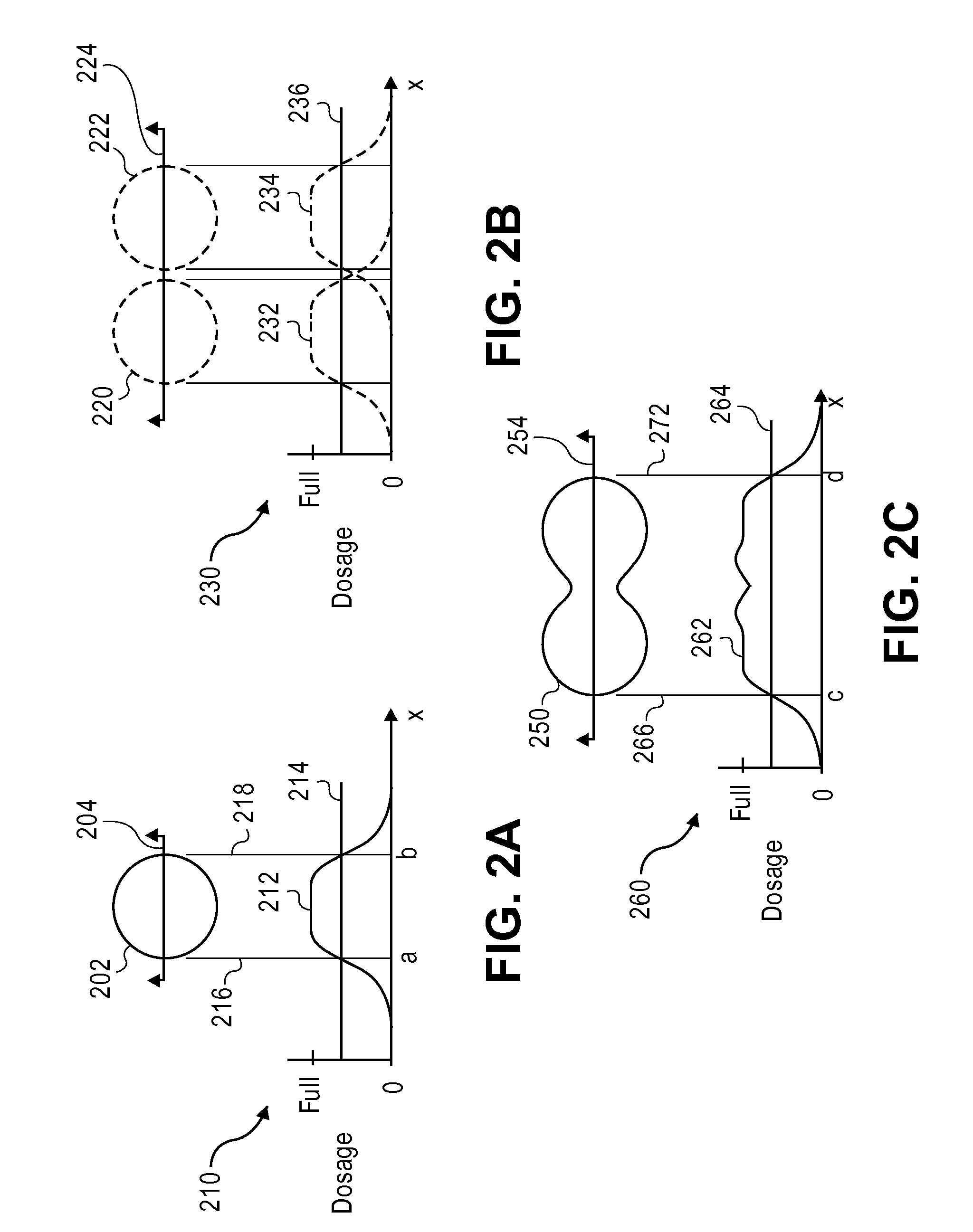

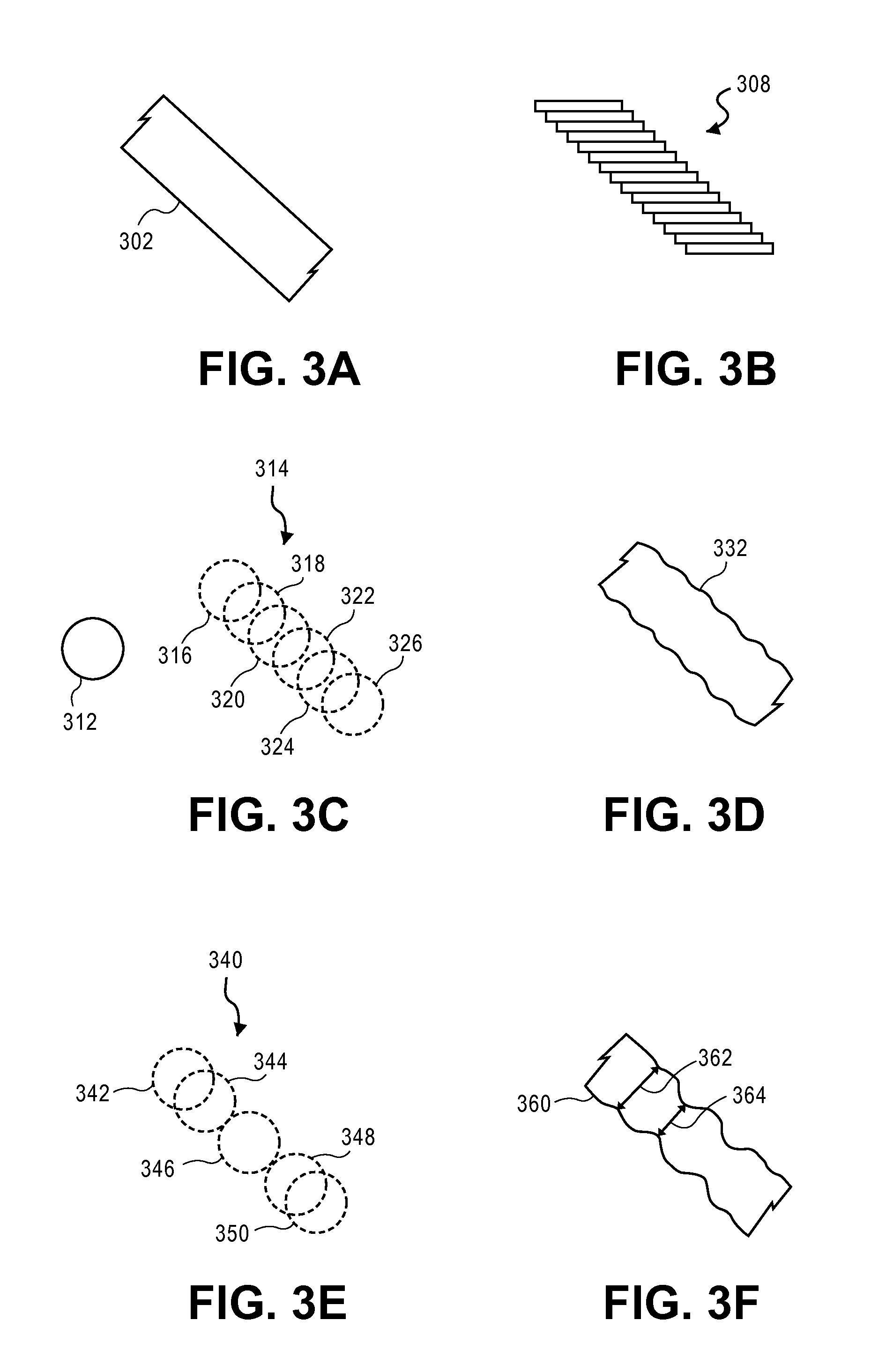

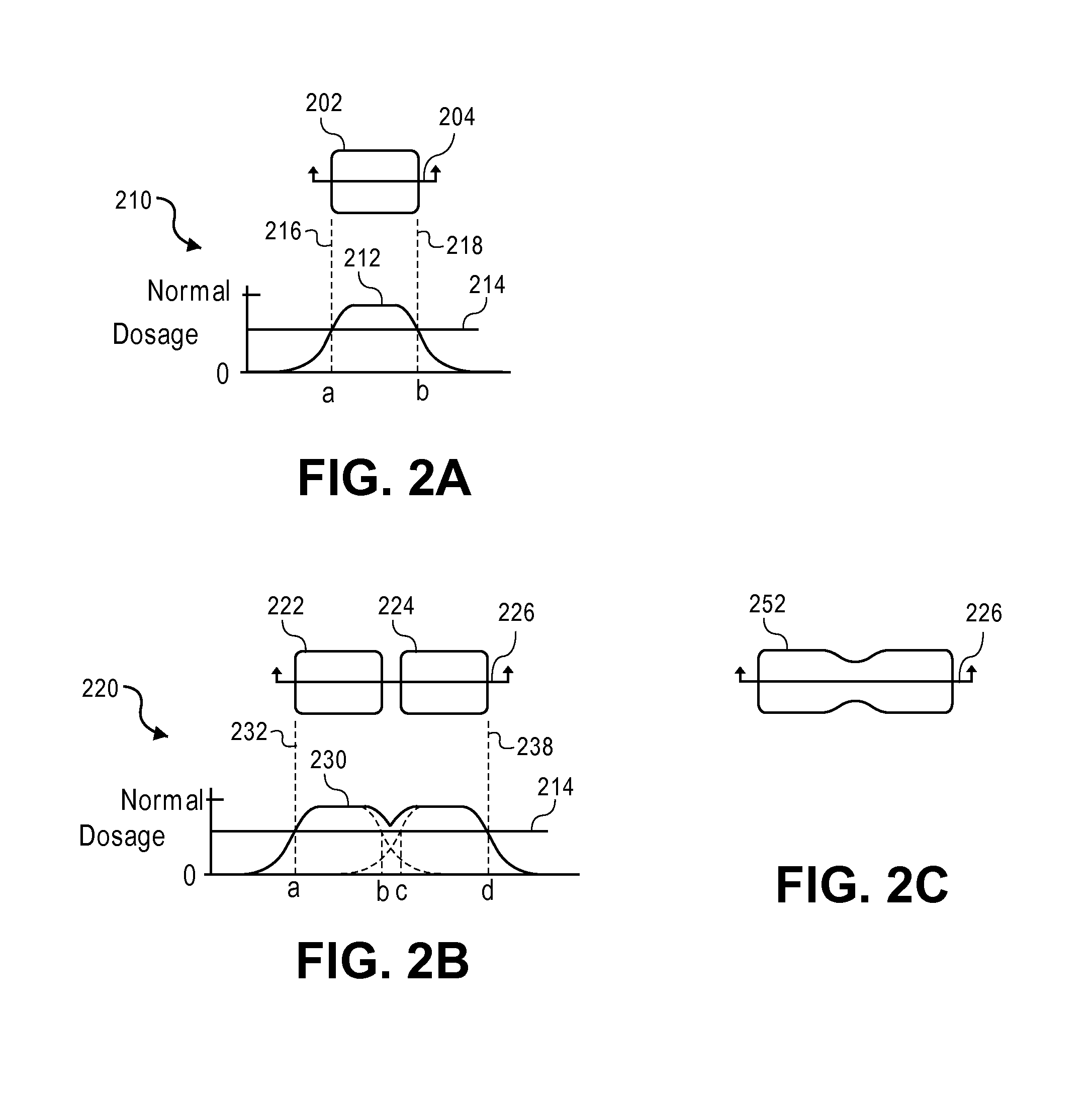

Method for Fracturing and Forming a Pattern Using Curvilinear Characters with Charged Particle Beam Lithography

InactiveUS20110053056A1Photo-taking processesElectric discharge tubesMask data preparationCamera lens

In the field of semiconductor production using shaped charged particle beam lithography, a method and system for fracturing or mask data preparation or proximity effect correction is disclosed, wherein a series of curvilinear character projection shots are determined for a charged particle beam writer system, such that the set of shots can form a continuous track, possibly of varying width, on a surface. A method for forming a continuous track on a surface using a series of curvilinear character projection shots is also disclosed. Methods for manufacturing a reticle and for manufacturing a substrate such as a silicon wafer by forming a continuous track on a surface using a series of curvilinear character projection shots is also disclosed.

Owner:D2S

Ceramic heater

InactiveUS20050016986A1Efficient transferEliminate temperature differenceSemiconductor/solid-state device manufacturingHot plates heating arrangementsElectrical resistance and conductanceSemiconductor

The invention is a ceramic heater provided with a resistor heating body formed in an interior of a ceramic substrate, characterized in that the resistor heating body is made of an electrically conductive ceramic and a sintering aid containing layer is existent at least on the surface of the resistor heating body. This heater does not generate crack even in the rapid temperature rise, and has an effect of uniformizing the heating and rapidly increasing the temperature rising rate, and is used in an industrial field of semiconductor production-inspection apparatuses including an electrostatic chuck or plasma generating device, optical apparatuses and the like.

Owner:IBIDEN CO LTD

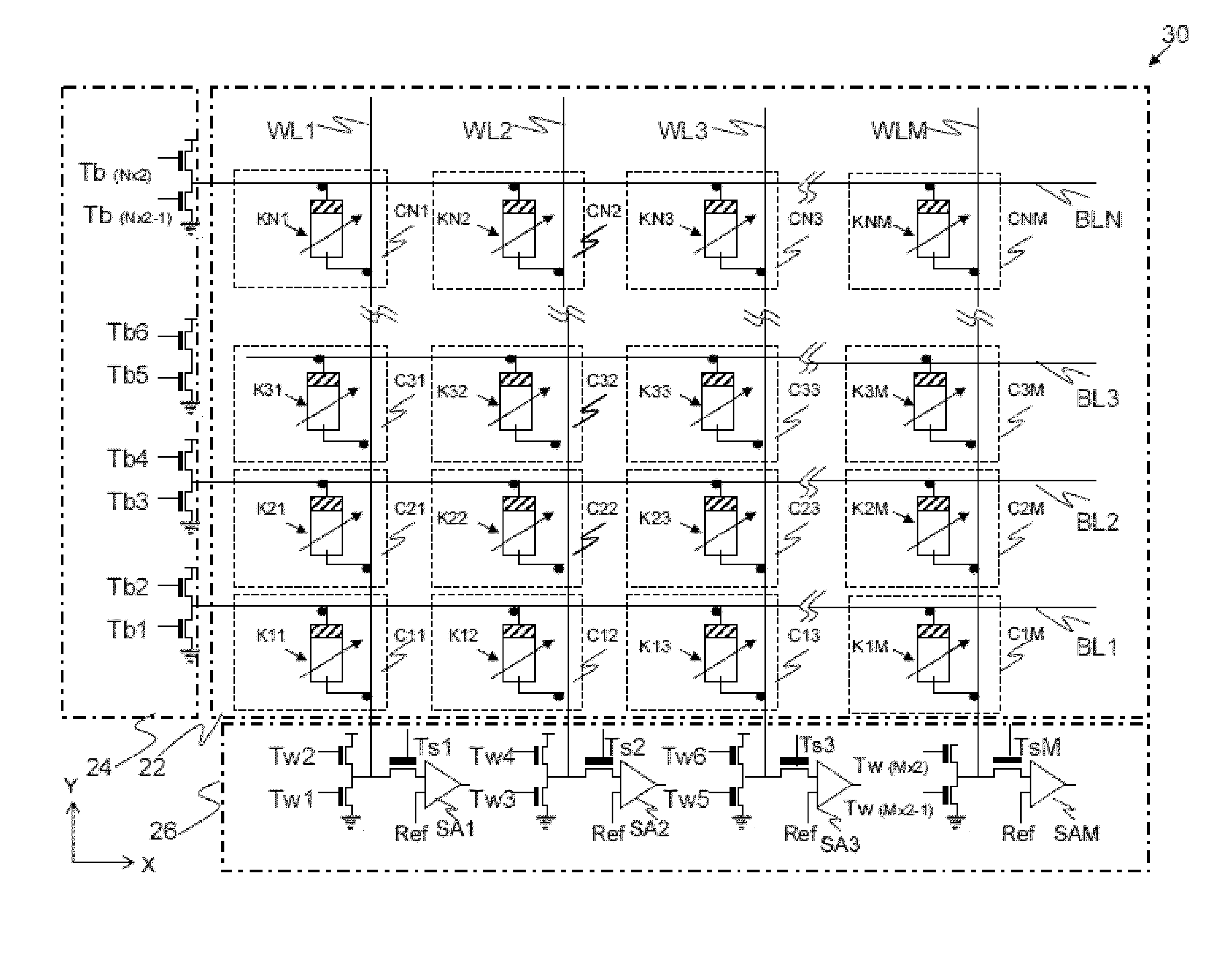

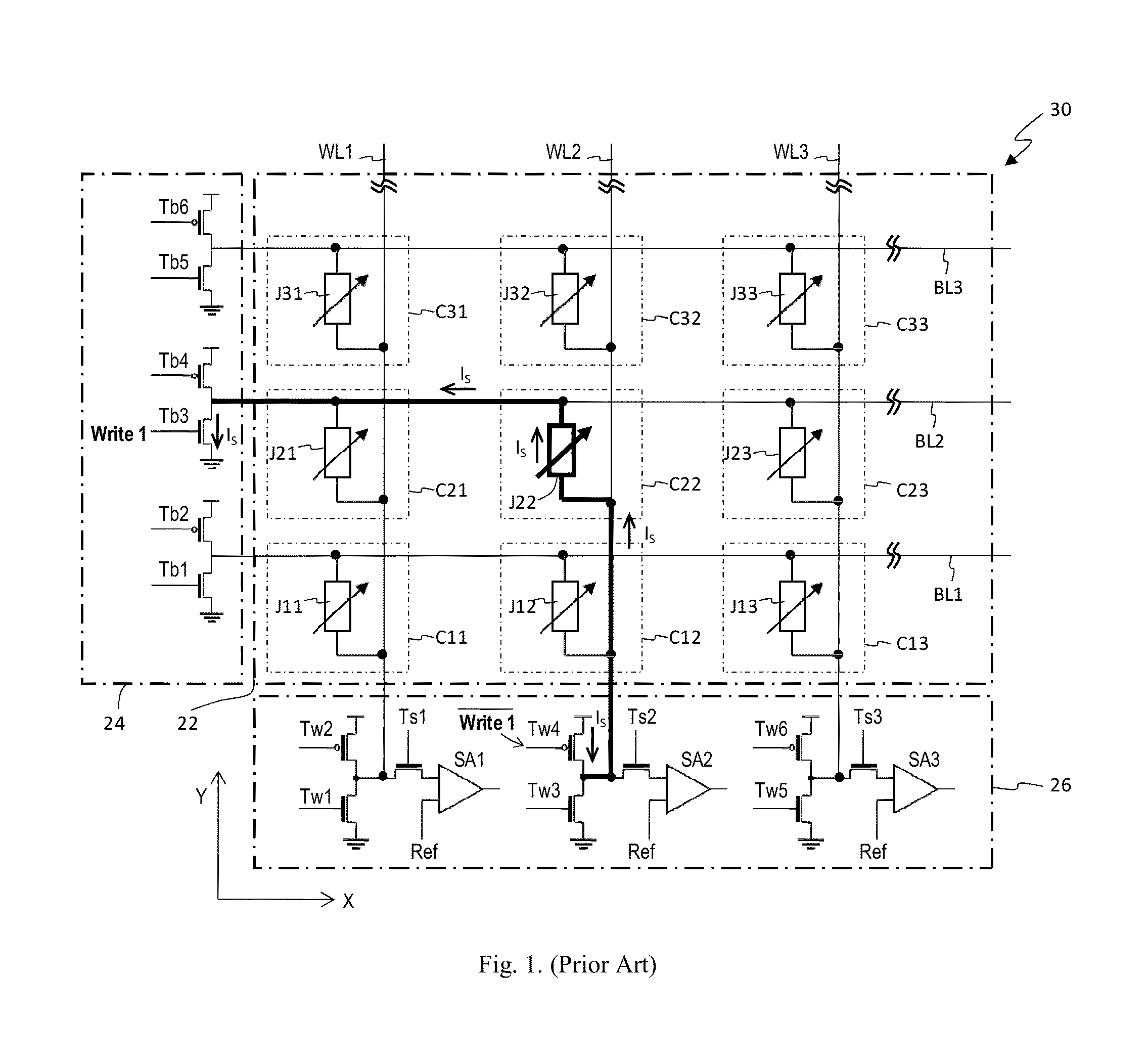

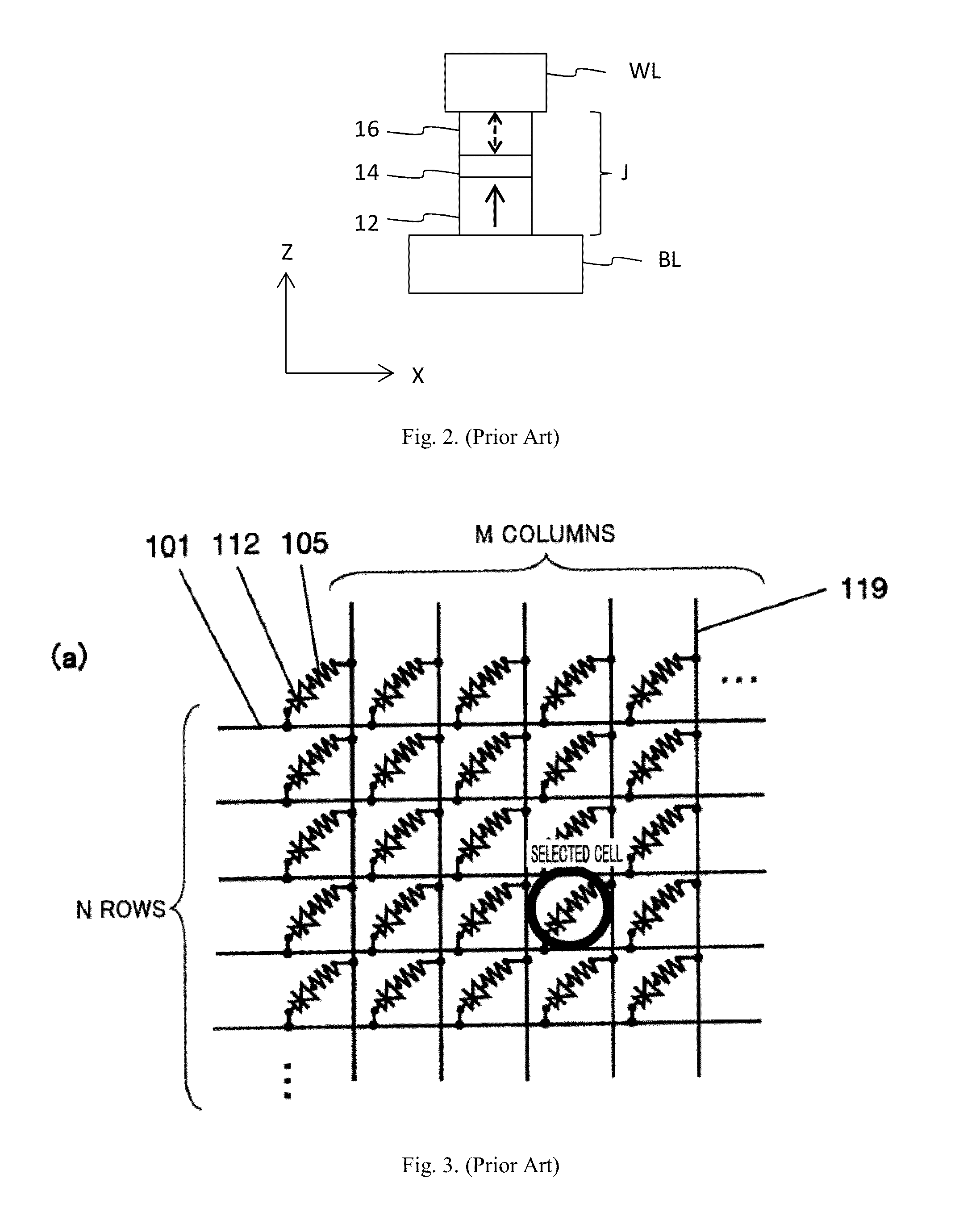

Low Cost High Density Nonvolatile Memory Array Device Employing Thin Film Transistors and Back to Back Schottky Diodes

InactiveUS20140103471A1Low costEliminate needSolid-state devicesDigital storageHigh densityEngineering

An improved crosspoint memory array device comprising a plurality of memory cells, each memory cell being disposed at an intersection region of bit and word conductive lines, electrically coupled to one of the first conductive lines at a first terminal and to one of the second conductive lines at a second terminal, and comprising a controllable electrical resistance, wherein a back to back Schottky diode is located between each memory cell and one of the said conductive lines, and wherein each conductive line is electrically coupled to at least two thin film transistors (TFTs). The device is substantially produced in BEOL facilities without need of front end semiconductor production facilities, yet can be made with ultra high density and low cost.

Owner:TACHO HLDG LLC

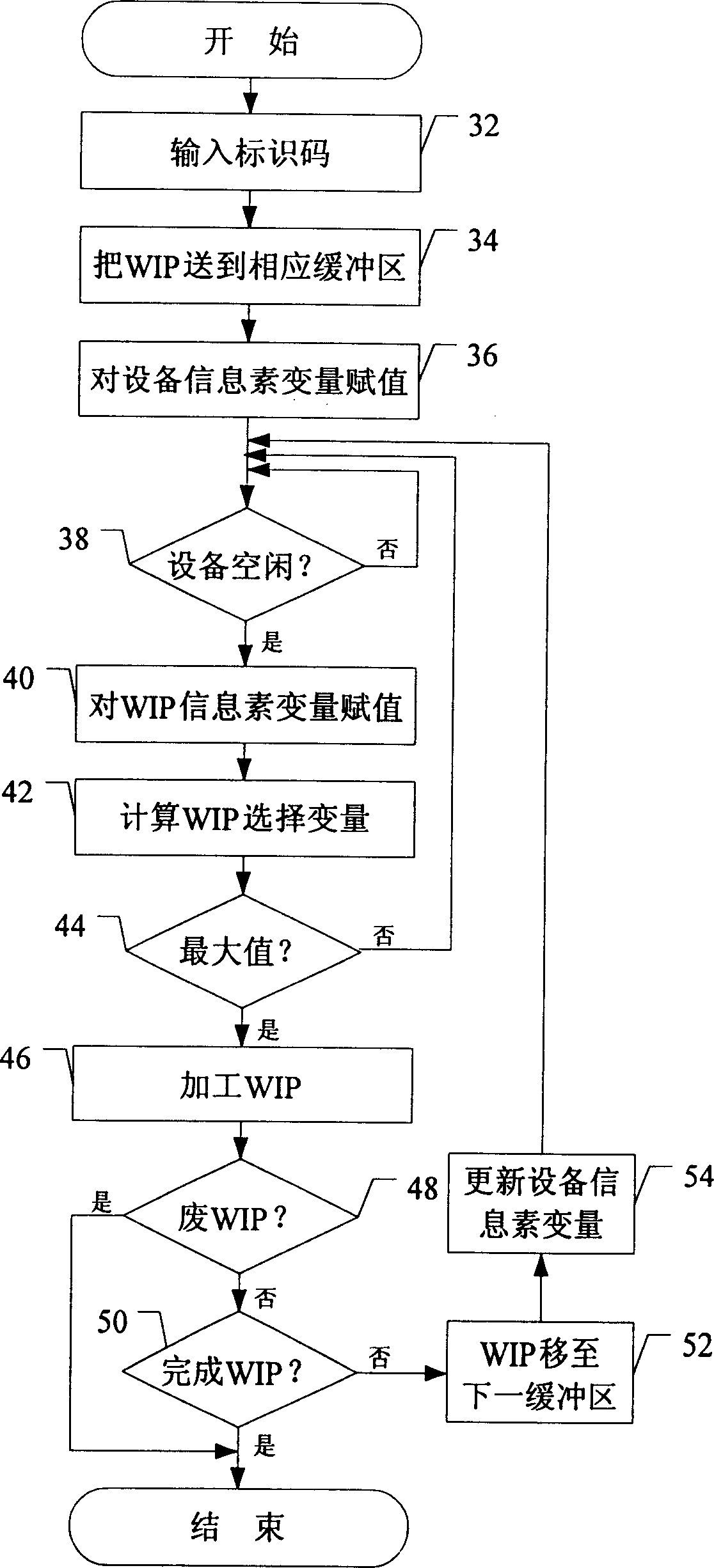

Dynamic scheduling method based on pheromone for semiconductor production line

InactiveCN1734382AScheduling method is stableRobust and stableData processing applicationsTotal factory controlShort termsComputer science

The invention discloses a dynamic dispatching method on the base of pheromone in semi-conductive product line, which comprises the following steps: first, storing pheromone variation of each WIP which relates to the WIP delivery date, holding time of waiting processing equipment, pure processing time and production periodic multiplication factor; second, storing pheromone variation which relates to equipment load; then, integrating the WIP pheromone variation and relating equipment pheromone variation, generating a selective variation of each WIP; finally, elaborating them on the equipment according to the method which consists of short-term and long-term function index to improve multi-function index production or making system.

Owner:TONGJI UNIV

Ceramic substrate, ceramic heater, electrostatic chuck and wafer prober for use in semiconductor producing and inspecting devices

InactiveUS20050029244A1Remarkable effectReduce resistanceSemiconductor/solid-state device testing/measurementSolid-state devicesMetallurgySemiconductor

A ceramic substrate for semiconductor manufacture and / or inspection which is conducive to decrease in α-rays radiated, to prevent electrical errors, and to decrease an electrostatic chucking force such as heater or wafer prober, generation of particles, and circuit defects. The ceramic substrate is configured such that the level of α-rays radiated from the surface of the ceramic substrate is not higher than 0.250 c / cm2·hr.

Owner:IBIDEN CO LTD

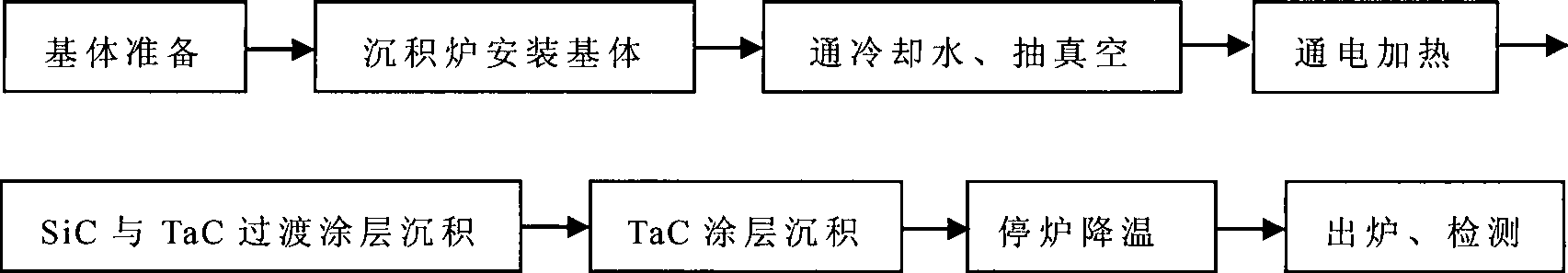

Graphite matrix flawless TaC coating and manufacturing method thereof

InactiveCN101445392AImprove corrosion resistanceImprove diffusion resistanceGraphite substrateThermal stability

The invention discloses a graphite matrix flawless TaC coating and a manufacturing method thereof. A tie coat is deposited on a graphite matrix. A TaC main coating is deposited on the outer layer of the tie coat. The tie coat is composed of a SiC-TaC codeposition coating or compounded by two transition layers of the SiC-TaC codeposition coating and a SiC-TaC laminated coating. When the tie coat is compounded by two transition layers of the SiC-TaC codeposition coating and the SiC-TaC laminated coating, the SiC-TaC codeposition coating serves as a first transition layer, and the SiC-TaC laminated coating serves as a second transition layer; and then the deposition of the tie coat is ended; or the SiC-TaC codeposition coating and the SiC-TaC laminated coating are alternatively deposited many times. Good TaC coating which has small heat stress, no macroscopic cracking, corrosion-resistance, and good thermal stability is deposited out of the surface of the graphite material. The method is suitable for preparing graphite substrate, graphite crucible, graphite windpipe, graphite guide shell coating in the crystal and semiconductor production, protecting and cleaning coating such as antisepsis, anti-pollution, anti-infiltration, anti-oxidation of graphite parts in other various hot environments.

Owner:CENT SOUTH UNIV

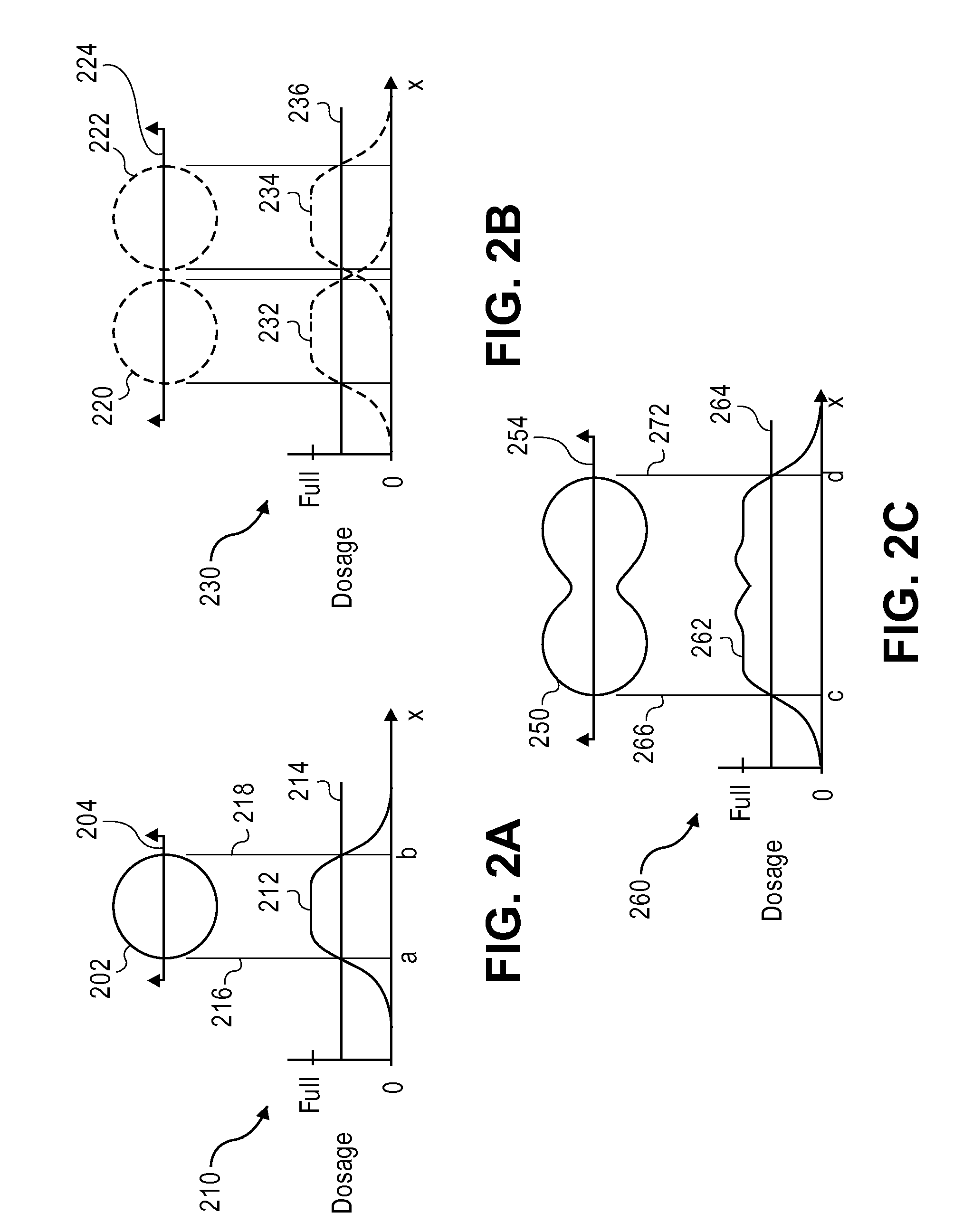

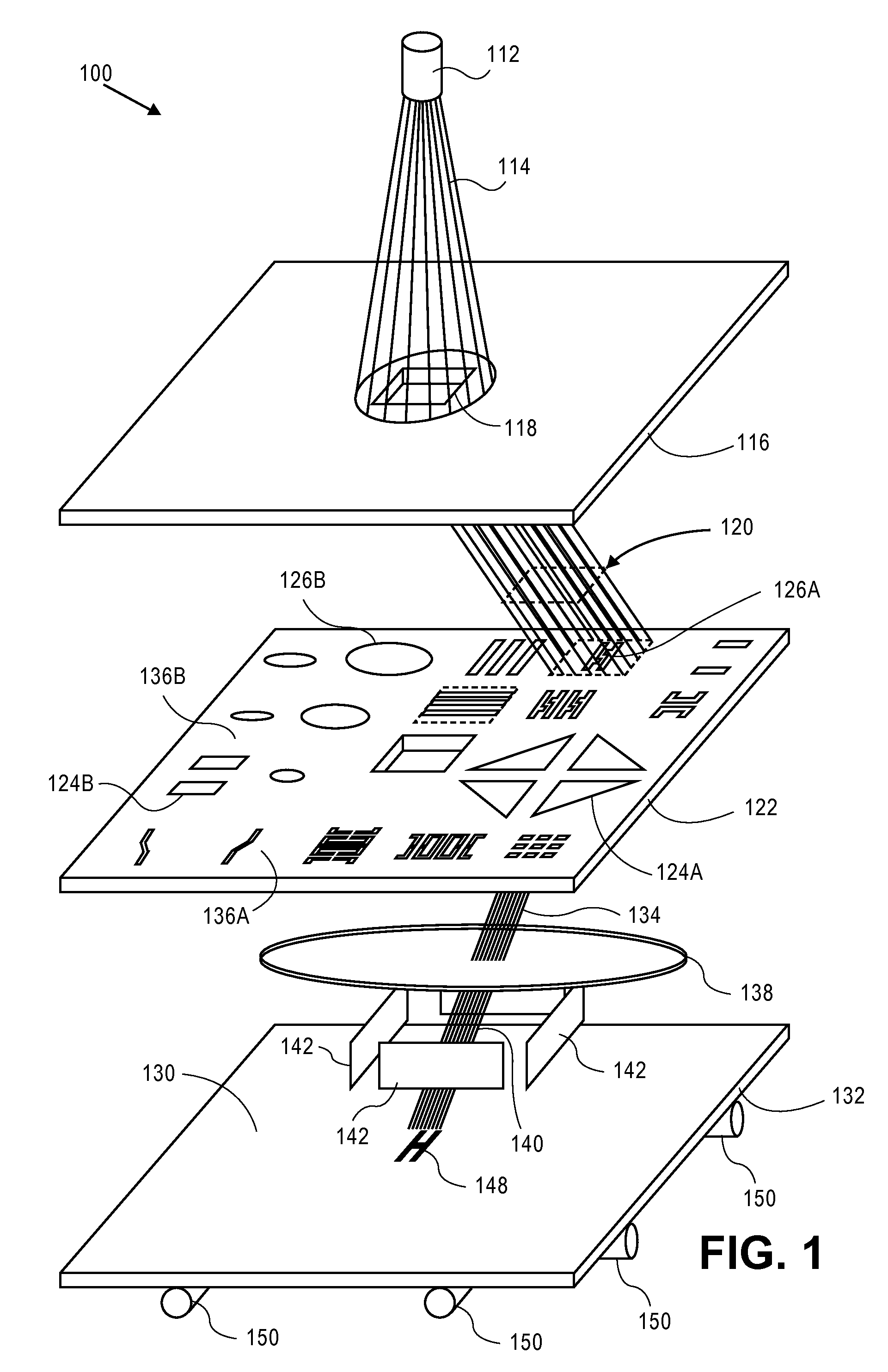

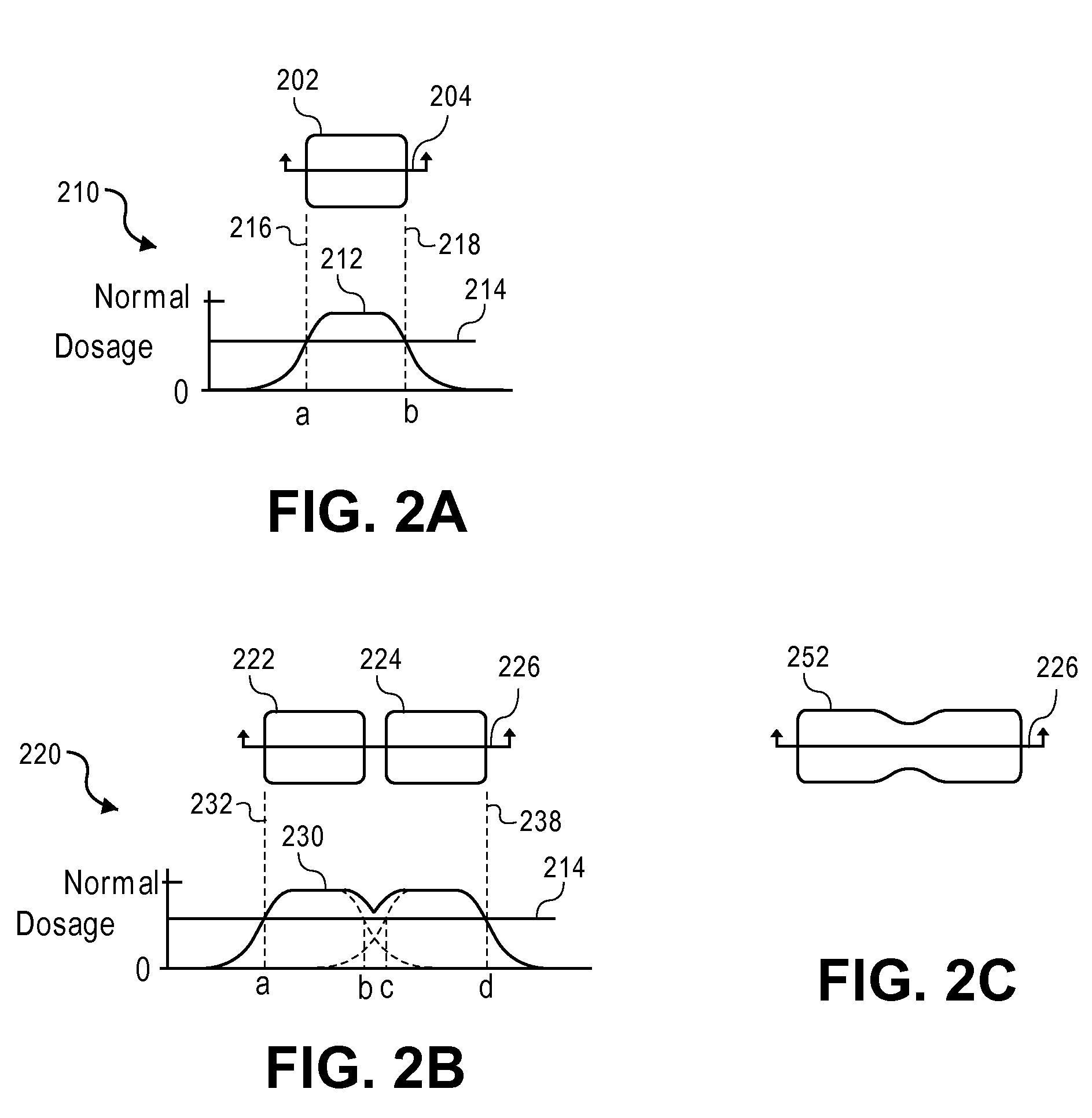

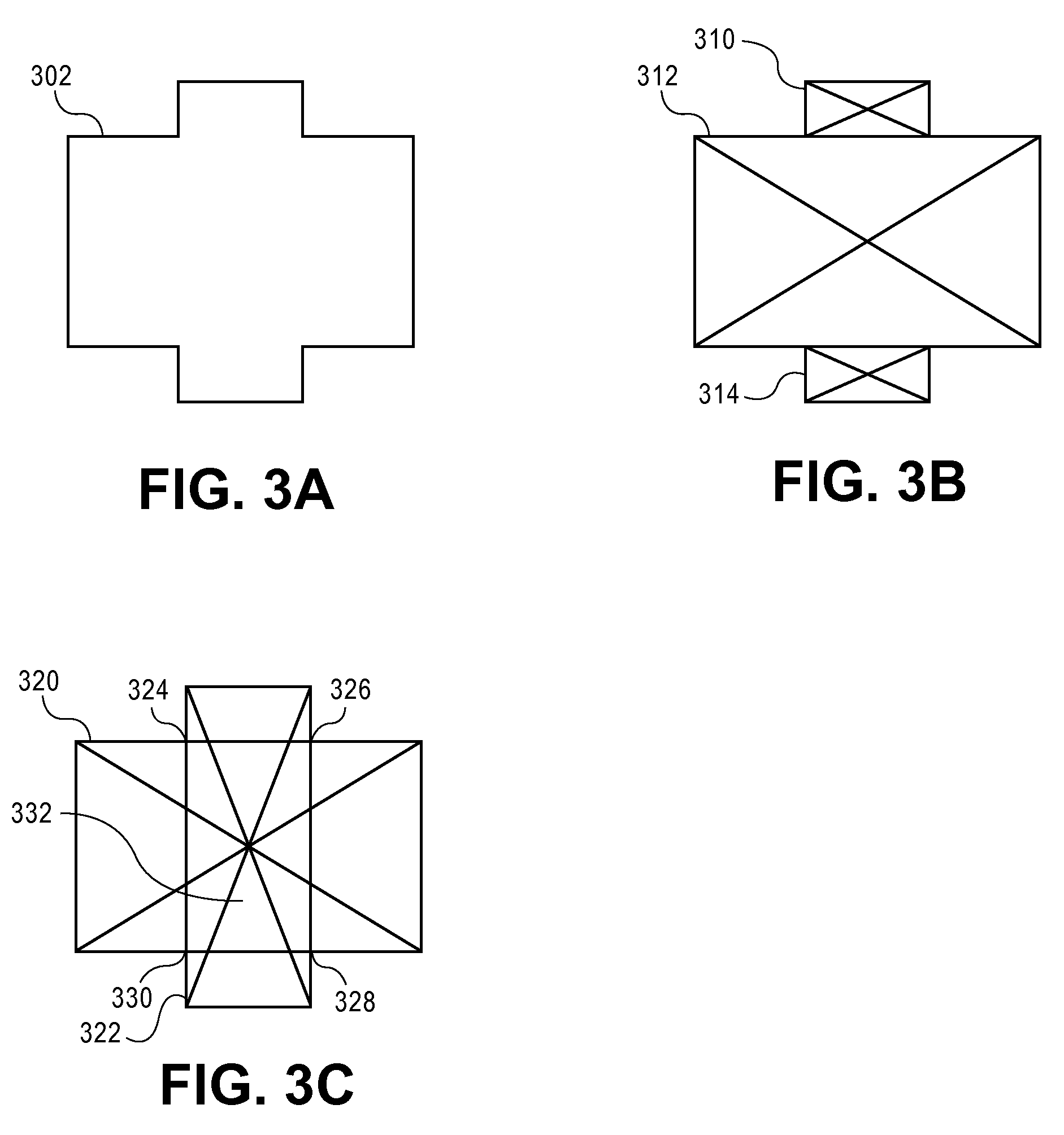

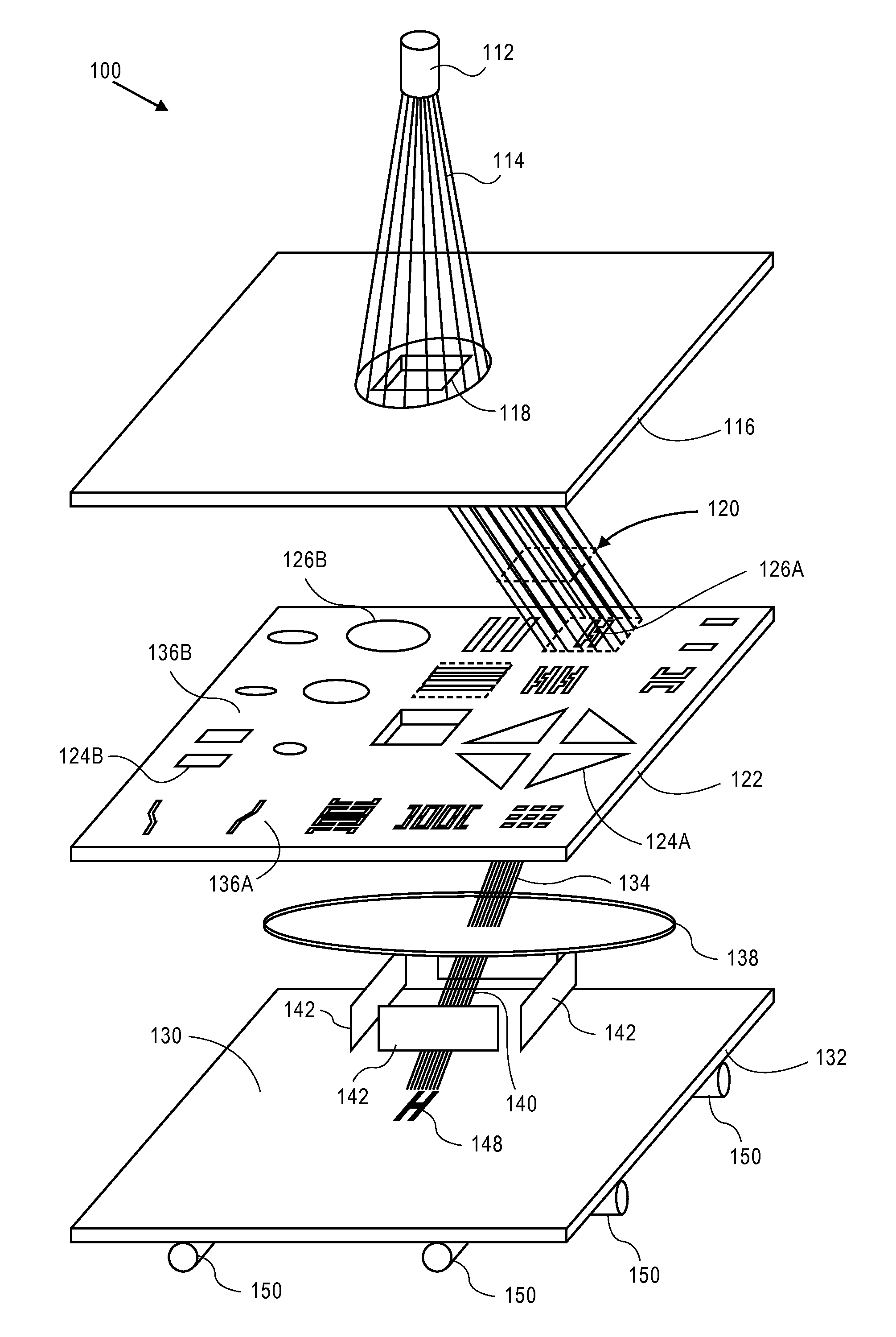

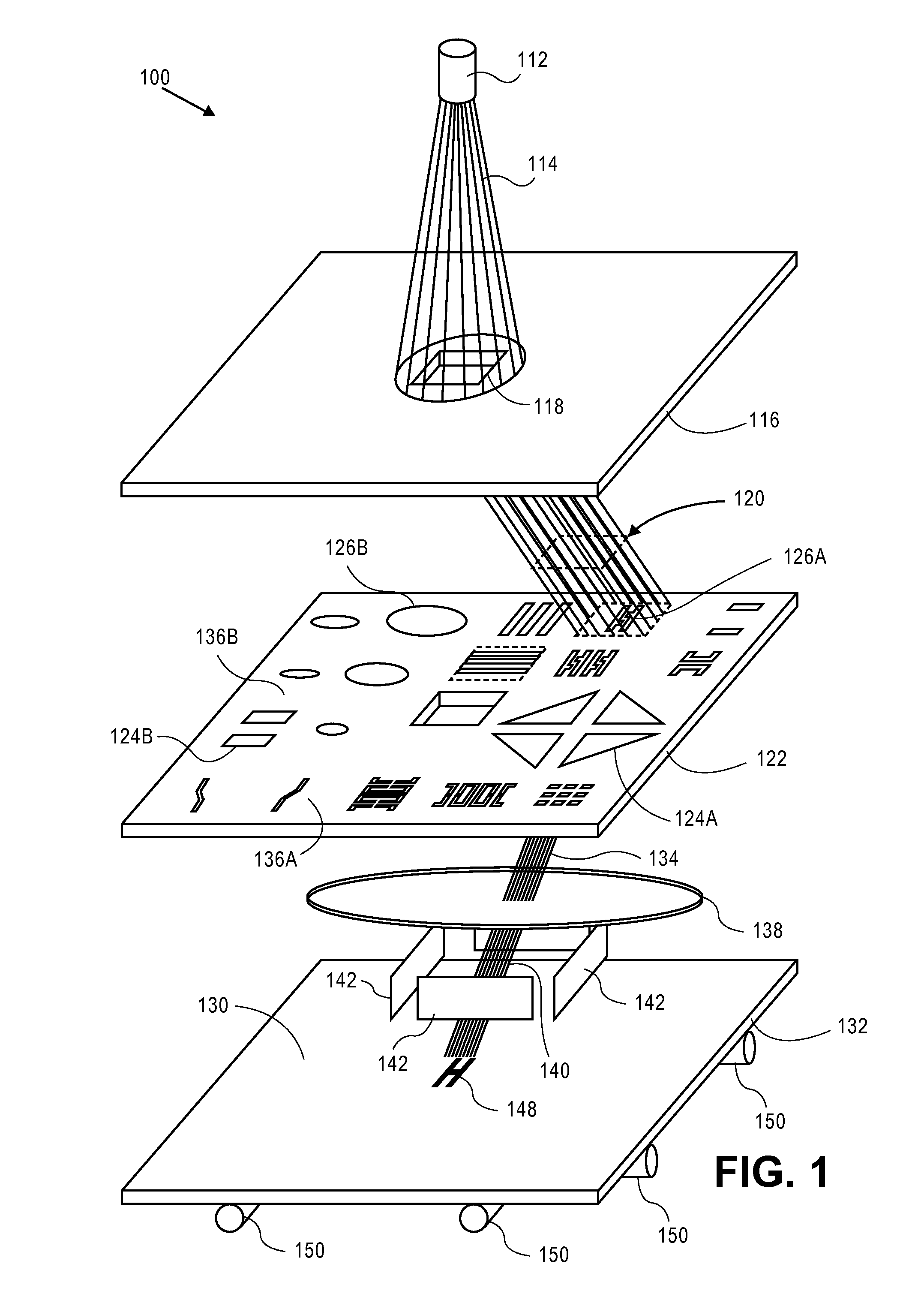

Method and system for fracturing a pattern using charged particle beam lithography with multiple exposure passes which expose different surface area

ActiveUS8137871B2Reduce in quantityElectric discharge tubesRadiation applicationsMask data preparationLithographic artist

In the field of semiconductor production using charged particle beam lithography, a method and system for fracturing or mask data preparation or proximity effect correction is disclosed, in which the union of shots from one of a plurality of exposure passes is different than the union of shots from a different exposure pass. Methods for manufacturing a reticle and for manufacturing an integrated circuit are also disclosed, in which the union of shots from one of a plurality of charged particle beam exposure passes is different than the union of shots from a different exposure pass.

Owner:D2S

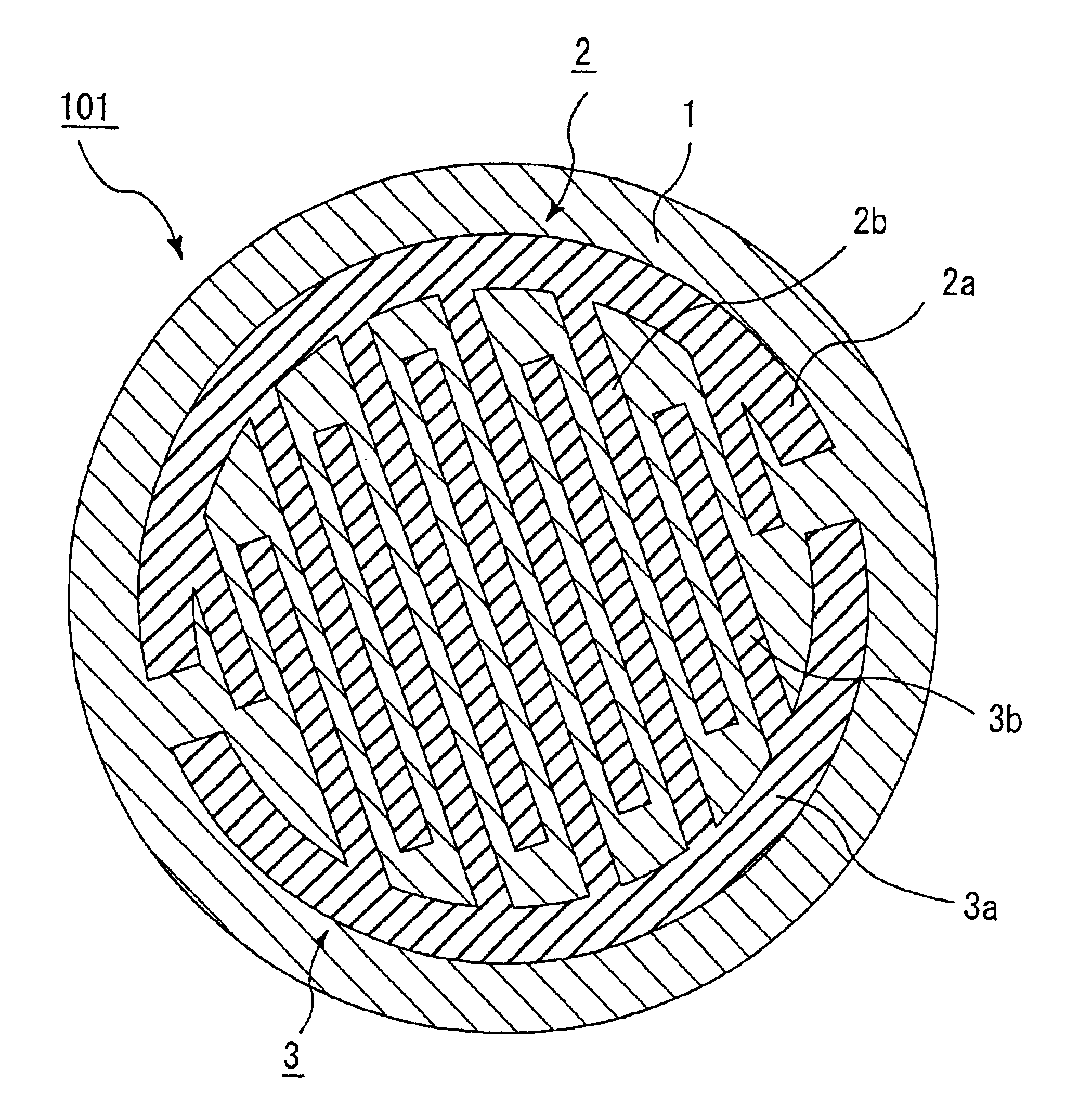

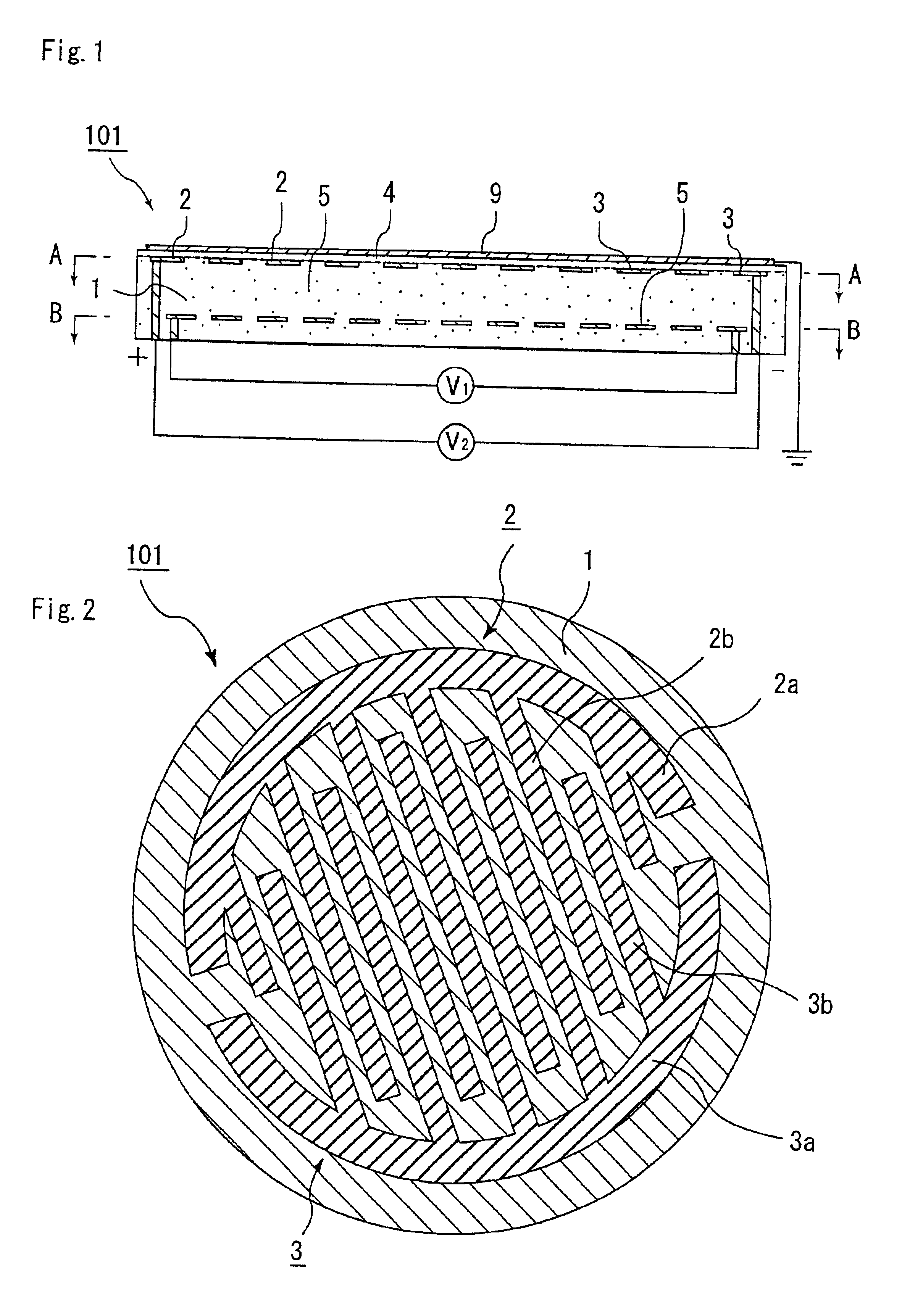

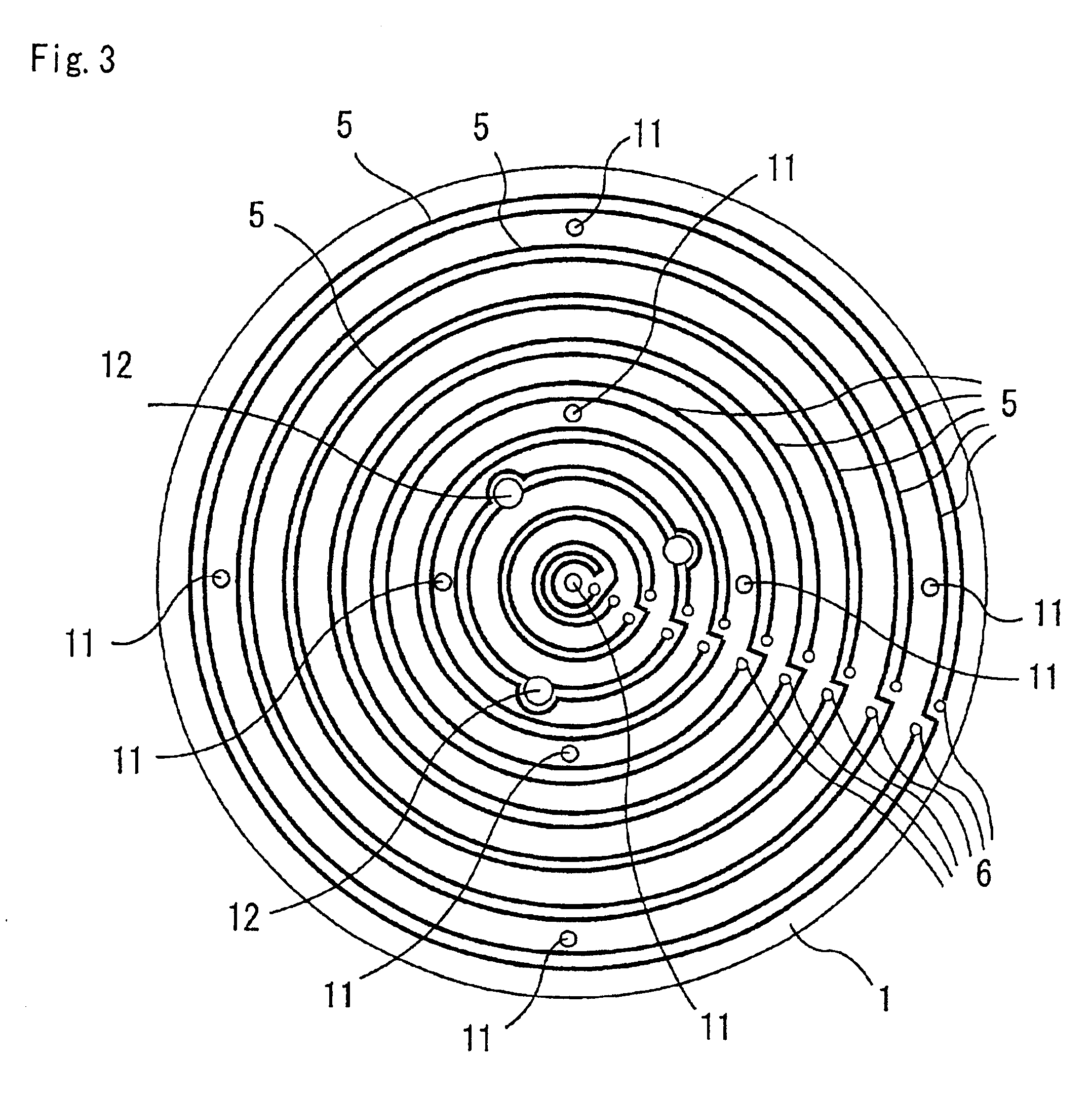

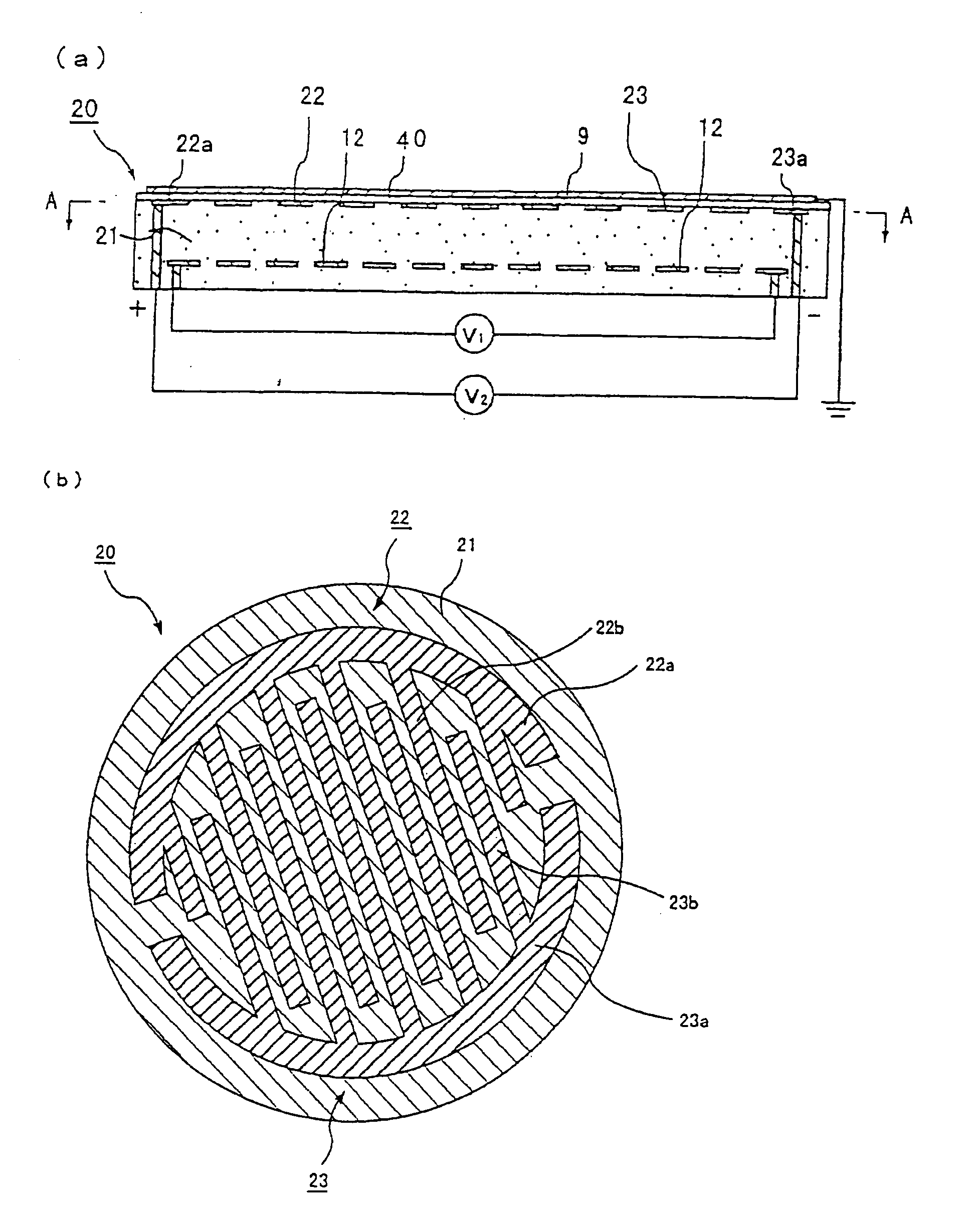

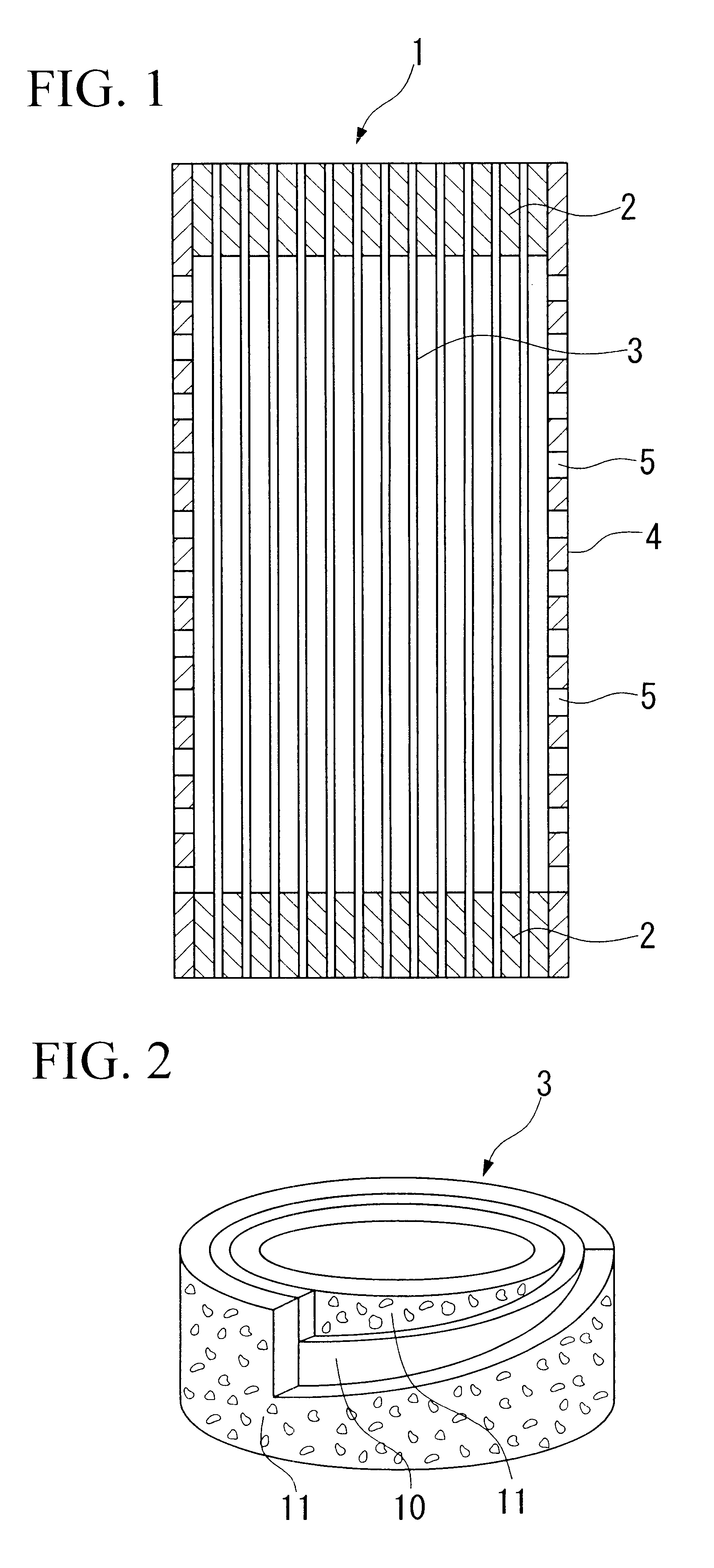

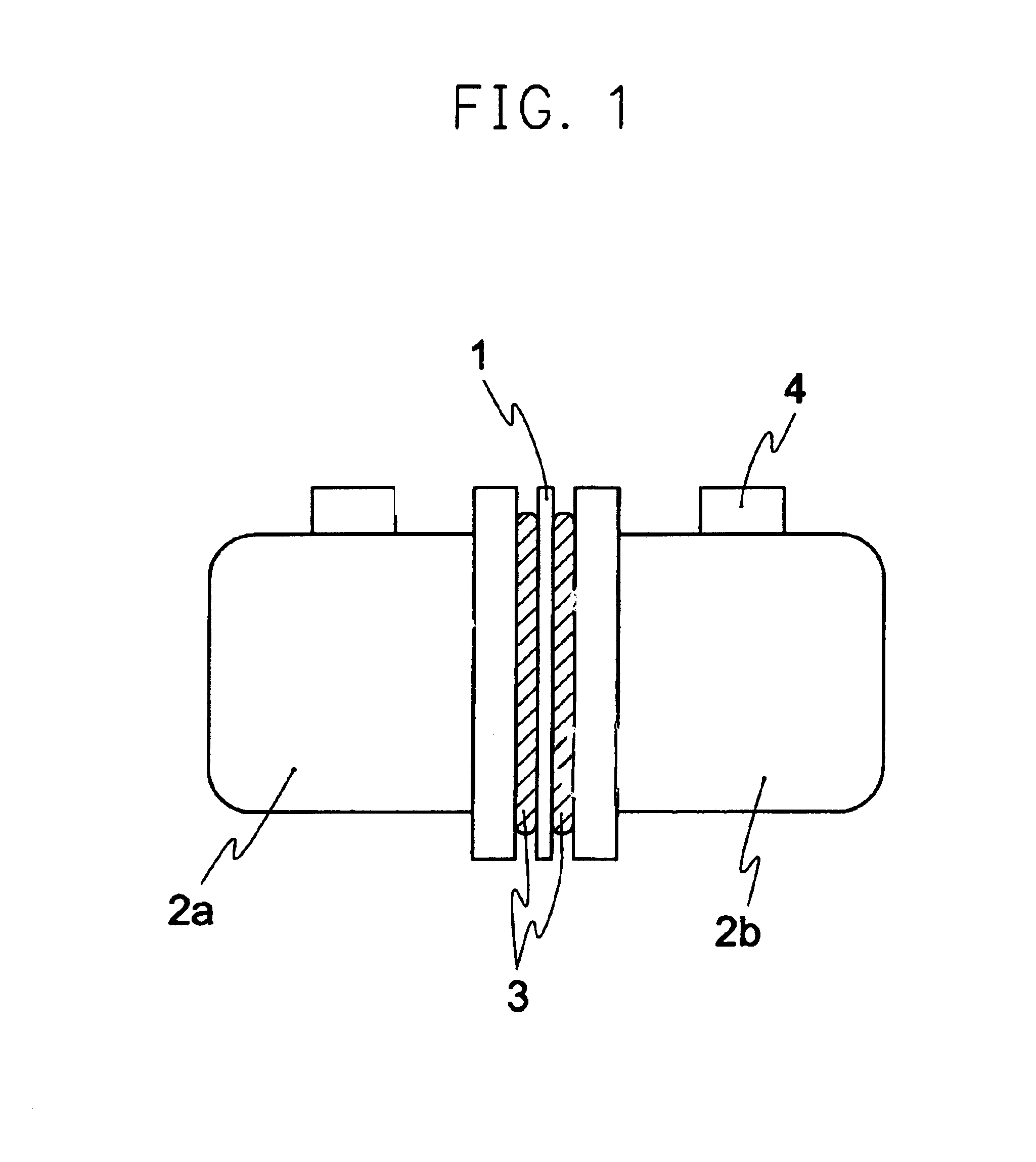

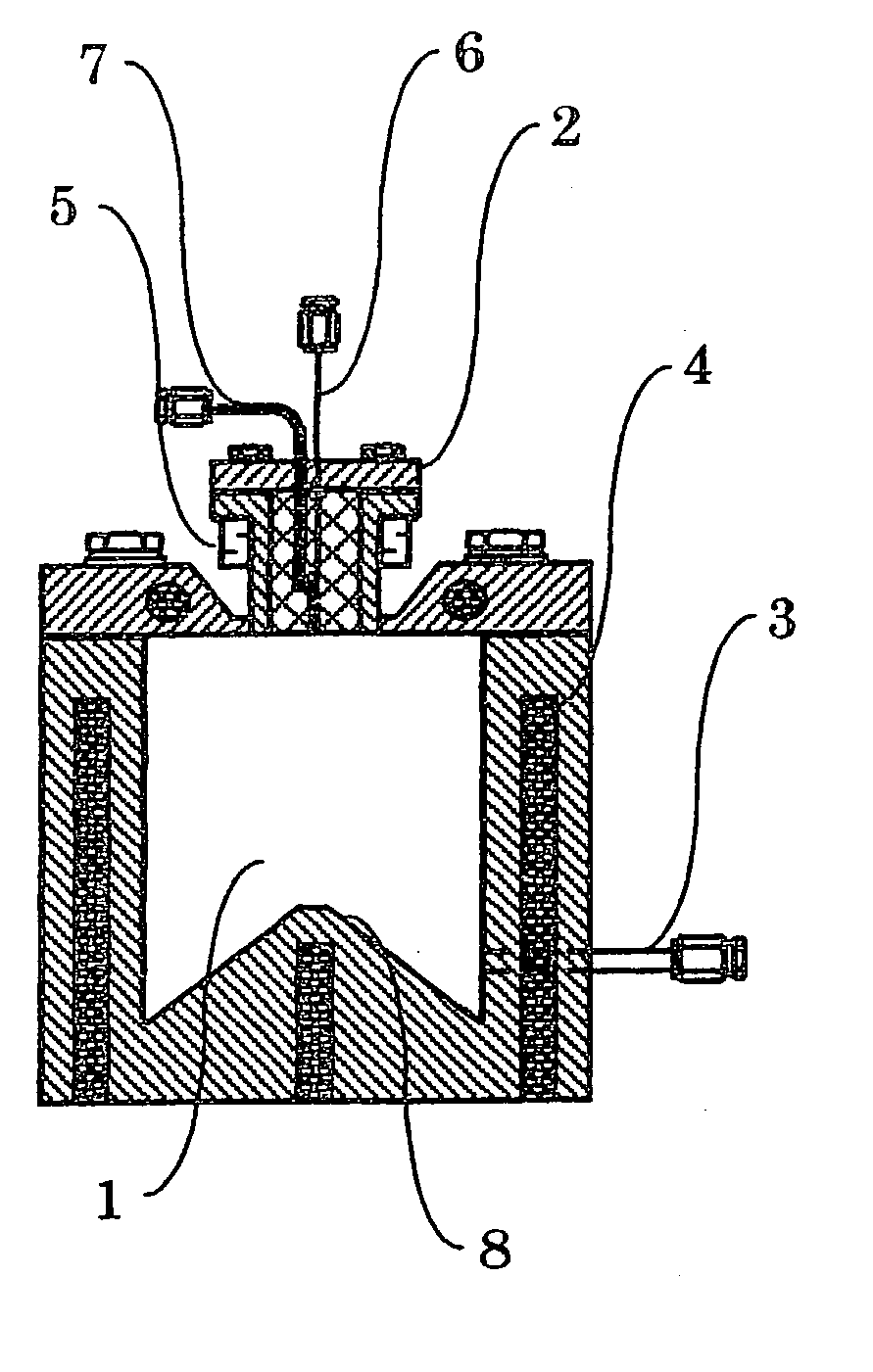

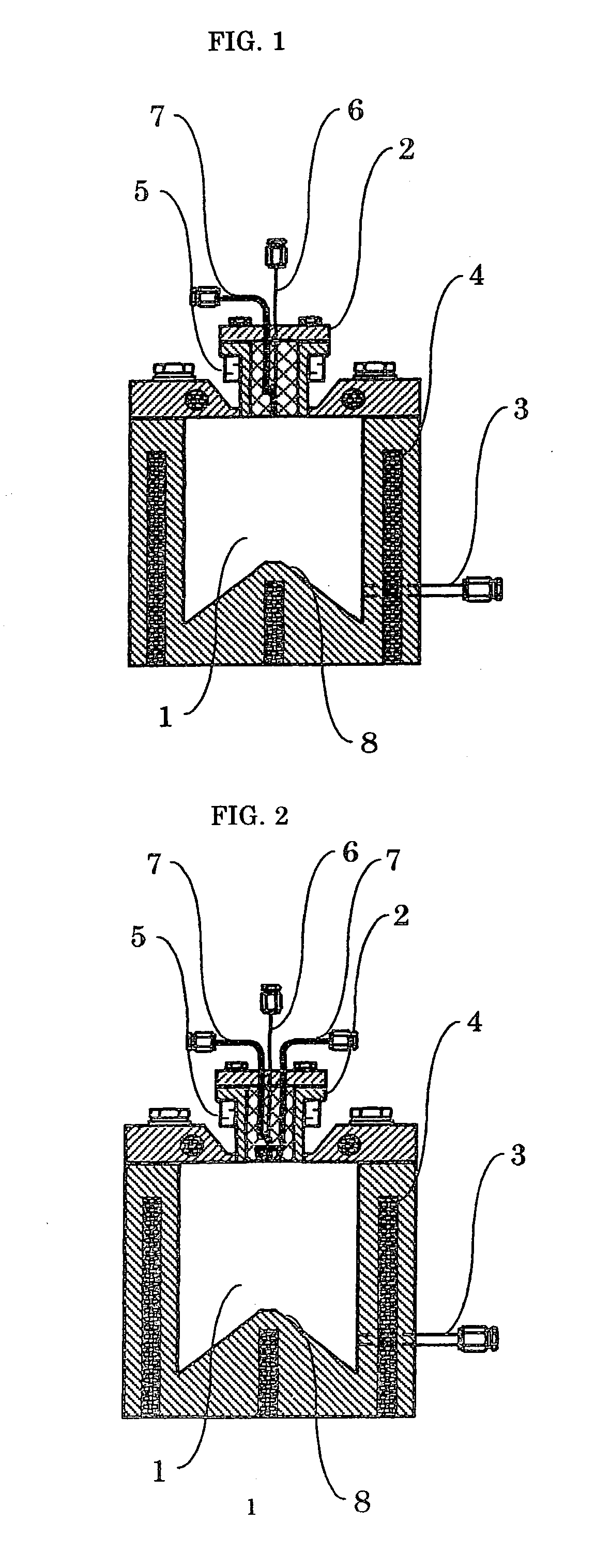

Hollow yarn membrane module, potting agent therefor and method for deaeration of liquid chemicals

InactiveUS6648945B1Good chemical resistanceSolve the blockageMembranesSemi-permeable membranesChemical treatmentEpoxy

A hollow fiber membrane module and potting material can be used for chemical deaeration in a semiconductor production process, in printers, in a liquid crystal sealing process or in a chemical production process. A hollow fiber membrane module 1 includes, as potting material 2, an epoxy resin cured product in which the weight change per unit surface area of a potting material test piece after immersing the test piece in a chemical for 6 months at room temperature is within the range of -20 to +20 mg / cm<2>, and as housing 4, a polyolefin in which the weight change per unit surface area of a test piece after immersing the test piece in a chemical for 6 months at room temperature is within the range of -20 to +20 mg / cm<2>, and the total metal content is 300 ppm or less. The module has a long service life when used for chemical treatment without leakage.

Owner:MITSUBISHI CHEM CORP

Device used to produce or examine semiconductors

InactiveUS7071551B2Easy to disassembleMaintained satisfactorilySemiconductor/solid-state device detailsSolid-state devicesElastomerElectrical conductor

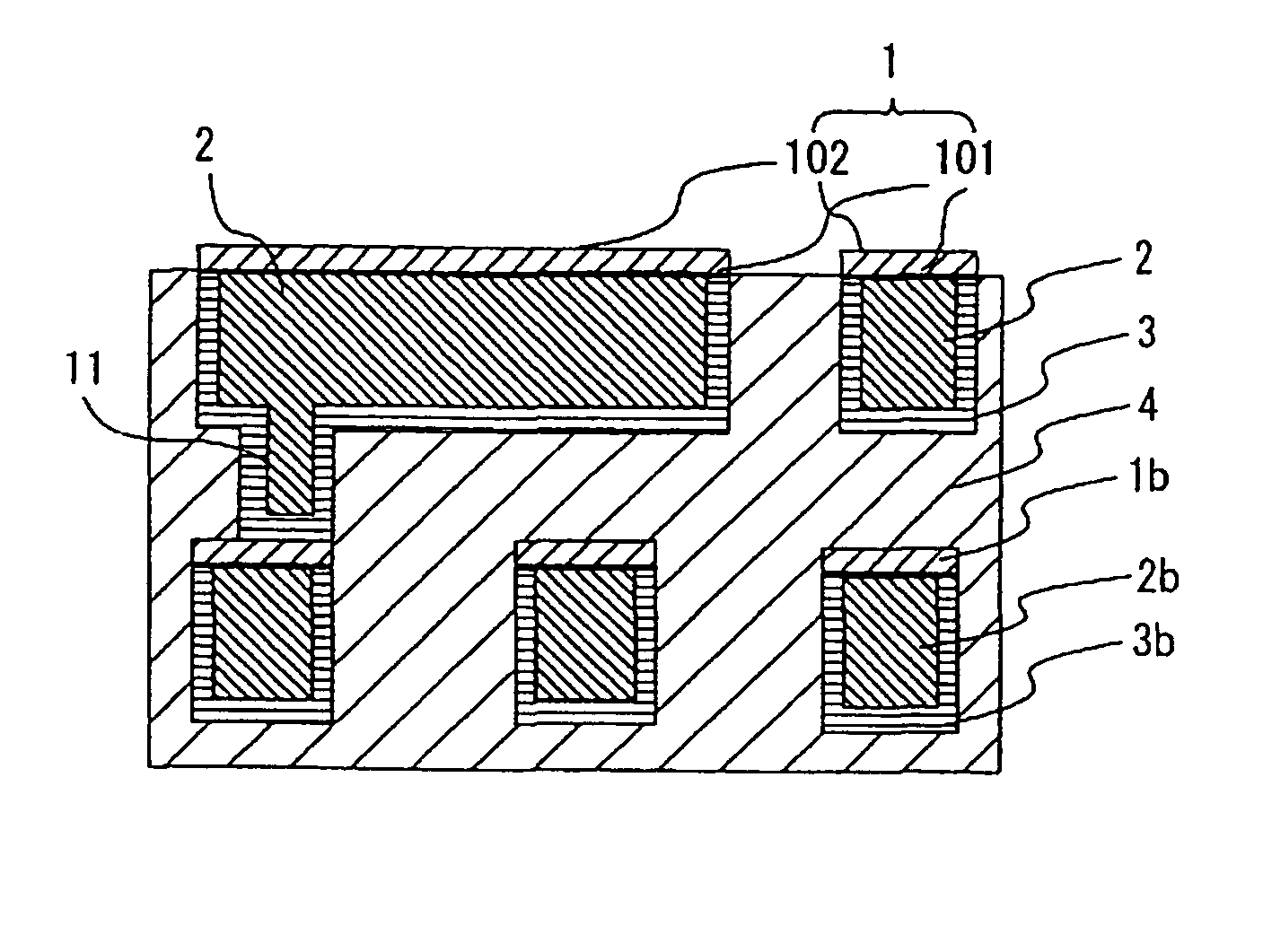

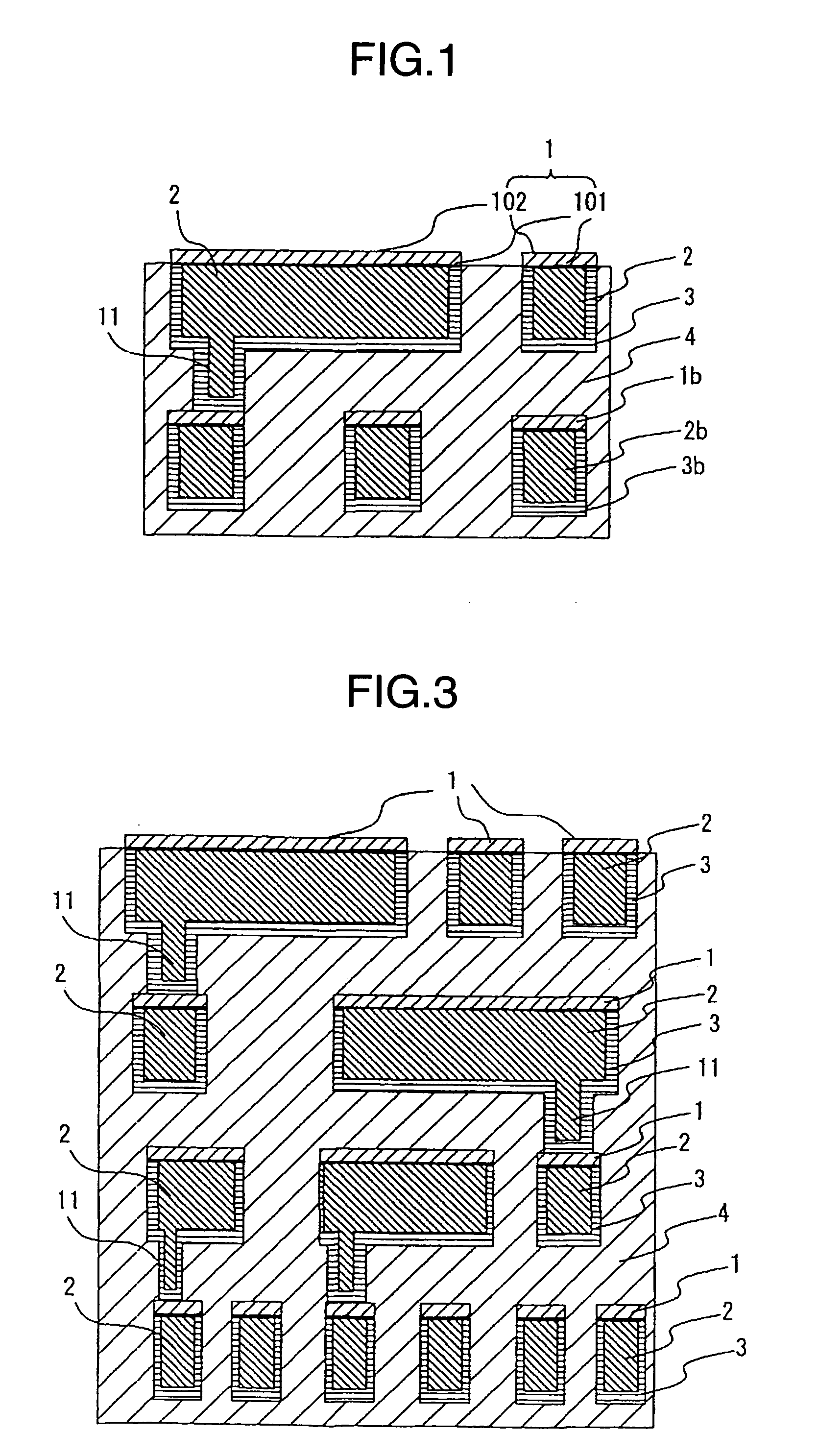

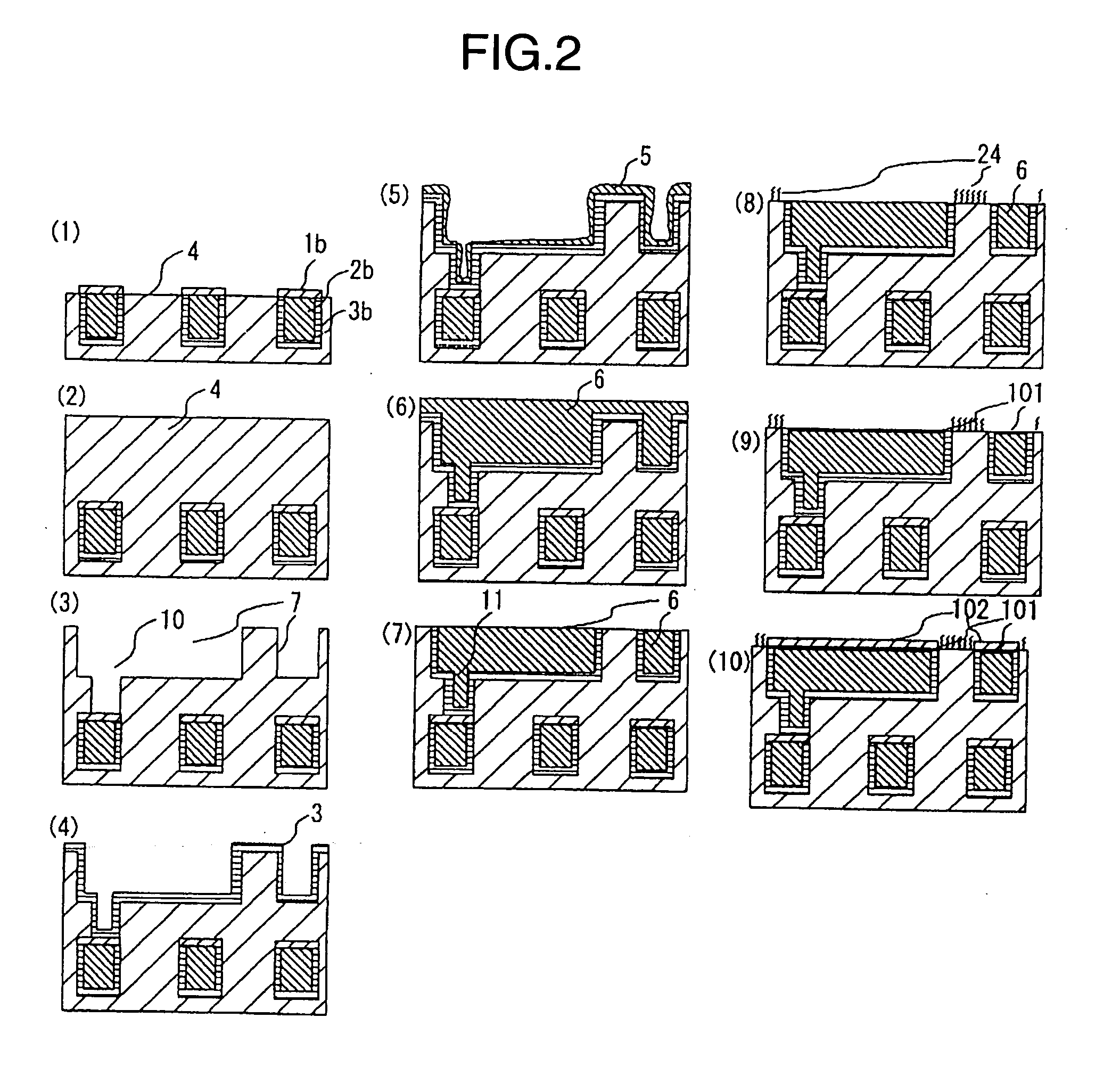

A semiconductor-producing / examining device that can maintain a preferable connection state for a predetermined period of time and that can easily remove a ceramic substrate from a supporting case. The semiconductor producing / examining device includes a ceramic substrate having a conductor layer formed on the surface thereof or inside thereof and a supporting case. An external terminal is connected to the conductor layer. A connection between the conductor layer and the external terminal is performed such that the external terminal is pressed on the conductor layer or the external terminal is pressed on another conductor layer connected to the conductor layer by using the elastic force and the like of an elastic body.

Owner:IBIDEN CO LTD

Method for fracturing and forming a pattern using curvilinear characters with charged particle beam lithography

In the field of semiconductor production using shaped charged particle beam lithography, a method and system for fracturing or mask data preparation or proximity effect correction is disclosed, wherein a series of curvilinear character projection shots are determined for a charged particle beam writer system, such that the set of shots can form a continuous track, possibly of varying width, on a surface. A method for forming a continuous track on a surface using a series of curvilinear character projection shots is also disclosed. Methods for manufacturing a reticle and for manufacturing a substrate such as a silicon wafer by forming a continuous track on a surface using a series of curvilinear character projection shots is also disclosed.

Owner:D2S

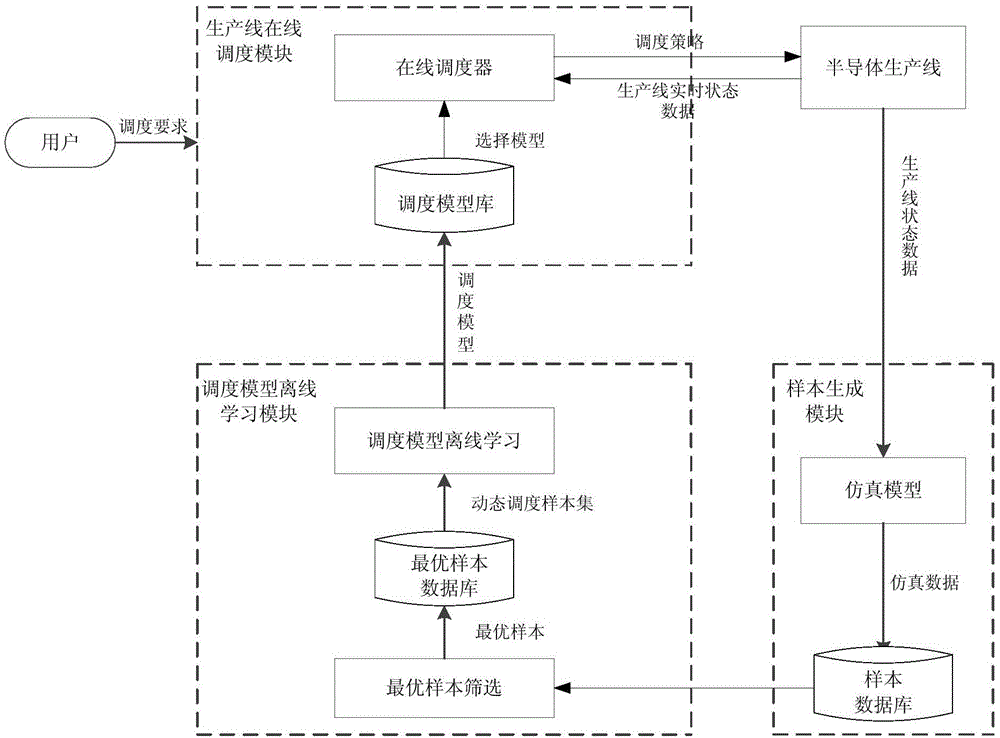

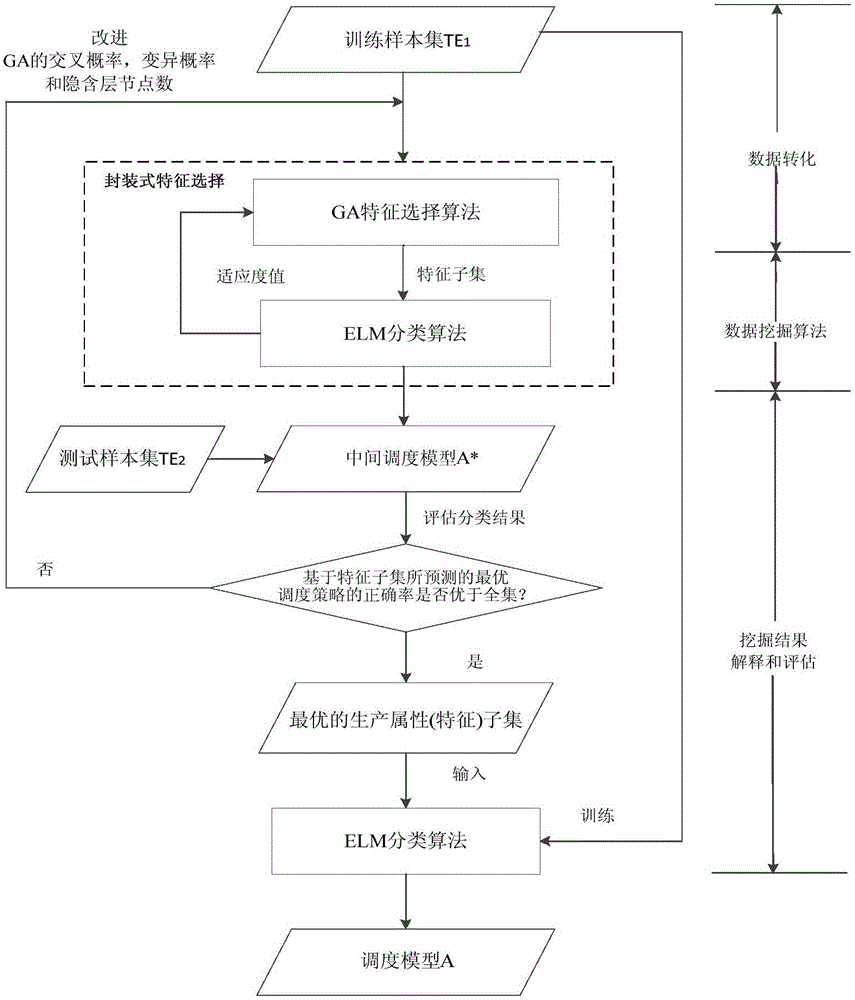

Semiconductor production line dynamic scheduling device

InactiveCN105045243AFast Optimal Scheduling StrategyQuickly provide the optimal scheduling strategyTotal factory controlProgramme total factory controlOptimal schedulingApplication scheduling

The invention relates to a semiconductor production line dynamic scheduling device, comprising a sample generation module for generating data samples, a scheduling model off-line learning module for building a scheduling module according to the data sample, and a production online scheduling module used for generating a real-time scheduling strategy according to the user scheduling target and the scheduling model to perform online scheduling of the semiconductor production line. A matched scheduling model is chosen from a scheduling model database according to the user requirements; the system state information of the semiconductor production line is inputted; and the application scheduling model chooses an optimal or a close-to-optimal scheduling strategy from the candidate scheduling strategies to be applied to the operation of the production line. Compared with the prior art, the semiconductor production line dynamic scheduling device achieves the real-time performance and optimization of the scheduling, satisfies the effectiveness of the scheduling and improves the overall performance of the production line.

Owner:TONGJI UNIV

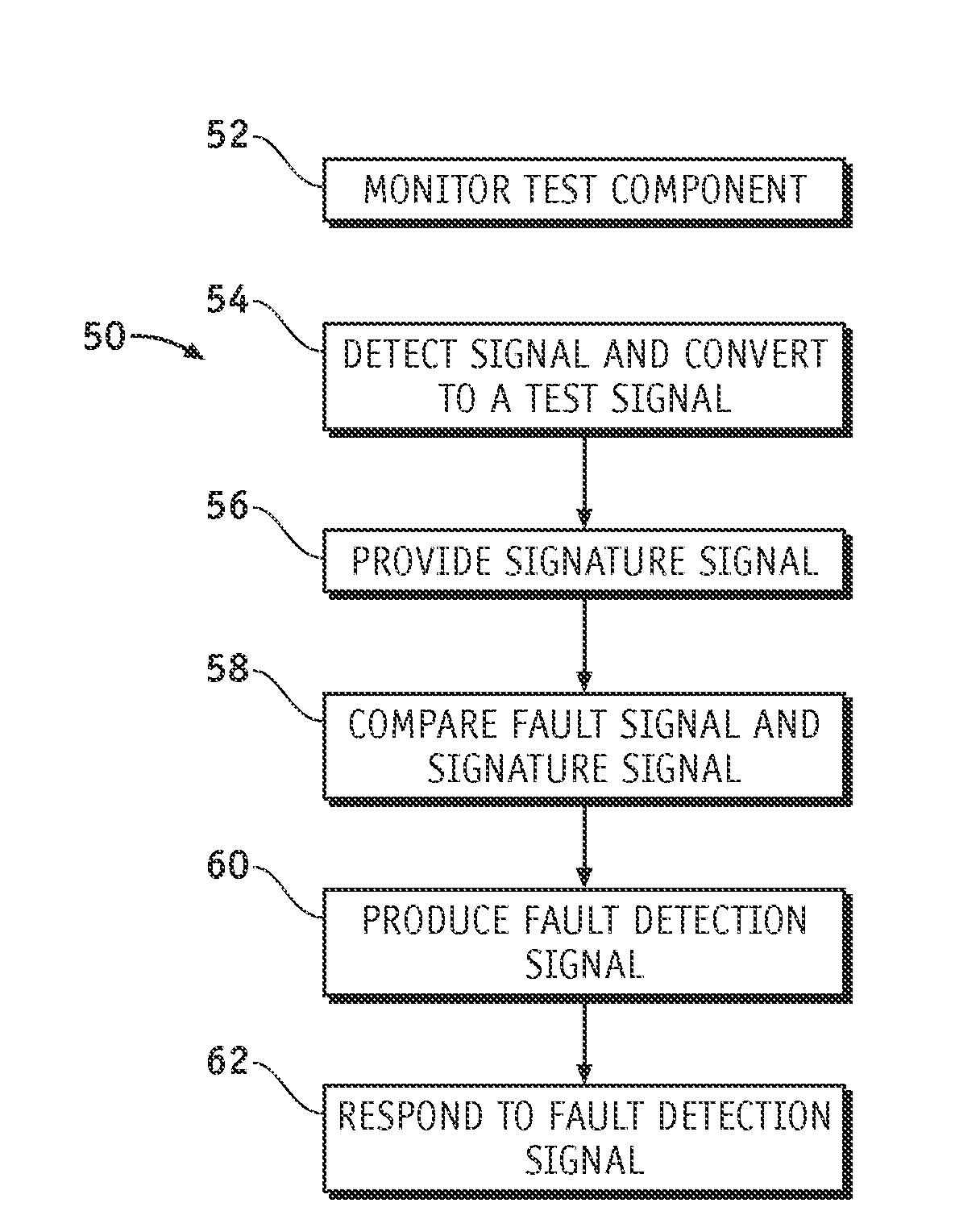

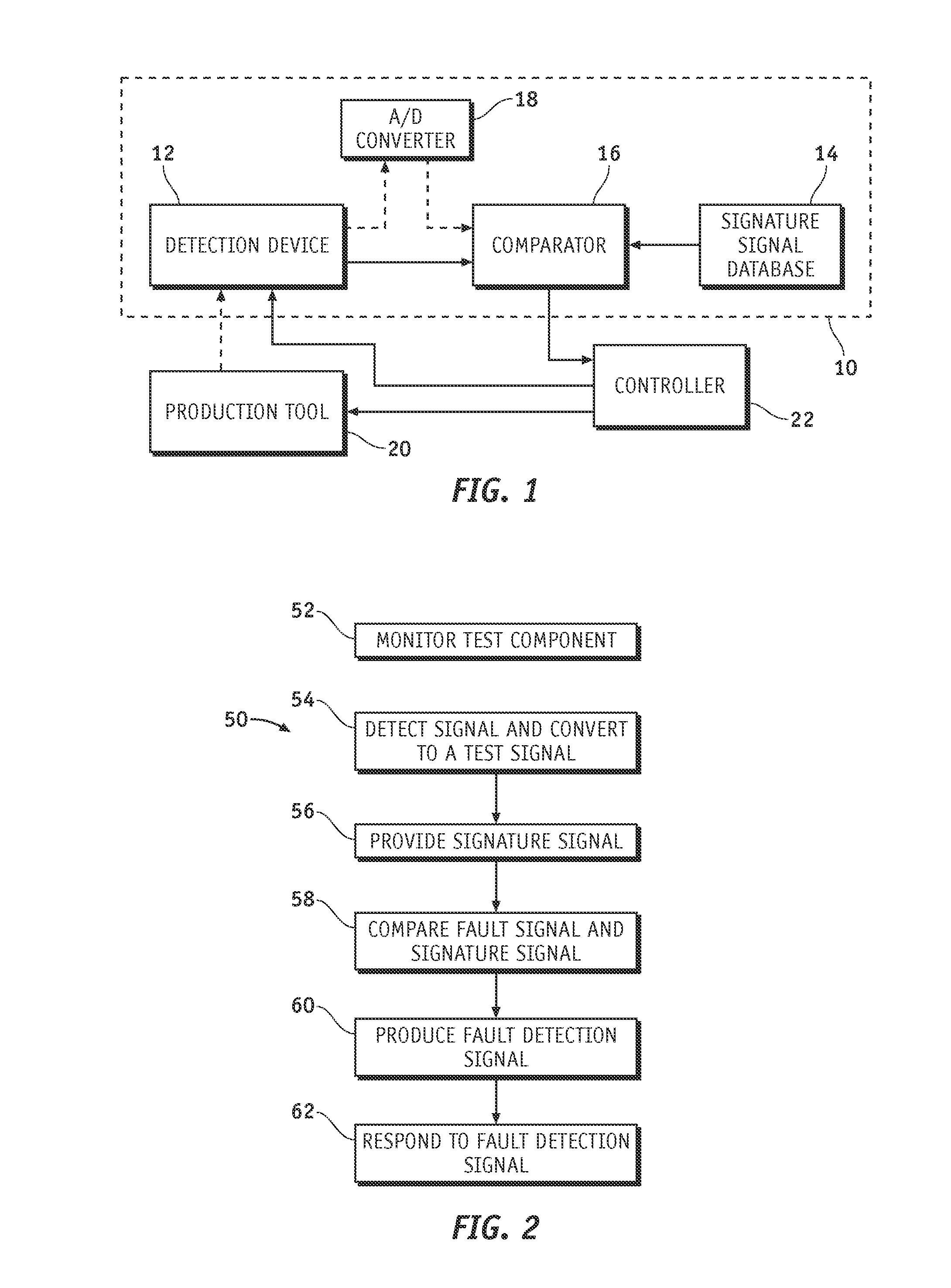

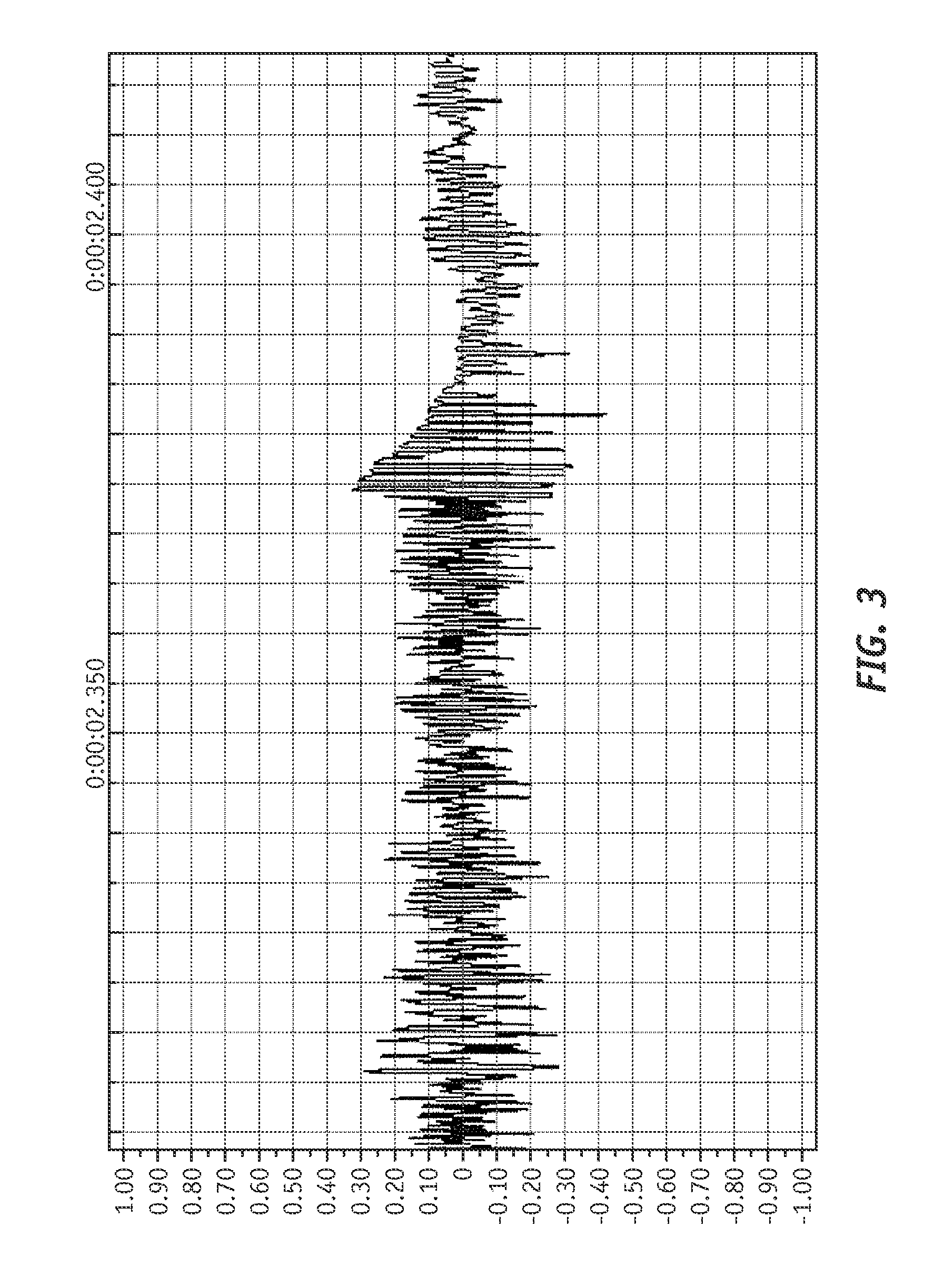

Fault detection apparatuses and methods for fault detection of semiconductor processing tools

ActiveUS20090153144A1Programme controlSemiconductor/solid-state device testing/measurementComparative testSemiconductor

Fault detection apparatuses and methods for detecting a processing or hardware performance fault of a semiconductor production tool have been provided. In an exemplary embodiment, a method for detecting a fault of a semiconductor production tool comprises sensing a signal associated with a test component of the production tool during operation of the production tool and converting the signal to an electronic test signal. A prerecorded signature signal corresponding to the test component is provided and the test signal and the prerecorded signature signal are compared.

Owner:NOVELLUS SYSTEMS

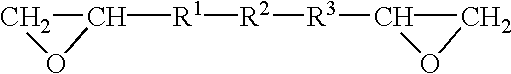

Fluorocopolymer and fluororesin composition lowly permeable to liquid chemical

To provide a novel PFA-based fluorine-containing copolymer having improved impermeability to liquid chemicals while retaining the excellent heat resistance, stress cracking resistance and processability inherent in PFA-based fluororesins, a material and a molded article useful in the field of semiconductor production apparatus and the like, using the copolymer. The present invention provides a fluorine-containing copolymer comprising 90 to 99.4% by mole of a repeating unit derived from tetrafluoroethylene, 0.5 to 5% by mole of a repeating unit derived from at least one lower perfluoro(alkyl vinyl ether) represented by the formula (1):in which Rf<1 >is a perfluoroalkyl group having 2 to 4 carbon atoms, and 0.1 to 5% by mole of a repeating unit derived from at least one higher perfluoro(vinyl ether) represented by the formula (2):in which Rf<2 >is a perfluoroalkyl group having 5 to 10 carbon atoms or a perfluoro(alkoxy alkyl) group having 4 to 17 carbon atoms, wherein the fluorine-containing copolymer has a melt flow rate of 0.1 g / 10 minutes to 100 g / 10 minutes and melting point of 290° to 325° C., and a resin composition using the same.

Owner:DAIKIN IND LTD

Vaporizer and apparatus for vaporizing and supplying

InactiveUS20030209201A1Reduce and stabilize pressure fluctuation in and flow rate fluctuationAvoid depositionMixing methodsUsing liquid separation agentVaporizationProduct gas

The present invention provides a vaporizer comprising a vaporization chamber for a CVD material, a CVD material feed portion supplying the CVD material for the vaporization chamber, a vaporized gas exhaust port and a heating means for heating the vaporization chamber, characterized in that the CVD material feed portion has passageways for the CVD material and for a carrier gas respectively and the passageway for the CVD material has a pressure loss-inducing means for the CVD material. At the same time, the present invention provides an apparatus for vaporizing and supplying that feeds a CVD material to a vaporizer via a liquid flow controller, and after vaporizing the CVD material that supplies the vaporized gas for a semiconductor production apparatus, characterized in having a pressure loss-inducing means for the CVD material between the liquid flow controller and the vaporizer. According to the present invention, even in the case of vaporizing and supplying with a decrease in a feed amount of a carrier gas to be supplied accompanying the CVD material employing a solid CVD material, reducing and stabilizing both the pressure fluctuation in the vaporizer and the flow rate fluctuation in the liquid flow controller and efficiently vaporizing a CVD material at a desirable concentration and flow rate without causing deposit or adhesion of the solid material in the vaporization chamber can be achieved.

Owner:JAPAN PIONICS

Method and system for fracturing a pattern using charged particle beam lithography with multiple exposure passes which expose different surface area

ActiveUS20110159435A1Reduce in quantityElectric discharge tubesRadiation applicationsMask data preparationLithographic artist

In the field of semiconductor production using charged particle beam lithography, a method and system for fracturing or mask data preparation or proximity effect correction is disclosed, in which the union of shots from one of a plurality of exposure passes is different than the union of shots from a different exposure pass. Methods for manufacturing a reticle and for manufacturing an integrated circuit are also disclosed, in which the union of shots from one of a plurality of charged particle beam exposure passes is different than the union of shots from a different exposure pass.

Owner:D2S

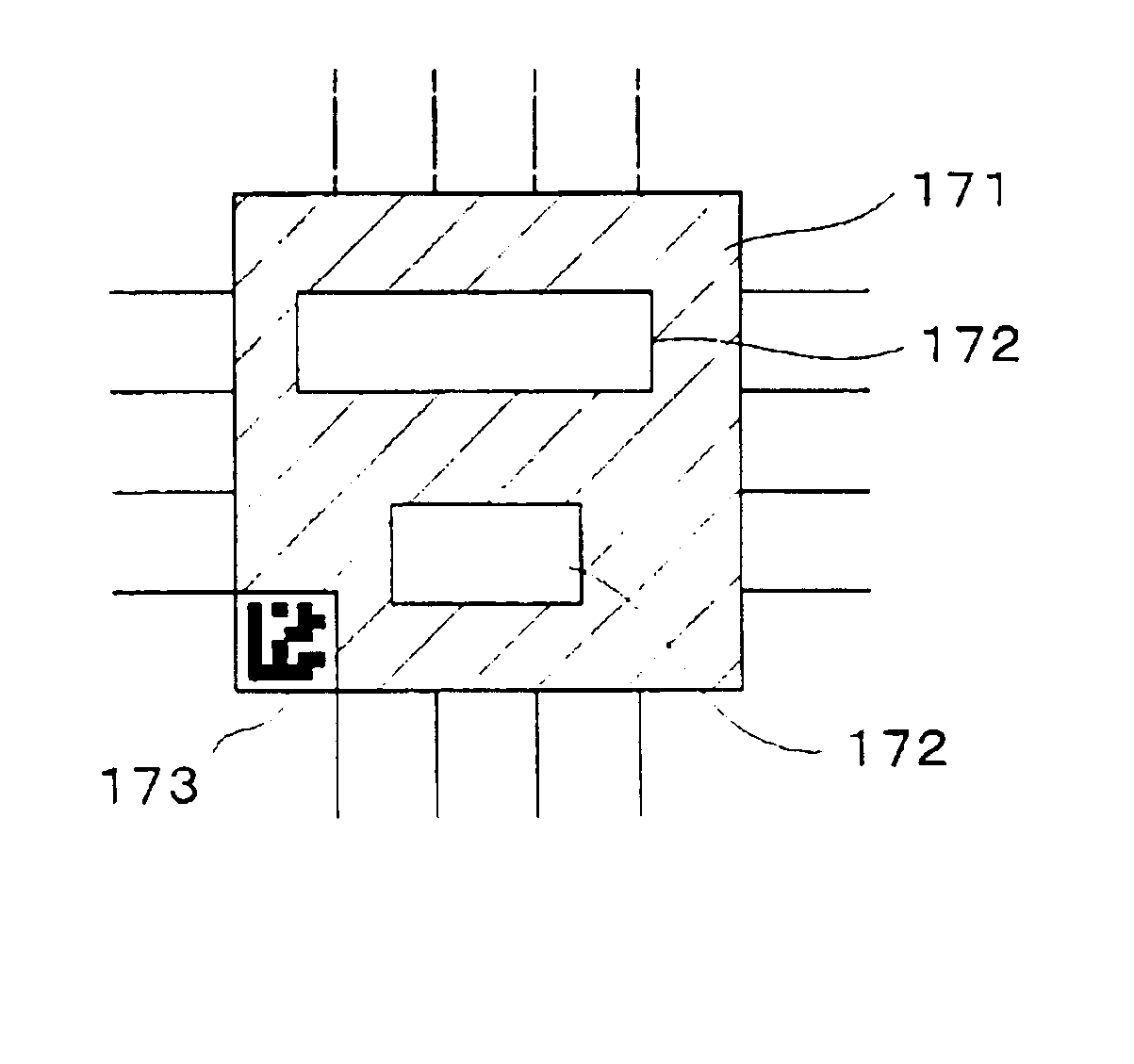

Semiconductor device and an information management system thereof

InactiveUS6896186B2Increase flexibilityAccurate and efficient distributionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsBarcodeSemiconductor chip

Individual two-dimensional barcodes 30, 91 and 173 are provided for individual chips 31 arrayed on a wafer 50, individual lead frames 93 to each of which chips 92 are bonded and individual packaged products 171 constituted of resin sealed semiconductor chips based upon chip ID information to enable information management to be implemented separately for individual chips 31, individual frames 93 and individual chip products 171. Thus, a higher degree of efficiency and a higher degree of accuracy in the information management for semiconductor devices are achieved in all processes of semiconductor production including the individual manufacturing processes, the physical distribution process, the shipping process and the claim handling process.

Owner:HPLP TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com