Scheduling method for semiconductor production line based on multi-ant-colony optimization

A production line and semiconductor technology, applied in the field of semiconductor production line scheduling based on multi-ant colony optimization, can solve problems such as scheduling solutions for semiconductor production lines that have not yet been found

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

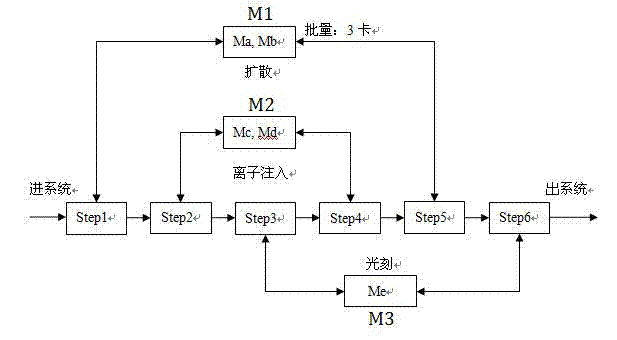

[0070] Below through the embodiment in conjunction with the attached image 3 The present invention is further described.

[0071] attached image 3 A simplified model Mini-Fab of a semiconductor production line is given. The model includes 3 device groups ( M 1 , M 2 , M 3 ),in: M 1 There are two interchangeable devices ( M a , M b ), simulating the diffusion processing area of a semiconductor production line, is a batch processing equipment; M 2 There are two interchangeable devices ( M a , M b ), which simulates the ion implantation processing area of the semiconductor production line, which is a non-batch processing equipment; M 3 There is a device ( M e ), which simulates the lithography processing area of a semiconductor production line, and is a non-batch processing equipment. The processing flow of the workpiece processed on this model is exactly the same, including 6 processing steps, respectively in M 1 , M 2 , M 3 The processing is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com