Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

66 results about "Parallel processing architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Published on Sep 16, 2017. What Is Parallel Processing In Computer Architecture And Organization : Parallel Processing is the processing of program instructions by dividing them among multiple processors with the objective of running a program in less time. In the earliest computers, only one program ran at a time.

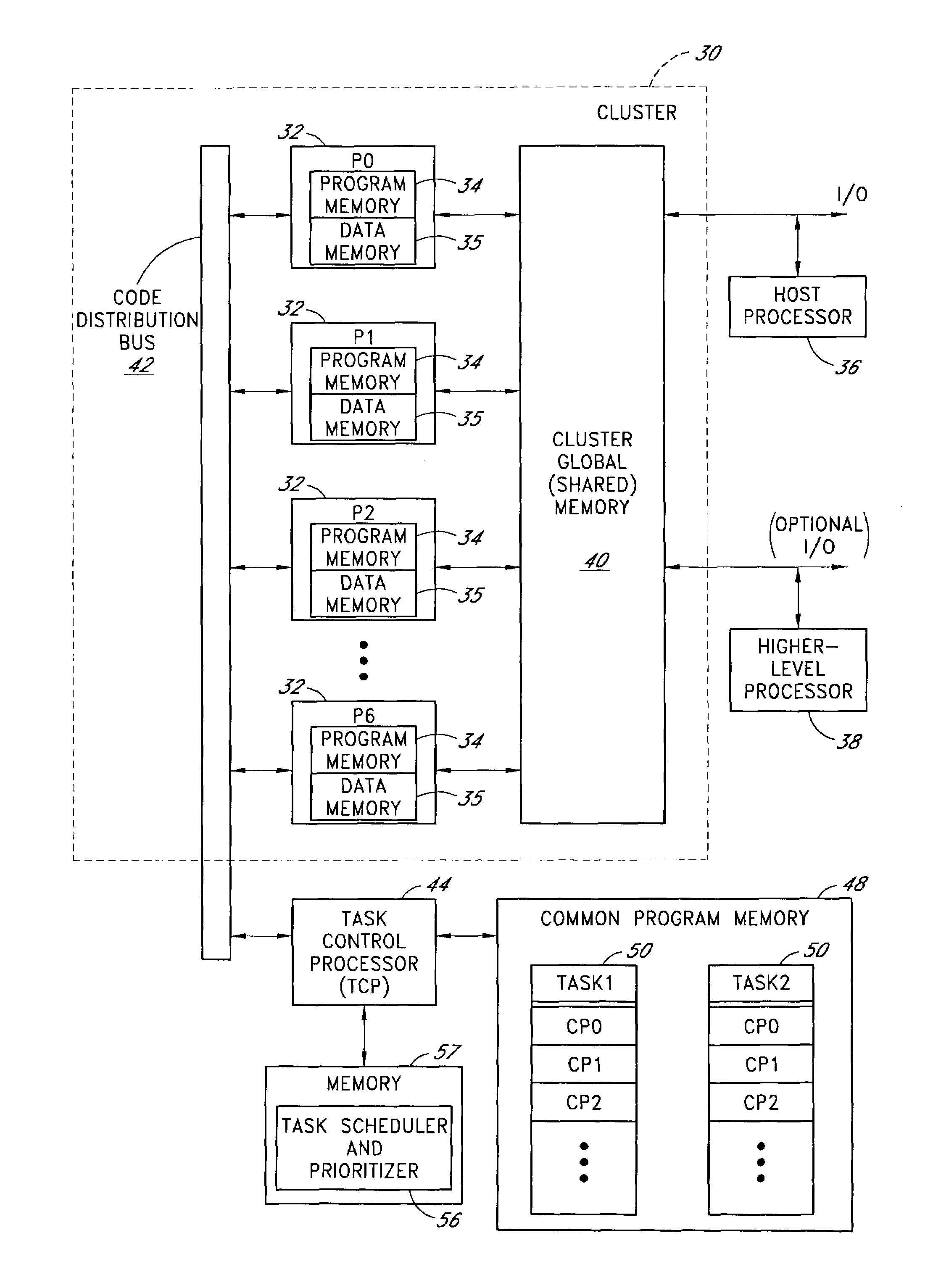

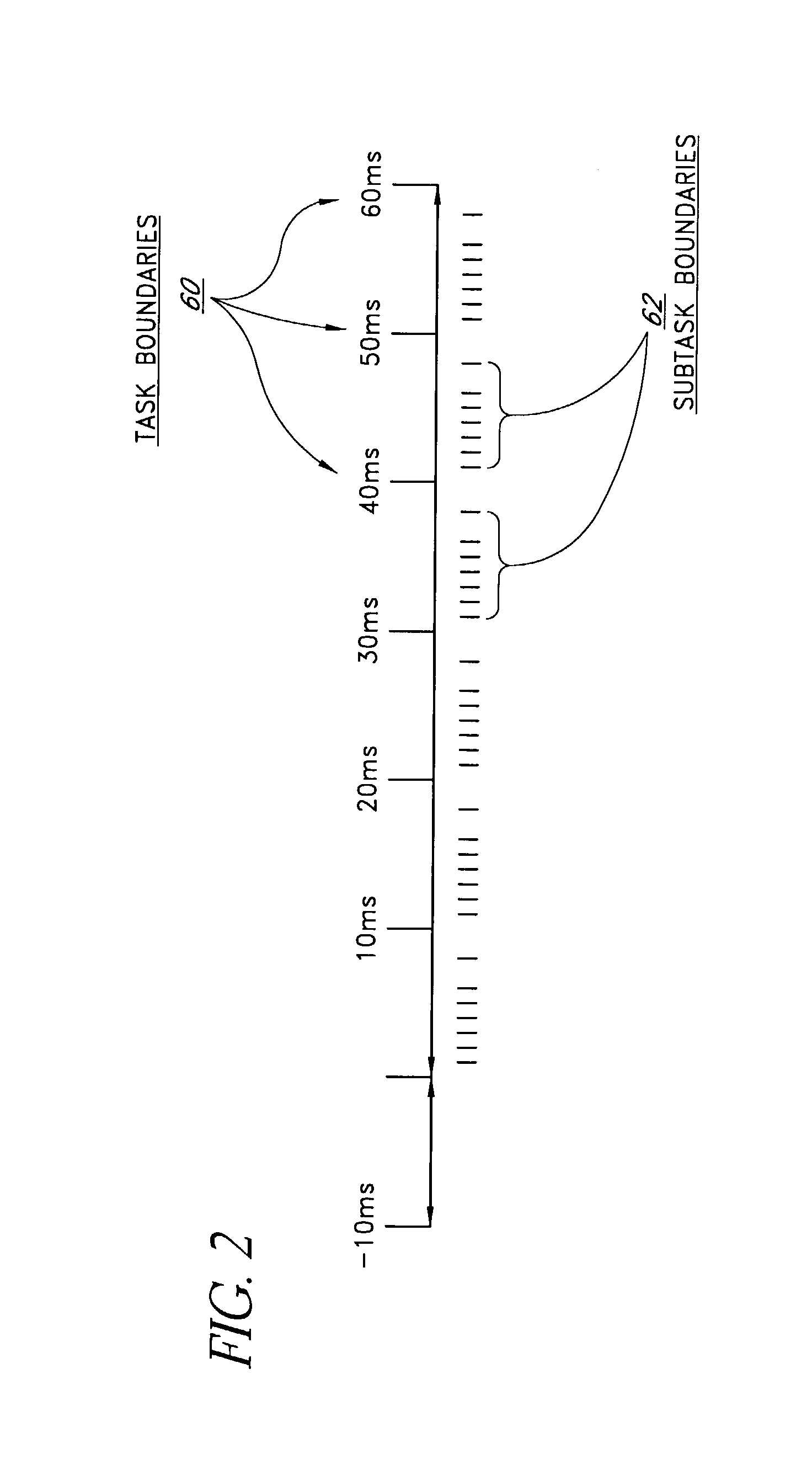

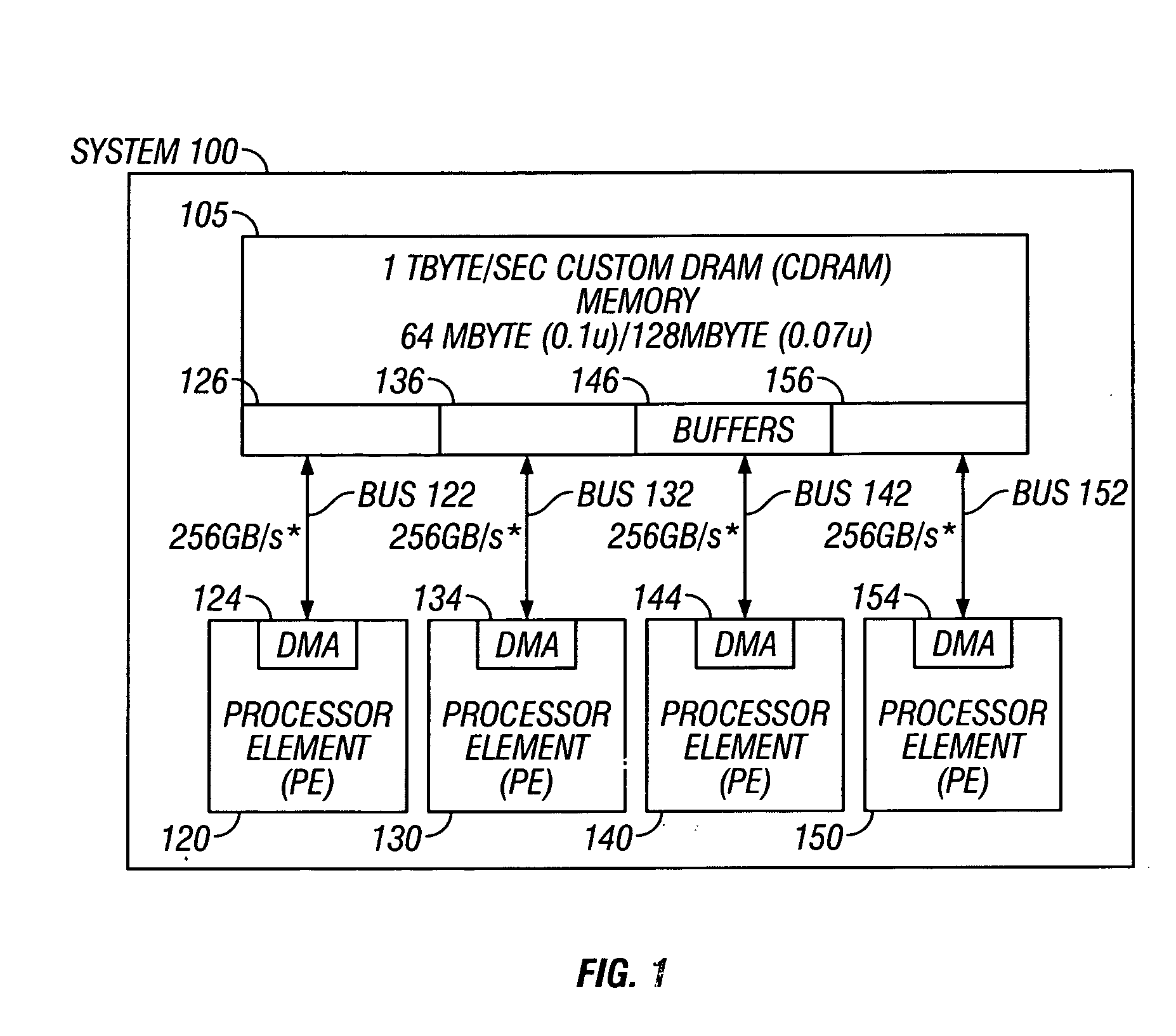

Processor cluster architecture and associated parallel processing methods

ActiveUS6959372B1High level of performanceGeneral purpose stored program computerProgram loading/initiatingCode distributionComputer science

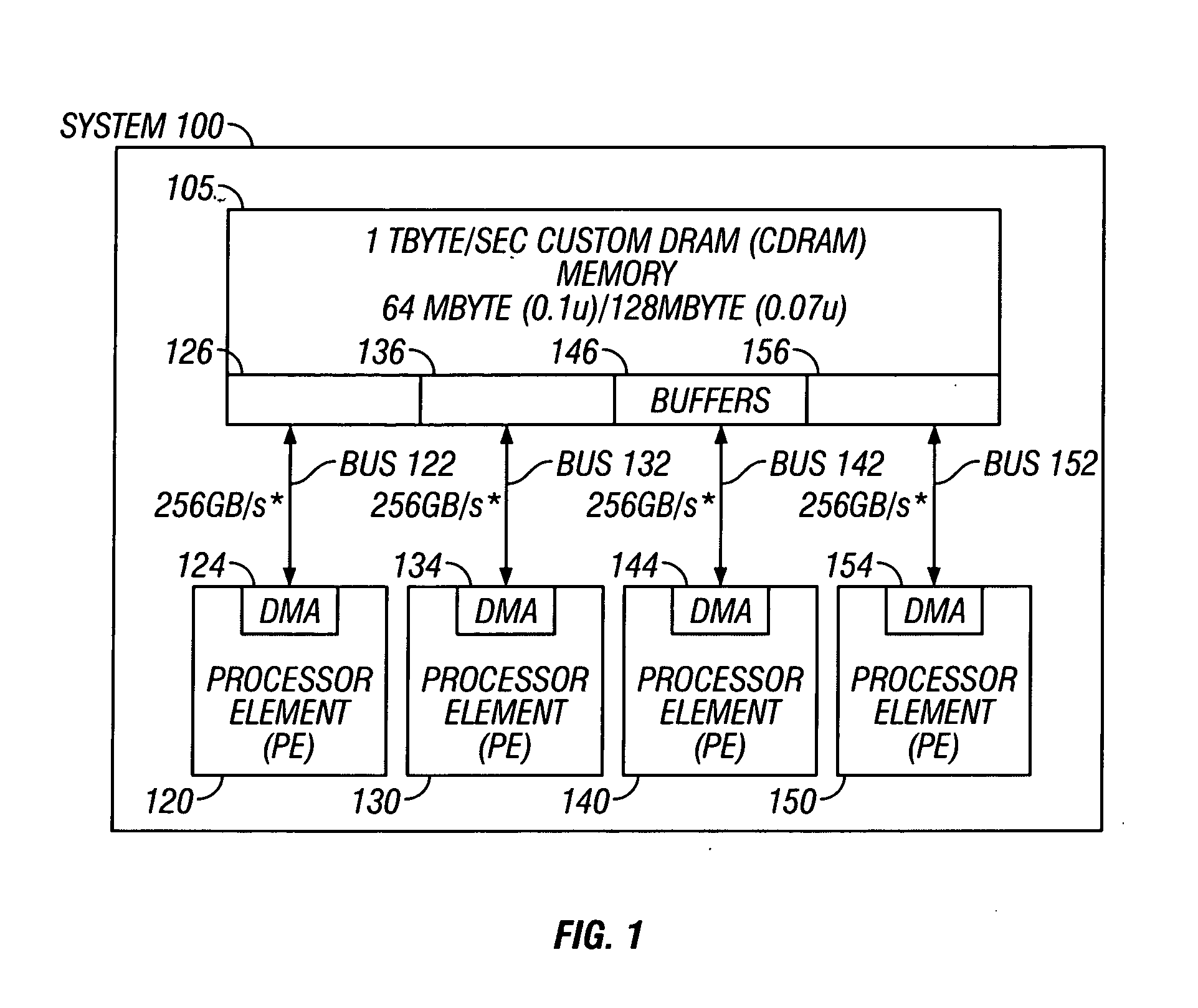

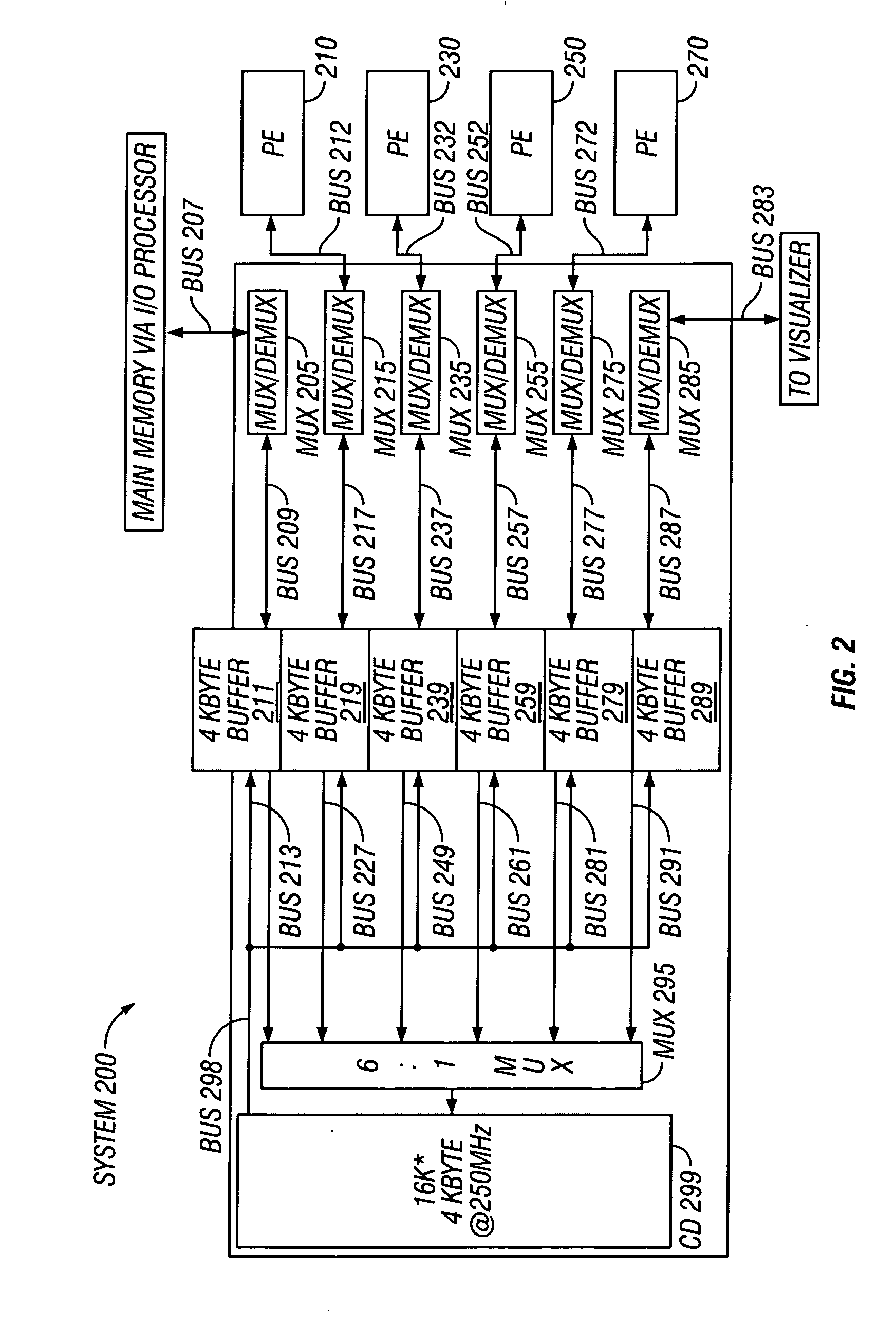

A parallel processing architecture comprising a cluster of embedded processors that share a common code distribution bus. Pages or blocks of code are concurrently loaded into respective program memories of some or all of these processors (typically all processors assigned to a particular task) over the code distribution bus, and are executed in parallel by these processors. A task control processor determines when all of the processors assigned to a particular task have finished executing the current code page, and then loads a new code page (e.g., the next sequential code page within a task) into the program memories of these processors for execution. The processors within the cluster preferably share a common memory (1 per cluster) that is used to receive data inputs from, and to provide data outputs to, a higher level processor. Multiple interconnected clusters may be integrated within a common integrated circuit device.

Owner:NVIDIA CORP

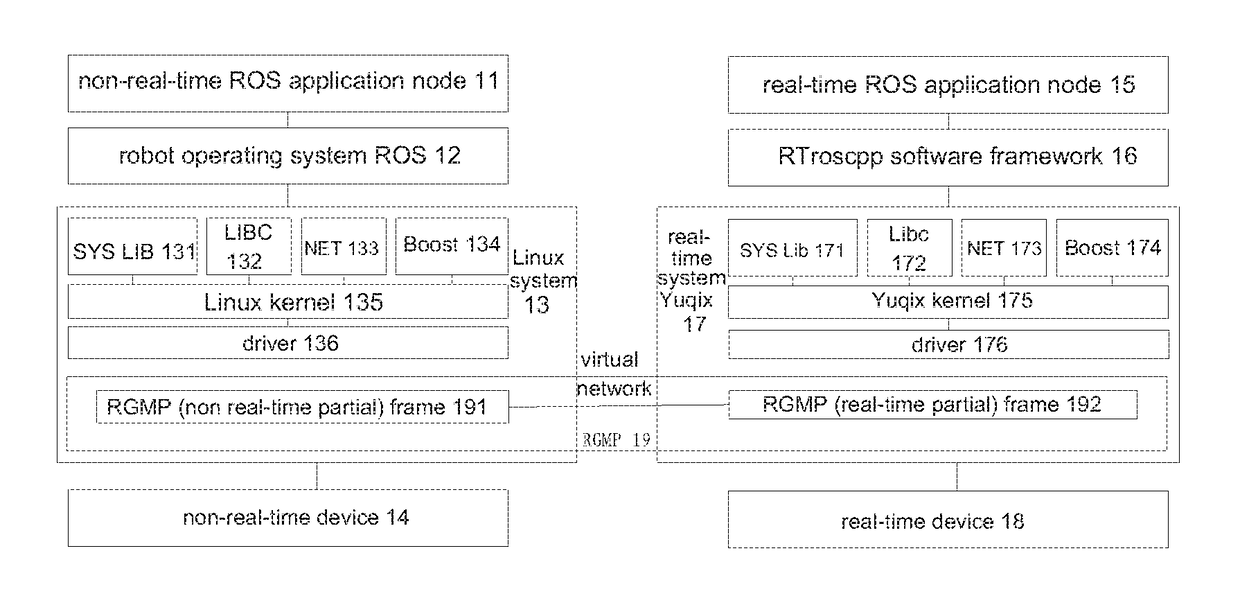

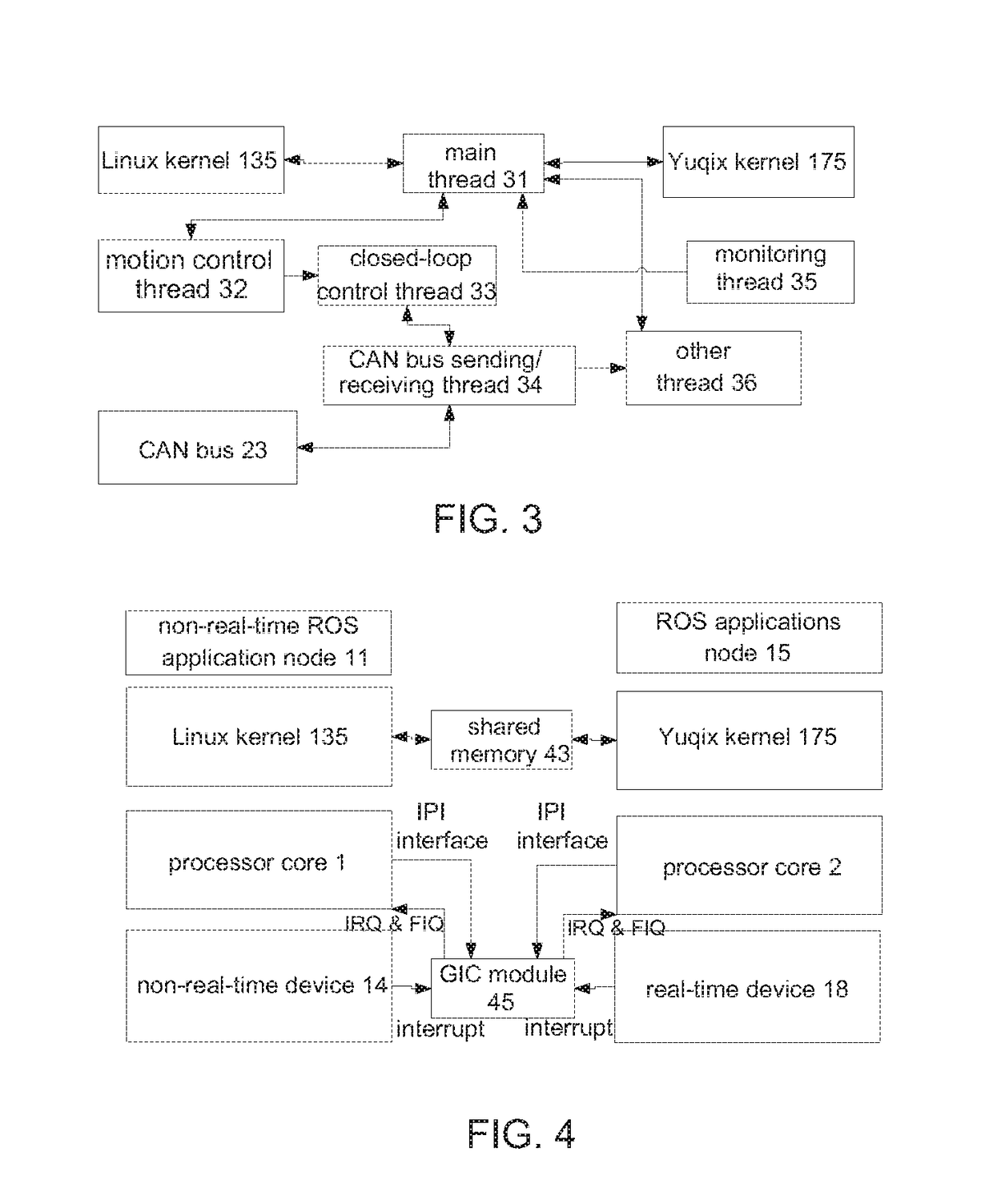

Robotic hybrid system application framework based on multi-core processor architecture

ActiveUS20170203436A1Improve development efficiencyLow costProgramme controlProgramme-controlled manipulatorOperational systemEmbedded operating system

The present invention relates to a robot hybrid system application framework based on a multi-core processor architecture. In the robot system with ARM / X86 multi-core processor as the controller, multi-core parallel processing architecture of the ARM / X86 multi-core processor is used to run the robotic hybrid system application framework comprising real-time operating system, non-real-time operating system and system supporting frame in the whole robot controller, so as to provide improved operating system services. In this application framework, a real-time operating system runs independently in one ARM / X86 core, while several non-real-time operating systems run on other ARM / X86 cores. The operating systems occupy processor resources and peripherals separately and run robotic applications with different real-time requirements. The application program can be used as a unified robot operating system (ROS) application node.

Owner:AUBO BEIJING ROBOTICS TECH CO LTD

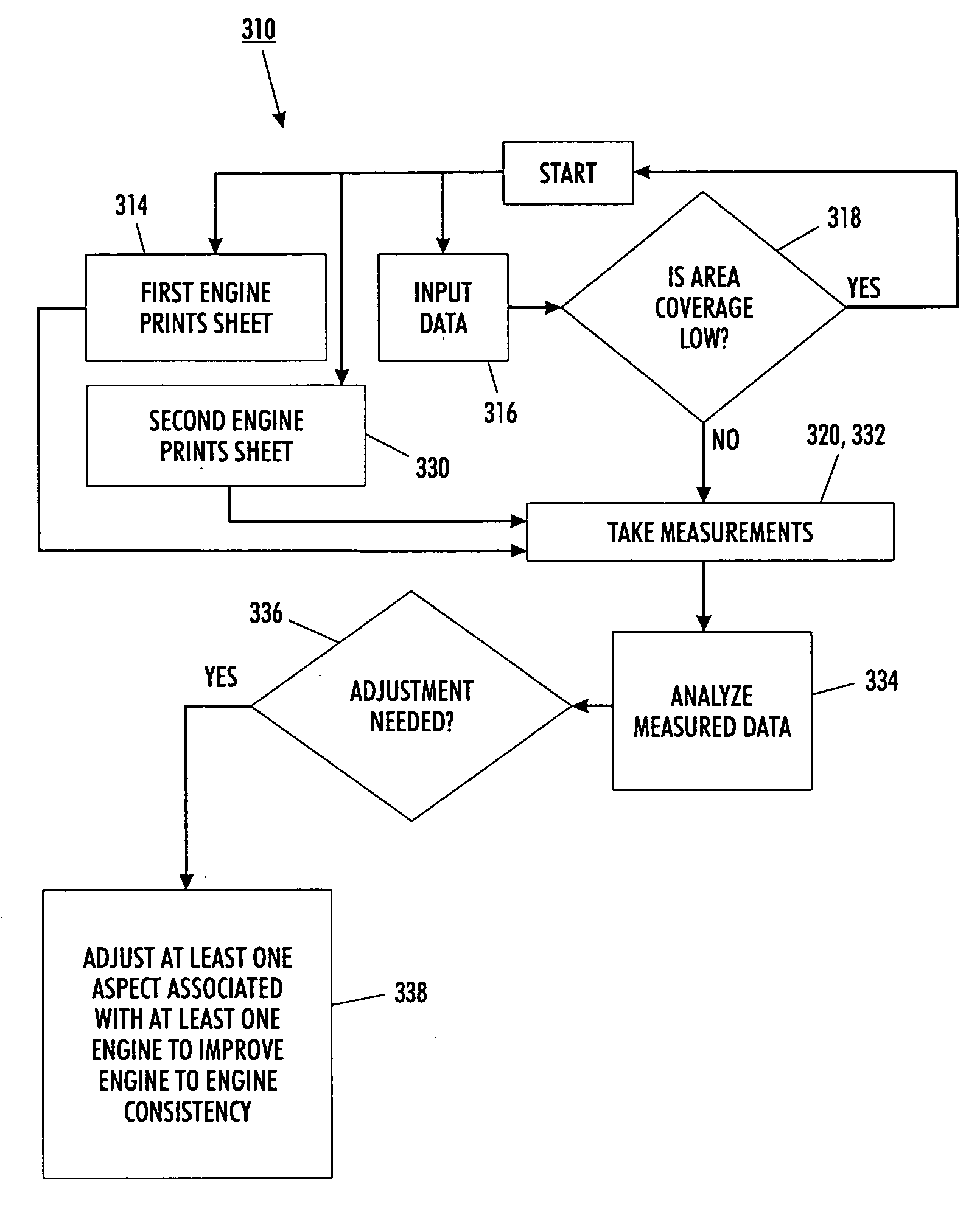

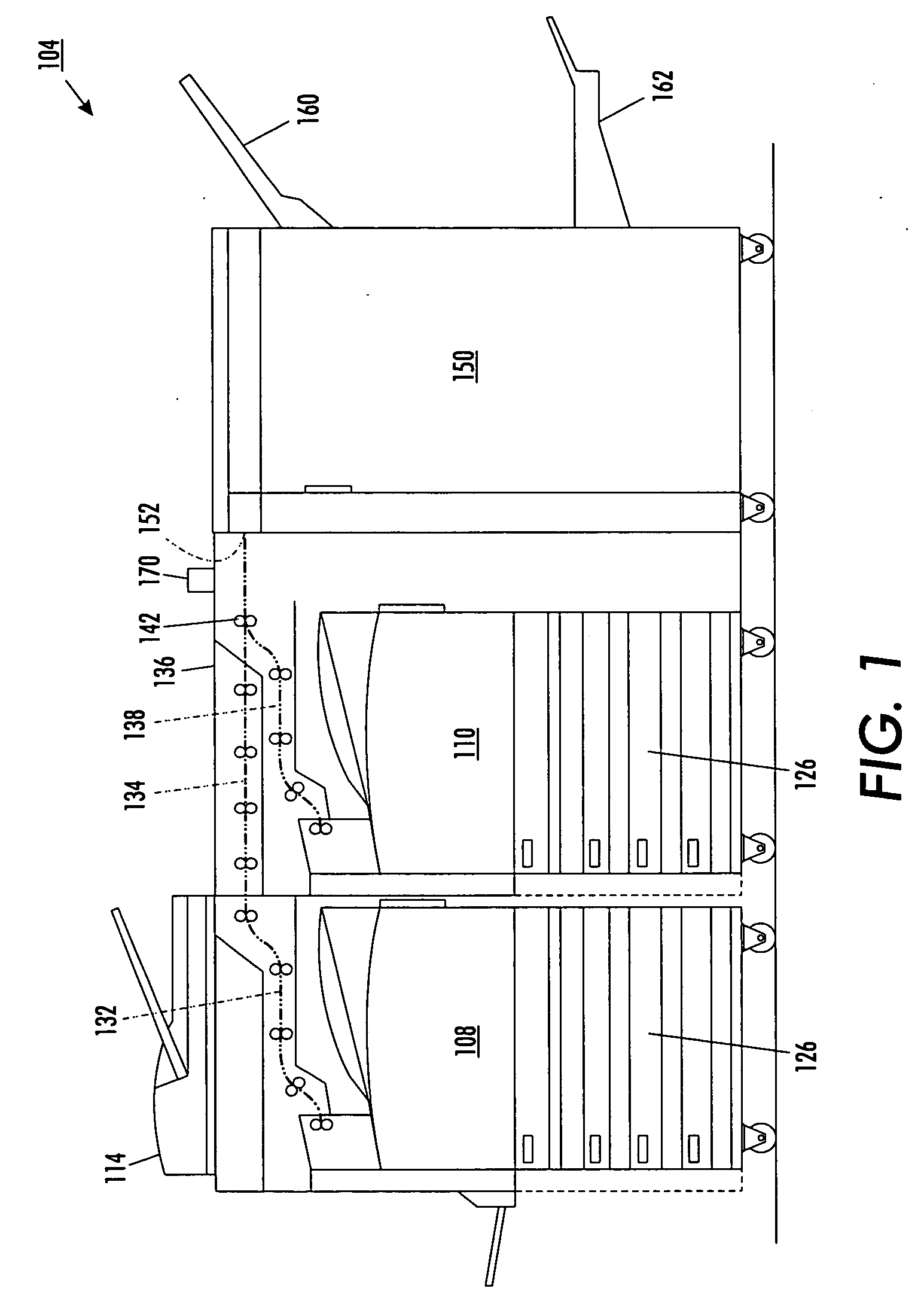

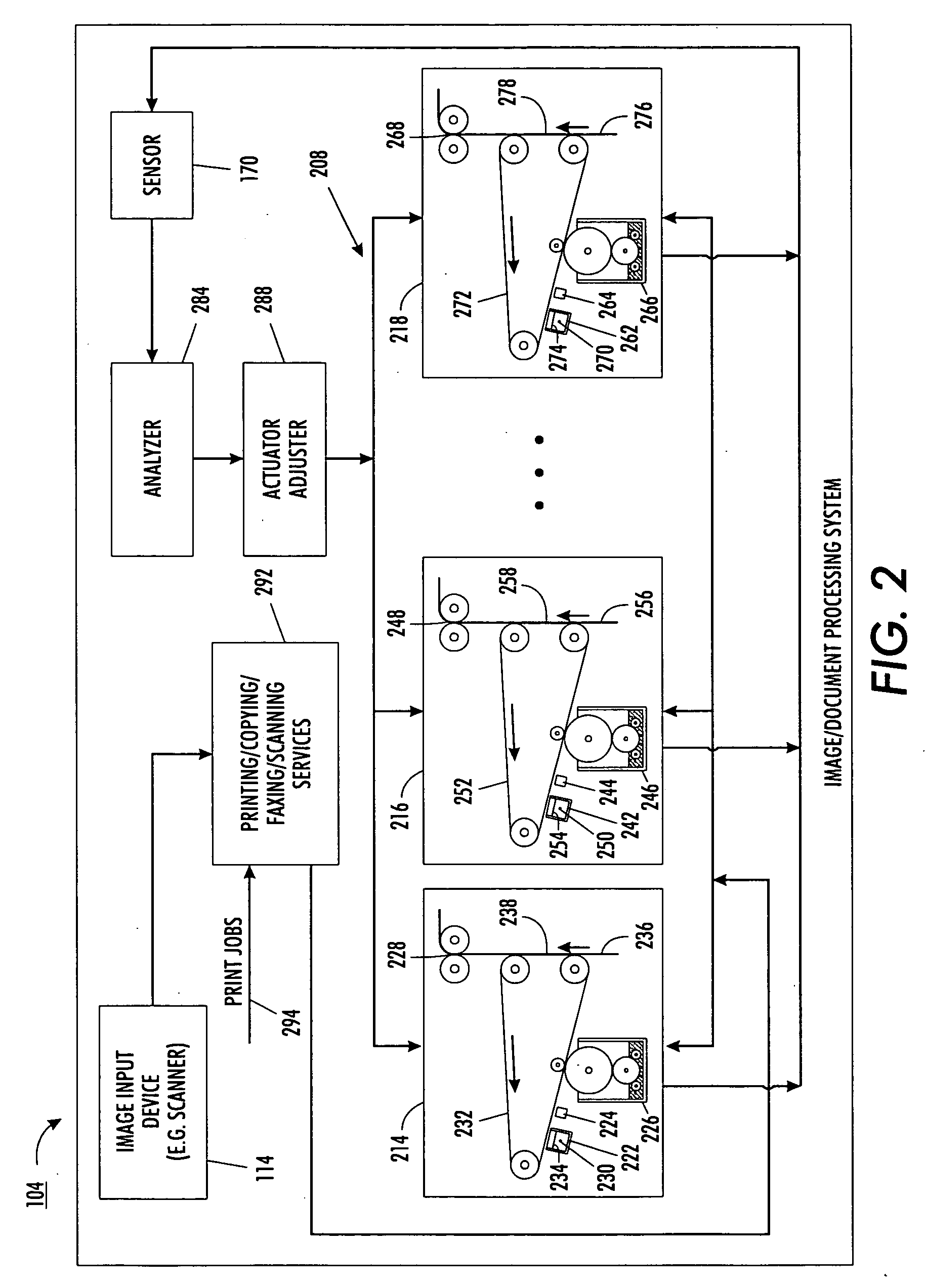

Image quality control method and apparatus for multiple marking engine systems

A full width array CCD sensor is incorporated in the media path to monitor fused pages by calculating area coverage from multiple engines in a Tightly Integrated Parallel Process (TIPP) architecture. With knowledge of the area coverage differences between print engines for a given pixel count to the ROS, a relative density difference of each engine is determined. Based on the determined relative density difference, an adjustment is calculated and applied to the engine with the largest error to match the area coverage(s) of the other engine(s).

Owner:XEROX CORP

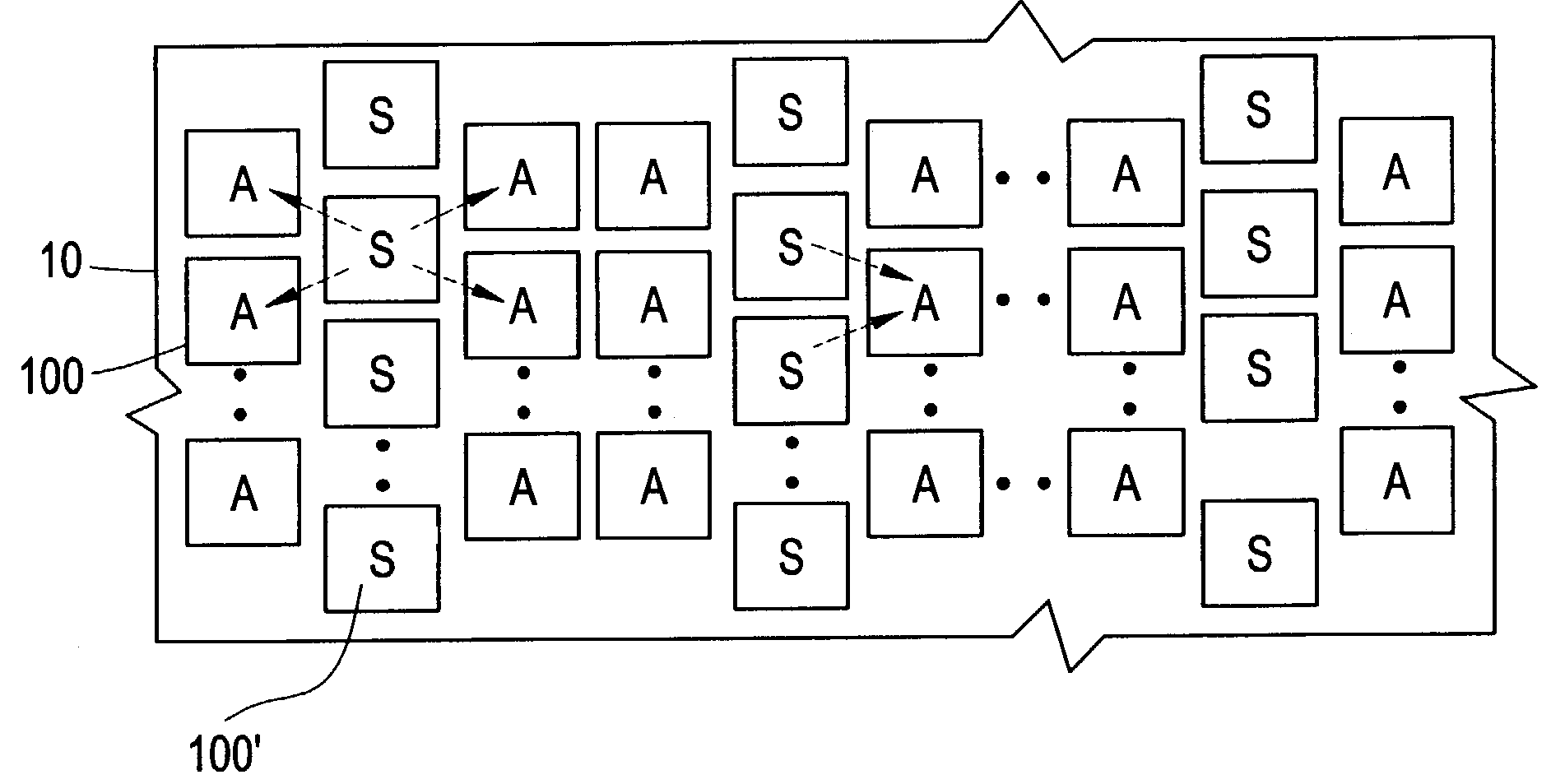

Fault tolerant cell array architecture

InactiveUS7299377B2Single instruction multiple data multiprocessorsStatic indicating devicesData processing systemComputer architecture

A data processing system containing a monolithic network of cells with sufficient redundancy provided through direct logical replacement of defective cells by spare cells to allow a large monolithic array of cells without uncorrectable defects to be organized, where the cells have a variety of useful properties. The data processing system according to the present invention overcomes the chip-size limit and off-chip connection bottlenecks of chip-based architectures, the von Neumann bottleneck of uniprocessor architectures, the memory and I / O bottlenecks of parallel processing architectures, and the input bandwidth bottleneck of high-resolution displays, and supports integration of up to an entire massively parallel data processing system into a single monolithic entity.

Owner:NORMAN RICHARD S

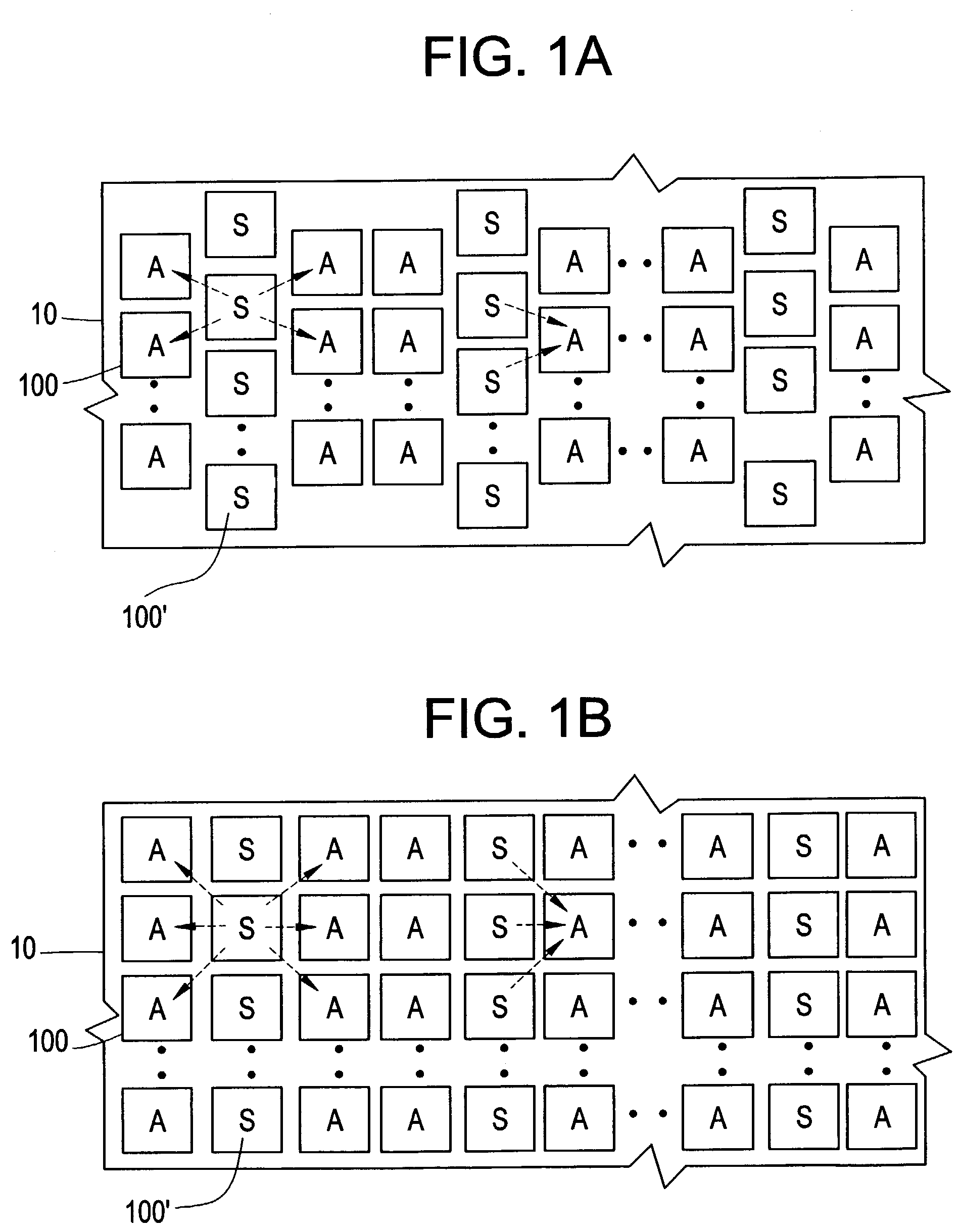

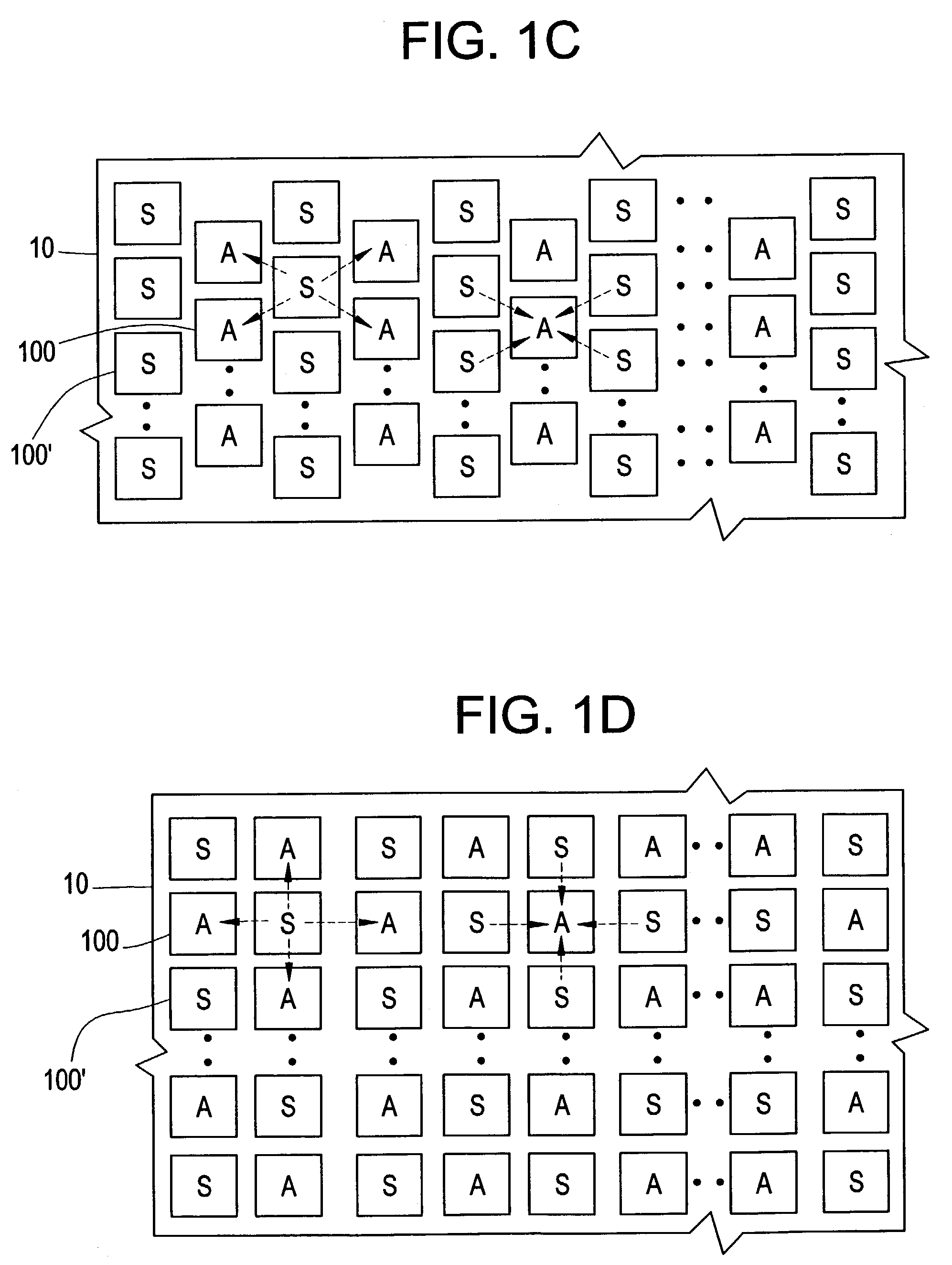

Method for matrix operation and rigorous wave coupling analysis through parallel processing architecture

ActiveCN103631761AOptically investigating flaws/contaminationUsing optical meansComputer moduleParallel computing

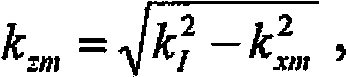

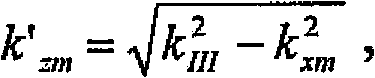

The invention provides a method for matrix operation and rigorous wave coupling analysis through a parallel processing architecture, so that a matrix operation and rigorous wave coupling analysis technology which is high in speed and low in cost is provided. The parallel processing architecture comprises a plurality of processor modules which are related to independent shared storages respectively to execute independent thread blocks. The matrix operation method comprises the following steps that i, the processors modules execute operation orders called by the parallel processing architecture respectively, wherein the operation orders are in one-to-one correspondence to operation parts in matrix operation, and the operation parts can be executed in parallel and are not related to one another; ii, data used in the operation parts are read to shared storages of corresponding processor modules respectively; iii, the processor modules read corresponding data in the shared storages based on corresponding operation orders, and execute thread blocks in parallel to complete the operation parts in the matrix operation.

Owner:RAINTREE SCI INSTR SHANGHAI

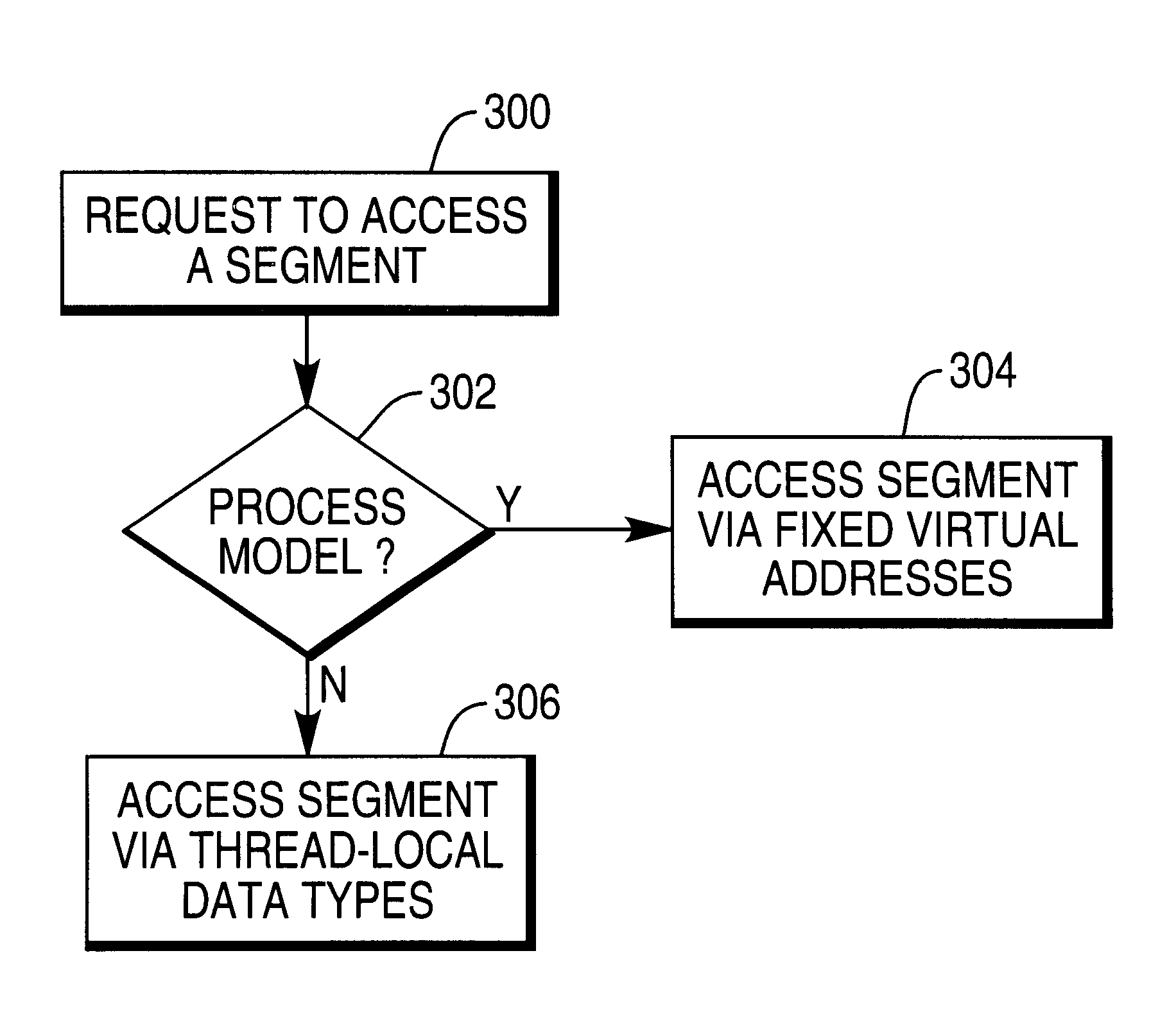

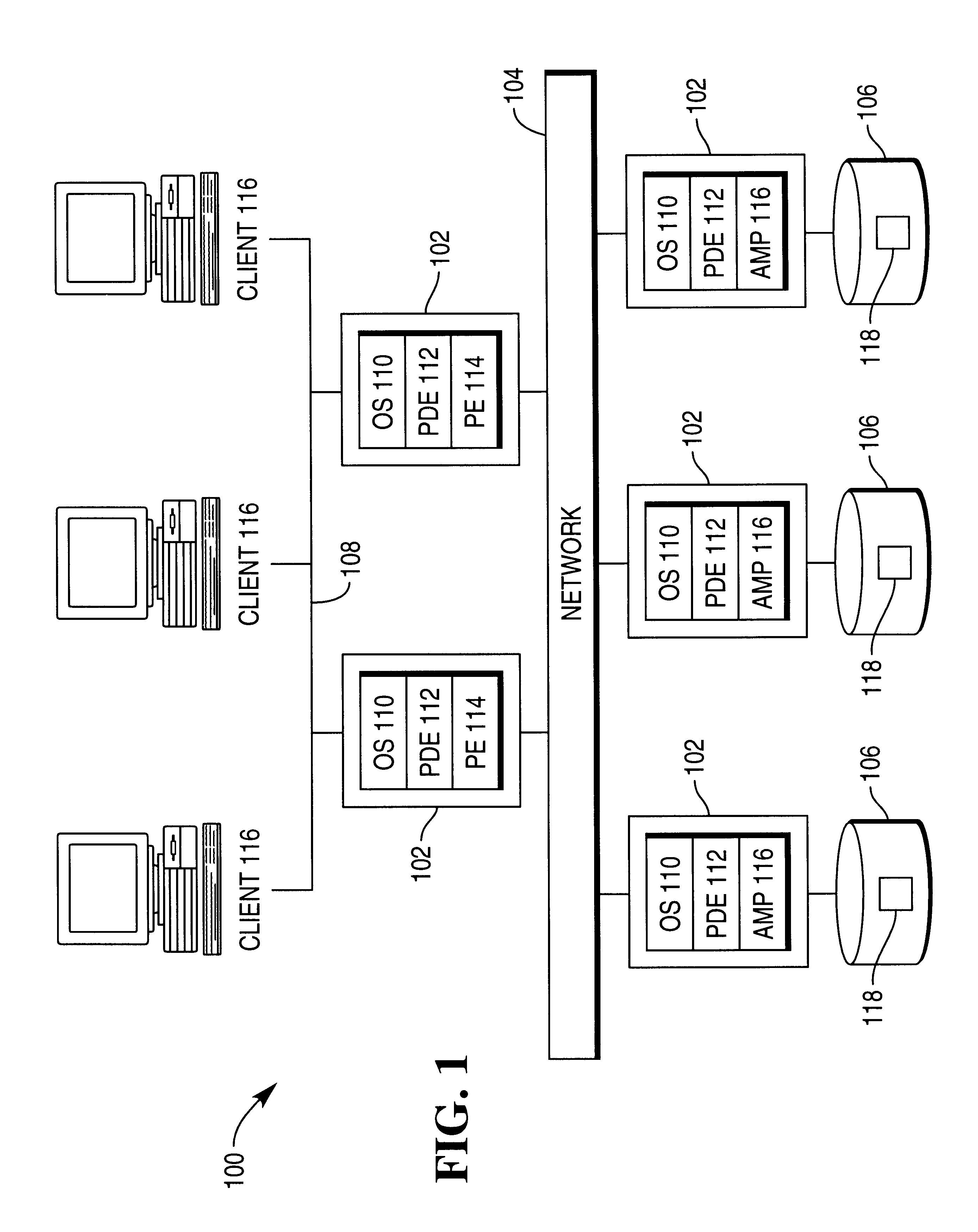

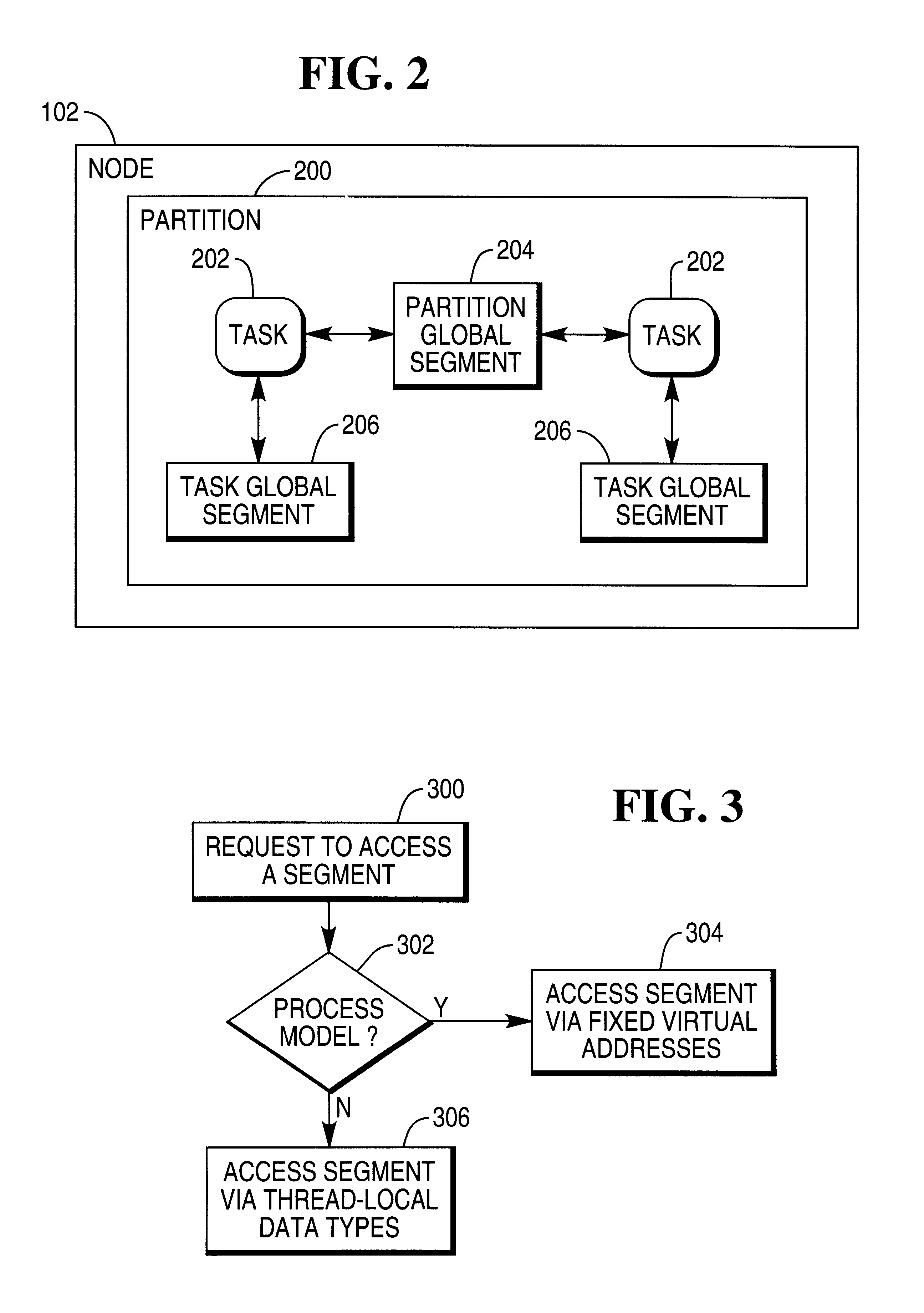

Multi-threading, multi-tasking architecture for a relational database management system

InactiveUS6351749B1Data processing applicationsRelational databasesOperational systemRelational database management system

A parallel processing architecture for a relational database management system (RDBMS) that supports both a process model operating system and a thread model operating system. The RDBMS is implemented as a shared nothing, single database image utilizing Parallel Database Extensions (PDEs) that insulate the RDBMS from the specifics of the operating system and that provide the necessary techniques for accessing common memory segments.

Owner:TERADATA US

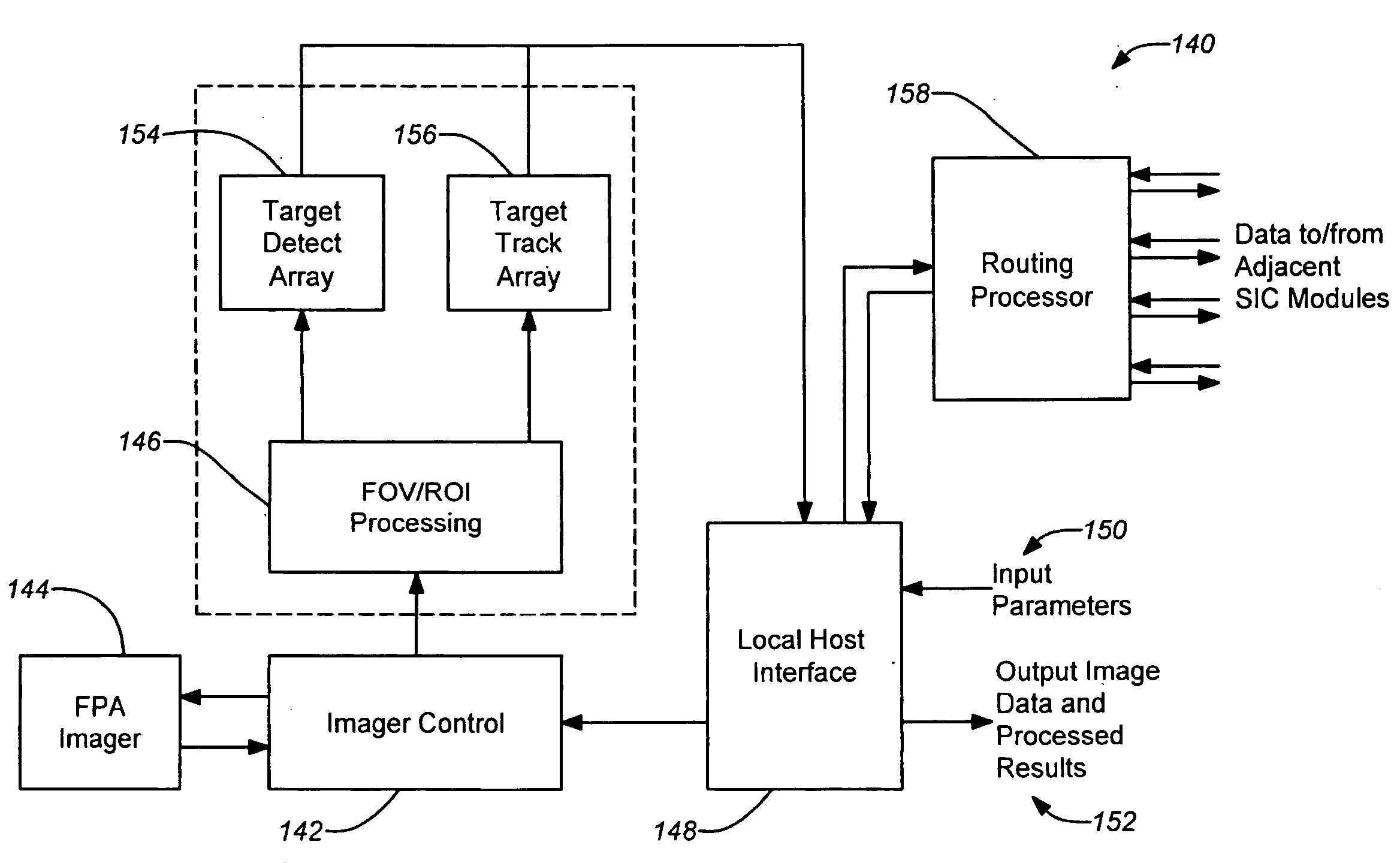

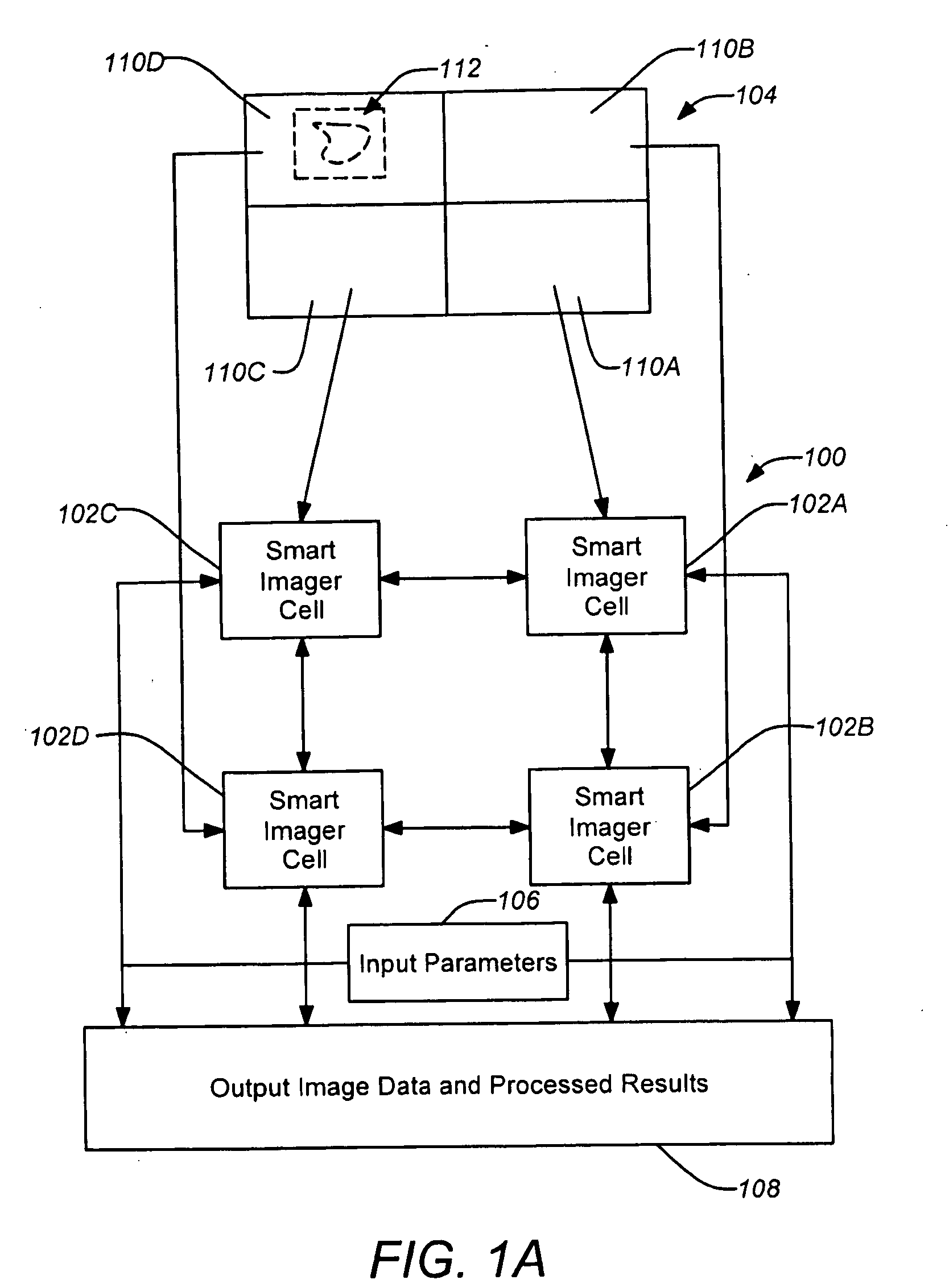

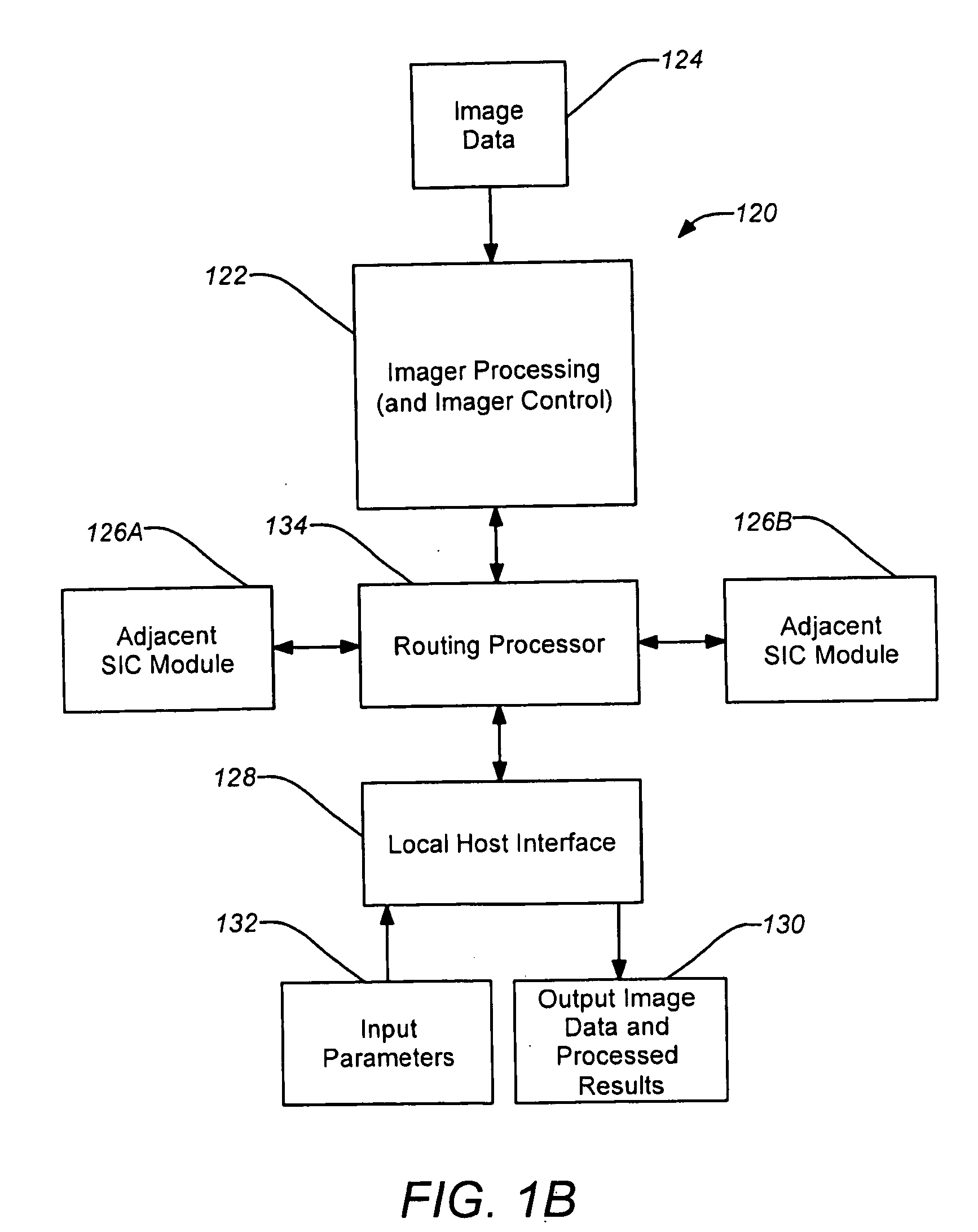

Synthetic foveal imaging technology

InactiveUS20090116688A1Rapid responseImage enhancementImage analysisImaging processingApplication software

Apparatuses and methods are disclosed that create a synthetic fovea in order to identify and highlight interesting portions of an image for further processing and rapid response. Synthetic foveal imaging implements a parallel processing architecture that uses reprogrammable logic to implement embedded, distributed, real-time foveal image processing from different sensor types while simultaneously allowing for lossless storage and retrieval of raw image data. Real-time, distributed, adaptive processing of multi-tap image sensors with coordinated processing hardware used for each output tap is enabled. In mosaic focal planes, a parallel-processing network can be implemented that treats the mosaic focal plane as a single ensemble rather than a set of isolated sensors. Various applications are enabled for imaging and robotic vision where processing and responding to enormous amounts of data quickly and efficiently is important.

Owner:CALIFORNIA INST OF TECH

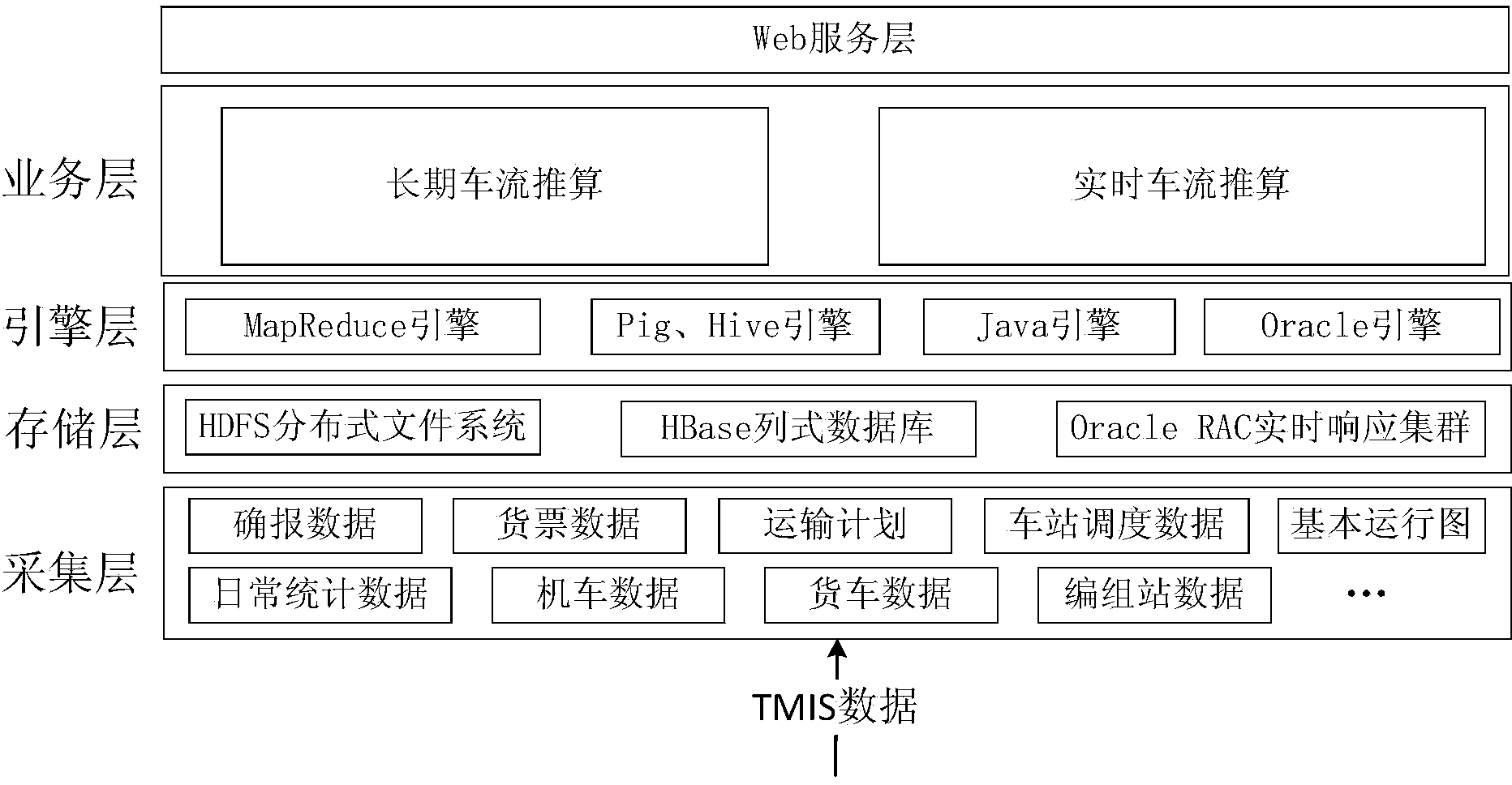

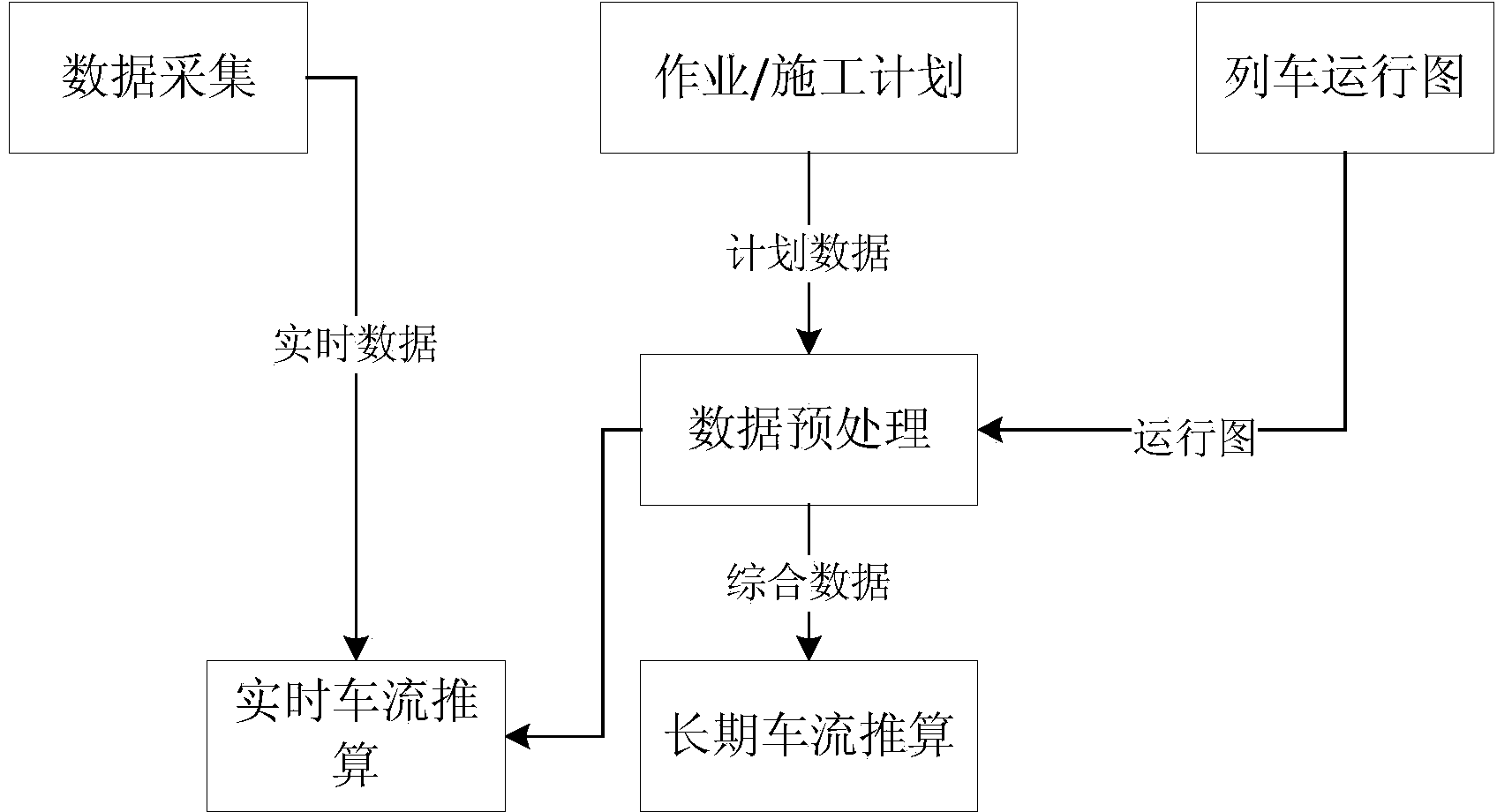

TMIS traffic flow determination method and system based on cloud computing

ActiveCN103902838ARealize long-term extrapolationReal-timeDetection of traffic movementSpecial data processing applicationsResource poolWeb service

The invention relates to a TMIS traffic flow determination method and system based on cloud computing. The TMIS traffic flow determination method comprises the steps of (1) constructing a distributed storage resource pool on the basis of a cloud platform, collecting and storing monitoring data related to traffic flow calculation through a TMIS, (2) preprocessing the collected monitoring data through a concurrent processing framework, (3) writing a traffic flow calculation algorithm under the concurrent processing framework, utilizing static data for calculating the result of long-term traffic flow calculation, (4) utilizing the static data and dynamic data under the distributed environment for calculating the result of real-time traffic flow calculation corresponding to each station, and (5) providing a traffic flow calculation inquiry service externally through the cloud platform. The TMIS traffic flow determination system comprises a collecting layer, a storage layer, an engine layer, a service layer and a web service layer. According to the TMIS traffic flow determination method and system based on cloud computing, the cloud platform is utilized for obtaining various data required by traffic flow calculation in the TMIS, the concurrent computation is utilized for rapid data processing, and long-term and real-time traffic flow calculation and determination of railway transportation can be achieved.

Owner:BEIJING TAILEDE INFORMATION TECH

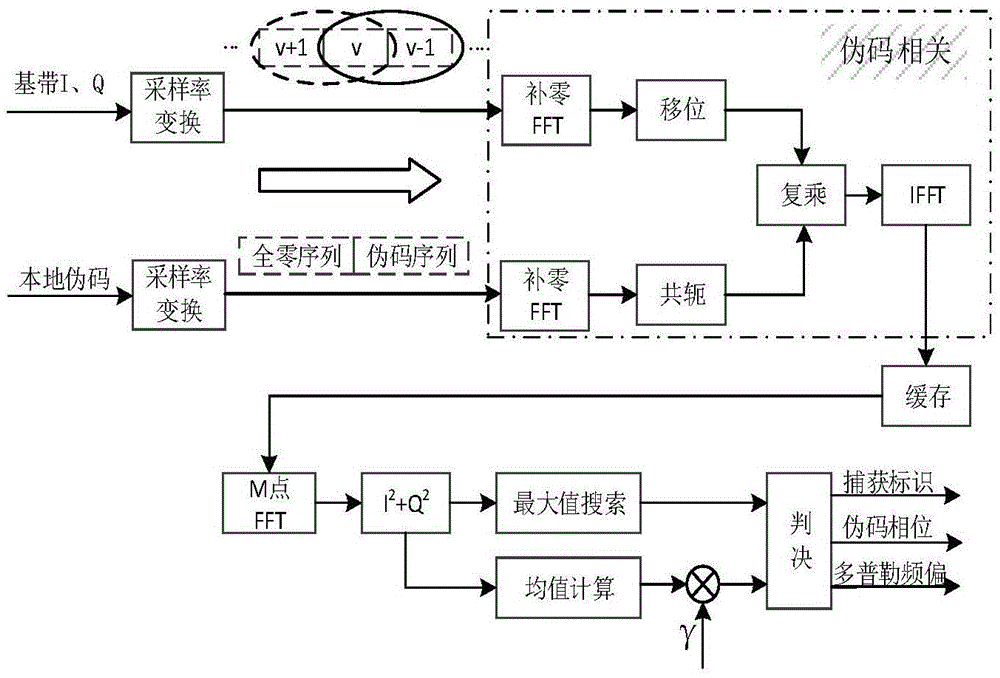

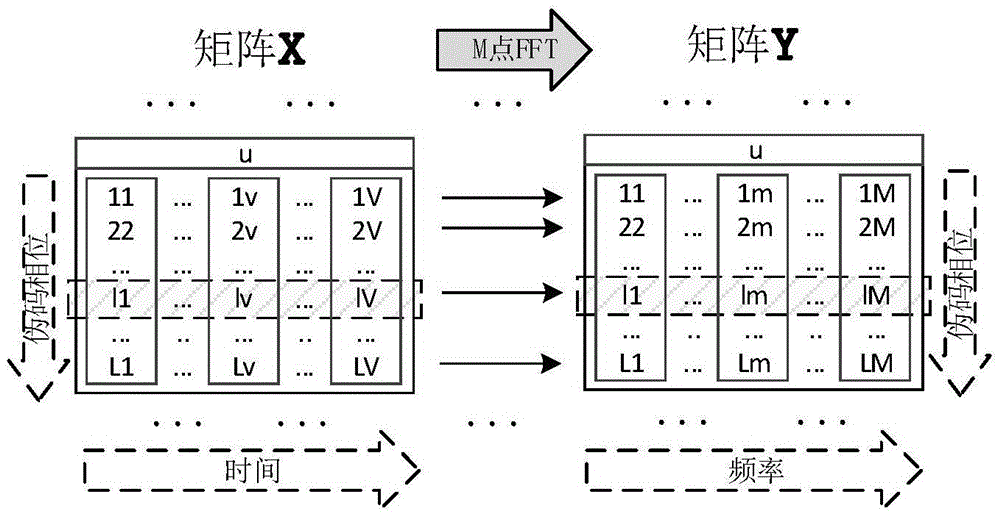

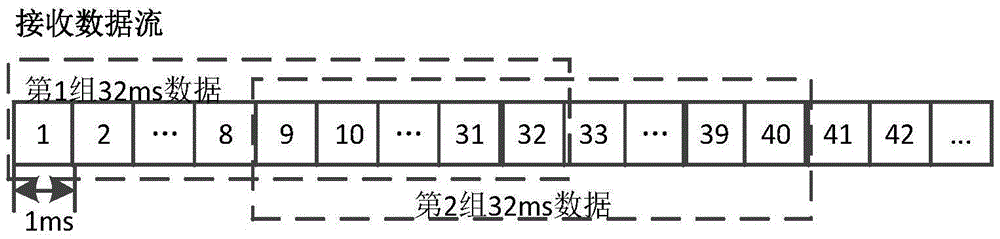

Full coherence accumulation time-frequency domain parallel capturing method based on FFT

InactiveCN105553507AReduce overheadAchieve unified optimizationTransmissionSignal-to-noise ratio (imaging)Data information

The invention discloses a full coherence accumulation time-frequency domain parallel capturing method based on FFT, in order to quickly capture a burst direct sequence spread spectrum signal with low signal to noise ratio and large frequency offset. The full coherence accumulation time-frequency domain parallel capturing method disclosed by the invention comprises two realization parts: pseudo code correlation based on FFT and full coherence accumulation based on FFT. Two methods of symbol correlation and zero complement FFT are used for further reducing the sinc loss in a pseudo code correlation process and the scallop loss in an accumulation process. The parallel capturing method is used for reducing the consumption of processing resources by the buffer of a large amount of intermediate data information and a parallel processing architecture based on FFT, obtaining a very high signal to noise ratio of a correlation peak within a short time, precisely evaluating Doppler frequency offset in a parallel search process of a pseudo code phase and reducing the average capturing time.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

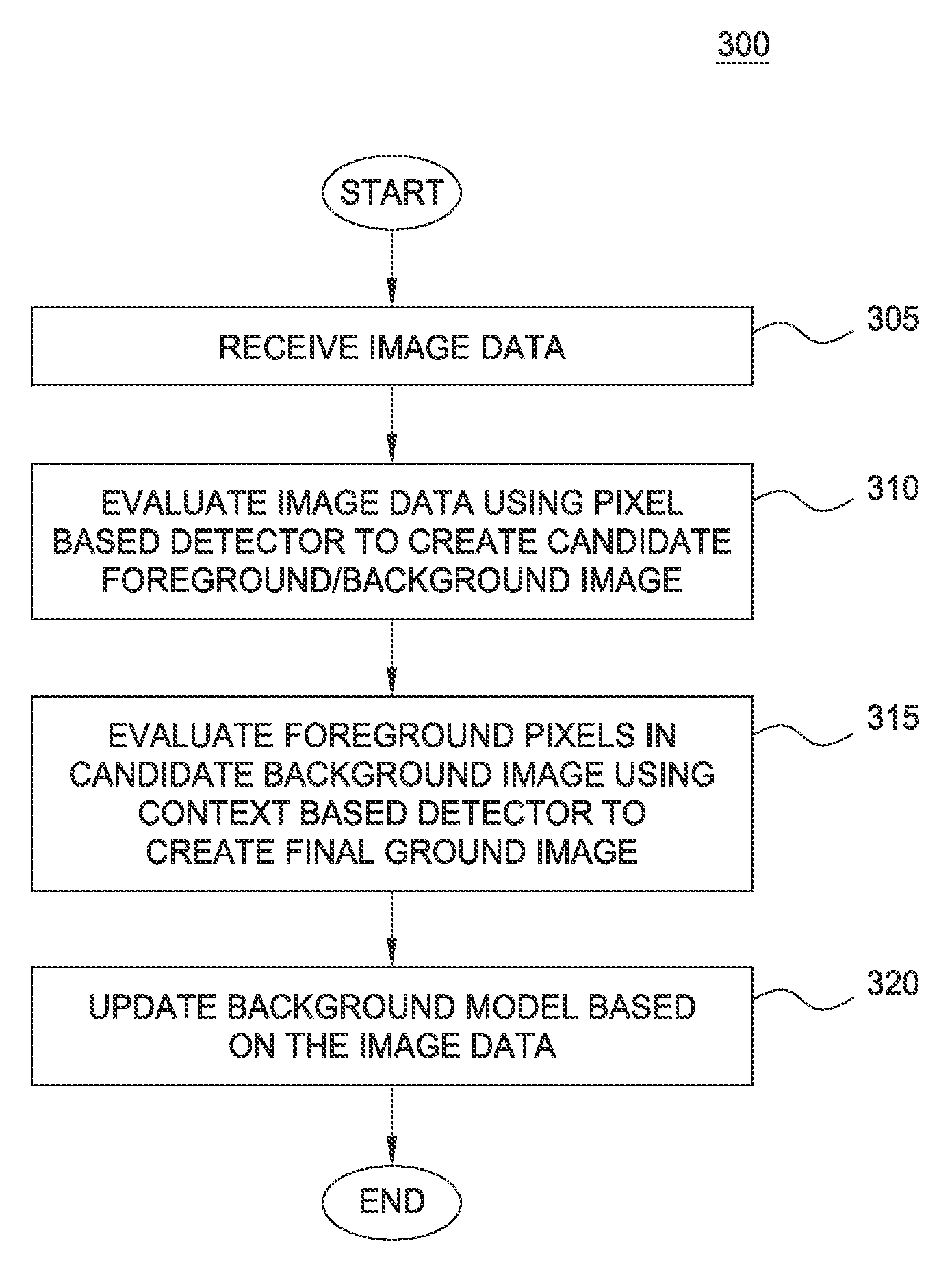

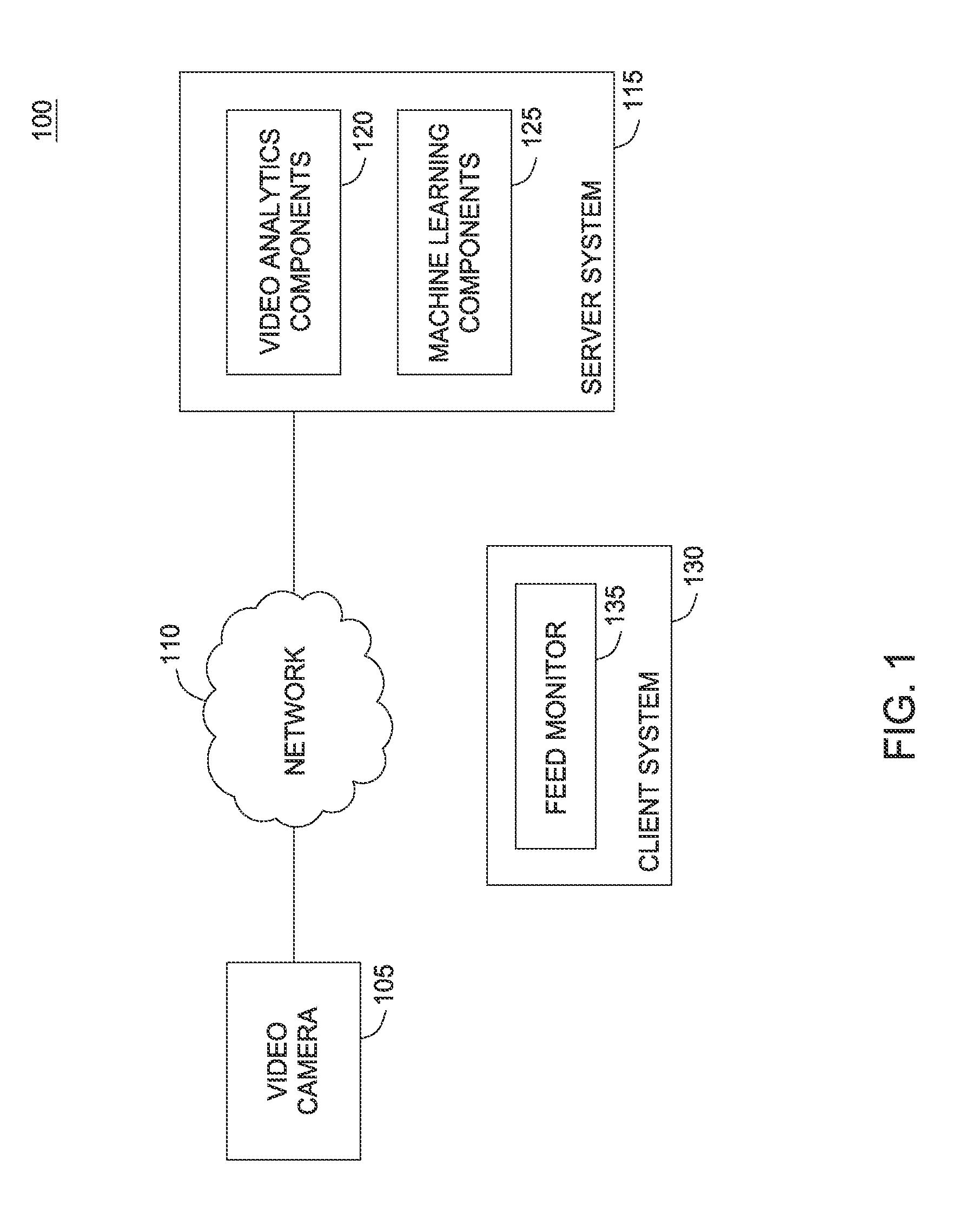

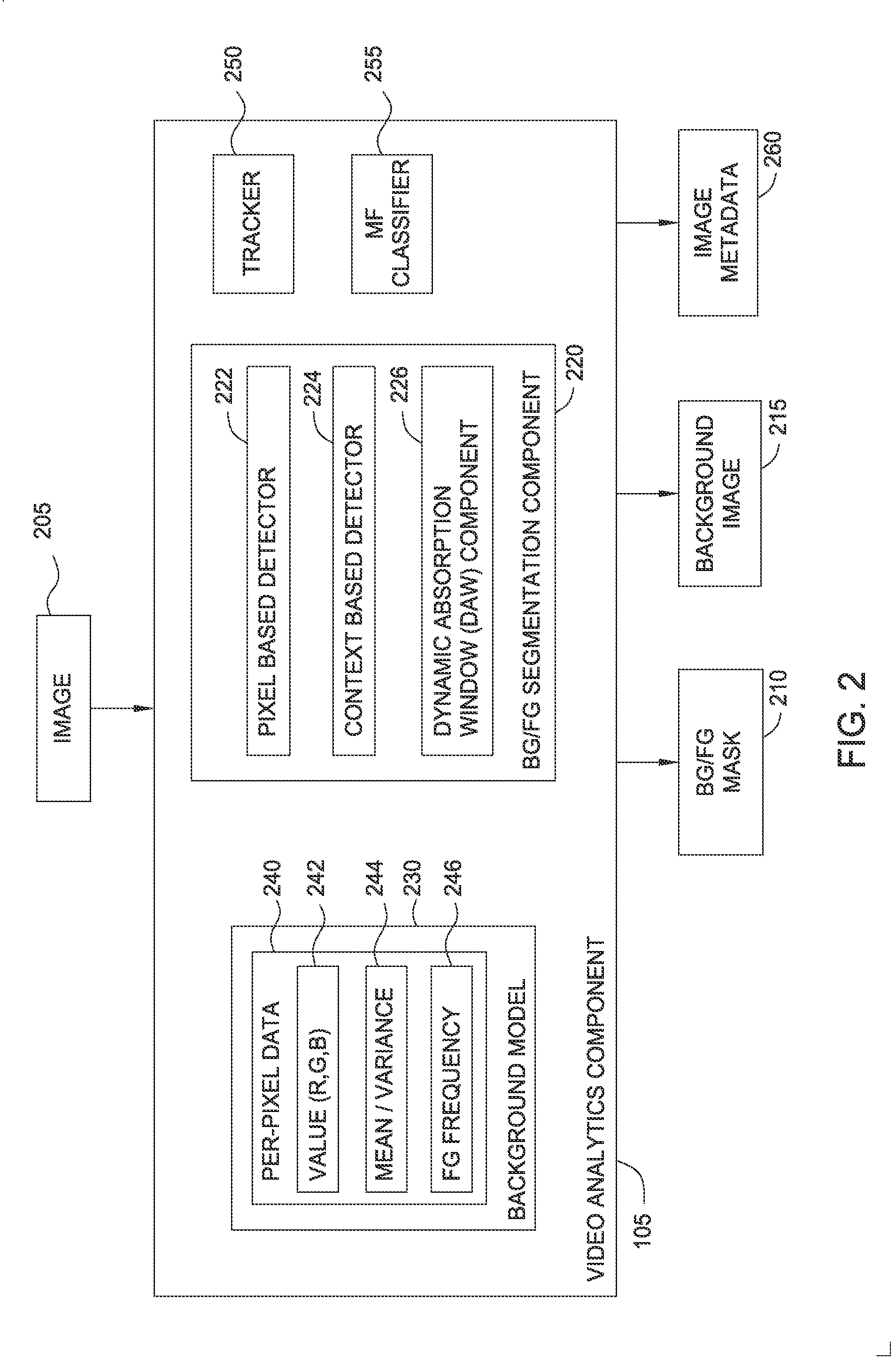

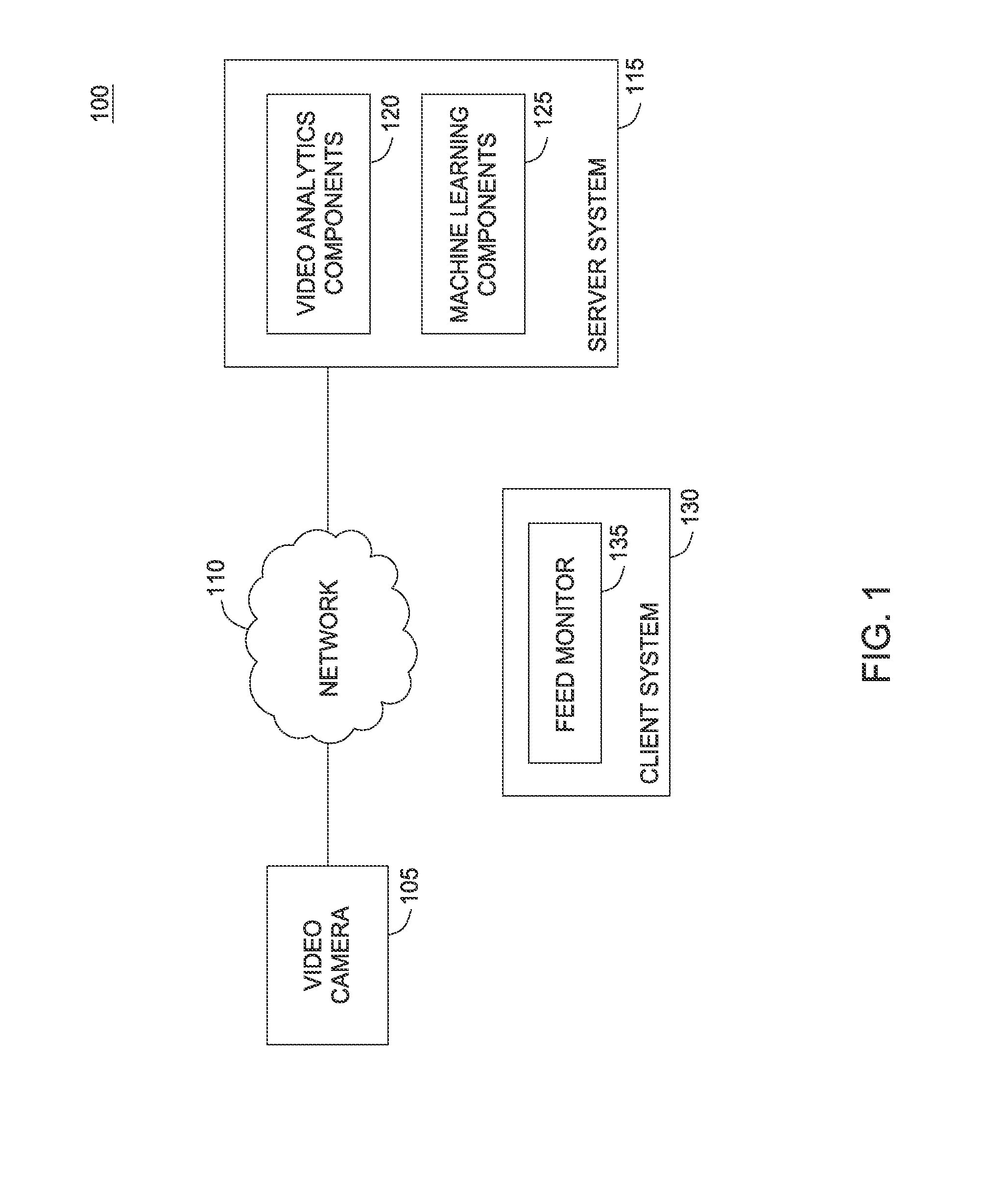

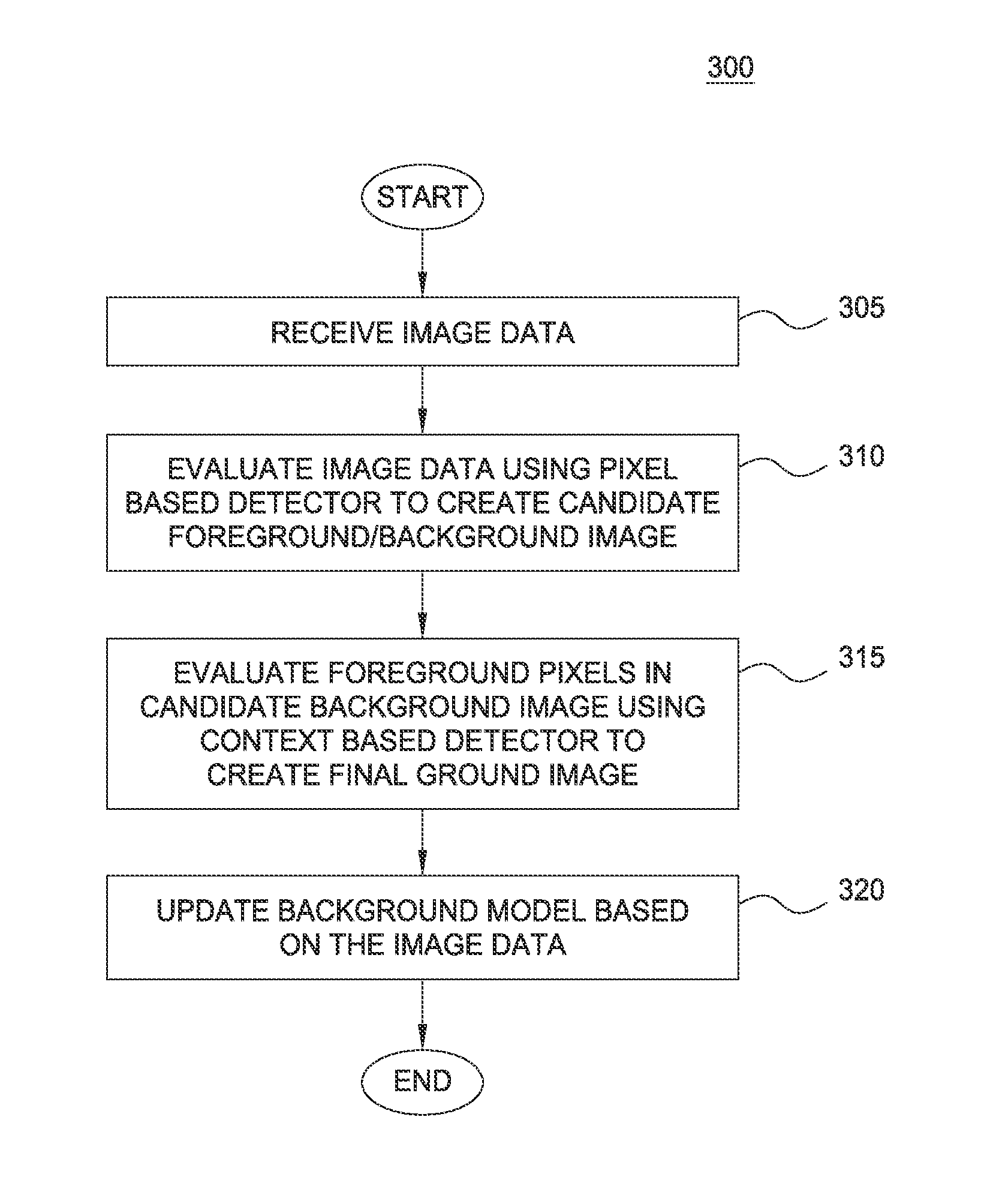

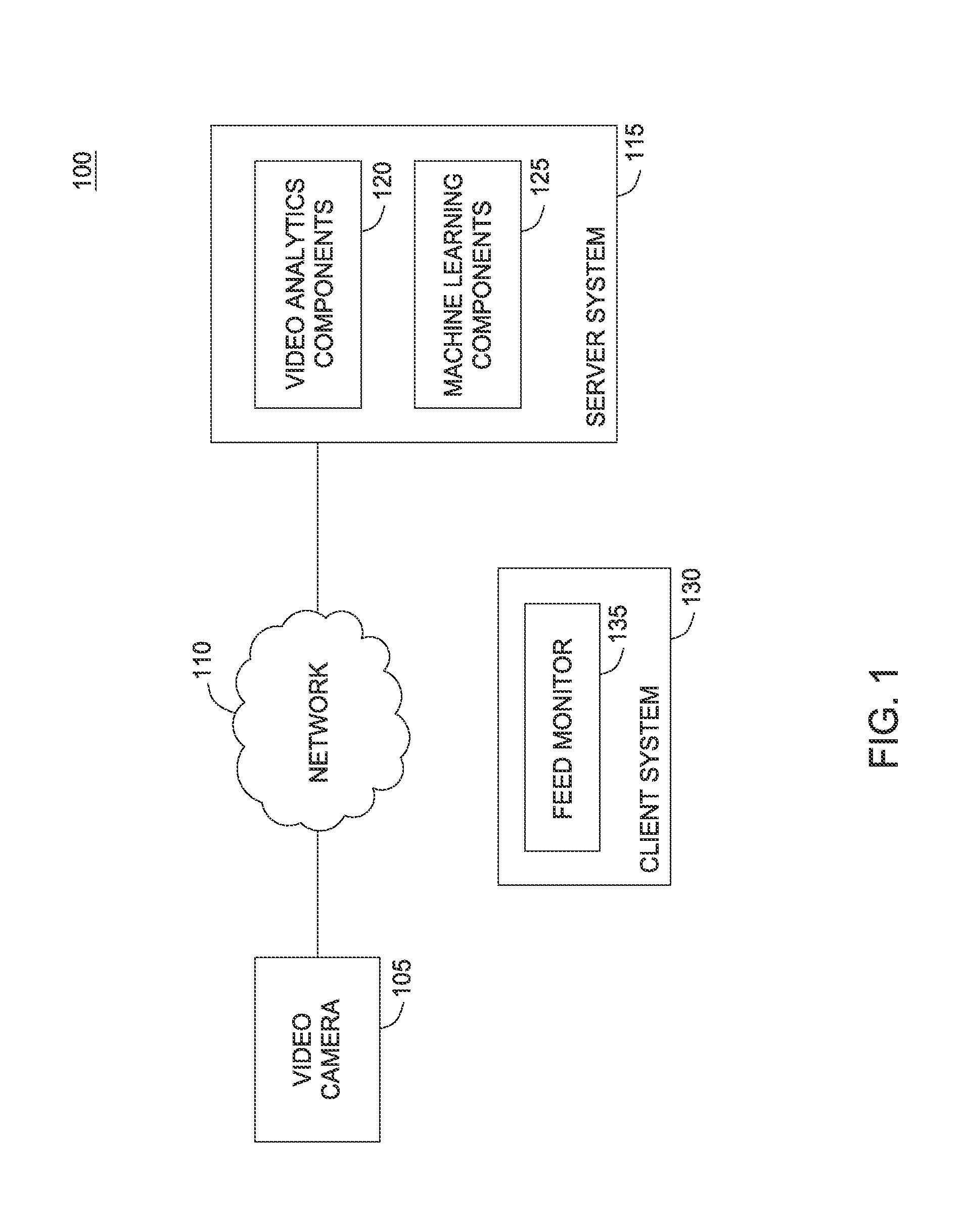

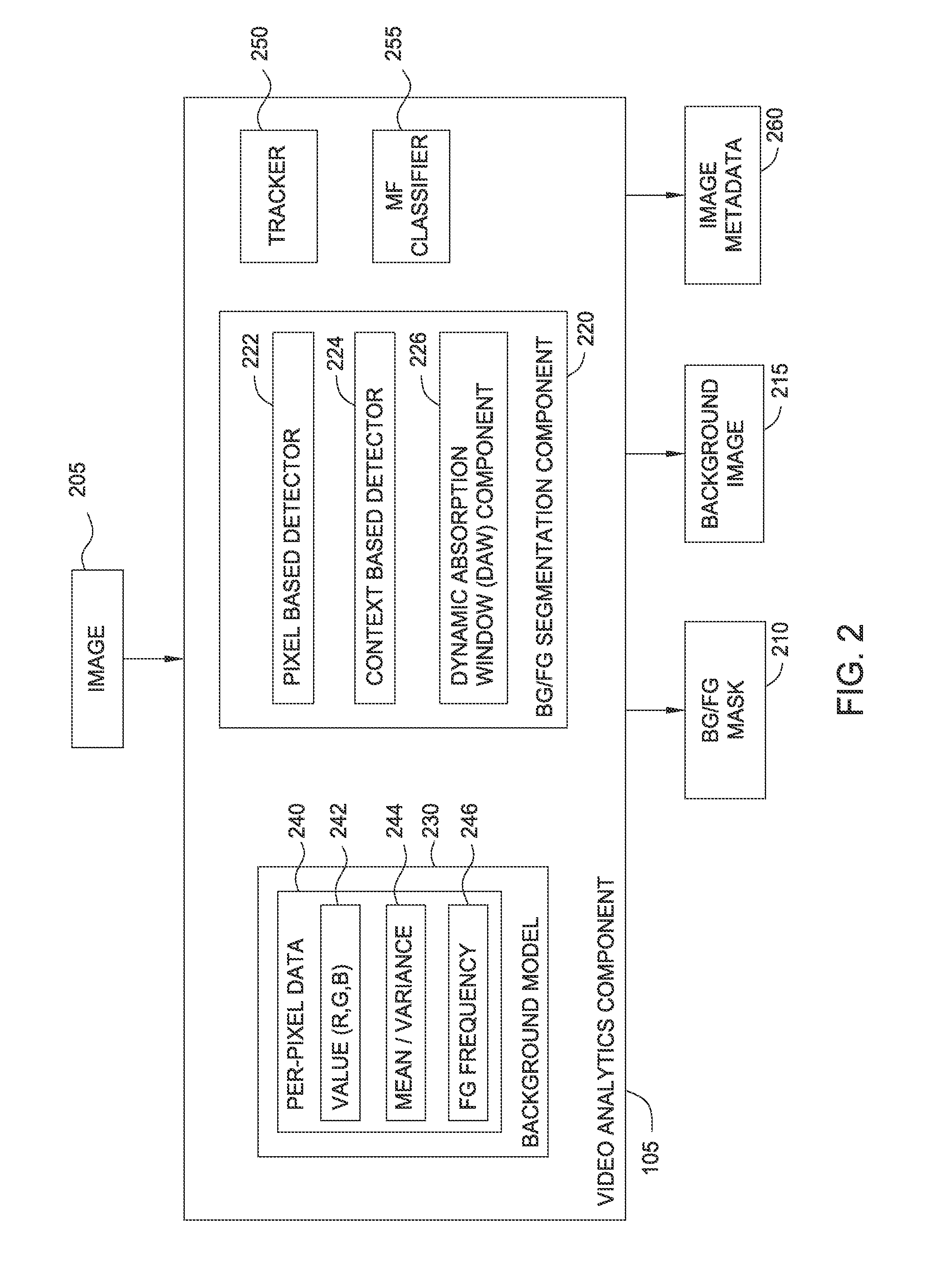

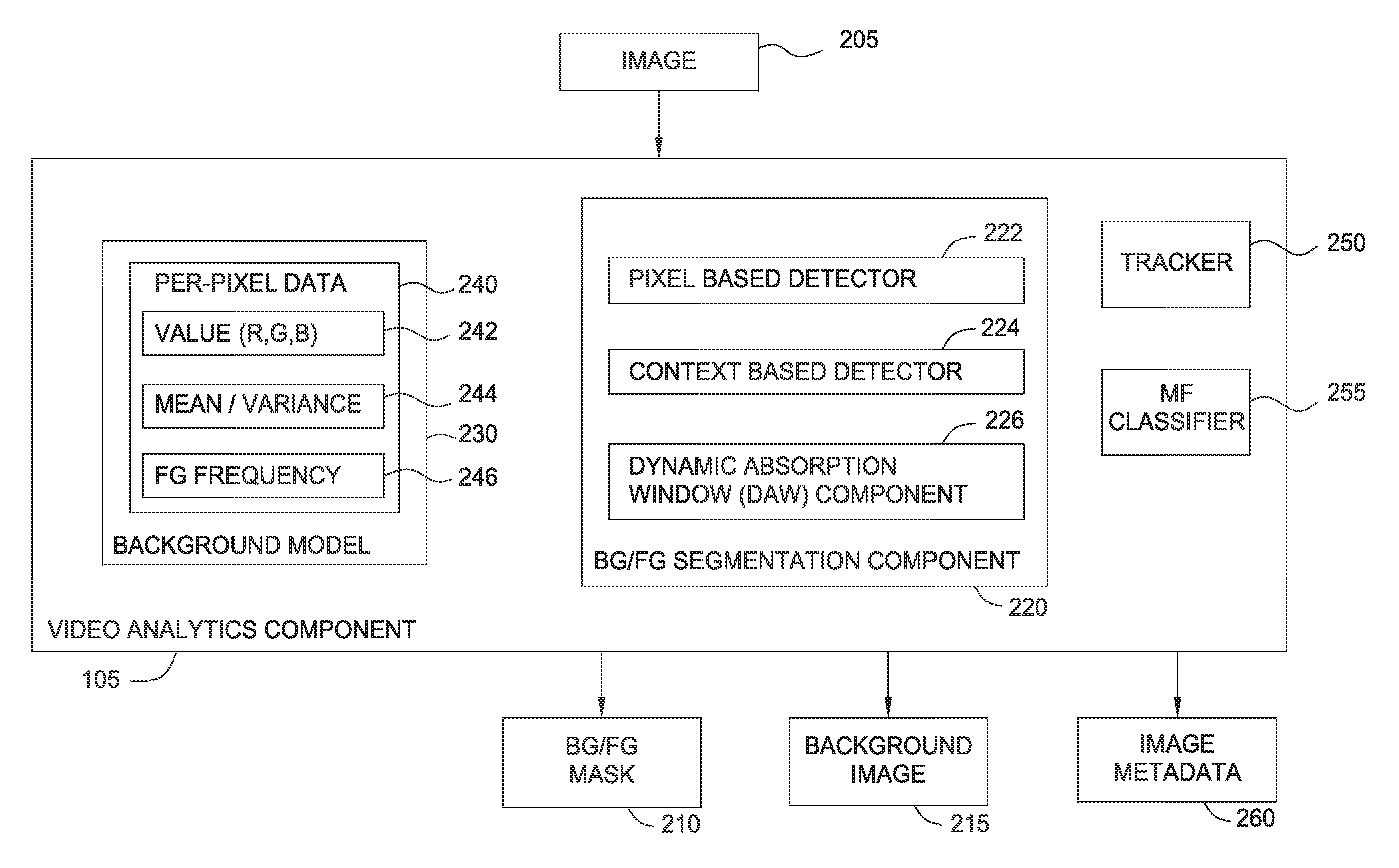

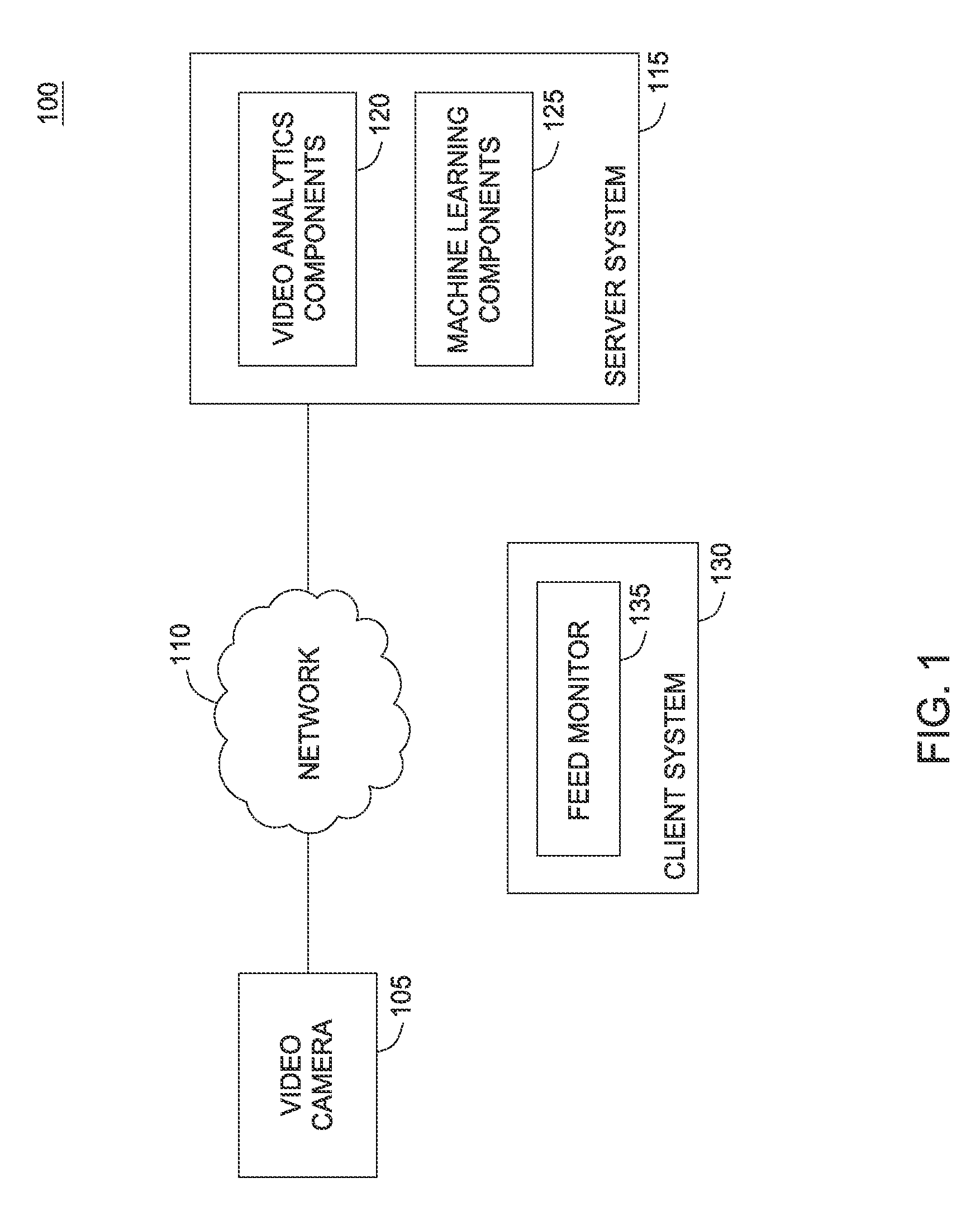

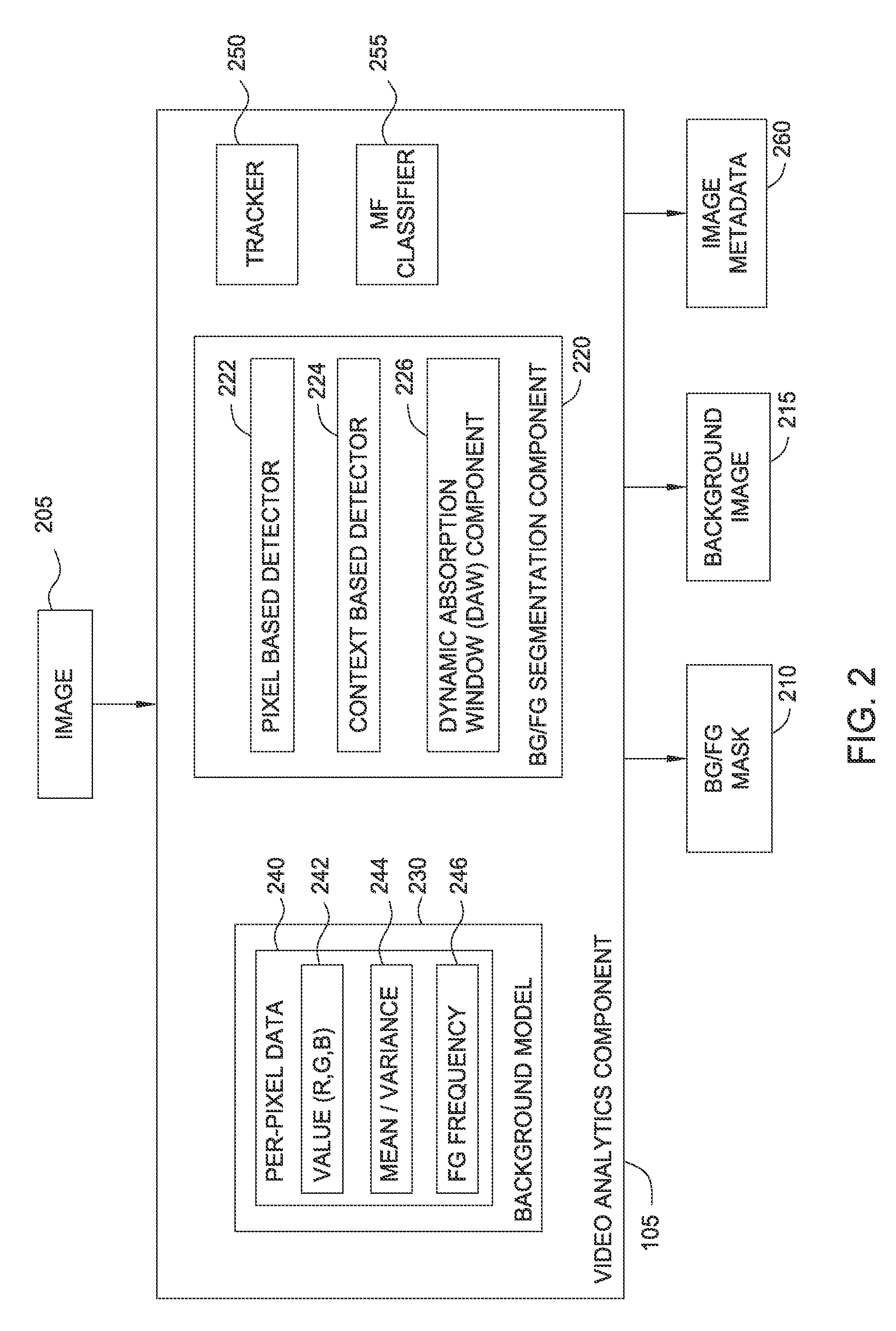

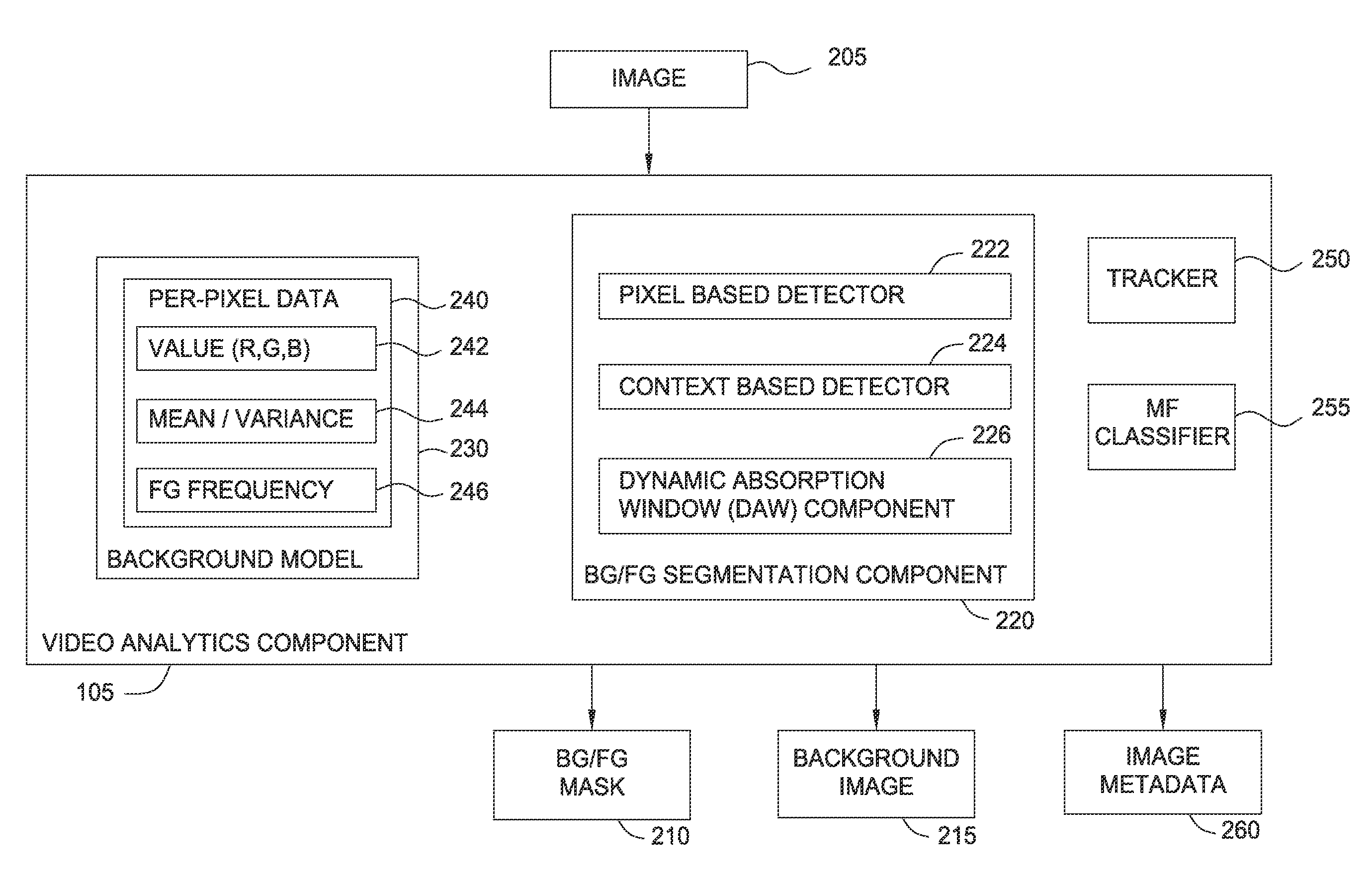

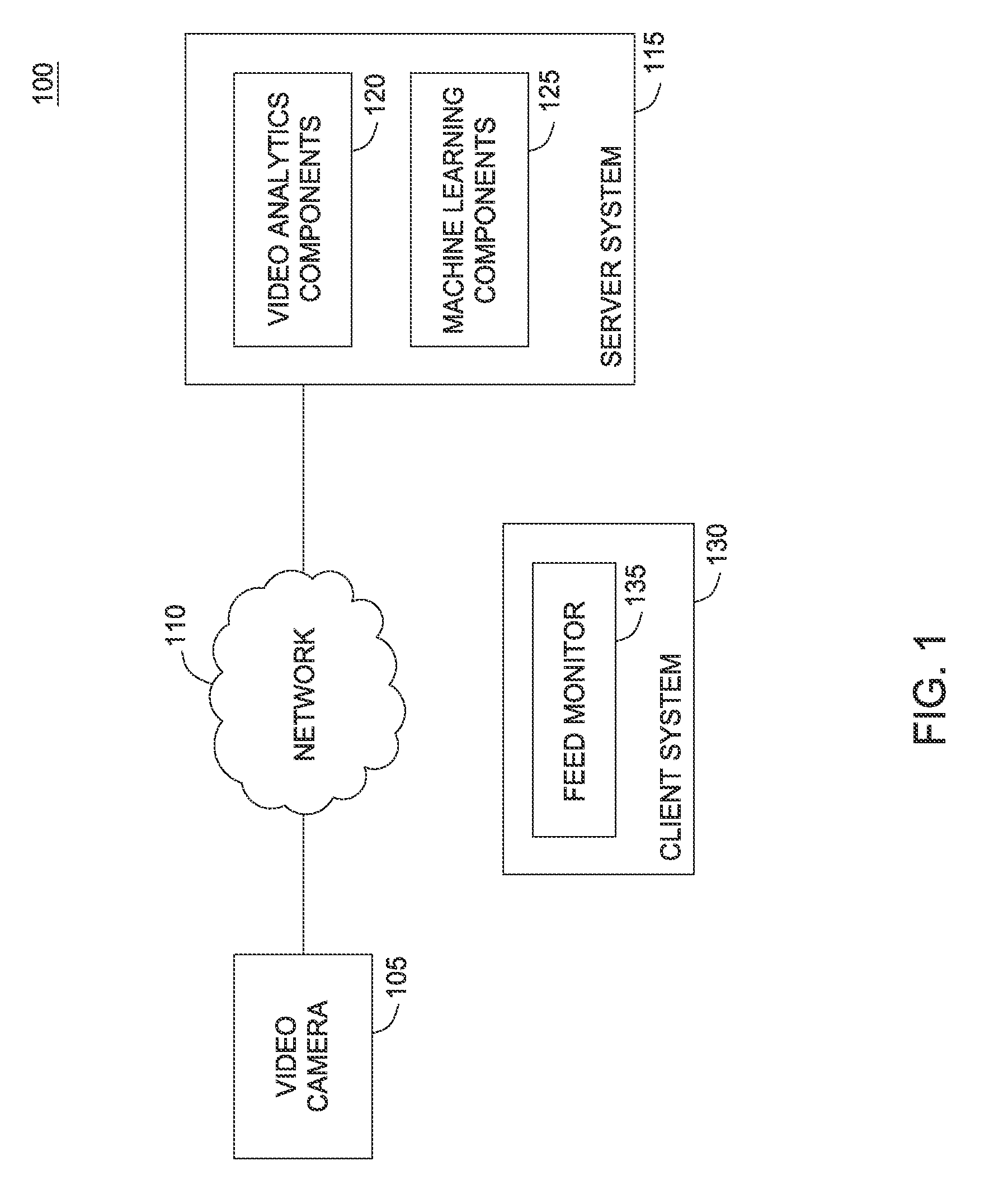

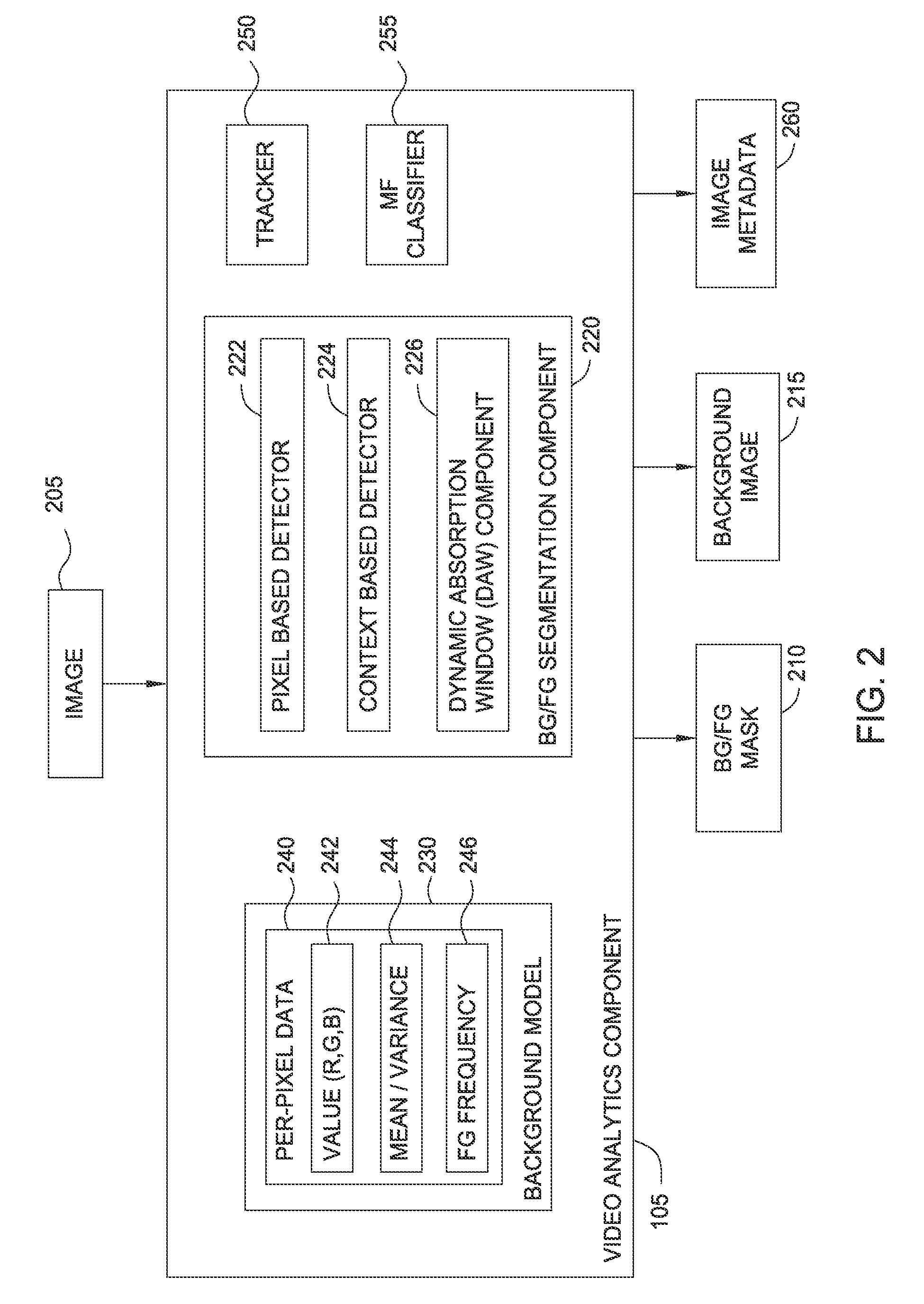

Incremental update for background model thresholds

Techniques are disclosed for creating a background model of a scene using both a pixel based approach and a context based approach. The combined approach provides an effective technique for segmenting scene foreground from background in frames of a video stream. Further, this approach can scale to process large numbers of camera feeds simultaneously, e.g., using parallel processing architectures, while still generating an accurate background model. Further, using both a pixel based approach and context based approach ensures that the video analytics system can effectively and efficiently respond to changes in a scene, without overly increasing computational complexity. In addition, techniques are disclosed for updating the background model, from frame-to-frame, by absorbing foreground pixels into the background model via an absorption window, and dynamically updating background / foreground thresholds.

Owner:INTELLECTIVE AI INC

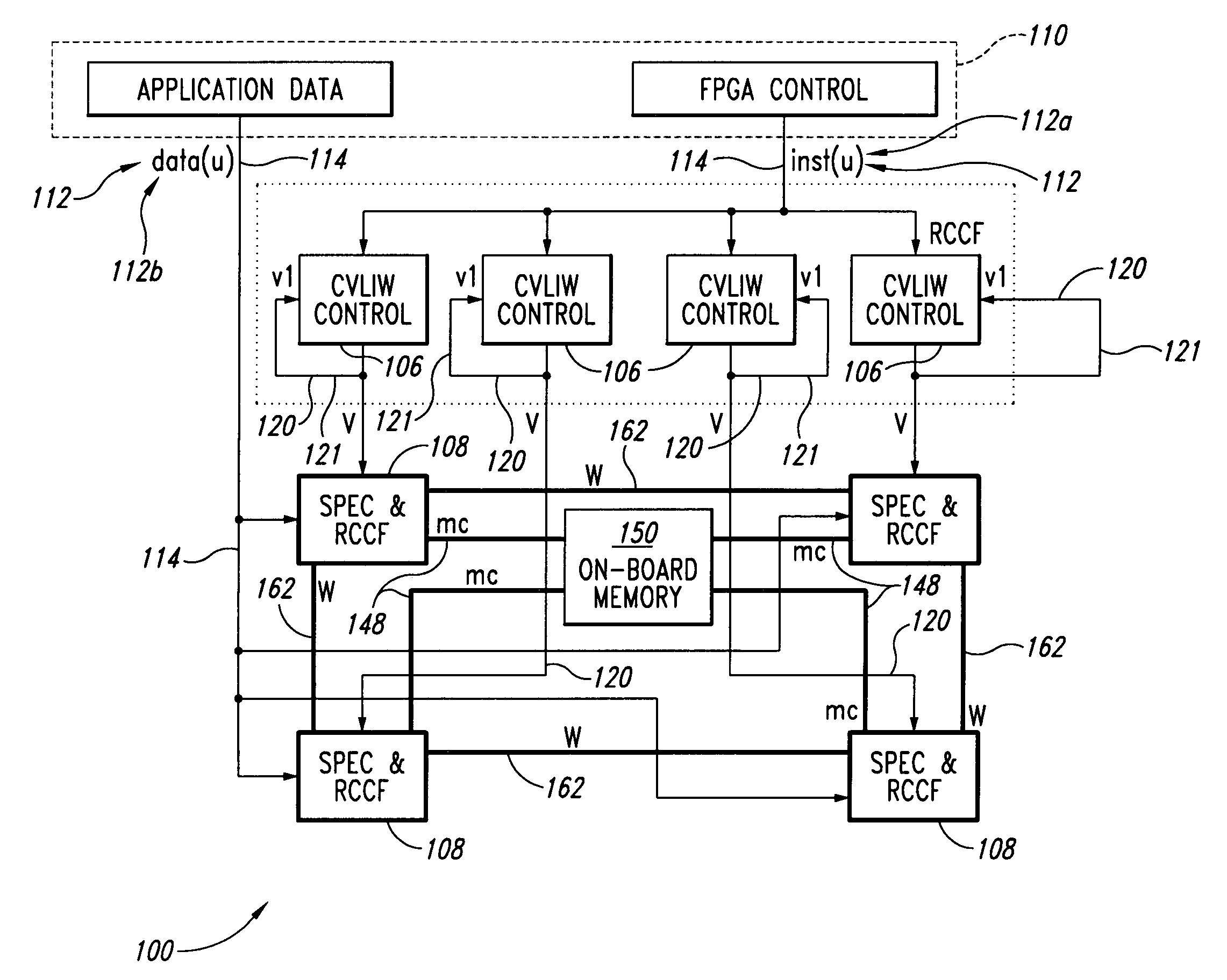

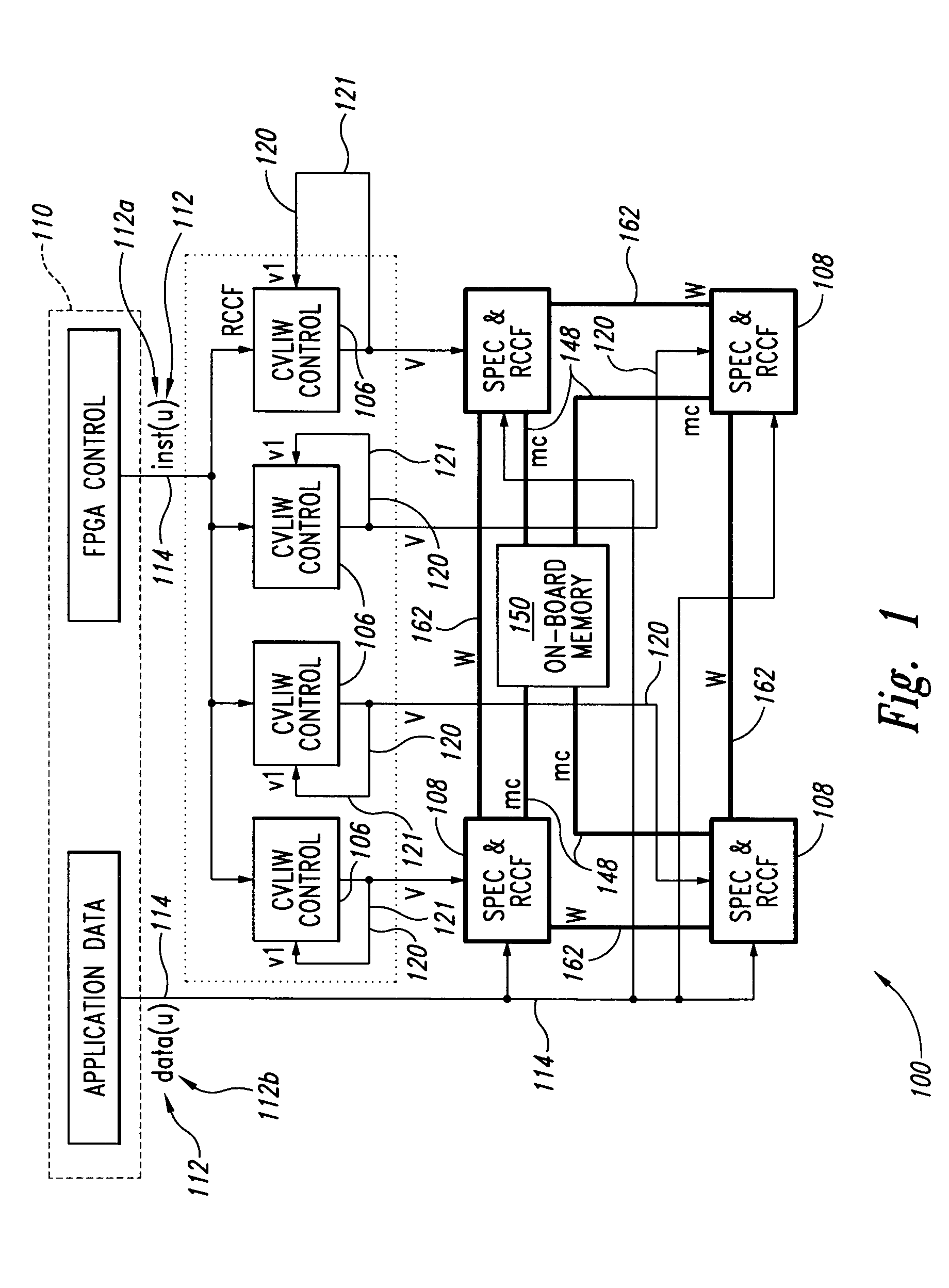

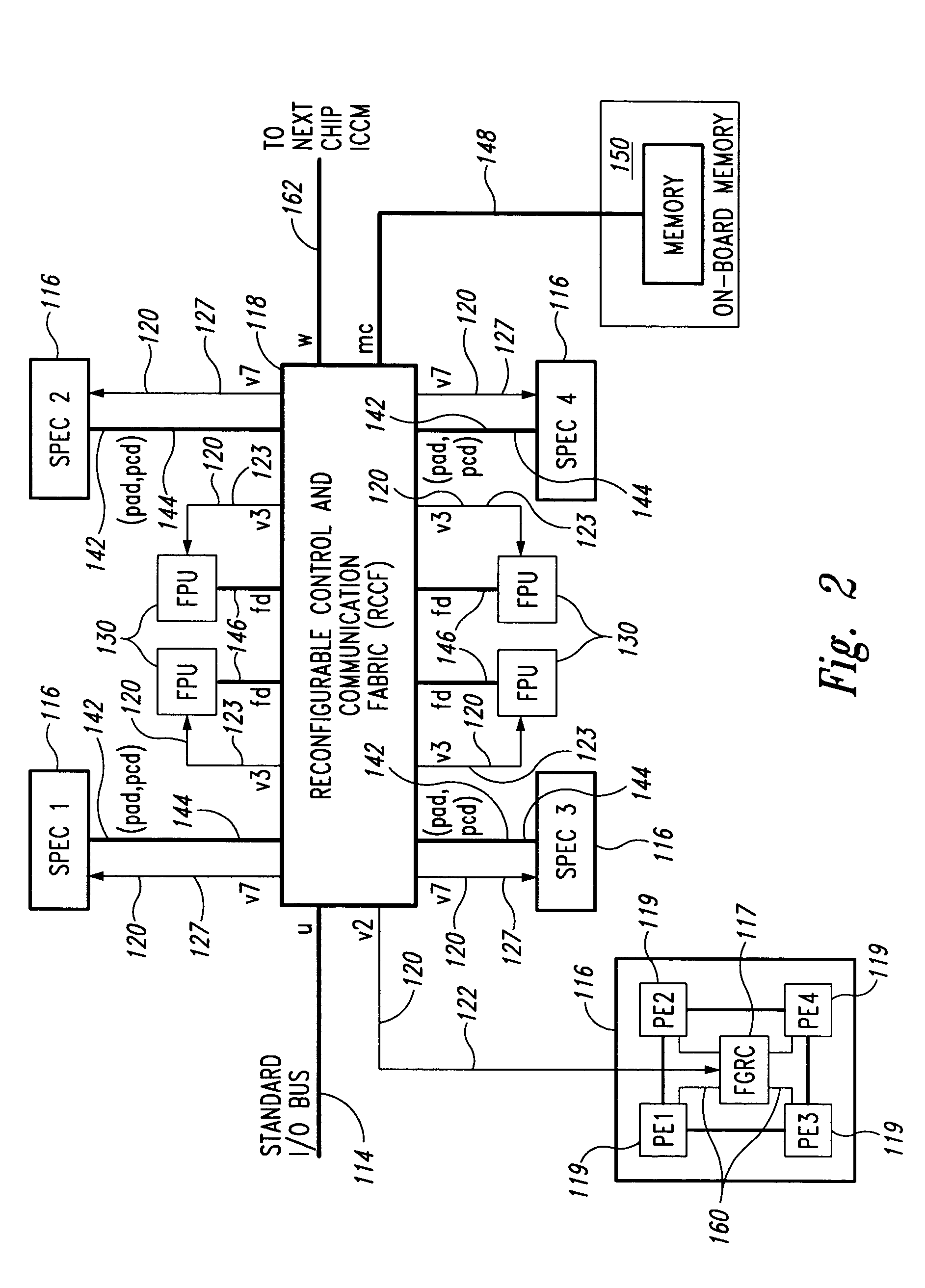

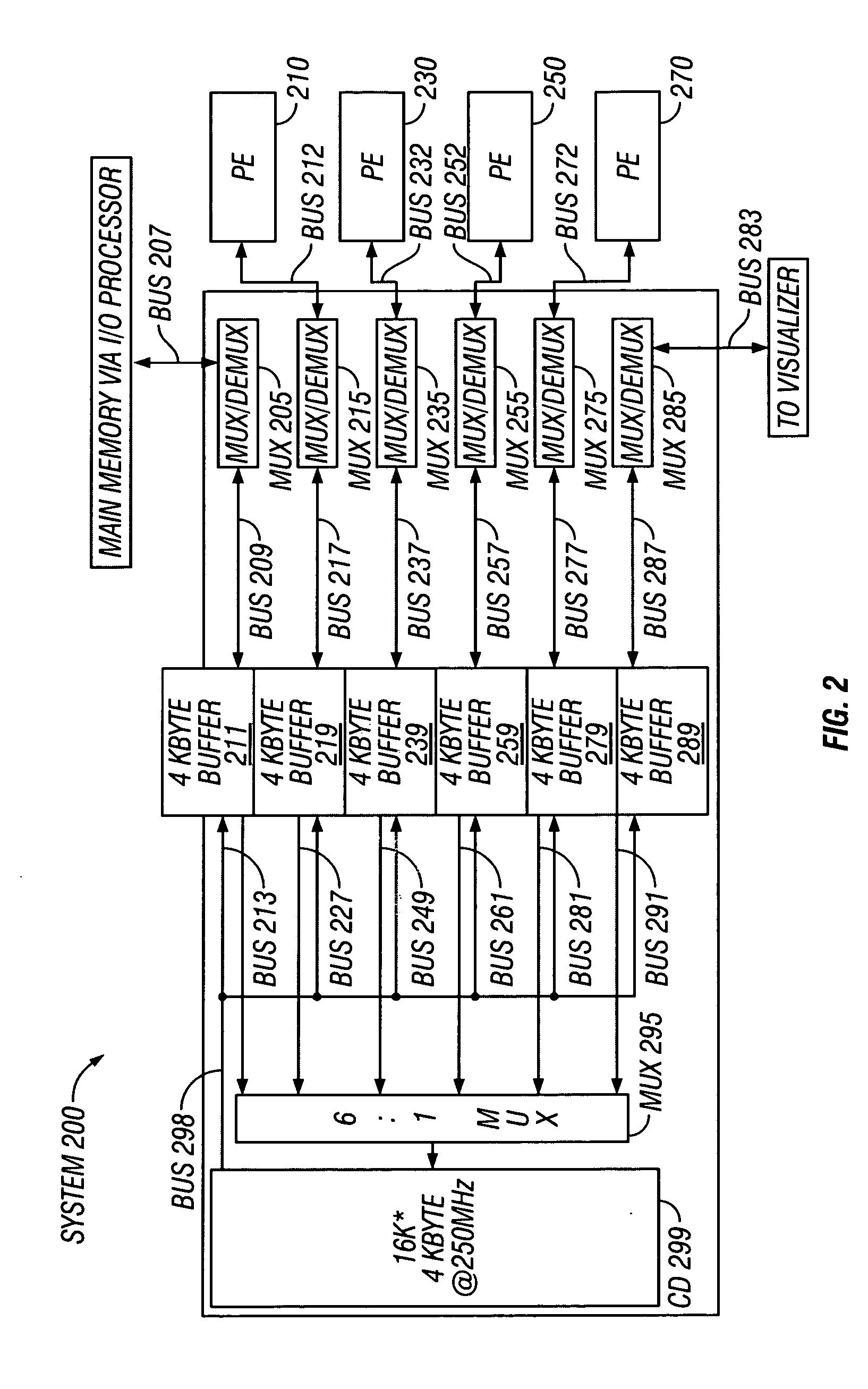

Super-reconfigurable fabric architecture (SURFA): a multi-FPGA parallel processing architecture for COTS hybrid computing framework

InactiveUS7299339B2Single instruction multiple data multiprocessorsMemory adressing/allocation/relocationBus interfaceProcessing element

A field programmable gate array includes a virtual bus interface that receives a control word from a host processor over a standard I / O bus. A configurable very long instruction word (VLIW) controller receives the control word via virtual bus interface signals mapped from the virtual bus interface. A reconfigurable communication and control fabric controls the data paths and programming modes of single instruction-multiple data (SIMD) processing element cells. The configurable VLIW controller has an interface with the reconfigurable communication and control fabric. SIMD processing element cells are controlled by the configurable VLIW controller through the reconfigurable communication and control fabric via the interface.

Owner:THE BOEING CO

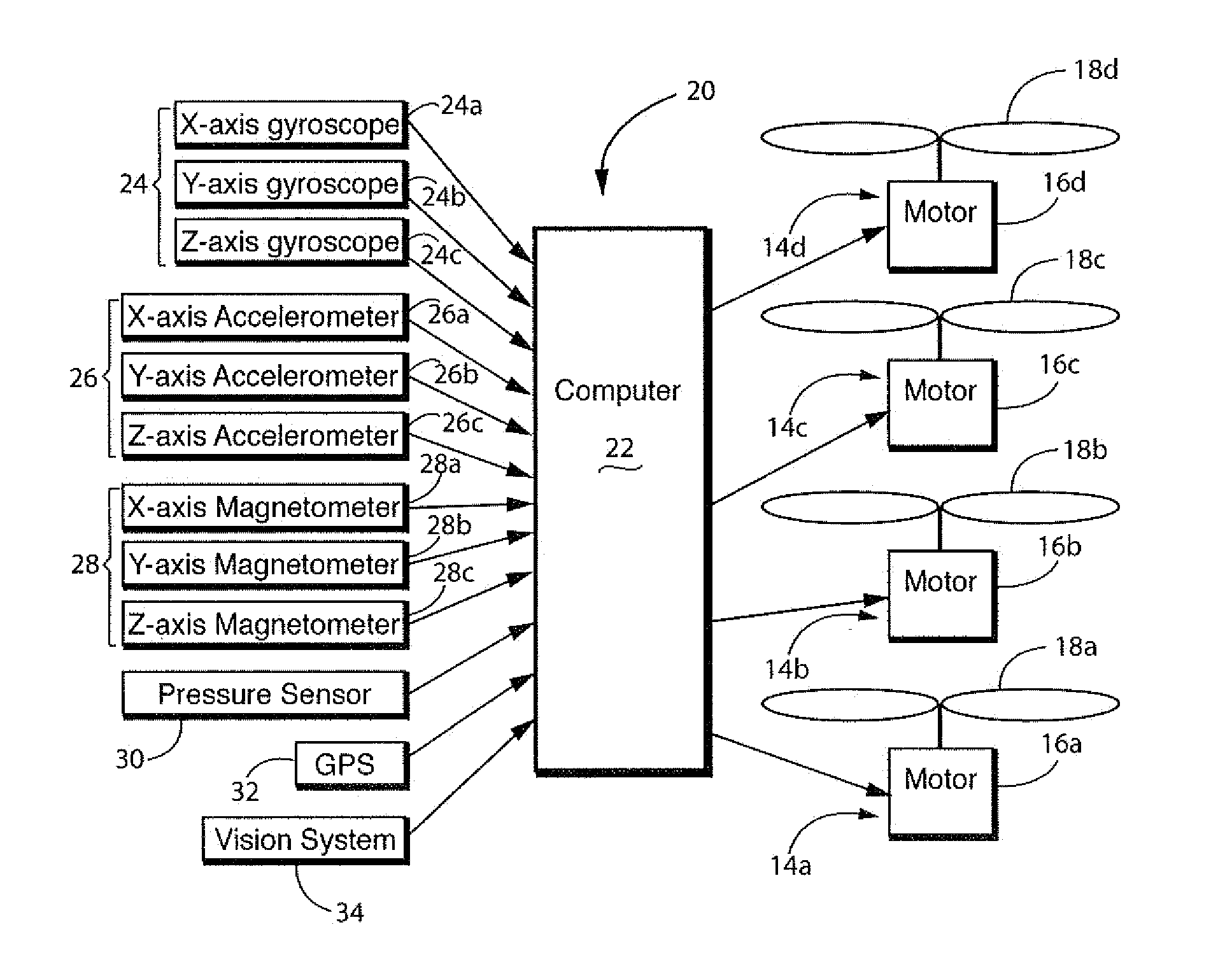

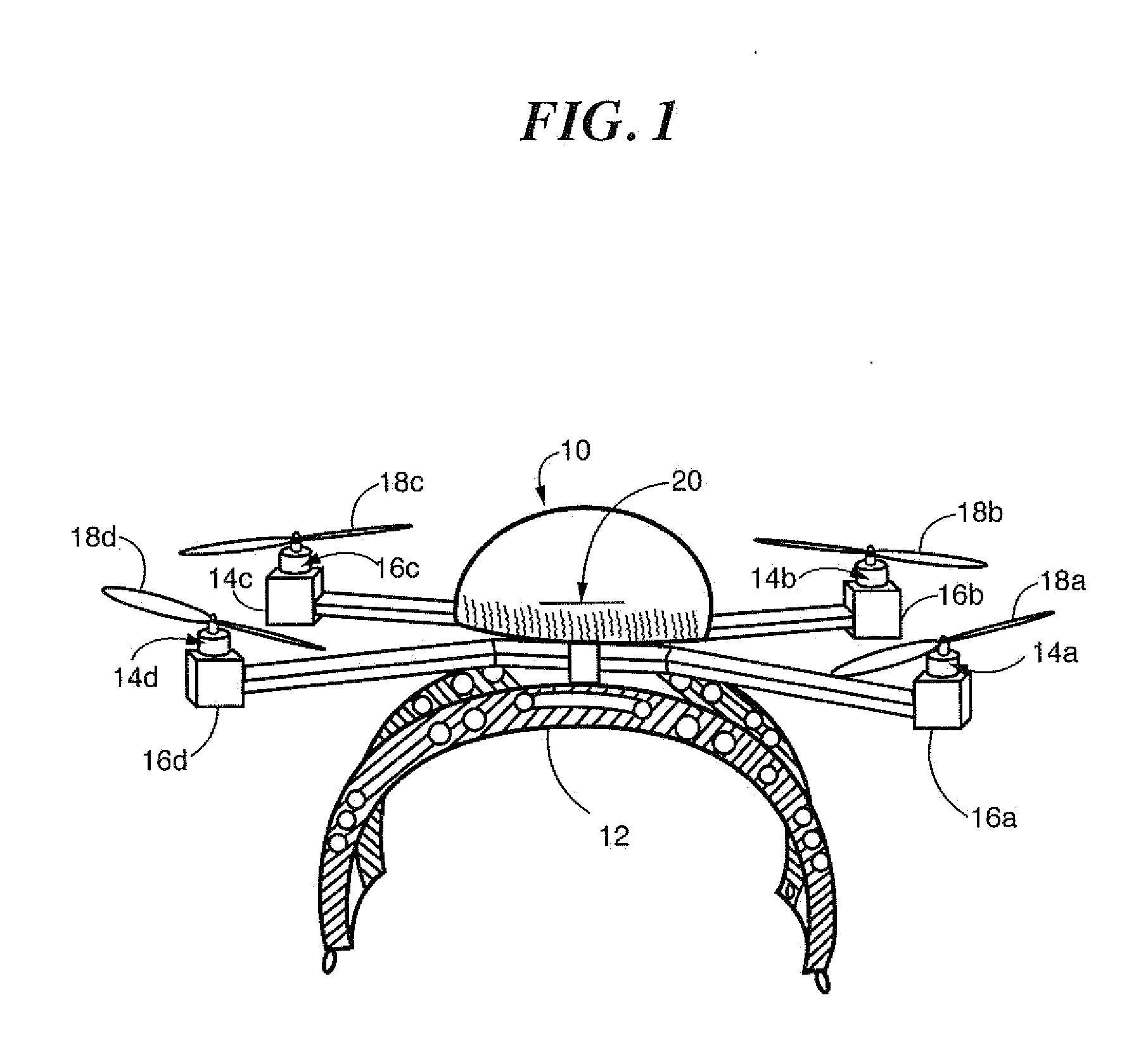

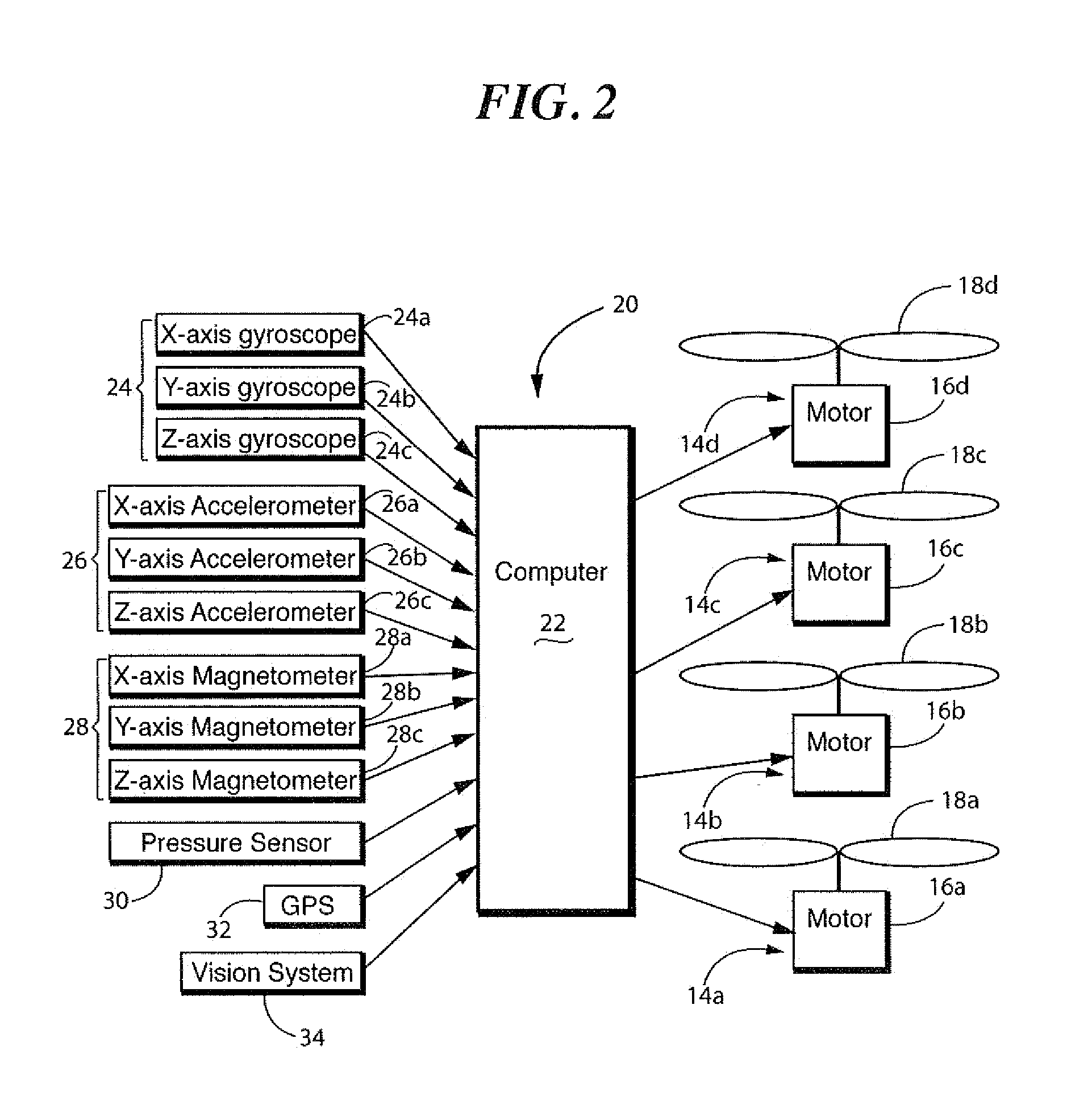

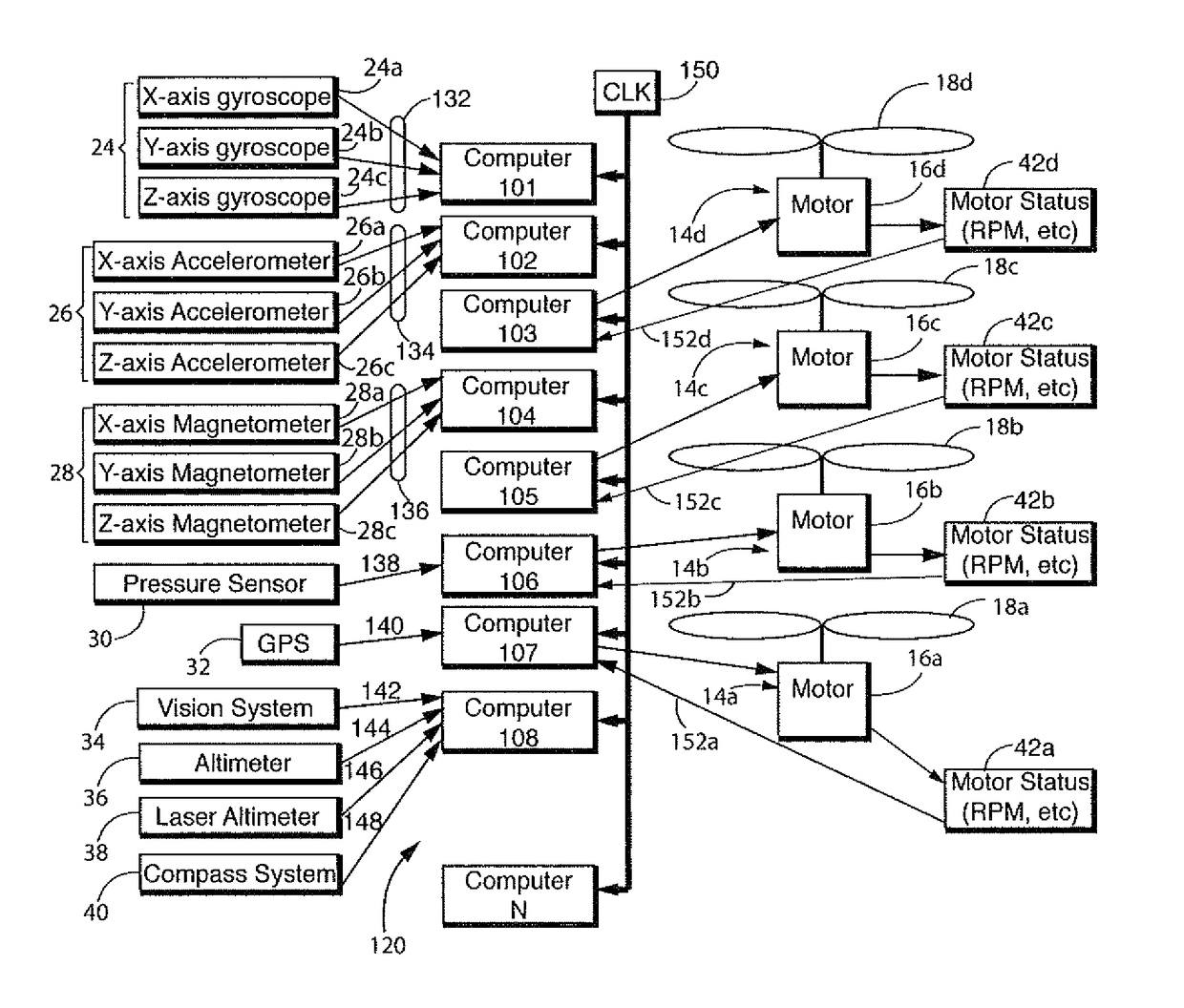

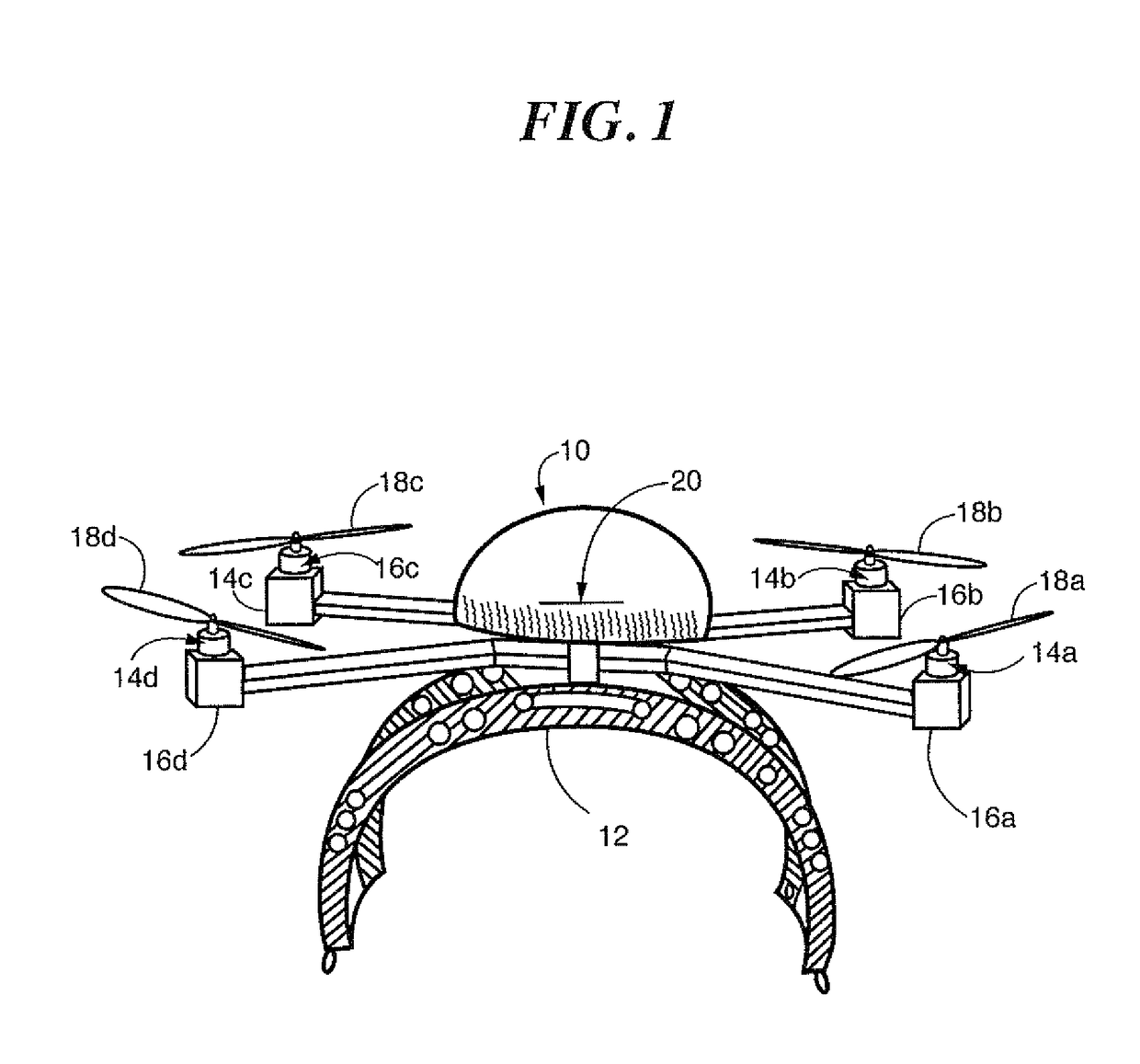

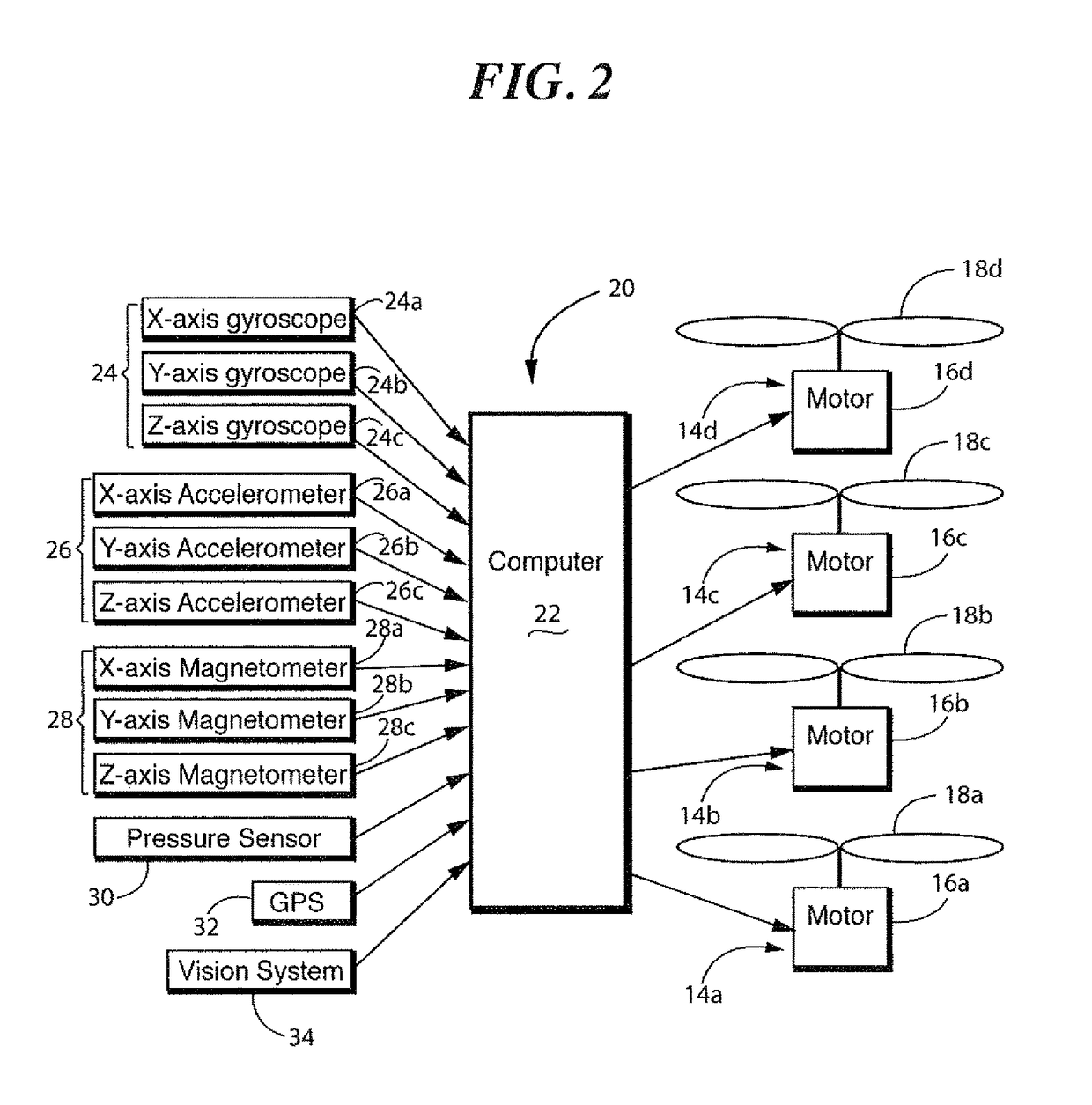

Control system for unmanned aerial vehicle utilizing parallel processing architecture

ActiveUS20130110325A1Autonomous decision making processDigital data processing detailsDistribution controlControl signal

A UAV has two rotors. First and second sensors sense a first and second type of input respectively. The second type of input is different than the first type, the first sensor providing a first sensor output and the second sensor providing a second sensor output. The first sensor output is input to a first computer and the second sensor output is input to a second computer. The first and second computer communicate in parallel to process the first and second sensor outputs to create a control signal having a predetermined number of variables therein, each variable having an exclusive position within the signal. The first computer outputs a first variable and the second computer outputs a second variable, each output being assigned an exclusive position within the control signal. At least one of the first and second computers outputting the control signal to the rotors.

Owner:HOVERFLY TECH INC

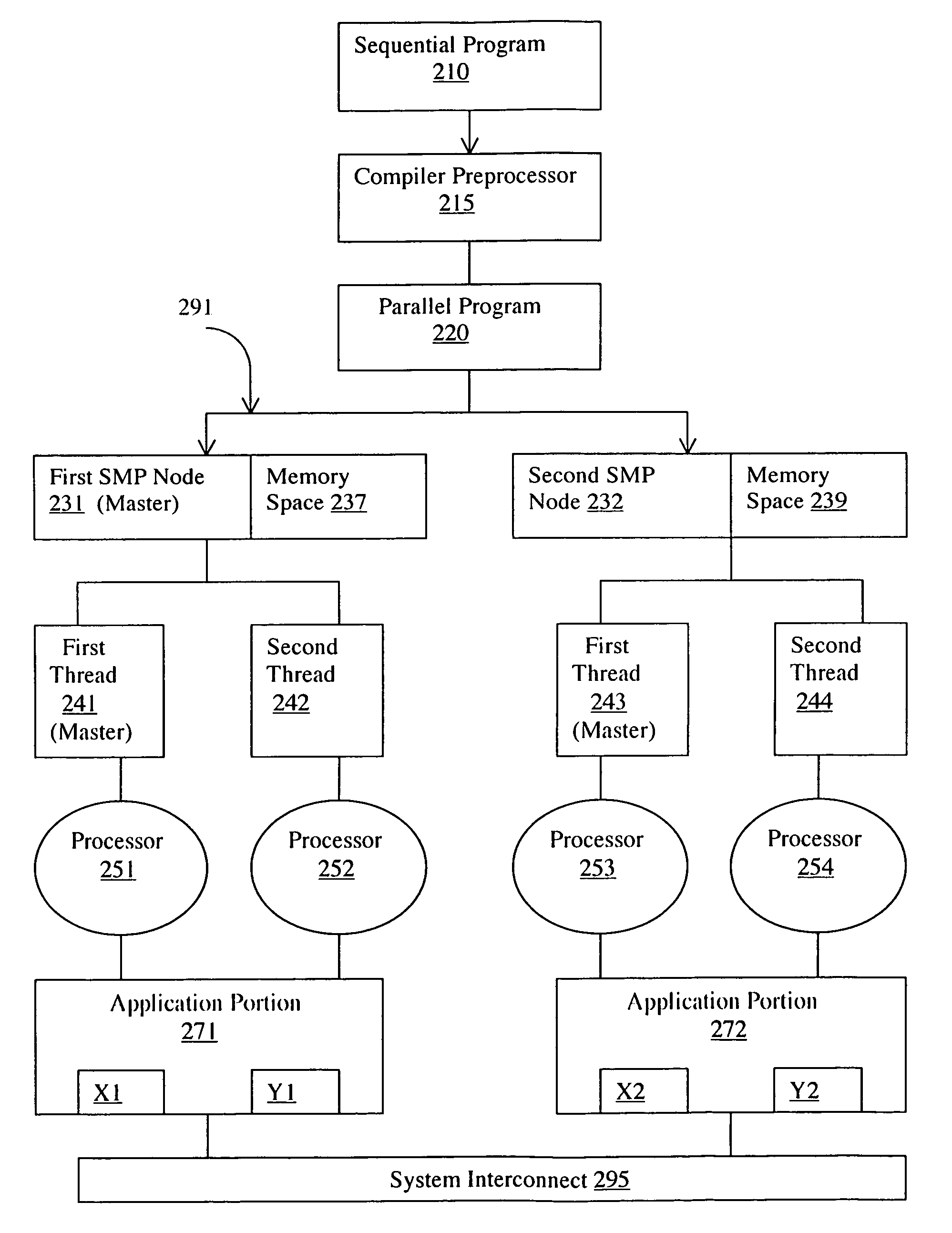

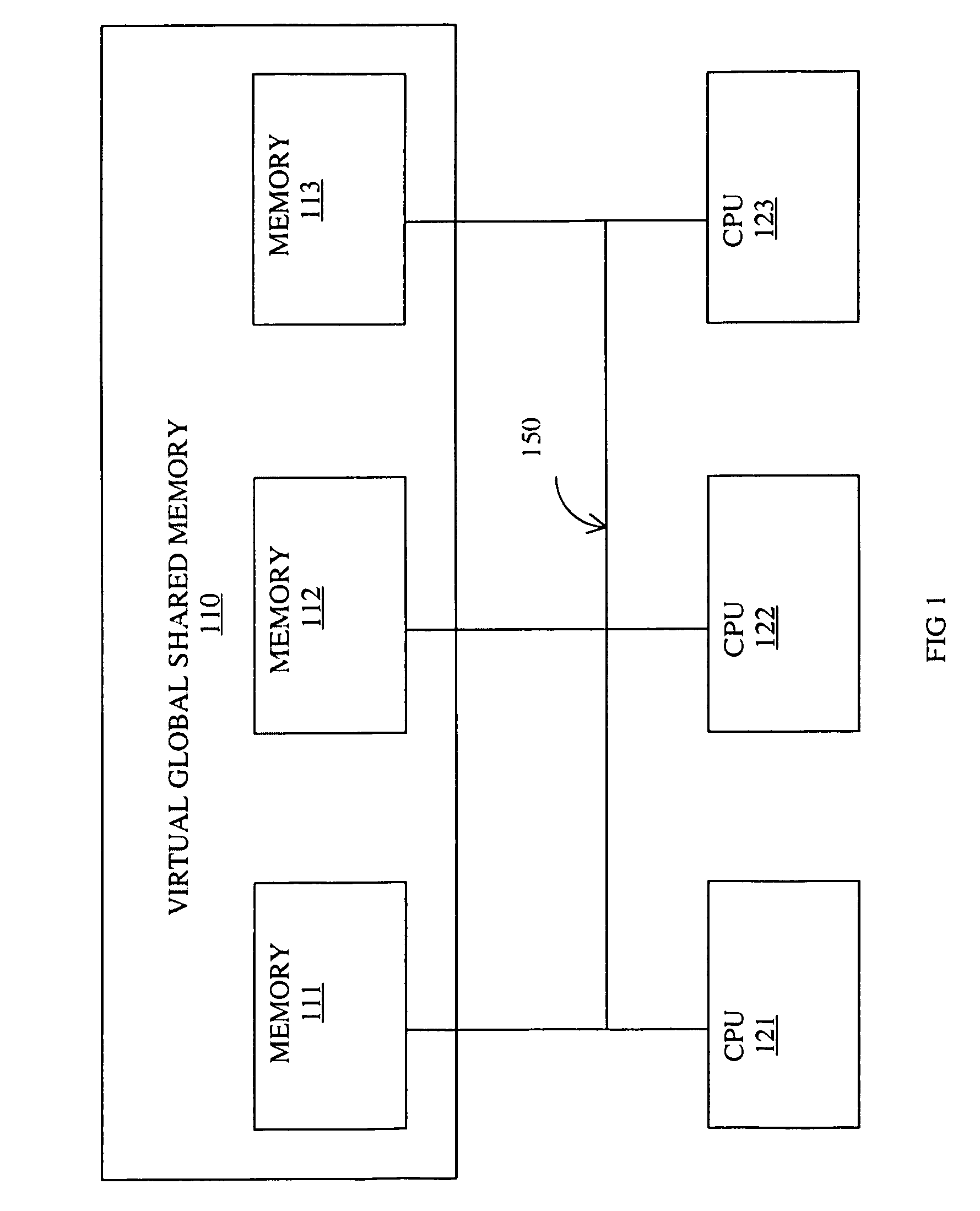

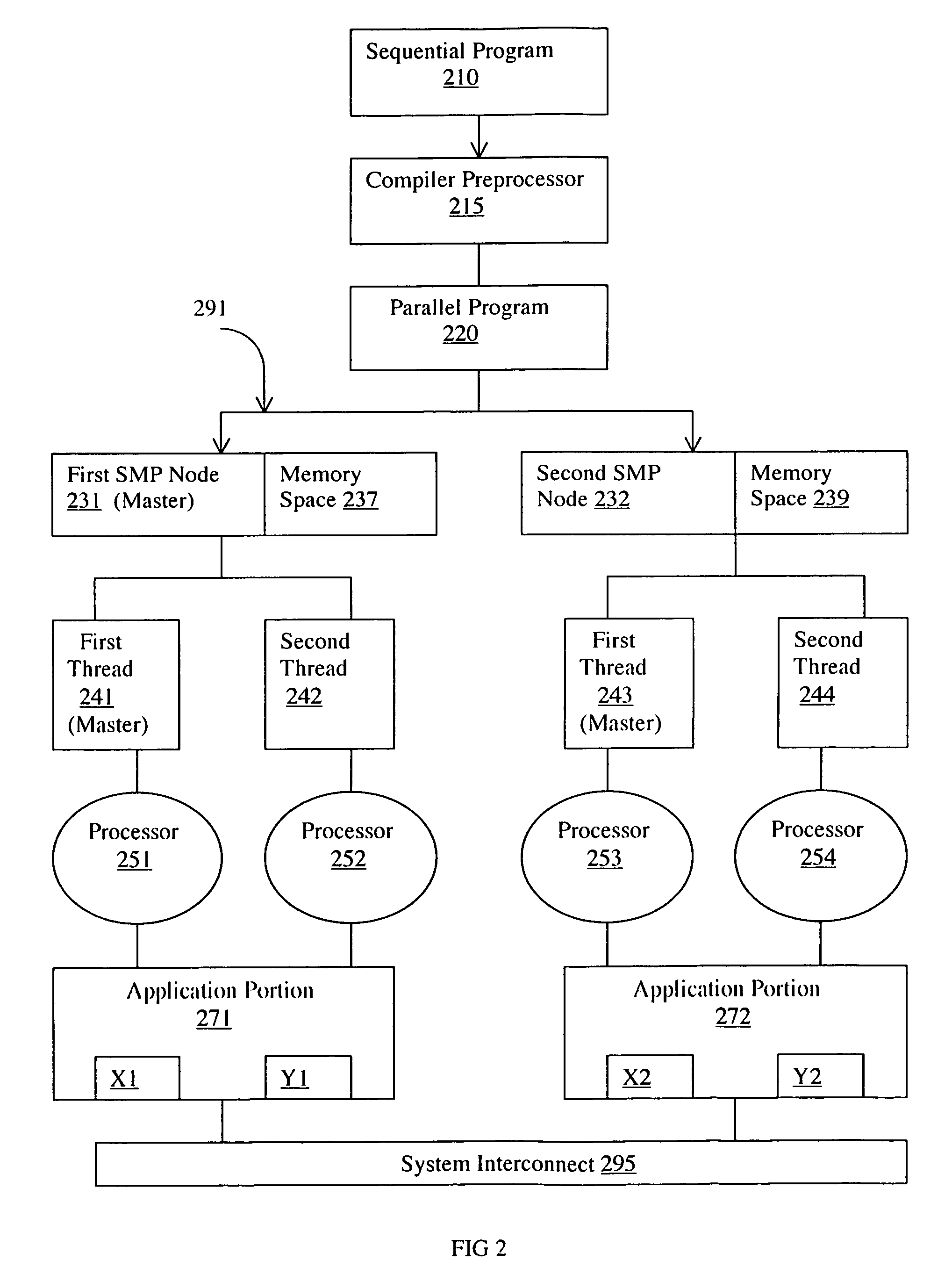

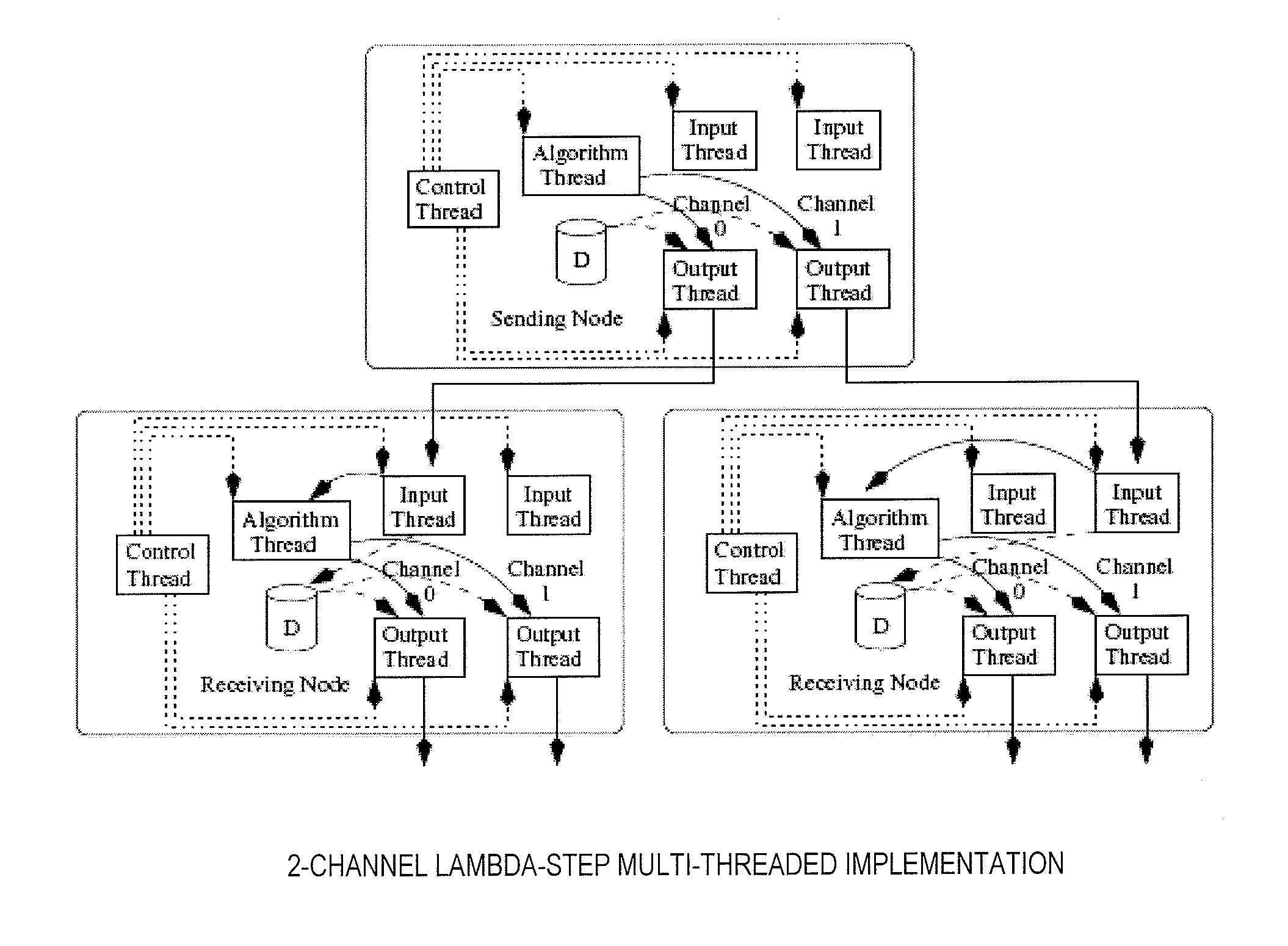

Unity parallel processing system and method

Present invention unity parallel processing systems and methods facilitate flexible utilization of sequential program applications in a distributed multi-computer parallel processing environment. The new unity parallel processing architecture enables multiple processing nodes (e.g., SMPs) to perform multi-thread processing within the multiple processing nodes while providing a shared virtual global memory space. Symmetric multiprocessors run shared memory applications with modified runtime guidance directives that permit the memories to emulate a virtual global memory across the plurality of symmetric multiprocessors. Within each SMP node, programs utilize multiple threads according to directives and library calls. Across multiple SMP nodes, each SMP node is treated as a single process with one-way communication to other SMP nodes. Portions of the program data are stored in memories associated with the SMP nodes and communication of the program data across multiple SMP nodes is controlled by unity compiler directives.

Owner:XENOGENIC DEV LLC

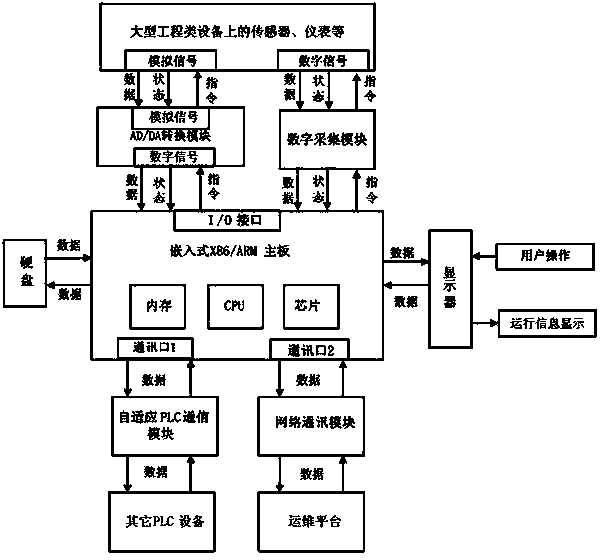

Intelligent controller system for large engineering equipment

ActiveCN103592880AImprove stabilityHigh precisionProgramme controlComputer controlSystems designThe Internet

The invention discloses an intelligent controller system for large engineering equipment. The intelligent controller system comprises a mainboard, a signal acquisition unit and a self-adaptive PLC communication module. A CPU which is based on an embedded parallel processing framework is arranged on the mainboard. The mainboard is connected with a sensor or an instrument in the large engineering equipment through the signal acquisition unit, acquires equipment operating state signals or detection data detected and output by the sensor or the instrument, outputs a control instruction to a controlled device in the large engineering equipment, and controls the controlled device to operate automatically. The mainboard is connected and in communication with a PLC in peripheral equipment through the self-adaptive PLC communication module, forms an internet of things, conducts configuration monitoring on the PLC, and synchronously backups all data in peripheral controllers in the internet of things by means of a distributed data storage technology. The intelligent controller system for the large engineering equipment has the advantages of being high in system data processing speed, high in system operational stability, safe, and high in efficiency, and lowering the difficulty in system design, development and maintenance at a later period.

Owner:OCEAN UNIV OF CHINA

System and method for parallel processing using dynamically configurable proactive co-processing cells

ActiveUS20140337850A1Facilitates communication among system resourcesImprove interoperabilityProgram initiation/switchingInterprogram communicationCoprocessorProcessing element

A parallel processing architecture includes a CPU, a task pool populated by the CPU, and a plurality of autonomous co-processing cells each having an agent configured to proactively interrogate the task pool to retrieve tasks appropriate for a particular so-processor. Each co-processor communicates with the task pool through a switching fabric, which facilitates connections for data transfer and arbitration between all system resources. Each so-processor notifies the task pool when a task or task thread is completed, whereupon the task pool notifies the CPU.

Owner:SWARM TECH

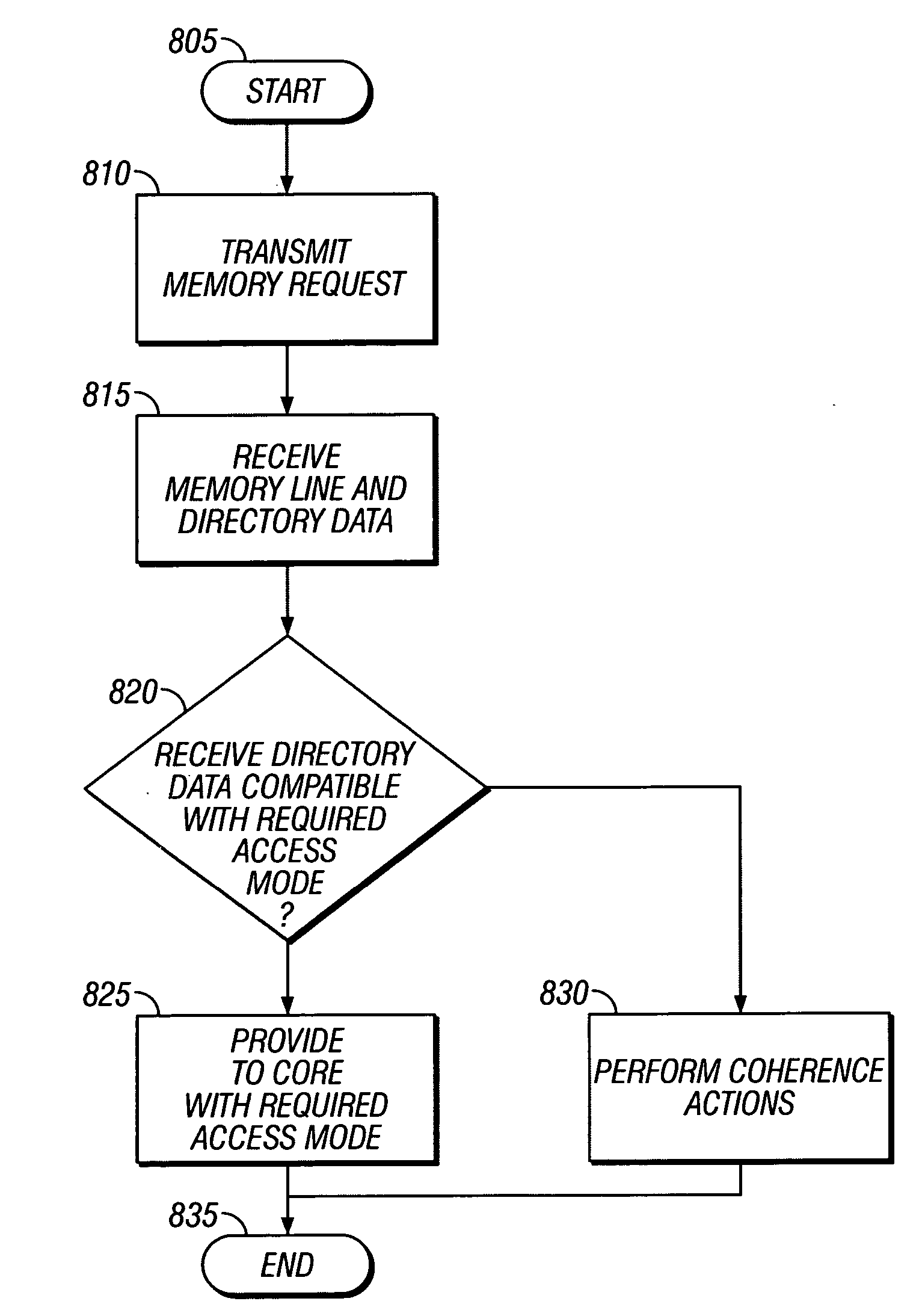

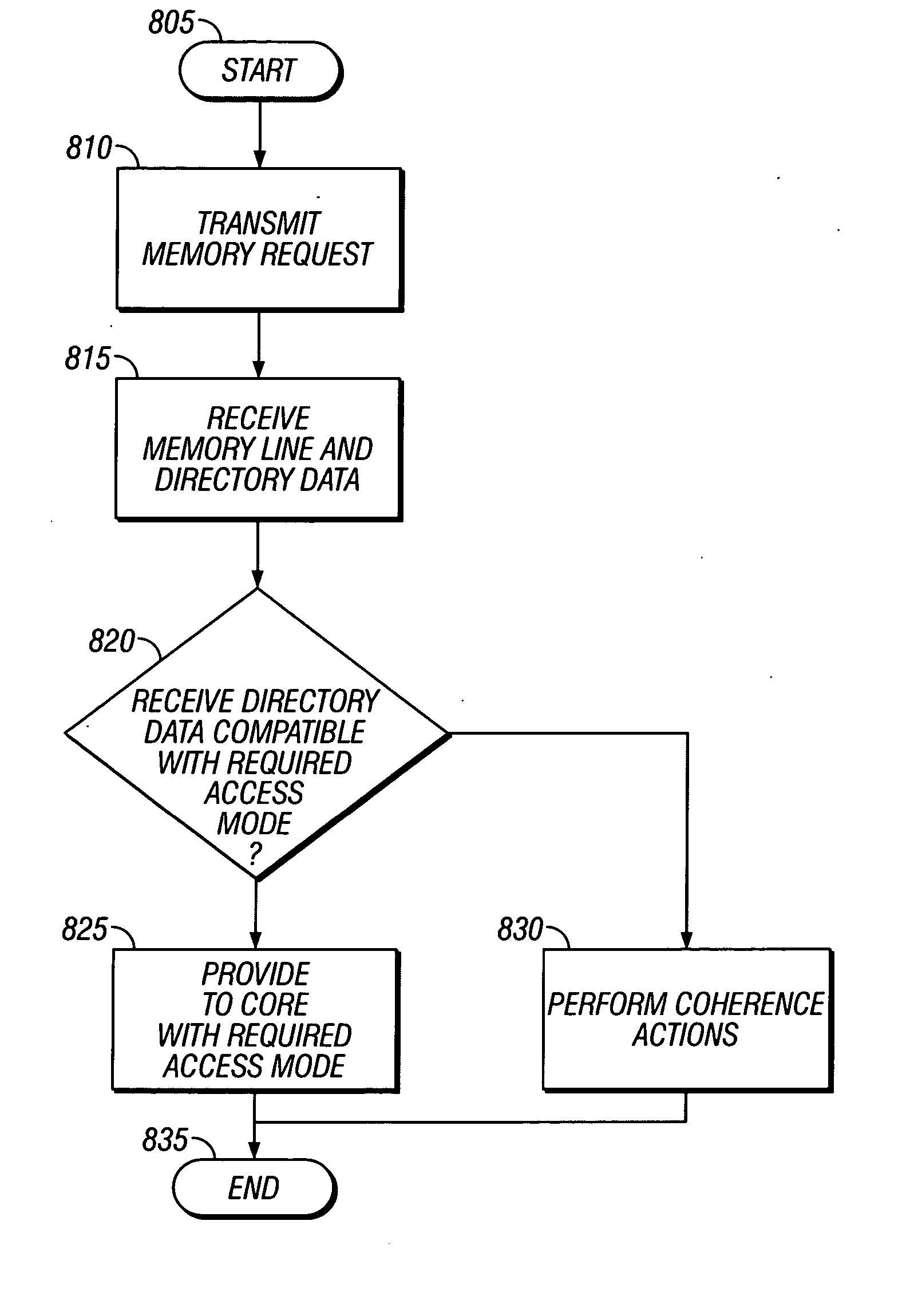

Method and apparatus for directory-based coherence with distributed directory management utilizing prefetch caches

ActiveUS20050216672A1Memory adressing/allocation/relocationParallel processing architectureProcessor element

The present invention provides for a type of parallel processing architecture in which a plurality of processors has access to a shared memory hierarchy level. A memory hierarchy level has a coherence directory and associated directory data with a plurality of cachelines each associated with different data. Prefetch caches are interconnected to processor memory and a plurality of processor elements, each element interconnected to different buffers. Cache lines are requested from memory, and the requests, responses, and detections therein are available for particular access modes, therein providing additional coherence of the data. Processing of said directory data is performed by processing elements. In one embodiment, the system comprises an integrated prefetch cache.

Owner:META PLATFORMS INC

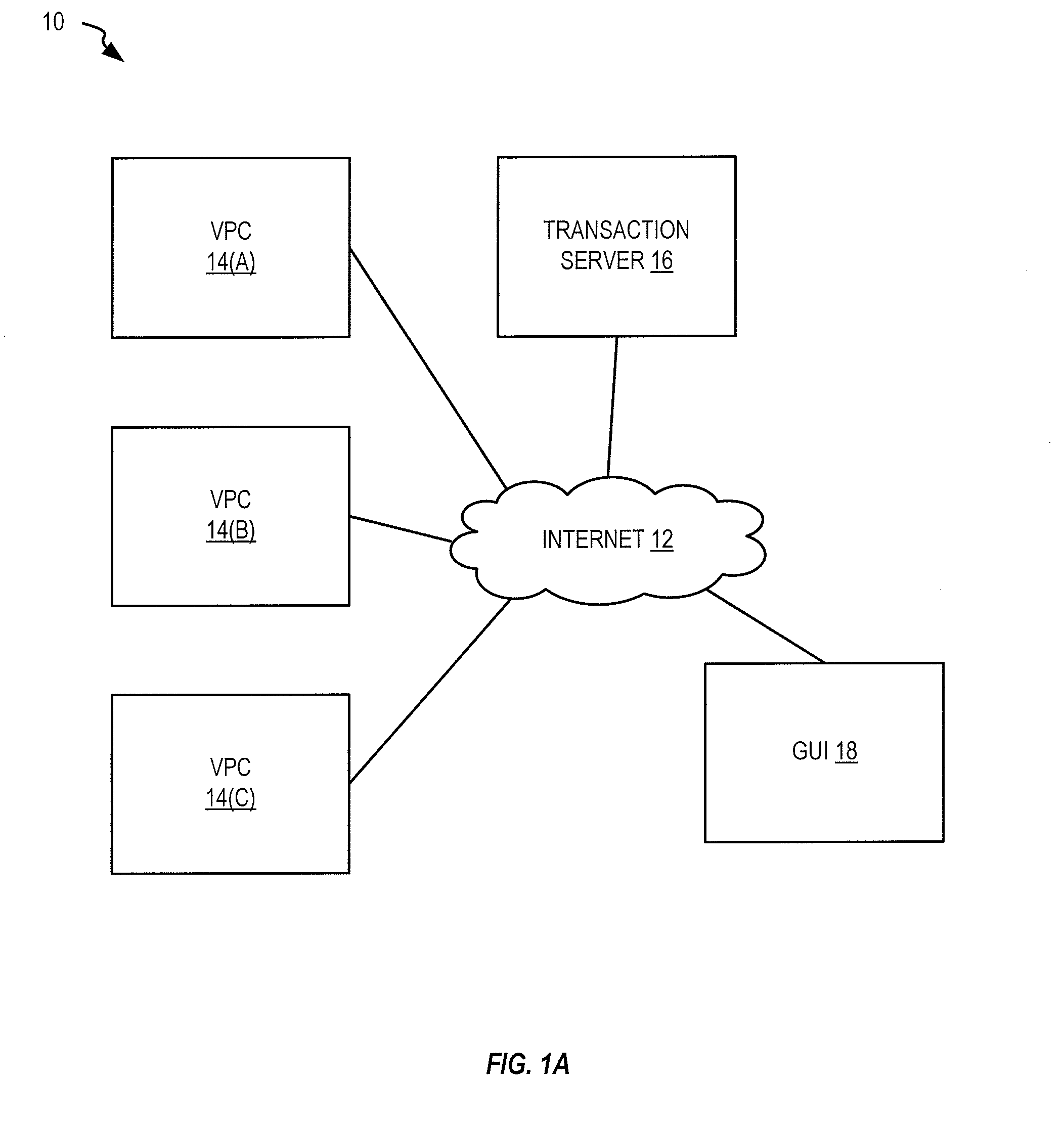

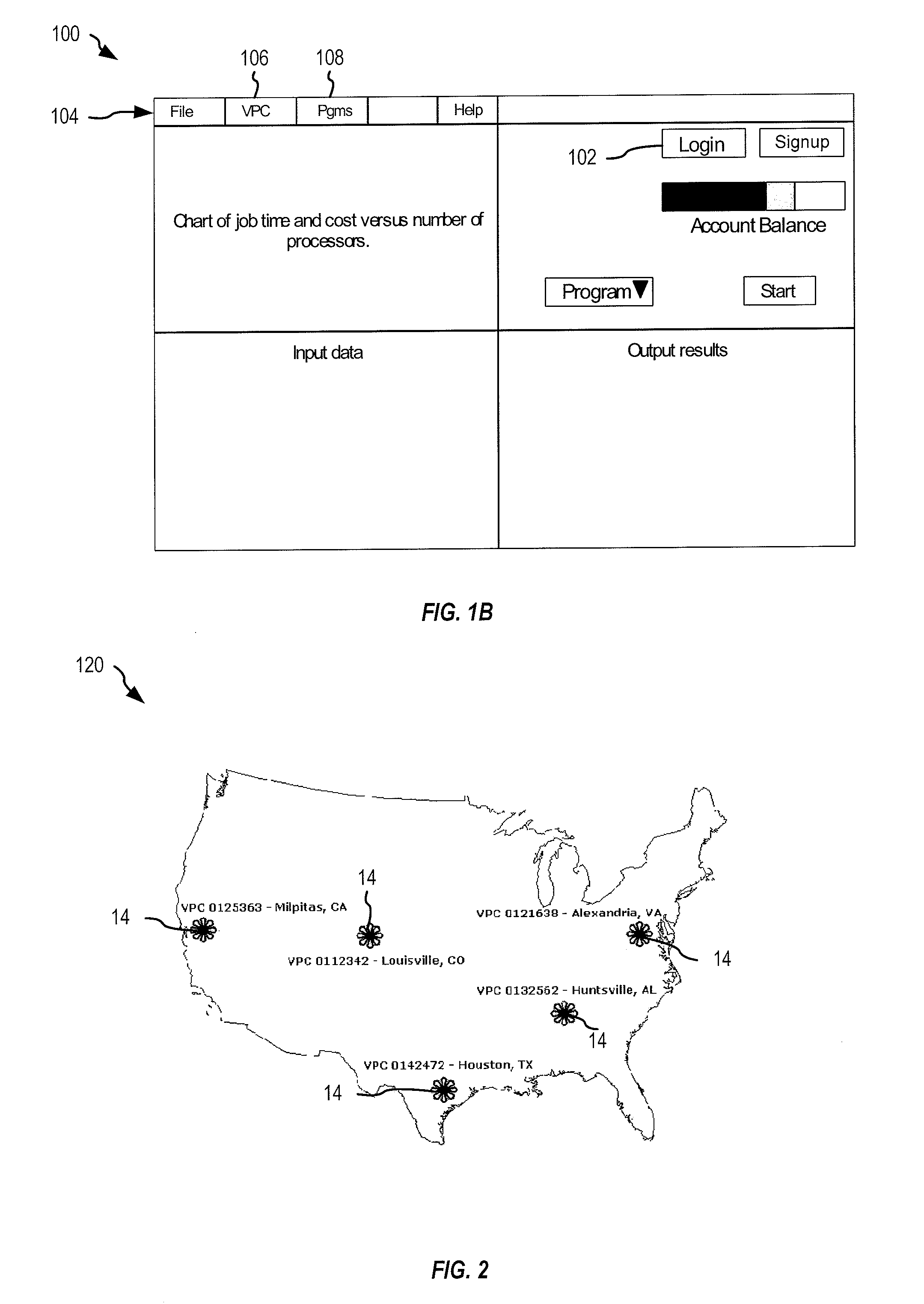

System And Method For Accessing And Using A Supercomputer

ActiveUS20090077483A9Minimum delayResource allocationProgram control using wired connectionsGraphicsSupercomputer

Systems and methods form and control a supercomputer based upon a parallel processing architecture such as a Howard cascade. A graphical user interface allows a user to interact with one or more virtual power centers of the supercomputer facility. A plurality of processing nodes self-organize into one or more virtual power centers. The processing nodes utilize overlapped input and output for improved communication.

Owner:MASSIVELY PARALLEL TECH

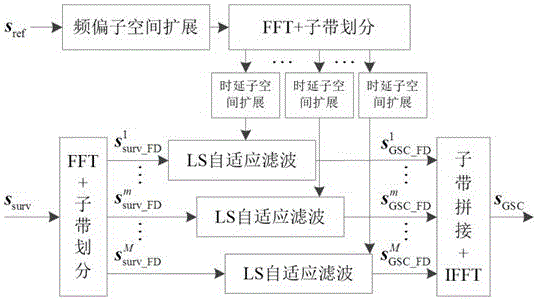

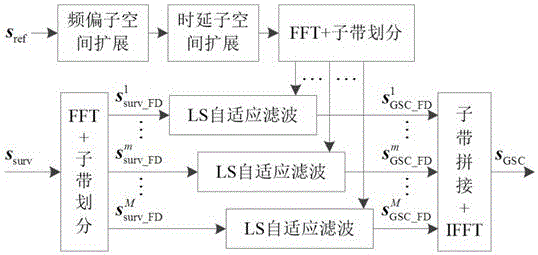

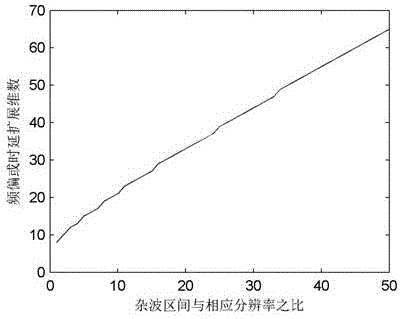

Sub-band-processing-based clutter suppression method and apparatus for passive radar

ActiveCN106226745ASuitable for real-time implementationImprove robustnessWave based measurement systemsPassive radarDecomposition

The invention discloses a sub-band-processing-based clutter suppression method and apparatus for a passive radar. The method comprises the four steps of sub band decomposition, over-sampling clutter sub space construction, LS adaptive filtering, and sub band synthesis. To be specific, a monitoring signal is composed into multi-path sub band signals; a clutter sub space is constructed in an over sampling mode by using a reference signal; sub band decomposition is carried out; LS adaptive filtering is carried out on each sub band; and then the filtered sub band signals are synthesized to obtain a monitoring signal after clutter suppression. According to the method, the robustness on non-ideal factors like a carrier frequency offset, a sampling rate frequency offset, a fractional delay, and a channel frequency response and the like is high; the clutter suppression performance is close to the theoretical upper limit; the calculation load is low; the parallel processing architecture is provided; and thus the method and apparatus are suitable for engineering real-time implementation and have the popularization and application values.

Owner:WUHAN UNIV

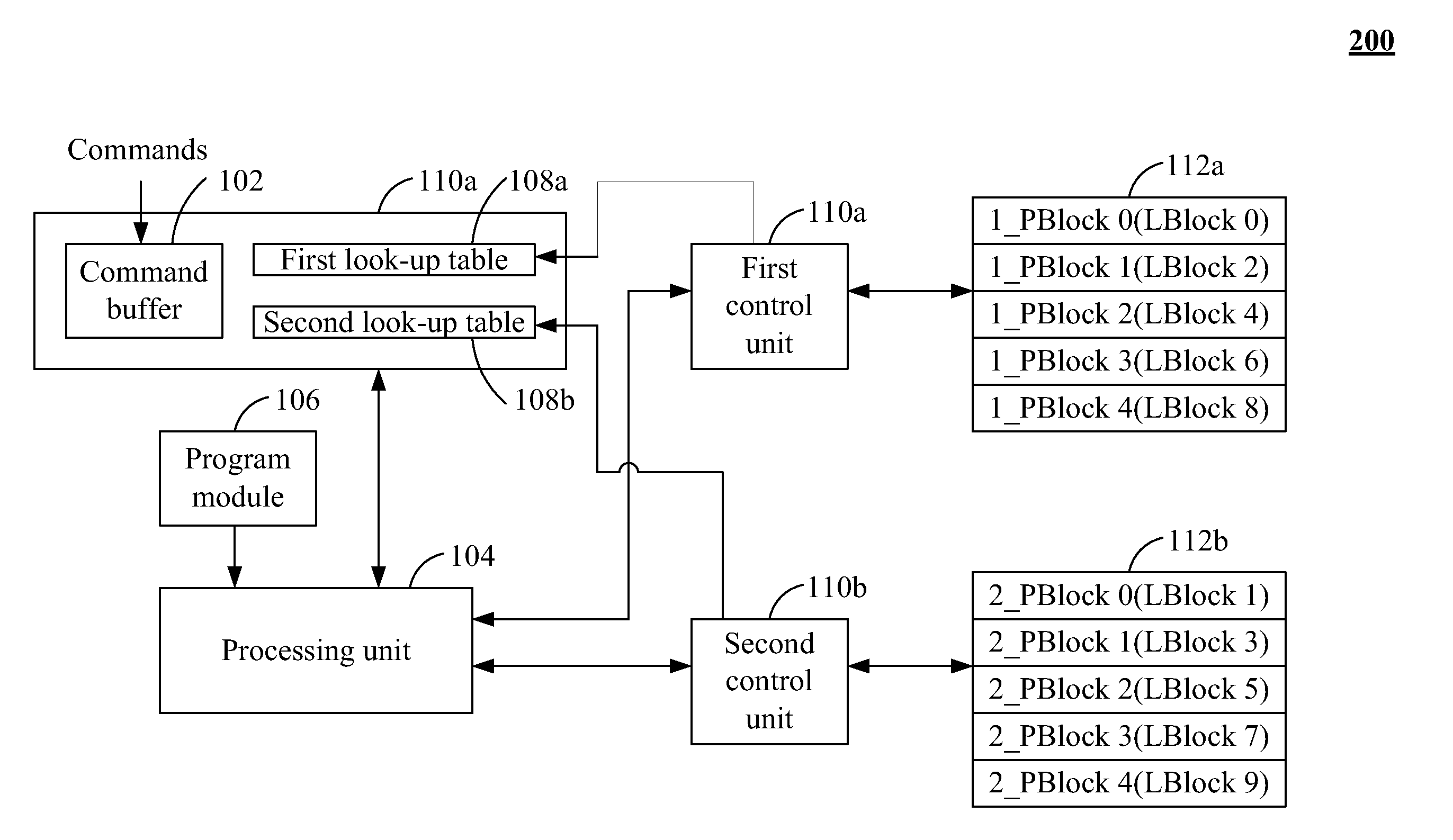

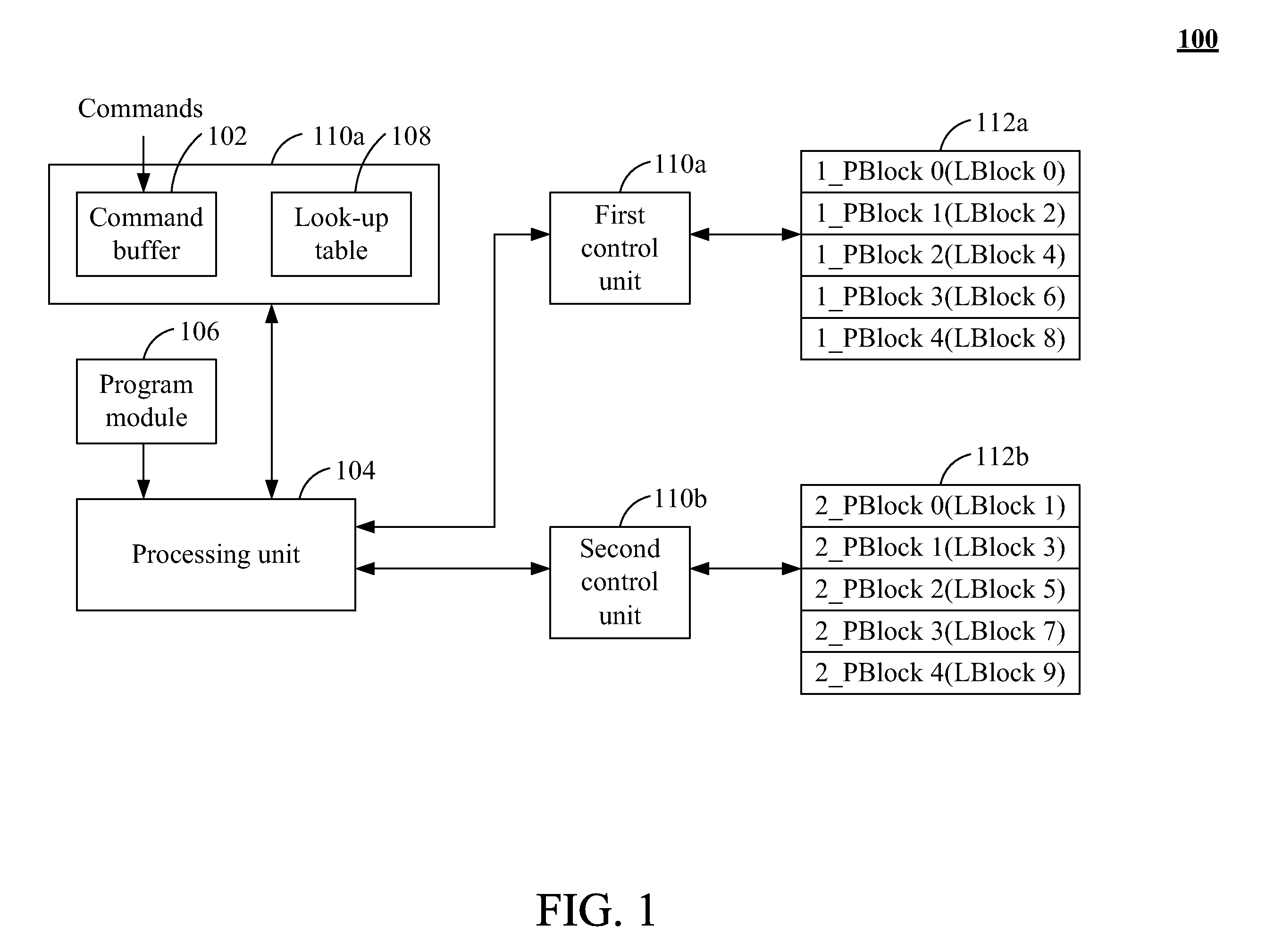

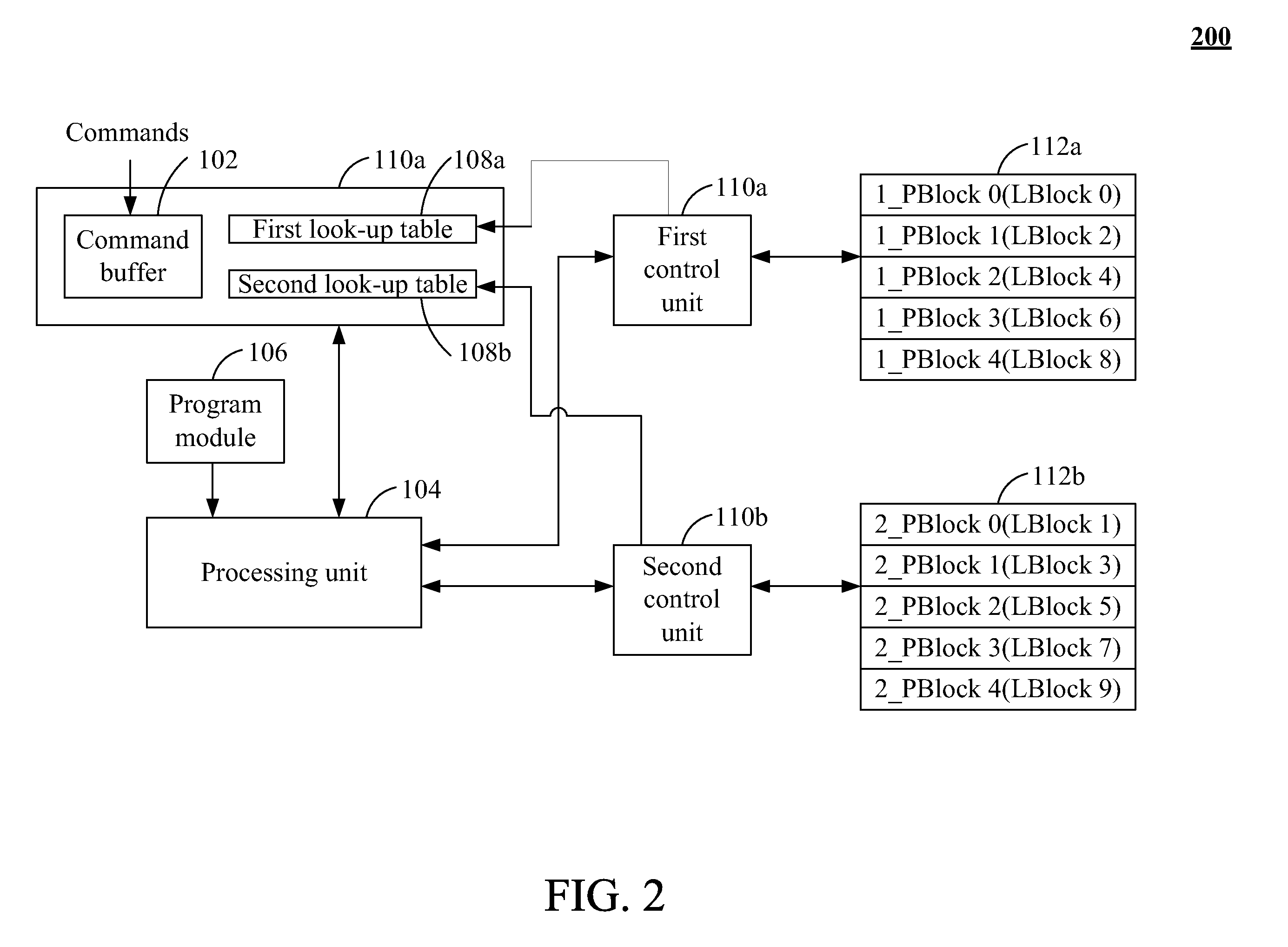

Parallel processing architecture of flash memory and method thereof

InactiveUS20110016261A1Improve access speedImprove access efficiencyMemory architecture accessing/allocationMemory adressing/allocation/relocationData storingData store

A parallel processing architecture of flash memory and method thereof are described. A processing unit classifies a plurality of commands to generate a first command group and a second command group respectively. The processing unit executes the first command group and the second command group. A first control unit performs the first command group to access the data stored in the first memory unit, and a second control unit simultaneously performs the second command group to access the data stored in the second memory unit for processing the data stored in the first and the second memory units in parallel.

Owner:GENESYS LOGIC INC

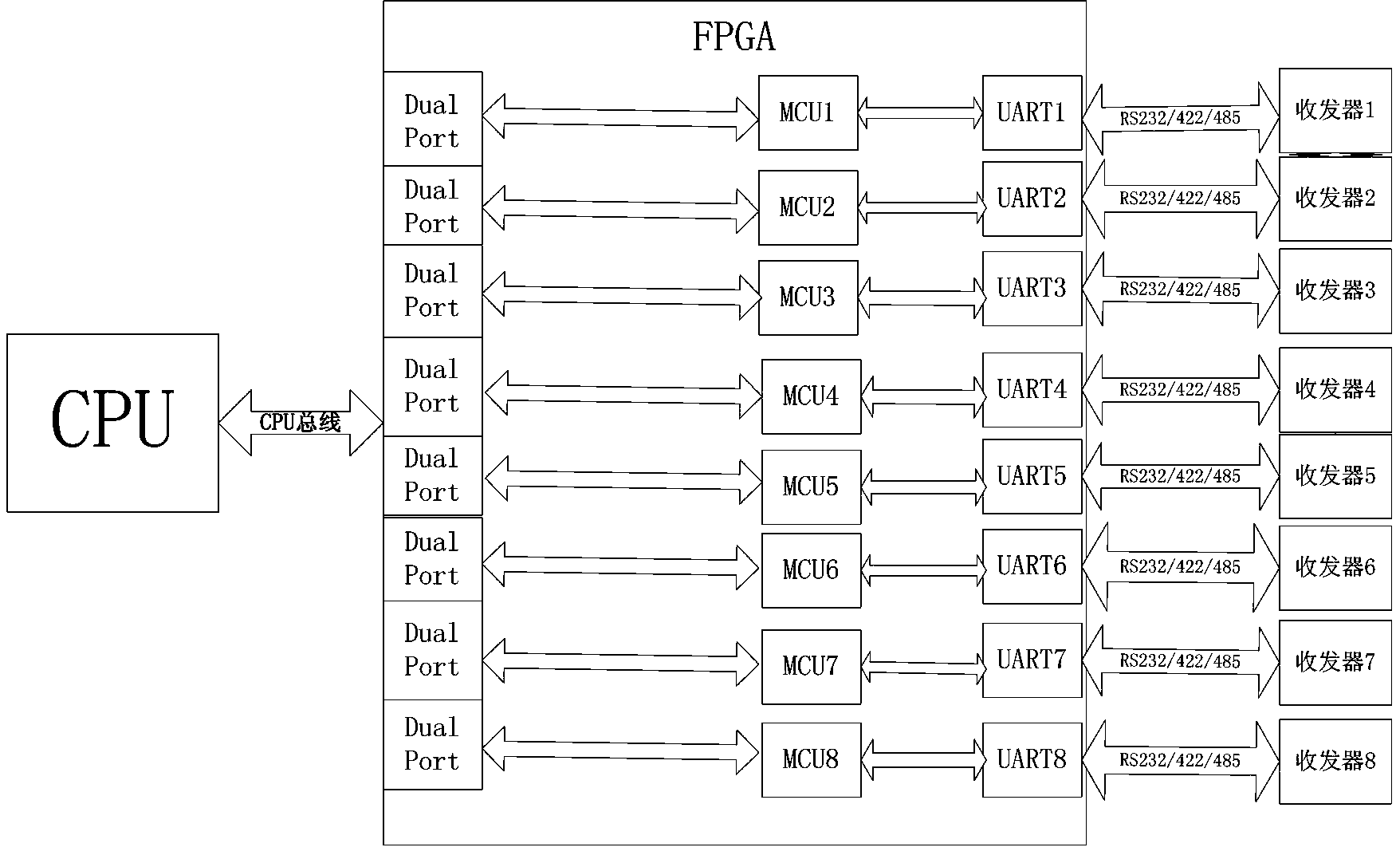

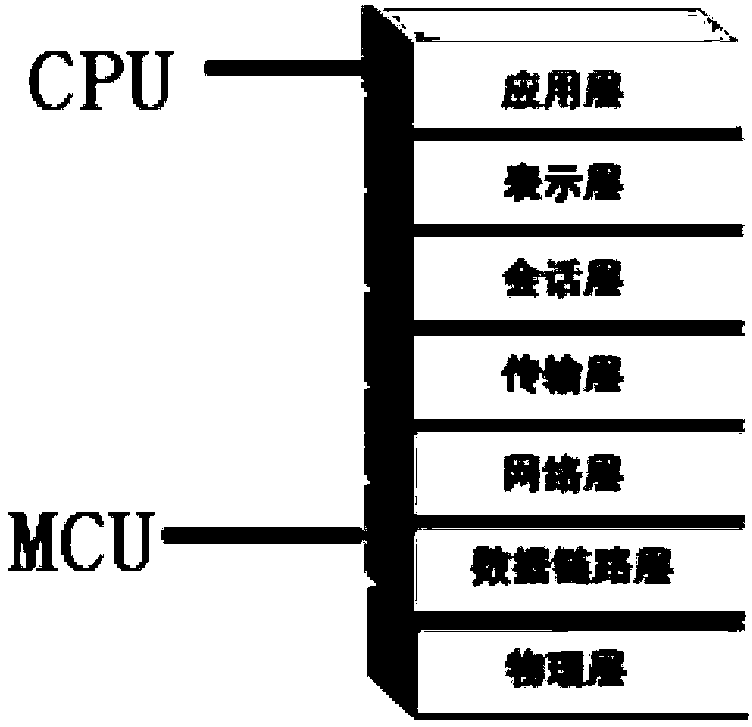

Multi-serial-port parallel processing framework based on FPGA

InactiveCN103713543AReduce loadFlexibility to increase or decrease the quantityProgramme controlComputer controlTransceiverFpga chip

The invention belongs to the technical field of distributed industrial control, and relates to a multi-serial-port parallel processing framework based on an FPGA. The framework comprises transceivers, an FPGA programmable logic chip and a processor CPU. The CPU is connected with the FPGA chip via a CPU interface bus. The framework is characterized in that: multiple UART cores and multiple co-processor MCUs which are corresponding to all the UART cores are designed in the FPGA chip via a hardware description language; multiple embedded type storage devices which are corresponding to all the co-processor MCUs are embedded in the FPGA, and each embedded type storage device is configured to be a dual-port mode capable of performing read-write operation; and the multiple UART cores are connected with the multiple corresponding transceivers via RS232 / RS422 / RS485 interfaces. The framework is low in hardware design cost so that a CPU load can be effectively reduced, serial bus data transmission bandwidth can be enhanced and multipath serial channels can be flexibly expanded.

Owner:STATE NUCLEAR POWER AUTOMATION SYST ENGCO

Dynamic absorption window for foreground background detector

Techniques are disclosed for creating a background model of a scene using both a pixel based approach and a context based approach. The combined approach provides an effective technique for segmenting scene foreground from background in frames of a video stream. Further, this approach can scale to process large numbers of camera feeds simultaneously, e.g., using parallel processing architectures, while still generating an accurate background model. Further, using both a pixel based approach and context based approach ensures that the video analytics system can effectively and efficiently respond to changes in a scene, without overly increasing computational complexity. In addition, techniques are disclosed for updating the background model, from frame-to-frame, by absorbing foreground pixels into the background model via an absorption window, and dynamically updating background / foreground thresholds.

Owner:INTELLECTIVE AI INC

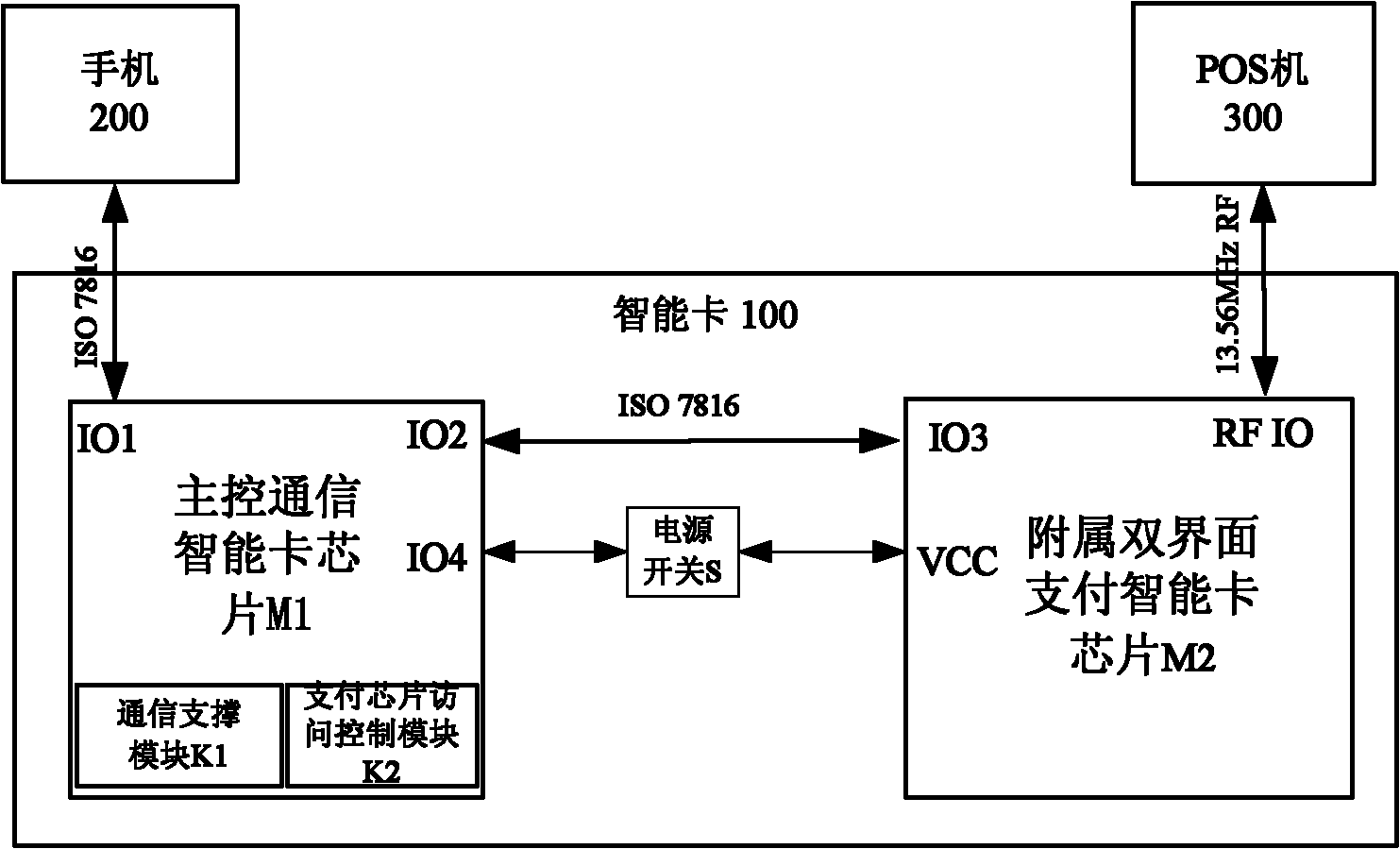

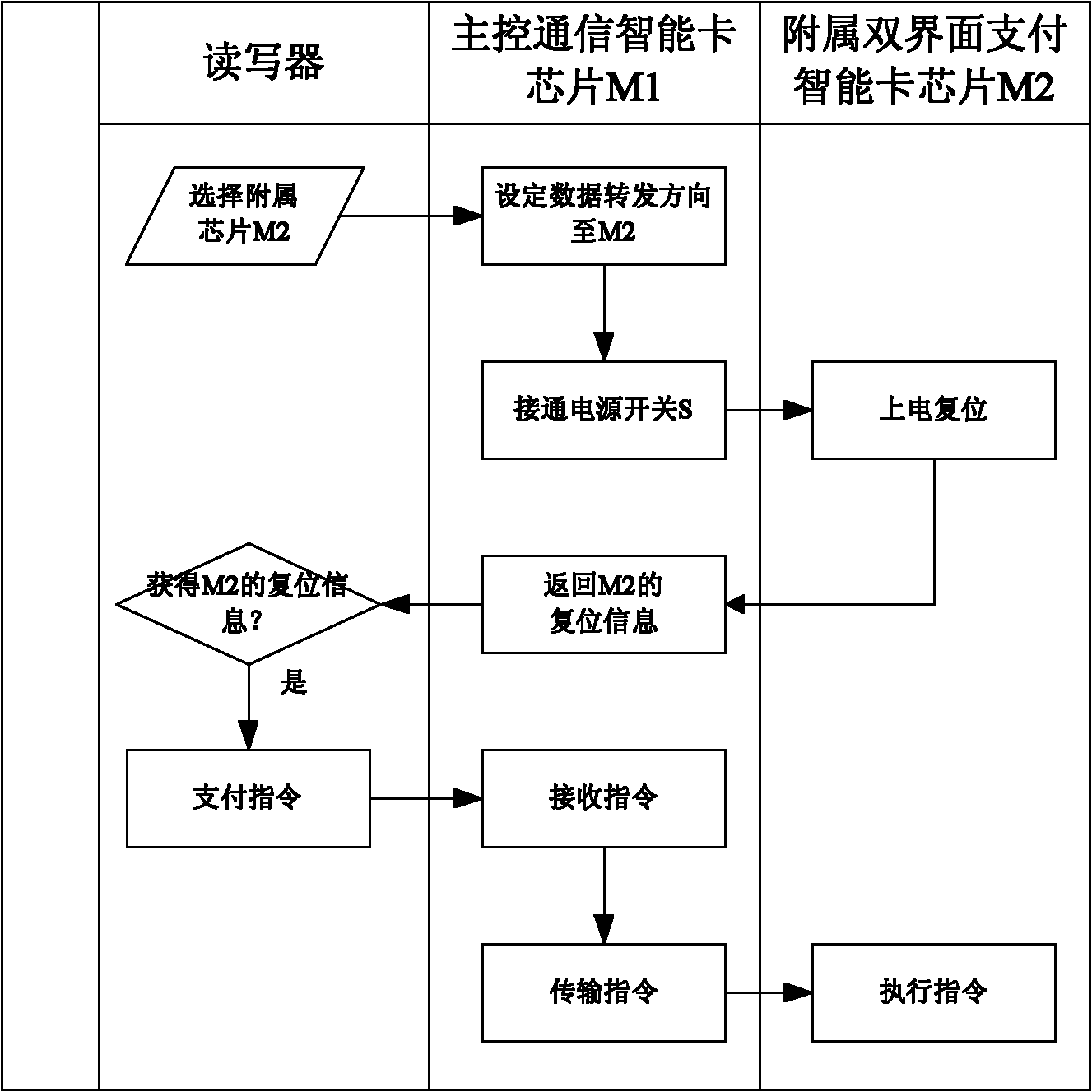

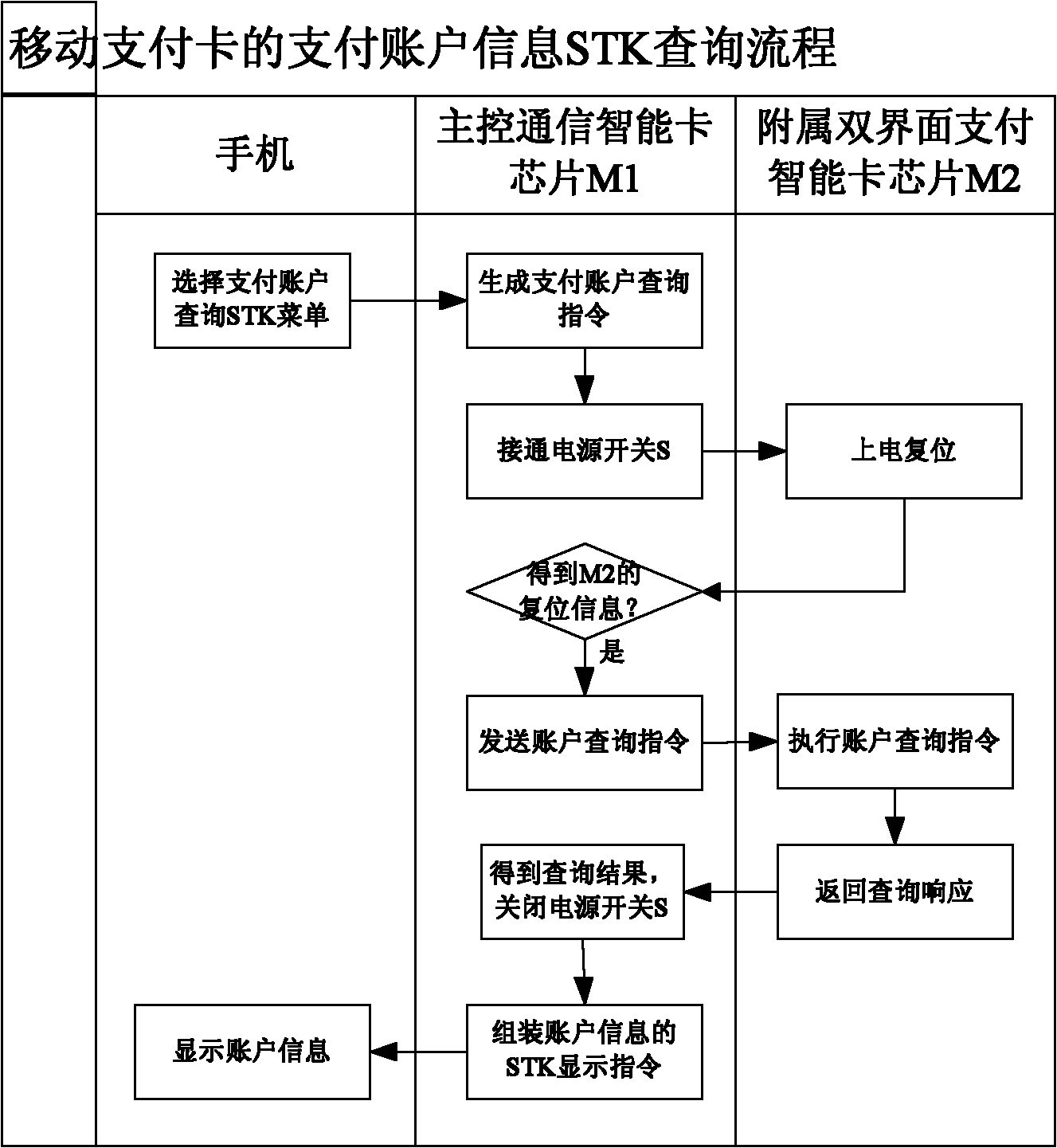

Mobile payment smart card and control method thereof

ActiveCN101916391AAdapt to changing needsExpand application spaceRecord carriers used with machinesSmart cardInformation searching

The invention discloses a mobile payment smart card. The mobile payment smart card is integrated with a main control communication smart card chip and a financial smart card chip with payment function in an SIP mode, wherein the main control chip is communicated with a mobile phone or other external equipment and performs access control on an affiliated payment smart card chip. The mobile paymentsmart card has contact and non-contact functions, the contact function is controlled by the main control chip, and the non-contact function is controlled by the financial smart card chip. The main control chip is a high-capacity soft mask chip and can support changeful communication application requirements, and the access control of the main control chip on the affiliated payment chip enables the mobile payment smart card to realize STK extension such as financial account information search, aerial earmark and the like by the telecommunication function provided by the main control chip. The affiliated payment chip independent from the main control chip executes the non-contact function, and the mobile payment smart card has higher comprehensive stability due to a parallel processing architecture of the two chips; and the physical independence of the affiliated payment chip ensures that the data has high security of financial level.

Owner:WUHAN TIANYU INFORMATION IND

Foreground detector for video analytics system

Techniques are disclosed for creating a background model of a scene using both a pixel based approach and a context based approach. The combined approach provides an effective technique for segmenting scene foreground from background in frames of a video stream. Further, this approach can scale to process large numbers of camera feeds simultaneously, e.g., using parallel processing architectures, while still generating an accurate background model. Further, using both a pixel based approach and context based approach ensures that the video analytics system can effectively and efficiently respond to changes in a scene, without overly increasing computational complexity. In addition, techniques are disclosed for updating the background model, from frame-to-frame, by absorbing foreground pixels into the background model via an absorption window, and dynamically updating background / foreground thresholds.

Owner:INTELLECTIVE AI INC

Control system for unmanned aerial vehicle utilizing parallel processing architecture

A UAV has two rotors. First and second sensors sense a first and second type of input respectively. The second type of input is different than the first type, the first sensor providing a first sensor output and the second sensor providing a second sensor output. The first sensor output is input to a first computer and the second sensor output is input to a second computer. The first and second computer communicate in parallel to process the first and second sensor outputs to create a control signal having a predetermined number of variables therein, each variable having an exclusive position within the signal. The first computer outputs a first variable and the second computer outputs a second variable, each output being assigned an exclusive position within the control signal. At least one of the first and second computers outputting the control signal to the rotors.

Owner:HOVERFLY TECH INC

Fault tolerant cell array architecture

InactiveUS20080034184A1Moderate yieldArray is largeSingle instruction multiple data multiprocessorsStatic indicating devicesMassively parallelData processing system

A data processing system containing a monolithic network of cells with sufficient redundancy provided through direct logical replacement of defective cells by spare cells to allow a large monolithic array of cells without uncorrectable defects to be organized, where the cells have a variety of useful properties. The data processing system according to the present invention overcomes the chip-size limit and off-chip connection bottlenecks of chip-based architectures, the von Neumann bottleneck of uniprocessor architectures, the memory and I / O bottlenecks of parallel processing architectures, and the input bandwidth bottleneck of high-resolution displays, and supports integration of up to an entire massively parallel data processing system into a single monolithic entity.

Owner:NORMAN RICHARD S

Dynamic absorption window for foreground background detector

Owner:INTELLECTIVE AI INC

Incremental update for background model thresholds

Techniques are disclosed for creating a background model of a scene using both a pixel based approach and a context based approach. The combined approach provides an effective technique for segmenting scene foreground from background in frames of a video stream. Further, this approach can scale to process large numbers of camera feeds simultaneously, e.g., using parallel processing architectures, while still generating an accurate background model. Further, using both a pixel based approach and context based approach ensures that the video analytics system can effectively and efficiently respond to changes in a scene, without overly increasing computational complexity. In addition, techniques are disclosed for updating the background model, from frame-to-frame, by absorbing foreground pixels into the background model via an absorption window, and dynamically updating background / foreground thresholds.

Owner:INTELLECTIVE AI INC

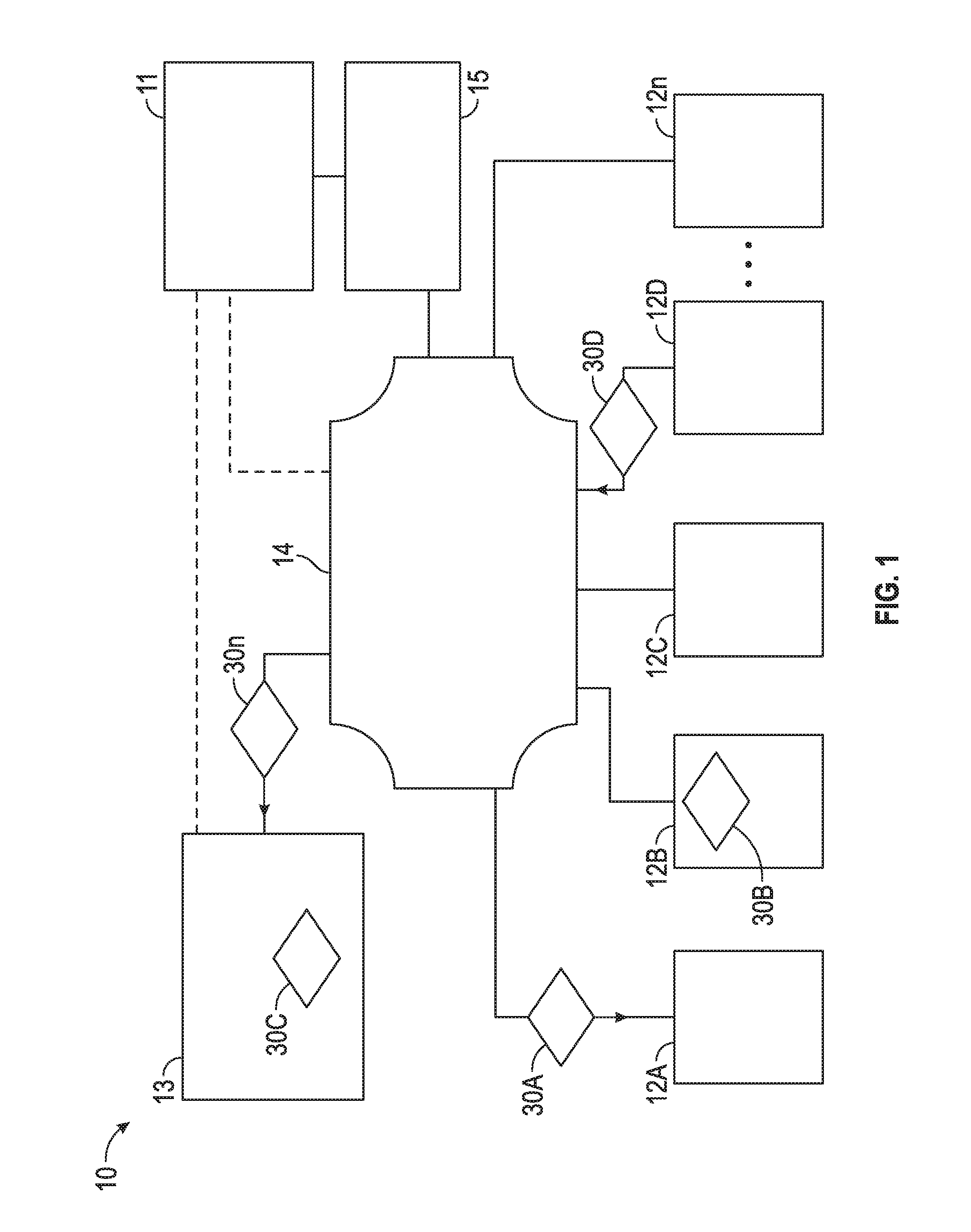

Method and apparatus for directory-based coherence with distributed directory management

The present invention provides for a type of parallel processing architecture in which a plurality of processors has access to a shared memory hierarchy level. A memory hierarchy level has a coherence directory and associated directory data with a plurality of cachelines each associated with different data. Buffers are interconnected to processor memory and a plurality of processor elements, each element interconnected to different buffers. Cache lines are requested from memory, and the requests, responses, and detections therein are available for particular access modes, therein providing additional coherence of the data. Processing of the directory data is performed by processing elements.

Owner:META PLATFORMS INC

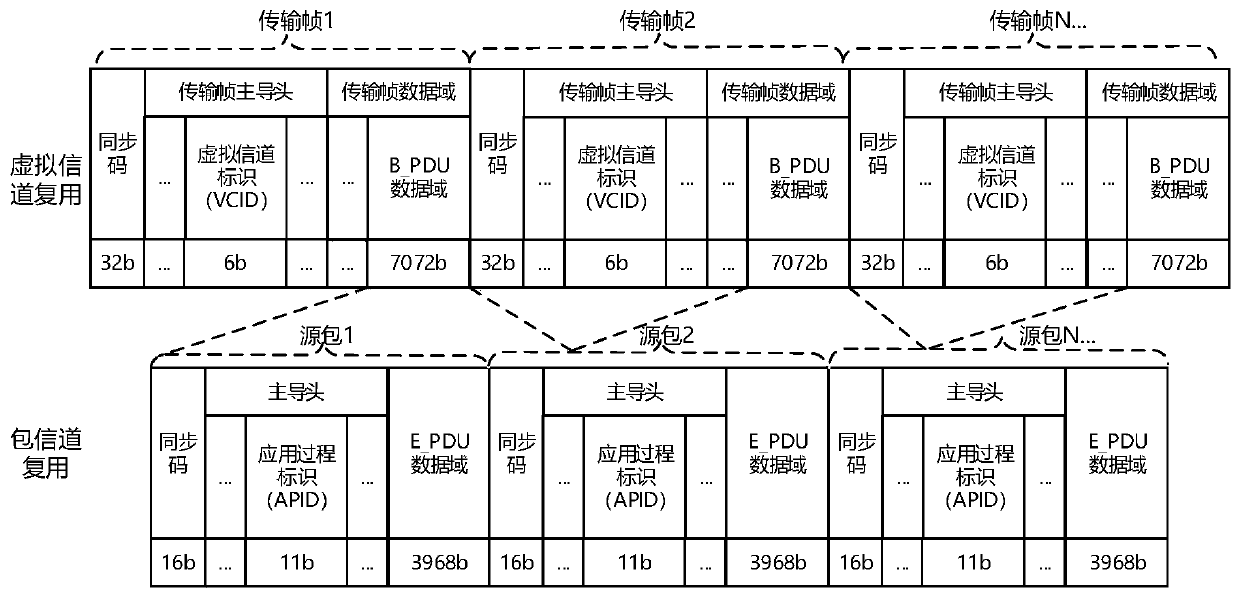

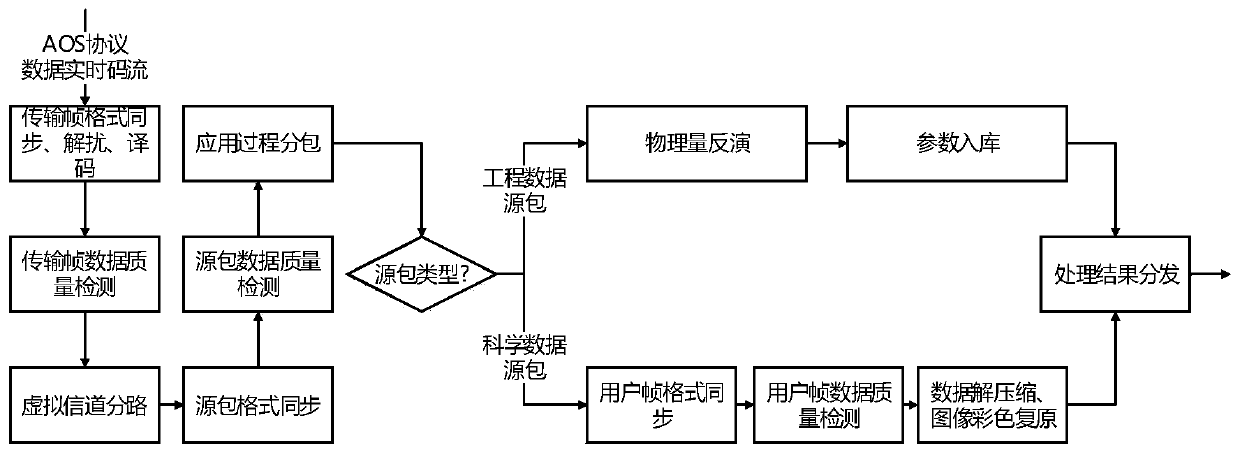

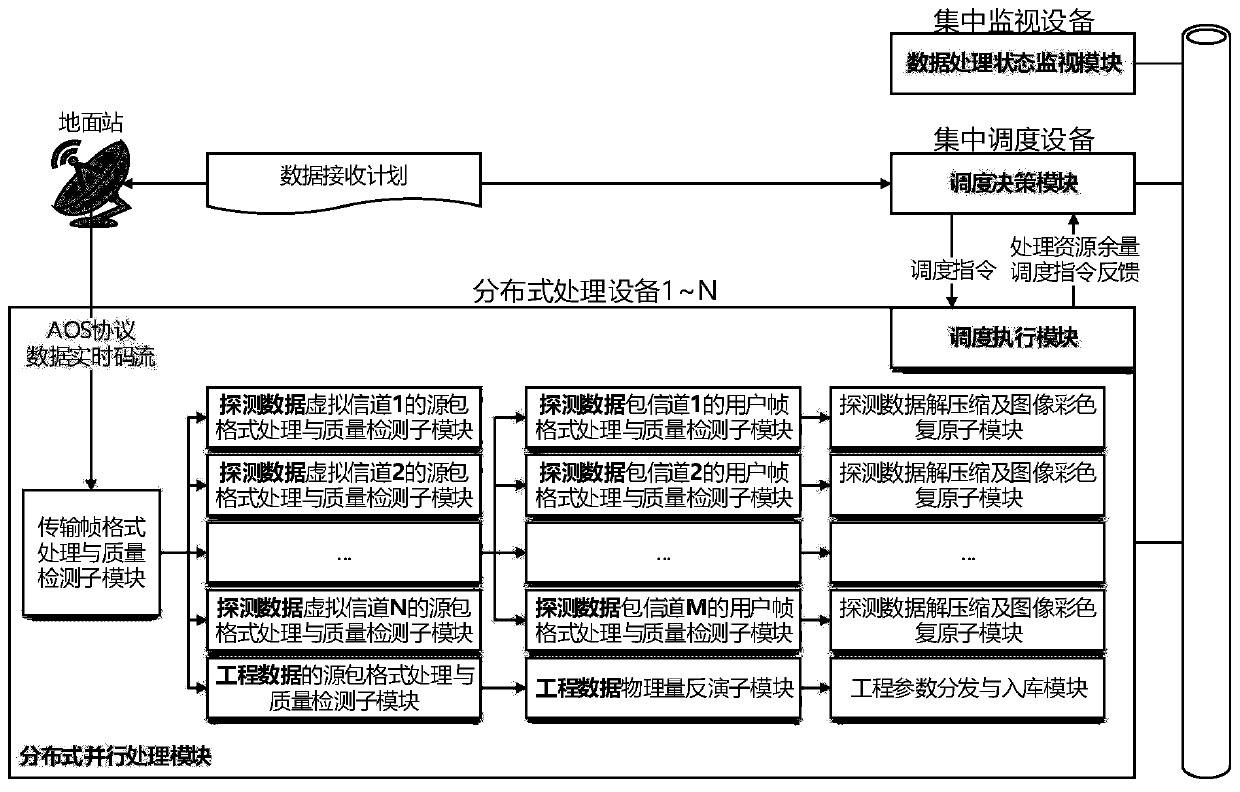

CCSDS AOS protocol data real-time processing method and system

ActiveCN110049020AImprove performanceImplement parallel processingResource allocationRadio transmissionComputer moduleTime processing

The invention discloses a CCSDS AOS protocol data real-time processing system. Protocol data are processed in real time based on a centralized scheduling and distributed parallel processing architecture. The system comprises: a scheduling decision module which is used for collecting real-time processing operation, distributing hardware processing resources and sending a starting or stopping instruction of a processing module; a scheduling execution module which is used for executing a task of starting or stopping the processing module according to the instruction sent by the scheduling decision module; a distributed parallel processing module which is used for implementing tasks of frame transmission, source package, user frame format processing and quality detection, engineering data physical quantity inversion, detection data decompression and image color restoration, and processing result distribution and storage; and a data processing state monitoring module which is used for monitoring the operation state of the processing module, processing statistics and processing logs. The treatment performance of the system is superior to 300 Mbps.

Owner:NAT SPACE SCI CENT CAS

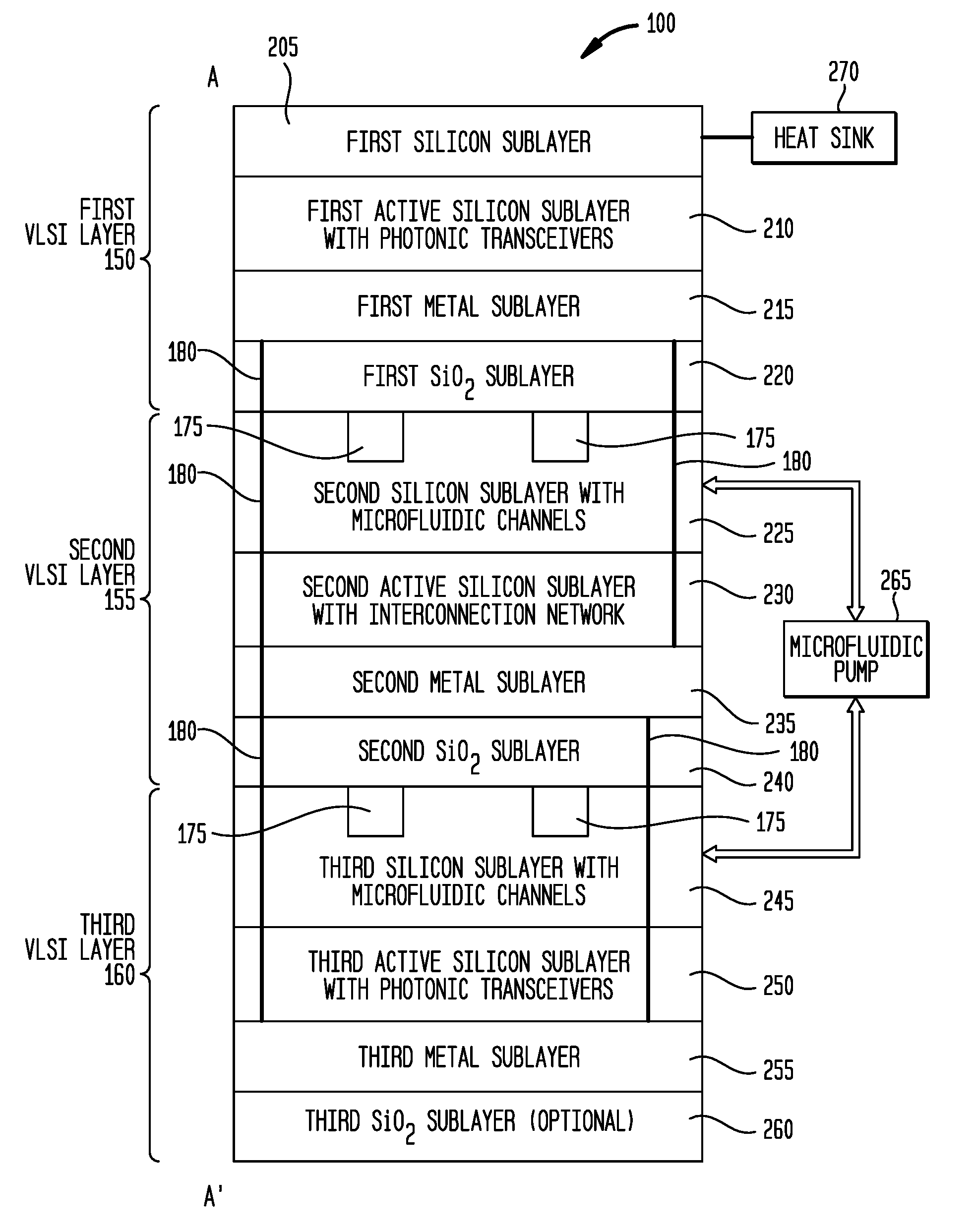

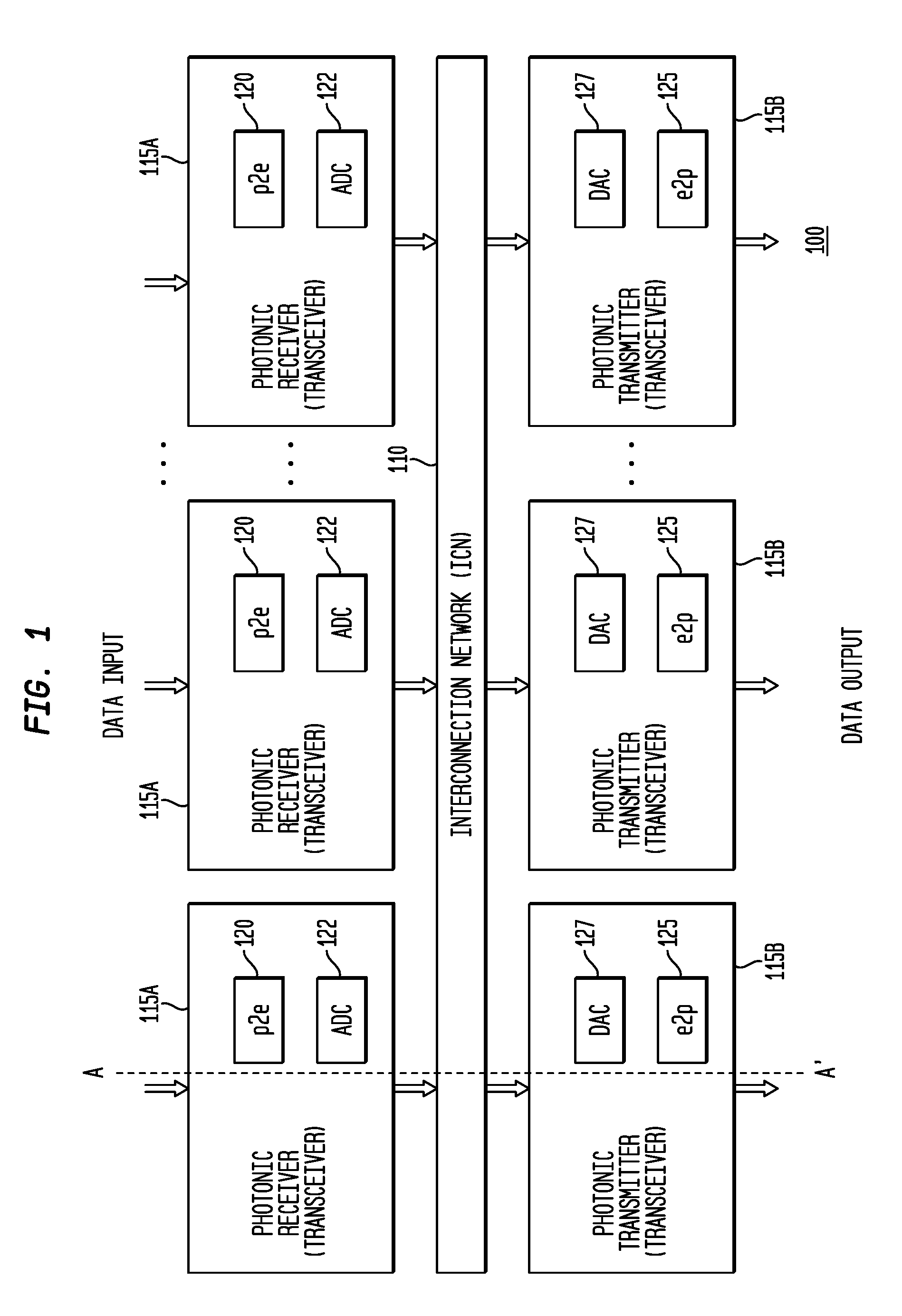

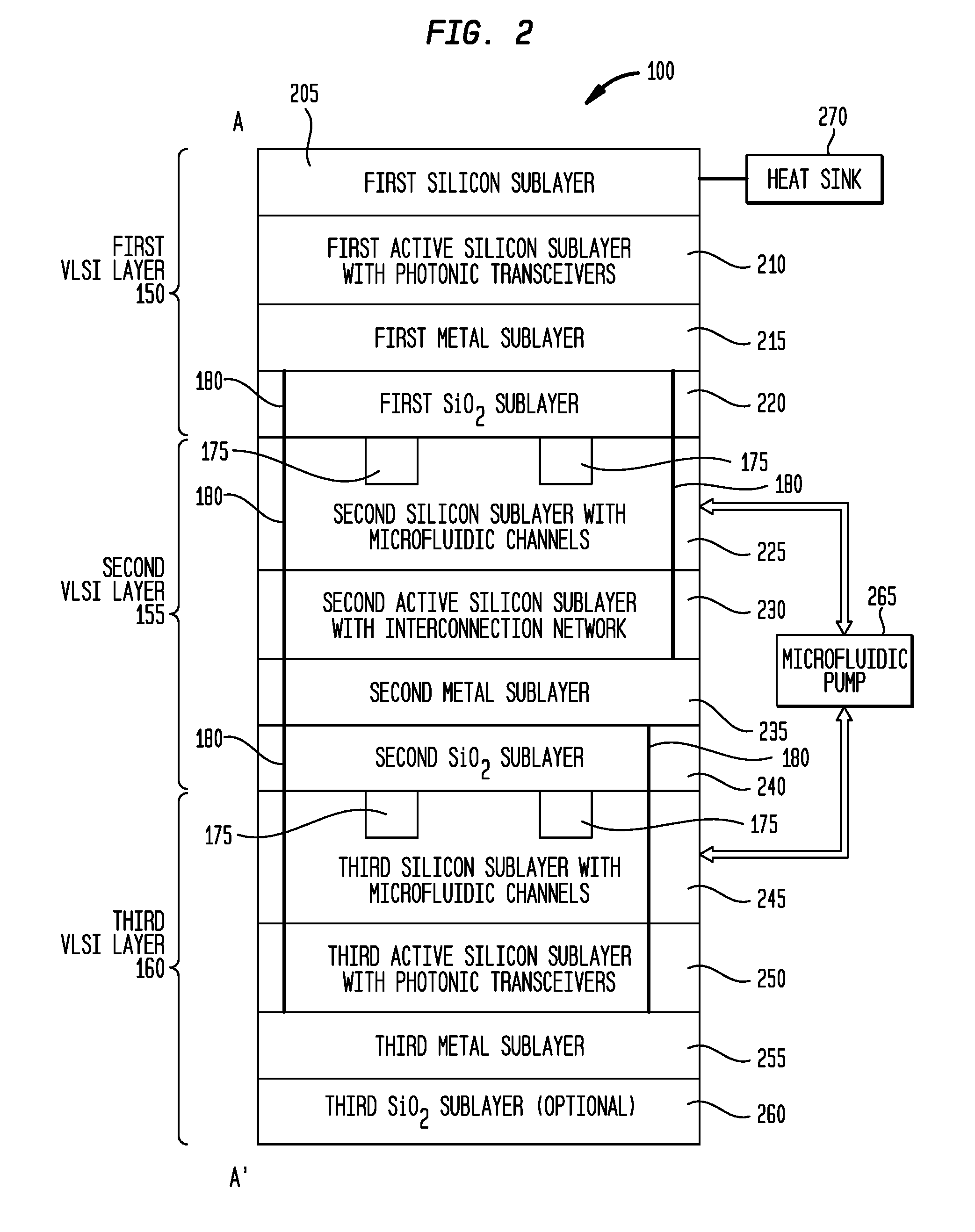

3D VLSI Interconnection Network with Microfluidic Cooling, Photonics and Parallel Processing Architecture

A three-dimensional VLSI integrated circuit apparatus is disclosed having a plurality of VLSI layers. A first VLSI layer includes a first silicon sublayer coupleable to at least one heat sink, and a first active silicon sublayer having a (first) plurality of photonic receivers (or transceivers); and a second VLSI layer including a second silicon sublayer having a first plurality of microfluidic cooling channels, and a second active silicon sublayer of the plurality of second VLSI sublayers having an interconnection network. Additional VLSI layers may also include a third VLSI layer having a third silicon sublayer having a second plurality of microfluidic cooling channels and a third active silicon sublayer having a (second) plurality of photonic transmitters (or transceivers). Additional VLSI layers may also include a third VLSI layer having microfluidic cooling channels and memory circuits, and a fourth VLSI layer having microfluidic cooling channels and parallel processing circuitry.

Owner:VISHKIN UZI Y

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com