Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

950 results about "Real-time operating system" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A real-time operating system (RTOS) is an operating system (OS) intended to serve real-time applications that process data as it comes in, typically without buffer delays. Processing time requirements (including any OS delay) are measured in tenths of seconds or shorter increments of time. A real-time system is a time bound system which has well defined fixed time constraints. Processing must be done within the defined constraints or the system will fail. They either are event driven or time sharing. Event driven systems switch between tasks based on their priorities while time sharing systems switch the task based on clock interrupts. Most RTOSs use a pre-emptive scheduling algorithm.

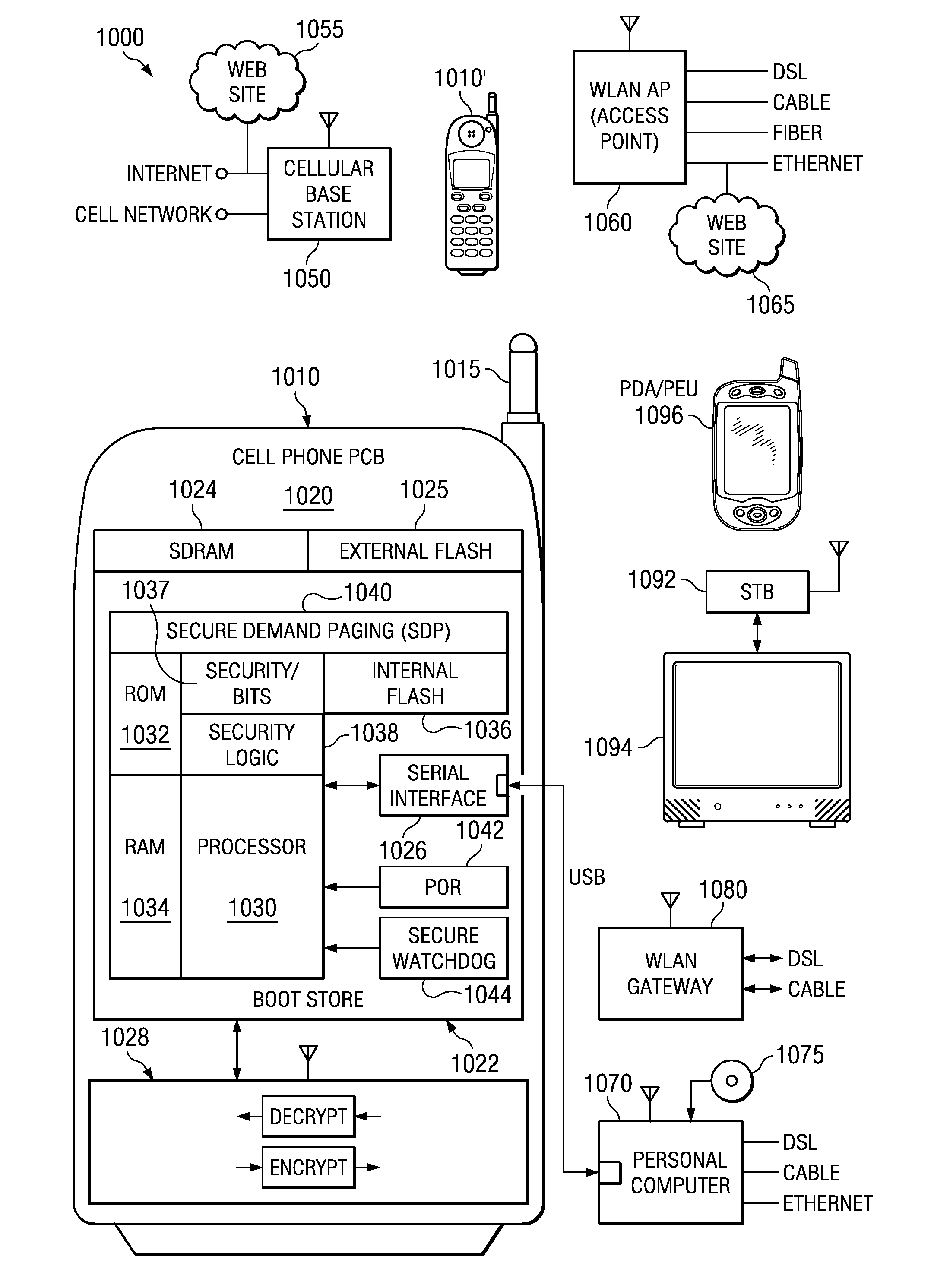

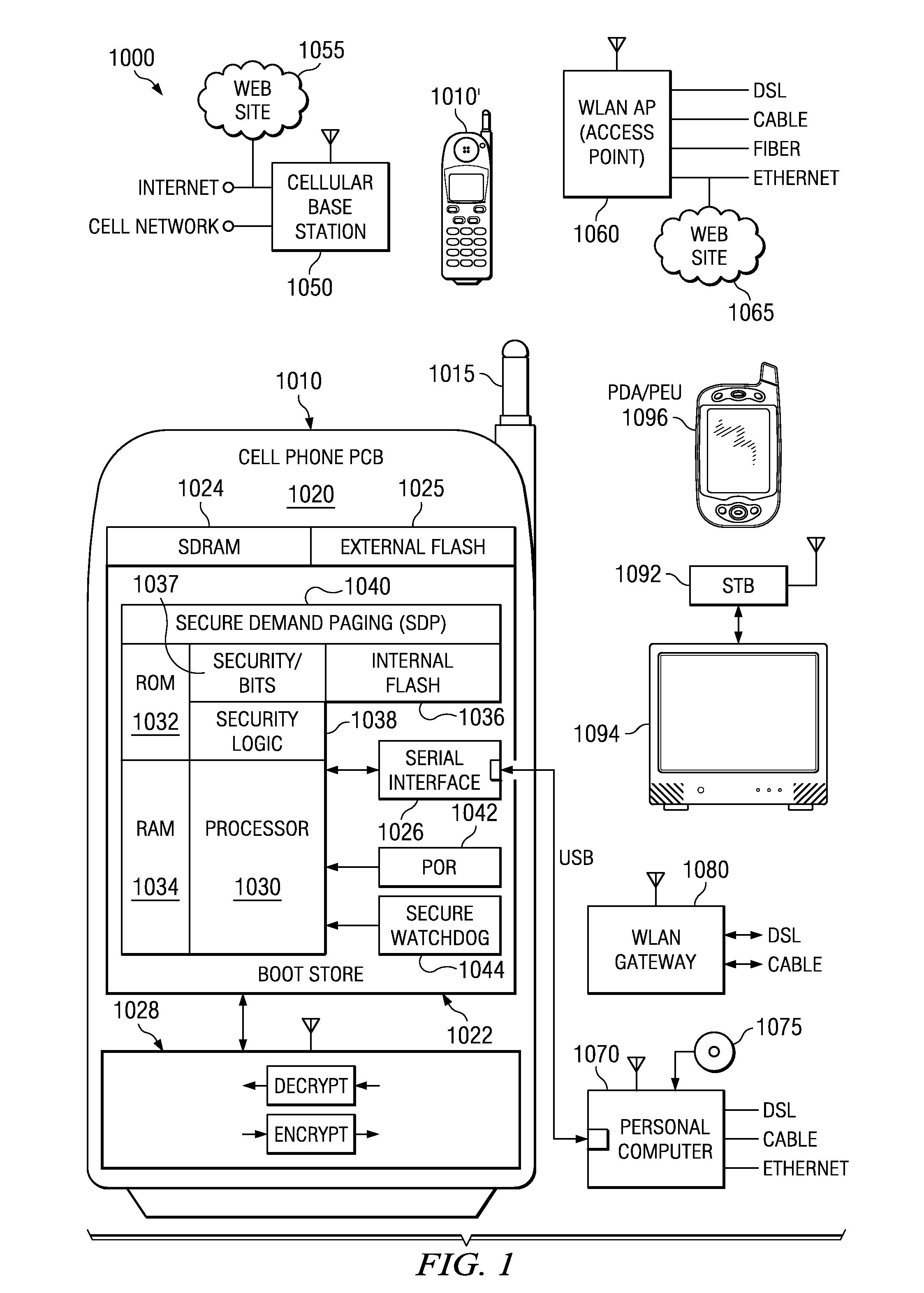

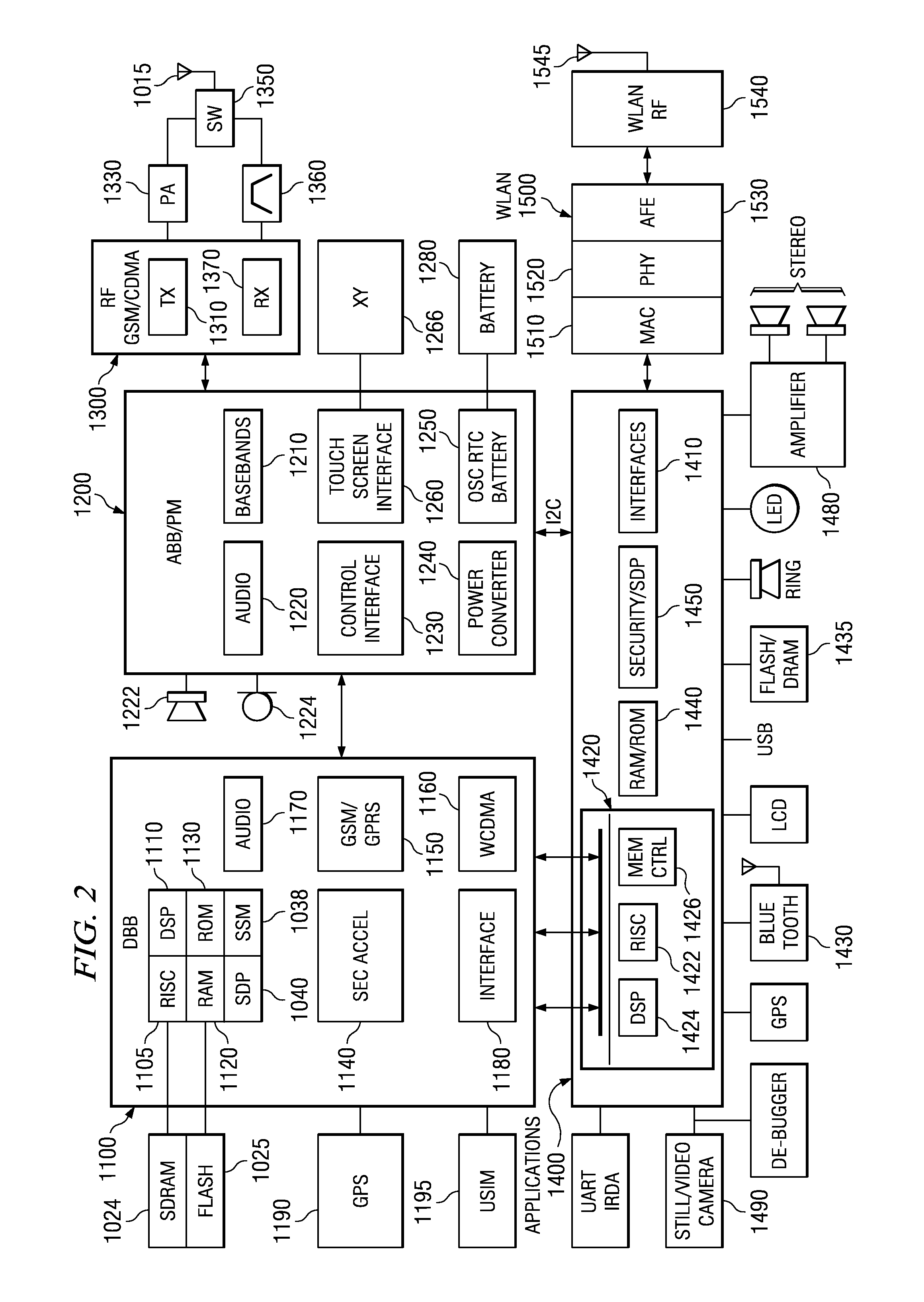

Virtual cores and hardware-supported hypervisor integrated circuits, systems, methods and processes of manufacture

InactiveUS20070226795A1Alteration can be preventedMemory loss protectionError detection/correctionNon real timeElectronic systems

An electronic system (1400) includes a processor (1422, 2610) having a pipeline, a bus (2655) coupled to the pipeline, a storage (1435, 1440, 2650) coupled to the bus (2655), the storage (1435, 2650) having a real time operating system (RTOS) and a real-time application, a non-real-time operating system (HLOS), a secure environment kernel (SE), and a software monitor (2310); and protective circuitry (2460) coupled to the processor and operable to establish a first signal (VP1_Active) and a second signal (NS) each having states and together having combinations of the states representing a first category (2430) for the real-time operating system and the real-time application, a second category (2420) for the non-real-time operating system, and a third category (2450) for the secure environment kernel.

Owner:TEXAS INSTR INC

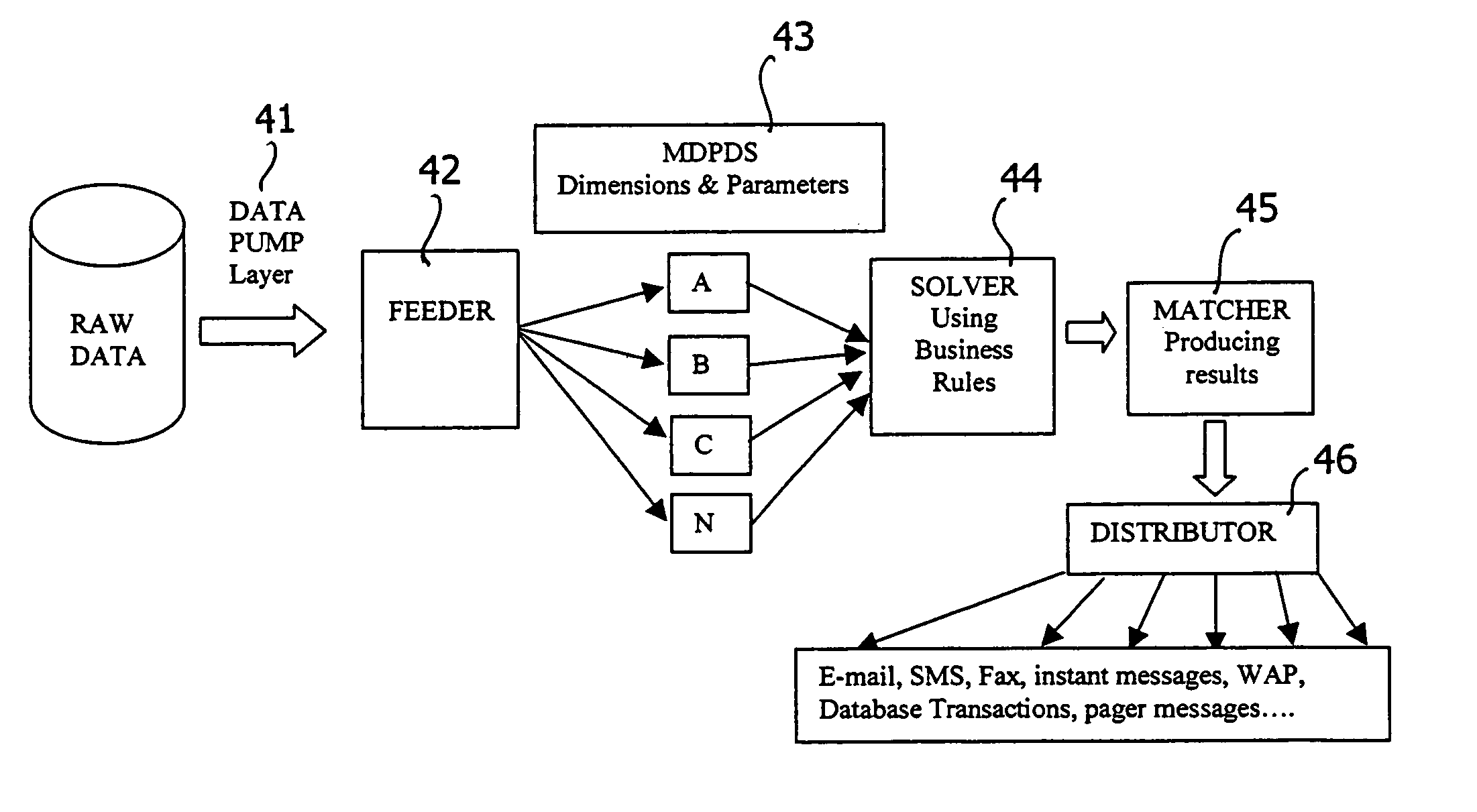

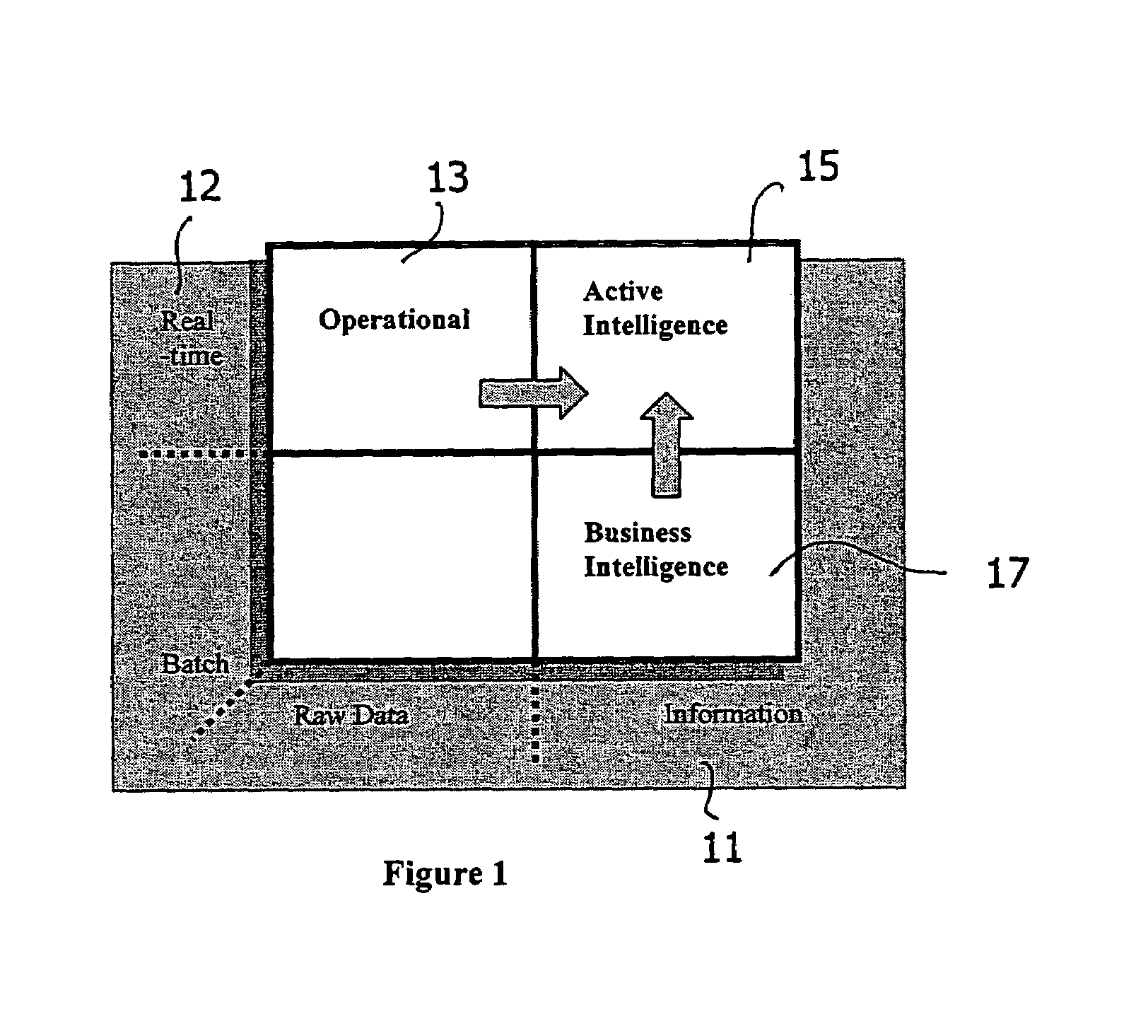

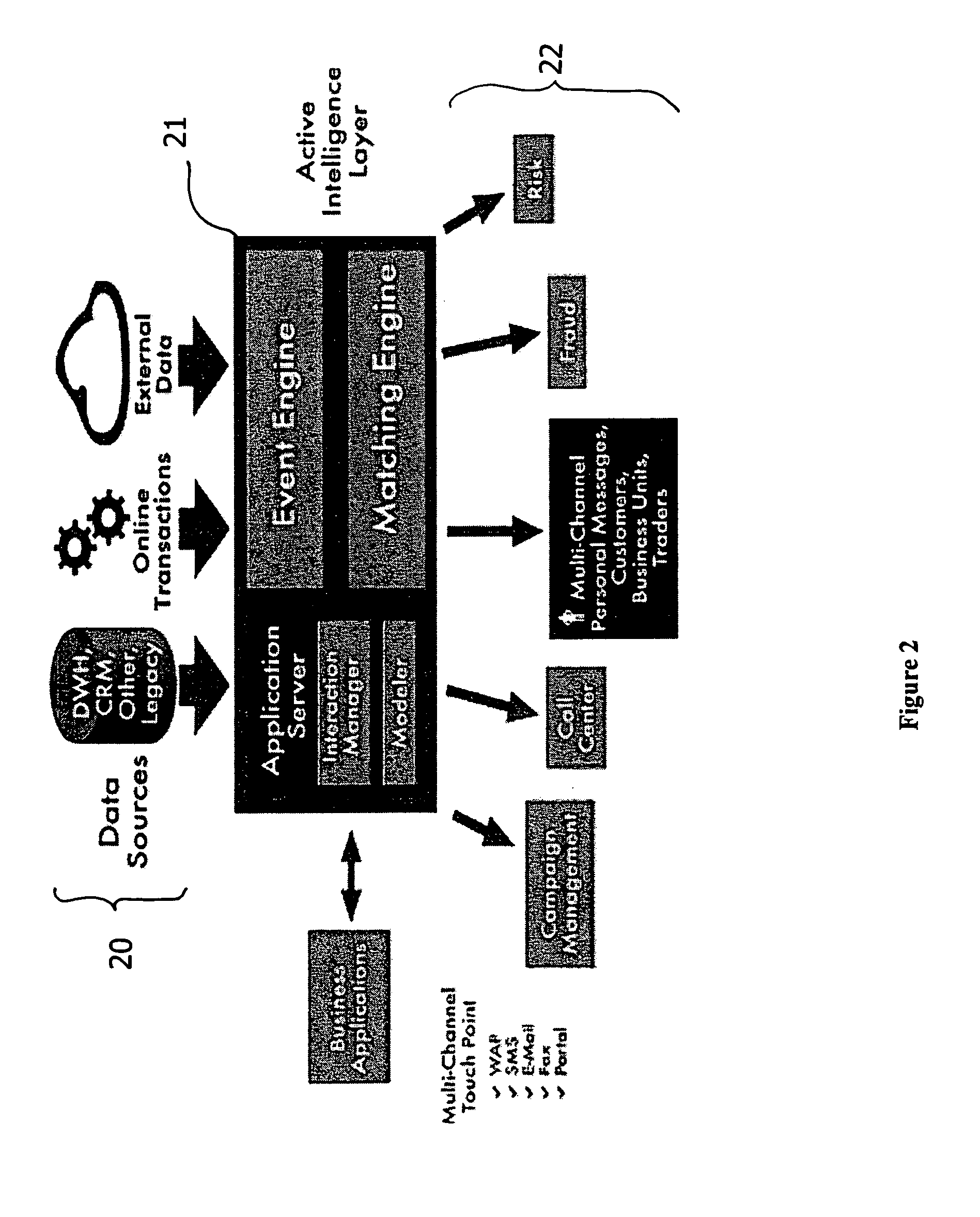

System and method for analyzing and utilizing data, by executing complex analytical models in real time

InactiveUS6965886B2Efficiently distributedIncrease opportunitiesDigital computer detailsOffice automationOperational systemReal-time data

A system and method for collecting, filtering, analyzing, distributing and effectively utilizing highly relevant events (such as key business events) in real time, from huge quantities of data. The present invention analyzes both historic and real-time data stemming from operational activity, by interfacing with internal data repositories (such as Enterprise Resource Planning (ERP) and Customer Relationship Management (CRM)), external data sources (such as suppliers and clients), and real time operational systems in order to create an Active Intelligence Platform. This Active Intelligence Platform is positioned as a layer between the organization's data sources and its applications, monitoring inputs and relaying only the important data items to the relevant individuals and / or systems. This allows individuals and systems to respond immediately and effectively to key events.

Owner:ACTIMIZE

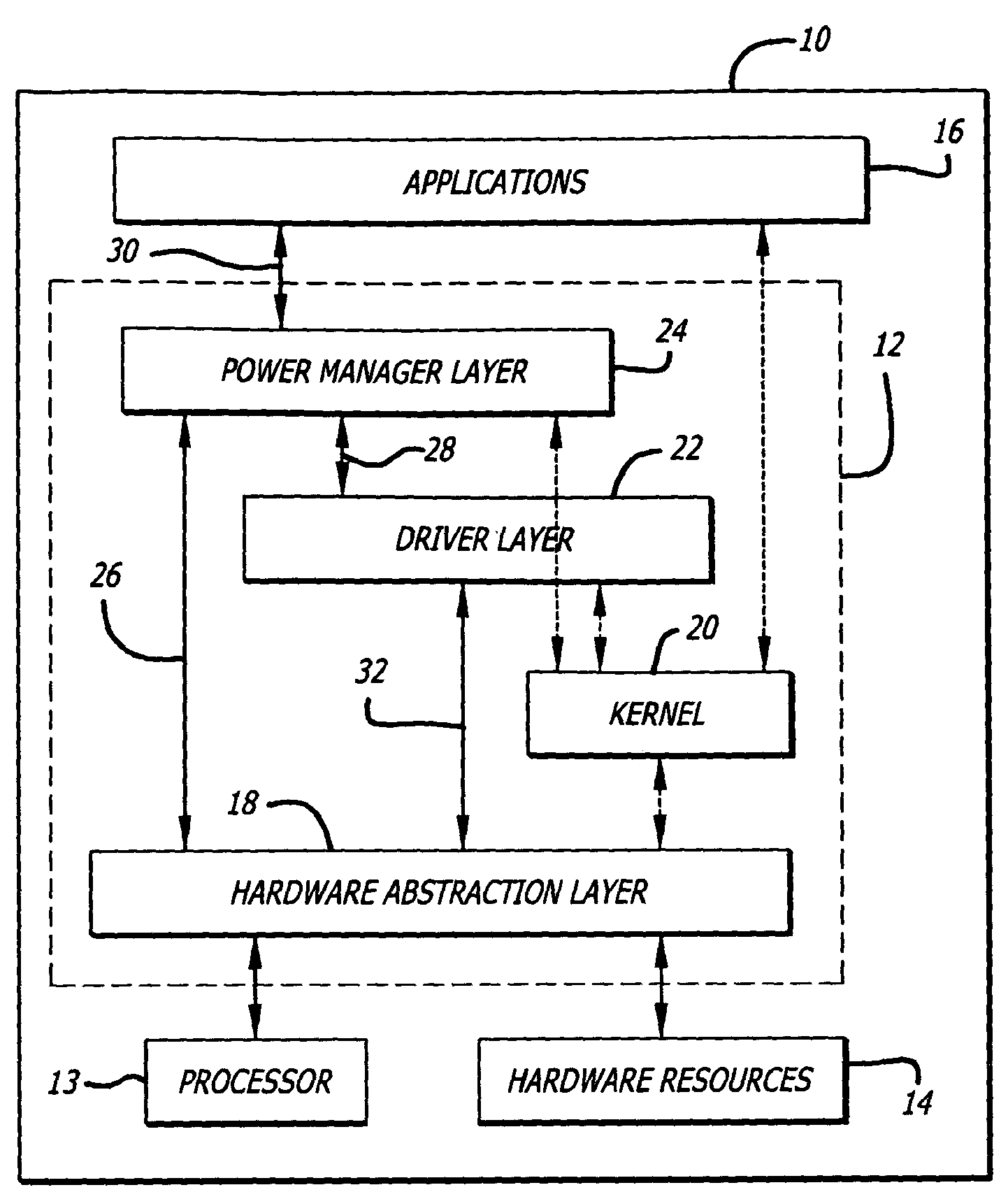

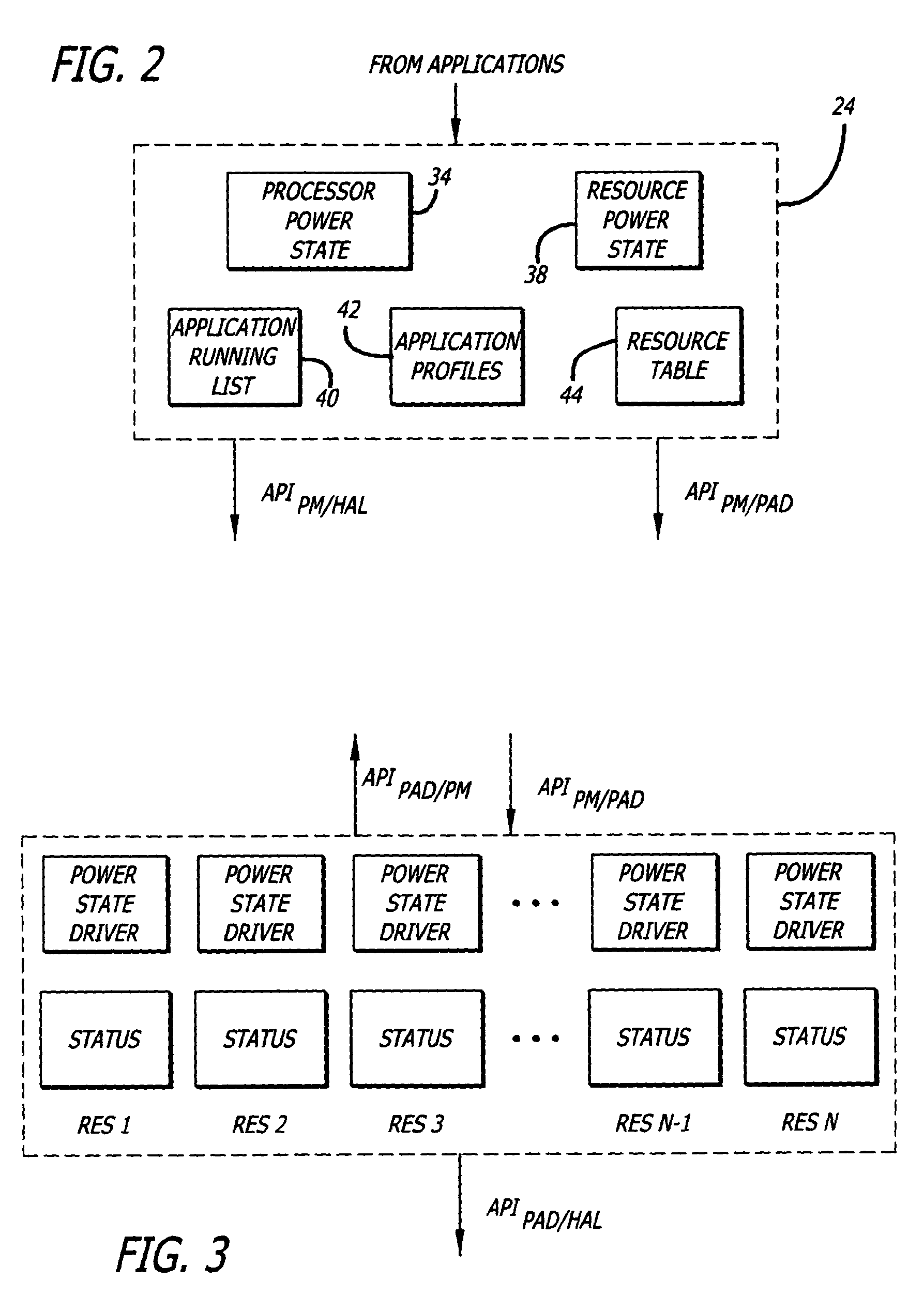

Application-driven method and apparatus for limiting power consumption in a processor-controlled hardware platform

ActiveUS7272730B1Volume/mass flow measurementPower supply for data processingOperational systemApplication software

An improvement in a real time operating system for supporting at least one application, a processor and at least one hardware resource. The operating system includes a power manager layer. Such power manager layer is arranged to exchange information with an application, the processor and at least one hardware resource to provide real time power management responsive to the information.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

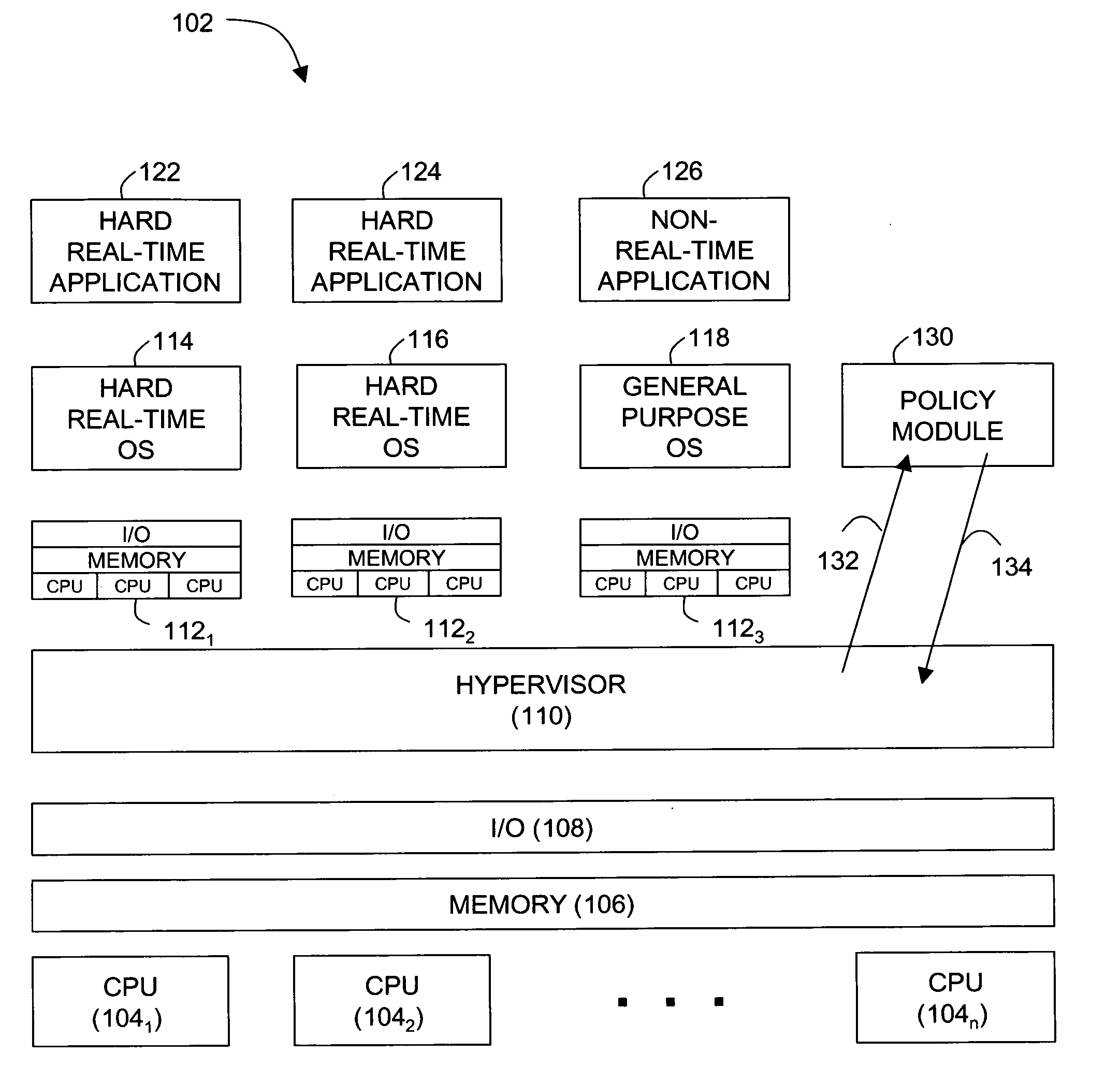

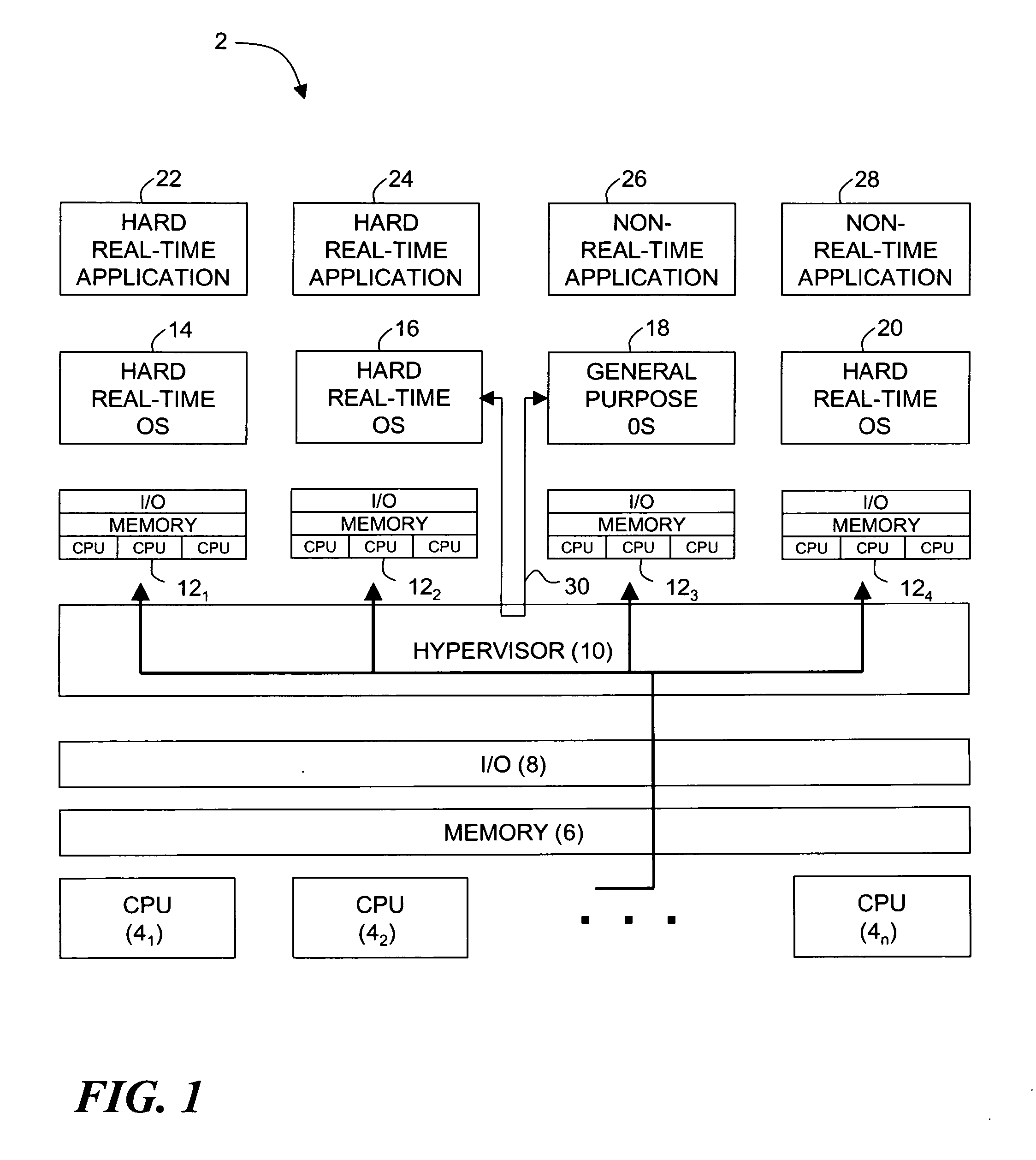

Enhancement of real-time operating system functionality using a hypervisor

InactiveUS20050251806A1Improve robustnessImprove securityProgram initiation/switchingSoftware simulation/interpretation/emulationScheduling functionOperational system

A system, method and computer program product for enhancing a real-time operating system (RTOS) with functionality normally associated with a general purpose operating system (GPOS). A hypervisor that is adapted to perform a real-time scheduling function supports concurrent execution of an RTOS and a GPOS on a system of shared hardware resources. The RTOS or its applications can utilize services provided by the GPOS. Such services may include one or more of file system organization, network communication, network management, database management, security, user-interface support and others. To enhance operational robustness and security, the hypervisor can be placed in read-only storage while maintaining the ability to update scheduling mechanisms. A programmable policy manager that is maintained in read-write storage can be used to dictate scheduling policy changes to the hypervisor as required to accommodate current needs.

Owner:IBM CORP

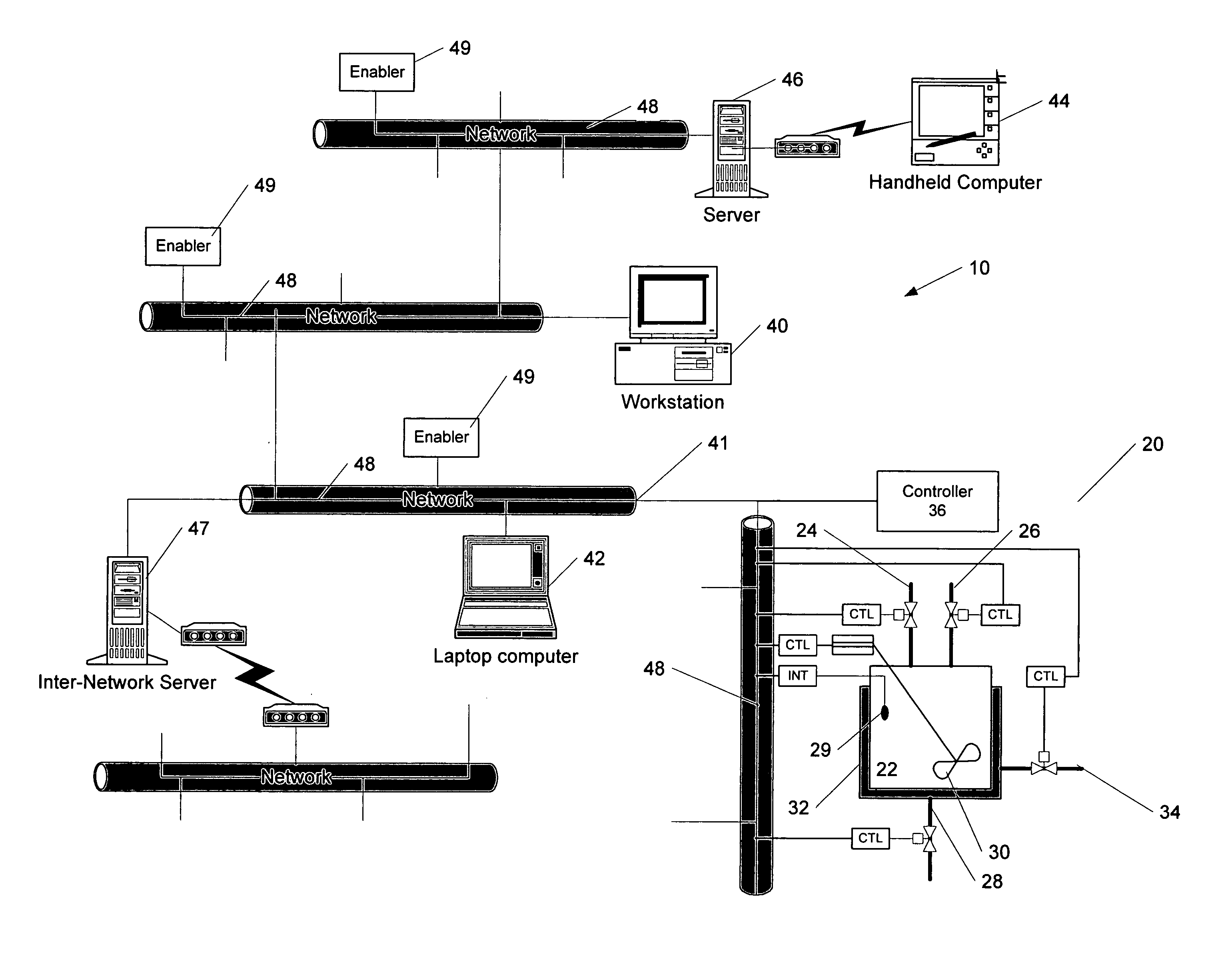

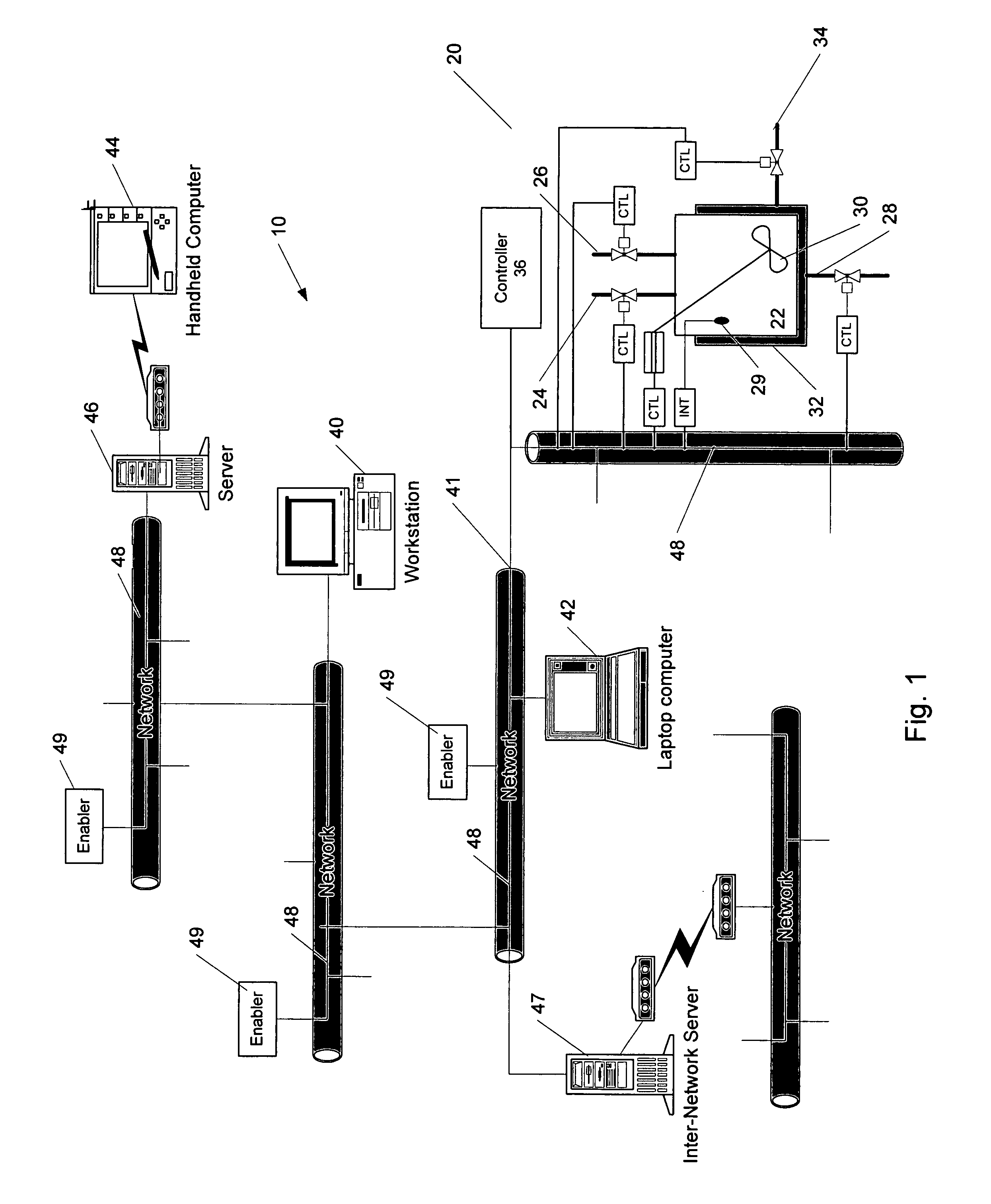

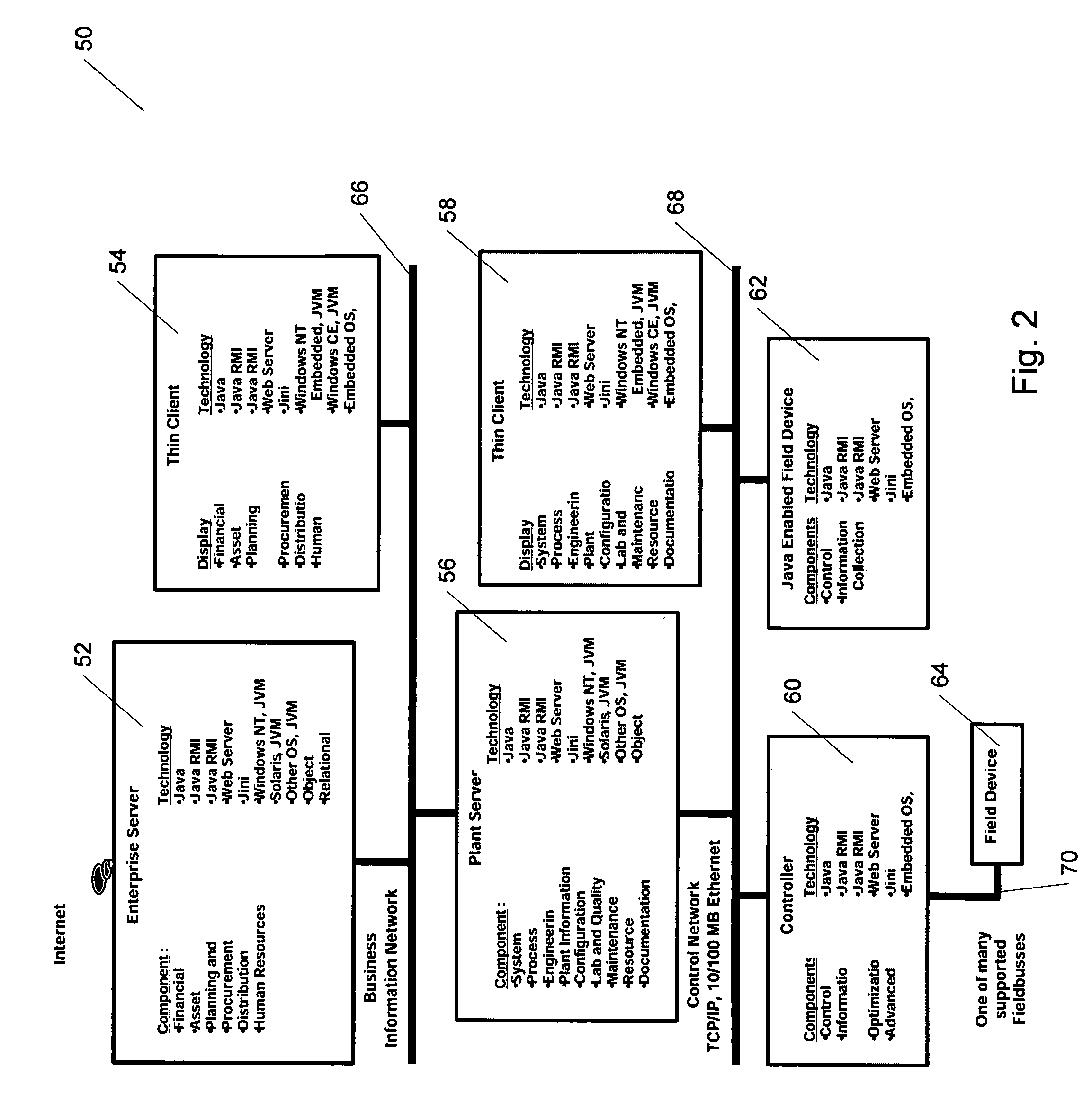

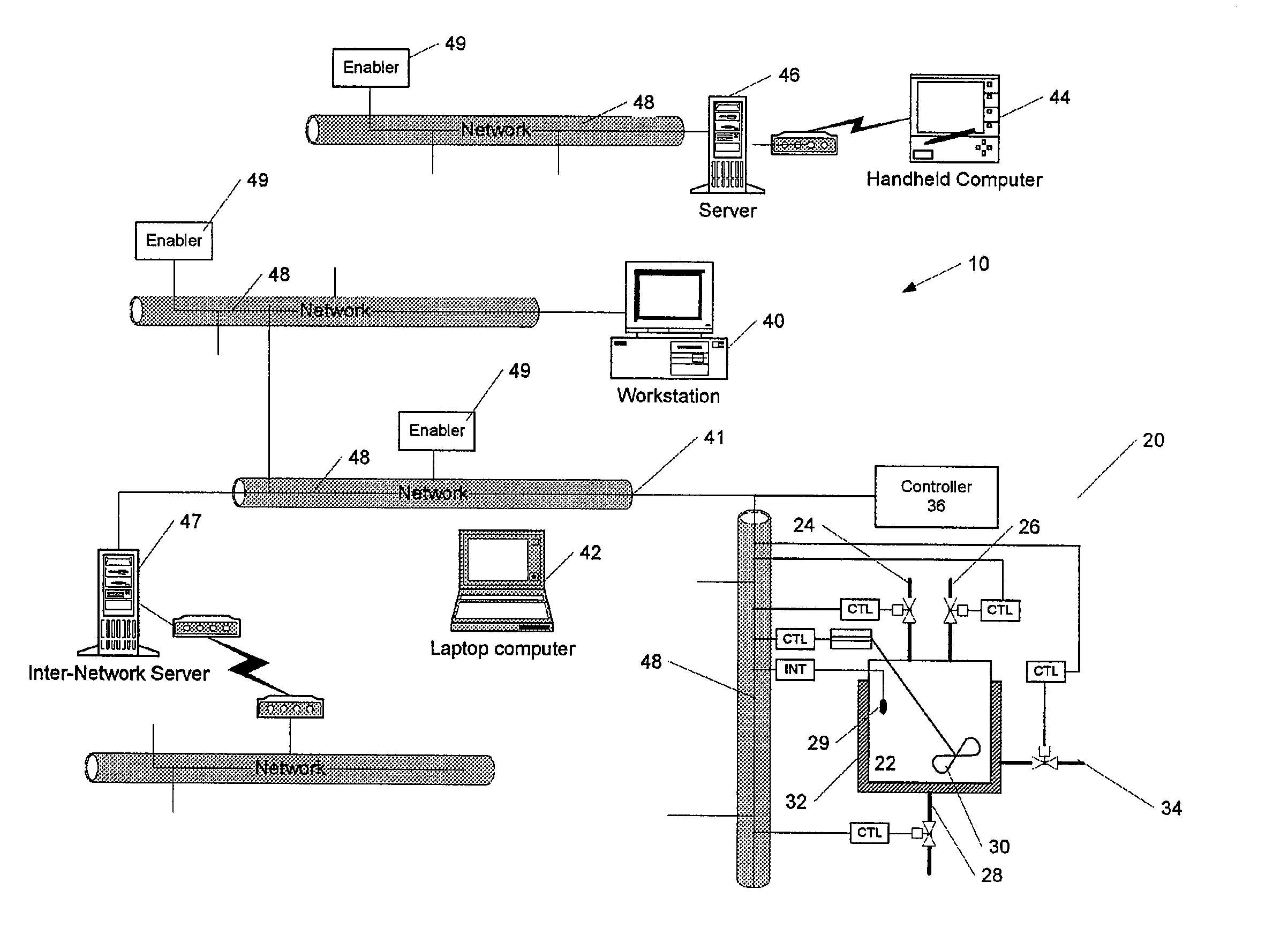

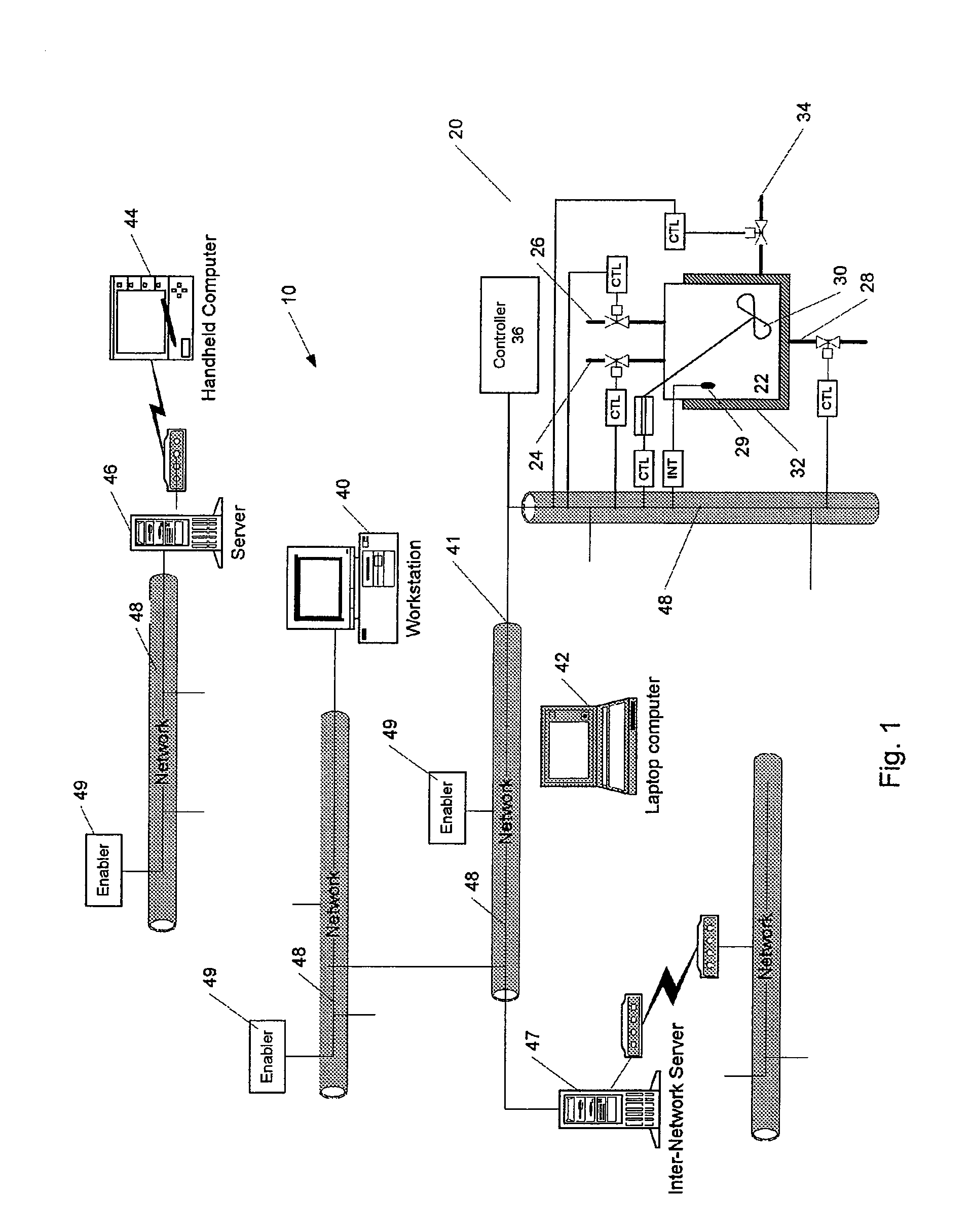

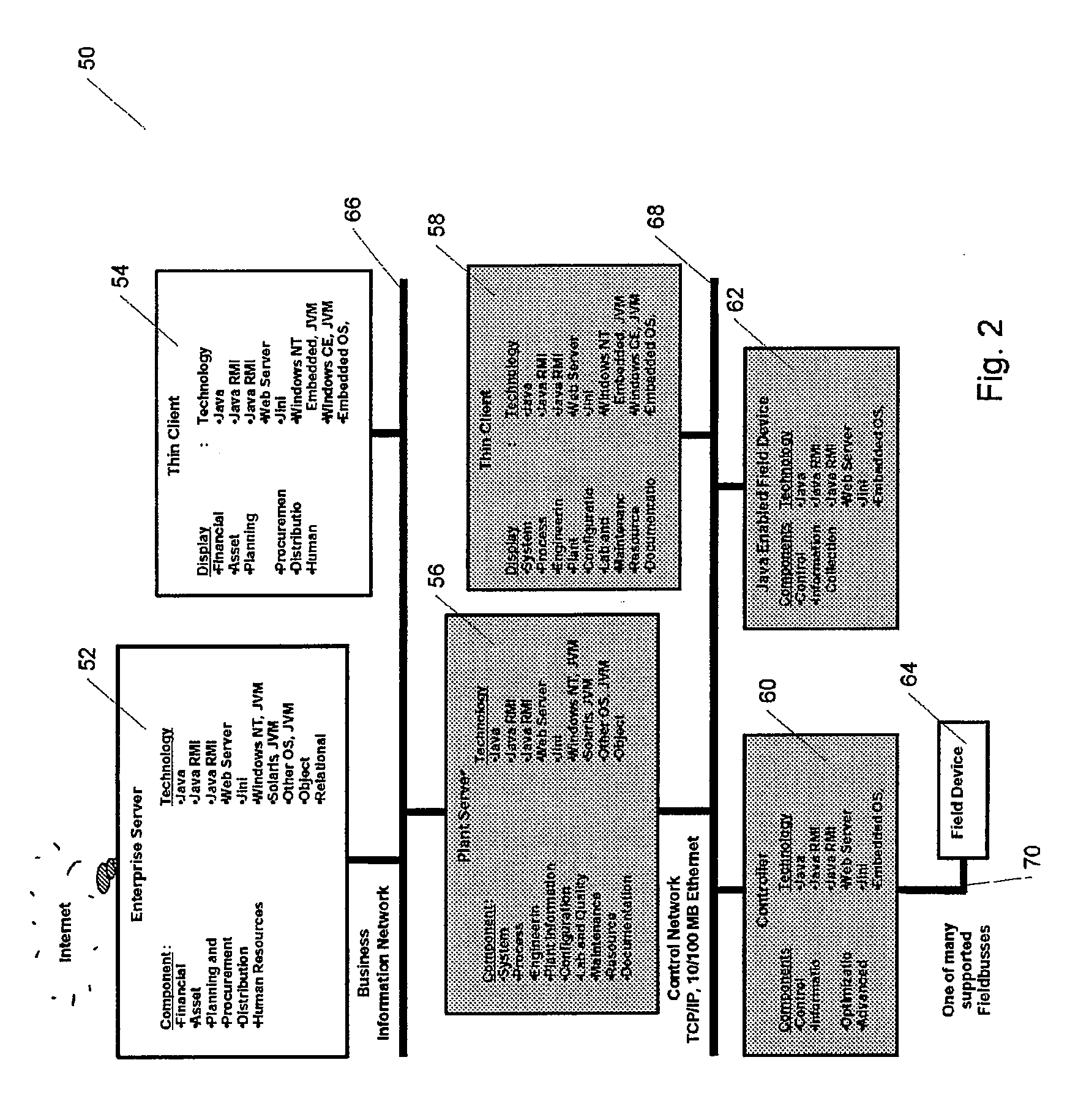

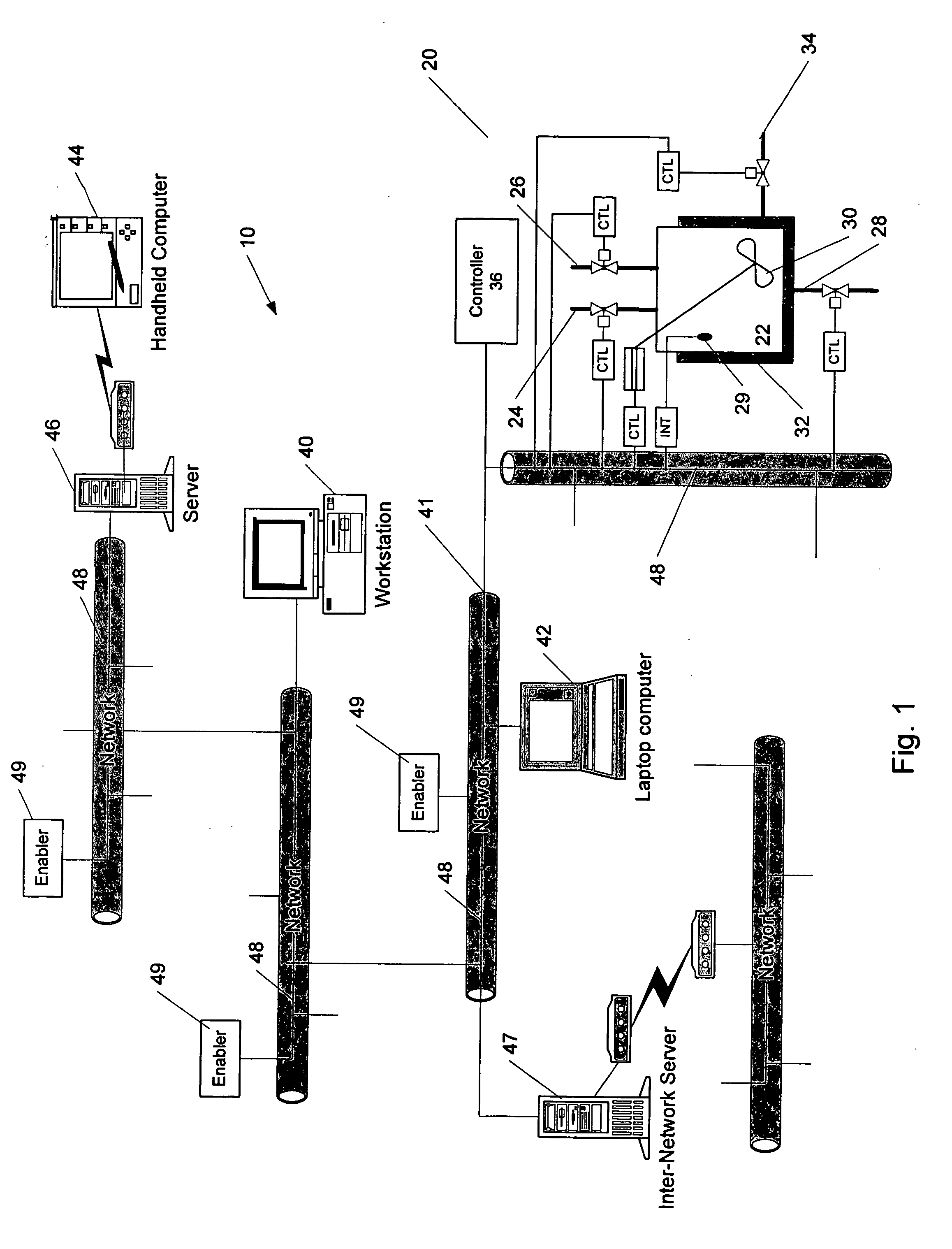

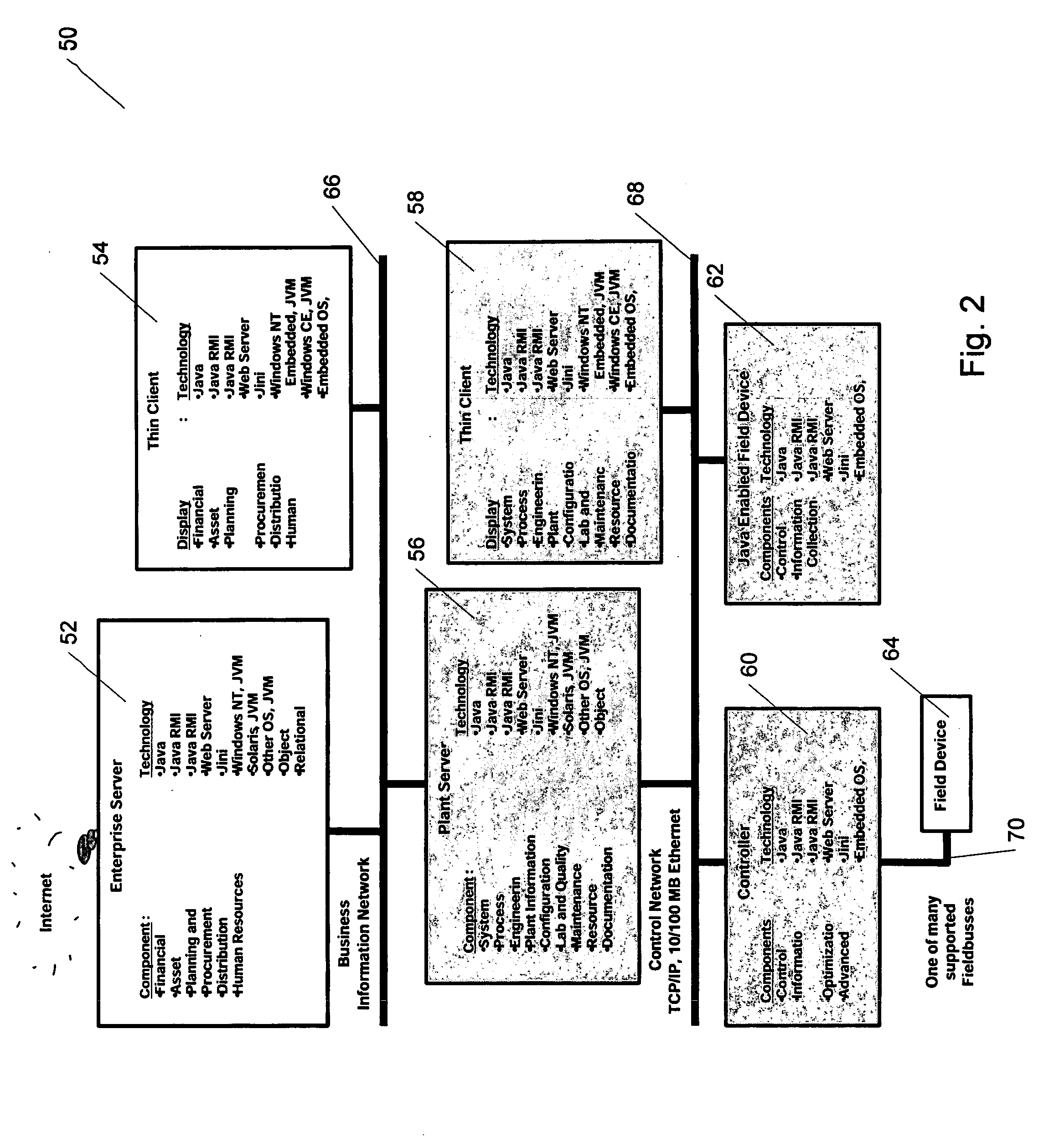

Methods and apparatus for control using control devices that provide a virtual machine environment and that communicate via an IP network

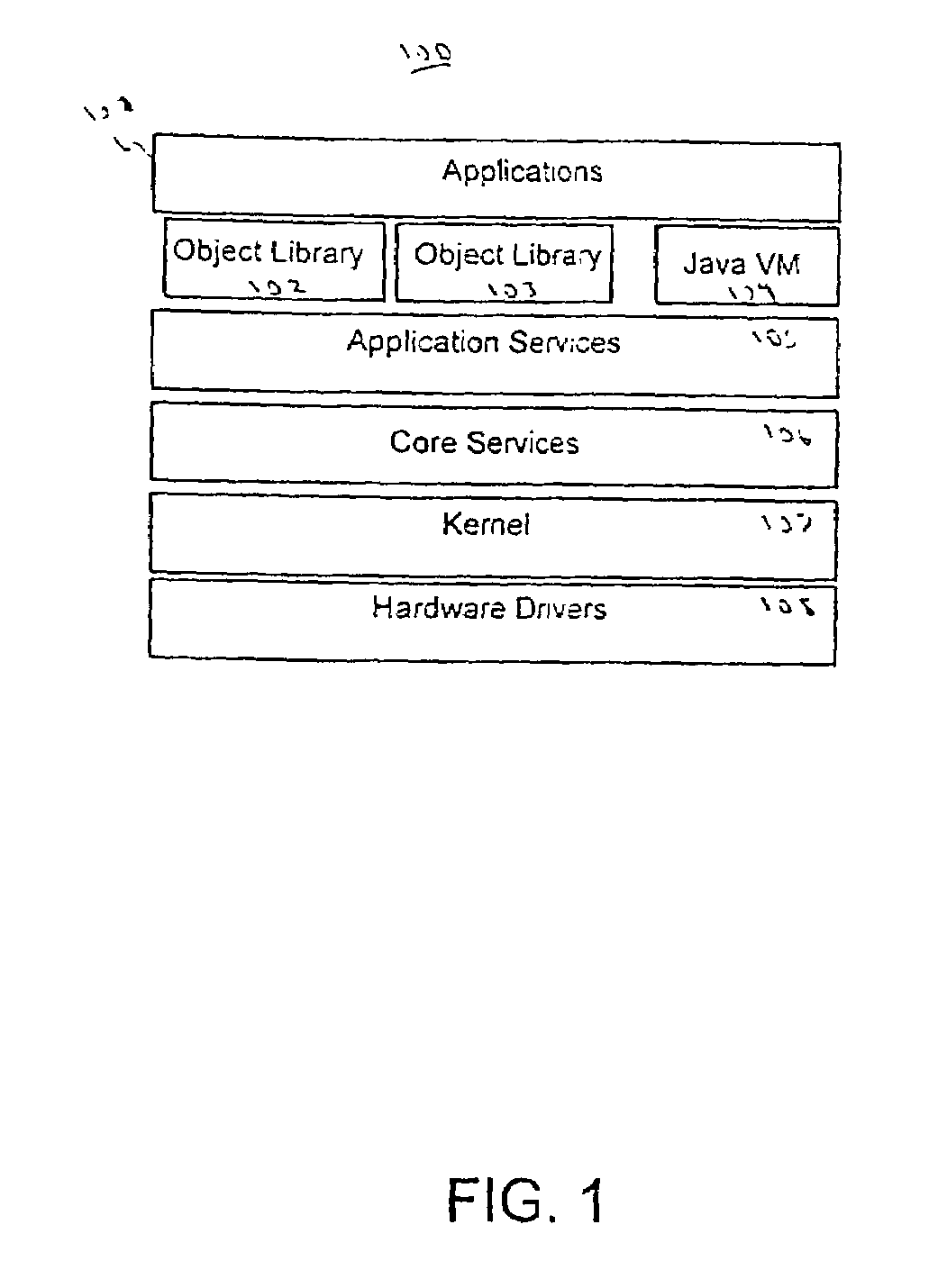

The invention provides improved methods and apparatus for control using field and control devices that provide a virtual machine environment and that communicate via an IP network. By way of non-limiting example, such field device can be an “intelligent” transmitter or actuator that includes a low power processor, along with a random access memory, a read-only memory, FlashRAM, and a sensor interface. The processor can execute a real-time operating system, as well as a Java virtual machine (JVM). Java byte code executes in the JVM to configure the field device to perform typical process control functions, e.g., for proportional integral derivative (PID) control and signal conditioning. Control networks can include a plurality of such field and control devices interconnected by an IP network, such as an Ethernet.

Owner:SCHNEIDER ELECTRIC SYST USA INC

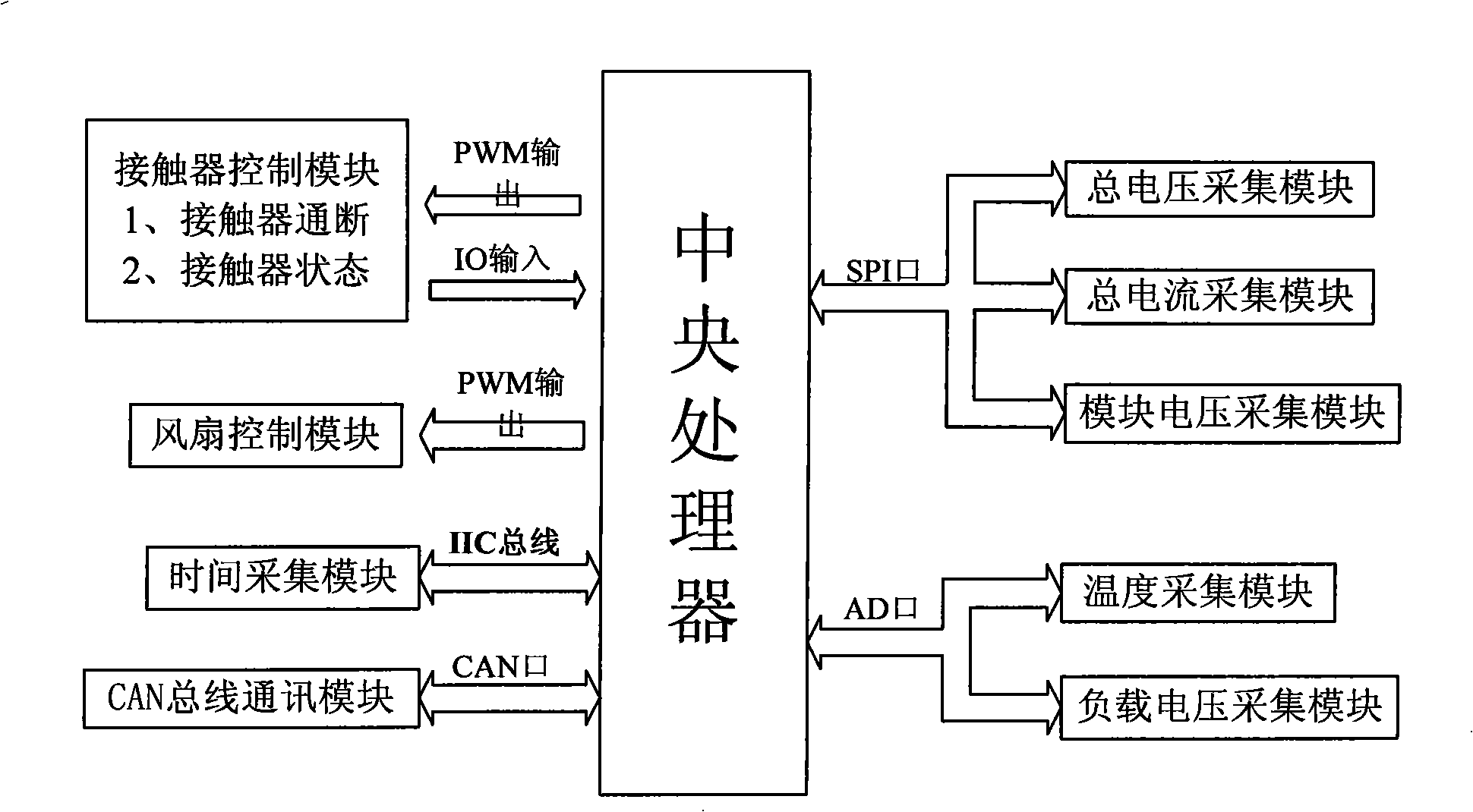

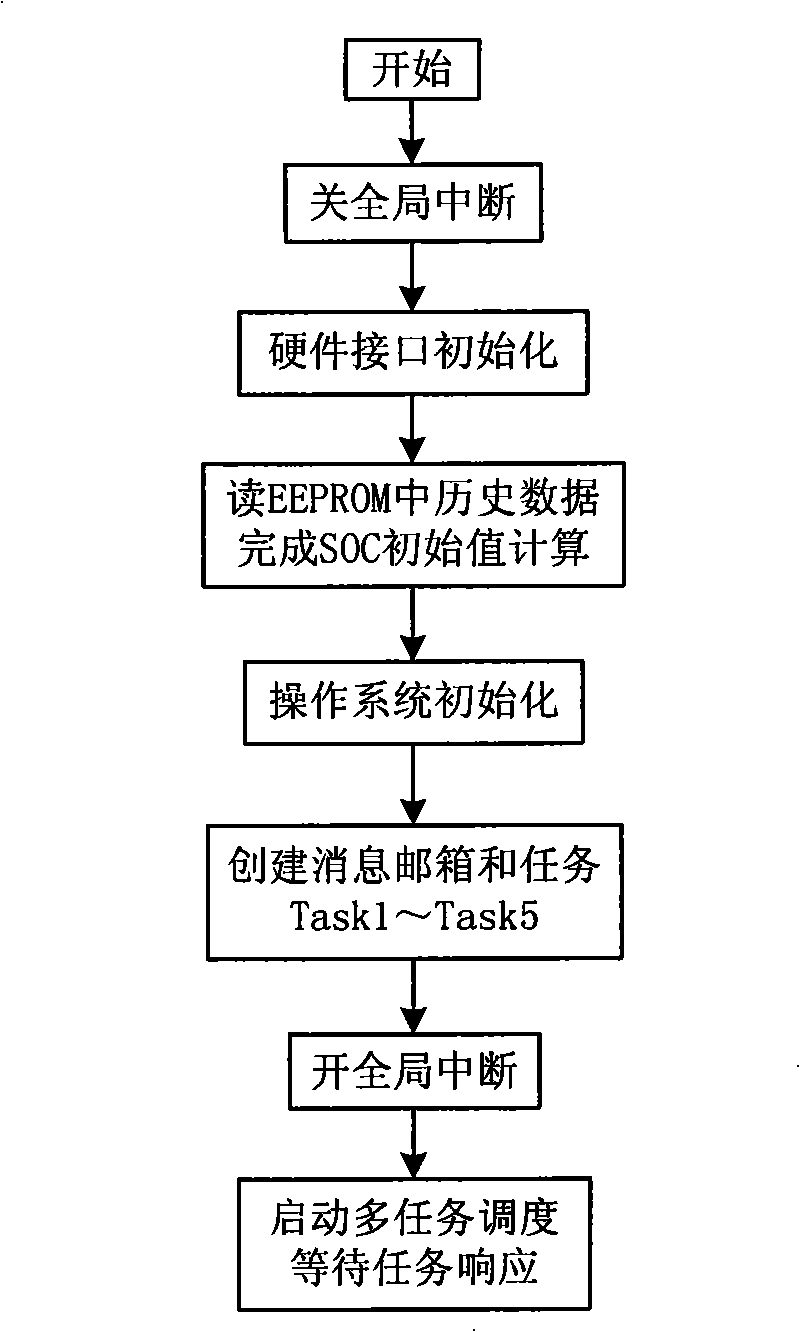

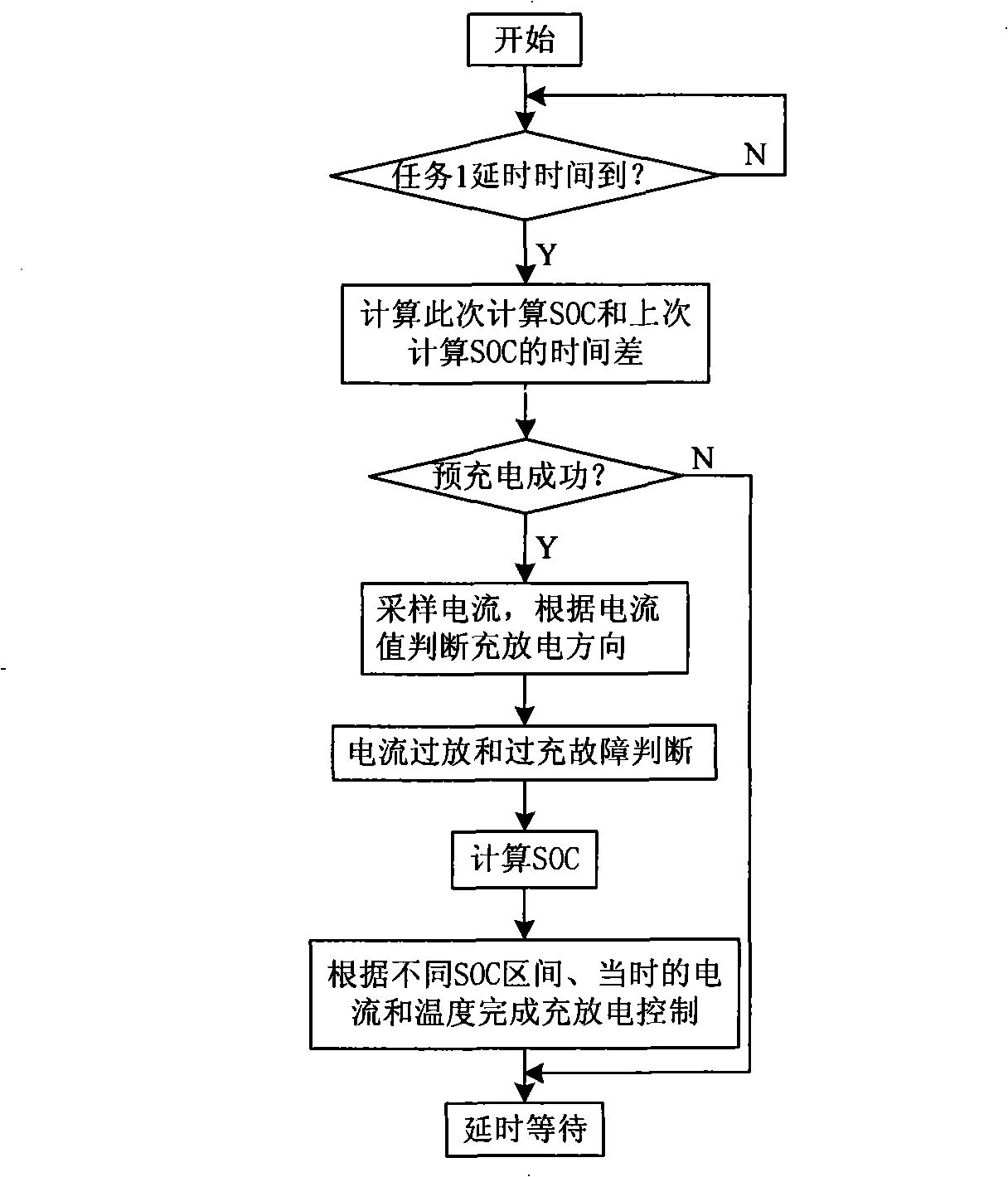

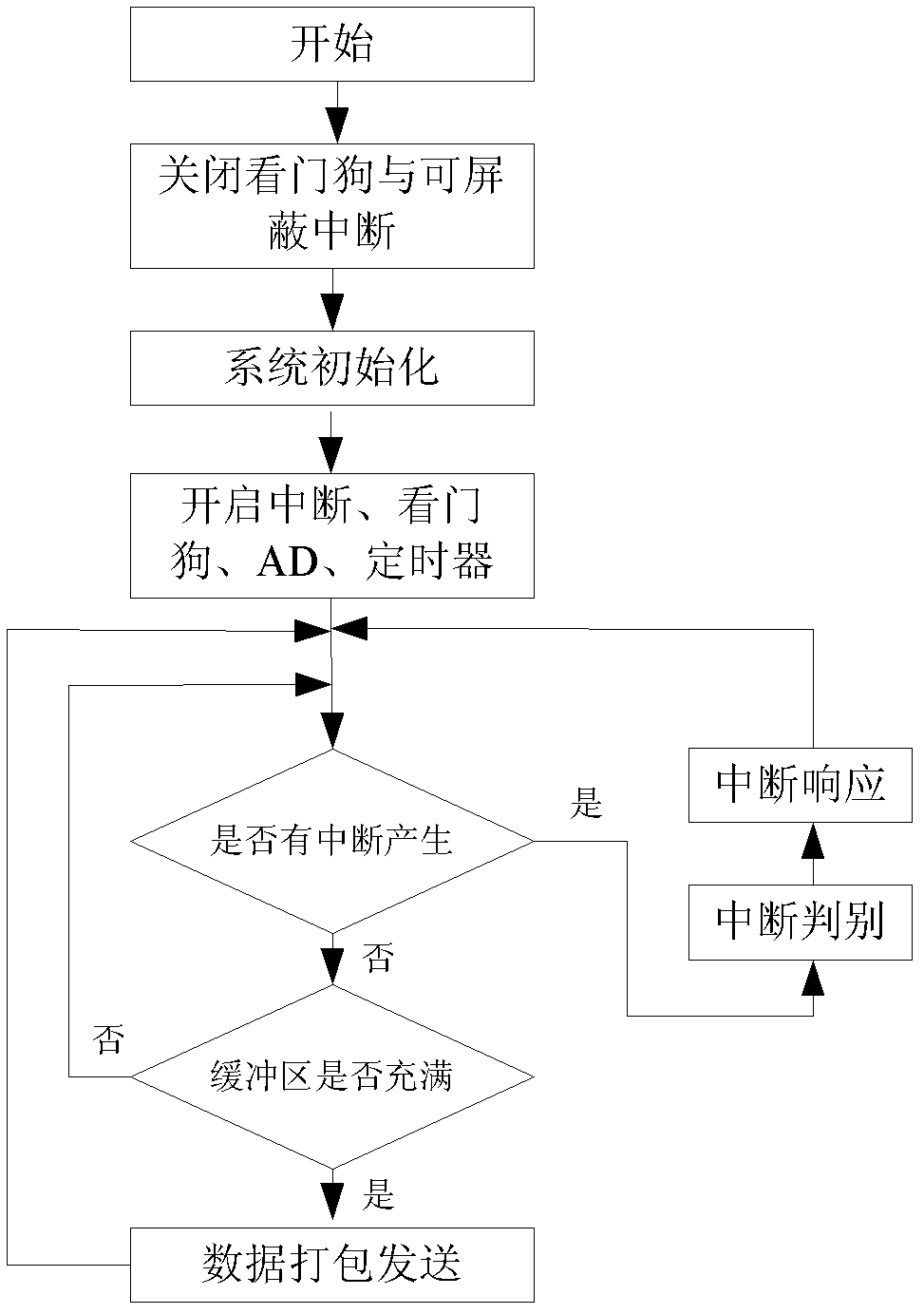

Vehicle mounted battery management system control method

ActiveCN101318489AImprove execution efficiencyEasy to compileSecondary cells servicing/maintenanceElectric vehicle charging technologyOperational systemData acquisition

A battery management system based on a real time operation system which belongs to the technical field of vehicle storage battery management includes a CPU, a load voltage collecting module, a total voltage collecting module, a module voltage collecting module, a current collecting module, a temperature collecting module, a time collecting module, a CAN bus communicating module and a contactor control module. The CPU is respectively connected with a voltage collecting module, the current collecting module, the temperature collecting module, the time collecting module, the CAN bus communicating module and the contactor control module. The battery management system based on a real time operation system transplants a uc / OS-II multi-task real time operation system into the CPU, thus simplifying the software programming of a vehicle storage battery management system under the dispatching of the real time operation system, improving the execution efficiency to manage the system software, ensuring the real time property of data collection and enhancing the working stability of the system.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

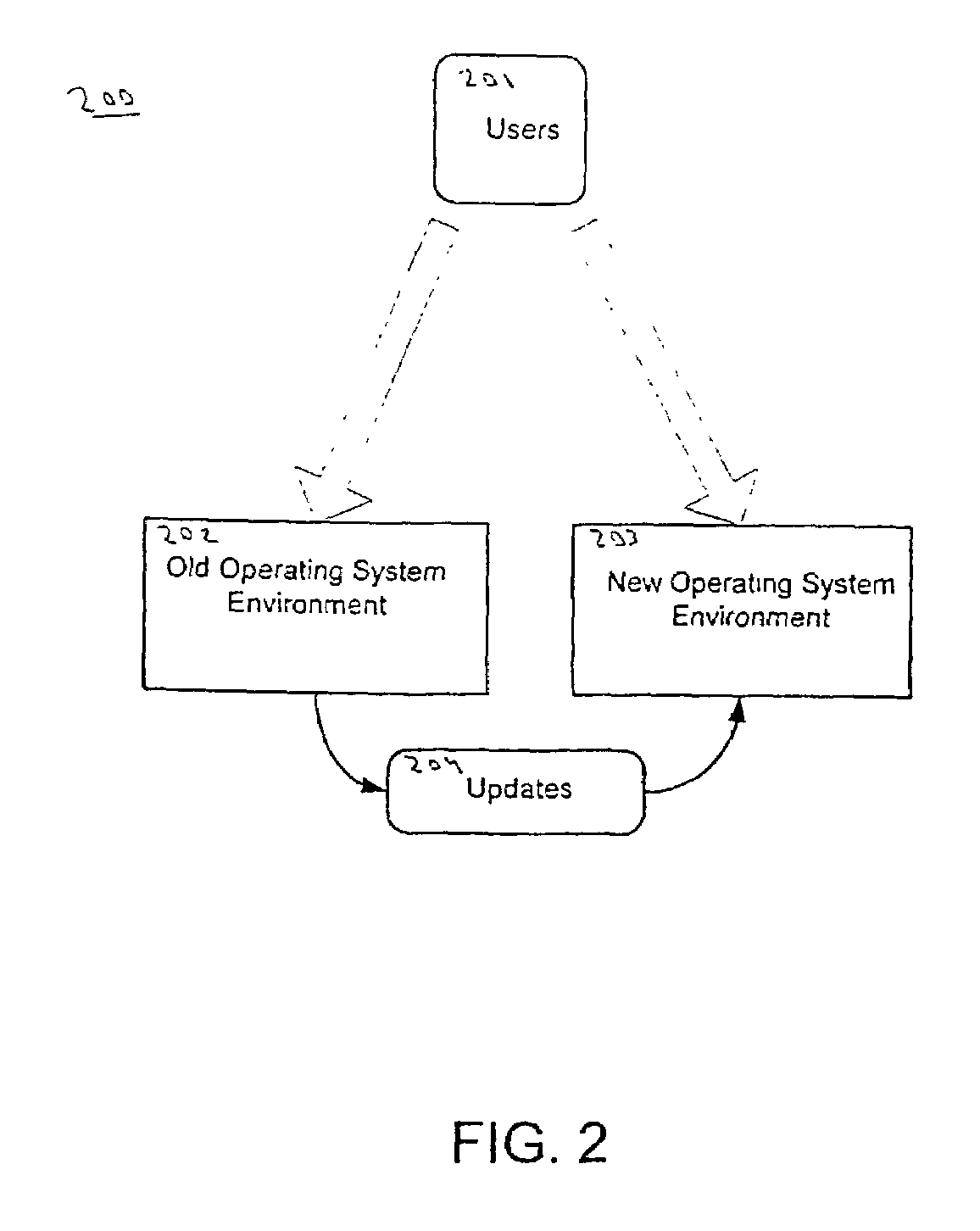

Method and system for live operating environment upgrades

ActiveUS7000229B2Safe recoveryData processing applicationsError preventionOperational systemComputerized system

A method and system for implementing a live operating system upgrade of a computer system. The method includes generating a first copy of a previous operating system environment of the computer system. The computer system is then booted to a subsequent operating system environment. A second copy of the previous operating system environment at the time of the booting is then generated. Additionally, a third copy of the subsequent operating system environment, at the time of the booting is generated. The copies function by ensuring the subsequent operating system environment is synchronized with the previous operating system environment by comparing the first copy, the second copy, and the third copy to detect any intervening changes and allow decisions to be made regarding such changes.

Owner:ORACLE INT CORP

Methods and apparatus for control using control devices that provide a virtual machine environment and that communicate via an IP network

InactiveUS20080040477A1Reduce complexityReduce confusionMultiple digital computer combinationsResourcesOperational systemActuator

Owner:SCHNEIDER ELECTRIC SYST USA INC

Method for multi-tasking multiple Java virtual machines in a secure environment

InactiveUS7178049B2Operational securitySpecific access rightsError detection/correctionOperational systemReal-time operating system

The present invention allows construction of a secure, real-time operating system from a portable language such as Java that appears to be a Java virtual machine from a top perspective but provides a secure operating system from a bottom perspective. This allows portable languages, such as Java, to be used for secure embedded multiprocessor environments.

Owner:MICROPAIRING TECH LLC

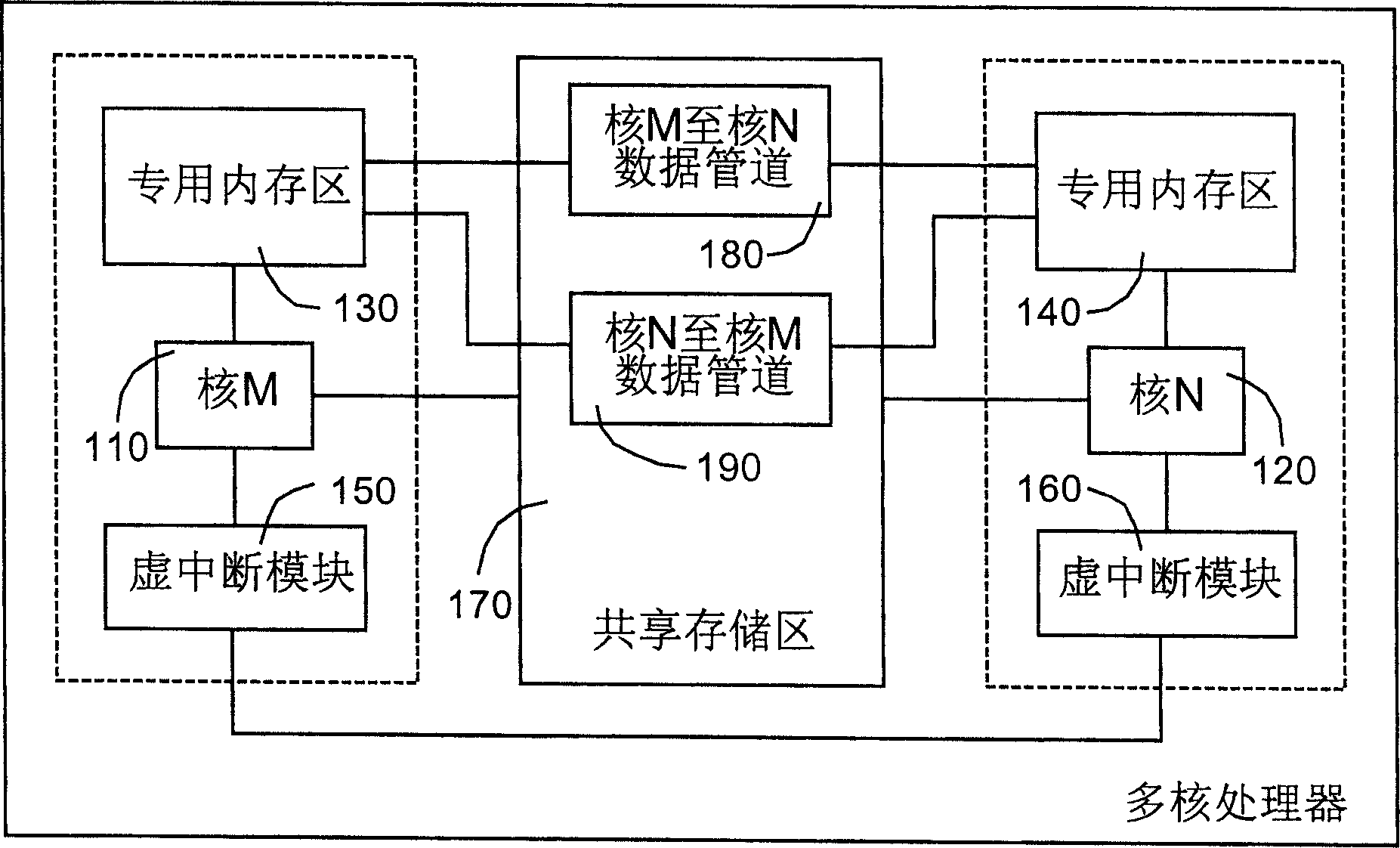

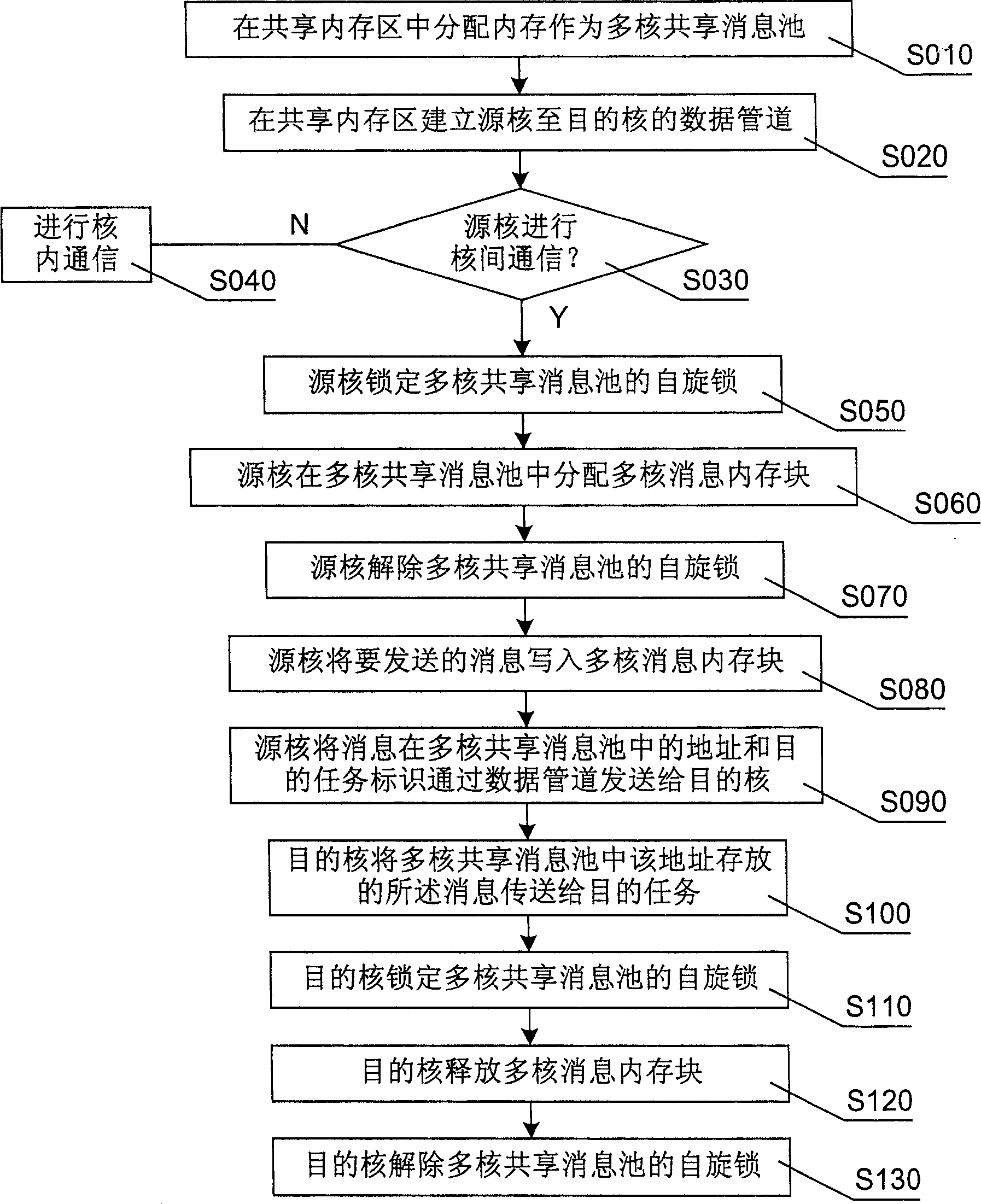

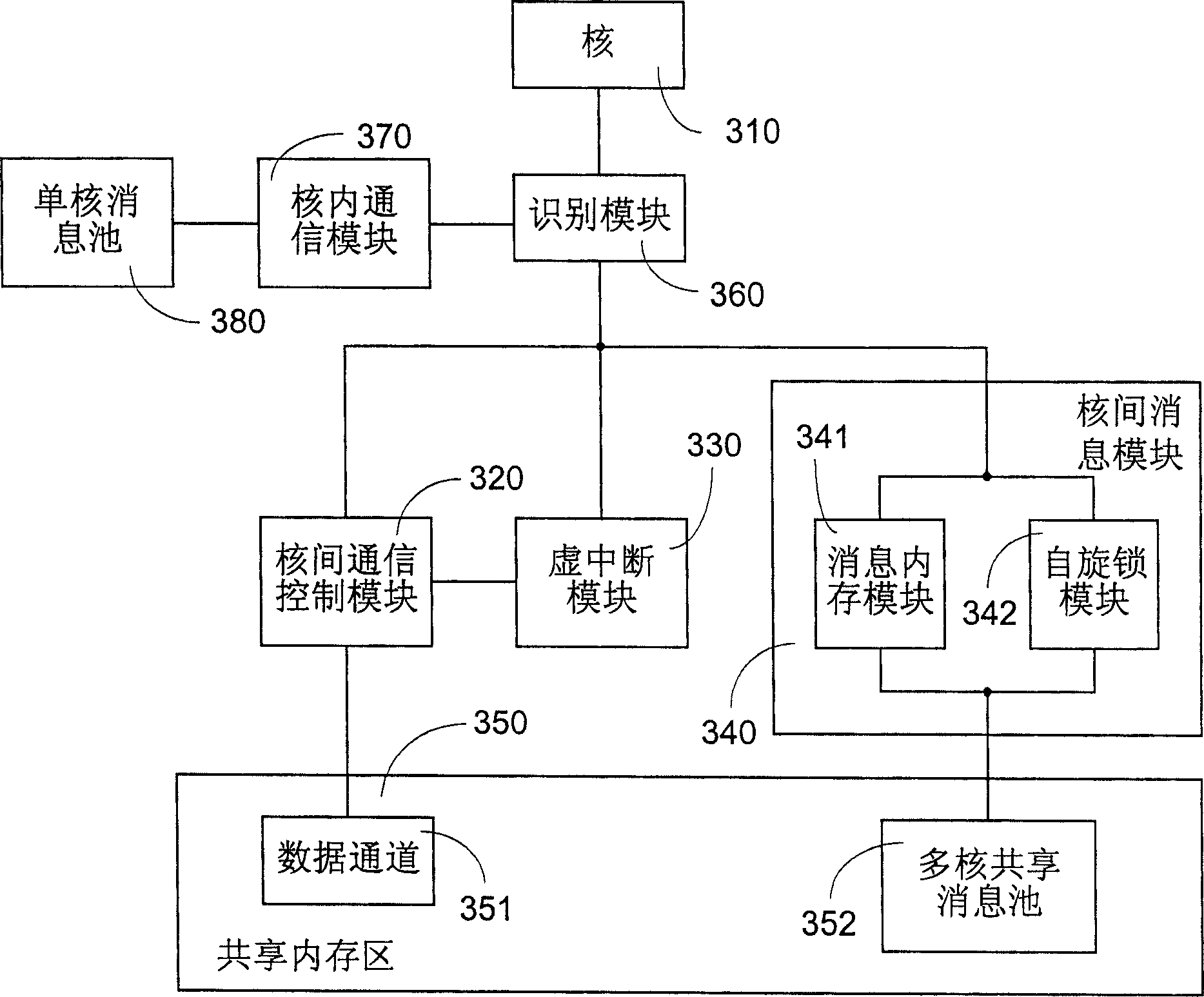

Inter core communication method and apparatus for multi-core processor in embedded real-time operating system

ActiveCN1904873APrevent copyingImprove efficiencyDigital computer detailsElectric digital data processingMessage queueDistributed memory

The invention discloses an inter-core communicating method of multi-core processor in embedded real time operation system. It includes following steps: distributing memory as multi-core information sharing pool; writing information the source core would send into the pool; sending the information to target core; target core sending the information storing in pool to target mission. The invention also discloses an inter-core communicating device. It improves the inter-core communicating efficiency and realizes the unification of inner core communication and inter-core communication.

Owner:DATANG MOBILE COMM EQUIP CO LTD

Methods and apparatus for control using control devices that provide a virtual machine environment and that communicate via an IP network

Owner:INVENSYS SYST INC

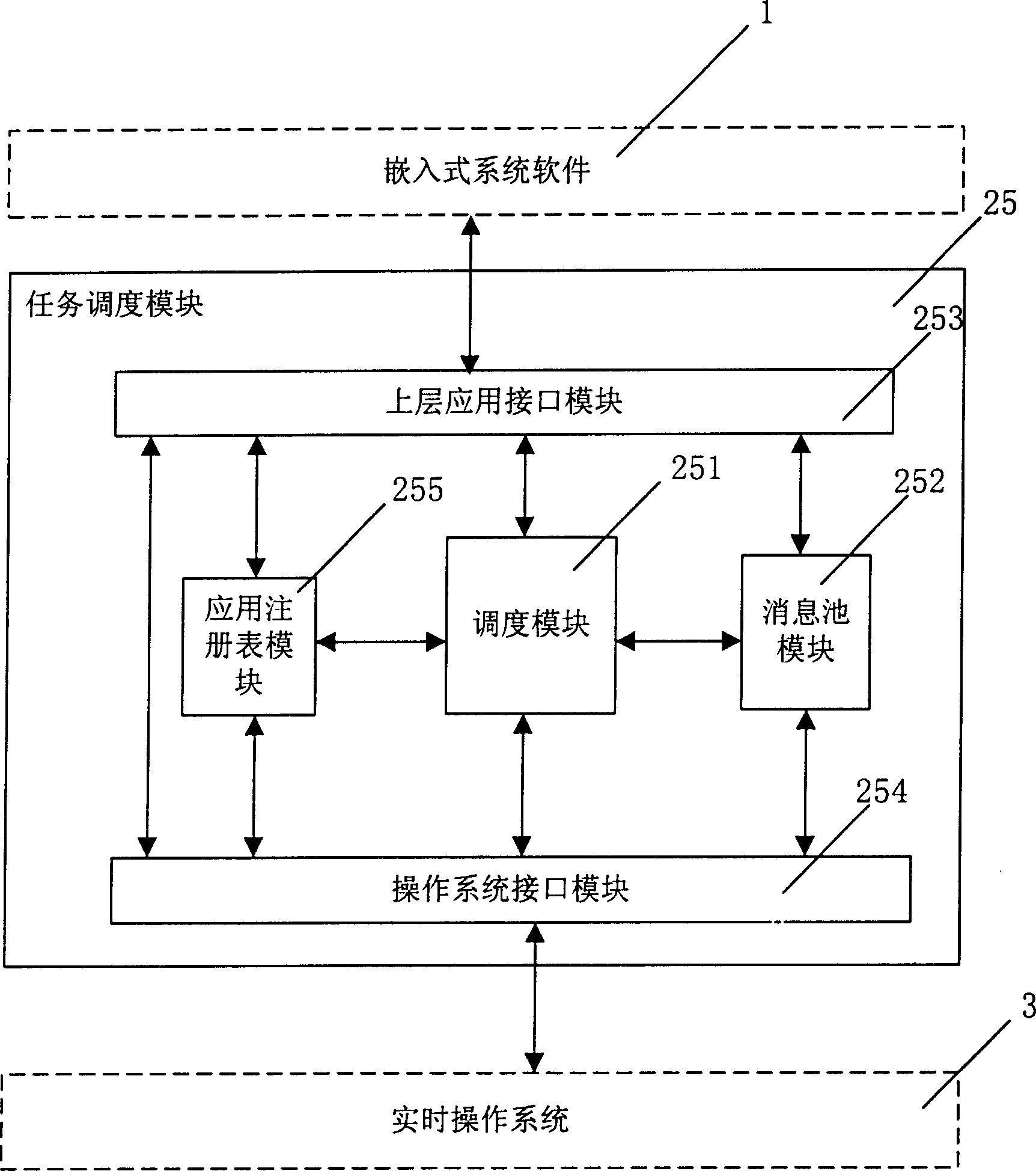

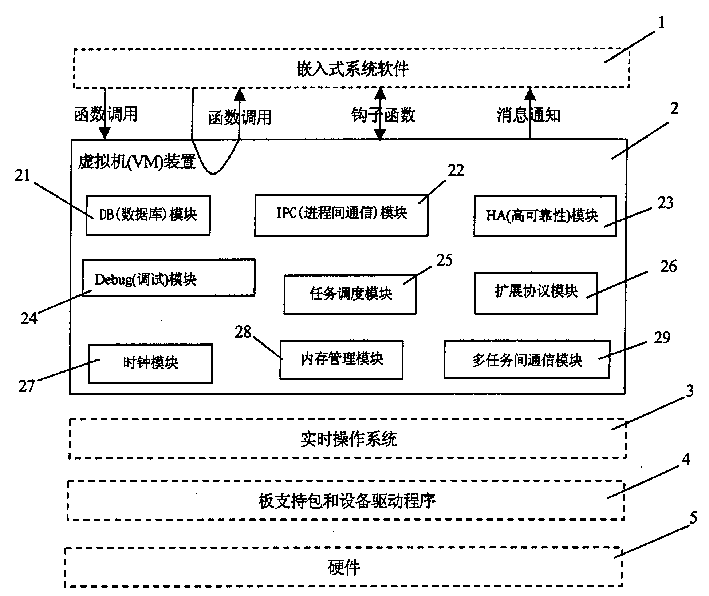

Virtual machine for embedded systemic software development

InactiveCN1490724AImprove development efficiencyImprove reliabilitySoftware testing/debuggingInternal memoryComputer architecture

The unit comprises databank module, interprocess communication module, high reliability module, debugging module, task dispatching module, expension protocol module, clock module, internal memory module and multiintertask communication module. The unit not only provides an operation and development platform with strong function for system software in top large-scale of embedded type to realize independence of top and bottom layers and to increase portability of top application code, but also can collectively transfer the function of some universal modules in top application software into the virtulizer for realization through intermediate component contained with generality in the virtualizer.

Owner:ALCATEL LUCENT SHANGHAI BELL CO LTD

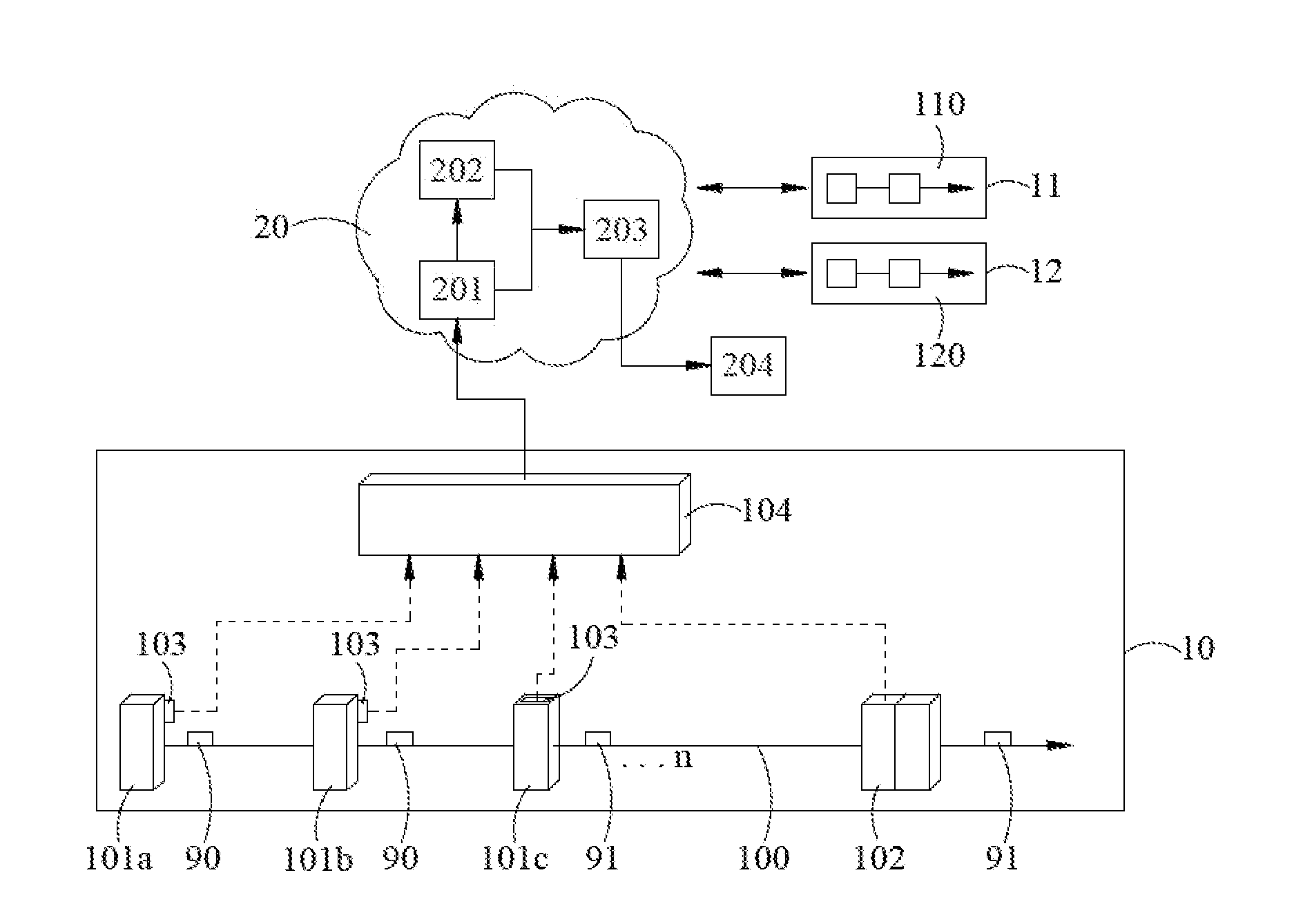

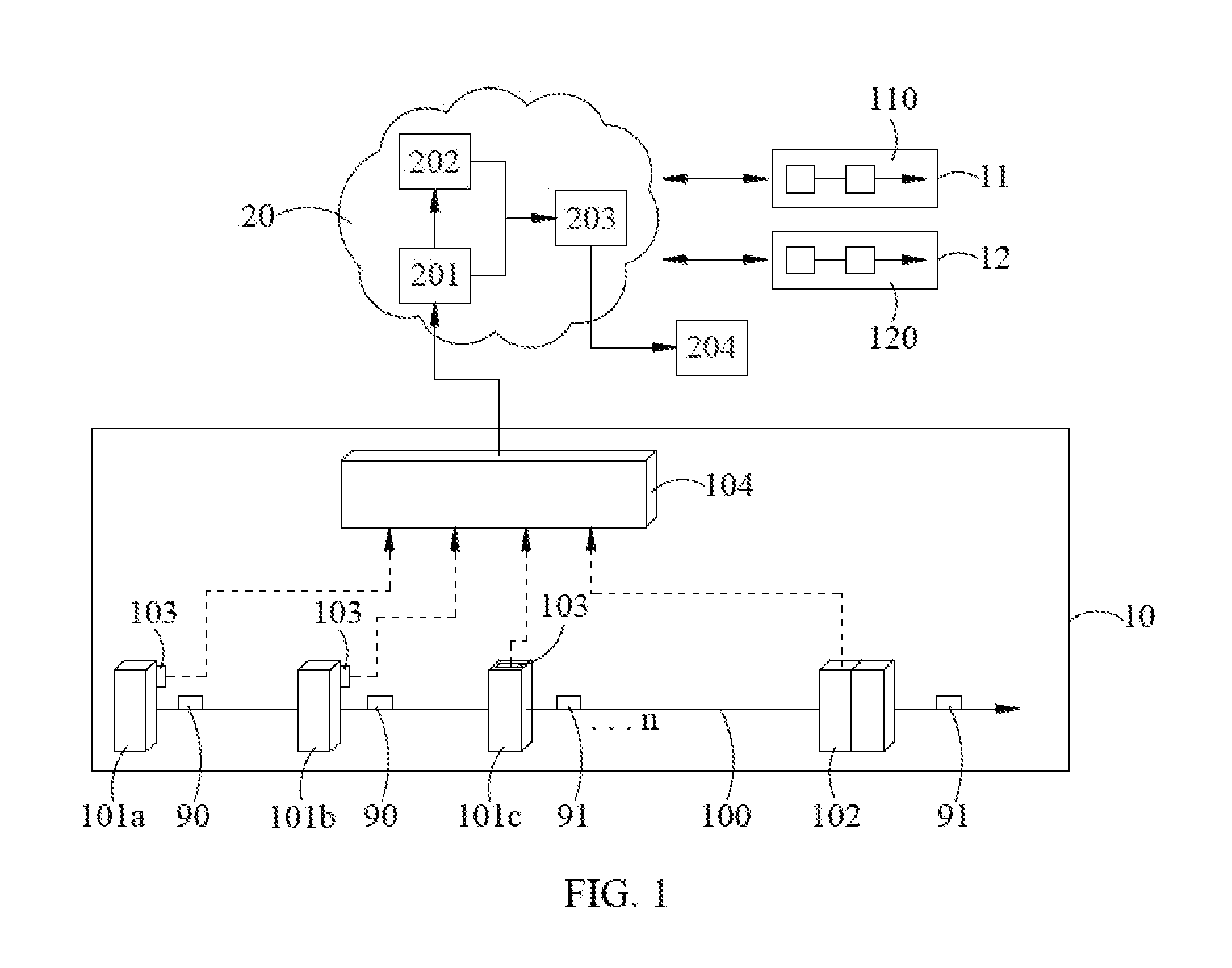

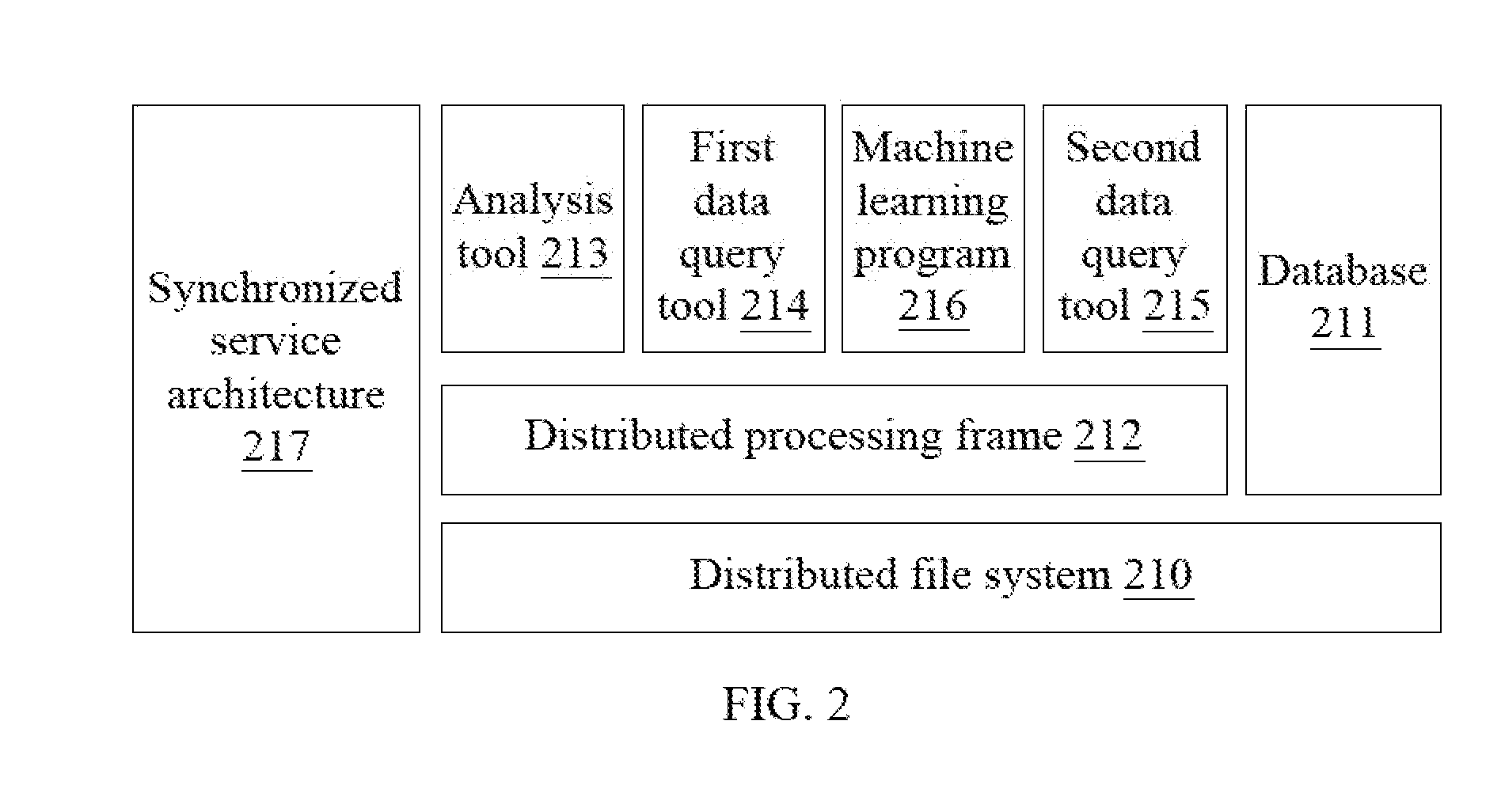

Real Time Monitoring System and Method Thereof of Optical Film Manufacturing Process

InactiveUS20170003677A1Improve accuracyImprove yieldTesting/monitoring control systemsOptically investigating flaws/contaminationProduction lineData platform

A real time monitoring system and a method thereof of an optical film manufacturing process are provided. The real time monitoring system includes a plurality of production systems and a cloud big data platform which connects to the plurality of production systems. The process data of the production line is collected by as production line data collector of the production system. The process data is uploaded to a database of the cloud big data platform. The historical process data across the plurality of production systems can be combined as a process waveform feature by a profile database. A processor connects to the database and the profile database. The differences between the process data and the process waveform feature are compared in real time. When the difference value exceeds a threshold value, an abnormal message is sent to the corresponding production line.

Owner:YUAN ZE UNIV

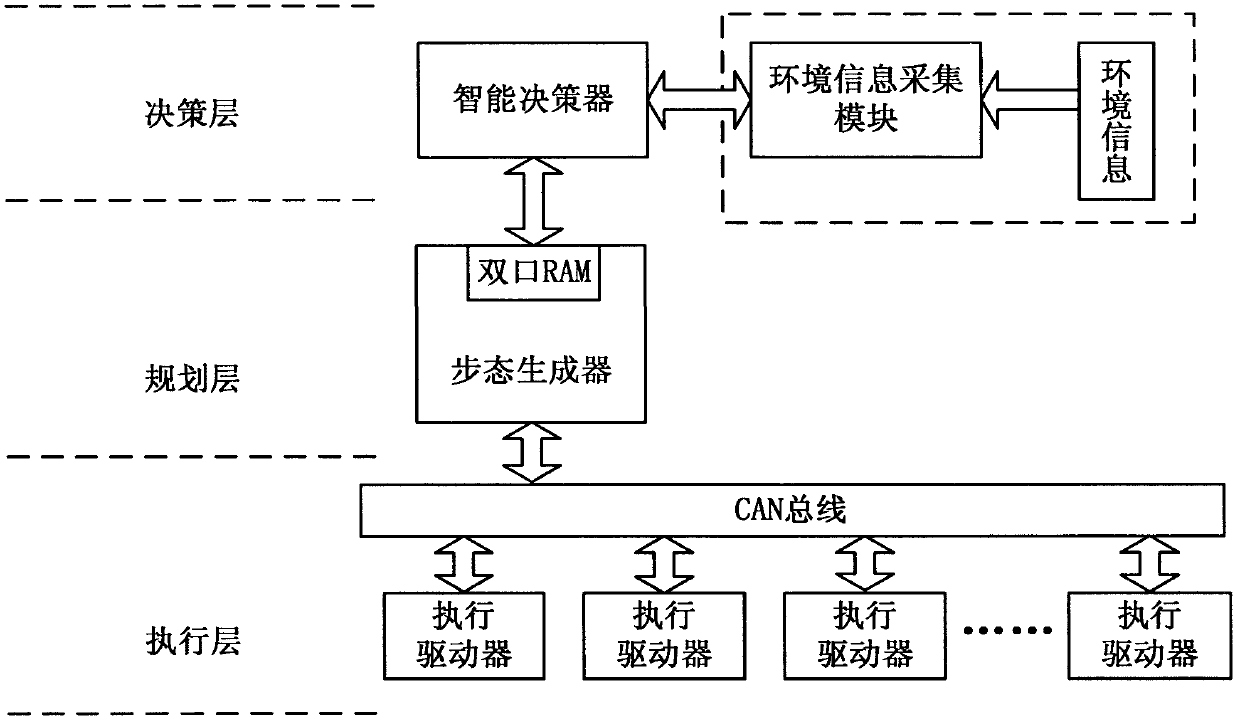

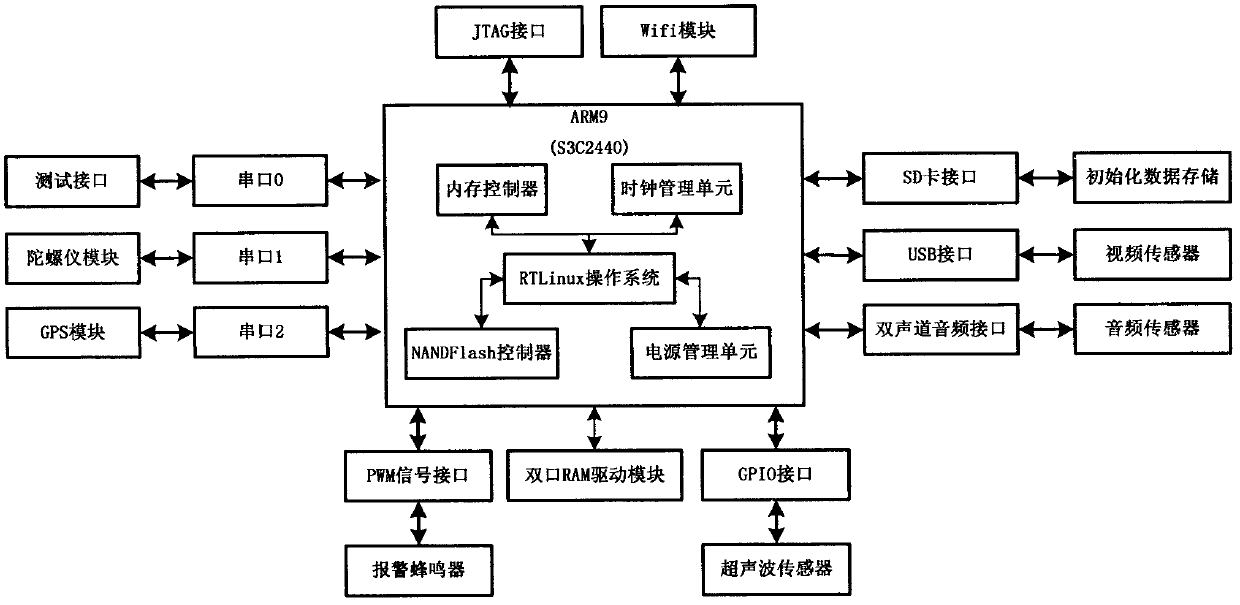

Combined type bionic quadruped robot controller

InactiveCN102637036AIntegrity guaranteedImprove adaptabilityPosition/course control in two dimensionsOperational systemNervous system

The invention relates to a combined type bionic quadruped robot controller, which is in a structure similar to a vertebrate nervous system, wherein the controller is divided into a decision layer, a planning layer and an execution layer which respectively correspond to a higher nervous center, a lower nervous center and a motor nerve of an animal. The decision layer for realizing that the robot senses the working environment and generates corresponding motion decision instructions consists of an ARM9 (advanced RISC (reduced instruction-set computer) machine 9) and an environmental information acquisition system, and a real-time operating system is embedded in the ARM9. The core of the planning layer is a walking pattern generator, and is used for planning and solving the motion parameters of each joint according to the decision instructions from the upper layer. The execution layer for controlling the current, the position and the speed of a driving motor in three closed loops consists of a motor controller using a digital signal processor as the core. Data can be effectively transmitted among the three layers in real time through a dual-port RAM (random-access memory) and a CAN (controller area network) bus network. The combined type bionic quadruped robot controller disclosed by the invention has the characteristics of high reliability, high flexibility, extension easiness and maintenance easiness, and has a broad application prospect in the technical field of bionic legged robots.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

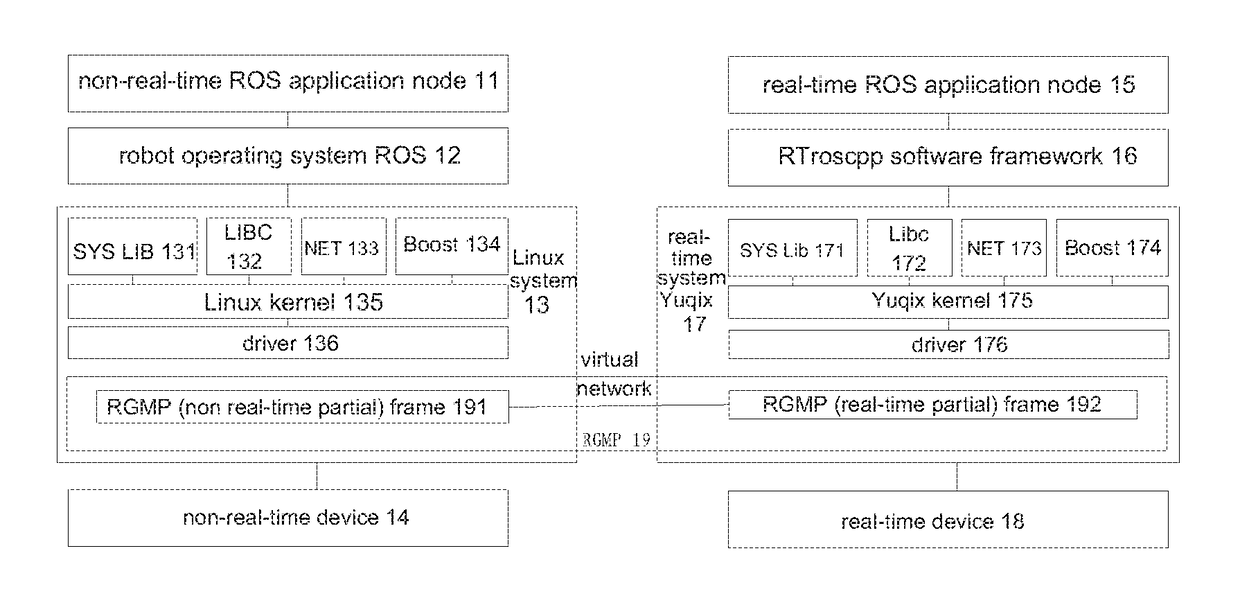

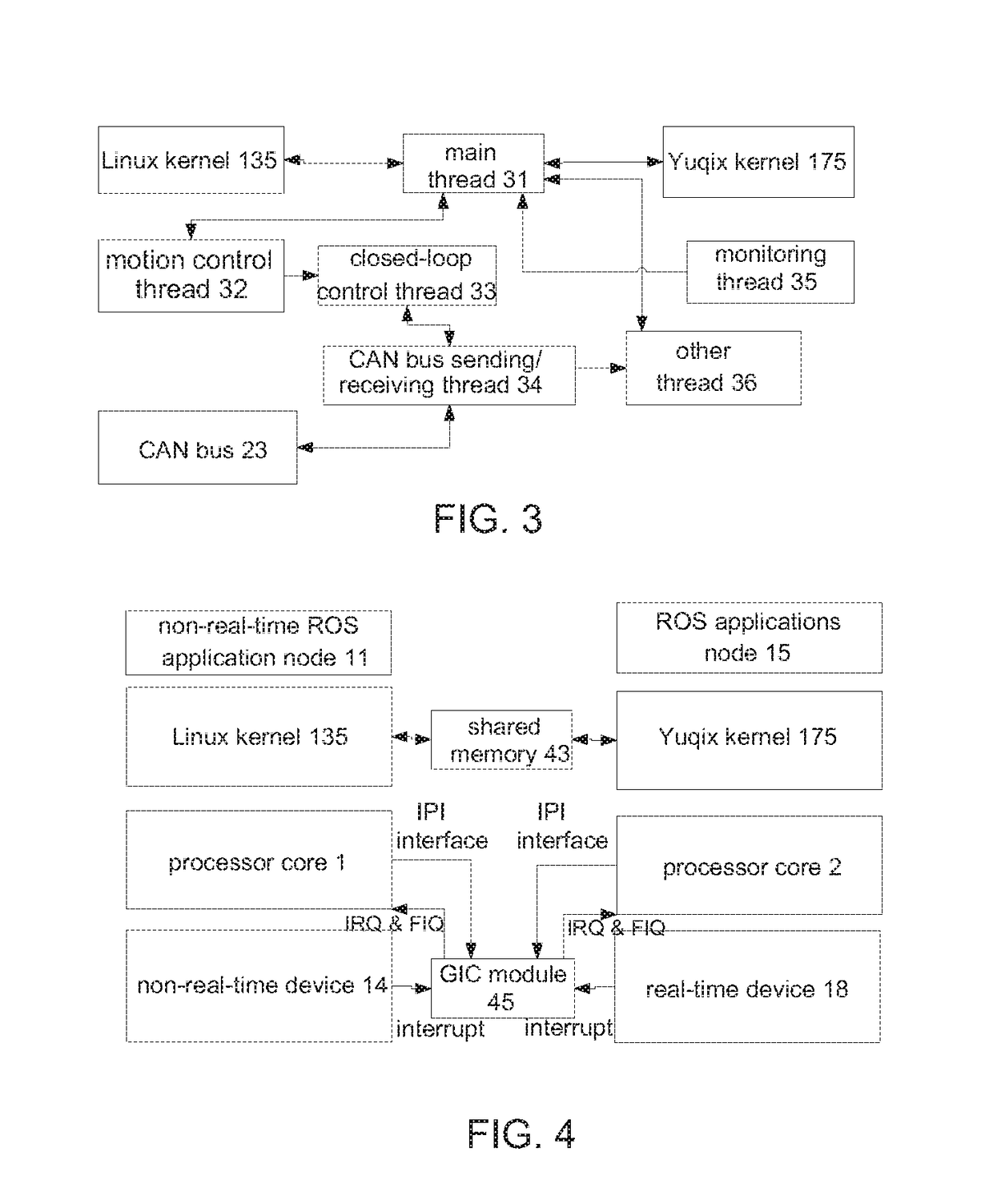

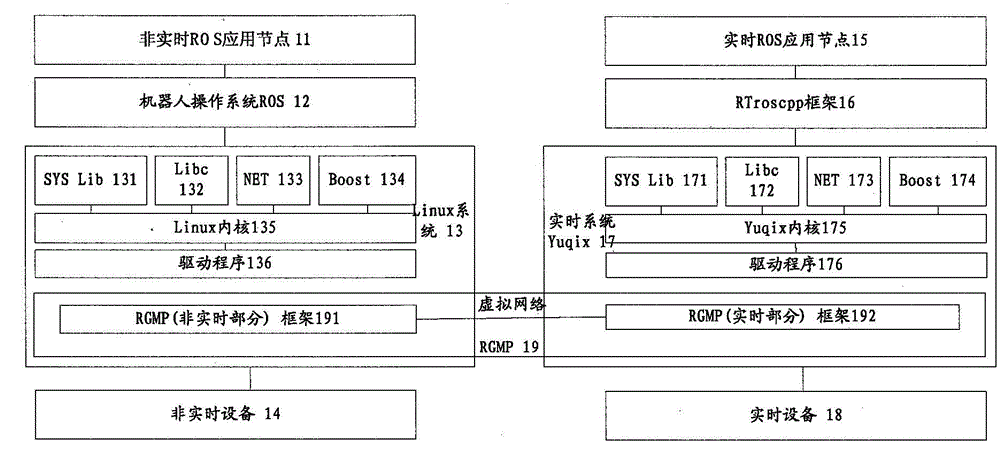

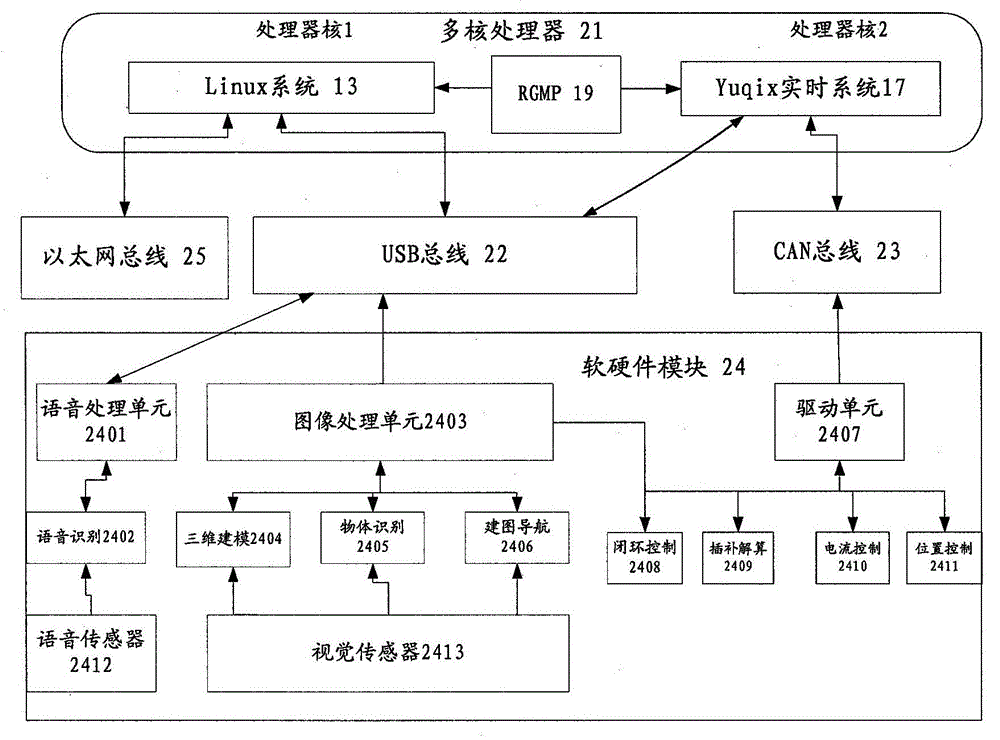

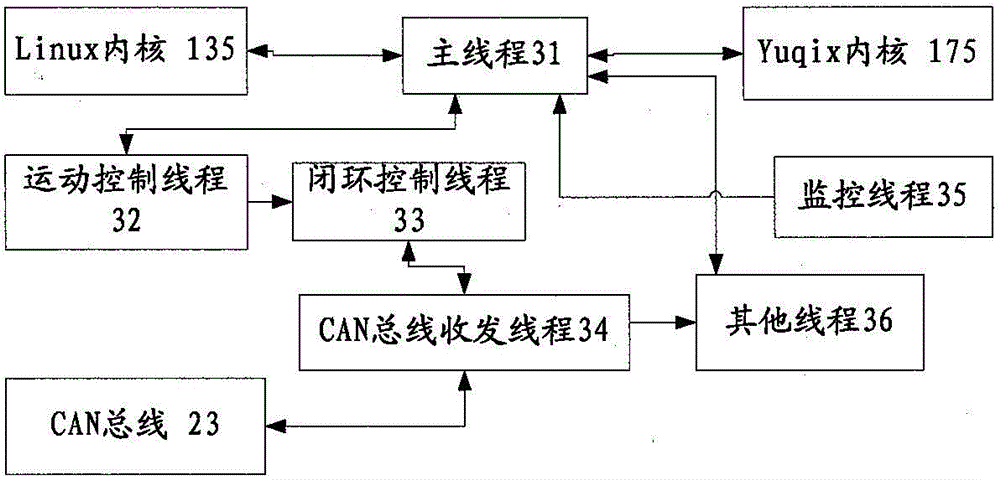

Robotic hybrid system application framework based on multi-core processor architecture

ActiveUS20170203436A1Improve development efficiencyLow costProgramme controlProgramme-controlled manipulatorOperational systemEmbedded operating system

The present invention relates to a robot hybrid system application framework based on a multi-core processor architecture. In the robot system with ARM / X86 multi-core processor as the controller, multi-core parallel processing architecture of the ARM / X86 multi-core processor is used to run the robotic hybrid system application framework comprising real-time operating system, non-real-time operating system and system supporting frame in the whole robot controller, so as to provide improved operating system services. In this application framework, a real-time operating system runs independently in one ARM / X86 core, while several non-real-time operating systems run on other ARM / X86 cores. The operating systems occupy processor resources and peripherals separately and run robotic applications with different real-time requirements. The application program can be used as a unified robot operating system (ROS) application node.

Owner:AUBO BEIJING ROBOTICS TECH CO LTD

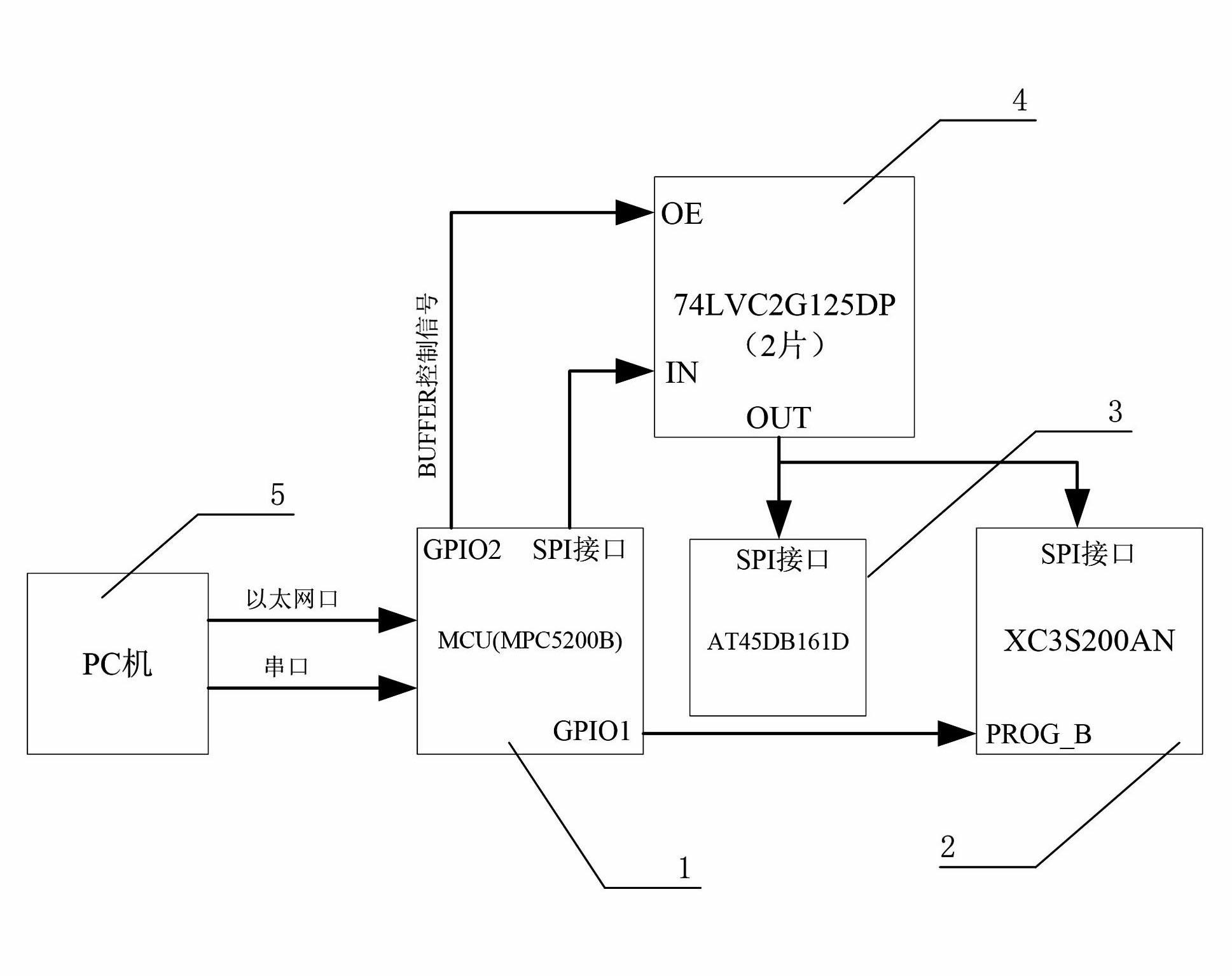

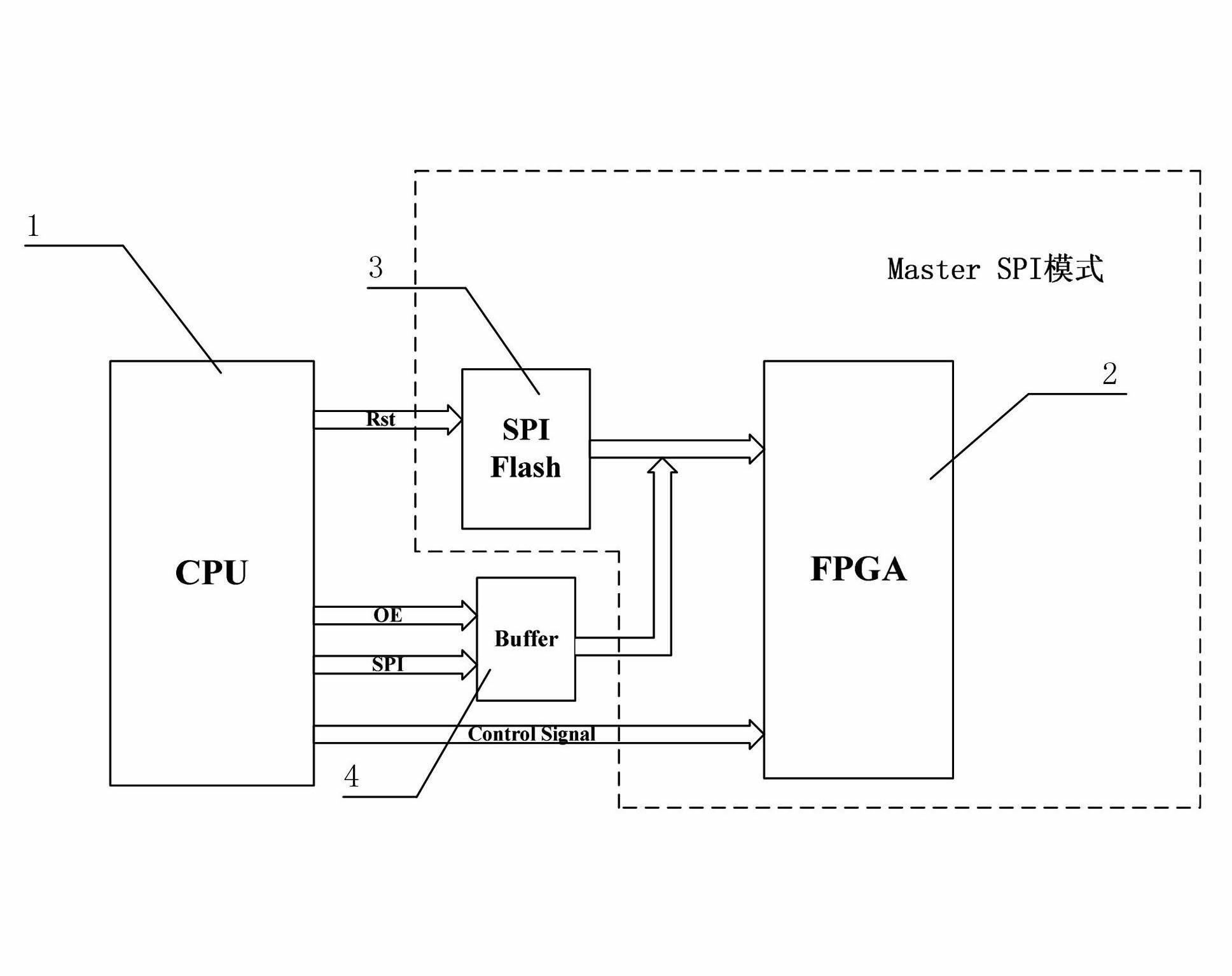

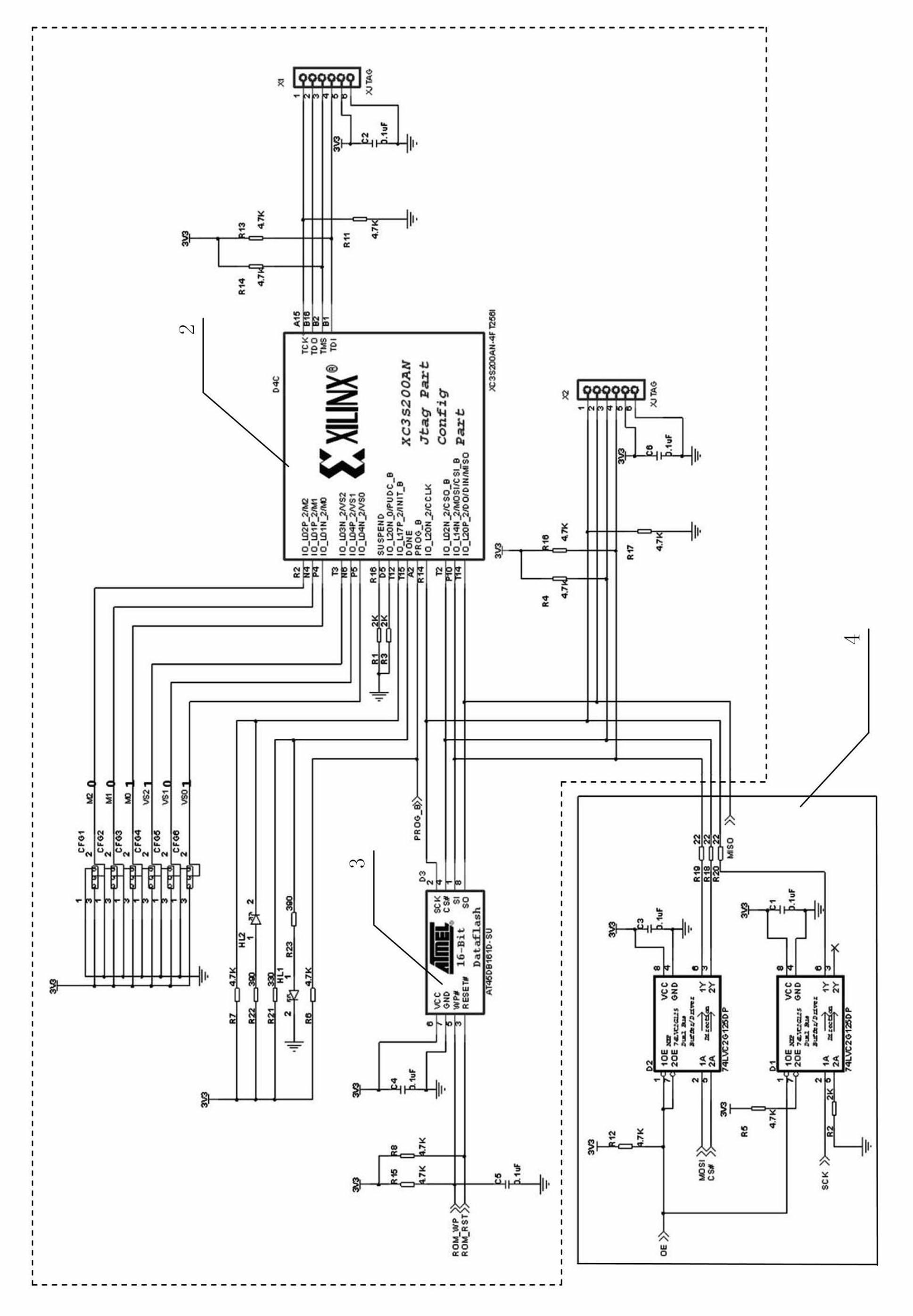

Device for updating FPGA (Field Programmable Gate Array) from a long distance by CPU (Central Processing Unit) and method therefor

ActiveCN102609287ALow costEasy to operateProgram loading/initiatingOperabilityReal-time operating system

The invention discloses a device for updating an FPGA (Field Programmable Gate Array) from a long distance by a CPU (Central Processing Unit) and a method for updating the FPGA from a long distance by the CPU. The device comprises a controller module, an FPGA module, a configuration module and a buffer module, wherein the controller module is connected with an upper computer in a wired / wireless way, a second GPIO (General Purpose Input / Output) interface of the controller module is connected with an enable pin of the buffer controller, an SPI (Serial Peripheral Interface) of the controller module is connected with a data input end of the buffer module, a first GPIO interface of the controller module is connected with a configuration signal of the FPGA module, a data output end of the buffer module is connected with SPIs of the FPGA module and the configuration module respectively, a FPGA configuration file is updated from a long distance based on MPC5200B and a real-time operation system VxWorks. According to the device and the method, the cost is saved, the operability of the system is improved, the design difficulty is reduced, the on-line updating of the FPGA is easily realized, and the configuration efficiency and the configuration flexibility of the FPGA are improved.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

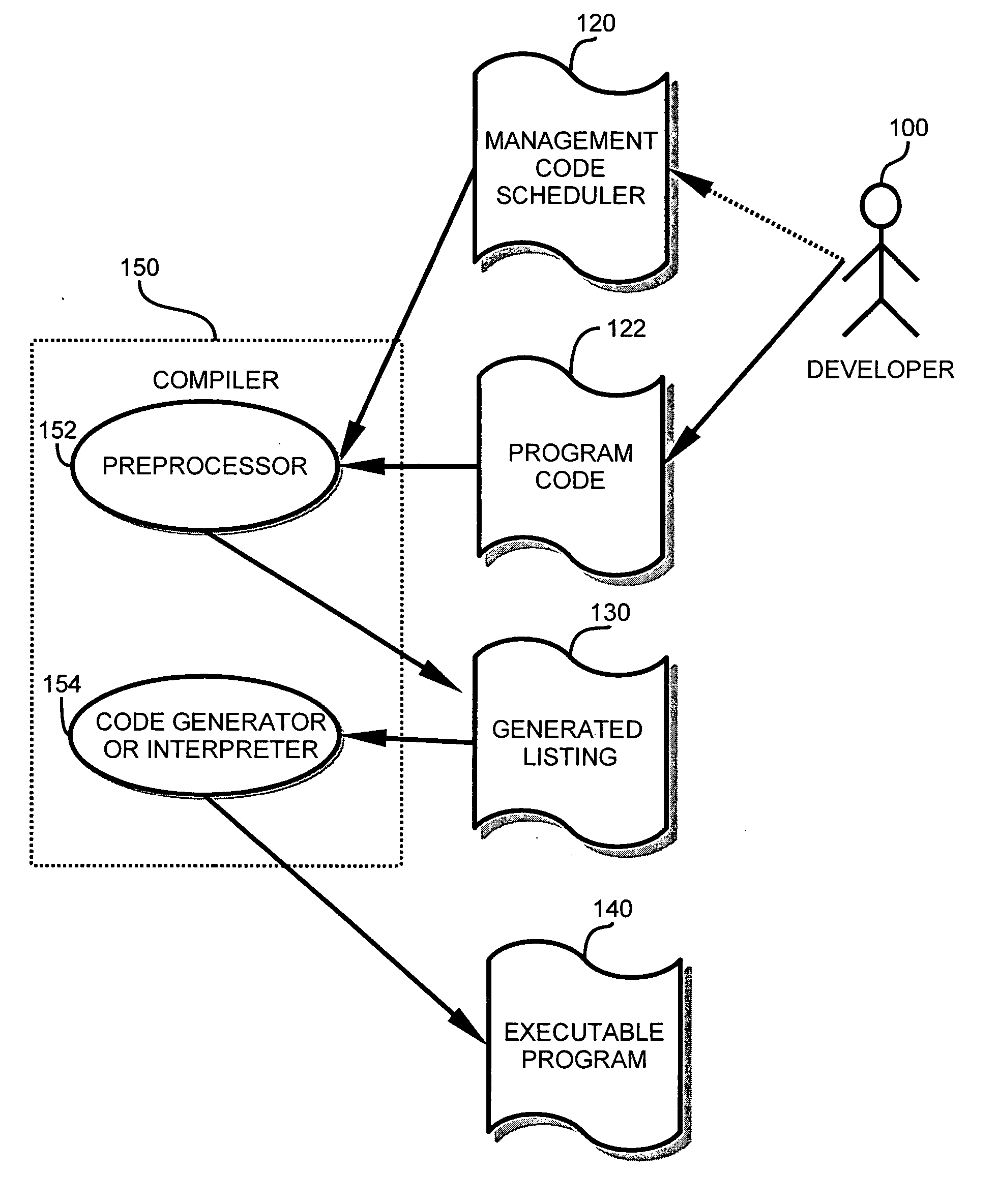

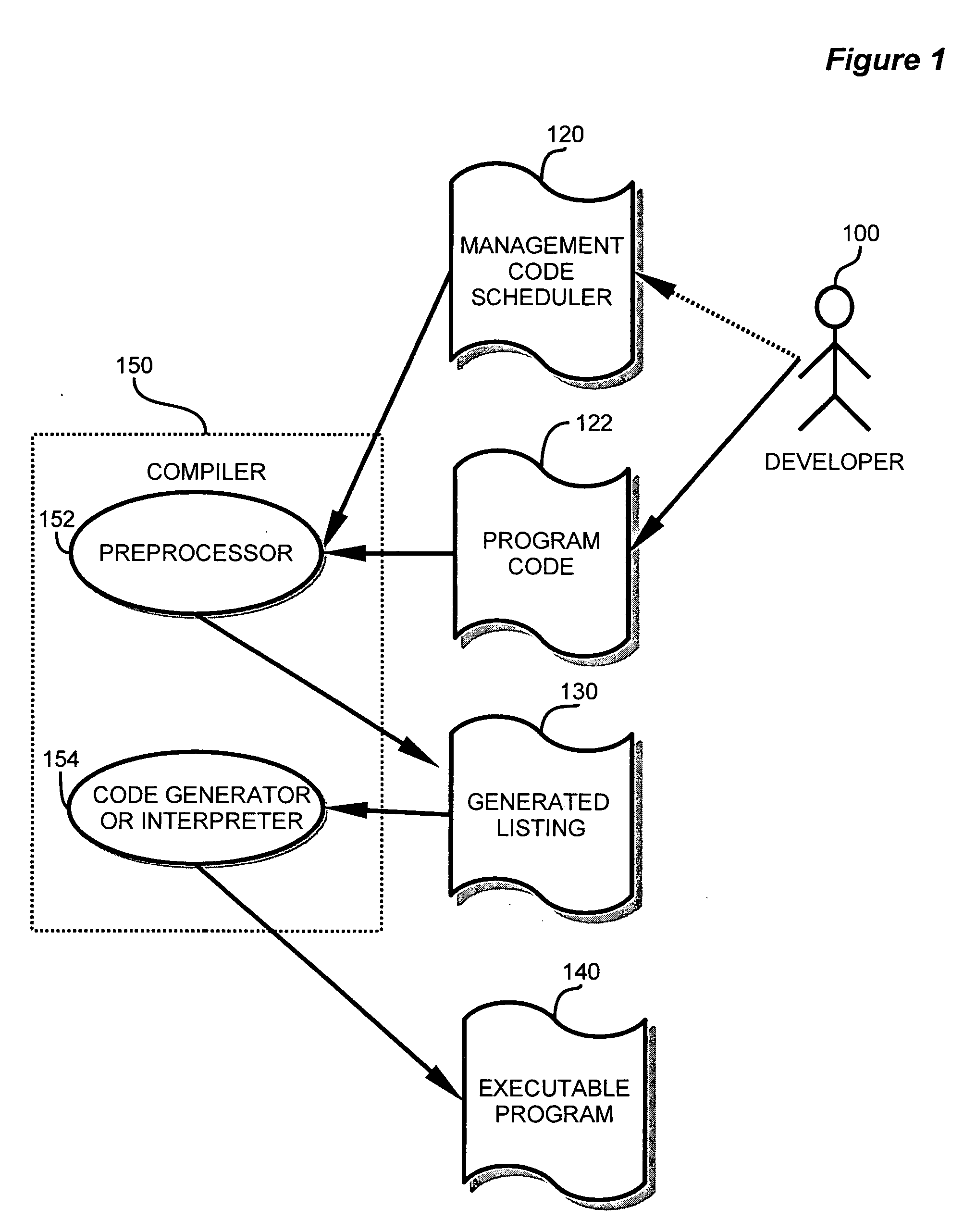

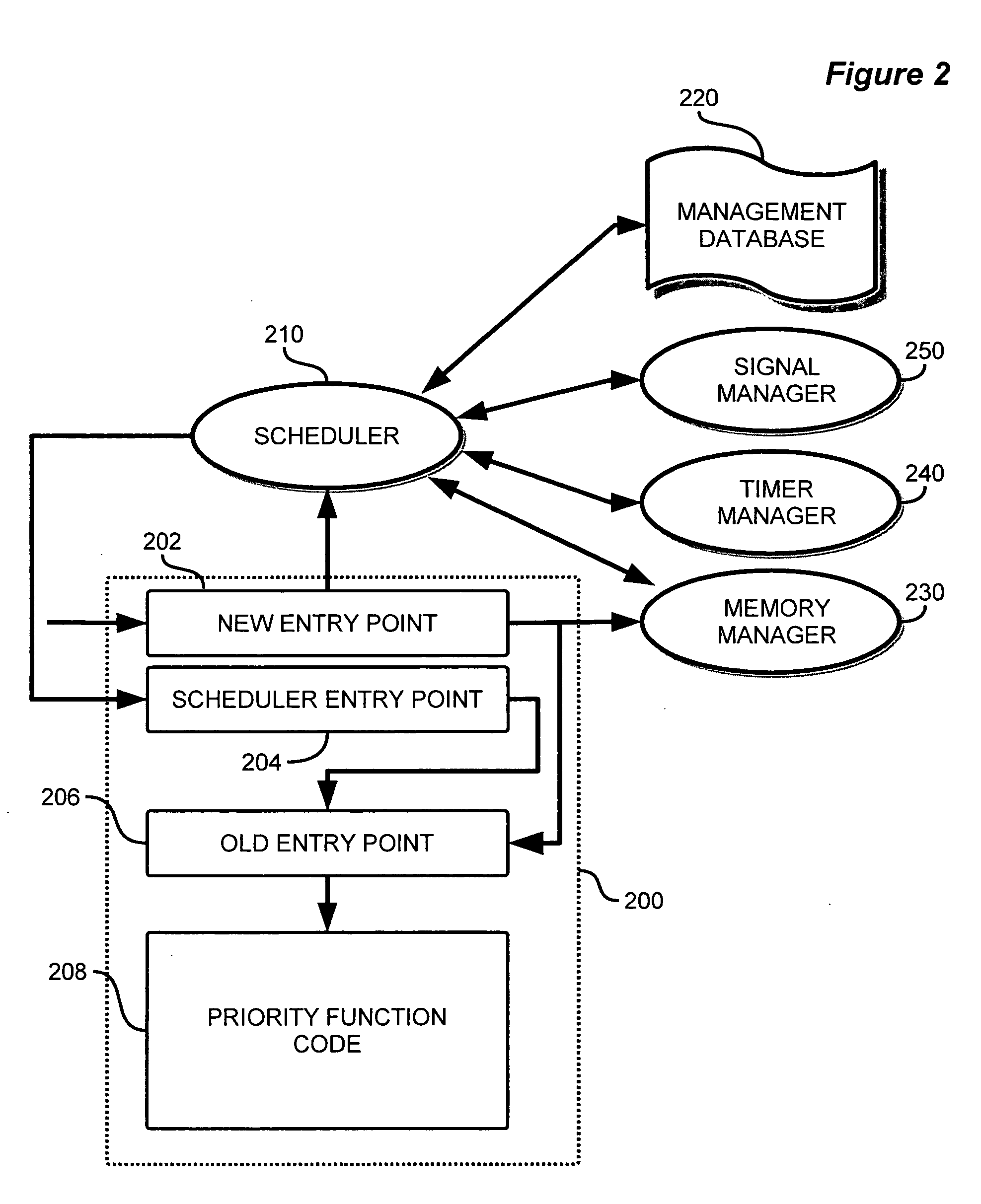

Method and apparatus for implementing task management of computer operations

InactiveUS20060107268A1Easily includedImprove performanceMultiprogramming arrangementsSpecific program execution arrangementsOperational systemPre processor

A development and runtime framework for applications that execute in real-time operating systems. Application development is enhanced through simple instructions that allow a programmer to declare functions and sets of functions as tasks and supertasks, respectively, and manage the execution of functions, tasks and supertasks with priorities. A compiler or pre-processor provides tools for generating the code for tasks and supertasks, and the management code for managing execution. Function calls may be made directly to functions within supertasks via respective entrypoints, and the tasks are managed based on the functions being invoked. Within a supertask, a higher priority function may be runnable while a lower priority function of that supertask is suspended. A cookie is used to recognize when a register update for a supertask may be omitted, enabling more efficient context switching.

Owner:SOFTWARE WIRELESS

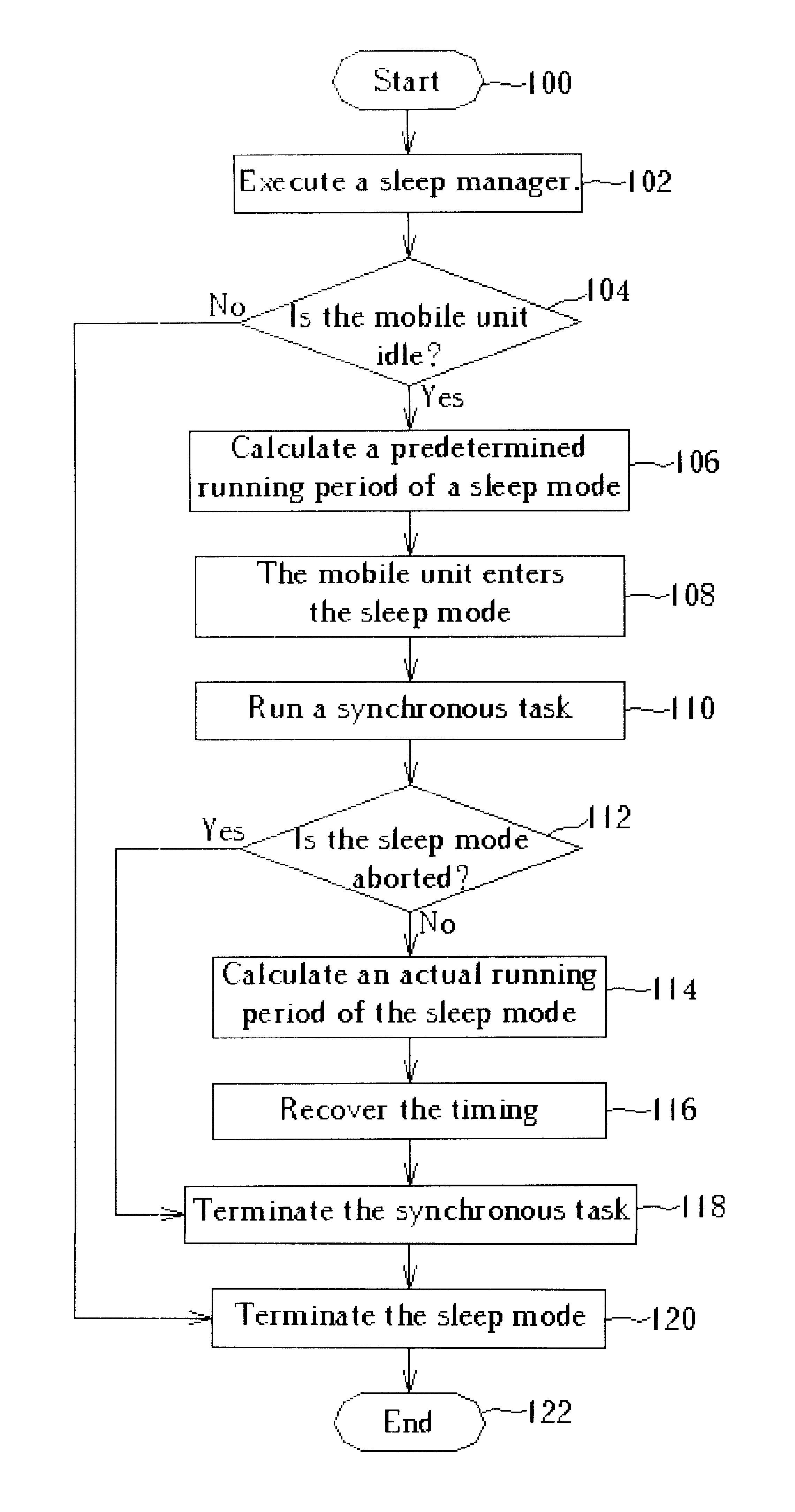

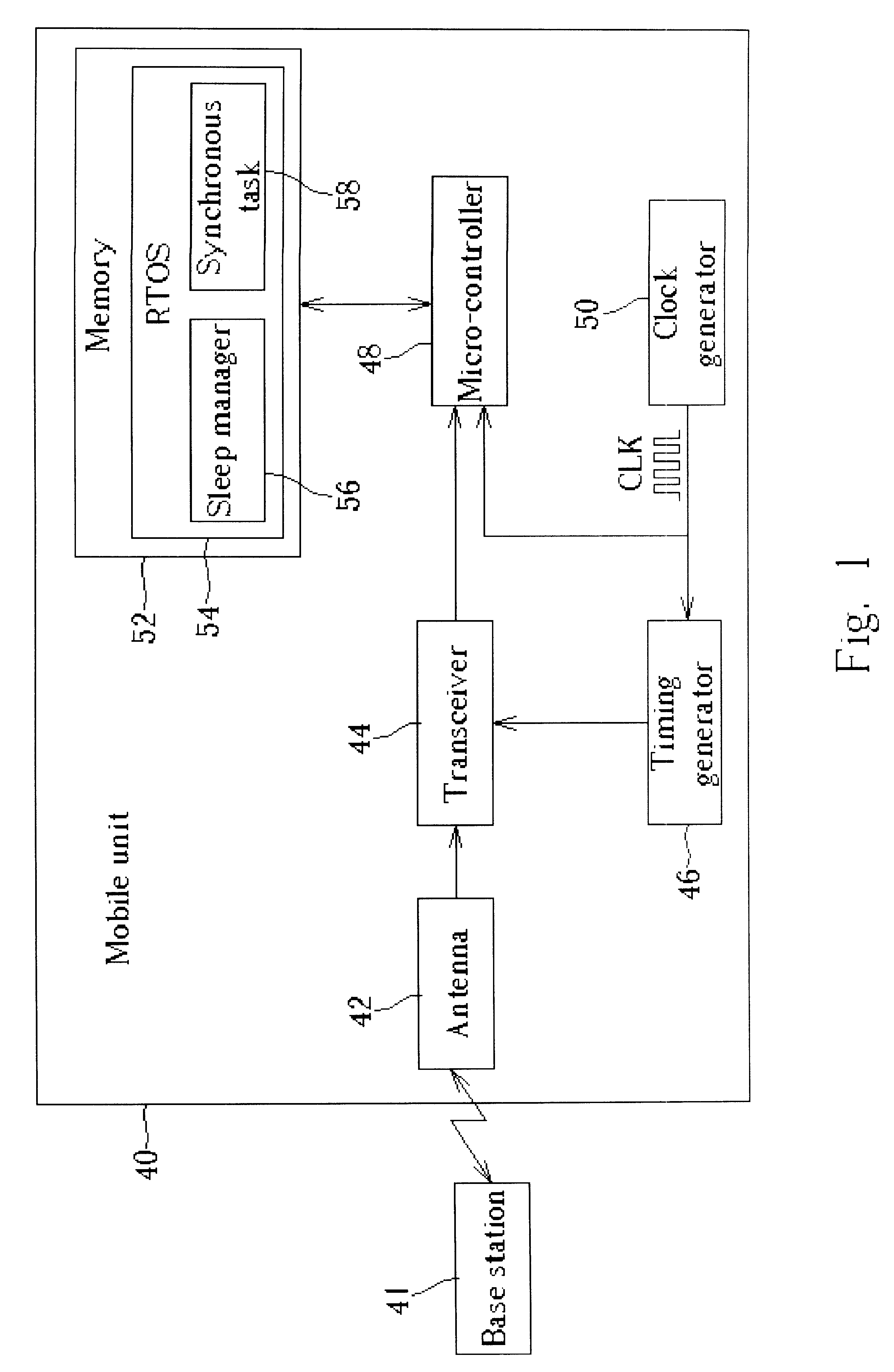

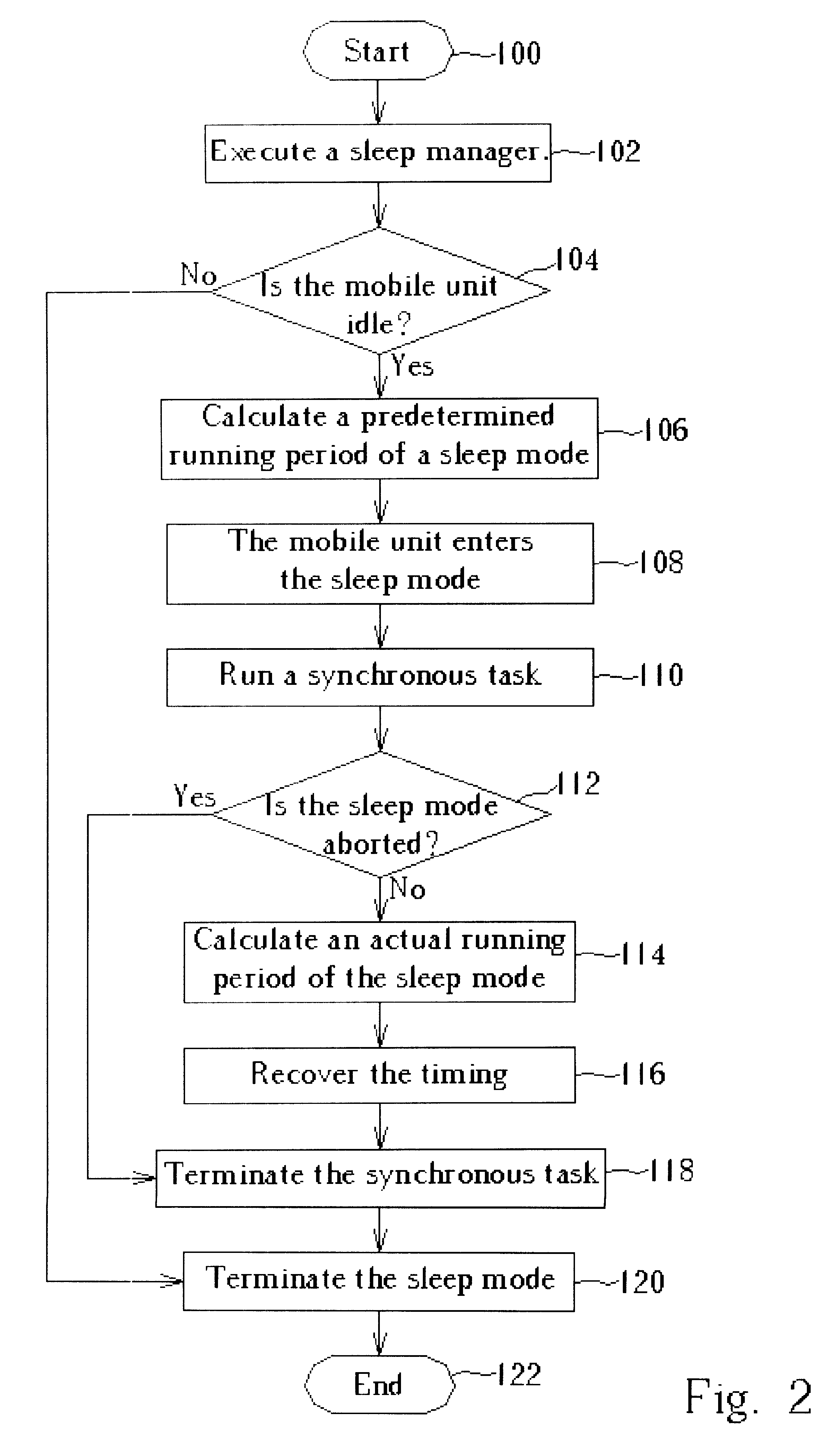

Method for switching a time frame based mobile unit to a sleep mode

InactiveUS7260068B2Reduce power consumptionSimple planEnergy efficient ICTPower managementOperational systemCommunications system

Method for recovering frame timing of a mobile communication device performing a sleep mode. The mobile communication device communicates with a base station through a communication system so that wireless signals are transmitted via frames. The method includes executing a synchronous task for interrupting currently loaded control processes in a real-time operating system and for calculating a predetermined sleep period for the sleep mode, executing the synchronous task for driving the mobile communication device to enter the sleep mode during an actual sleep period, and executing the synchronous task for synchronizing frame timing of the mobile communication with frame timing of the base station according to the actual sleep period.

Owner:MEDIATEK INC

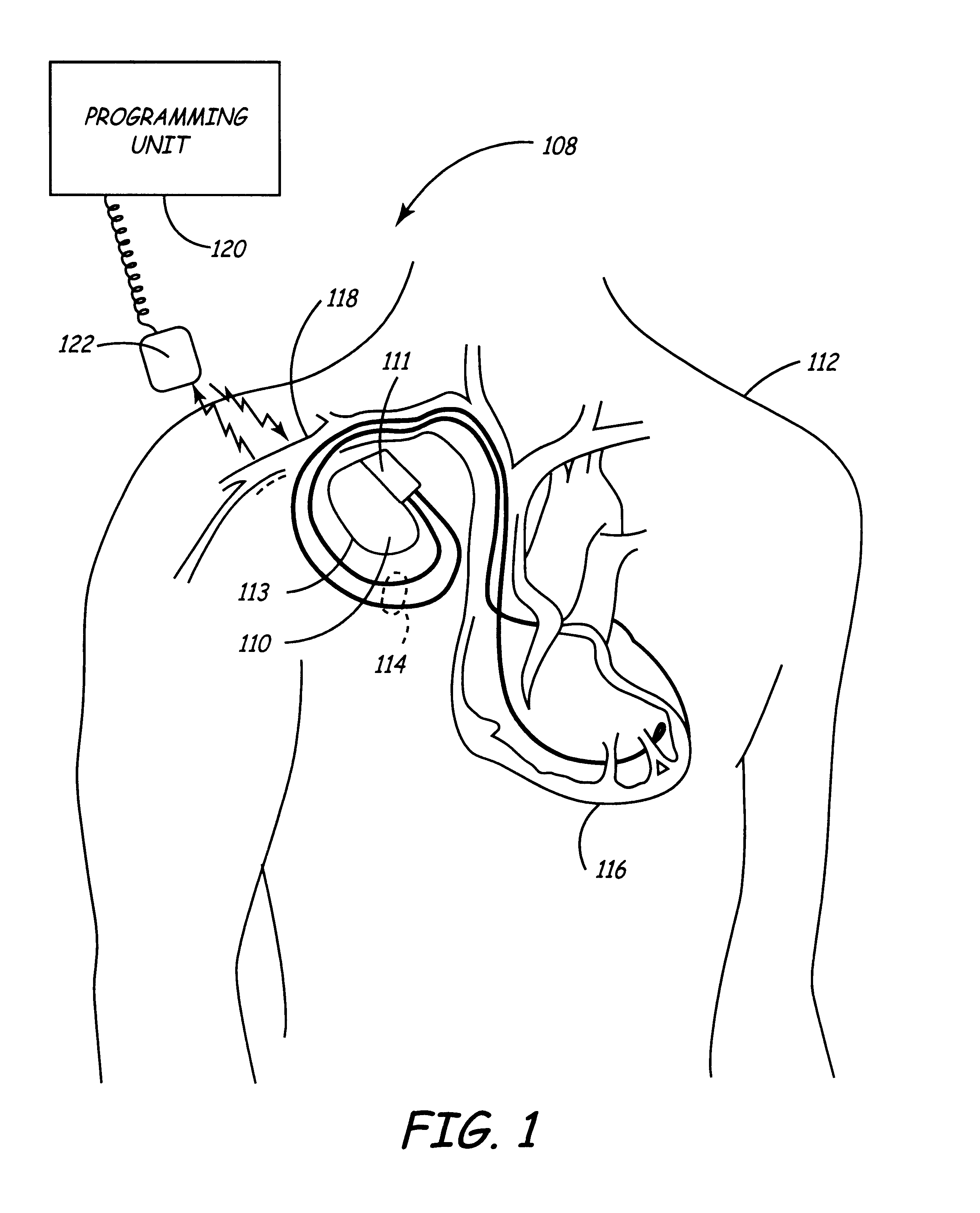

Downloadable software support in a pacemaker

InactiveUS6584356B2Program initiation/switchingHeart stimulatorsOperational systemCardiac pacemaker electrode

Owner:MEDTRONIC INC

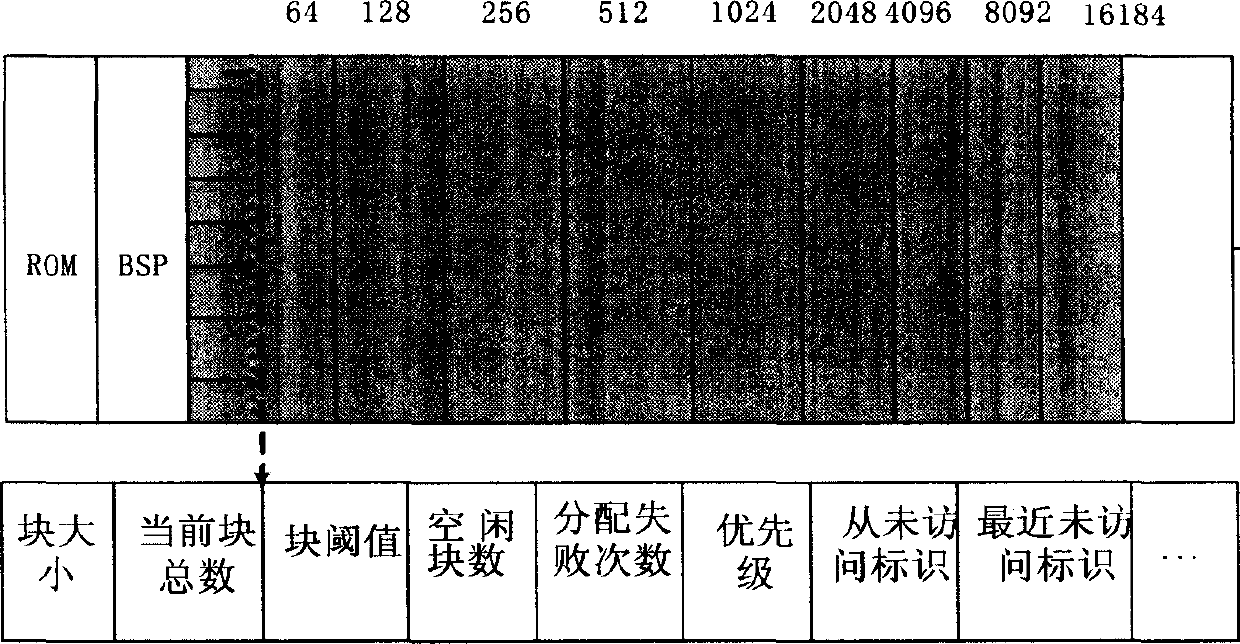

Method for internal memory allocation in the embedded real-time operation system

InactiveCN1722106AGuaranteed real-timeImprove reliabilityMultiprogramming arrangementsMemory systemsInternal memoryOperational system

The invention relates to a method for allocating internal memory of real time operating system, which comprises the following steps: applying a big internal memory area from operating system, dividing the big internal memory area into internal memory polls with different sizes and the same internal memory poll comprises internal memory block with the same size, initialing each internal memory poll controlling bar. When it needs internal memory block, it finds the corresponding internal memory poll according to the size of internal memory block, and quotes weather the internal memory poll has free block, if it has free block, it fetches a block from the head of the team and modifies the referent information of internal memory poll controlling bar, and then the allocation finishes; if not, it dose dynamic adjustment to internal memory; when it releases the internal memory, it finds the corresponding internal memory poll according to the size of internal memory and returns it into the tail of the team and rewrites the referent information of internal memory poll controlling bar.

Owner:GLOBAL INNOVATION AGGREGATORS LLC

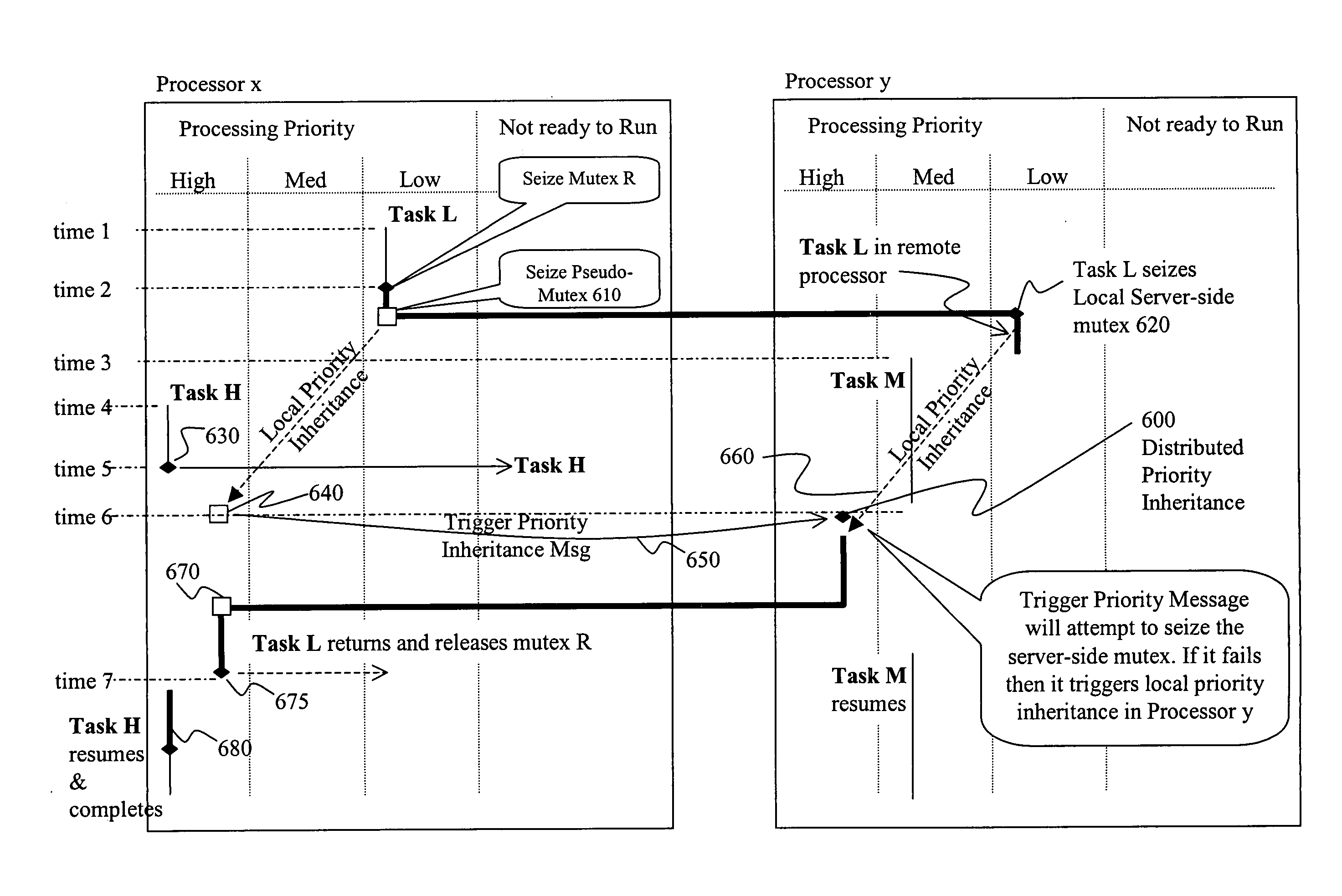

System and method for implementing distributed priority inheritance

ActiveUS20060282836A1Advanced conceptEasy to transportMultiprogramming arrangementsMemory systemsOperational systemReal-time operating system

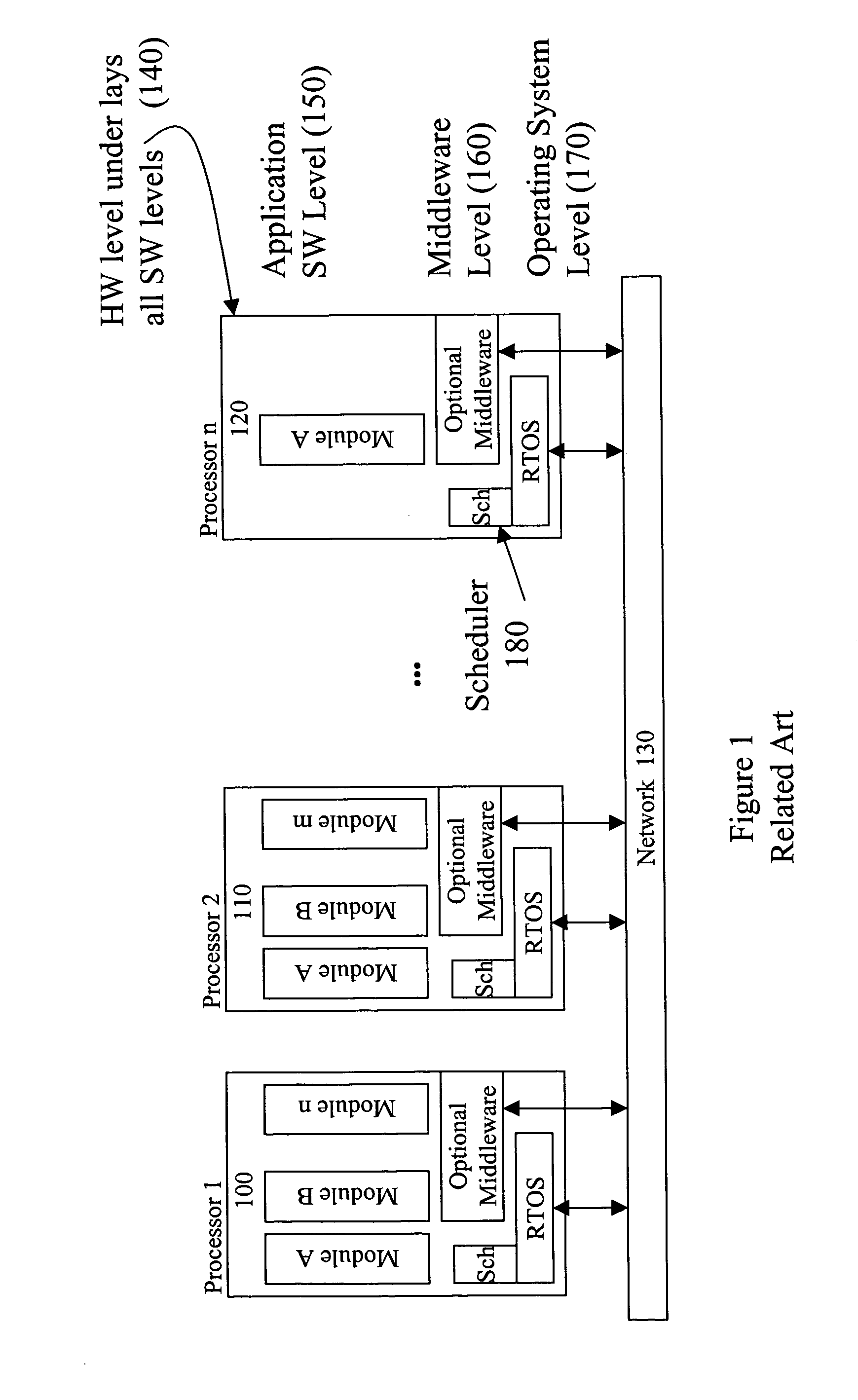

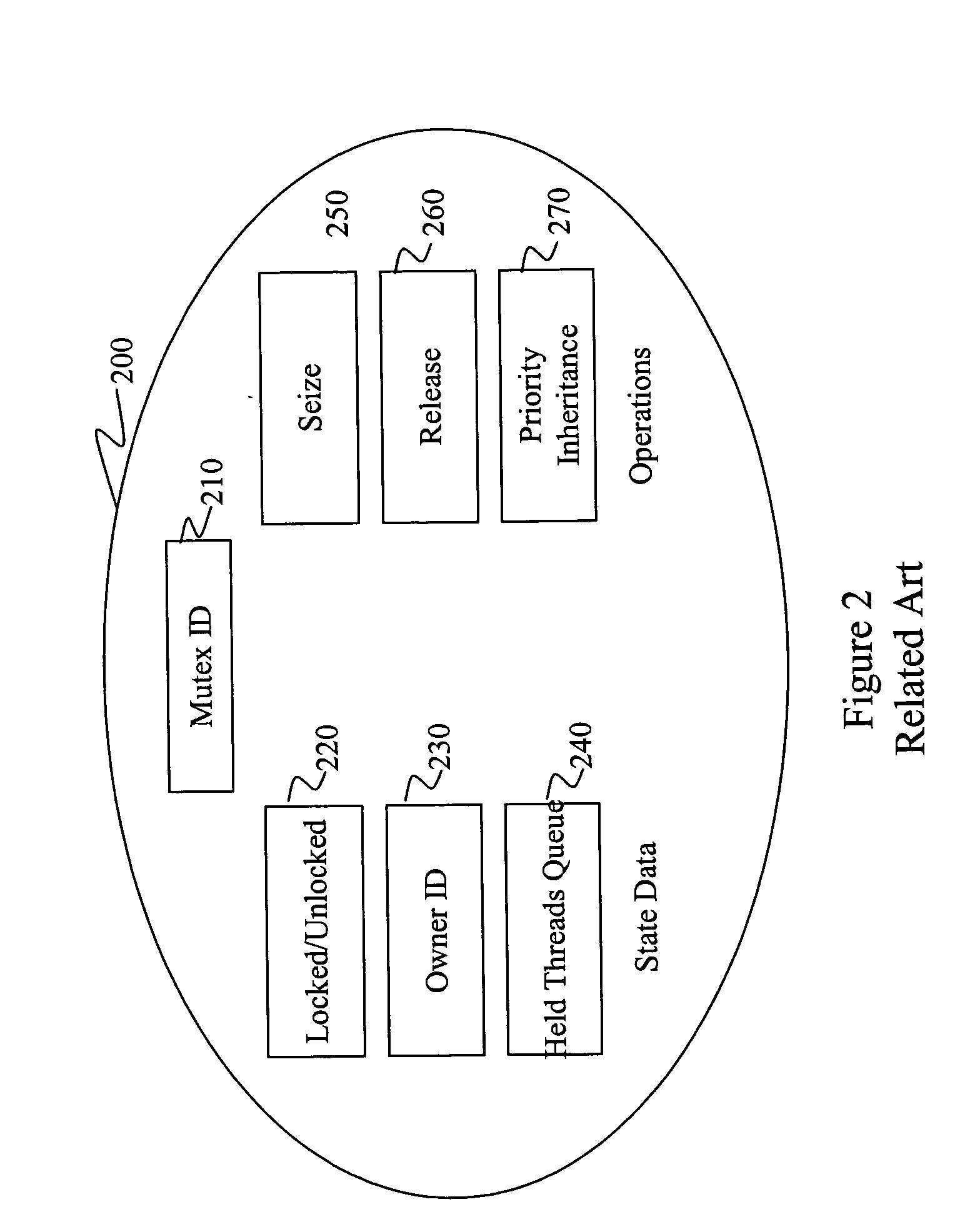

Priority inheritance is implemented across a distributed system, preferably by use of a mutual exclusion object, referred to as a pseudo-mutex, which provides operations for communicating priority of a task which is held to a different connected processor or node of a network and generating a dummy local command of priority at least equal to that of the held task at the remote processor or node in collaboration with a real-time operating system and middleware. The remote real time operating system then carries out priority inheritance in the normal manner to raise the priority of a blocked task, thus reversing any preemption of that task at the remote processor or node. The increase in priority avoids preemption of lower priority processes and thus increases the execution speed of the executing thread to release the existing lock at an earlier time; allowing a lock to be obtained by the higher priority thread. The middleware serves as an intermediary, communicating messages that include pseudo-mutex arguments or similar communications and requests for enabling priority inheritance across nodes.

Owner:LOCKHEED MARTIN CORP

Versatile semiconductor manufacturing controller with statistically repeatable response times

ActiveUS20060259259A1Ensure correct executionEffectively reduces jitterProgramme controlVoltage-current phase angleOperational systemMonitoring and control

The present invention relates to process I / O controllers for semiconductor manufacturing to which a tool host can delegate data collection, monitoring and control tasks. In particular, it relates to process I / O controllers that can perform more than one of data collection, monitoring, control and response to commands from a tool host with statistically repeatable performance and precision. Embodiments described use prioritized real time operating systems to control of semiconductor manufacturing tools and data collection from tool associated with the sensors. Statistically repeatable responsiveness to selected commands and to sensor inputs during selected recipe steps effectively reduces jitter.

Owner:MKS INSTR INC

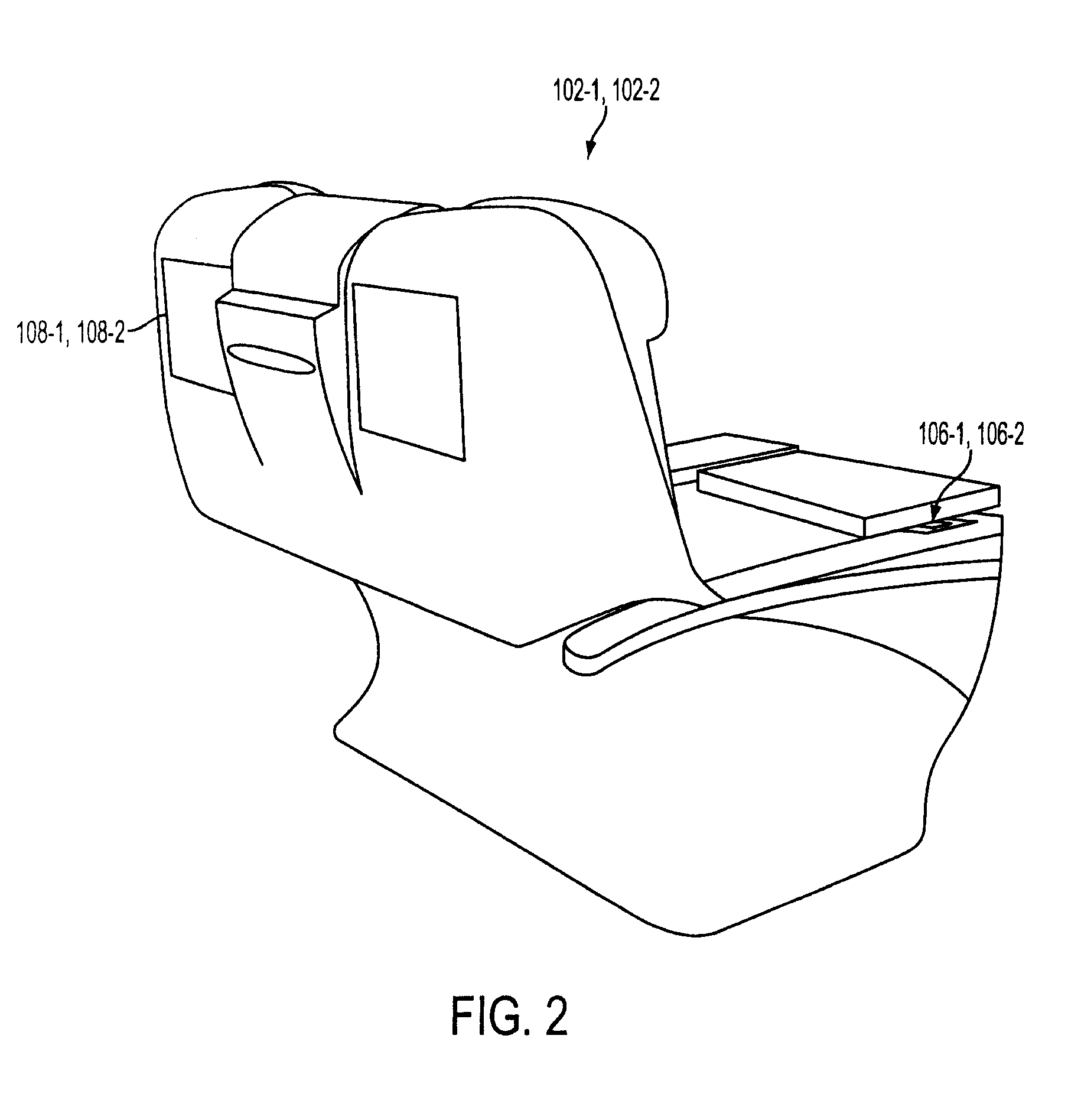

Server design and method

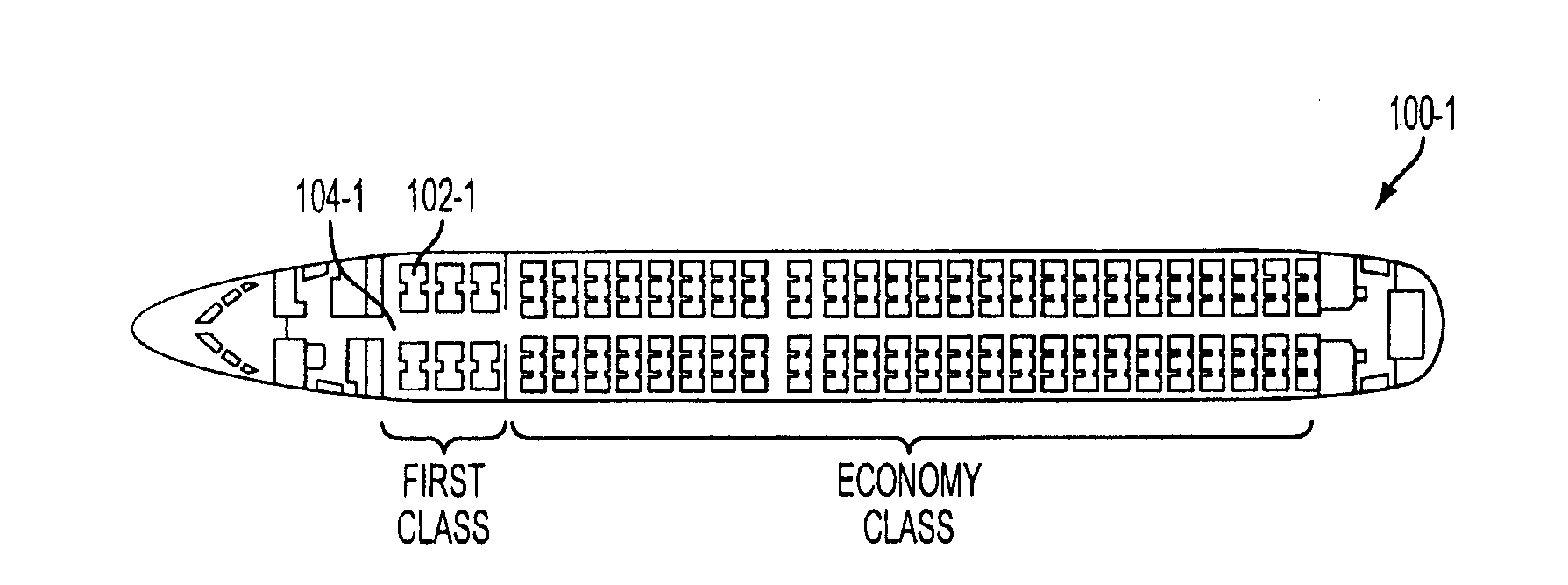

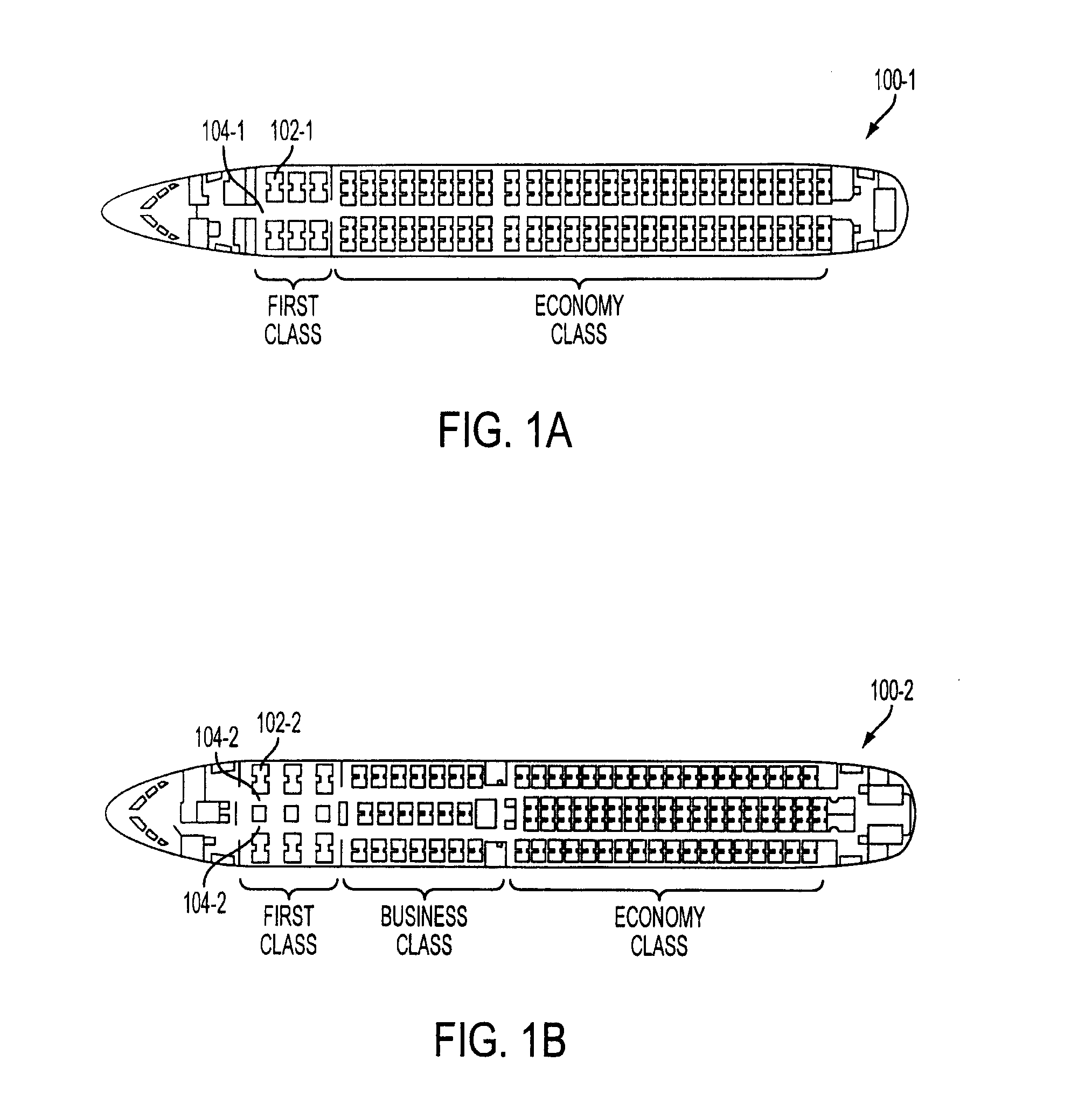

ActiveUS20080312778A1Low costImprove performanceDigital data processing detailsBroadcast specific applicationsCommunications systemOperational system

A communication system for a vehicle includes a server that includes a real time operating system, at least one cabin function application that runs on the real time operating system, and at least one in-flight entertainment application that runs on another operating system on top of the real time operating system. Thus, an in-operation entertainment system is capable of providing audio and / or visual content to a large number of locations in a cabin of the vehicle, and a cabin function system is capable of providing various cabin applications, e.g., lighting level control, attendant calling, air conditioning control, etc. at different locations in the vehicle cabin in a manner that is isolated and prioritized over the entertainment system.

Owner:THALES AVIONICS INC

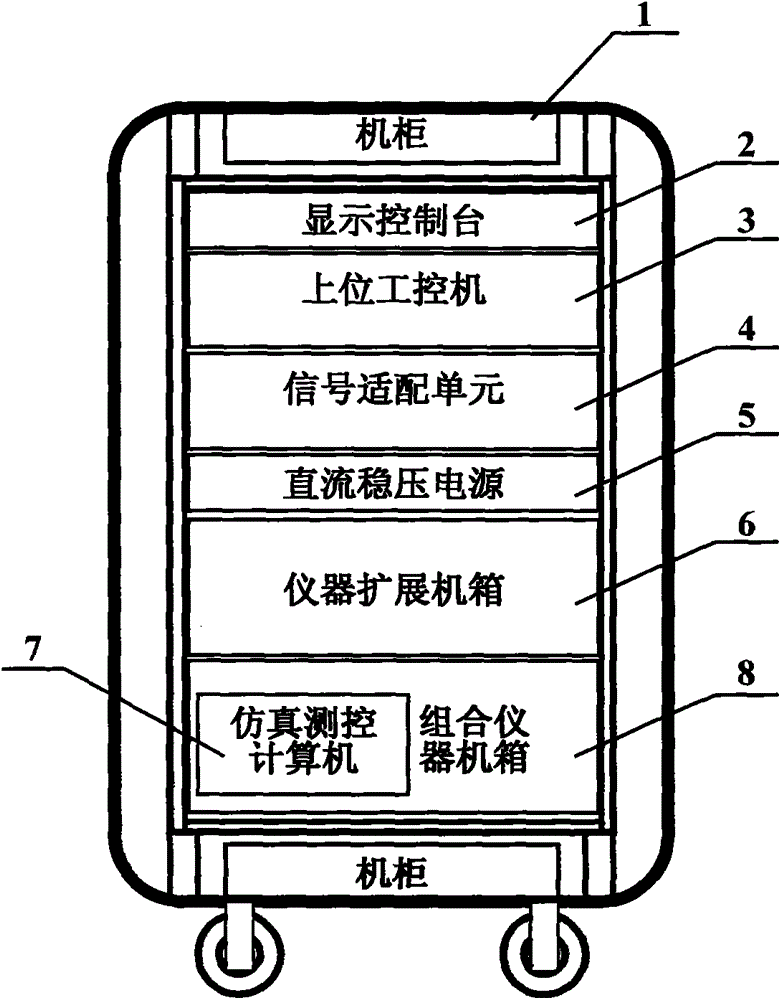

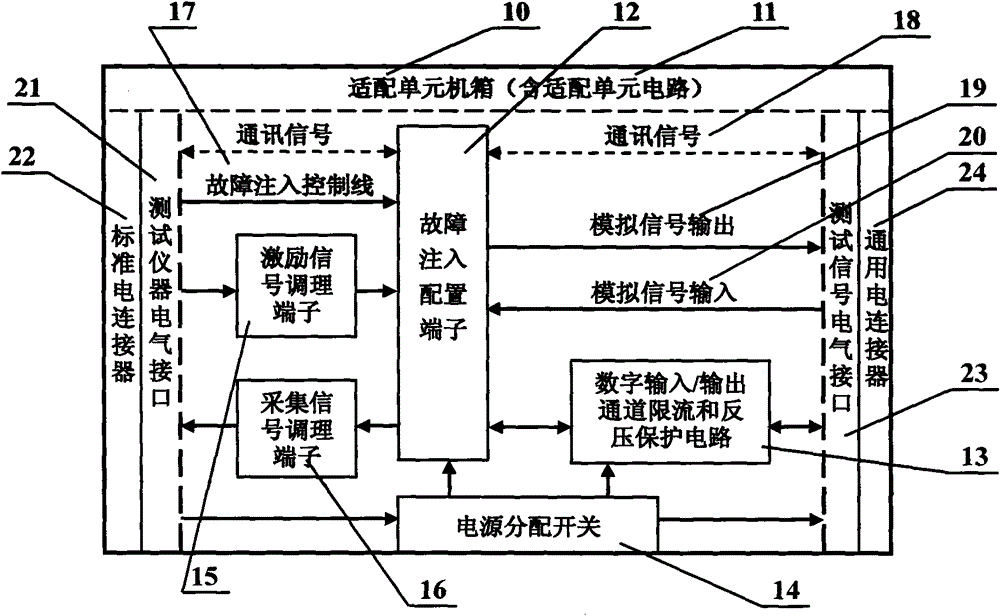

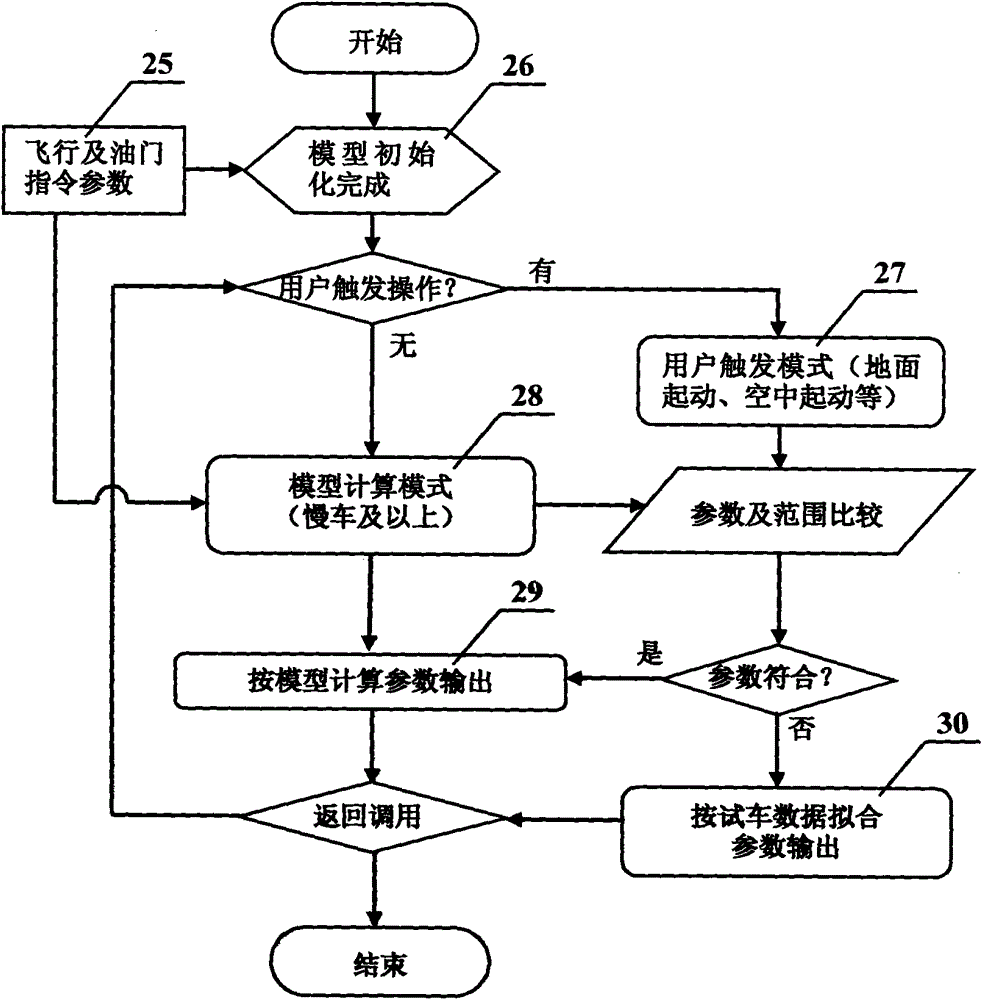

Universal simulator for aircraft engines

InactiveCN104699068AImprove compatibilityImprove scalabilityElectric testing/monitoringAviationMathematical model

The invention discloses a universal simulator for aircraft engines. The universal simulator comprises an upper industrial personal computer, a simulation measurement and control computer, a display control desk, a combination instrument case with a plurality of instrument hardware modules, an instrument extension case, a signal adaptation unit, a direct-current voltage-stabilized source and a special testing cable. The universal simulator has the advantages that mathematical models of the engines are operated by an embedded high-performance real-time operating system of the simulation measurement and control computer, so that the real-time performance and the effectiveness of simulation experiments can be guaranteed; hardware architectures for forming testing systems are standard PXI [PCI (peripheral component interconnect) extensions for instrumentation] bus open architectures, accordingly, the hardware modules of various mature PXI bus interfaces can be extended and configured according to particular testing application, and the universal simulator is high in automation degree, extensibility and compatibility and good in maintainability; the signal adaptation unit is configured with standard and universal electric connectors by means of integration, and only corresponding matched testing connecting cables need to be replaced, so that electric connection of the testing systems can be quickly reconstructed by the simulator for the engines, and requirements of platforms on the universality can be met.

Owner:GUIZHOU AERONAUTICAL ENGINE INST

Robotic hybrid system application frame based on multi-core processor architecture

InactiveCN105278940ARun independently of each otherDebug each other independentlySpecific program execution arrangementsFrame basedStructure of Management Information

The invention describes a robotic hybrid system application frame based on a multi-core processor architecture. In a robotic system which takes an ARM (Advanced RISC Machines) / X86 multi-core processor as a controller, a multi-core parallel processing structure of the ARM / X86 multi-core processor is used for operating the robotic hybrid system application architecture consisting of a real-time operating system, non-real-time operating systems and a system supporting frame on a whole robotic controller so as to provide improved operating system service, wherein the real-time operating system, non-real-time operating systems and the system supporting frame simultaneously operate. In the application frame, one real-time operating system independently operates in one ARM / X86 core, meanwhile, a plurality of non-real-time operating systems operate in other ARM / X86 cores, the operating systems mutually individually occupy processor resources and peripherals, robotic application programs with different real time requirements are independently operated, and the application programs can be used (drawing 1) in a uniform ROS (Robotic Operating System) application node form.

Owner:BEIHANG UNIV

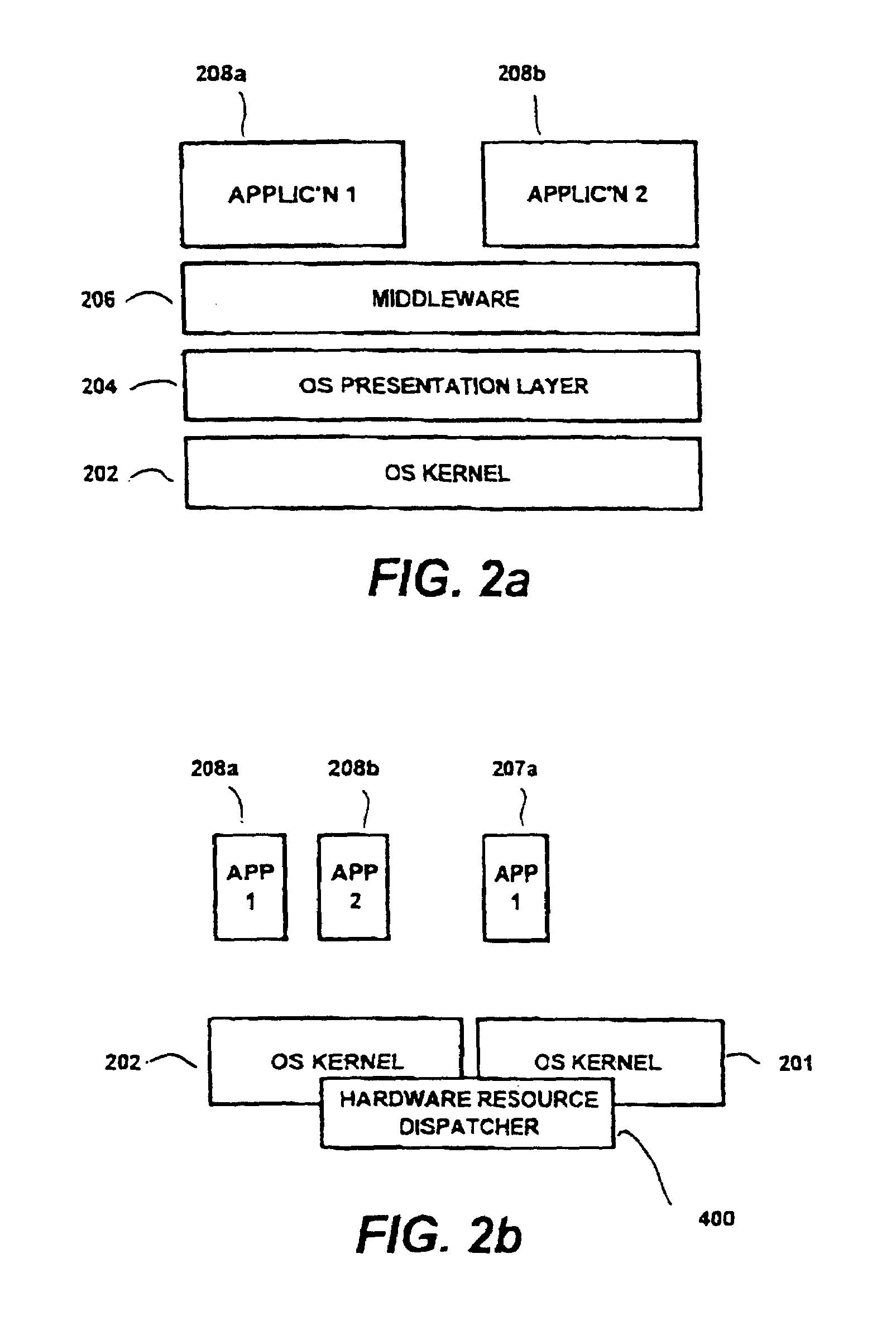

Plural operating systems having interrupts for all operating systems processed by the highest priority operating system

ActiveUS7434224B2Possible to performProgram initiation/switchingError detection/correctionGeneral purposeOperational system

Multiple different operating systems are enabled to run concurrently on the same computer. A first operating system is selected to have a relatively high priority (the realtime operating system, such as C5). At least one secondary operating system is selected to have a relatively lower priority (the general purpose operating system, such as Linux). A common program (a hardware resource dispatcher similar to a nanokernel) is arranged to switch between these operating systems under predetermined conditions and modifications are provided to the first and second operating systems to allow them to be controlled by the common program.

Owner:VIRTUALLOGIX

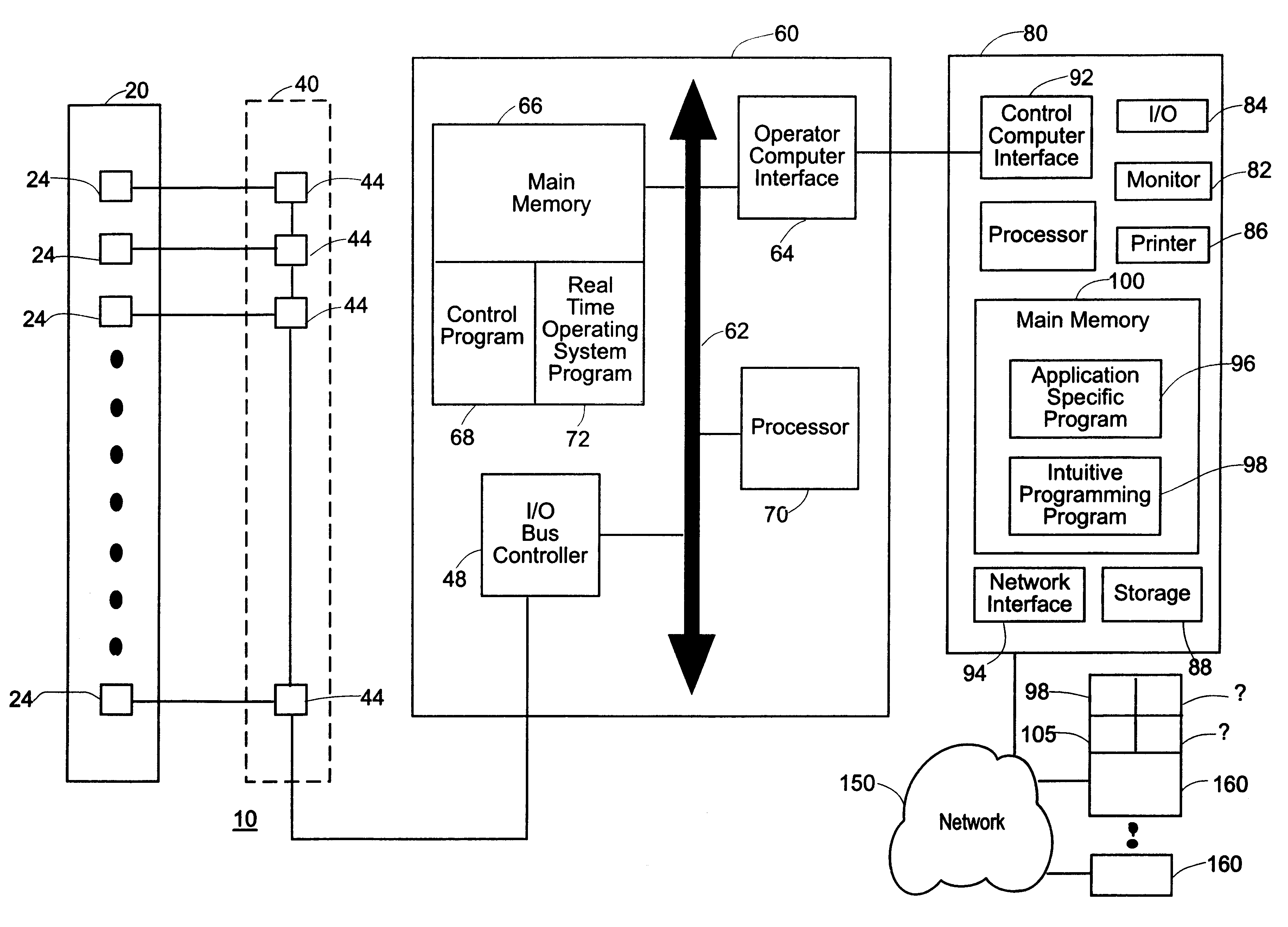

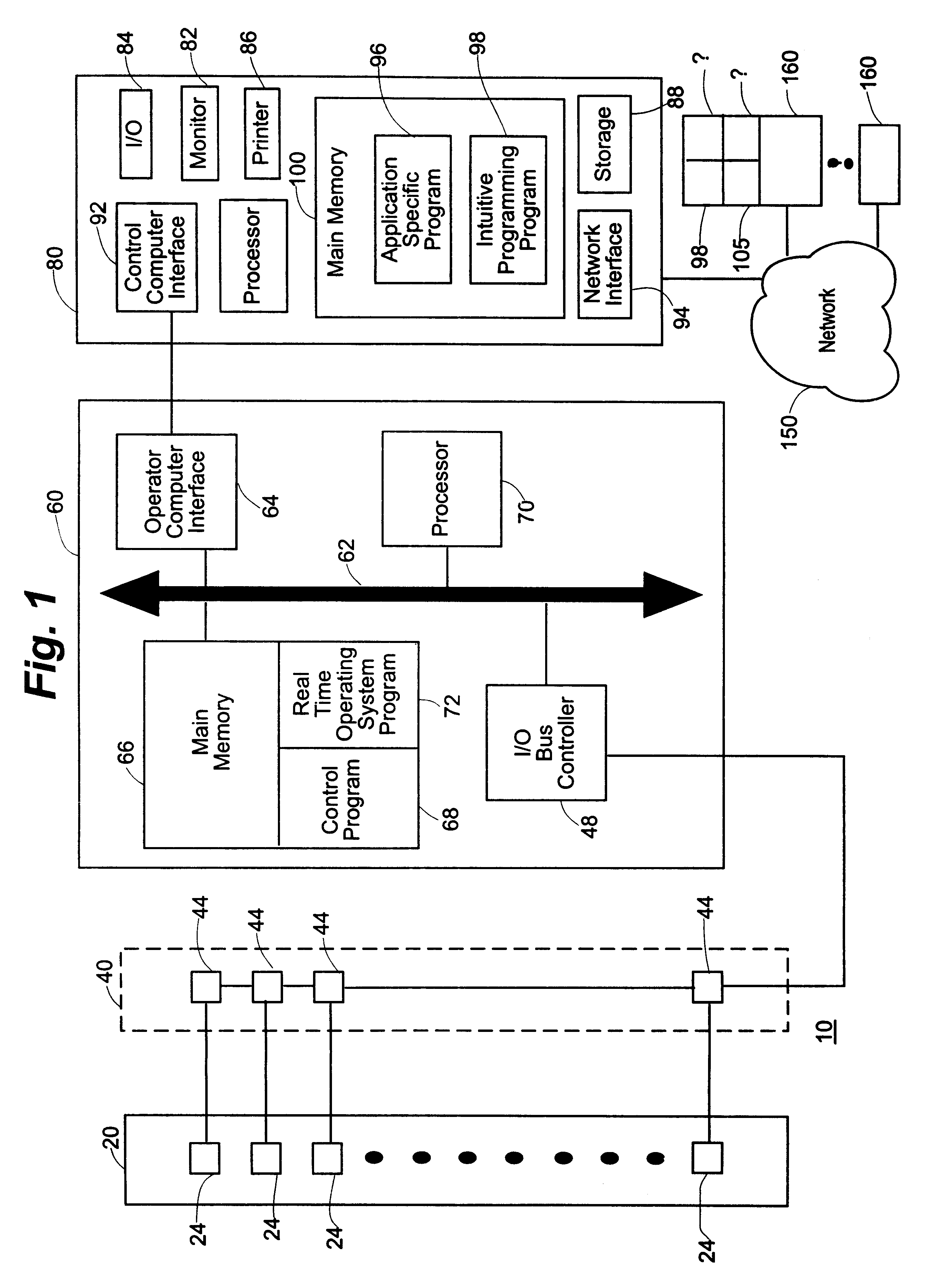

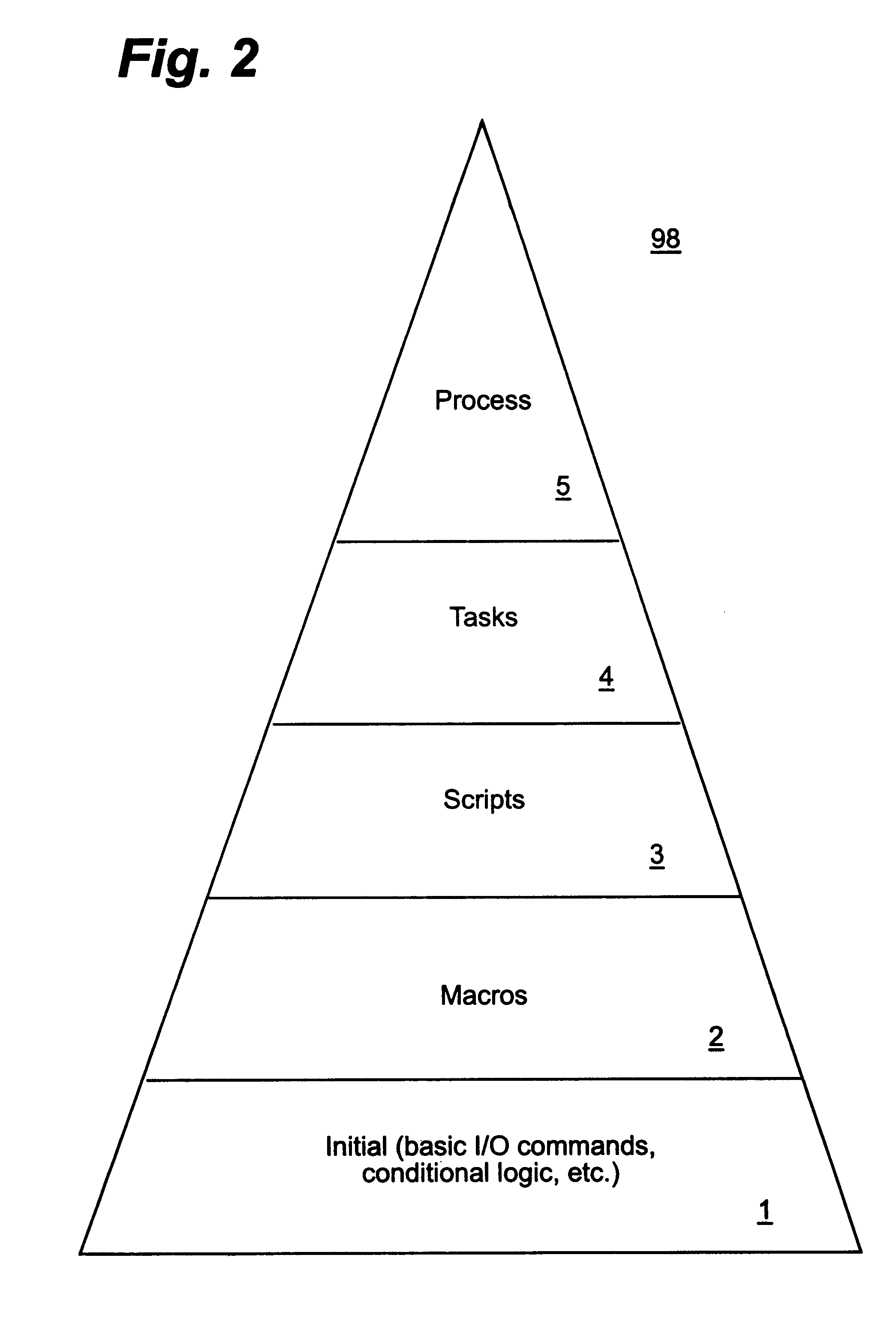

Processor-based process control system with intuitive programming capabilities

A system having a processor-based process control system for a plastic injection molding machine performing a plastic injection molding process having an I / O bus network containing a plurality of I / O modules operably connected to a corresponding I / O device associated with the plastic injection molding machine and a first computer having and I / O bus controller directly connected to the I / O bus network, a real-time operating system, and a first processor executing a plastic injection molding control program for controlling the plastic injection molding process.

Owner:HETTINGA SIEBOLT

Task scheduler system and method for managing tasks in an embedded system without a real time operating system

InactiveUS20070143761A1Low costLimited memory spaceMultiprogramming arrangementsMemory systemsOperational systemReal-time operating system

A task scheduler system and method for managing tasks in an embedded system executes both unscheduled and scheduled tasks in their respective queues in a prescribed order without dependence on a Real Time Operating System (RTOS).

Owner:AVAGO TECHNOLOGIED FIBER IP SINGAPORE PTE LTD

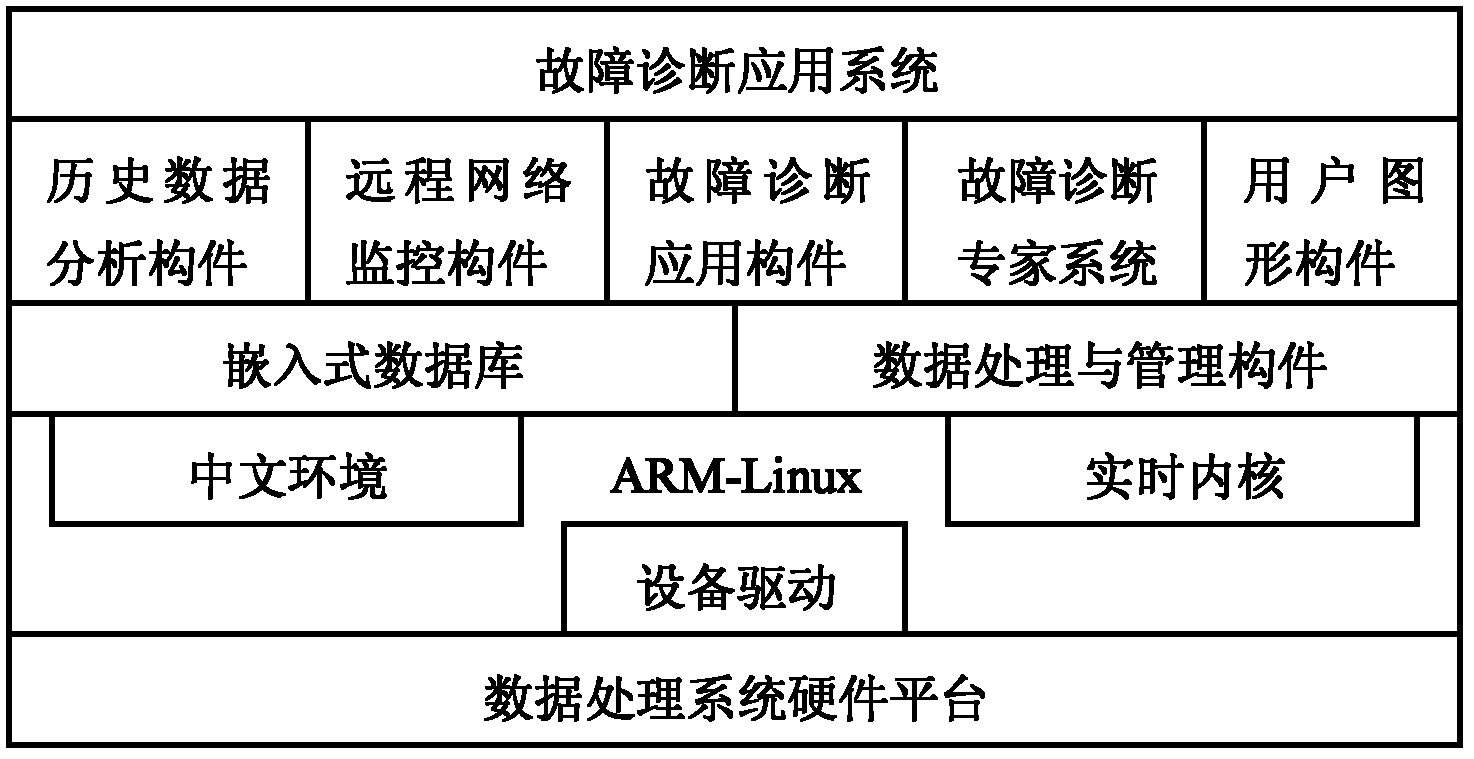

Embedded control platform for inspection instrument

ActiveCN102436205AMeet the needs of versatilitySatisfy functional task requirementsProgramme controlComputer controlEmbedded databaseOperational system

The invention discloses an embedded control platform for an inspection instrument. A tool chain of the control platform comprises a cuttable embedded real-time operating system, an embedded database management system (EDMS) and a data acquisition / communication and processing system; and the control platform comprises an embedded data acquisition module and an embedded analysis processing module, wherein the embedded data acquisition module acquires multi-path real-time data of target equipment and preprocesses and uploads the data to the embedded analysis processing module, and the embedded analysis processing module is a simplified expert system facing round target monitoring and is used for data processing of a monitored target, state judgment, confidence evaluation, report generation and timely processing measures and suggestions. The embedded control platform for the inspection instrument has high generality and configurability and is oriented to an intelligent round monitoring instrument.

Owner:ZHEJIANG UNIV OF TECH

Method and apparatus for implementing priority management of computer operations

InactiveUS20060031838A1Reduce amountReduce overheadMultiprogramming arrangementsSpecific program execution arrangementsOperational systemReal-time operating system

A development framework and runtime environment for applications that execute in real-time operating systems. Application development is enhanced by providing simple instructions that allow a programmer to declare any function as a function managed with priority. Compiler tools implement priority function and the management code for managing execution at runtime. At runtime, priority functions are managed based on their respective priority level. The priority function information is stored when execution is to be delayed.

Owner:CHRABIEH RABIH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com