Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39 results about "Dual-modulus prescaler" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

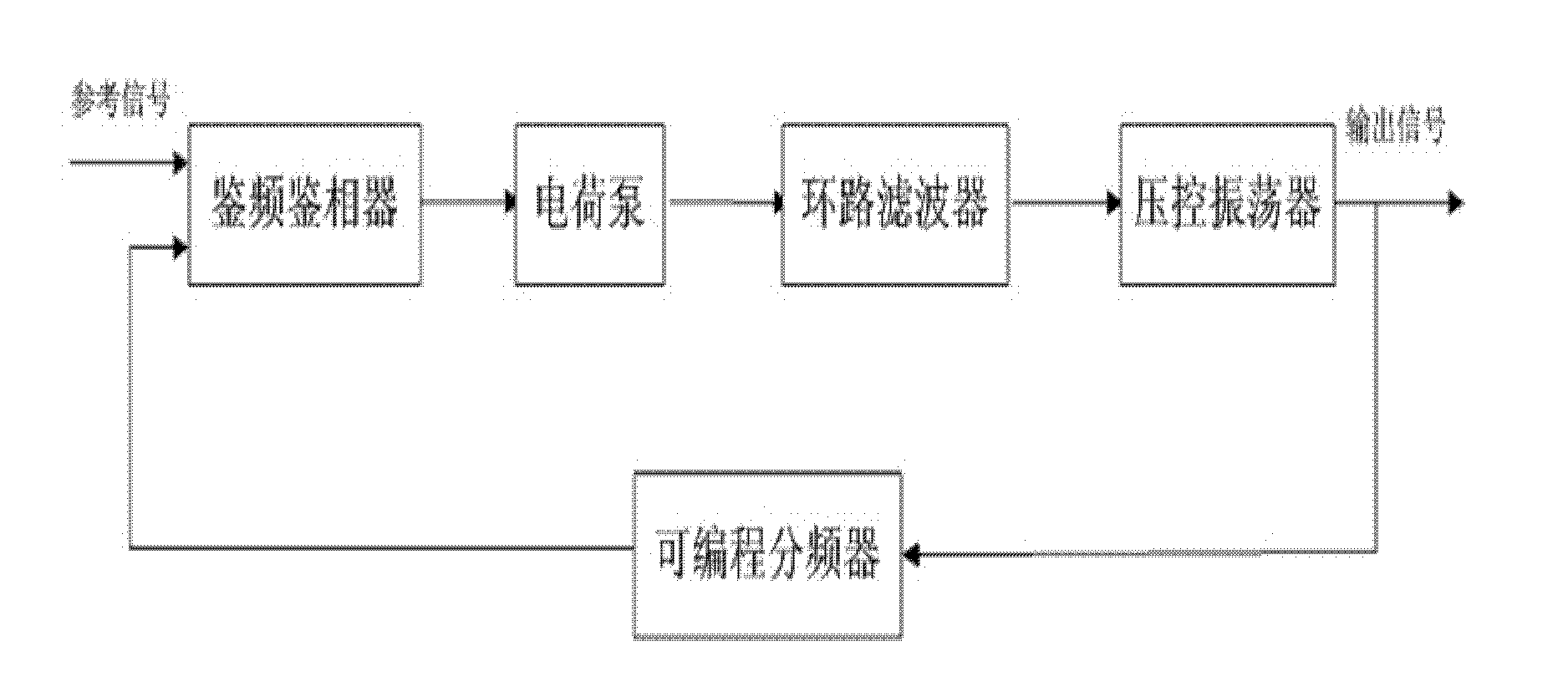

A dual modulus prescaler is an electronic circuit used in high-frequency synthesizer designs to overcome the problem of generating narrowly spaced frequencies that are nevertheless too high to be passed directly through the feedback loop of the system. The modulus of a prescaler is its frequency divisor. A dual-modulus prescaler has two separate frequency divisors, usually M and M+1.

Co-prime division prescaler and frequency synthesizer

InactiveUS6845139B2Pulse automatic controlCounting chain pulse countersControl signalFrequency synthesizer

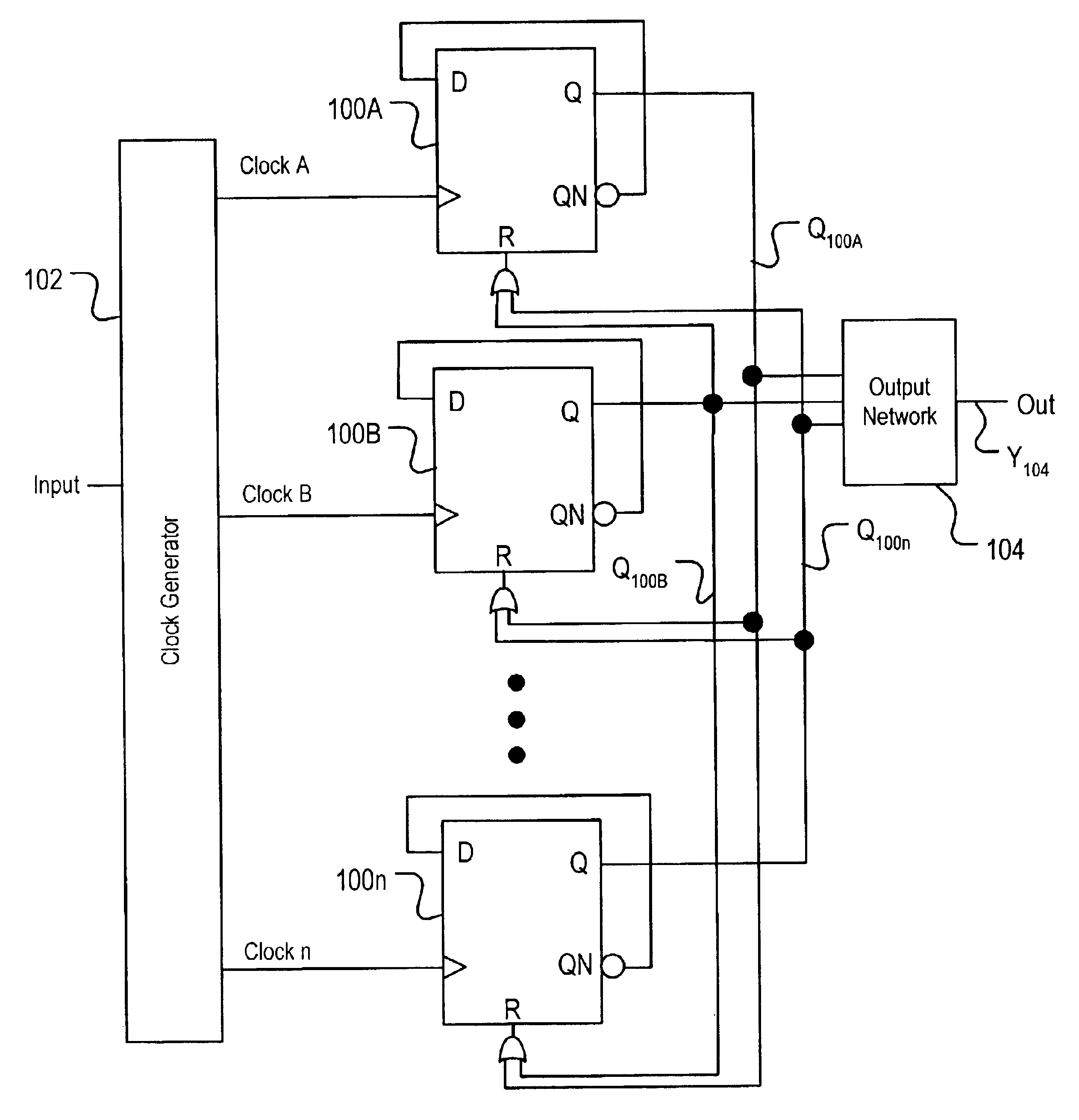

A system may include a control unit and a dual modulus prescaler. The control unit may generate a modulus control signal. The dual modulus prescaler may be configured to divide the frequency of an input signal by Q when the modulus control signal has a first value and to divide the frequency of the input signal by (Q+V) when the modulus control signal has a second value. Q is an irreducible fraction. The sum (Q+V) may be an integer or a fraction. The dual-modulus prescaler includes several clocked storage units (e.g., flip-flops) that are each clocked by a respective one of several equally spaced phases of the input signal. Each clocked storage unit operates in a toggle mode.

Owner:DSP GROUP

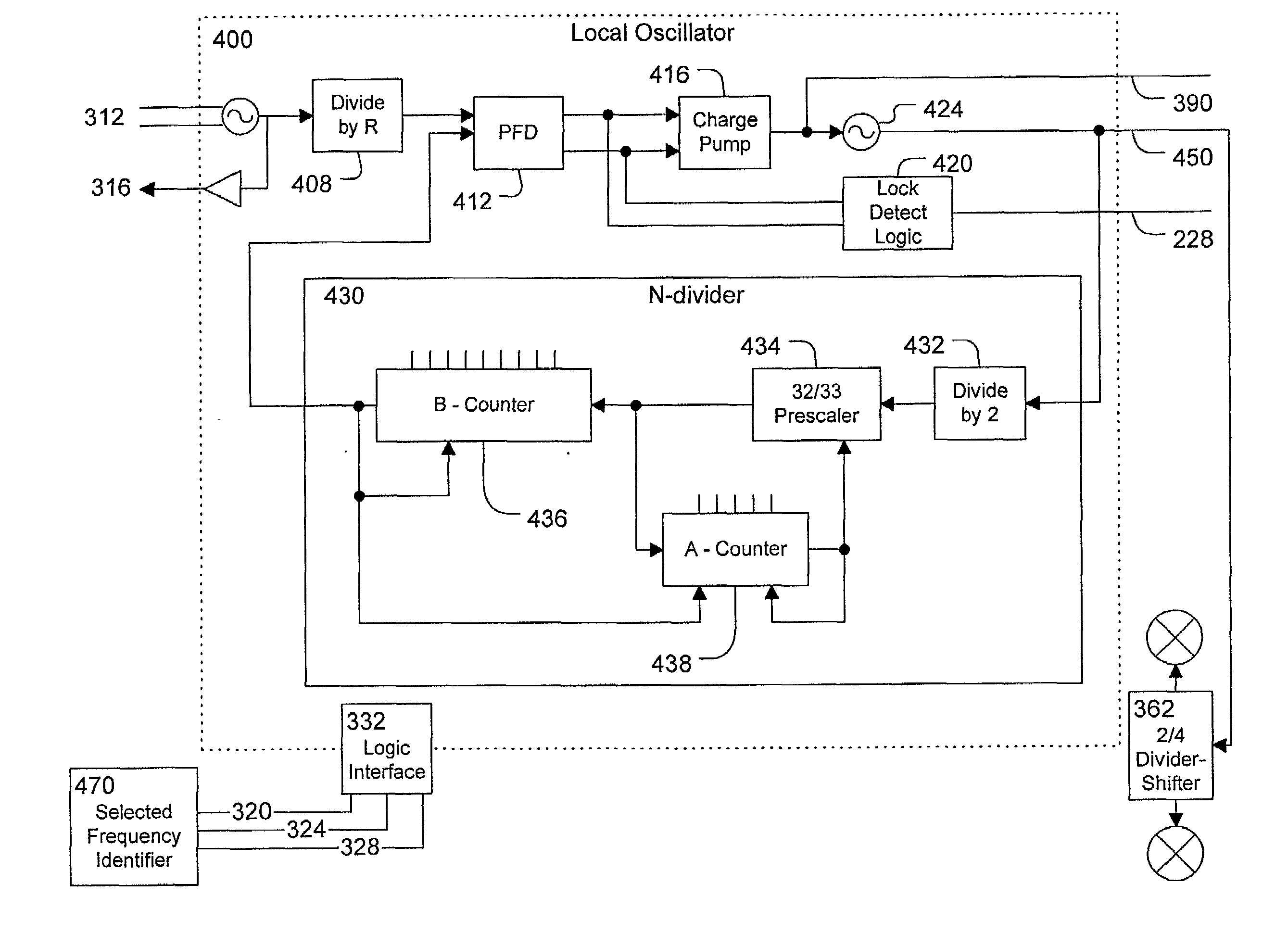

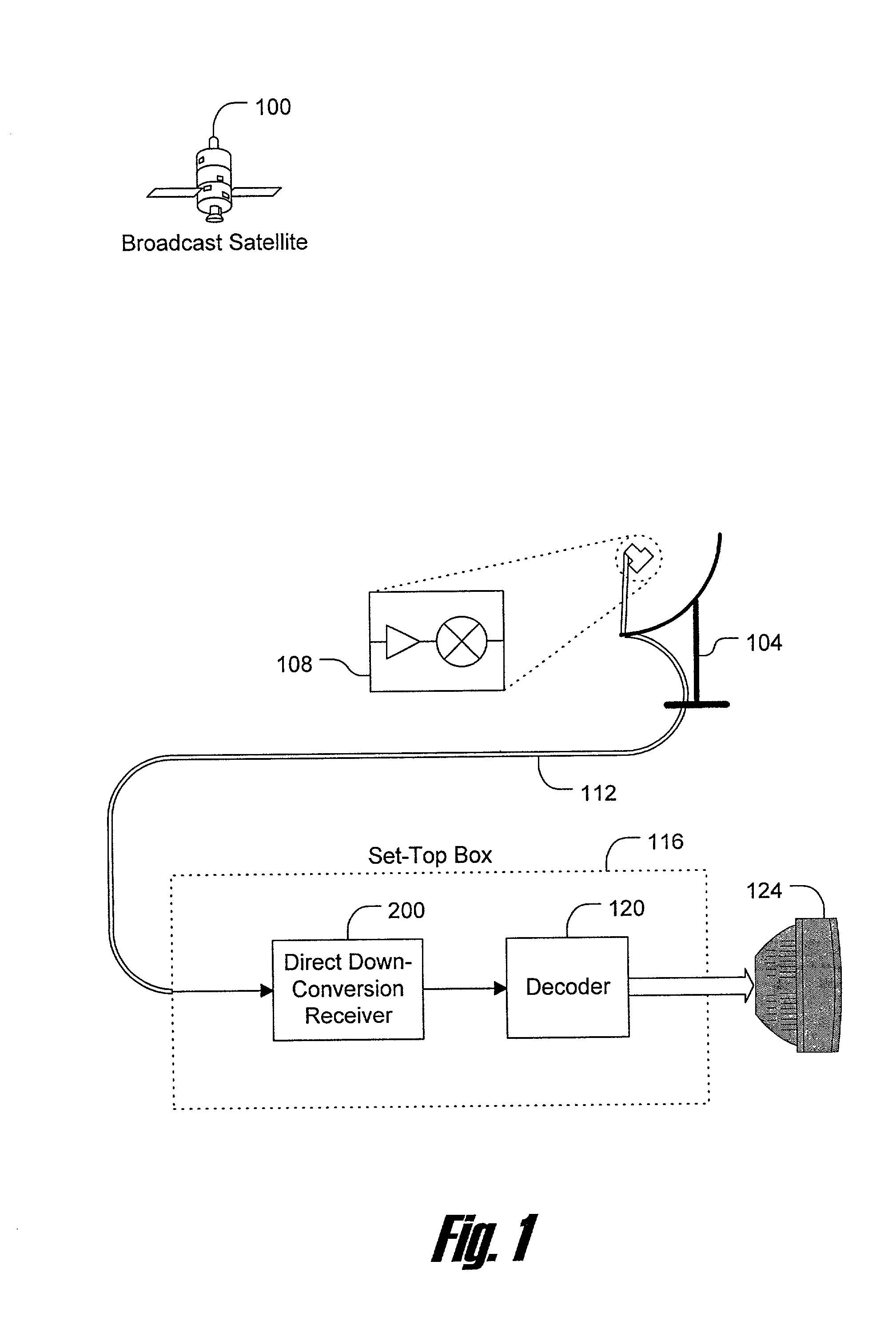

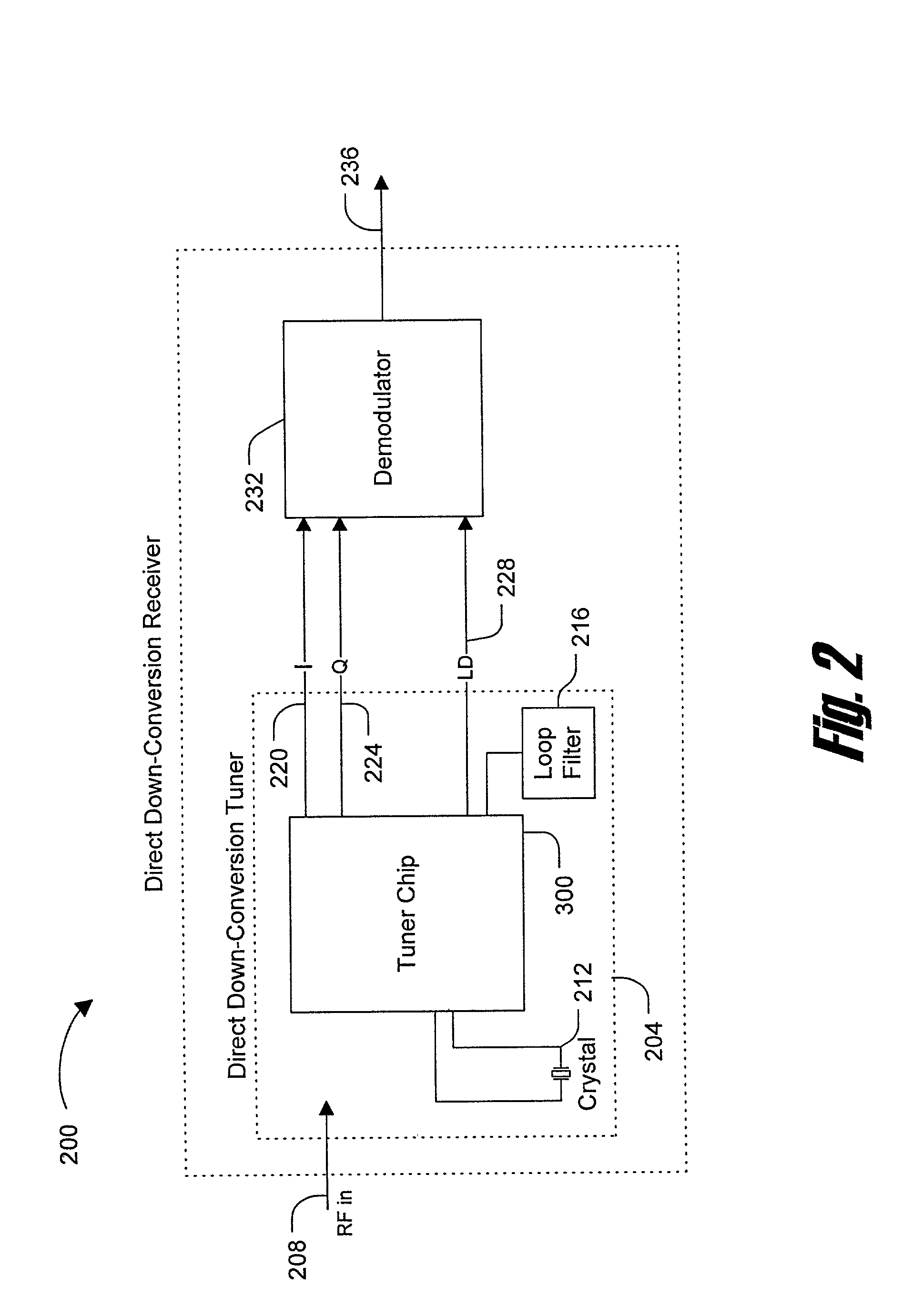

System and method of frequency synthesis to avoid gaps and VCO pulling in direct broadcast satellite systems

ActiveUS6968020B1Reduced VCO pullingVCO pulling within the broadband tuner is reducedTransmissionAngle demodulation by phase difference detectionFrequency coverageFrequency spectrum

A system and method for designing a broadband tuner such that VCO pulling is minimized and gaps in frequency coverage are avoided, while total power consumption is reduced, is disclosed. A broadband spectrum is divided into sub-bands and various multipliers to a local oscillator output are introduced. In this fashion, the present invention allows a local oscillator within the broadband tuner to always generate signals that lie outside of the broadband spectrum for a particular broadband application. Additionally, a modulus ratio for a dual modulus prescaler with the local oscillator is maximized, thereby reducing power consumption.

Owner:SYNAPTICS INC

Co-prime division prescaler and frequency synthesizer

InactiveUS20040036513A1Pulse automatic controlCounting chain pulse countersControl signalFrequency synthesizer

A system may include a control unit and a dual modulus prescaler. The control unit may generate a modulus control signal. The dual modulus prescaler may be configured to divide the frequency of an input signal by Q when the modulus control signal has a first value and to divide the frequency of the input signal by (Q+V) when the modulus control signal has a second value. Q is an irreducible fraction. The sum (Q+V) may be an integer or a fraction. The dual-modulus prescaler includes several clocked storage units (e.g., flip-flops) that are each clocked by a respective one of several equally spaced phases of the input signal. Each clocked storage unit operates in a toggle mode.

Owner:DSP GROUP

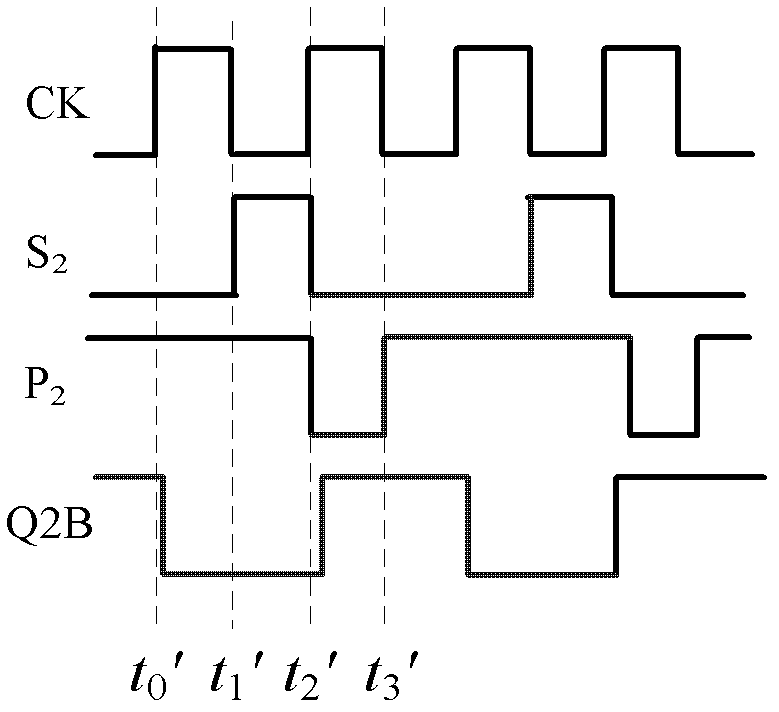

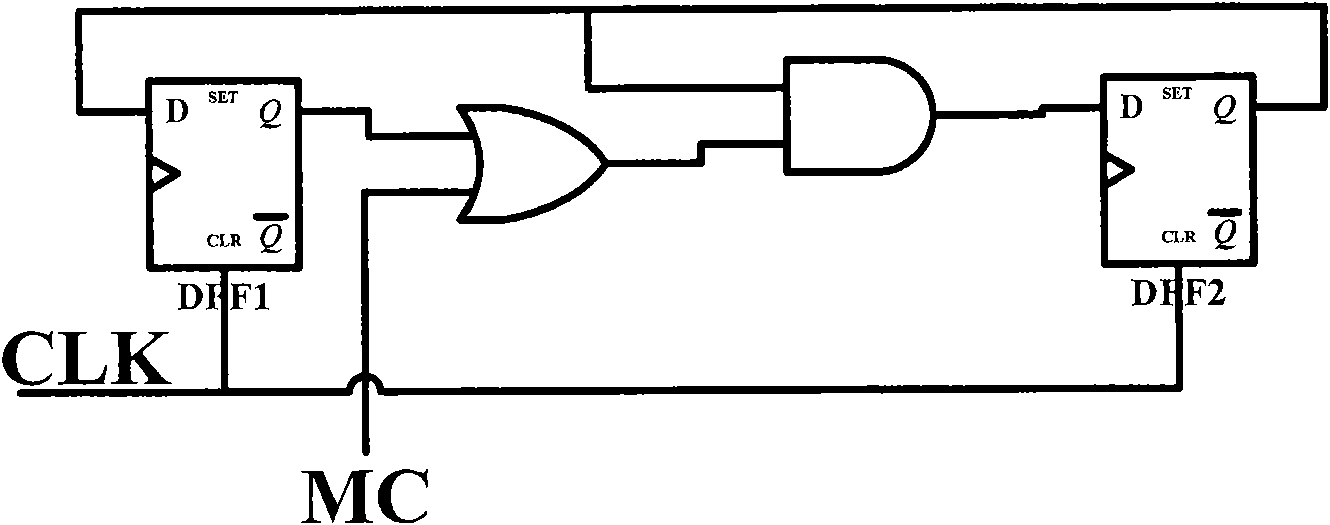

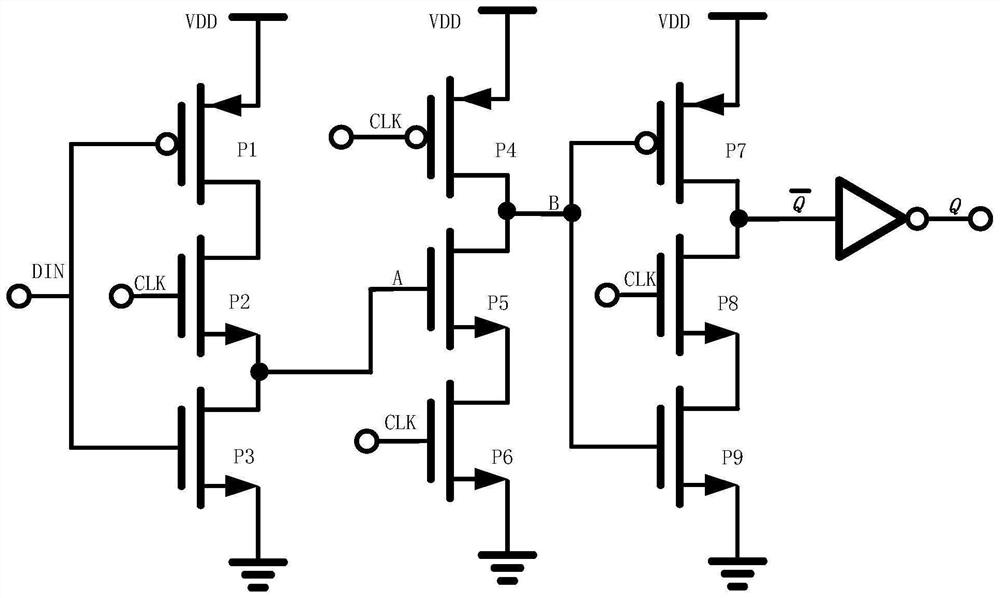

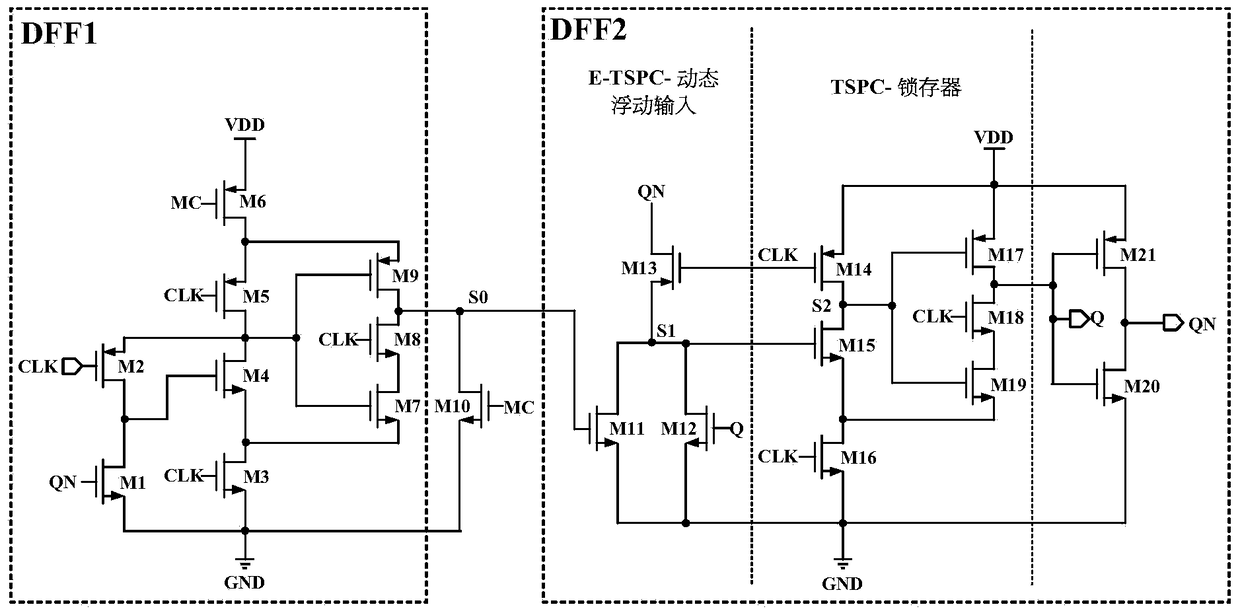

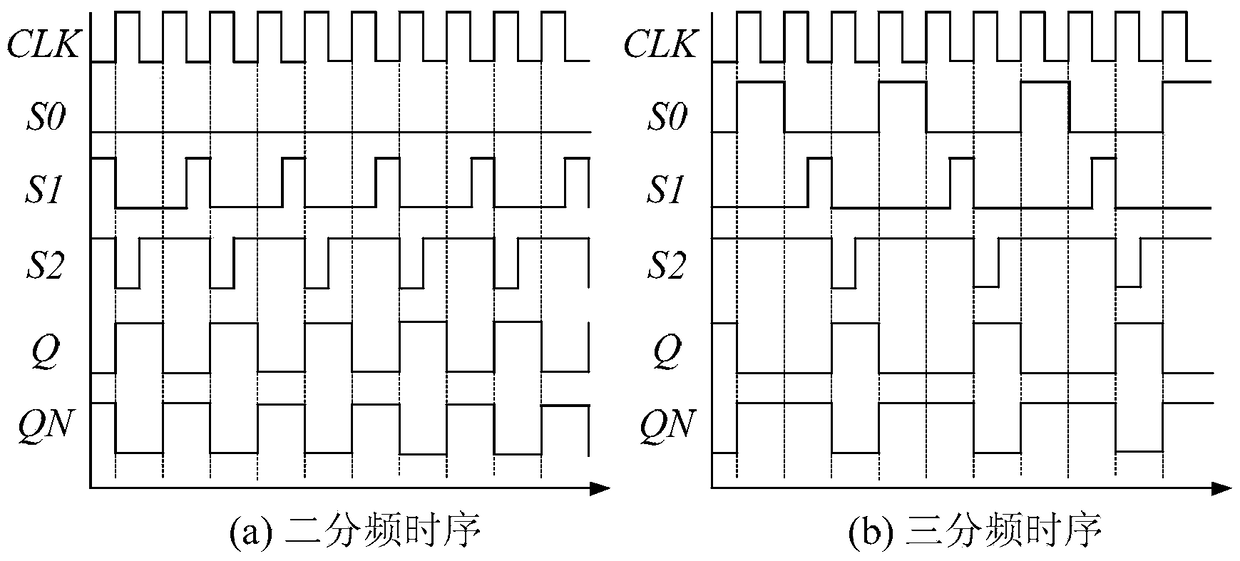

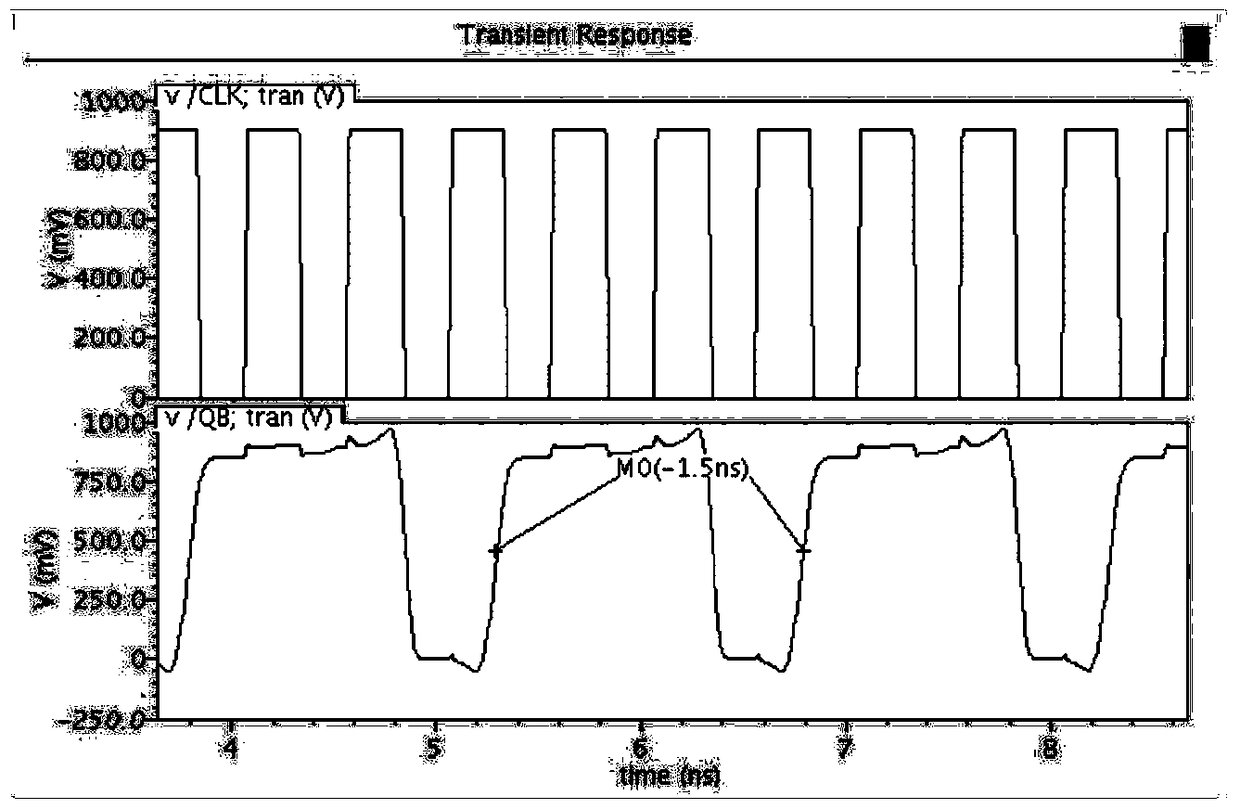

True Single-Phase Clock (TSPC) 2/3 dual-mode prescaler with high speed and low power consumption

InactiveCN102497201AWork fasterRealize three-way operationCounting chain synchronous pulse countersDual modePre-charge

The invention discloses a True Single-Phase Clock (TSPC) 2 / 3 dual-mode prescaler with a high speed and low power consumption. The TSPC 2 / 3 dual-mode prescaler comprises six-stage dynamic phase inverters, a D trigger DFF1 in a TSPC structure which is formed by serially connecting a first-stage dynamic phase inverter, a second-stage dynamic phase inverter and a third-stage dynamic phase inverter and a D trigger DFF2 in a TSPC structure which is formed by serially connecting a fourth-stage dynamic phase inverter, a fifth-stage dynamic phase inverter and a sixth-stage dynamic phase inverter. The TSPC 2 / 3 dual-mode prescaler with the high speed and the low power consumption, disclosed by the invention, removes an AND gate and an OR gate in the traditional TSPC 2 / 3 dual-mode prescaler structure and directly sends outputs of the first D trigger to the fifth-stage dynamic phase inverter in the second D trigger to control pre-charge from the fifth-stage dynamic phase inverter to a node P2 and delay high electric level output by the 2 / 3 dual-mode prescaler for one more clock period. Therefore, three-way frequency division operation is realized and working speed for the three-way frequency division of the 2 / 3 dual-mode prescaler is improved.

Owner:SOUTHEAST UNIV

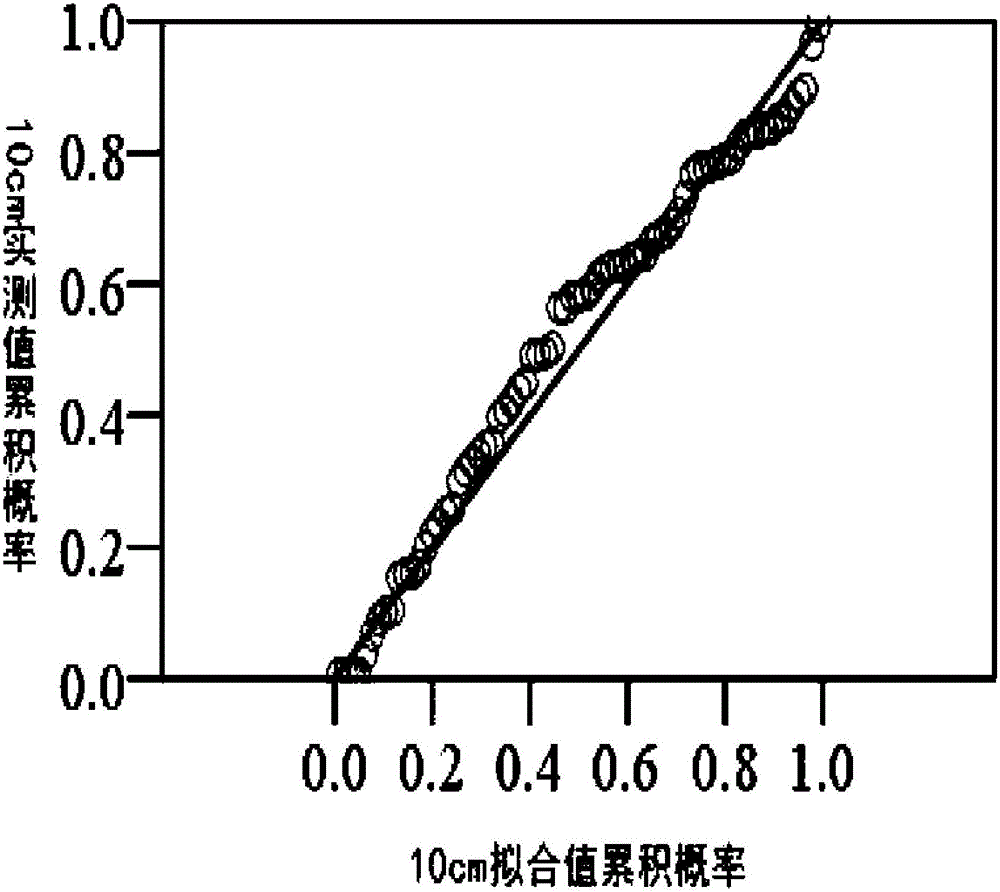

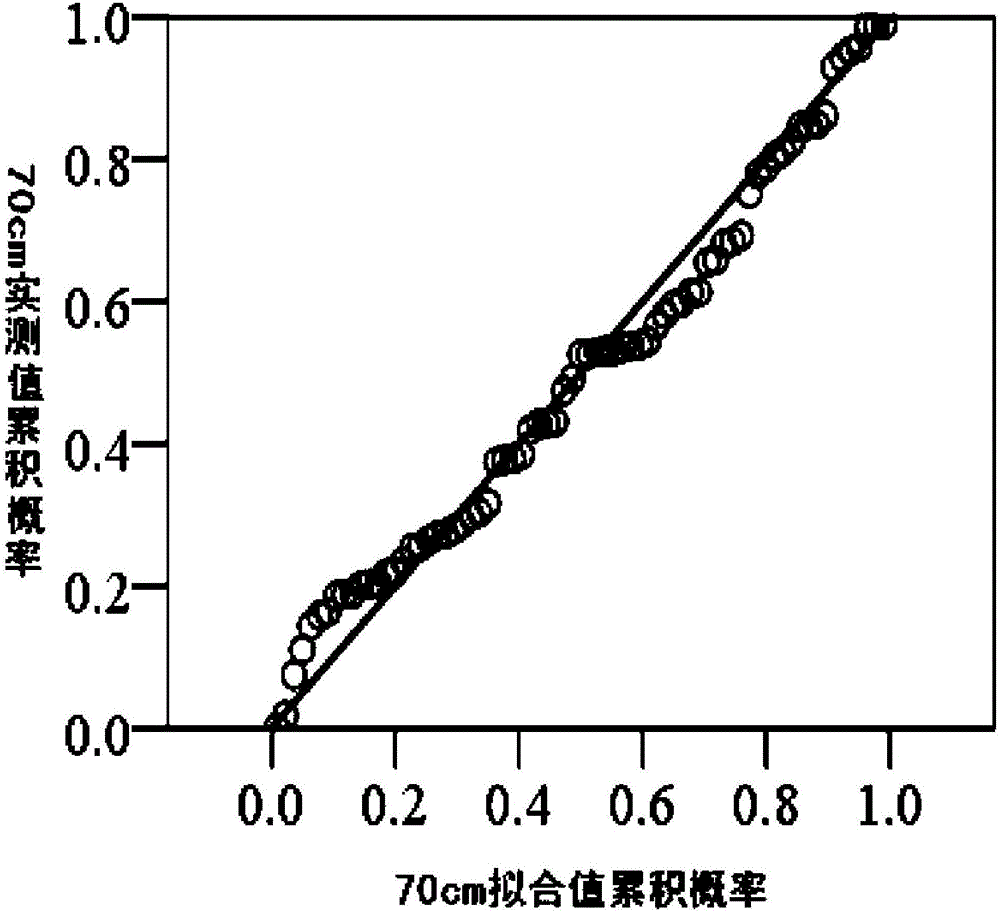

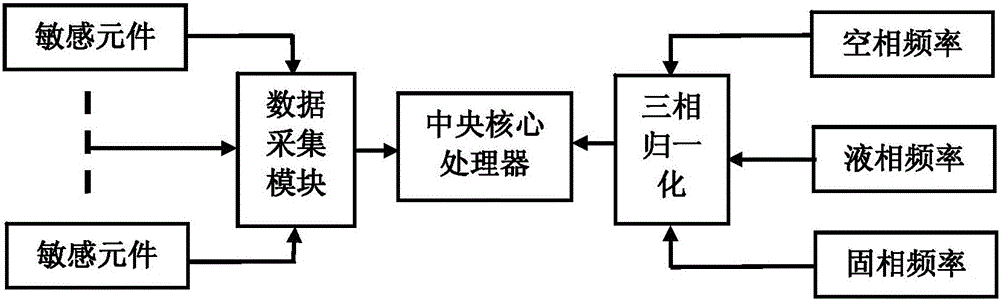

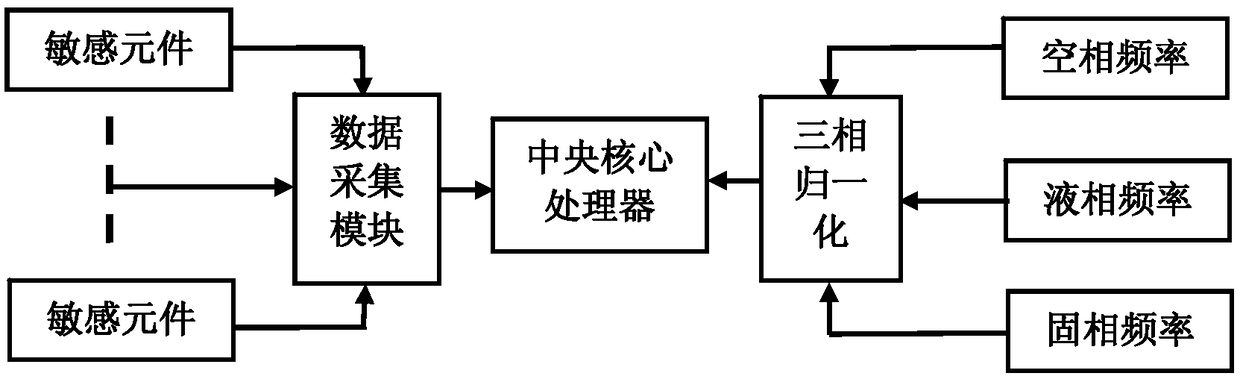

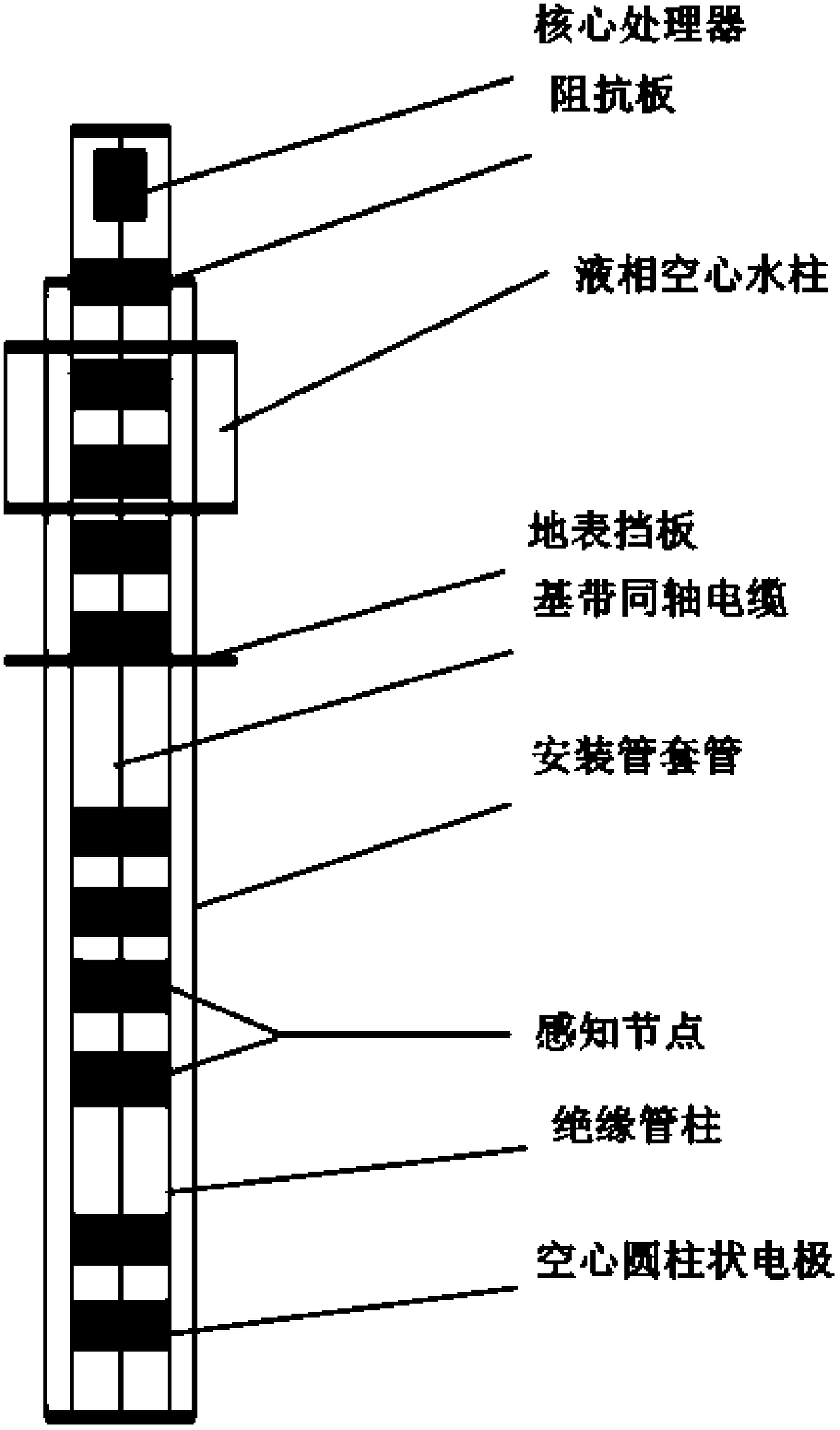

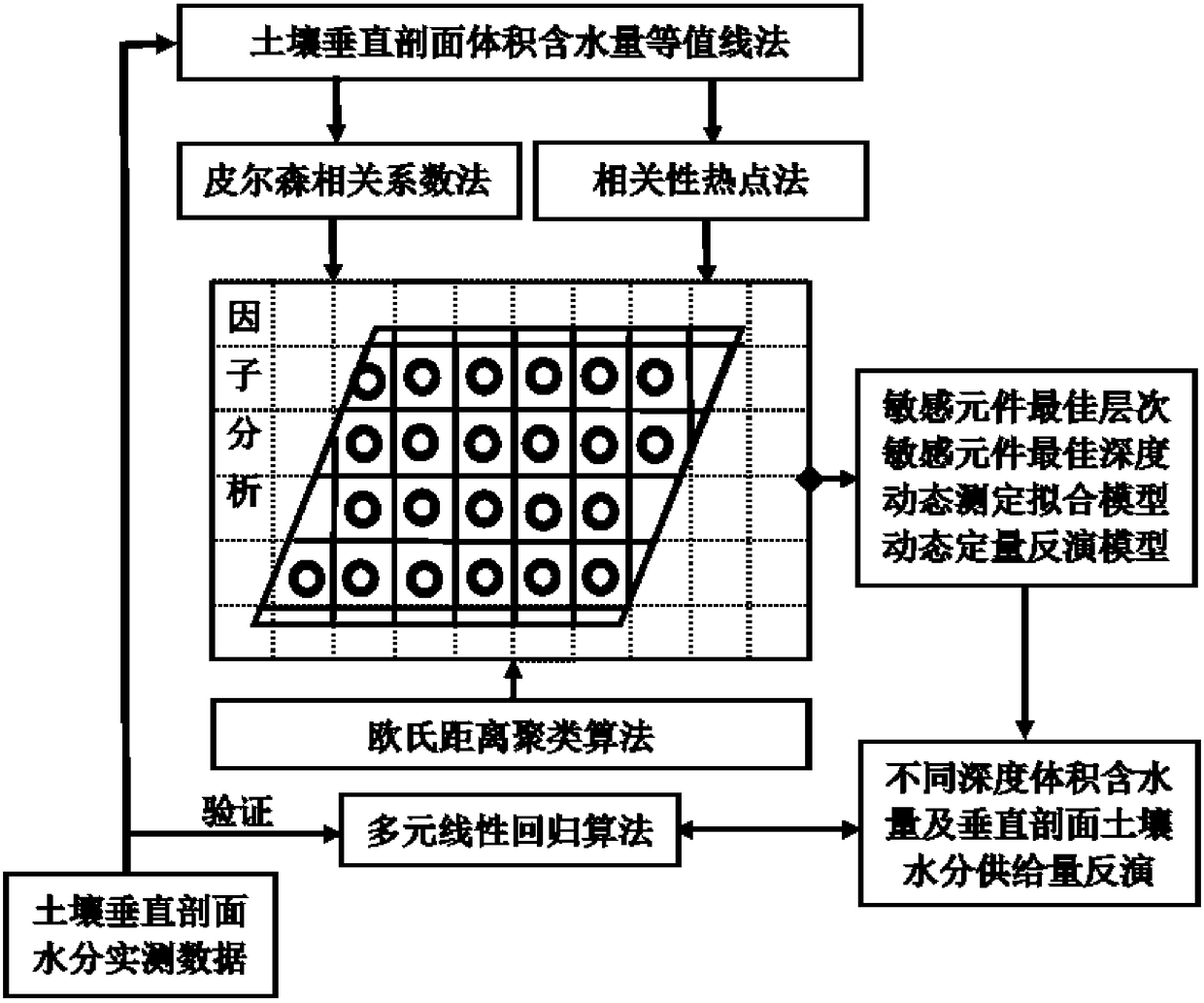

Moisture measurement method and device of vertical section of farmland soil

ActiveCN105758901ARealize precise perceptionStrong spatial integrityMaterial capacitanceLow noiseMeasurement device

The invention discloses a moisture measurement method and device of a vertical section of farmland soil. The device is characterized by comprising a mounting pipe sleeve, a hollow cylindrical electrode, an insulating pipe column, a base band coaxial cable, a liquid-phase hollow water column, a resisting plate and a core processor; the moisture measurement device of the vertical section of the soil is controlled by a voltage-controlled oscillator to generate a high-frequency oscillation signal; a low-frequency square wave signal is obtained through silicon epitaxy high-frequency and low-noise amplitude amplification, and shaping and frequency division of a dual-modulus prescaler; accurate sensing of the volume moisture content of the soil is realized through a mathematical model between the frequency and the volume moisture content of the soil. A cylindrical stereoscopic type multilayered structure is adopted, and a moisture dynamic determination fitting and quantitative inversion technology of the vertical section of the farmland oil is integrated, so that the volume moisture convent of different heights of the vertical section of the farmland oil and the moisture supply amount of the soil of the vertical section are dynamically sensed in real time by utilizing the fewest layers; the moisture measurement method and device has the greatest advantages that the moisture condition of the vertical section of the soil can be continuously sensed in real time, the space integrity is strong and real-time calibration can be realized.

Owner:NANJING AGRICULTURAL UNIVERSITY

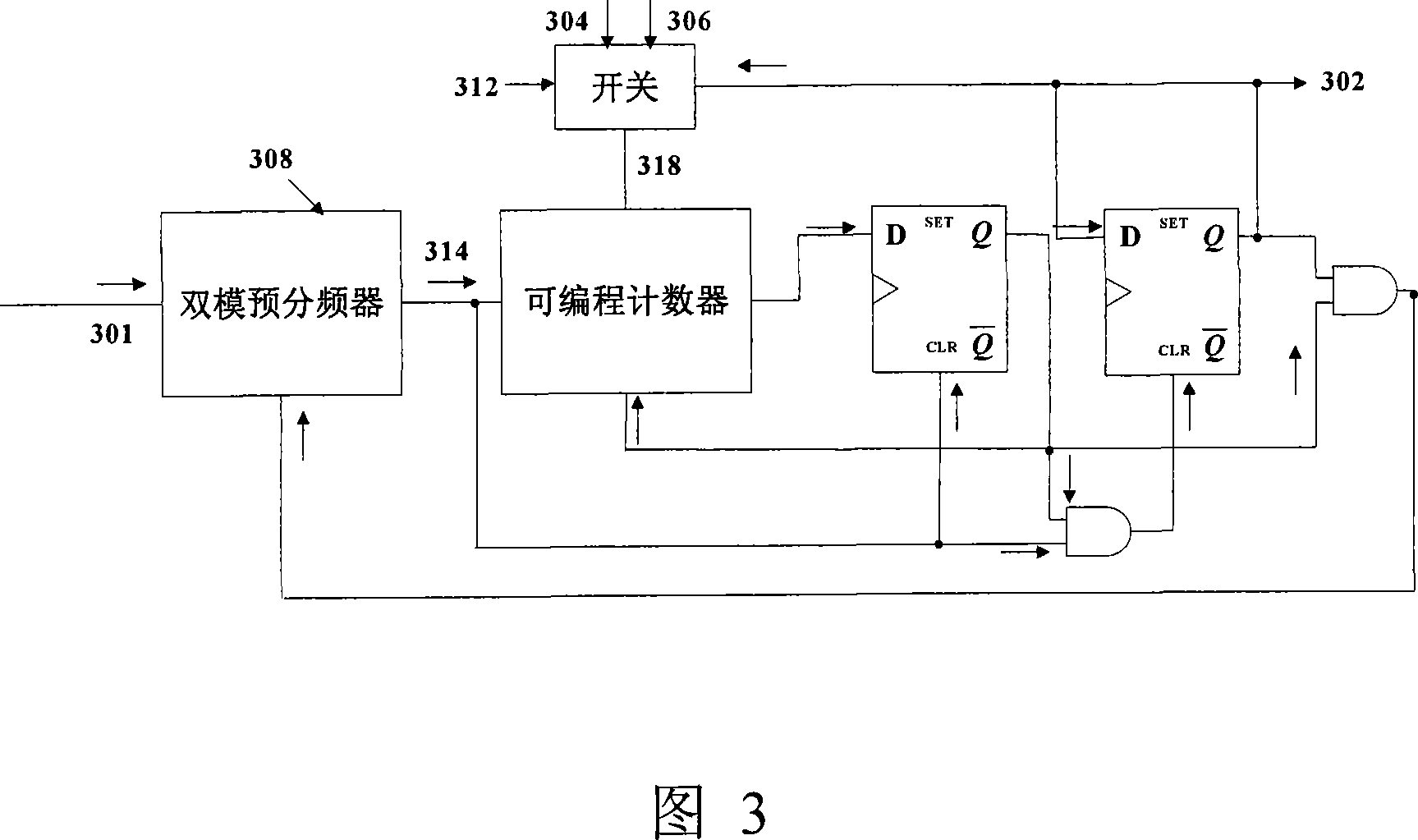

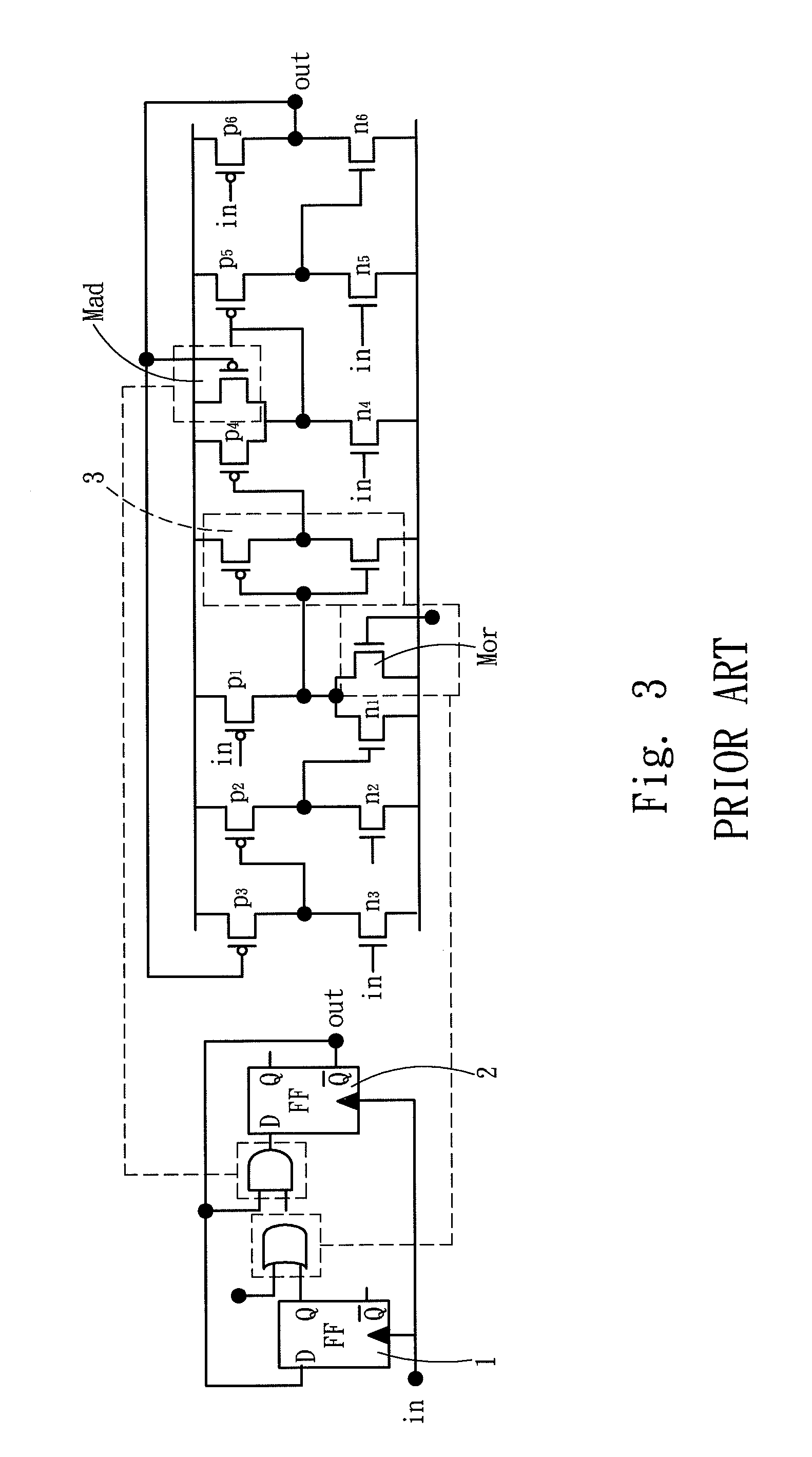

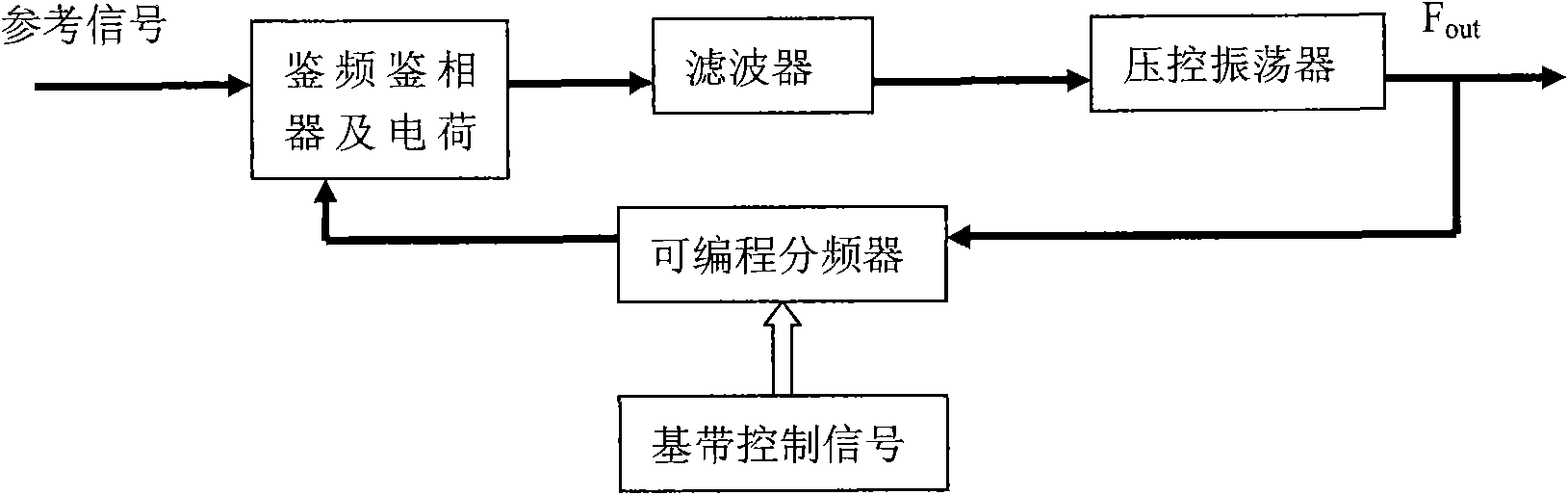

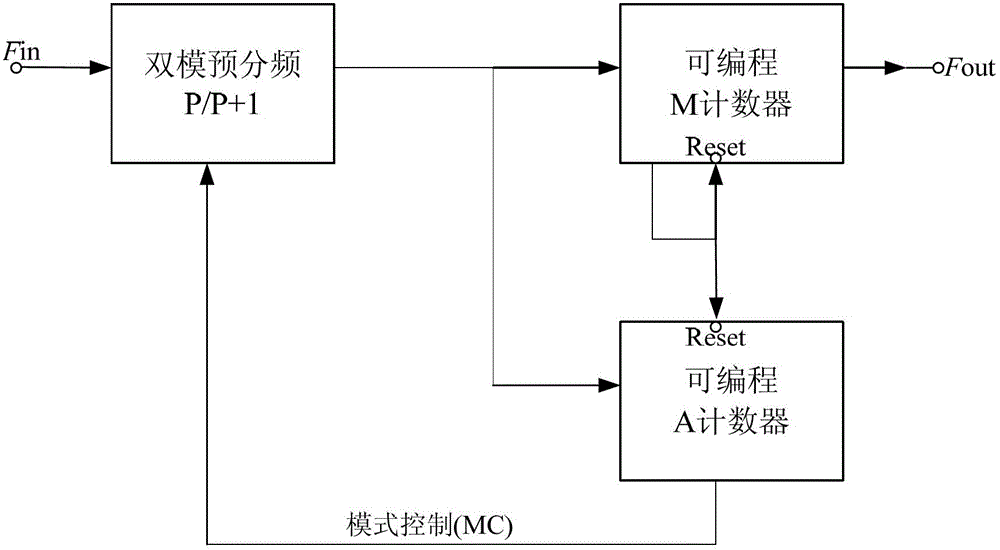

A dual-mode frequency divider

ActiveCN101079631AWork fasterSimple structurePulse automatic controlCounting chain pulse countersDual modeMode control

The invention discloses a double-mode frequency divider, which comprises the following parts: double-mode frequency predivider, which divides frequency for high-frequency signal input by exterior to output the frequency dividing signal to programmable counter; programmable counter, which counts the input frequency dividing signal to generate output metering signal to signal selector at the first signal output end when the counter reaches N or generate output metering signal to signal selector at the second signal output end when the counter reaches M; signal selector, which gates the first or second signal output ends of programmable counter under mode control signal to continuously invert the condition of output end acted by clock to output the mode control signal. The invention realizes the function of programming frequency division, which elevates the working speed of circuit and simplifies the circuit structure.

Owner:锐立平芯微电子(广州)有限责任公司

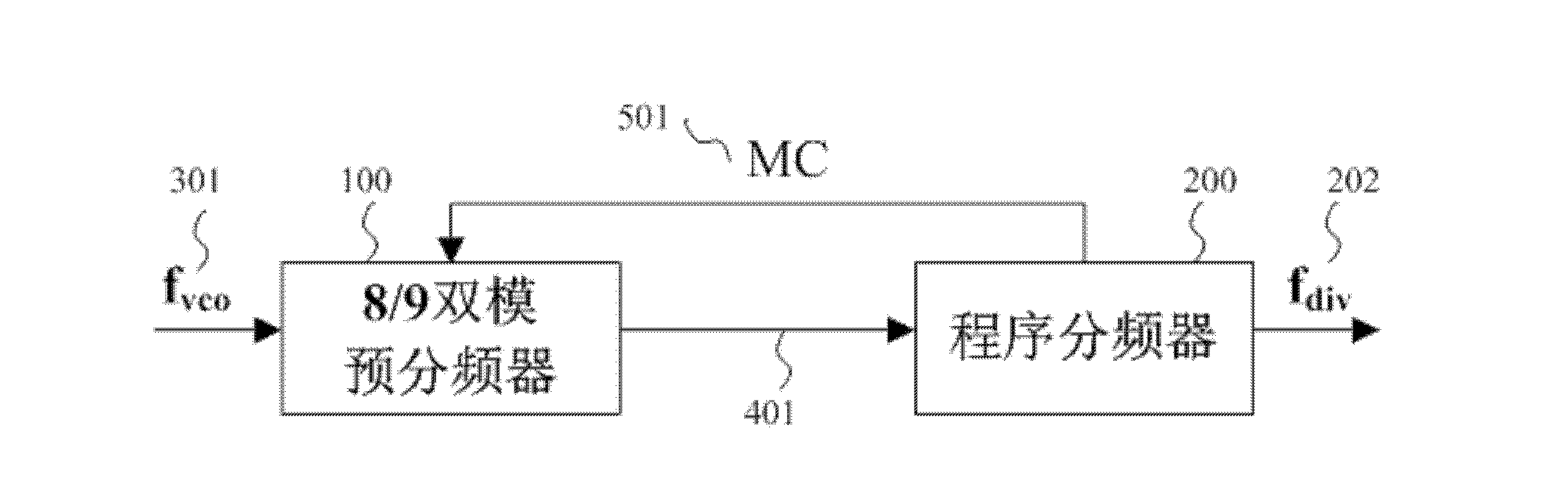

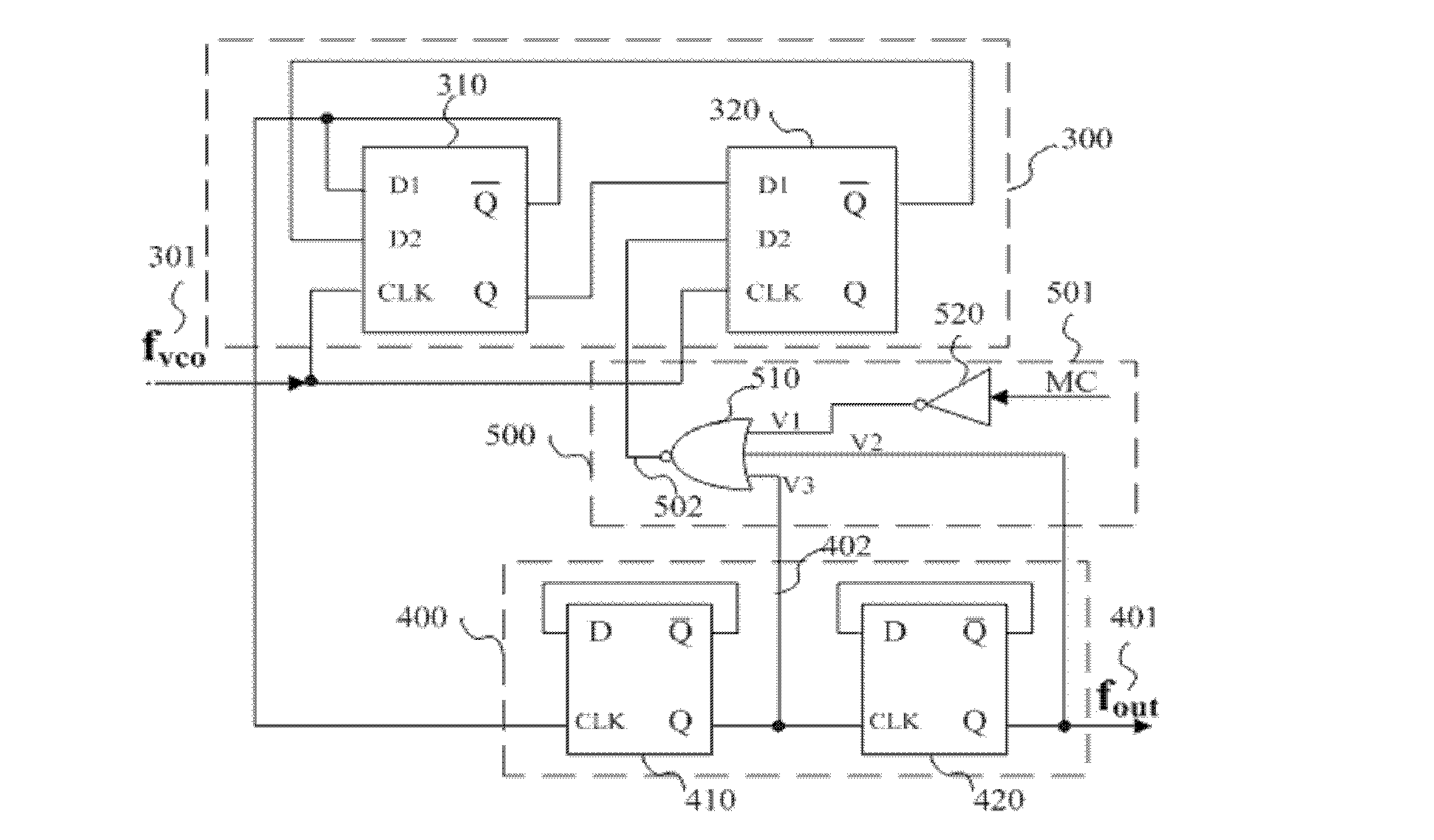

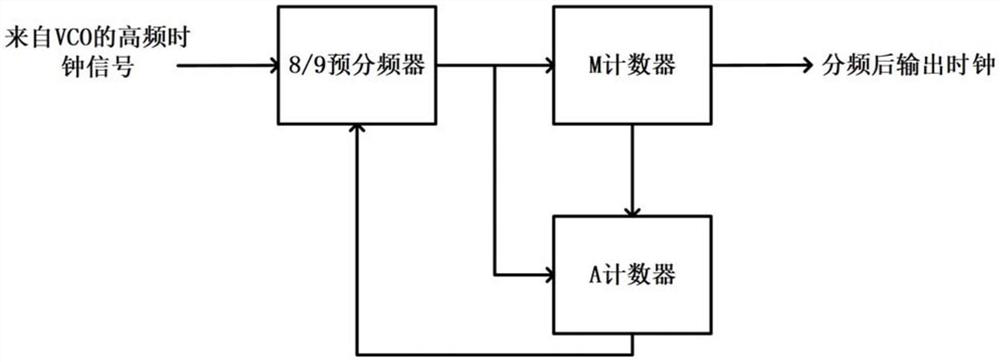

Superspeed 8/9 bimodule prescaler based on GaAa hetero junction bipolar transistor (HBT) device

InactiveCN102324930ARaise the eigenfrequencyReduce phase noisePulse automatic controlPhase noiseFrequency synthesizer

The invention discloses a superspeed 8 / 9 bimodule prescaler based a GaAa hetero junction bipolar transistor (HBT) device, which mainly solves the problems of low working frequency and high phase noise of the prior art. The superspeed 8 / 9 bimodule prescaler based on the GaAa HBT device comprises a 2 / 3 bimodule prescaler, an asynchronous 4 division frequency divider and a mode selection logic circuit. The 2 / 3 bimodule prescaler is formed by two D triggers which are embedded with NADN gates, the 4 division frequency divider is formed by two D triggers which are asynchronously connected with each other, and the mode selection logic circuit is formed by a triple-input NOR gate and a NOT gate. All the transistors in a prescaler path adopt GaAs single hetero junction bipolar transistors the hetero junction materials of which are InGaP / GaAs. The superspeed 8 / 9 bimodule prescaler based on the GaAa HBT device can realize the 8 frequency division or 9 frequency division function, has high working efficiency, low phase noise, quick working speed, excellent high and low temperature characteristics and better irradiation-resistant performance, and can be applied in a frequency synthesizer in a high-frequency section transmit-receive system.

Owner:XIDIAN UNIV

Prescaler

ActiveUS7248665B2Increase working frequencyReduce power consumptionCounting chain pulse countersPulse counters with static storageAsynchronous circuitSynchronous motor

Owner:WINBOND ELECTRONICS CORP

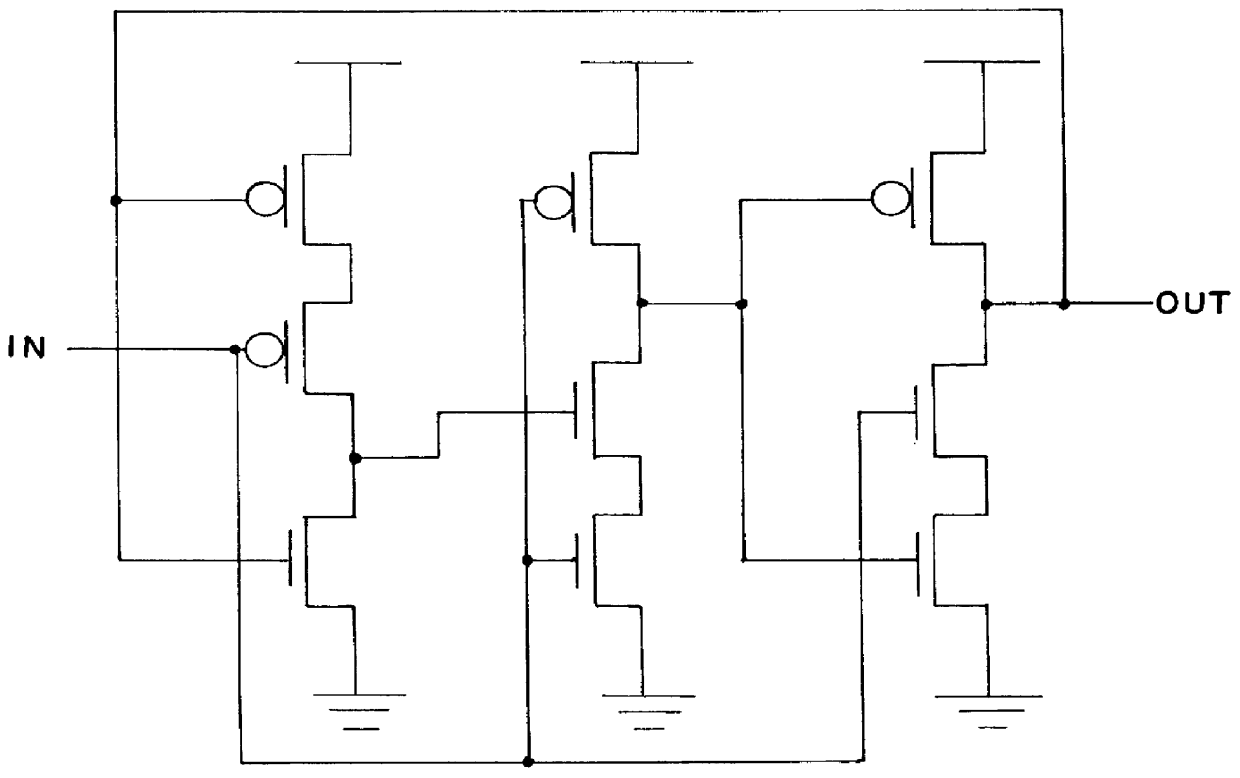

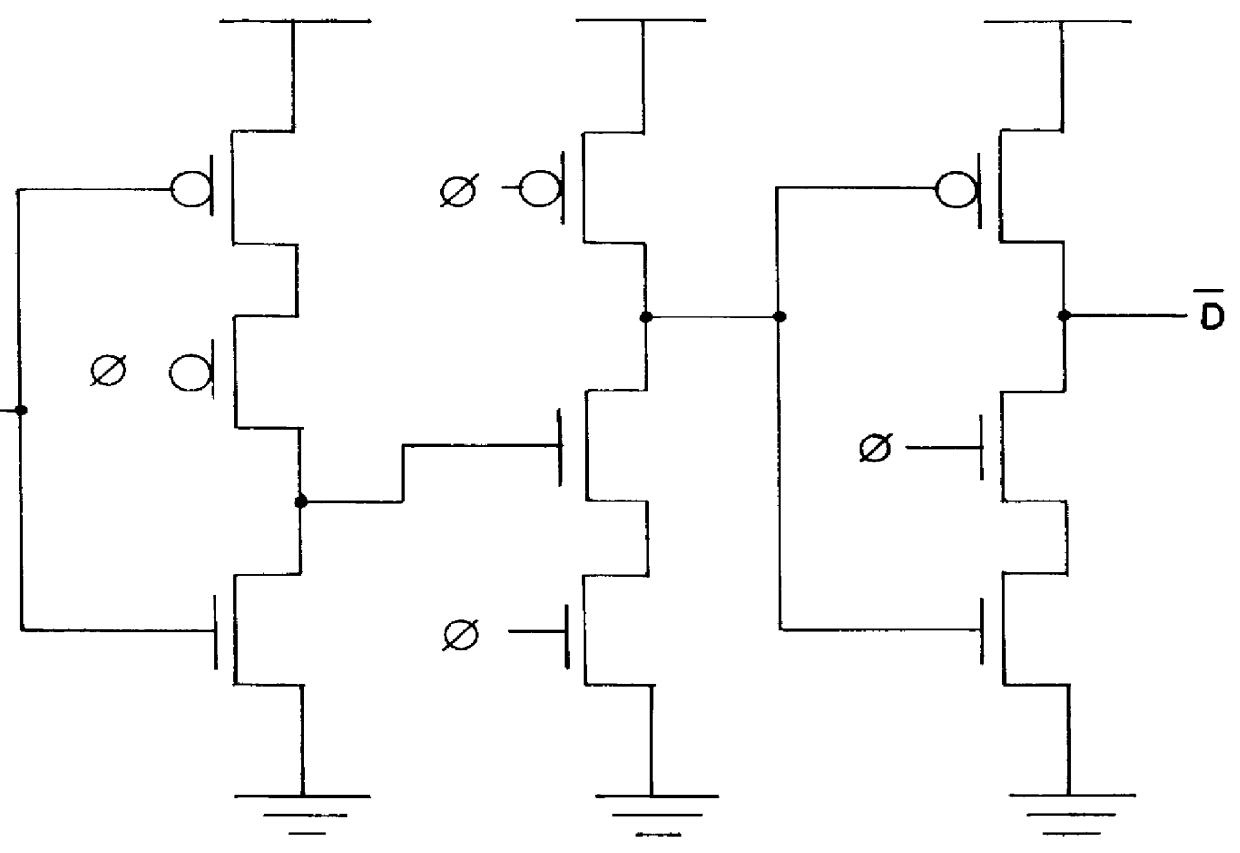

High-frequency CMOS dual/multi modulus prescaler

InactiveUS6094466AAvoid low frequency operationCounting chain synchronous pulse countersCMOSTelecommunications

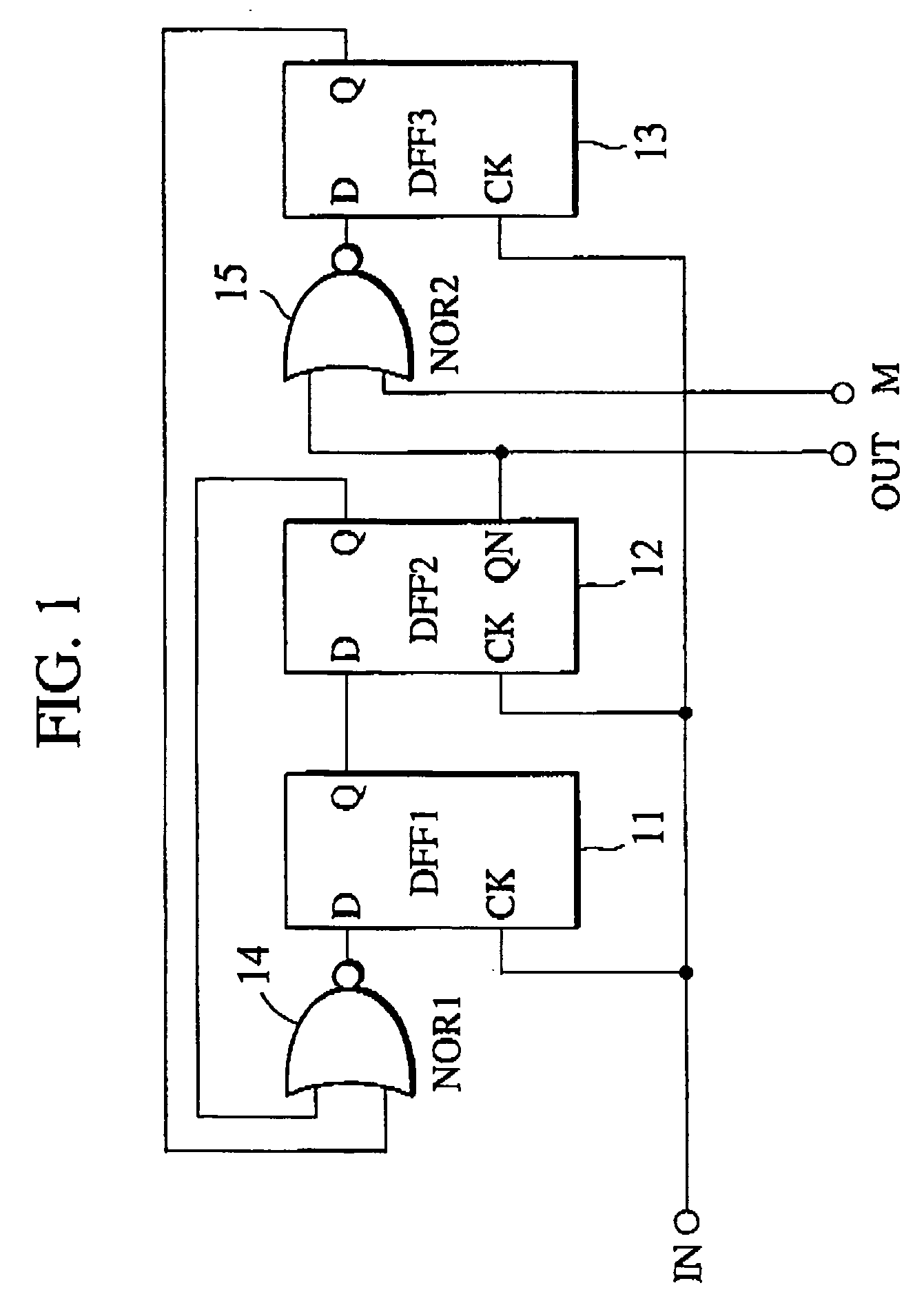

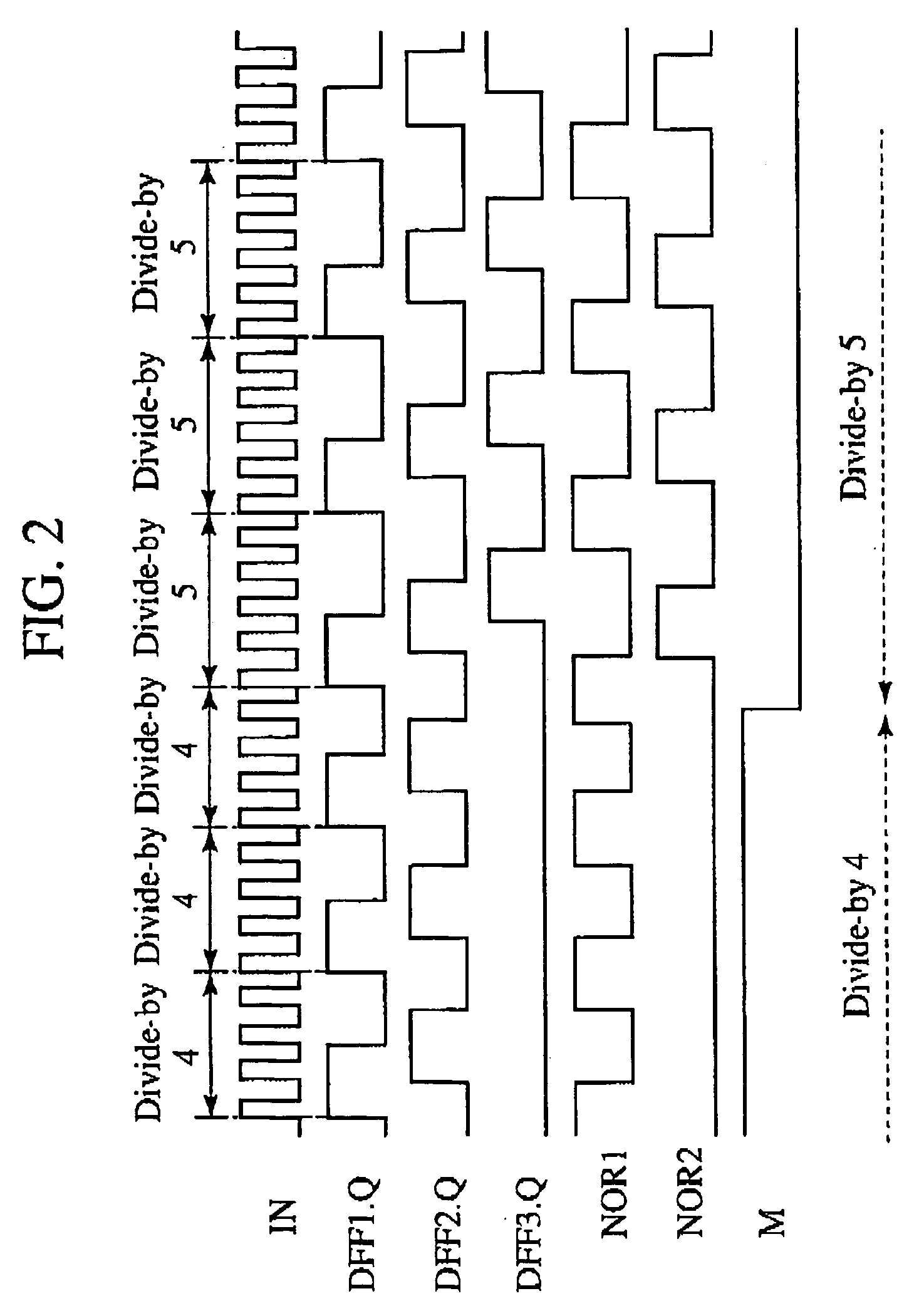

The invention of the "high-frequency CMOS dual / multi modulus prescaler" is a new application in this field. Compared to other transistors which have CMOS technology, this invention has a greater potential for high frequency operations. Additionally, it has a low-power consumption property and can be easily integrated with CMOS technology. We propose a general construction of the prescaler which can be applied to dual-modulus prescaler. First, a divide-by-3 / 4 dual-modulus prescaler and a divide-by-4 / 5 one are presented. Consequently, a general dual-modulus prescaler is developed based on the same technique. Moreover, a general multi-modulus prescaler will also be achieved. The operating frequency can be up to 1 GHz for the proposed dual / multiple modulus prescalers which are fabricated in a 0.8- mu m SPDM CMOS technology.

Owner:NAT SCI COUNCIL

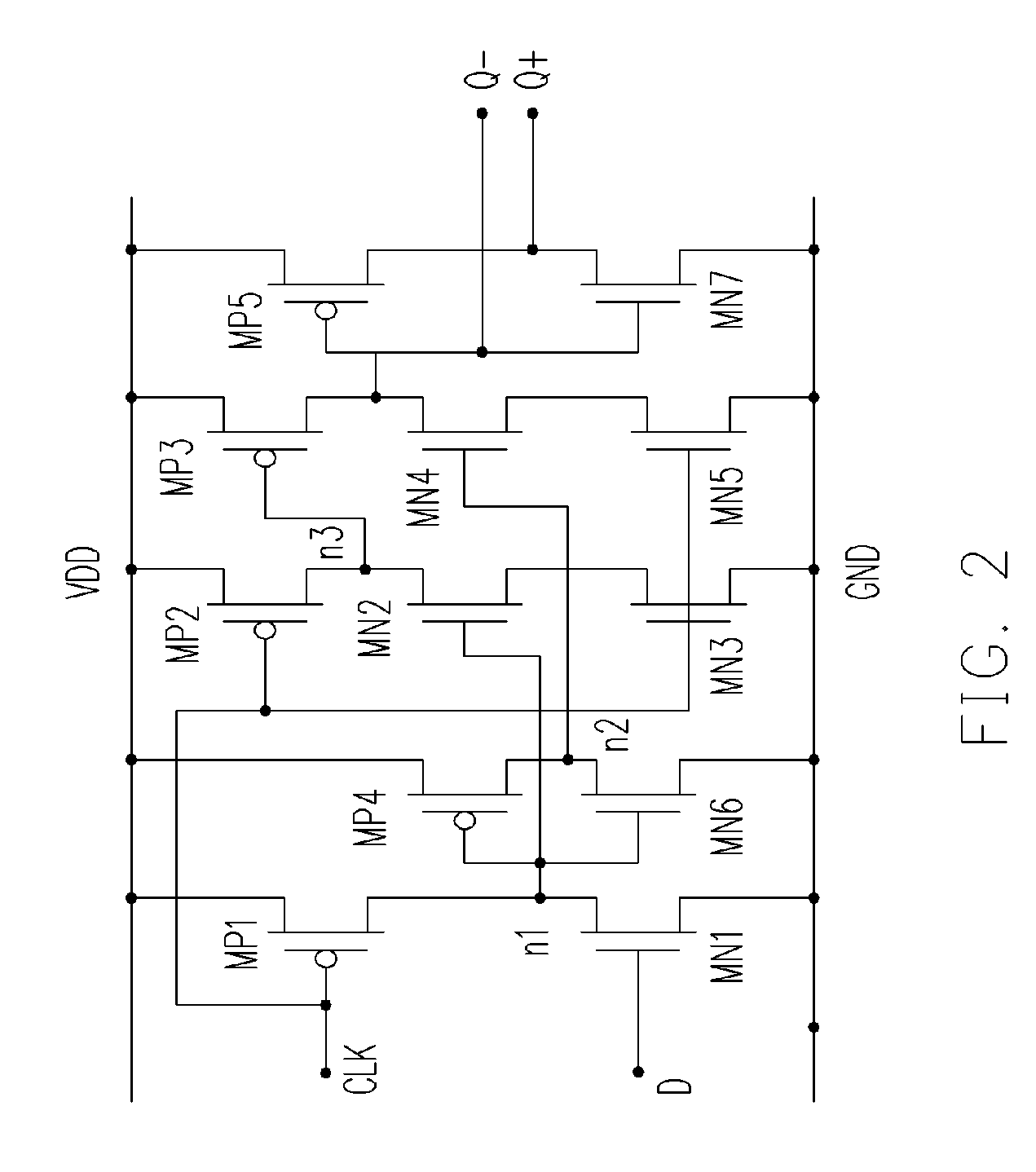

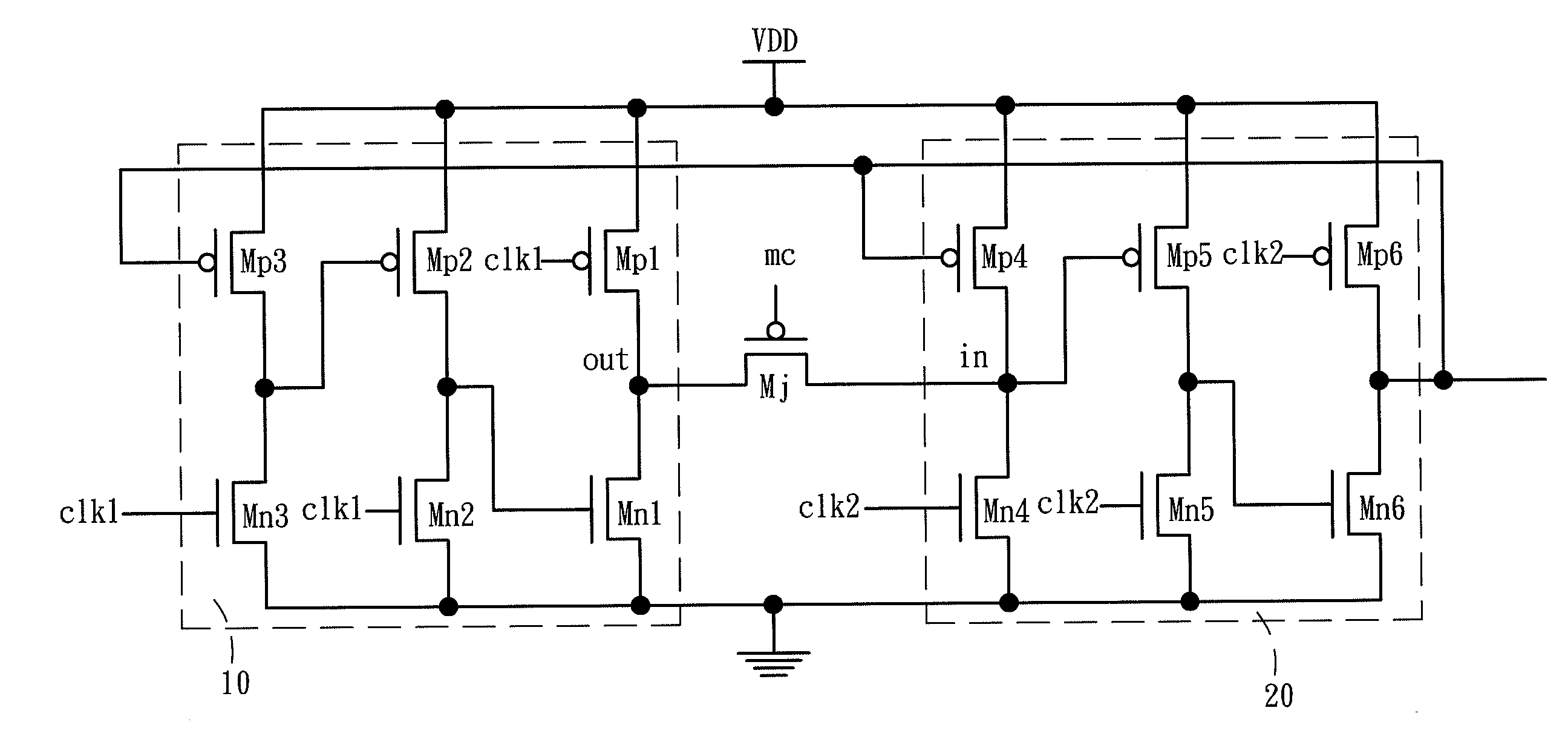

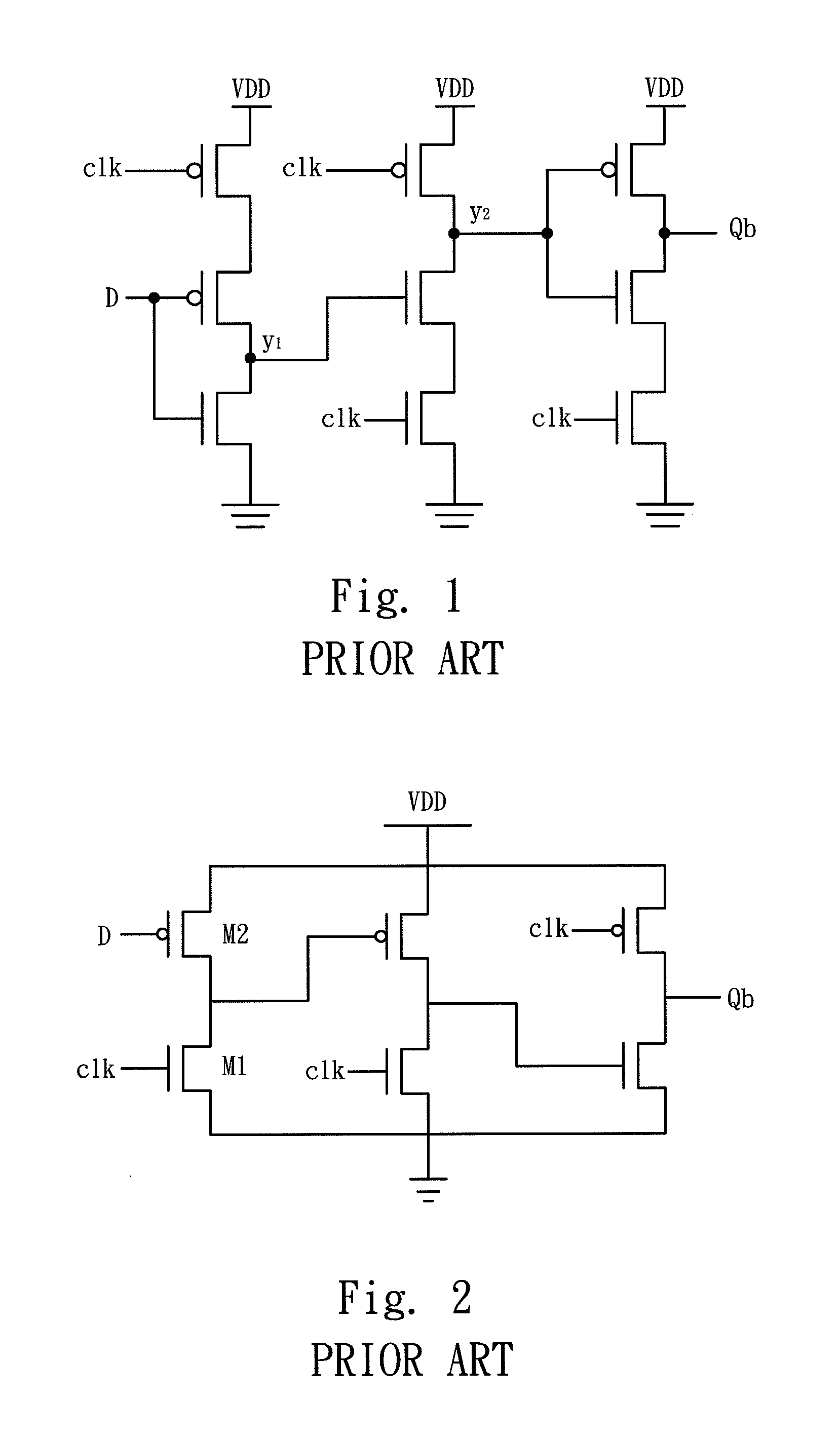

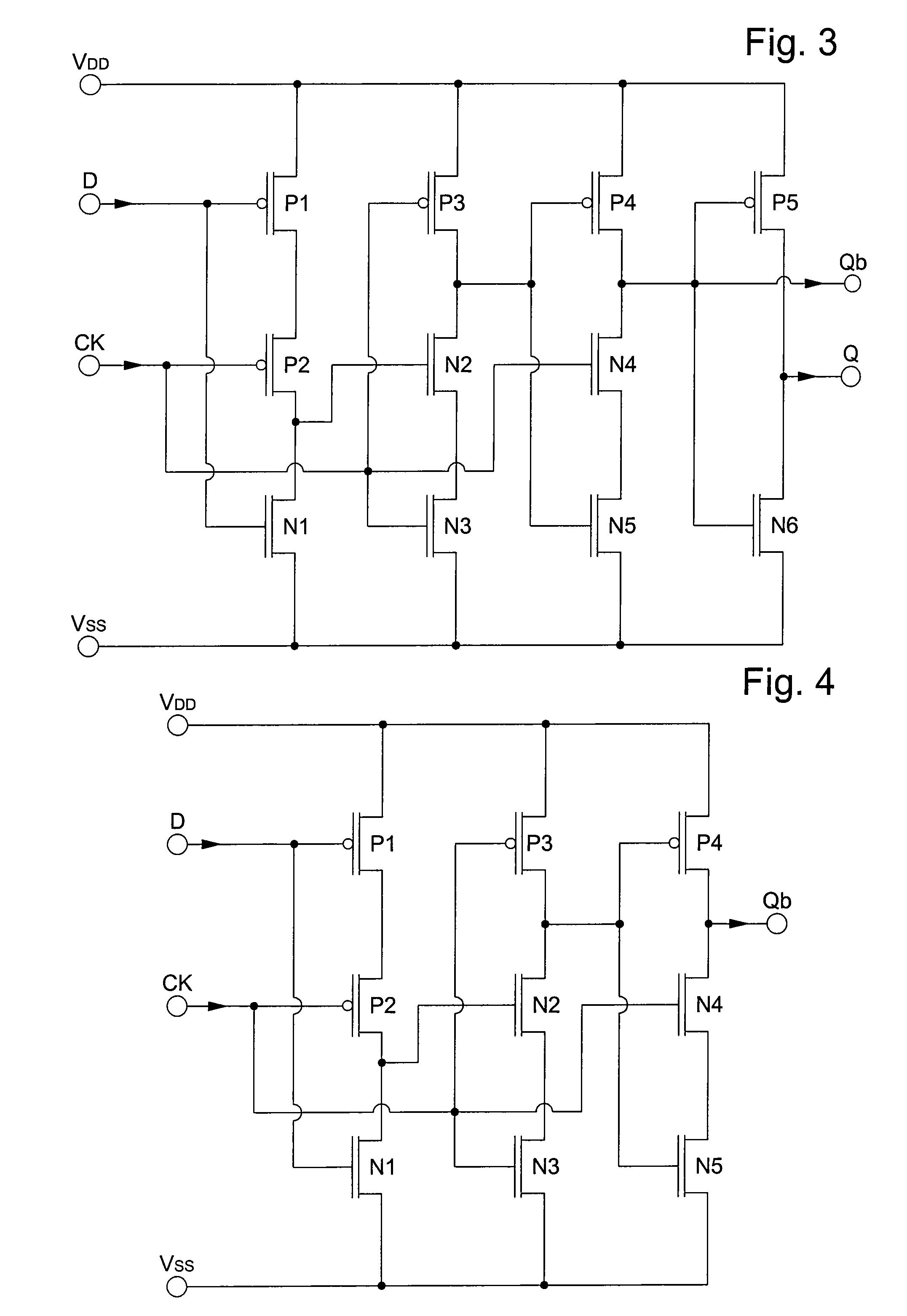

High speed dual modulus prescaler

InactiveUS20110254605A1Save electricityReduce in quantityEnergy efficient ICTCounting chain pulse countersCommunications systemFrequency synthesizer

A high speed dual modulus prescaler aims to be used on a frequency synthesizer of wireless communication systems to divide frequency of input signals. The high speed dual modulus prescaler includes a first D flip-flop, a second D flip-flop and a main control transistor. The main control transistor switches connection of the first D flip-flop and second D flip-flop. The main control transistor provides an OR gate state and an AND gate state to form an OR gate circuit and an AND gate circuit in the prescaler. Thereby the number of transistors in the prescaler can be reduced to increase operation speed and lower power consumption.

Owner:NATIONAL YUNLIN UNIVERSITY OF SCIENCE AND TECHNOLOGY

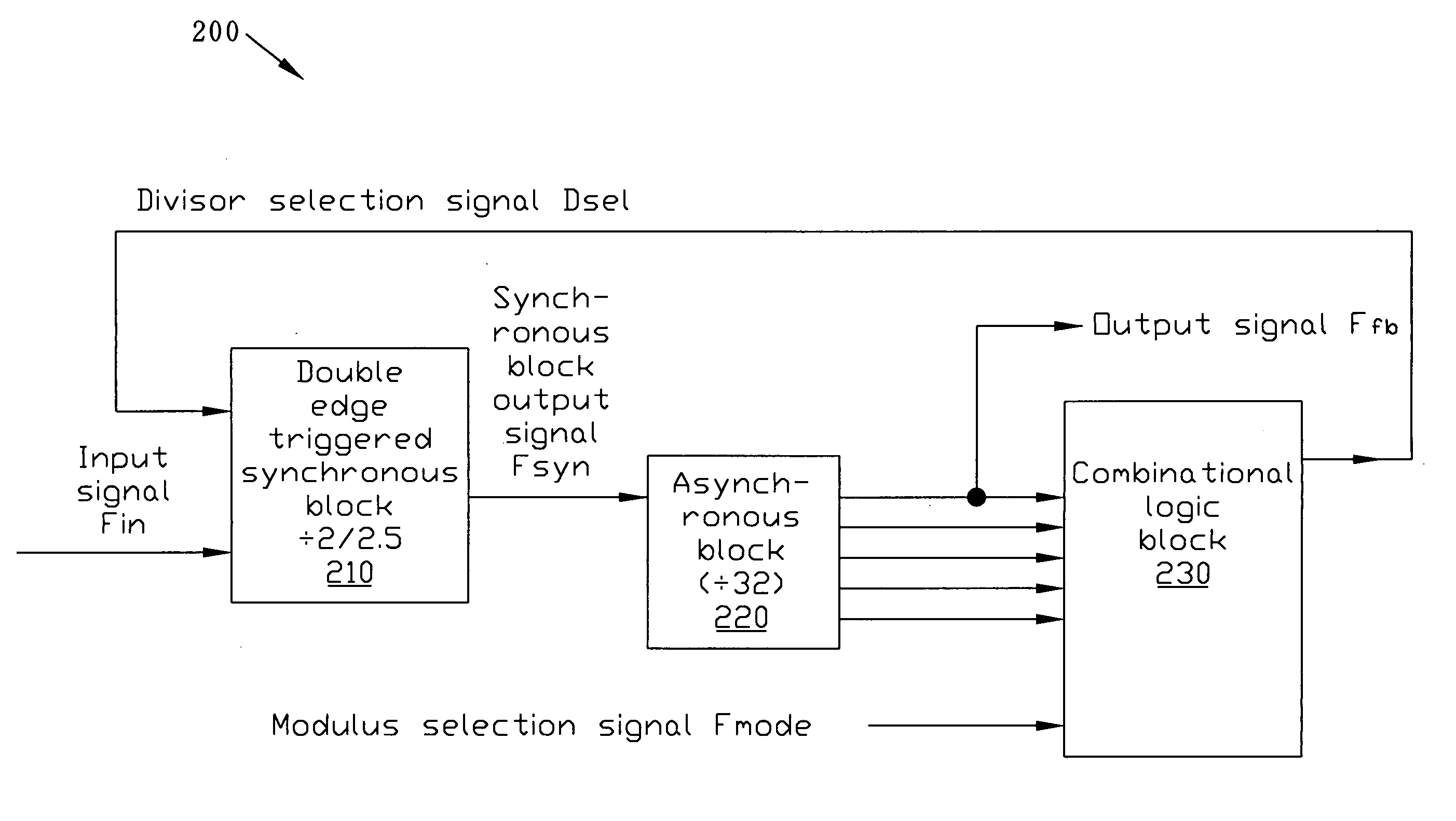

Dual-modulus prescaler using double edge triggered D-flip-flops

InactiveUS20050253630A1Reduce rateReduce energy consumptionCounting chain pulse countersPulse counters with static storageLogic blockDual-modulus prescaler

The present invention provides one dual-modulus prescaler using double edge triggered D-flip-flops. The dual-modulus prescaler comprises one double edge triggered synchronous block, one asynchronous block, and one combination logic block. The double edge triggered synchronous block is used to receive an input signal and a divisor selection signal from the combination logic block, and output a synchronous block output signal to the asynchronous block. The asynchronous block is used to receive the synchronous block output signal and output a plurality of signals to the combination logic block. One of the output signals of the asynchronous block is the output signal of the dual-modulus prescaler. The combination logic block is used to receive all the output signals of the asynchronous block and a modulus selection signal. Then, the combination logic block outputs the divisor selection signal and feeds it back to the double edge triggered synchronous block. The double edge triggered synchronous blockish composed of a plurality of D-flip-flops.

Owner:PERICOM TECH (SHANGHAI) CO LTD

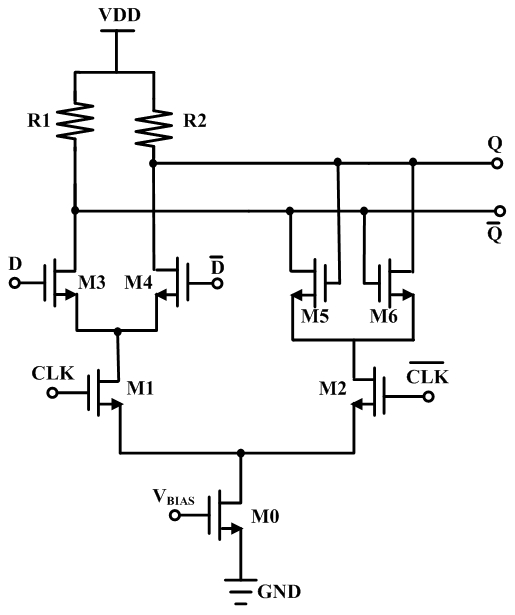

A high-speed large-swing divide-by-two frequency divider circuit based on current-mode logic

InactiveCN102291132AImprove anti-interference abilityReduce noisePulse automatic controlDual modeP channel

The invention discloses a high speed high-oscillation amplitude divide-by-two frequency divider circuit, which belongs to the technical fields of integrated circuit designing and signal processing. Specifically, the circuit mainly comprises two high speed high-oscillation amplitude D triggers which are cascaded. The D trigger of each stage eliminates the bias of a tail current source based on theconventional D trigger having a current-mode logic (CML) structure, and adopts a P-channel metal oxide semiconductor (PMOS) transistor as a load; and simultaneously, a PMOS and N-channel metal oxide semiconductor (NMOS) complementary cross coupling pair structure and the like are adopted by the output stage of the circuit to finally achieve the aims of increasing the oscillation amplitude of an output signal and making the oscillation amplitude of the output signal approximate to full oscillation amplitude under the condition of ensuring the high speed working of the circuit. The circuit not only can directly drive a post circuit, reduces system power consumption to a certain extent, compensates for the shortcomings of a conventional divide-by-two frequency divider, and is suitable for a high speed frequency divider part in a low-power consumption preposed dual-mode prescaler front-end without any additional level conversion amplification circuit.

Owner:EAST CHINA NORMAL UNIV

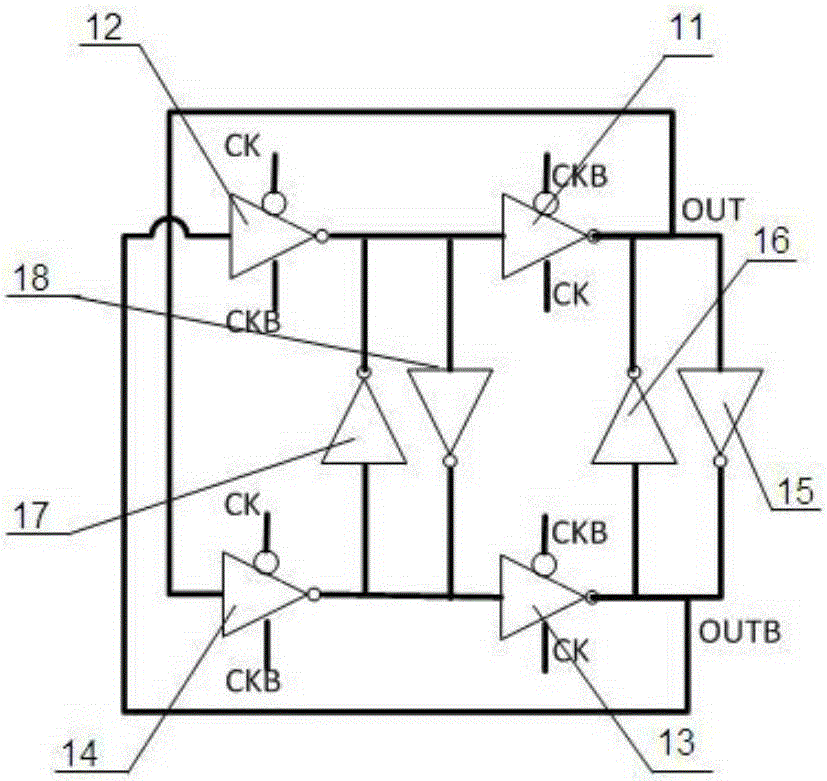

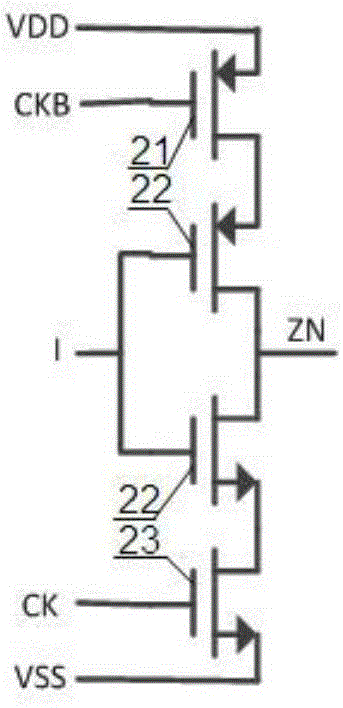

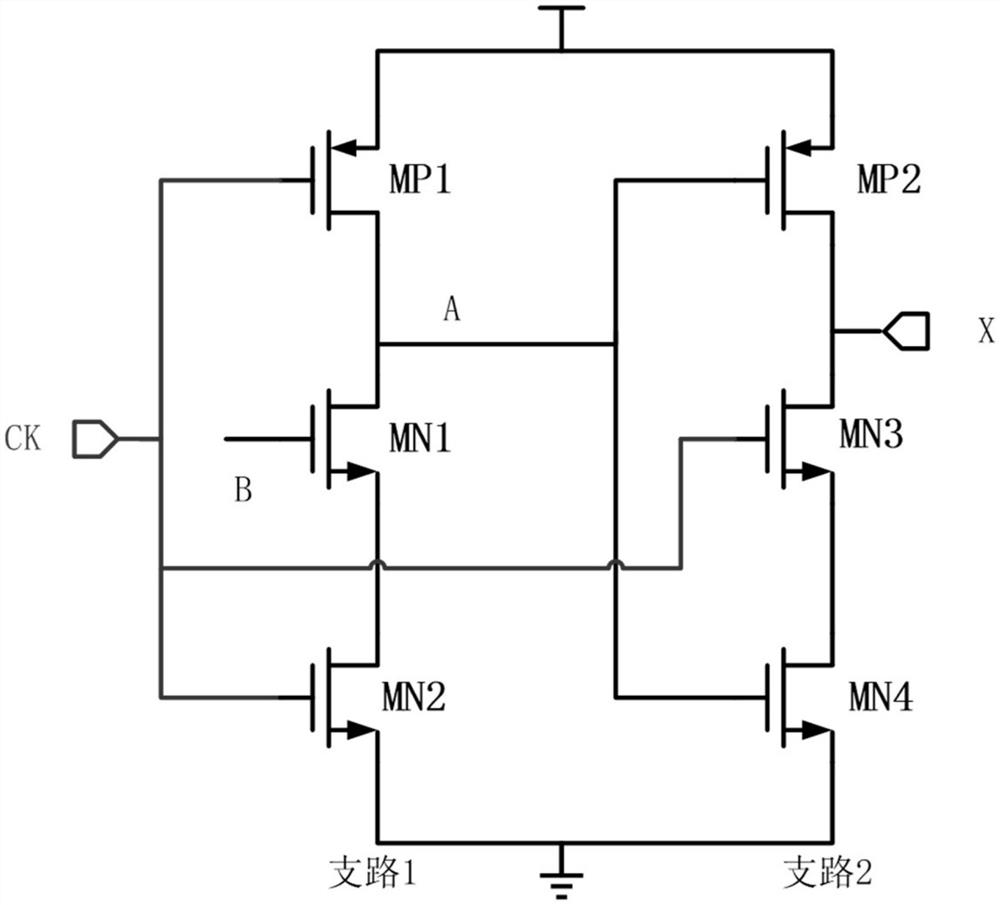

Dual-modulus prescaler circuit operating at a very high frequency

ActiveUS7719326B2Simple structureHigh frequencyPulse automatic controlCounting chain synchronous pulse countersNegative feedbackNAND logic

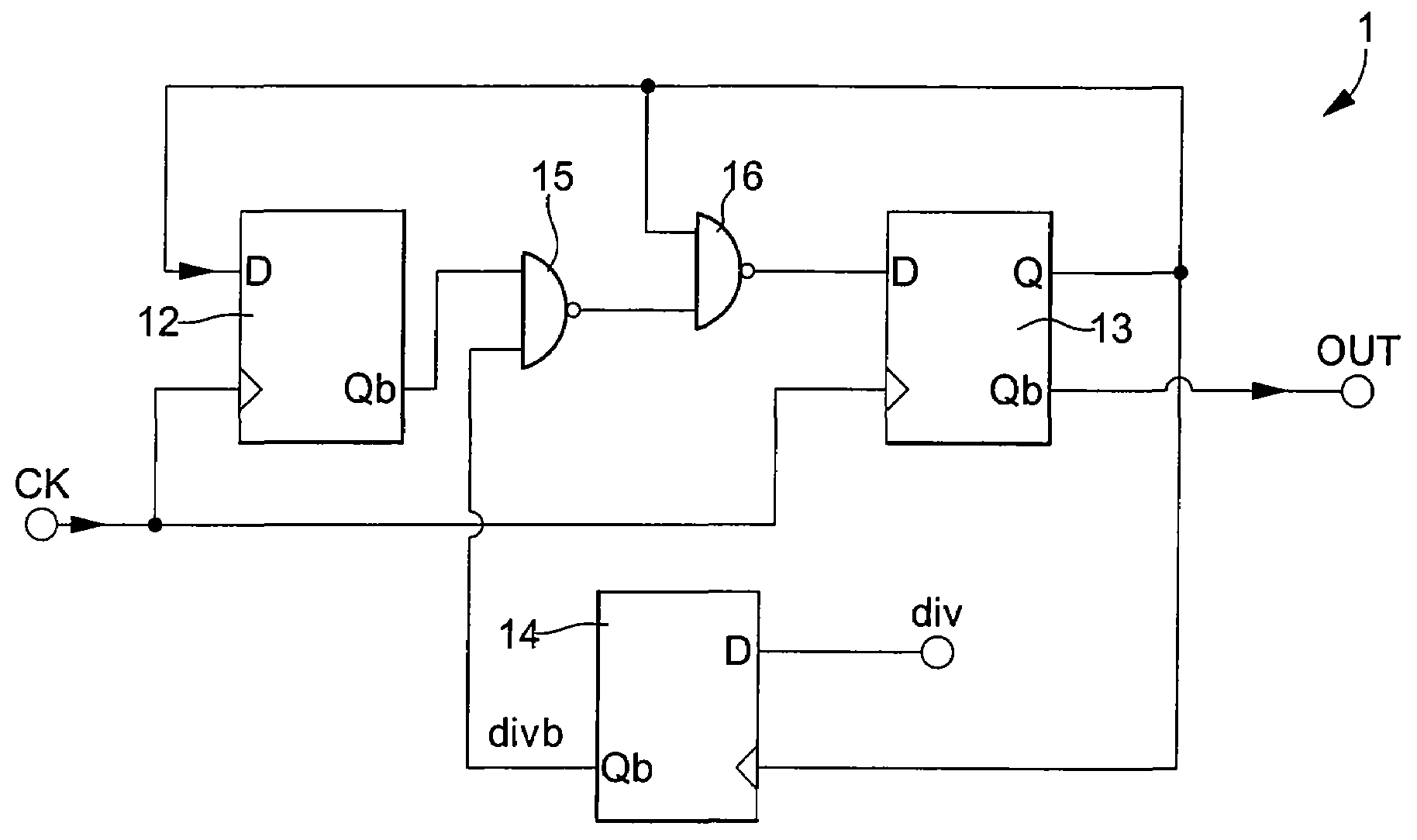

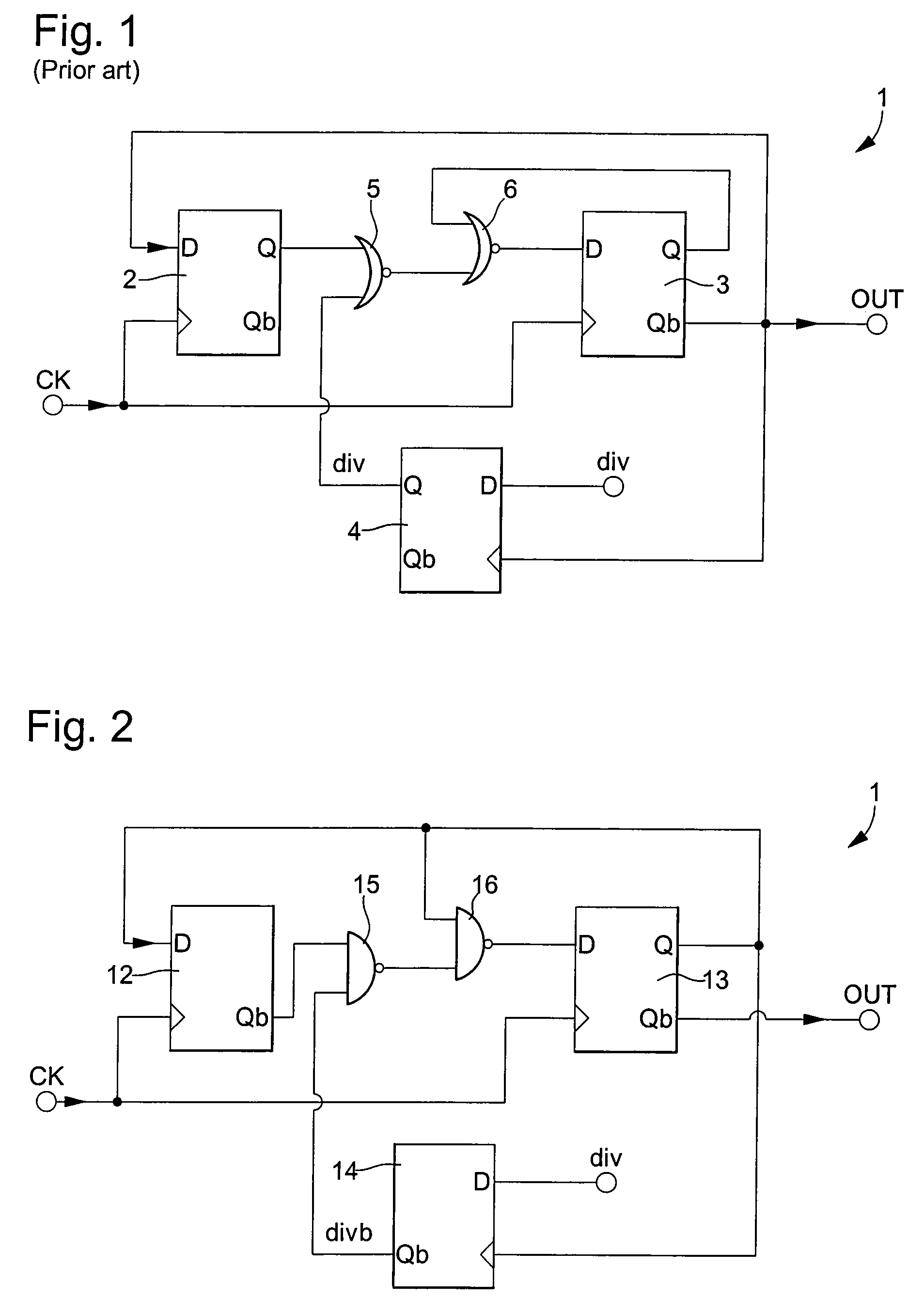

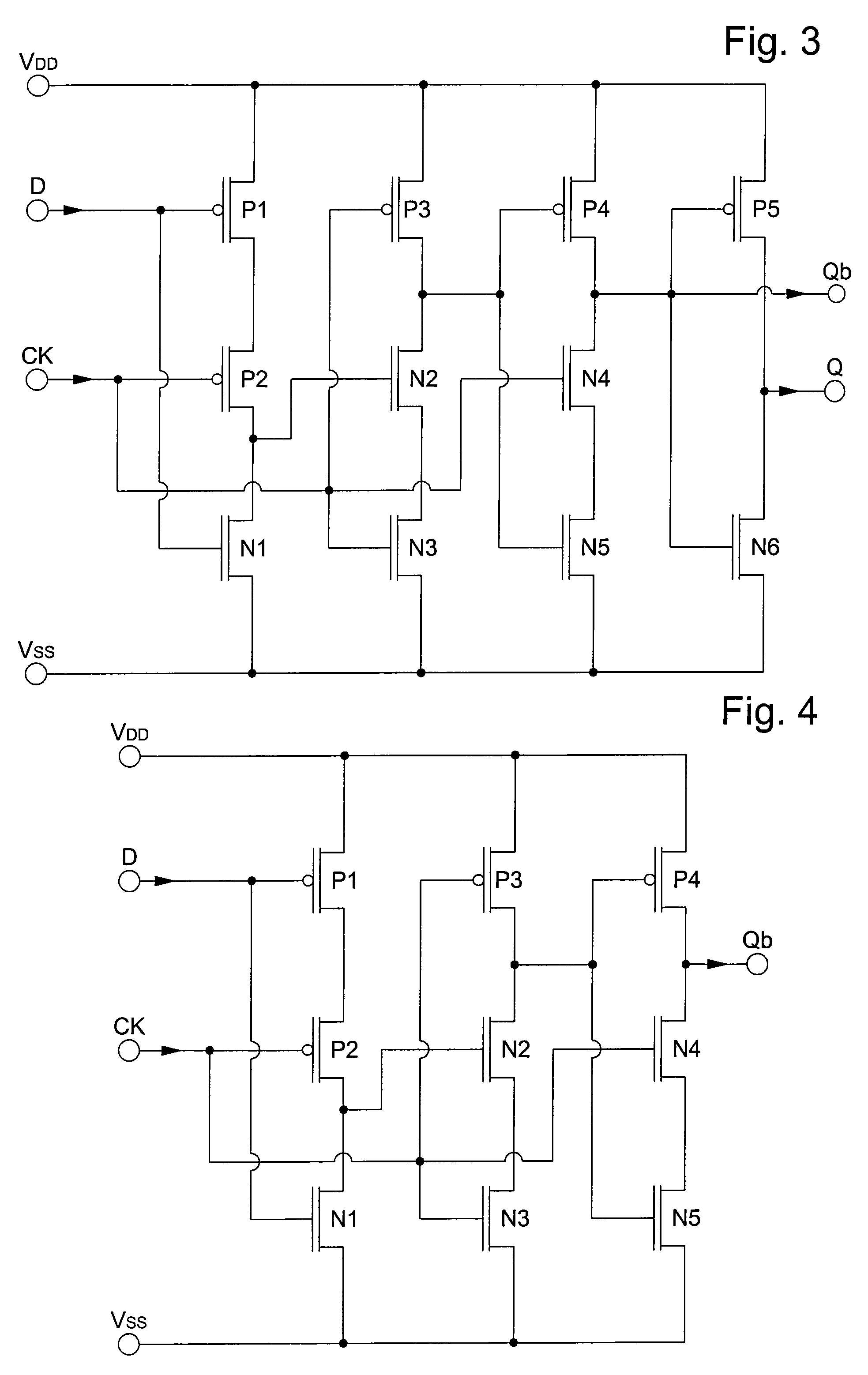

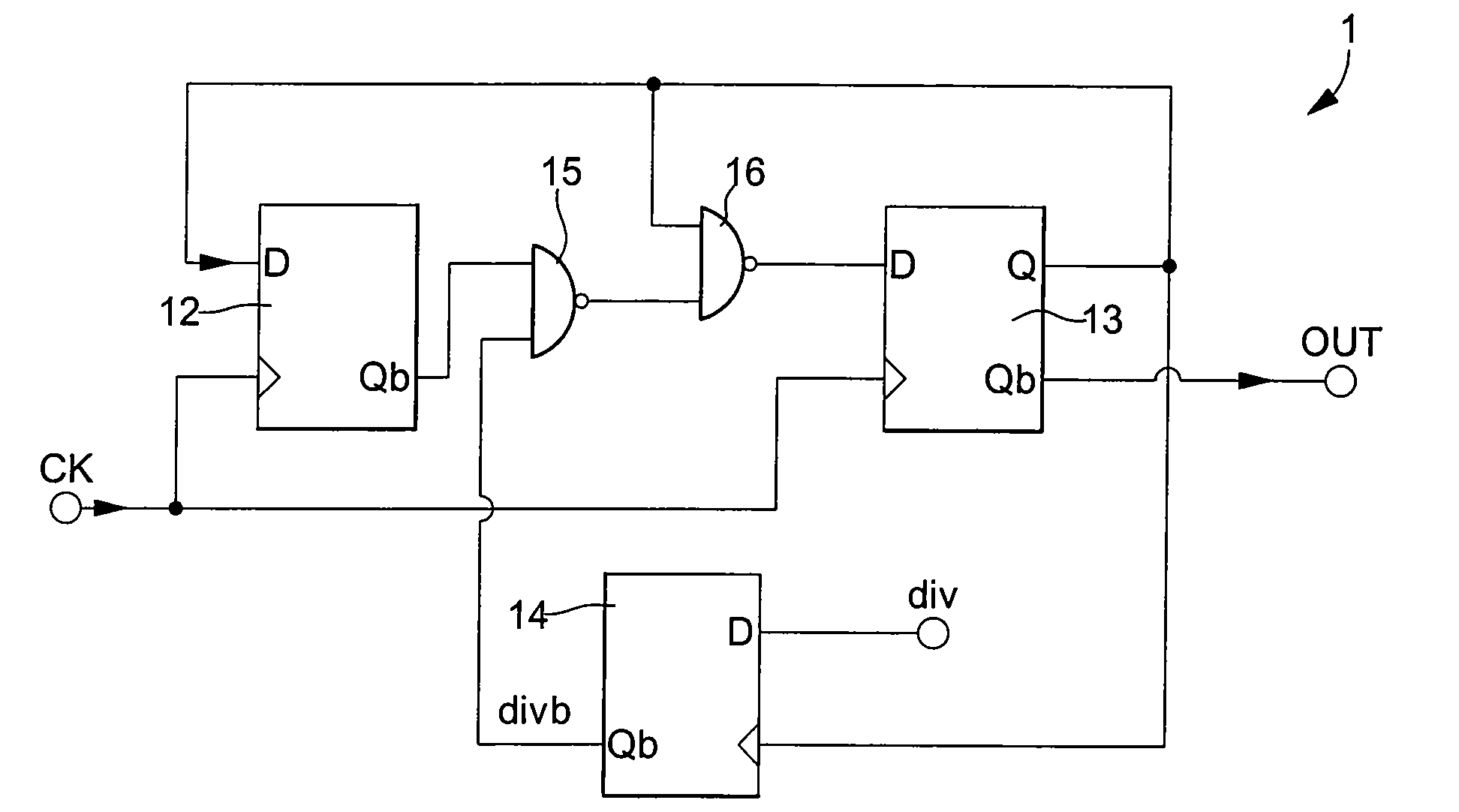

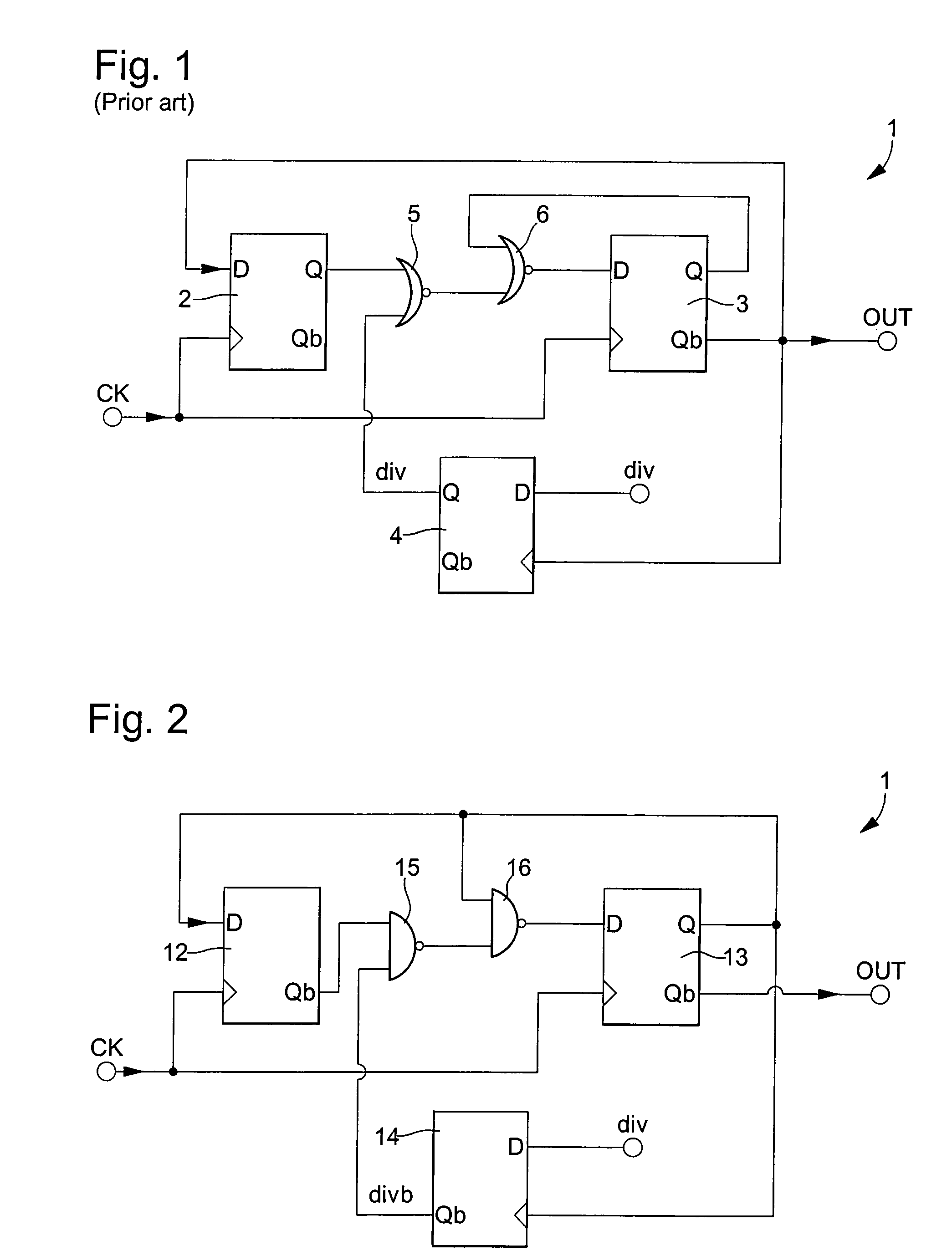

The dual-modulus prescaler circuit (1) is devised to operate at a very high frequency. This circuit includes an assembly formed of two dynamic D-type flip flops (12, 13), and two NAND logic gates (15, 16) arranged in negative feedback between the two flip flops. The two flip flops are clocked by an input clock signal (CK) to supply a divided output signal (OUT) whose frequency matches the input clock frequency divided by 2 or by 3 as a function of a division mode selection signal (divb) applied to the input of the first NAND logic gate (15). One non-inverted output of the second flip flop is connected to one input of the first flip flop (12). The first dynamic flip flop includes three active branches and supplies a single inverted output signal. A third flip flop (14) with three active branches receives an inverted mode selection signal (div) at input in order to supply the mode selection signal to the inverted output thereof, clocked by the non-inverted output signal of the second flip flop.

Owner:THE SWATCH GRP RES & DEVELONMENT LTD

Two-modulus prescaler circuit

InactiveUS20050116258A1Reduce signal amplitudeReduce power supply voltageCounting chain pulse countersSolid-state devicesMulti inputSwitching signal

In the dual modulus prescaler circuit, an output terminal of the first multi-input logic gate circuit is connected to a data input terminal of a first D flip-flop circuit; output terminals of the first to (n-2)th D flip-flop circuits are, respectively, connected to data input terminals of the second to (n-1)th D flip-flop circuits; output terminals of the (n-1)th and nth D flip-flop circuits are connected to input terminals of the first multi-input logic gate circuit; the second multi-input logic gate circuit is connected to the output terminal of the (n-1)th D flip-flop circuit and receives a switching signal; and an output terminal of the second multi-input logic gate circuit is connected to a data input terminal of the nth D flip-flop circuit. Moreover, all the aforementioned connections are connections using differential signals.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP +1

Dual-modulus prescaler circuit operating at a very high frequency

ActiveUS20090146699A1High frequencyReduce power consumptionPulse automatic controlCounting chain synchronous pulse countersNegative feedbackNAND logic

The dual-modulus prescaler circuit (1) is devised to operate at a very high frequency. This circuit includes an assembly formed of two dynamic D-type flip flops (12, 13), and two NAND logic gates (15, 16) arranged in negative feedback between the two flip flops. The two flip flops are clocked by an input clock signal (CK) to supply a divided output signal (OUT) whose frequency matches the input clock frequency divided by 2 or by 3 as a function of a division mode selection signal (divb) applied to the input of the first NAND logic gate (15). One non-inverted output of the second flip flop is connected to one input of the first flip flop (12). The first dynamic flip flop includes three active branches and supplies a single inverted output signal. A third flip flop (14) with three active branches receives an inverted mode selection signal (div) at input in order to supply the mode selection signal to the inverted output thereof, clocked by the non-inverted output signal of the second flip flop.

Owner:THE SWATCH GRP RES & DEVELONMENT LTD

Dual-modulus prescaler with self-adaptive dormancy

ActiveCN101630957ANo power consumptionAvoid wasting powerCounting chain pulse countersControl signalMode control

The invention discloses a dual-modulus prescaler with self-adaptive dormancy, which consists of a plurality of high-speed logic units, a logic control circuit and a plurality of MOS transistors used as current sources, wherein each high-speed logic unit has a clock triggering end, a signal input end and a signal output end; the clock triggering end of each high-speed logic unit is connected with an external clock signal CLK, and the signal input end of each high-speed logic unit is connected with the output end of the logic control end; and the input end of the logic control circuit is connected with the signal output end of the high-speed logic unit and an external mode control signal. In the dual-modulus prescaler with the self-adaptive dormancy, one high-speed trigger is in the state of dormancy due to the cutting-off of the MOS transistors which are used as the current sources according to a specific digital value of a fractional frequency value and the mode control signal, so the consumption of electric energy is reduced, unnecessary waste of power consumption is avoided, and the aim of reducing the power consumption is achieved.

Owner:锐立平芯微电子(广州)有限责任公司

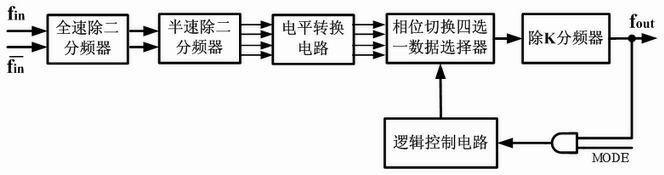

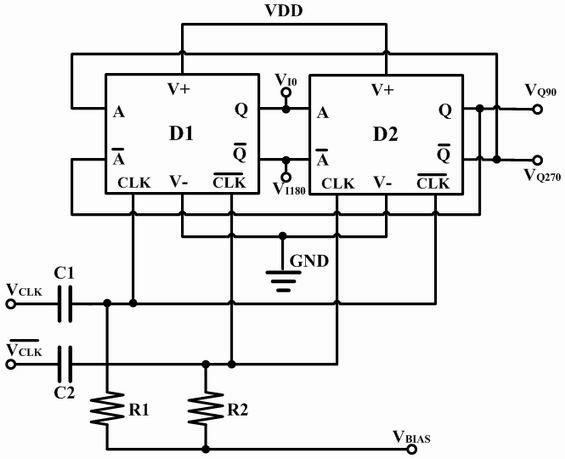

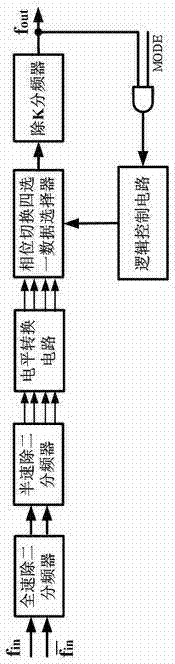

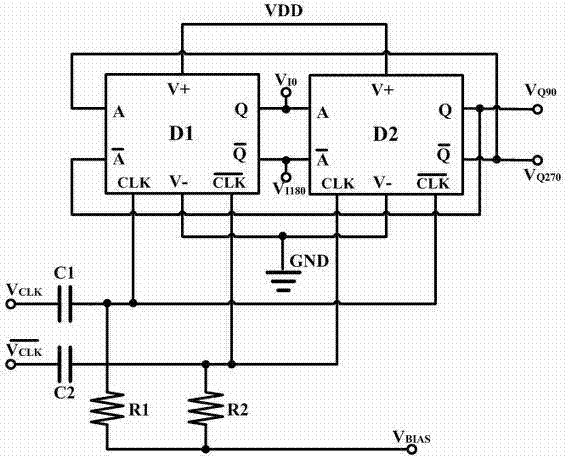

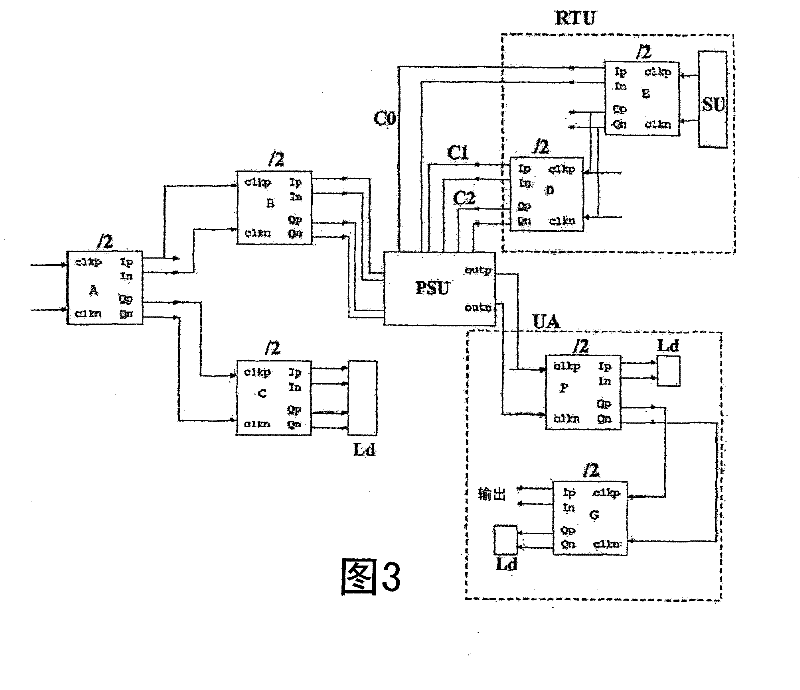

Phase-switched dual-mode counter circuit for a frequency synthesizer

InactiveUS7116747B2Easy to implementAvoid voltage dropPulse automatic controlCounting chain pulse countersPhase shiftedControl signal

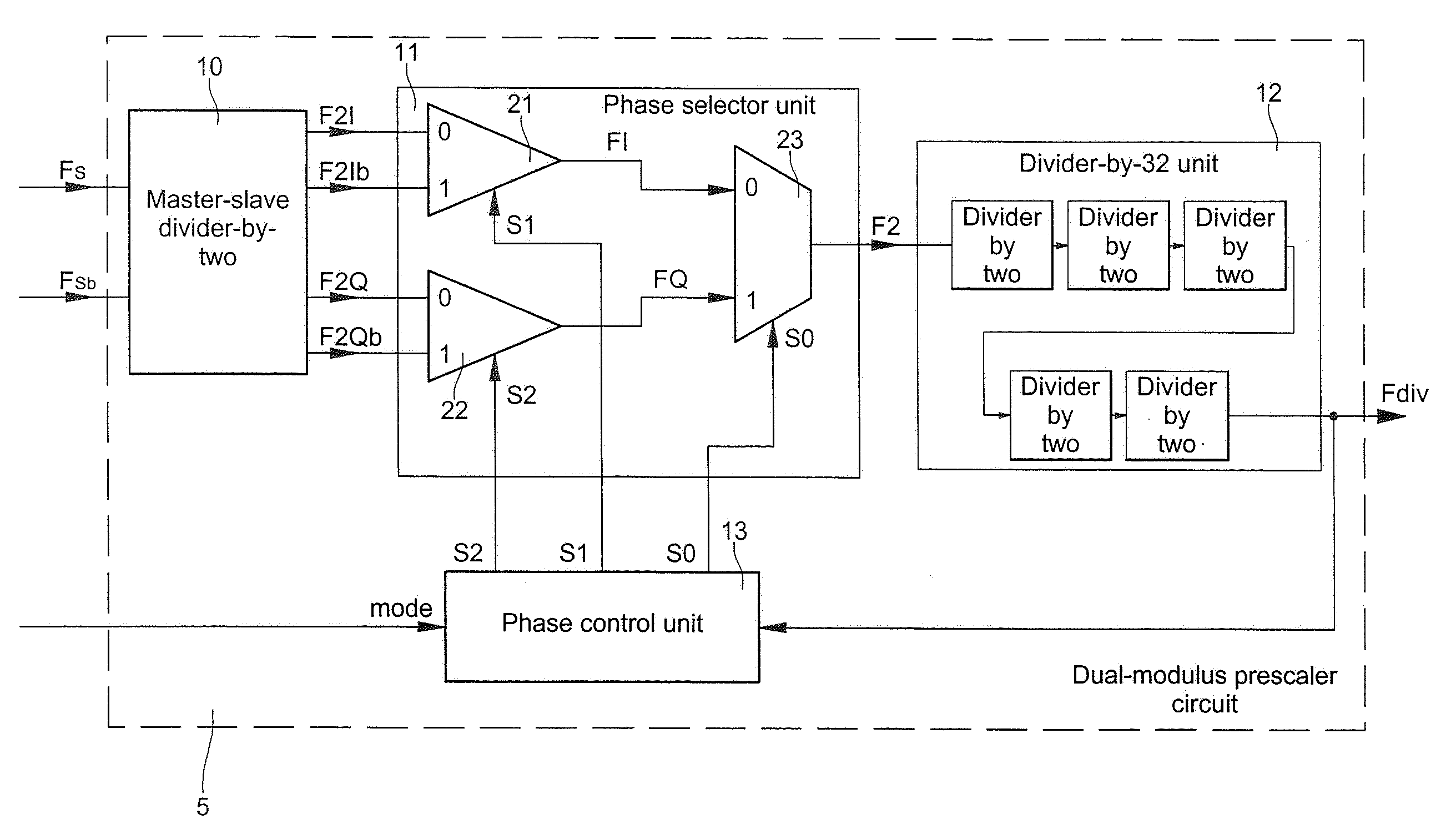

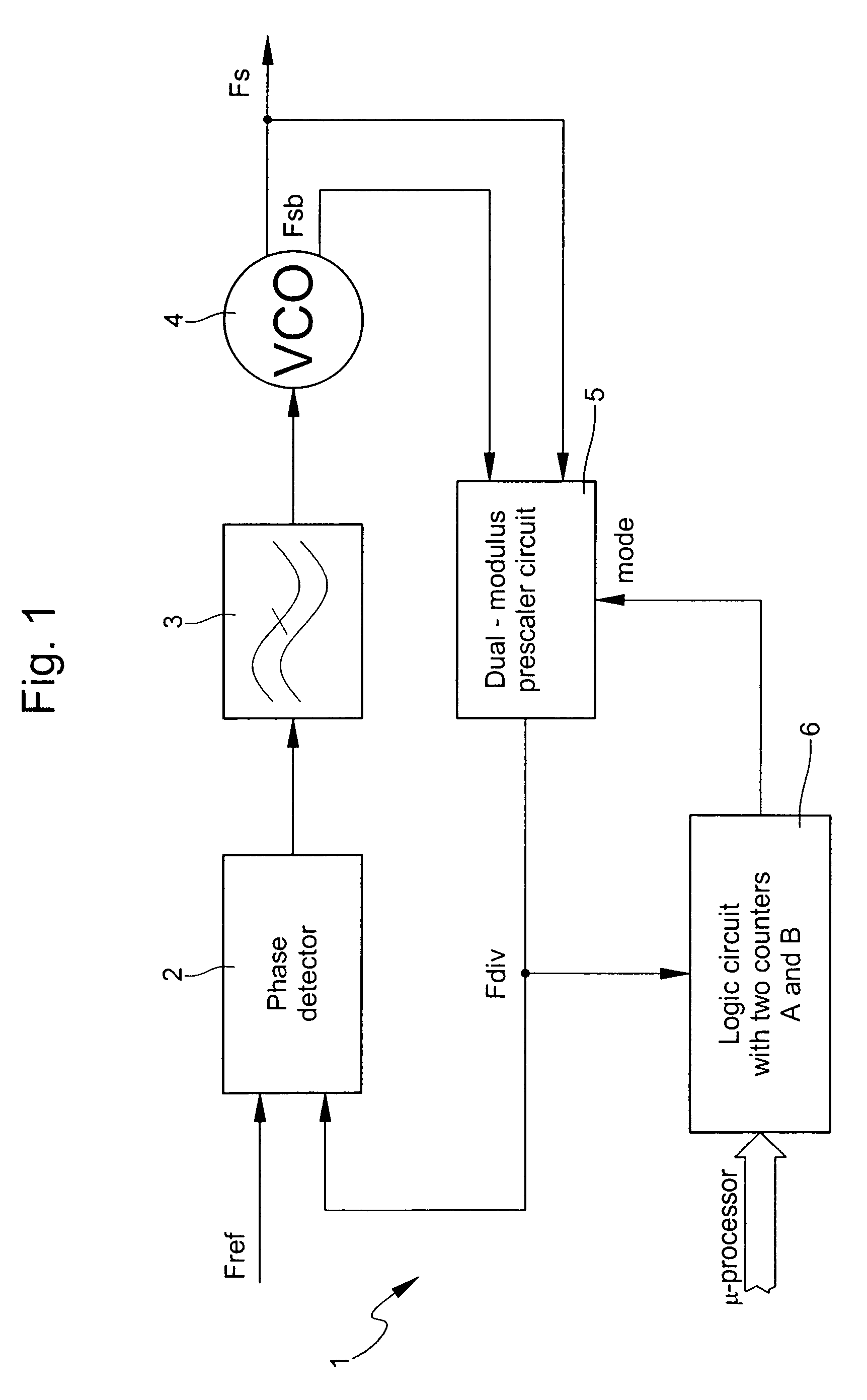

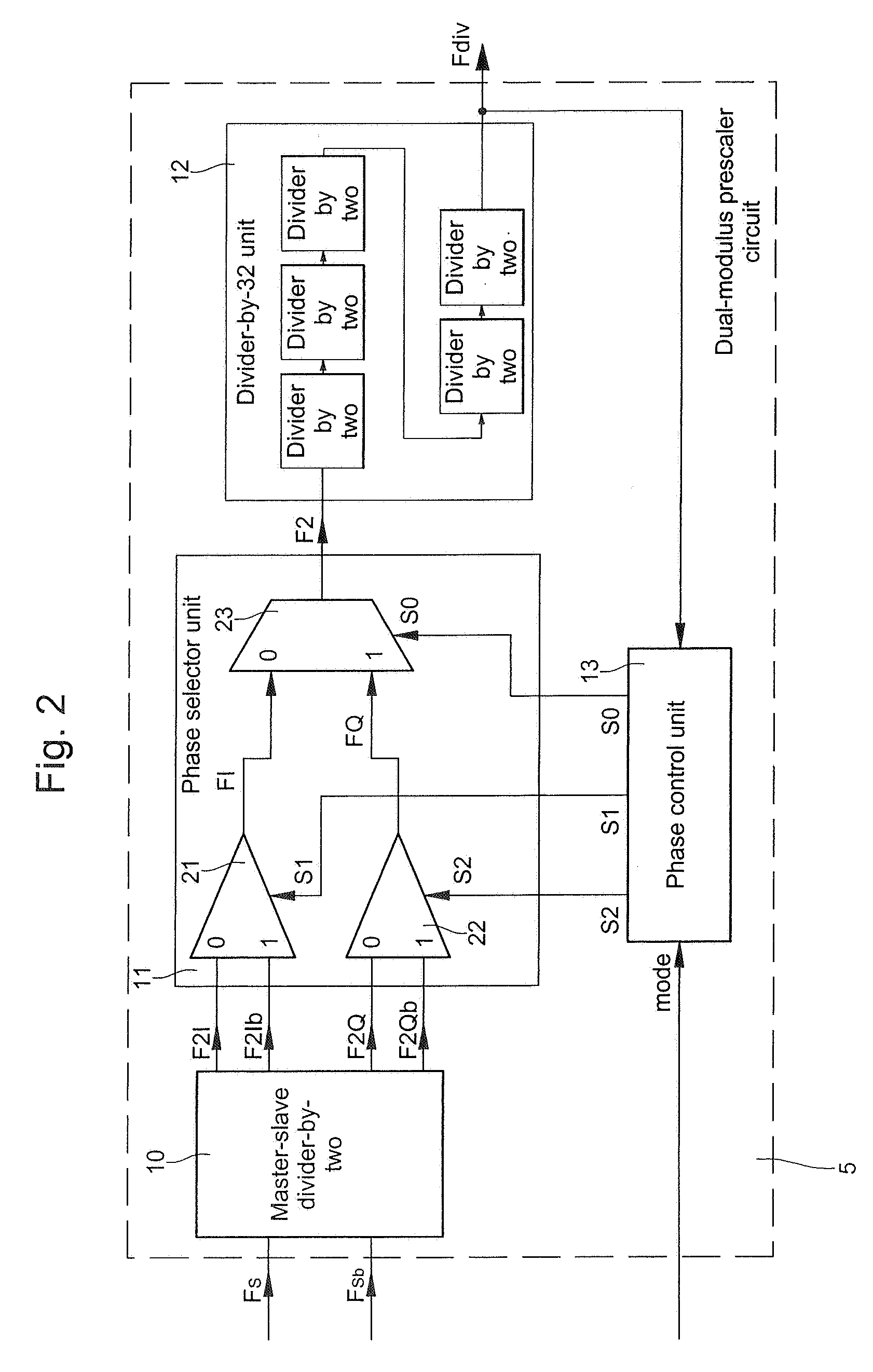

A dual-modulus prescaler circuit for a frequency synthesizer comprises a plurality of asynchronous dividers-by-two connected in series, a phase selector unit (11) between two dividers-by-two (10, 12) and a control unit (13) for supplying control signals (S0, S1, S2) to the selector unit as a function of a selected mode. Said selector unit receives four signals phase shifted by 90° in relation to each other from a master-slave first divider and supplies a selected one of the four phase shifted signals. The control signals (S0, S1, S2) are supplied to the selector unit for selecting one of the four phase shifted signals (F2) at the output in a particular division period. As a function of the control signals supplied by the control unit (13) in one selected of the modes, the selector unit effects phase switching in each division period between two phase shifted signals selected by each branch. The second phase shifted signal i in phase lead of 90° in relation to the first phase shifted signal.

Owner:THE SWATCH GRP RES & DEVELONMENT LTD

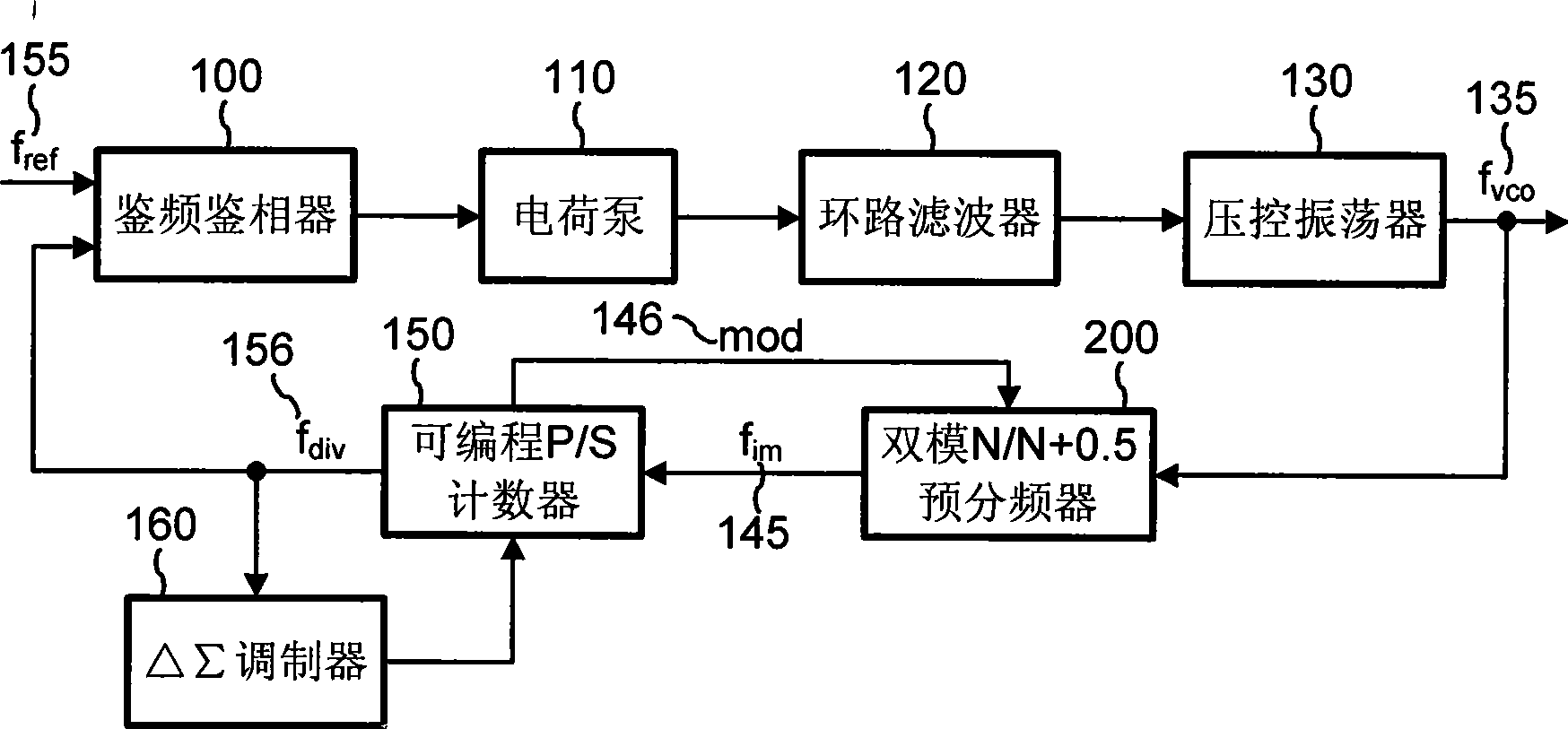

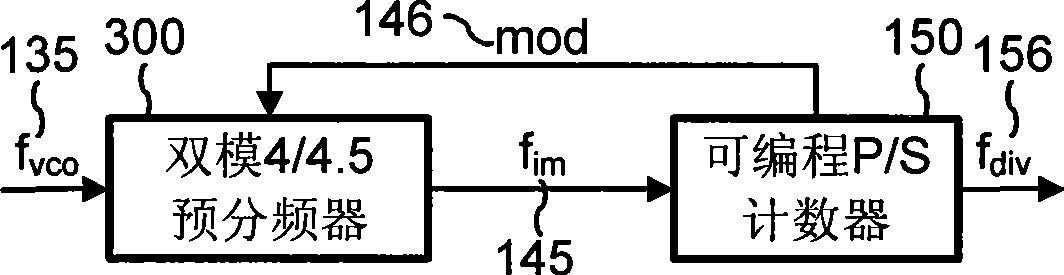

Dual mode 4/4.5 pre-divider

InactiveCN101478307AReduce contributionHigh-resolutionPulse automatic controlControl signalDual mode

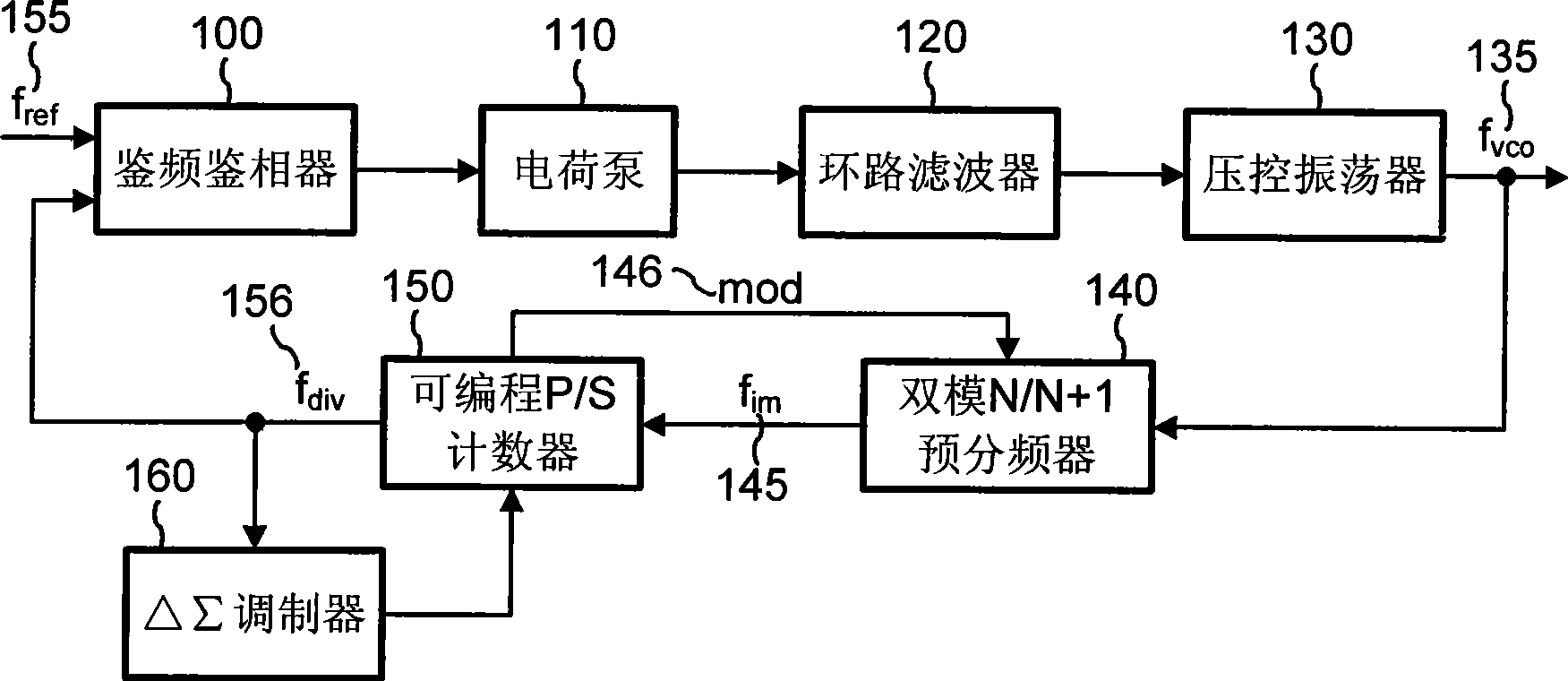

The invention relates to a dual-mode 4 / 4.5 dual-modulus prescaler circuit, which belongs to the phase-locked frequency synthesis technology field in IC design, and comprises four two-input AND gates, two rising edge D-triggers, two descending edge D-triggers, two flip-latches and two two-input signal selectors, wherein, two of the two-input AND gates, the rising edge D-triggers, the two descending edge D-triggers and one two-input signal selector form a prescaler logic circuit; two two-input AND gates, the two flip-latches and one two-input signal selector form a loop termination logic circuit; and the prescaler logic circuit and the loop termination logic circuit realize 4 frequency division or 4.5 frequency division under the action of external control signals. The dual-mode 4 / 4.5 dual-modulus prescaler circuit reduces the step length of frequency dividing ratio and the quantum step of a Delta-Sigma modulator to reach 0.5, increases the system resolution, reduces the phase noises produced by the Delta-Sigma modulator, and can increase the loop bandwidth and accelerate the system generated time with the same phase noises being kept.

Owner:FUDAN UNIV

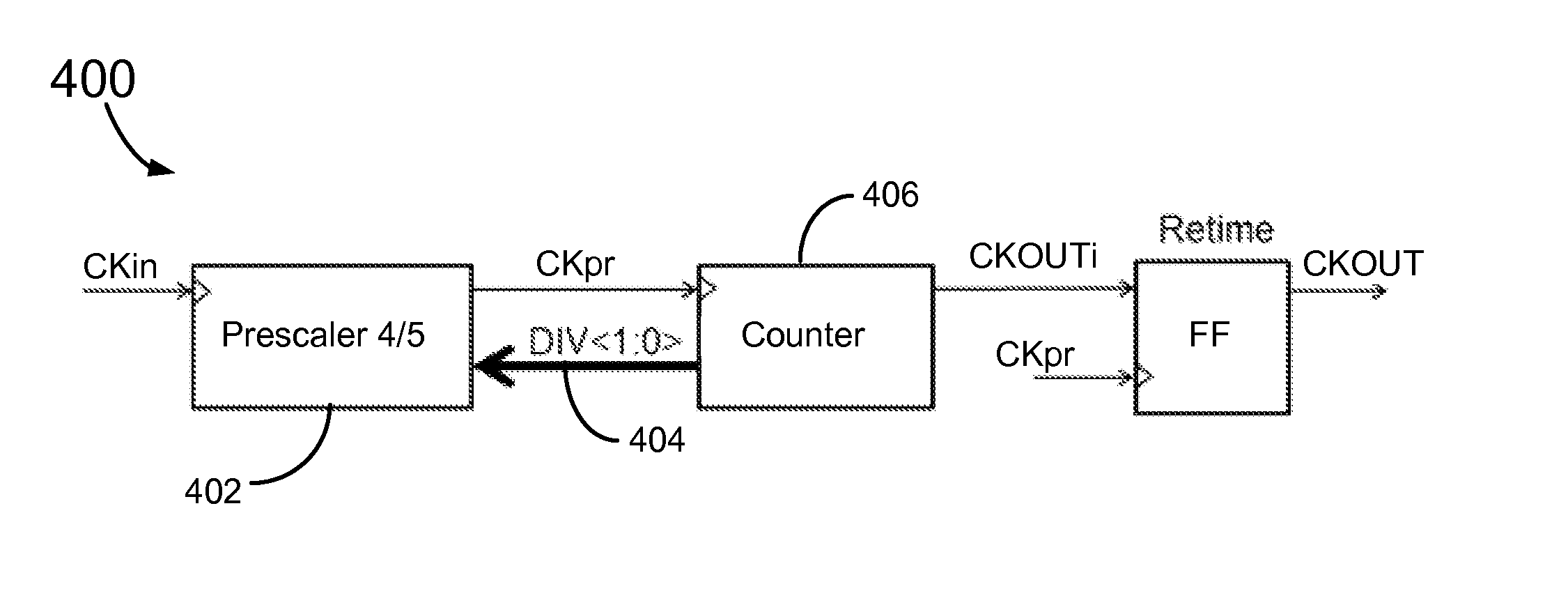

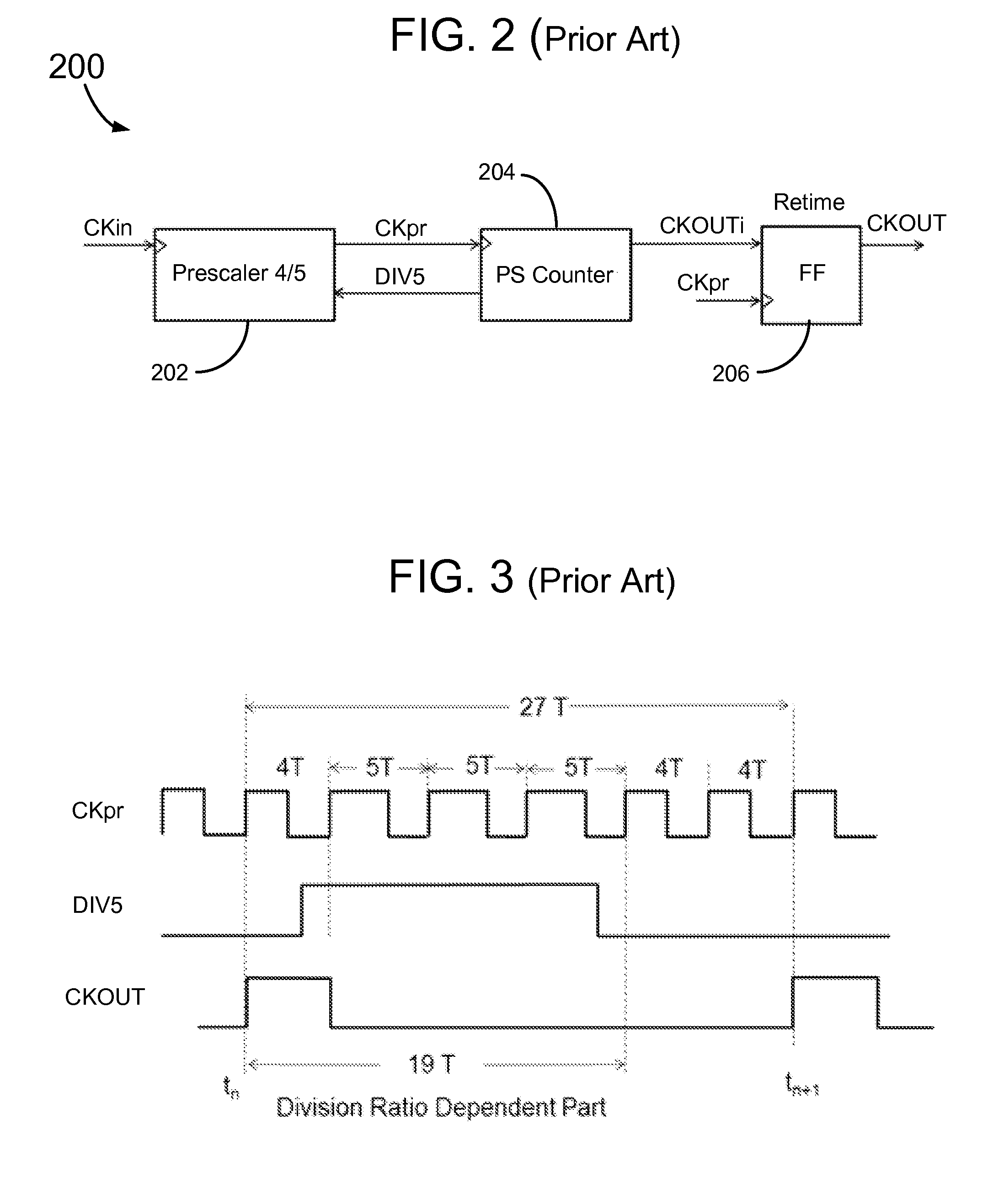

Frequency divider with improved linearity for a fractional-N synthesizer using a multi-modulus prescaler

ActiveUS8891725B2Counting chain pulse counters using semiconductor devicesPulse automatic controlLinearityDual-modulus prescaler

A frequency divider is disclosed. The frequency divider includes a multi-modulus prescaler to perform a frequency division by a modulus M, wherein M is an integer between N and 2*N−1 and N is a power of 2. The frequency divider also includes a programmable counter to output the digital representation of M and an output clock signal. For the frequency divider, M equals N plus D minus D\N for each edge of the multi-modulus prescaler output clock CKpr wherein the counter samples the digital representation of D and D\N denotes an integer part of D divided by N, and M equals N for each subsequent edge of the prescaler output clock CKpr wherein the counter does not sample the digital representation of D.

Owner:QUALCOMM INC

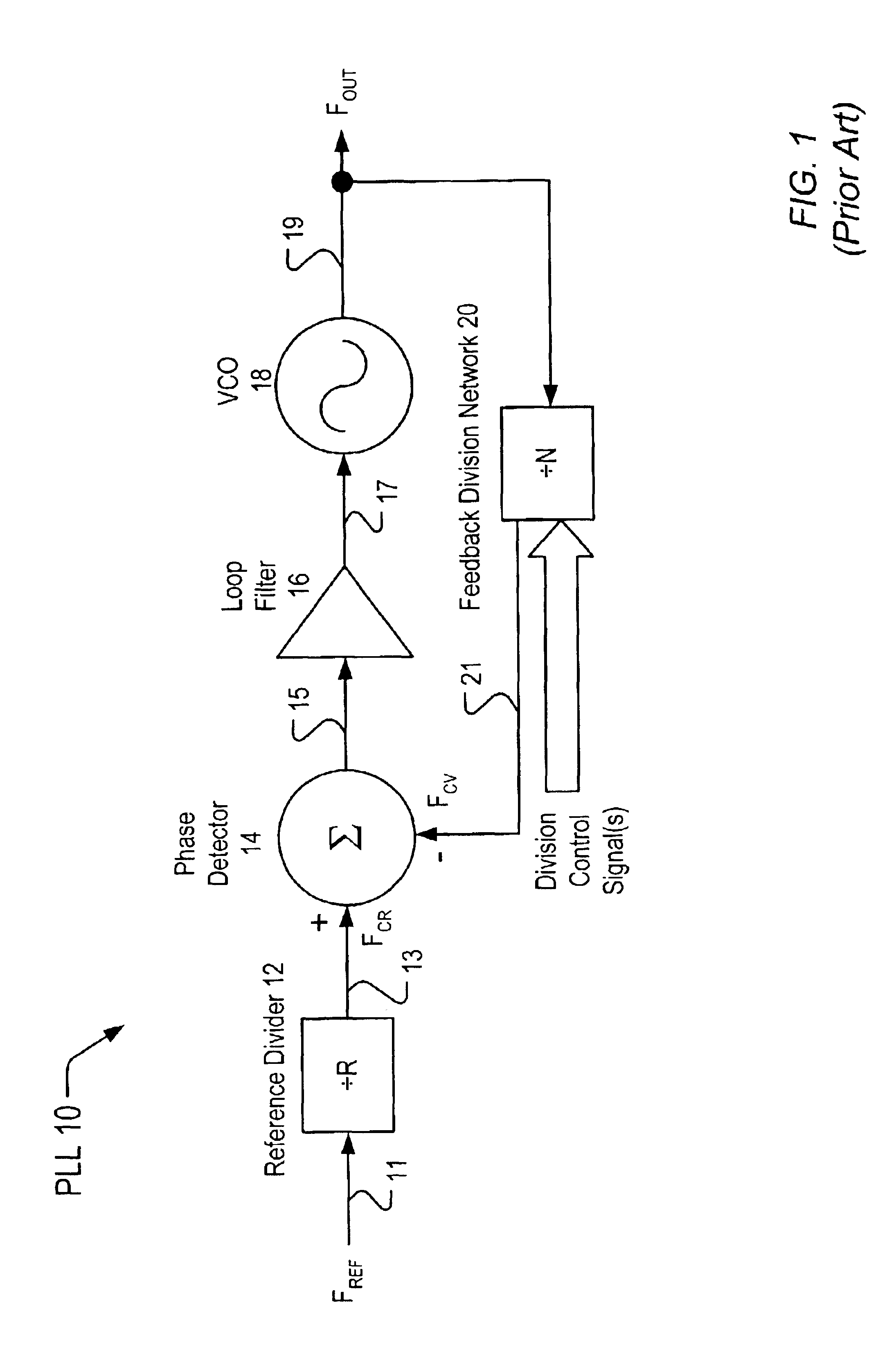

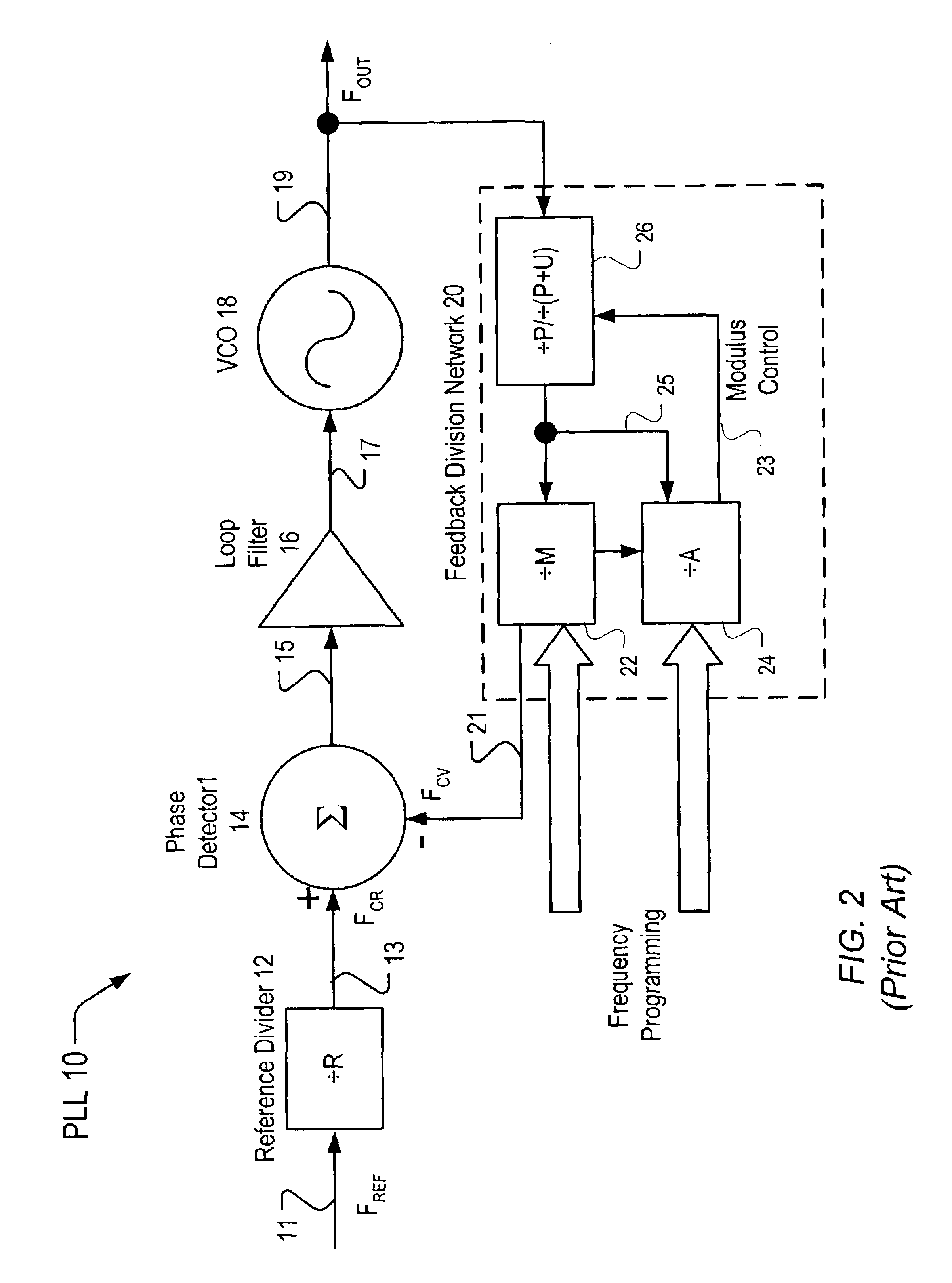

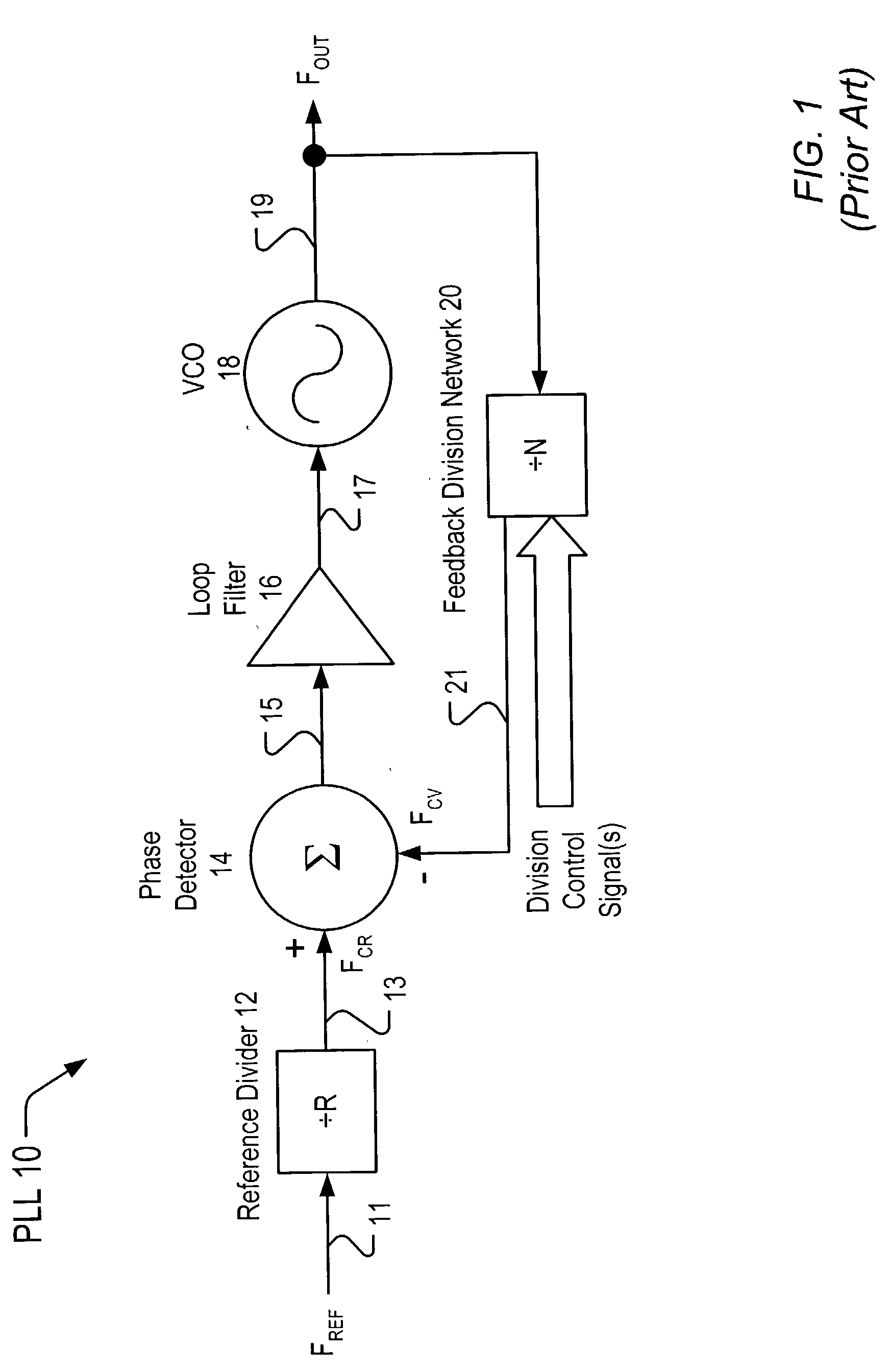

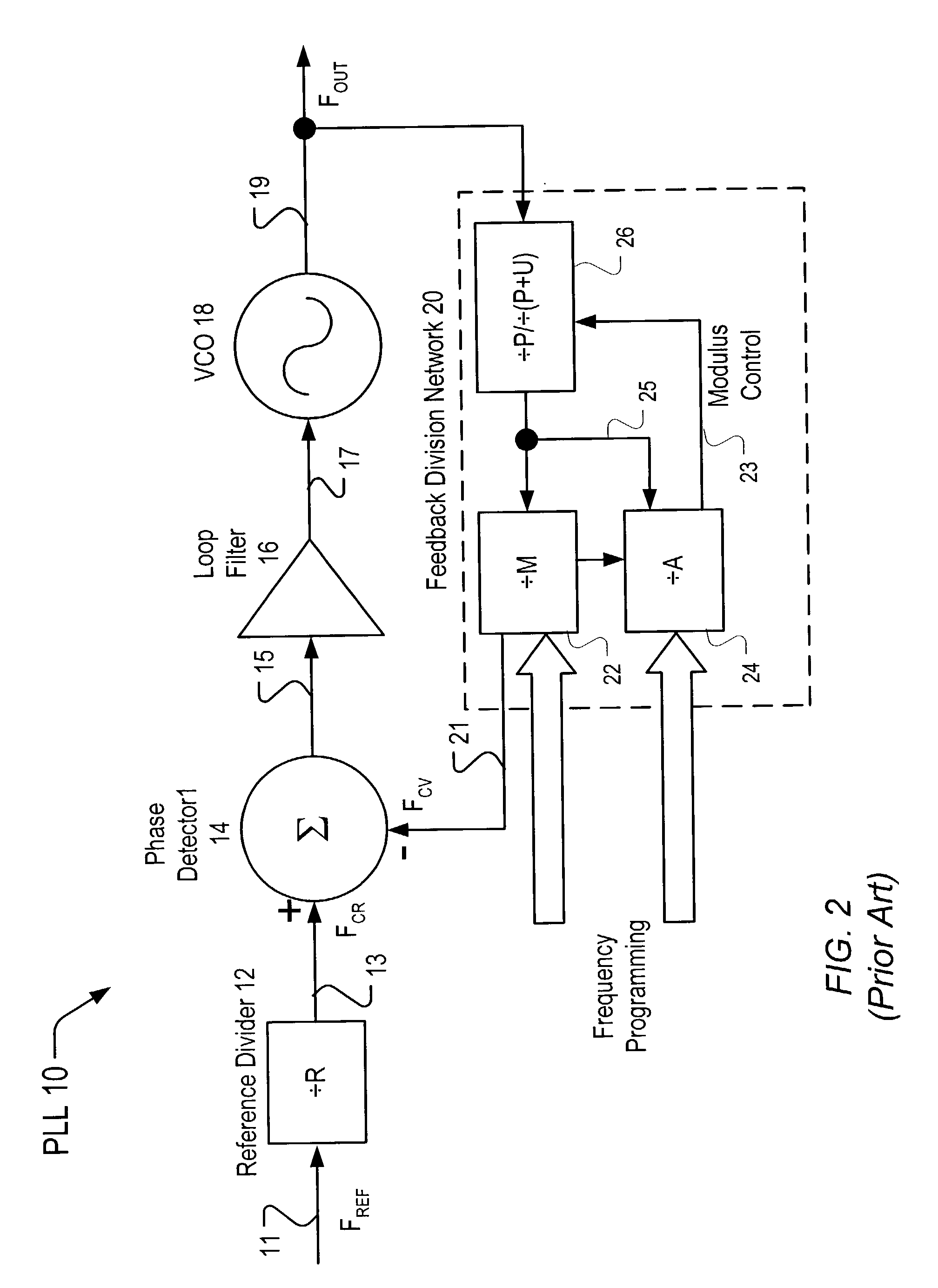

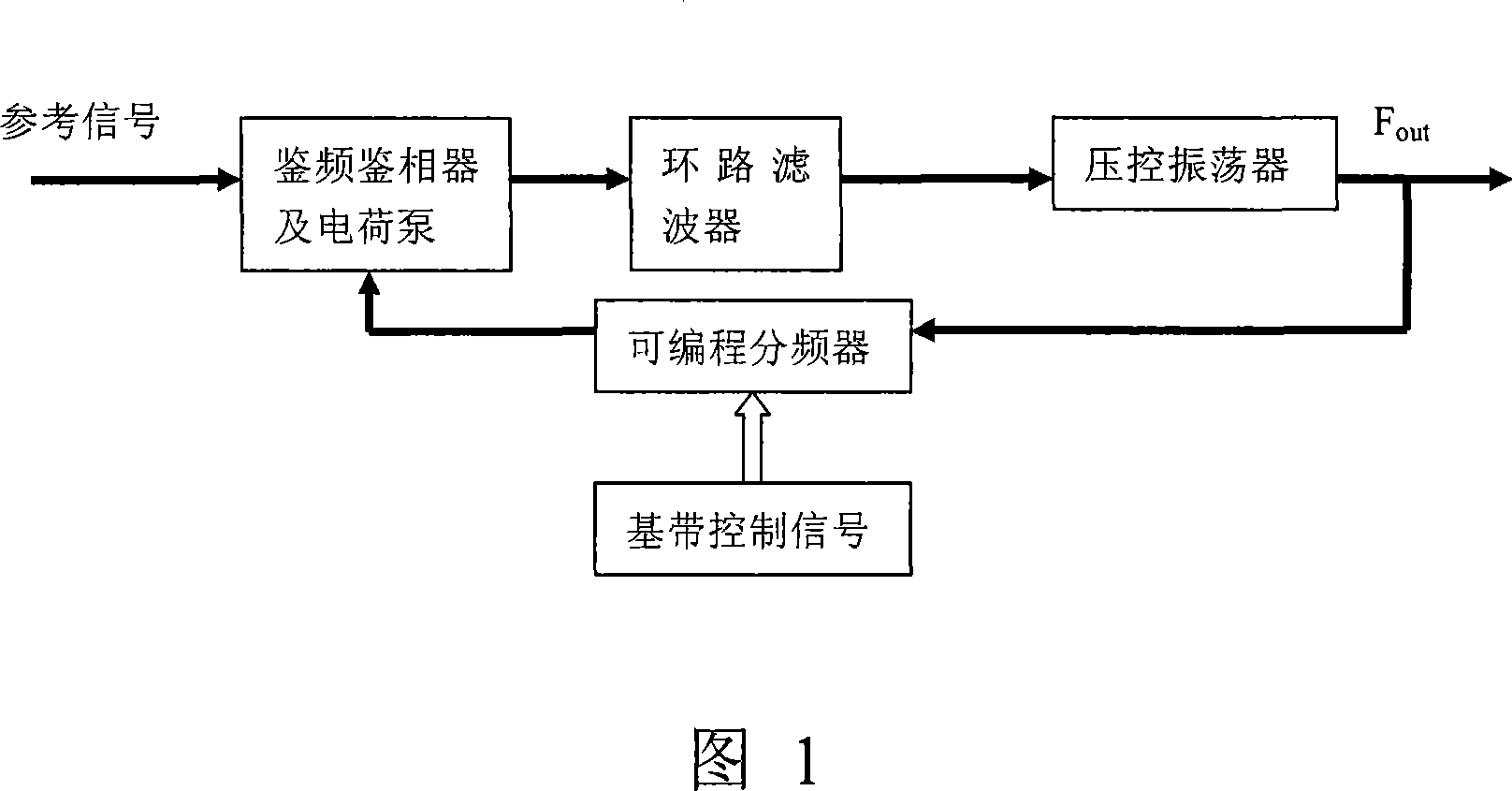

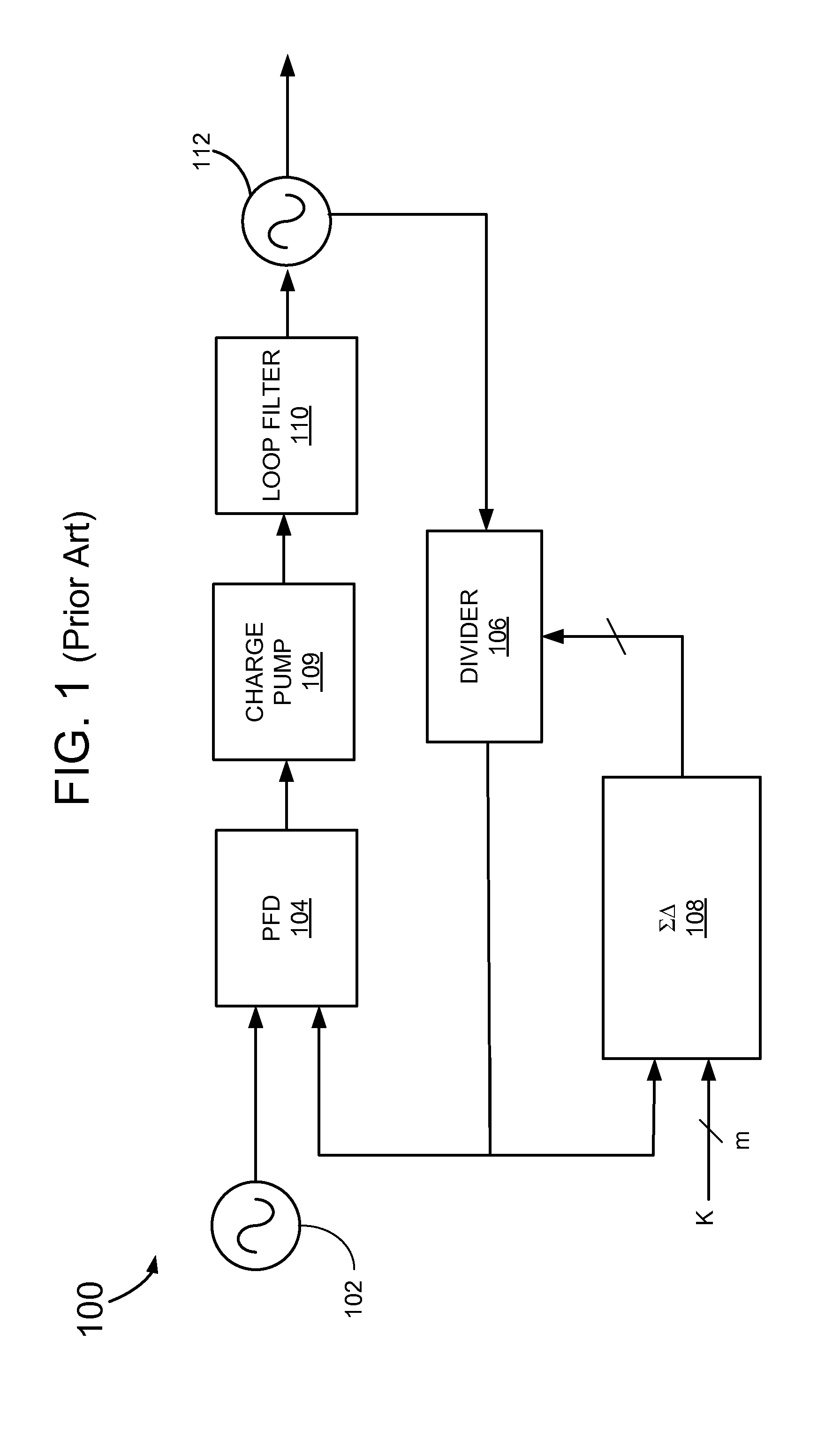

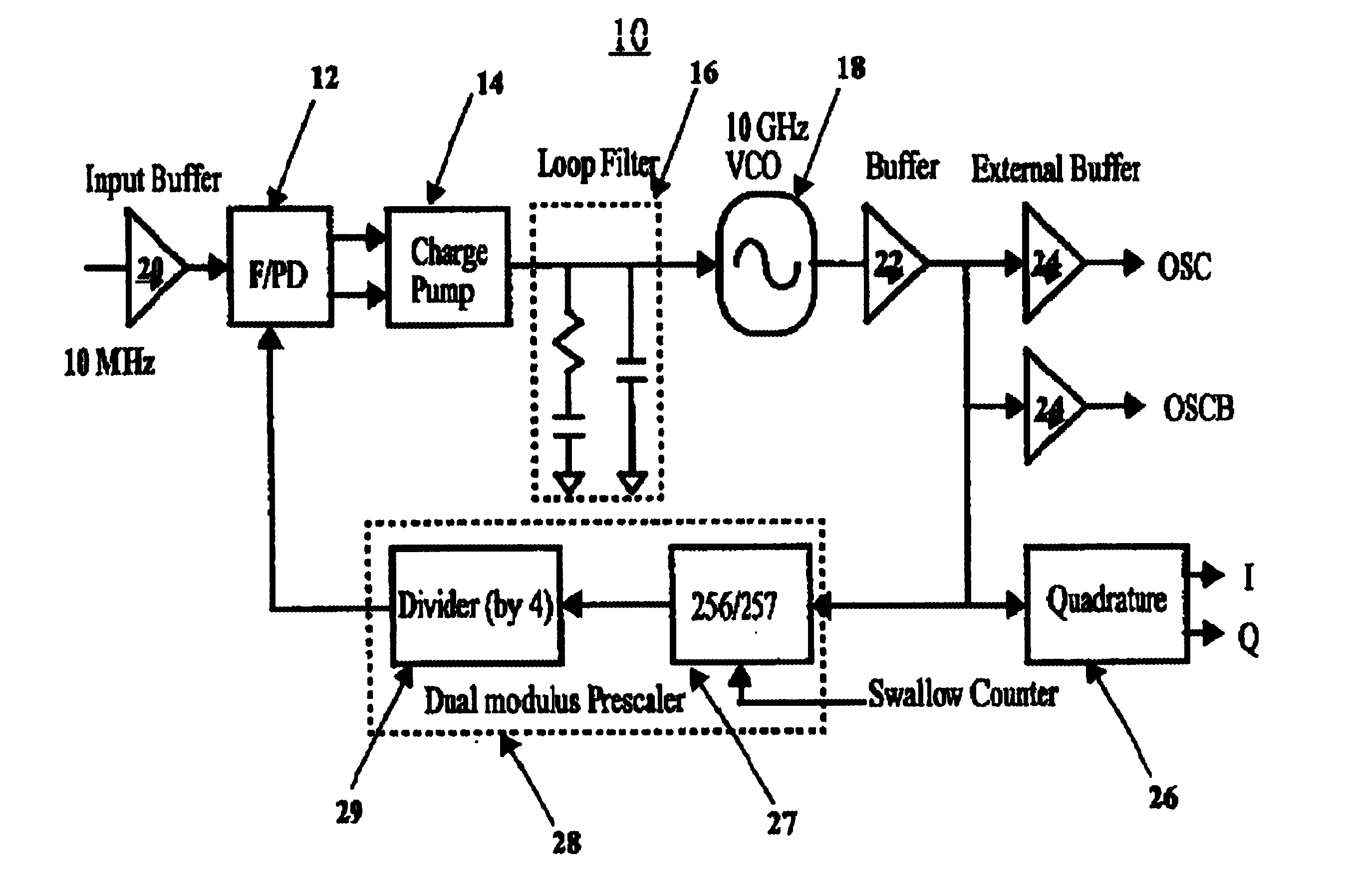

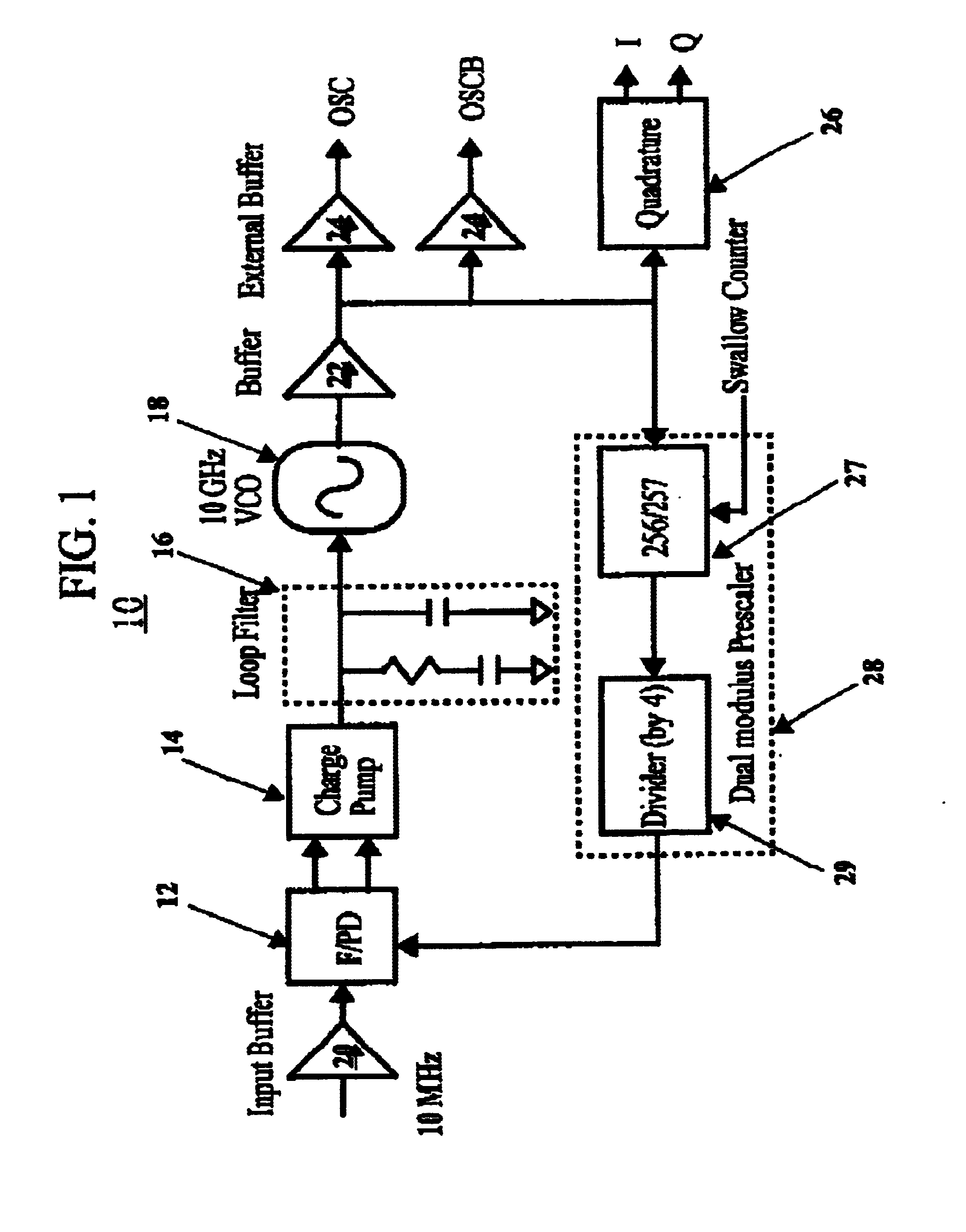

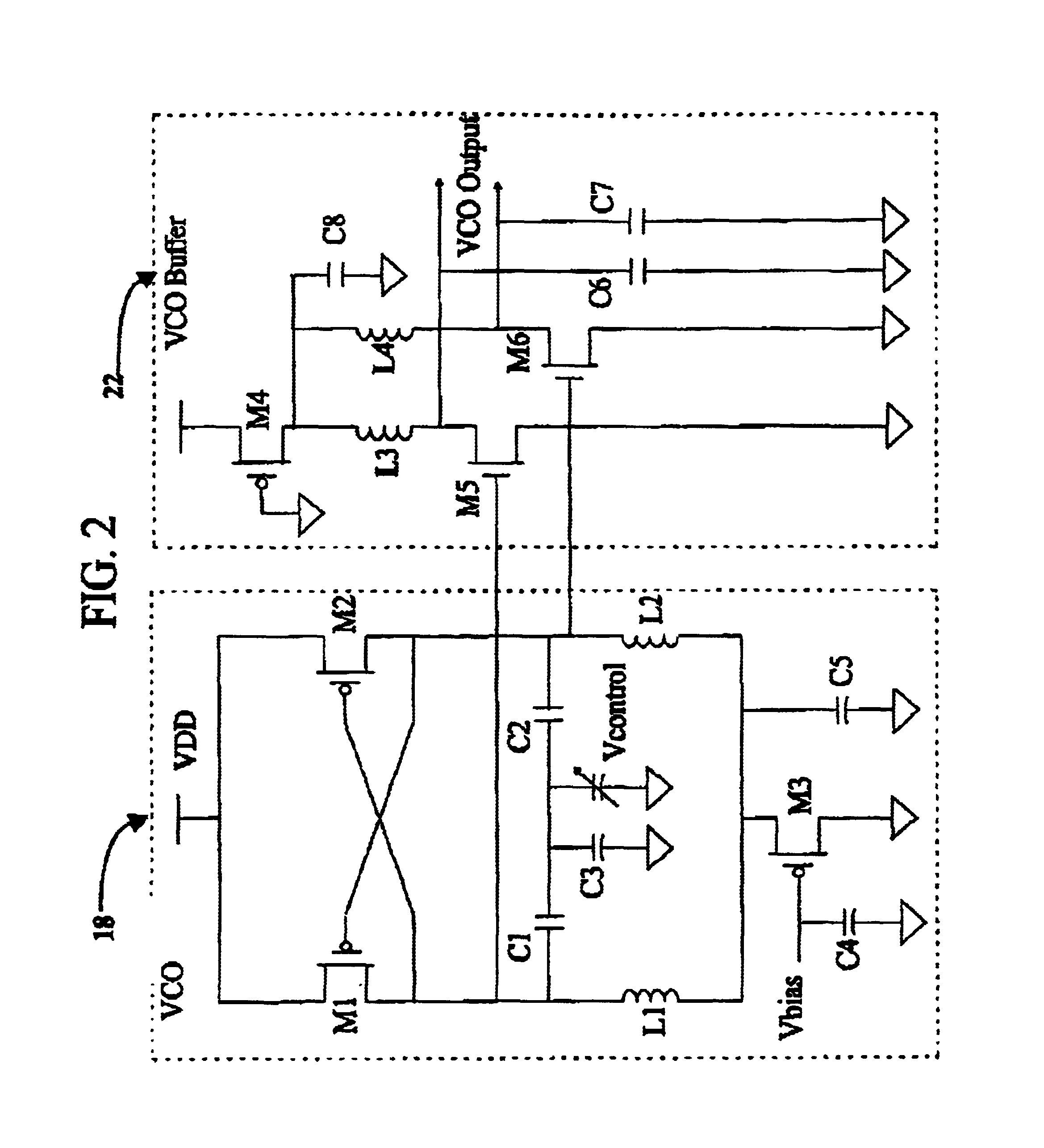

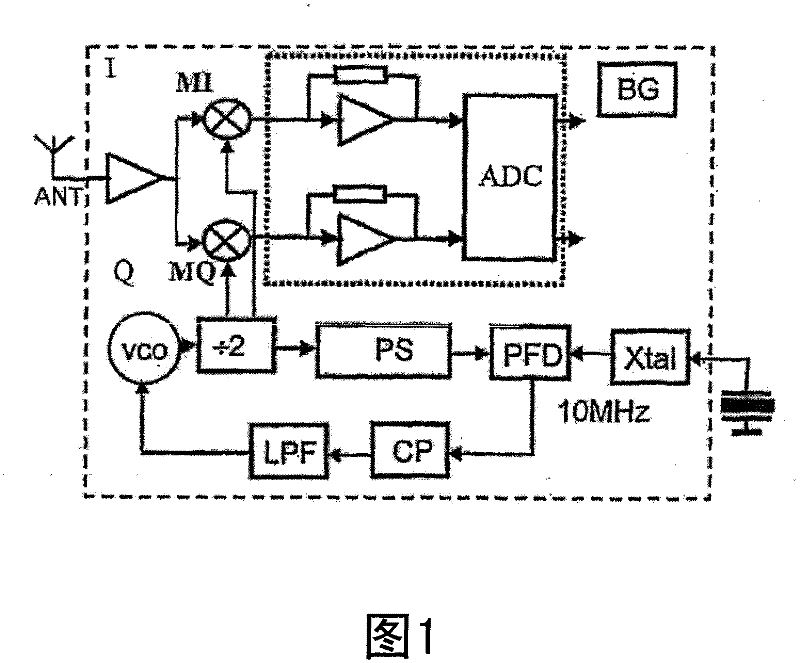

High speed phase locked loop

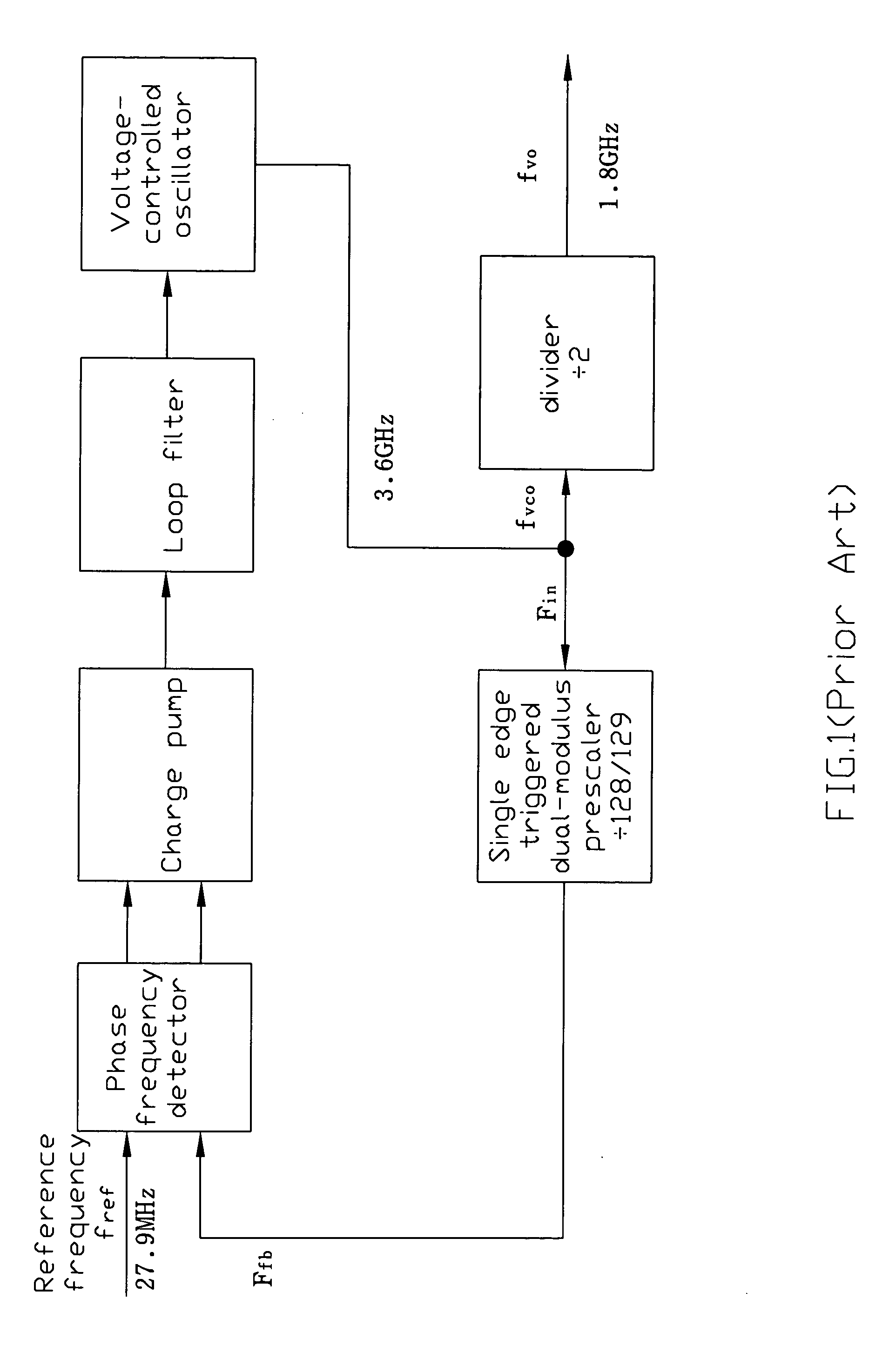

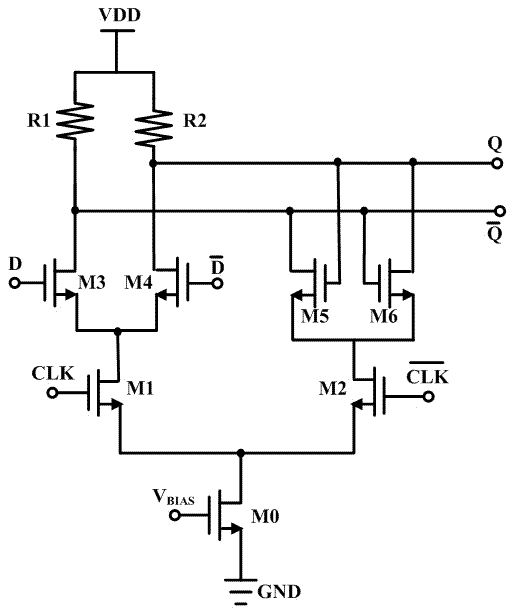

InactiveUS6940322B2Increase working frequencyReduce signal amplitudePulse automatic controlCounting chain pulse countersLoop filterCMOS

A high speed CMOS phase locked loop (PLL) (10) includes a three-state phase detection circuit having a frequency phase detector (12) coupled to a charge pump (14) for monitoring the phase differences between a reference frequency signal and a divided output frequency signal. The PLL can further include a loop filter (16)coupled to the three-state phase detection circuit, a VCO (18) coupled to the output of the loop filter, a VCO buffer (22) coupled to the output of the VCO for providing an output frequency signal, and a dual modulus prescaler (28) having a synchronous counter (27 and 29) using feedback among D flip-flops (30 and 32) for generating the divided output frequency signal.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

Current-mode-logic-based high speed high-oscillation amplitude divide-by-two frequency divider circuit

InactiveCN102291132BImprove anti-interference abilityReduce noisePulse automatic controlDual modeP channel

The invention discloses a high speed high-oscillation amplitude divide-by-two frequency divider circuit, which belongs to the technical fields of integrated circuit designing and signal processing. Specifically, the circuit mainly comprises two high speed high-oscillation amplitude D triggers which are cascaded. The D trigger of each stage eliminates the bias of a tail current source based on theconventional D trigger having a current-mode logic (CML) structure, and adopts a P-channel metal oxide semiconductor (PMOS) transistor as a load; and simultaneously, a PMOS and N-channel metal oxide semiconductor (NMOS) complementary cross coupling pair structure and the like are adopted by the output stage of the circuit to finally achieve the aims of increasing the oscillation amplitude of an output signal and making the oscillation amplitude of the output signal approximate to full oscillation amplitude under the condition of ensuring the high speed working of the circuit. The circuit not only can directly drive a post circuit, reduces system power consumption to a certain extent, compensates for the shortcomings of a conventional divide-by-two frequency divider, and is suitable for a high speed frequency divider part in a low-power consumption preposed dual-mode prescaler front-end without any additional level conversion amplification circuit.

Owner:EAST CHINA NORMAL UNIV

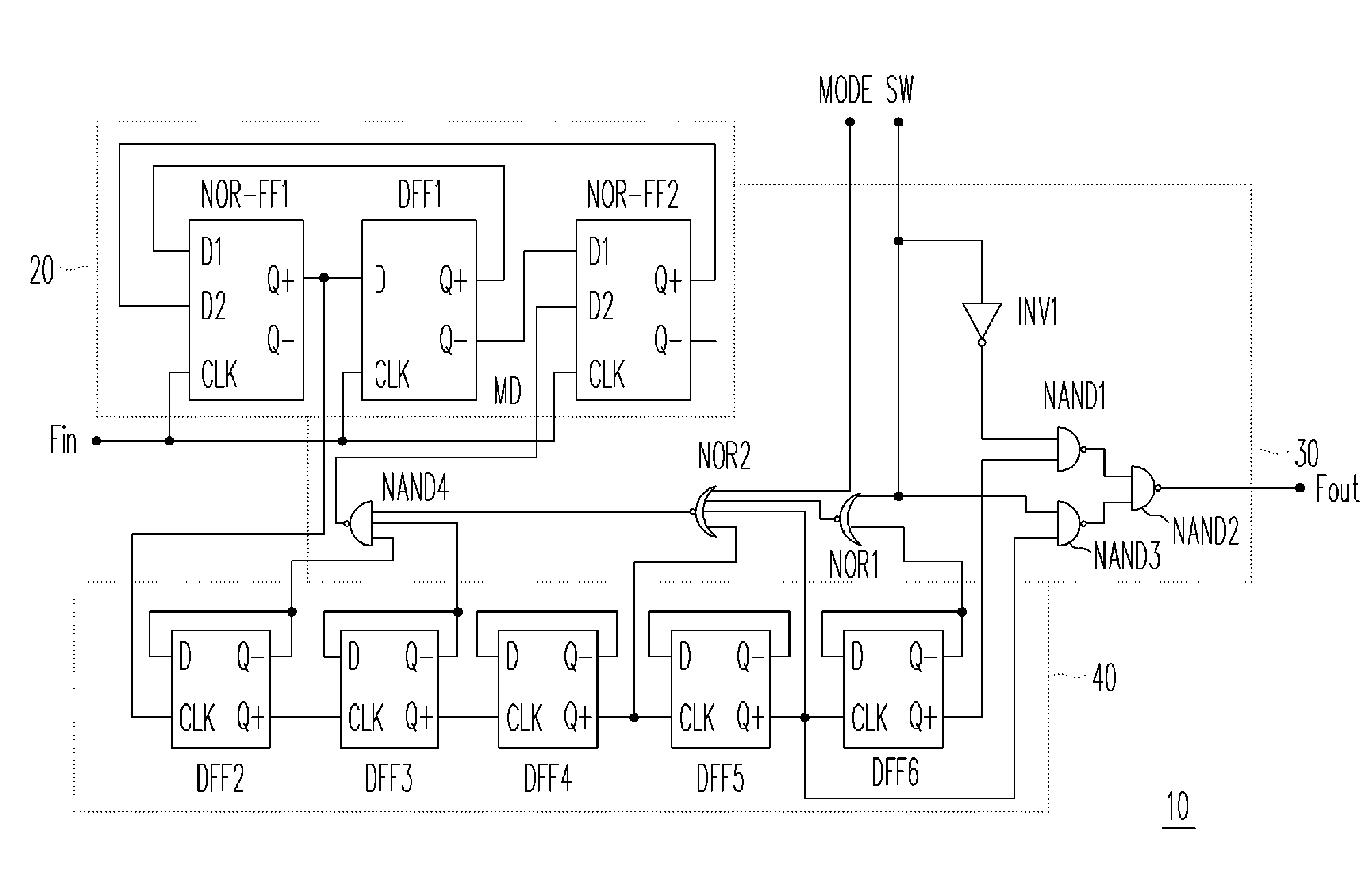

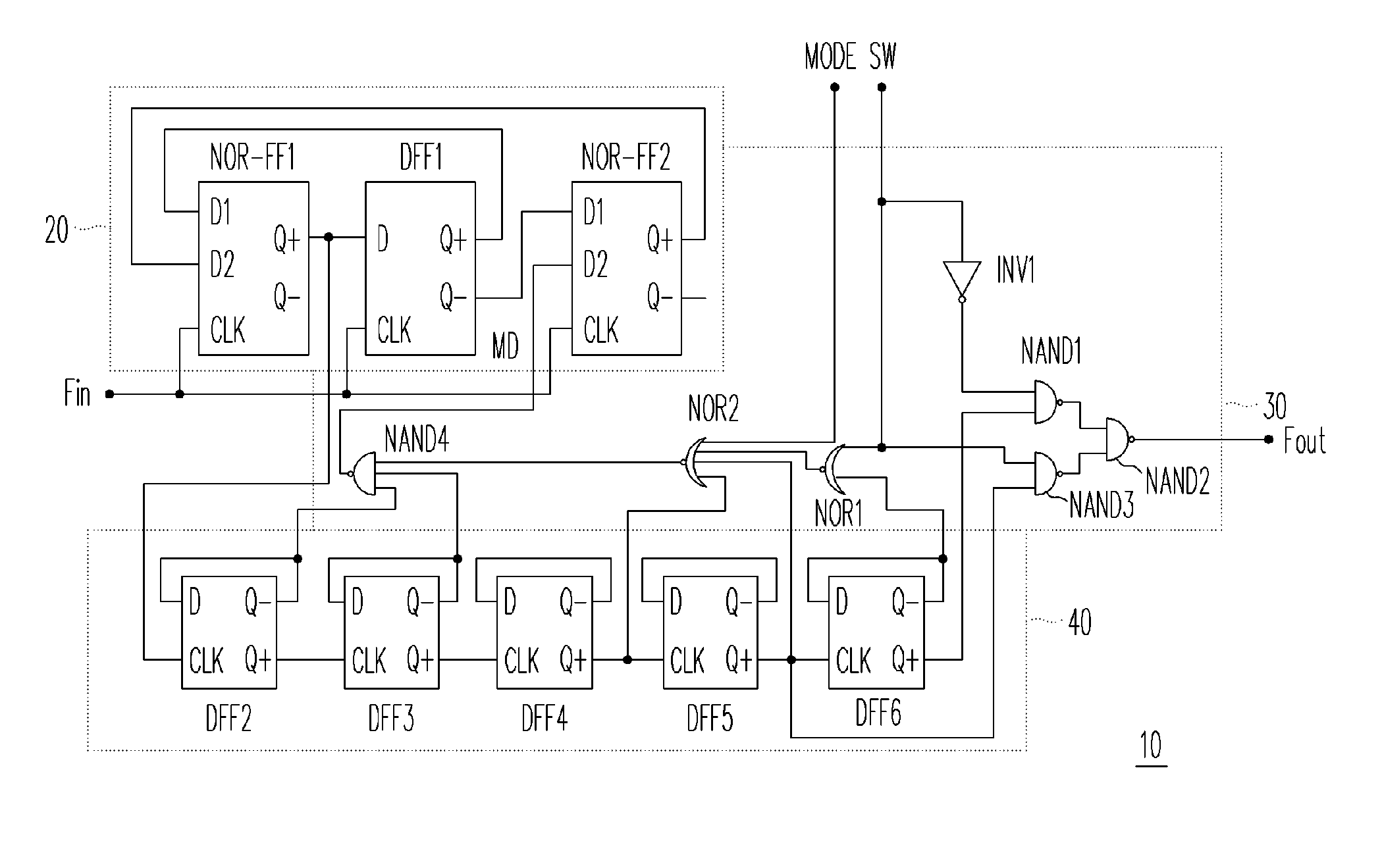

prescaler

ActiveUS20060245534A1Increase working frequencyReduce power consumptionCounting chain pulse countersPulse counters with static storageControl signalComputer science

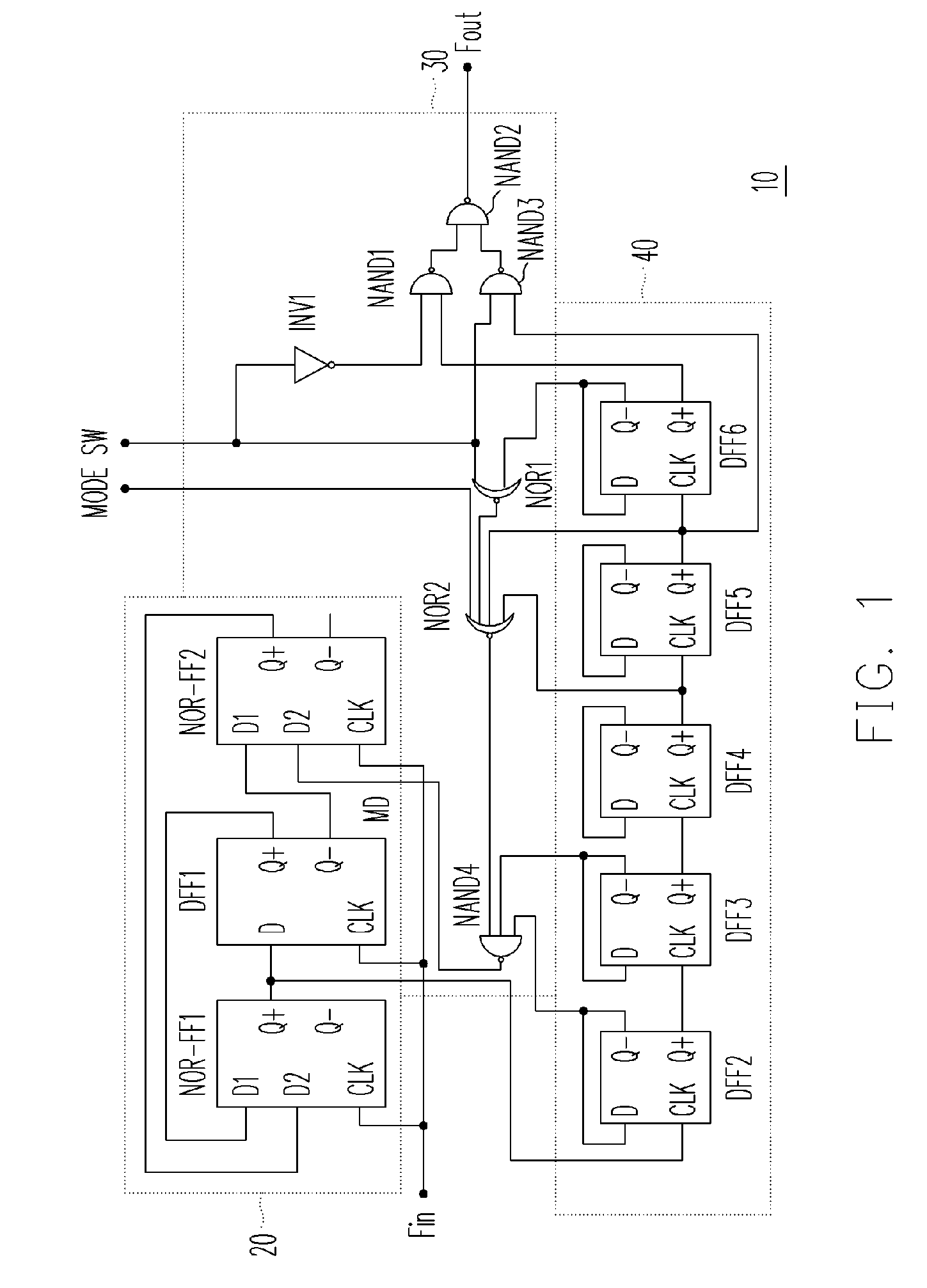

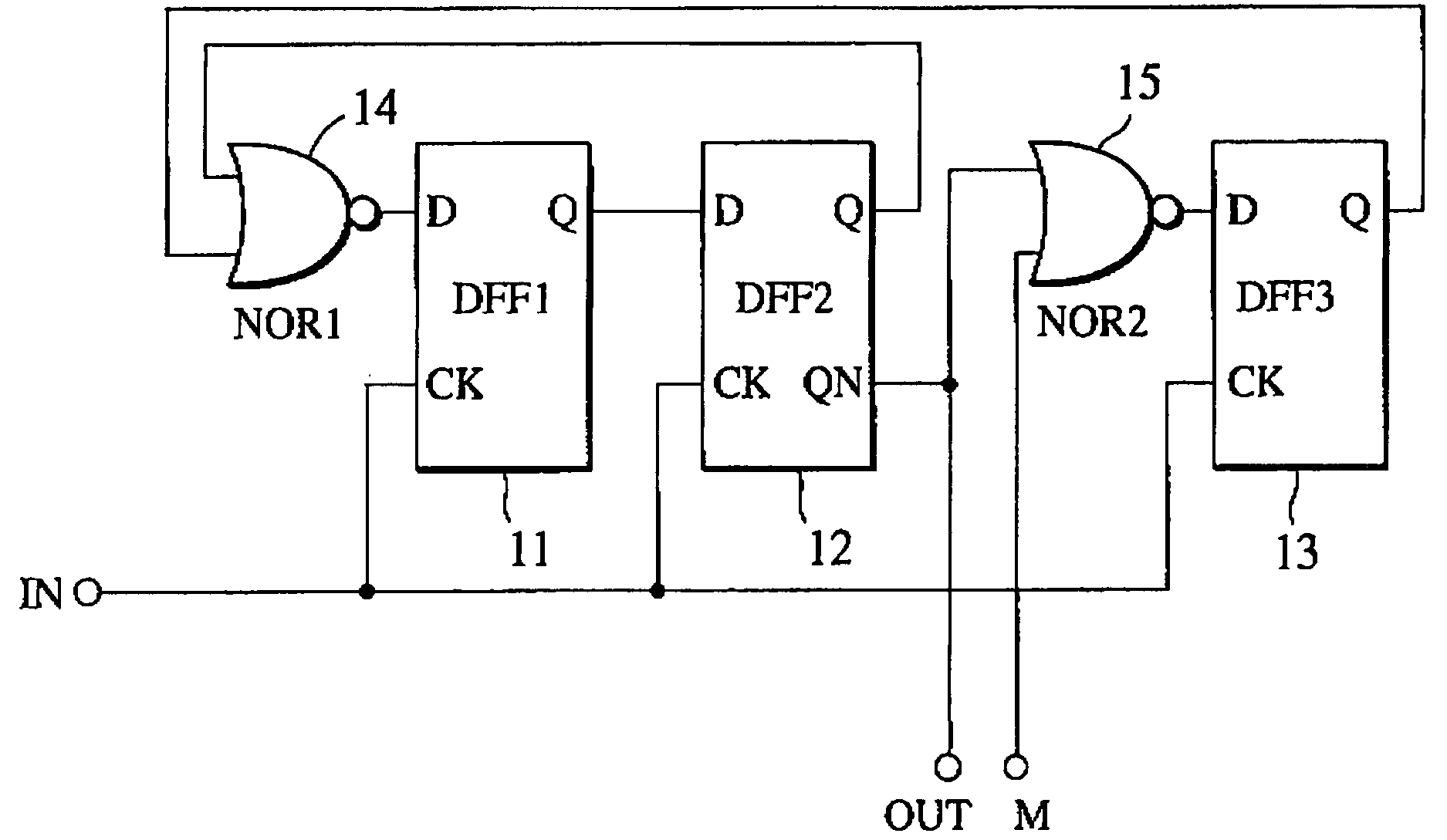

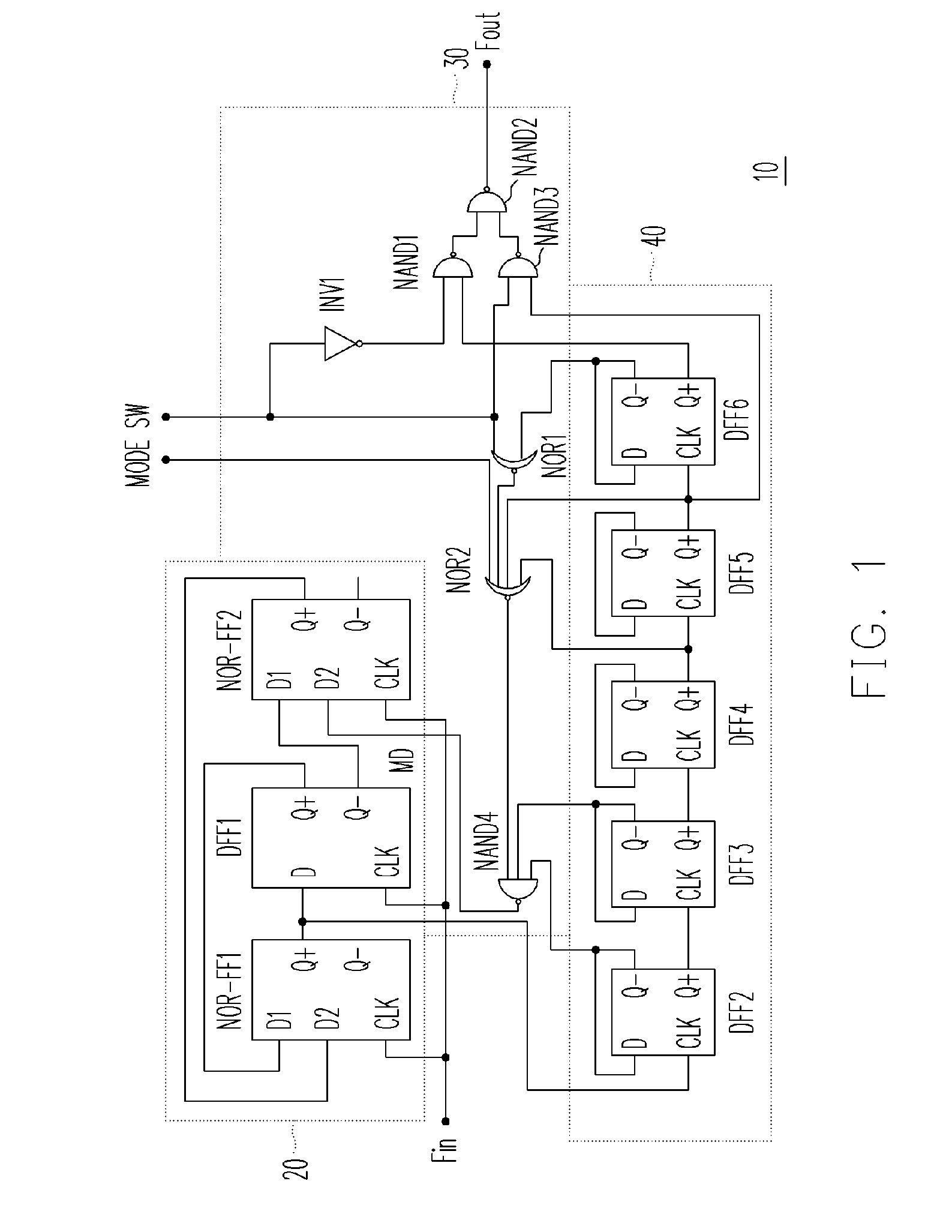

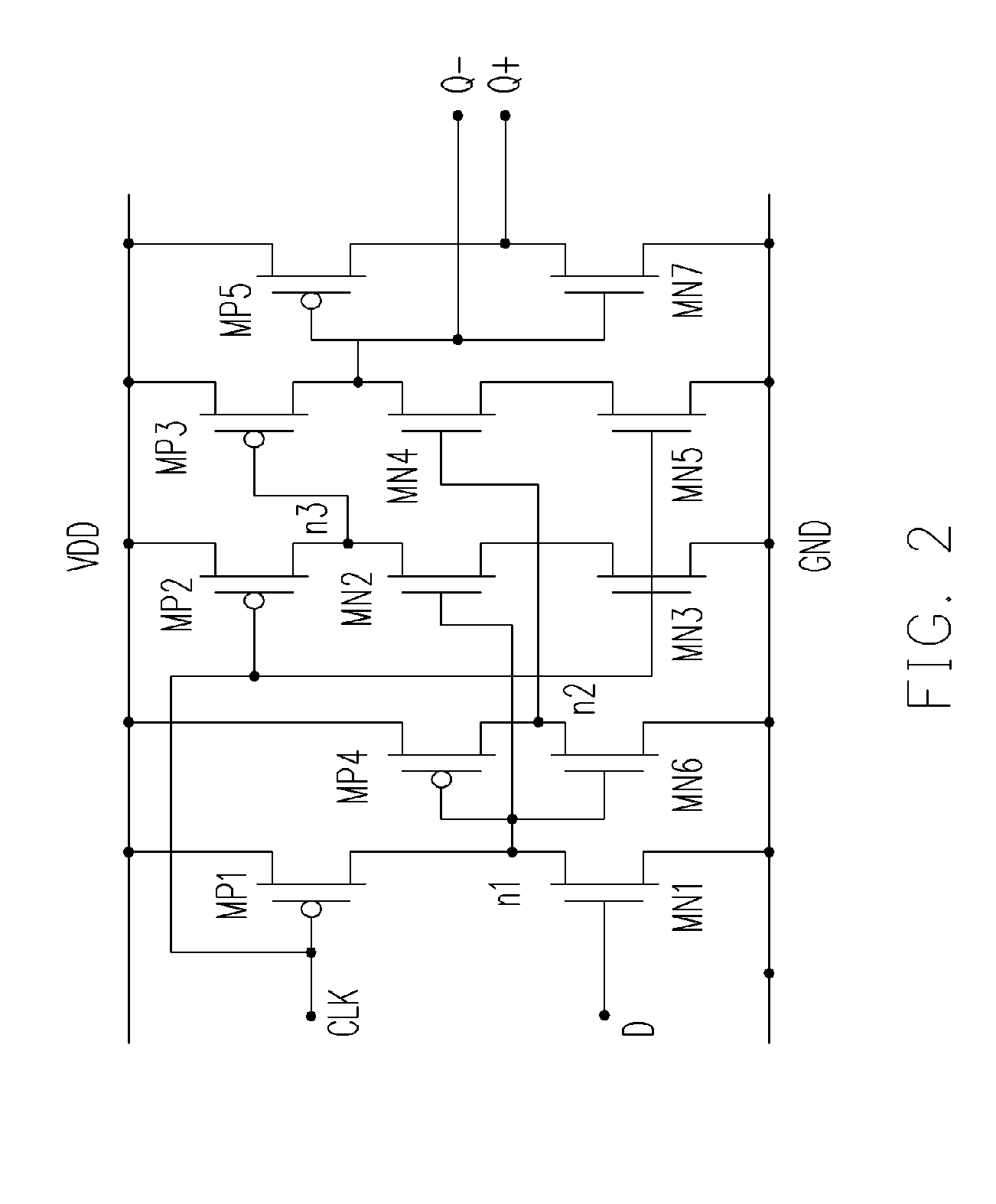

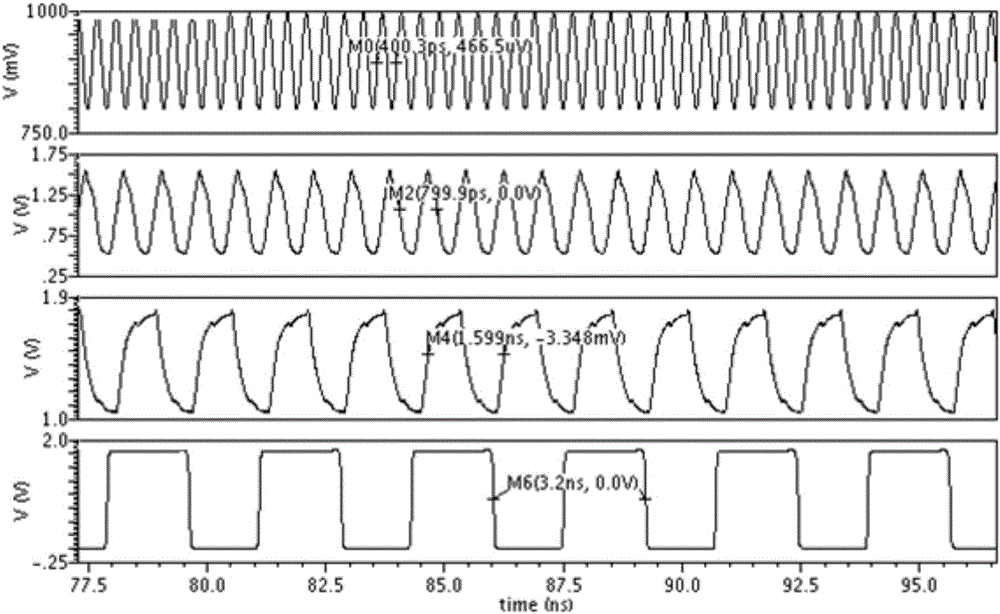

Disclosed is a Dual-Modulus Prescaler (DMP) dividing an input signal into an output signal, comprising: a synchronous counter, including a D-Flip-Flop (DFF), a first NOR-Flip-Flop and a second NOR-Flip-Flop, receiving the input signal, the division ratio thereof being based on an intermediate signal; a control logic, controlling the division ratio of the synchronous counter and selecting the output frequency based on first and second control signals, and outputting the intermediate signal to the synchronous counter; and an asynchronous counter, coupled to the control logic and the synchronous counter, having a chain of five DFFs.

Owner:WINBOND ELECTRONICS CORP

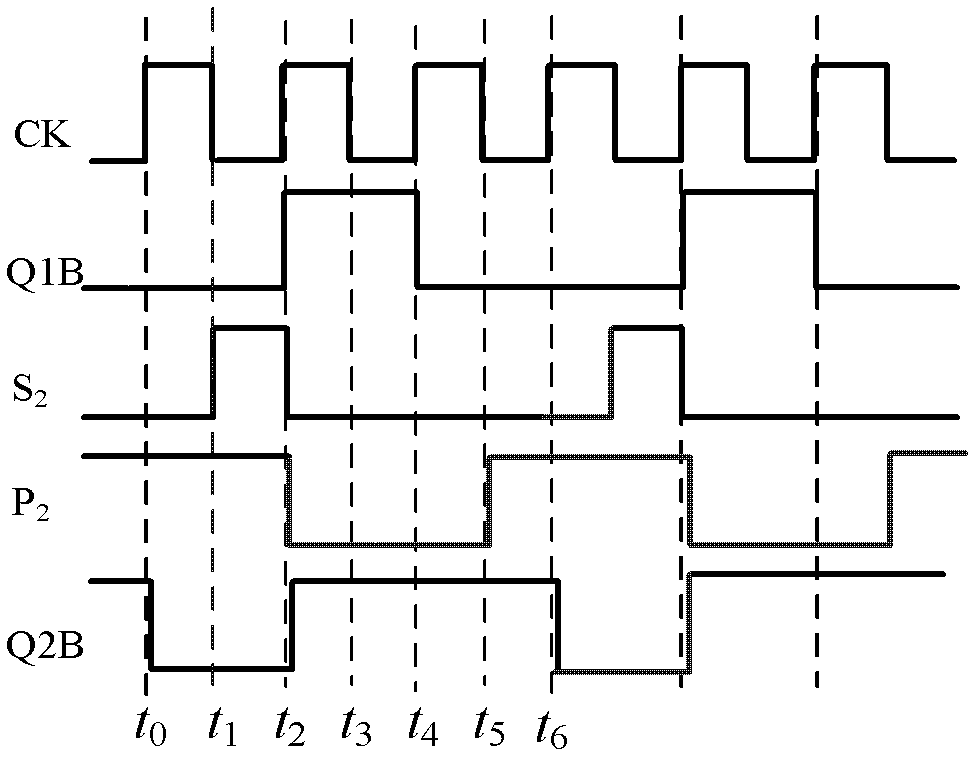

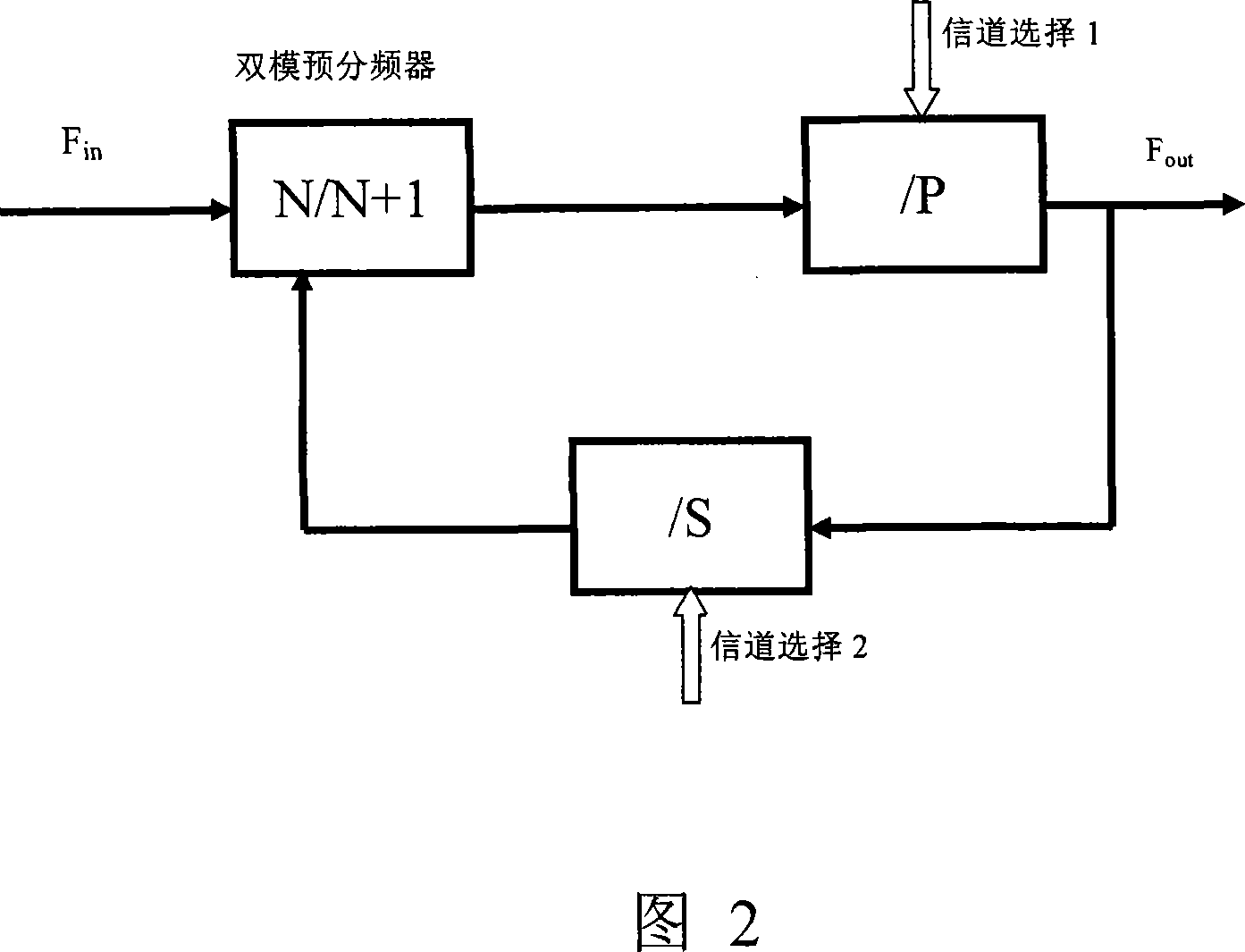

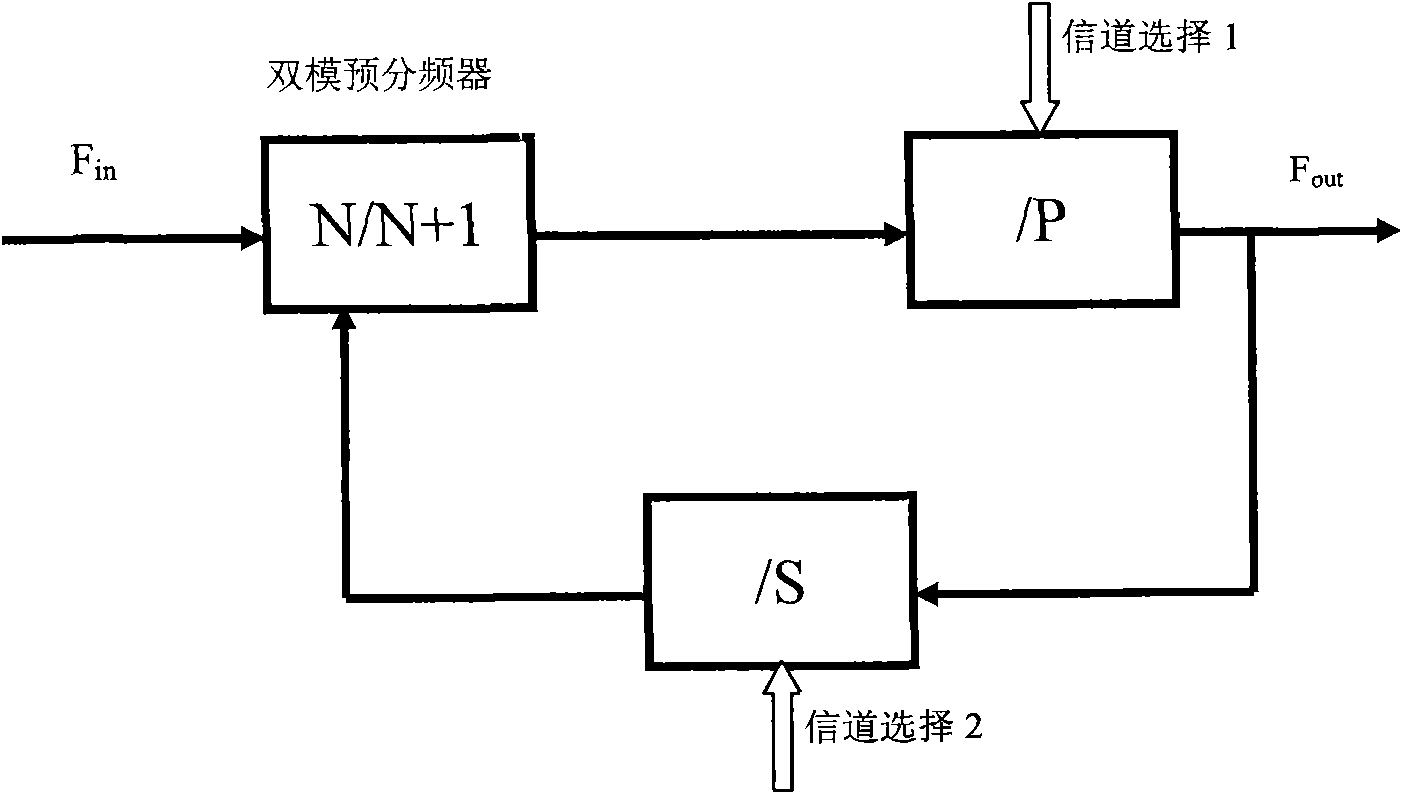

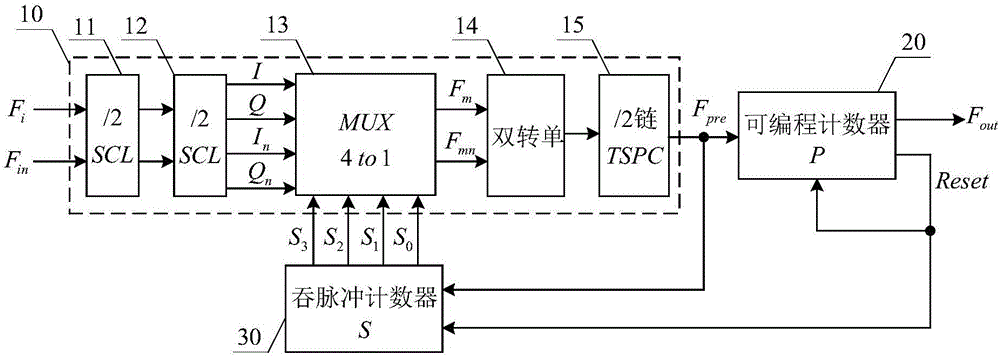

Multi-modulus programmable frequency divider structure with counter directly controlling phase switching

ActiveCN106100637AEliminate the effects ofSimple structurePulse automatic controlMode controlTime delays

The invention discloses a multi-modulus programmable frequency divider structure with a counter directly controlling phase switching. The structure comprises a N / N+1 phase switching type dual-modulus prescaler, a programmable counter P and a pulse-swallow counter S, wherein a prescale signal F<pre> output by the N / N+1 phase switching type dual-modulus prescaler is used as a work clock of the programmable counter P and the pulse-swallow counter S at the same time, a frequency divided signal F<out> output by the programmable counter P is used as total output of the multi-modulus programmable frequency divider structure, and a reset signal output by the programmable counter P is used as the reset signal of the programmable counter P and the pulse-swallow counter S at the same time. Compared with the conventional structure, in the structure provided by the invention, an independent prescale mode control signal MC and a phase selection logical circuit are eliminated, influence of time delay of the phase selection logical circuit on a switching window is directly eliminated, thus, the prescaler is restrained from outputting glitch, and correct frequency division is guaranteed when performing phase switching.

Owner:SOUTHEAST UNIV

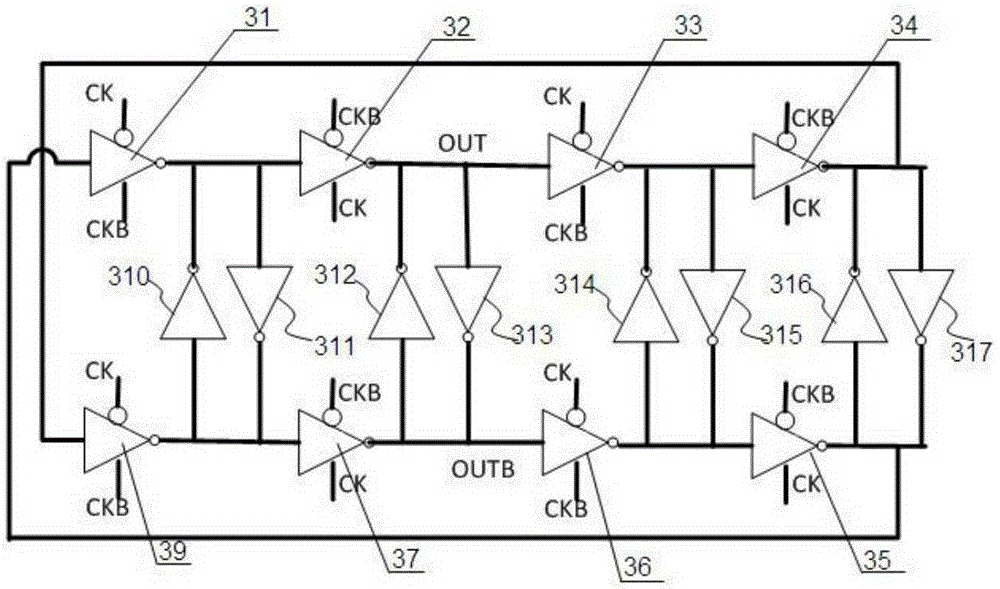

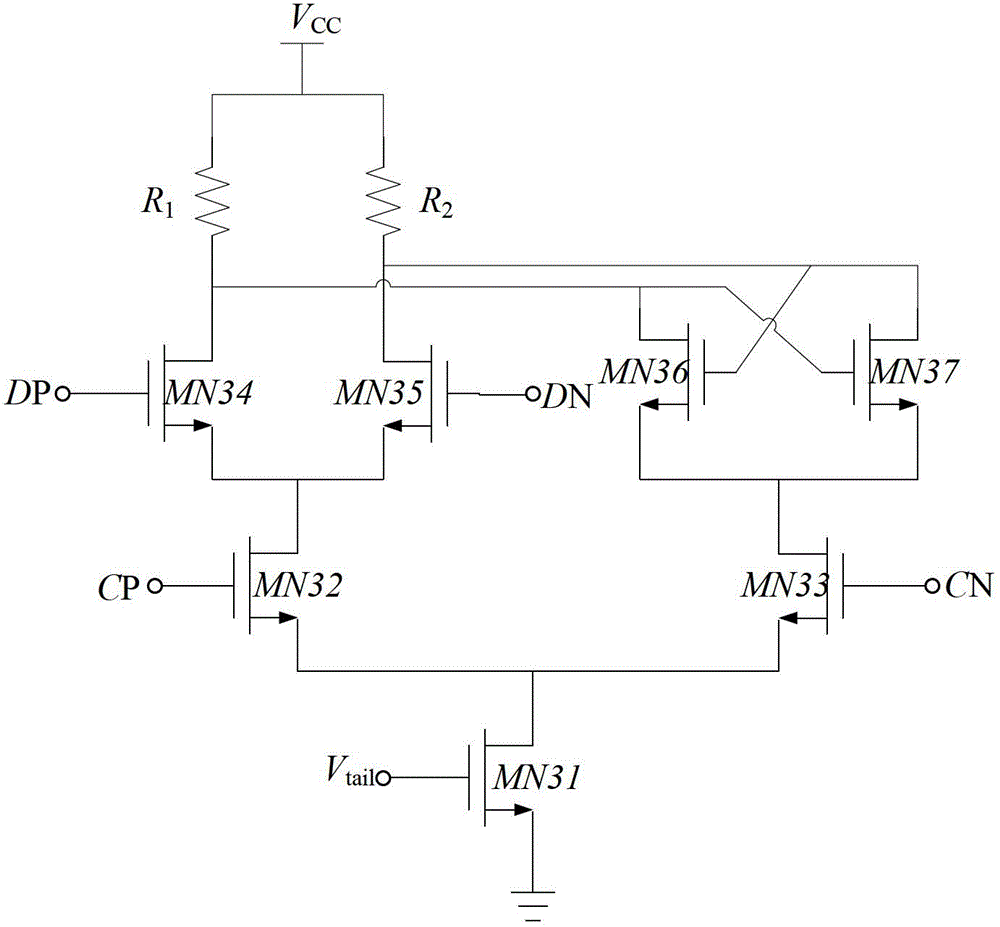

High-speed differential dual-modulus prescaler

ActiveCN105207672AMeet the design requirements of frequency divisionReduce power consumptionPulse automatic controlLocal oscillatorFrequency synthesizer

The invention belongs to the technical field of radio frequency communication chips, and particularly relates to a high-speed differential dual-modulus prescaler which is used for a multi-GHz frequency comprehensive phase-locked loop design technology. According to the high-speed differential dual-modulus prescaler, a logic gate of a trigger input end is combined with input-stage clock enable inverters, and a logic gate conversion rule that input and output are in inverse relationships is utilized. By means of latches between differential circuits, high-speed dynamic circuits are converted to high-speed static steady-state circuits. According to the technical scheme, a high-speed and low-power dual-modulus prescaler design technology which is suitable for a novel deep submicron process is provided, and the design requirement of frequency division of a frequency synthesizer and a local oscillator in a wireless radio frequency communication chip at present is effectively met.

Owner:SHANGHAI SIFLOWER COMM TECH CO LTD

True single-phase clock dual-mode prescaler with high speed and low power consumption

ActiveCN102710259BIncrease working frequencyReduce power consumptionPulse automatic controlCapacitanceMode control

The invention discloses a true single-phase clock dual-mode prescaler with high speed and low power consumption. The prescaler comprises a trigger unit consisting of a plurality of static complementary metal oxide semiconductor (CMOS) D triggers, a mode switching control unit and an adaptive power consumption control unit; the static CMOS D triggers are synchronously triggered, the CK ends of the static CMOS D triggers are connected with an input clock, and the D ends of the static CMOS D triggers are connected with the output of the mode switching control unit; the input of the mode switching control unit is connected with a frequency division and mode control end and the output of the trigger unit; and the input of the adaptive power consumption control unit is connected with a module power-off control word and the output of the mode switching control unit. Specific logic is adopted in the D triggers to reduce capacitive load so as to improve the working speed, the current of a true single-phase clock is reduced from milliamperes to microamperes at the same high speed compared with a current mode logic structure, and the power consumption of the dual-mode prescaler is also reduced by 15 to 50 percent through an adaptive power consumption control mode according to total frequency dividing ratio configuration.

Owner:JIANGSU CAS INTERNET OF THINGS TECH VENTURECAPITAL

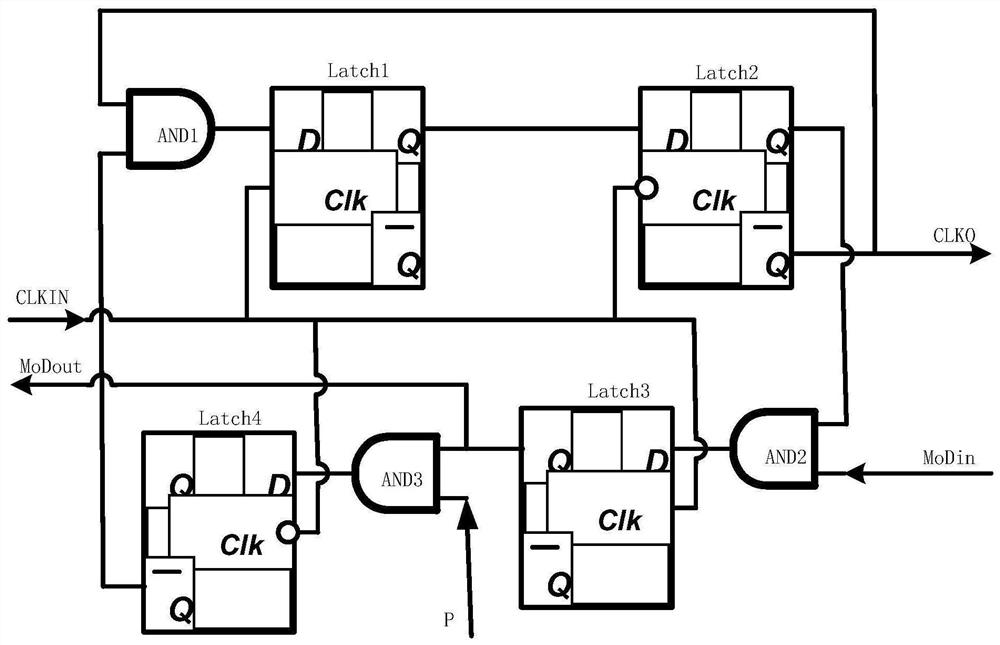

TSPC trigger, dual-mode prescaler and related devices of frequency divider

ActiveCN112260682AWork fasterEfficient power electronics conversionCounting chain synchronous pulse countersTelecommunicationsComputer architecture

The invention provides a TSPC trigger, a dual-mode prescaler and a frequency divider. The TSPC trigger comprises a first-stage structure, wherein the first-stage structure comprises a first transistorand a second transistor, and the size of the second transistor is larger than that of the first transistor, a first end of the first transistor is connected with a power supply, a grid of the first transistor is connected with a clock signal end, a second end of the first transistor is connected with a first end of the second transistor, a second end of the second transistor is grounded, and a grid of the second transistor is connected with a first signal end. Because the first end of the first transistor connected with the clock signal end is connected with the power supply, compared with the prior art, the TSPC trigger has the advantages that the transistor, namely the first transistor, connected with the clock signal end is closer to the power supply, and when the clock signal input bythe clock signal end controls the first transistor to be conducted, the power supply voltage can be transmitted to the output end of the first-stage structure more quickly, so that the working speedsof the TSPC trigger, the dual-mode prescaler and the frequency divider are increased.

Owner:CALTERAH SEMICON TECH SHANGHAI CO LTD

Phase-switching dual-mode frequency divider and frequency synthesizer including the frequency divider

Owner:NXP BV

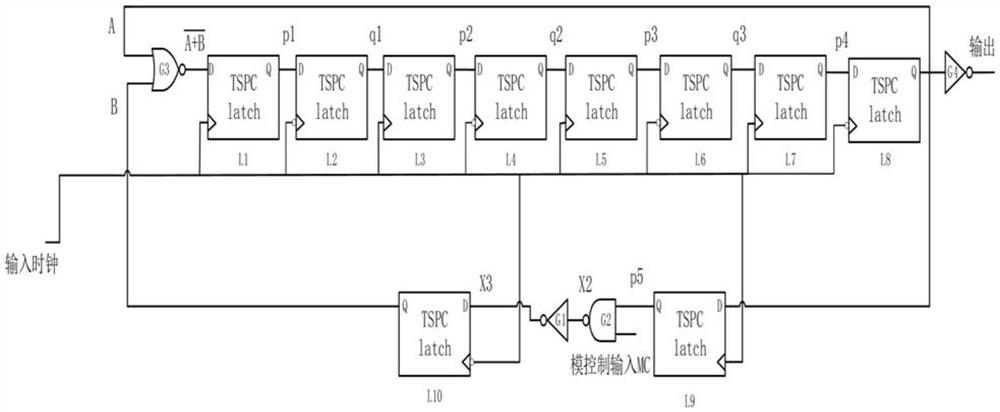

A high-speed 8/9 prescaler circuit, its control method and its phase-locked loop

The invention discloses a high-speed 8 / 9 dual-mode prescaler, comprising 10 TSPC latches L1‑L10, 1 NAND gate (G2), 1 NOR gate (G3), a first NOT gate (G1) and the second NOT gate (G4); it is characterized in that: TSPC latches L1, L3, L5, L7 and L9 are first type latches, TSPC latches L2, L4, L6, L8 and L10 for the second type of latch. The high-speed 8 / 9 dual-mode prescaler proposed by the invention has high operating frequency and wide frequency band coverage.

Owner:SOUTH CHINA UNIV OF TECH

A 2/3 dual-mode prescaler with high speed and low power consumption

ActiveCN105071805BWork fasterReduce power consumptionPulse automatic controlCounting chain pulse countersMode controlEngineering

Owner:SOUTHEAST UNIV

Method and device for measuring moisture in vertical section of farmland soil

ActiveCN105758901BRealize precise perceptionStrong spatial integrityMaterial capacitanceLow noiseMeasurement device

The invention discloses a moisture measurement method and device of a vertical section of farmland soil. The device is characterized by comprising a mounting pipe sleeve, a hollow cylindrical electrode, an insulating pipe column, a base band coaxial cable, a liquid-phase hollow water column, a resisting plate and a core processor; the moisture measurement device of the vertical section of the soil is controlled by a voltage-controlled oscillator to generate a high-frequency oscillation signal; a low-frequency square wave signal is obtained through silicon epitaxy high-frequency and low-noise amplitude amplification, and shaping and frequency division of a dual-modulus prescaler; accurate sensing of the volume moisture content of the soil is realized through a mathematical model between the frequency and the volume moisture content of the soil. A cylindrical stereoscopic type multilayered structure is adopted, and a moisture dynamic determination fitting and quantitative inversion technology of the vertical section of the farmland oil is integrated, so that the volume moisture convent of different heights of the vertical section of the farmland oil and the moisture supply amount of the soil of the vertical section are dynamically sensed in real time by utilizing the fewest layers; the moisture measurement method and device has the greatest advantages that the moisture condition of the vertical section of the soil can be continuously sensed in real time, the space integrity is strong and real-time calibration can be realized.

Owner:NANJING AGRICULTURAL UNIVERSITY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com