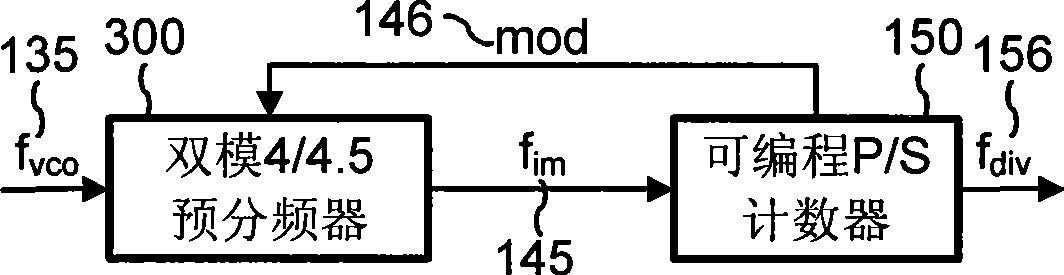

Dual mode 4/4.5 pre-divider

A prescaler and flip-flop technology, applied in the direction of electrical components, automatic power control, etc., can solve the problem of large quantization noise of the ΔΣ modulator, and achieve the effect of improving resolution, satisfying fast settling time, and reducing contribution.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

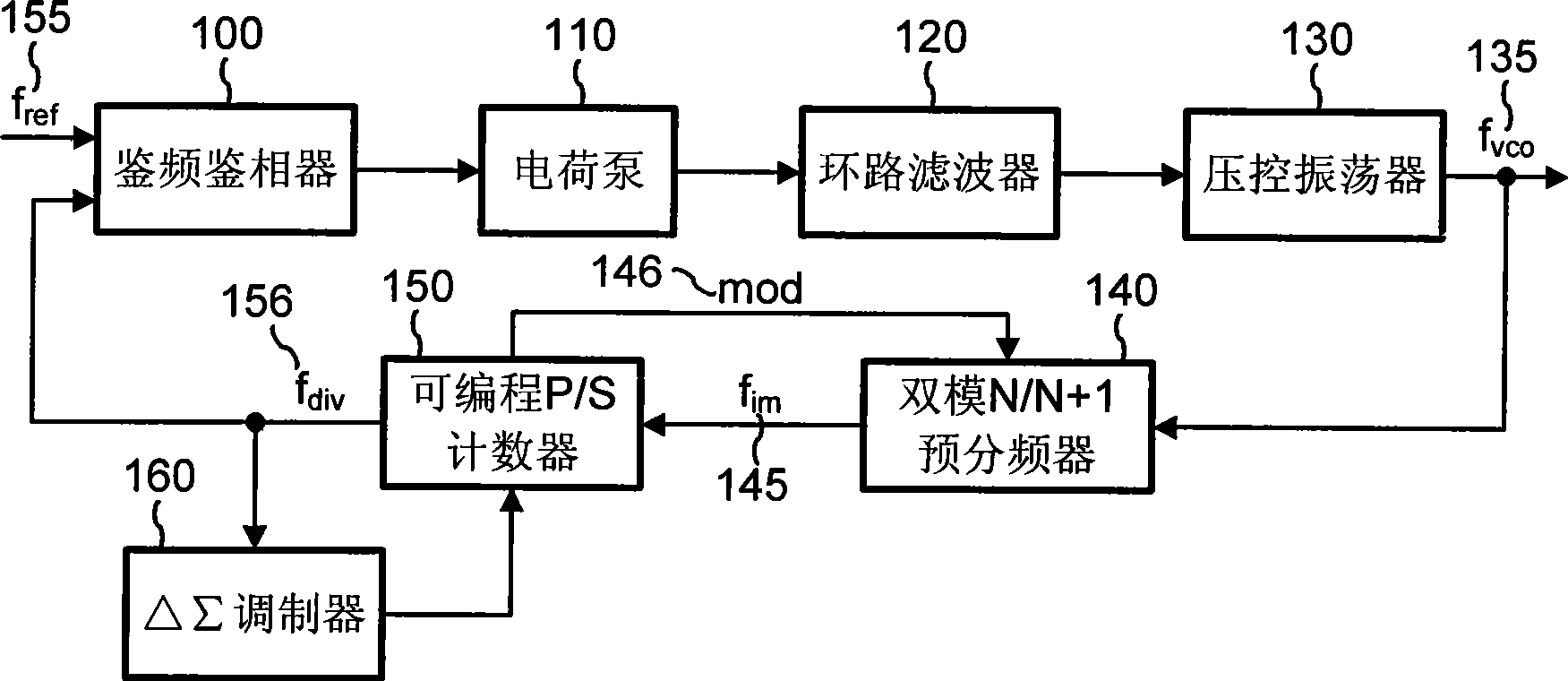

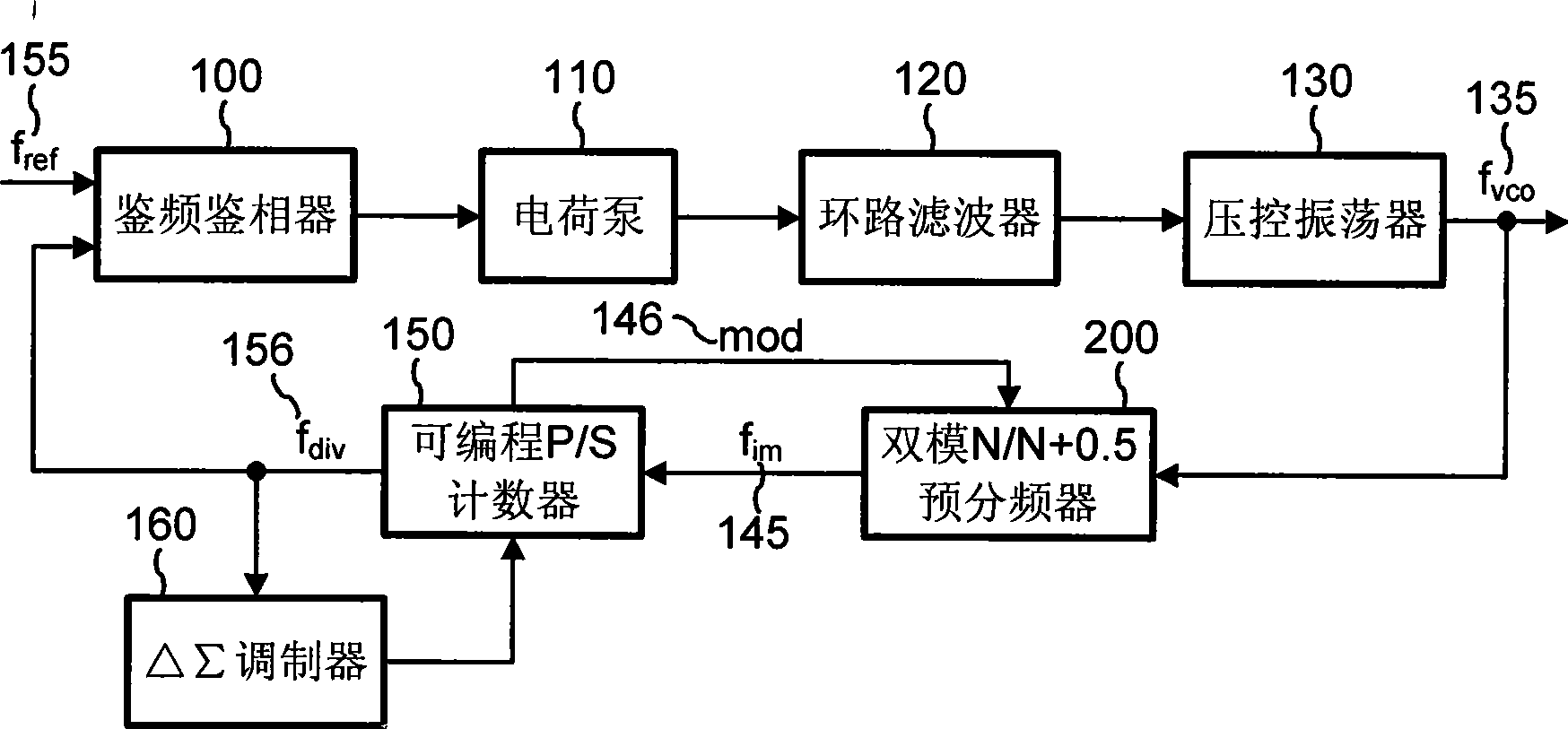

[0032] figure 2 Schematic diagram of the system structure of the fractional frequency synthesizer used in the present invention, including frequency and phase detector 100, charge pump 110, loop filter 120, voltage controlled oscillator 130, dual-mode N / N+0.5 prescaler 200 . Programmable P / S counter 150 and ΔZ modulator 160 . The output signal f can be obtained vco =[S*(N+0.5)+(P-S)*N]*f div =(P*N+0.5*S)*f div , and when the integer frequency division is locked, f div equal to f ref , so get the output signal f vco =(P*N+0.5*S)*f ref , the resolution of the output signal is increased to 0.5*f ref . In the fractional frequency division mode, since the ΔΣ modulator 160 produces a variable integer frequency division ratio, f div is not always equal to f ref , but dynamic equality. At this moment, the output of ΔΣ modulator 160 is equivalent to a quantization step on the frequency division ratio of 0.5, so its output quantization noise is relative to figure 1 Reduced ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com