Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

34results about "Counting chain pulse counters using semiconductor devices" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Frequency divider with improved linearity for a fractional-n synthesizer using a multi-modulus prescaler

ActiveUS20140003570A1Counting chain pulse counters using semiconductor devicesPulse automatic controlEngineeringLinearity

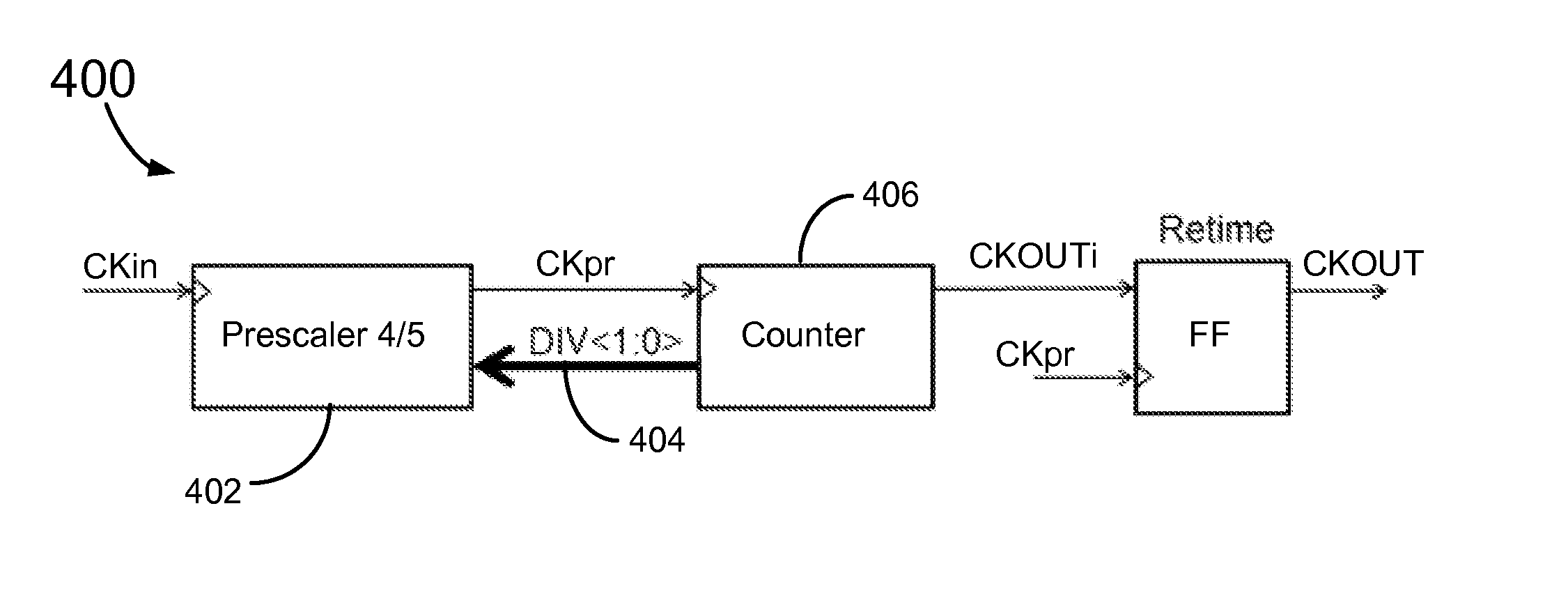

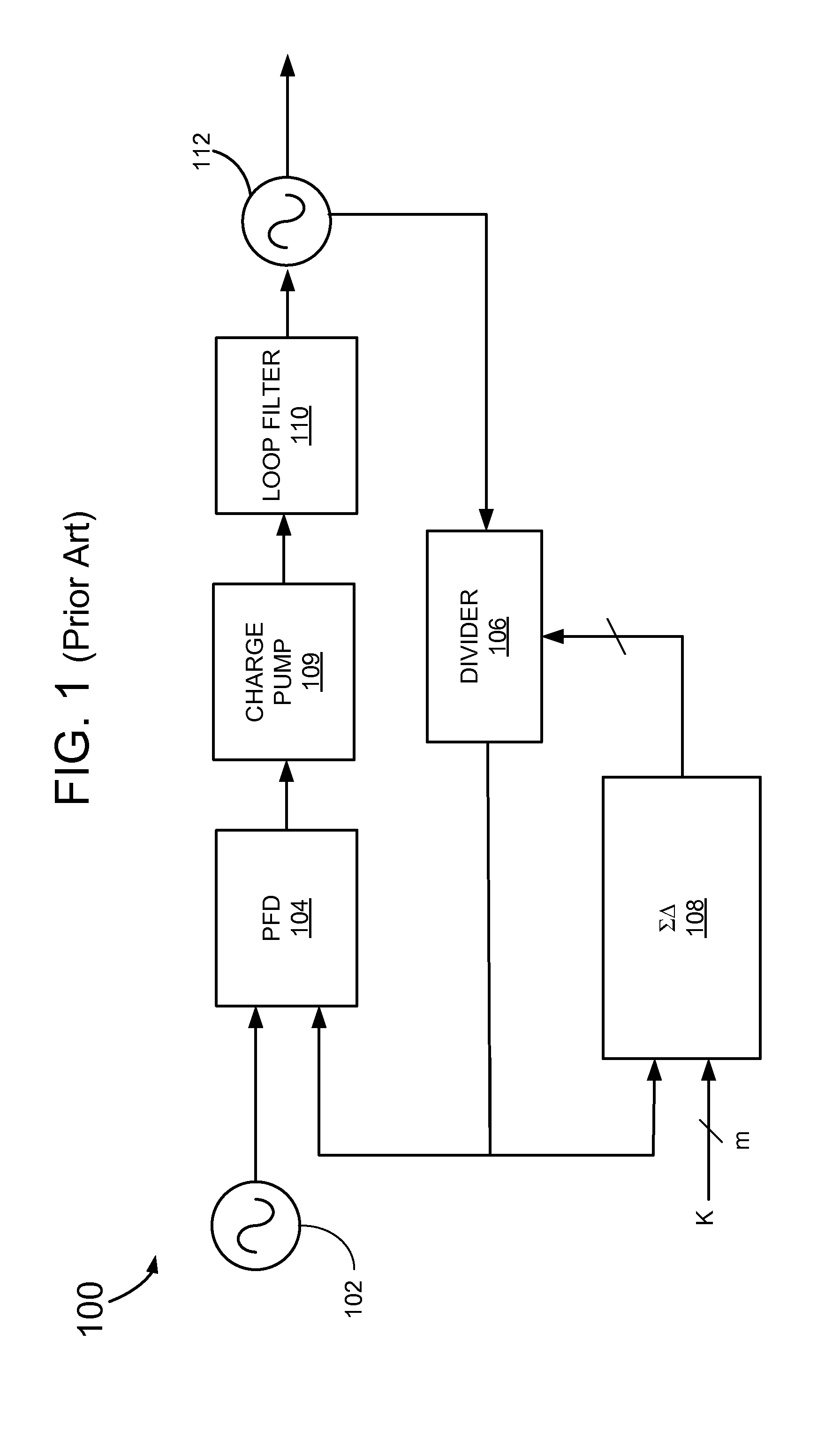

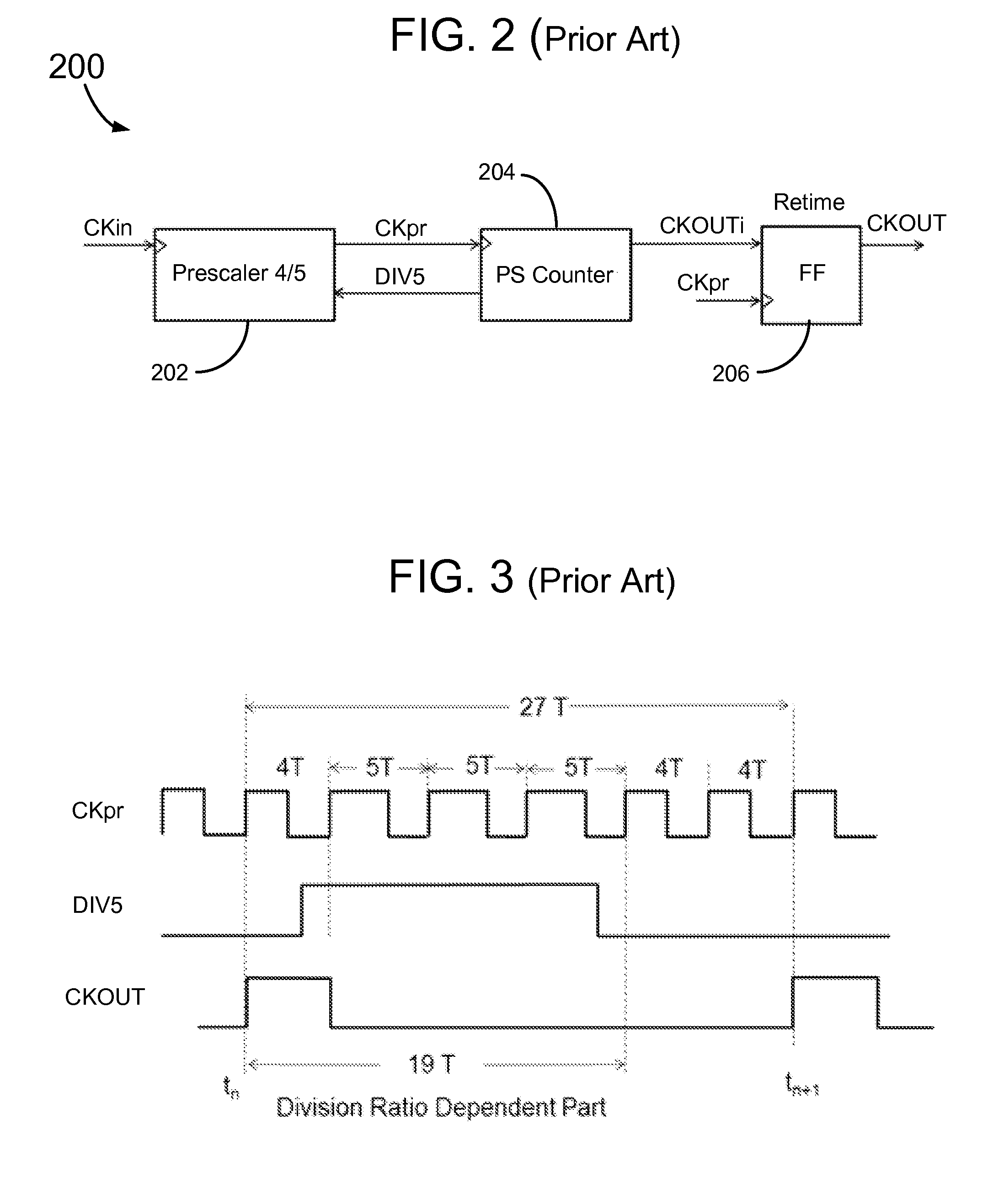

A frequency divider is disclosed. The frequency divider includes a multi-modulus prescaler to perform a frequency division by a modulus M, wherein M is an integer between N and 2*N−1 and N is a power of 2. The frequency divider also includes a programmable counter to output the digital representation of M and an output clock signal. For the frequency divider, M equals N plus D minus D\N for each edge of the multi-modulus prescaler output clock CKpr wherein the counter samples the digital representation of D and D\N denotes an integer part of D divided by N, and M equals N for each subsequent edge of the prescaler output clock CKpr wherein the counter does not sample the digital representation of D.

Owner:QUALCOMM INC

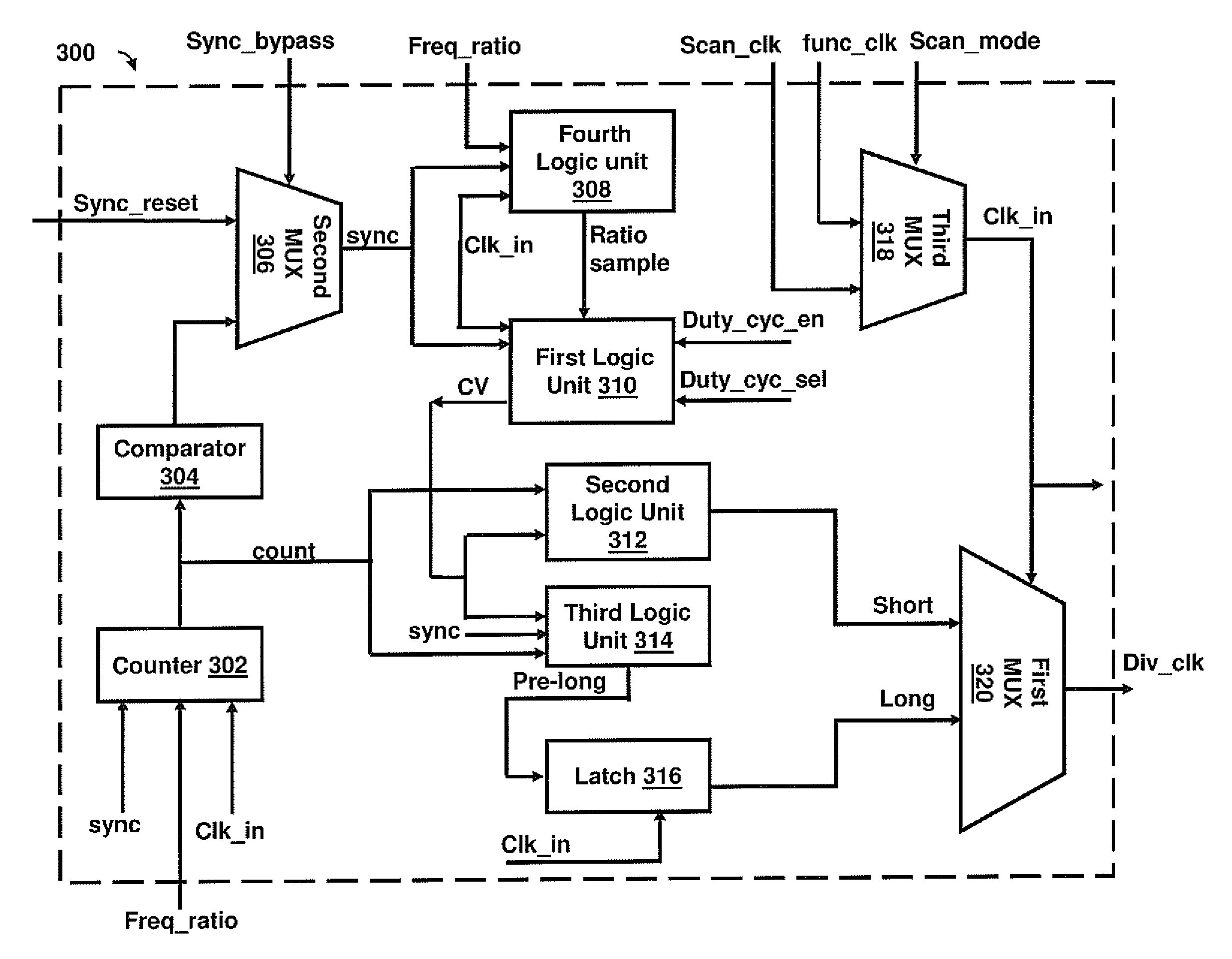

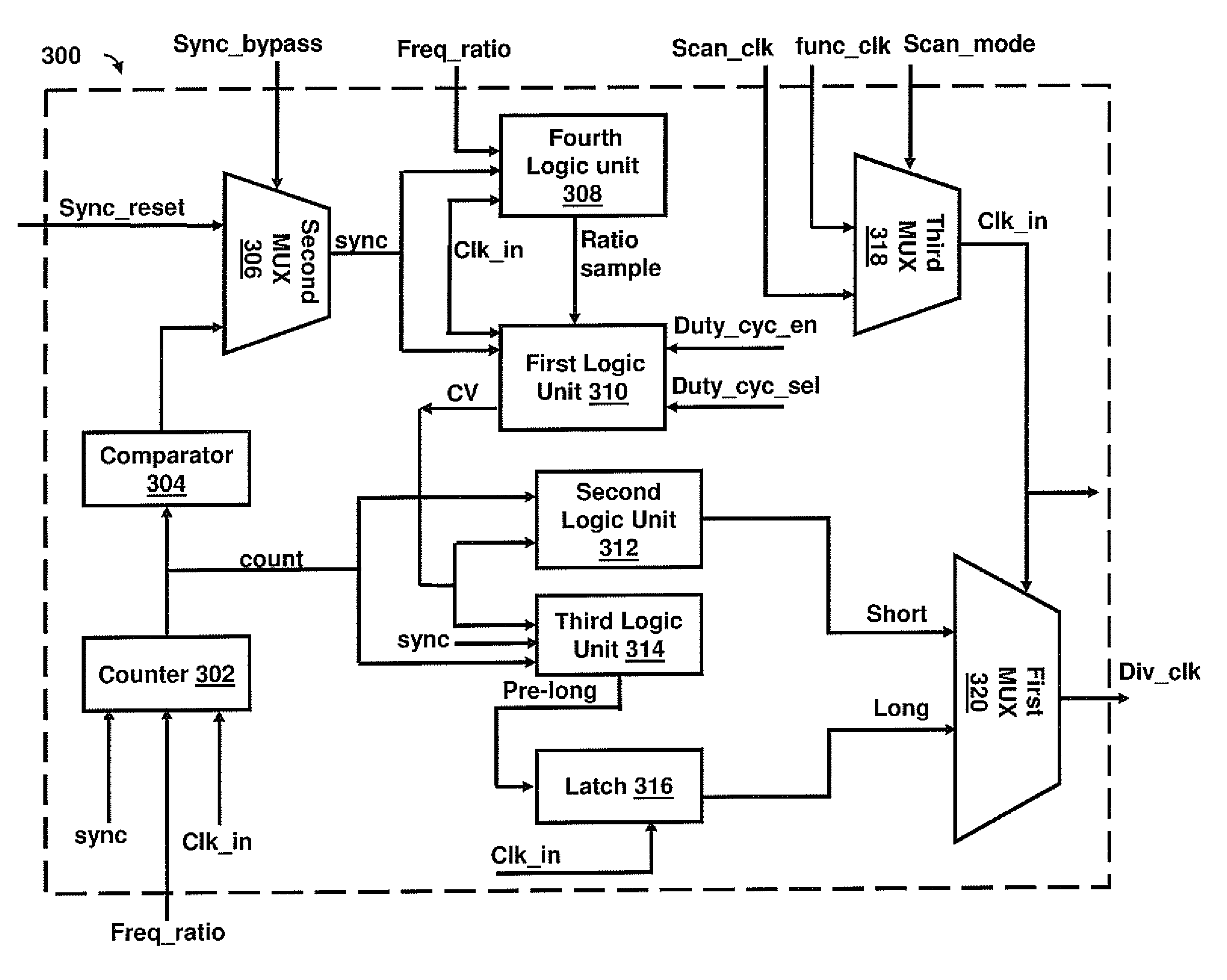

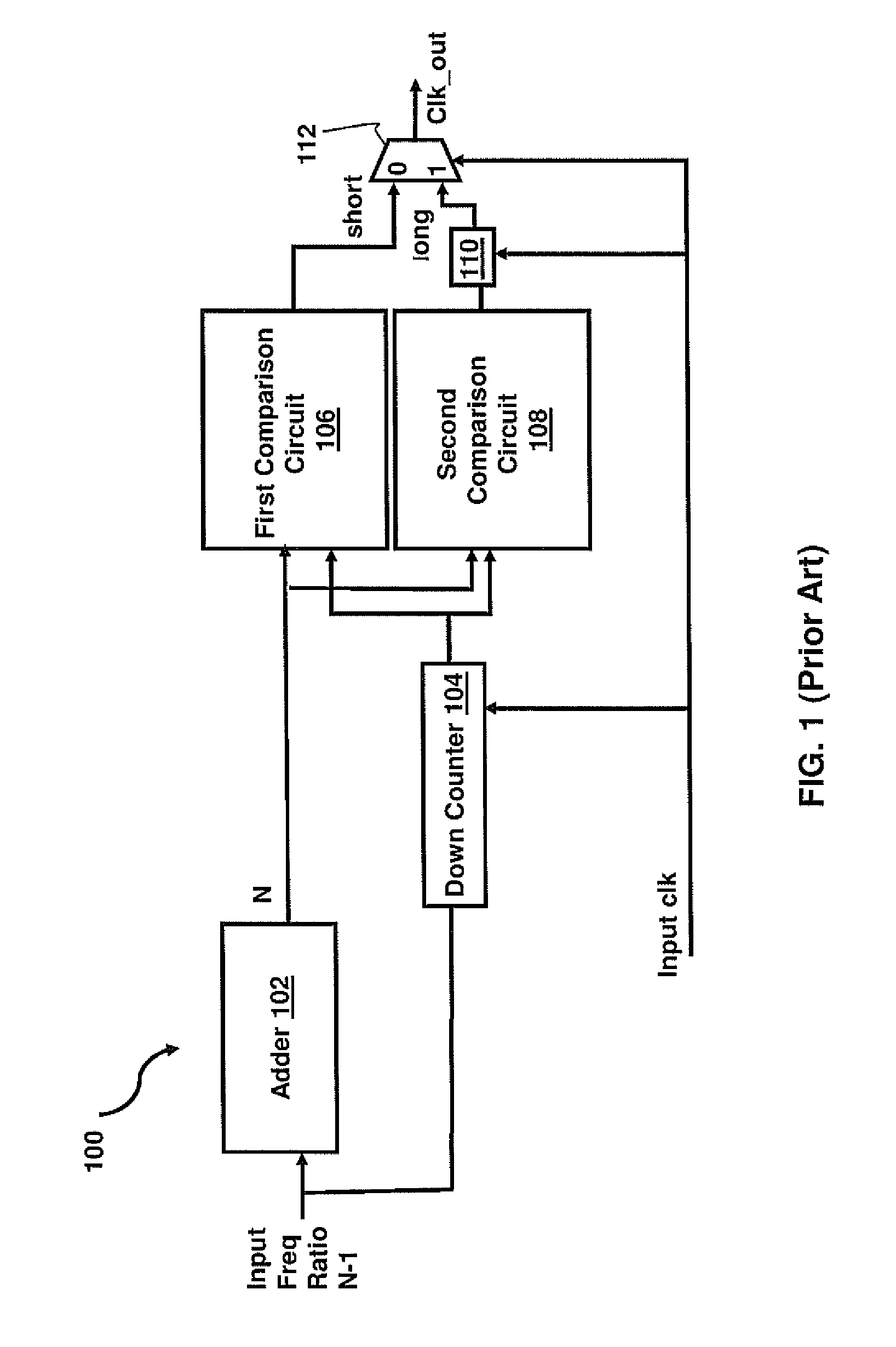

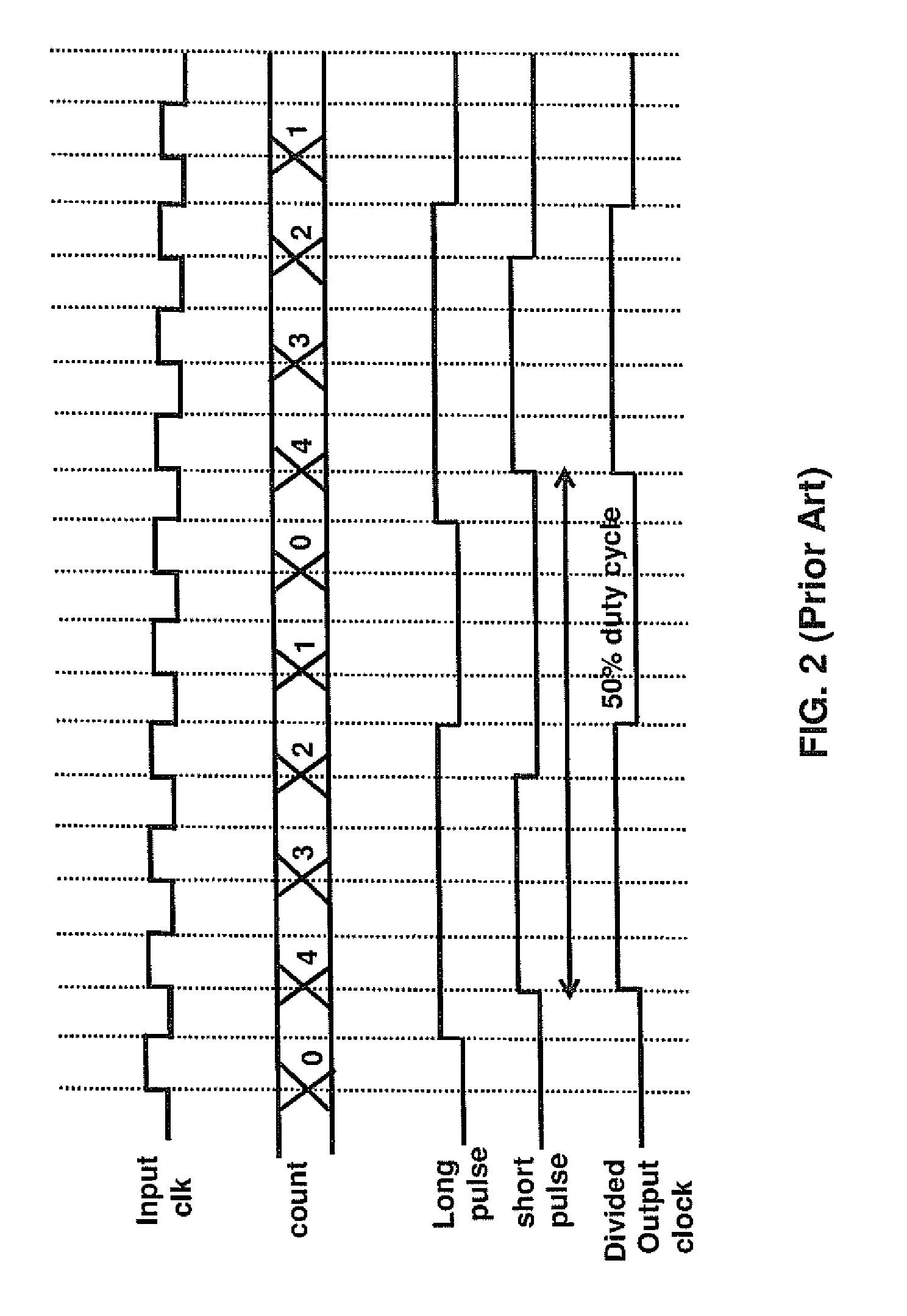

Programmable synchronous clock divider

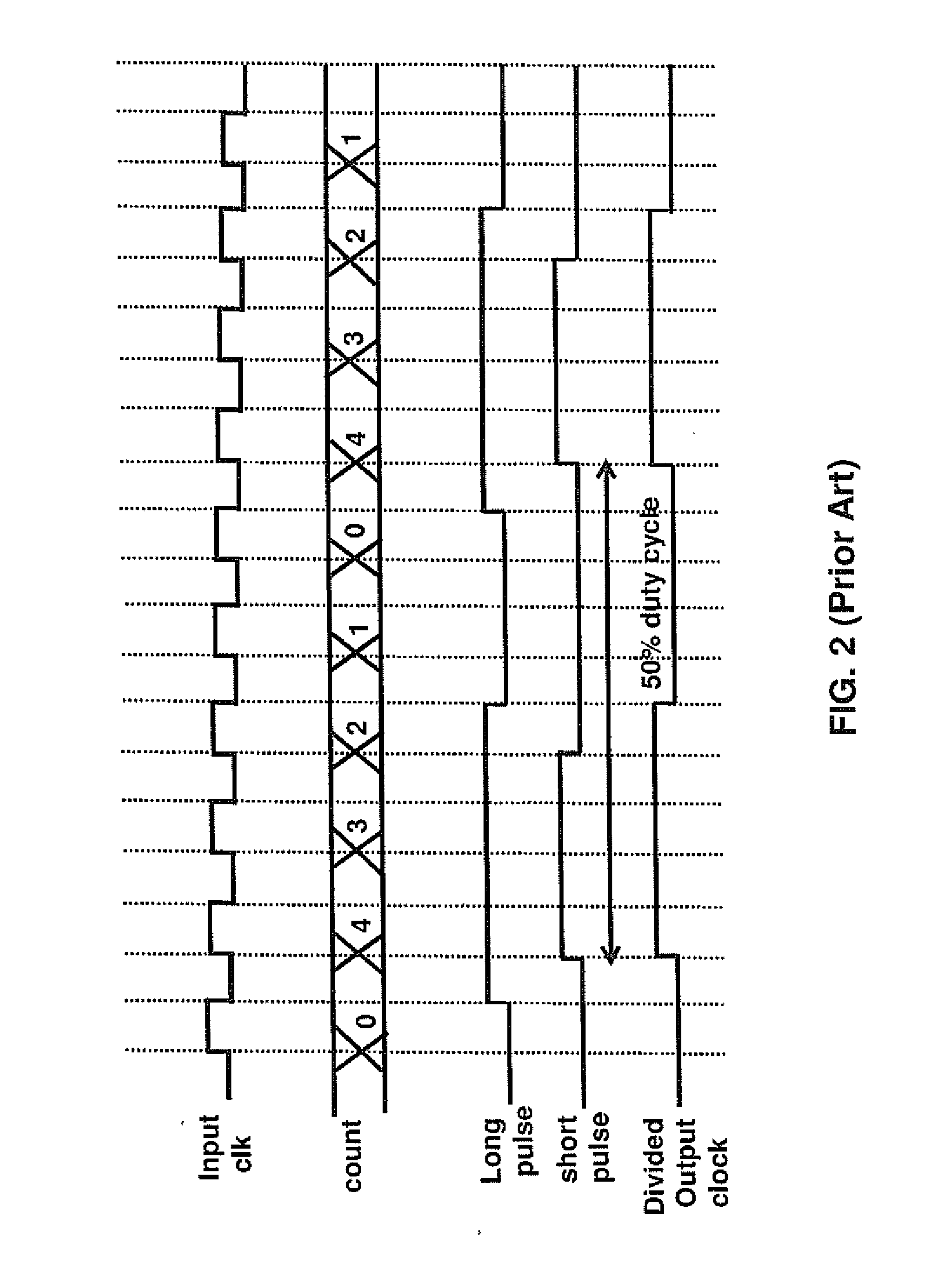

ActiveUS20160233852A1Counting chain pulse counters using semiconductor devicesElectric pulse generatorLong pulseClock signal

A divided clock signal is generated from an input clock signal. The duty cycle of the divided clock signal is programmed by generating a compare value based on values of duty cycle input and a divide value of the input clock signal. The compare value is compared to a count value to generate short and long pulse signals. The divided clock signal is generated based on the short and long pulse signals. The duty cycle of the divided clock signal varies in accordance with the compare value.

Owner:NXP USA INC

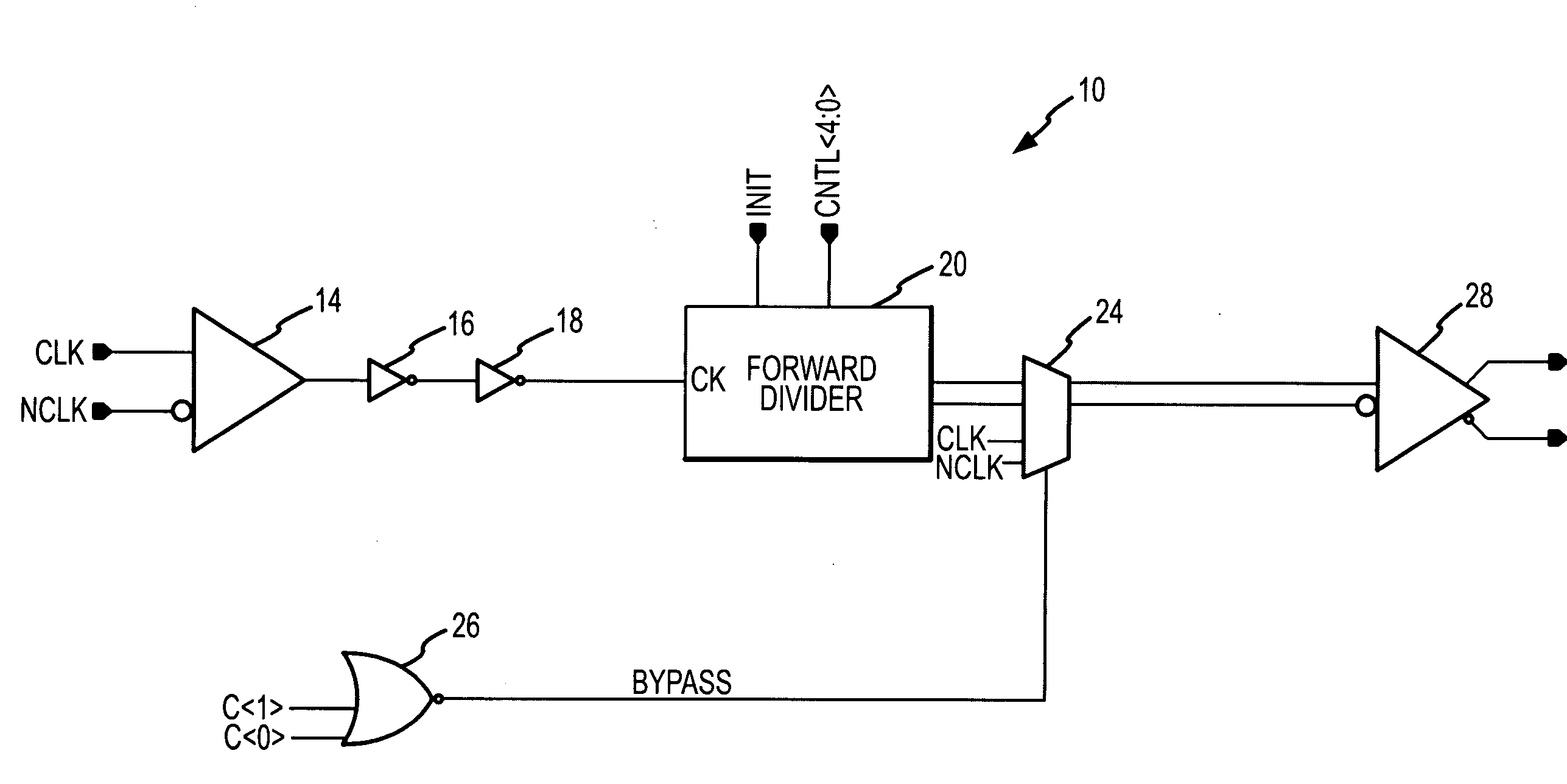

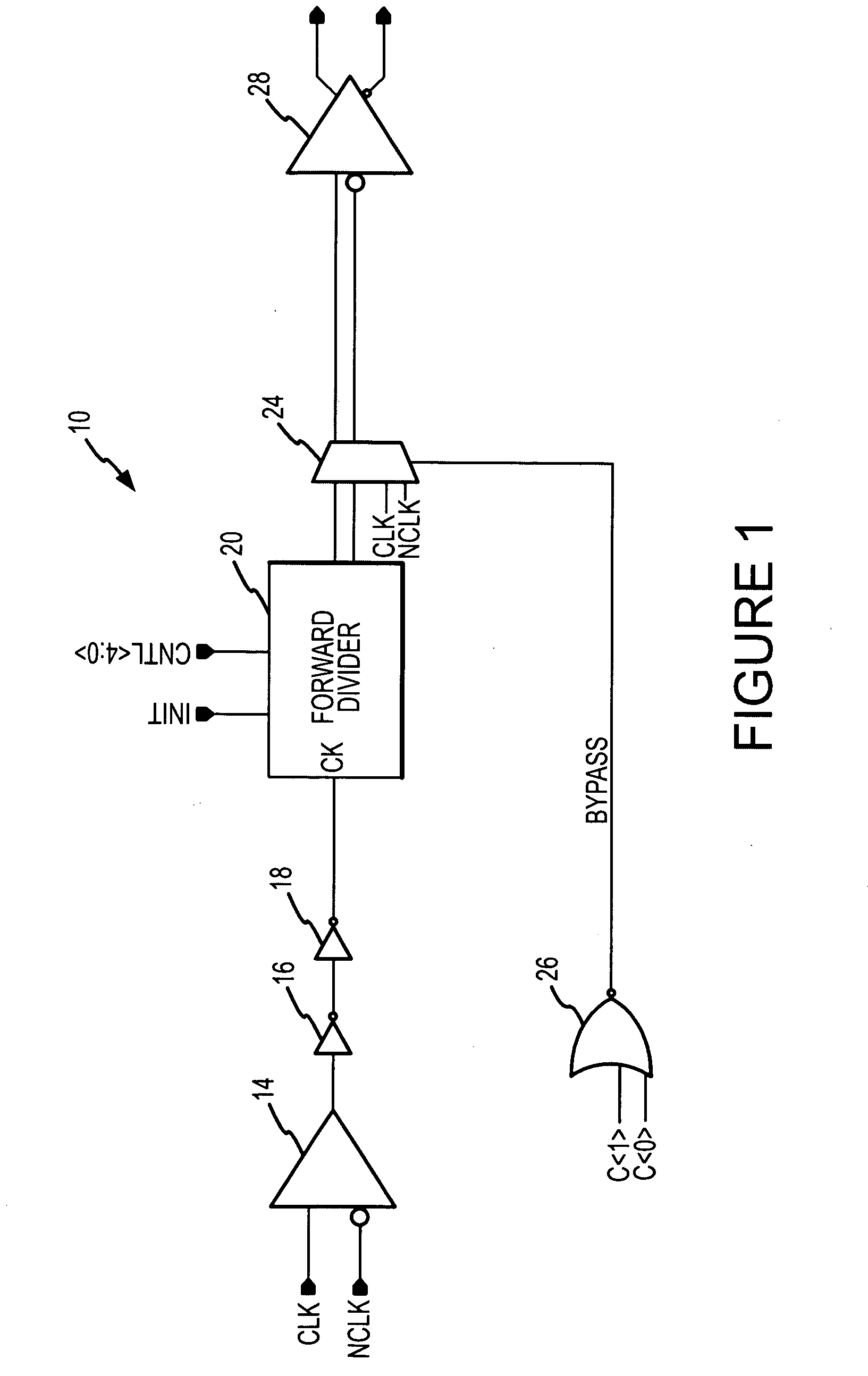

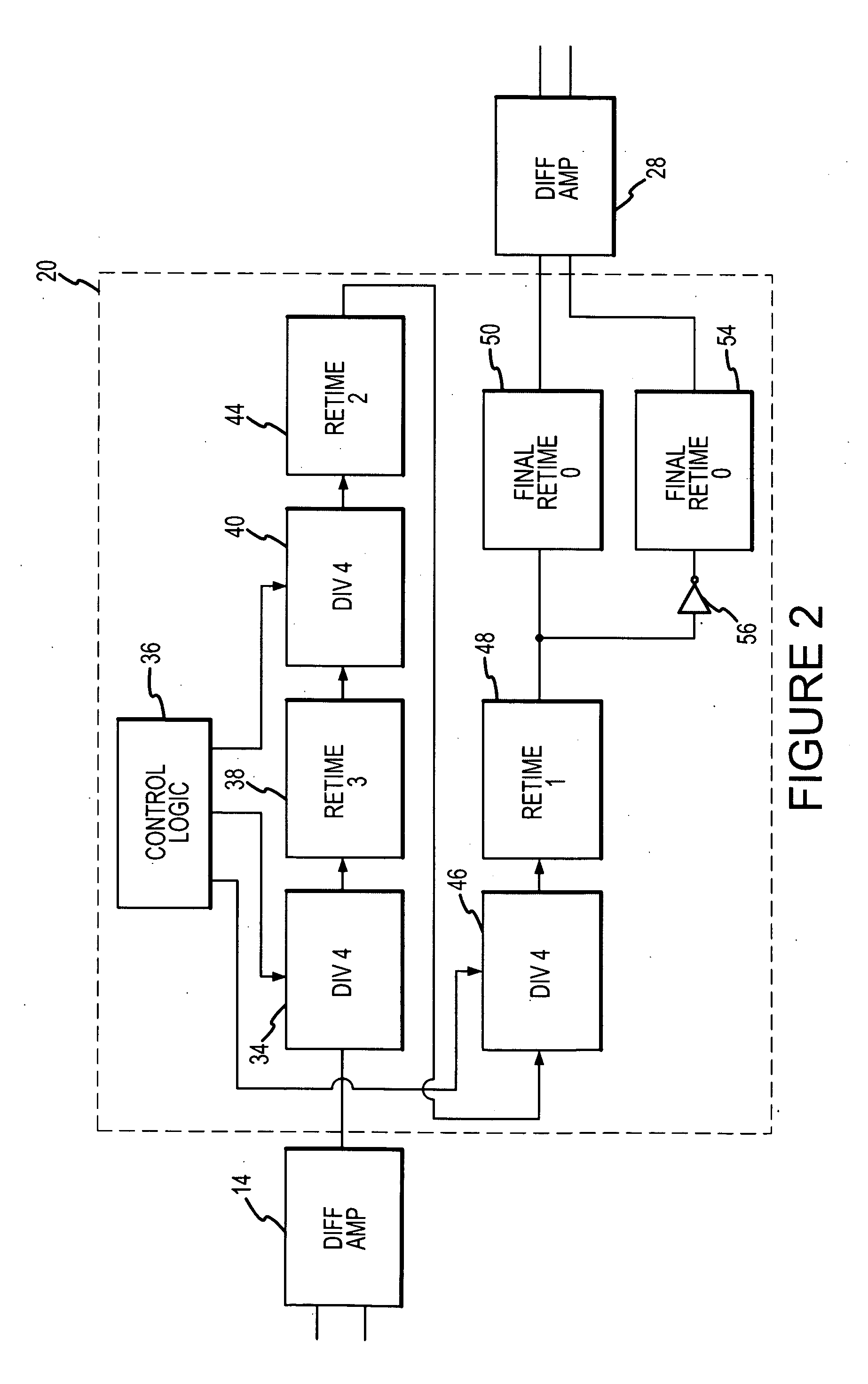

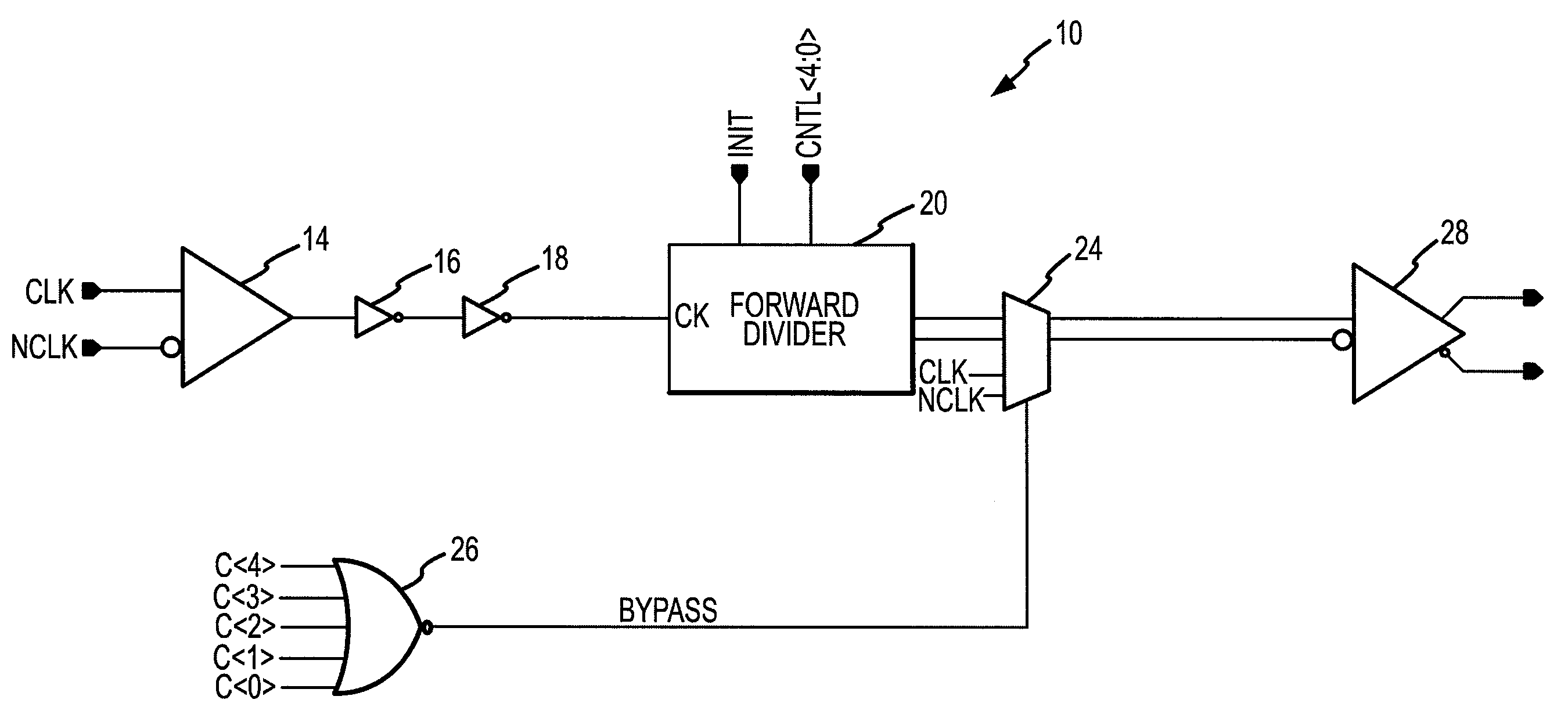

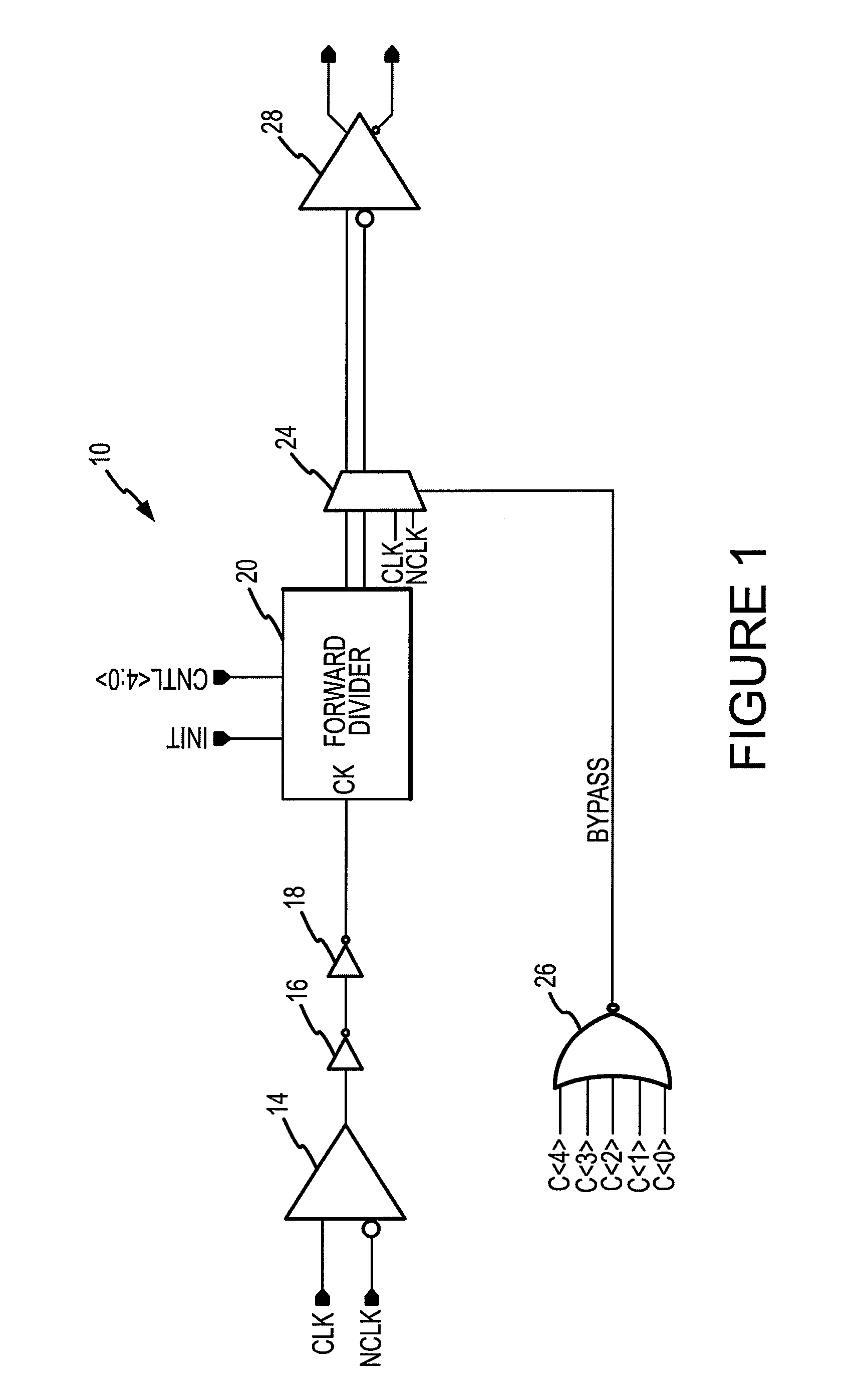

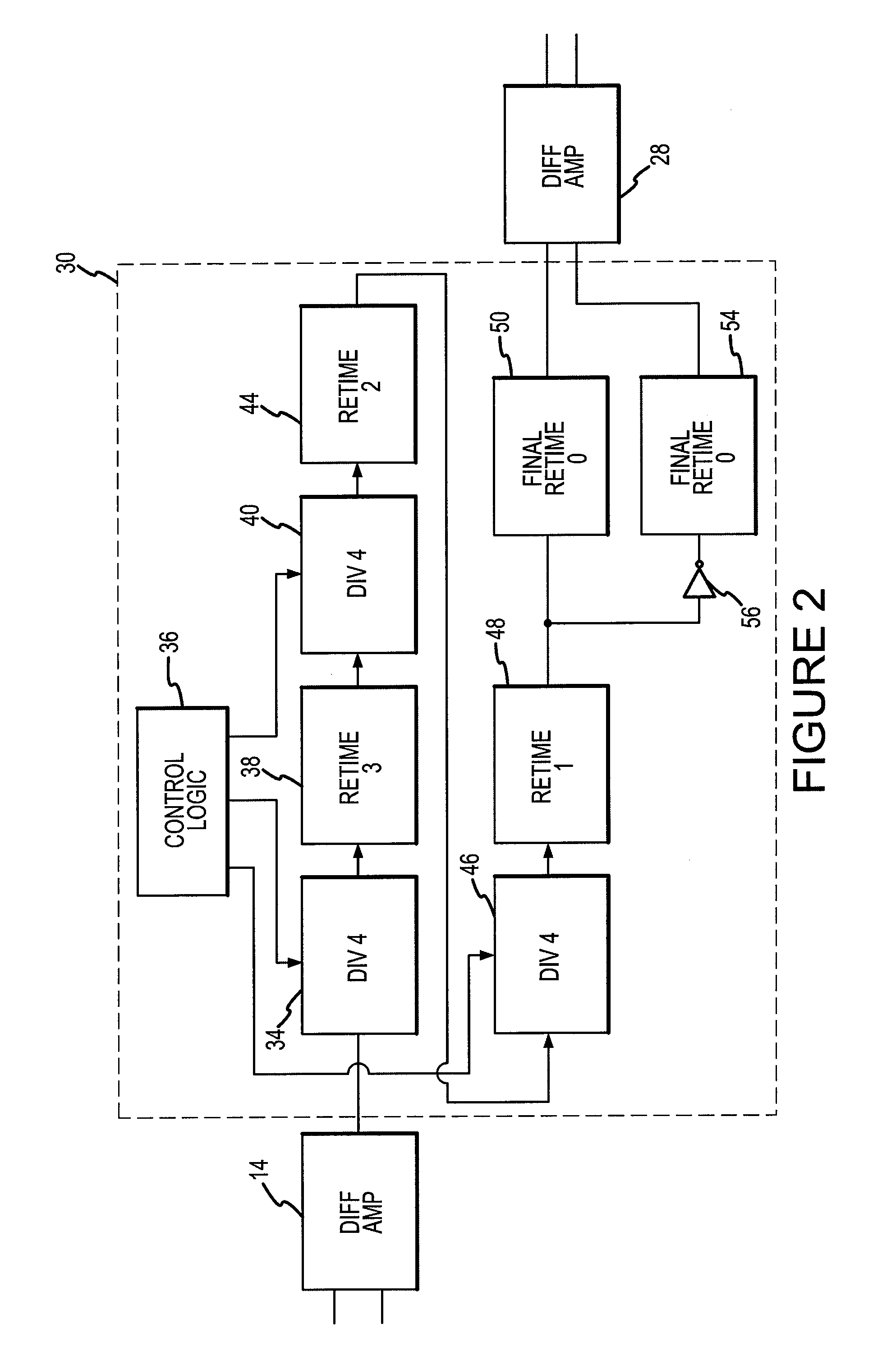

Wide frequency range signal generator and method, and integrated circuit test system using same

ActiveUS20070300111A1Counting chain pulse counters using semiconductor devicesElectronic circuit testingSignal generatorTimer

A signal generator produces an output clock signal by coupling an input clock signal through a plurality of divider circuits each of which is formed by a toggling flip-flop. The frequency of the output clock signal is adjusted by selecting the flip-flop to which the input clock signal is coupled. Retimer flip-flops may be coupled between adjacent flip-flips to resynchronize the signal being coupled through the flip-flops. Each of the retimer flip-flops receives a respective signal from the output of an upstream flip-flop at its data input, and it receives the input clock signal at its clock input. The flip-flop then applies the signal to a downstream flip-flop in synchronism with the input clock signal. The final two flip-flops through which the input signal is coupled may be preset to various states to set the phase of the output clock signal to one of four phases.

Owner:MICRON TECH INC

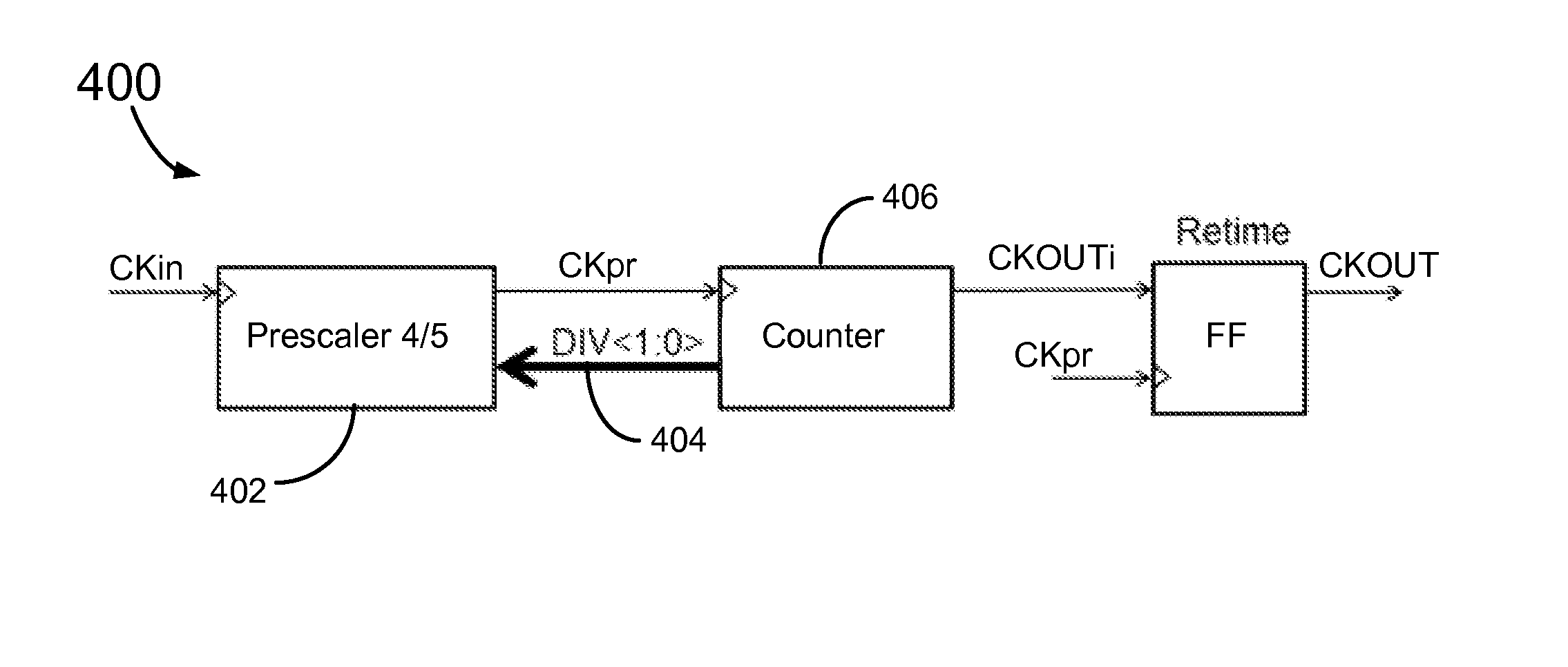

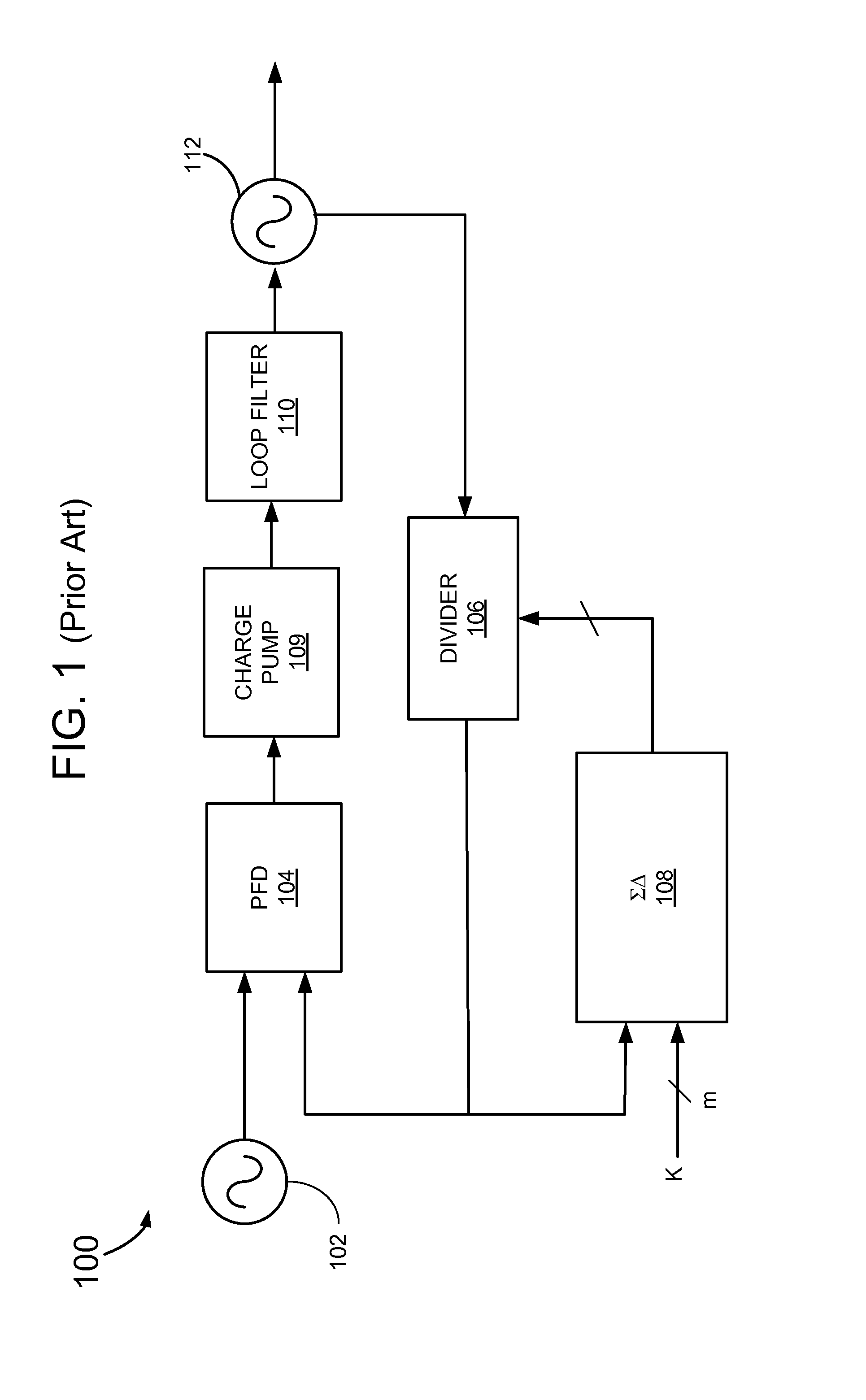

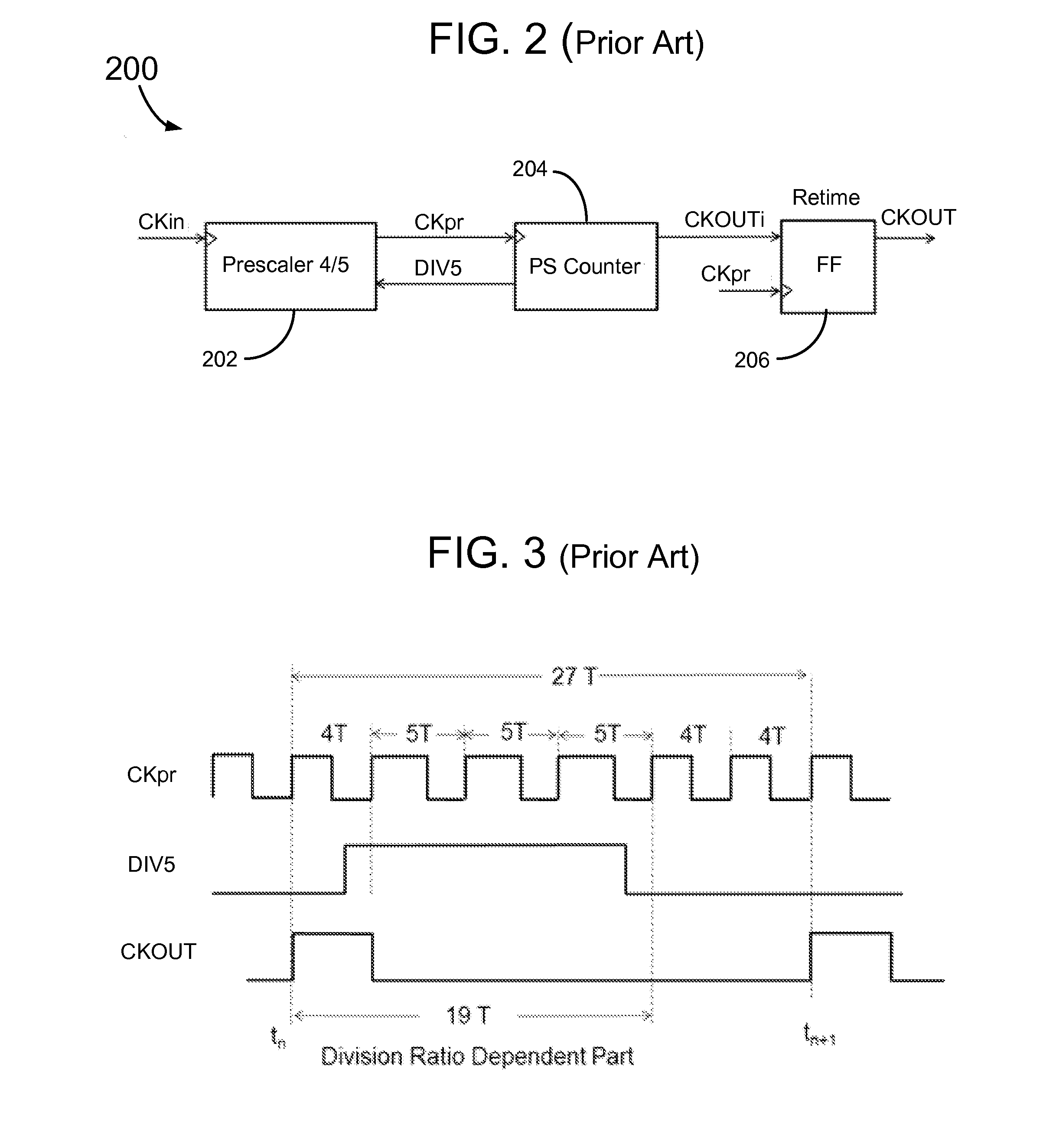

Frequency divider with improved linearity for a fractional-N synthesizer using a multi-modulus prescaler

ActiveUS8891725B2Counting chain pulse counters using semiconductor devicesPulse automatic controlLinearityDual-modulus prescaler

A frequency divider is disclosed. The frequency divider includes a multi-modulus prescaler to perform a frequency division by a modulus M, wherein M is an integer between N and 2*N−1 and N is a power of 2. The frequency divider also includes a programmable counter to output the digital representation of M and an output clock signal. For the frequency divider, M equals N plus D minus D\N for each edge of the multi-modulus prescaler output clock CKpr wherein the counter samples the digital representation of D and D\N denotes an integer part of D divided by N, and M equals N for each subsequent edge of the prescaler output clock CKpr wherein the counter does not sample the digital representation of D.

Owner:QUALCOMM INC

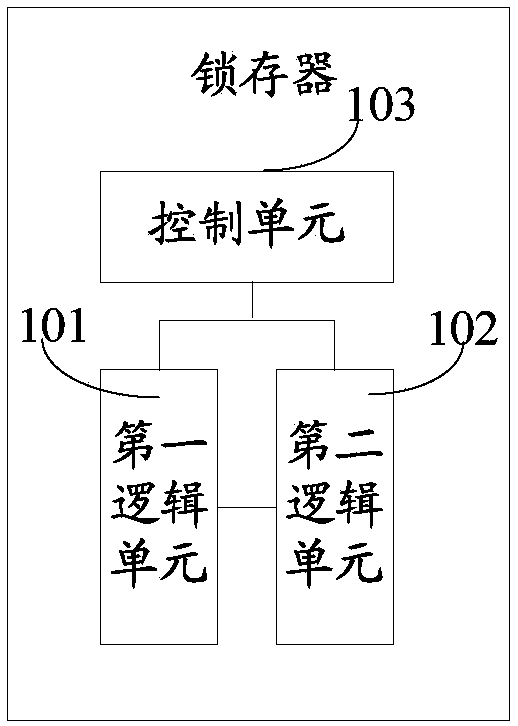

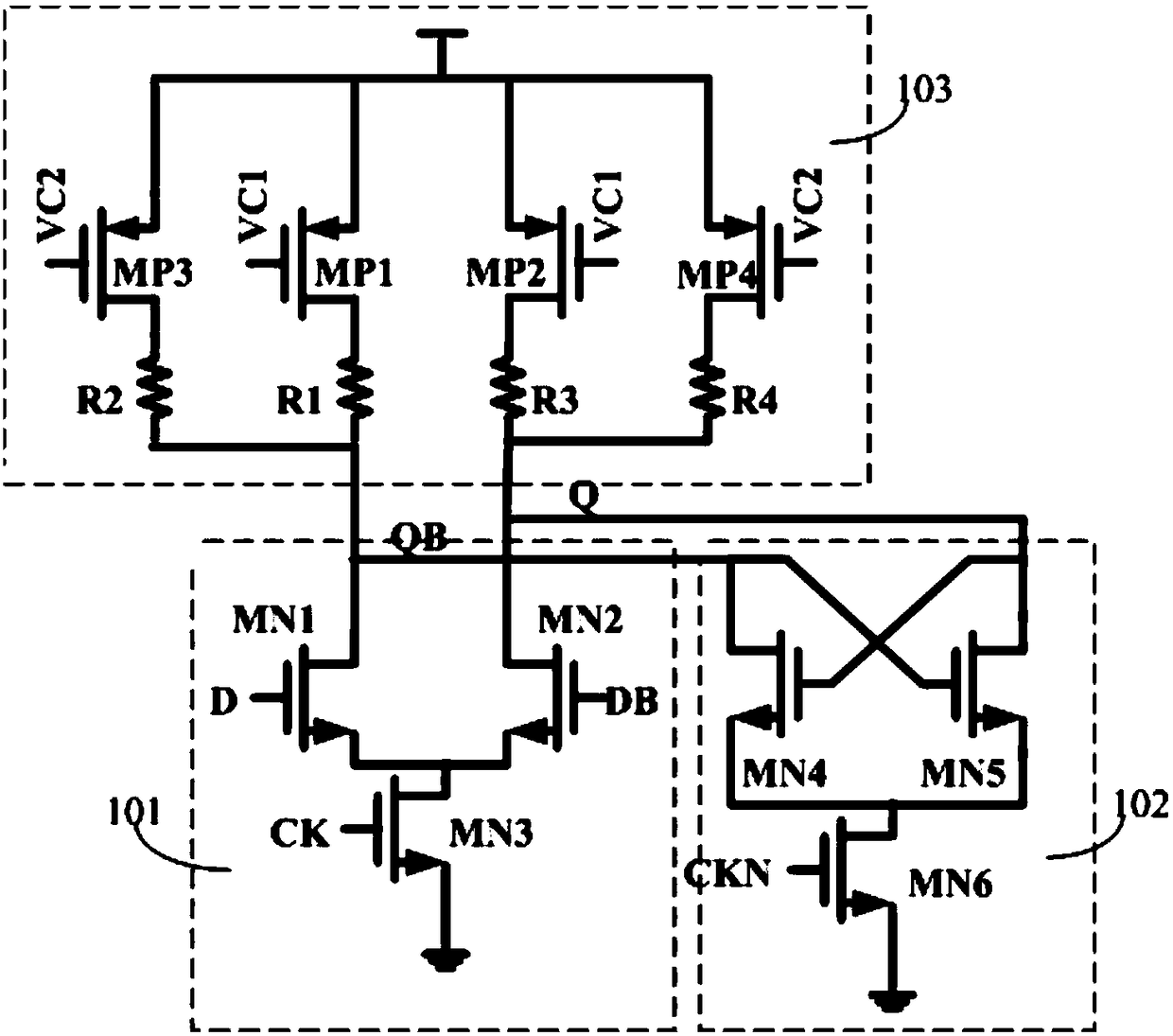

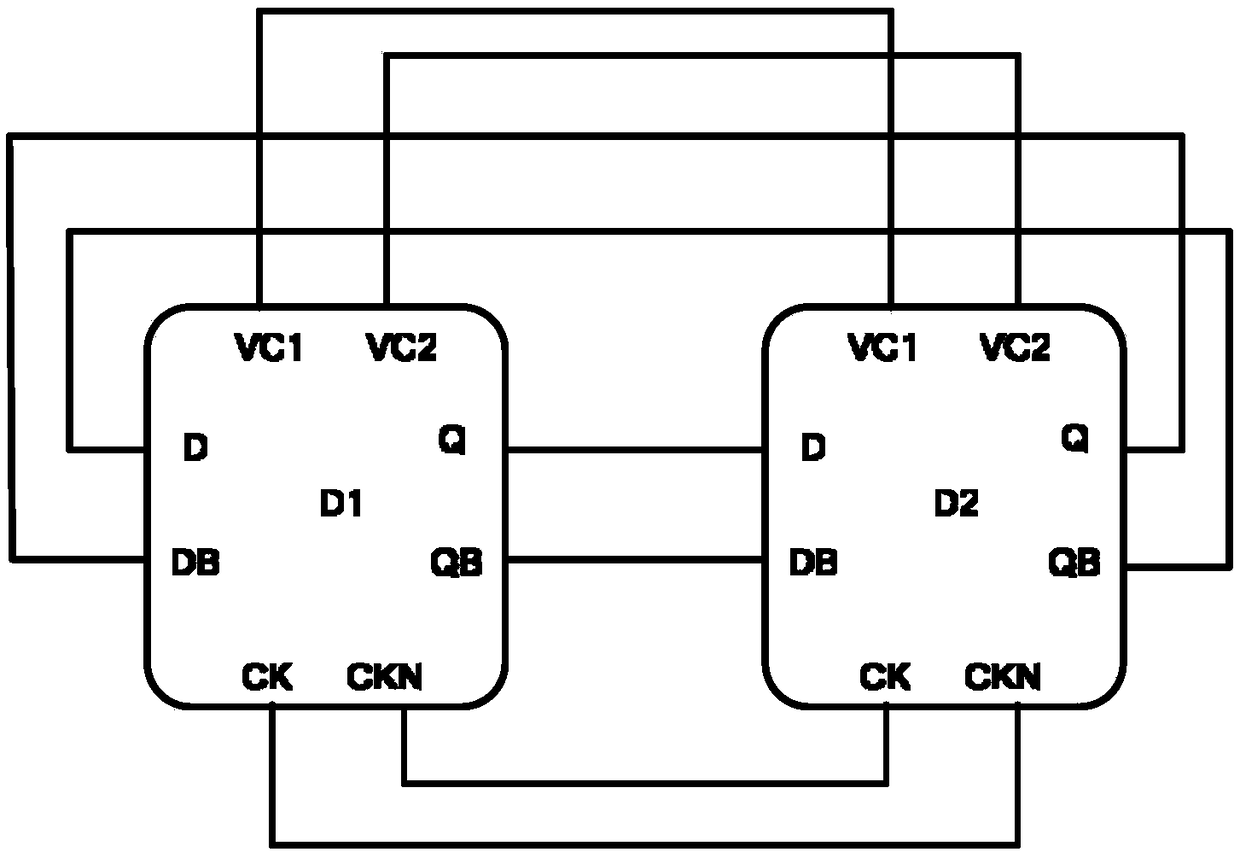

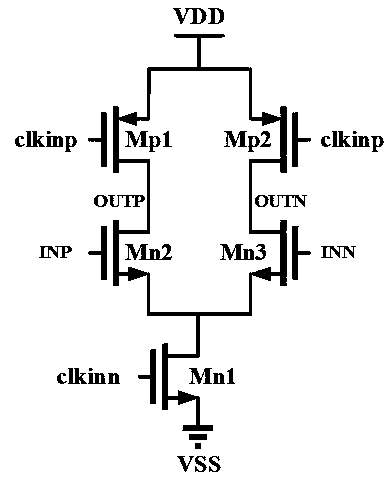

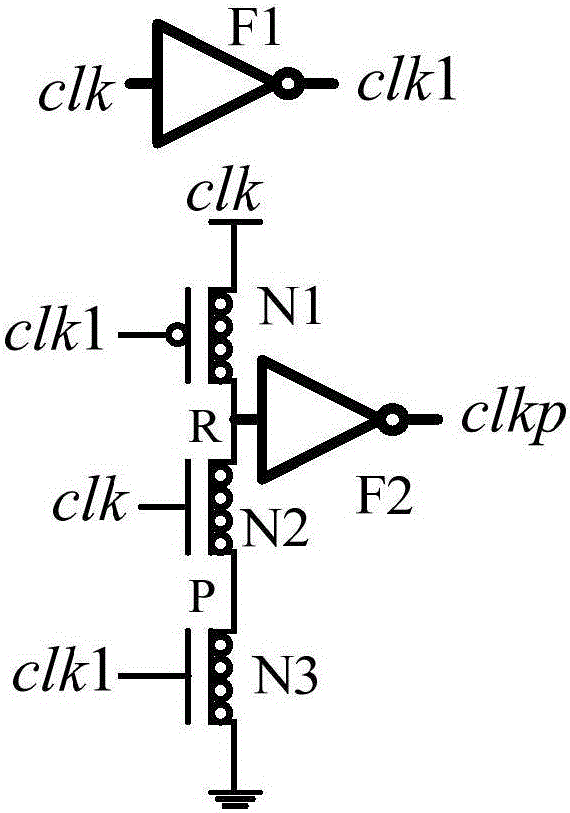

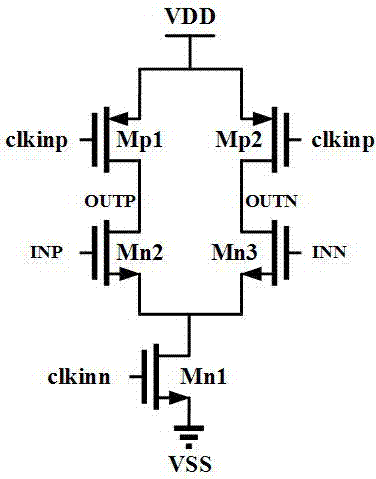

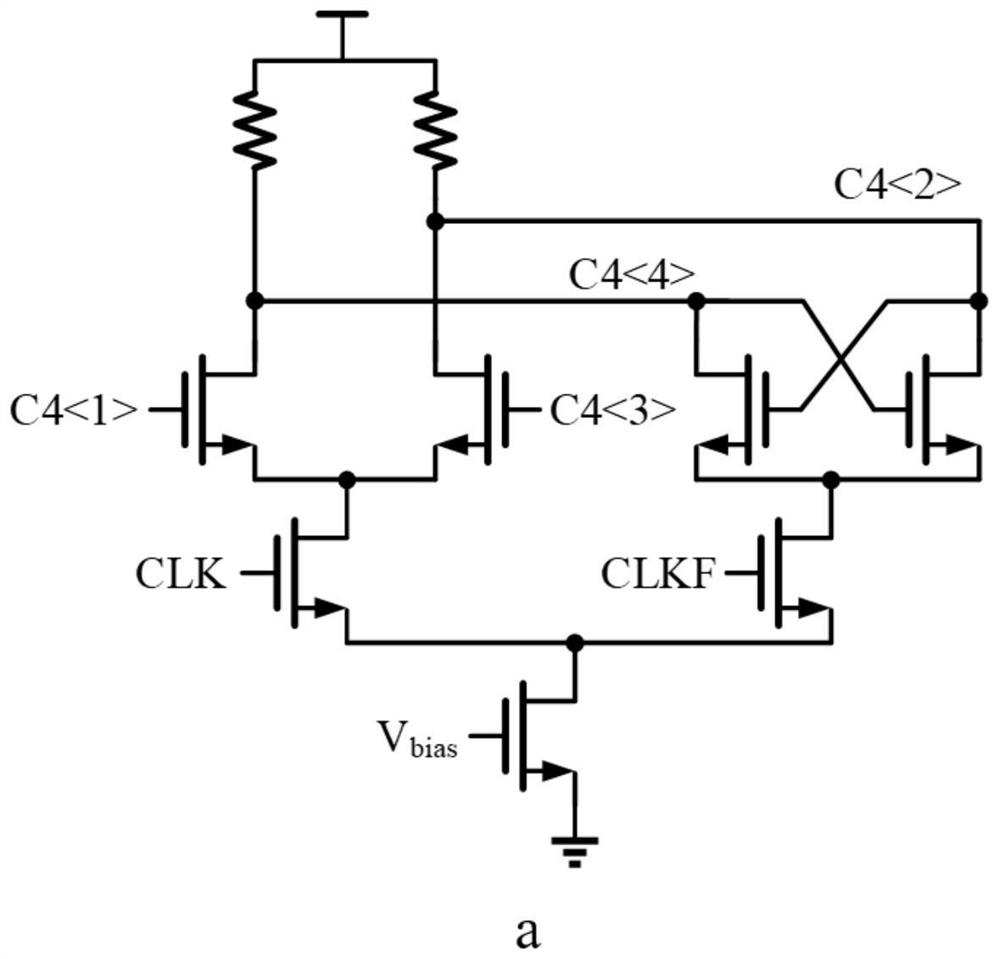

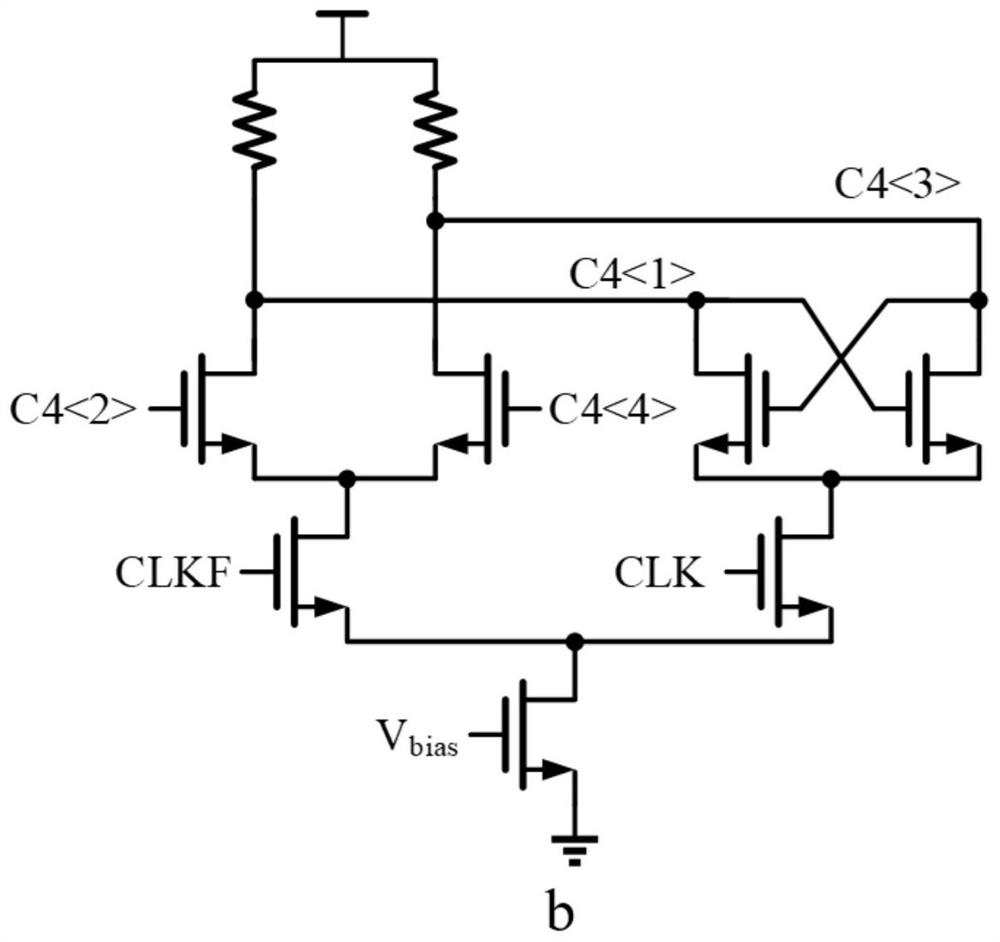

Latch, two-frequency divider circuit based on current mode logic and frequency divider

InactiveCN108599757AEliminates problems with narrow crossover rangesIncreased crossover rangeCounting chain pulse counters using semiconductor devicesLogic circuitsLogic cellEngineering

The invention discloses a latch, a two-frequency divider circuit based on current mode logic and a frequency divider. The latch comprises a first logic unit, a second logic unit and a control unit, wherein the first logic unit comprises a first input end, a second input end, a first output end, a second output end and a clock signal positive input end; the second logic unit comprises a third inputend, a fourth input end, a third output end, a fourth output end and a clock signal negative input end; the first output end is coupled with the third input end and the fourth output end; the secondoutput end is coupled with the third output end and the fourth input end; and the control unit is coupled between the first logic unit and a power supply and between the second logic unit and the power supply, and a current path between the power supply and a ground wire is controlled by resistance regulation. The invention provides a latch with a controllable resistance value at the output end; and the frequency divider realized based on the latch can eliminate the problem of narrow frequency division ranges of existing frequency dividers, and can greatly improve the frequency division rangeof the frequency divider.

Owner:北京何氏咨询策划有限公司

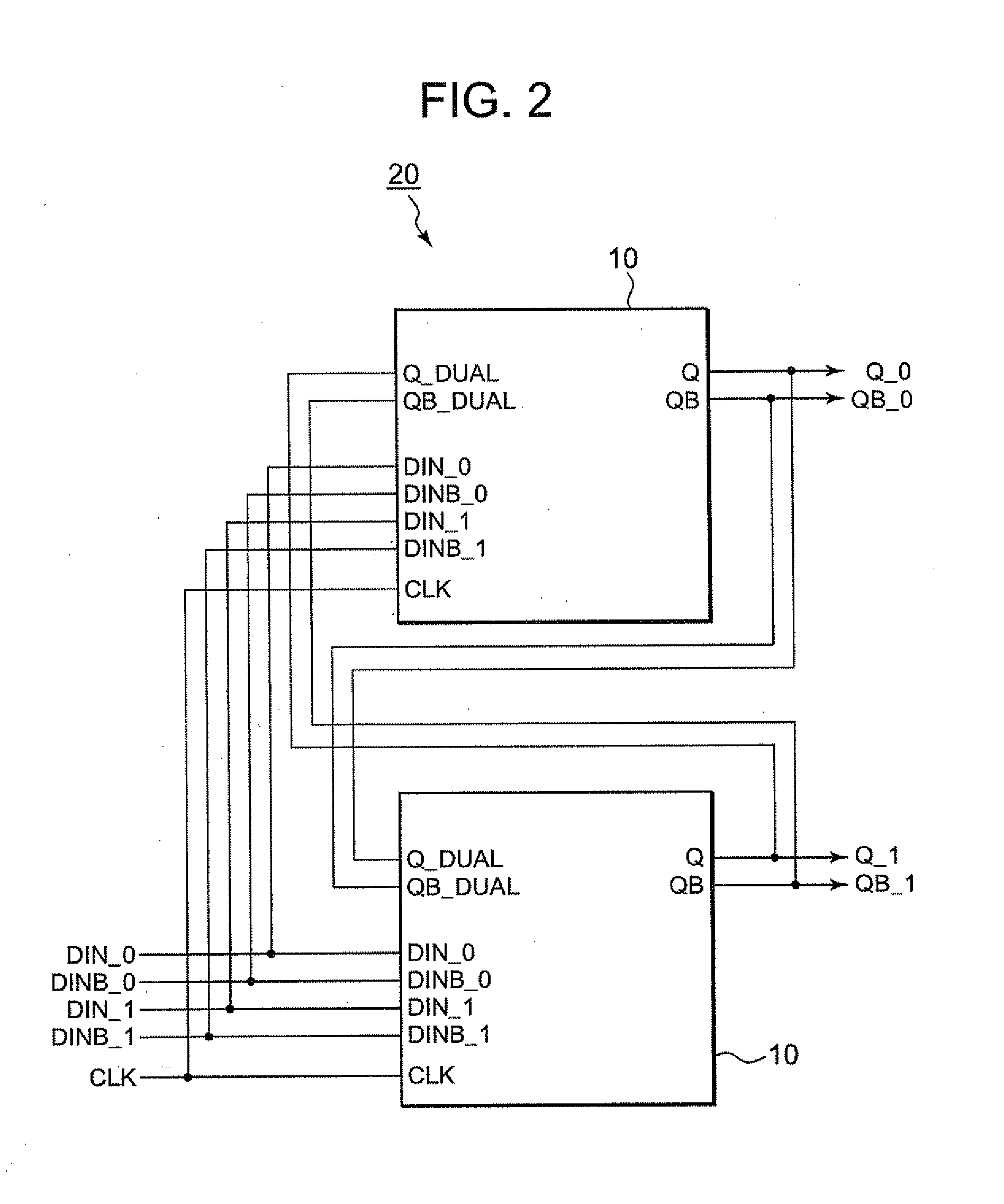

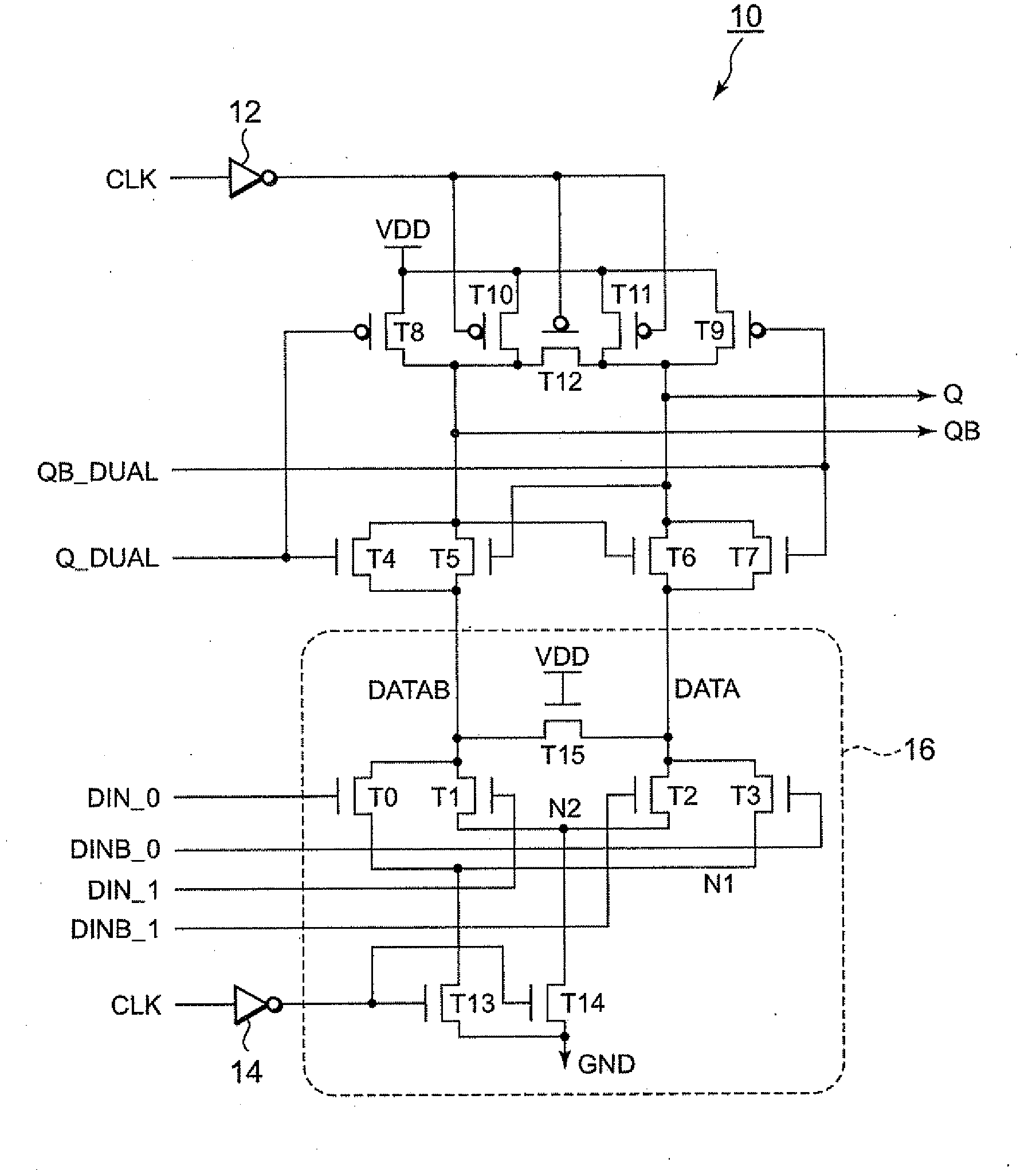

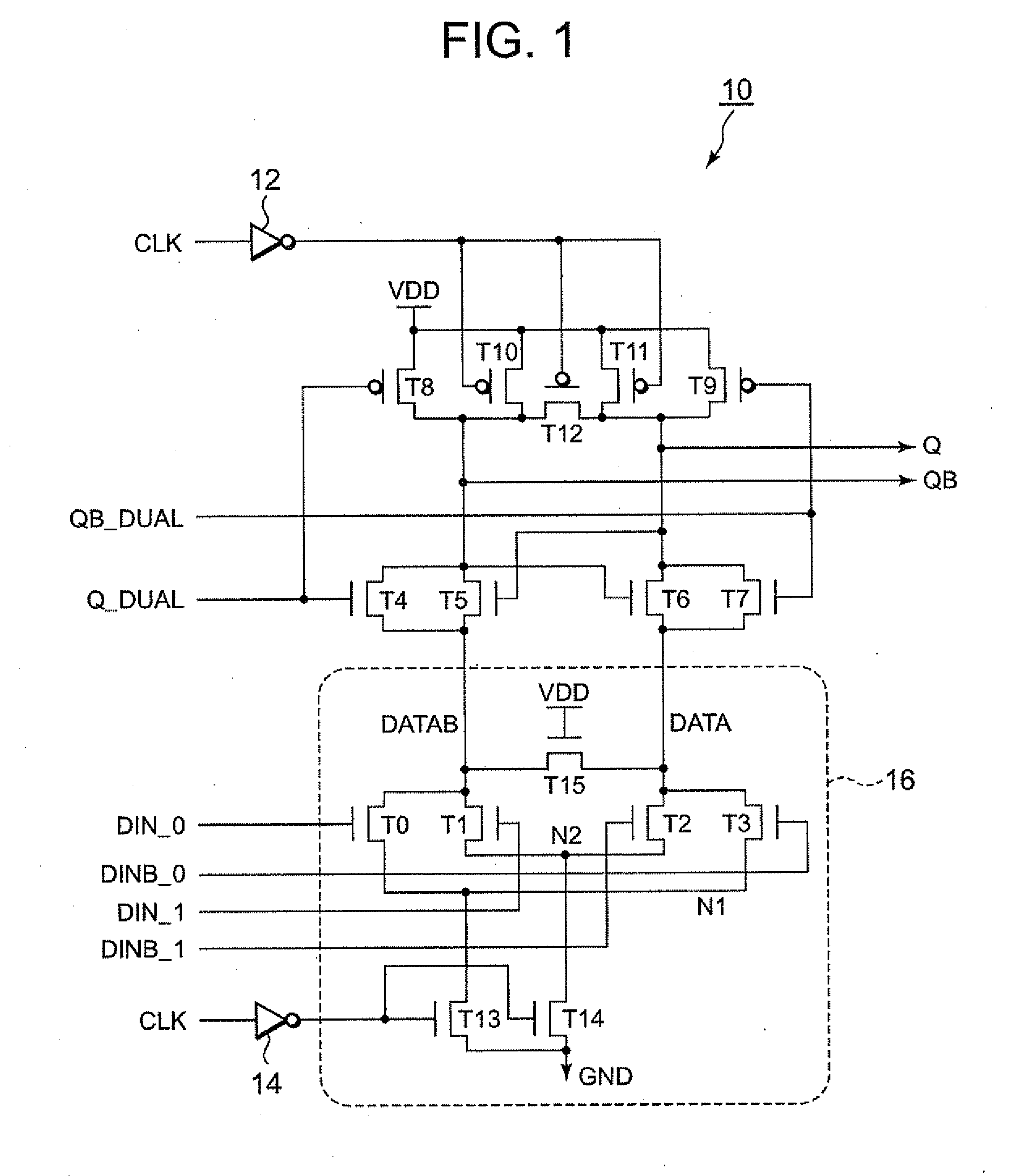

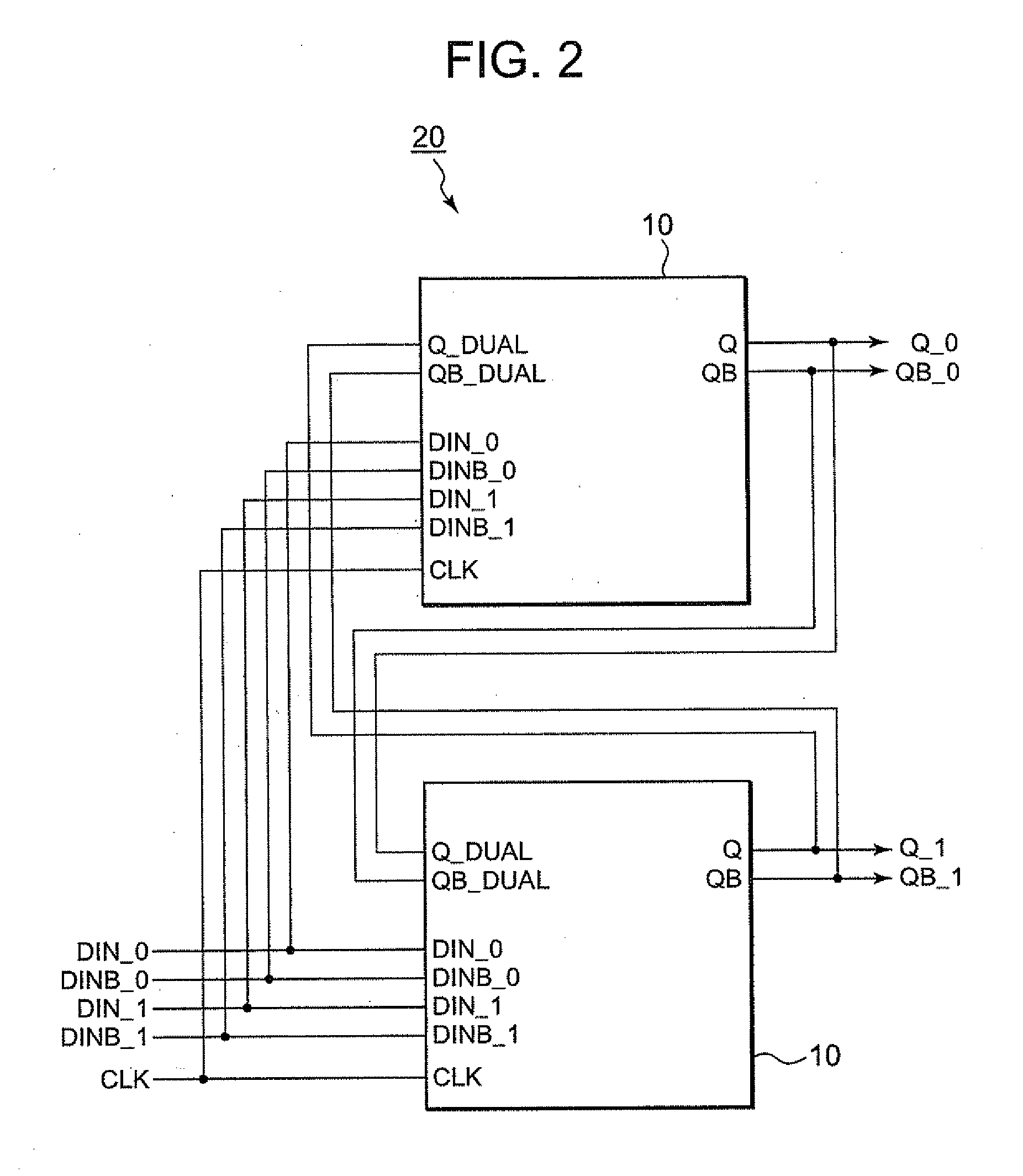

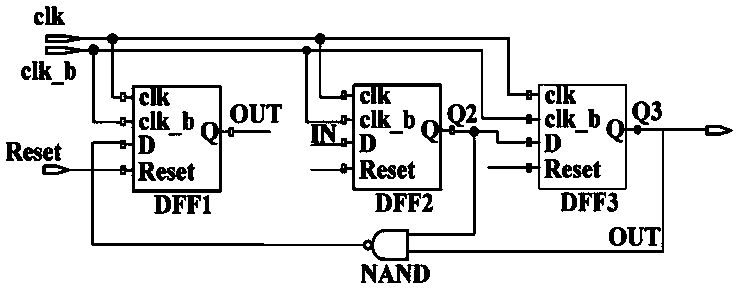

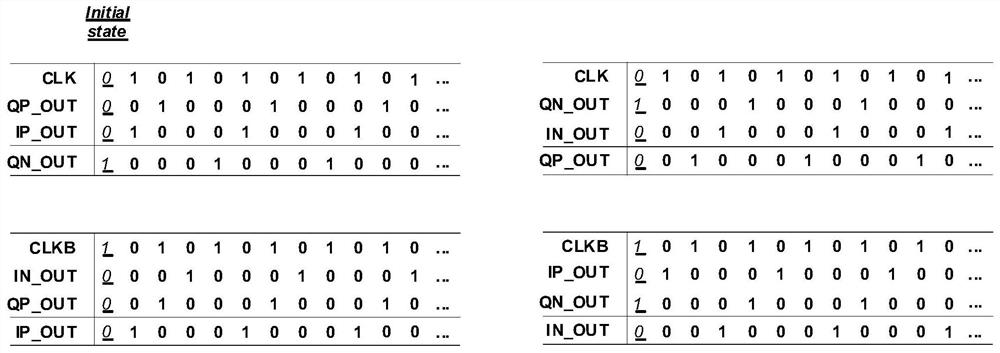

Design Structure for Radiation Hardened Programmable Phase Frequency Divider Circuit

ActiveUS20080048745A1Counting chain pulse counters using semiconductor devicesPulse counters with static storageCMOSEngineering

A design structure embodied in a machine readable medium includes information for designing, manufacturing and / or testing a programmable phase frequency divider circuit implemented in CMOS technology for space applications. The programmable phase frequency divider consists of three radiation hardened D-type flip flops and combinational logic circuits to provide the feedback controls that allow programmable frequency division ratios from 1 to 8. The radiation hardened D-type flip flop circuits are designed to keep on running properly at GHz frequencies even after a single event upset (SEU) hit. The novel D-type flip flop circuits each have two pairs of complementary inputs and outputs to mitigate SEU's. The combinational logic circuits are designed to utilize the complementary outputs in such a way that only one of the four dual complementary inputs to any D-type flip flop gets flipped at most after an SEU hit.

Owner:MARVELL ASIA PTE LTD

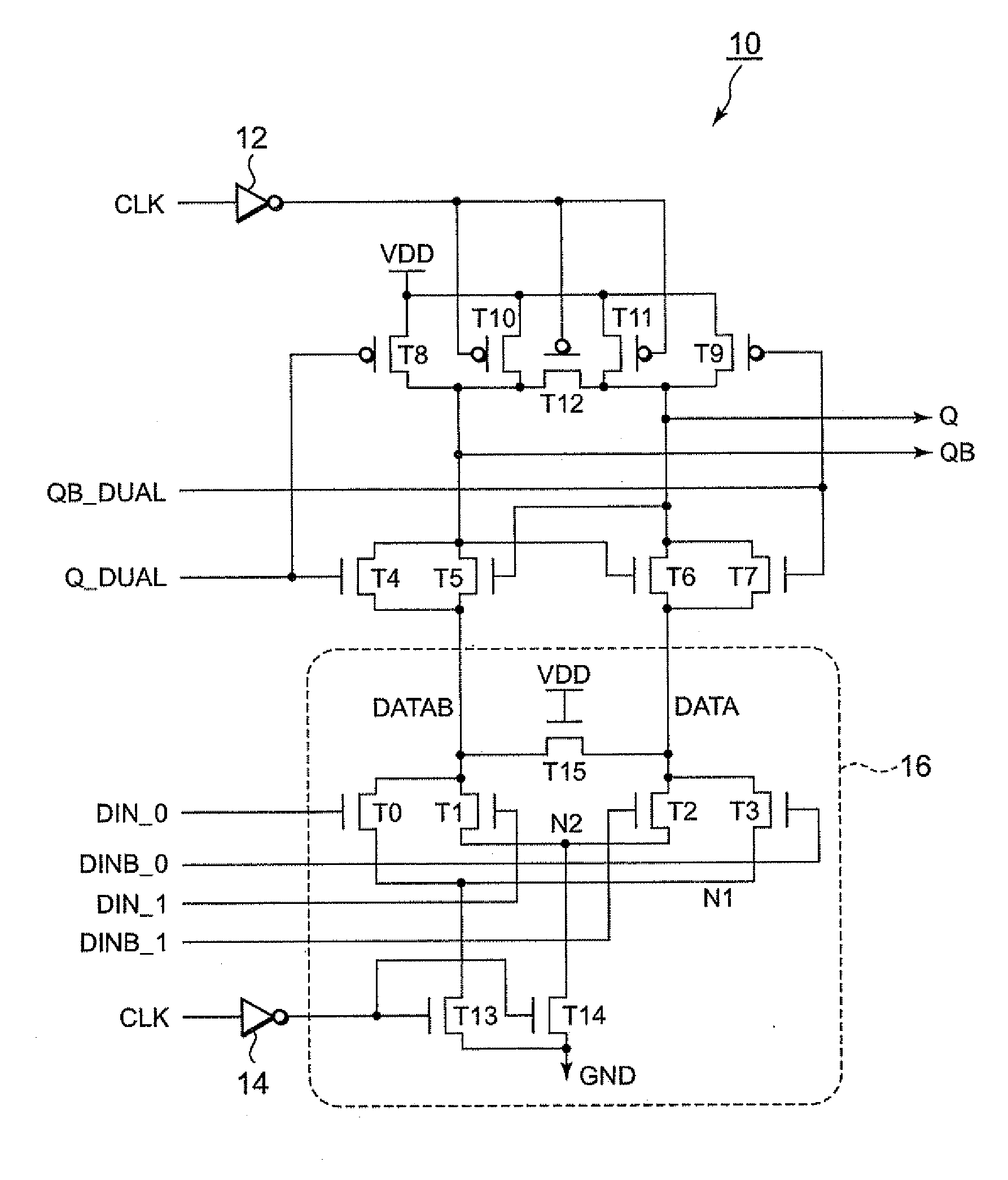

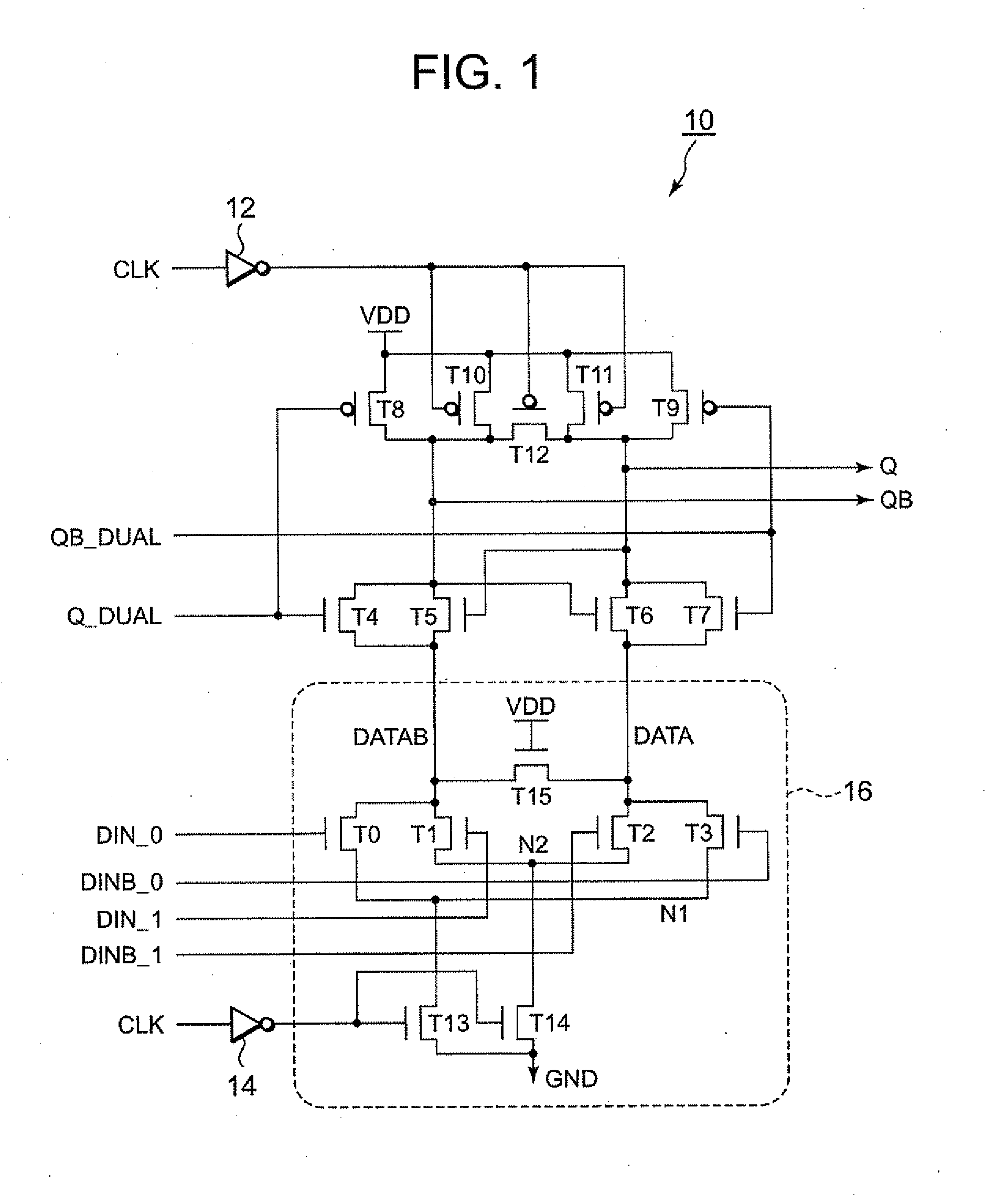

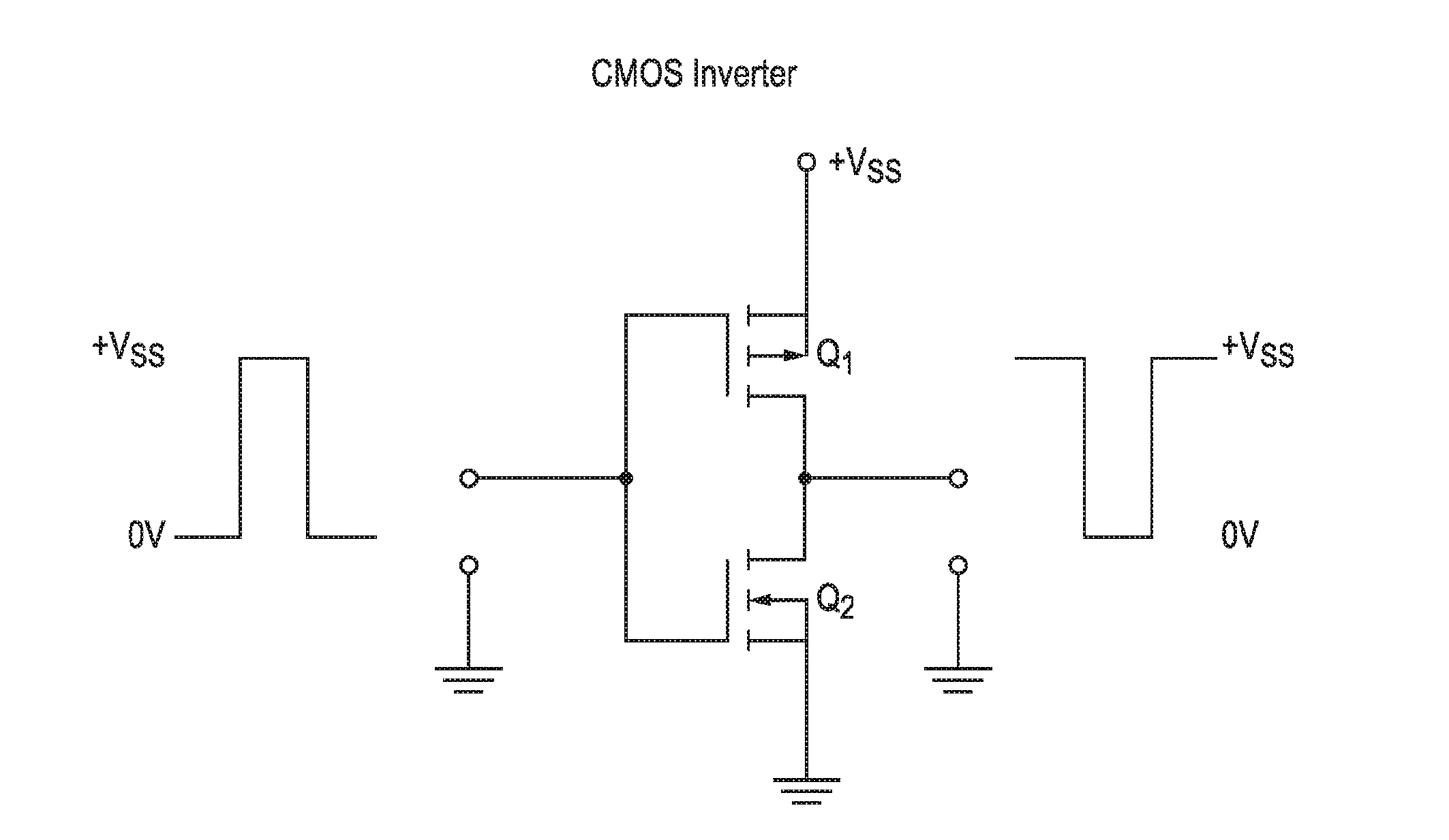

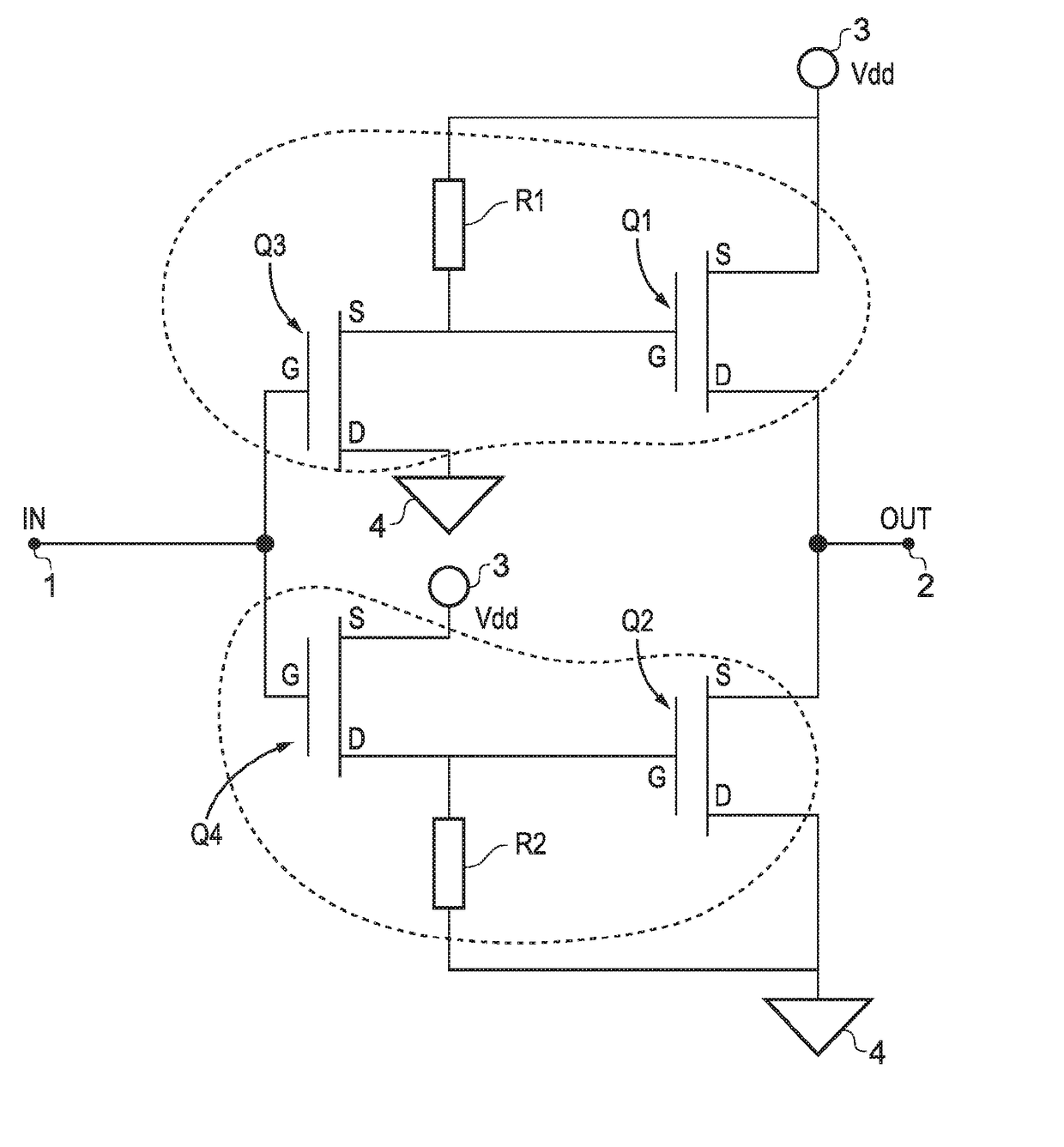

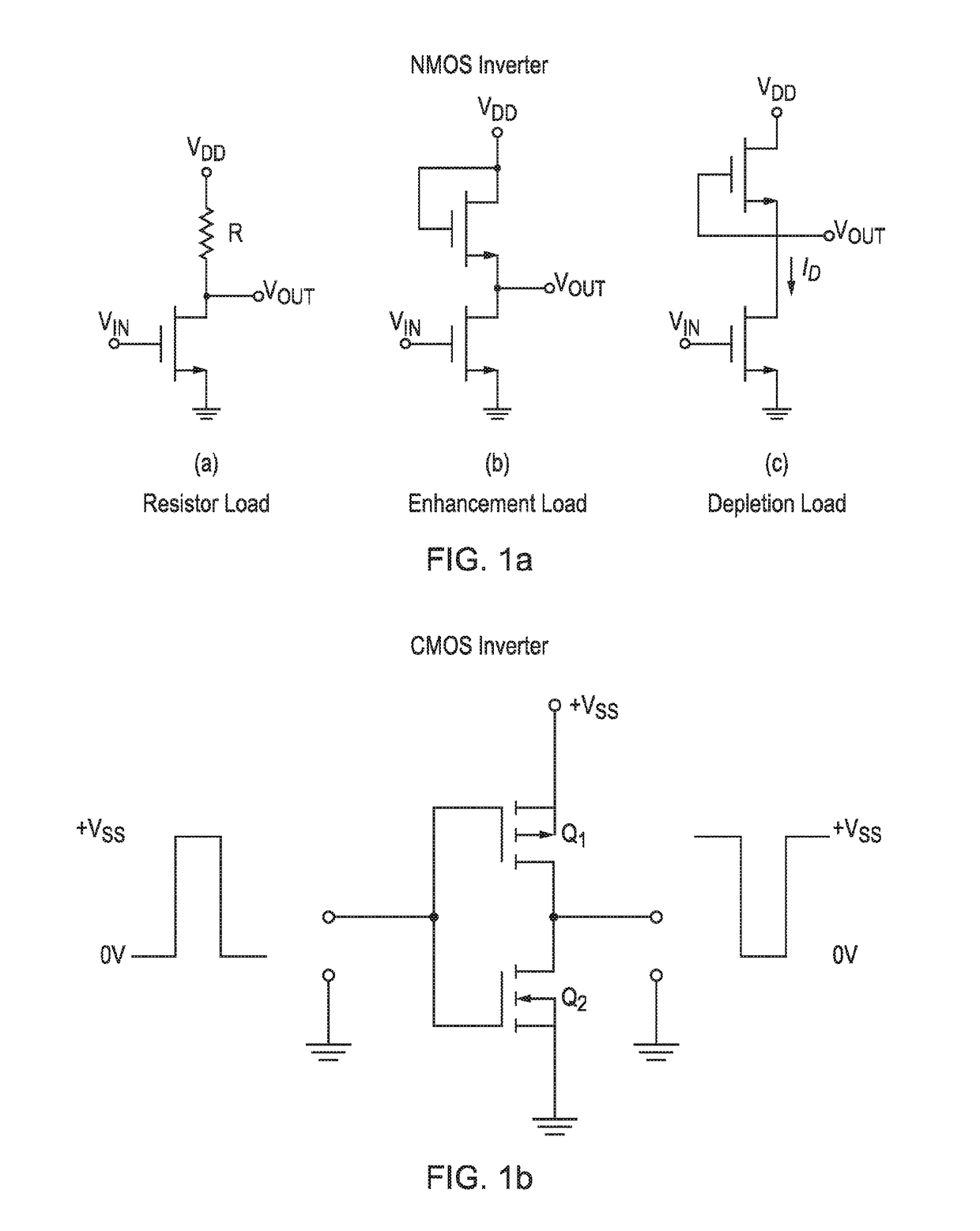

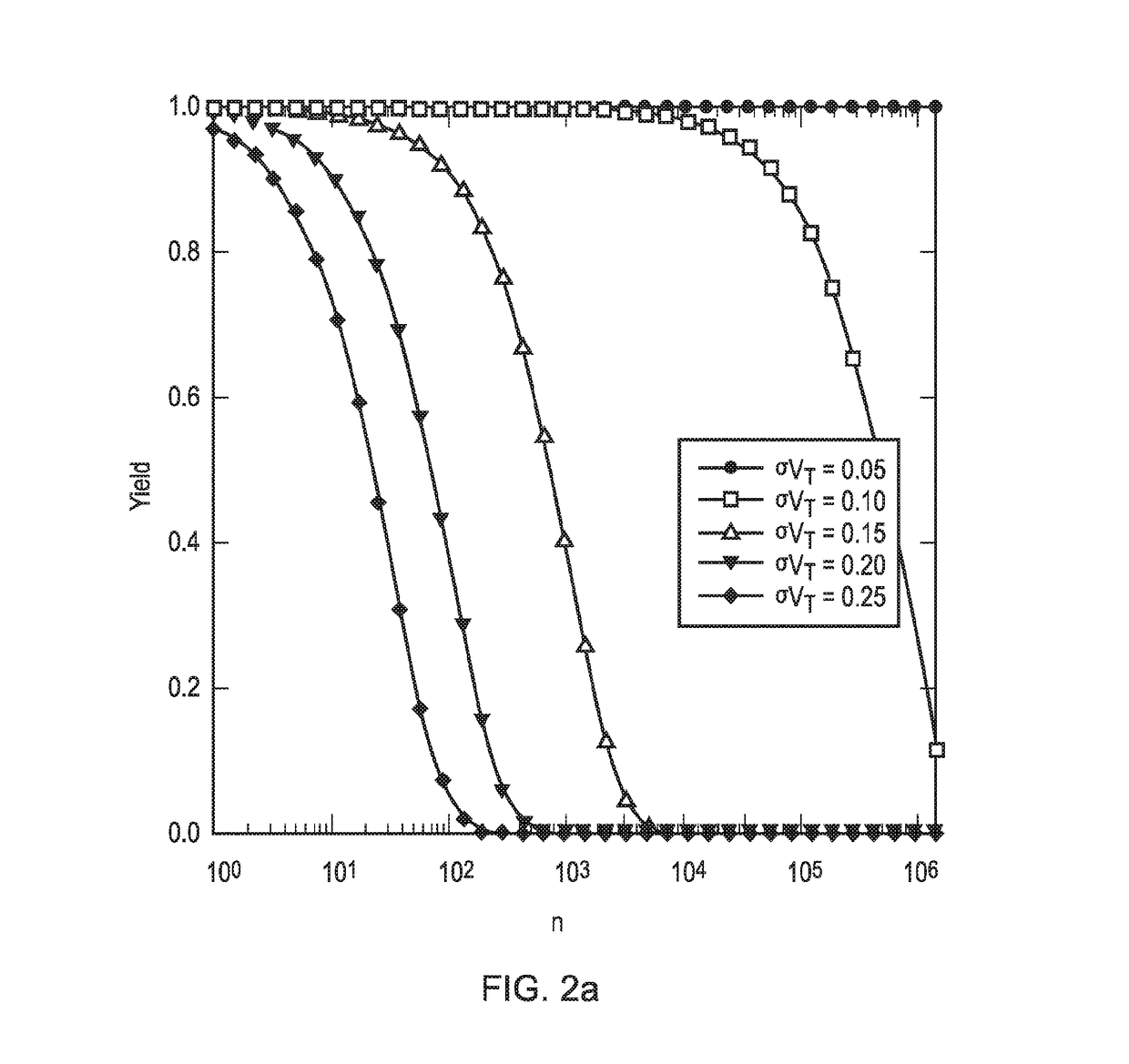

Electronic circuits

ActiveUS20160173099A1Directly appliedLogic circuits characterised by logic functionCounting chain pulse counters using semiconductor devicesEngineeringField-effect transistor

An electronic circuit comprises: an input terminal; an output terminal; first and second supply rails; first, second, third, and fourth field effect transistors, FETs, each of a first type and each having respective gate, source and drain terminals; and first and second loads. The source of the first FET is connected to the first supply rail, the drain of the first FET and the source of the second FET are connected to the output terminal, the drain of the second FET is connected to the second supply rail, the gate of the third FET and the gate of the fourth FET are connected to the input terminal, the drain of the third FET is connected to the second supply rail, the first load is connected between the first supply rail and the source of the third FET, and the second load is connected between the drain of the fourth FET and the second supply rail. In one aspect of the invention, the gate of the first FET is connected to a node between the source of the third FET and the first load such that a voltage at the source of the third FET is applied to the gate of the first FET, and the gate of the second FET is connected to a node between the drain of the fourth FET and the second load such that a voltage at the drain of the fourth FET is applied to the gate of the second FET.

Owner:PRAGMATIC PRINTING

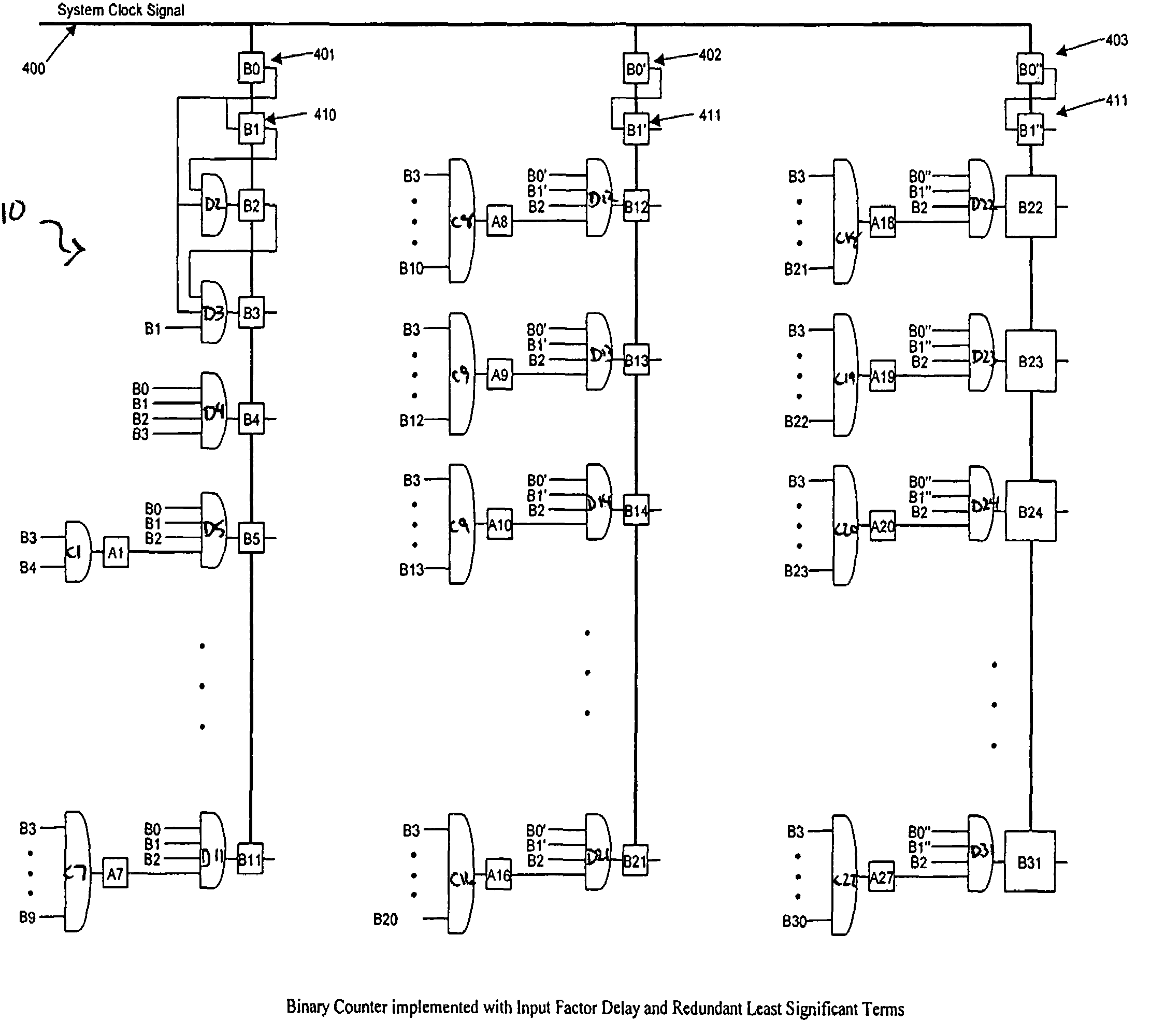

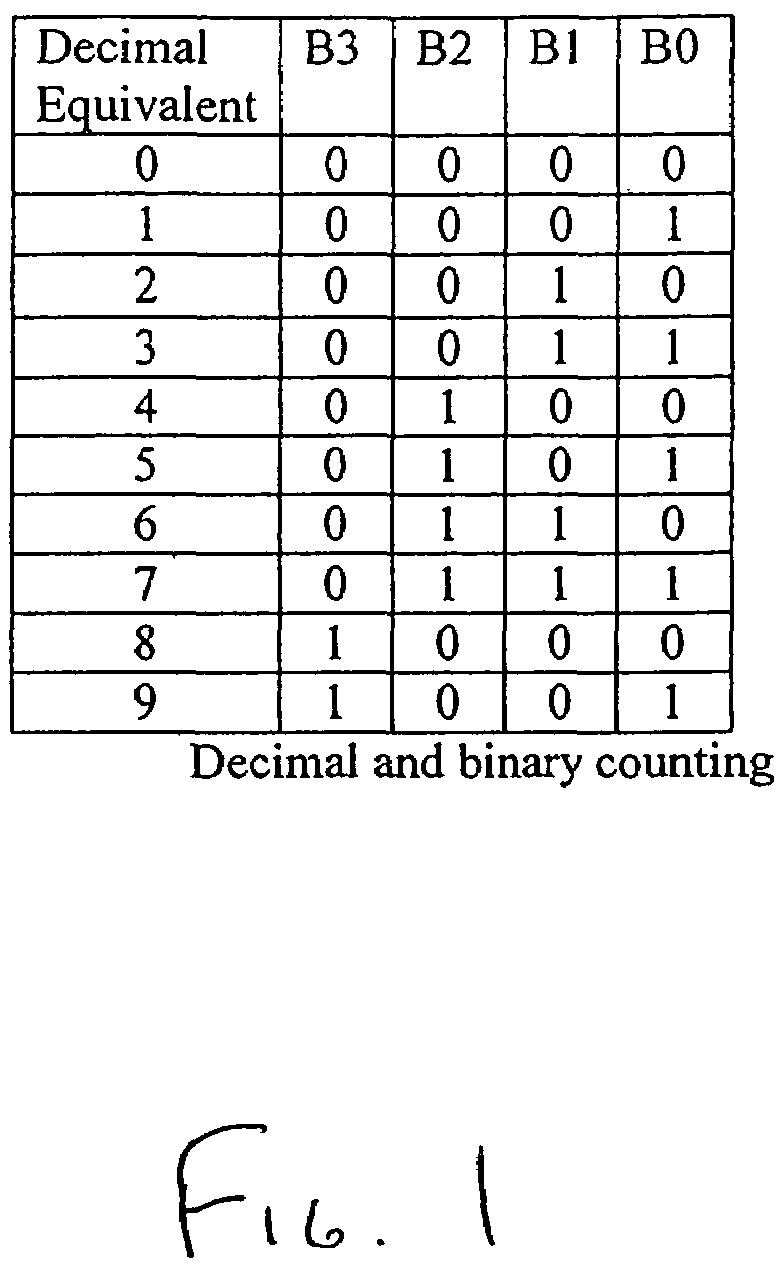

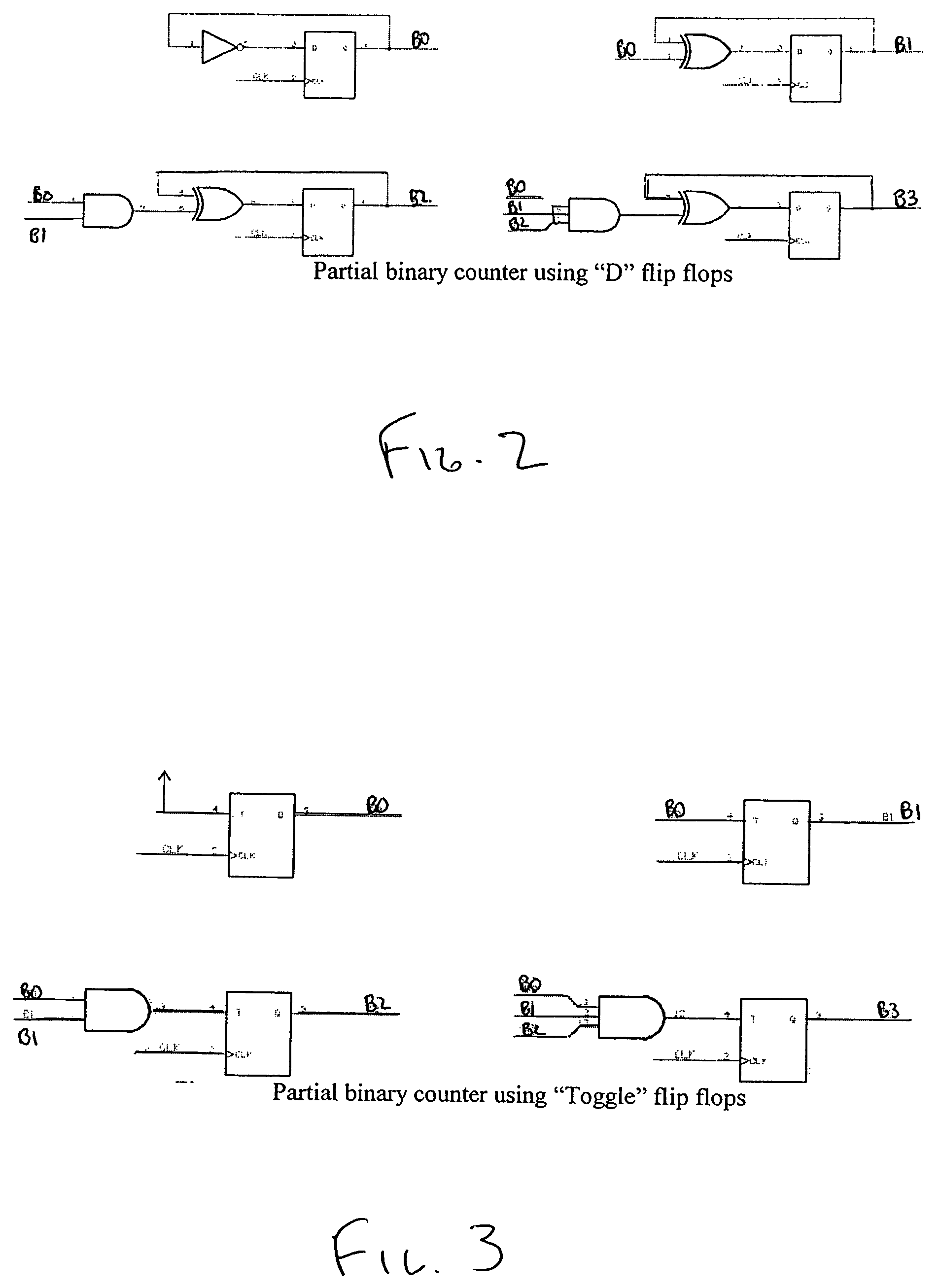

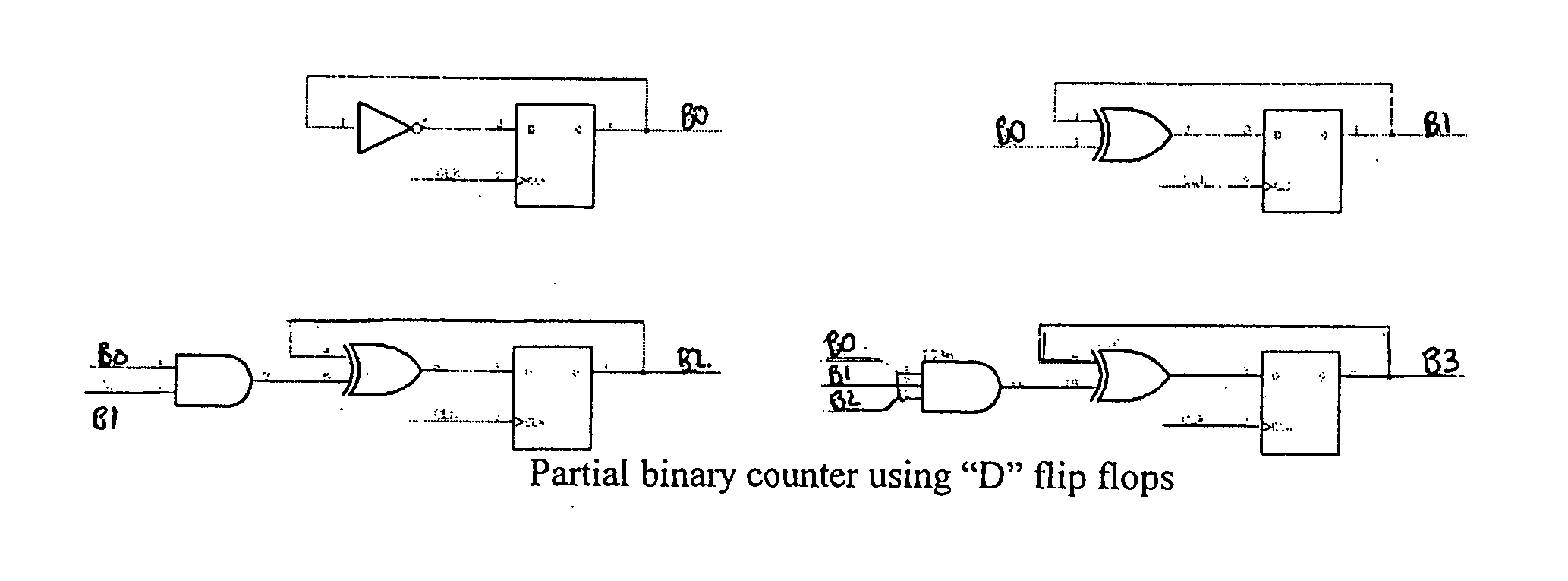

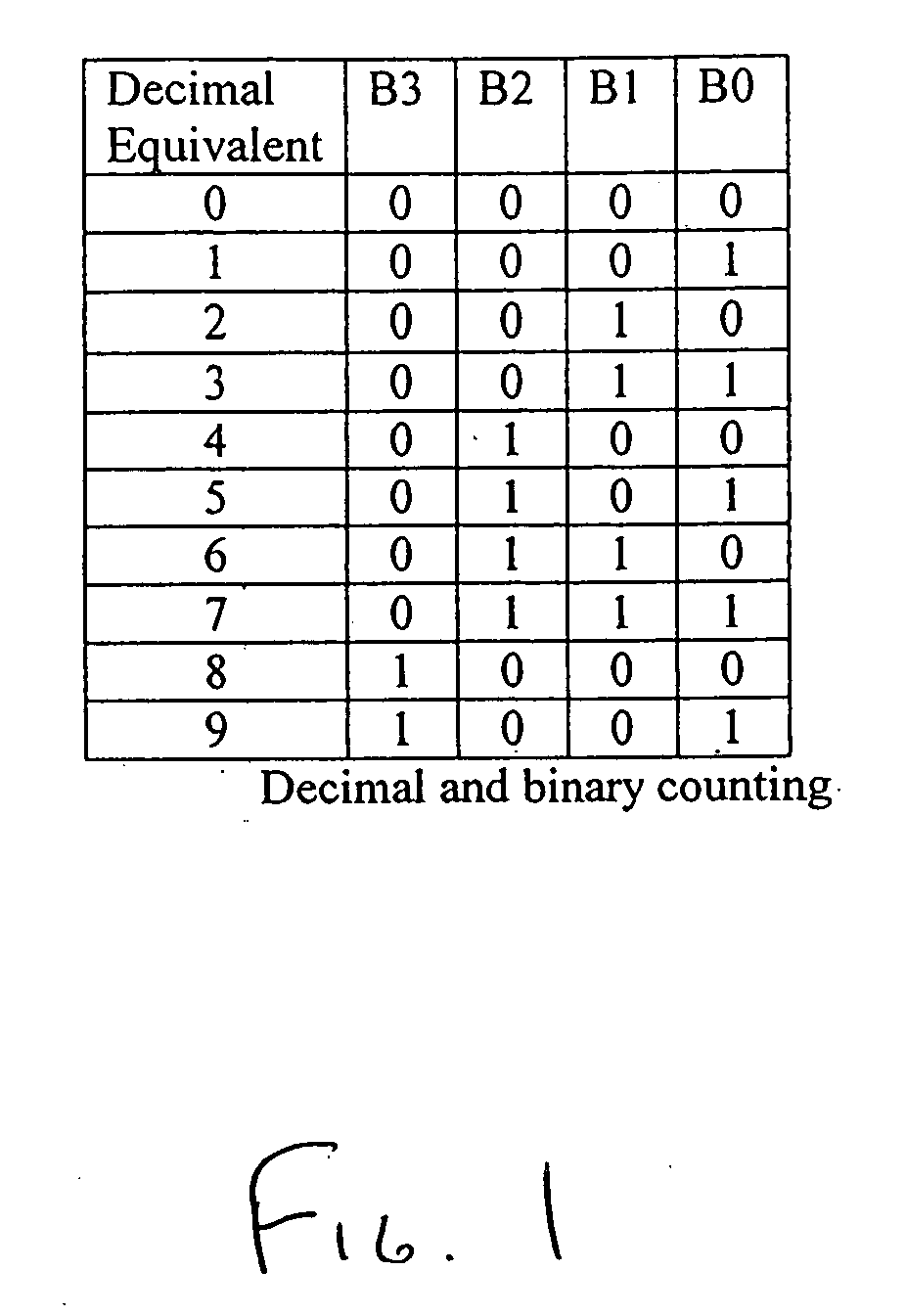

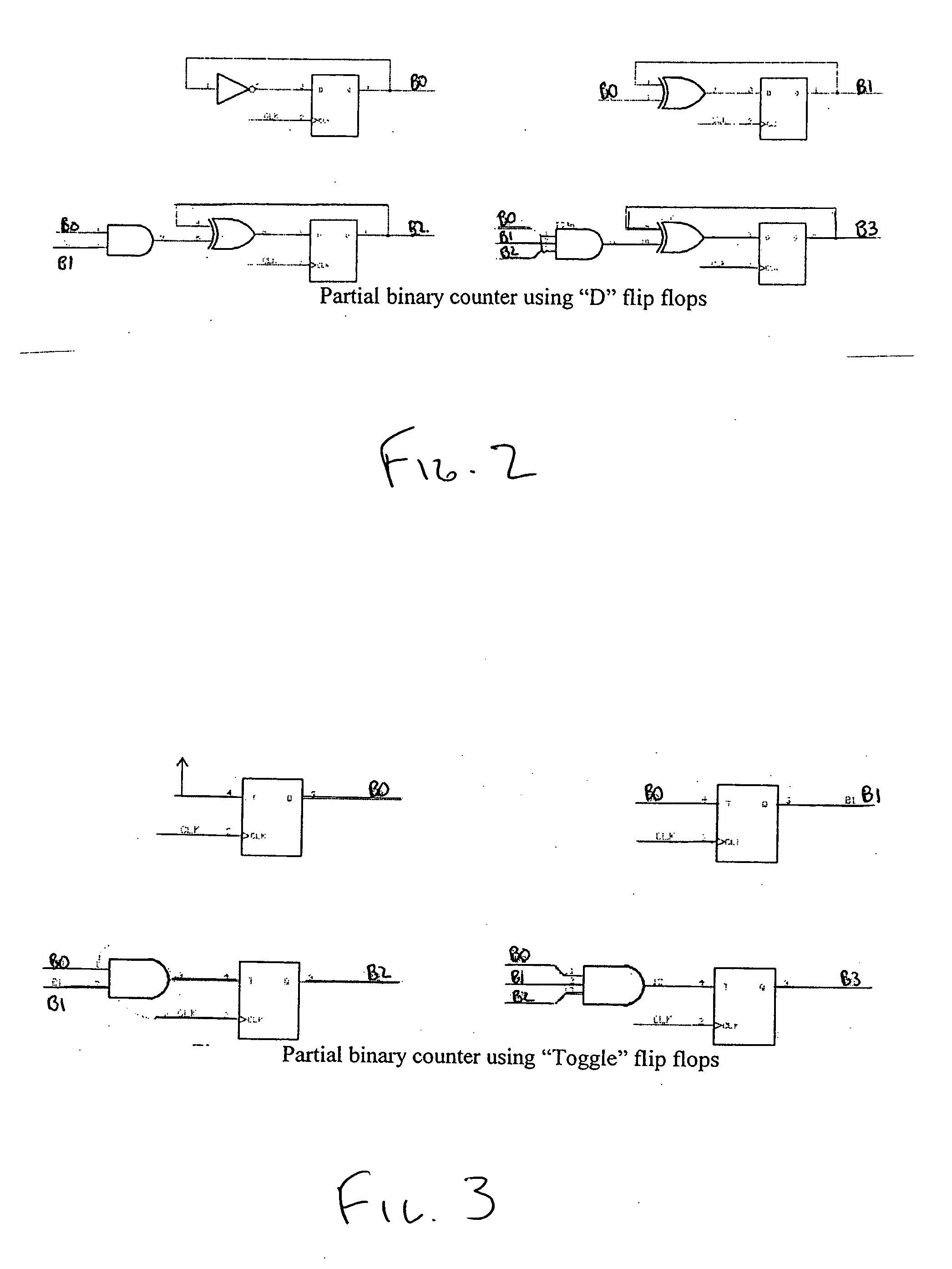

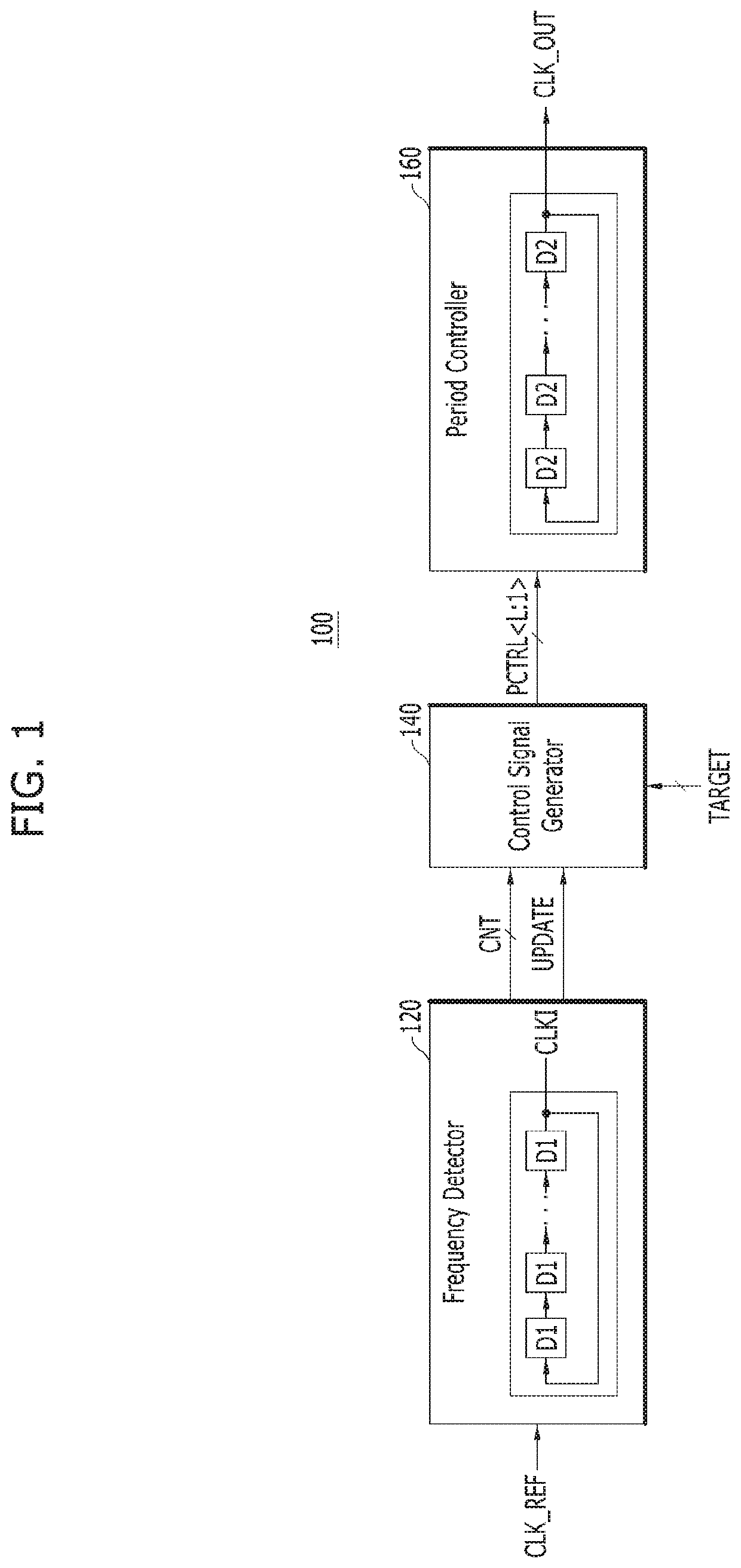

High speed binary counter

A high speed binary counter includes a counting first flip-flop for each binary bit, a single AND gate for each lower order binary bit beyond B0 and B1, and at least two AND gates for each higher order binary bit. The counter also includes an input factor delay second flip-flop. The counter is further provided with a mechanism for redundant least significant terms for lesser order bits.

Owner:MERCURY DEFENSE SYST INC

High speed binary counter

ActiveUS20060104405A1Increase speedCounting chain pulse counters using semiconductor devicesCounting chain synchronous pulse countersComputer scienceAND gate

A high speed binary counter includes a counting first flip-flop for each binary bit, a single AND gate for each lower order binary bit beyond B0 and B1, and at least two AND gates for each higher order binary bit. The counter also includes an input factor delay second flip-flop. The counter is further provided with a mechanism for redundant least significant terms for lesser order bits.

Owner:MERCURY DEFENSE SYST INC

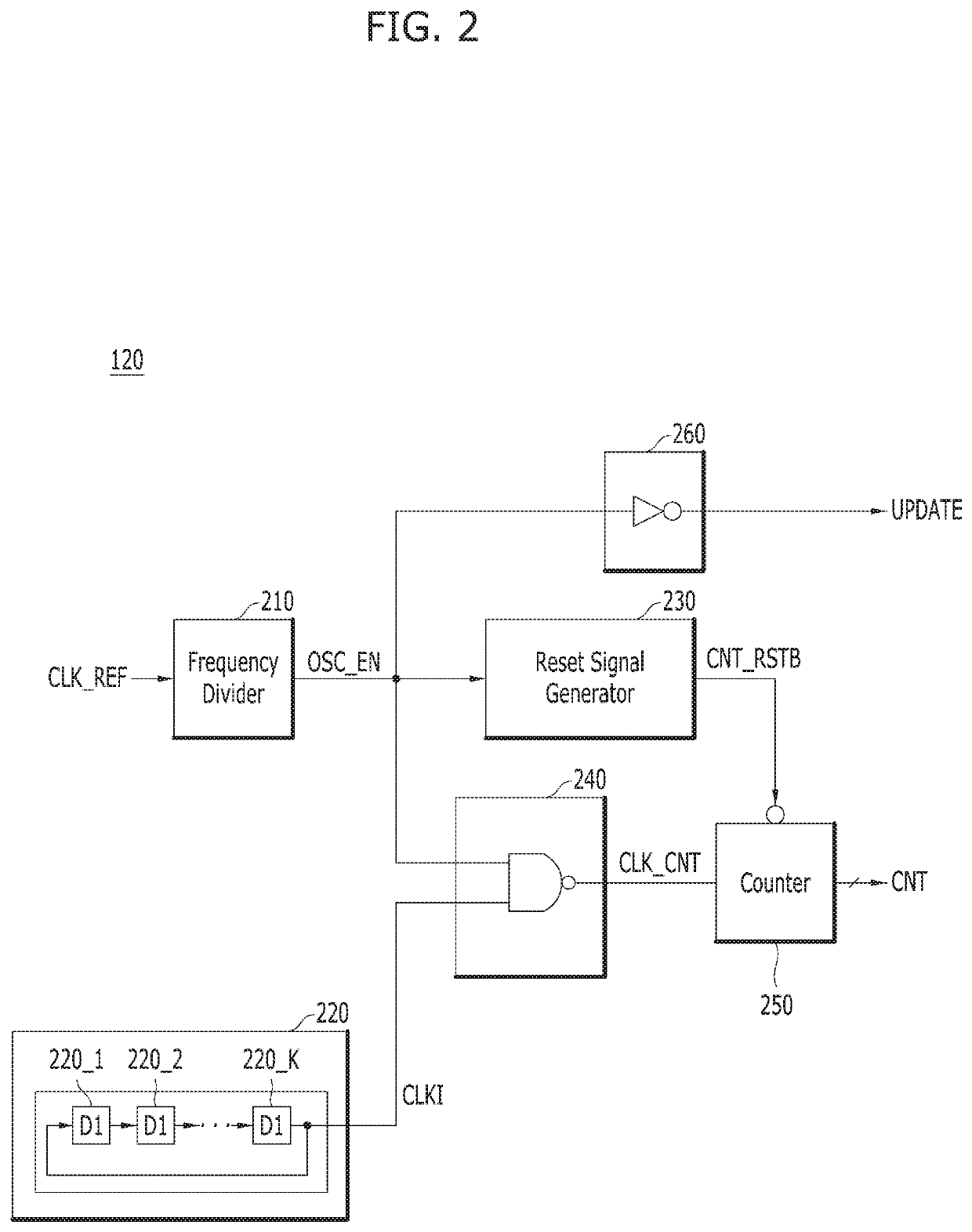

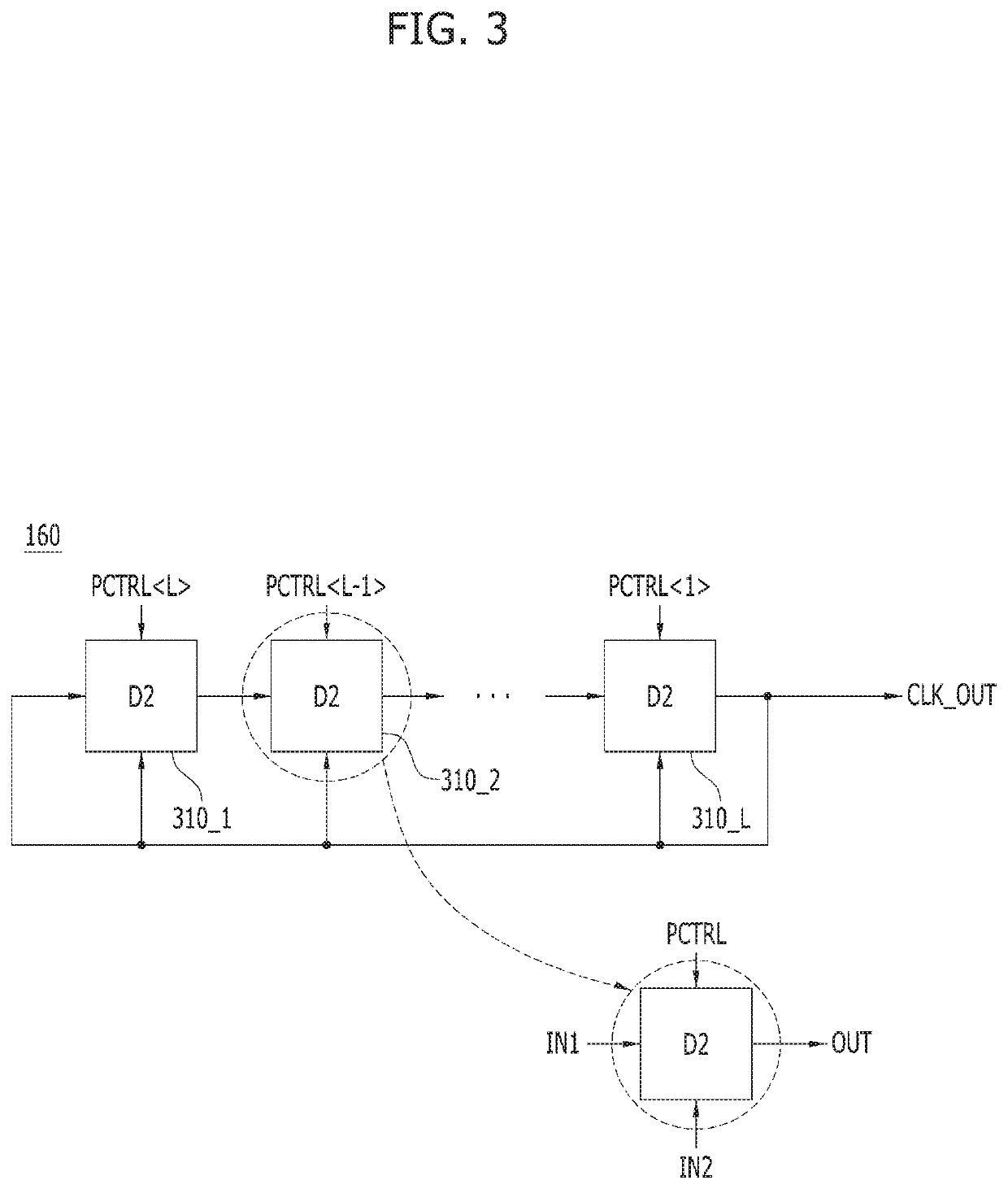

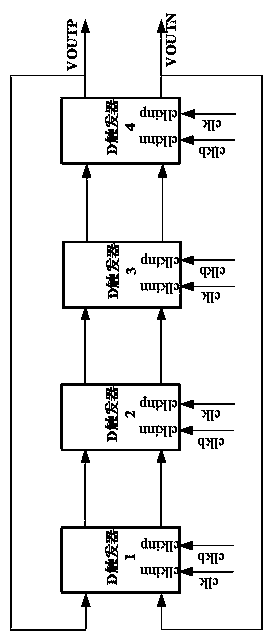

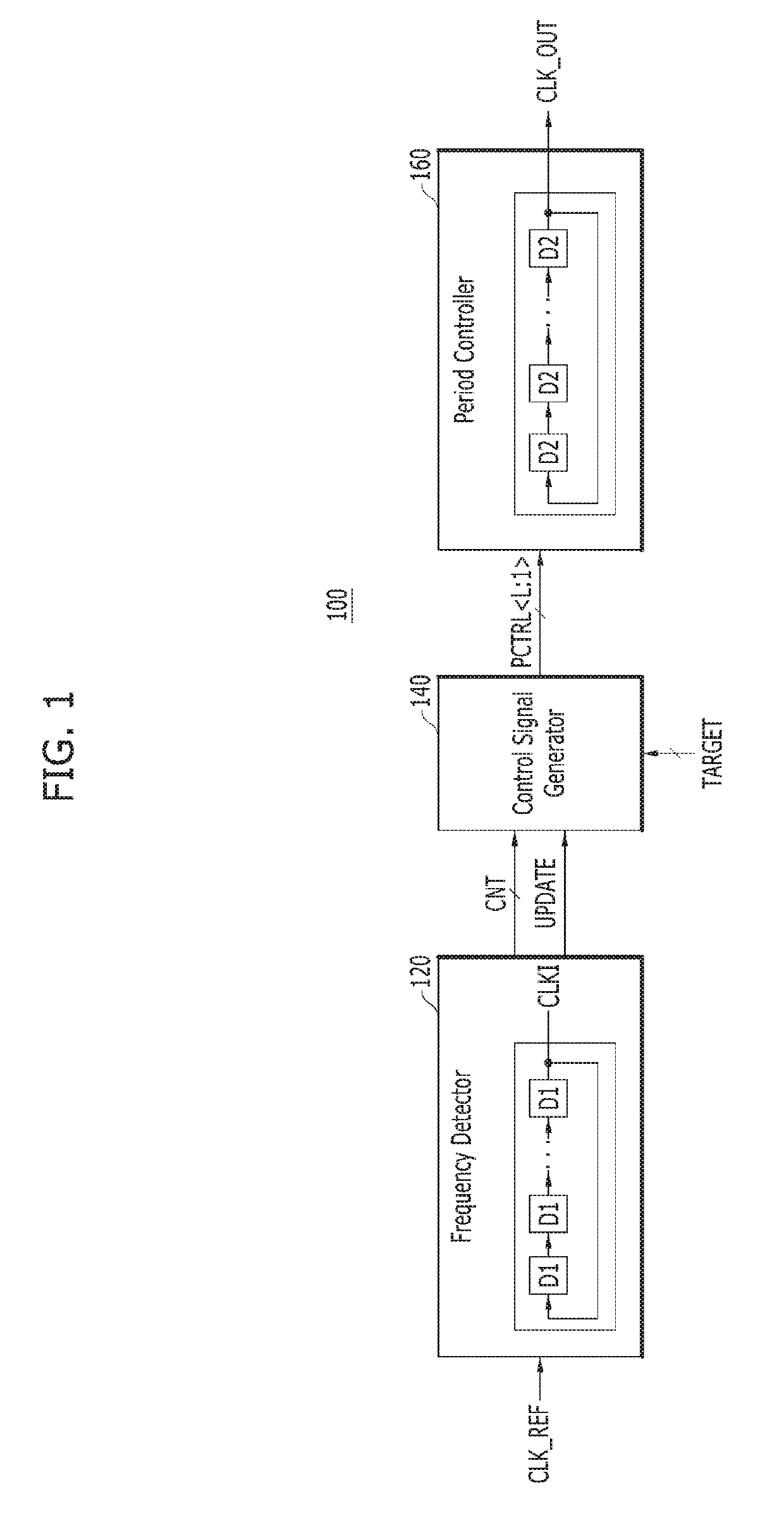

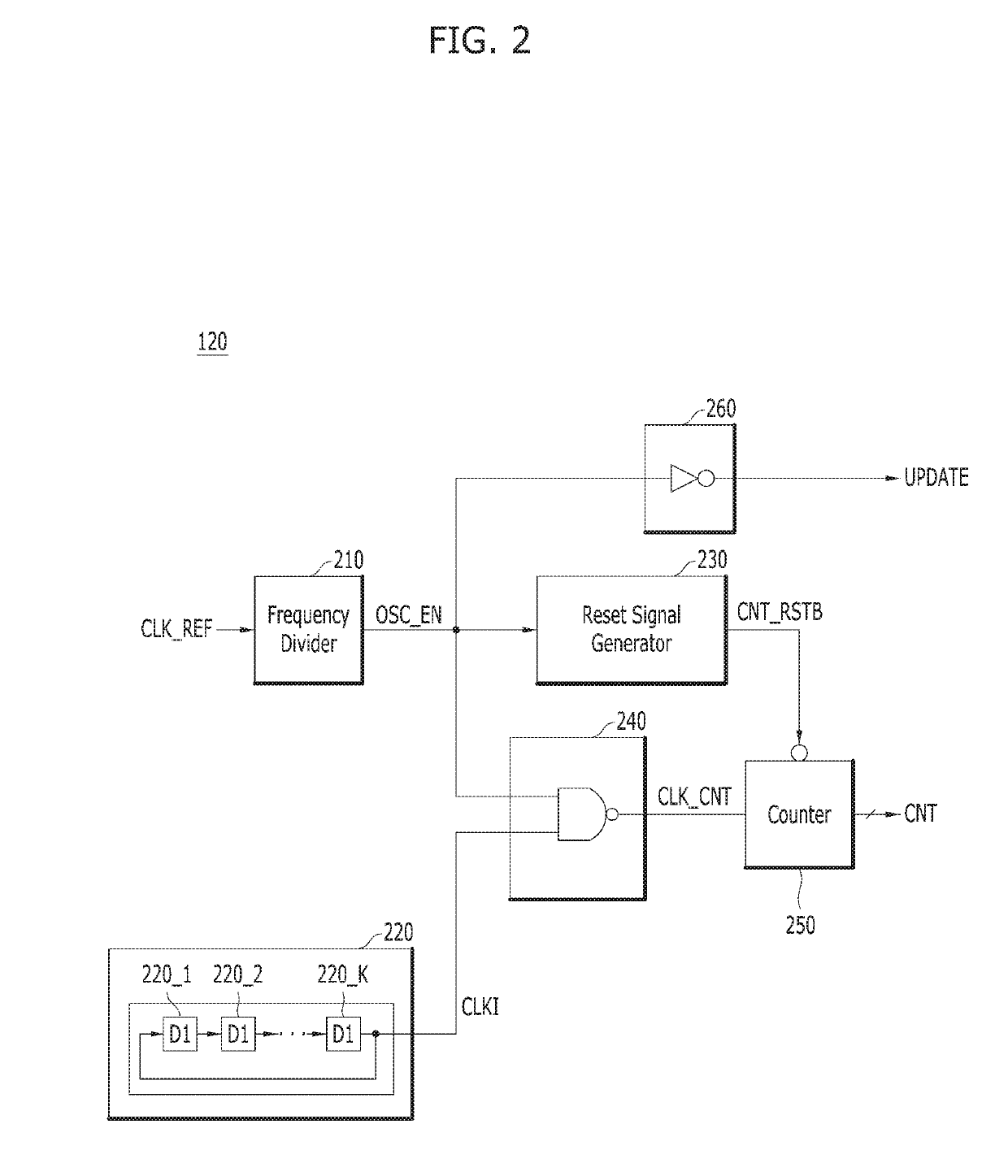

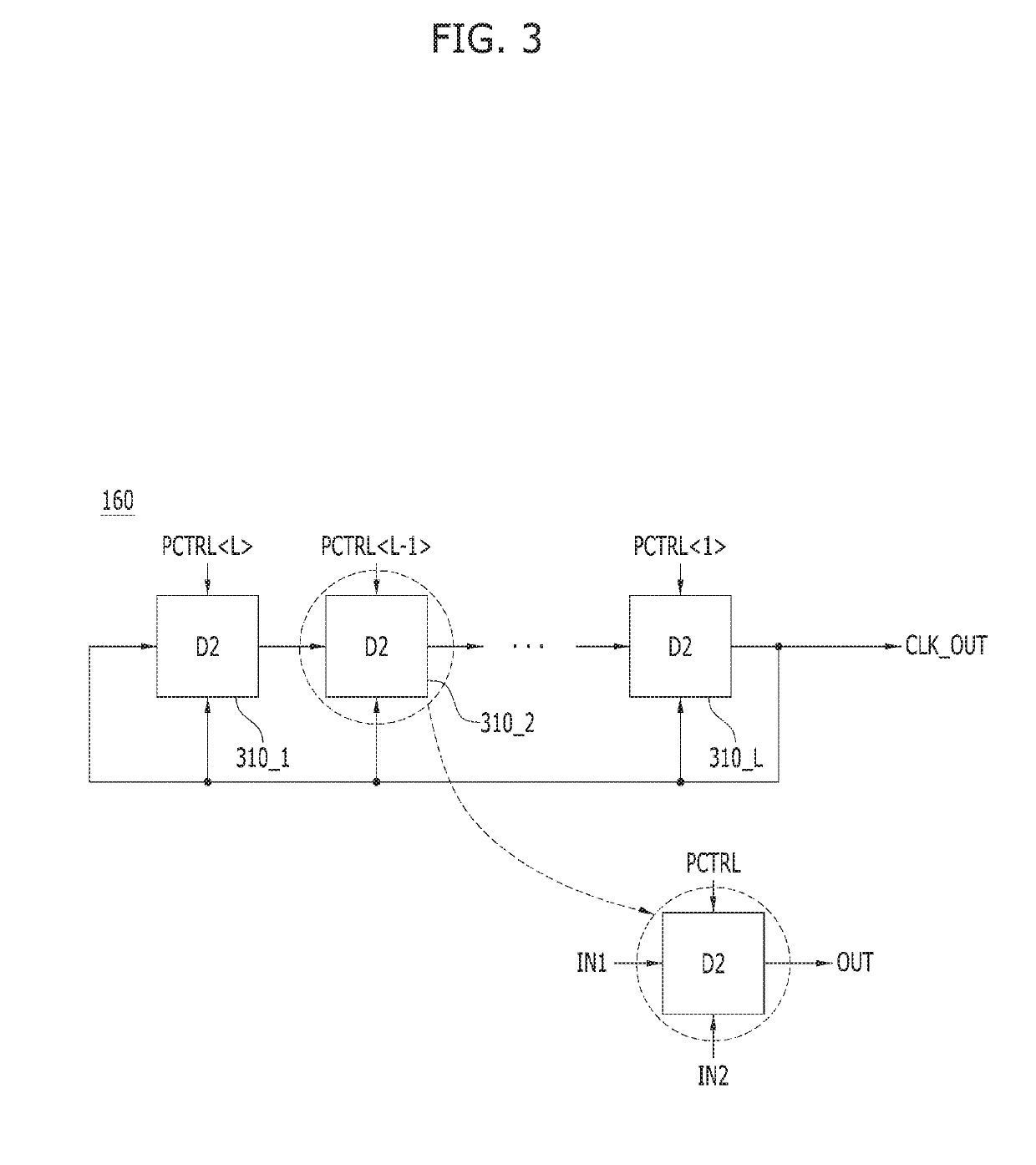

Semiconductor device including clock generation circuit

ActiveUS10637452B2Digital circuit testingCounting chain pulse counters using semiconductor devicesComputer hardwareDevice material

A clock generation circuit includes: a frequency detector suitable for generating an internal clock, and generating a counting signal indicating a toggling number of the internal clock during an activation period of an input clock; a control signal generator suitable for generating a plurality of period control signals based on a target signal and the counting signal, the target signal indicating a target frequency of an output clock; and a period controller suitable for generating the output clock based on the period control signals.

Owner:SK HYNIX INC

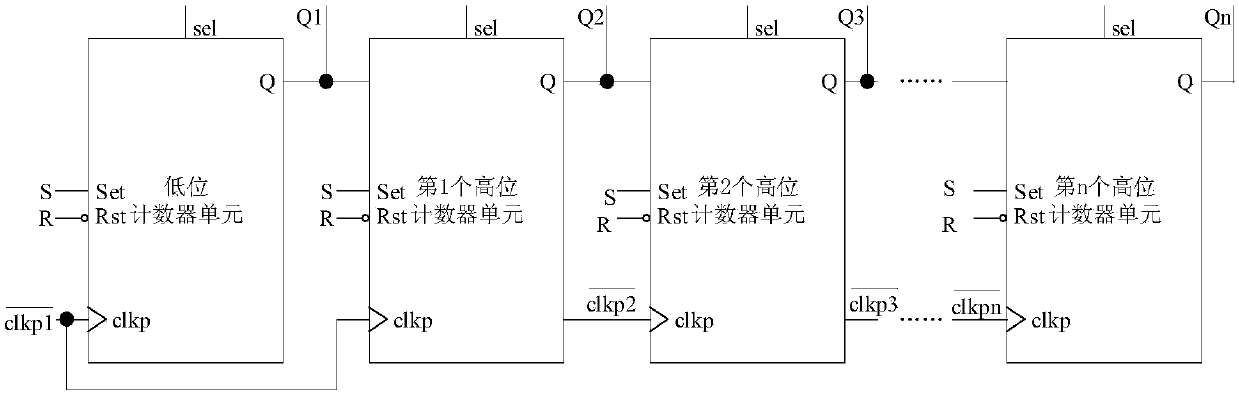

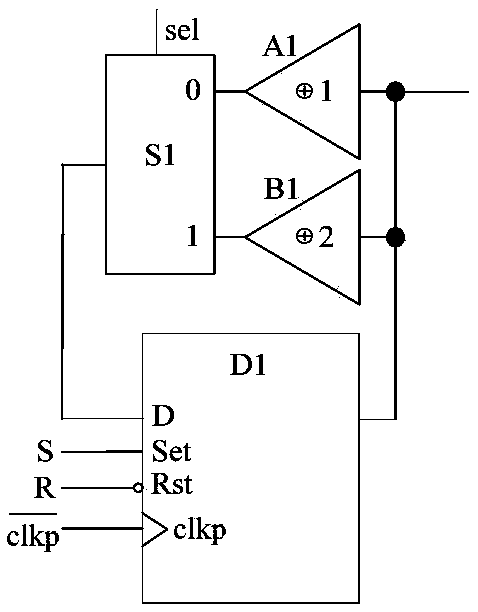

Three-valued reversible counter using carbon nano-field effect transistor

ActiveCN107682006AReduce redundant jumpsReduce dynamic power consumptionCounting chain pulse counters using semiconductor devicesCounting chain reversible pulse countersField-effect transistorComputer science

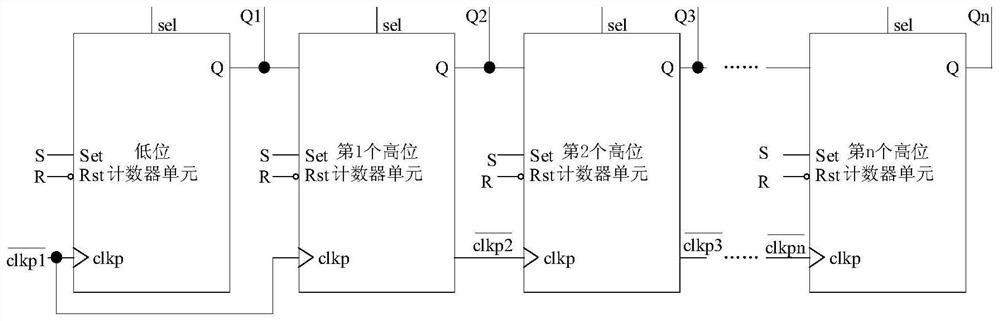

The invention discloses a three-valued reversible counter using a carbon nano-field effect transistor. The three-valued reversible counter comprises a low-bit counting unit and n high-bit counting units with the same circuit structure, wherein the low-bit counting unit comprises a three-valued pulse type D trigger, a first alternative selector, a first modulo-1 circuit, and a first modulo-2 circuit; the high-bit counting unit comprises a second three-valued pulse type D trigger, a second alternative selector, a second modulo-1 circuit, a second modulo-2 circuit and a carry / borrow circuit. Thethree-valued reversible counter disclosed by the invention has the advantage that the clock signal of each level of counting unit is input after the clock signal of the former level of counting unit is processed through the carry / borrow circuit, thereby guaranteeing that each level of counting unit only needs to receive the clock signal in the counting time, the redundancy hop of the counter produced by the change of the clock signal is reduced, and the dynamic power consumption of the circuit is lowered.

Owner:NINGBO UNIV

Programmable synchronous clock divider

ActiveUS9490777B2Counting chain pulse counters using semiconductor devicesElectric pulse generatorLong pulseClock signal

Owner:NXP USA INC

Structure for Radiation Hardened Programmable Phase Frequency Divider Circuit

InactiveUS20080211558A1Counting chain pulse counters using semiconductor devicesElectric pulse generatorCMOSSoi cmos technology

A design structure embodied in a machine readable medium includes information for designing, manufacturing and / or testing a programmable phase frequency divider circuit implemented in CMOS technology for space applications. The programmable phase frequency divider consists of three radiation hardened D-type flip flops and combinational logic circuits to provide the feedback controls that allow programmable frequency division ratios from 1 to 8. The radiation hardened D-type flip flop circuits are designed to keep on running properly at GHz frequencies even after a single event upset (SEU) hit. The novel D-type flip flop circuits each have two pairs of complementary inputs and outputs to mitigate SEU'S. The combinational logic circuits are designed to utilize the complementary outputs in such a way that only one of the four dual complementary inputs to any D-type flip flop gets flipped at most after an SEU hit.

Owner:GLOBALFOUNDRIES INC

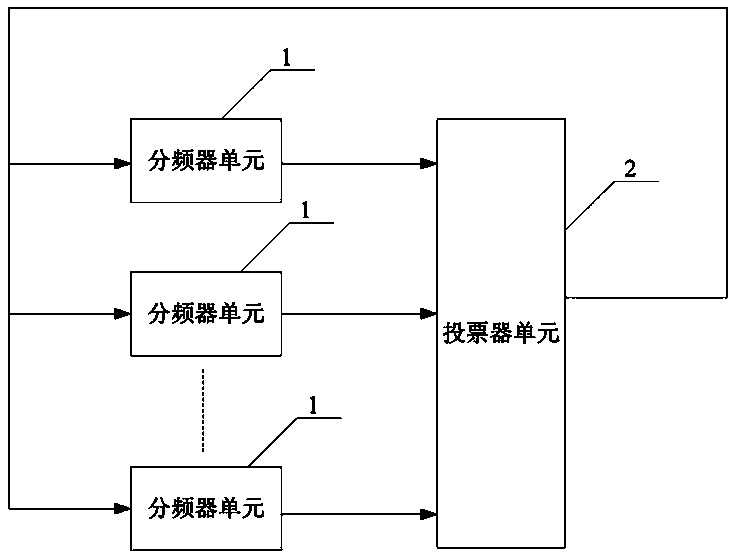

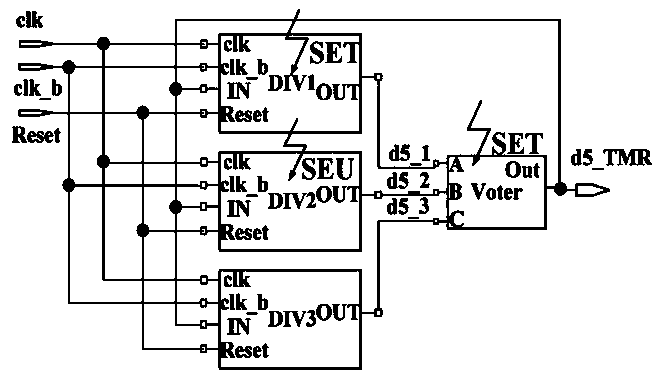

Frequency divider circuit with anti-irradiation function

ActiveCN109525243AWith anti-irradiation functionSuppression of single event effectsCounting chain pulse counters using semiconductor devicesEngineeringIrradiation

The invention discloses a frequency divider circuit with anti-irradiation function, comprising more than three frequency divider units and a voting unit, wherein the output ends of each frequency divider unit are respectively connected to the input end of the voting unit, and the output end of the voting unit is in feedback connection to the input ends of each frequency divider unit. The frequencydivider circuit has the advantages such as simple structure, low cost, anti-irradiation function and low soft error rate.

Owner:NAT UNIV OF DEFENSE TECH

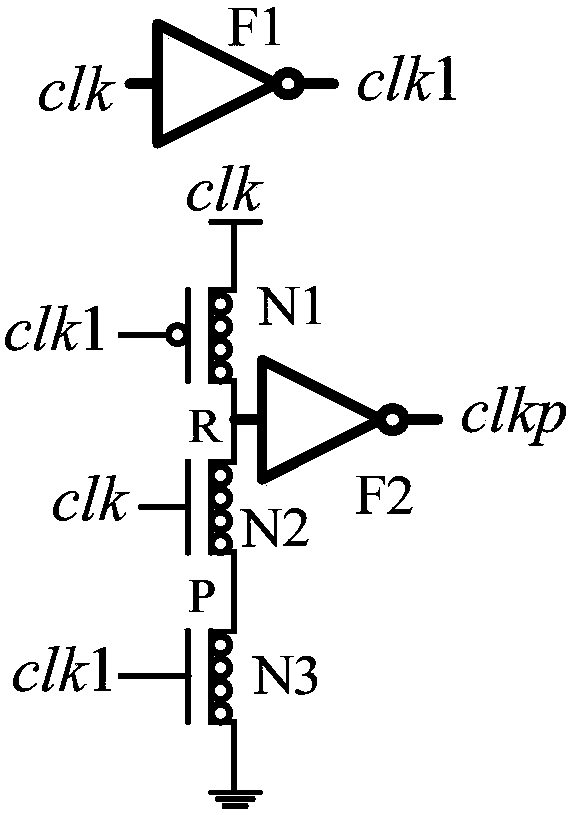

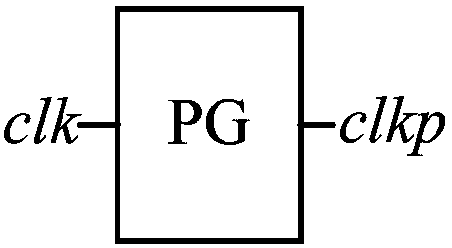

A millimeter wave high-speed frequency divider

ActiveCN107276580BReduce areaLarge frequency division rangeCounting chain pulse counters using semiconductor devicesElectric pulse generatorSoftware engineeringFlip-flop

Owner:江苏微远芯微系统技术有限公司

Semiconductor device including clock generation circuit

ActiveUS20190267975A1Digital circuit testingCounting chain pulse counters using semiconductor devicesCycle controlTarget signal

A clock generation circuit includes: a frequency detector suitable for generating an internal clock, and generating a counting signal indicating a toggling number of the internal clock during an activation period of an input clock; a control signal generator suitable for generating a plurality of period control signals based on a target signal and the counting signal, the target signal indicating a target frequency of an output clock; and a period controller suitable for generating the output clock based on the period control signals.

Owner:SK HYNIX INC

Wide frequency range signal generator and method, and integrated circuit test system using same

ActiveUS7536618B2Counting chain pulse counters using semiconductor devicesElectronic circuit testingSignal generatorTimer

A signal generator produces an output clock signal by coupling an input clock signal through a plurality of divider circuits each of which is formed by a toggling flip-flop. The frequency of the output clock signal is adjusted by selecting the flip-flop to which the input clock signal is coupled. Retimer flip-flops may be coupled between adjacent flip-flips to resynchronize the signal being coupled through the flip-flops. Each of the retimer flip-flops receives a respective signal from the output of an upstream flip-flop at its data input, and it receives the input clock signal at its clock input. The flip-flop then applies the signal to a downstream flip-flop in synchronism with the input clock signal. The final two flip-flops through which the input signal is coupled may be preset to various states to set the phase of the output clock signal to one of four phases.

Owner:MICRON TECH INC

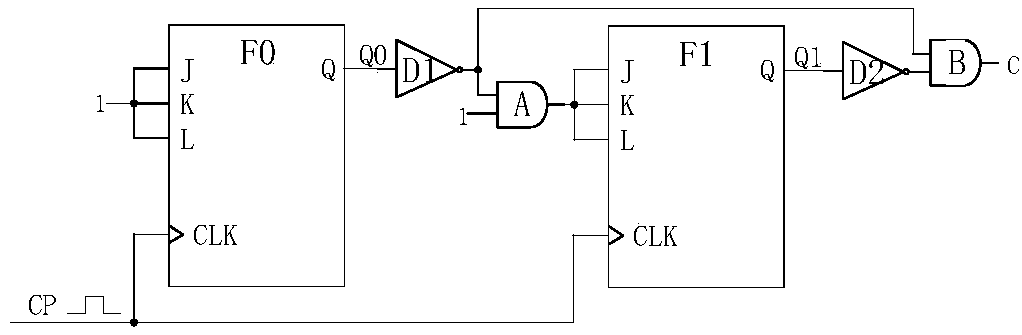

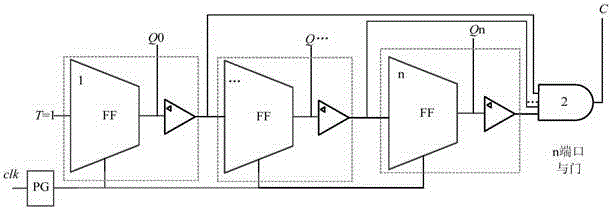

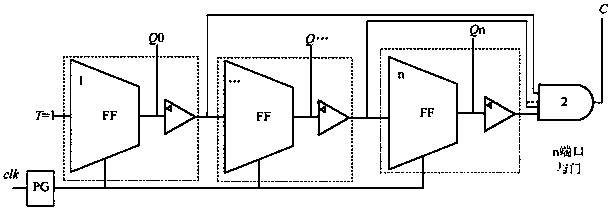

Three-valued addition counter based on CNFETs

ActiveCN106067807AReduce power consumptionLower latencyCounting chain pulse counters using semiconductor devicesTime delaysEngineering

The invention discloses a three-valued addition counter based on CNFETs. The three-valued addition counter comprises a pulse signal generator, n addition counting units, and an n input AND gate. The pulse signal generator has an input end and output end. Each addition counting unit has an input end, an output end, a clock control end, and a carry output end. The n input AND gate has n input ends and an output end. The output end of the pulse signal generator is connected with the clock control ends of the n addition counting units. The carry output ends of the n addition counting units and the n input ends of the n input AND gate are connected in one-to-one correspondence. The output end of the n input AND gate is the carry output end of the three-valued addition counter. The carry output end of the kth addition counting unit is connected with the input end of the (k+1)th addition counting unit, wherein k=1, 2, ..., n-1. The output end of the jth addition counting unit is the jth output end of the three-valued addition counter, wherein j=1, 2, ..., n. The three-valued addition counter reduces invalid operation, decreases circuit power consumption and time delay, and has a high-speed low-power-consumption characteristic.

Owner:NINGBO UNIV

Millimeter wave high-speed frequency divider

ActiveCN107276580AReduce areaLarge frequency division rangeCounting chain pulse counters using semiconductor devicesElectric pulse generatorInductorEngineering

The invention discloses a millimeter wave high-speed frequency divider, and relates to the field of millimeter wave integrated circuits. The millimeter wave high-speed frequency divider is a frequency divider module applied in a millimeter wave transceiver chip, and solves the technical problems that the existing high-speed frequency divider is too large in area and too narrow in frequency division range. The millimeter wave high-speed frequency divider comprises four simple D triggers connected in sequence into a ring. The millimeter wave high-speed frequency divider not provided with passive devices such as an inductor occupying large area has the technical advantages of small area and large frequency division range.

Owner:江苏微远芯微系统技术有限公司

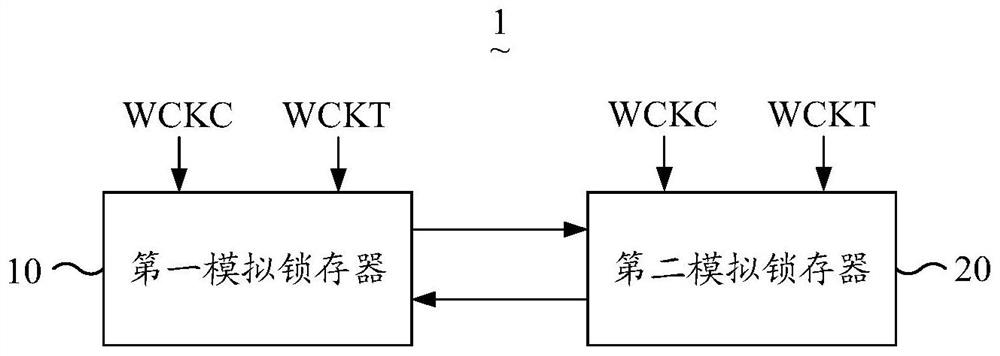

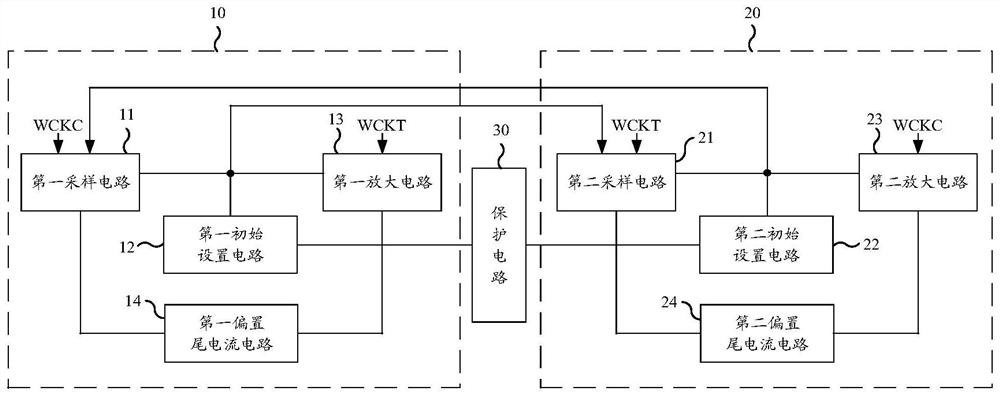

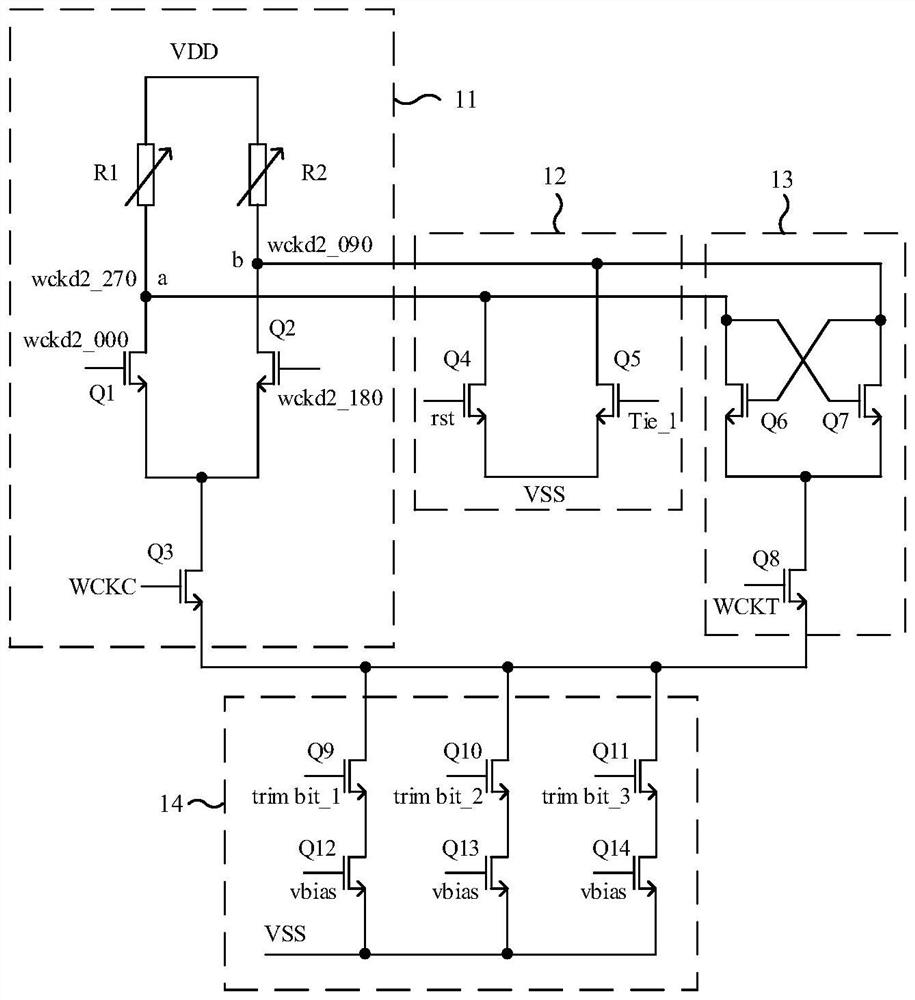

Analog frequency divider

PendingCN114665865ARealize frequency divisionCounting chain pulse counters using semiconductor devicesAnalog signalComputer science

The invention discloses an analog frequency divider which comprises a first analog latch and a second analog latch, the output end of the first analog latch is connected with the input end of the second analog latch, and the output end of the second analog latch is connected with the input end of the first analog latch; the analog frequency divider receives analog signals, and the analog signals are amplified and sampled through the first analog latch and the second analog latch so as to realize frequency division of the analog signals. According to the invention, the output end of the first analog latch is connected with the input end of the second analog latch, and the output end of the second analog latch is connected with the input end of the first analog latch, so that the frequency division of the analog signal is realized.

Owner:XI AN UNIIC SEMICON CO LTD

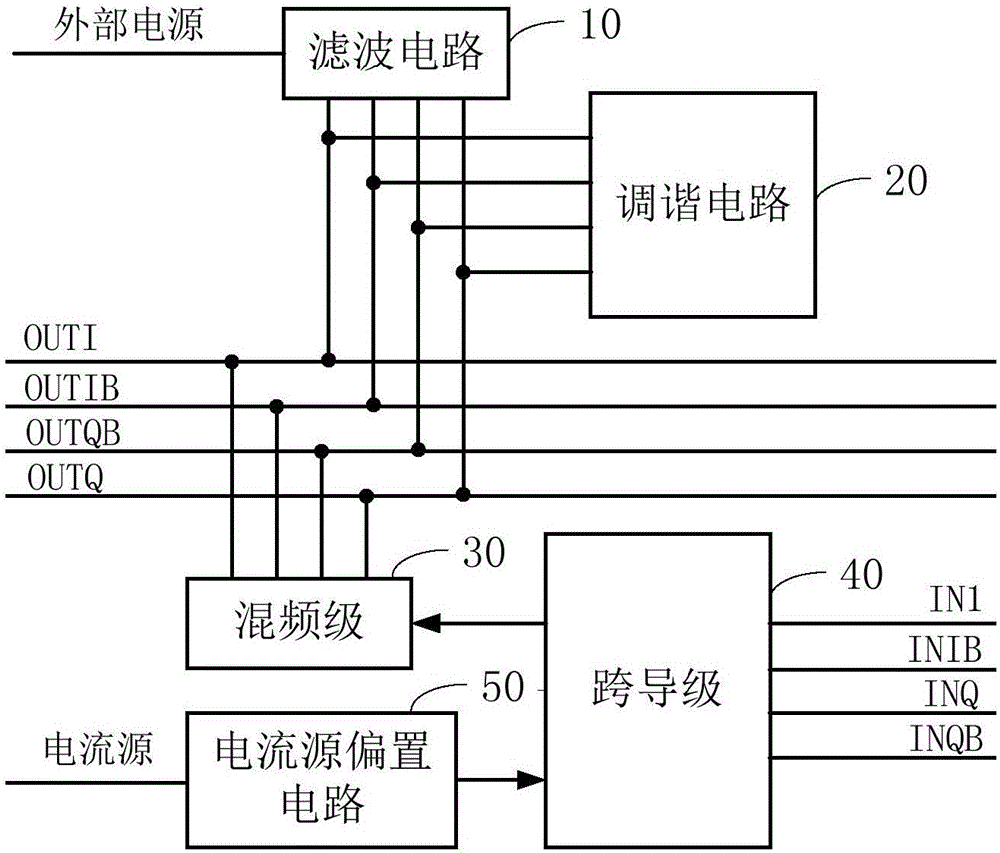

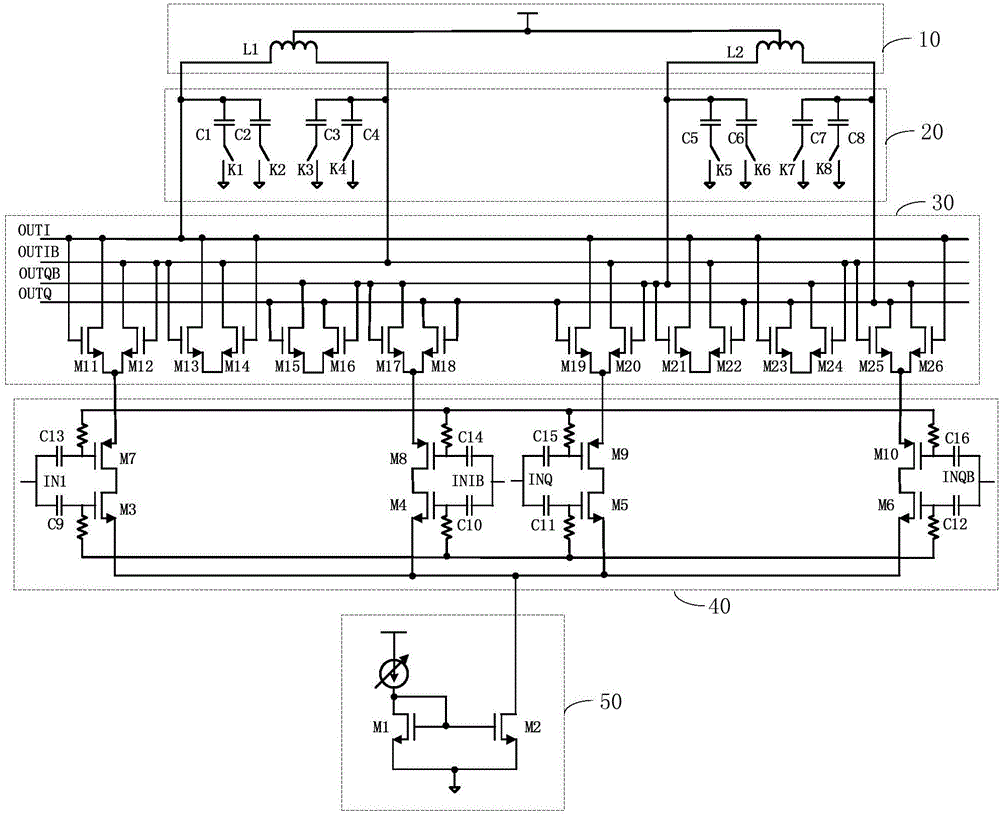

Orthogonal input divide-by-2 frequency divider

PendingCN106603067AHigh currentImprove conversion gainCounting chain pulse counters using semiconductor devicesEngineeringLinearity

The invention is suitable for the field of frequency dividers, and provides an orthogonal input divide-by-2 frequency divider, which comprises: a filter circuit for inputting an external power supply and performing output after filtering; a tuning circuit connected with an output end of the filter circuit; a mixer stage connected to an output end OUTI, an output end OUTIB, an output end OUTQB and an output end OUTQ of the orthogonal input divide-by-2 frequency divider together with the output end of the filter circuit; a transconductance stage connected with an input end INI, an input end INIB, an input end INQ and an input end INQB of the orthogonal input divide-by-2 frequency divider respectively to input a voltage signal, convert the voltage signal into a current signal and output the current signal to a common source end of the mixer stage; and a current source biasing circuit connected to the common source end of the transconductance stage and enabling the transconductance stage to form a variable current source by injecting an external current source. According to the orthogonal input divide-by-2 frequency divider provided by the invention, the external current source is injected into the current source biasing circuit to enable the transconductance stage to form the variable current source so as to increase the current of the transconductance stage, so that the conversion grain, the degree of linearity and the range of a working frequency of the orthogonal input divide-by-2 frequency divider can be effectively improved.

Owner:CHINA COMM MICROELECTRONICS TECH CO LTD +1

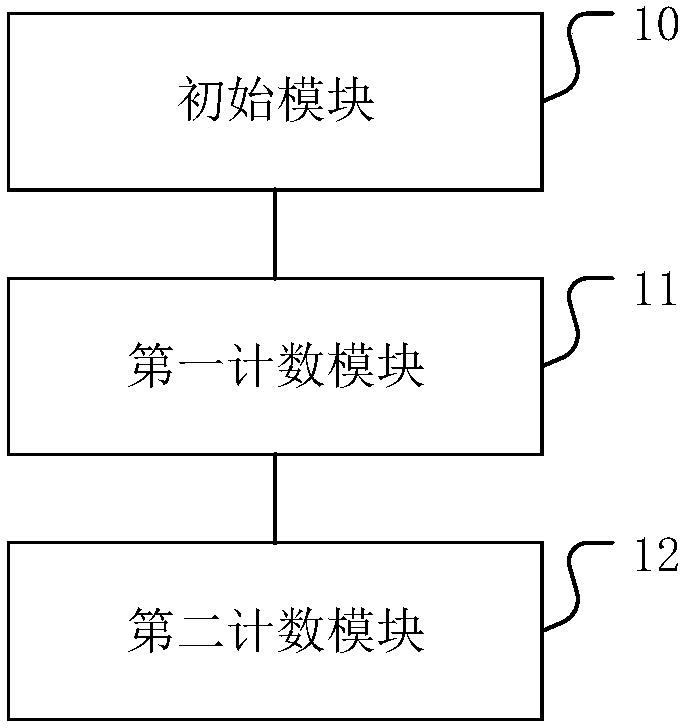

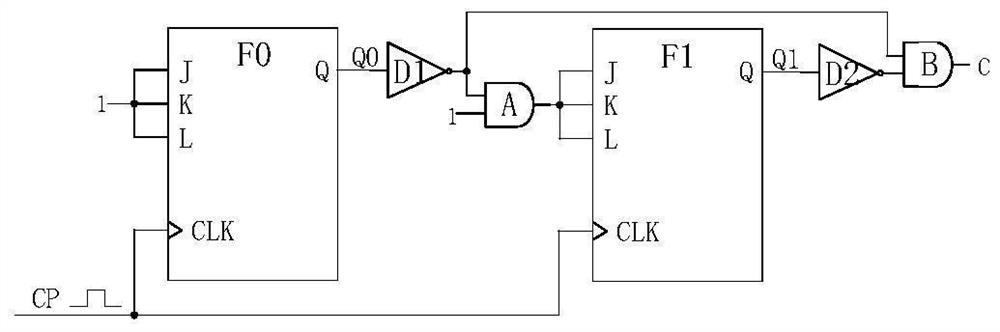

CPLD-based clock counting method and device, and medium

InactiveCN107659305AGuaranteed work efficiencyReduce resource usageCounting chain pulse counters using semiconductor devicesCurrent cycleComputer science

The invention discloses a CPLD-based clock counting method and device, and a medium. The method comprises the following steps: acquiring an event duration of a CPLD, and setting layers representing counting cycles according to the event duration, wherein the layers at least comprise two layers, the lowest layer represents a system cycle, durations of the counting cycles are positively related to layer levels, and the counting cycle represented by a higher layer is an integer multiple of the counting cycle represented by a lower layer; starting counting by using the counting cycle represented by the lowest of the layers as a current cycle, and using a target counting cycle represented by a next layer as the current cycle to continue the counting when a counting duration reaches the target counting cycle, until the current cycle is identical to the counting cycle represented by the highest of the layers; and continuing the counting according to the current cycle to reach the event duration. Therefore, the method provided by the invention has the beneficial effect that the overall work efficiency of the CPLD during clock counting is relatively improved. Moreover, the invention furtherprovides the CPLD-based clock counting device, and the medium, which achieve the above beneficial effect.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

A Three-value Reversible Counter Using Carbon Nano Field-Effect Transistor

ActiveCN107682006BReduce redundant jumpsReduce dynamic power consumptionCounting chain pulse counters using semiconductor devicesCounting chain reversible pulse countersHemt circuitsFlip-flop

The invention discloses a three-valued reversible counter using a carbon nano-field effect transistor. The three-valued reversible counter comprises a low-bit counting unit and n high-bit counting units with the same circuit structure, wherein the low-bit counting unit comprises a three-valued pulse type D trigger, a first alternative selector, a first modulo-1 circuit, and a first modulo-2 circuit; the high-bit counting unit comprises a second three-valued pulse type D trigger, a second alternative selector, a second modulo-1 circuit, a second modulo-2 circuit and a carry / borrow circuit. Thethree-valued reversible counter disclosed by the invention has the advantage that the clock signal of each level of counting unit is input after the clock signal of the former level of counting unit is processed through the carry / borrow circuit, thereby guaranteeing that each level of counting unit only needs to receive the clock signal in the counting time, the redundancy hop of the counter produced by the change of the clock signal is reduced, and the dynamic power consumption of the circuit is lowered.

Owner:NINGBO UNIV

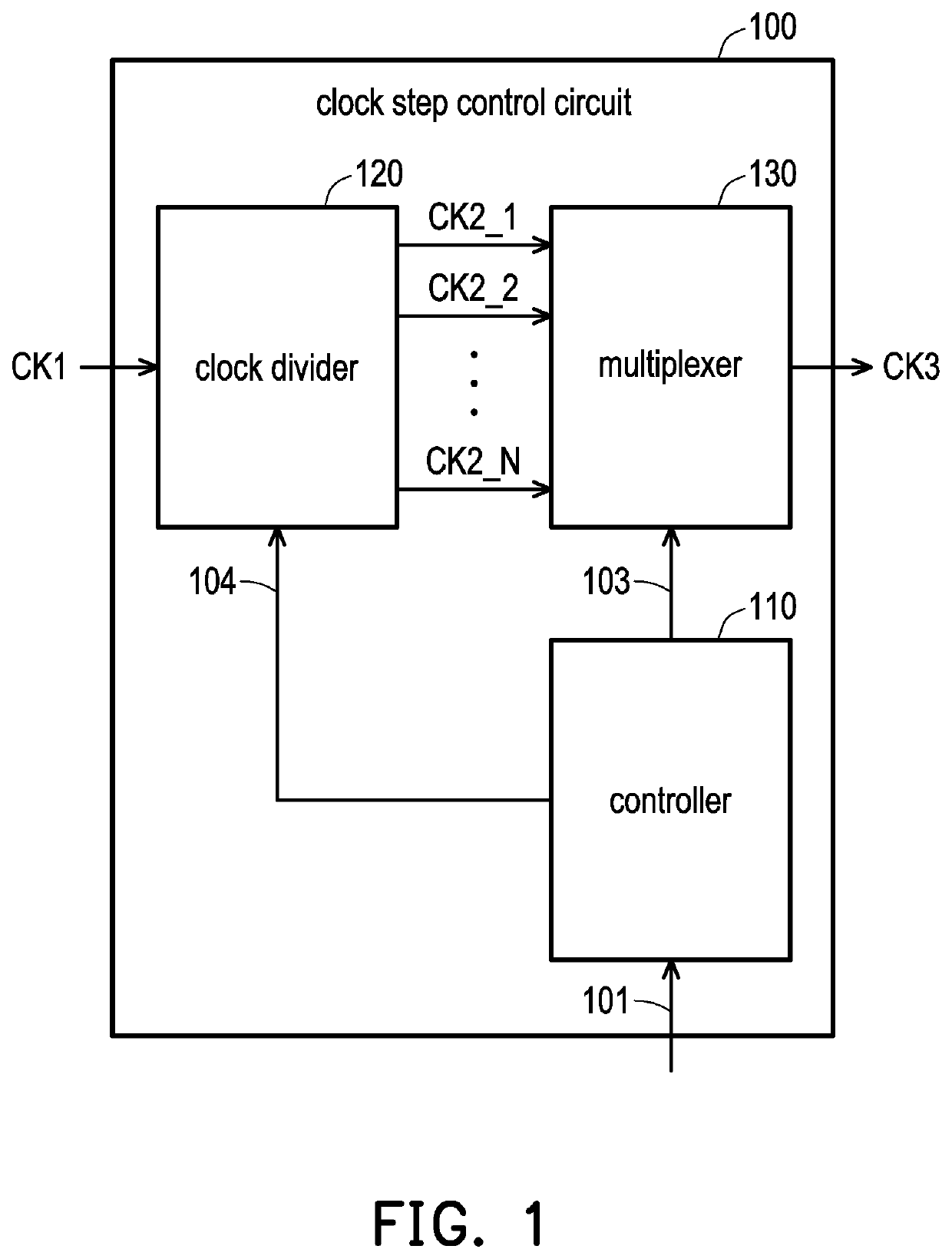

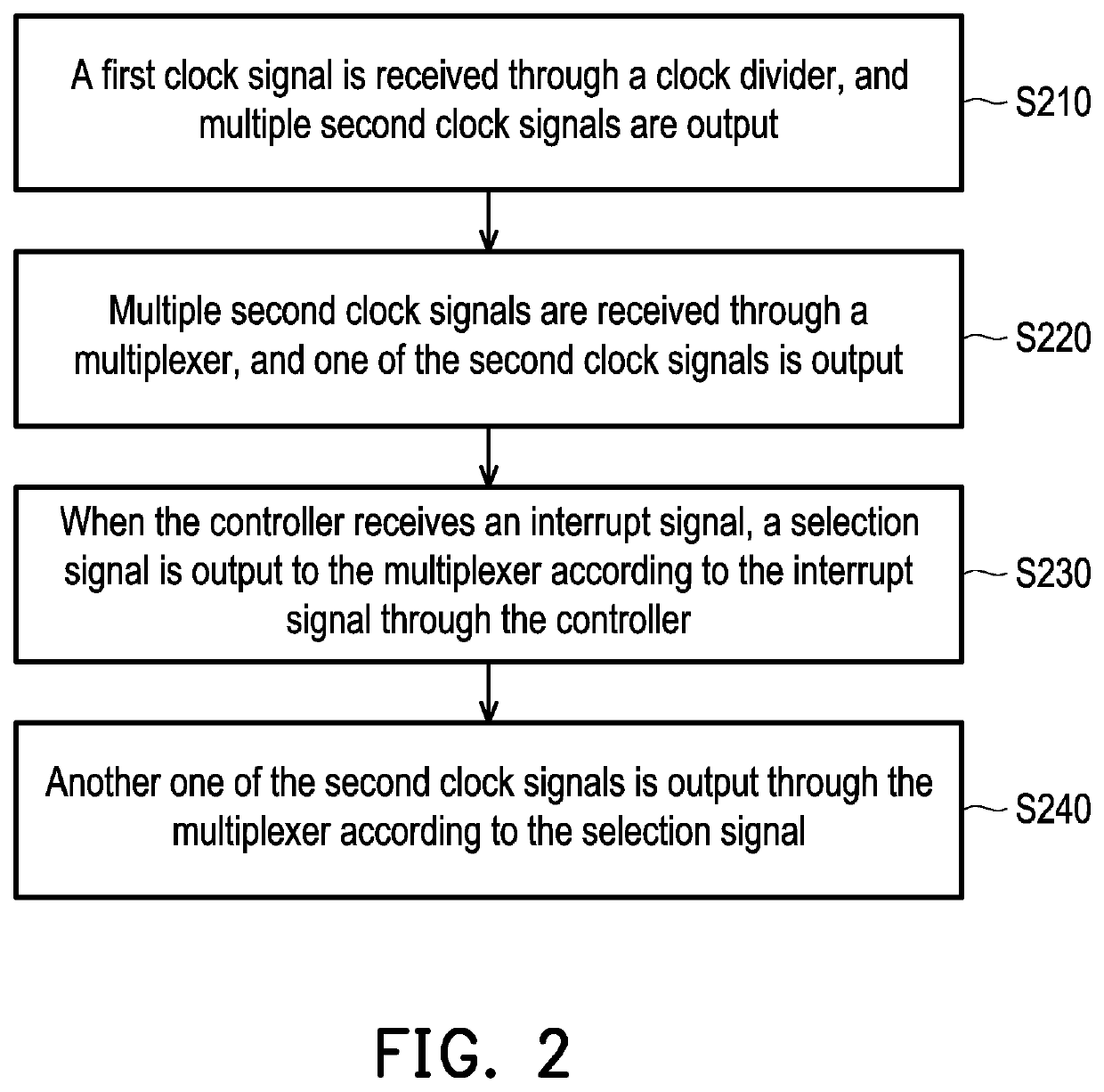

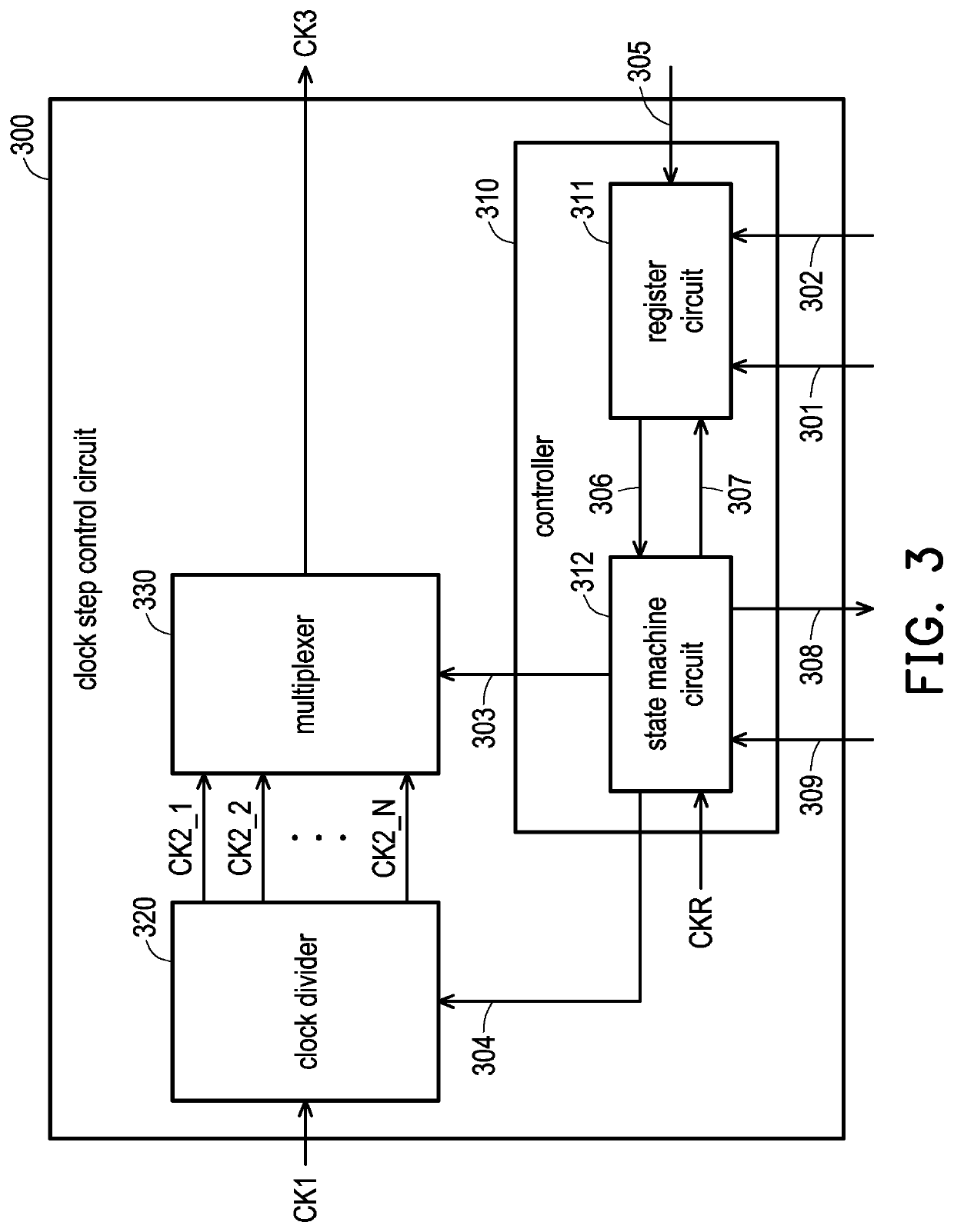

Clock step control circuit and method thereof

ActiveUS11381245B1Reduce clock frequencyCounting chain pulse counters using semiconductor devicesDigital computer detailsMultiplexerClock rate

The disclosure provides a clock step control circuit and a method thereof. The clock step control circuit includes a clock divider, a multiplexer, and a controller. The clock divider receives a first clock signal and outputs multiple second clock signals. The multiplexer receives the second clock signals and outputs one of the second clock signals. The controller is coupled to the clock divider and the multiplexer. When the controller receives an interrupt signal, the controller outputs a selection signal to the multiplexer according to the interrupt signal. The multiplexer outputs another one of the second clock signals according to the selection signal. The clock step control circuit and the method thereof in the disclosure can appropriately switch the clock signal to output a clock signal with an appropriate clock frequency.

Owner:SHANGHAI BIREN TECH CO LTD

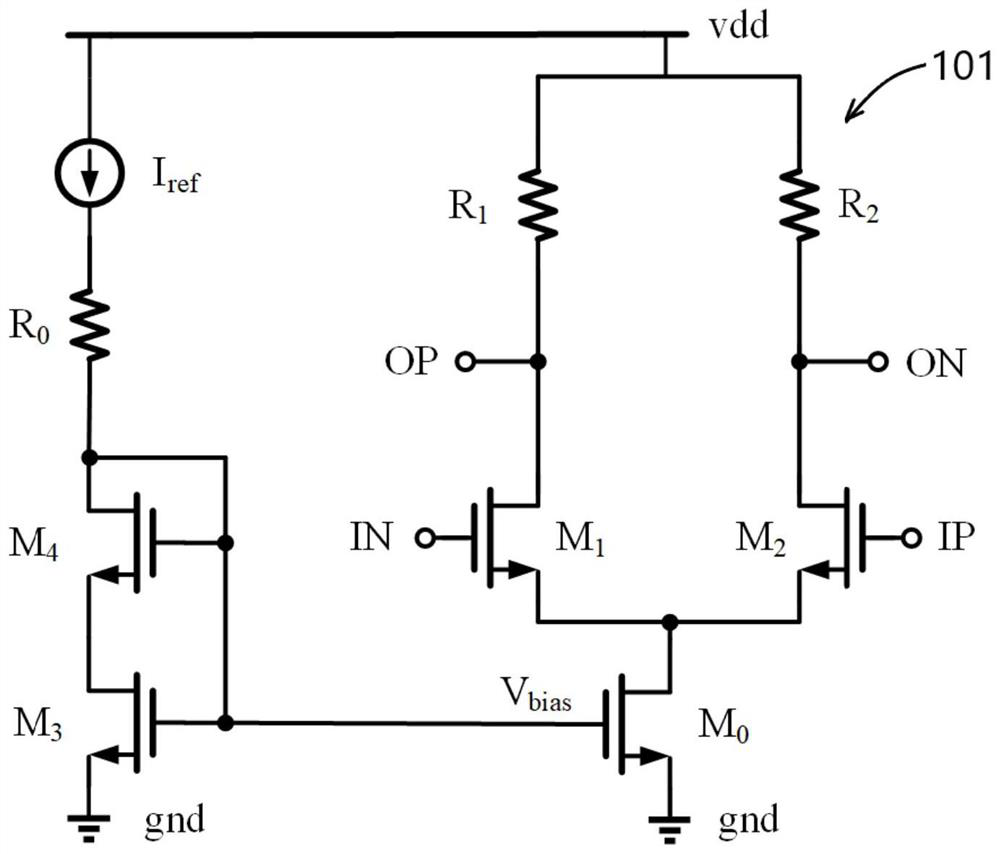

CML clock frequency dividing circuit, secondary clock frequency dividing circuit and analog-to-digital converter

PendingCN114142850AReduce power consumptionRun fastCounting chain pulse counters using semiconductor devicesAnalogue-digital convertersDividing circuitsDigital clock

One embodiment of the invention provides a CML clock frequency dividing circuit. The CML clock frequency dividing circuit comprises a buffer stage circuit and a frequency dividing stage circuit which are electrically connected. Wherein the buffer stage circuit is used for receiving an input clock signal, and the clock signal output by the buffer stage circuit is accessed to the control end of the clock signal input by the frequency division stage circuit. Wherein the input and the output of the buffer stage circuit are analog clock signals; the input of the frequency division level circuit is an analog clock signal, and the output of the frequency division level circuit is a digital clock signal. According to the CML clock frequency dividing circuit, a two-stage circuit structure is adopted, only one set of fixed bias current Ibias needs to be arranged, and compared with the mode that two sets of fixed bias current Ibias are arranged in the prior art, the overall power consumption is obviously reduced.

Owner:苏州迅芯微电子有限公司

A three-valued addition counter based on cnfet

ActiveCN106067807BReduce power consumptionLower latencyCounting chain pulse counters using semiconductor devicesTime delaysSignal generator

The invention discloses a three-valued addition counter based on CNFETs. The three-valued addition counter comprises a pulse signal generator, n addition counting units, and an n input AND gate. The pulse signal generator has an input end and output end. Each addition counting unit has an input end, an output end, a clock control end, and a carry output end. The n input AND gate has n input ends and an output end. The output end of the pulse signal generator is connected with the clock control ends of the n addition counting units. The carry output ends of the n addition counting units and the n input ends of the n input AND gate are connected in one-to-one correspondence. The output end of the n input AND gate is the carry output end of the three-valued addition counter. The carry output end of the kth addition counting unit is connected with the input end of the (k+1)th addition counting unit, wherein k=1, 2, ..., n-1. The output end of the jth addition counting unit is the jth output end of the three-valued addition counter, wherein j=1, 2, ..., n. The three-valued addition counter reduces invalid operation, decreases circuit power consumption and time delay, and has a high-speed low-power-consumption characteristic.

Owner:NINGBO UNIV

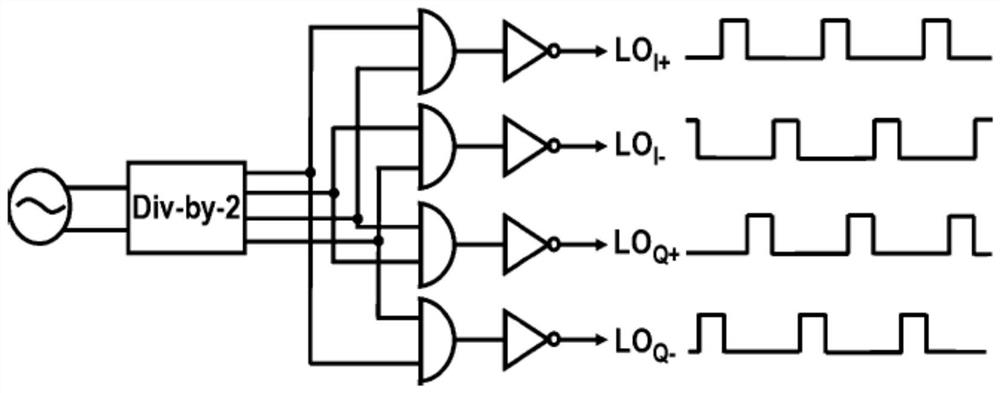

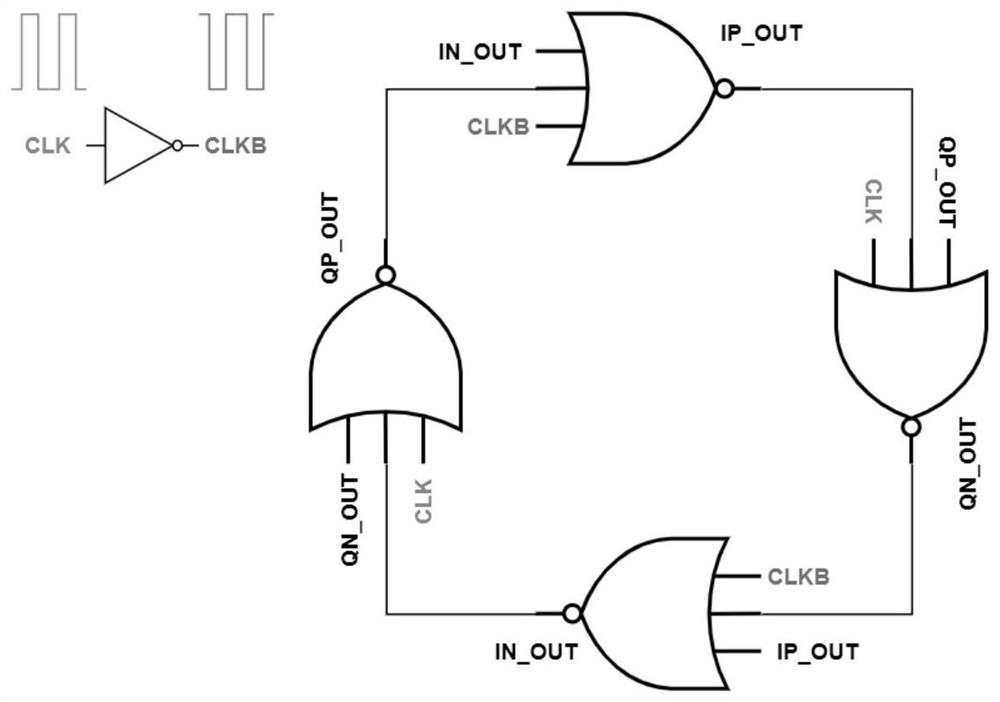

Novel frequency divider

PendingCN113472344ASave powerSave extra spaceLogic circuits characterised by logic functionCounting chain pulse counters using semiconductor devicesNOR gateNAND gate

The embodiment of the invention discloses a novel frequency divider which comprises four three-input NOR gates with the same specification, the four three-input NOR gates are annularly connected, and the output end of each three-input NOR gate is connected with one input end of the next adjacent three-input NOR gate. Only one-stage logic gate is needed, and compared with a common two-stage method that one frequency divider is needed and then a NAND gate or a NOR gate is used for synthesizing 25% duty ratio output, the power consumption and the region can be effectively saved.

Owner:北京北斗华大科技有限公司

Electronic circuits

ActiveUS9768782B2Directly appliedLogic circuits characterised by logic functionCounting chain pulse counters using semiconductor devicesField-effect transistorElectronic circuit

An electronic circuit comprises: an input terminal; an output terminal; first and second supply rails; first, second, third, and fourth field effect transistors, FETs, each of a first type and each having respective gate, source and drain terminals; and first and second loads. The source of the first FET is connected to the first supply rail, the drain of the first FET and the source of the second FET are connected to the output terminal, the drain of the second FET is connected to the second supply rail, the gate of the third FET and the gate of the fourth FET are connected to the input terminal, the drain of the third FET is connected to the second supply rail, the first load is connected between the first supply rail and the source of the third FET, and the second load is connected between the drain of the fourth FET and the second supply rail. In one aspect of the invention, the gate of the first FET is connected to a node between the source of the third FET and the first load such that a voltage at the source of the third FET is applied to the gate of the first FET, and the gate of the second FET is connected to a node between the drain of the fourth FET and the second load such that a voltage at the drain of the fourth FET is applied to the gate of the second FET.

Owner:PRAGMATIC PRINTING

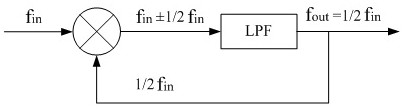

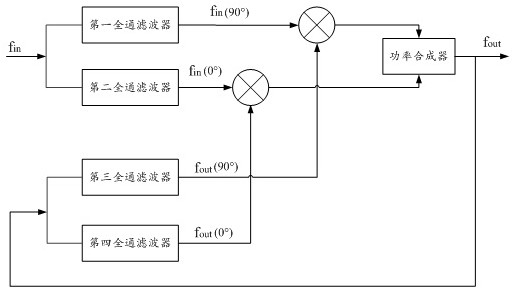

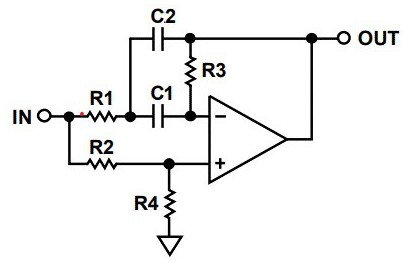

Regenerative frequency divider of broadband topological structure

PendingCN113949382AAvoid influenceEnhanced inhibitory effectCounting chain pulse counters using semiconductor devicesPulse automatic controlPower combinerFrequency mixer

The invention discloses a regenerative frequency divider of a broadband topological structure. The regenerative frequency divider comprises a first all-pass filter, a second all-pass filter, a third all-pass filter, a fourth all-pass filter, a first frequency mixer, a second frequency mixer and a power synthesizer. Orthogonal mode driving is achieved through the two frequency mixers and the feedback ends of the input port and the output port through the first all-pass filter, the second all-pass filter, the third all-pass filter and the fourth all-pass filter respectively, so that single side band conversion (SSB) is achieved, and signals output by the two frequency mixers are synthesized through the power synthesizer. And the unnecessary upper single frequency is eliminated, and only the lower side band frequency is left. Therefore, the lower frequency is not limited by the upper side band frequency and is only limited by the bandwidth of the all-pass filter, so that the regenerative frequency divider with a broadband topological structure is provided.

Owner:CHENGDU GOLDSKY MICROWAVE TECH

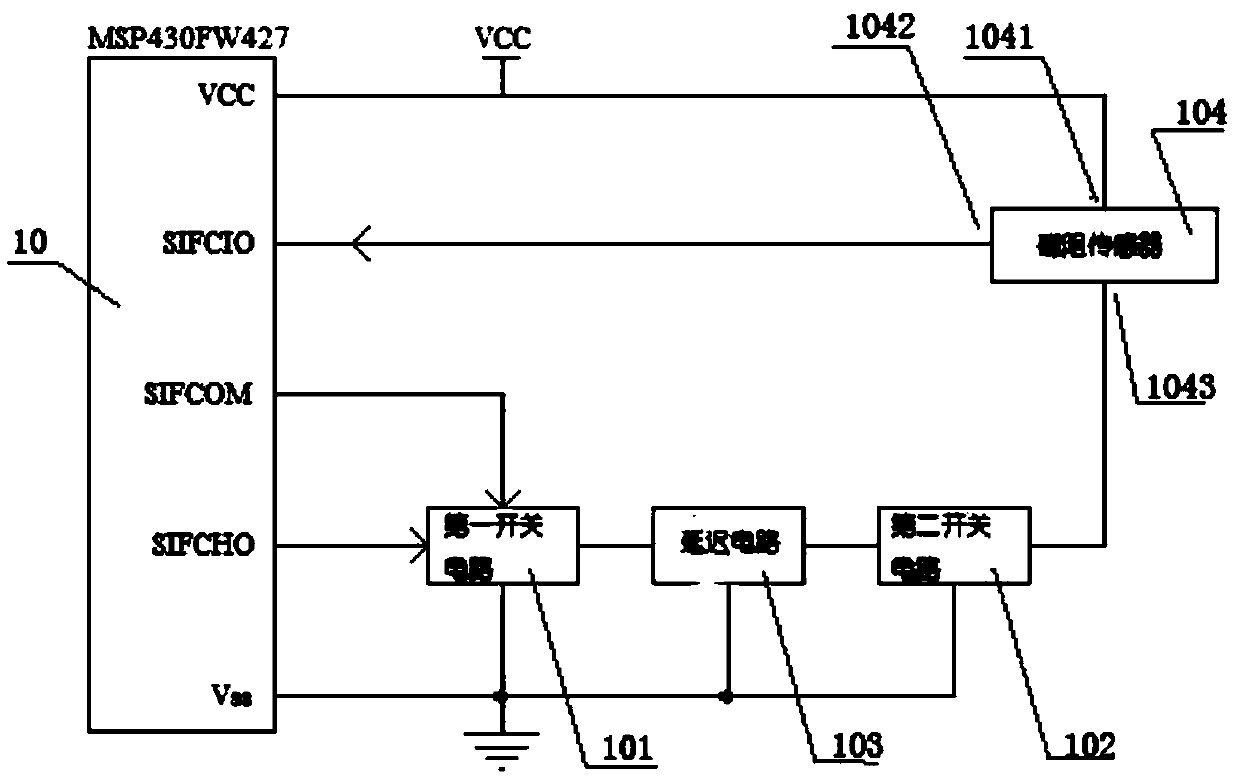

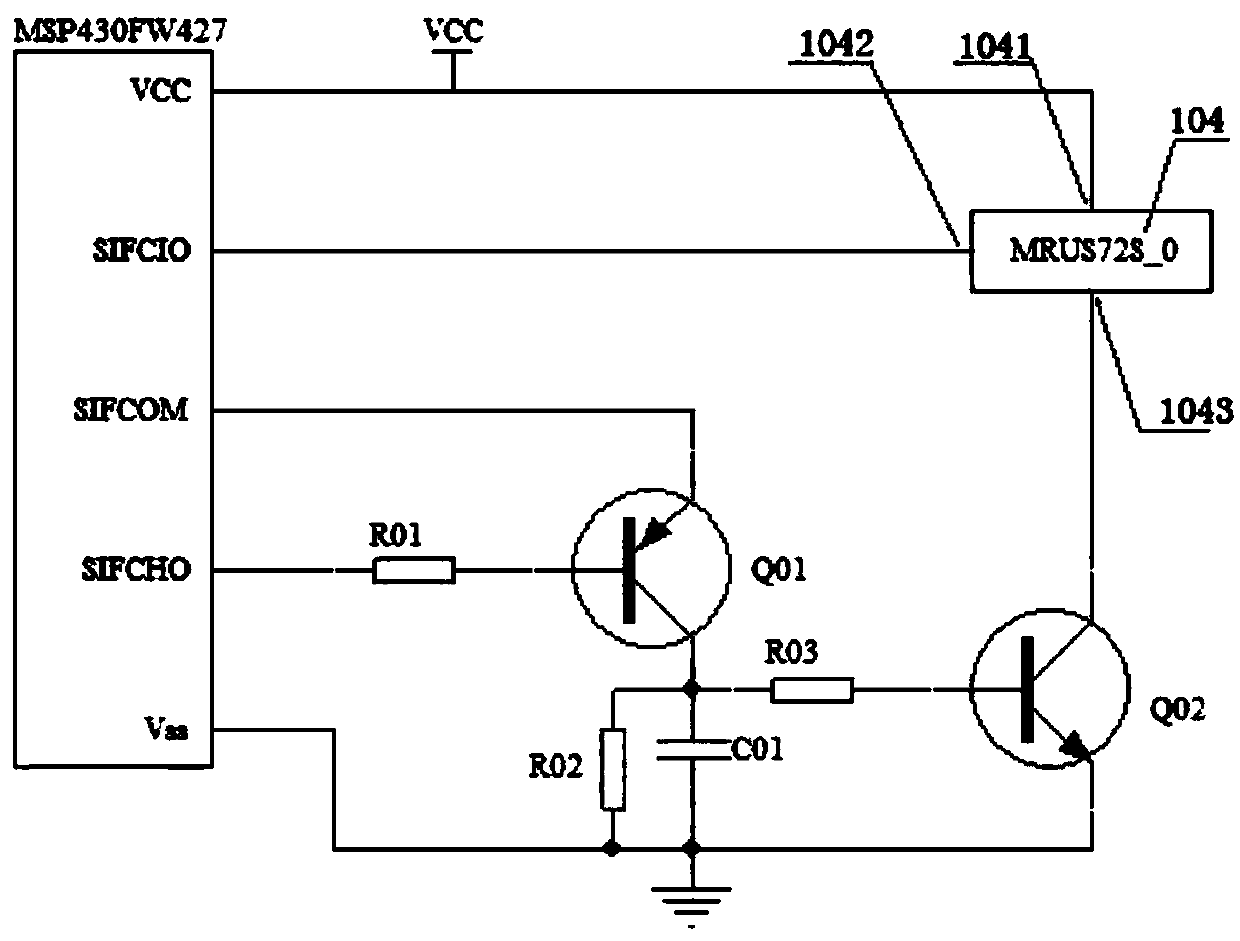

A counting device for automatically controlling sampling and detection of magnetoresistive sensors with low power consumption

ActiveCN106374913BCounting chain pulse counters using semiconductor devicesConverting sensor output electrically/magneticallyMicrocomputerMicrocontroller

The invention relates to the technical field of smart metering systems, and especially relates to a low-power counting device automatically controlling sampling detection by a magnetic resistance sensor. The counting device comprises a single chip microcomputer, a first switching circuit, a second switching circuit, a delay circuit, and a magnetic resistance sensor. The single chip microcomputer includes a signal acquisition pin, an excitation power pin, an excitation control pin, a power supply pin, and a grounding pin. The excitation control pin and the excitation power pin of the single chip microcomputer are connected with the first switching circuit. The first switching circuit is connected with the delay circuit. The delay circuit is connected with the second switching circuit. The second switching circuit is connected with the grounding end of the magnetic resistance sensor. The power input end of the magnetic resistance sensor is connected with the power supply pin of the single chip microcomputer. The signal output end of the magnetic resistance sensor is connected with the signal acquisition pin of the single chip microcomputer. The first switching circuit, the delay circuit and the second switching circuit are connected with the grounding pin of the single chip microcomputer. Low-power counting in the dormant state of the single chip microcomputer is realized.

Owner:优艾特仪表科技成都有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com