Novel frequency divider

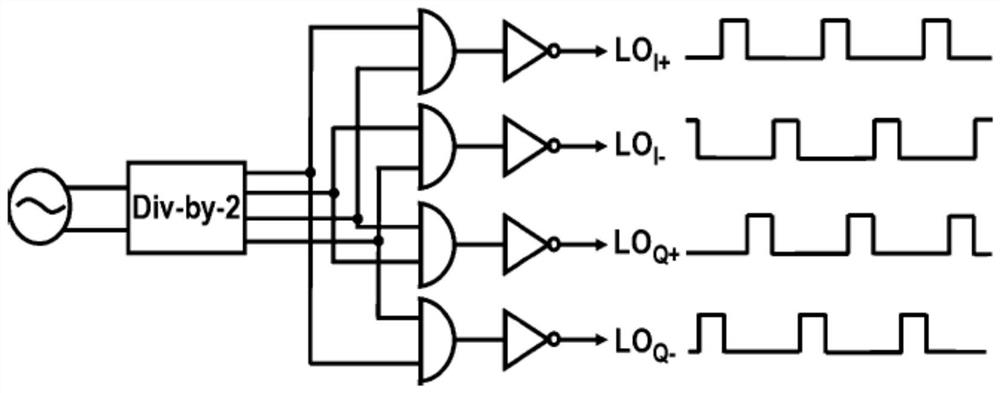

A frequency divider, a new type of technology, applied in pulse counters, counting chain pulse counters, pulse counters using semiconductor devices, etc., can solve the problems of high power consumption and large area, and achieve the effect of saving power consumption and area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

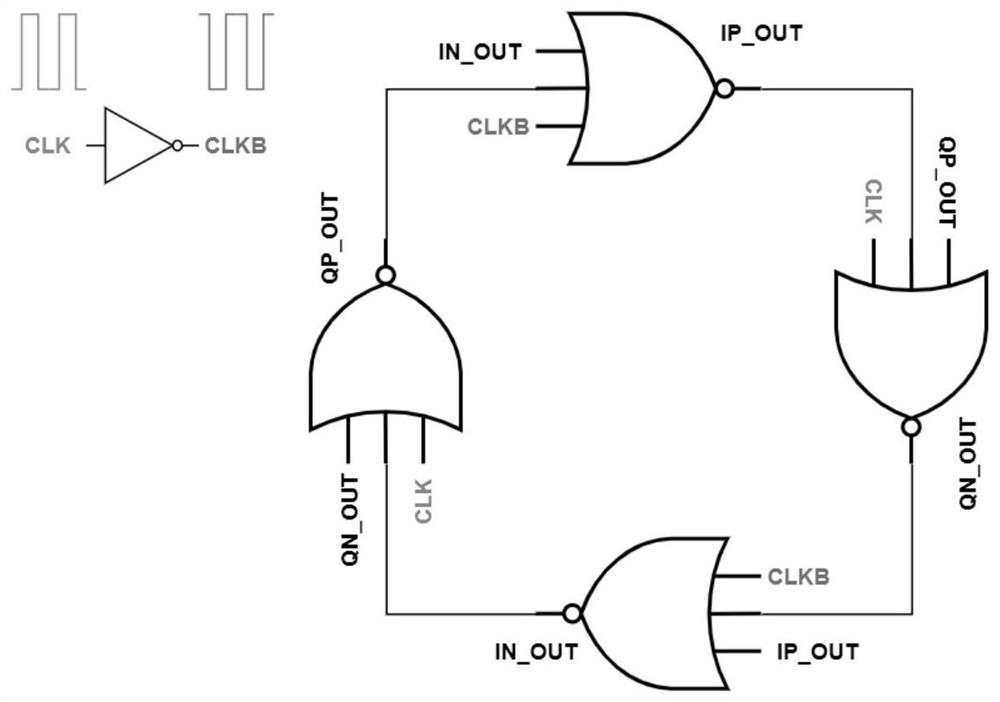

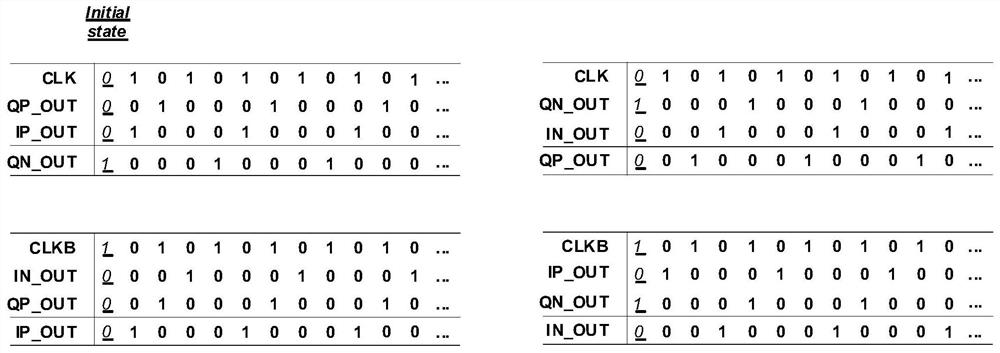

[0015] Example 1: Please refer to figure 2 , the novel frequency divider of the embodiment of the present invention includes four three-input NOR gates with the same specifications. The four three-input NOR gates are connected in a ring, and the output end of the three-input NOR gate is connected to an input end of the next adjacent three-input NOR gate. The novel frequency divider of the embodiment of the present invention utilizes an externally provided clock signal to directly generate four different phase signals whose frequency is 1 / 2 of the input clock and whose duty cycle is 25%.

[0016] The present invention uses four identical three-input NOR gates (3-input NOR gate) to be connected in a ring, and utilizes an externally provided clock signal to directly generate four kinds of frequency which are 1 / 2 of the input clock and duty ratios are all 1 / 2. 25% different phase signals. The overall circuit architecture is as figure 2 shown. Each of the four NORs in this ri...

Embodiment 2

[0022] Embodiment 2: According to De Morgan's law, this structure can also be implemented with a three-input NAND gate (3-input NAND gate). For the actual circuit structure, please refer to Figure 4 , the novel frequency divider of the embodiment of the present invention includes four three-input NAND gates with the same specifications. The four three-input NAND gates are connected in a ring, and the output end of the three-input NAND gate is connected to one input end of the next adjacent three-input NAND gate. The novel frequency divider of the embodiment of the present invention utilizes the externally provided clock signal to directly generate four different phase signals whose frequency is 1 / 2 of the input clock and whose duty ratio is 75%. Different phase signals with a duty cycle of 25% can be obtained by using a phase converter.

[0023] As an implementation manner, the three-input NAND gate includes two MOSs connected in parallel.

[0024] Such as Figure 5 As sho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com