A three-valued addition counter based on cnfet

A technology of adding counter and adding, which is applied to the pulse counter, pulse counter, counting chain pulse counter of semiconductor devices, etc., can solve the problems of increased power consumption and interconnection crosstalk.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

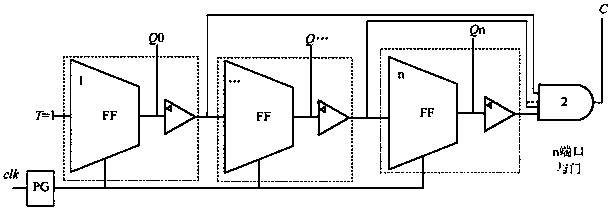

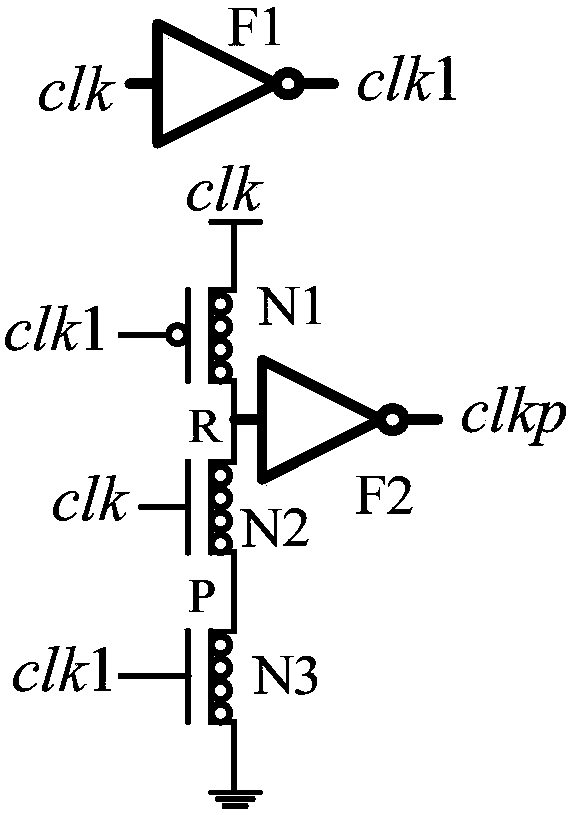

[0035] Embodiment one: if figure 1, Fig. 2 (a), Fig. 2 (b), Fig. 3 (a) and Fig. 3 (b) shown, a kind of ternary value addition counter based on CNFET, including pulse signal generator, n addition counting unit and n-input AND gate, wherein n is an integer greater than or equal to 1, the pulse signal generator has an input terminal and an output terminal, the addition and counting unit has an input terminal, an output terminal, a clock control terminal and a carry output terminal, and the n-input AND gate has n input terminals and output terminals; the output terminals of the pulse signal generator are respectively connected to the clock control terminals of the n addition and counting units, and the carry terminals of the n addition and counting units are in one-to-one correspondence with the n input terminals of the n input AND gate connection, the output terminal of the n-input AND gate is the carry output terminal of the three-value addition counter, the input terminal of th...

Embodiment 2

[0036] Embodiment two: if figure 1, Fig. 2 (a), Fig. 2 (b), Fig. 3 (a) and Fig. 3 (b) shown, a kind of ternary value addition counter based on CNFET, including pulse signal generator, n addition counting unit and n-input AND gate, wherein n is an integer greater than or equal to 1, the pulse signal generator has an input terminal and an output terminal, the addition and counting unit has an input terminal, an output terminal, a clock control terminal and a carry output terminal, and the n-input AND gate has n input terminals and output terminals; the output terminals of the pulse signal generator are respectively connected to the clock control terminals of the n addition and counting units, and the carry terminals of the n addition and counting units are in one-to-one correspondence with the n input terminals of the n input AND gate connection, the output terminal of the n-input AND gate is the carry output terminal of the three-value addition counter, the input terminal of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com