Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

68 results about "NAND logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Because the NAND function has functional completeness all logic systems can be converted into NAND gates – the mathematical proof for this was published by Henry M. Sheffer in 1913 in the Transactions of the American Mathematical Society (Sheffer 1913). This is also true for NOR gates. In principle, any combinatorial logic function can be realized with enough NAND gates.

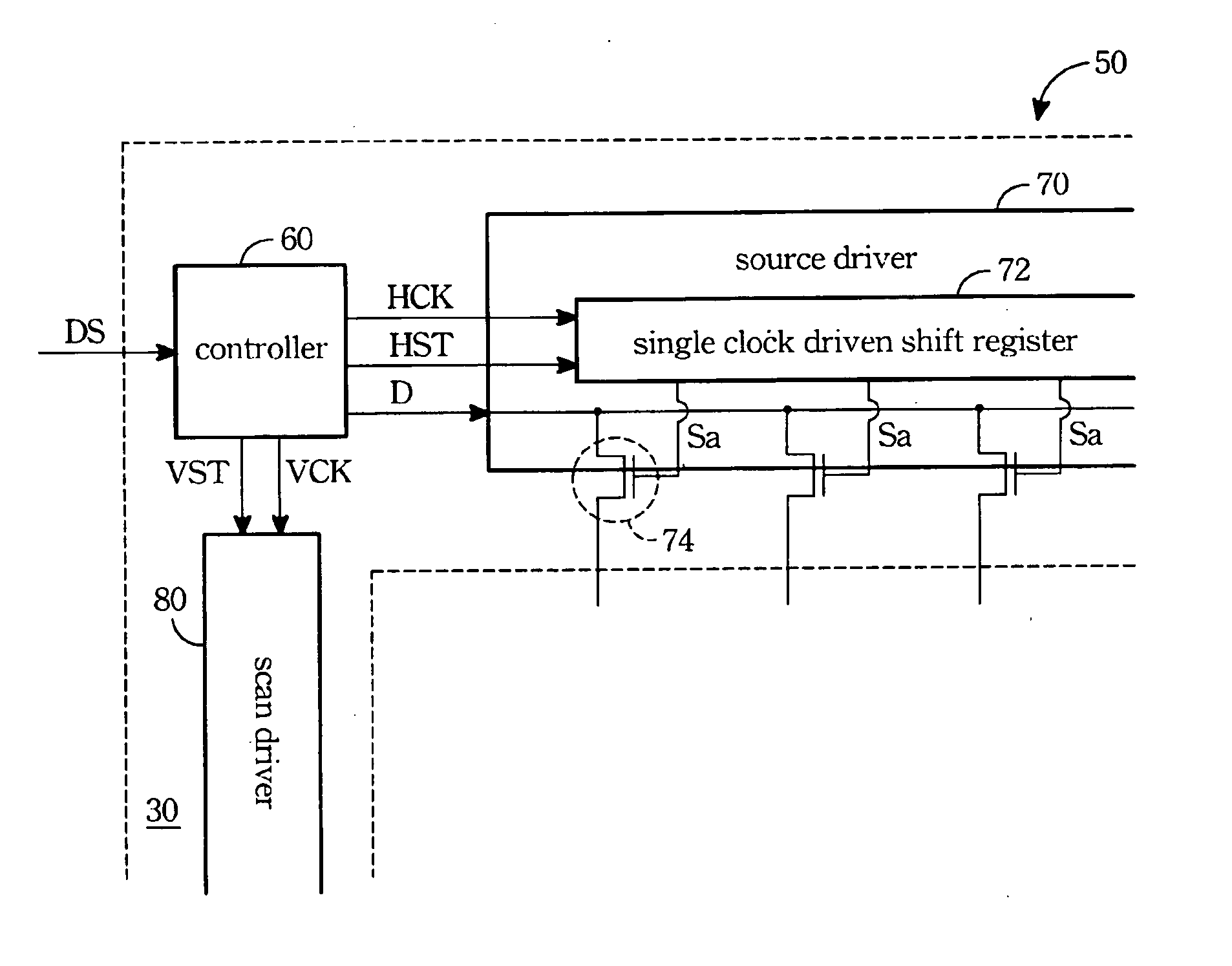

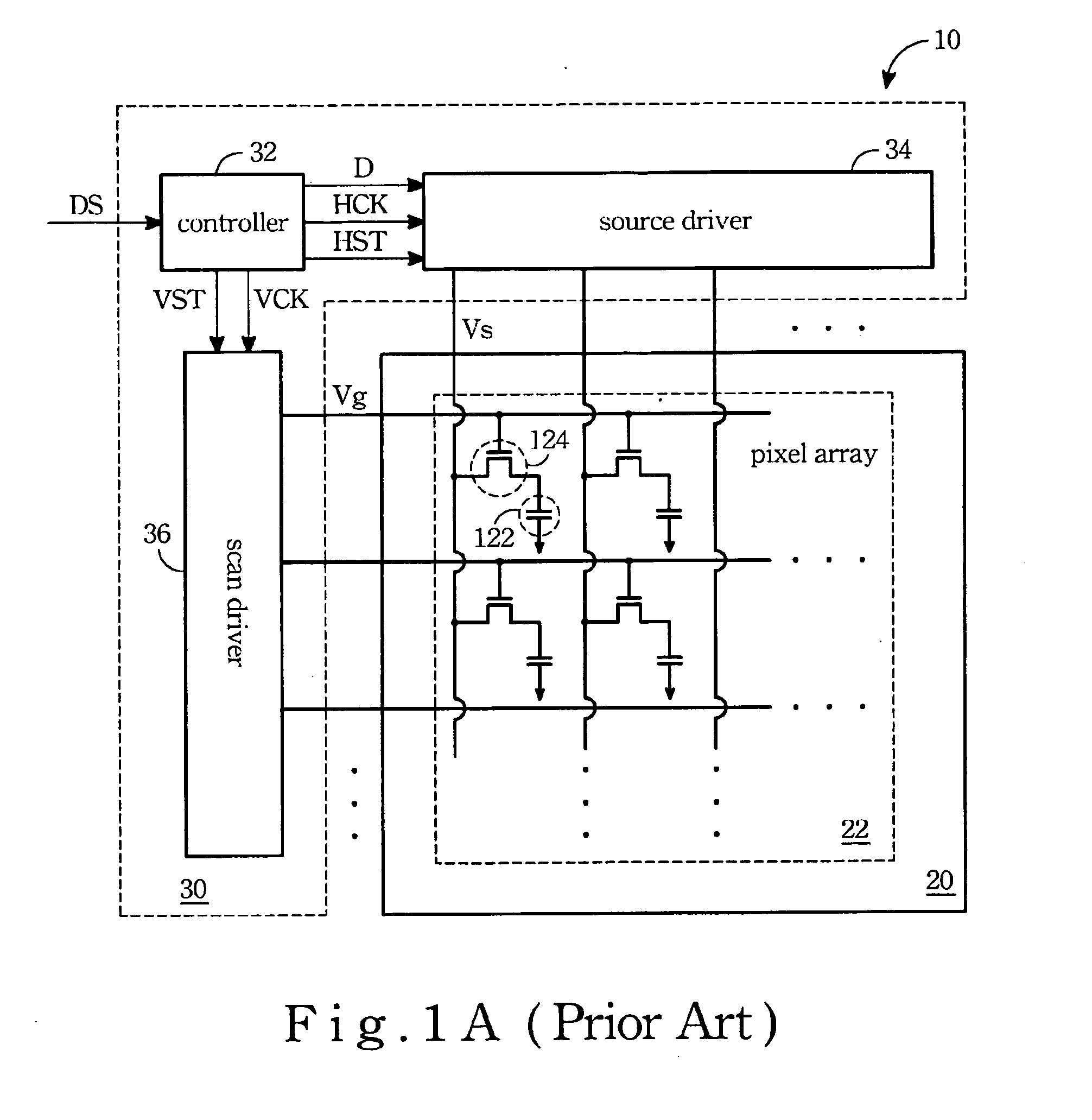

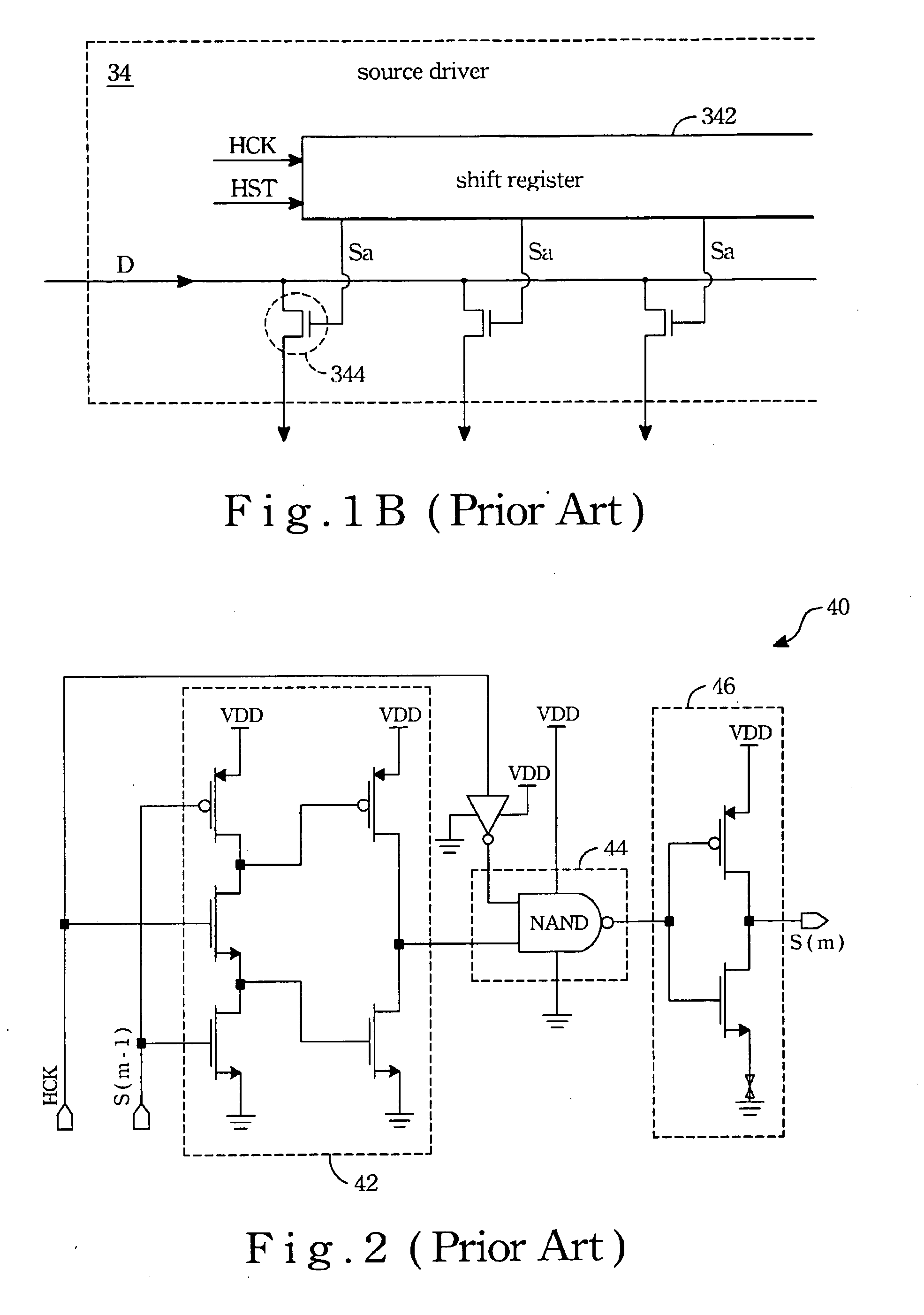

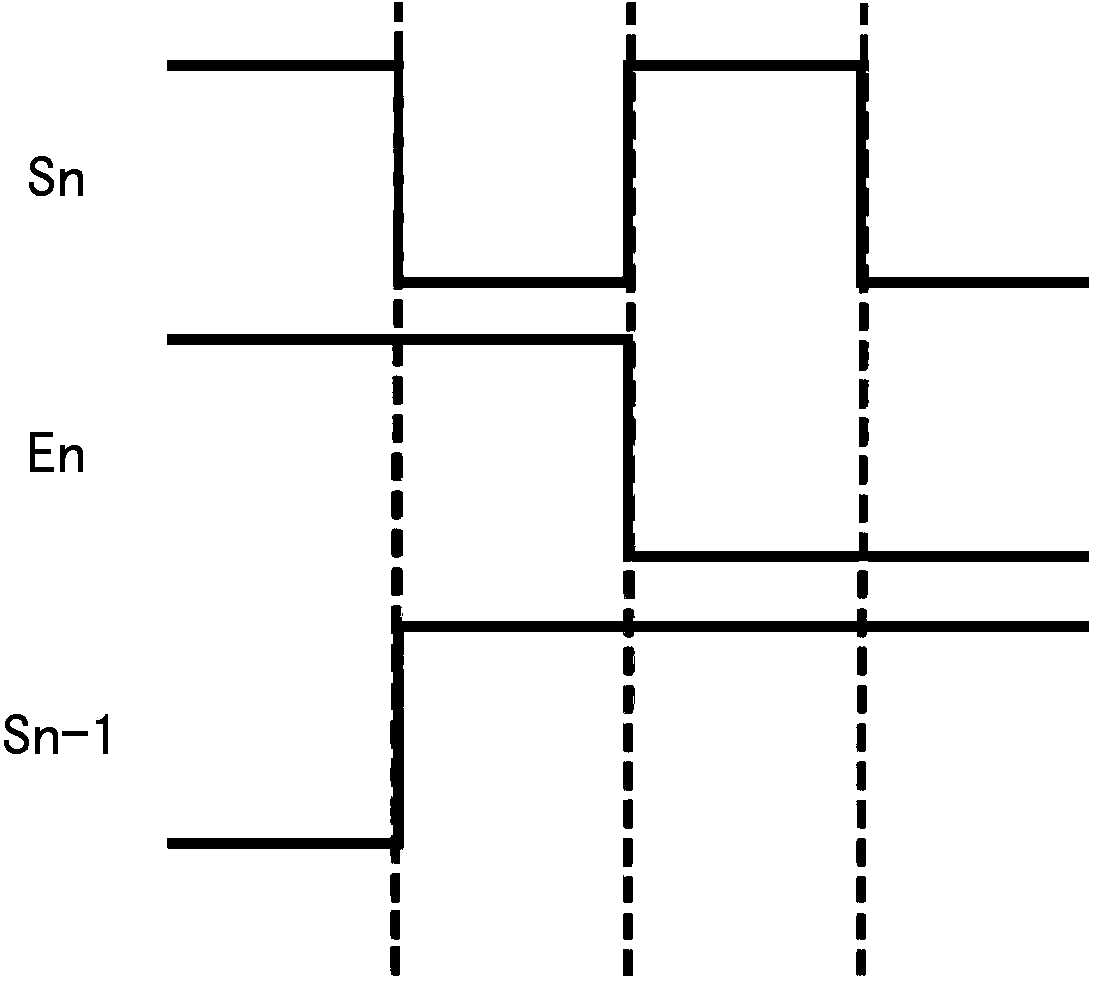

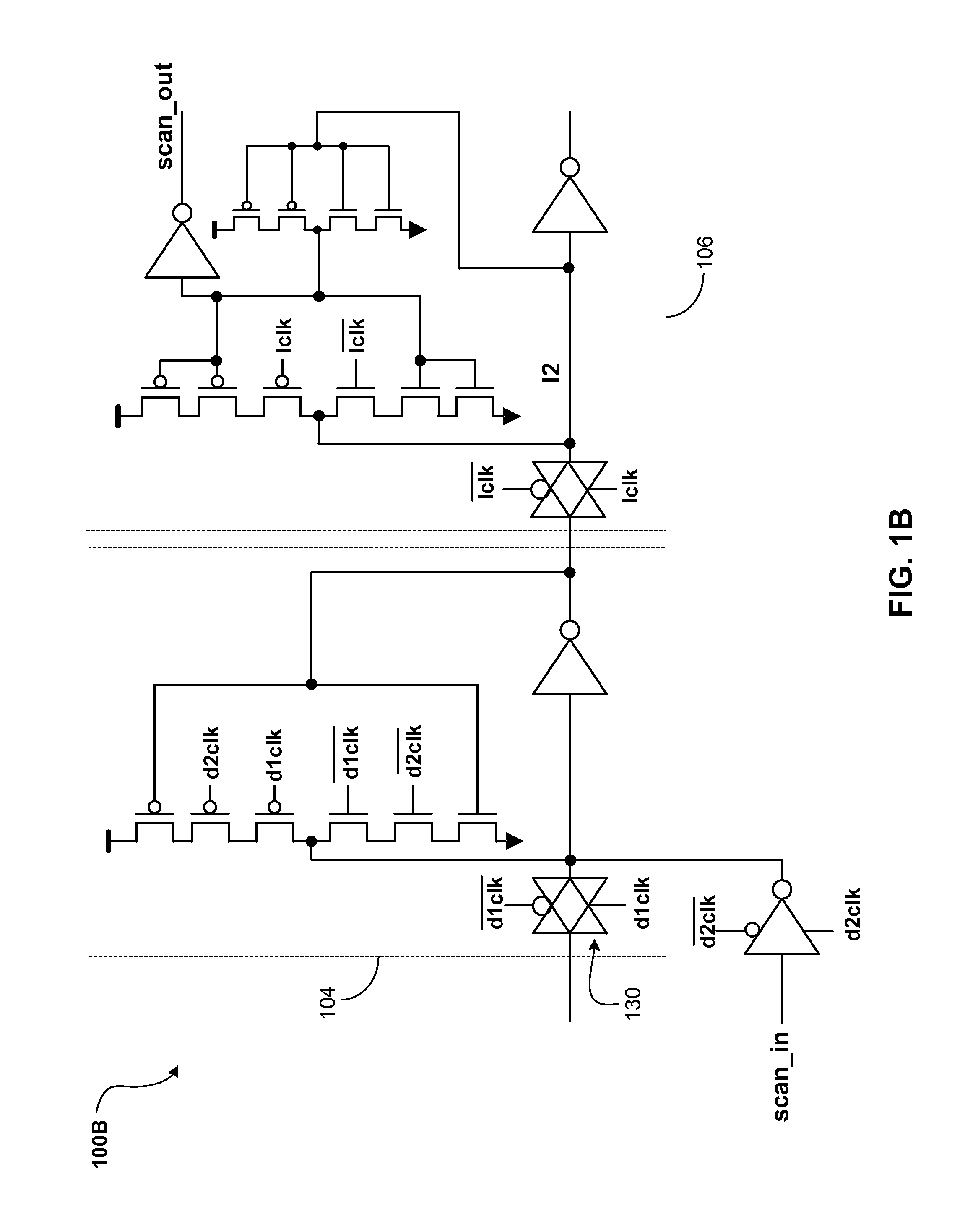

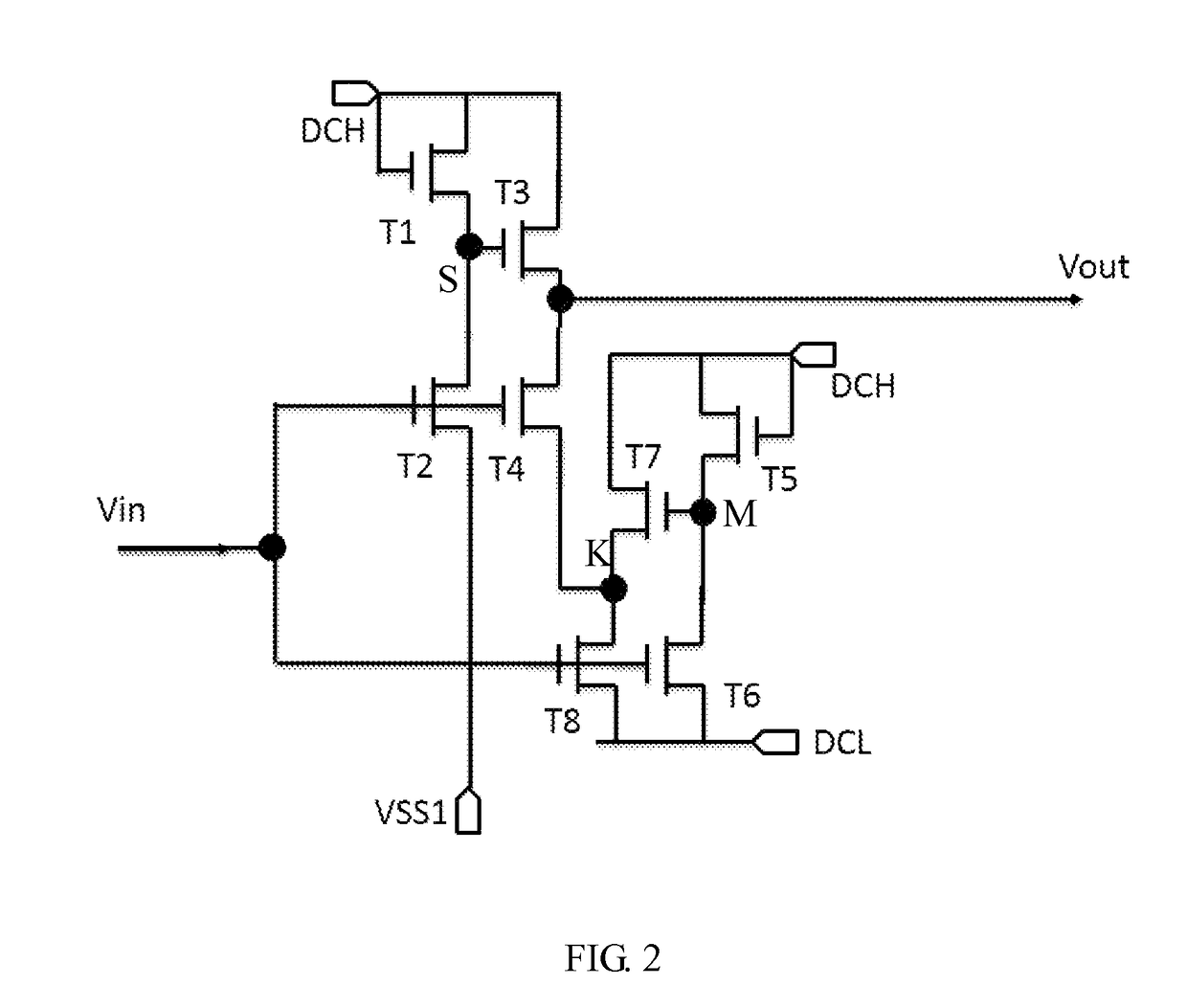

Single clock driven shift register and driving method for same

ActiveUS20060017685A1Affect qualityCathode-ray tube indicatorsDigital storageShift registerNAND logic

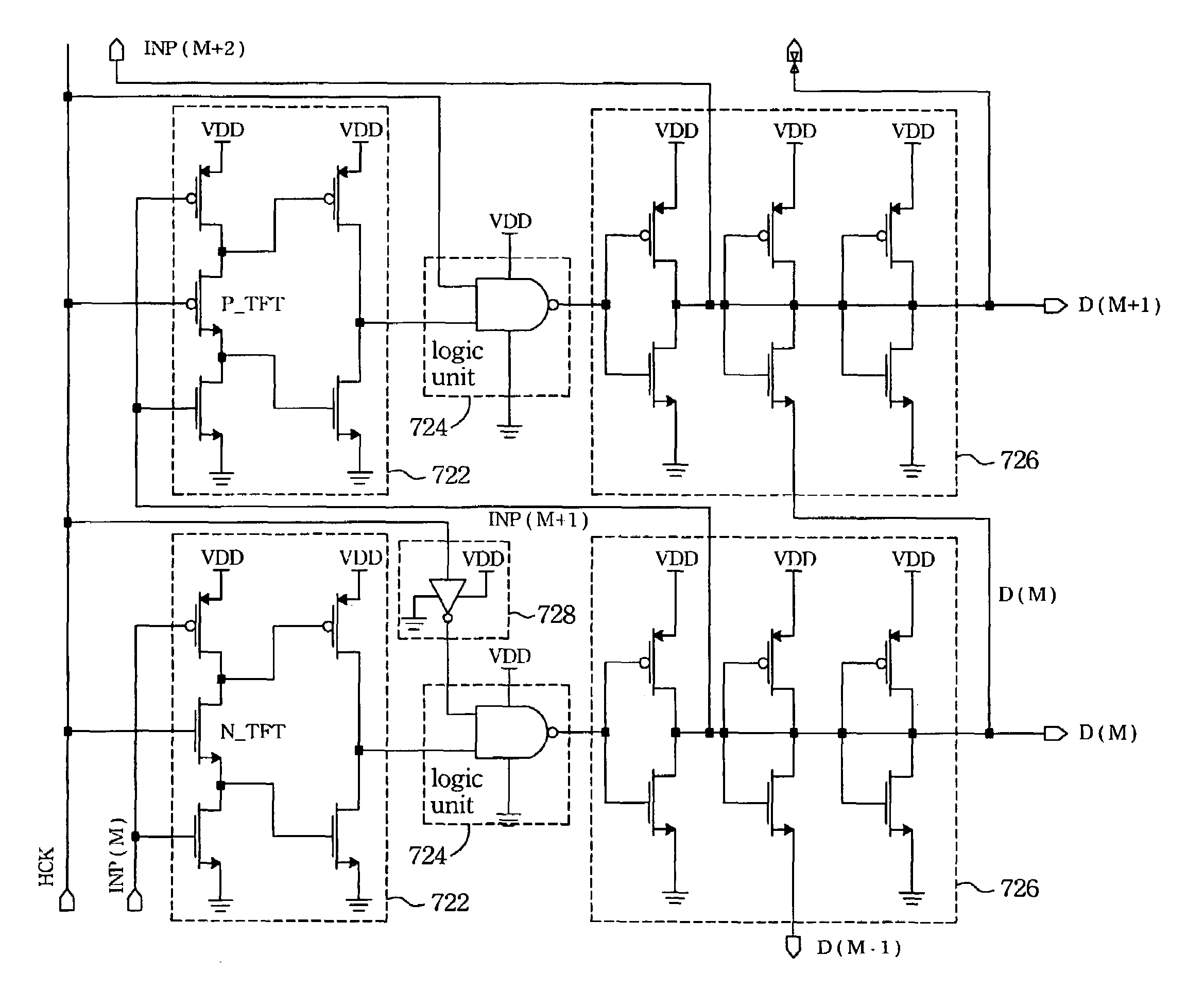

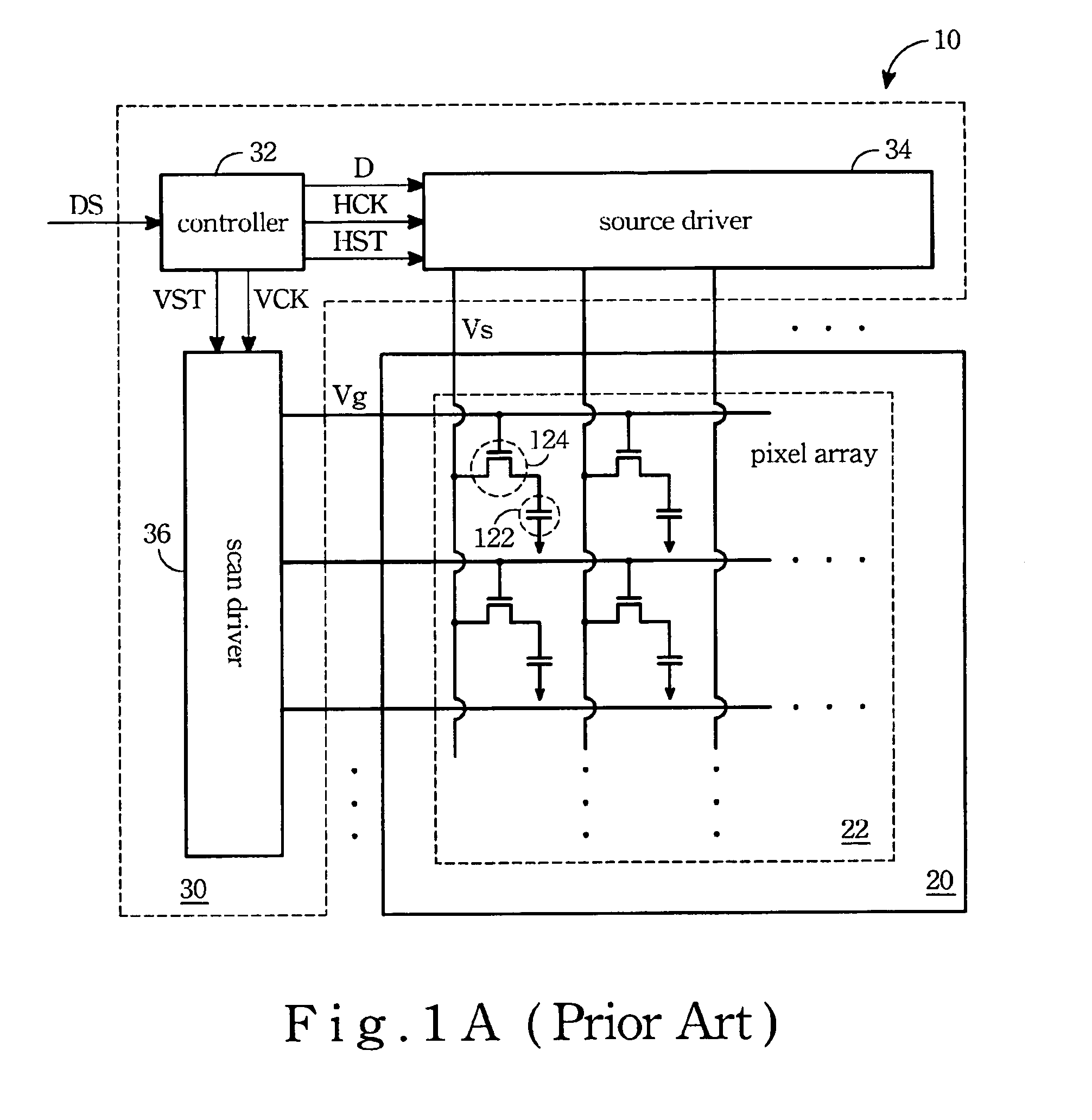

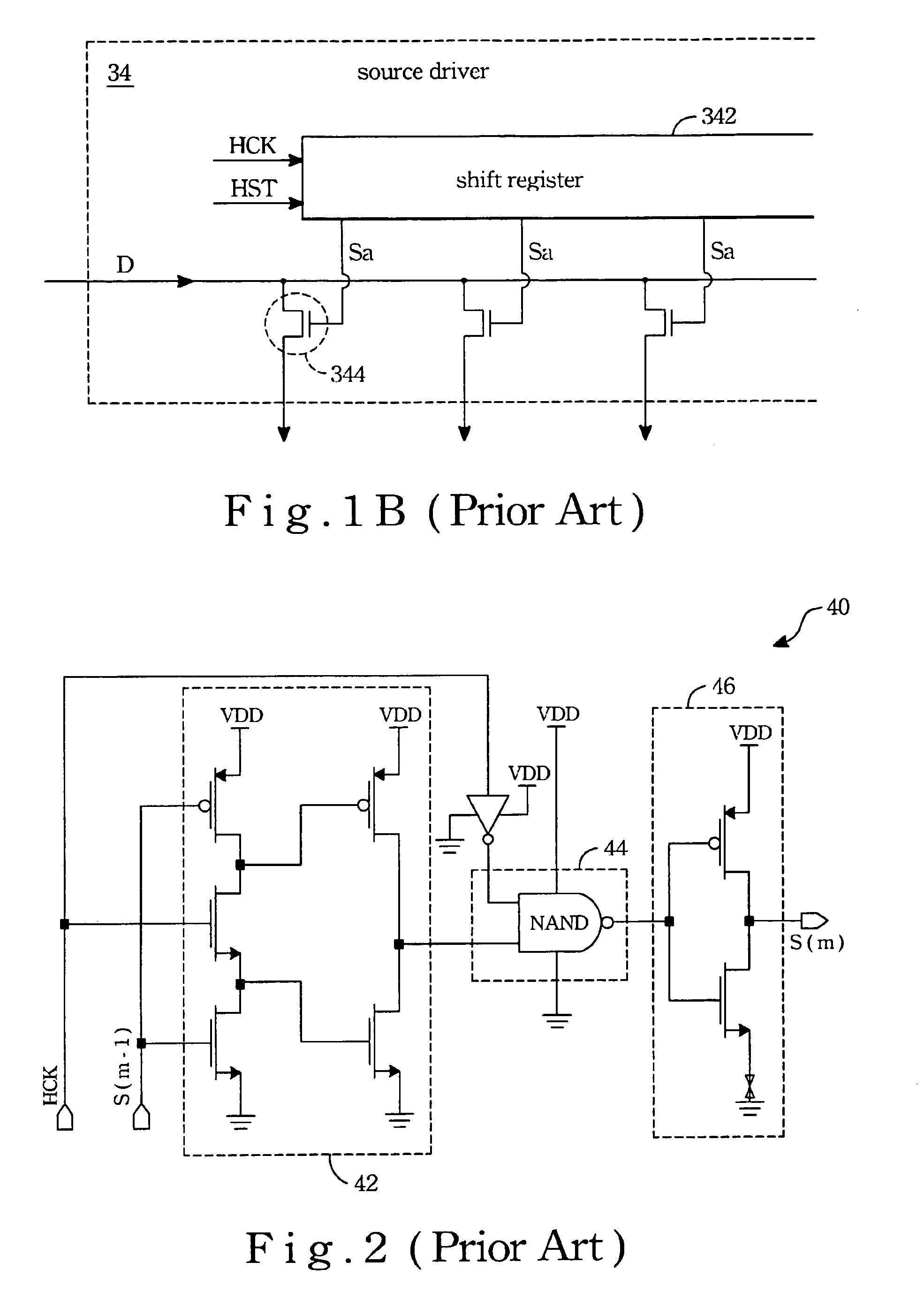

A single clock driven shift register comprising multiple stages is provided. The (M)th stage comprises a latch unit, a logic unit, and a non-overlap buffer. The latch unit latches an input signal from the (M−1)th stage according to a clock signal. The logic unit connecting to an output terminal of the latch unit deals with an output signal of the latch unit and the clock signal with an NAND logic calculation. The non-overlap buffer connecting to the output terminal of the logic unit comprises at least three inverters connected in a serial, and an output signal of the first inverter coupled to the output terminal of the logic unit is input to an latch unit of the (M+1)th stage. Meanwhile, an output signal of the non-overlap buffer of the (M−1)th stage is input to the non-overlap buffer or the logic unit to delay the output signal of the non-overlap buffer.

Owner:AU OPTRONICS CORP

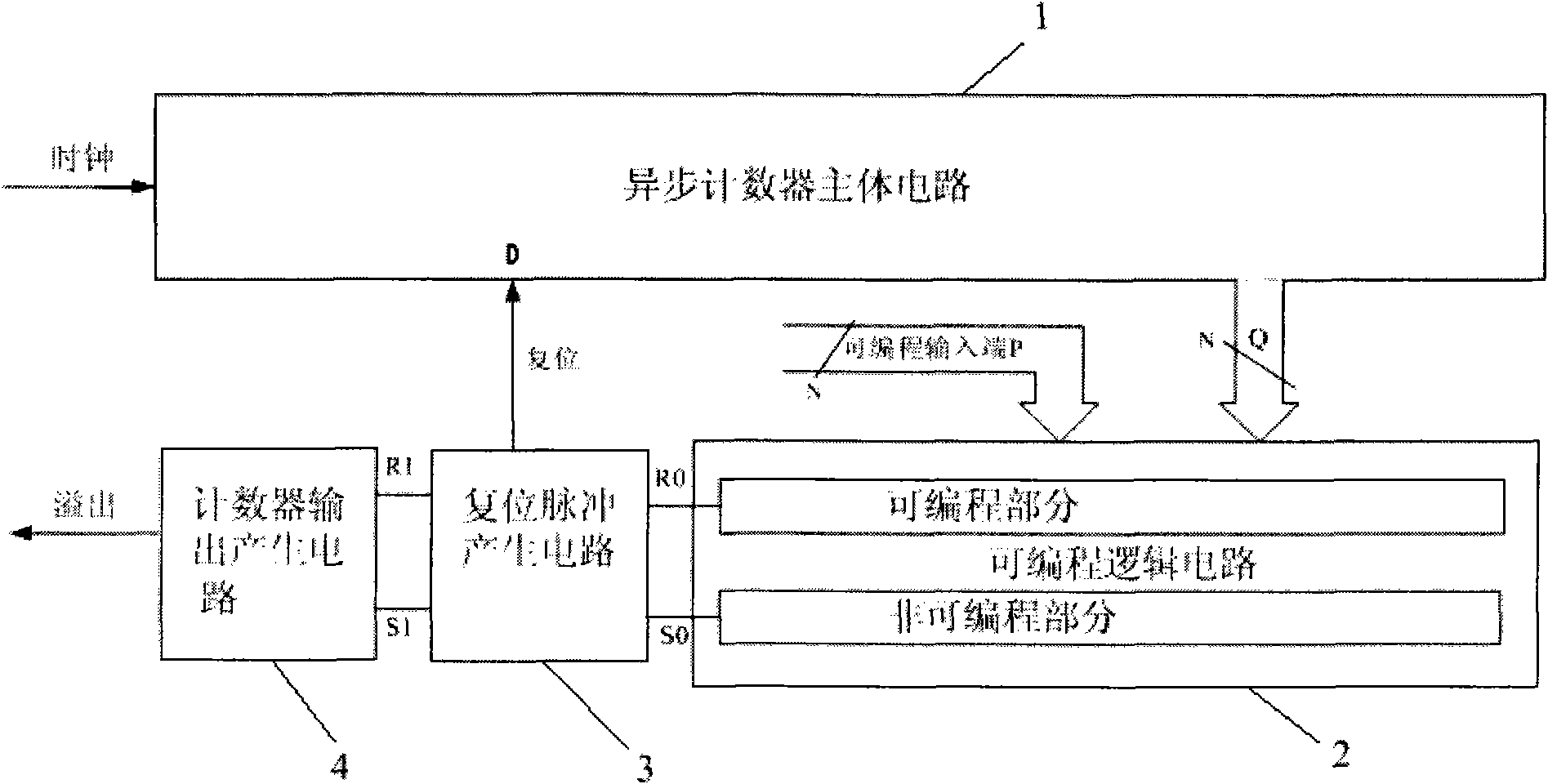

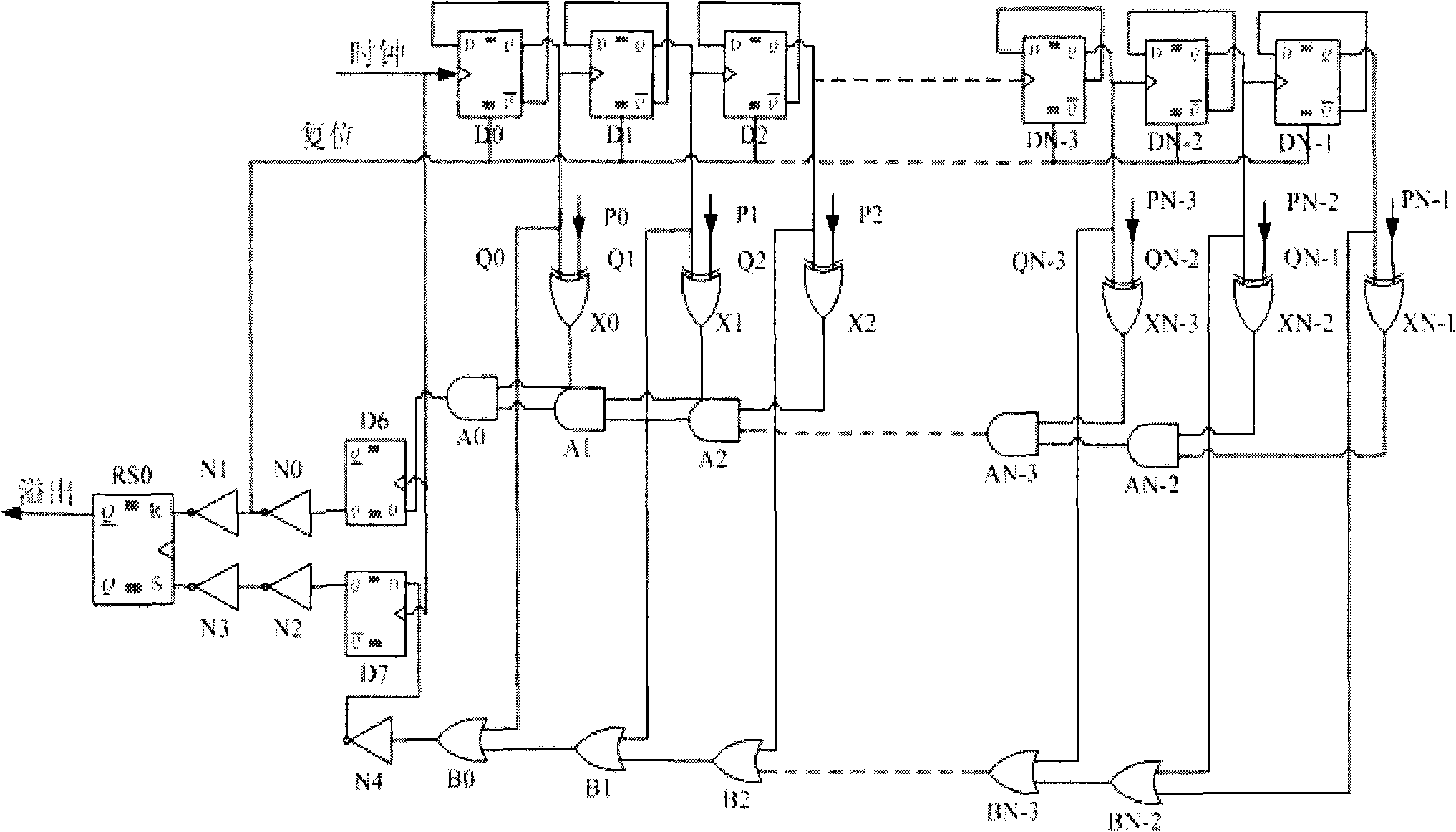

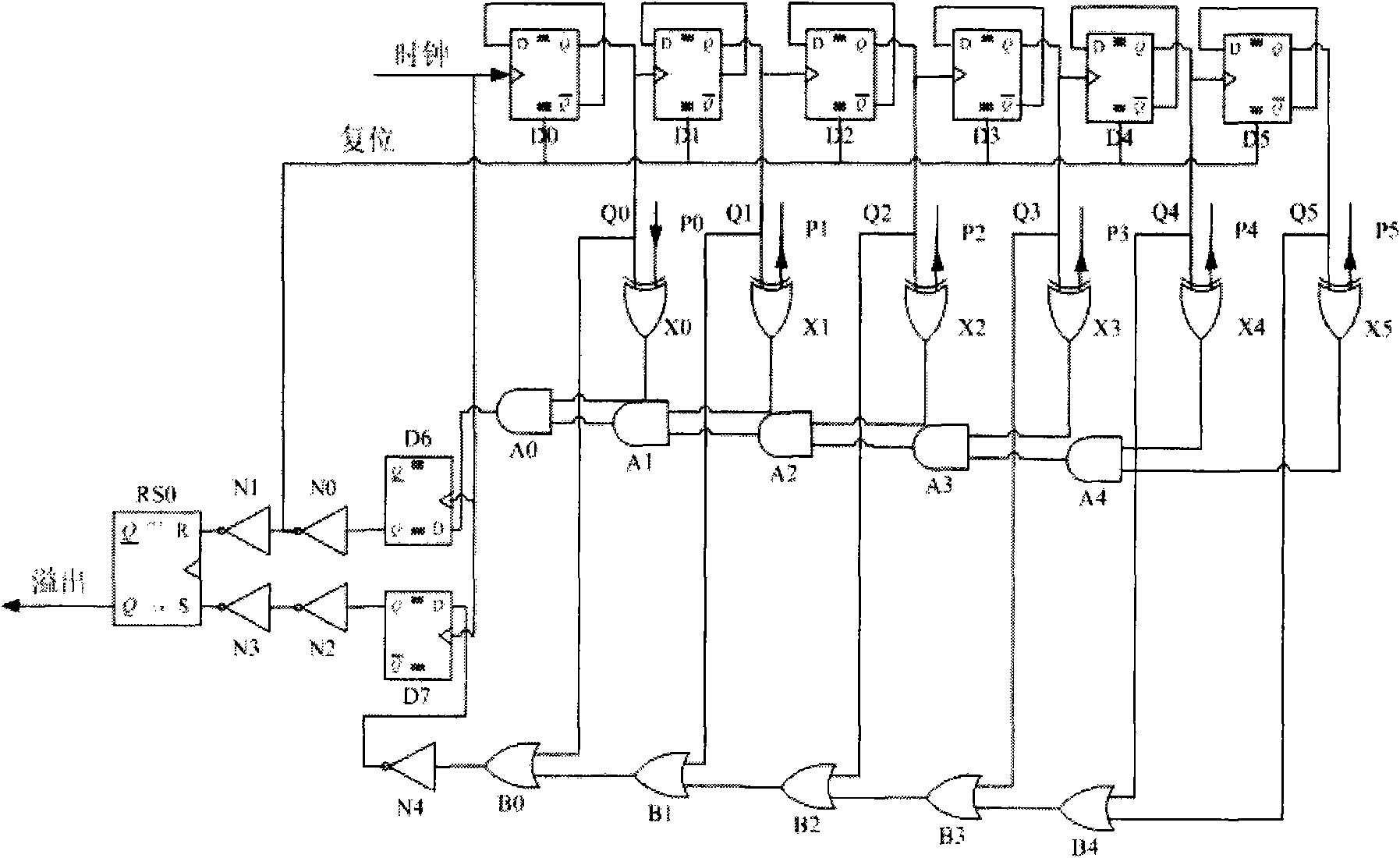

Glitch-eliminating programmable counter

InactiveCN101944907ANovel structureStrong elimination abilityCounting chain asynchronous pulse countersNAND logicNOR logic

The invention discloses a glitch-eliminating programmable counter, which comprises an asynchronous counter main body circuit, a programmable logic circuit, an reset pulse generation circuit and a counter output generation circuit, wherein the asynchronous counter main body circuit is provided with N-bit frequency division output end (Q0...QN-1), a programmable input end P and a trigger D; the programmable logic circuit is divided into a programmable part and a non-programmable part, the programmable part adopts a NAND logic, while the non-programmable part adopts a NOR logic; the reset pulse generation circuit is provided with two input ends R0 and S0 and three output ends; and the counter output generation circuit is provided with two input ends R1 and S1 and one outlet end. The glitch-eliminating programmable counter has the characteristics of simple design, novel circuit structure, high glitch-eliminating capability, easy realization and the like.

Owner:SOUTHEAST UNIV

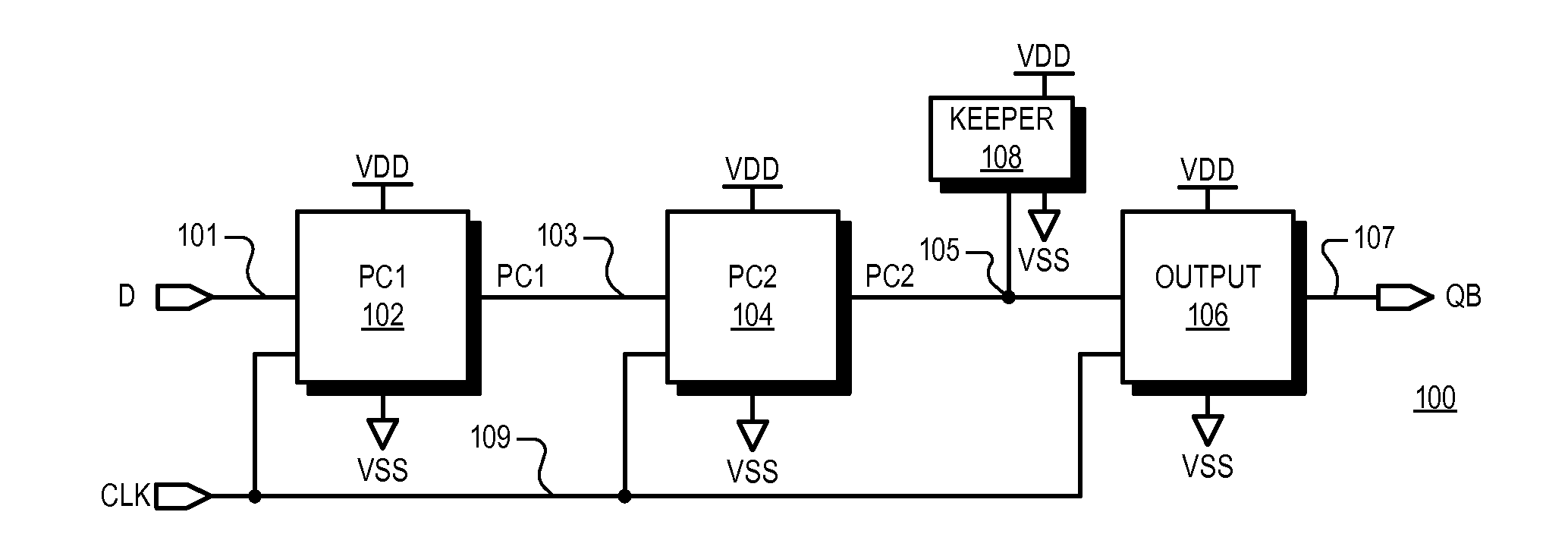

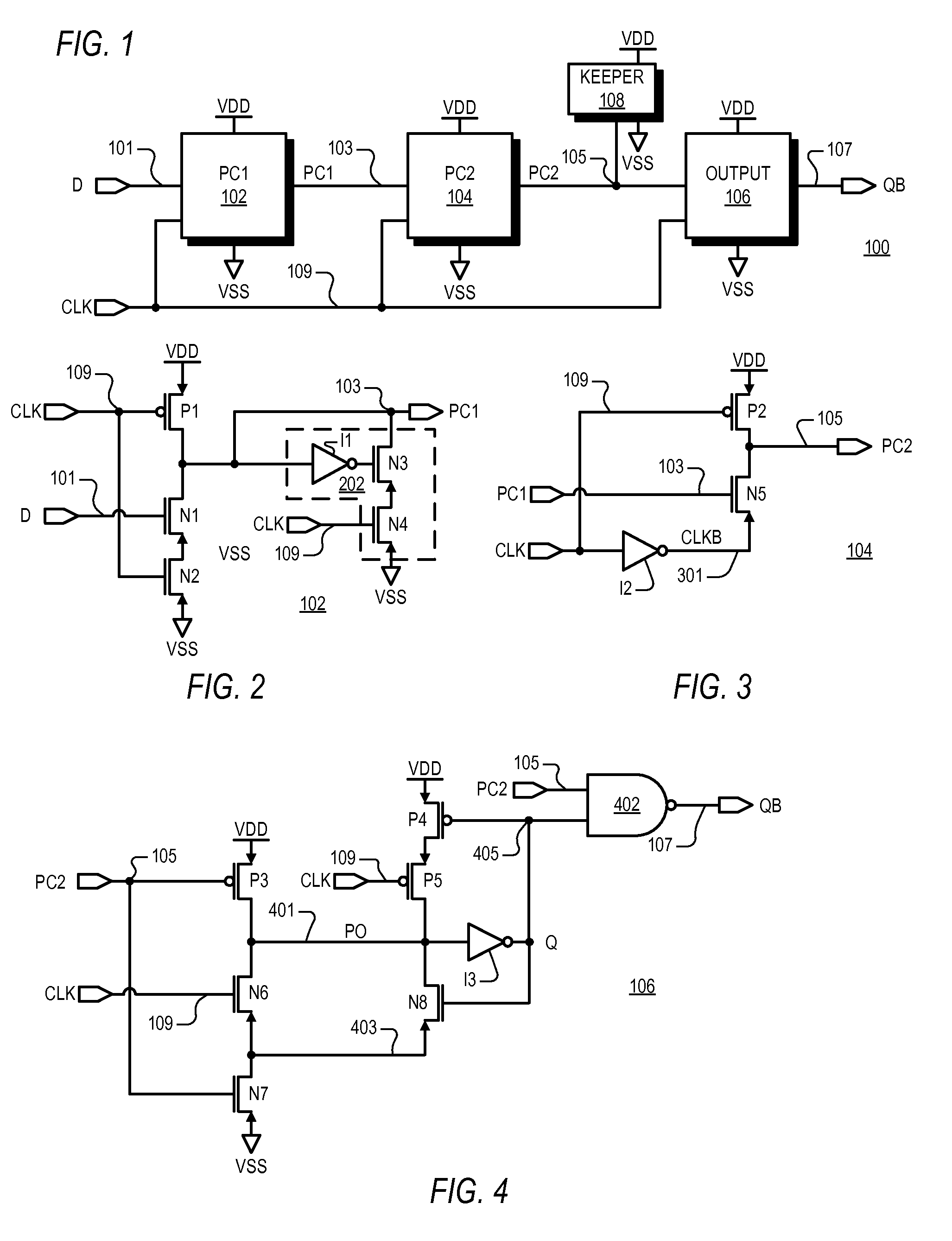

Fast dynamic register

A fast dynamic register circuit including first and second precharge circuits, a keeper circuit and an output circuit. The first and second precharge circuits each precharge a corresponding one of a pair of precharge nodes and cooperate to minimize setup and hold times. If an input data node is low when the clock goes high, the first precharge node remains high causing the second precharge node to be discharged. Otherwise if the input node is high, the first precharge node is discharged and the second remains charged. Once either precharge node is discharged, the output state of the register remains fixed until the next rising clock edge independent of changes of the input data node. The fast dynamic register may be implemented with multiple inputs to perform common logic operations, such as OR, NOR, AND and NAND logic operations.

Owner:VIA TECH INC

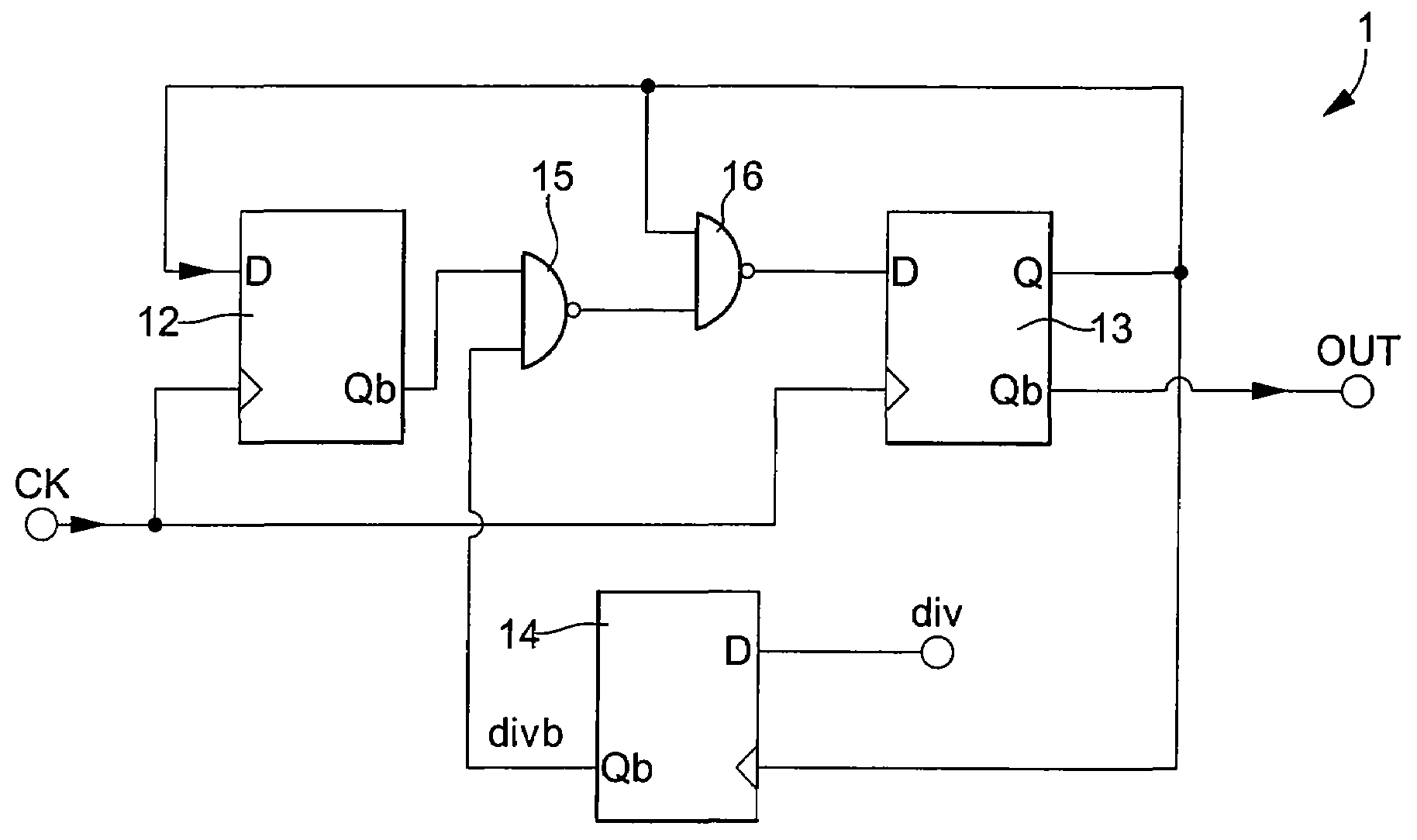

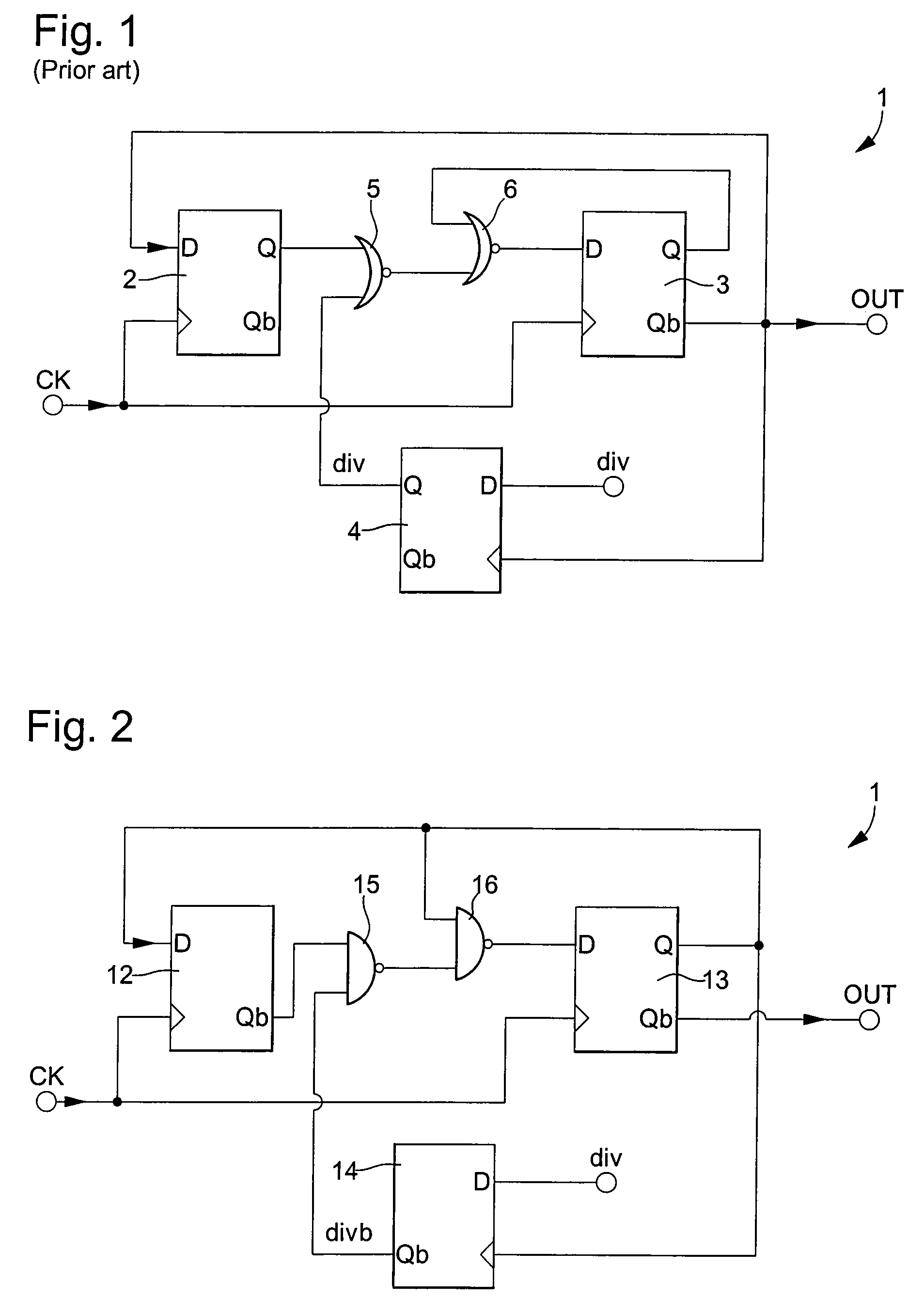

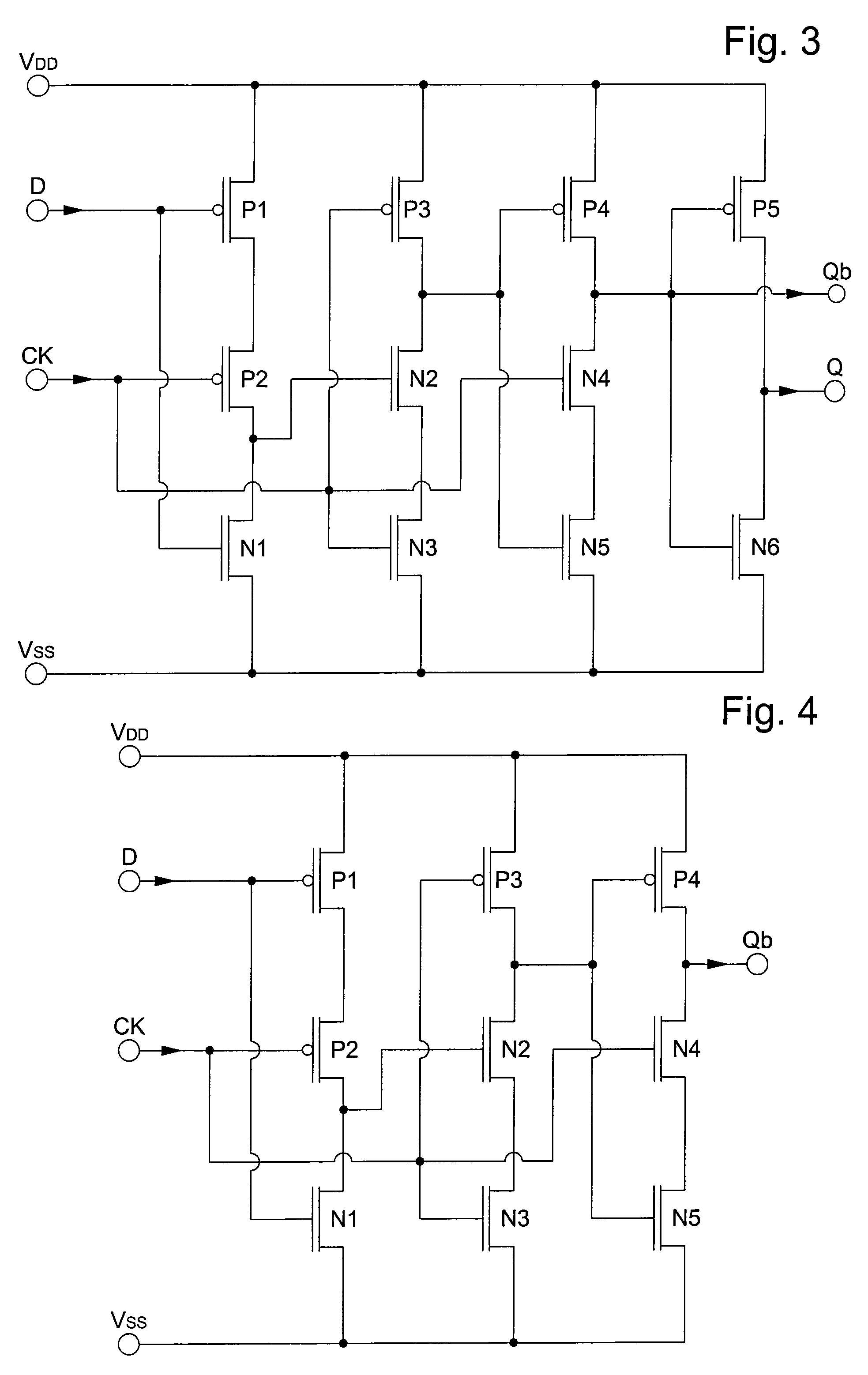

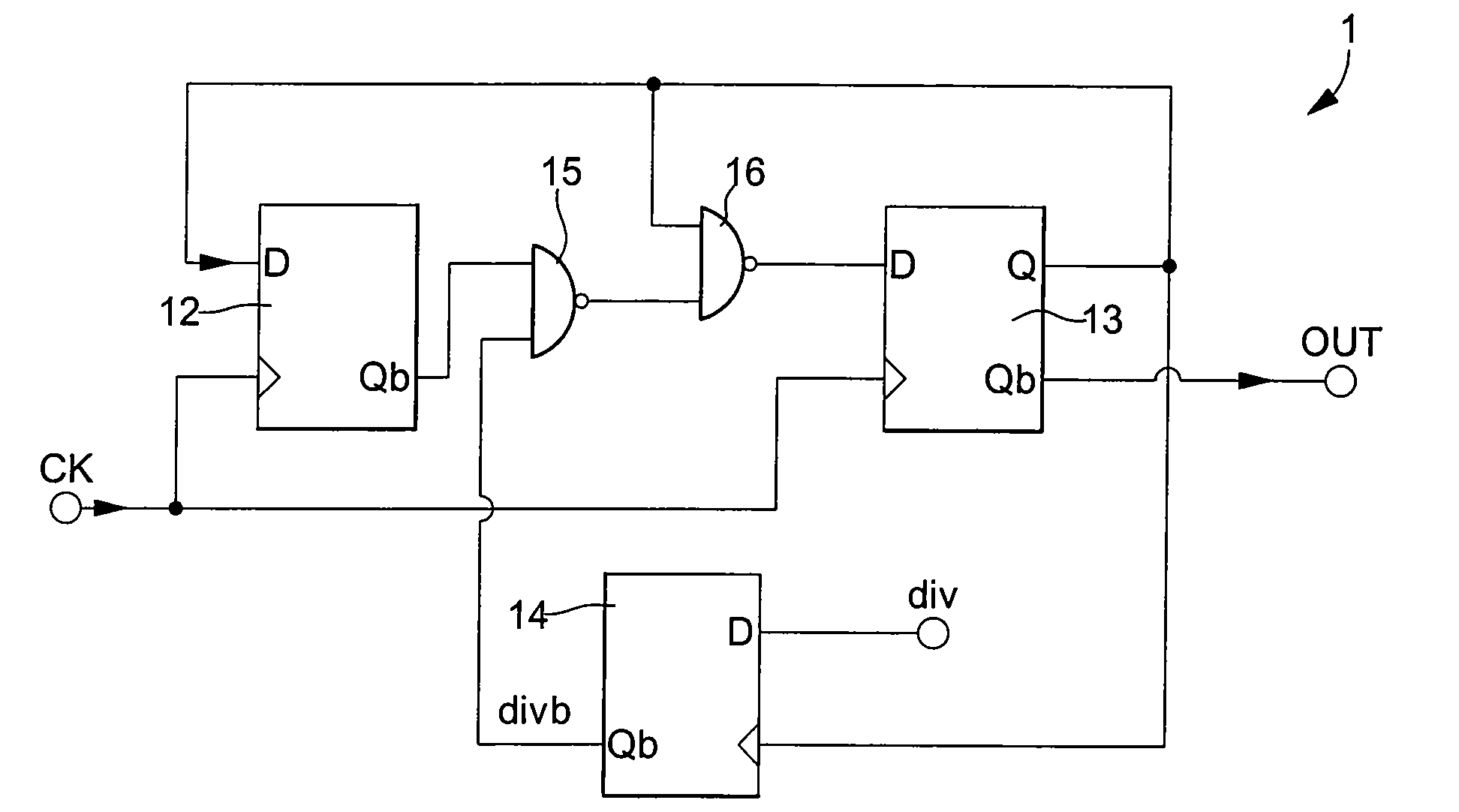

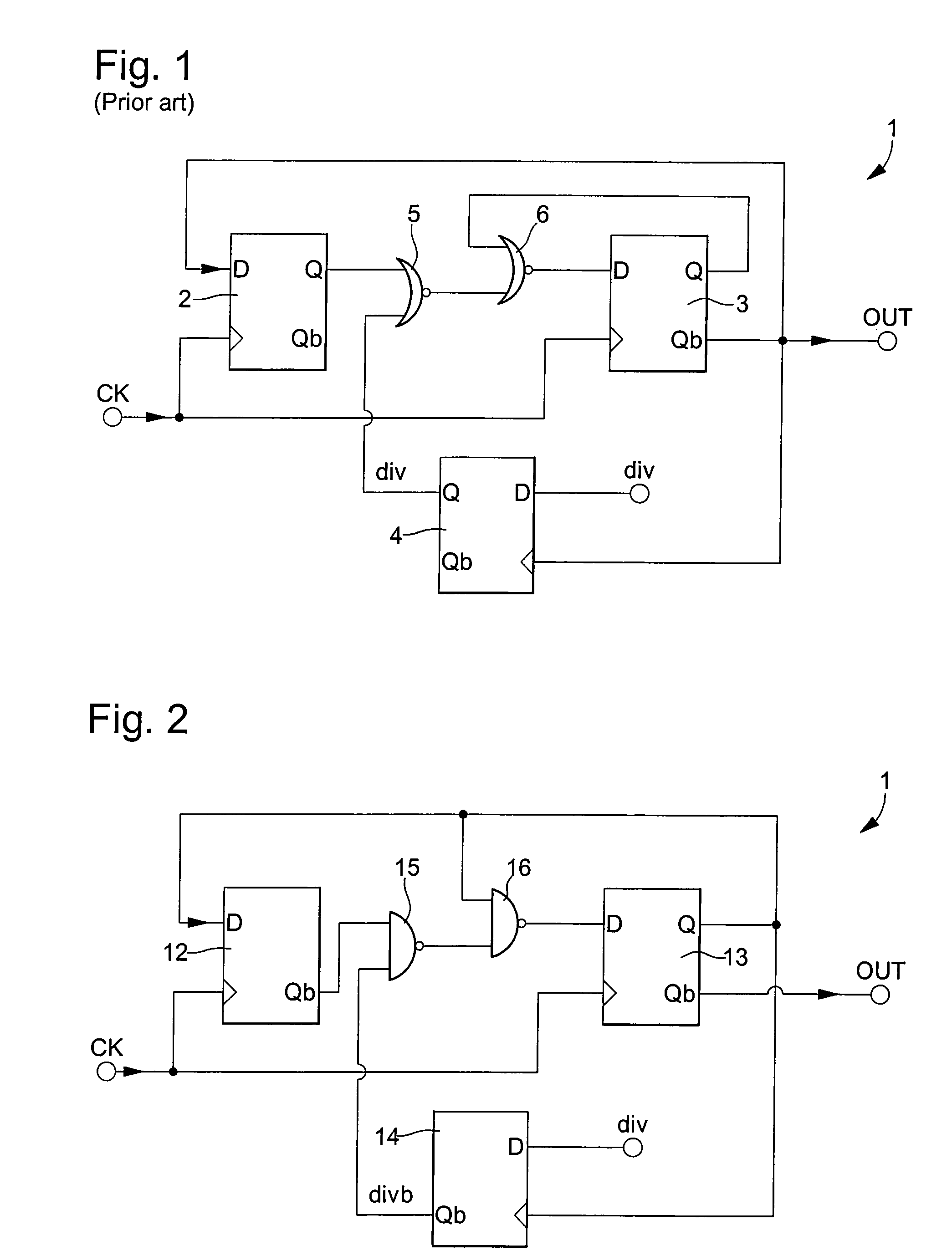

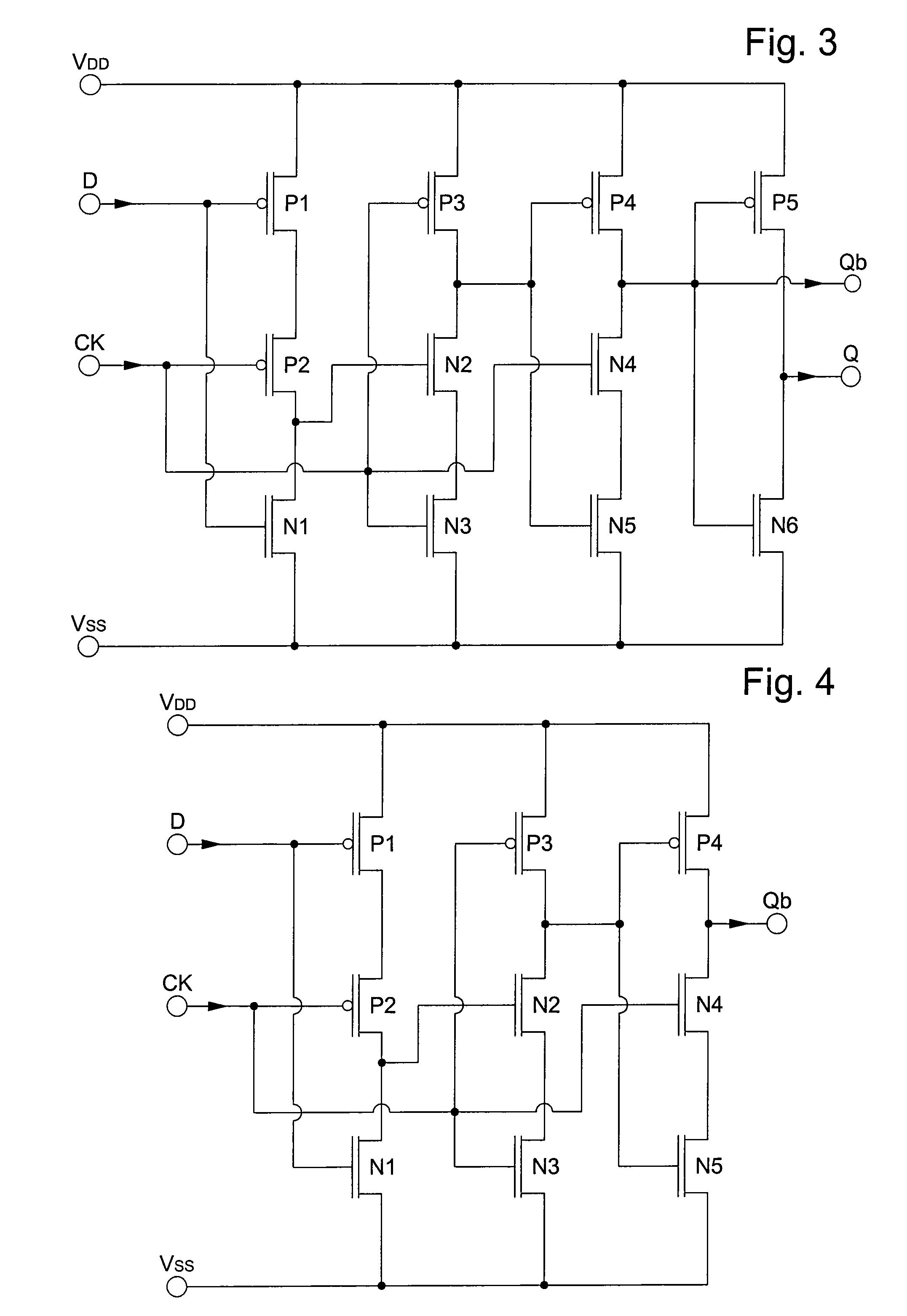

Dual-modulus prescaler circuit operating at a very high frequency

ActiveUS7719326B2Simple structureHigh frequencyPulse automatic controlCounting chain synchronous pulse countersNegative feedbackNAND logic

The dual-modulus prescaler circuit (1) is devised to operate at a very high frequency. This circuit includes an assembly formed of two dynamic D-type flip flops (12, 13), and two NAND logic gates (15, 16) arranged in negative feedback between the two flip flops. The two flip flops are clocked by an input clock signal (CK) to supply a divided output signal (OUT) whose frequency matches the input clock frequency divided by 2 or by 3 as a function of a division mode selection signal (divb) applied to the input of the first NAND logic gate (15). One non-inverted output of the second flip flop is connected to one input of the first flip flop (12). The first dynamic flip flop includes three active branches and supplies a single inverted output signal. A third flip flop (14) with three active branches receives an inverted mode selection signal (div) at input in order to supply the mode selection signal to the inverted output thereof, clocked by the non-inverted output signal of the second flip flop.

Owner:THE SWATCH GRP RES & DEVELONMENT LTD

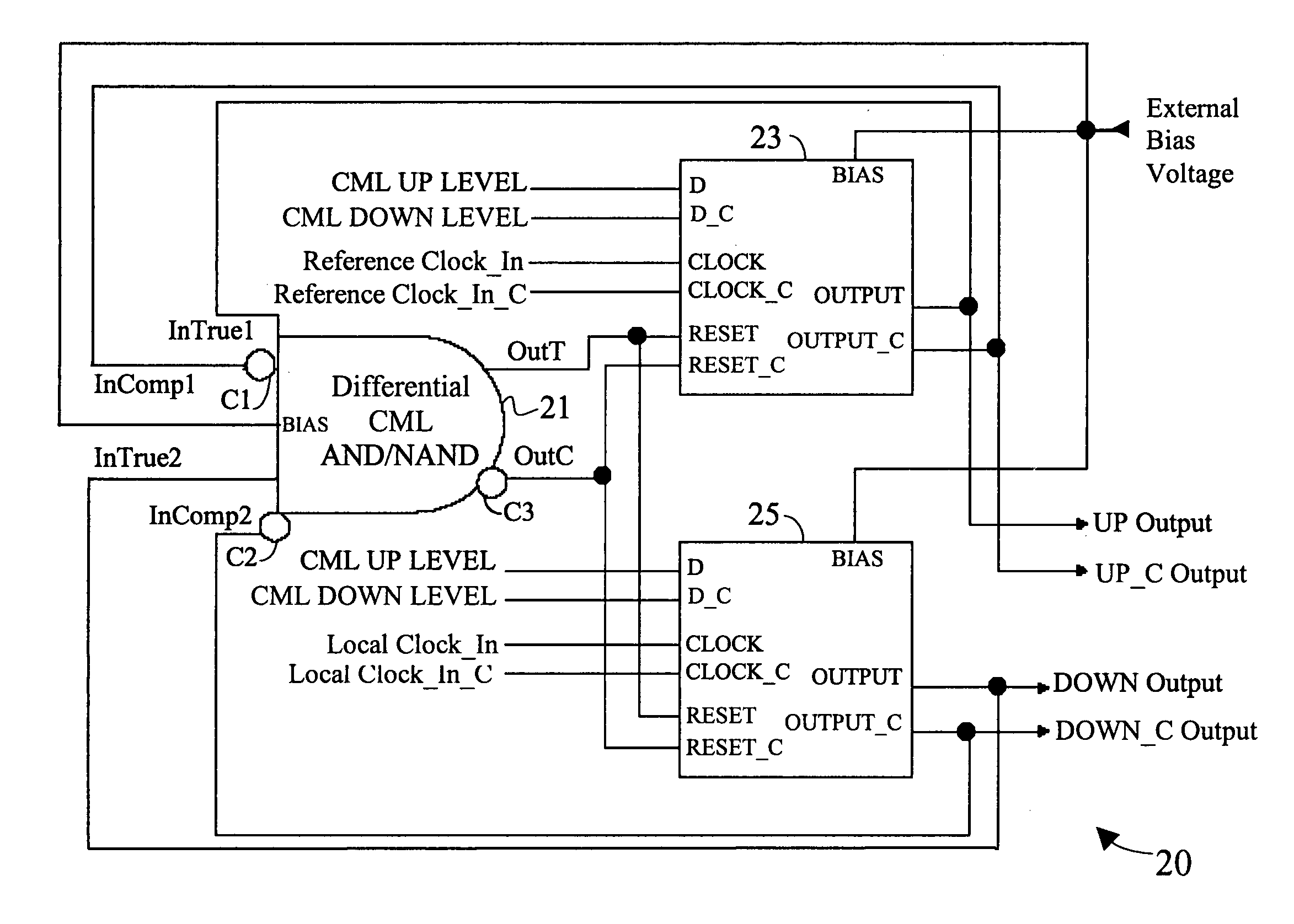

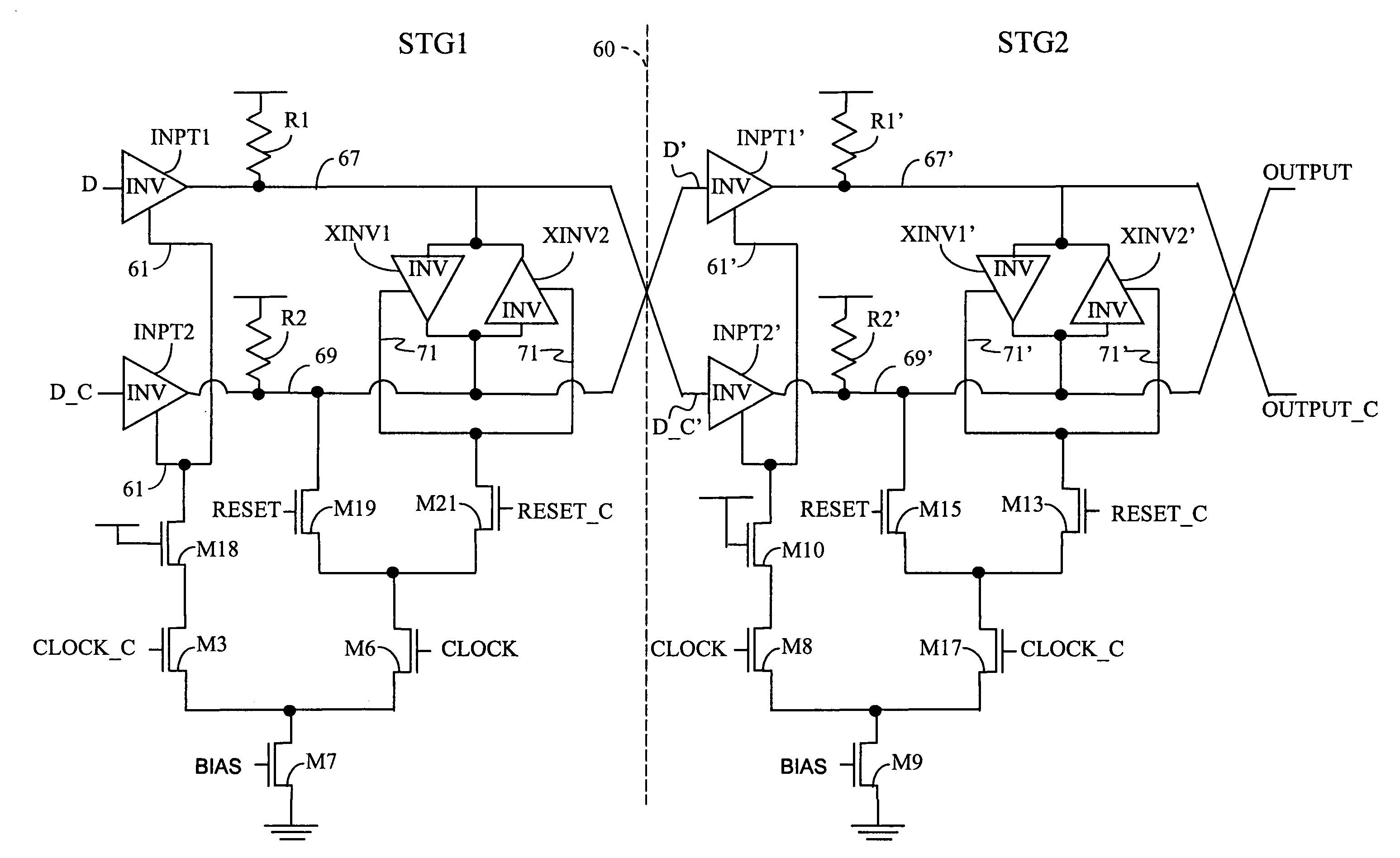

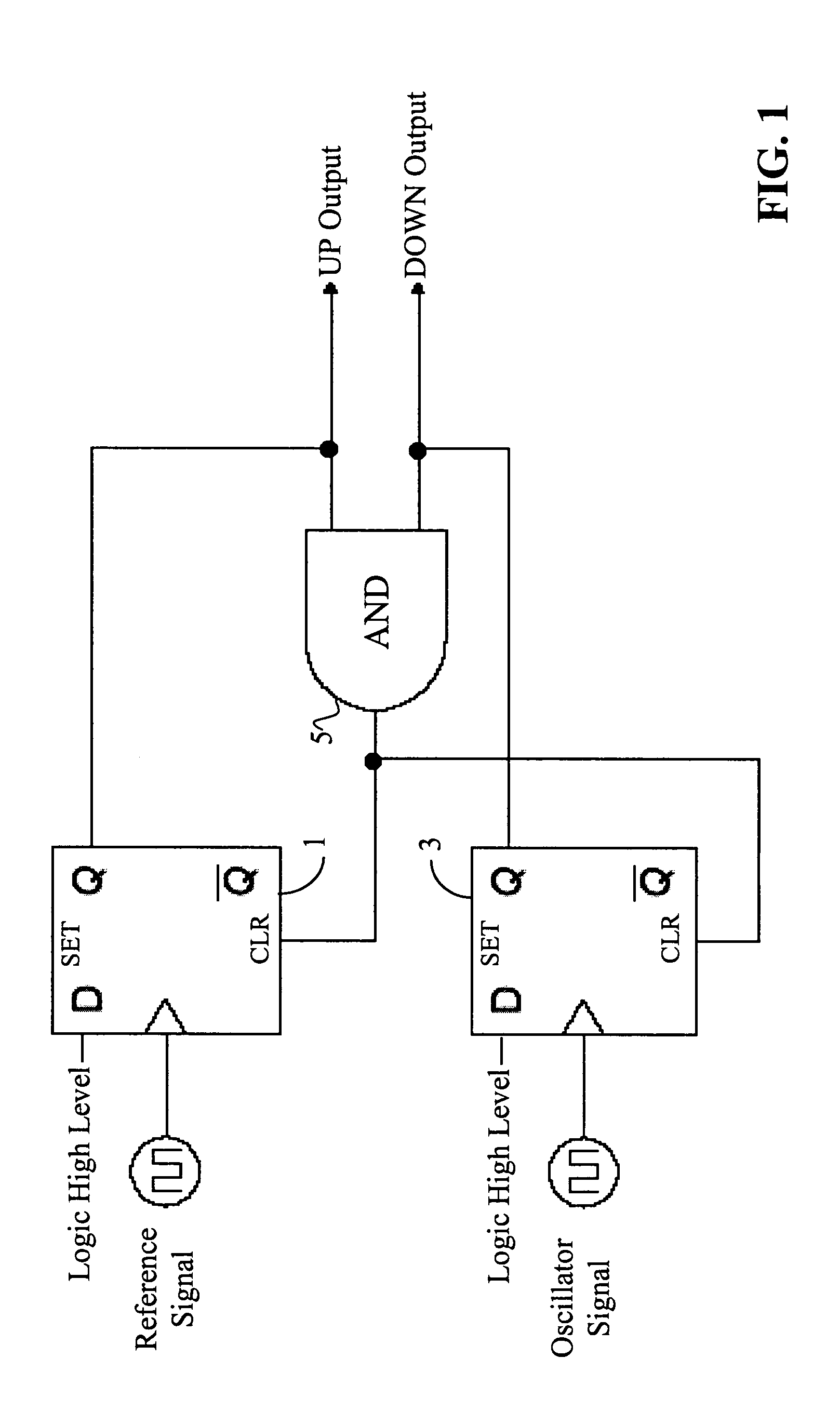

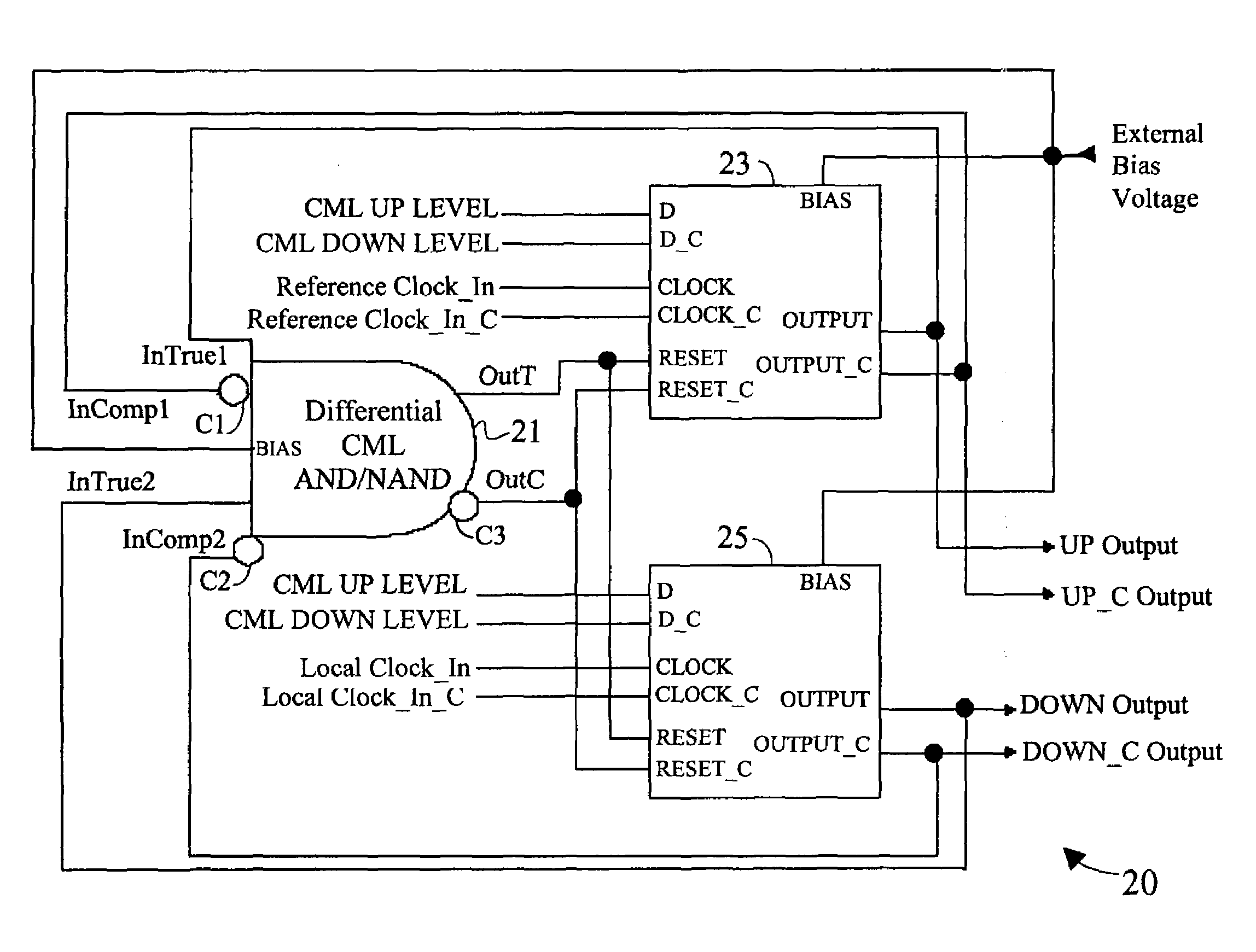

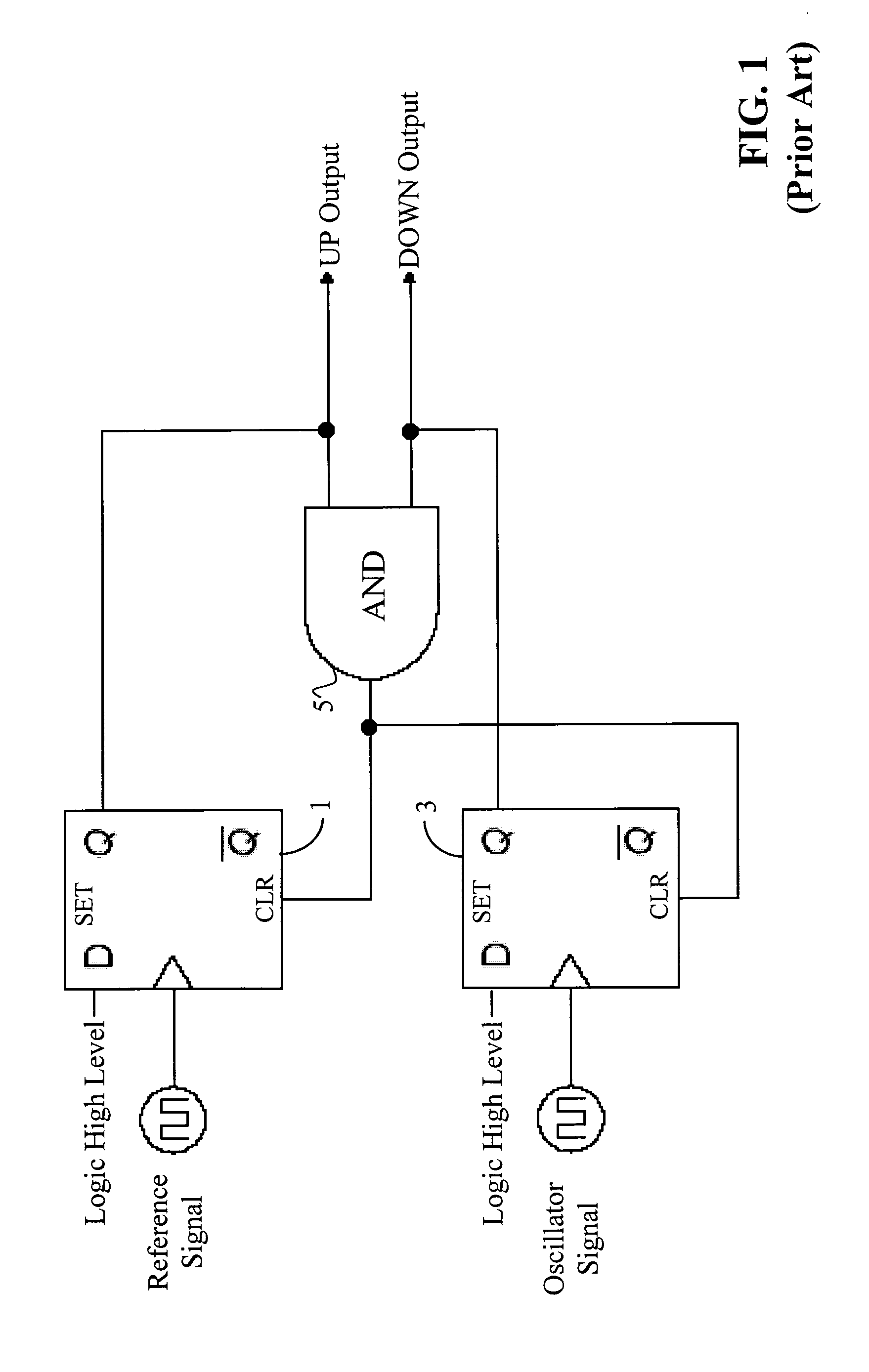

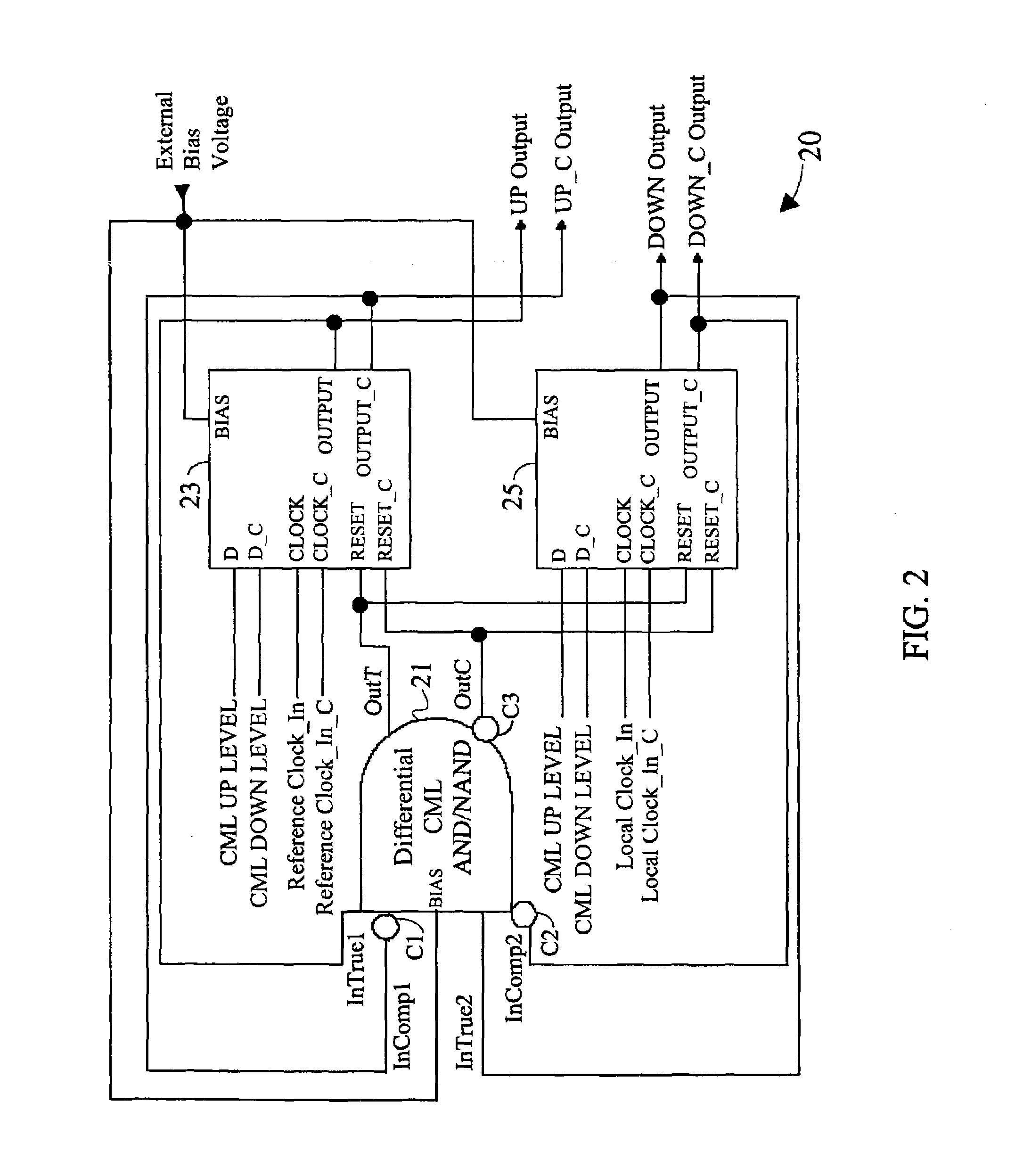

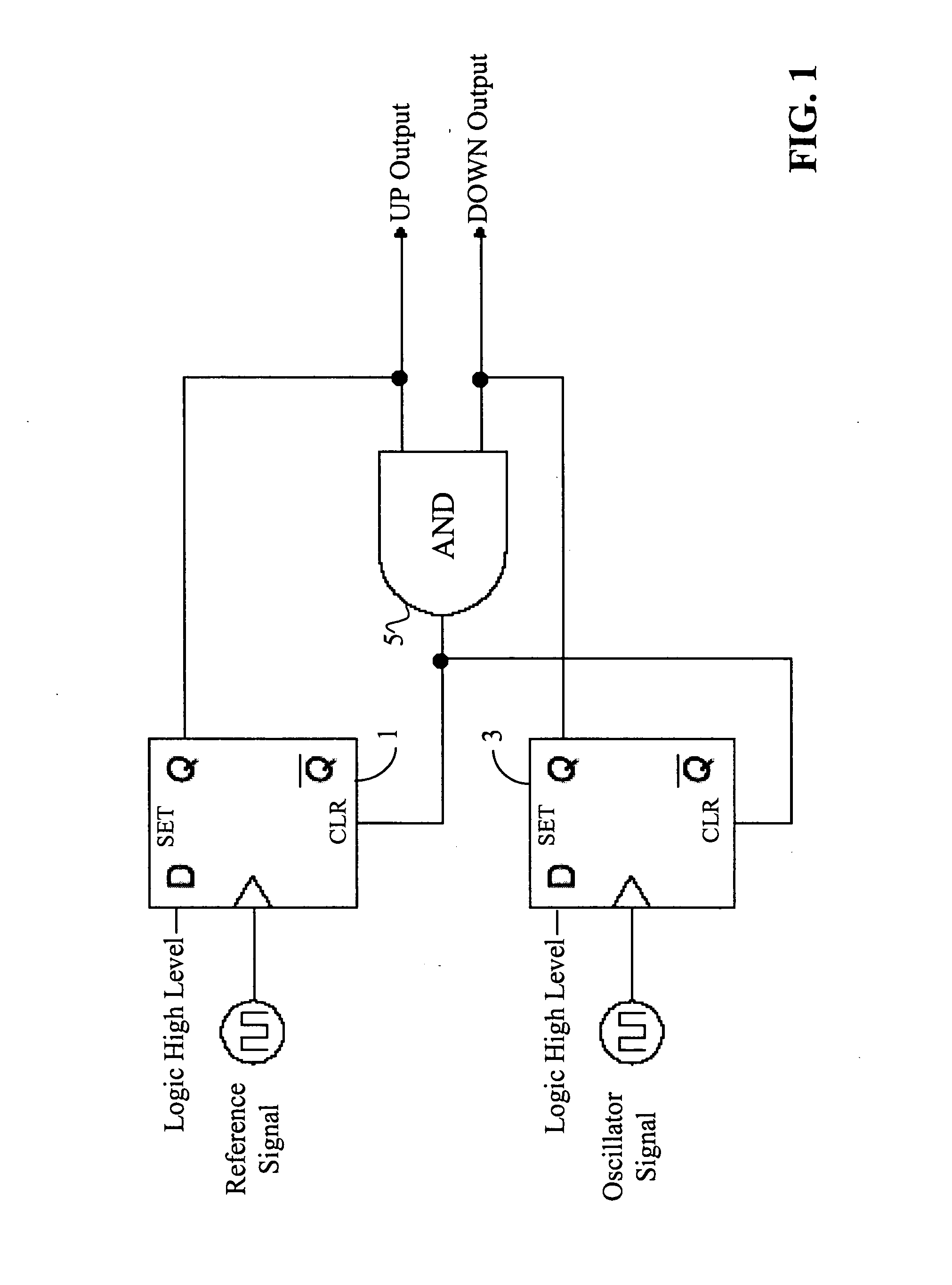

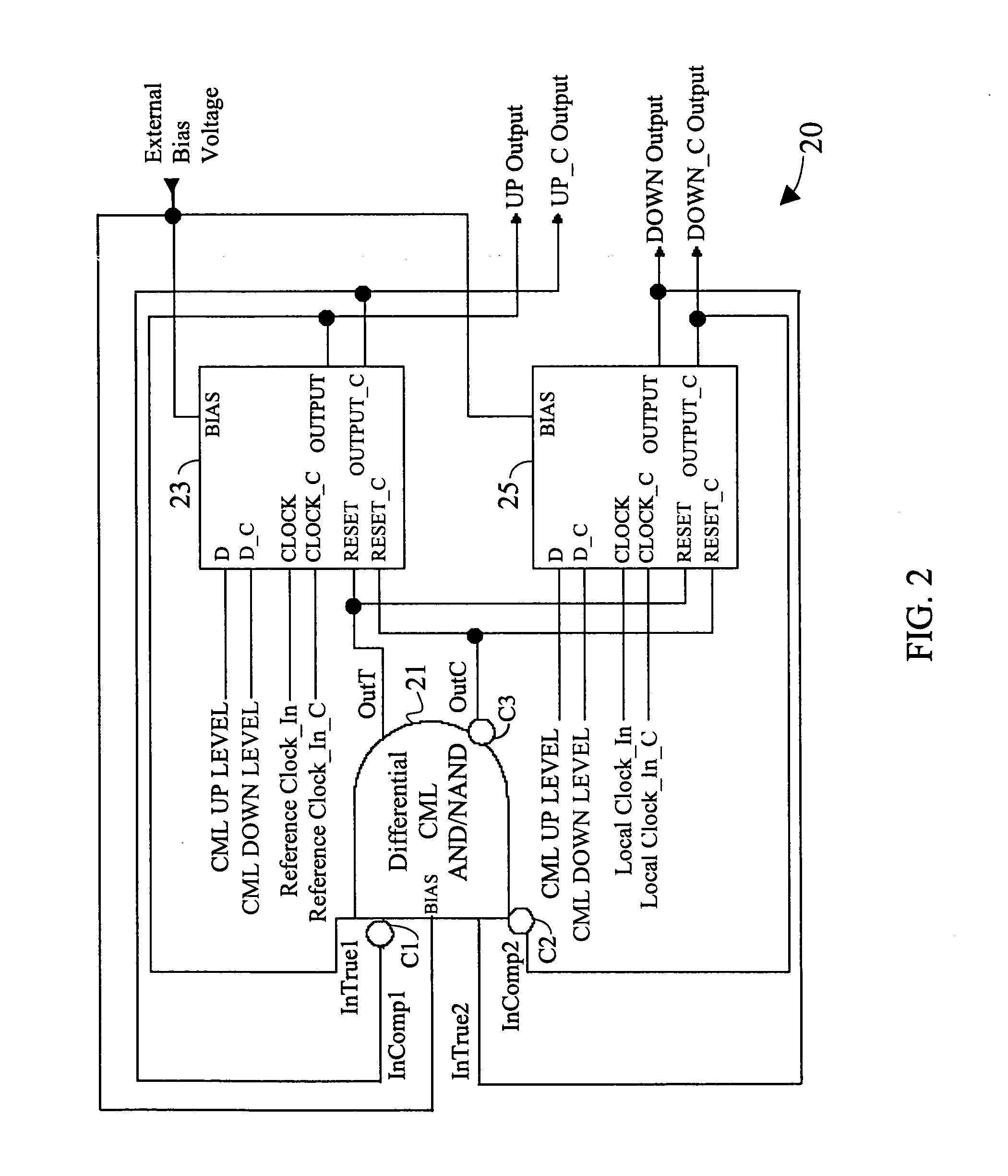

Differential master/slave CML latch

InactiveUS20050242859A1High frequencyReduce noiseReliability increasing modificationsMultiple input and output pulse circuitsDifferential phaseNAND logic

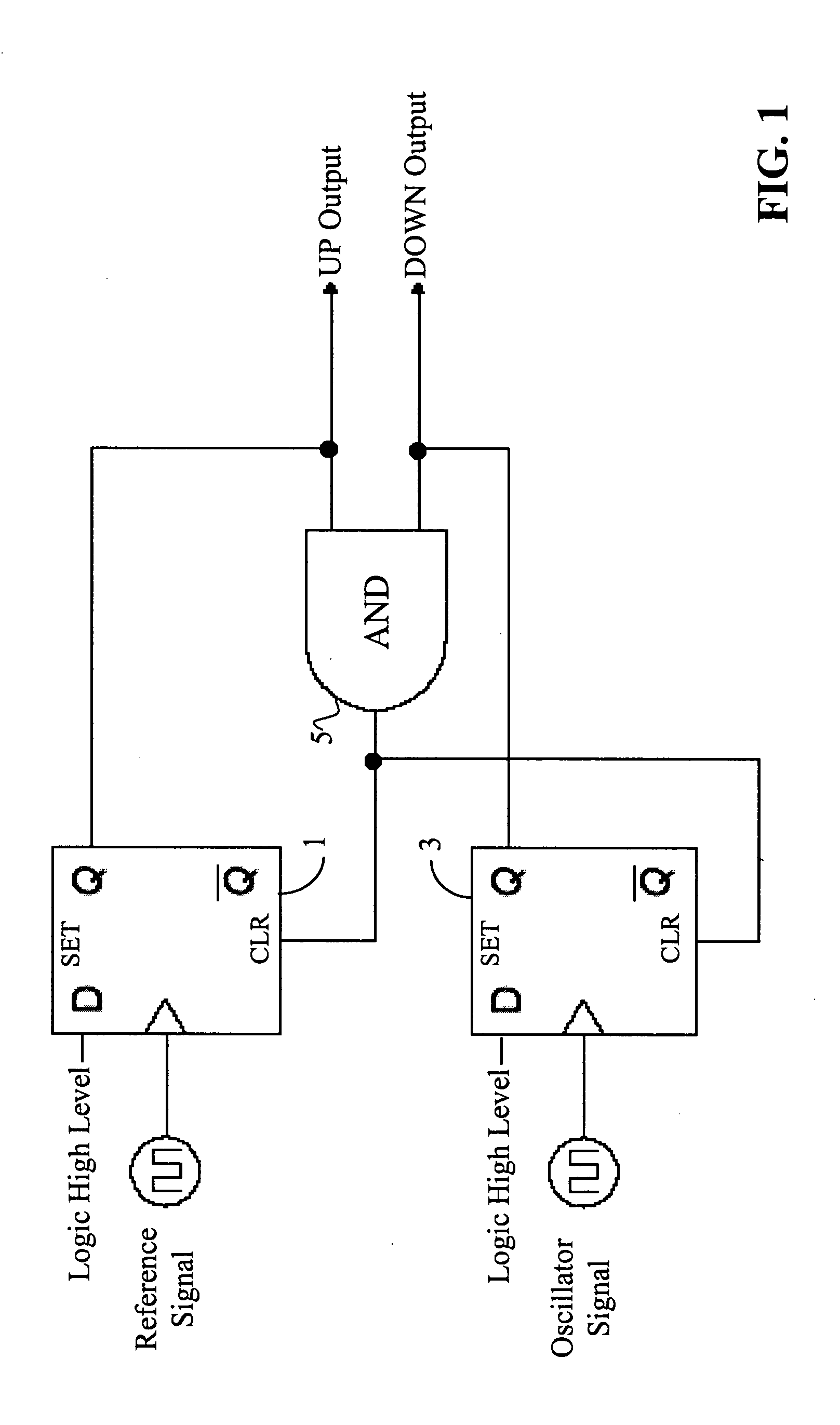

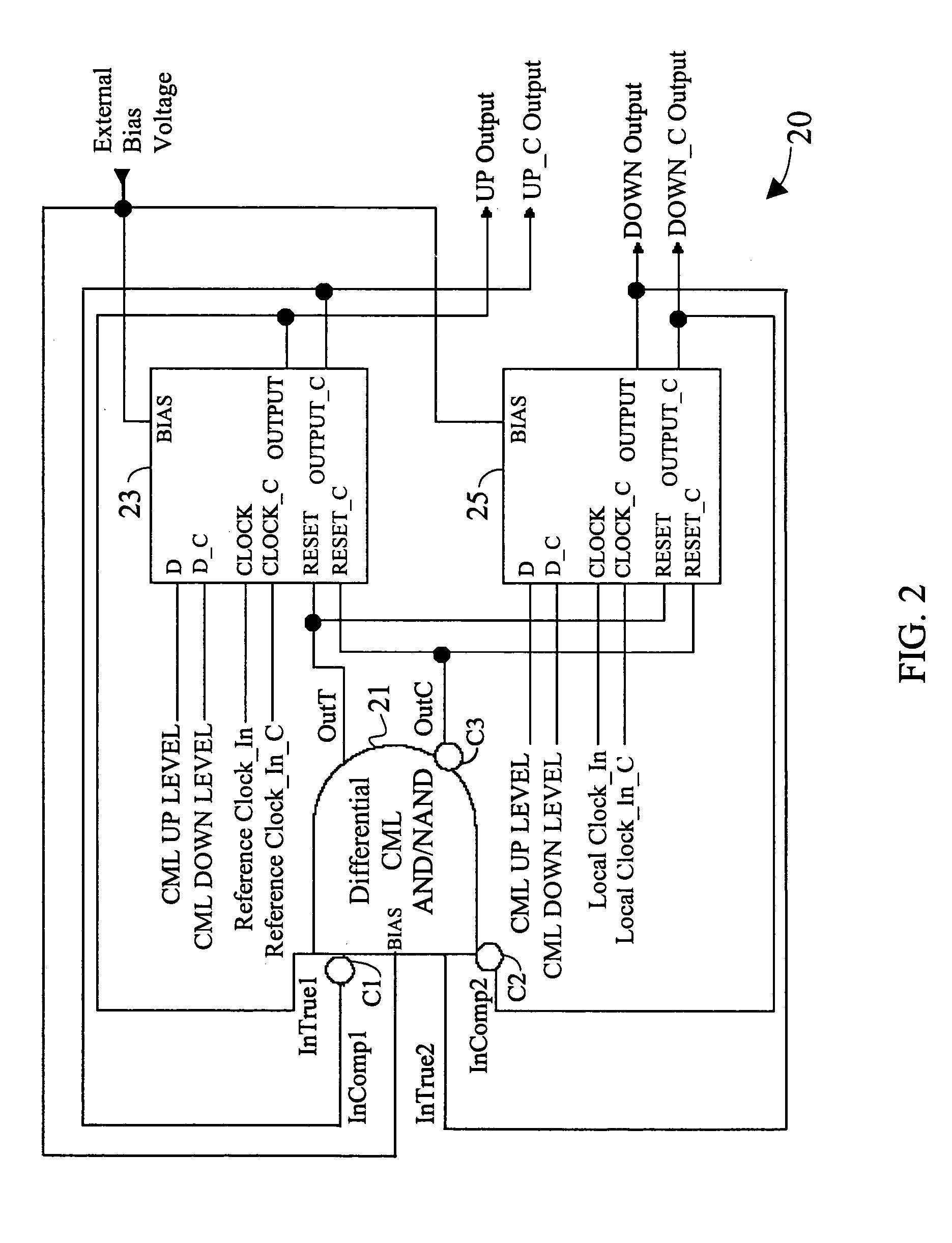

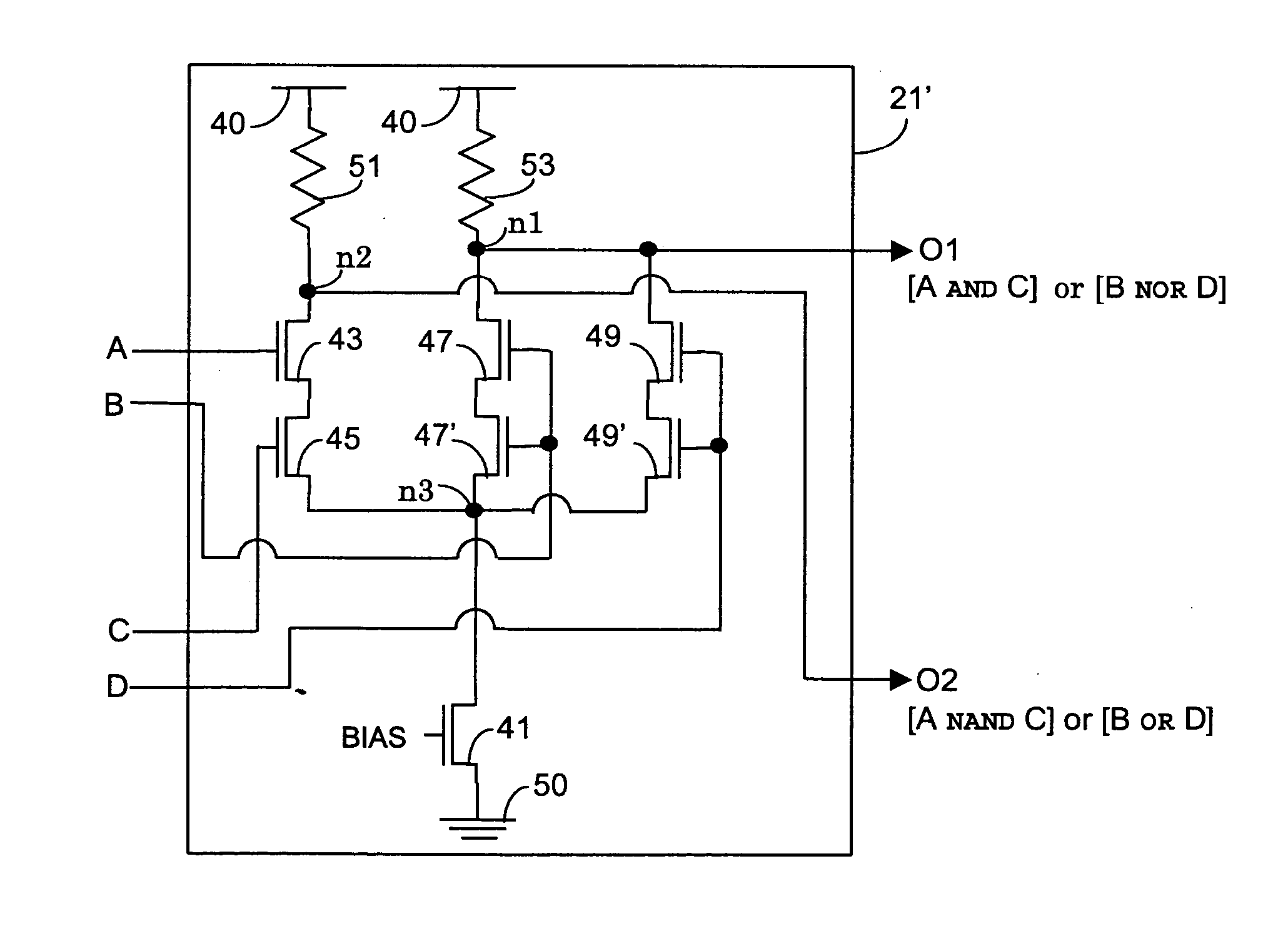

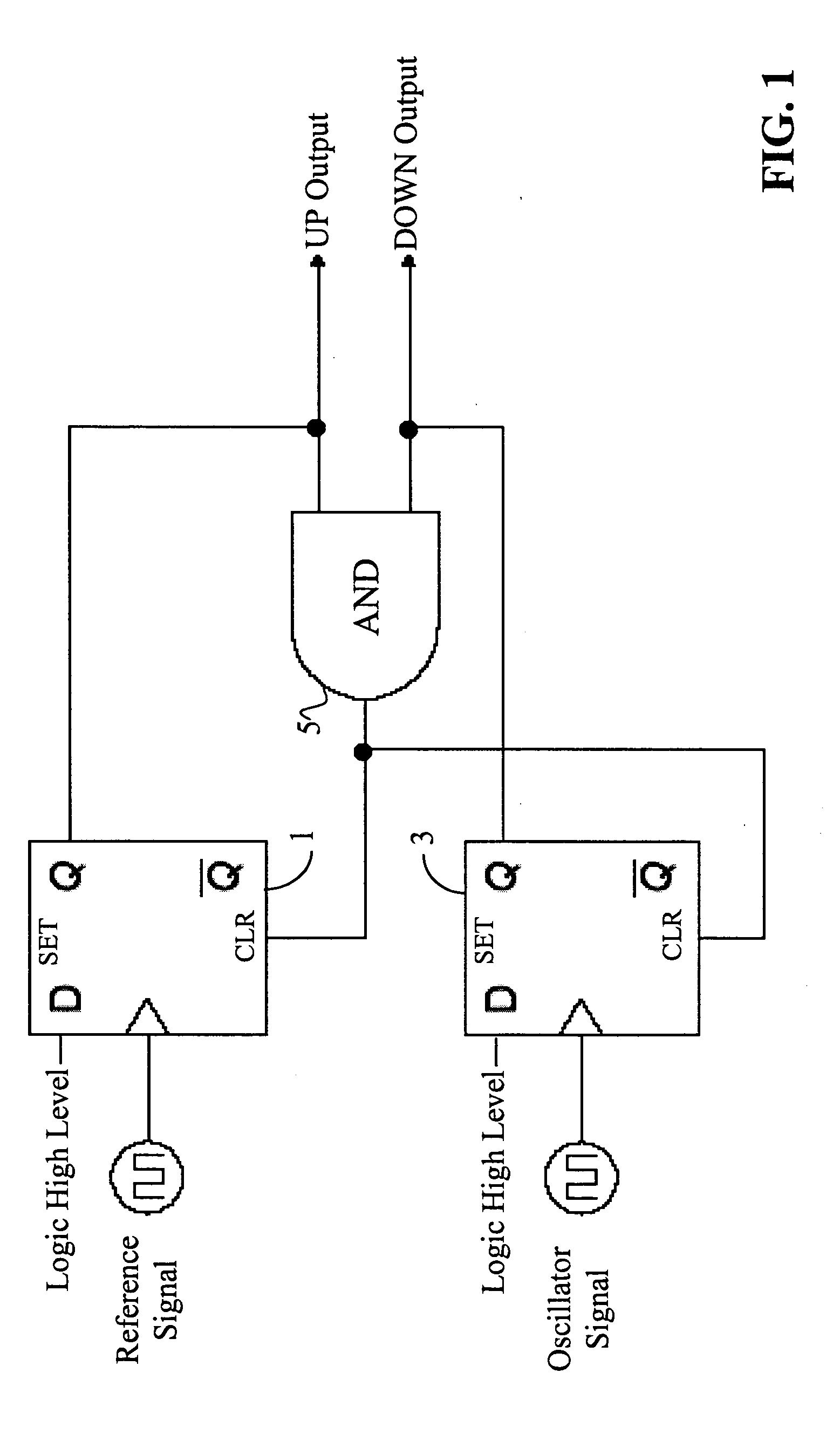

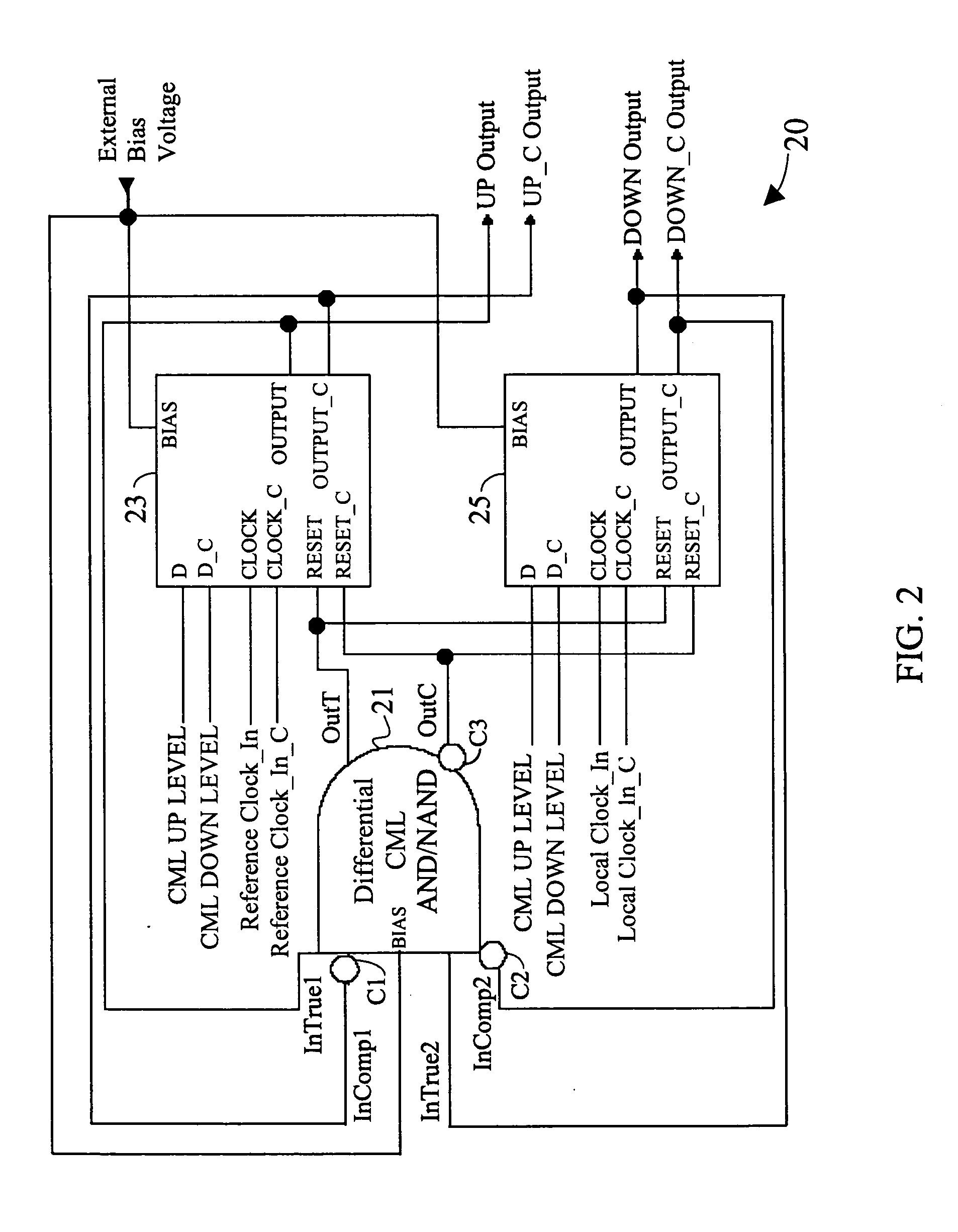

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

Chip and detection method thereof

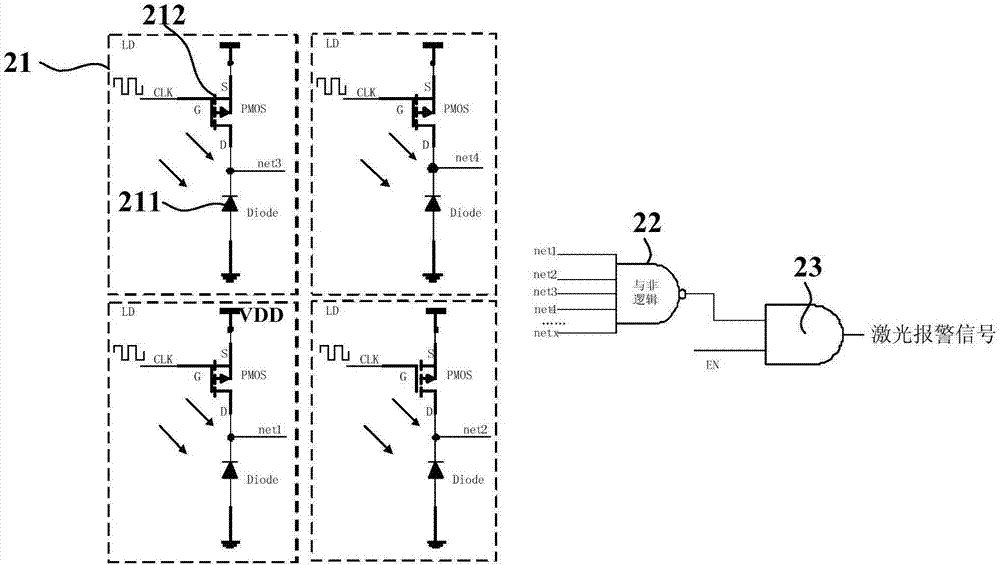

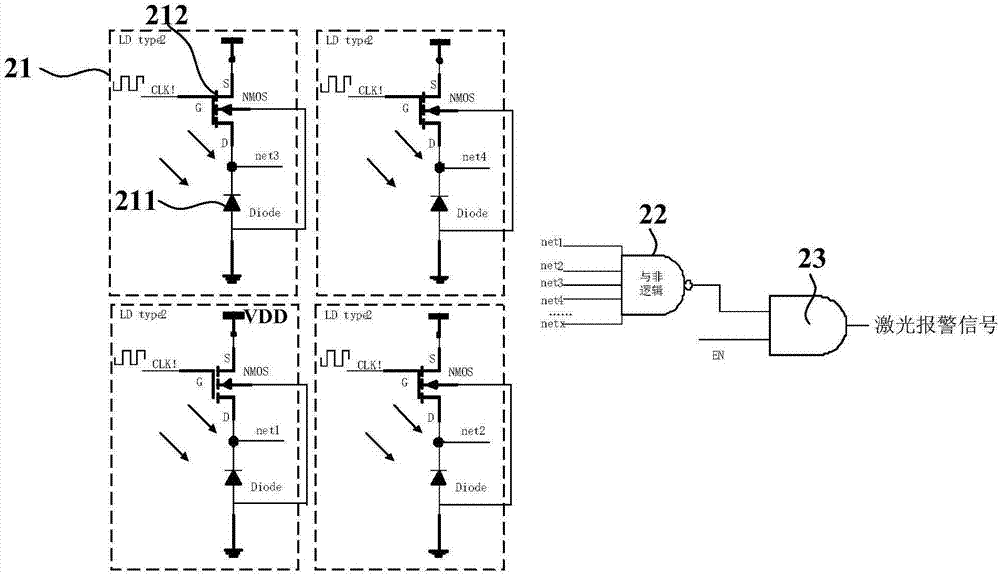

ActiveCN107403798AImprove securitySimple structureSolid-state devicesSemiconductor devicesElectricityNAND logic

The embodiments of the invention disclose a chip and a detection method thereof. The chip includes a substrate, at least one laser detection circuit, and multiple key circuit modules. The laser detection circuit includes laser detection units, a NAND logic unit, and an AND logic unit. Each laser detection unit includes a monitoring diode and a first charging transistor; the anode of the monitoring diode is grounded; the input end of the first charging transistor is electrically connected with a power supply; and the cathode of the monitoring diode and the output end of the first charging transistor are electrically connected and serve as the output end of the laser detection unit. Each input end of the NAND logic unit is electrically connected with the output end of one laser detection unit, a first input end of the AND logic unit is electrically connected with the output end of the NAND logic unit, and a second input end of the AND logic unit receives an enable signal. Each key circuit module is set adjacent to at least one laser detection unit. Through the implementation of the embodiments of the invention, the accuracy of laser detection is improved, and missing detection is avoided.

Owner:GIGADEVICE SEMICON (BEIJING) INC

Differential master/slave CML latch

InactiveUS7034594B2High frequencyReduce noiseReliability increasing modificationsMultiple input and output pulse circuitsDifferential phaseNAND logic

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

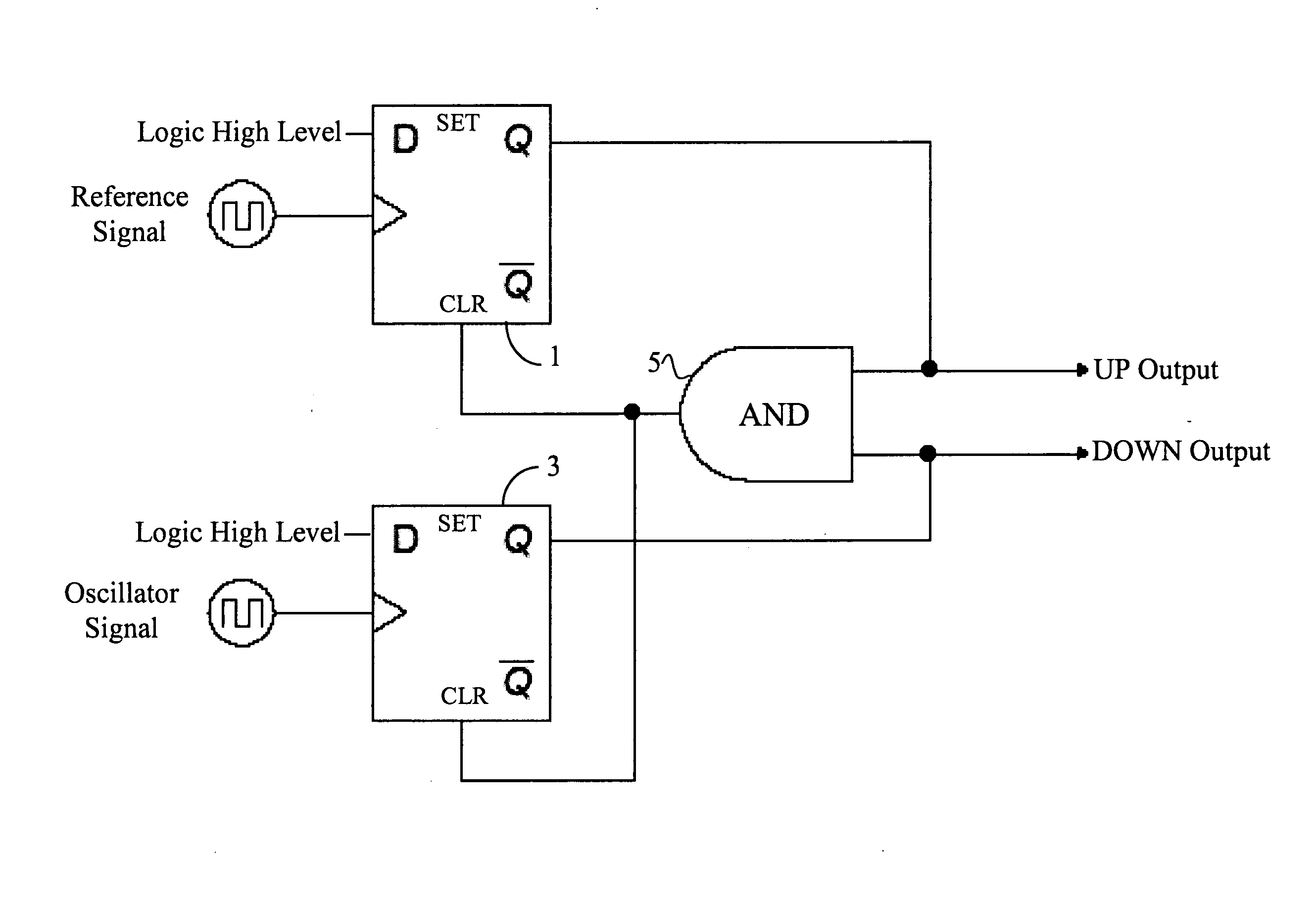

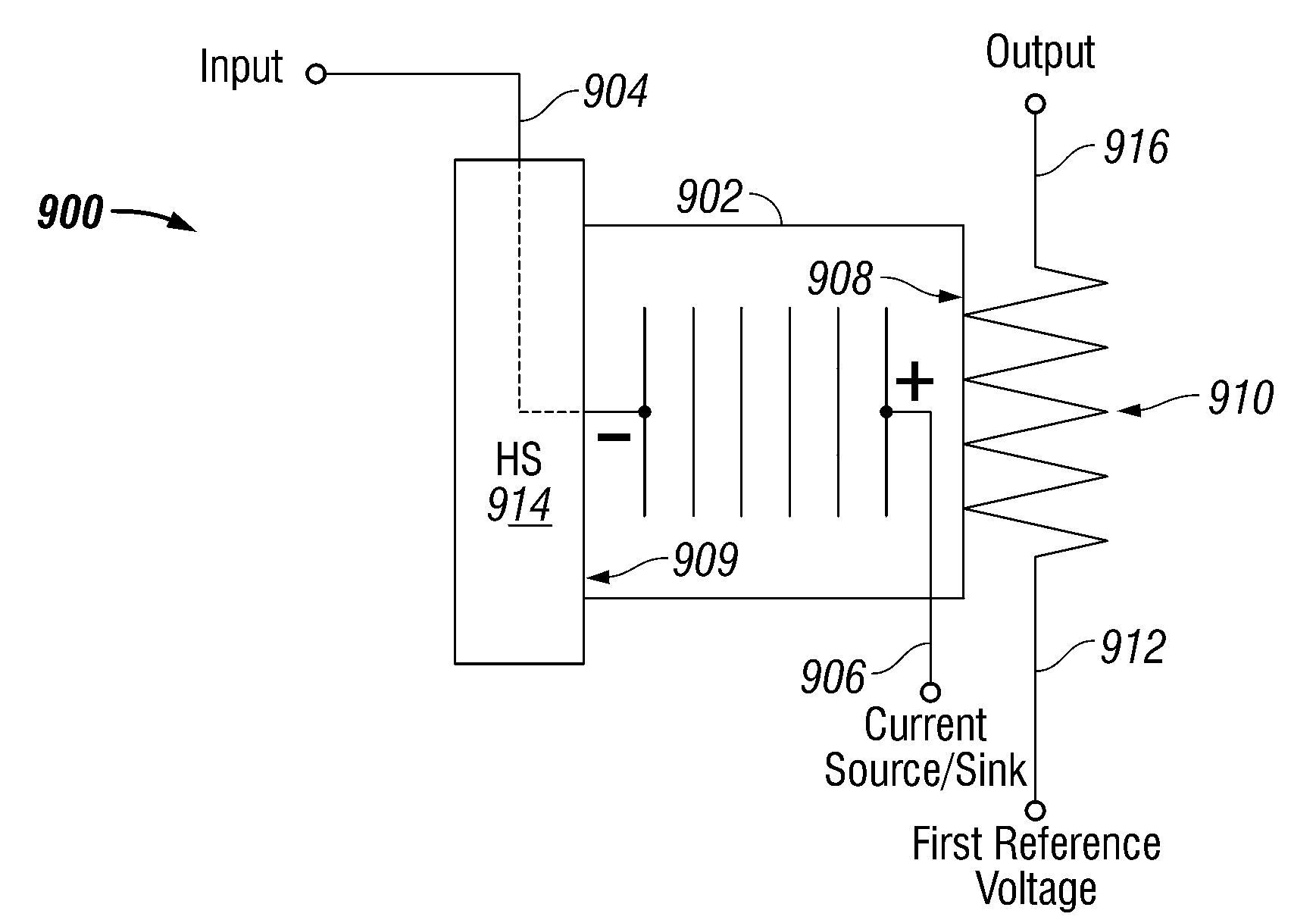

Differential current mode phase/frequency detector circuit

InactiveUS7038497B2High frequencyReduce noiseMultiple input and output pulse circuitsPulse automatic controlNAND logicDetector circuits

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

Dual-modulus prescaler circuit operating at a very high frequency

ActiveUS20090146699A1High frequencyReduce power consumptionPulse automatic controlCounting chain synchronous pulse countersNegative feedbackNAND logic

The dual-modulus prescaler circuit (1) is devised to operate at a very high frequency. This circuit includes an assembly formed of two dynamic D-type flip flops (12, 13), and two NAND logic gates (15, 16) arranged in negative feedback between the two flip flops. The two flip flops are clocked by an input clock signal (CK) to supply a divided output signal (OUT) whose frequency matches the input clock frequency divided by 2 or by 3 as a function of a division mode selection signal (divb) applied to the input of the first NAND logic gate (15). One non-inverted output of the second flip flop is connected to one input of the first flip flop (12). The first dynamic flip flop includes three active branches and supplies a single inverted output signal. A third flip flop (14) with three active branches receives an inverted mode selection signal (div) at input in order to supply the mode selection signal to the inverted output thereof, clocked by the non-inverted output signal of the second flip flop.

Owner:THE SWATCH GRP RES & DEVELONMENT LTD

Single clock driven shift register and driving method for same

A single clock driven shift register comprising multiple stages is provided. The (M)th stage comprises a latch unit, a logic unit, and a non-overlap buffer. The latch unit latches an input signal from the (M−1)th stage according to a clock signal. The logic unit connecting to an output terminal of the latch unit deals with an output signal of the latch unit and the clock signal with an NAND logic calculation. The non-overlap buffer connecting to the output terminal of the logic unit comprises at least three inverters connected in a serial, and an output signal of the first inverter coupled to the output terminal of the logic unit is input to an latch unit of the (M+1)th stage. Meanwhile, an output signal of the non-overlap buffer of the (M−1)th stage is input to the non-overlap buffer or the logic unit to delay the output signal of the non-overlap buffer.

Owner:AU OPTRONICS CORP

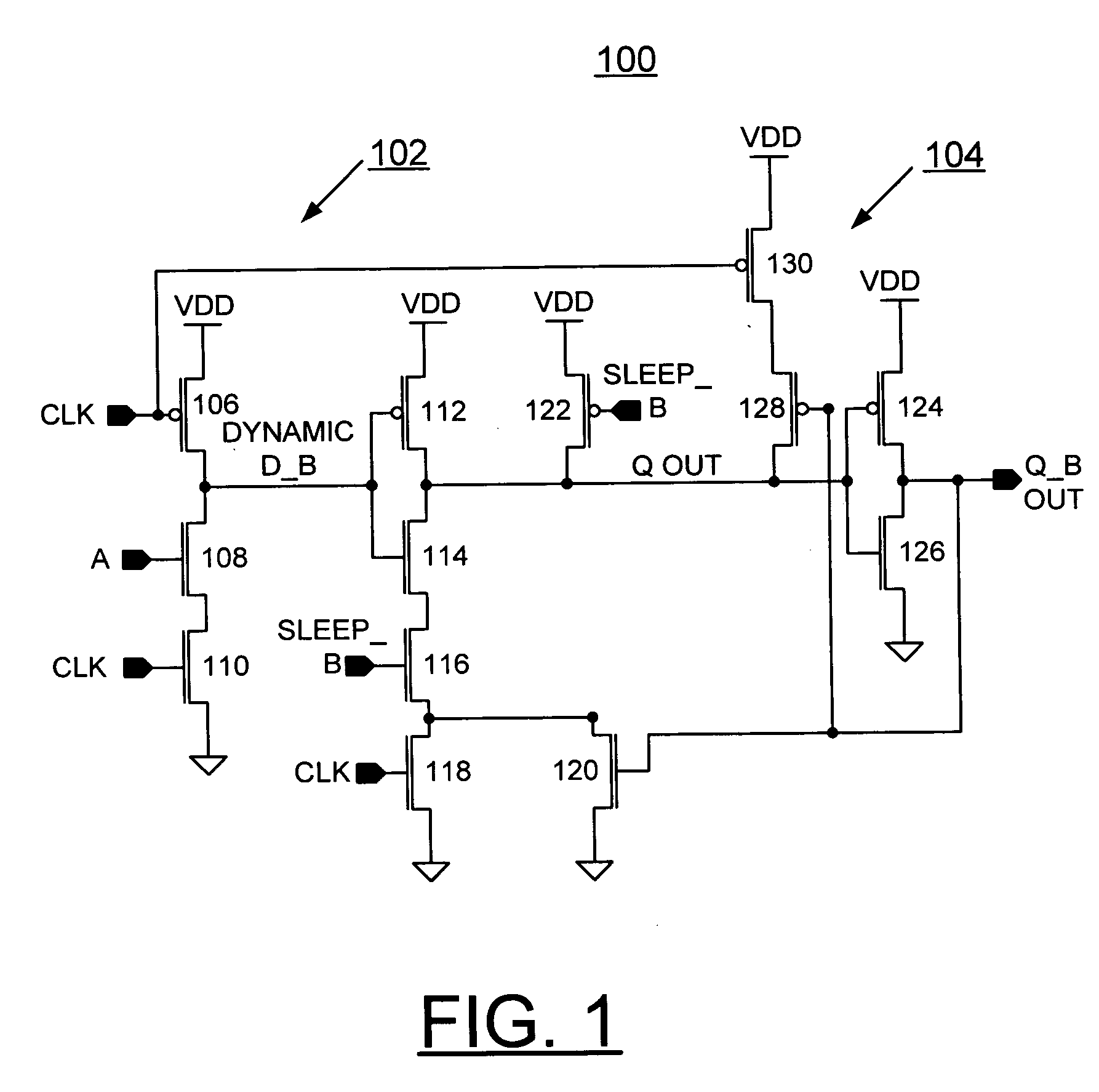

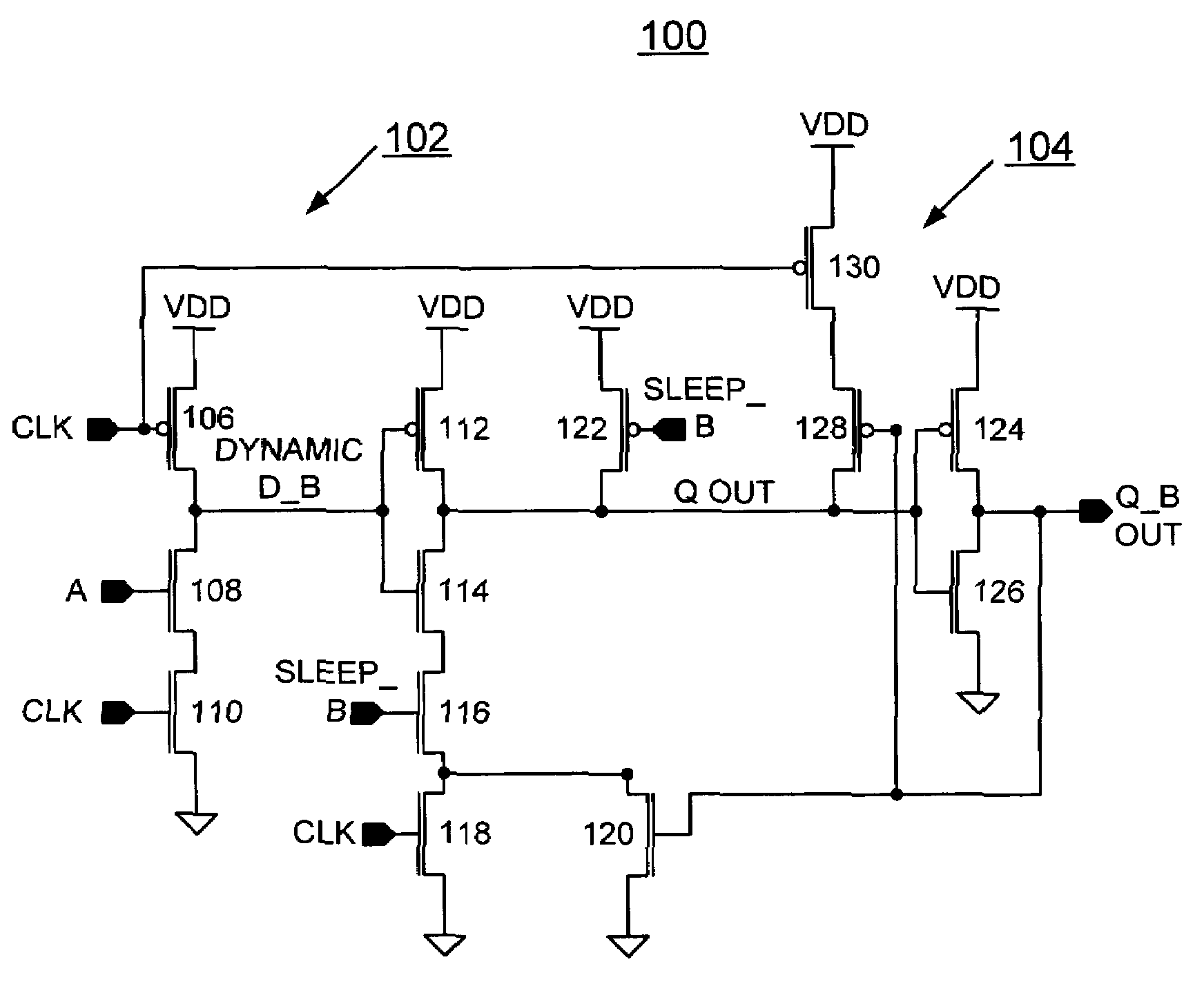

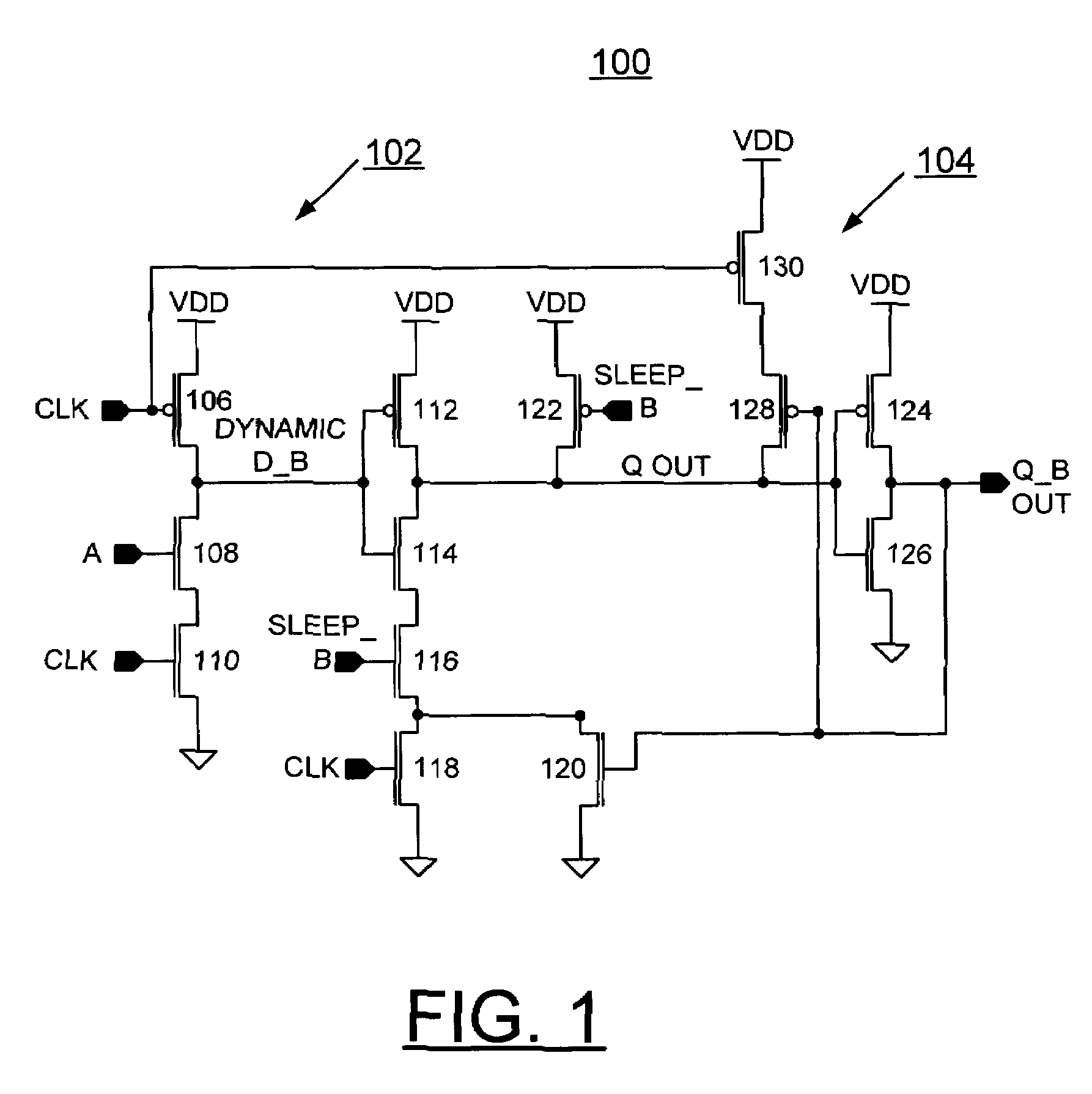

Method and apparatus for implementing subthreshold leakage reduction in LSDL

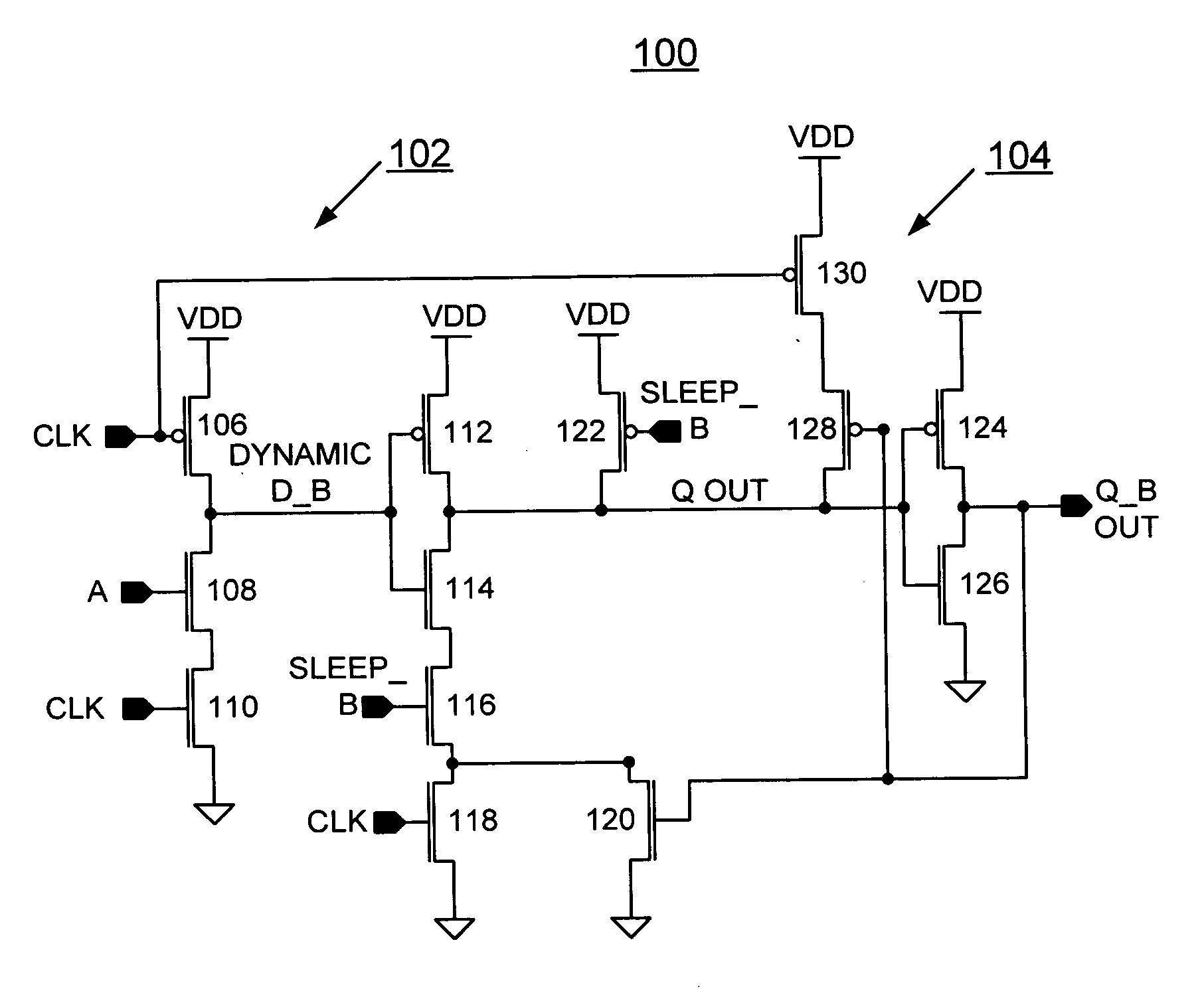

InactiveUS20070139082A1Power reduction in field effect transistorsSubthreshold leakage currentNAND logic

A method and apparatus are provided for implementing subthreshold leakage current reduction in limited switch dynamic logic (LSDL). A limited switch dynamic logic circuit includes a cross-coupled NAND and inverter logic. A dynamic node provides a first input to the NAND. A sleep signal provides a second input to the NAND. An output of the NAND provides an input to the inverter logic that inverts the NAND output and provides a complementary output. The NAND logic includes a series connected first sleep transistor receiving the sleep input. The first sleep transistor is turned OFF during the sleep mode. A second sleep transistor is connected between a voltage supply rail and the NAND output. The second sleep transistor is turned ON during the sleep mode to force high the NAND output and force low complementary output.

Owner:GOOGLE LLC

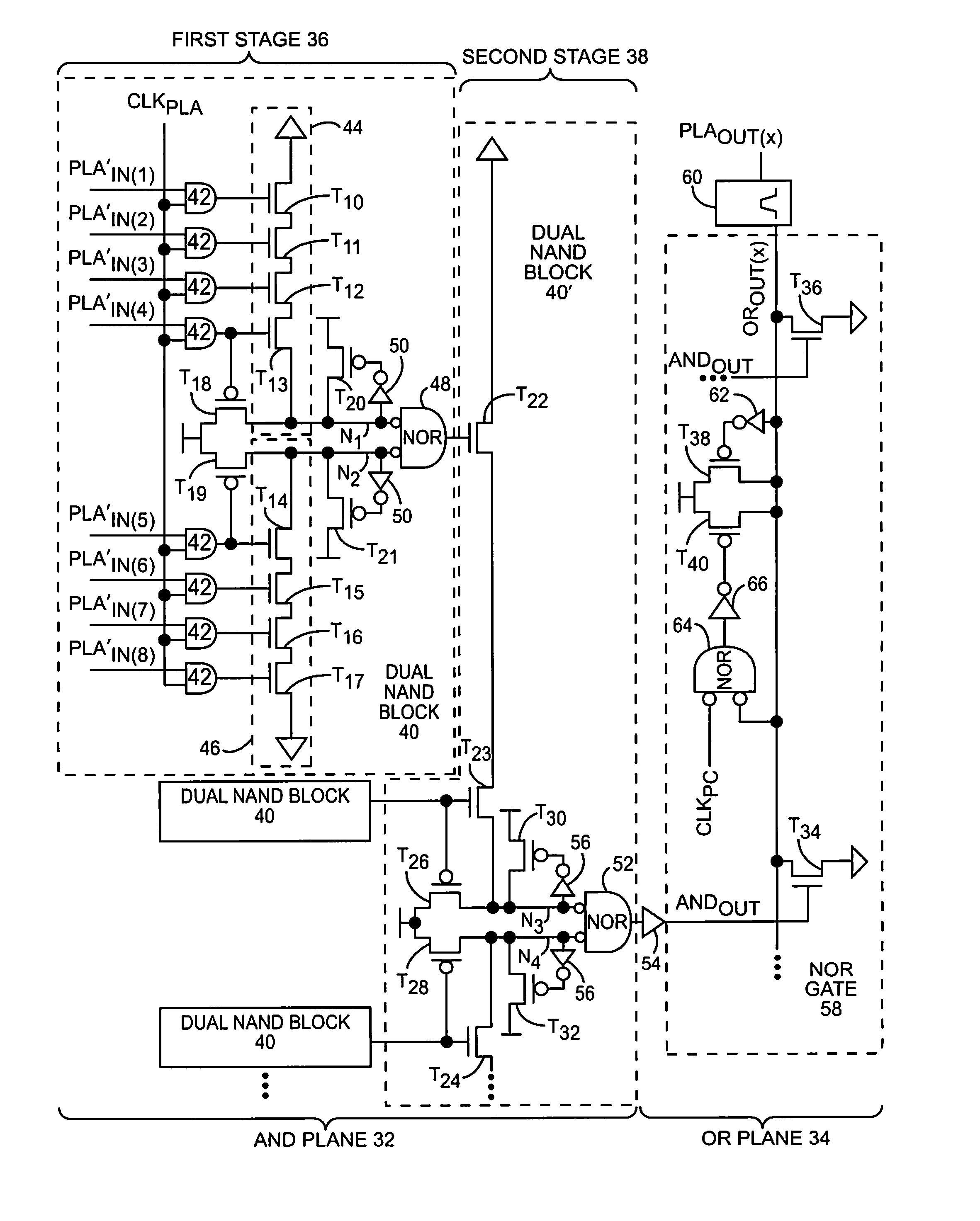

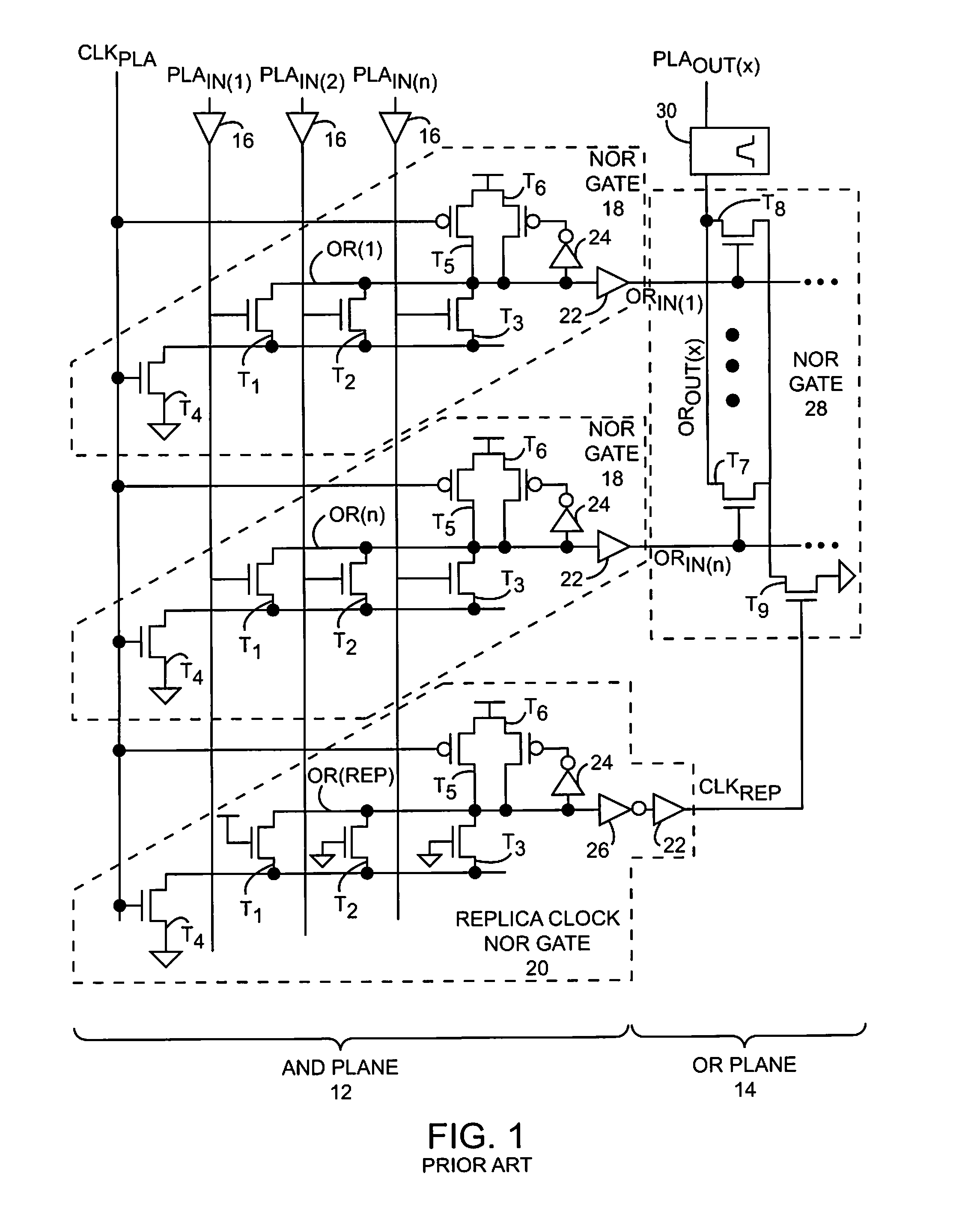

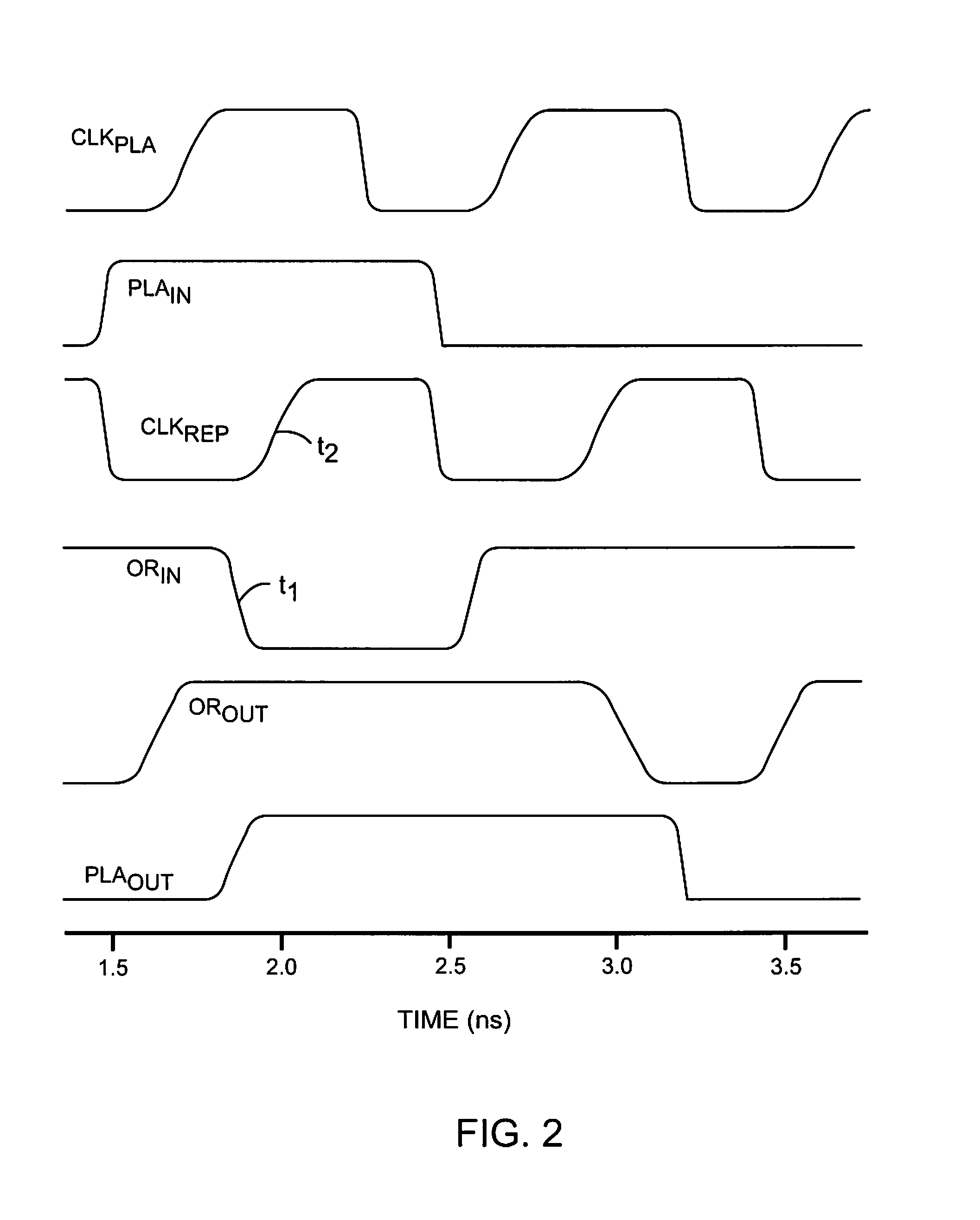

Low power, race free programmable logic arrays

InactiveUS7541832B1Reduce power consumptionQuantity minimizationLogic circuits using elementary logic circuit componentsComputation using denominational number representationLogic implementationNAND logic

The present invention provides a PLA architecture where the AND plane is implemented with NAND logic. The OR plane may be implemented with various logic, but in one embodiment, the OR plane is implemented with NOR logic. The AND plane may have multiple sequential stages providing hierarchical NAND logic. The NAND logic may be broken into a hierarchy of NAND logic blocks. Each NAND logic block may include one or more series-connected NAND transistor stacks. Each transistor in the transistor stack may receive an input signal representing the product of a PLA clock signal and either a direct PLA input or the complement thereof. As such, the PLA clock is inherently integrated with the input signals that drive the various transistors of the NAND transistor stacks.

Owner:ARIZONA STATE UNIVERSITY

Differential current mode phase/frequency detector circuit

InactiveUS20050242843A1Reduce noiseHigh frequencyReliability increasing modificationsMultiple input and output pulse circuitsDetector circuitsNAND logic

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

Method and apparatus for implementing subthreshold leakage reduction in LSDL

InactiveUS7268590B2Power reduction in field effect transistorsNAND logicSubthreshold leakage current

A method and apparatus are provided for implementing subthreshold leakage current reduction in limited switch dynamic logic (LSDL). A limited switch dynamic logic circuit includes a cross-coupled NAND and inverter logic. A dynamic node provides a first input to the NAND. A sleep signal provides a second input to the NAND. An output of the NAND provides an input to the inverter logic that inverts the NAND output and provides a complementary output. The NAND logic includes a series connected first sleep transistor receiving the sleep input. The first sleep transistor is turned OFF during the sleep mode. A second sleep transistor is connected between a voltage supply rail and the NAND output. The second sleep transistor is turned ON during the sleep mode to force high the NAND output and force low complementary output.

Owner:GOOGLE LLC

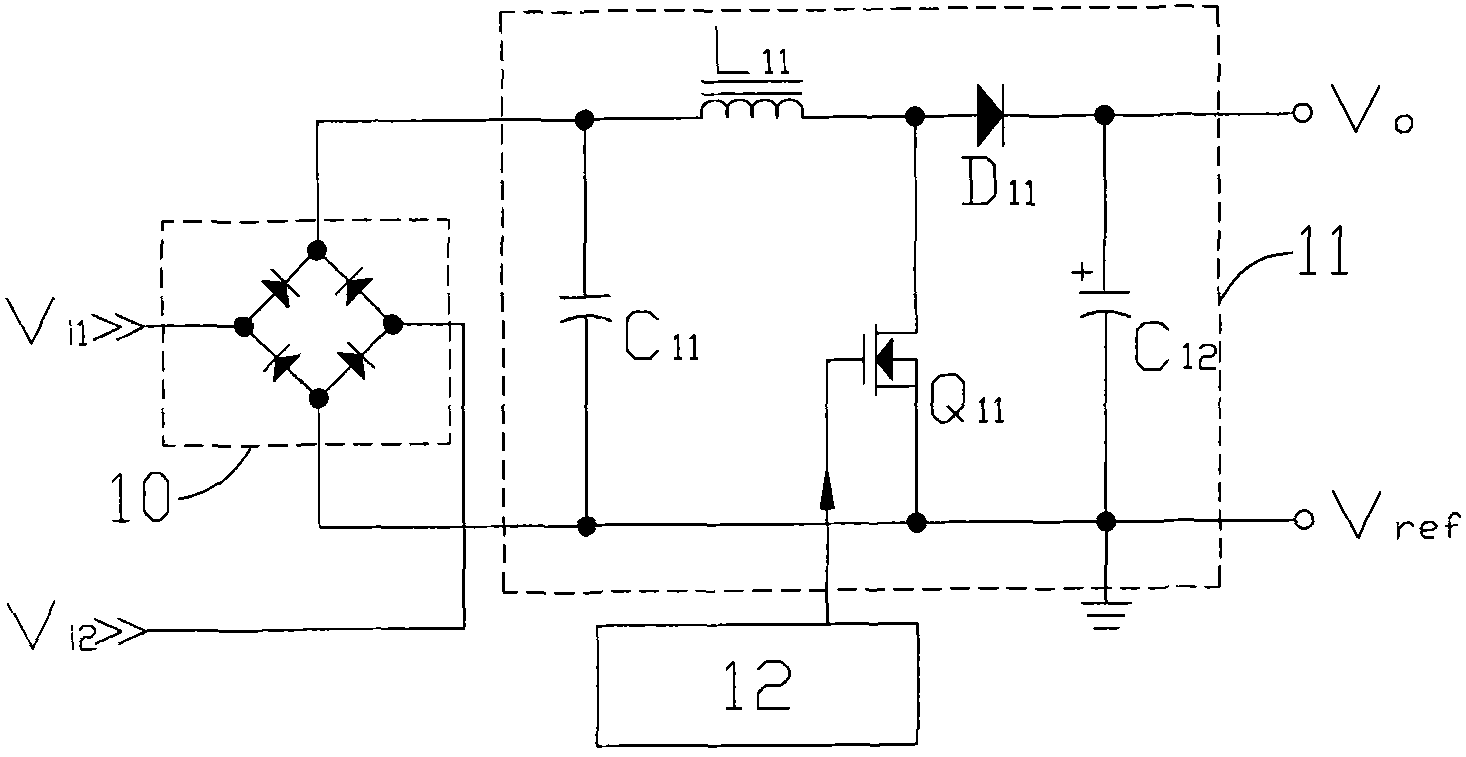

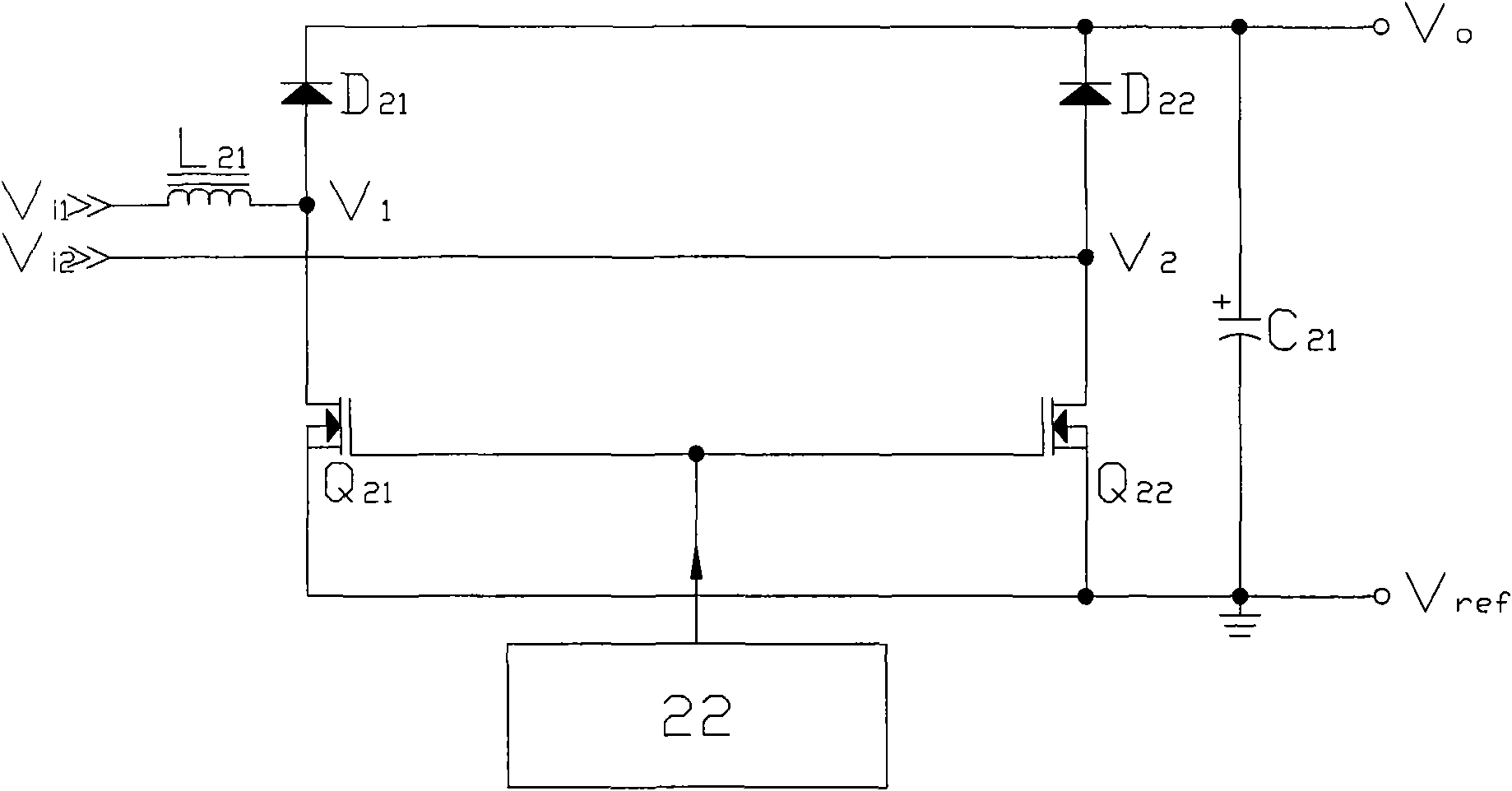

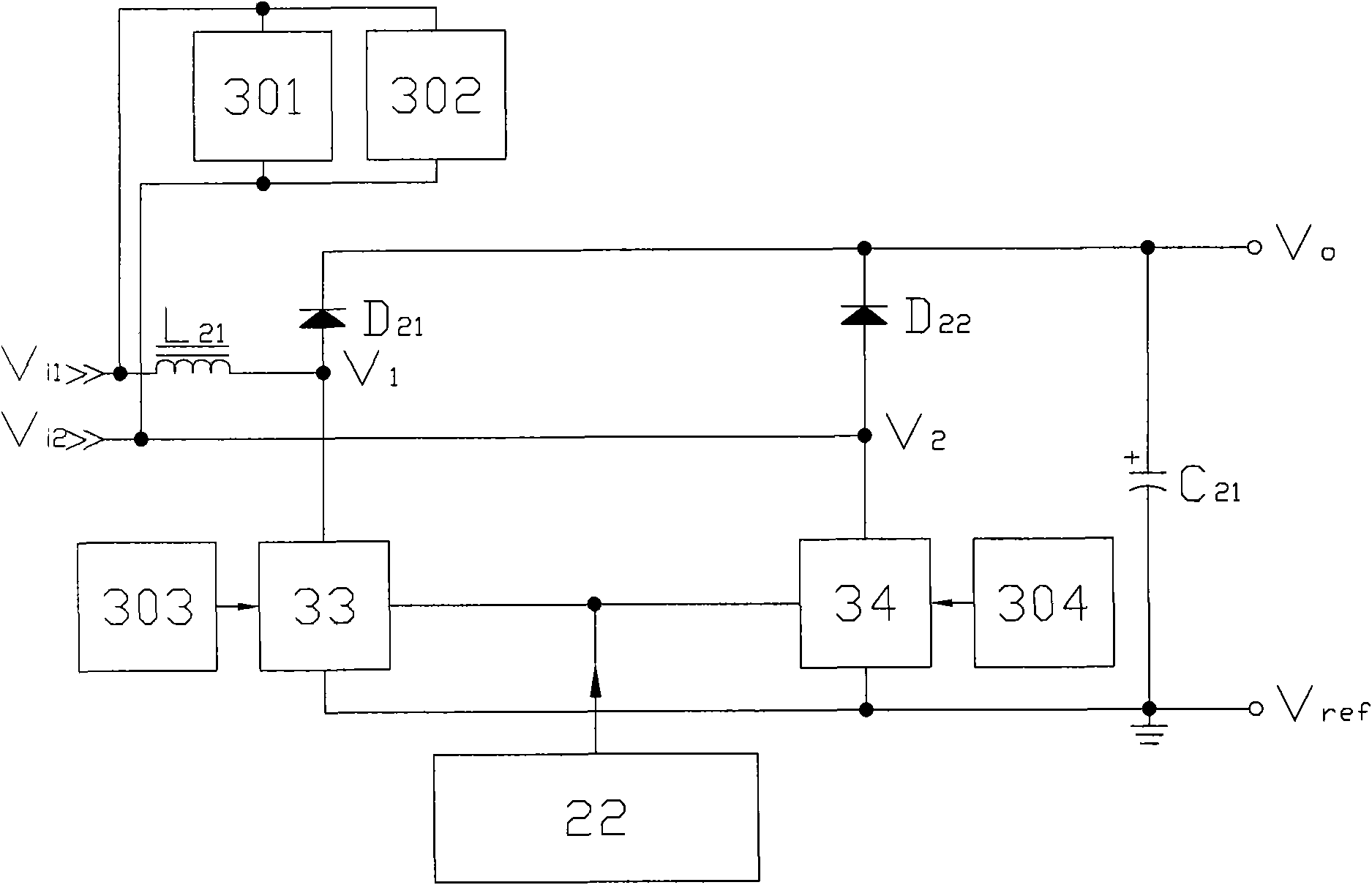

No bridge type power factor corrector with logical control

InactiveCN101888171AReduce conduction lossEfficient power electronics conversionEnergy industryNAND logicVoltage polarity

The invention discloses a no bridge type power factor corrector with logical control, comprising a high frequency switch controller, a boosting inductor, a filter capacitor, two boosting transistor assemblies, two boosting diodes, two line voltage polarity detectors and two low frequency switch drivers. The two line voltage polarity detectors control the two low frequency switch drivers by signal coupling (optical coupling, magnetic coupling and the like), and the two line voltage polarity detectors and the high frequency switch controller drive the two boosting transistor assemblies by a control logic (or logic, nand logic and the like), so that the boosting inductor can release the stored energy by virtue of the channel of the two boosting transistor assemblies, intrinsic-barrier diode conduction loss can be reduced, and efficiency is improved.

Owner:GLACIALTECH +1

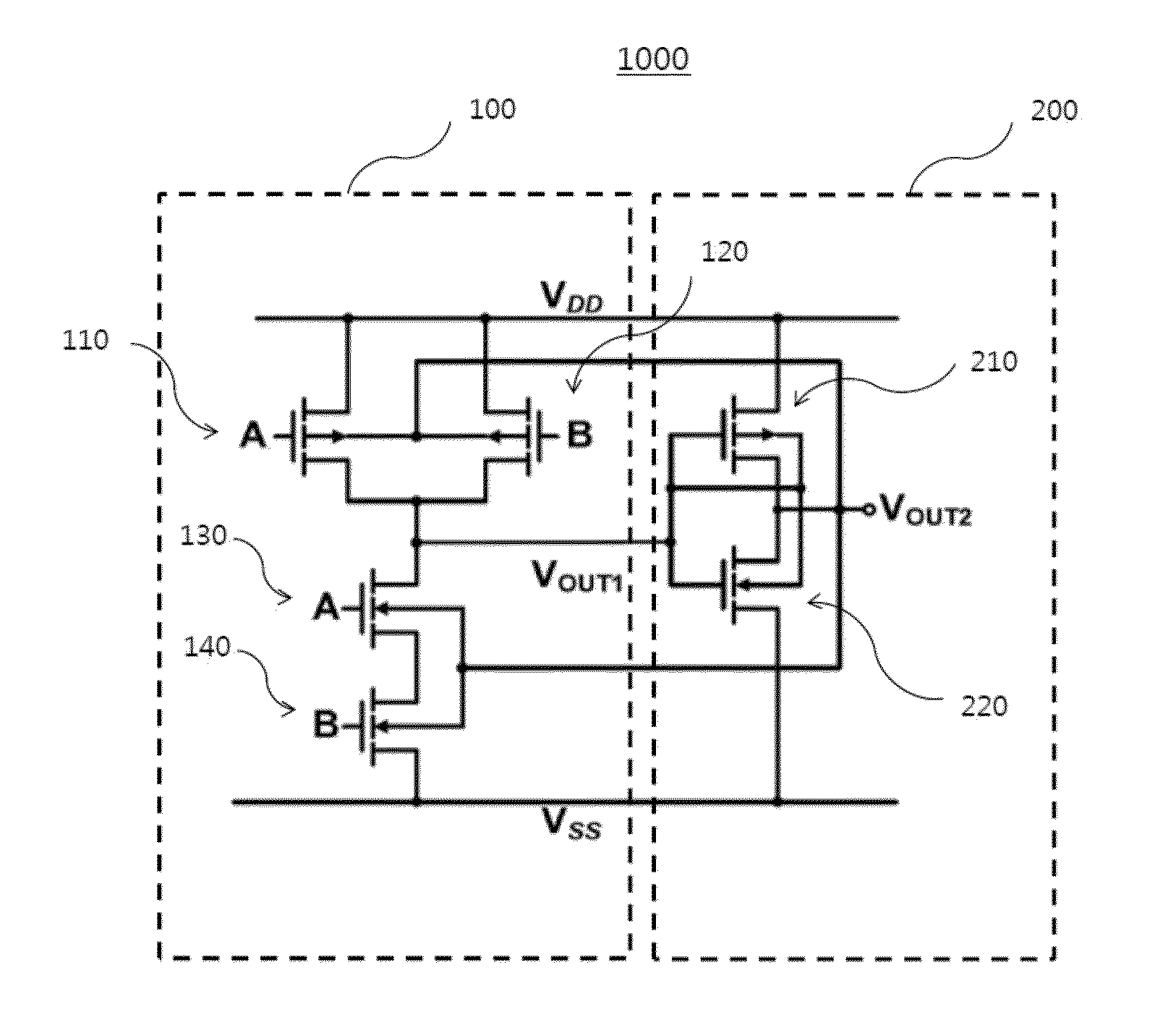

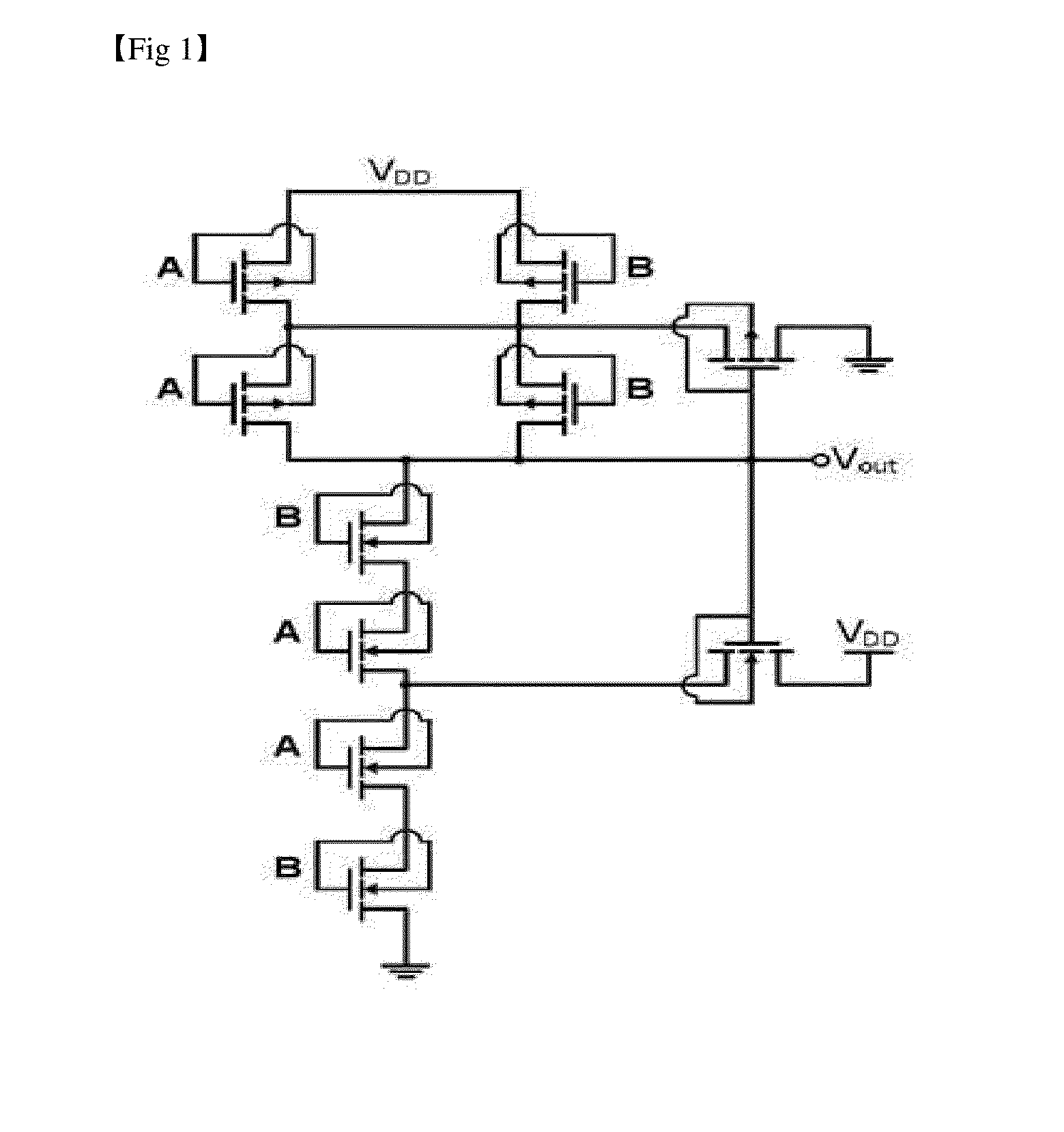

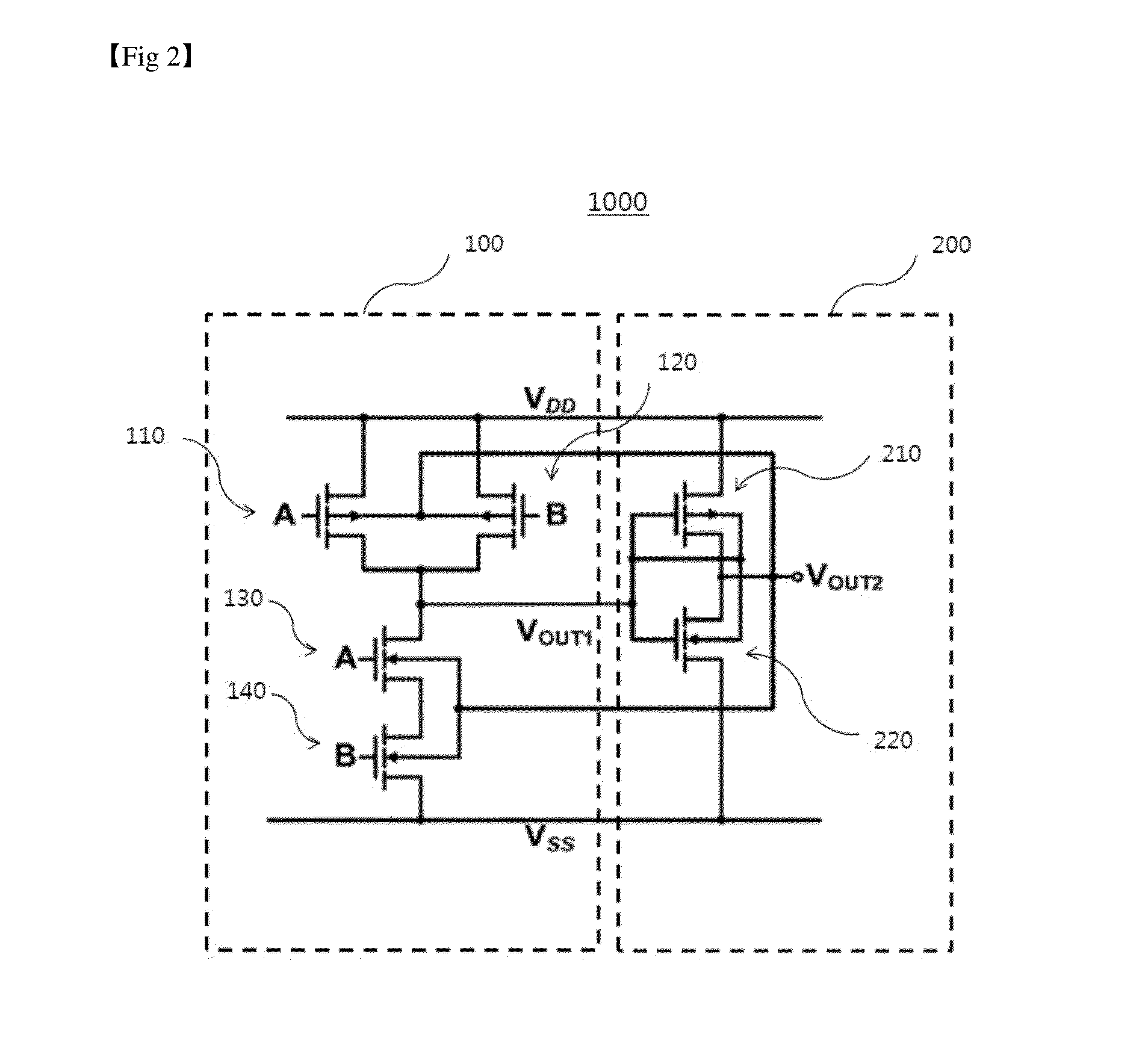

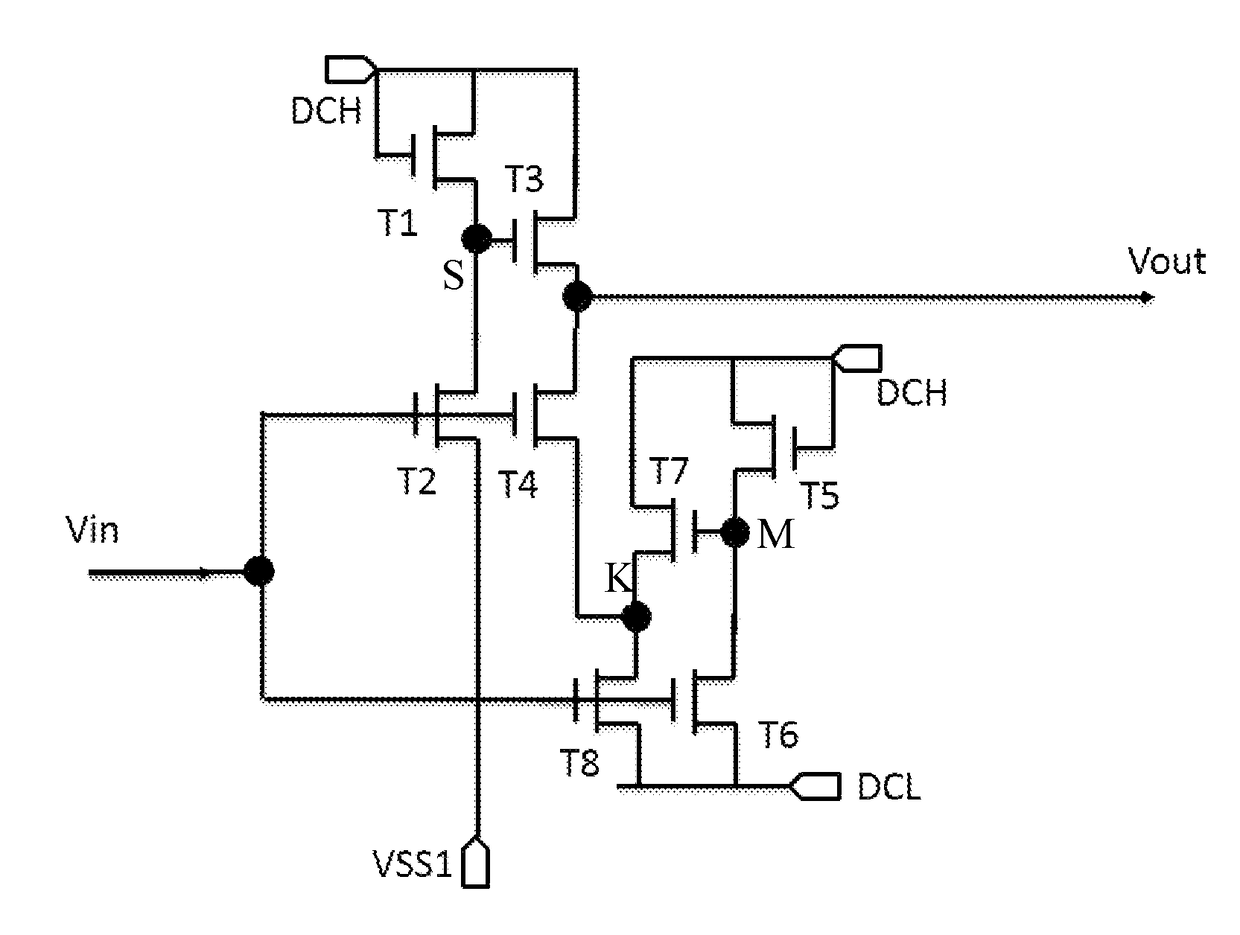

Logic gate using schmitt trigger circuit

ActiveUS20150303918A1Low noise immunityReduce power consumptionPower reduction by control/clock signalLogic circuits characterised by logic functionSchmitt triggerNAND logic

Logic gates using Schmitt trigger circuits are provided. An AND gate using the Schmitt trigger circuit includes: a NAND gate configured to receive two input signals, perform a NAND logic operation, and output a first output signal; and a DTMOS inverter configured to invert the first output signal, and output the inverted first output signal as a second output signal, and a threshold voltage of the NAND gate is controlled using the second output signal. A OR gate using the Schmitt trigger circuit includes: a NOR gate configured to receive two input signals, perform a NOR logic operation, and output a first output signal; and a DTMOS inverter configured to invert the first output signal, and output the inverted first output signal as a second output signal, and a threshold voltage of the NOR gate is controlled using the second output signal.

Owner:RES & BUSINESS FOUND SUNGKYUNKWAN UNIV

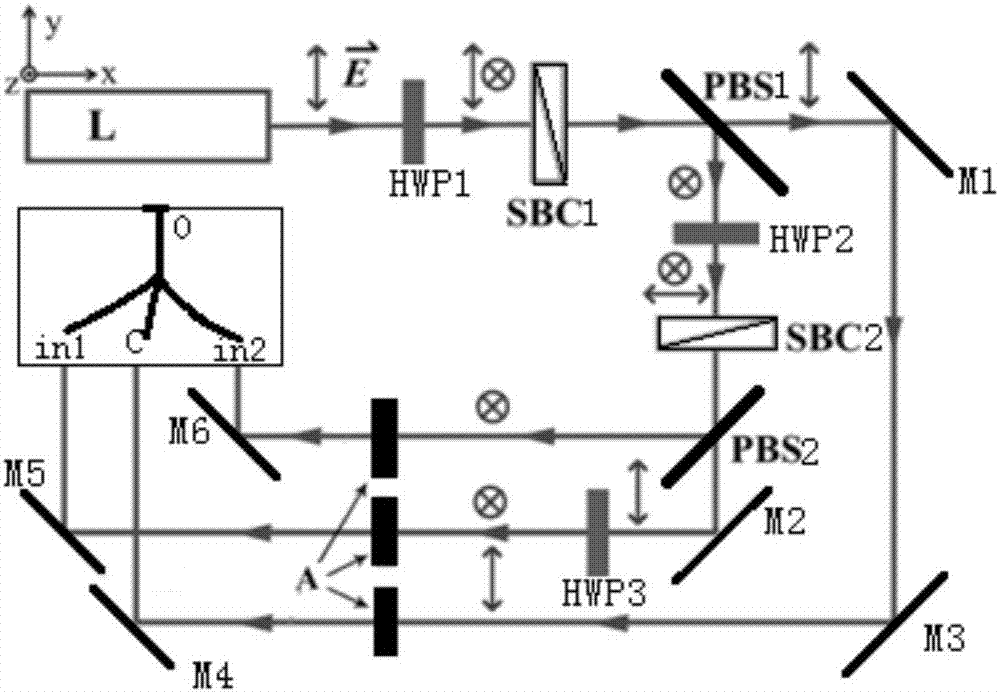

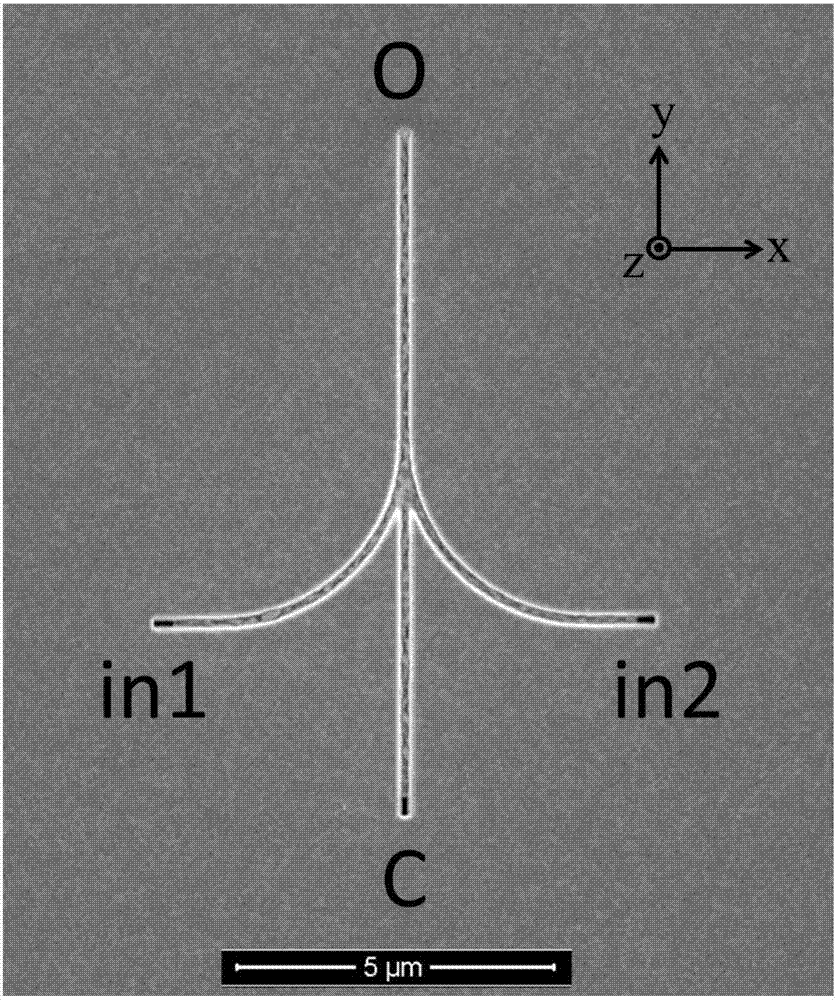

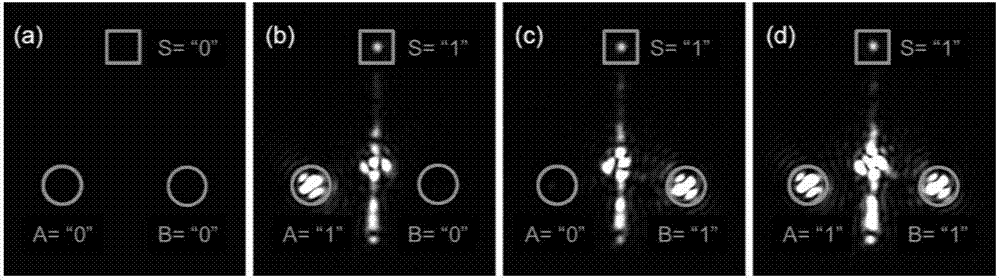

Universal linear optical all-optical logic gate and implement method thereof

PendingCN107976855ALogic circuits using opto-electronic devicesInstrumentsComplex amplitudeNAND logic

The invention discloses a universal linear optical all-optical logic gate and an implement method thereof. According to the universal linear optical all-optical logic gate, a first logic input port, asecond logic input port and an invariant input port are adopted and connected to a main waveguide through first to third waveguides respectively, the main waveguide is connected to an output port, and therefore an all-optical logic gate structure is formed; the light intensity of first excitation light, the light intensity of second excitation light and the light intensity of third excitation light are adjusted separately, the phase difference from the first excitation light to the third excitation light is adjusted, optical-field complex amplitude which is contributed by the first and secondlogic input ports and the invariant input port to the output port is controlled, and therefore seven kinds of different linear optical all-optical logic gates are achieved on the single all-optical logic gate structure; regarding OR-logic gates, NOT-logic gates, XOR-logic gates, XNOR-logic gates and NAND-logic gates, under the two conditions that the output sates of the linear optical all-opticallogic gates are logic '1' and logic '0', theoretically, the maximum output signal beam intensity ratio is infinity.

Owner:PEKING UNIV

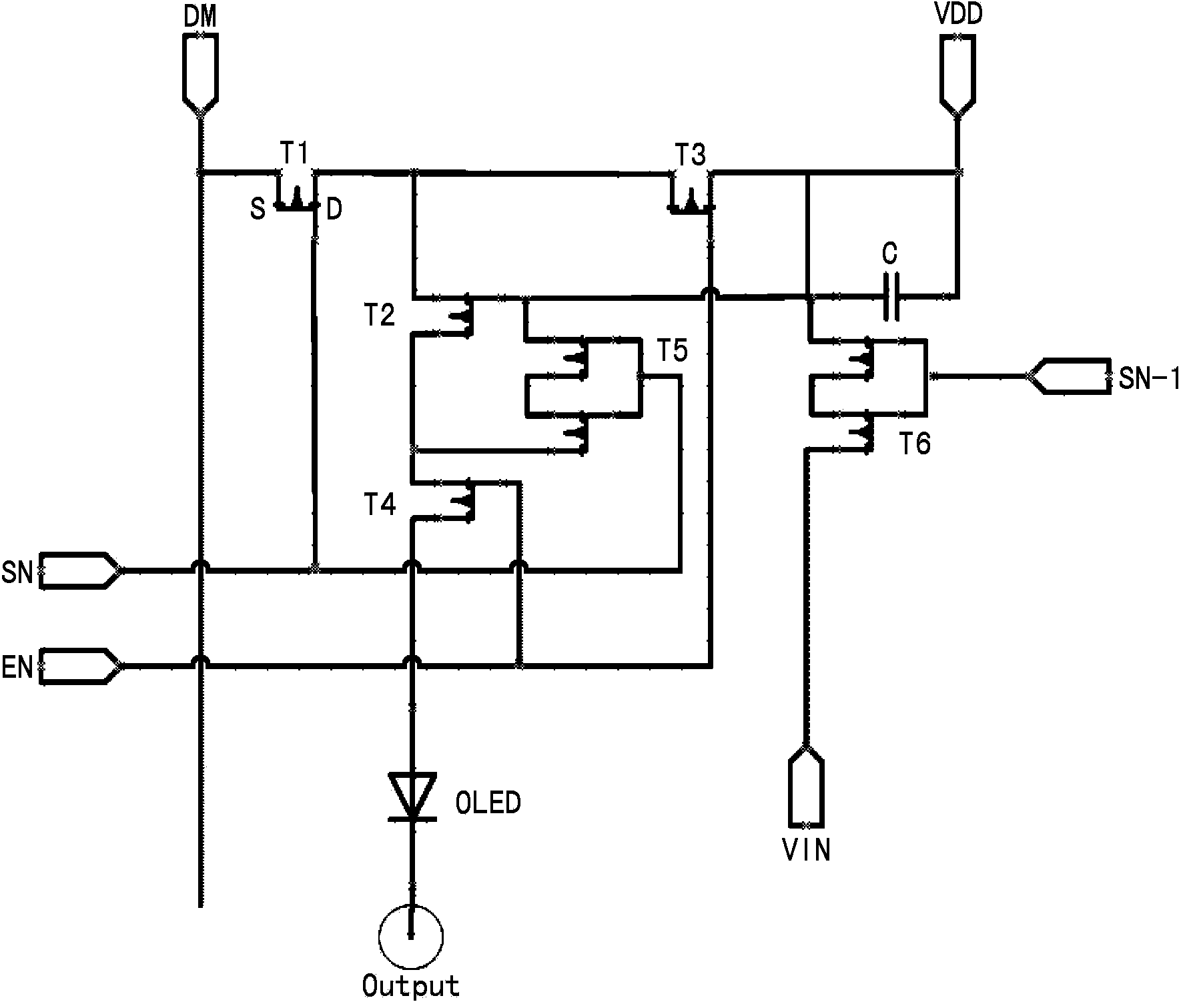

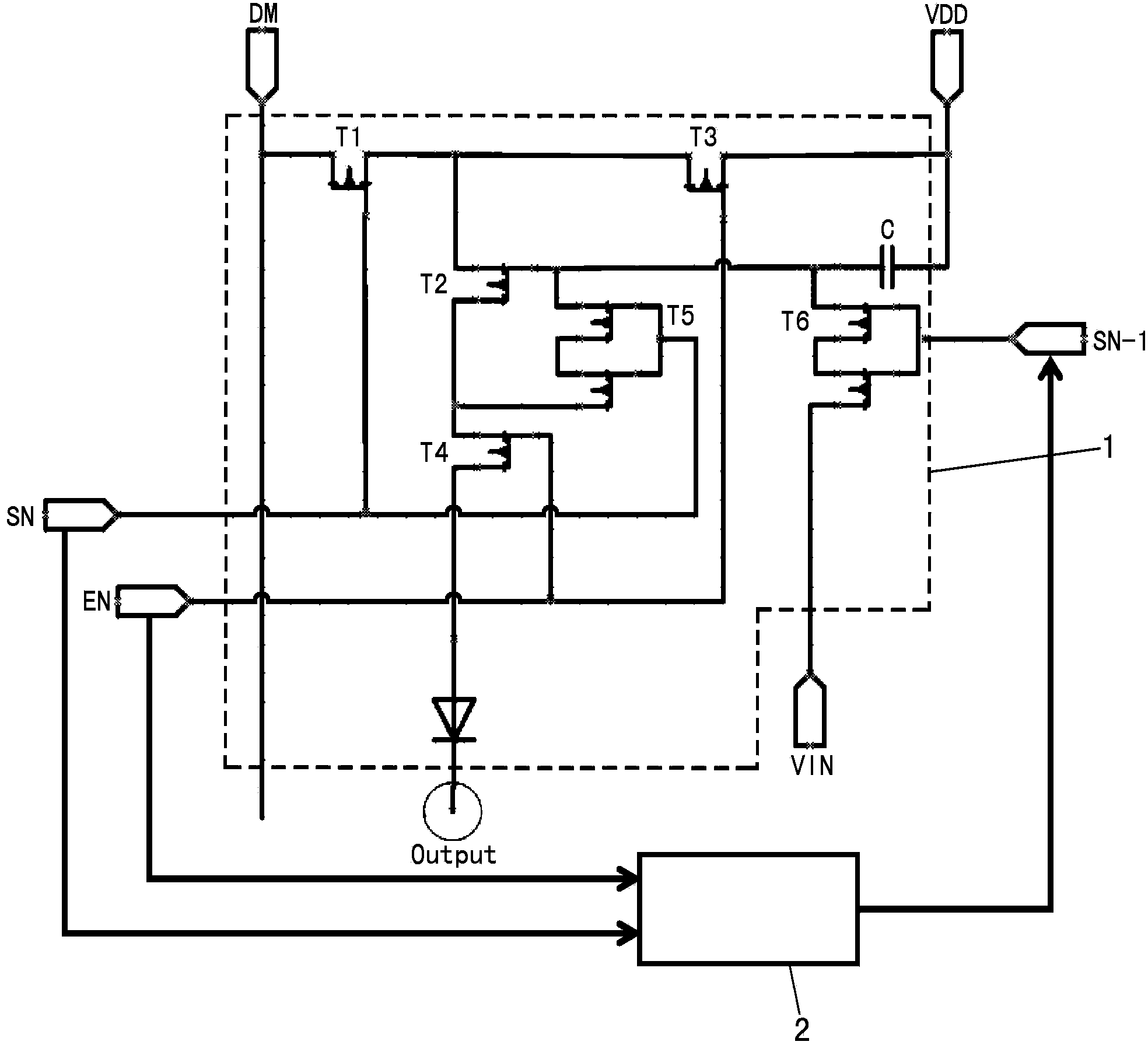

Pixel test circuit for AMOLED

ActiveCN104036730AReduce the number of independent probesLow costStatic indicating devicesNAND logicControl signal

The invention provides a pixel test circuit for an AMOLED. The pixel test circuit comprises a pixel driving module and a NAND logic circuit module. A pixel driving circuit is connected with the power supply end, the data signal end, the current scanning signal end, the front row scanning signal end, the preset voltage end, the light-emitting control signal input end and the output end. Signals of the light-emitting control signal input end of the pixel driving module and signals of a current scanning signal input end serve as input signals of the NAND logic circuit module, and the output end of the NAND logic circuit module is connected with the front row scanning signal input end of the pixel driving module. According to the pixel test circuit for the AMOLED, when a TEG measuring machine table is utilized to perform measurement, the signals of the front row scanning signal input end do not need measuring, and accordingly the number of independent probes needed for measurement is reduced.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

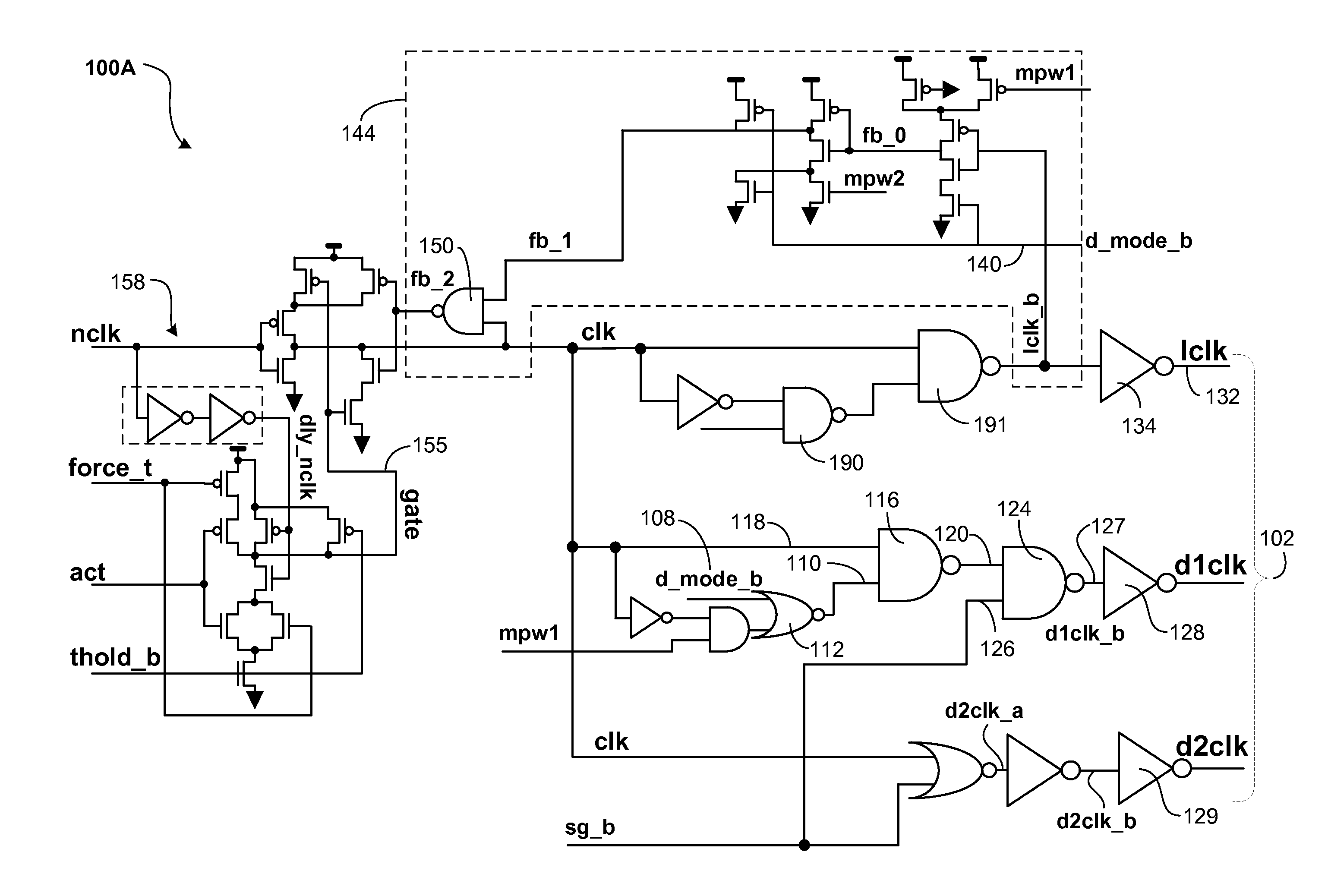

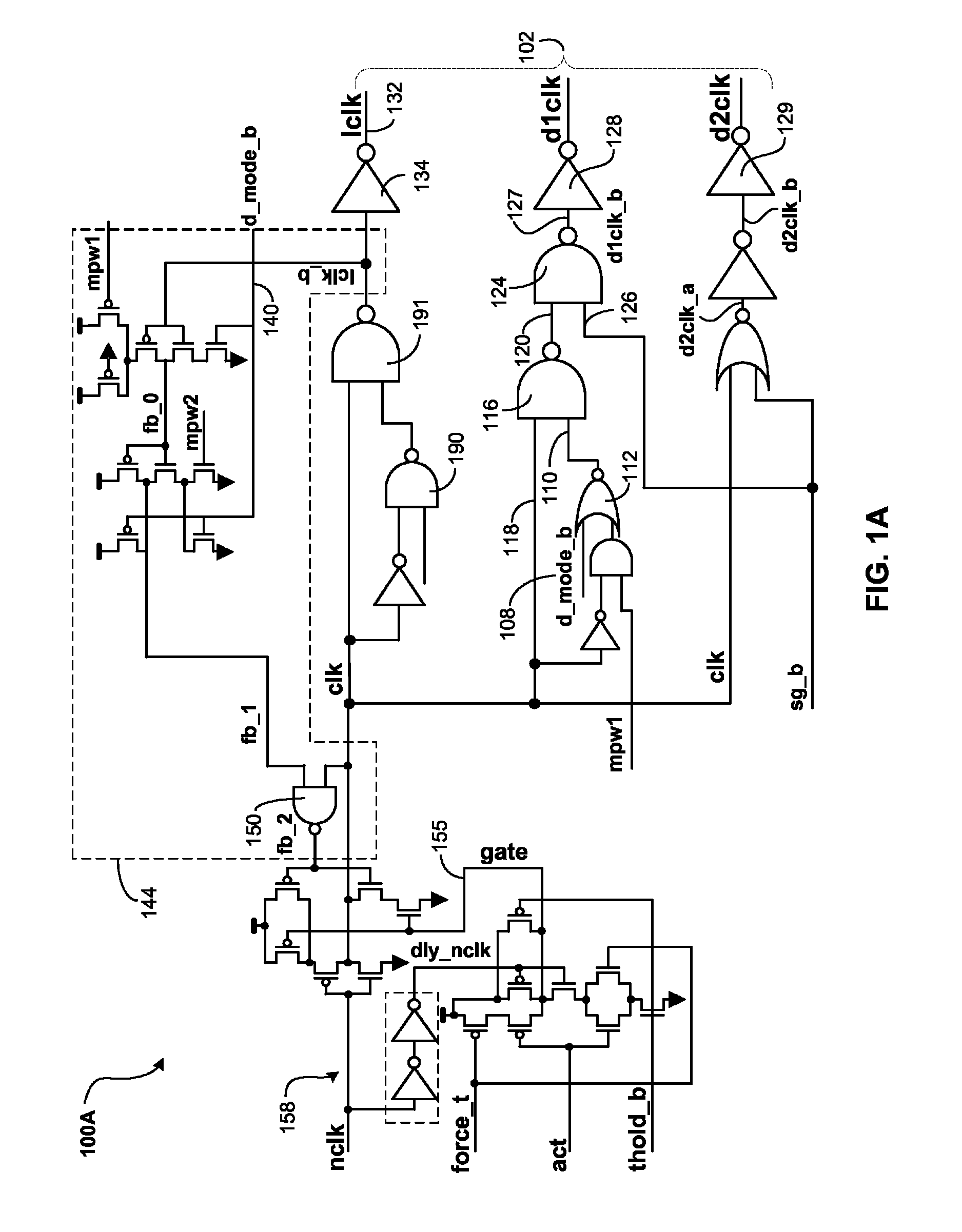

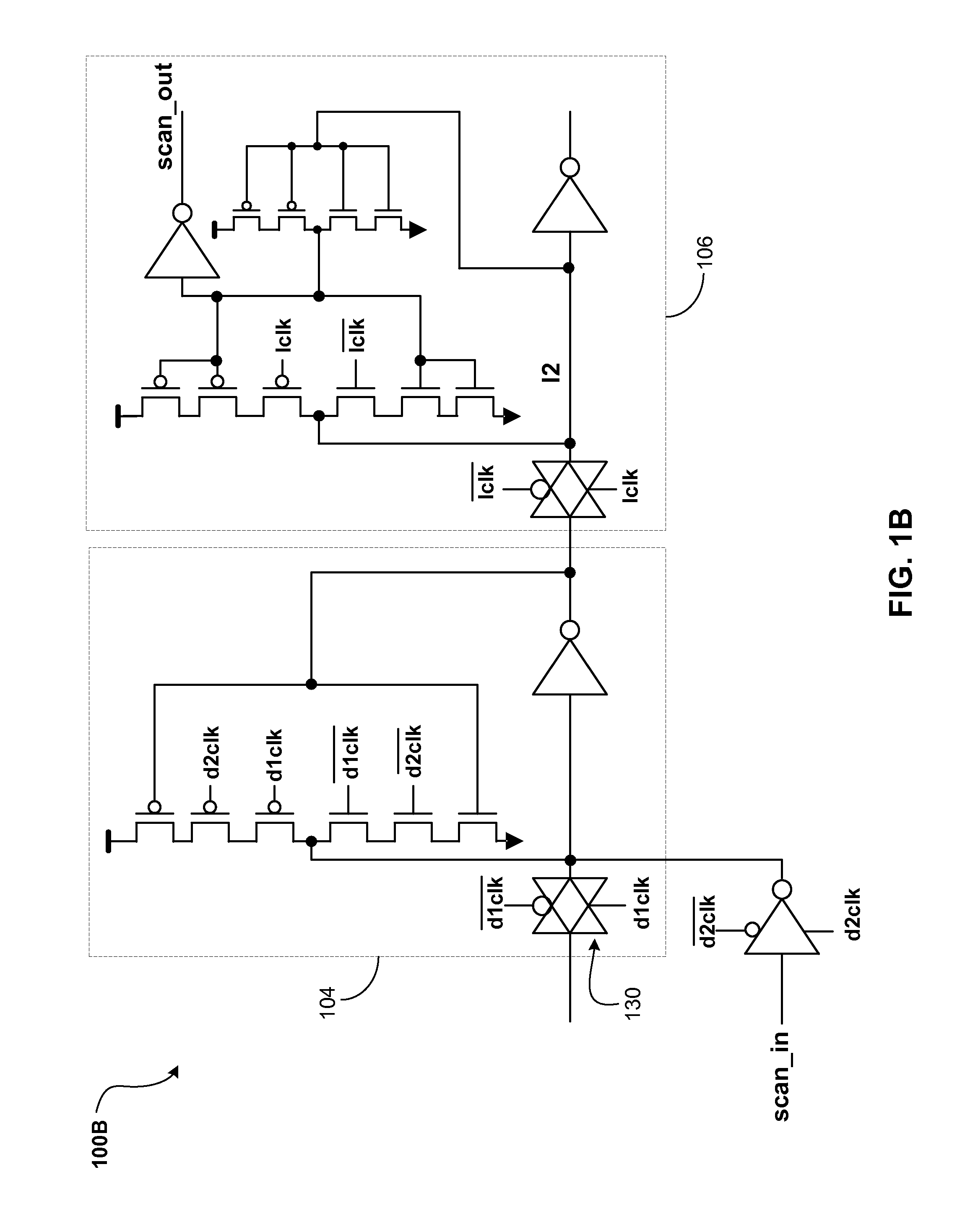

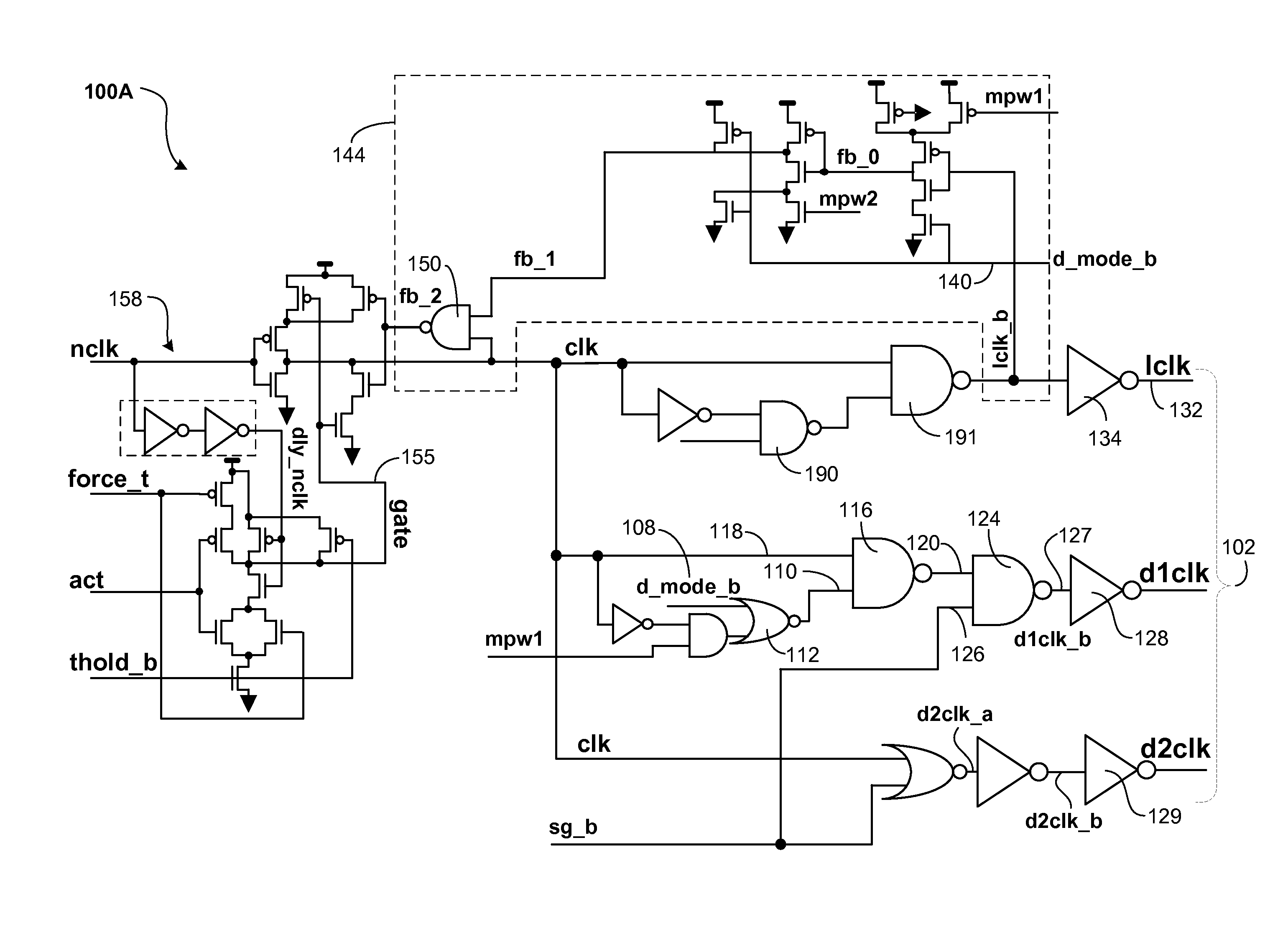

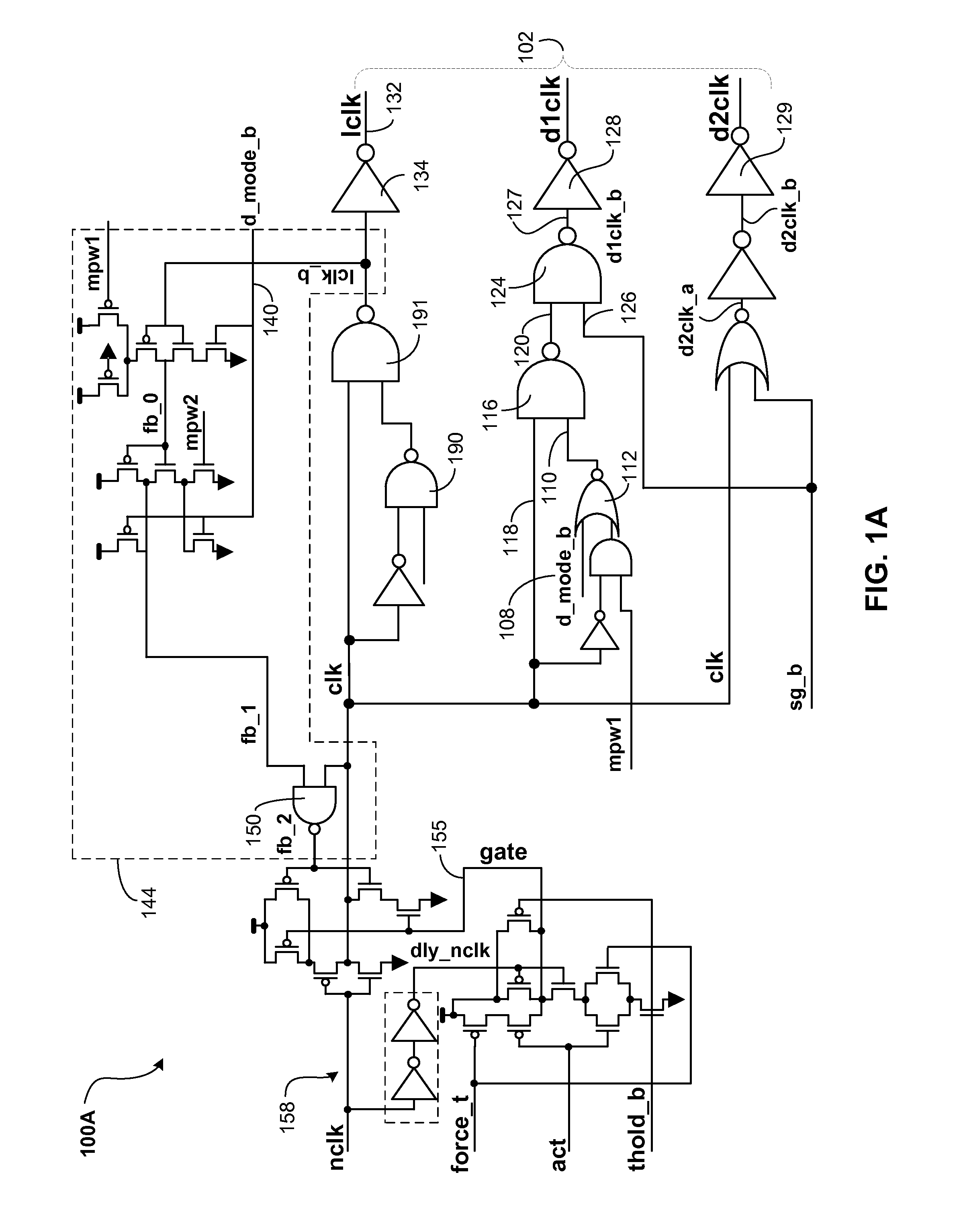

Margin improvement for configurable local clock buffer

Owner:GLOBALFOUNDRIES INC

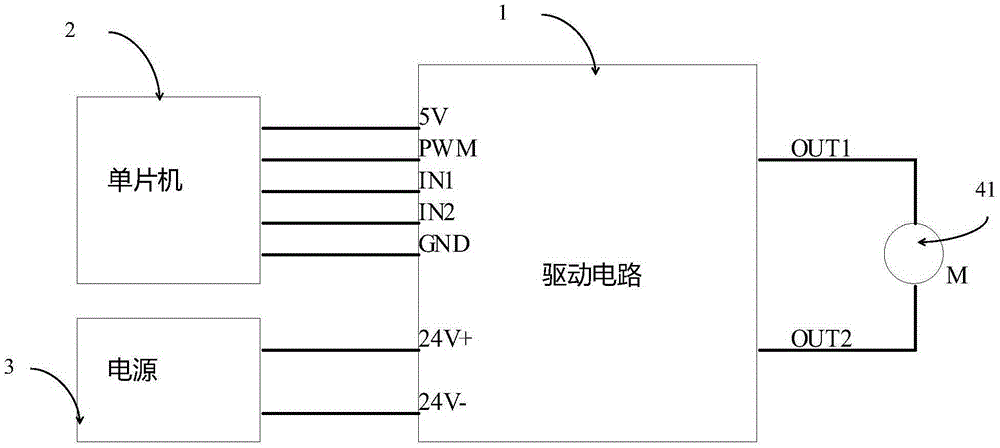

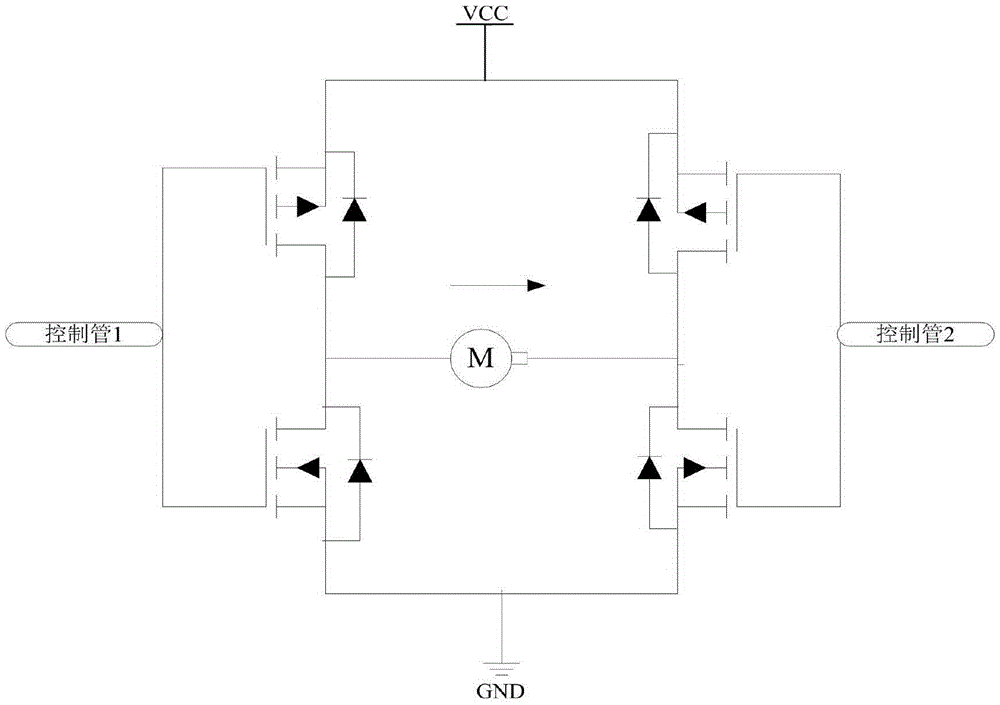

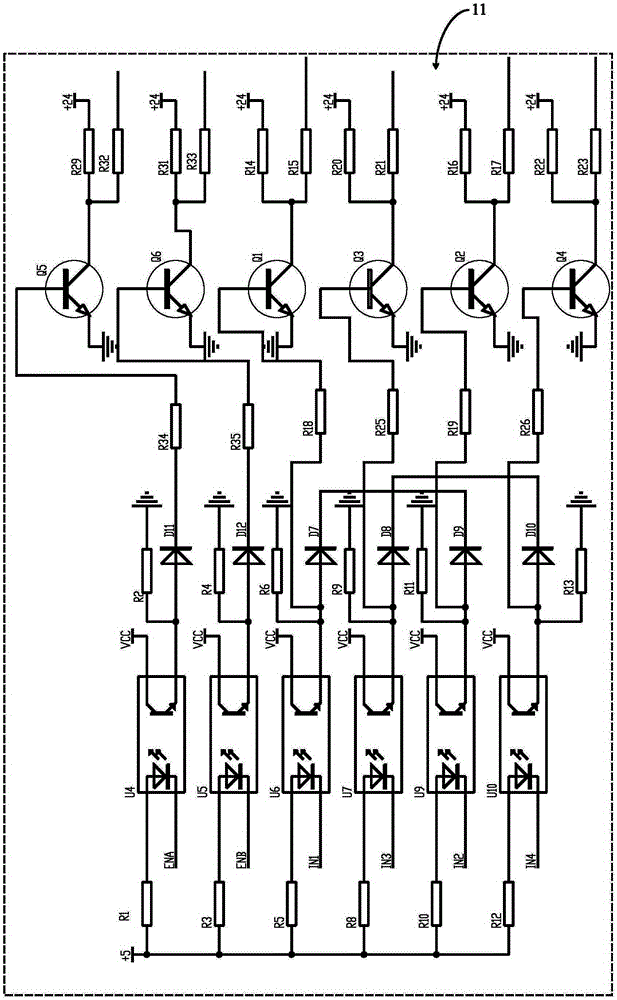

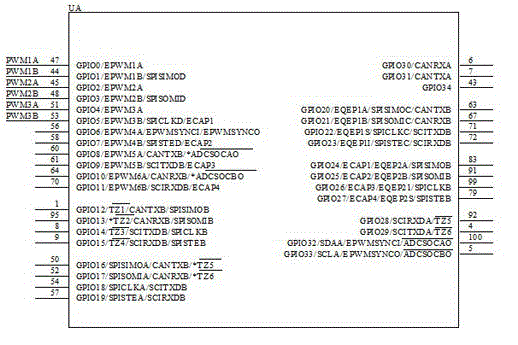

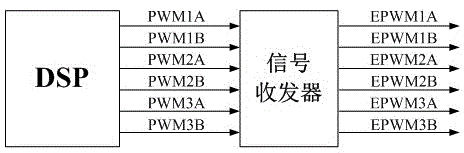

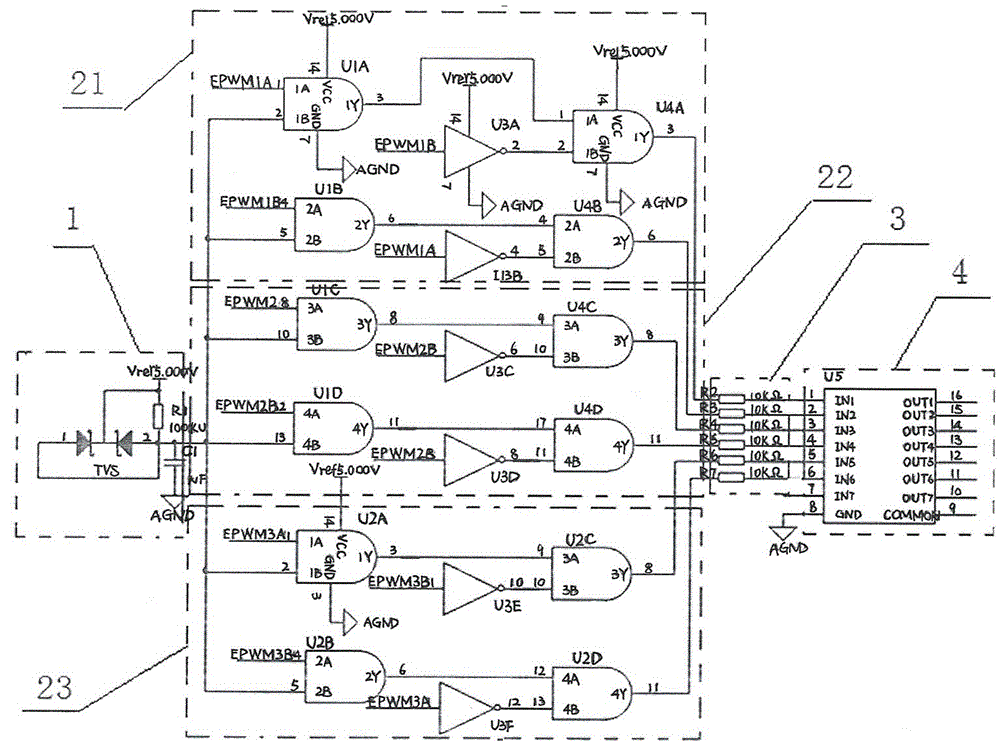

DC motor driving circuit

PendingCN106887975ASupports direct driveAdjust speedDC motor rotation controlMultiple dc dynamo-electric motors controlNAND logicLow voltage

The invention provides a DC motor driving circuit. The DC motor driving circuit comprises an H bridge circuit of which an output end is connected with a first motor and a second motor, the H bridge circuit is used for controlling the first motor and the second motor for positive rotation, negative rotation and braking; an NAND logic circuit used for controlling conduction or closing of an H bridge of the H bridge circuit, an optical coupler isolation circuit used for isolating a single-chip microcomputer control circuit from the H bridge circuit to guarantee stability of the single-chip microcomputer control circuit; and a power source circuit used for converting a high voltage into a low voltage for supply for the optical coupler isolation circuit, the NAND logic circuit and the H bridge circuit. The DC motor driving circuit is advantaged in that a sink current driving mode is utilized, direct driving of most of single-chip microcomputers is supported, the large power tube H bridge principle is employed to control positive rotation, negative rotation and braking of the motors, moreover, rotation speeds of two DC motors can be further adjusted, photoelectric isolation is employed, stability of the single-chip microcomputer control circuit is guaranteed, a driving problem of a large power DC motor is solved, and the DC motor is enabled to realize safe, stable and high-efficiency operation in various occasions.

Owner:ANHUI SANLIAN ROBOT TECH CO LTD

Margin improvement for configurable local clock buffer

A timing margin circuit of a local clock buffer circuit may include an inverter logic gate having an inverter input and an inverter output, whereby the inverter input receives an input clock signal. A NAND logic gate includes a first NAND input coupled to the inverter output, a second NAND input, and a NAND output. The circuit also includes a logic device having a first logic device input that is coupled to the inverter output, a second logic device input that receives a mode selection signal, and a logic device output that couples to the second NAND input, whereby the NAND logic gate generates a first time delayed input clock signal and a second time delayed input clock signal, such that the first and the second time delayed input clock signal control a falling edge transition of a local clock signal derived from the input clock signal.

Owner:GLOBALFOUNDRIES INC

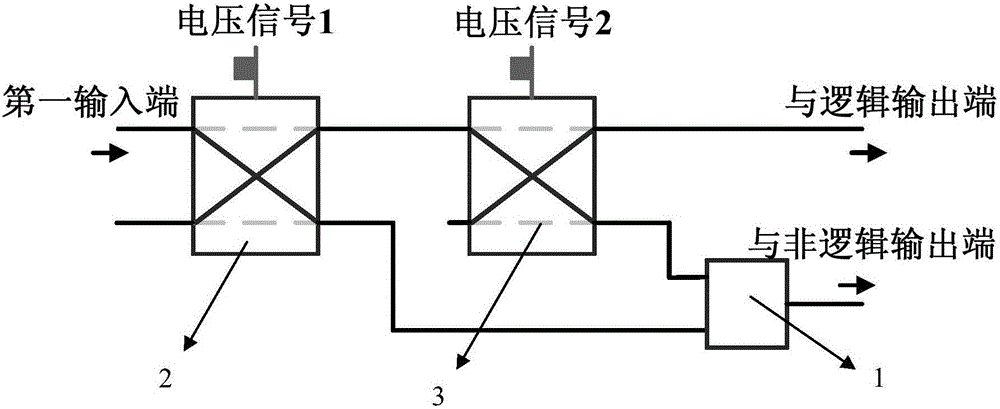

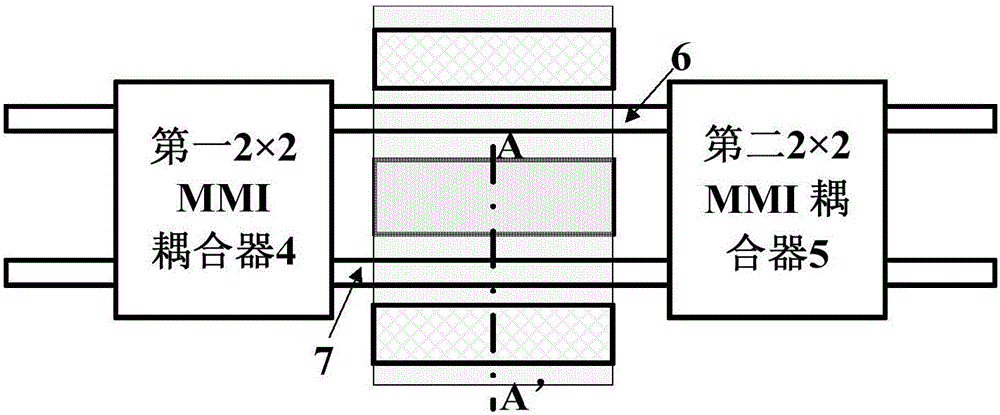

Silicon-based electro-optic logic AND/NAND gate

ActiveCN105759534AHigh extinction ratioLogic circuits using opto-electronic devicesOptical bistable devicesNAND logicBroadband

The invention discloses a silicon-based electro-optic logic AND / NAND gate. The silicon-based electro-optic logic AND / NAND gate comprises a first 2*2MZI type electro-optic switch, a second 2*2MZI type electro-optic switch and a 2*1MMI coupler. Each of the first and second 2*2MZI type electro-optic switches comprises a first input end, a second input end, a first output end and a second output end, and the 2*1MMI coupler comprises a first input end, a second input and an output end. The first output end of the first 2*2MZI type electro-optic switch is connected with the first input end of the second 2*2MZI type electro-optic switch, and the first output end of the second 2*2MZI type electro-optic switch is an AND logic output end. The second output end of the second 2*2MZI type electro-optic switch is connected with the first input end of the 2*1MMI coupler, the second output end of the first 2*2MZI type electro-optic switch is connected with the second input end of the 2*1MMI coupler, and the output end of the 2*1MMI coupler is an NAND logic output end. The silicon-based electro-optic logic AND / NAND gate has the advantages of high extinction ratio, high speed, large broadband and large fabrication tolerance.

Owner:NINGBO UNIV

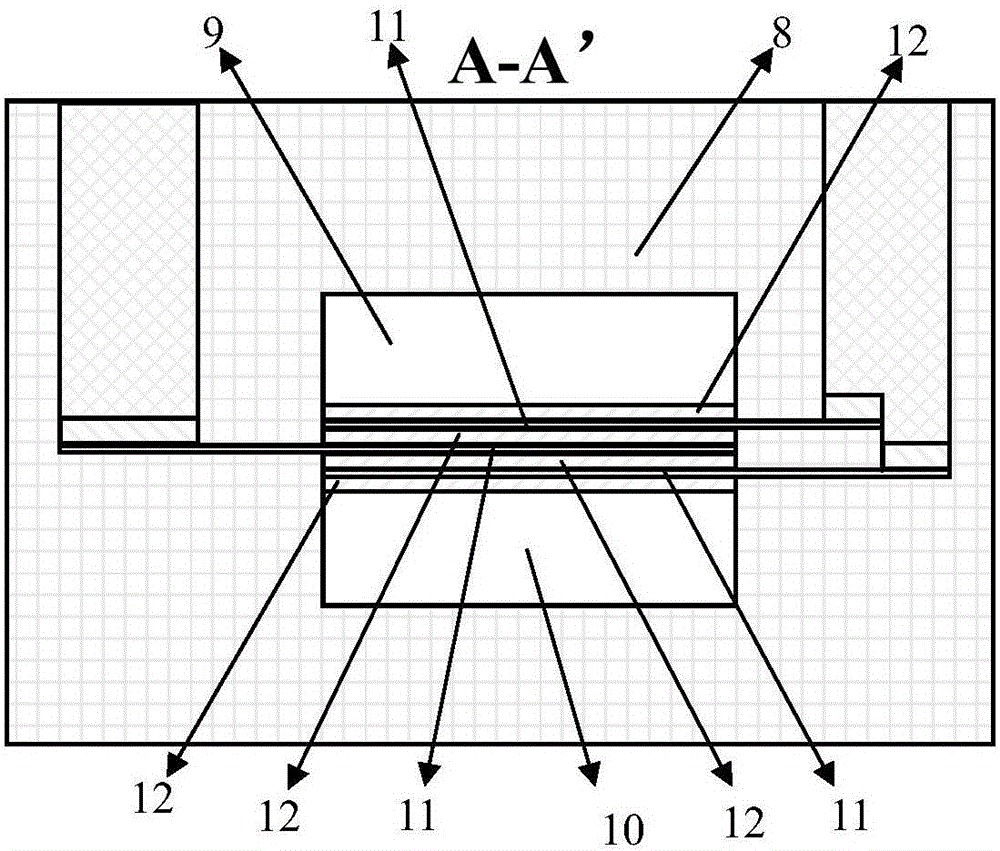

Insulated Gate Bipolar Transistor (IGBT) driver interlock circuit with power-on time delay function

InactiveCN105048794AAvoid Simultaneous On ConditionsAvoid short circuit failurePower conversion systemsDriver circuitElectricity

The invention discloses an IGBT driver interlock circuit with a power-on time delay function, including a time delay circuit module 1, an NAND logic circuit module, a plurality of resistors 3s, an inverting drive 4 which are successively connected; the NAND logic circuit module includes a plurality of NAND logic circuit groups composed of an upper pipe and a lower pipe. According to the invention, a drive signal which is sent by a Digital Signal Processor (DSP) chip is subject to a certain time delay, and then is output to a drive board for driving an IGBT module so as to enable the IGBT to have a reliable turn-off within the time period. The circuit is also provided with an interlock circuit, and constitutes a logic relationship with an NAND gate chip such that once one signal turns to be a high level signal, another signal will be a low level signal,thereby guaranteeing the upper and lower pipes of the IGBT are not powered on at the same time and preventing short circuit breakdown of the IGBT. The IGBT driver interlock circuit with the power-on time delay function precludes the short circuit breakdown of the IGBT, effectively protects the bridge arm of the IGBT, and increases the reliability of the IGBT driver circuit.

Owner:ZT YUPIN TECH CO LTD

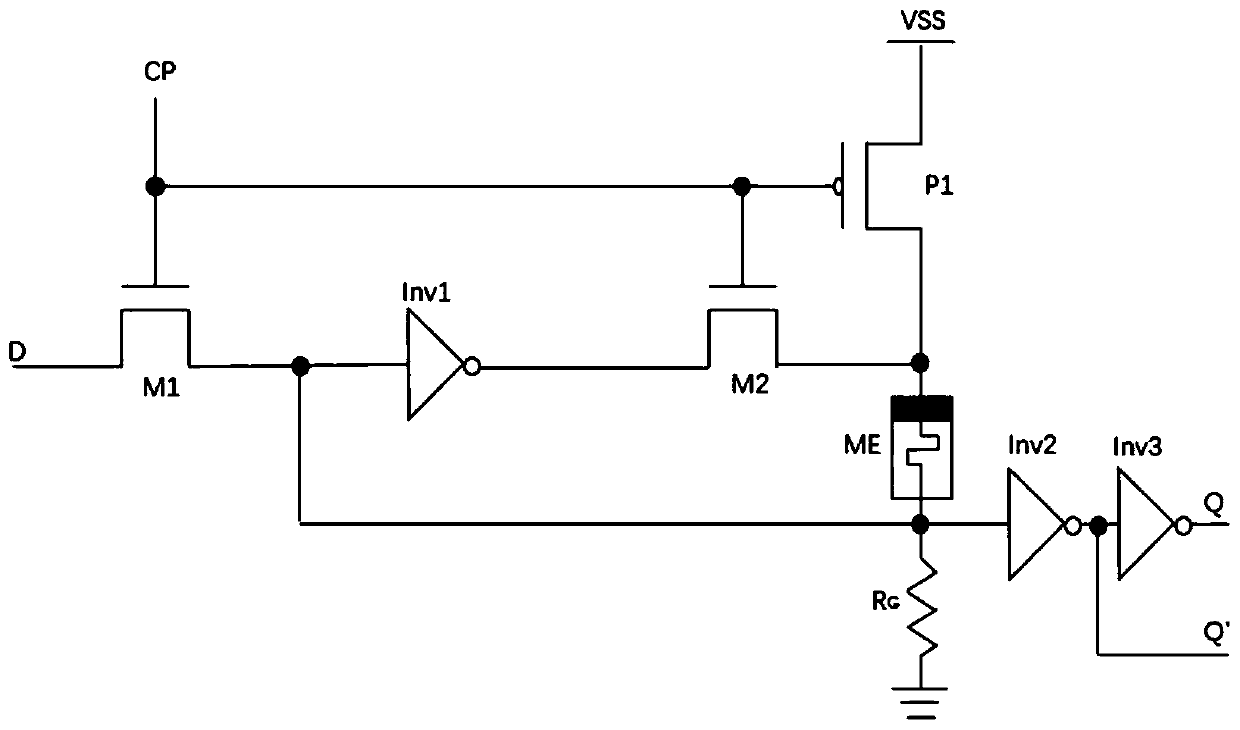

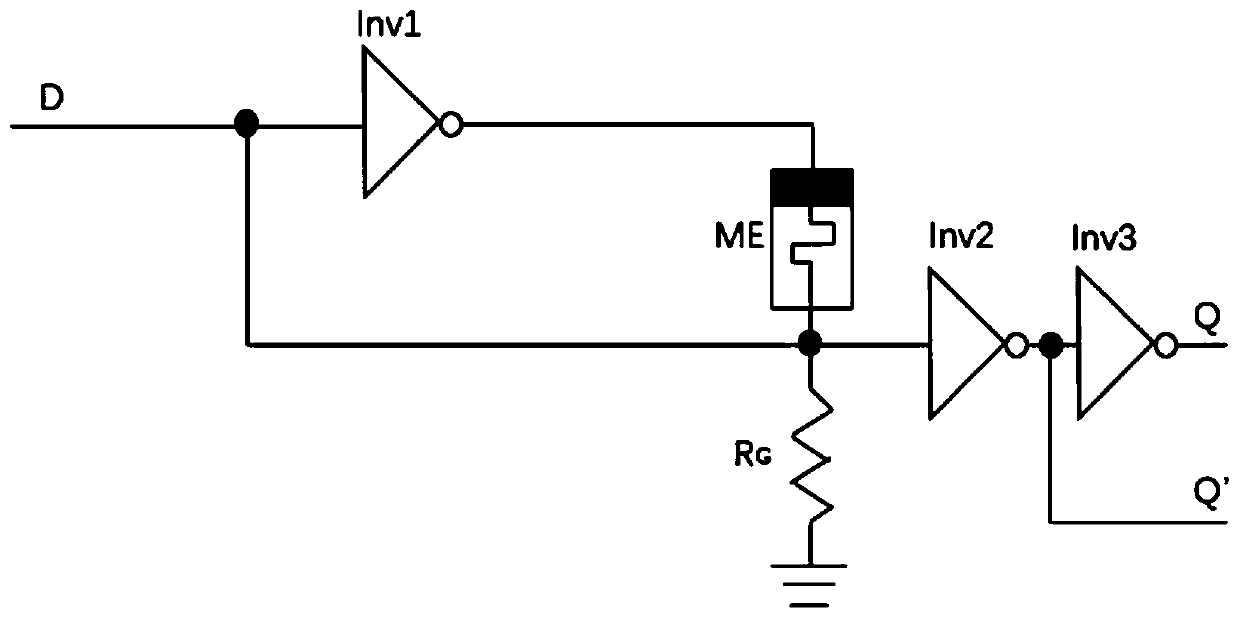

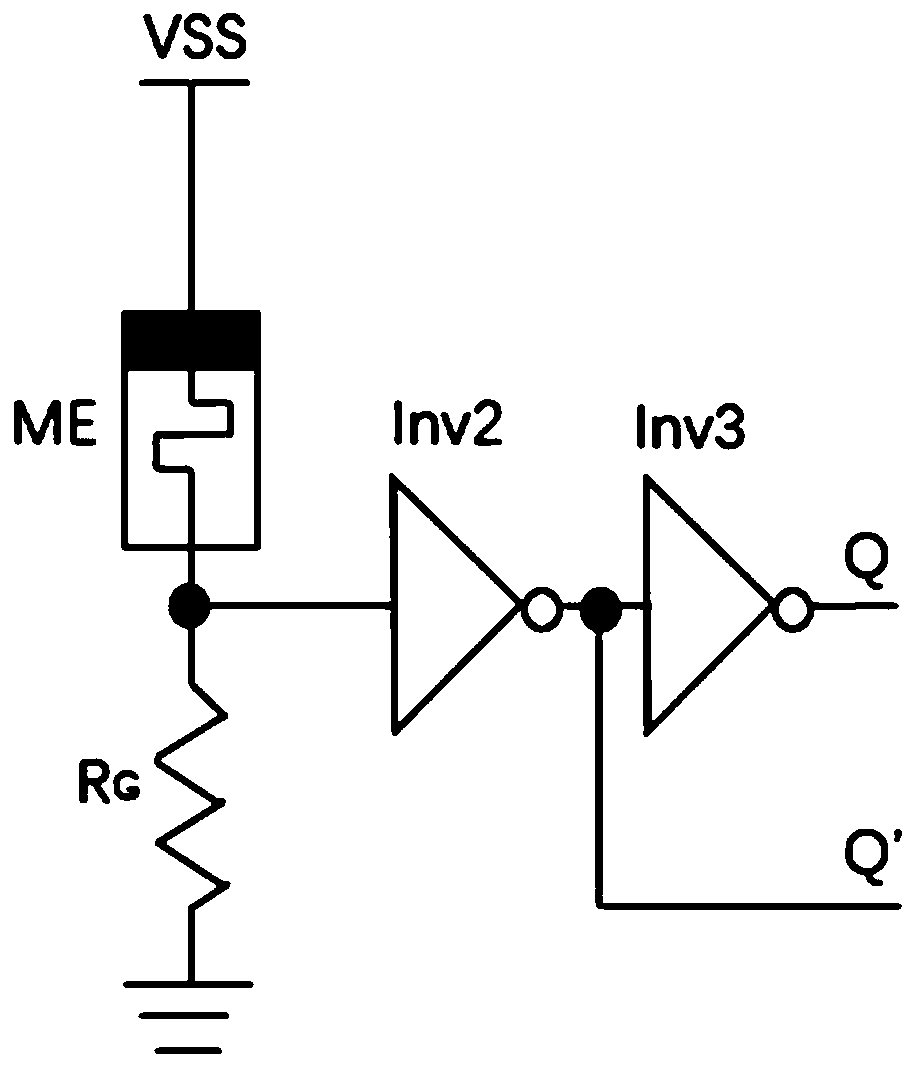

Level-triggered D flip-flop circuit based on resistive memory

PendingCN111130508ASimple structureStructural refinementElectric pulse generator detailsEnergy efficient computingMOSFETNAND logic

The invention discloses a level triggered D flip-flop circuit based on a resistive memory. The level triggered D flip-flop circuit comprises an MOSFET, a first memristor, a resistor, a first phase inverter and a second phase inverter. The source electrode of the MOSFET is electrically connected with an input signal; the grid electrode of the MOSFET is electrically connected with a clock pulse signal; the drain electrode of the MOSFET is electrically connected to the positive electrode of the first memristor, one end of the resistor and the input end of the first inverter. The output end of thefirst phase inverter is electrically connected to the input end of the second phase inverter; the output end of the second phase inverter is electrically connected with an output signal; the negativeelectrode of the first memristor is electrically connected to the output end of the NAND logic circuit used for conducting auxiliary setting on the first memristor, one input end of the NAND logic circuit is electrically connected with an input signal, the other input end of the NAND logic circuit is electrically connected with a clock pulse signal, and the other end of the resistor is grounded.According to the invention, the structure of the circuit is simpler and more refined, and the layout area has greater advantages.

Owner:SUZHOU UNIV

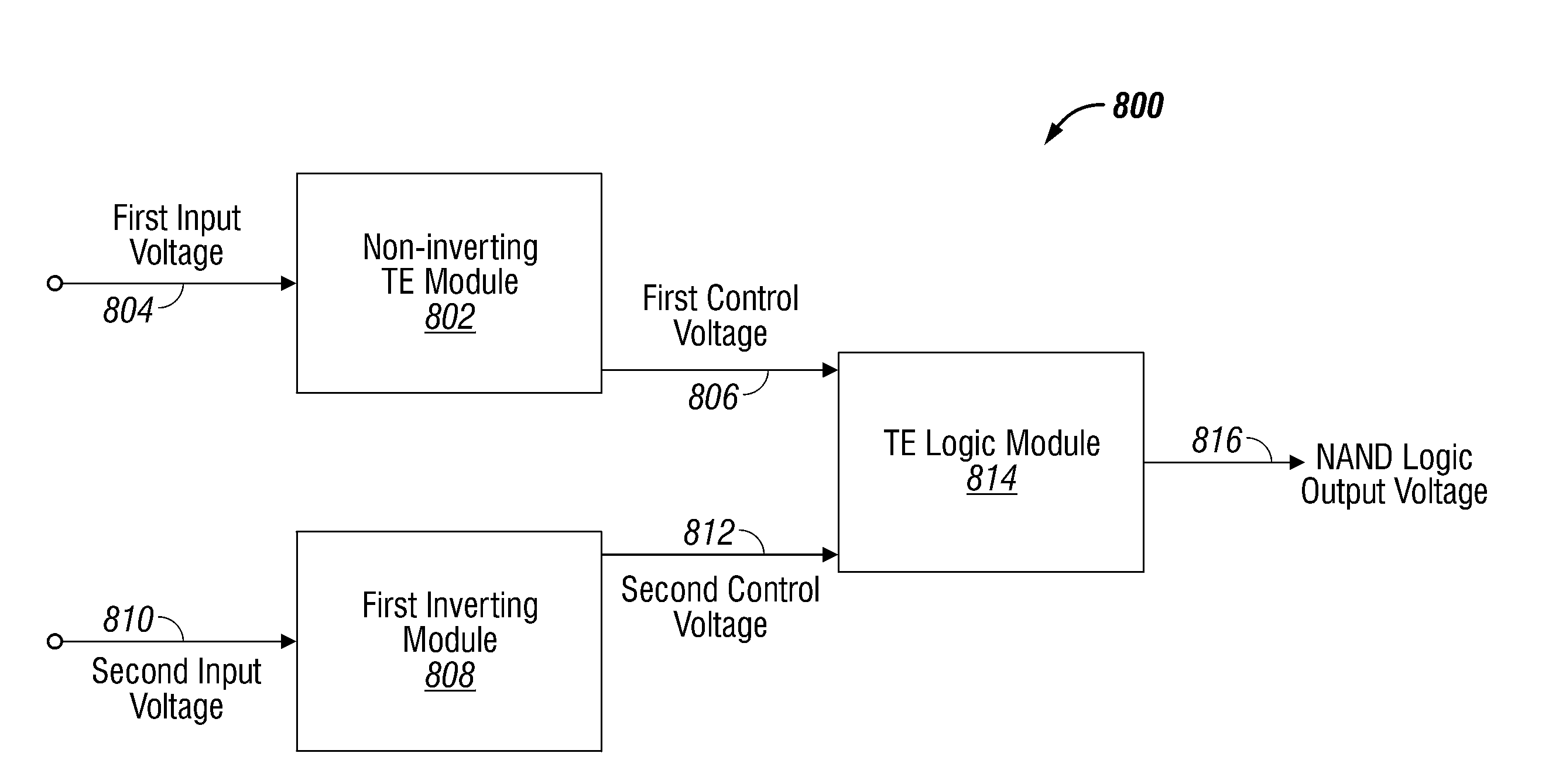

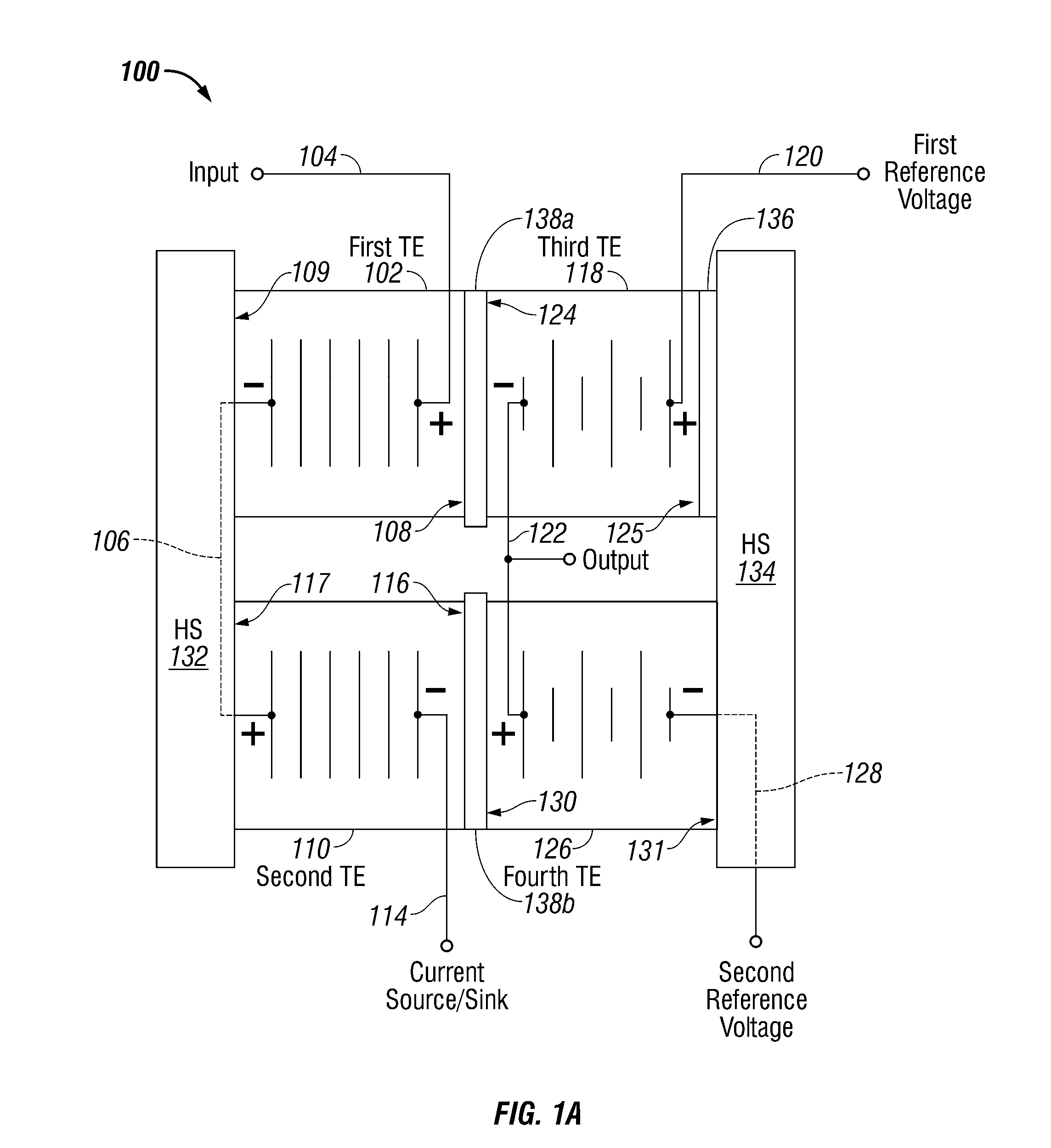

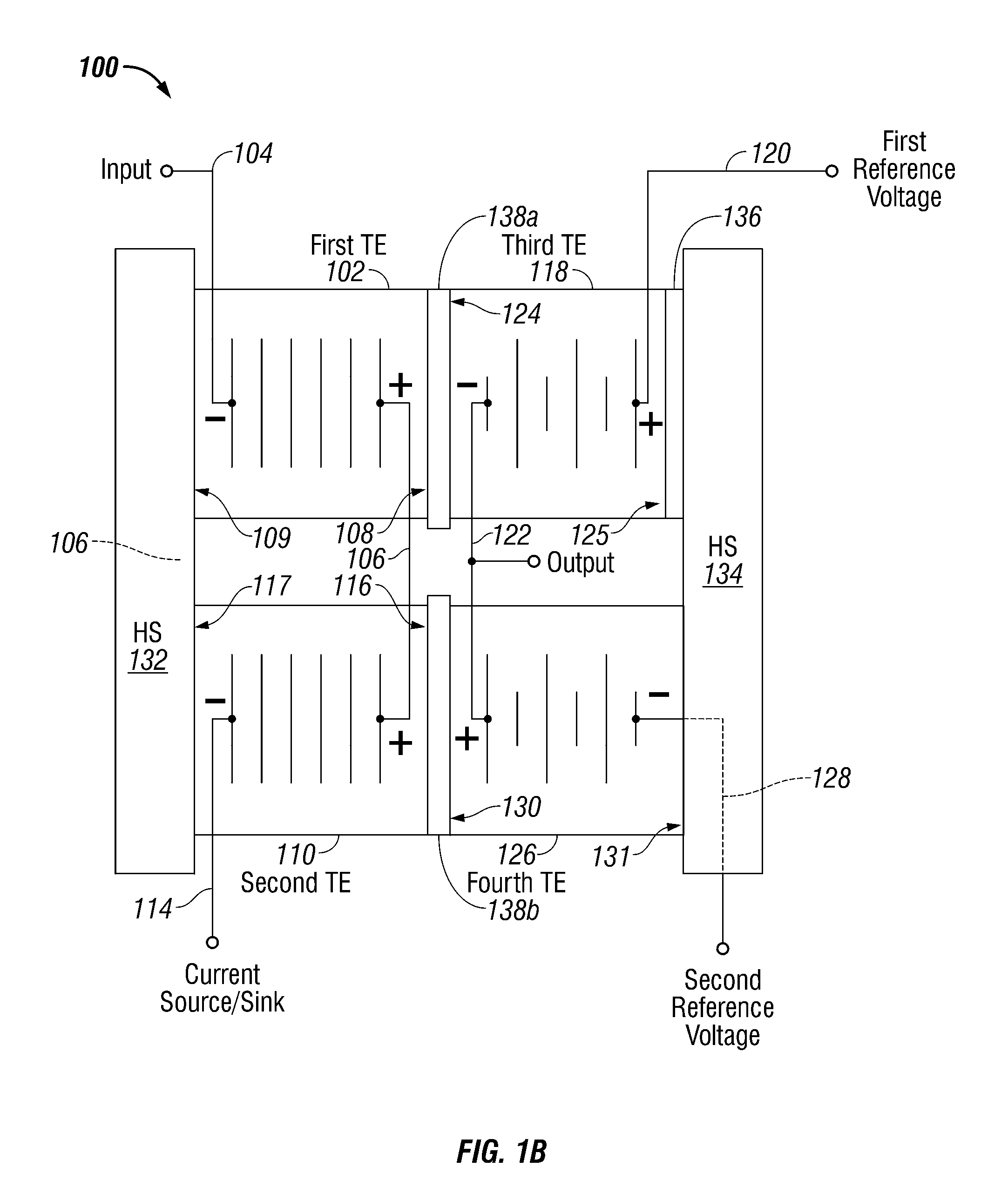

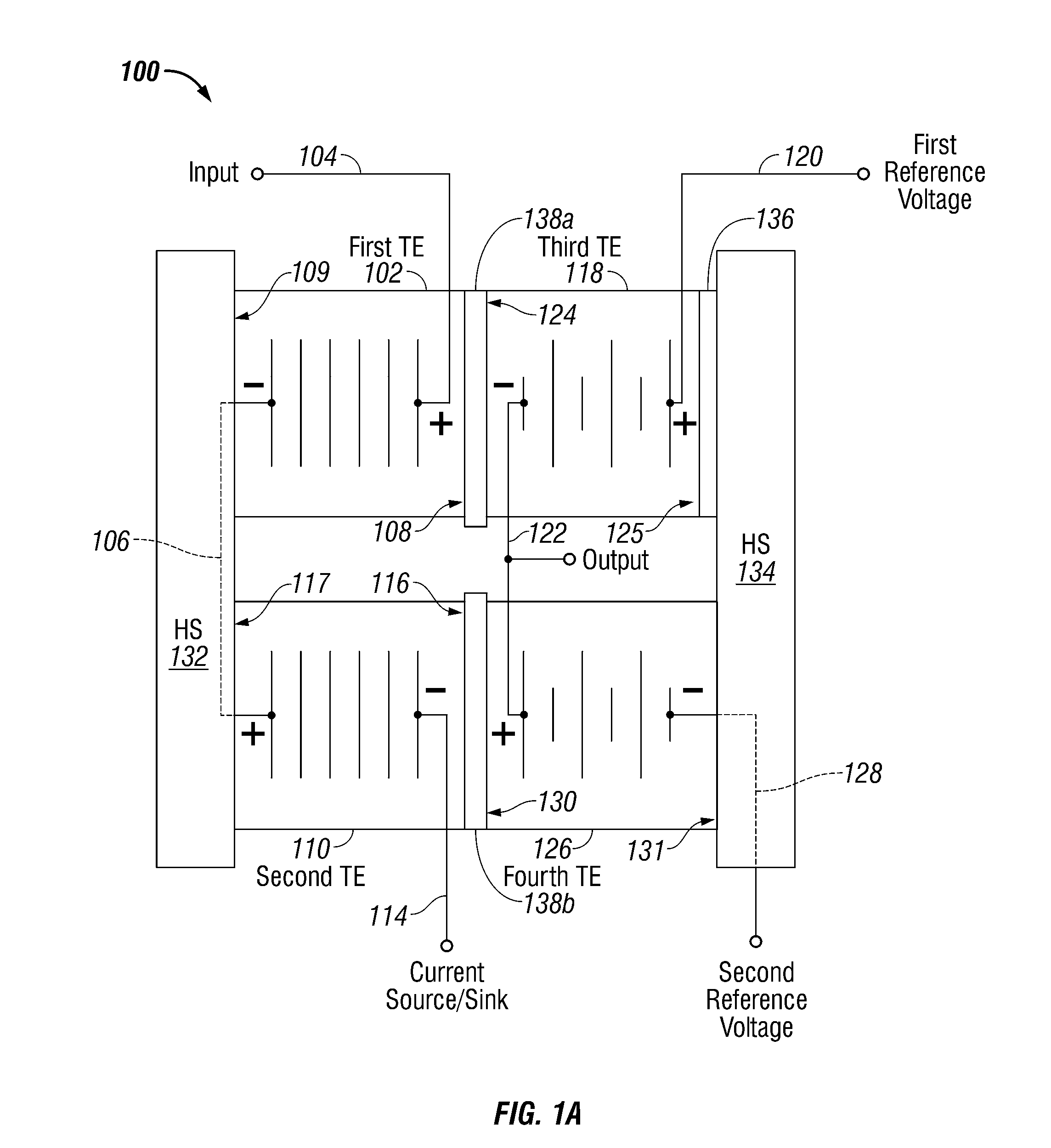

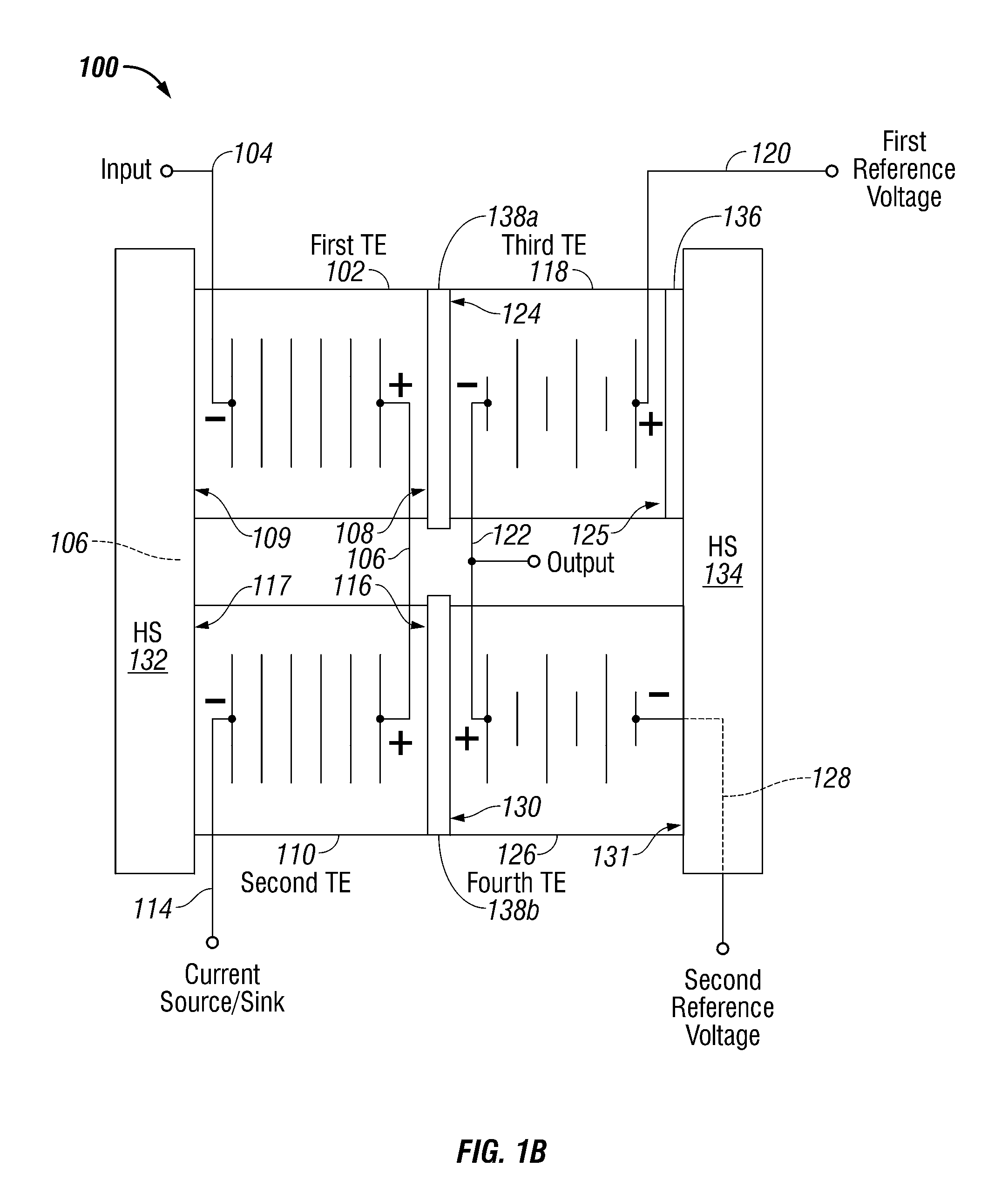

Thermal electric NAND gate

InactiveUS7602218B2Low volumeLess overall consumptionLogic circuits characterised by logic functionLogic circuits using superconductive devicesNAND logicVoltage

A thermal electric (TE) binary NAND gate logic circuit is provided with a method for NAND logic gating. The method accepts a first input voltage representing an input binary logic state and generates a first thermal electric (TE) temperature in response to the first input voltage. A second input voltage is accepted representing an input binary logic state, and a second TE temperature is generated in response to the second input voltage. In response to the first and second TE temperatures, a NAND logic state output voltage is generated. More explicitly, a first control voltage is generated in response to the first TE temperature, and a second control voltage is generated in response to the second TE temperature. Then, a third TE temperature is generated in response to the first and second control voltages, which in turn generates the output voltage.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

Scan driving circuit and NAND logic operation circuit thereof

ActiveUS20170229081A1Suitable for integrationLogic circuits characterised by logic functionStatic indicating devicesCMOSNAND logic

The invention provides a scan driving circuit for an oxide semiconductor thin film transistor and a NAND logic operation circuit thereof. The NAND logic operation circuit includes: a first inverter and a second inverter applied to a pull-down holding circuit of a GOA circuit, and multiple transistors. The invention uses the combination of NFTF and inverter to replace a function of original PMOS elements and thereby achieves characteristics similar to that of the original CMOS NAND operation circuit. Accordingly, the invention can solve the design problem of IGZO TFT single type of device logic operation circuit and thus is more suitable for integrating a large scale digital integrated circuit on a liquid crystal display device.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Thermal Electric NAND Gate

InactiveUS20090206883A1Less overall consumptionHigh densityLogic circuits characterised by logic functionLogic circuits using superconductive devicesNAND logicVoltage

A thermal electric (TE) binary NAND gate logic circuit is provided with a method for NAND logic gating. The method accepts a first input voltage representing an input binary logic state and generates a first thermal electric (TE) temperature in response to the first input voltage. A second input voltage is accepted representing an input binary logic state, and a second TE temperature is generated in response to the second input voltage. In response to the first and second TE temperatures, a NAND logic state output voltage is generated. More explicitly, a first control voltage is generated in response to the first TE temperature, and a second control voltage is generated in response to the second TE temperature. Then, a third TE temperature is generated in response to the first and second control voltages, which in turn generates the output voltage.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

Multi-function differential logic gate

InactiveUS20050242842A1Control inputLogic circuits characterised by logic functionPulse automatic controlDifferential phaseNAND logic

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

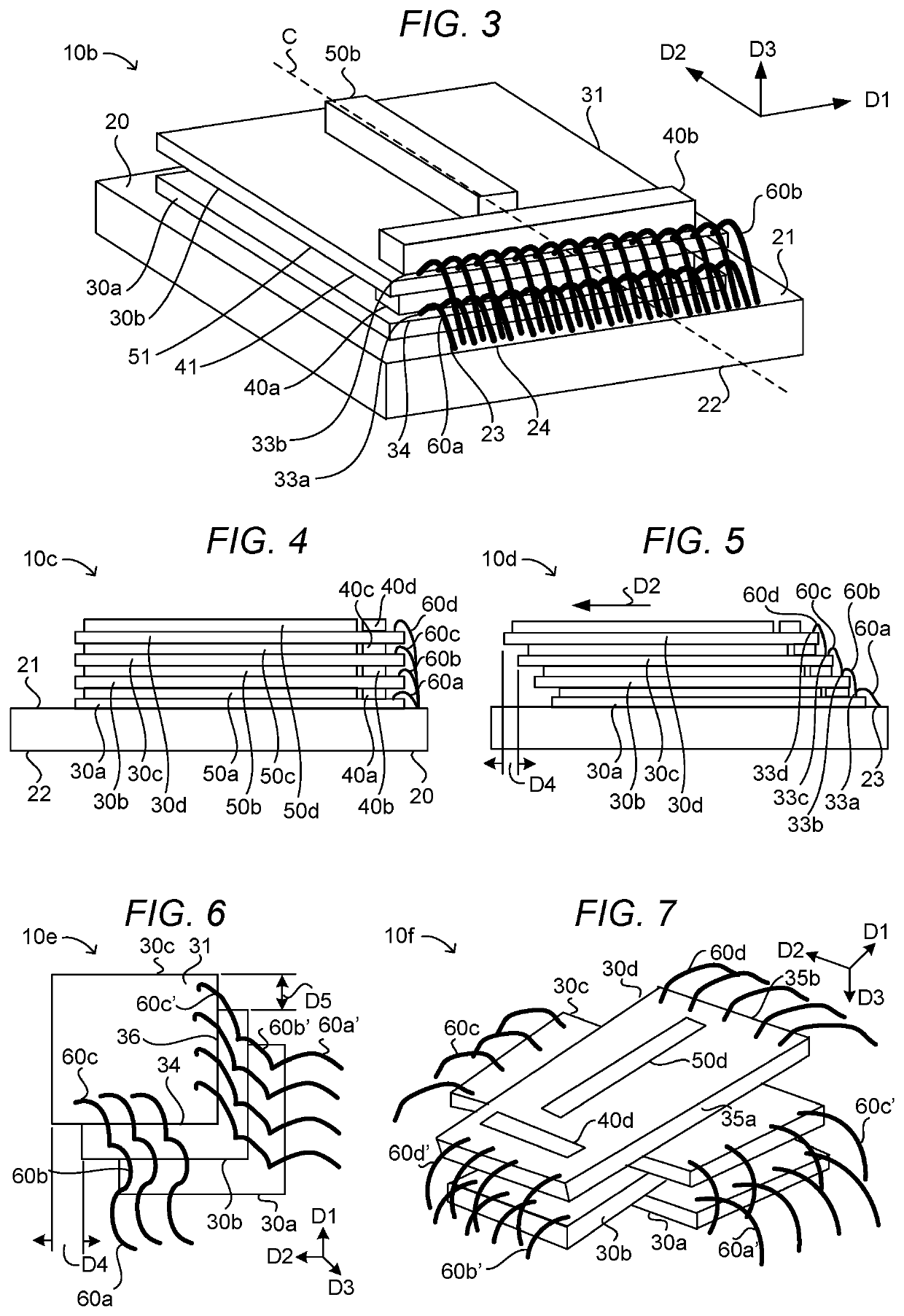

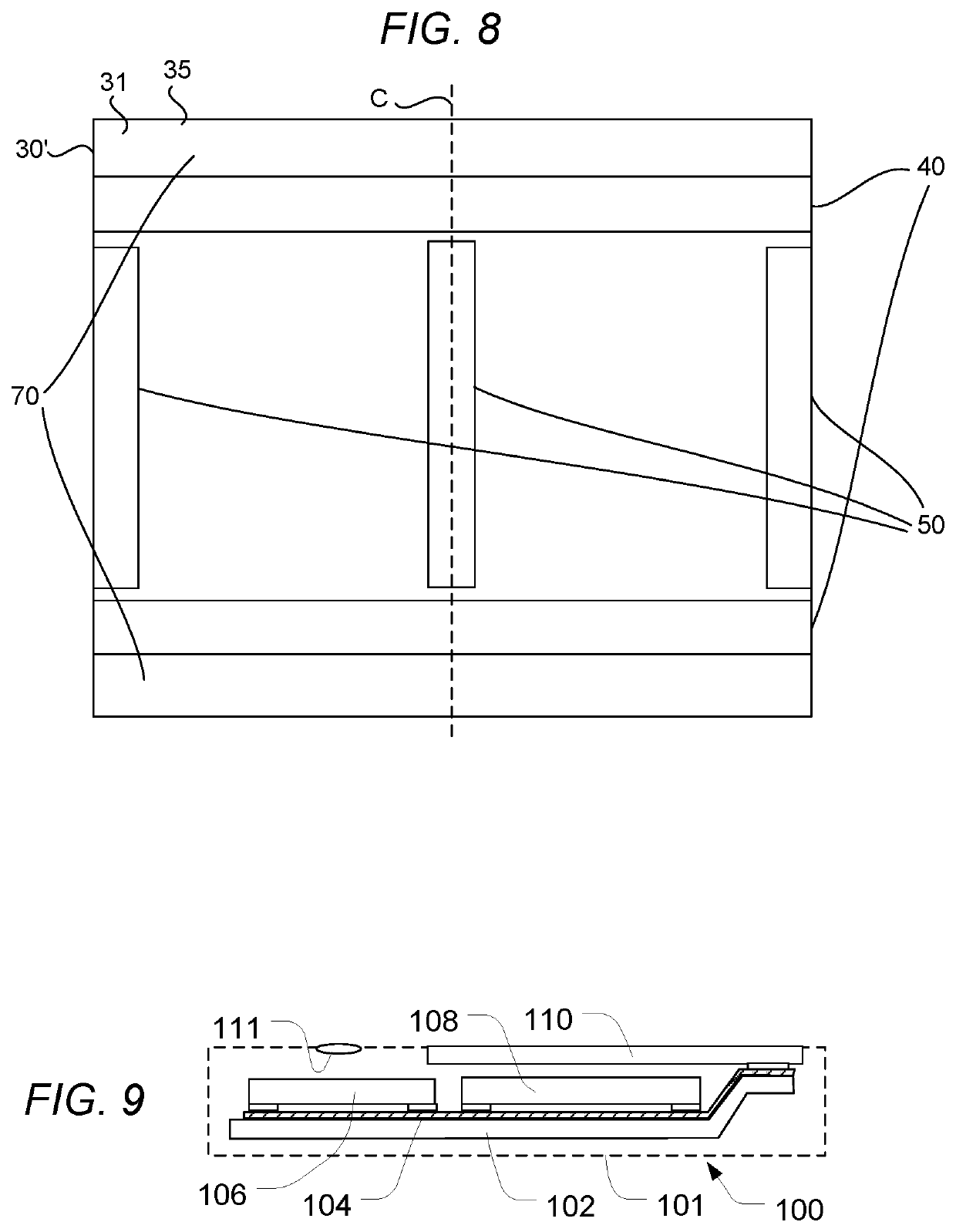

Abstracted NAND logic in stacks

A microelectronic package may include a substrate having first and second surfaces each extending in first and second directions, a NAND wafer having a memory storage array, a bitline driver chiplet configured to function as a bitline driver, and a wordline driver chiplet configured to function as a wordline driver. The NAND wafer may be coupled to the first surface of the substrate, and the bitline and wordline driver chiplets may each be mounted to a front surface of the NAND wafer. The NAND wafer may have element contacts electrically connected with conductive structure of the substrate. The bitline and wordline driver chiplets may be elongated along the first and second directions, respectively. Front surfaces of the bitline driver chiplet and the wordline driver chiplet may be arranged in a single common plane and may be entirely contained within an outer periphery of the front surface of the NAND wafer.

Owner:ADEIA SEMICON INC

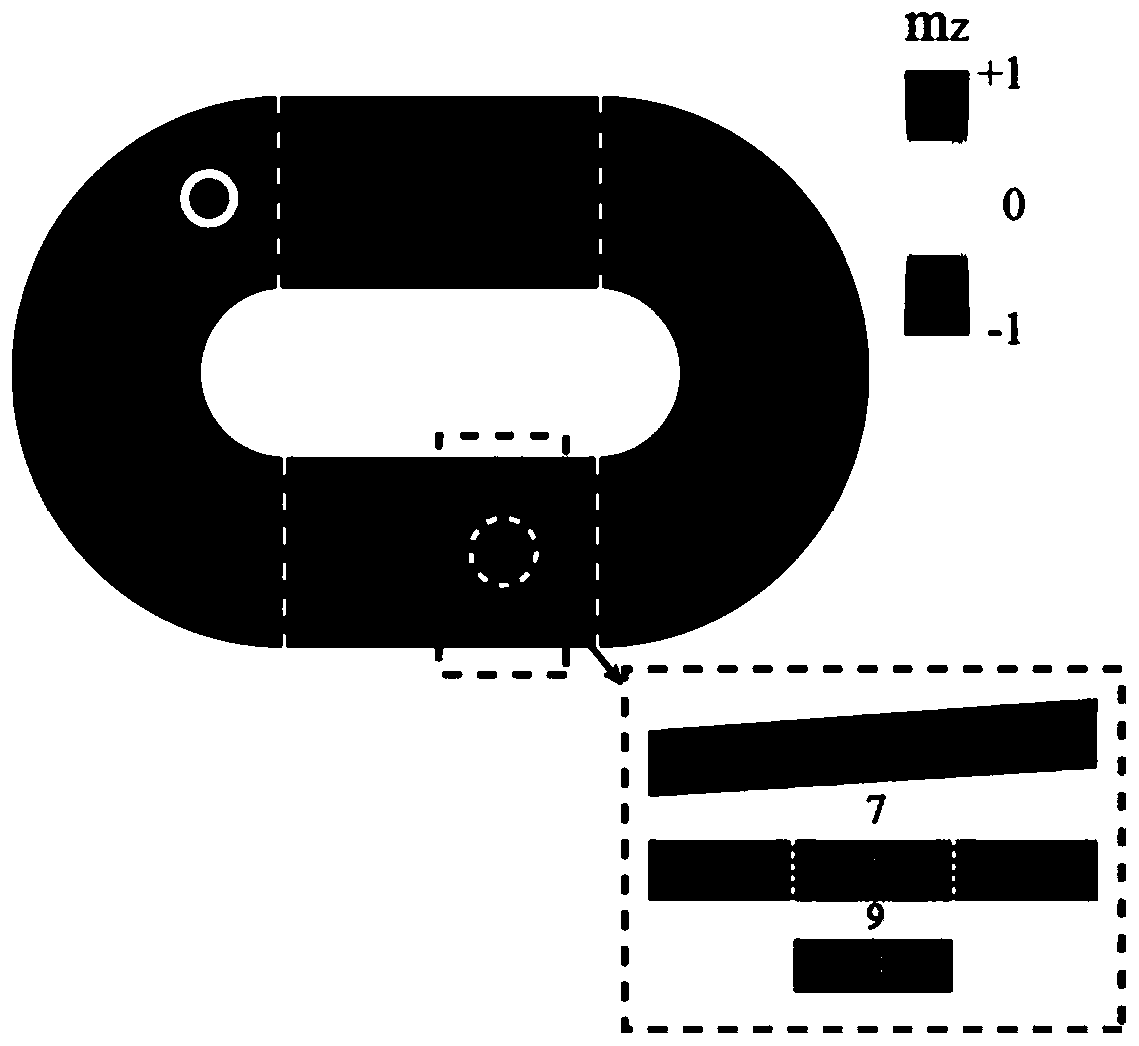

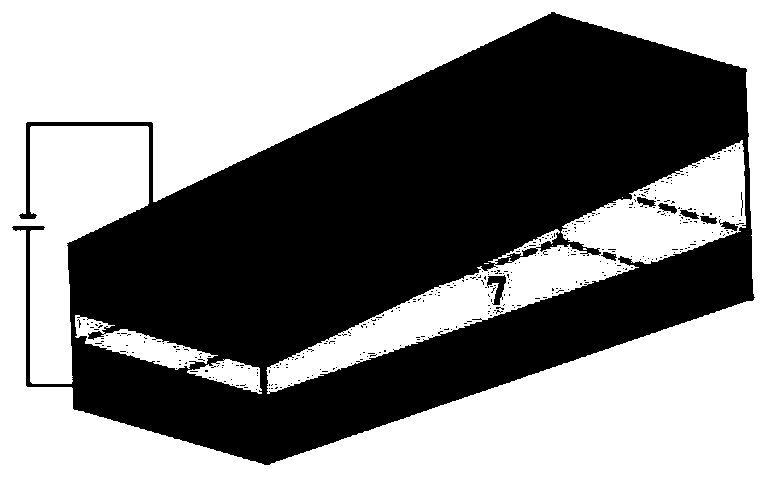

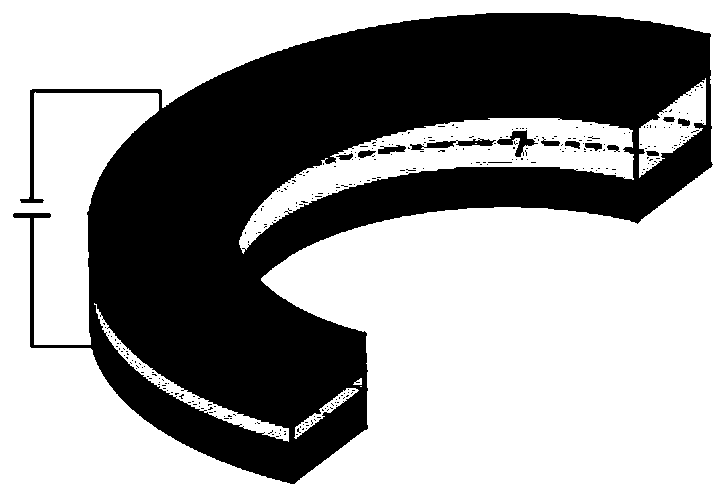

AND logic gate and NAND logic gate based on magnetic skyrmion

InactiveCN110233617ARealize the logic functionGuaranteed stabilityLogic circuits characterised by logic functionNAND logicMagnetic skyrmion

The invention discloses an AND logic gate and an NAND logic gate based on magnetic skyrmion. The magnetic skyrmion is placed in the annular magnetic racing track. A voltage driving mode is adopted toenable the skyrmion to circularly move in the magnetic racing track, and the state of the skyrmion in the magnetic racing track is read through the magnetic tunnel junction, so that the logic functions of the AND gate and the NAND gate are realized, and the stability of the NOT gate based on the skyrmion and the AND gate in use is ensured.

Owner:CHINA UNIV OF GEOSCIENCES (WUHAN)

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com