True Single-Phase Clock (TSPC) 2/3 dual-mode prescaler with high speed and low power consumption

A dual-mode prescaler, true single-phase clock technology, applied in pulse counters, synchronous pulse counters, counting chain pulse counters, etc. effect of speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

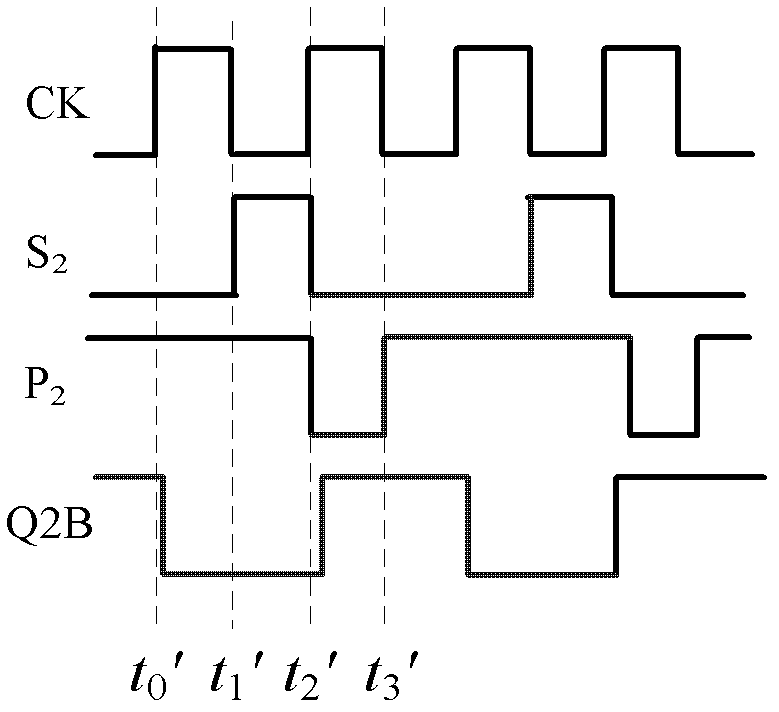

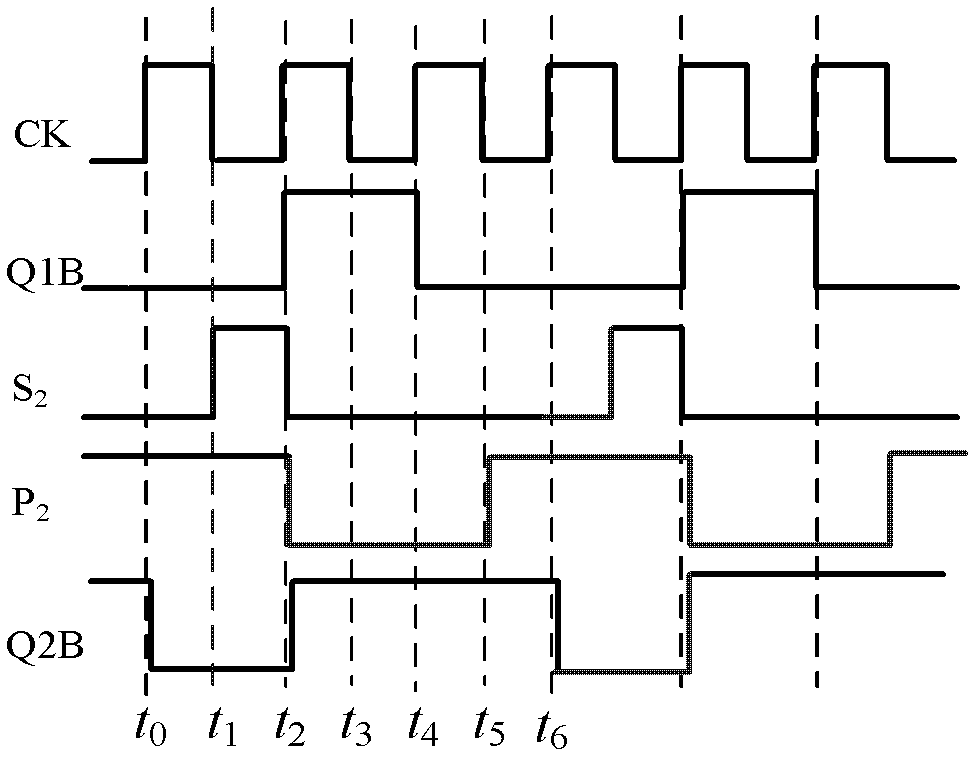

[0023] The present invention will be further described below in conjunction with the accompanying drawings.

[0024] Such as figure 1 Shown is a high-speed and low-power true single-phase clock 2 / 3 dual-mode prescaler, including six-stage dynamic inverters, and the first-stage, second-stage, and third-stage dynamic inverters are connected in series to form a true The D flip-flop DFF1 with a single-phase clock structure, and the fourth, fifth, and sixth-stage dynamic inverters are connected in series to form a D flip-flop DFF2 with a true single-phase clock structure;

[0025]In the present invention, by delaying the precharging operation of the true single-phase clock trigger by one cycle to realize the three-frequency division operation, the working speed of the true single-phase clock 2 / 3 dual-mode prescaler can be significantly improved, and the frequency divider performs two During frequency division, one of the unused D flip-flops can also be turned off to reduce circuit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com