Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33 results about "Core level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Core-level (plural core-levels) (chemistry) The energy level of the electrons (core electrons) occupying the completely filled shells under the valence shell.

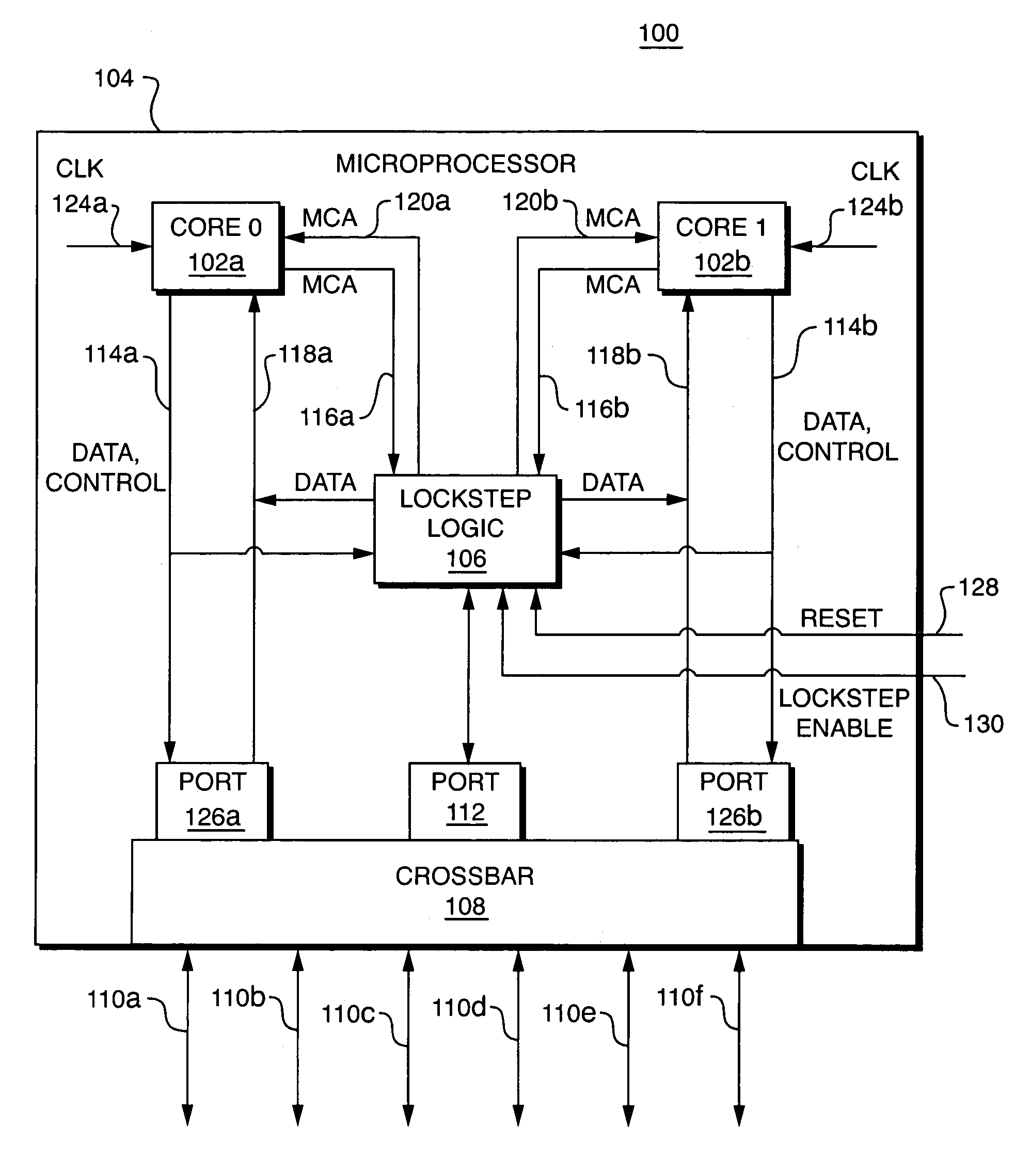

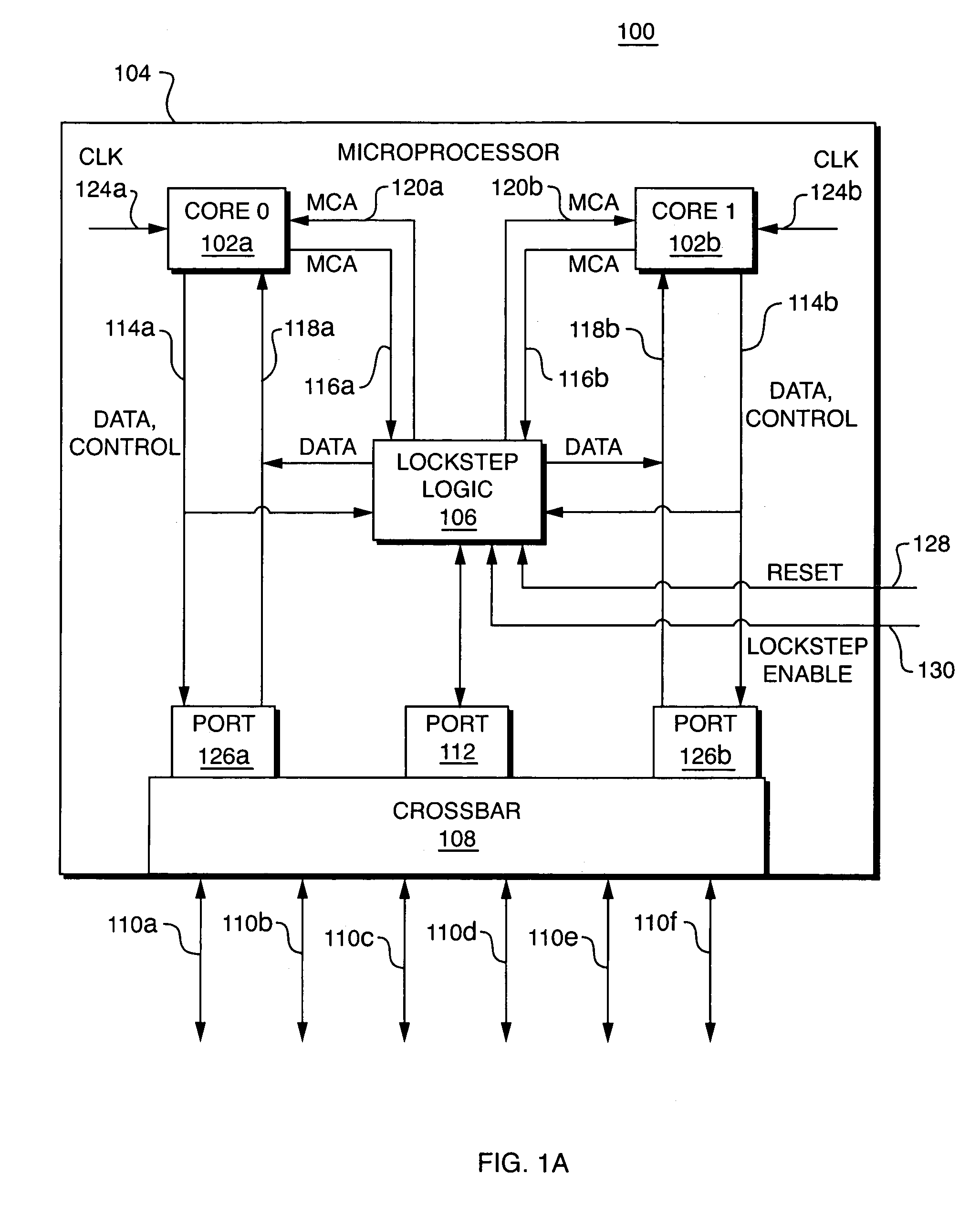

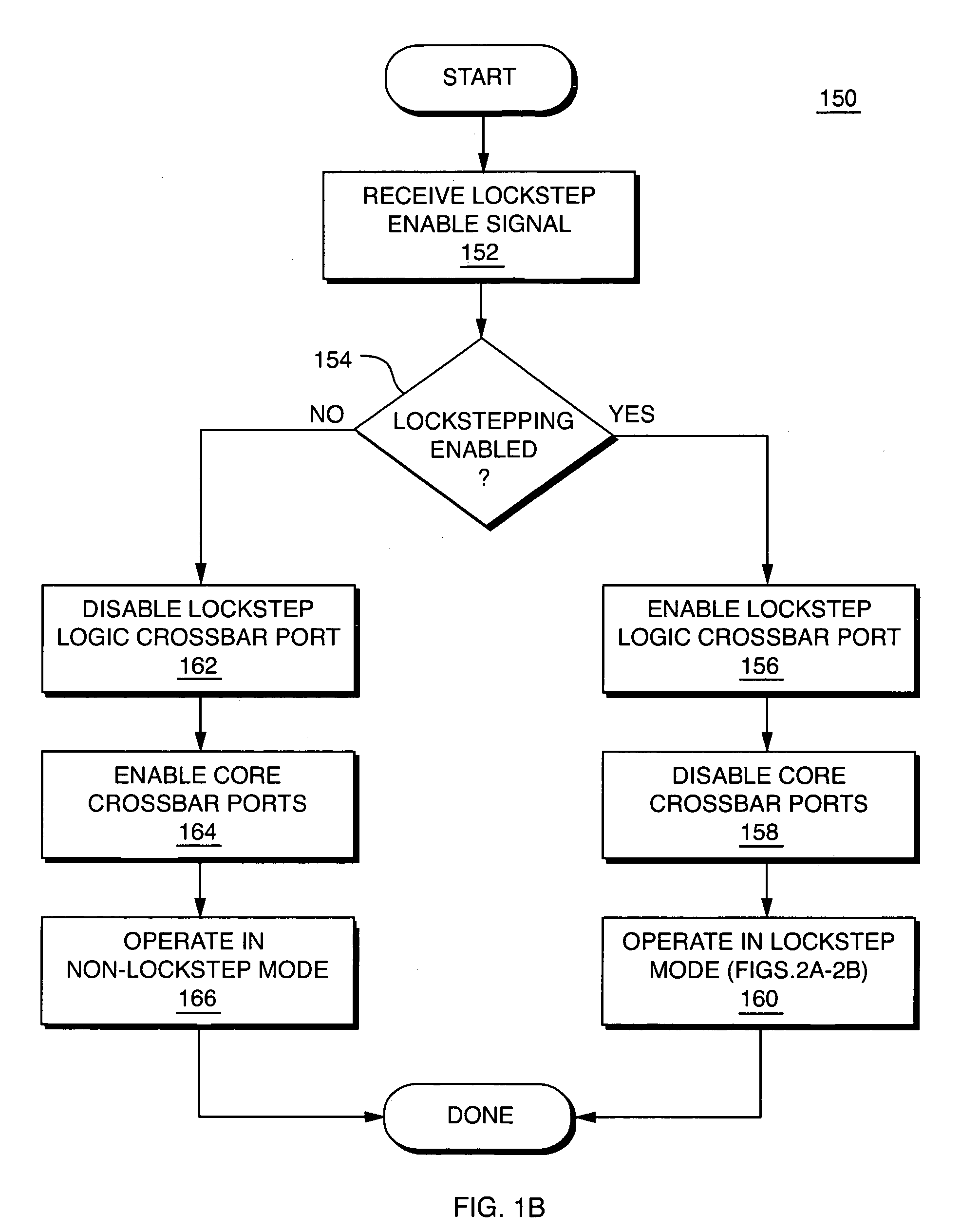

Core-level processor lockstepping

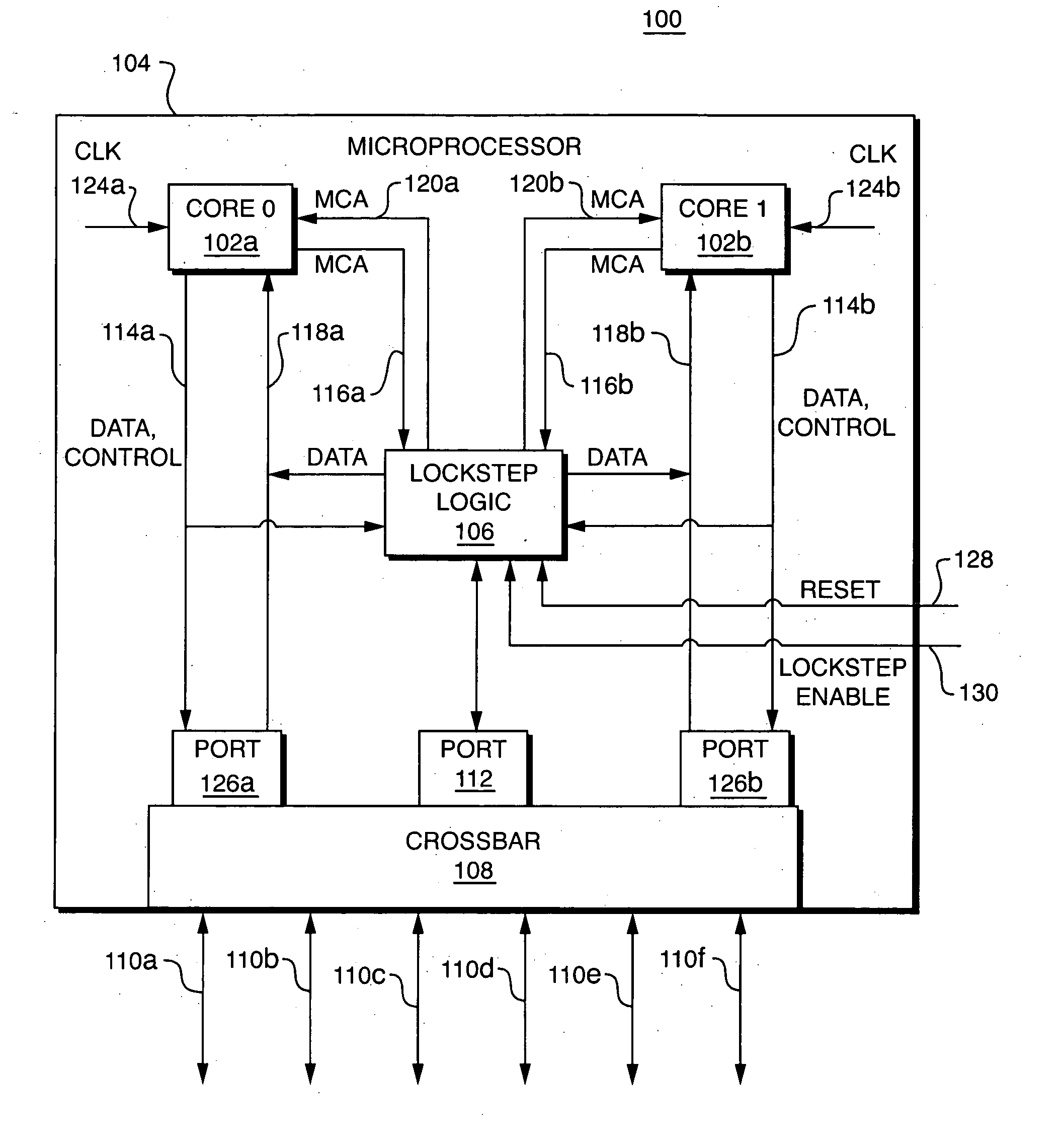

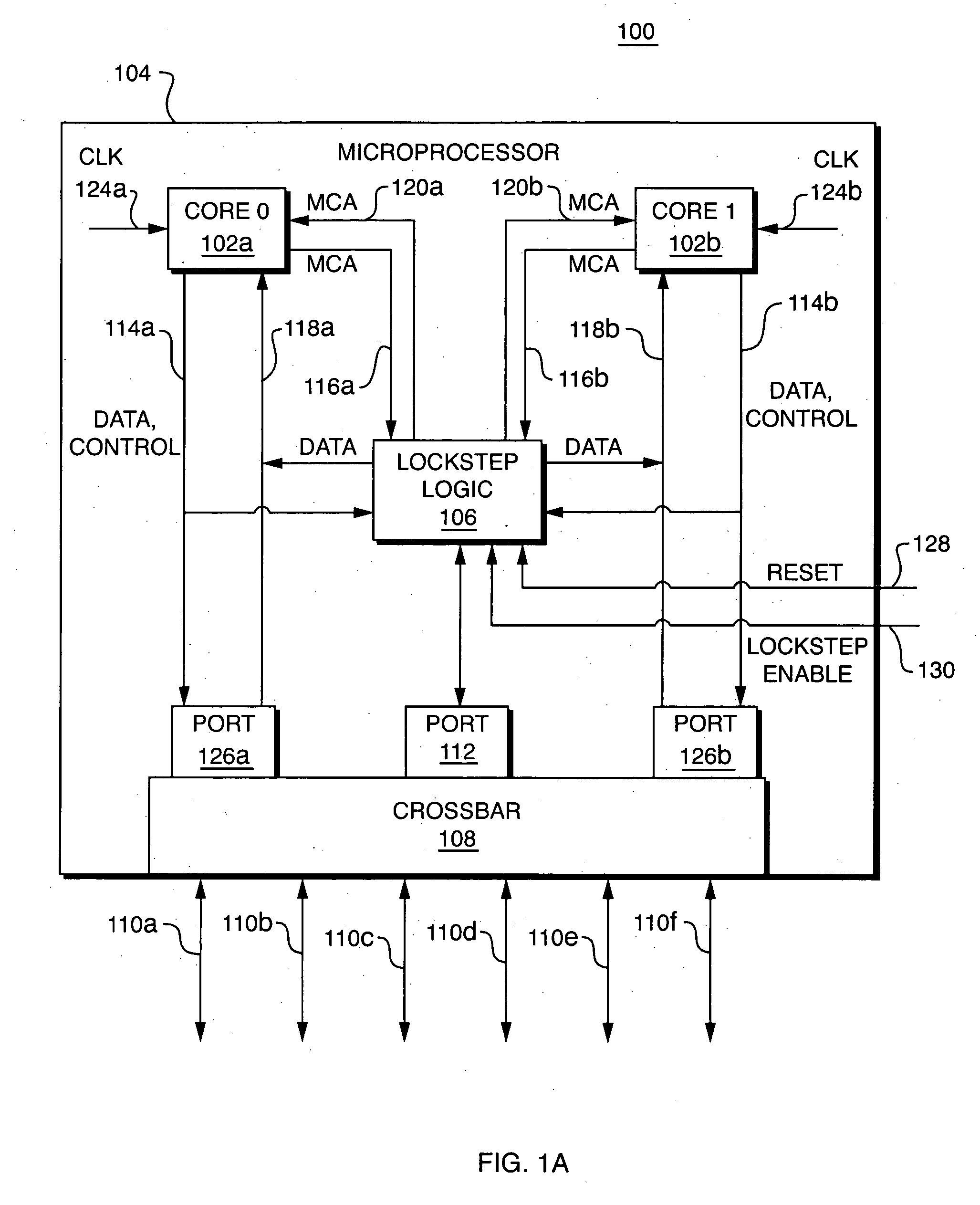

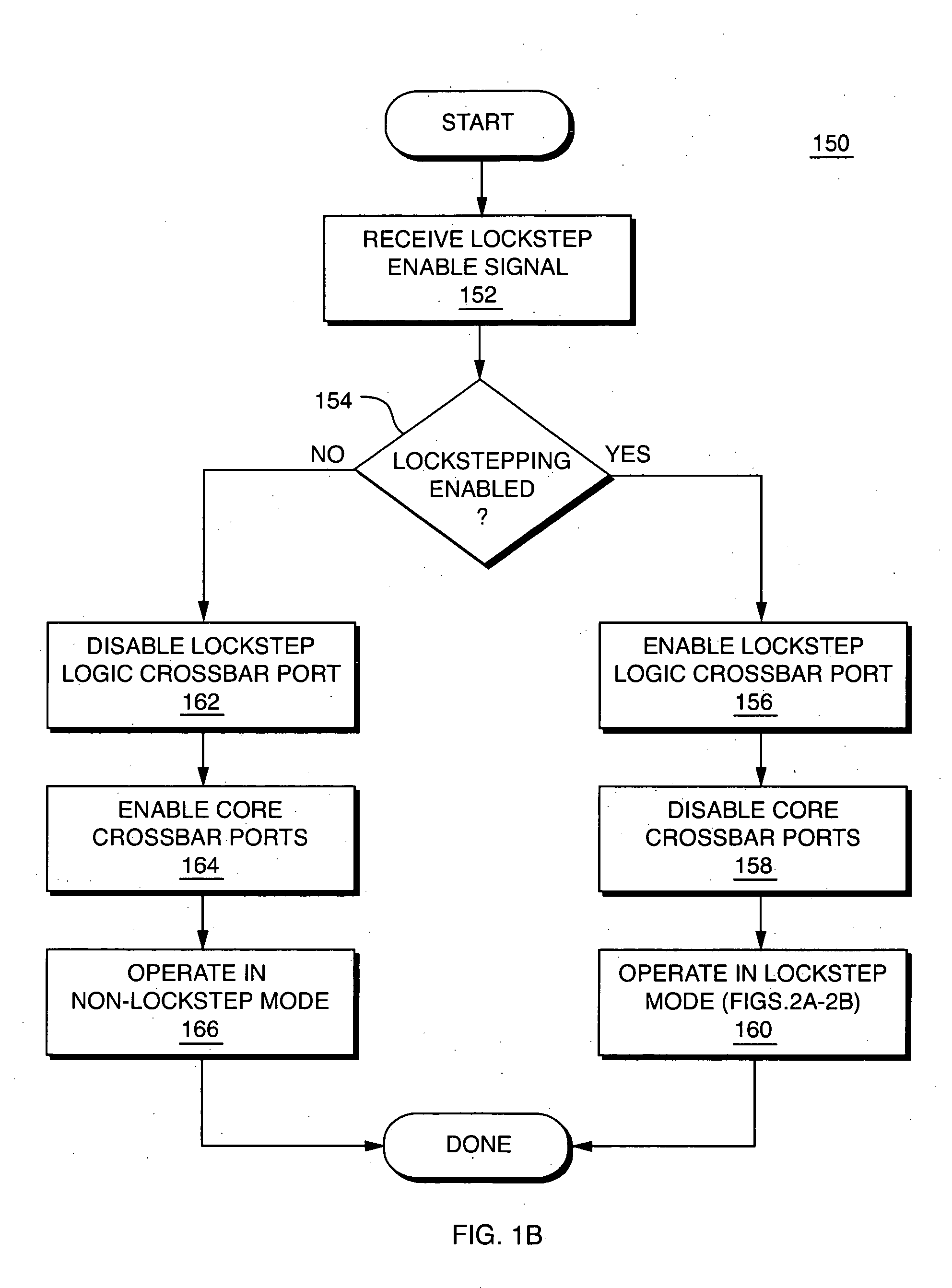

A device is provided which includes a first microprocessor core to generate a first output signal; a second microprocessor core to generate a second output signal; a switching fabric having a first input / output port; and lockstep logic, coupled between the first input / output port of the switching fabric and the first and second microprocessor cores, to detect whether the first output signal differs from the second output signal.

Owner:SK HYNIX INC

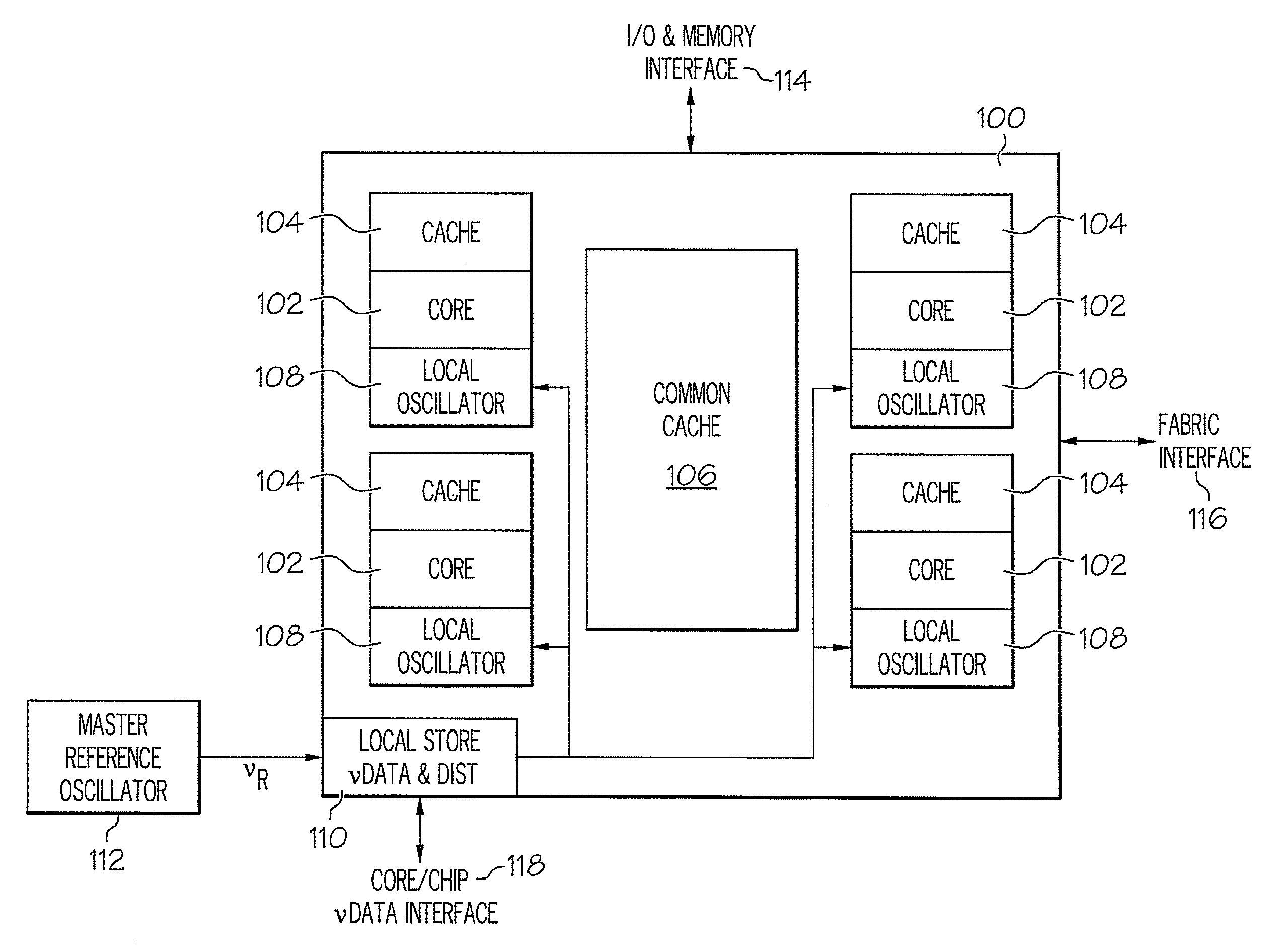

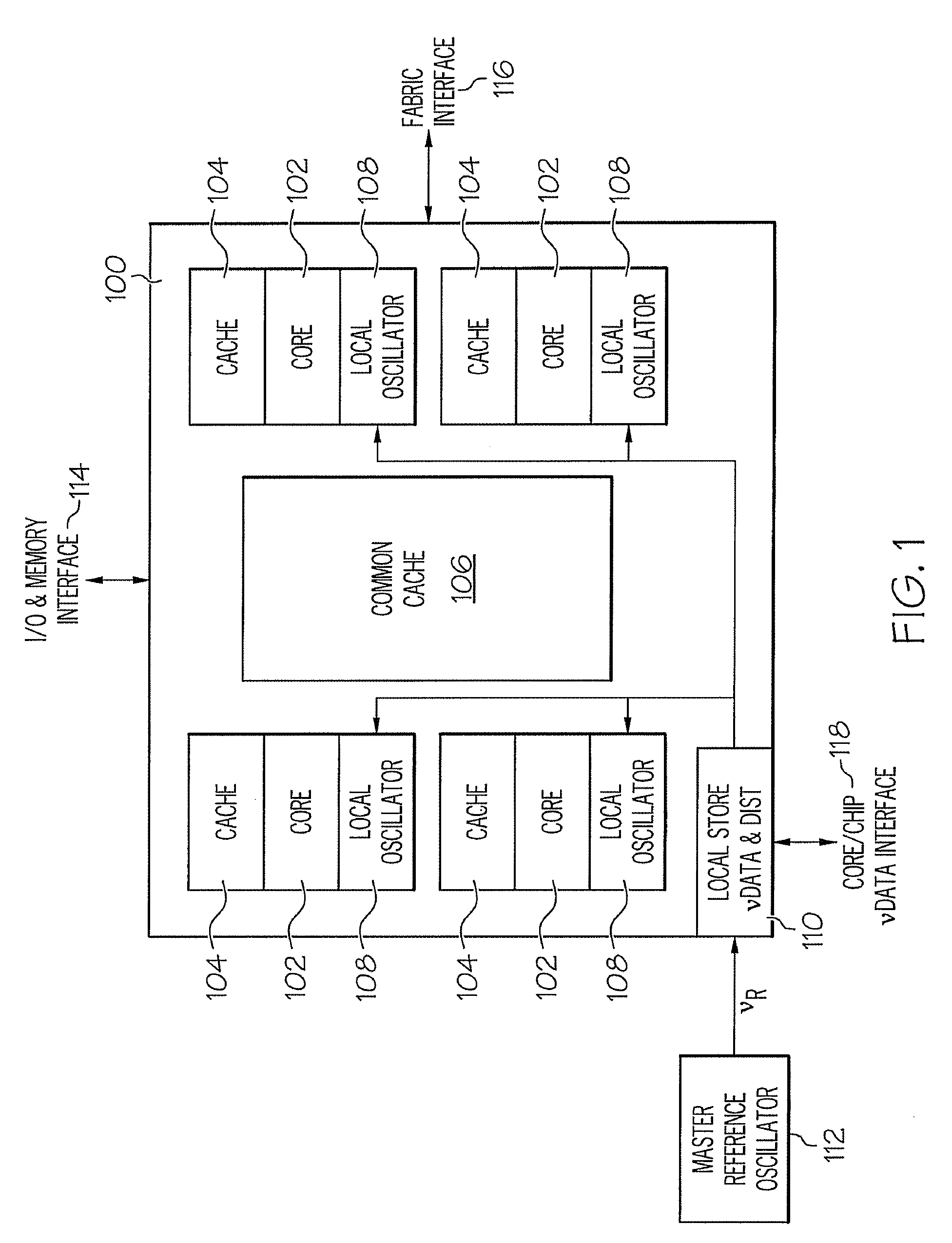

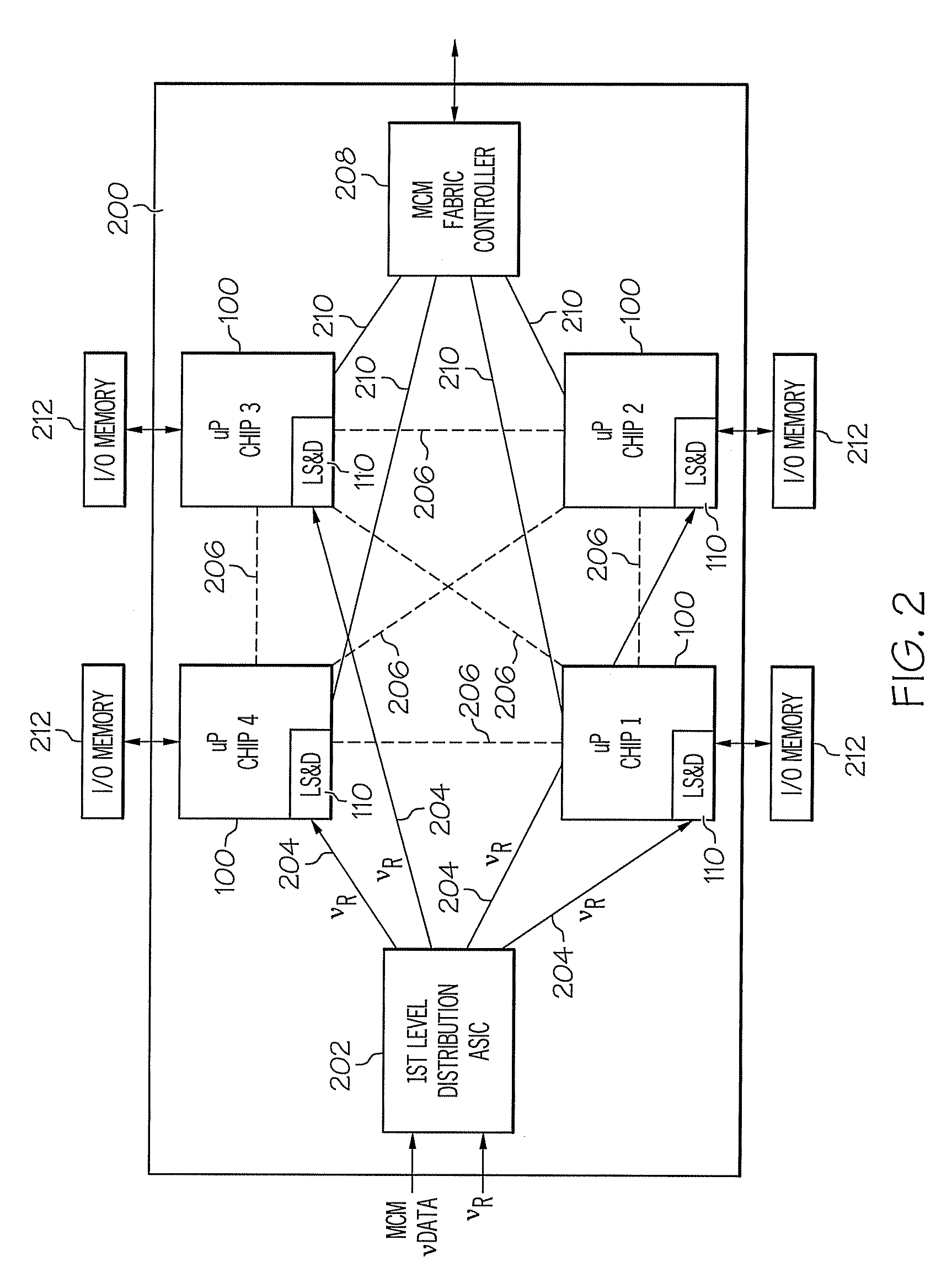

Methods and systems for digitally controlled multi-frequency clocking of multi-core processors

ActiveUS20090106576A1Convenient power managementEnergy efficient ICTMultiple digital computer combinationsLocal oscillatorEngineering

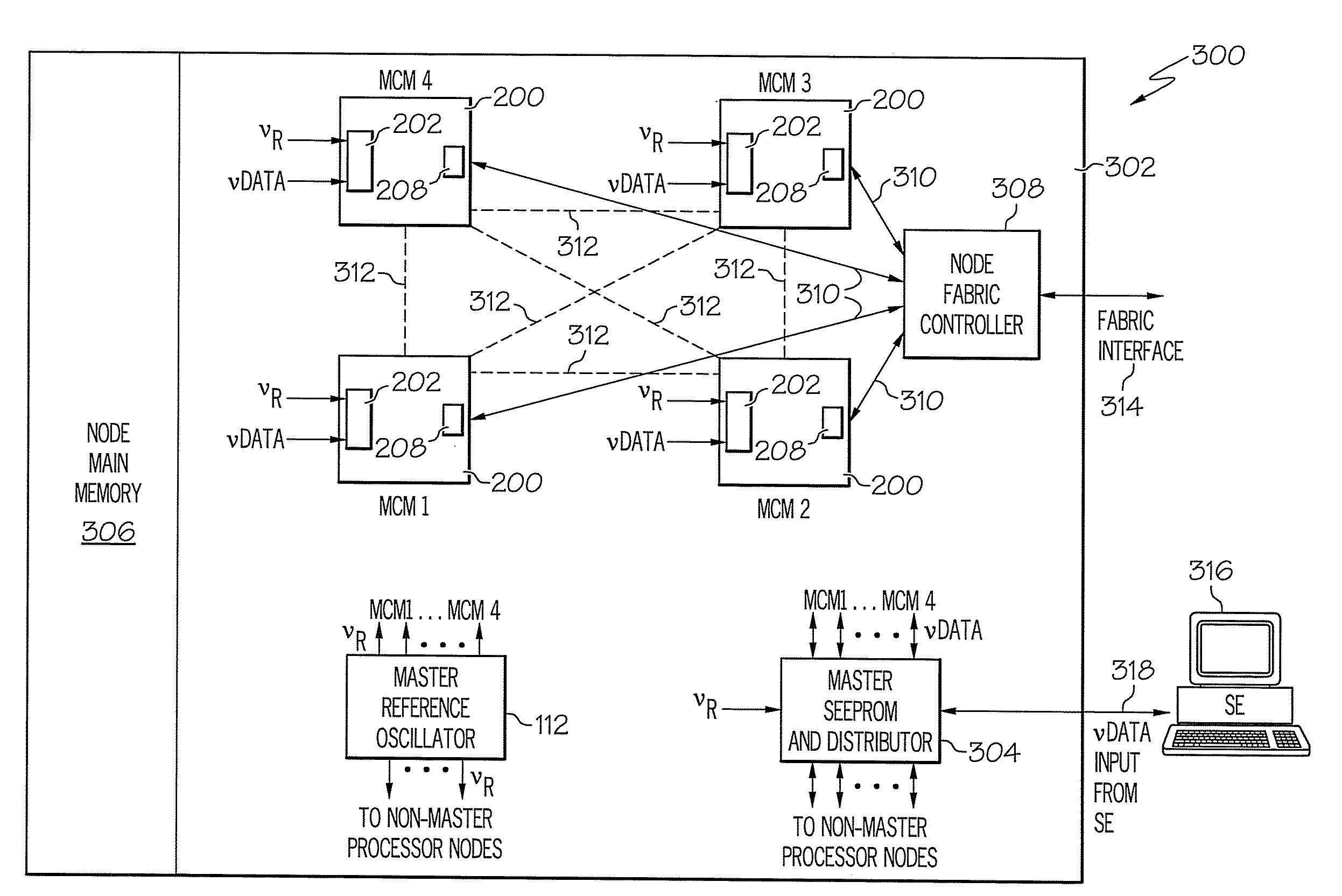

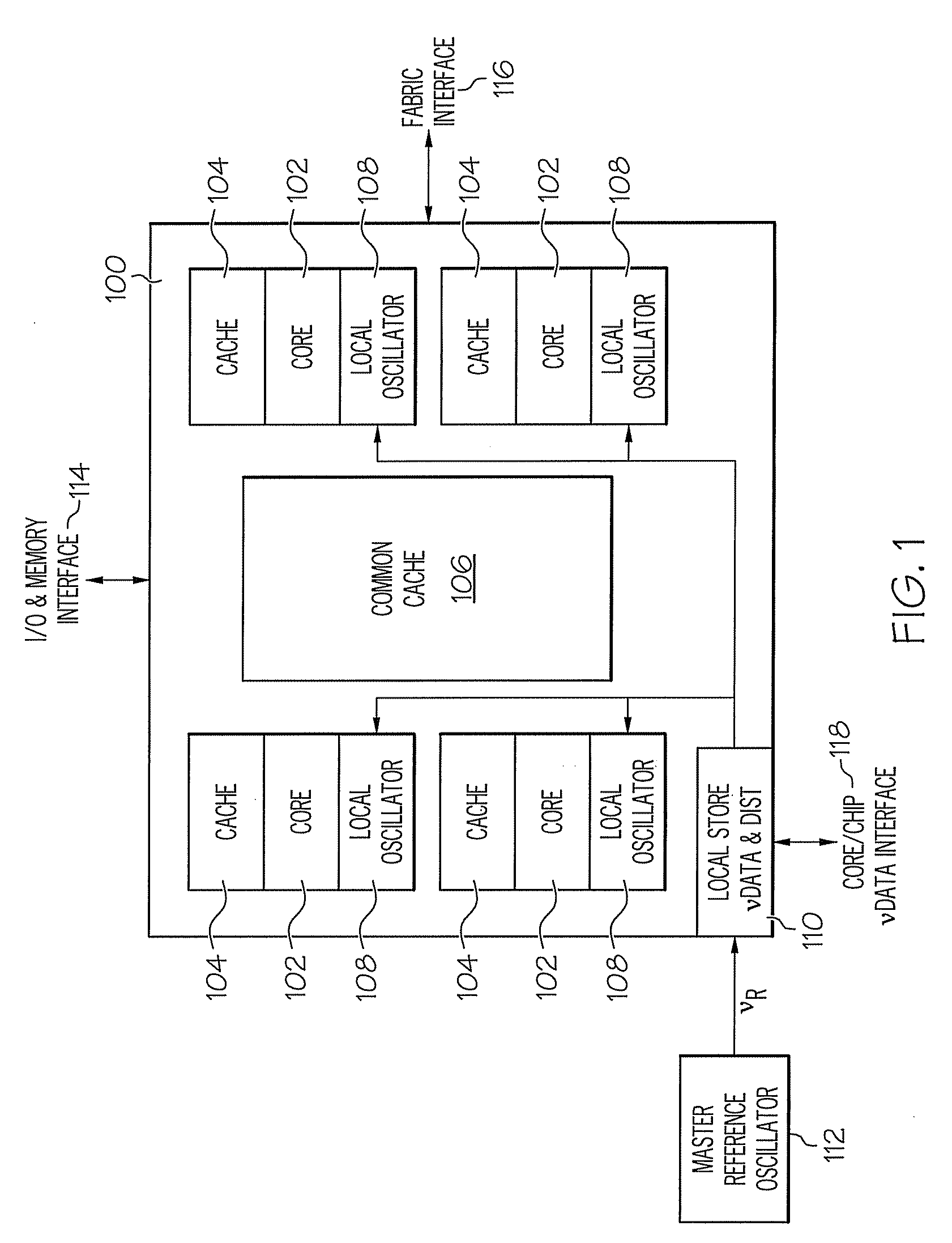

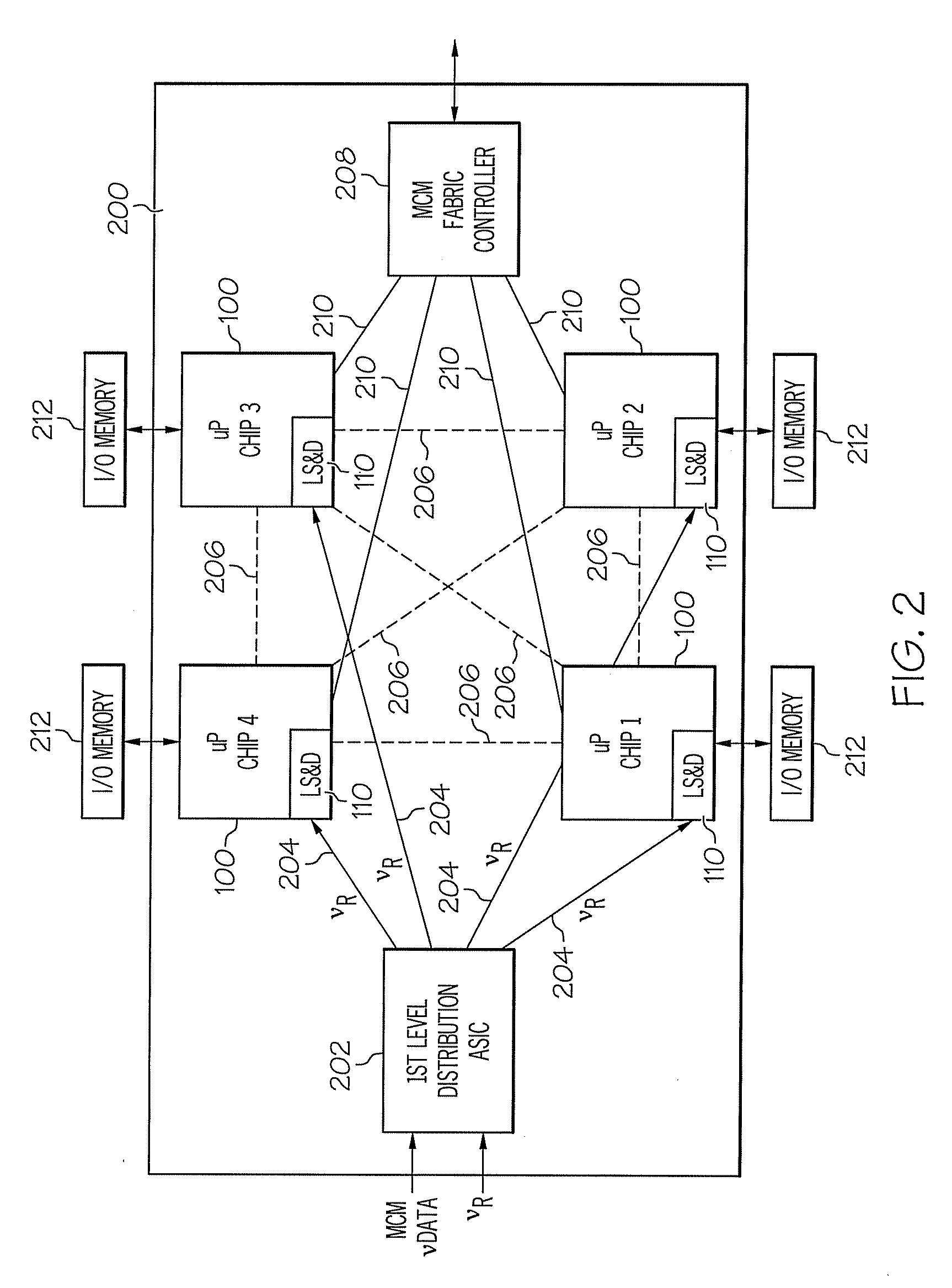

A method and system for digitally controlled multi-frequency clocking are provided. The method includes receiving a system reference oscillator clock frequency at a microprocessor including multiple cores. The system reference oscillator clock frequency provides a reference frequency to a local oscillator. The local oscillator supplies a core clock frequency to at least one of the cores. The method further includes adjusting the local oscillator to output the core clock frequency at a frequency greater than the system reference oscillator clock frequency as a function of digital frequency characteristic data associated with the core or cores. The method supports extendibility to larger systems and may support enhanced power management through frequency adjustments at the core level.

Owner:IBM CORP

Core-level processor lockstepping

A device is provided which includes a first microprocessor core to generate a first output signal; a second microprocessor core to generate a second output signal; a switching fabric having a first input / output port; and lockstep logic, coupled between the first input / output port of the switching fabric and the first and second microprocessor cores, to detect whether the first output signal differs from the second output signal.

Owner:SK HYNIX INC

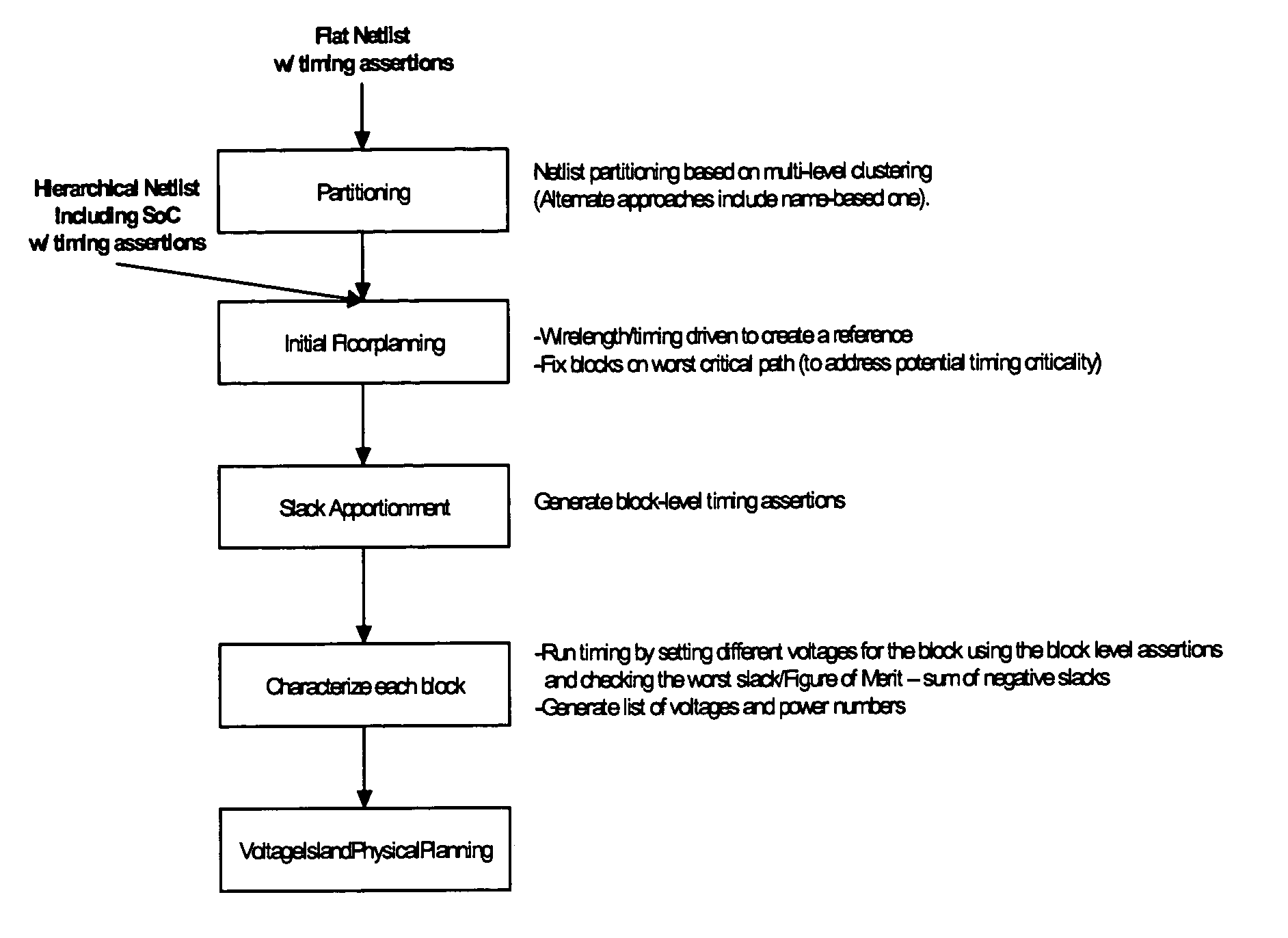

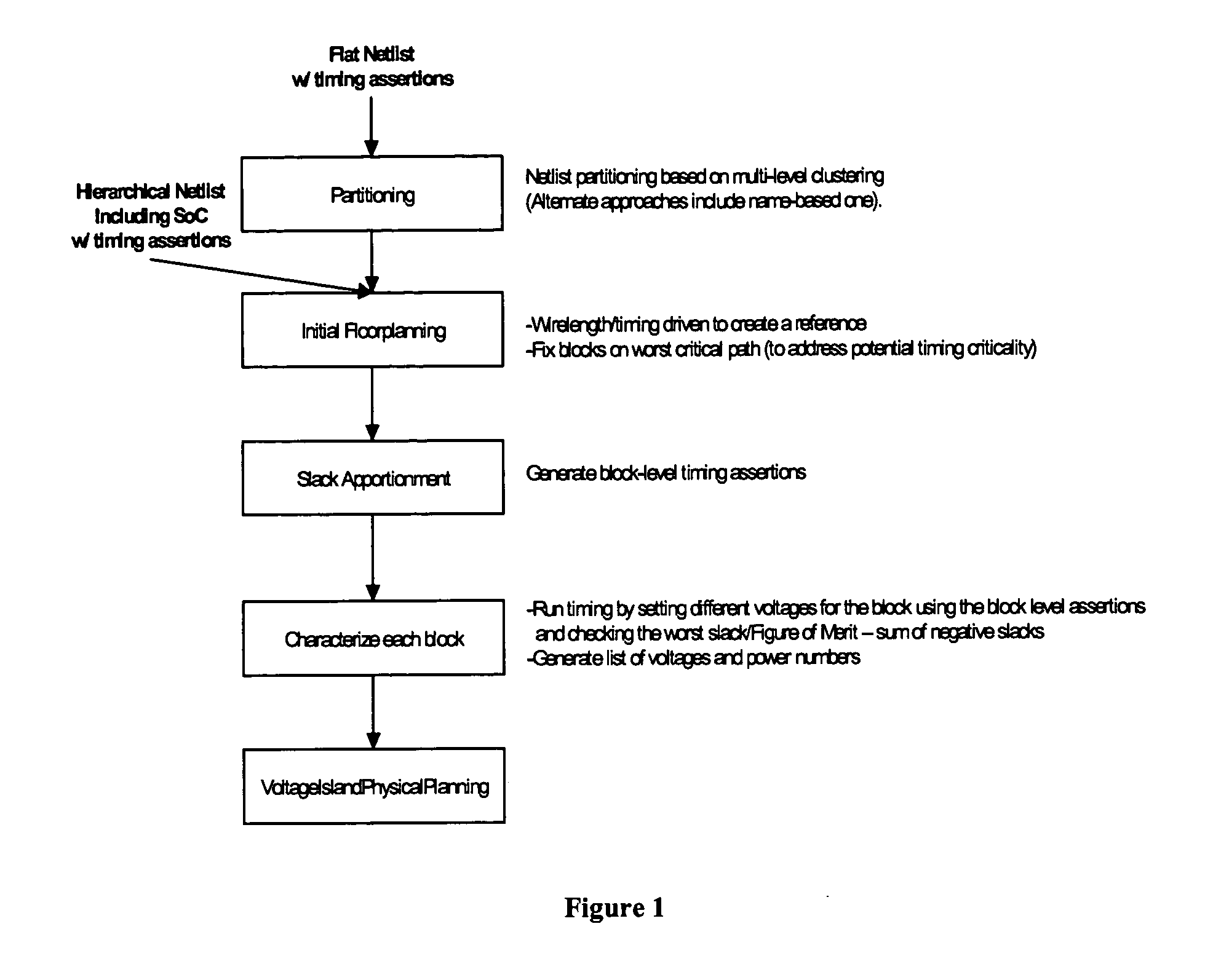

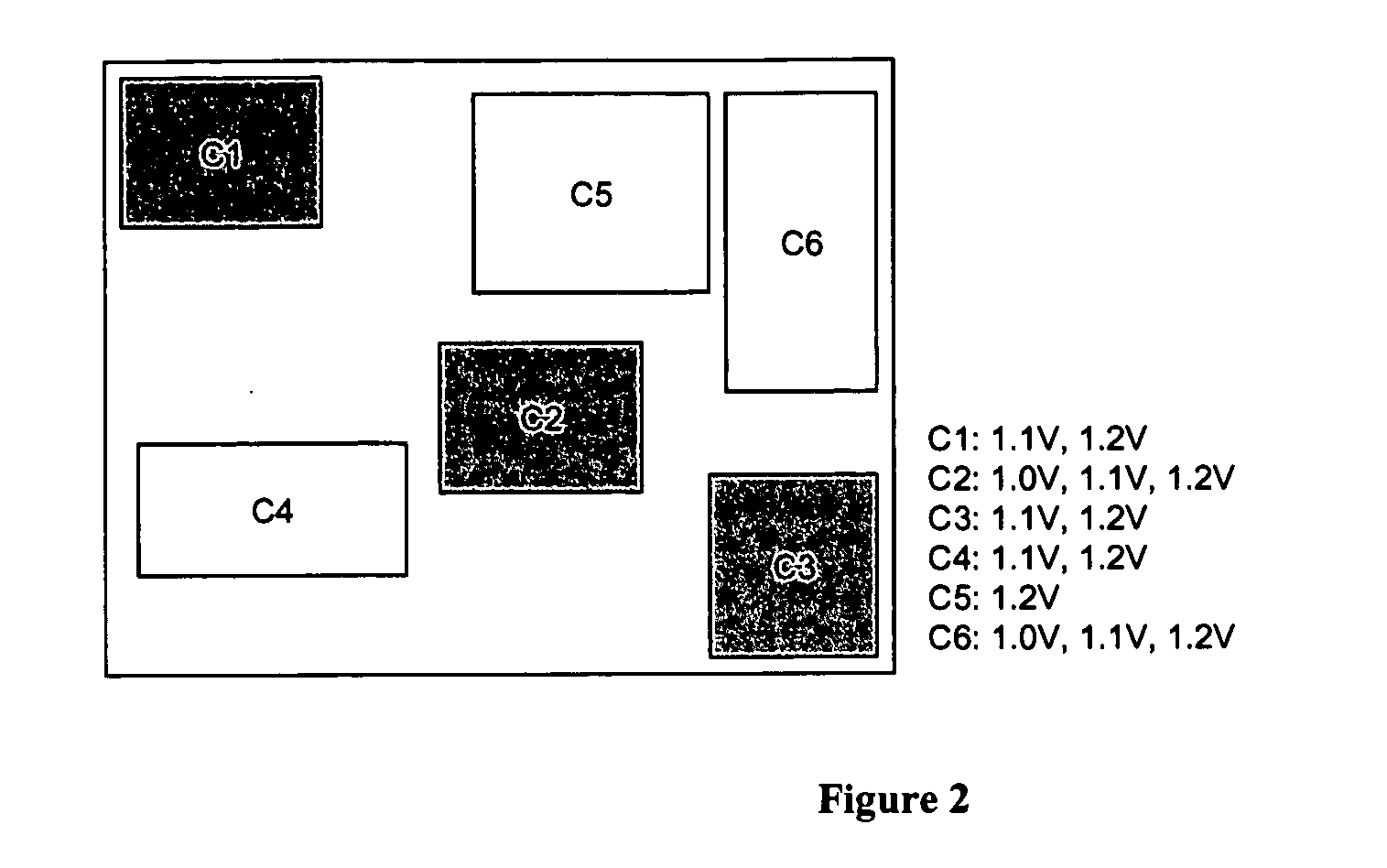

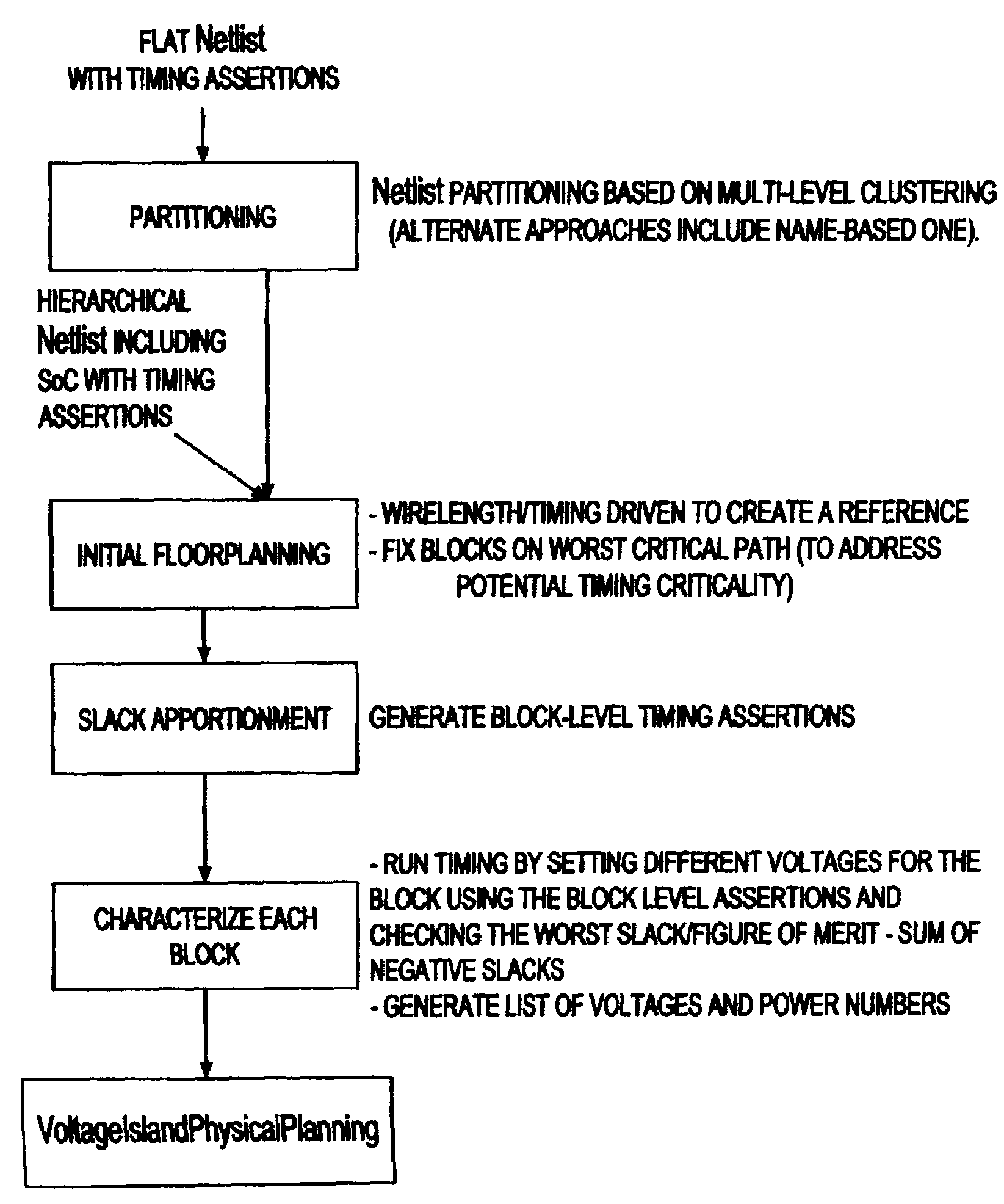

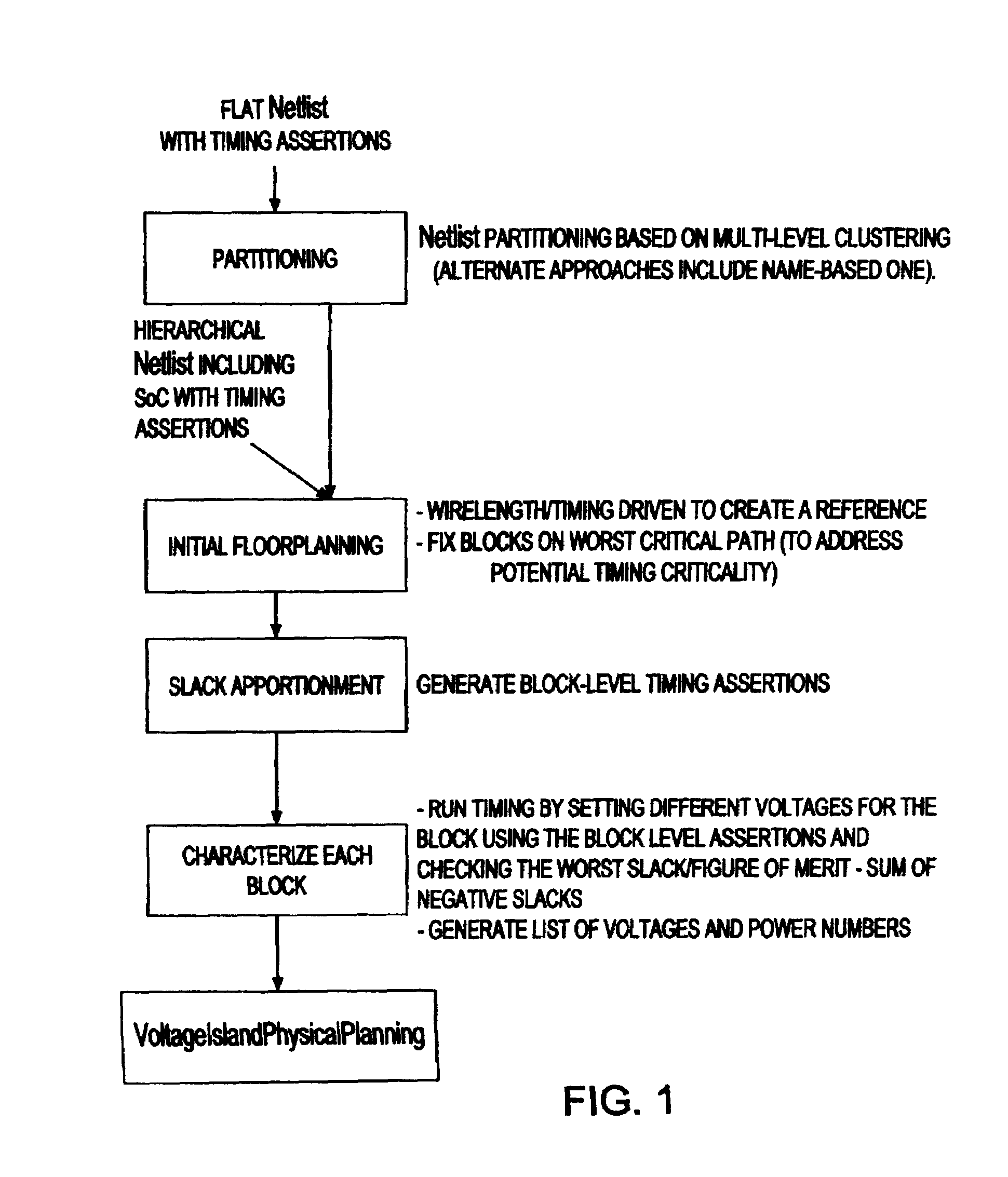

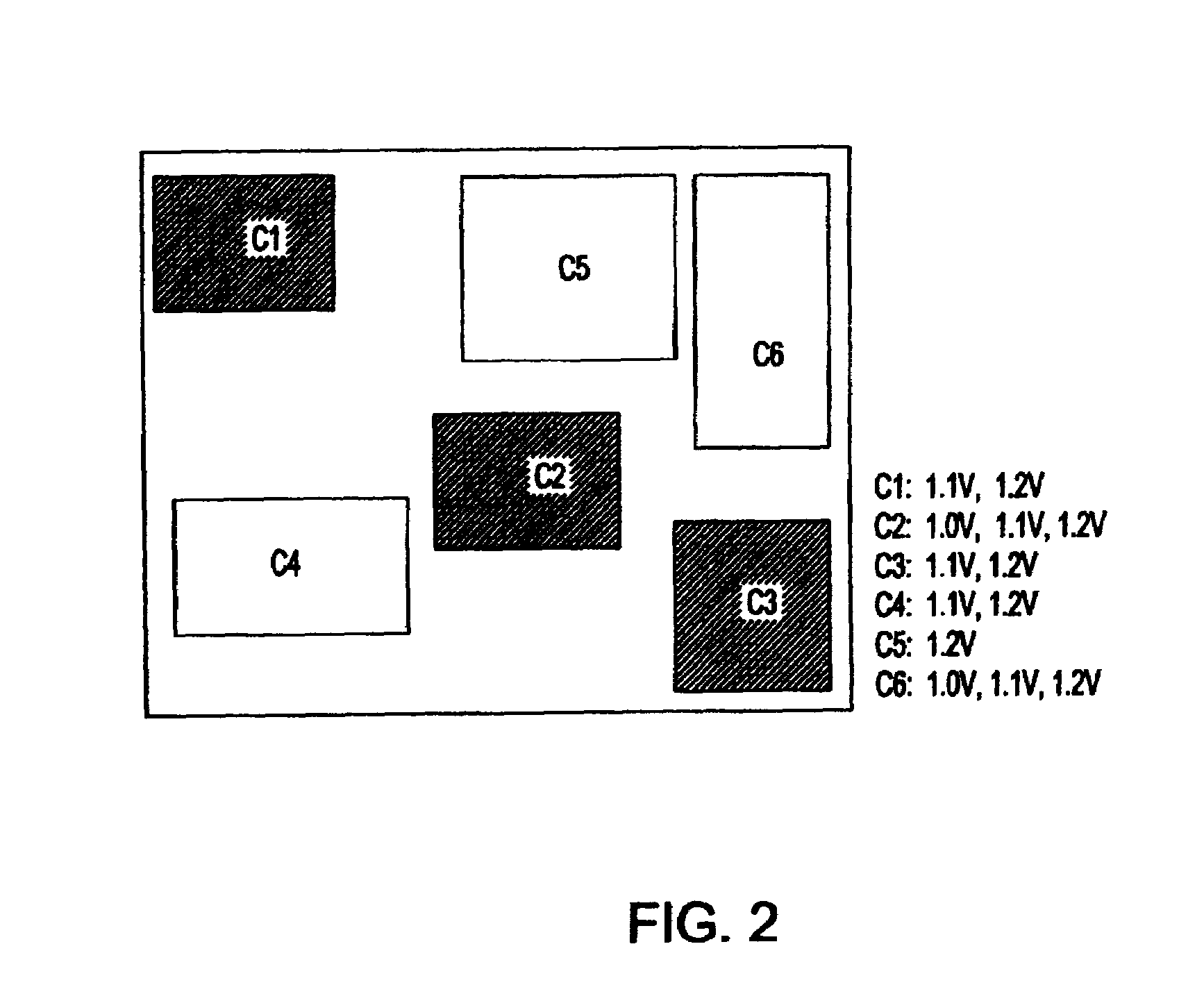

Method of physical planning voltage islands for ASICs and system-on-chip designs

InactiveUS20050278676A1Minimize power consumptionCAD circuit designSoftware simulation/interpretation/emulationPhysical planningIslanding

Voltage islands enable a core-level power optimization of ASIC / SoC designs by utilizing a unique supply voltage for each cluster of the design. Creating voltage islands in a chip design for optimizing the overall power consumption consists of generating voltage island partitions, assigning voltage levels and floorplanning. The generation of voltage island partitions and the voltage level assignment are performed simultaneously in a floorplanning context due to the physical constraints involved. This leads to a floorplanning formulation that differs from the conventional floorplanning for ASIC designs. Such a formulation of a physically aware voltage island partitioning and method for performing simultaneous voltage island partitioning, level assignment and floorplanning are described, as are the definition and the solution of floorplanning for voltage island based designs executed under area, power, timing and physical constraints. The physical planning of voltage islands includes: a) characterizing cell clusters in terms of voltages and power consumption values; b) providing a set of cell clusters that belong to a single voltage island Random Logic Macro (RLM); and c) assigning voltages for the voltage island RLMs, all within the context of generating a physically realizable floorplan for the design.

Owner:GOOGLE LLC

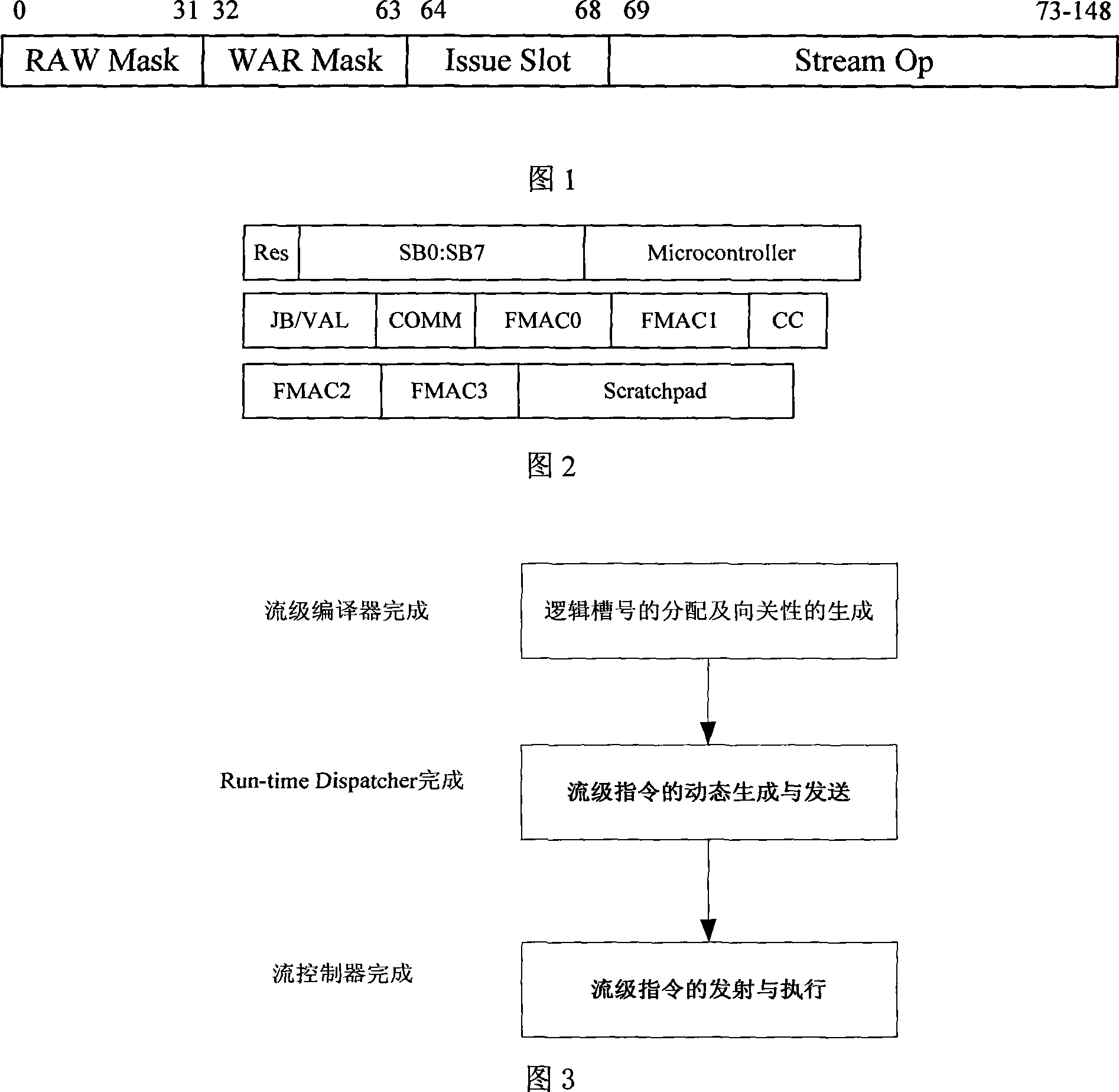

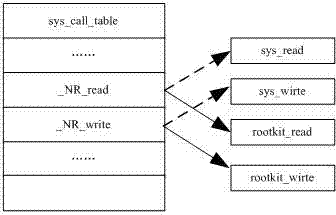

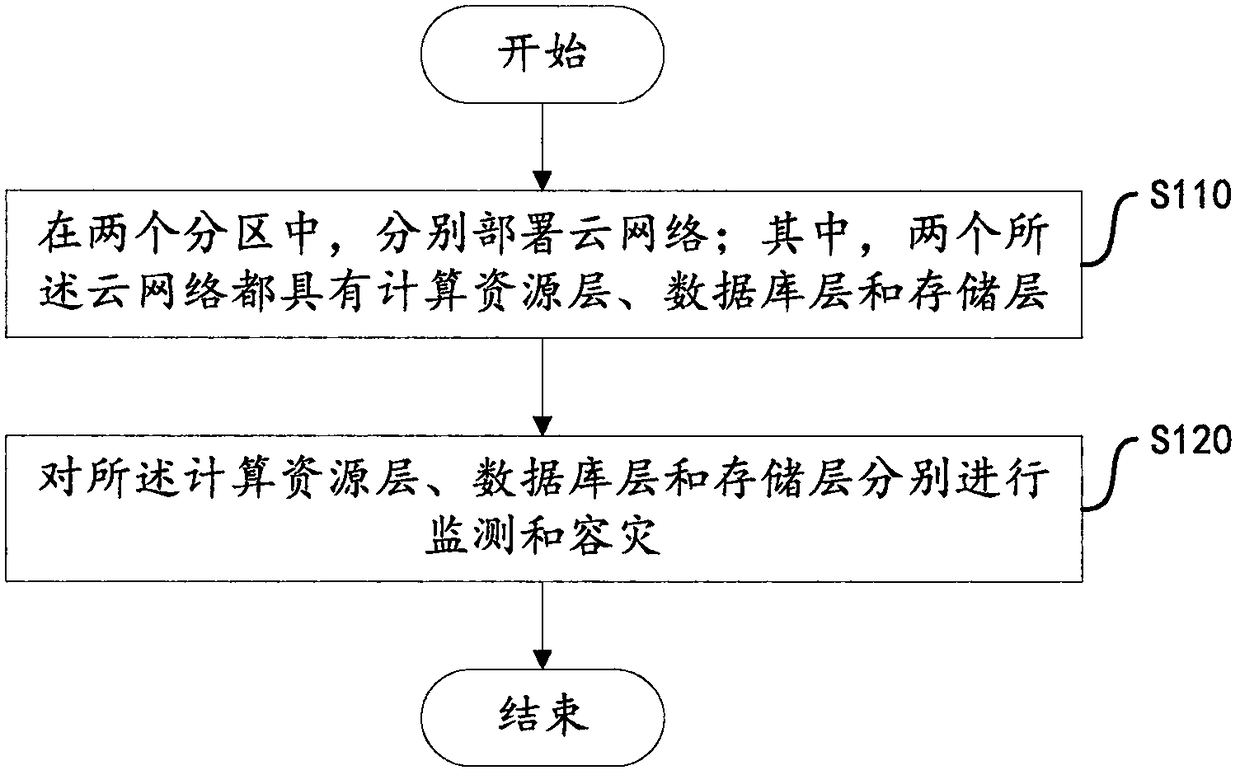

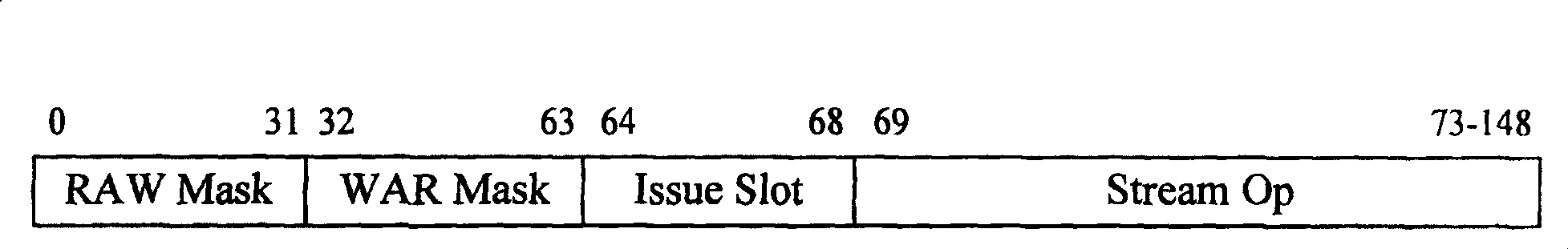

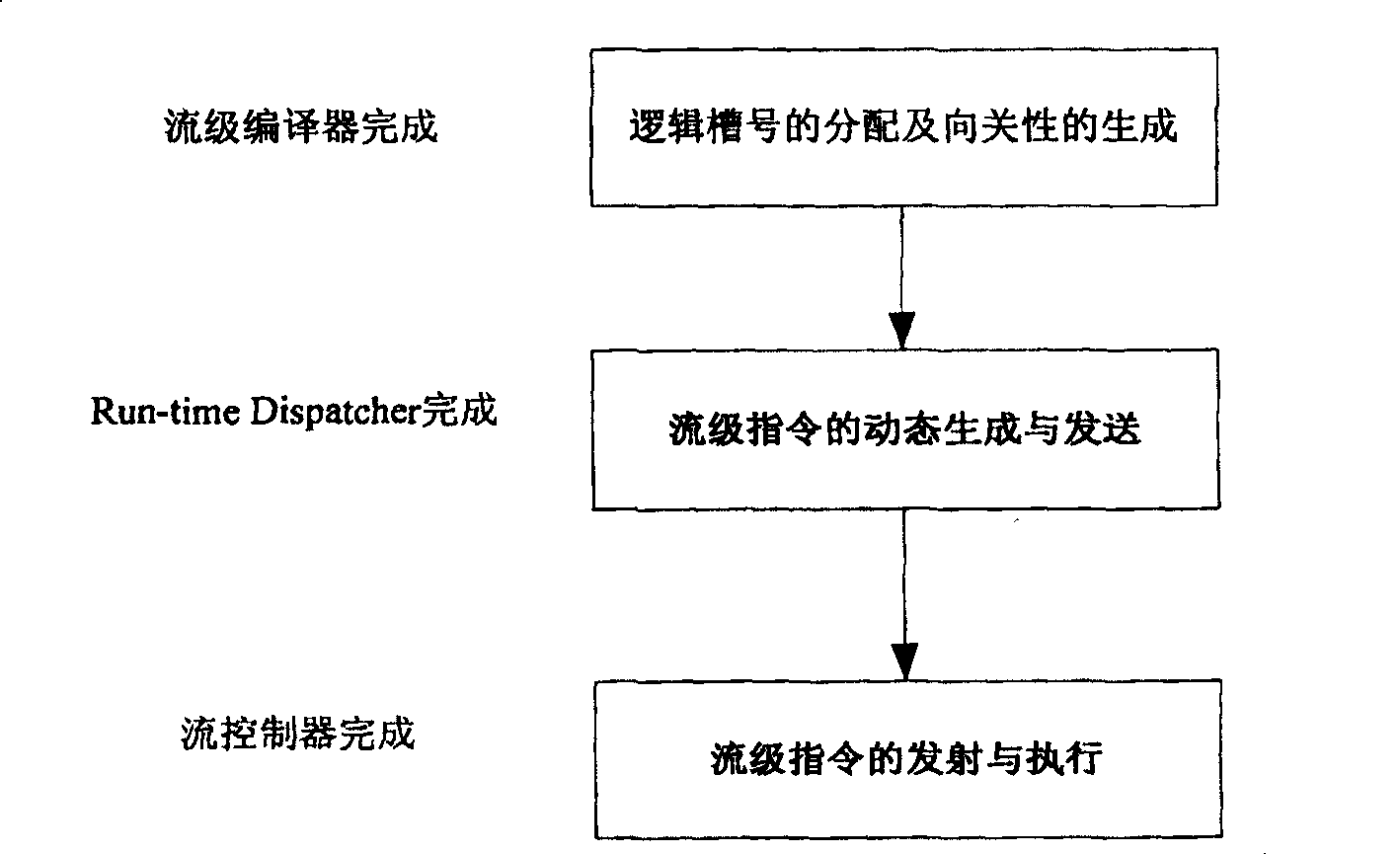

Instruction control method aimed at stream processor

InactiveCN101021779AHide Access LatencyEasy to manageConcurrent instruction executionComplete dataParallel computing

This invention discloses a instruction control method for streaming processor, which divides the instruction control into flow-level process and core-level process, the flow-level process is responsible for data scheduling between calculation core and off-chip memory, the core-level process completes data calculation, and the steps is: (1) initializing scalar data of the core-level procedure, (2) preparing vector data for the core-level procedure, (3) start executing the core-level procedure, (4) executing the procedure, (5) storing vector data generated by the procedure into the off-chip memory, (6) reading scalar result of the procedure.

Owner:NAT UNIV OF DEFENSE TECH

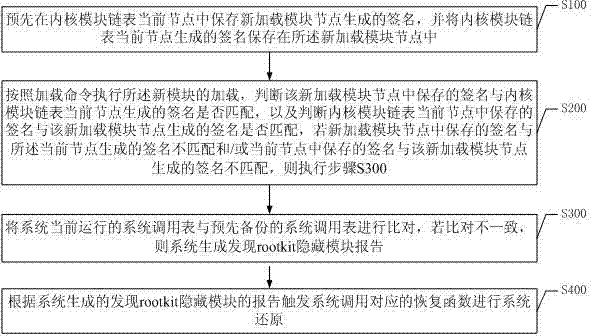

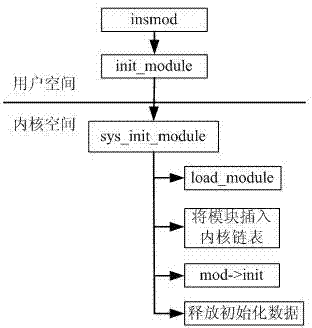

Method and device of detection processing of core-level rootkit

InactiveCN103699839AImprove reliabilityGuaranteed safe operationPlatform integrity maintainanceComputer hardwareOperational system

The invention discloses a method and a device of detection processing of a core-level rootkit. The method comprises the following steps of A, pre-storing a new loading module node signature at a current node of a core module chain table, and storing a current node signature into a new loading module node; B, loading a new module, judging whether the signature stored in the new loading module node is matched with the current node signature or not, judging whether the signature stored in the current node is matched with the new loading module node signature or not, if one is not matched, preforming the step C; C, comparing a currently operational system call table with a spare system call table, if not consistent, generating a report of discovering a hidden module. According to the method and the device, invasion of the rootkit is detected by setting a mutually matching mechanism of the new loading module and the current node signature of the chain table, and the report is further affirmed through comparing the system call table with a spare reference file, so that the reliability of a detection result is improved, and meanwhile, through setting a system recovery method, safety operation of the system is ensured.

Owner:TCL CORPORATION

Method of physical planning voltage islands for ASICs and system-on-chip designs

InactiveUS7296251B2Minimize power consumptionCAD circuit designSoftware simulation/interpretation/emulationPhysical planningCore level

Owner:GOOGLE LLC

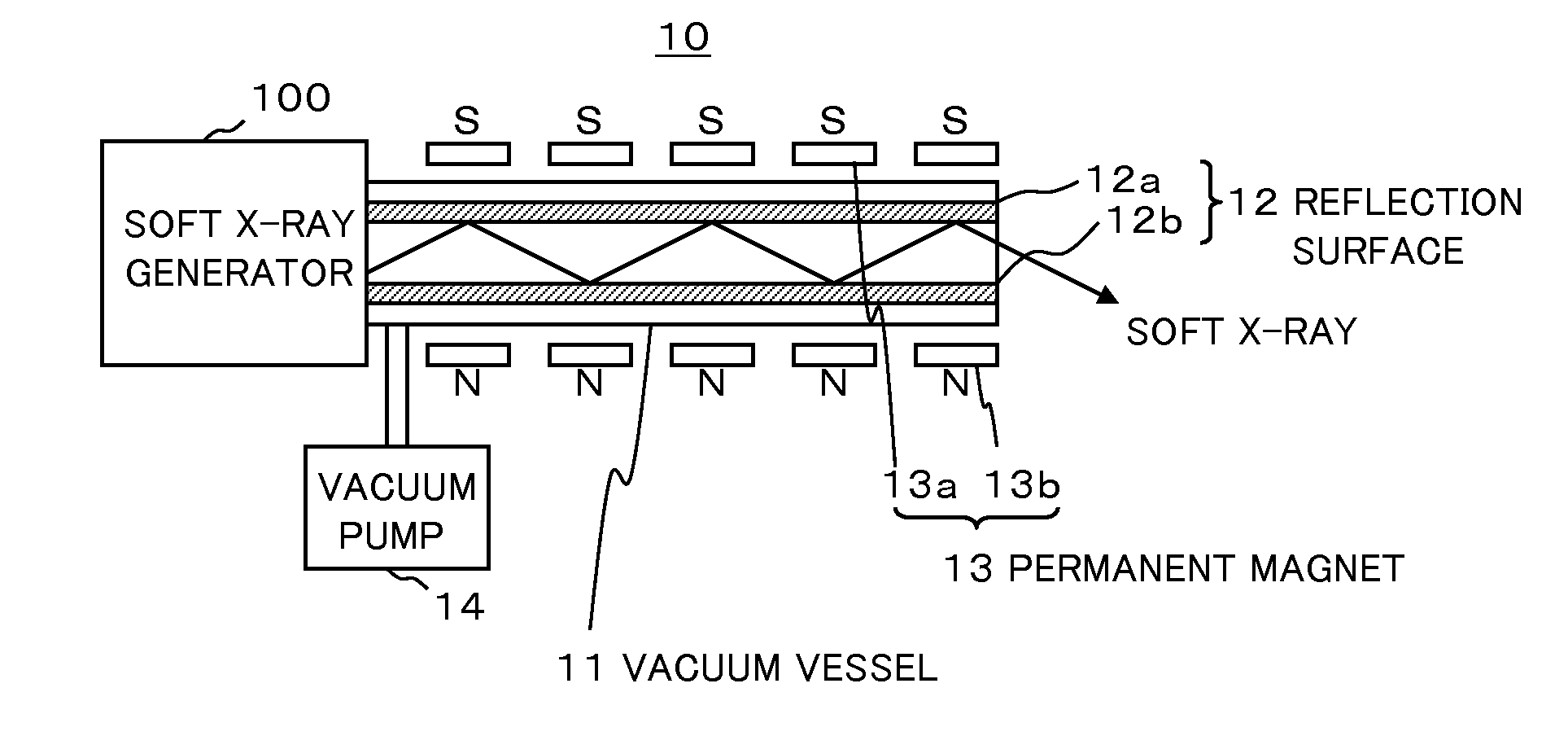

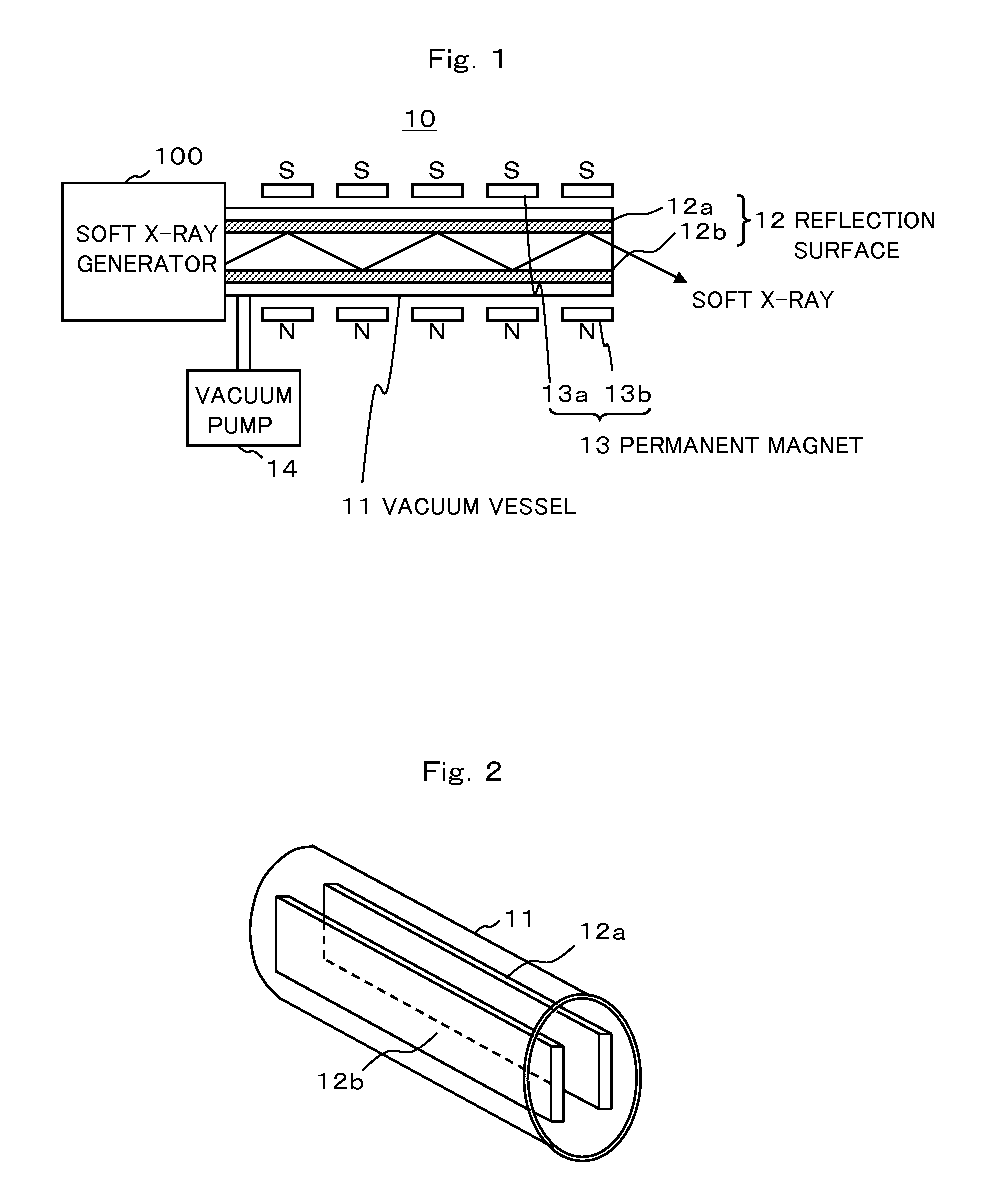

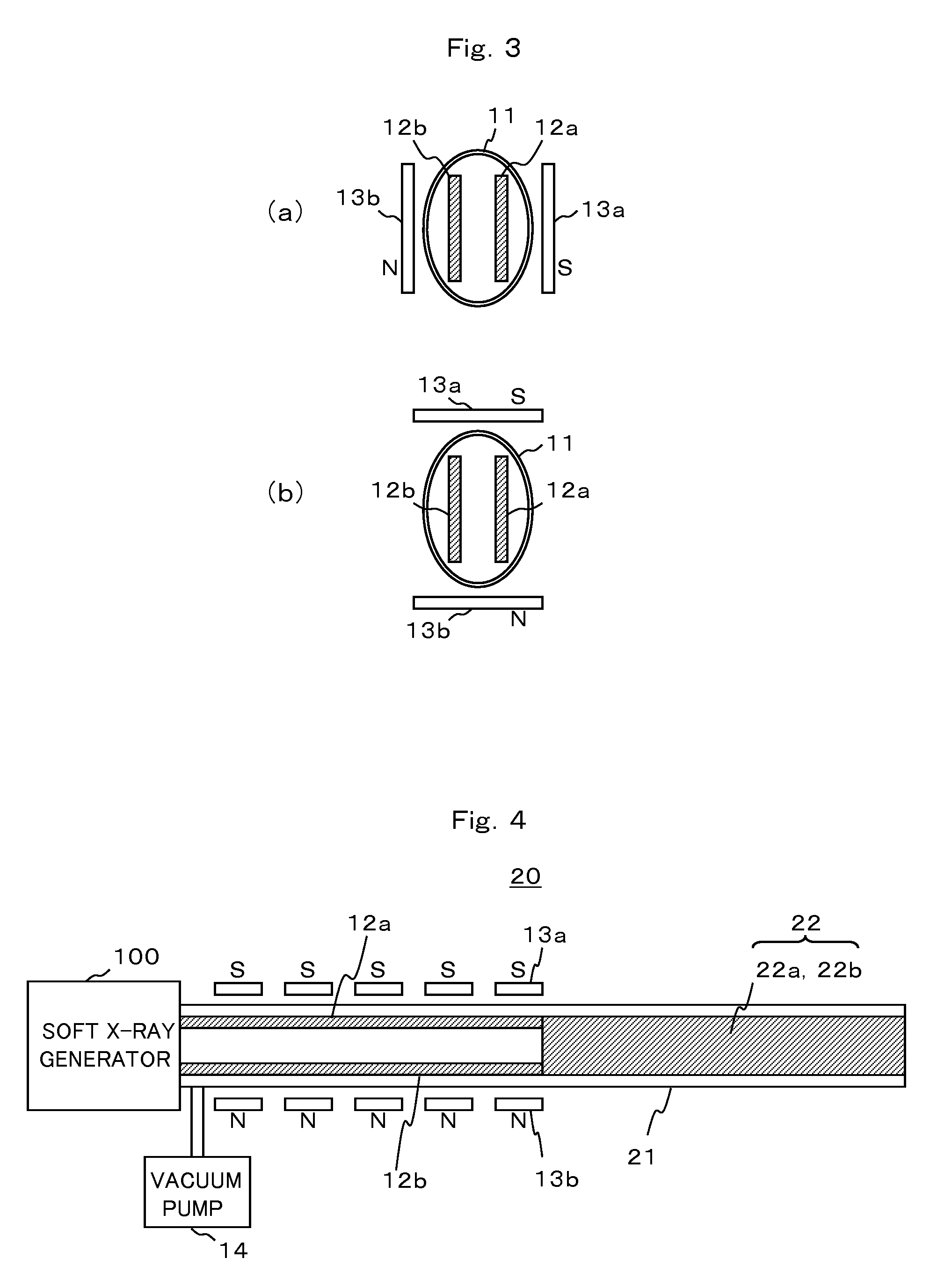

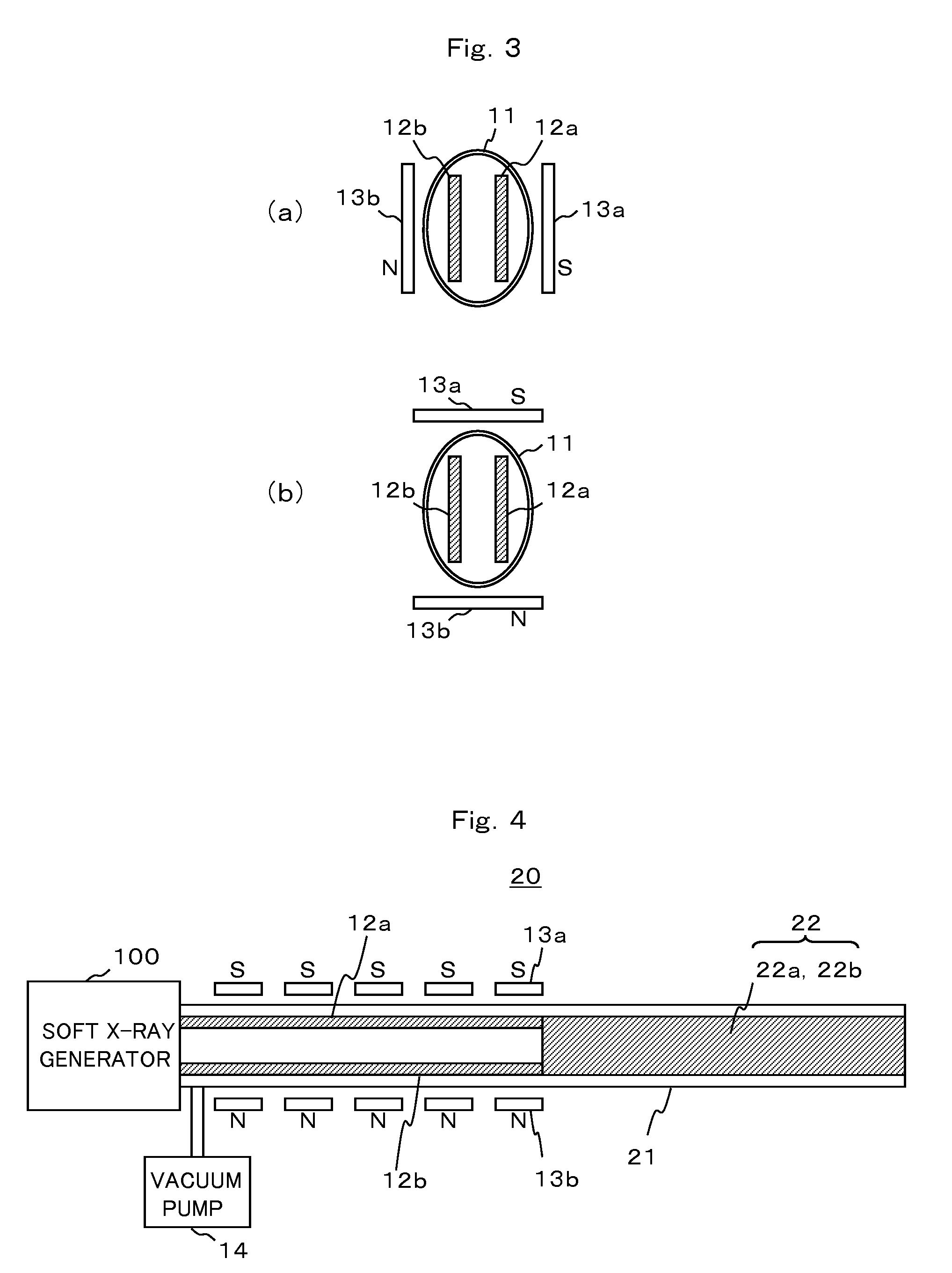

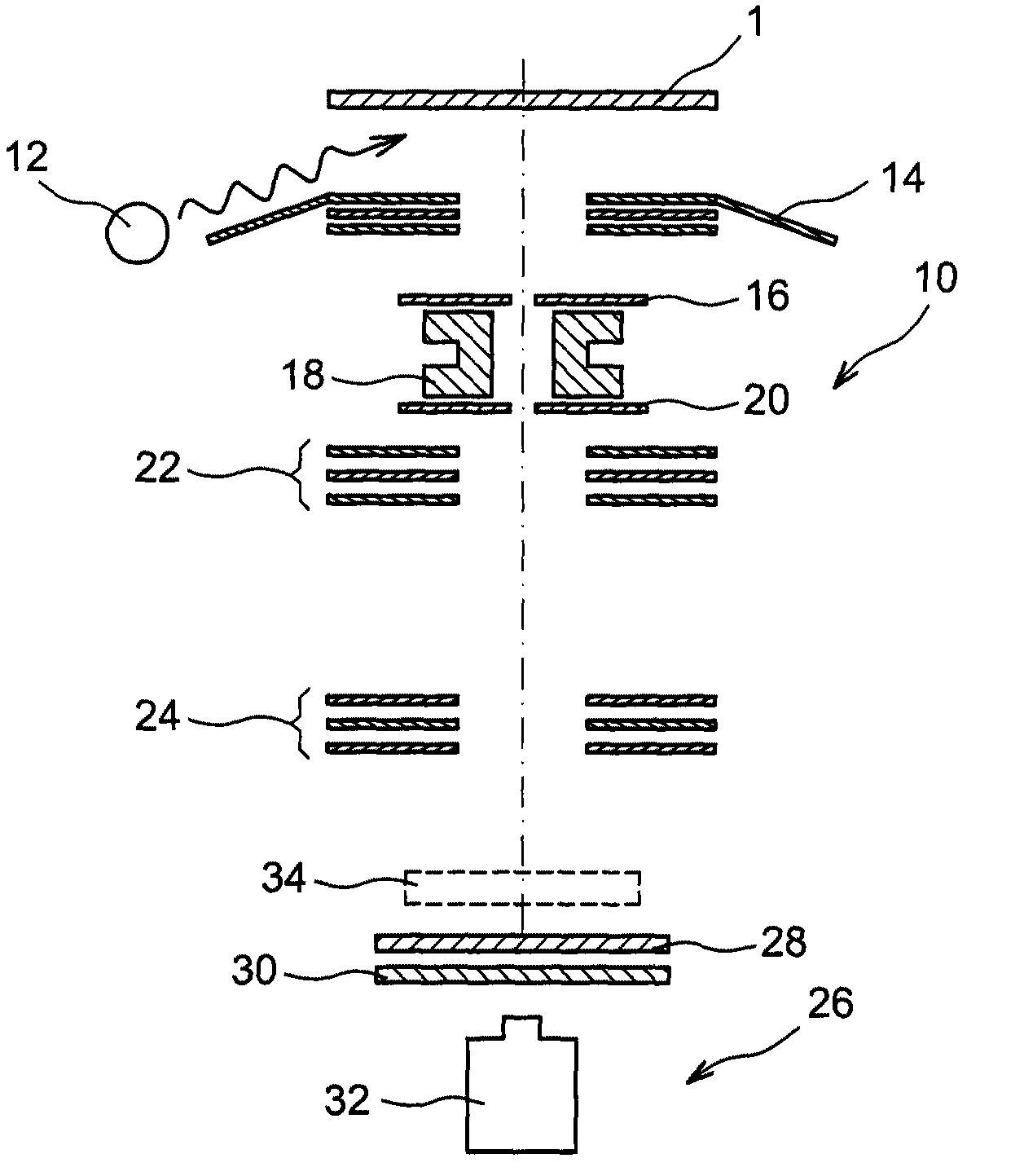

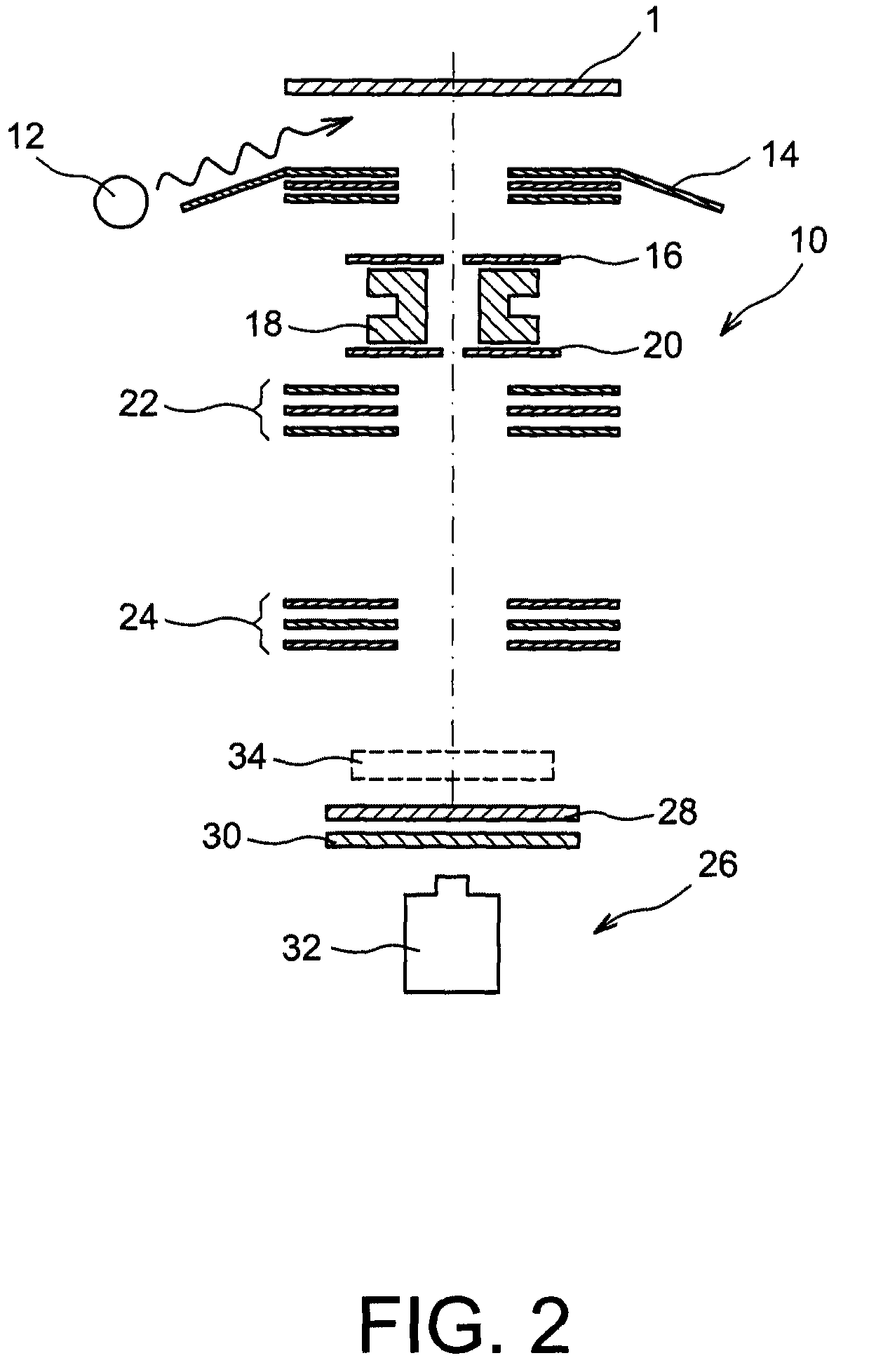

Phase controller

InactiveUS20120281816A1Increase the differenceSmall sizeHandling using polarising devicesHandling using diffraction/refraction/reflectionPhase differenceRefractive index

A reflection surface 12 constituted by a transition metal having a core level absorption edge in the vicinity of a wavelength of a soft X-ray is formed on an inside of a vacuum vessel 14, and furthermore, there is provided a permanent magnet 13 for generating a magnetic field in a perpendicular direction to a longitudinal direction of the vacuum vessel 14 in a position of the reflection surface 12 by which the soft X-ray is to be reflected, and the soft X-ray to be linearly polarized light incident on the vacuum vessel 14 is reflected at plural times over the reflection surface 12 in a position where the magnetic field is applied in such a manner that magnetic scattering is increased by a resonant effect of a magnetic circular dichroism when the soft X-ray is reflected by the reflection surface 12. Thus, a great difference in a refractive index is made between circularly polarized counterclockwise light and circularly polarized clockwise light which constitute the linearly polarized light, and a phase difference between the circularly polarized counterclockwise light and the circularly polarized clockwise light is obtained at a time. Consequently, it is possible to reversibly convert the soft X-ray from the linearly polarized light into the circularly polarized light or from the circularly polarized light into the linearly polarized light by a reflection to be carried out at only several times.

Owner:SAITAMA MEDICAL UNIVERSITY

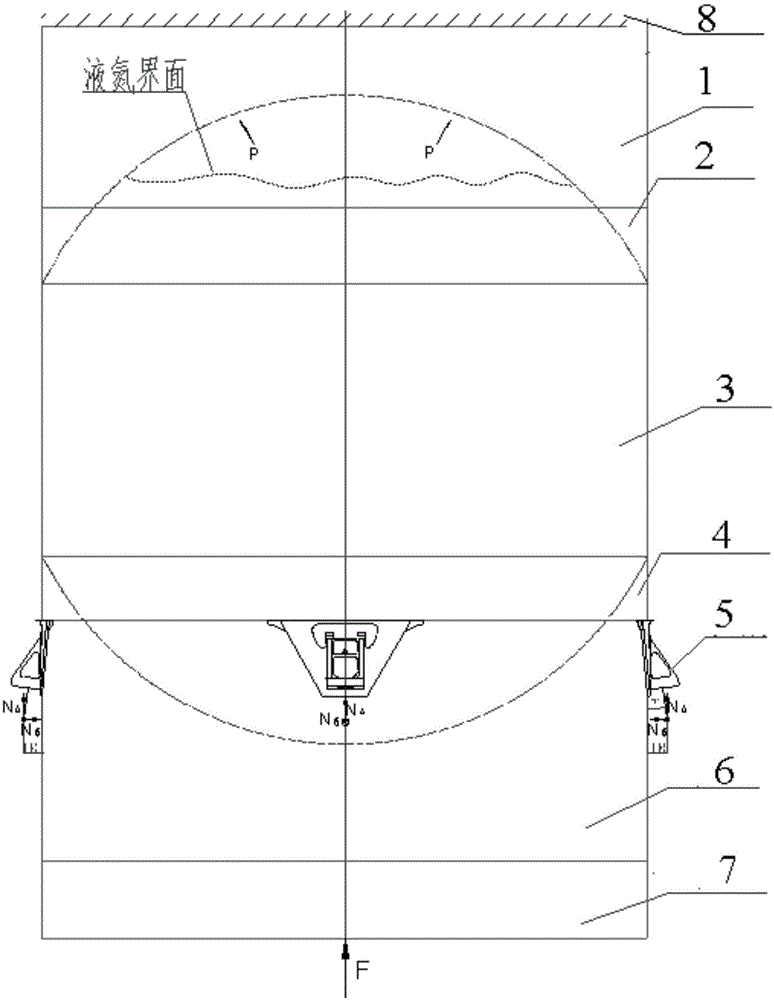

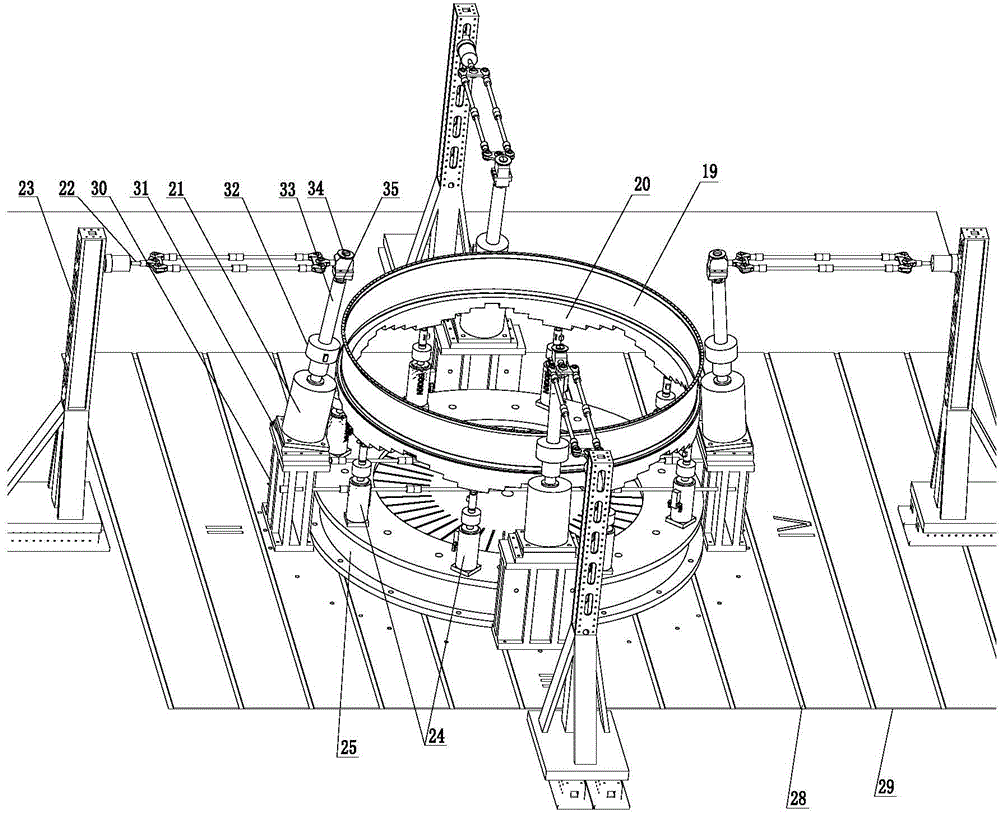

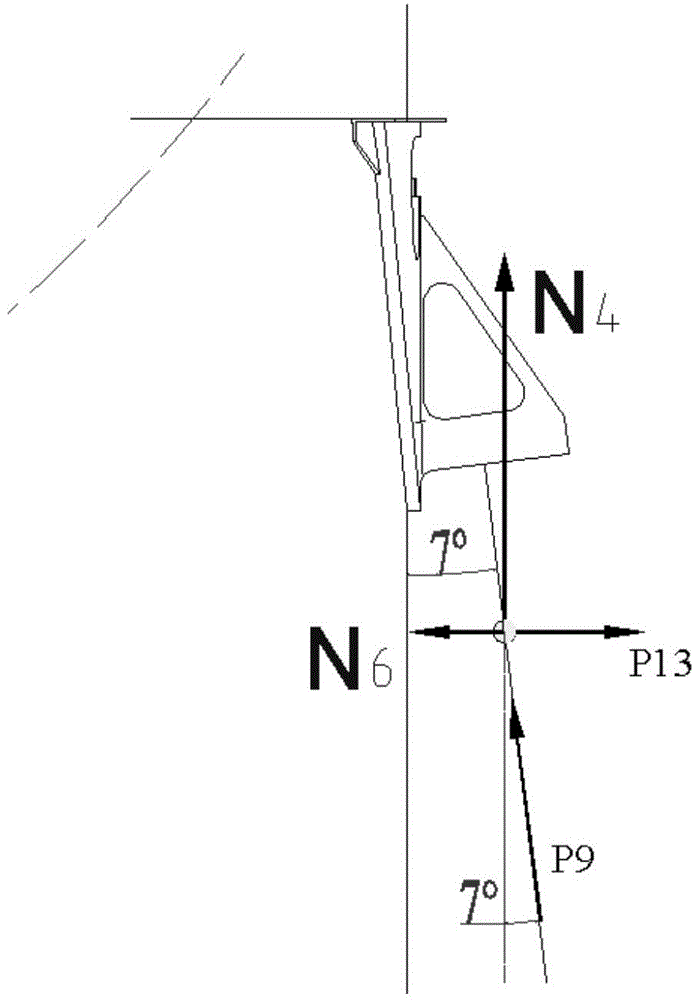

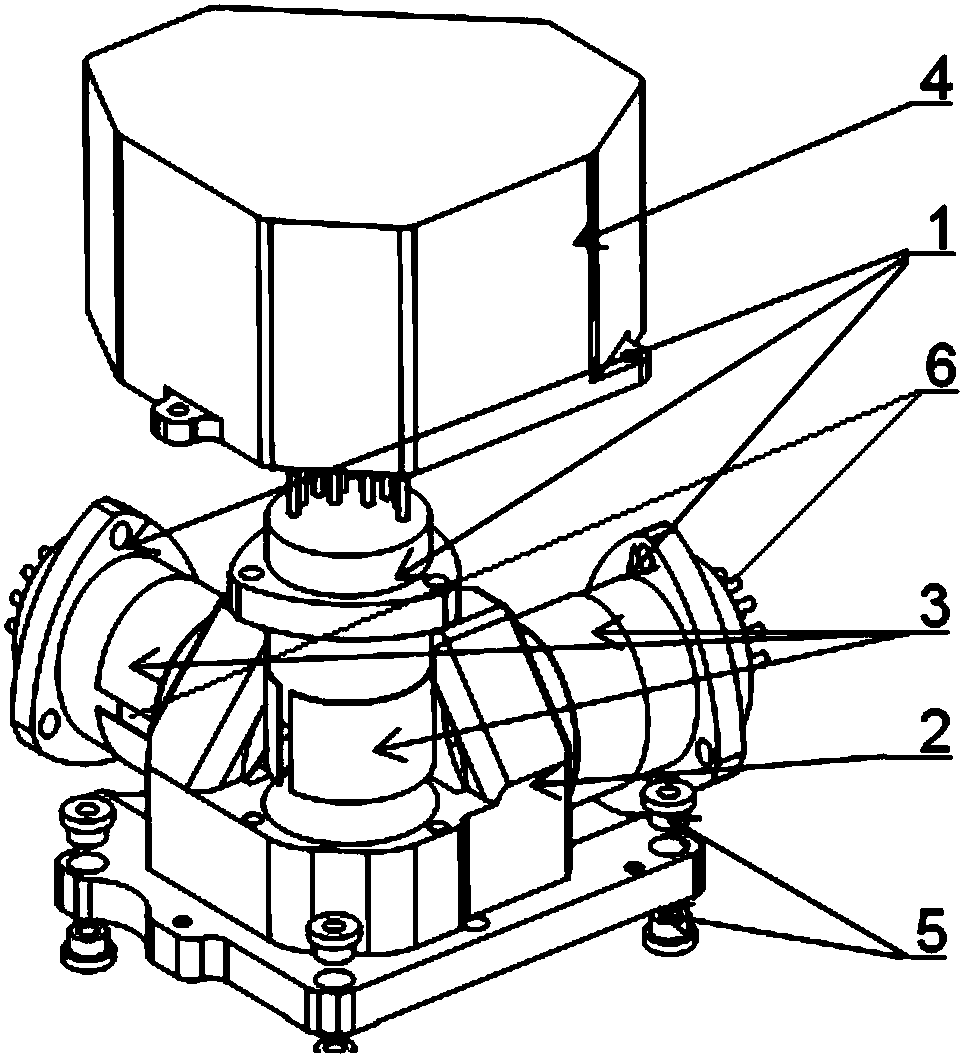

Multi-bonding point high-load inclined pushing-type loading device

InactiveCN105223003AStrong test technology reserveGuaranteed uptimeMachine part testingDynamometerTest platform

The invention relates to the structure static load test technology and particularly relates to a multi-bonding point high-load inclined pushing-type loading device. The device comprises a step type force transmission tool (20), inclined columns (23), P1-P8 loading equipment (24), a test platform (25), a foundation (29), P3-P16 loading equipment (22), P9-P12 loading equipment (21), bearing bases (30), wedge form supports (31), 400 ton pressure type dynamometers (32), force transmission pressure bars (33), high bearing bulb nest combinations (35) and loading tools (34). The P1-P8 loading equipment (24) provide upward loads in an axial direction. The loading tools (34) are connected to a test piece and provide upward loads in an oblique direction for the test piece. With the adoption of the multi-bonding point high-load inclined pushing-type loading device, the core level front bonding low temperature combined static load test can be smoothly completed, and a sound test technical reserve is provided for enforcement and conduction of the follow-up type low temperature static load test.

Owner:BEIJING INST OF STRUCTURE & ENVIRONMENT ENG +1

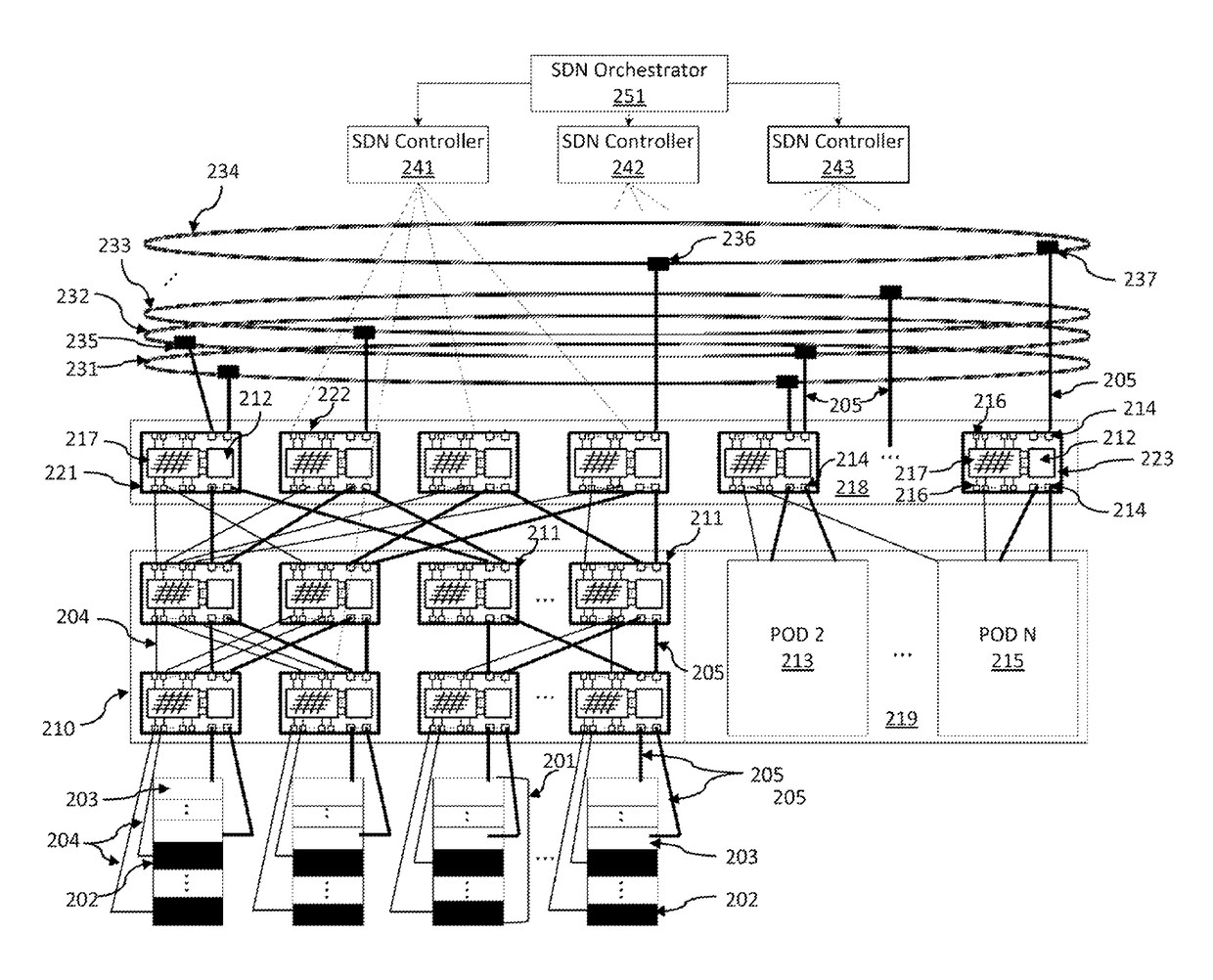

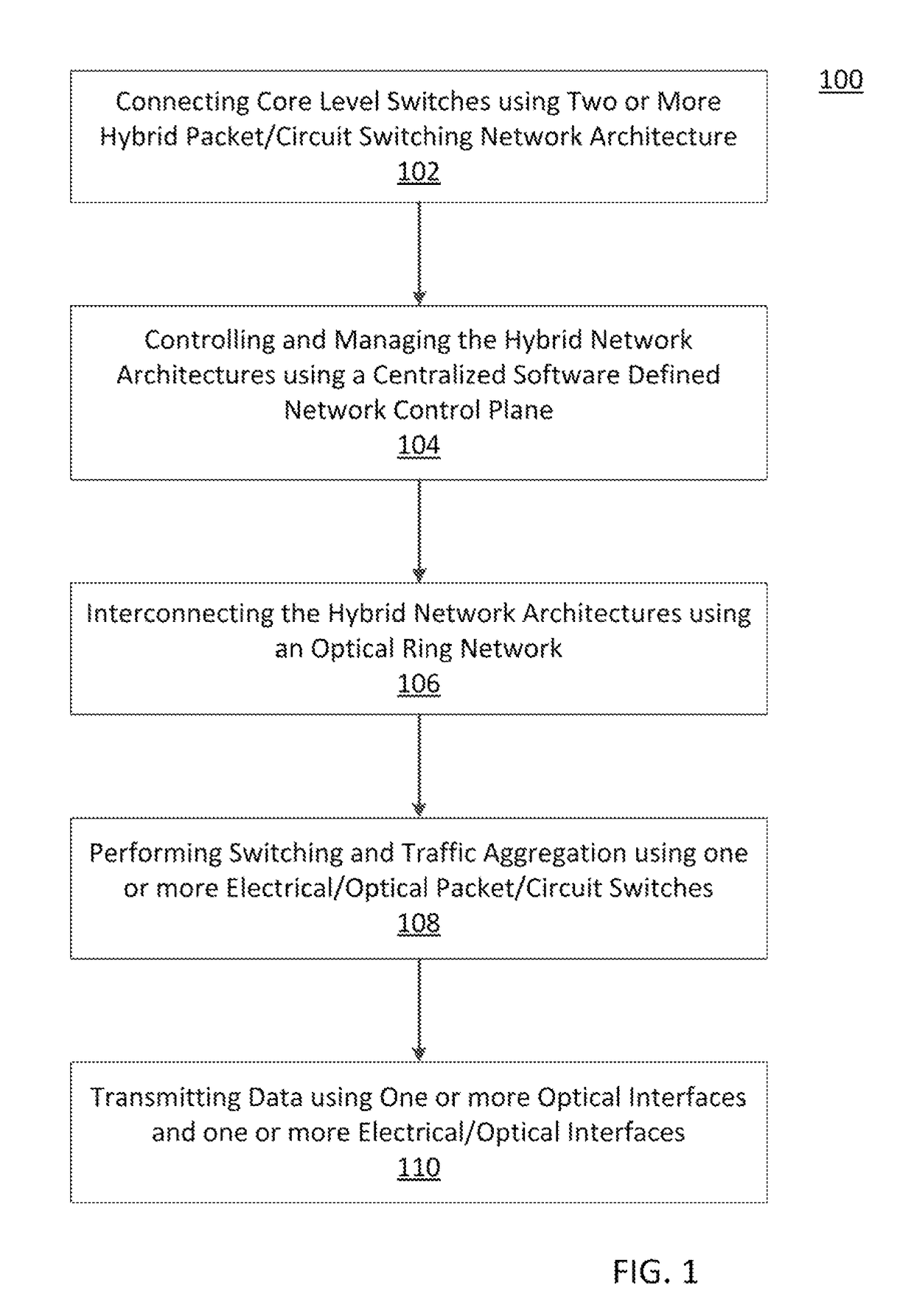

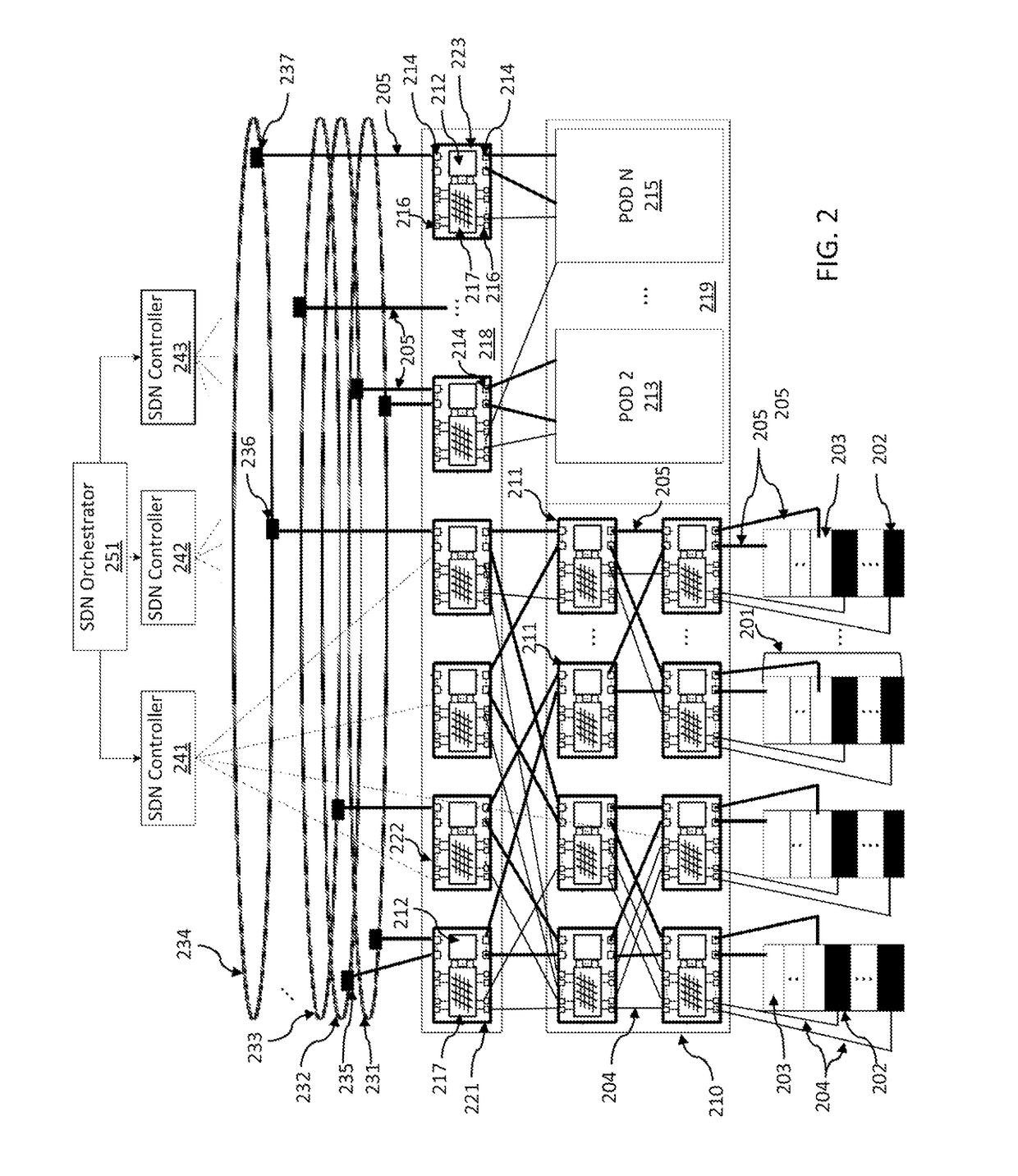

Scalable hybrid packet/circuit switching network architecture

ActiveUS9654852B2Multiplex system selection arrangementsWavelength-division multiplex systemsLow speedNetwork architecture

Systems and methods for packet switching in a network, including two or more hybrid packet / circuit switching network architectures configured to connect two or more core level switches in the network architectures, the network architectures being controlled and managed using a centralized software defined network (SDN) control plane. An optical ring network may be configured to interconnect the two or more hybrid network architectures, and one or more hybrid electrical / optical packet / circuit switches configured to perform switching and traffic aggregation. One or more high-speed optical interfaces and one or more low-speed electrical / optical interfaces may be configured to transmit data.

Owner:NEC CORP

Methods and systems for digitally controlled multi-frequency clocking of multi-core processors

ActiveUS7945804B2Convenient power managementEnergy efficient ICTMultiple digital computer combinationsLocal oscillatorEngineering

Owner:INT BUSINESS MASCH CORP

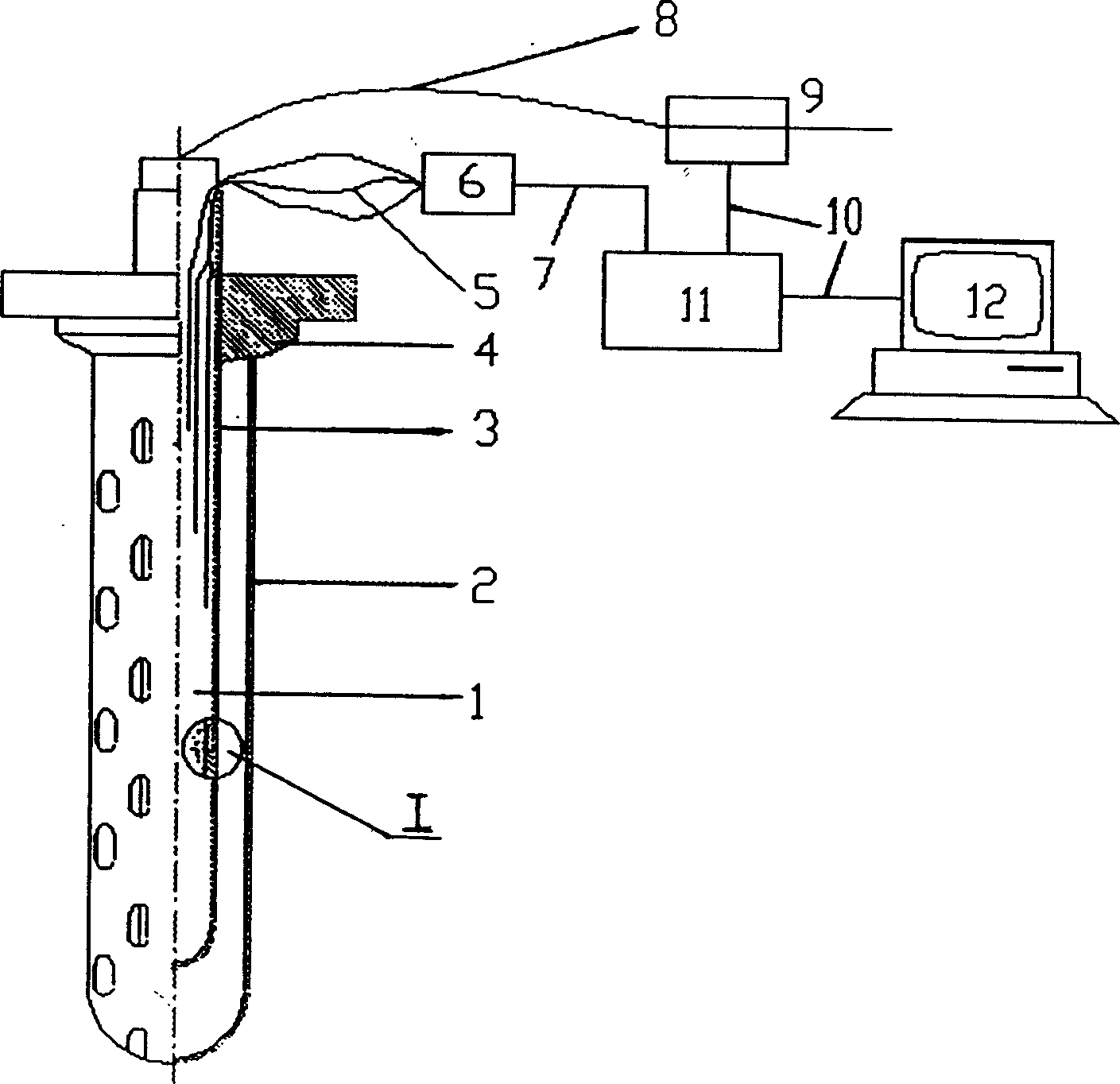

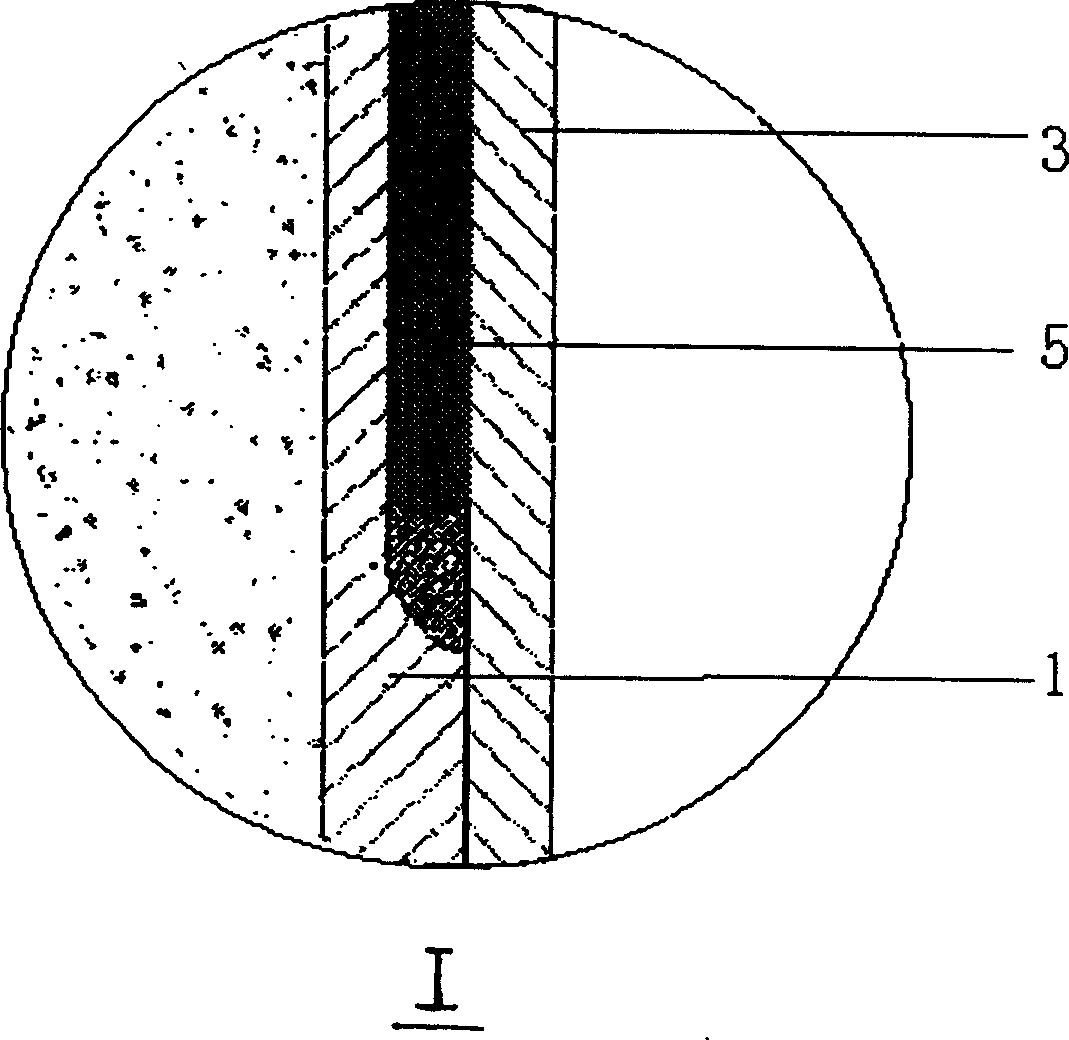

Core level monitoring device for reactor

InactiveCN1477648AImprove reliabilityExtended service lifeNuclear energy generationNuclear monitoringElectricityThermocouple

The reactor core level monitoring equipment includes level detector and secondary instrument, its level detector includes electric heater, thermocouple and sealing component welded on the electric heater, the level detector is connected with secondary instrument by means of connector, electric heater cable and signal cable, on the outer wall of electric heater of the level detector the longitudinal recessed grooves with different heights are cut, the thermocouples can be welded in the recessed grooves, and the exterior of the electric heater is equipped with thin-wall case pipe.

Owner:NUCLEAR POWER INSTITUTE OF CHINA

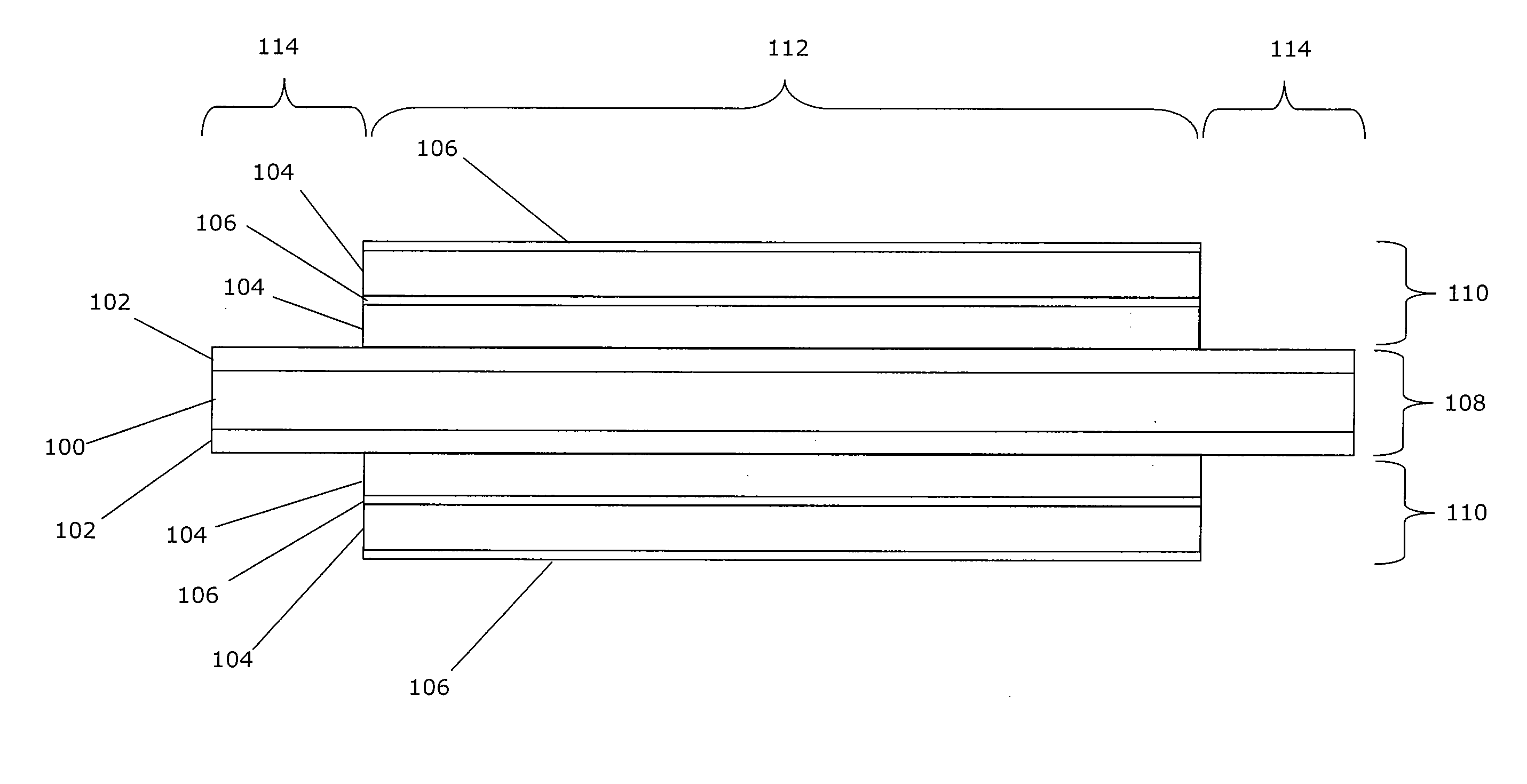

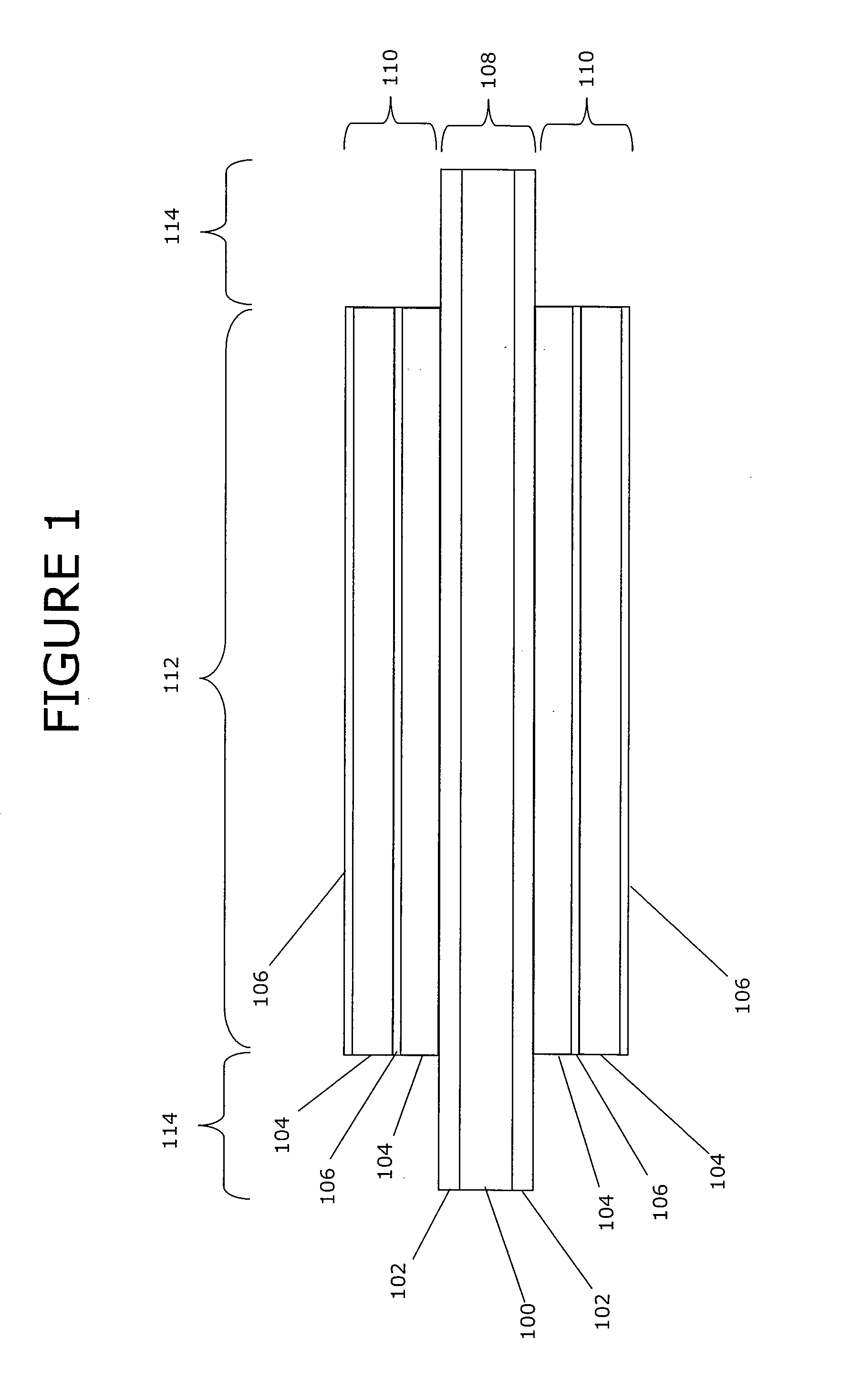

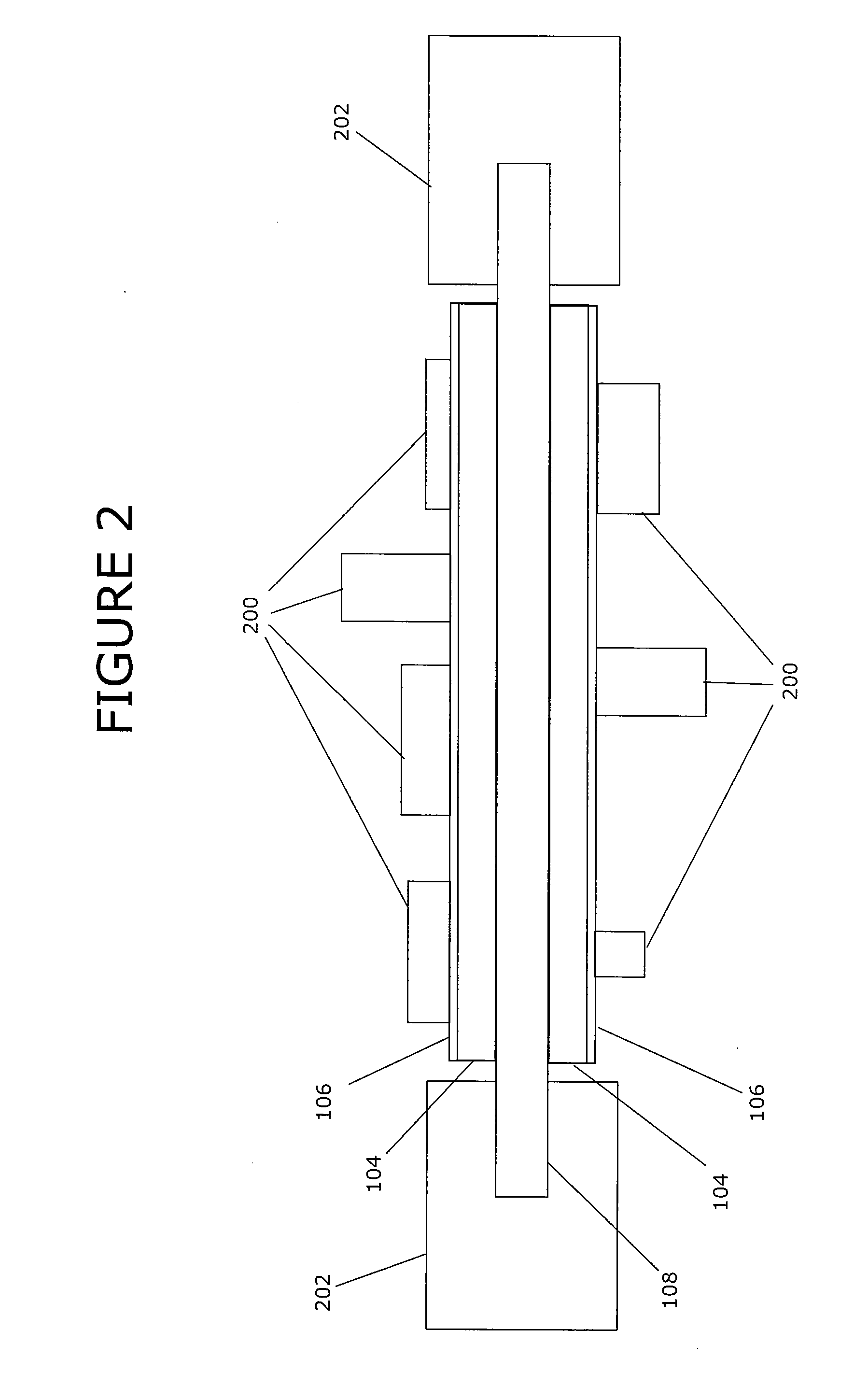

Multilayer, thermally-stabilized substrate structures

InactiveUS20090141456A1Semiconductor/solid-state device detailsPrinted circuit aspectsThermal expansionEngineering

A multilayer, thermally-stabilized substrate, including: a thermally-conductive core structure, including a central section located horizontally between two edge sections; a top multilayer circuit board connected to the top surface of the central portion of the core structure; and a bottom multilayer circuit board connected to the bottom surface of the central portion of the core structure. The core structure has a core thermal conductance and a effective core horizontal thermal expansion coefficient. The top and bottom multilayer circuit boards each include at least one dielectric layer and at least one electrically-conductive layer, and each have a circuit board thermal conductance that is less than the core thermal conductance of the core structure. The electrically-conductive layers of the top and the bottom circuit boards each have a conductive layer horizontal thermal expansion coefficient that is less than or equal to the effective core horizontal thermal expansion coefficient of the core structure.

Owner:ITT MFG ENTERPRISES LLC

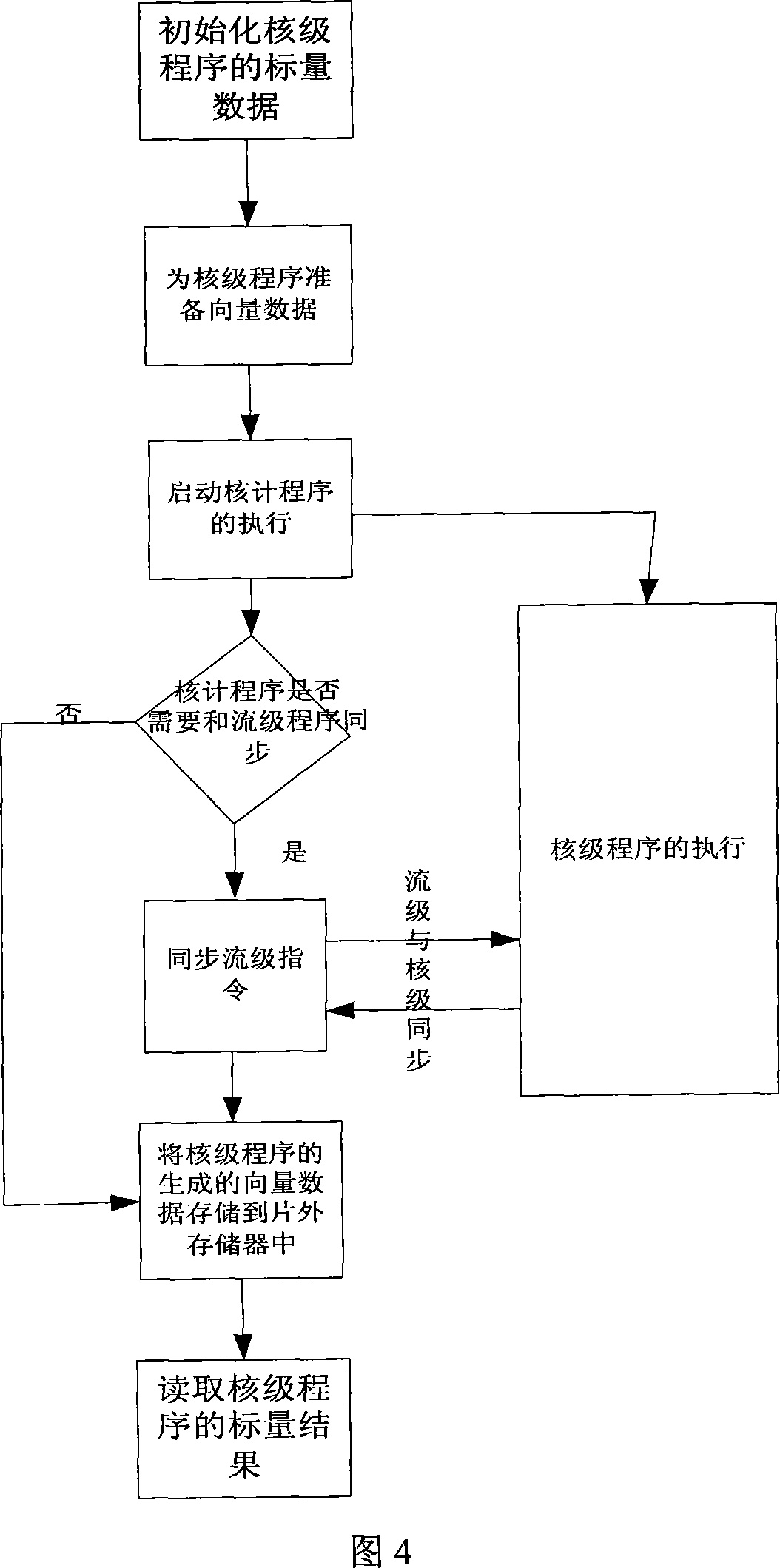

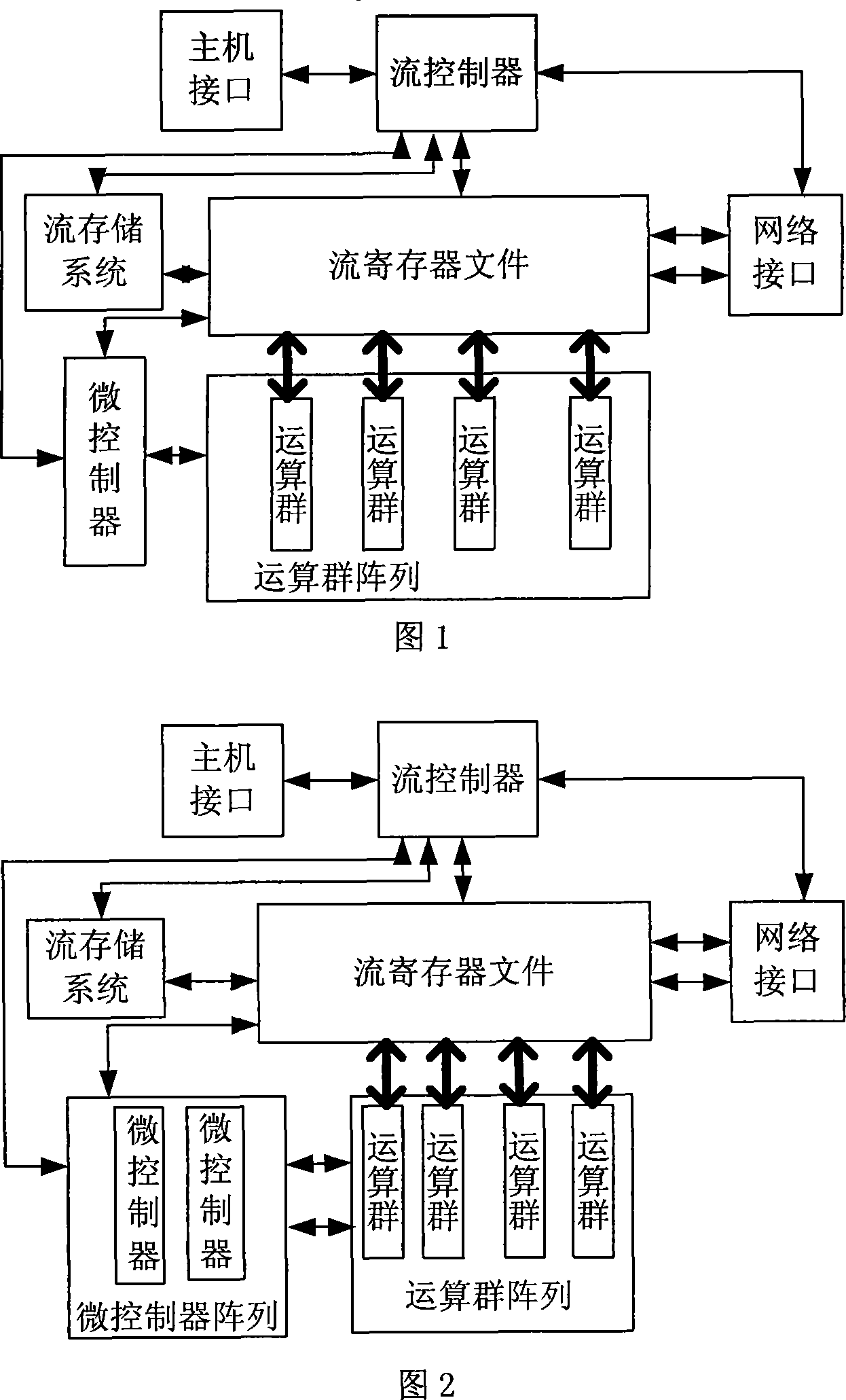

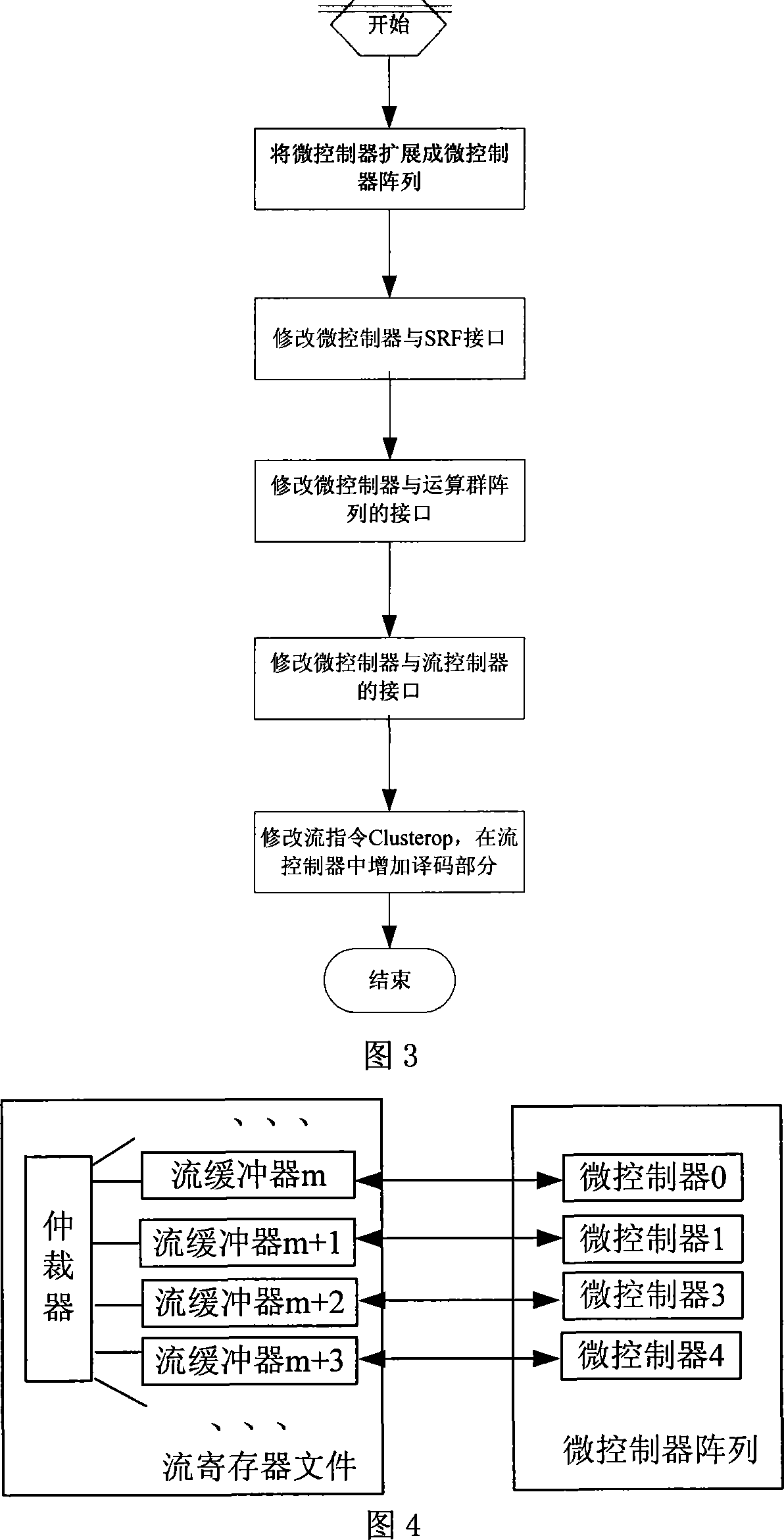

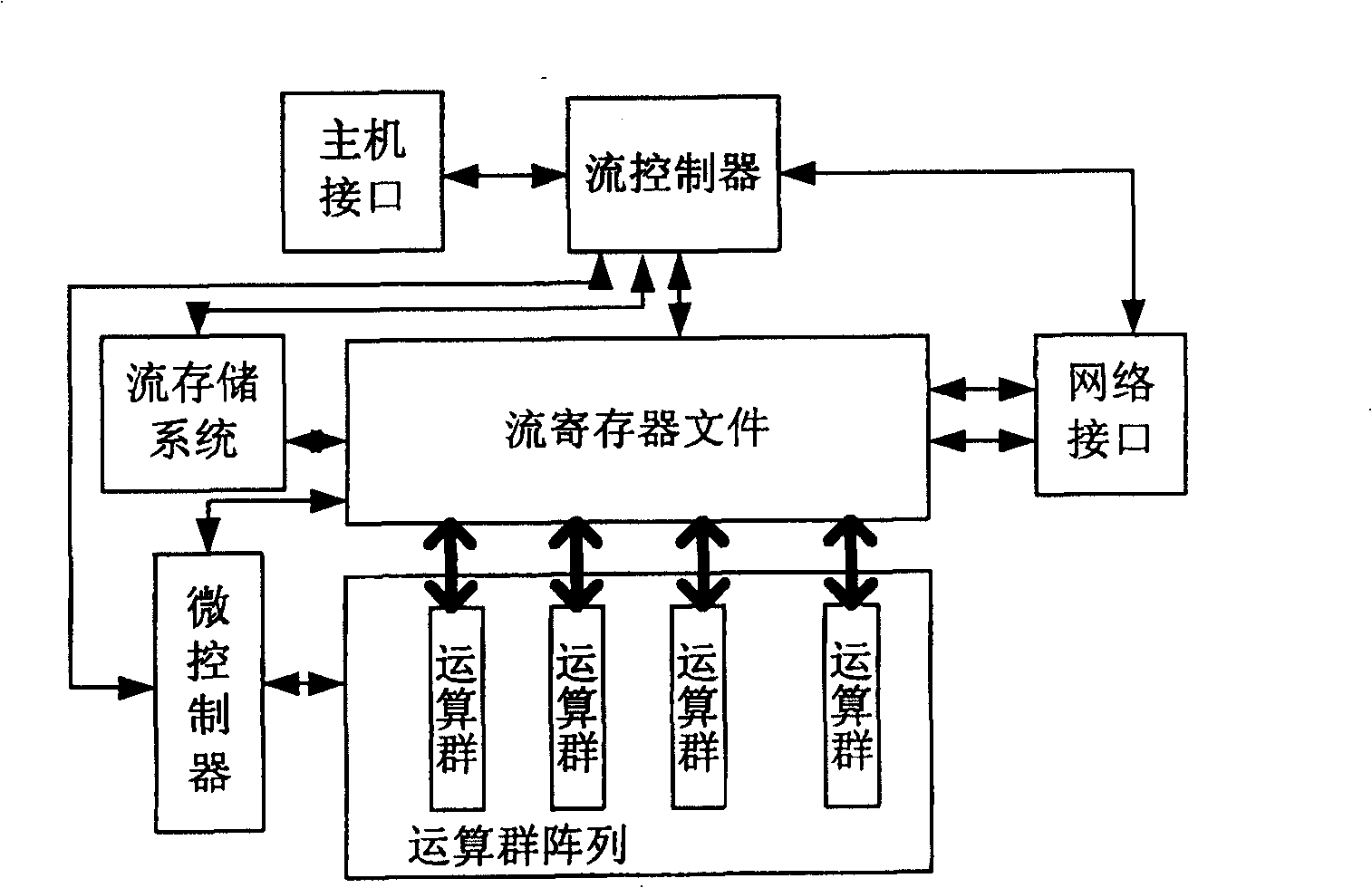

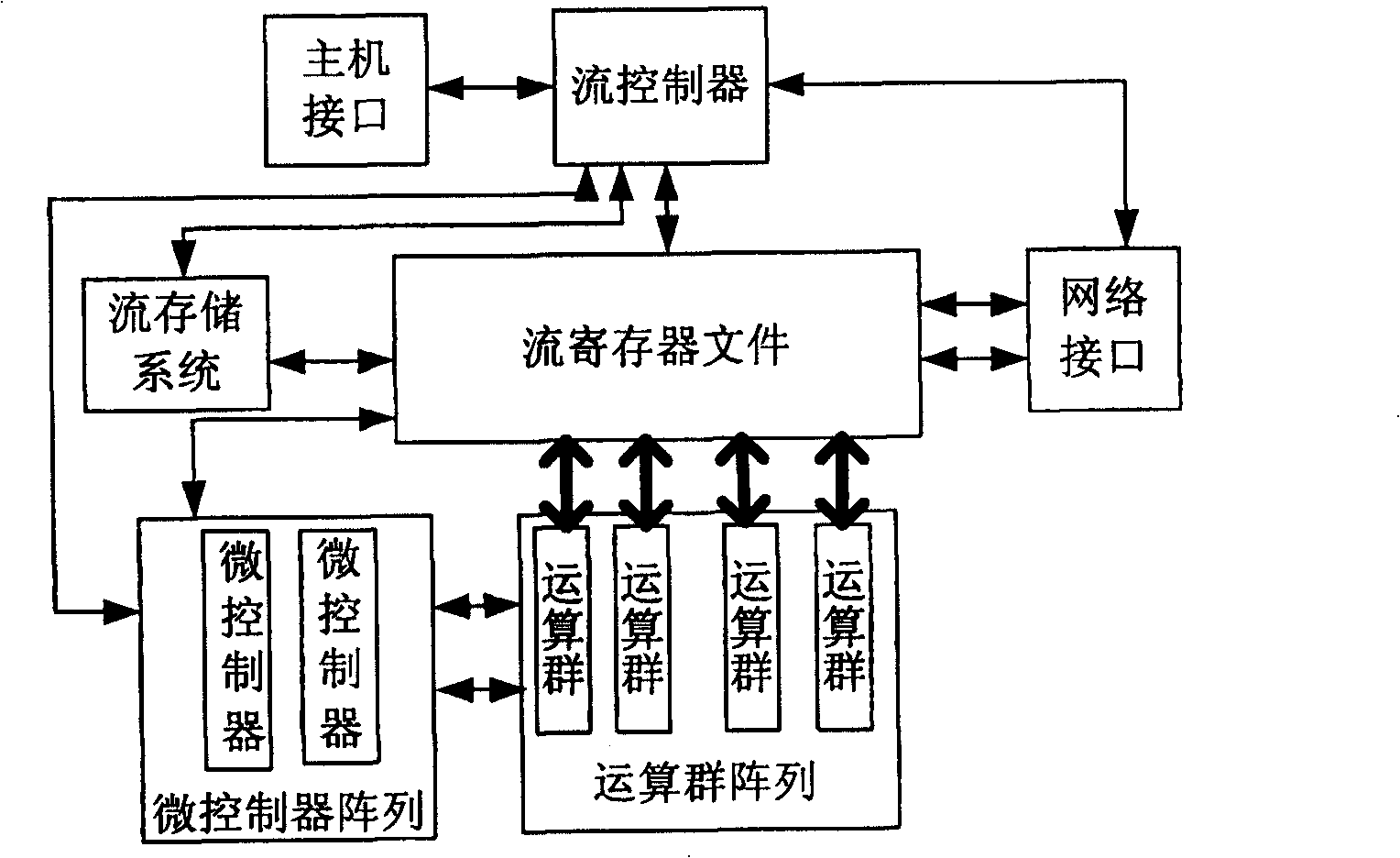

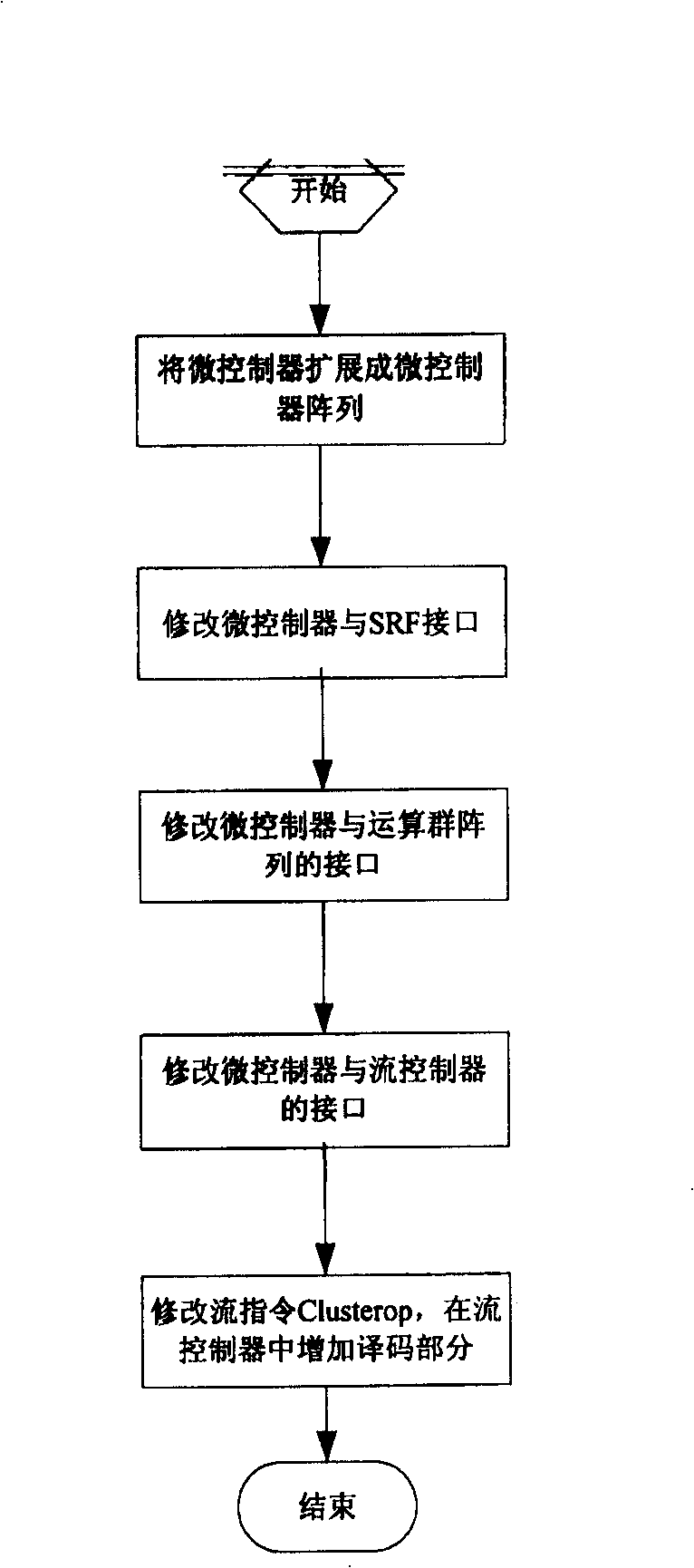

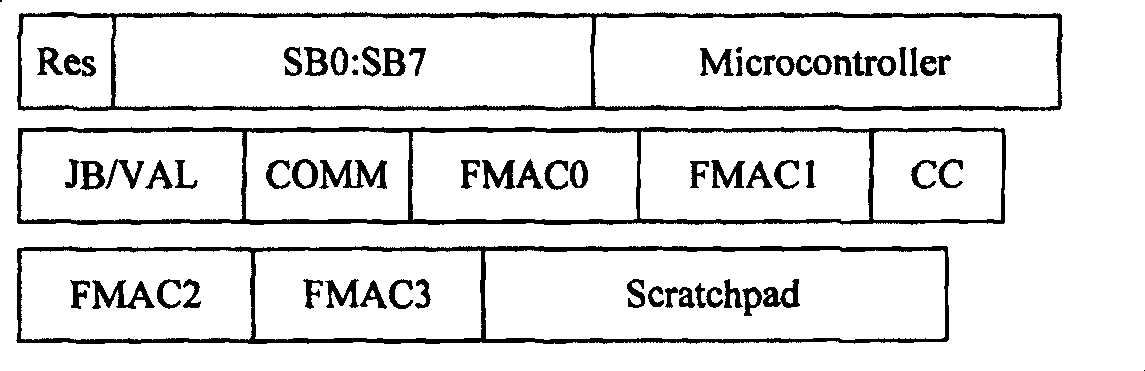

Stream processor expanding method for flexible distribution operating group resource

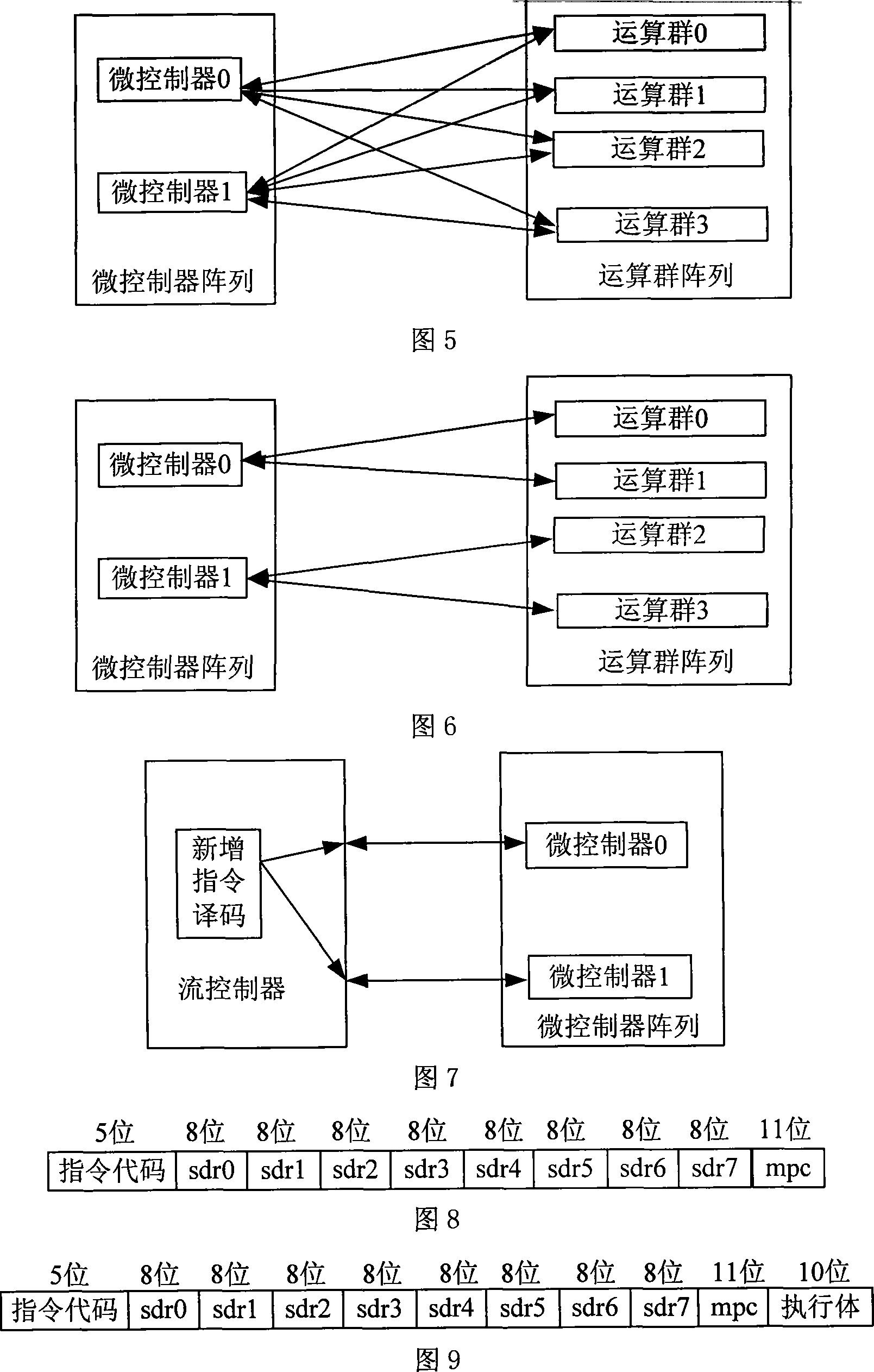

InactiveCN101021781ASave on multi-core scalingEasy to handleConcurrent instruction executionArchitecture with multiple processing unitsMicrocontrollerParallel computing

This invention discloses a cluster-processor expansion method by flexible allocation of computing resource, and its steps are: (1) setting the array of microcontroller, which is composed of two or more microcontrollers, adding a reading cluster interface for each microcontroller in SRF, and each microcontroller has the same structure and same interface with cluster controller, to start implementation of a core-level procedure under the control of cluster controller, (2)setting interfaces between microcontroller and operational group, (3) setting the cluster controller and adding interfaces connected with each microcontroller on it,(4) setting Clusterop in the controller, to make a core-level procedure implement only in a microcontroller and some computing group ensuring that many microcontrollers executes the procedure at the same time with the permission of computing resources.

Owner:NAT UNIV OF DEFENSE TECH

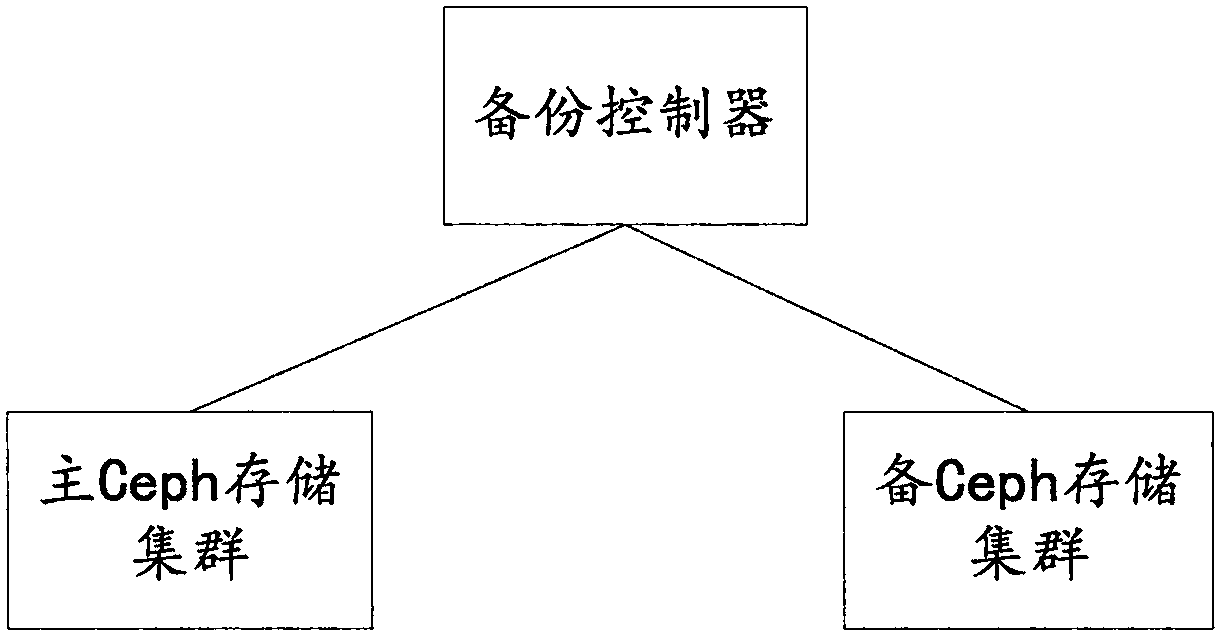

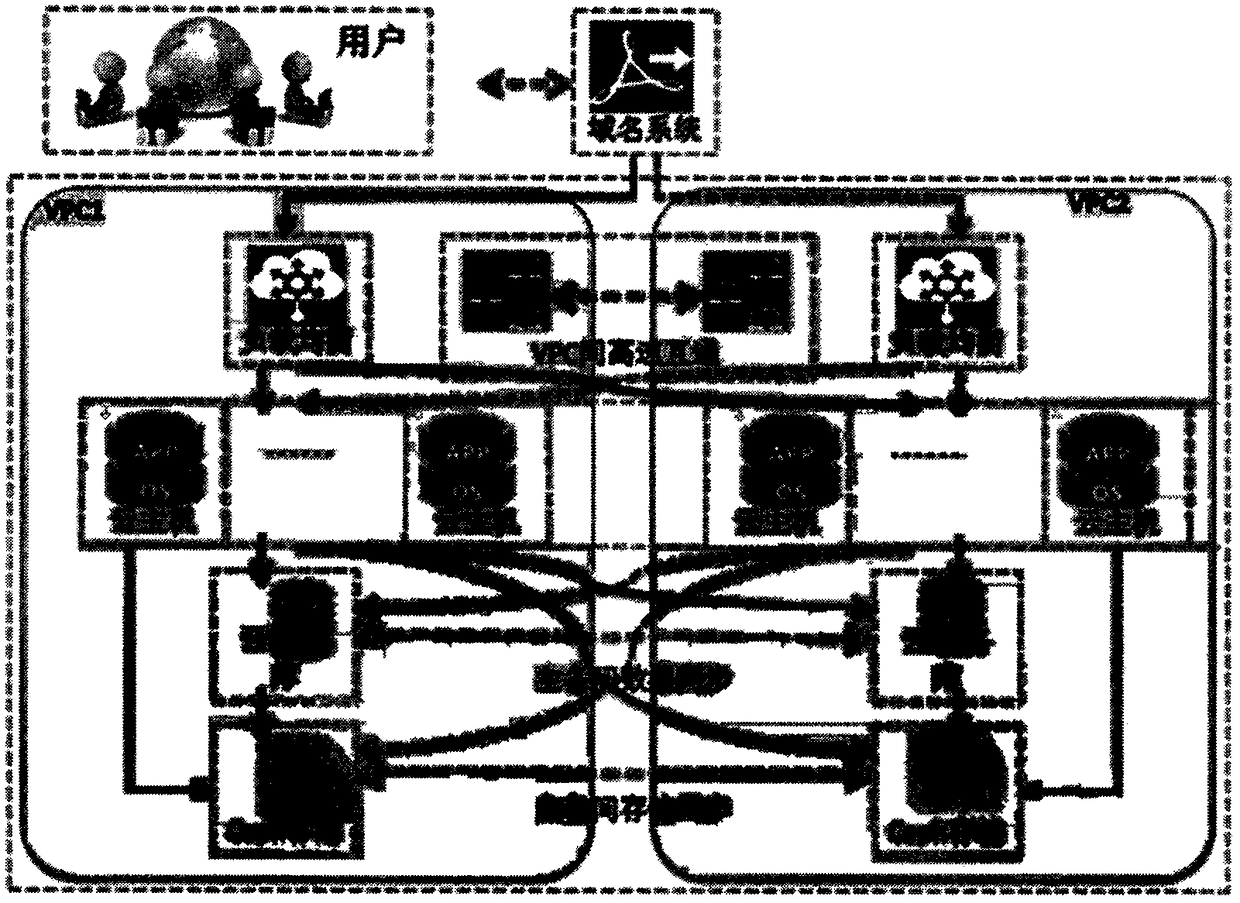

Cross-regional disaster recovery method and device

InactiveCN108512693ADisaster recovery in the same city or even in different placesLower deployment costsData switching networksCore levelSwitching time

The invention discloses a cross-regional disaster recovery method and device. The method comprises the following steps of respectively deploying cloud networks in two partitions, wherein each of the two cloud networks is provided with a computing resource layer, a database layer and a storage layer; and respectively carrying out monitoring and disaster recovery on the computing resource layer, thedatabase layer and the storage layer. According to the method and the device, the cross-regional disaster recovery of hierarchical management is realized through the cloud network, the deployment cost is low, the switching time is short, no negative influence is generated on services, and the time for cross-regional disaster recovery can be shortened. Furthermore, cross-regional disaster recoveryis achieved on the computing resource layer, the database layer and the storage layer respectively, so that a complete cloud disaster recovery scheme is achieved, and a problem of local disaster recovery and even remote disaster recovery of the important and core-level services and above is solved.

Owner:NAT COMP NETWORK & INFORMATION SECURITY MANAGEMENT CENT

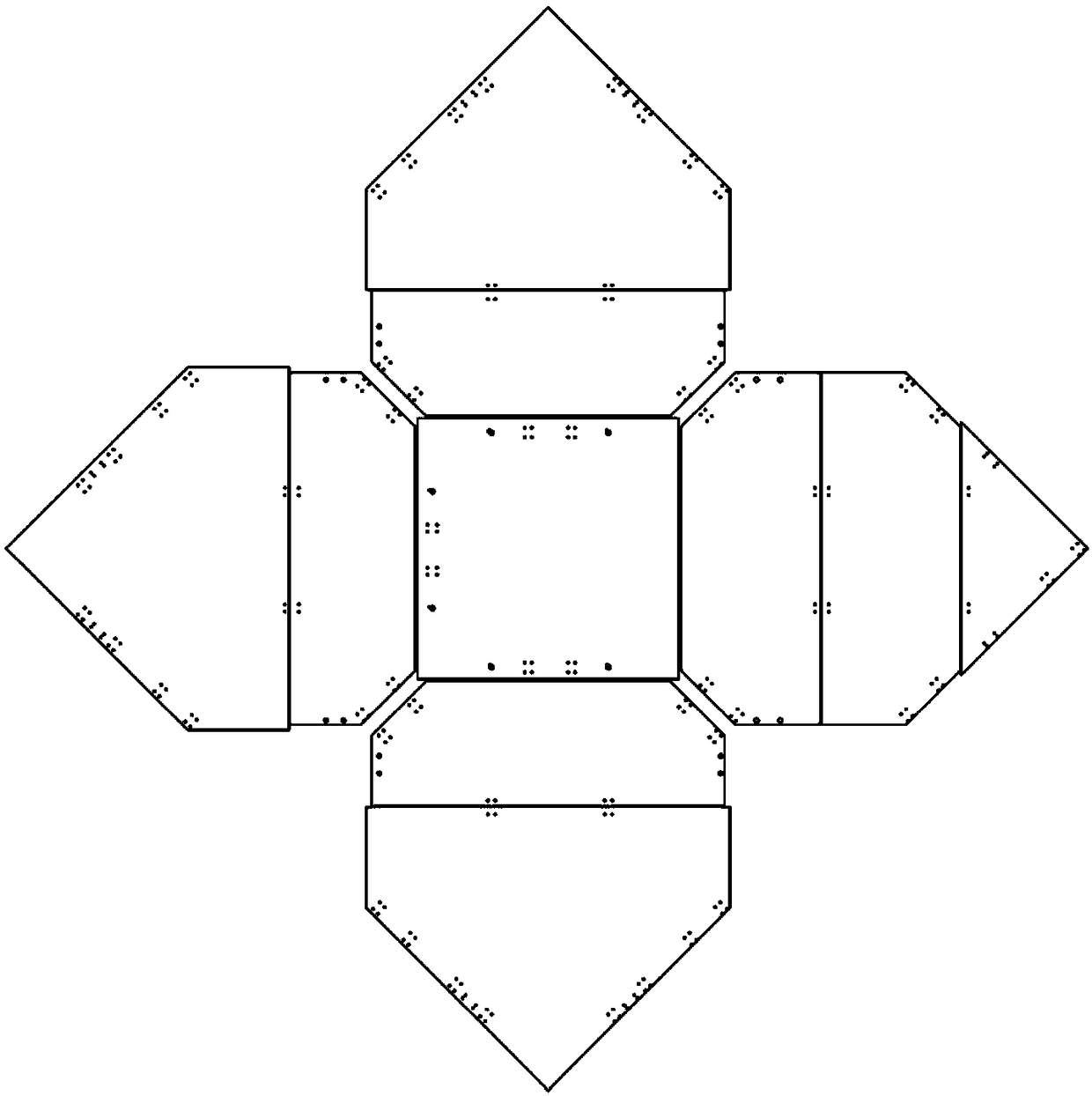

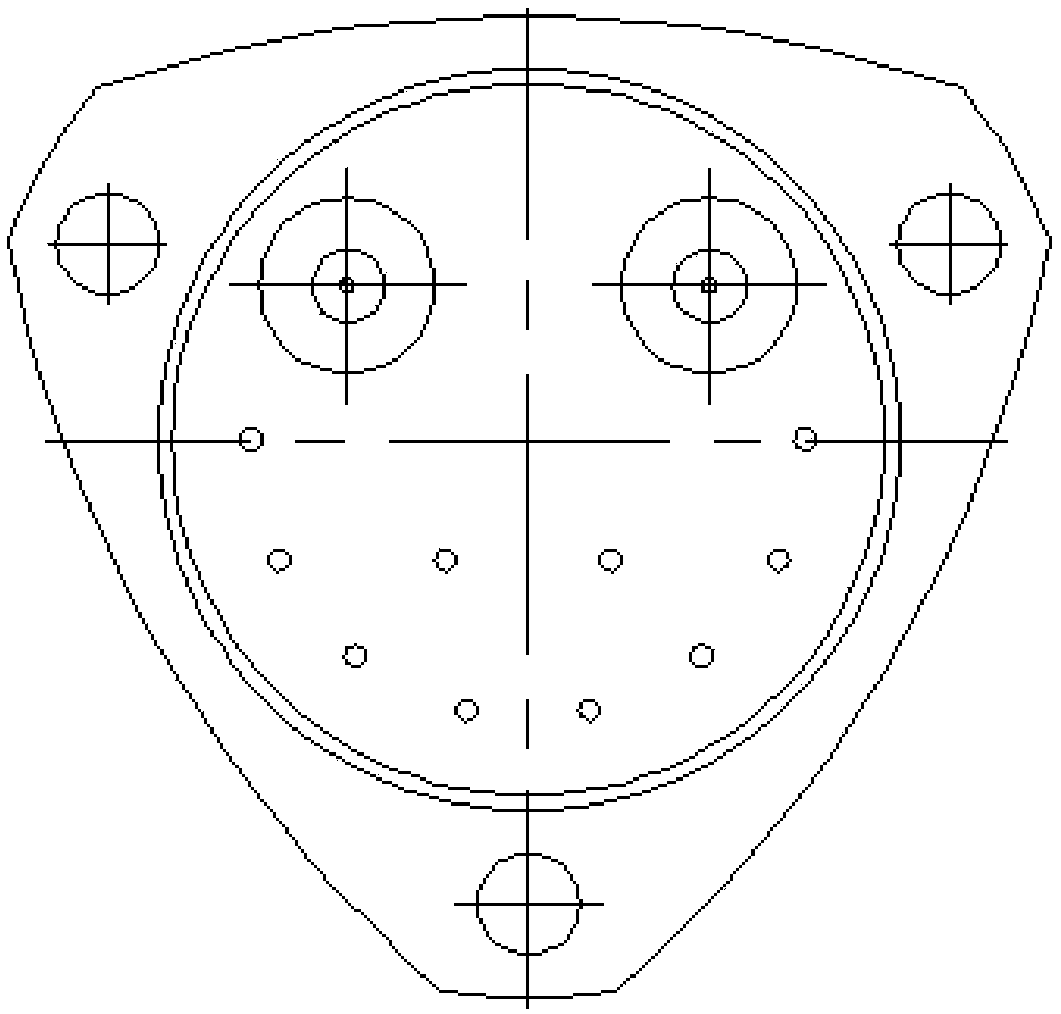

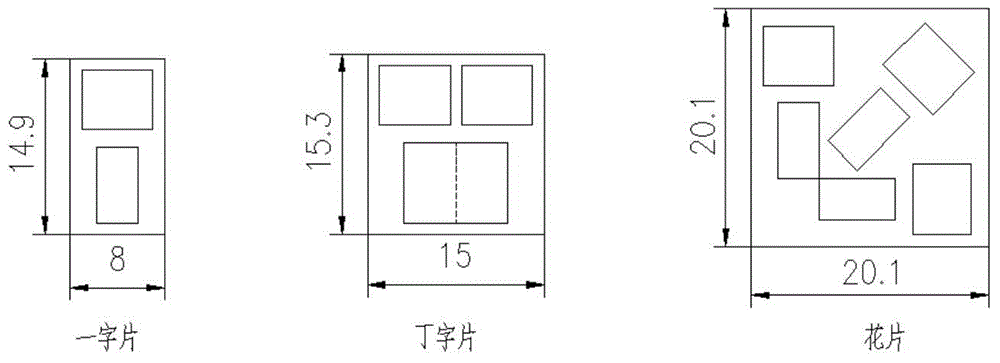

Composite-material core-level cover plate for rocket, and preparation method thereof

The invention discloses a composite-material core-level cover plate for a rocket, and a preparation method thereof. The cover plate comprises nine detachable units, wherein each detachable unit is a composite-material interlayer structure containing an inner framework; and one is a central quadrilateral unit and the other eight detachable units are divided into four groups, the two detachable units in each group are connected together through a hinge, the four sides of the central quadrilateral unit are lapped and fixed to one turned edge of the four groups of detachable units separately, theother sides of the four groups of detachable units are placed on a launching platform installation frame and fixed, and the whole outer edge outline is determined by an installation connector space where the cover plate is located. The invention puts forward for the first time that a light-weight foam interlayer structure containing the inner framework is applied to the core-level cover plate forthe rocket. The composite-material core-level cover plate has the advantages of being convenient to transport, simple to install, rapid to detach, and the like; and the disclosed preparation method has the advantages of ensuring the good forming quality of products, realizing integrated forming, and achieving low cost.

Owner:AEROSPACE RES INST OF MATERIAL & PROCESSING TECH +1

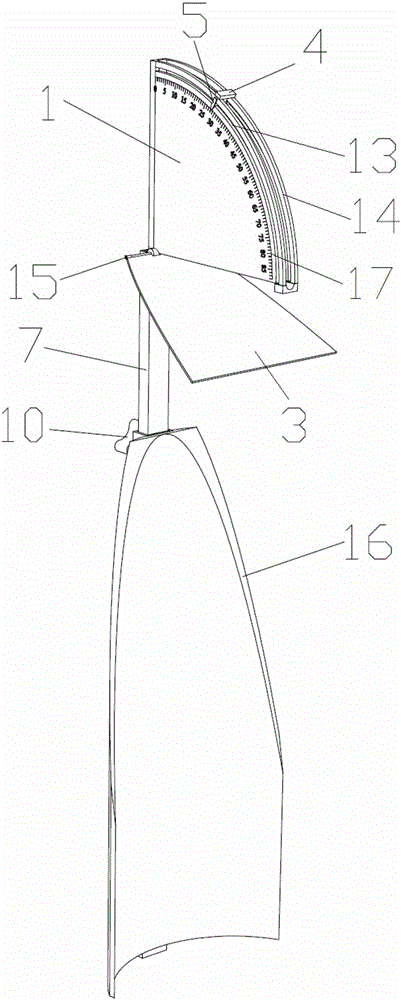

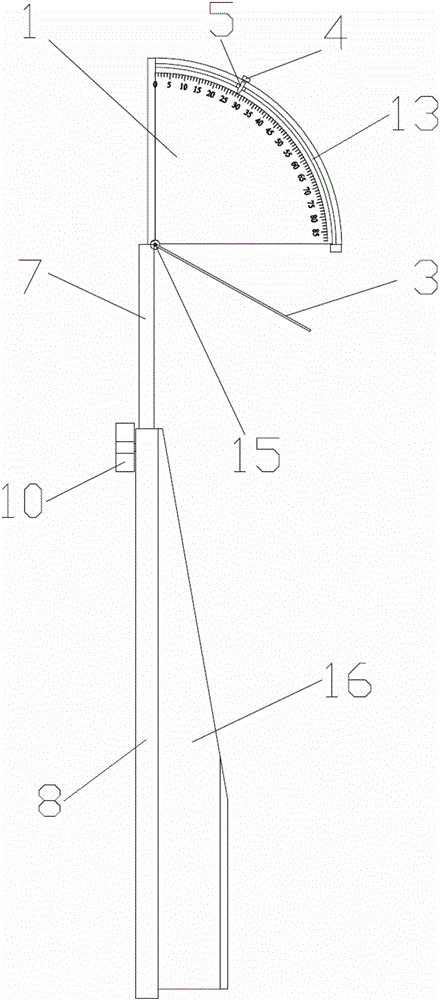

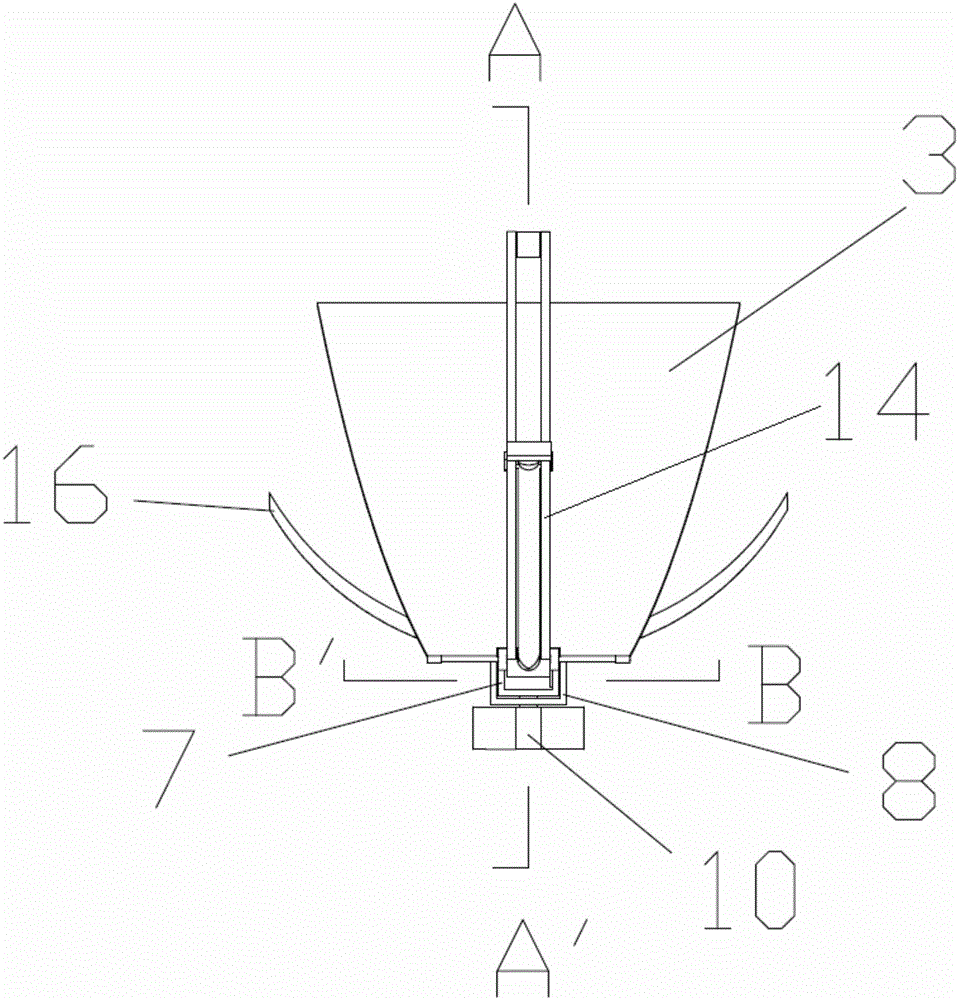

Drilling rock core level dip meter

The invention provides a drilling rock core level dip meter. The drilling core level dip meter comprises a measuring unit, an adjusting unit and a rock core fixing assembly which are connected in sequence. The measuring unit comprises a reading dial, an indication rod and a fit plate. The reading dial is in a fan shape. An arc-shaped side edge of the reading dial is provided with angle scales. End parts of the indication rod and the fit plate are fixedly connected and are perpendicular to each other. The connection part between the indication rod and the fit plate is hinged with the circle center of the reading dial. The adjusting unit comprises an upper shaft frame, a lower shaft frame, an adjusting handle and a rack and pinion mechanism. The dip meter is designed in strict accordance with principles related to rock core dip measurement, the fit plate and the indication rod perpendicular to each other are designed, and the rock core is placed in a pallet in the rock core measuring process, so that the dip reading can be rapidly read only if the rock core level is fit with the fit plate; and in this way, a tedious process in conventional dip measurement that the instruments needs to be repeatedly adjusted to determine the inclination is omitted, and the dip measuring efficiency is greatly improved.

Owner:CHINA UNIV OF GEOSCIENCES (WUHAN)

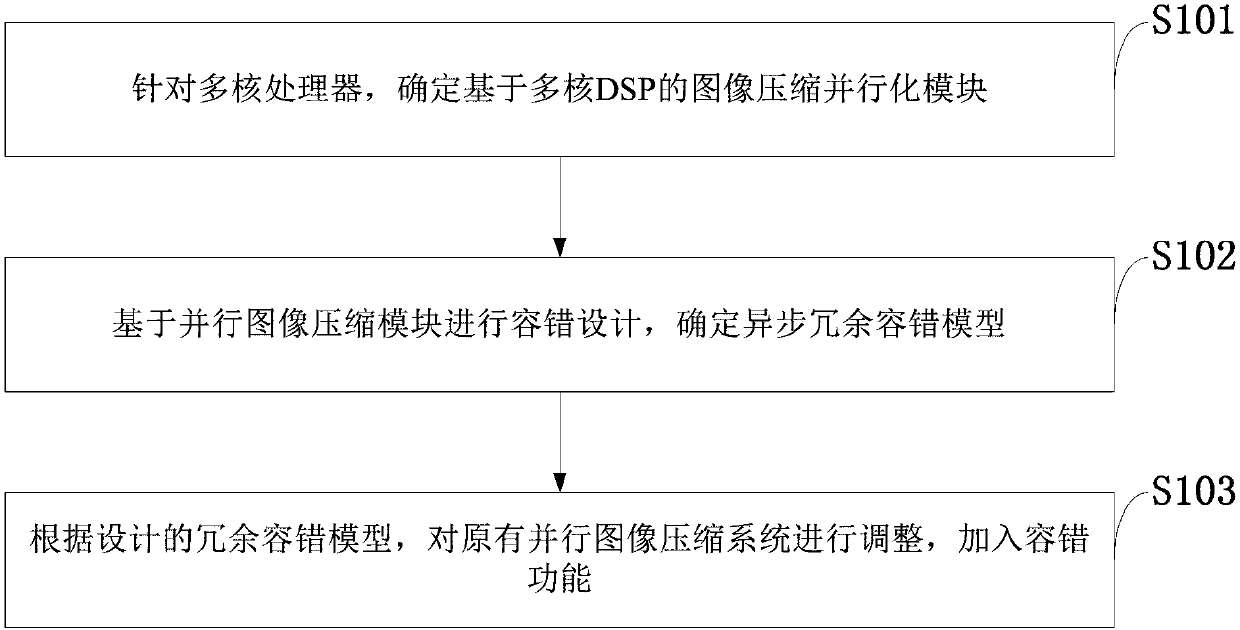

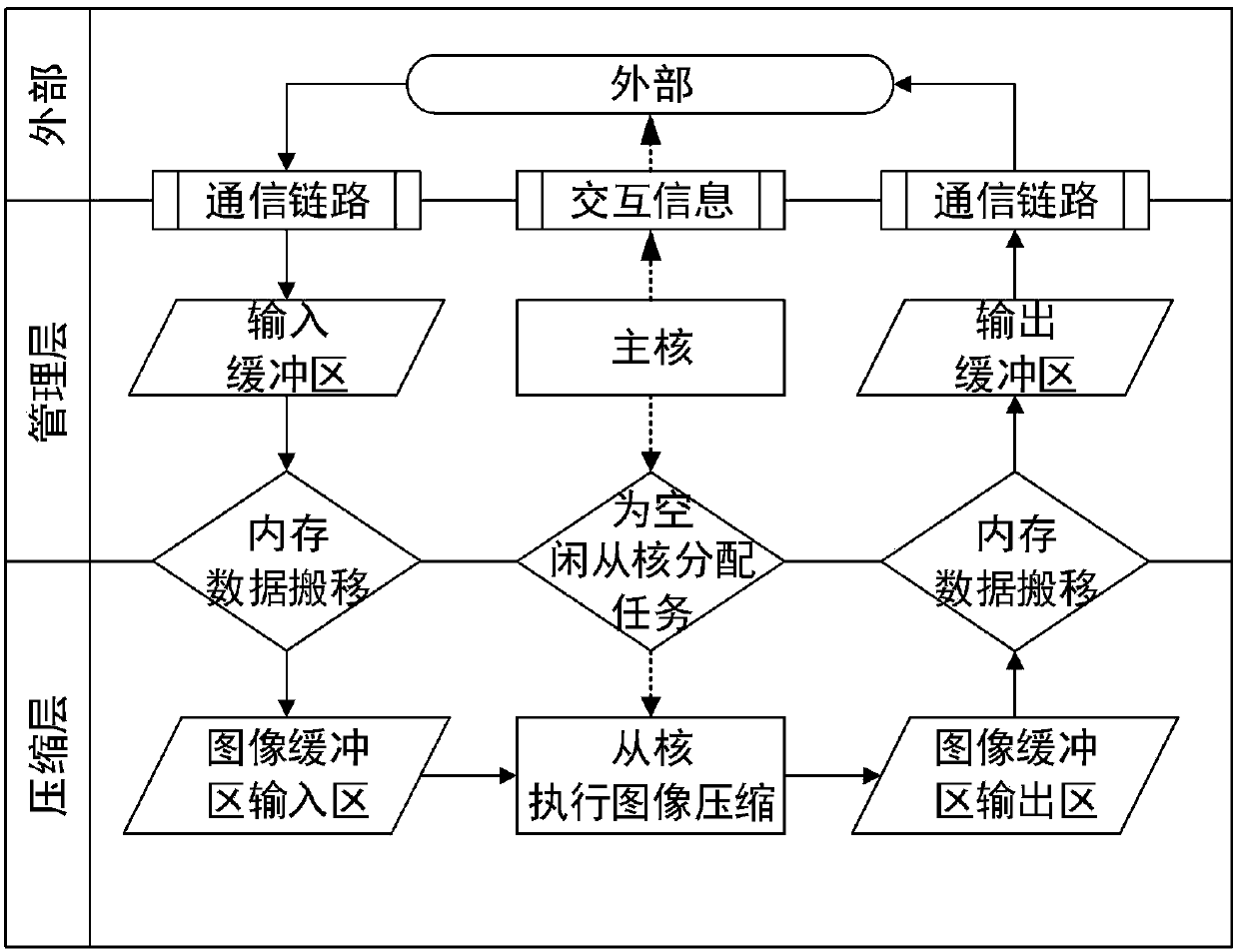

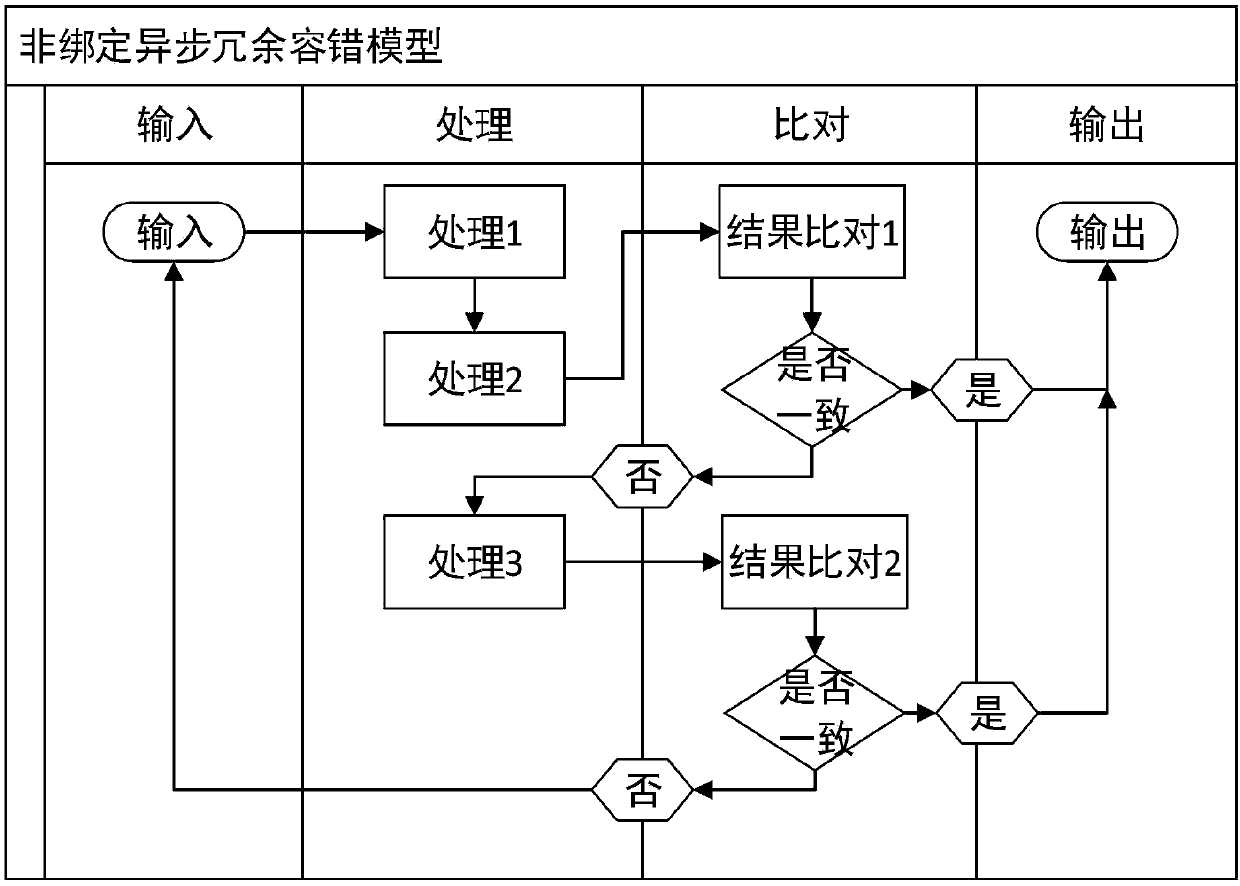

Image compression multi-core synchronous fault-tolerance method, computer and processor

InactiveCN108038014AGuaranteed uptimeImplement image compression tasksProcessor architectures/configurationNon-redundant fault processingFault toleranceImaging processing

The invention belongs to the technical field of hardware transient fault detection and recovery, and discloses an image compression multi-core synchronous fault-tolerance method, a computer and a processor. The method comprises the steps of constructing a synchronous image compression module, and making a single-core image processing program to conduct transplantation and optimization on a multi-core processor; according to existing core-level redundancy fault-tolerance characteristics, determining an unbounded asynchronous redundancy fault-tolerance model; according to the unbounded asynchronous redundancy fault-tolerance model, combining the synchronous image compression module to add a redundancy fault-tolerance function to an image compression system. According to the image compressionmulti-core synchronous fault-tolerance method, by achieving multi-core synchronous work on a main-core design management layer, the processor can be flexibly and conveniently transplanted on different kinds of hardware; the situations that there is a core being vacant to wait for data transmission and comparison is completed during synchronous redundancy fault tolerance are avoided; result comparison is conducted after two times of calculation; the extra expenditure caused by the data transmission is avoided, and memory access pressure of the system can also be reduced because the two operations are not overlapped in terms of time.

Owner:NAT UNIV OF DEFENSE TECH

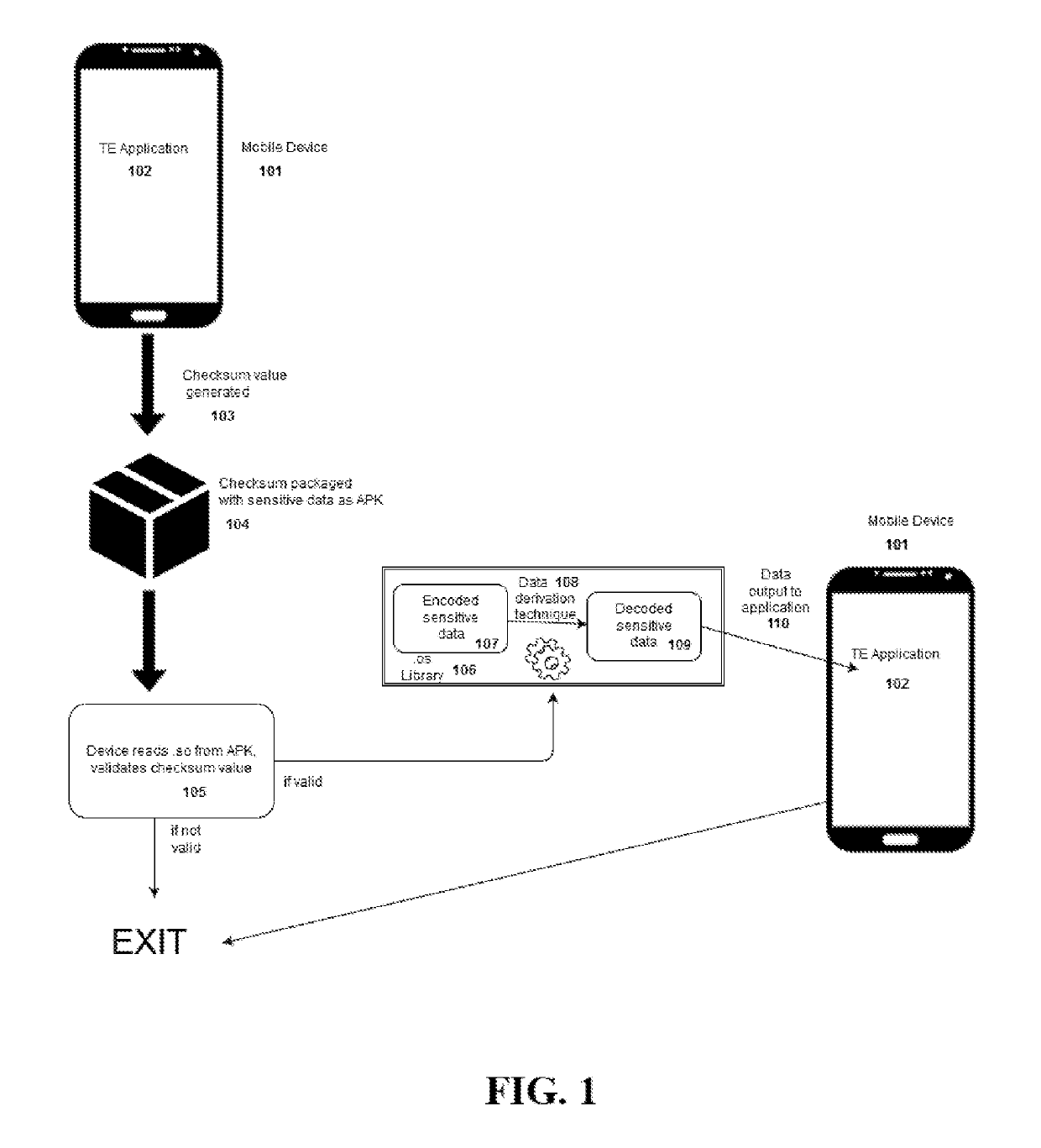

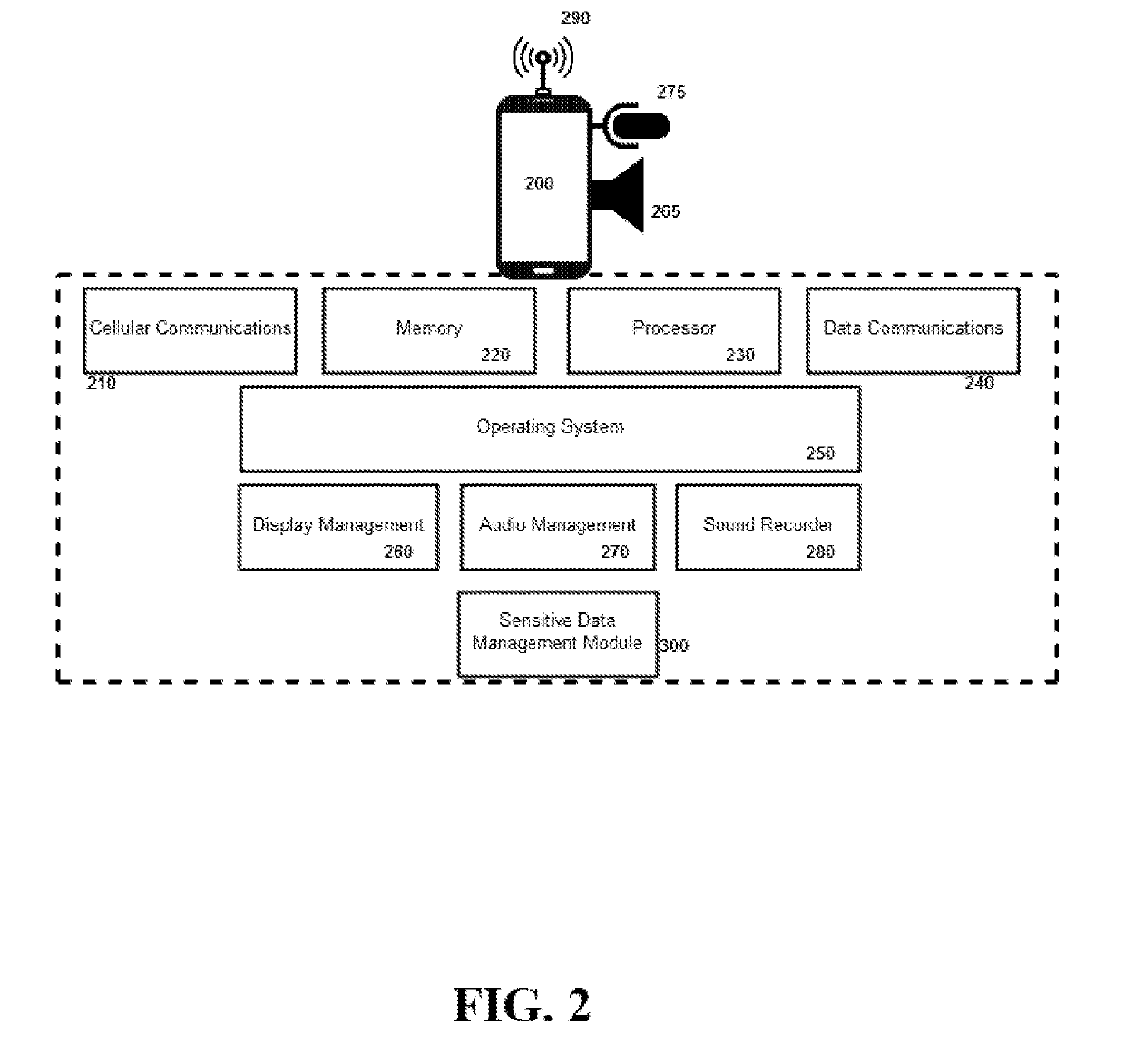

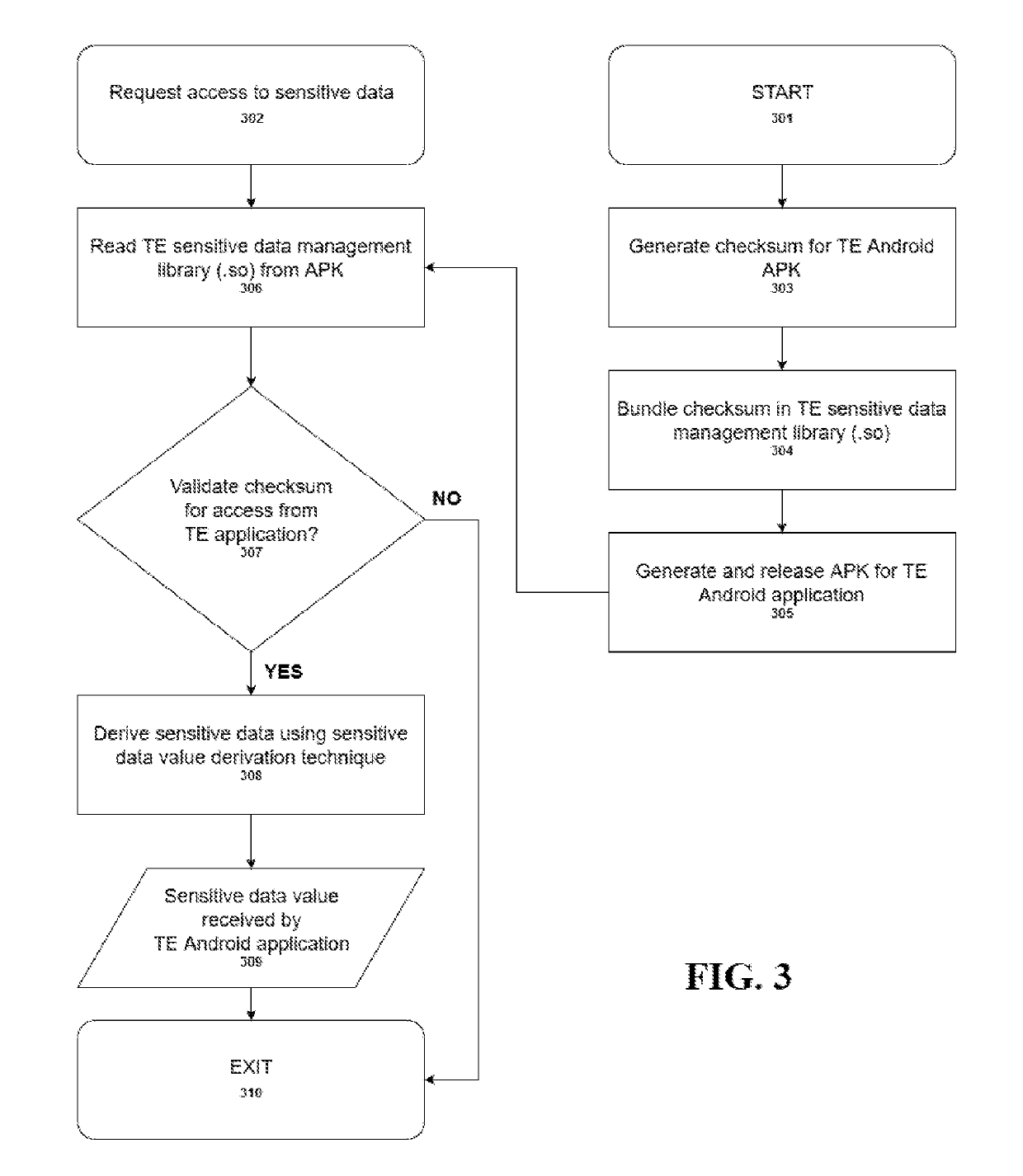

Theater ears android app sensitive data management

InactiveUS20190102573A1Digital data protectionProgram controlTheoretical computer scienceInterface layer

In one aspect of the embodiment, the method includes an algorithm to derive sensitive data values through a series of complex calculations based on various iterations of byte dissociation followed by complex mathematical operations and byte concatenations. In another aspect of the embodiment, the sensitive data management algorithm protects data by creating a library coded in the C programming language which on decompilation gives native machine learning code. This sensitive data protection library is coded and compiled as .so files which reside at the core level deep inside the application layer, thus being only accessible through the application layer code by proper access interface layer.

Owner:THEATER EARS

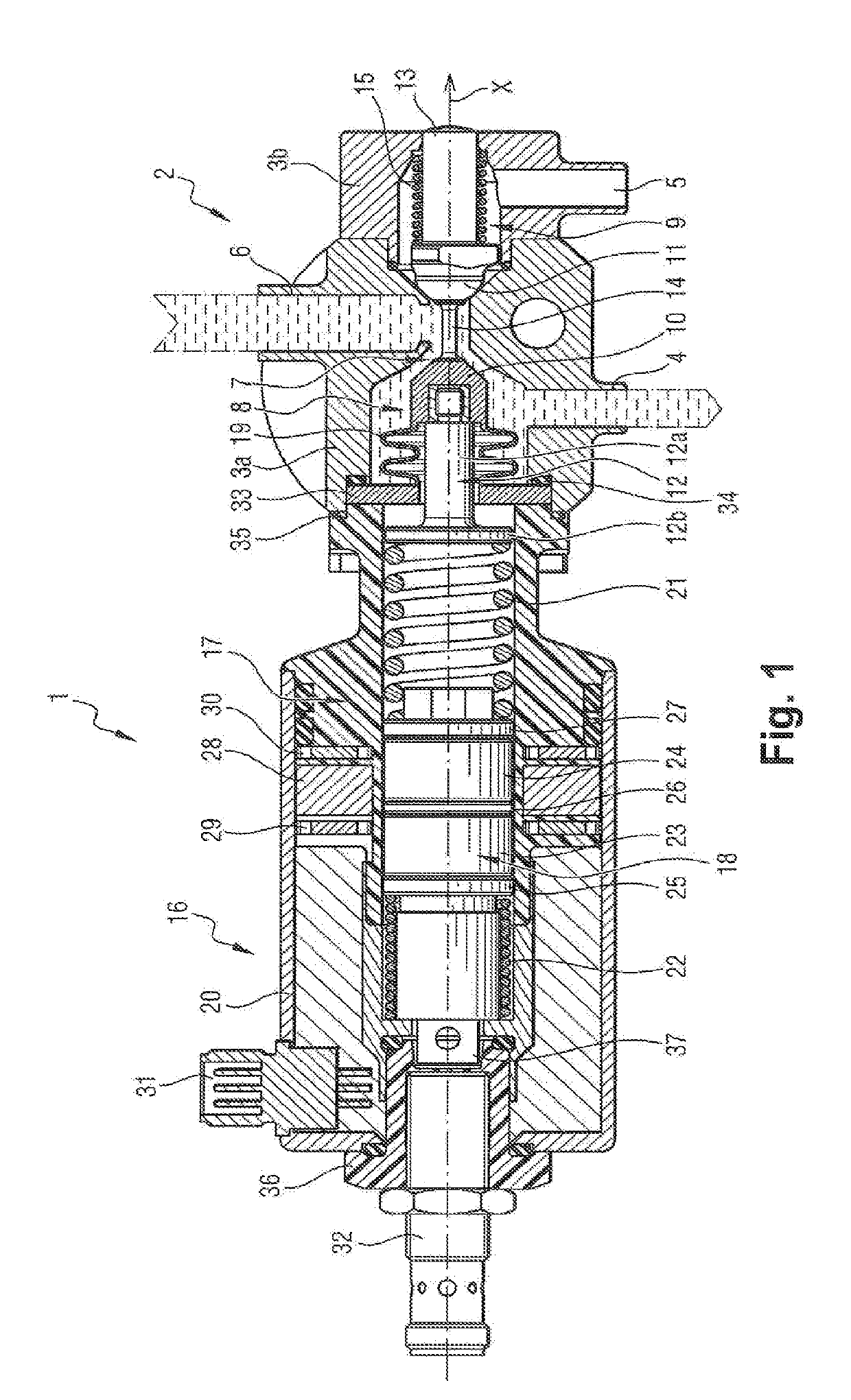

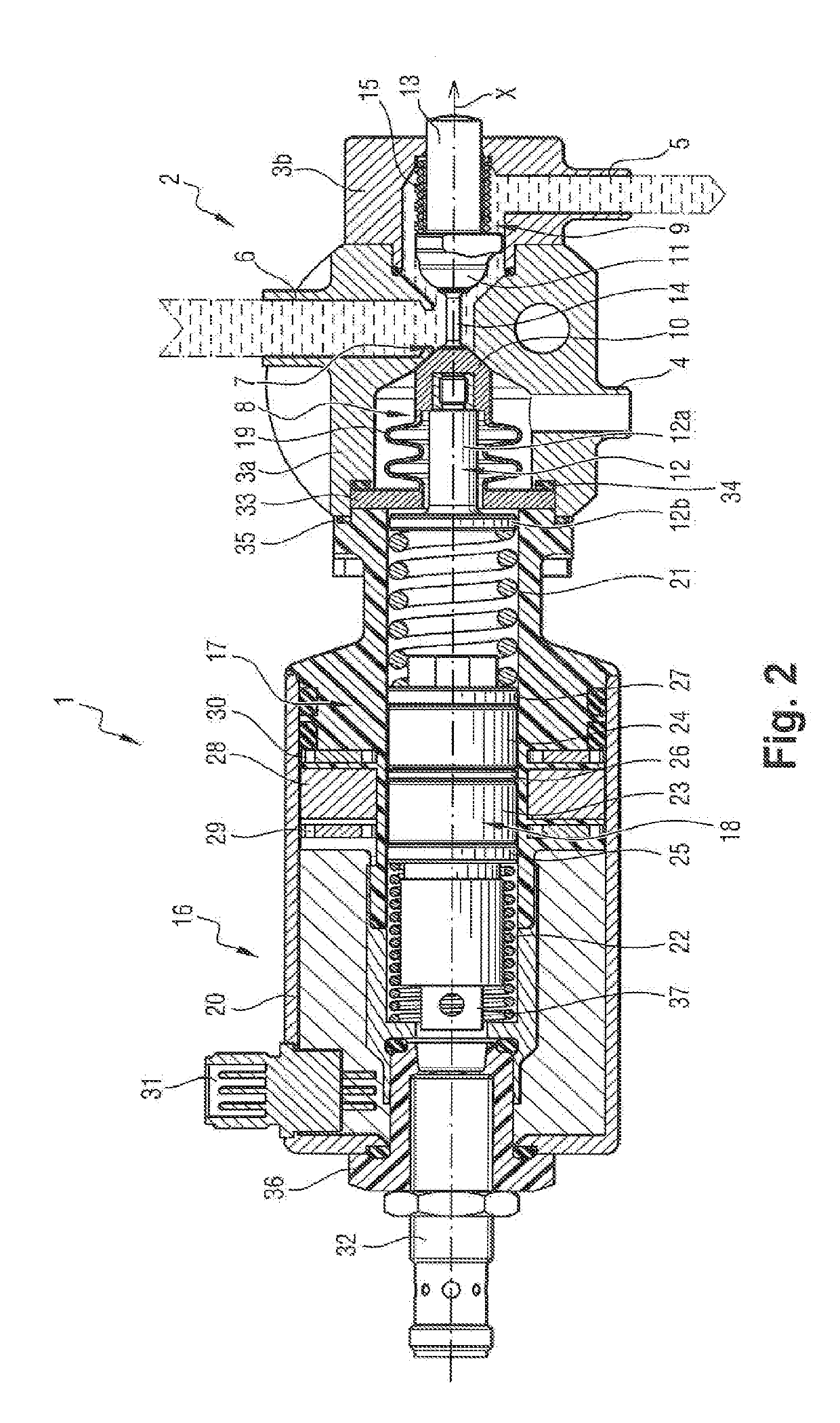

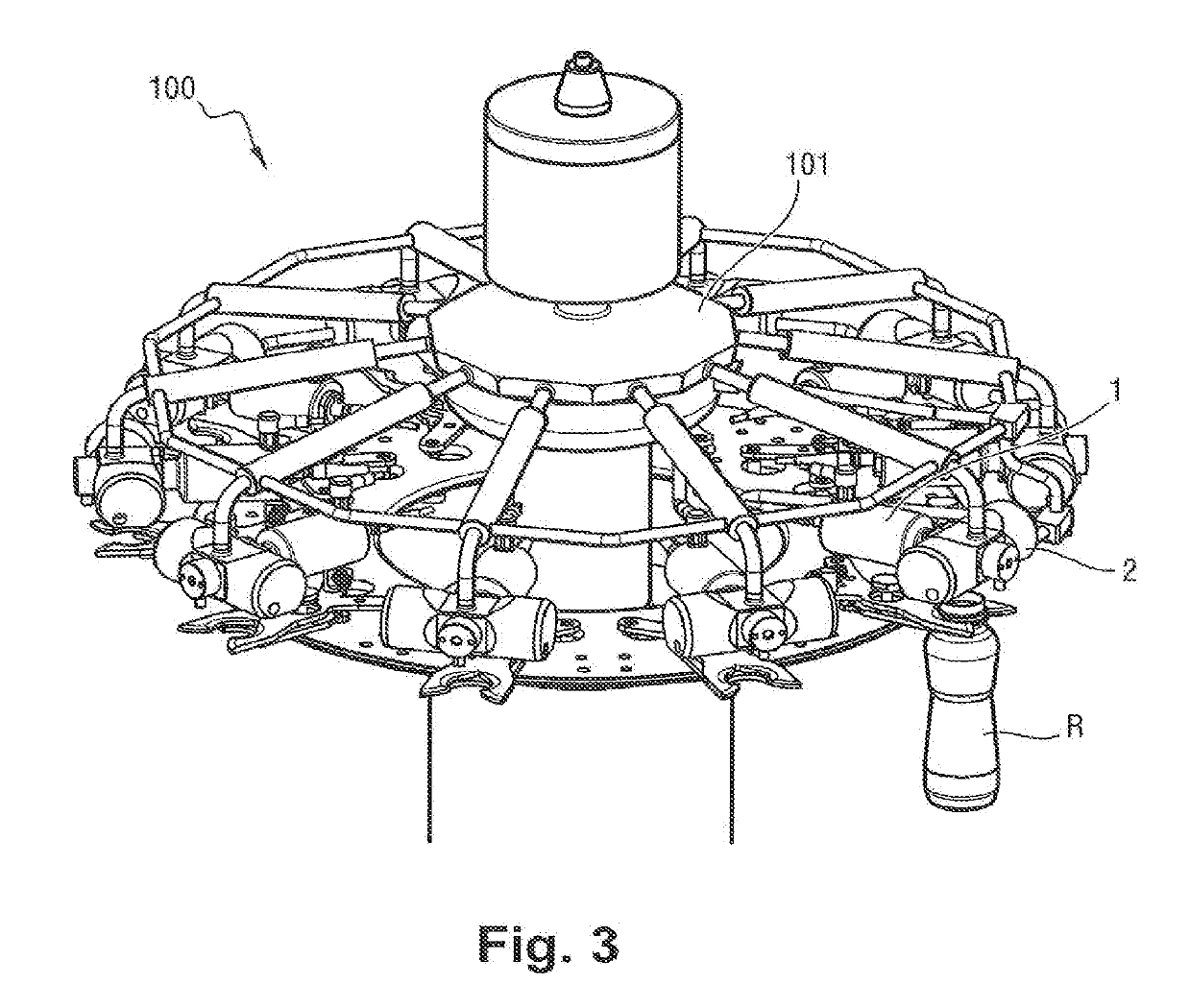

Valve actuator, valve, and machine consisting thereof

ActiveUS20190285193A1Easy to switchControlling the riskOperating means/releasing devices for valvesLiquid bottlingValve actuatorEngineering

A valve actuator includes moving equipment arranged to cause a plug of said equipment to slide along a given axis between two end positions. The moving equipment includes a core constrained to move in translation with the plug along the given axis. The actuator also includes a coil lying between two rings of ferromagnetic material, all three of which are secured to a frame of the actuator so as to surround the core, which itself carries two magnets mounted in opposition on the core level with the coil, a ring of ferromagnetic material lying between the two magnets that also lie between two other rings of ferromagnetic material. A valve and a machine may be fitted with such an actuator.

Owner:SERAC GROUP

Temperature control device and temperature control method thereof for high-precision quartz accelerometers

ActiveCN108363430AReduce startup timeExtended stabilization timeTemperatue controlTemperature controlAccelerometer

The invention discloses a temperature control device and a temperature control method thereof for high-precision quartz accelerometers. The temperature control device comprises the quartz accelerometers, a body, heating sheets, a thermally-insulated cover, cushion blocks and temperature sensors, wherein the body adopts a solid cubic structure, and three quartz accelerometers which are mutually orthogonal are mounted on the body separately; a meter case of each quartz accelerometer is adhered with one heating sheet for heating, the meter case of each quartz accelerometer is adhered with one temperature sensor, and one temperature sensor is adhered to the interior of each quartz accelerometer; the thermally-insulated cover sleeve the quartz accelerometers, the body and the heating sheets, and is used for isolating heat exchange with the external environment; and the body is fixedly connected to an inertial measurement device, and isolates heat exchange with the external environment by means of the cushion blocks. Through adopting the temperature control method of case-level temperature control and core-level temperature compensation, the contradiction between rapidity of temperaturerise of the accelerometers and influence of high current on accelerometer precision is eliminated, and the defects of the traditional temperature control and temperature compensation method are offset.

Owner:BEIJING AEROSPACE TIMES OPTICAL ELECTRONICS TECH

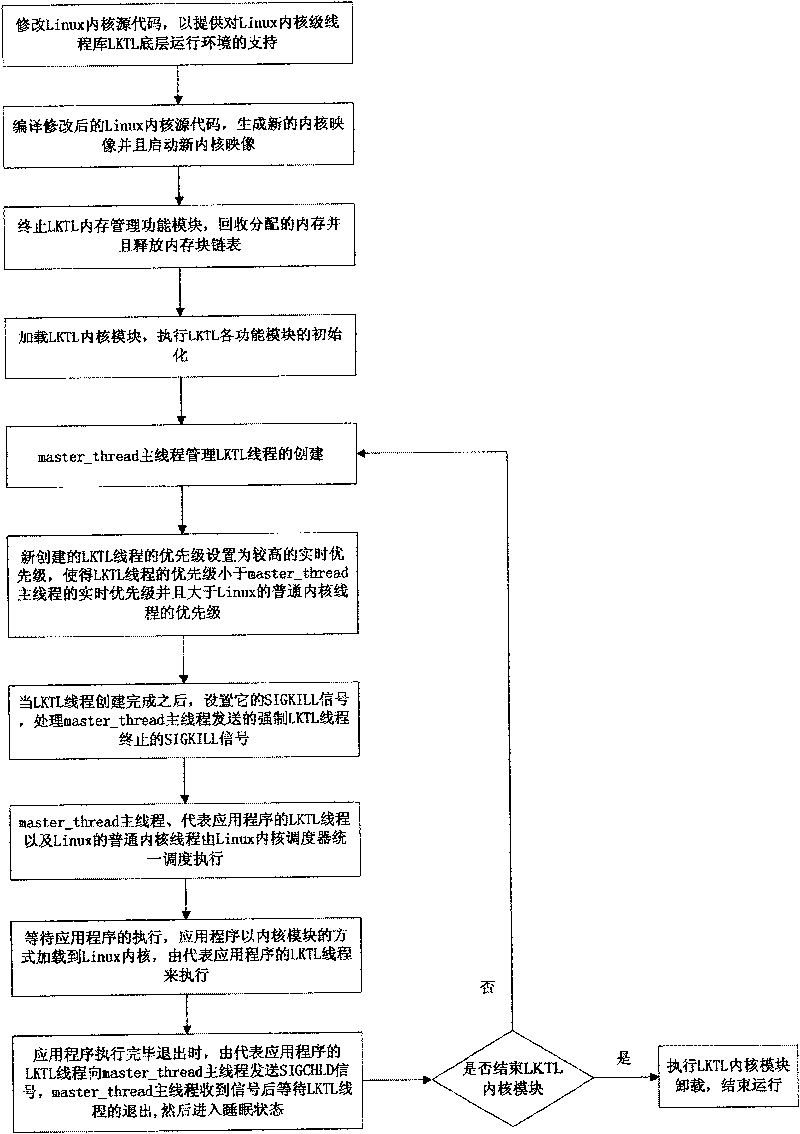

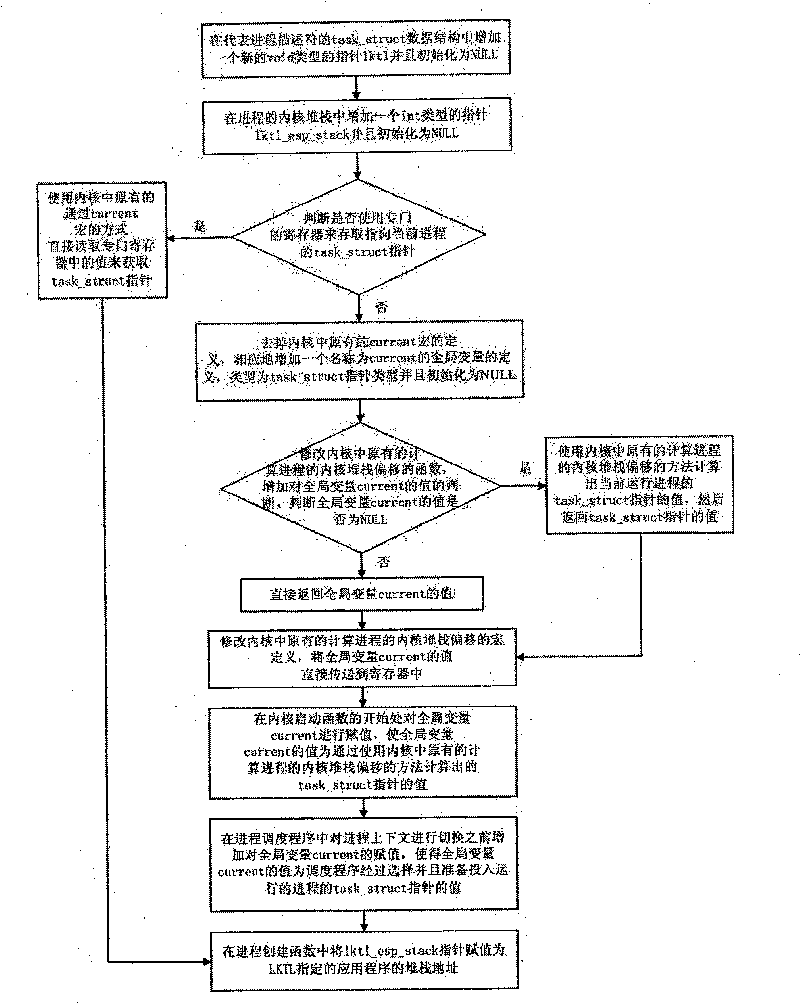

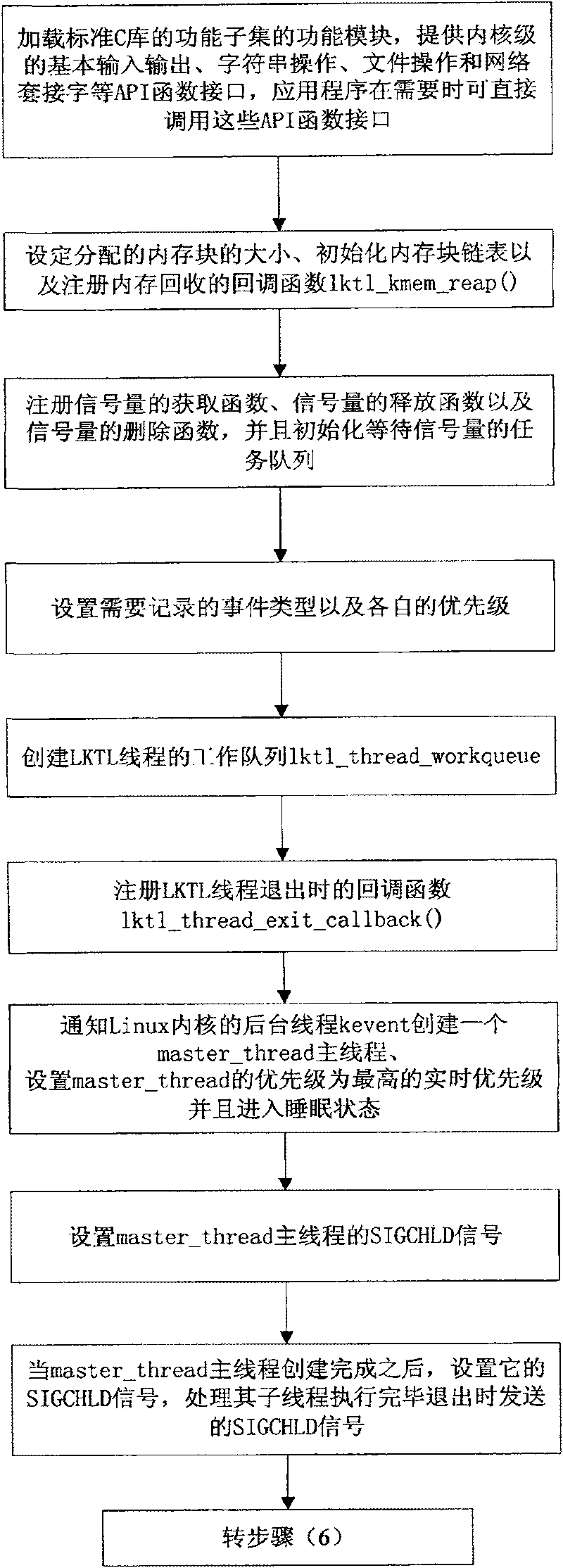

Method for implementing inner core level thread library based on built-in Linux operating system

InactiveCN101226487BImprove performanceEliminate overheadProgram initiation/switchingOperational systemLog management

The invention relates to a method for realizing kernel level process lib based on embedded Linux operating system, which realizes an integral kernel process manage system, provides kernel process management, signal amount management, memory management and log management, and AIP function interface of the function subgroup of standard C lib. The invention has the advantages that 1, the invention can modify little on kernel to support the software real-time or hardware real-time calling mechanism of prior embedded Linux operating system and confirm the application real-time demand, 2, the invention can completely eliminate the consumption of repeated switch of application process between user state and kernel state, to improve the integral performance of embedded Linux application system, 3,the invention shields the complexity of kernel module programming, to provide a development frame for developers and a series of programming interfaces (API), thereby reducing development and application complexity and improving development efficiency.

Owner:NO 709 RES INST OF CHINA SHIPBUILDING IND CORP

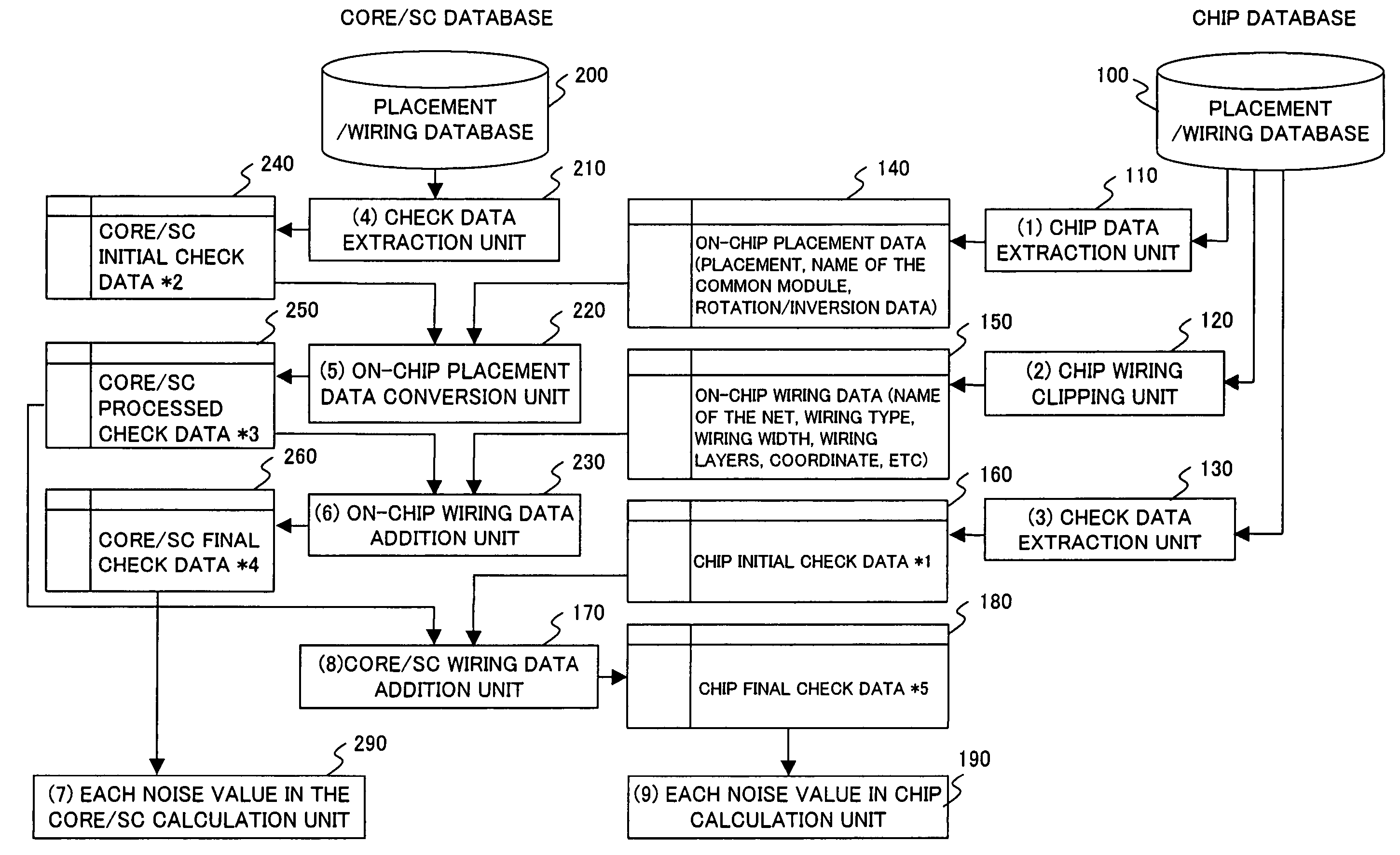

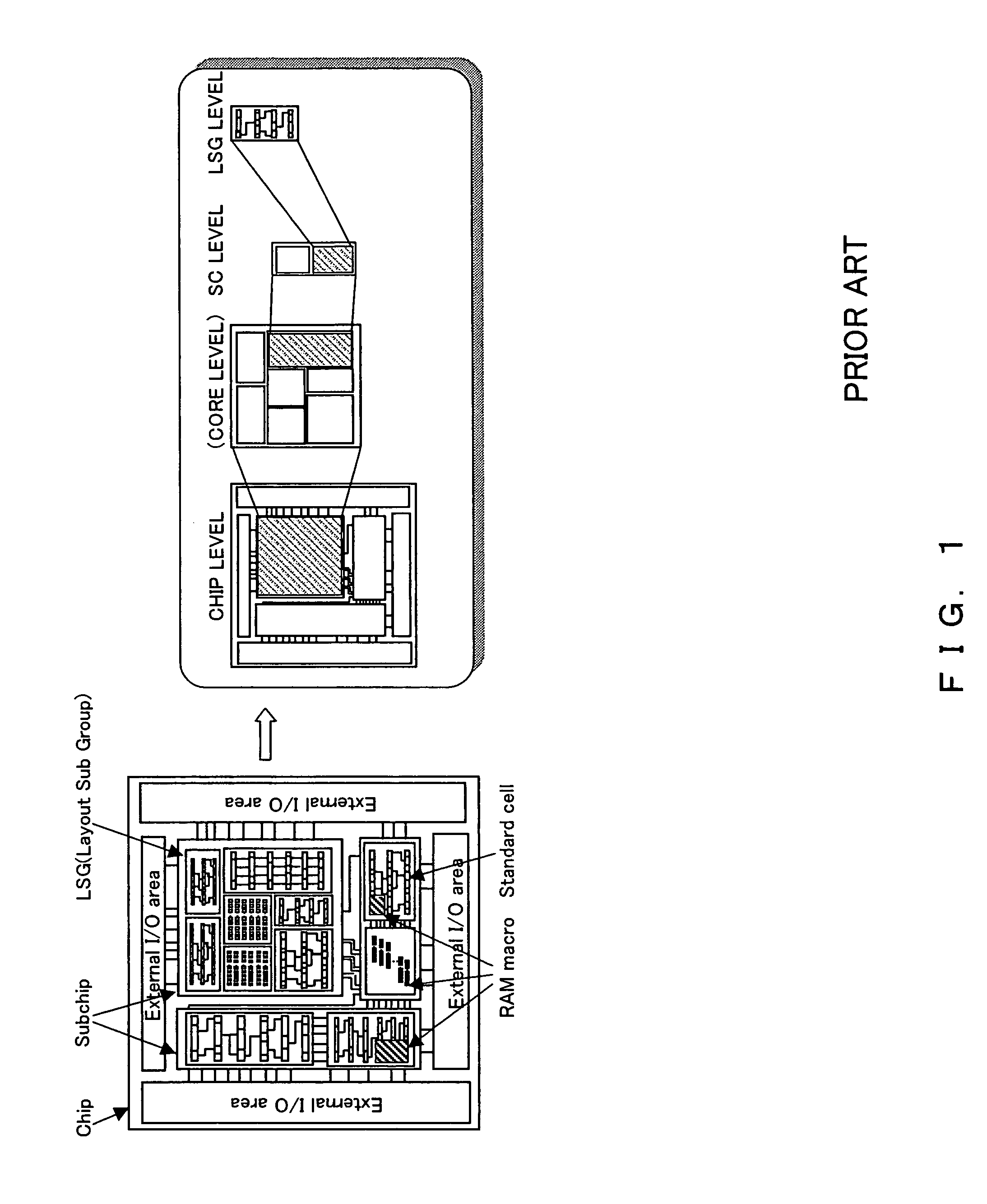

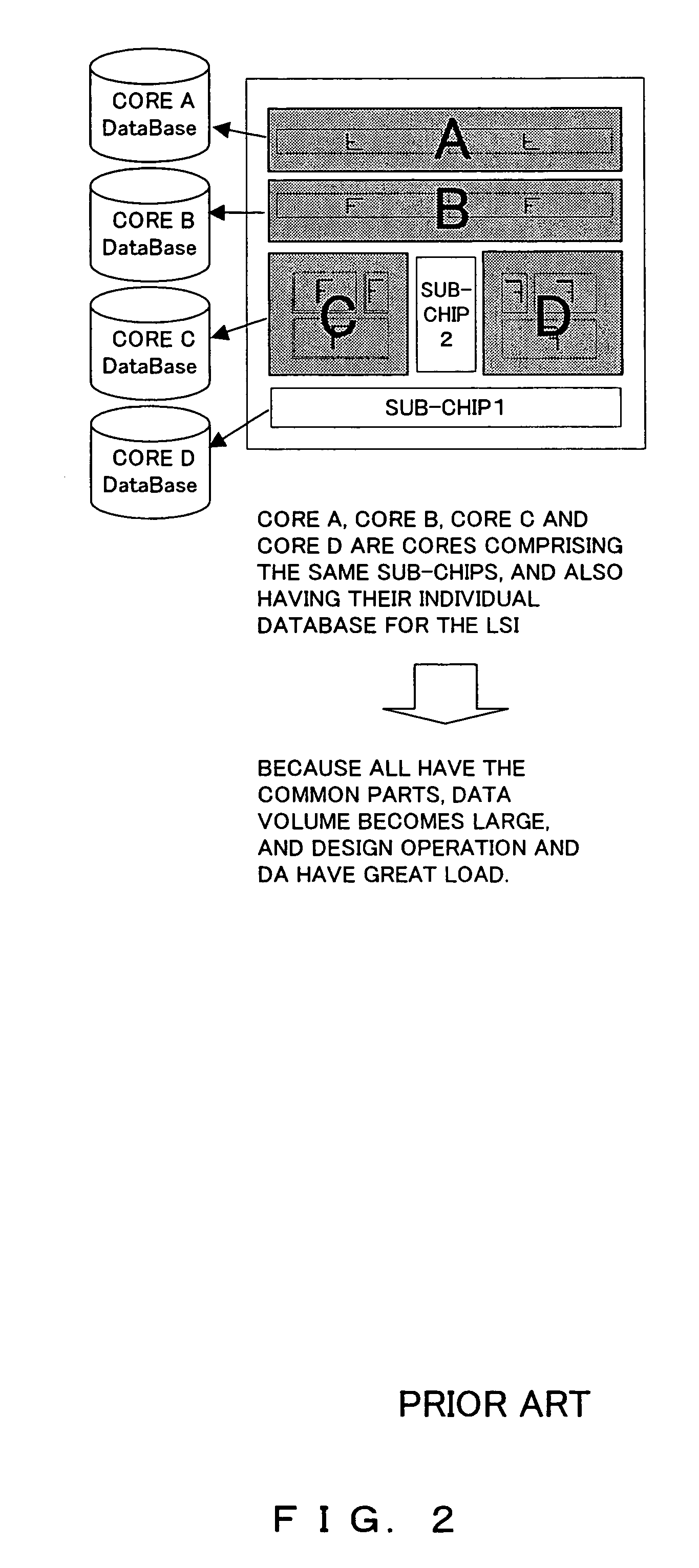

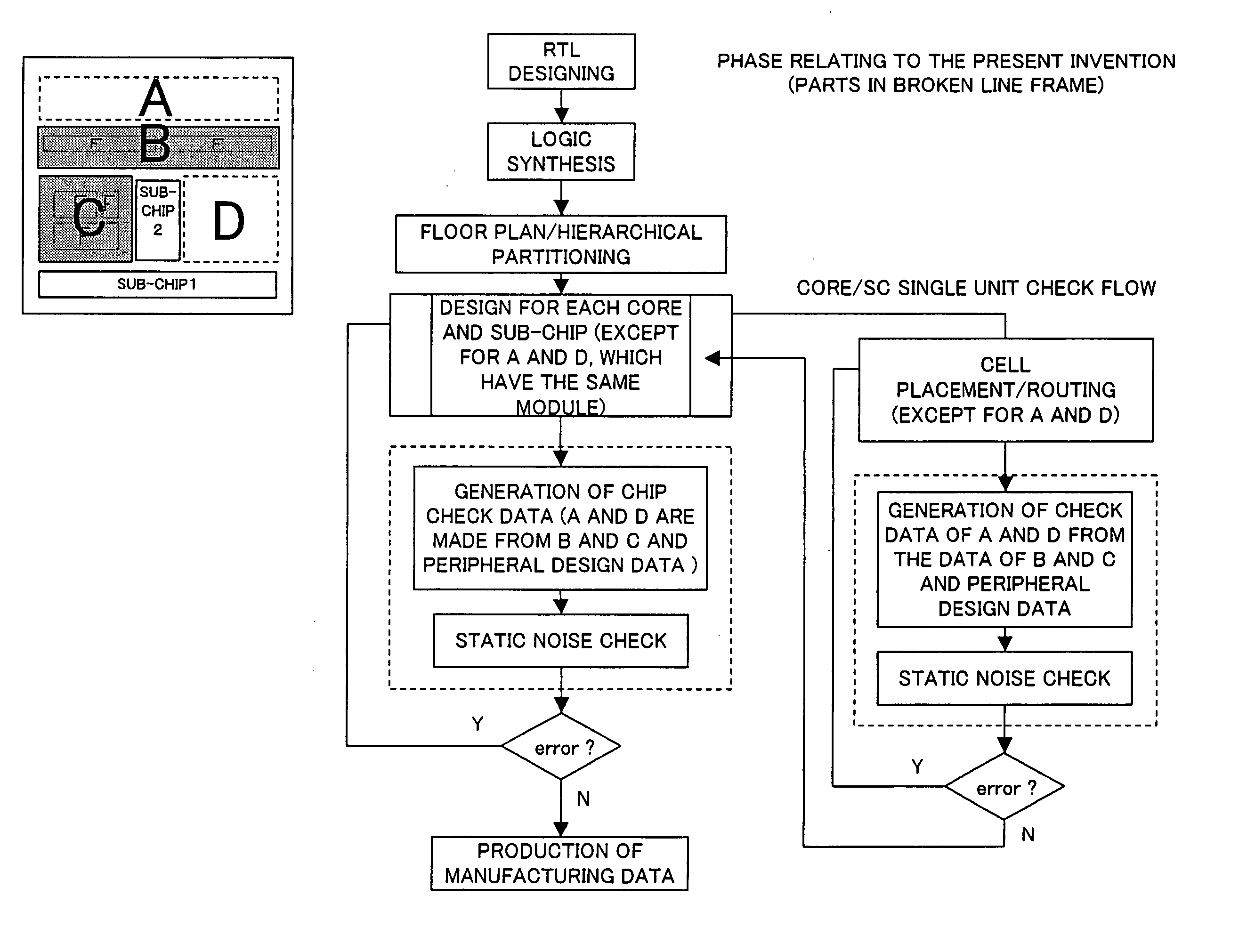

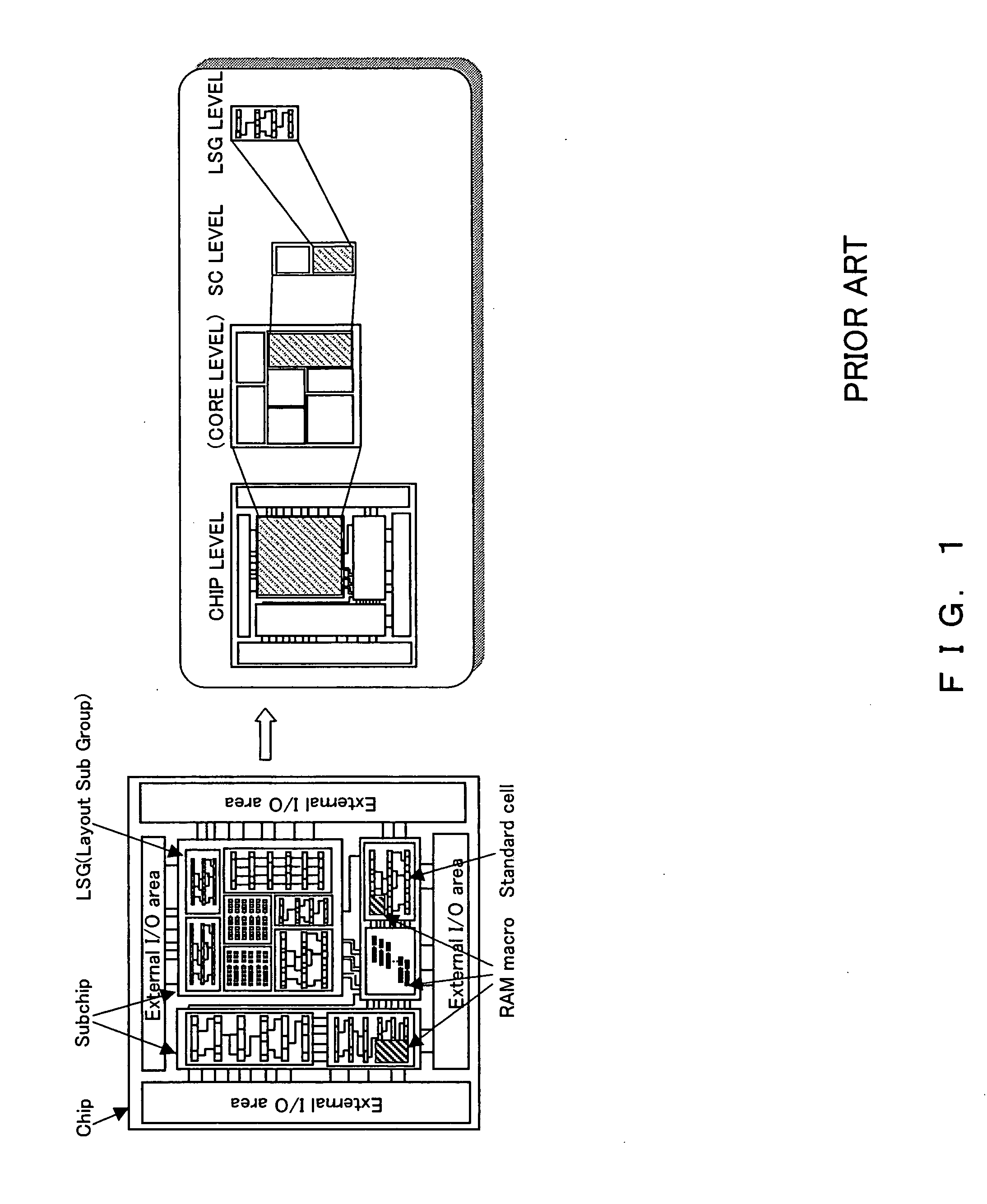

Method for the generation of static noise check data in the layout hierarchical design of an LSI

InactiveUS7493579B2Reduce dataReduce loadComputer aided designSpecial data processing applicationsEngineeringHierarchical design

Owner:FUJITSU LTD

Phase controller

InactiveUS8781076B2Increase the differenceSimple vacuum pumpHandling using polarising devicesHandling using diffraction/refraction/reflectionPhase differenceRefractive index

A reflection surface 12 constituted by a transition metal having a core level absorption edge in the vicinity of a wavelength of a soft X-ray is formed on an inside of a vacuum vessel 14, and furthermore, there is provided a permanent magnet 13 for generating a magnetic field in a perpendicular direction to a longitudinal direction of the vacuum vessel 14 in a position of the reflection surface 12 by which the soft X-ray is to be reflected, and the soft X-ray to be linearly polarized light incident on the vacuum vessel 14 is reflected at plural times over the reflection surface 12 in a position where the magnetic field is applied in such a manner that magnetic scattering is increased by a resonant effect of a magnetic circular dichroism when the soft X-ray is reflected by the reflection surface 12. Thus, a great difference in a refractive index is made between circularly polarized counterclockwise light and circularly polarized clockwise light which constitute the linearly polarized light, and a phase difference between the circularly polarized counterclockwise light and the circularly polarized clockwise light is obtained at a time. Consequently, it is possible to reversibly convert the soft X-ray from the linearly polarized light into the circularly polarized light or from the circularly polarized light into the linearly polarized light by a reflection to be carried out at only several times.

Owner:SAITAMA MEDICAL UNIVERSITY

Stream processor expanding method for flexible distribution operating group resource

InactiveCN100456231CSave on multi-core scalingEasy to handleConcurrent instruction executionArchitecture with multiple processing unitsMicrocontrollerParallel computing

This invention discloses a cluster-processor expansion method by flexible allocation of computing resource, and its steps are: (1) setting the array of microcontroller, which is composed of two or more microcontrollers, adding a reading cluster interface for each microcontroller in SRF, and each microcontroller has the same structure and same interface with cluster controller, to start implementation of a core-level procedure under the control of cluster controller, (2)setting interfaces between microcontroller and operational group, (3) setting the cluster controller and adding interfaces connected with each microcontroller on it,(4) setting Clusterop in the controller, to make a core-level procedure implement only in a microcontroller and some computing group ensuring that many microcontrollers executes the procedure at the same time with the permission of computing resources.

Owner:NAT UNIV OF DEFENSE TECH

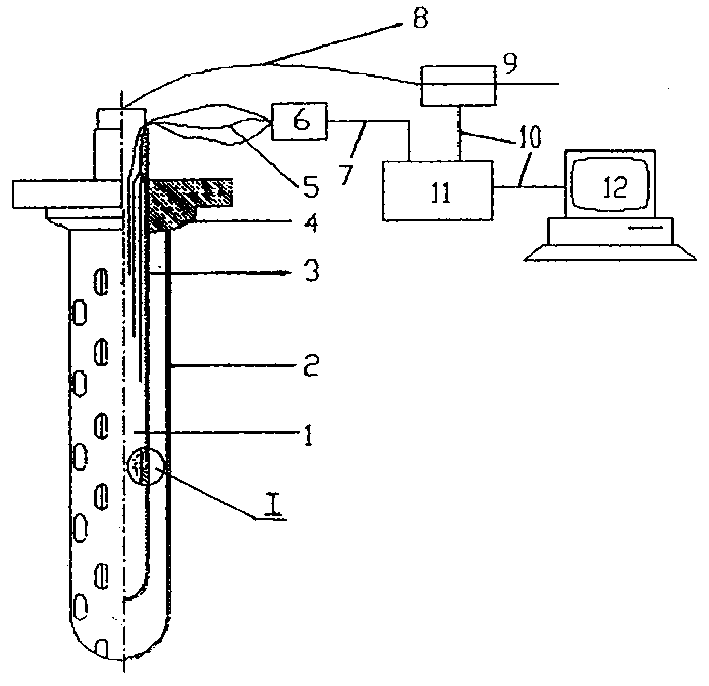

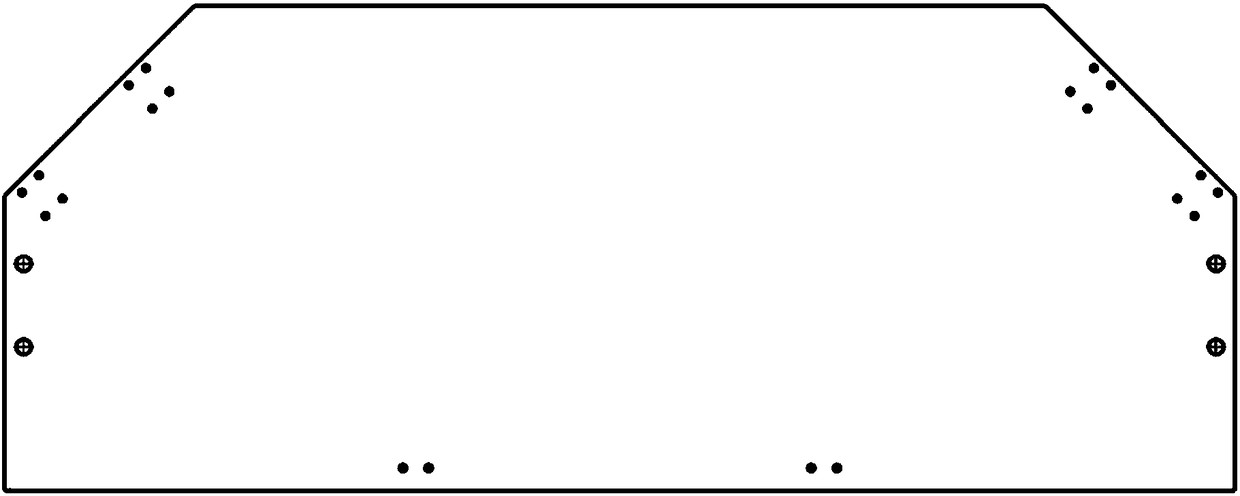

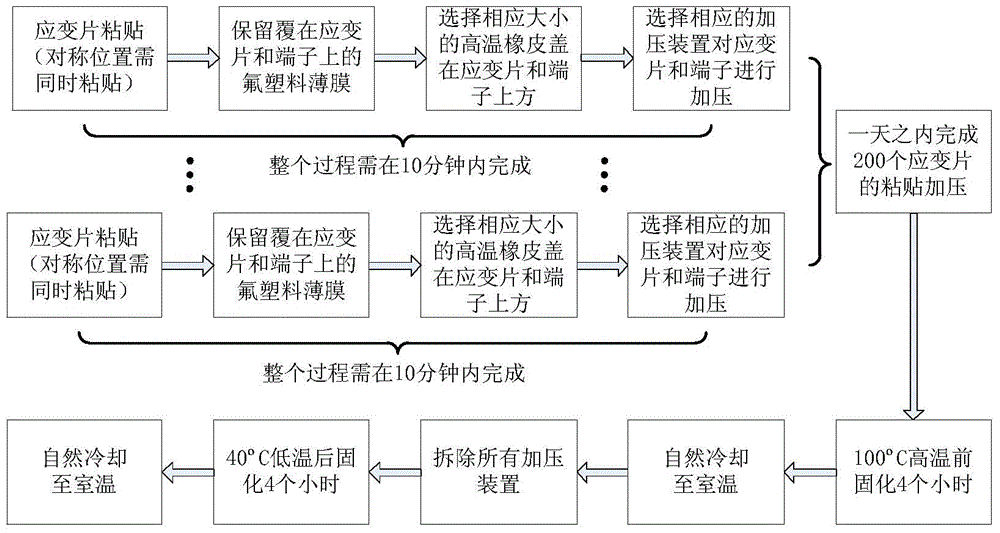

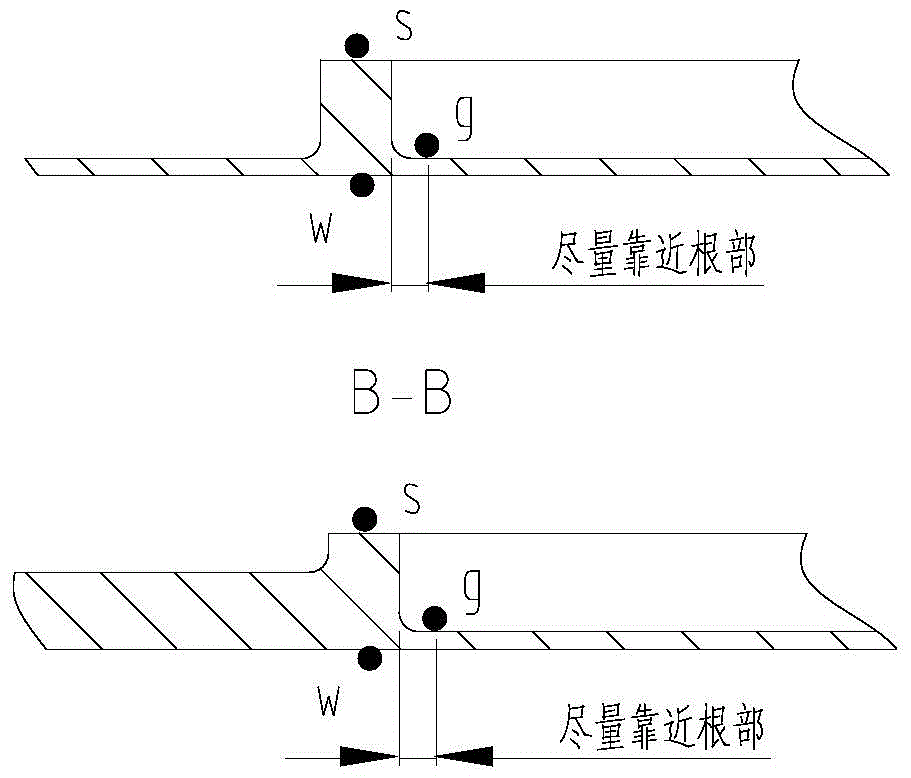

Pressurization device for adherence and solidification of low-temperature test strainometer of large storage tank

The invention belongs to the technical field of strain tests and specifically relates to a pressurization device for adherence and solidification of a low-temperature test strainometer of a large storage tank. The device comprises an upper cover plate (1), a pressing plate (2), magnets (3), an upper pressurization block (4), two high-temperature rubber blocks (5), a lower pressurization block (6) and a handle (7), wherein the upper pressurization block (4) is a hollow aluminum box structure, the lower side is sealed and equipped with a sunken area in the middle, and the upper side is opened and covered by the pressing plate (2) and the upper cover plate (1); the two magnets (3) are disposed on two sides of the sunken area in the aluminum box; the lower pressurization block (6) has an iron block structure, and the upper side is equipped with a sunken area in the middle and disposed oppositely to the upper pressurization block (4); and the handle (7) is disposed on the lower side of the lower pressurization block (6). In a working condition experiment which binds sextic liquid nitrogen media having been completed in a low-temperature static combined experiment in front of a second-level hydrogen tank, a first-level oxygen tank and a core level, valid data is acquired in strain measurement in order to provide an experiment basis for a design department to design the storage tank and carry out assessment.

Owner:BEIJING INST OF STRUCTURE & ENVIRONMENT ENG +1

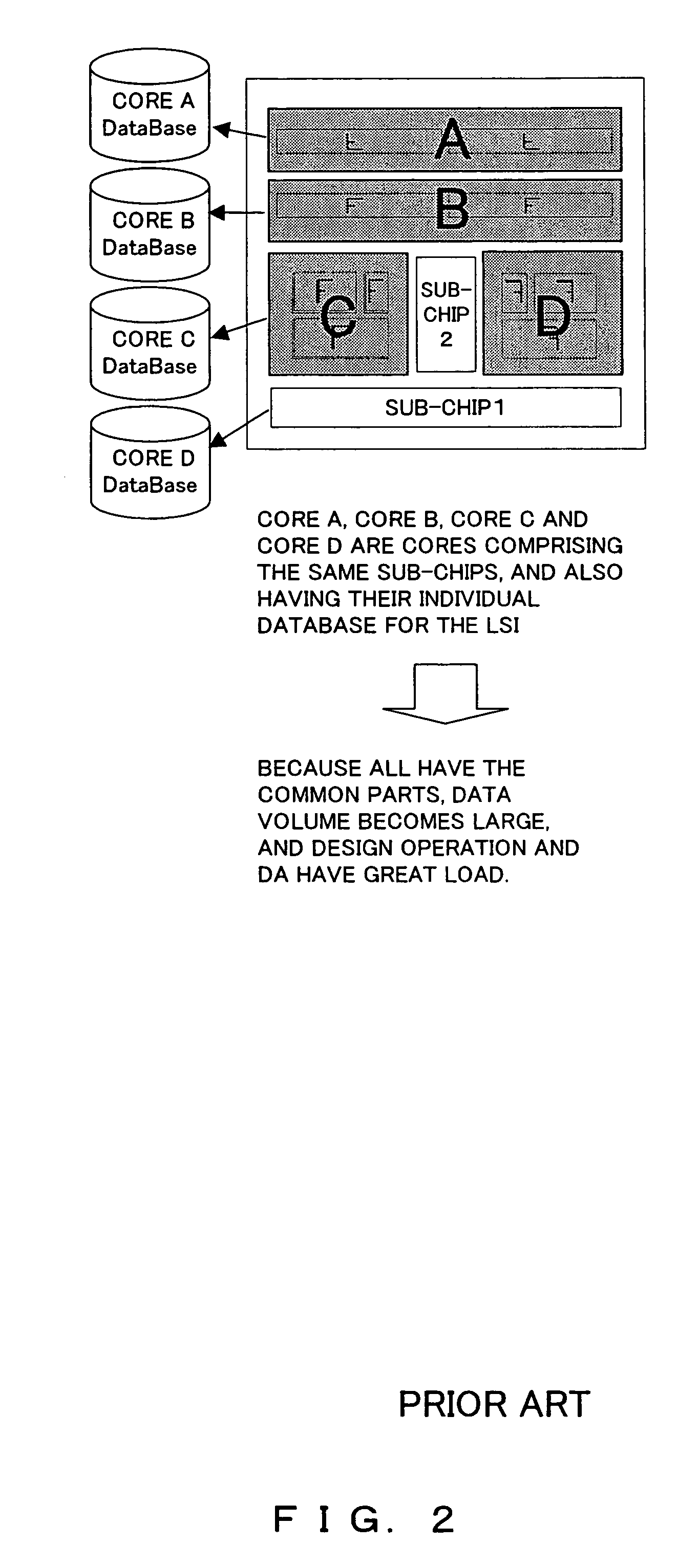

Method for the generation of static noise check data

InactiveUS20060136851A1Reduce data volumeReduce loadProgram controlComputer aided designEngineeringHierarchical design

In the static noise check of the LSI hierarchical design, in order to reduce the data volume of the common parts and load of the design operation and DA, when a plurality of cores, comprising the same sub-chips, are present, the static noise check data for the whole chip is generated from the core-level design data of one of the cores, and the chip-level design data.

Owner:FUJITSU LTD

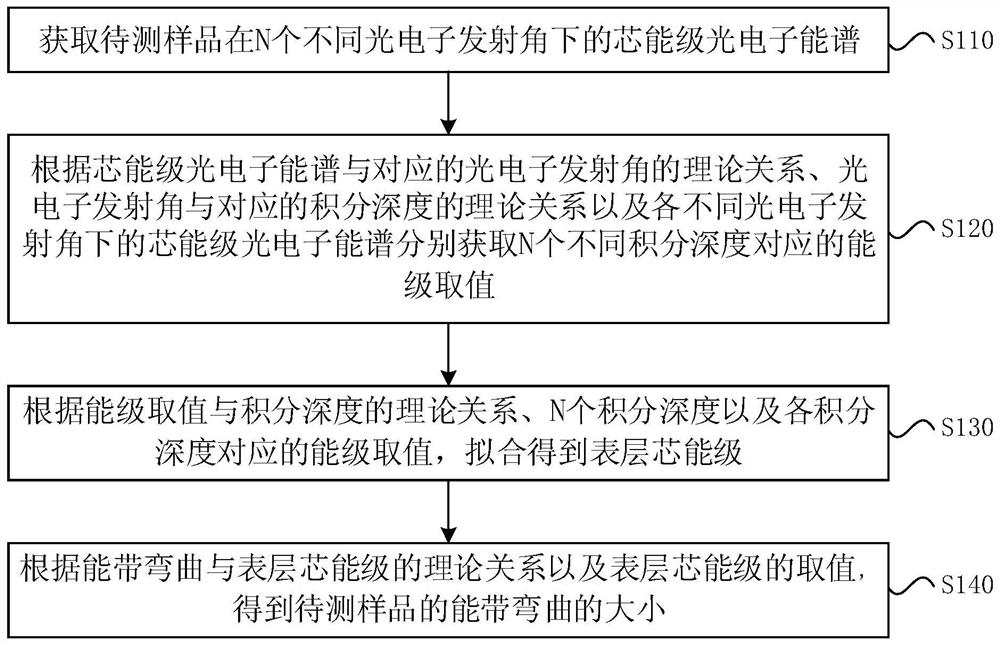

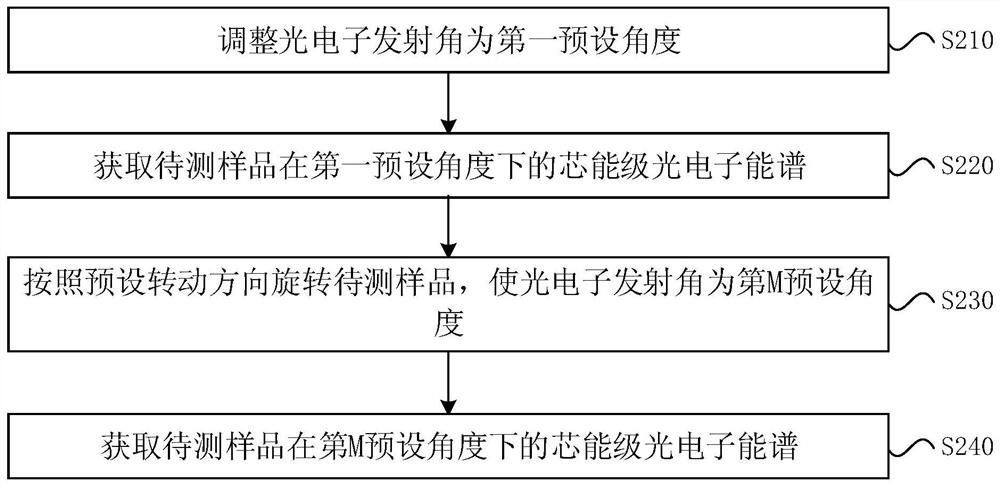

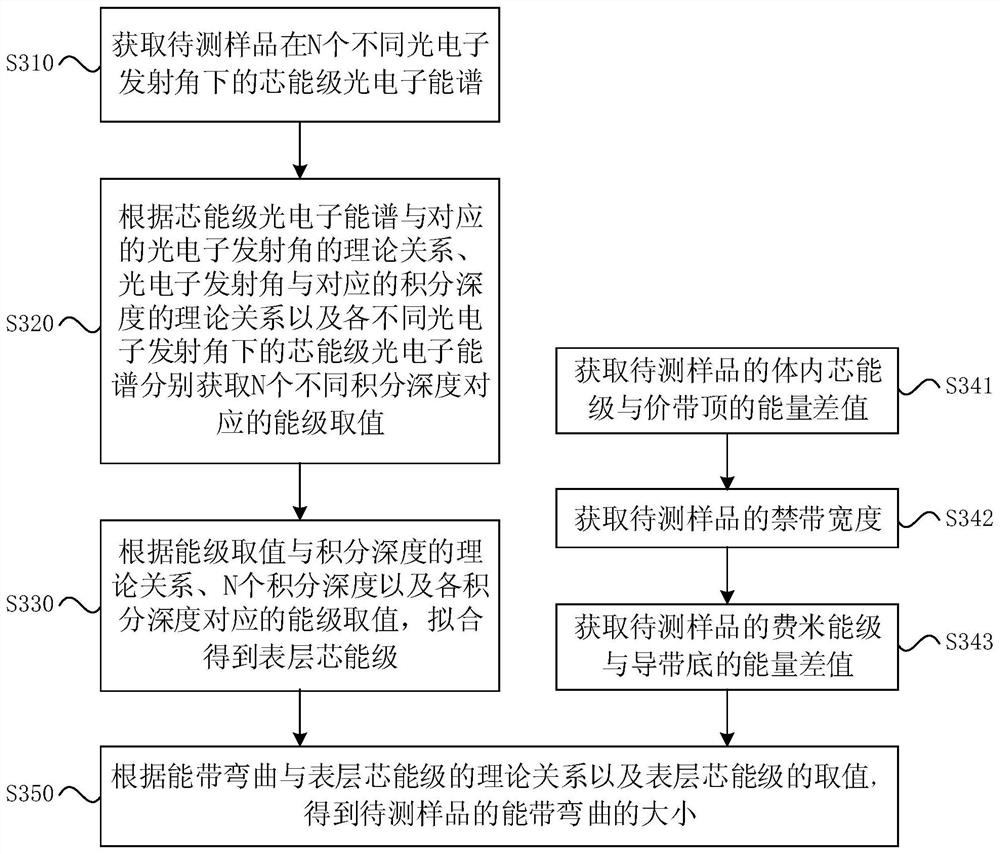

A method and device for measuring energy band bending by photoelectron spectroscopy

ActiveCN110161070BImprove measurement accuracyMaterial analysis using wave/particle radiationBand bendingParticle physics

The invention discloses a method and a device for measuring energy band bending by photoelectron energy spectrum. The method includes: obtaining the core level photoelectron spectrum of the sample to be tested under N different photoelectron emission angles; N is an integer and N≥4; according to the theoretical relationship between the core level photoelectron spectrum and the corresponding photoelectron emission angle, the photoelectron The theoretical relationship between the emission angle and the corresponding integration depth and the core level photoelectron spectrum under different photoelectron emission angles respectively obtain the energy level values corresponding to N different integration depths; the photoelectron emission angle corresponds to the integration depth one by one; according to the energy The theoretical relationship between the level value and the integration depth, the N integration depths and the energy level values corresponding to each integration depth are fitted to obtain the surface core energy level; the surface core energy level is the corresponding core energy level when the integration depth is 0; according to The theoretical relationship between the energy band bending and the surface core energy level and the value of the surface core energy level can be used to obtain the size of the energy band bending of the sample to be tested. Thereby, the measurement accuracy of band bending can be improved.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Instruction control method aimed at stream processor

InactiveCN100461094CHide Access LatencyEasy to manageConcurrent instruction executionComplete dataParallel computing

Owner:NAT UNIV OF DEFENSE TECH

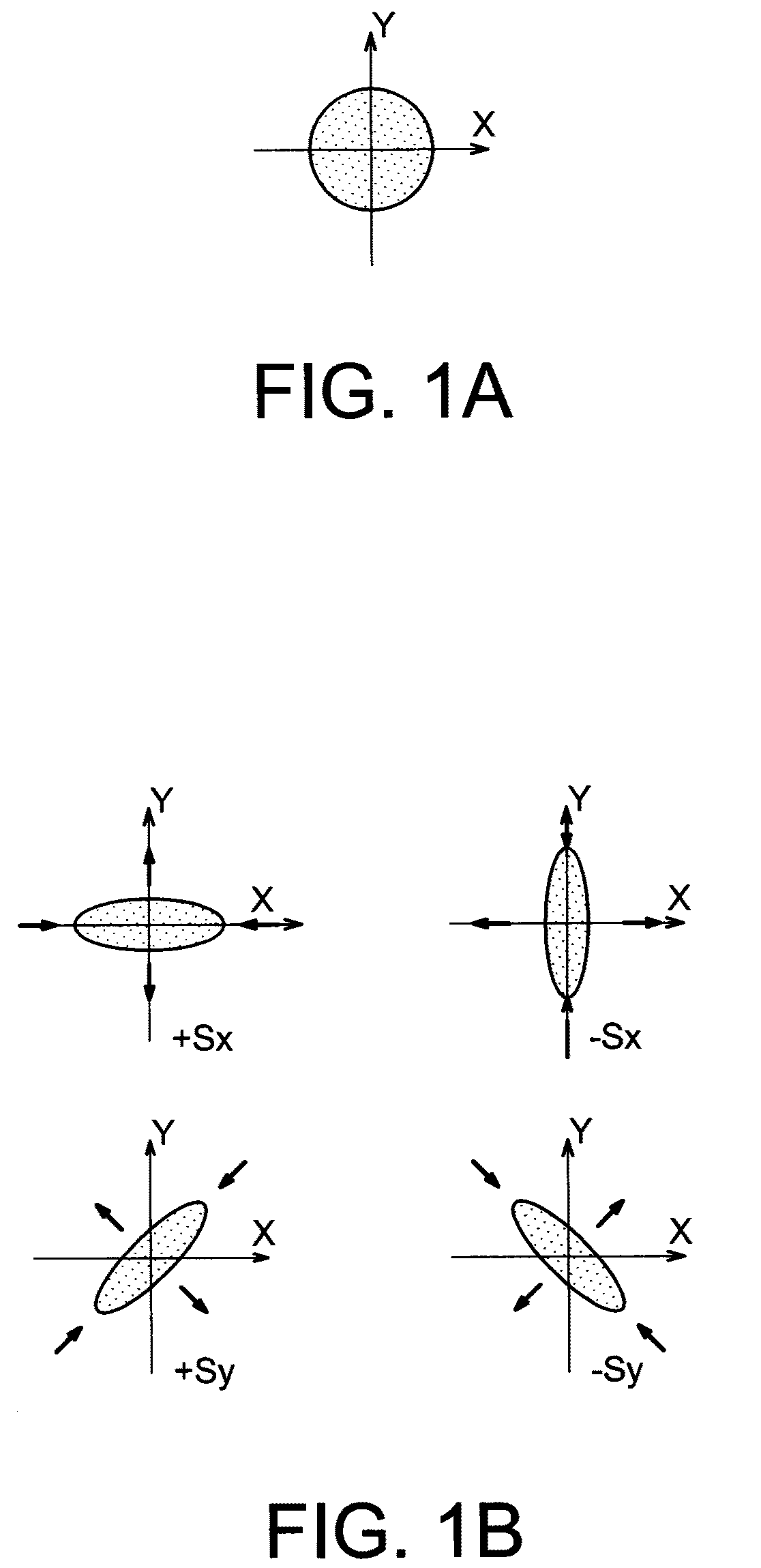

Method for correcting astigmatism in electron emission spectromicroscopy imaging

InactiveUS8089044B2Eliminating astigmatism defectsIncrease contrastThermometer detailsMaterial analysis using wave/particle radiationMicro imagingSecondary electrons

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com