Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38 results about "Lockstep" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Lockstep systems are fault-tolerant computer systems that run the same set of operations at the same time in parallel. The redundancy (duplication) allows error detection and error correction: the output from lockstep operations can be compared to determine if there has been a fault if there are at least two systems (dual modular redundancy), and the error can be automatically corrected if there are at least three systems (triple modular redundancy), via majority vote. The term "lockstep" originates in the army usage, where it refers to the synchronized walking, in which the marchers walk as closely together as physically practical.

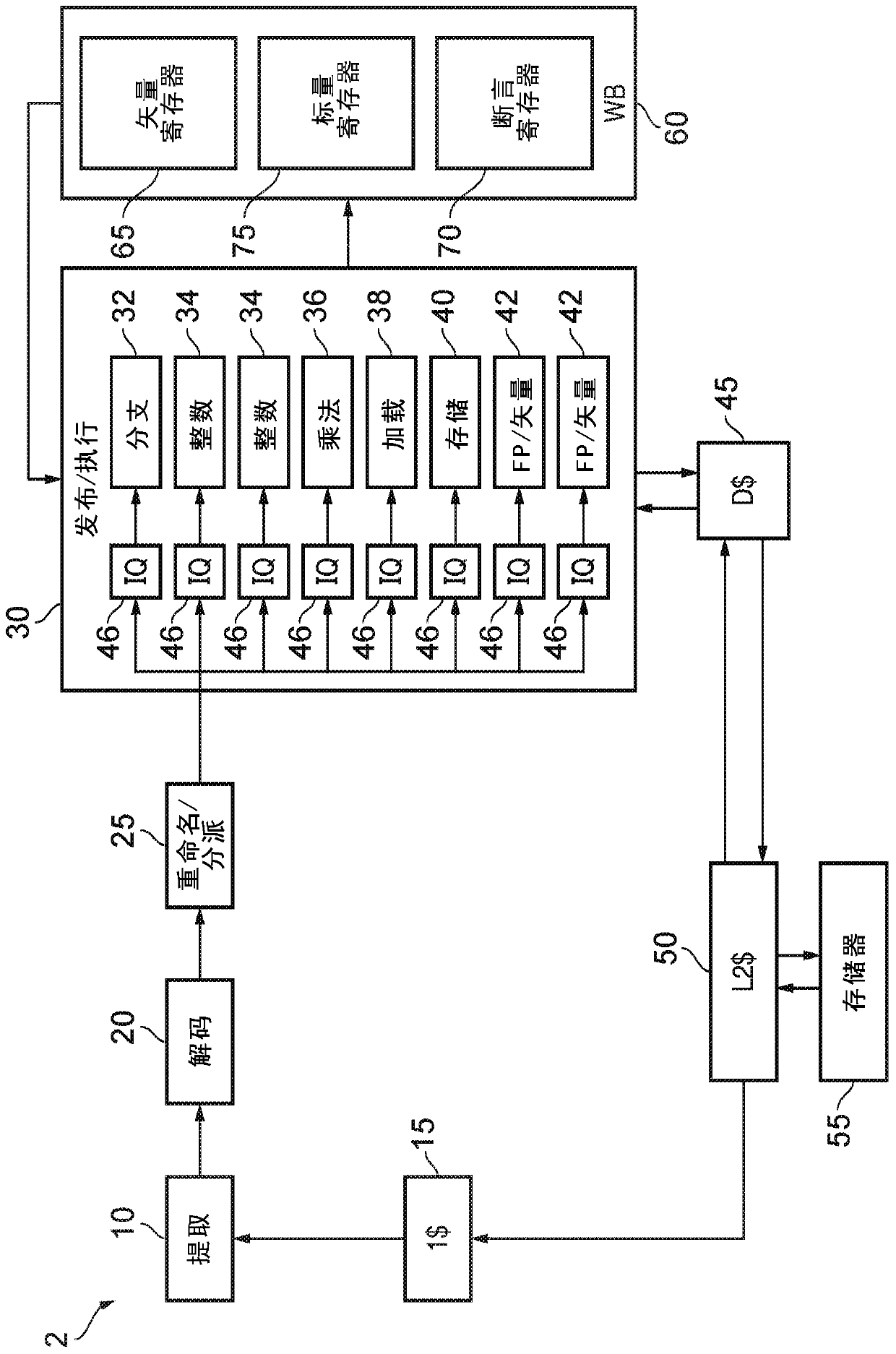

Reliable execution using compare and transfer instruction on an smt machine

ActiveUS20100281239A1Digital computer detailsConcurrent instruction executionLockstepComputer architecture

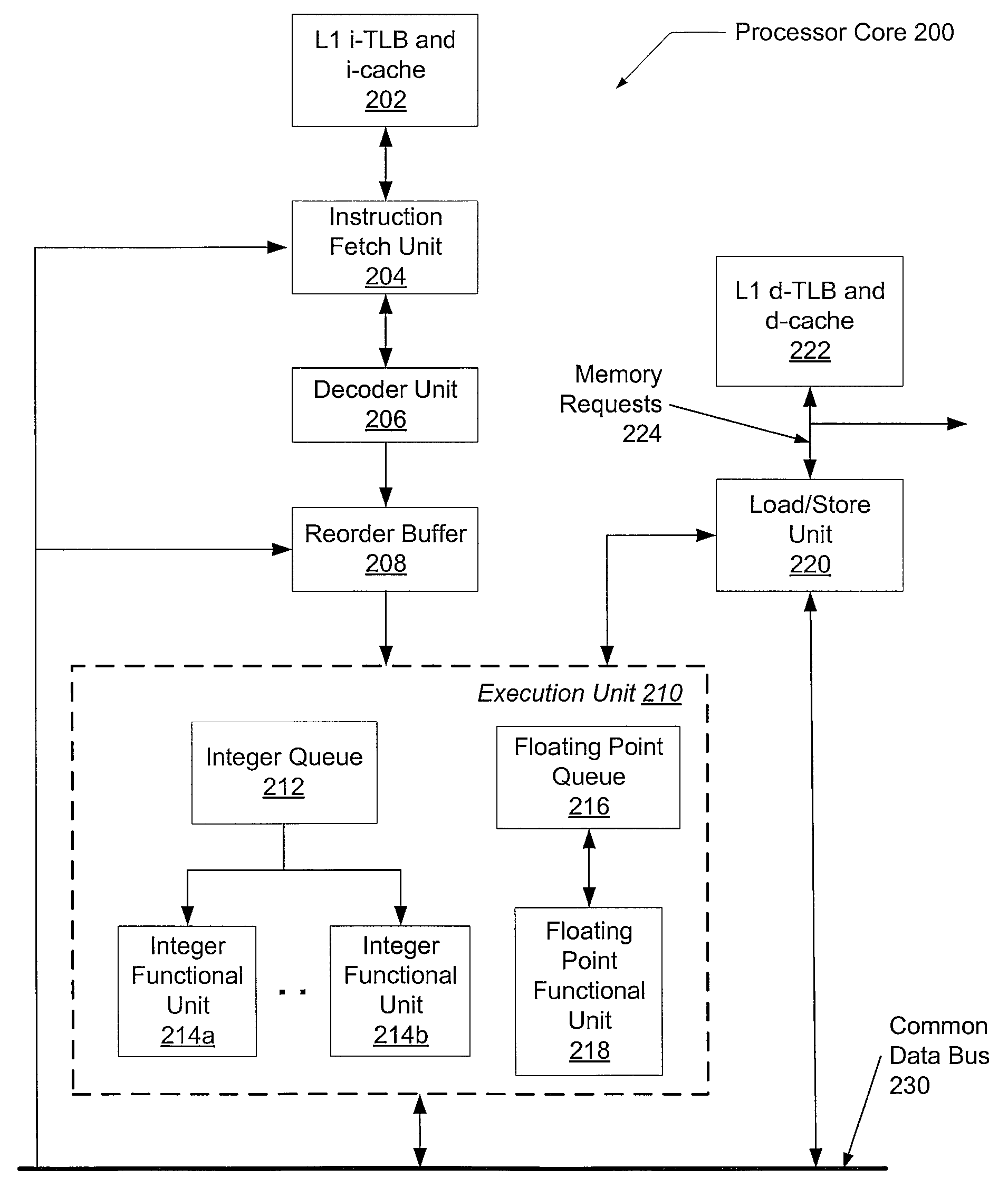

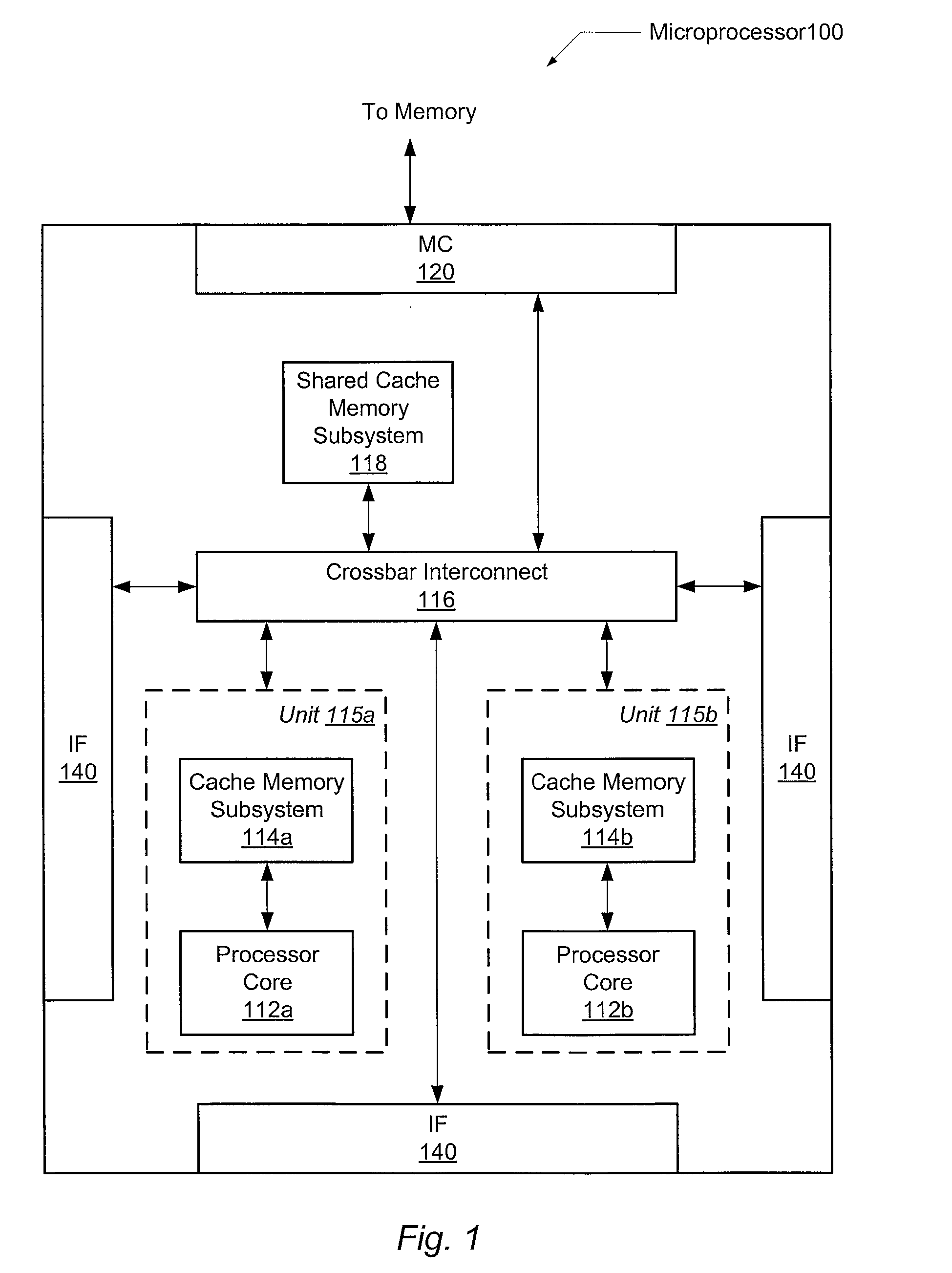

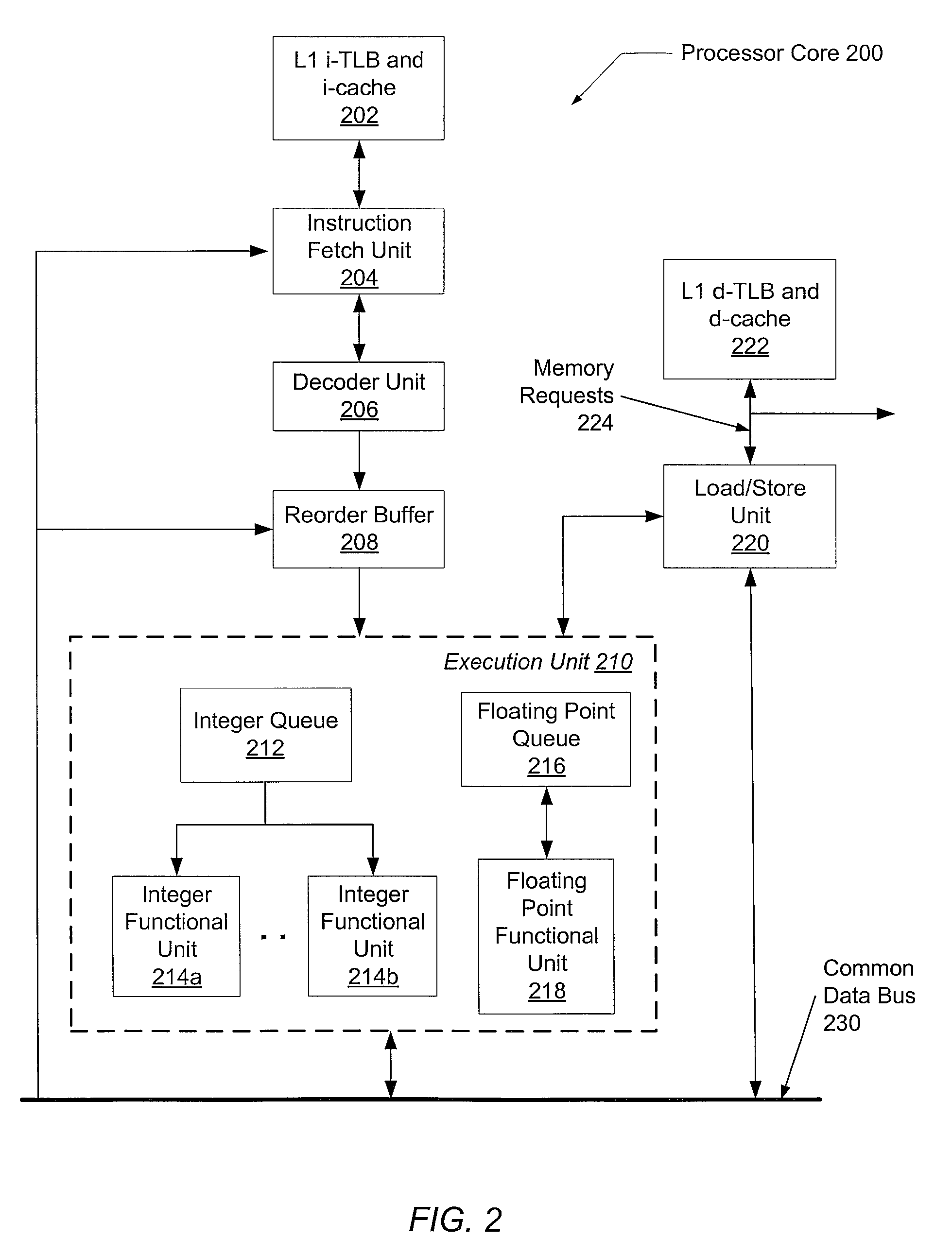

A system and method for efficient reliable execution on a simultaneous multithreading machine. A processor is placed in a reliable execution mode (REM) to detect possible errors during execution of a mission critical software application. Only two threads may be configured to operate in this mode. Floating-point store and integer-transfer unary instructions may be converted to new binary instructions. Each new instruction has two source operands, each one corresponding to a different thread is specified by a same logical register number as a single source operand of the original unary instruction. All other instructions are replicated, wherein the original instruction and its twin are assigned to different threads. Simultaneous multi-threaded (SMT) floating-point logic may only be able to provide lockstep execution when it communicates using the new instruction with instantiated integer independent clusters. The new instruction cannot begin until both source operands are ready, which are subsequently compared to determine any mismatches or errors.

Owner:ADVANCED MICRO DEVICES INC

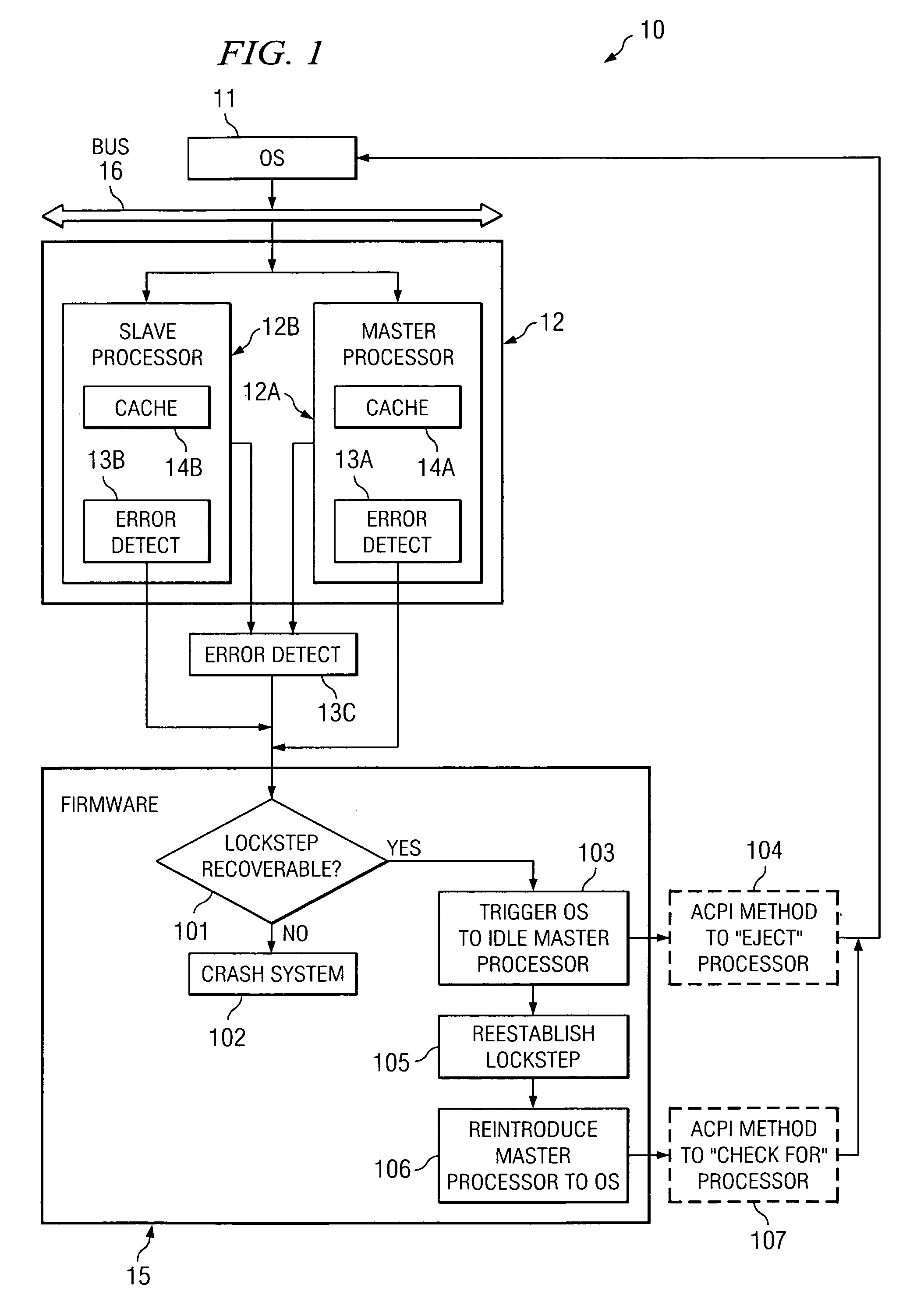

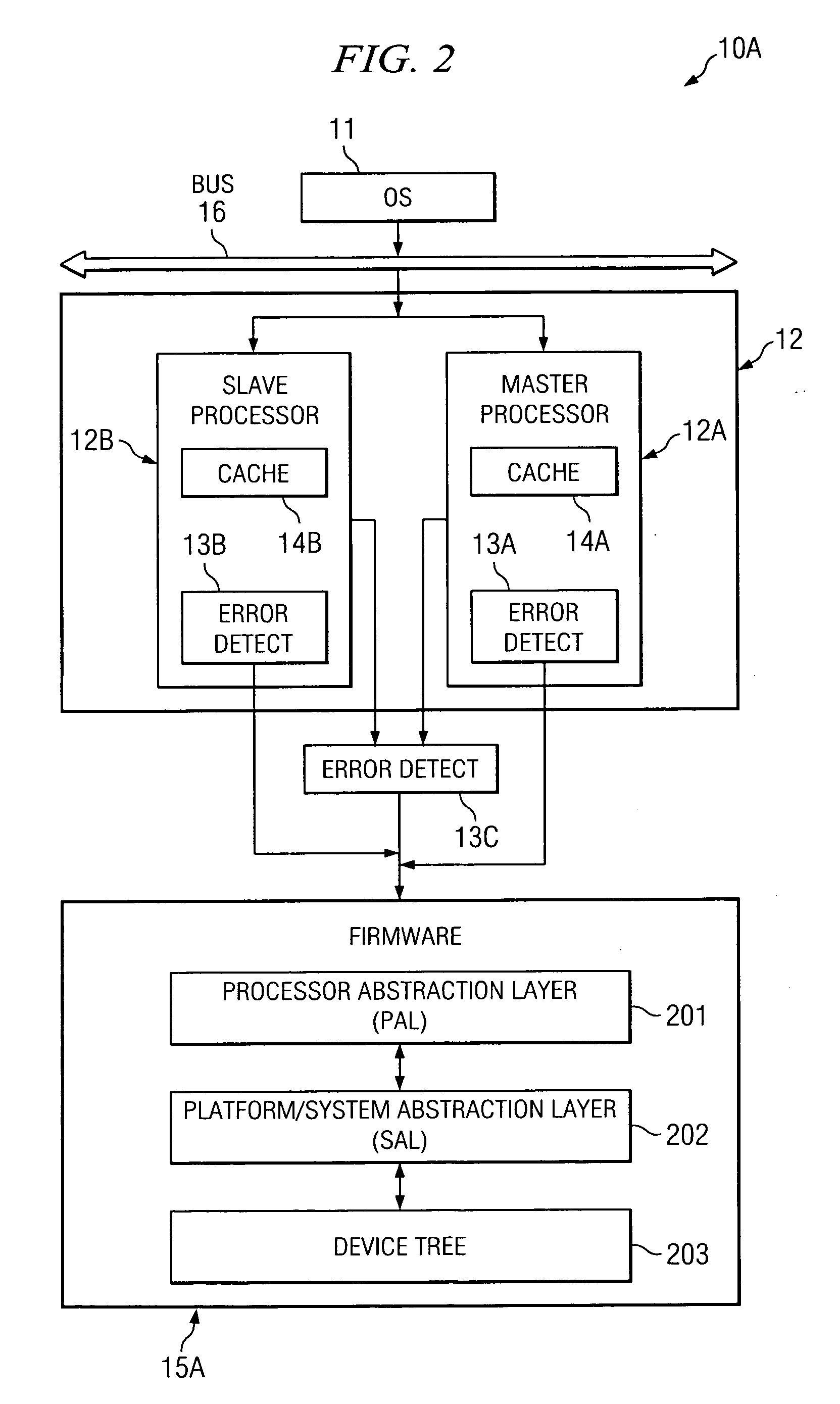

System and method for providing firmware recoverable lockstep protection

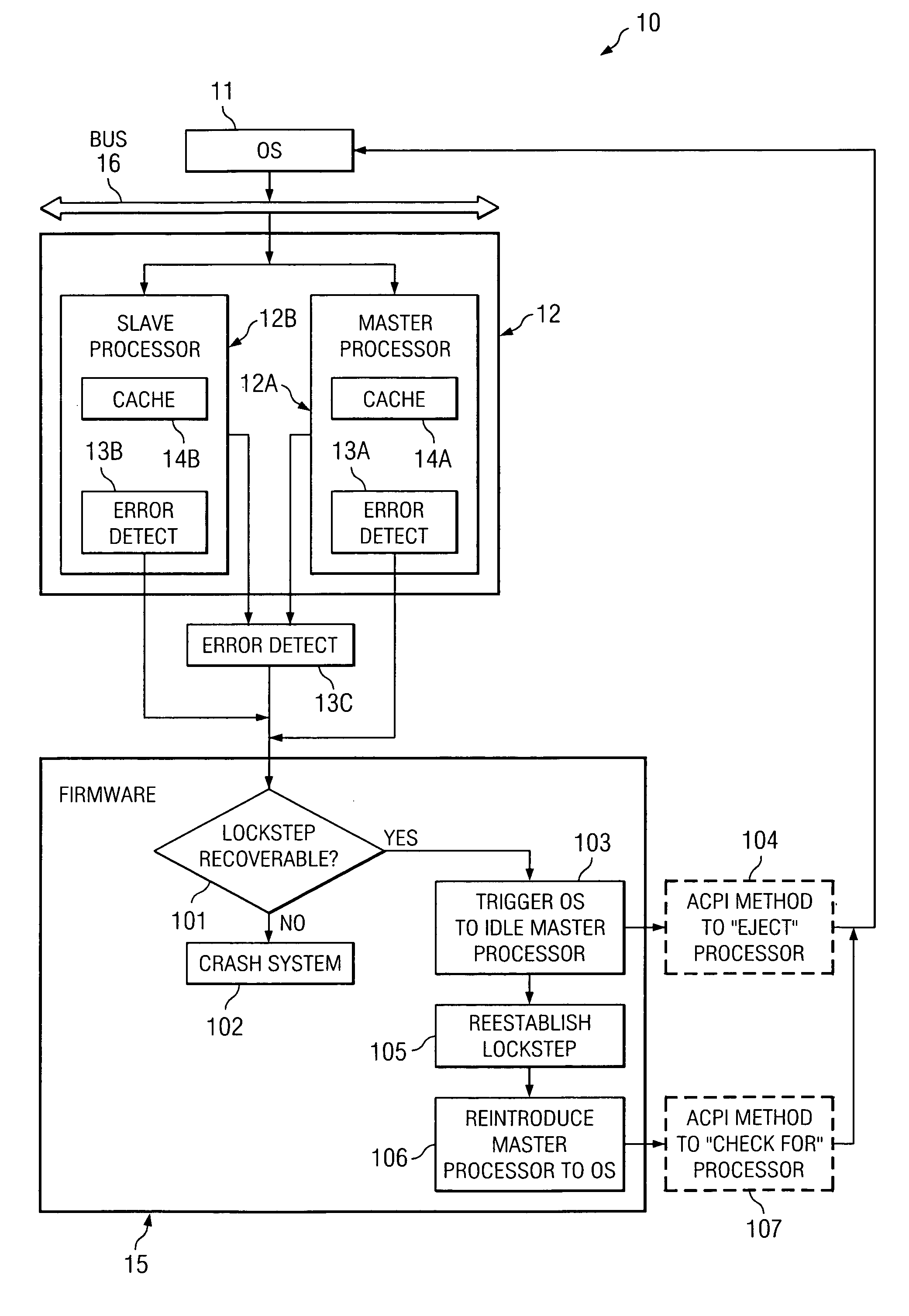

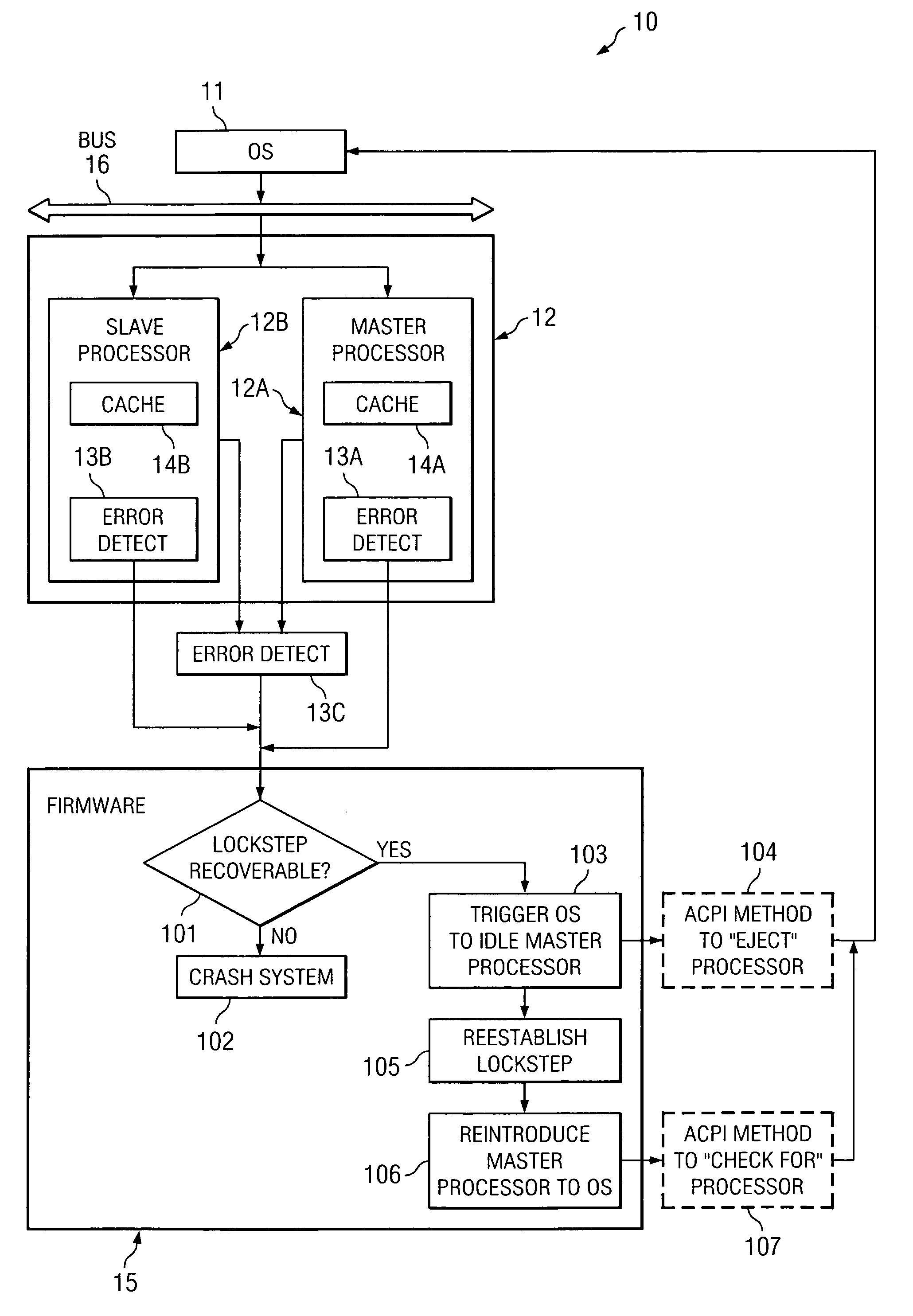

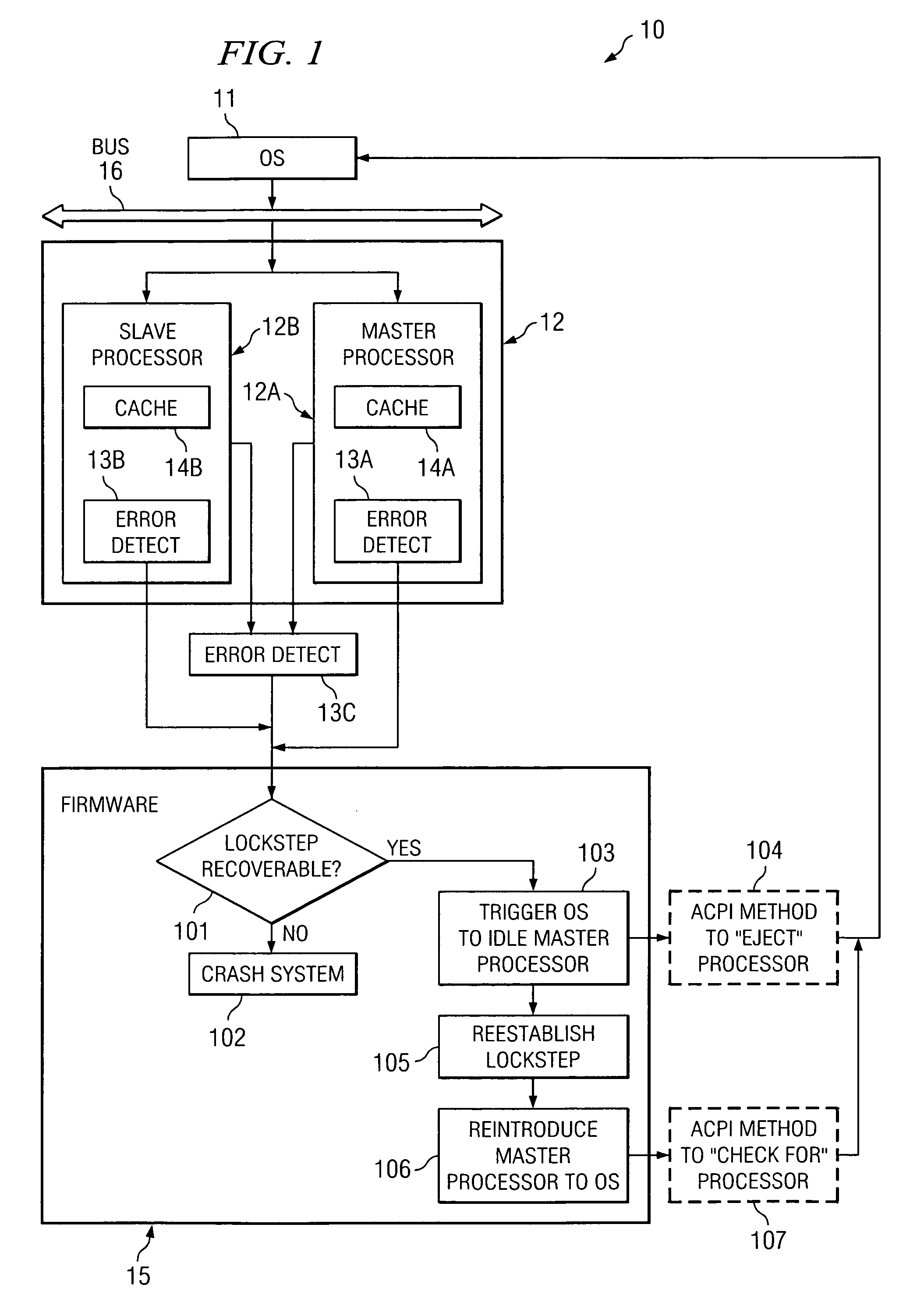

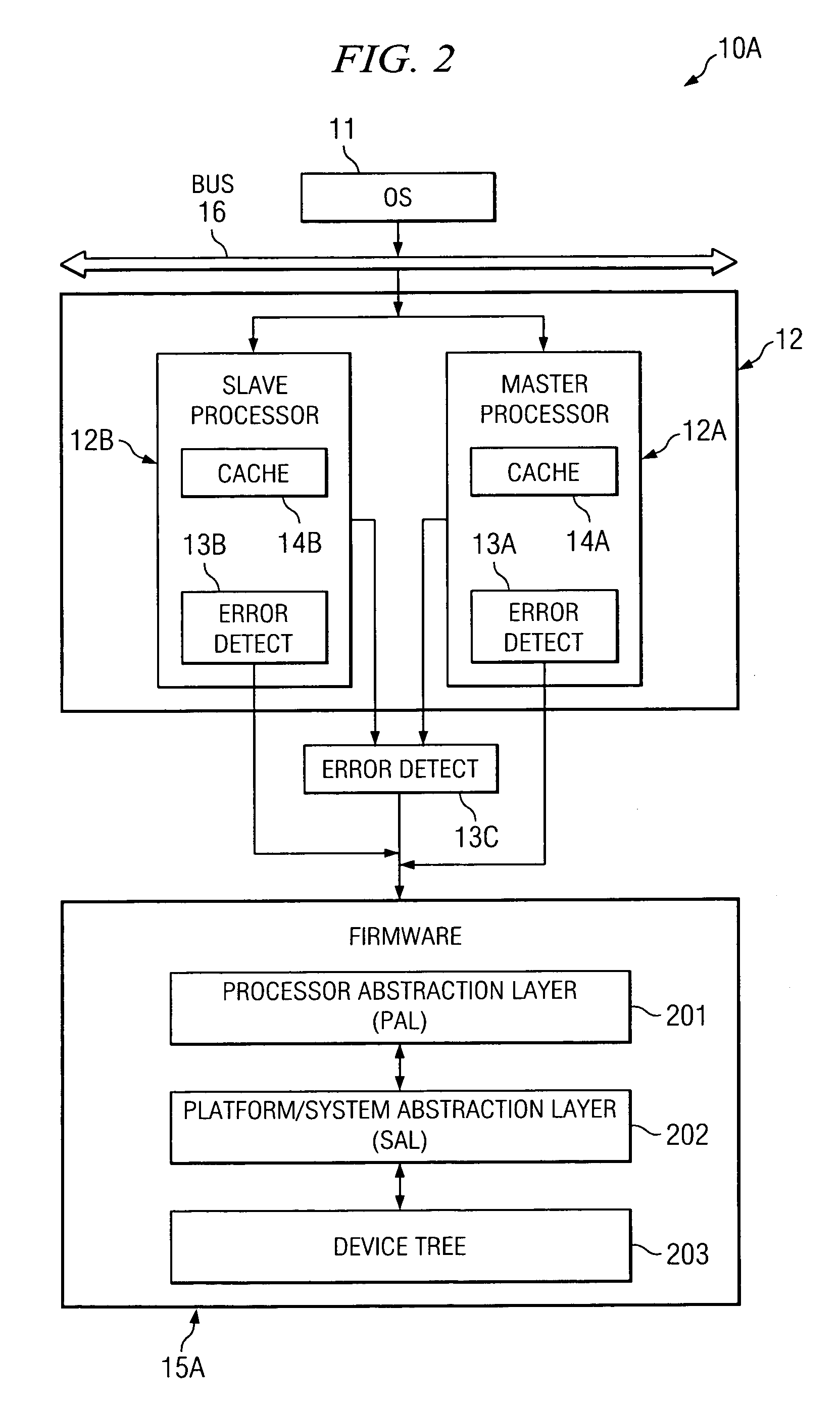

ActiveUS20060107107A1Error detection/correctionGeneral purpose stored program computerFirmwareOperational system

According to at least one embodiment, a method comprises detecting loss of lockstep for a pair of processors. The method further comprises triggering, by firmware, an operating system to idle the processors, and recovering, by the firmware, lockstep between the pair of processors. After lockstep is recovered between the pair of processors, the method further comprises triggering, by the firmware, the operating system to recognize the processors as being available for receiving instructions.

Owner:FORAS TECH LTD

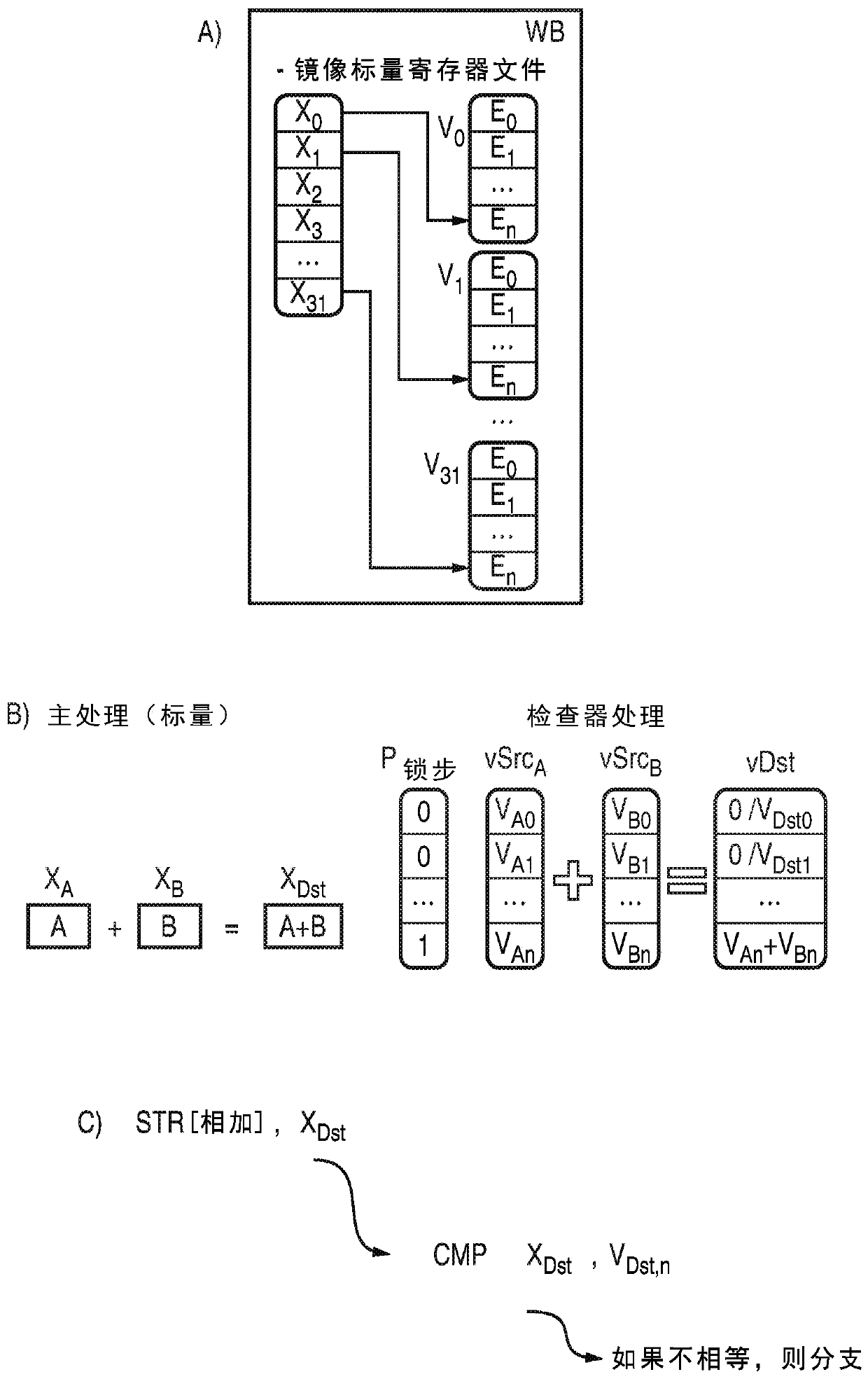

Error detection using vector processing circuitry

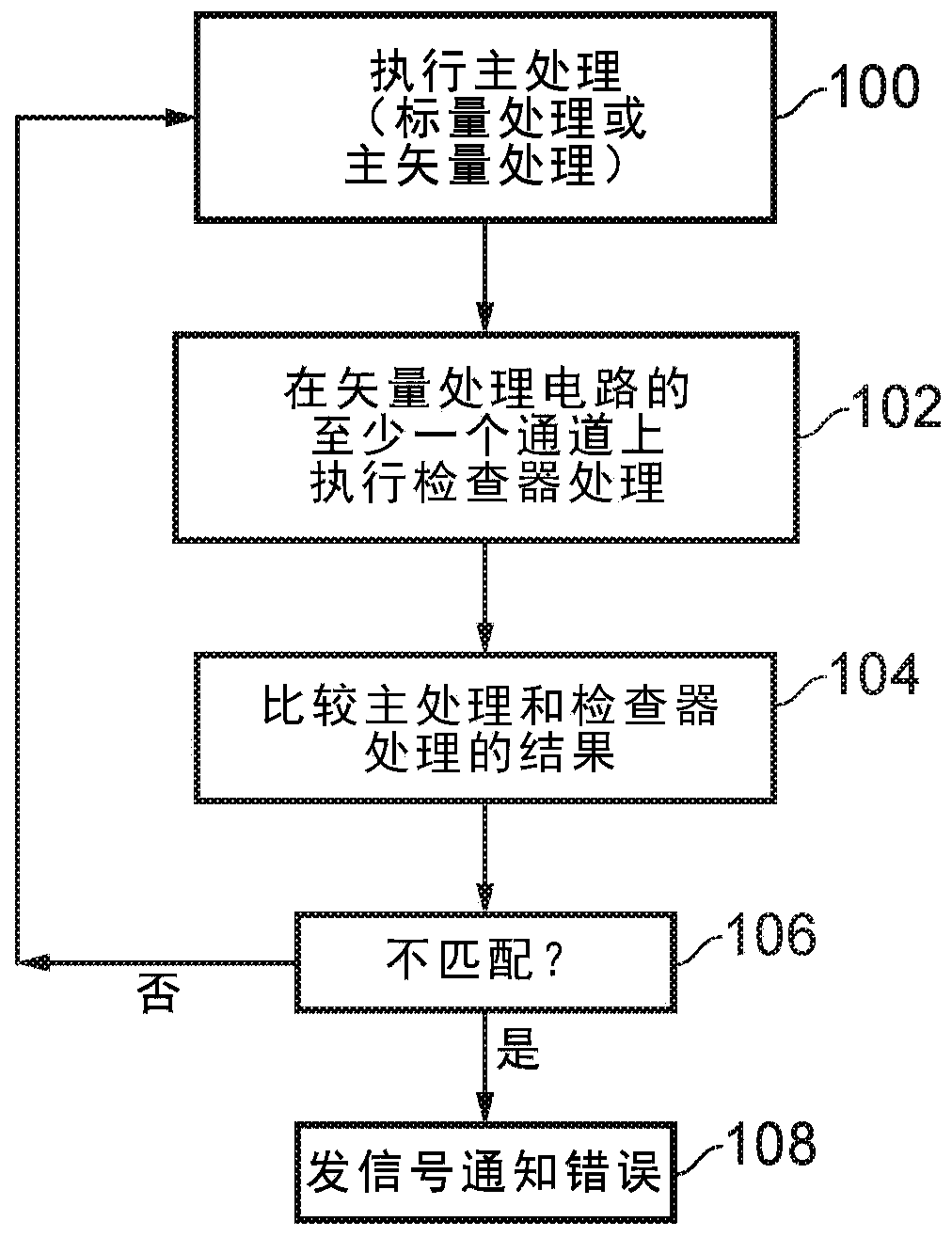

A data processing apparatus (2) has scalar processing circuitry (32-42) and vector processing circuitry (38, 40, 42). When executing main scalar processing on the scalar processing circuitry (32-42),or main vector processing using a subset of said plurality of lanes on the vector processing circuitry (38, 40, 42), checker processing is executed using at least one lane of the plurality of lanes onthe vector processing circuitry (38, 40, 42), the checker processing comprising operations corresponding to at least part of the main scalar / vector processing. Errors can then be detected based on acomparison of an outcome of the main processing and an outcome of the checker processing. This provides a technique for achieving functional safety in a high end processor with better performance andreduced hardware cost compared to a dual / triple core lockstep approach.

Owner:ARM LTD

Automatic bug reproduction using replication and CPU lockstep

InactiveUS20200034284A1Software testing/debuggingSoftware simulation/interpretation/emulationLockstepAlgorithm

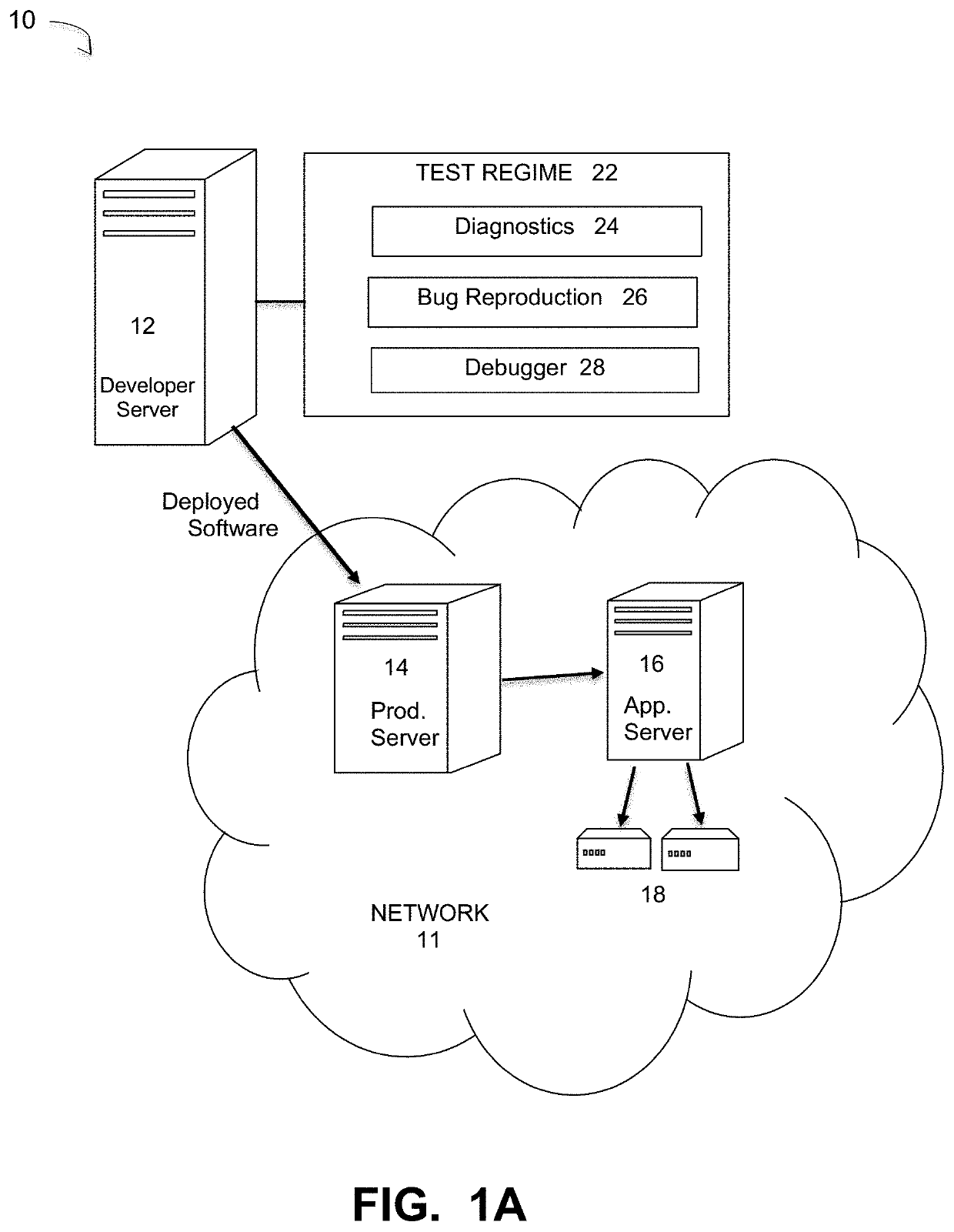

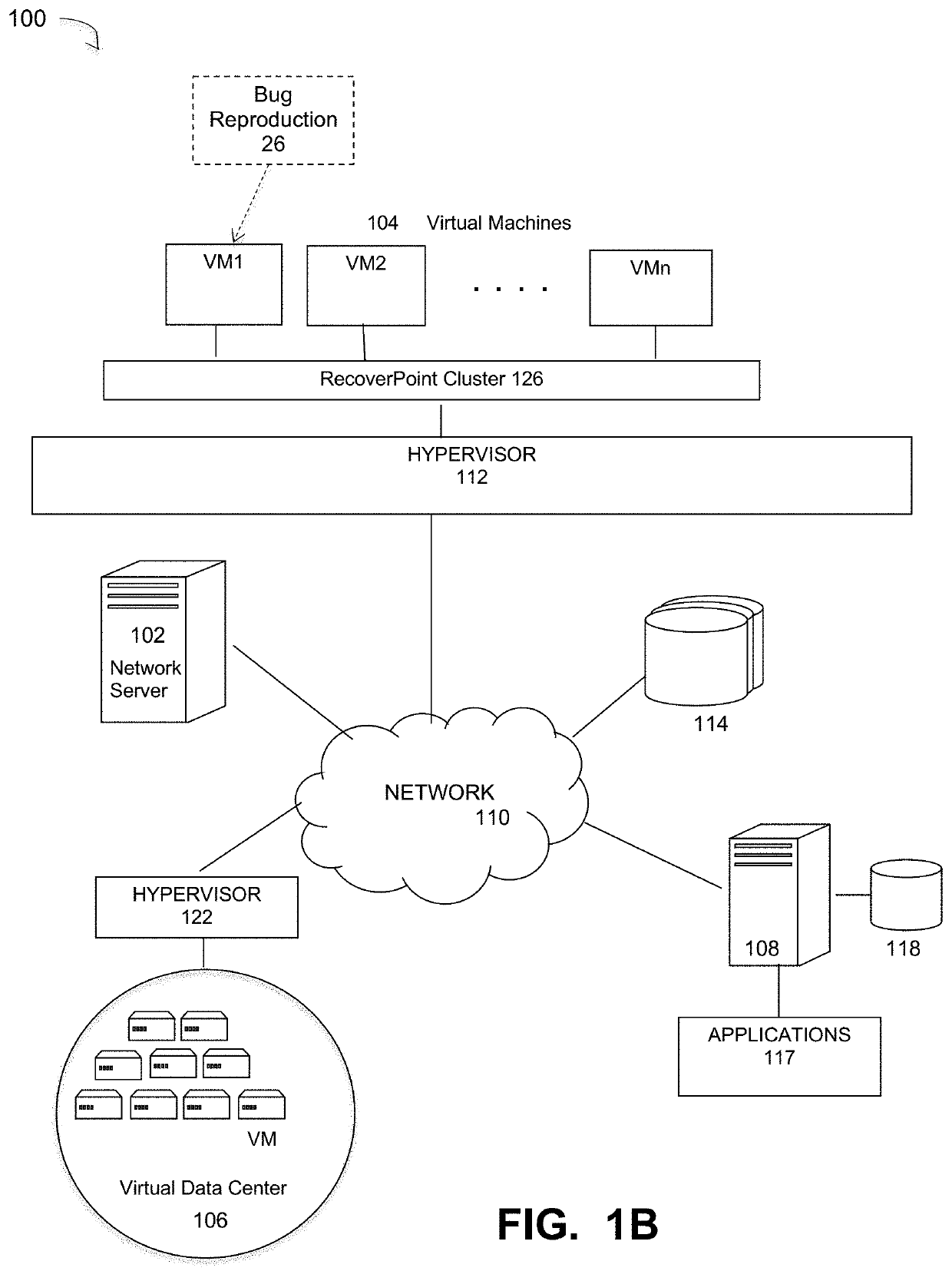

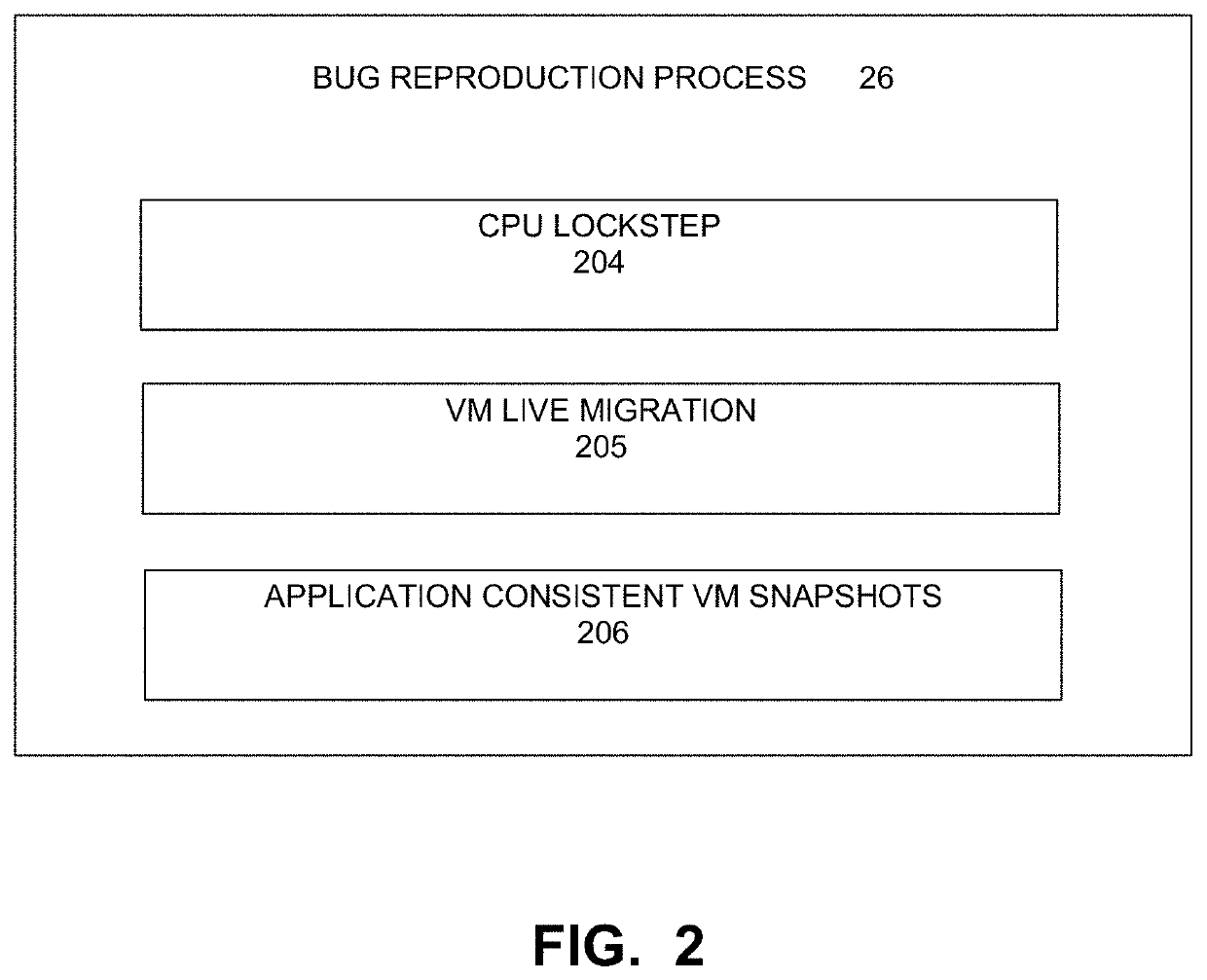

Embodiments are directed to a bug reproduction system and method to reproduce non-probabilistic bug conditions in programs, such as those that involve multi-threaded race conditions and / or containerized systems. To consistently reproduce a phenomenon that usually happens with low probability, embodiments provide an effective approach to consistently reproducing bugs by combining multi-point-in-time replication (like RecoverPoint), CPU lockstep and the same constructs used in implementing VMware VMotion functionality. The result is a system that once there is an initial reconstruction, will be able to consistently reproduce the same issue one hundred percent of the time.

Owner:EMC IP HLDG CO LLC

System and method for providing firmware recoverable lockstep protection

ActiveUS7502958B2Error detection/correctionGeneral purpose stored program computerLockstepComputer engineering

According to at least one embodiment, a method comprises detecting loss of lockstep for a pair of processors. The method further comprises triggering, by firmware, an operating system to idle the processors, and recovering, by the firmware, lockstep between the pair of processors. After lockstep is recovered between the pair of processors, the method further comprises triggering, by the firmware, the operating system to recognize the processors as being available for receiving instructions.

Owner:FORAS TECH LTD

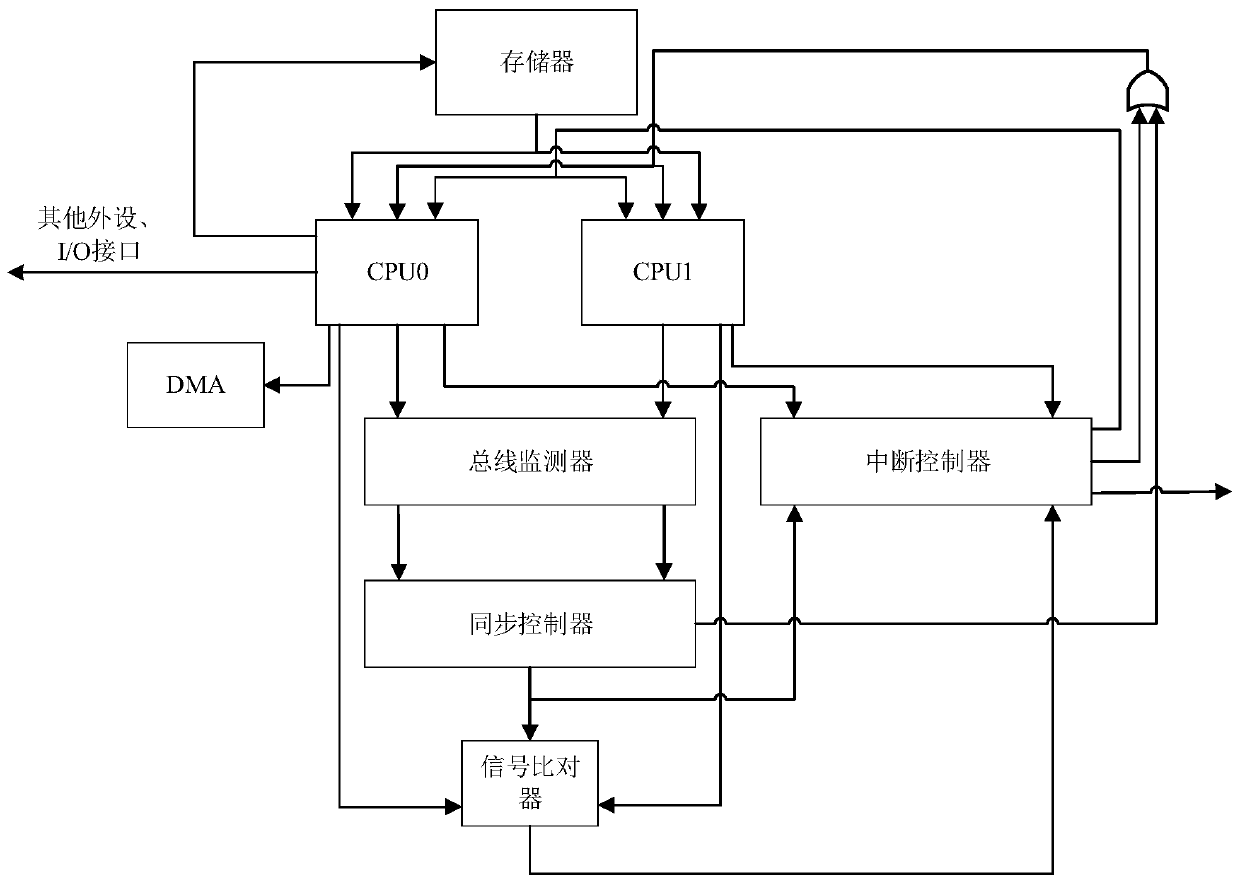

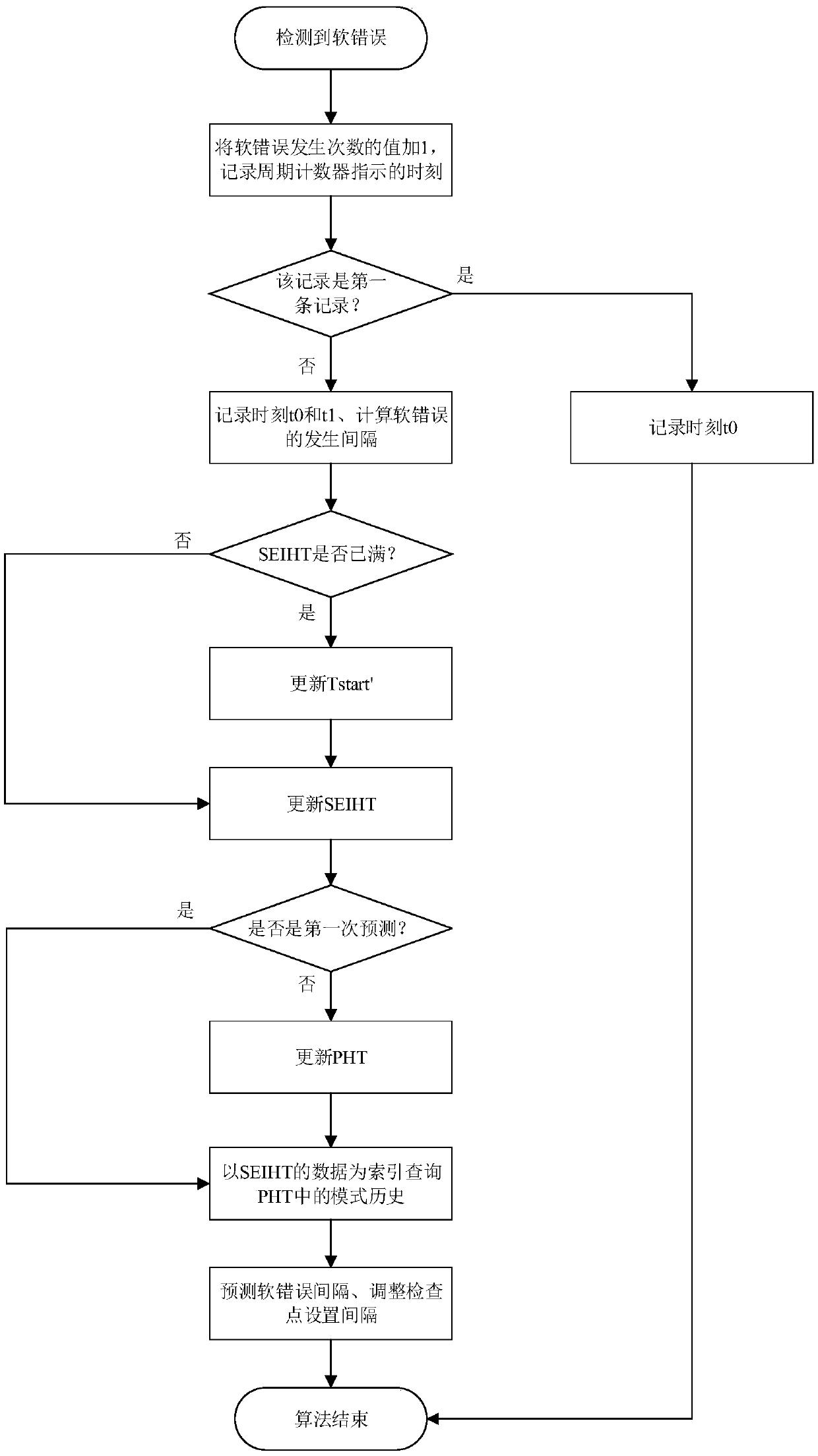

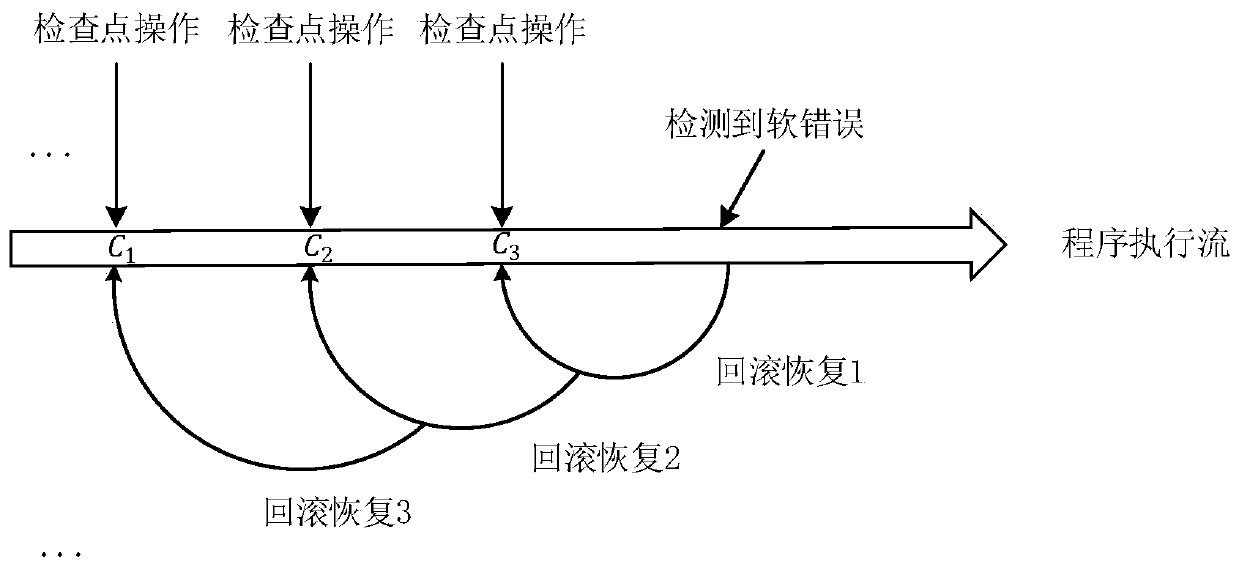

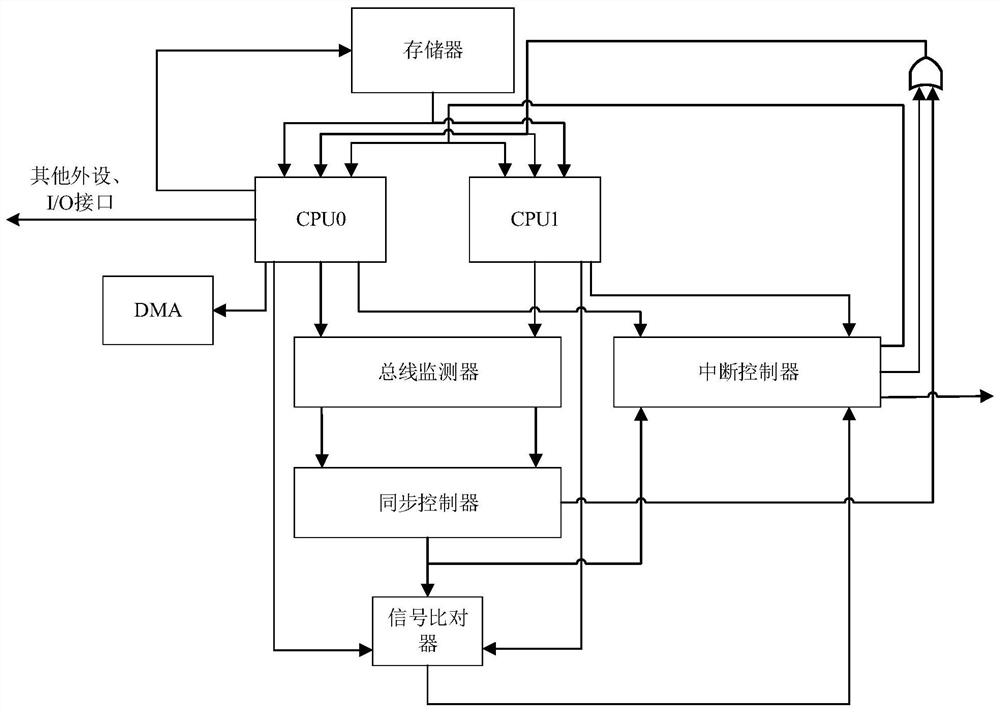

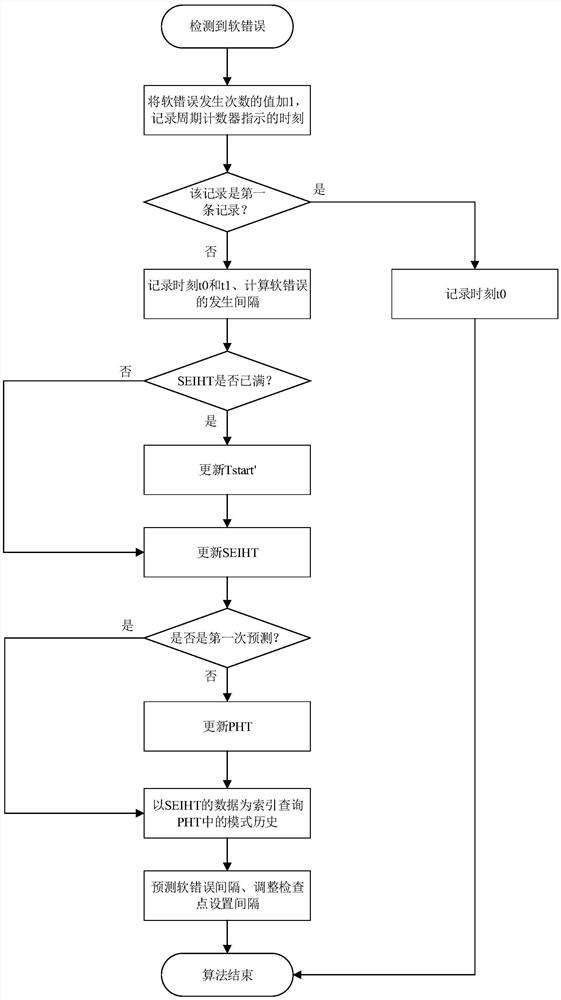

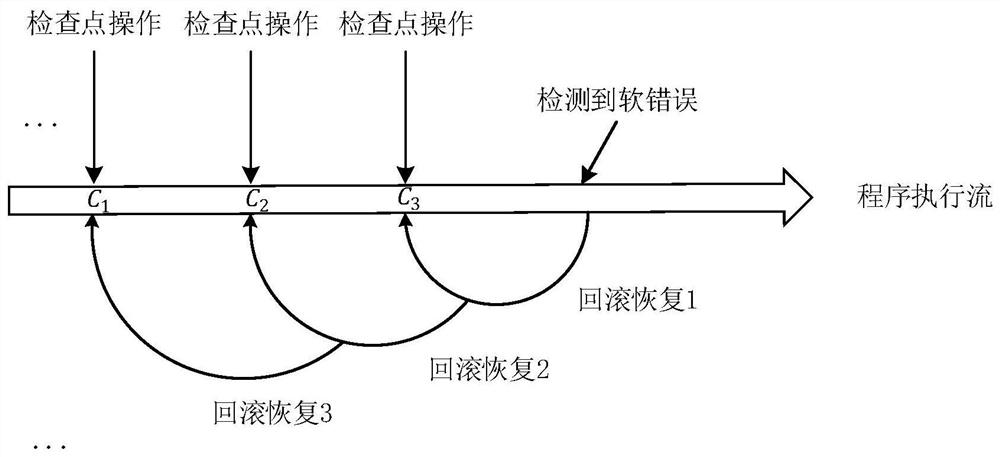

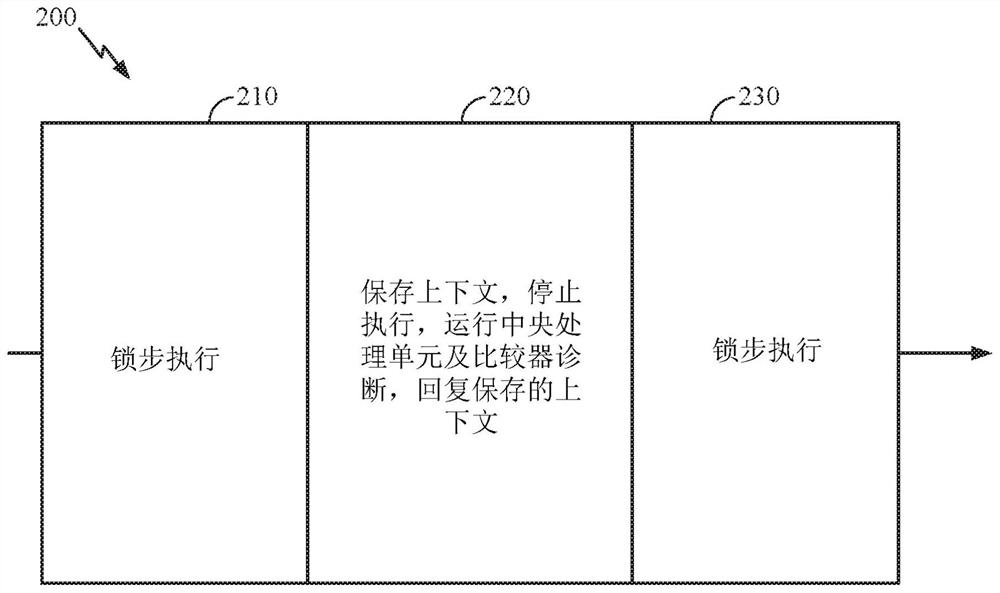

Low-delay dual-mode lockstep soft error tolerance processor system

ActiveCN111104243AImprove universalityReduce time overheadNon-redundant fault processingLockstepSelf adaptive

The invention discloses a low-delay dual-mode lockstep soft error tolerance processor system, and belongs to the technical field of processor fault tolerance. According to the system, soft errors in aprocessor system are detected through a dual-mode lockstep architecture; by adopting the universal check points and the rollback recovery algorithm, the system can deal with various soft errors, andthe universality of the fault recovery method is improved; according to the system, a self-adaptive dynamic check point method is adopted, predicting the next soft error interval is performed by usinga soft error interval history table SEIHT and a mode history table PHT, the setting frequency of the check points is increased or decreased according to the prediction result, the long-term characteristics and the short-term characteristics of the soft error history are considered at the same time, the average execution time of processor tasks is effectively shortened, and the problem that largedelay time is introduced into an existing processor-oriented dual-mode lockstep fault-tolerant technology is solved.

Owner:JIANGNAN UNIV

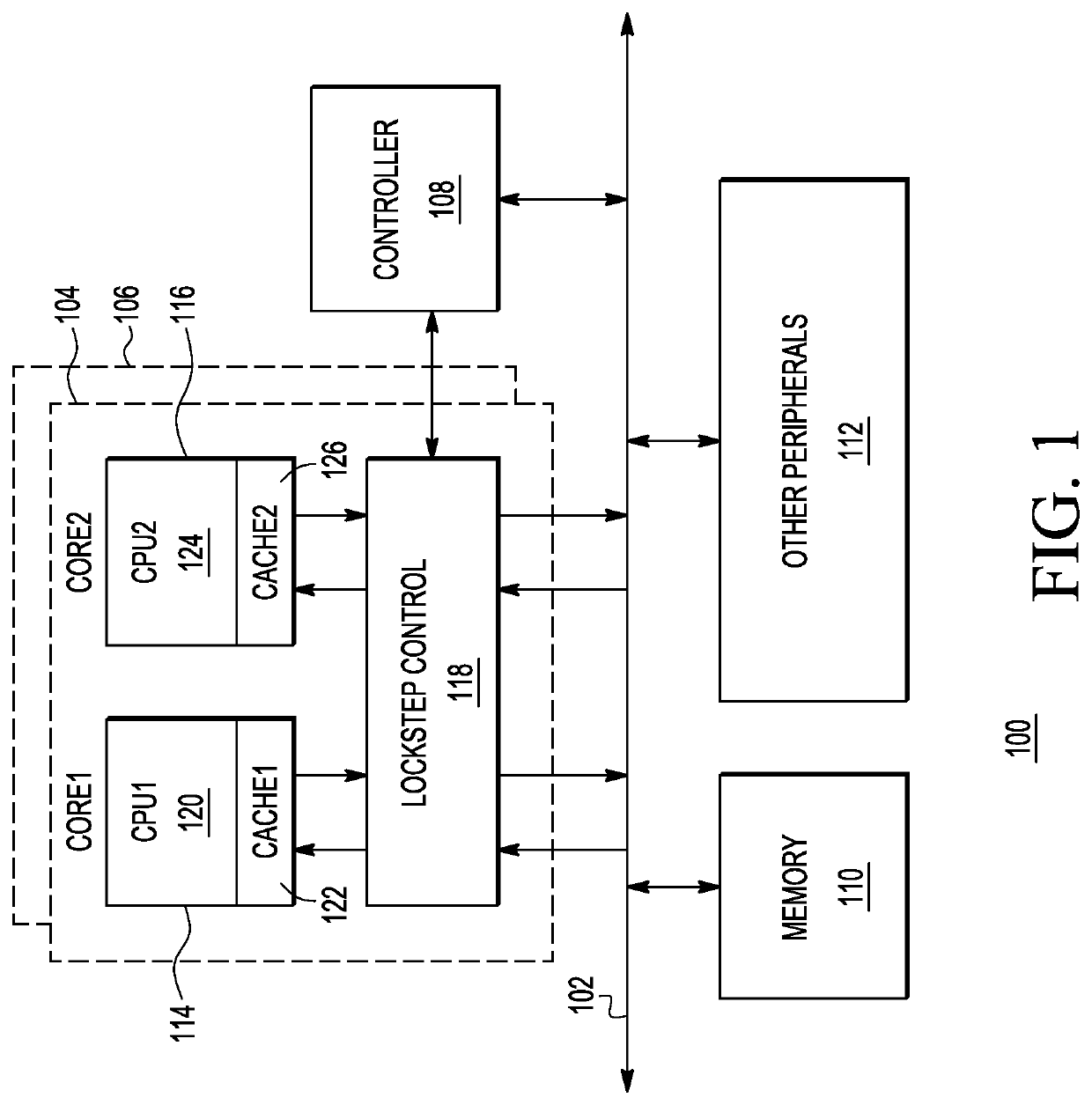

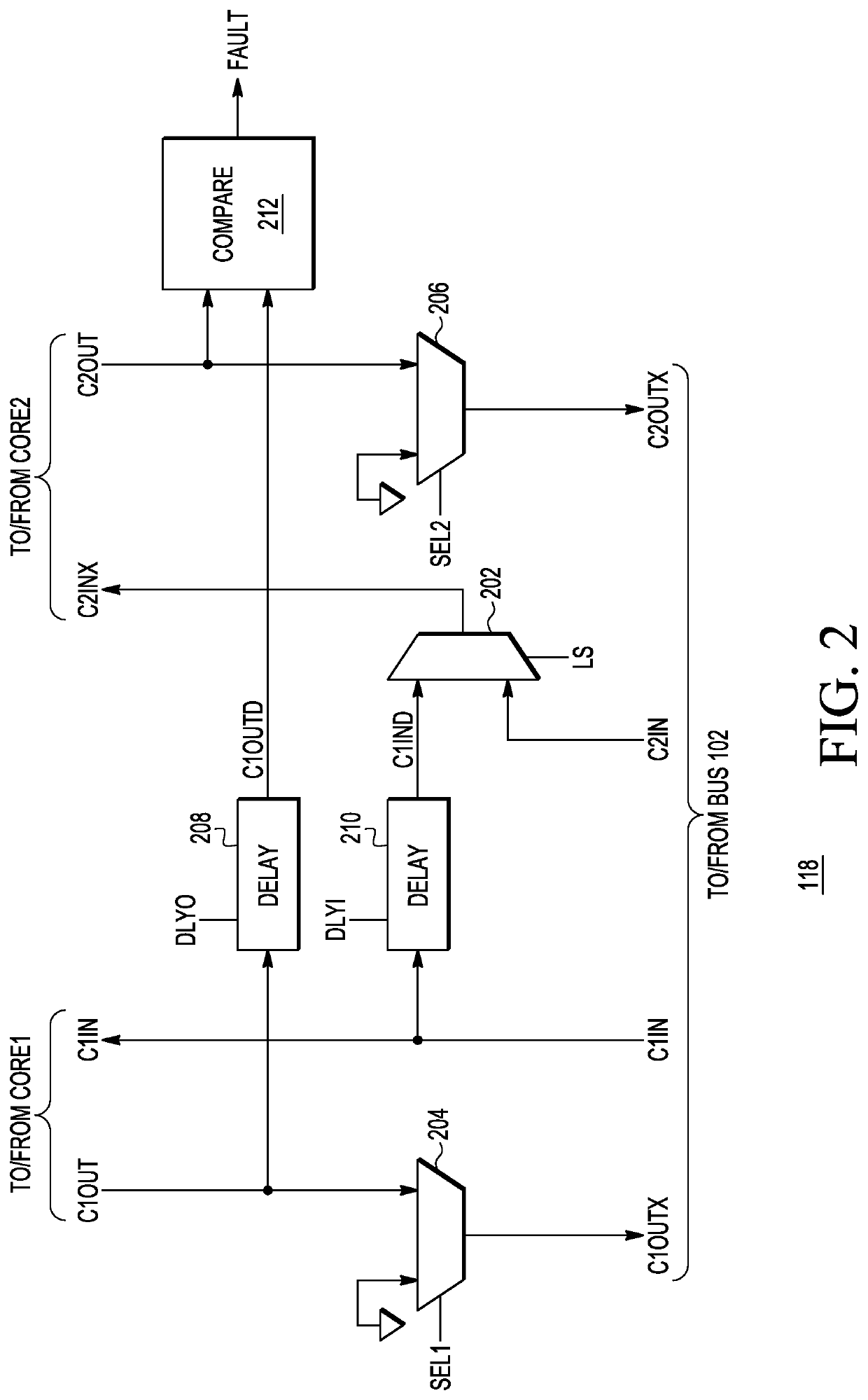

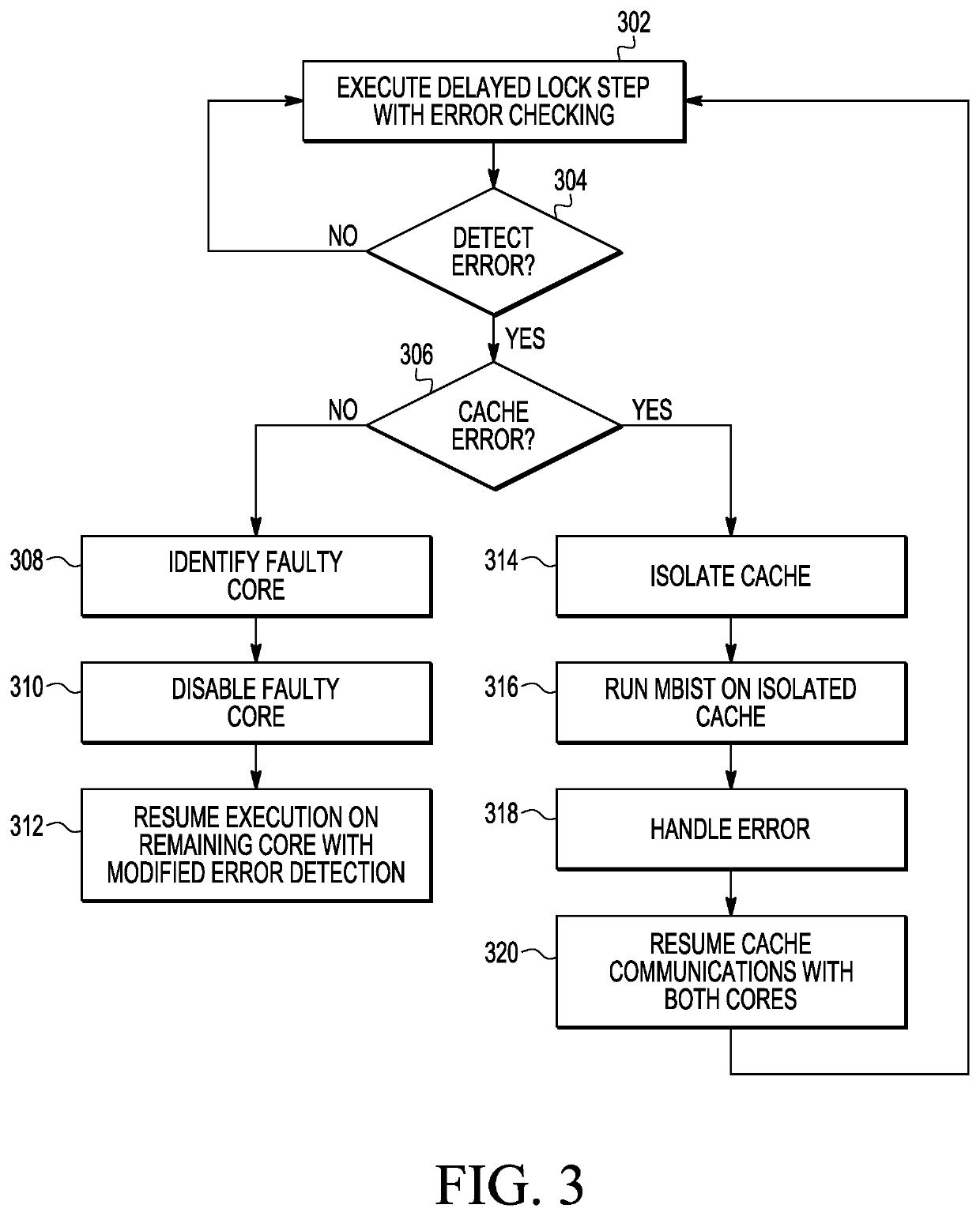

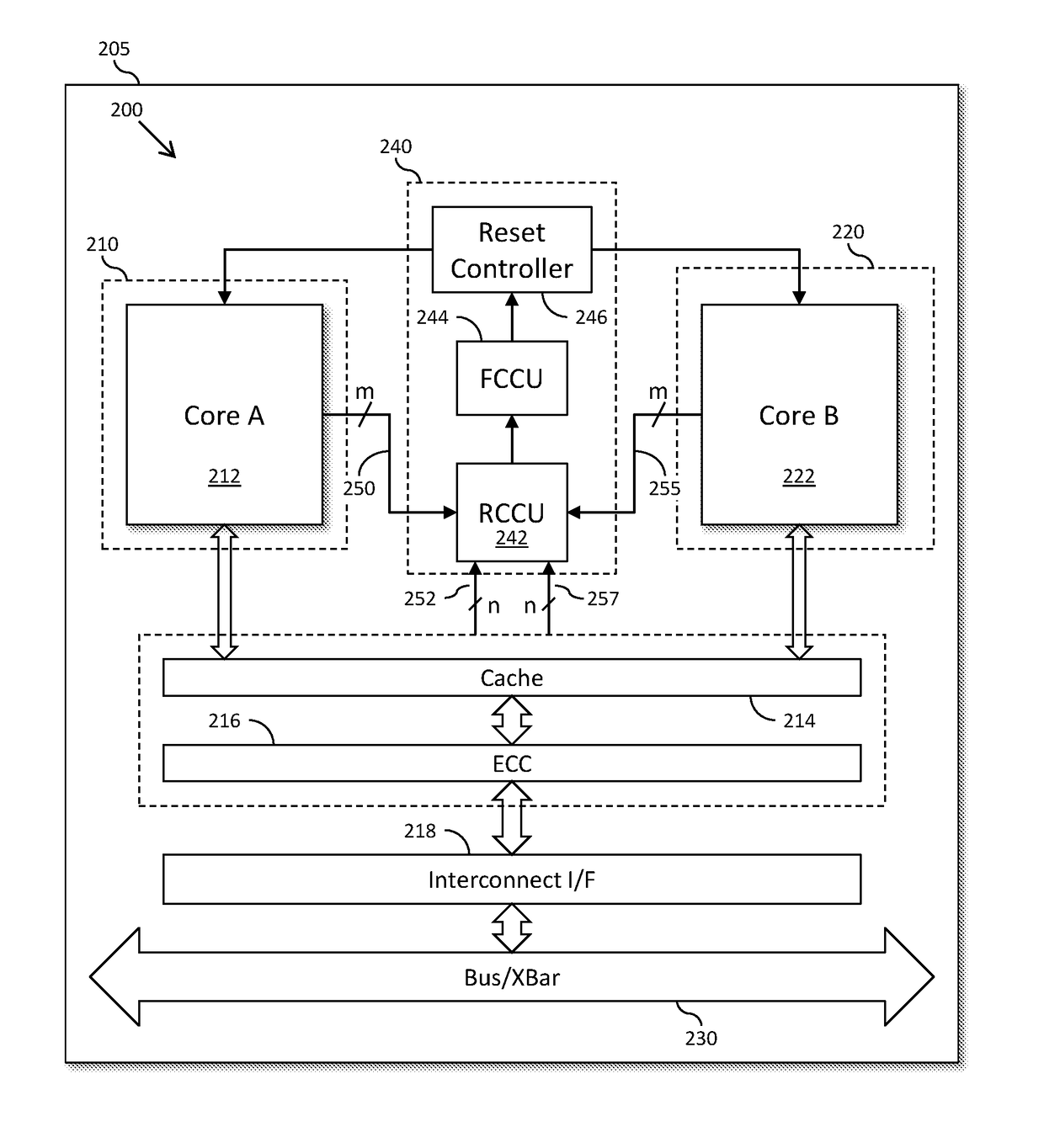

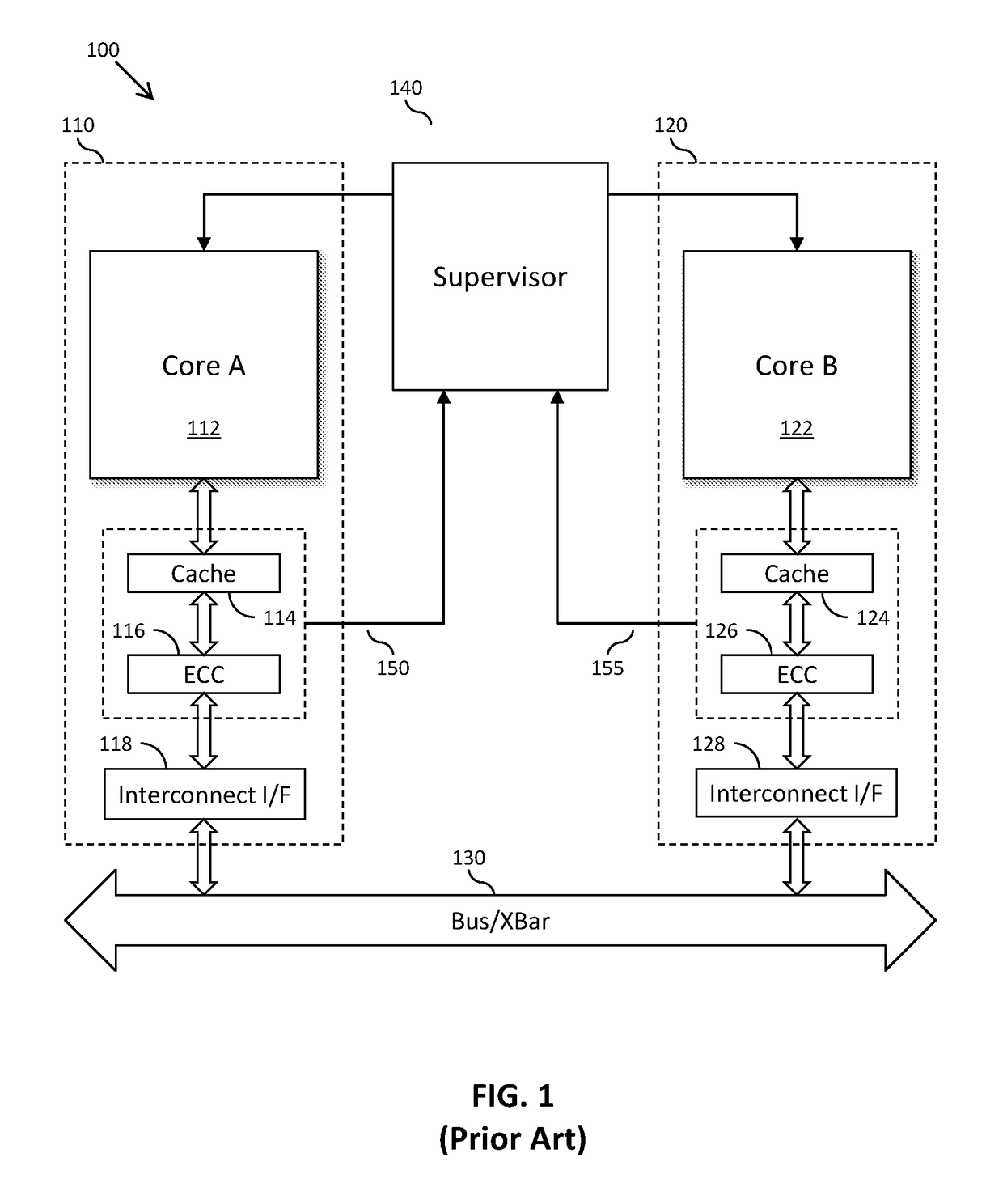

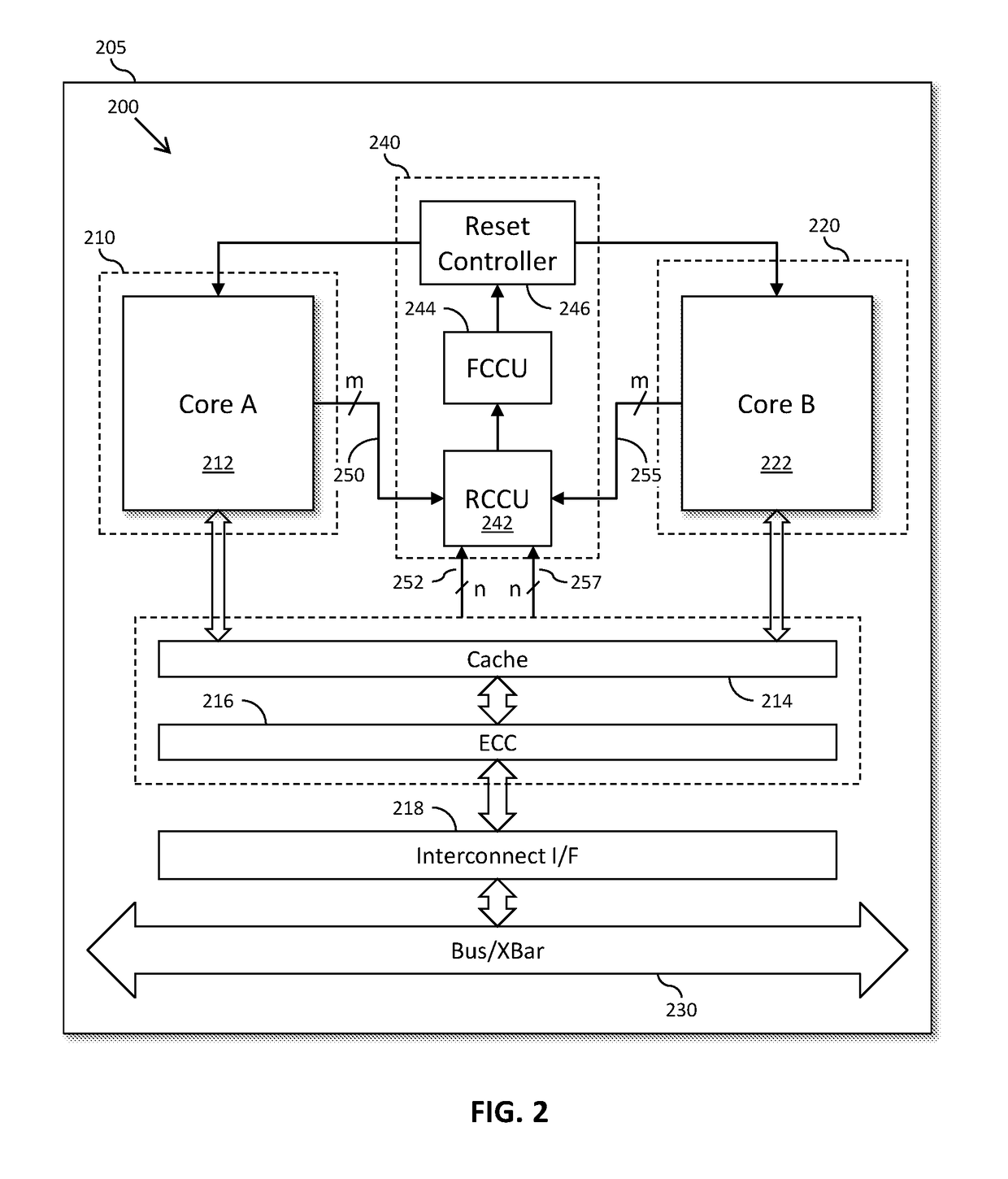

Data processing system having lockstep operation

A data processing system and methods for operating the same are disclosed. The method includes detecting a fault by comparing output signals from a first processing core and a second processing core, entering a safe mode based upon detecting the fault, completing transactions while in the safe mode, and determining whether the fault corresponds to a hard error. Based upon the fault corresponding to a hard error, one of processing cores is identified as a faulty core. The faulty core is inhibited from executing instructions and the other processing core is allowed to execute instructions.

Owner:NXP USA INC

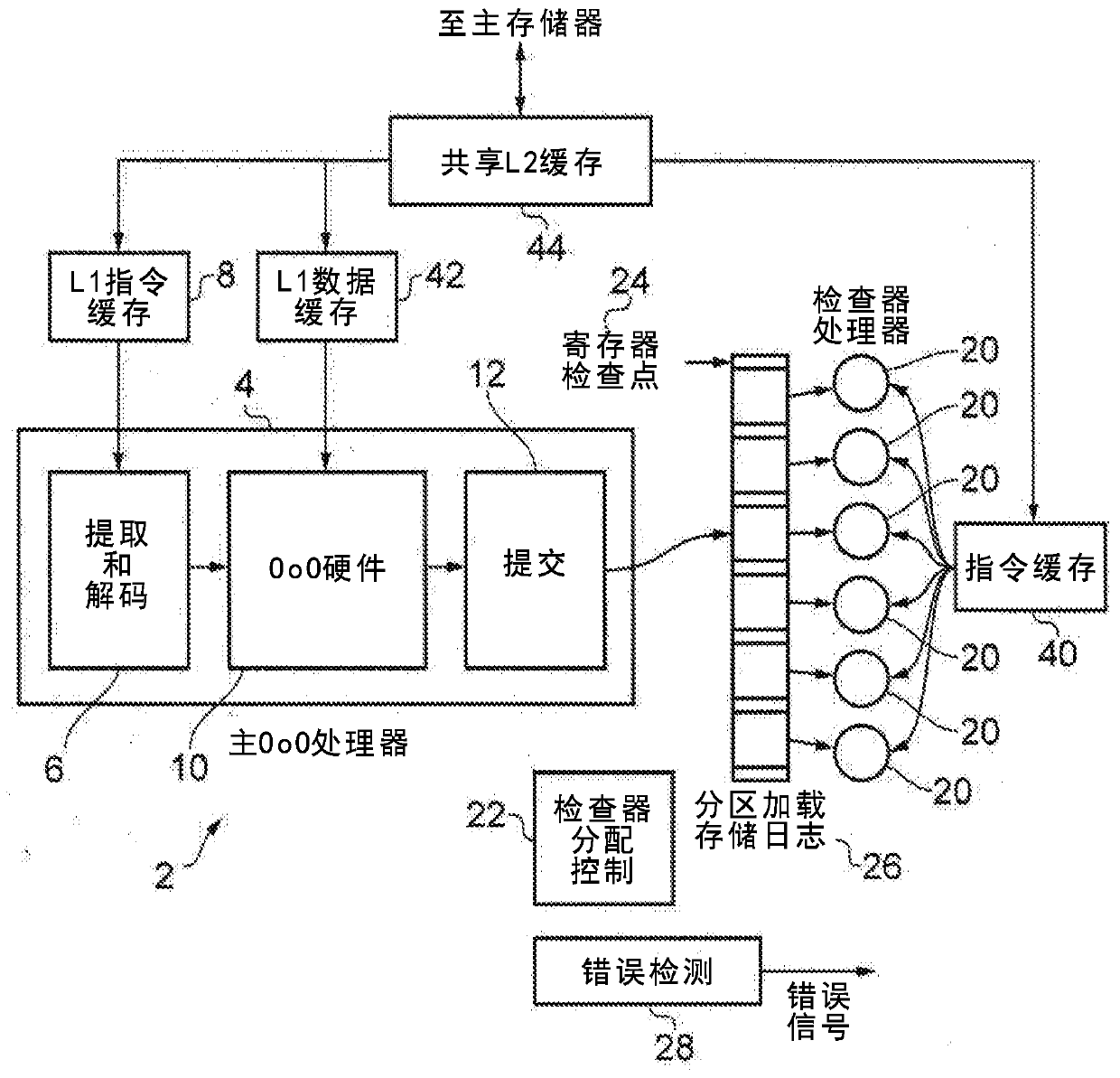

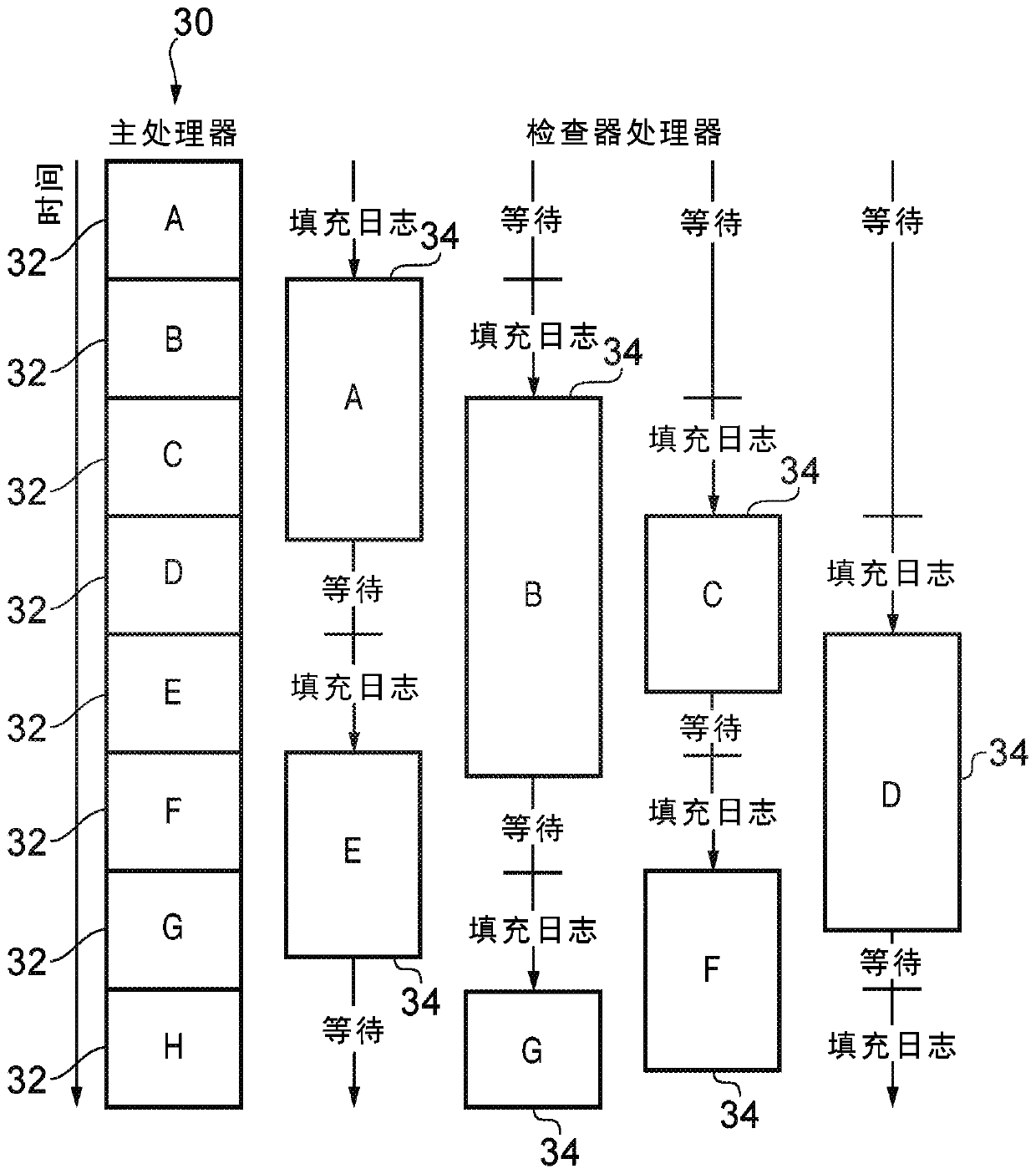

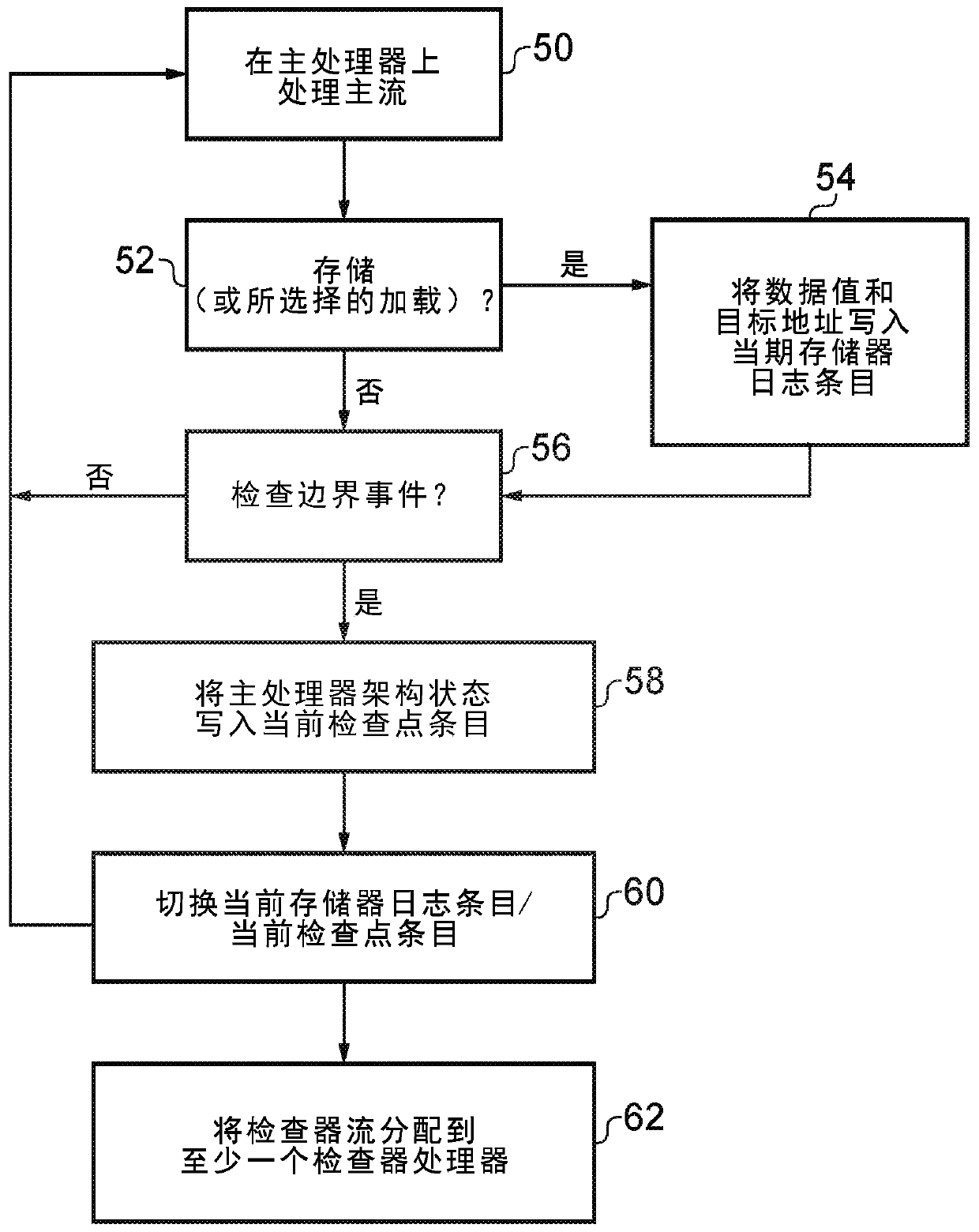

Main processor error detection using checker processors

An apparatus (2) comprises a main processor (4) to execute a main stream (30) of program instructions, two or more checker processors (20) to execute respective checker streams (34) of program instructions in parallel with each other, the checker streams corresponding to different portions (32) of the main stream executed by the main processor, and error detection circuitry (28) to detect an errorwhen a mismatch is detected between an outcome of a given portion (32) of the main stream executed on the main processor (4) and an outcome of the corresponding checker stream (34) executed on one ofthe plurality of checker processors (20). This approach enables high performance main processors (4) to be checked for errors with lower circuit area and power consumption overhead than a dual-core lockstep technique.

Owner:ARM LTD +1

Multi-channel network-on-a-chip

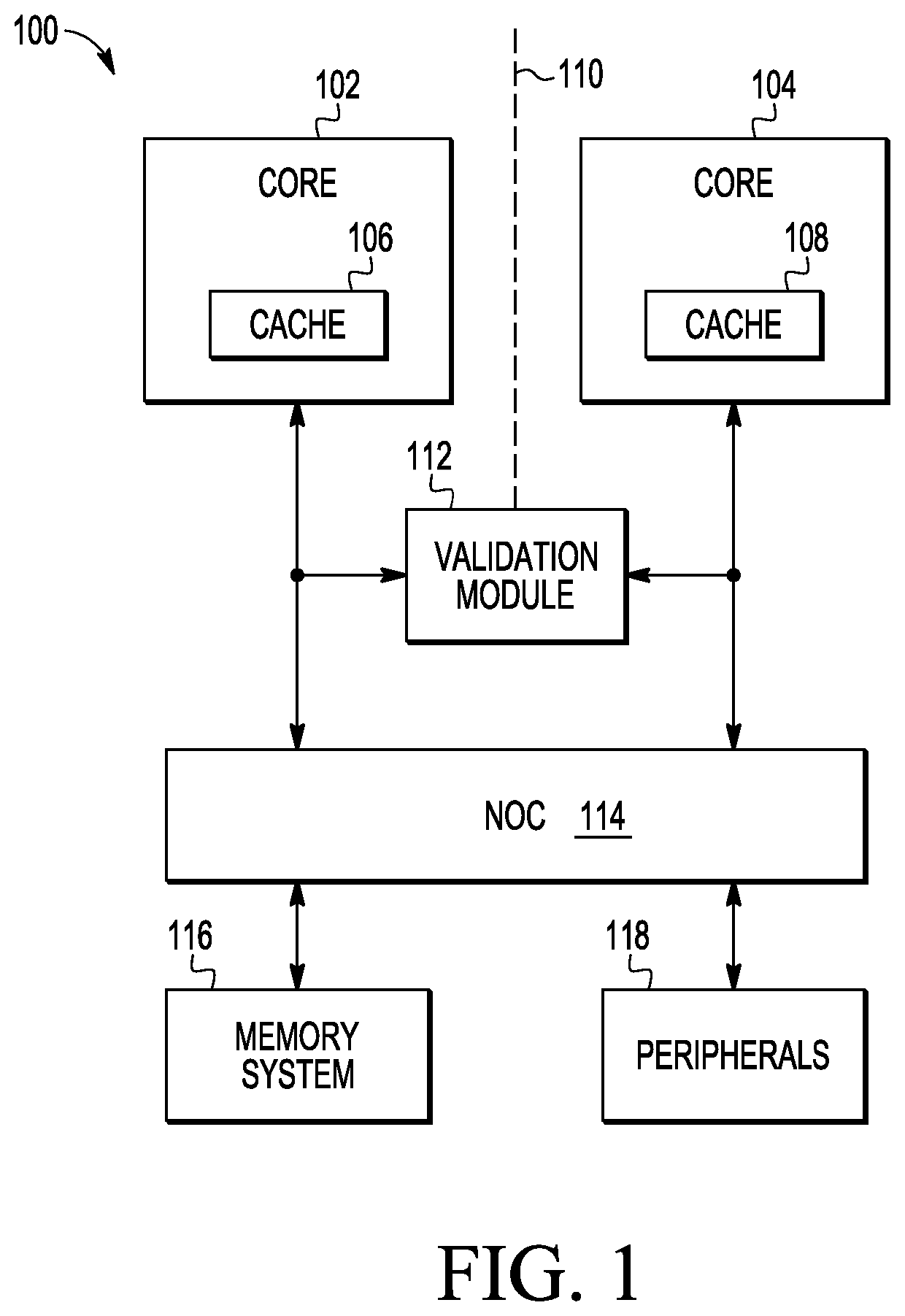

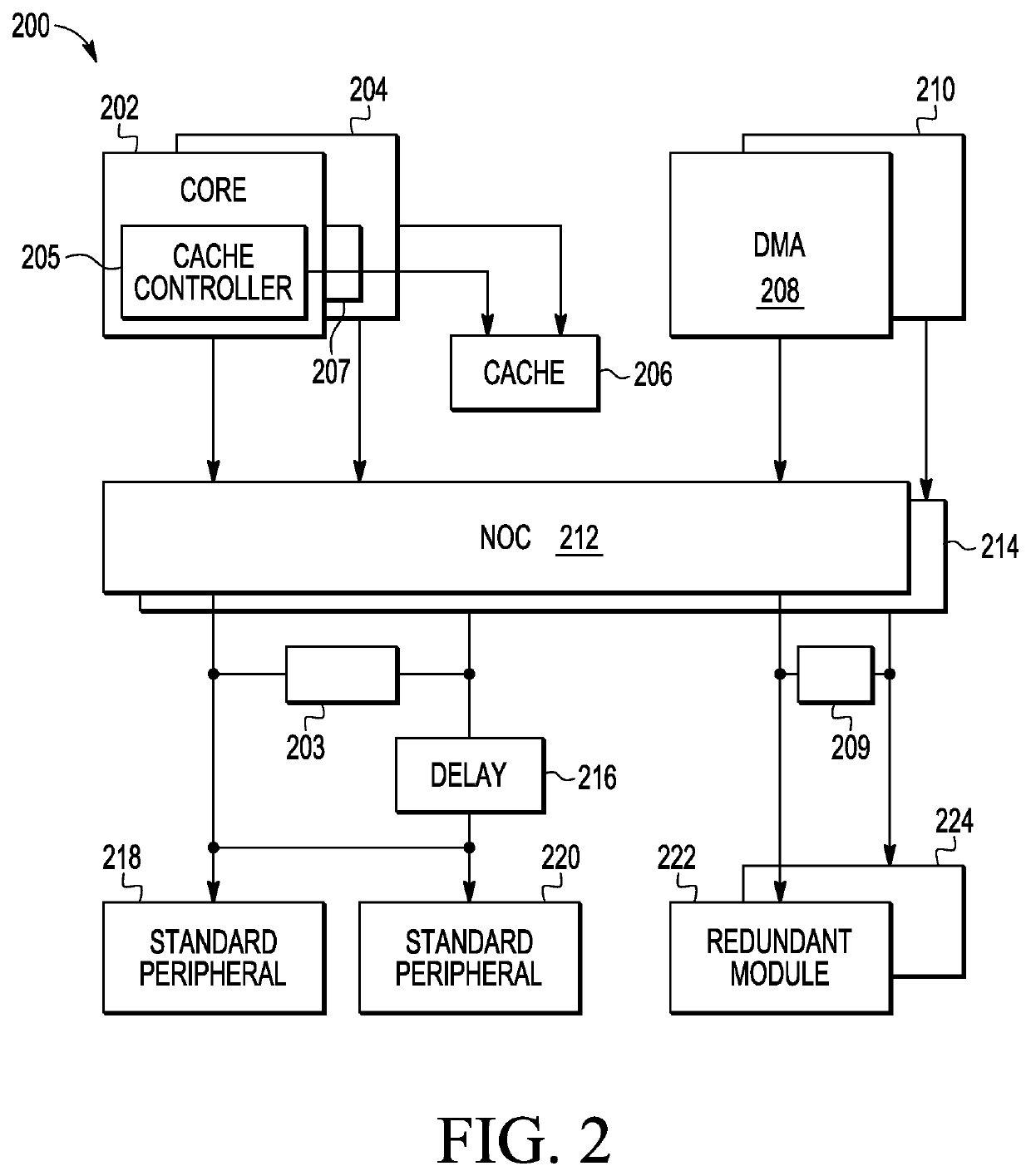

ActiveUS10761925B2Non-redundant fault processingFault response safety measuresLockstepComputer architecture

In at least one embodiment of the disclosure, a method includes detecting an error in a local memory shared by redundant computing modules executing in delayed lockstep. The method includes pausing execution in the redundant computing modules and handling the error of the local memory. The method includes resuming execution in delayed lockstep of the redundant computing modules in response to the handling of the error.

Owner:NXP USA INC

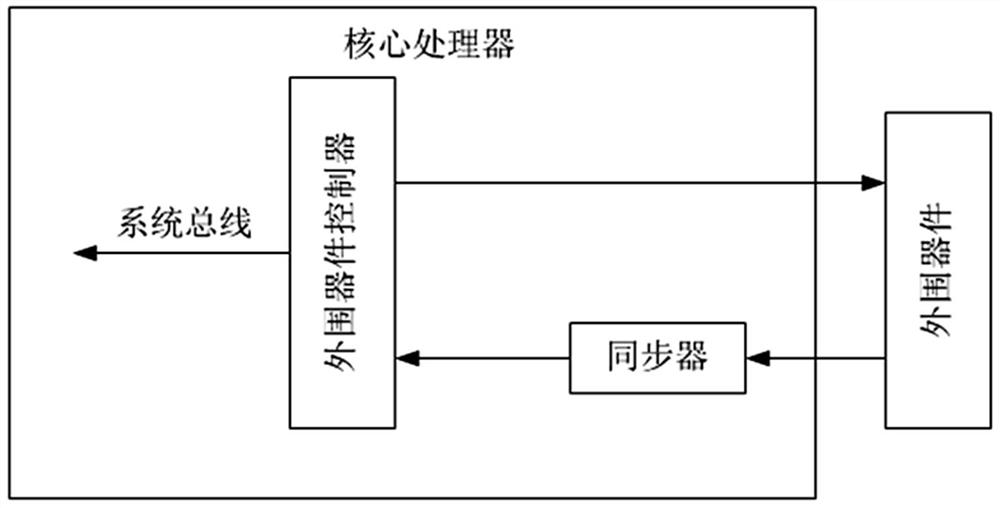

In-loop dual backup system

ActiveCN111930572AImprove fault diagnosis rateReduce the risk of common cause failureRedundant operation error correctionLockstepDual core

The invention discloses an in-loop dual-backup system. Two peripheral device controllers and two peripheral device structures are adopted; the two peripheral device controllers work in a dual-core lock step mode; the peripheral devices are respectively controlled by different peripheral device controllers; and one of the peripheral devices negates the written data according to bits. According to the in-loop dual-backup system, the dual-backup peripheral device is seamlessly connected to the loop of the dual-core lockstep peripheral device controller, so that the fault diagnosis rate of peripheral device access is greatly improved, and meanwhile, due to the isomerism of data stored in the peripheral device, the risk of common cause failure is greatly reduced.

Owner:NANJING SEMIDRIVE TECH CO LTD

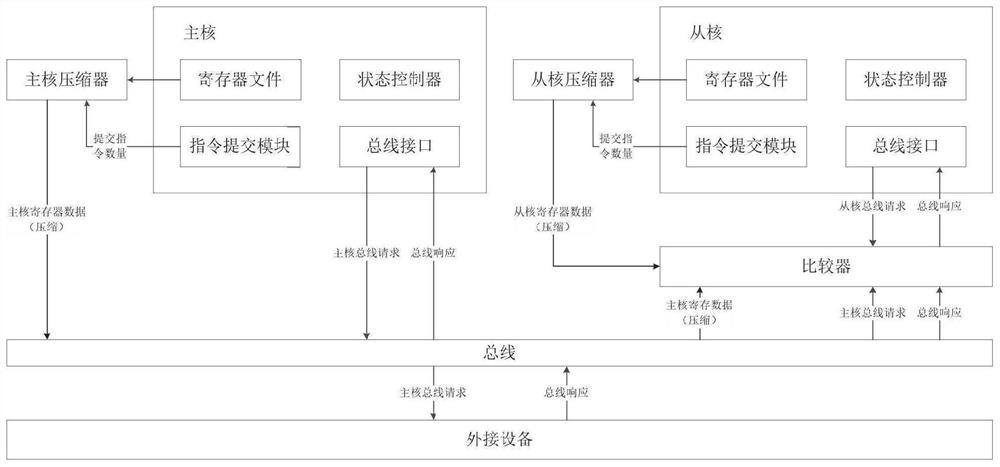

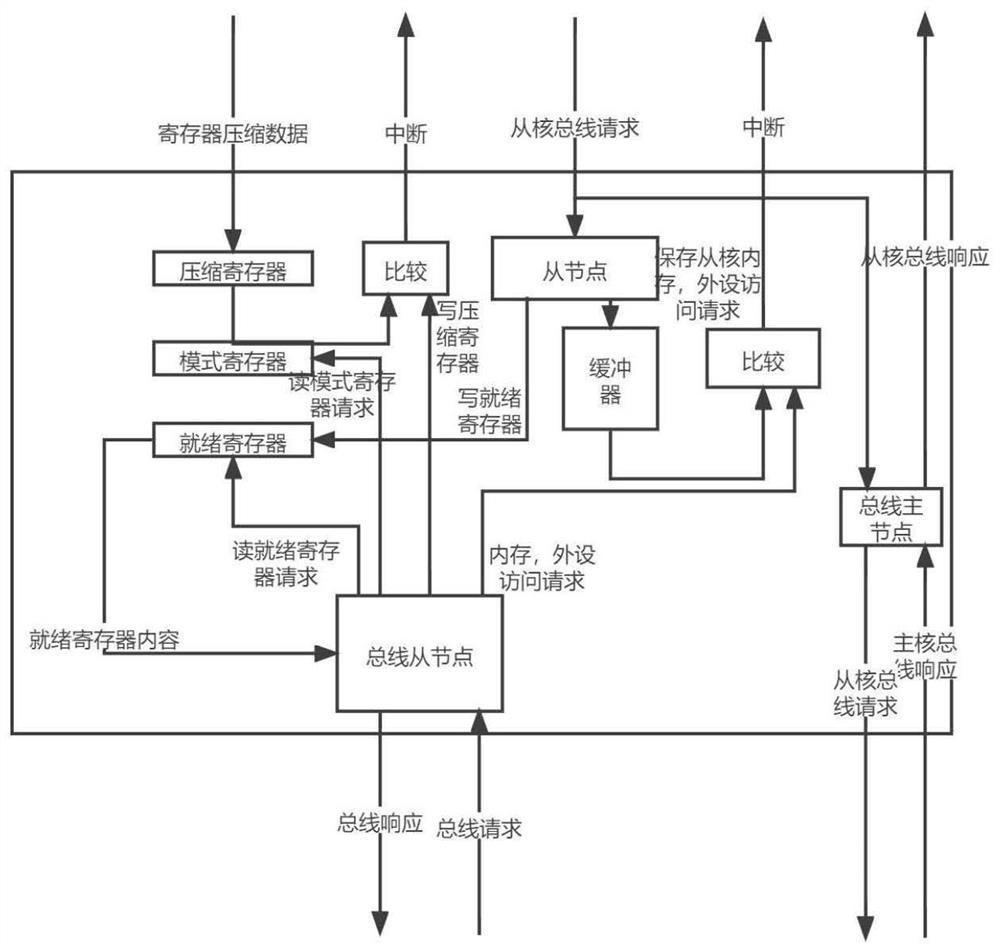

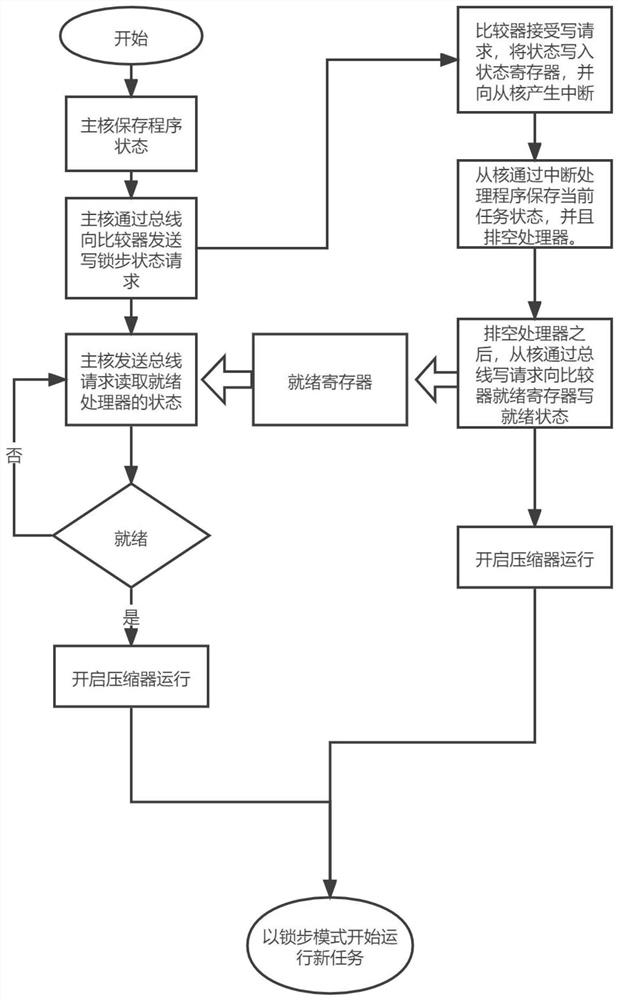

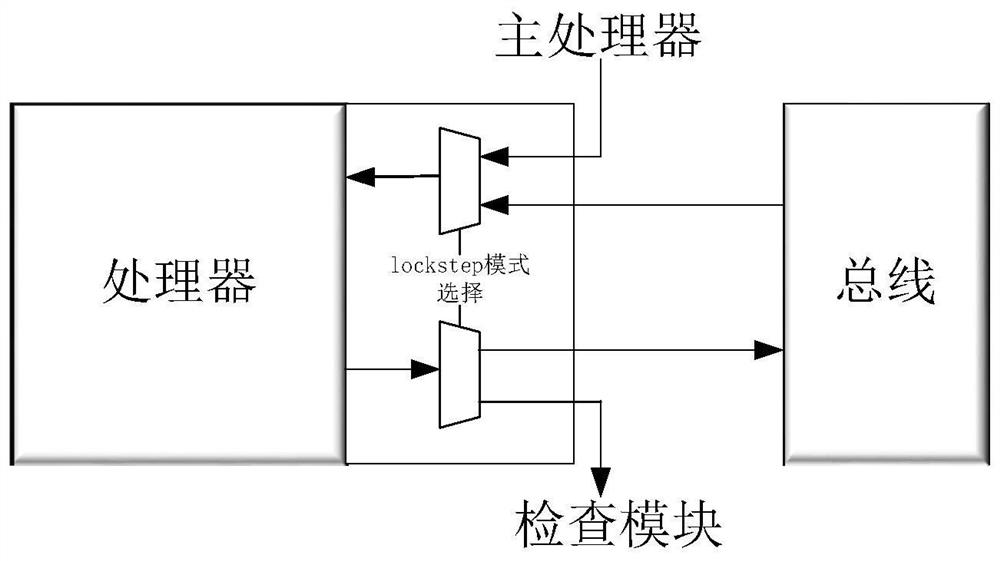

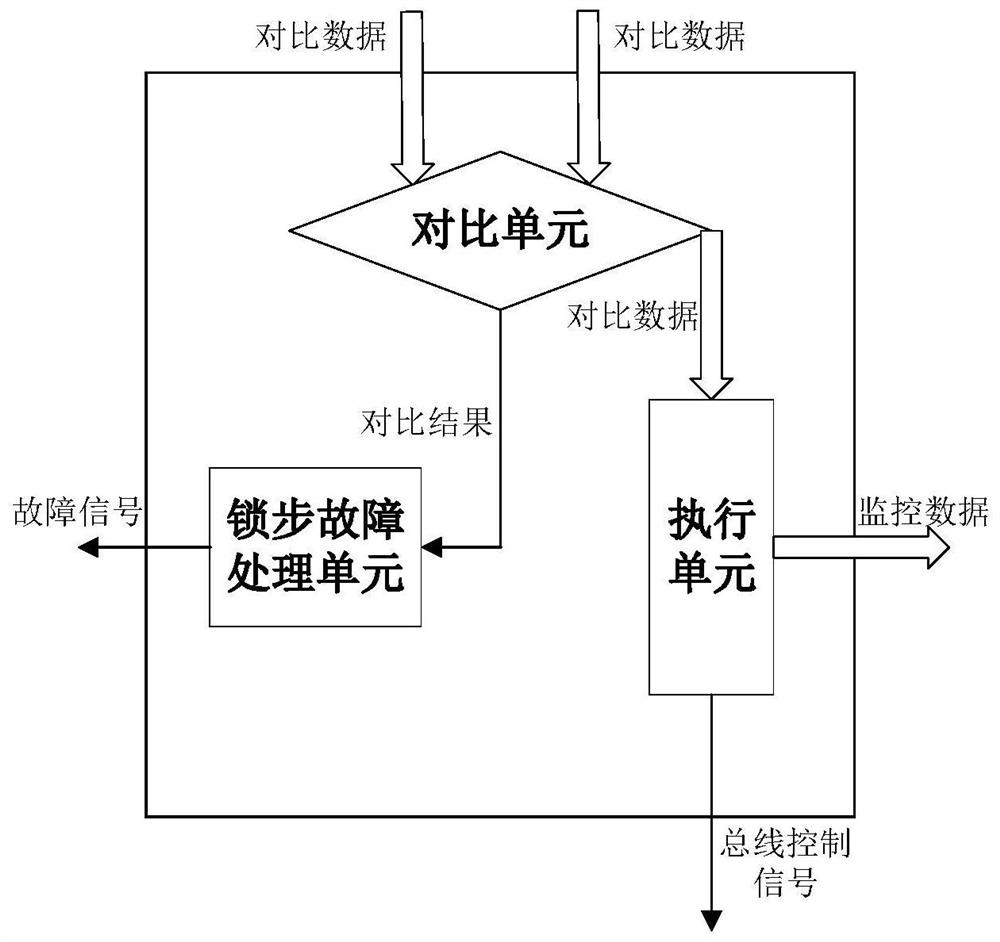

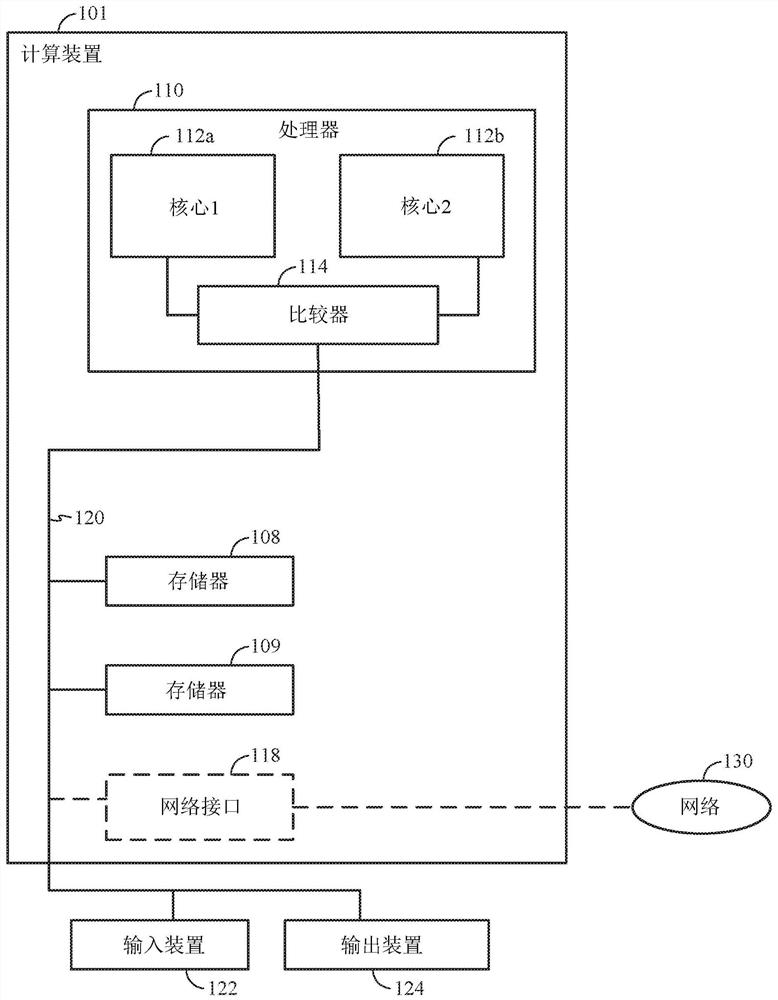

Microprocessor architecture and microprocessor fault detection method

The invention provides a microprocessor architecture which comprises a master core, a slave core, a bus and a comparator, the master core and the comparator are respectively in communication connection with the bus, and the slave core is in communication connection with the comparator; when the microprocessor is in a lockstep mode, the comparator blocks an access request of the slave core to the bus, the master core and the slave core both execute a master core task, and the comparator compares master core operation data of the master core with slave core operation data of the slave core so as to perform fault detection on the execution state of the master core task. The microprocessor fault detection method comprises the steps that the operation mode of the microprocessor is set according to the task requirement, and the operation mode comprises the lockstep mode and the non-lockstep mode; and if the microprocessor is in a lock step mode, the master core and the slave core both execute the master core task, and the master core operation data of the master core is compared with the slave core operation data of the slave core to perform fault detection on the execution state of the master core task.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

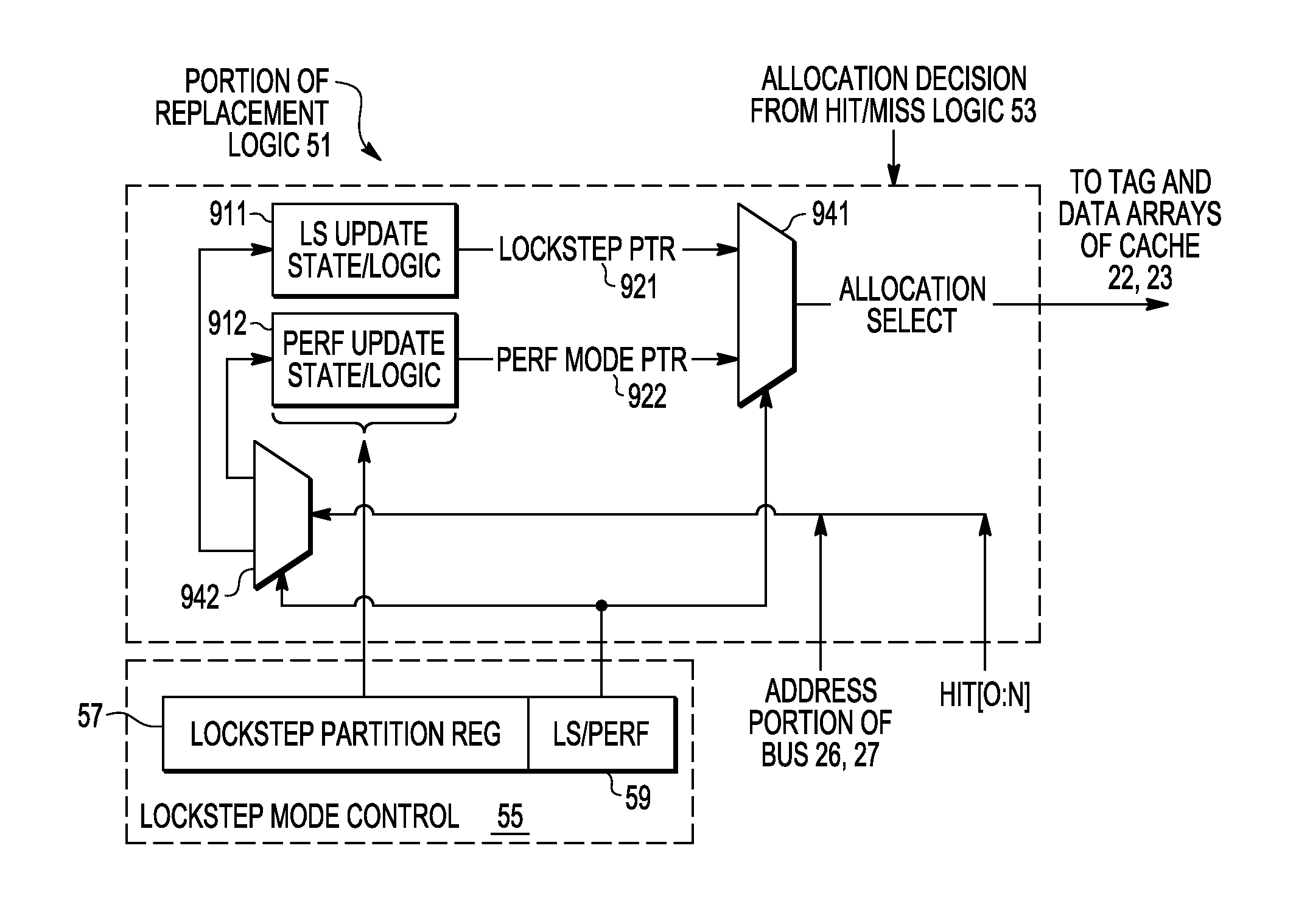

Dynamic lockstep cache memory replacement logic

ActiveUS9208036B2Memory architecture accessing/allocationMemory adressing/allocation/relocationLockstepTheoretical computer science

Owner:NXP USA INC

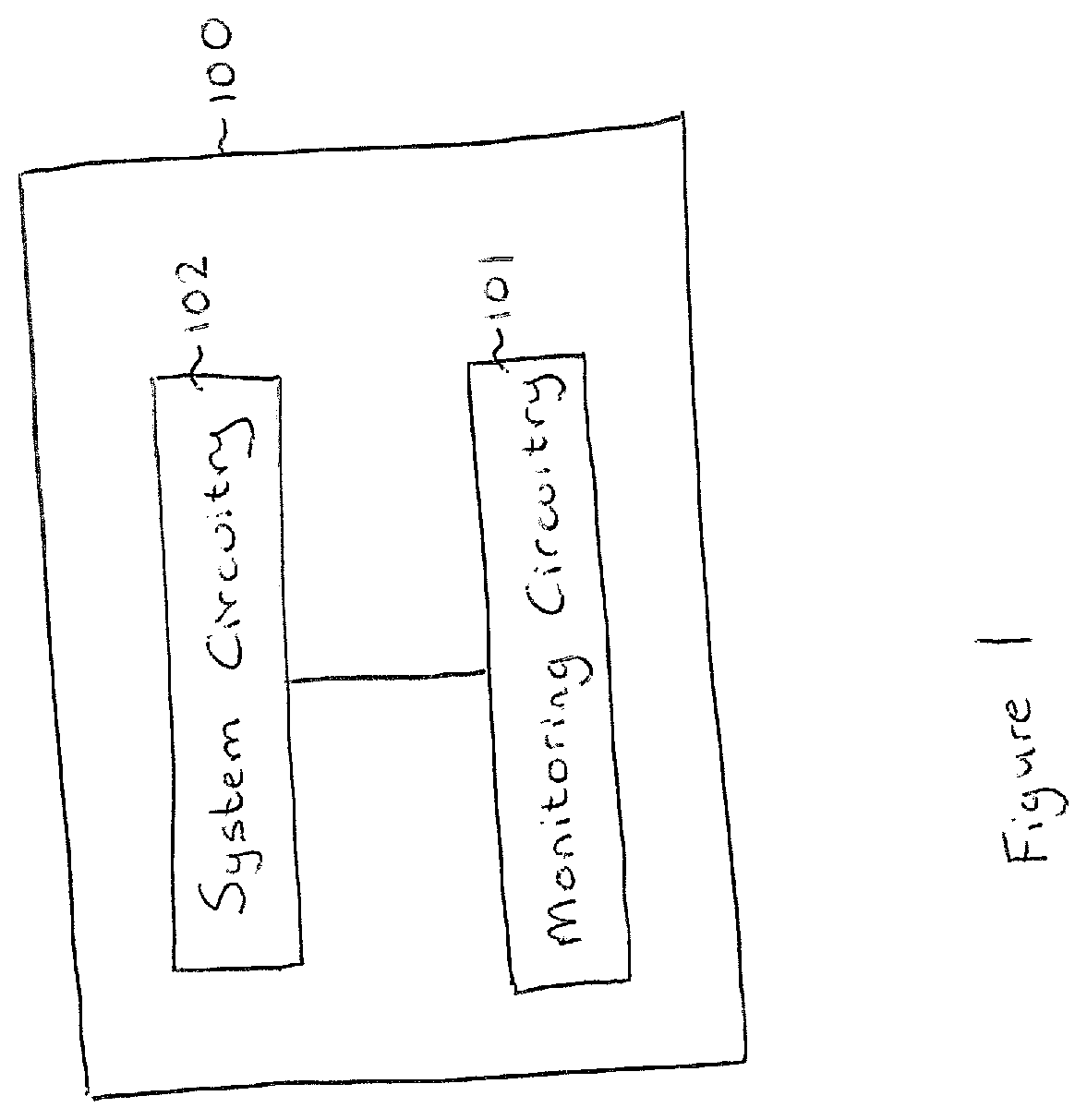

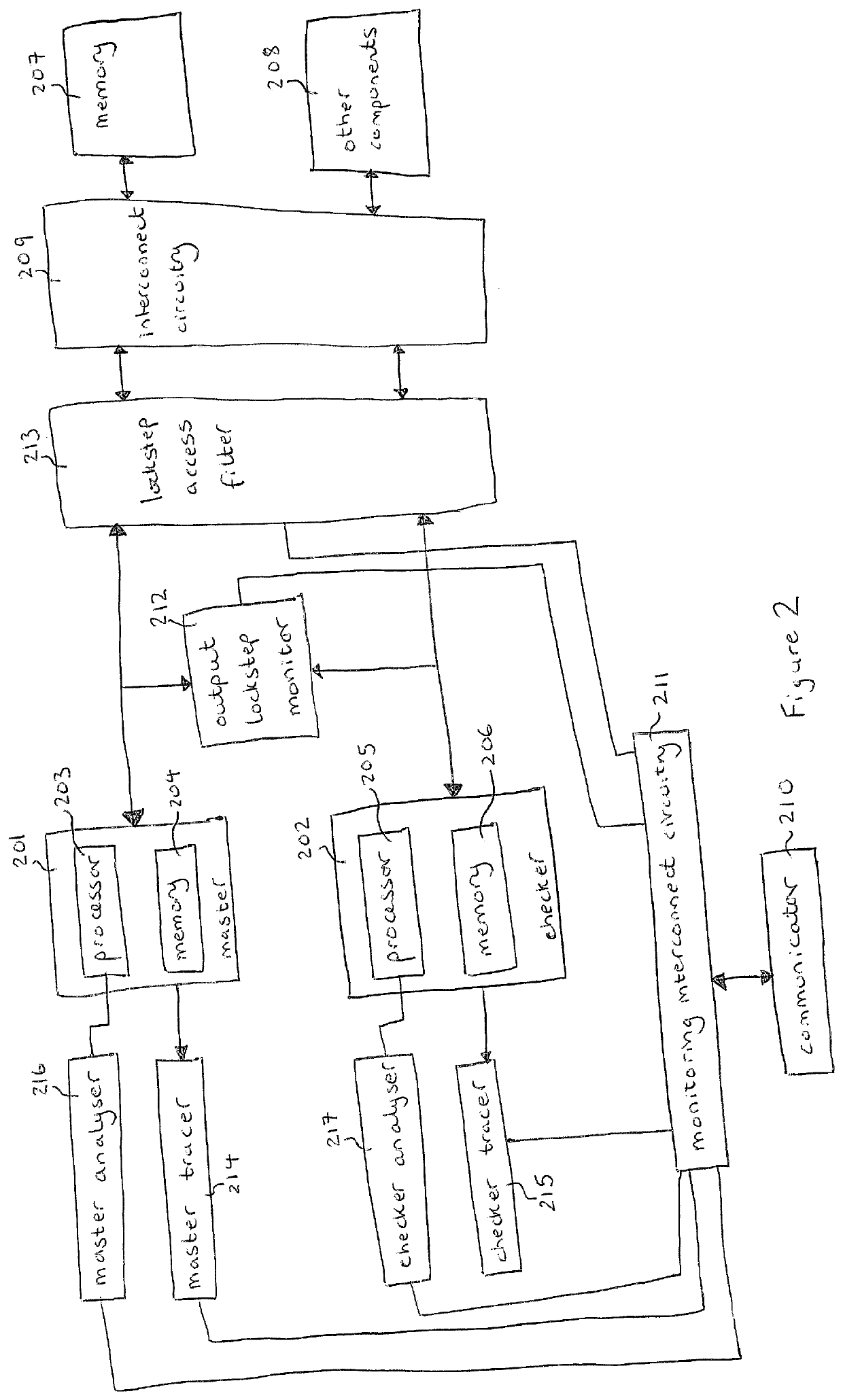

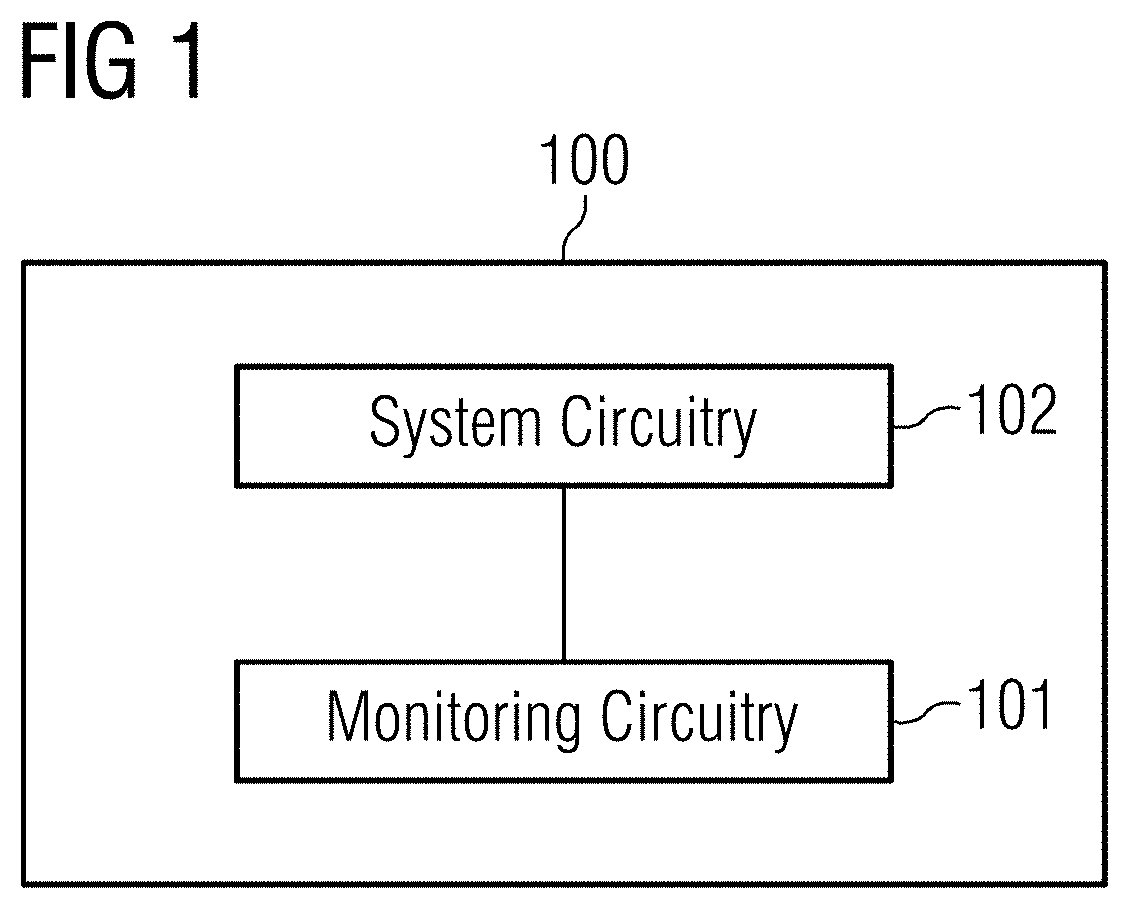

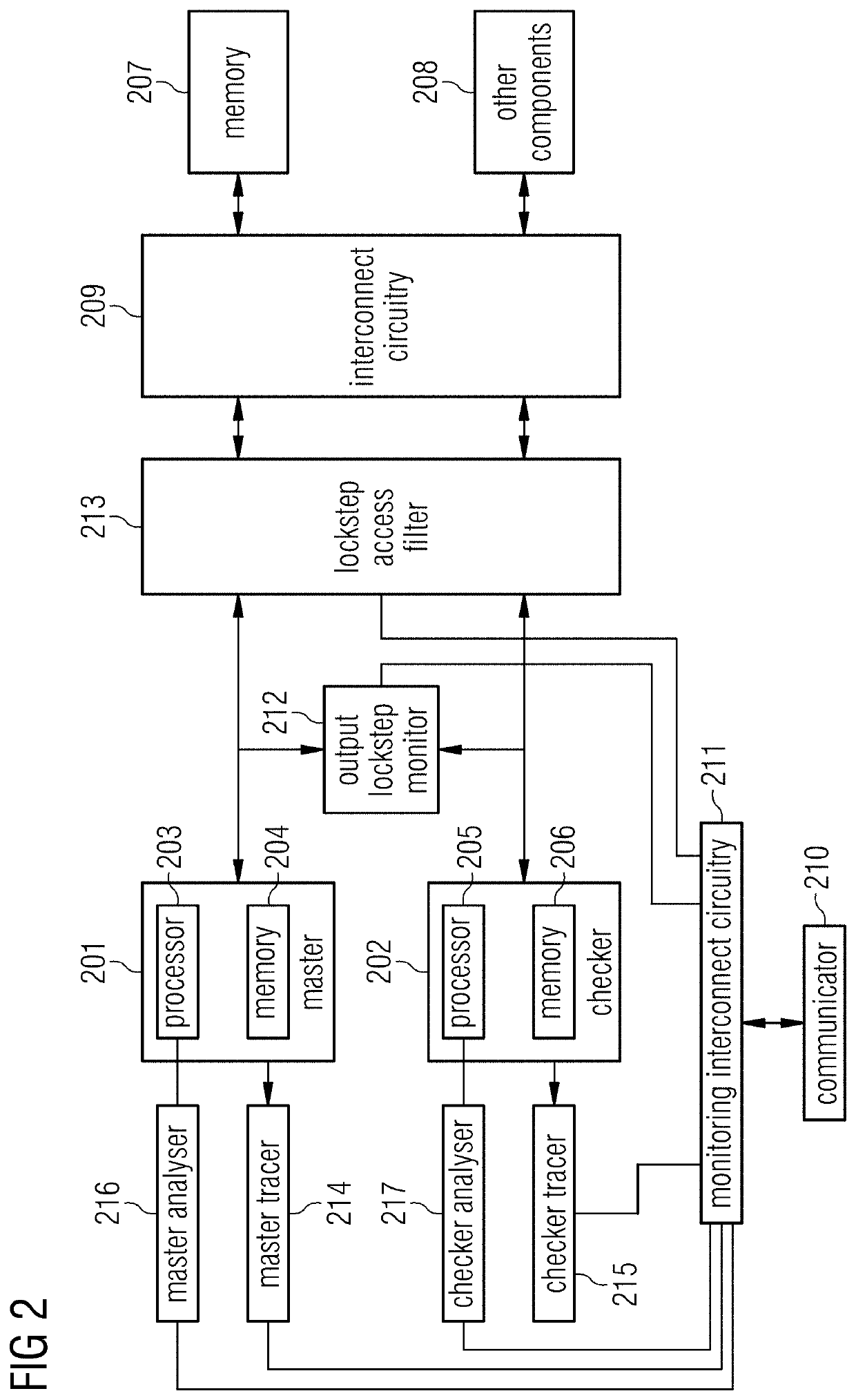

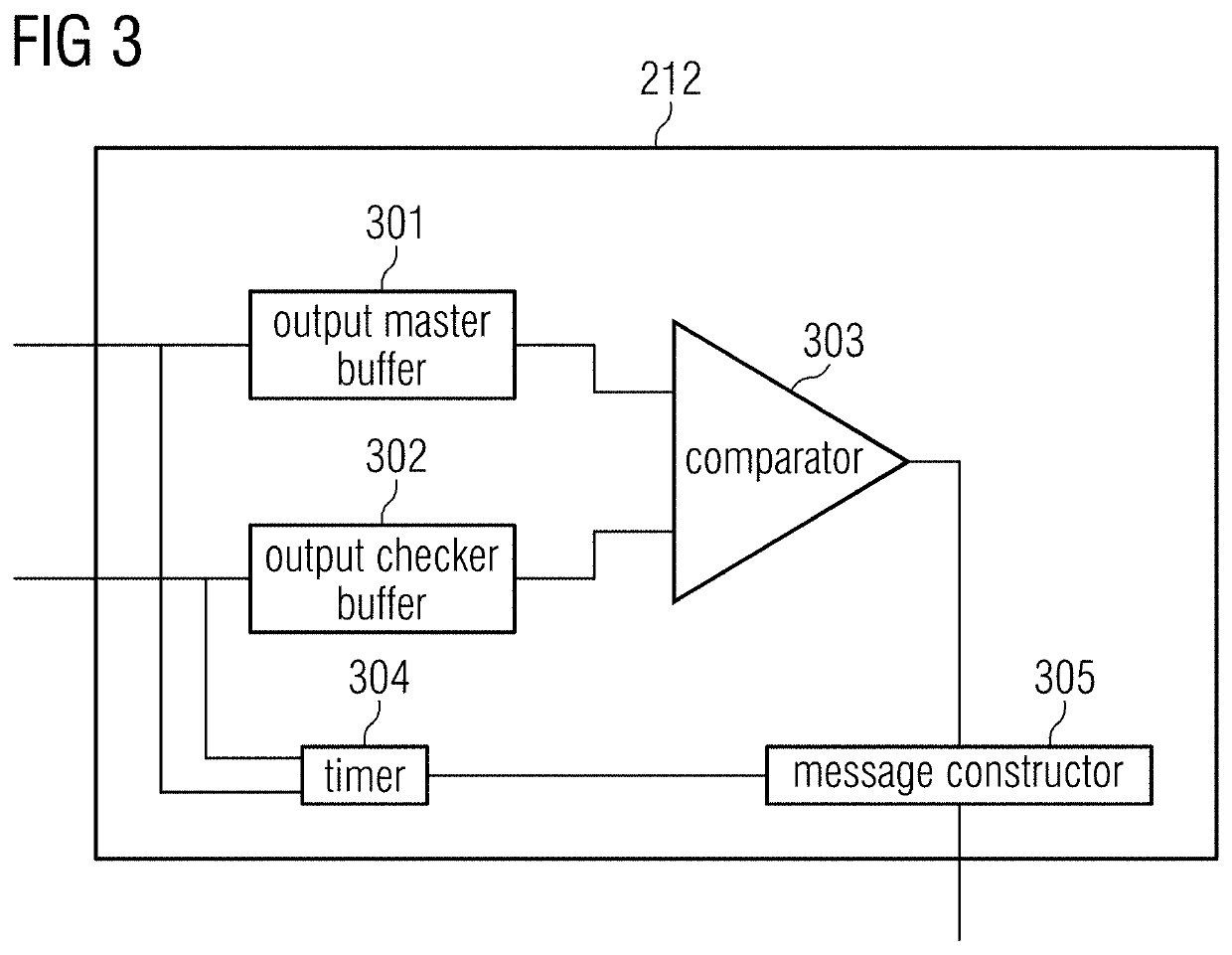

Monitoring Processors Operating in Lockstep

An integrated circuit (IC) chip includes system circuitry having system memory, and a master processor and a checker processor configured to operate in lockstep; and monitoring circuitry comprising an internal lockstep monitor, a master tracer and a checker tracer. The internal lockstep monitor is configured to: observe states of internal signals of the master processor and the checker processor, compare corresponding observed states of the master processor and the checker processor, and if the corresponding observed states differ: trigger the master tracer to output stored master trace data recorded from the output of the master processor, and trigger the checker tracer to output stored checker trace data recorded from the output of the checker processor.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

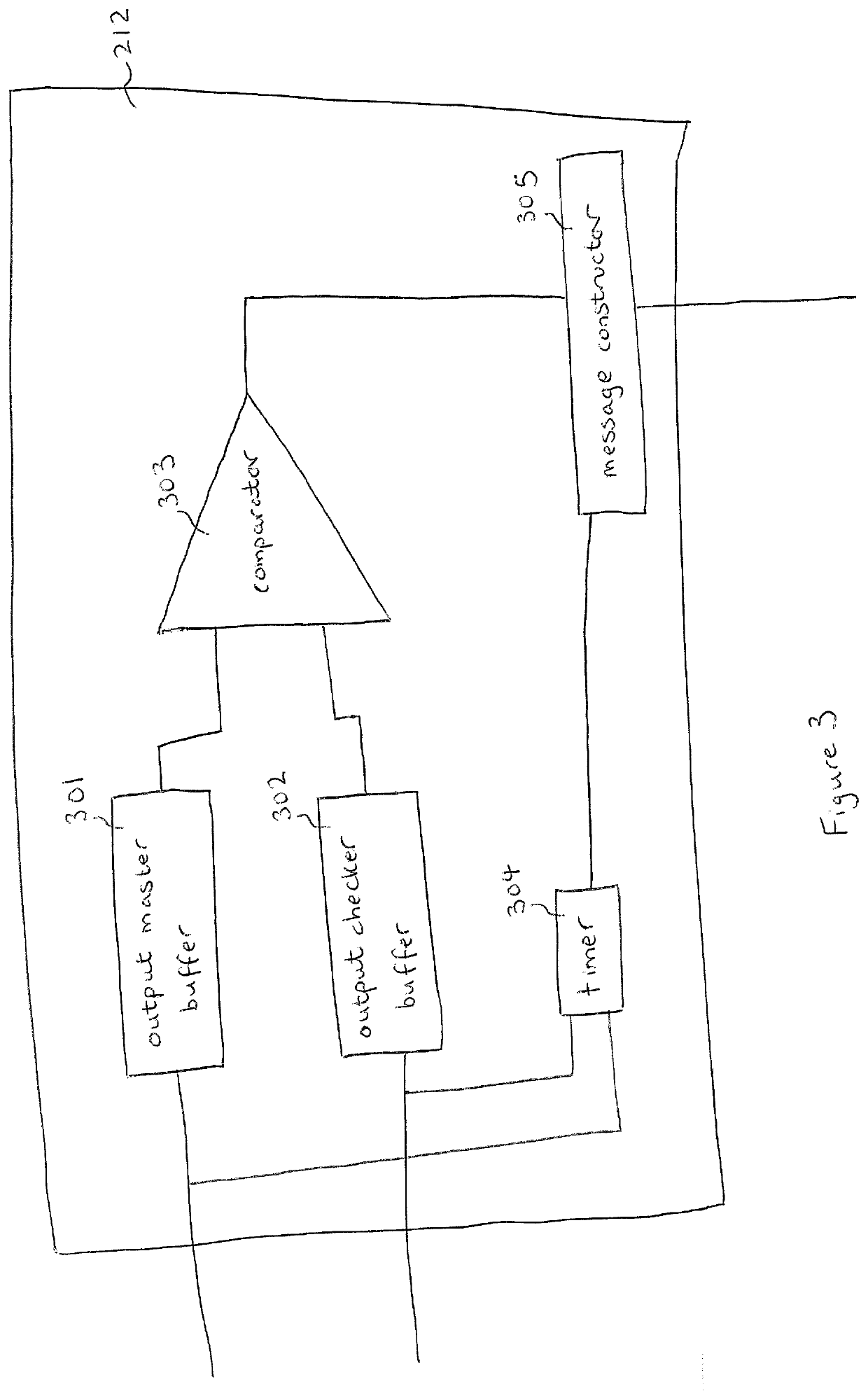

Monitoring processors operating in lockstep

An integrated circuit (IC) chip includes system circuitry having system memory, and a master processor and a checker processor configured to operate in lockstep; and monitoring circuitry comprising an internal lockstep monitor, a master tracer and a checker tracer. The internal lockstep monitor is configured to: observe states of internal signals of the master processor and the checker processor, compare corresponding observed states of the master processor and the checker processor, and if the corresponding observed states differ: trigger the master tracer to output stored master trace data recorded from the output of the master processor, and trigger the checker tracer to output stored checker trace data recorded from the output of the checker processor.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Method and apparatus for managing mismatches within a multi-threaded lockstep processing system

A processing system comprising a first processing domain and a second processing domain. Each of the first processing domain and the second processing domain comprises a multi-threaded processor core arranged to output a set of internal state signals representative of current states of internal components of the respective processor core. The processing system further comprises a supervisor component arranged to receive the sets of internal state signals output by the processor cores of the first and second processing domains, compare internal state signals output by the processor core of the first processing domain to corresponding internal state signals output by the processor core of the second processing domain, and upon detection of a mismatch between compared internal state signals to initiate a reset of a thread under the execution of which the detected mismatch of internal state signals occurred.

Owner:NXP USA INC

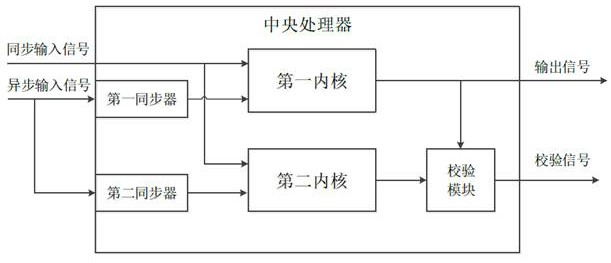

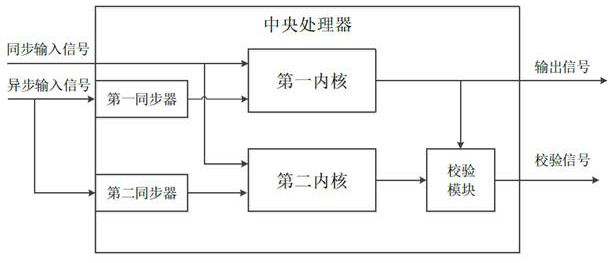

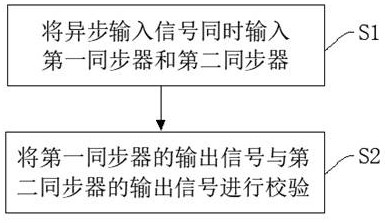

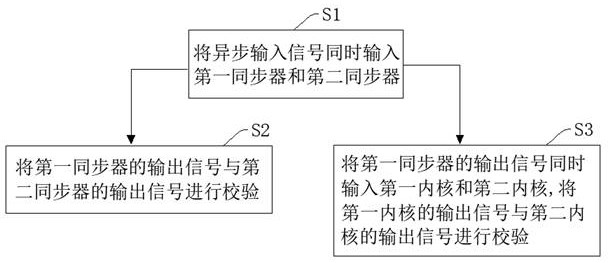

Asynchronous input signal synchronization method and device, central processing unit and chip

ActiveCN113253796AFix bugs with false warningsEffective awarenessGenerating/distributing signalsSynchronizerLockstep

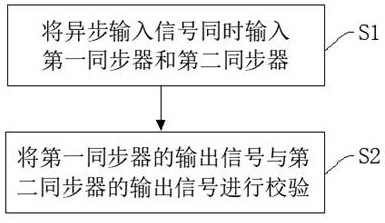

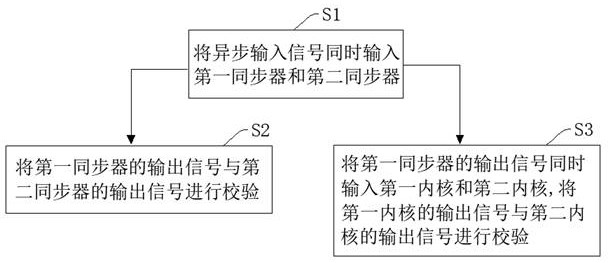

The invention relates to the field of chips, and provides an asynchronous input signal synchronization method and device, a central processing unit and a chip. The asynchronous input signal synchronization method is used for a dual-core lockstep system, the dual-core lockstep system comprises a first core and a second core, and the method comprises the following steps: inputting asynchronous input signals into a first synchronizer and a second synchronizer at the same time; and verifying the output signal of the first synchronizer and the output signal of the second synchronizer. The two synchronizers are adopted for comparison detection, the fault of any synchronizer can be captured according to the comparison verification result information of the output signals of the two synchronizers, and the safety and reliability of the dual-core lockstep system are guaranteed.

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +1

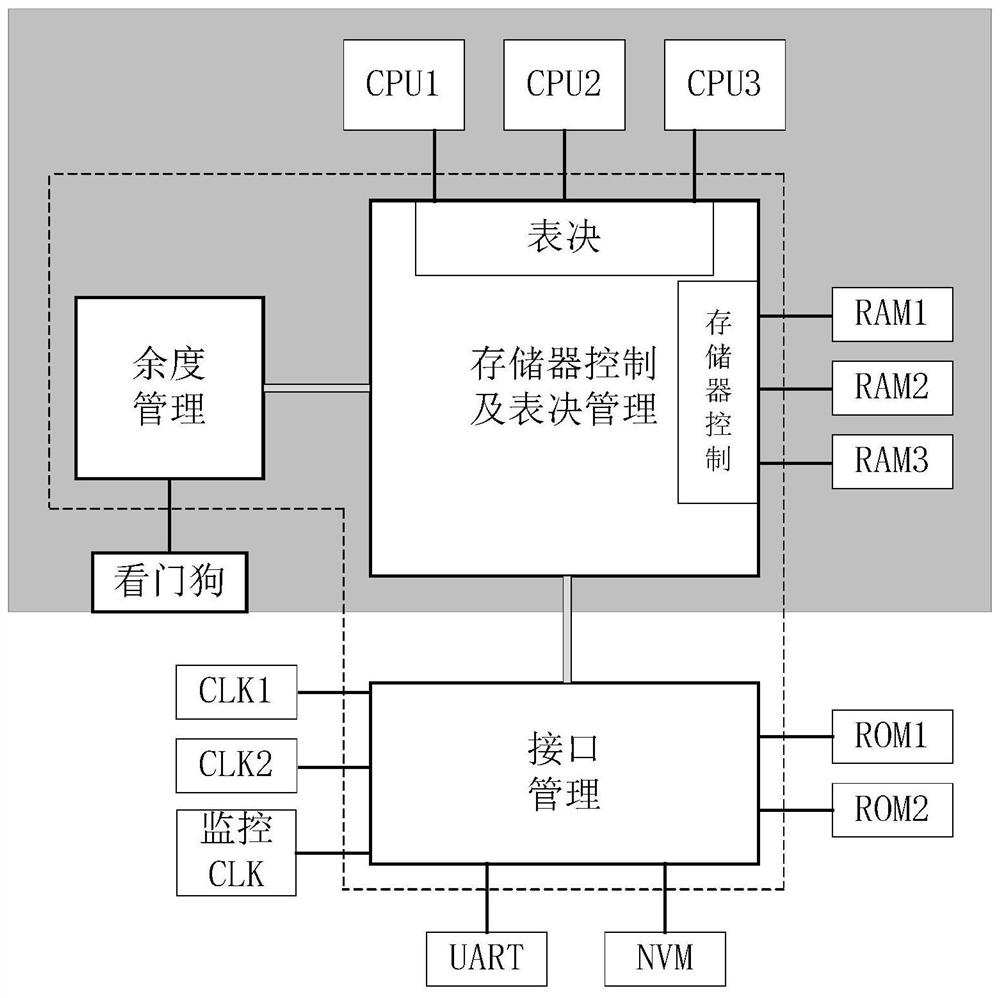

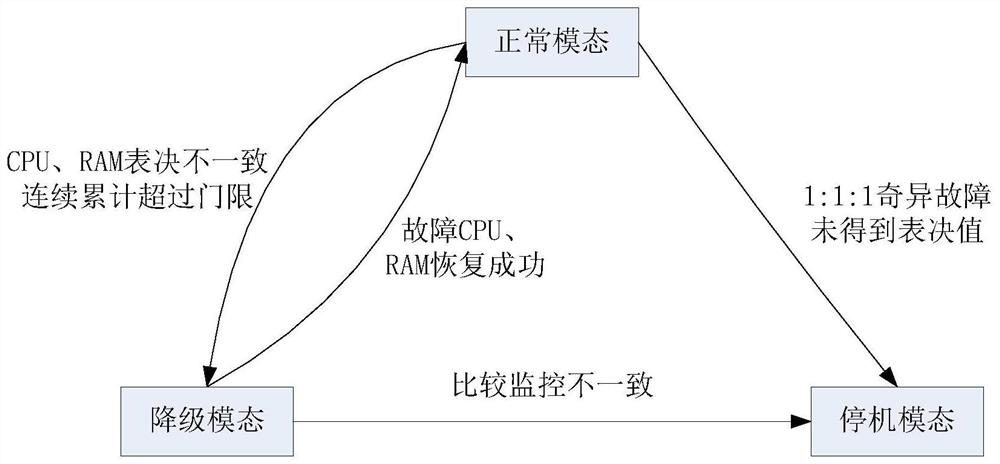

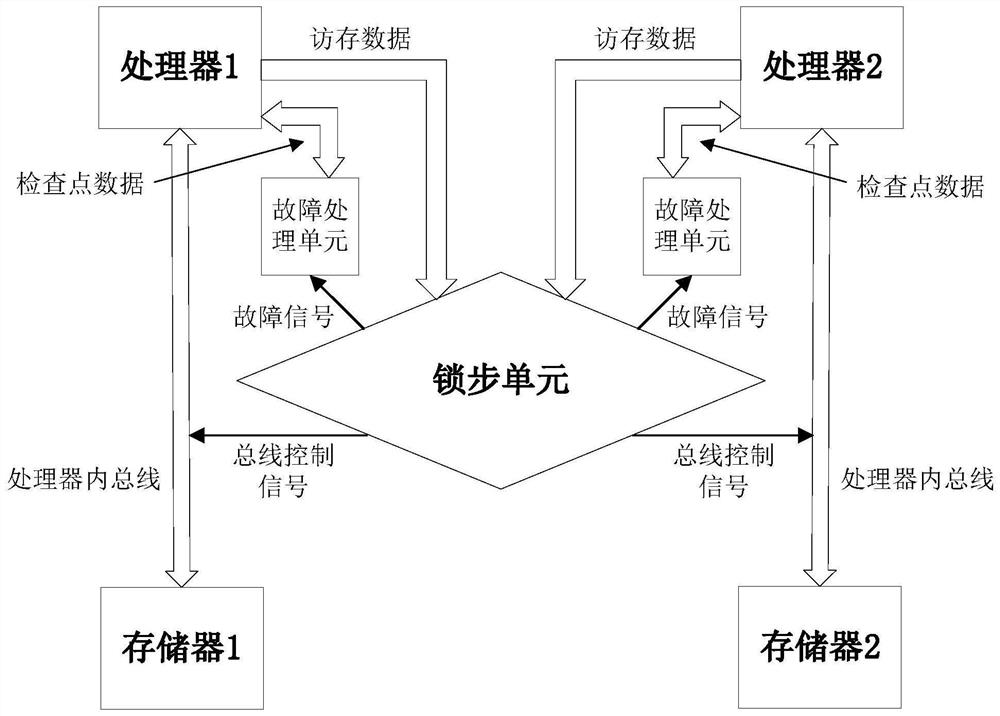

An error recovery method for multiprocessor chips based on three-mode lockstep

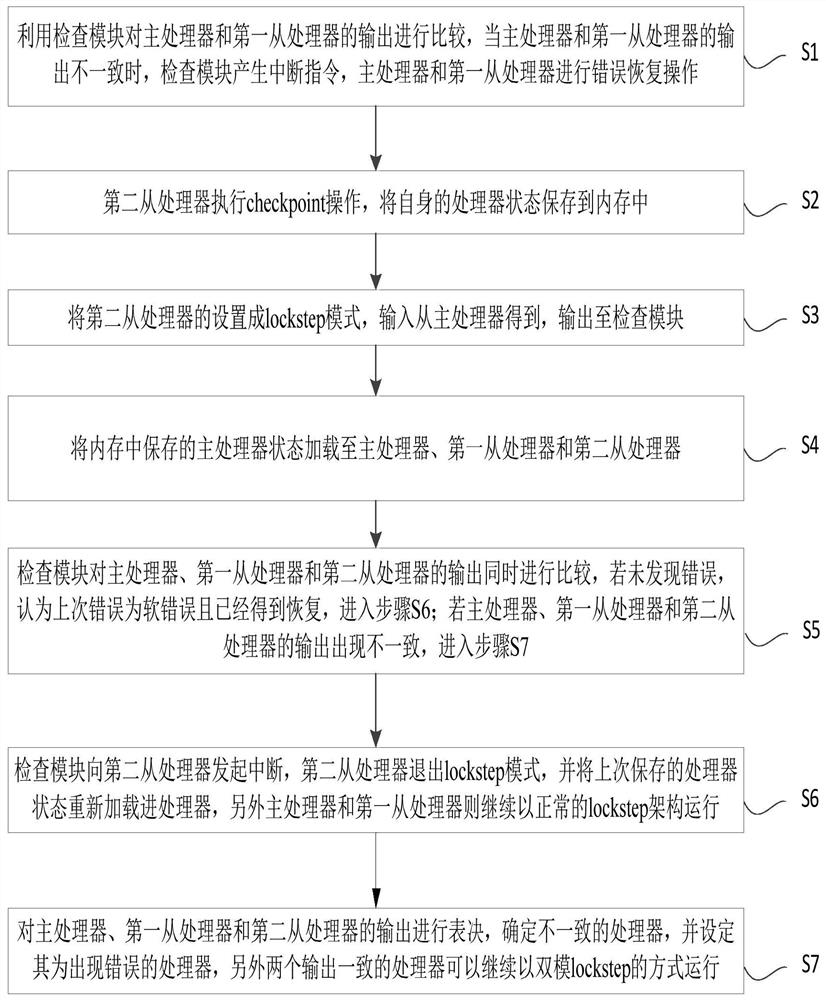

ActiveCN112506701BQuick checkImprove reliabilityResource allocationRedundant operation error correctionLockstepDual core

The invention discloses a multi-processor chip error recovery method based on three-mode lockstep. The dual-core lockstep structure based on checkpoint rollback error recovery can quickly check out the wrong CPU through the second slave processor, and can also be performed through subsequent operations. It has a certain ability to detect CPU hard errors, greatly improves the reliability and real-time performance of processor error handling, and at the same time reduces the resource consumption of the three-mode lockstep.

Owner:FOSHAN POWER SUPPLY BUREAU GUANGDONG POWER GRID

Synchronization method and device for asynchronous input signal, central processing unit, chip

The invention relates to the field of chips, and provides a synchronization method and device for an asynchronous input signal, a central processing unit, and a chip. The method for synchronizing the asynchronous input signal is used in a dual-core lockstep system, the dual-core lockstep system includes a first core and a second core, and the method includes: simultaneously inputting the asynchronous input signal into the first synchronizer and the second synchronizer ; Checking the output signal of the first synchronizer and the output signal of the second synchronizer. The present invention uses two synchronizers for comparative detection, and can capture the failure of any synchronizer according to the comparison verification result information of the output signals of the two synchronizers, thereby ensuring the safety and reliability of the dual-core lockstep system.

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +1

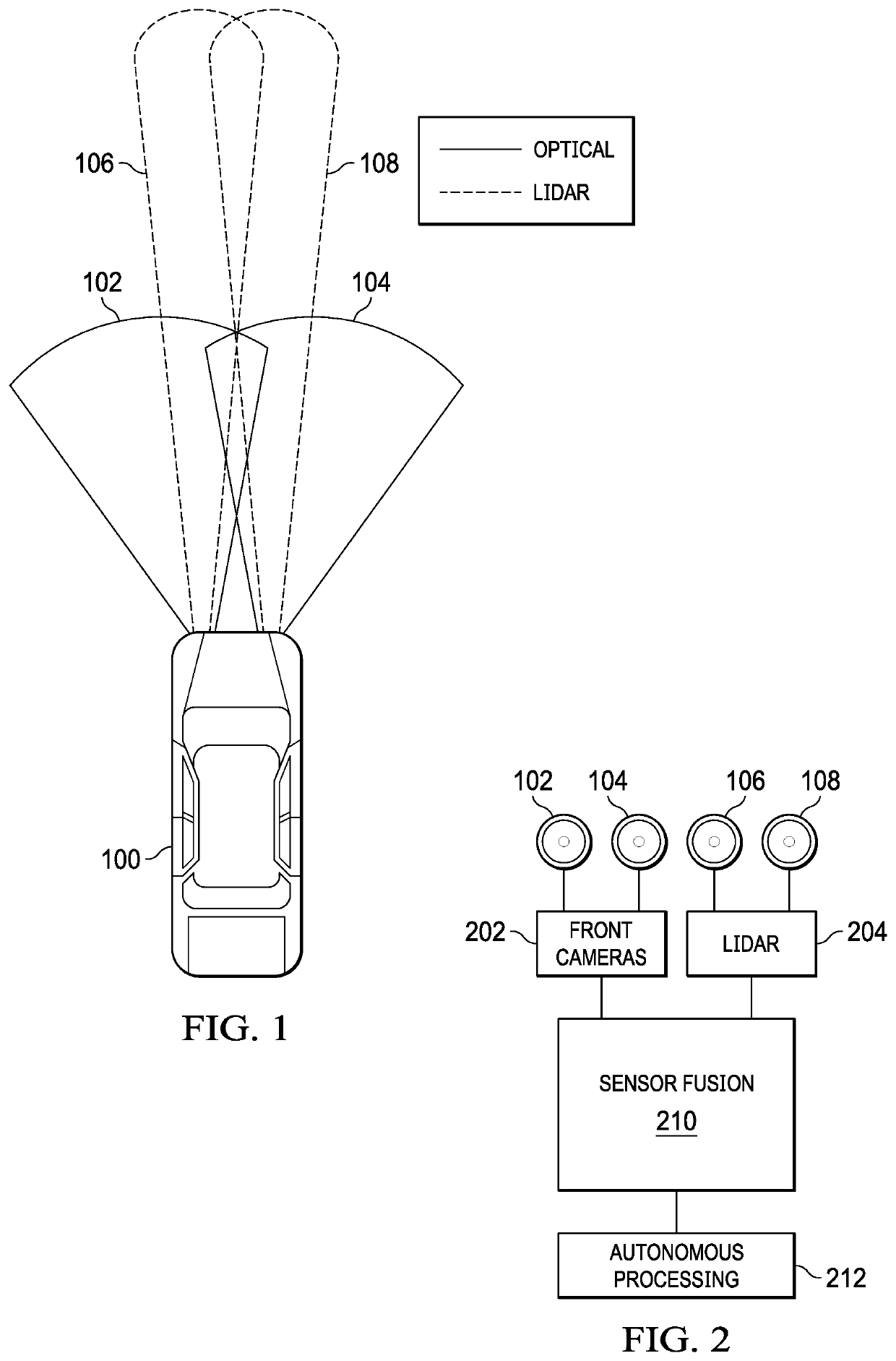

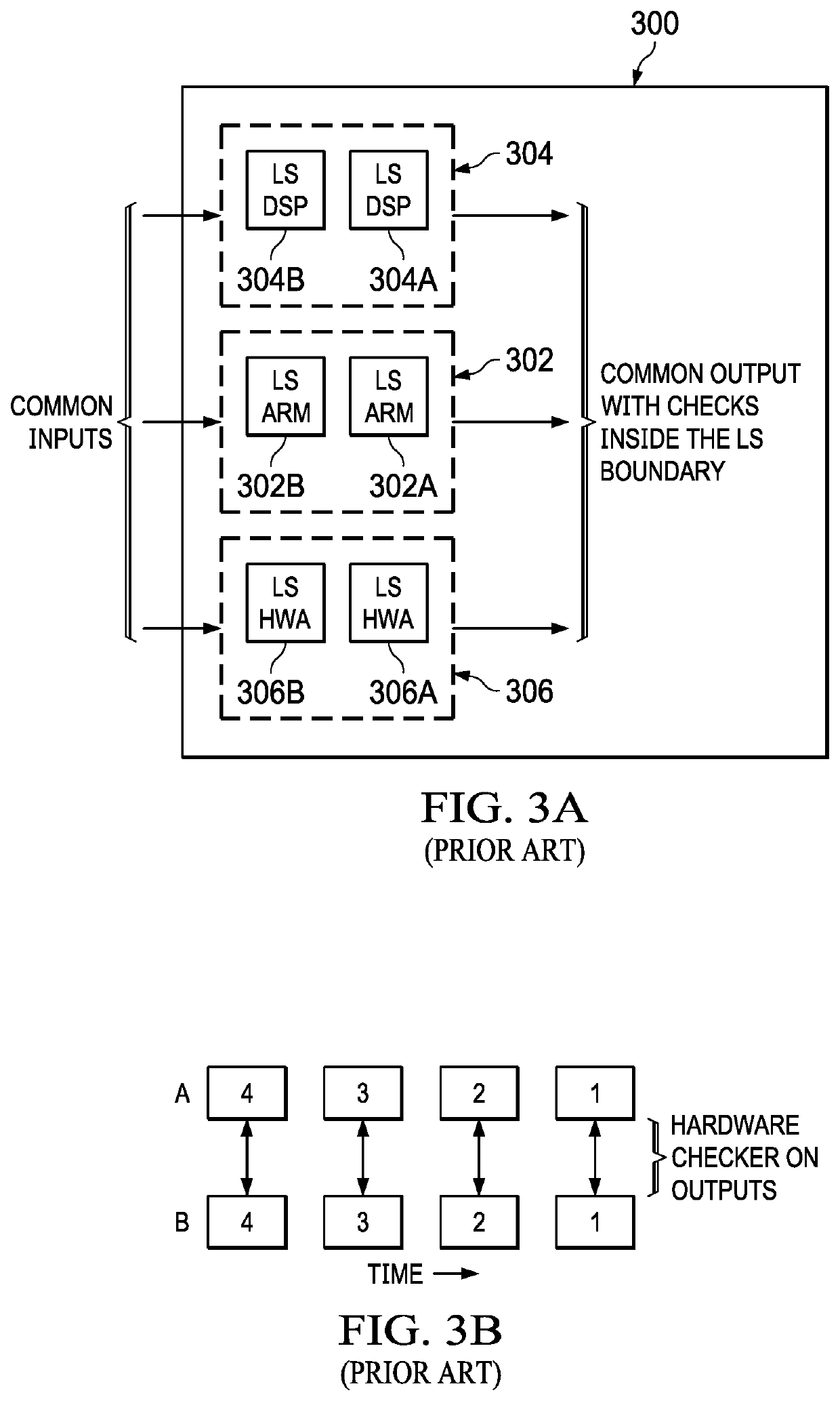

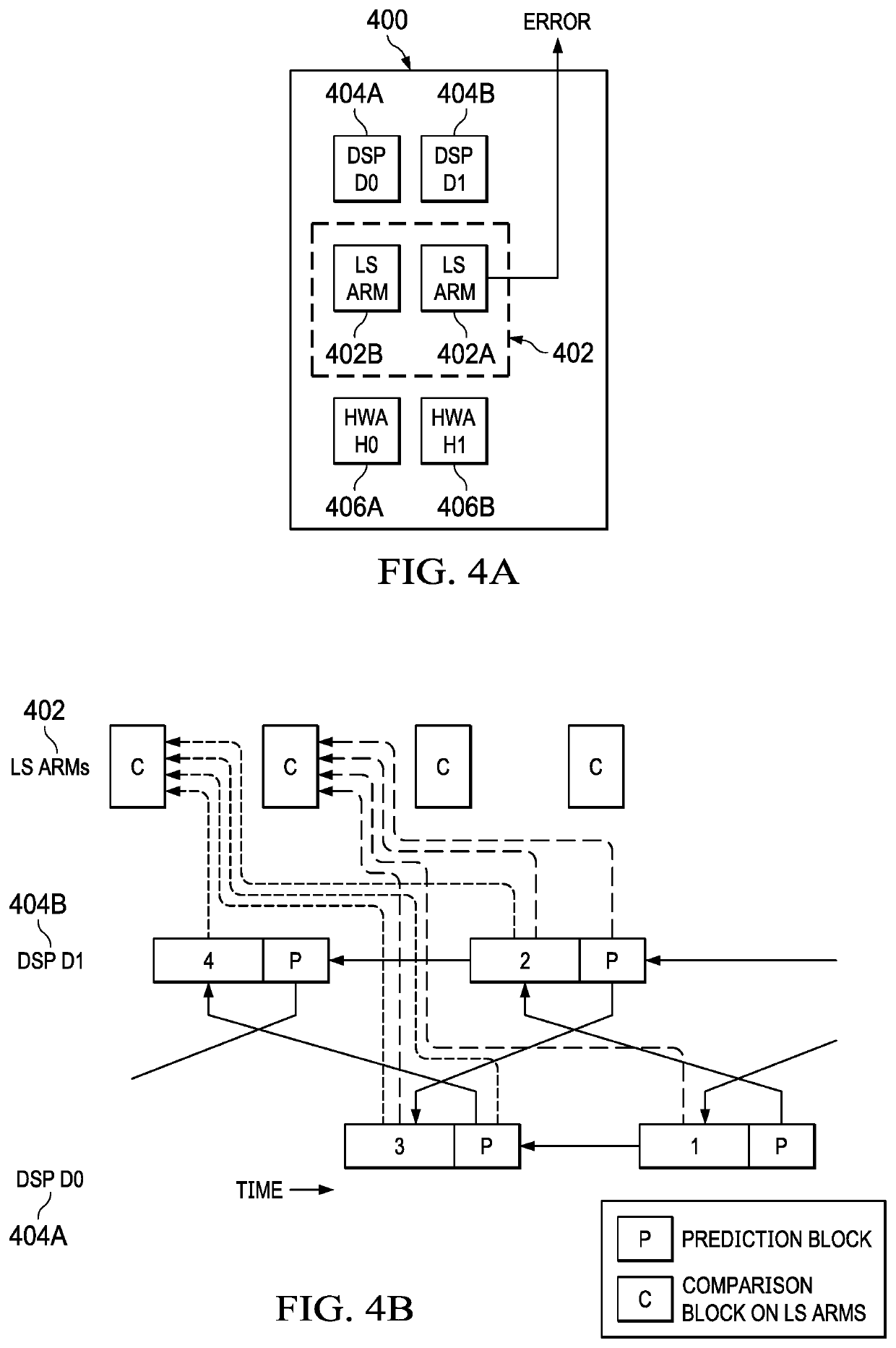

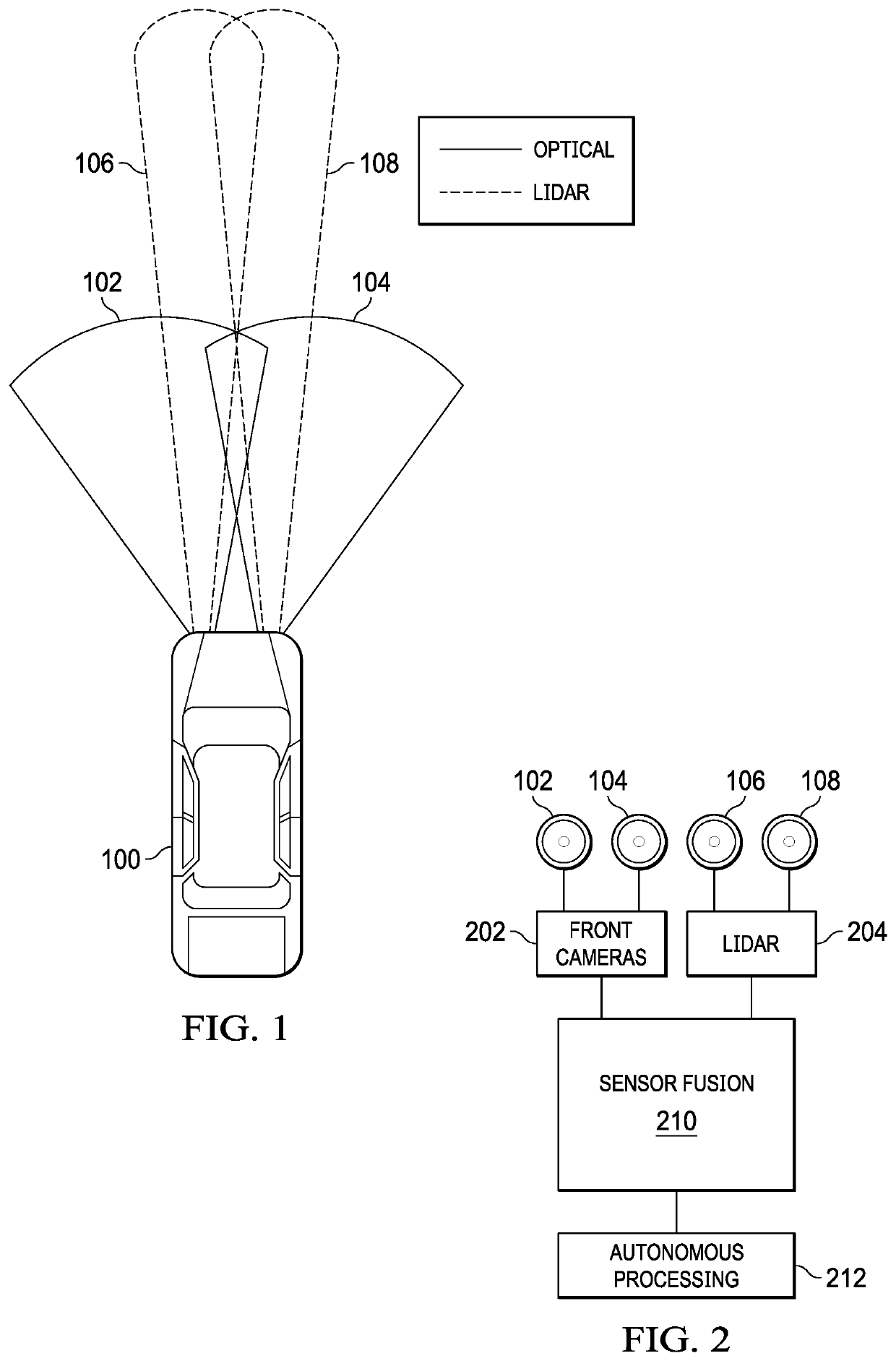

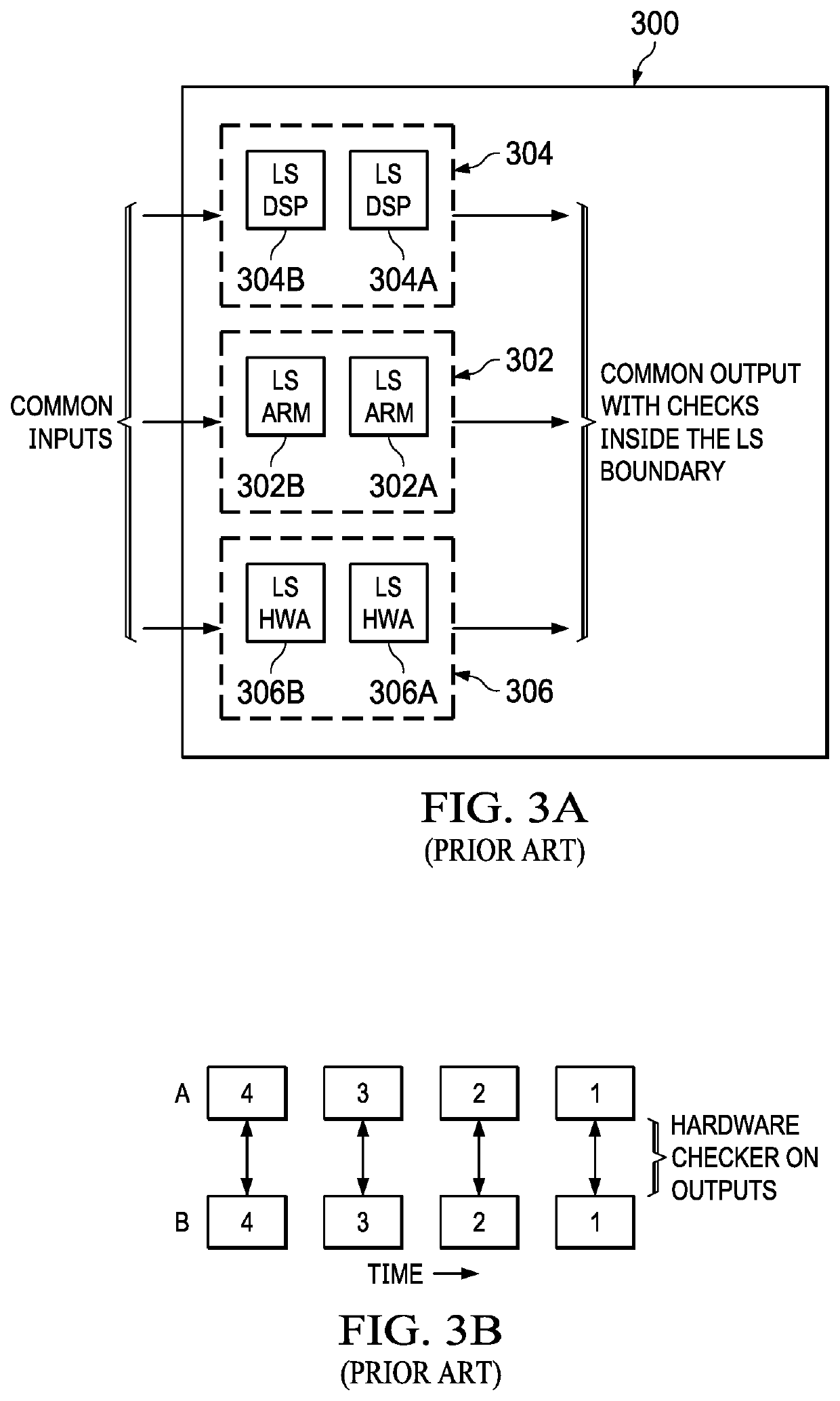

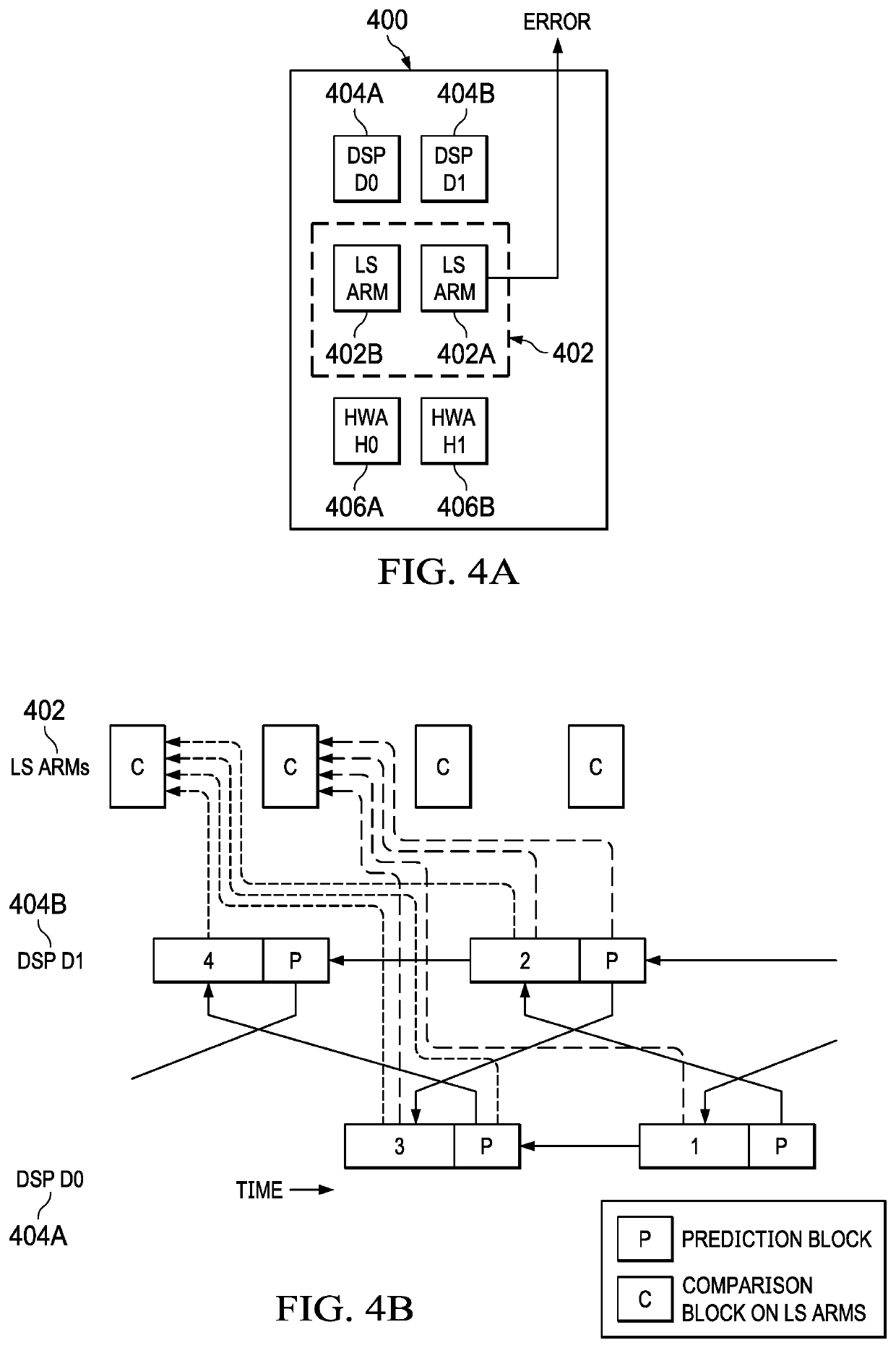

Alternating frame processing operation with predicted frame comparisons for high safety level use

ActiveUS11172219B2Improve securityLarge capacityError detection/correctionDigital computer detailsLockstepImage flow

Frames from an image stream or streams are processed by independently operating digital signal processors (DSPs), with only frame checking microprocessors operating in a lockstep mode. In one example, two DSP are operating on alternate frames. Each DSP processes the frames and produces prediction values for the next frame. The lockstep microprocessors develop their own next frame prediction. The lockstep processors compare issued frames and previously developed predicted frames for consistency. If the predictions are close enough, the issued frame passes the test. The lockstep processors then compare the issued frame to the preceding two frames for a similar consistency check. If the prior frames are also close enough, the issued frame is acceptable. In another example, hardware checkers are provided to compare the present frame with a larger number of prior frames. The hardware checkers provide comparison results to the lockstep processors to compare against allowable variation limits.

Owner:TEXAS INSTR INC

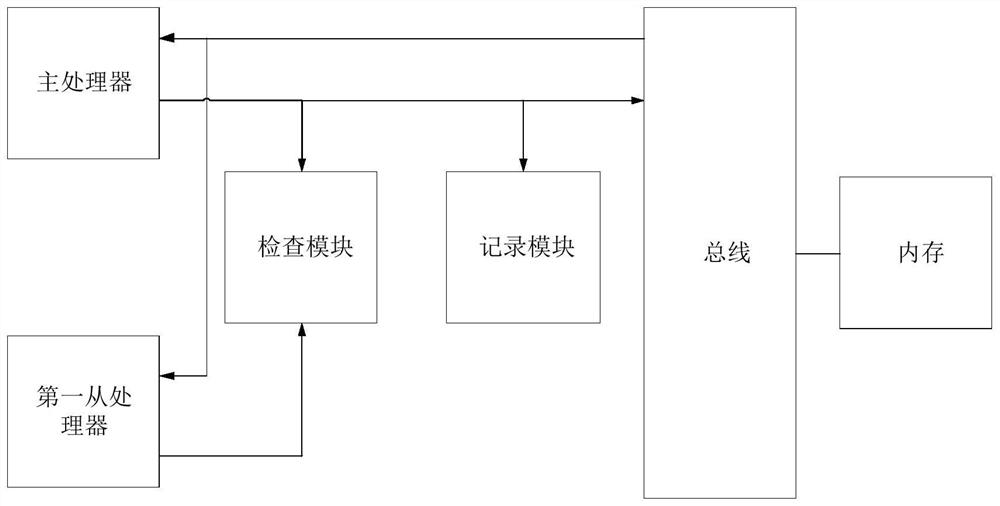

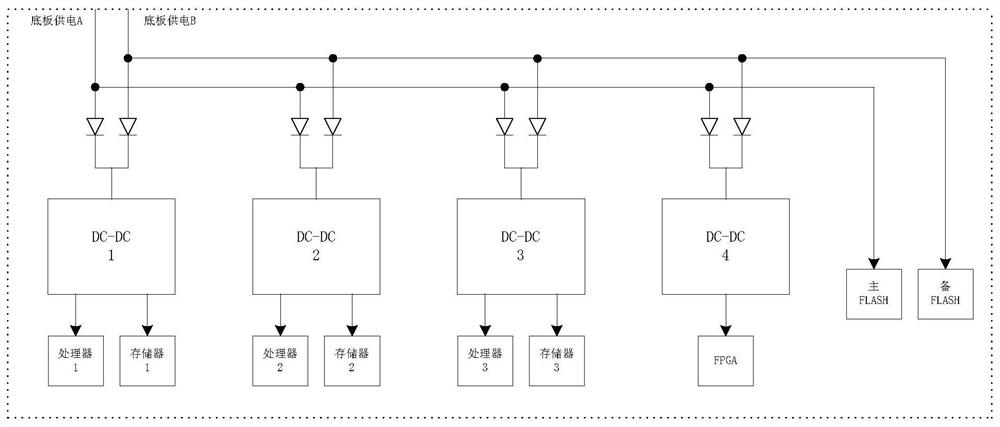

A lockstep processor and management method

ActiveCN108228391BImprove fault detection rateReduce development costsRedundant hardware error correctionLockstepComputer architecture

The invention belongs to computer system reliability design technology, and relates to a high-reliability multi-processor computer architecture for real-time monitoring of faults and real-time fault recovery. Including that the processor system adopts a single module design, including a processor unit, a memory unit, a power supply management unit, a clock unit, and a system management unit; the processor unit includes 3 similar or non-similar processor CPUs working in parallel; the The memory unit is composed of 3 random access memory RAMs working in parallel, 2 active and standby read-only memories ROM, and 1 non-volatile memory NVM; the power supply management unit realizes the monitoring and management of the system's dual redundant power supply and Power conversion and management; the clock unit realizes the monitoring and management of dual redundant clock circuits; the system management unit is responsible for monitoring the working conditions of system resources, locating, isolating and recovering resource failures.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

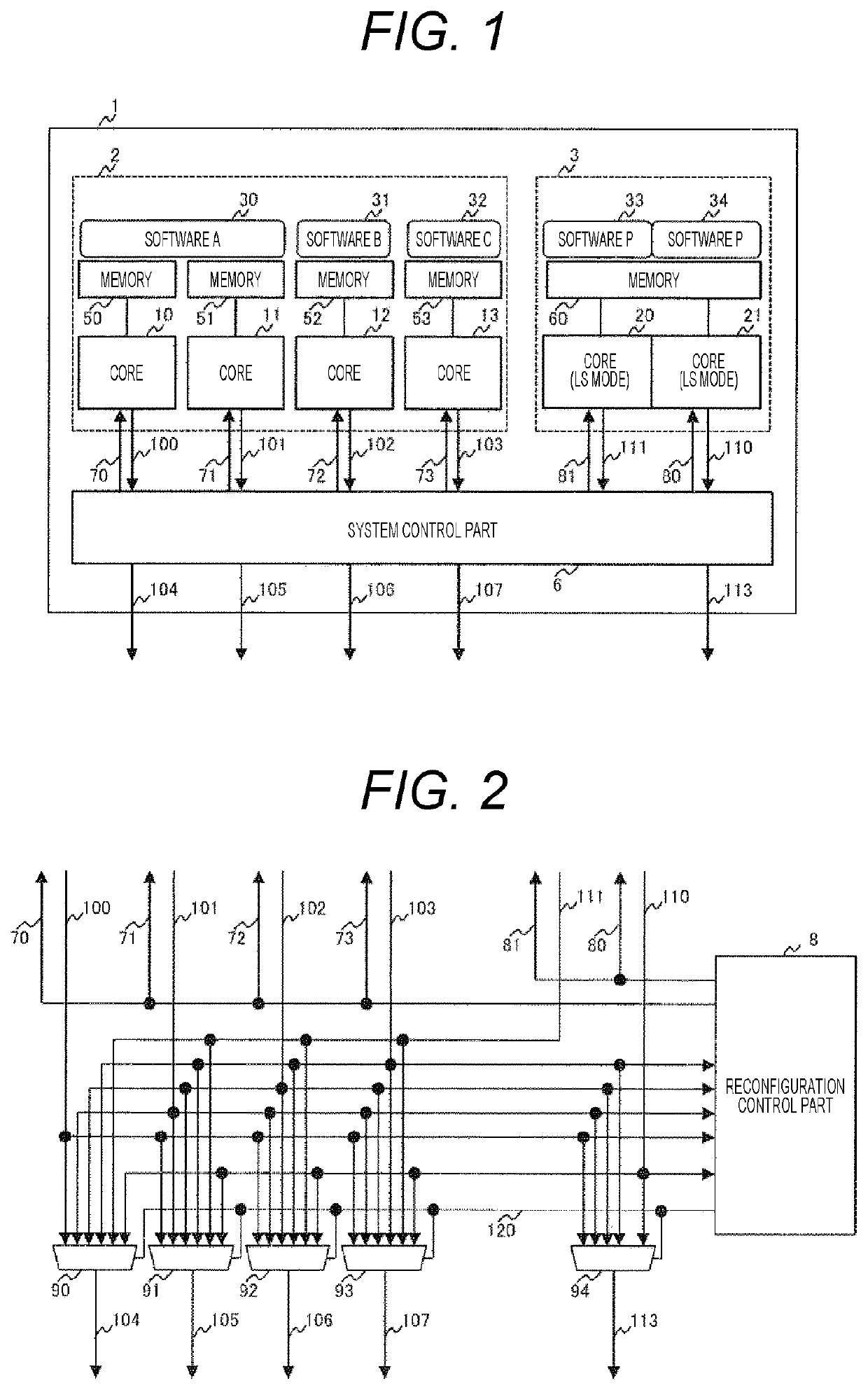

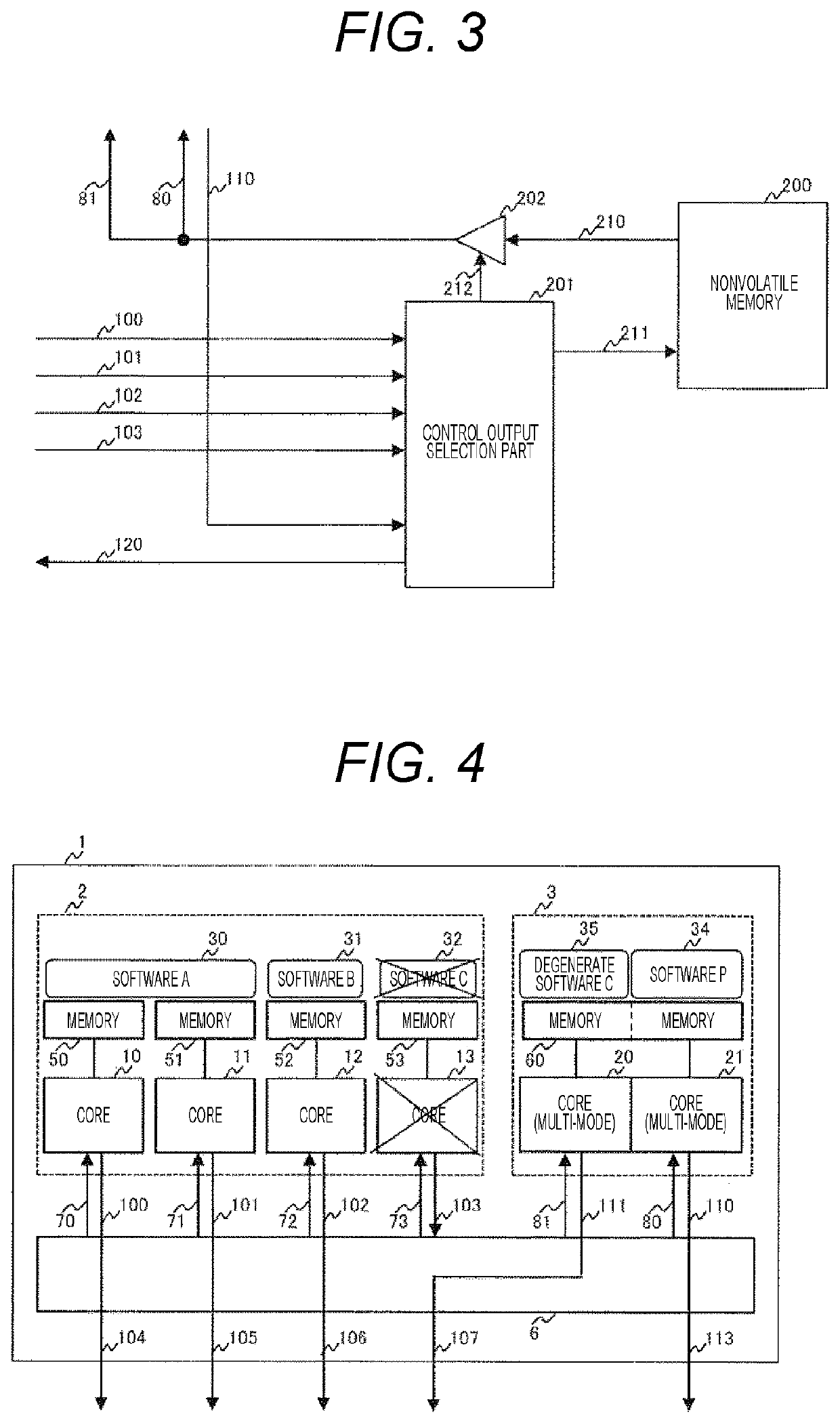

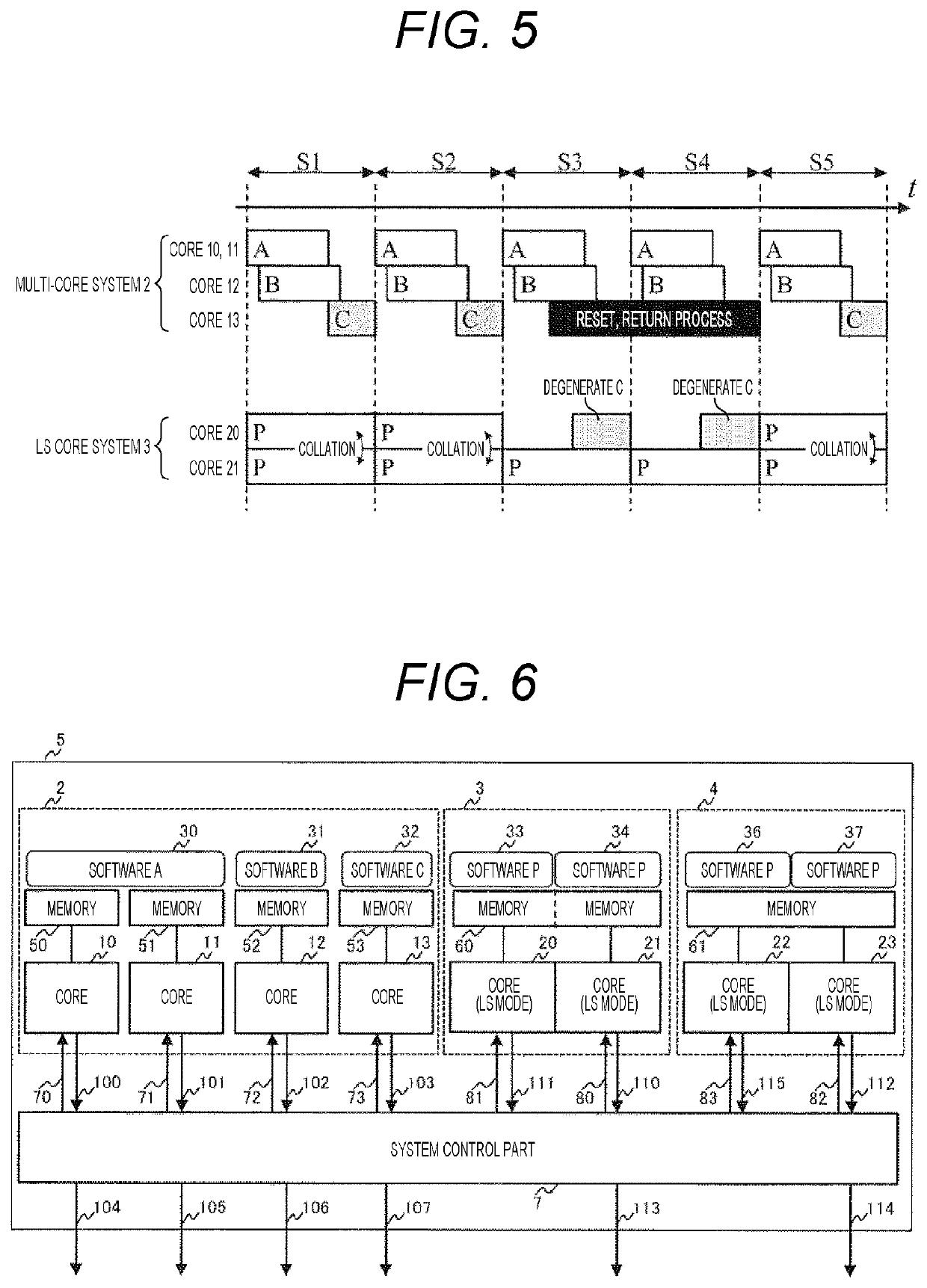

Reconfiguration control device

ActiveUS11385977B2Improve performanceImprove reliabilityProgramme controlRedundant hardware error correctionLockstepControl system

In the invention, a problem is solved in which, in order to achieve high performance and high reliability with the conventional multi-core and lockstep core, a redundant lockstep core is necessarily prepared to execute a multi-core program in which an error has occurred, a circuit area increases, and a cost and a power consumption increase. In the invention, a safe operation of a control system is secured by operating a software program operating on a multi-core in which an error has occurred as degenerate software on a core switched from a lockstep operation to a multi-core operation.

Owner:HITACHI LTD

Alternating frame processing operation with predicted frame comparisons for high safety level use

ActiveUS20210203979A1Improve securityLarge capacityError detection/correctionDigital computer detailsDigital signalMicroprocessor

Frames from an image stream or streams are processed by independently operating digital signal processors (DSPs), with only frame checking microprocessors operating in a lockstep mode. In one example, two DSP are operating on alternate frames. Each DSP processes the frames and produces prediction values for the next frame. The lockstep microprocessors develop their own next frame prediction. The lockstep processors compare issued frames and previously developed predicted frames for consistency. If the predictions are close enough, the issued frame passes the test. The lockstep processors then compare the issued frame to the preceding two frames for a similar consistency check. If the prior frames are also close enough, the issued frame is acceptable. In another example, hardware checkers are provided to compare the present frame with a larger number of prior frames. The hardware checkers provide comparison results to the lockstep processors to compare against allowable variation limits.

Owner:TEXAS INSTR INC

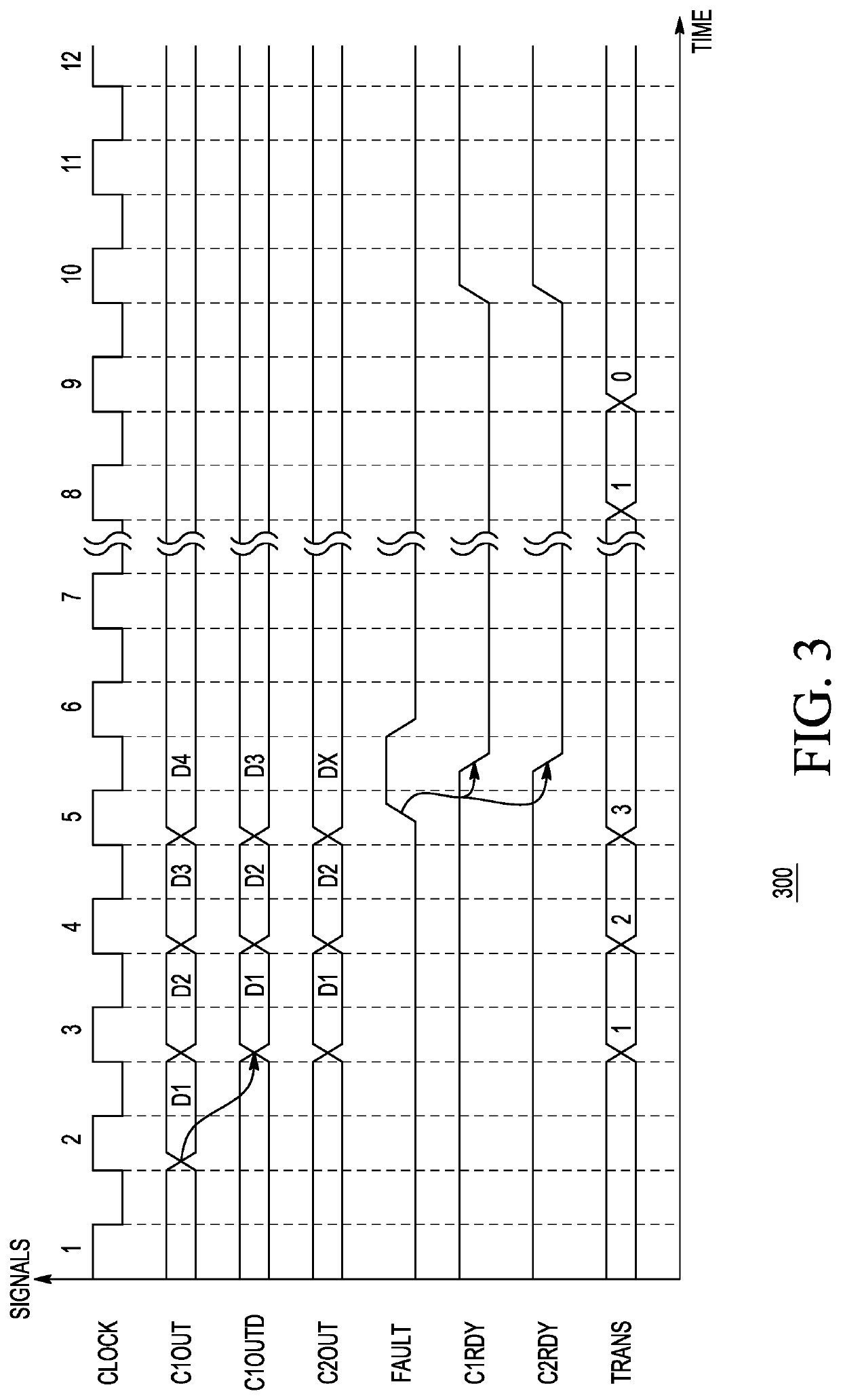

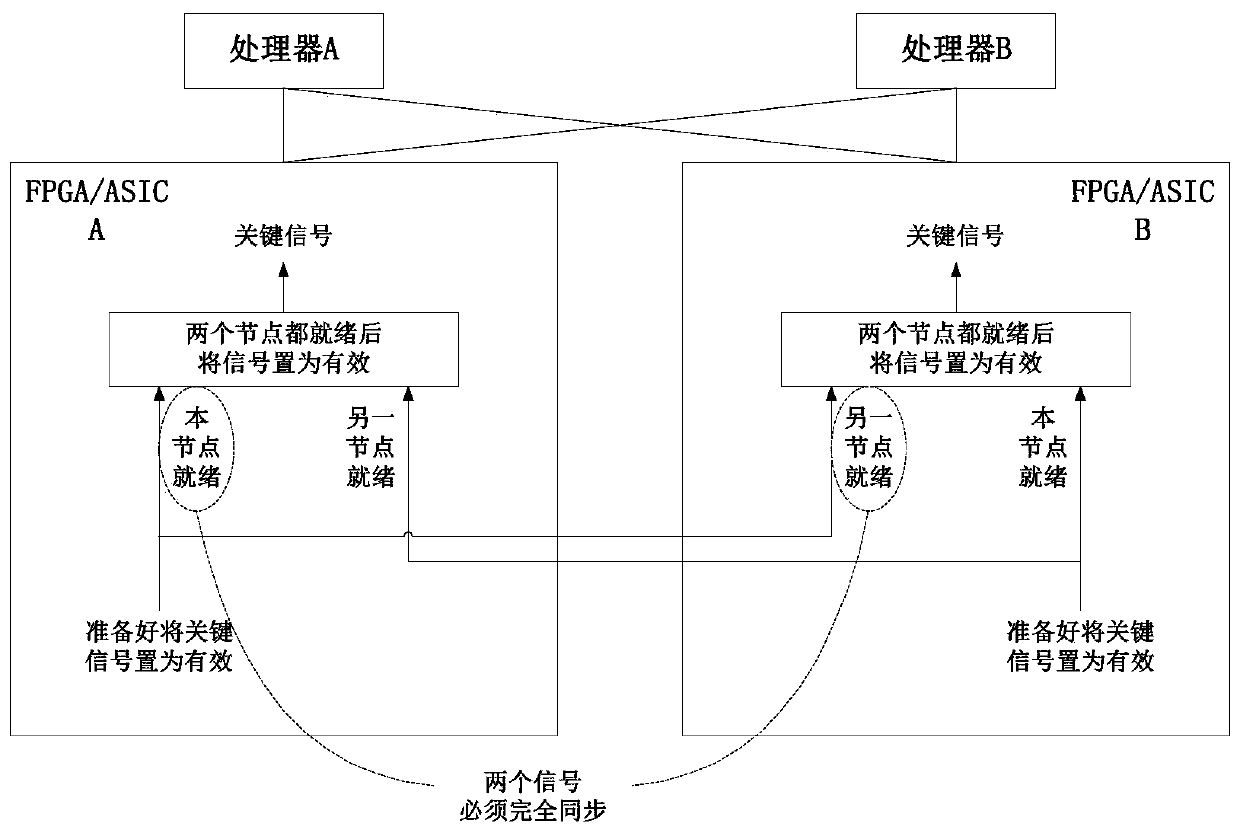

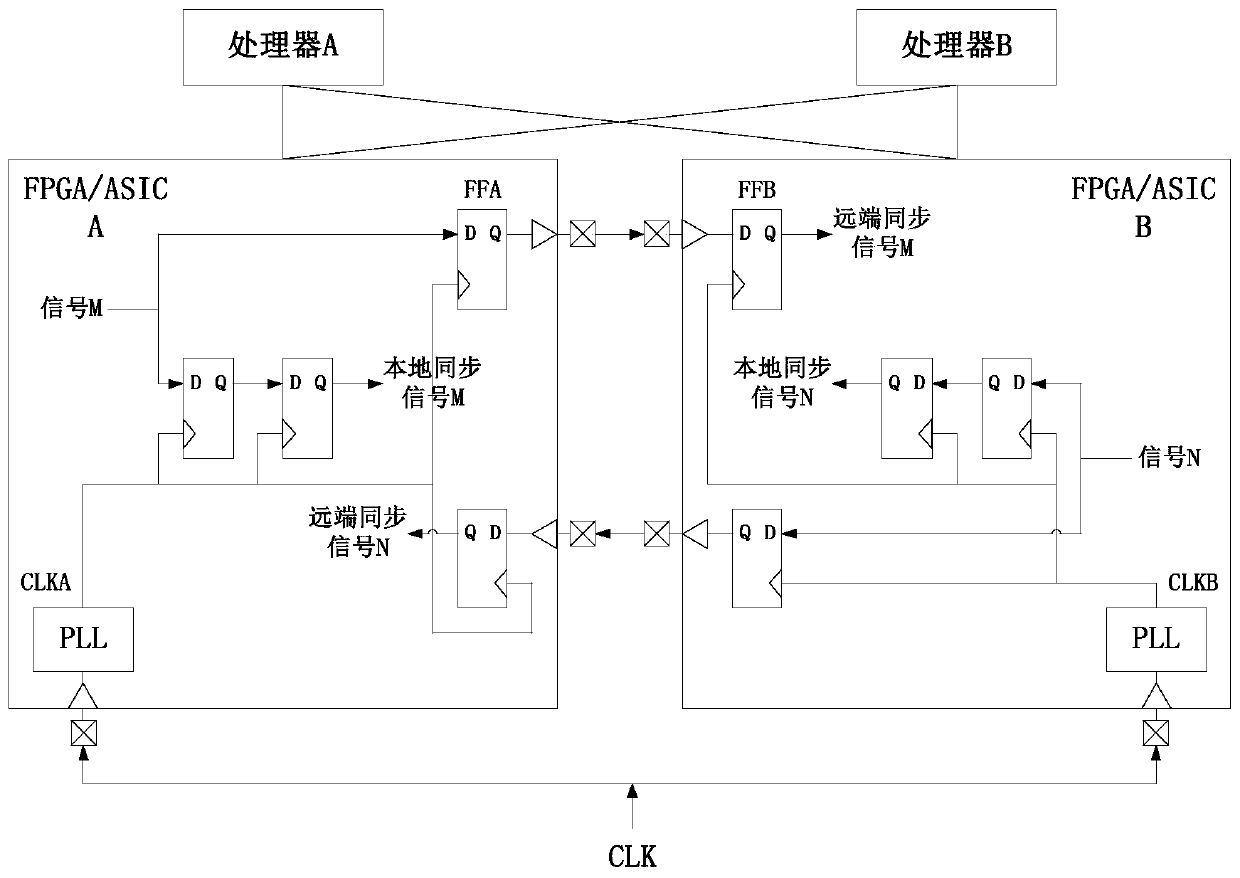

Method, device and circuit for synchronizing signals between nodes under Lockstep architecture

ActiveCN110175091AImprove running stabilityAvoid lockstep alignment errorsRedundant hardware error correctionComputer scienceVIT signals

The invention provides a method, device and circuit for synchronizing signals between nodes under a Lockstep architecture. The method comprises the following steps of: receiving a first ready signal for representing whether a first node is ready or not; carrying out delay of n clock periods on the first ready signal to obtain a local synchronization signal; wherein n is an integer greater than 1;delay of m clock periods is carried out on the first ready signal to obtain a delay ready signal of the first node, and m is a positive integer smaller than n; sending a delay ready signal of the first node to a second node; the structure of the second node is completely the same as that of the first node; receiving a delay ready signal of a second node sent by the second node; performing n-m clock period delay on the delay ready signal of the second node to obtain a far-end synchronization signal; and when the local synchronization signal and the remote synchronization signal are valid at thesame time, setting the target key signal of the first node to be valid.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

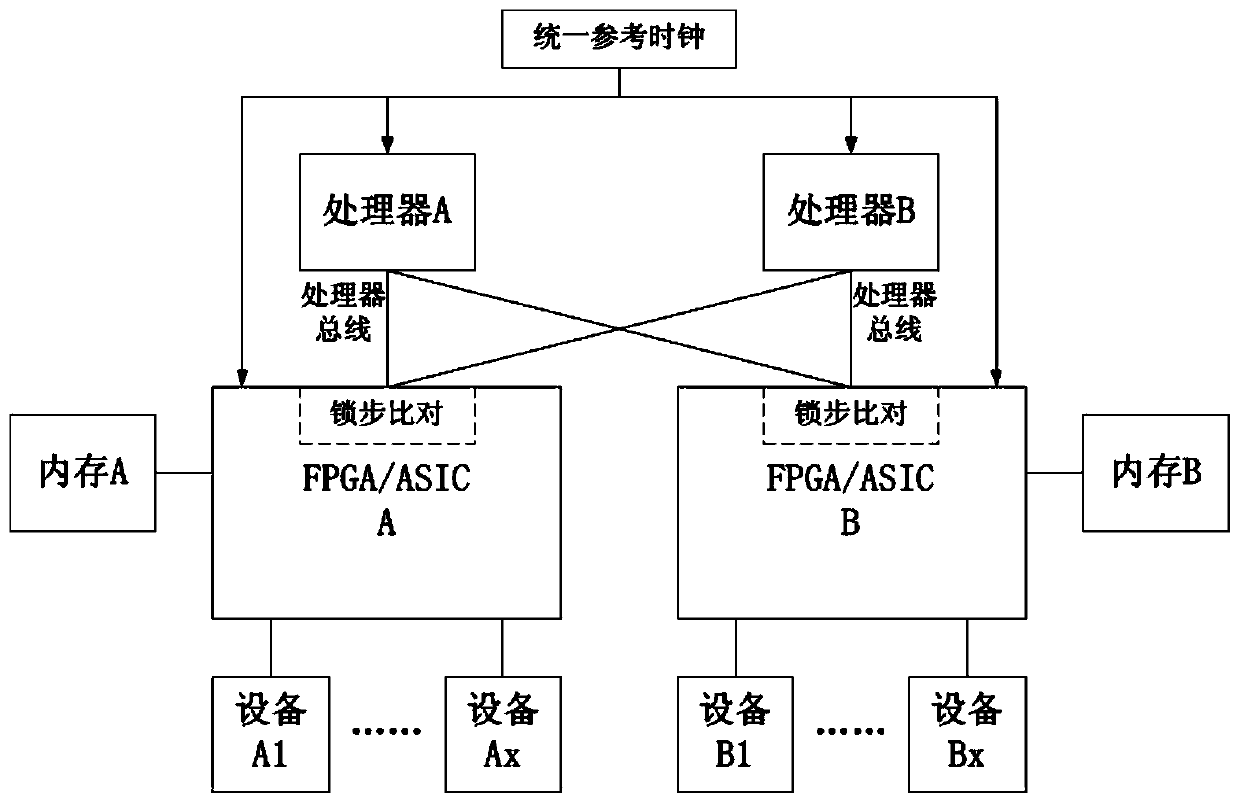

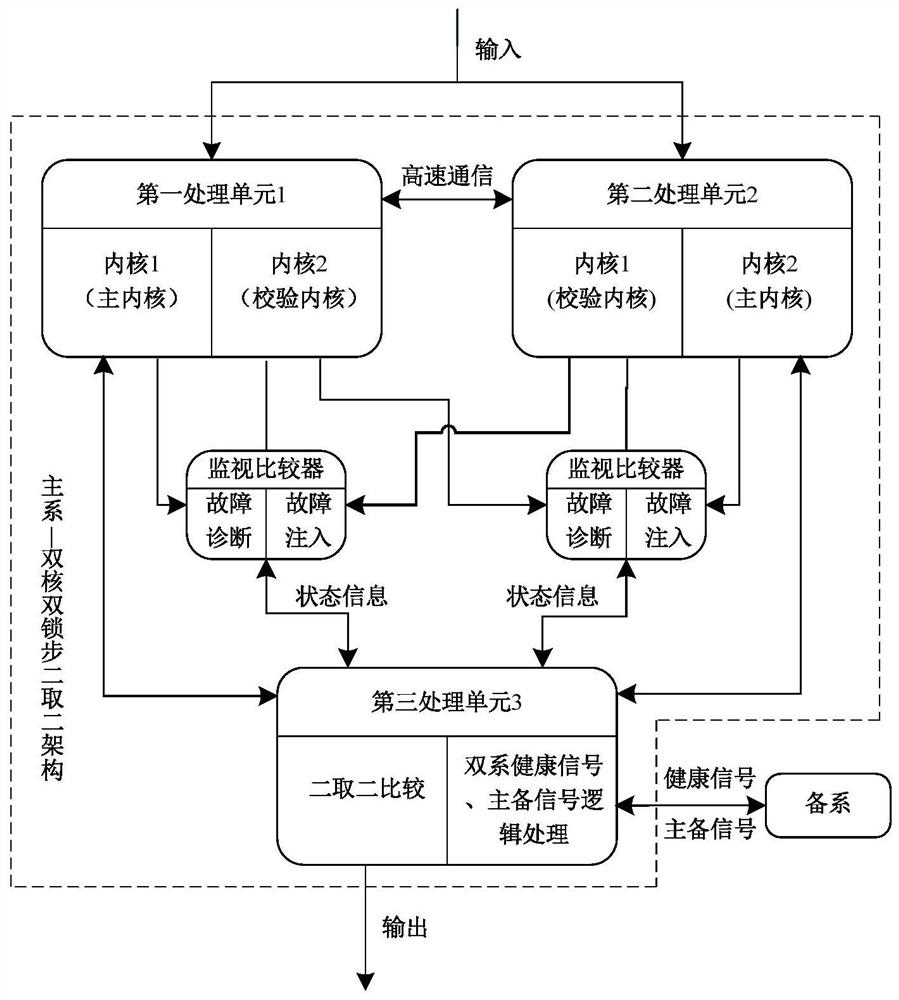

Dual-core dual-lockstep two-out-of-two architecture and its security platform

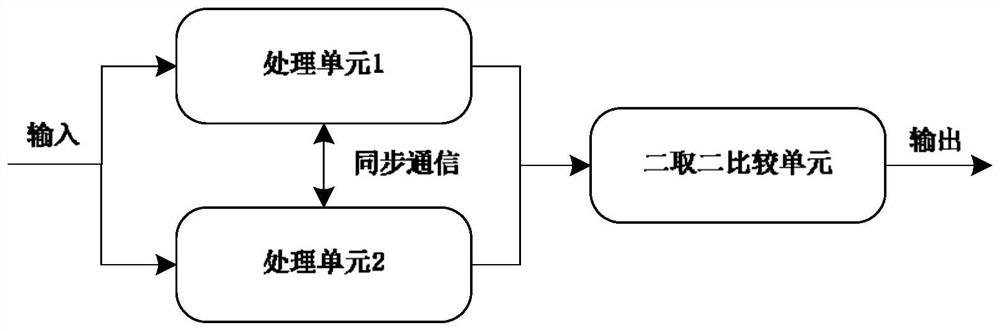

ActiveCN109634171BReduce common cause failureAvoid single point of failure problemsProgramme controlComputer controlLockstepDual core

The invention relates to a double-core double-lock-step two multiply two structure and a safety platform thereof. The structure comprises a main system and a standby system with the same structure, wherein each of the main system and the standby system adopts a double-core double-lock-step two multiply two structure. The double-core double-lock-step two multiply two structure comprises three processing units, specifically, a first processing unit, a second processing unit and a third processing unit. According to the structure, the double-lock step is realized on the basis of the two double-core processing units, a safe structure which is voted by two multiply two is realized through the third processing unit, the safety platform of the two multiply two structure is realized, and the platform meets the requirements of high safety and high reliability in the safety key field.

Owner:CRSC WANQUAN SIGNAL EQUIP

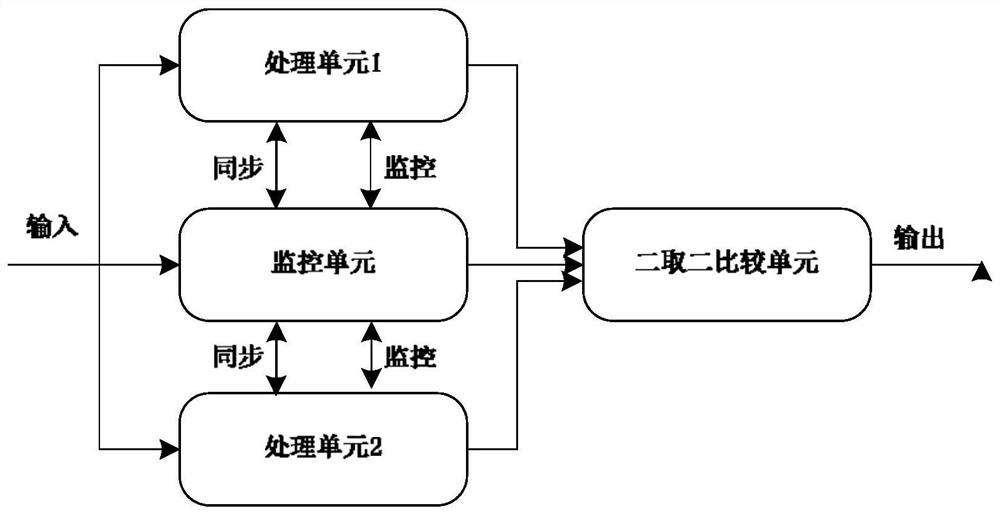

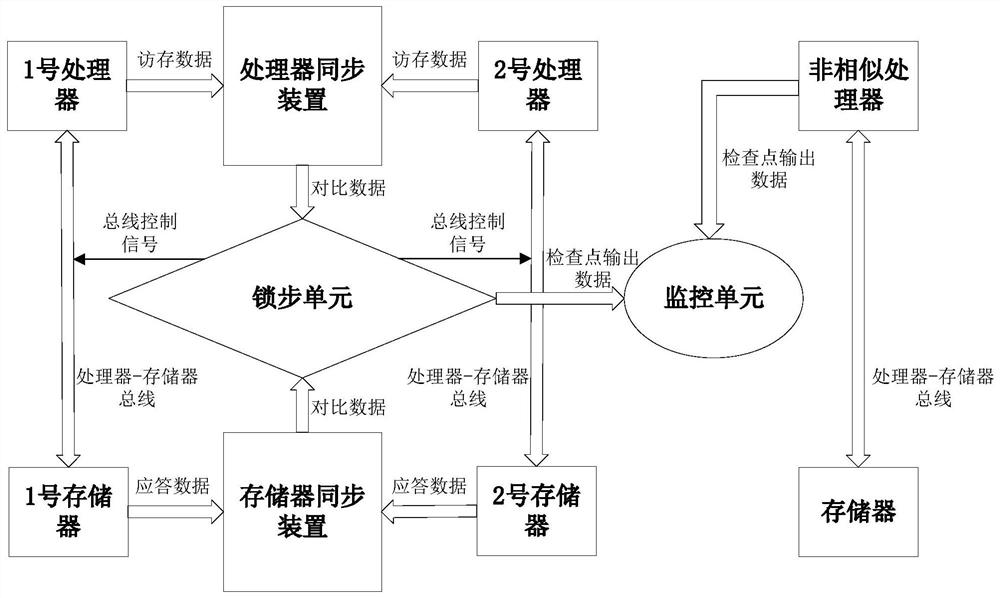

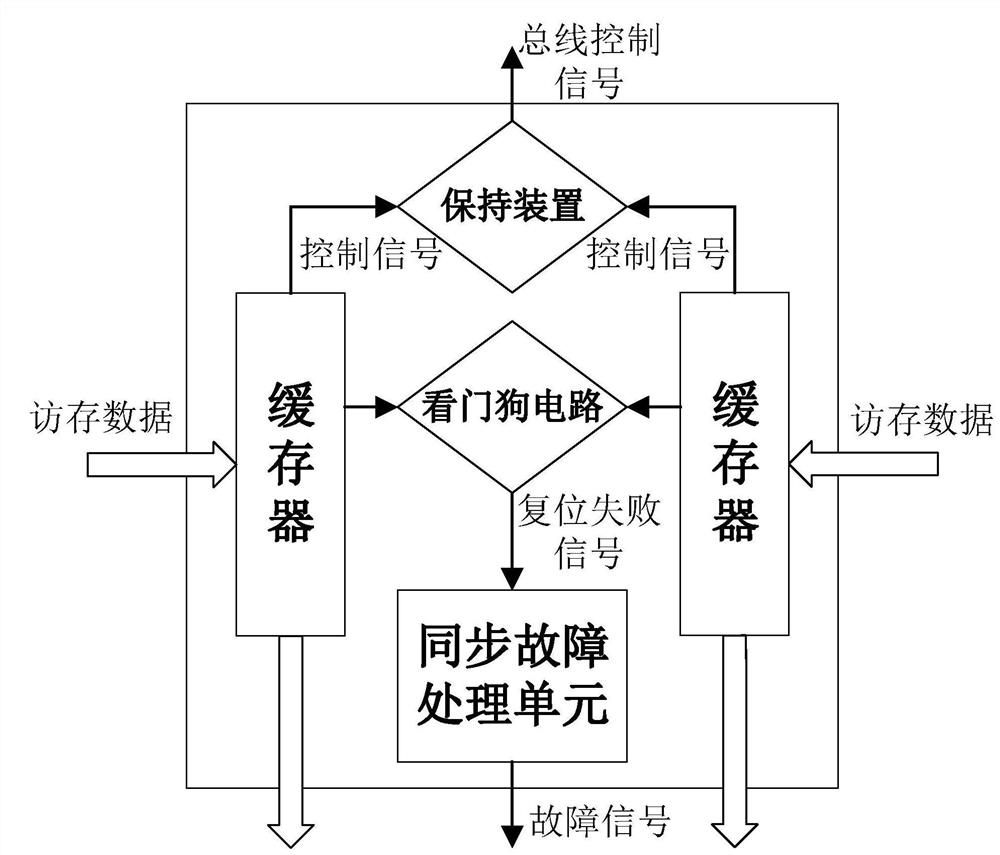

A high-security computer system based on lockstep and monitoring and its design method

ActiveCN109815040BImprove detection rateReduce busy waiting timeRedundant hardware error correctionTerm memorySystem failure

The invention provides a high-security computer system based on lock-step and monitoring and a design method thereof. When the processor performs a read operation, the dual processors respectively read data from the same address of the two memories and compare them. If the comparison is correct, the data is sent to the corresponding processor. If the comparison is wrong, the fault handling operation is performed; the comparison module for monitoring and lockstep is set up, and the checkpoint output is added to the load. When the checkpoint arrives, the cross comparison is performed. If the comparison is correct, the system is based on operation; if the comparison is incorrect, the troubleshooting operation is performed. The invention realizes fault detection and location at the instruction level, greatly reduces system faults caused by random faults in the memory, improves the detection rate of the dual-processor common-mode faults of the lockstep module, and further improves the safety of the entire system, effectively It solves the problem that the running speed of dissimilar processors does not match, and reduces the busy waiting time of the monitoring unit.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

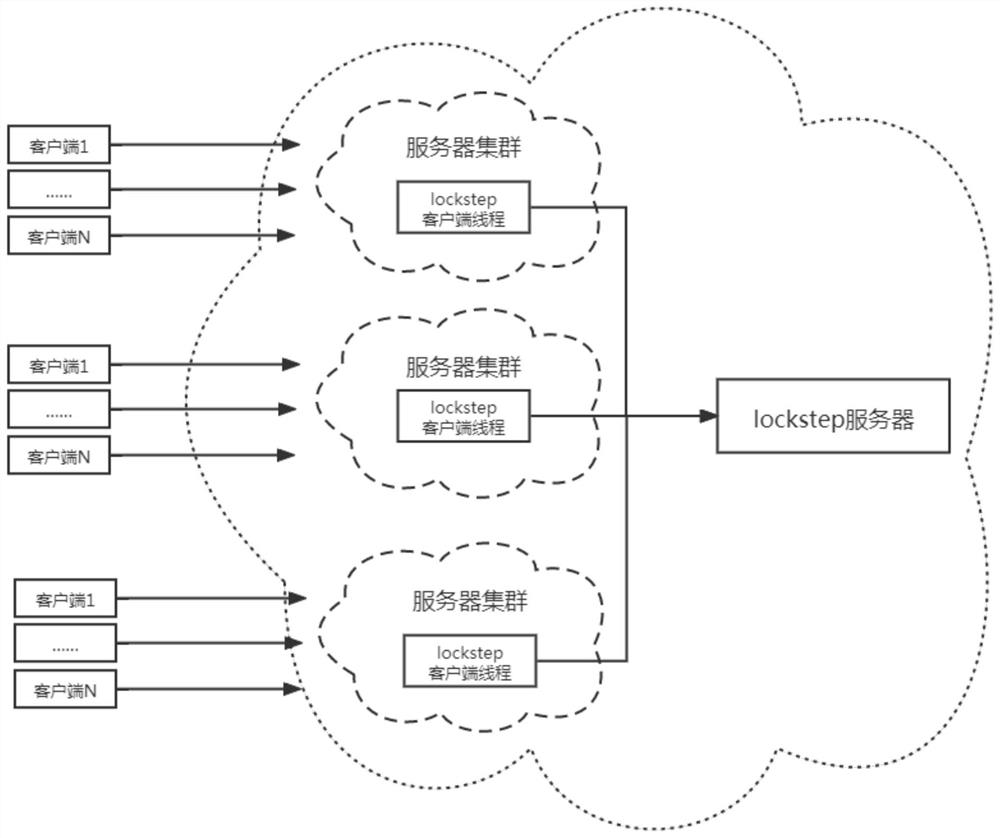

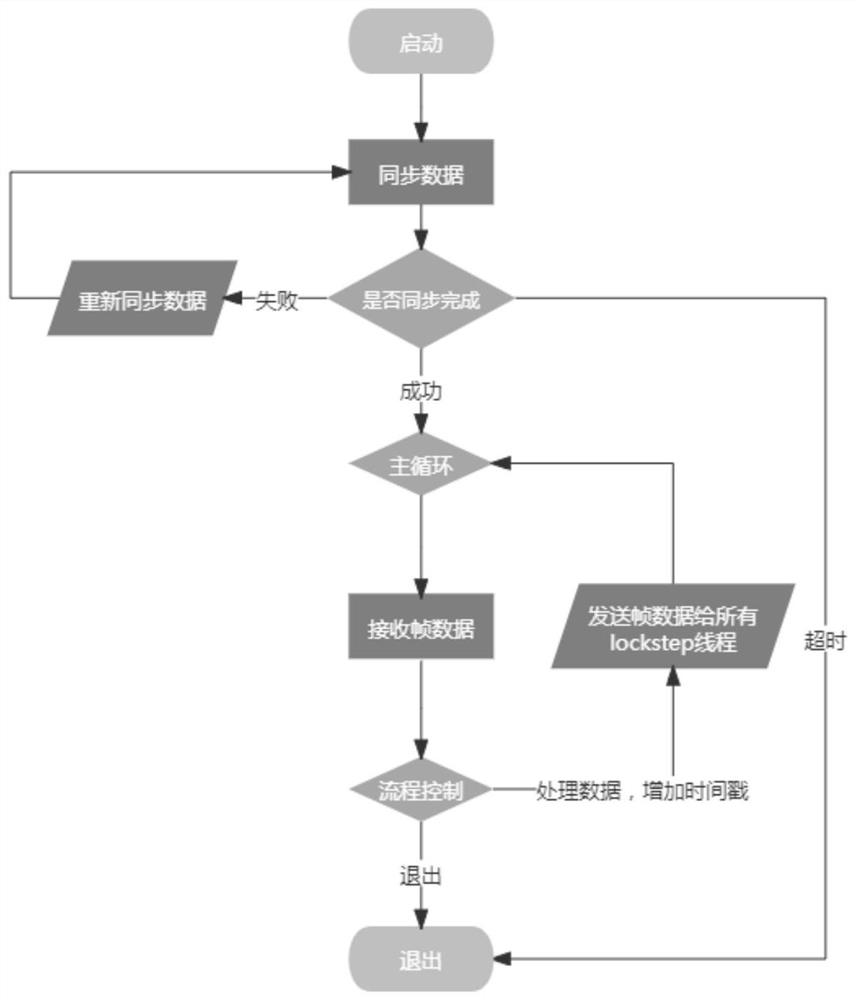

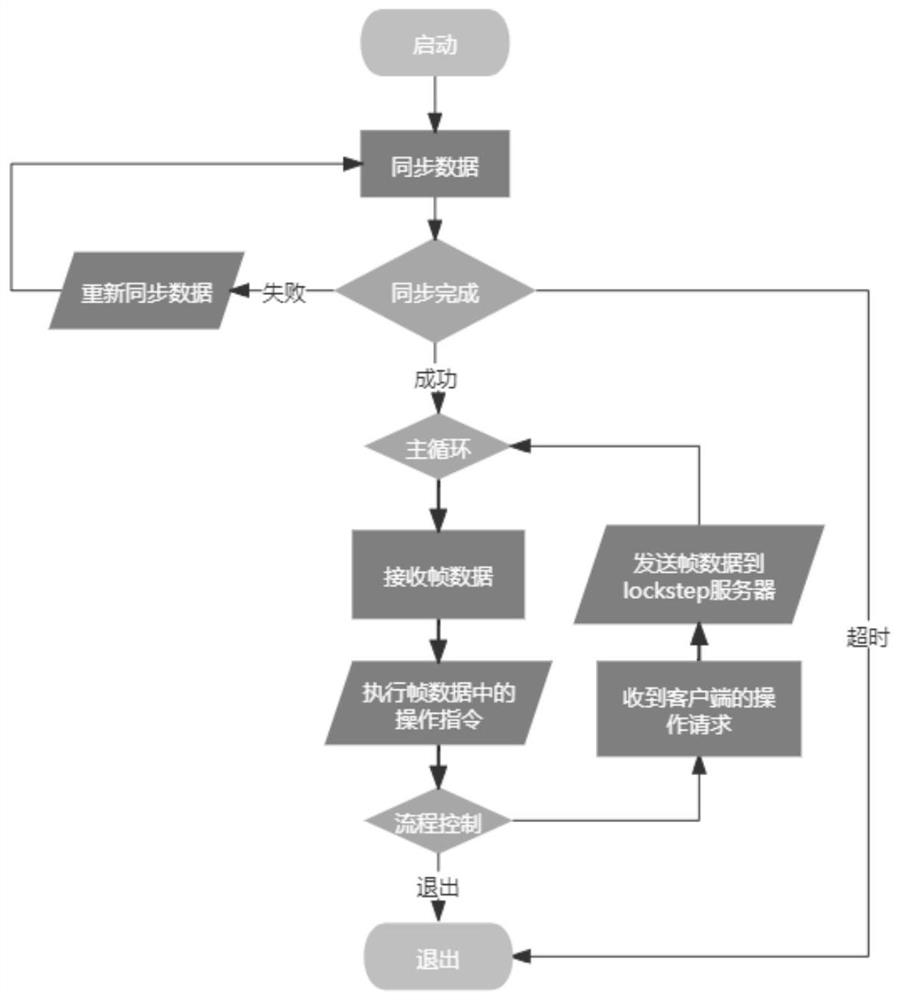

System and method for synchronizing key data between server clusters based on lockstep

The invention discloses a system for synchronizing key data among server clusters based on lockstep, which comprises a lockstep server and a plurality of server clusters connected with the lockstep server, each server cluster is connected with a plurality of clients, each server cluster comprises a lockstep client thread, and the lockstep client thread is connected with the lockstep server. The lockstep client thread is used for carrying out polling with a fixed frame rate; the invention further provides a method for synchronizing the key data between the server clusters based on the lockstep. According to the invention, the data among the server clusters are ensured to be completely consistent.

Owner:四川启睿克科技有限公司

A low-latency dual-mode lockstep-tolerant soft error handler system

ActiveCN111104243BImprove universalityReduce time overheadNon-redundant fault processingLockstepDual mode

The invention discloses a low-delay dual-mode lockstep soft error tolerance processor system, which belongs to the technical field of processor error tolerance. The system realizes the detection of soft errors in the processor system through a dual-mode lockstep architecture; by adopting a universal checkpoint and rollback recovery algorithm, the system can cope with a variety of soft errors and improve the reliability of the fault recovery method Universality: The system adopts an adaptive dynamic checkpoint method, predicts the next soft error interval with the soft error interval history table SEIHT and the pattern history table PHT, and increases or decreases the setting frequency of the checkpoint according to the prediction result , this method considers the long-term and short-term characteristics of soft error history at the same time, effectively reduces the average execution time of processor tasks, and solves the problem of large delay time introduced by the current dual-mode lockstep fault-tolerant technology for processors.

Owner:JIANGNAN UNIV

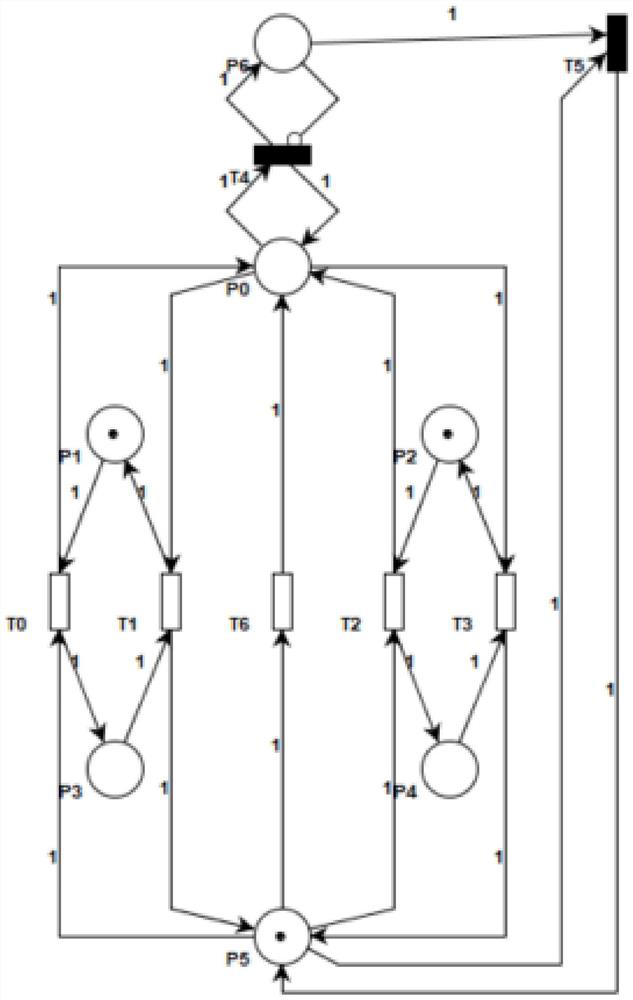

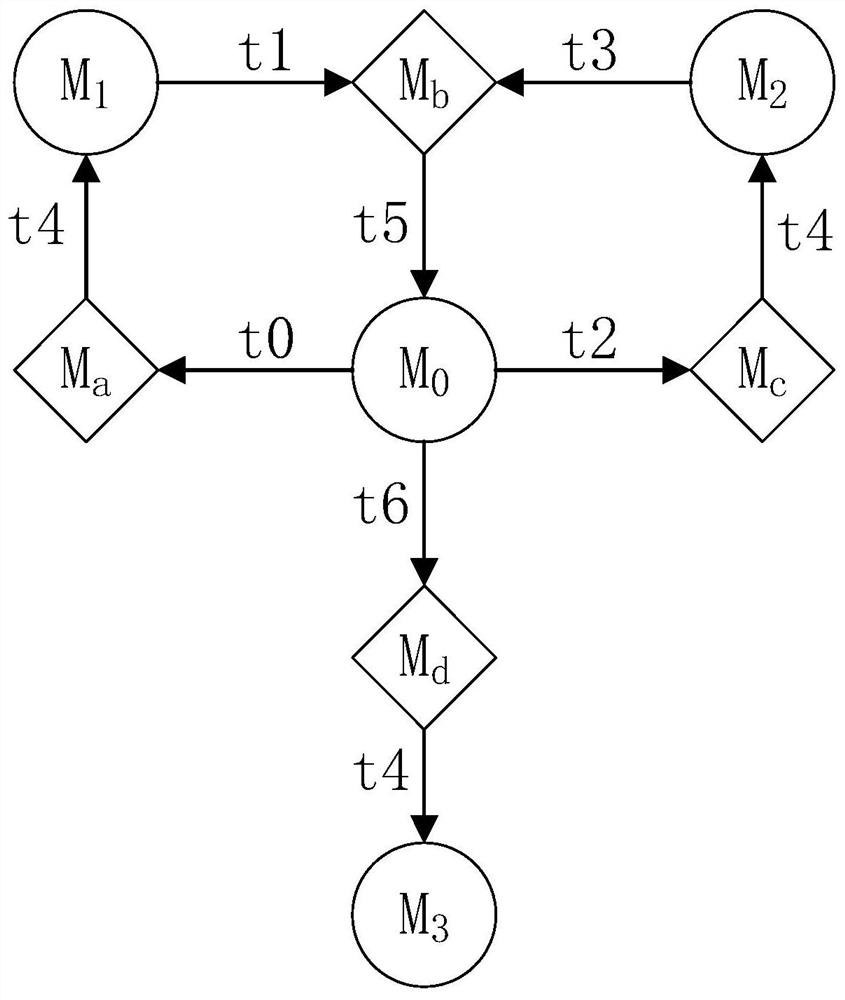

A Reliability Modeling and Analysis Method of Self-healing Processor-to-Lockstep System

ActiveCN109508260BAdd supportAccurate solutionRedundant hardware error correctionFailure rateLockstep

The present invention provides a method for modeling and analyzing the reliability of a self-repairing processor to a lockstep system. Firstly, the state of the lockstep system and the self-repairing processor is abstracted into a library set, and the faults of the processor and other components The occurrence and repair actions are abstracted into a transition set, and then the relationship between the place set and the transition set is abstracted into a directed arc set and ignition transition rules between them, and then the failure rate and repair rate information of each component is abstracted into a delay time The average implementation rate of transition elements, thus the GSPN reliability model of the lock-step system is obtained. After the model is initialized, according to the ignition transition rules, all the states reachable by the lockstep system are obtained, and then the isomorphic Markov chain of the GSPN reliability model is constructed, and the cumulative probability function equation of the reachable states of the GSPN reliability model is obtained and solved , to obtain the reliability function of the lock-step system, so as to complete the reliability analysis of the lock-step system. The modeling process of the invention is simple, and the reliability function of the system can be obtained accurately.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

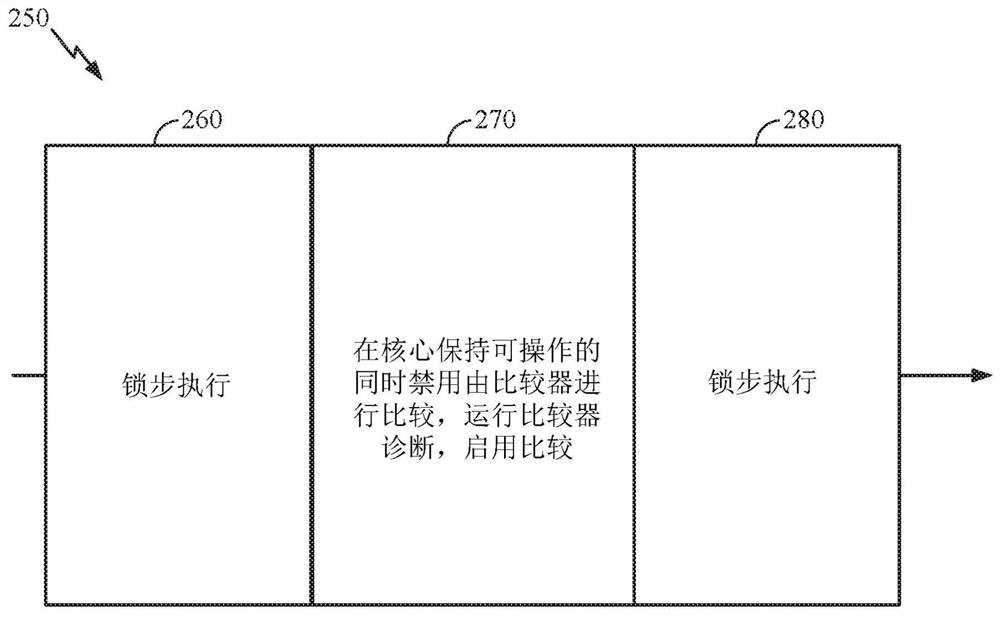

Periodic non-invasive diagnostics of lockstep systems

ActiveCN110140112BDetecting faulty computer hardwareRedundant hardware error correctionDiagnostic programLockstep

Aspects disclosed herein relate to periodic non-invasive diagnostics of lockstep systems. An exemplary method includes comparing execution of a program on a first processing system of a plurality of processing systems to execution of the program on a second processing system of the plurality of processing systems using a first comparator circuit , comparing said execution of said program on said first processing system to said execution of said program on said second processing system using a second comparator circuit, and using said first comparison A diagnostic routine is run on the second comparator circuit while the comparison by the second comparator circuit is in progress.

Owner:QUALCOMM INC

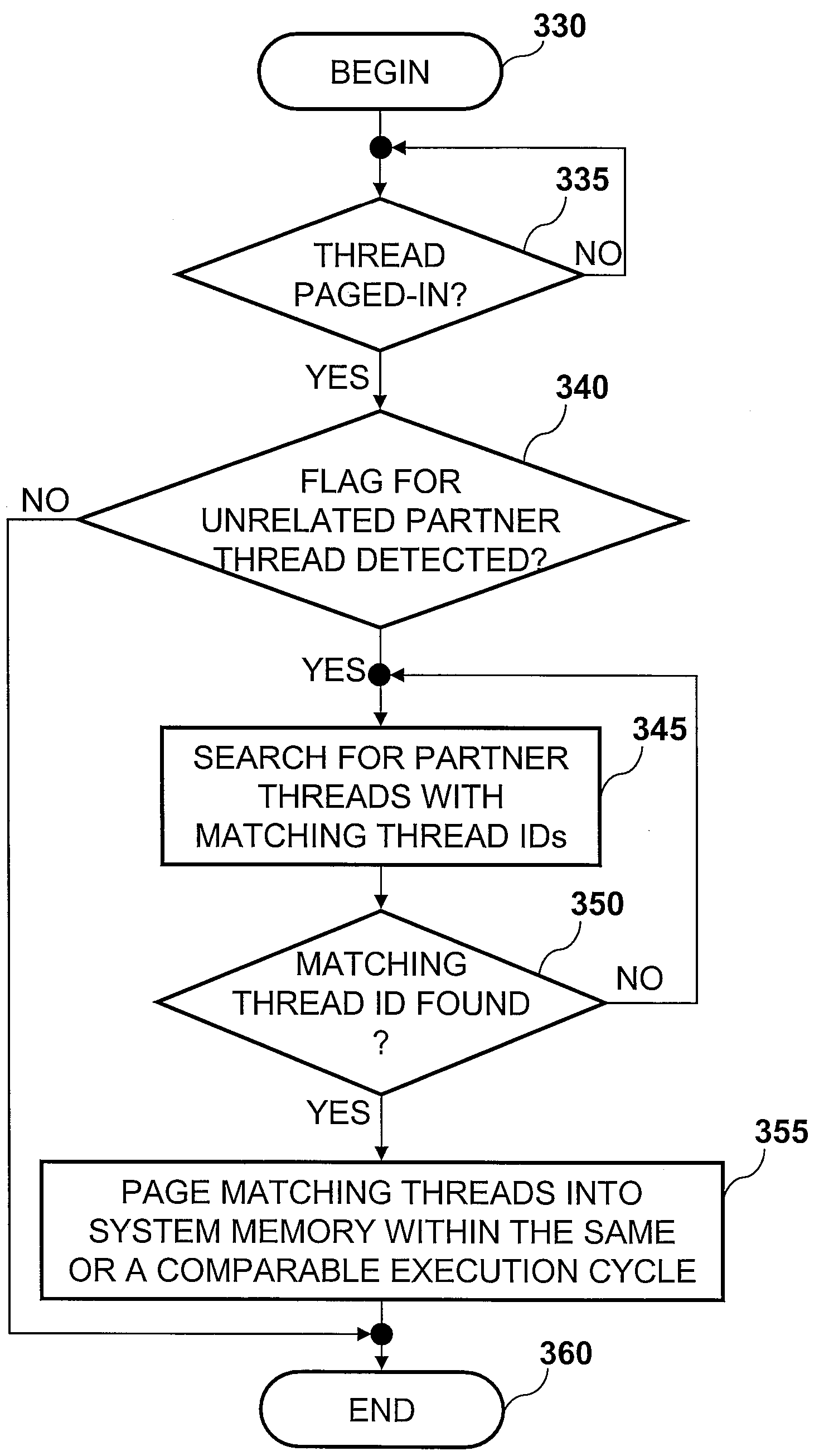

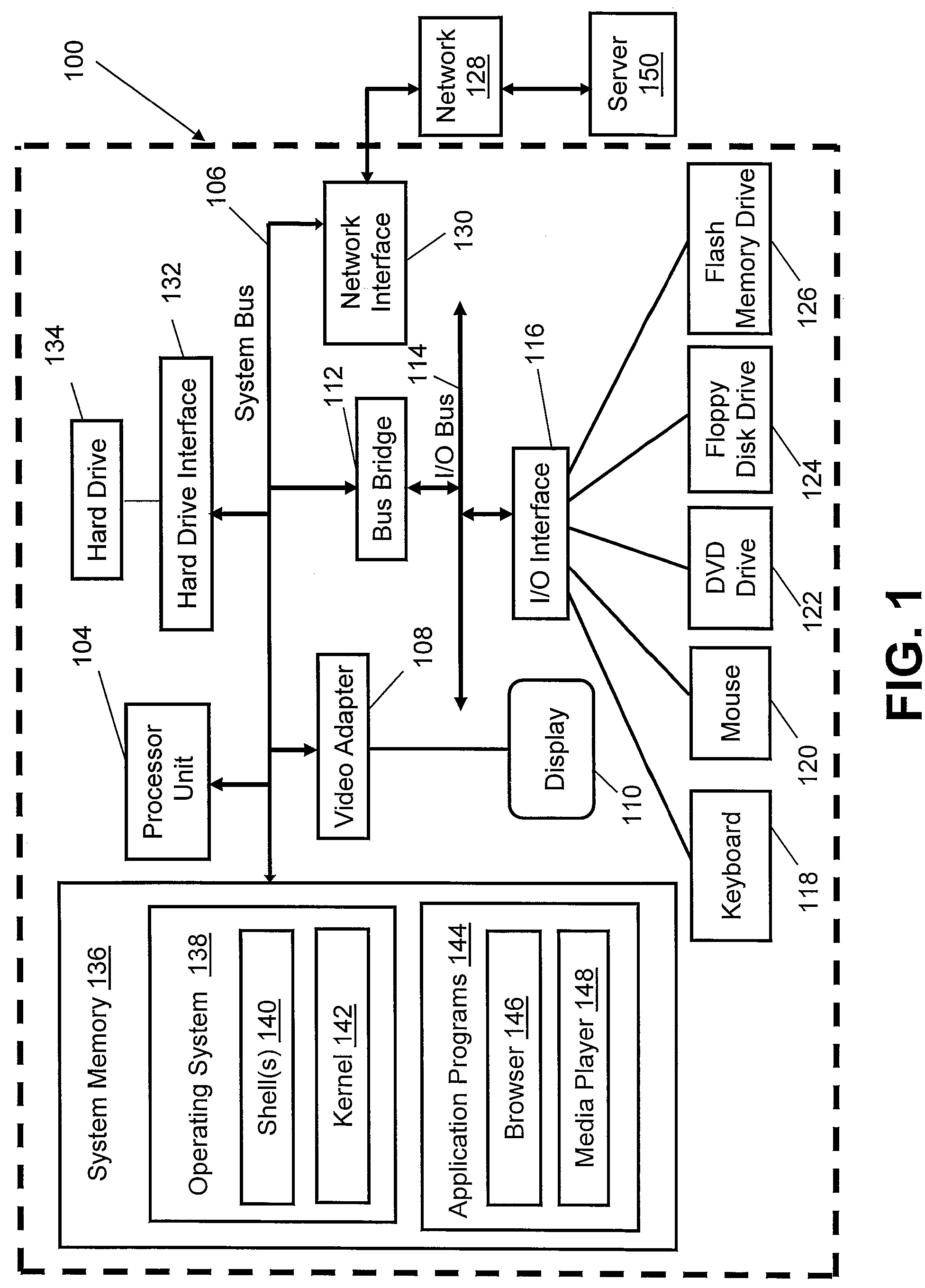

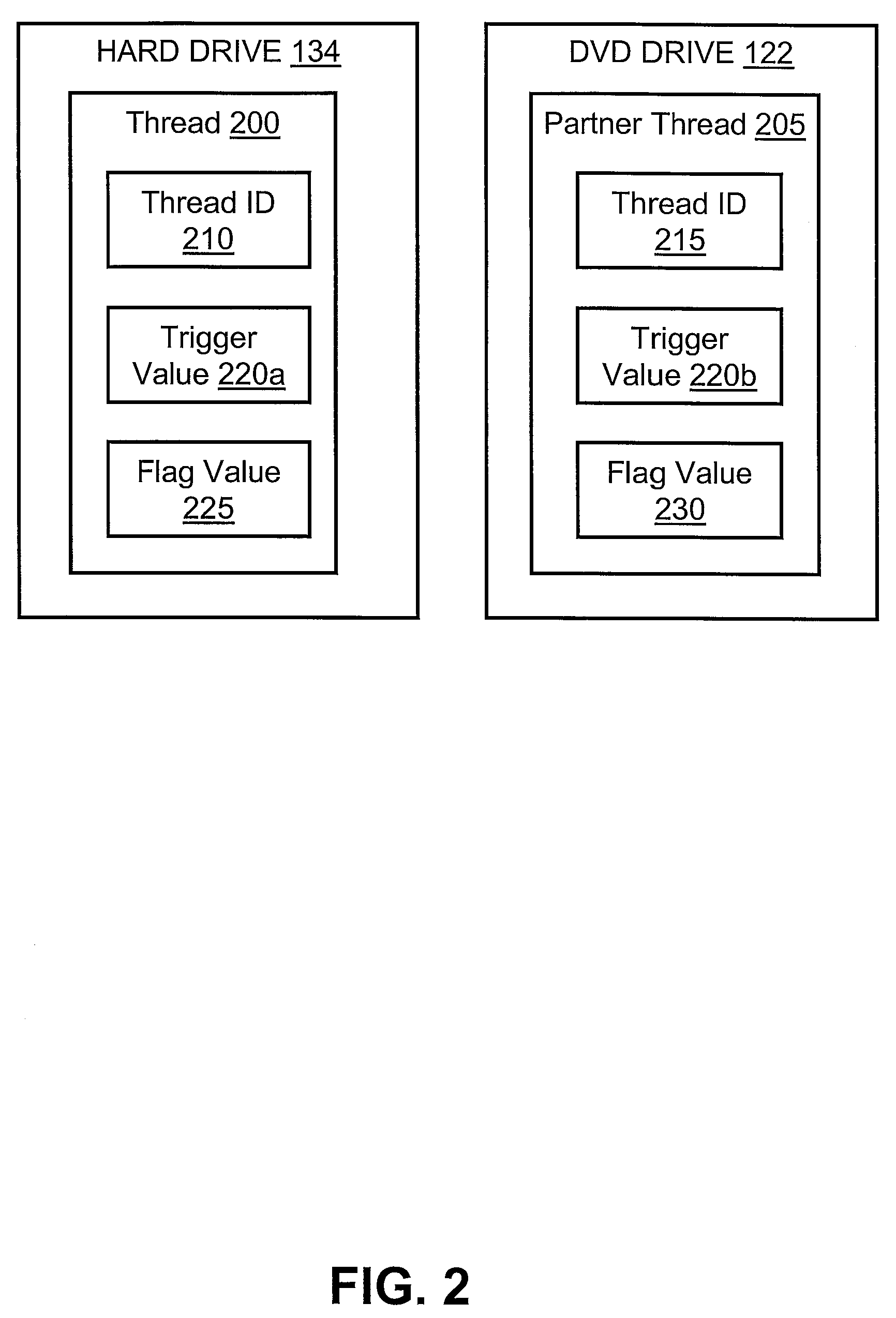

Method, system and program product for associating threads within non-related processes based on memory paging behaviors

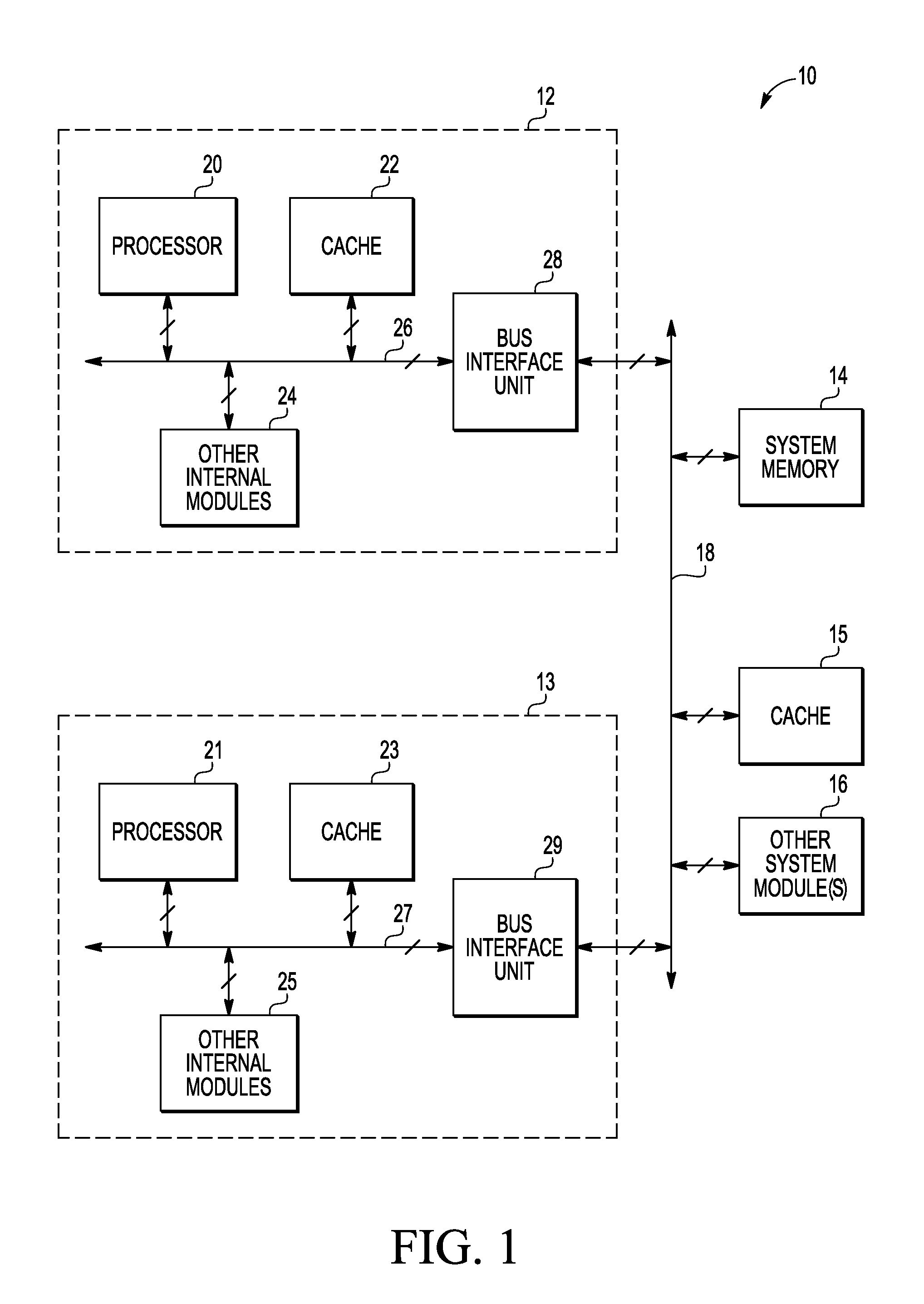

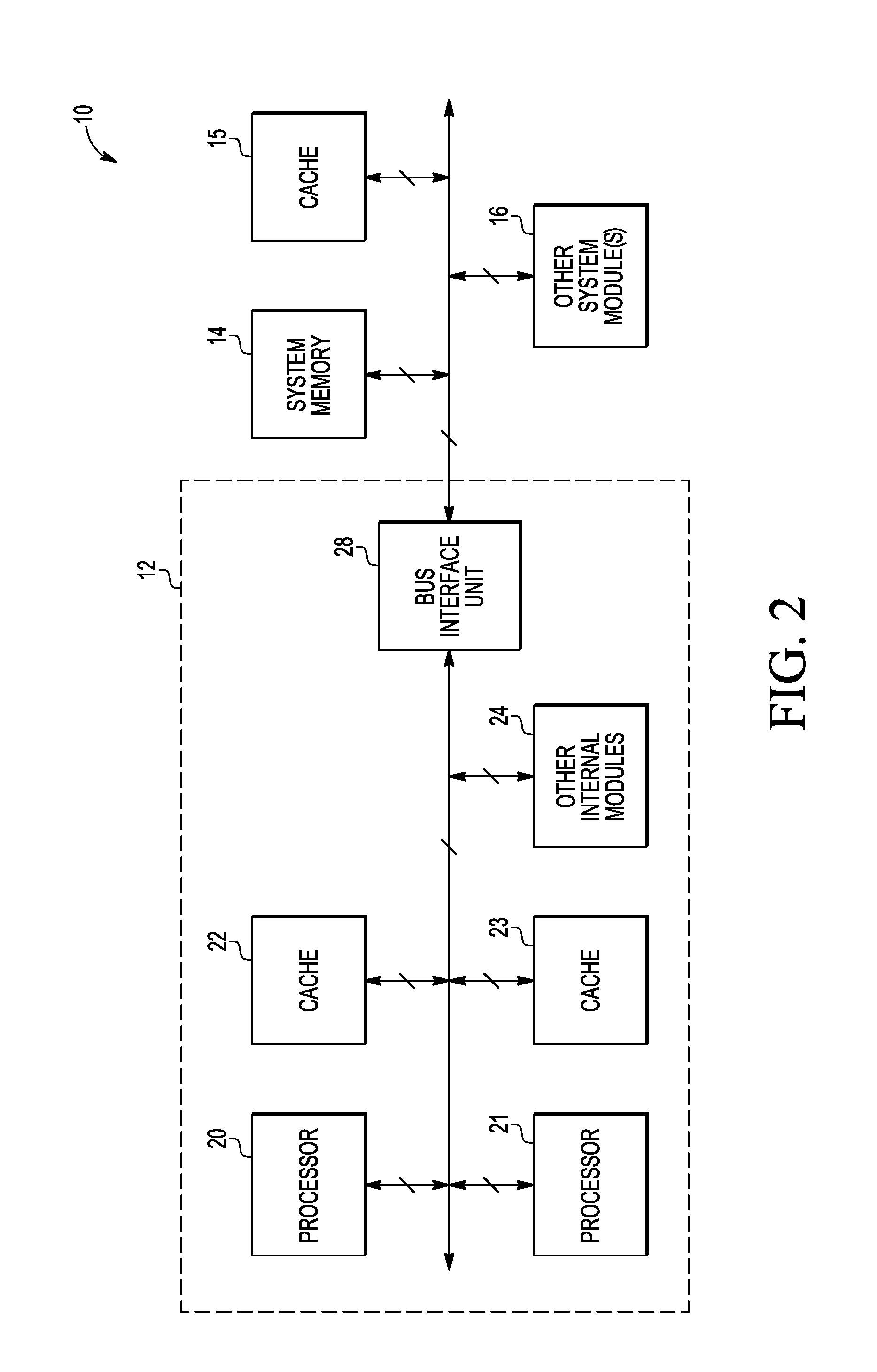

InactiveUS7596668B2Eliminate delaysExecution efficiency is improvedMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemUser input

A method of tying related process threads within non-related applications together in terms of memory paging behavior. In a data processing system, a first process thread is related to one or more “partner” threads within separate high latency storage locations. The kernel analyzes the memory “page-in” patterns of multiple threads and identifies one or more partner threads of the first thread based on user input, observed memory page-in patterns, and / or pre-defined identification information within the thread data structures. The kernel marks the first thread and its corresponding related partner threads with a unique thread identifier. When the first thread is subsequently paged into a lower latency memory, the kernel also pages-in the related partner threads that are marked with the unique thread identifier in lockstep. Tying related threads from non-related applications together in terms of memory paging behavior thus eliminates memory management delays.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com