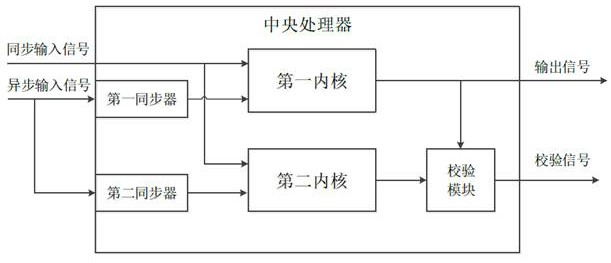

Asynchronous input signal synchronization method and device, central processing unit and chip

A technology of asynchronous input and synchronous devices, applied in the direction of generating/distributing signals, etc., can solve problems such as failure to find synchronizer failures, and achieve the effect of ensuring safety and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

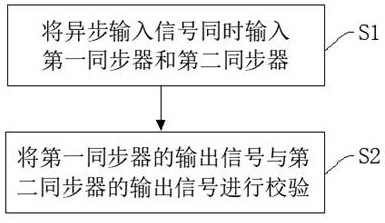

[0050] figure 2 It is a flowchart of a method for synchronizing an asynchronous input signal provided by Embodiment 1 of the present invention. The method for synchronizing an asynchronous input signal in this embodiment is used in a dual-core lockstep system, and the dual-core lockstep system includes a first core and a second core. like figure 2 As shown, the method includes the following steps:

[0051] S1. Input the asynchronous input signal into the first synchronizer and the second synchronizer at the same time, the first synchronizer is the same as the second synchronizer, that is, the structures, functions and parameters of the first synchronizer and the second synchronizer are the same same.

[0052] S2. Check the output signal of the first synchronizer and the output signal of the second synchronizer.

[0053] Step S2 includes the following sub-steps:

[0054] S21. Determine whether the output signal of the first synchronizer is the same as the output signal o...

Embodiment 2

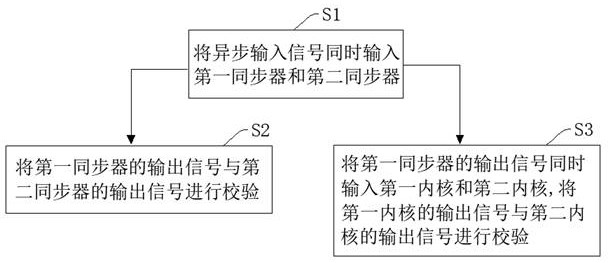

[0065] image 3 It is a flowchart of a method for synchronizing an asynchronous input signal provided by Embodiment 2 of the present invention. The method for synchronizing an asynchronous input signal in this embodiment is used in a dual-core lockstep system, and the dual-core lockstep system includes a first core and a second core. like image 3 As shown, the method includes the following steps:

[0066] S1. Input the asynchronous input signal into the first synchronizer and the second synchronizer at the same time, the first synchronizer is the same as the second synchronizer, that is, the structures, functions and parameters of the first synchronizer and the second synchronizer are the same same.

[0067] S2. Check the output signal of the first synchronizer and the output signal of the second synchronizer.

[0068] Step S2 includes the following sub-steps:

[0069] S21. Determine whether the output signal of the first synchronizer is the same as the output signal of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com