Image compression multi-core synchronous fault-tolerance method, computer and processor

An image compression and image processing technology, applied in the direction of processor architecture/configuration, computing, electrical digital data processing, etc., can solve the problems of performance waste, inflexible and inflexible binding mechanism between main core and redundant core, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

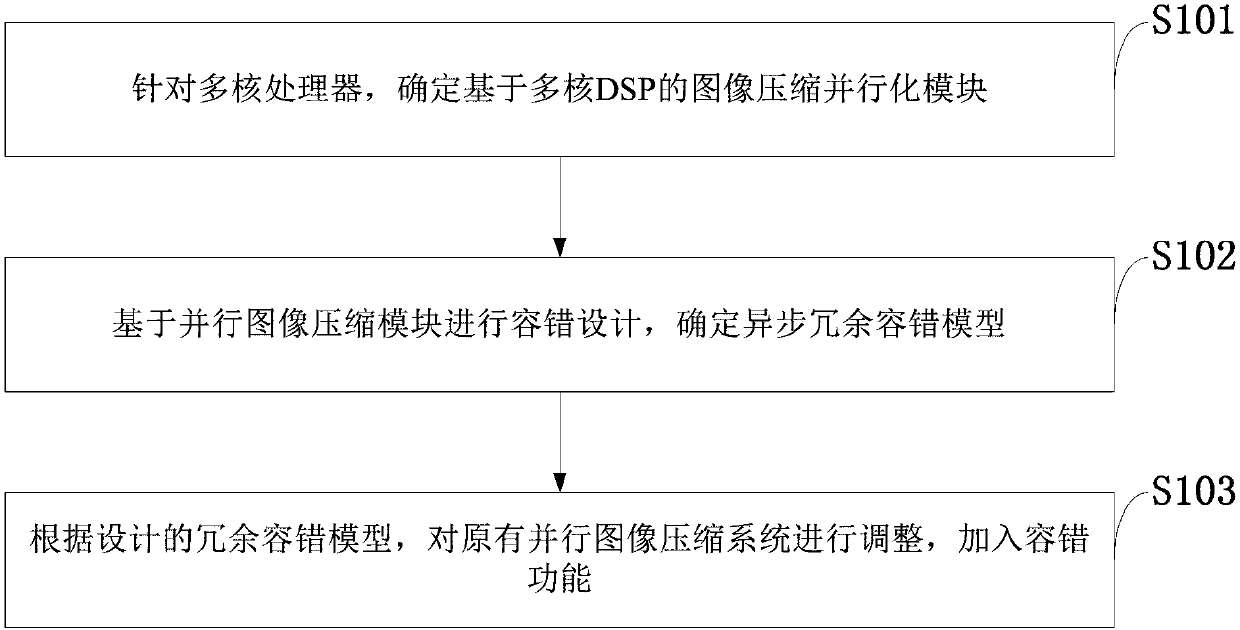

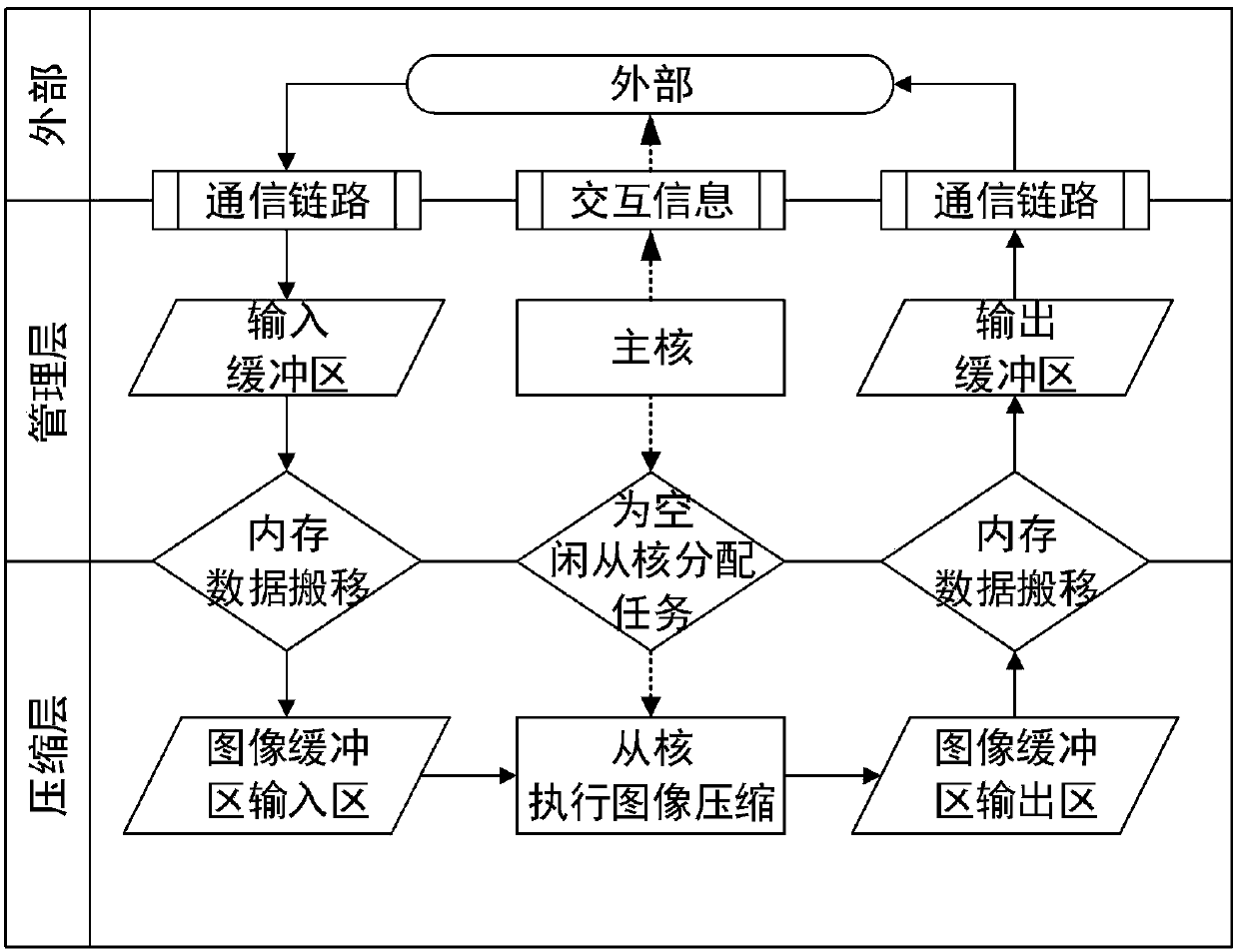

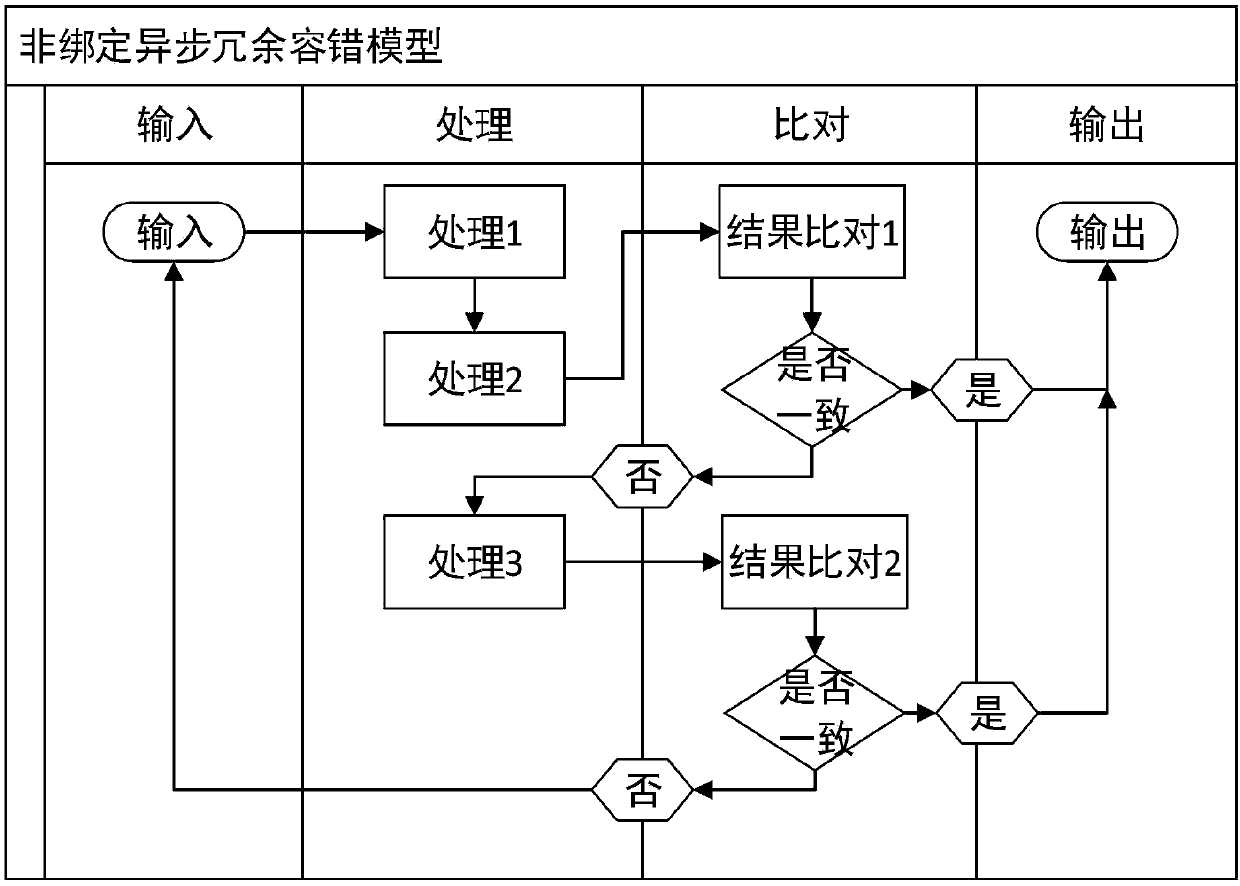

Method used

Image

Examples

Embodiment Construction

[0042] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0043] The history of computer development shows that many methods that were originally implemented in hardware can also be implemented in software. On COTS microprocessors, the lack of fault tolerance of COTS devices can be made up for by implementing software fault-tolerant technology for hardware transient faults. Many experiments have been carried out at home and abroad to explore the application of COTS processors in the space environment. The results show that the software fault-tolerant method for hardware faults can effectively improve the reliability of space computers based on COTS devices, and can well cope with t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com