Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38 results about "Boron penetration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for forming a thin film and method for fabricating a semiconductor device

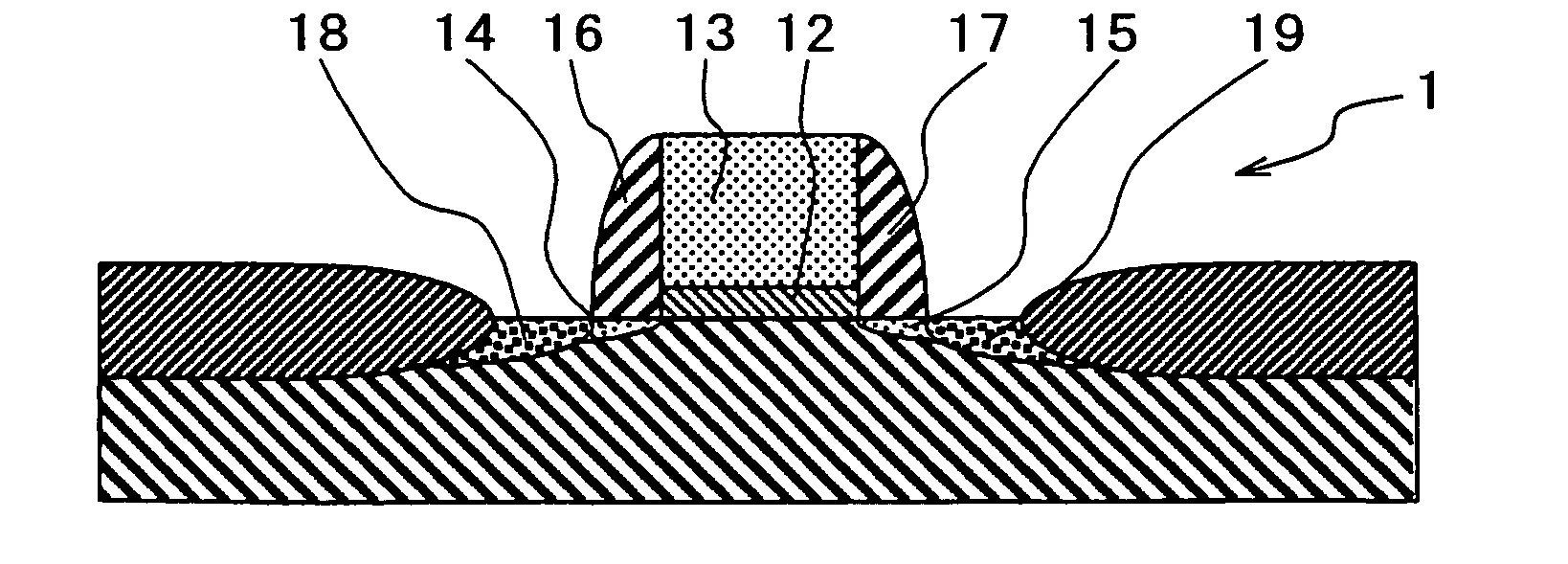

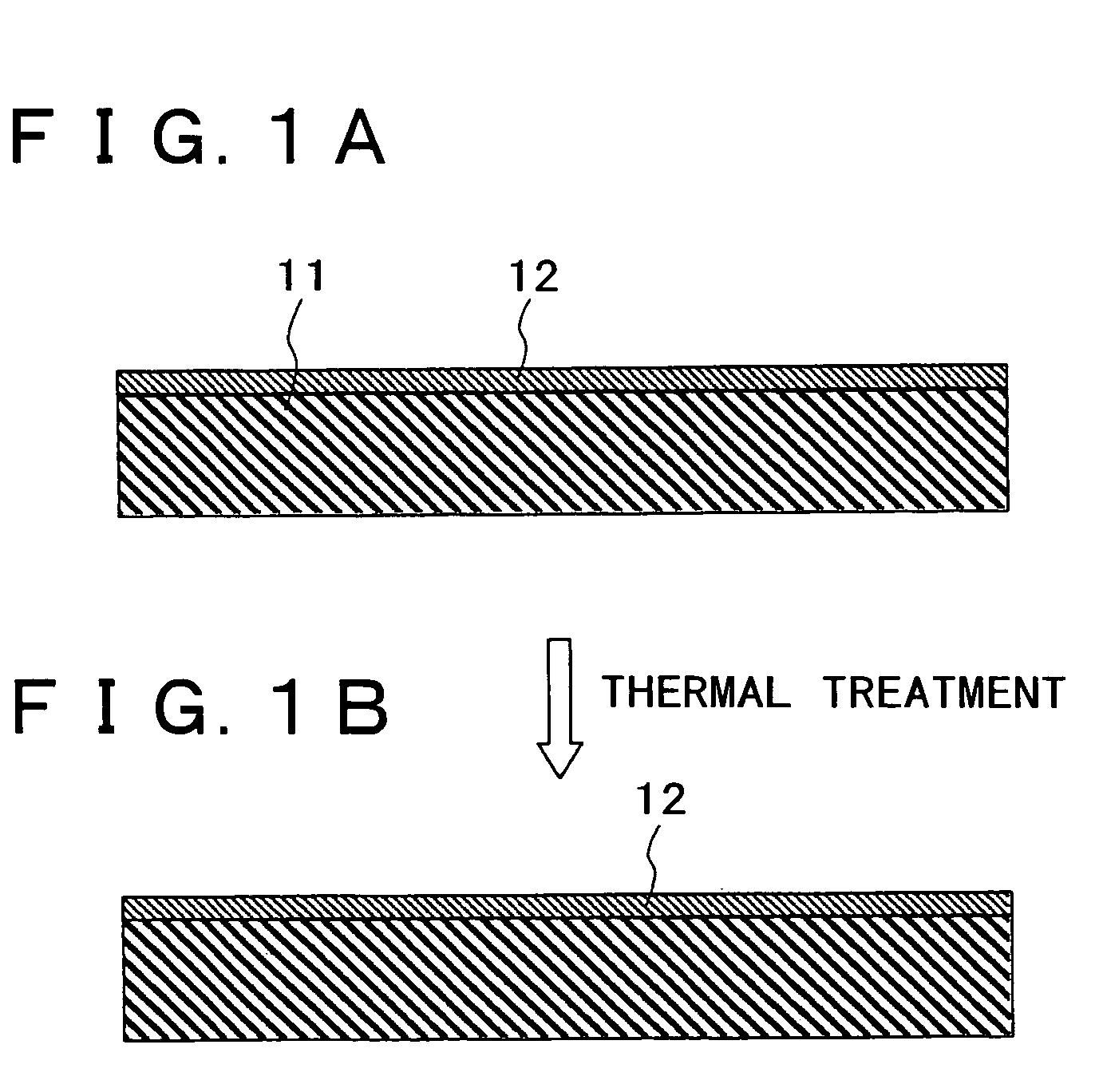

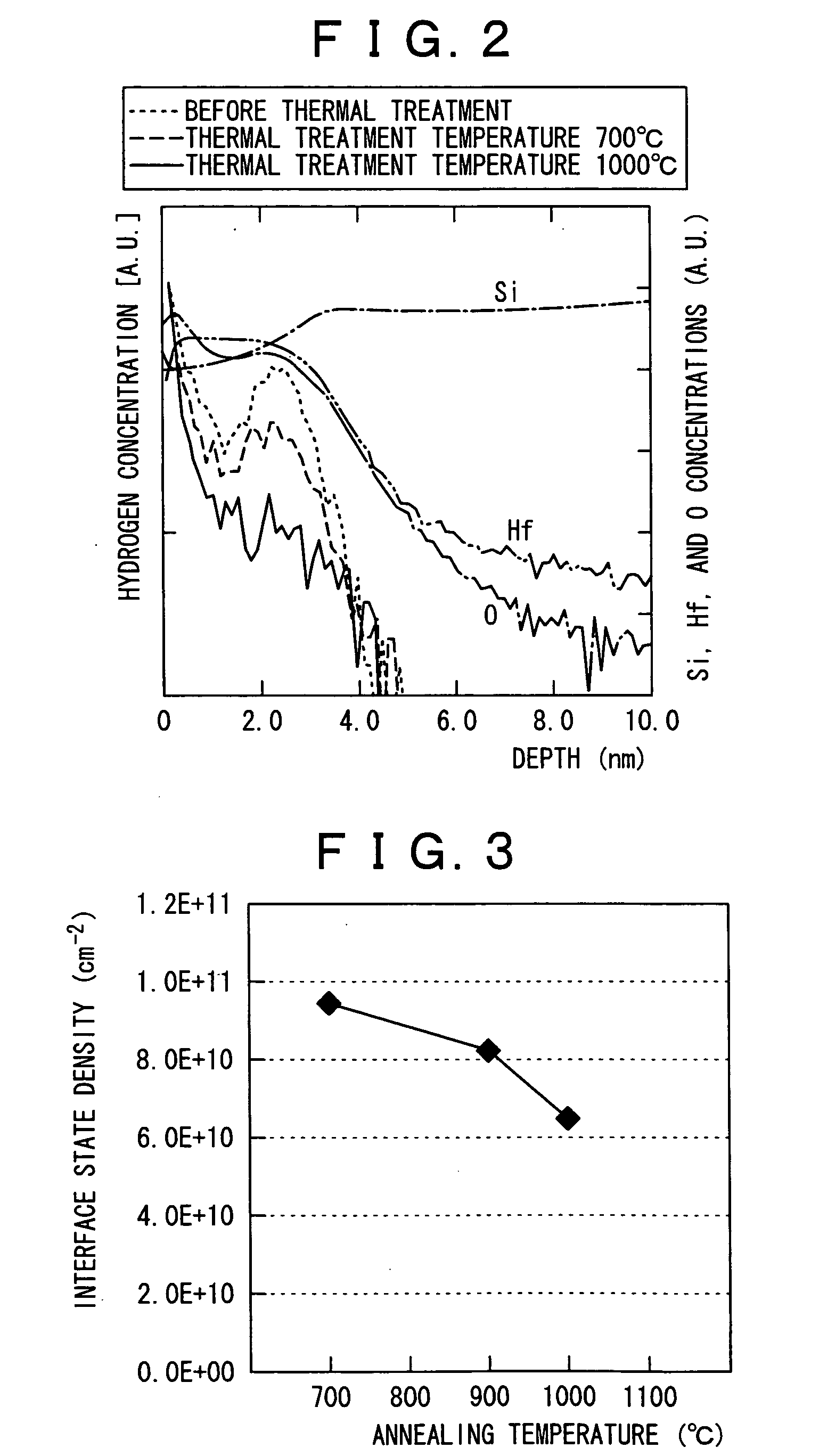

InactiveUS20050070123A1Improve mobility and reliabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricHafnium

By conducting a high temperature annealing in a nitrogen atmosphere at a temperature at which a hafnium silicate film undergoes no phase separation, hydrogen contained in the film is removed and prevention of boron penetration is made possible. The present invention provides a method for forming a thin film including a step of forming a hafnium silicate film on a substrate by an atomic layer deposition method and a step of carrying out thermal treatment on the hafnium silicate film at a thermal treatment temperature equal to or higher than a temperature at which hydrogen contained in the hafnium silicate film is removed and lower than a temperature at which the hafnium silicate film undergoes no phase separation, and a method for fabricating a semiconductor device for forming a gate dielectric film using the method for forming a thin film.

Owner:SONY CORP

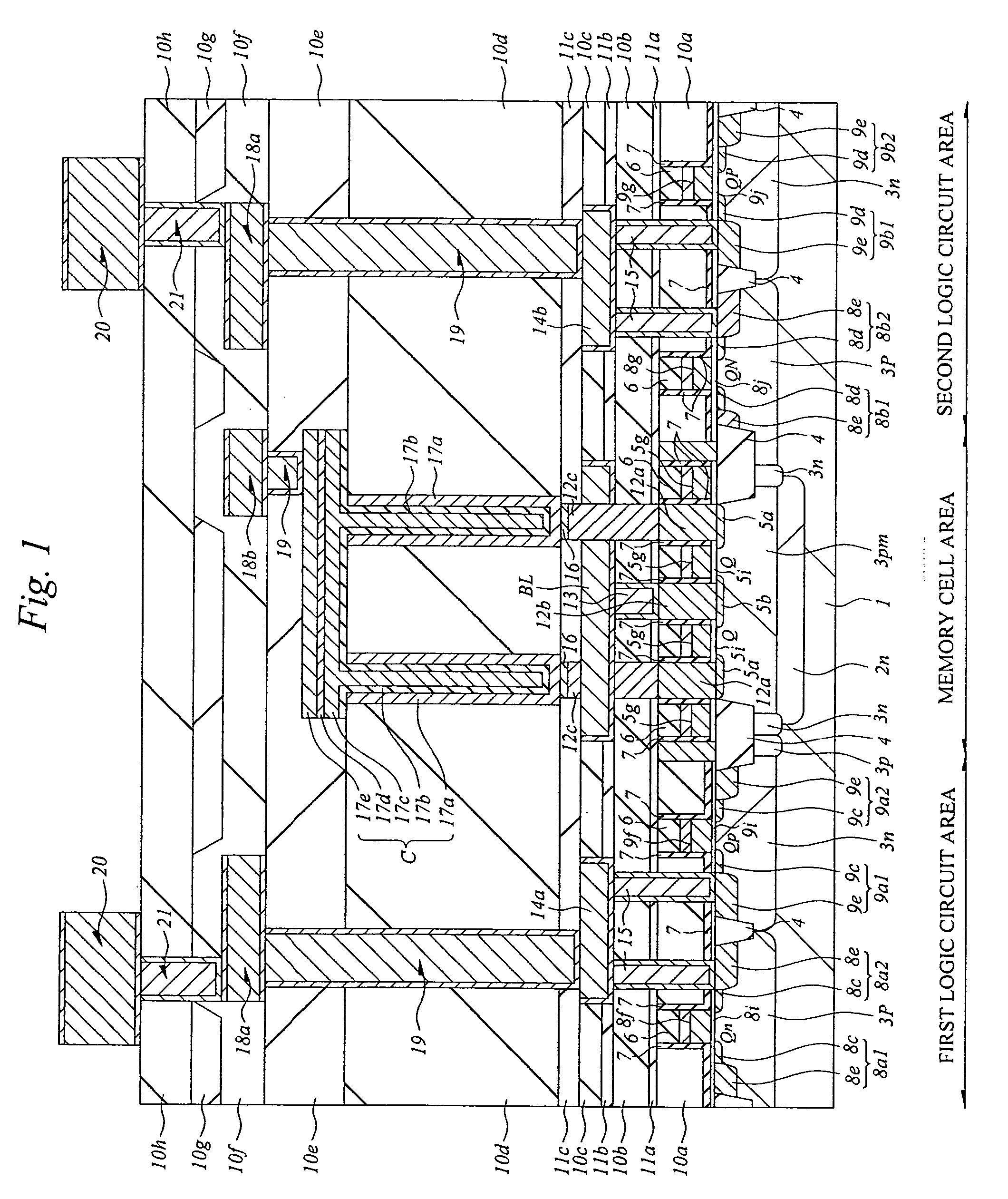

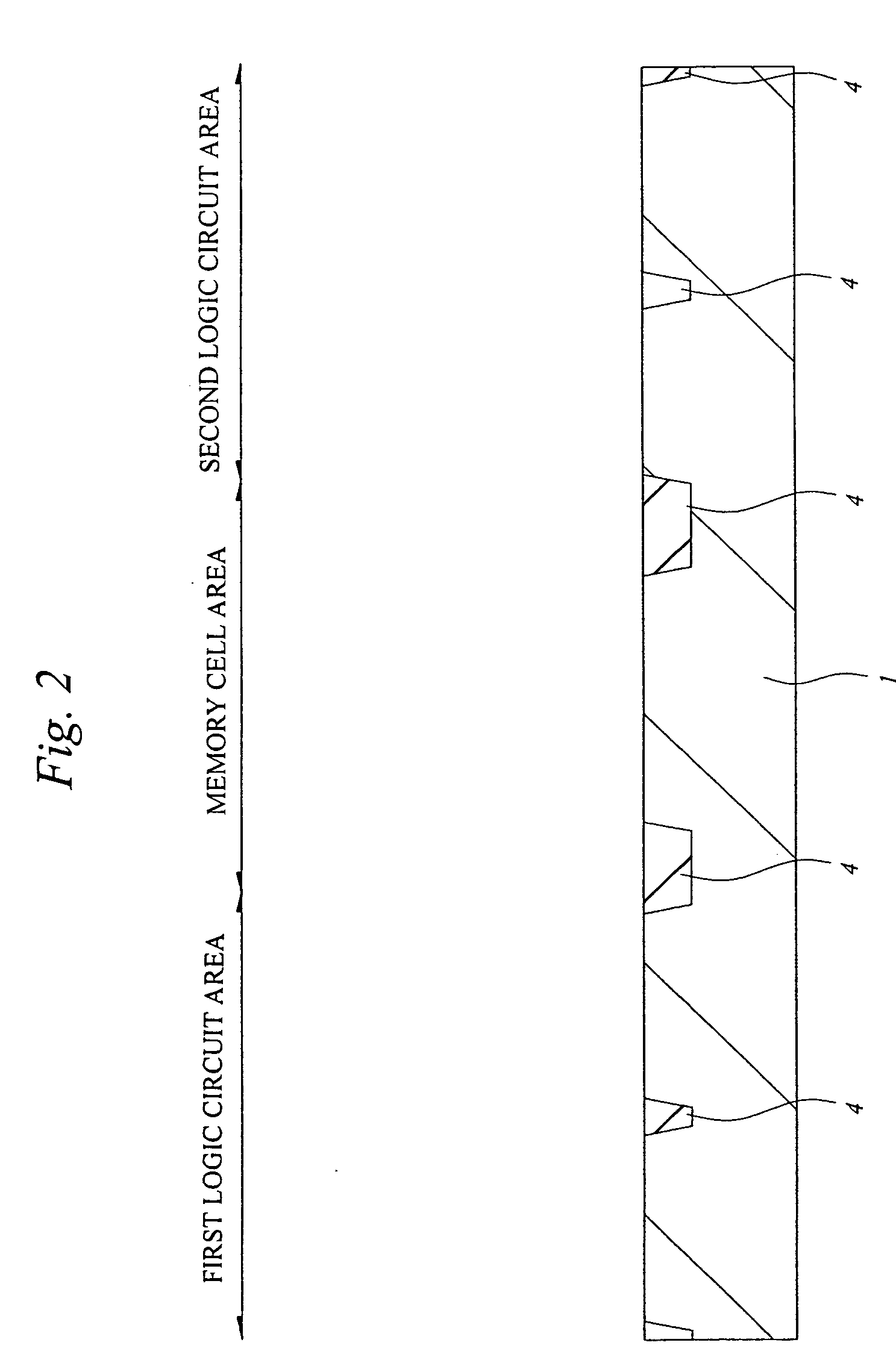

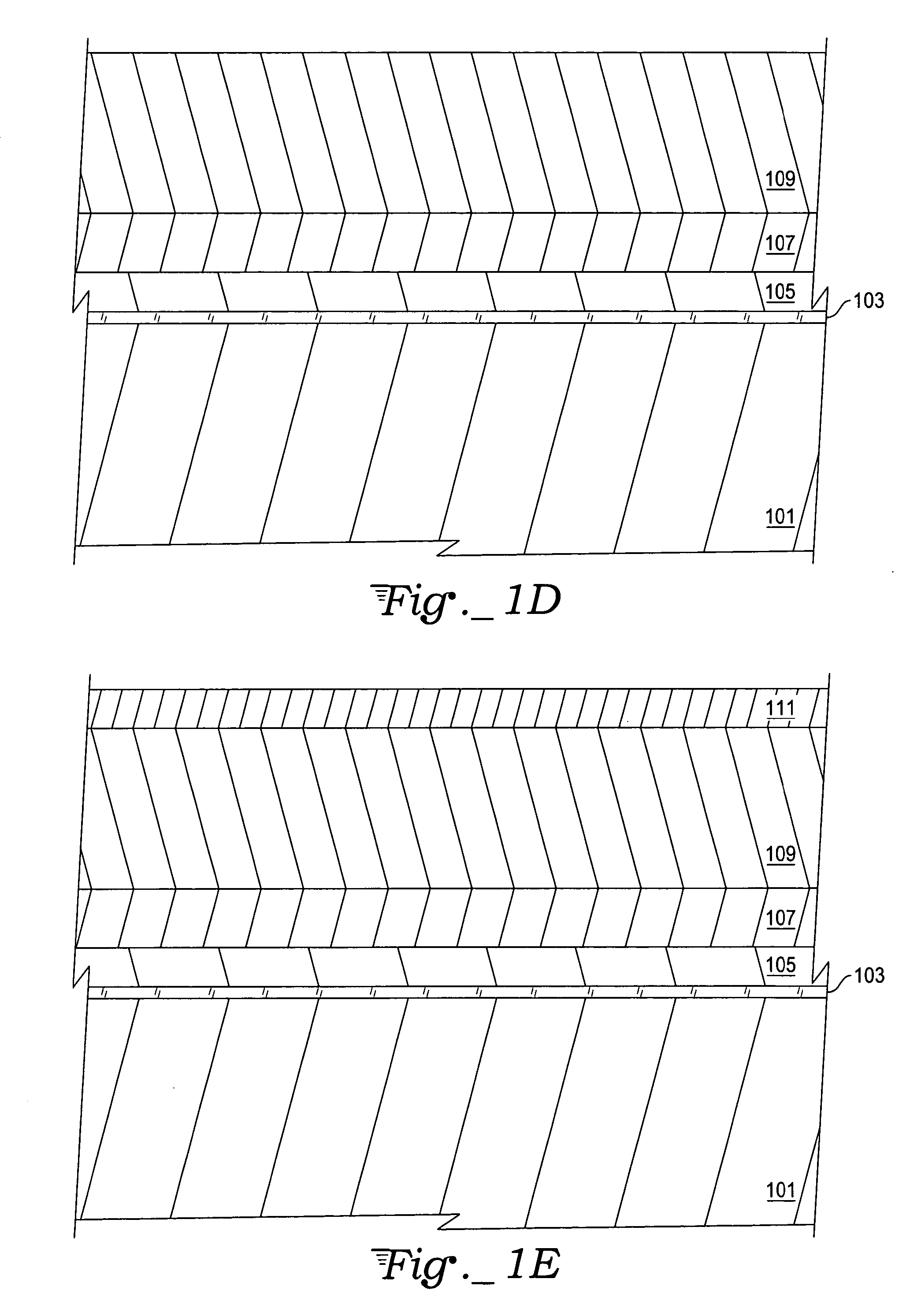

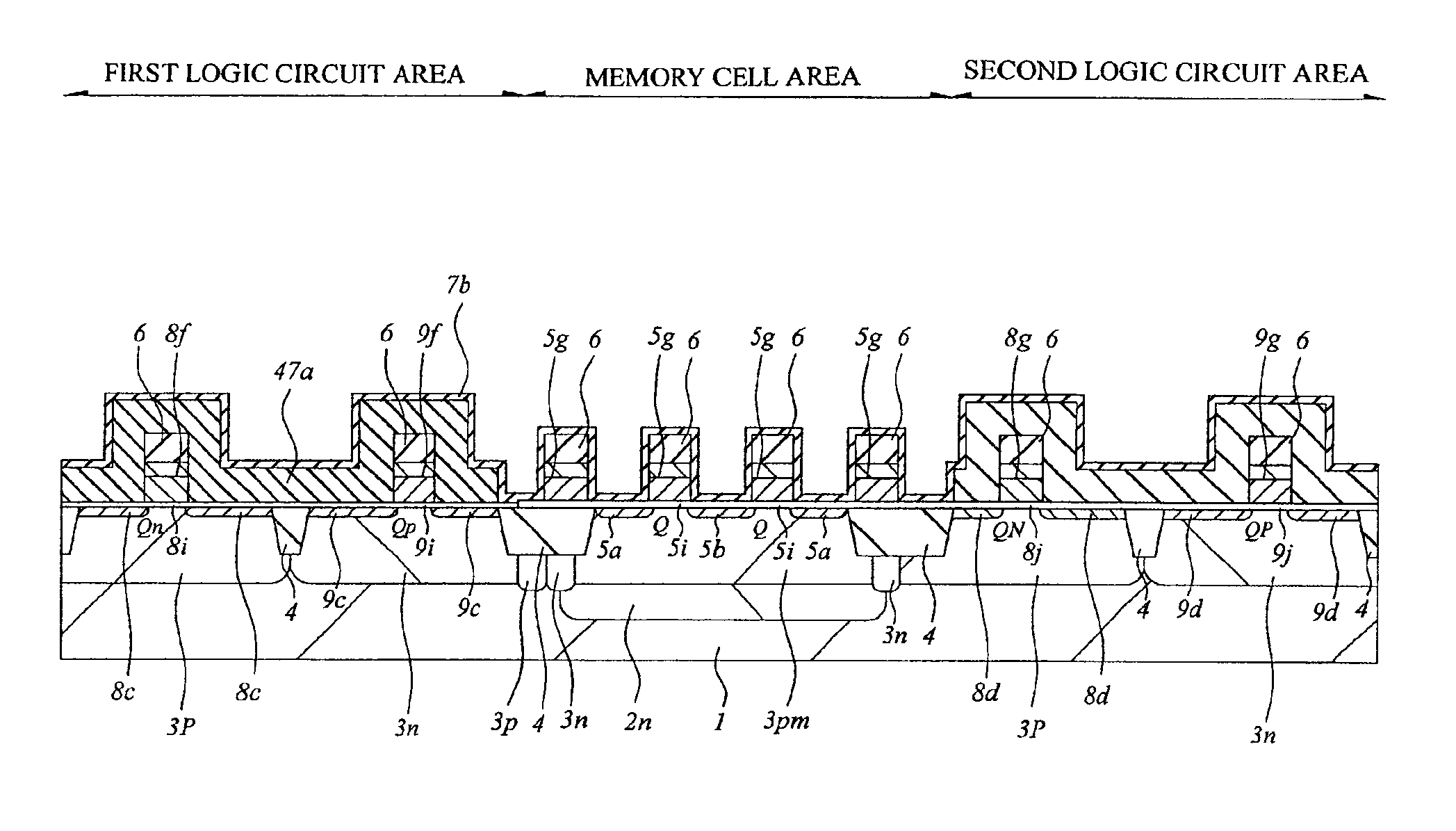

Semiconductor integrated circuit device and production method thereof

InactiveUS20050208716A1Improve refresh featureEasy to integrateTransistorSolid-state devicesDram memoryEngineering

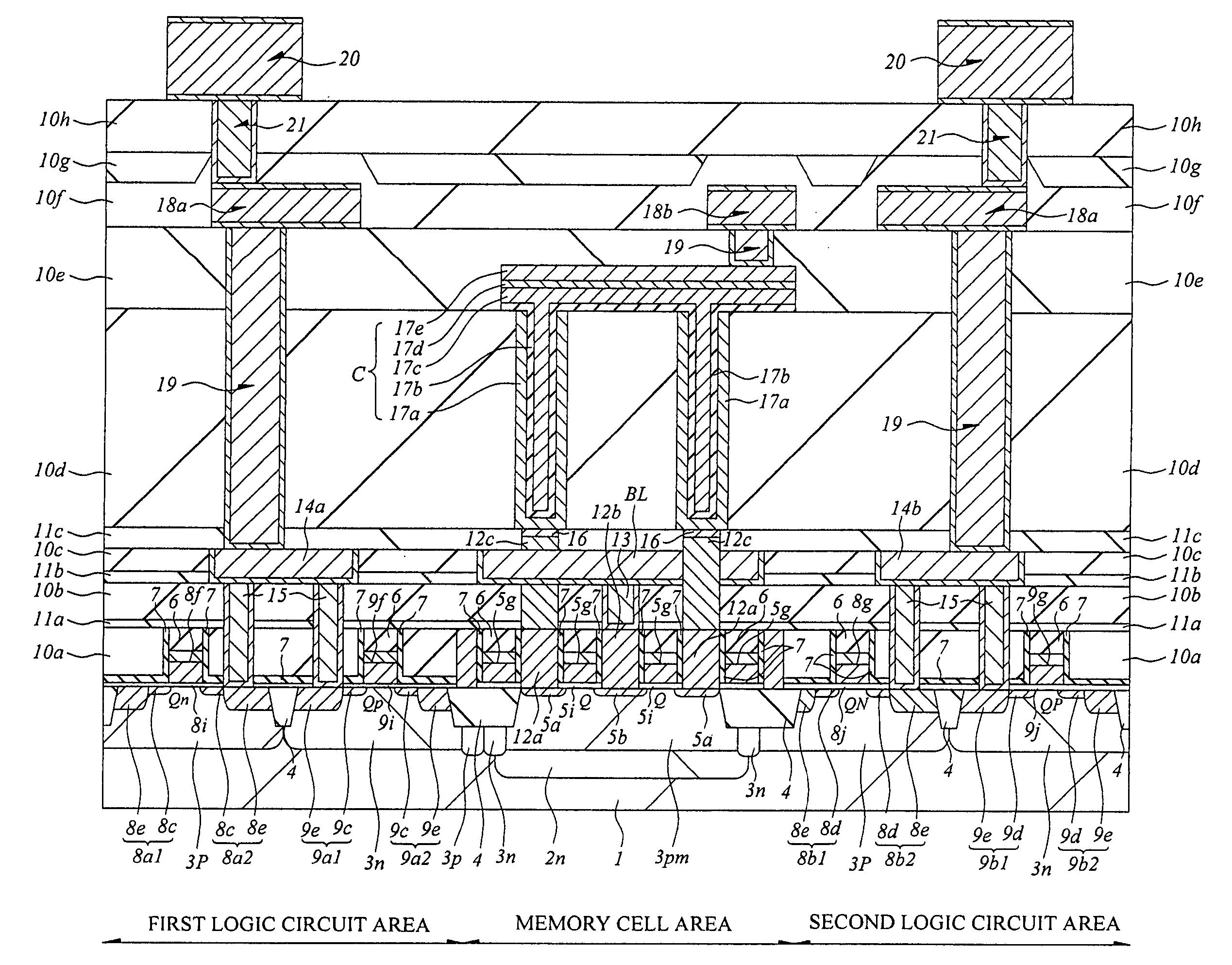

A refresh characteristic of a DRAM memory cell is improved and the performance of a MISFET formed in the periphery thereof and constituting a logic circuit is improved. Each gate electrode in a memory cell area is formed of p type polycrystalline silicon, and a cap insulating film on each gate electrode and a sidewall film on the sidewall thereof are formed of a silicon oxide film. A polycrystalline silicon film formed on the gate electrodes and between the gate electrodes is polished by a CMP method, and thereby contact electrodes are formed. Also, sidewall films each composed of a laminated film of the silicon oxide film and the polycrystalline silicon film are formed on the sidewall of the gate electrodes in the logic circuit area, and these films are used as a mask to form semiconductor areas. As a result, it is possible to reduce the boron penetration and form contact electrodes in a self-alignment manner. In addition, the performance of the MISFET constituting the logic circuit can be improved.

Owner:ELPIDA MEMORY INC

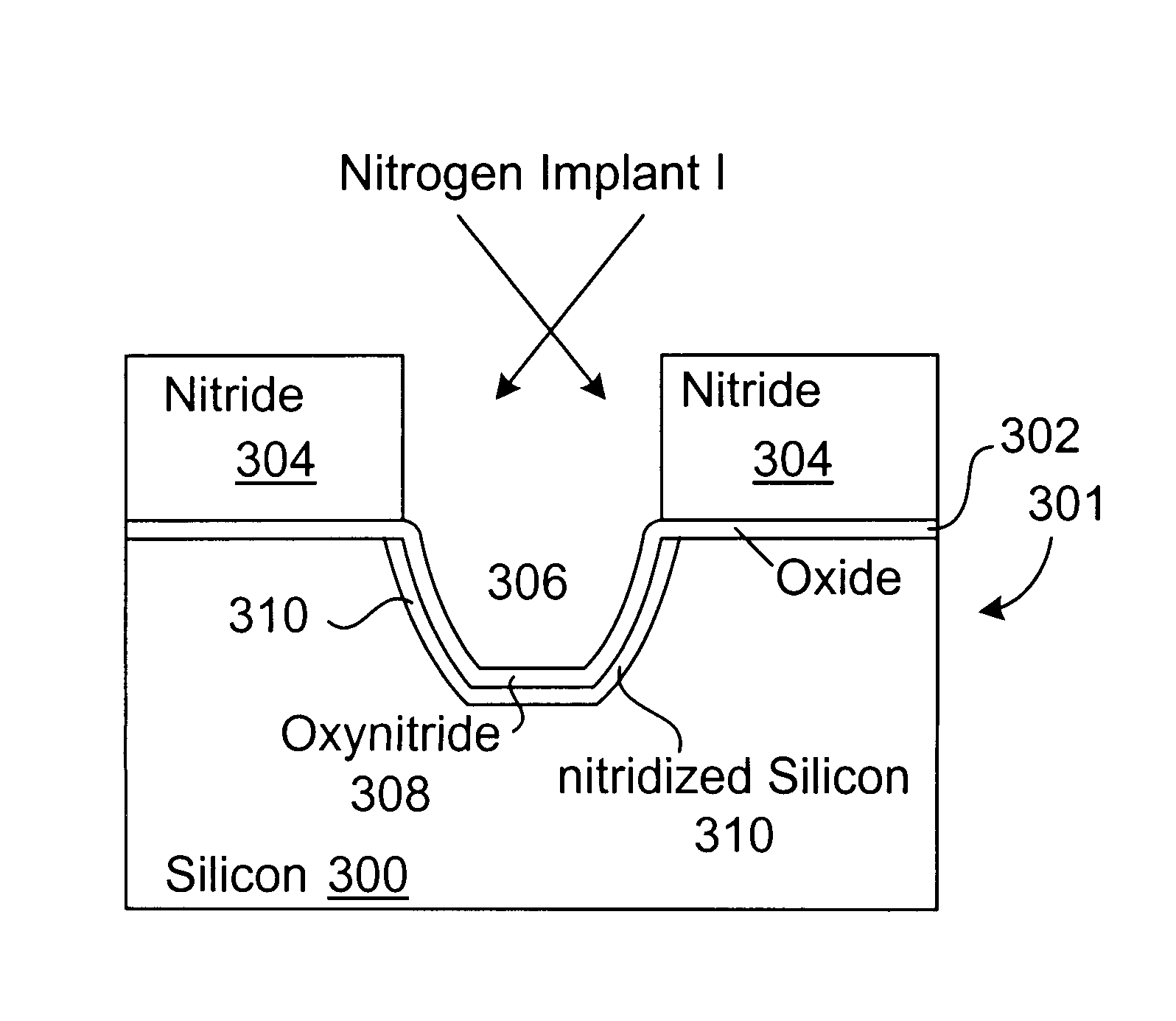

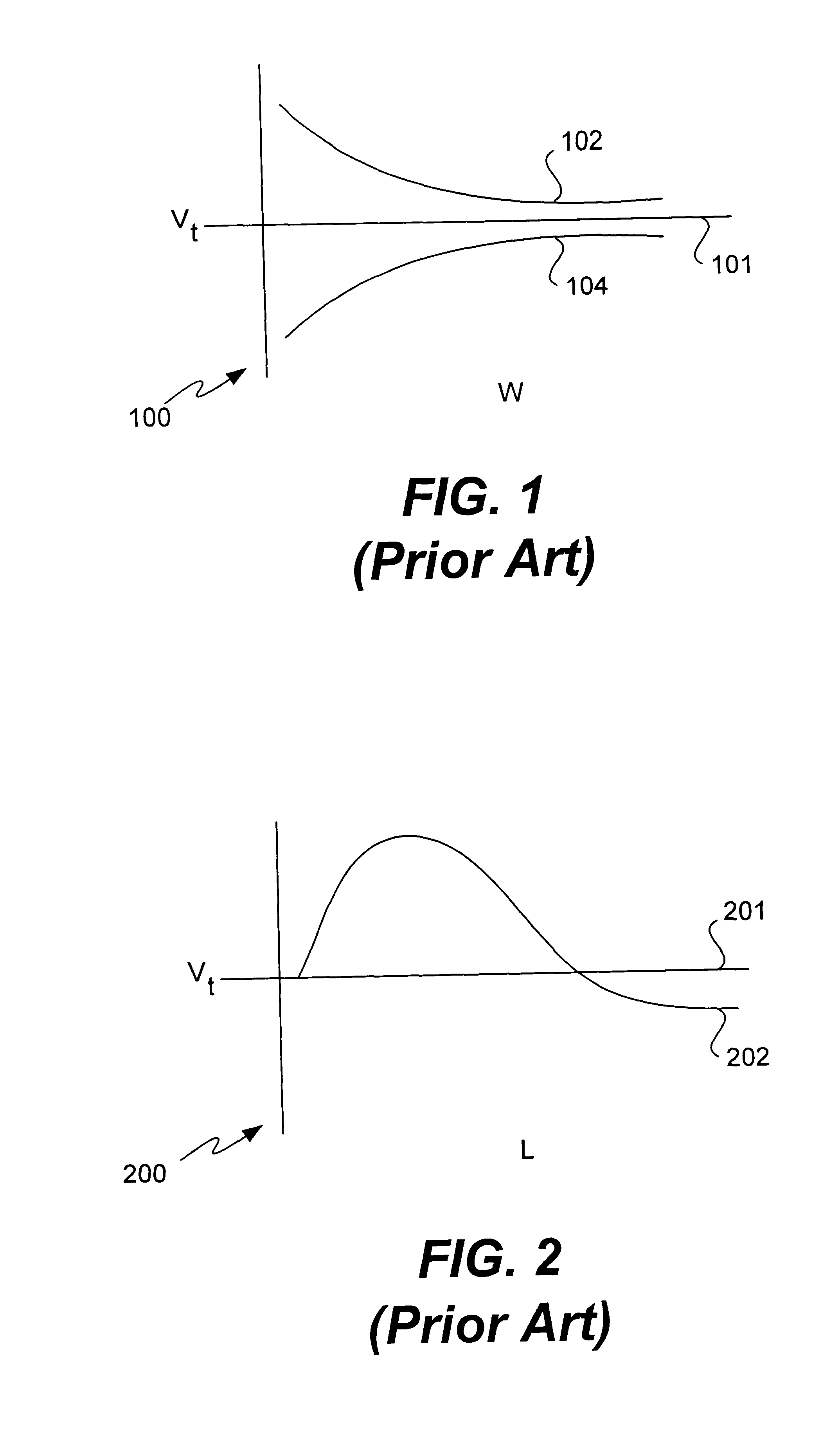

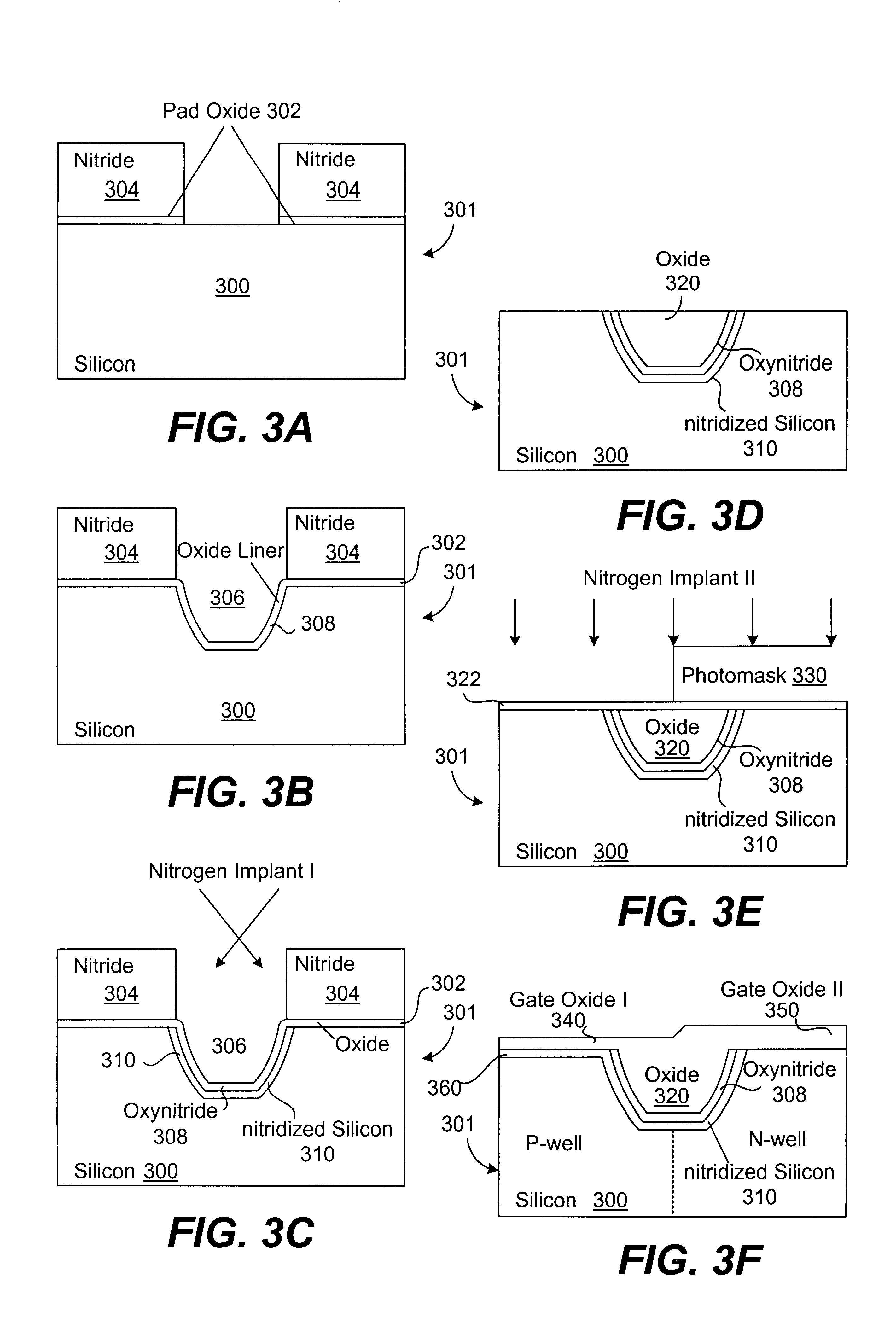

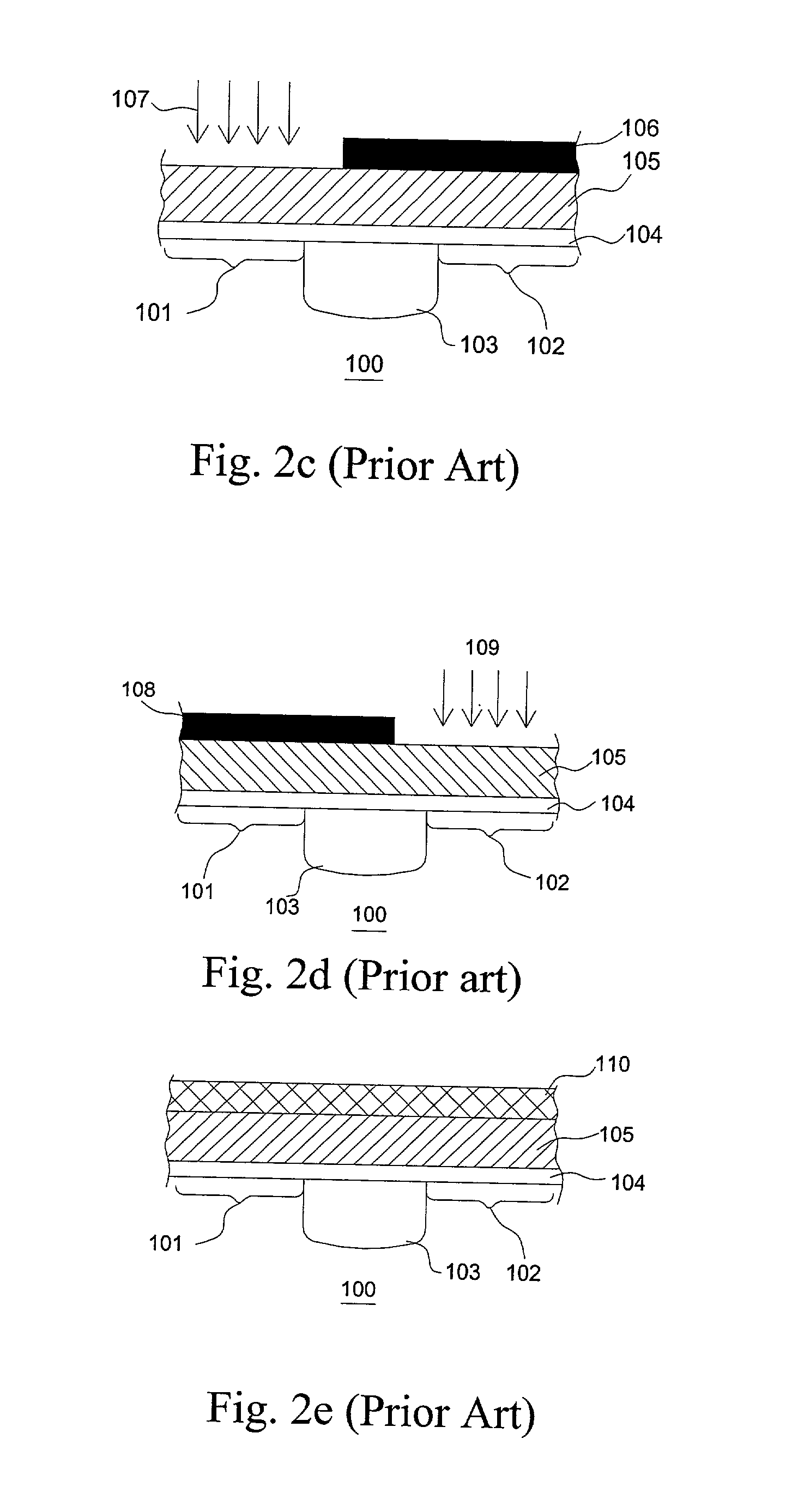

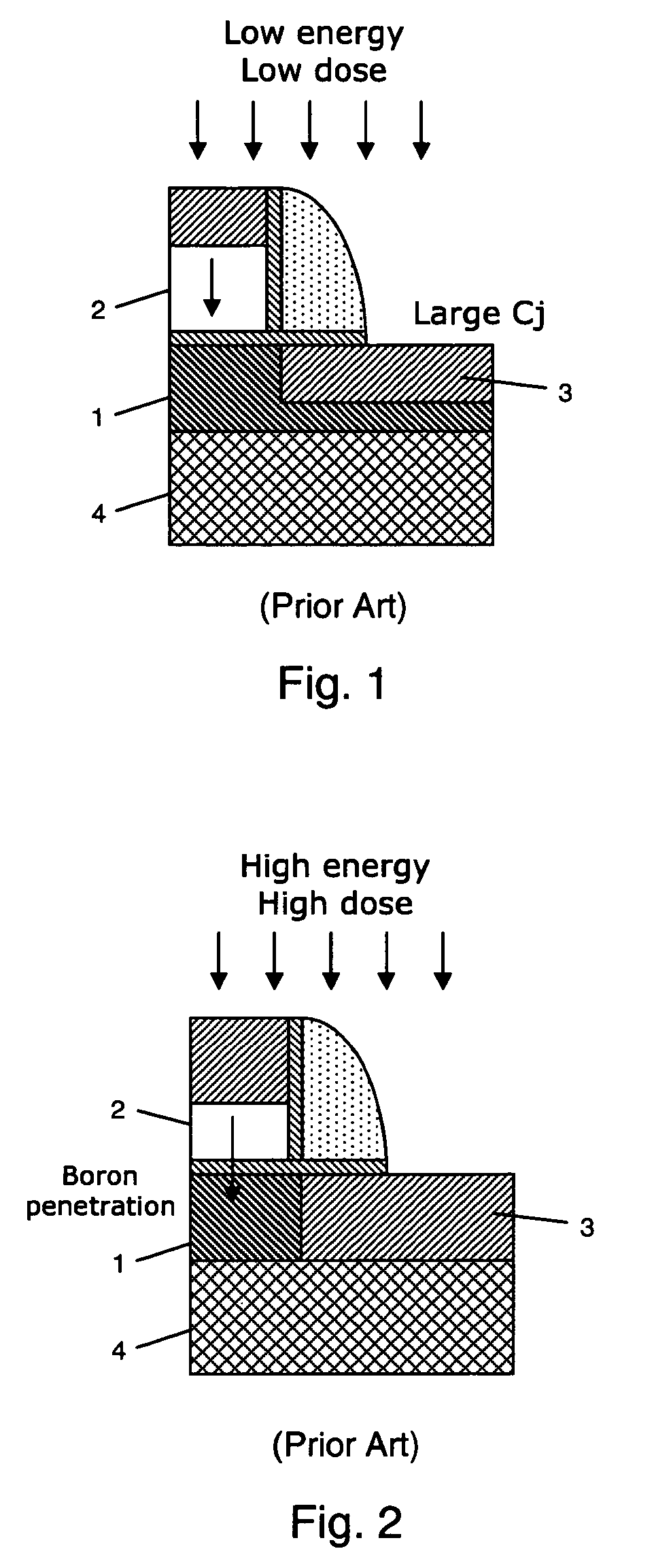

Dual nitrogen implantation techniques for oxynitride formation in semiconductor devices

InactiveUS6323106B1Suppress boron penetrationGood effectSemiconductor/solid-state device manufacturingCMOSNitrogen

Provided is a technique for fabrication of a nitrided gate oxide and shallow trench isolation (STI) oxide liner in a semiconductor depletion into STI oxide and the RNCE in CMOS devices by introducing nitrogen to the STI edges of the p-well. This technique improves isolation performance and is also effective to harden the oxide to reduce boron penetration. Nitridization of the STI liner may be conducted on its own or in combination with gate oxide nitridization, both with beneficial effect with regard to the RNCE. The nitridization may also be focussed on the channel region of the gate oxide in particular in order to mitigate RSCE.

Owner:BELL SEMICON LLC

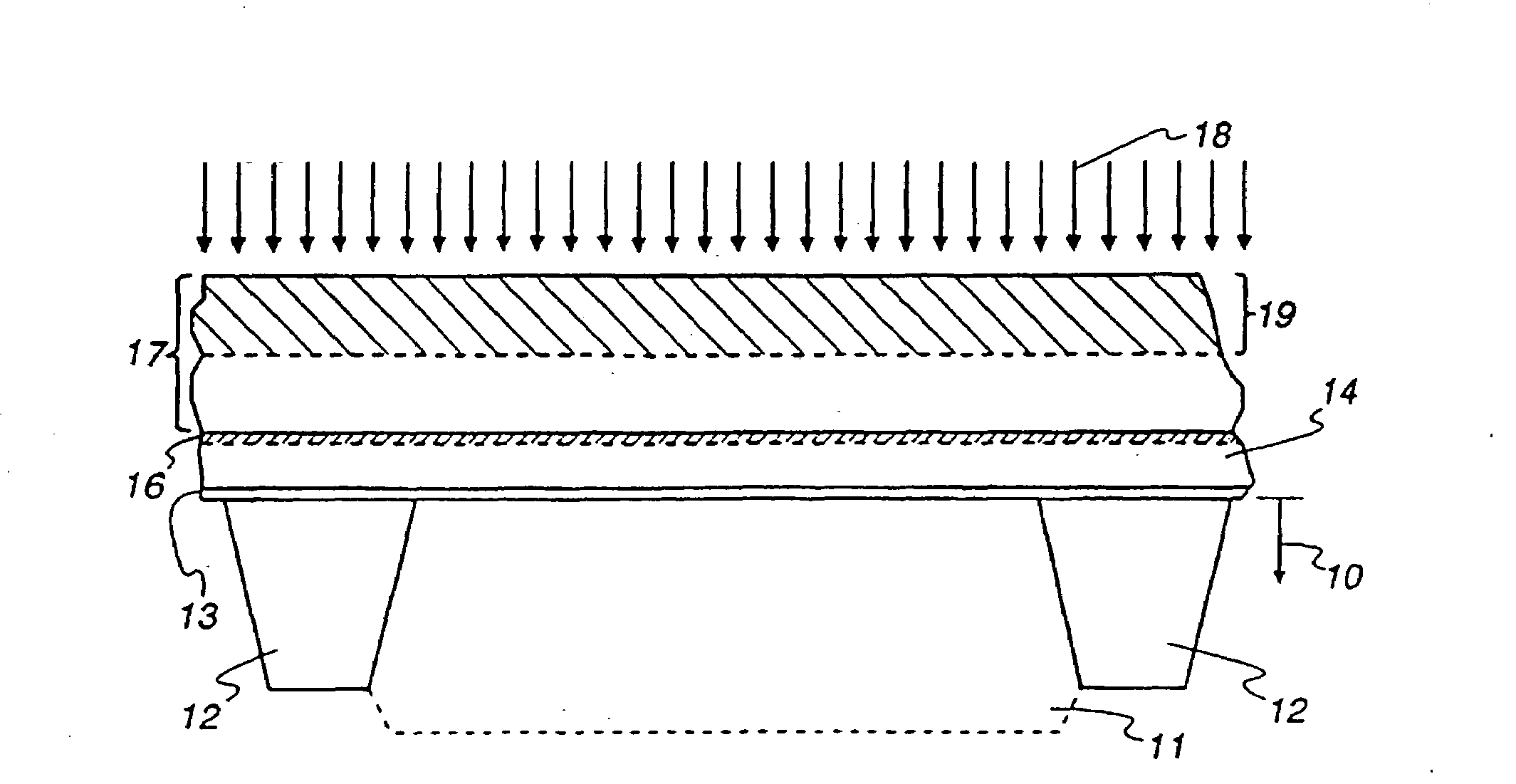

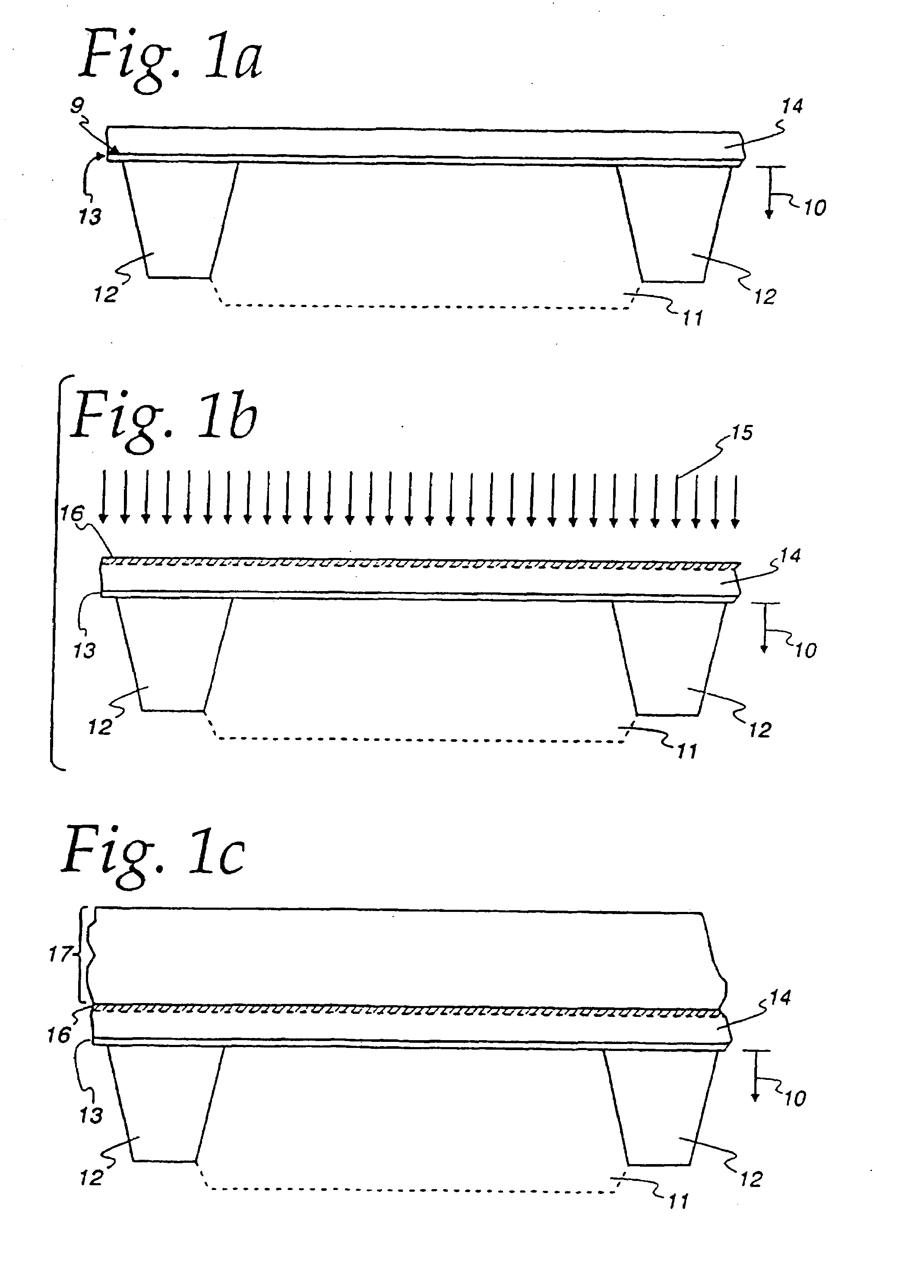

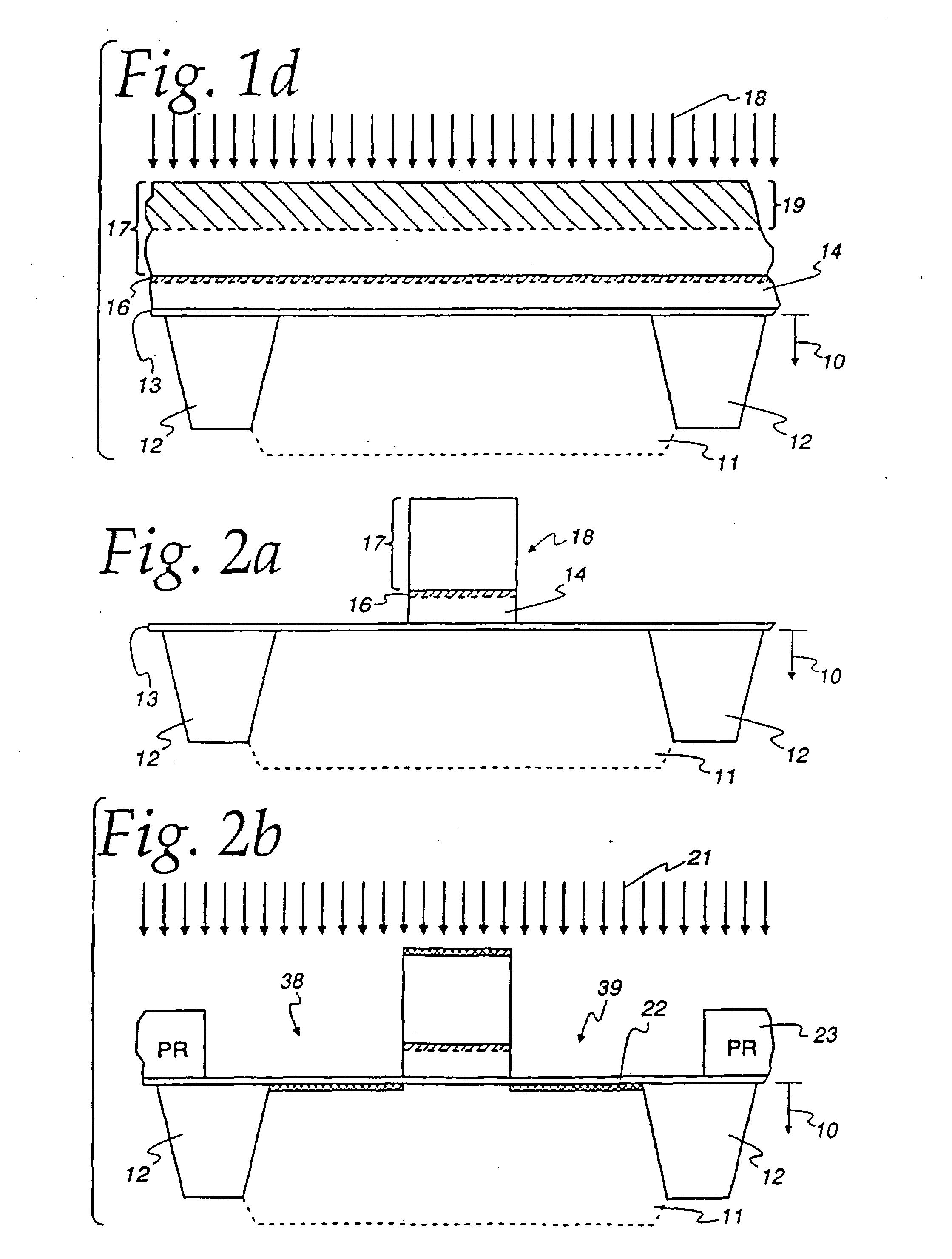

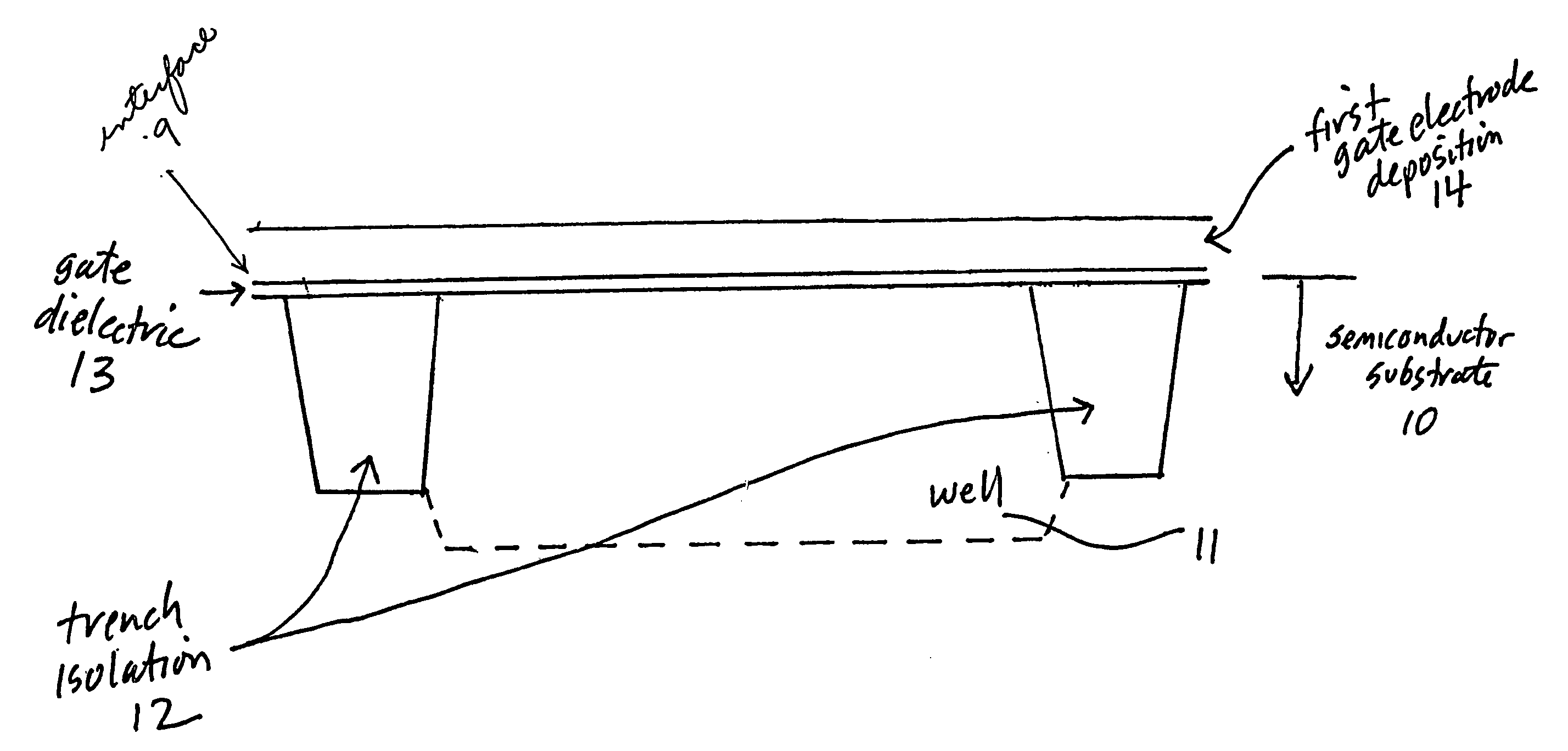

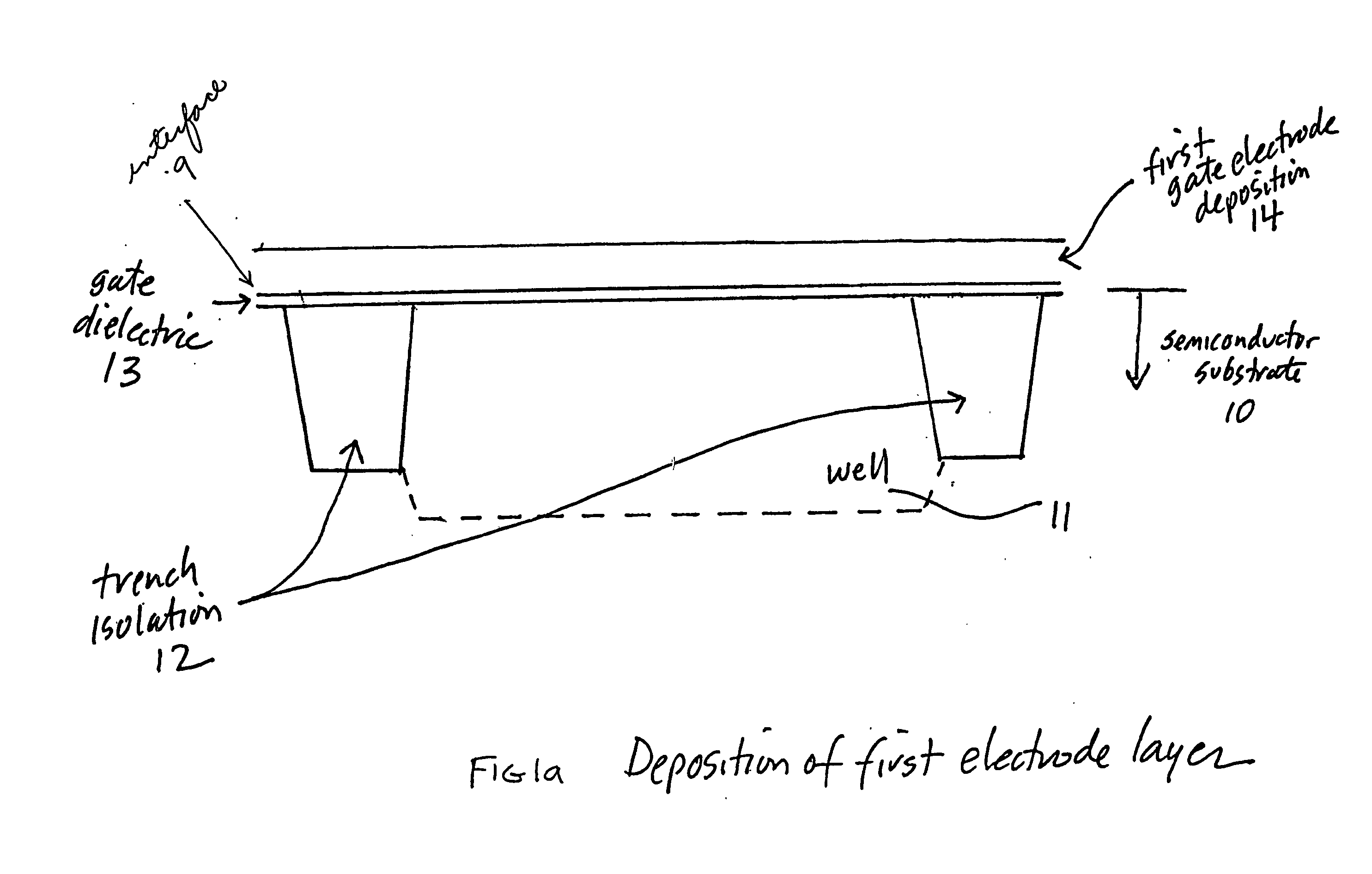

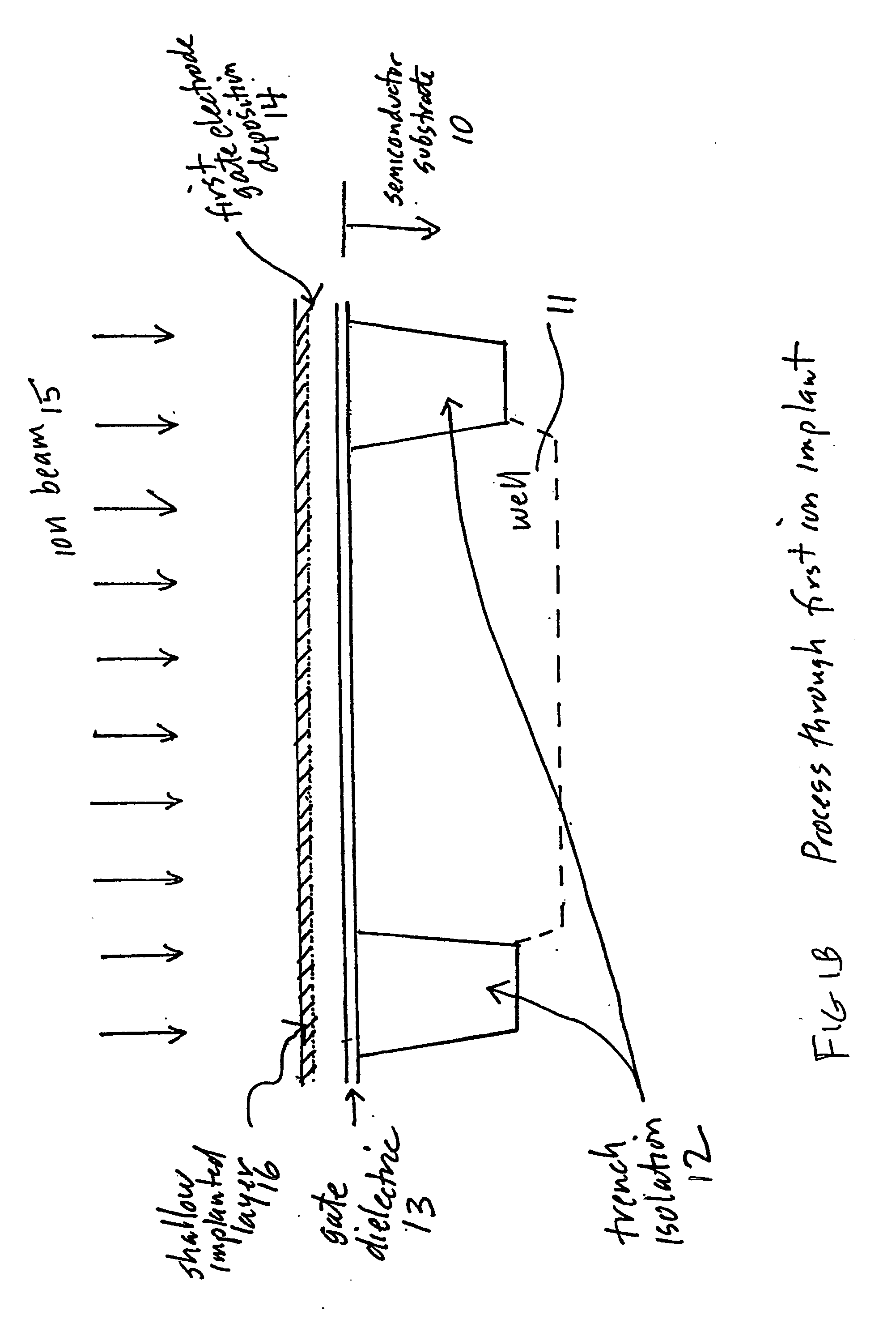

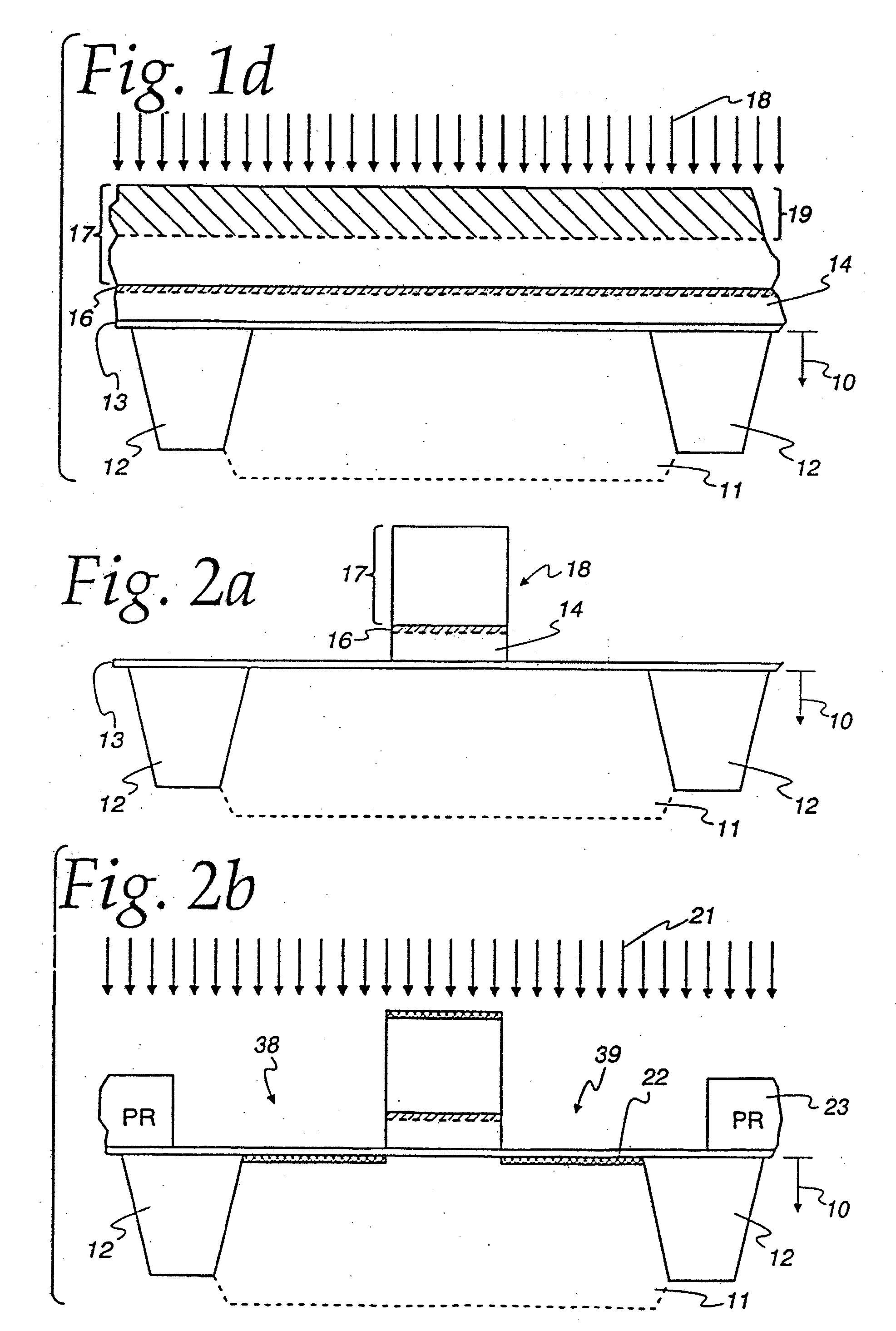

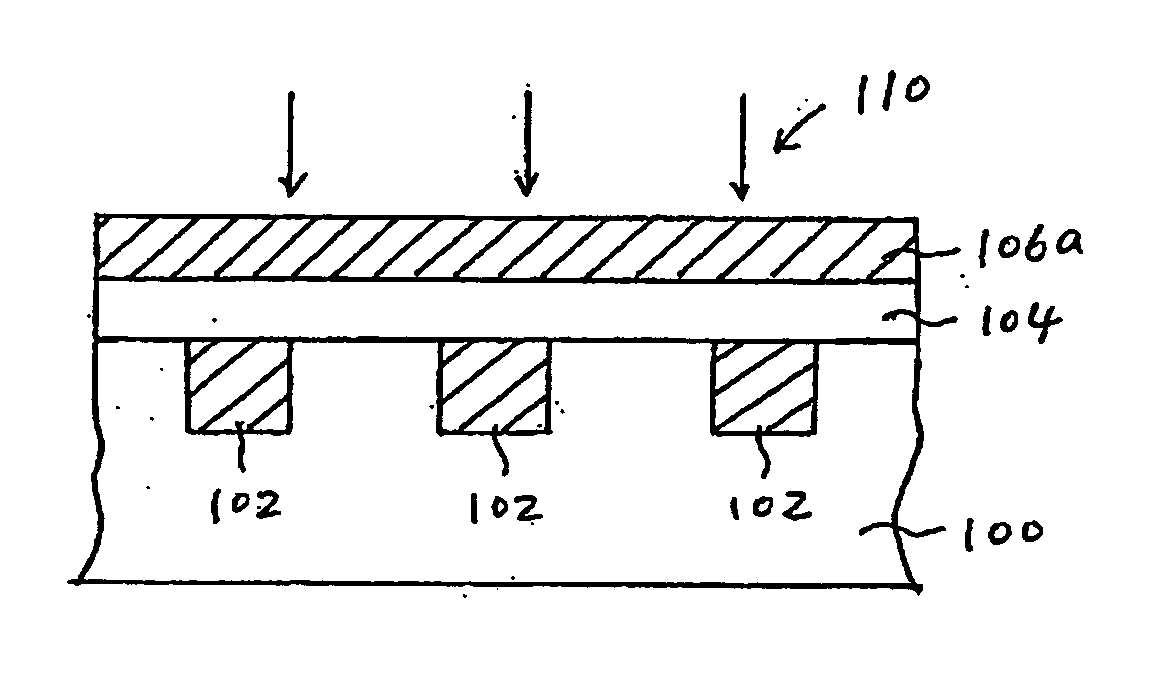

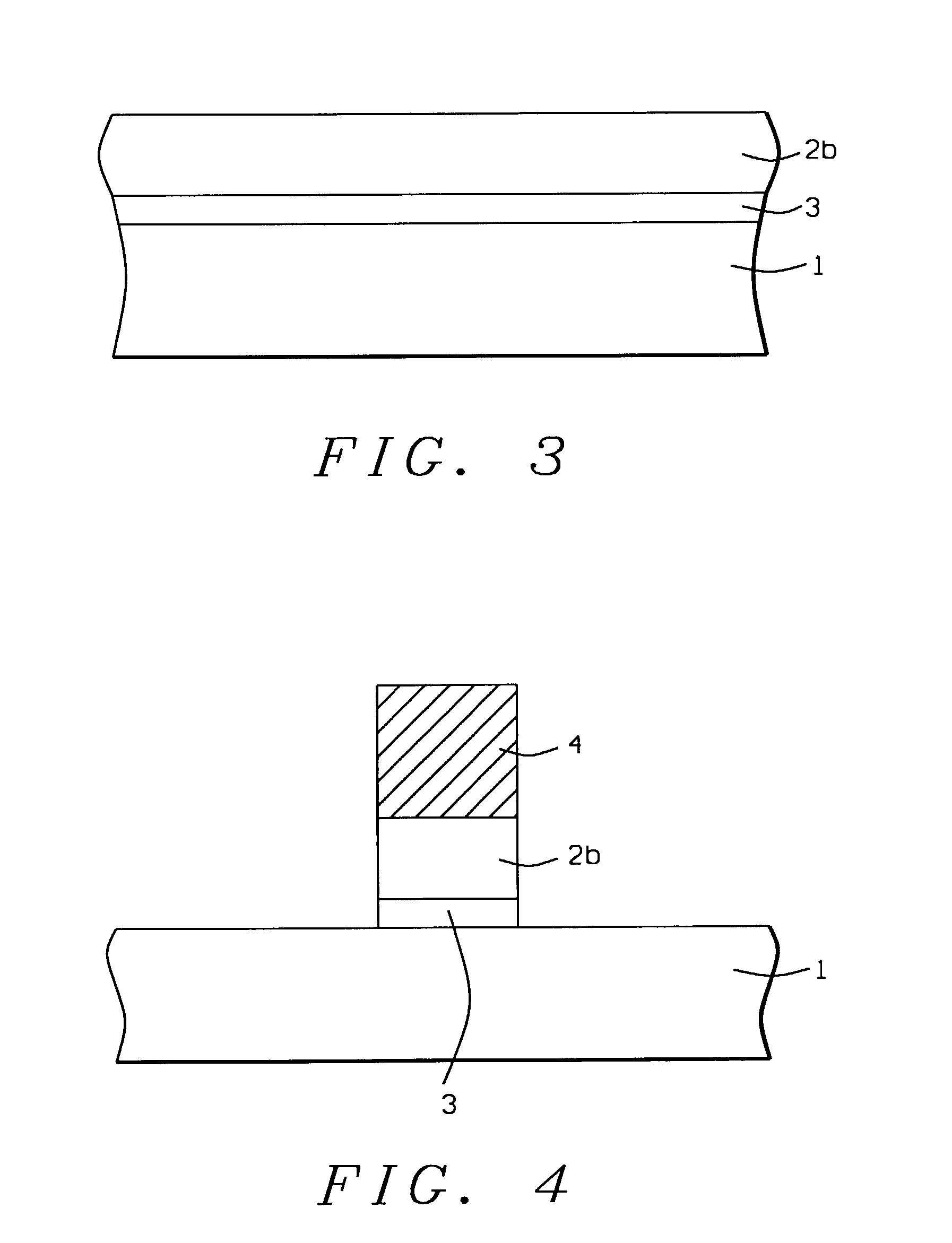

Semiconductor device and method of fabricating a semiconductor device

InactiveUS20080200020A1Increase doseLow effective-energy implant processesTransistorSemiconductor/solid-state device manufacturingDopantGate dielectric

A method is proposed for the fabrication of the gate electrode of a semiconductor device such that the effects of gate depletion are minimized. The method is comprised of a dual deposition process wherein the first step is a very thin layer that is doped very heavily by ion implantation. The second deposition, with an associated ion implant for doping, completes the gate electrode. With the two-deposition process, it is possible to maximize the doping at the gate electrode / gate dielectric interface while minimizing risk of boron penetration of the gate dielectric. A further development of this method includes the patterning of both gate electrode layers with the advantage of utilizing the drain extension and source / drain implants as the gate doping implants and the option of offsetting the two patterns to create an asymmetric device. A method is also provided for the formation of shallow junctions in a semiconductor substrate by diffusion of dopant from an implanted layer contained within a dielectric layer into the semiconductor surface. Further, the ion implanted layer is provided with a second implanted species, such as hydrogen, in addition to the intended dopant species, wherein said species enhances the diffusivity of the dopant in the dielectric layer.

Owner:SERMEQUIP INC

Semiconductor device and method of fabricating a semiconductor device

InactiveUS20060099812A1Increase doseRemove constraintsTransistorSolid-state devicesDopantGate dielectric

A method is proposed for the fabrication of the gate electrode of a semiconductor device such that the effects of gate depletion are minimized. The method is comprised of a dual deposition process wherein the first step is a very thin layer that is doped very heavily by ion implantation. The second deposition, with an associated ion implant for doping, completes the gate electrode. With the two-deposition process, it is possible to maximize the doping at the gate electrode / gate dielectric interface while minimizing risk of boron penetration of the gate dielectric. A further development of this method includes the patterning of both gate electrode layers with the advantage of utilizing the drain extension and source / drain implants as the gate doping implants and the option of offsetting the two patterns to create an asymmetric device. A method is also provided for the formation of shallow junctions in a semiconductor substrate by diffusion of dopant from an implanted layer contained within a dielectric layer into the semiconductor surface. Further, the ion implanted layer is provided with a second implanted species, such as hydrogen, in addition to the intended dopant species, wherein said species enhances the diffusivity of the dopant in the dielectric layer.

Owner:SEMEQUIP

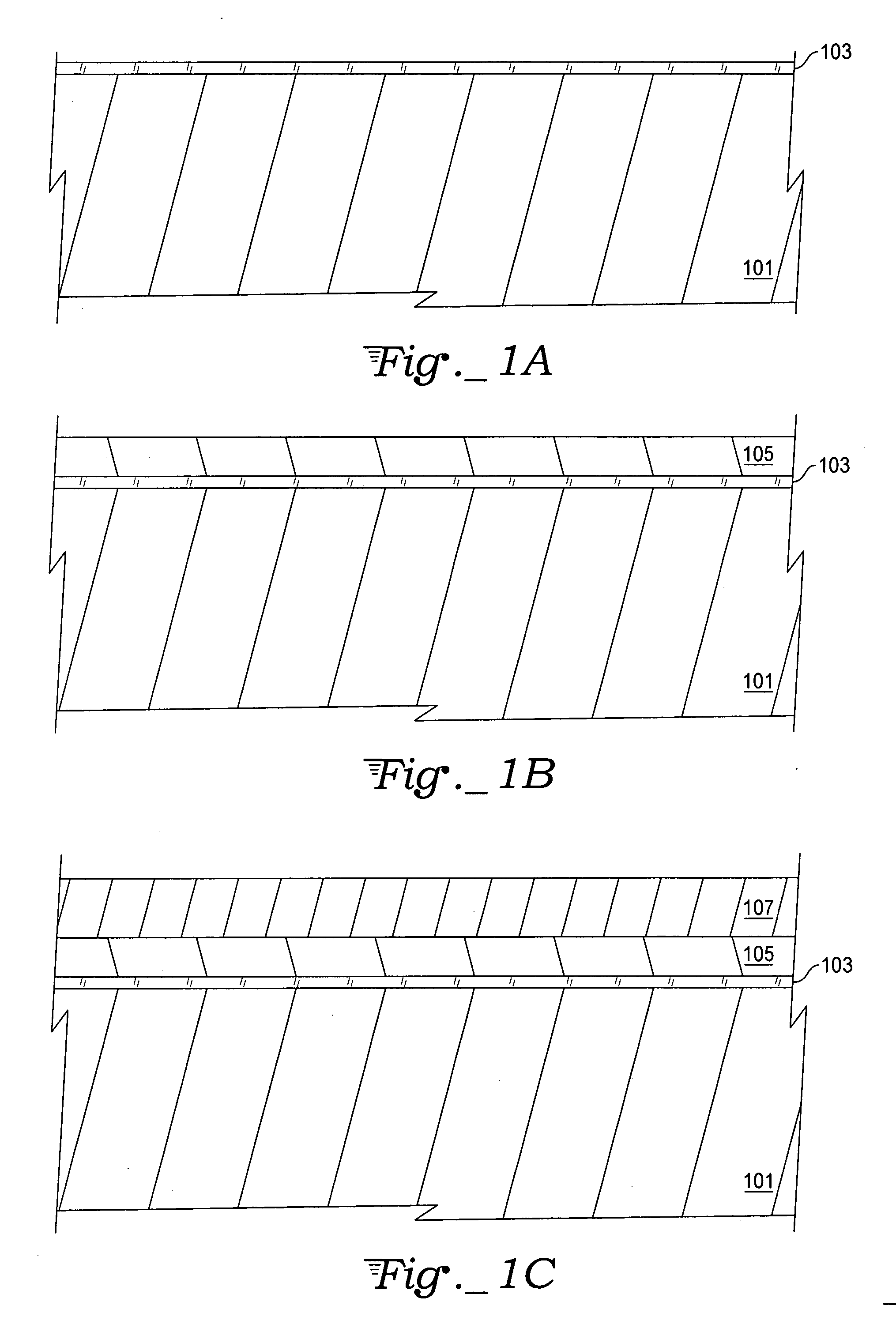

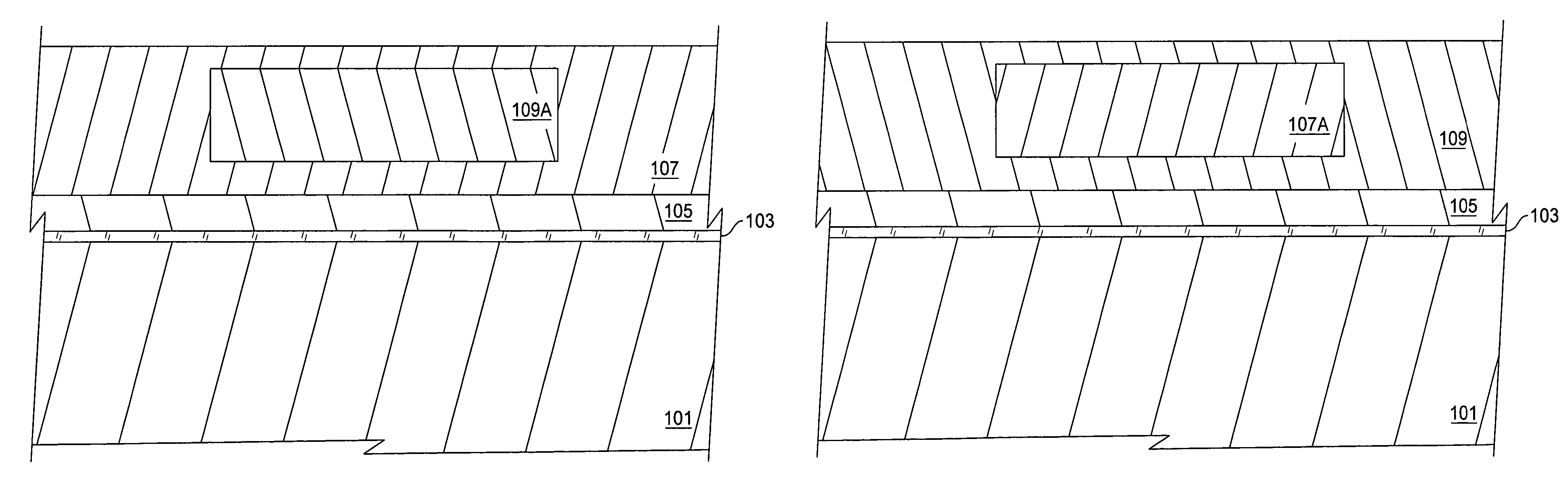

Semiconductive film with dopant diffusion barrier and tunable work function

ActiveUS20070080411A1Inhibition effectSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricBlocking layer

A method of fabricating a semiconductive film stack for use as a polysilicon germanium gate electrode to address problems associated with implant and diffusion of dopants. Achieving a sufficiently high active dopant concentration at a gate-dielectric interface while avoiding gate penetration of dopants such as boron is problematic. A higher gate implant dosage or annealing temperature is needed, and boron penetration through the thin gate oxide is inevitably enhanced. Both problems are exacerbated as the gate dielectric becomes thinner. In order to achieve a high level of active dopant concentration next to the gate dielectric without experiencing problems associated with gate depletion and penetration, a method and procedures of applying a diffusion-blocking layer is described with respect to an exemplary MOSFET application. However, a diffusion-blocking concept is also presented, which is readily amenable to a variety of semiconductor related technologies.

Owner:ATMEL CORP

Semiconductor device and method of fabricating a semiconductor device

InactiveUS20100022077A1Increase doseLow effective-energy implant processesTransistorSemiconductor/solid-state device manufacturingDopantGate dielectric

A method is proposed for the fabrication of the gate electrode of a semiconductor device such that the effects of gate depletion are minimized. The method is comprised of a dual deposition process wherein the first step is a very thin layer that is doped very heavily by ion implantation. The second deposition, with an associated ion implant for doping, completes the gate electrode. With the two-deposition process, it is possible to maximize the doping at the gate electrode / gate dielectric interface while minimizing risk of boron penetration of the gate dielectric. A further development of this method includes the patterning of both gate electrode layers with the advantage of utilizing the drain extension and source / drain implants as the gate doping implants and the option of offsetting the two patterns to create an asymmetric device. A method is also provided for the formation of shallow junctions in a semiconductor substrate by diffusion of dopant from an implanted layer contained within a dielectric layer into the semiconductor surface. Further, the ion implanted layer is provided with a second implanted species, such as hydrogen, in addition to the intended dopant species, wherein said species enhances the diffusivity of the dopant in the dielectric layer.

Owner:SEMEQUIP

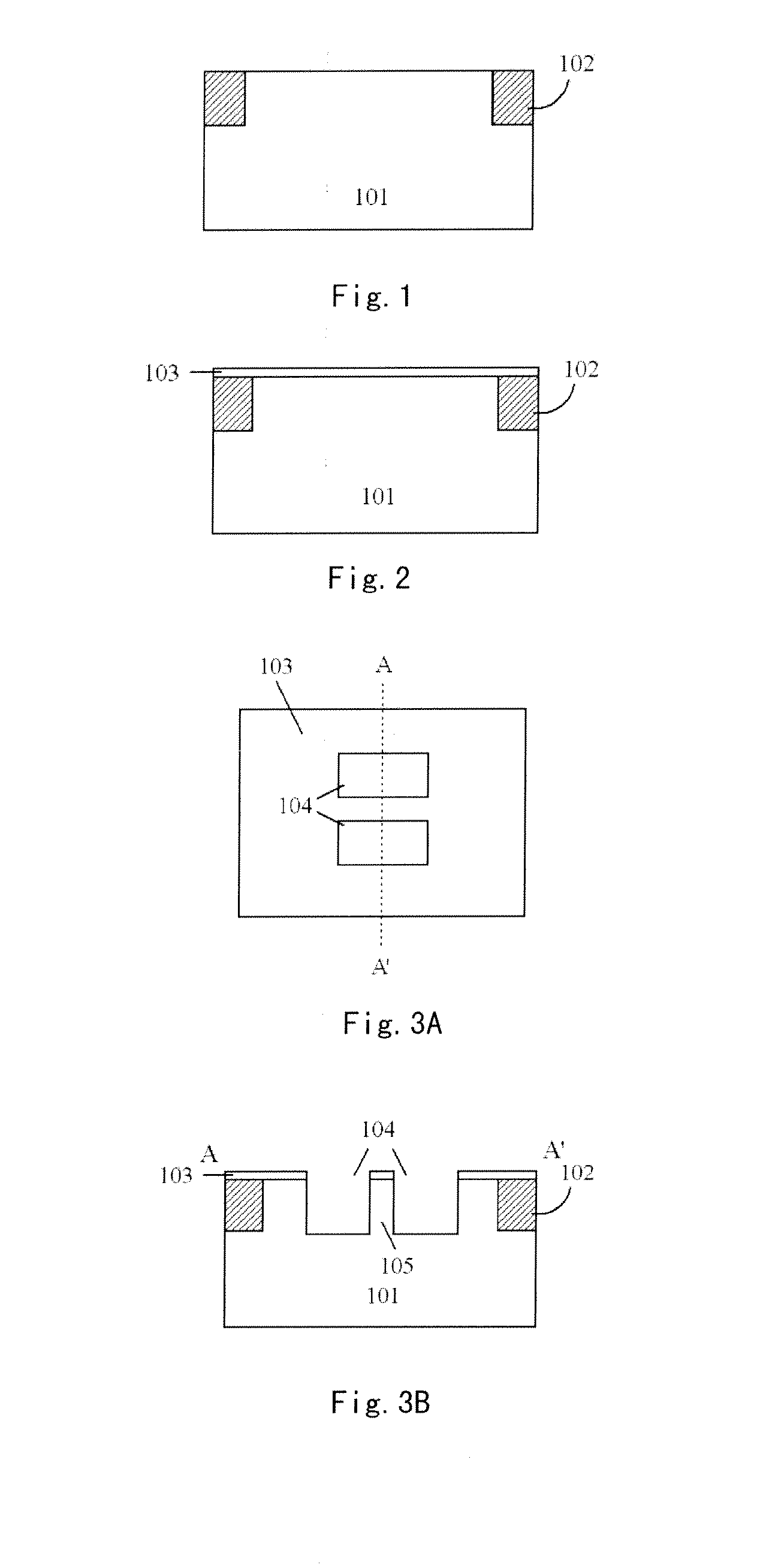

Method for Manufacturing Full Silicide Metal Gate Bulk Silicon Multi-Gate Fin Field Effect Transistors

InactiveUS20130011986A1Reduce manufacturing costLow gate sheet resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesFloating body effectGate stack

The present application discloses a method for manufacturing a full silicide metal gate bulk silicon multi-gate fin field effect transistor, which comprises the steps of: forming at least one fin on the semiconductor substrate; forming a gate stack structure on top and side surfaces of the fin; forming a source / drain extension area in the fin on both sides of the gate stack structure; forming a source / drain area on both sides of the source / drain extension area; forming silicide on the source / drain area; forming a full silicide metal gate electrode; and forming contact and implementing metalization. The present invention eliminates the self-heating effect and the floating body effect of SOI devices, then has a much lower cost, overcomes such defects as the polysilicon gate depletion effect, Boron penetration effect, and large series resistance of polysilicon gate electrodes, and has good compatibility with the planar COMS technology, thus it can be easily integrated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Integrated circuit device with P-type gate memory cell having pedestal contact plug and peripheral circuit

InactiveUS6900492B2Increase heightReduce substrate concentrationTransistorSolid-state devicesDram memorySilicon oxide

A refresh characteristic of a DRAM memory cell is improved and the performance of a MISFET formed in the periphery thereof and constituting a logic circuit is improved.Each gate electrode in a memory cell area is formed of p type polycrystalline silicon, and a cap insulating film on each gate electrode and a sidewall film on the sidewall thereof are formed of a silicon oxide film. A polycrystalline silicon film formed on the gate electrodes and between the gate electrodes is polished by a CMP method, and thereby contact electrodes are formed. Also, sidewall films each composed of a laminated film of the silicon oxide film and the polycrystalline silicon film are formed on the sidewall of the gate electrodes in the logic circuit area, and these films are used as a mask to form semiconductor areas. As a result, it is possible to reduce the boron penetration and form contact electrodes in a self-alignment manner. In addition, the performance of the MISFET constituting the logic circuit can be improved.

Owner:NEC ELECTRONICS CORP +2

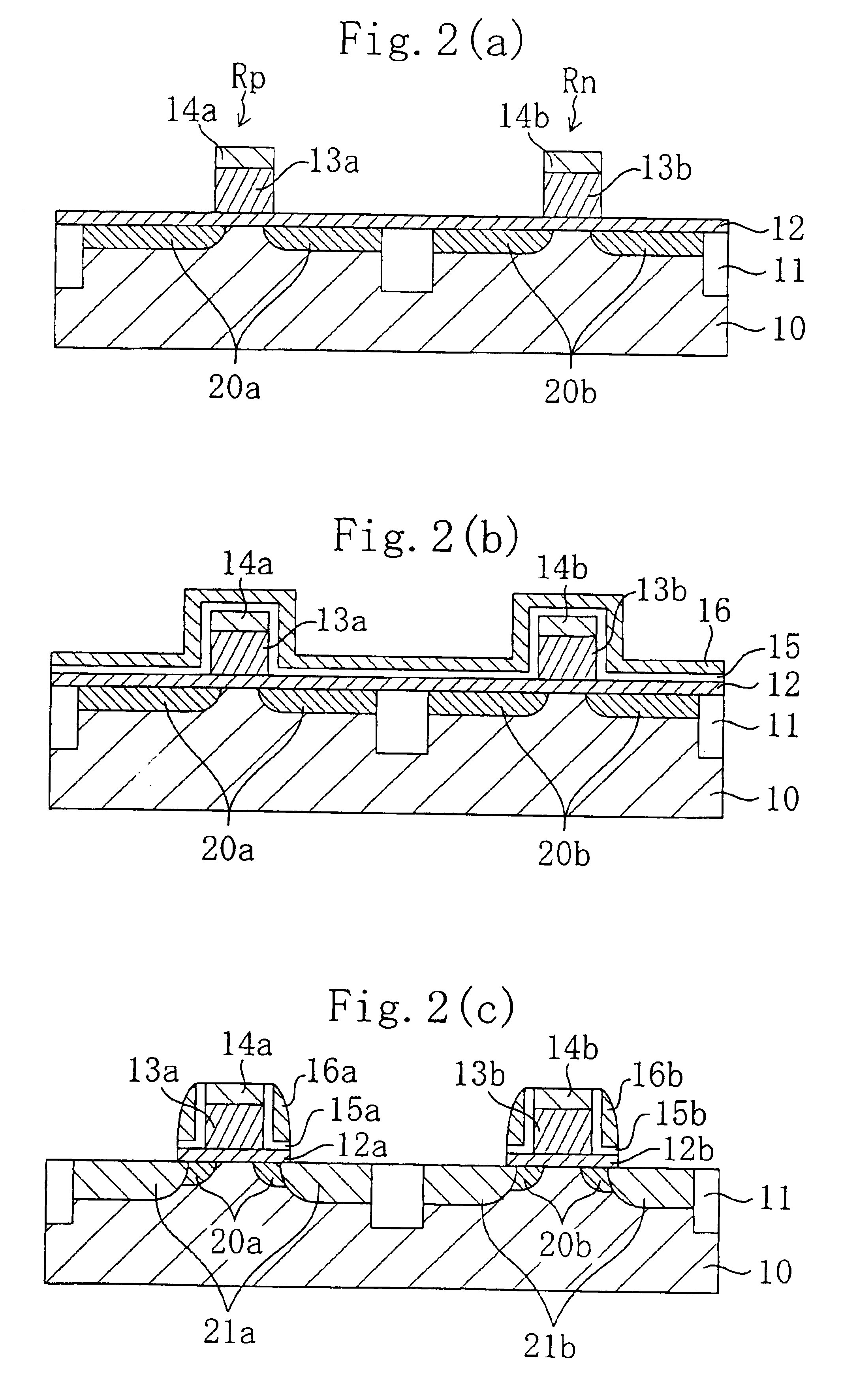

Manufacturing method of CMOS type semiconductor device, and CMOS type semiconductor device

ActiveUS20060273401A1Improvement in NBTI lifeEnhancing boron penetrationSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSDevice material

The manufacturing method of the CMOS type semiconductor device which can suppress the boron penetration from the gate electrode of the pMOS transistors to the semiconductor substrate in the case that boron is contained in the gate electrodes, while enabling the improvement in the NBTI lifetime of the pMOS transistors, without degrading the performance of the nMOS transistors, is offered. The manufacturing method of the CMOS type semiconductor device concerning the present invention has the following process steps. Halogen is introduced to the semiconductor substrate of pMOS transistor formation areas. Next, a gate insulating film is formed on the semiconductor substrate of the pMOS transistor formation areas. Next, nitrogen is introduced to the gate insulating film.

Owner:RENESAS ELECTRONICS CORP

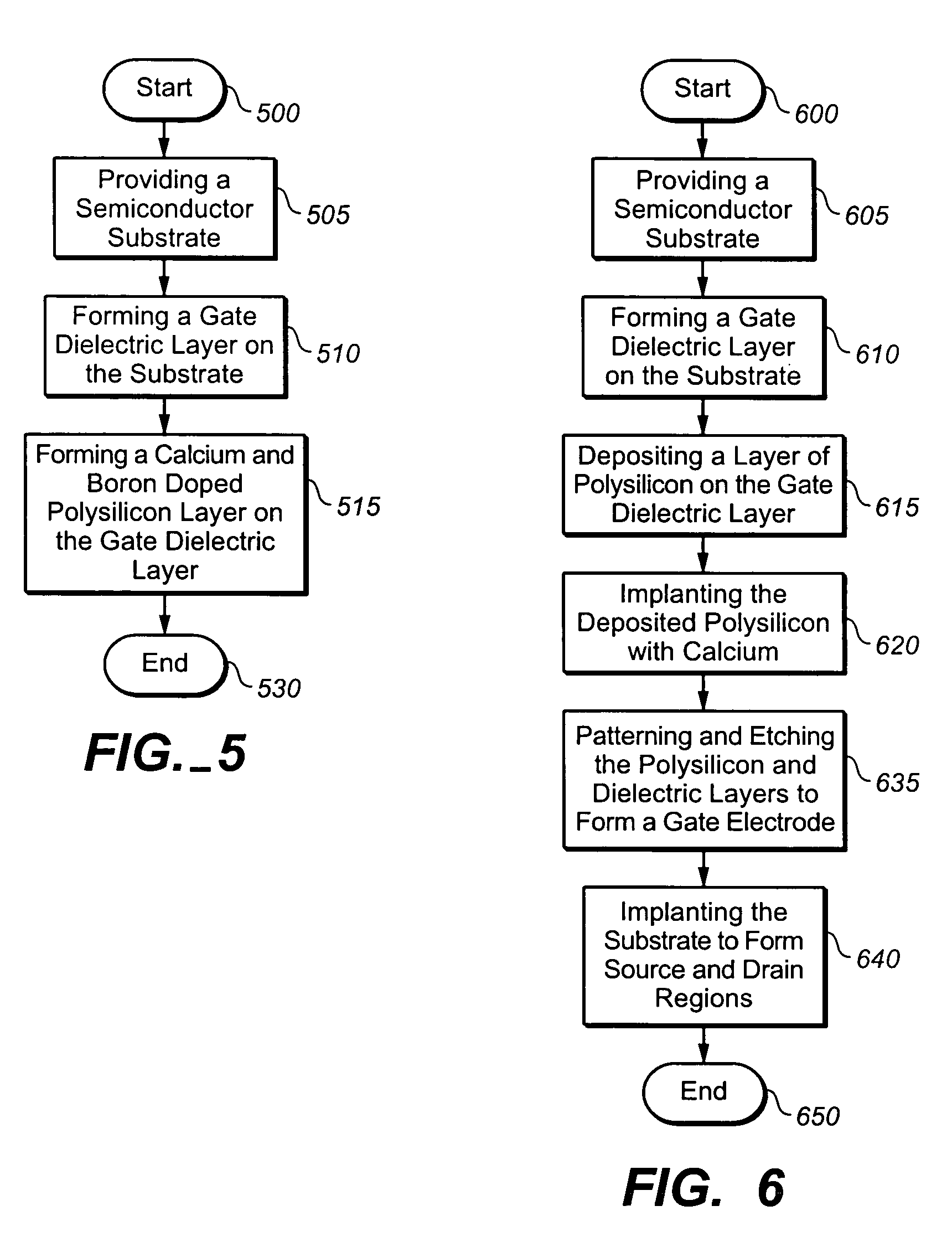

Method for suppressing boron penetration by implantation in P+ MOSFETS

InactiveUS20050054182A1Semiconductor/solid-state device manufacturingSemiconductor devicesKryptonDevice material

A method for manufacturing a semiconductor device includes providing a first layer, forming a plurality of isolation regions in the first layer, forming an insulating layer over the first layer, forming a second layer over the insulating layer, implanting one of helium, neon, krypton or xenon ions into the second layer, implanting boron ions into the second layer, patterning and etching the implanted second layer and the insulating layer, annealing at least the layer of implanted second layer to activate the implanted boron ions, and forming source and drain regions in the first layer.

Owner:MACRONIX INT CO LTD

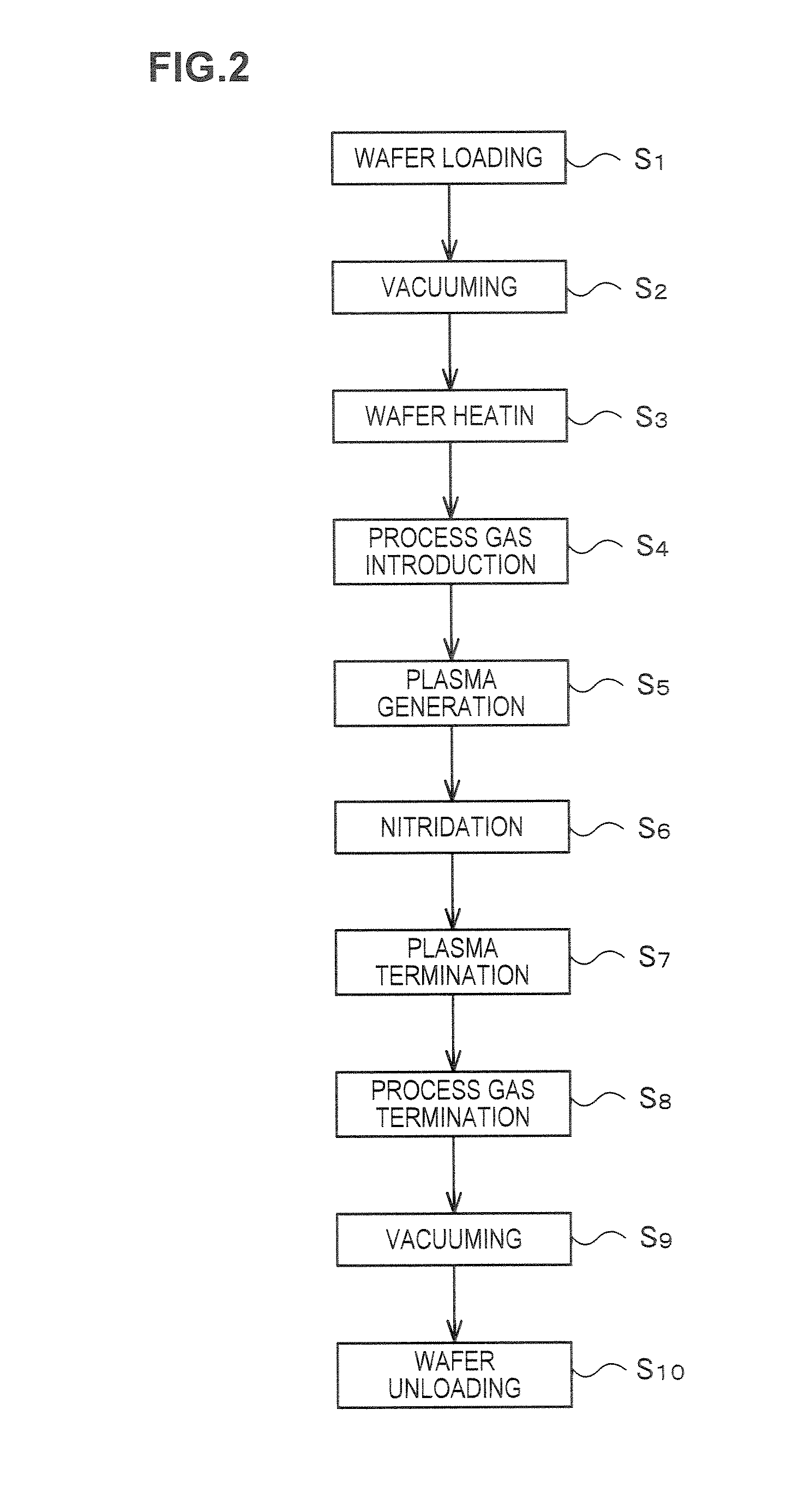

Method of forming gate insulating film, semiconductor device and computer recording medium

InactiveUS7674722B2Deteriorating capability of deviceReduced driving abilitySolid-state devicesSemiconductor/solid-state device manufacturingMicrowaveNitrogen

In the present invention, when a gate insulation film in a DRAM is formed, an oxide film constituting a base of the gate insulation film is plasma-nitrided. The plasma nitridation is performed with microwave plasma generated by using a plane antenna having a large number of through holes. Nitrogen concentration in the gate insulation film formed by the plasma nitridation is 5 to 20% in atomic percentage. Even without subsequent annealing, it is possible to effectively prevent a boron penetration phenomenon in the DRAM and to reduce traps in the film causing deterioration in driving capability of the device.

Owner:TOKYO ELECTRON LTD

Method of fabricating semiconductor device

InactiveUS6861375B1Great driving forceTransistorSemiconductor/solid-state device manufacturingOxygenNitrogen gas

A silicon oxynitride film is formed on a substrate. Then, a heat treatment is performed, while keeping a surface of the silicon oxynitride film in contact with a gas containing nitrogen, such as an NO gas, to introduce at least nitrogen into the silicon oxynitride film and produce a steeply sloped distribution of nitrogen. A semiconductor film containing an impurity, such as an amorphous silicon film, is formed on the silicon oxynitride film. By forming a CMOS device with, in particular, a dual gate structure which comprises p-type and n-type MIS transistors each having a gate oxide film composed of the silicon oxynitride film and a gate electrode composed of a polysilicon film, a high driving force is provided, while boron penetration in the p-type MIS transistor is suppressed.

Owner:PANASONIC CORP

Lightly-insitu-doped amorphous silicon applied in DRAM gates

InactiveUS20030092249A1Prevent penetrationSemiconductor/solid-state device manufacturingIn situ dopingAmorphous silicon

The present invention forms a polysilicon by first forming then thermally processing a lightly in-situ doped amorphous silicon layer, thus suppressing boron penetration and lateral diffusion of N-type and P-type impurities.

Owner:PROMOS TECH INC

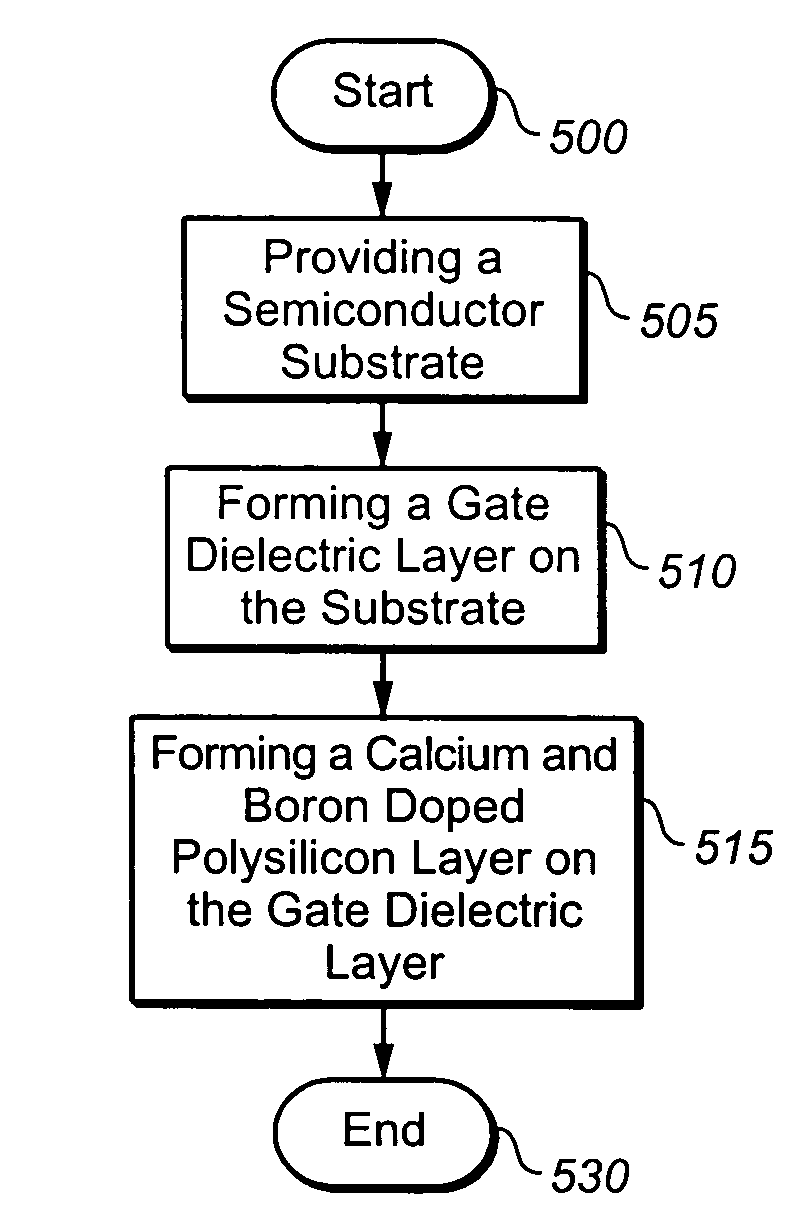

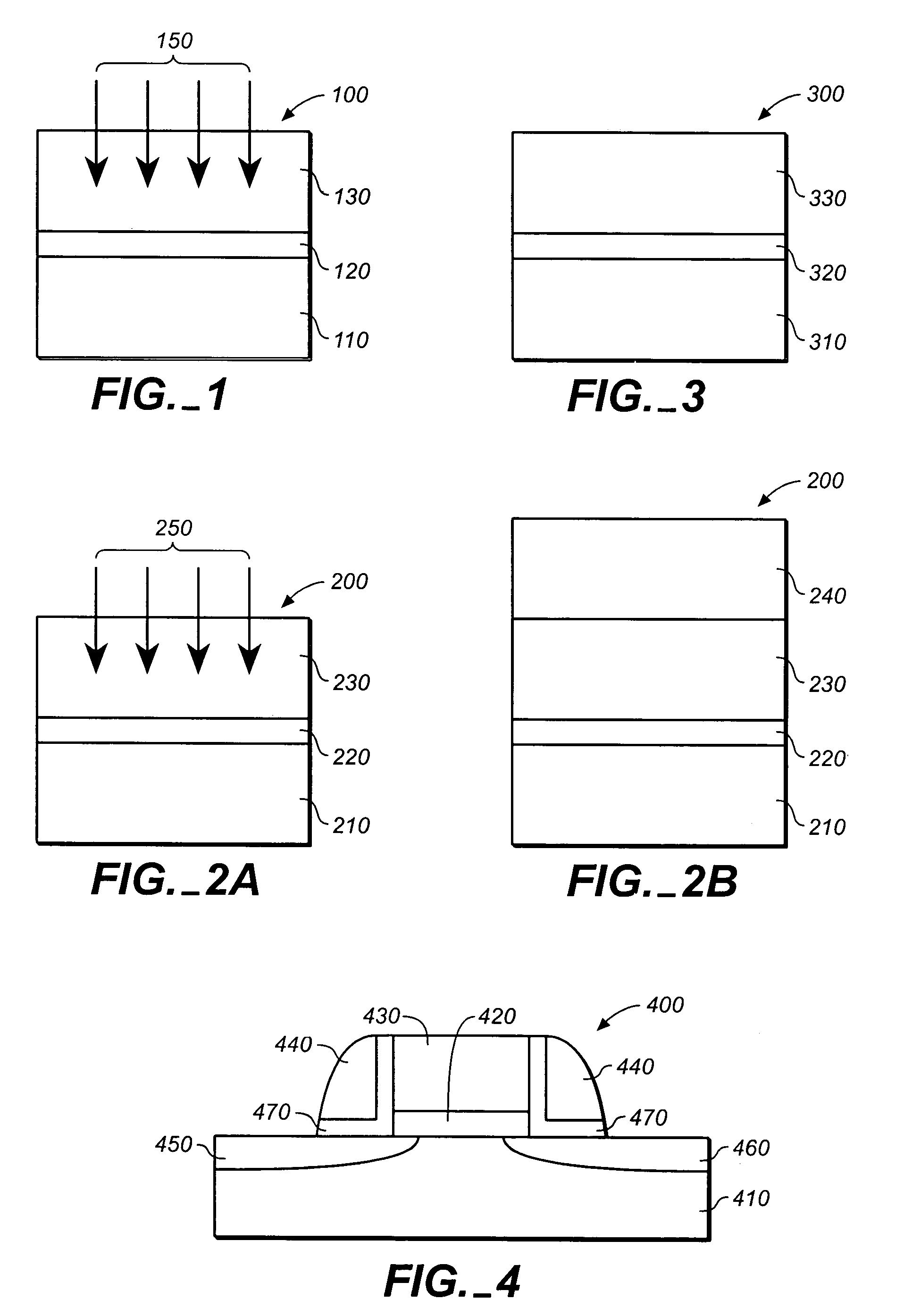

Calcium doped polysilicon gate electrodes

InactiveUS6930362B1Promote migrationReduce decreaseSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDopant Activation

A calcium doped polysilicon gate electrodes for PMOS containing semiconductor devices. The calcium doped PMOS gate electrodes reduce migration of the boron dopant out of the gate electrode, through the gate dielectric and into the substrate thereby reducing the boron penetration problem increasingly encountered with smaller device size regimes and their thinner gate dielectrics. Calcium doping of the gate electrode may be achieved by a variety of techniques. It is further believed that the calcium doping may improve the boron dopant activation in the gate electrode, thereby further improving performance.

Owner:BELL SEMICON LLC

Method of Forming Gate Insulating Film, Semiconductor Device and Computer Recording Medium

InactiveUS20070290247A1Deteriorating capability of deviceReduced driving abilityTransistorSolid-state devicesMicrowaveDevice material

In the present invention, when a gate insulation film in a DRAM is formed, an oxide film constituting a base of the gate insulation film is plasma-nitrided. The plasma nitridation is performed with microwave plasma generated by using a plane antenna having a large number of through holes. Nitrogen concentration in the gate insulation film formed by the plasma nitridation is 5 to 20% in atomic percentage. Even without subsequent annealing, it is possible to effectively prevent a boron penetration phenomenon in the DRAM and to reduce traps in the film causing deterioration in driving capability of the device.

Owner:TOKYO ELECTRON LTD

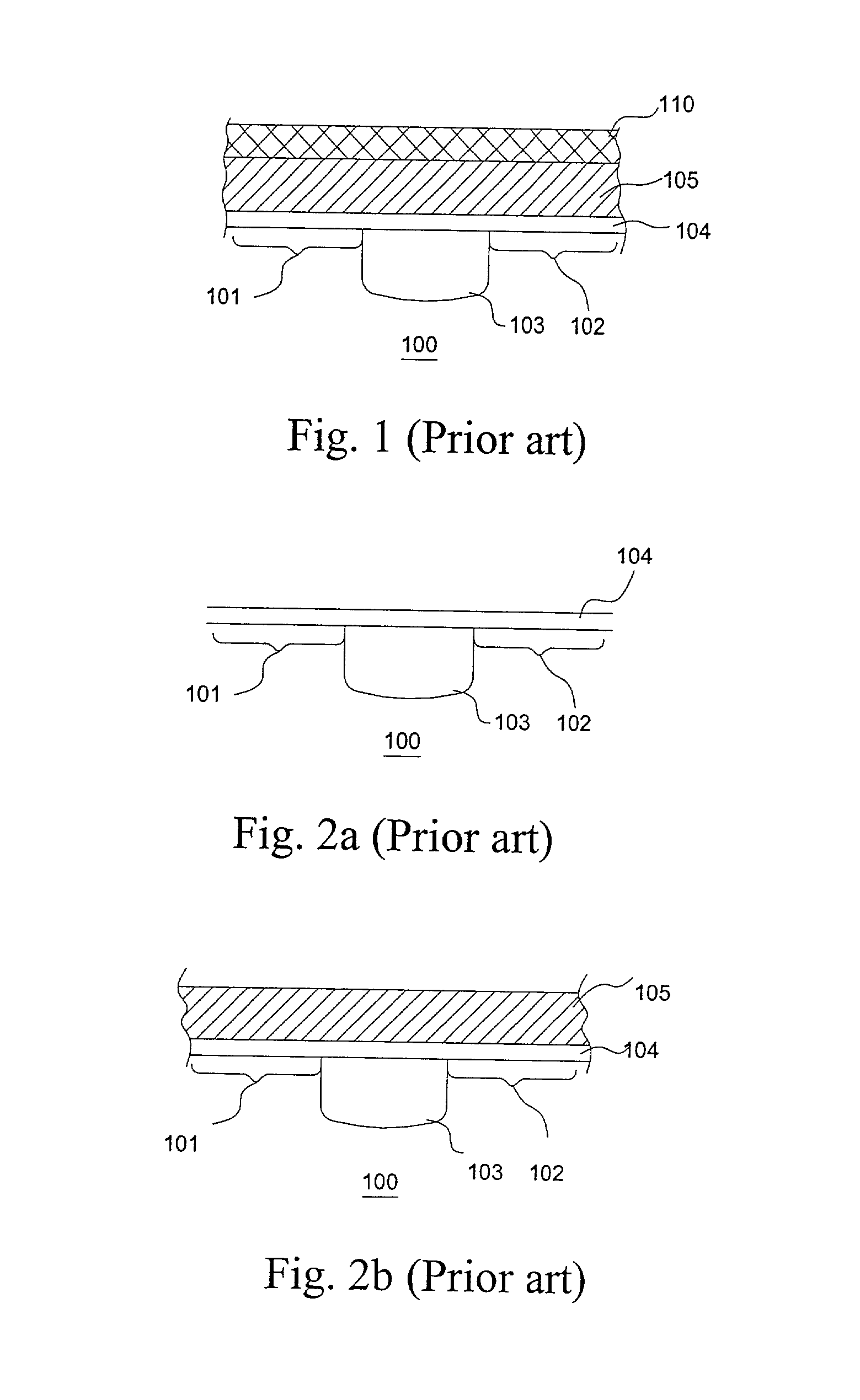

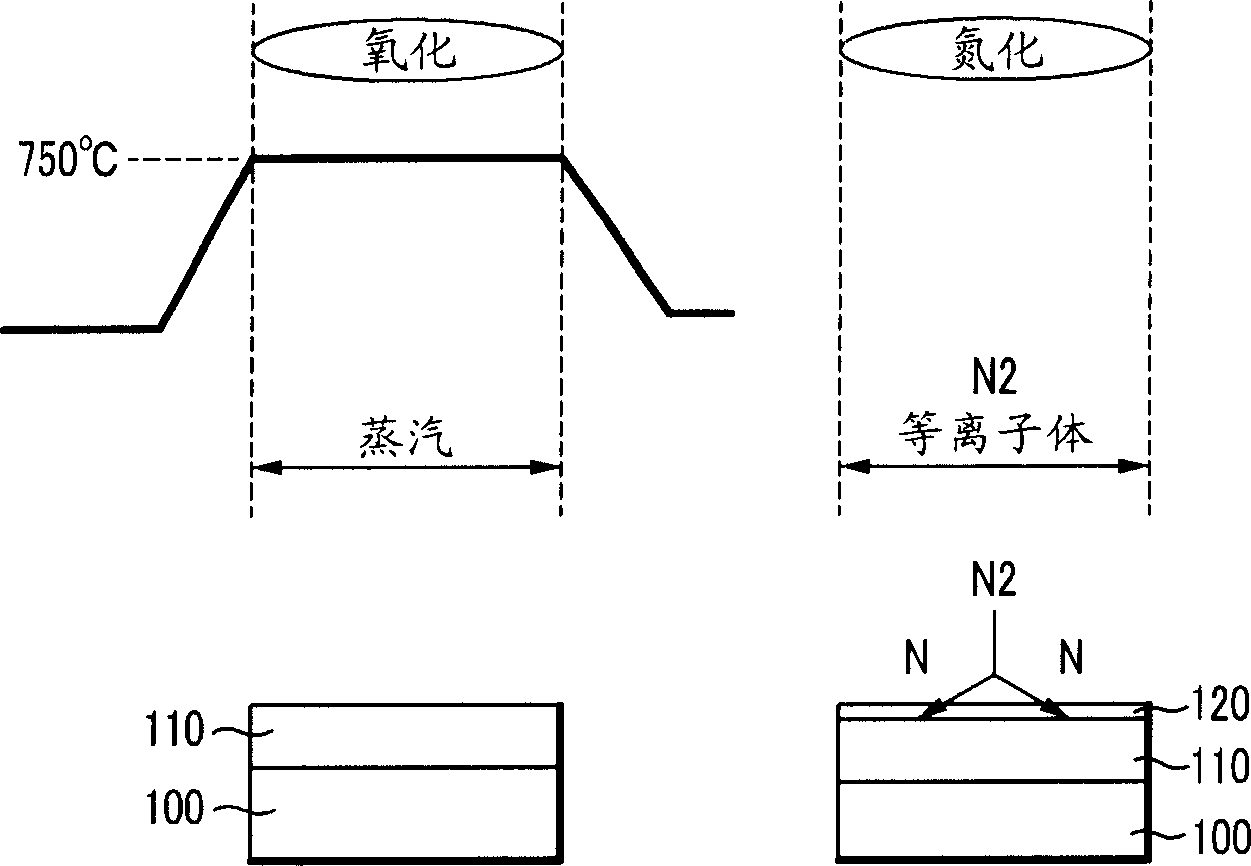

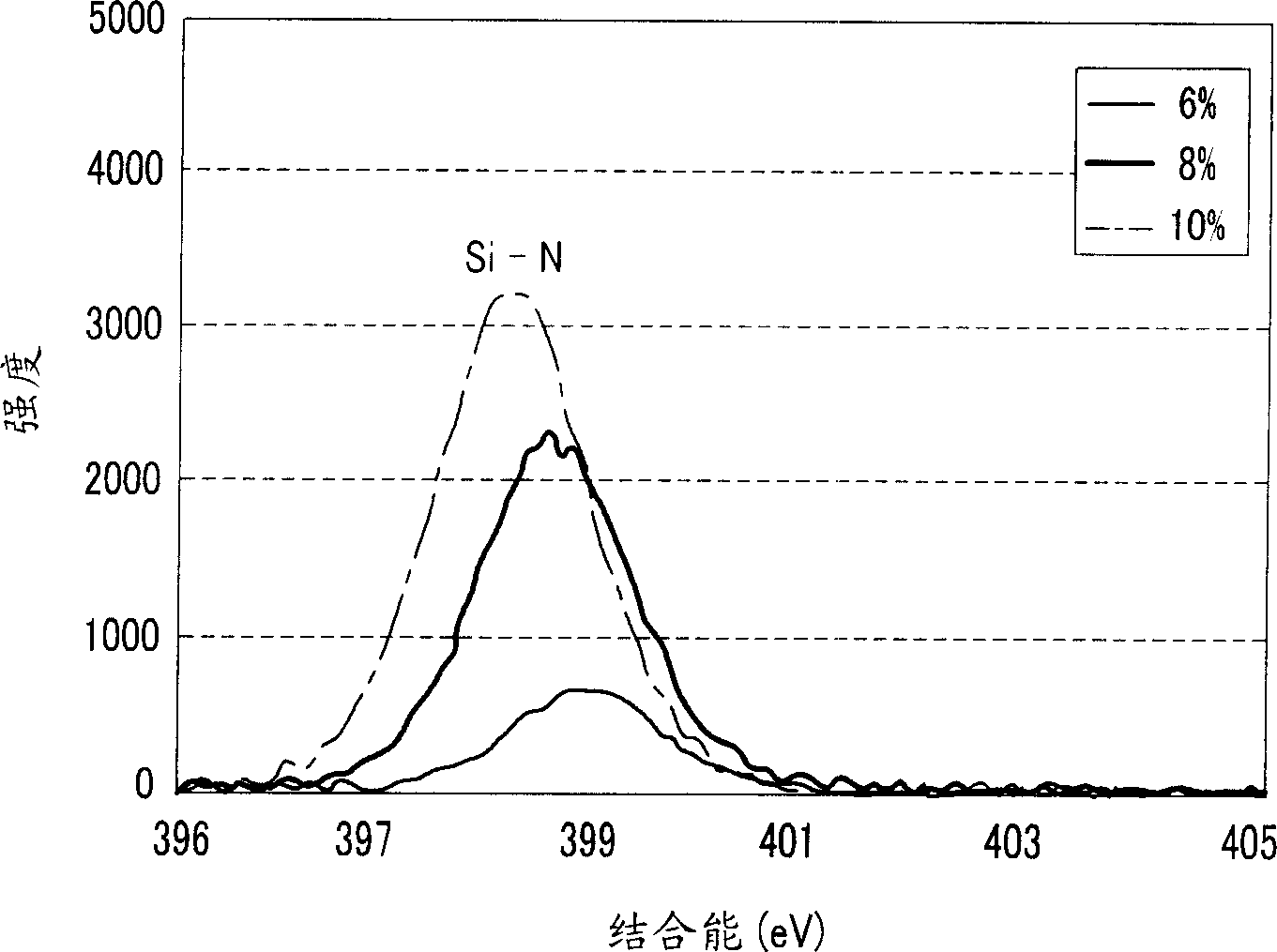

Semiconductor device and manufacturing method thereof

InactiveCN1750238ASemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenPlasma nitridation

A method of manufacturing a semiconductor device includes forming a gate oxide layer on a substrate and forming a nitride layer on the surface of the oxide layer using nitrogen at a concentration of 9 to 11% as a plasma gas. With such scheme, the plasma nitridation method is used so that charge mobility can be preserved for an NMOS transistor and the boron penetration is prevented for a PMOS transistor in a semiconductor having a gate length of 100 nm or less.

Owner:DONGBUANAM SEMICON

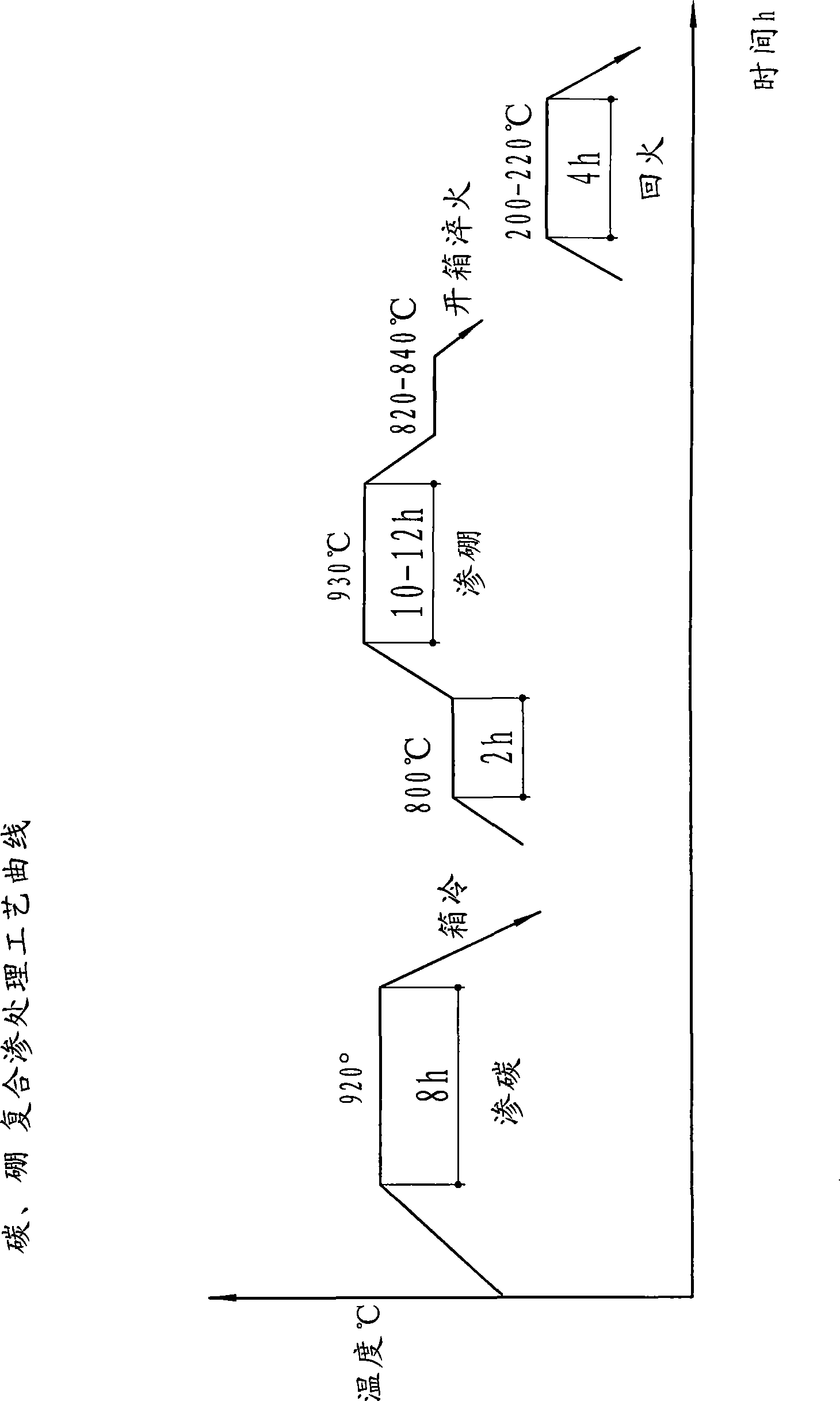

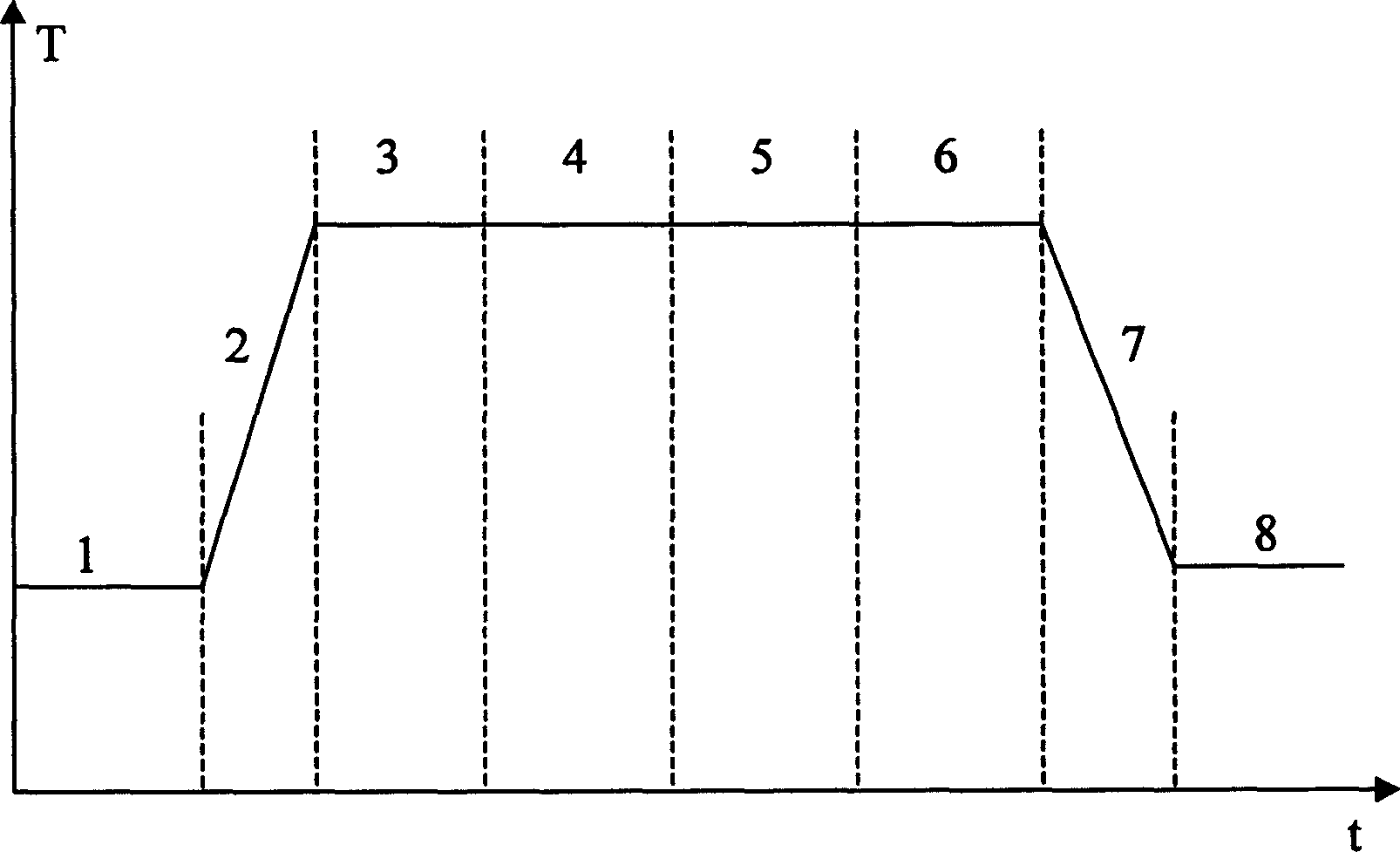

Carbon and boron complex seeping treatment process of Mg-Cr refractory product mould

InactiveCN101423925AImprove wear resistanceIncreased durabilitySolid state diffusion coatingAlcoholRefractory

The invention provides a magnesium chromium fireproof product die carbon and a boron combined penetration treatment process suitable for mass industrial production. In the process, the die is subjected to carburizing treatment and then the boriding treatment; before packaging, impurities and oxides remained on the surface of the die are milled and polished, and cleaned by alcohol and dried; and the die is placed in a boriding box, and the boriding box is placed in a box furnace for boriding treatment. The process has the advantages that for the abnormal 20Cr magnesium chromium fireproof product die with large overall dimension of more than 500 to 1,000mm and complex shape, after the combined treatment of carbon penetration and boron penetration, the depth of penetration is between 0.08 and 0.12mm, the hardness is between 1,300 and 1,500HV, and the wearing resistance and the endurance are both sunstantially improved.

Owner:JINZHOU BEIFANG REFRACTORY MOLD

Preparation method for full-silicification metal gate silicon multi-gate fin field effect transistor

ActiveCN102867751AReduce manufacturing costOvercoming the Polysilicon Depletion EffectSemiconductor/solid-state device manufacturingSemiconductor devicesFloating body effectEngineering

The invention discloses a preparation method for a full-silicification metal gate silicon multi-gate fin field effect transistor. The preparation method comprises the steps: forming fins on a semiconductor substrate; forming gate piling structures at the top and on the side surfaces of the fins; forming source / drain extension area structures in the fins at two sides of the gate piling structures; forming source / drain structures at two sides of the source / drain extension areas; carrying out source / drain silicification; forming full-silicification metal gate electrodes; and contacting and metalizing. According to the preparation method, self-heating effect and floating body effect of SOI (Silicon-On-Insulator) device can be eliminated, and lower cost can be realized; the defects of polycrystalline silicon depletion effect, boron penetration effect, large series resistance and the like can be overcome; and the full-silicification metal gate silicon multi-gate fin field effect transistor can be well compatible with CMOS (Complementary Metal-Oxide-Semiconductor Transistor) plane process, thus being easy to integrate.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Silicon-rich low thermal budget silicon nitride for integrated circuits

A low-thermal budget, silicon-rich silicon nitride film may include a concentration of hydrogen in Si—H bonds being at least 1.5 times as great as a concentration of hydrogen in N—H bonds. The silicon nitride film suppresses boron diffusion in boron-doped devices when such devices are processed using high-temperature processing operations that conventionally urge boron diffusion. The low-thermal budget, silicon-rich silicon nitride film may be used to form spacers in CMOS devices, it may be used as part of a dielectric stack to prevent shorting in tightly packed SRAM arrays, and it may be used in BiCMOS processing to form a base nitride layer and / or nitride spacers isolating the base from the emitter. Furthermore the low-thermal budget, silicon-rich silicon nitride film may remain covering the CMOS structure while bipolar devices are being formed, as it suppresses the boron diffusion that results in boron penetration and boron-doped poly depletion.

Owner:BELL SEMICON LLC

Semiconductor device and manufacturing method thereof

InactiveUS20060063337A1Preventing boron penetrationMinimizing decrease of charge mobilitySemiconductor/solid-state device manufacturingDevice materialNitrogen

A method of manufacturing a semiconductor device includes forming a gate oxide layer on a substrate and forming a nitride layer on the surface of the oxide layer using nitrogen at a concentration of 9 to 11% as a plasma gas. With such scheme, the plasma nitridation method is used so that charge mobility can be preserved for an NMOS transistor and the boron penetration is prevented for a PMOS transistor in a semiconductor having a gate length of 100 nm or less.

Owner:DONGBU ELECTRONICS CO LTD

A preparation method of nanometer scale W/TiN compound refractory metal bar

InactiveCN101217112AGood density of surface statesOvercoming the phenomenon that the threshold voltage is too highSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSilicon oxide

The invention relates to a preparation method of a nanometer scale W / TiN composite refractory metal gate, the steps are as follows: a device source / leakage area cobalt silicide is formed, after that, the flattening process is carried out, a gate groove is corroded, a gate silicon oxide is bleached and replaced, then the gate is oxidized again; the vacuum thermal annealing processing is carried out; a refractory metal TiN is sputtered, the thickness is 25 to 45nm; a W thin film is sputtered, the thickness is 90 to 110nm; the acetone and the anhydrous ethanol are used for ultrasonic cleaning, the deionized water is used for flushing, and the drying is carried out in hot N2; the W / TiN T-shaped gate is done with the lithography; the W / TiN T-shaped gate is etched by reaction ions, the etching gas is C12 and SF6; a chemical vapor deposition SiO2 is strengthened by a plasma, the thickness of SiO2 is 500 to 700nm; a contact hole is formed; and the metallizing annealing is carried out. The invention solves a series of serious problems of excessive high gate resistance, serious boron penetration of a PMOS device, polysilicon gate depletion, incompatibility with a high k gate dielectric and so on which exist in the conventional polysilicon gate, so the invention can obtain excellent device properties.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

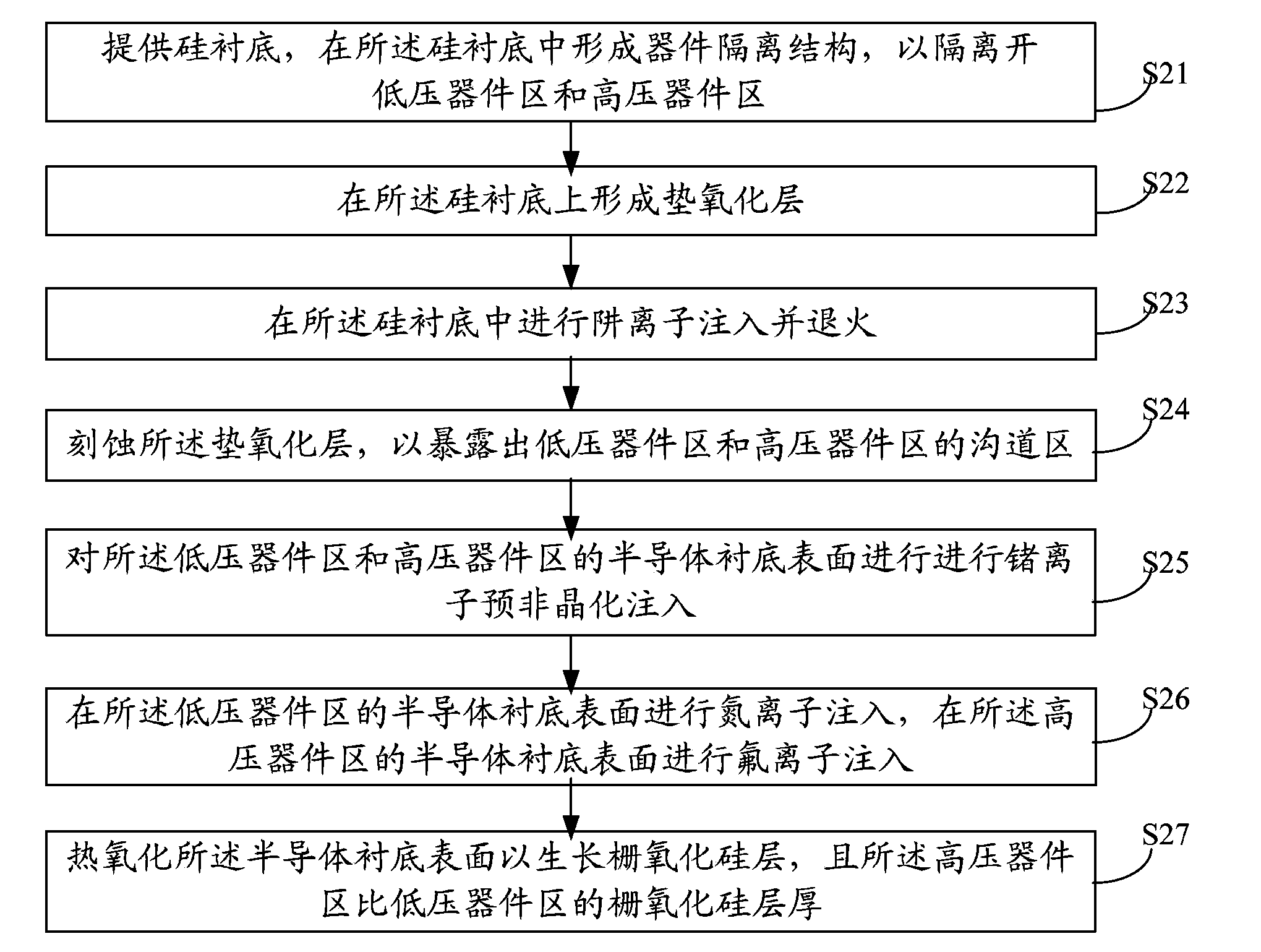

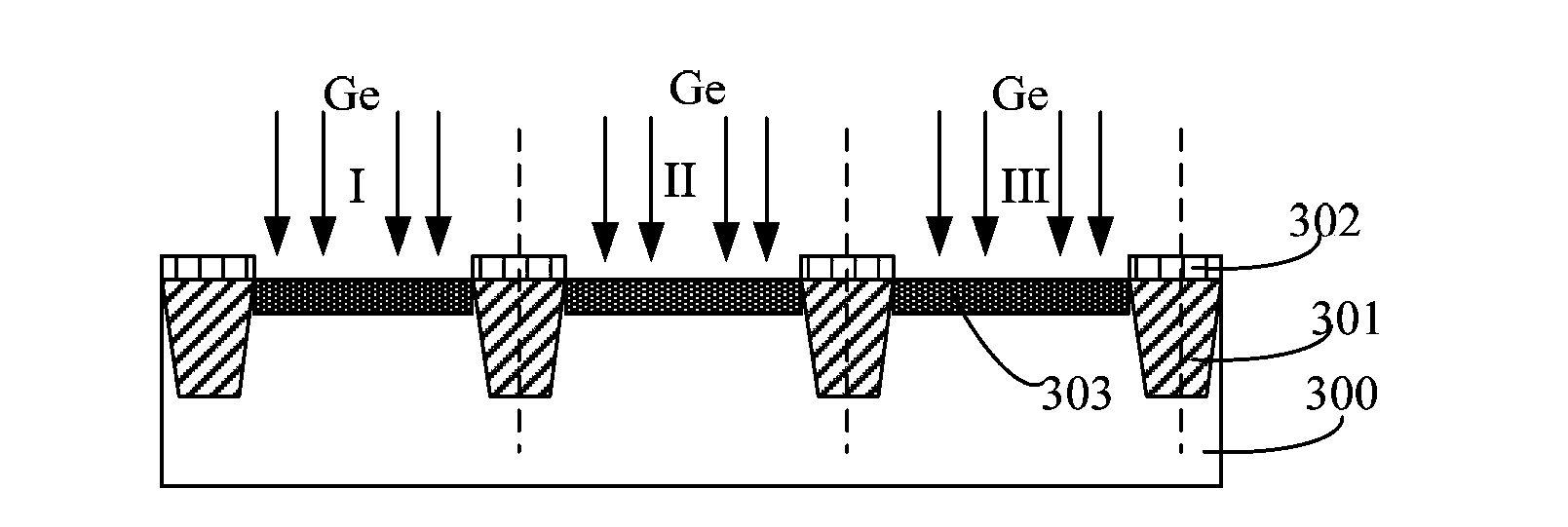

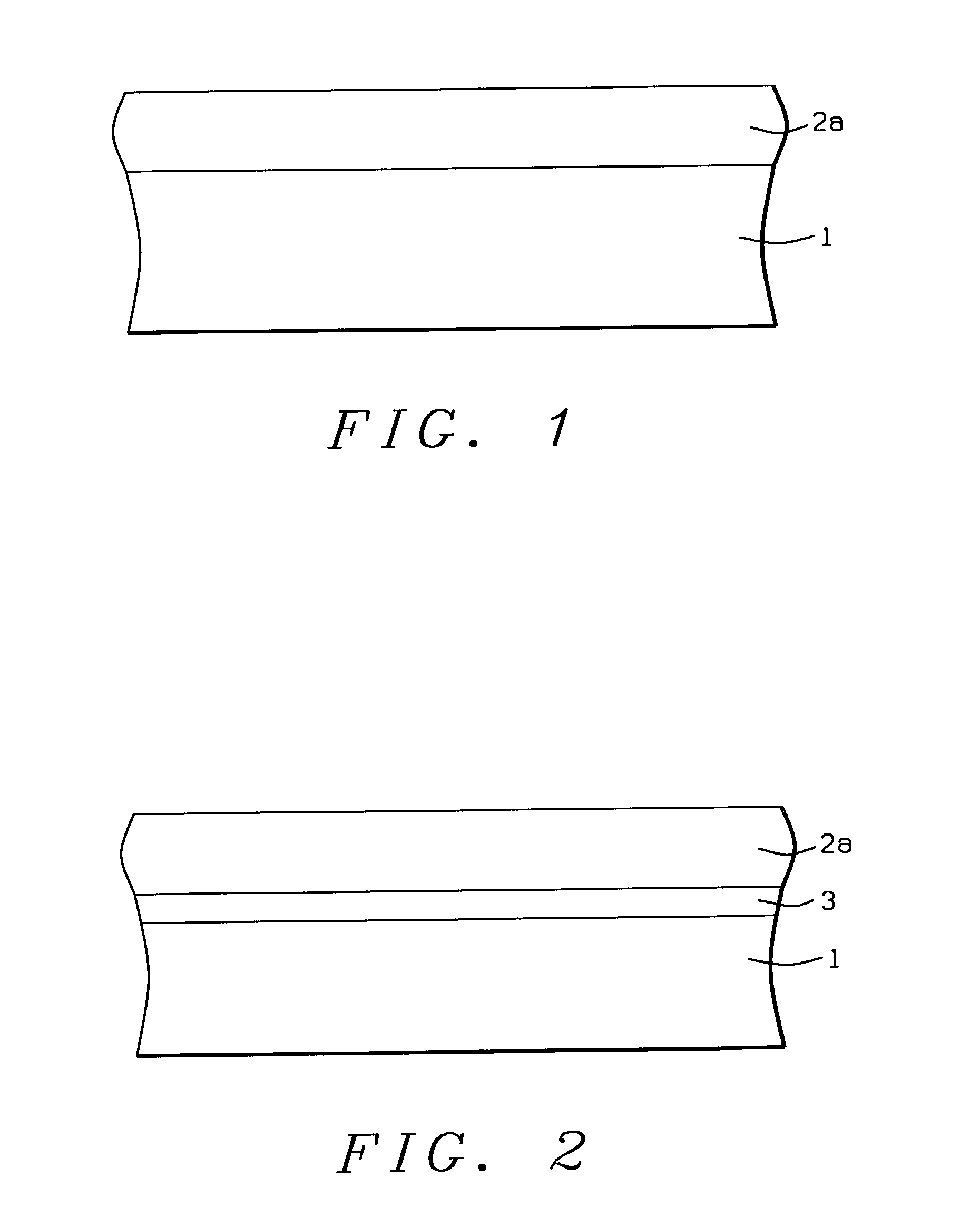

Method for preparing gate silicon oxide layers and method for processing semiconductor substrate

InactiveCN103390548AImprove reliabilityReduce channelingSemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrier mobilitySilicon oxide

The invention provides a method for preparing gate silicon oxide layers and a method for processing a semiconductor substrate. Nitrogen ions are injected into a low-pressure device area in advance and fluorine ions are injected in a high-pressure device area in advance, so that when the gate silicon oxide layers grow on the surface of the thermal oxidation semiconductor substrate, growth of the gate silicon oxide layers in the low-pressure device area is restrained, growth of the gate silicon oxide layers in the high-pressure device area is promoted, therefore, the gate silicon oxide layers with different thicknesses are formed, and the technological process is greatly simplified; further germanium and / or silicon is injected into the semiconductor substrate in a pre-non-crystallizing mode, and the channel carrier mobility is improved; in the annealing recrystallization process after non-crystallizing injection and nitrogen and fluoride ion injection, the characteristics of the surface of the silicon substrate are optimized, and the method is beneficial to improving the reliability of the gate oxide layers. The fabrication processing enables the peak value of the nitrogen concentration distribution of the low-pressure device area to be close to the surfaces of the gate silicon oxide layers, the follow-up boron penetration from P+ polycrystalline silicon can be effectively blocked, and the reliability of the thin gate silicon oxide layers in the low-pressure device area can be enhanced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

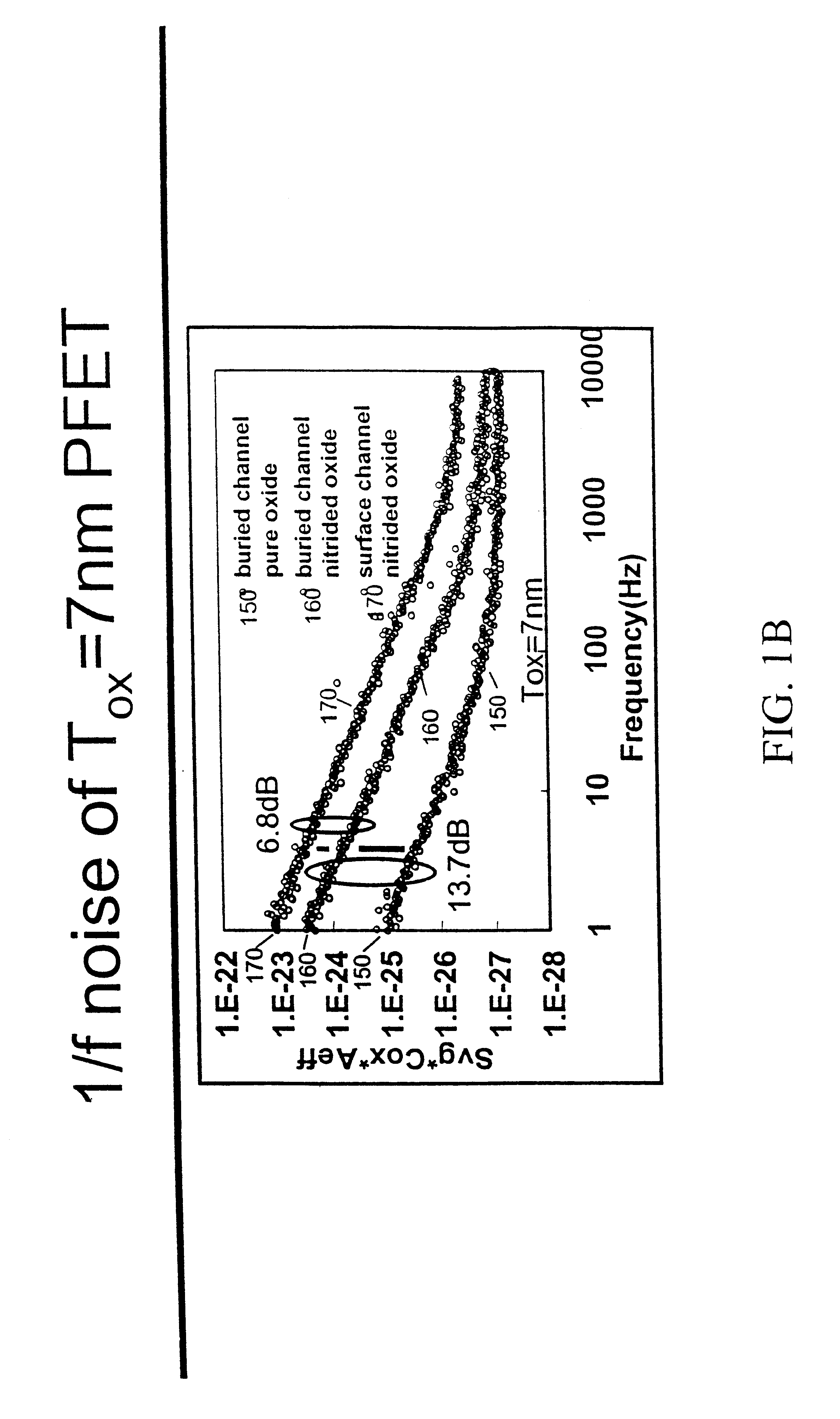

Reduced 1/f noise in MOSFETs

InactiveUS6653679B2Reducing noiseTransistorSemiconductor/solid-state device detailsNitrogenEngineering

An improved gate structure for a MOSFET device exhibits a reduced level of 1 / f noise or "flicker noise", while maintaining the control of boron penetration into the substrate of the MOSFET device. The gate structure for the MOSFET device includes a gate electrode and a gate oxide layer wherein nitrogen is selectively implanted into the gate oxide / device substrate interface prior to oxidation of the gate oxide layer. The nitrogen is selectively implanted so that the nitrogen is implanted into thin gate oxide regions and masked from thick gate oxide regions so that the benefits of controlling the boron penetration are realized while the 1 / f noise is reduced due to the selective implantation of the nitrogen.

Owner:NEWPORT FAB

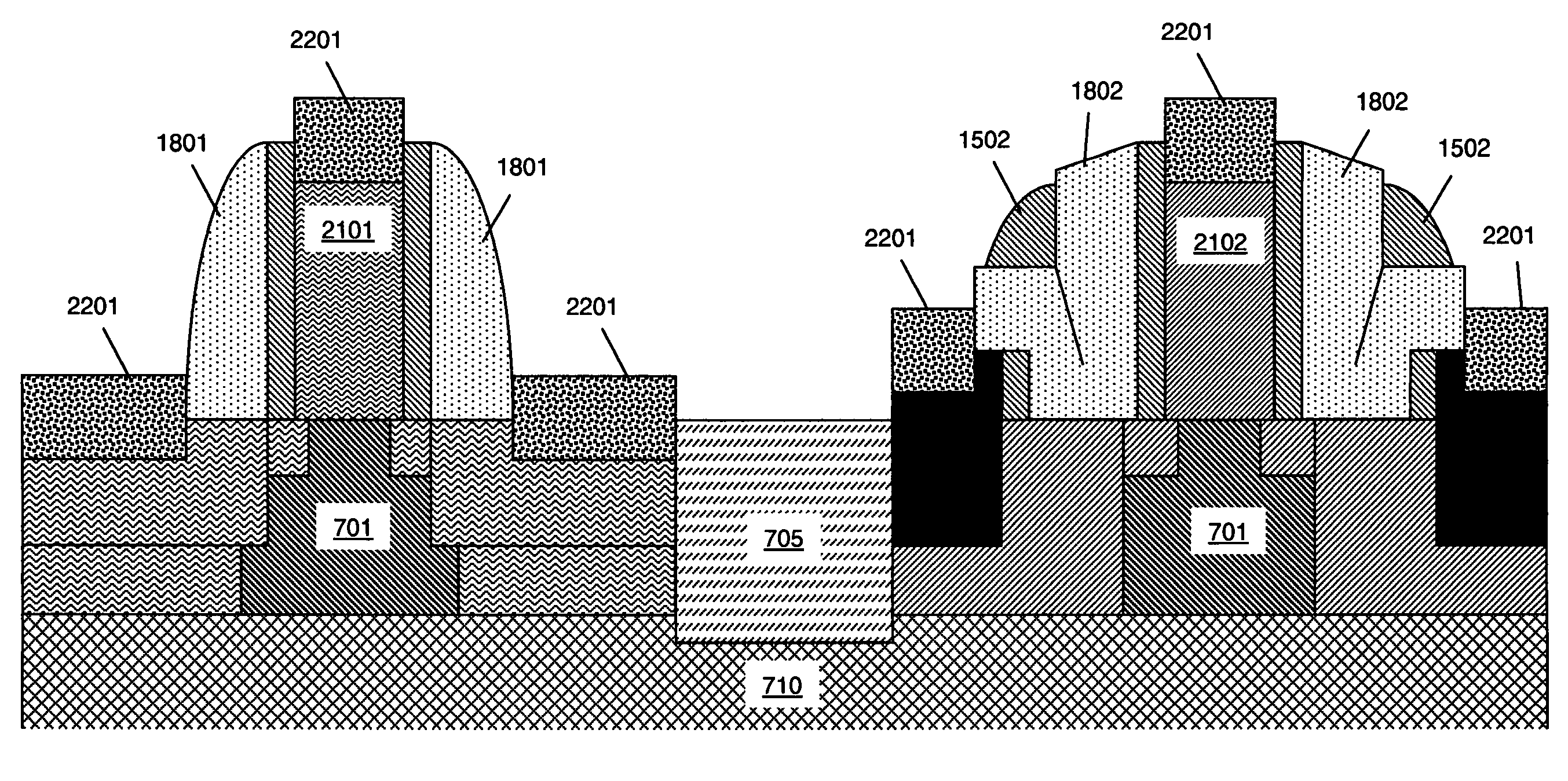

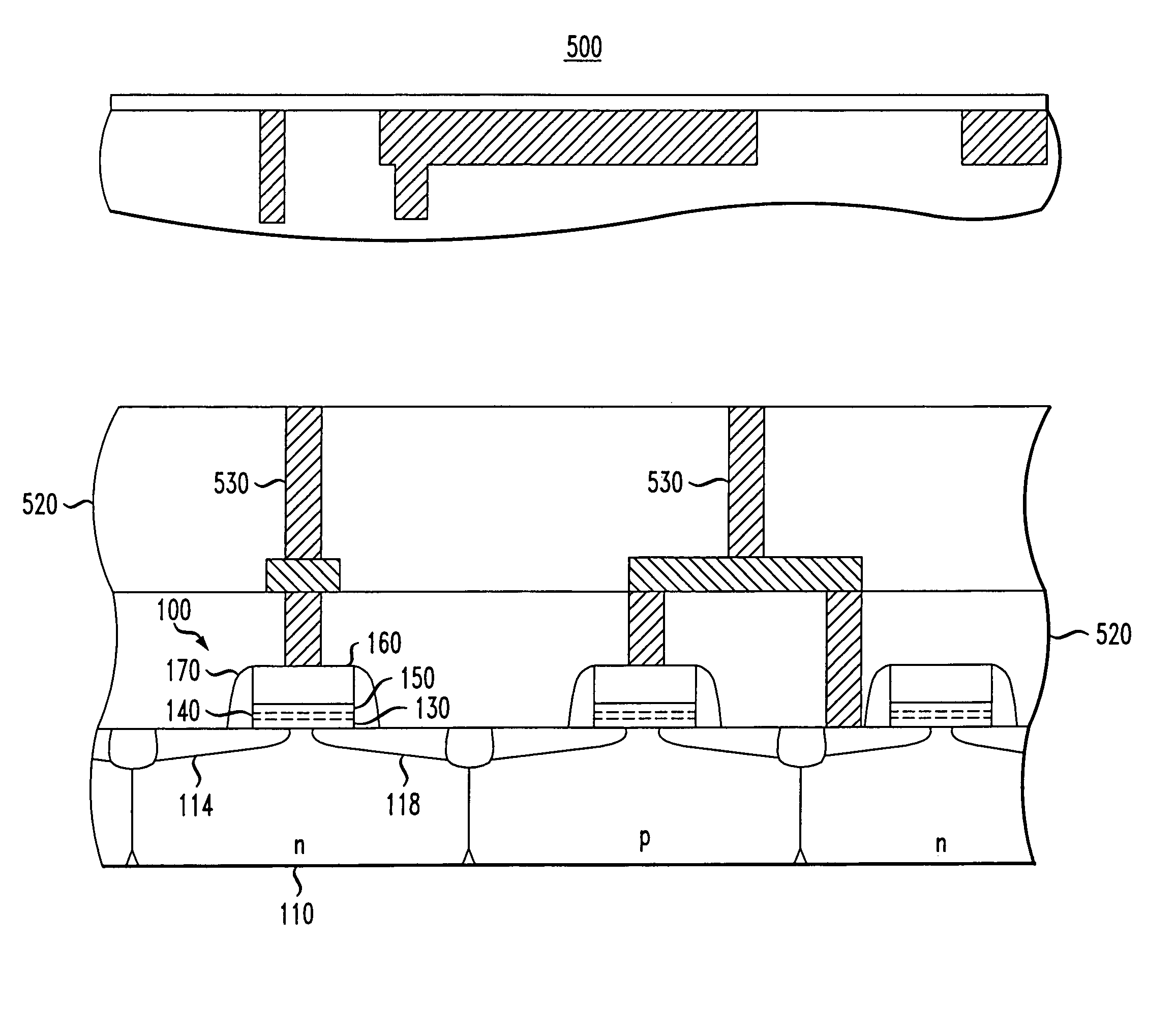

SOI bottom pre-doping merged e-SiGe for poly height reduction

InactiveUS7605042B2Reducing and even avoiding boron penetrationImprove operating characteristicsTransistorSolid-state devicesEngineeringBoron

Owner:KK TOSHIBA

Integrated method of surface channel CMOS (complementary metal oxide semiconductor) logic device and SONOS (silicon-oxide-nitride-oxide-silicon) device

ActiveCN104576522ARealize self-aligned contact holesAchieve integrationSemiconductor/solid-state device manufacturingSilicon oxideP channel

The invention discloses an integrated method of a surface channel CMOS (complementary metal oxide semiconductor) logic device and an SONOS (silicon-oxide-nitride-oxide-silicon) device. The method comprises steps as follows: a gate oxide layer, an ONO layer and a polycrystalline silicon layer are formed; a gate polycrystalline silicon layer of the SONOS device is subjected to N type ion implantation; a fourth silicon nitride film is grown; a photoresist pattern of a first part of a first polysilicon gate is defined; the fourth silicon nitride film is etched; photoresist patterns of a second part of the first polysilicon gate and a polysilicon gate of the CMOS device are defined; polysilicon gates of the devices are formed while the polycrystalline silicon layer is etched; LDD (lightly doped drain) injection is performed; side walls are formed; source drain injection is performed; polysilicon gate doping of the CMOS logic device is realized while the source drain injection is performed; PSG (phosphosilicate glass) is grown and flattened; USG (undoped silicon glass) is grown; and contact holes are formed. With the adoption of the integrated method, a thermal process of boron penetration of a PMOS (P-channel metal oxide semiconductor) device can be reduced, the number of photoetching models is reduced, and a small-size surface channel device and a high-density storage device can be integrated.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Gate dielectric structure for reducing boron penetration and current leakage

InactiveUS7081419B2Reduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The present invention provides a semiconductor device capable of substantially retarding boron penetration within the semiconductor device and a method of manufacture therefor. In the present invention the semiconductor device includes a gate dielectric located over a substrate of a semiconductor wafer, wherein the gate dielectric includes a nitrided layer and a dielectric layer. The present invention further includes a nitrided transition region located between the dielectric layer and the nitrided layer and a gate located over the gate dielectric.

Owner:BELL SEMICON LLC

Method of fabricating a gate dielectric layer with reduced gate tunnelling current and reduced boron penetration

InactiveUS7022625B2Reduce riskTotal current dropSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNitrogen

A method of forming a silicon nitride-silicon dioxide, composite gate dielectric layer, offering reduced risk of boron penetration from an overlying boron doped polysilicon gate structure, has been developed. A porous, silicon rich silicon nitride layer is first deposited on a semiconductor substrate, allowing a subsequent thermal oxidation procedure to grow a thin silicon dioxide layer on the semiconductor substrate, underlying the porous, silicon rich silicon nitride layer. A two step anneal procedure is then employed with a first step performed in a nitrogen containing ambient to densify the porous, silicon rich silicon nitride layer, while a second step of the anneal procedure, performed in an inert ambient at a high temperature, reduces the foxed charge at the silicon dioxide-semiconductor interface.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Electronic device with dopant diffusion barrier and tunable work function and methods of making same

ActiveUS7612421B2Inhibition effectSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricElectron

A method of fabricating a semiconductive film stack for use as a polysilicon germanium gate electrode to address problems associated with implant and diffusion of dopants. Achieving a sufficiently high active dopant concentration at a gate-dielectric interface while avoiding gate penetration of dopants such as boron is problematic. A higher gate implant dosage or annealing temperature is needed, and boron penetration through the thin gate oxide is inevitably enhanced. Both problems are exacerbated as the gate dielectric becomes thinner. In order to achieve a high level of active dopant concentration next to the gate dielectric without experiencing problems associated with gate depletion and penetration, a method and procedures of applying a diffusion-blocking layer is described with respect to an exemplary MOSFET application. However, a diffusion-blocking concept is also presented, which is readily amenable to a variety of semiconductor related technologies.

Owner:ATMEL CORP

Structure of for preparing gate containing nitrogen in silicon oxide layer of semiconductor device and preparation technique

InactiveCN1540724AAccurate distributionPrecisely control the distributionSemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenSilicon oxide

Technique of preparing gate silicon oxide layer is key technique of fabricating IC. A small quantity of nitrogen element doped into traditional gate silicon oxide improves its characteristics. Rapid tempering oven (RTO) is adopted in the invention to control diffusibility of element accurately. Thickness of silicon oxide layer and distribution of nitrogen element are controlled through methods of multistep oxidation and annealing (diffusing). The preparing method solves issues of boron penetration, raises reliability, reduces leakage current, and does not effect on carrier mobility in channel obviously.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com