Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Stable duty cycle" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Clock generation circuit used in analog-to-digital converter (ADC) with high speed and high precision

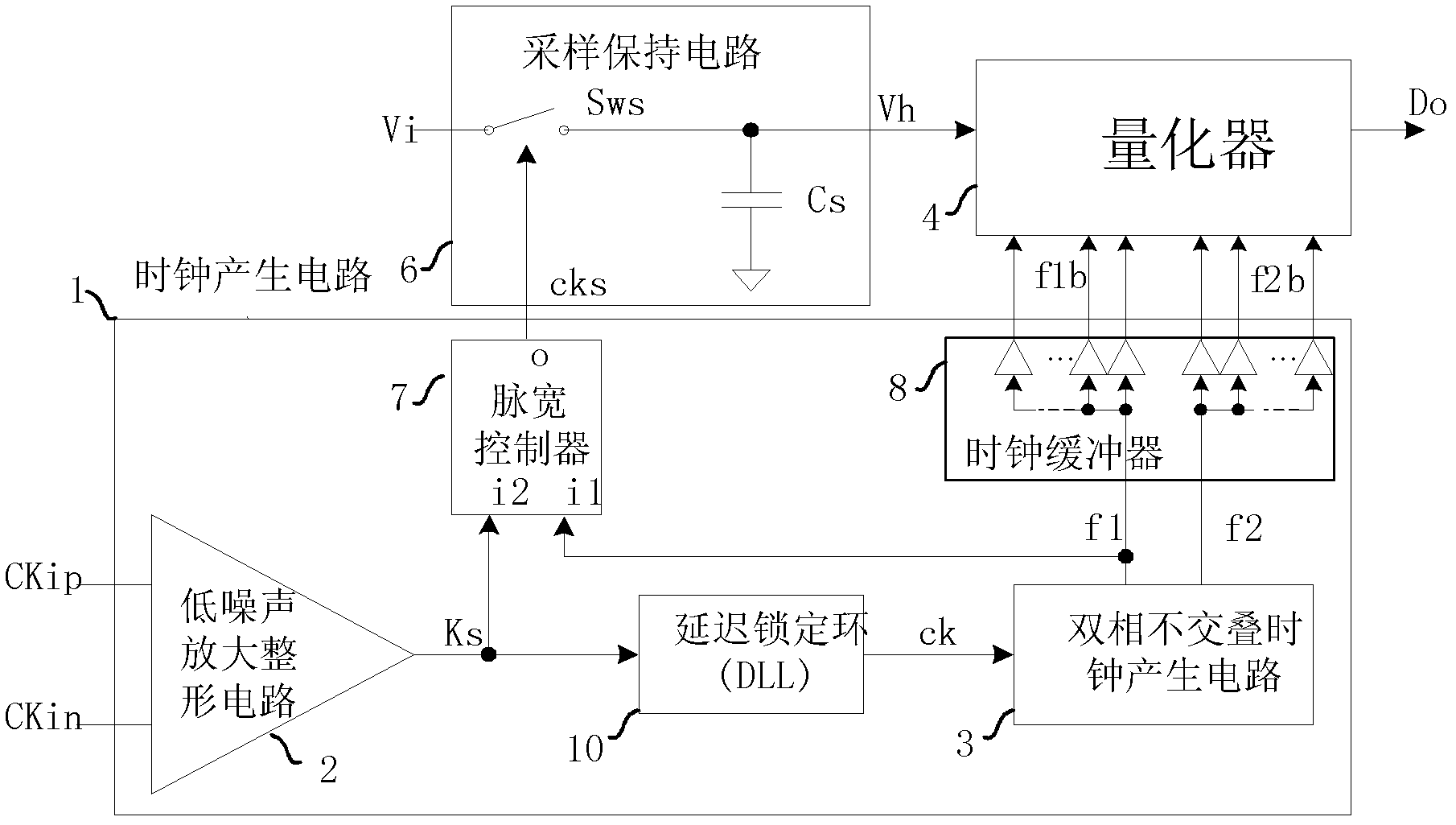

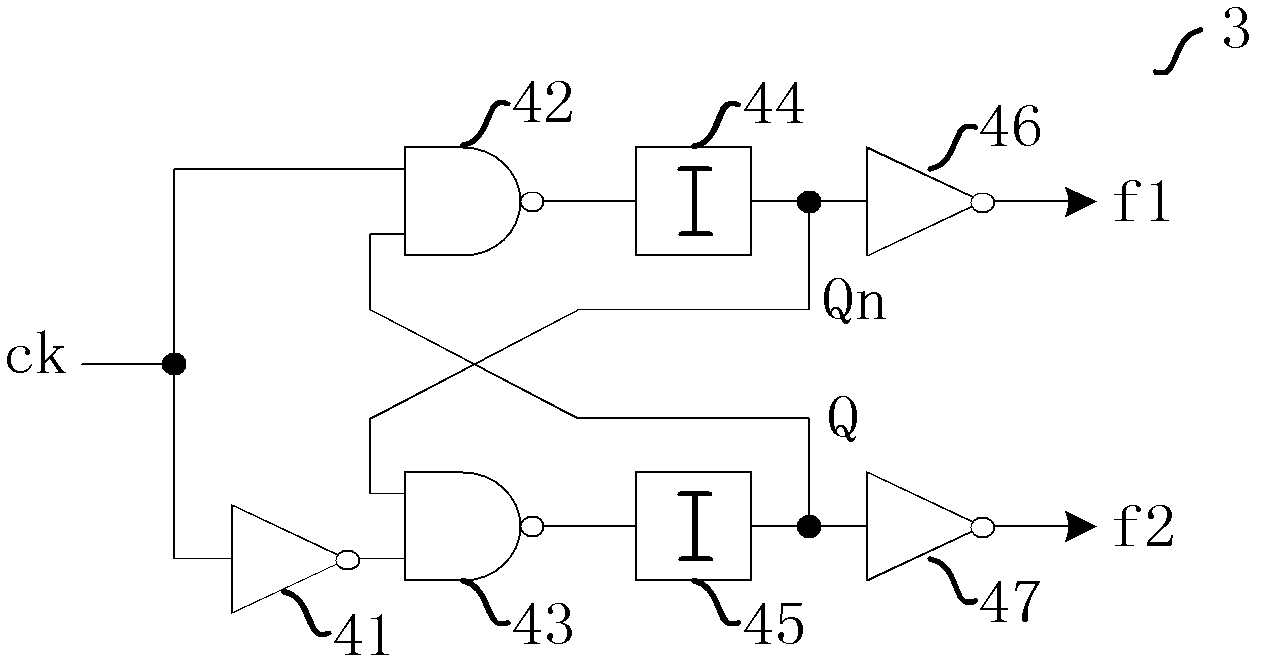

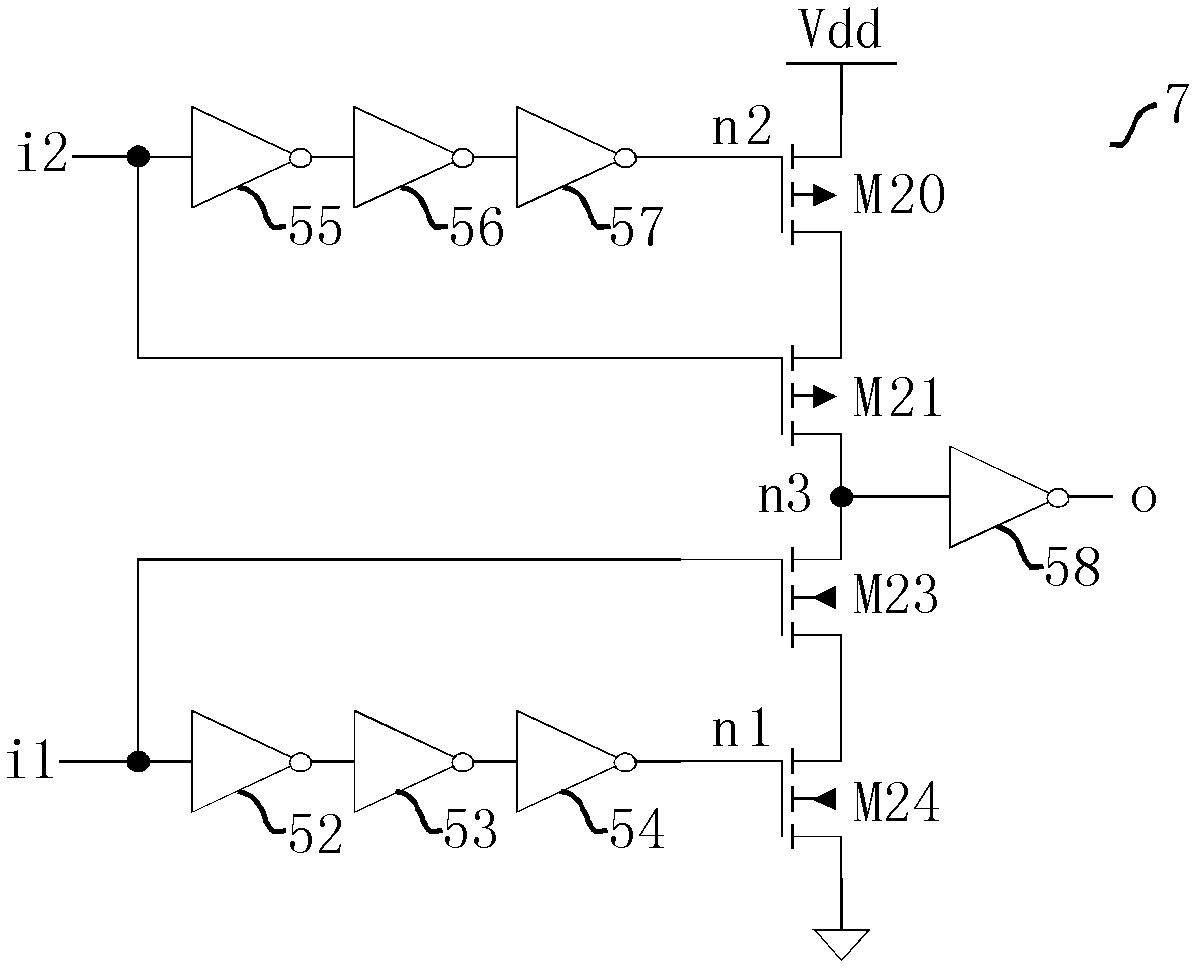

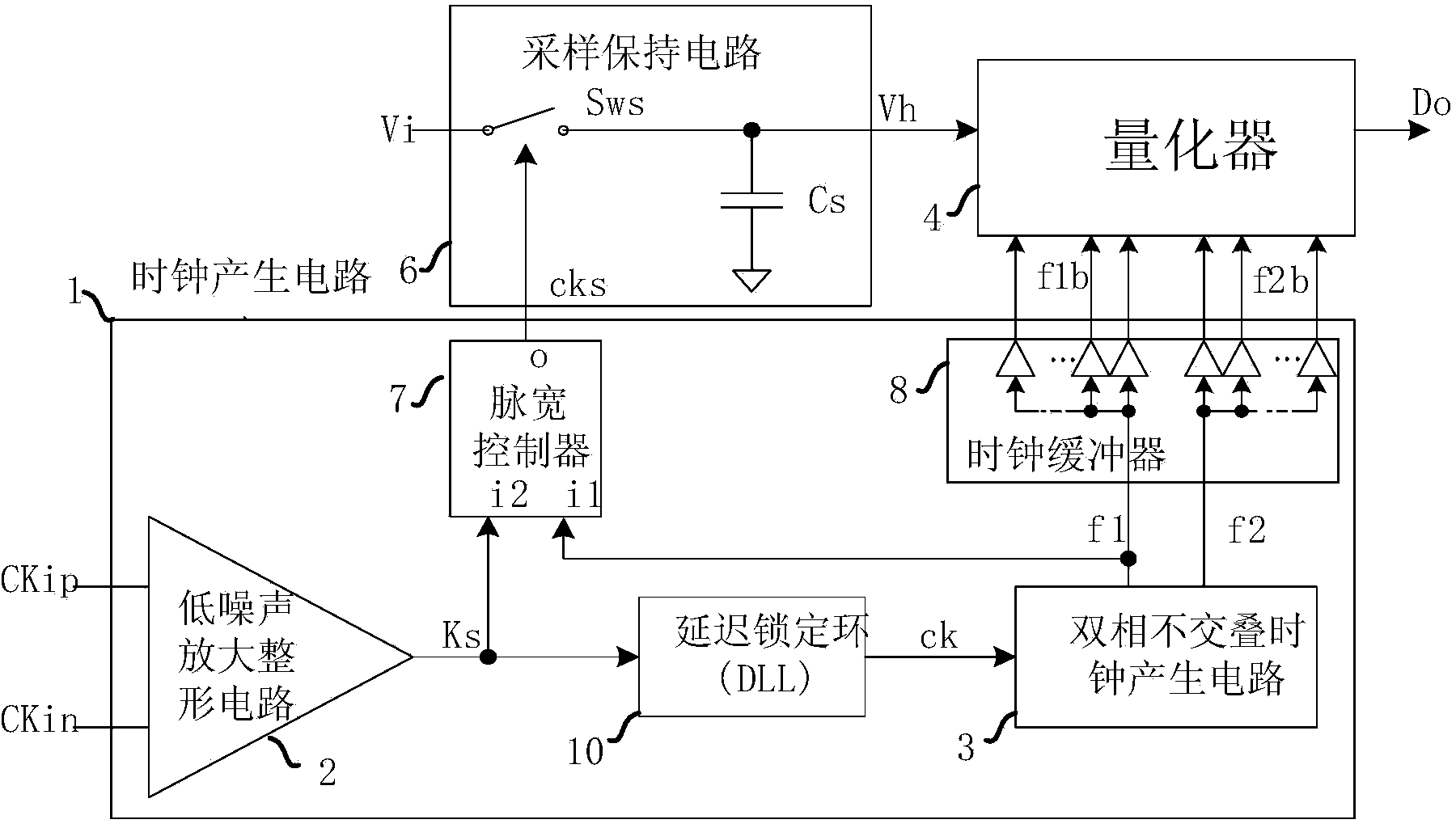

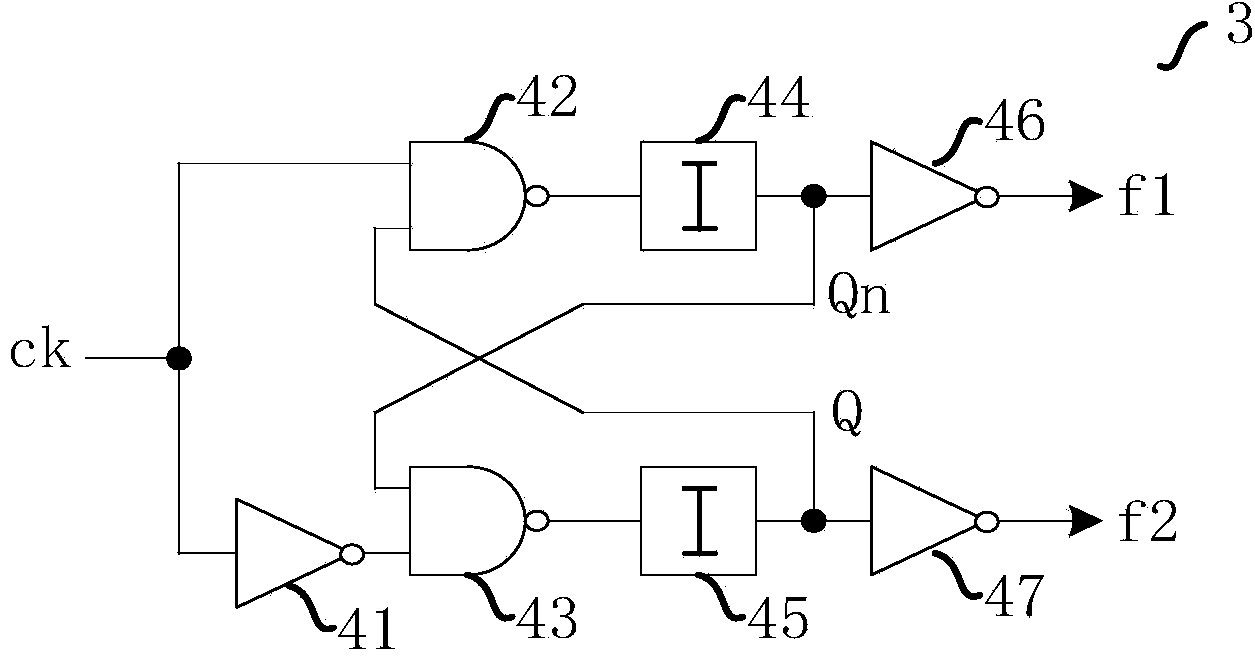

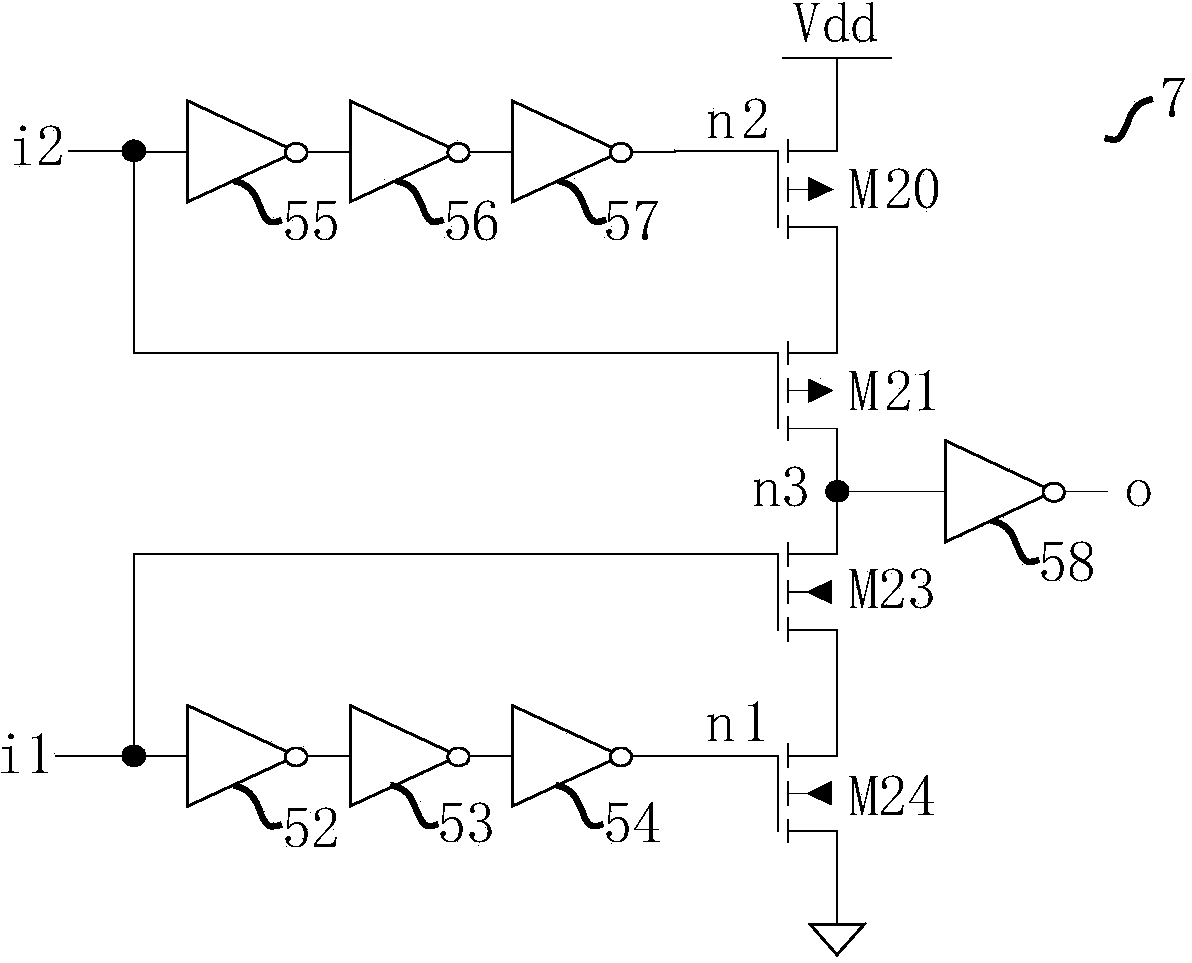

The invention discloses a clock generation circuit used in an analog-to-digital converter (ADC) with a high speed and high precision. The clock generation circuit comprises: a low noise amplification and shaping circuit, a pulse width controller, a DLL with pulse width calibration, a biphase non-overlapping clock generation circuit and a clock buffer. A voltage-controlled delay line (VCDL) with pulse width adjustment is designed in the DLL with the pulse width calibration. The VCDL can realize clock signal time delay and pulse width control based on a cascade group comprising same M improvement delay units. The DLL with the pulse width calibration and the biphase non-overlapping clock generation circuit together form a time-delay control and pulse width adjustment loop. Therefore, working sequences of an ADC sampling circuit and a quantizer can be synchronized and stable processing to an input clock duty ratio can be realized. By using the technical scheme of the invention, a bandwidth requirement to an ADC driving circuit can be reduced; difficulty for designing the system and power consumption can be reduced; realization precision of the ADC quantizer can be improved.

Owner:TSINGHUA UNIV

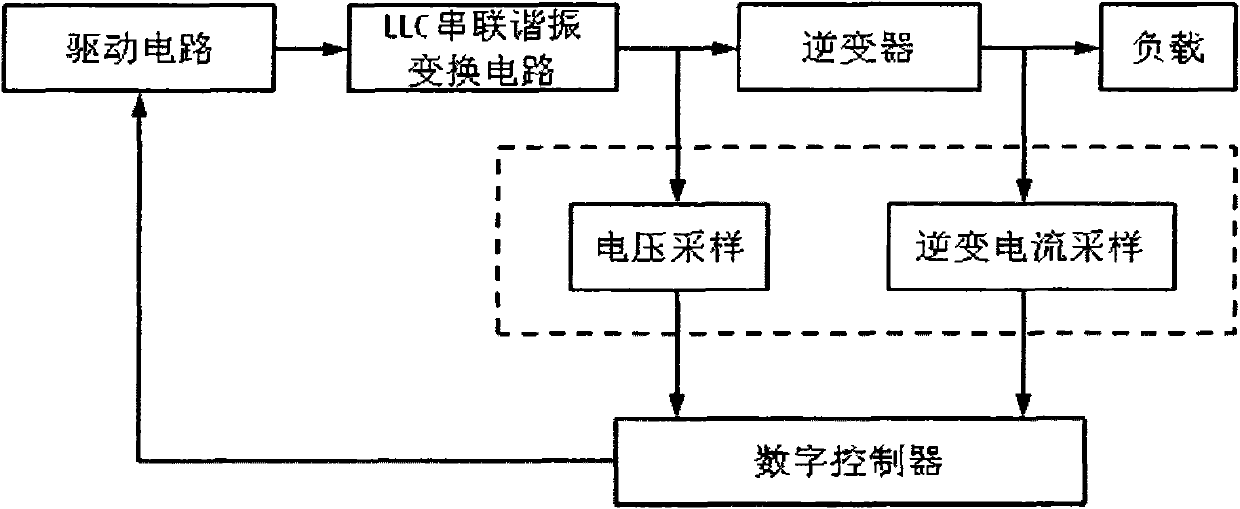

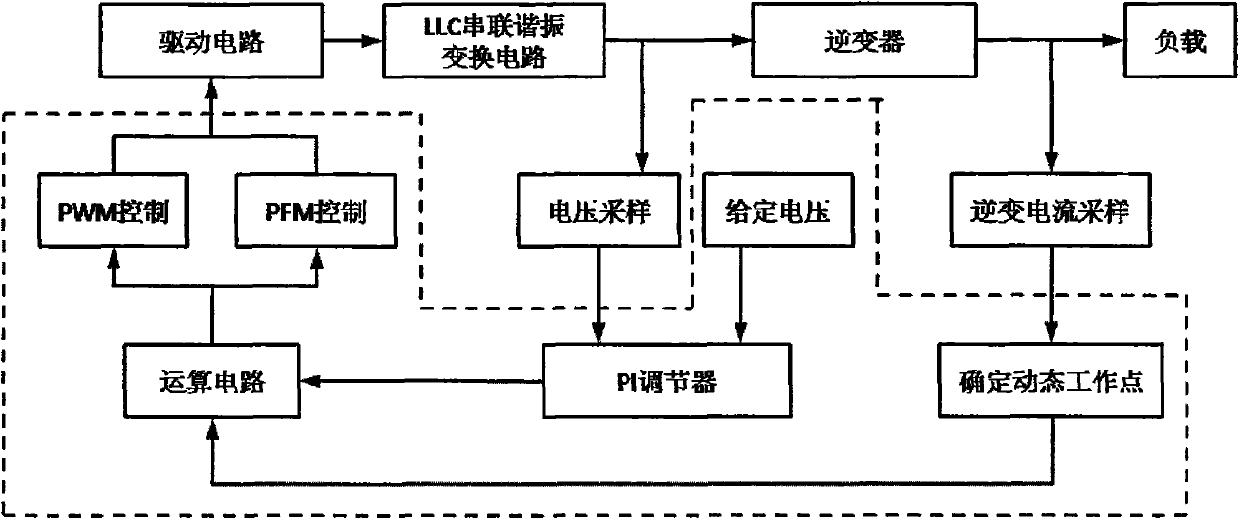

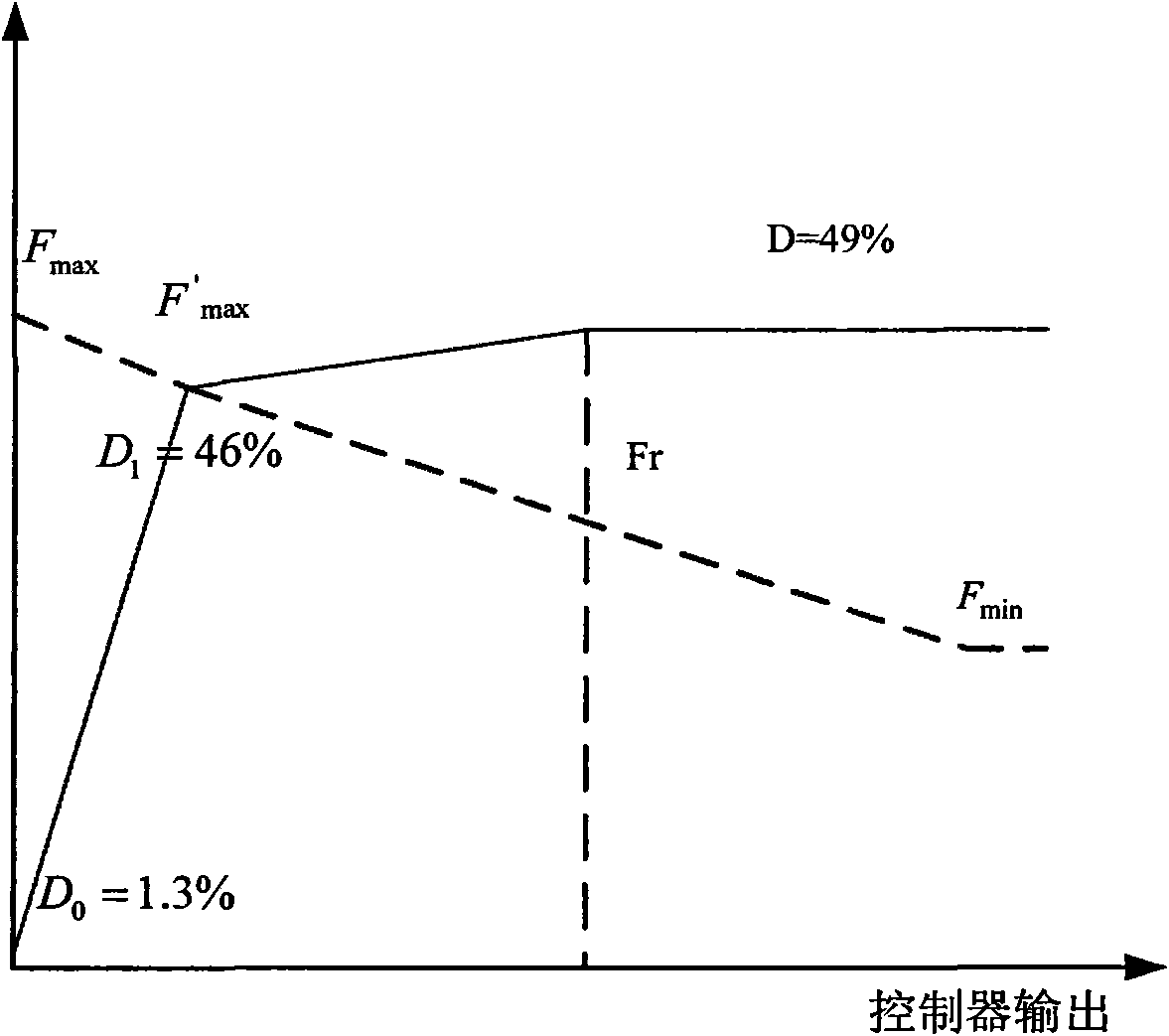

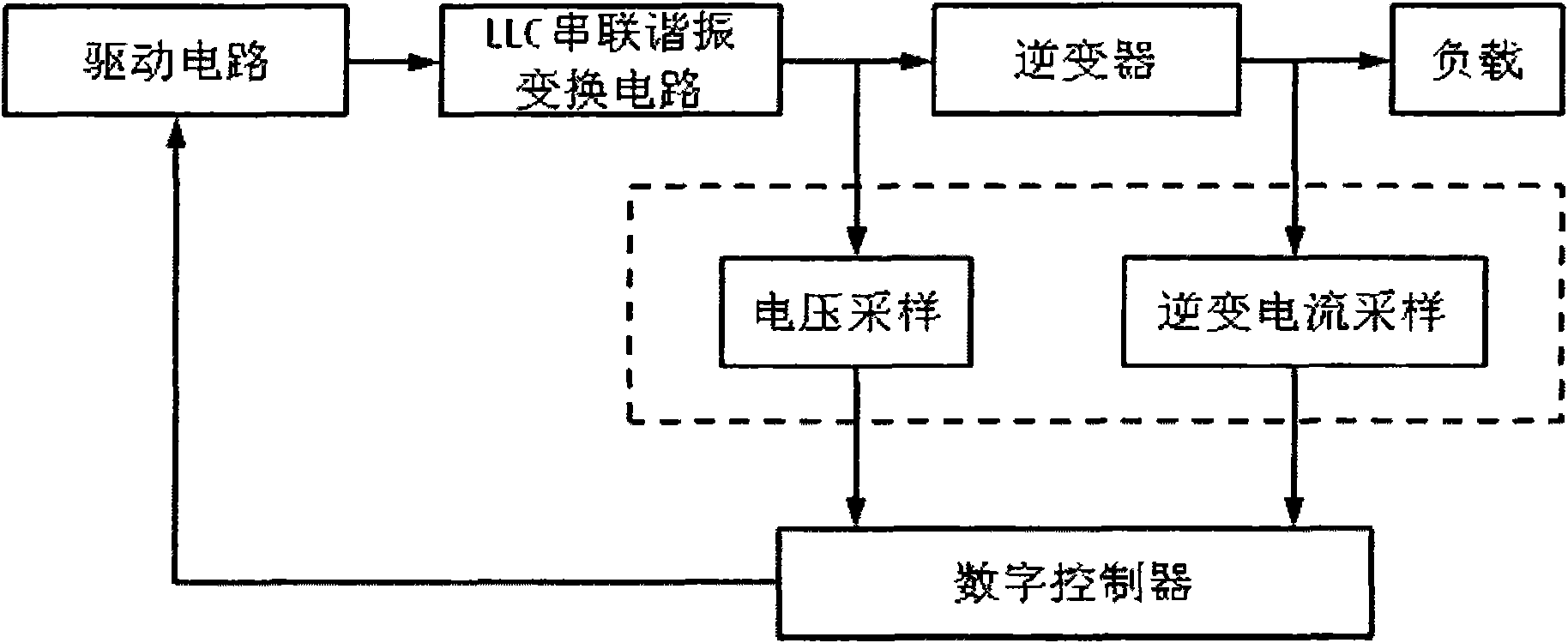

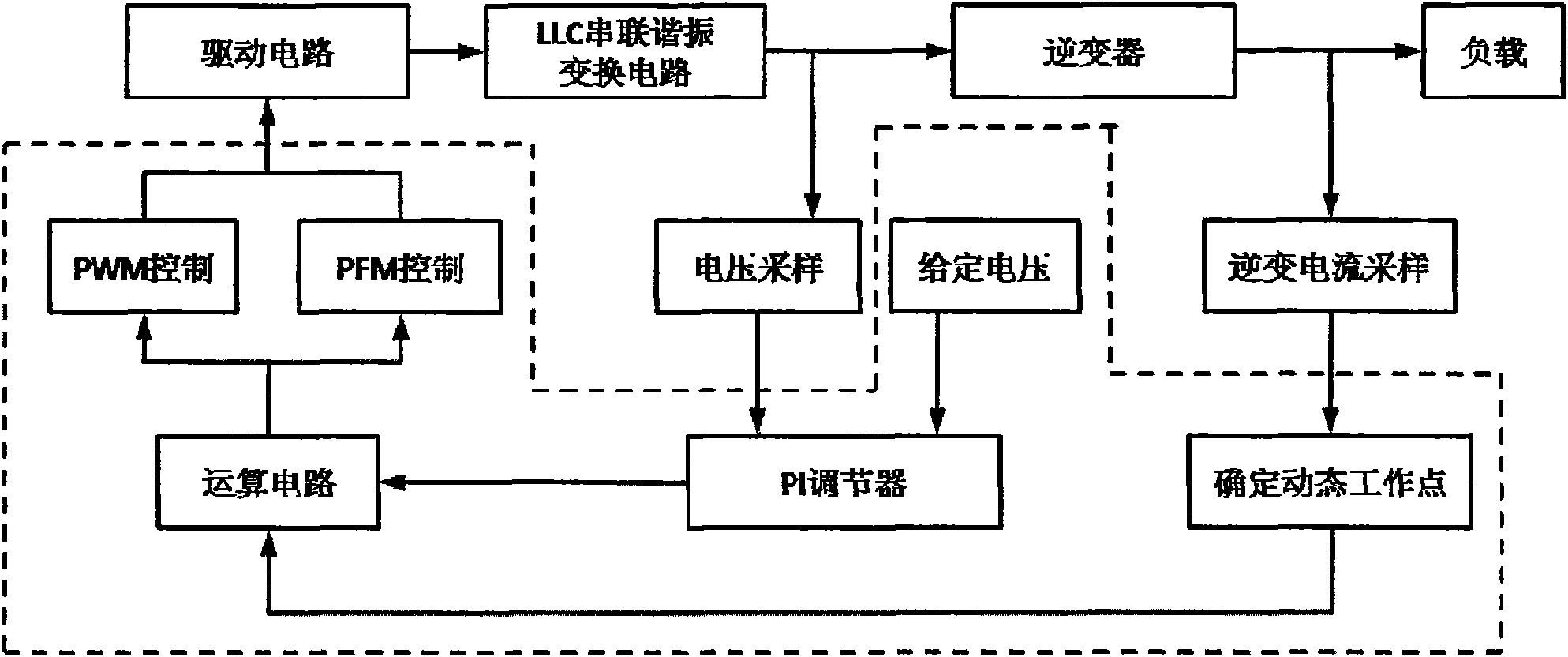

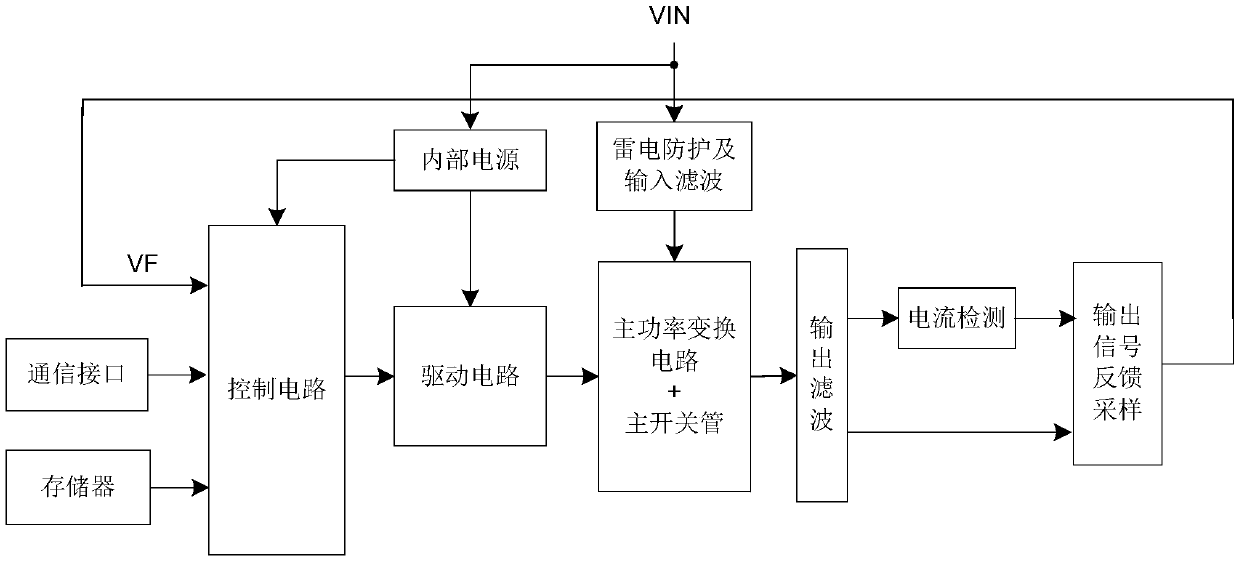

Numeric control method for liquid level control (LLC) resonant conversion circuit

ActiveCN102025266AStable duty cycleAvoid uncontrollableDc-dc conversionElectric variable regulationElectricityDriver circuit

The invention discloses a numeric control method for a liquid level control (LLC) resonant conversion circuit. The method comprises the following steps of: sampling an LLC series resonant conversion circuit and an inverter electrically connected with the LLC series resonant conversion circuit respectively by adopting a single voltage loop numeric control structure; after calculation, outputting to a numeric controller; calculating the input quantity by using the numeric controller and outputting a driving pulse; controlling the LLC series resonant conversion circuit by using the driving pulse through a driving circuit; during light load or no load, adopting a mode of combining a pulse width modulation (PWM) control strategy and a pulse frequency modulation (PFM) control strategy; and during heavy load, adopting the PFM control. By the method, load states can be judged quickly; adverse influence on system load judgment due to different loading time is screened; a dynamic working point is selected reasonably according to the judged load state and current is controlled, so that the voltage stress of the LLC series resonant conversion circuit is eliminated; the control method provided by the invention is simple; and error and instability can be effectively reduced.

Owner:VERTIV CORP

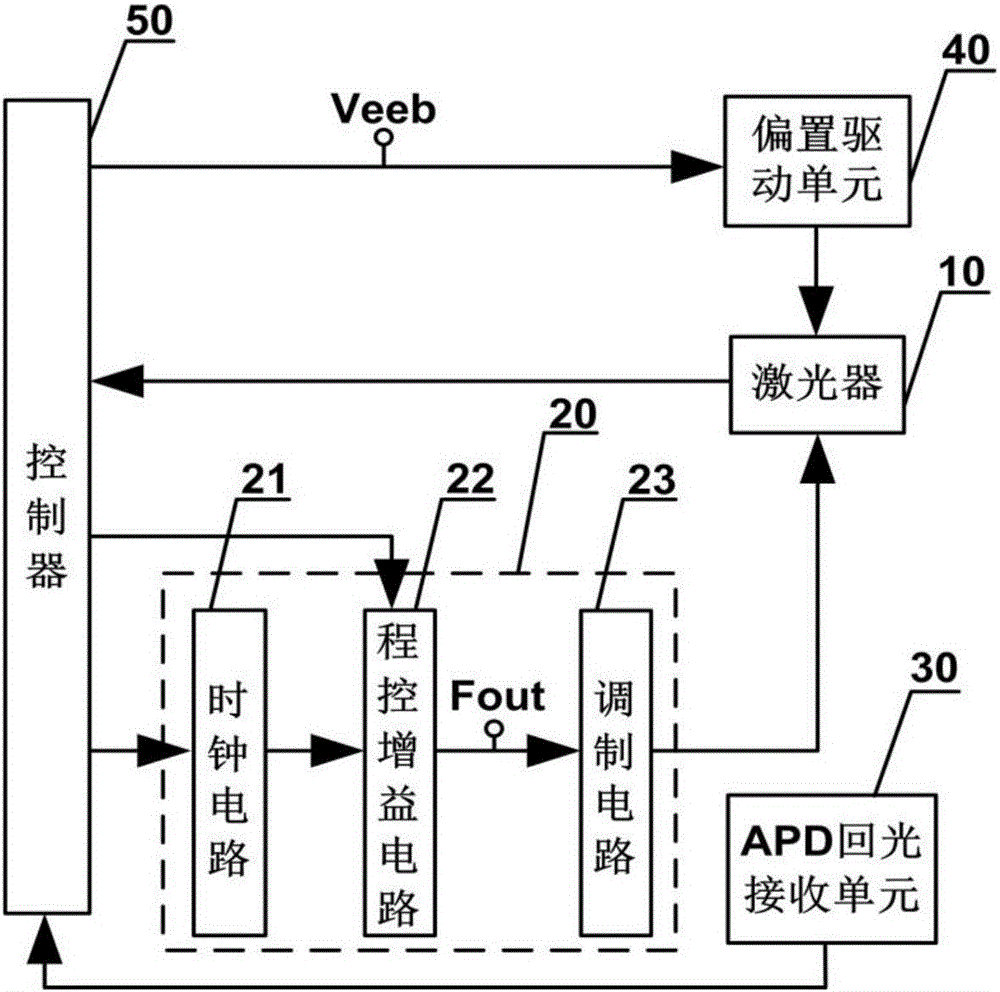

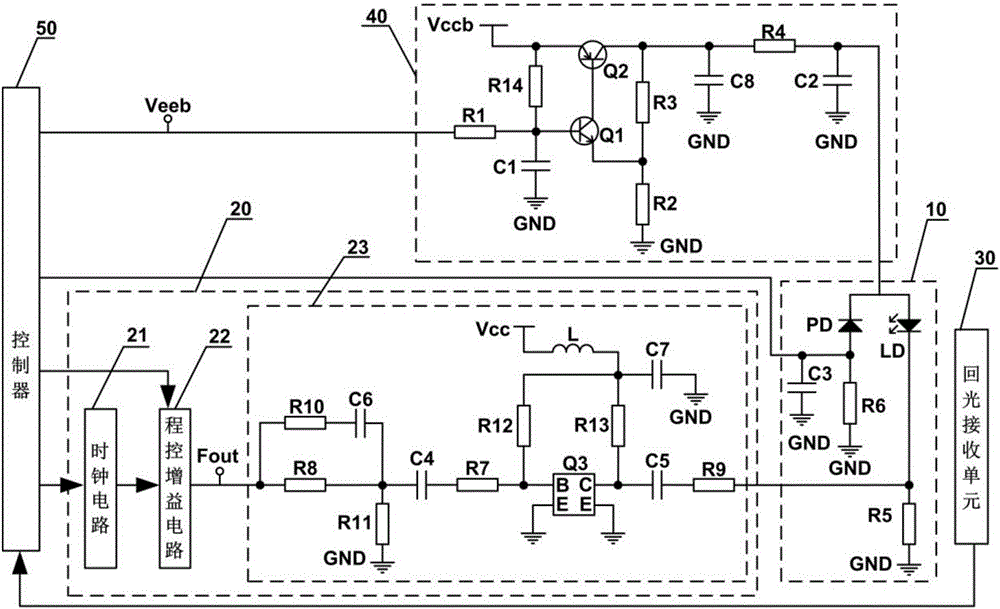

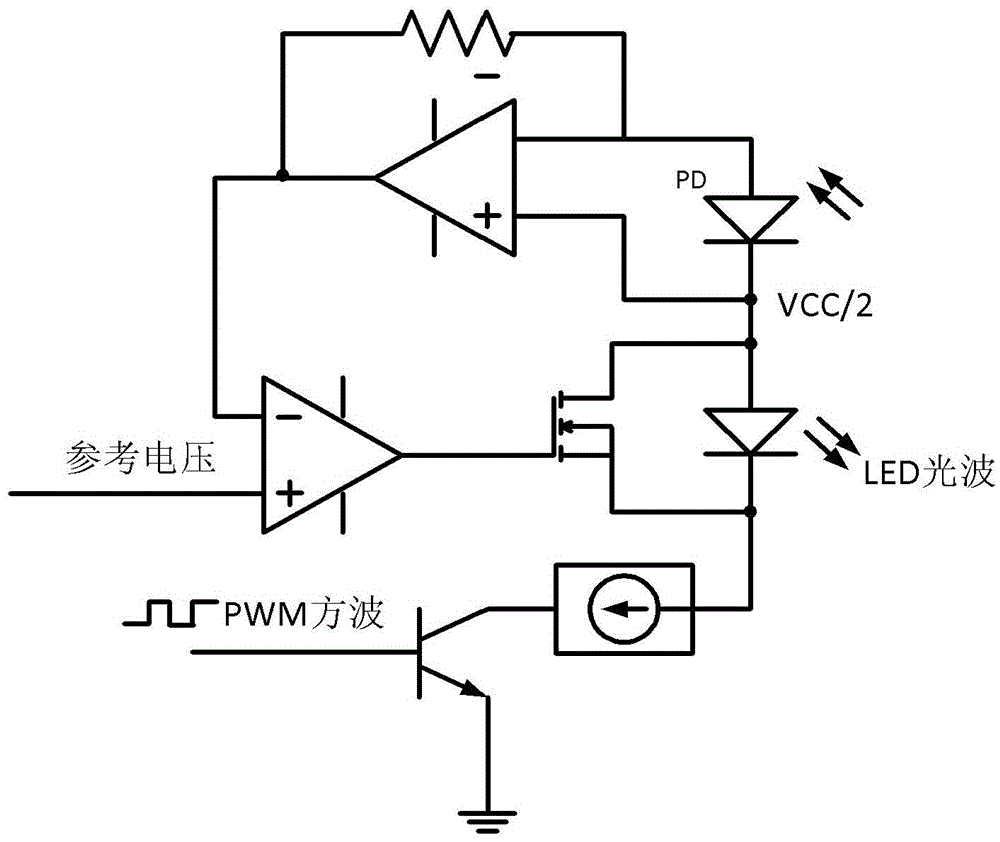

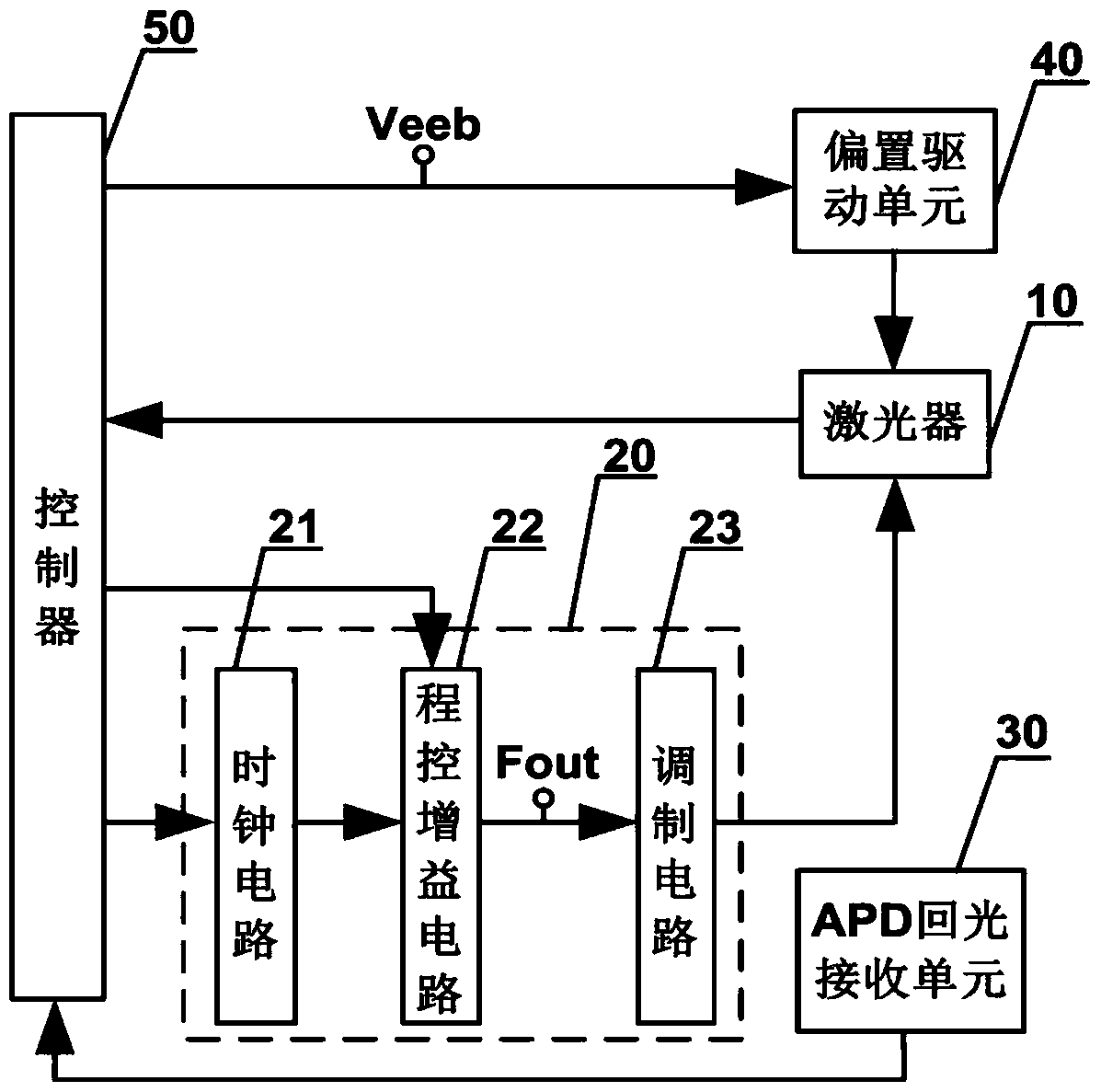

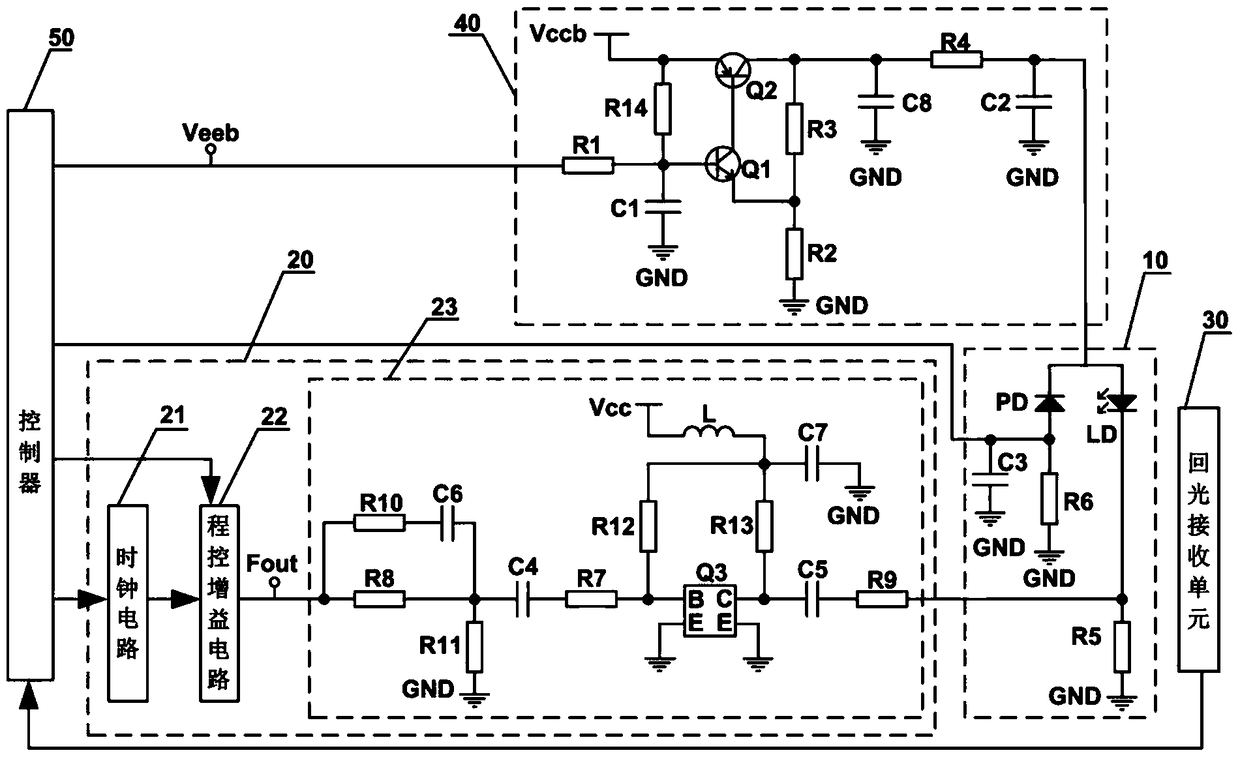

Phase type laser distance measuring system

ActiveCN105093233AIncreaseImprove ranging accuracyElectromagnetic wave reradiationLaser rangingPulse voltage

The invention discloses a phase type laser distance measuring system. The system comprises a laser for generating laser signals; an emission signal unit for generating emission signals and sending the emission signals to the laser after amplitude adjustment and power amplification are successively performed on the emission signals; a returning light receiving unit for receiving reflection signals of laser signals; a bias driving unit for providing offset voltages for driving the laser to emit the laser signals; and a controller for outputting PWM pulse voltage signals with an adjustable duty ratio to the bias driving unit to form the offset voltages and receive the emission signals. When the controller receives that the emission signals involves weak reflection, the controller reduces the duty ratio of the PWM pulse voltage signals and improves the amplitude of the emission signals in a linkage mode; and when the controller receives that the emission signals involves strong reflection, the controller increases the duty ratio of the PWM pulse voltage signals and reduces the amplitude of the emission signals in a linkage mode. The system provided by the invention has the advantages of simple system, high anti-interference capability and high distance measuring accuracy.

Owner:SUZHOU YISEN PHOTOELECTRIC TECH CO LTD

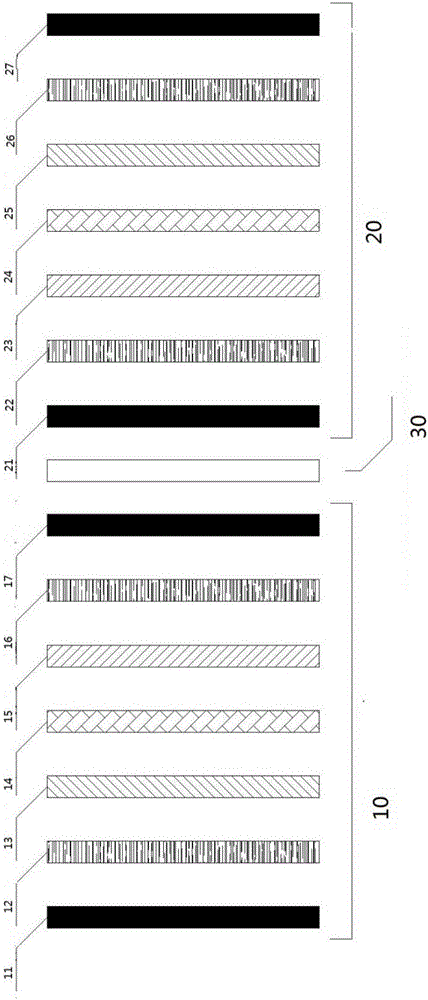

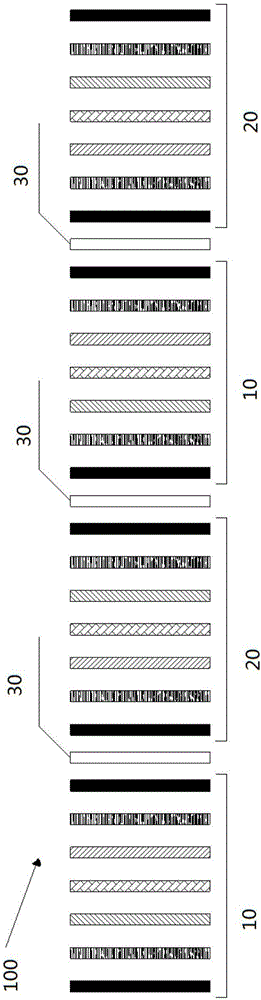

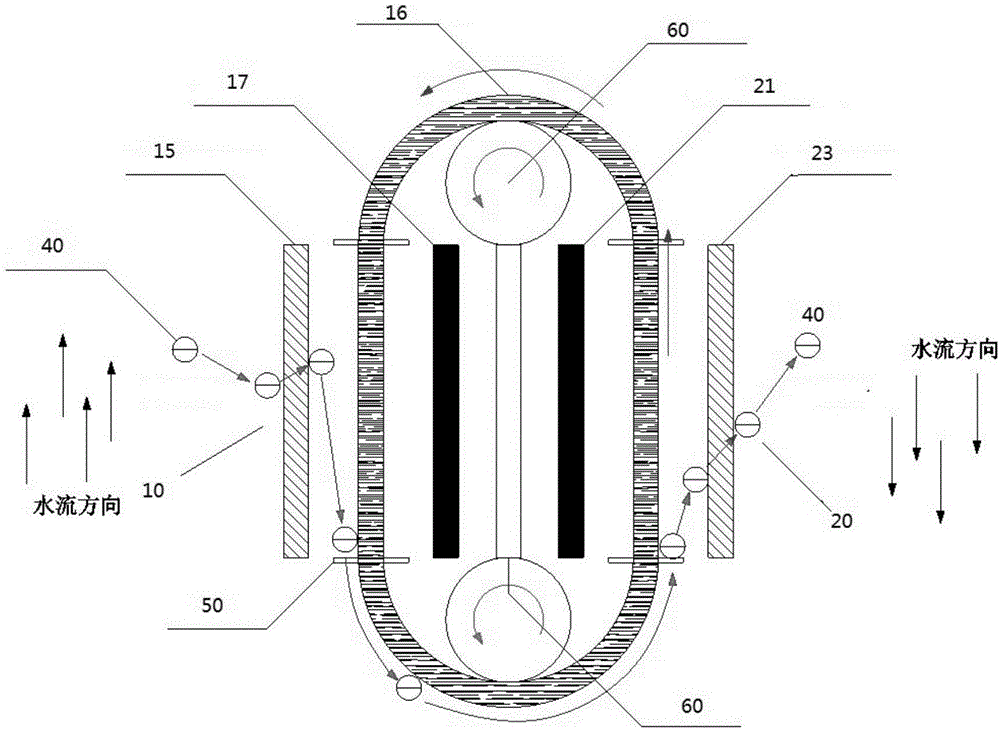

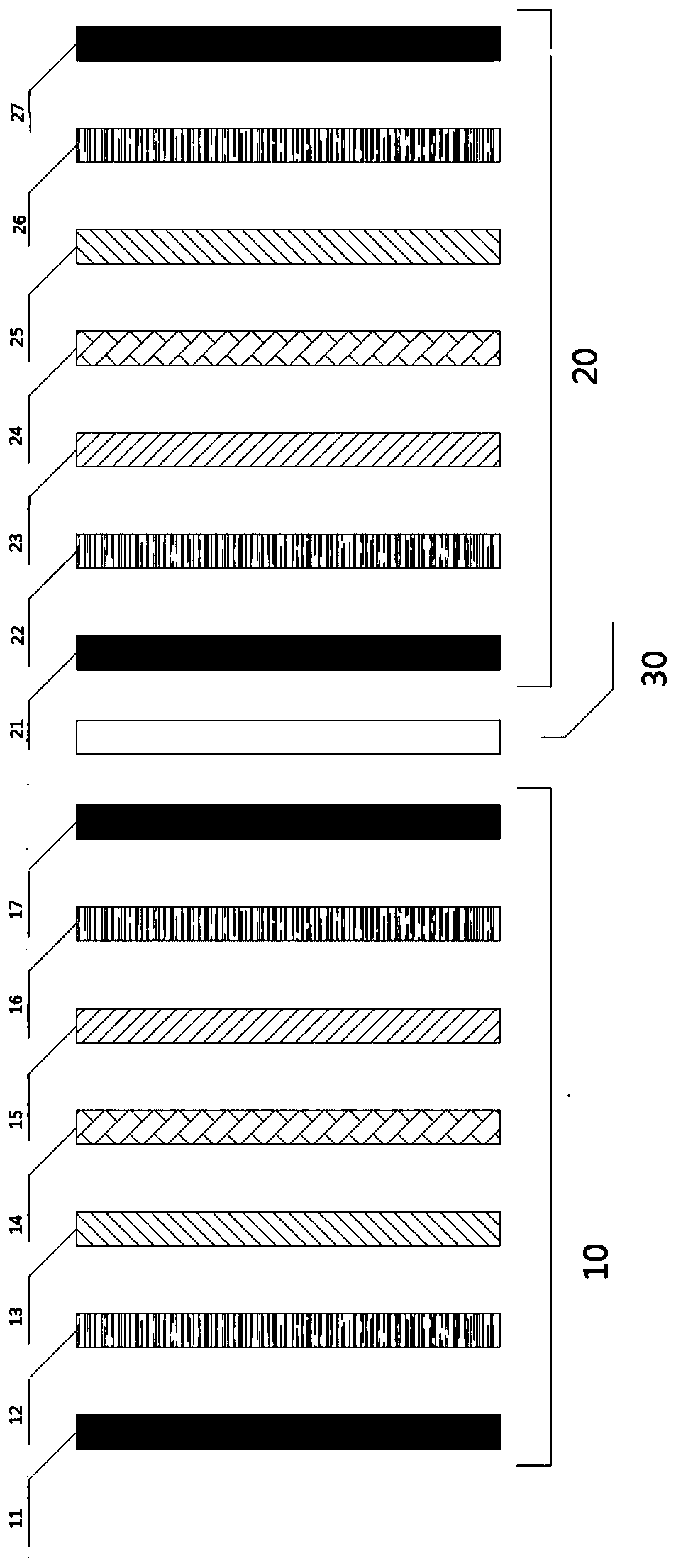

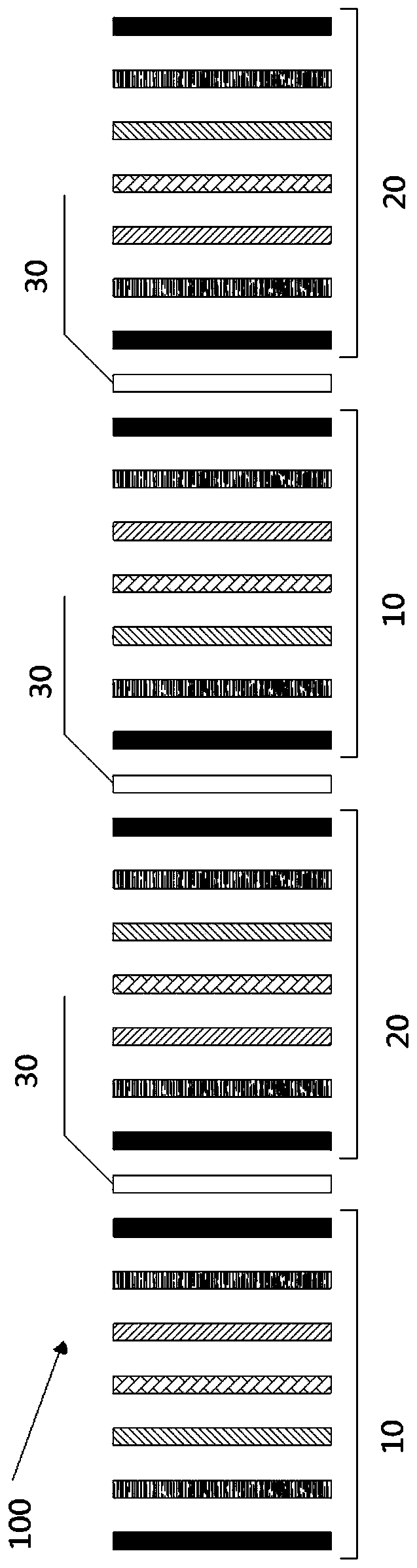

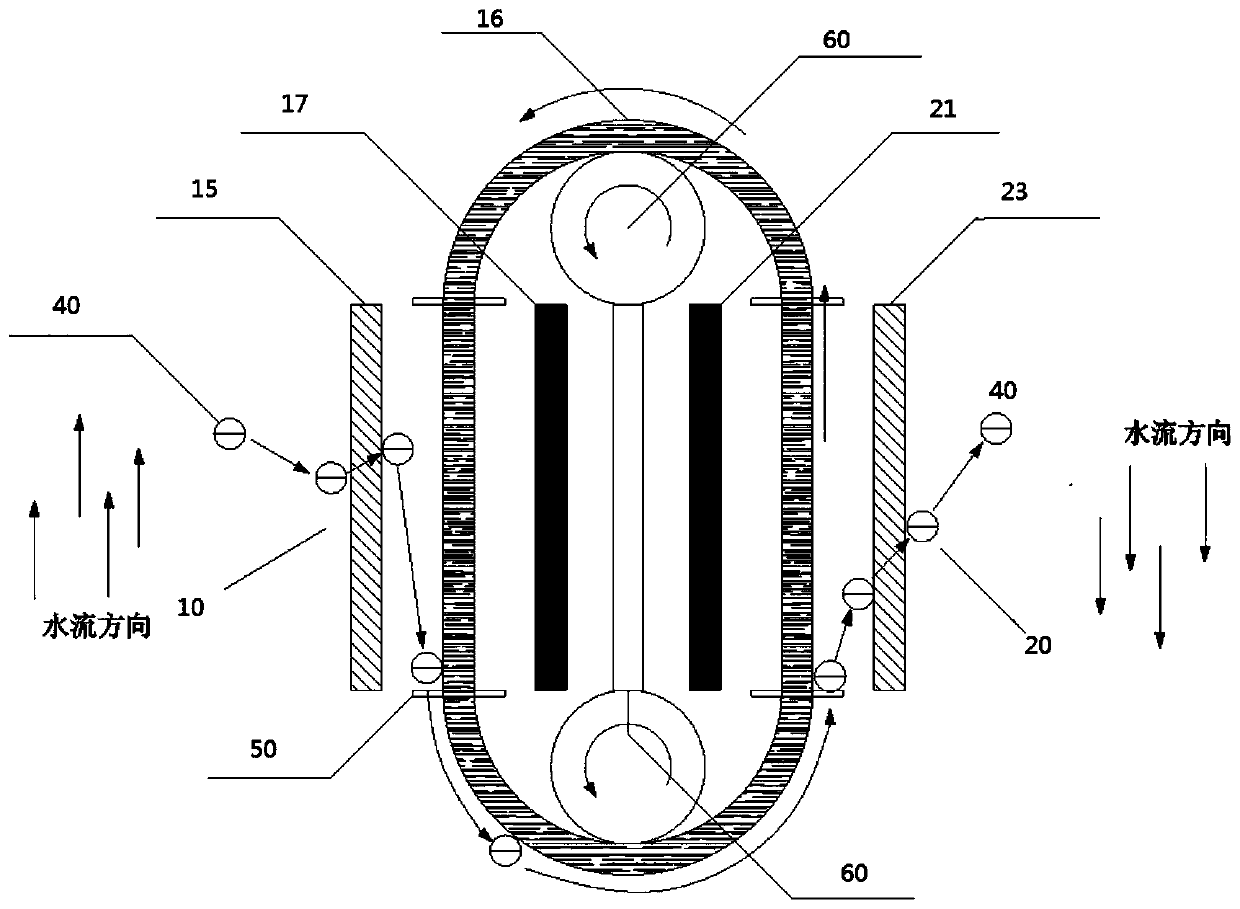

Membrane capacitive deionization array with movable type electrodes and deionization method thereof

ActiveCN106673142ALong runStable duty cycleDispersed particle separationWater/sewage treatmentCapacitanceCapacitive deionization

The invention discloses a membrane capacitive deionization array with movable type electrodes and a deionization method thereof. The array comprises the following components: adsorption modules and desorption modules are mutually spaced and alternatively arranged into an array, and the movable type electrodes are periodically positioned in the adsorption modules and the desorption modules. The traditional membrane capacitive deionization technology is used as a prototype, adsorption modules are arranged, arrangement sequence of an ion-exchange membrane is changed, the desorption modules are arranged, originally fixed electrodes are innovatively changed into movable type electrodes, the electrodes are periodically arranged in the adsorption modules and the desorption modules, so that the purpose that the deionization process is stably efficient for a long time is realized; the adsorption modules and the desorption modules work simultaneously in different regions, in order to form a stable working cycle, and circuit with reversal connection is not needed for backwashing; the deionization method can be operated continuously with high efficiency and stabilization, and the deionization efficiency is high.

Owner:HOHAI UNIV

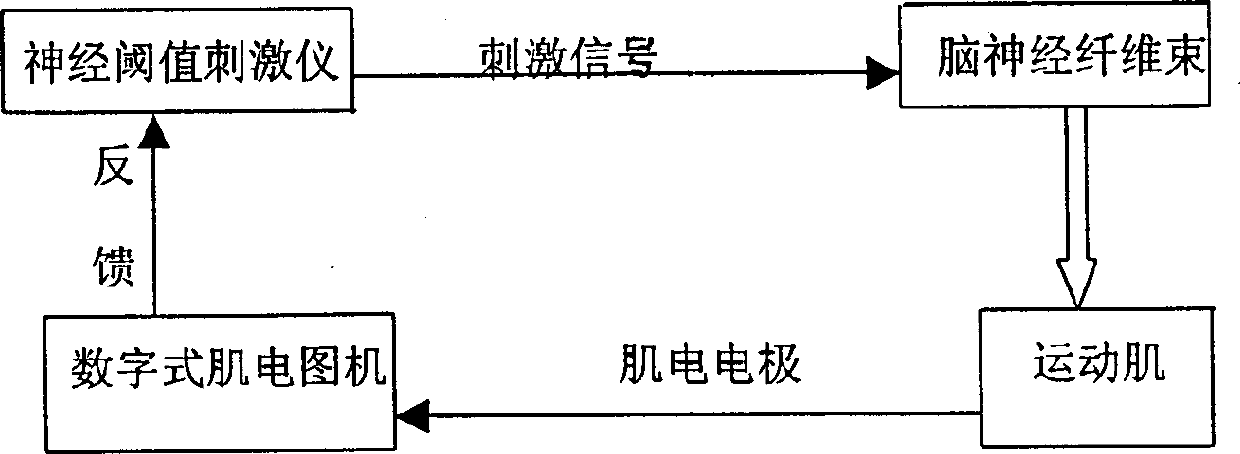

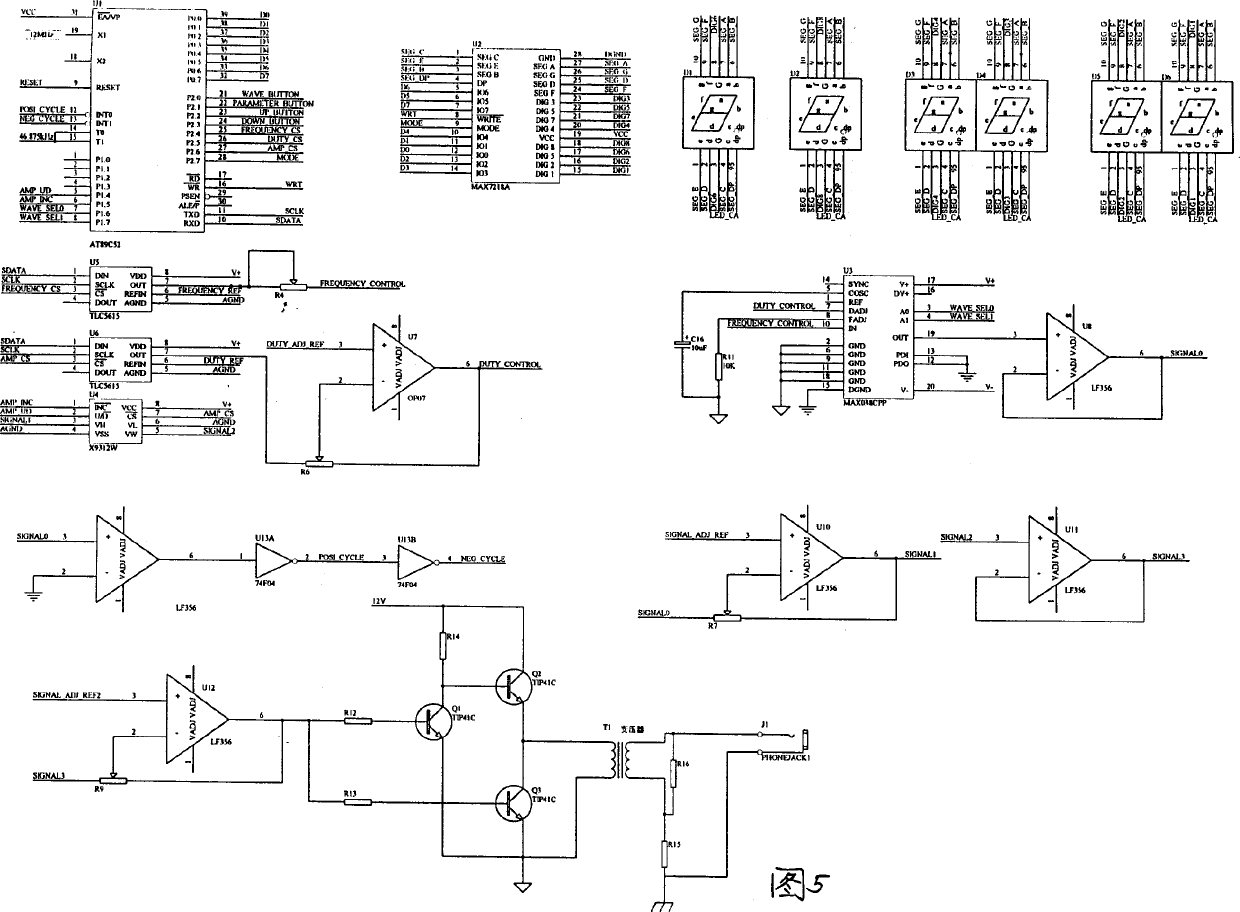

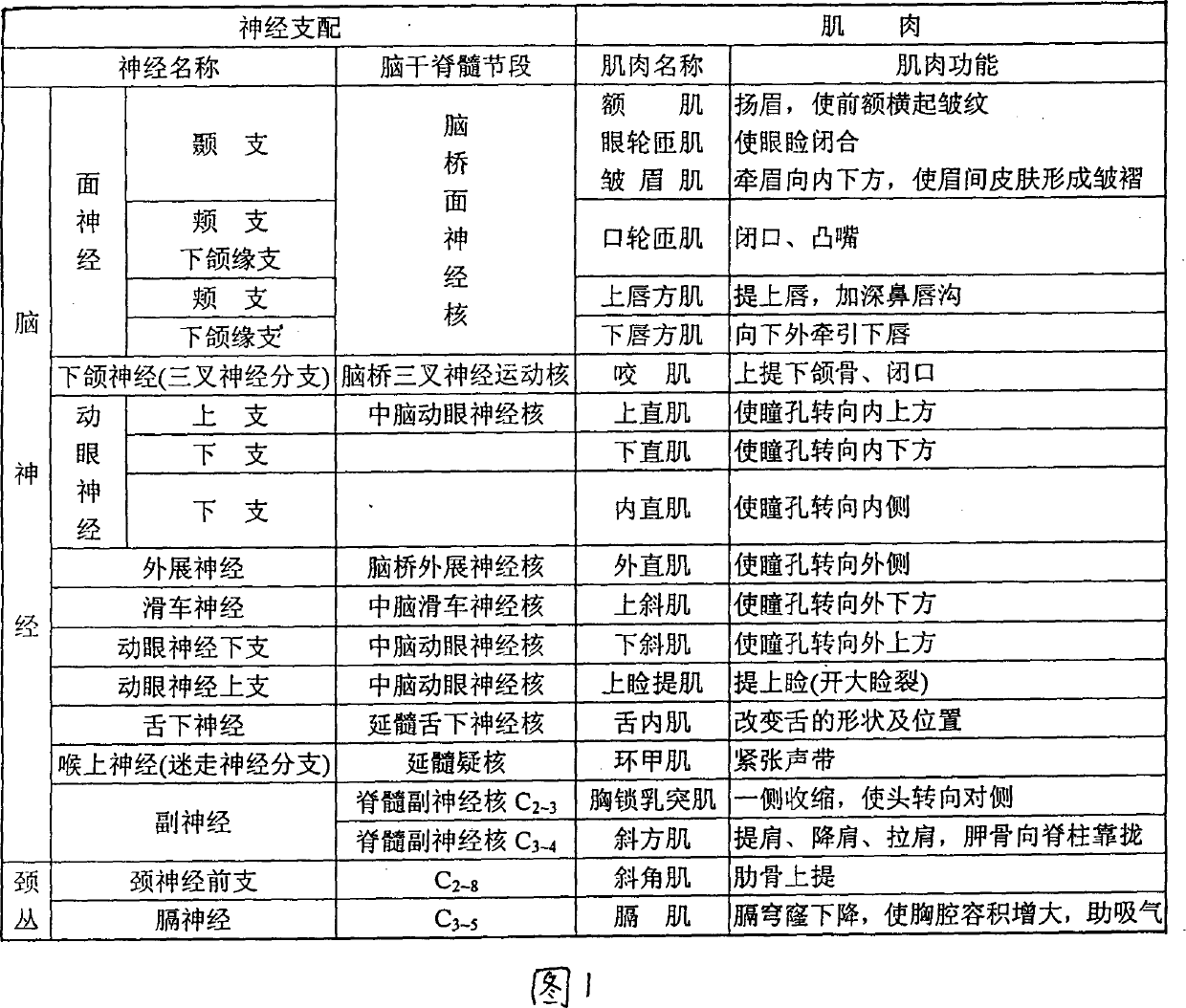

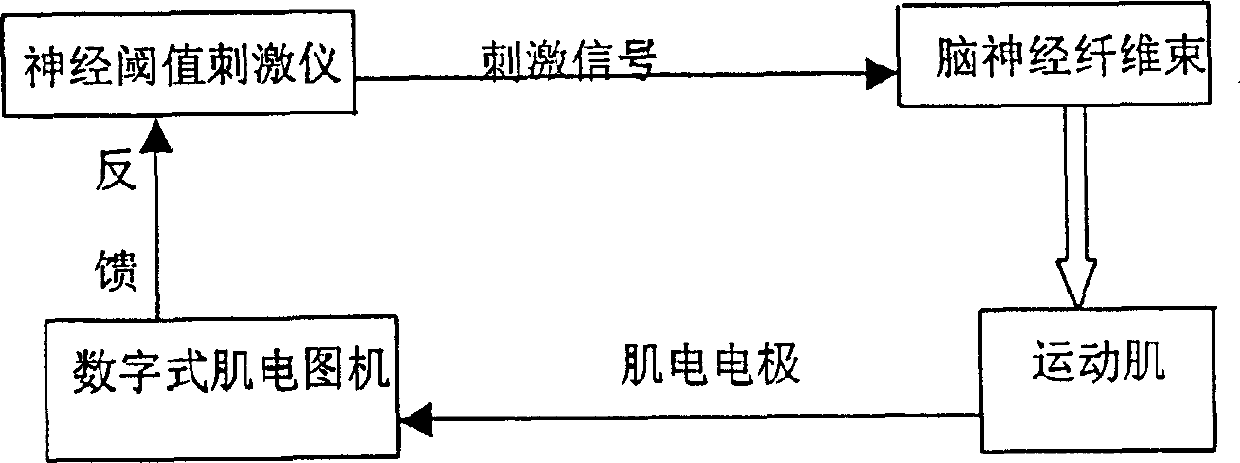

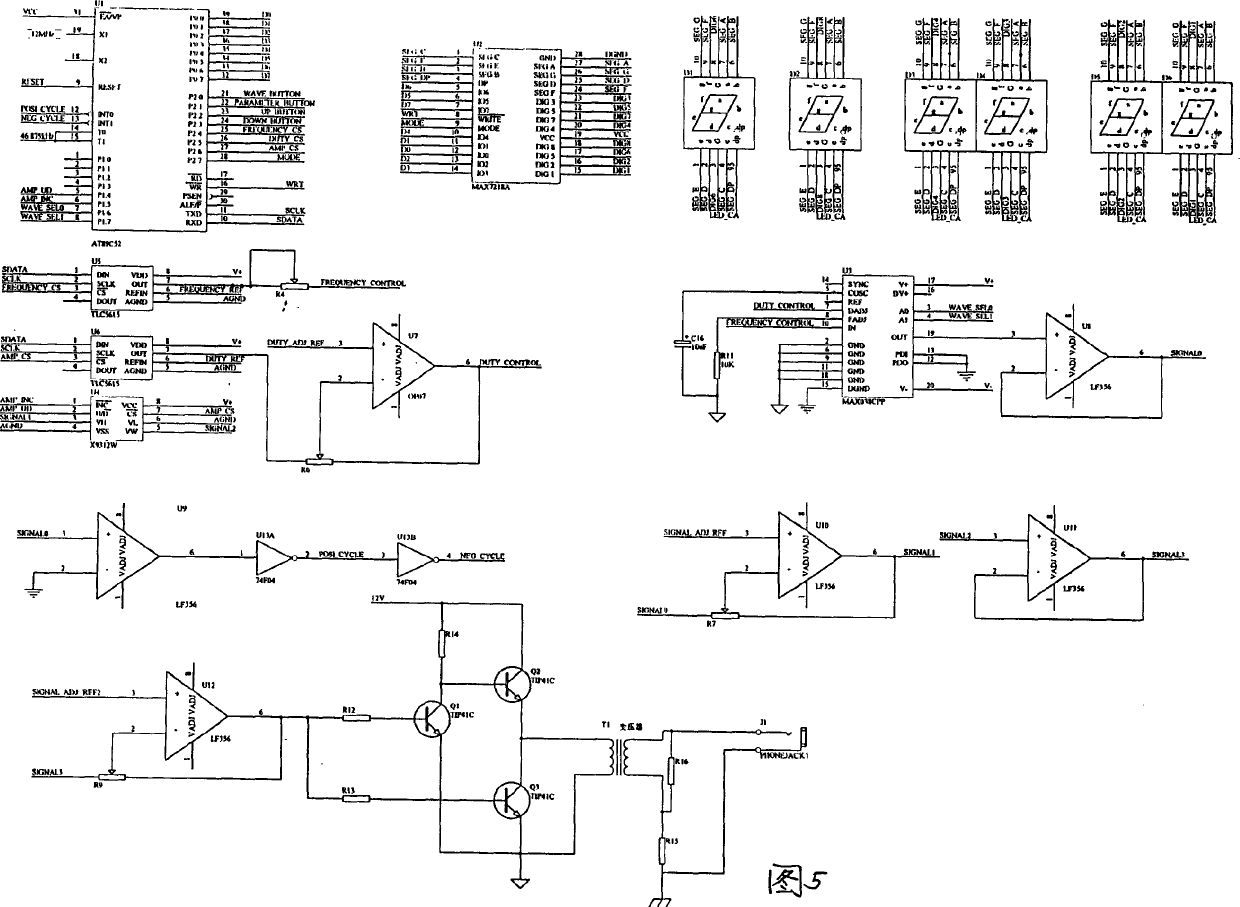

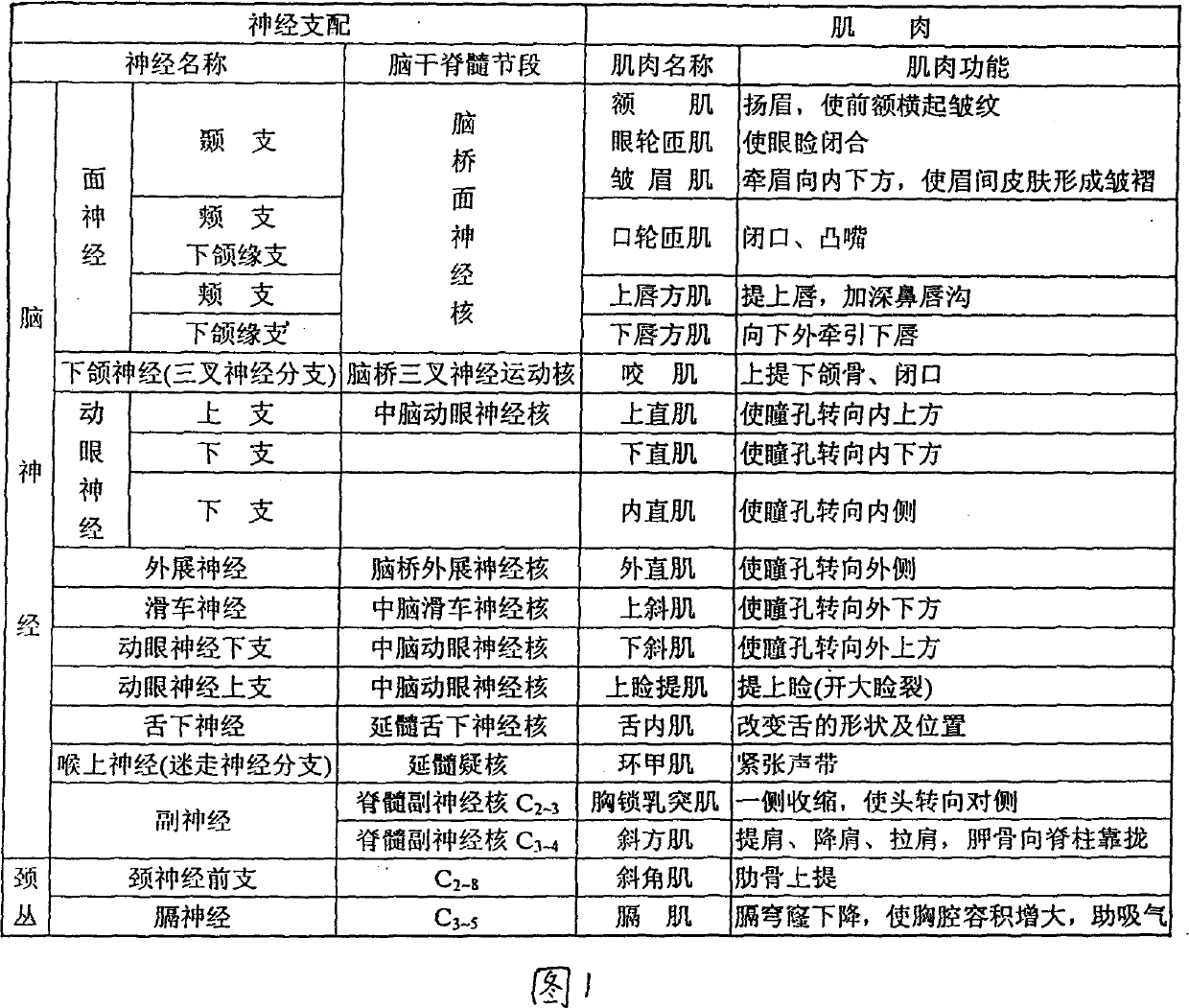

Method and system for testing human nerve threshold value

InactiveCN1401294APrecise digital adjustmentAccurate amplitudeDiagnostic recording/measuringSensorsNerve thresholdThreshold potential

A method for measuring the threshold value of human nerve includes opening human skull, applying electric stimualting signal to the nerve to be measured, measuring the electromyographic signal of the muscle controlled by said nerve, and finding out the threshold value and relative parameters. Its system is composed of a nerve threshold stimulator, a digital electromyograph and a computer.

Owner:NANJING GENERAL HOSPITAL NANJING MILLITARY COMMAND P L A +1

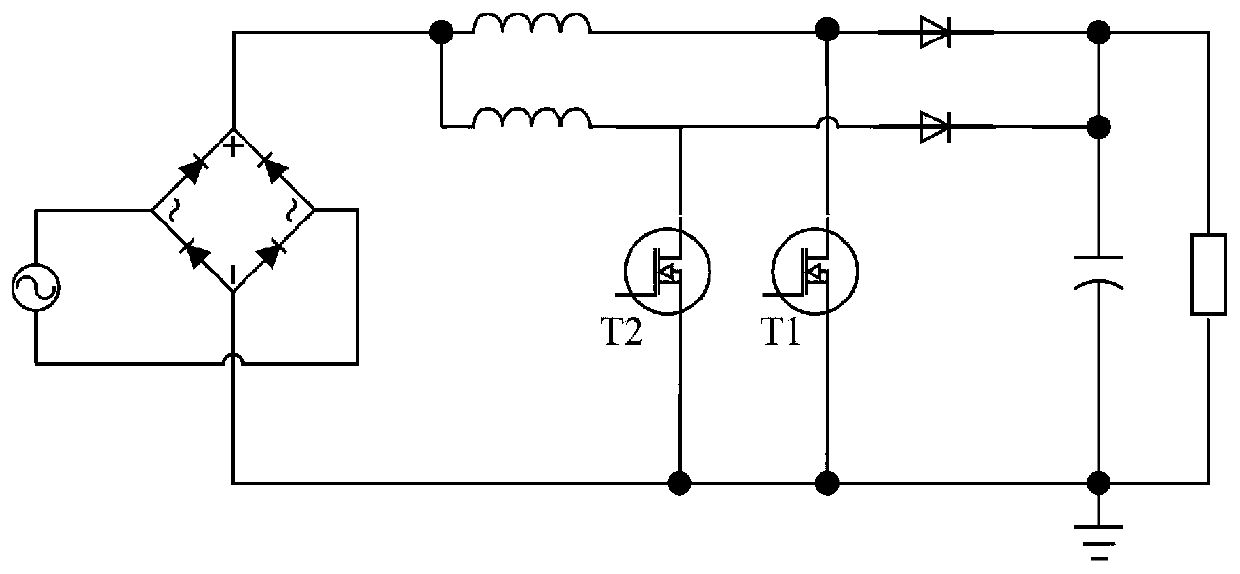

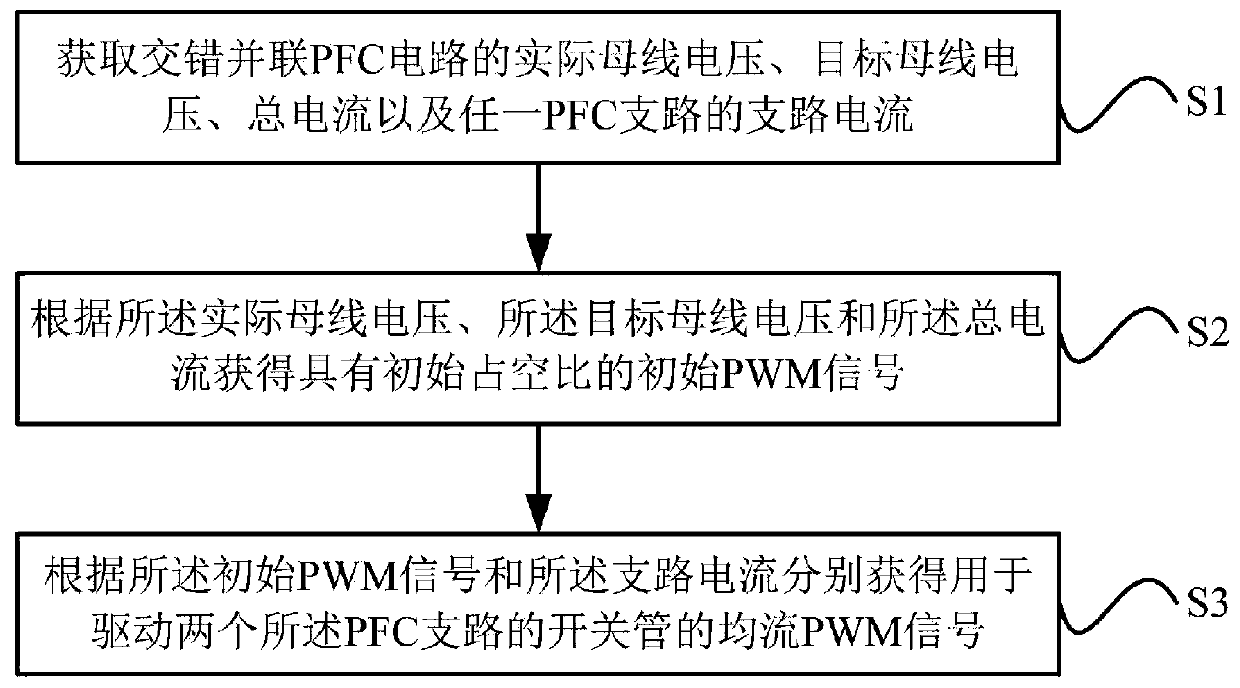

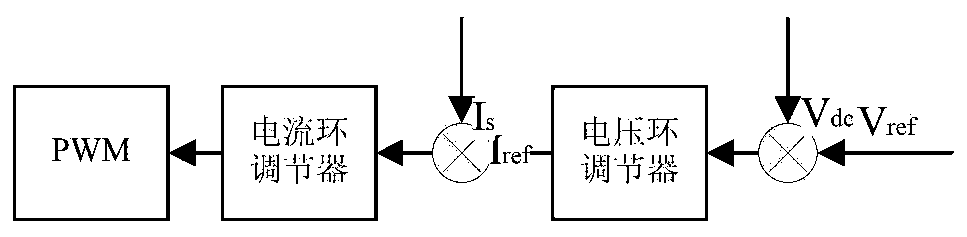

Current sharing control method and device for interleaved parallel PFC circuit and air conditioner

InactiveCN110677032ASolve uneven flowStable duty cycleEfficient power electronics conversionSpace heating and ventilation safety systemsHemt circuitsControl engineering

The invention provides a current sharing control method and device for an interleaved parallel PFC circuit and an air conditioner. The interleaved parallel PFC circuit comprises two symmetrically arranged PFC branches. The method comprises the following steps: acquiring the actual bus voltage, the target bus voltage and the total current of the interleaved parallel PFC circuit and the branch current of any PFC branch; obtaining the initial PWM signal having an initial duty cycle according to the actual bus voltage, the target bus voltage and the total current; and obtaining the current sharingPWM signal for driving the switching tubes of the two PFC branches according to the initial PWM signal and the branch current. The technical scheme can simply and effectively solve the problem of uneven current of the branches of the interleaved parallel PFC circuit and ensure that electrical appliances such as the air conditioner are in a reliable operation state.

Owner:NINGBO AUX ELECTRIC +1

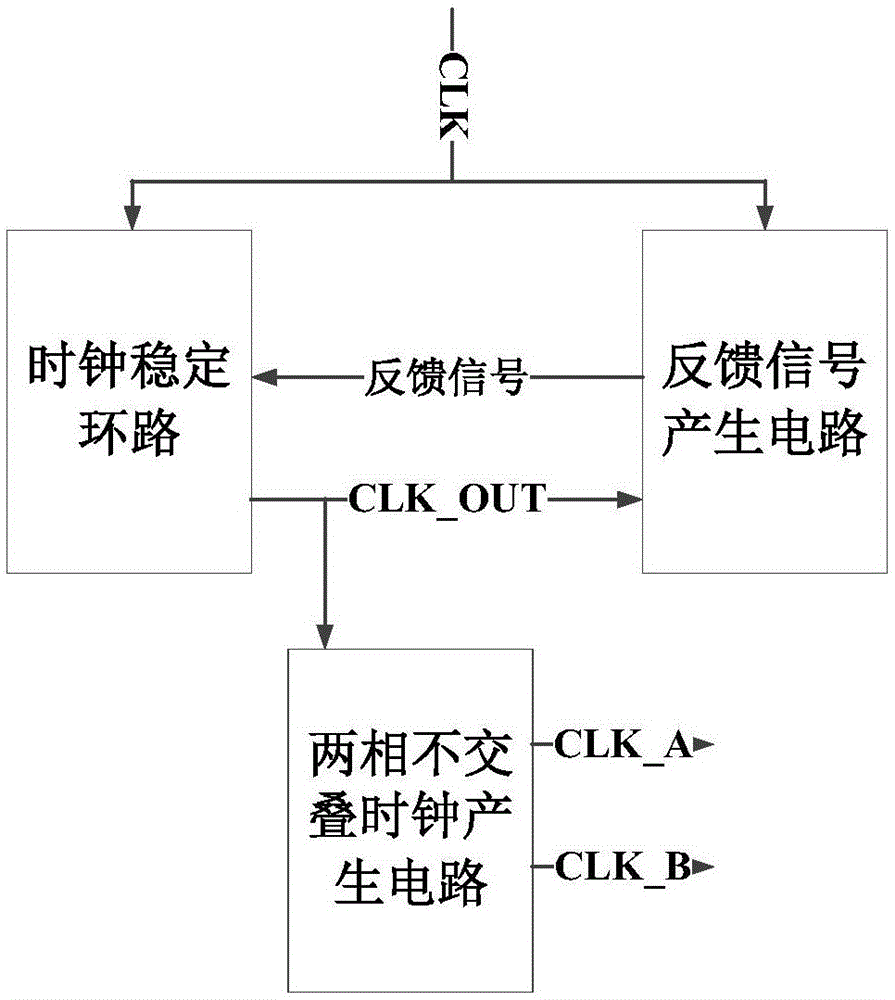

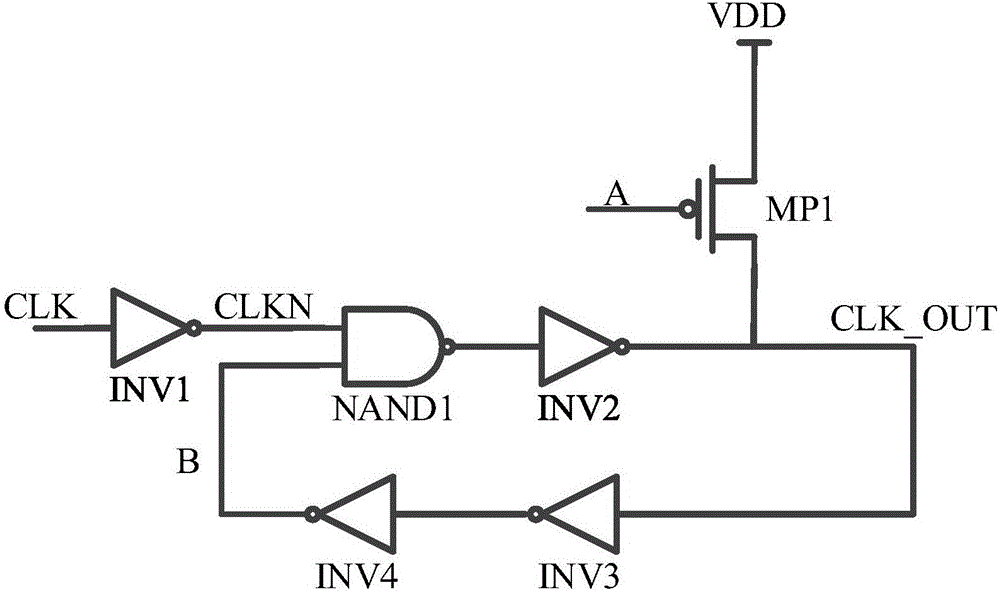

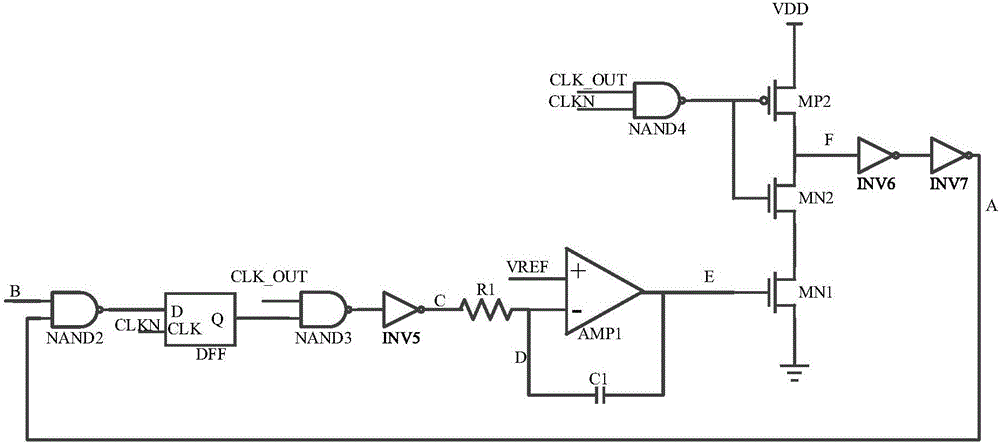

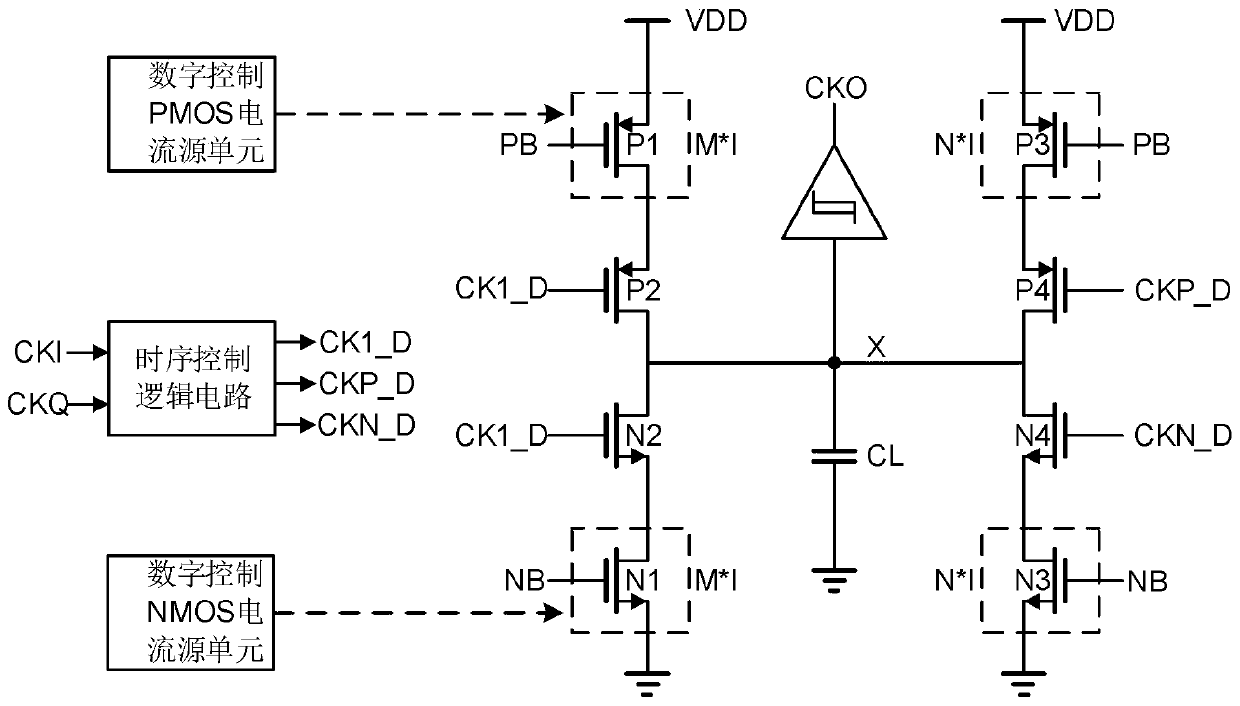

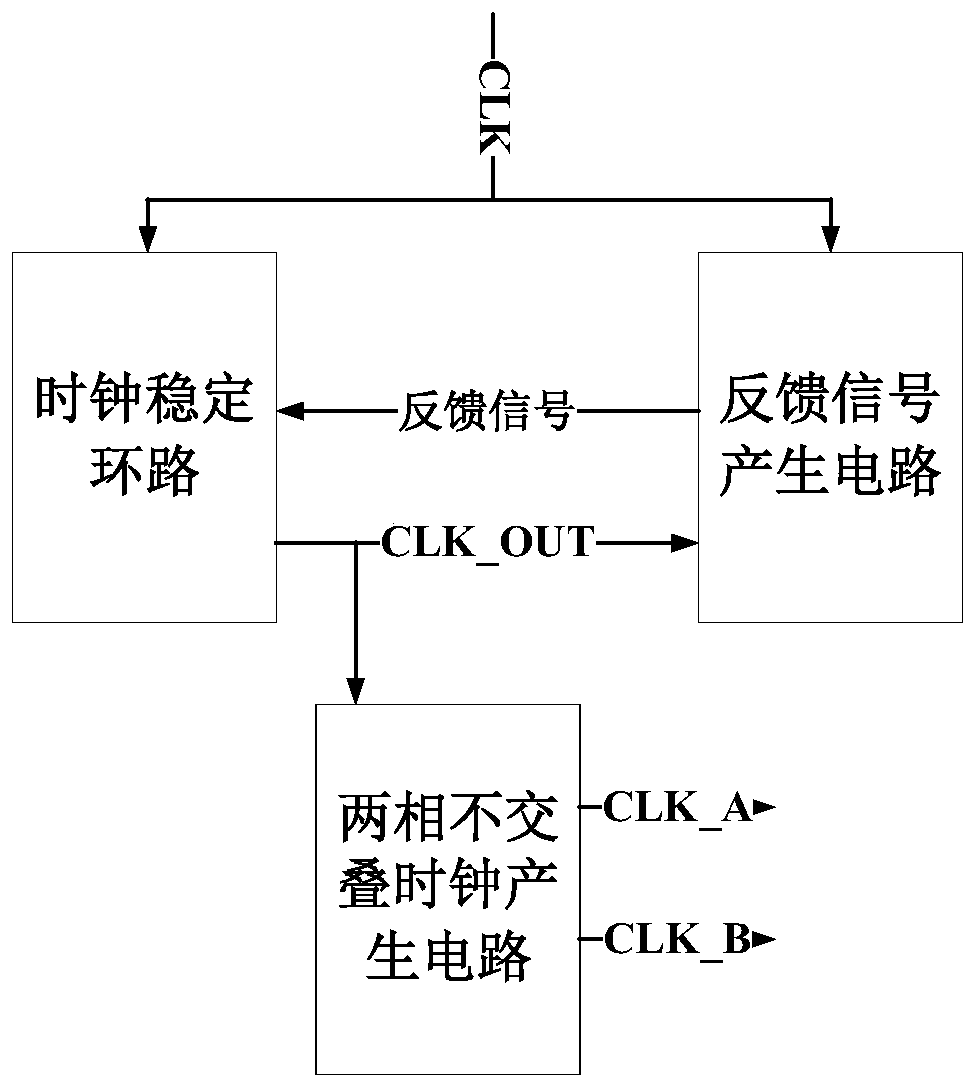

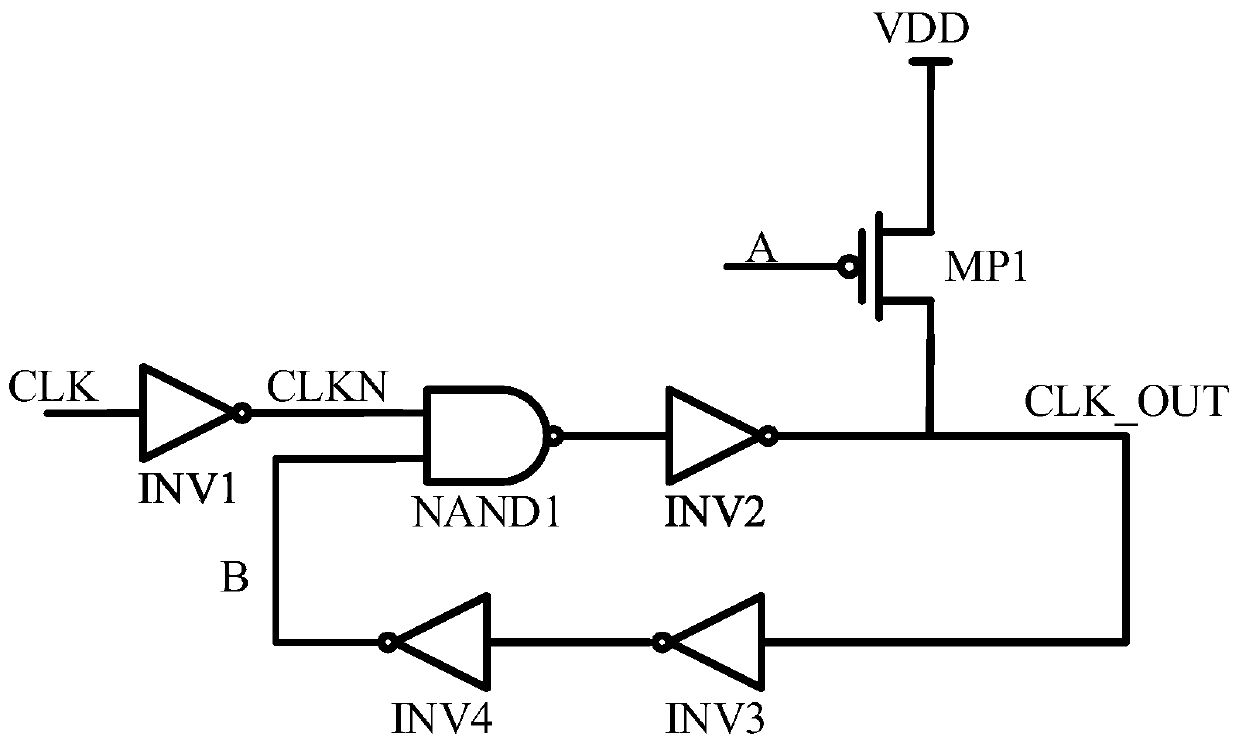

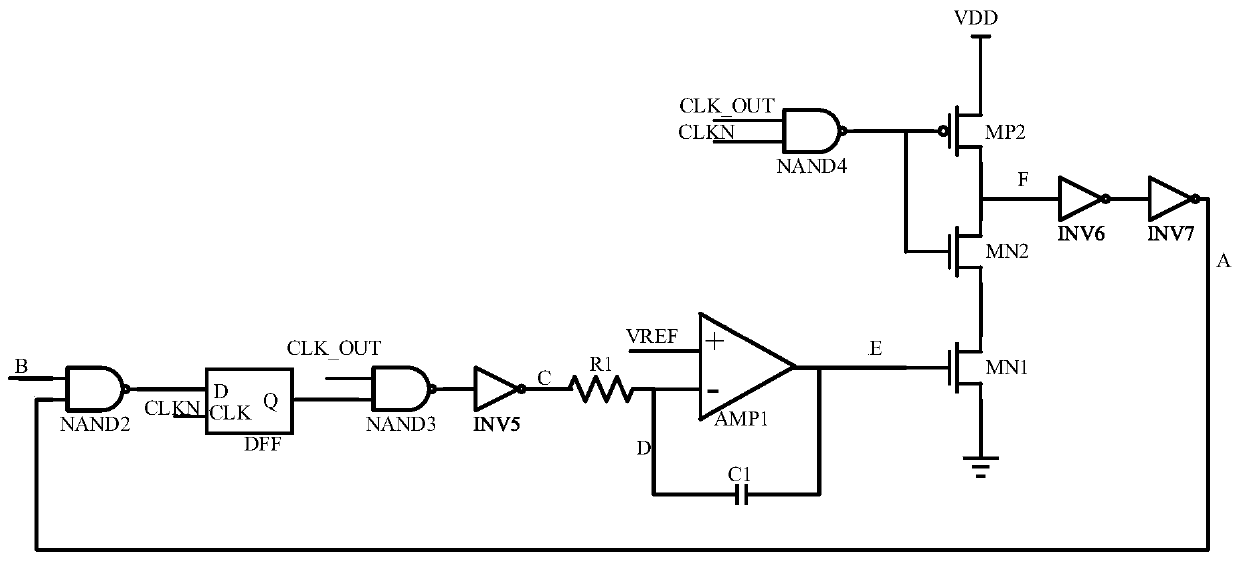

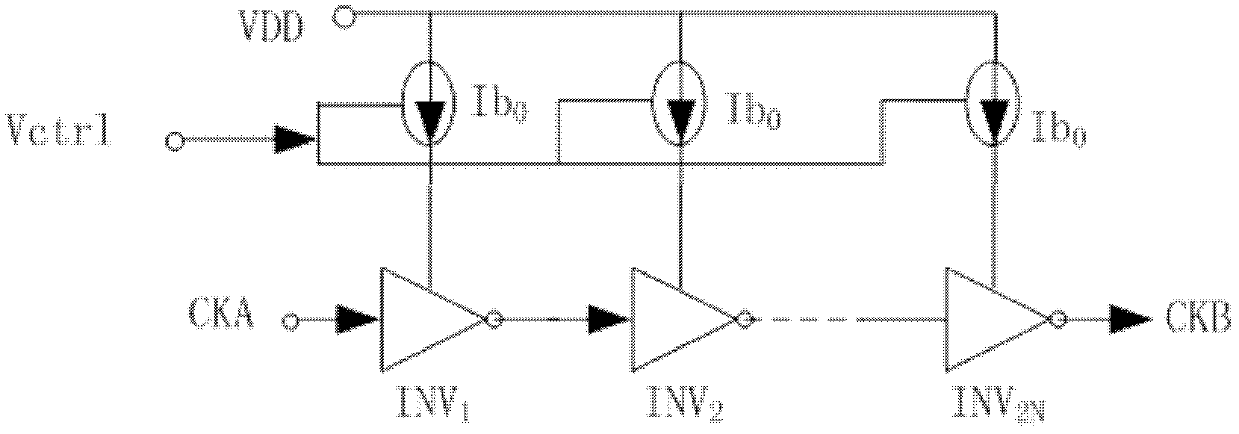

Clock generation circuit for analog-to-digital converter

ActiveCN106411319AStable duty cycleReduce jitterElectric pulse generatorPhysical parameters compensation/preventionDigital down converterSignal-to-noise ratio (imaging)

The invention discloses a clock generation circuit for an analog-to-digital circuit, which comprises a clock stabilizing circuit and a two-phase non-overlapping clock generation circuit. The clock stabilizing circuit comprises a clock stabilizing loop and a feedback signal generation circuit. In the feedback signal generation circuit, a control signal is generated by an active low-pass filter to control an N tube current modulation inverter, the clock stabilizing loop is used for generating a stable clock signal, and by a filtering technology and a current modulation technology, accurate modulation on a feedback signal is implemented. In the clock stabilizing loop, by a loop structure, a duty ratio of an output clock can be reduced; under the regulation of the feedback signal, by pulling up a PMOS tube MP1, the duty ratio of the output clock is increased, and finally, the duty ratio of 50% of the output clock is achieved; and the clock is stabilized and vibration is reduced. According to the clock generation circuit disclosed by the invention, the clock stabilizing circuit can be integrated into an ADC circuit; and by adopting the structure disclosed by the invention, clock signal quality can be obviously improved, the strict requirement of an ADC for clock quality is reduced, and a signal-to-noise ratio of the ADC is improved.

Owner:TIANJIN UNIV

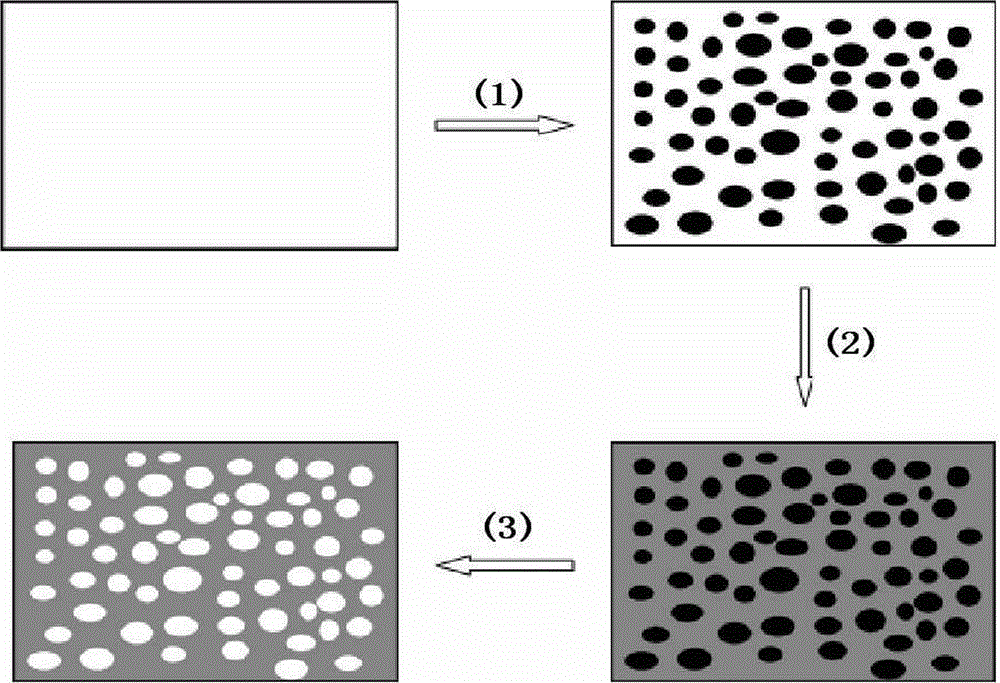

Method for modifying indium tin oxide electrochemiluminescence reaction electrodes

InactiveCN104897759AEvenly distributedStable duty cycleMaterial electrochemical variablesElectrochemiluminescenceIndium

The invention provides a method for modifying indium tin oxide electrochemiluminescence reaction electrodes. An ink spot-spray protective coating process is adopted as a film coating mode for the method which includes (1), covering the surface of each indium tin electrode with a discontinuous spot ink protective layer in an inkjet mode; (2), coating metal films on the surfaces, uncovered by the ink protective layer, of the indium tin oxide electrodes; (3), removing ink on the surfaces of the electrodes by the aid of a physical stripping process or a chemical stripping process, and covering the surface of each treated electrode with a latticed gold-plated layer jto enable the indium tin oxide electrodes to be high in surface adhesion property and electroconductivity; (4), fixing capture probe molecules to the surfaces of the modified electrodes in a physical adsorption manner or chemical coupling manner. The method has the advantages that the bonding strength of the electrodes and the probe molecules can be improved while the transparency and the electroconductivity of the indium tin oxide electrodes are guaranteed, surface hydrolysis of the electrodes can be resisted, and the stability of the electrodes can be improved.

Owner:彭梓 +1

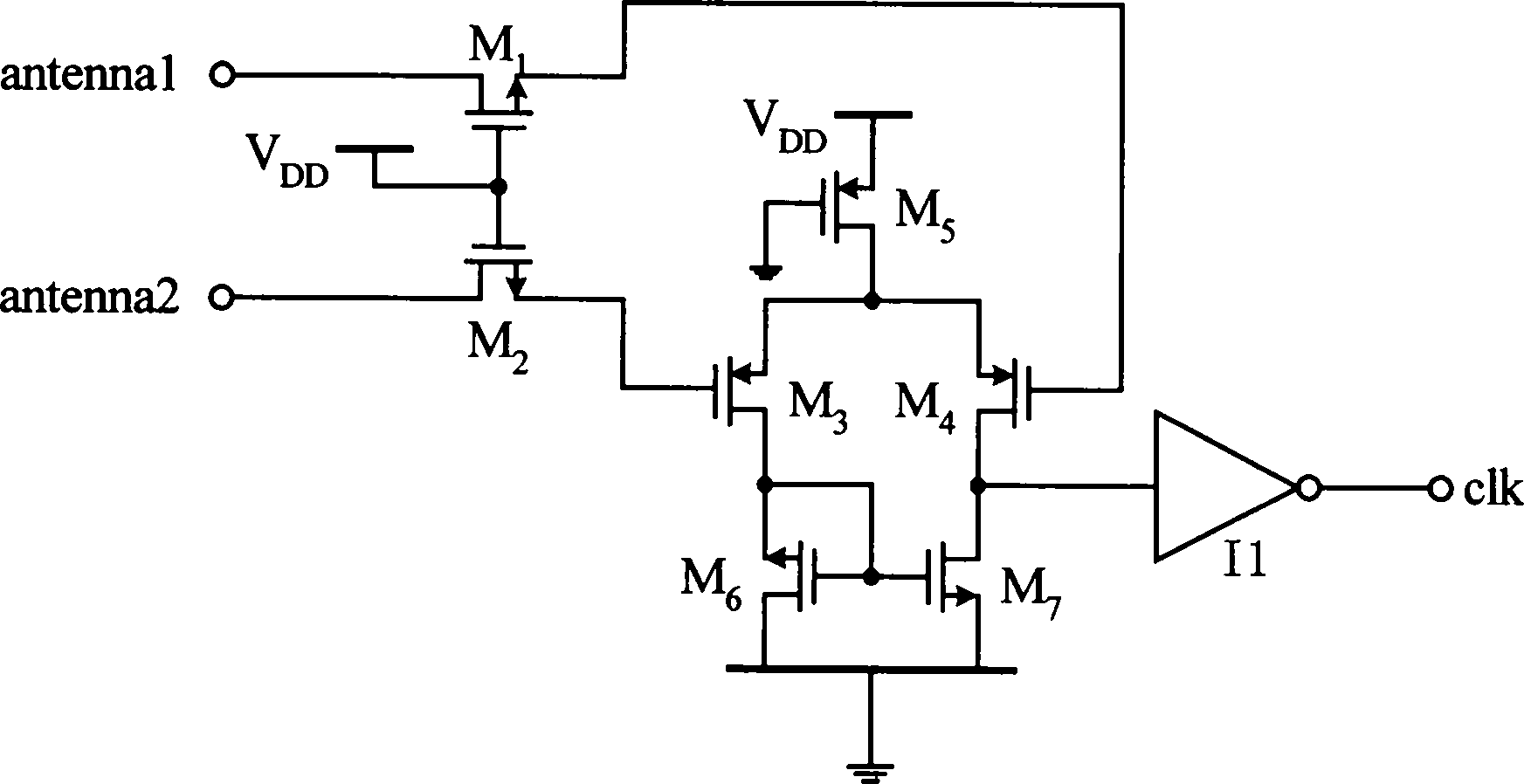

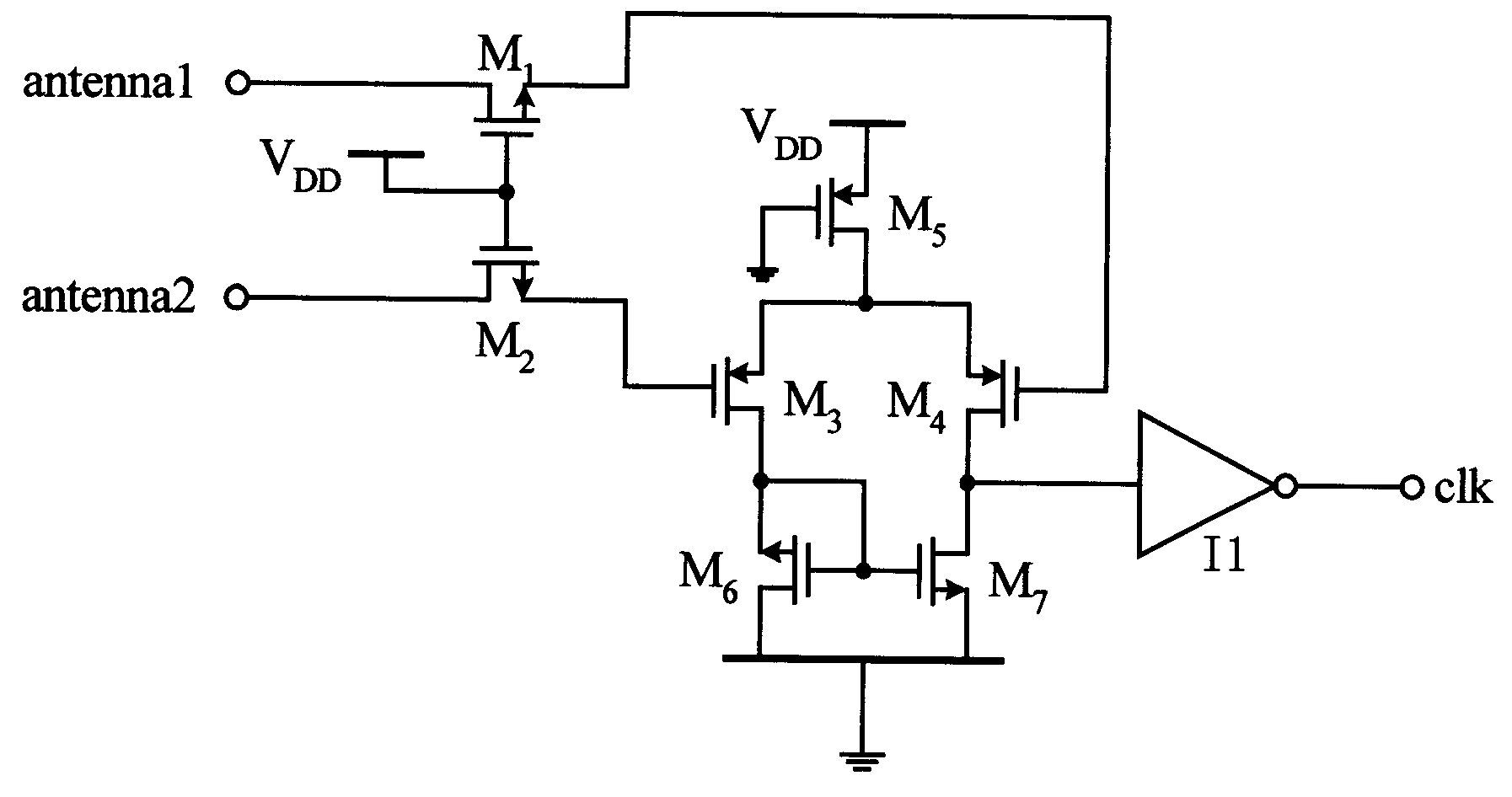

Clock recovery circuit used in non-contact IC card and radio frequency identification label

ActiveCN101038617BPlay a limiting roleSensitivity is not affectedPulse automatic controlSensing record carriersEngineeringRadio frequency

The invention discloses a clock recovery circuit for non-contact type IC card and radio frequency identified tag chip, wherein one ends of two transfer gates are connected to the terminal end of the chip, the other ends of which are connected to the two input ends of a comparator, the signal outputted from the comparator is reshaped by a phase inverter and outputted from the output end as a clocksignal. The invention has a stable duty ratio and can be adaptable to the field density with wider range.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

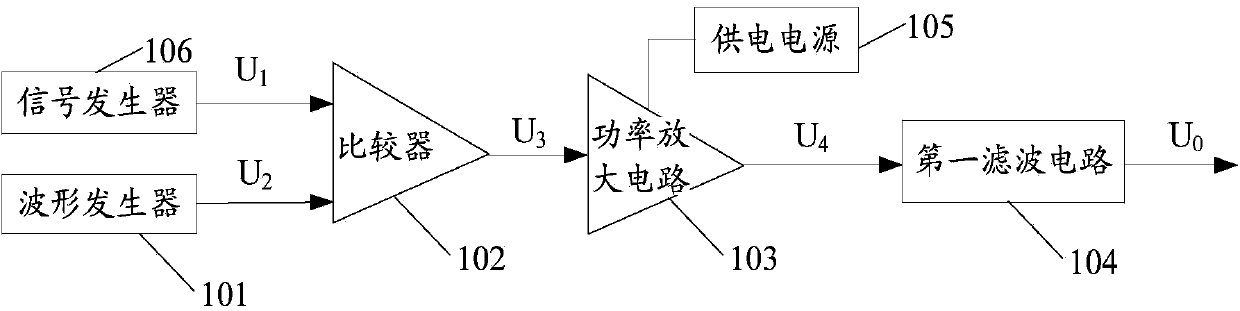

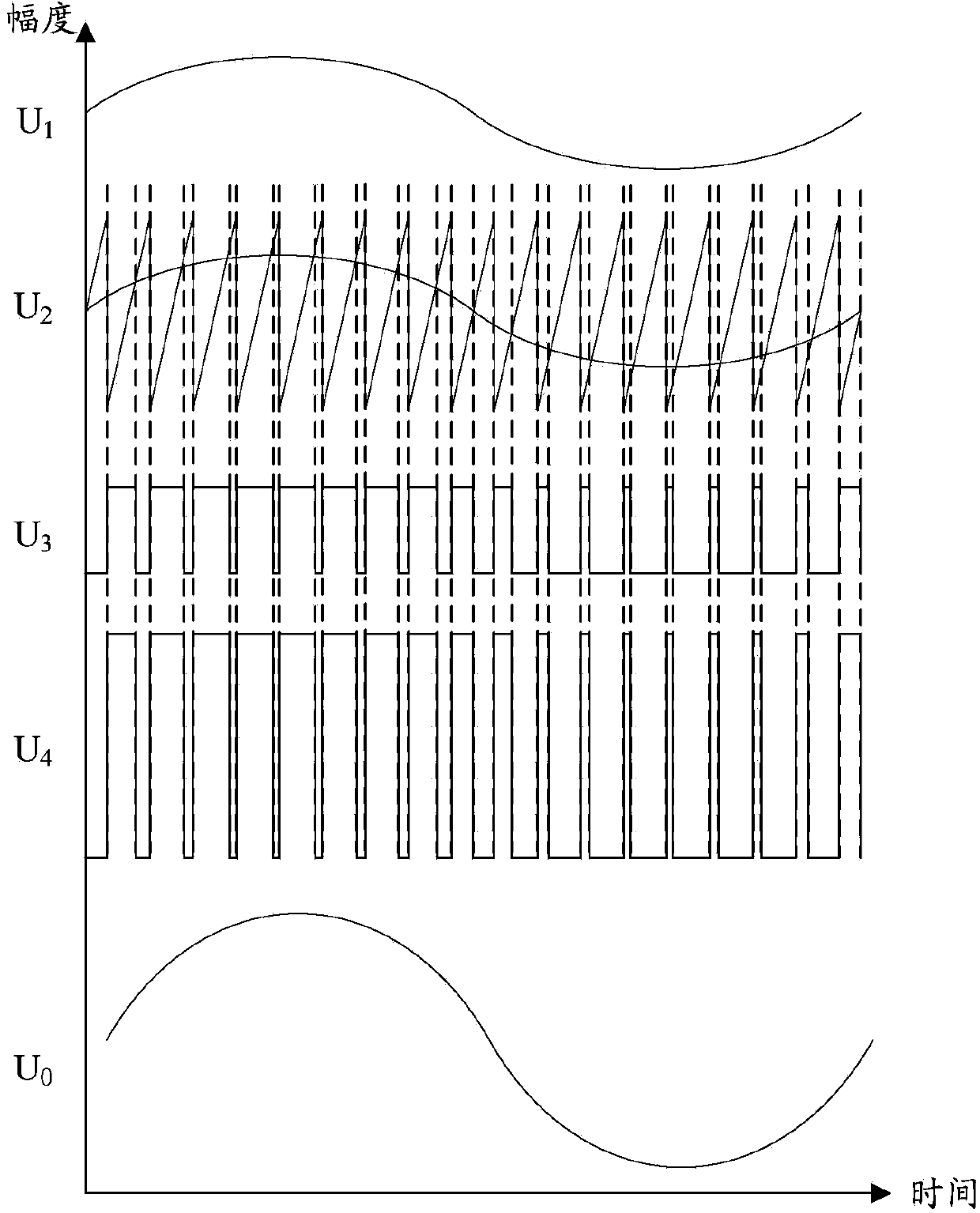

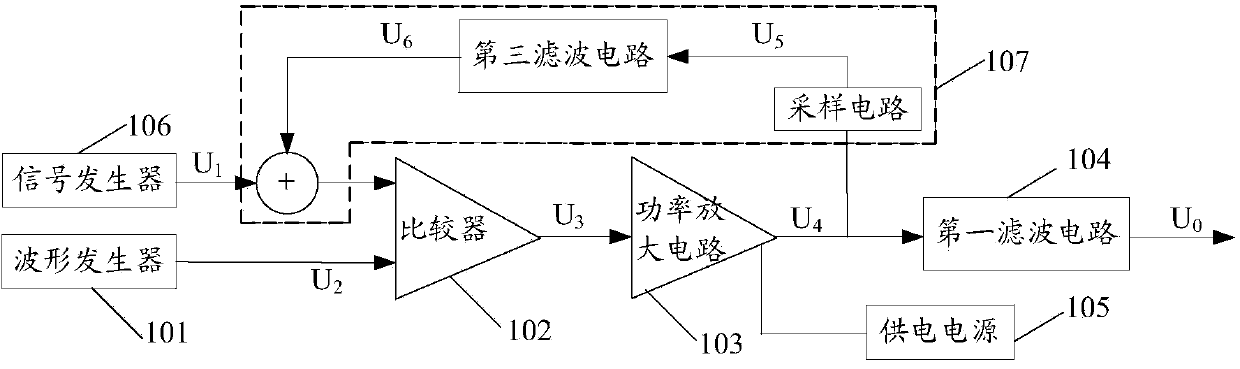

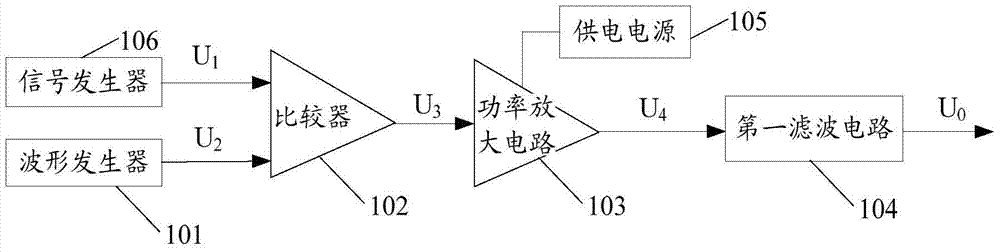

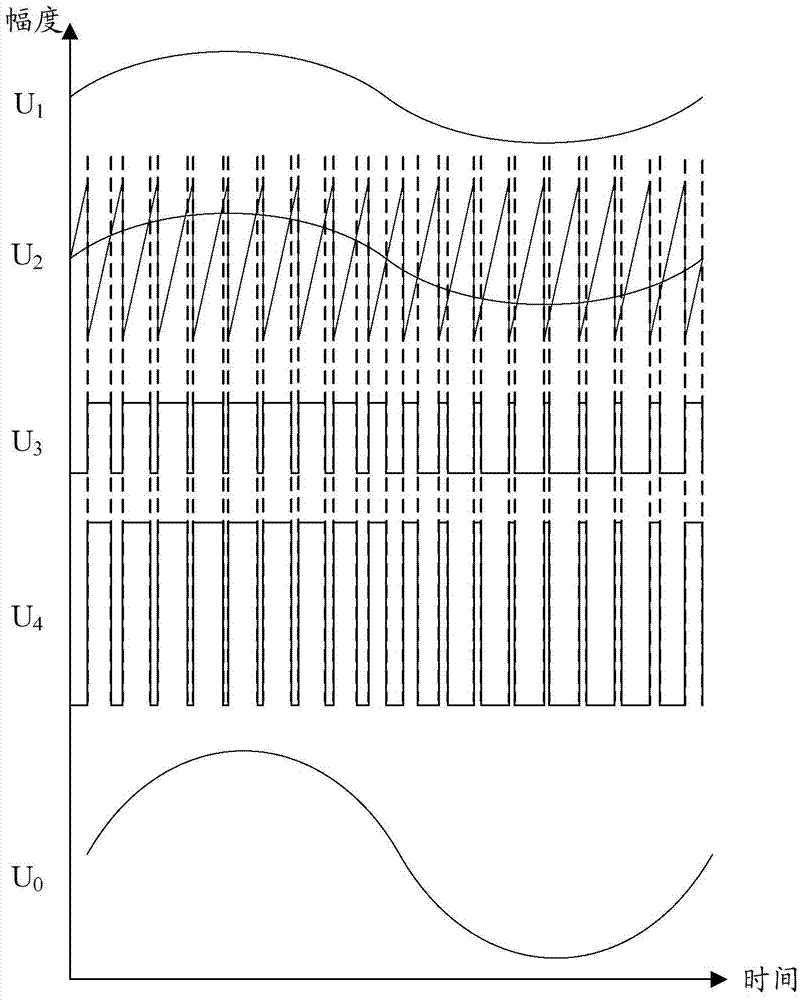

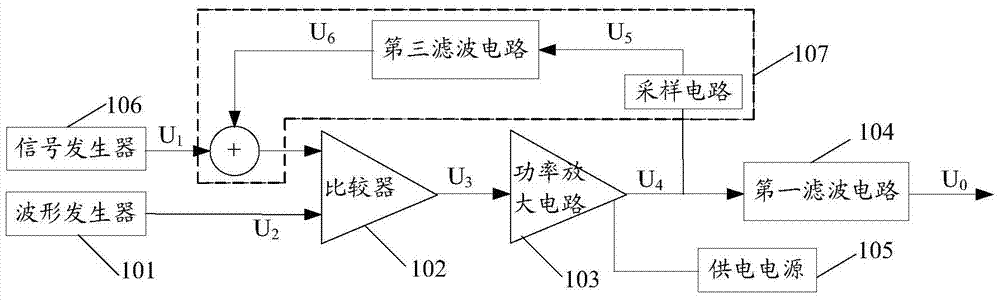

Feedback circuit for D type power amplifier and electronic equipment

ActiveCN104201996AStable duty cycleStable powerAmplifier with semiconductor-devices/discharge-tubesAmplifier detailsAudio power amplifierVoltage regulation

The invention discloses a feedback circuit for a D type power amplifier and electronic equipment and relates to the technical field of power amplifiers. The problem that a feedback circuit of an existing D type power amplifier is complex in design and high in cost is solved. The feedback circuit comprises a sampling circuit. The input end of the sampling circuit is connected with a power supply. The output end of the sampling circuit is connected with the input end of a waveform generator. The output end of the waveform generator is connected with a first input end of a comparer. A signal generator is connected with a second input end of the comparer. The output end of the comparer is connected with the input end of a power amplifying circuit. The output end of the power amplifying circuit is used for outputting signals. The sampling circuit is used for carrying out smoothing and voltage dividing on voltage output by the power supply. The voltage obtained after smoothing and voltage dividing adjusts the range generated by the waveform generator. The circuit can be used in the electronic equipment of the D type power amplifier.

Owner:HISENSE VISUAL TECH CO LTD

Numeric control method for liquid level control (LLC) resonant conversion circuit

ActiveCN102025266BStable duty cycleAvoid uncontrollableDc-dc conversionElectric variable regulationPower inverterElectricity

The invention discloses a numeric control method for a liquid level control (LLC) resonant conversion circuit. The method comprises the following steps of: sampling an LLC series resonant conversion circuit and an inverter electrically connected with the LLC series resonant conversion circuit respectively by adopting a single voltage loop numeric control structure; after calculation, outputting to a numeric controller; calculating the input quantity by using the numeric controller and outputting a driving pulse; controlling the LLC series resonant conversion circuit by using the driving pulse through a driving circuit; during light load or no load, adopting a mode of combining a pulse width modulation (PWM) control strategy and a pulse frequency modulation (PFM) control strategy; and during heavy load, adopting the PFM control. By the method, load states can be judged quickly; adverse influence on system load judgment due to different loading time is screened; a dynamic working point is selected reasonably according to the judged load state and current is controlled, so that the voltage stress of the LLC series resonant conversion circuit is eliminated; the control method provided by the invention is simple; and error and instability can be effectively reduced.

Owner:VERTIV CORP

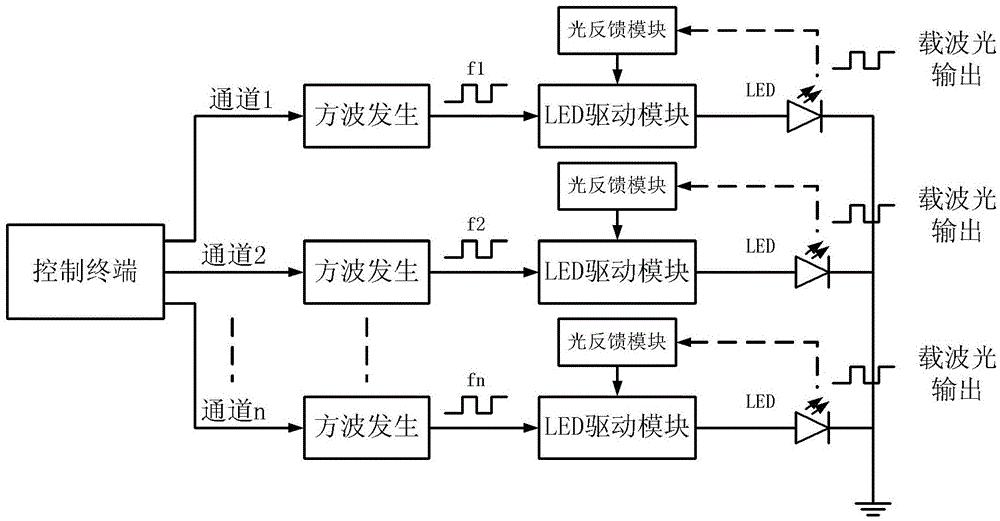

A method and system for parallel transmission of multi-channel carrier optical signals

ActiveCN103166904BFast frequency conversionSmall phase noiseElectromagnetic transmittersMultiple carrier systemsCarrier signalInstability

The invention discloses a method and a system of parallel emission of multichannel carrier light signals. The system drives a direct numerical frequency synthesizer chip to generate a square signal through intellectualized control of a control terminal, wherein frequency and phase positions of the square signal are continuous and controllable, and the system outputs the square signal to control a light emitting diode (LED) to flicker in fixed frequency. During the working process of the LED, an LED drive module and an optical feedback module act together and enable the LED to output carrier light signals which are stable in power in long power mode, the optical feedback module feeds received LED power instability fluctuation back by using a photovoltaic conversion diode and restrains power fluctuation by being combined with the LED drive module, and furthermore the multichannel carrier light signals which are controllable in frequency and phase position are generated by arranging a multichannel square signal generator and an LED module in parallel. The whole system is intelligent and controllable, high in integration level, low in power consumption, stable and reliable in work, and wide in application scope, can be extended in multiple channels, and is an integrated carrier light generating system.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

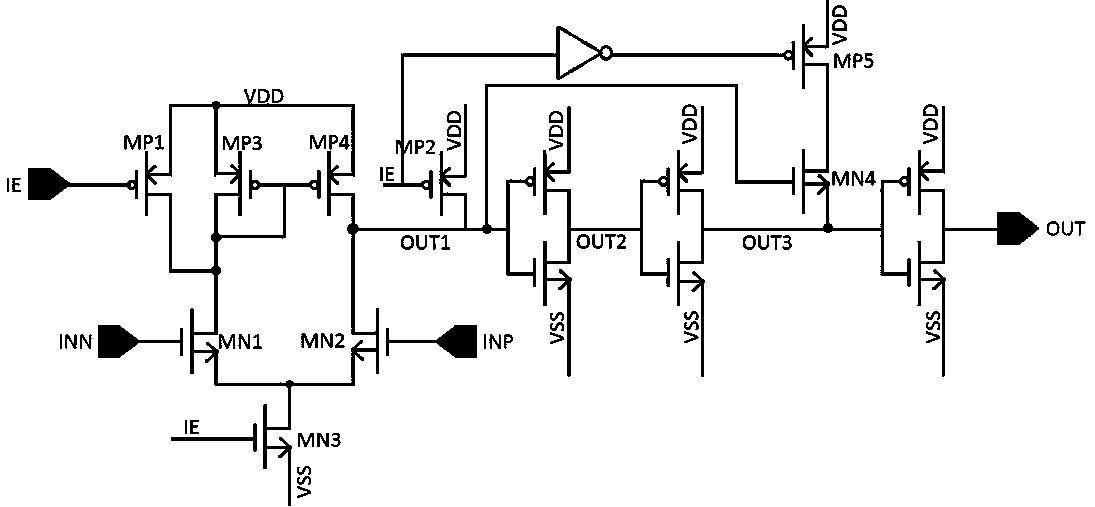

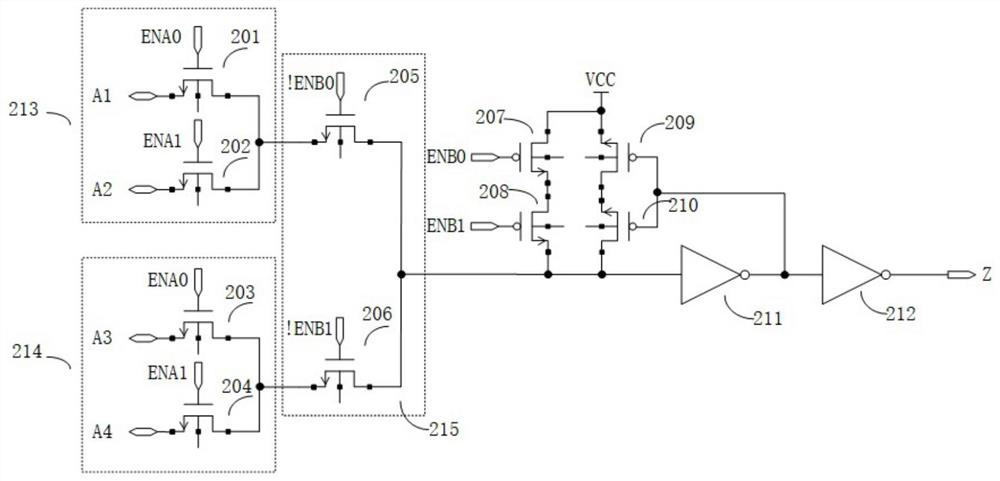

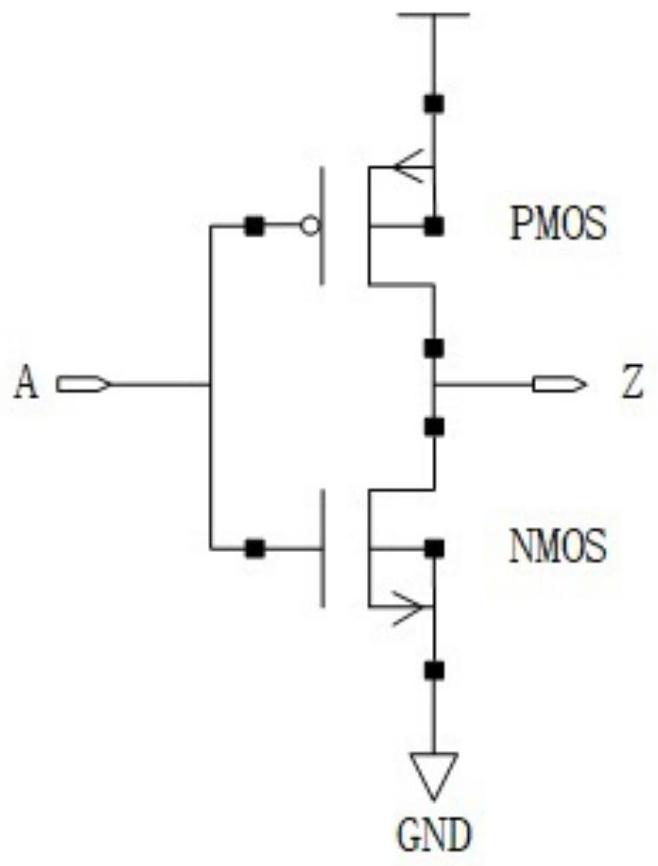

High-speed receiver circuit of DDR4 standard

PendingCN108305648ASimple structureImprove transmission bandwidthDigital storageDifferential amplifiersHigh transmissionTransistor

The invention discloses an input receiver circuit of a DDR4 standard. The input receiver circuit comprises a first transistor MP1, a second transistor MP2, a third transistor MP3, a fourth transistorMP4, a fifth transistor MP5, a sixth transistor MN1, a seventh transistor MN2, an eighth transistor MN3, a ninth transistor MN4, a first phase inverter, a second phase inverter, a third phase inverterand a fourth phase inverter, wherein MN4 and MP5 form a duty ratio adjusting circuit for improving the output duty ratio. The high-speed receiver circuit of the DDR4 standard has the advantages of asimple structure, high transmission bandwidth, low transmission delay and the like.

Owner:南京胜跃新材料科技有限公司

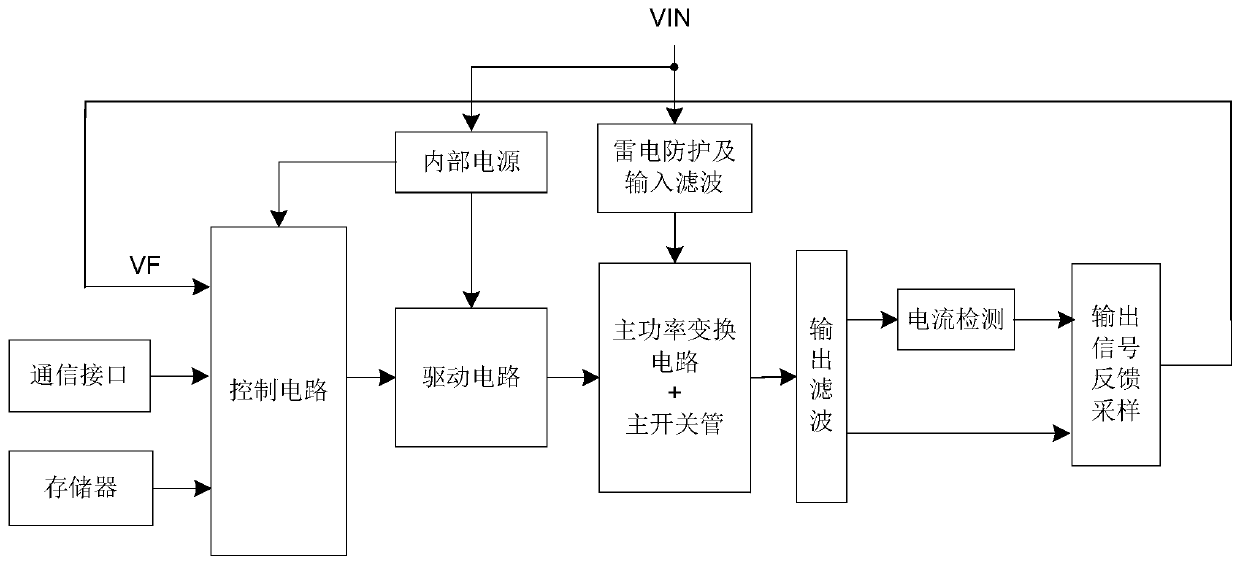

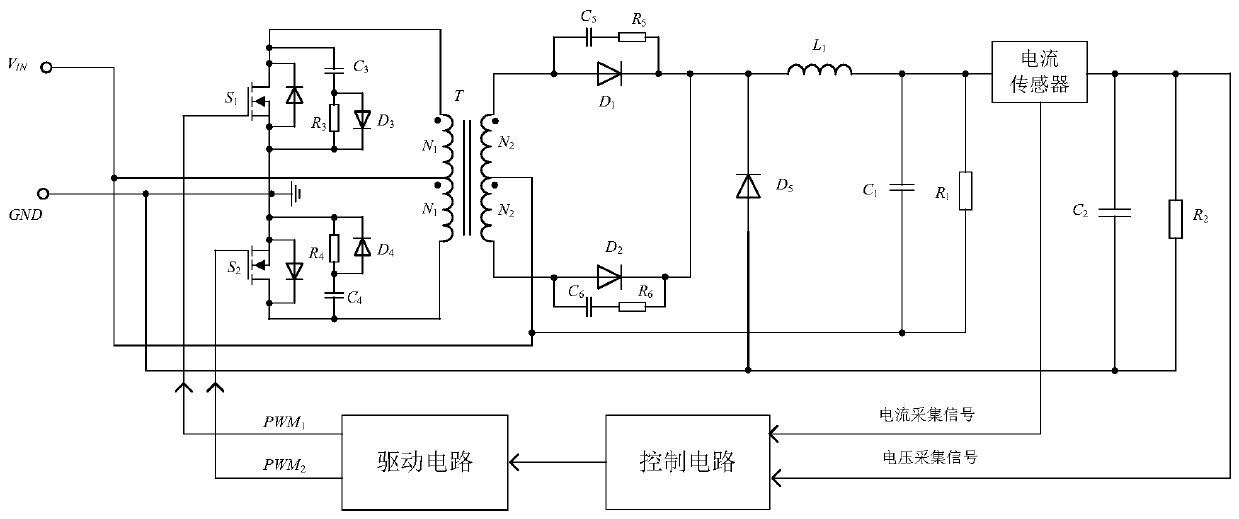

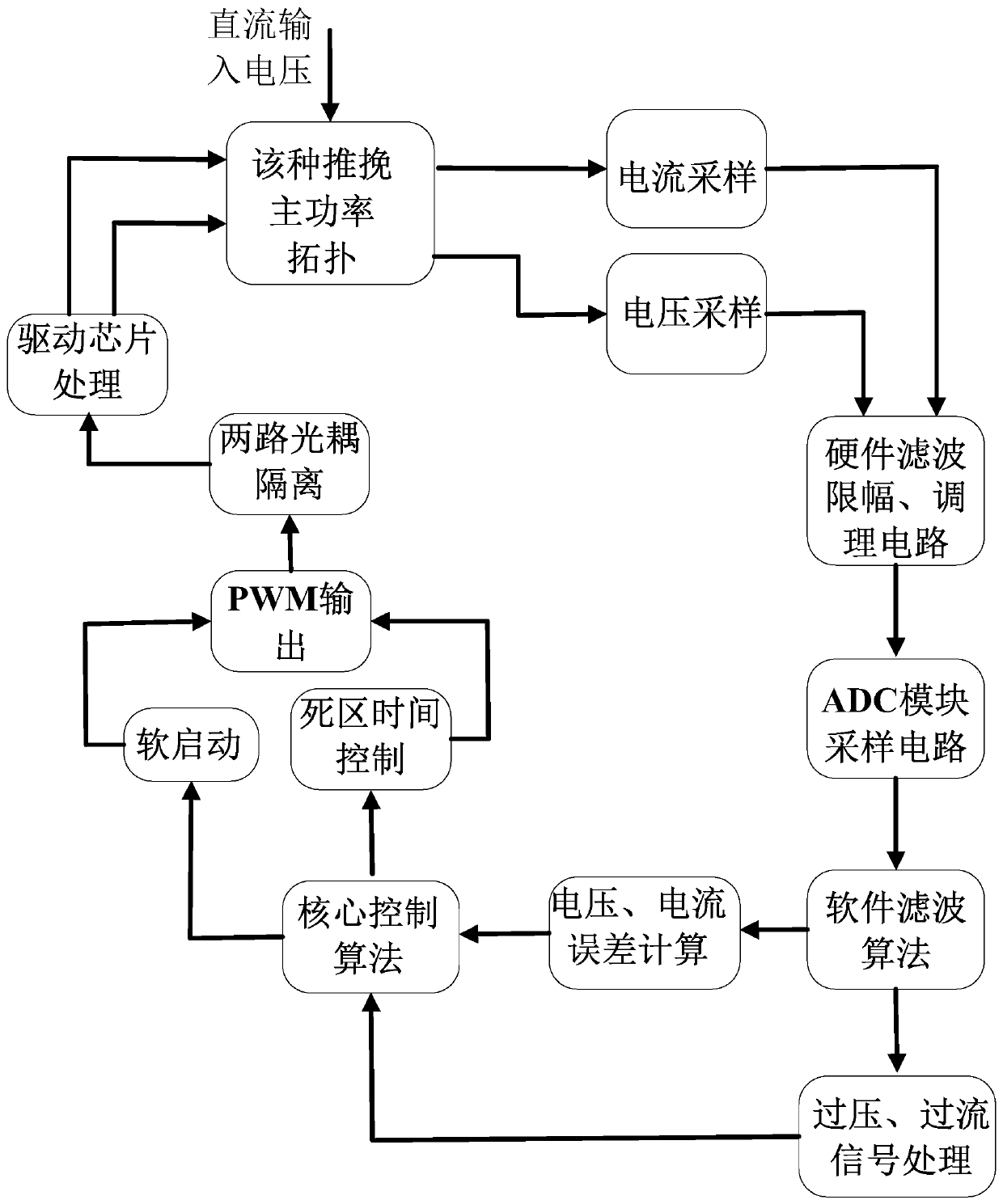

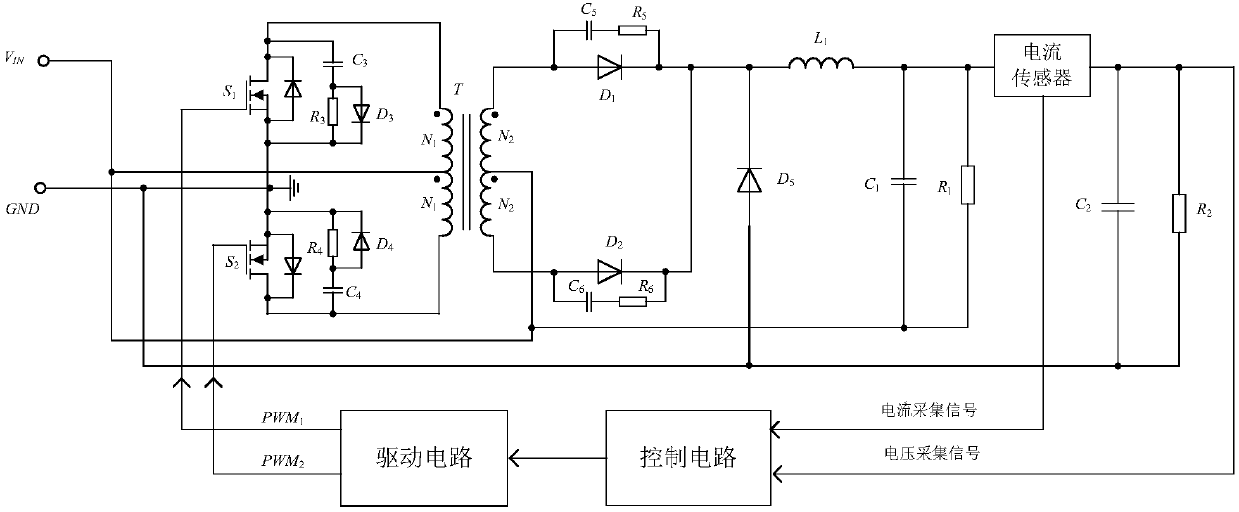

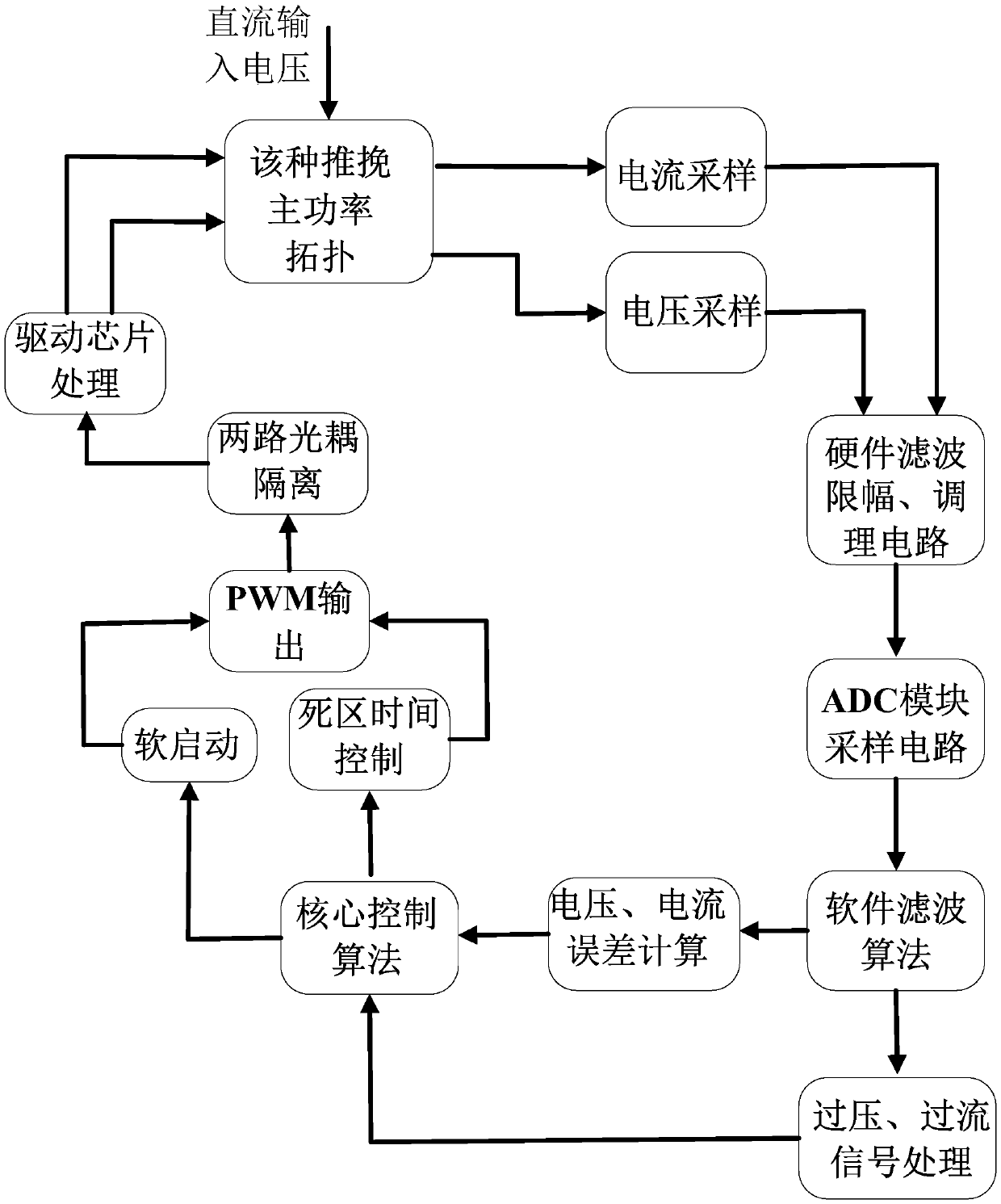

An Improved Push-Pull Converter Based on Sliding Mode Control

ActiveCN107769580BImprove work efficiencySmall rippleDc-dc conversionElectric variable regulationControl systemPush pull

The invention provides an improved push-pull converter based on sliding mode control. The push-pull converter is improved on the basis of an original push-pull circuit. DC input voltage is directly imported to the midpoint of the secondary side of a transformer and is used to increase the secondary voltage of the transformer. Thus, the product output voltage is the sum of the input voltage and theconversion voltage of a power conversion circuit. The power conversion circuit only provides the difference between the input voltage and the output voltage. Such topology can significantly improve the efficiency of a product. In addition, the system uses voltage-current double loop control based on a sliding mode control algorithm, and designs a sliding mode surface according to desired dynamiccharacteristics. By designing a sliding mode control law, a controlled system converges along the sliding mode surface. Thus, good robustness, stability and dynamic quality of the system are guaranteed.

Owner:SHAANXI AVIATION ELECTRICAL

A kind of feedback circuit and electronic equipment for d class power amplifier

ActiveCN104201996BStable duty cycleStable powerAmplifier with semiconductor-devices/discharge-tubesAmplifier detailsAudio power amplifierClass-D amplifier

The invention discloses a feedback circuit and electronic equipment for class D power amplifiers, relates to the technical field of power amplifiers and is used to solve the problems of complex design and high cost of the feedback circuit of the existing class D power amplifiers. Wherein, the feedback circuit includes a sampling circuit; the input end of the sampling circuit is connected to the power supply, the output end is connected to the input end of the waveform generator, the output end of the waveform generator is connected to the first input end of the comparator, and the signal generator is connected to the comparator The second input terminal of the comparator is connected, the output terminal of the comparator is connected with the input terminal of the power amplifier circuit, and the output terminal of the power amplifier circuit is used for outputting signals; wherein, the sampling circuit is used for filtering and dividing the voltage output by the power supply , the filtered and divided voltage adjusts the amplitude of the waveform generated by the waveform generator. The circuit provided by the invention can be used in electronic equipment using class D power amplifiers.

Owner:HISENSE VISUAL TECH CO LTD

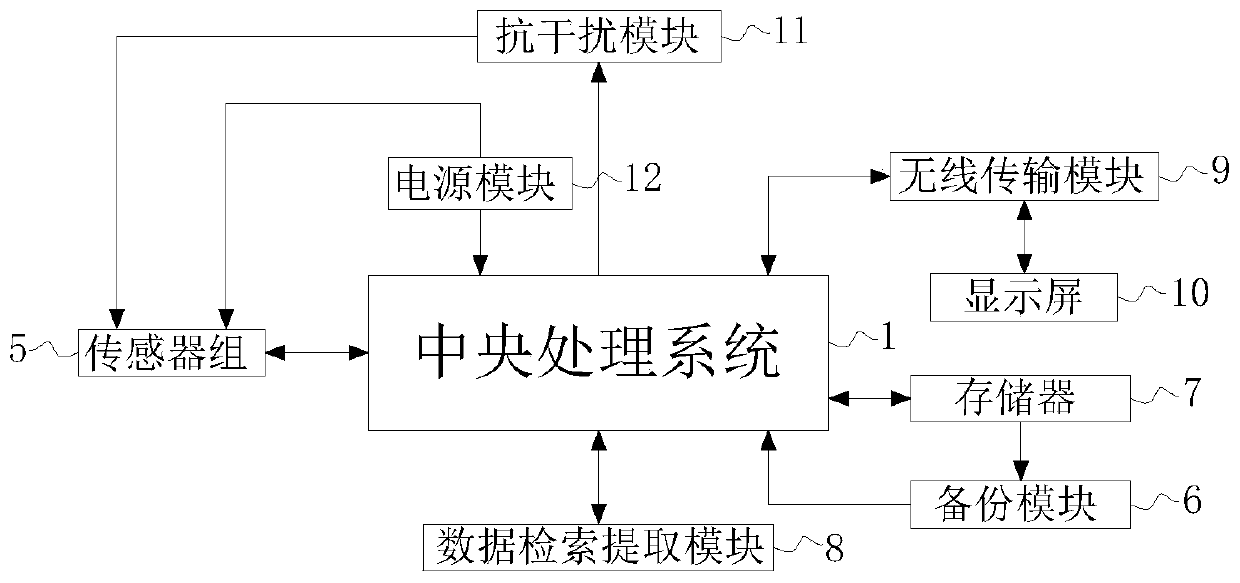

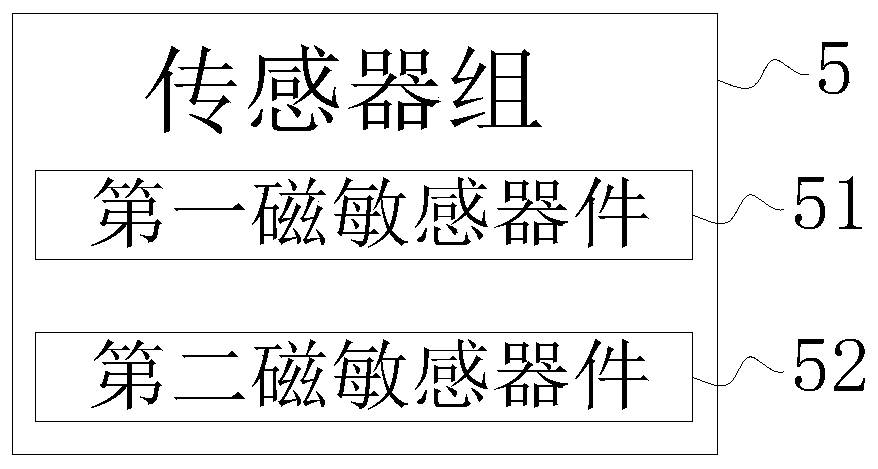

Pulse collection intelligent device in which positive rotation and negative rotation are measured by single sensor

PendingCN110398270AEnsure consistencyStable duty cycleVolume meteringSemiconductor chipMagnetic line

The invention discloses a pulse collection intelligent device in which positive rotation and negative rotation are measured by a single sensor. The device comprises a central processing system and a movement. Magnet is rotationally connected with a front of the movement. A pointer is fixedly connected with one side of the magnet. A sensor group is fixedly connected with the front of the movement.The invention relates to the technical field of remote intelligent meter reading. According to the pulse collection intelligent device in which the positive rotation and the negative rotation are measured by the single sensor, the positive rotation and the negative rotation are measured by the single sensor, two magnetic sensitive devices are packaged in the single sensor, so consistency of collection sensitivity of the magnetic sensitive devices is ensured; when the two magnetic sensitive devices leave a factory, relative positions are fixed; the magnetic sensitive devices are integrated in asemiconductor chip, so consistency of a duty cycle of each state is ensured; and even if a magnetic line of force is weakened by aging of the magnet, influence on each magnetic sensitive device is consistent, so the duty cycle of each state under various bad situations is kept relatively stably, and signal missing condition is avoided.

Owner:武汉力拓达科技有限公司

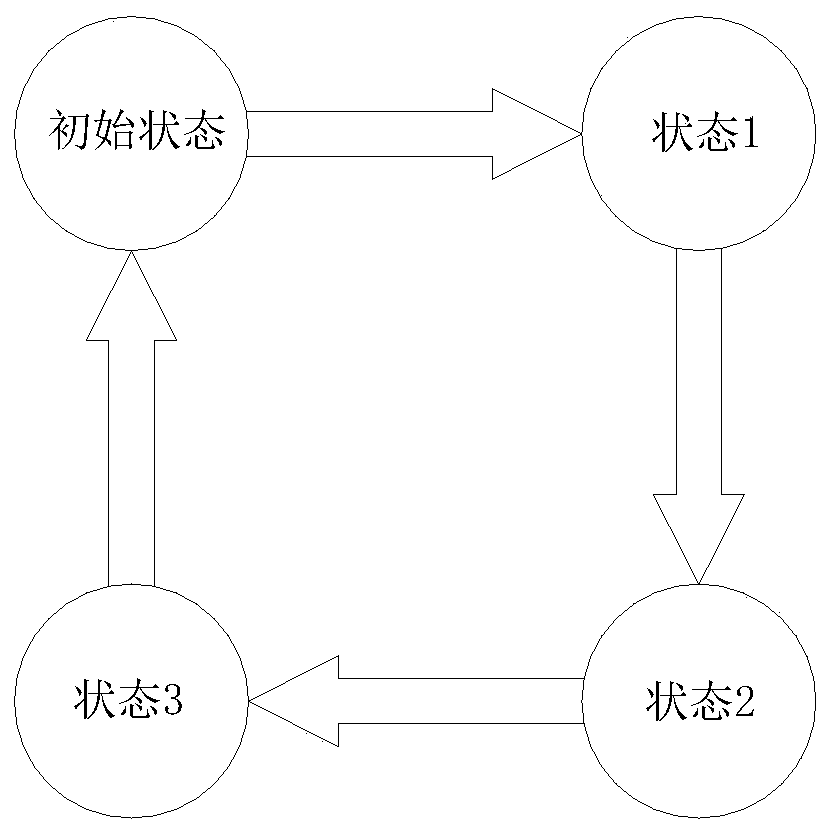

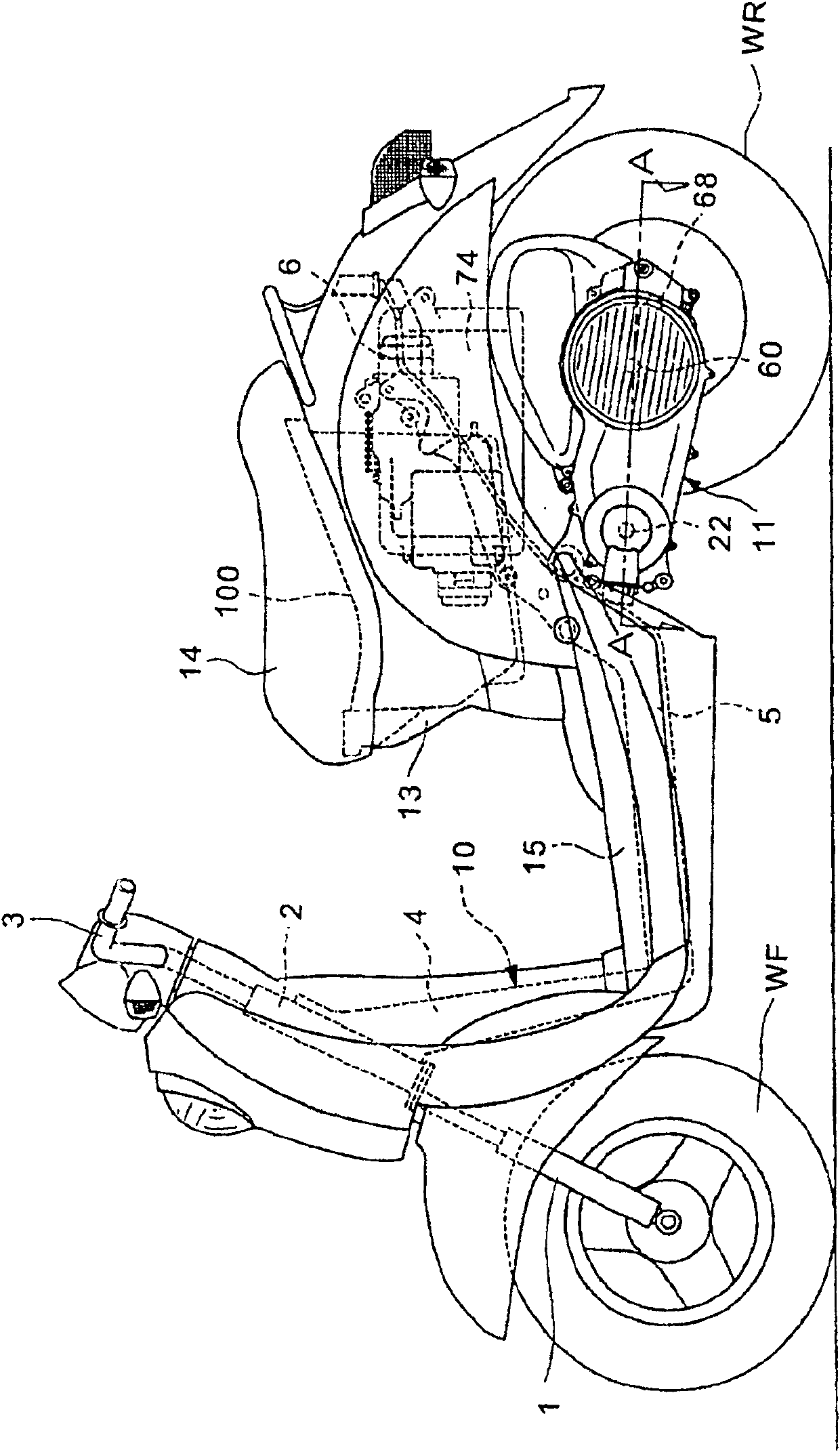

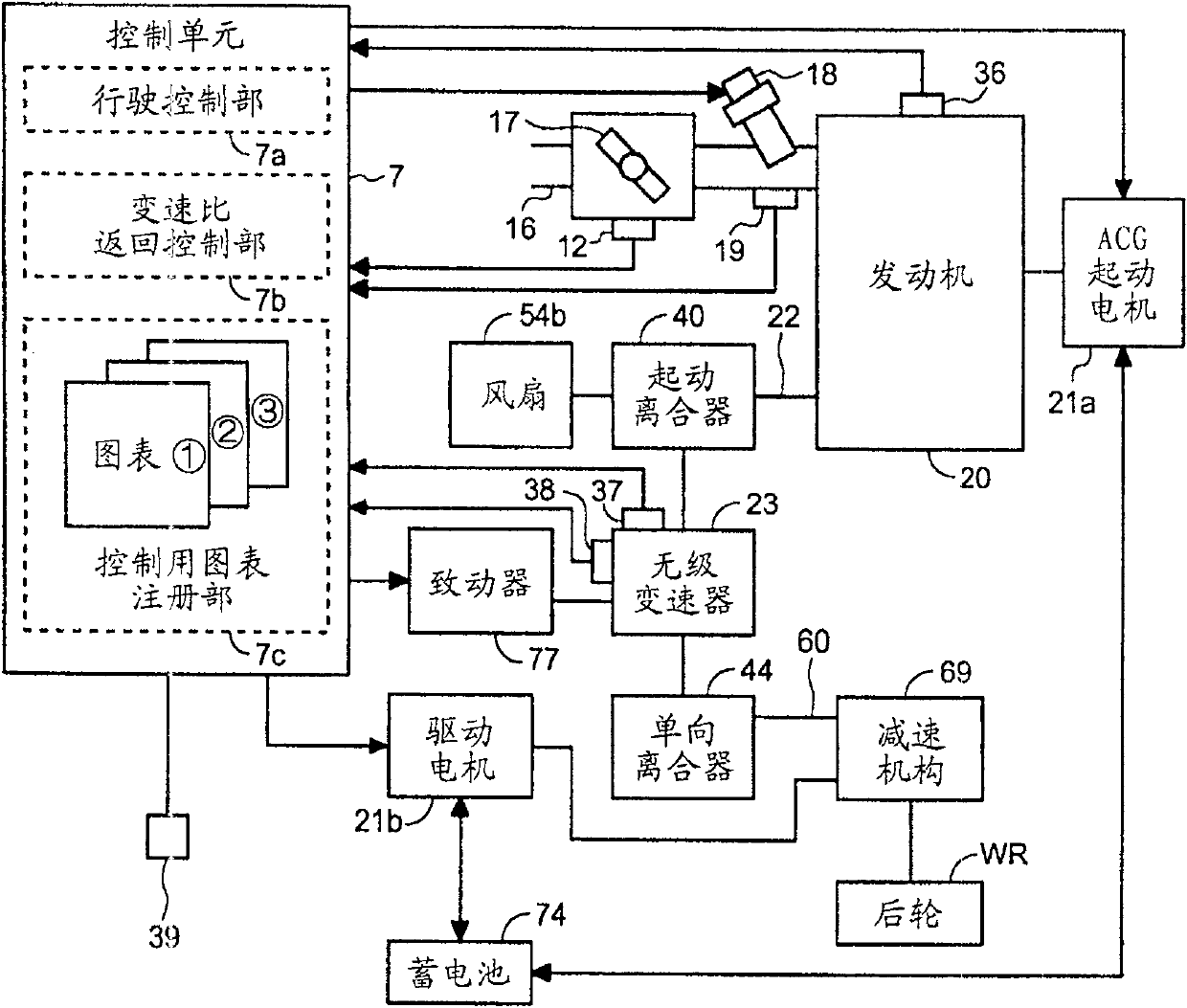

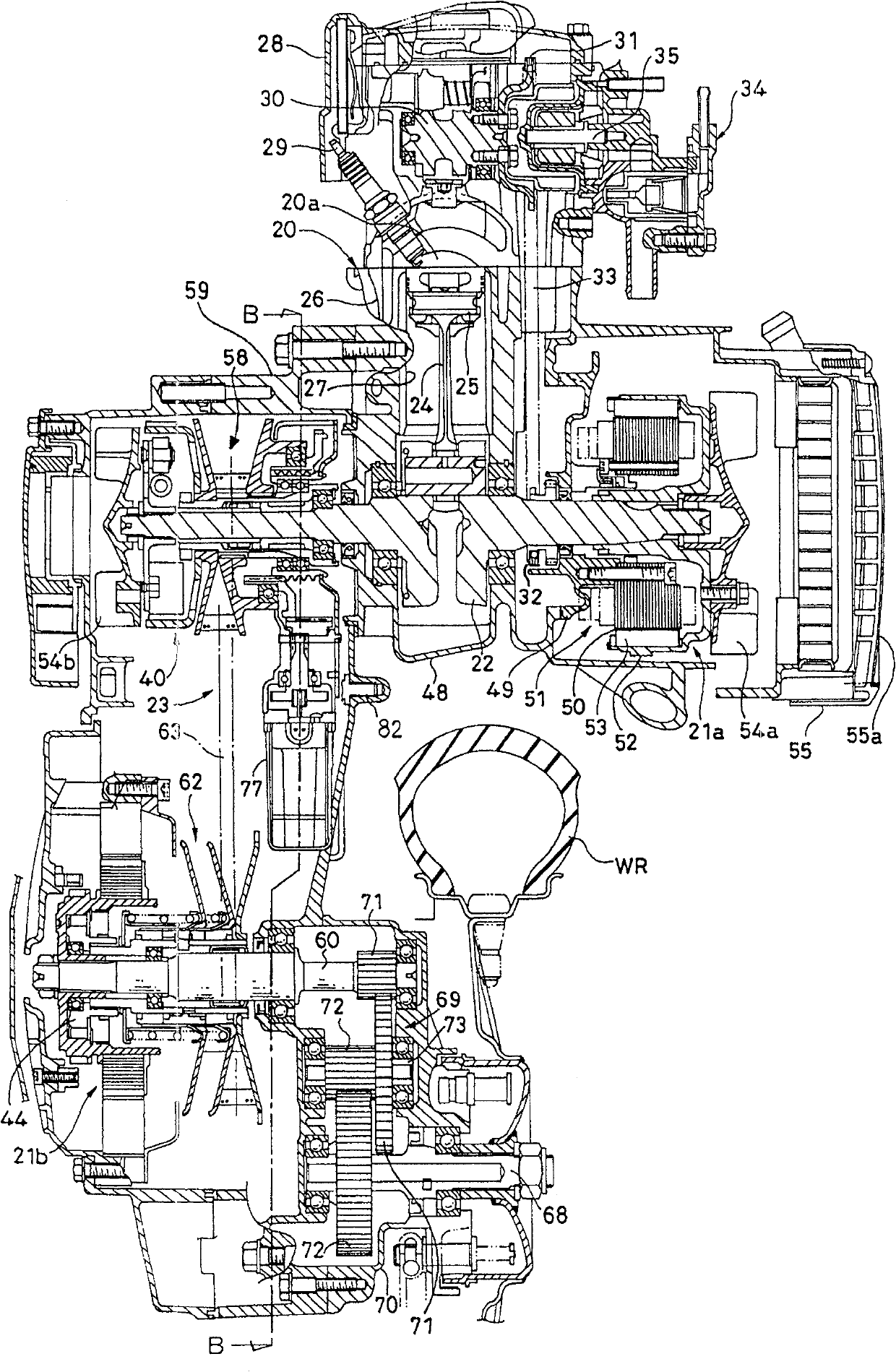

Transmission controller for continuously variable transmission system

InactiveCN100592991CIncrease duty cycleSufficient accelerationGearingGas pressure propulsion mountingEngineeringActuator

The invention provides a variable speed control device of a variable speed case, which can lead the variation ratio to stably return to a low ratio side even in a hybrid vehicle that an engine is stopped when in deceleration. The variable speed control device comprises a control unit (7); wherein, according to detecting signals from a variation ratio sensor (38) and a belt pulley revolution transmitter at a driving side (37), a control chart logged in a controlling chart registration part (7c) ensures the starting running speed of a belt pulley at the driving side after being returned and thedutyfactor of an actuator, and a control instruction is sent to the actuator (77) which changes the variation ratio through changing the groove width of the belt pulley at the driving side. The control instruction is set to be sent after an engine stopping instruction from a driving control part, the closer to a high ratio side the variation ratio is drew, the higher the starting running speed ofthe actuator is. Based on the control, the variation ratio is closer to the high ratio side, and the rotary speed change rate of the belt pulley at the driving side is higher, thus a big dutyfactor isprovided until the rotation of the belt pulley at the driving side stops, to lead the variation ratio to return to the low ratio side.

Owner:HONDA MOTOR CO LTD

Clock generation circuit used in analog-to-digital converter (ADC) with high speed and high precision

InactiveCN102522994BStable duty cycleHigh precisionAnalogue conversionLow noiseDigital down converter

The invention discloses a clock generation circuit used in an analog-to-digital converter (ADC) with a high speed and high precision. The clock generation circuit comprises: a low noise amplification and shaping circuit, a pulse width controller, a DLL with pulse width calibration, a biphase non-overlapping clock generation circuit and a clock buffer. A voltage-controlled delay line (VCDL) with pulse width adjustment is designed in the DLL with the pulse width calibration. The VCDL can realize clock signal time delay and pulse width control based on a cascade group comprising same M improvement delay units. The DLL with the pulse width calibration and the biphase non-overlapping clock generation circuit together form a time-delay control and pulse width adjustment loop. Therefore, working sequences of an ADC sampling circuit and a quantizer can be synchronized and stable processing to an input clock duty ratio can be realized. By using the technical scheme of the invention, a bandwidth requirement to an ADC driving circuit can be reduced; difficulty for designing the system and power consumption can be reduced; realization precision of the ADC quantizer can be improved.

Owner:TSINGHUA UNIV

Phase laser ranging system

ActiveCN105093233BAvoid loweringImprove ranging accuracyElectromagnetic wave reradiationLaser rangingPulse voltage

The invention discloses a phase type laser distance measuring system. The system comprises a laser for generating laser signals; an emission signal unit for generating emission signals and sending the emission signals to the laser after amplitude adjustment and power amplification are successively performed on the emission signals; a returning light receiving unit for receiving reflection signals of laser signals; a bias driving unit for providing offset voltages for driving the laser to emit the laser signals; and a controller for outputting PWM pulse voltage signals with an adjustable duty ratio to the bias driving unit to form the offset voltages and receive the emission signals. When the controller receives that the emission signals involves weak reflection, the controller reduces the duty ratio of the PWM pulse voltage signals and improves the amplitude of the emission signals in a linkage mode; and when the controller receives that the emission signals involves strong reflection, the controller increases the duty ratio of the PWM pulse voltage signals and reduces the amplitude of the emission signals in a linkage mode. The system provided by the invention has the advantages of simple system, high anti-interference capability and high distance measuring accuracy.

Owner:SUZHOU YISEN PHOTOELECTRIC TECH CO LTD

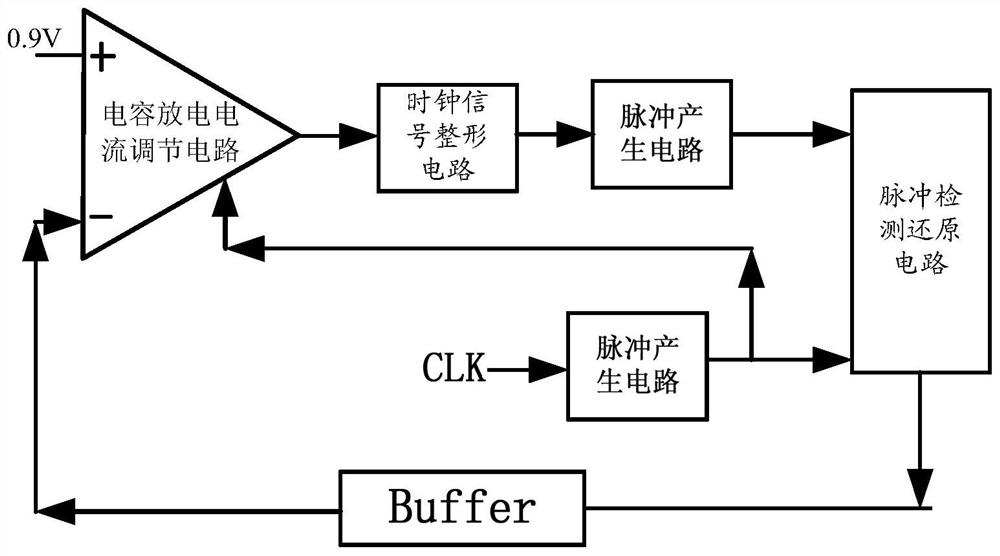

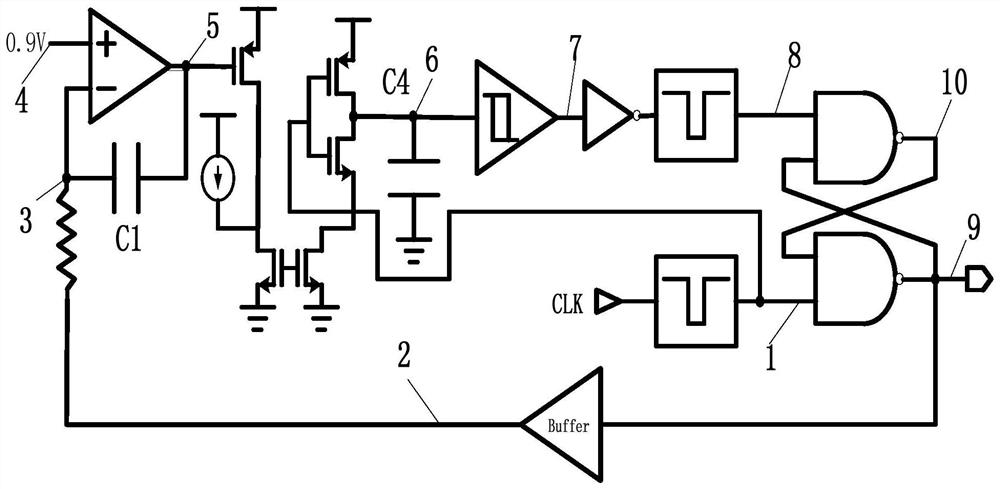

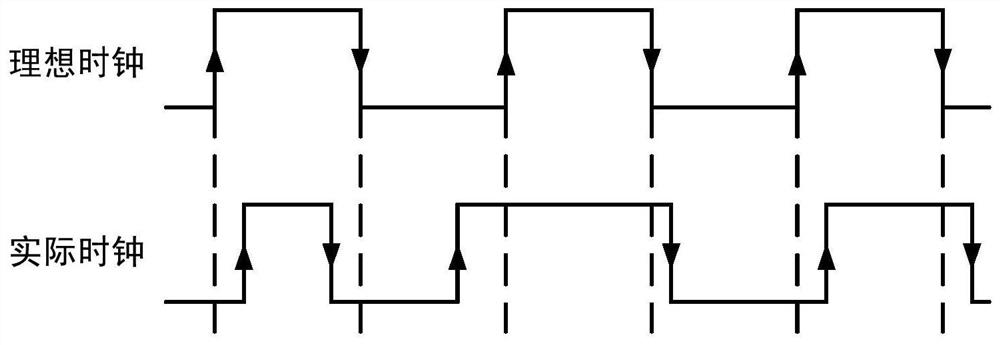

Wide-range low-jitter high-precision clock signal proportion stabilizer circuit and adjusting method

ActiveCN114157275AStable ratioStable duty cycleContinuous to patterned pulse manipulationPulse shapingCapacitanceConverters

The invention discloses a wide-range low-jitter high-precision clock signal ratio stabilizer circuit, which is characterized in that an original clock signal generates a narrow pulse signal with a corresponding duty ratio through a pulse generation circuit, one path of the narrow pulse signal enters a capacitor discharge current regulation circuit, and the other path of the narrow pulse signal enters a pulse detection and reduction circuit; the two narrow pulse signals generate reduction square waves through the pulse detection reduction circuit, the reduction square waves enter the capacitor discharge current adjusting circuit, the descending slope of triangular wave signals output by an inverter is adjusted, the triangular wave signals enter the clock signal shaping circuit, and then the phases of the narrow pulse signals are adjusted. And finally, the two narrow pulse signals pass through a pulse detection and reduction circuit to generate reduction square waves with the duty ratio of 1: 1. The circuit well solves the problem of duty ratio of an input clock, and provides an accurate clock signal for a core circuit of the converter. The invention also provides a clock signal adjusting method realized by adopting the wide-calibration-range low-jitter high-precision clock signal proportion stabilizer circuit.

Owner:BEIJING MXTRONICS CORP +1

System for testing human nerve threshold value

InactiveCN1180744CPrecise digital adjustmentAccurate amplitudeDiagnostic recording/measuringSensorsNerve thresholdMedicine

Owner:NANJING GENERAL HOSPITAL NANJING MILLITARY COMMAND P L A +1

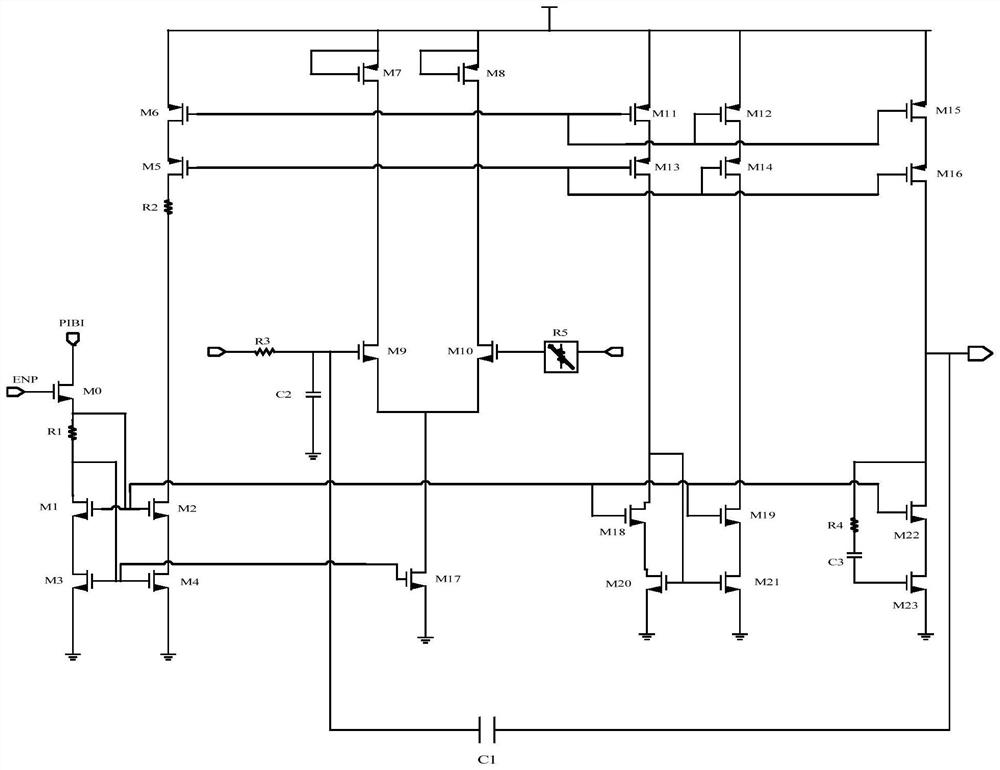

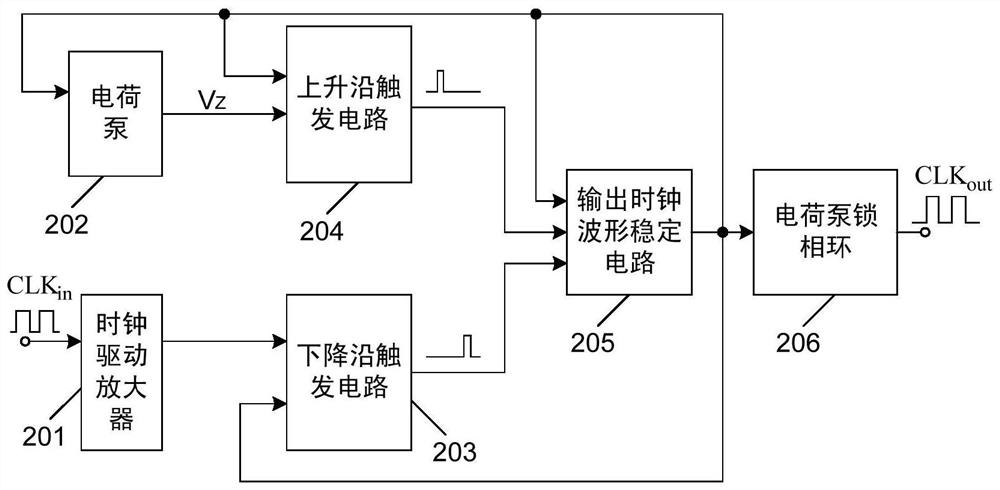

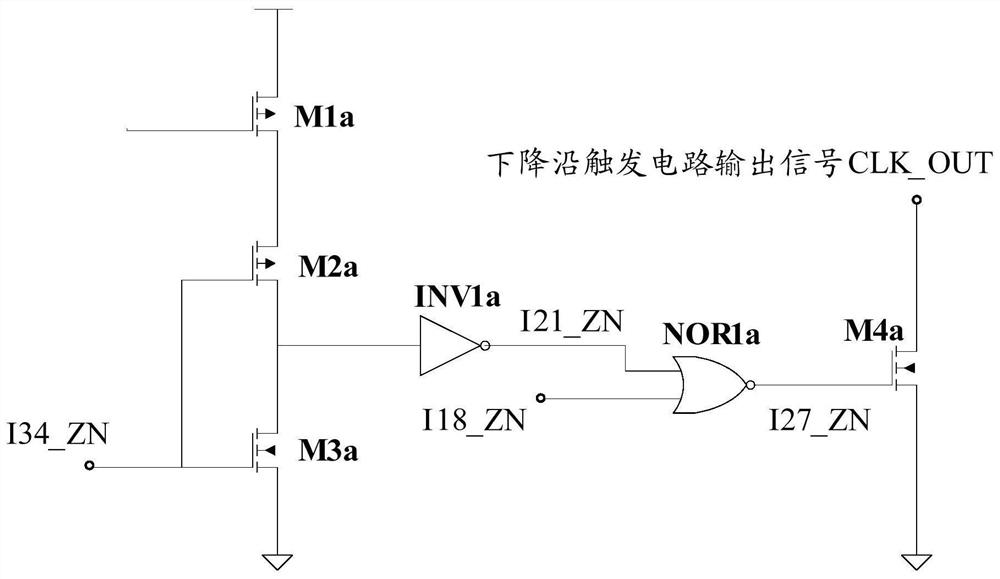

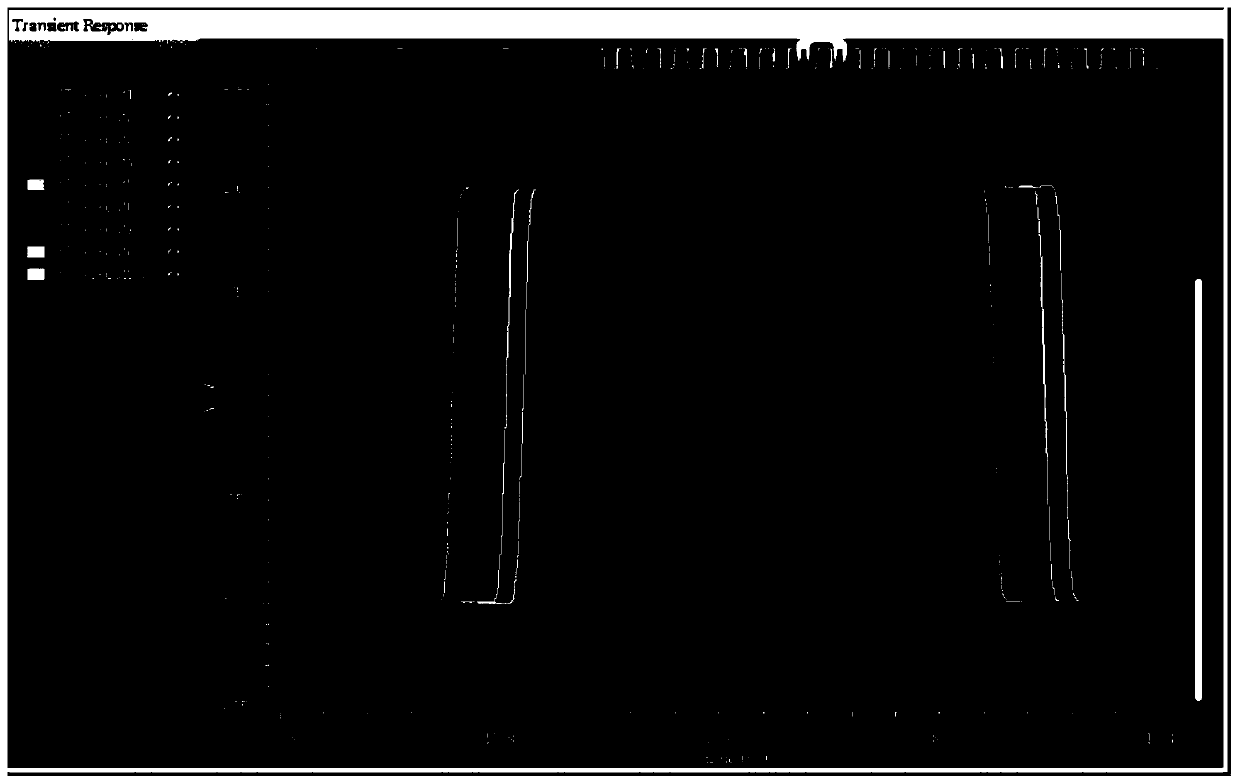

A duty cycle stable and low jitter clock circuit

ActiveCN108199699BStable duty cycleMeet demanding requirementsContinuous to patterned pulse manipulationPulse shapingLow jitterHemt circuits

The invention discloses a clock circuit with stable duty cycle and low jitter. The whole clock circuit is composed of a clock driving amplifier module, a charge pump module, an output clock falling edge trigger circuit module, an output clock rising edge trigger circuit module, an output clock waveform stabilization circuit module and a charge pump phase-locked loop module. The clock waveform stabilization circuit generates a complete output clock according to the edge control pulse generated by the rising edge and falling edge control circuit; the falling edge trigger circuit keeps the falling edge of the output clock consistent with the falling edge of the input clock; the rising edge trigger circuit can be based on the input clock. The duty cycle detection result is based on the falling edge of the output clock, and the position of the rising edge of the output clock is adjusted so that the duty cycle of the output clock is finally stabilized to 50%; the charge pump phase-locked loop receives the output clock of the output clock waveform stabilization circuit module, Generates high-speed low-jitter clock signals. The clock circuit can meet the stringent requirements for clock signals in high-frequency applications.

Owner:BEIJING MXTRONICS CORP +1

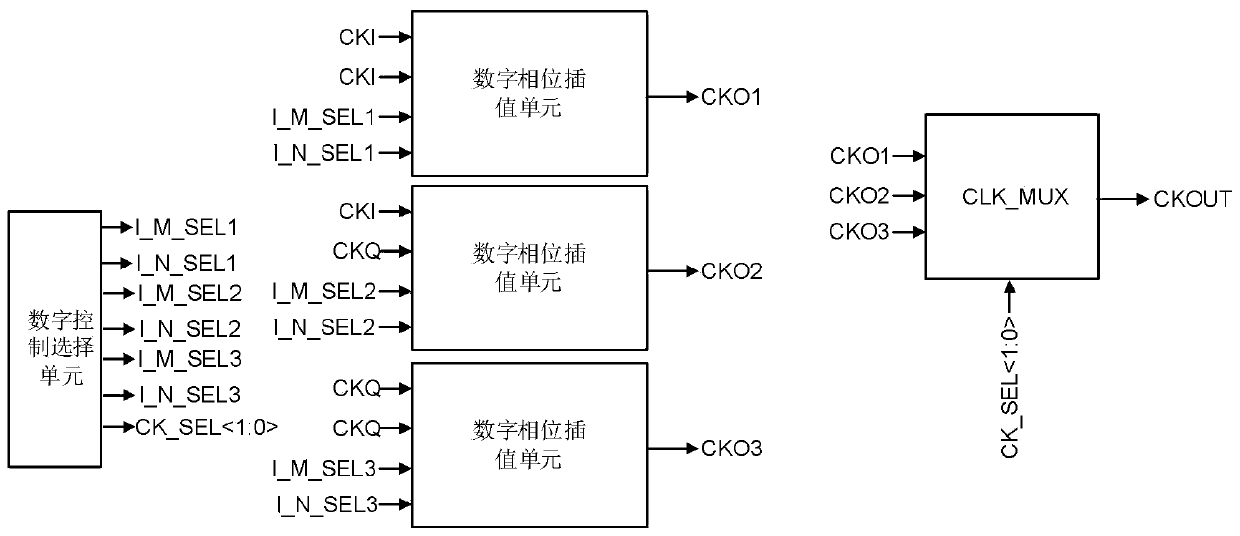

A Duty Cycle Stable Digitally Controlled Single-Stage Multi-Clock Phase Interpolator

Owner:上海奥令科电子科技有限公司

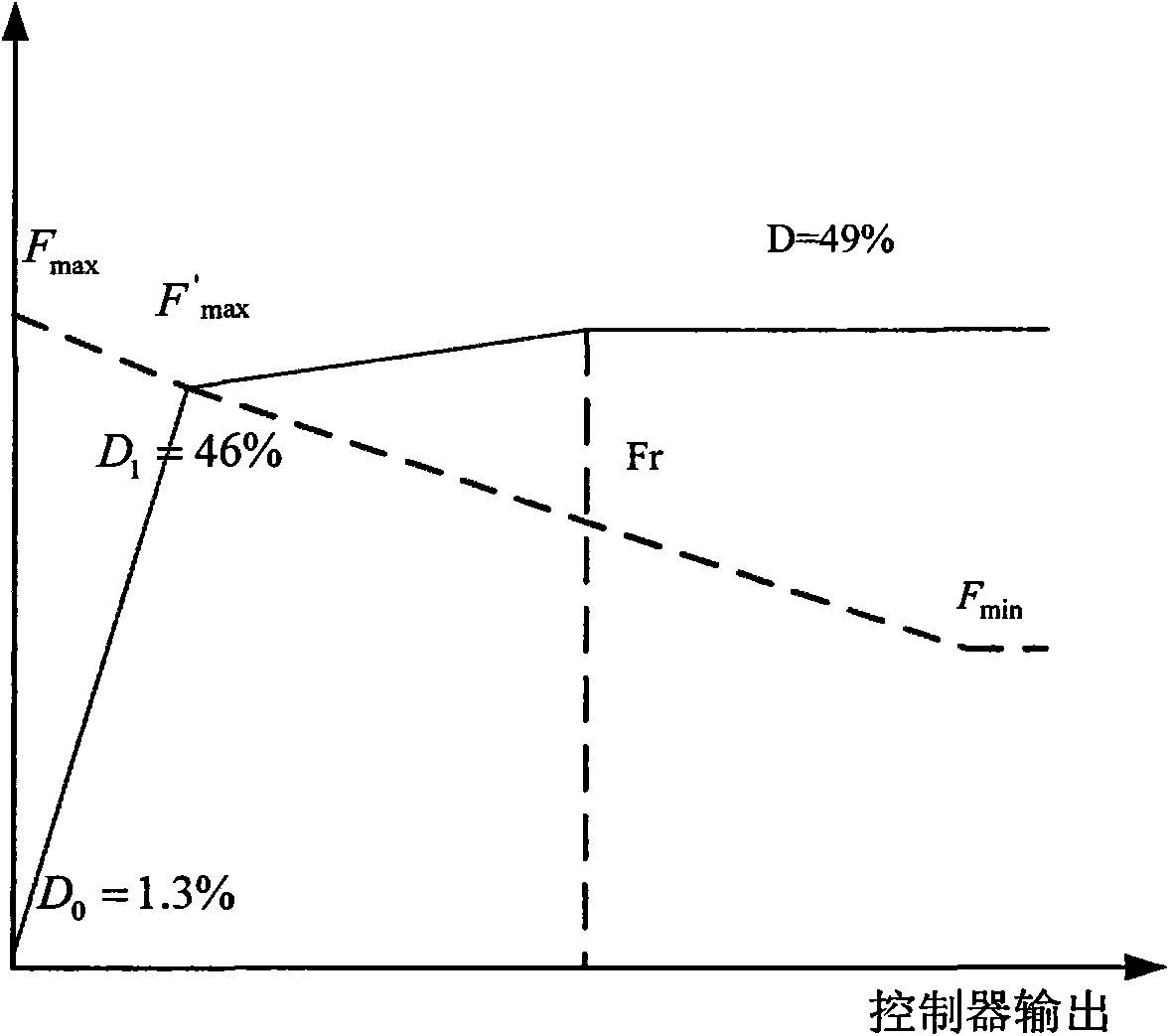

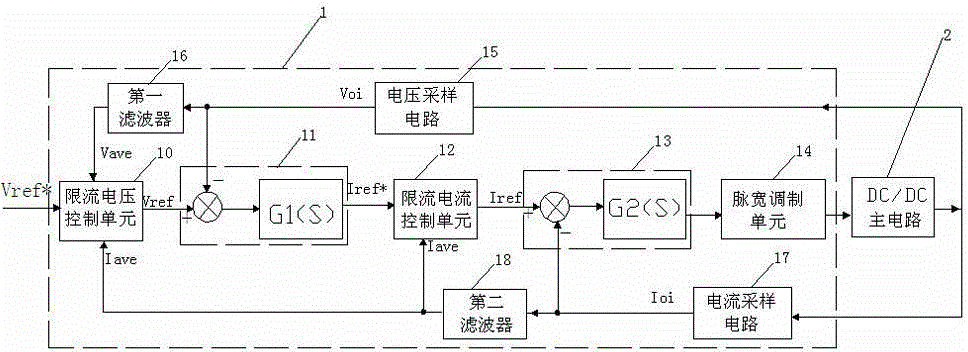

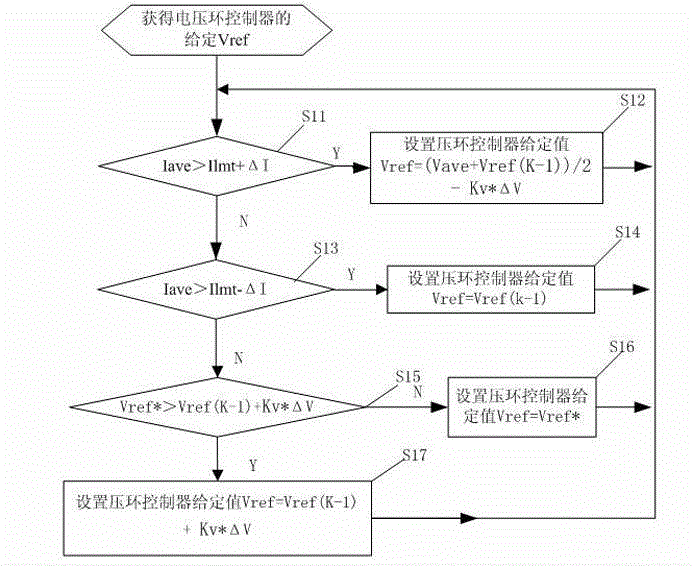

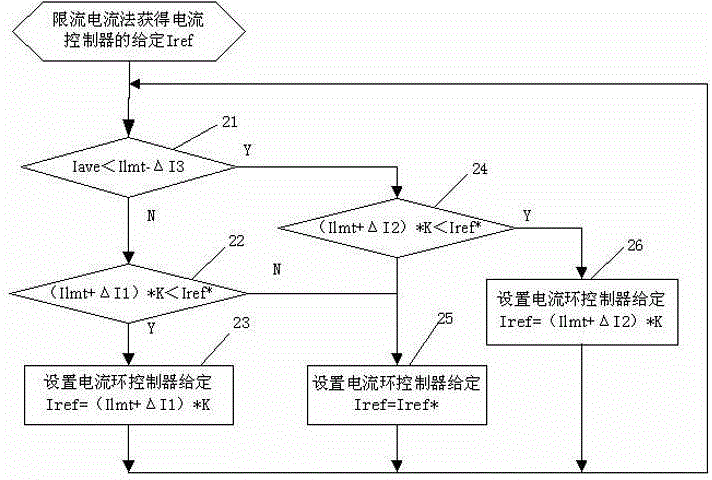

Control system and control method for stepless current limiting of switch power supply

ActiveCN103746552BReduce noiseAvoid shockDc-dc conversionElectric variable regulationClosed loopPeak value

The invention discloses a control system for the stepless current limiting of a switch power supply. The system comprises a current limiting voltage control unit, a voltage loop controller, a current limiting current control unit, a current loop controller and a pulse width modulation unit; the output end of the pulse width modulation unit is connected with a DC (direct current) / DC main circuit of the switch power supply. The system also comprises a voltage sampling unit, a first filter, a current sampling circuit and a second filter. The control method for the stepless current limiting of the switch power supply is used for performing dual-closed loop control, namely voltage loop control on the outer loop and current loop control on the inner loop, on the DC-DC main circuit of the switch power supply, so the current limiting function of software is realized. Driving oscillation of a power switch caused by the current limiting is avoided, and the system has the characteristics of precise current limiting, capability of setting a current limiting point, reduction of output ripple wave voltage (peak-peak value noise voltage) under the current limiting condition, small system noise, high reliability and the like.

Owner:厦门华睿晟智能科技有限责任公司

Improved push-pull converter based on sliding mode control

ActiveCN107769580AImprove efficiencyRobustDc-dc conversionElectric variable regulationSliding mode controlDesign systems

The invention provides an improved push-pull converter based on sliding mode control. The push-pull converter is improved on the basis of an original push-pull circuit. DC input voltage is directly imported to the midpoint of the secondary side of a transformer and is used to increase the secondary voltage of the transformer. Thus, the product output voltage is the sum of the input voltage and theconversion voltage of a power conversion circuit. The power conversion circuit only provides the difference between the input voltage and the output voltage. Such topology can significantly improve the efficiency of a product. In addition, the system uses voltage-current double loop control based on a sliding mode control algorithm, and designs a sliding mode surface according to desired dynamiccharacteristics. By designing a sliding mode control law, a controlled system converges along the sliding mode surface. Thus, good robustness, stability and dynamic quality of the system are guaranteed.

Owner:SHAANXI AVIATION ELECTRICAL

A Clock Generating Circuit for Analog-to-Digital Converter

ActiveCN106411319BStable duty cycleReduce jitterElectric pulse generatorPhysical parameters compensation/preventionDigital down converterSignal-to-noise ratio (imaging)

The invention discloses a clock generation circuit for an analog-to-digital circuit, which comprises a clock stabilizing circuit and a two-phase non-overlapping clock generation circuit. The clock stabilizing circuit comprises a clock stabilizing loop and a feedback signal generation circuit. In the feedback signal generation circuit, a control signal is generated by an active low-pass filter to control an N tube current modulation inverter, the clock stabilizing loop is used for generating a stable clock signal, and by a filtering technology and a current modulation technology, accurate modulation on a feedback signal is implemented. In the clock stabilizing loop, by a loop structure, a duty ratio of an output clock can be reduced; under the regulation of the feedback signal, by pulling up a PMOS tube MP1, the duty ratio of the output clock is increased, and finally, the duty ratio of 50% of the output clock is achieved; and the clock is stabilized and vibration is reduced. According to the clock generation circuit disclosed by the invention, the clock stabilizing circuit can be integrated into an ADC circuit; and by adopting the structure disclosed by the invention, clock signal quality can be obviously improved, the strict requirement of an ADC for clock quality is reduced, and a signal-to-noise ratio of the ADC is improved.

Owner:TIANJIN UNIV

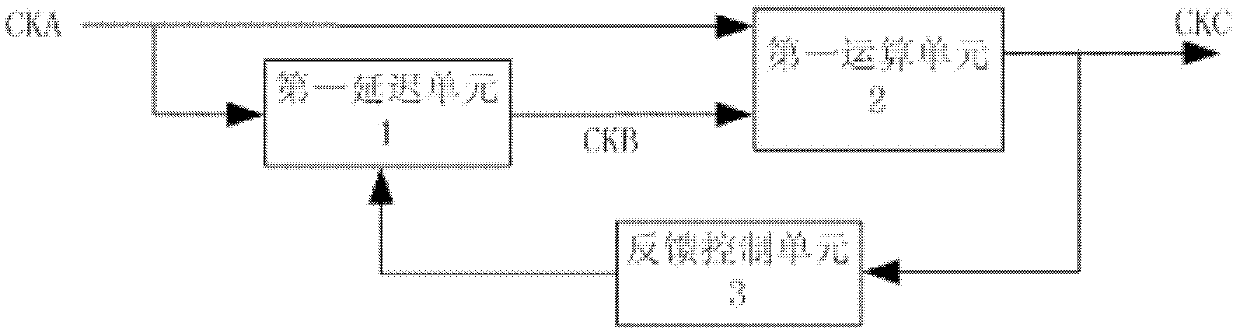

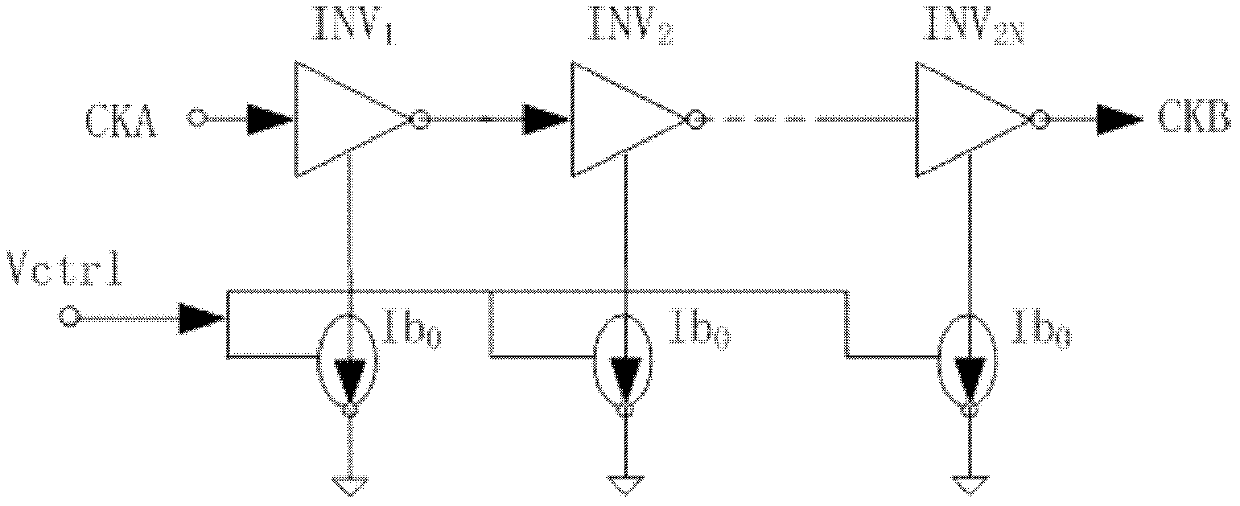

A clock multiplier circuit

ActiveCN103326697BReduce design costAvoid frequency range requirementsPulse manipulationFeedback controlSignal delay

The invention discloses a clock frequency multiplication circuit. The clock frequency multiplication circuit includes a first delay unit, a first operation unit and a feedback control unit, wherein, under the control of the feedback control unit, the first delay unit converts the externally input clock The signal is delayed and processed to obtain and output a delayed clock signal; the first computing unit performs logic operations according to the clock signal input from the outside and the delayed clock signal output by the first delay unit to obtain and output a multiplied clock signal; the feedback control unit according to The multiplied clock signal output by the first operation unit controls the delay processing of the first delay unit. Through the above technical solutions, the present invention provides a more complete clock frequency multiplication circuit.

Owner:NATIONZ TECH INC

A membrane capacitive deionization array with movable electrodes and its deionization method

ActiveCN106673142BLong runStable duty cycleDispersed particle separationWater/sewage treatmentCapacitive deionizationHemt circuits

The invention discloses a membrane capacitive deionization array with movable type electrodes and a deionization method thereof. The array comprises the following components: adsorption modules and desorption modules are mutually spaced and alternatively arranged into an array, and the movable type electrodes are periodically positioned in the adsorption modules and the desorption modules. The traditional membrane capacitive deionization technology is used as a prototype, adsorption modules are arranged, arrangement sequence of an ion-exchange membrane is changed, the desorption modules are arranged, originally fixed electrodes are innovatively changed into movable type electrodes, the electrodes are periodically arranged in the adsorption modules and the desorption modules, so that the purpose that the deionization process is stably efficient for a long time is realized; the adsorption modules and the desorption modules work simultaneously in different regions, in order to form a stable working cycle, and circuit with reversal connection is not needed for backwashing; the deionization method can be operated continuously with high efficiency and stabilization, and the deionization efficiency is high.

Owner:HOHAI UNIV

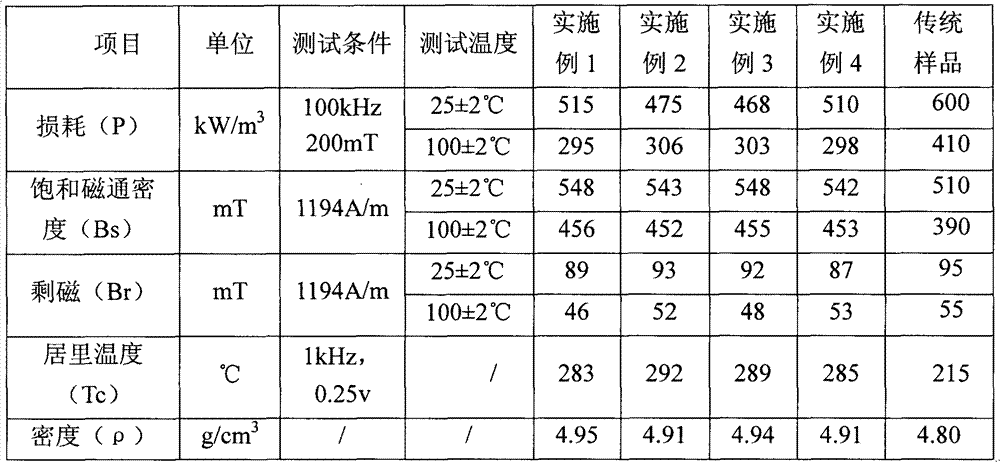

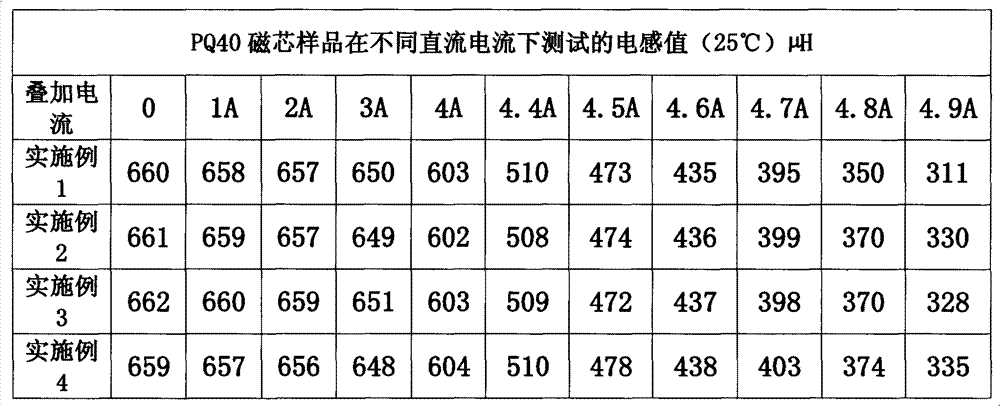

High-saturation magnetic flux, high-direct current superposition and low-loss soft magnetic material and preparation method thereof

The invention relates to a high-saturation magnetic flux, high-direct current superposition and low-loss soft magnetic material and a preparation method thereof. The soft magnetic material comprises the following main components: 53.5 to 55 molar percent of Fe2O3, 4 to 9.5 molar percent of ZnO, and the balance of MnO; and based on the total weight of the main components, the soft magnetic material comprises the following auxiliary components: 0.01 to 0.05 weight percent of WO3, 0.005 to 0.03 weight percent of NiO, and 0.02 to 0.06 weight percent of ZrO2. The soft magnetic material has higher saturation magnetic flux density Bs in a wide temperature range and a larger difference between the saturation magnetic flux density Bs of the soft magnetic material and residual magnetic flux densityBr exists, power consumption is greatly reduced in the wide temperature range particularly, the superposition performance is high, and Curie temperature is relatively high, so that a plurality of electromagnetic parameters are matched more optimally, and the soft magnetic material is particularly suitable for realizing the higher and more stable electrical inductance function on various occasionswith large direct current superposition.

Owner:RUYUAN DONGYANGGUANG MAGNETIC MATERIAL

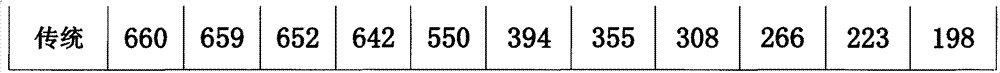

FPGA high-performance interconnection circuit

PendingCN112234959AGuaranteed Signal IntegritySignal Integrity AssuranceMultiple input and output pulse circuitsElectronic switchingSoftware engineeringHemt circuits

The invention discloses an FPGA high-performance interconnection circuit, and relates to an integrated circuit technology. The circuit comprises i secondary NMOS tubes connected in parallel, wherein the output end of each secondary switch NMOS tube is connected to a common reference point; the input end of each secondary NMOS transistor is connected with a primary NMOS transistor group, the primary NMOS transistor group is composed of m primary NMOS transistors which are connected in parallel, the output end of each primary NMOS transistor in the same primary NMOS transistor group is connectedwith the corresponding secondary NMOS transistor, and the input end of each primary NMOS transistor in the same primary NMOS transistor group is used as the input end of the interconnection circuit;in each primary NMOS tube group, the primary NMOS tubes with the same serial number are controlled by the same primary SRAM unit, and each secondary NMOS tube is connected to the corresponding secondary SRAM; wherein the common reference point is connected to the output end through the pull-up circuit and the level recovery circuit, and i and m are integers greater than 1. According to the invention, the performance of the interconnection circuit in the aspects of area, power consumption, speed and signal integrity is more excellent.

Owner:CHENGDU SINO MICROELECTRONICS TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com