FPGA high-performance interconnection circuit

A high-performance, circuit technology, applied in multiple input and output pulse circuits, electrical components, electronic switches, etc., can solve the problems of large chip area, limited power consumption improvement of interconnected circuits, large area, etc., and achieve superior performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0031] For ease of reading, the "device referred to by 101" is abbreviated as "101" hereinafter, and the other symbols are the same.

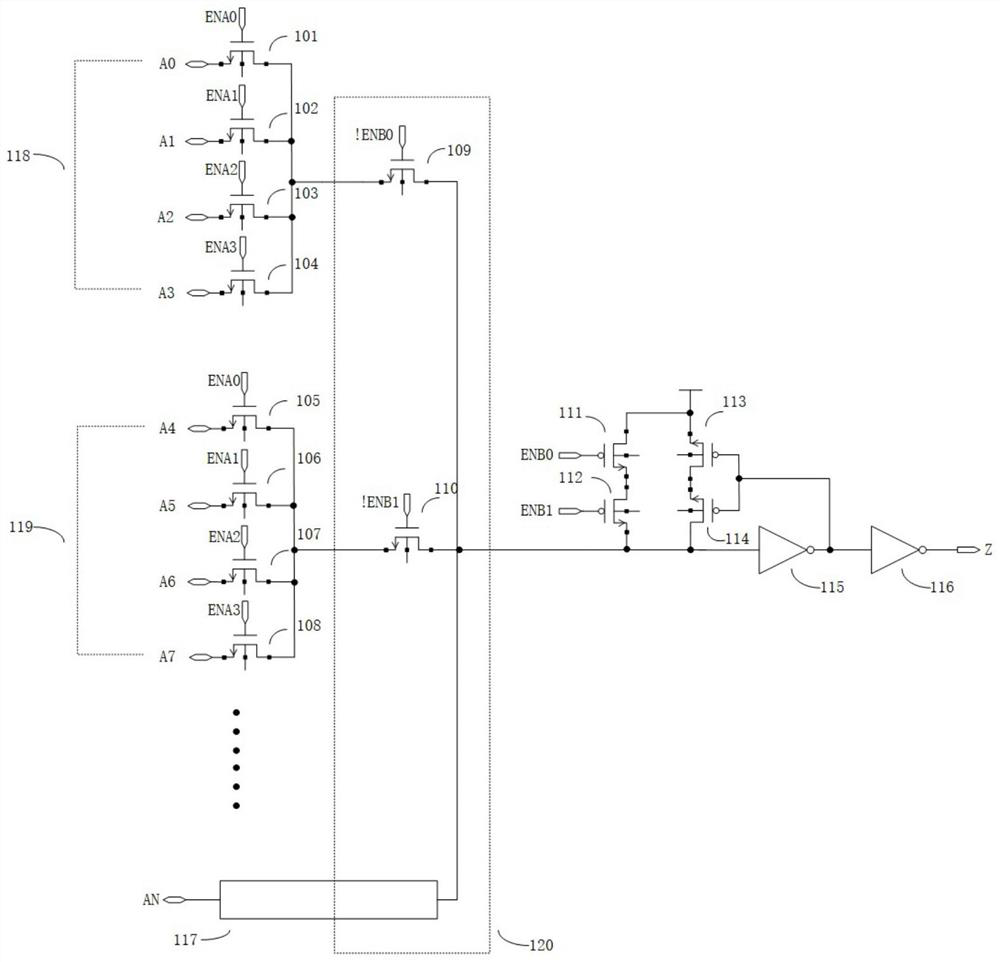

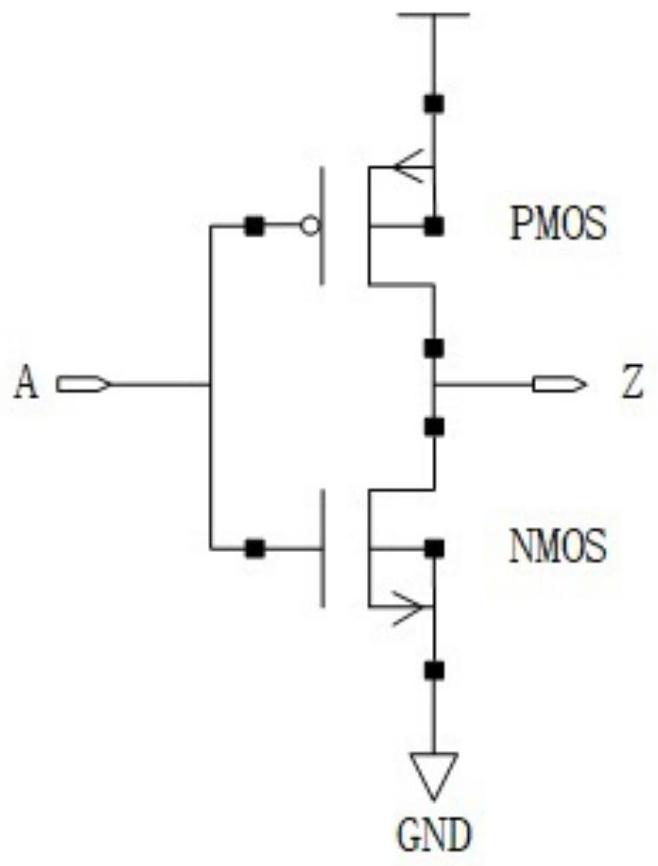

[0032] figure 1 118 and 119 are two sets of the same 4-select-one MUX, and the device types are all NMOS transistors. The gate terminals of 101 and 105, 102 and 106, 103 and 107, 104 and 108 are controlled by the same SRAM; 120 is the first Secondary MUX, the device type is also NMOS transistor, 111 and 112 are pull-up PMOS transistors, of which 109 and 111, the gate terminals of 110 and 112 come from the opposite output of the same SRAM; 113~116 are level recovery circuits, 113 and 112 114 is a PMOS tube, and the inverter structure in the level restoration circuit is composed of image 3 shown. The MUX of this circuit can be expanded.

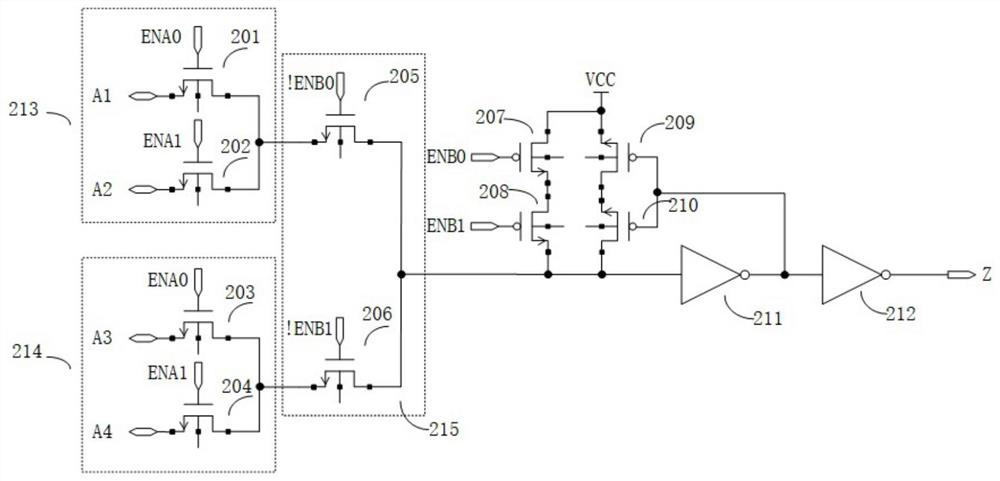

[0033] figure 2 It is the most basic circuit structure of the present invention (two-stage 4 select one MUX), 213 and 214 are two groups of the same 2 select one MUX, the device type is NMOS, and the gate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com