Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

47results about How to "Significant energy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

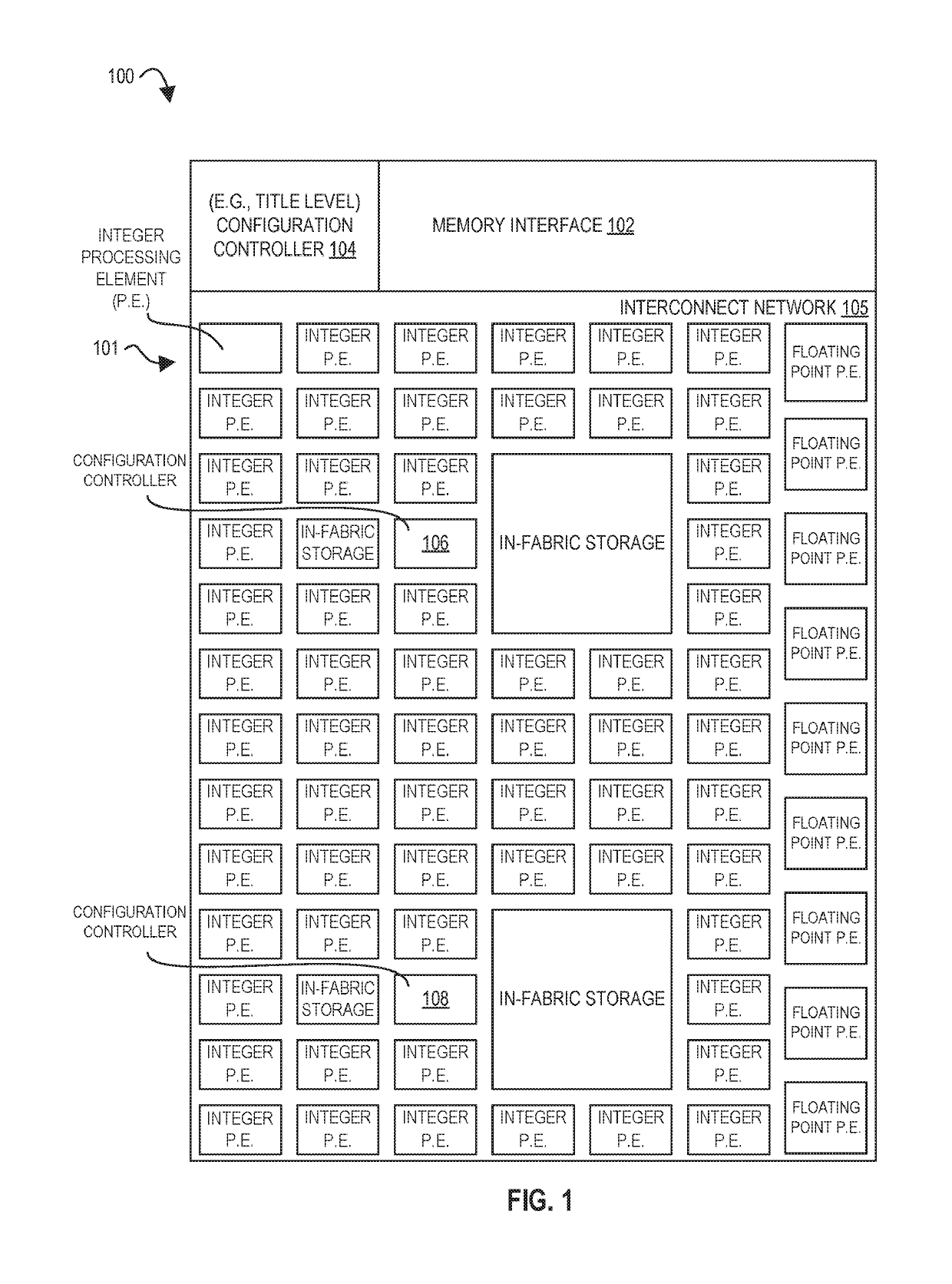

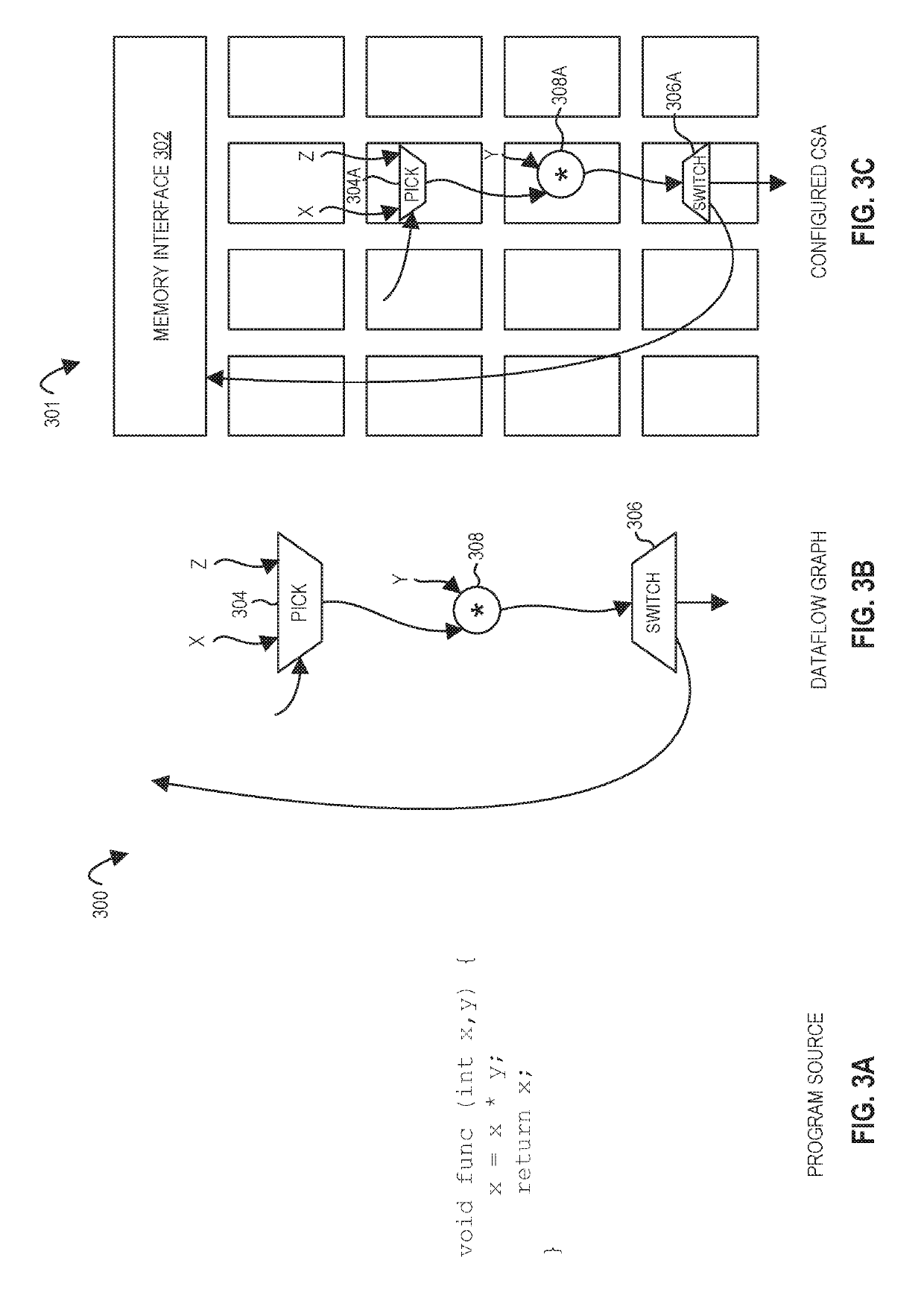

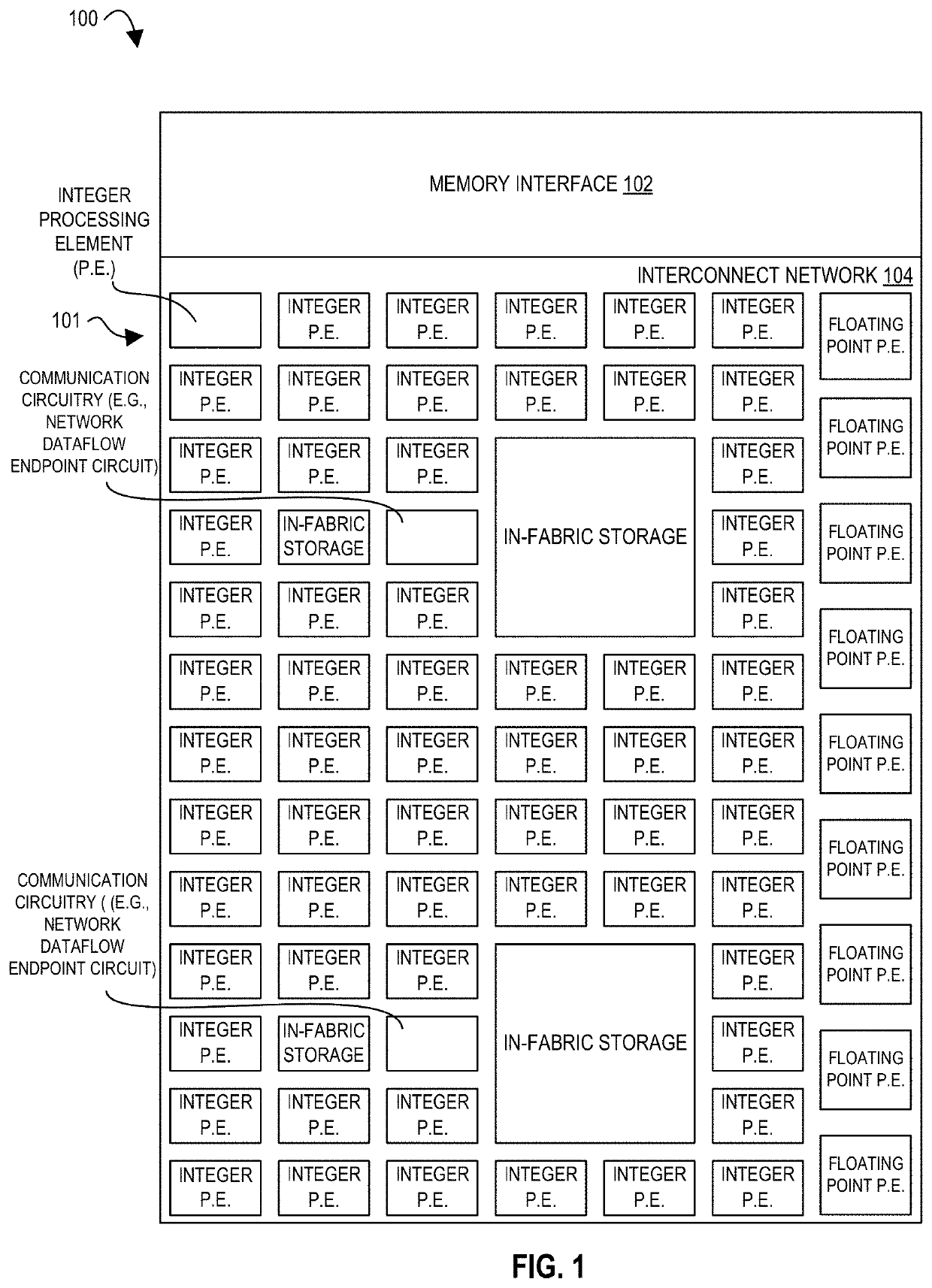

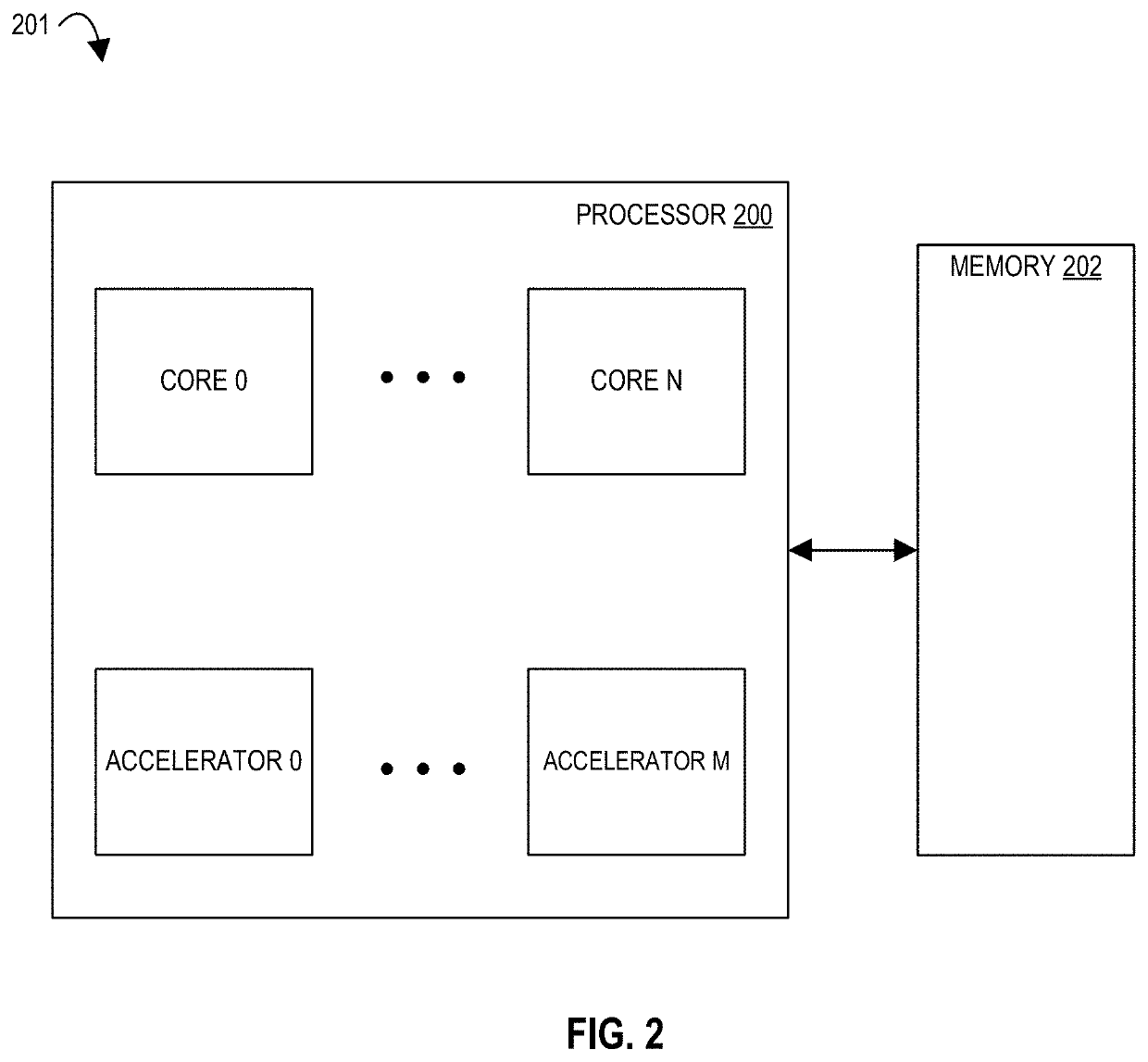

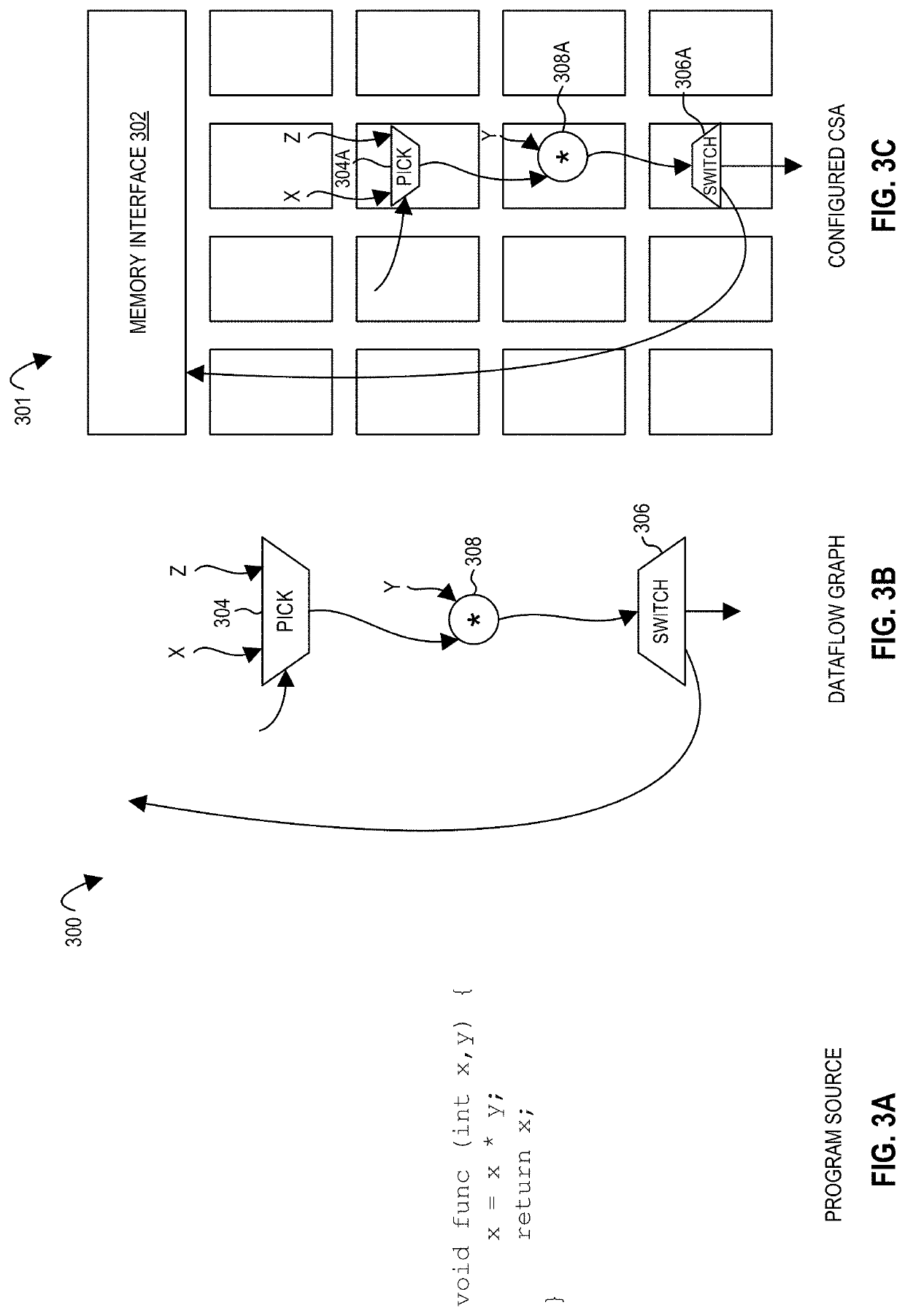

Processors, methods, and systems with a configurable spatial accelerator

ActiveUS20190018815A1Easy to adaptImprove performanceDataflow computersResource allocationComputer scienceVoltage

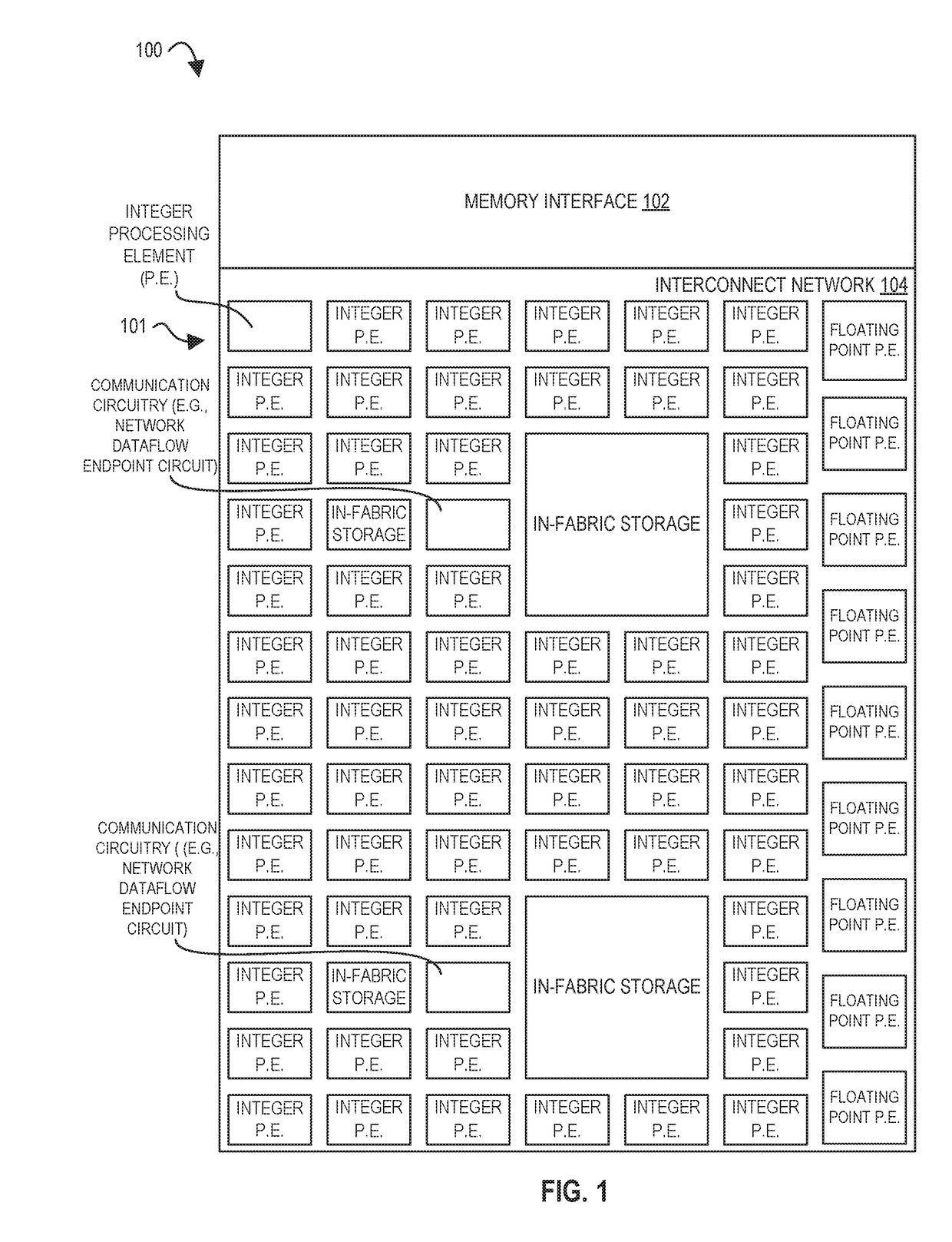

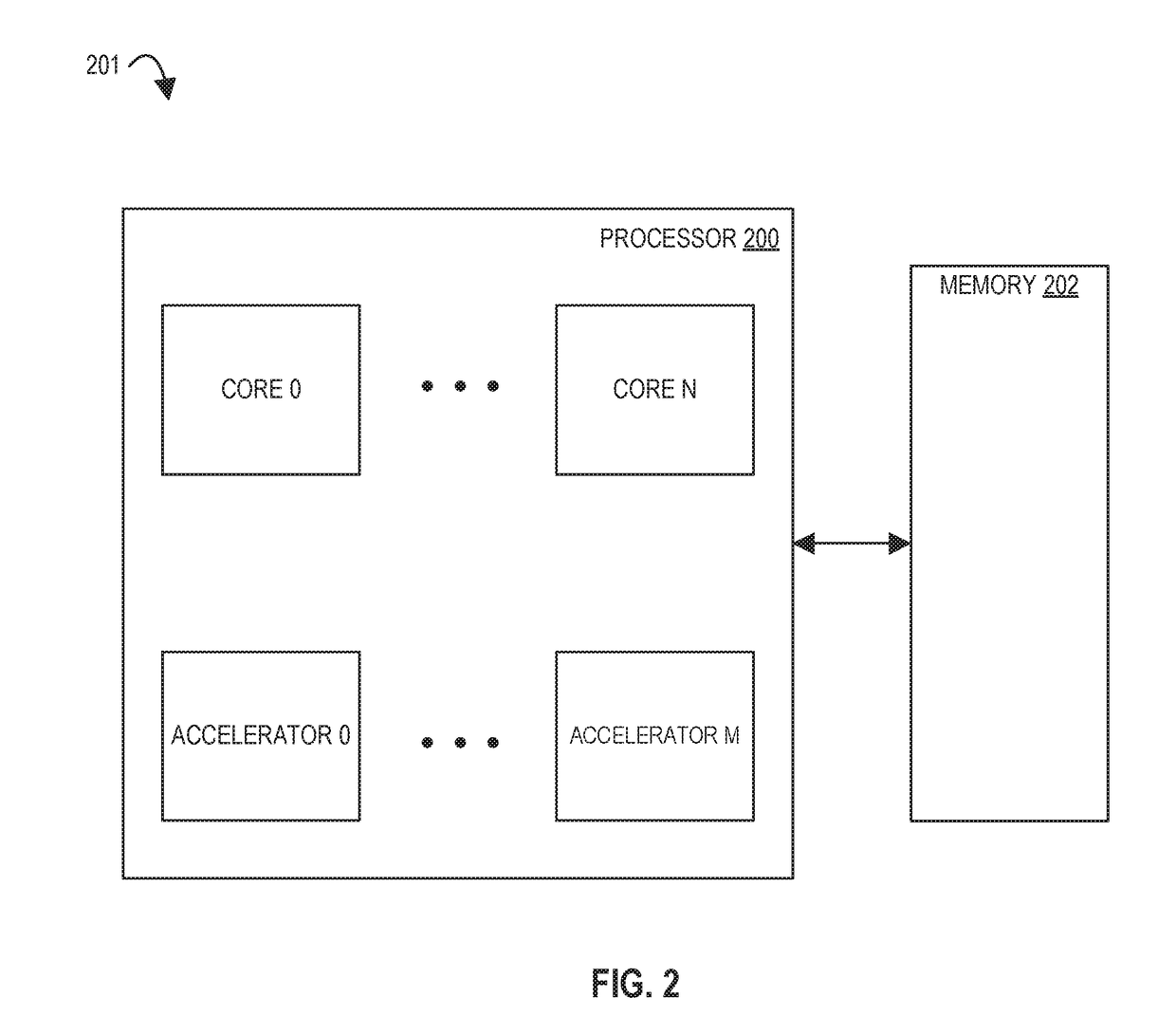

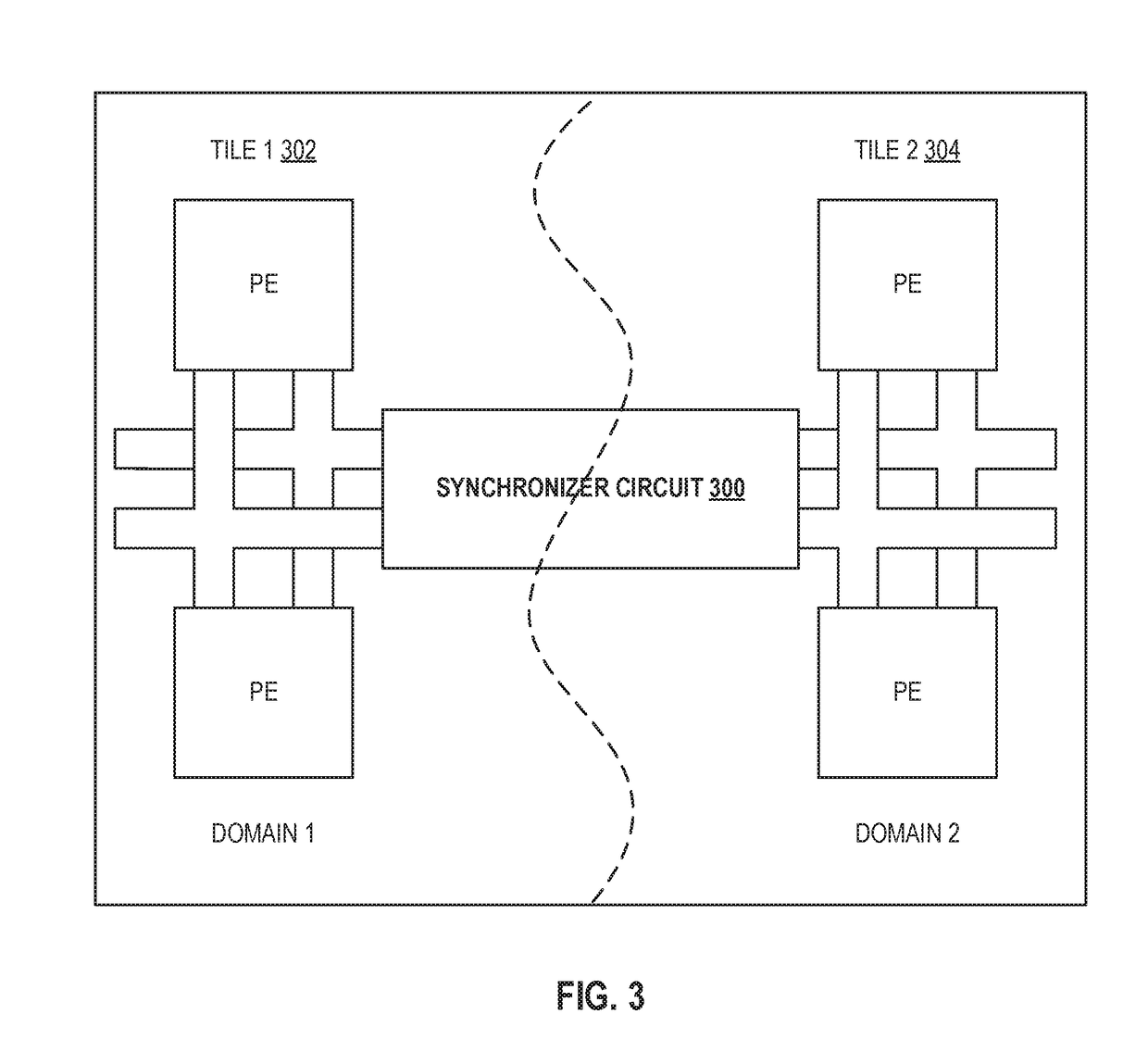

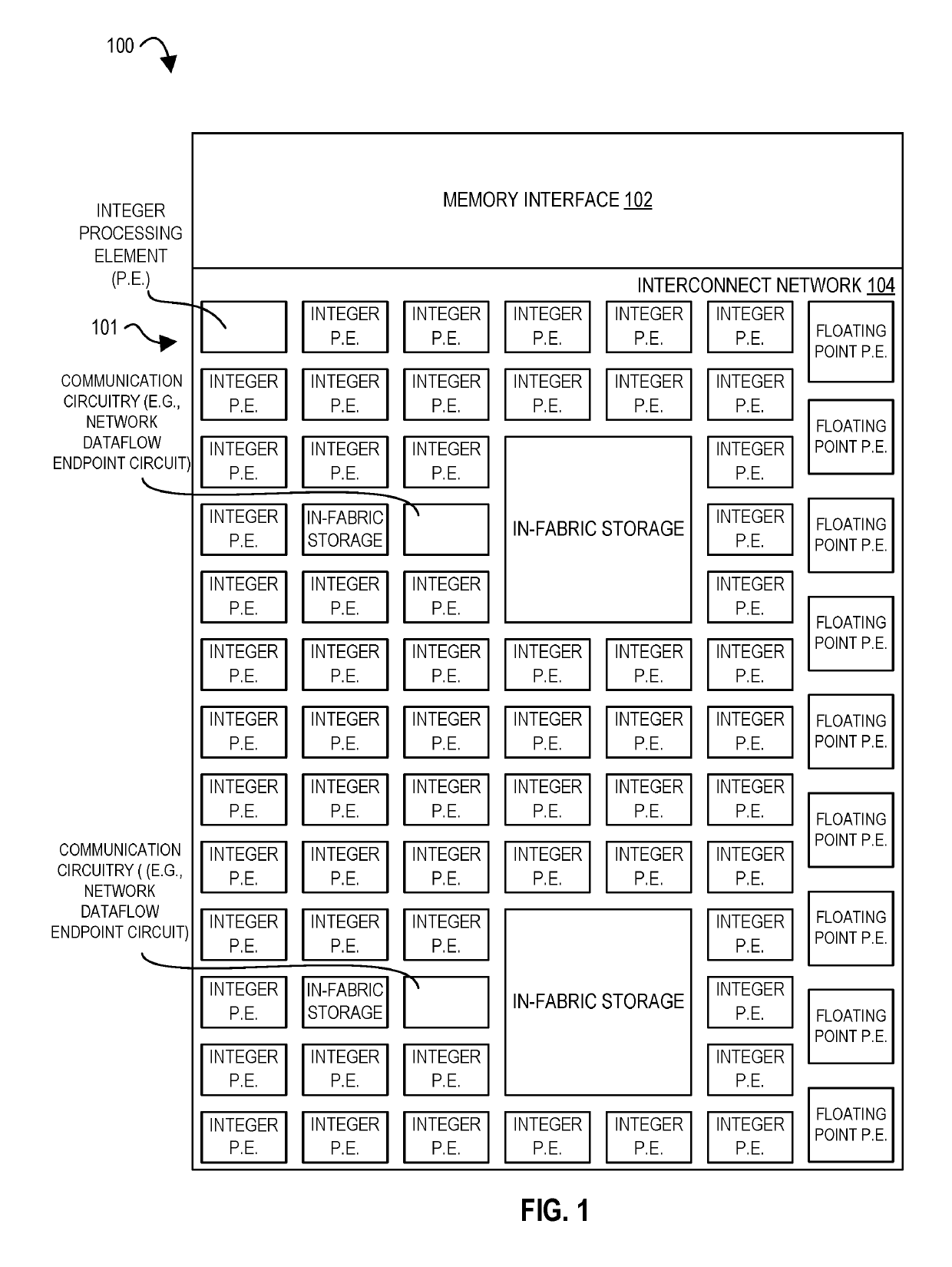

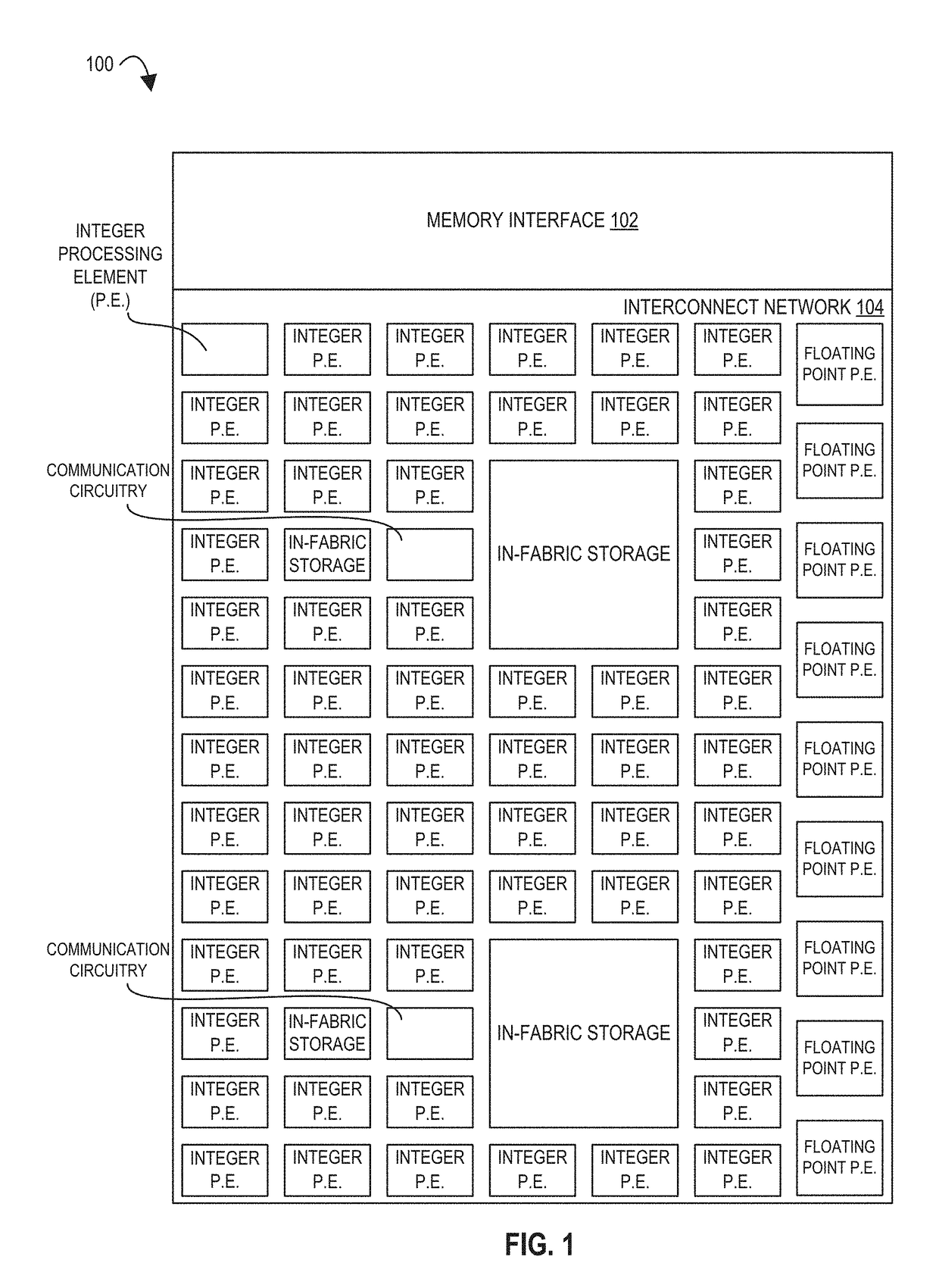

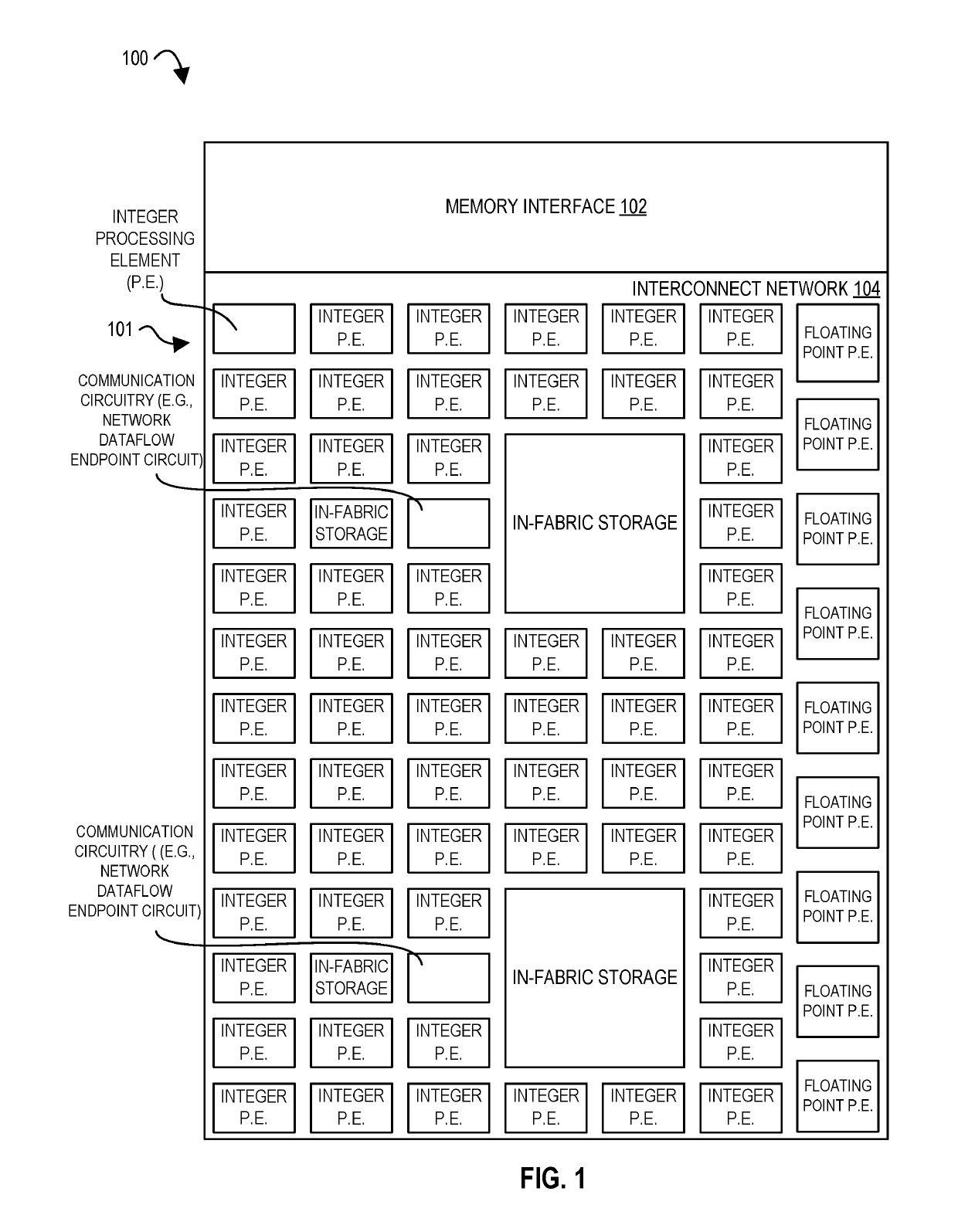

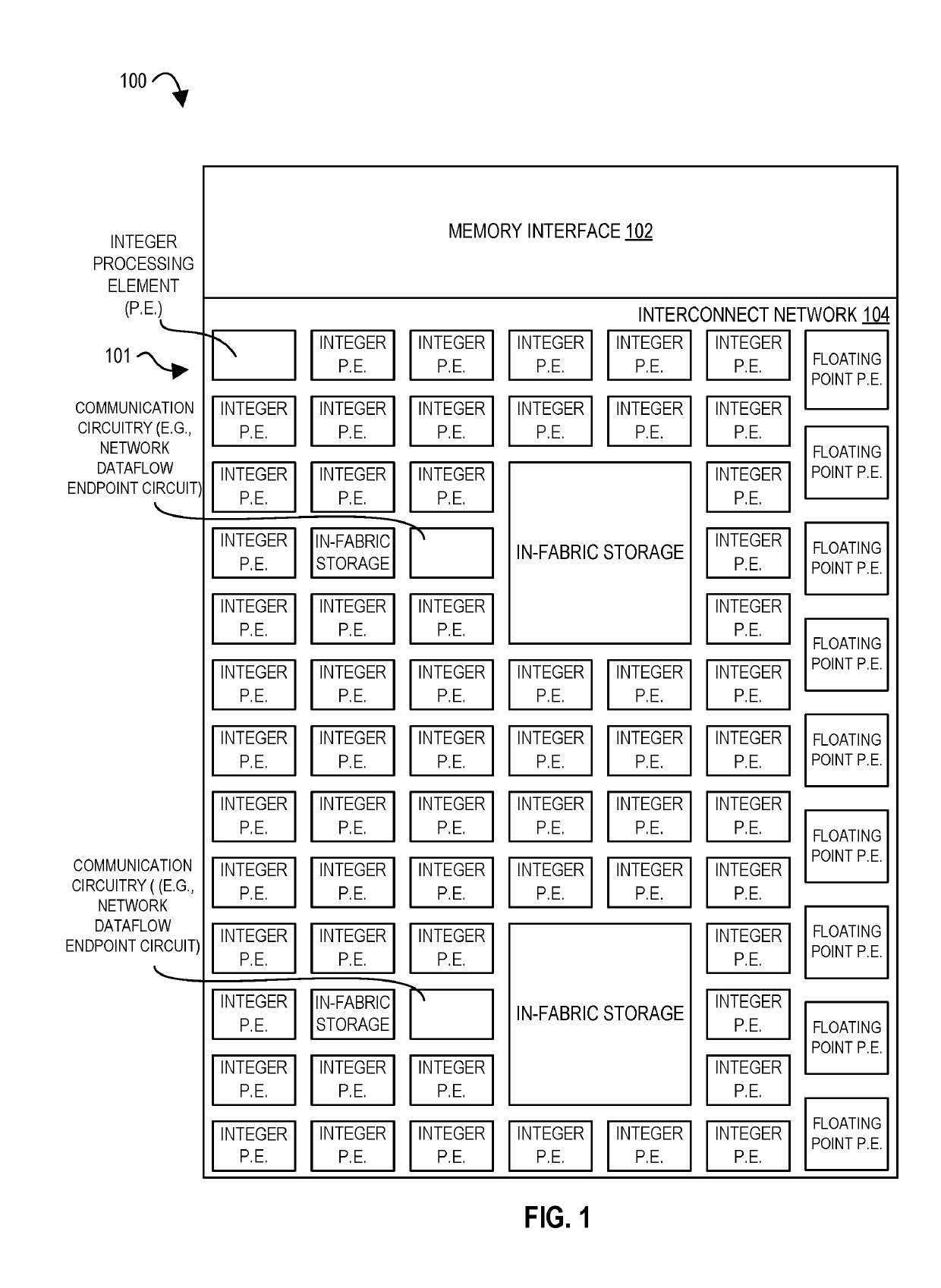

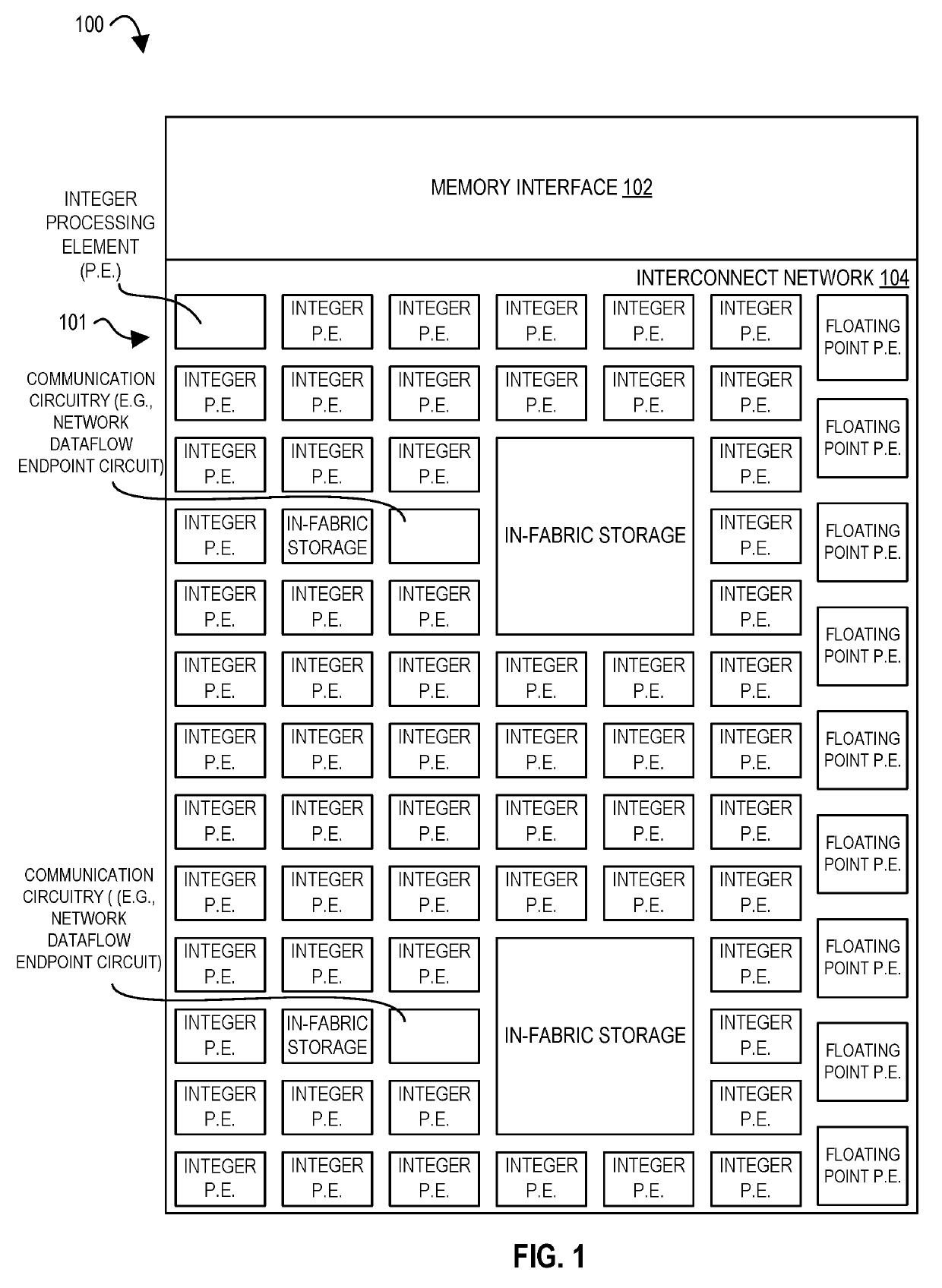

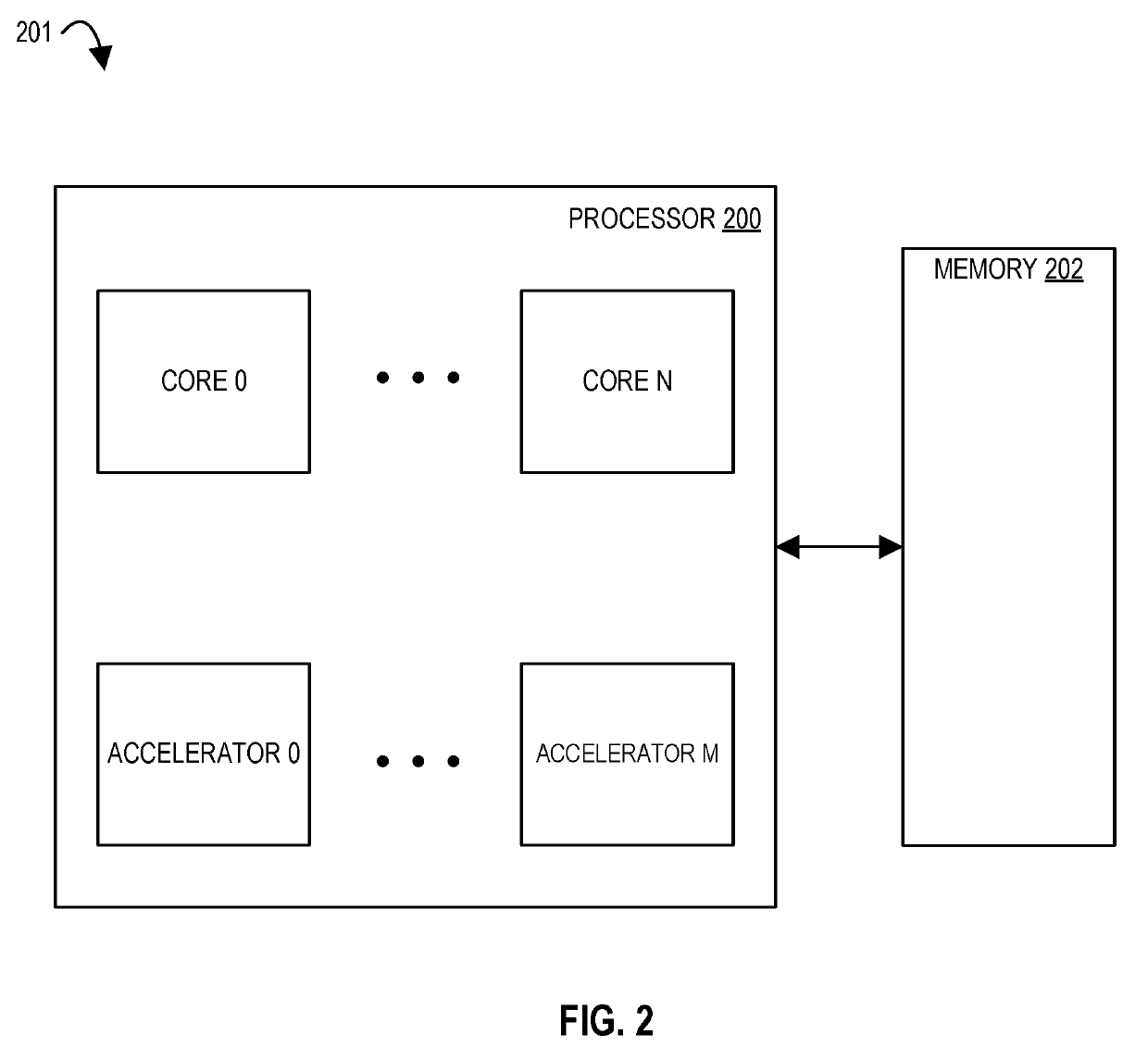

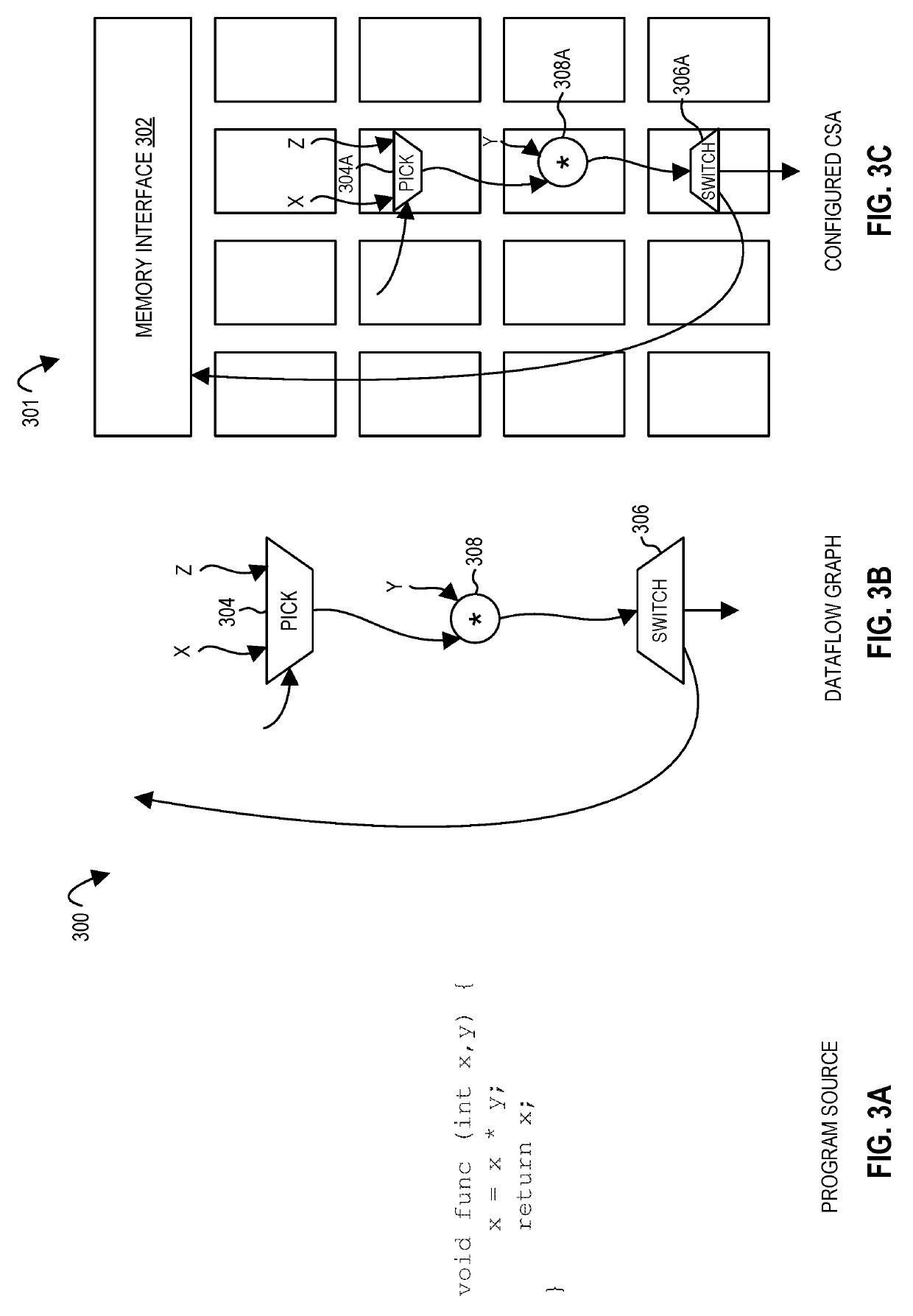

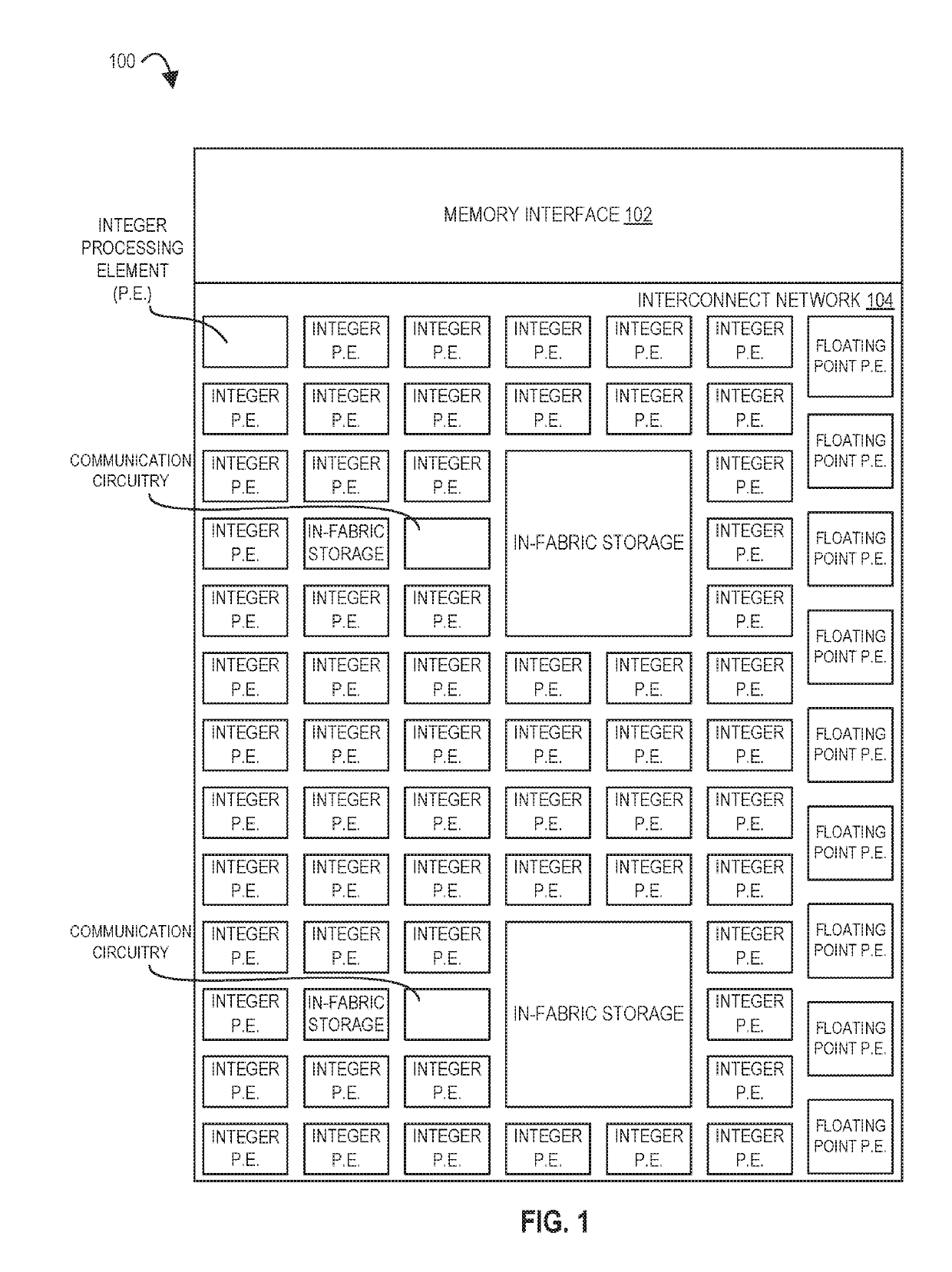

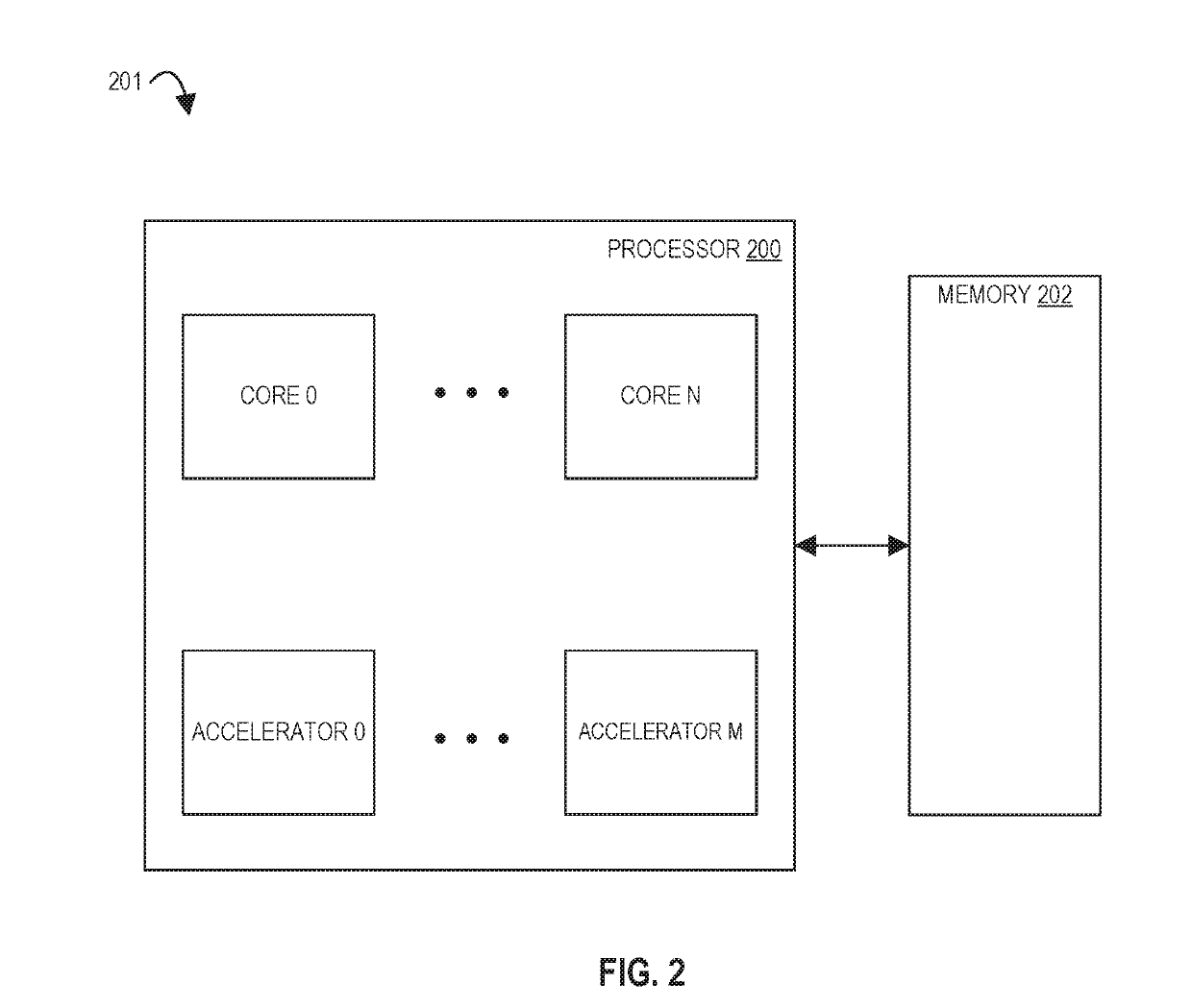

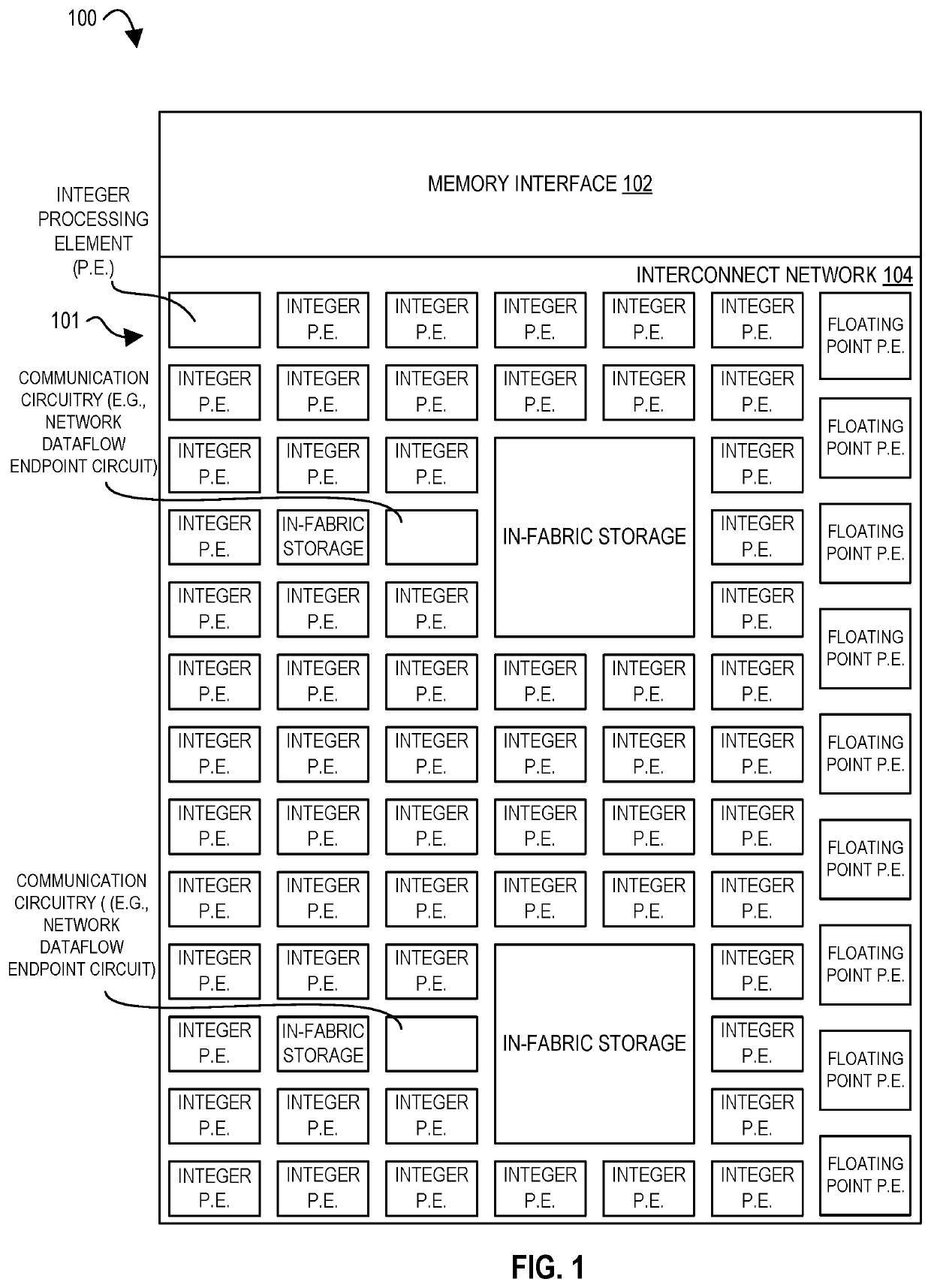

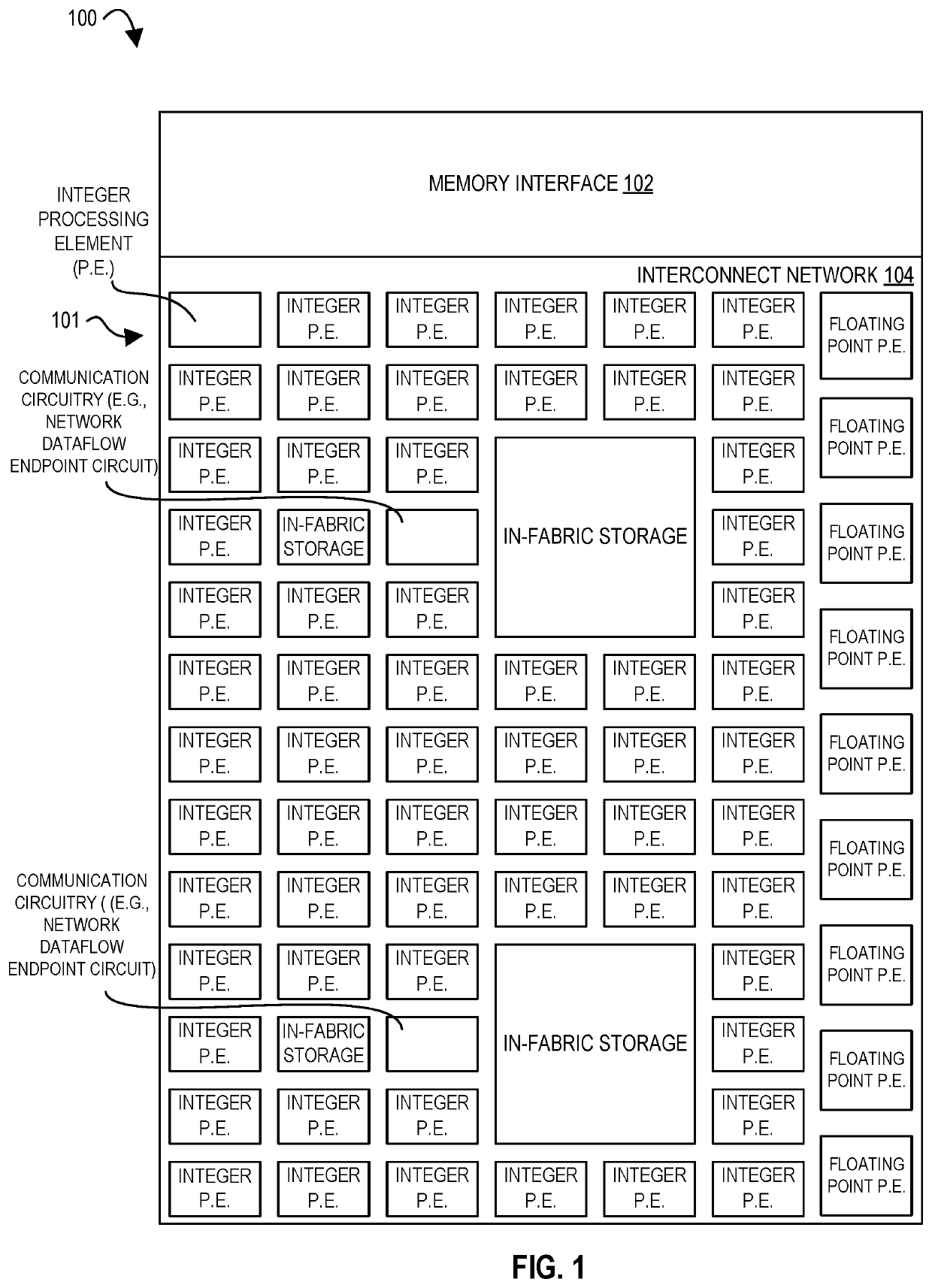

Systems, methods, and apparatuses relating to a configurable spatial accelerator are described. In one embodiment, a processor includes a synchronizer circuit coupled between an interconnect network of a first tile and an interconnect network of a second tile and comprising storage to store data to be sent between the interconnect network of the first tile and the interconnect network of the second tile, the synchronizer circuit to convert the data from the storage between a first voltage or a first frequency of the first tile and a second voltage or a second frequency of the second tile to generate converted data, and send the converted data between the interconnect network of the first tile and the interconnect network of the second tile

Owner:INTEL CORP

Green biodiesel

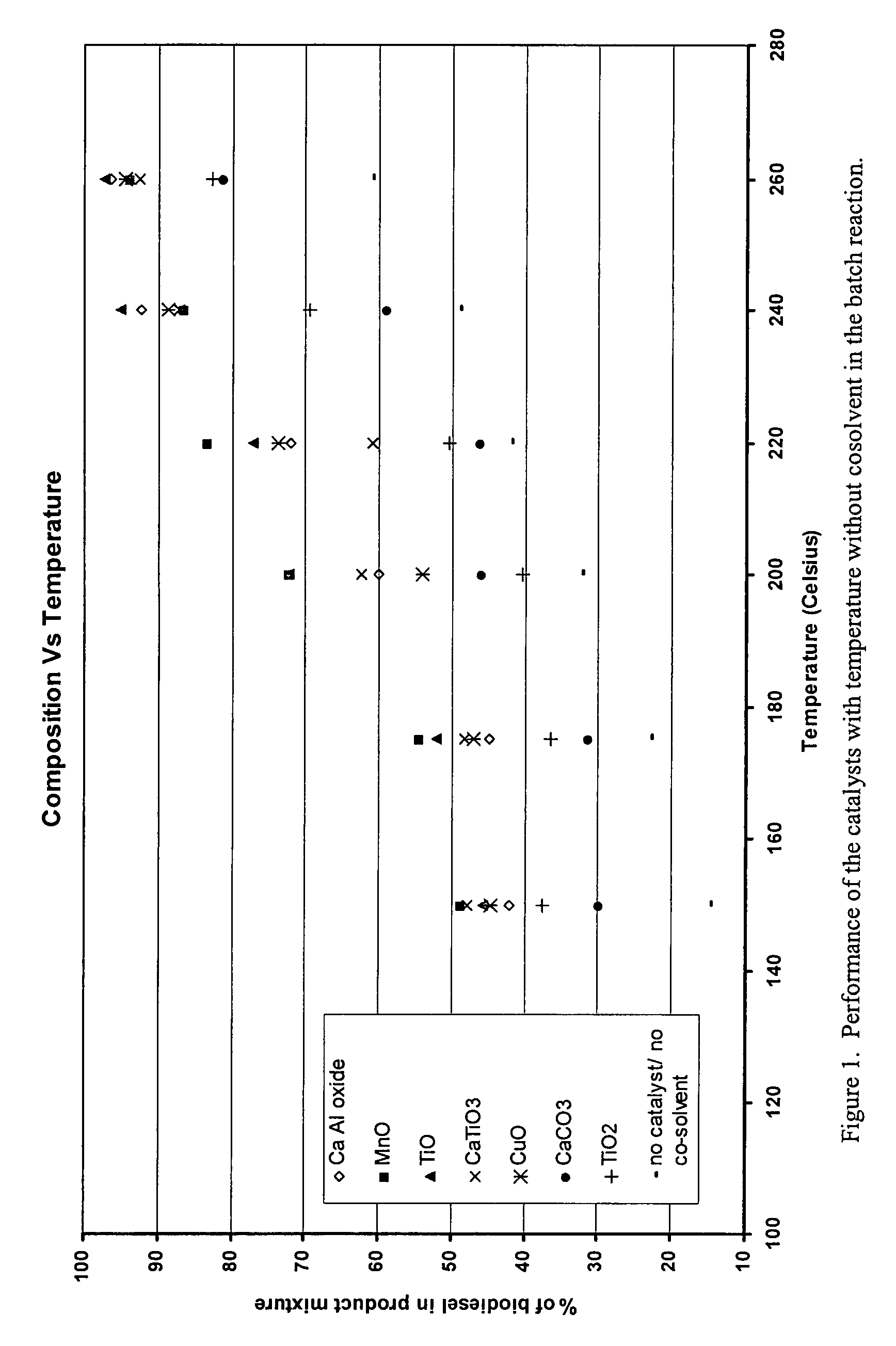

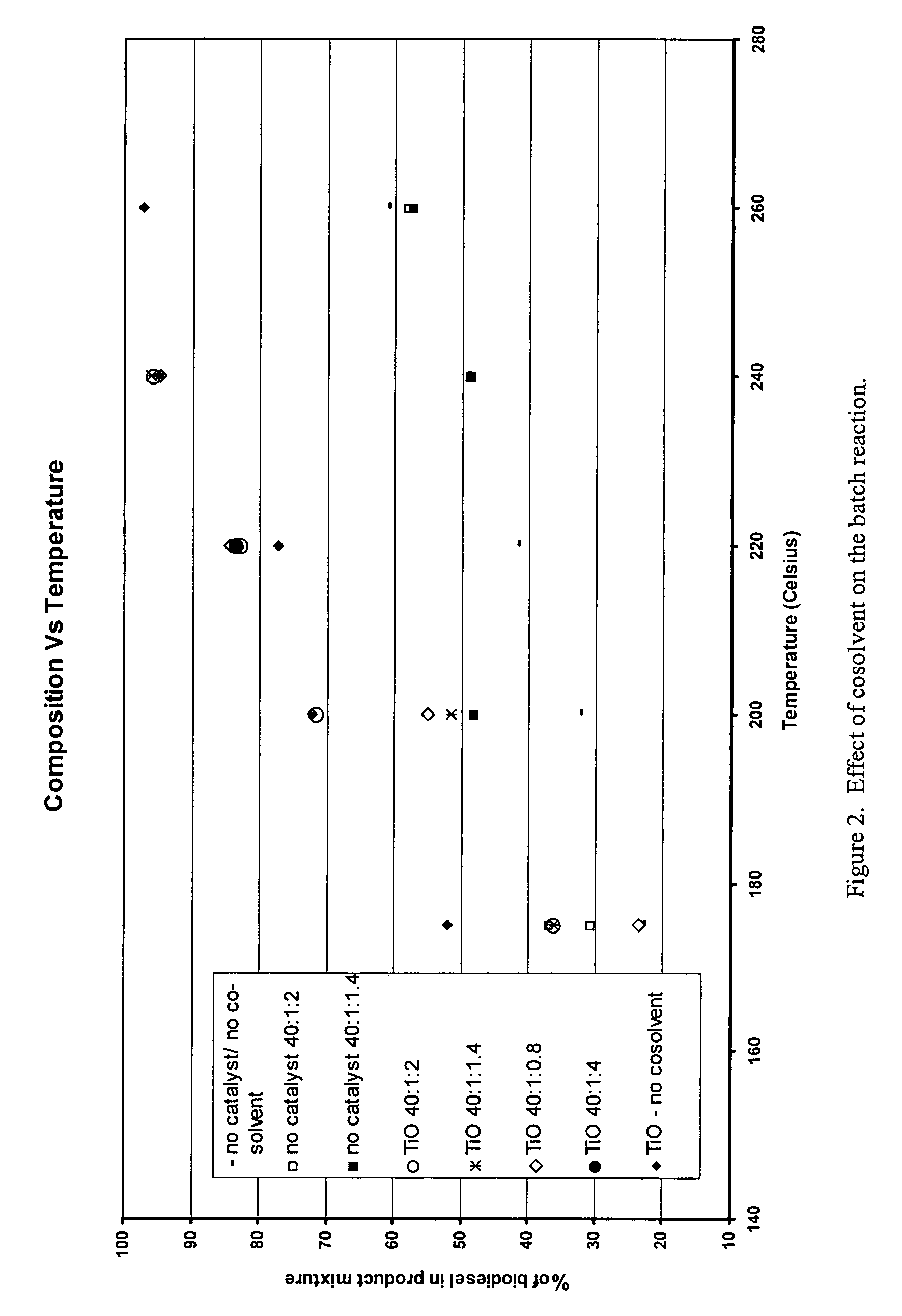

InactiveUS7563915B2Reduce wasteSignificant energyFatty oils/acids recovery from wasteFatty acid esterificationCalcium silicateBiodiesel

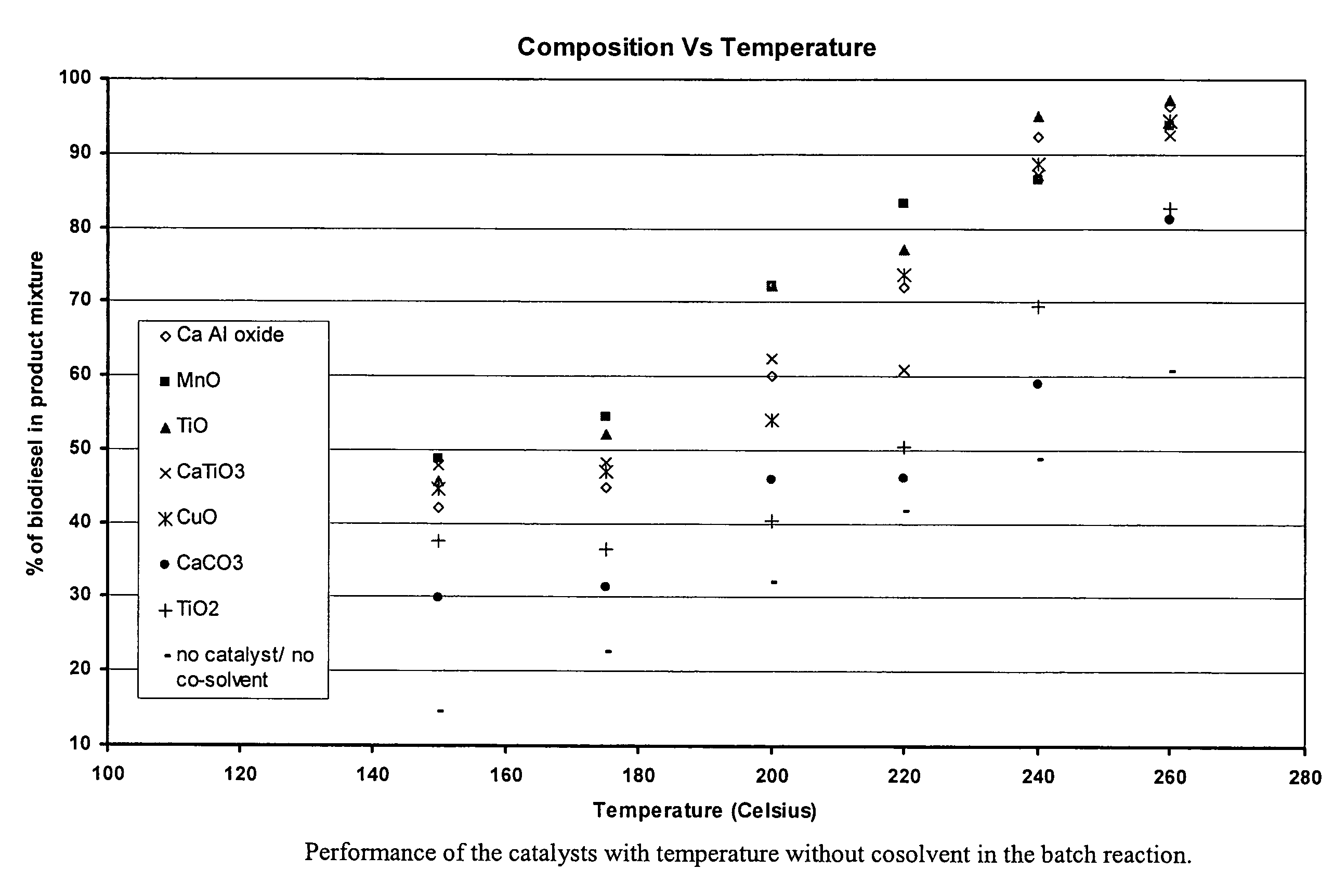

Methods for improved manufacture of green biodiesel focus on the selection and use of one or more solid metallic oxide base catalyst(s) selected from the group consisting of calcium oxide (CaO), calcium aluminum oxide (CaO—Al2O3), calcium titanate (CaTiO3), barium titanate (BaTiO3), magnesium aluminum oxide (MgO—Al2O3), zinc oxide (ZnO), copper (II) oxide (CuO), nickel oxide (NiO), manganese oxide (MnO), titanium oxide (TiO), vanadium oxide (VO), cobalt oxide (CoO), iron oxide (FeO), chromite (FeCr2O4), hydrotalcite (Mg6Al2(CO3)(OH)16.4(H2O), magnetite (Fe3O4), magnesium silicate and calcium silicate.

Owner:PENN STATE RES FOUND

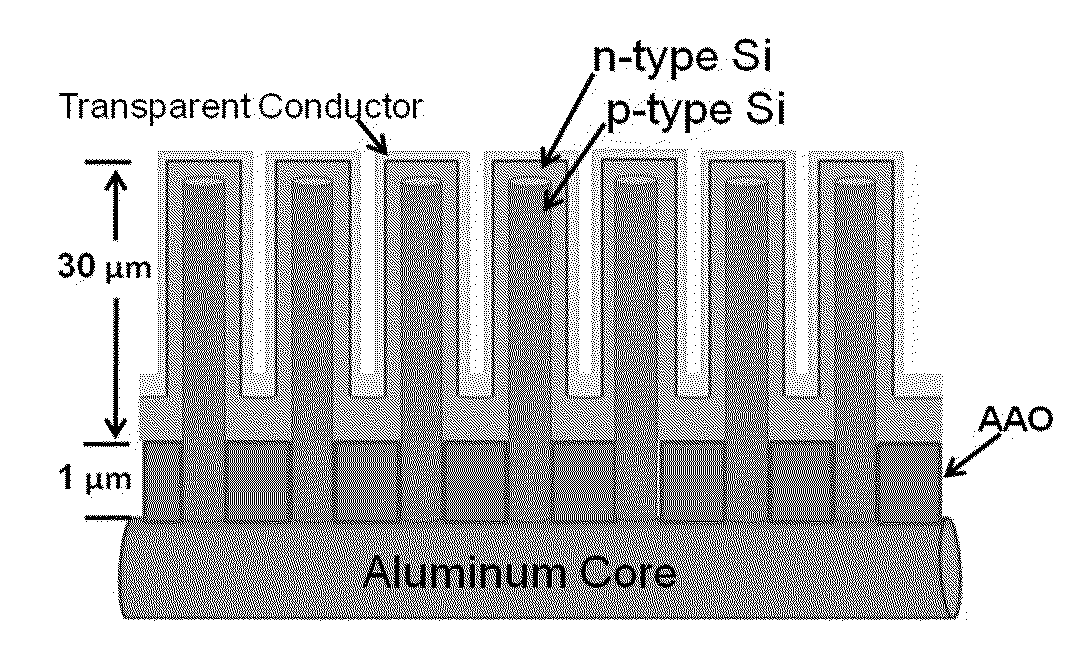

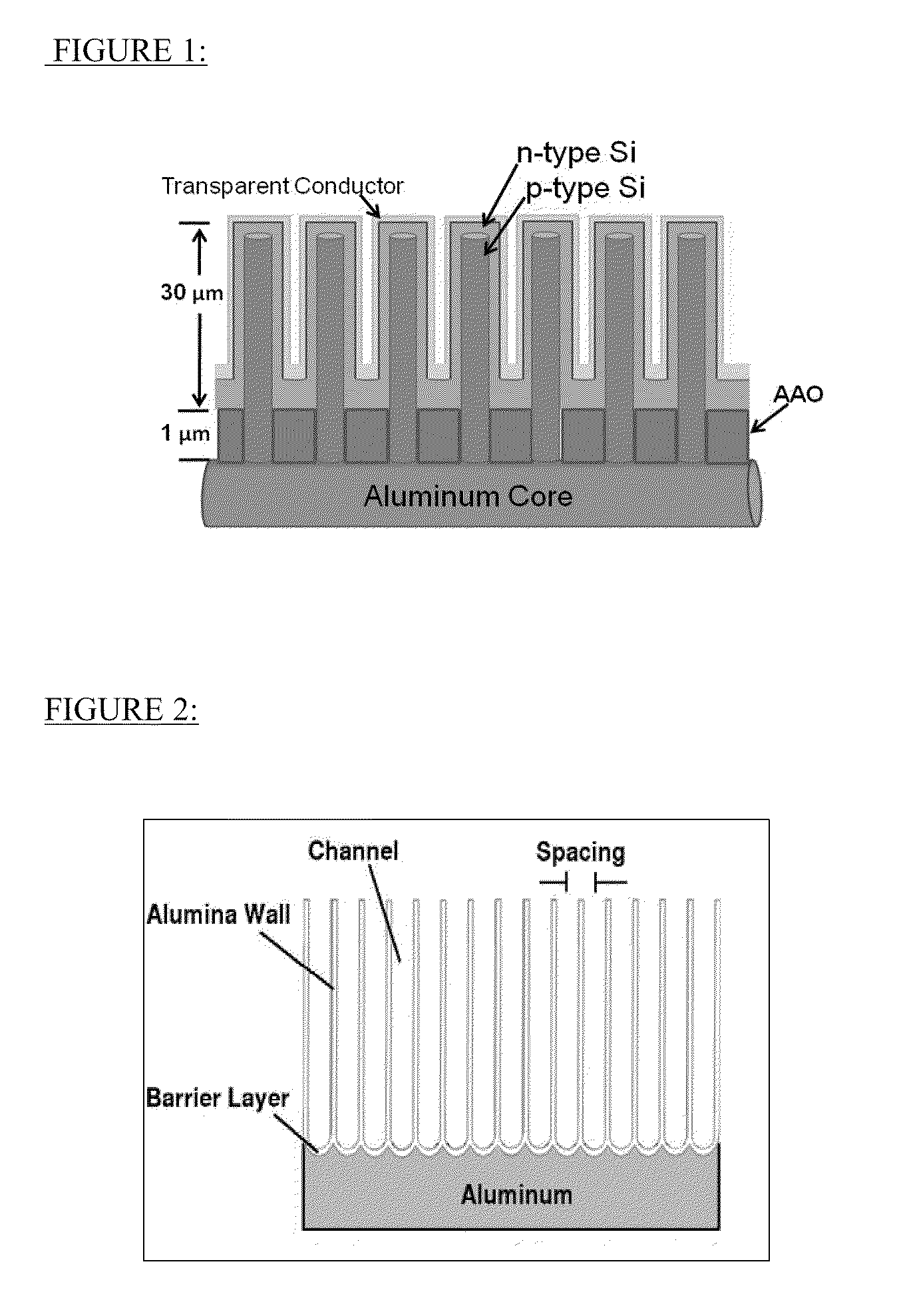

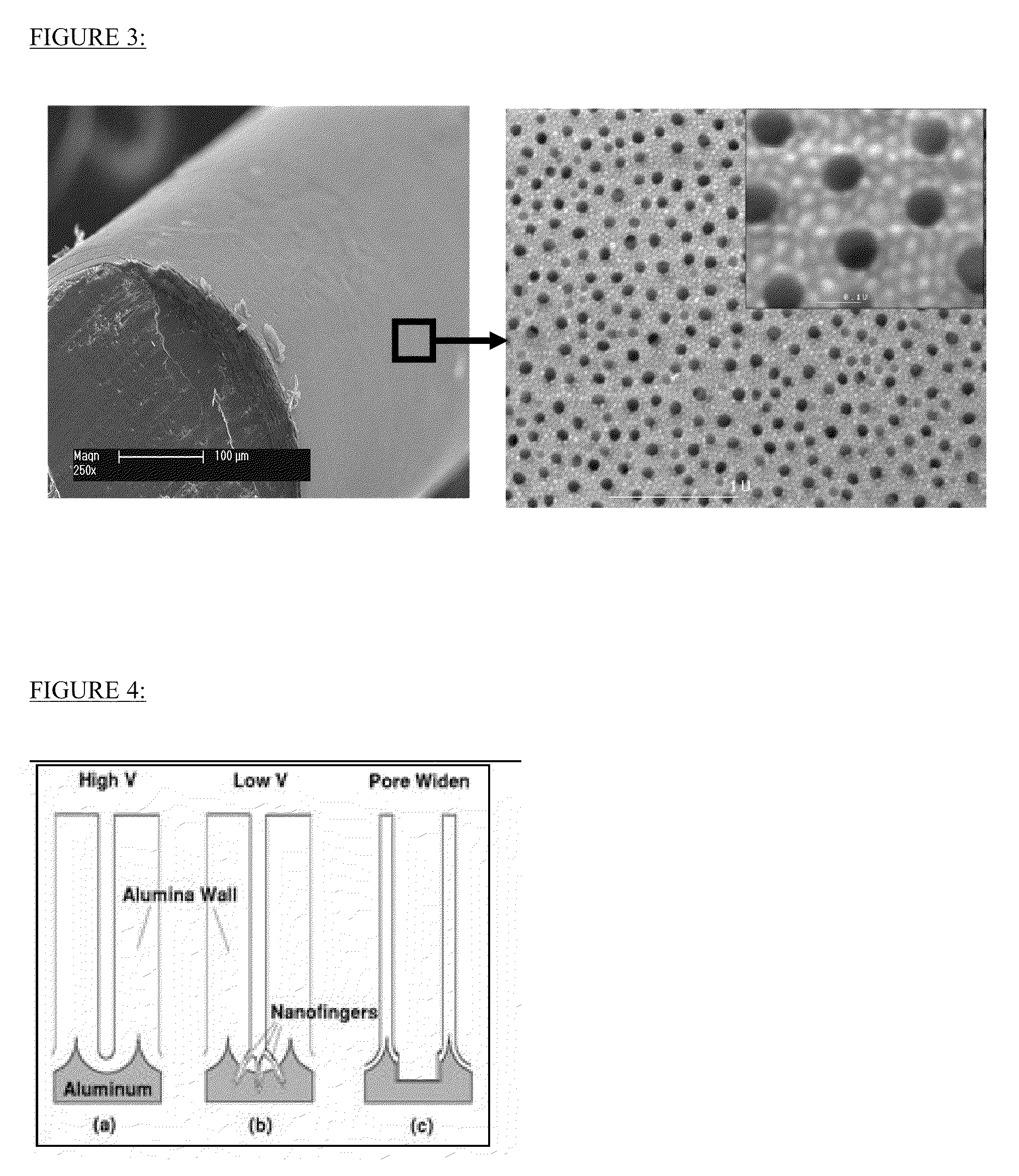

Semiconducting nanowire arrays for photovoltaic applications

InactiveUS20100193768A1Novel design attributeEasy to produceSolid-state devicesSemiconductor/solid-state device manufacturingDopantSilicon nanowires

This invention relates to the fabrication of nanowires for electrical and electronic applications. A method of growing silicon nanowires using an alumina template is disclosed whereby the aluminum forming the alumina is also used as the catalyst for growing the silicon nanowires in a VLS (CVD) process and as the semiconductor dopant. In addition, various techniques for masking off parts of the aluminum and alumina in order to maintain electrical isolation between device layers is disclosed.

Owner:ILLUMINEX CORP

Processors and methods for privileged configuration in a spatial array

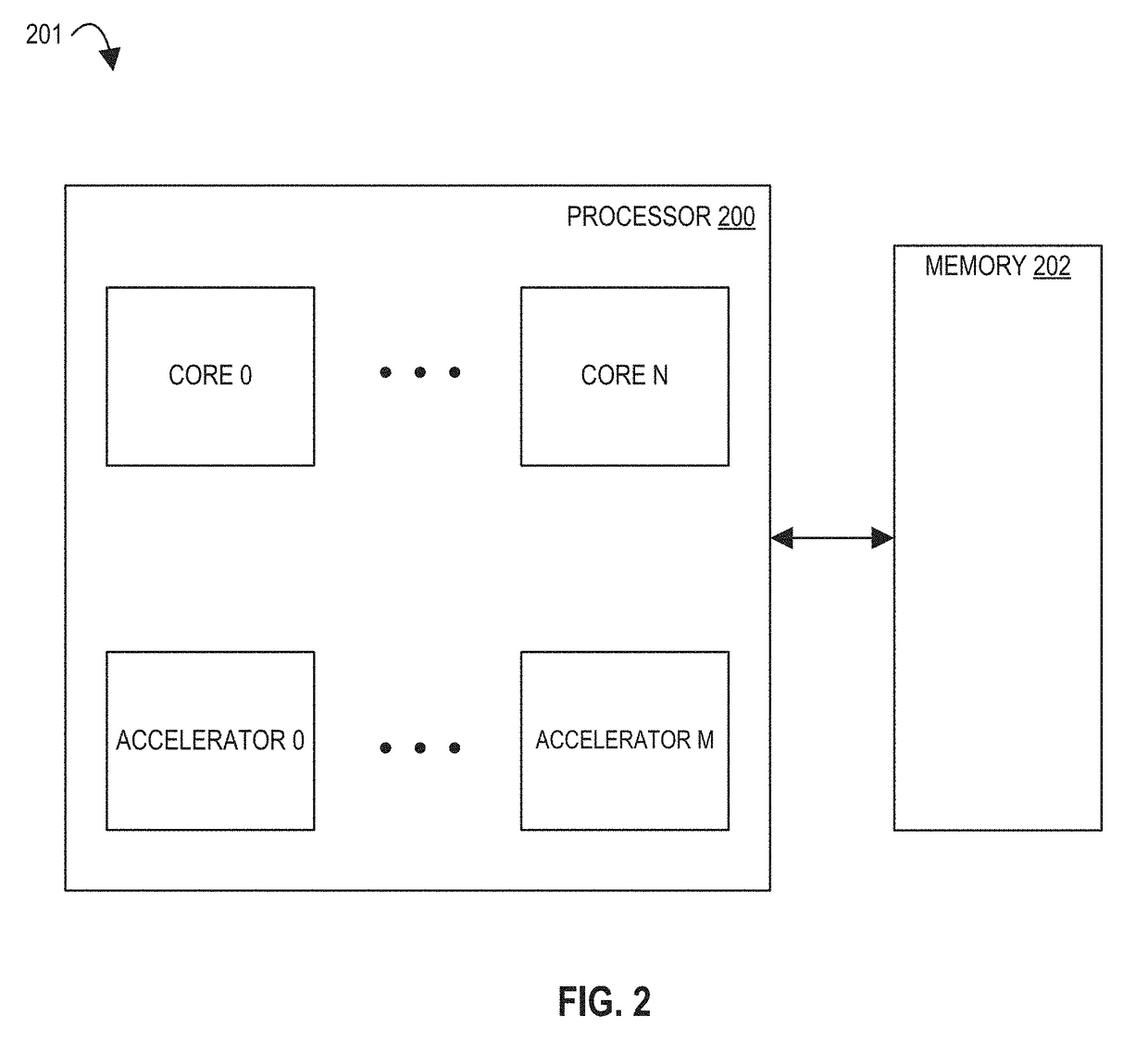

ActiveUS20190102179A1Easy to adaptImprove performanceResource allocationRuntime instruction translationArray data structureProcessing element

Methods and apparatuses relating to privileged configuration in spatial arrays are described. In one embodiment, a processor includes processing elements; an interconnect network between the processing elements; and a configuration controller coupled to a first subset and a second, different subset of the plurality of processing elements, the first subset having an output coupled to an input of the second, different subset, wherein the configuration controller is to configure the interconnect network between the first subset and the second, different subset of the plurality of processing elements to not allow communication on the interconnect network between the first subset and the second, different subset when a privilege bit is set to a first value and to allow communication on the interconnect network between the first subset and the second, different subset of the plurality of processing elements when the privilege bit is set to a second value.

Owner:INTEL CORP

Apparatus, methods, and systems for remote memory access in a configurable spatial accelerator

InactiveUS20190303297A1Easy to adaptImprove performanceMemory architecture accessing/allocationDigital computer detailsDirect memory accessRemote memory access

Systems, methods, and apparatuses relating to remote memory access in a configurable spatial accelerator are described. In one embodiment, a configurable spatial accelerator includes a first memory interface circuit coupled to a first processing element and a cache, the first memory interface circuit to issue a memory request to the cache, the memory request comprising a field to identify a second memory interface circuit as a receiver of data for the memory request; and the second memory interface circuit coupled to a second processing element and the cache, the second memory interface circuit to send a credit return value to the first memory interface circuit, to cause the first memory interface circuit to mark the memory request as complete, when the data for the memory request arrives at the second memory interface circuit and a completion configuration register of the second memory interface circuit is set to a remote response value.

Owner:INTEL CORP

Processors, methods, and systems for a configurable spatial accelerator with security, power reduction, and performace features

InactiveUS20190004878A1Easy to adaptImprove performanceInterprogram communicationDigital computer detailsArray data structurePower consumption

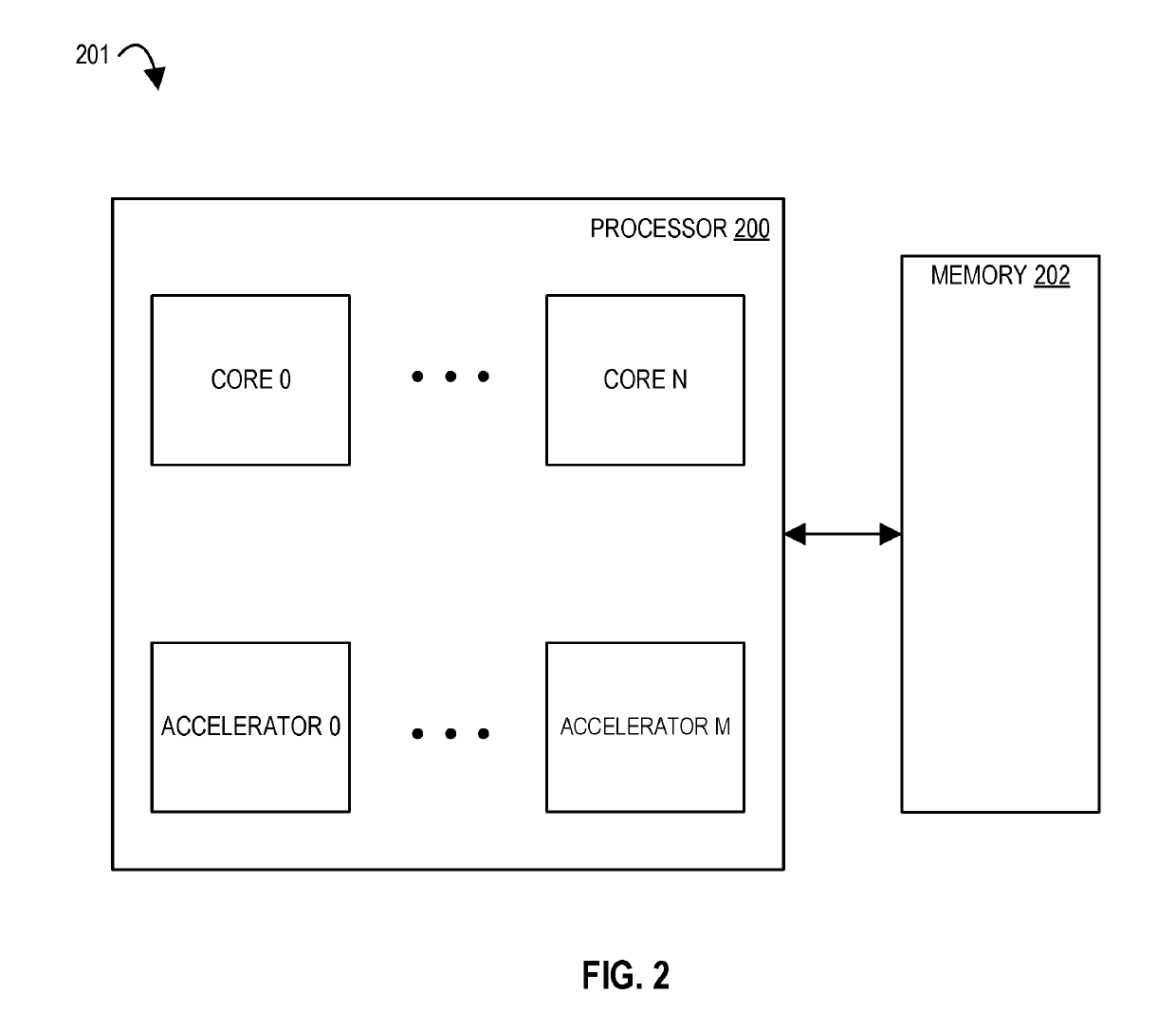

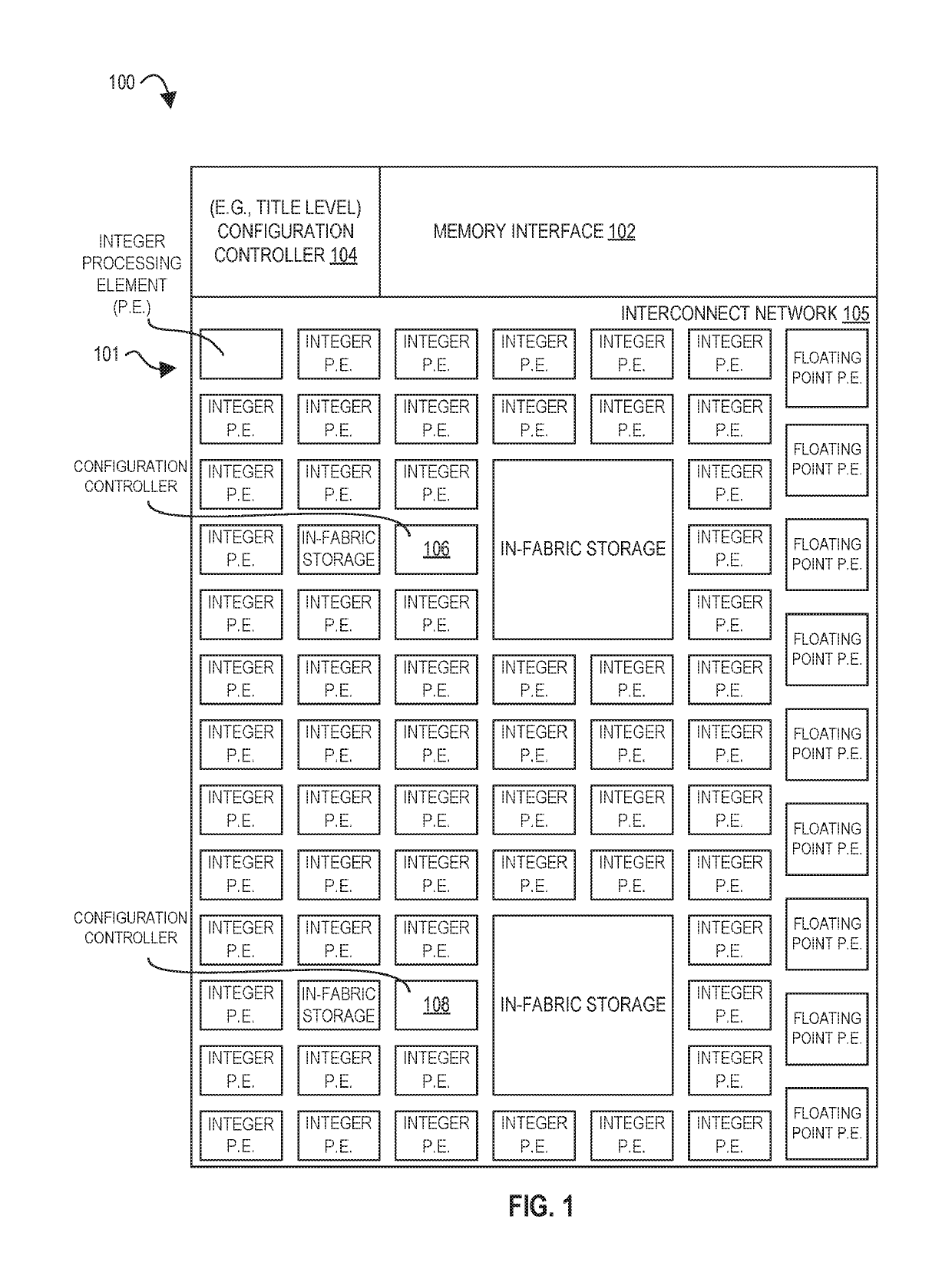

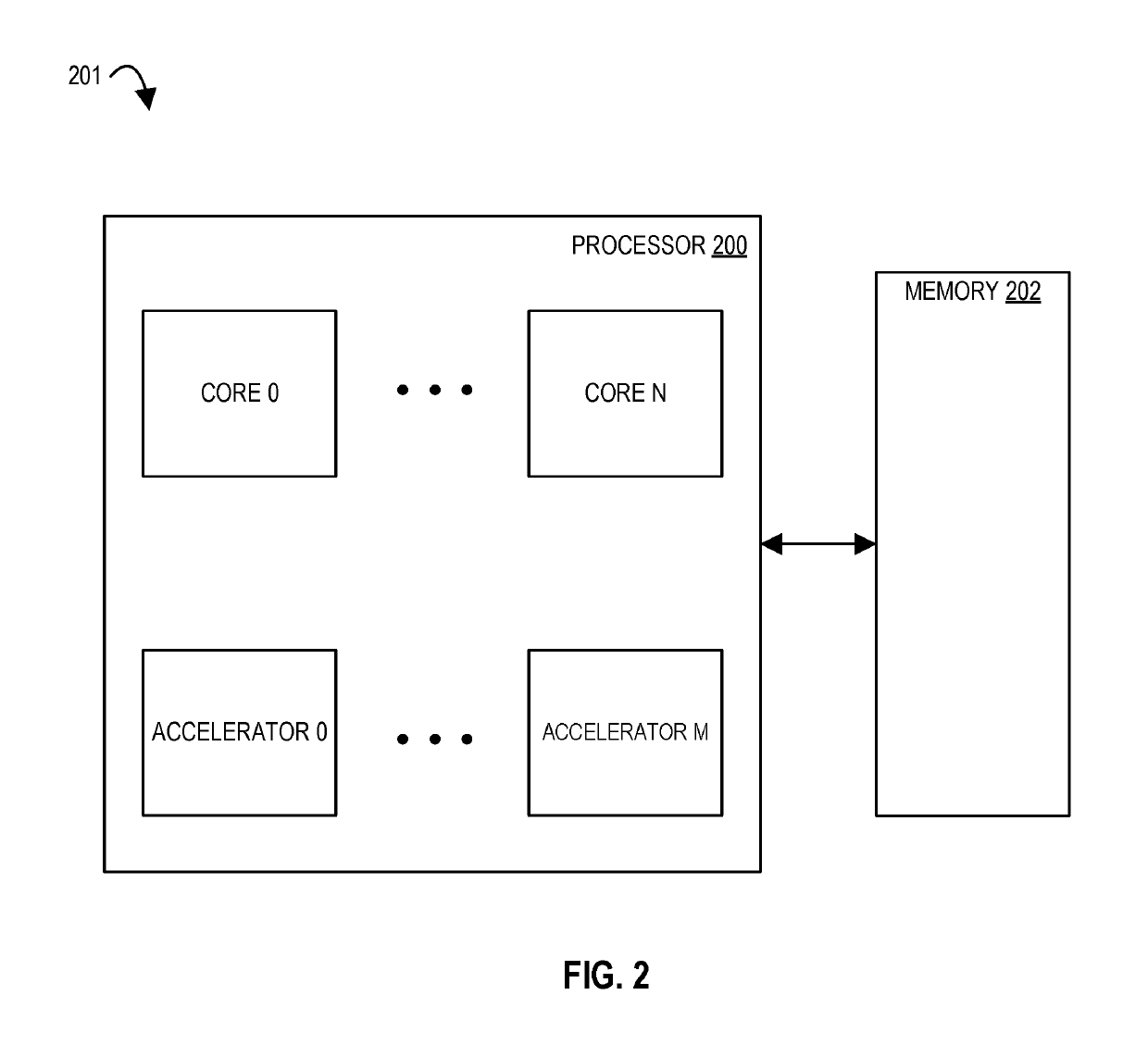

Systems, methods, and apparatuses relating to a configurable spatial accelerator are described. In one embodiment, a processor includes a plurality of processing elements; and an interconnect network between the plurality of processing elements to receive an input of two dataflow graphs each comprising a plurality of nodes, wherein a first dataflow graph and a second dataflow graph are be overlaid into a first and second portion, respectively, of the interconnect network and a first and second subset, respectively, of the plurality of processing elements with each node represented as a dataflow operator in the plurality of processing elements, and the first and second subsets of the plurality of processing elements are to perform a first and second operation, respectively, when incoming first and second, respectively, operand sets arrive at the plurality of processing elements.

Owner:INTEL CORP

Processors and methods for configurable clock gating in a spatial array

InactiveUS20190101952A1Easy to adaptImprove performanceDataflow computersSingle instruction multiple data multiprocessorsSignal onParallel computing

Methods and apparatuses relating to configurable clock gating in spatial arrays are described. In one embodiment, a processor includes processing elements; an interconnect network between the processing elements; and a configuration controller, coupled to a first processing element and a second processing element of the plurality of processing elements and the first processing element having an output coupled to an input of the second processing element, to configure the second processing element to clock gate at least one clocked component of the second processing element, and configure the first processing element to send a reenable signal on the interconnect network to the second processing element to reenable the at least one clocked component of the second processing element when data is to be sent from the first processing element to the second processing element.

Owner:INTEL CORP

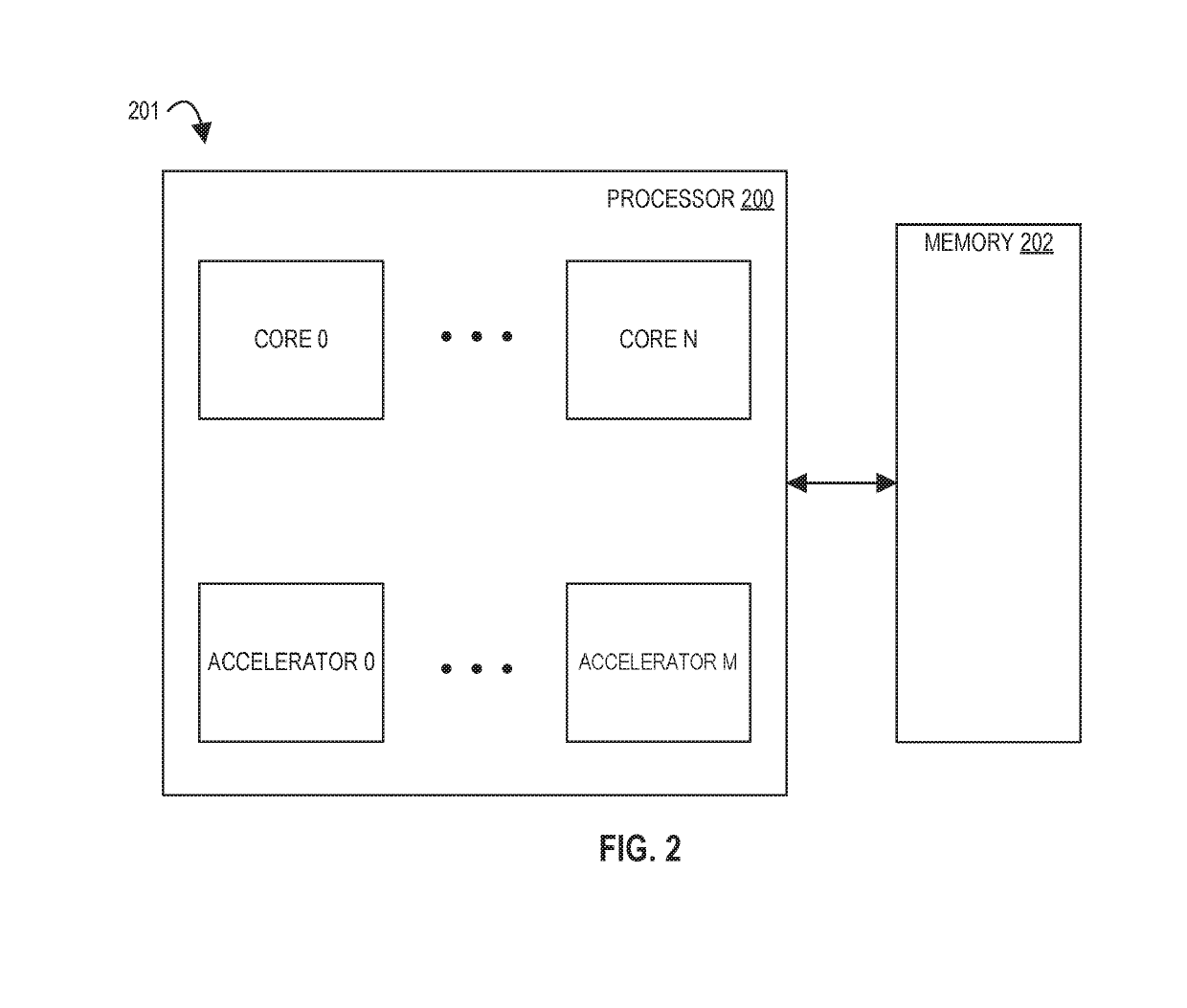

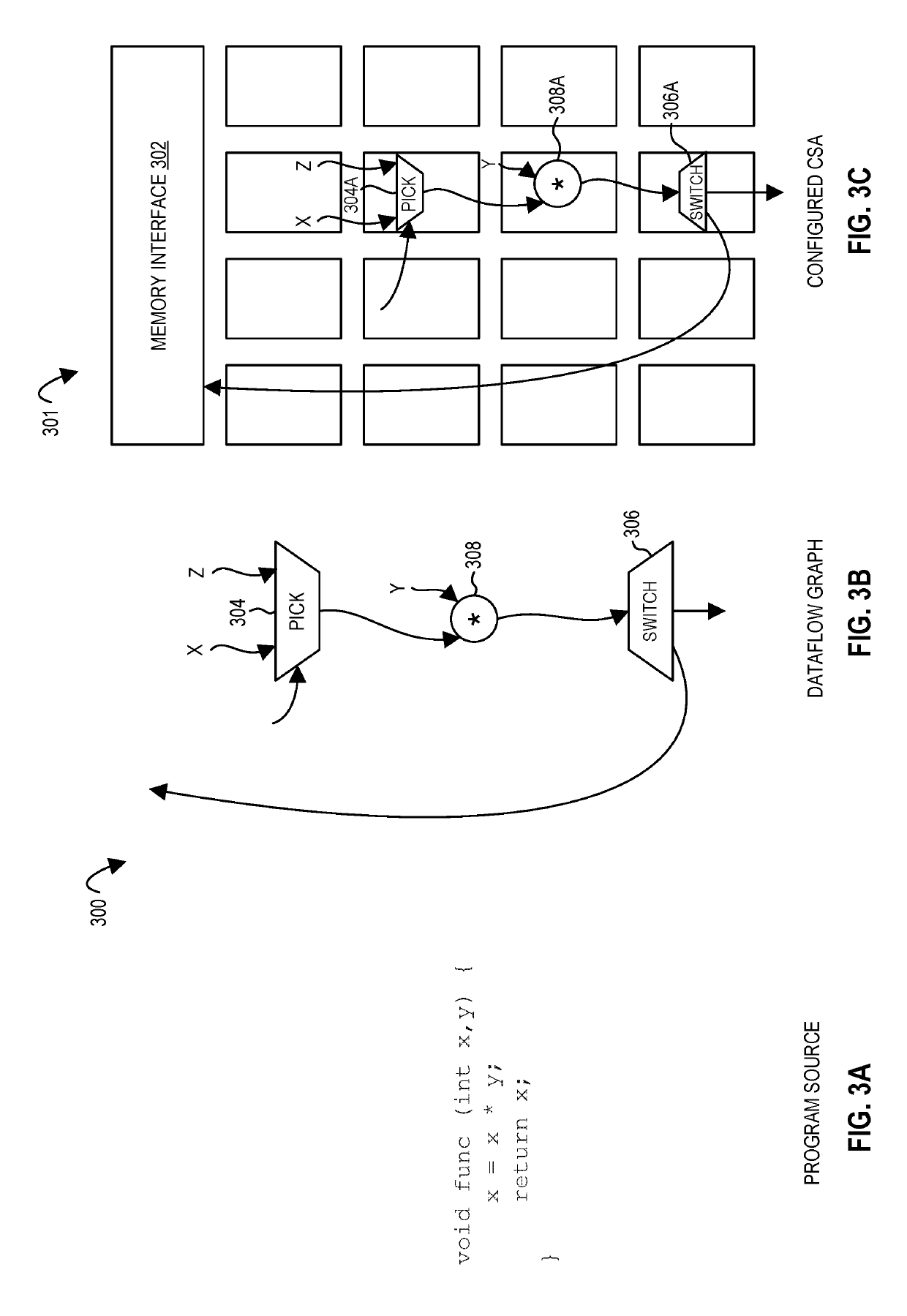

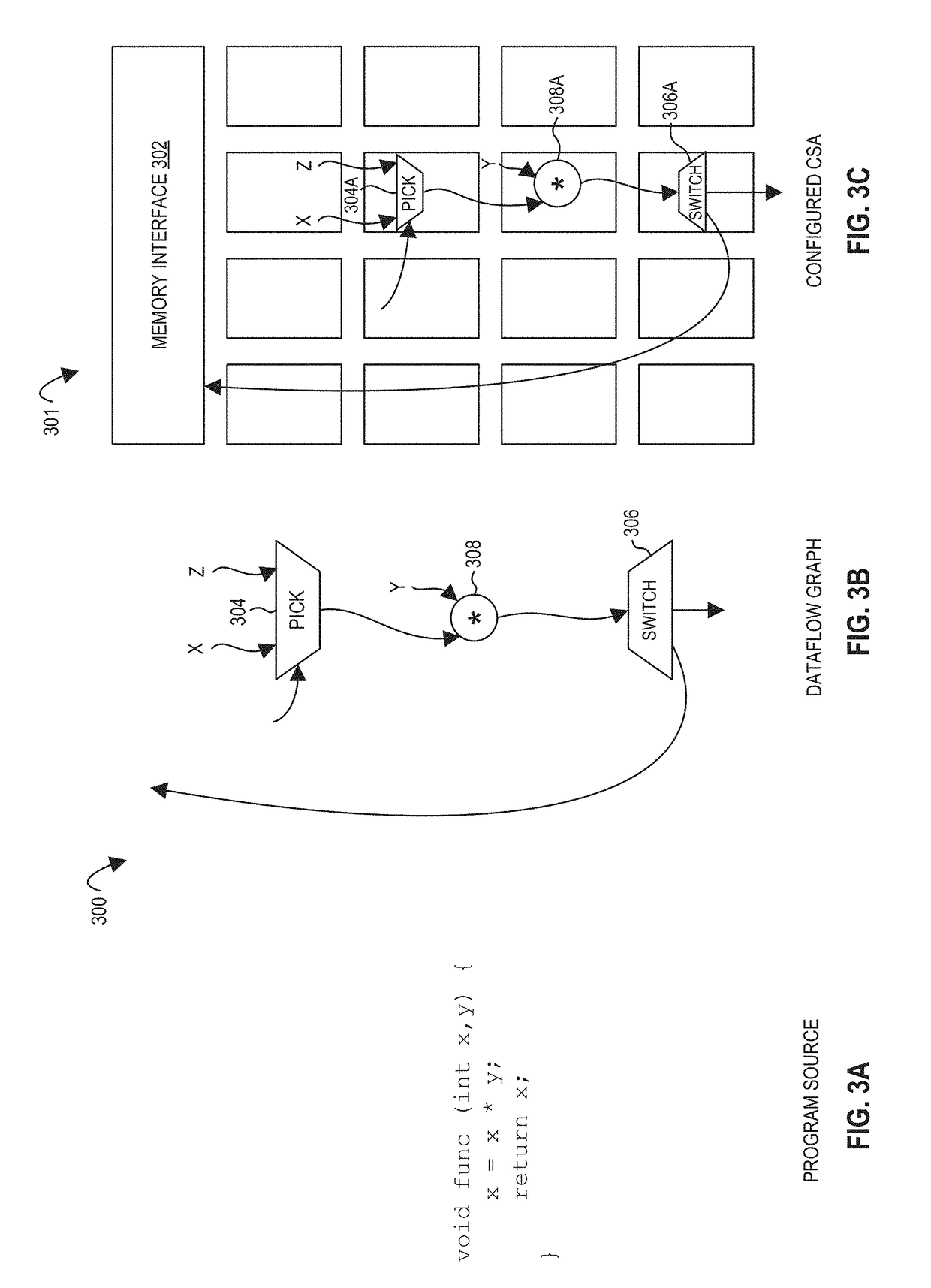

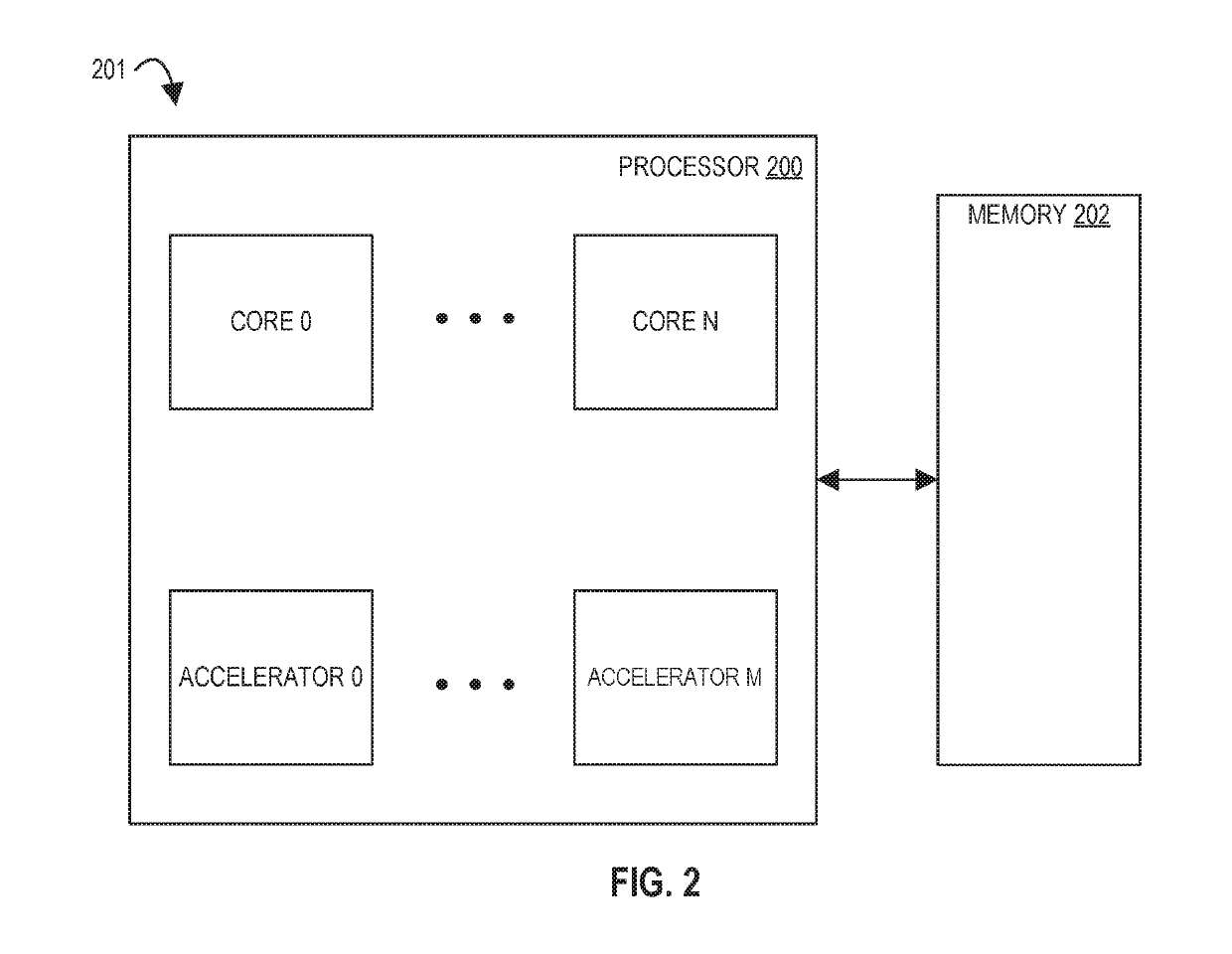

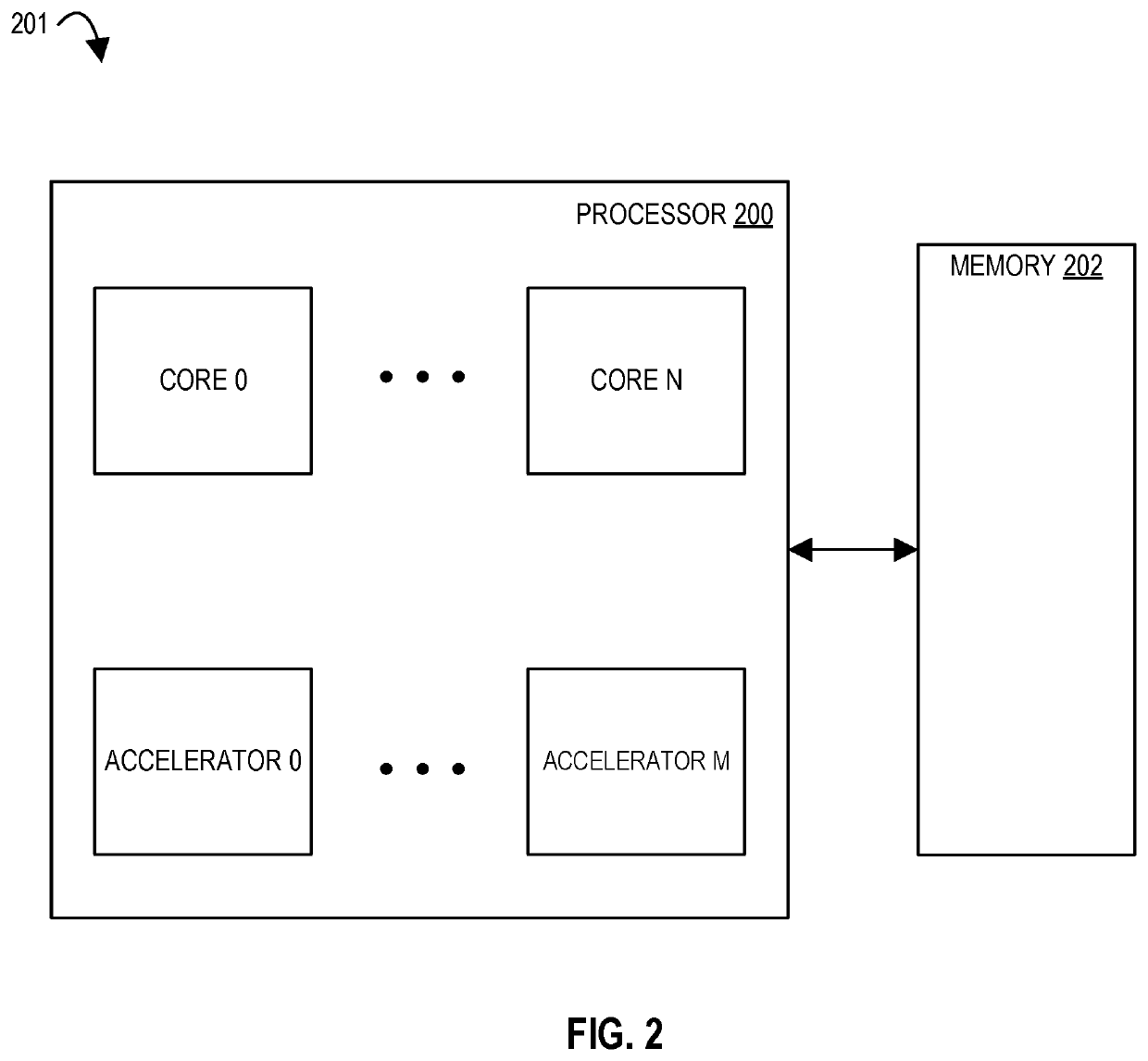

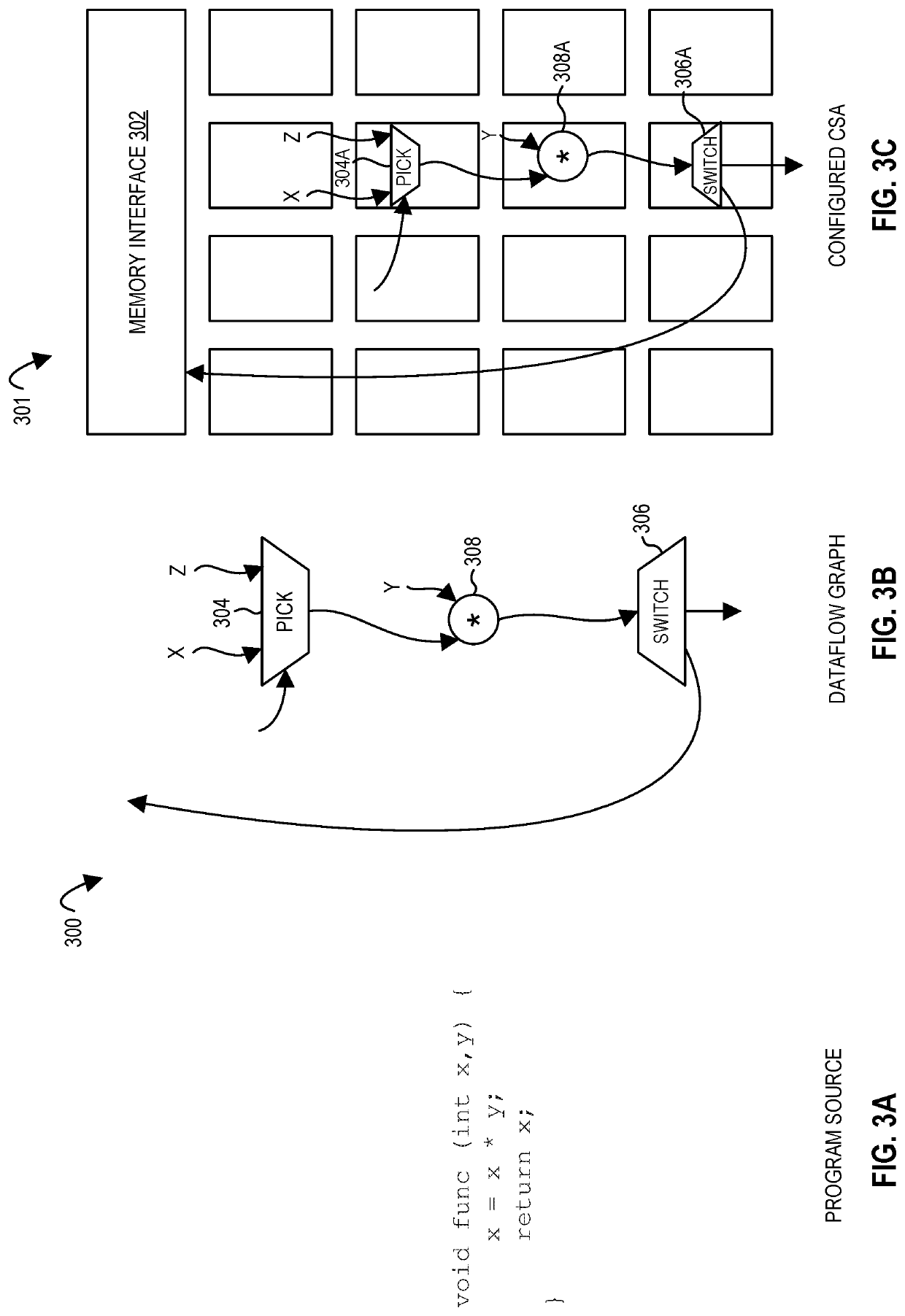

Apparatus, methods, and systems with a configurable spatial accelerator

ActiveUS20190205263A1Easy to adaptImprove performanceMemory architecture accessing/allocationEnergy efficient computingSystems approachesDataflow

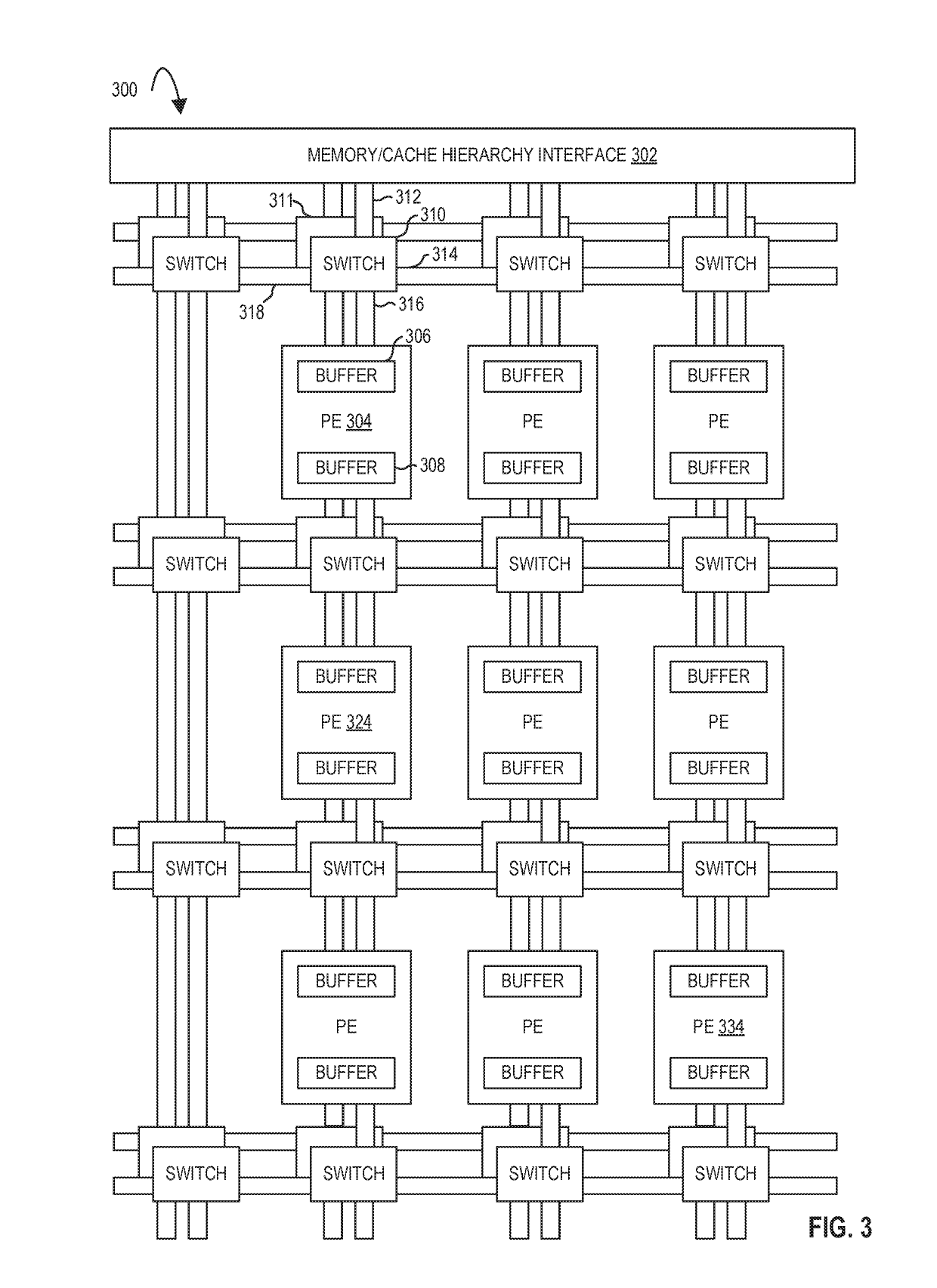

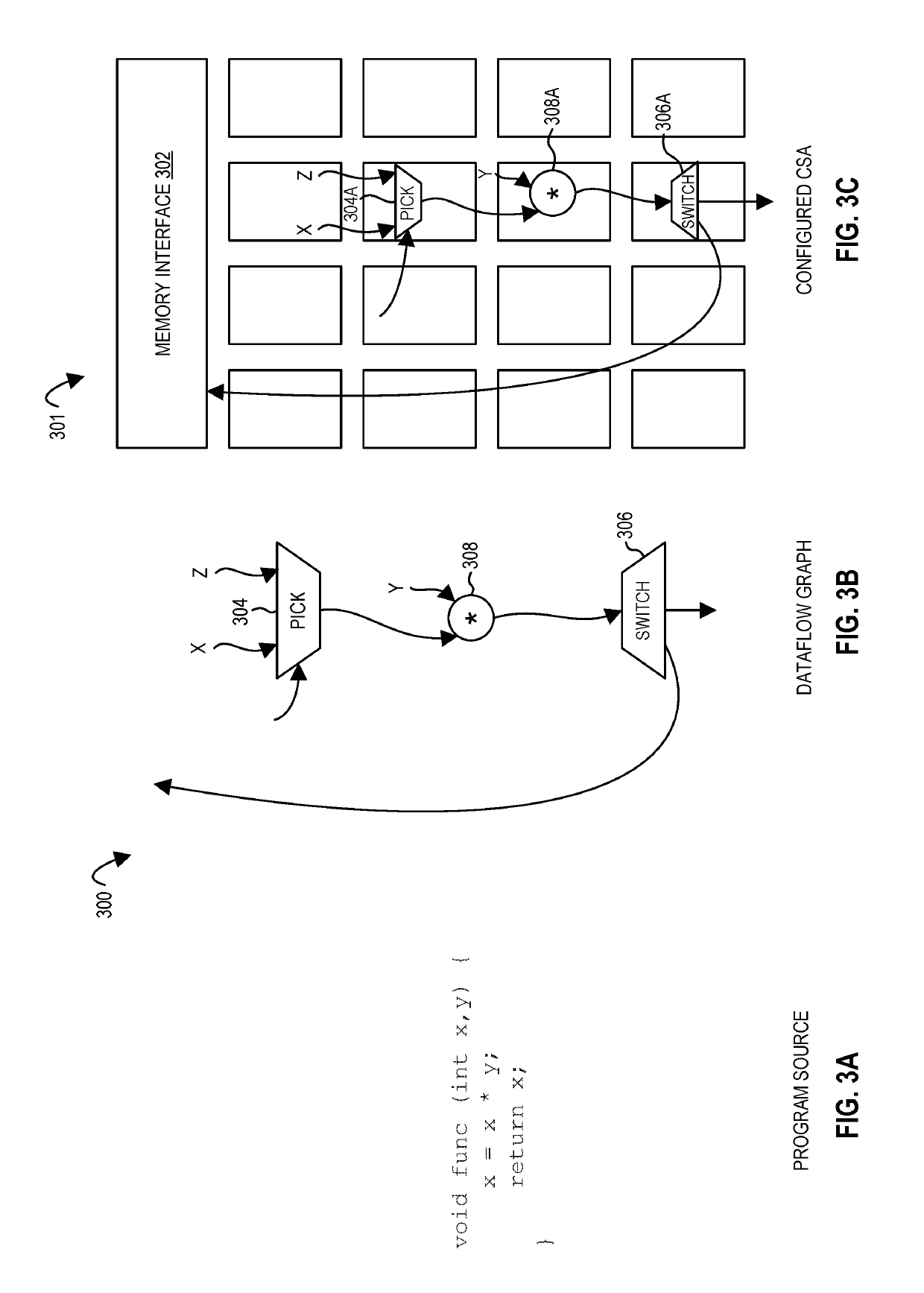

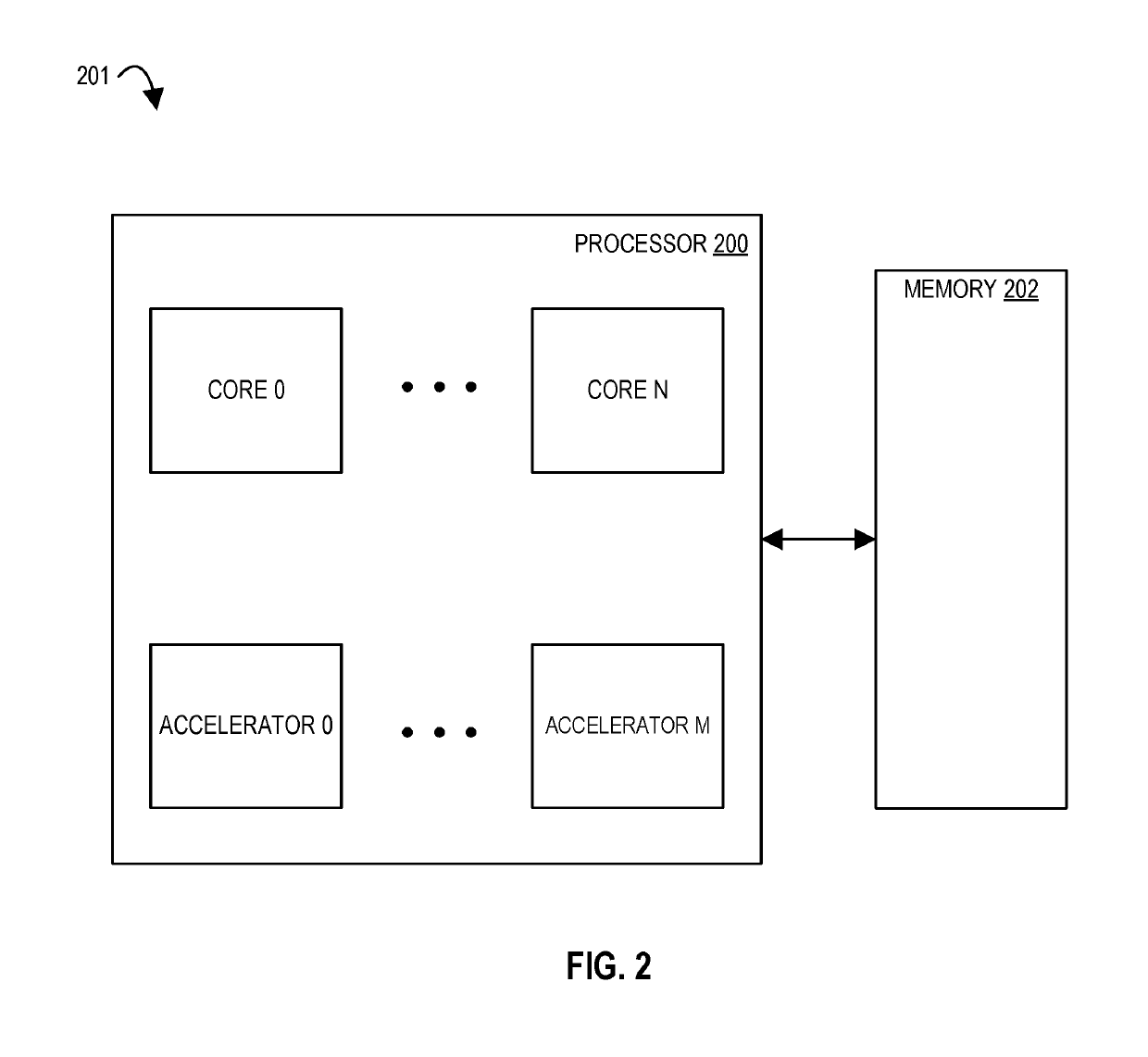

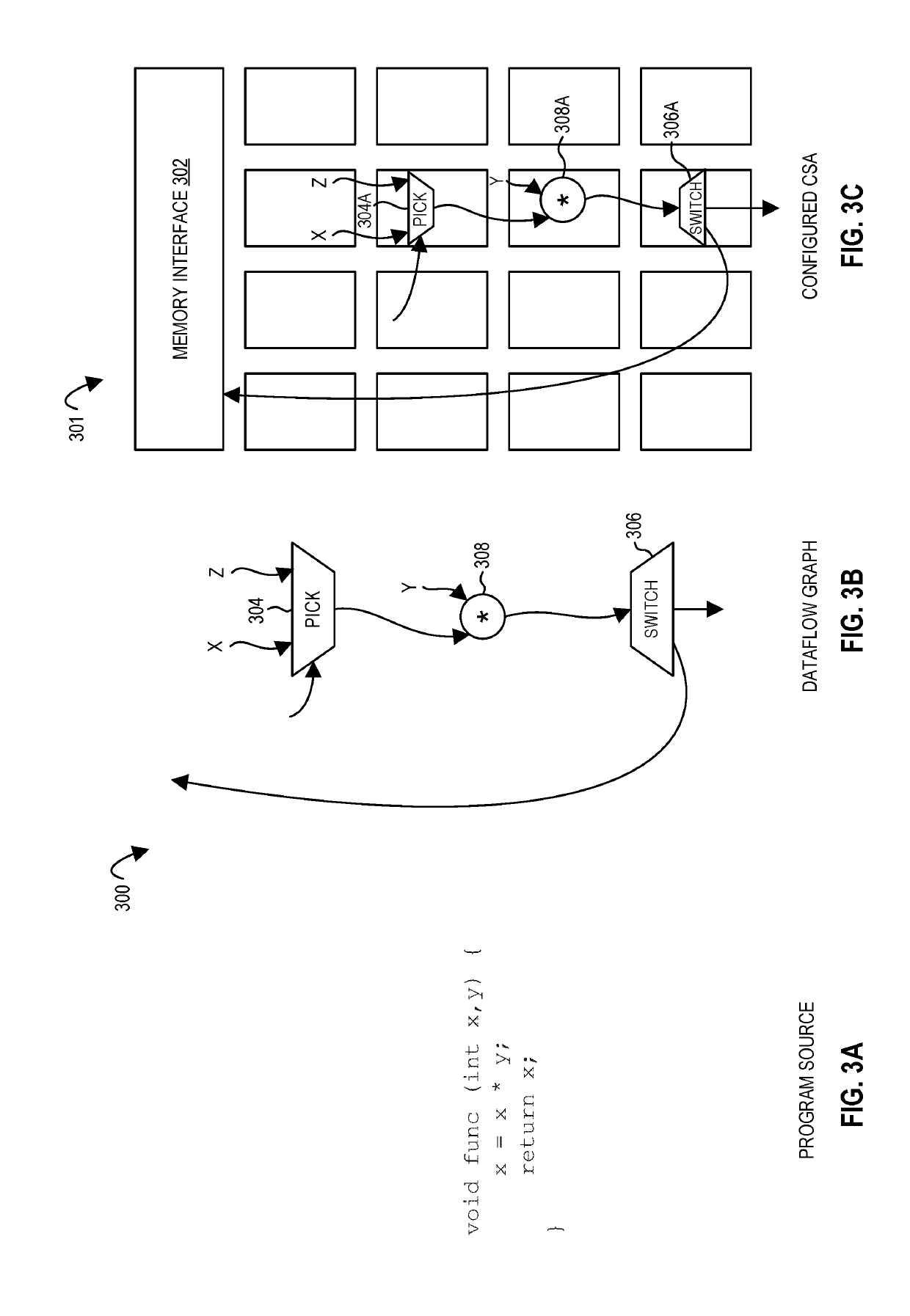

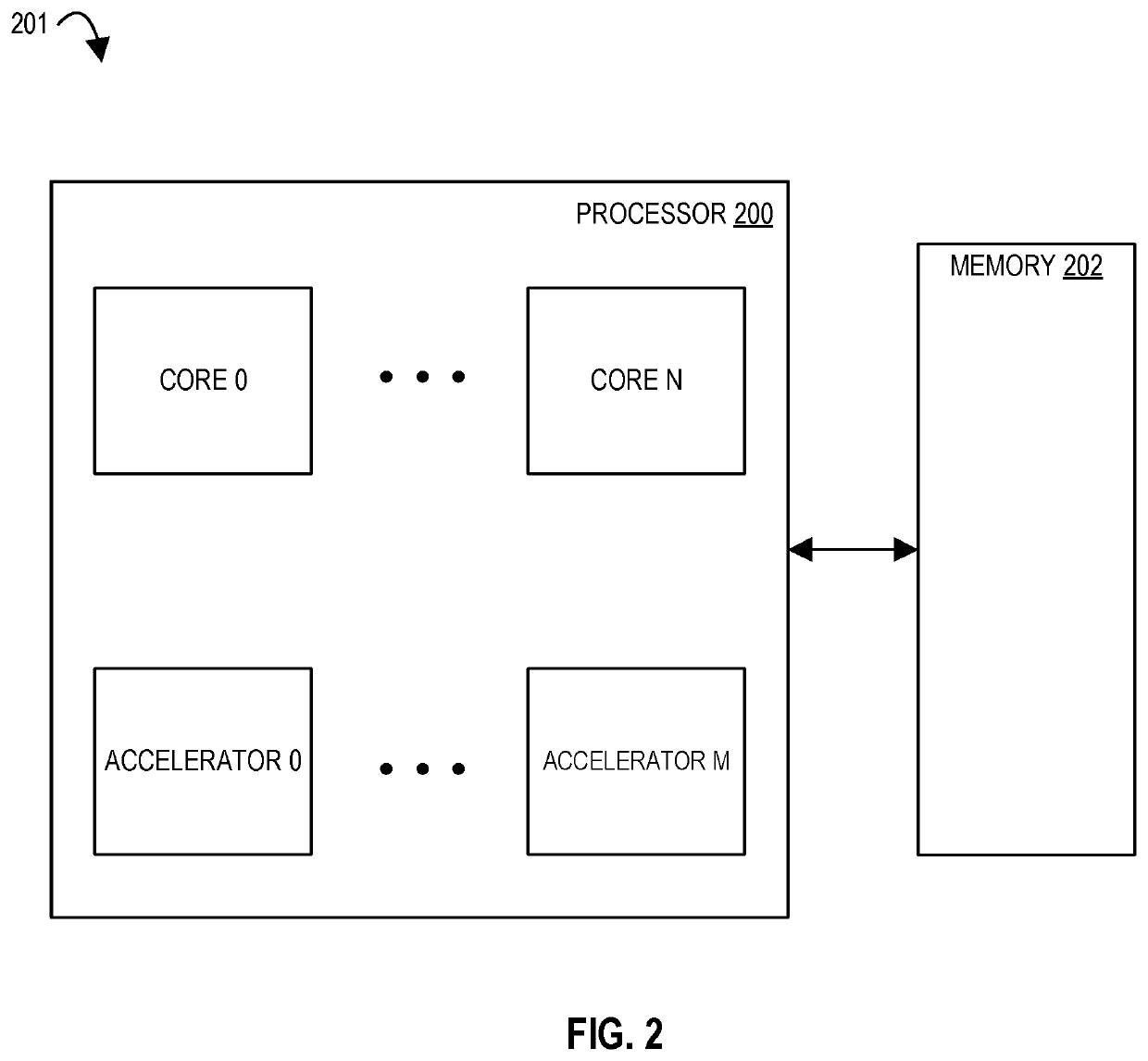

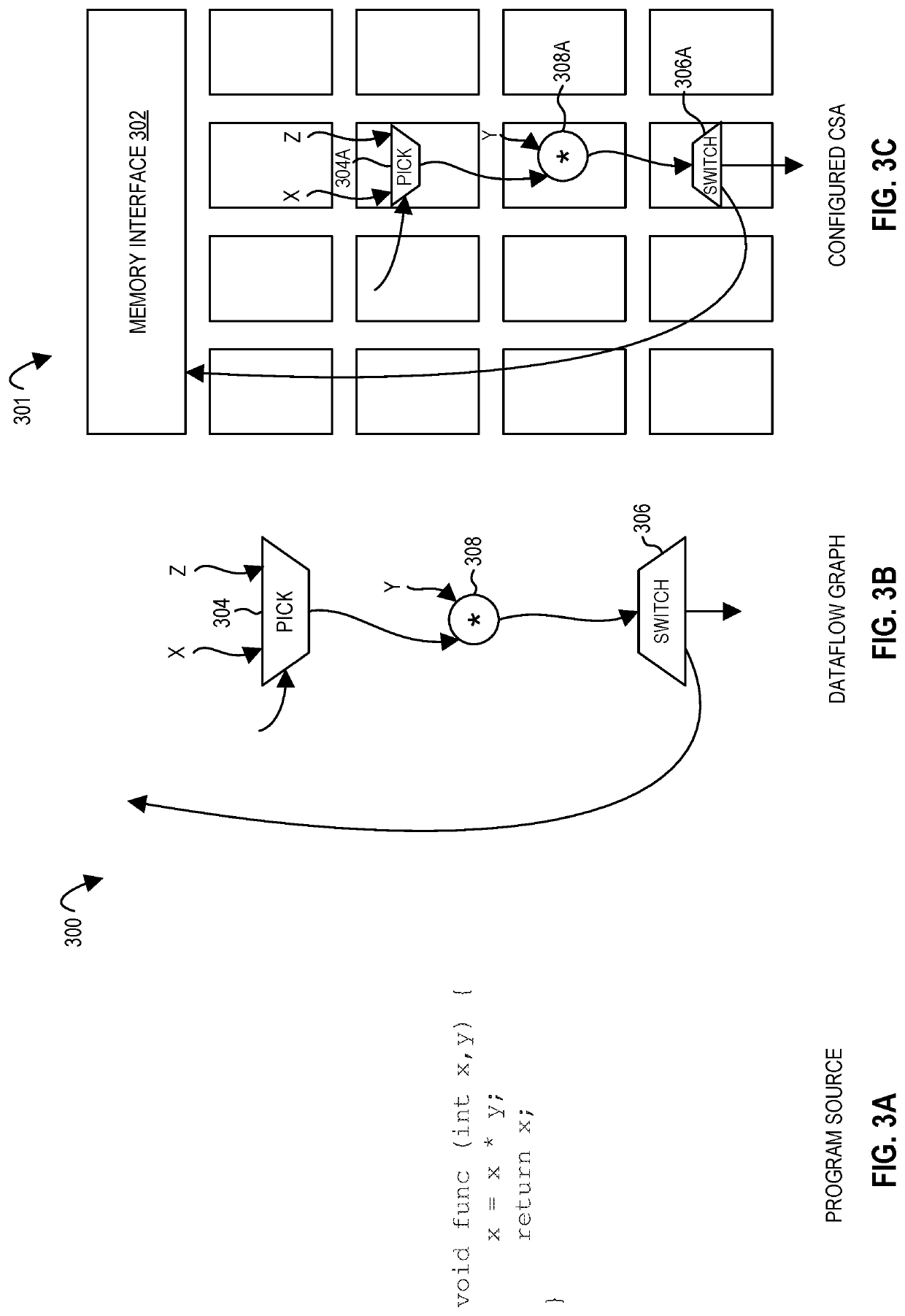

Systems, methods, and apparatuses relating to a configurable spatial accelerator are described. In one embodiment, a processor includes a core with a decoder to decode an instruction into a decoded instruction and an execution unit to execute the decoded instruction to perform a first operation; a plurality of processing elements; and an interconnect network between the plurality of processing elements to receive an input of a dataflow graph comprising a plurality of nodes, wherein the dataflow graph is to be overlaid into the interconnect network and the plurality of processing elements with each node represented as a dataflow operator in the plurality of processing elements, and the plurality of processing elements are to perform a second operation by a respective, incoming operand set arriving at each of the dataflow operators of the plurality of processing elements.

Owner:INTEL CORP

Apparatus, methods, and systems for conditional queues in a configurable spatial accelerator

ActiveUS20190303168A1Easy to adaptImprove performanceSingle instruction multiple data multiprocessorsConcurrent instruction executionDataflowDatapath

Systems, methods, and apparatuses relating to conditional queues in a configurable spatial accelerator are described. In one embodiment, a configurable spatial accelerator includes a first output buffer of a first processing element coupled to a first input buffer of a second processing element and a second input buffer of a third processing element via a data path that is to send a dataflow token to the first input buffer of the second processing element and the second input buffer of the third processing element when the dataflow token is received in the first output buffer of the first processing element; a first backpressure path from the first input buffer of the second processing element to the first processing element to indicate to the first processing element when storage is not available in the first input buffer of the second processing element; a second backpressure path from the second input buffer of the third processing element to the first processing element to indicate to the first processing element when storage is not available in the second input buffer of the third processing element; and a scheduler of the second processing element to cause storage of the dataflow token from the data path into the first input buffer of the second processing element when both the first backpressure path indicates storage is available in the first input buffer of the second processing element and a conditional token received in a conditional queue of the second processing element from another processing element is a true conditional token.

Owner:INTEL CORP

Apparatus, methods, and systems for memory consistency in a configurable spatial accelerator

ActiveUS20190205284A1Easy to adaptImprove performanceInterprogram communicationDigital computer detailsComputer scienceProcedure sequence

Owner:INTEL CORP

Processors, methods, and systems for debugging a configurable spatial accelerator

ActiveUS20190095383A1Easy to adaptImprove performanceAssociative processorsDataflow computersProcessing elementOperand

Systems, methods, and apparatuses relating to debugging a configurable spatial accelerator are described. In one embodiment, a processor includes a plurality of processing elements and an interconnect network between the plurality of processing elements to receive an input of a dataflow graph comprising a plurality of nodes, wherein the dataflow graph is to be overlaid into the interconnect network and the plurality of processing elements with each node represented as a dataflow operator in the plurality of processing elements, and the plurality of processing elements are to perform an operation by a respective, incoming operand set arriving at each of the dataflow operators of the plurality of processing elements. At least a first of the plurality of processing elements is to enter a halted state in response to being represented as a first of the plurality of dataflow operators.

Owner:INTEL CORP

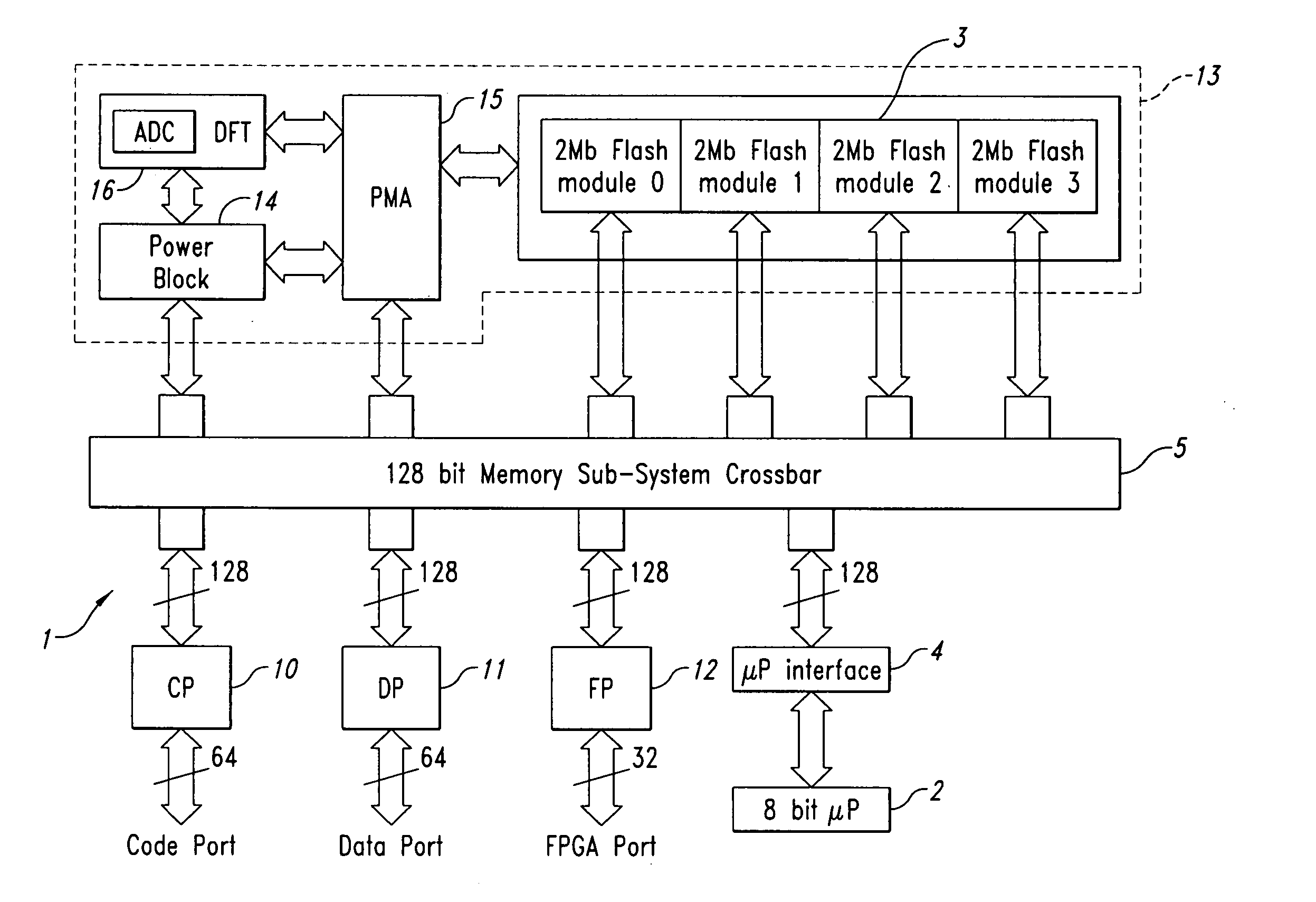

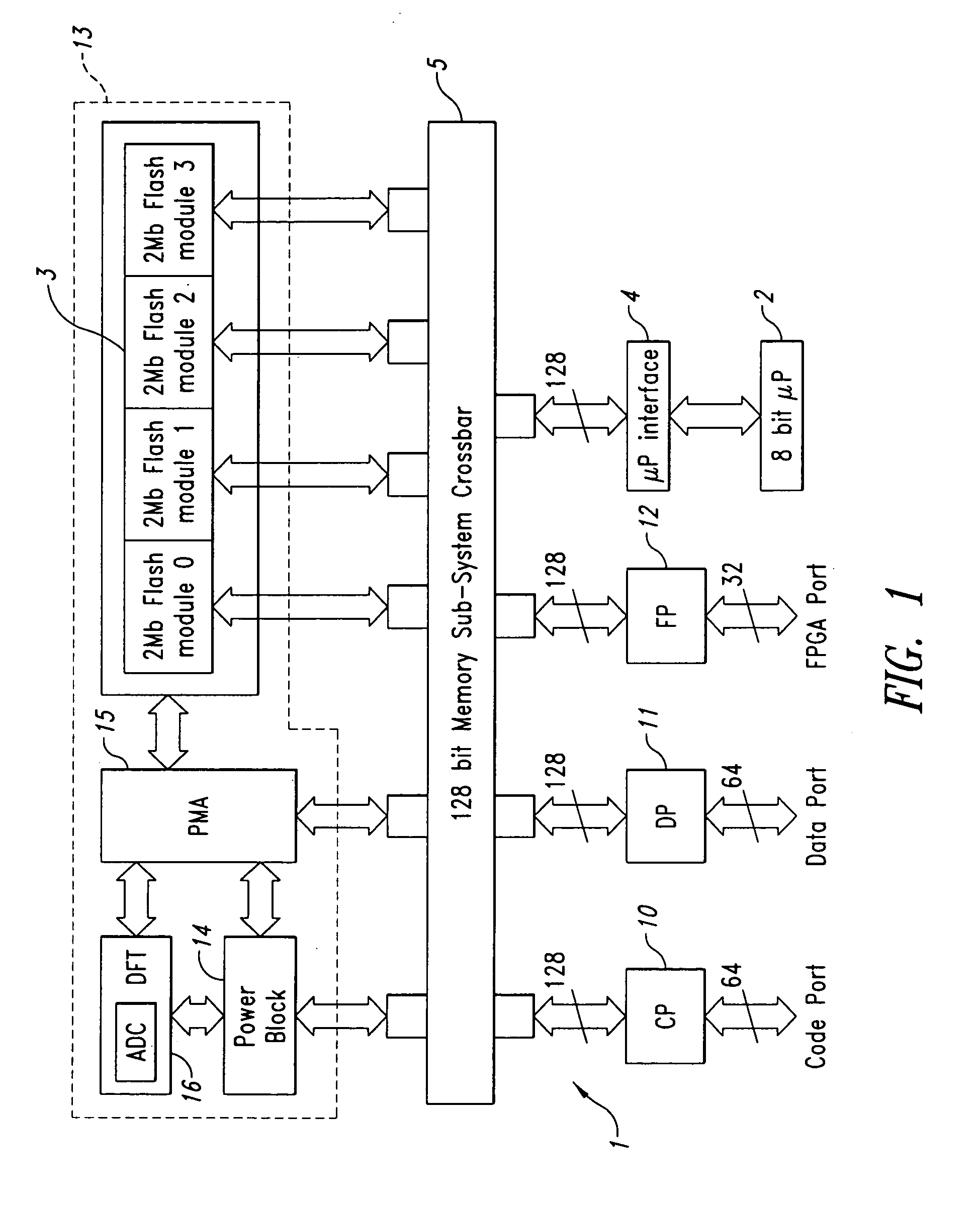

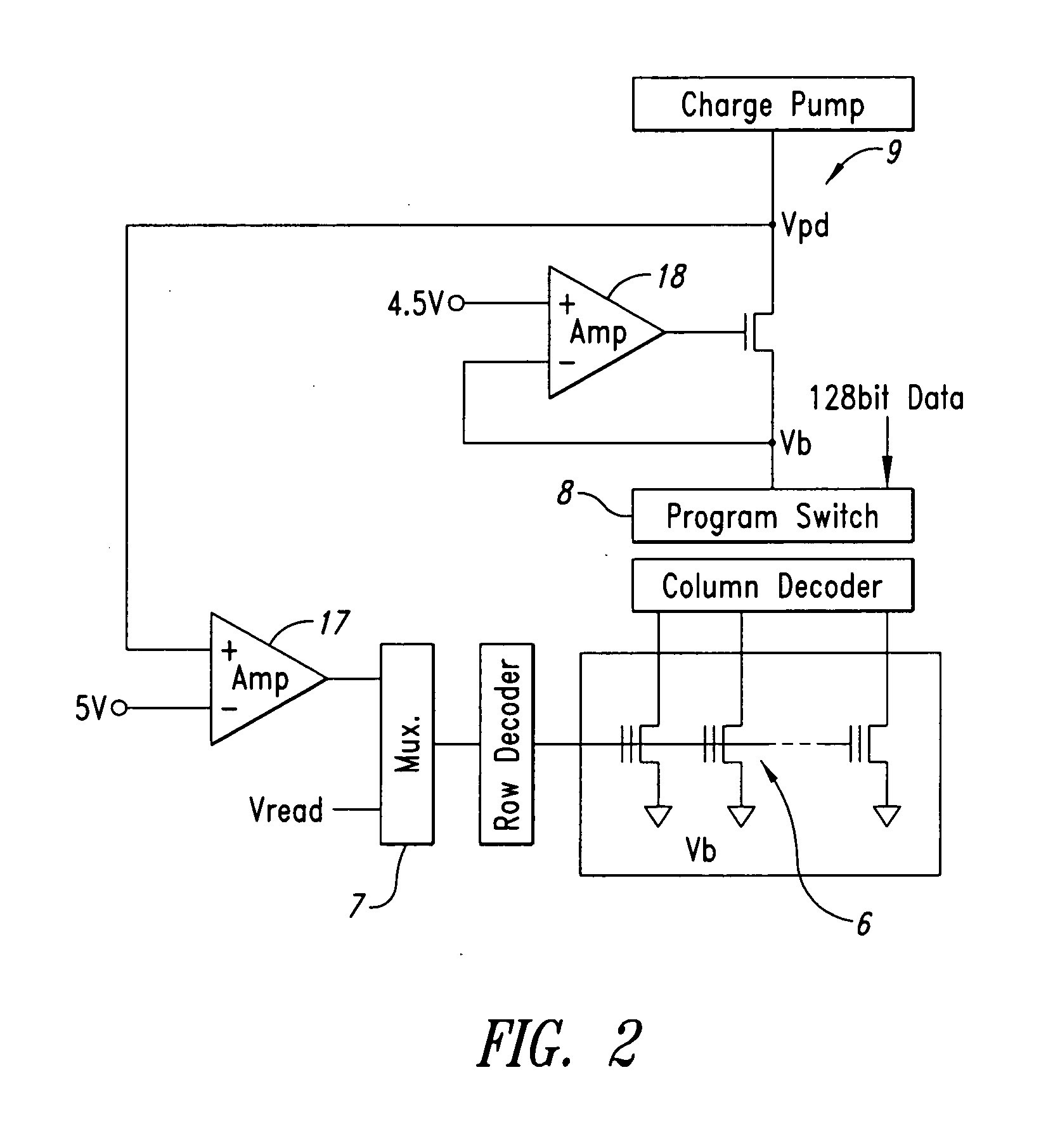

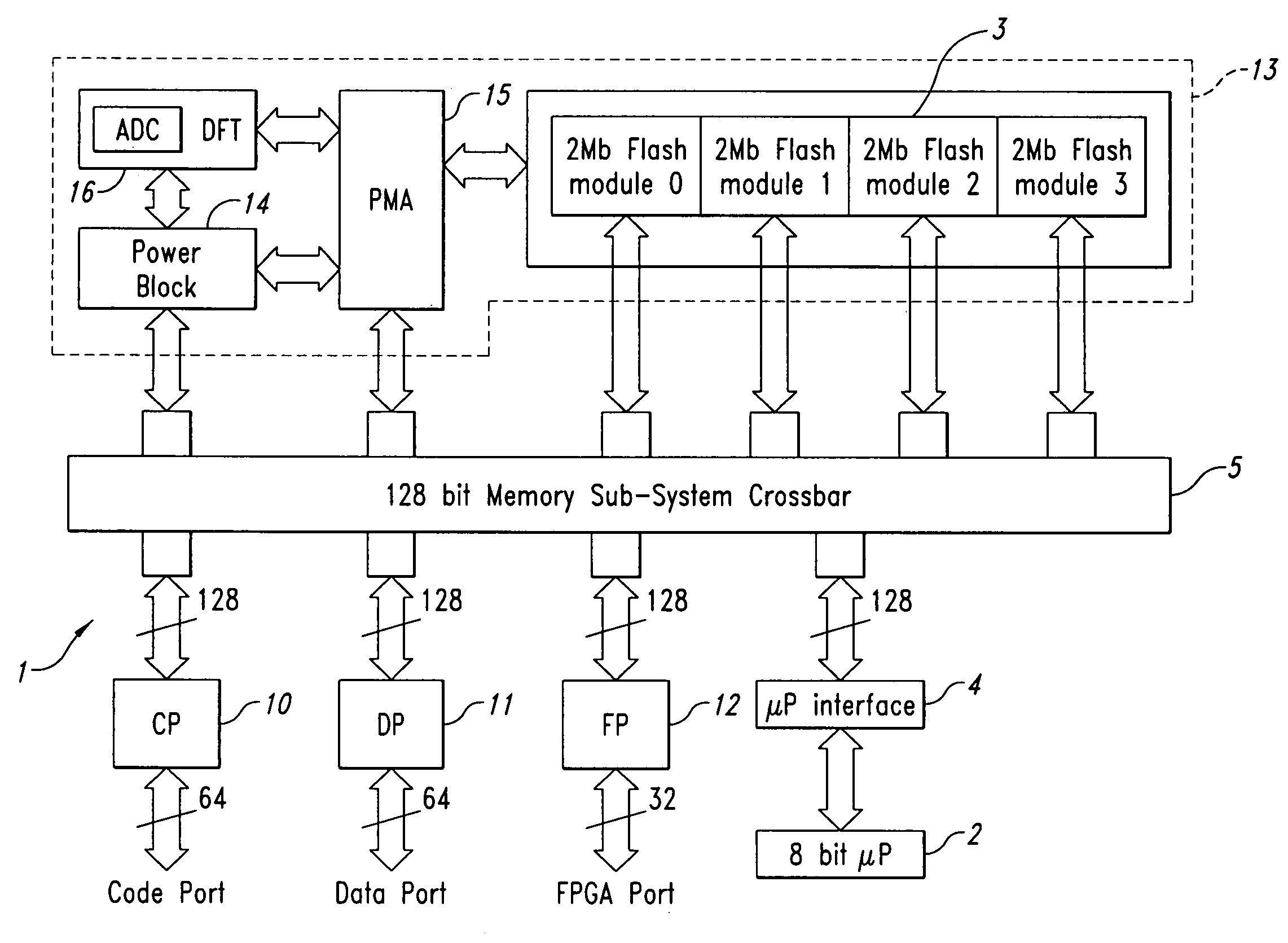

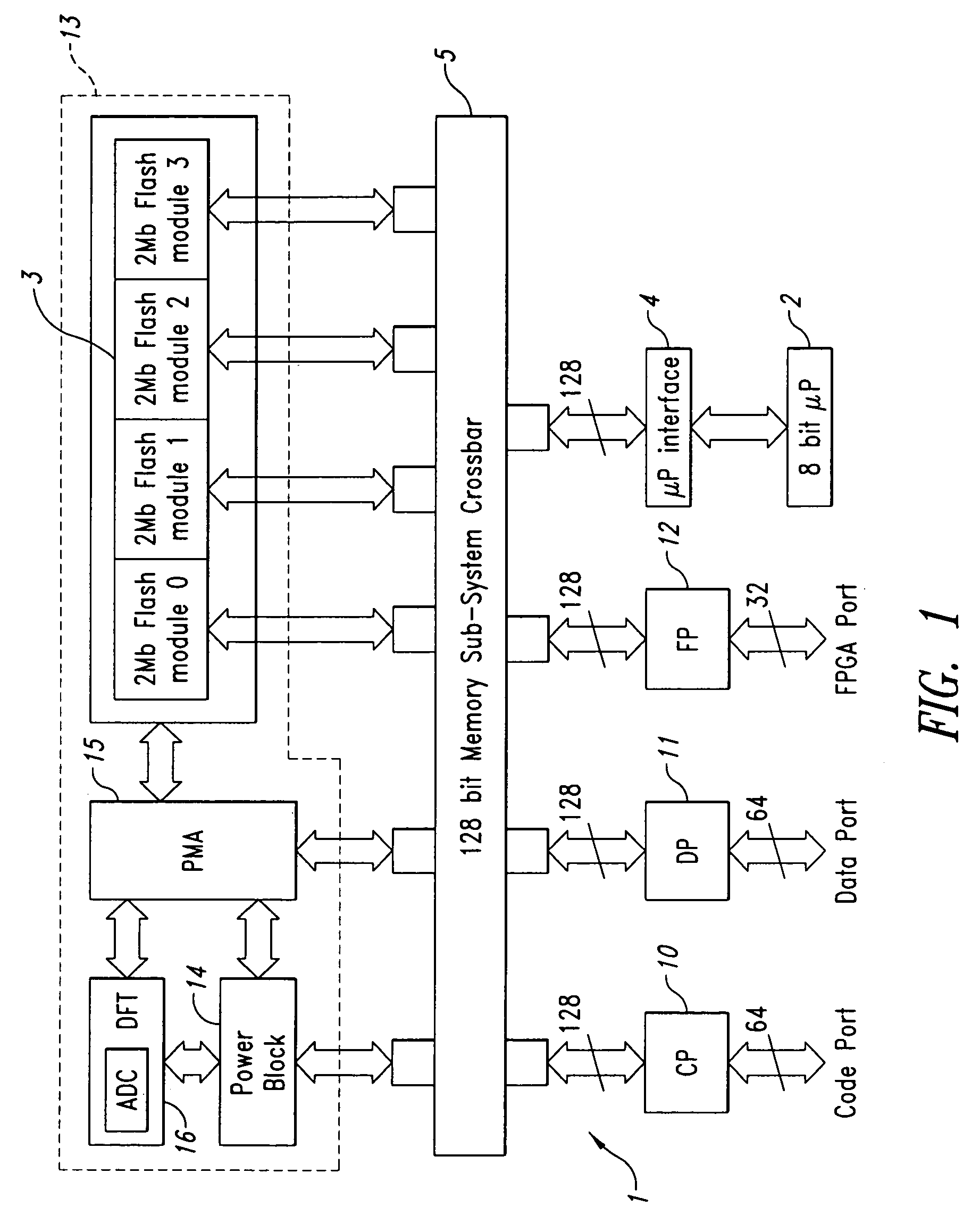

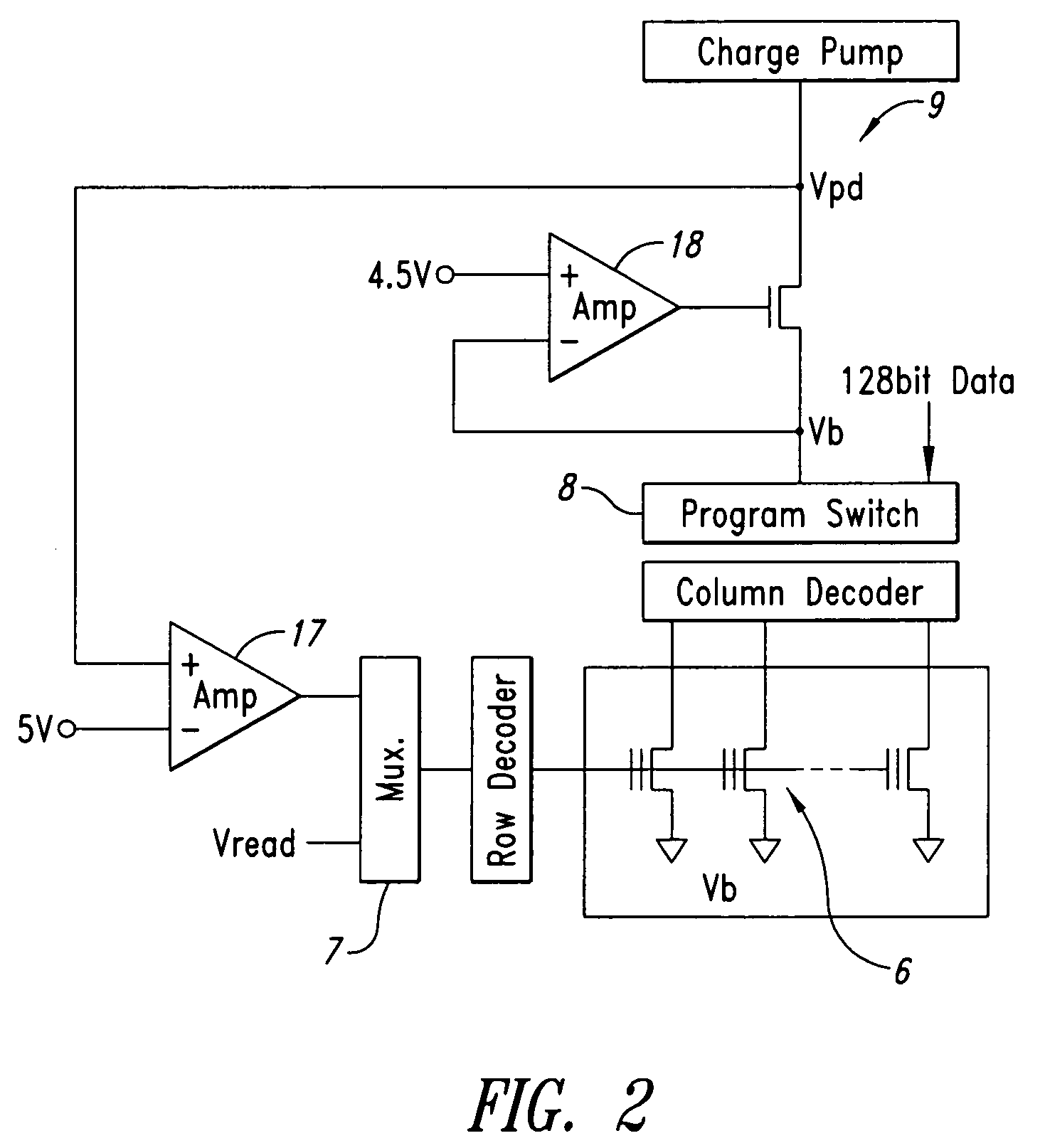

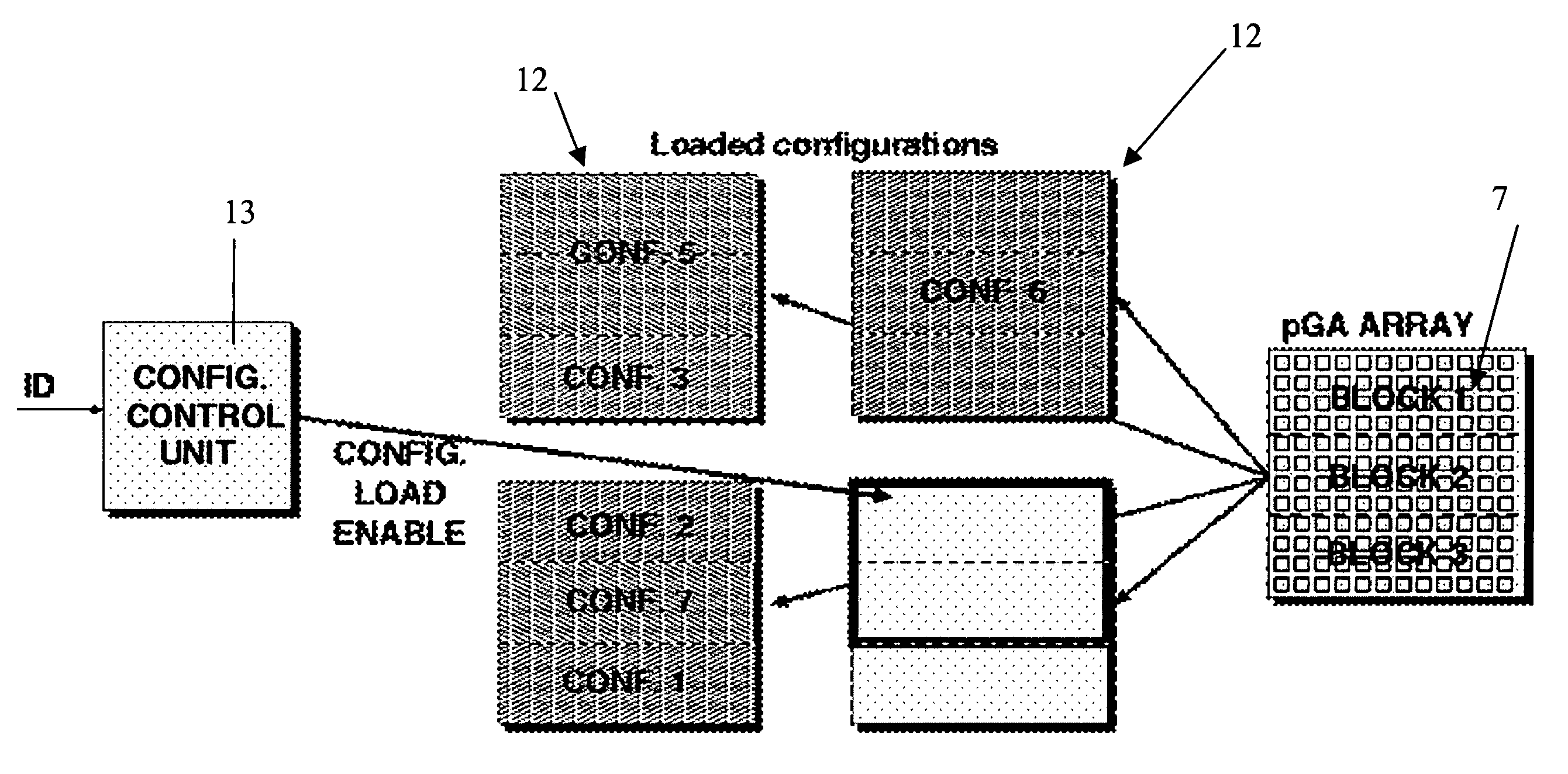

Embeddable flash memory system for non-volatile storage of code, data and bit-streams for embedded FPGA configurations

InactiveUS20050005055A1Significant energySignificant performanceMemory adressing/allocation/relocationRead-only memoriesEmbedded technologyApplication specific

An application-specific embeddable flash memory having three content-specific I / O ports and delivering a peak read throughput of 1.2 GB / s. The memory is combined with a special automatic programming gate voltage ramp generator circuit having a programming rate of 1 Mbyte / s for non-volatile storage of code, data, and embedded FPGA bit stream configurations. The test chip uses a NOR-type 0.18 μm flash embedded technology with 1.8V power supply, two poly, six metal and memory cell size of 0.35 μm2.

Owner:STMICROELECTRONICS SRL

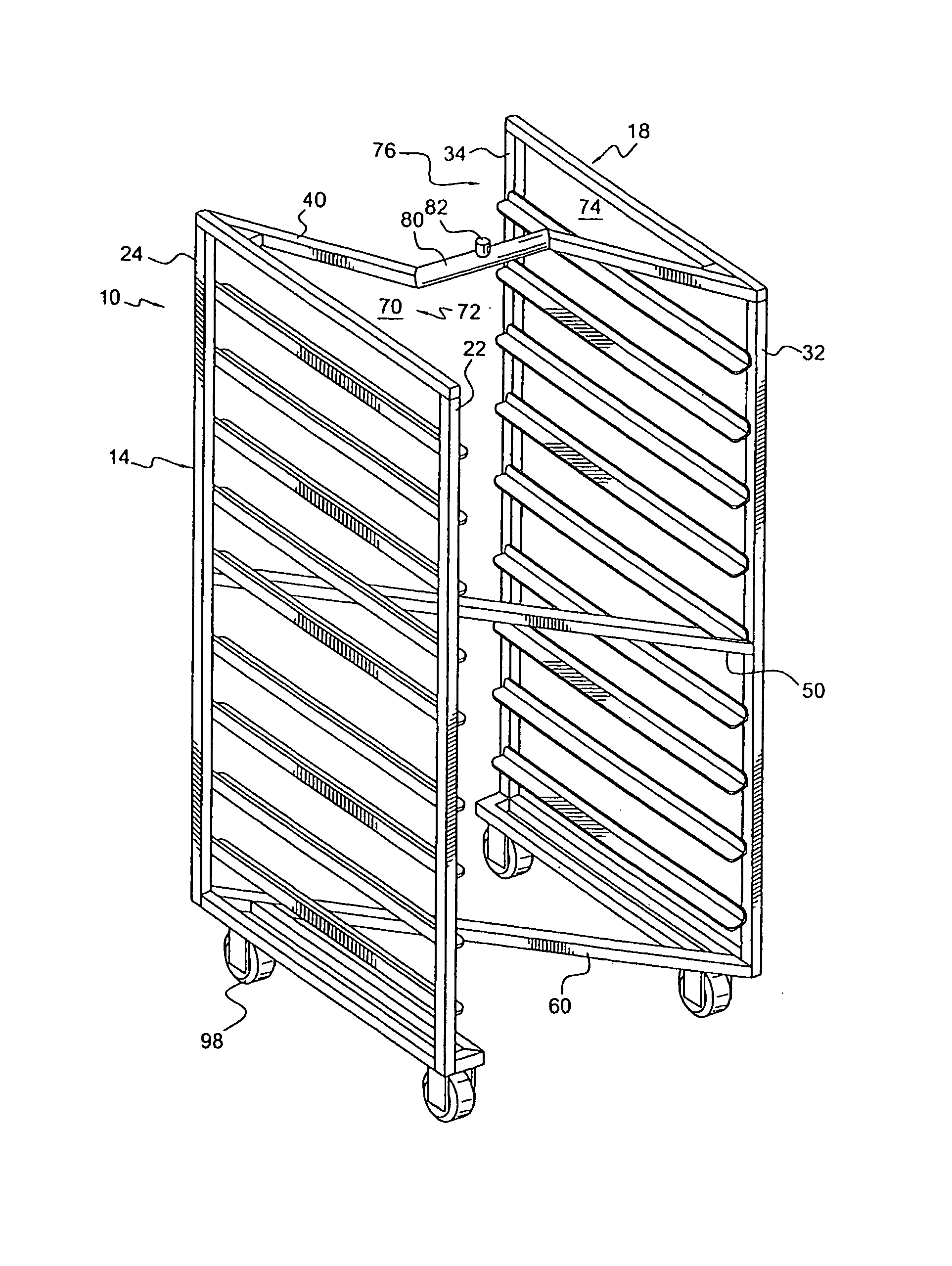

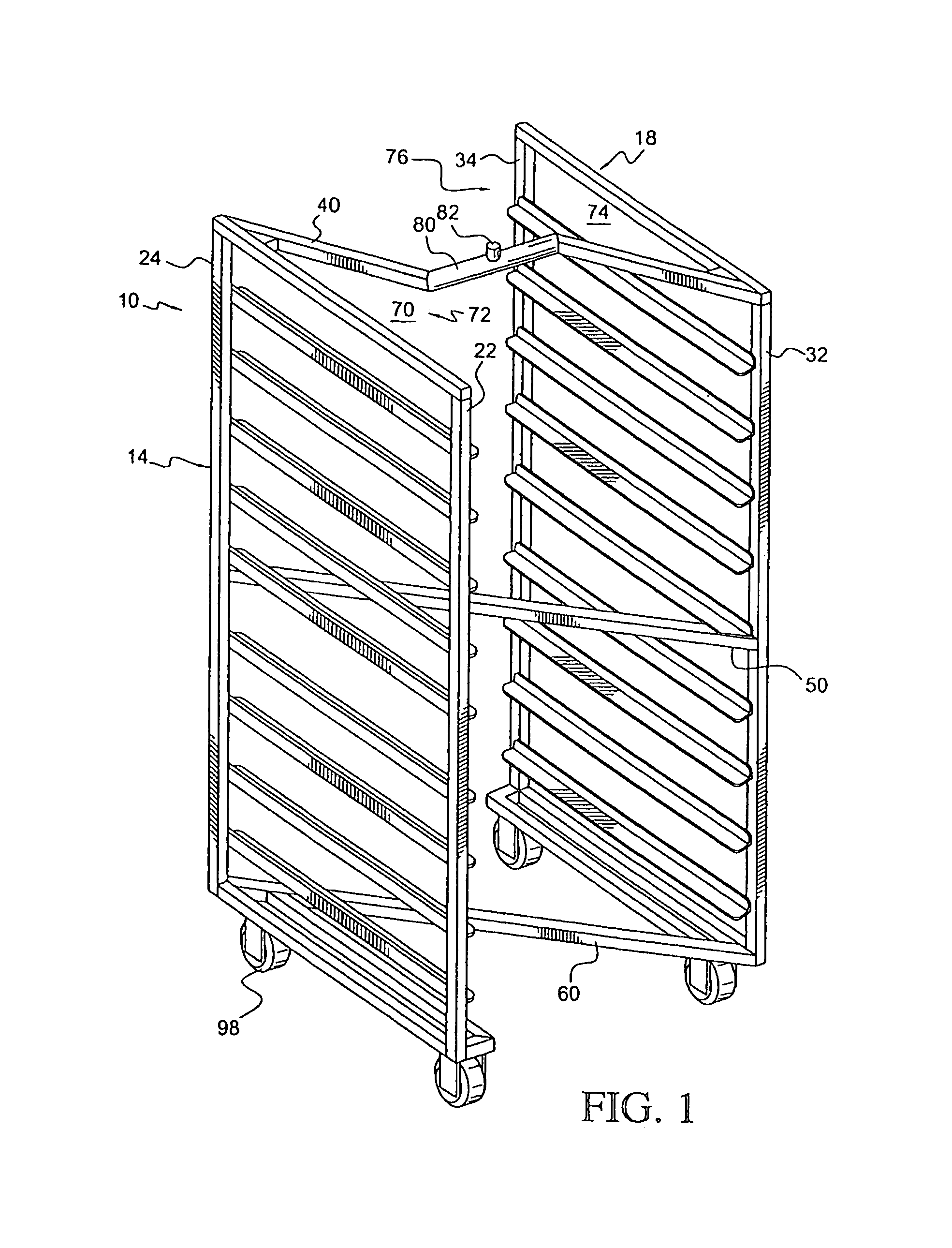

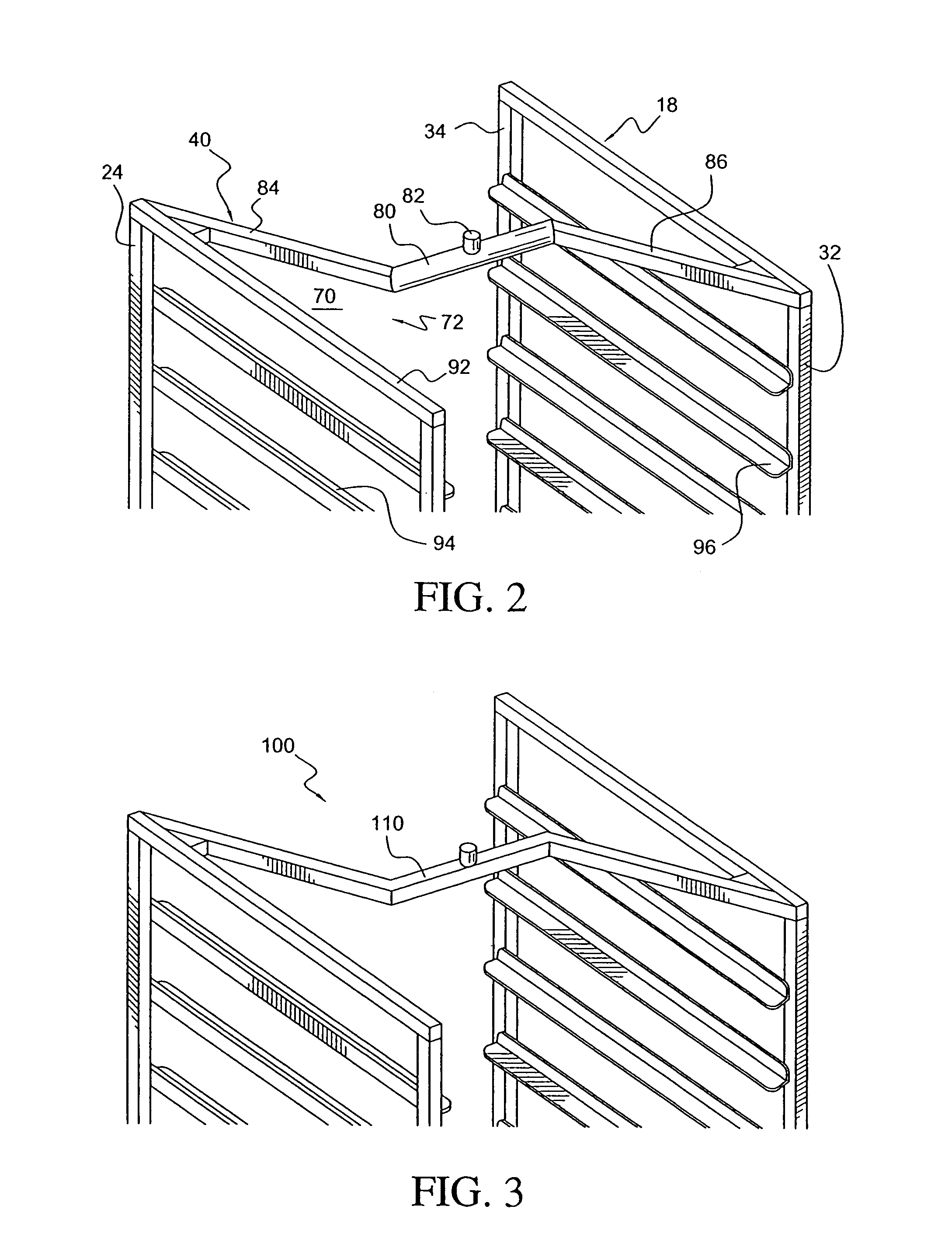

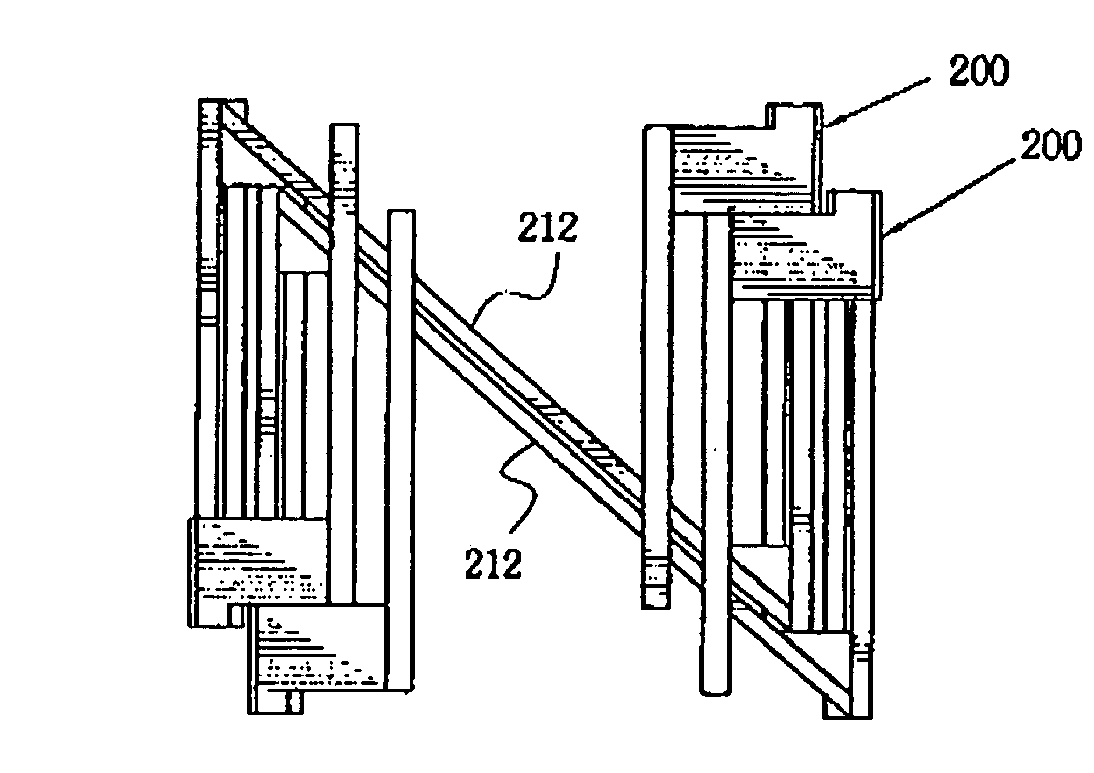

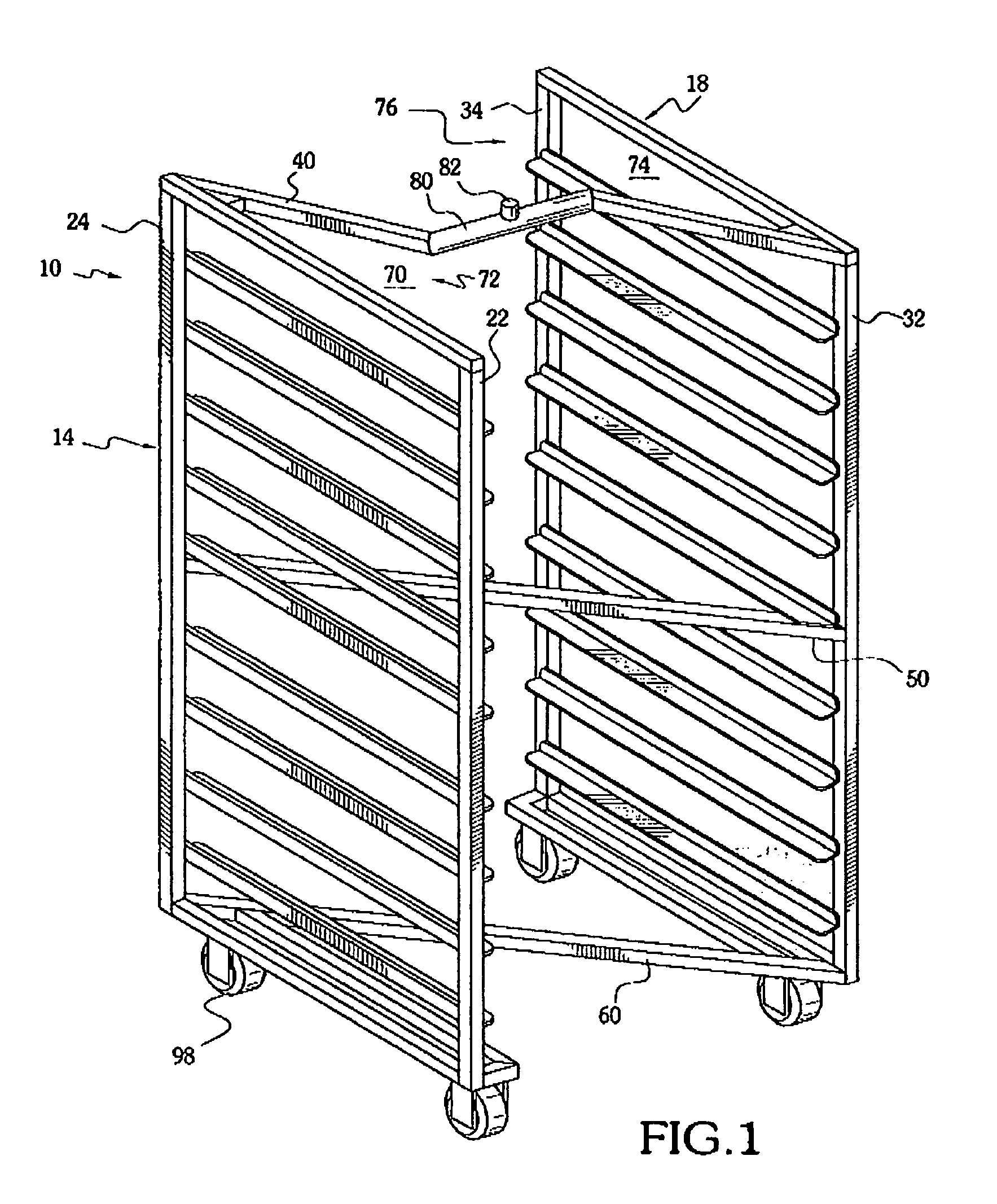

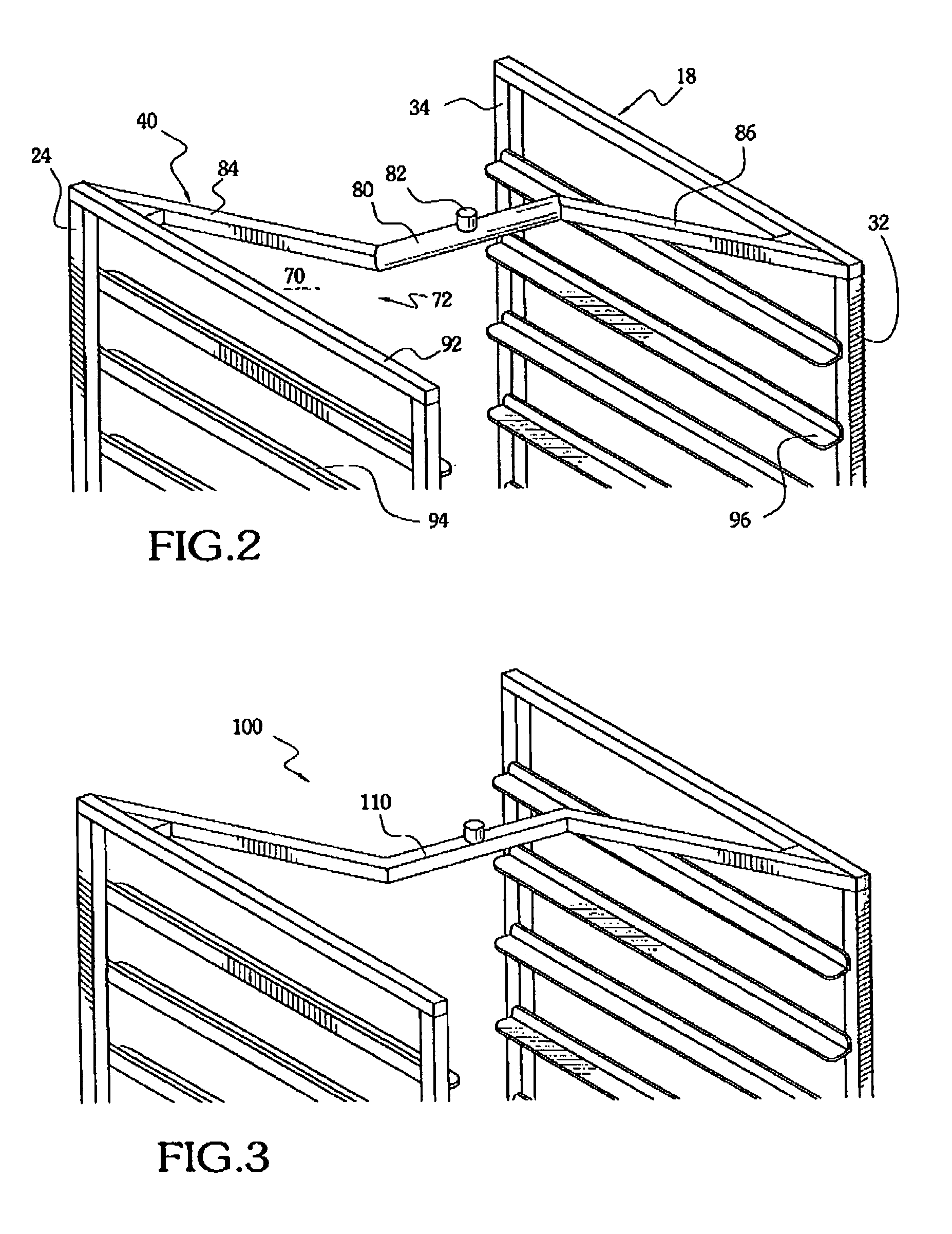

Nestable and liftable oven rack

InactiveUS7419063B1Lower the volumeSignificant costShow cabinetsBaking ovenEngineeringSpace requirements

Rack includes a left upright frame, a right upright frame, and a connector extending between and joining the left and right frames. The connector defines at least one passage extending along the left upright frame, for example, so that another rack may be nested within a volume defined by the rack for reducing storage space requirements. The rack may have its connector oriented so that the rack has a substantially Z-shaped frame, a substantially X-shaped frame, a substantially U-shaped frame, a substantially V-shaped frame, or a substantially H-shaped frame, for example, when viewed from above. A lifting element may be provided on an upper portion of the rack for use with institutional and industrial lifting mechanisms. The lifting element may be mounted on the rack so as to avoid interference with another rack when the racks are nesting.

Owner:M & E MFG

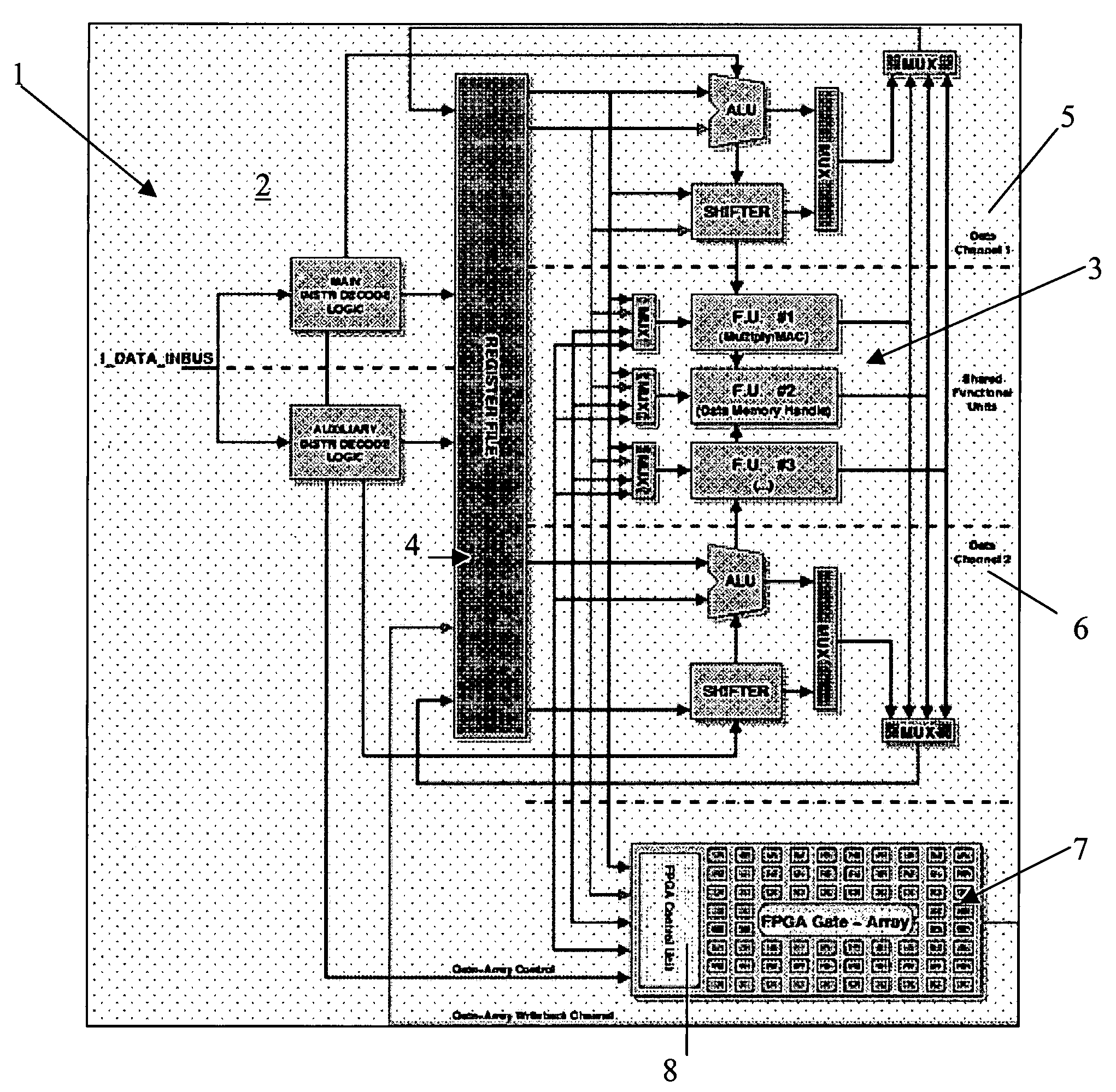

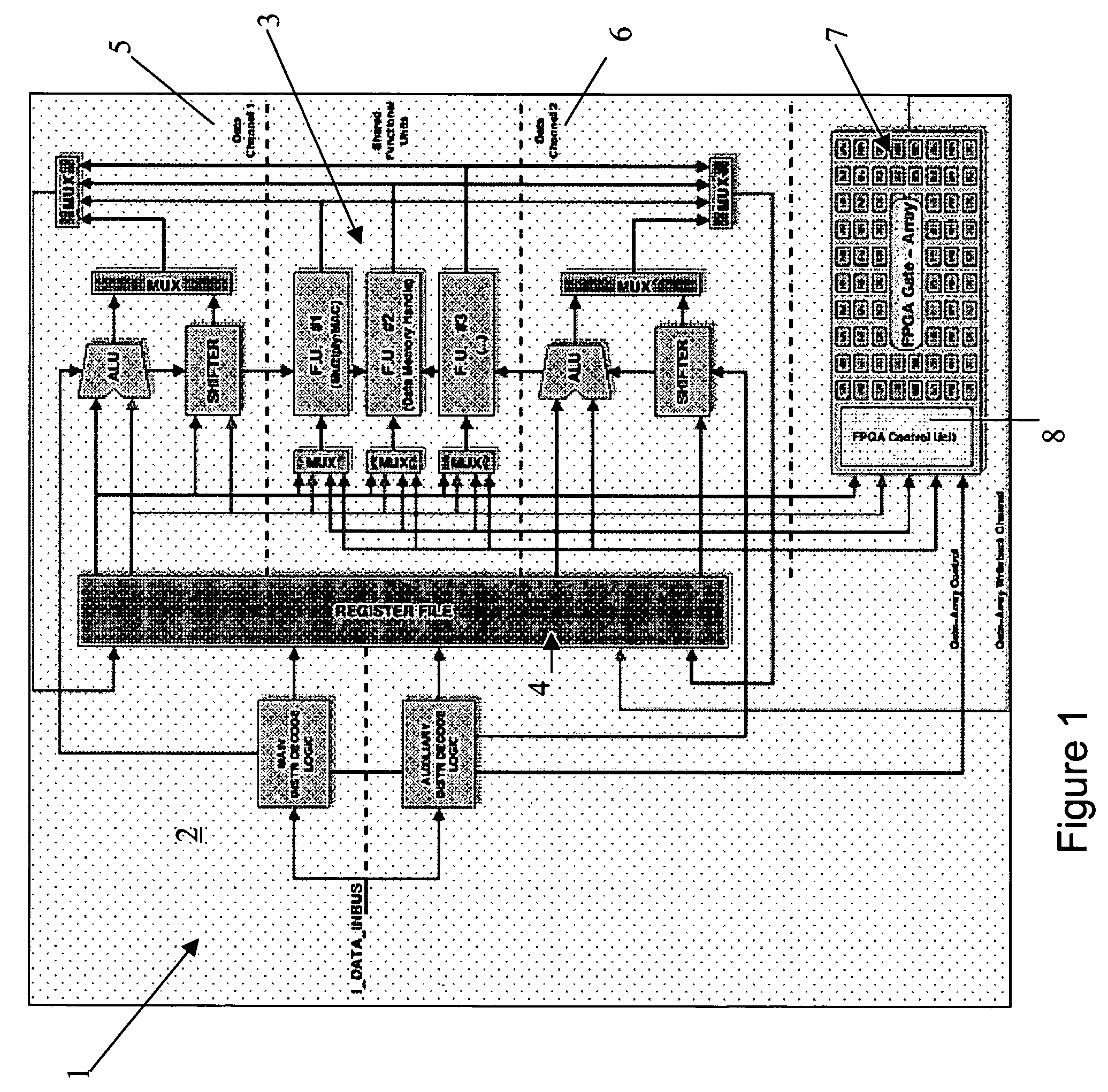

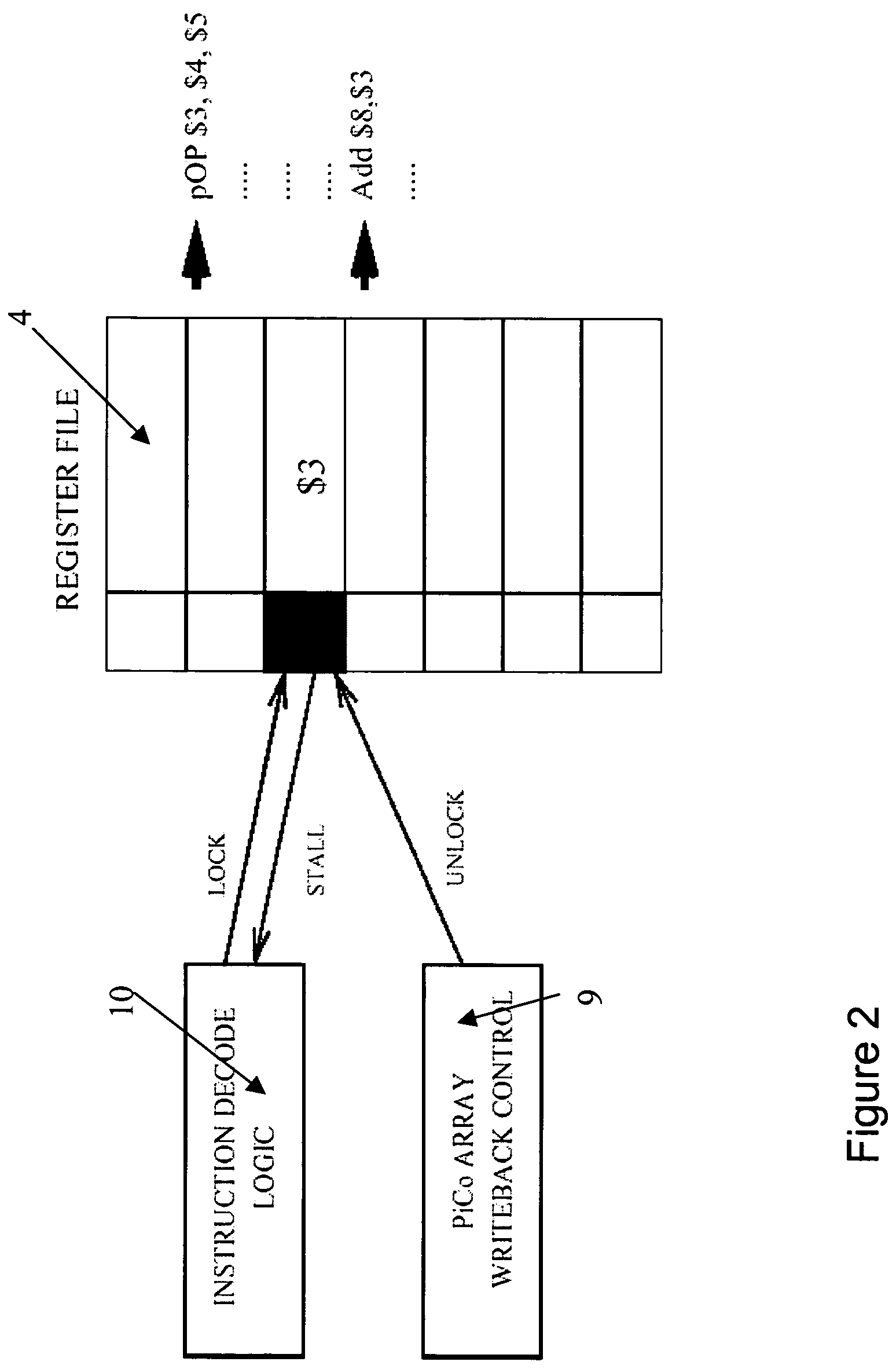

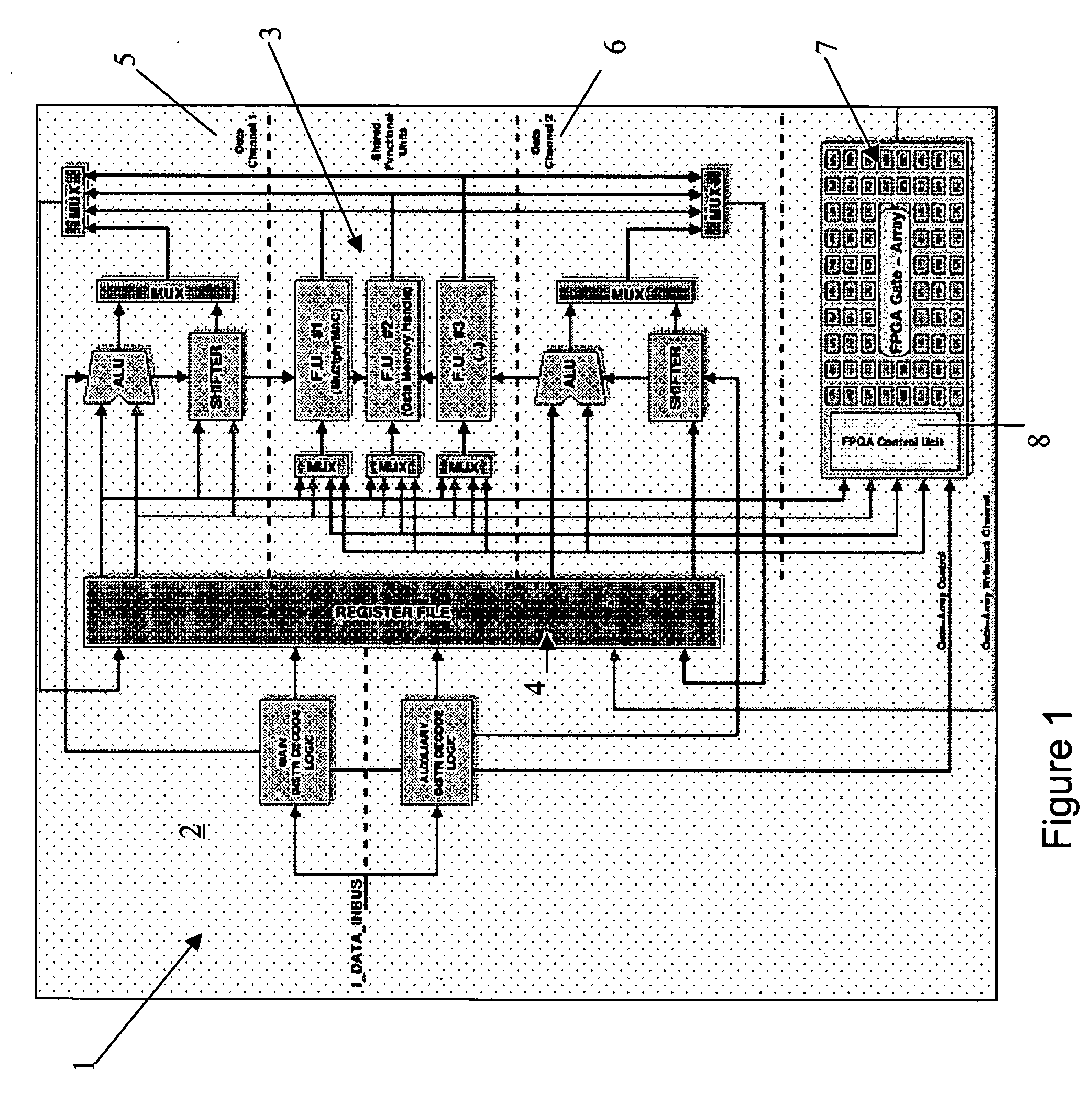

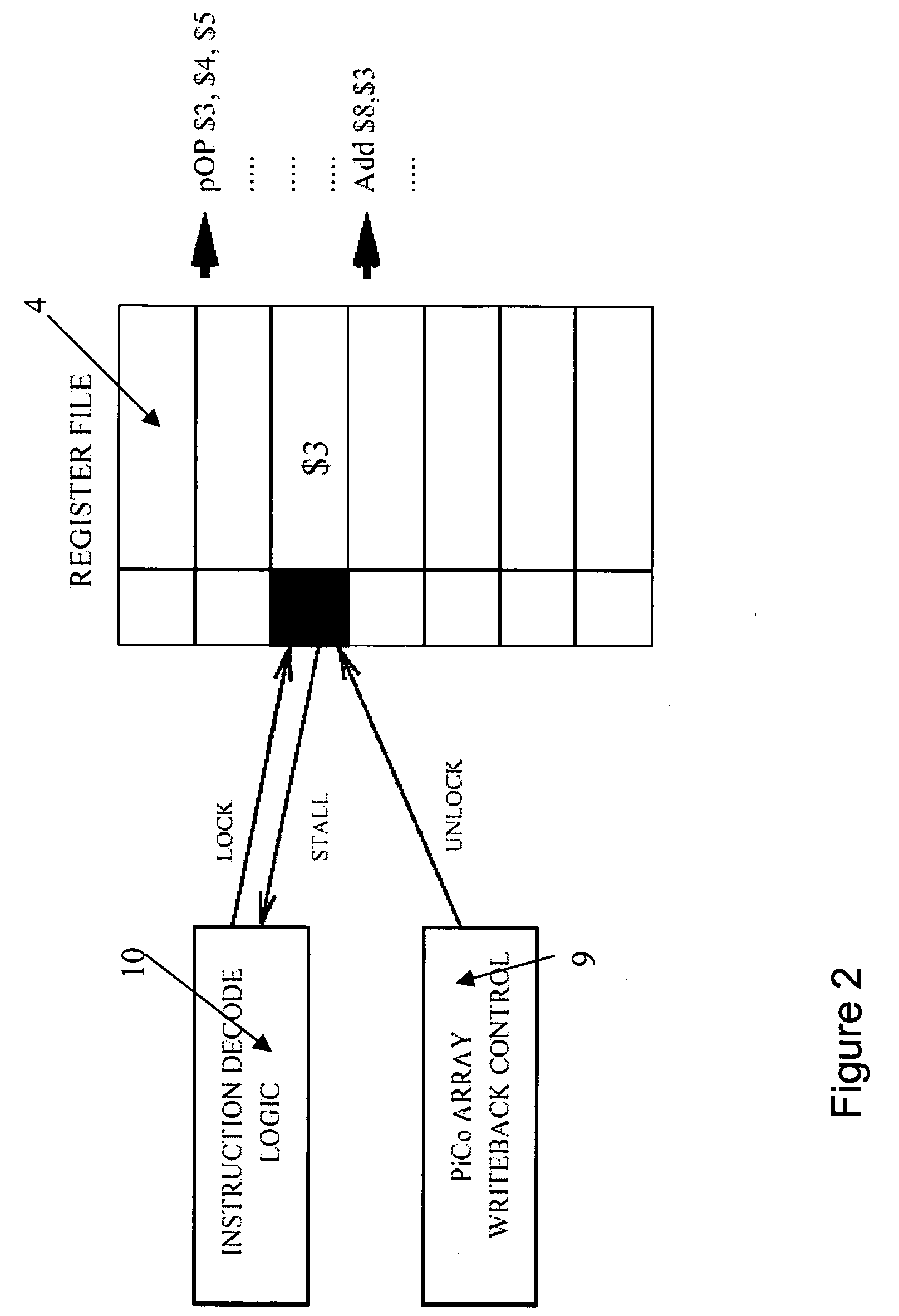

Digital architecture for reconfigurable computing in digital signal processing

ActiveUS7225319B2Significant energySignificant performanceConcurrent instruction executionArchitecture with single central processing unitMicrocontrollerDigital signal processing

A digital embedded architecture, includes a microcontroller and a memory device, suitable for reconfigurable computing in digital signal processing and comprising: a processor, structured to implement a Very Long Instruction Word elaboration mode by a general purpose hardwired computational logic, and an additional data elaboration channel comprising a reconfigurable function unit based on a pipelined array of configurable look-up table based cells controlled by a special purpose control unit, thus easing the elaboration of critical kernels algorithms.

Owner:STMICROELECTRONICS SRL

Nestable and/or liftable rack

InactiveUS6974042B2Lower the volumeSignificant costShow cabinetsKitchen equipmentTight frameEngineering

Rack includes a left upright frame, a right upright frame, and a connector extending between and joining the left and right frames. The connector defines at least one (1) passage extending along the left upright frame, for example, so that another rack may be nested within a volume defined by the rack for reducing storage space requirements. The rack may have its connector oriented so that the rack has a substantially Z-shaped frame, when viewed from above. Wheels may be provided to ease movement of the rack, and a lifting element may be provided on an upper portion of the rack for use with institutional and industrial lifting mechanisms.

Owner:M & E MFG

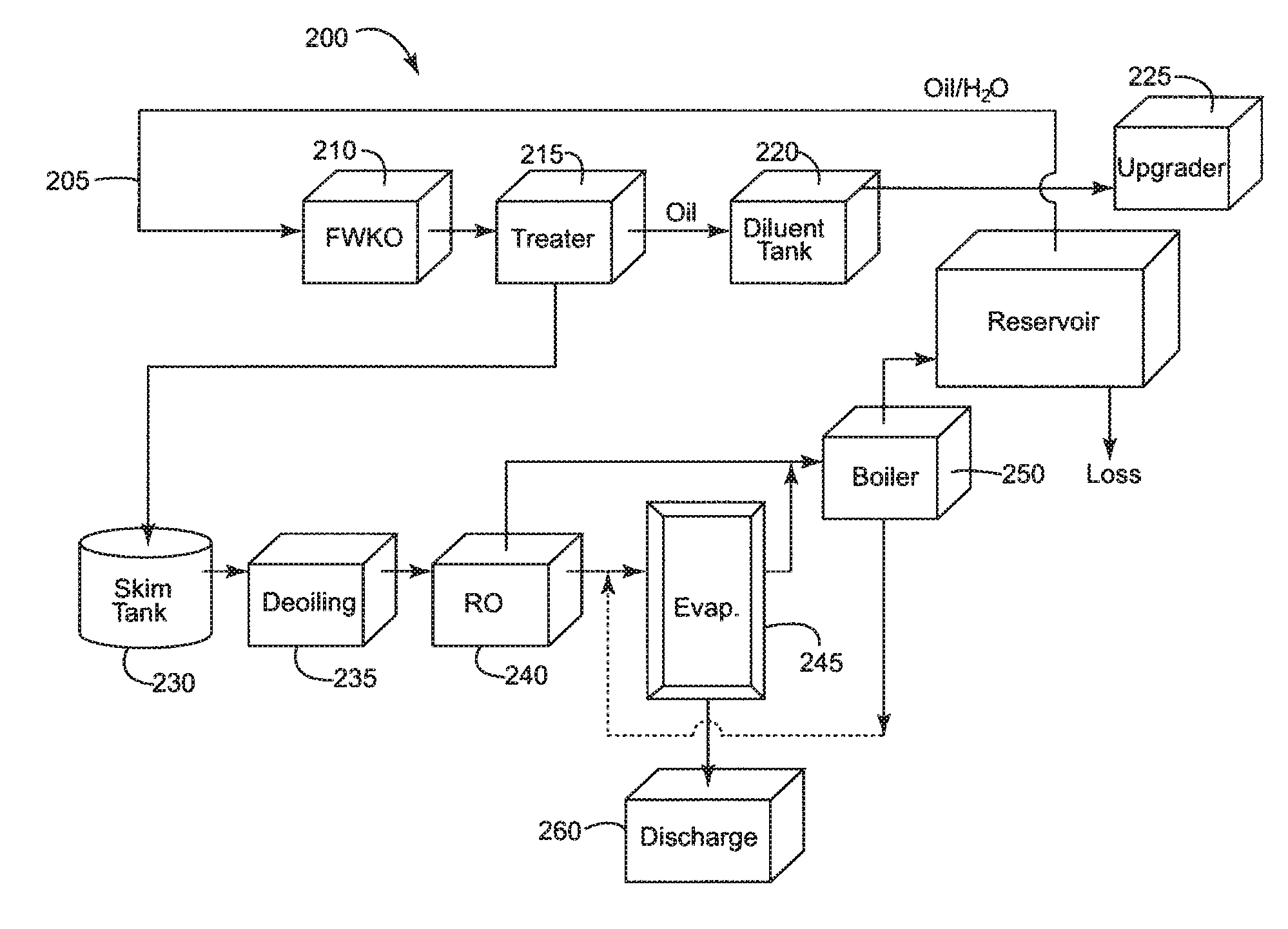

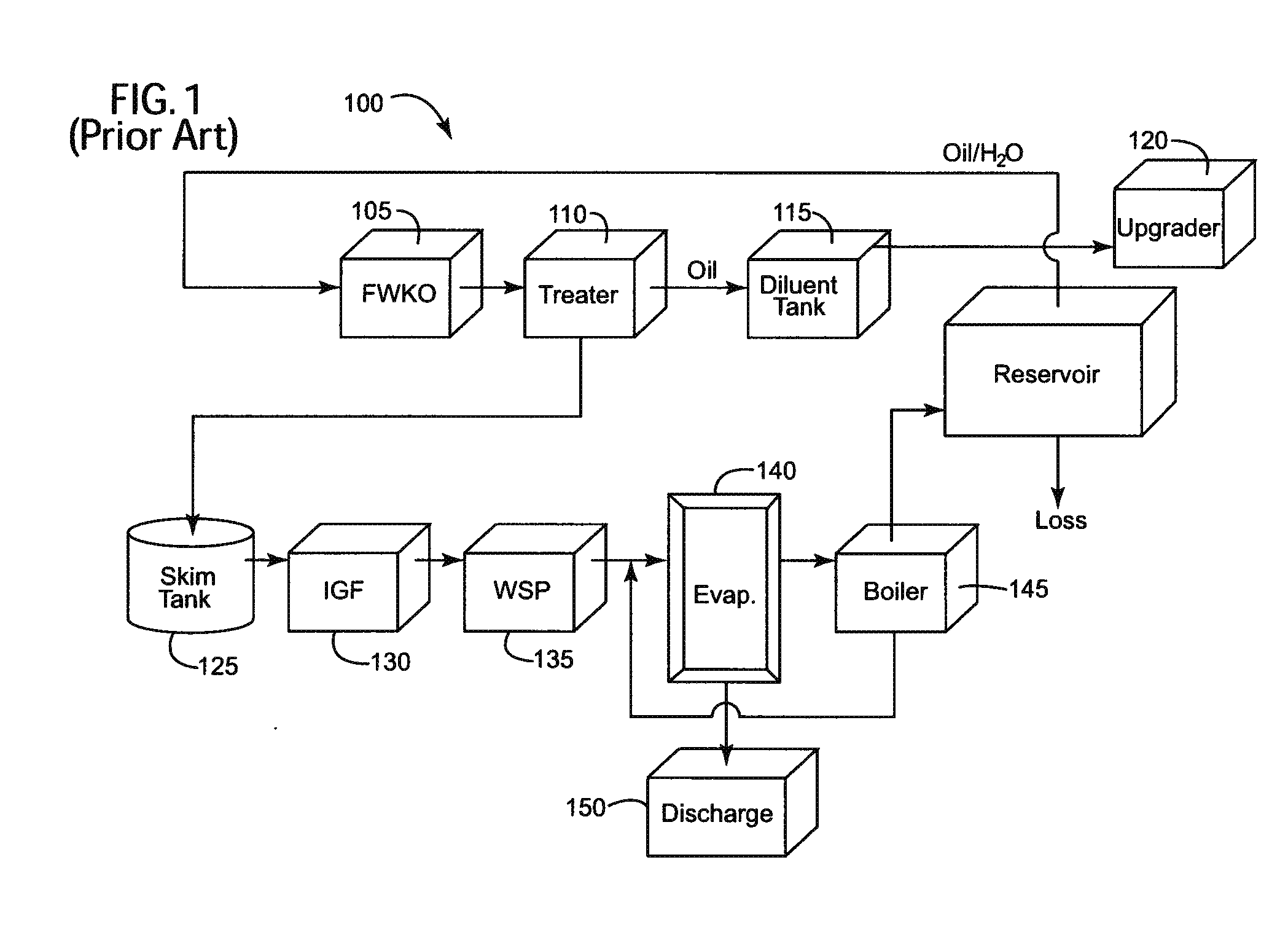

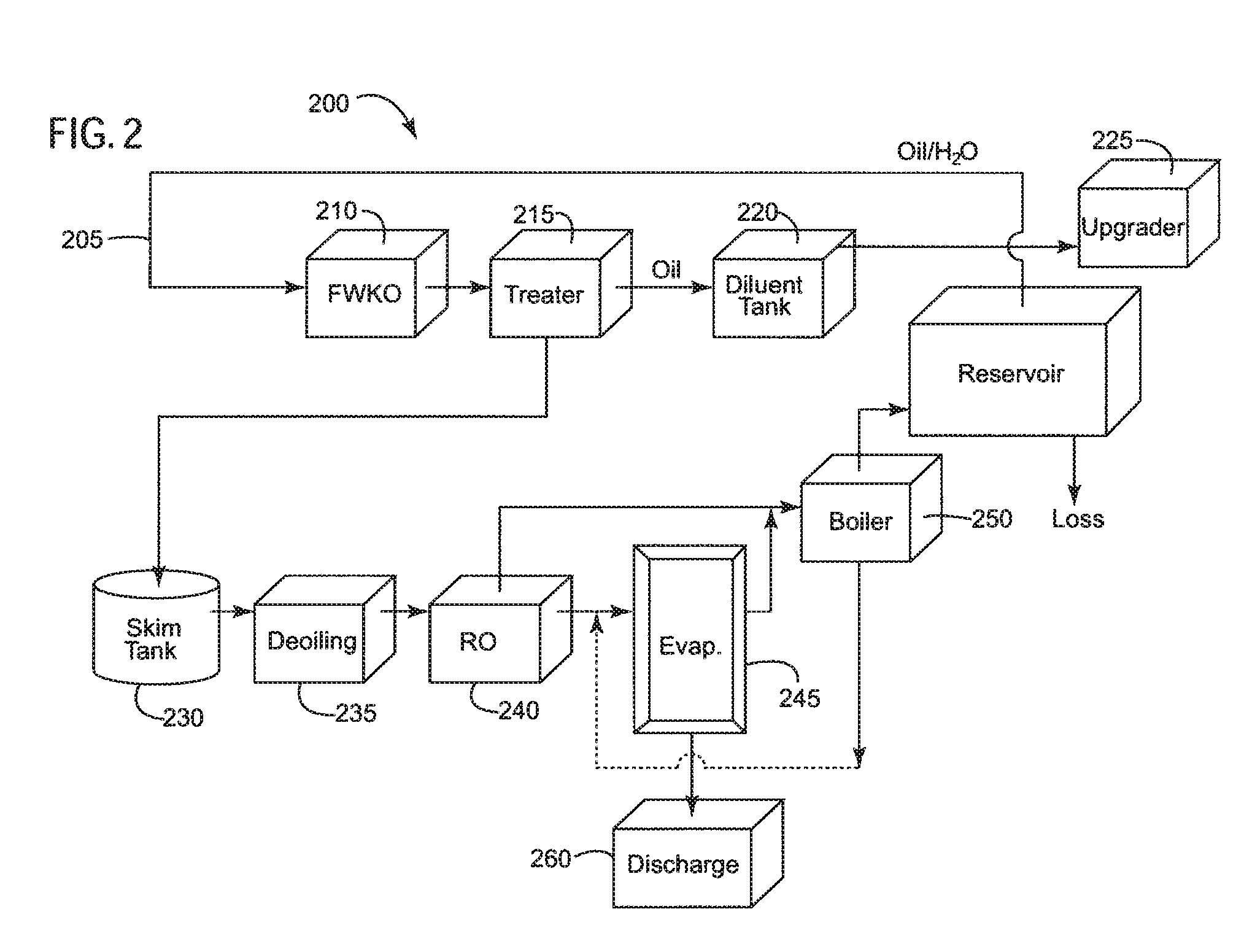

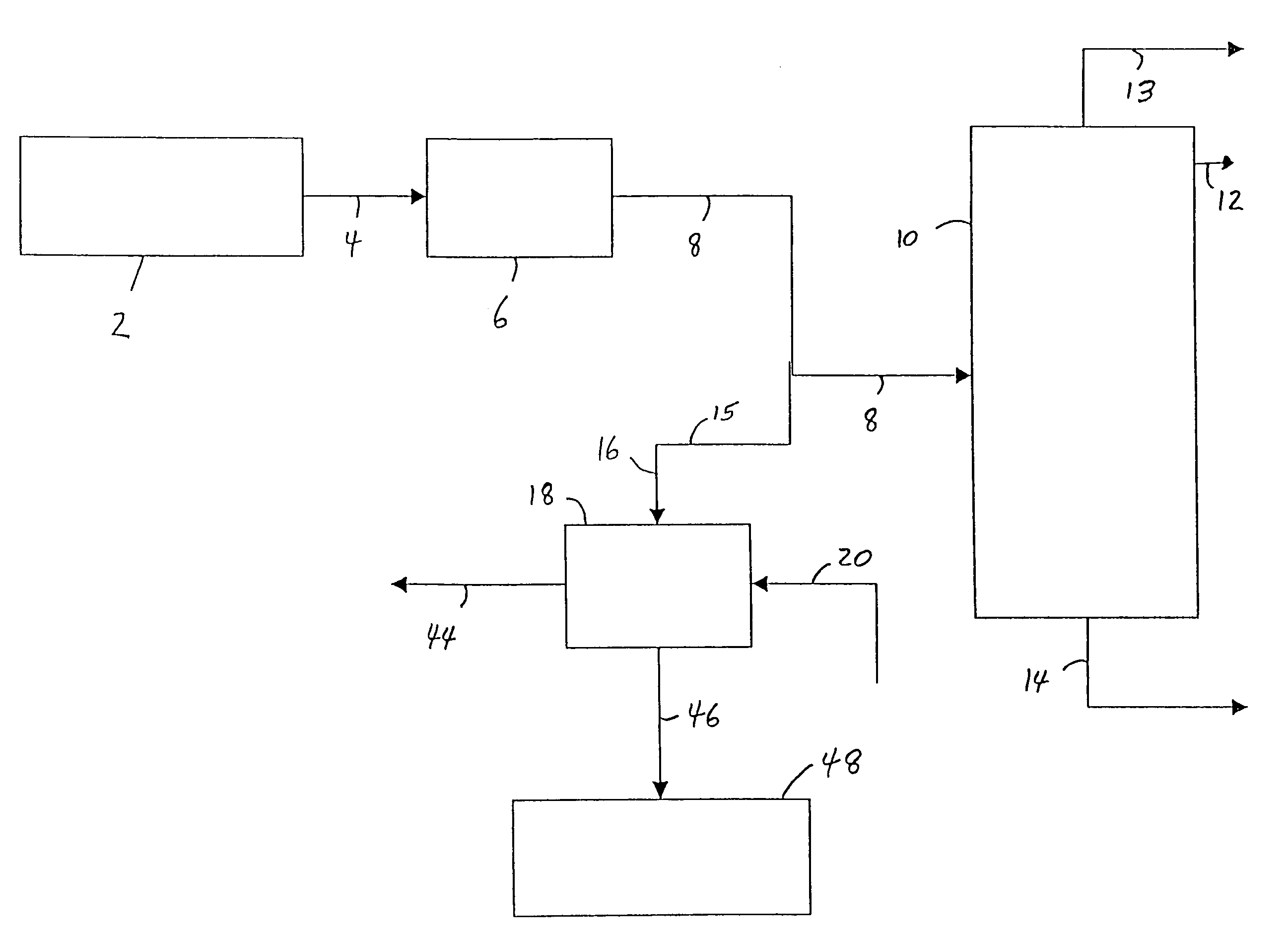

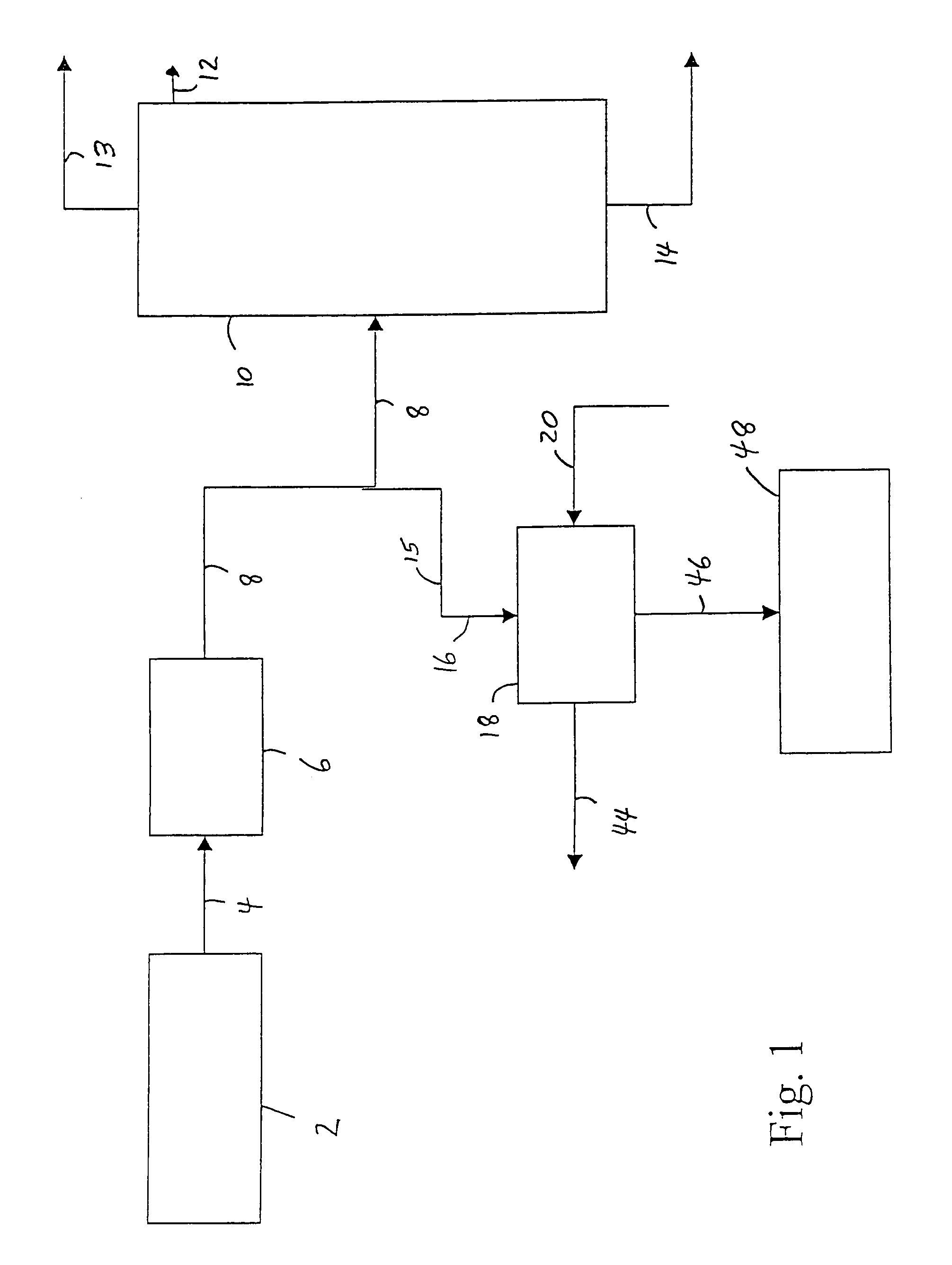

Process for treatment of produced water

InactiveUS20100294719A1Reduce amountEfficient and cost-effectiveWaste water treatment from quariesSemi-permeable membranesDistilled waterFuel oil

A process for treating produced water in heavy oil production comprises, providing an oil / water mixture gathered from an oil / water collection well, whereby oil from said oil / water mixture is separated to provide an oil product and a produced water product containing oil, dissolved gases and dissolved solutes. Said produced water product is then deoiled, and the deoiled water subsequently passes though a membrane system, resulting in permeate water and reject. The resulting permeate water is sent on to a boiler system for production of steam, and the reject is introduced into an evaporator to result in distillate water and blow down. Thereafter, the blow down may be charged into zero liquid discharge treatment; and the distillate water added to the membrane permeate.

Owner:GENERAL ELECTRIC CO

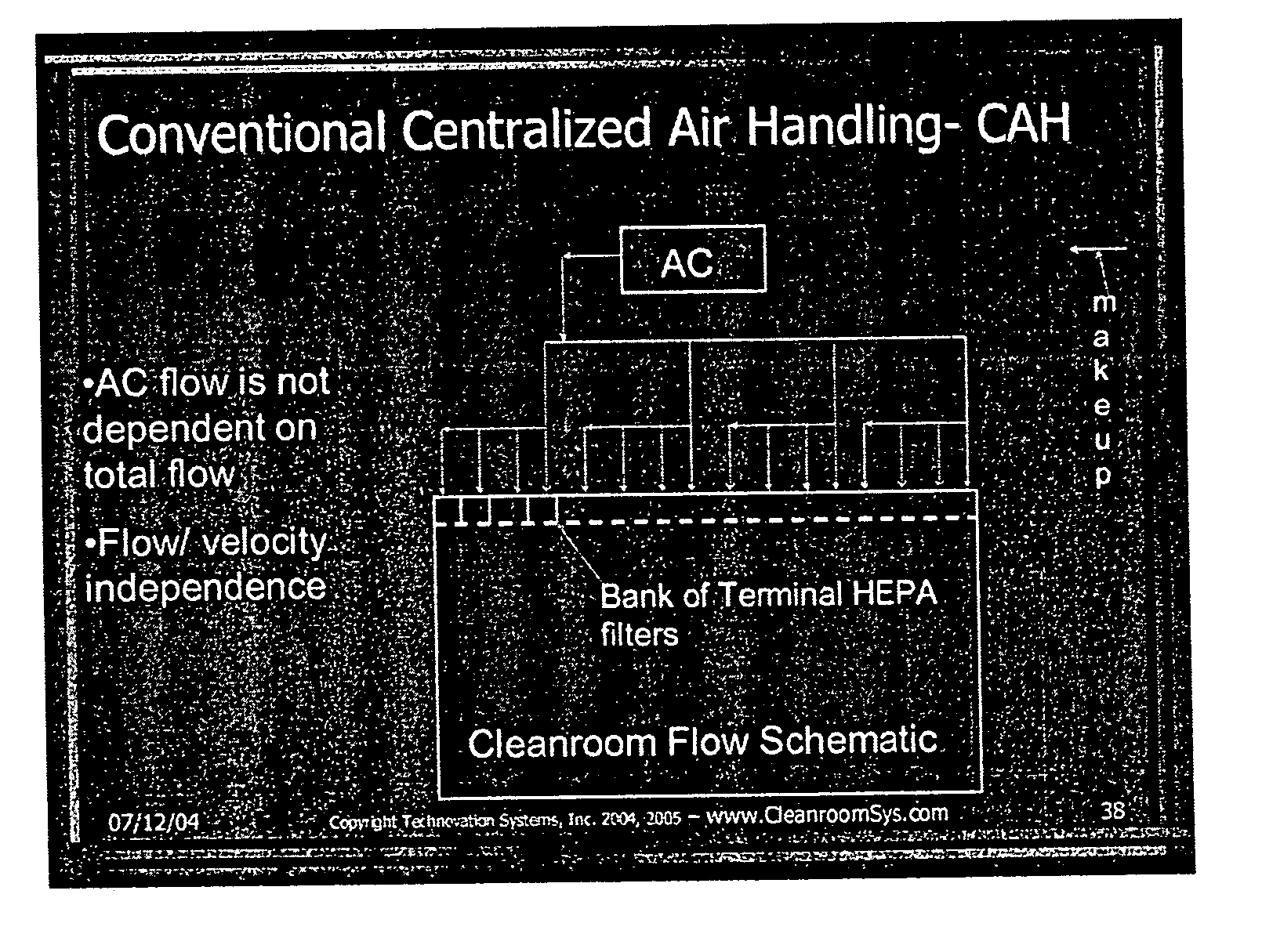

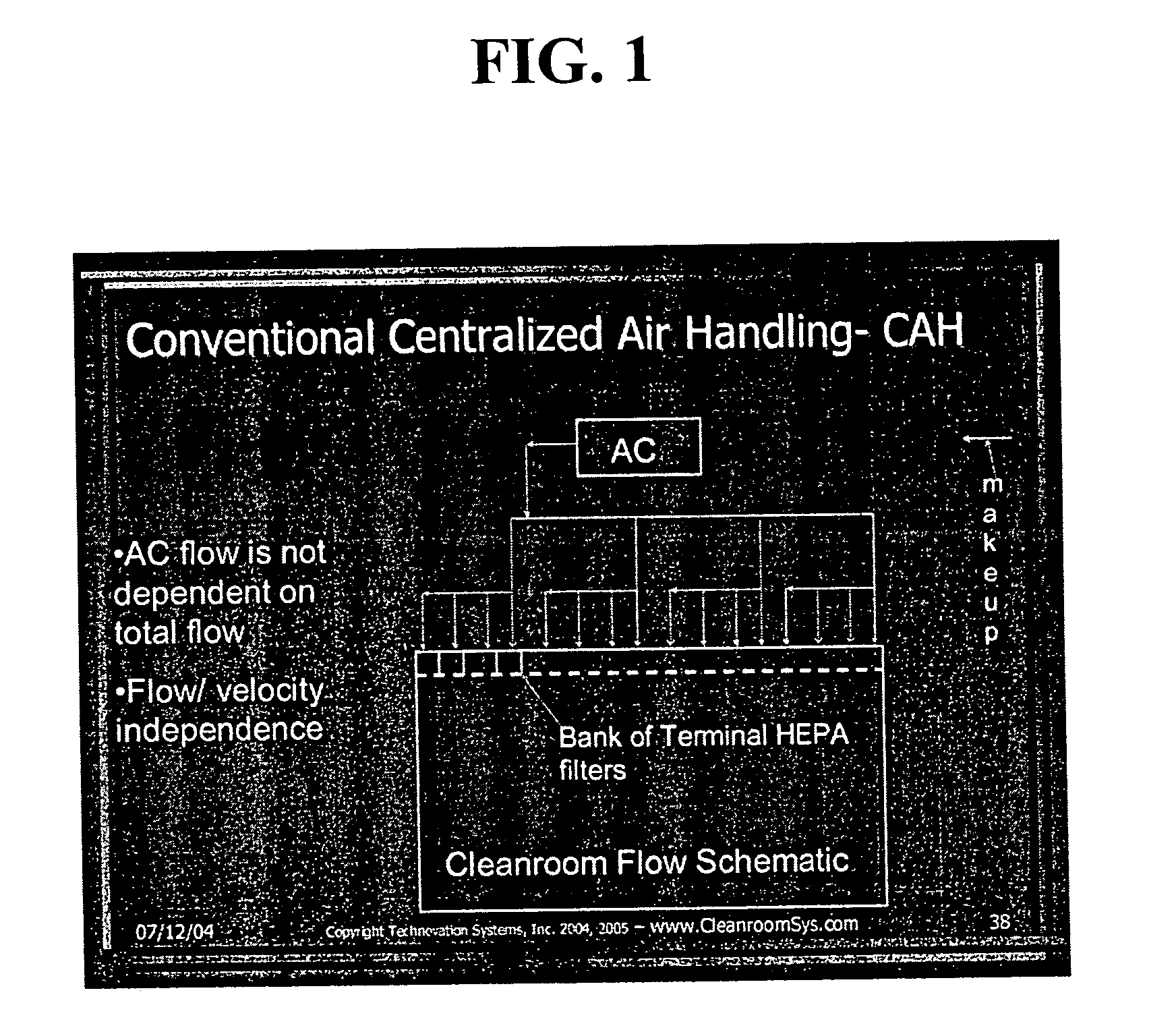

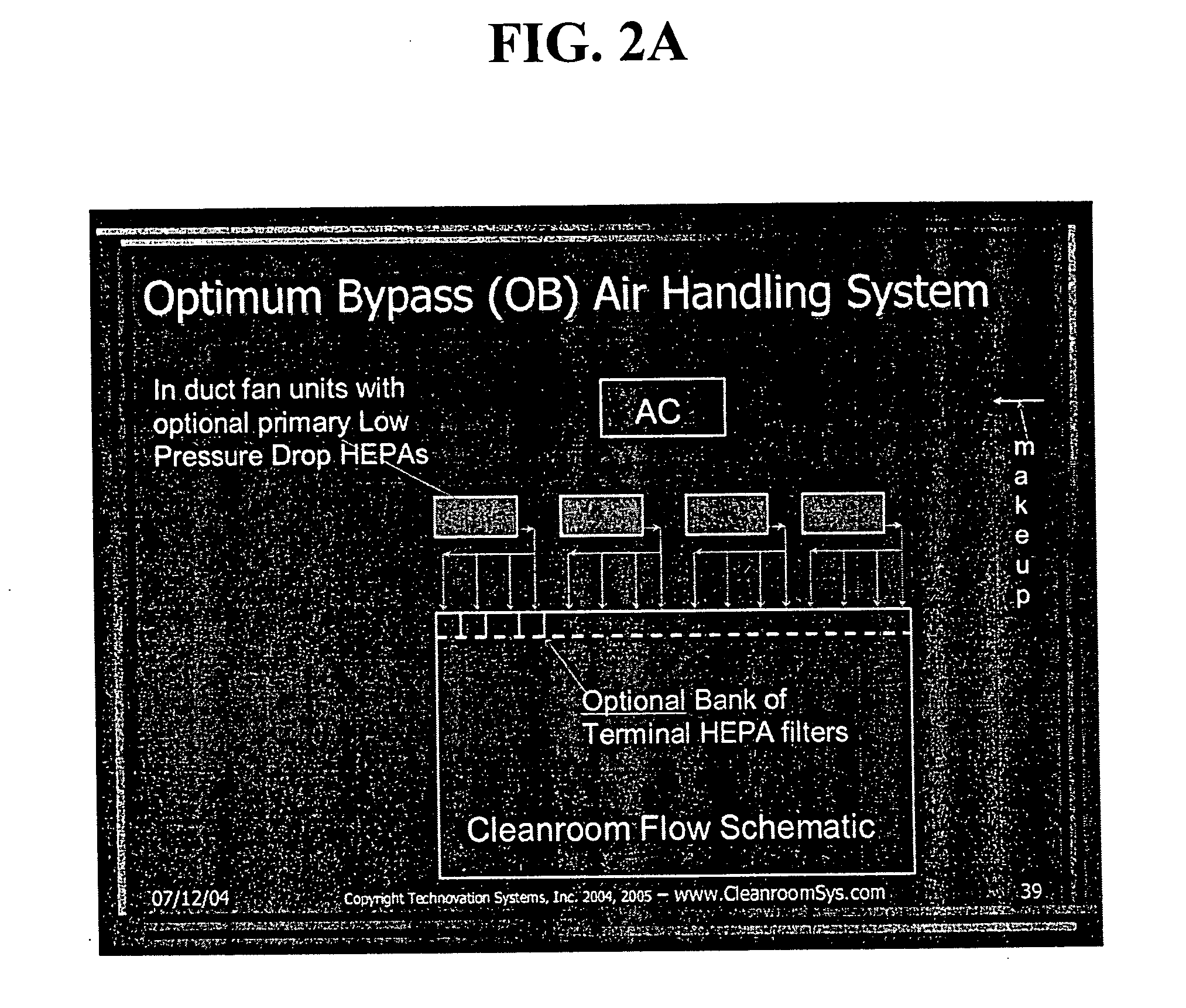

Energy efficient air handling system for cleanrooms

InactiveUS20070089854A1Low costEliminate useMechanical apparatusMilk preservationEngineeringAir change

A refrigeration based air handling system design process for significant energy and cost savings in cleanroom and other applications requiring large air change rates is presented. The process utilizes a by pass around the air conditioning system, the ratio of bypass to air conditioning flow being such that minimal or no reheat of the air is required for applications having relative humidity (RH) control requirements and with RH control being achieved via cooling. If dehumidification is achieved by adsorptive processes, then the by pass ratio is varied so as to minimize cooling of the heated dry air. In other non relative humidity control applications the bypass is varied to minimize the air conditioning flow, thereby decreasing cost, but by using optimum cooling coil velocities in a manner such that system energy for airflow is minimized. The energy and cost savings achieved by this process vary between 65% to 15% depending on the Class of the cleanroom and / or on the number of air changes per hour required.

Owner:JAISINGHANI RAJAN A

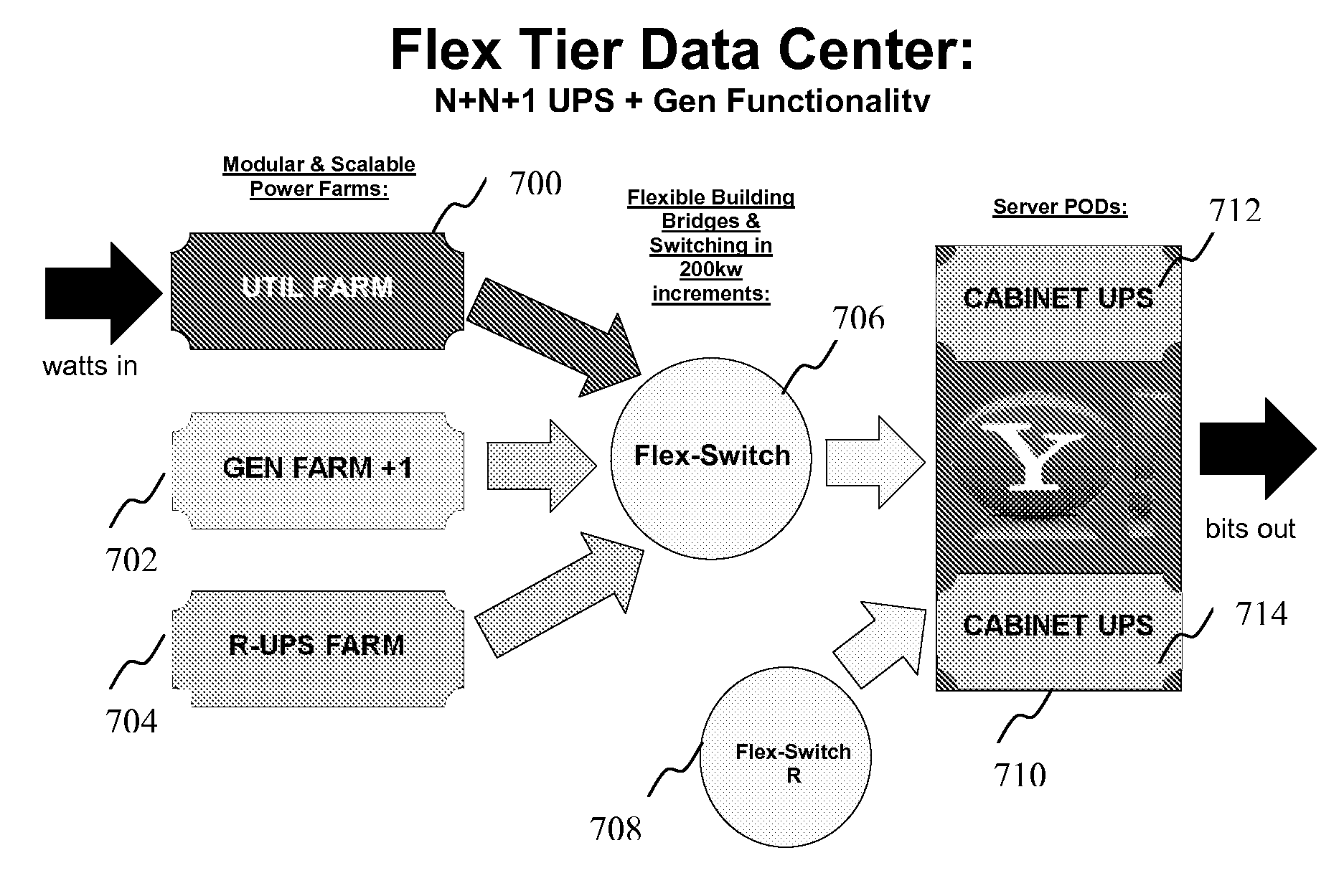

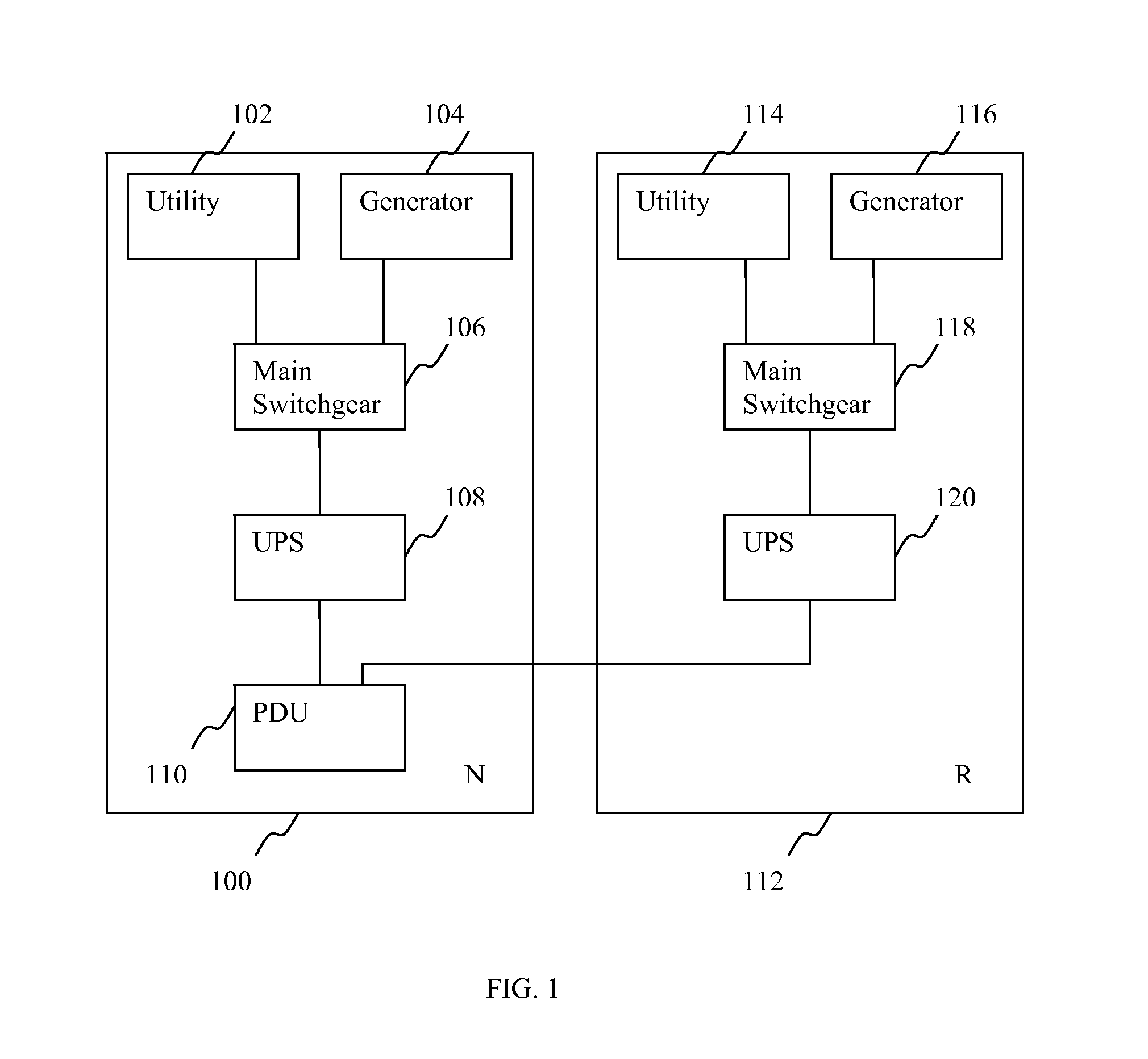

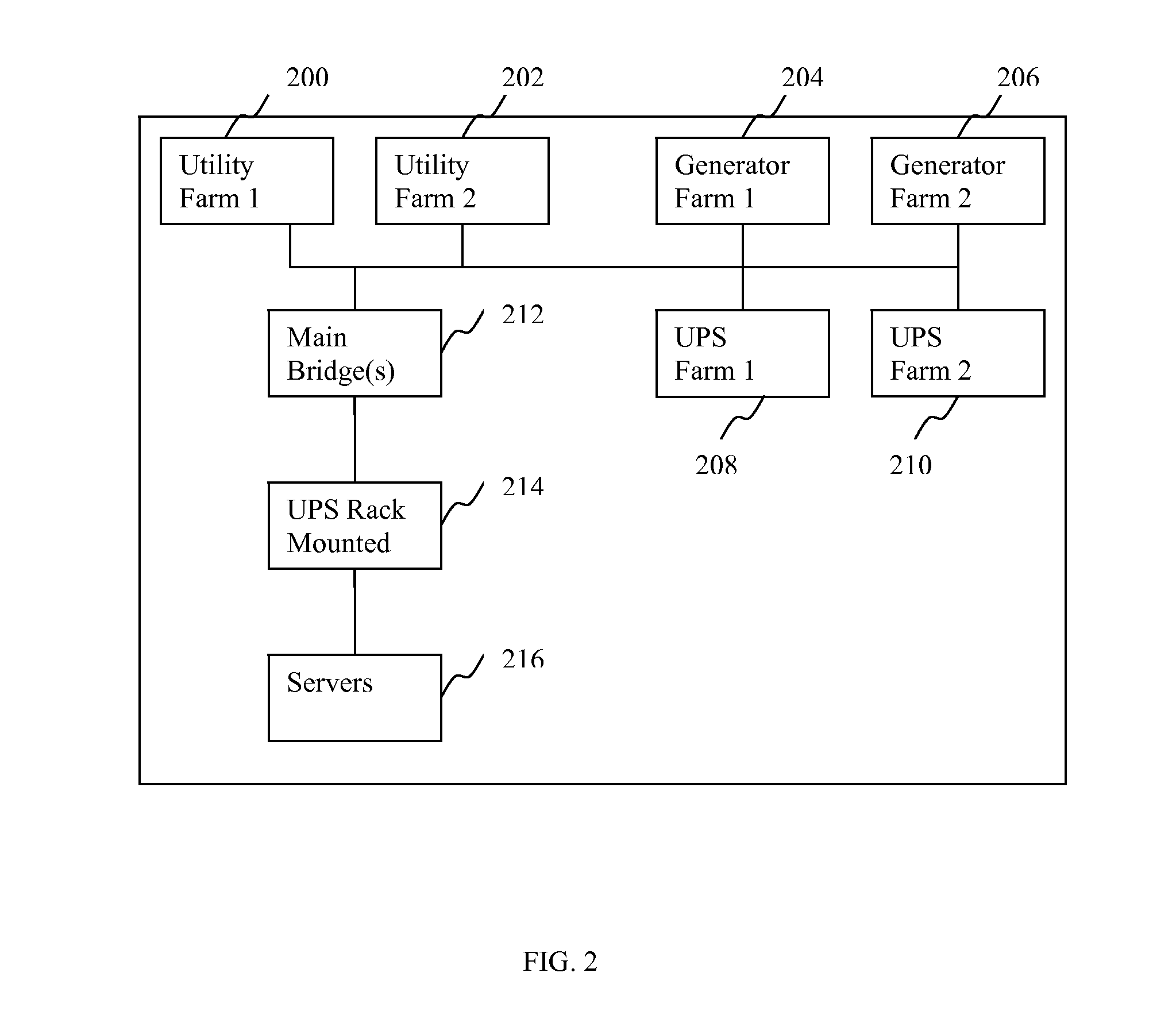

Flexible Tier Data Center

InactiveUS20130120929A1Building cost is highSignificant costDigital processing power distributionCooling/ventilation/heating modificationsData centerComputer science

A server cooling system includes: a flex-switch with one or more flexible building bridges; one or more utility farms coupled with the flex-switch; a power distribution unit operably connected to the flex-switch; and a server POD including one or more racks operably connected to the power distribution unit. The flex-switch is configurable to include additional utility farms, one or more generator farms, and one or more UPS farms.

Owner:R2 SOLUTIONS

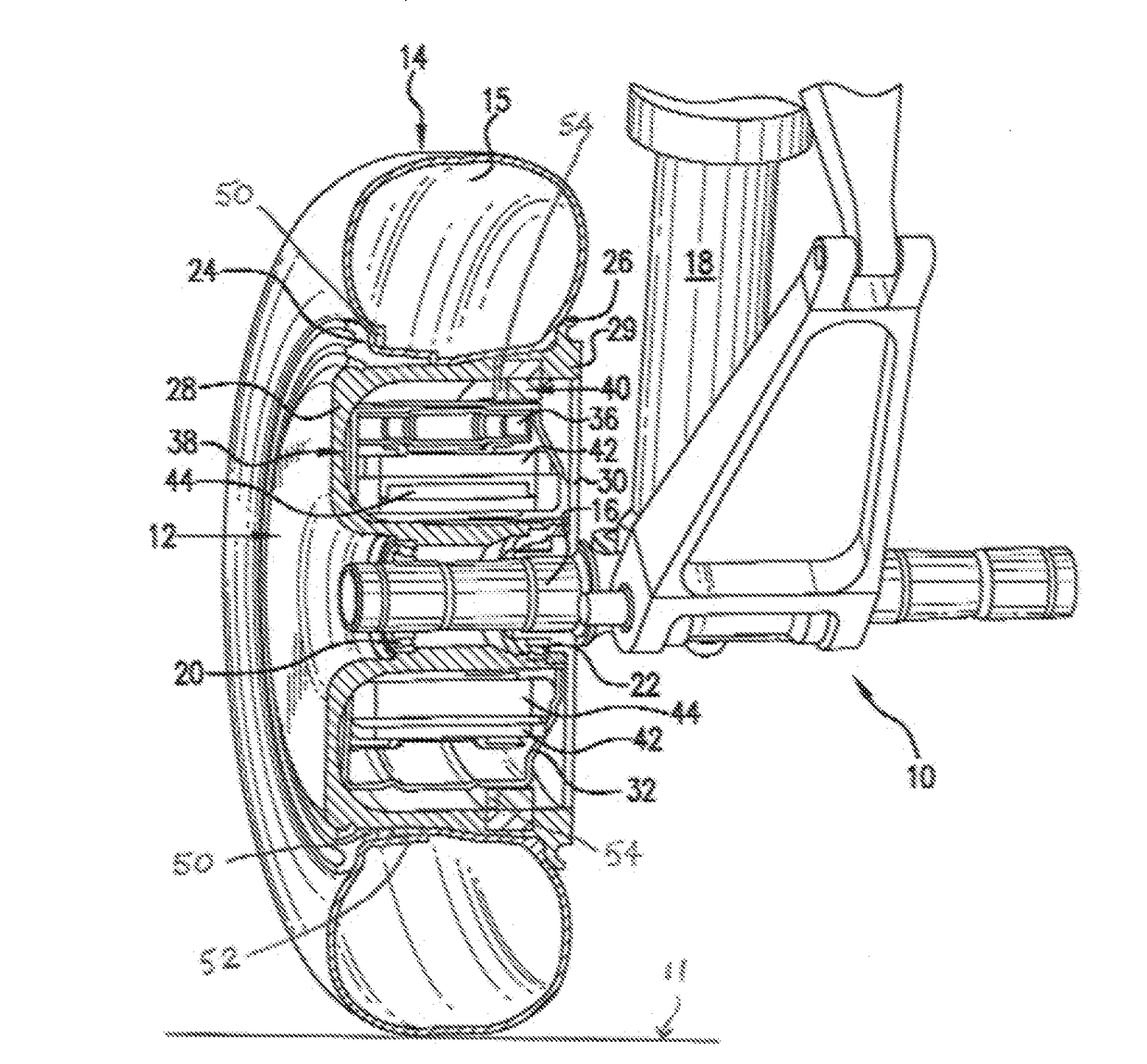

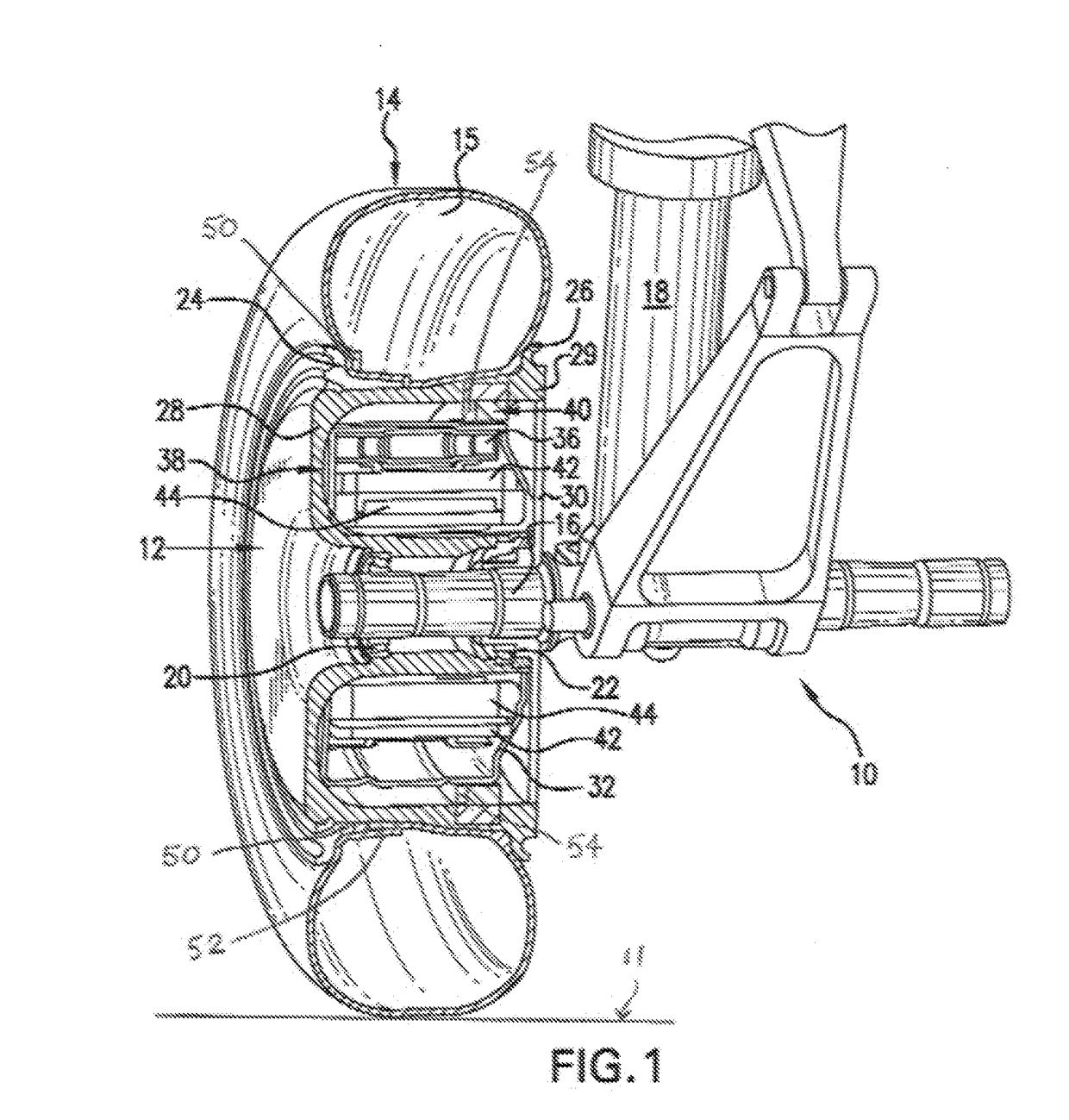

Method for using aircraft wheel tyre pressure to improve aircraft energy efficiency and drive system performance

ActiveUS20170217572A1Improve efficiencyImprove performanceEnergy efficient operational measuresDigital data processing detailsPresent methodGear wheel

A method is provided for improving both landing gear wheel drive assembly performance and energy efficiency performance in an aircraft equipped with one or more landing gear wheel drive assemblies to move the aircraft autonomously on the ground without reliance on the aircraft's engines. Aircraft moved on the ground by thrust from aircraft engines may also show improved energy efficiency. The present method employs a discovered relationship between aircraft tyre pressure and landing gear wheel drive assembly performance and maintains aircraft tyre inflation pressure at an optimum high pressure that enhances both landing gear wheel drive assembly performance and aircraft energy efficiency while the aircraft are driven on the ground by the landing gear wheel drive assemblies. Operation of the landing gear wheel drive assembly may be automatically prevented by a failsafe mechanism when optimum high tyre inflation pressure levels are not maintained during aircraft ground travel.

Owner:BOREALIS TECH LTD

Apparatuses, methods, and systems for configurable operand size operations in an operation configurable spatial accelerator

ActiveUS11029958B1Easy to adaptImprove performanceInstruction analysisHardware accelerationElectrical and Electronics engineering

Systems, methods, and apparatuses relating to configurable operand size operation circuitry in an operation configurable spatial accelerator are described. In one embodiment, a hardware accelerator includes a plurality of processing elements, a network between the plurality of processing elements to transfer values between the plurality of processing elements, and a first processing element of the plurality of processing elements including a first plurality of input queues having a multiple bit width coupled to the network, at least one first output queue having the multiple bit width coupled to the network, configurable operand size operation circuitry coupled to the first plurality of input queues, and a configuration register within the first processing element to store a configuration value that causes the configurable operand size operation circuitry to switch to a first mode for a first multiple bit width from a plurality of selectable multiple bit widths of the configurable operand size operation circuitry, perform a selected operation on a plurality of first multiple bit width values from the first plurality of input queues in series to create a resultant value, and store the resultant value in the at least one first output queue.

Owner:INTEL CORP

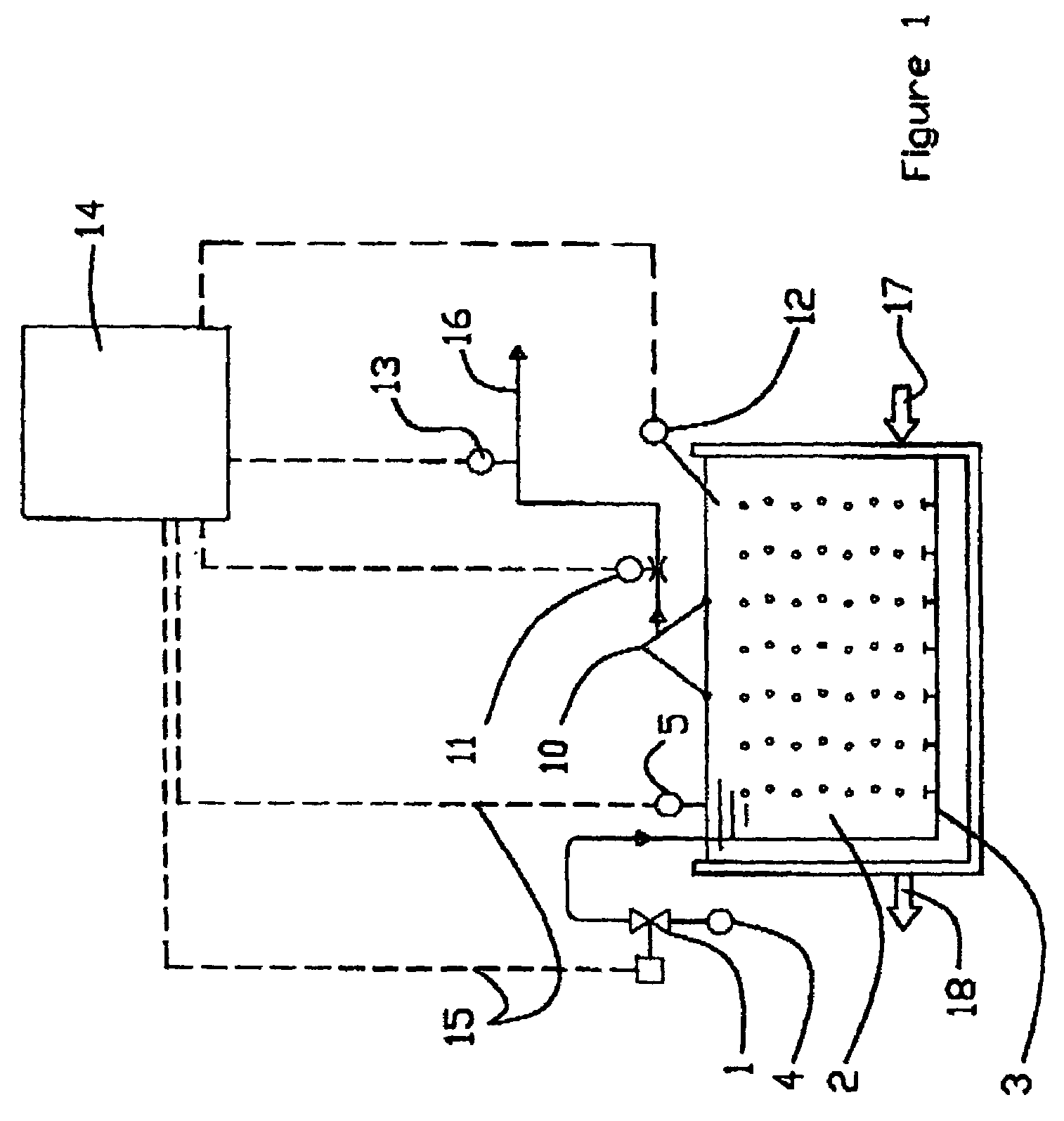

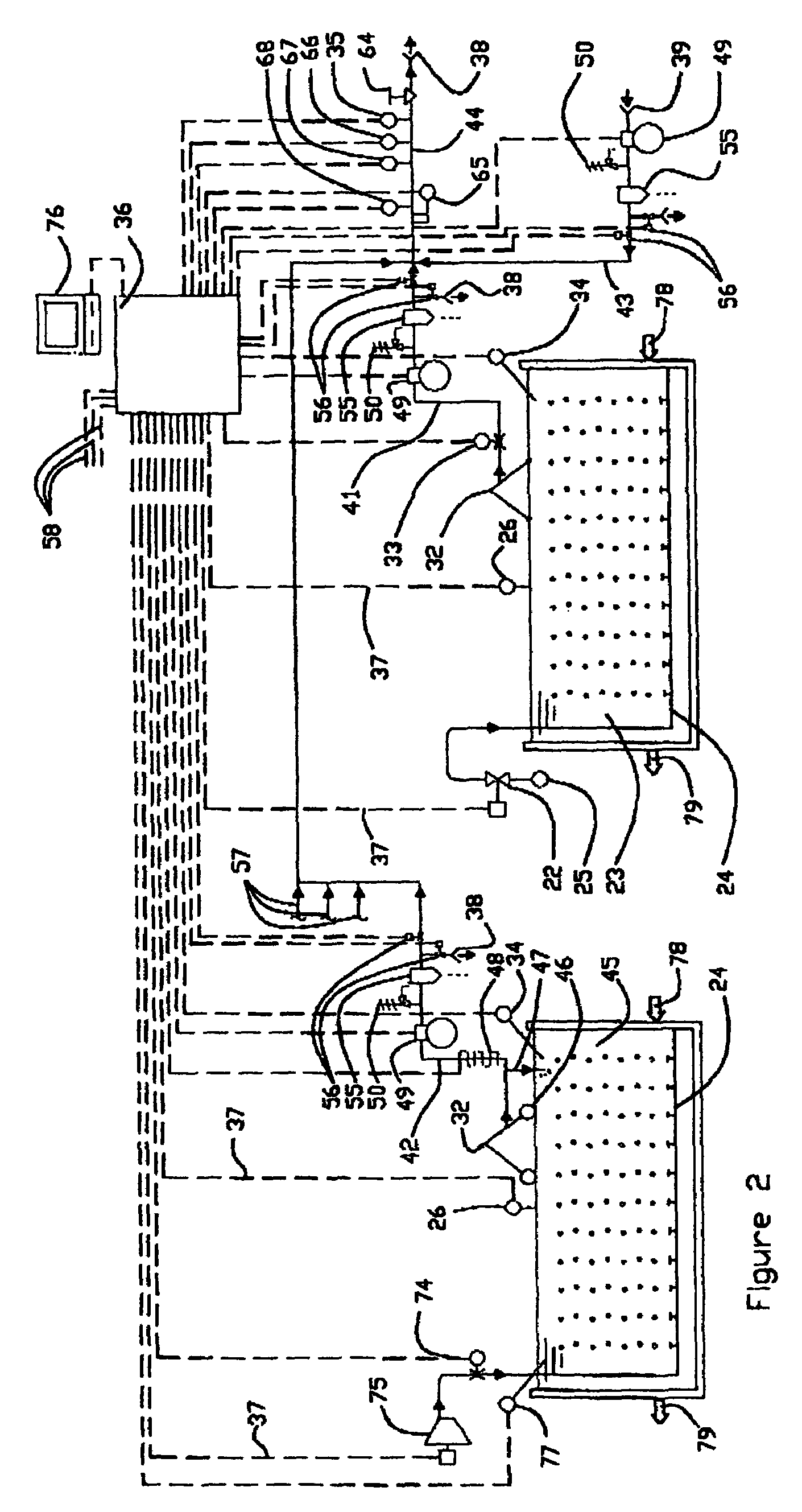

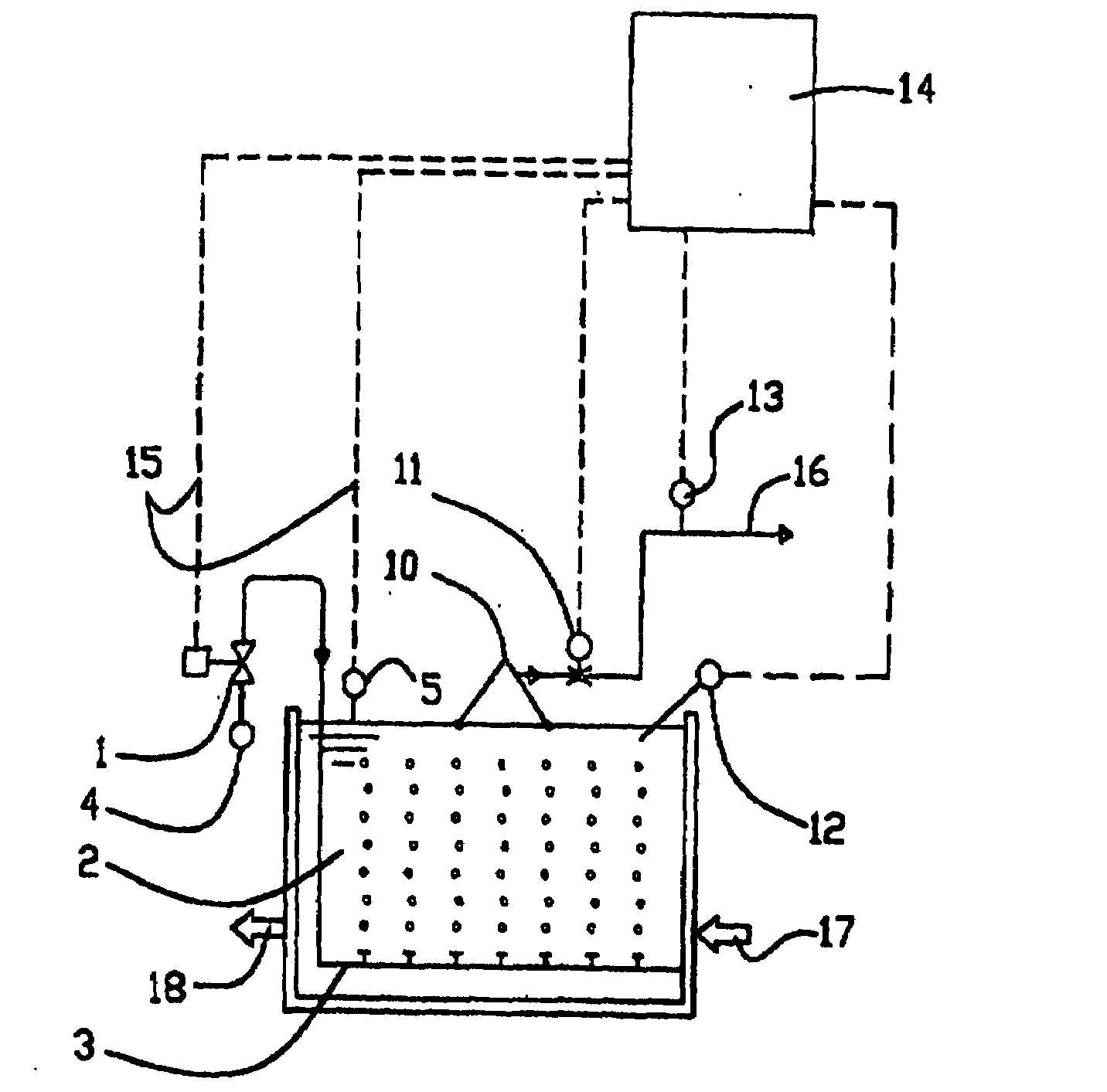

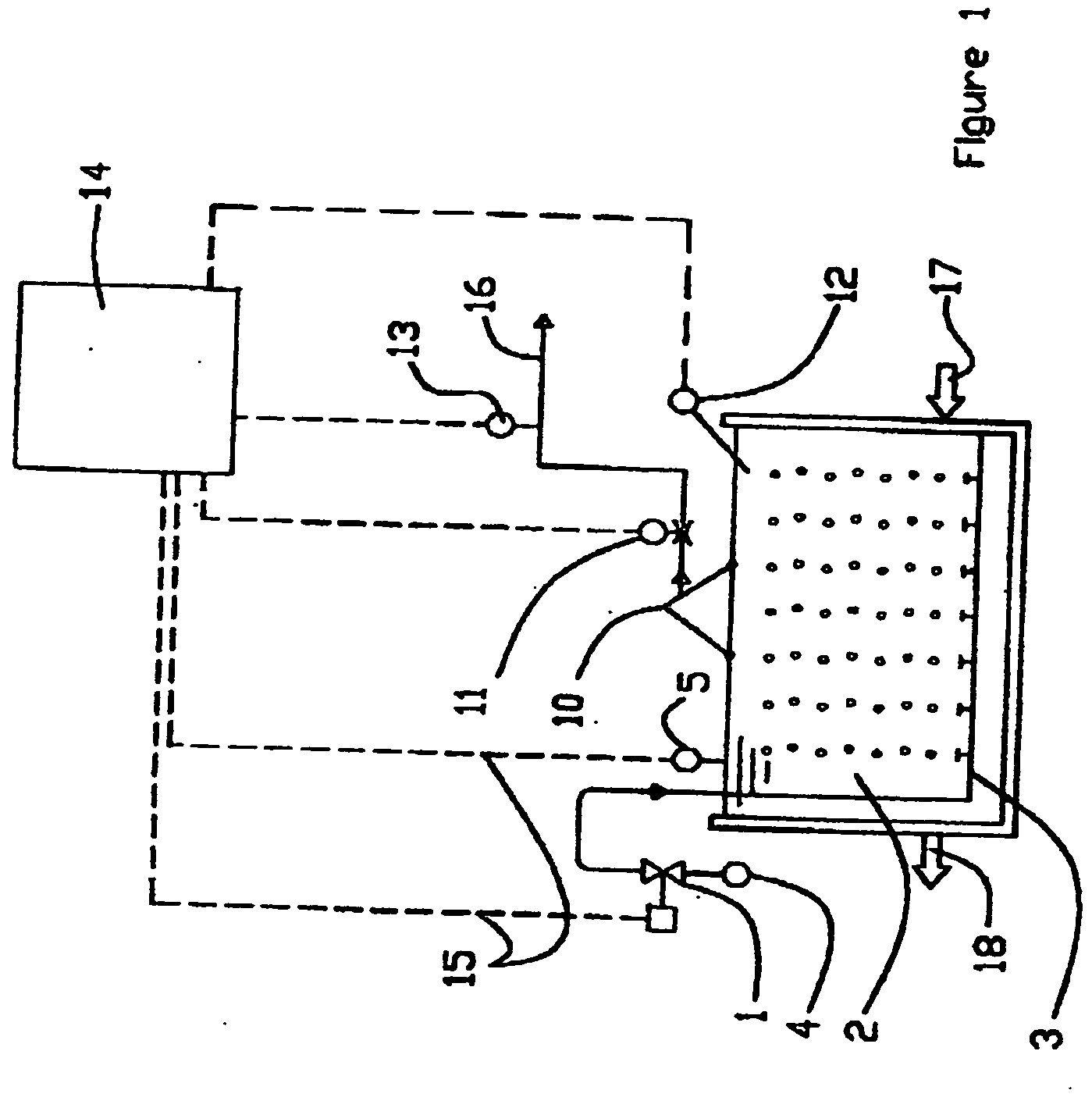

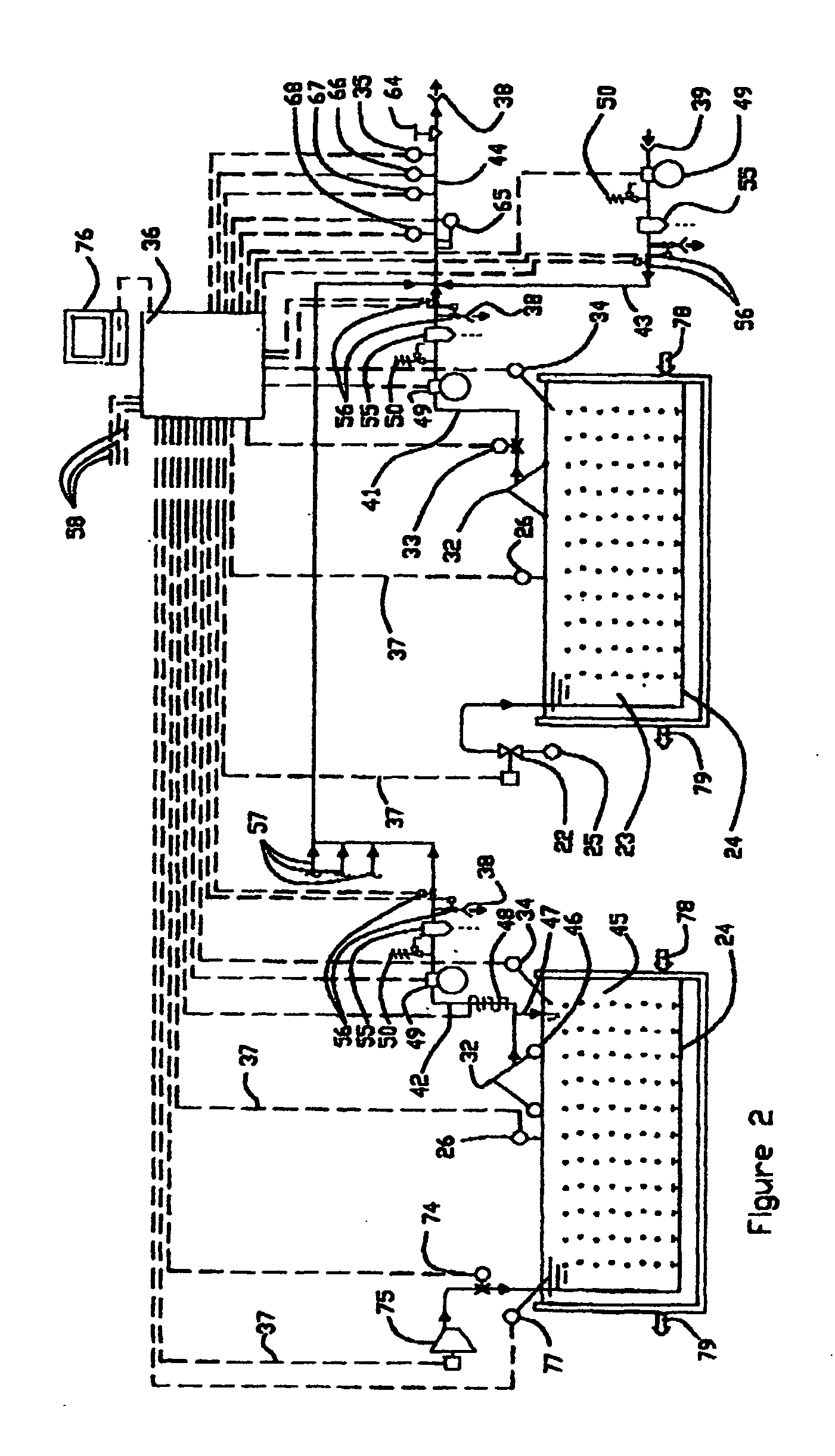

Controlling wastewater treatment processes

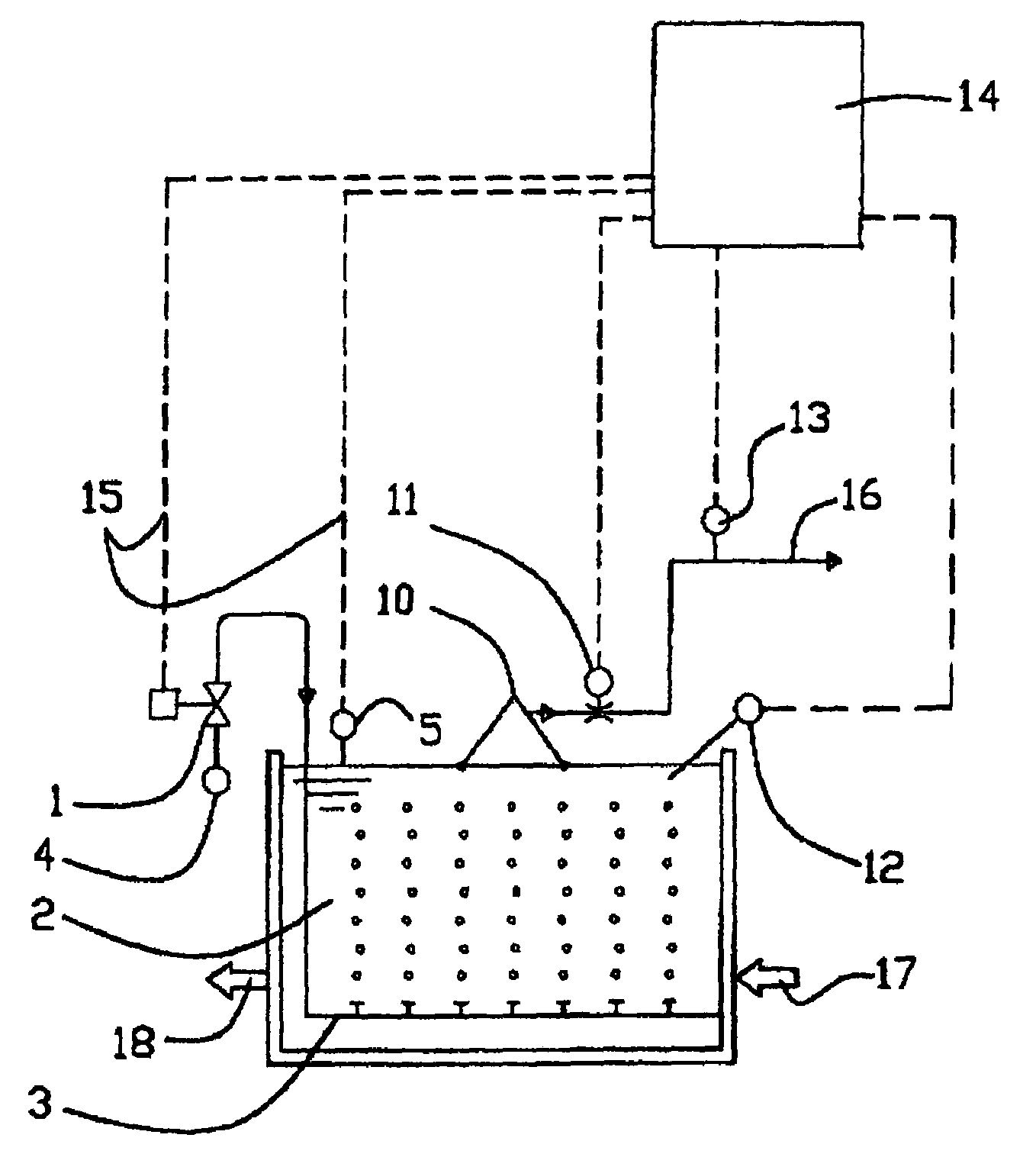

ActiveUS7449113B2Minimize impactAvoid loadWater treatment parameter controlTreatment using aerobic processesActivated sludgeAutomatic control

Methods and apparatus for continuing, automated control of wastewater treatment processes. In certain preferred embodiments, method and apparatus for control of aeration in suspended growth biological treatment processes, especially in activated sludge processes.

Owner:ADVANCED AERATION CONTROL

Controlling wastewater treatment processes

InactiveUS20090230055A1Minimize impactAvoid loadWater treatment parameter controlTreatment using aerobic processesActivated sludgeAutomatic control

Methods and apparatus for continuing, automated control of wastewater treatment processes. In certain preferred embodiments, method and apparatus for control of aeration in suspended growth biological treatment processes, especially in activated sludge processes.

Owner:ADVANCED AERATION CONTROL

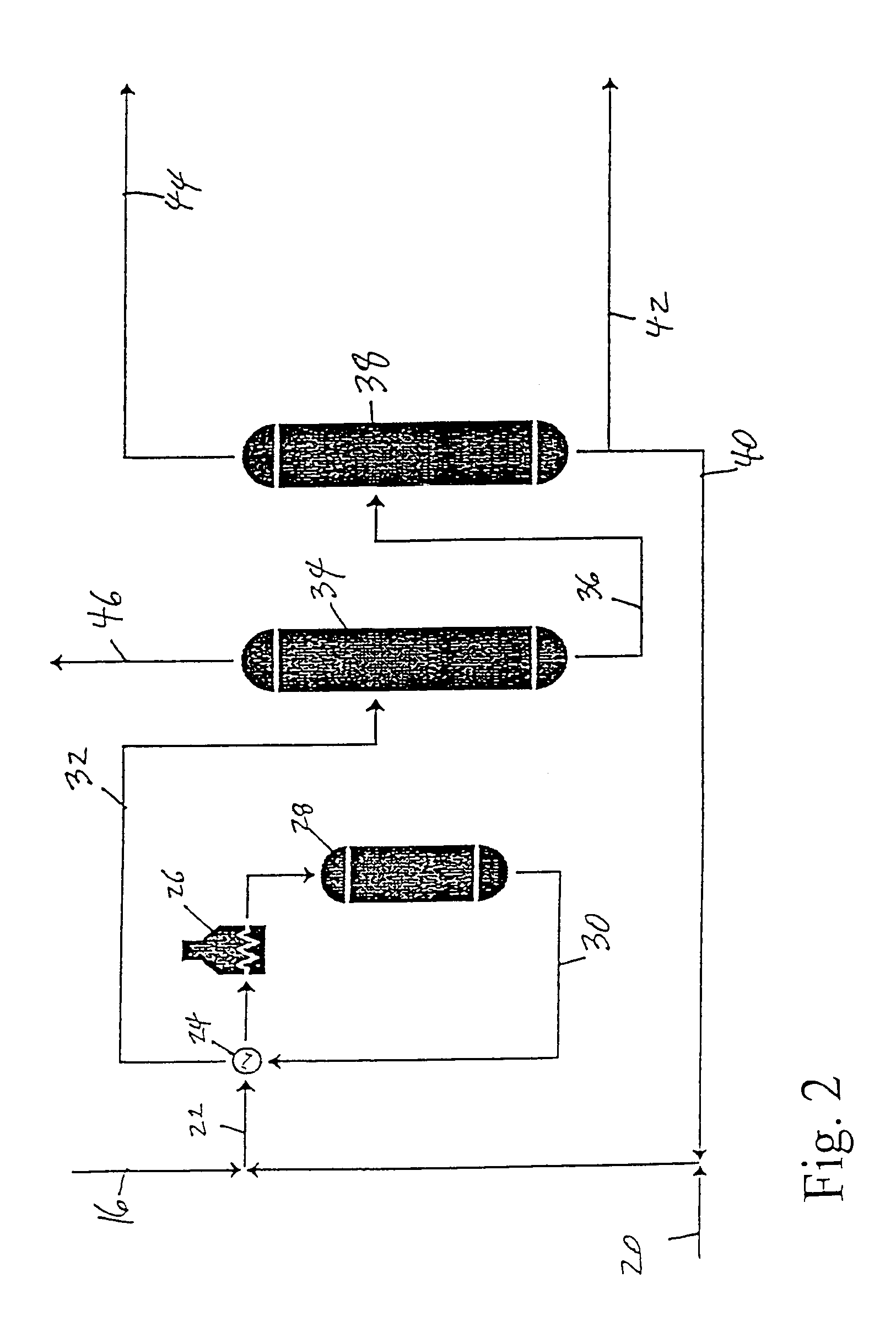

Process for production of propylene and ethylbenzene from dilute ethylene streams

InactiveUS7608745B2Significant costSignificant energyChemical industryHydrocarbon purification/separationReaction zoneEthylene

A process for producing propylene is provided which includes directing an ethylene stream from an ethylene reaction zone to a propylene reaction zone; directing a butene stream to the propylene reaction zone; reacting the ethylene stream with the butene stream in the propylene reaction zone to produce a propylene reaction stream; and subjecting the propylene reaction stream to a recovery operation to recover propylene. A processes is also provided for producing an alkylaromatic by directing an ethylene stream from a propylene reaction zone to an alkylaromatic reaction zone; directing an aromatic stream to the alkylaromatic reaction zone; reacting the ethylene stream with the aromatic stream in the alkylaromatic reaction zone to produce an alkylaromatic reaction stream; and subjecting the alkylaromatic reaction stream to a recovery operation to recover alkylaromatics. A process for producing propylene and an alkylaromatic is also provided.

Owner:LUMMUS TECH INC

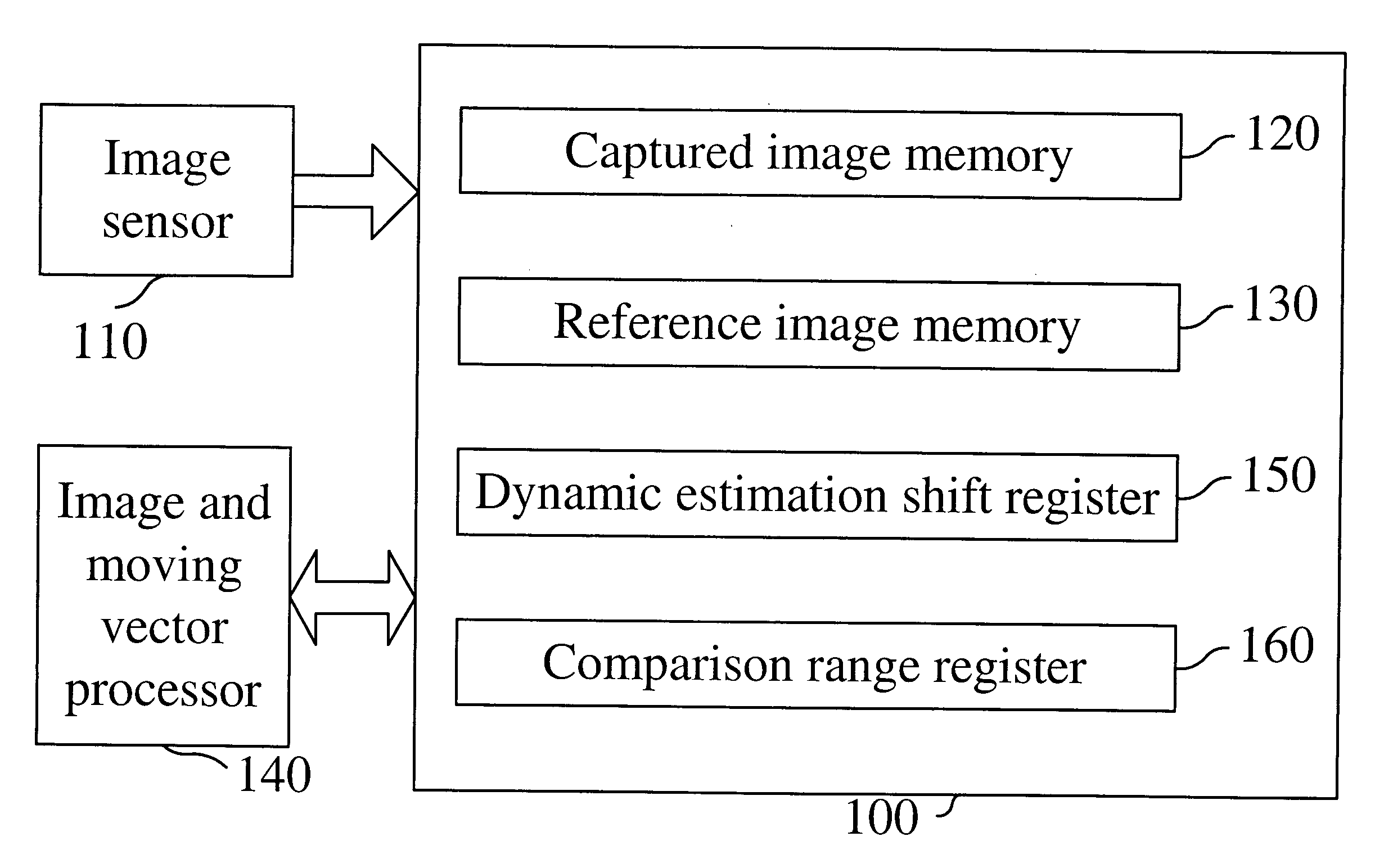

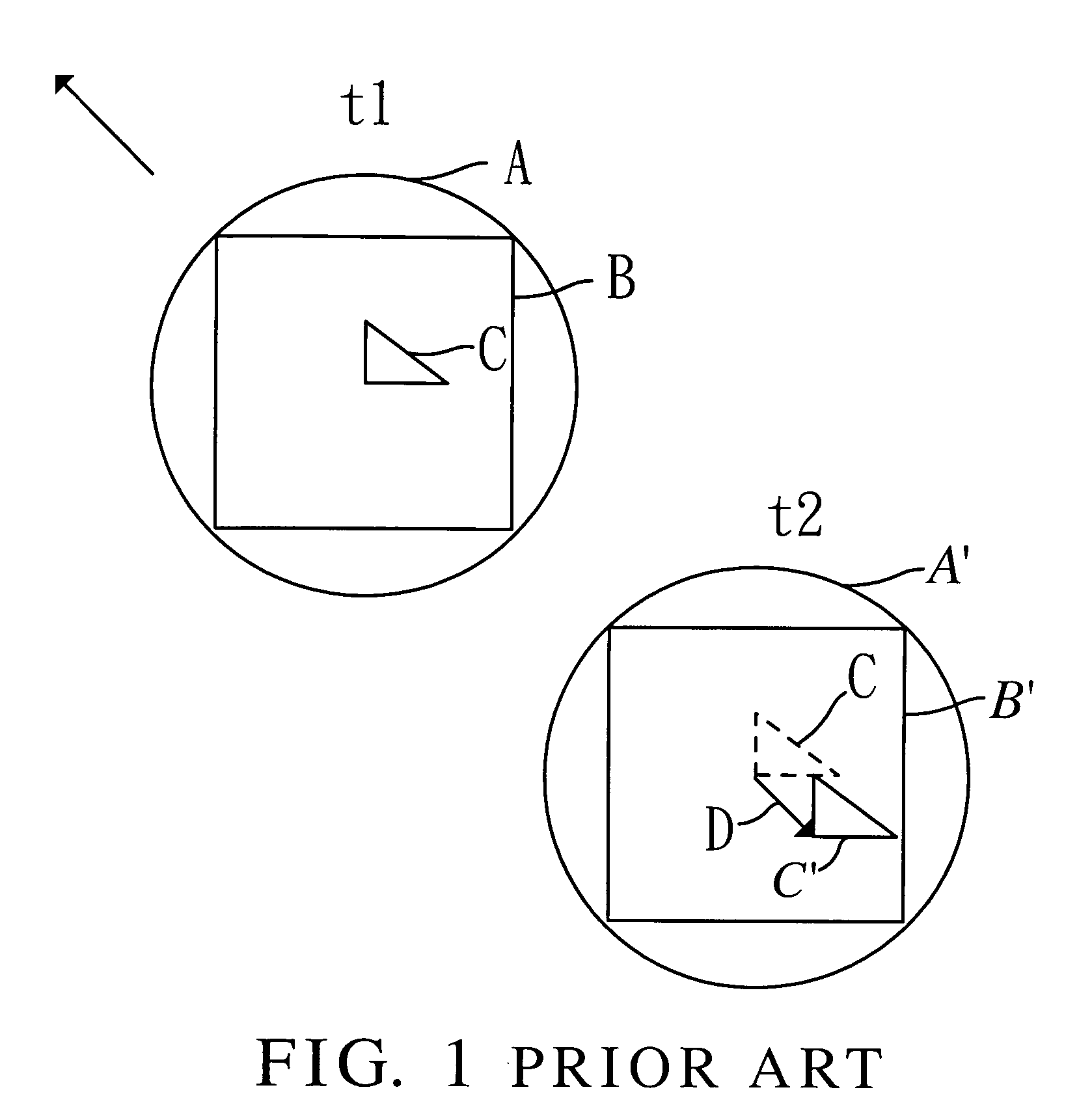

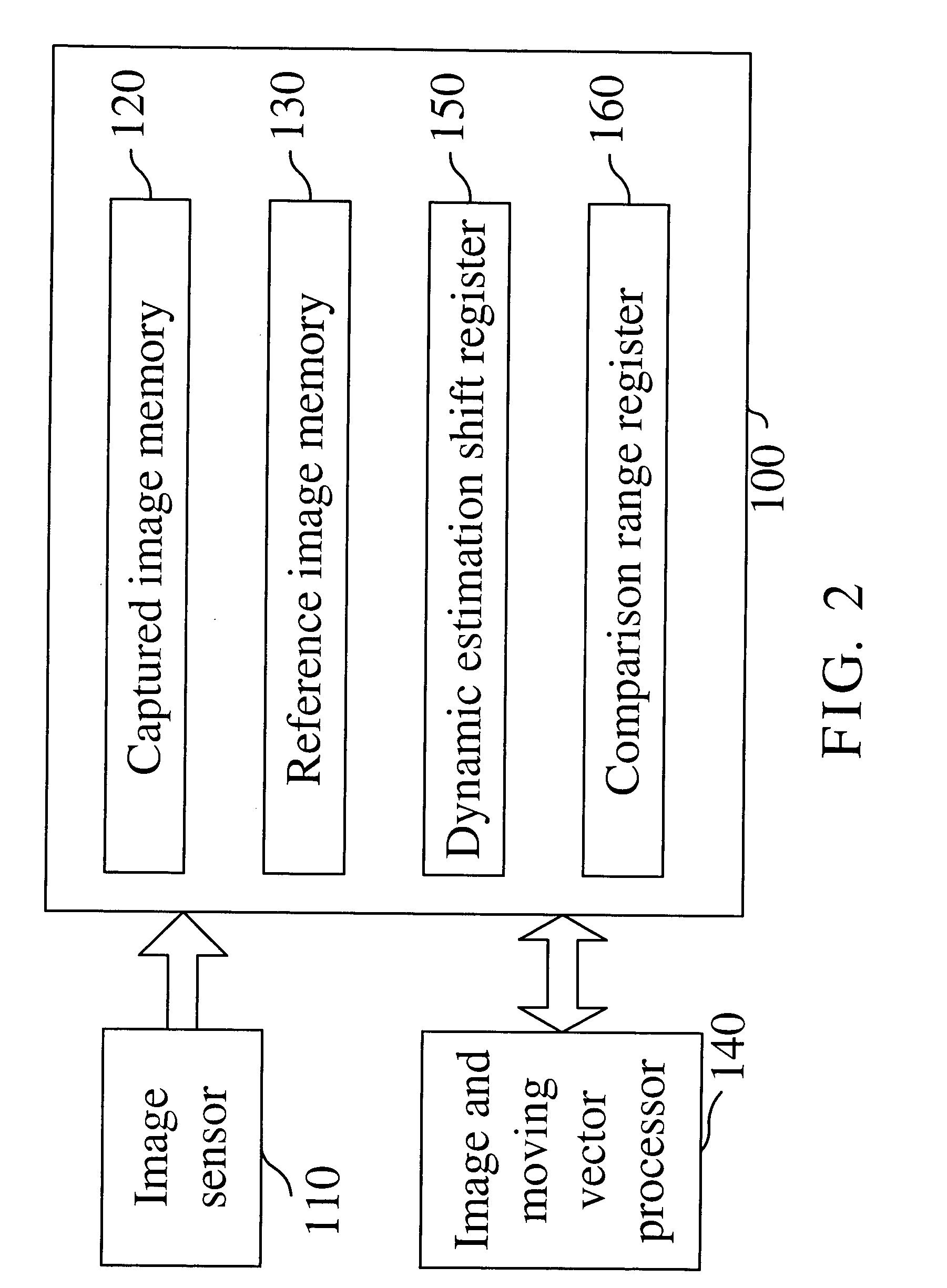

Method and apparatus for dynamically searching a moving vector of an image stream

InactiveUS20050083304A1Significant energySignificant timeInput/output for user-computer interactionImage analysisMotion vector

A method and apparatus for dynamically searching moving vector of an image stream, which captures a previous image for determining a target area in the previous image, captures a current image at a next sampling time for comparing the previous image and the current image so that a matched area with the target area is found to accordingly determine a moving vector and offset in the image stream, captures a next image at a next sampling time for determining an estimated area in the next image in accordance with the moving vector and further updates the moving vector and offset in the image stream in accordance with matched part found in the estimated area as compared with the target area.

Owner:SUNPLUS TECH CO LTD

Embeddable flash memory system for non-volatile storage of code, data and bit-streams for embedded FPGA configurations

InactiveUS7251705B2Significant energySignificant performanceMemory adressing/allocation/relocationRead-only memoriesEmbedded technologyApplication specific

An application-specific embeddable flash memory having three content-specific I / O ports and delivering a peak read throughput of 1.2 GB / s. The memory is combined with a special automatic programming gate voltage ramp generator circuit having a programming rate of 1 Mbyte / s for non-volatile storage of code, data, and embedded FPGA bit stream configurations. The test chip uses a NOR-type 0.18 μm flash embedded technology with 1.8V power supply, two poly, six metal and memory cell size of 0.35 μm2.

Owner:STMICROELECTRONICS SRL

Apparatuses, methods, and systems for a configurable accelerator having dataflow execution circuits

PendingUS20220100680A1Easy to adaptImprove performanceEnergy efficient computingElectric digital data processingData streamData memory

Systems, methods, and apparatuses relating to a configurable accelerator having dataflow execution circuits are described. In one embodiment, a hardware accelerator includes a plurality of dataflow execution circuits that each comprise a register file, a plurality of execution circuits, and a graph station circuit comprising a plurality of dataflow operation entries that each include a respective ready field that indicates when an input operand for a dataflow operation is available in the register file, and the graph station circuit is to select for execution a first dataflow operation entry when its input operands are available, and clear ready fields of the input operands in the first dataflow operation entry when a result of the execution is stored in the register file; a cross dependence network coupled between the plurality of dataflow execution circuits to send data between the plurality of dataflow execution circuits according to a second dataflow operation entry; and a memory execution interface coupled between the plurality of dataflow execution circuits and a cache bank to send data between the plurality of dataflow execution circuits and the cache bank according to a third dataflow operation entry.

Owner:INTEL CORP

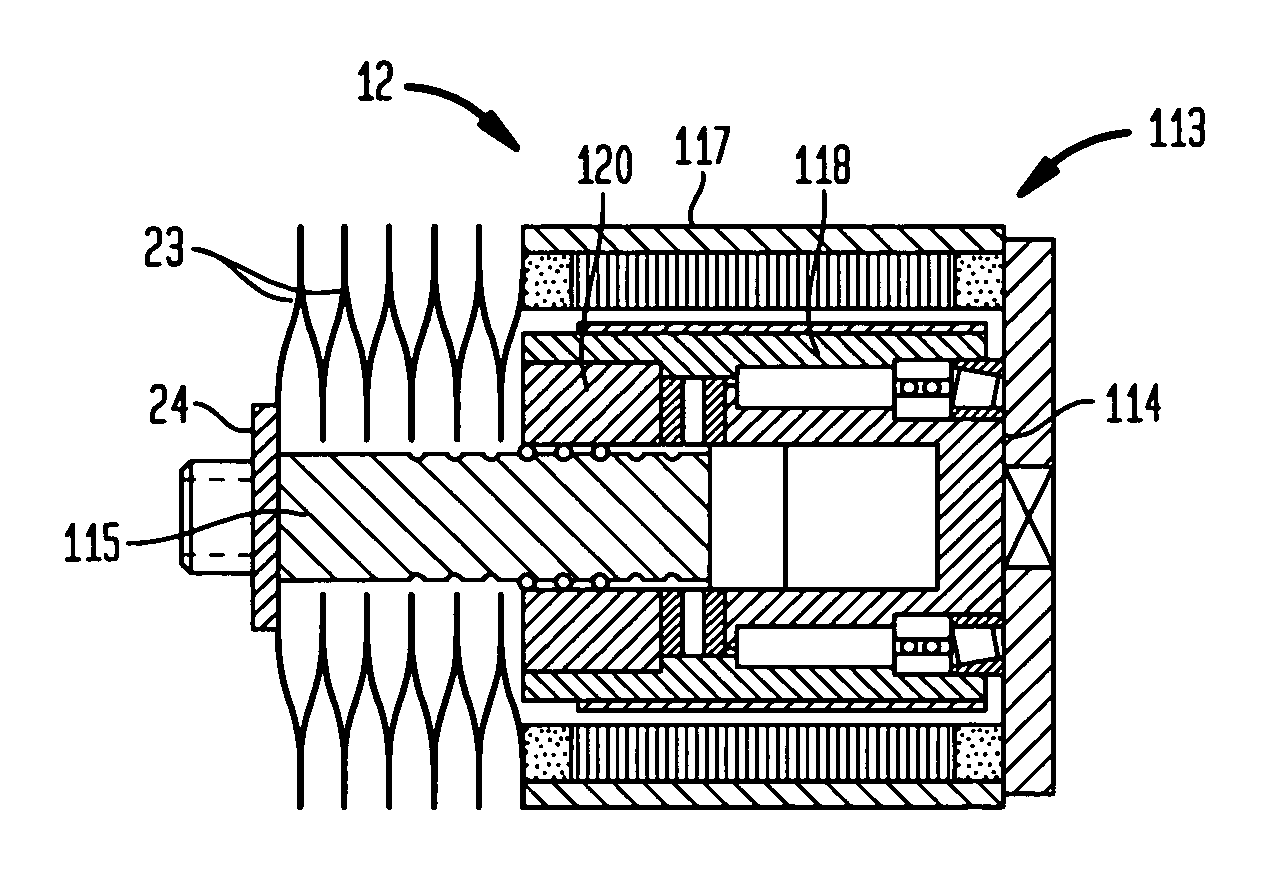

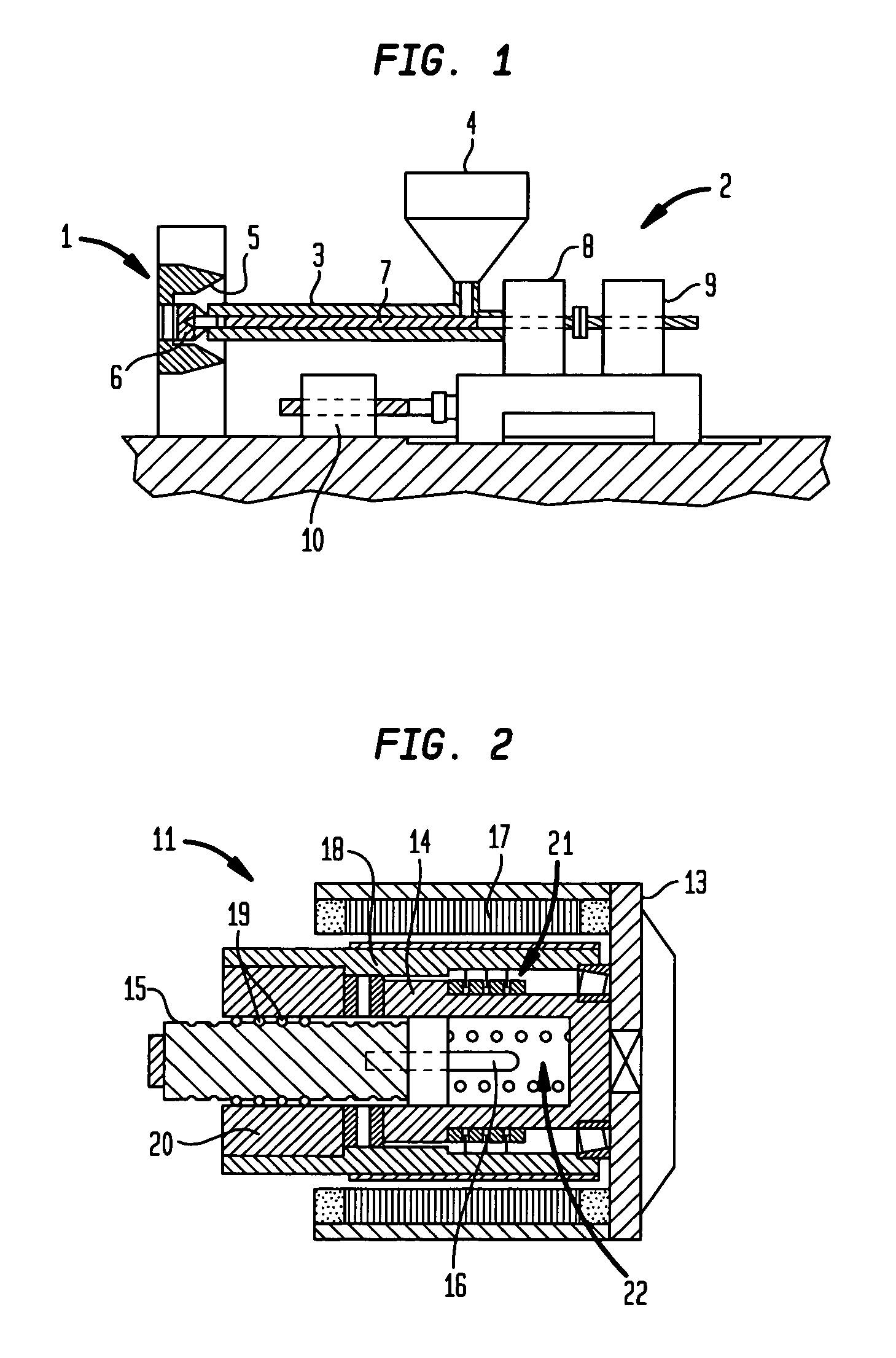

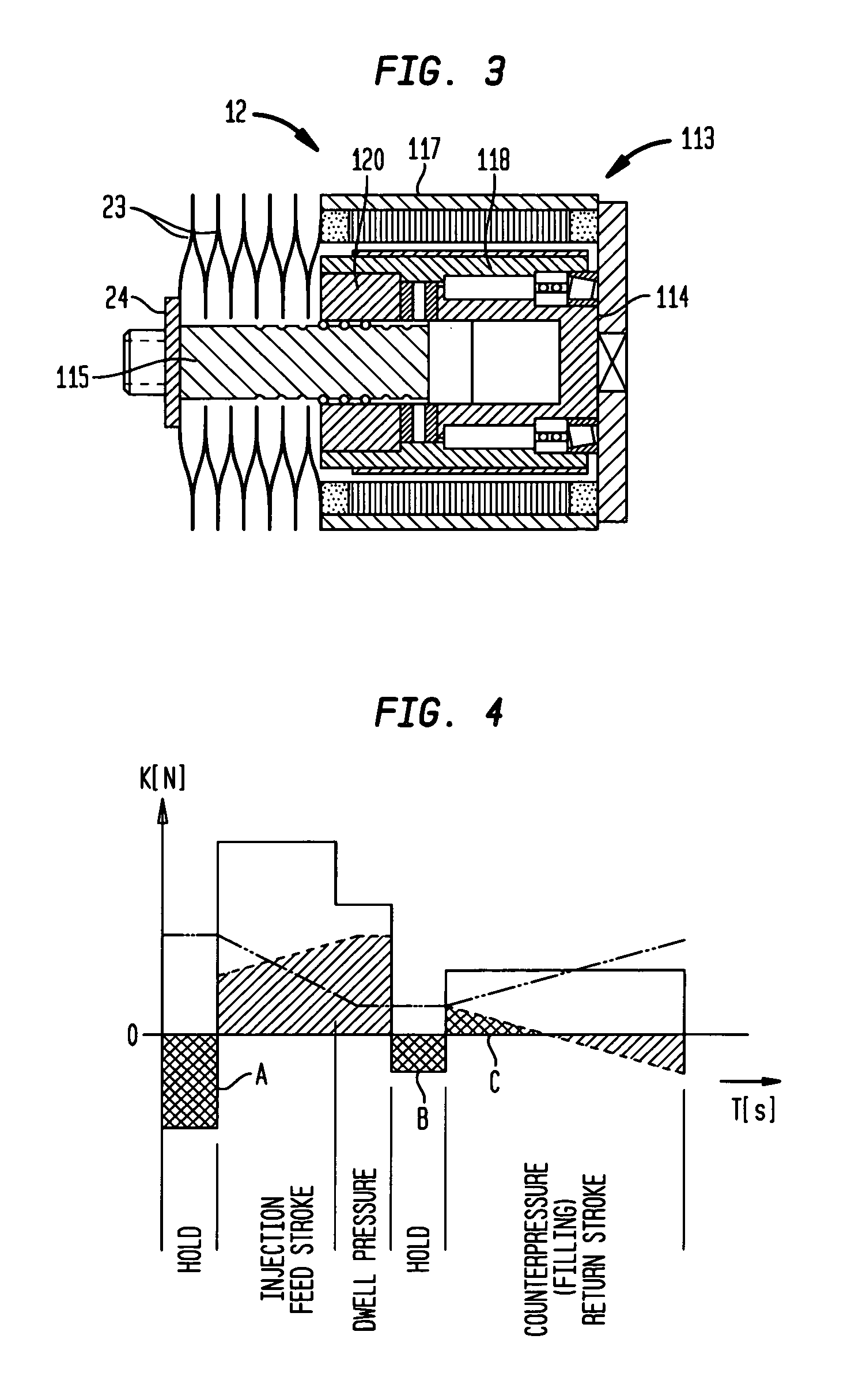

Plasticizing unit with an electromotive spindle drive for an injection molding machine

InactiveUS7112056B2High strengthDoes not consume energyFood shapingElectrical energy consumptionEngineering

An actuating drive for a plasticizing unit of an injection molding machine is disclosed. The actuating drive includes a spindle drive with an electric motor and a control mechanism. An energy storage device is coupled with the spindle drive for force transmission therebetween. The energy storage device is loaded by the spindle drive in a return stroke phase and is unloaded in a forward feed phase, boosting the power of an electric motor. The actuator drive can be used, for example, for pulsating actuation of a mold ejector of the injection molding machine, significantly reducing the electrical energy consumption compared to conventional drives.

Owner:SUMITOMO SHI DEMAG PLASTICS MACHINERY

Digital architecture for reconfigurable computing in digital signal processing

ActiveUS20050015573A1Easing elaborationSignificant energyConcurrent instruction executionArchitecture with single central processing unitDigital signal processingComputational logic

A digital embedded architecture, includes a microcontroller and a memory device, suitable for reconfigurable computing in digital signal processing and comprising: a processor, structured to implement a Very Long Instruction Word elaboration mode by a general purpose hardwired computational logic, and an additional data elaboration channel comprising a reconfigurable function unit based on a pipelined array of configurable look-up table based cells controlled by a special purpose control unit, thus easing the elaboration of critical kernels algorithms.

Owner:STMICROELECTRONICS SRL

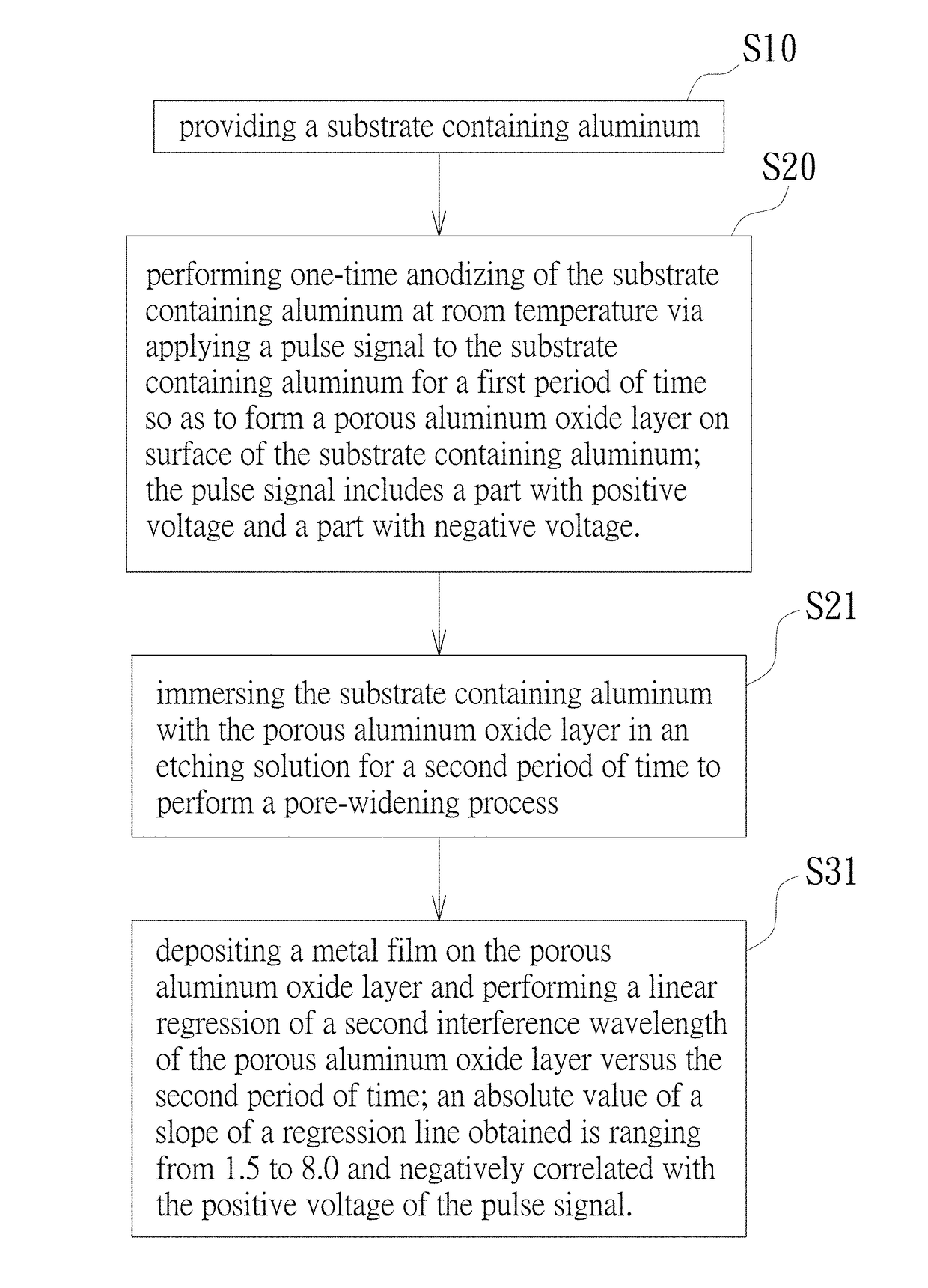

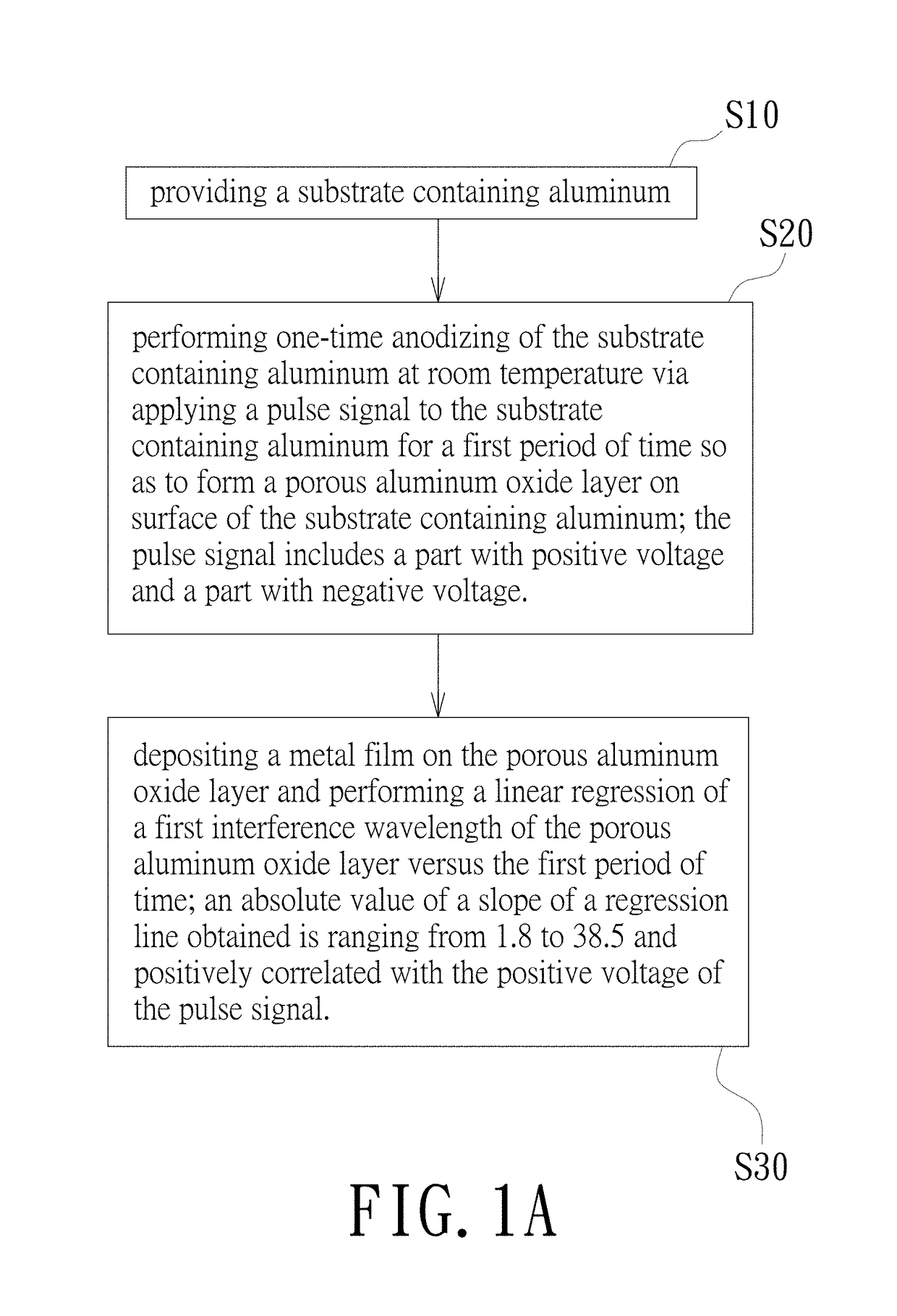

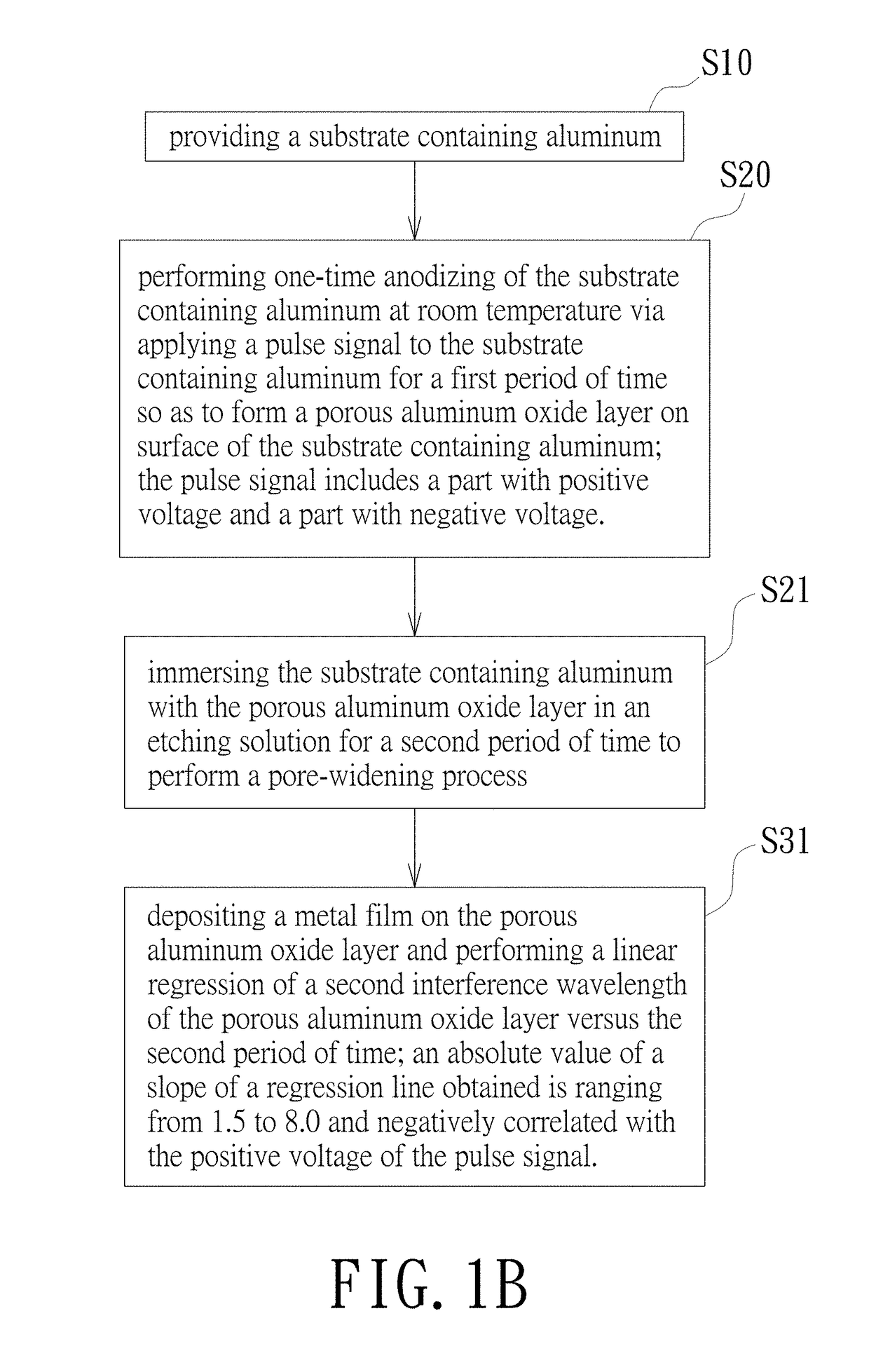

Method for dye-free coloring of one-time anodic aluminum oxide surface

ActiveUS20180016696A1Reduction in production timeEnergy and cost savingAnodisationSignal onAnodic oxidation

A method for dye-free coloring of one-time anodic aluminum oxide surface is revealed. First provide a substrate containing aluminum. The substrate containing aluminum is anodized once at room temperature. The anodizing process includes a step of applying a pulse signal on the substrate containing aluminum for a first period of time. Thus a porous aluminum oxide layer is formed on surface of the substrate containing aluminum. The pulse signal includes a part with positive voltage and a part with negative voltage. Then a metal layer is deposited on the surface of the porous aluminum oxide layer. The porous aluminum oxide layer has a first interference wavelength. Next perform a linear regression of the first interference wavelength versus the first period of time. The absolute value of the slope of the regression line obtained ranges from 1.8 to 38.5. The absolute value is positively correlated with the positive voltage.

Owner:NAT CHENG KUNG UNIV

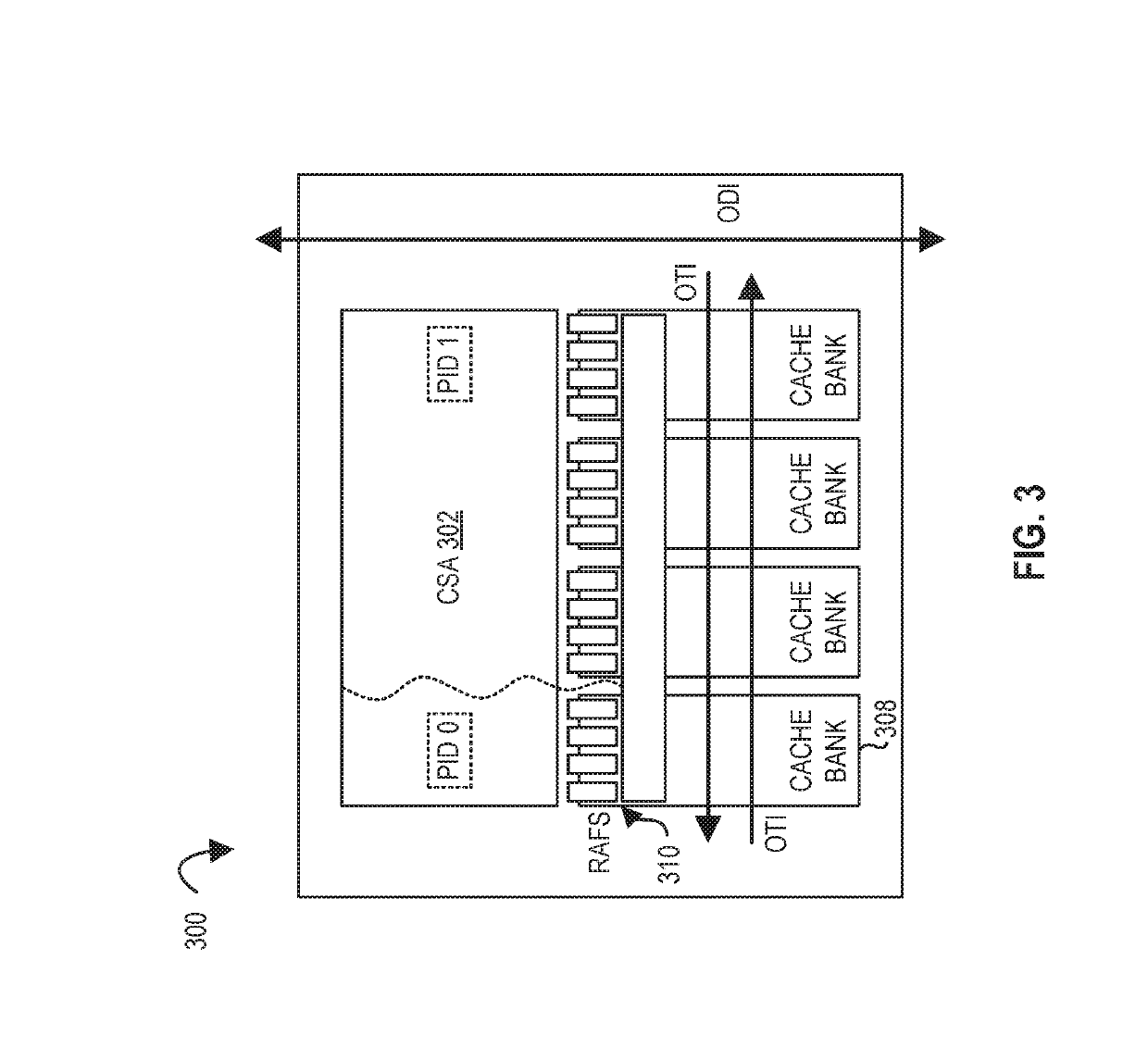

Apparatuses, methods, and systems for swizzle operations in a configurable spatial accelerator

ActiveUS20200310797A1Easy to adaptImprove performanceSingle instruction multiple data multiprocessorsInstruction analysisSoftware engineeringProcessing element

Systems, methods, and apparatuses relating to swizzle operations and disable operations in a configurable spatial accelerator (CSA) are described. Certain embodiments herein provide for an encoding system for a specific set of swizzle primitives across a plurality of packed data elements in a CSA. In one embodiment, a CSA includes a plurality of processing elements, a circuit switched interconnect network between the plurality of processing elements, and a configuration register within each processing element to store a configuration value having a first portion that, when set to a first value that indicates a first mode, causes the processing element to pass an input value to operation circuitry of the processing element without modifying the input value, and, when set to a second value that indicates a second mode, causes the processing element to perform a swizzle operation on the input value to form a swizzled input value before sending the swizzled input value to the operation circuitry of the processing element, and a second portion that causes the processing element to perform an operation indicated by the second portion the configuration value on the input value in the first mode and the swizzled input value in the second mode with the operation circuitry.

Owner:INTEL CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com