Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Shortened TAT" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

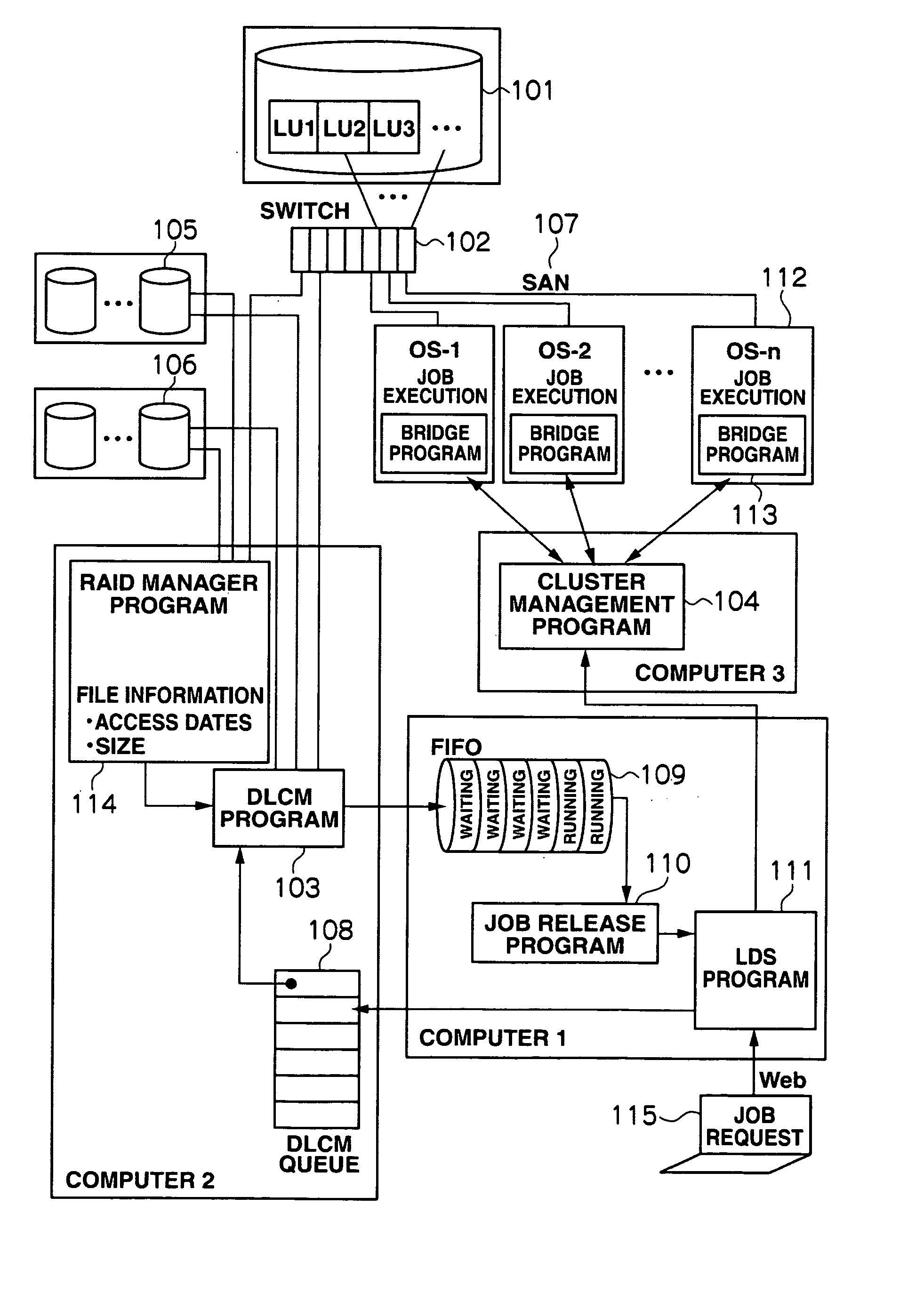

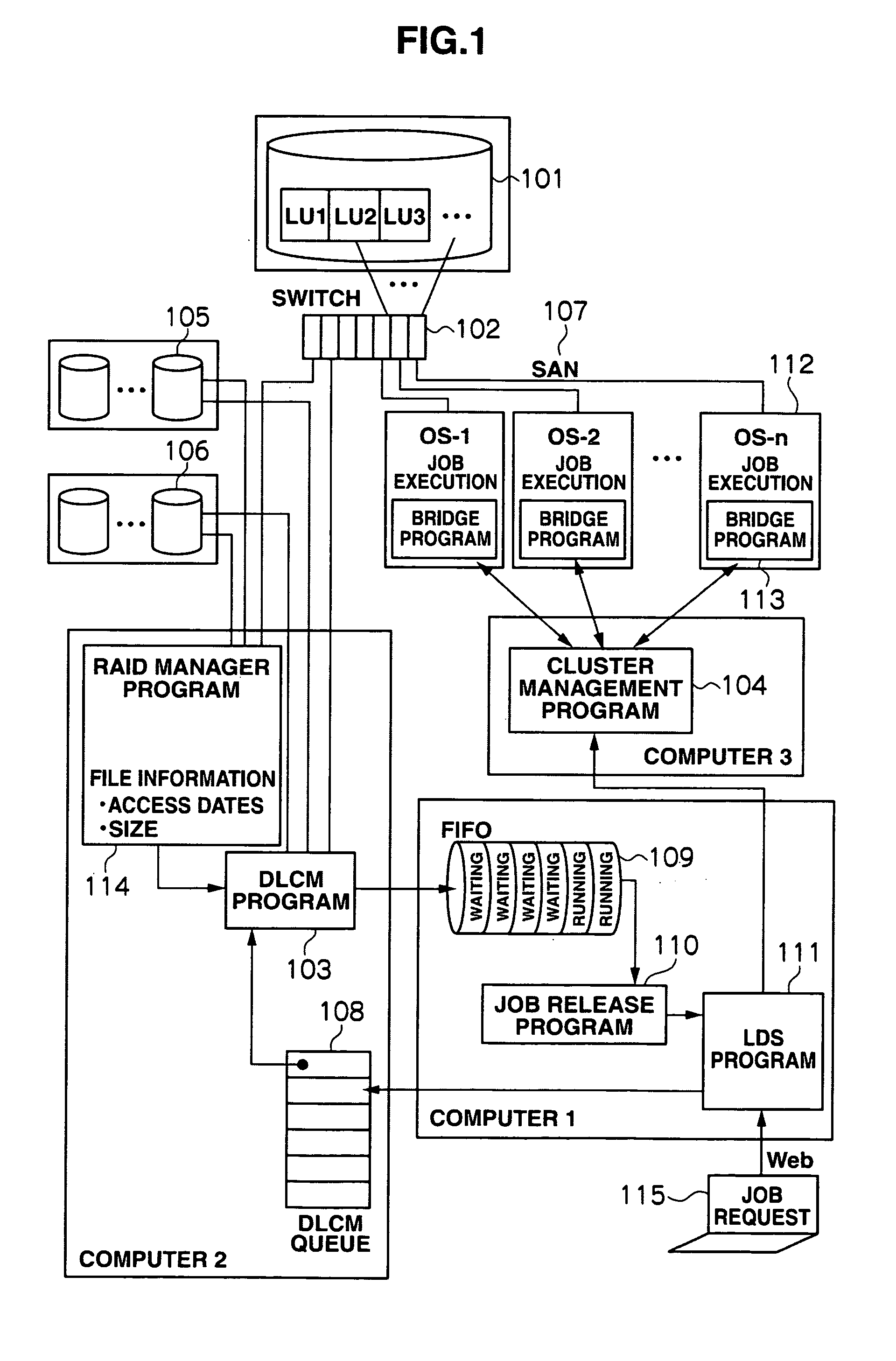

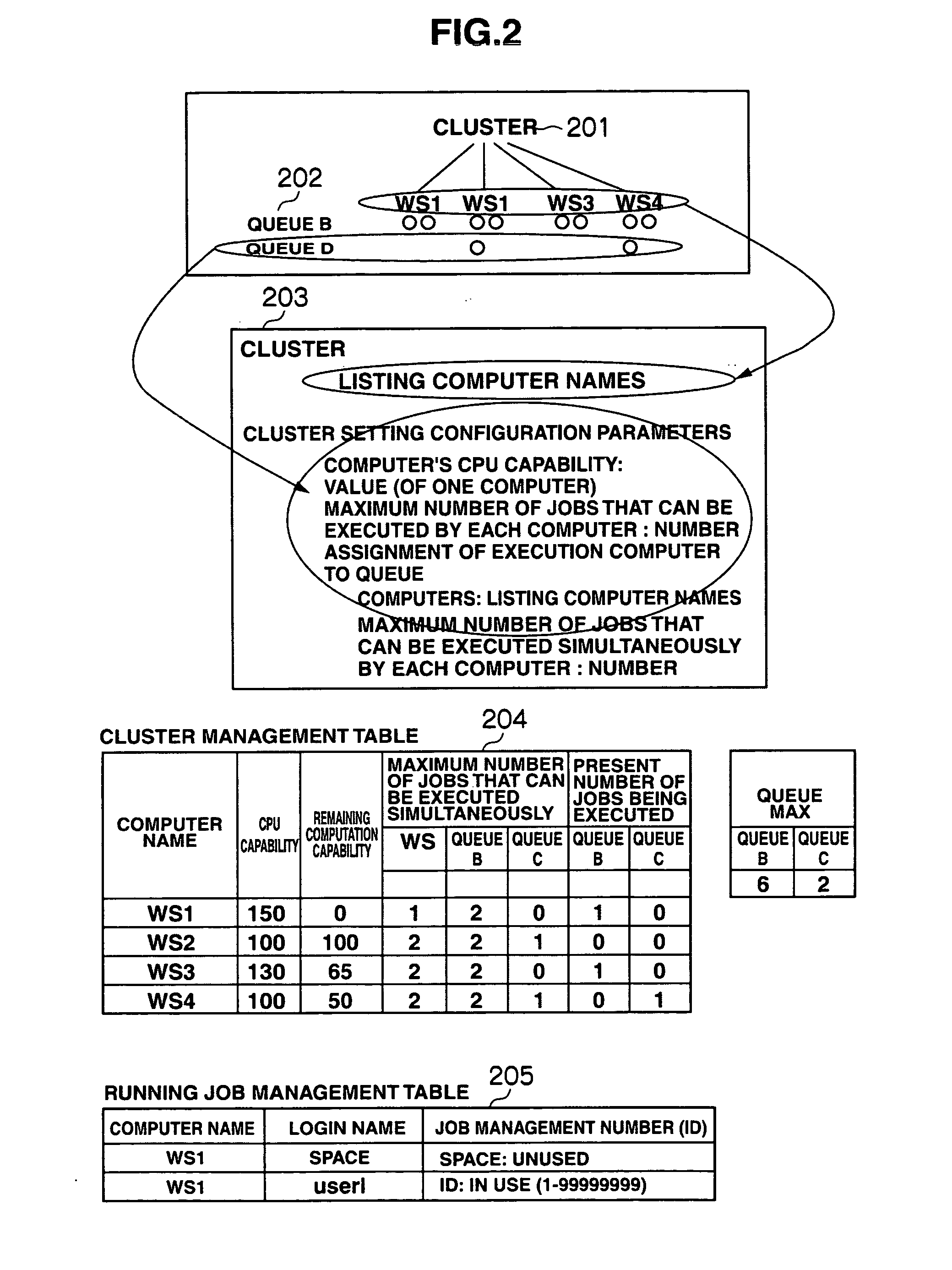

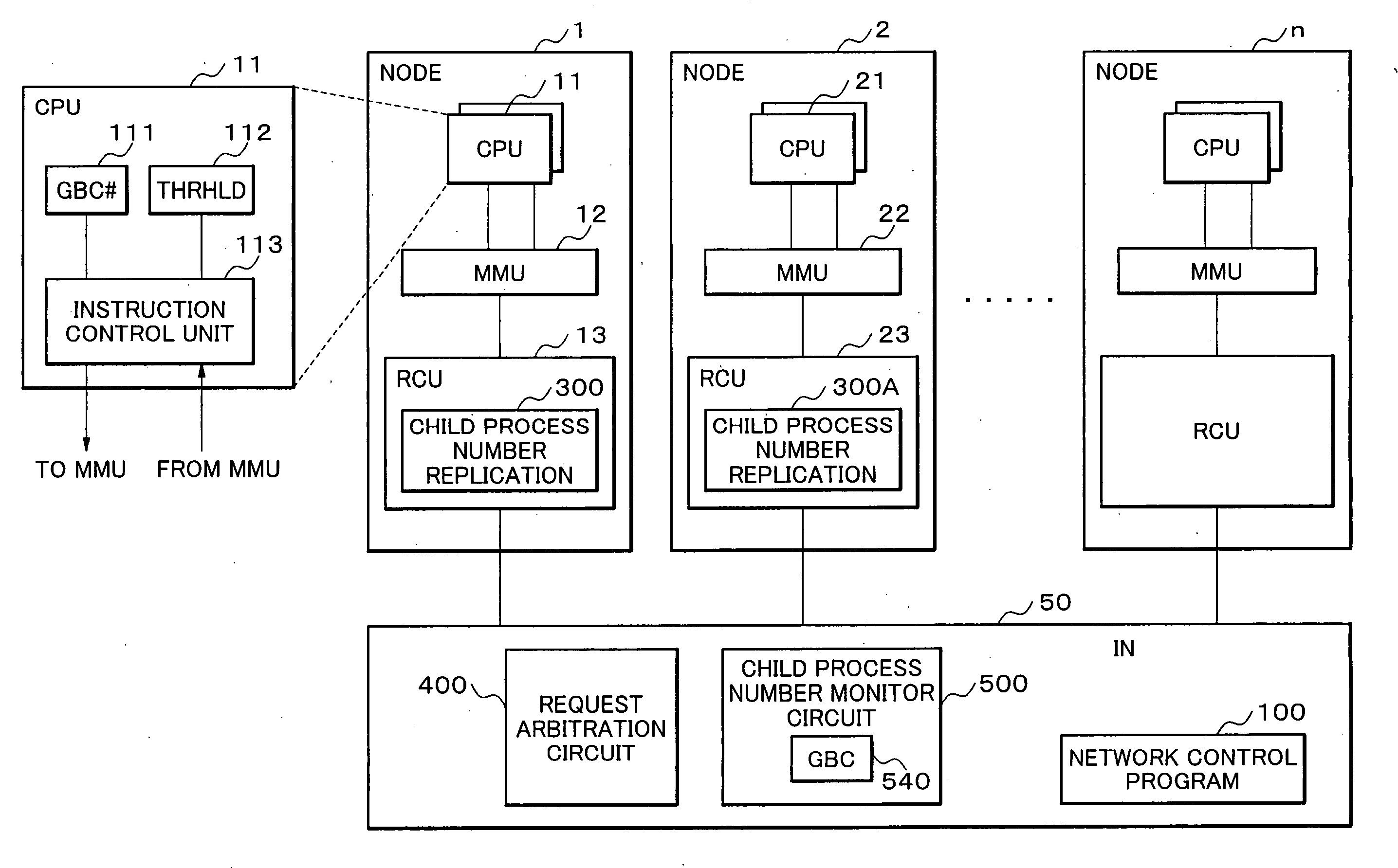

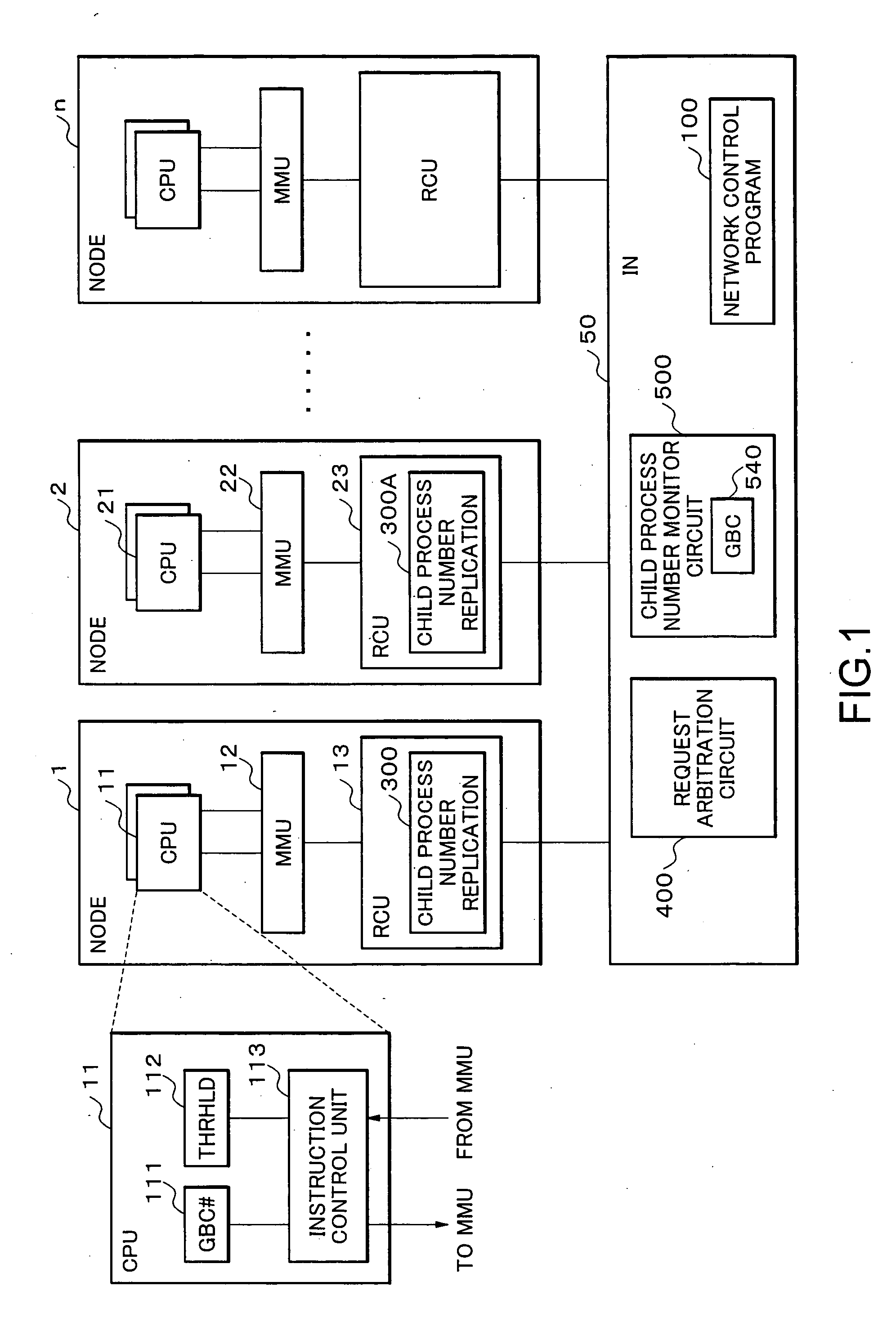

Load distribution control system and method

InactiveUS20080007765A1Efficient processingImprove access performanceDigital computer detailsMultiprogramming arrangementsDistribution controlControl system

Processing time for job execution is shortened by using computation capability to the maximum extent possible.When a user makes a job request, the job request is sent from an LDS program of a first computer to a second computer; the second computer executes data preparation processing and empty area reservation processing with regard to a storage unit (disk A) and stores the results to an the FIFO of the first computer; when the output from the FIFO is transferred via a job release program to the LDS program, the transferred content is then transferred to a third computer; and the third computer selects a computer that should execute the job, from among a group of computers and commands the selected computer to execute the job.

Owner:HITACHI LTD

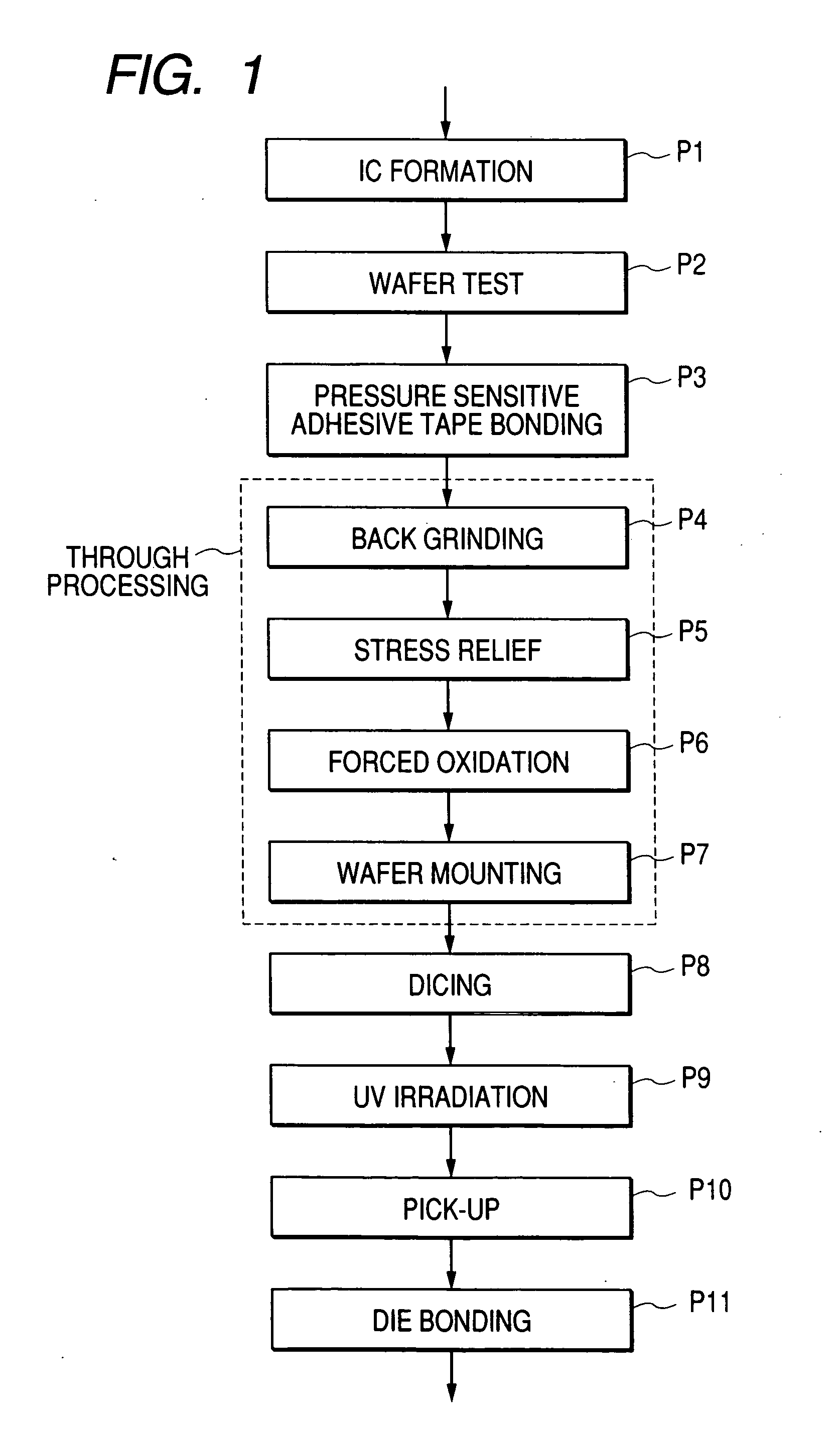

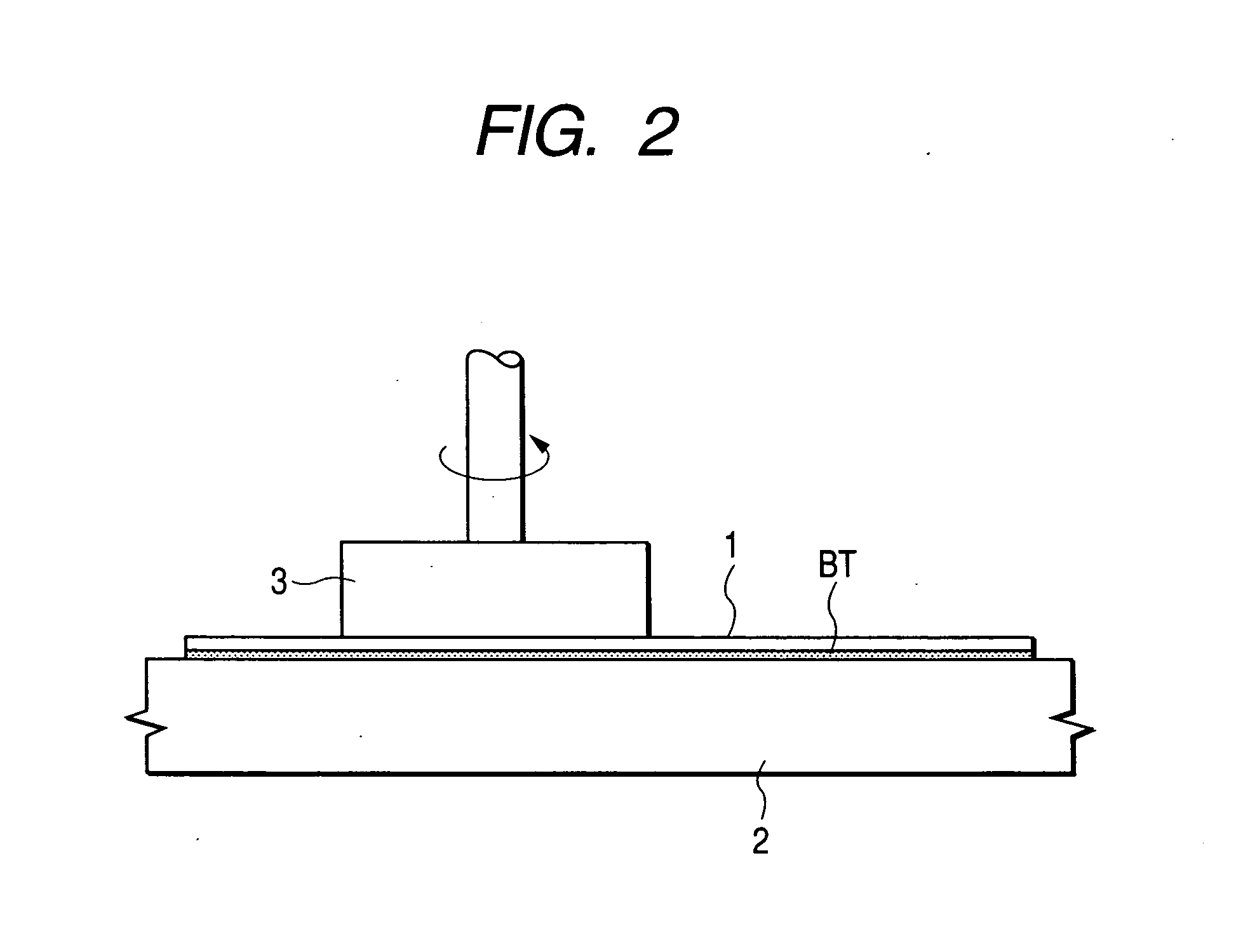

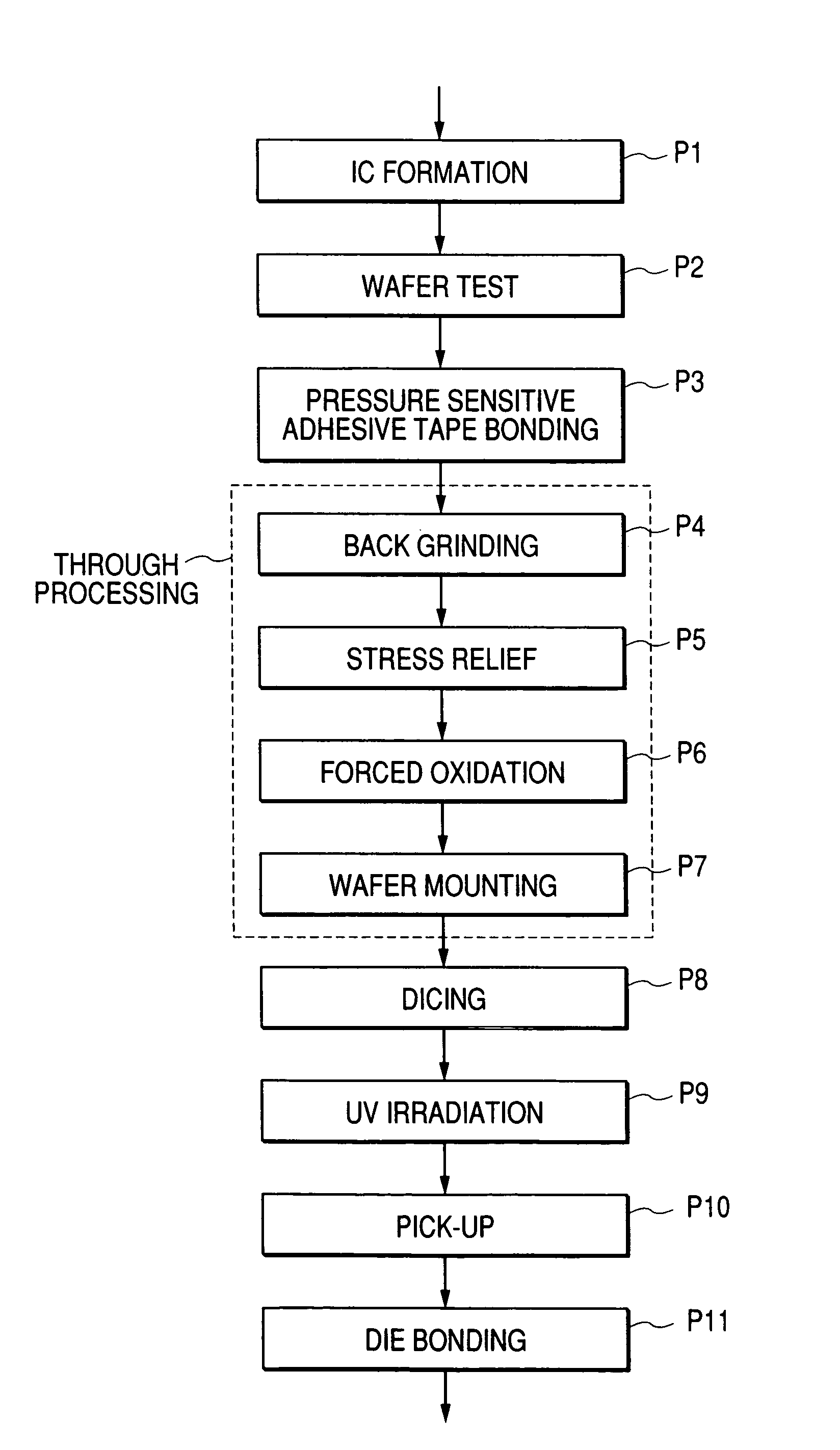

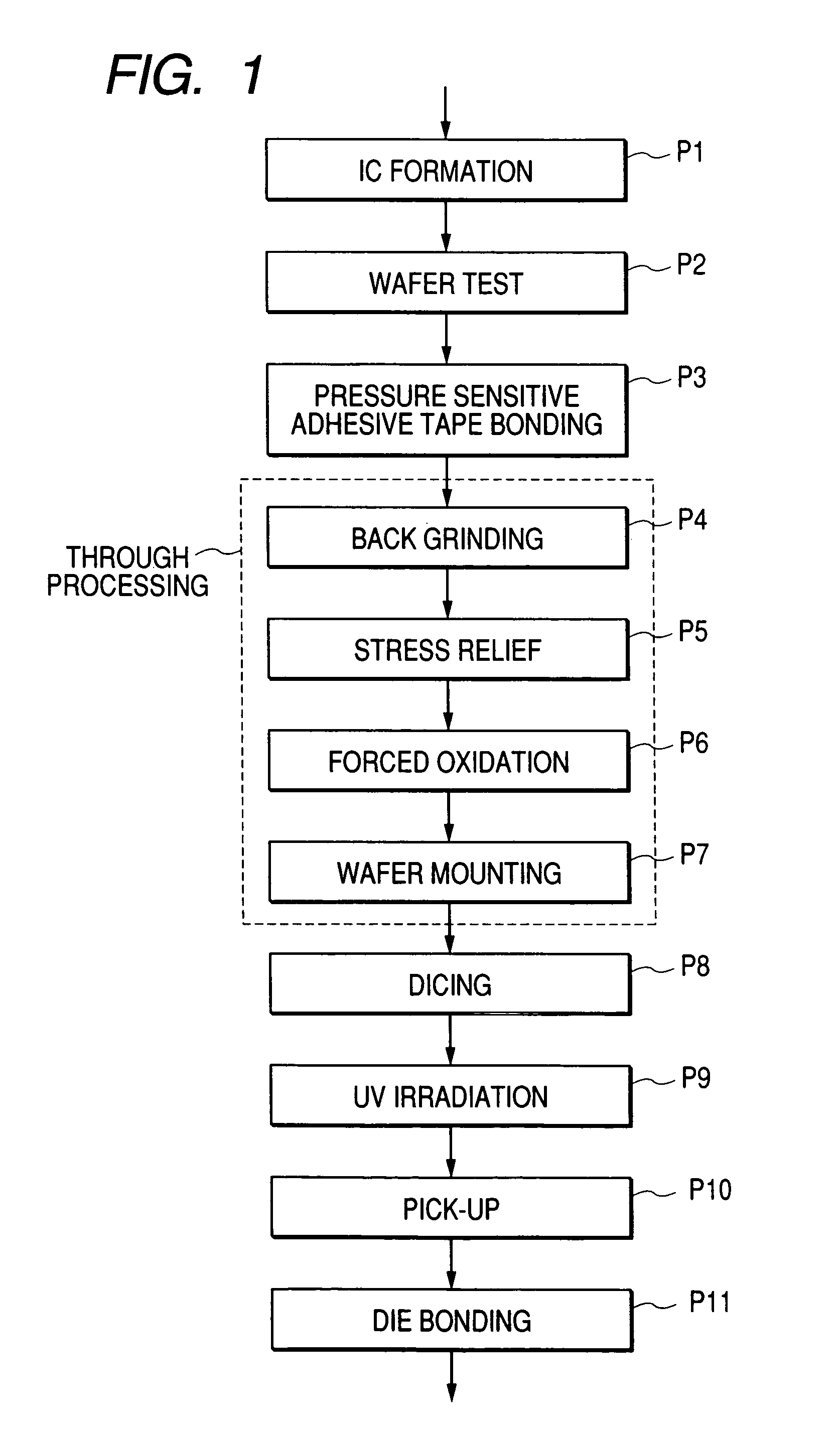

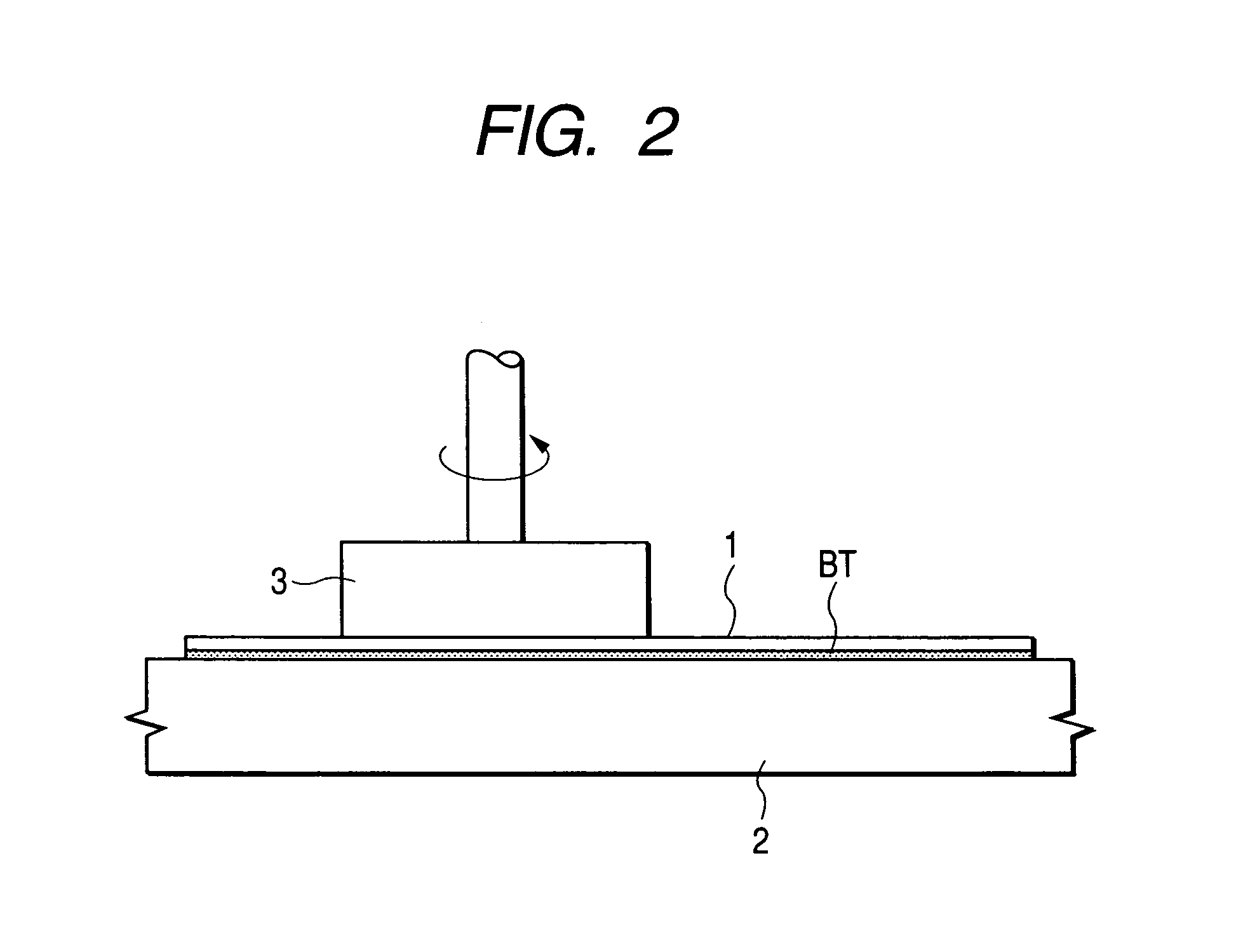

Fabrication method of semiconductor integrated circuit device

InactiveUS20050142815A1Wafer thickness reductionEasy to separateSolid-state devicesSemiconductor/solid-state device manufacturingWaferingDicing tape

A technique capable of stably releasing chips from a dicing tape, includes grinding a back surface of a semiconductor wafer, while adhering a pressure sensitive adhesive tape to a circuit forming surface of the semiconductor wafer formed with an integrated circuit, to achieve a predetermined thickness and forcibly oxidizing the back surface of the semiconductor wafer. Then, the pressure sensitive adhesive tape adhered to the circuit forming surface of the semiconductor wafer is released, and a dicing tape is adhered to the back surface of the semiconductor wafer. Further, the semiconductor wafer is divided by dicing it into individual chips, and then the back surface of the chip is pressed by way of the dicing tape, thereby releasing the chips from the dicing tape.

Owner:RENESAS ELECTRONICS CORP

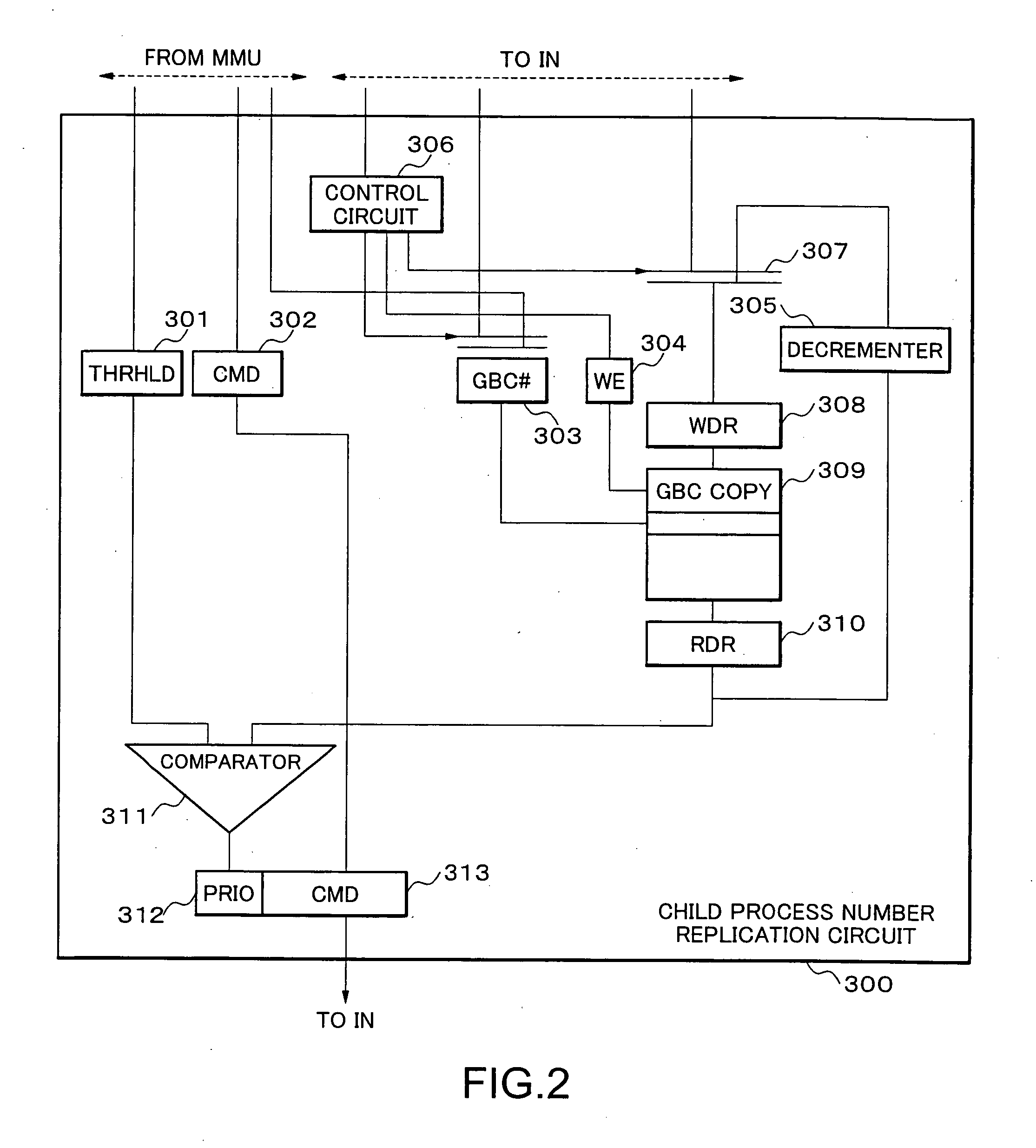

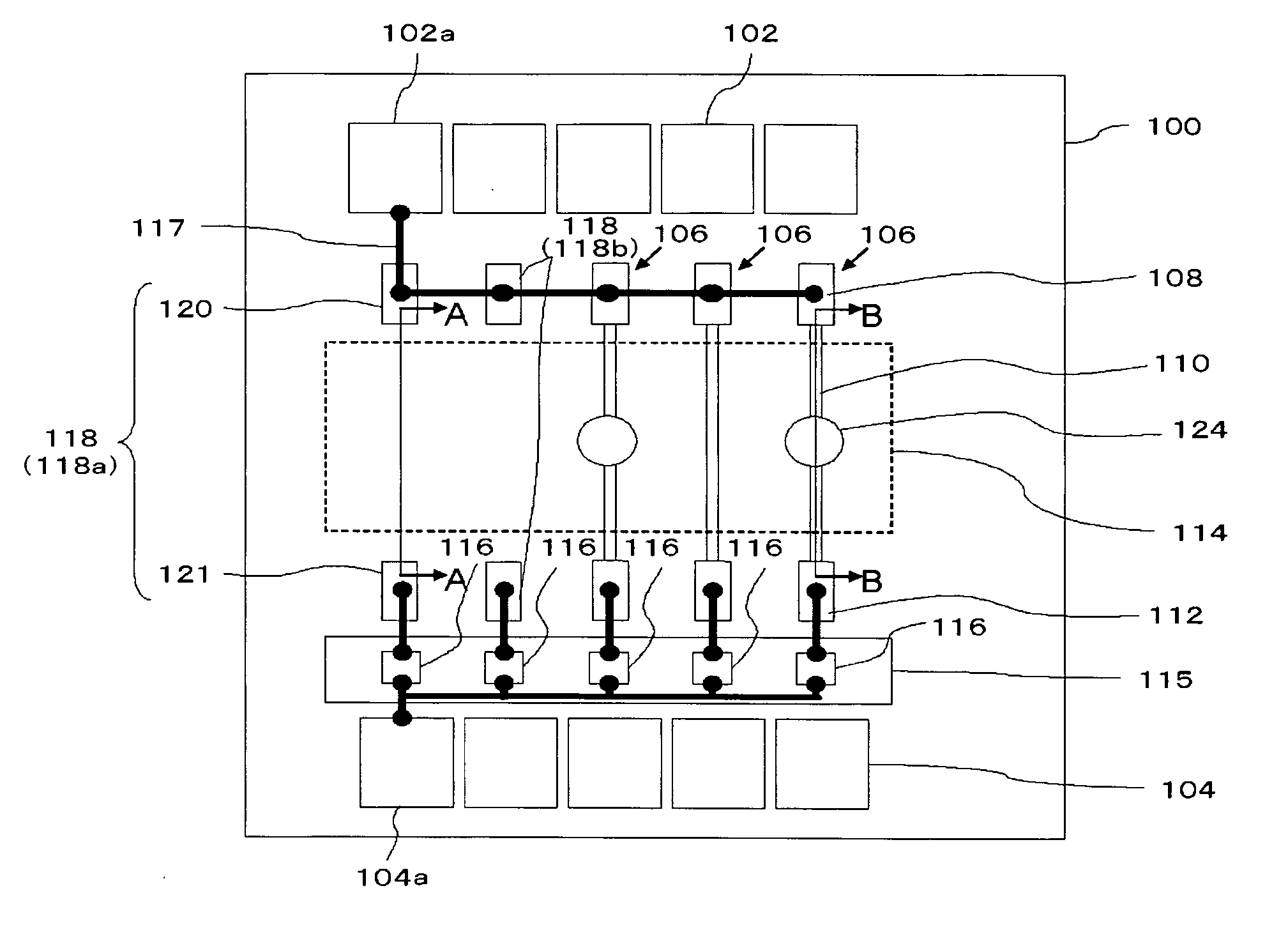

Parallel processing system, interconnection network, node and network control method, and program therefor

InactiveUS20060059489A1Shortened TATImprove system efficiencyProgram synchronisationMemory systemsNetwork controlInterconnection

The parallel processing system includes a plurality of nodes which are interconnected over an interconnection network; wherein the parallel processing system divides a computer job into parallel jobs by a parent process performed by a computer arranged in the nodes, and the parallel jobs are processed by the plurality of child processes using the plurality of computers arranged in the plurality of nodes; and a transfer process through the interconnection network from a slow child process in the child processes is performed on a basis of priority over other transfer processes.

Owner:NEC CORP

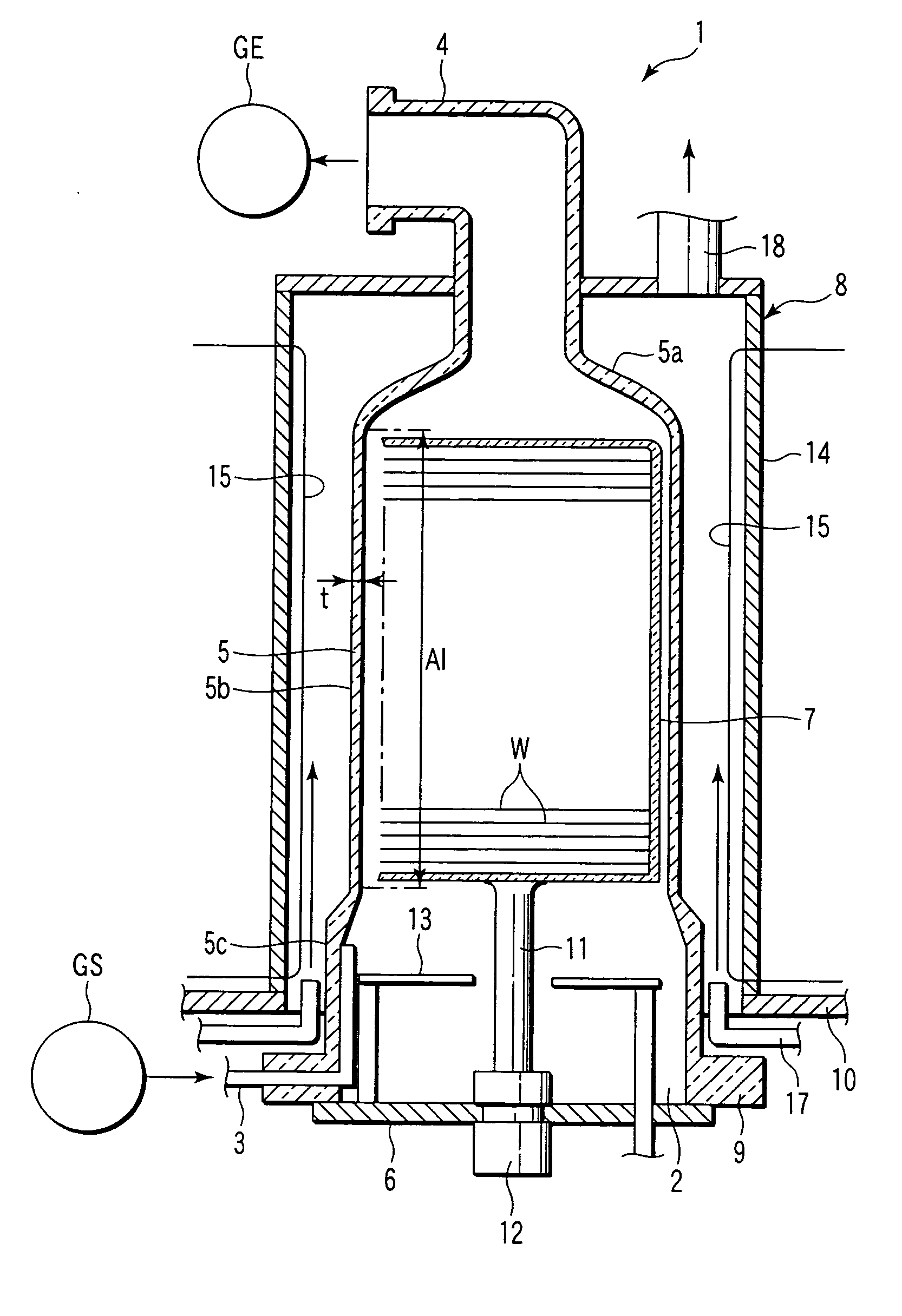

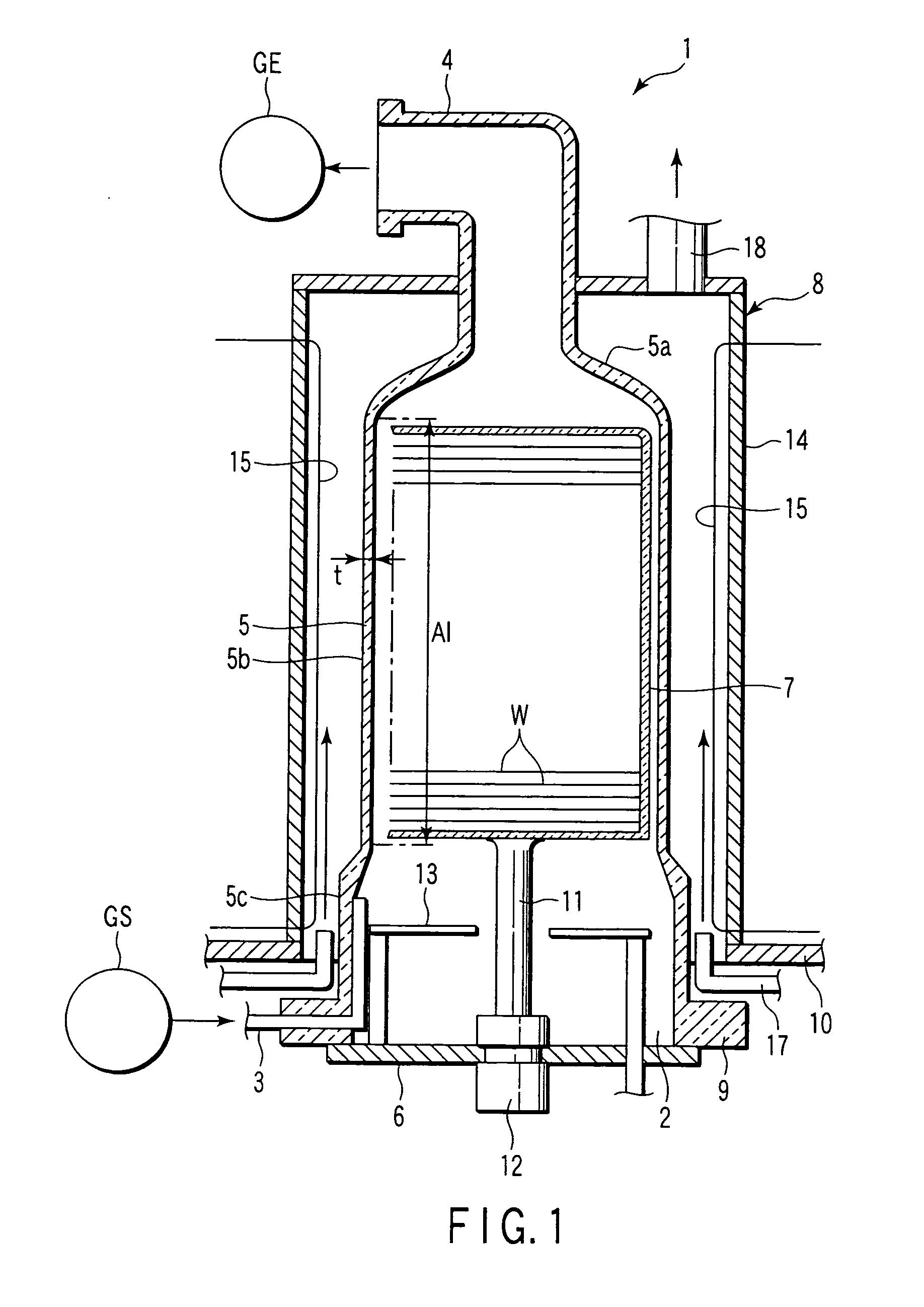

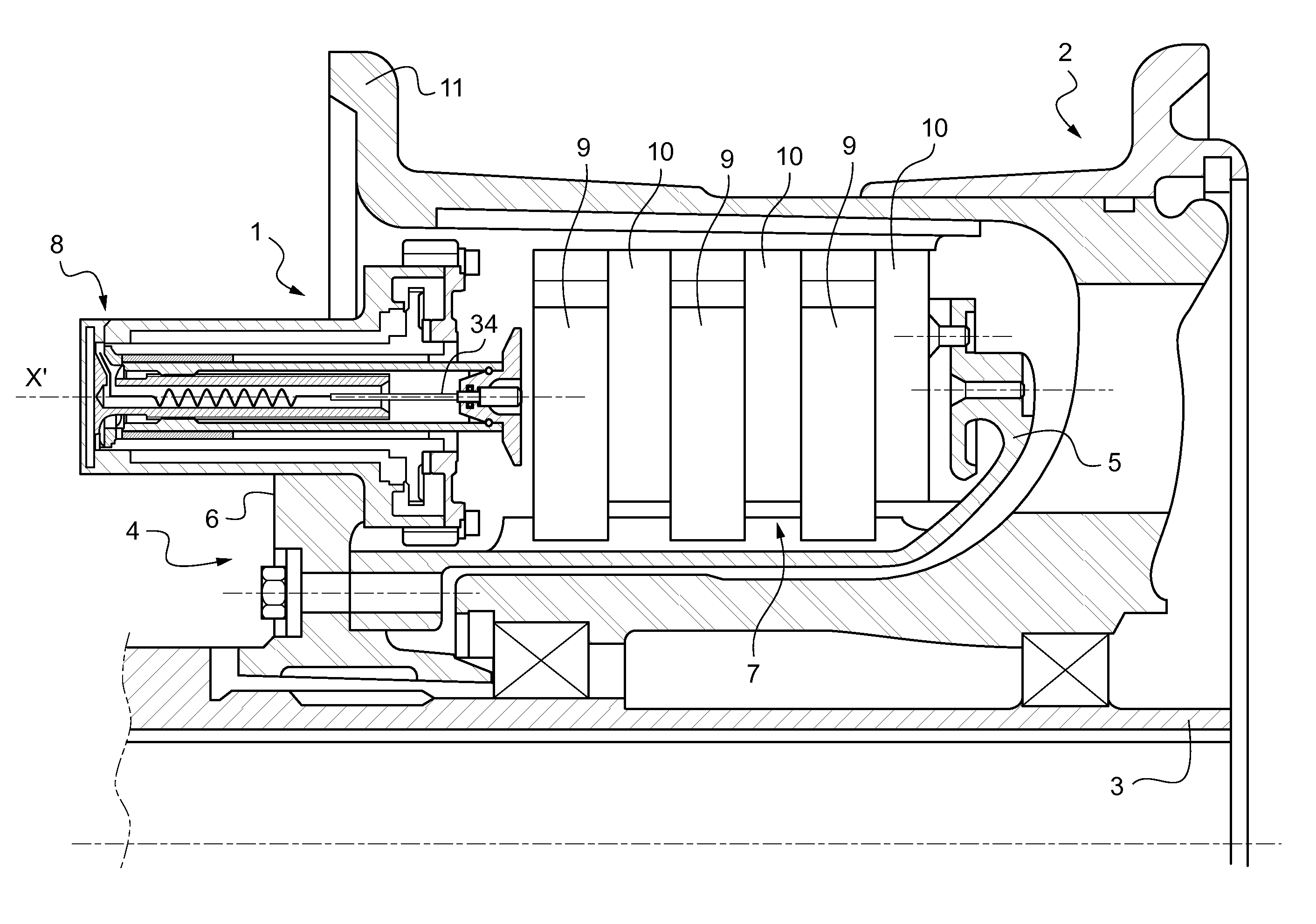

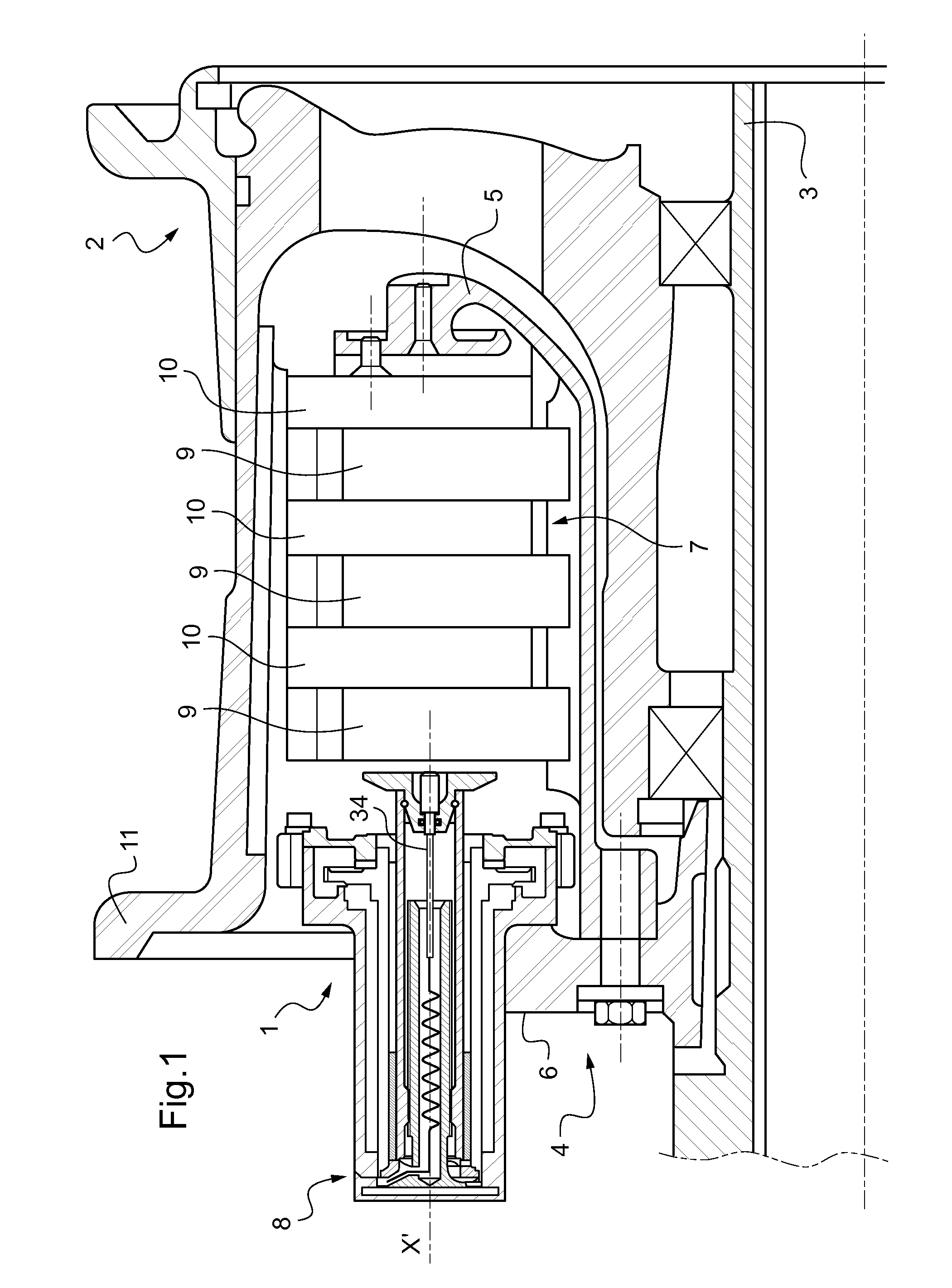

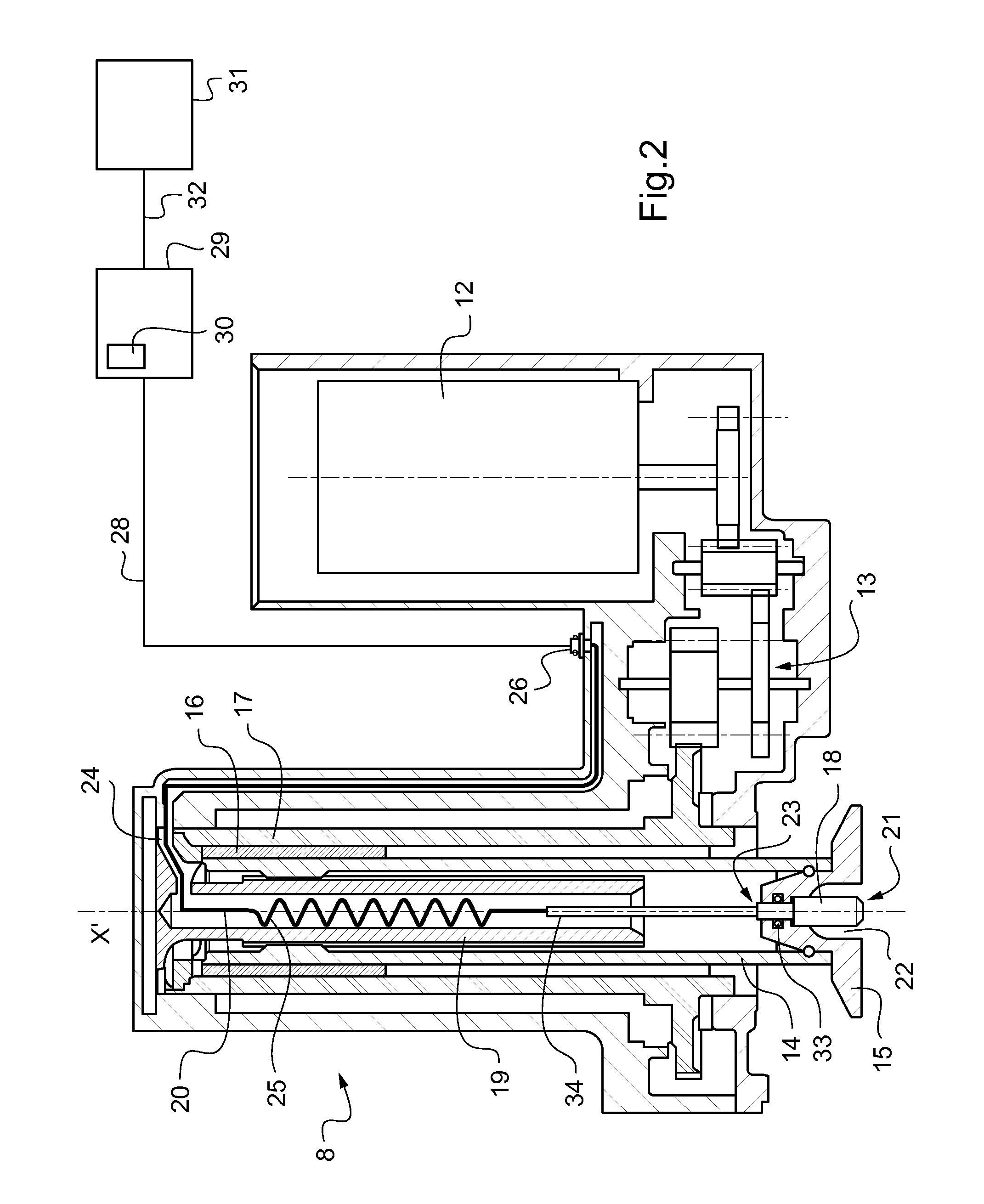

Vertical heat treatment device and method controlling the same

ActiveUS7432475B2Shorten convergence timeShortened TATDrying solid materials with heatMuffle furnacesProcess regionProcess engineering

Owner:TOKYO ELECTRON LTD

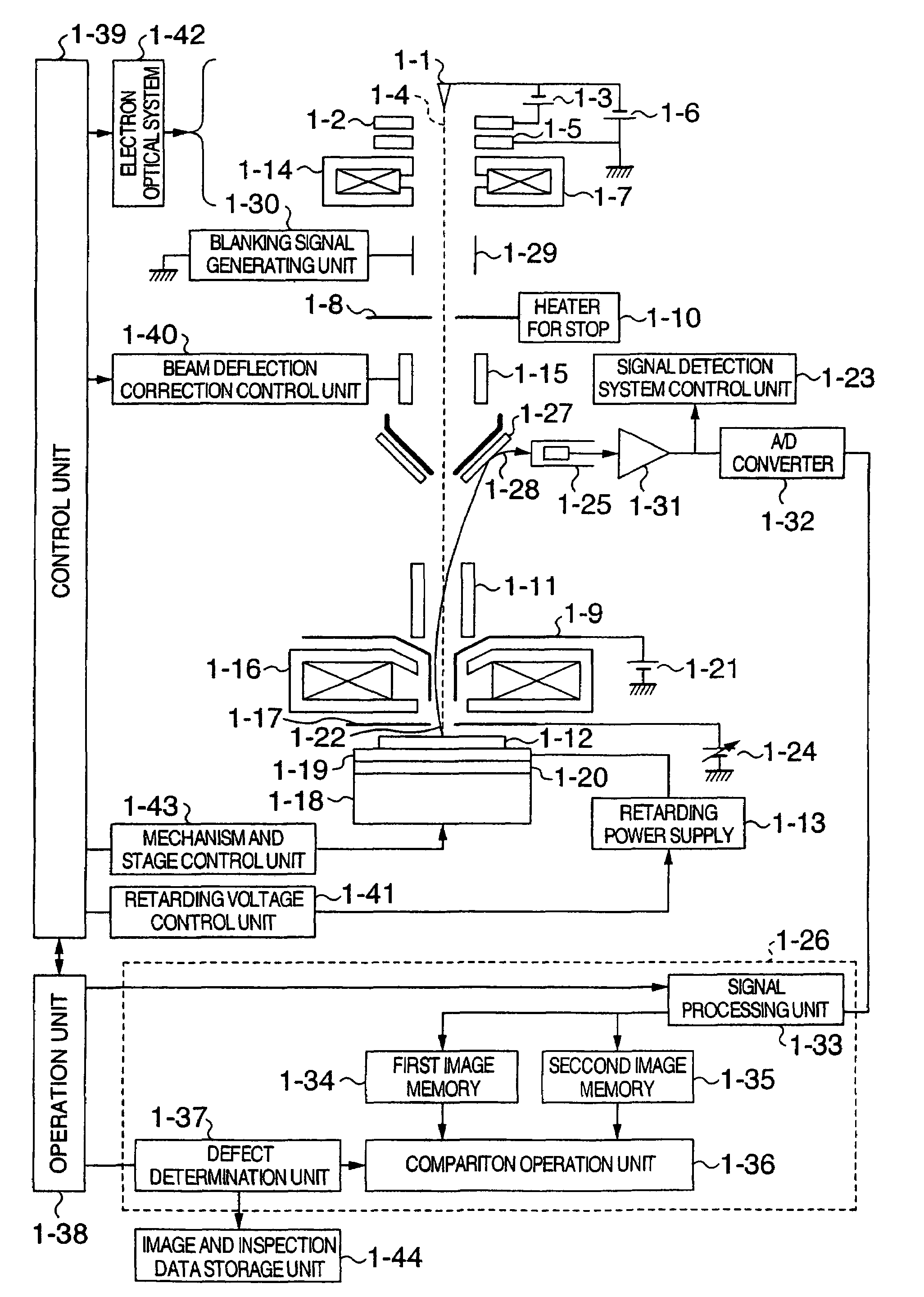

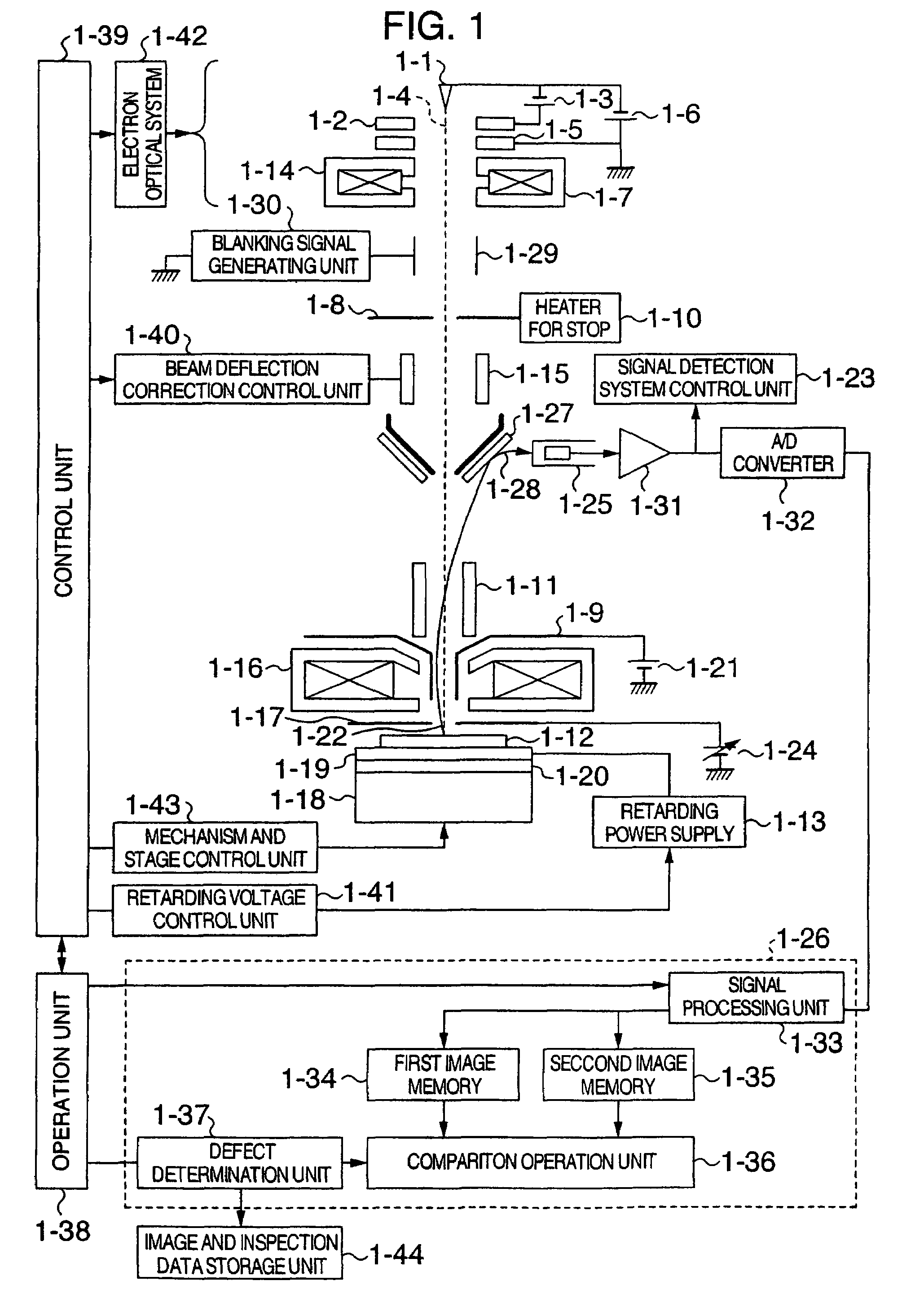

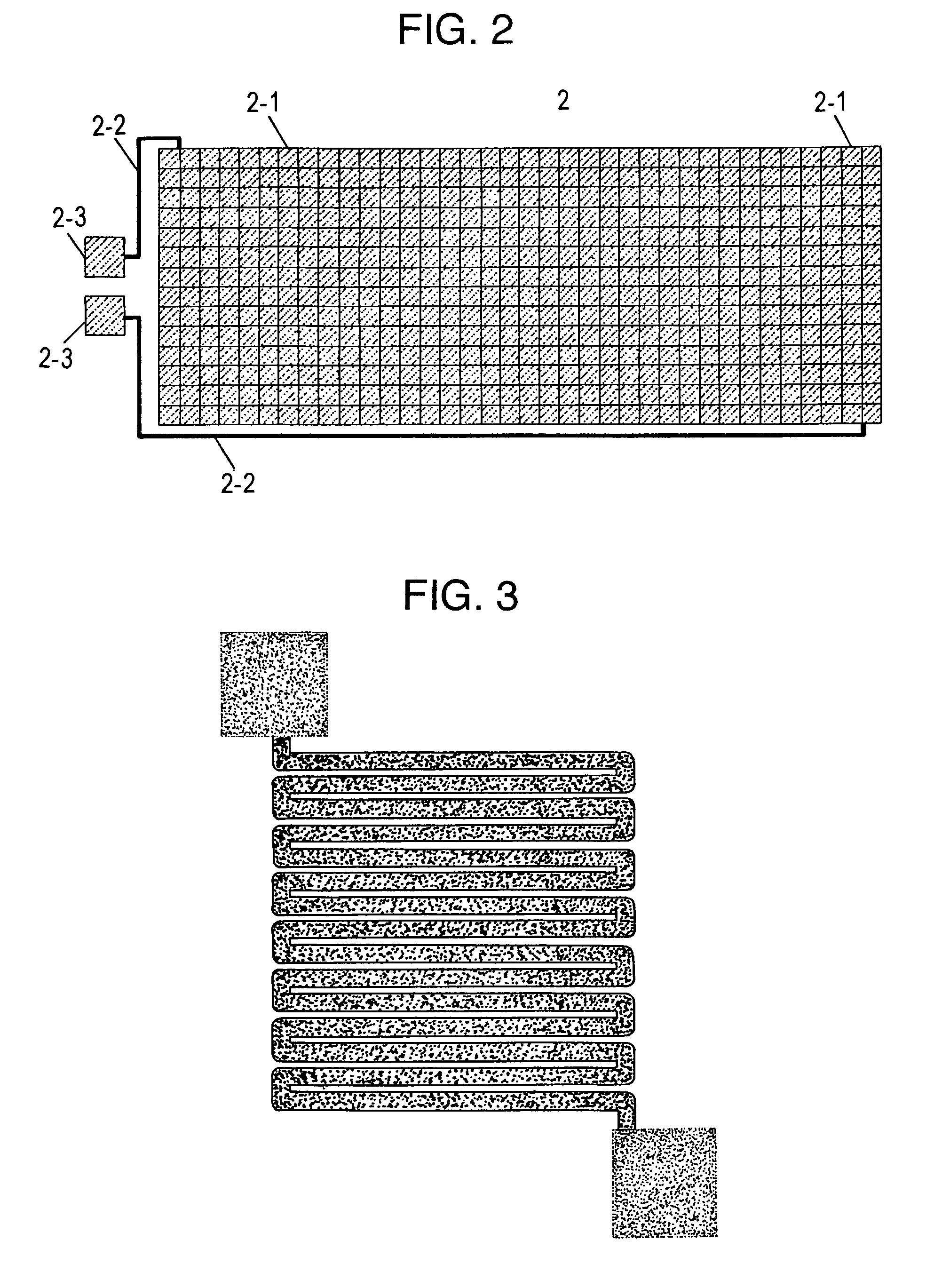

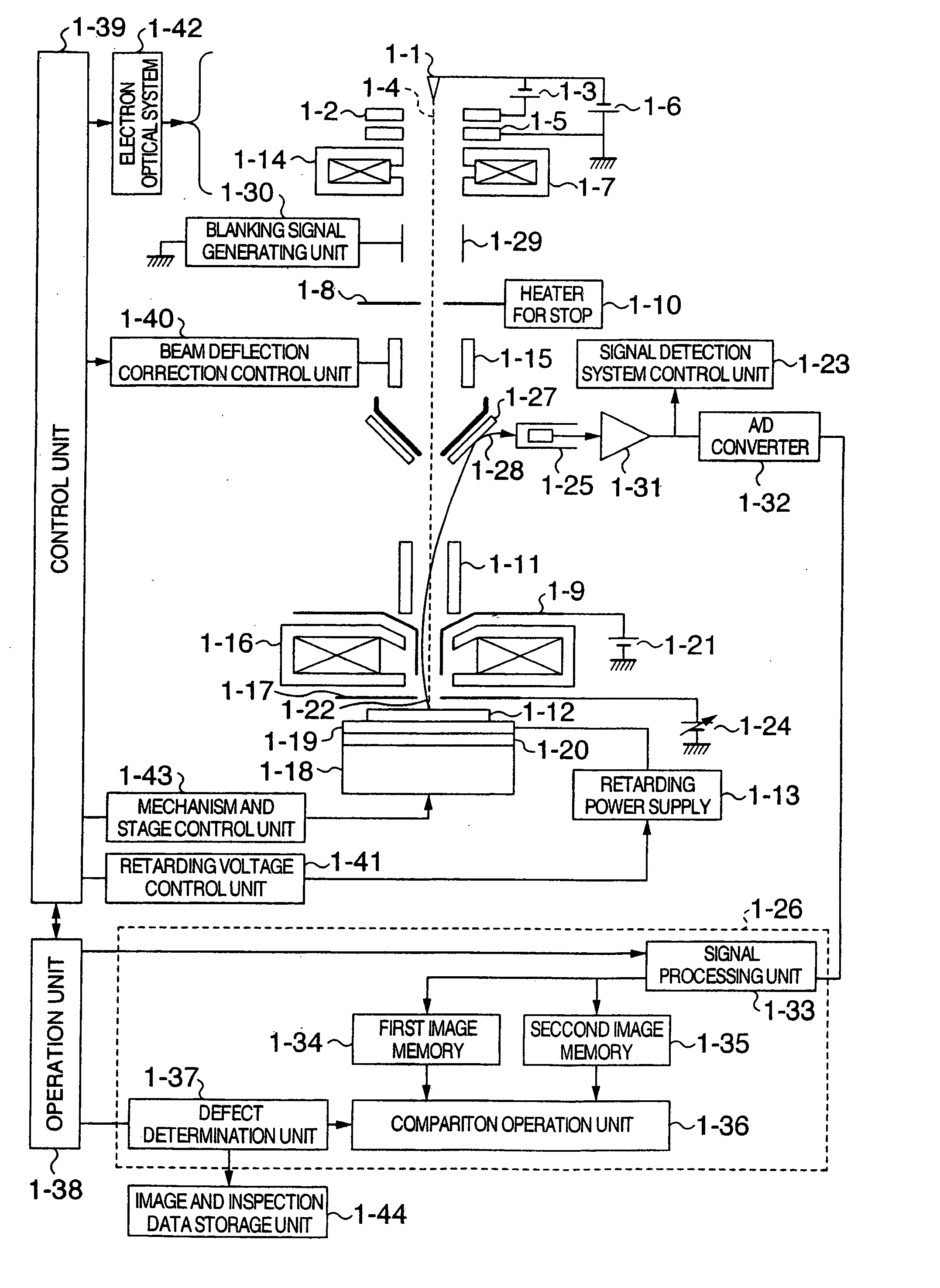

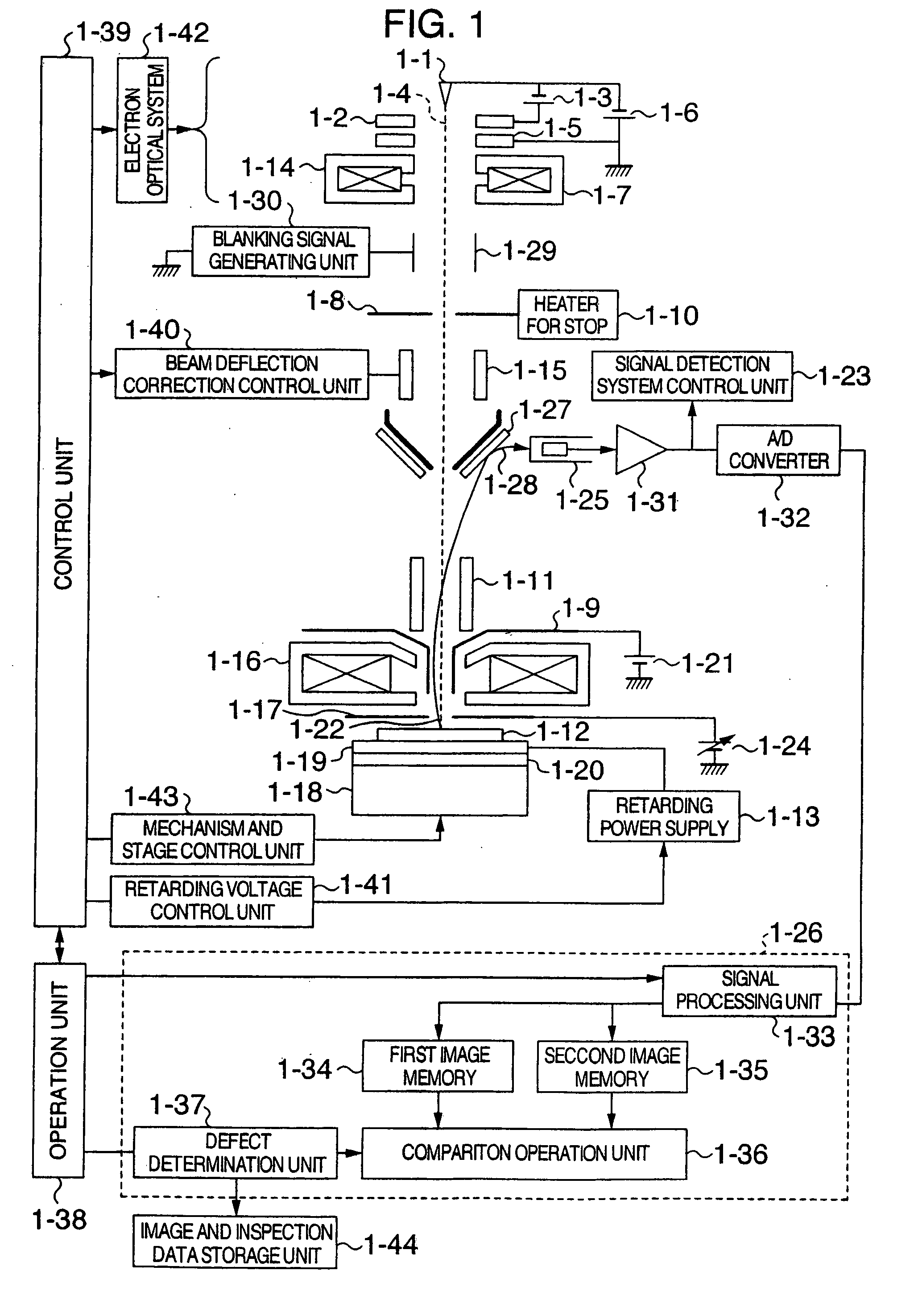

Method and apparatus for inspecting patterns

InactiveUS7394070B2Reduce impactGood conditionMaterial analysis using wave/particle radiationElectric discharge tubesElectrode potentialCharge control

When the electrode potential of a charge control electrode above a wafer is reduced, image brightness is reduced. A point of change in the image brightness is a switching point between a positively charged state of the image and a negatively charged state of the image, showing the weakly charged state of the image. By setting this point of change as an inspecting condition, the amount of electric charges on the surface of the wafer can be reduced, and stable wafer inspection can be performed. It is estimated that an applied voltage V1 in FIG. 14 corresponds to the point of the change and is roughly included in the voltage range of a region enclosed by a broken line in the vicinity of the applied voltage V1. Within this voltage range, the influence of charge on an inspection under the inspecting condition can be reduced.

Owner:HITACHI HIGH-TECH CORP

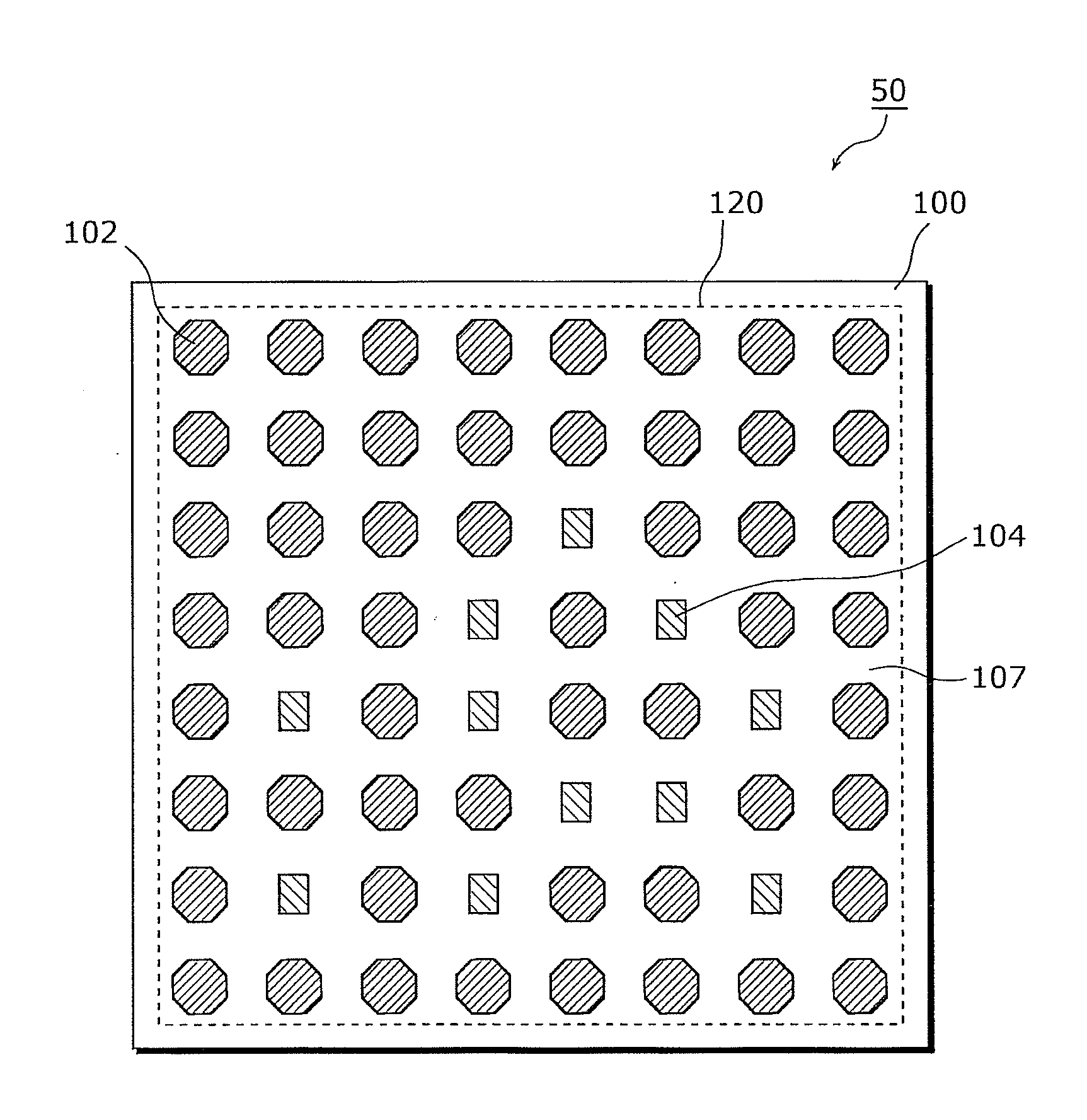

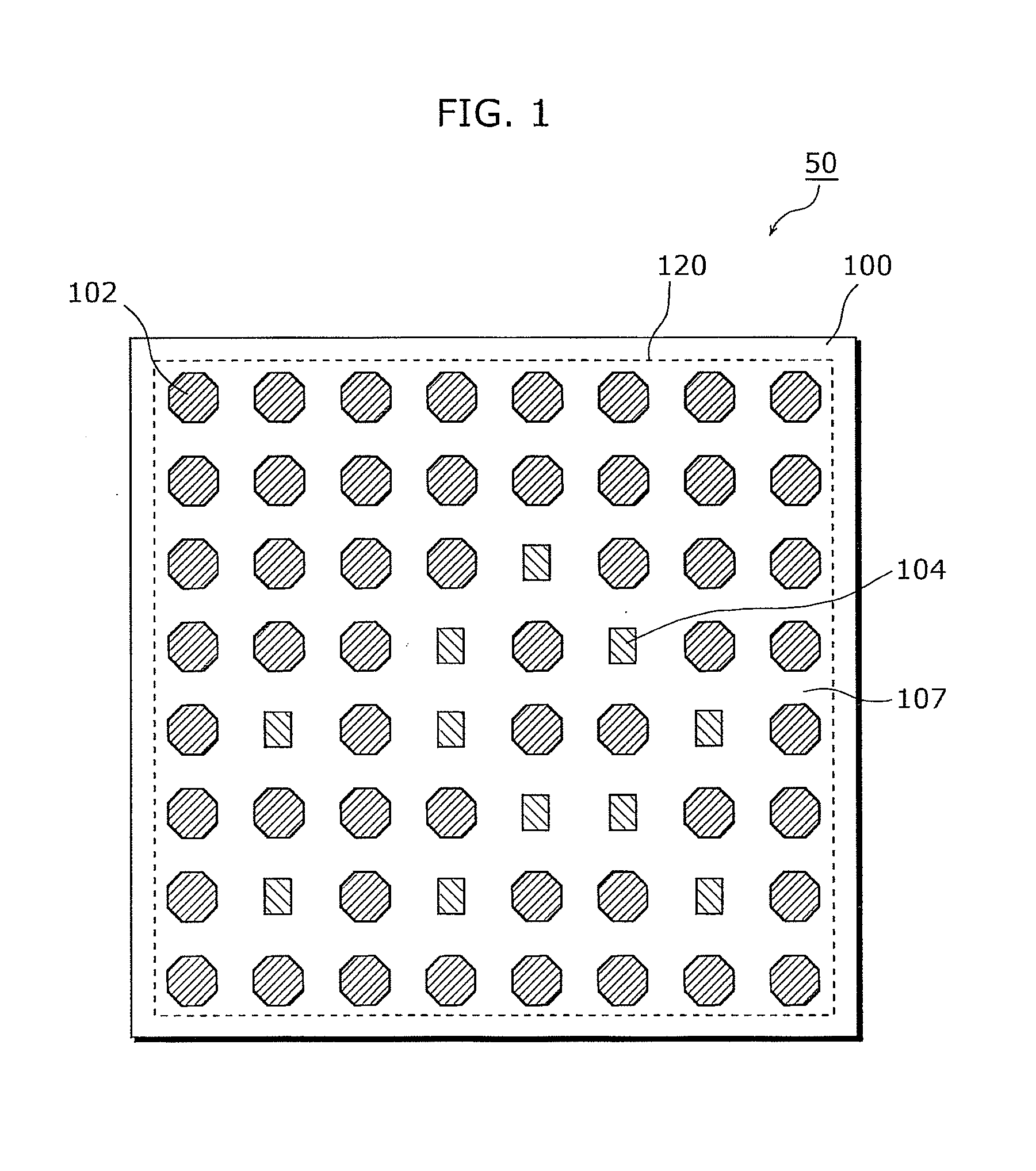

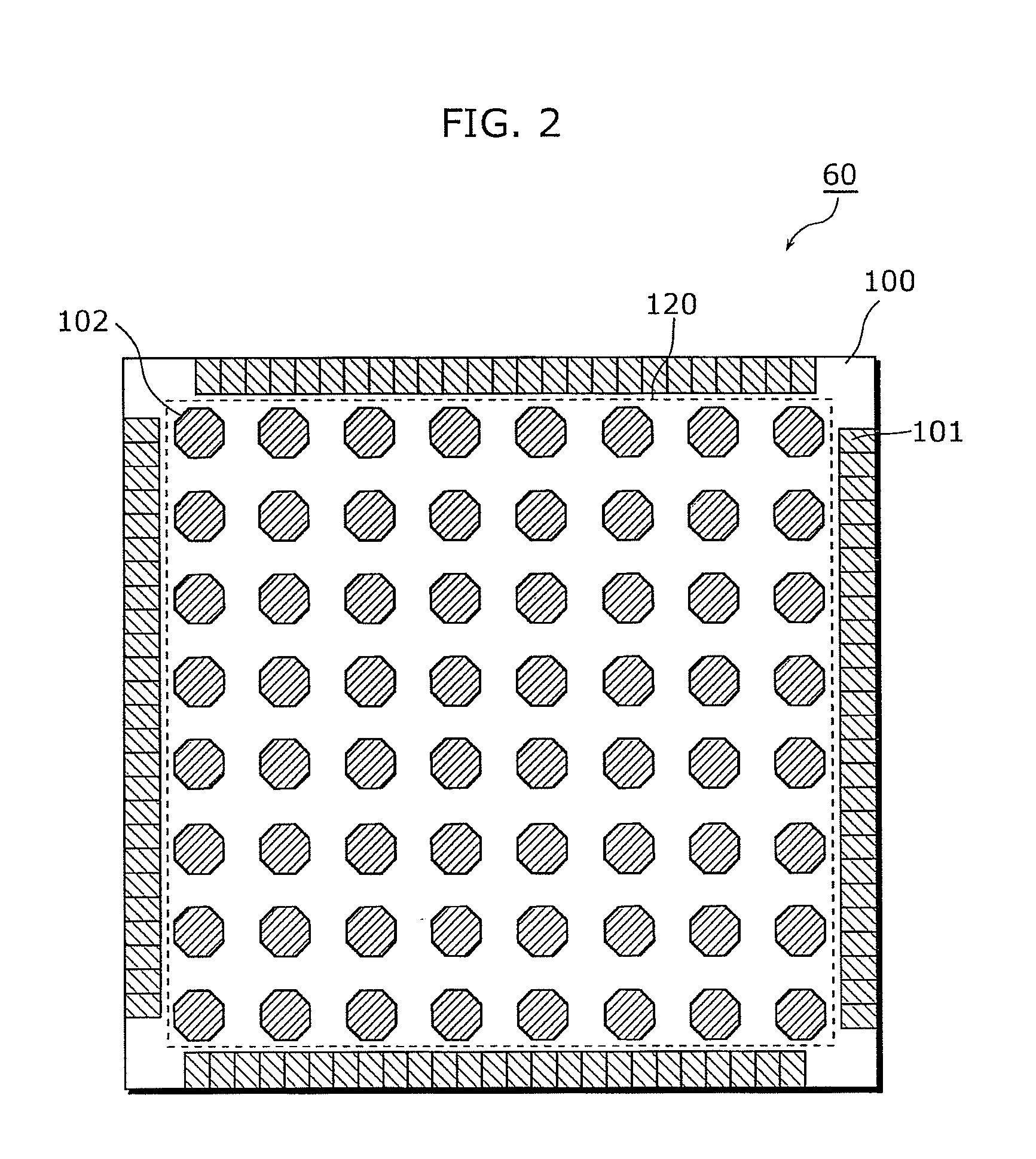

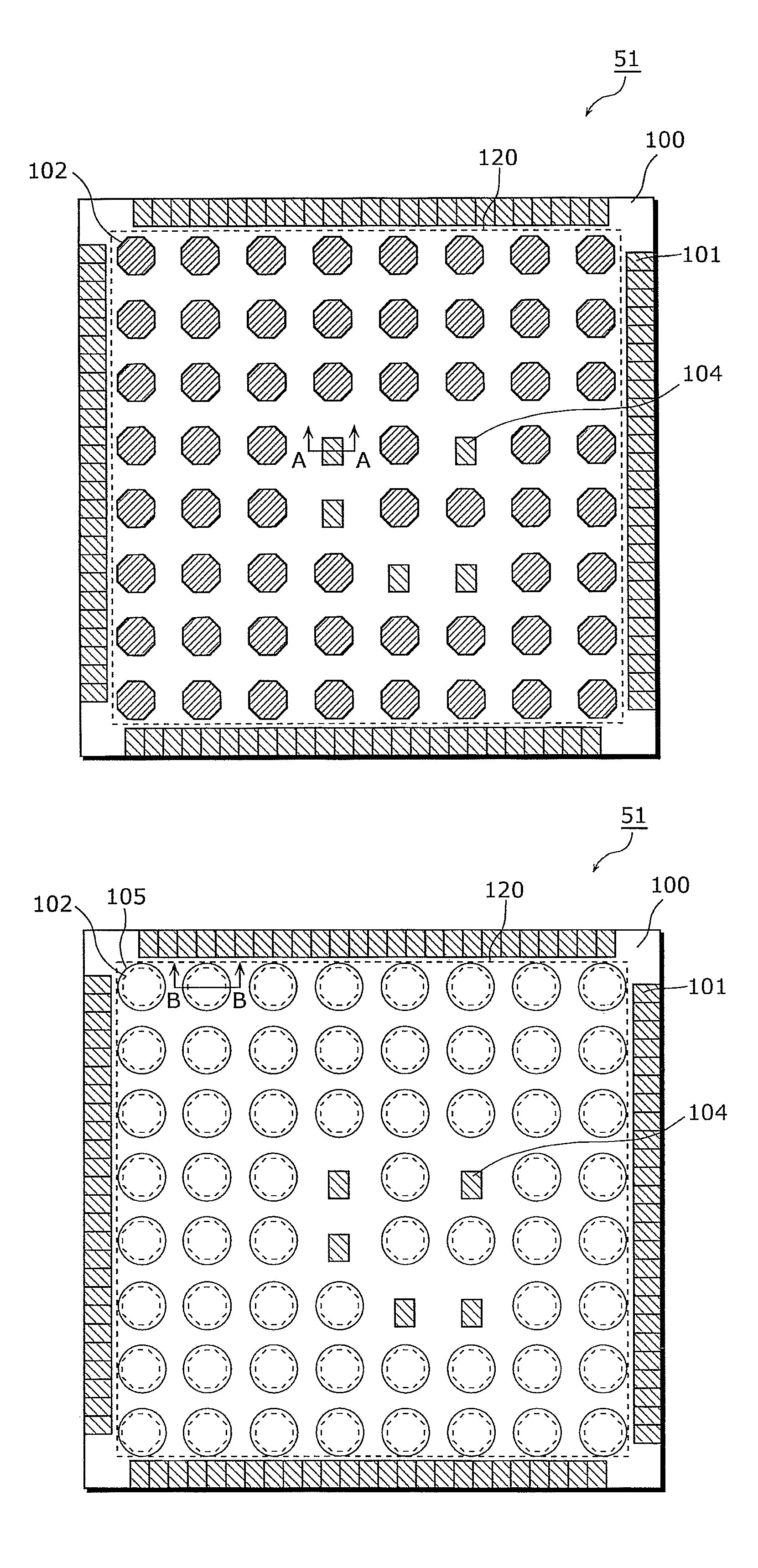

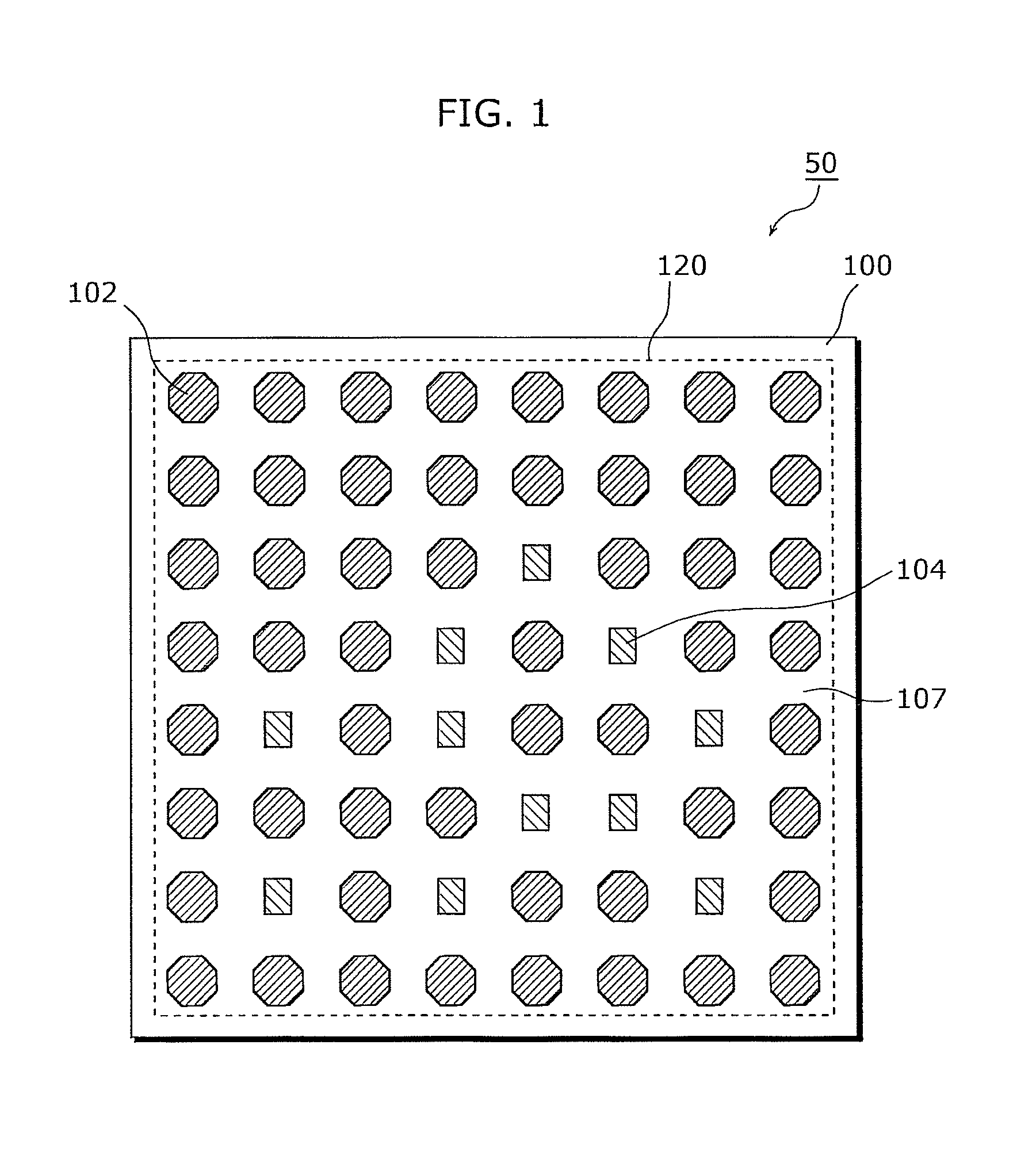

Semiconductor device and method of manufacturing the same

ActiveUS20110284841A1Tested and reliableEasy to implementSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor chipExternal connection

A semiconductor device according to one embodiment of this invention includes: a semiconductor chip; a plurality of external connection pads and a plurality of first test pads, both of which are formed in a central region of a top surface of the semiconductor chip; a plurality of external connection electrodes each formed on a corresponding one of the external connection pads, the external connection electrodes being for connecting the external connection pads and an outside of the semiconductor device.

Owner:PANASONIC CORP

Method and apparatus for inspecting patterns

InactiveUS20060163477A1Optimal inspecting conditionImprove efficiencyMaterial analysis using wave/particle radiationElectric discharge tubesElectrode potentialCharge control

When the electrode potential of a charge control electrode above a wafer is reduced, image brightness is reduced. A point of change in the image brightness is a switching point between a positively charged state of the image and a negatively charged state of the image, showing the weakly charged state of the image. By setting this point of change as an inspecting condition, the amount of electric charges on the surface of the wafer can be reduced, and stable wafer inspection can be performed. It is estimated that an applied voltage V1 in FIG. 14 corresponds to the point of the change and is roughly included in the voltage range of a region enclosed by a broken line in the vicinity of the applied voltage V1. Within this voltage range, the influence of charge on an inspection under the inspecting condition can be reduced.

Owner:HITACHI HIGH-TECH CORP

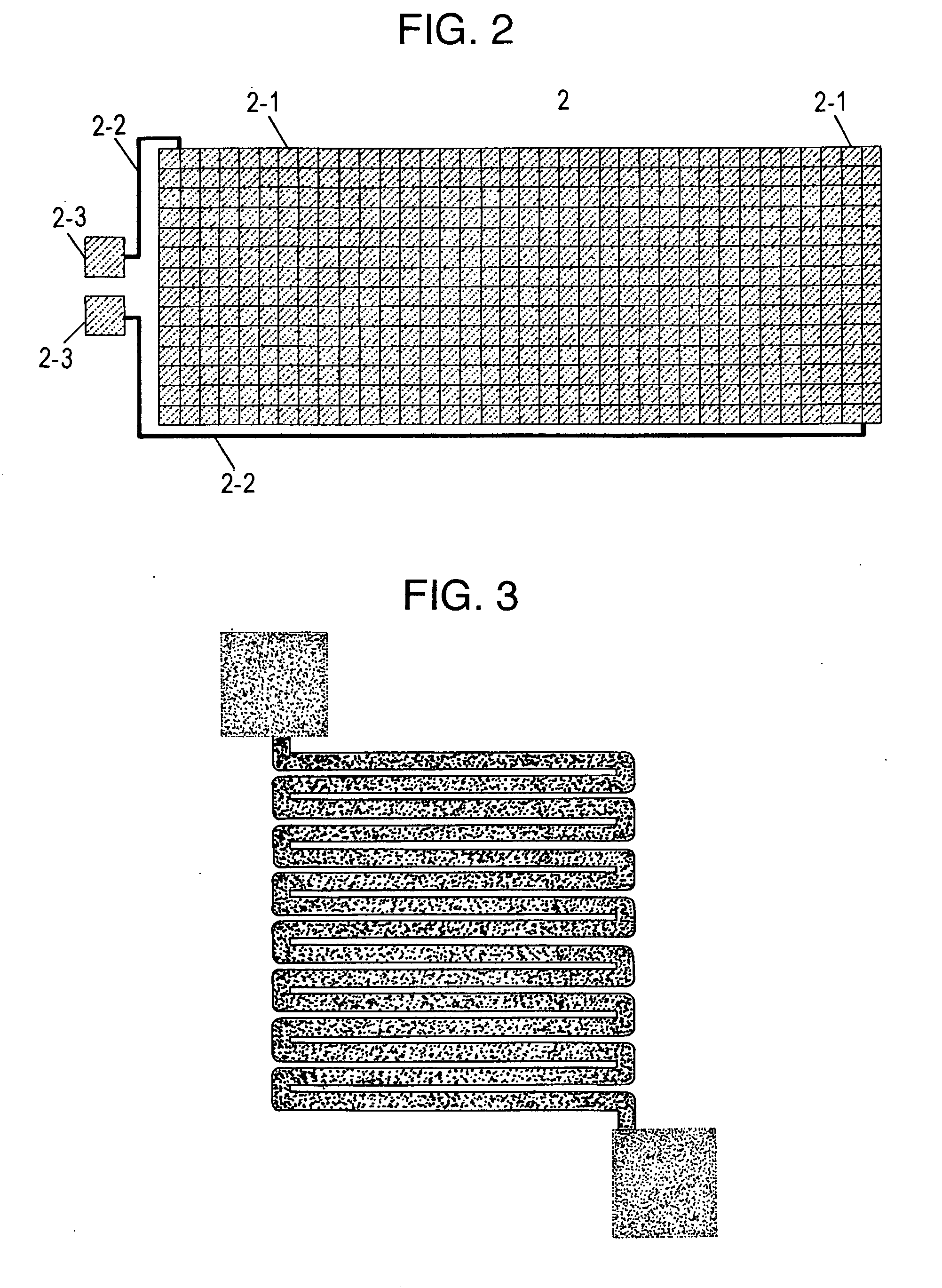

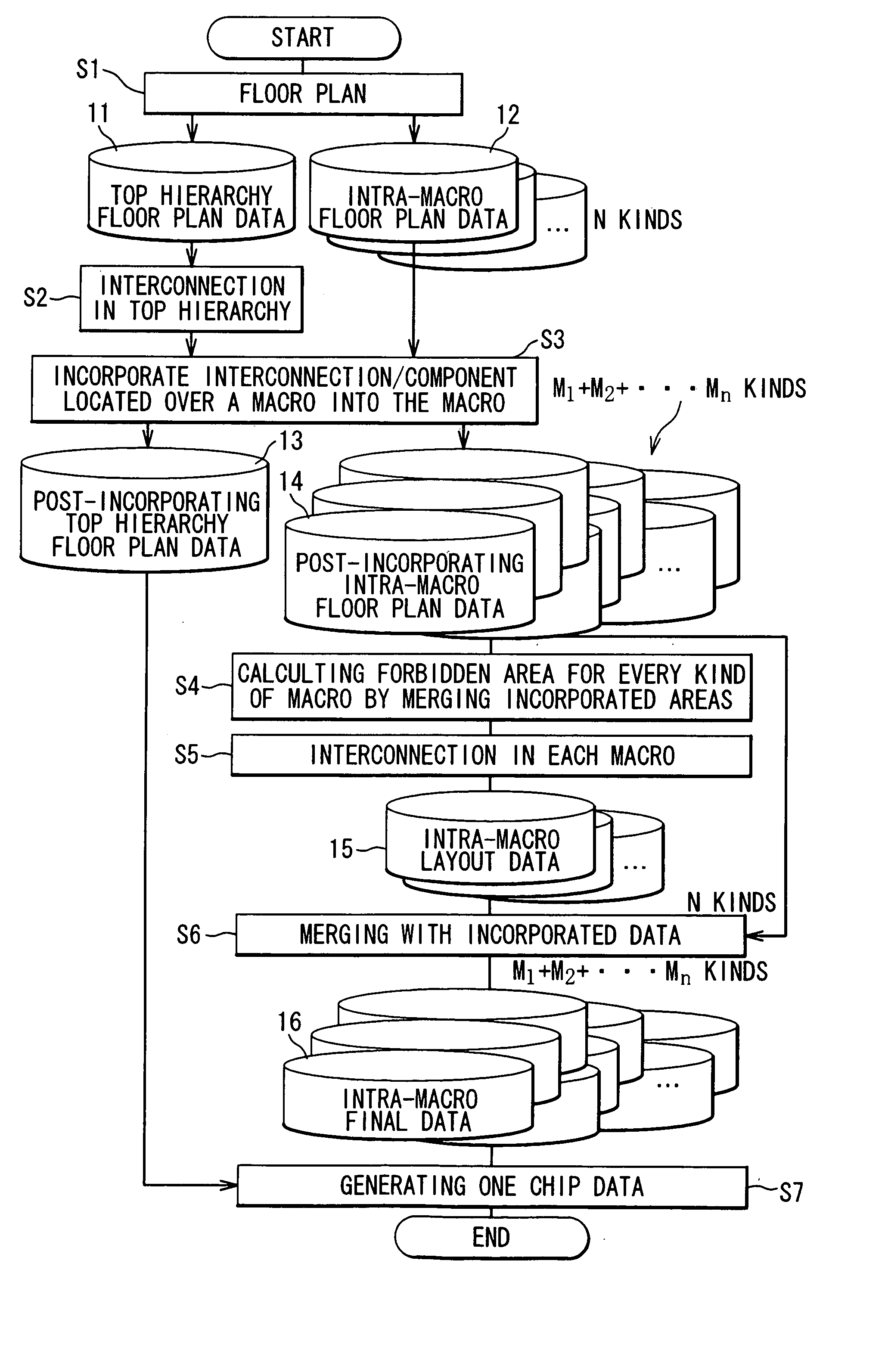

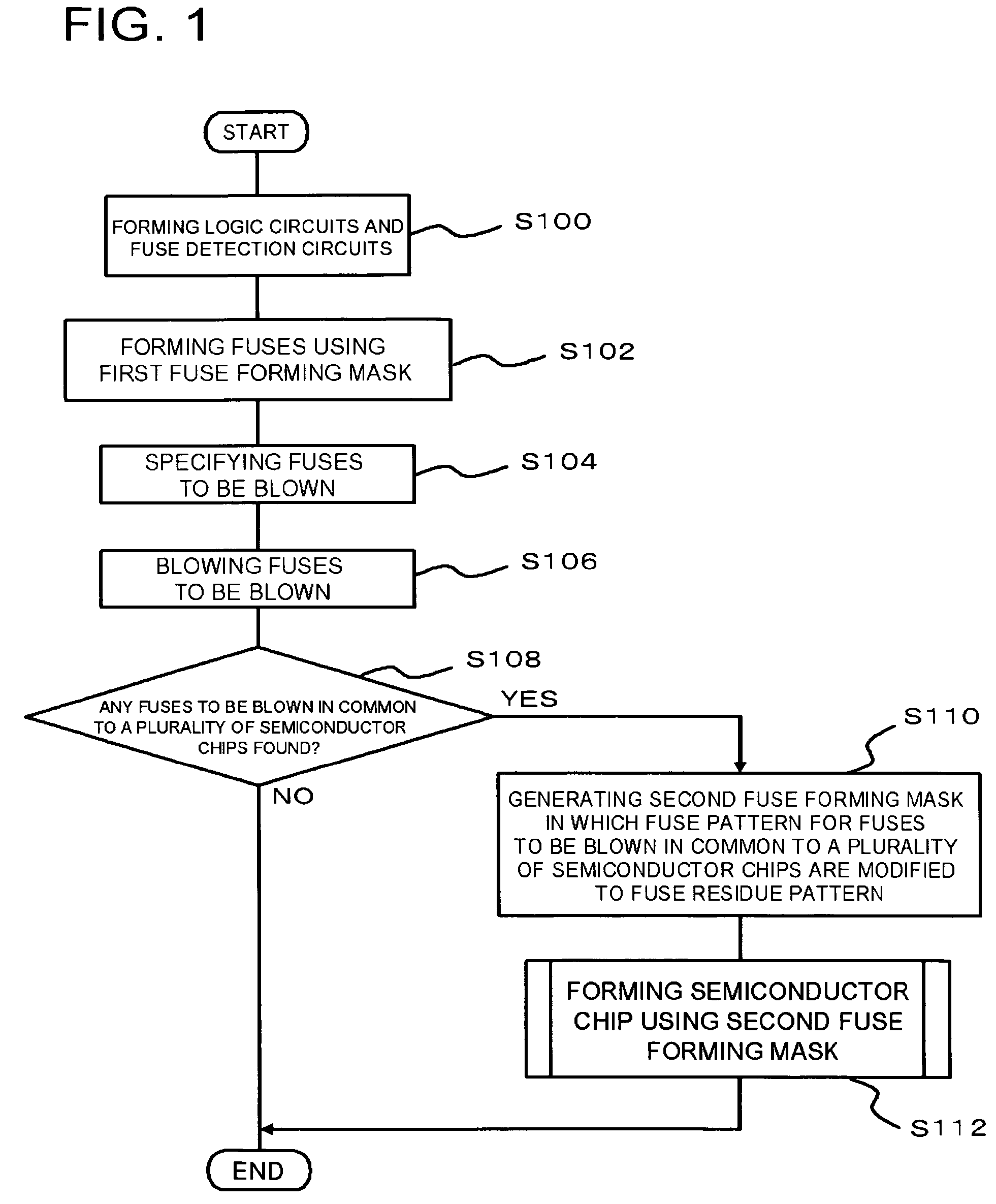

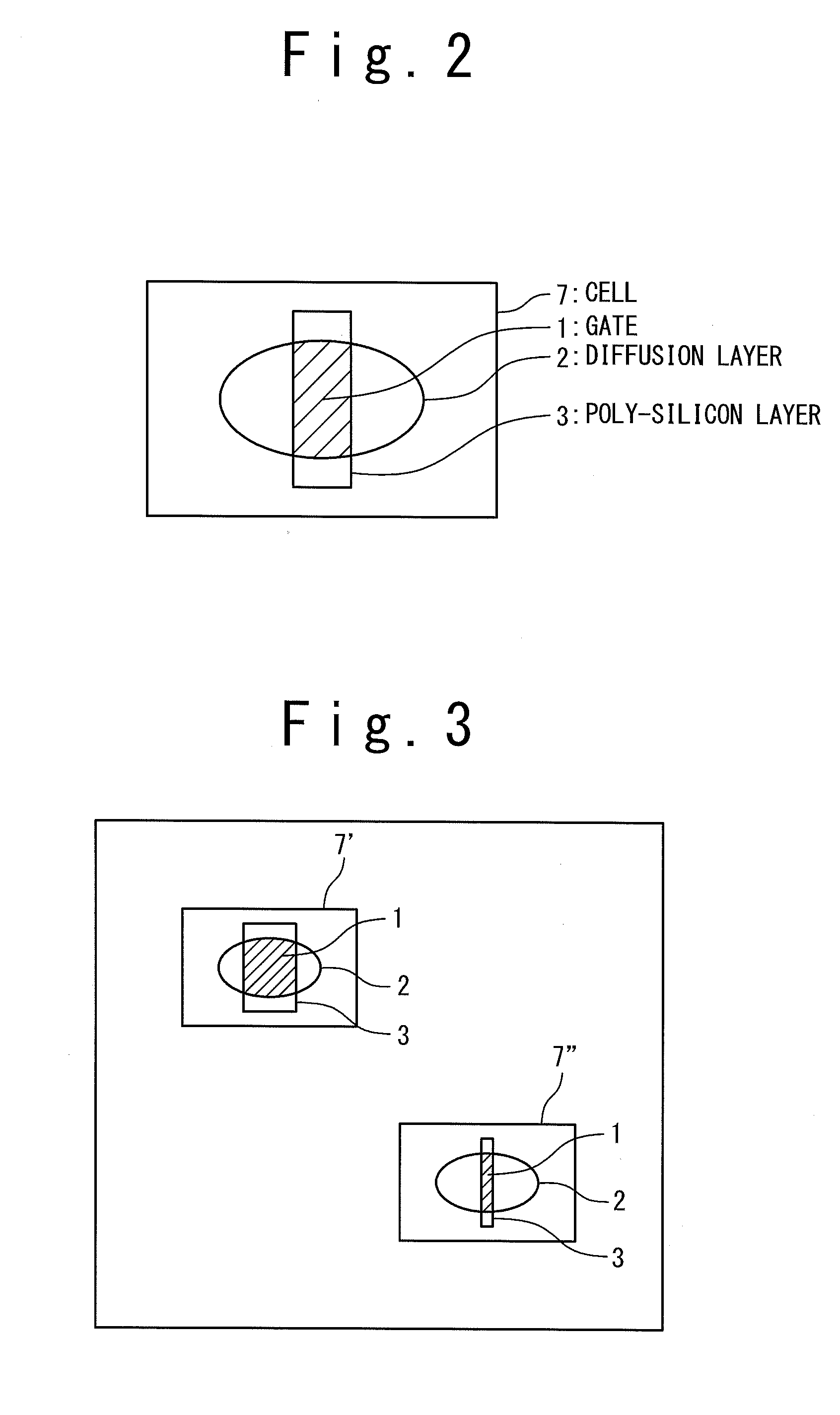

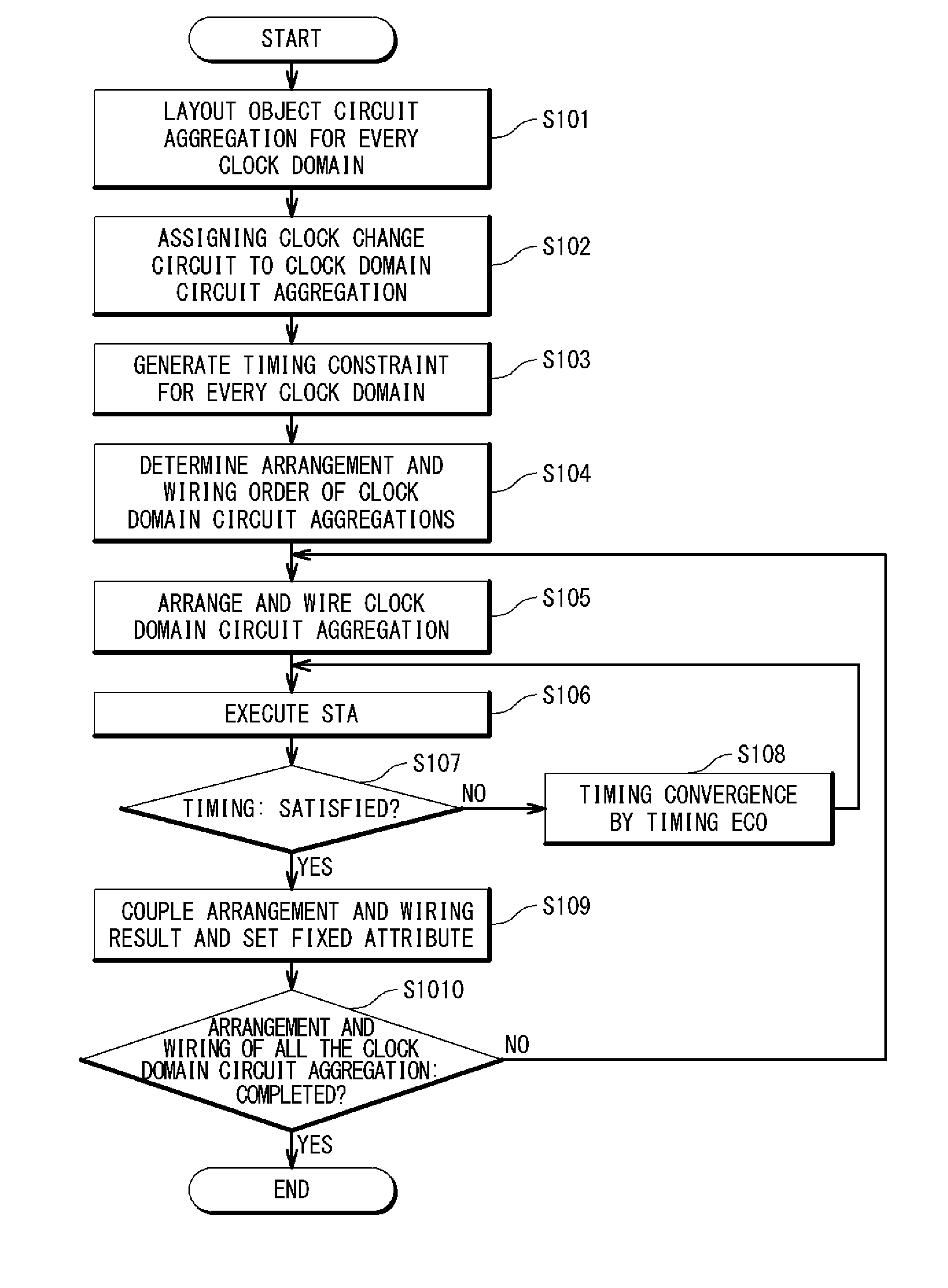

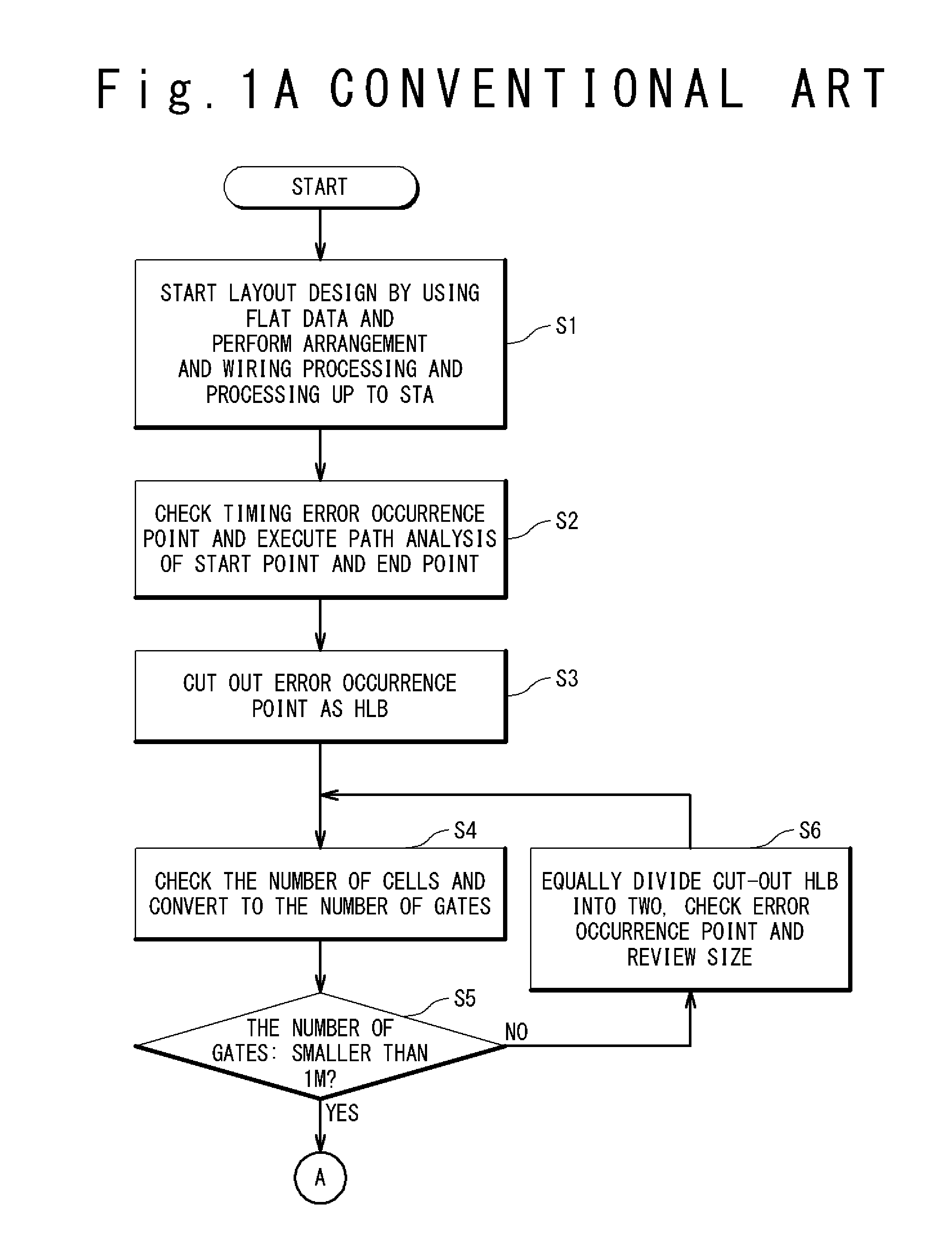

Software product for and method of laying-out semiconductor device

InactiveUS20050183053A1Shorten the timeShortened TATSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

A software product for laying-out a semiconductor device includes the functions of: (A) locating a plurality of macros including a plurality of first macros of the same kind belonging to a first hierarchy; (B) arranging interconnections connecting between the plurality of macros; (C) extracting from the interconnections a plurality of overlapping sections which overlap with the plurality of first macros, respectively; (D) incorporating respective of the overlapping sections into the first macros; (E) calculating a forbidden area associated with any overlapping section by superposing the plurality of overlapping sections with reference to orientations of the first macros; and (F) arranging interconnections / components belonging to a lower hierarchy within each first macro such that the interconnections / components are not provided in the forbidden area.

Owner:NEC ELECTRONICS CORP

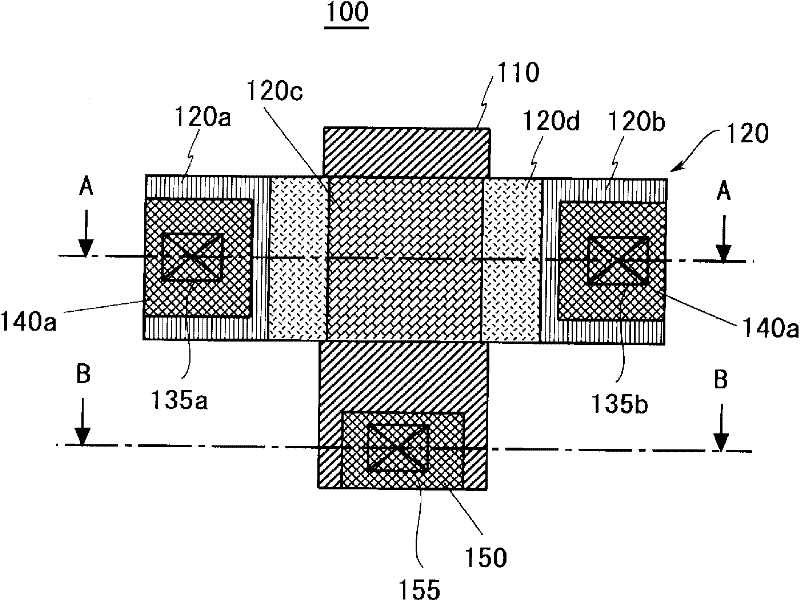

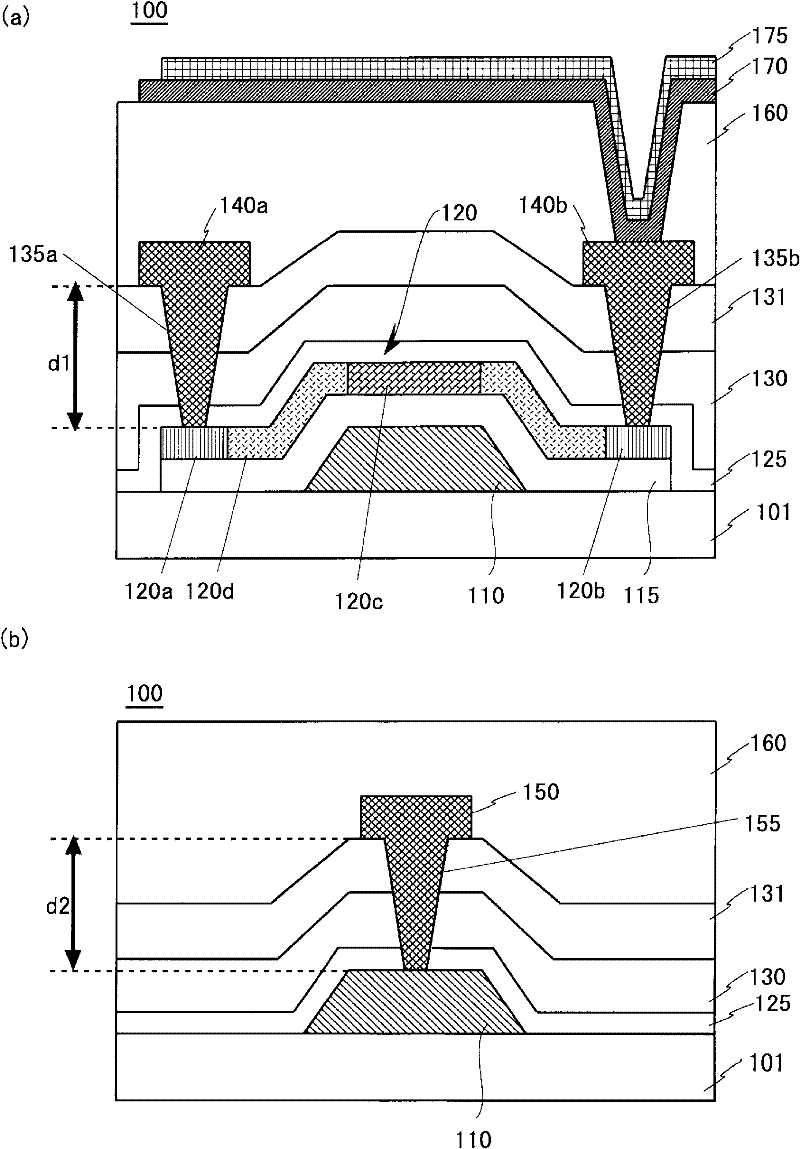

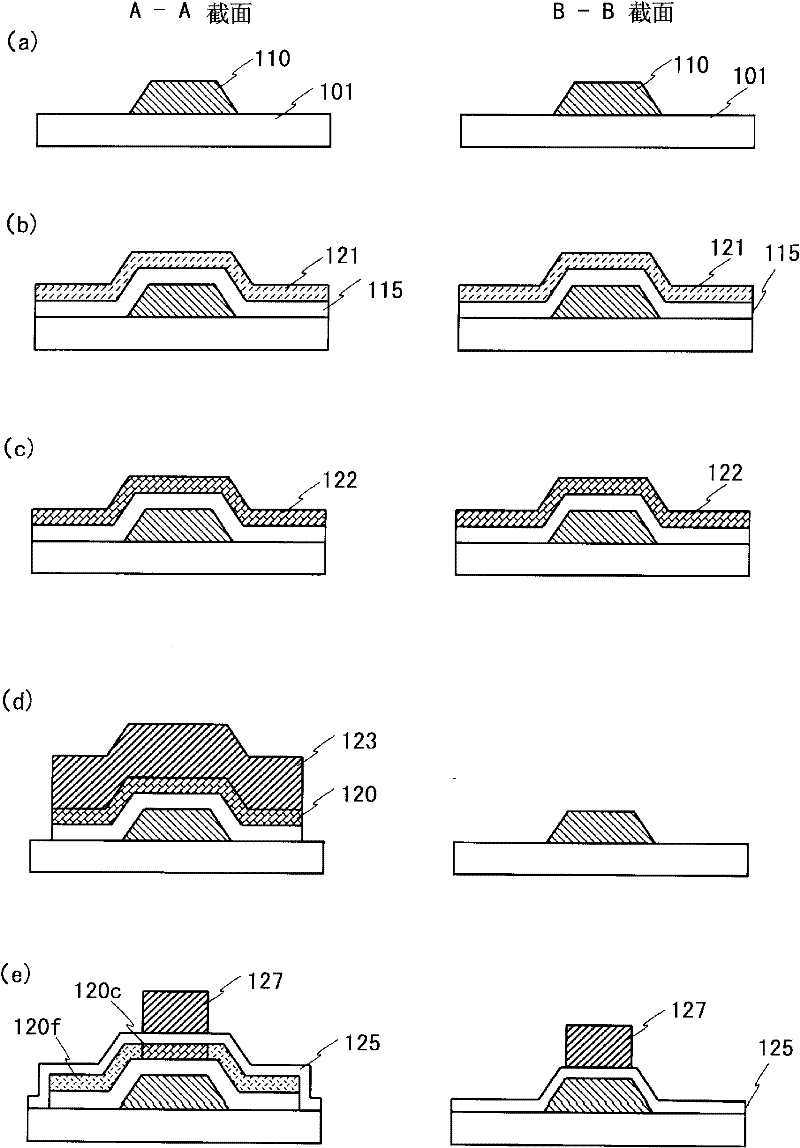

Thin film transistor and manufacturing method for same, semiconductor device and manufacturing method for same, and display device

InactiveCN102576739AAvoid contact resistanceIncrease contact resistanceTransistorSolid-state devicesDisplay deviceEngineering

Disclosed is a thin film transistor manufacturing method in which the process for opening contact holes has been simplified. Due to the removal in advance of a gate insulating film (115) which is formed on a gate electrode (110) not covered by a channel layer (120) of a TFT (100), the film thickness of the insulating film formed on the gate electrode (110) which is not covered by the channel layer (120) is the same as the film thickness of the insulating film formed on the source region (120a) and the drain region (120b). Therefore, it is possible to simultaneously open a contact hole (155) which reaches the surface of the gate electrode (110), a contact hole (135a) which reaches the surface of the source region (120a), and a contact hole (135b) which reaches the surface of the drain region (120b).

Owner:SHARP KK

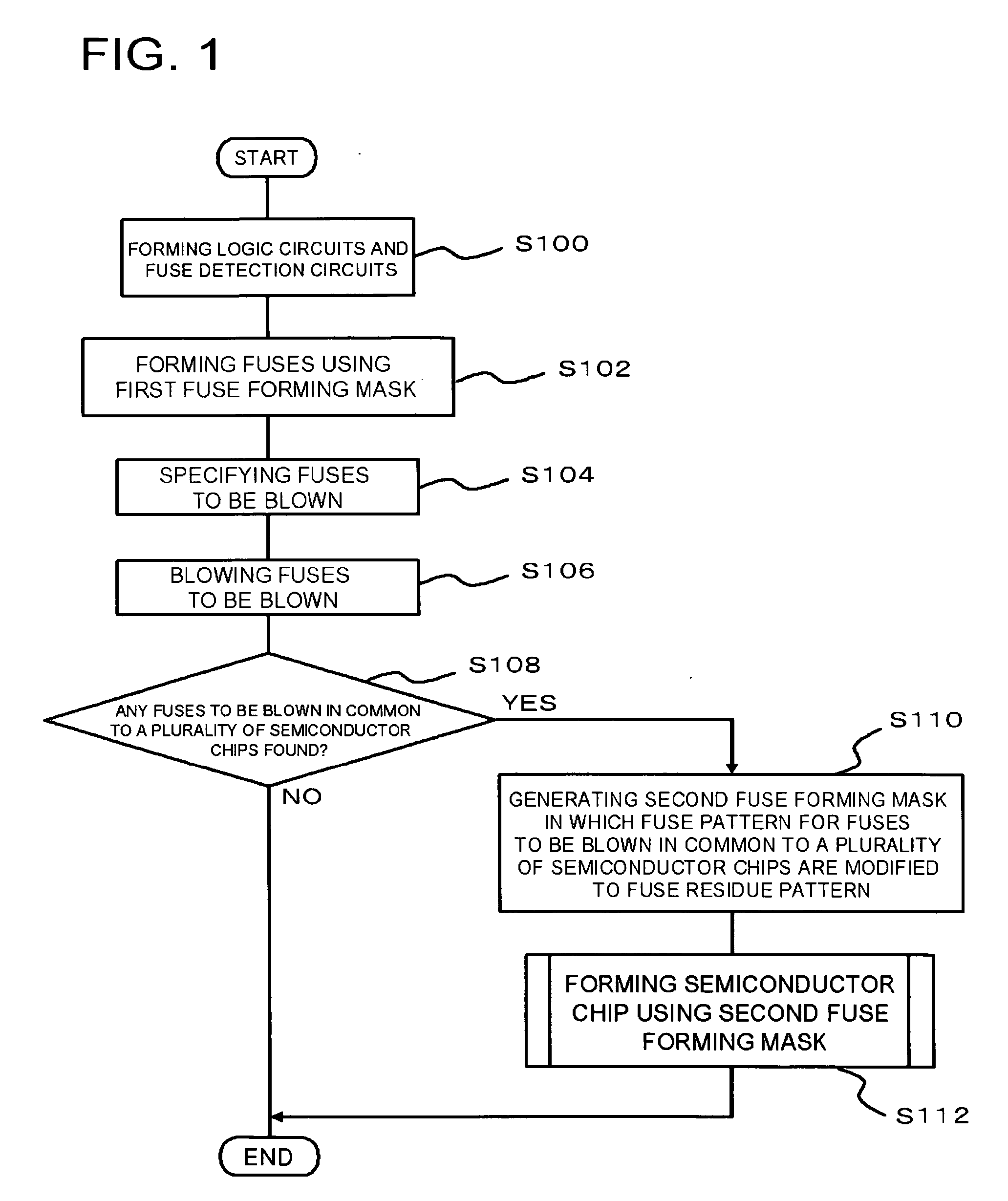

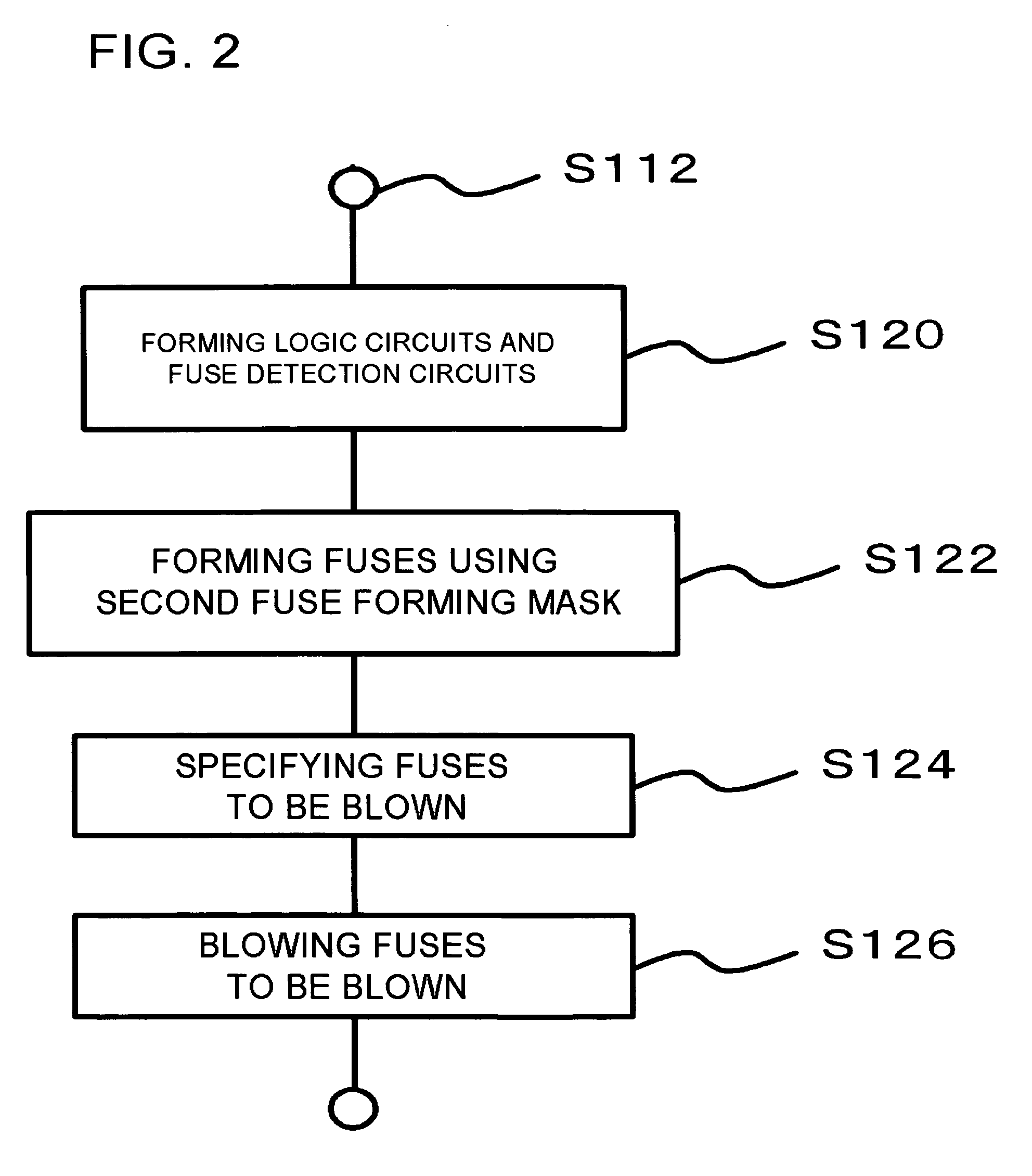

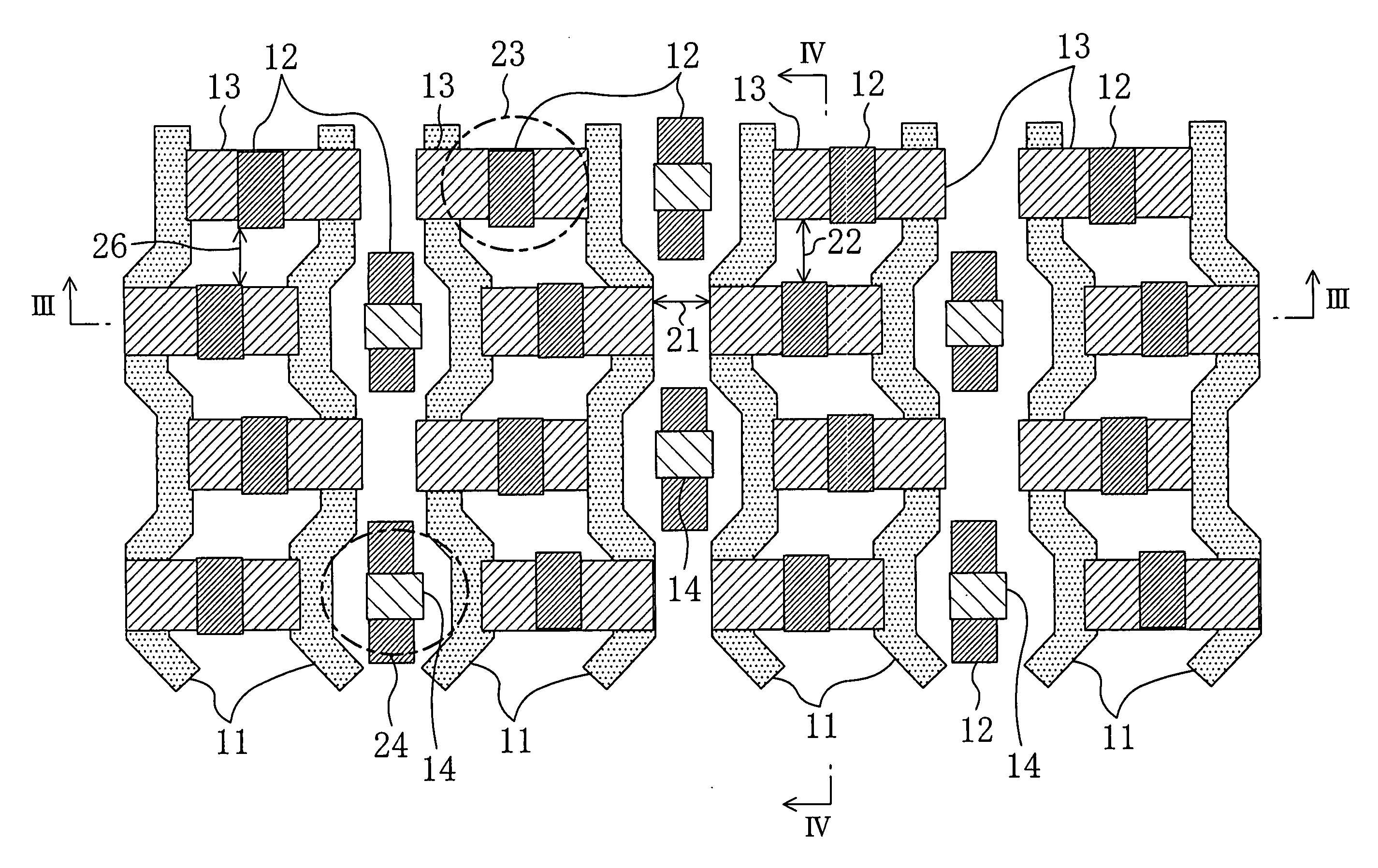

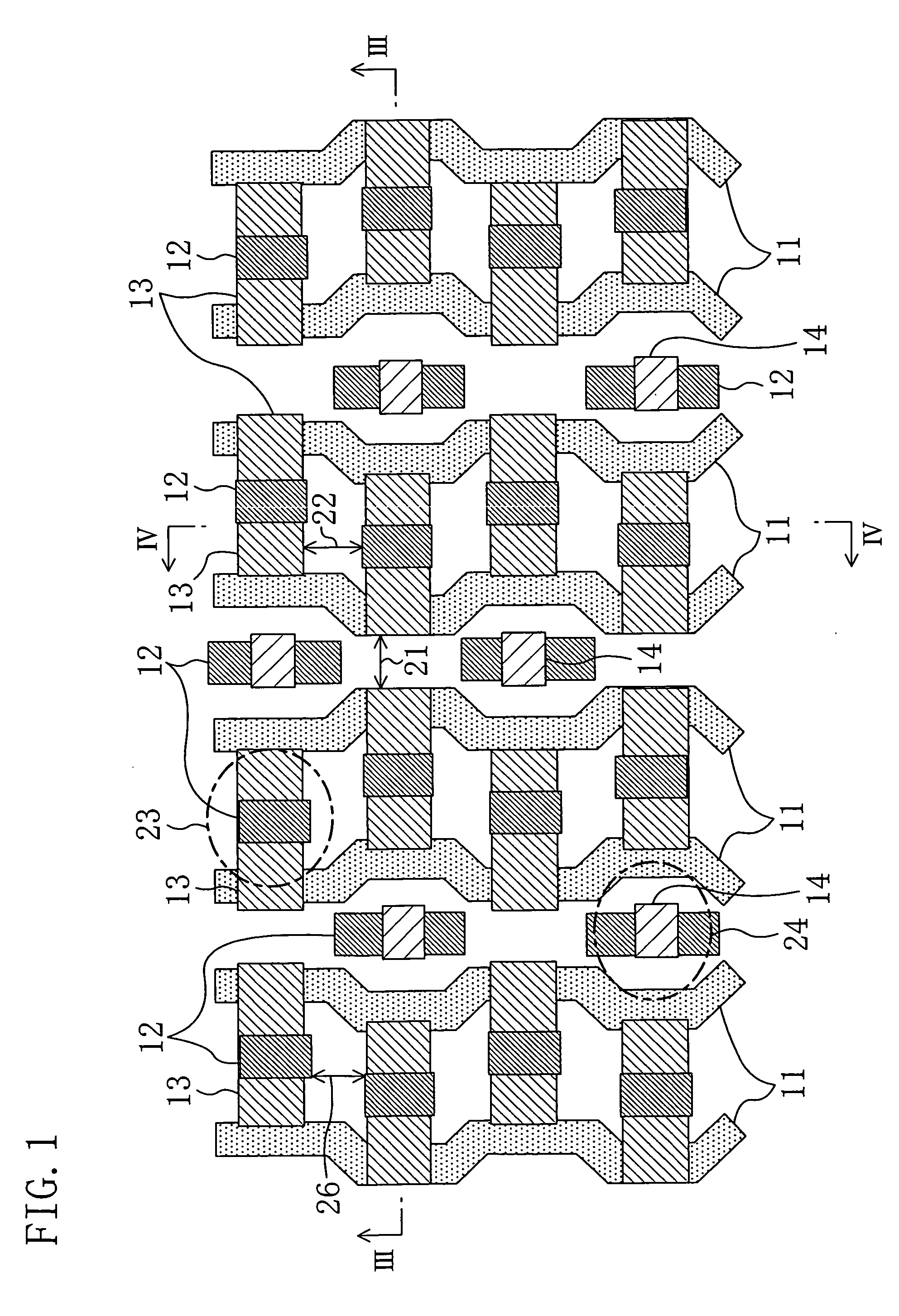

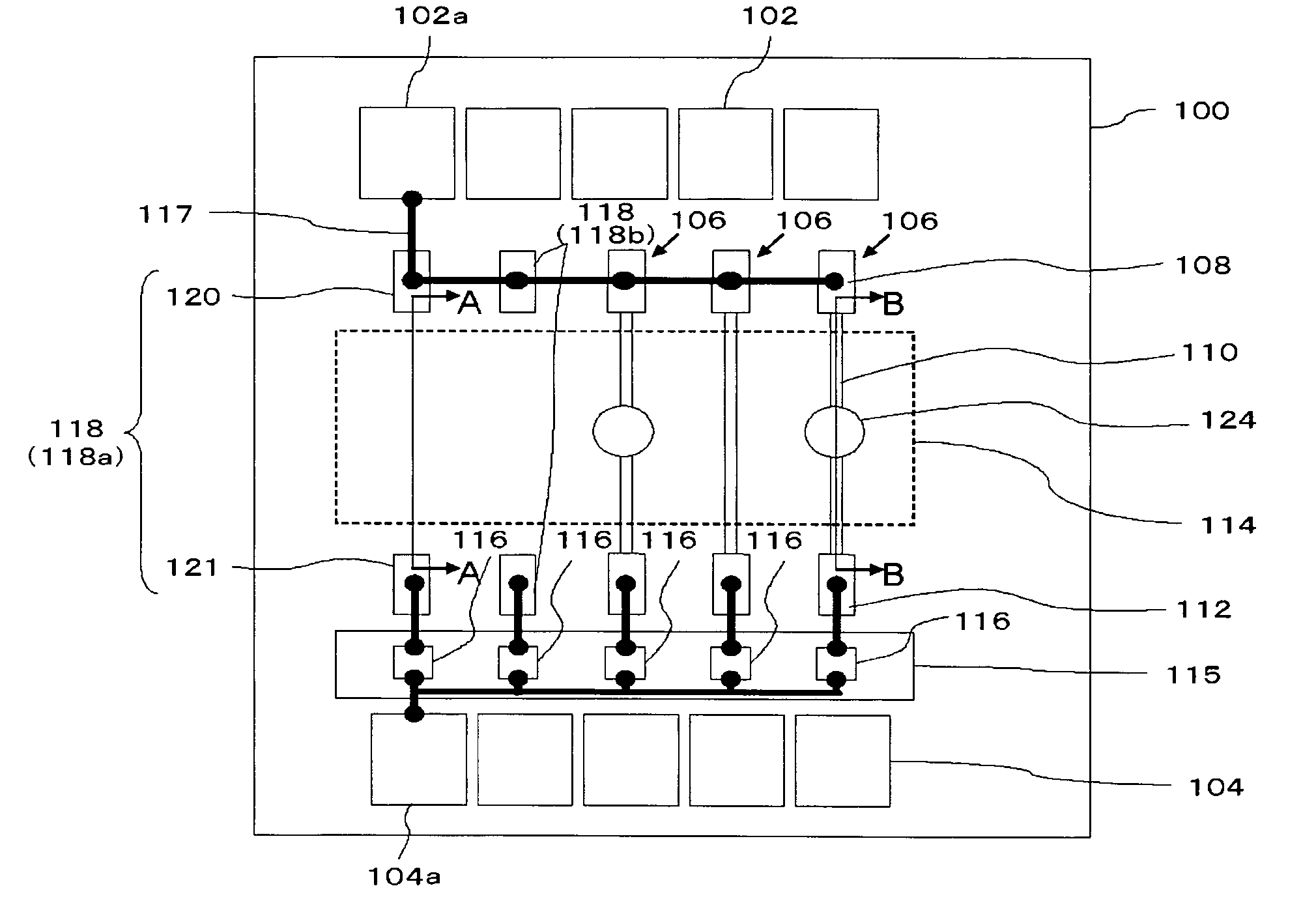

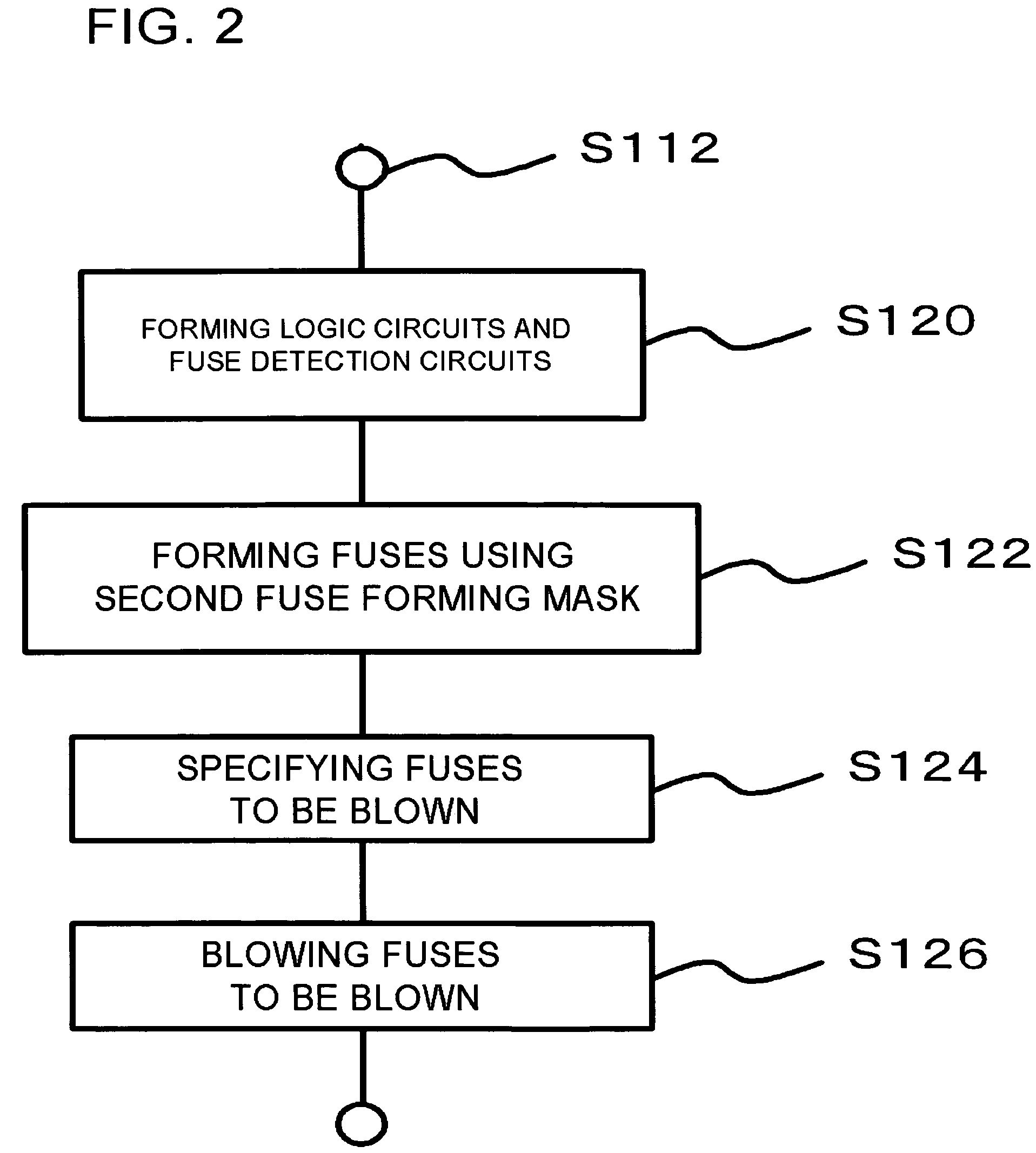

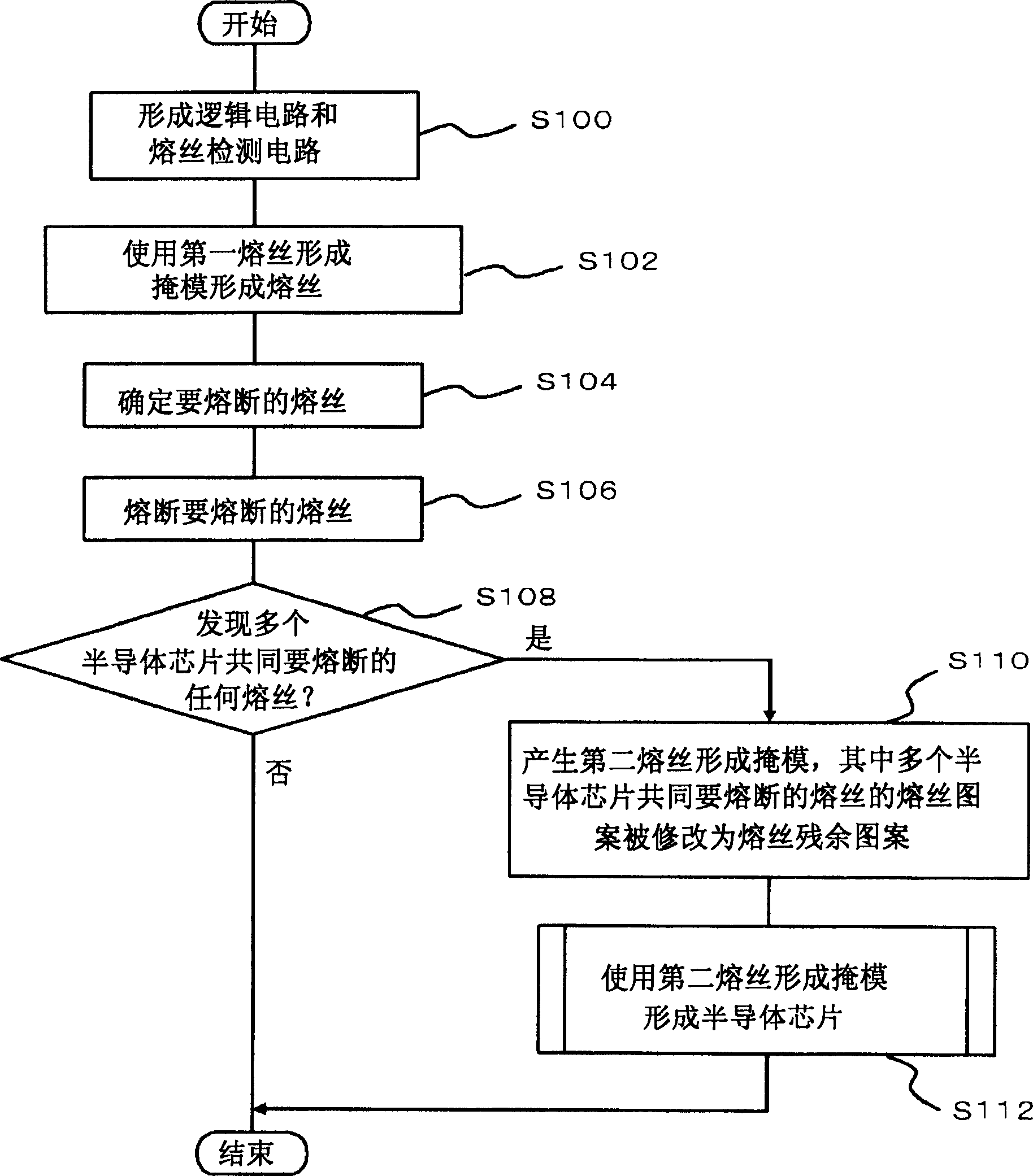

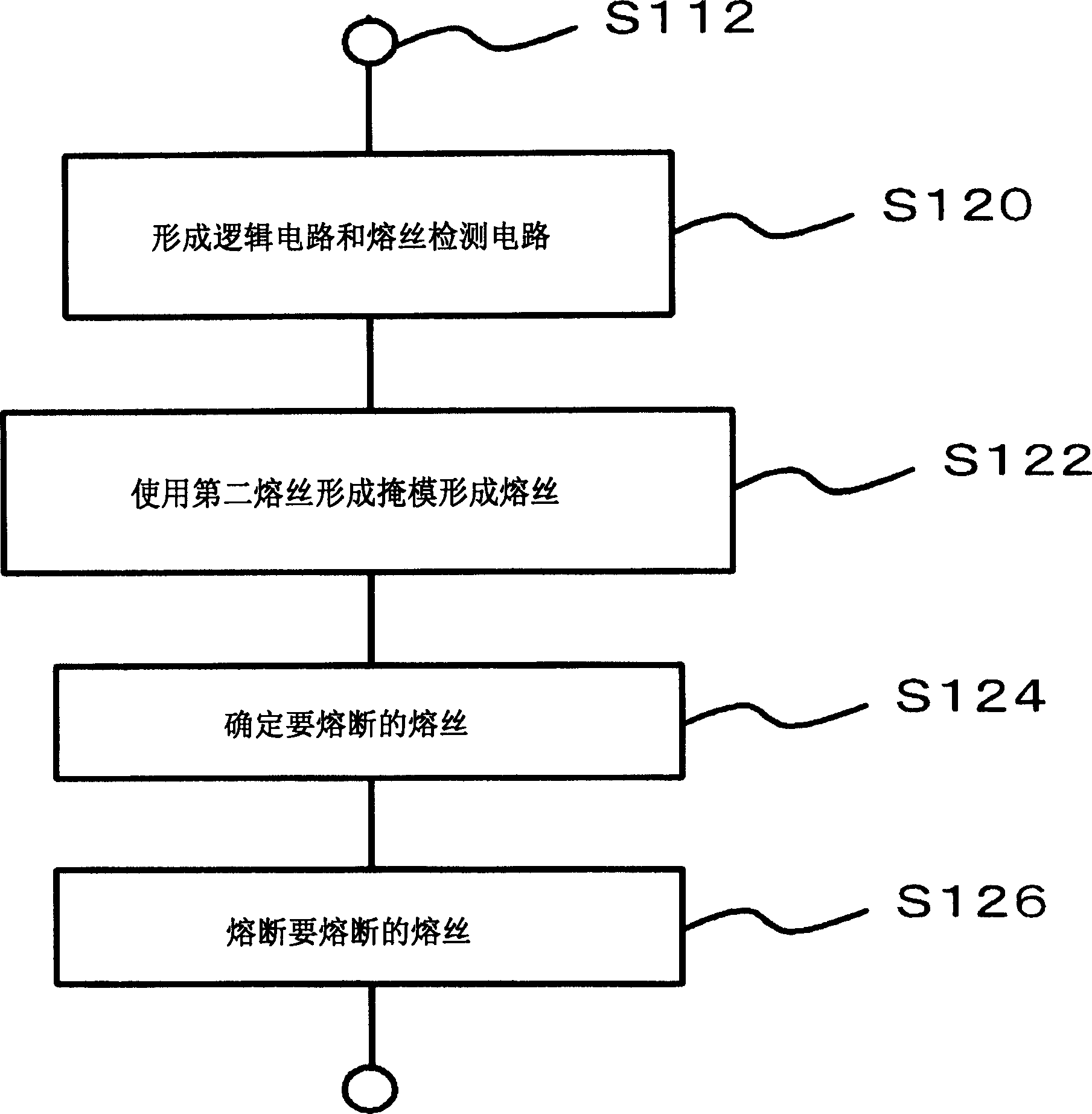

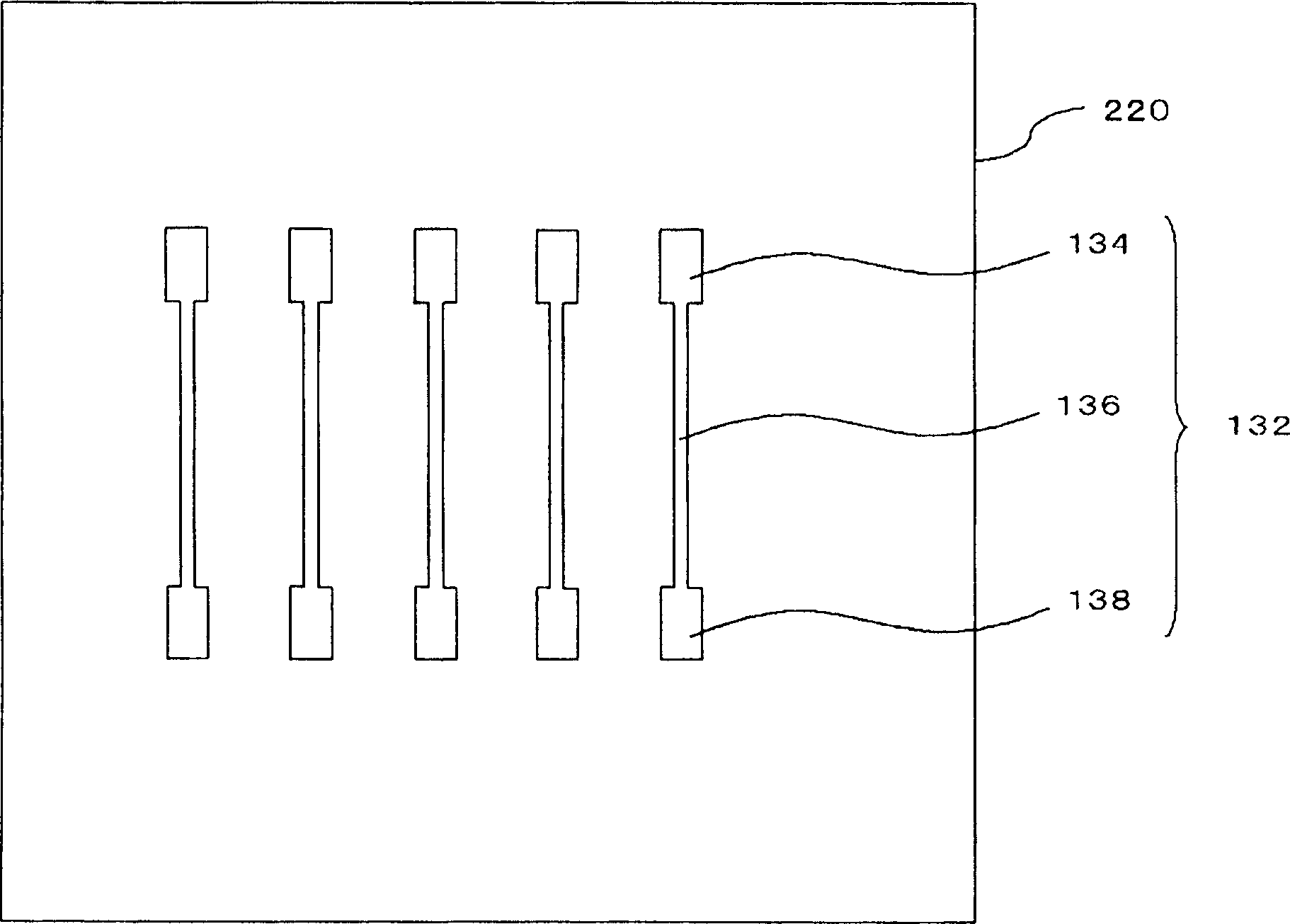

Semiconductor chip and method of fabricating the same

InactiveUS20060189042A1Processing time be shortenEfficiently fabricateSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor chip

There is provided a semiconductor chip having fuses. The semiconductor chip includes fuses each having a first terminal electrically connected to a first logic circuit, a second terminal electrically connected to a second logic circuit, and a blowable region formed between the first terminal and the second terminal; and fuse residues each having the same patterns with those of the first terminal and the second terminal of the fuses, and configured so that patterns corresponded to the first terminals and the second terminals are electrically disconnected from each other.

Owner:RENESAS ELECTRONICS CORP

Evaluation semiconductor device

InactiveUS20060273371A1Improve current performanceImprove accuracyTransistorSolid-state devicesDevice materialEngineering

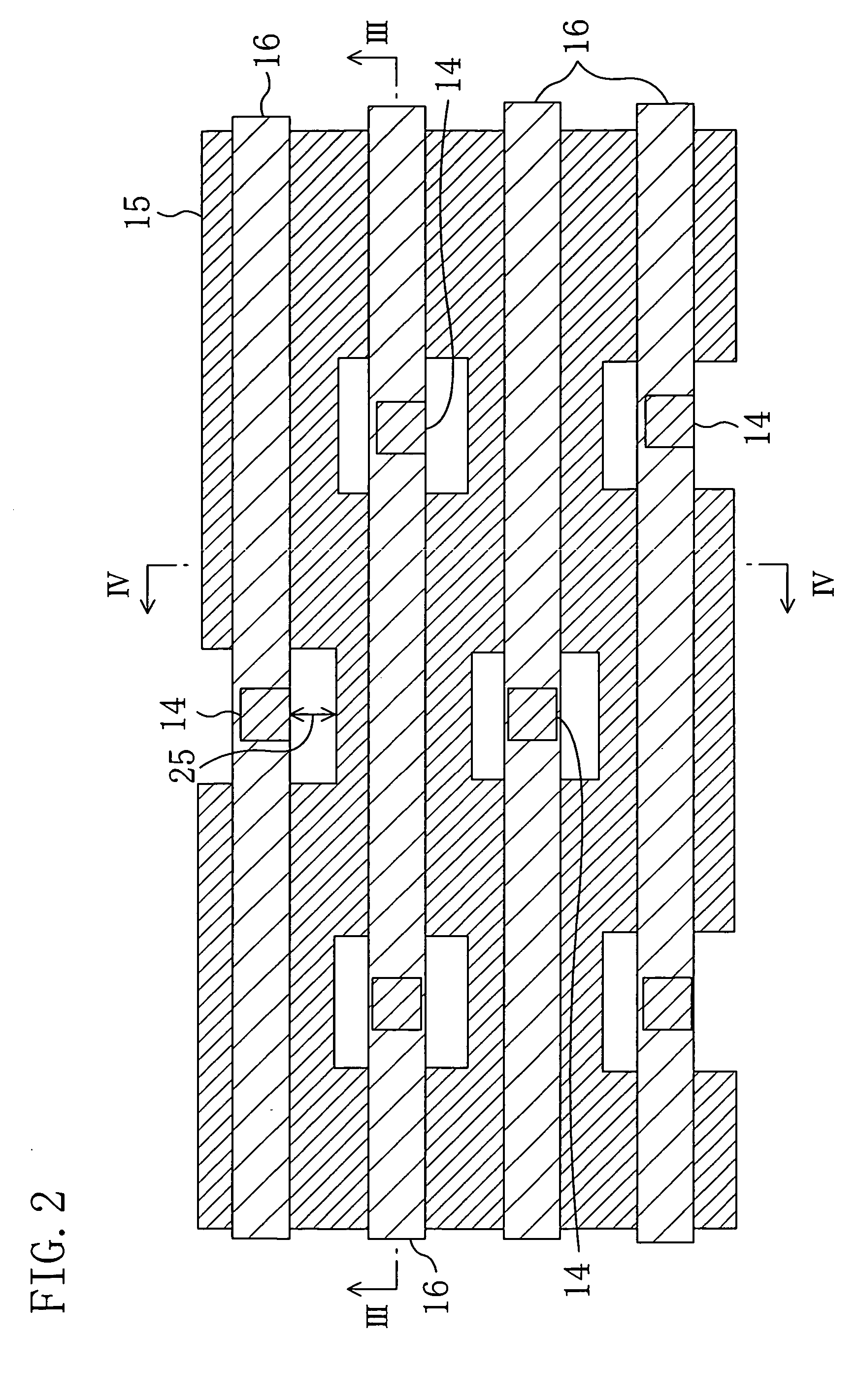

An evaluation semiconductor device is used for evaluating a yield of a DRAM portion of an integrated circuit device. The evaluation semiconductor device includes an evaluation gate interconnect provided in a layer corresponding to a gate interconnect layer of the DRAM portion; and an evaluation source contact corresponding to a source contact of a capacitor included in the DRAM portion and connected to the evaluation gate interconnect.

Owner:PANASONIC CORP

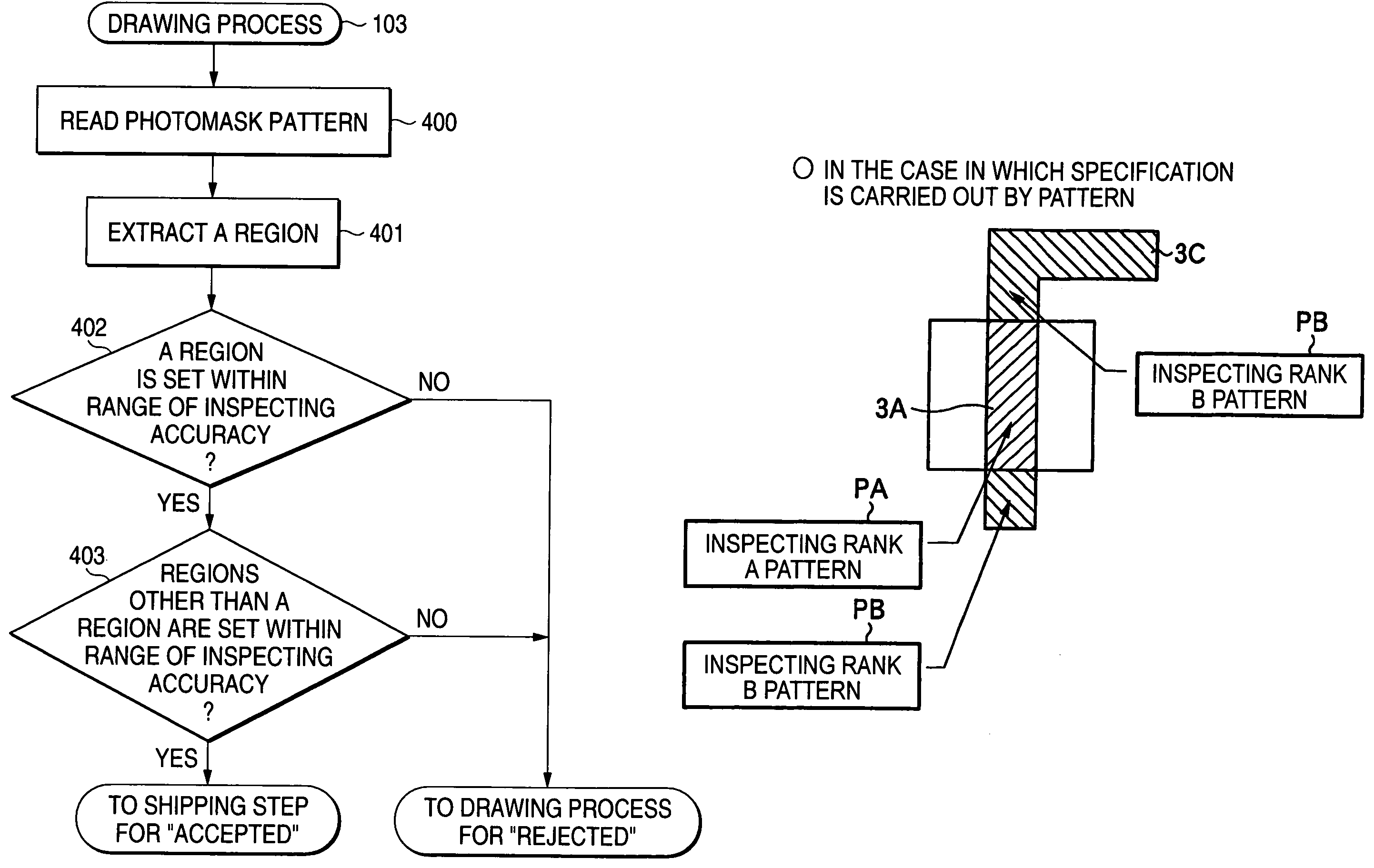

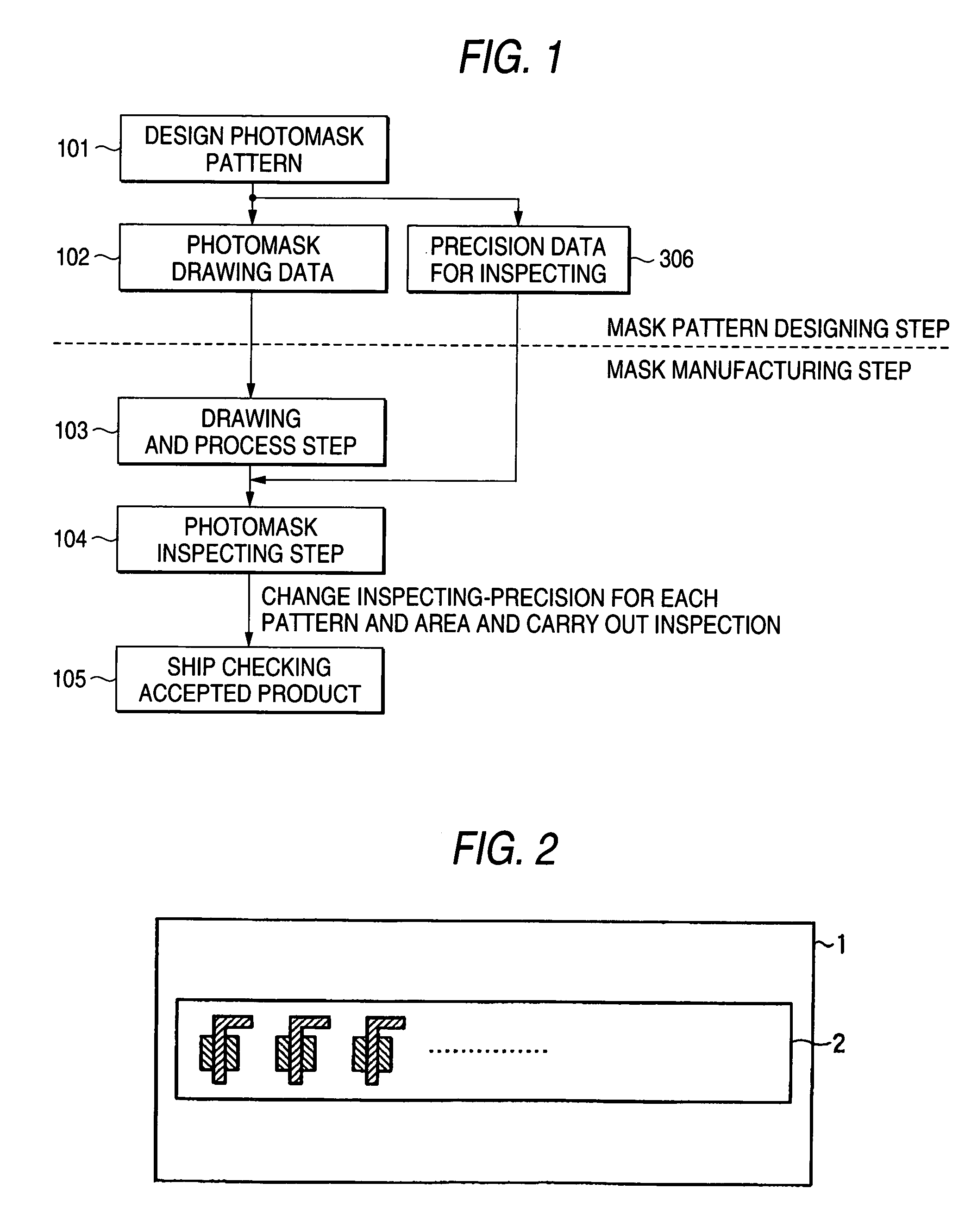

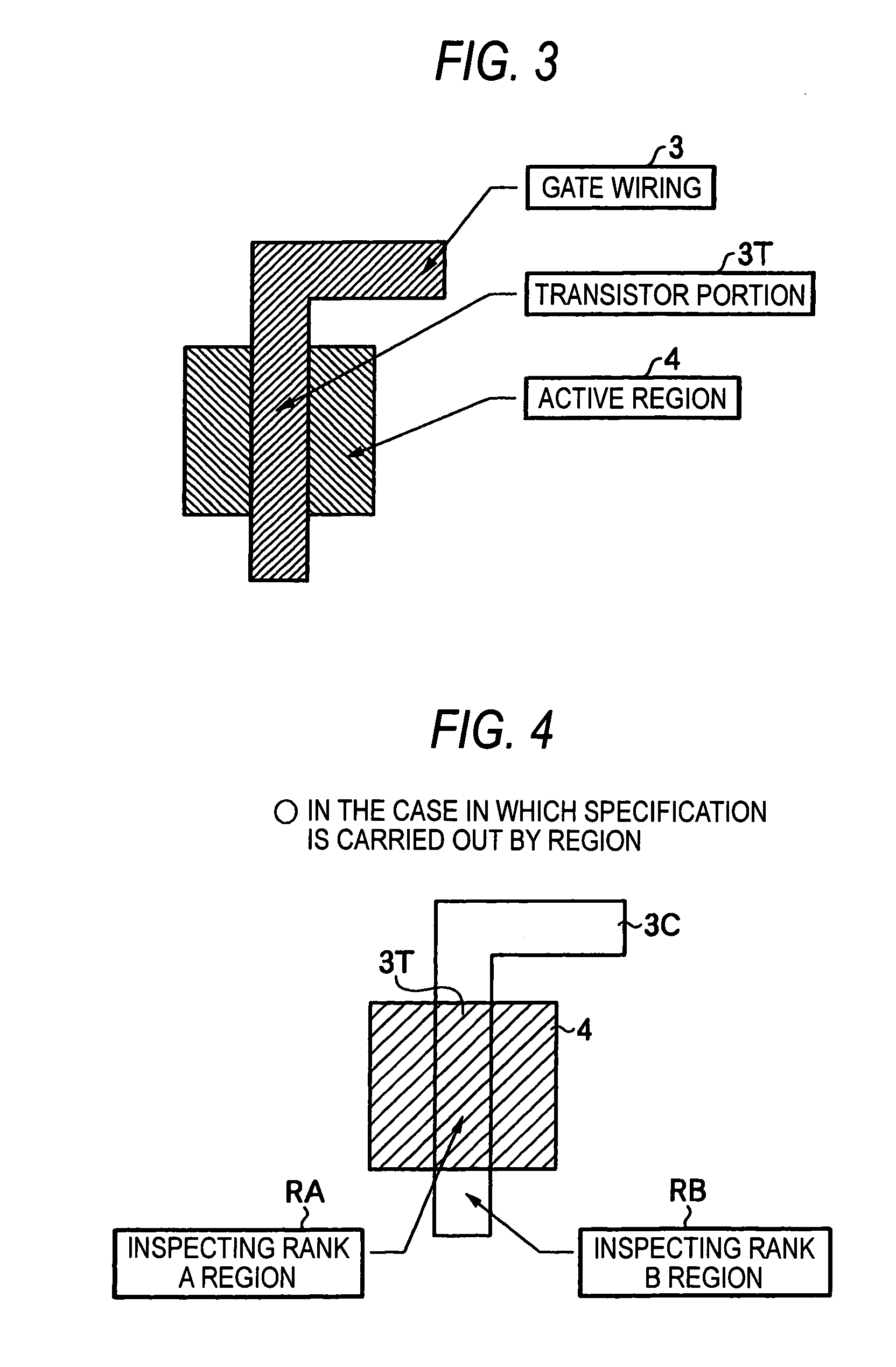

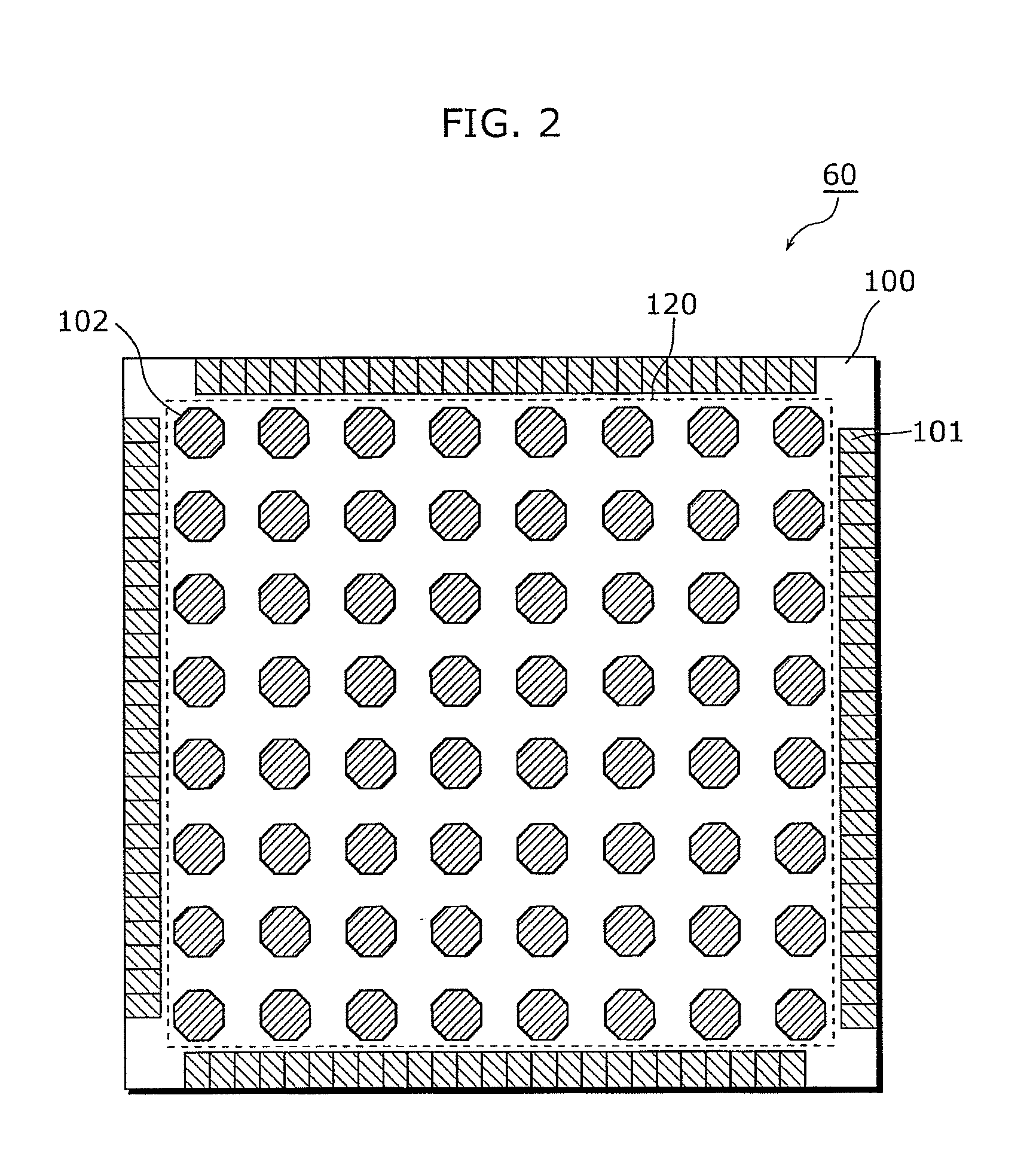

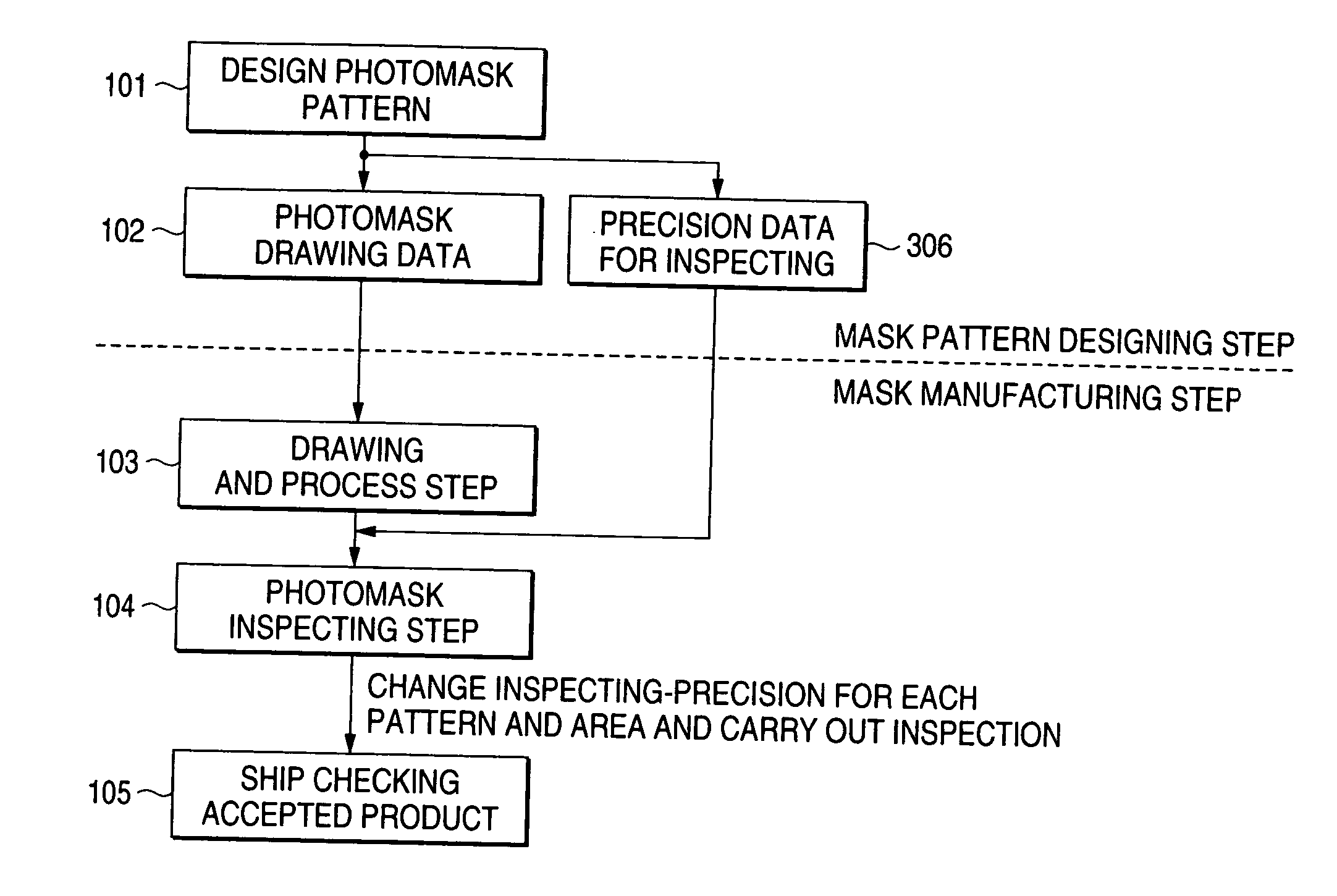

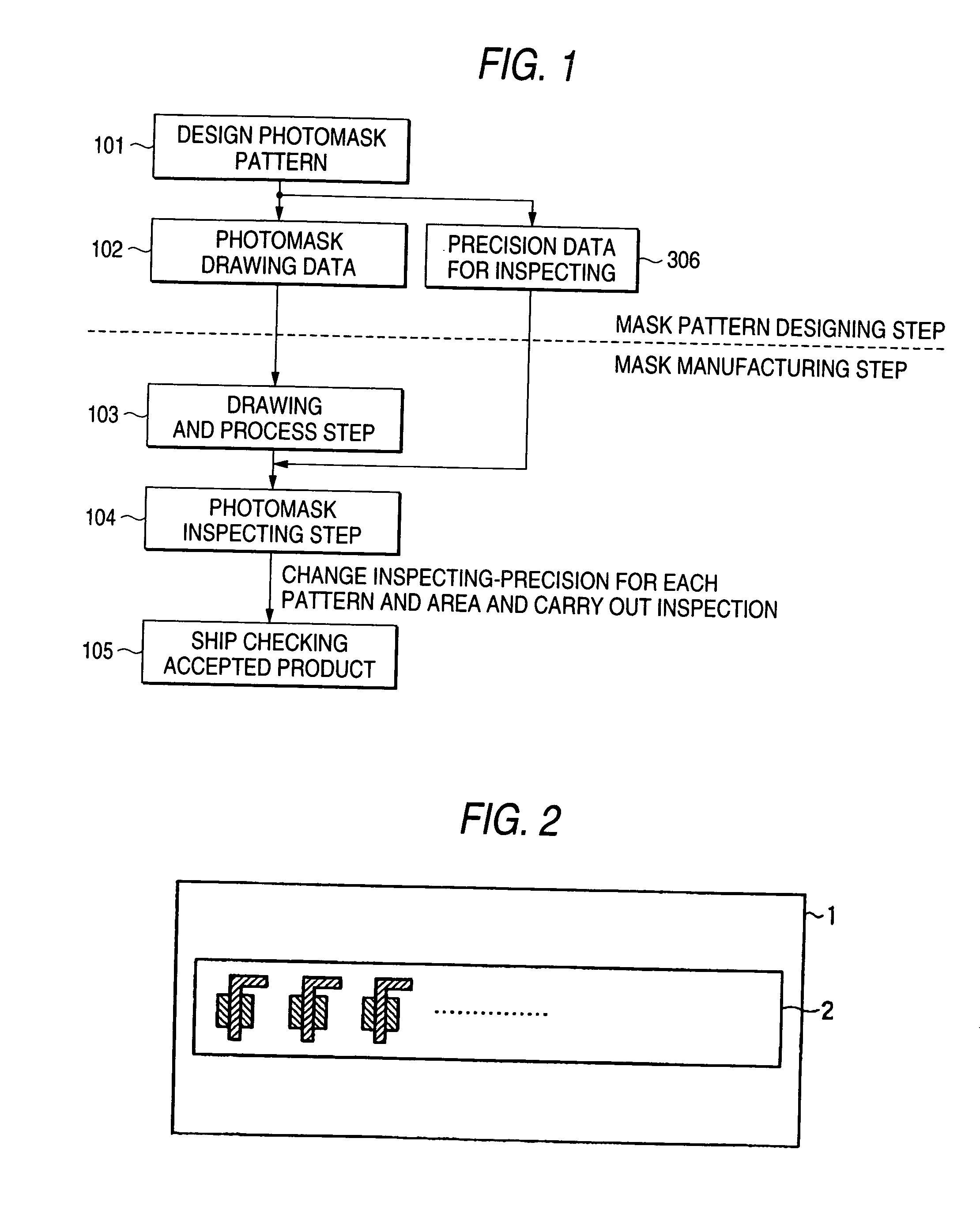

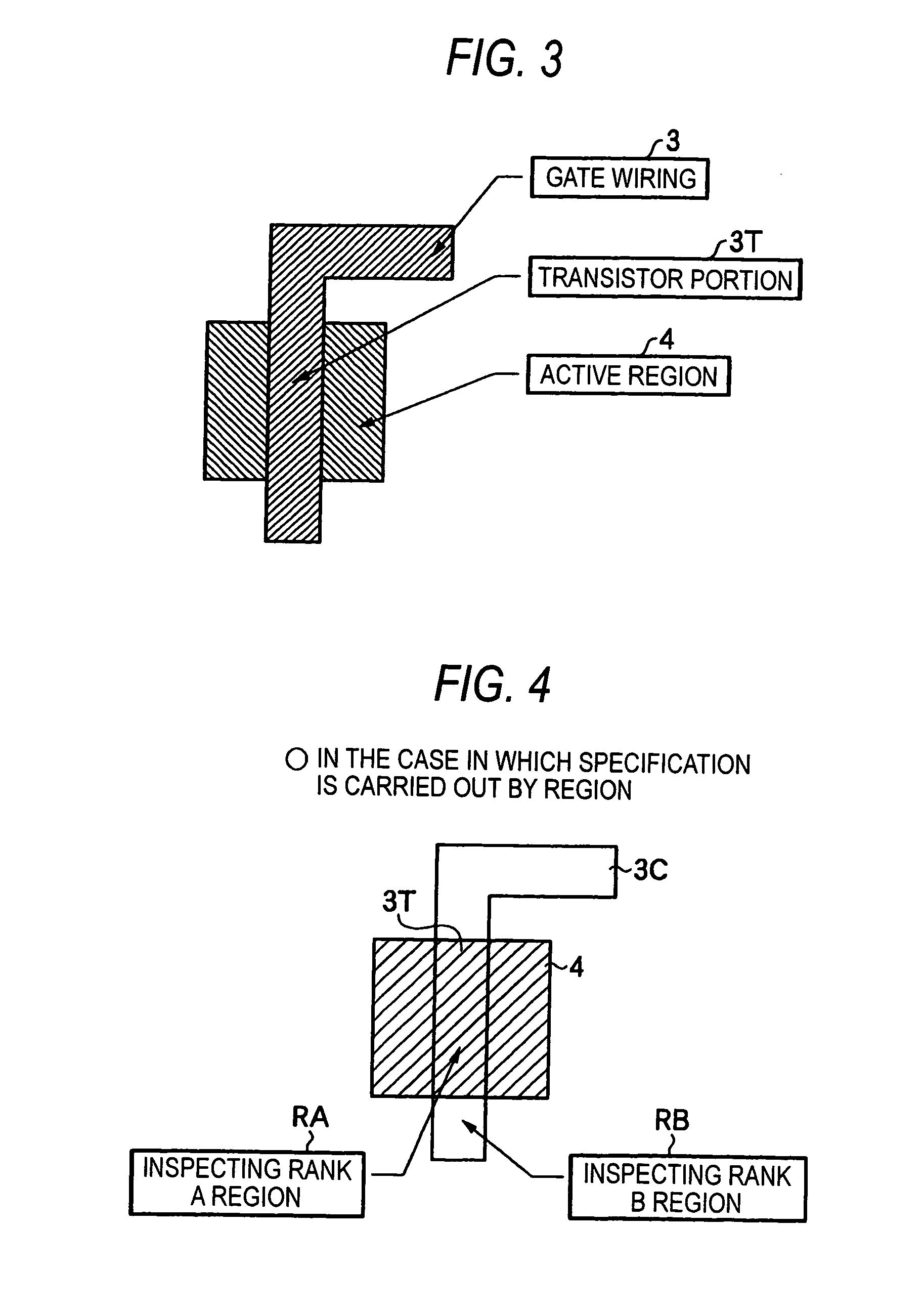

Mask pattern inspecting method, inspection apparatus, inspecting data used therein and inspecting data generating method

InactiveUS7114144B2Shorten TATDecrease costImage enhancementImage analysisIntegrated circuitEngineering

A method of inspecting a photomask for a semiconductor integrated circuit formed based on drawing pattern data, includes the steps of classifying a drawing pattern of the semiconductor integrated circuit into a plurality of ranks in accordance with a predetermined reference and extracting the same, determining inspecting accuracy for each of the ranks, and deciding quality of the photomask depending on whether the determined inspecting accuracy is satisfied.

Owner:SOCIONEXT INC

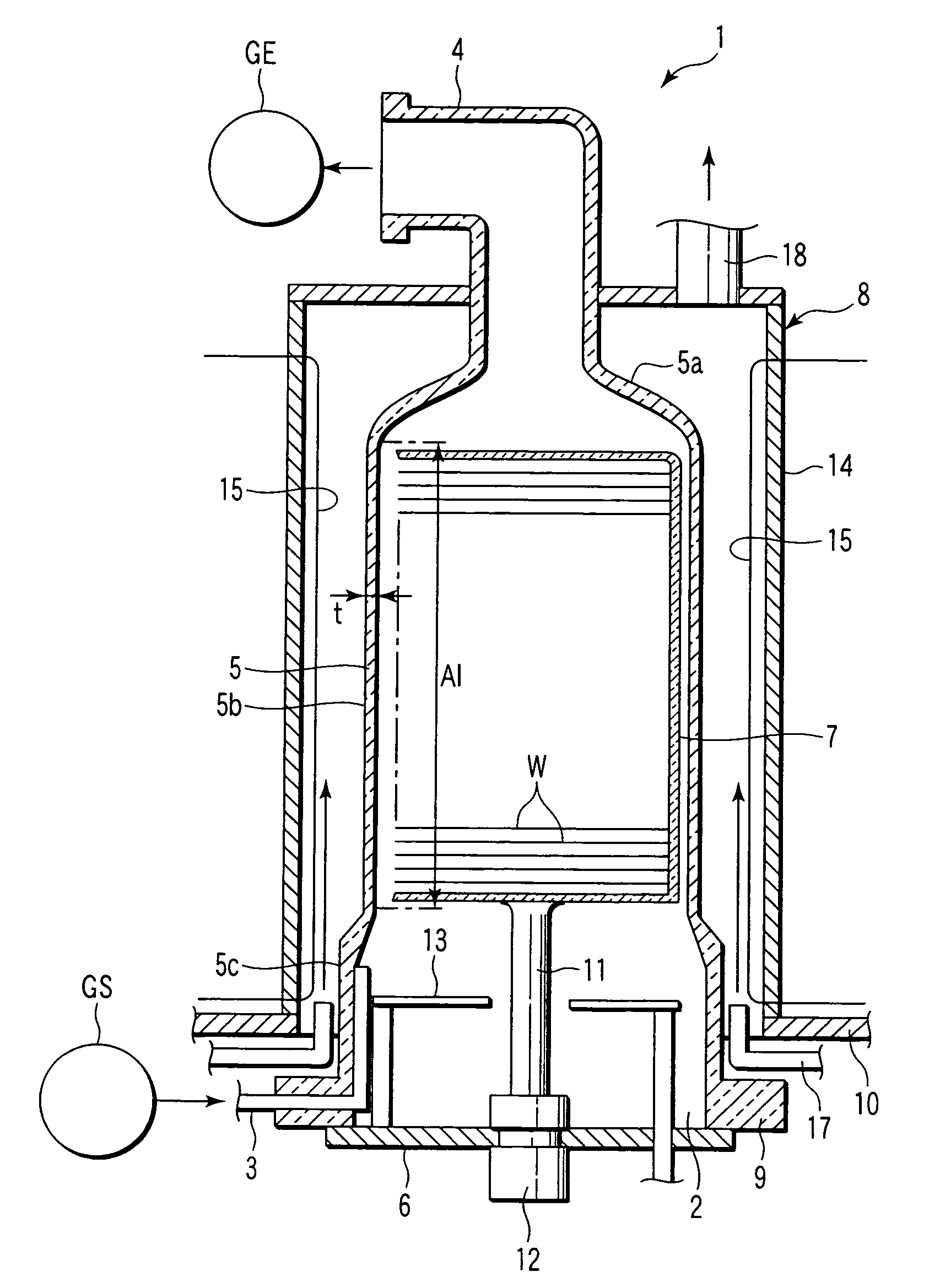

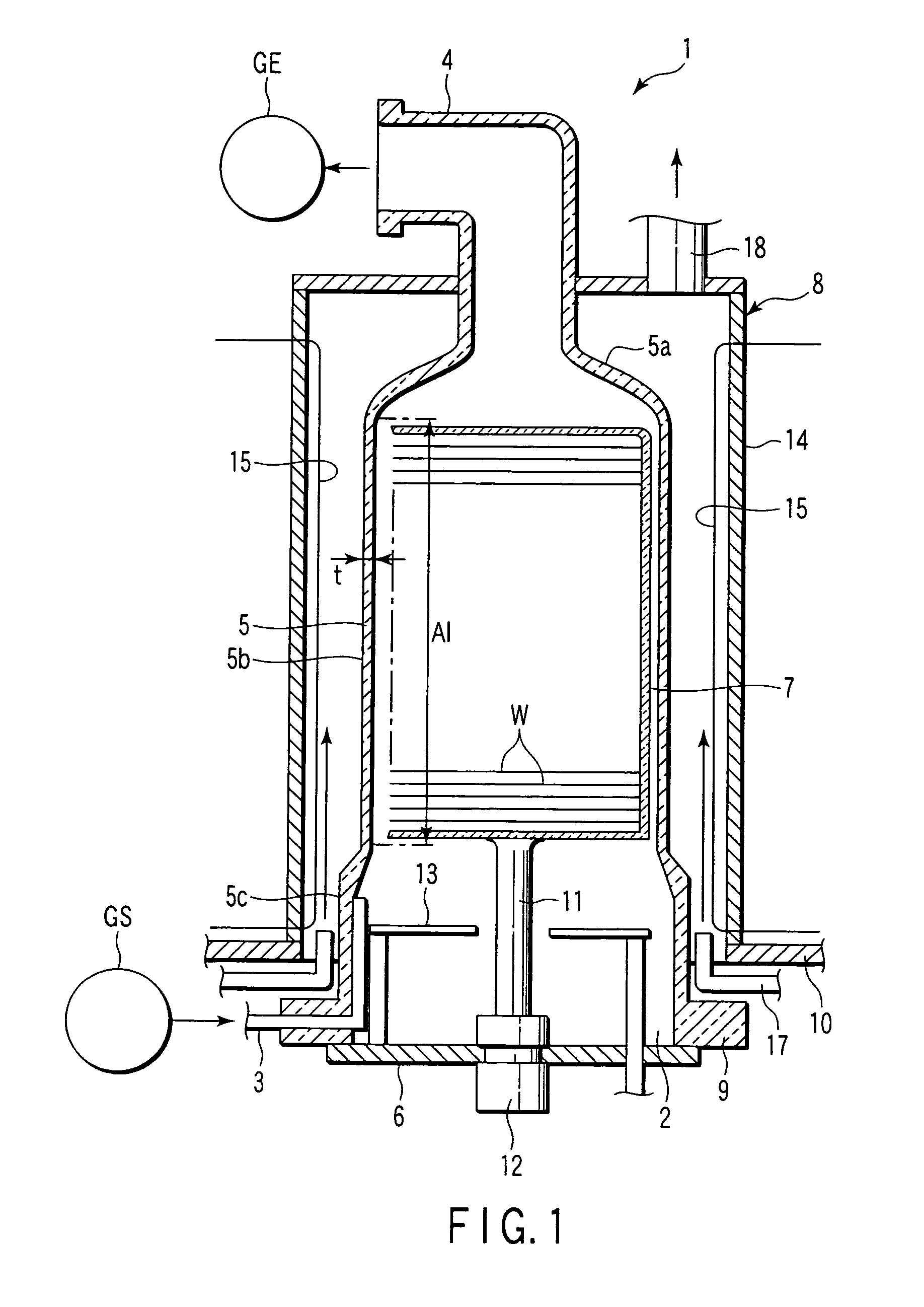

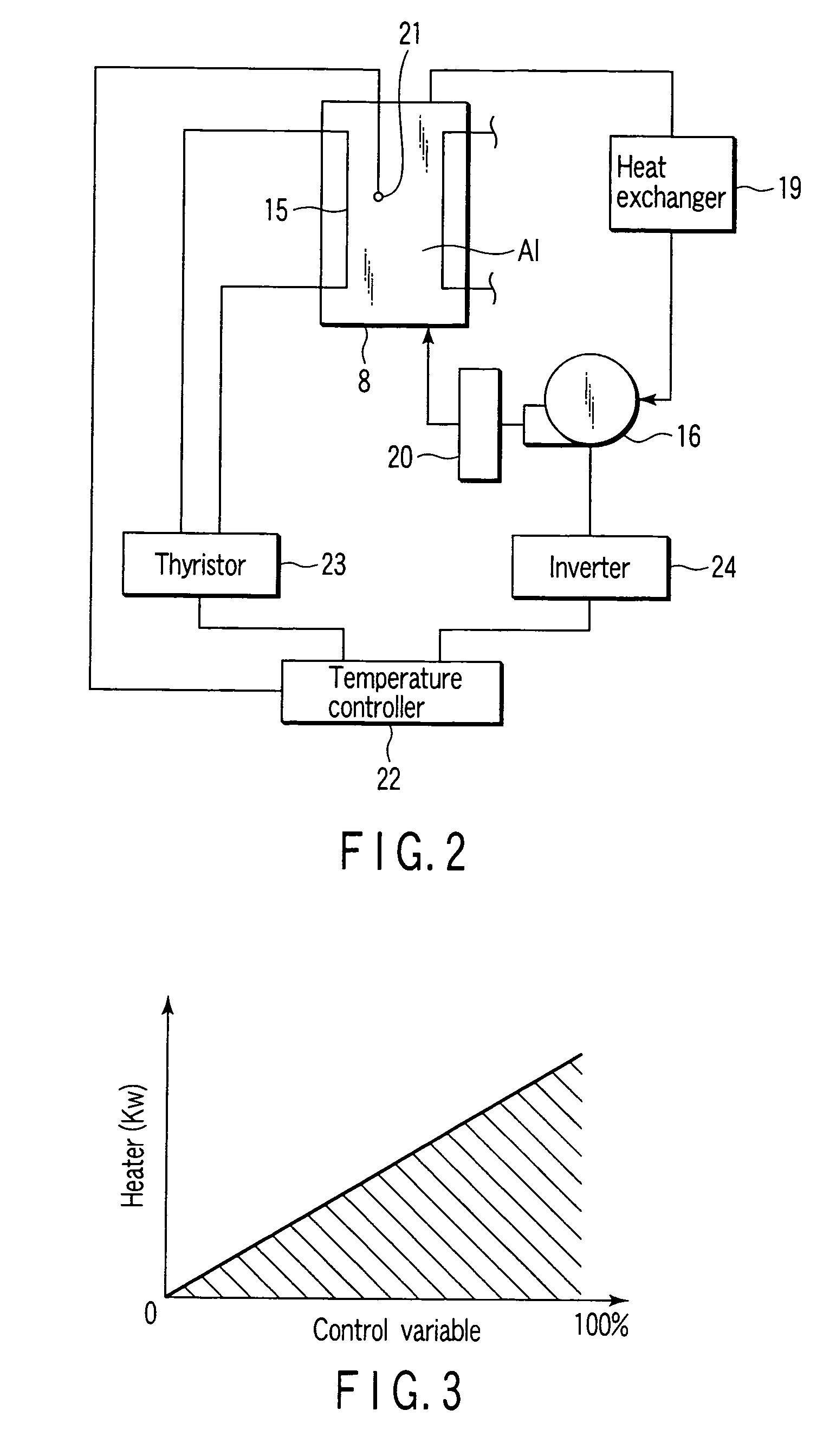

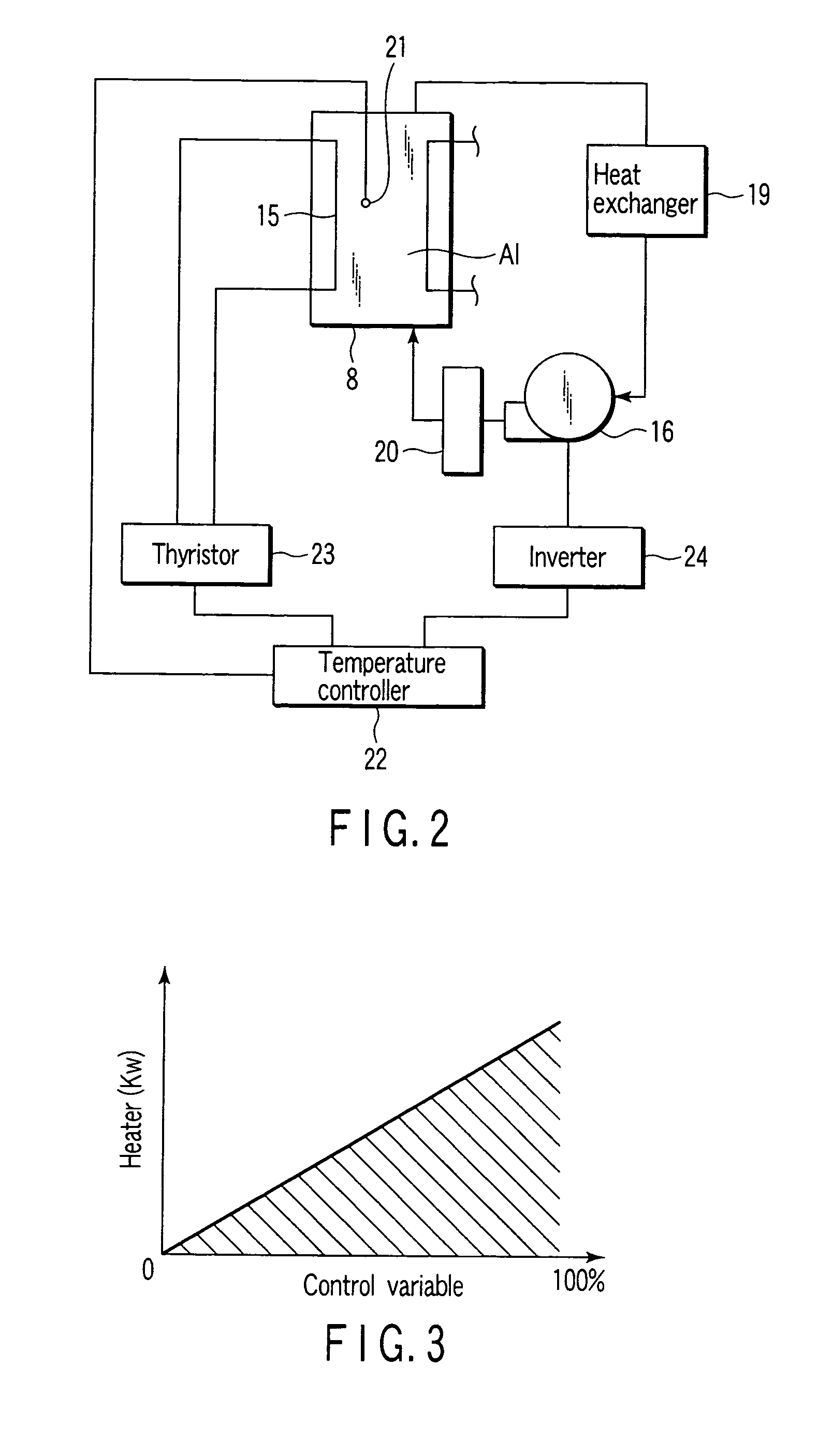

Vertical heat treatment device and method controlling the same

ActiveUS20070148606A1Shorten convergence timeShortened TATDrying solid materials with heatMuffle furnacesProcess engineeringHeating furnace

A vertical heat processing apparatus includes a process chamber (5) defining a process field (A1) configured to accommodate a plurality of target substrates (W) supported at intervals in a vertical direction. The apparatus further includes a heating furnace (8) surrounding the process chamber (5) and including an electric heater (15), and an electric blower (16) configured to send a cooling gas into the heating furnace (8). A control section (22) executes, in order to converge the process field (A1) to a target temperature, performing power feeding to the heater (15) to heat up the process field (A1) to a predetermined temperature immediately below the target temperature, and at a time point when the process field (A1) reaches the predetermined temperature, decreasing the power feeding to the heater (15), and supplying the cooling gas from the blower (16) to forcibly cool the process field (A1).

Owner:TOKYO ELECTRON LTD

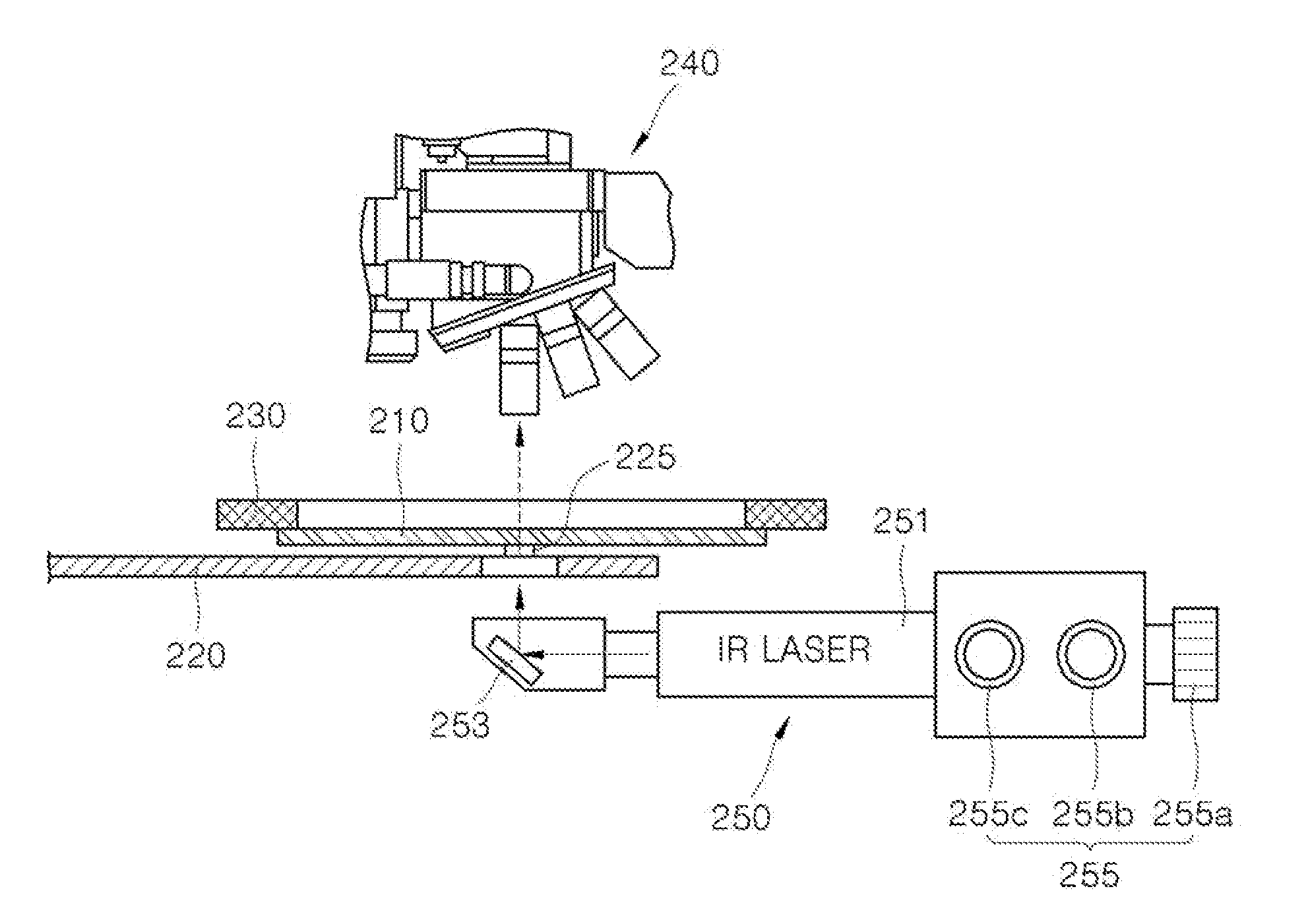

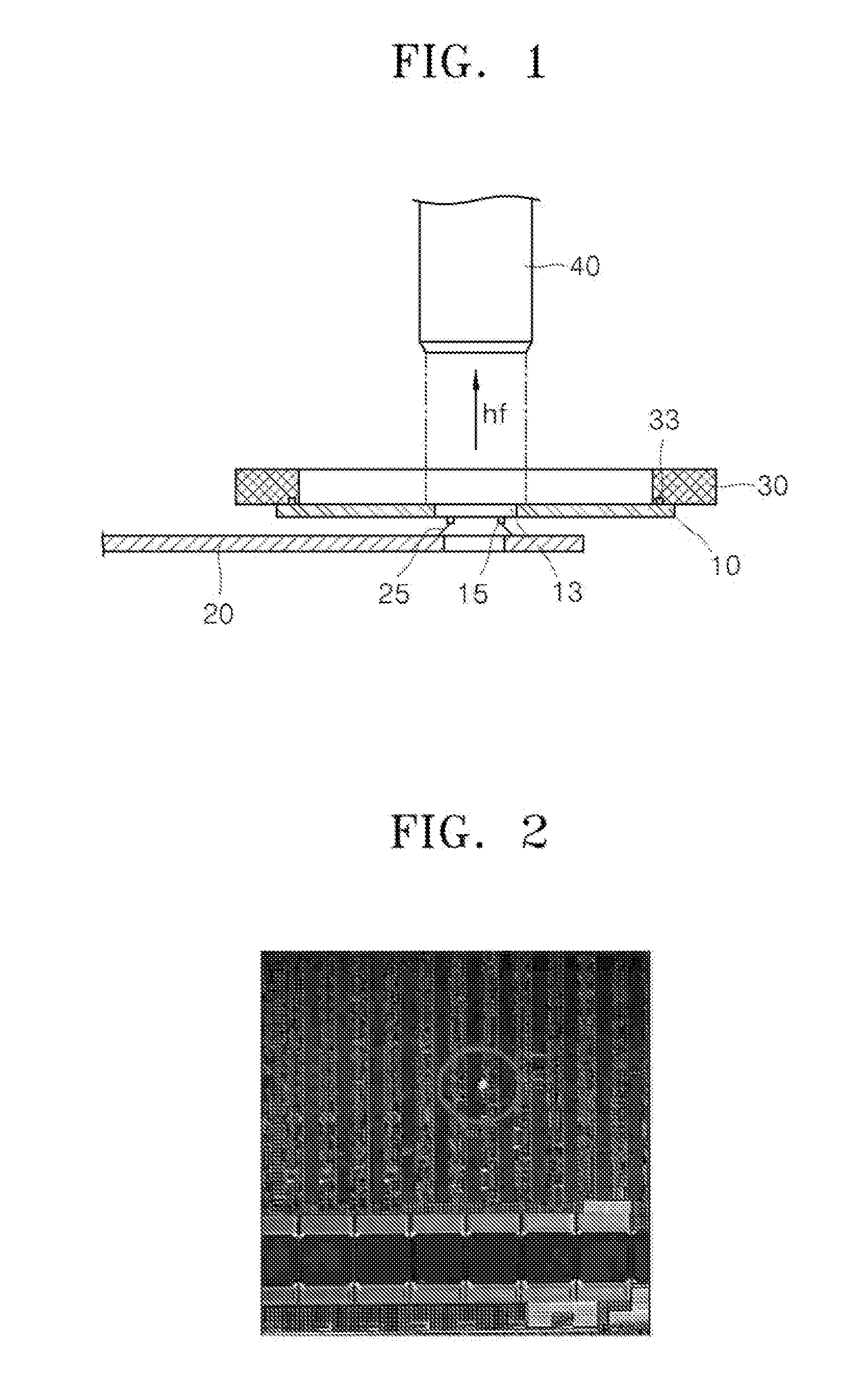

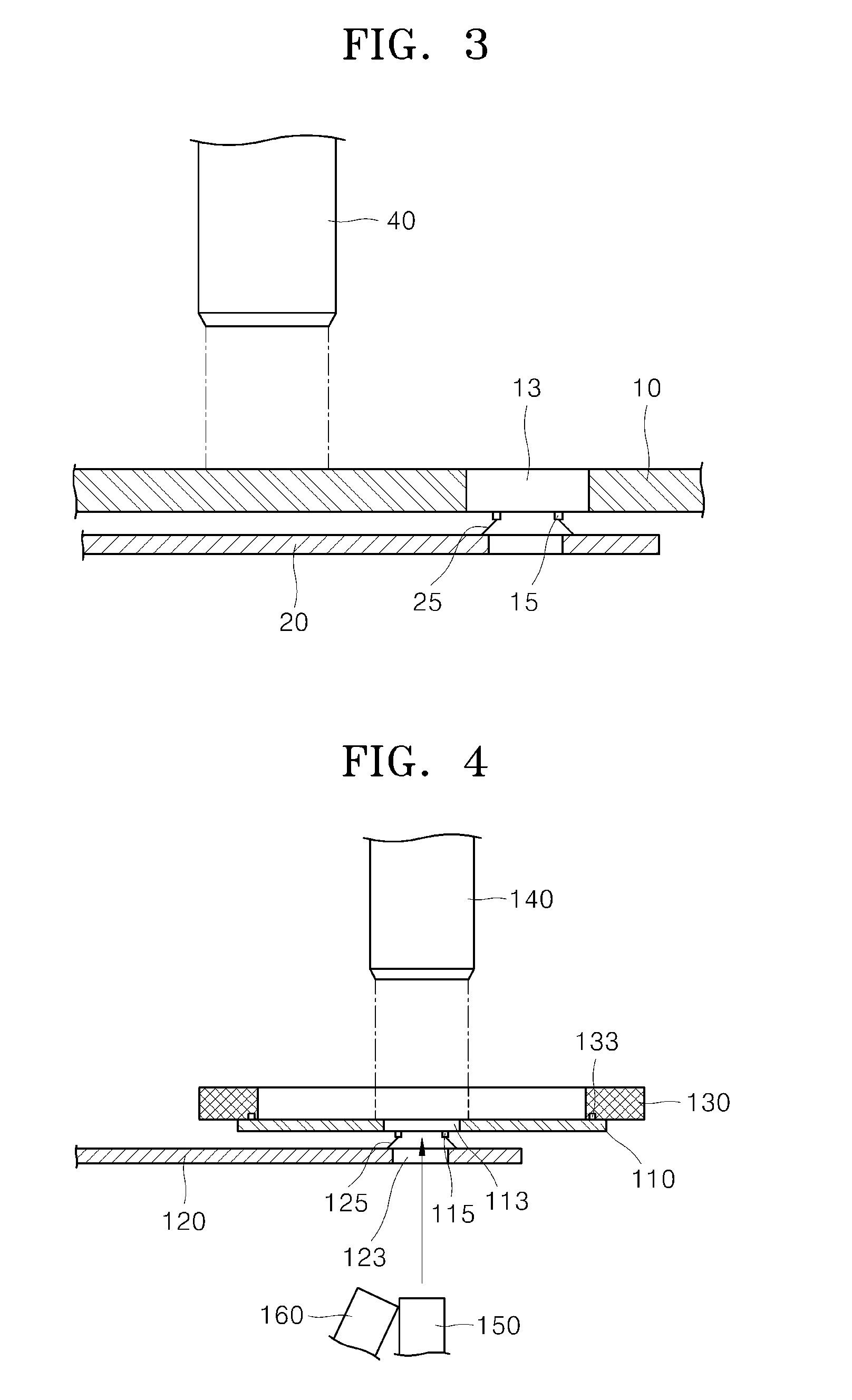

Device for detecting chip location and method of detecting chip location using the device

InactiveUS20080094087A1Reduction of informationShorten the timeRadiation pyrometrySemiconductor/solid-state device testing/measurementProbe cardTurnover time

In a device for detecting a chip location and a method of detecting a chip location using the device, the device includes a chuck to which a wafer to be inspected is fixable, an infrared irradiation unit capable of irradiating infrared light to a target semiconductor chip of the wafer from the backside of the wafer, and a scope disposed opposite to the infrared irradiation unit with respect to the wafer. In this manner, it can be readily be determined whether the scope is aligned with a target semiconductor chip to which a probe card is connected for inspection by a backside emission method. Furthermore, the target semiconductor chip to be inspected can be readily detected among semiconductor chips viewed through the scope. Therefore, TAT (turn around time) for inspection can be largely reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

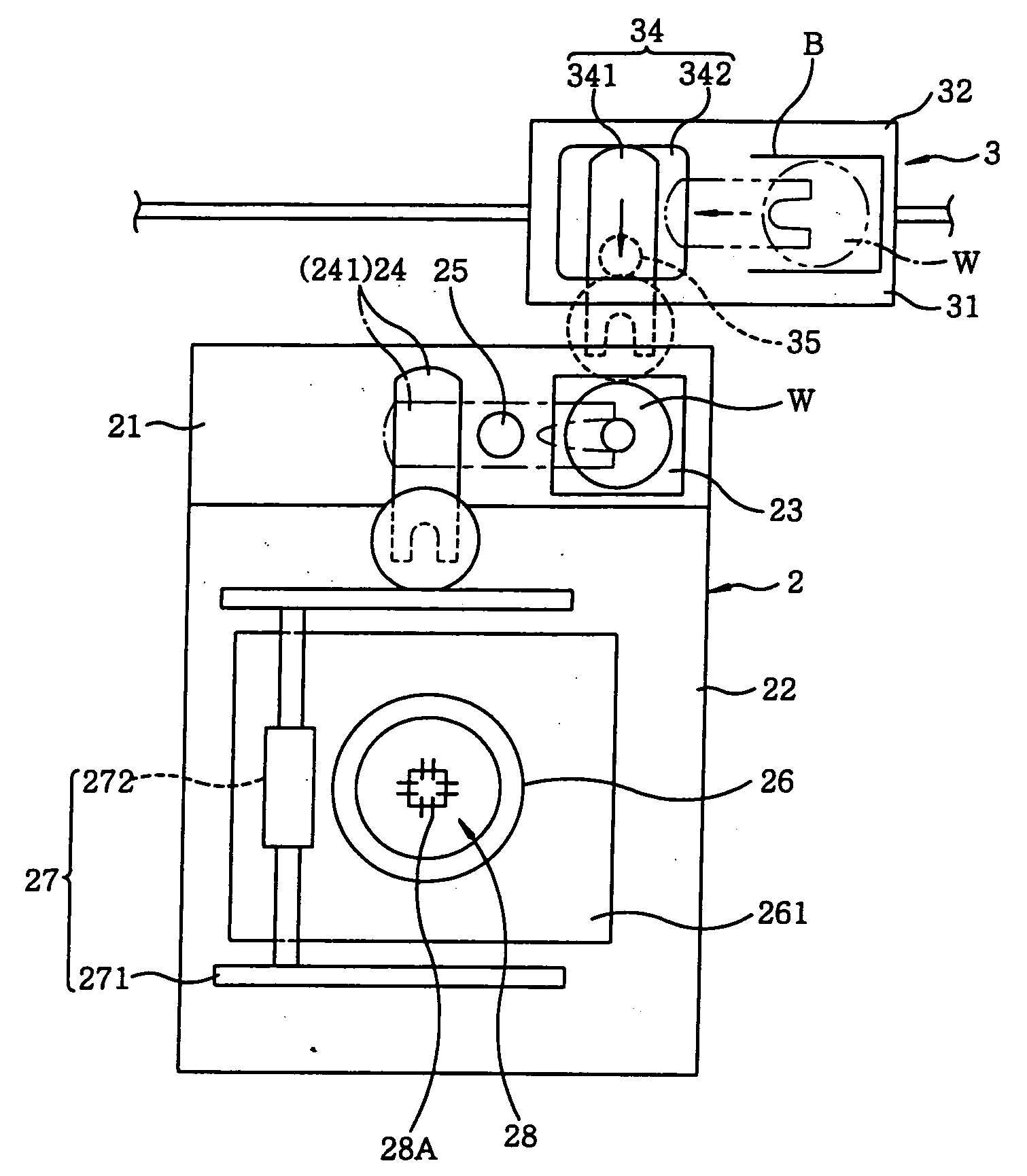

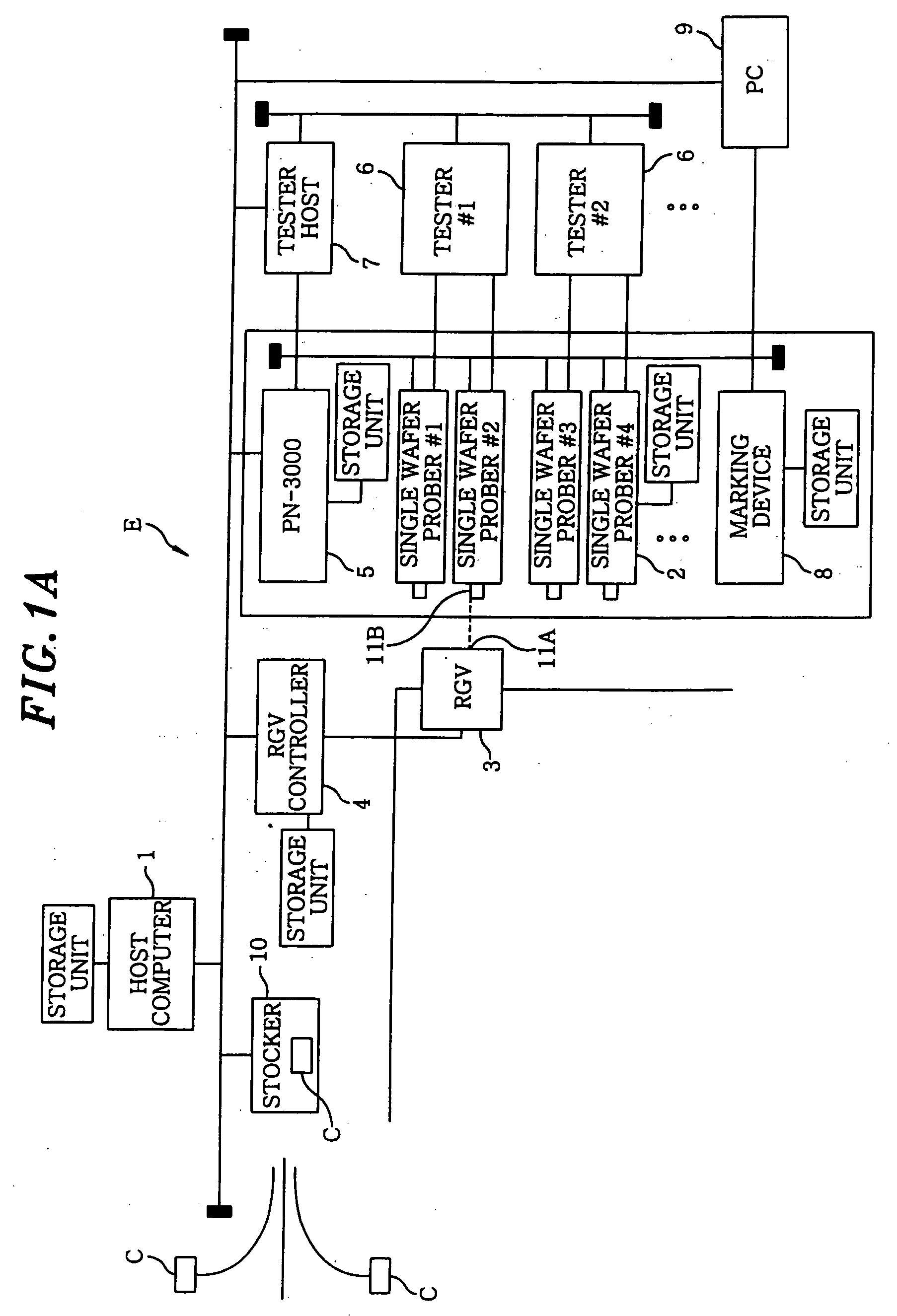

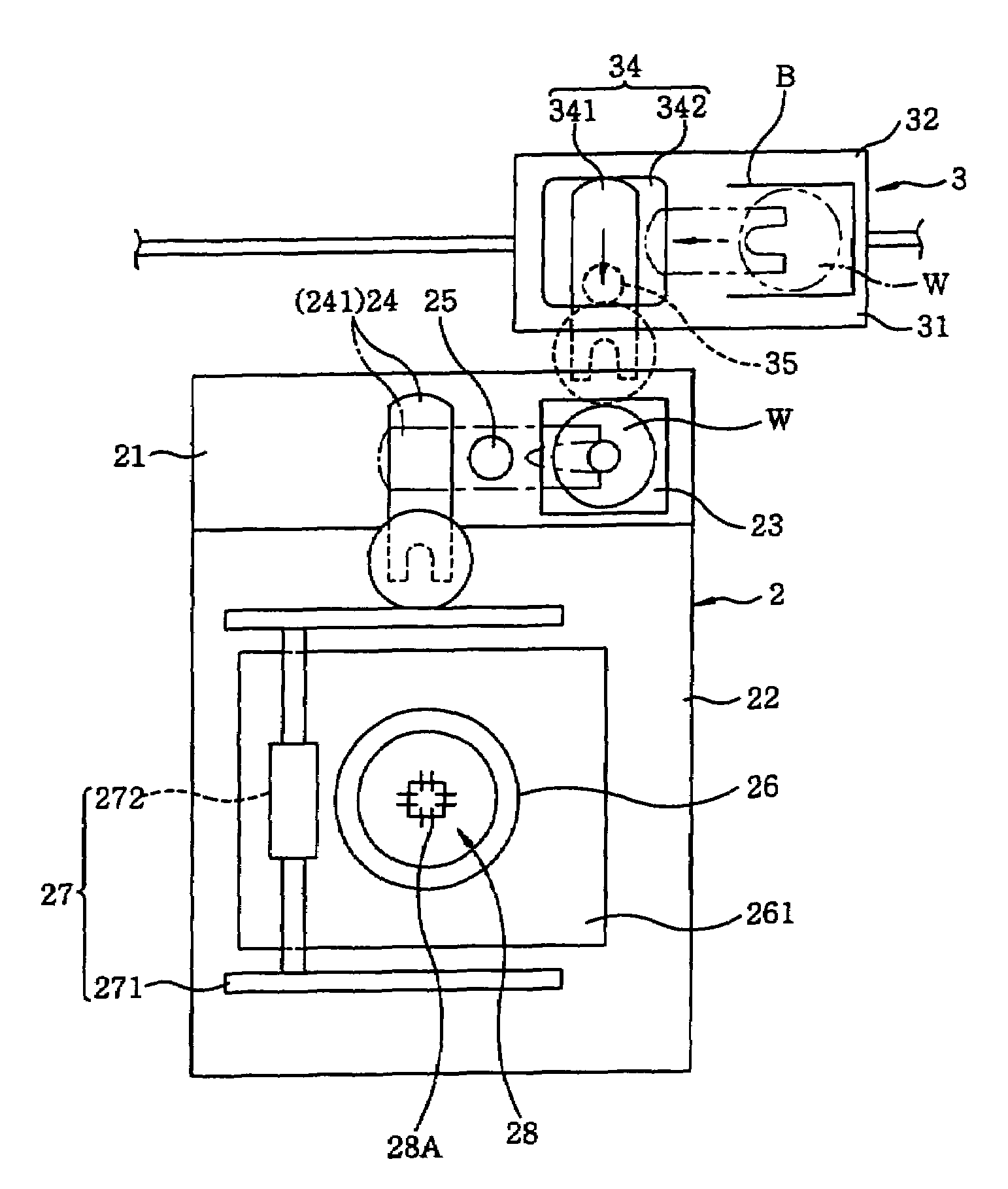

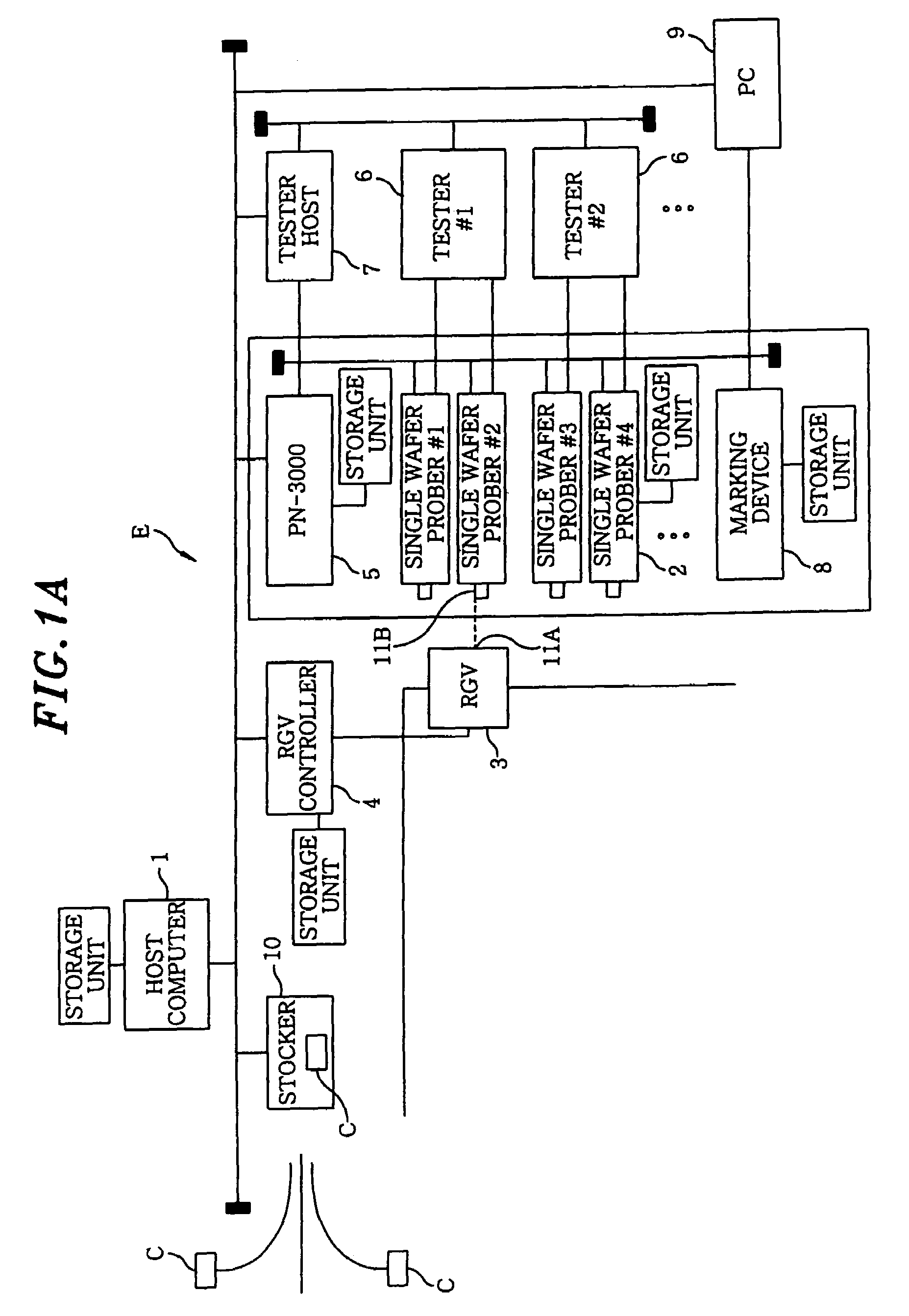

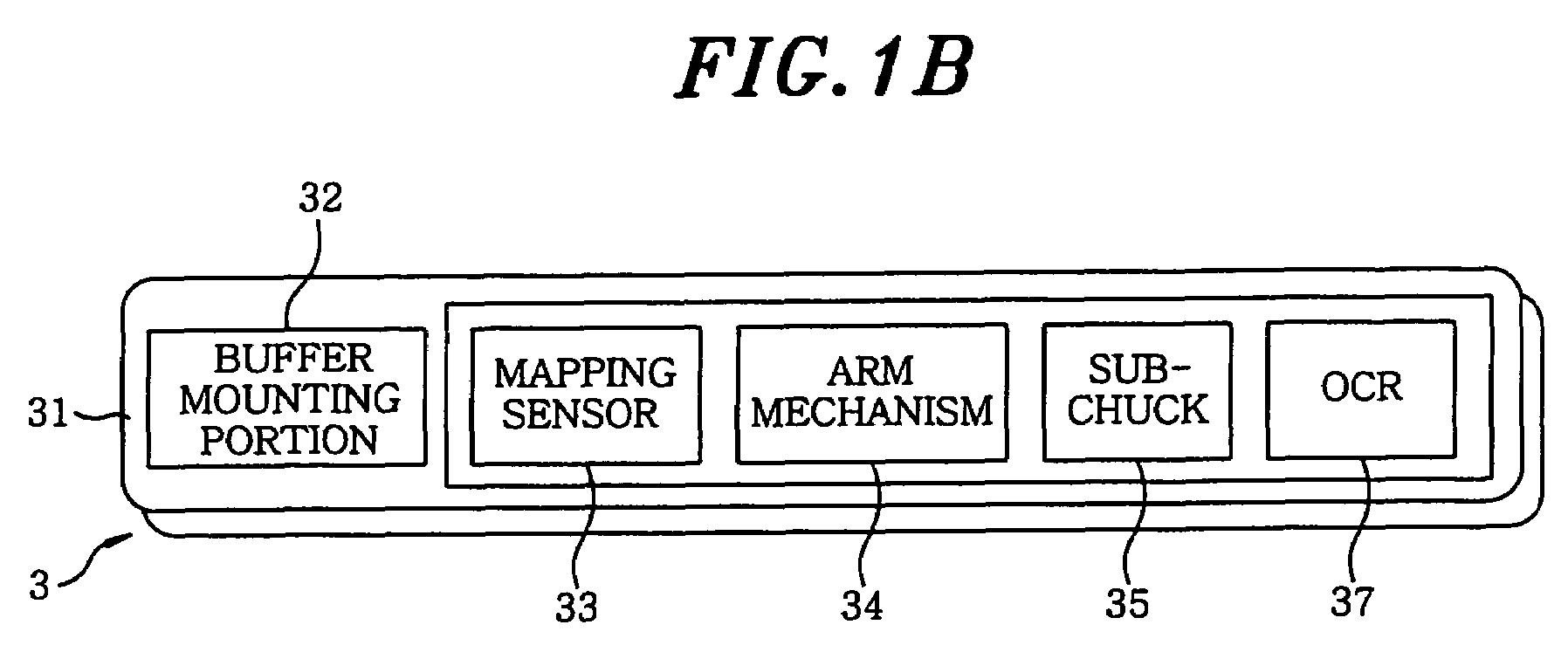

Transfer system and transfer method of object to be processed

InactiveUS20060152211A1Enhance transfer efficiencyCommunication efficiency be improveElectronic circuit testingDigital data processing detailsTransfer systemCommunication interface

A transfer method employs a transfer system including a semiconductor handling device and an automatic transfer device. The semiconductor handling device includes a first transfer mechanism and a first optically coupled parallel I / O communications interface. The automatic transfer device includes a second transfer mechanism and a second optically coupled parallel I / O communications interface. The transfer method includes a successive transfer notifying step wherein the automatic transfer device and the semiconductor handling device notify each other that a successive transfer is possible via an optical communications between the first and the second optically coupled parallel I / O communications interface in case where a plurality of objects to be processed are able to be successively transferred one by one between the first and the second transfer mechanism; and a successive transfer step wherein the objects are transferred one by one between the first and the second transfer mechanism.

Owner:TOKYO ELECTRON LTD

Semiconductor chip and method of fabricating the same

InactiveUS7638369B2Shortened TATImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

There is provided a semiconductor chip having fuses. The semiconductor chip includes fuses each having a first terminal electrically connected to a first logic circuit, a second terminal electrically connected to a second logic circuit, and a blowable region formed between the first terminal and the second terminal; and fuse residues each having the same patterns with those of the first terminal and the second terminal of the fuses, and configured so that patterns corresponded to the first terminals and the second terminals are electrically disconnected from each other.

Owner:RENESAS ELECTRONICS CORP

Fabrication method of semiconductor integrated circuit device

InactiveUS7452787B2Shortened TATGuaranteed stable releaseSolid-state devicesSemiconductor/solid-state device manufacturingWaferingDicing tape

A technique capable of stably releasing chips from a dicing tape, includes grinding a back surface of a semiconductor wafer, while adhering a pressure sensitive adhesive tape to a circuit forming surface of the semiconductor wafer formed with an integrated circuit, to achieve a predetermined thickness and forcibly oxidizing the back surface of the semiconductor wafer. Then, the pressure sensitive adhesive tape adhered to the circuit forming surface of the semiconductor wafer is released, and a dicing tape is adhered to the back surface of the semiconductor wafer. Further, the semiconductor wafer is divided by dicing it into individual chips, and then the back surface of the chip is pressed by way of the dicing tape, thereby releasing the chips from the dicing tape.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device including external connection pads and test pads

ActiveUS8927987B2Improve screening efficiencyShortened TATSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor chipExternal connection

A semiconductor device according to one embodiment of this invention includes: a semiconductor chip; a plurality of external connection pads and a plurality of first test pads, both of which are formed in a central region of a top surface of the semiconductor chip; a plurality of external connection electrodes each formed on a corresponding one of the external connection pads, the external connection electrodes being for connecting the external connection pads and an outside of the semiconductor device.

Owner:PANASONIC CORP

Mask pattern inspecting method, inspection apparatus, inspecting data used therein and inspecting data generating method

A method of inspecting a photomask for a semiconductor integrated circuit formed based on drawing pattern data, includes the steps of classifying a drawing pattern of the semiconductor integrated circuit into a plurality of ranks in accordance with a predetermined reference and extracting the same, determining inspecting accuracy for each of the ranks, and deciding quality of the photomask depending on whether the determined inspecting accuracy is satisfied.

Owner:PANASONIC CORP

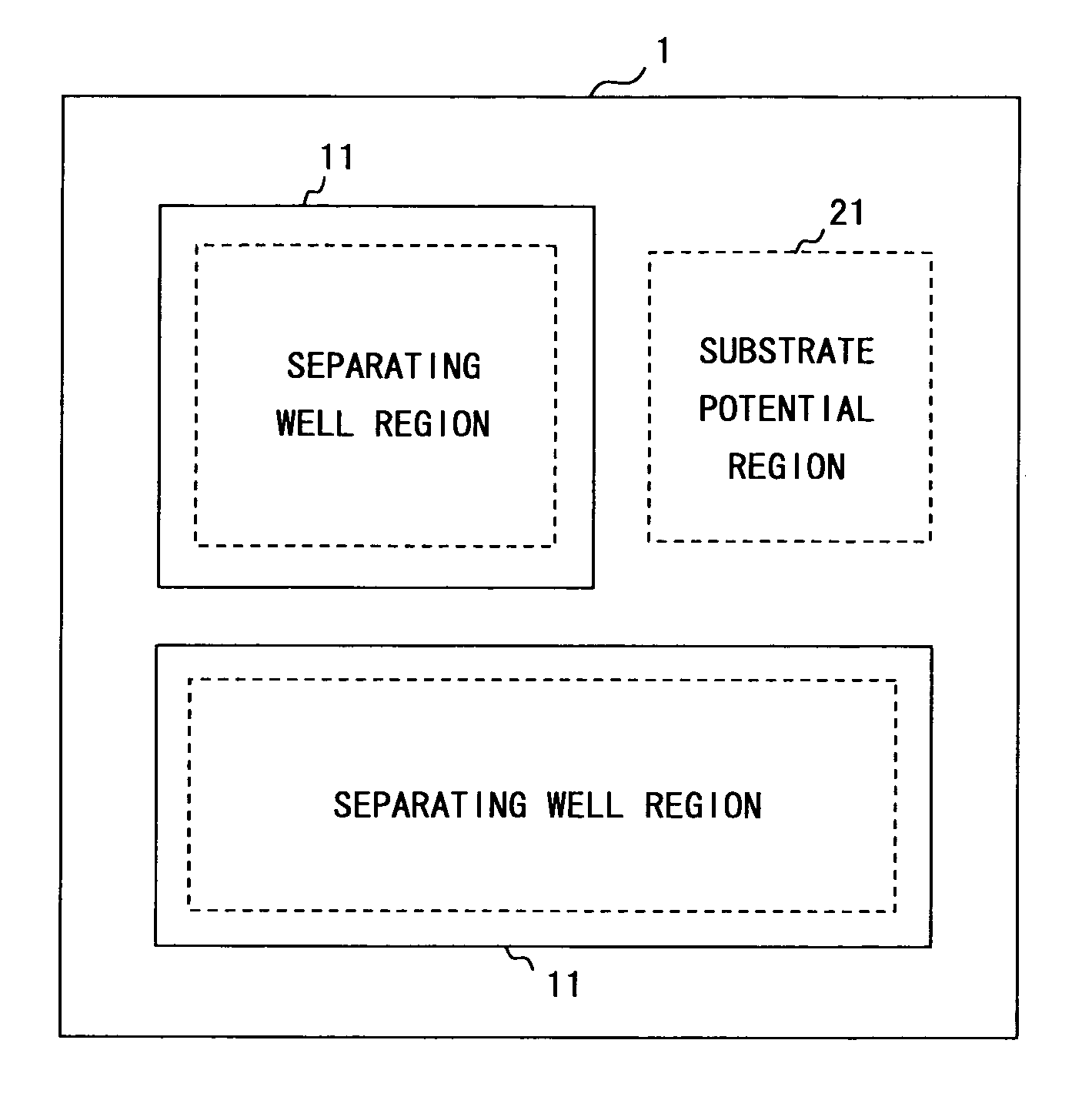

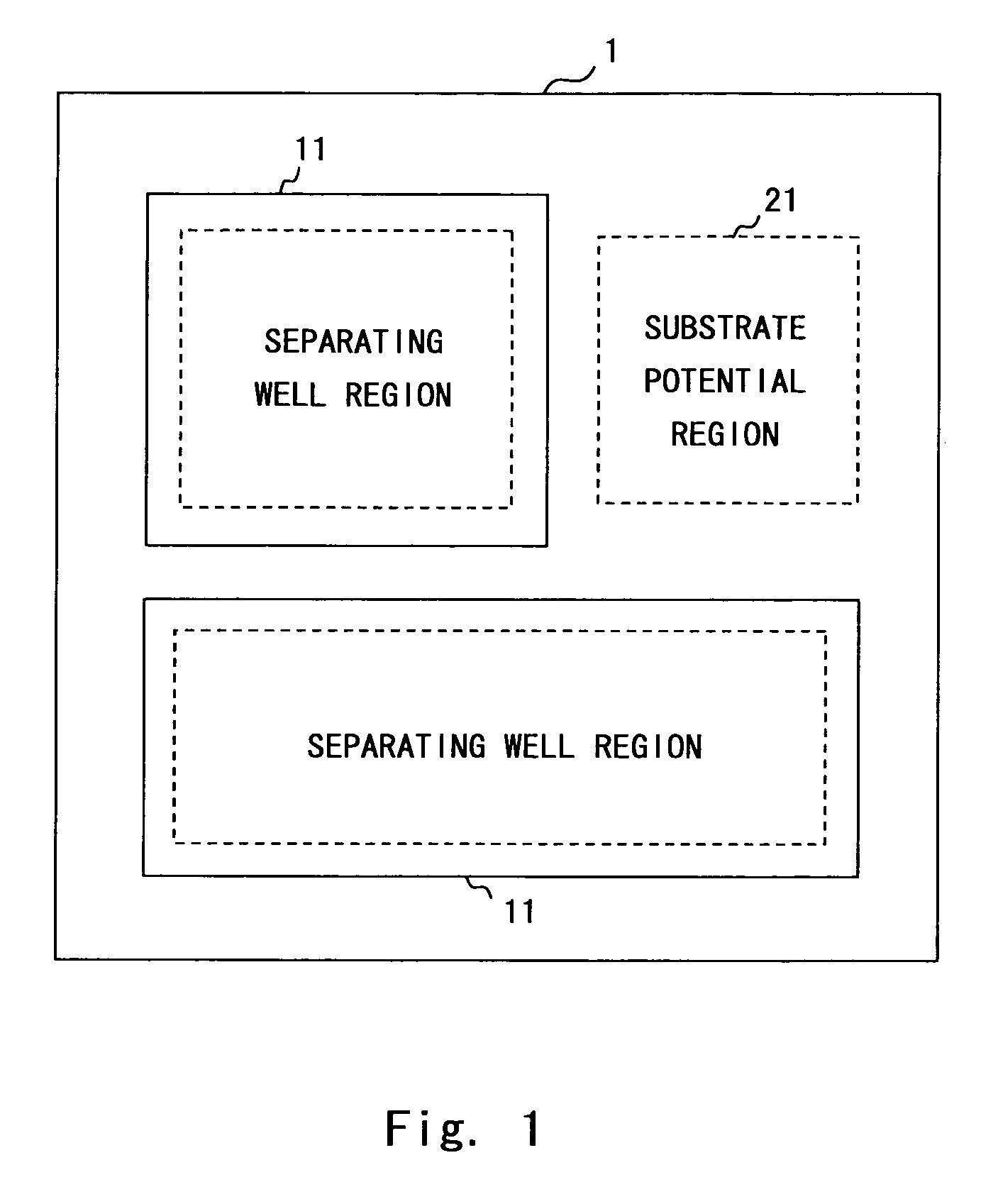

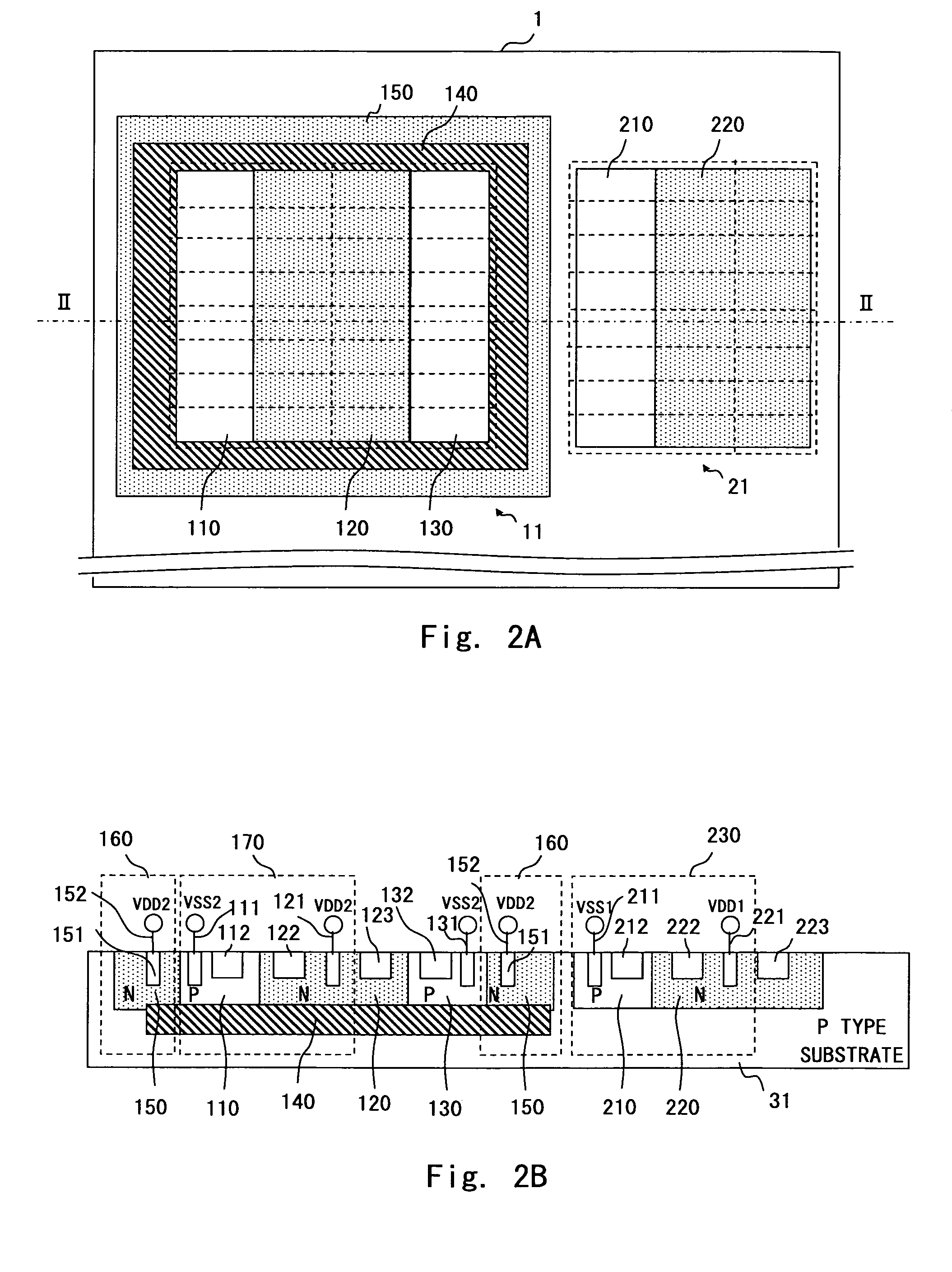

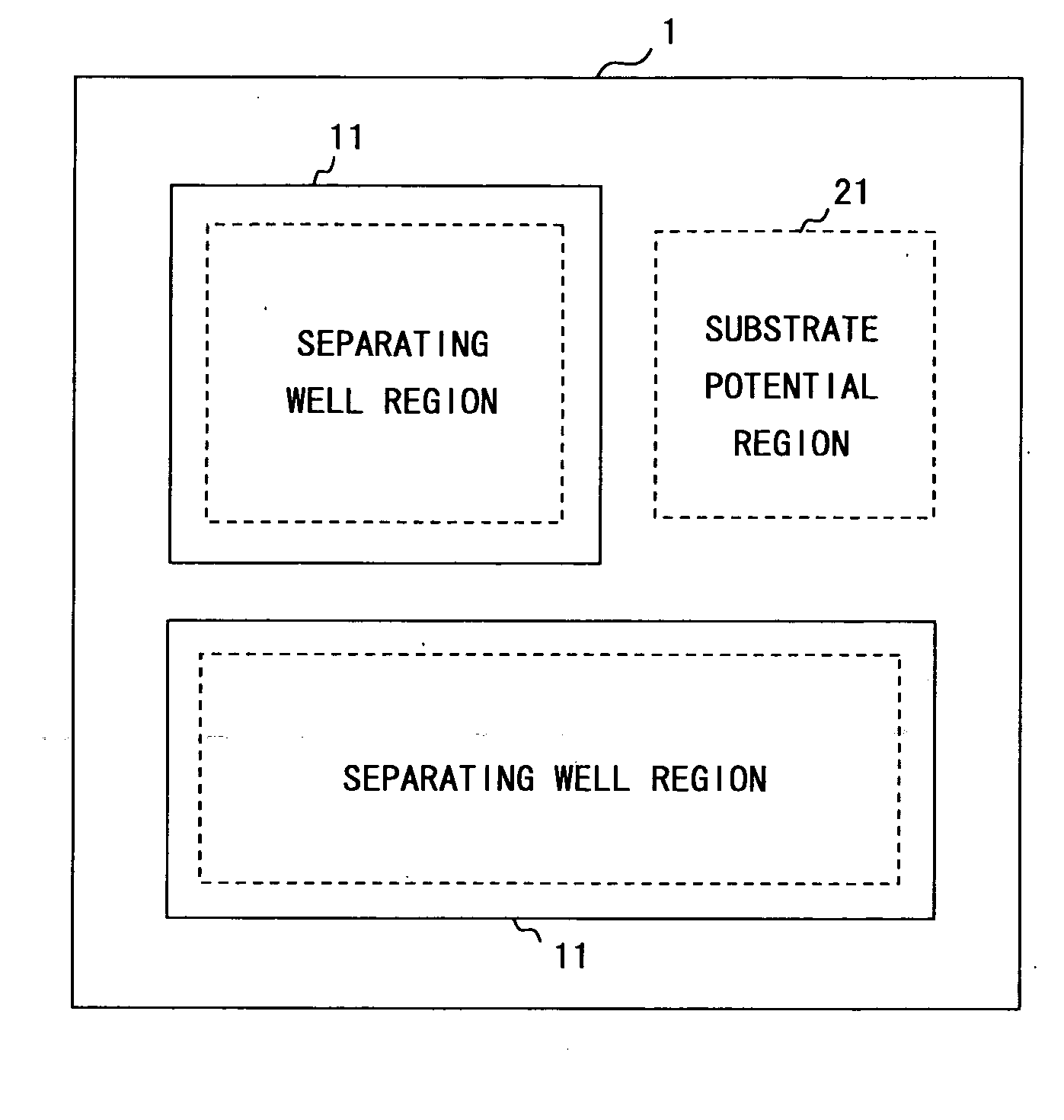

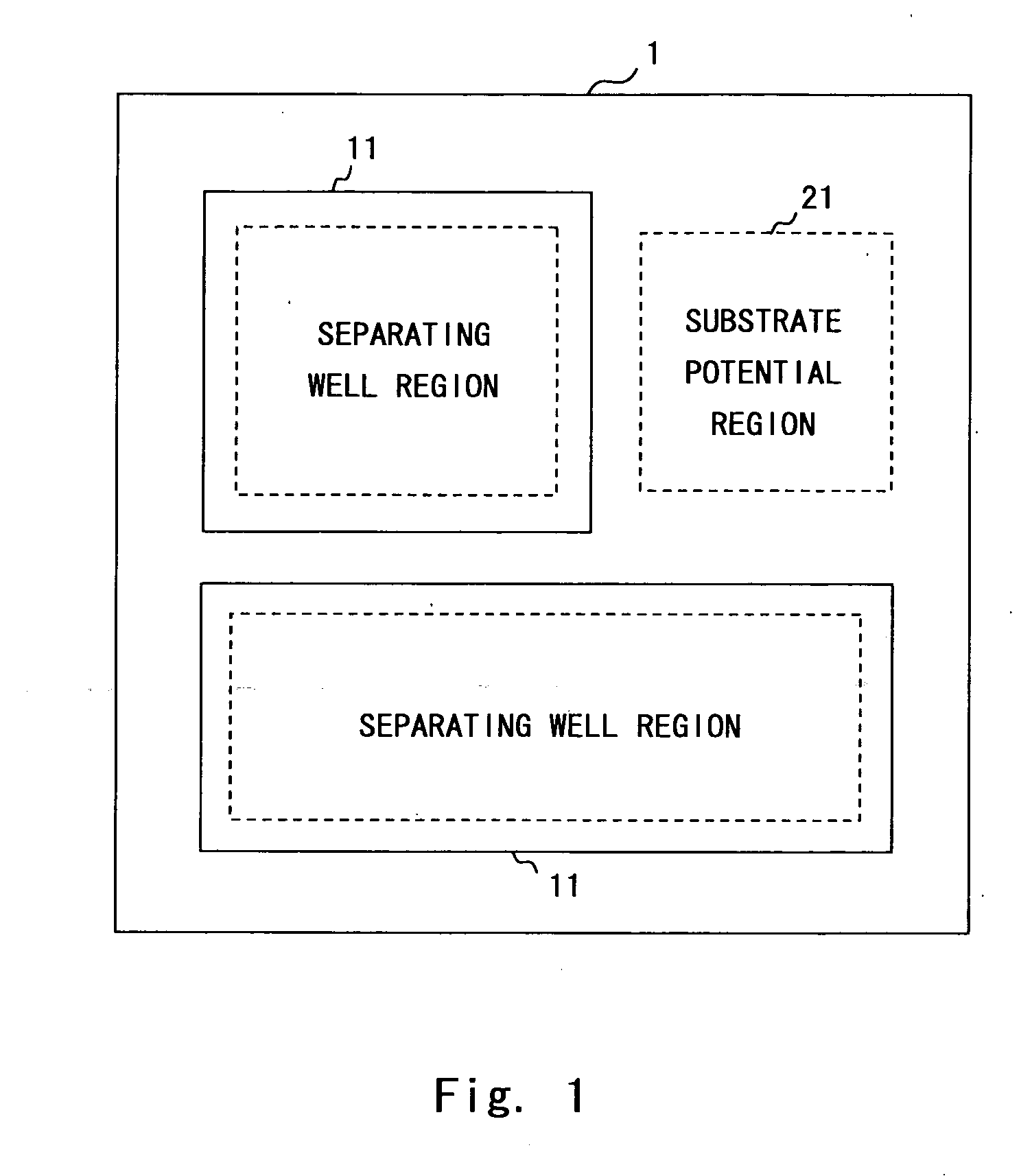

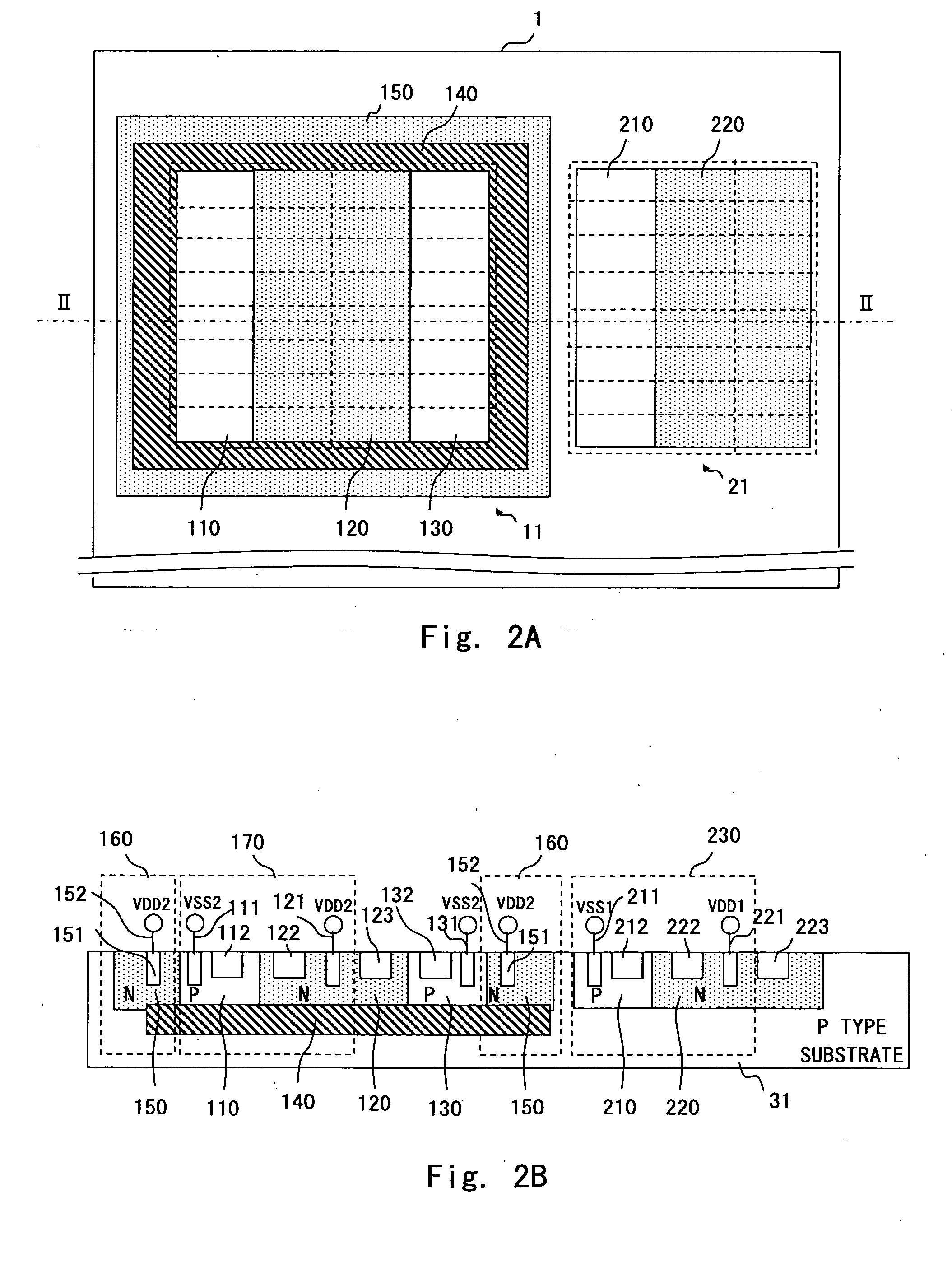

Layout design method of semiconductor integrated circuit having well supplied with potential different from substrate potential

Design time (TAT) is reduced in a layout design of a semiconductor integrated circuit having a well supplied with a potential different from a substrate potential. A layout design method of the present invention includes preparing a first cell pattern placed on a semiconductor substrate of a first conductive type, preparing a second cell pattern having a deep well of a second conductive type, placing the first cell pattern in a first circuit region, and placing the second cell pattern in a second region different from the first circuit region. This reduces TAT in chip design.

Owner:RENESAS ELECTRONICS CORP

Electric brake for an aircraft wheel, the brake including an electromechanical actuator fitted with a temperature sensor

ActiveUS9114791B2Reduce the temperatureShortened TATThermometer detailsDynamo-electric brakes/clutchesCircular discEngineering

Owner:SAFRAN LANDING SYSTEMS

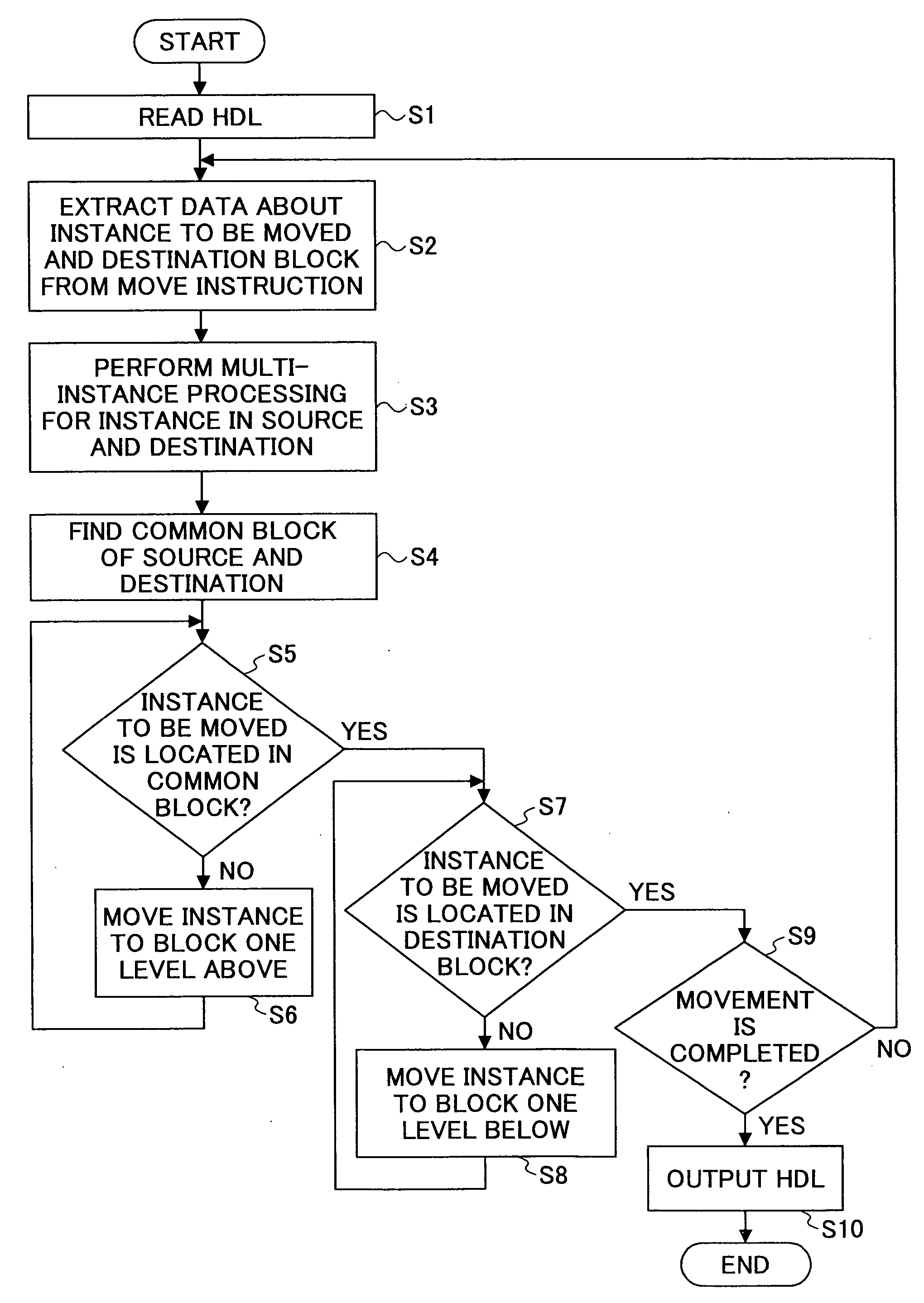

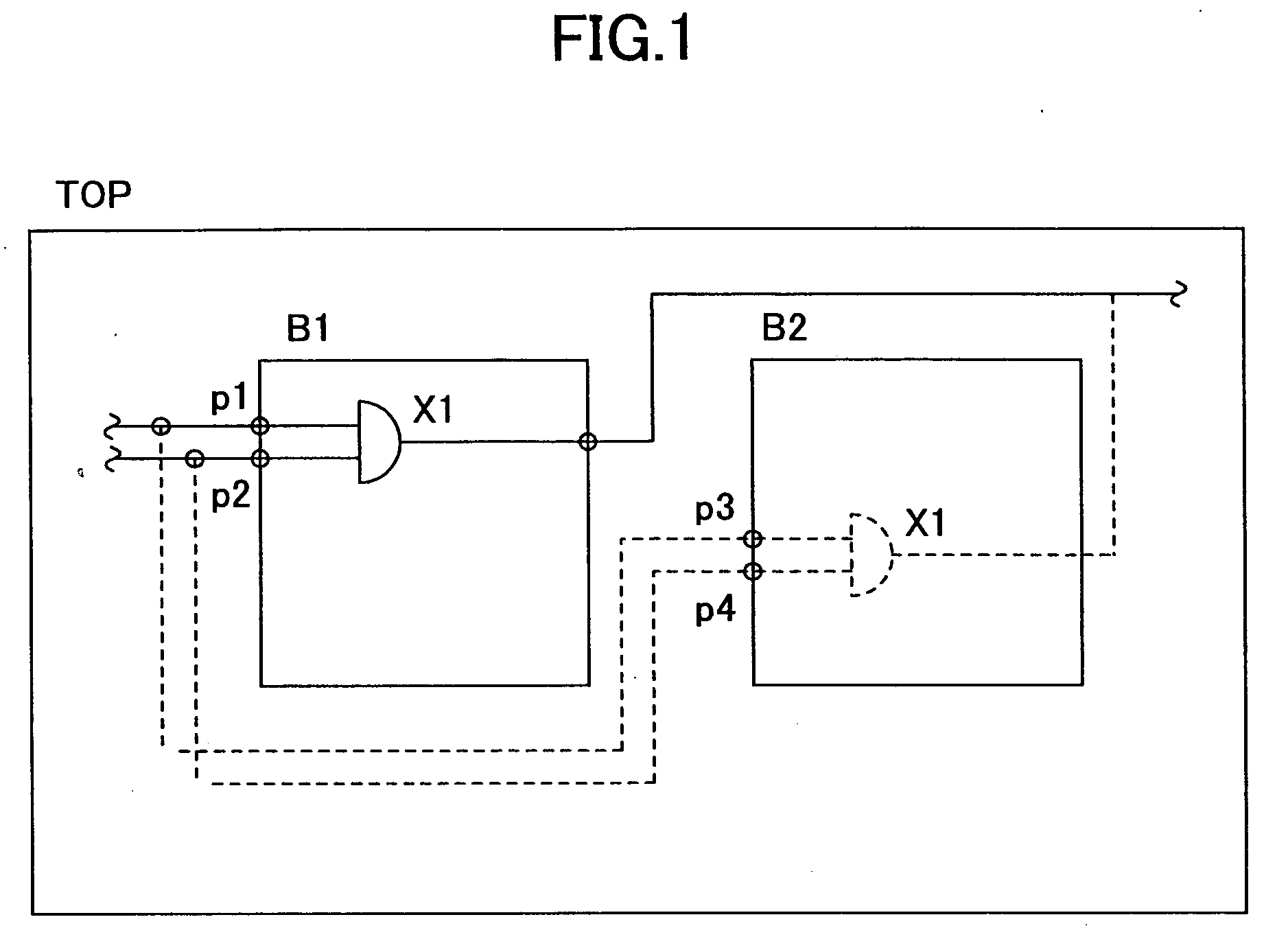

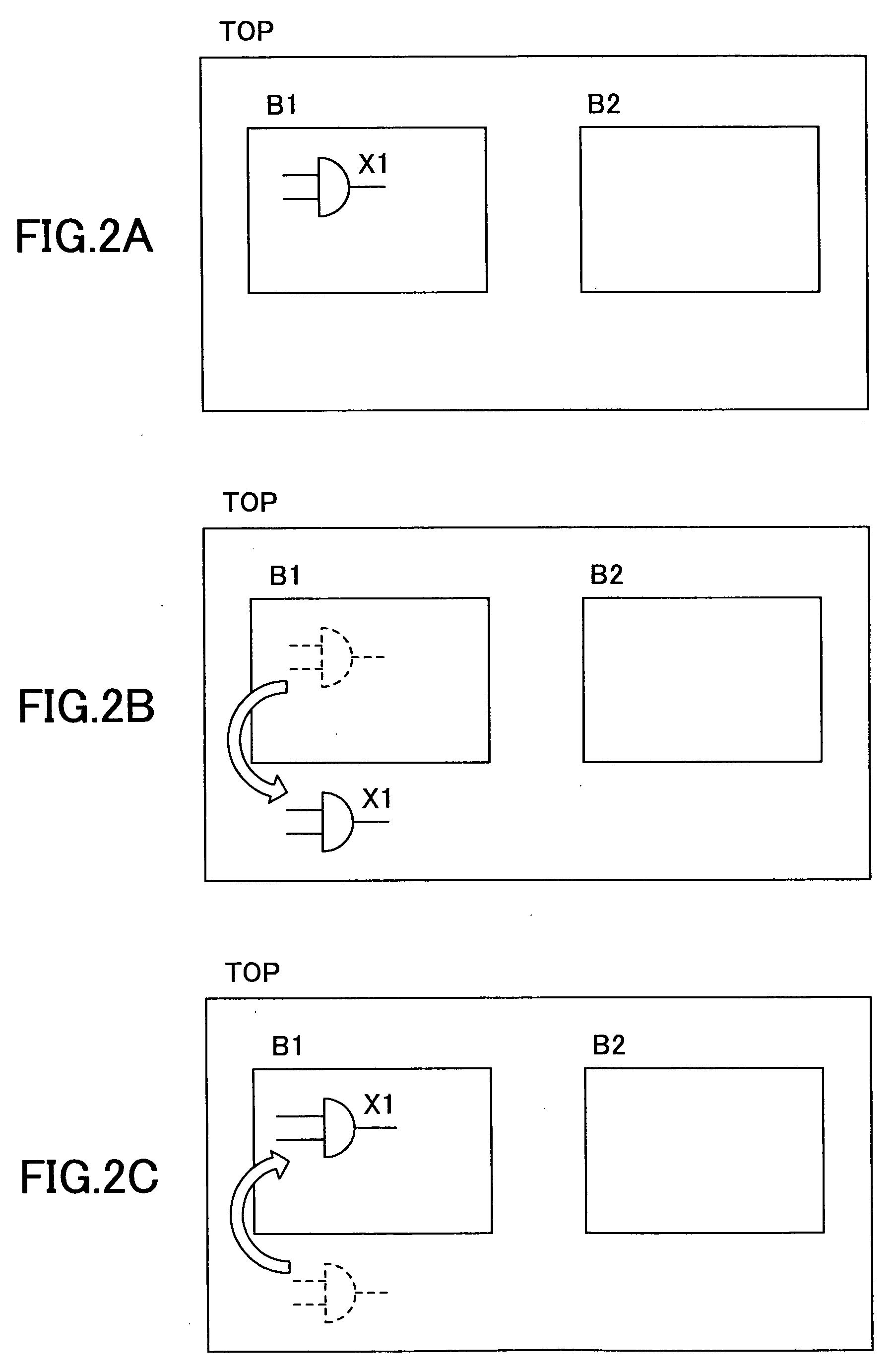

Logic circuit design method, computer-readable recording medium having logic circuit design program stored therein, and logic circuit design device

InactiveUS20060236281A1Simple configurationSimple designElectrical testingCAD circuit designComputer architectureLogic circuit design

A logic circuit design method for use in a logic circuit having a hierarchical structure including an instance, a first block, and a second block is disclosed. The logic circuit design method includes the steps of reading information about the logic circuit, moving an instance which has a signal connection and a first hierarchical port connected thereto from a first block to a second block in accordance with the read information, creating a second hierarchical port in accordance with the movement of the instance, and disconnecting the instance from the first hierarchical port and connecting the instance to the second hierarchical port while maintaining the signal connection to the instance that the instance had at the time when the instance was moved from the first block to the second block.

Owner:FUJITSU LTD

Transfer system and transfer method of object to be processed

InactiveUS7826918B2Improve transmission efficiencyShortened TATElectronic circuit testingDigital data processing detailsCommunication interfaceEngineering

Owner:TOKYO ELECTRON LTD

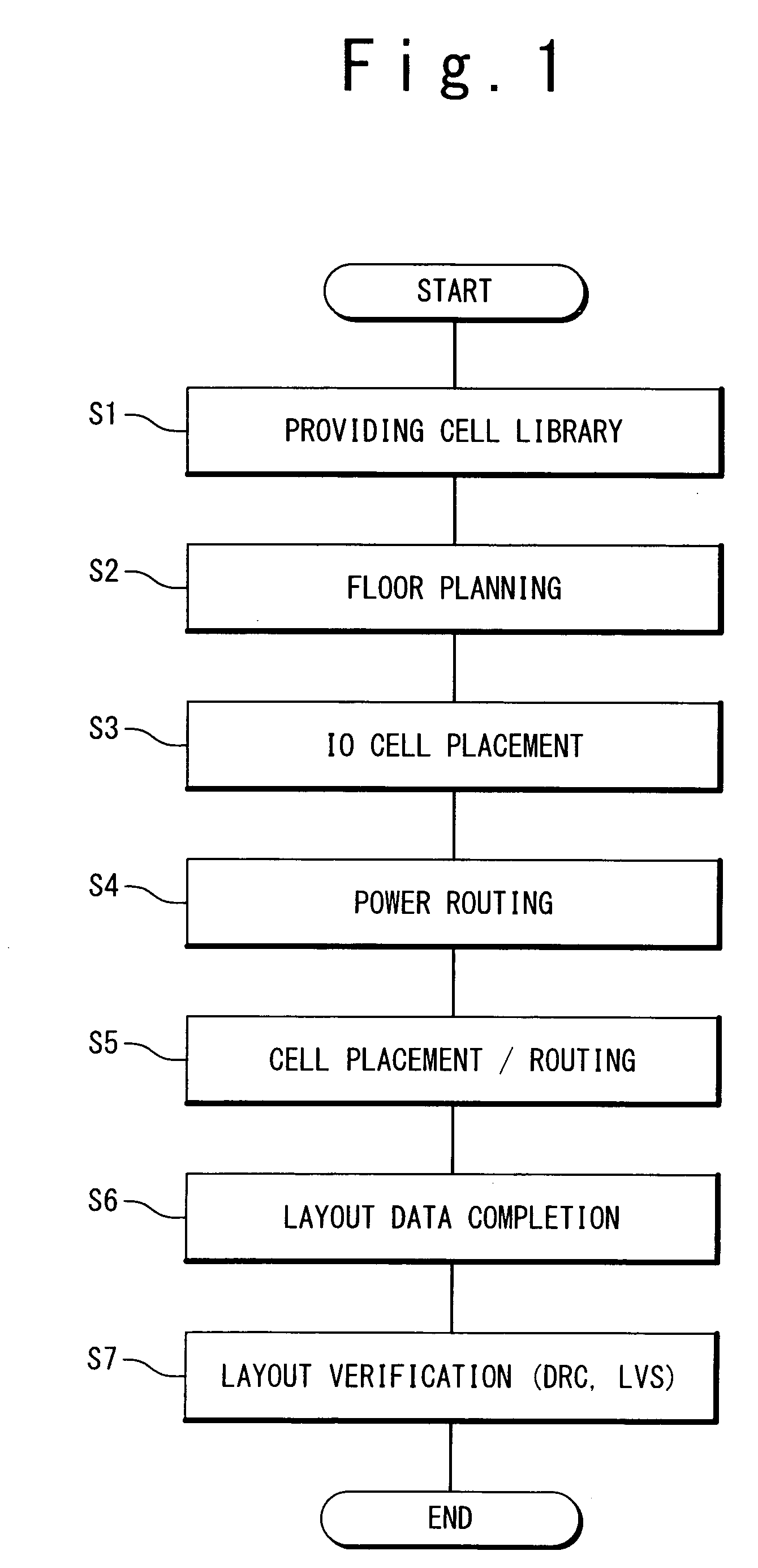

Method of verifying semiconductor integrated circuit and design program

InactiveUS20080313585A1Improve production yieldAvoid placement errorsSolid-state devicesComputer aided designControl signalControl cell

A method of verifying a semiconductor integrated circuit is provided. A controlling cell and a controlled cell controlled by a control signal output from the controlling cell are placed in an IO region of the semiconductor integrated circuit. The method includes: (A) providing a library that includes requirement information specifying the controlling cell required by the controlled cell; (B) obtaining a region information indicating a region within the IO region in which a signal interconnection through which the control signal is transmitted is provided; and (C) verifying whether or not the specified controlling cell is placed within the region, in a case where the controlled cell is placed within the region.

Owner:RENESAS ELECTRONICS CORP

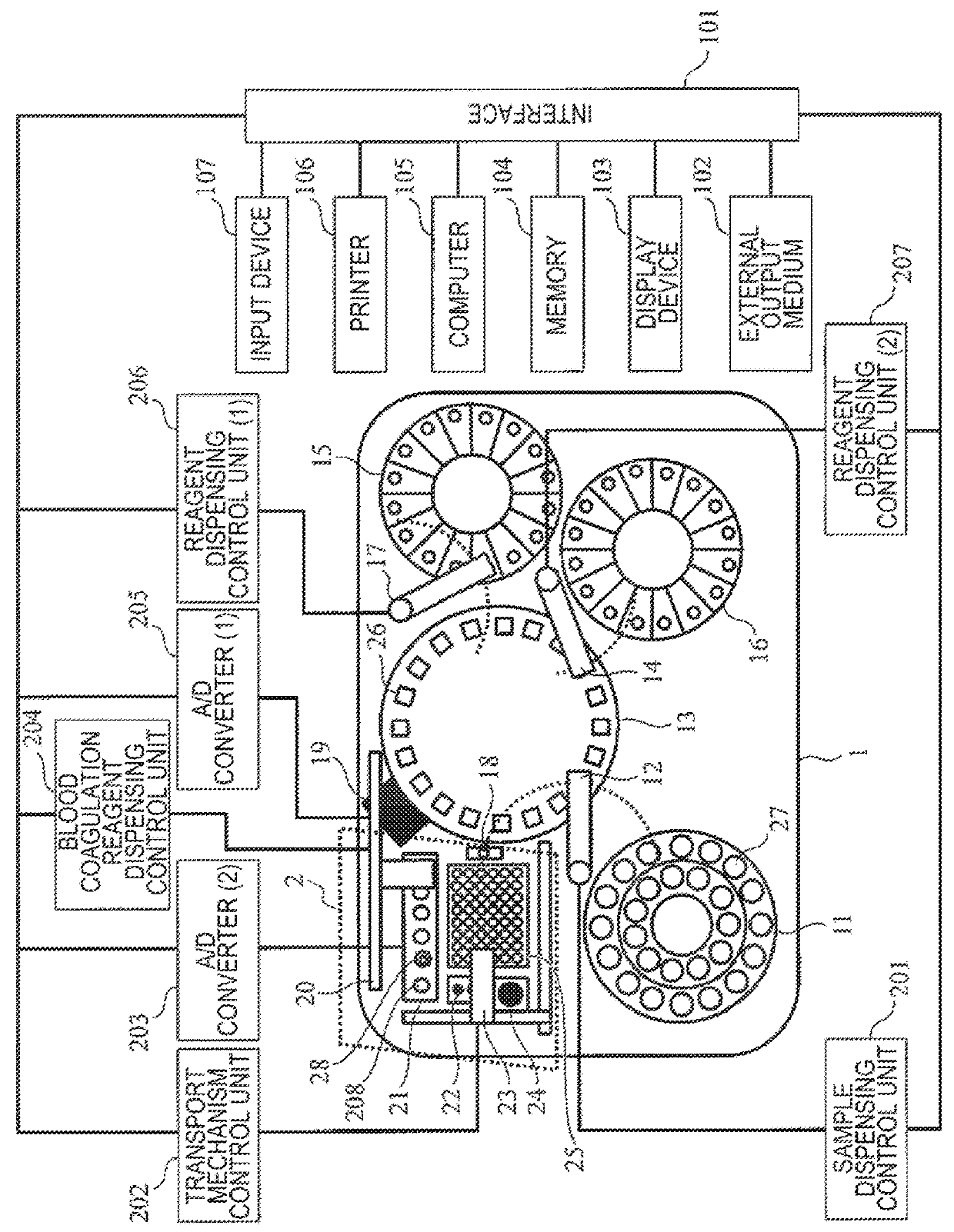

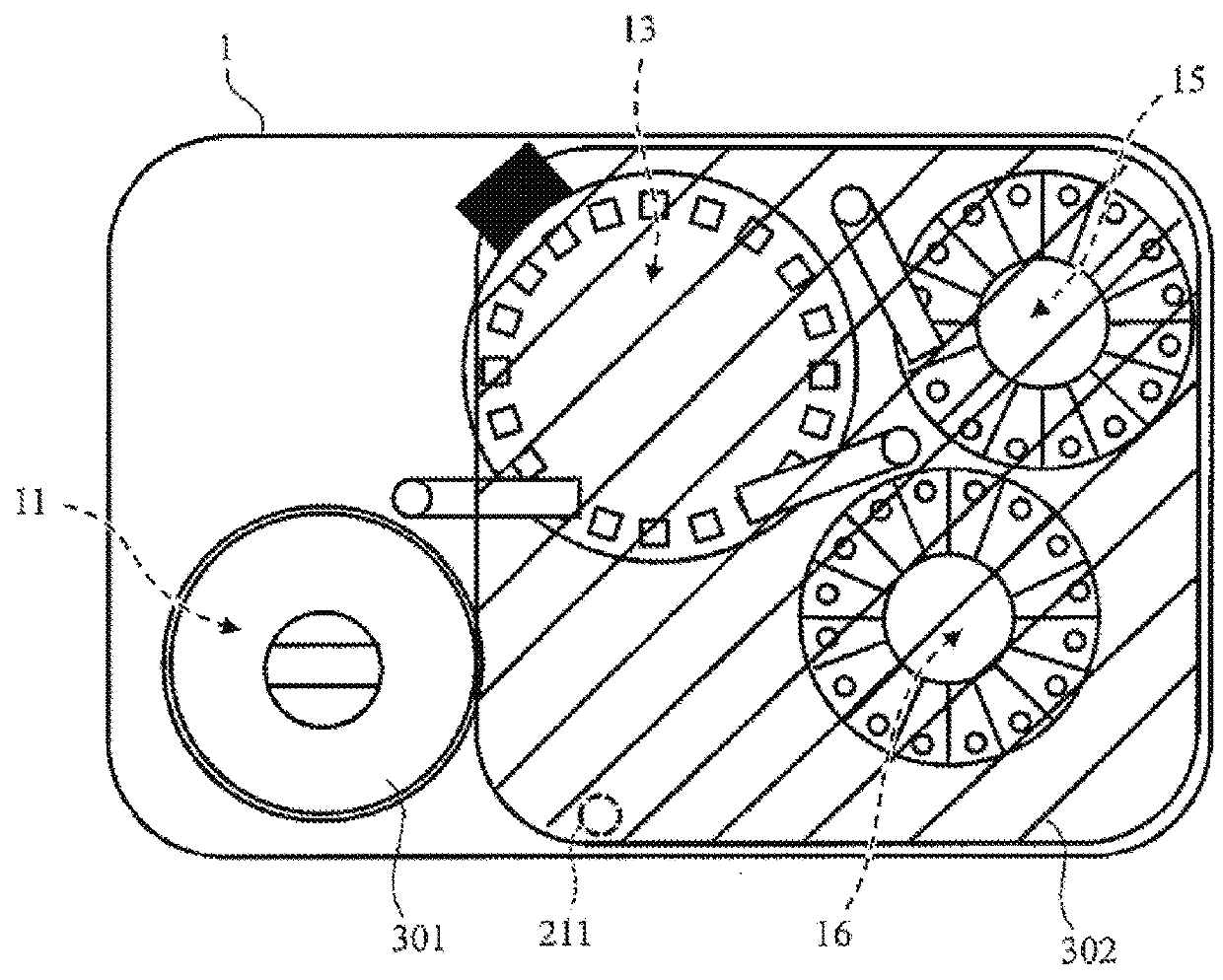

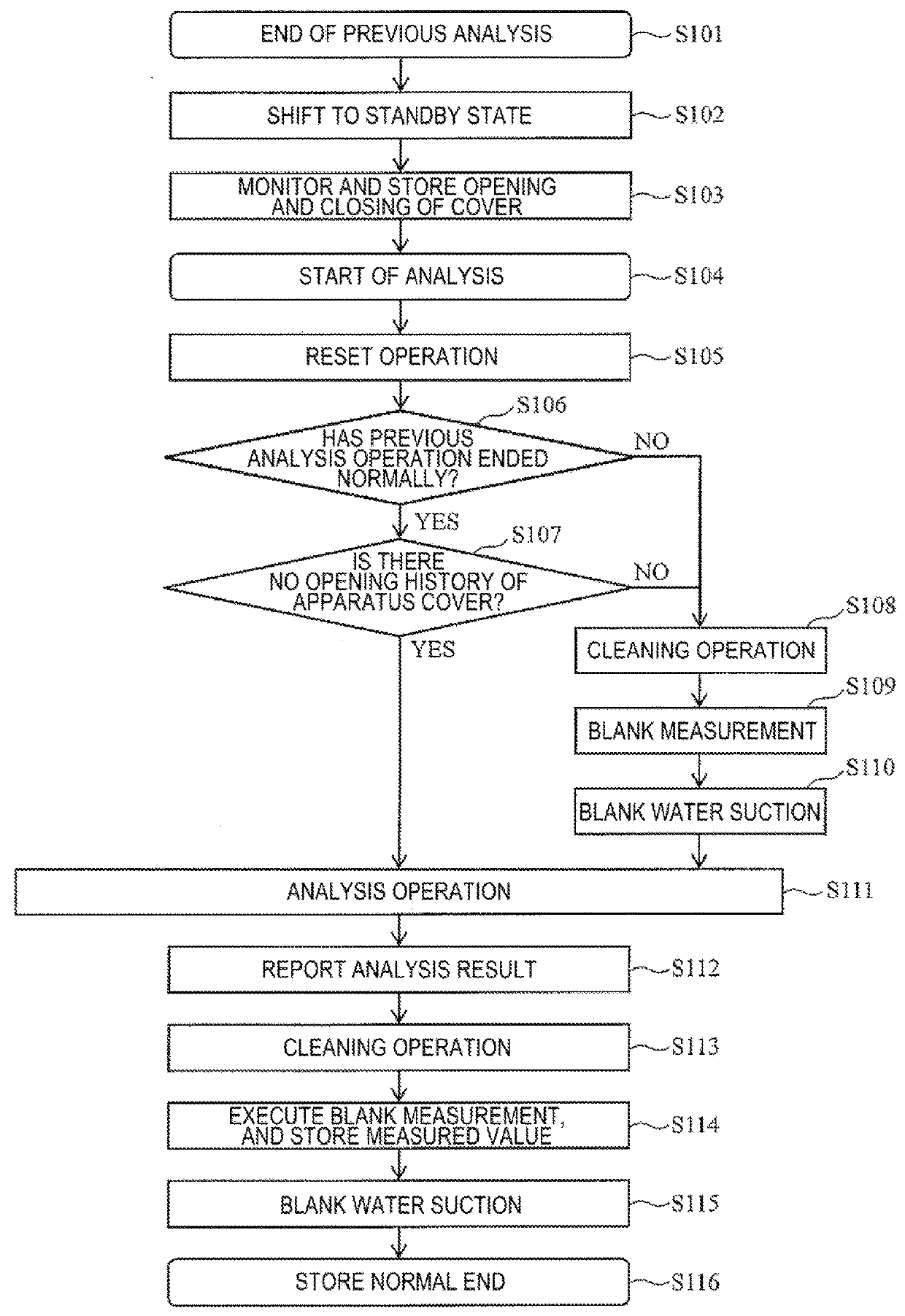

Automated Analyzer and Control Method for Same

ActiveUS20180275155A1Reduce the number of executionsShortened TATSamplingMaterial analysis by optical meansExecution controlEngineering

An automated analyzer has a reaction disk on which a plurality of reaction vessels capable of holding sample and reagent mixtures can be placed, a first cover for covering at least a portion of the area above the reaction disk, a second cover that can be opened and closed independently from the first cover, at least one sensor for monitoring the opening and closing of the first cover, and a control unit for monitoring a signal from the sensor and carrying out control such that if the first cover has not been opened and closed during the period until a new analysis operation is started, a pre-analysis cleaning operation, blank measurement operation, or both, are skipped.

Owner:HITACHI HIGH-TECH CORP

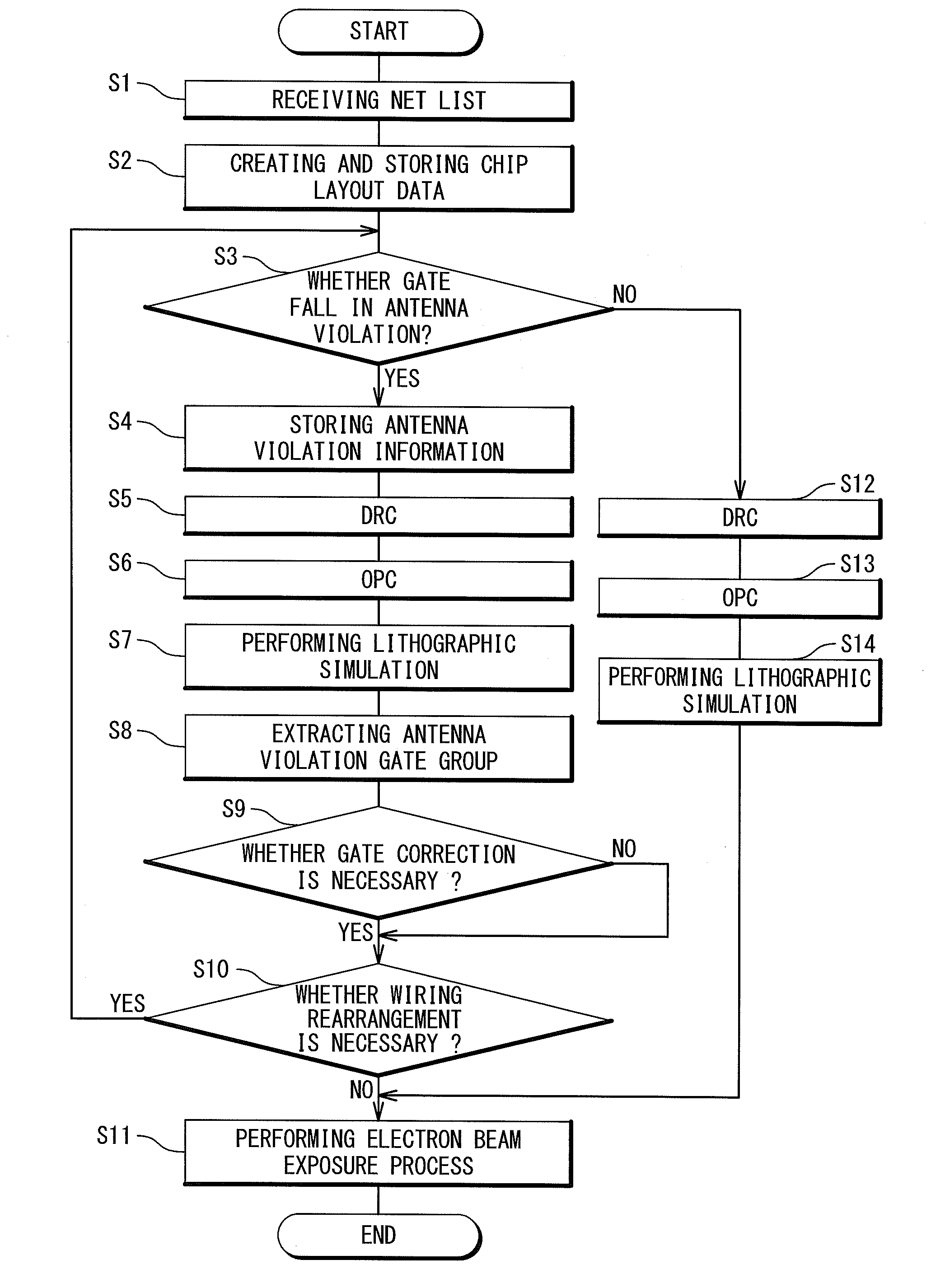

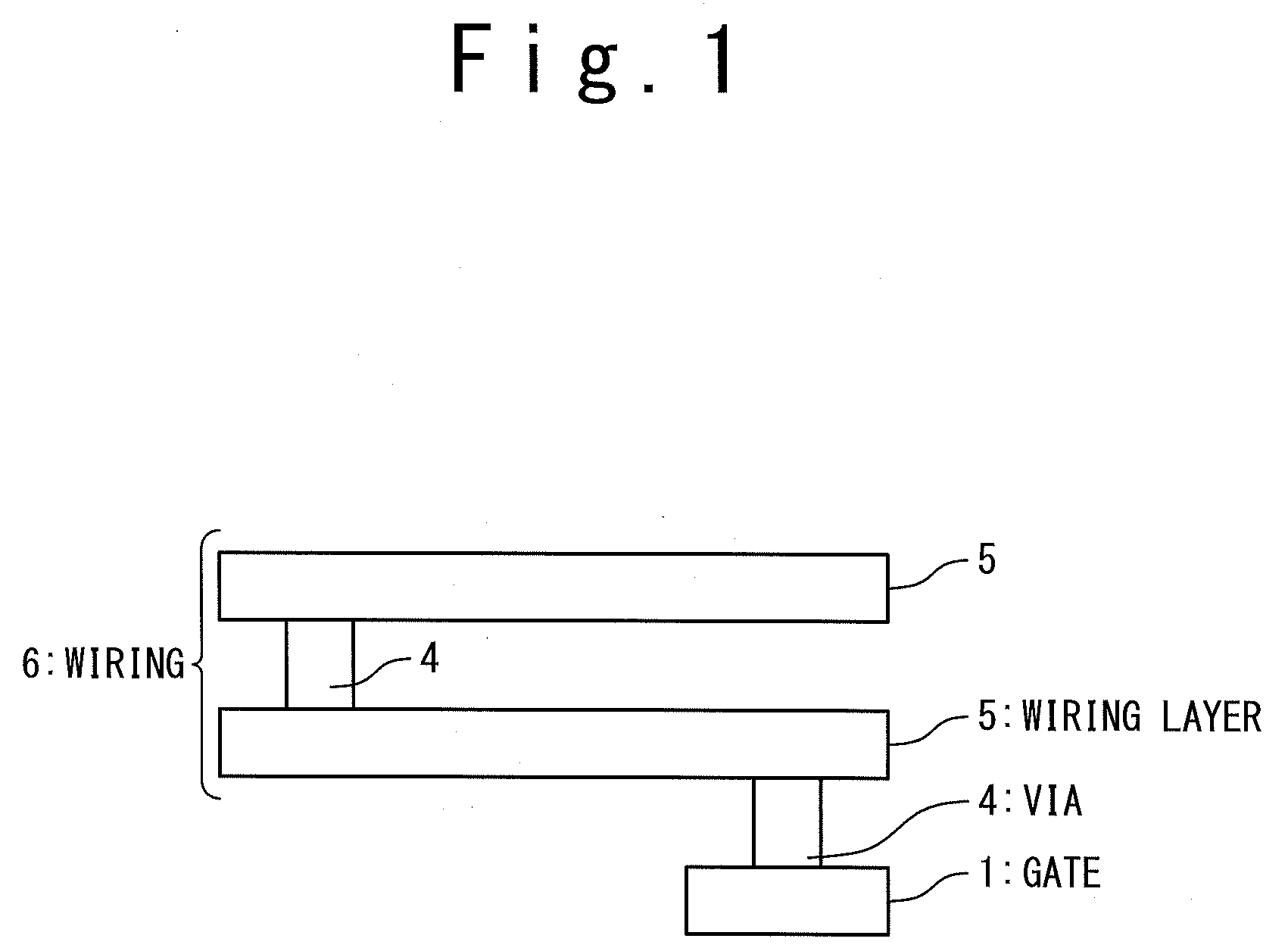

Method of designing semiconductor device

InactiveUS20110055776A1Small sizeShortened TATSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentLithographic artistEngineering

This is a method of designing a semiconductor device. The method includes: arranging cells used for an electric circuit and wirings respectively connected to gates of the cells in a coordinate region to create chip layout data including the cells, gates and wirings; checking whether each gate included in the chip layout data is in antenna violation; storing antenna violation information in an error-remaining portion library, the antenna violation information representing an antenna violation gate group, in which gates in the antenna violation are contained, in the gates included in the chip layout data; performing lithography simulation for the chip layout data to create predicted layout data after photoresist exposure; selecting the antenna violation gate group from the gates included in the predicted layout data, with reference to the error-remaining library; calculating a calculated value representing a ratio of an area of an wiring of the wirings with respect to an area of a gate of the antenna violation gate group connected to the wiring, for each gate of the antenna violation group; and adjusting a size of the gate of the antenna violation gate group, when the calculated value of the antenna violation group included in the predicted layout data is in a range between a first and second setting value.

Owner:RENESAS ELECTRONICS CORP

Layout design method and layout design tool

ActiveUS20070111426A1Simple designImprove design qualityTransistorSolid-state devicesCell patternEngineering

Design time (TAT) is reduced in a layout design of a semiconductor integrated circuit having a well supplied with a potential different from a substrate potential. A layout design method of the present invention includes preparing a first cell pattern placed on a semiconductor substrate of a first conductive type, preparing a second cell pattern having a deep well of a second conductive type, placing the first cell pattern in a first circuit region, and placing the second cell pattern in a second region different from the first circuit region. This reduces TAT in chip design.

Owner:RENESAS ELECTRONICS CORP

Semiconductor chip and method of fabricating the same

InactiveCN1825563AEfficient manufacturingPrevent intrusionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipElectrical connection

There is provided a semiconductor chip having fuses. The semiconductor chip includes fuses each having a first terminal electrically connected to a first logic circuit, a second terminal electrically connected to a second logic circuit, and a blowable region formed between the first terminal and the second terminal; and fuse residues each having the same patterns with those of the first terminal and the second terminal of the fuses, and configured so that patterns corresponded to the first terminals and the second terminals are electrically disconnected from each other.

Owner:RENESAS ELECTRONICS CORP

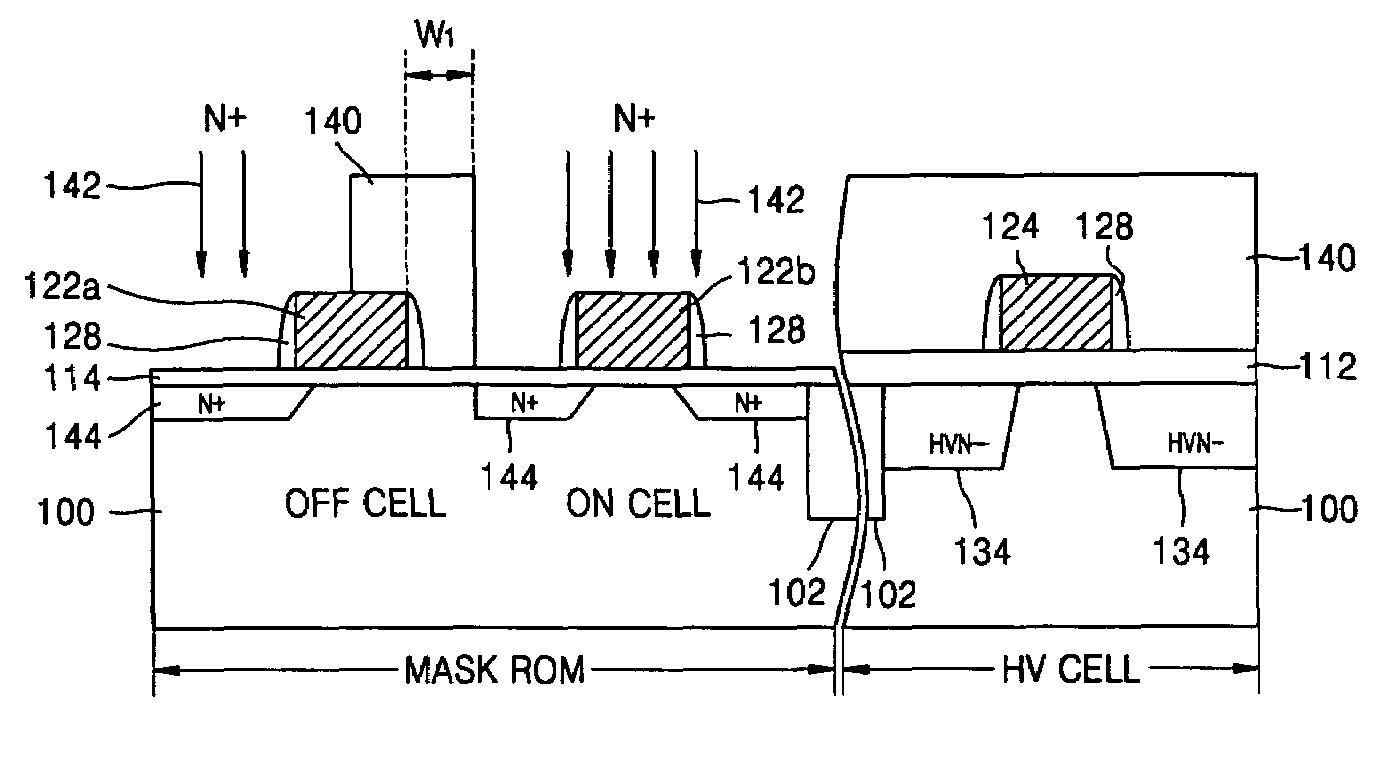

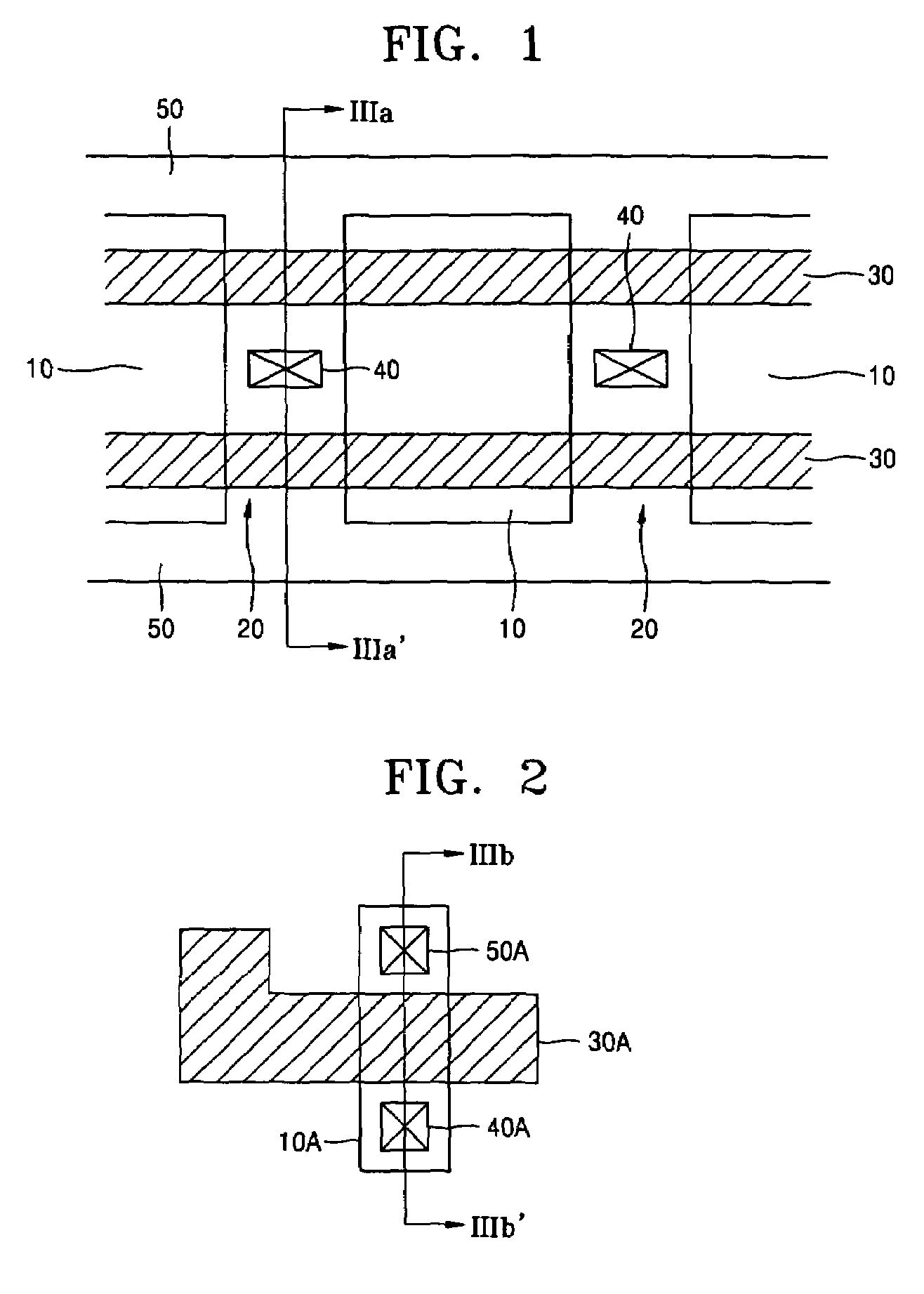

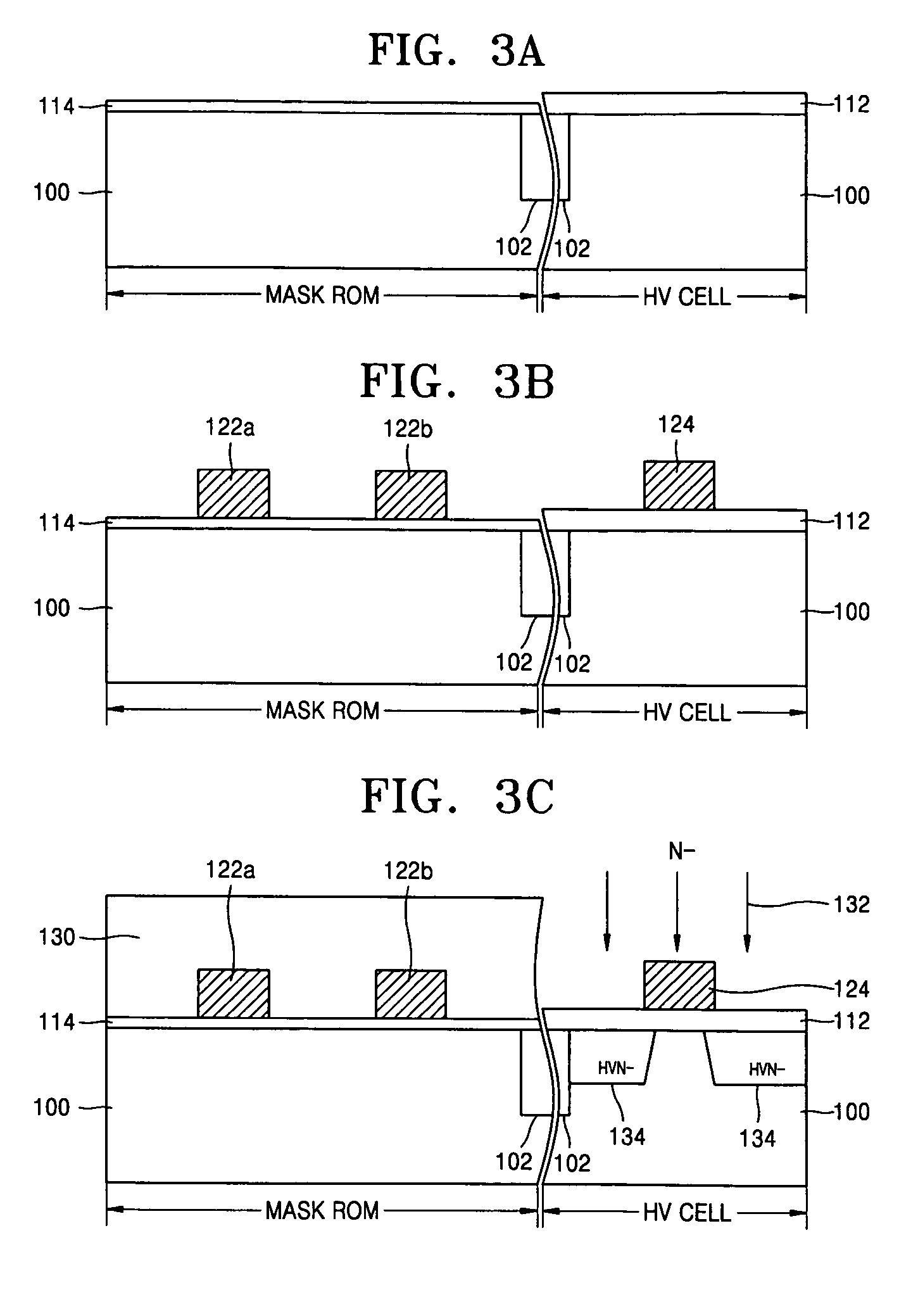

Method of manufacturing NOR-type mask ROM device and semiconductor device including the same

InactiveUS7253058B2Reduce turnaround timeEliminate needSolid-state devicesSemiconductor/solid-state device manufacturingBit lineMask ROM

A method of manufacturing a NOR-type mask ROM device includes forming a first gate electrode for an OFF cell and a second gate electrode for an ON cell on a semiconductor substrate of a first conductivity type. To code the mask ROM device, a plurality of source / drain regions is formed by implanting impurities of a second conductivity type, opposite the first conductivity type, into the semiconductor substrate adjacent only to one side of the first gate electrode and adjacent to both sides of the second gate electrode. To prevent misalignment of a bit line contact hole with a contact region, additional impurities are implanted only into a bit line contact region of the mask ROM device region. When a semiconductor device formed on the same substrate as the mask ROM device includes a double diffused region, additional implantation for both may be realized simultaneously.

Owner:SAMSUNG ELECTRONICS CO LTD

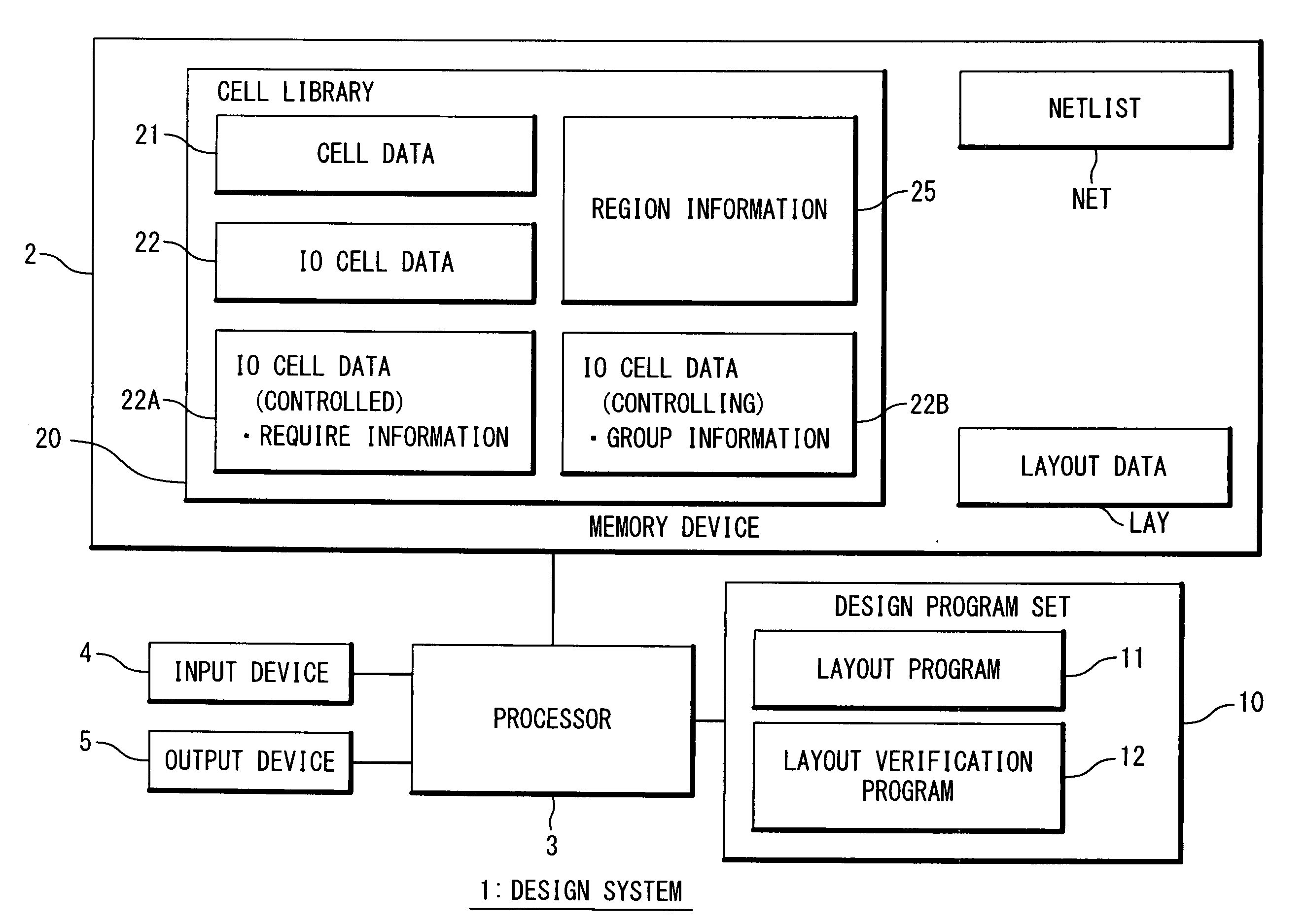

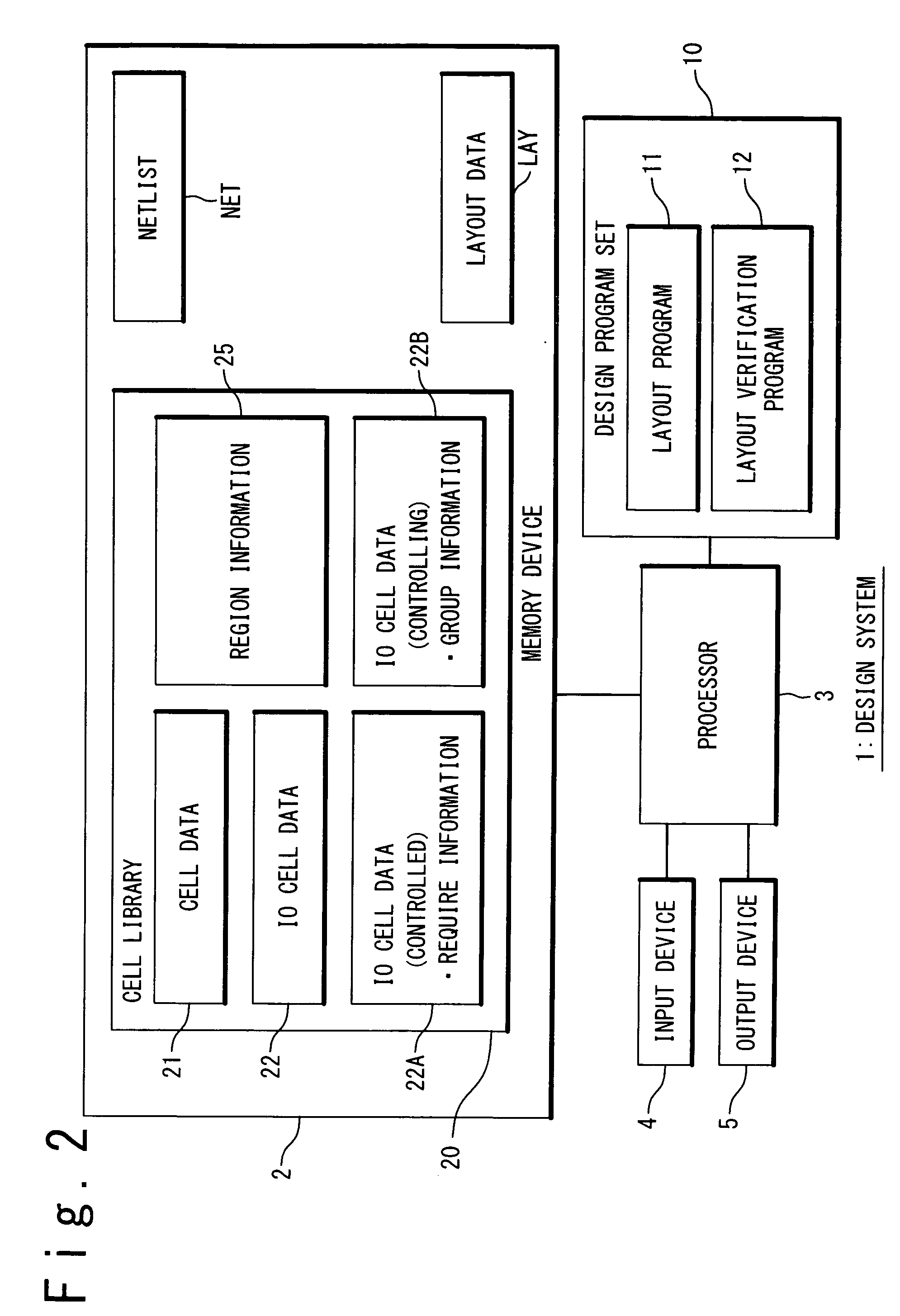

Method of supporting layout design of semiconductor integrated circuit

InactiveUS8499268B2Shorten the timeShortened TATCAD circuit designSoftware simulation/interpretation/emulationEngineeringNetlist

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com