Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

42results about How to "Performance penalty" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

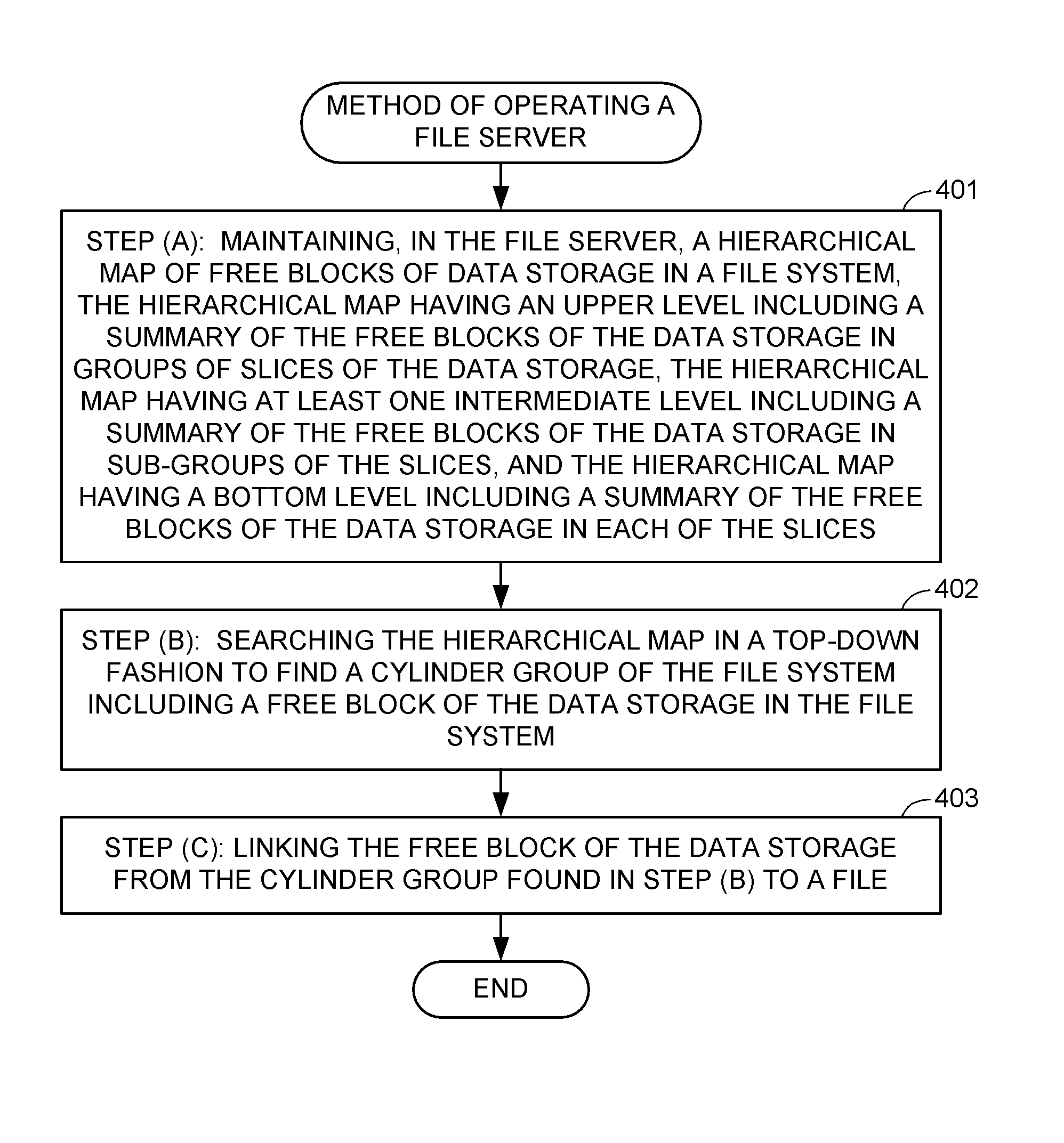

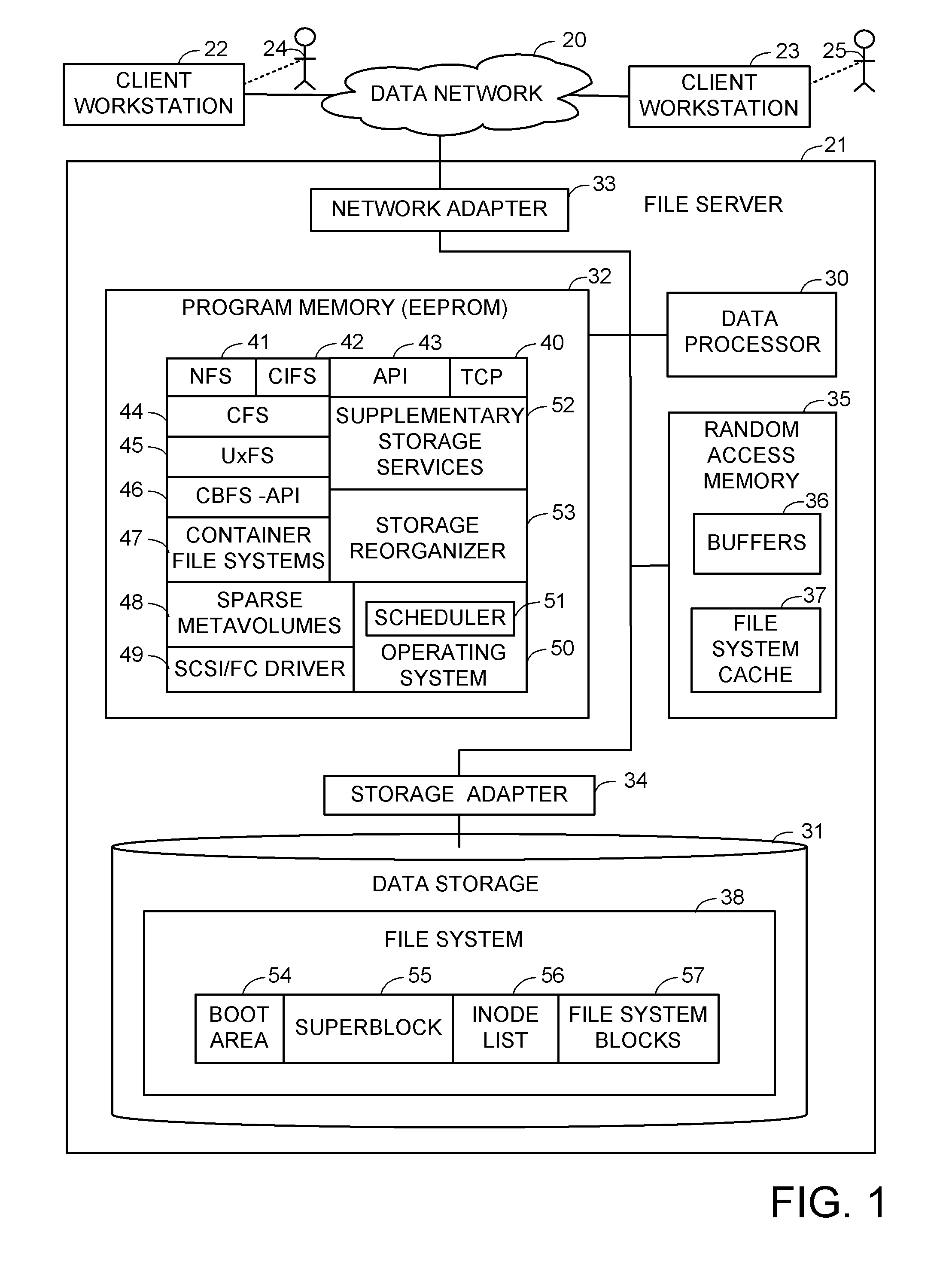

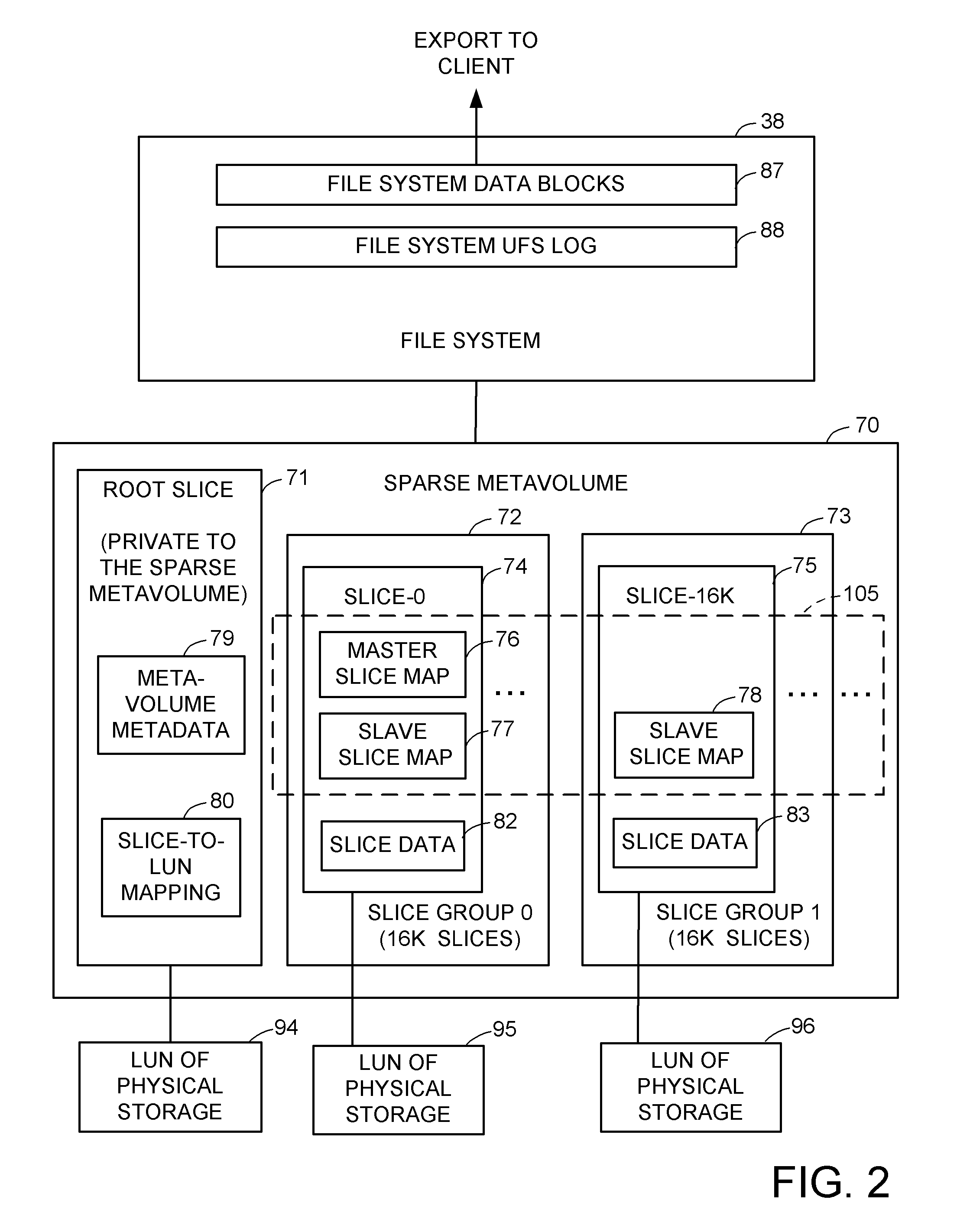

Hierarchical mapping of free blocks of cylinder groups of file systems built on slices of storage and linking of the free blocks

ActiveUS8407265B1Shorten the timePerformance penaltyDigital data information retrievalSpecial data processing applicationsFile systemIntermediate level

In a file server, a file system is built upon a volume of data storage. The file system includes multiple cylinder groups. Each cylinder group includes file system blocks. The file system blocks include allocated blocks and free blocks. The volume includes slices of storage, and each slice stores at least one of the cylinder groups. A hierarchical slice map has a top level that includes a count of free blocks in the file system, an upper level that includes a count of free blocks in groups of the slices, an intermediate level that includes a count of the free blocks in sub-groups of the slices, and a bottom level that includes a count of the free blocks in each slice of storage. To find a free block for allocation to a file, the slice map hierarchy is searched in a top-down fashion.

Owner:EMC IP HLDG CO LLC

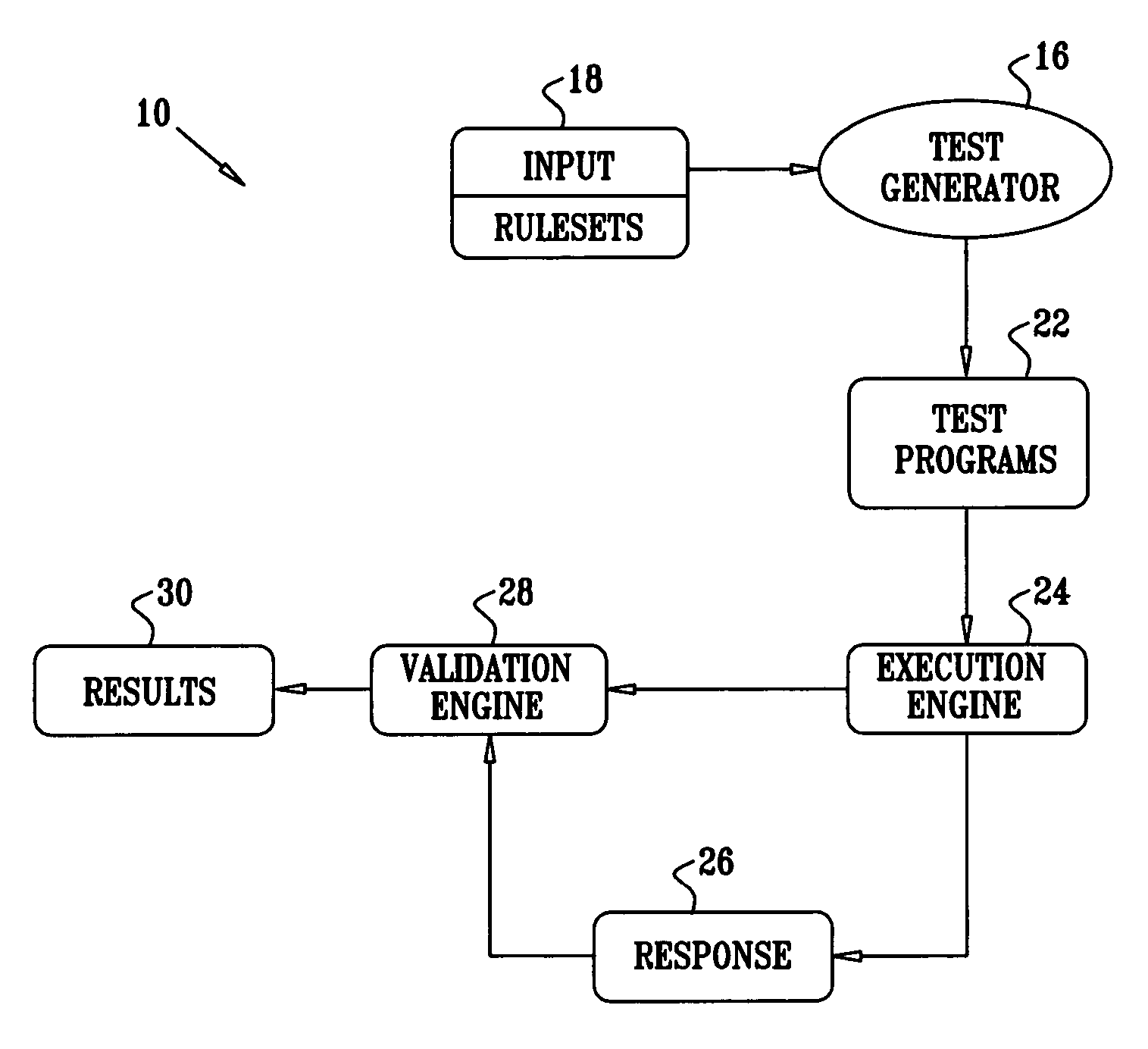

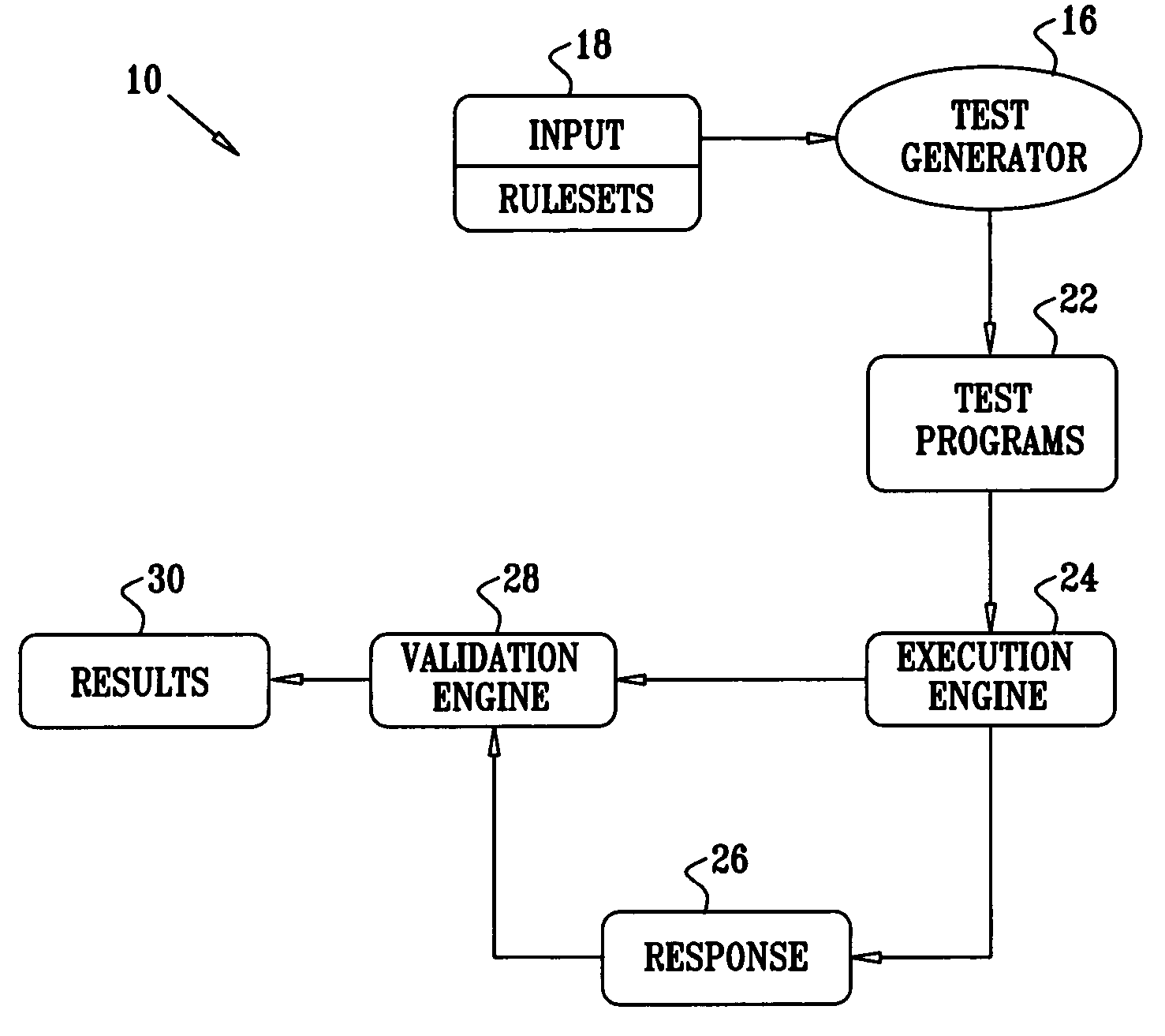

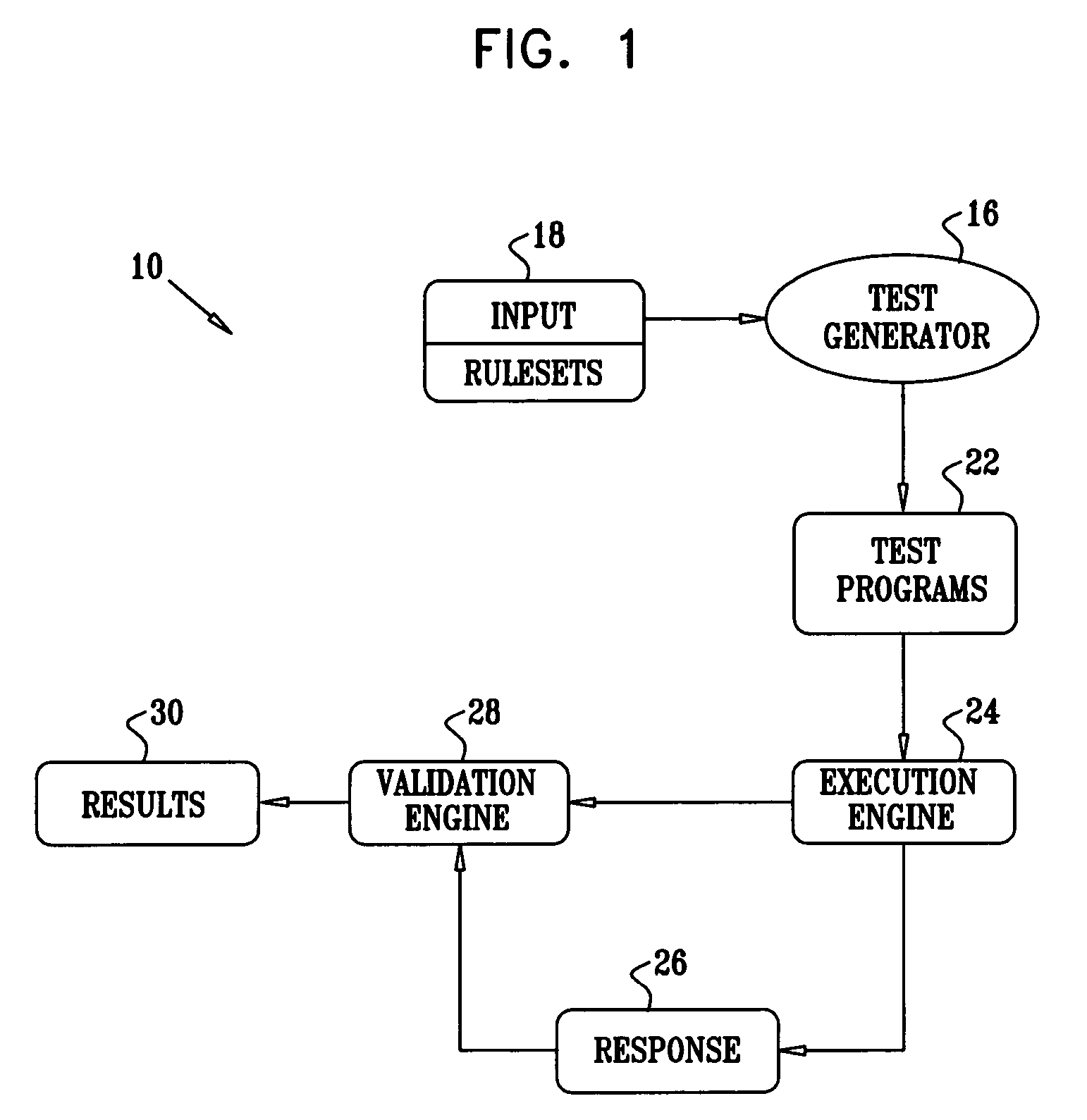

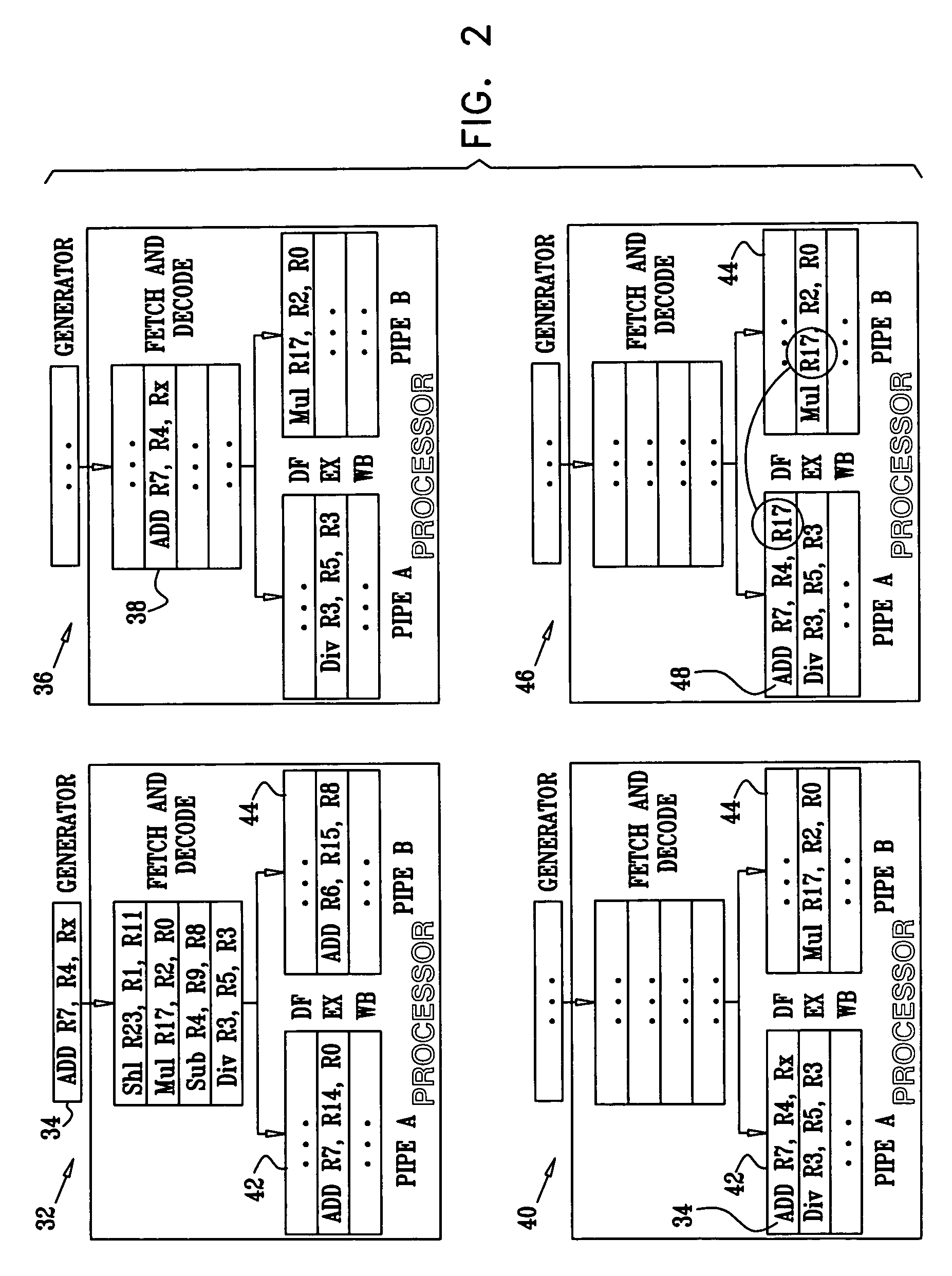

Late binding of variables during test case generation for hardware and software design verification

InactiveUS7003420B2Improves quality and rapidityPerformance penaltyResistance/reactance/impedenceCAD circuit designSoftware designTheoretical computer science

Methods and systems are provided that improve design verification by test generators by delaying assignment of values in the generated stimuli until these values are used in the design. Late binding allows the generator to have a more accurate view of the state of the design, and in order to choose correct values. Late binding can significantly improve test coverage with a reasonable performance penalty as measured by simulation time.

Owner:IBM CORP

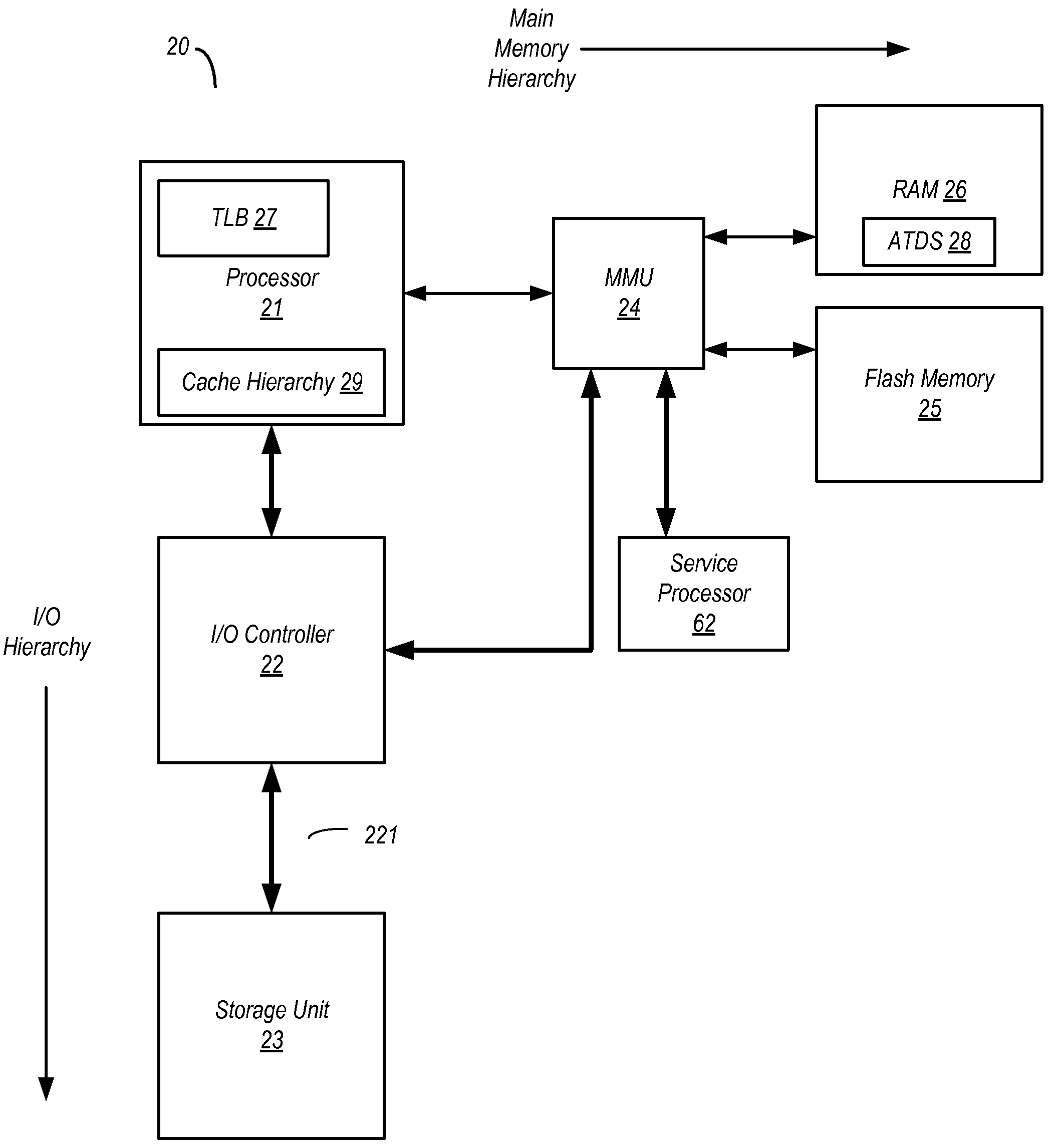

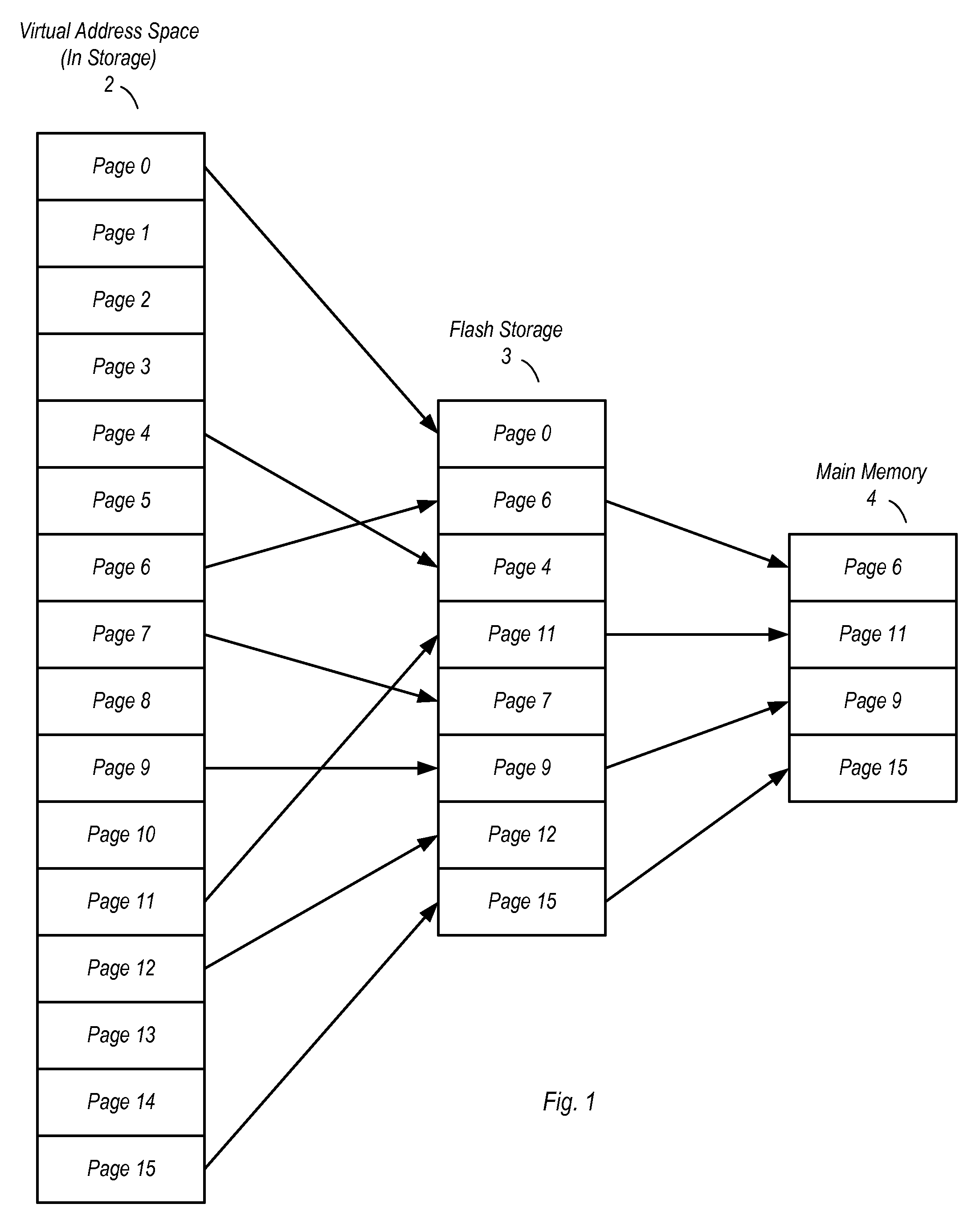

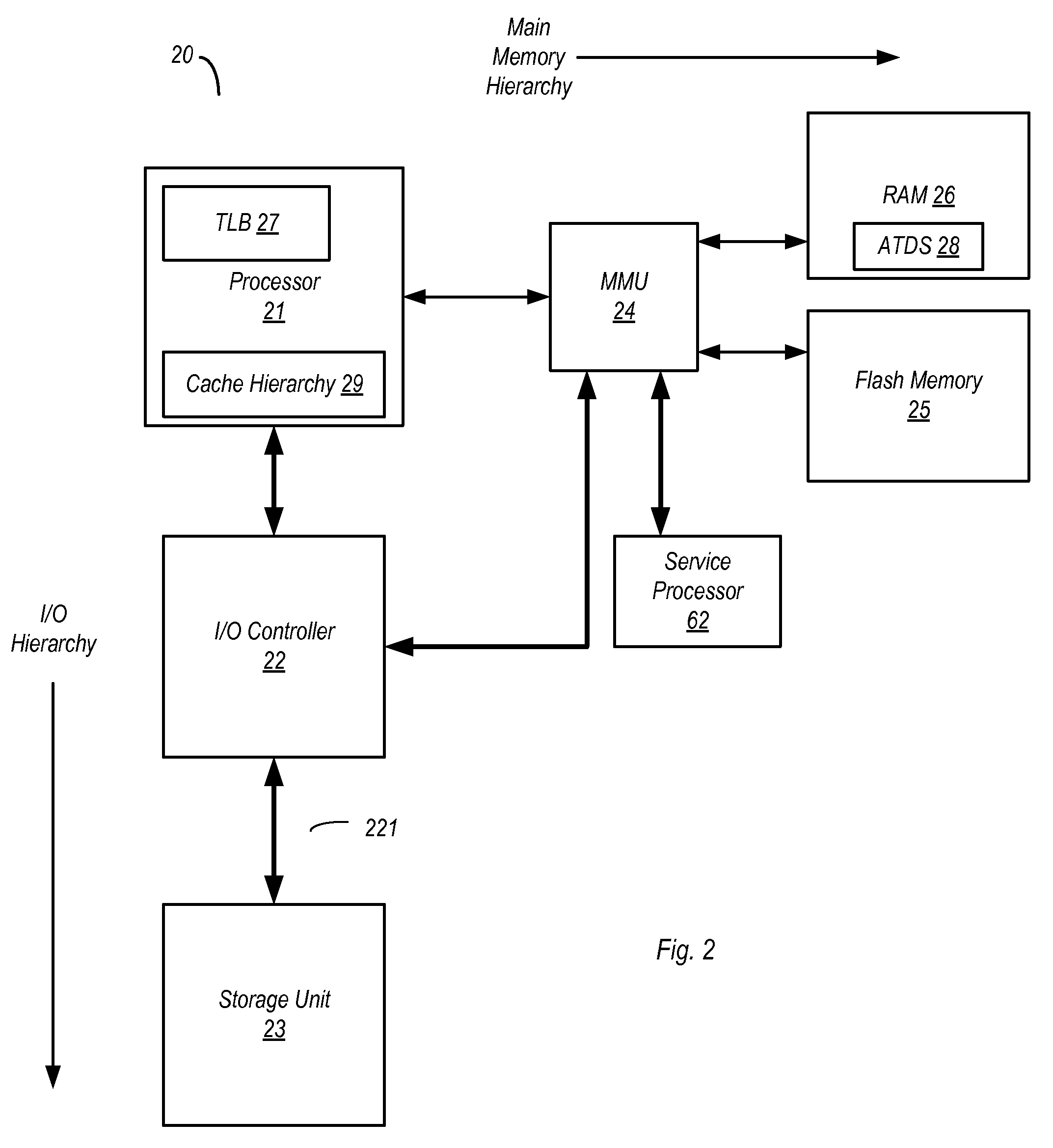

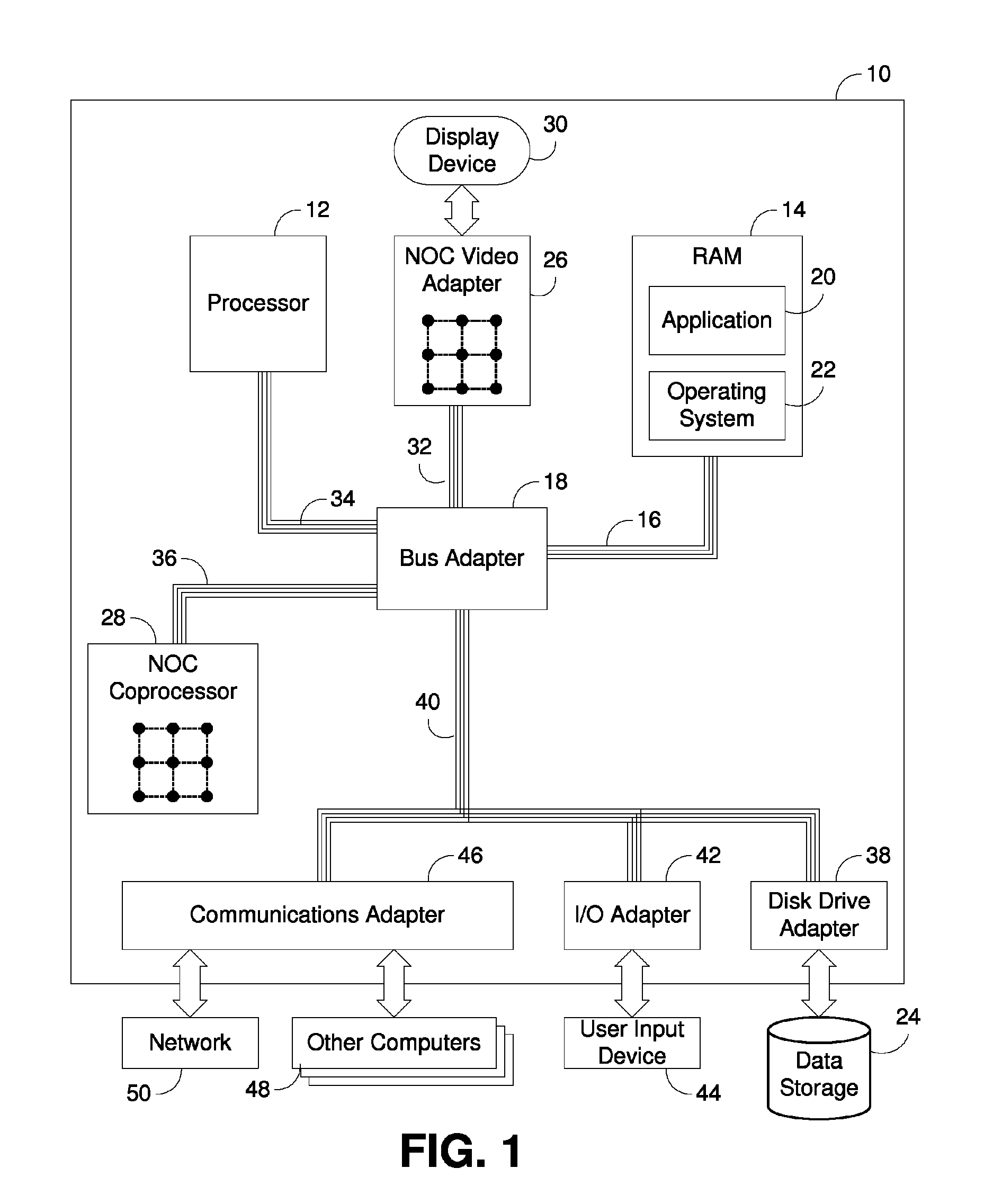

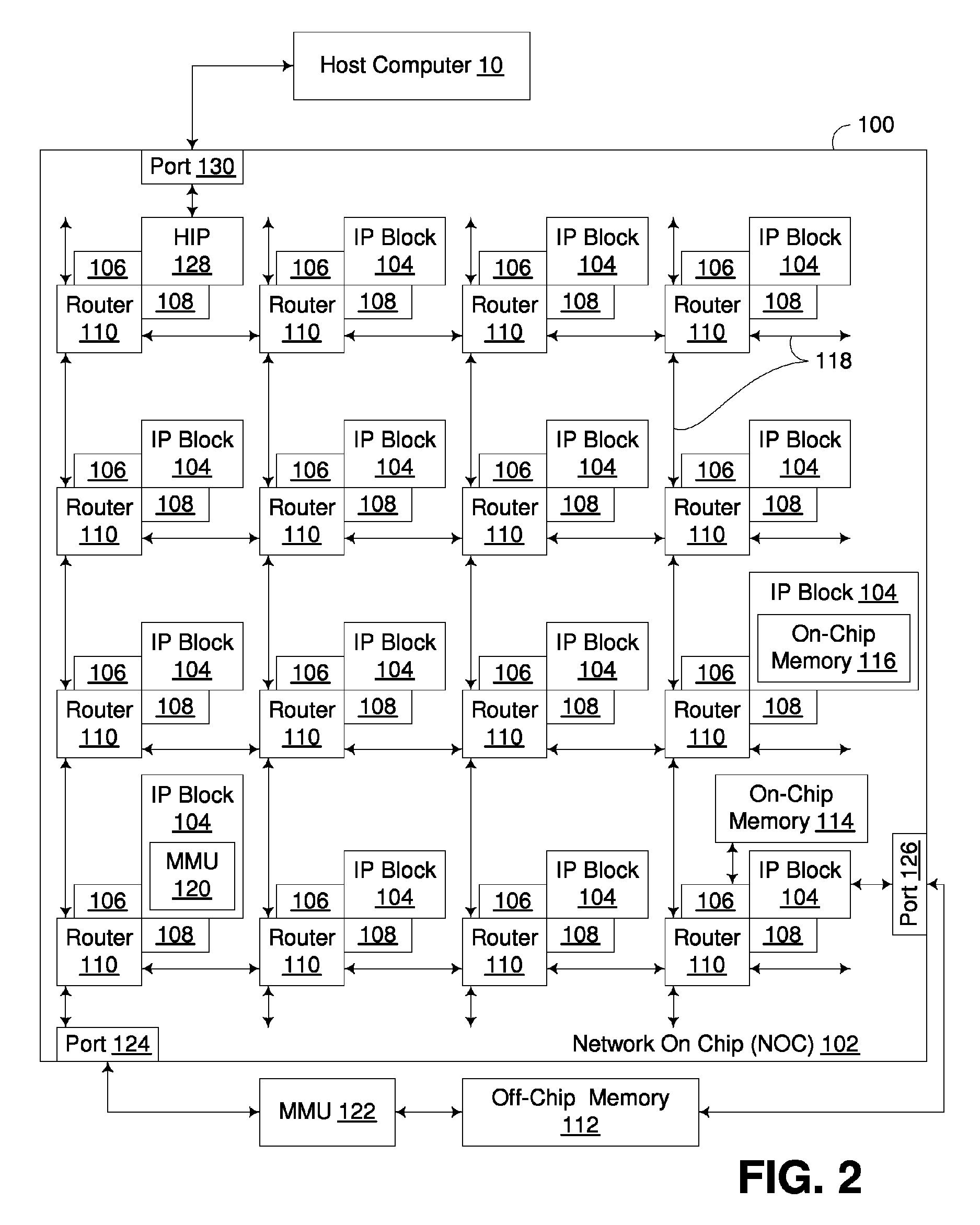

Extended main memory hierarchy having flash memory for page fault handling

ActiveUS20100332727A1Lower performance requirementsPerformance penaltyMemory architecture accessing/allocationEnergy efficient ICTMemory hierarchyManagement unit

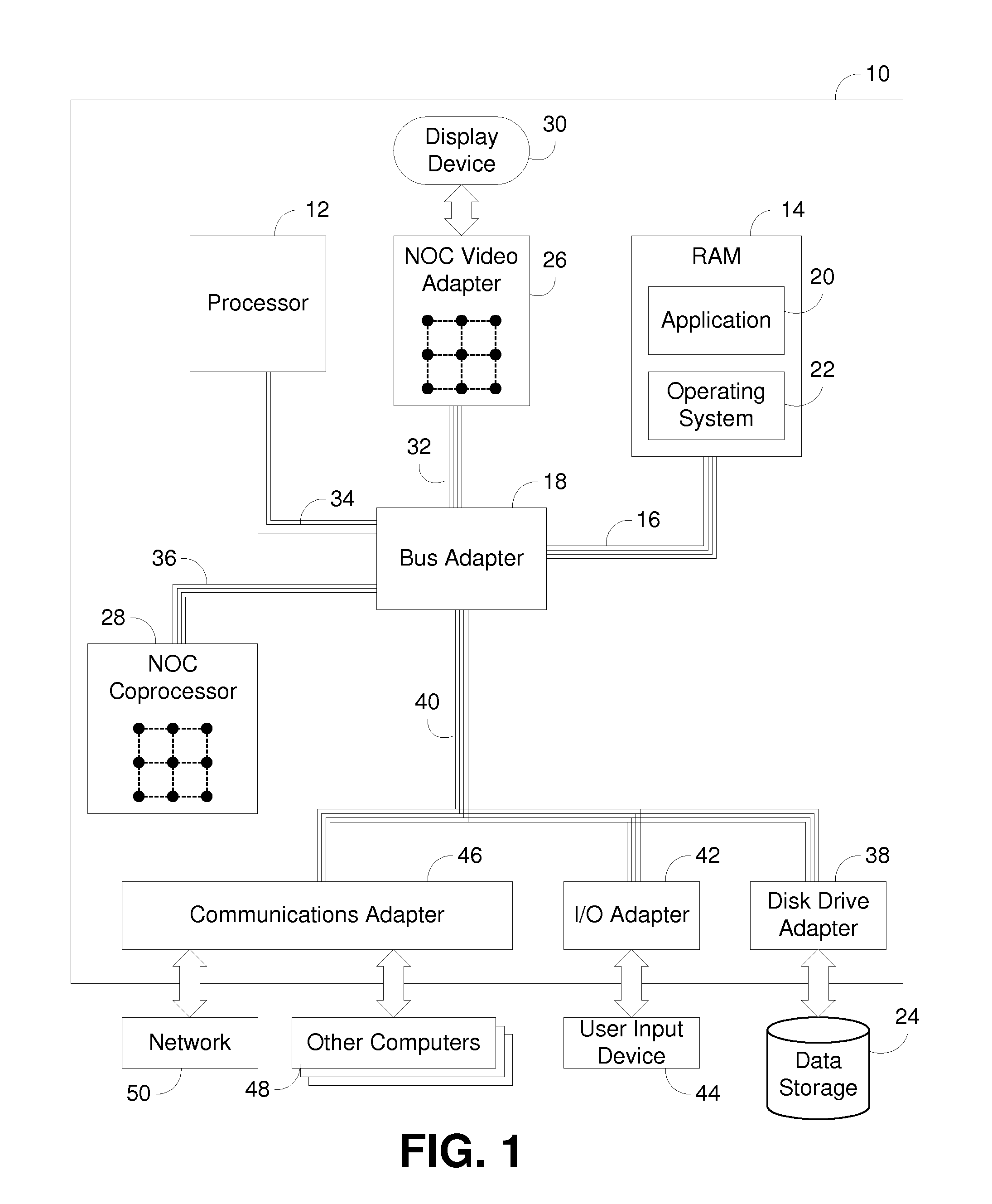

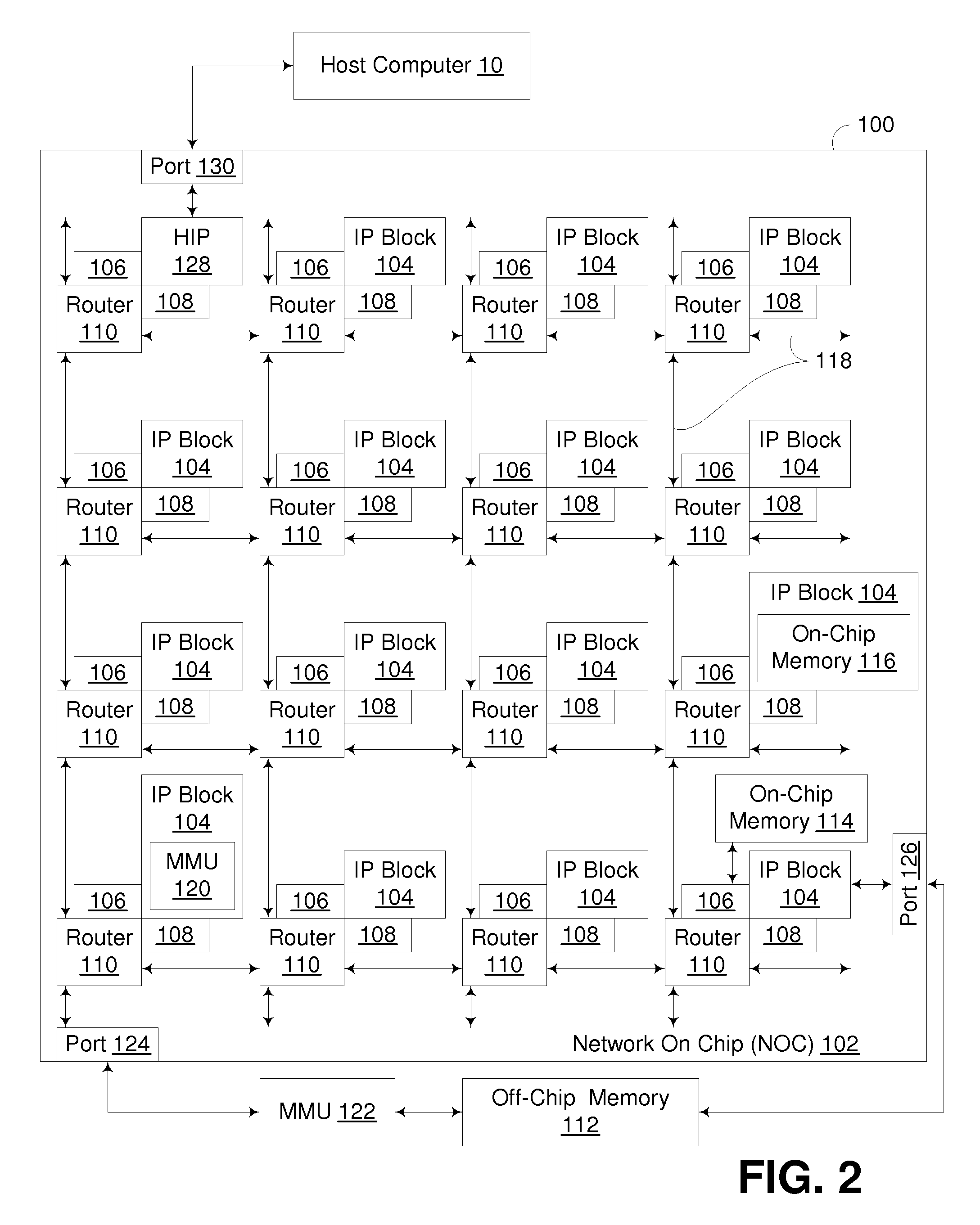

A computer system with flash memory in the main memory hierarchy is disclosed. In an embodiment, the computer system includes at least one processor, a memory management unit coupled to the at least one processor, and a random access memory (RAM) coupled to the memory management unit. The computer system may also include a flash memory coupled to the memory management unit, wherein the computer system is configured to store at least a subset of a plurality of pages in the flash memory during operation. Responsive to a page fault, the memory management unit may determine, without invoking an I / O driver, if a requested page associated with the page fault is stored in the flash memory and further configured to, if the page is stored in the flash memory, transfer the page into RAM.

Owner:SUN MICROSYSTEMS INC

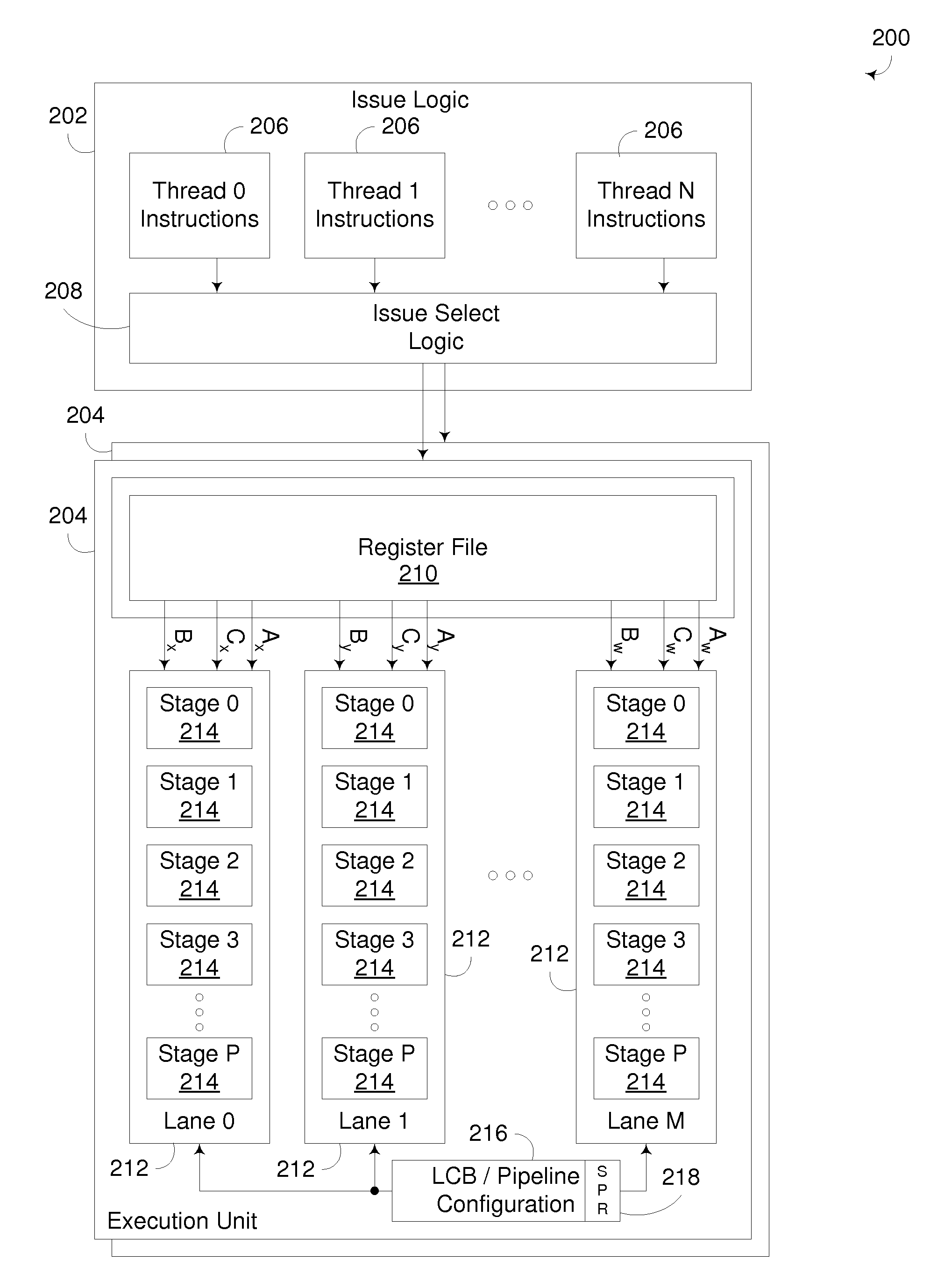

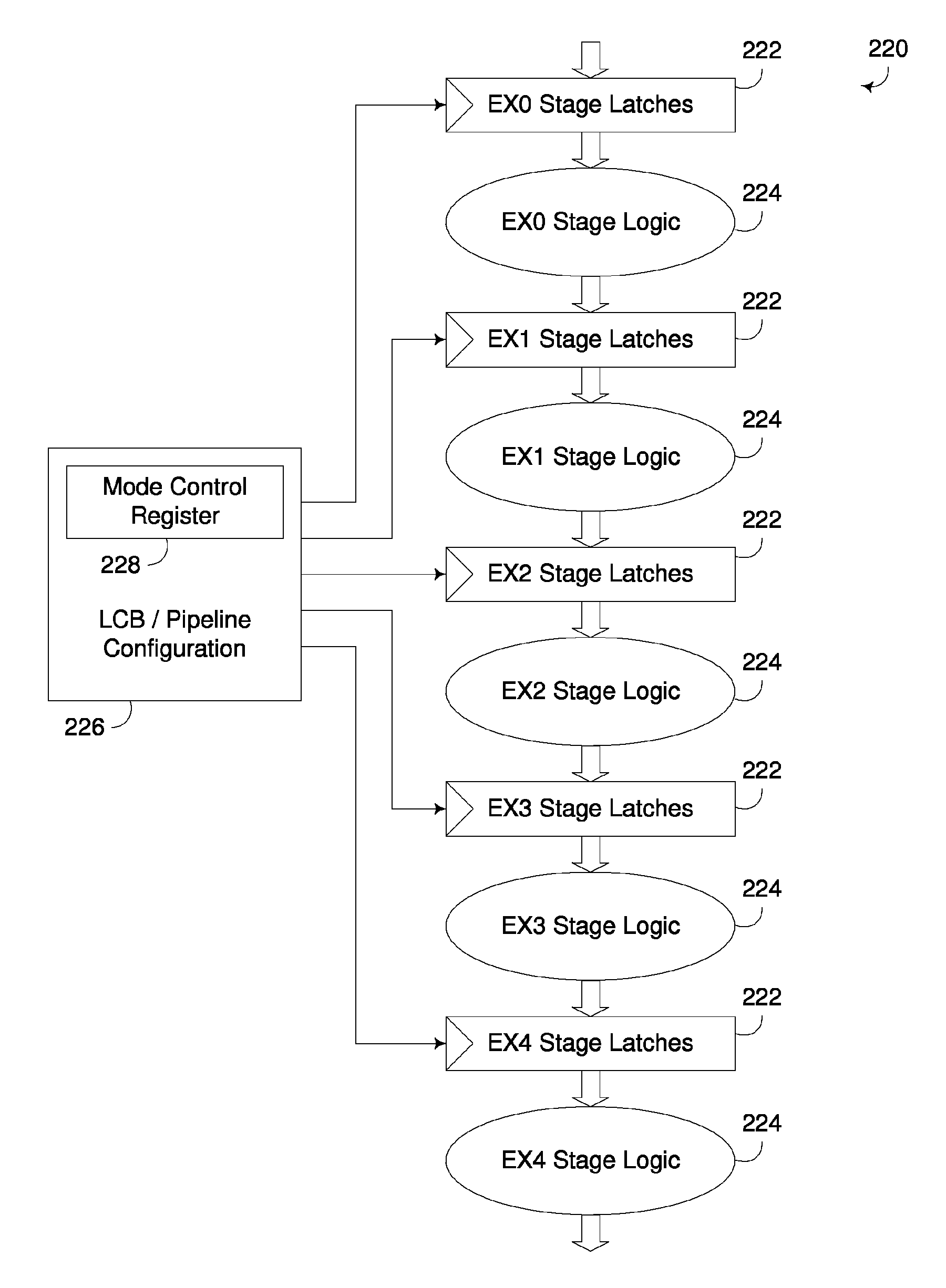

Dynamic Merging of Pipeline Stages in an Execution Pipeline to Reduce Power Consumption

InactiveUS20090292907A1Reduce power consumptionReduce switchingEnergy efficient ICTVolume/mass flow measurementPower modeClock rate

A pipelined execution unit incorporates one or more low power modes that reduce power consumption by dynamically merging pipeline stages in an execution pipeline together with one another. In particular, the execution logic in successive pipeline stages in an execution pipeline may be dynamically merged together by setting one or more latches that are intermediate to such pipeline stages to a transparent state such that the output of the pipeline stage preceding such latches is passed to the subsequent pipeline stage during the same clock cycle so that both such pipeline stages effectively perform steps for the same instruction during each clock cycle. Then, with the selected pipeline stages merged, the power consumption of the execution pipeline can be reduced (e.g., by reducing the clock frequency and / or operating voltage of the execution pipeline), often with minimal adverse impact on performance.

Owner:IBM CORP

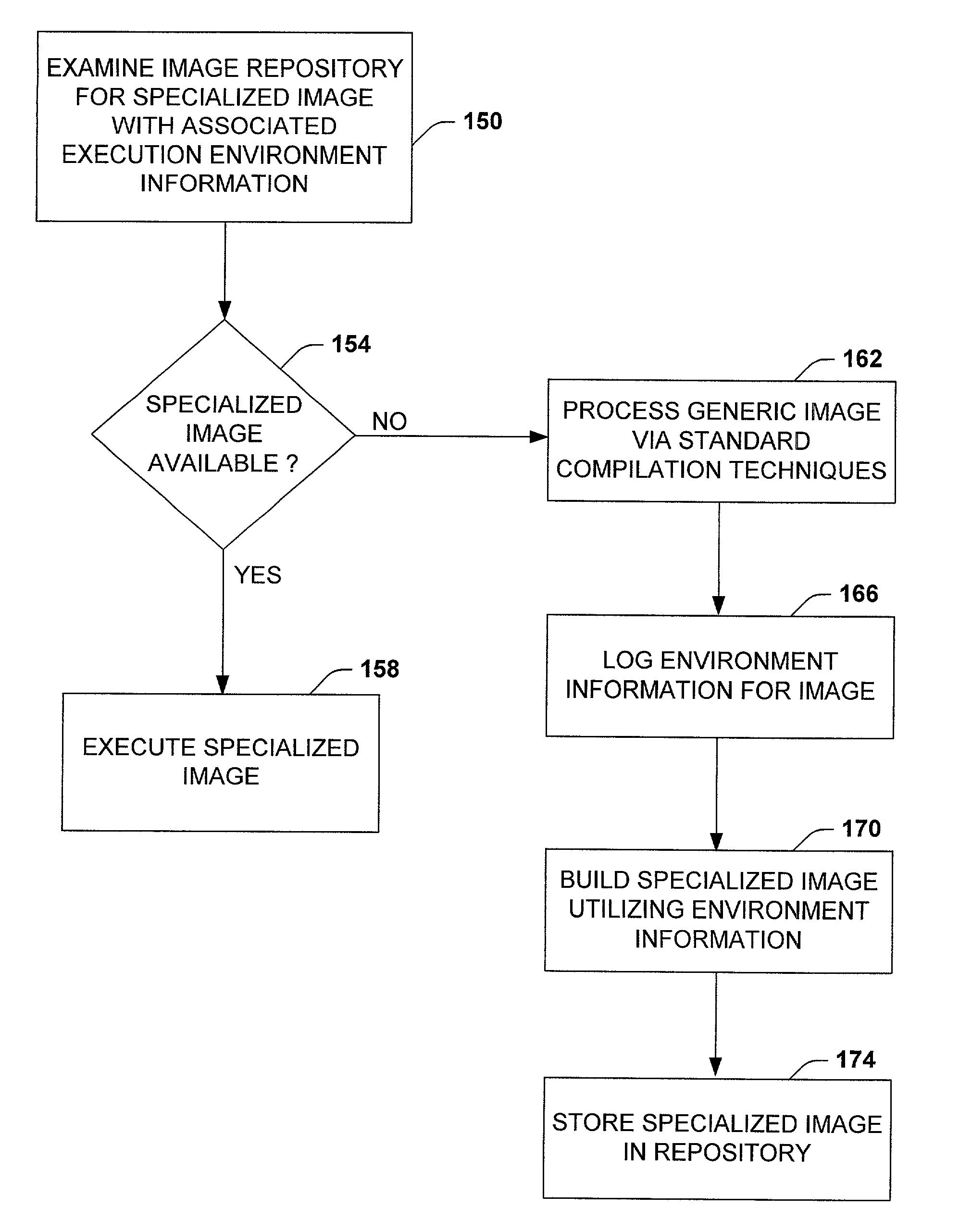

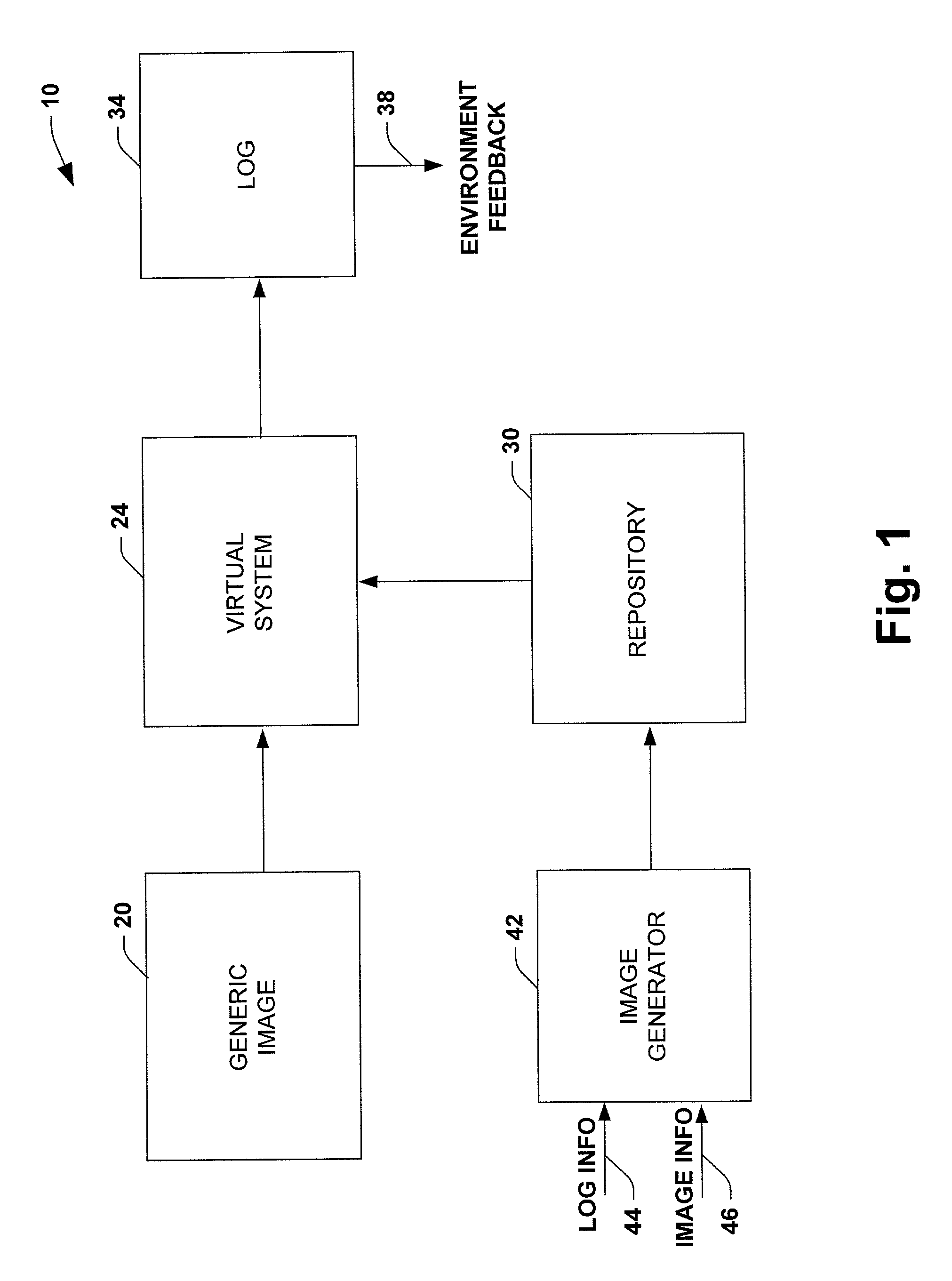

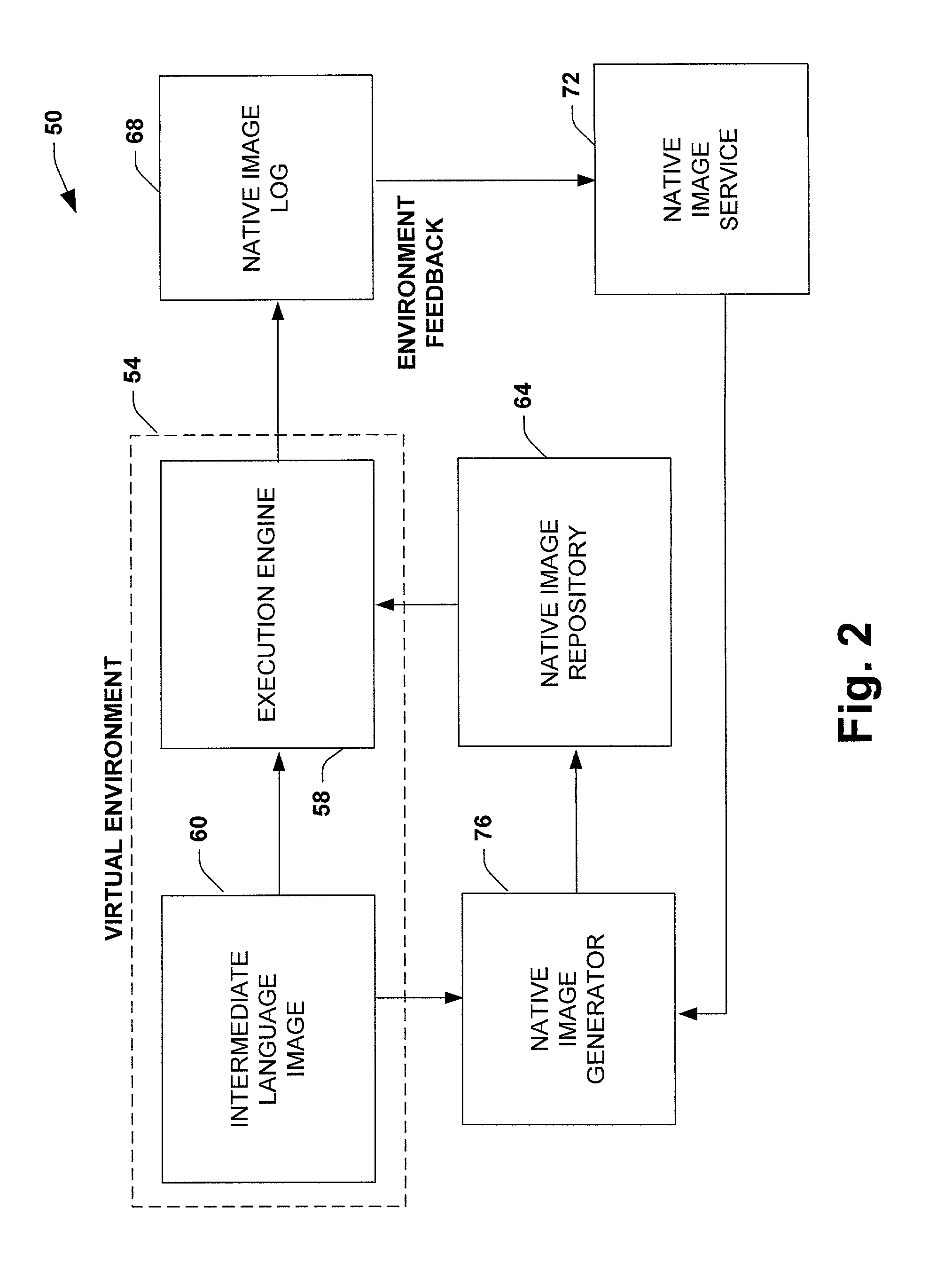

System and method providing on-demand generation of specialized executables

InactiveUS7730468B1Improved generationImprove performanceSpecific program execution arrangementsMemory systemsComputer scienceOn demand

A system and method is provided for generating and executing specialized code executables. The system includes a virtual subsystem that processes a generic code image and logs information relating to an operating environment of the virtual subsystem. The logged information is employed as feedback to generate a specialized native executable, wherein the specialized native executable is utilized to provide improved performance of the virtual subsystem. The specialized native executable is selected for execution by the virtual subsystem by matching a current operating environment setting with the logged information.

Owner:MICROSOFT TECH LICENSING LLC

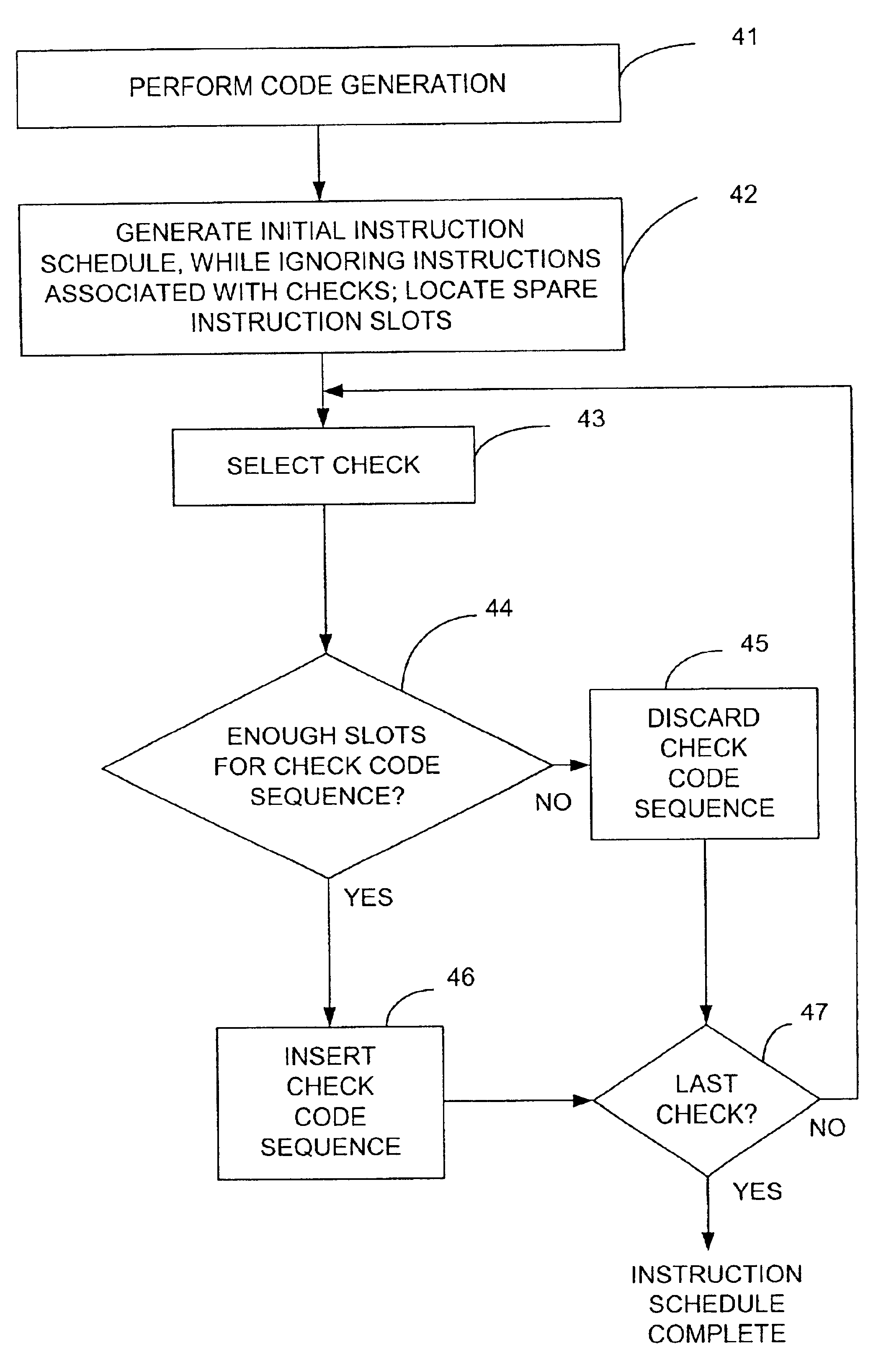

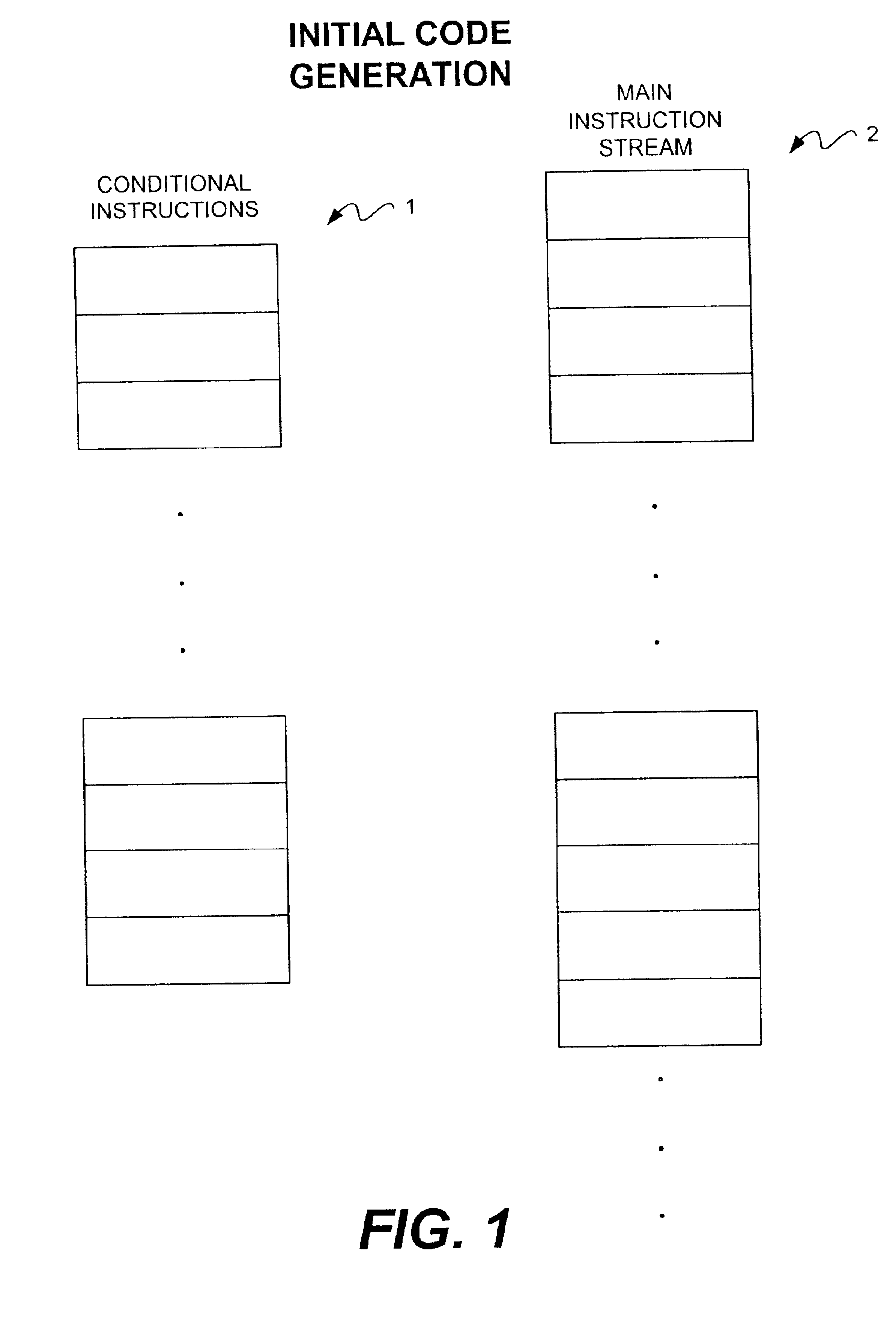

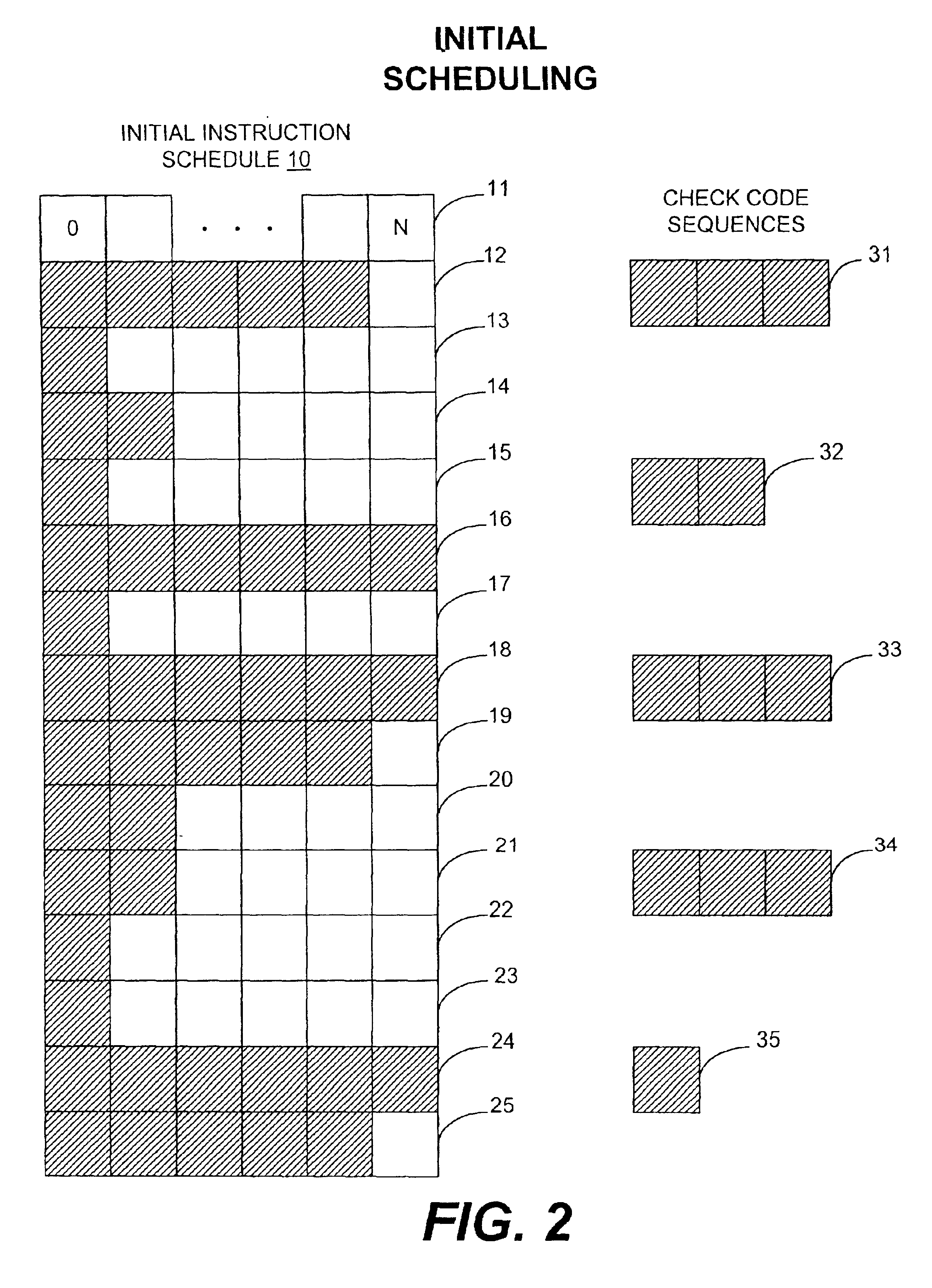

Method and apparatus for performing correctness checks opportunistically

InactiveUS6883166B1Performance penaltySoftware engineeringSoftware testing/debuggingCode moduleScheduling instructions

A method and an apparatus that enable spare instruction slots within a code module to be utilized opportunistically for insertion of instructions associated with correctness check functions. The apparatus comprises a compiler that generates code and an initial instruction schedule. During generation of the initial instruction schedule, the compiler ignores code sequences associated with correctness check functions. After the initial instruction schedule has been generated, the compiler examines the initial instruction schedule and determines locations of spare instruction slots in the initial instruction schedule that can potentially be utilized for insertion of the code sequences associated with the correctness checks. The code sequences associated with the correctness checks are then inserted into the instruction schedule to the extent that insertion of the code sequences does not lengthen the final instruction schedule. Consequently, no performance penalty is incurred at run time.

Owner:HEWLETT PACKARD DEV CO LP

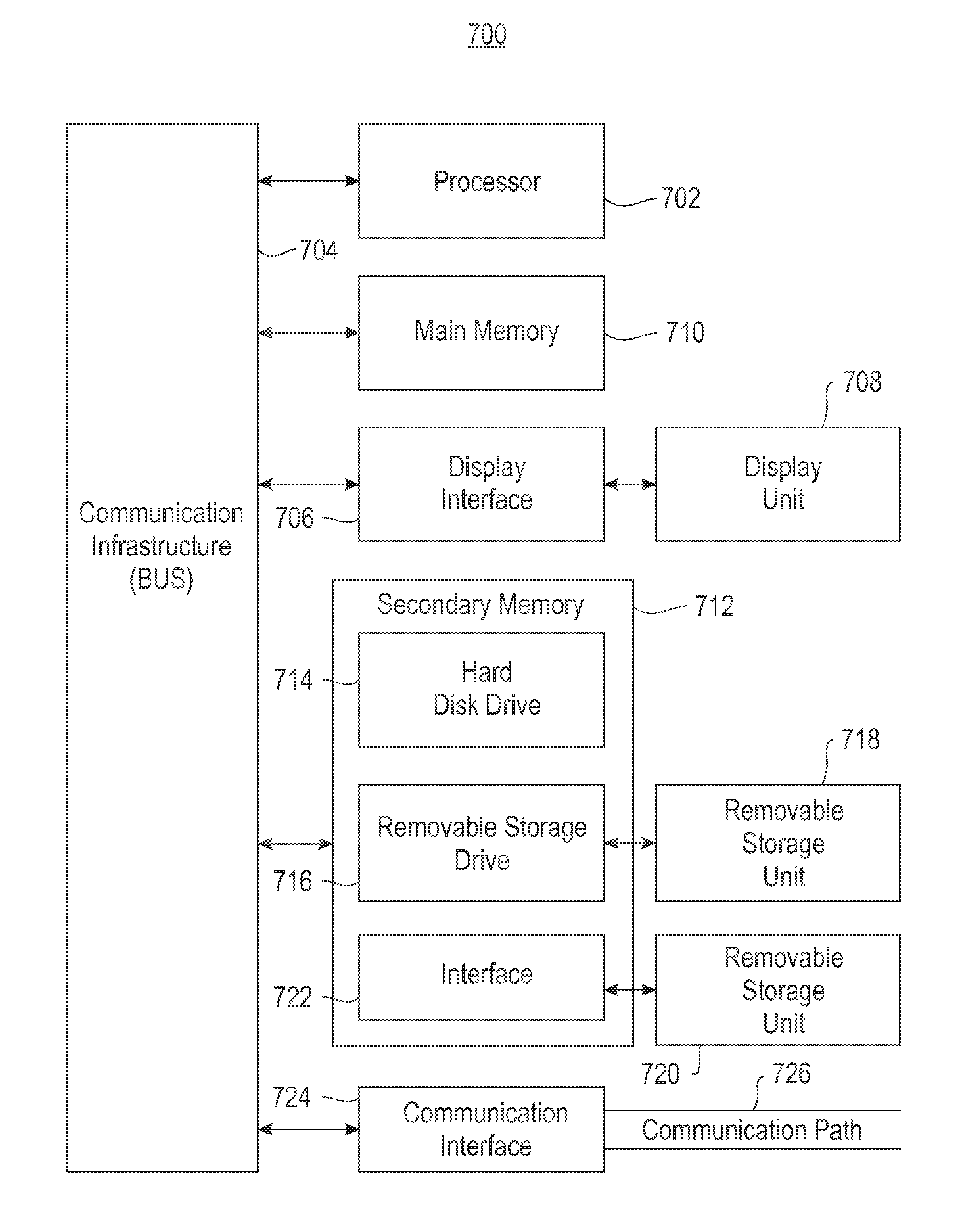

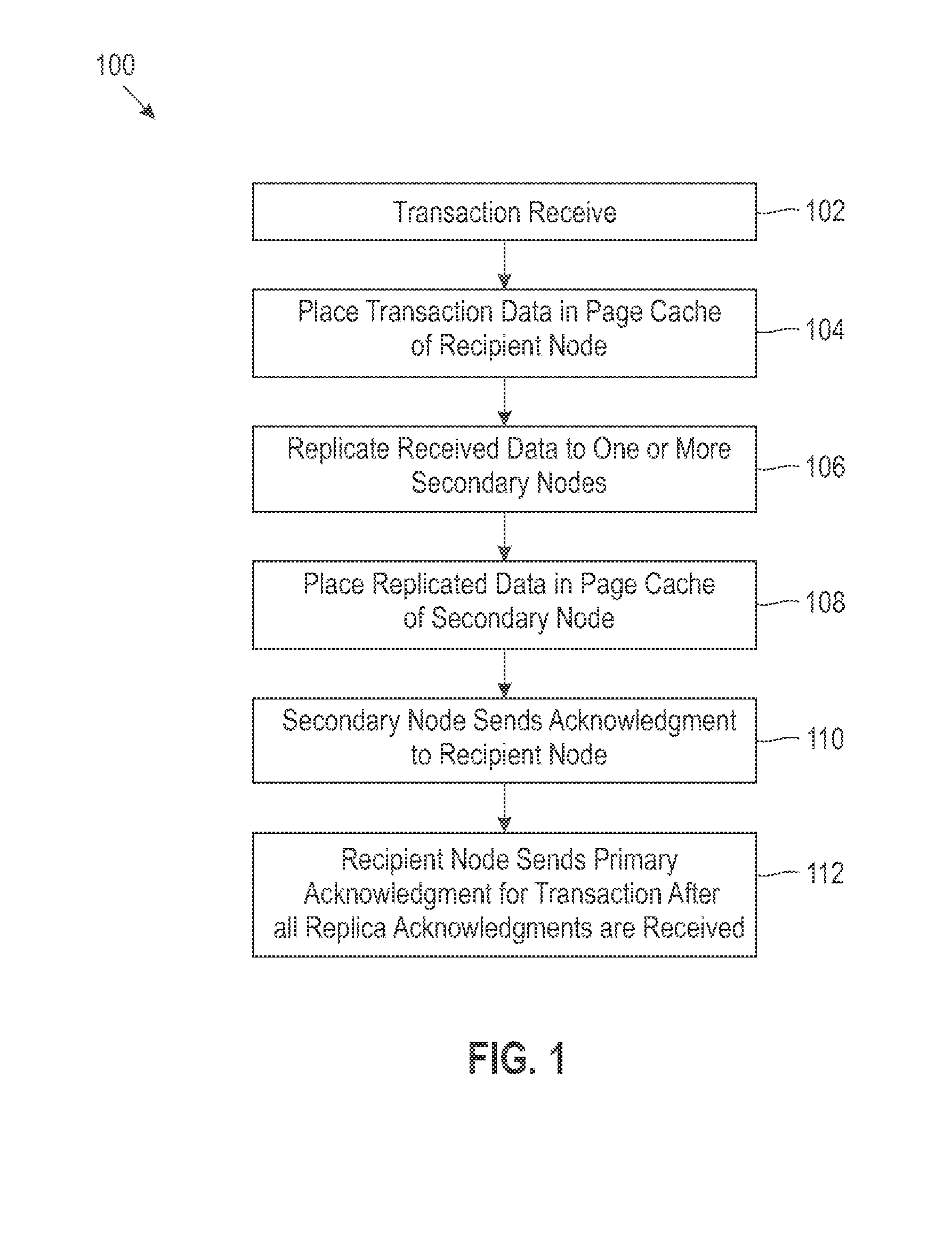

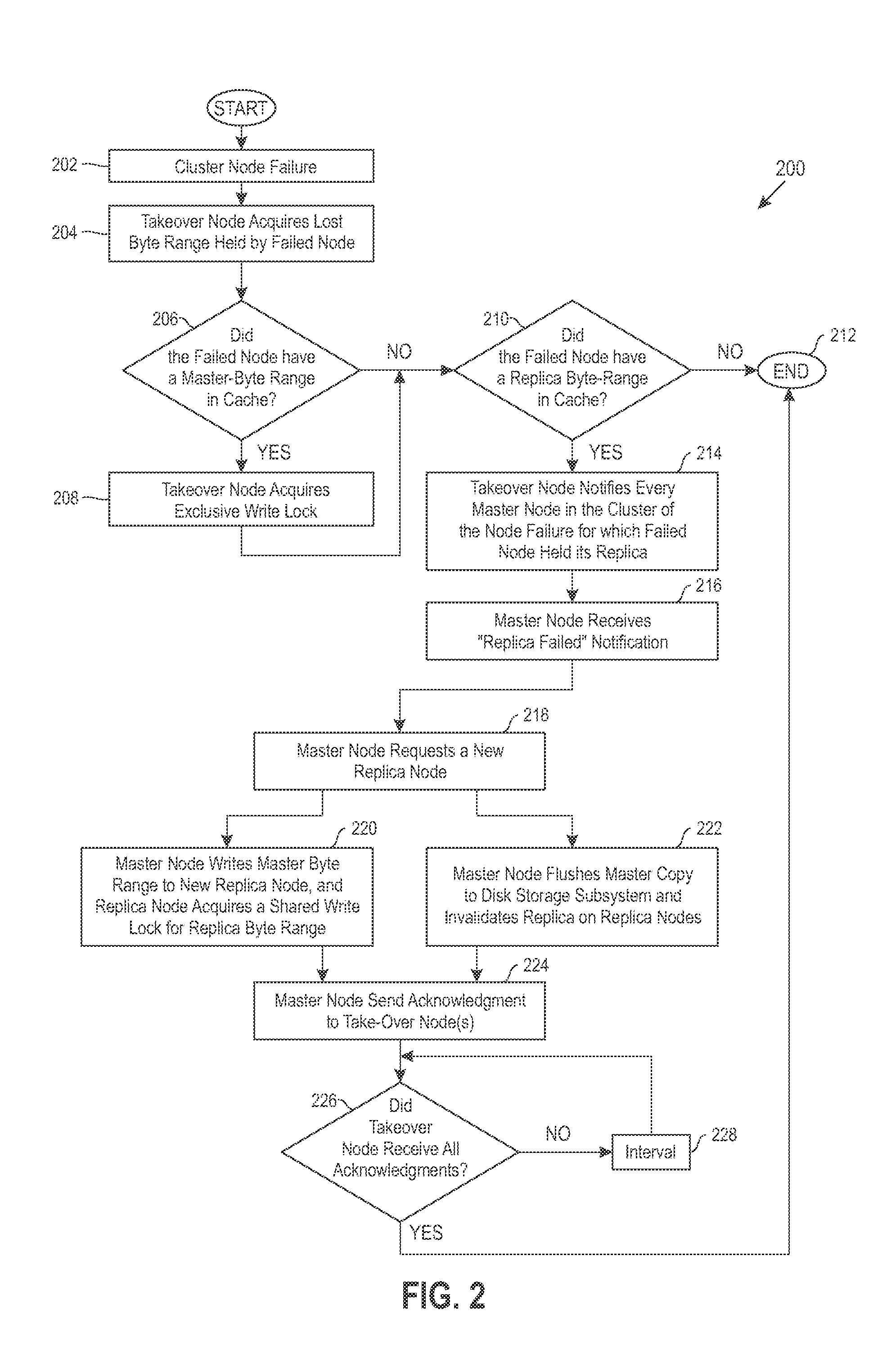

Write Performance in Fault-Tolerant Clustered Storage Systems

InactiveUS20140173185A1Reduce performance lossPerformance penaltyInput/output to record carriersMemory adressing/allocation/relocationFile systemTransaction data

Embodiments of the invention relate to supporting transaction data committed to a stable storage. Committed data in the cluster is stored in the persistent cache layer and replicated and stored in the cache layer of one or more secondary nodes. One copy is designated as a master copy and all other copies are designated as replica, with an exclusive write lock assigned to the master and a shared write lock extended to the replica. An acknowledgement of receiving the data is communicated following confirmation that the data has been replicated to each node designated to receive the replica. Managers and a director are provided to support management of the master copy and the replicas within the file system, including invalidation of replicas, fault tolerance associated with failure of a node holding a master copy, recovery from a failed node, recovered of the file system from a power failure, and transferring master and replica copies within the file system.

Owner:IBM CORP

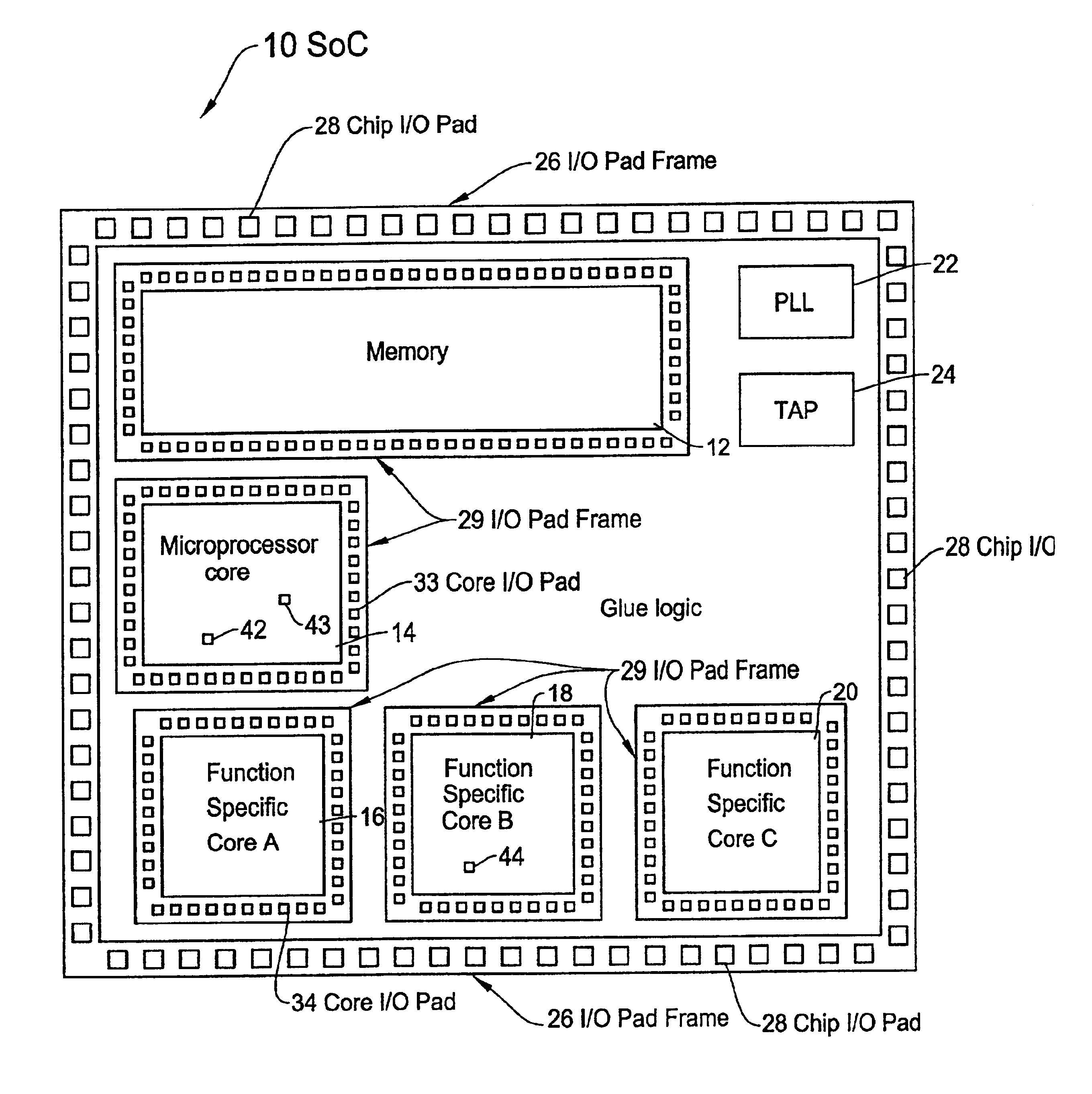

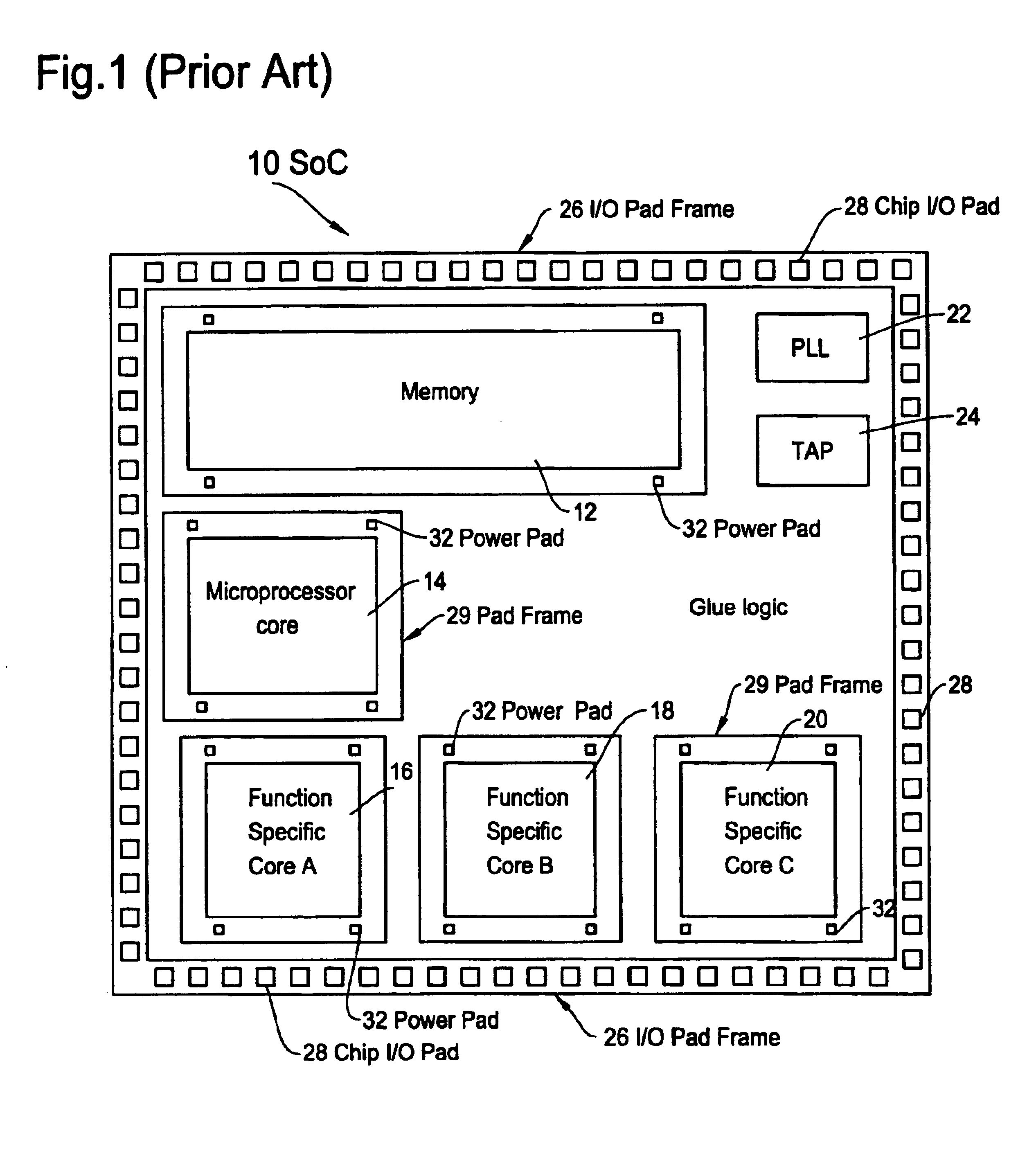

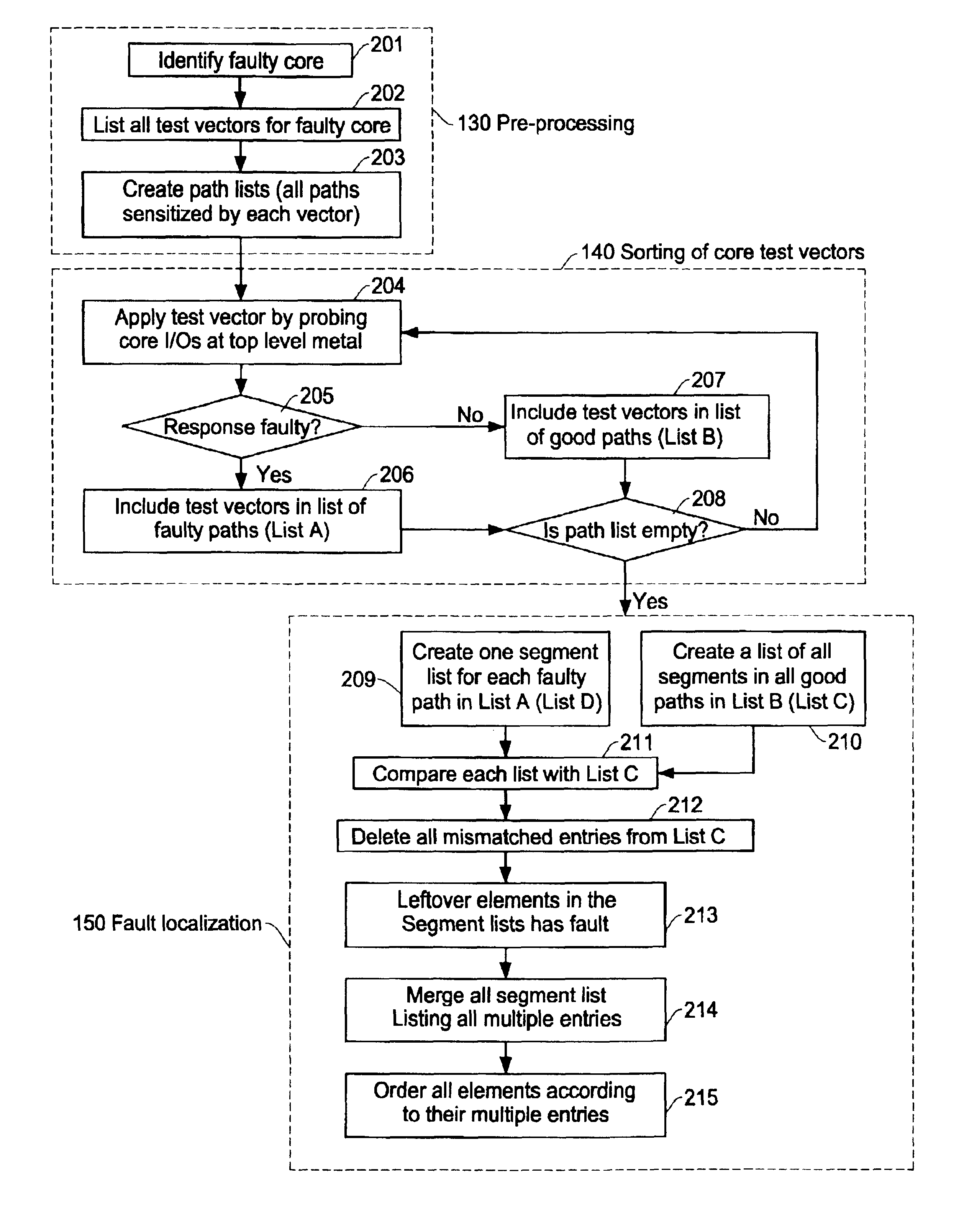

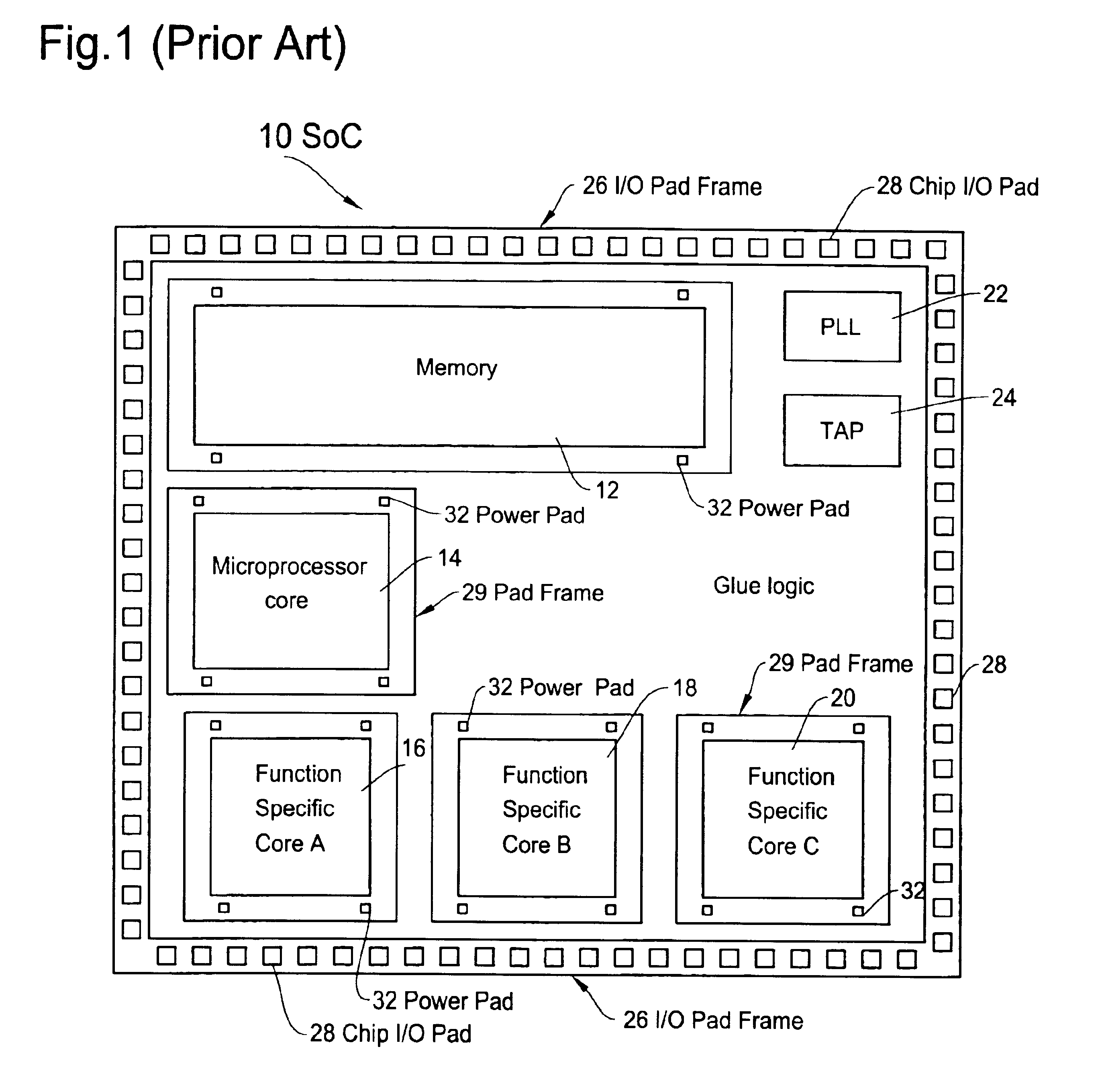

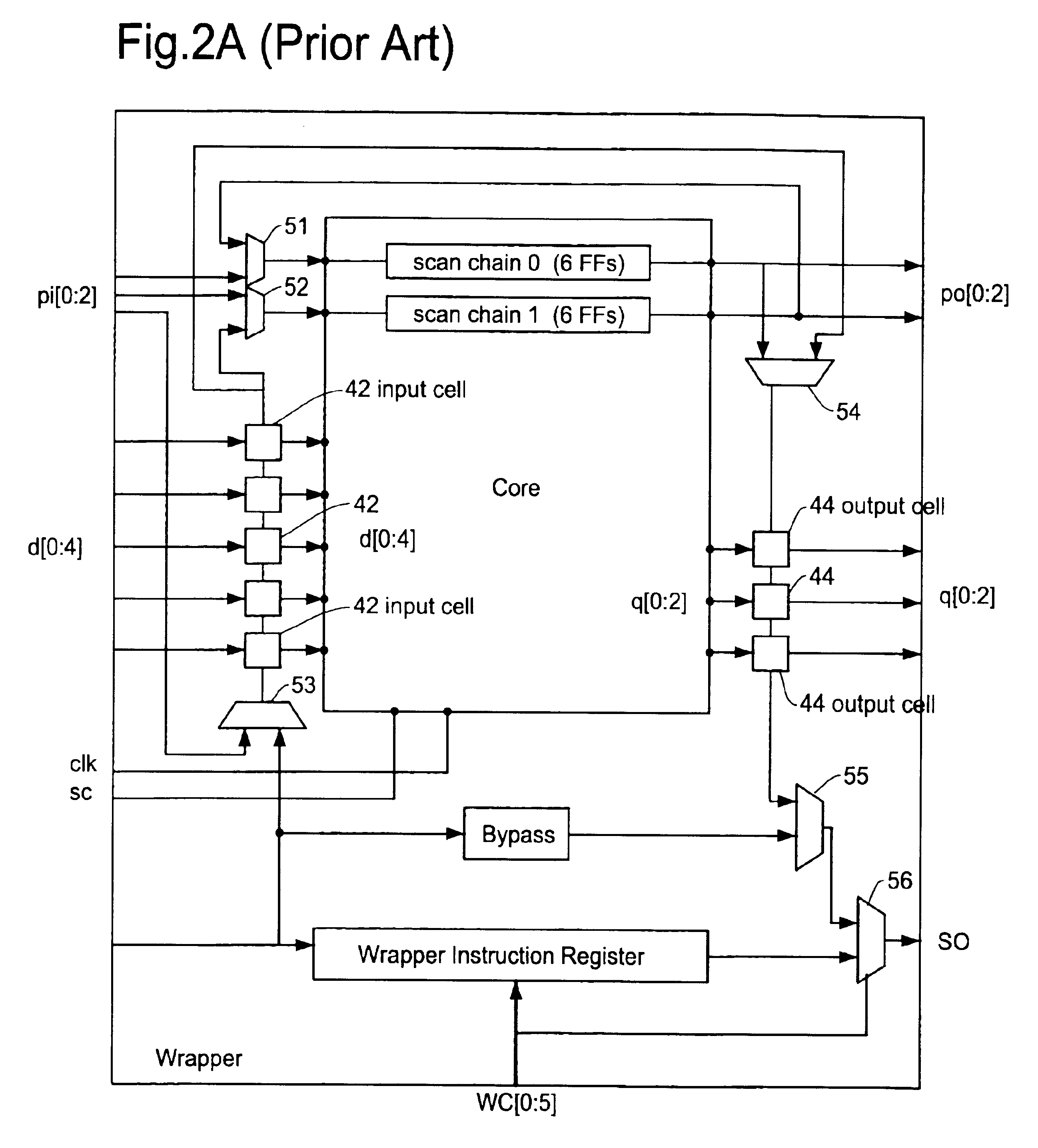

Method of evaluating core based system-on-a-chip (SoC) and structure of SoC incorporating same

InactiveUS6948105B2Easy to implementPerformance penaltyDigital circuit testingSemiconductor/solid-state device detailsObservabilitySystem on a chip

A method of debugging an individual core in core based system-on-a-chip (SOC) ICs with high accuracy and observability, and a structure of SOC incorporating the method. The method includes the steps of building two or more metal layers of a pad frame for each core in an SoC while connecting I / O (input and output) pads on a lower metal layer to a top metal layer, thereby exposing all I / O pads and power pads on a surface of the top metal layer of the pad frame of each core, and applying test vector to each core through the I / O pads on the top metal layer of the core and evaluating response outputs of the core received through the I / O pads on the top metal layer.

Owner:ADVANTEST CORP

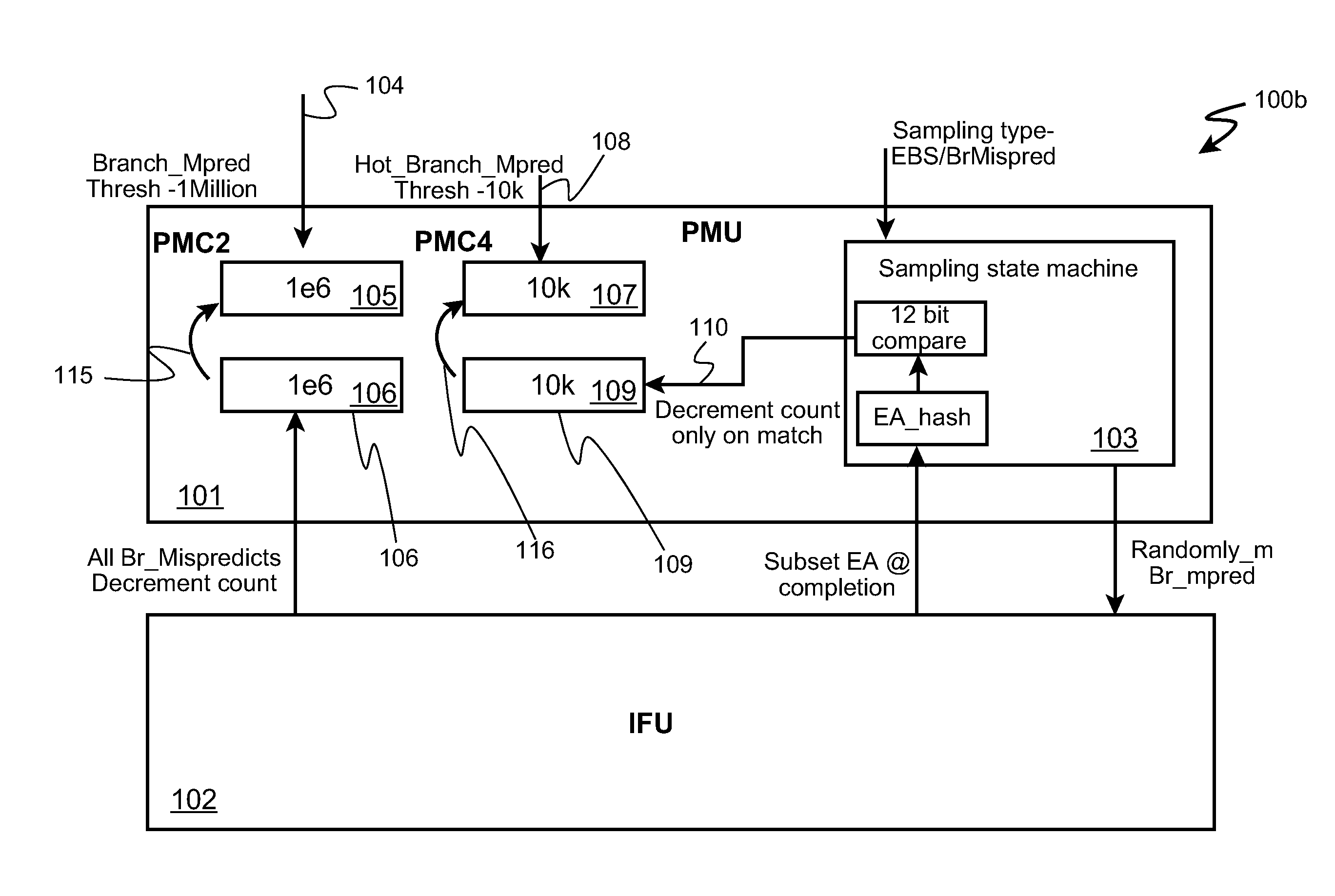

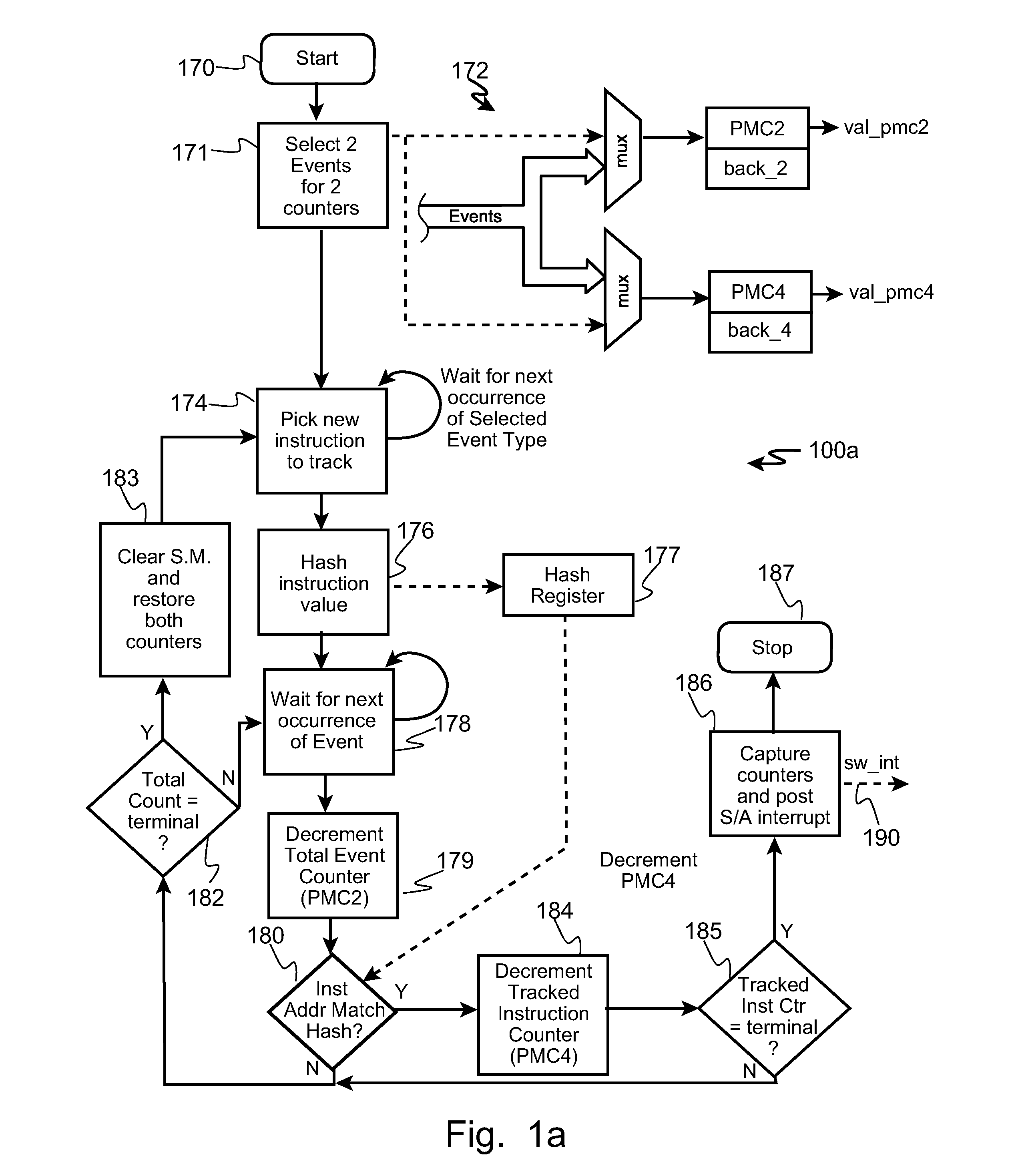

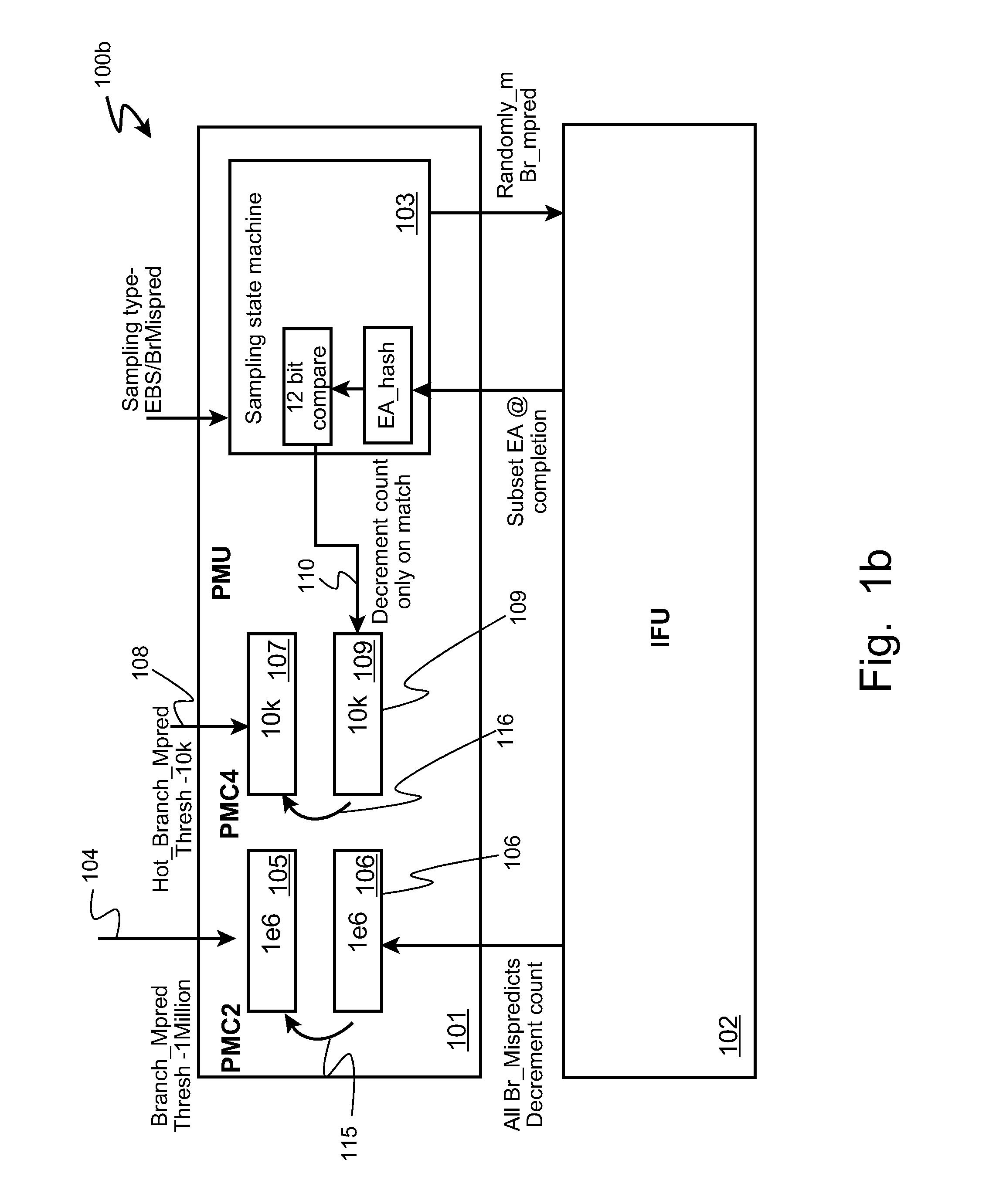

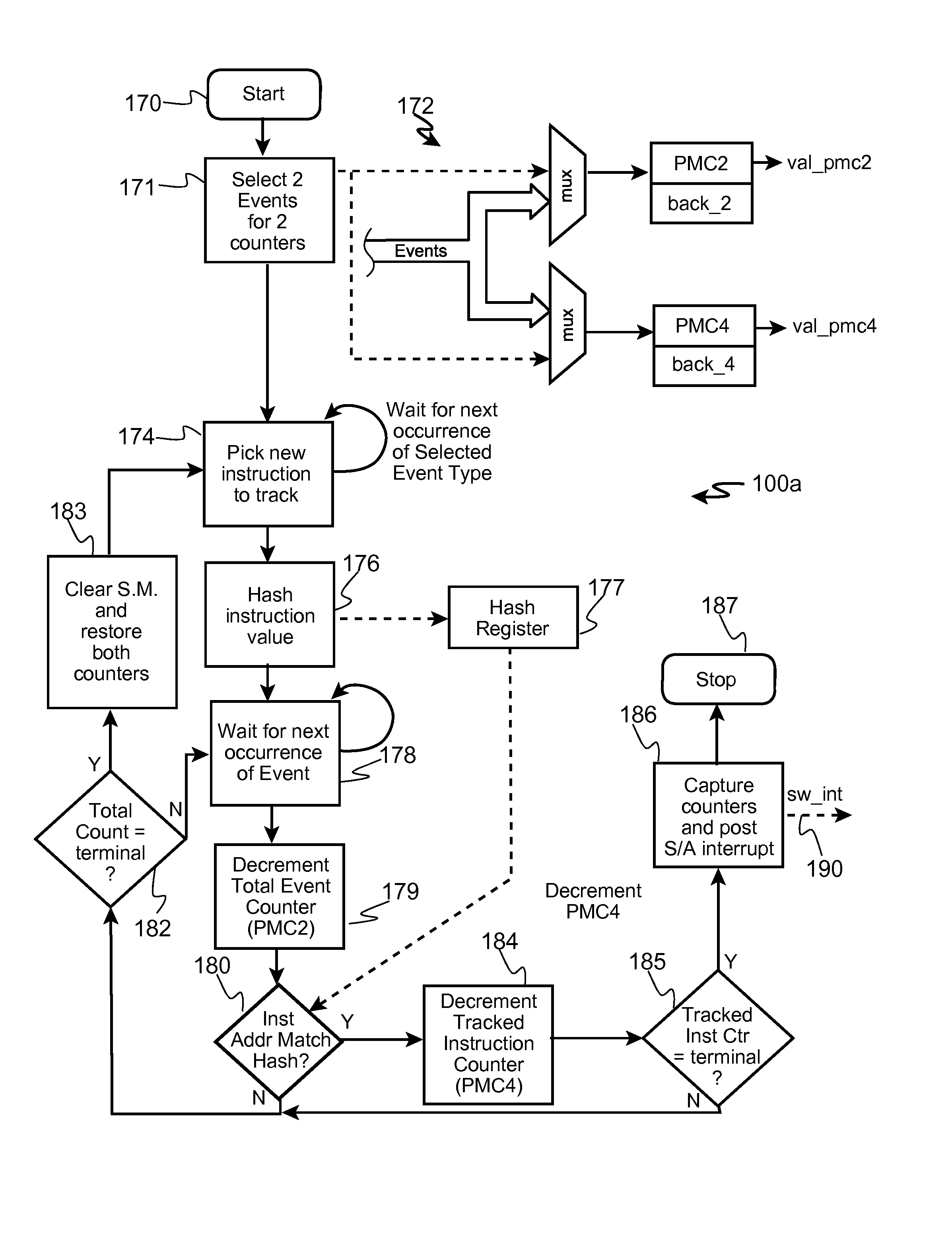

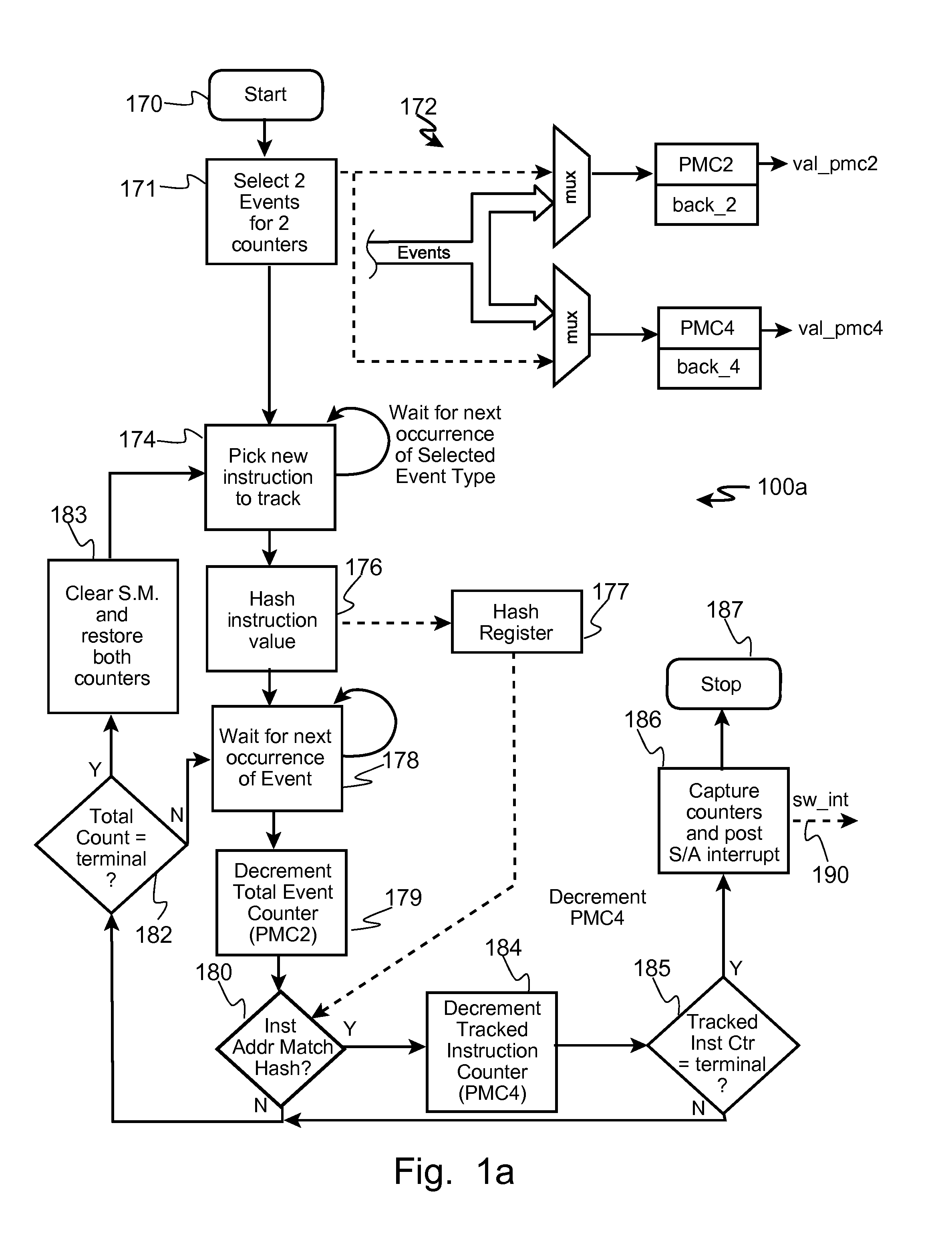

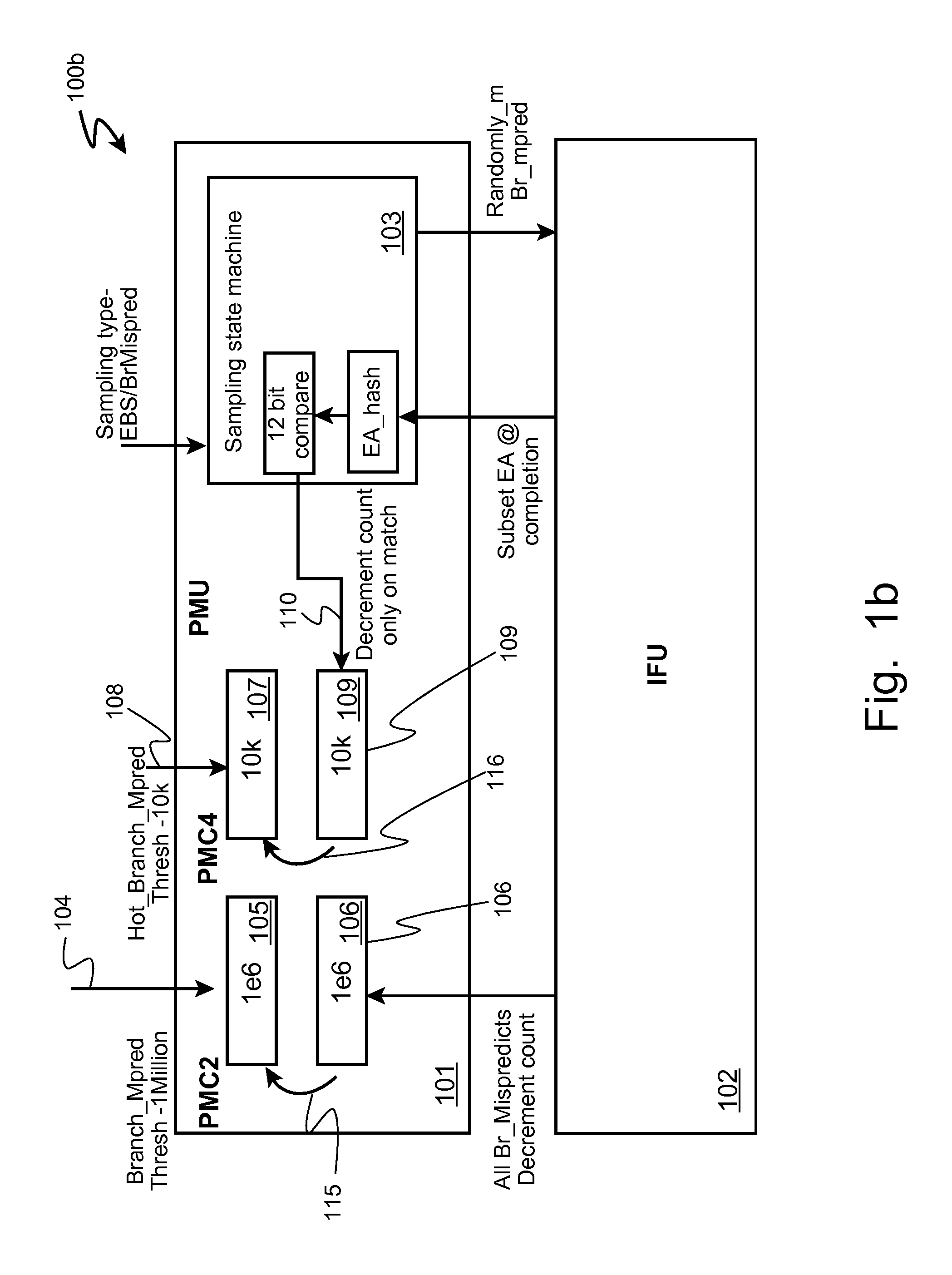

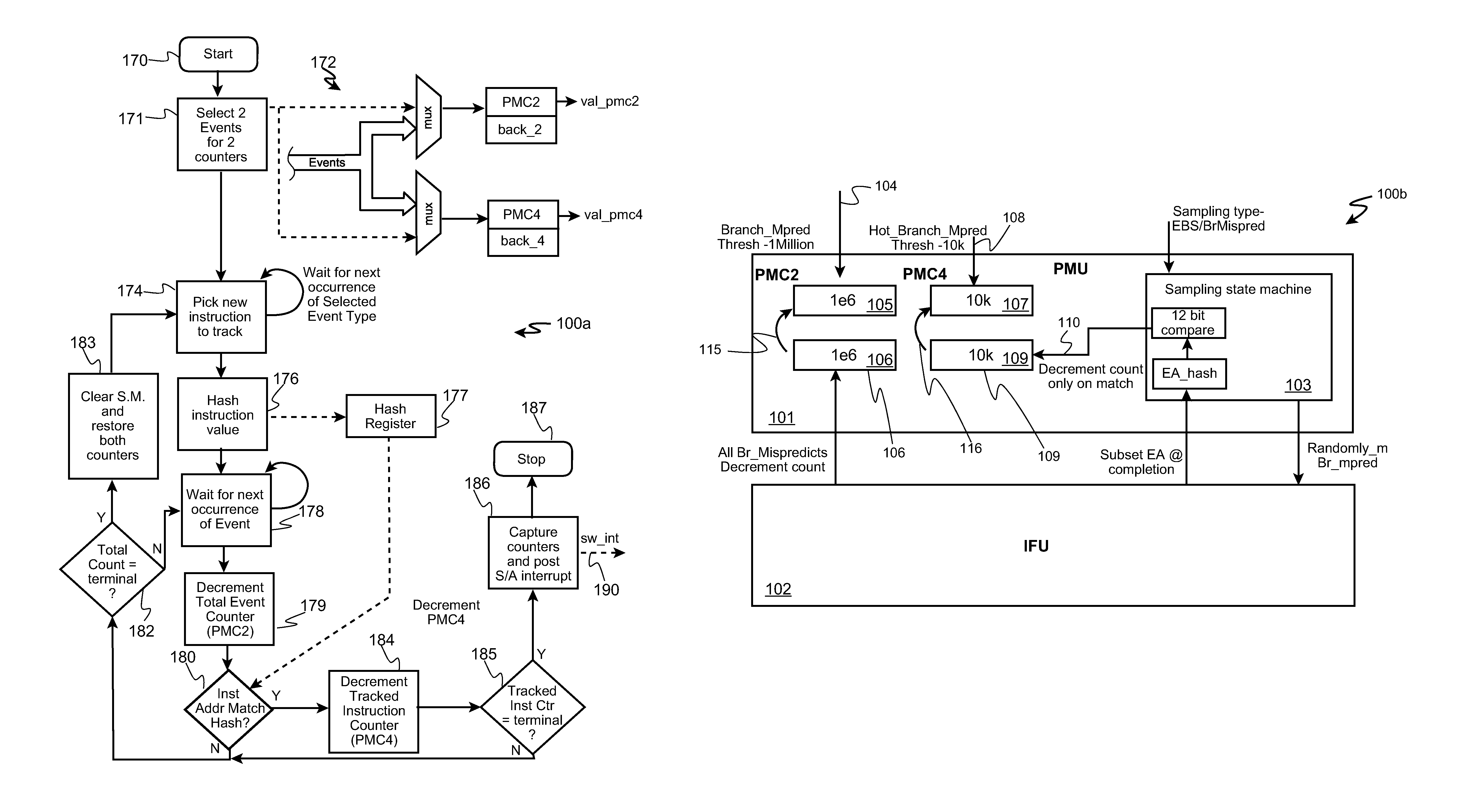

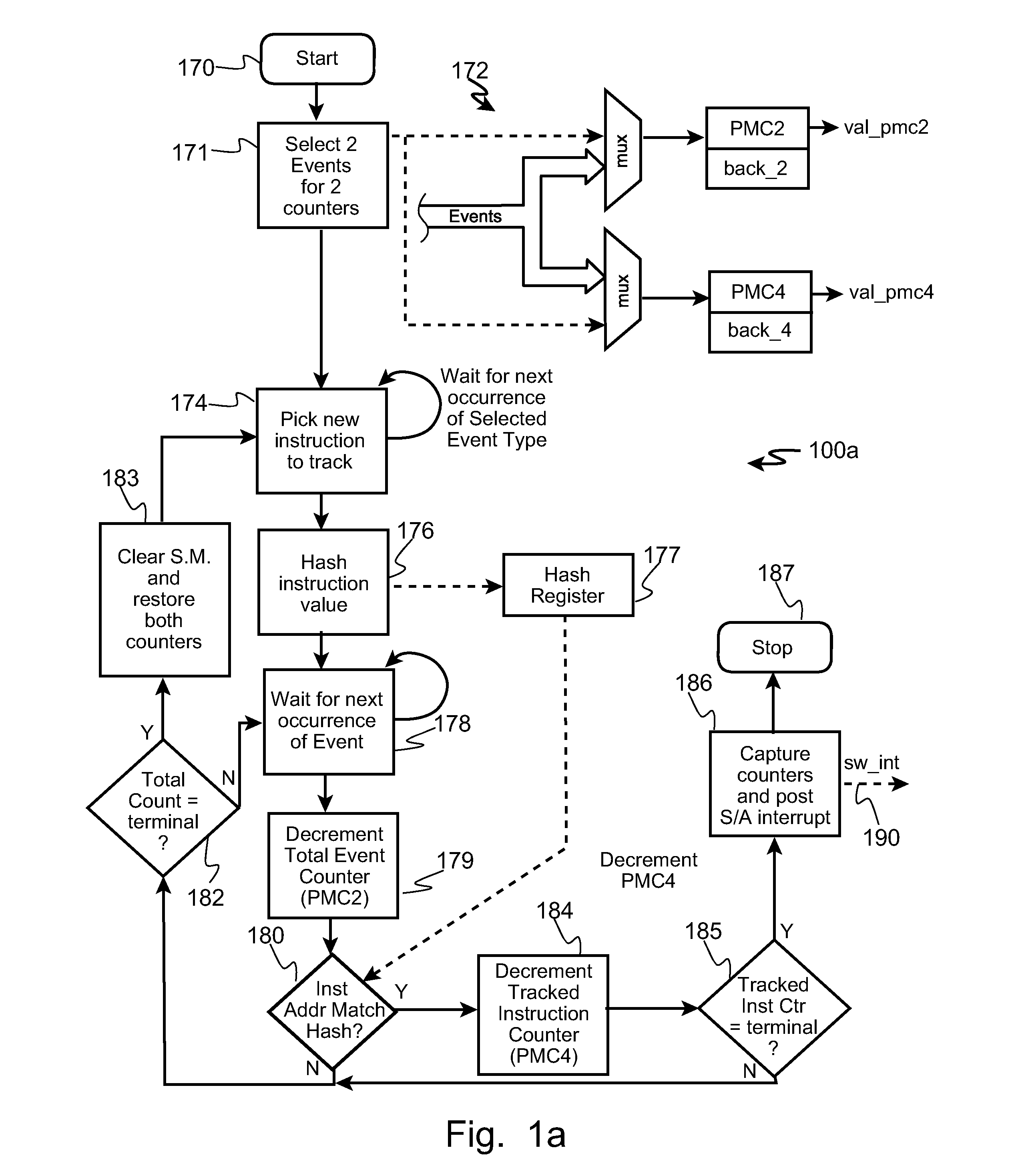

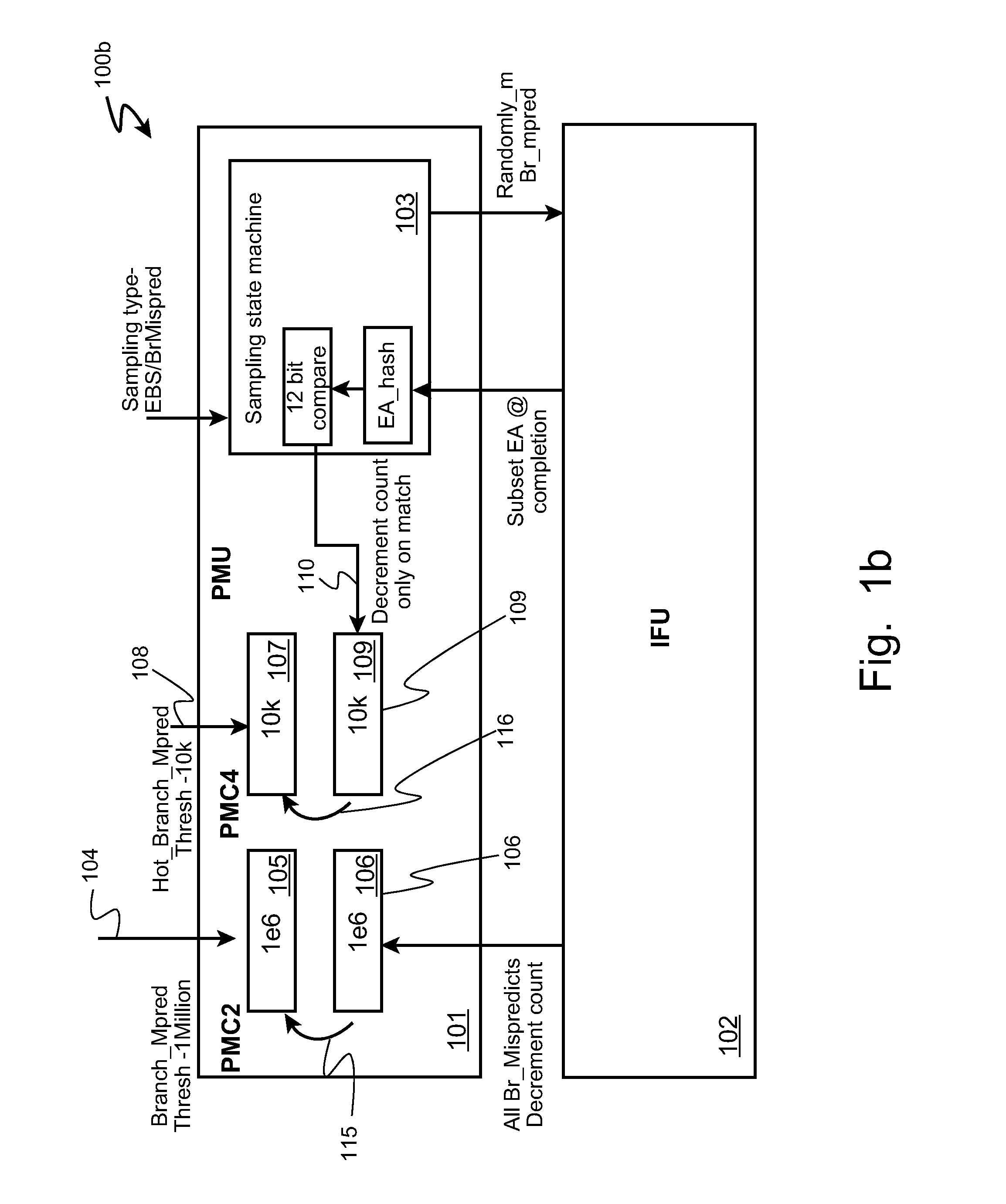

Autonomic Hotspot Profiling Using Paired Performance Sampling

InactiveUS20120124560A1Reduced performance impactReduce complexitySoftware engineeringHardware monitoringEvent typeParallel computing

A processor performance profiler is enabled to for identify specific instructions causing performance issues within a program being executed by a microprocessor through random sampling to find the worst-case offenders of a particular event type such as a cache miss or a branch mis-prediction. Tracking all instructions causing a particular event generates large data logs, creates performance penalties, and makes code analysis more difficult. However, by identifying and tracking the worst offenders within a random sample of events without having to hash all events results in smaller memory requirements for the performance profiler, lower performance impact while profiling, and decreased complexity to analyze the program to identify major performance issues, which, in turn, enables better optimization of the program in shorter developer time.

Owner:IBM CORP

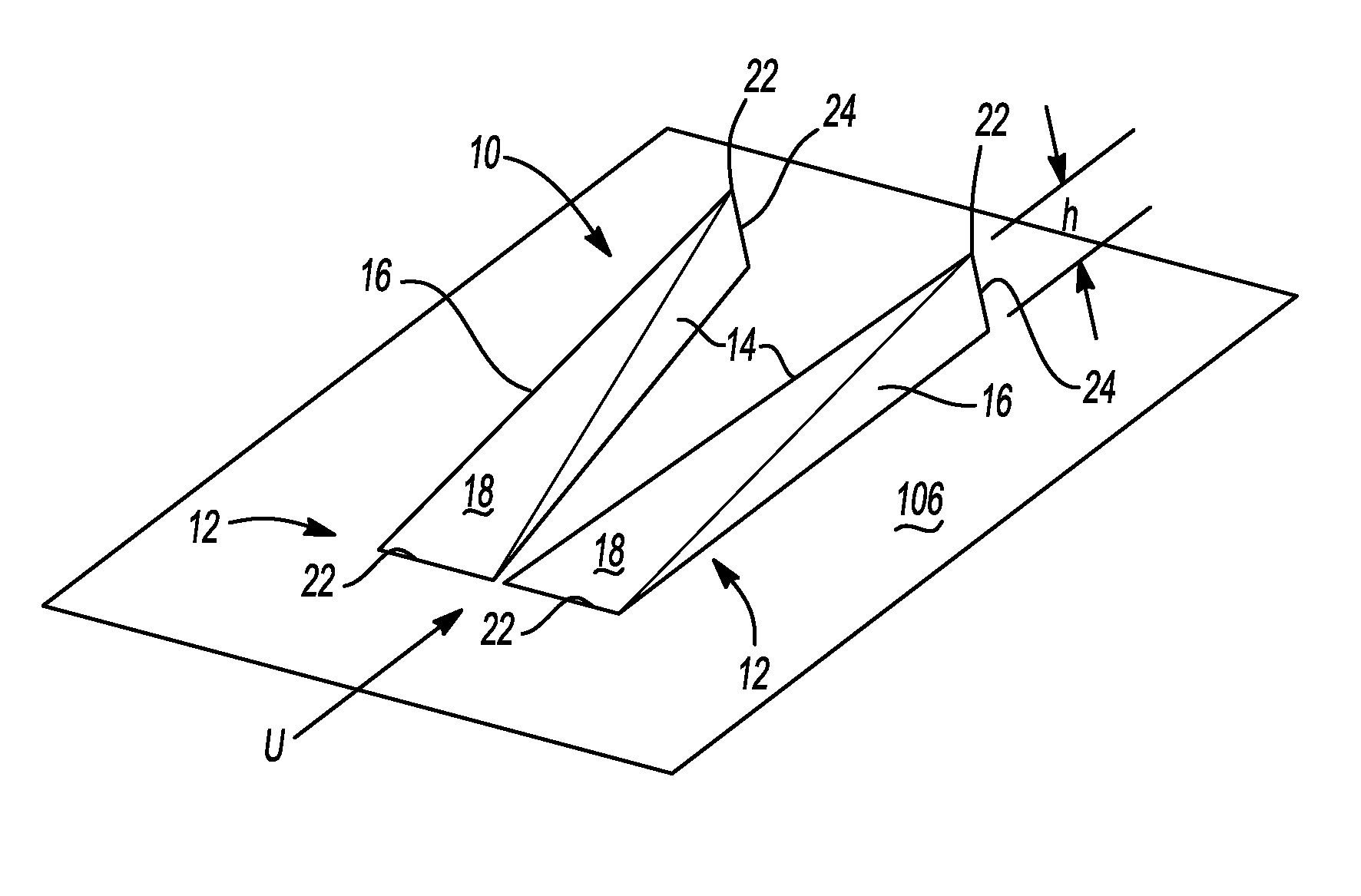

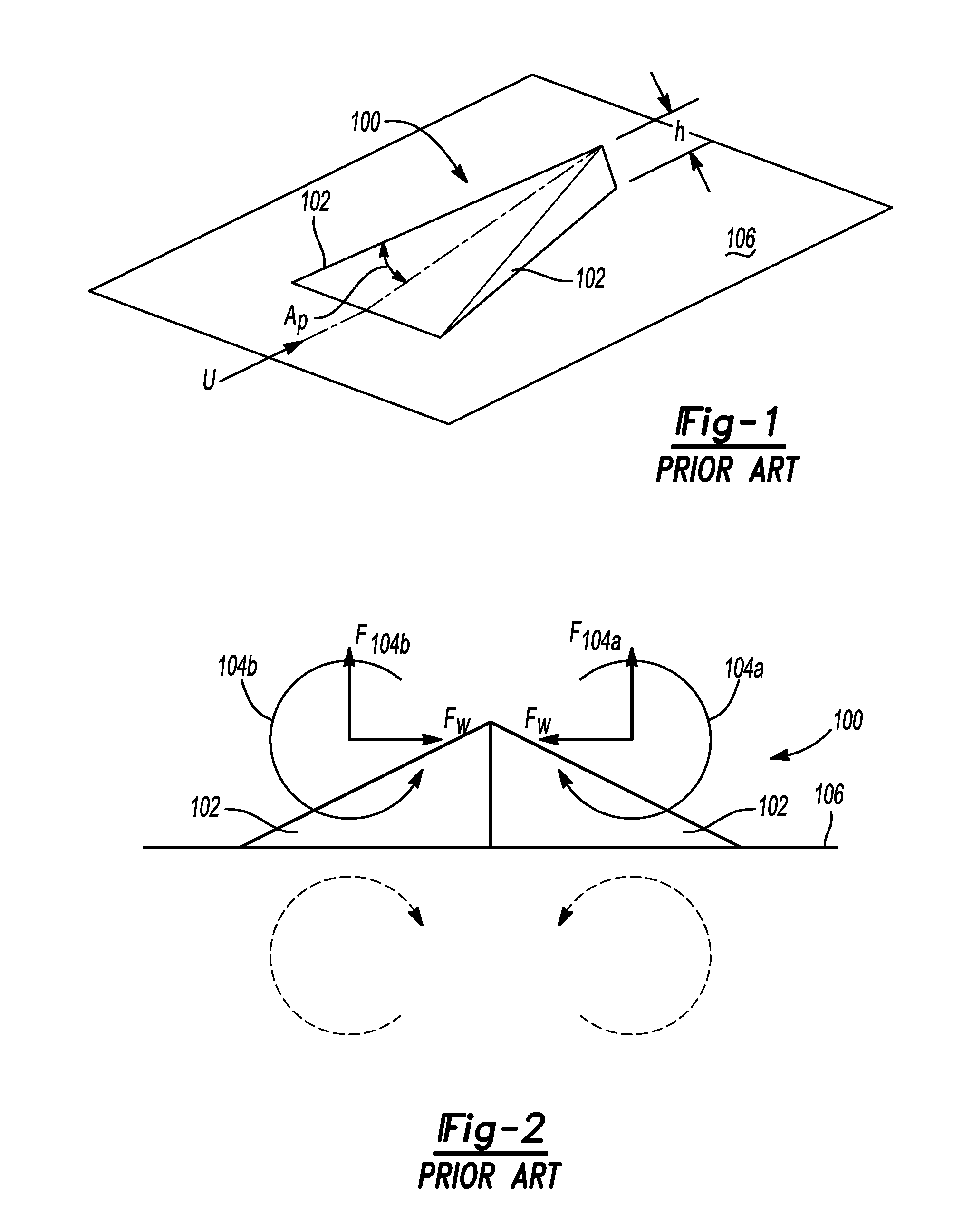

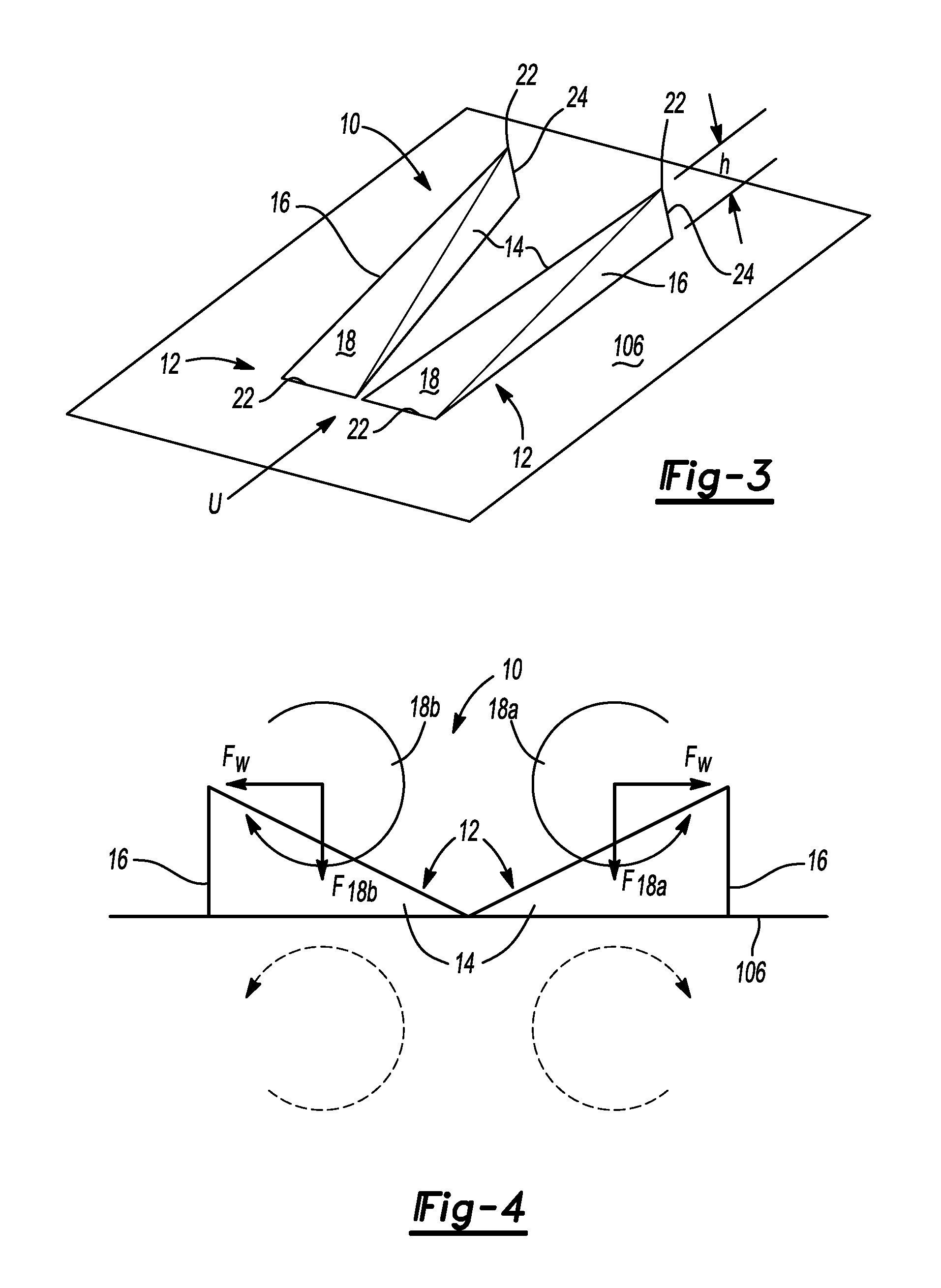

Passive boundary layer control elements

InactiveUS20100288379A1Reduce volatilityFluctuating levelInfluencers by generating vorticesEngine manufactureAirplaneHigh momentum

Sub-boundary-layer-scale ramp-like vortex generators that can be mounted on any surface such as the wing of an airplane, the inlet to a propulsion system, the hull of a ship, or any other surface over which a fluid moves, when the objective is to minimize drag, irreversibility losses, or other performance penalties that can occur for reasons such as boundary layer separation or other undesirable boundary layer properties. The disclosed devices acts to passively induce streamwise vortices in the boundary layer, thereby transferring high-momentum fluid toward the surface in such a way as to alter the shape of the velocity profile within the boundary layer and thereby avoid or delay separation or alter other properties of the boundary layer.

Owner:RGT UNIV OF MICHIGAN

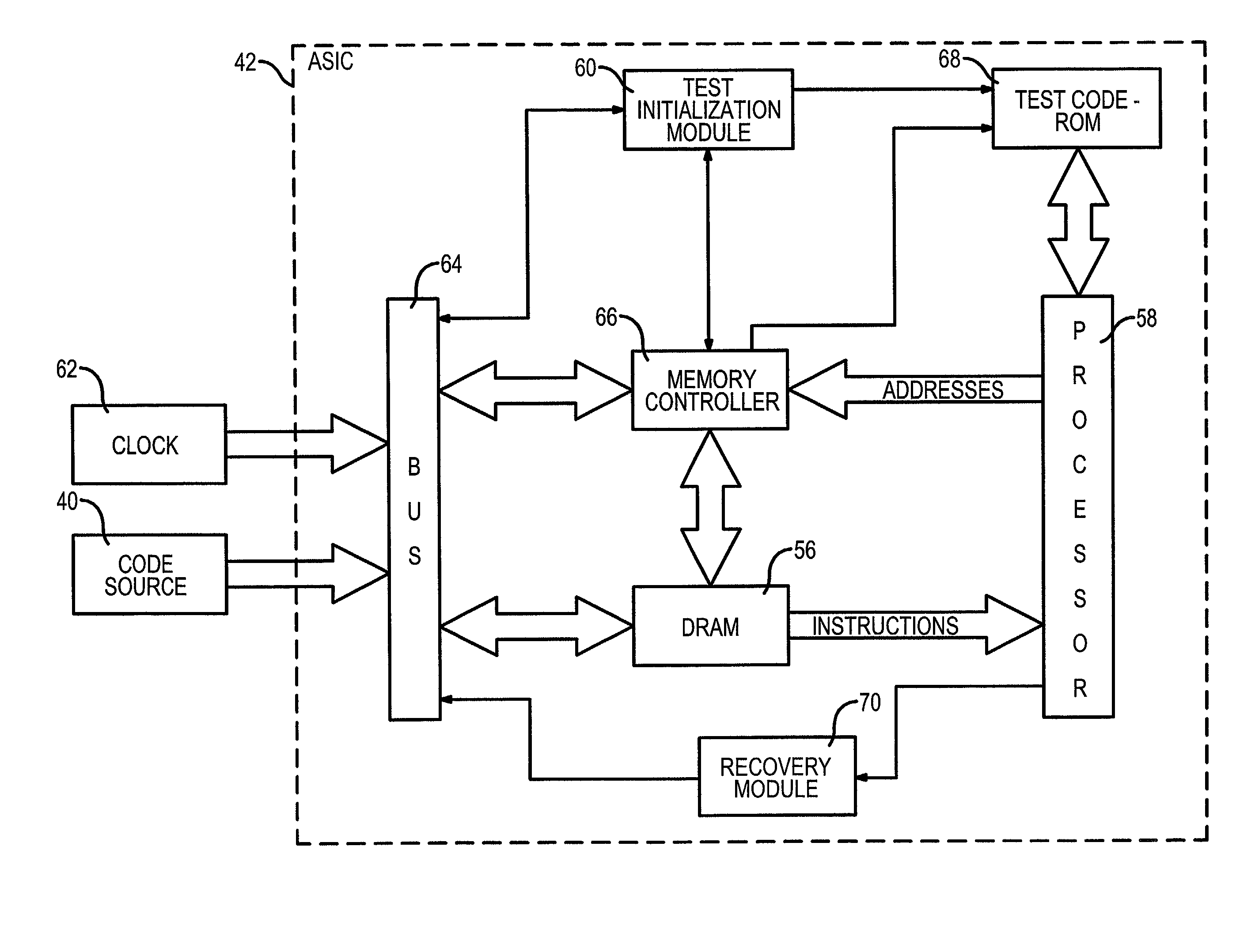

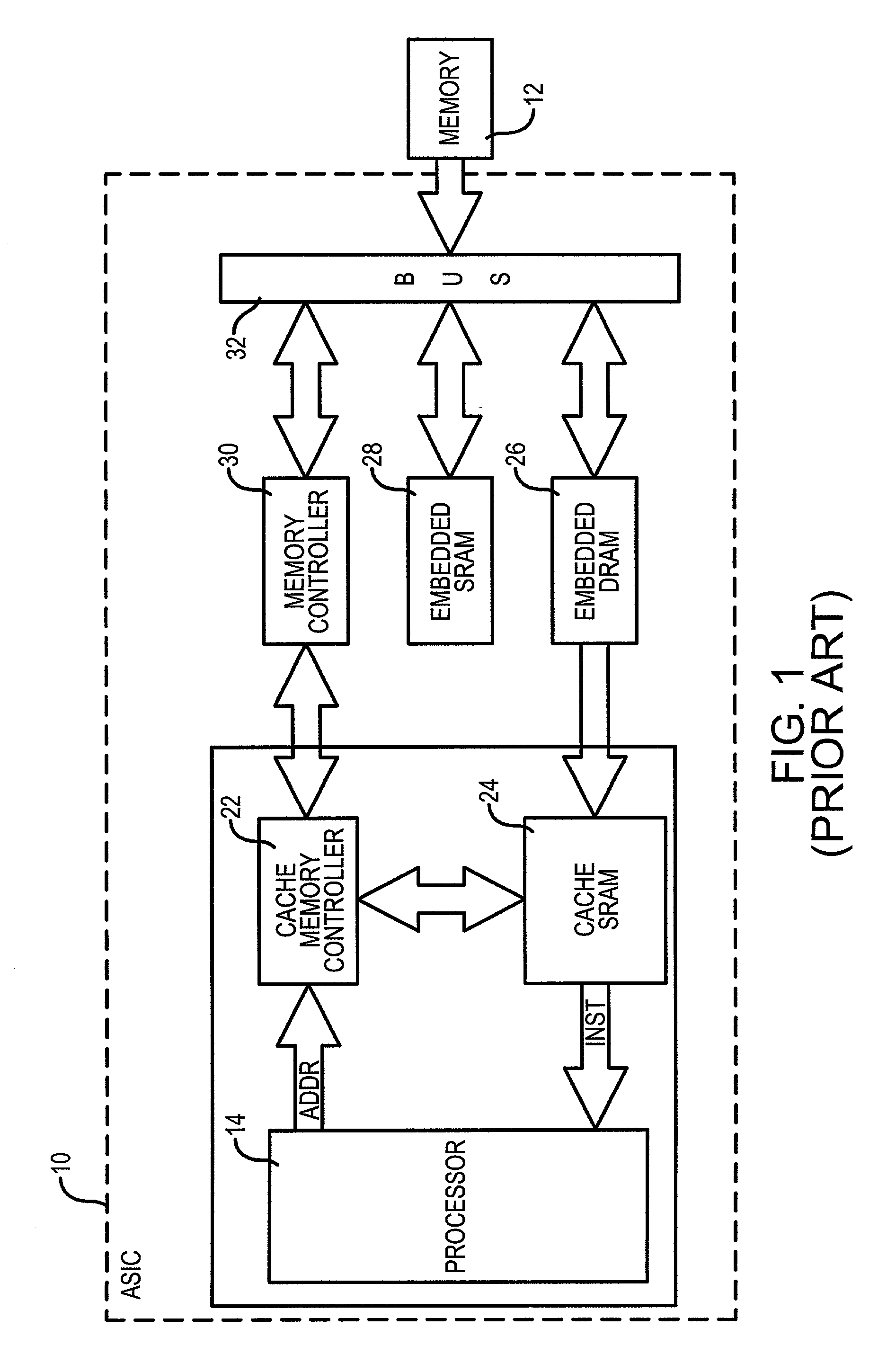

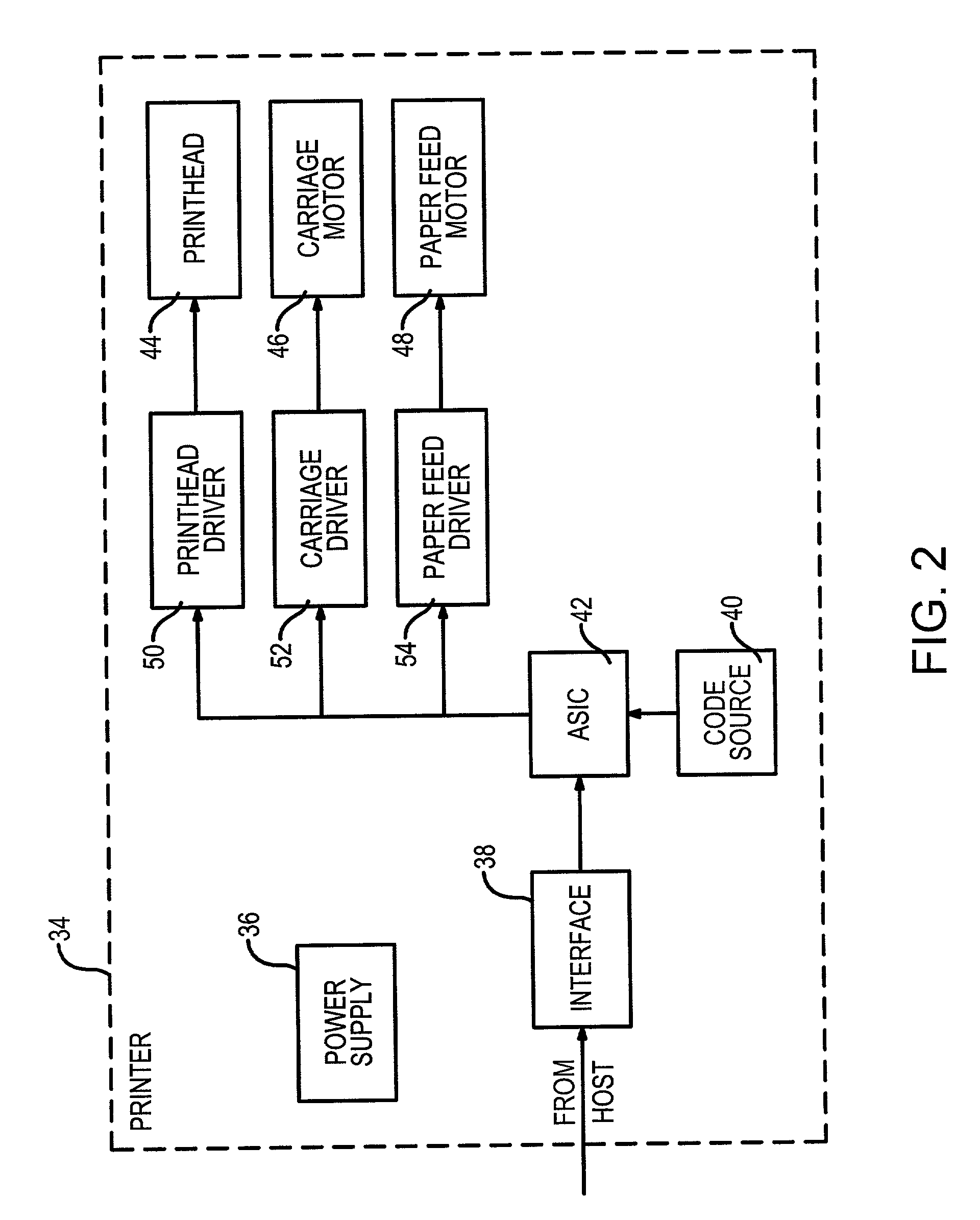

System and method of recovering from soft memory errors

InactiveUS6971051B2Performance penaltyIncreased power consumptionDigital storageApplication-specific integrated circuitBad memory

Managing volatile storage of information, such as executable code within dynamic random access memory (DRAM) embedded within an application specific integrated circuit (ASIC), includes systematically checking the contents of the volatile memory during periods of extended inactivity. Volatile memory checking routines may be initiated on the basis of time, on the basis of a specific event, or on a combination of timing and event occurrences. If a specific error condition is detected, the device in which the volatile memory resides may be automatically reinitialized, so that the corrupt executable code is not used. The information management techniques may be extended to other types of semi-permanent memory i.e., memory that is susceptible to losses in the form of soft errors.

Owner:AVAGO TECH INT SALES PTE LTD

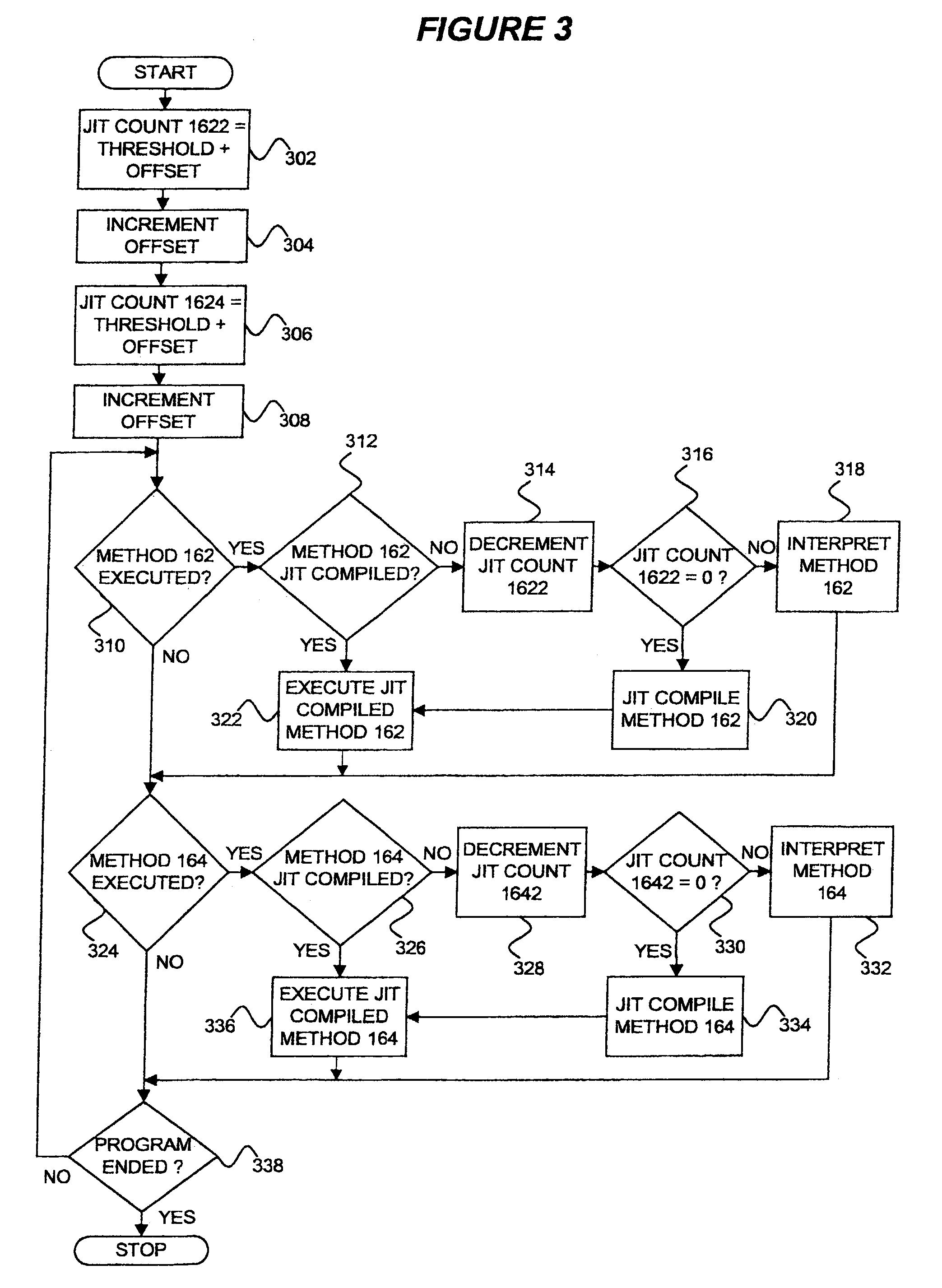

Just in time compilation of java software methods

InactiveUS7089544B2Performance penaltyProgram controlMemory systemsJust-in-time compilationSoftware engineering

A method to just-in-time (JIT) compile Java software methods, the method having the steps of: initializing a first counter for a first software method to a first value, the first value being adjusted each time the first software method is invoked; initializing a second counter for a second software method to a second value, the second value being different from the first value, and the second value being adjusted each time the second software method is invoked; responsive to a determination that the first value exceeds a particular value, JIT compiling the first software method; responsive to a determination that the second value exceeds the particular value, JIT compiling the second software method.

Owner:LINKEDIN

Dynamic merging of pipeline stages in an execution pipeline to reduce power consumption

InactiveUS8291201B2Reduce power consumptionLow powerEnergy efficient ICTVolume/mass flow measurementPower modeClock rate

A pipelined execution unit incorporates one or more low power modes that reduce power consumption by dynamically merging pipeline stages in an execution pipeline together with one another. In particular, the execution logic in successive pipeline stages in an execution pipeline may be dynamically merged together by setting one or more latches that are intermediate to such pipeline stages to a transparent state such that the output of the pipeline stage preceding such latches is passed to the subsequent pipeline stage during the same clock cycle so that both such pipeline stages effectively perform steps for the same instruction during each clock cycle. Then, with the selected pipeline stages merged, the power consumption of the execution pipeline can be reduced (e.g., by reducing the clock frequency and / or operating voltage of the execution pipeline), often with minimal adverse impact on performance.

Owner:INT BUSINESS MASCH CORP

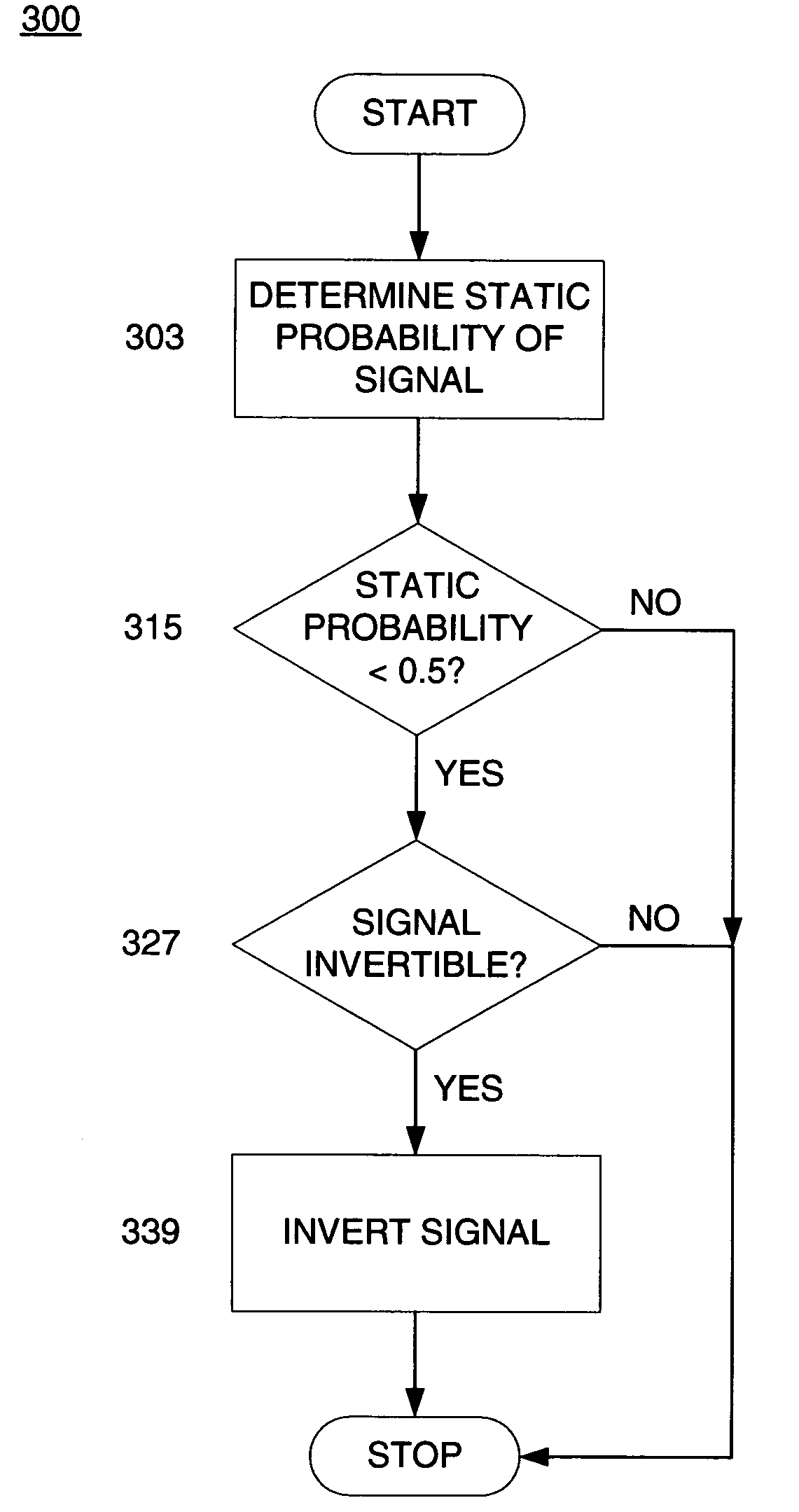

Leakage power optimization for integrated circuits

ActiveUS6993737B1Reduce leakage powerArea penaltyCAD circuit designSoftware simulation/interpretation/emulationProgrammable logic deviceDigital signal

A method for reducing leakage power in a system comprises determining the static probability for a signal in the system. If the static probability of the signal is in a high power range, then the signal is modified such that the static probability of the modified signal is in a low power range, and such that functionality of the system is not affected. In some embodiments, where the signal is a digital signal, modifying the signal comprises inverting the signal. In some embodiments, where the system comprises a programmable logic device, modifying the signal has no area or performance penalty.

Owner:XILINX INC

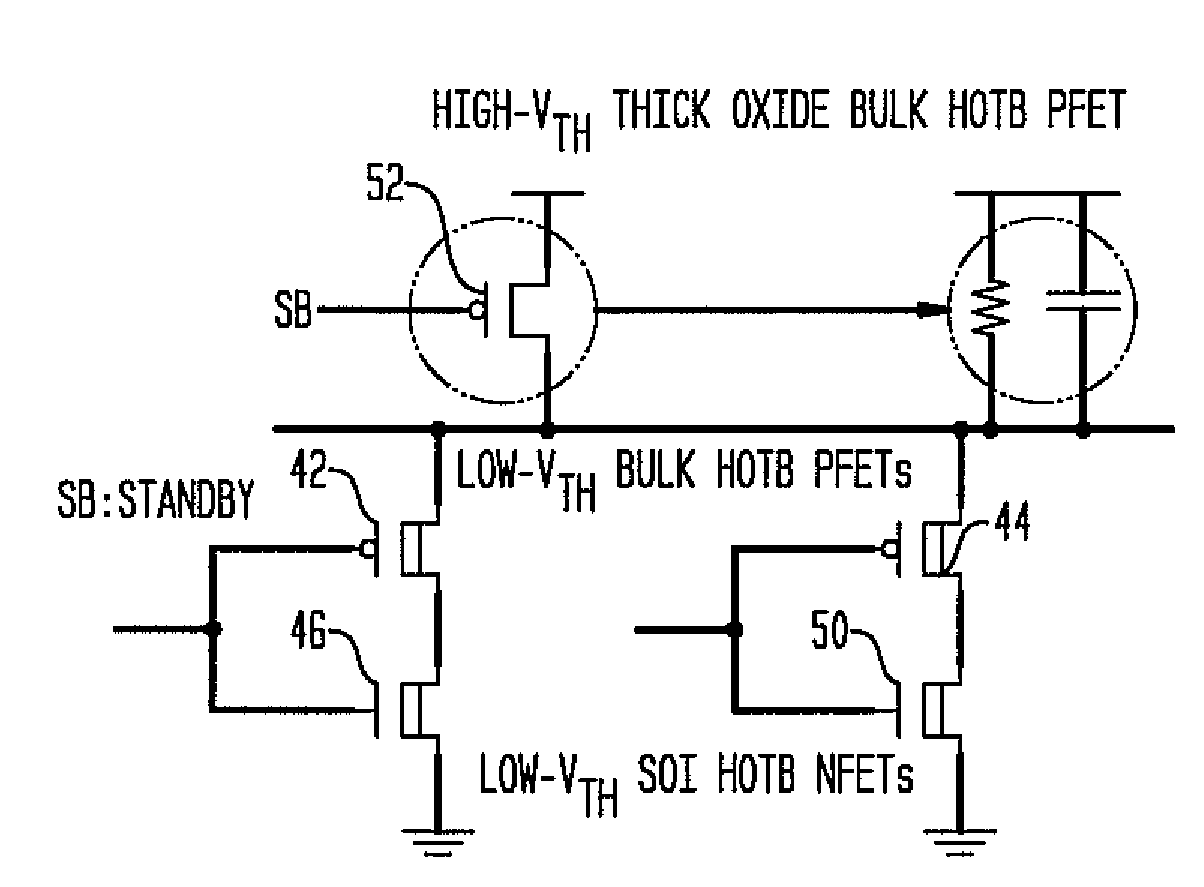

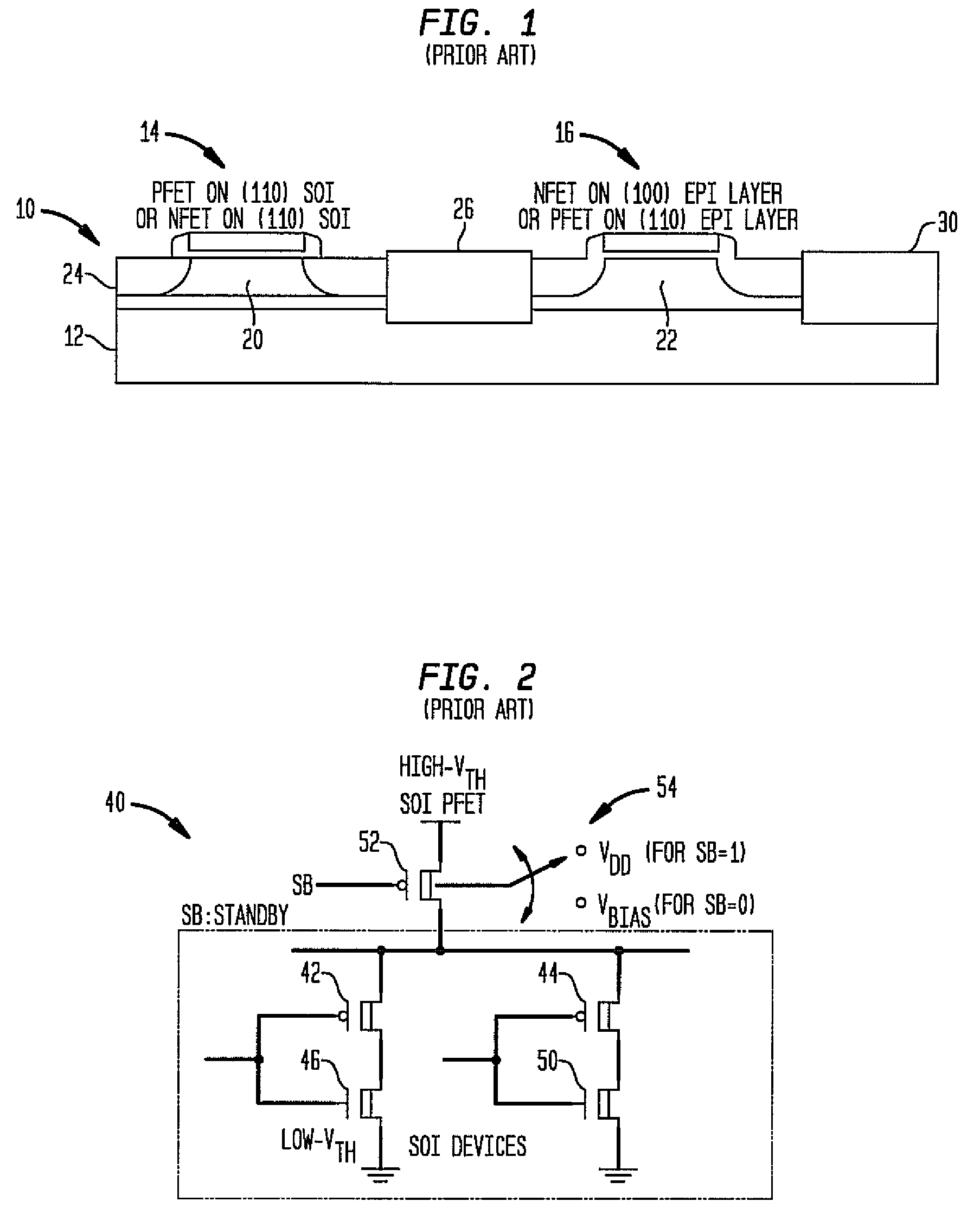

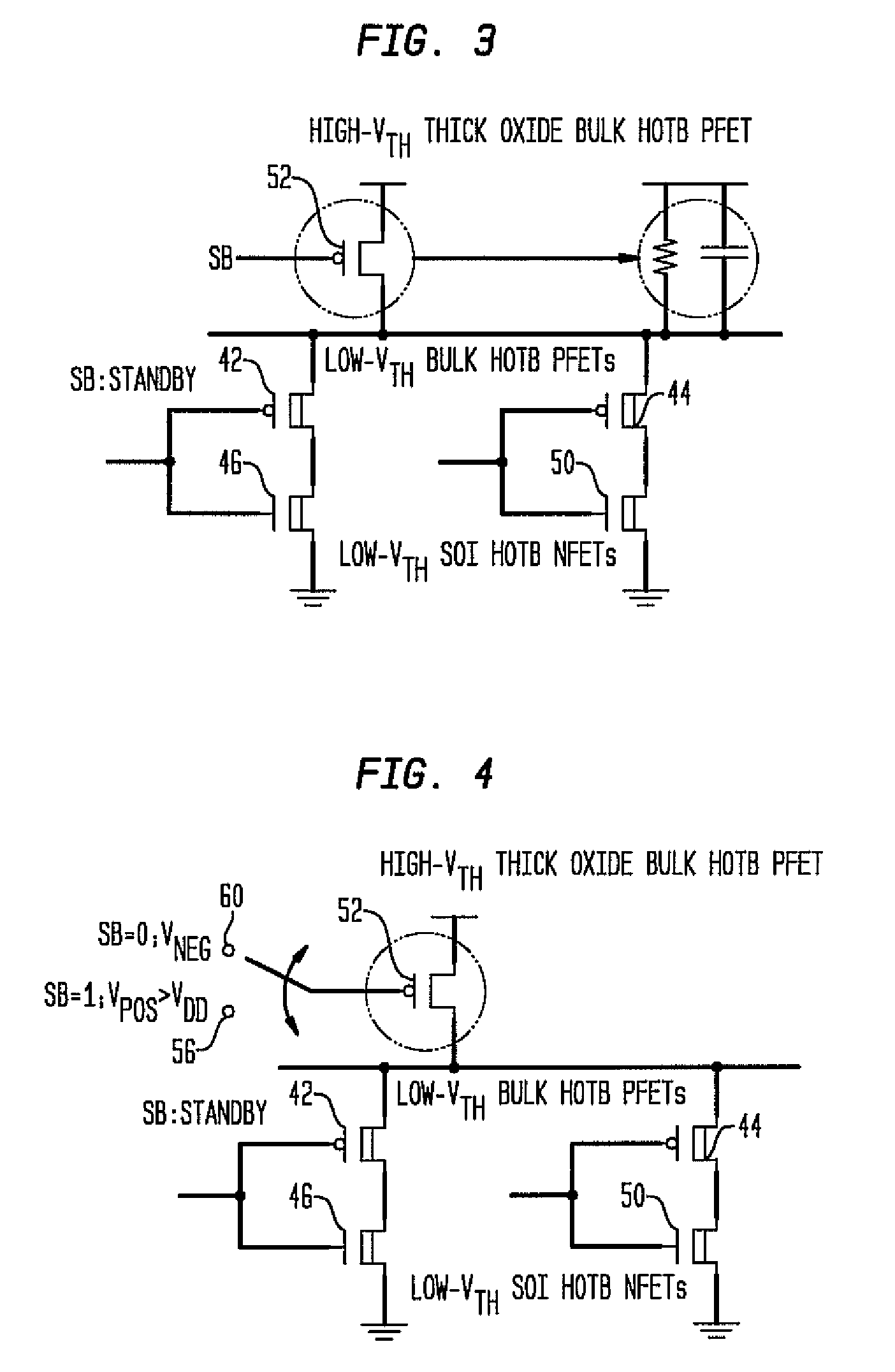

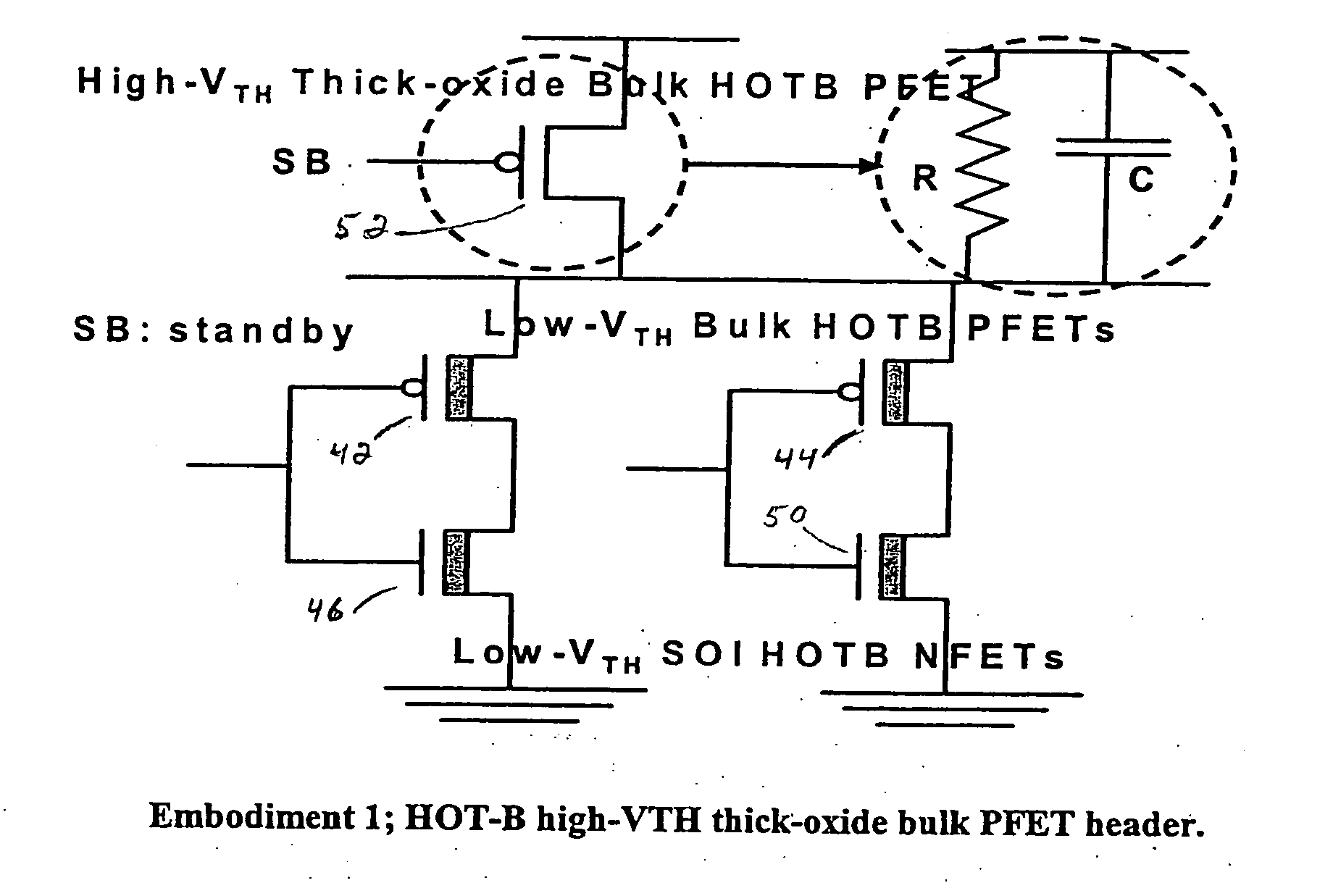

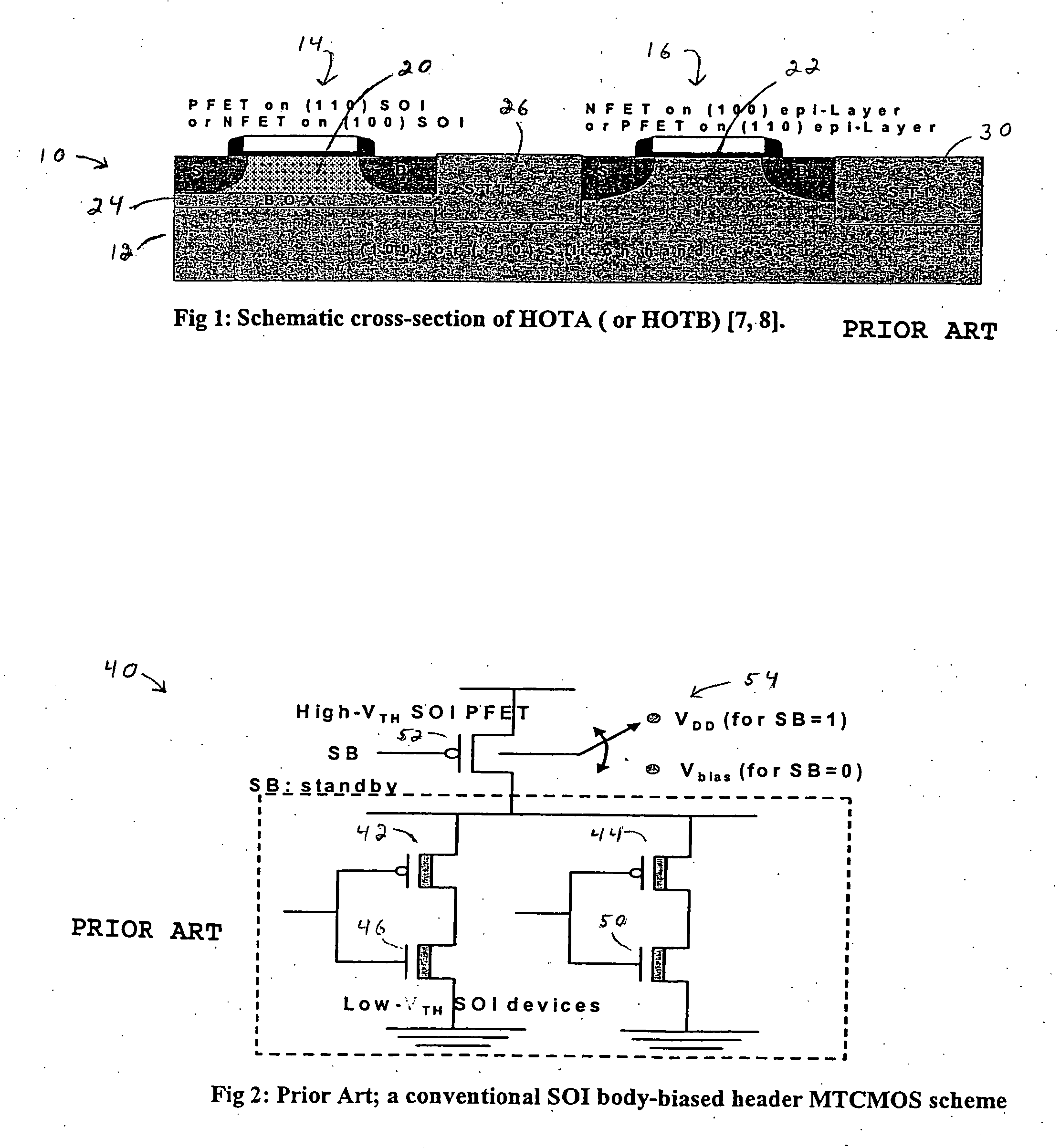

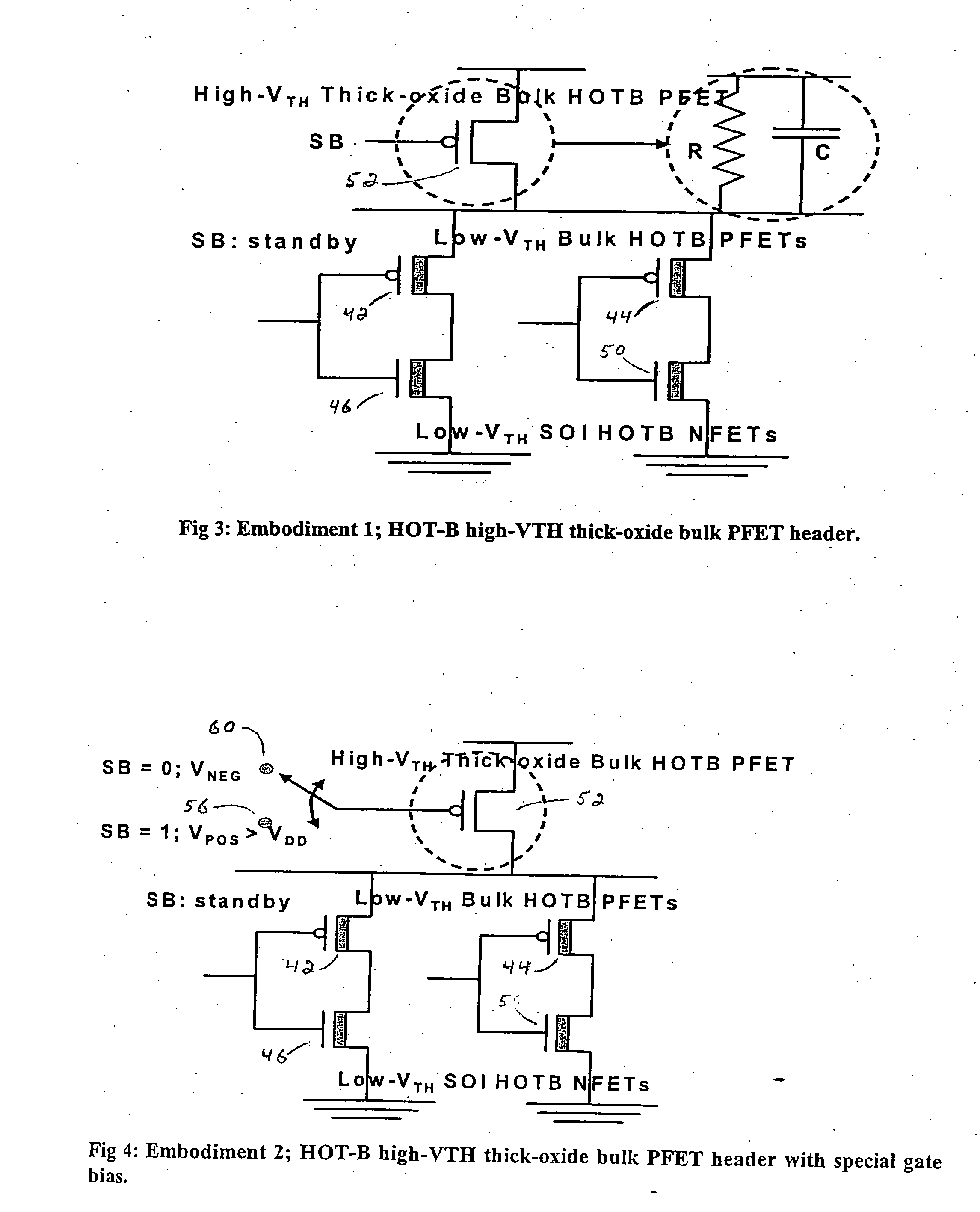

High performance PFET header in hybrid orientation technology for leakage reduction in digital CMOS VLSI designs

InactiveUS7274217B2Improve performanceLeakage powerReliability increasing modificationsPower reduction by control/clock signalEngineeringCmos vlsi

Discloses are CMOS circuit designs that combine MTCMOS and hybrid orientation technology to achieve the dual objectives of high performance and low standby leakage power. The invention utilizes novel combinations of a thick-oxide high-VTH PFET header with various gate- and body-biased schemes in HOT technology to significantly reduce the performance penalty associated with conventional PFET headers. A first embodiment of the invention provides a HOT-B high-VTH thick oxide bulk PFET header scheme. This header scheme can be expanded by application of a positive gate bias VPOS (VPOS>VDD) to the HOT-B PFET header during standby mode and a negative gate bias VNEG (VNEG<GND) in active mode. Another embodiment provides a HOT-A high-VTH thick oxide SOI PFET header scheme. A further embodiment provides a HOT-A body biased high-VTH thick oxide SOI PFET header scheme.

Owner:INT BUSINESS MASCH CORP

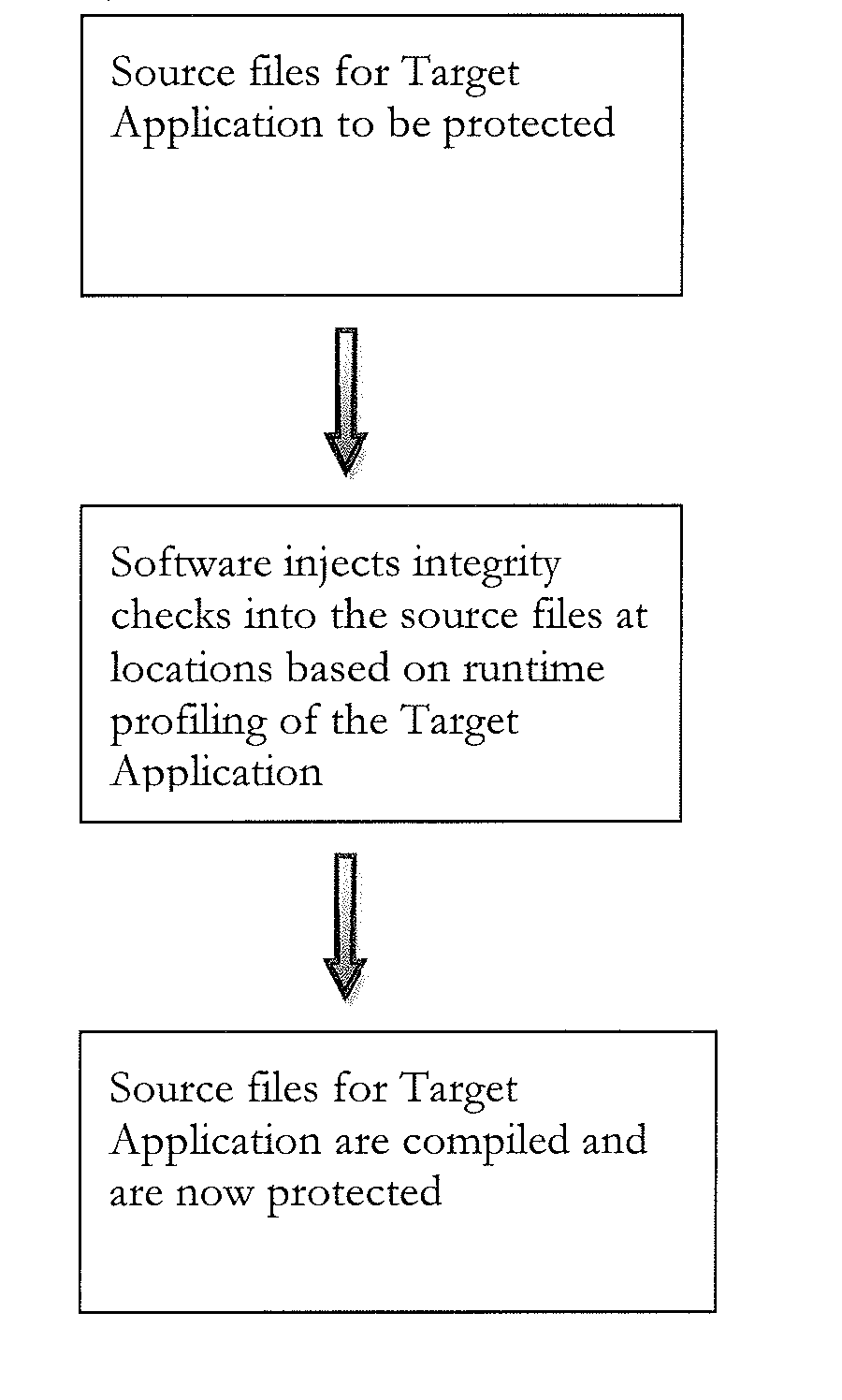

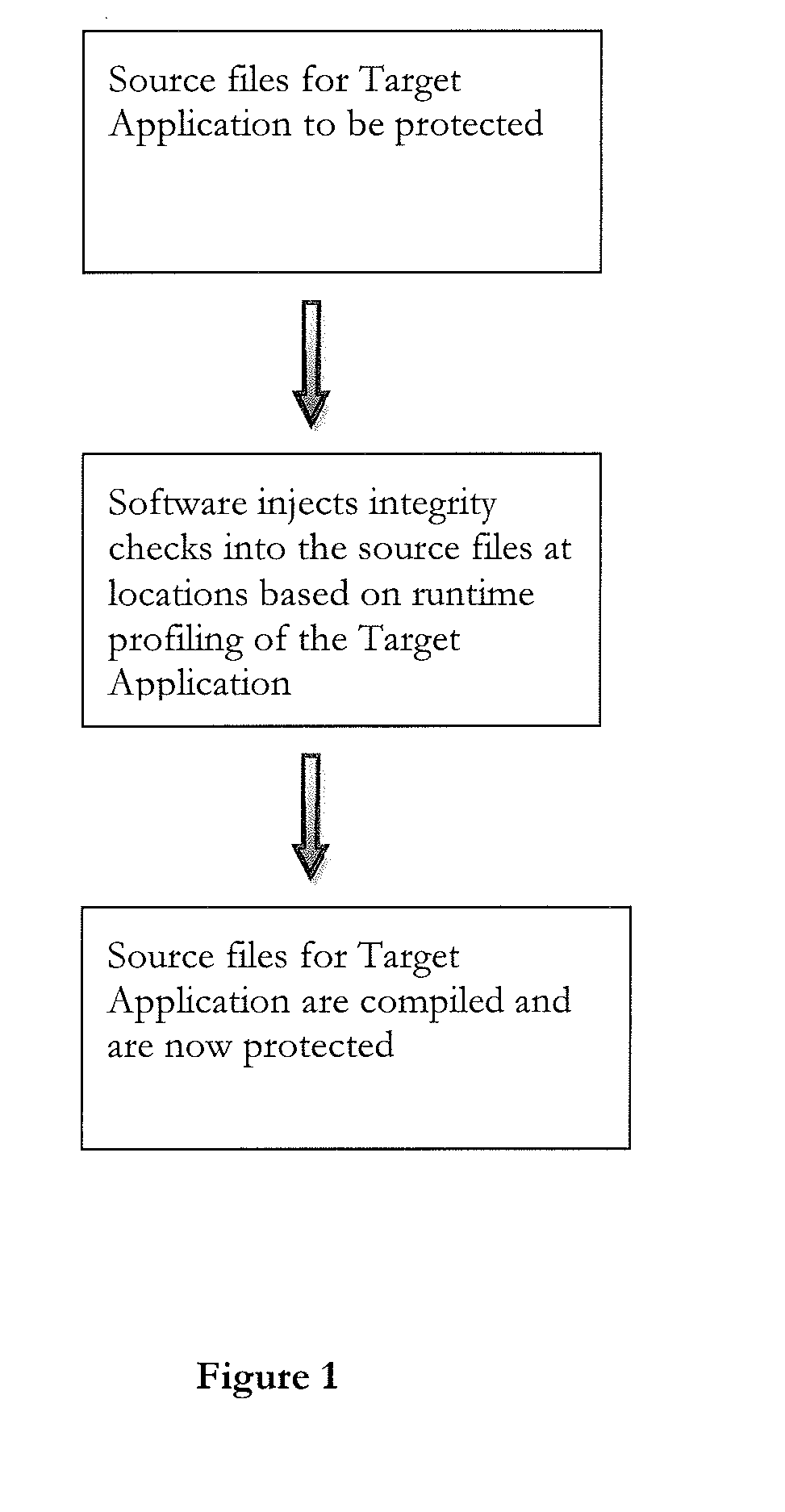

Anti-Tamper System Employing Automated Analysis

ActiveUS20110088095A1Improve efficacyPerformance penaltyMemory loss protectionError detection/correctionApplication softwareIntegrity check

A computer implemented anti-tamper system employing runtime profiling of software in order to decide where to inject integrity checks into the software, to enable verification of whether or not the software has been tampered with. Runtime profiling and analysis is used to record information about the application, in order to establish the locations and targets of runtime integrity checks in order to optimise protection security, while minimising the performance penalty and the need for hand configuration.

Owner:VERIMATRIX INC

Late binding of variables during test case generation for hardware and software design verification

InactiveUS20050096861A1Inhibiting bindingImproves quality and rapidityResistance/reactance/impedenceCAD circuit designSoftware designTest generator

Methods and systems are provided that improve design verification by test generators by delaying assignment of values in the generated stimuli until these values are used in the design. Late binding allows the generator to have a more accurate view of the state of the design, and in order to choose correct values. Late binding can significantly improve test coverage with a reasonable performance penalty as measured by simulation time.

Owner:IBM CORP

High performance PFET header in hybrid orientation technology for leakage reduction in digital CMOS VLSI designs

InactiveUS20060226493A1Improve performanceLeakage powerReliability increasing modificationsPower reduction by control/clock signalEngineeringCmos vlsi

Discloses are CMOS circuit designs that combine MTCMOS and hybrid orientation technology to achieve the dual objectives of high performance and low standby leakage power. The invention utilizes novel combinations of a thick-oxide high-VTH PFET header with various gate- and body-biased schemes in HOT technology to significantly reduce the performance penalty associated with conventional PFET headers. A first embodiment of the invention provides a HOT-B high-VTH thick oxide bulk PFET header scheme. This header scheme can be expanded by application of a positive gate bias VPOS (VPOS>VDD) to the HOT-B PFET header during standby mode and a negative gate bias VNEG (VNEG<GND) in active mode. Another embodiment provides a HOT-A high-VTH thick oxide SOI PFET header scheme. A further embodiment provides a HOT-A body biased high-VTH thick oxide SOI PFET header scheme.

Owner:IBM CORP

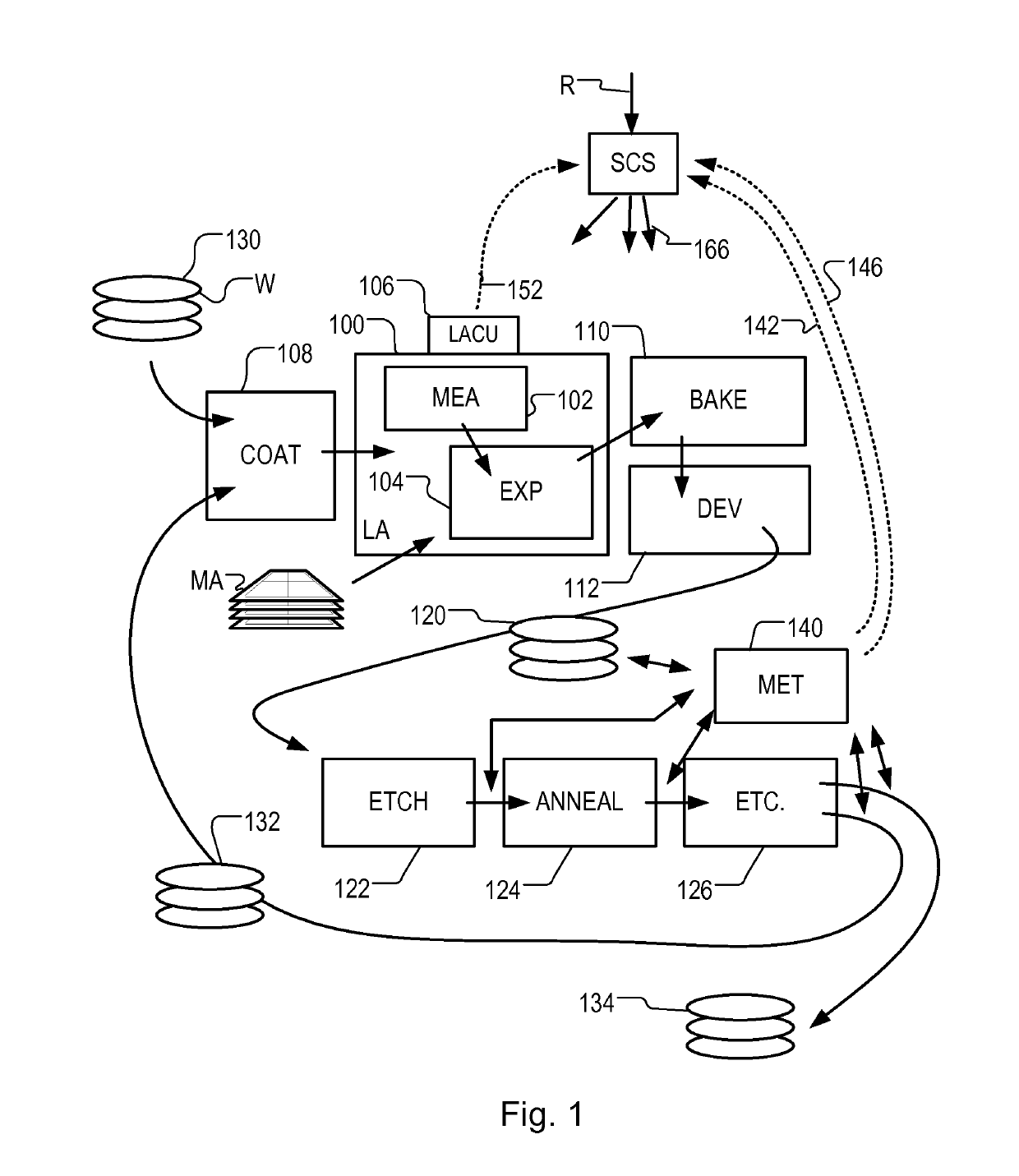

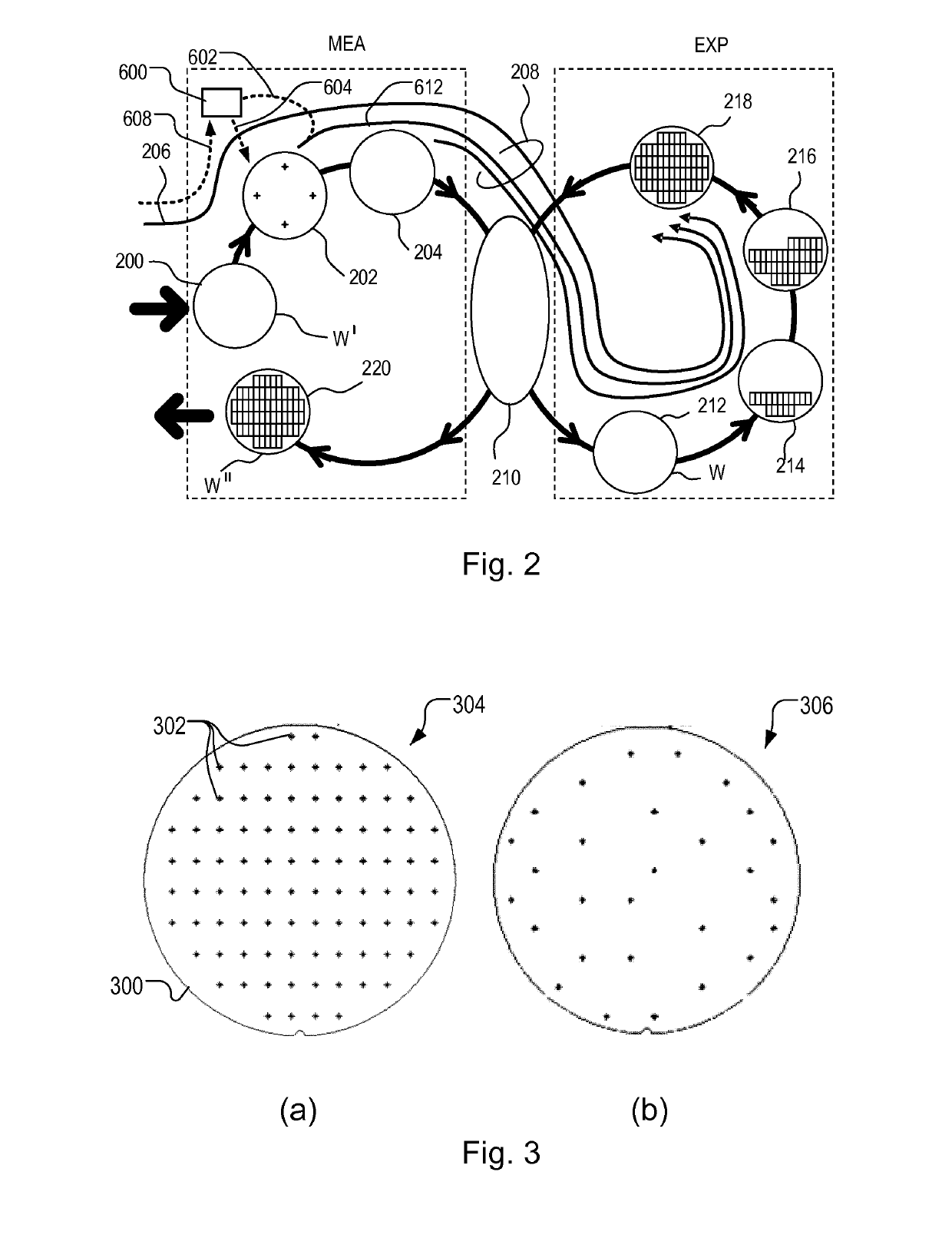

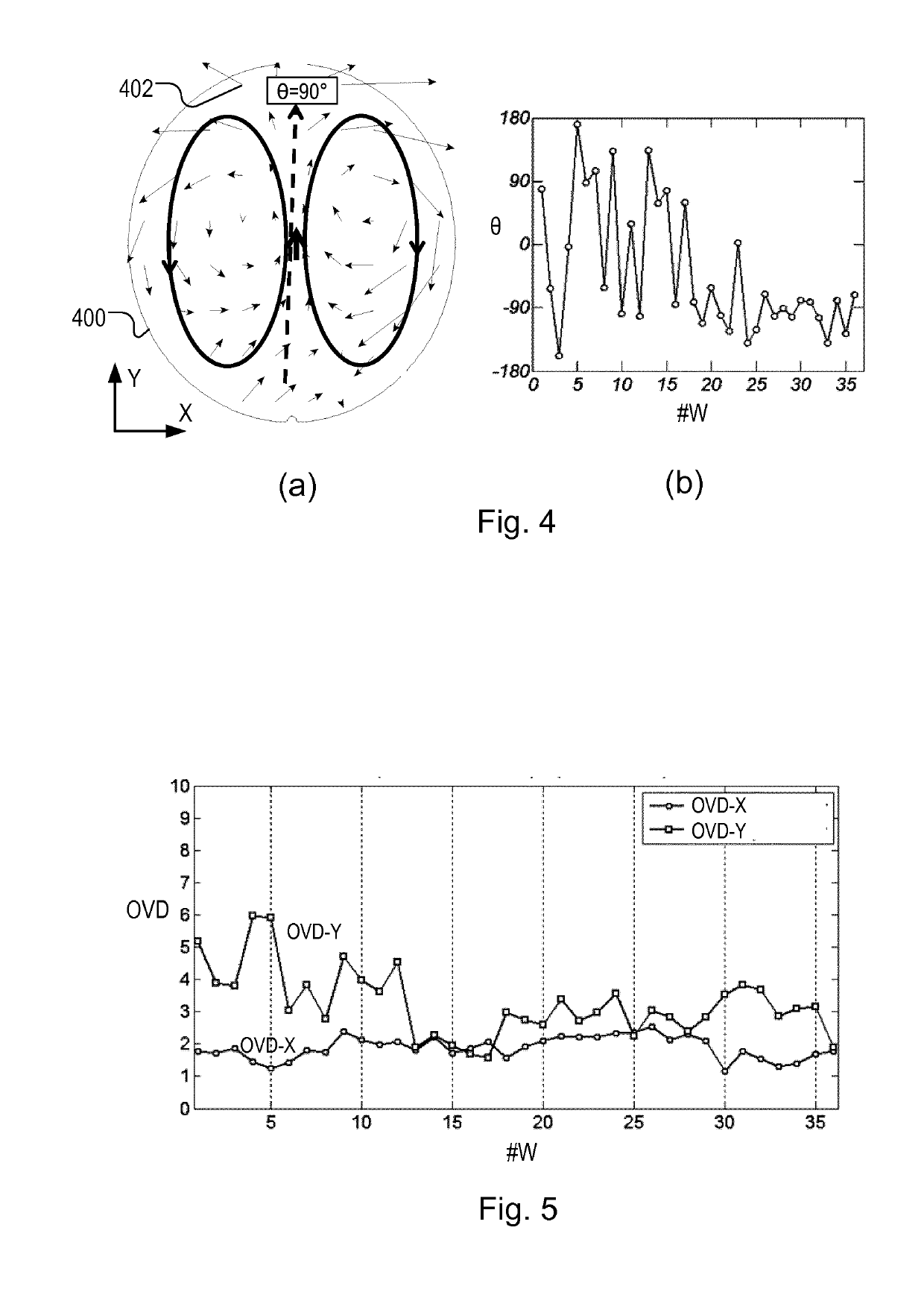

Method of obtaining measurements, apparatus for performing a process step, and metrology apparatus

ActiveUS20190137892A1Improve relevanceIncrease the number ofSemiconductor/solid-state device testing/measurementMaterial analysis by optical meansMetrologyEngineering

Measurements are obtained from locations across a substrate before or after performing a lithographic process step. Examples of such measurements include alignment measurements made prior to applying a pattern to the substrate, and measurements of a performance parameter such as overlay, after a pattern has been applied. A set of measurement locations is selected from among all possible measurement locations. At least a subset of the selected measurement locations are selected dynamically, in response to measurements obtained using a preliminary selection of measurement locations. Preliminary measurements of height can be used to select measurement locations for alignment. In another aspect, outlier measurements are detected based on supplementary data such as height measurements or historic data.

Owner:ASML NETHERLANDS BV

Autonomic Hotspot Profiling Using Paired Performance Sampling

InactiveUS20140059334A1Performance penaltyEasy to solveSoftware engineeringDigital computer detailsEvent typeParallel computing

A processor performance profiler is enabled to for identify specific instructions causing performance issues within a program being executed by a microprocessor through random sampling to find the worst-case offenders of a particular event type such as a cache miss or a branch mis-prediction. Tracking all instructions causing a particular event generates large data logs, creates performance penalties, and makes code analysis more difficult. However, by identifying and tracking the worst offenders within a random sample of events without having to hash all events results in smaller memory requirements for the performance profiler, lower performance impact while profiling, and decreased complexity to analyze the program to identify major performance issues, which, in turn, enables better optimization of the program in shorter developer time.

Owner:INT BUSINESS MASCH CORP

Autonomic hotspot profiling using paired performance sampling

InactiveUS8615742B2Performance penaltyEasy to solveSoftware engineeringHardware monitoringEvent typeParallel computing

A processor performance profiler is enabled to for identify specific instructions causing performance issues within a program being executed by a microprocessor through random sampling to find the worst-case offenders of a particular event type such as a cache miss or a branch mis-prediction. Tracking all instructions causing a particular event generates large data logs, creates performance penalties, and makes code analysis more difficult. However, by identifying and tracking the worst offenders within a random sample of events without having to hash all events results in smaller memory requirements for the performance profiler, lower performance impact while profiling, and decreased complexity to analyze the program to identify major performance issues, which, in turn, enables better optimization of the program in shorter developer time.

Owner:INT BUSINESS MASCH CORP

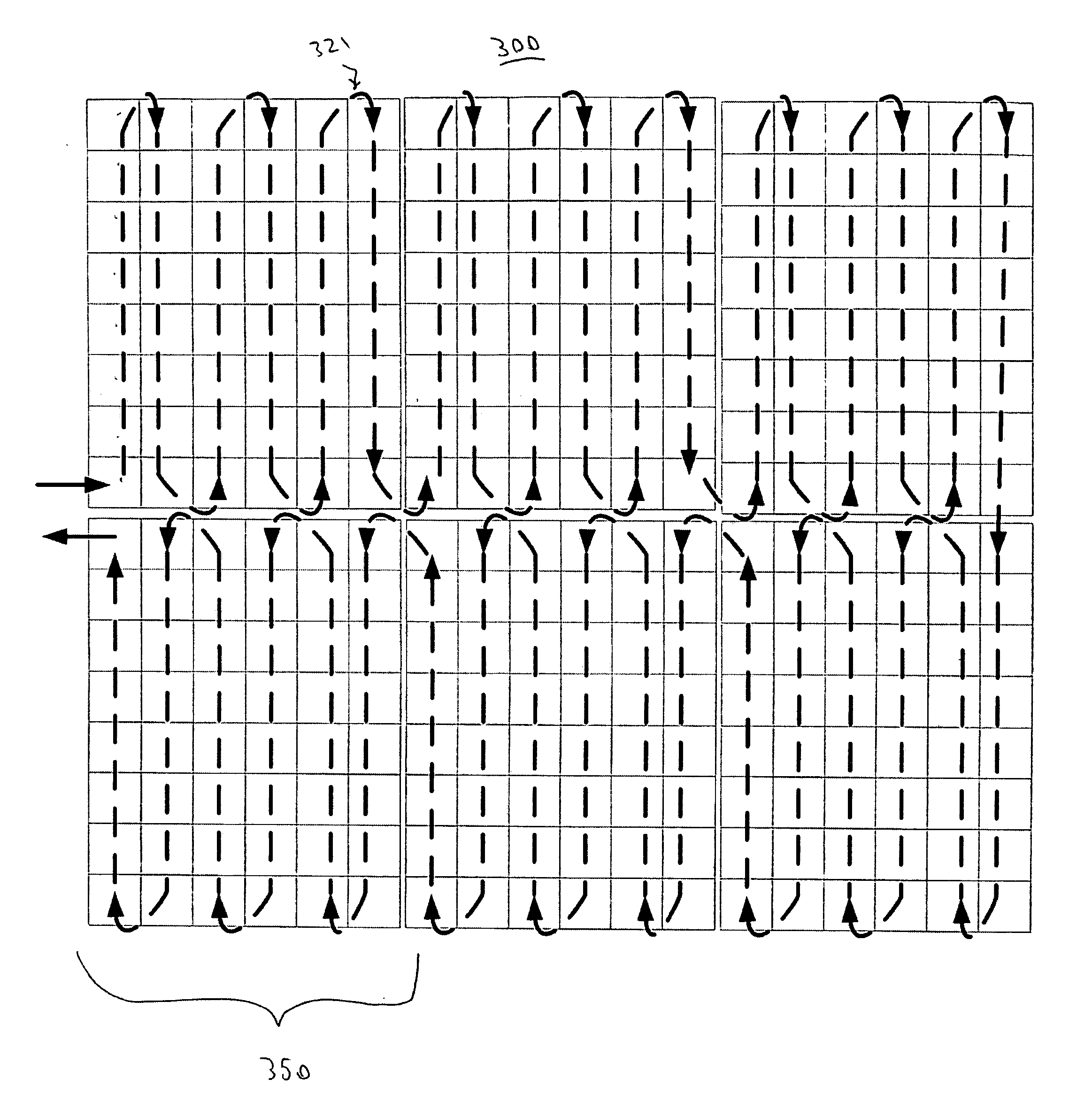

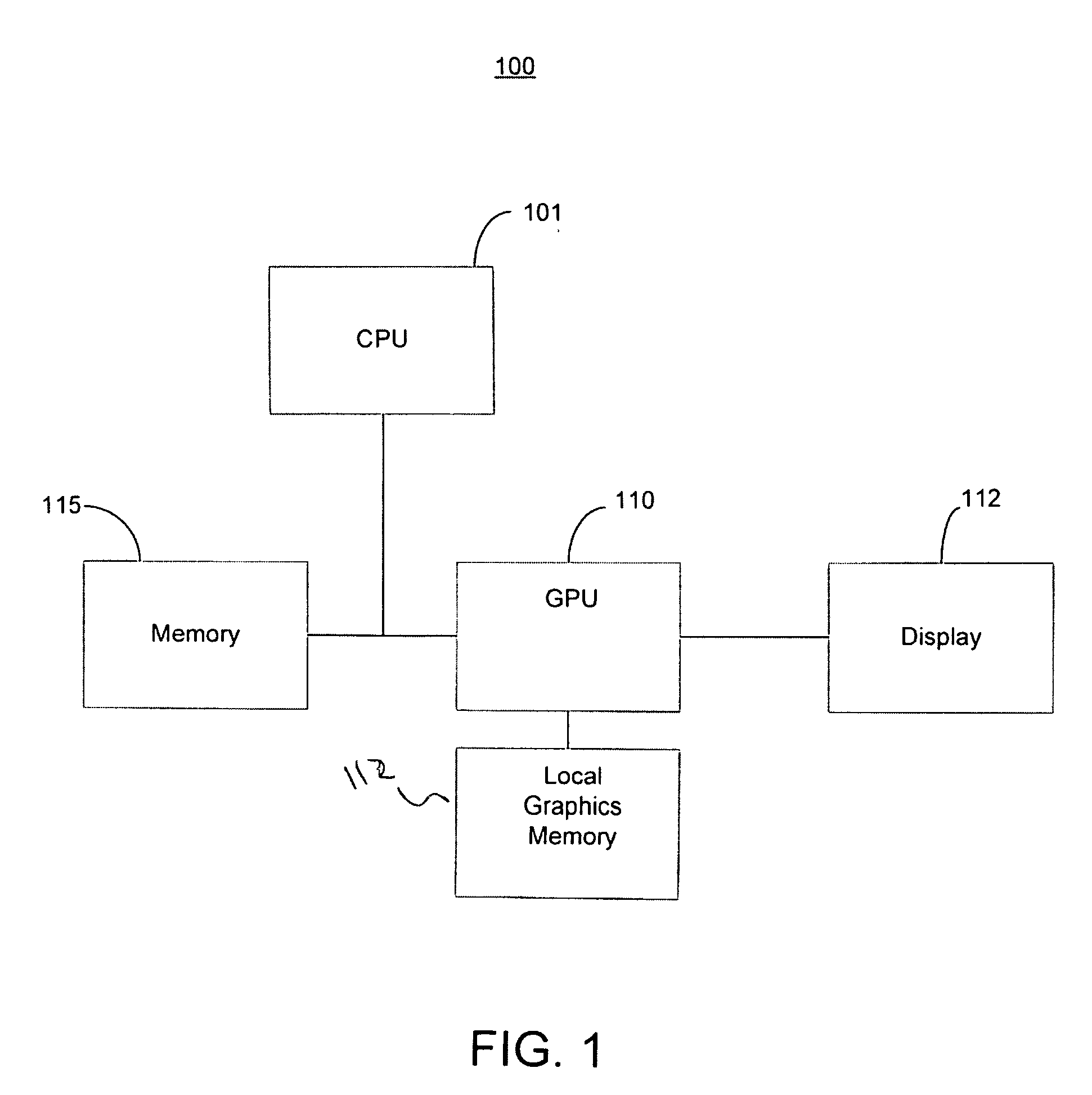

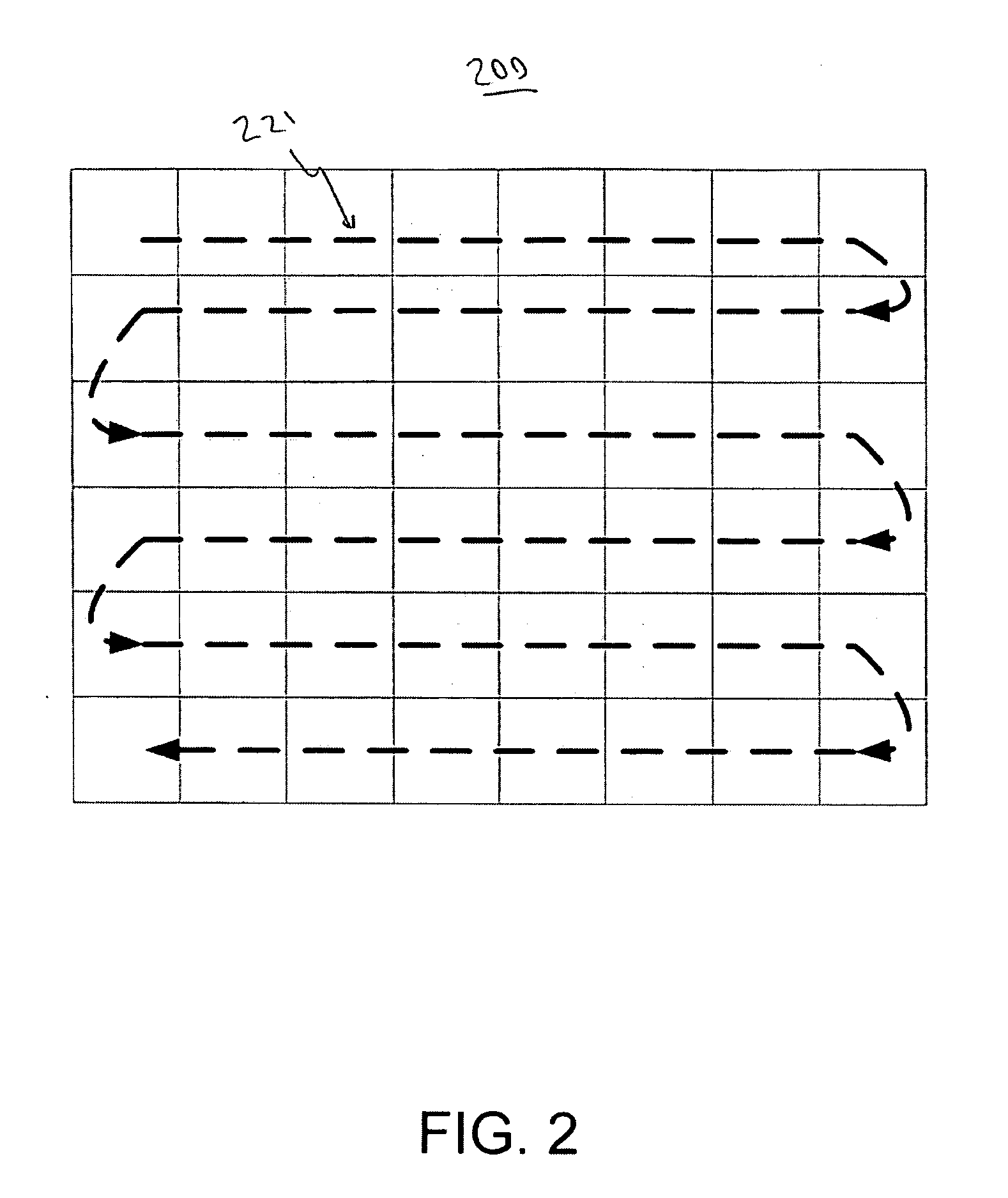

GPU having raster components configured for using nested boustrophedonic patterns to traverse screen areas

ActiveUS20070242070A1Efficient accessFast and efficient real-timeDigitally marking record carriersDrawing from basic elementsGratingComputer graphics (images)

In one embodiment, the present invention is implemented as a GPU configured for traversing pixels of an area. The GPU includes a set-up unit for generating polygon descriptions and a rasterizer unit coupled to the set-up unit for rasterizing the polygon descriptions. The rasterizer unit is configured to traverse a plurality of pixels of an image using a first boustrophedonic pattern along a predominant axis, and during the traversal using the first boustrophedonic pattern, traverse a plurality of pixels of the image using a second boustrophedonic pattern, wherein the second boustrophedonic pattern is nested within the first boustrophedonic pattern.

Owner:NVIDIA CORP

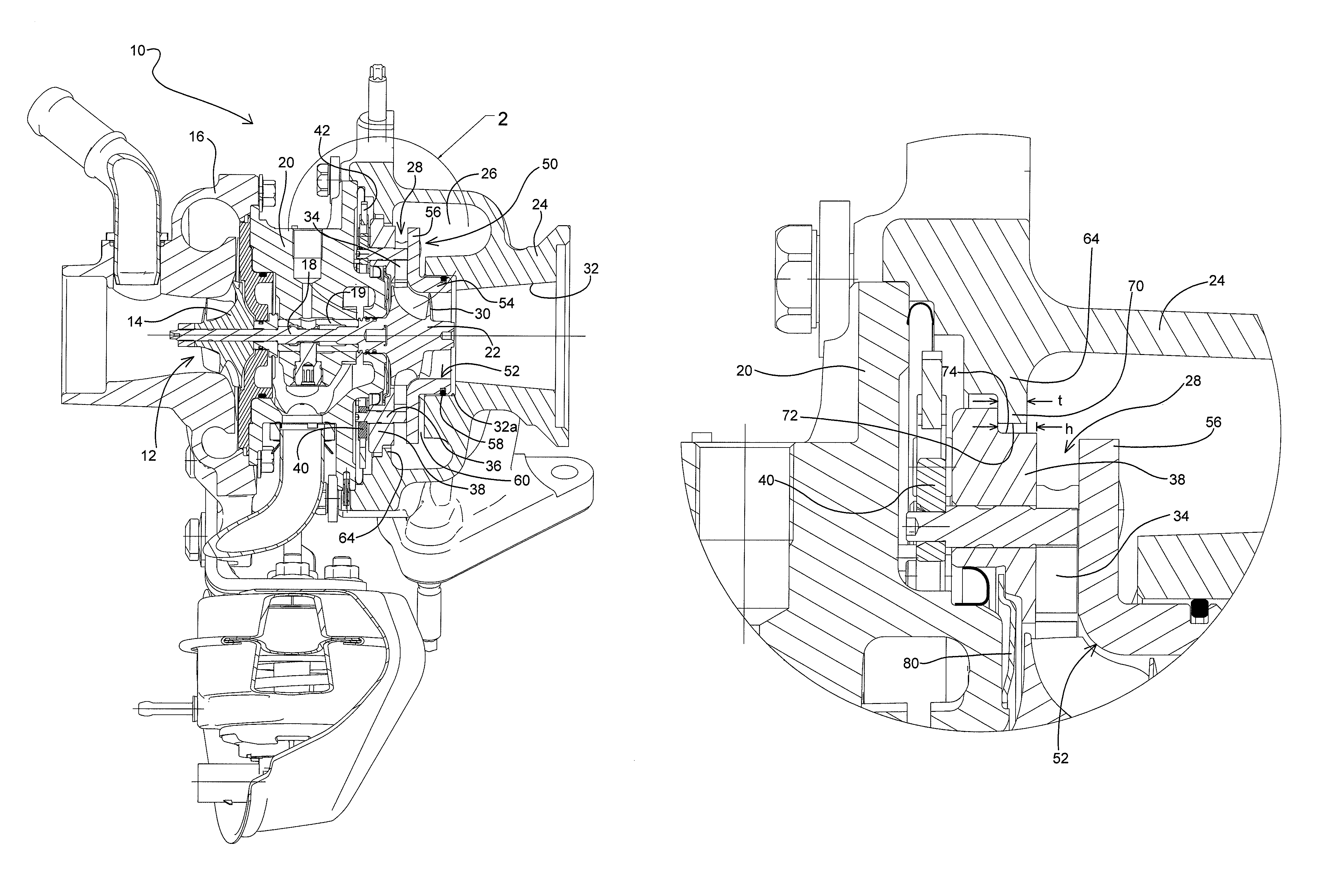

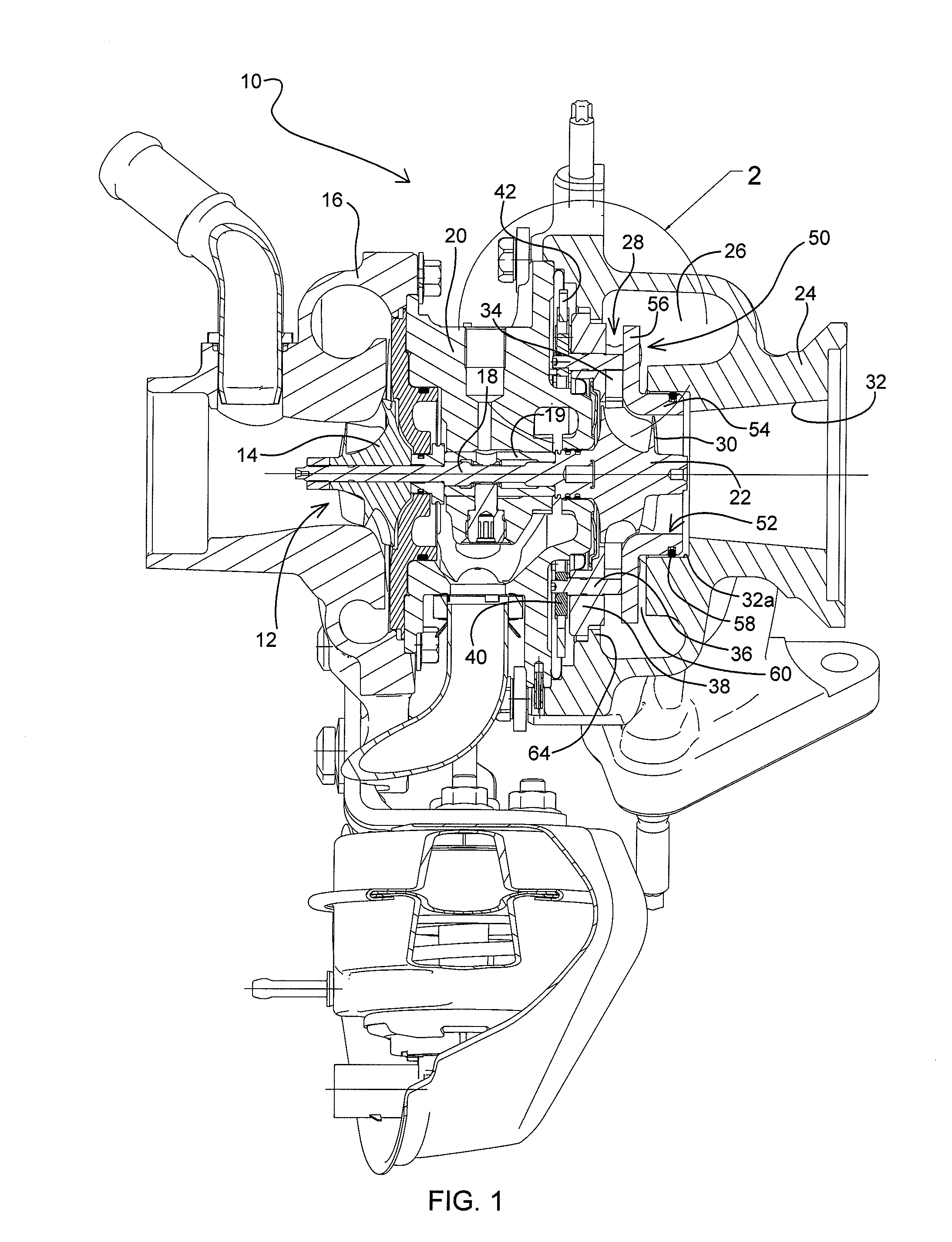

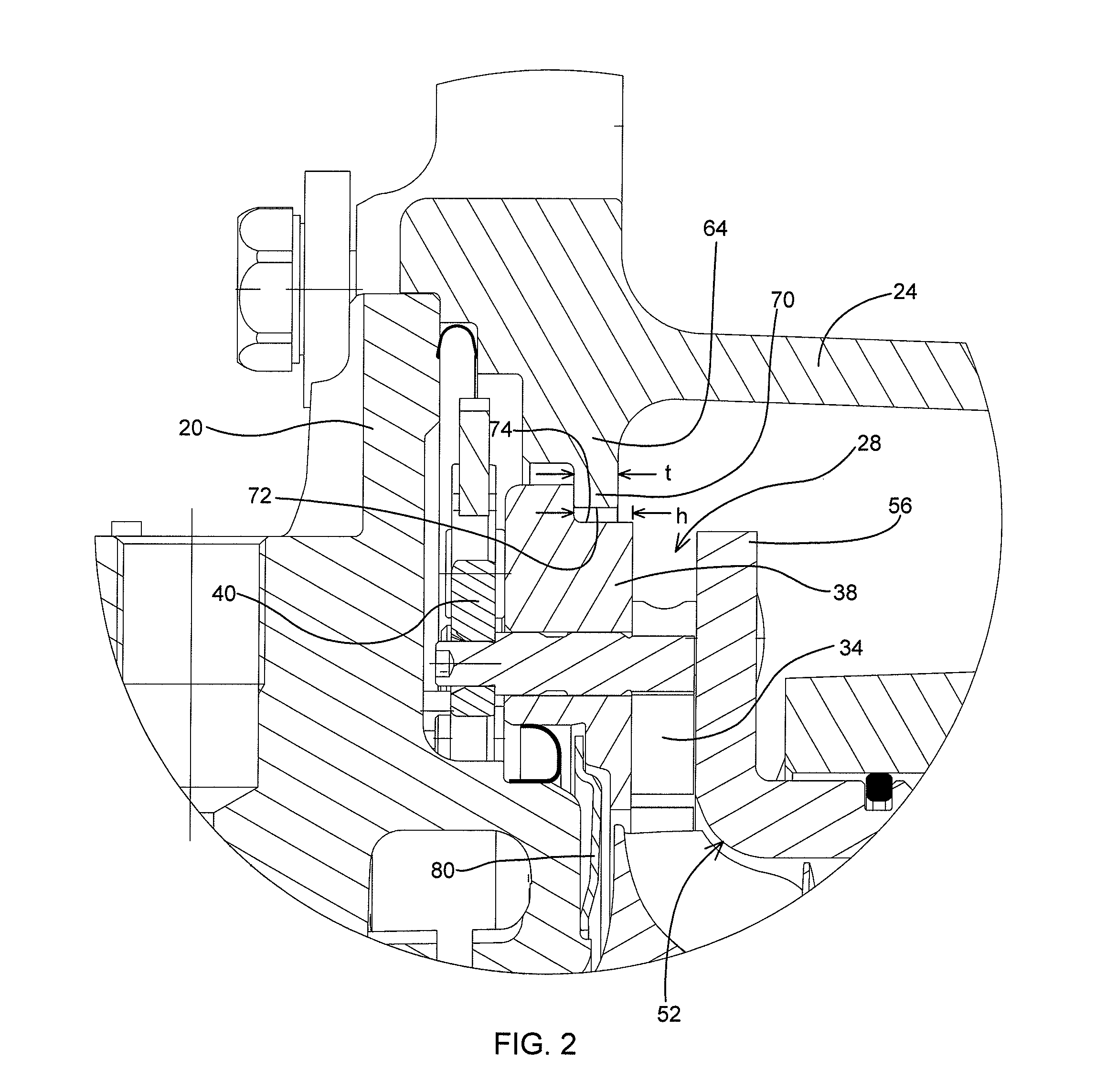

Turbocharger and variable-nozzle cartridge therefor

ActiveUS8979508B2Performance penaltyShorten speedWind motor controlPump componentsTurbochargerEngineering

A variable-vane assembly for a turbocharger includes an annular nozzle ring supporting an array of rotatable vanes, an insert having a tubular portion sealingly received into the bore of the turbine housing and having a nozzle portion extending radially out from one end of the tubular portion and being axially spaced from the nozzle ring with the vanes therebetween, and an annular retainer ring disposed radially outward of the nozzle ring and extending generally radially inwardly. The nozzle ring's face is stepped, and a radially inner edge of the retainer ring engages the face of the nozzle ring radially outward of the step, the radially inner edge of the retainer ring having an axial thickness that is less than the step height such that a remaining portion of the step is presented to the exhaust gas flowing through the nozzle.

Owner:GARRETT TRANSPORATION I INC

Method of evaluating core based system-on-a-chip

InactiveUS6944808B2Easy to implementPerformance penaltyDigital circuit testingSemiconductor/solid-state device testing/measurementSpecific testEngineering

A method of evaluating a core based SoC detects and localizes faults in the cores or interconnects between the cores with high accuracy and observability. The method includes the steps of building two or more metal layers to create core I / O pads having all I / O pads and power pads on a surface of the top metal layer of the pad frame of each core, testing the SoC as a whole by applying test vectors to the SoC through chip I / O pads and evaluating response outputs of the SoC, testing each core in the SoC by applying core specific test vectors to the core through the core I / O pads on the top metal layer of the core and evaluating response outputs of the core, and finding a location of a fault when the fault is detected when testing the SoC chip as a whole or when testing each of the cores.

Owner:ADVANTEST CORP

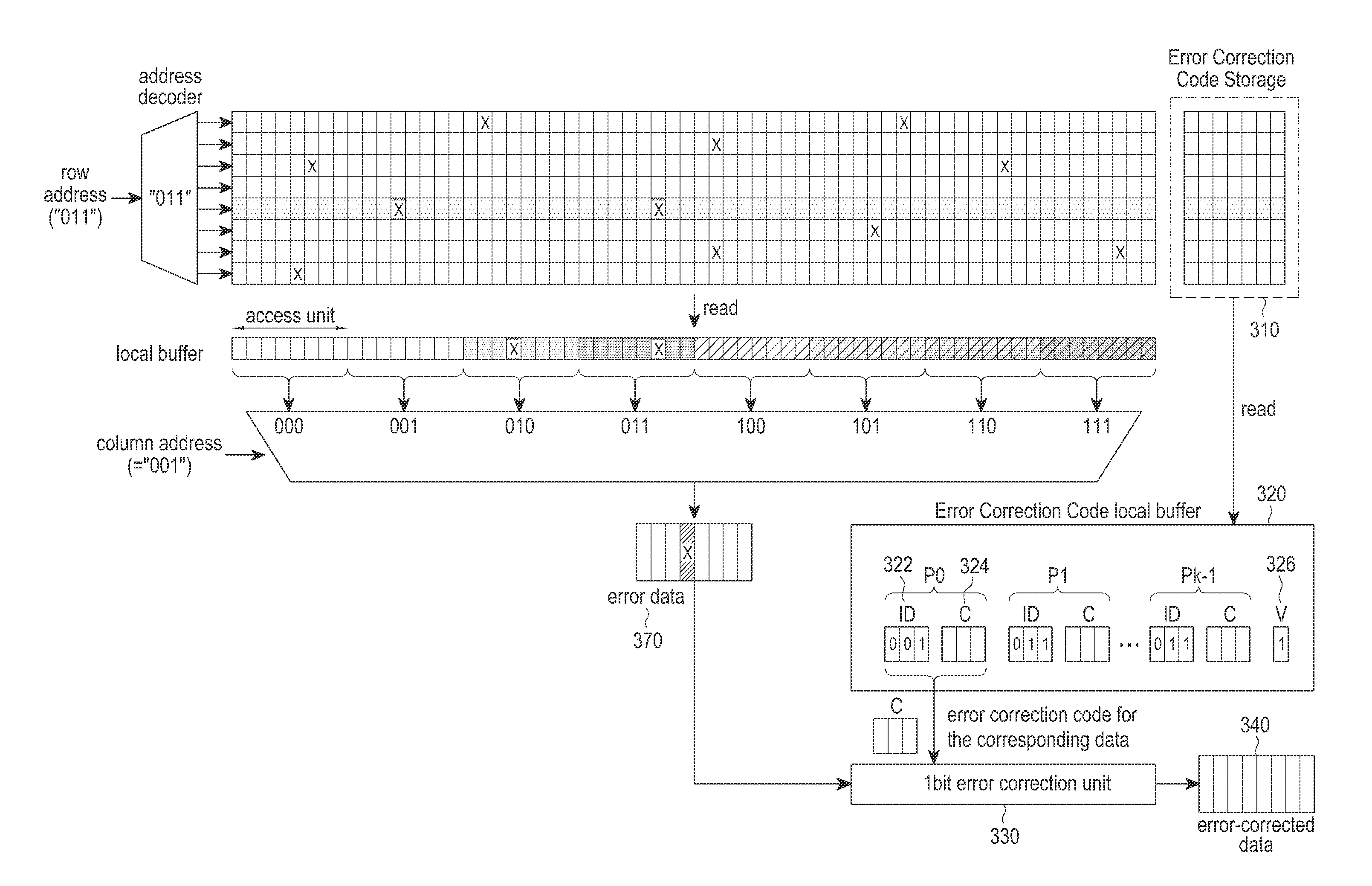

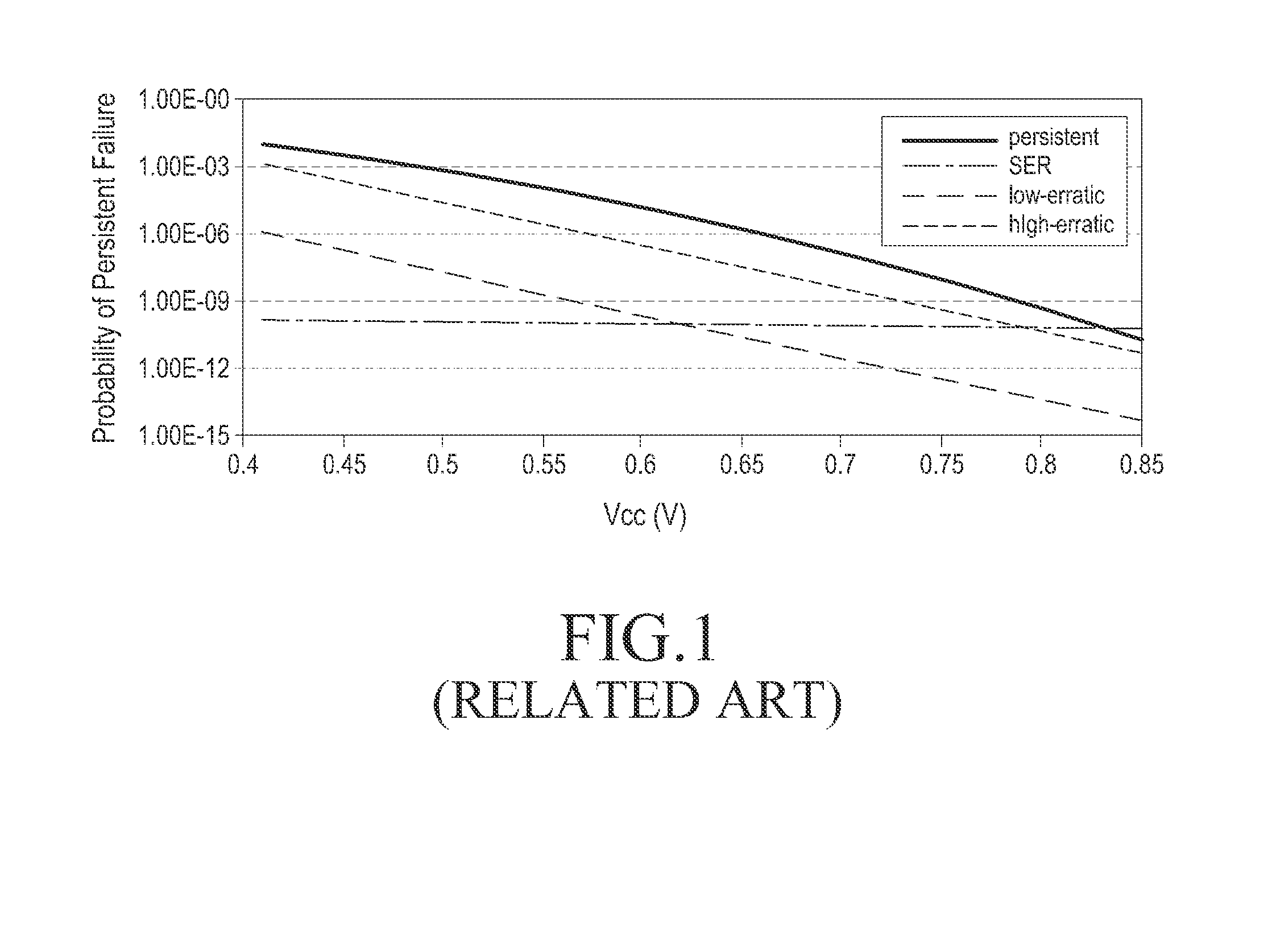

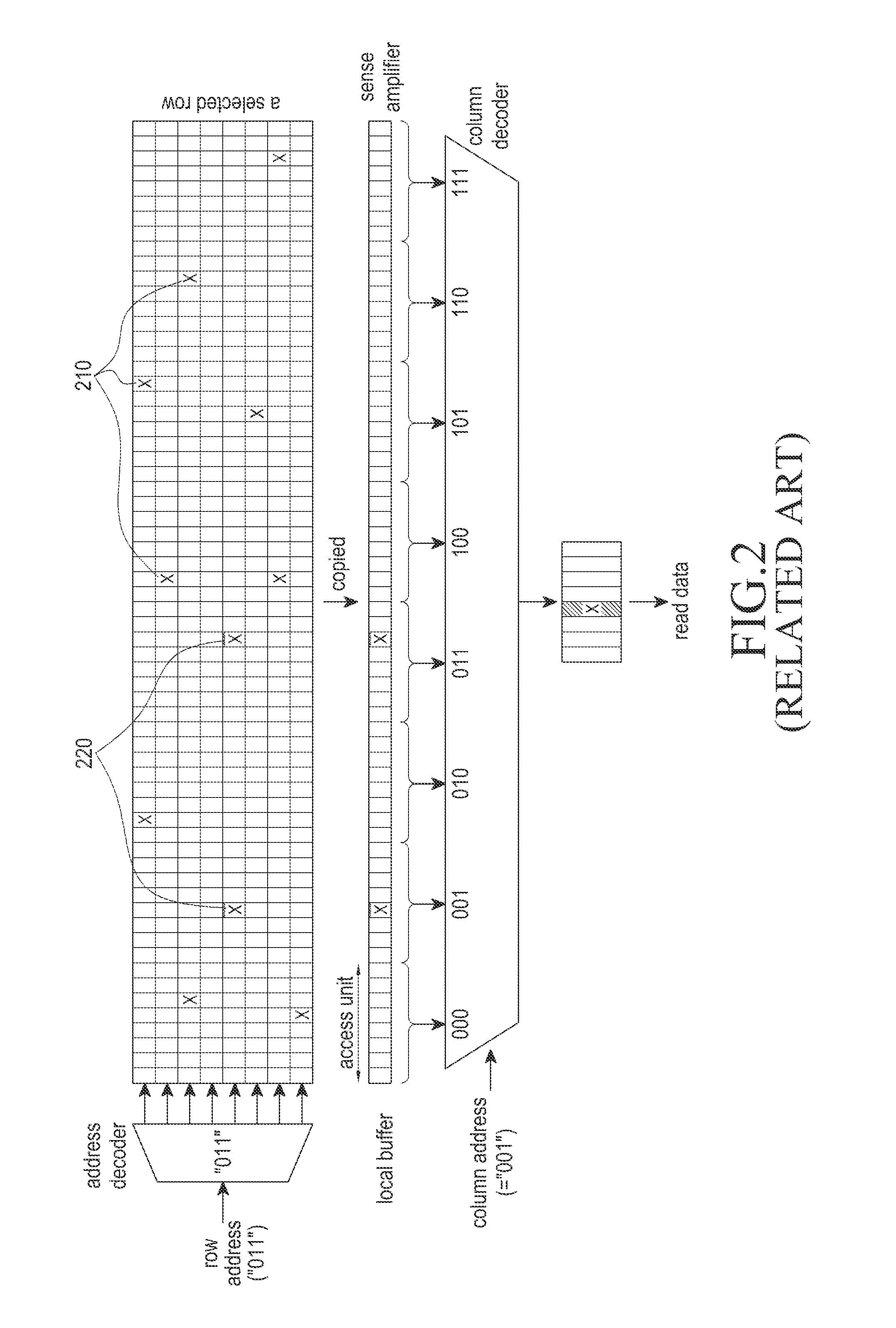

Apparatus and method for controlling memory in mobile communication system

ActiveUS20140250345A1Improve electricity efficiencyImprove powerStatic storageRedundant data error correctionLow voltageControl memory

An apparatus and method for controlling a low-voltage memory in a mobile communication system are provided. The apparatus includes a memory for storing data including at least one error caused by a low-voltage, and an error correction unit for identifying whether the at least one error exists in the memory according to a first bit set in a local buffer of an error correction code storage, for comparing location information on the error data read from the memory and location information on error data of at least one protection set in the local buffer of the error correction code storage when it is determined that the at least one error exists in the memory, for generating an error correction code as a result of the comparison, and for correcting the error data of the memory according to the error correction code.

Owner:SAMSUNG ELECTRONICS CO LTD +1

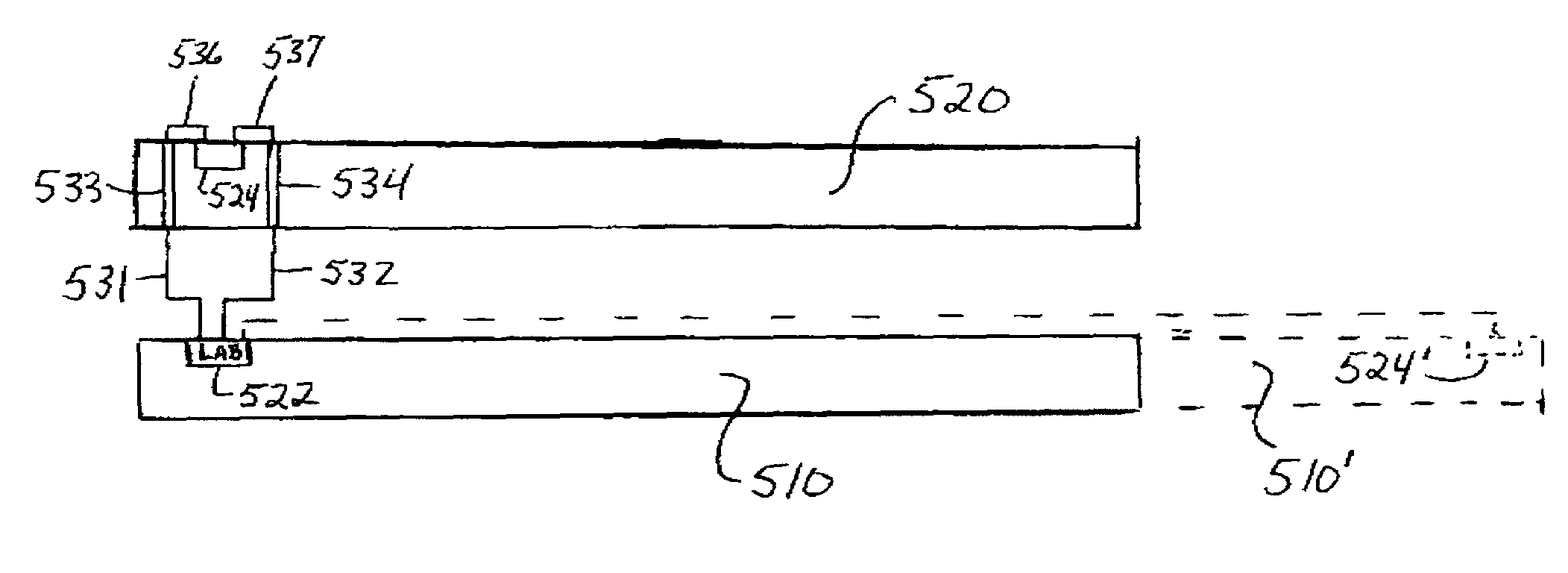

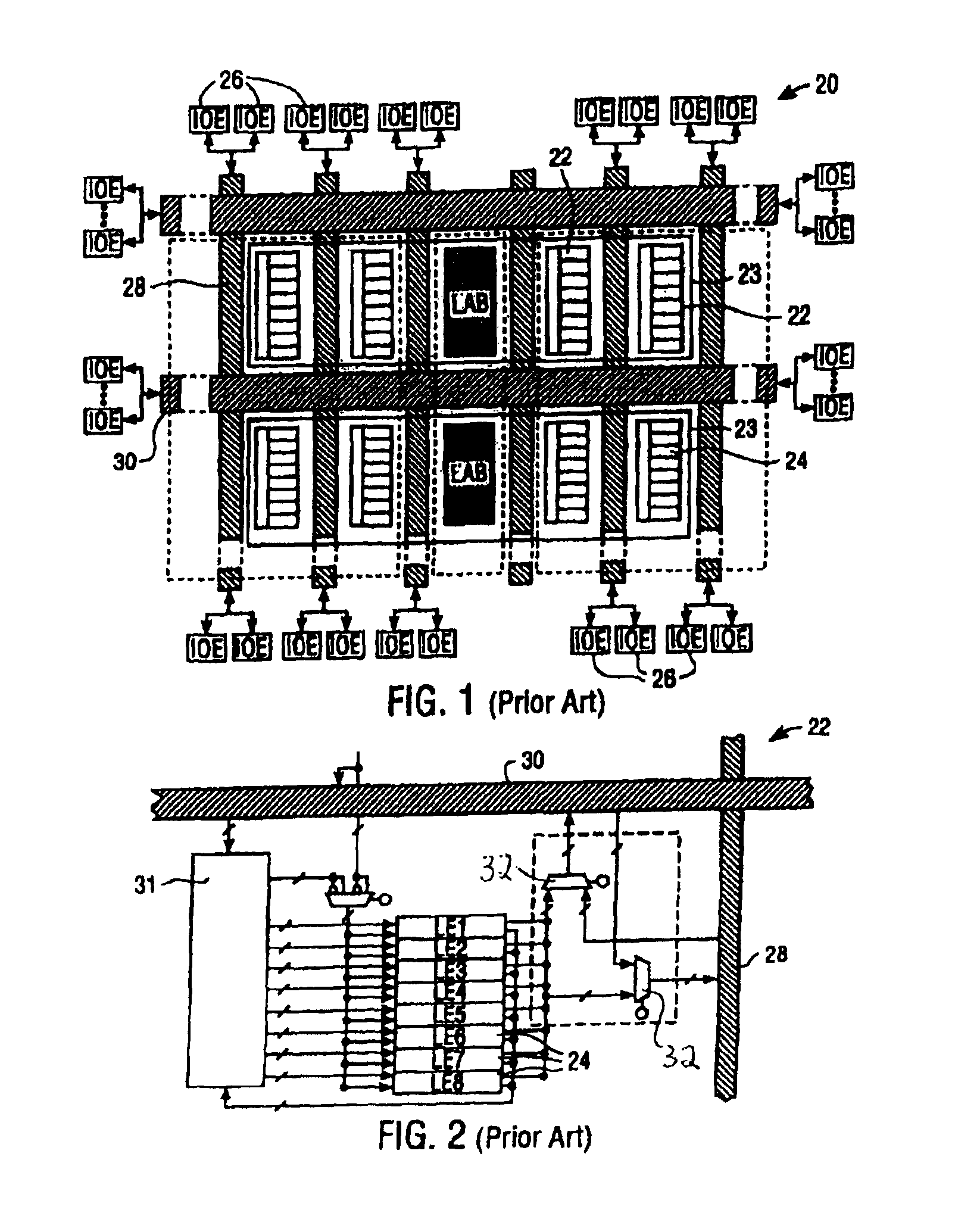

Circuit distribution to multiple integrated circuits

ActiveUS8000106B1Small sizeShorten the lengthSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

A semiconductor system in a package separates those circuits in a field programmable gate array (FPGA) into two substrates. In particular, the logic elements are formed in a first semiconductor substrate and certain non-logic elements are formed in a second semiconductor substrate that is in mechanical and electrical connection with the first substrate. The two substrates are enclosed in a suitable protective package and electrical connections are provided between one or both substrates and the exterior. The non-logic elements formed in the second substrate are located in circuits that would have a signal propagation delay in a conventional FPGA that is more than approximately twice the interconnect delay between the two substrates.

Owner:ALTERA CORP

Communication among agile and context-bound objects

InactiveUS7437711B2Efficient communicationPerformance penaltyMultiprogramming arrangementsSpecific program execution arrangementsObject-oriented programming

Communication among agile objects and context-bound objects within object-oriented programming environments, including communication across contextual boundaries, is disclosed. In one embodiment, a reference to a second object within a second context is wrapped in a proxy wrapper. A first object within a first context calls the second object via the wrapped reference. No direct reference is held by the first object to the second object. Other embodiments relate to agile objects. Agile objects called by context-bound objects execute in the contexts of their callers. The context of a calling context-bound object becomes the context of an agile object for calling of the agile object by the calling context-bound object. Direct reference to the agile object by the context-bound object is thus permitted.

Owner:MICROSOFT TECH LICENSING LLC

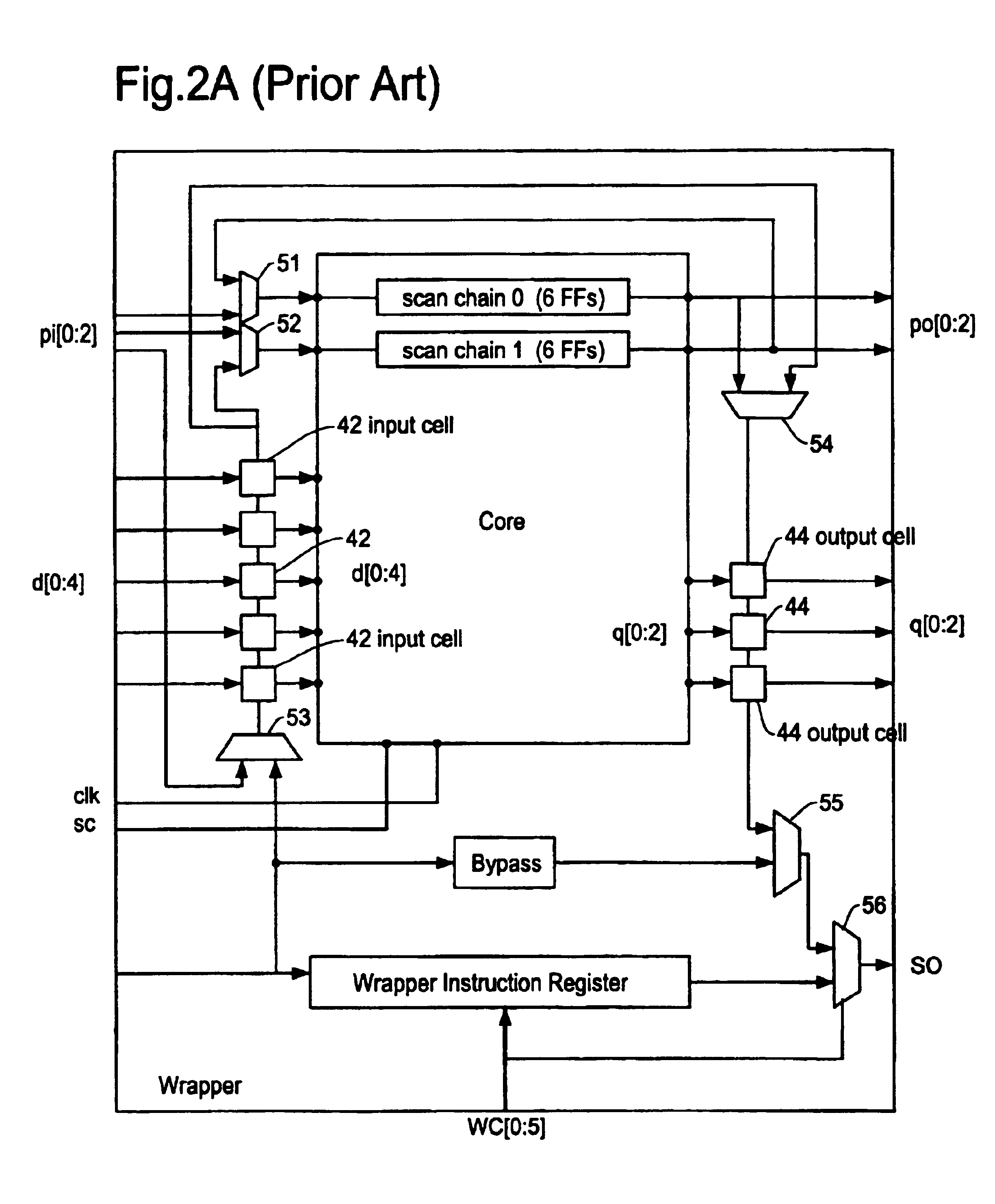

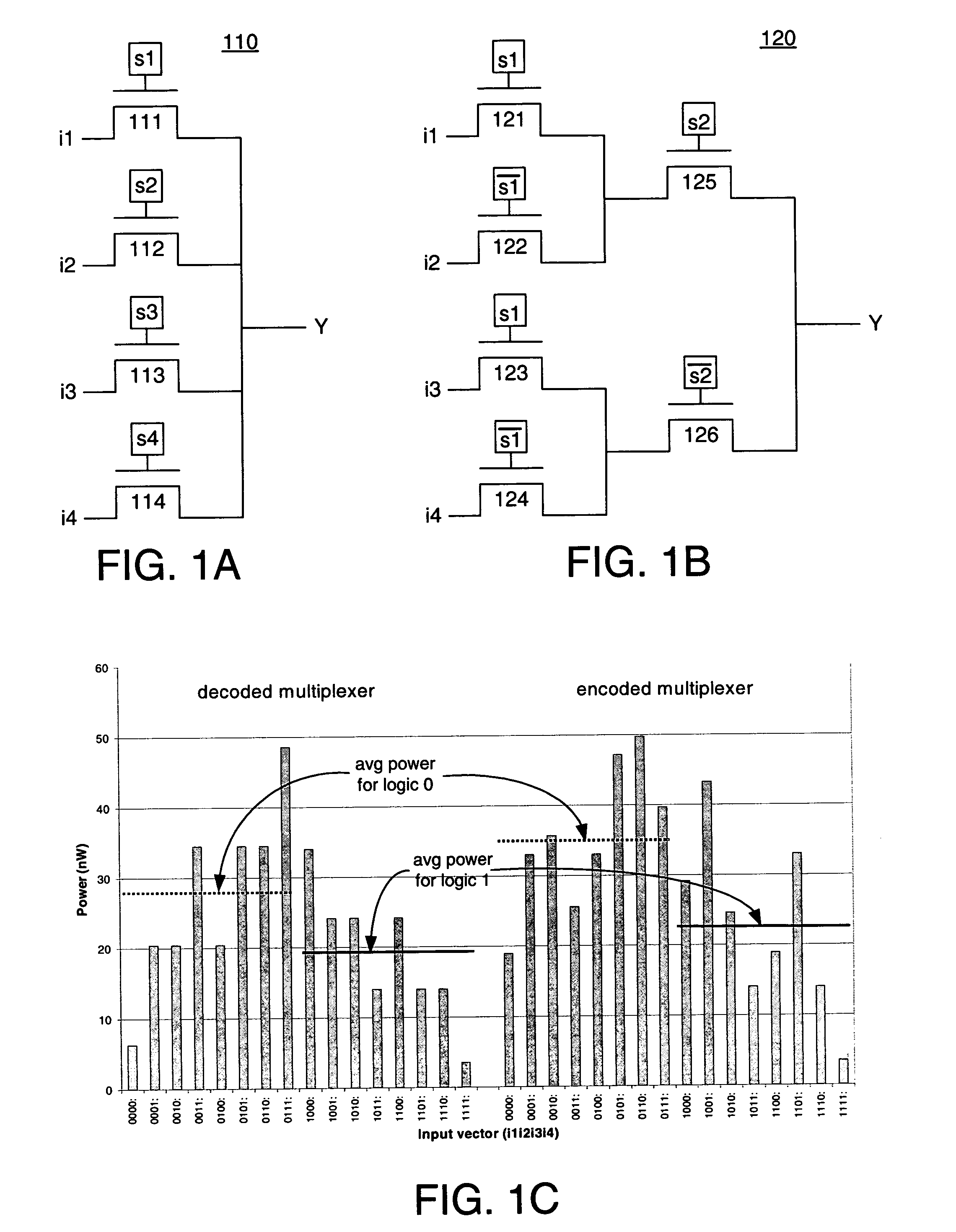

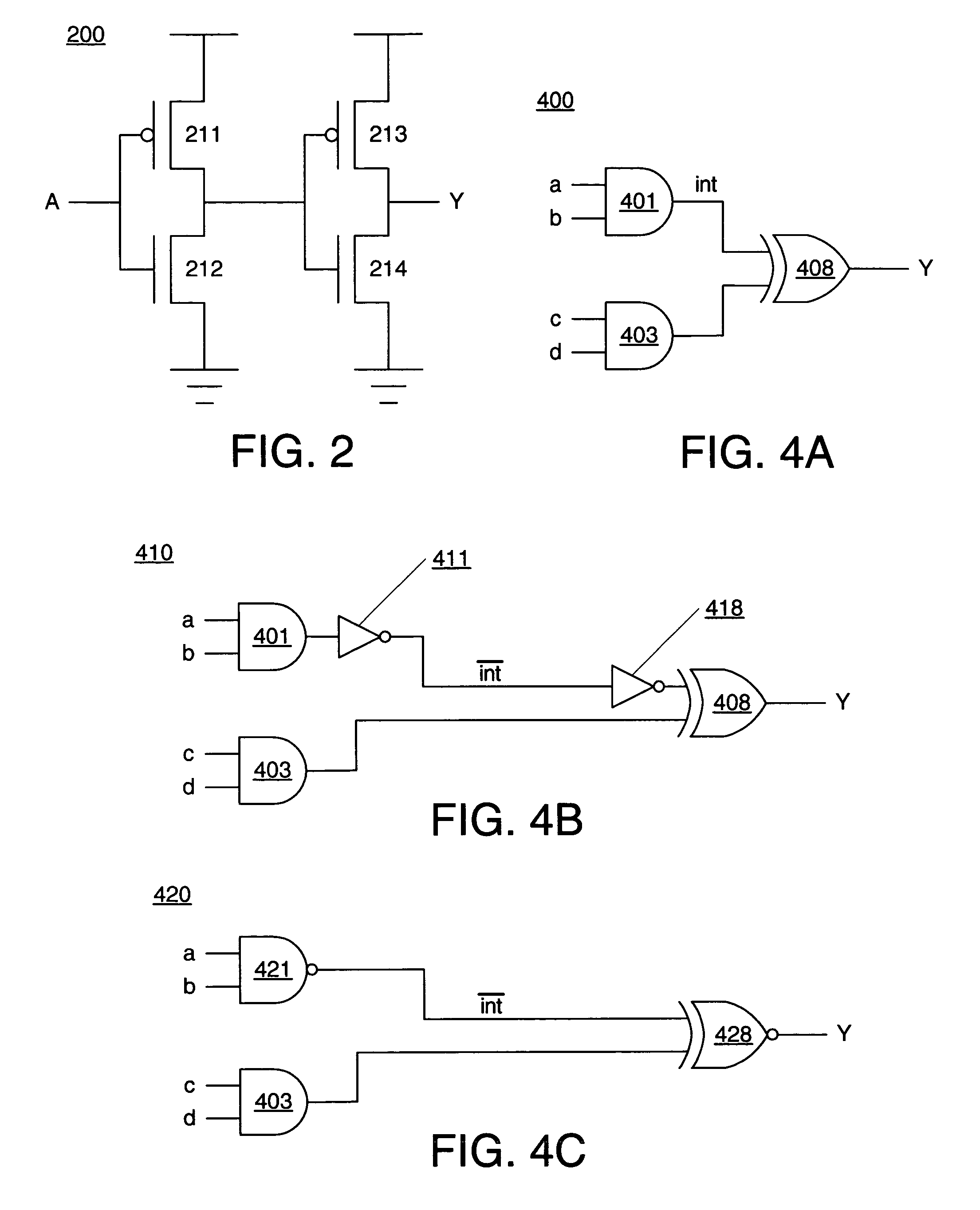

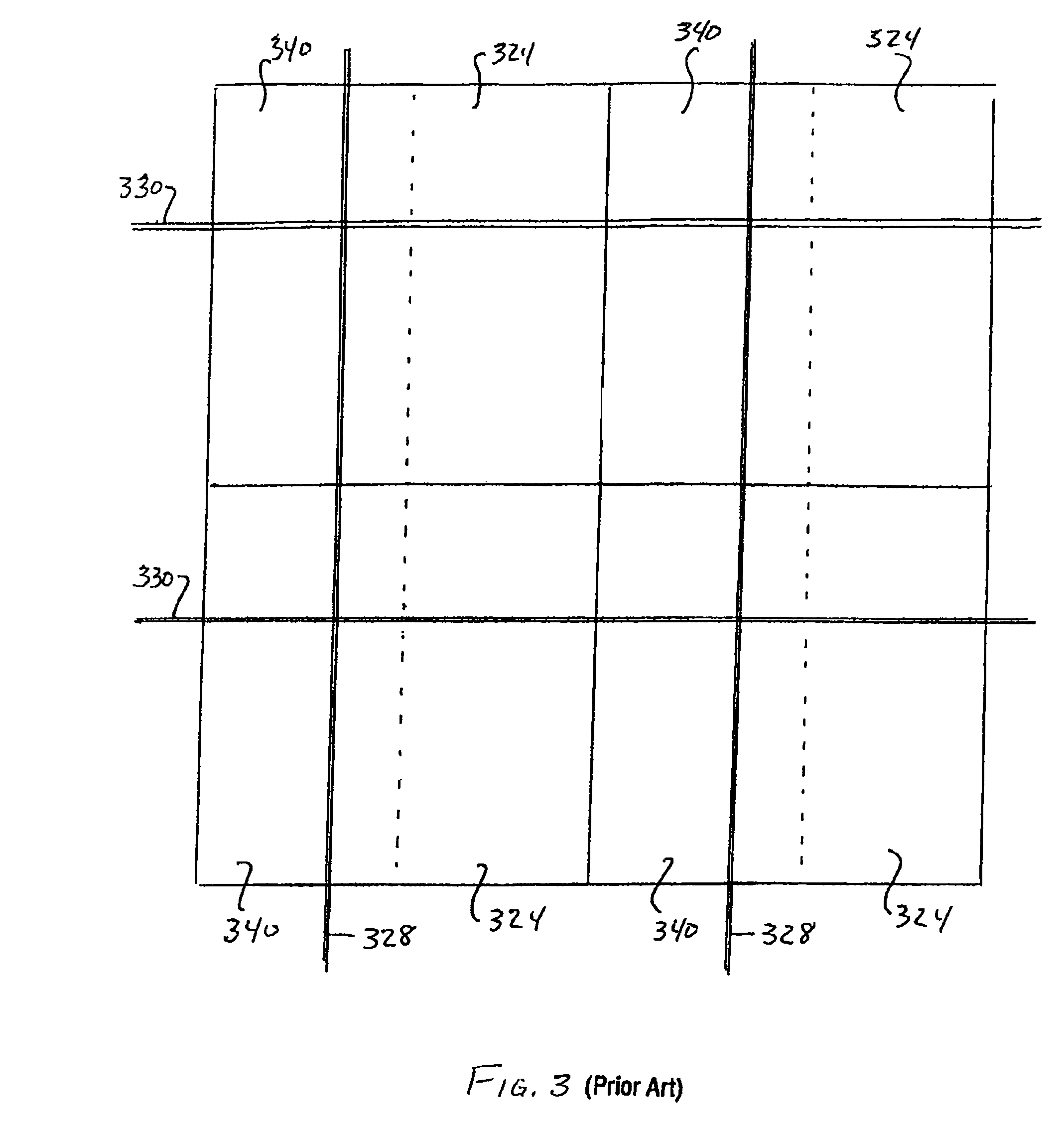

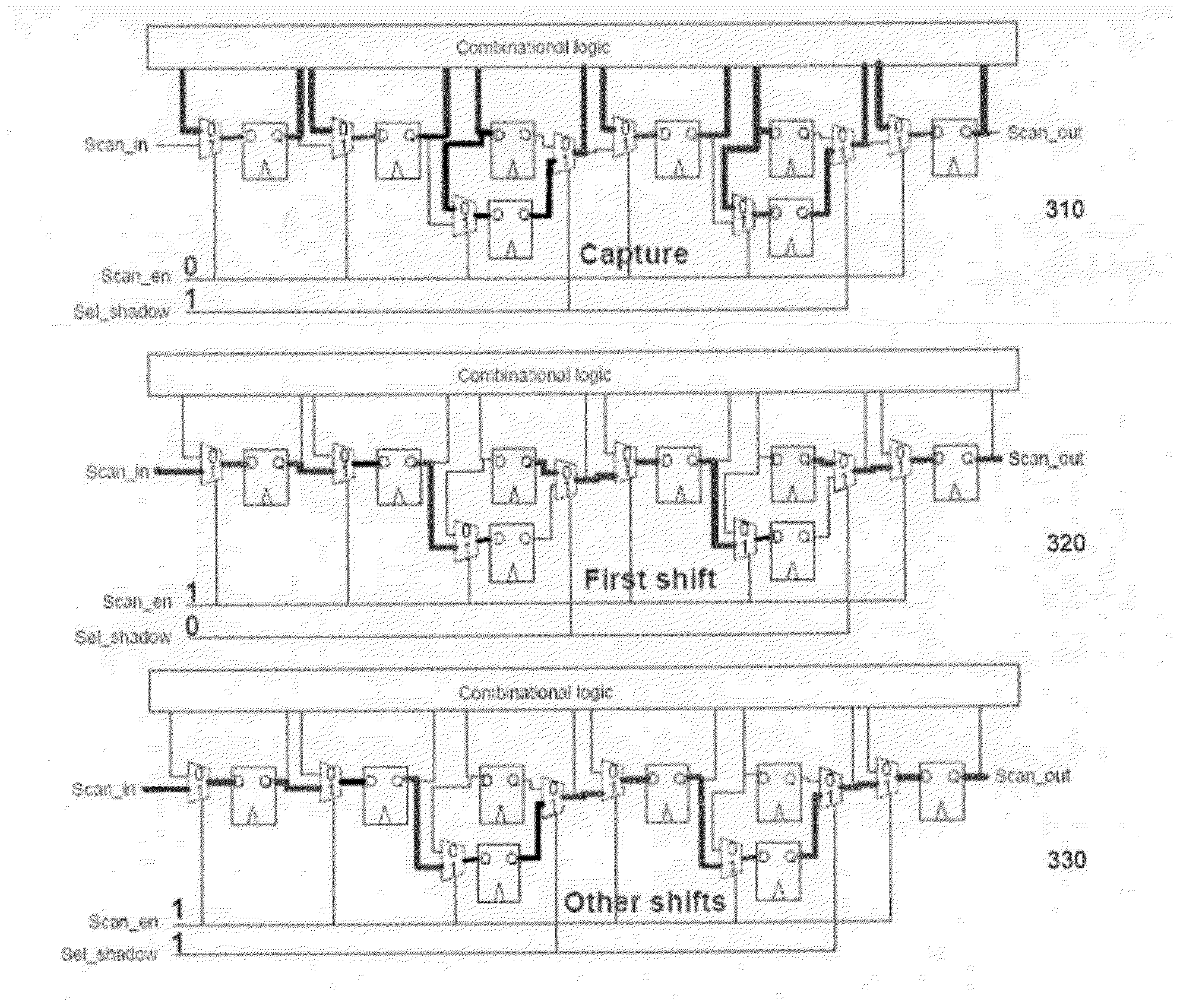

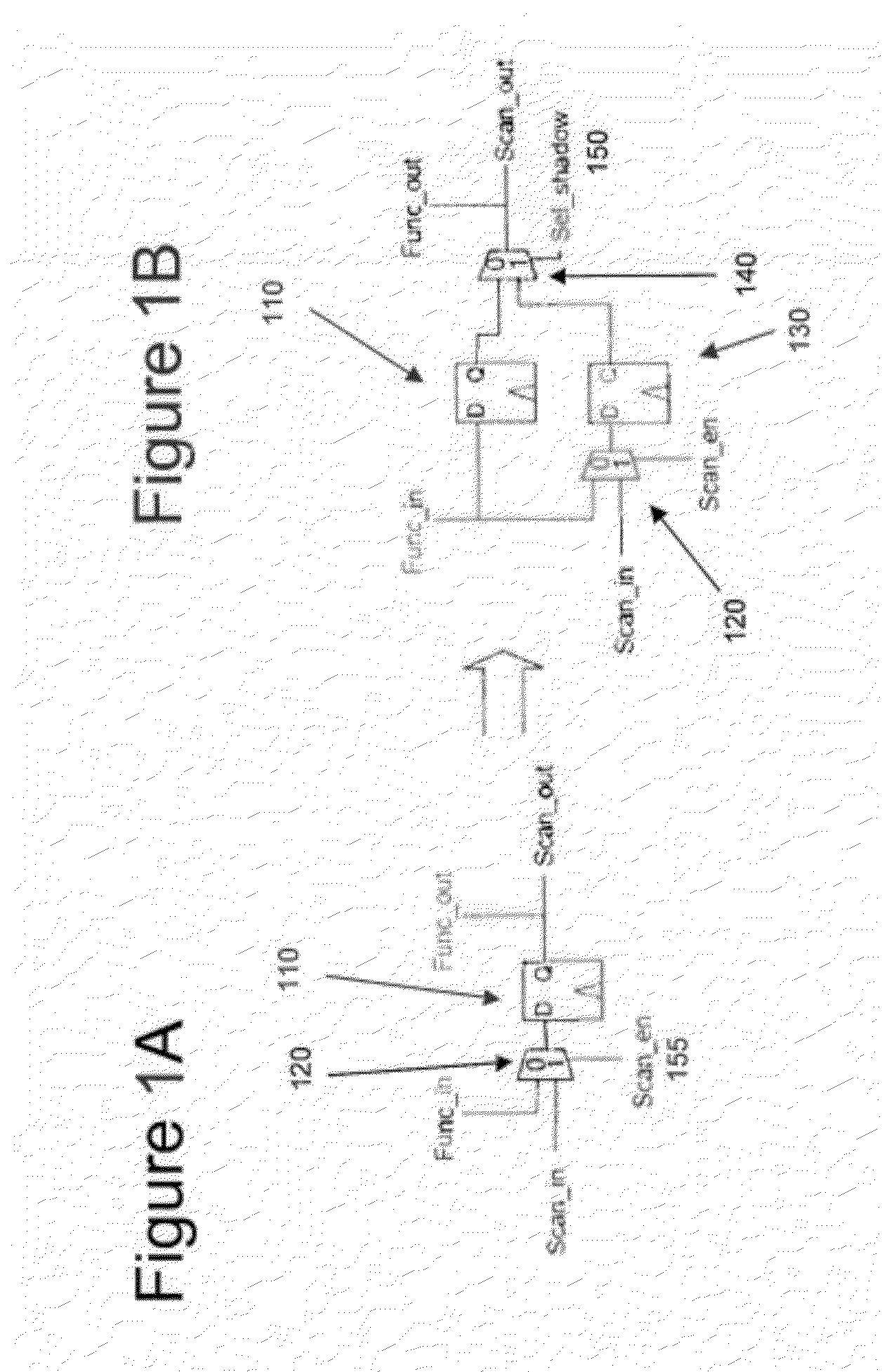

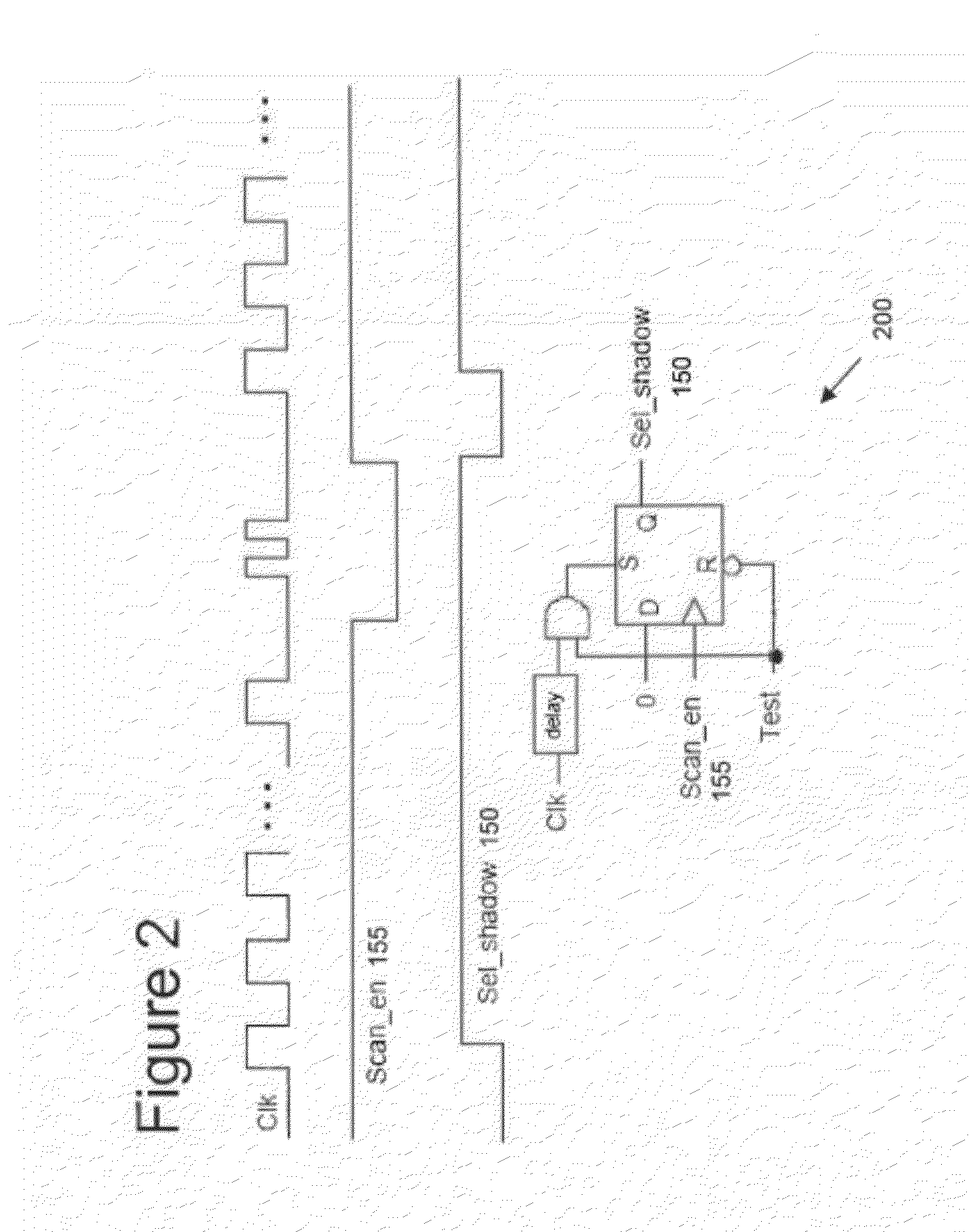

Architecture, system, method, and computer-accessible medium for eliminating scan performance penalty

ActiveUS20120284577A1Reduce performance lossShortening critical pathElectronic circuit testingMultiplexerComputer science

Exemplary apparatus, methods, and computer-accessible medium can be provided for transforming a circuit. For example, it is possible to select, from the circuit, at least one scan cell which includes a first multiplexer coupled to a first flip-flop. A second flip-flop and a second multiplexer can be inserted in the circuit. The first multiplexer can be coupled as an input to the second flip-flop, and the second multiplexer can be coupled to the output of the first flip-flop and the second flip-flop.

Owner:NEW YORK UNIV IN ABU DHABI CORP

Transportation vehicle and method operable with improved drag and lift

InactiveUS20050247250A1Performance penaltyImprovement in power/payload efficiencyWatercraft hull designFloating buildingsMarine engineeringGravity center

A powered transportation vehicle uses hydro and aero pressure lift on flat bottom surfaces for providing increased efficiency of operation. An elongate hull has a bottom surface having a large length to width aspect ratio operates in water, with a smaller aspect ratio for a second lifting body operating substantially in air. Trailing edges of the bottom surfaces form a seal with water for creating stagnation areas for the water and air for providing lift to the vehicle having a center of lift of the hull forward the center of gravity of the vehicle. A forward portion of the hull bottom surface is upwardly angled from an aft portion as measured from the center of gravity.

Owner:ERRECALDE GEORGE A

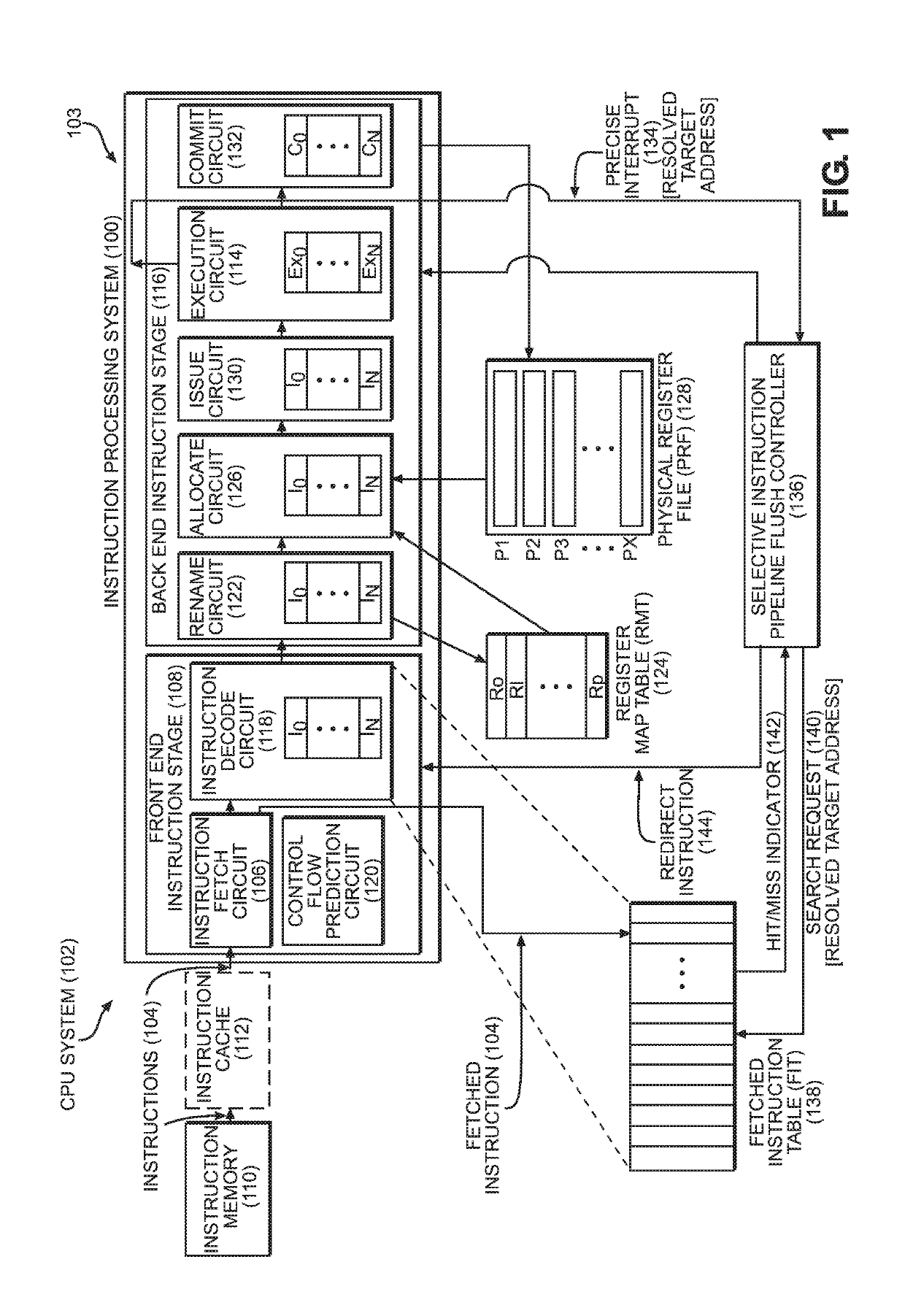

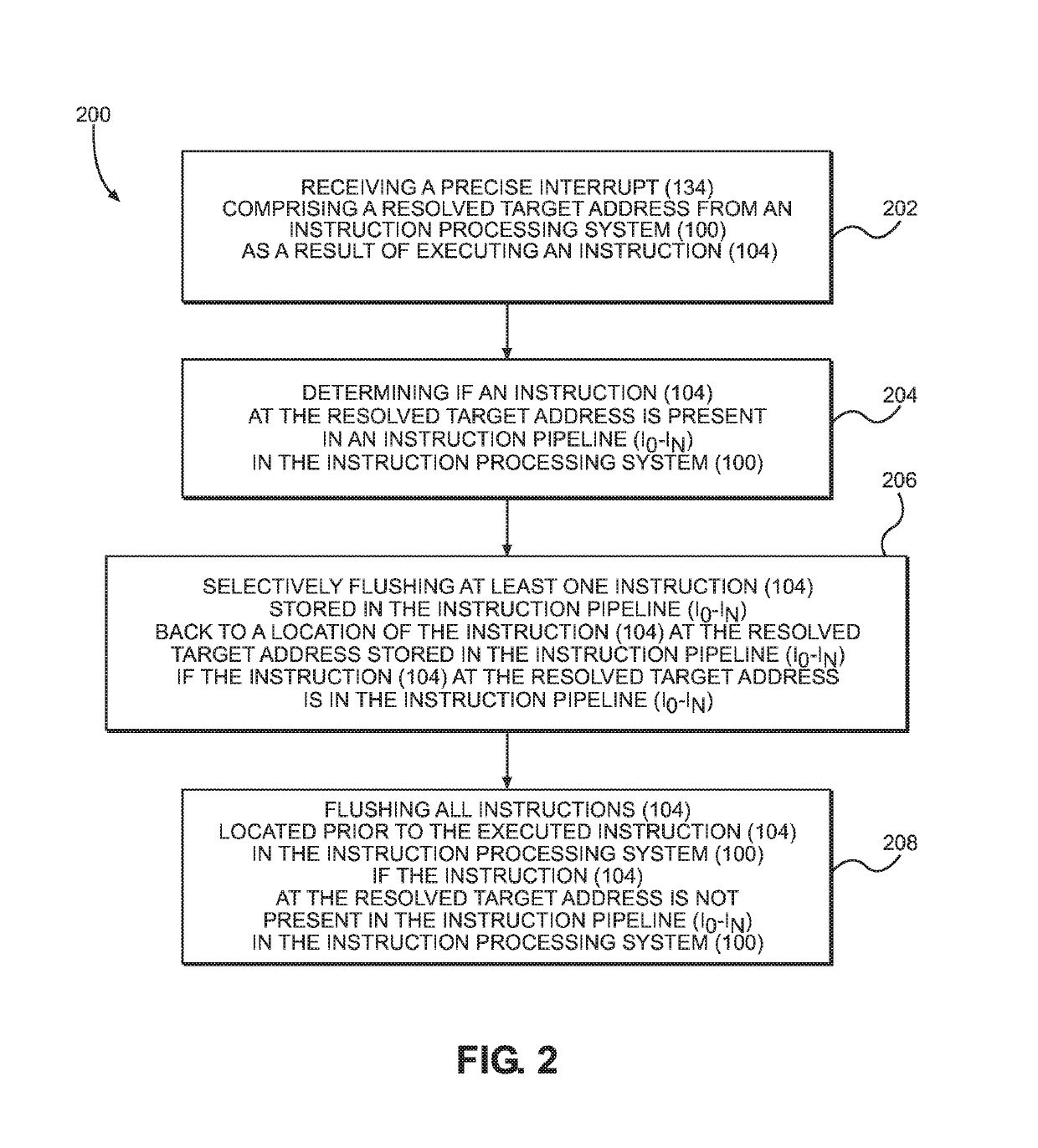

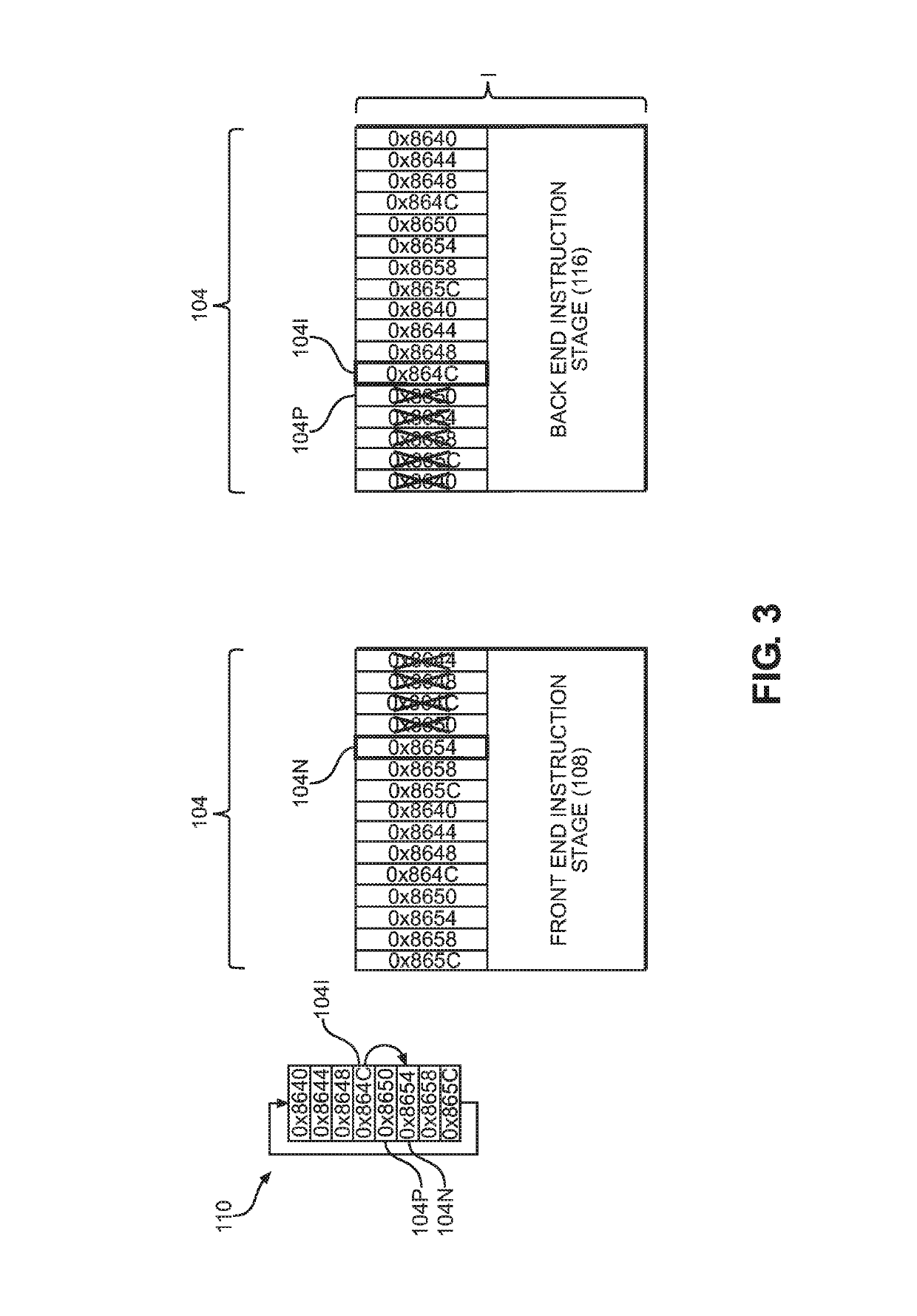

Selective flushing of instructions in an instruction pipeline in a processor back to an execution-resolved target address, in response to a precise interrupt

ActiveUS10255074B2Reduce the amount requiredReduce delaysConcurrent instruction executionInstruction pipelineInstruction selection

Owner:QUALCOMM INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com