Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32results about How to "No increase in area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

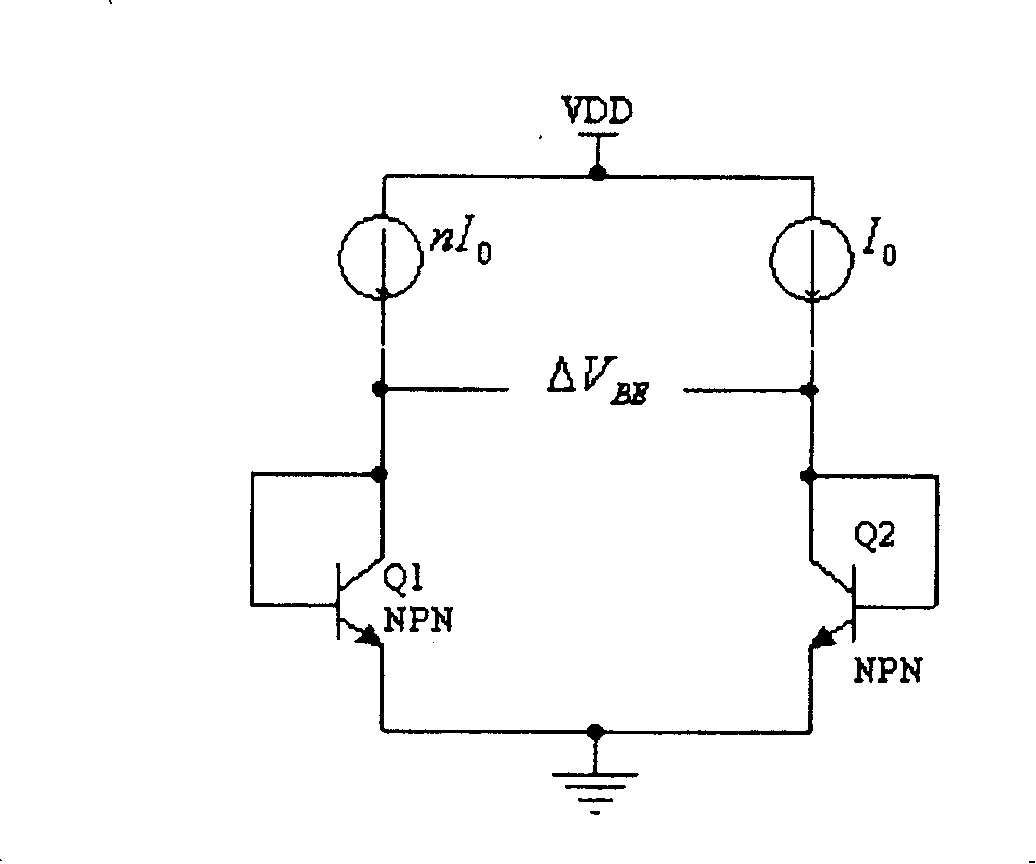

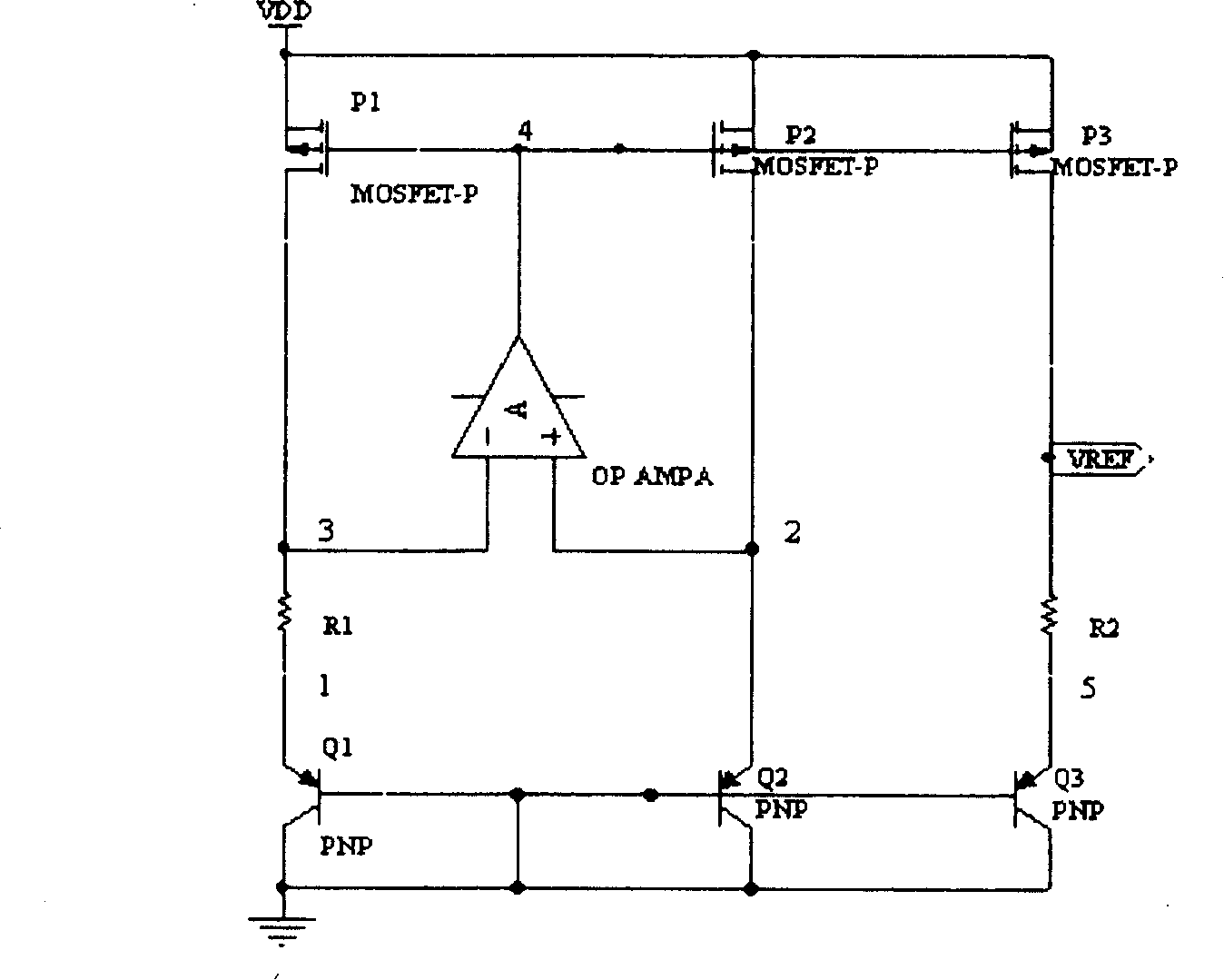

Output adjustable band-gap reference source circuit

An output adjustable band-gap reference source circuit is characterized by comprising: a high-gain operational amplification circuit; a voltage generation circuit independent of temperature and power source connected with the input end and output end of the high-gain operational amplification circuit by nodes, so as to implement output clamping effect; a start circuit, the output of which is connected to the node of the voltage generation circuit independent of temperature and power source to prevent the voltage generation circuit independent of temperature and power source entering a dead region; an output regulation circuit, the input of which is connected to the voltage generation circuit independent of temperature and power source, thereby to implement output clamping effect, and the output is the output of the whole band-gap reference source circuit.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

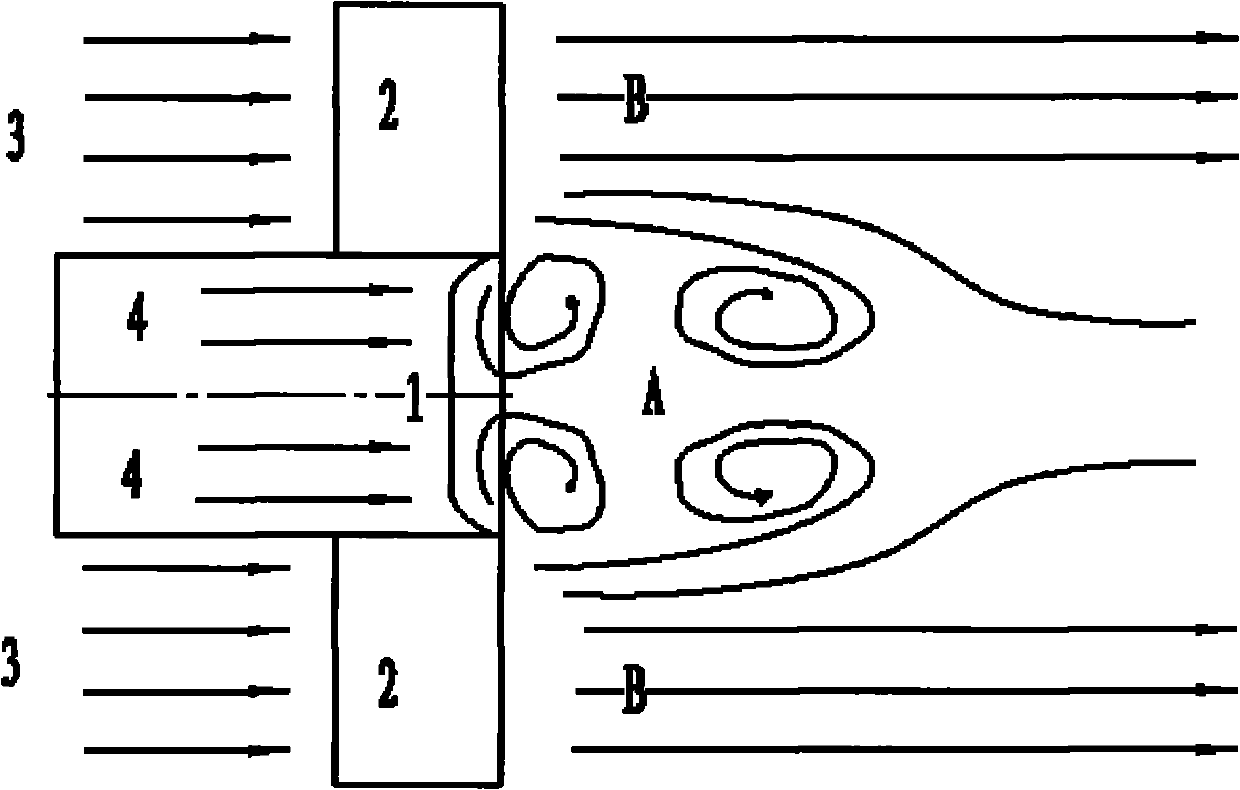

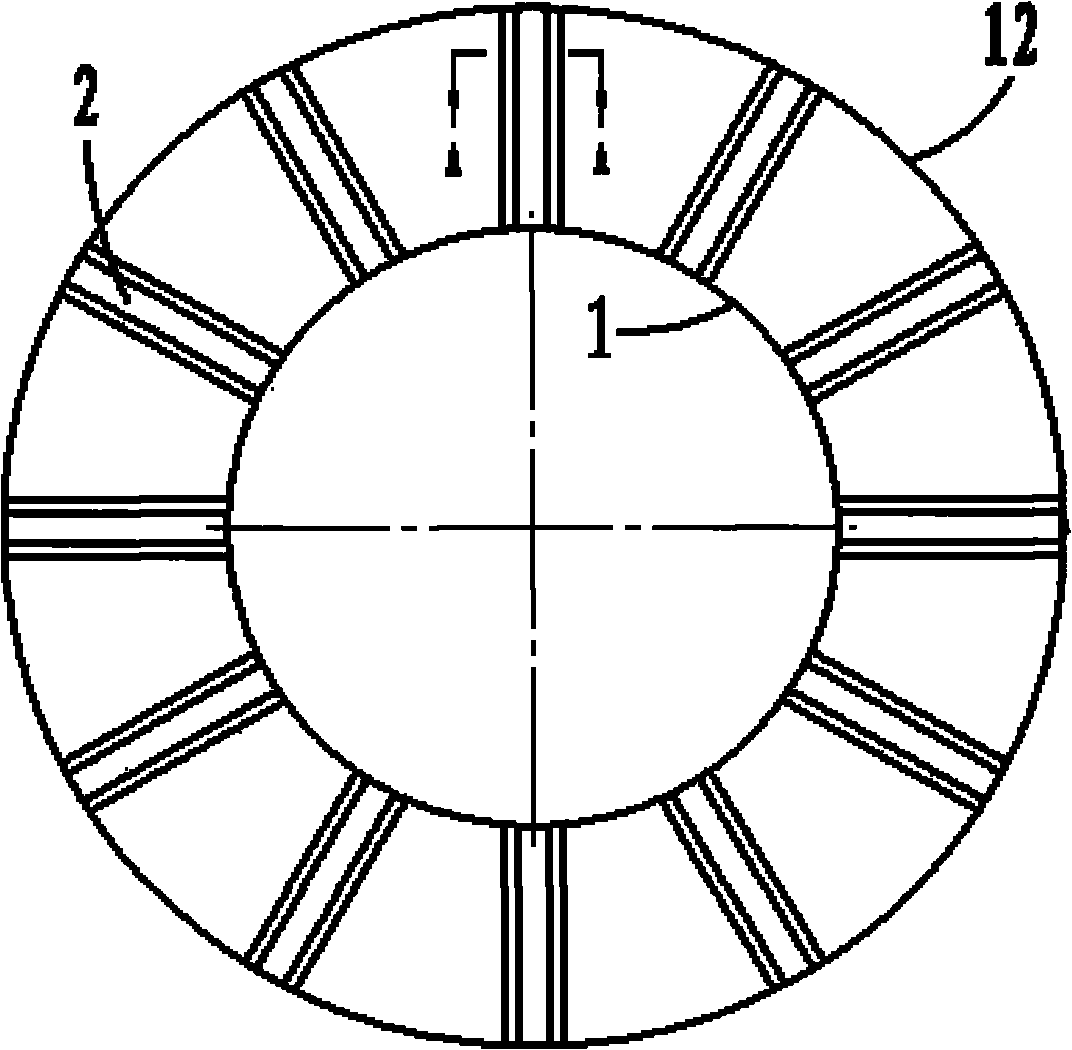

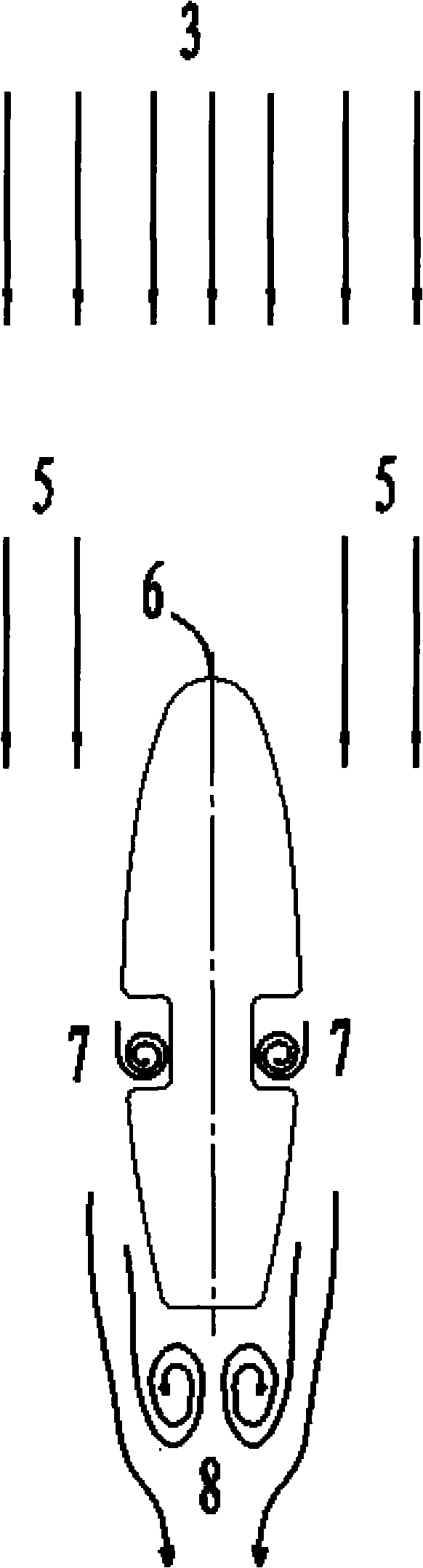

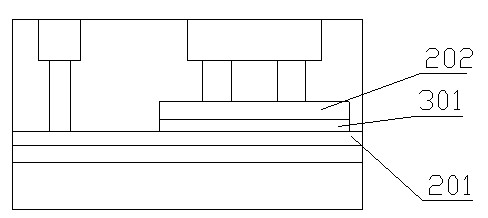

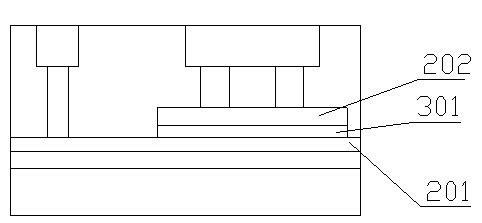

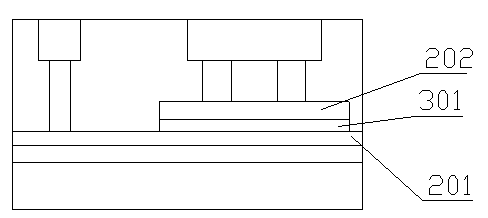

Flame stabilizing device and method for supporting plate with cavities

InactiveCN102200292AIncrease swirl areaExtended Radial Coverage AreaContinuous combustion chamberCombustion chamberLow speed

The invention provides a flame stabilizing device and method of an afterburner for a gas turbine engine. In the device, the original turbine rear frame supporting plate is replaced with the supporting plate with the cavities; and the device is characterized in that: the section of the supporting plate is in the shape of a wing with a suddenly expanded trailing edge and is provided with the cavities. The aim of stabilizing flame is fulfilled through a low-speed backflow region formed by flowing gas flow through the cavities of the supporting plate and the suddenly expanded part of the trailing edge. The invention provides the turbine rear frame supporting plate (2) of the afterburner for the gas turbine engine; the afterburner comprises a case (12), a turbine rear frame inner wall (1) and a plurality of turbine rear frame supporting plates (2), wherein the turbine rear frame supporting plates (2) are connected with the case (12) and the turbine rear frame inner wall (1); and the turbine rear frame supporting plate (2) is characterized by being provided with the cavities (9).

Owner:BEIHANG UNIV

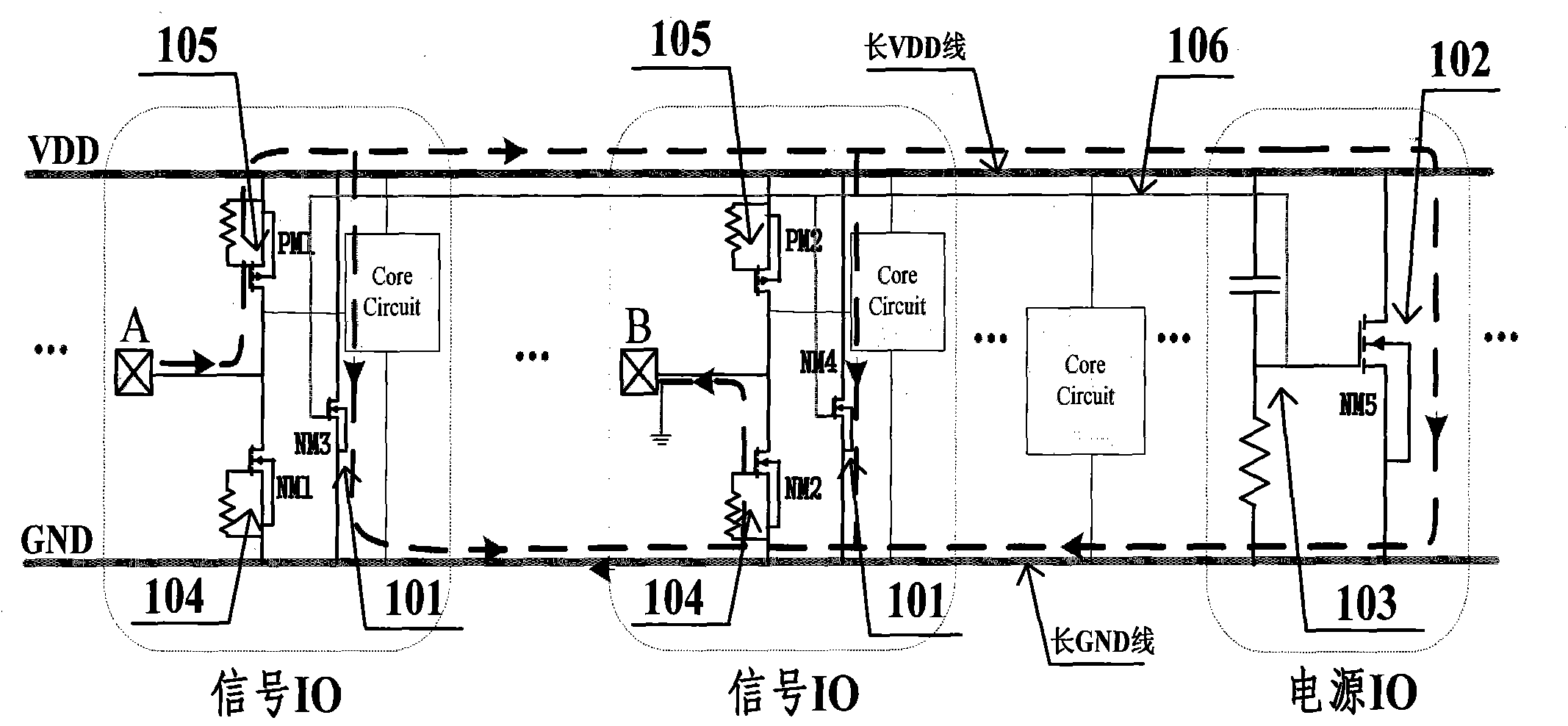

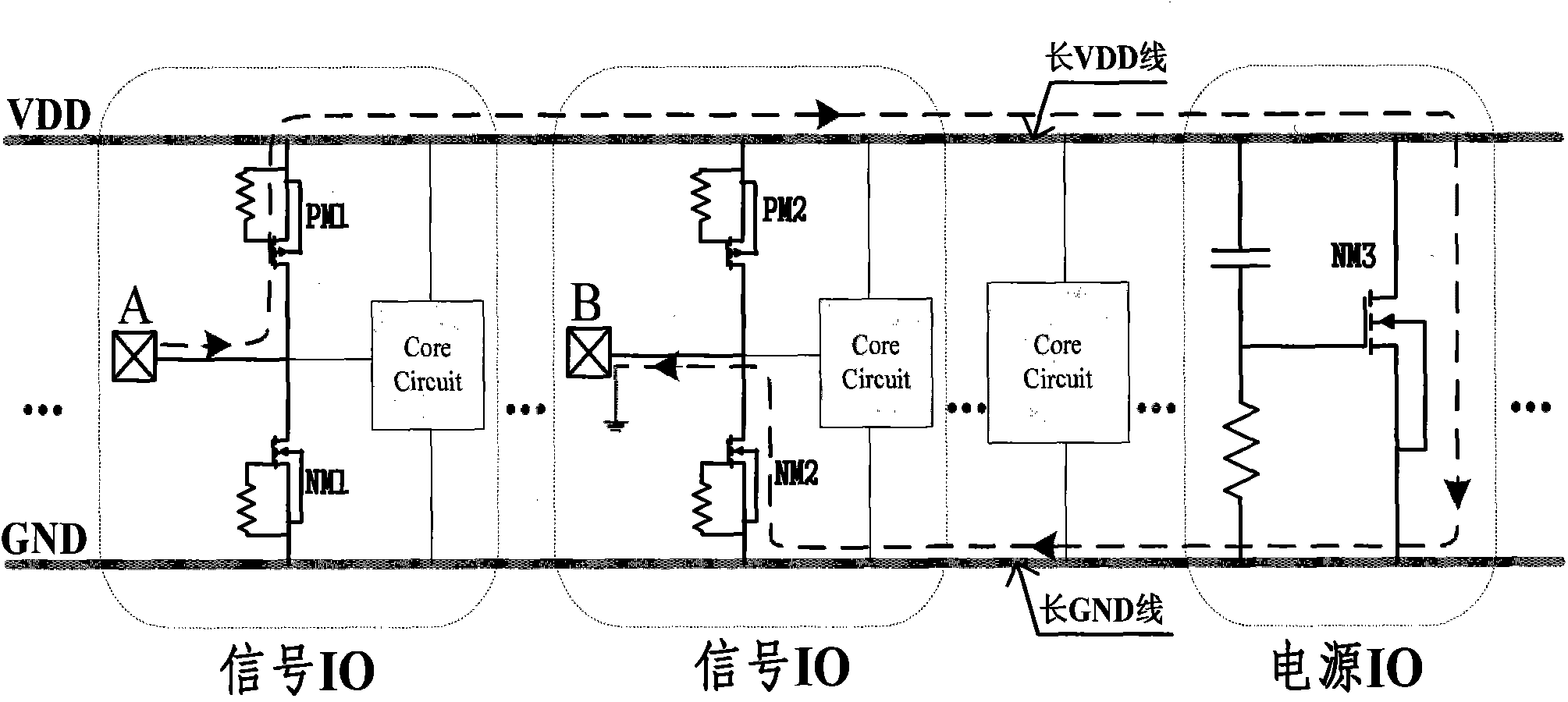

Integrated circuit full-chip electro static discharge protection method and circuit

InactiveCN103647265AReduce areaReduce voltage dropEmergency protective arrangements for limiting excess voltage/currentDischarge efficiencyEngineering

The invention is an integrated circuit full-chip electro static discharge (ESD, Electro Static Discharge) protection method. According to an integrated circuit full-chip ESD structure of the method, one power-ground ESD discharge path is added in each signal IO unit, namely, a full chip not only contains an electro static discharge path 102 in a power IO unit, but also contains the electro static discharge path 101 in each signal IO unit. Therefore, the number of the electro static discharge paths in the full chip is increased, the electro static discharge path between IO is shortened, the discharge resistance between IO is reduced, the full-chip electro static discharge efficiency is improved, and the full-chip ESD level is upgraded.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

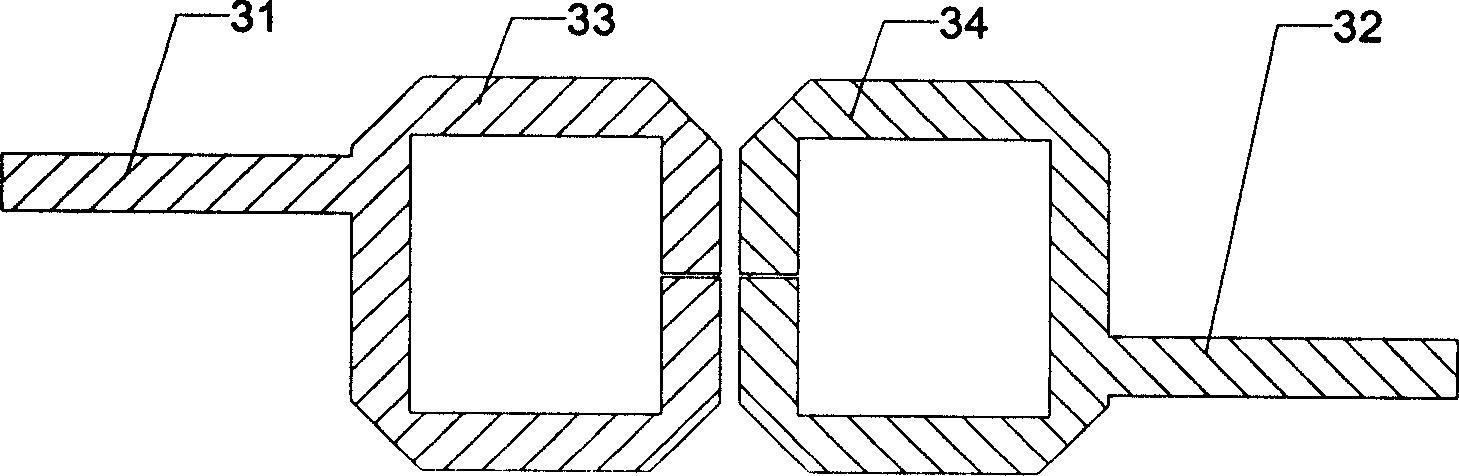

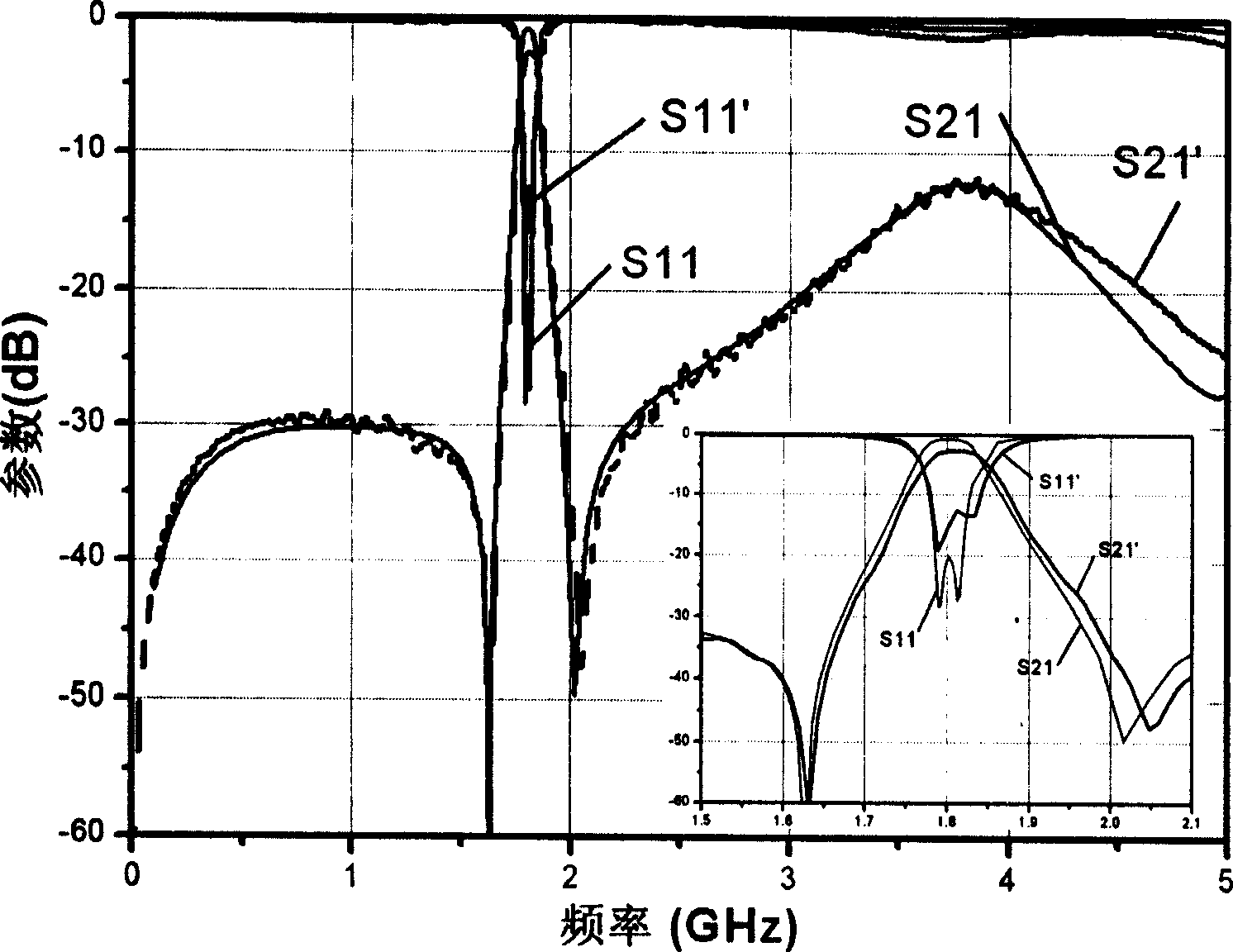

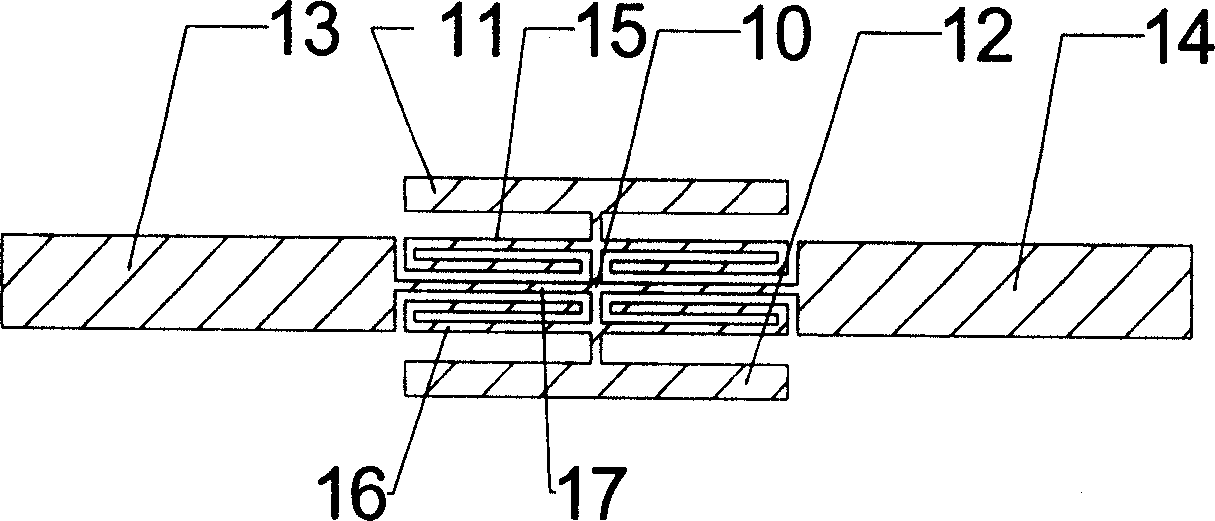

Compensated micro-band resonance device and microband open-loop coupled band filter with harmonic inhibition

InactiveCN1747227ANo increase in areaThe purpose of increasing the forbidden bandResonatorsResonanceHarmonic

The invention comprises incoming feeder, outgoing feeder, open circuit loop coupler and offset-type microstrip resonator. After connecting in series to offset-type microstrip resonator, the incoming and outgoing feeder connects to open circuit loop coupler. Base on conventional open circuit loop coupling band pass filter, the invention features an offset-type microstrip resonator connected in series between outgoing feeder and open circuit loop coupler to increase outband rejection ability of filter by forbidden band property of offset-type microstrip resonator.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

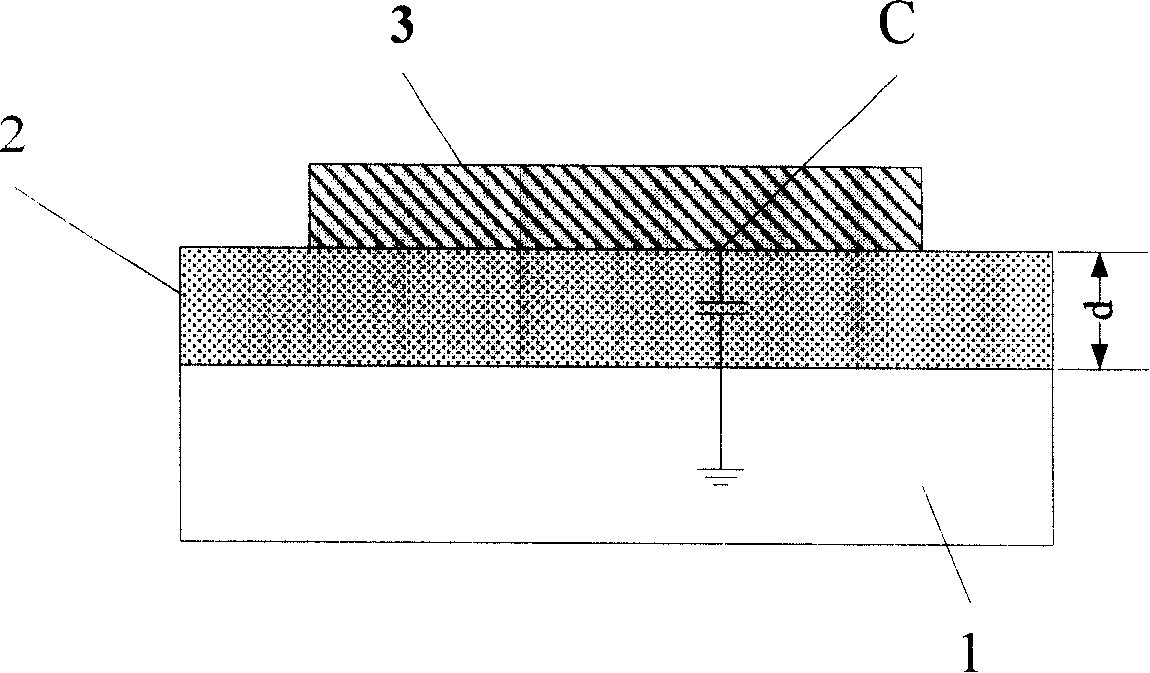

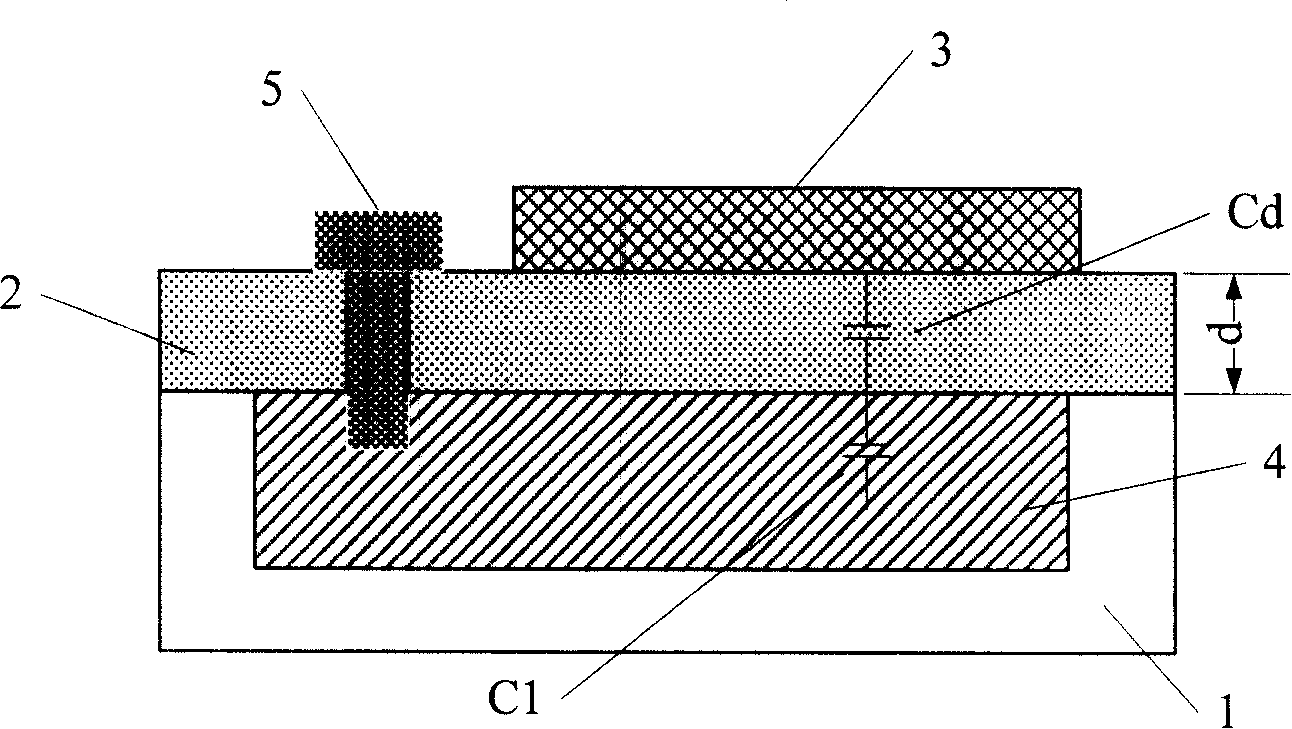

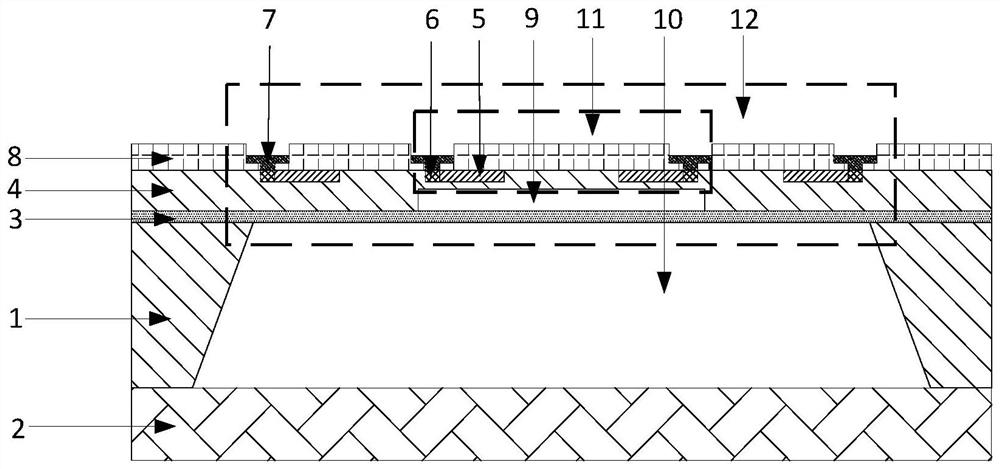

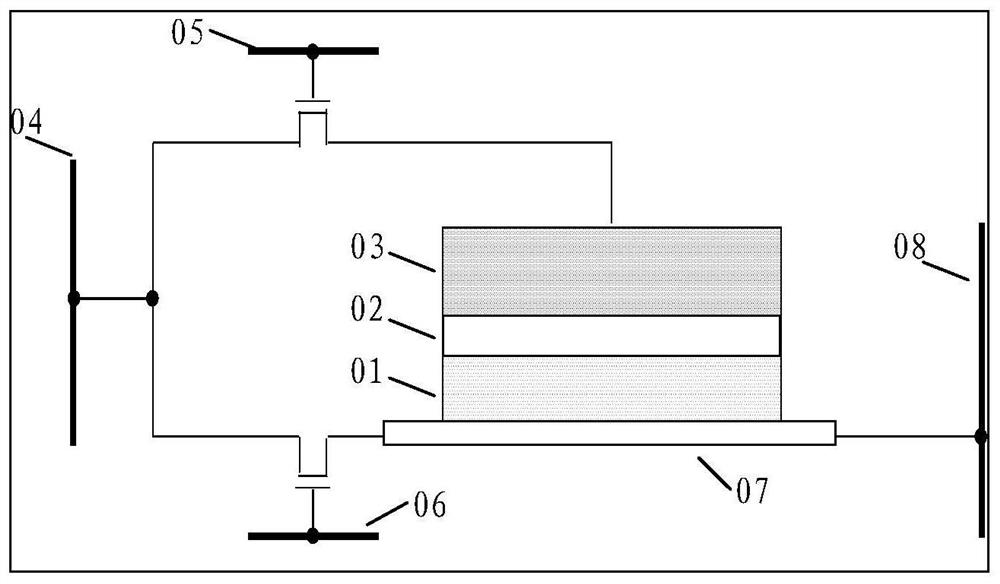

Method for increasing metal-insulating layer-metal (MIM) capacitor density in semiconductor device and structure thereof

ActiveCN102437015AIncrease capacitance densityImprove compatibilitySemiconductor/solid-state device detailsSolid-state devicesCapacitanceState of art

The invention discloses a method for increasing the metal-insulating layer-metal (MIM) capacitor density in a semiconductor device and the semiconductor device comprising a high-density MIM capacitor. An appearance layer is arranged on a blocking layer of a base, the appearance layer is etched so that the appearance layer is provided with a plurality of grooves, and a capacitor base plate covered on the appearance layer is in an appearance shape for increasing the area of the capacitor base plate, so the capacitor density is increased, and simultaneously, the matching of a high capacitor and a copper metal electrode plate is realized through the appearance layer. Compared with the prior art, the method and the semiconductor device have the advantages that the wafer area is not increased, and simultaneously, the method has high compatibility with the traditional process.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

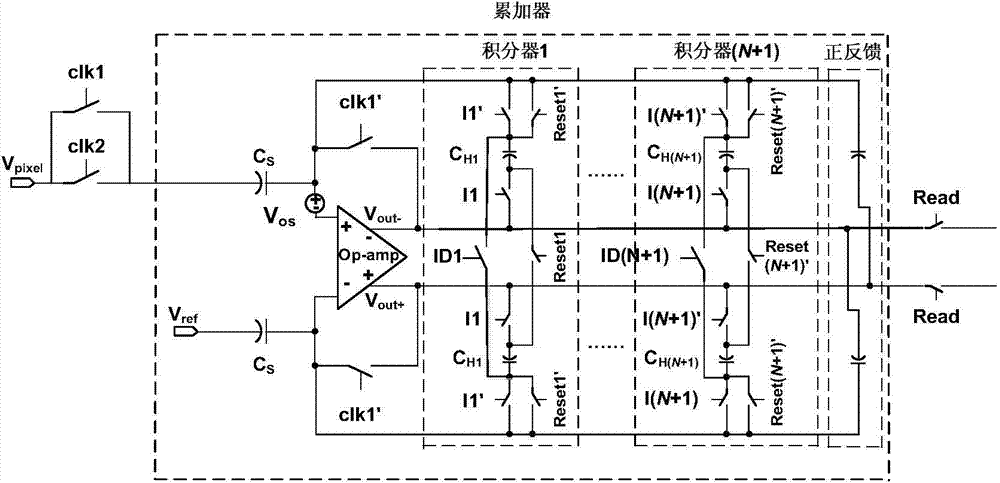

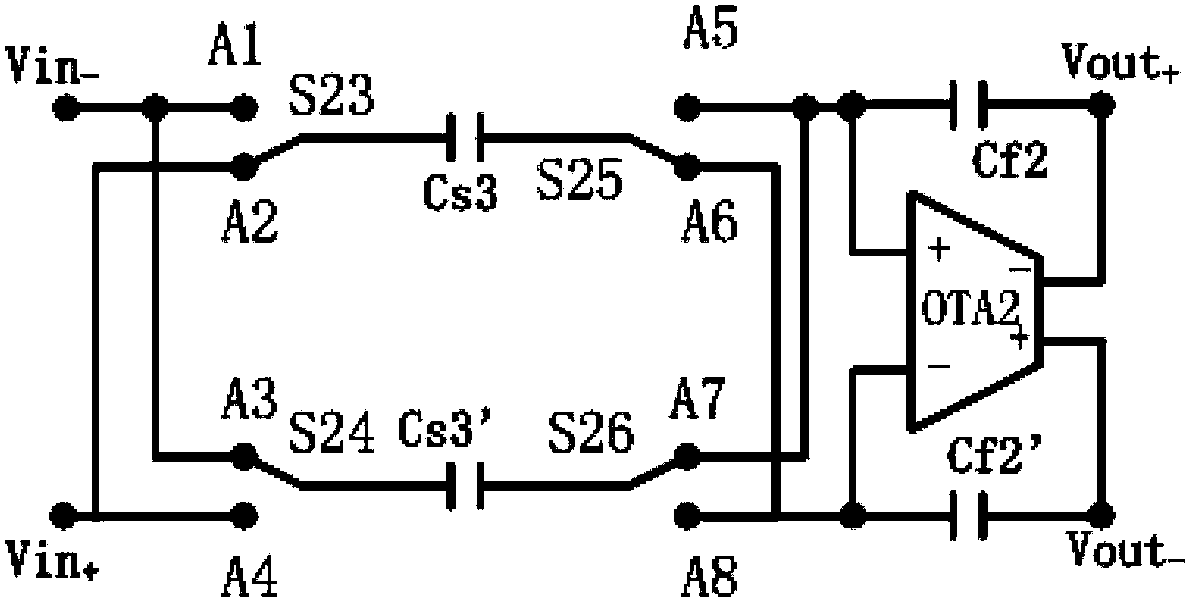

Analog accumulator applied to TDI (time delay integral)-type CMOS (complementary metal-oxide-semiconductor transistor) image sensor

ActiveCN104506785AIncrease the number of effective accumulative levelsAchieve compensationTelevision system detailsColor television detailsCapacitanceIntegrator

The invention relates to the field of integrated circuit design; in order to realize the compensation of the influence brought to parasitism, the effective accumulation series of the accumulator is greatly increased, and meanwhile, the area and the power consumption of a circuit are not increased excessively. Therefore, the technical scheme adopted by the invention is that an analog accumulator applied to a TDI (time delay integral)-type CMOS (complementary metal-oxide-semiconductor transistor) image sensor comprises an operational amplifier, an N+1-stage integrator, a sampling switch and an integral restrictor, and also comprises two positive feedback capacitors; one of the two positive feedback capacitors is connected between the positive input end and the positive output end of the operational amplifier, and the other positive feedback capacitor is connected between the negative input end and the negative output end of the positive feedback capacitor. The analog accumulator disclosed by the invention is mainly applied to the integrated circuit design.

Owner:TIANJIN UNIV

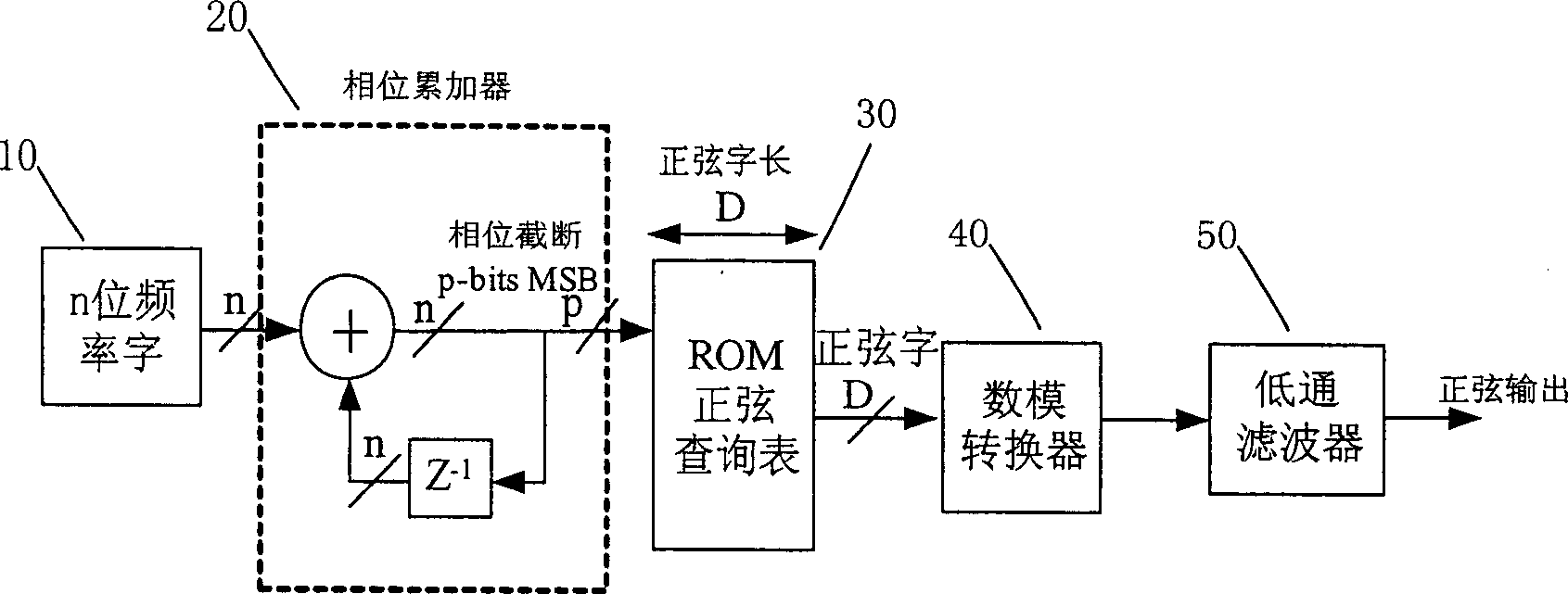

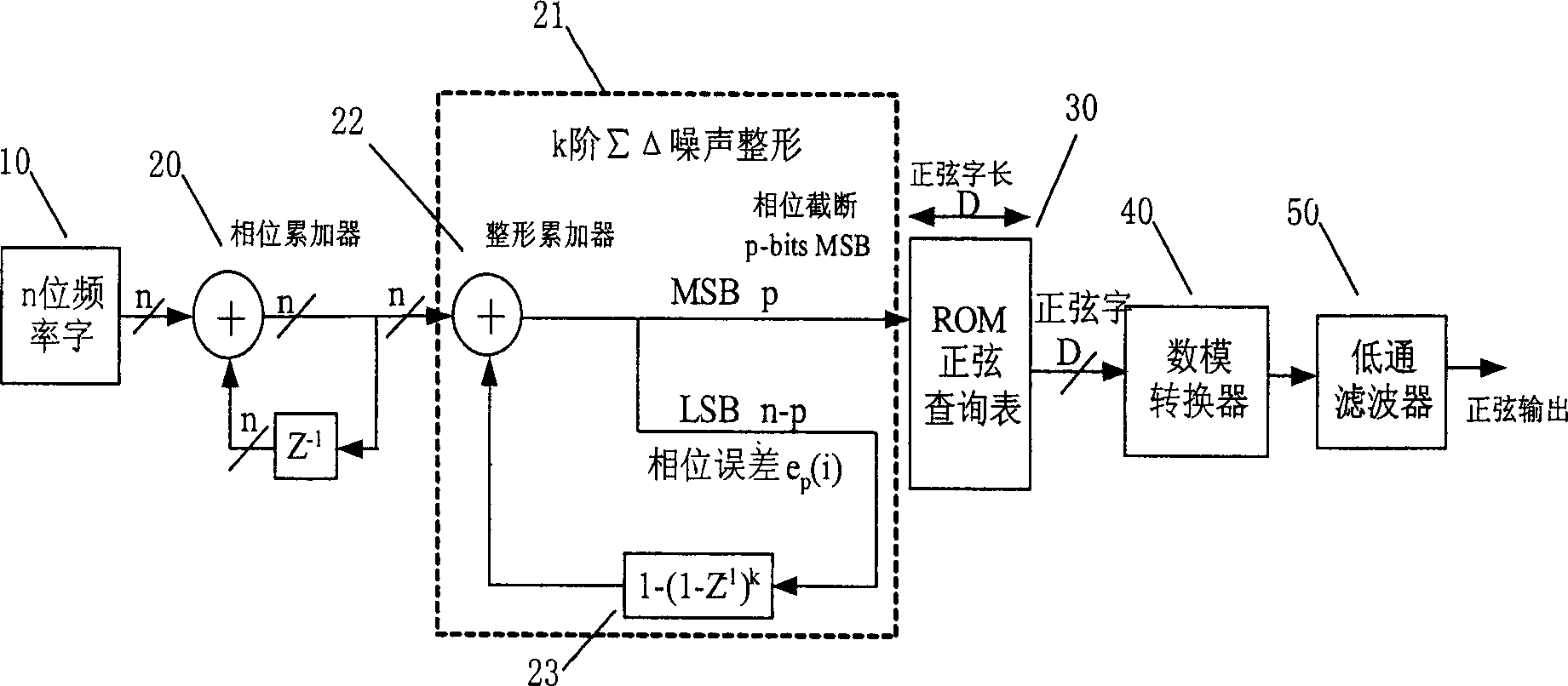

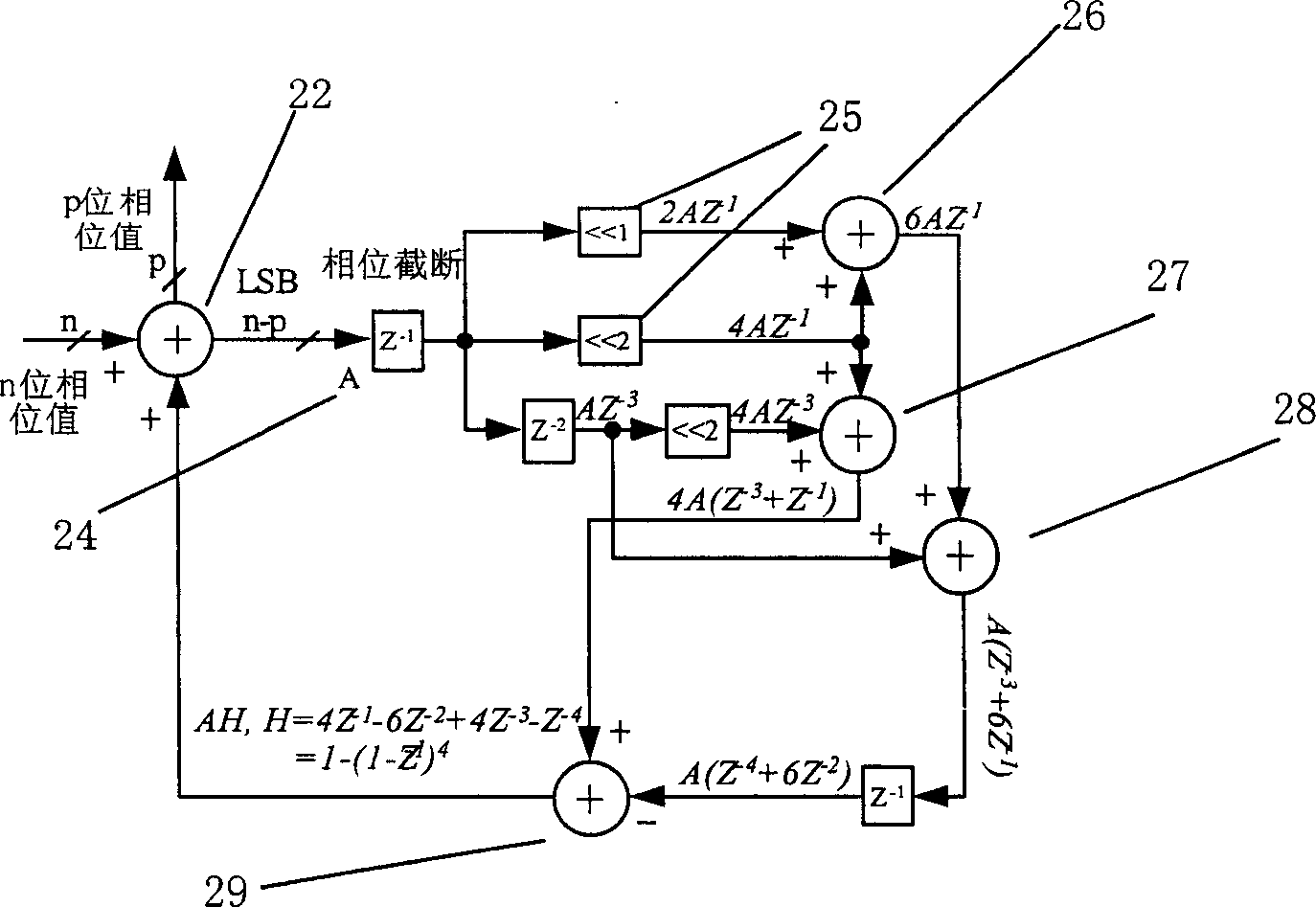

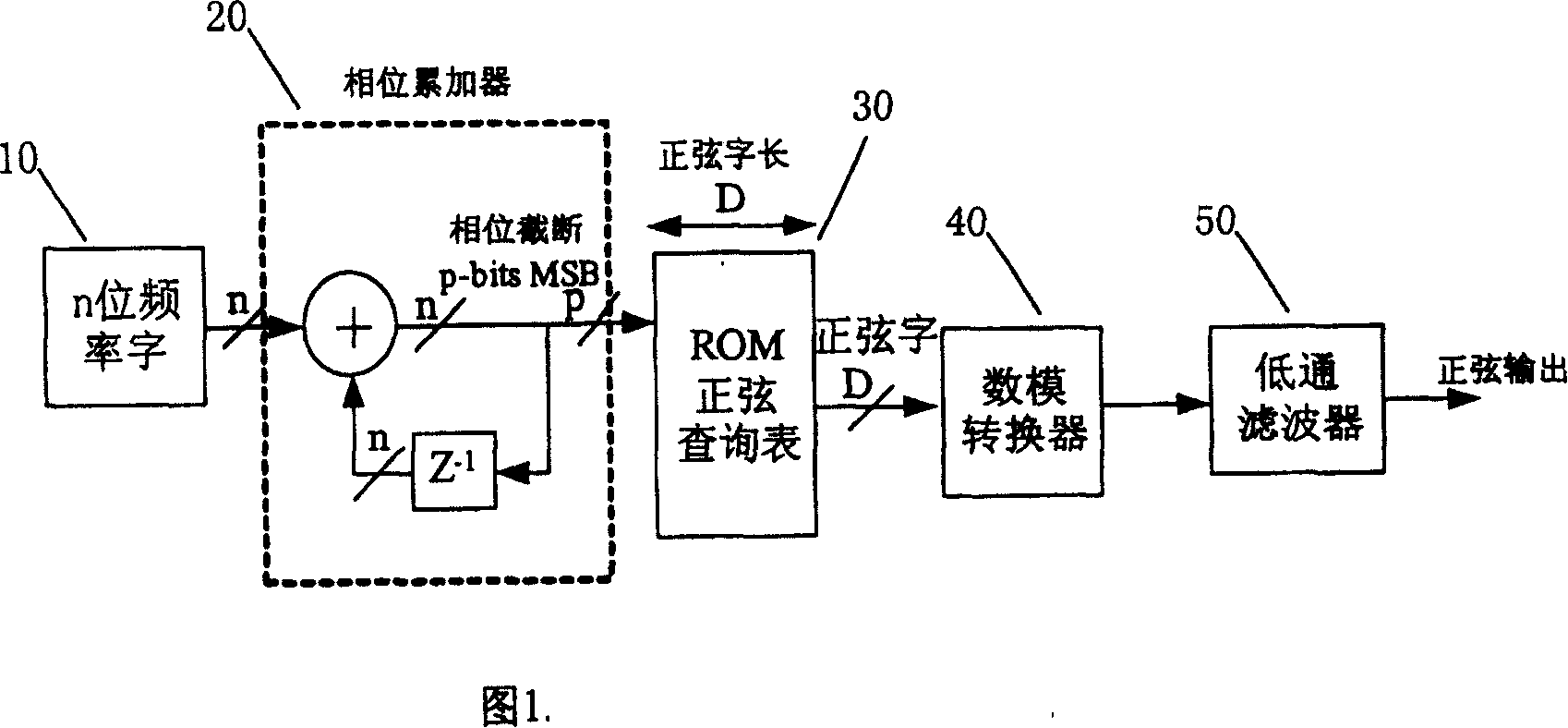

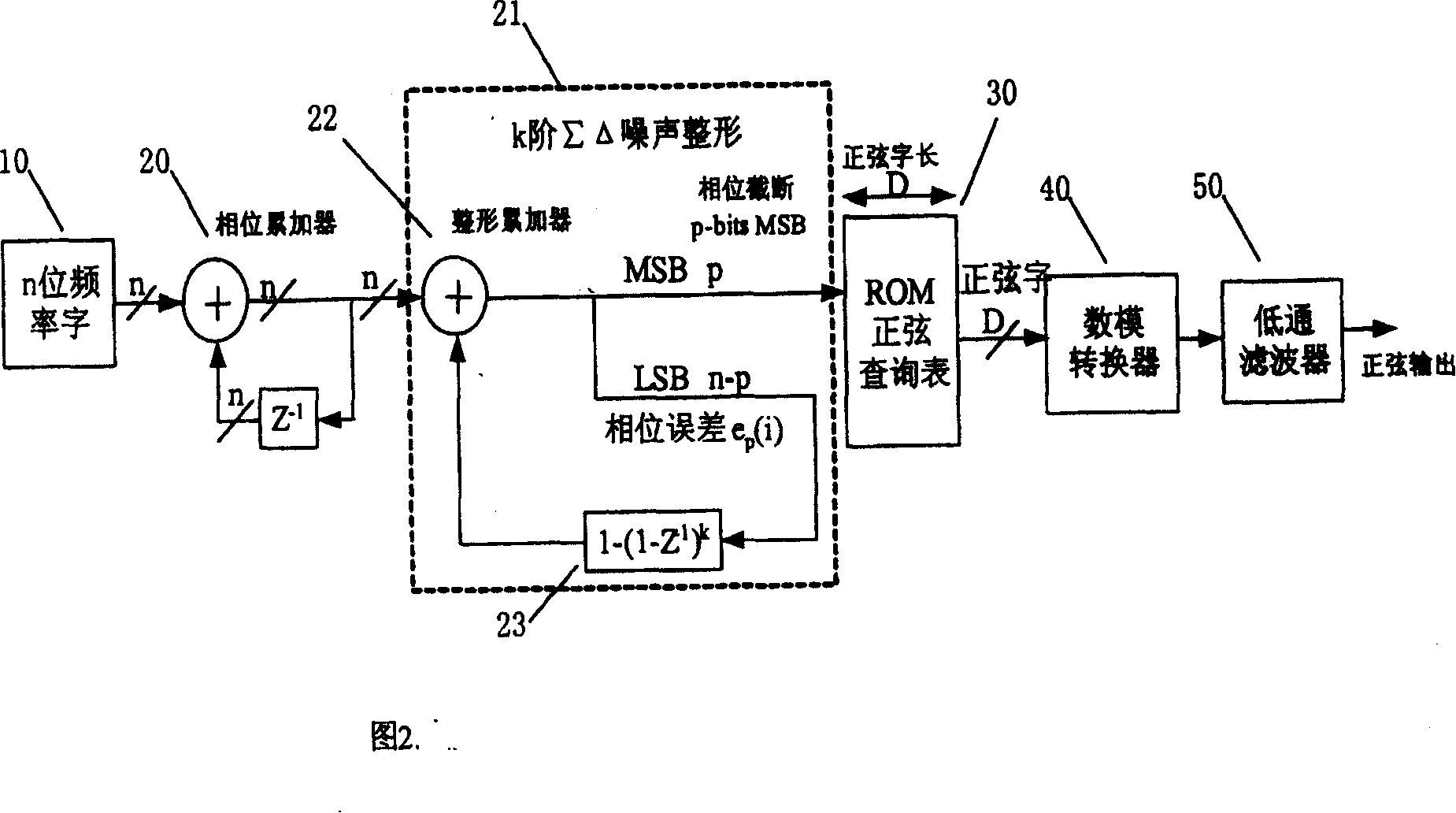

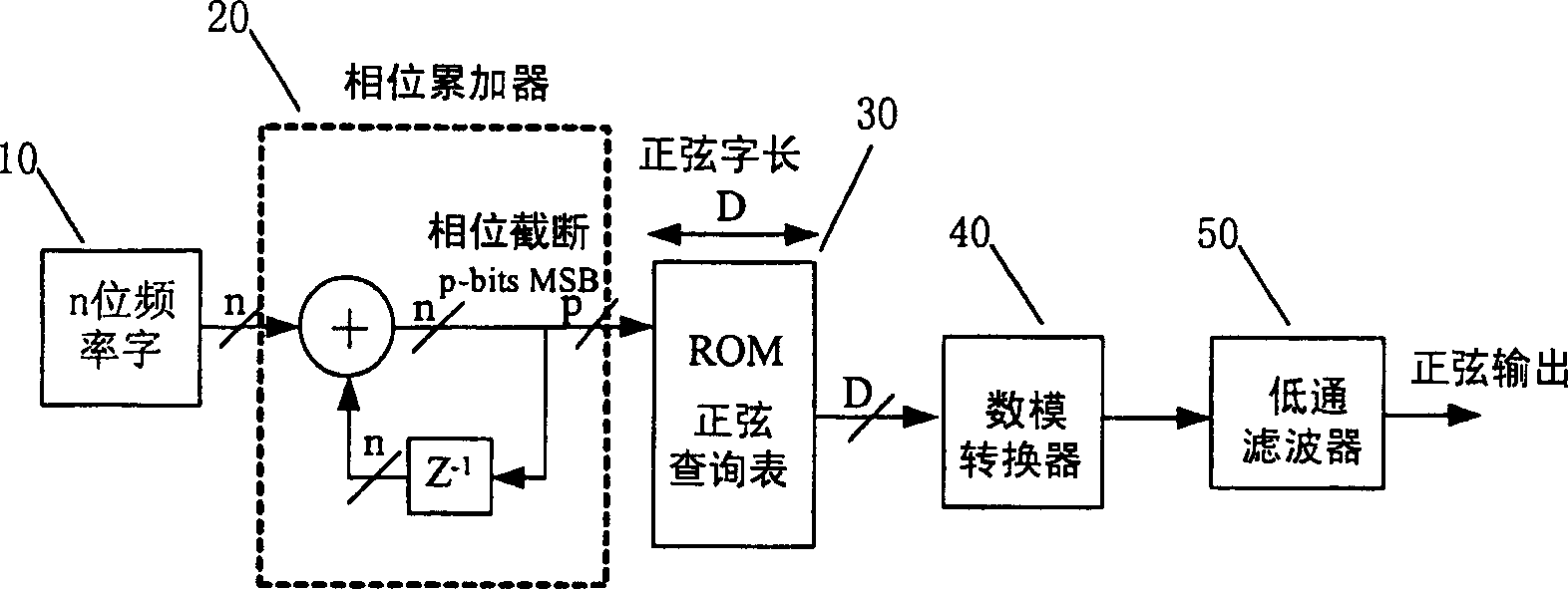

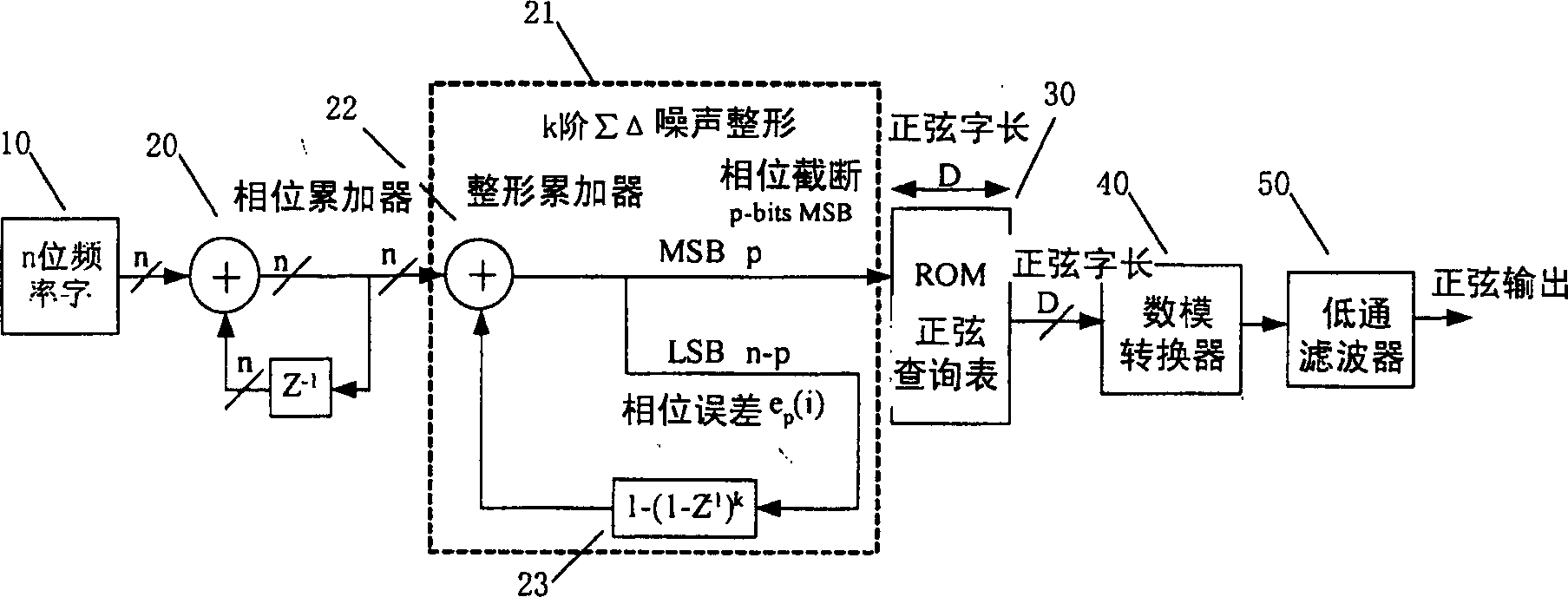

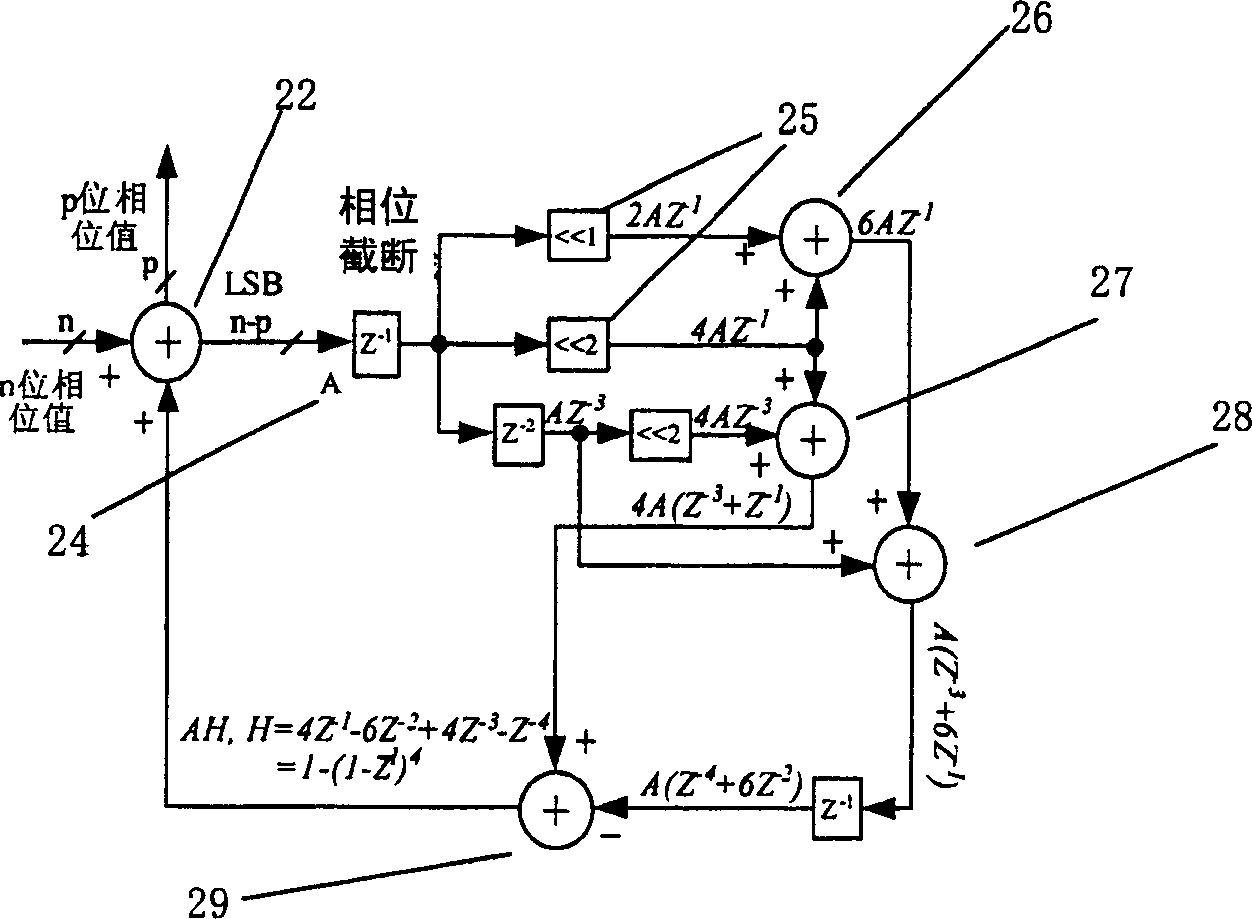

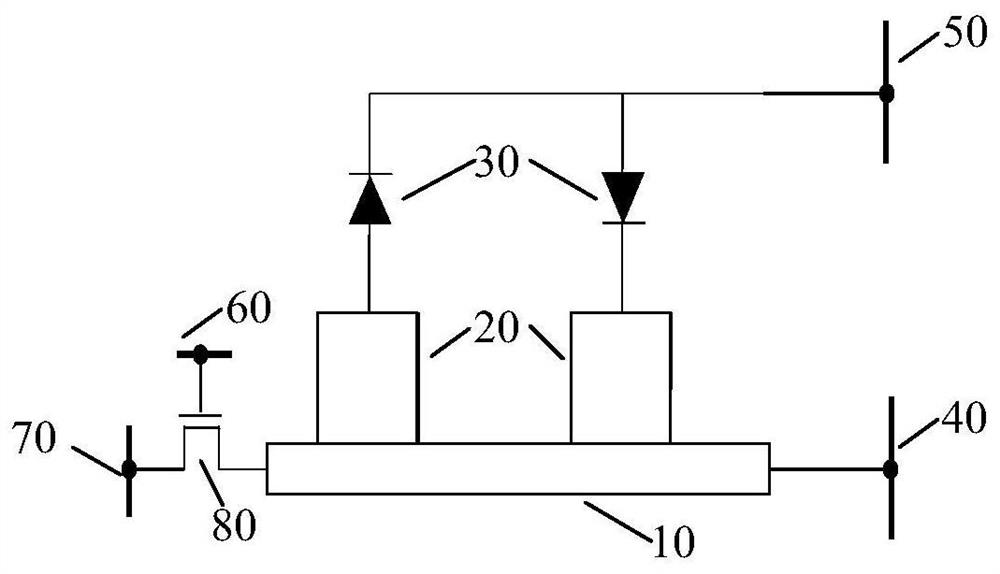

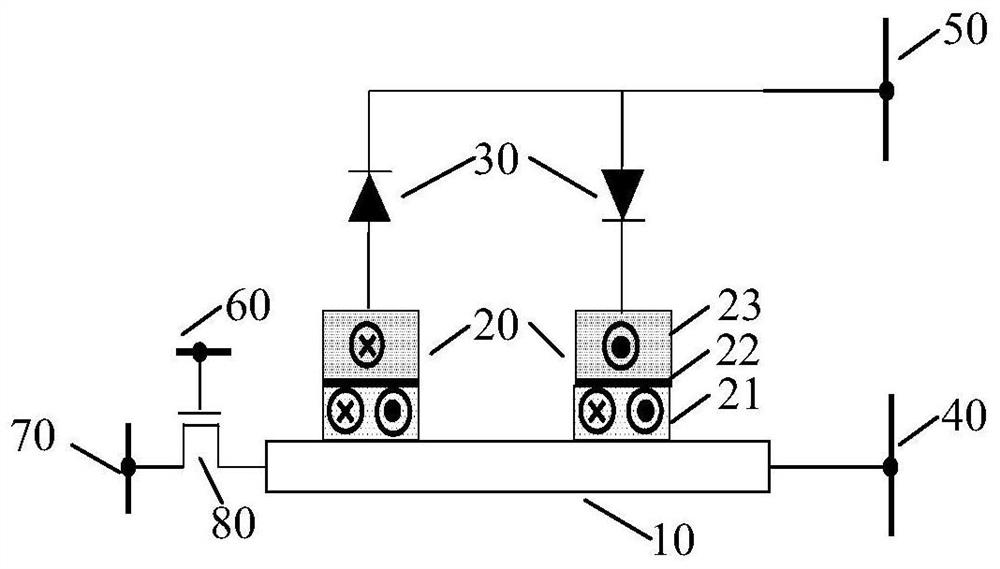

High order sigmatriangle noise shaping interpolator for direct digital frequency synthesis

InactiveCN1805271ANo increase in areaReduce areaPulse automatic controlDelta modulationLow noiseDigital analog converter

The invention relates to a high-order sigma delta noise rectification interpolator used in direct digital frequency synthesizer. The invention comprises a rectification accumulator (22), a delay circuit (23) and a phase accumulator (20). The external N bit frequency is input into the phase accumulator (20) whose output is connected to the rectification accumulator (22); the output of rectification accumulator (22) is used as the high p bits of the phase of sine or cosine and as the lower N-p bits of cut section, to connect the delay circuit (23) to process the transmission function as 1-(1-Z-1)n, to be output to the rectification accumulator (22); the output of rectified phase is connected to the sine or cosine look-up list (30) whose output via the digital / analogue converter (40) and the low-pass filter (50) is transformed to the sine or cosine wave with lower noise.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

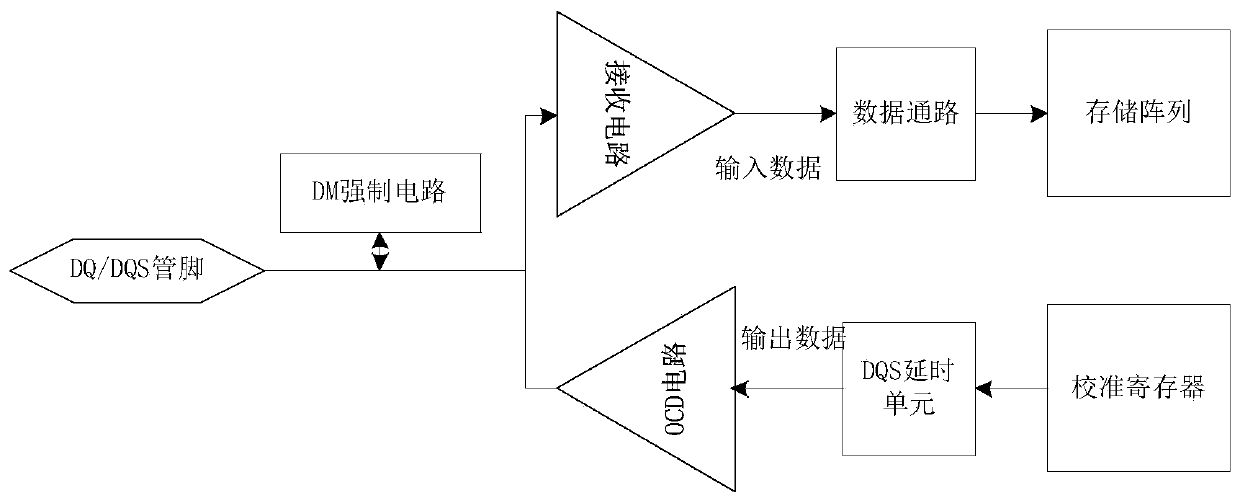

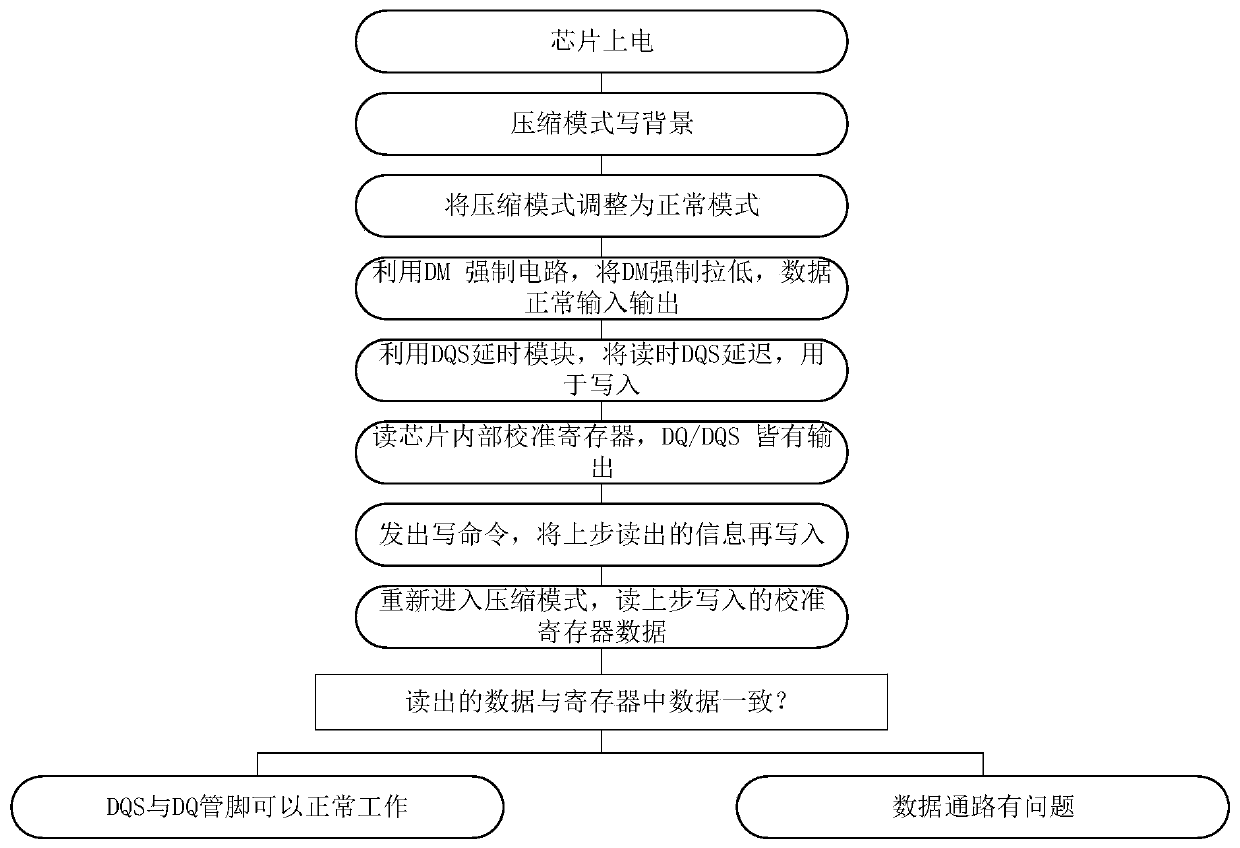

DRAM wafer level pin connectivity test circuit and method

ActiveCN110827911ANo increase in areaReduce difficultyStatic storageComputer architectureHemt circuits

The invention discloses a DRAM (dynamic random access memory) wafer-level pin connectivity test circuit and a method. The circuit structure comprises a calibration register, a delay unit, an OCD circuit, a receiving circuit, a data path and a storage array which are connected in sequence, input signals of a DQ pin and a DQS pin of a DRAM wafer level are transmitted into a chip through the receiving circuit, and output signals of the DQ pin and the DQS pin are driven through the OCD circuit. DM pin input signals of the DRAM wafer level are transmitted into the chip through the receiving circuit, and output signals of the DRAM wafer level control the level through the DM forced circuit. According to the invention, under the condition of not adding extra pin connection, the functions of all DQ data paths and DQS and DM pins are completely verified, the test comprehensiveness is improved, and the design difficulty and cost of the test pin card are not increased; for subsequent back-end testing, the bad chips are screened out in advance, the packaging cost is reduced, and the back-end testing yield is improved. And for KGD type products, the DPM is reduced, and the product quality is ensured.

Owner:XI AN UNIIC SEMICON CO LTD

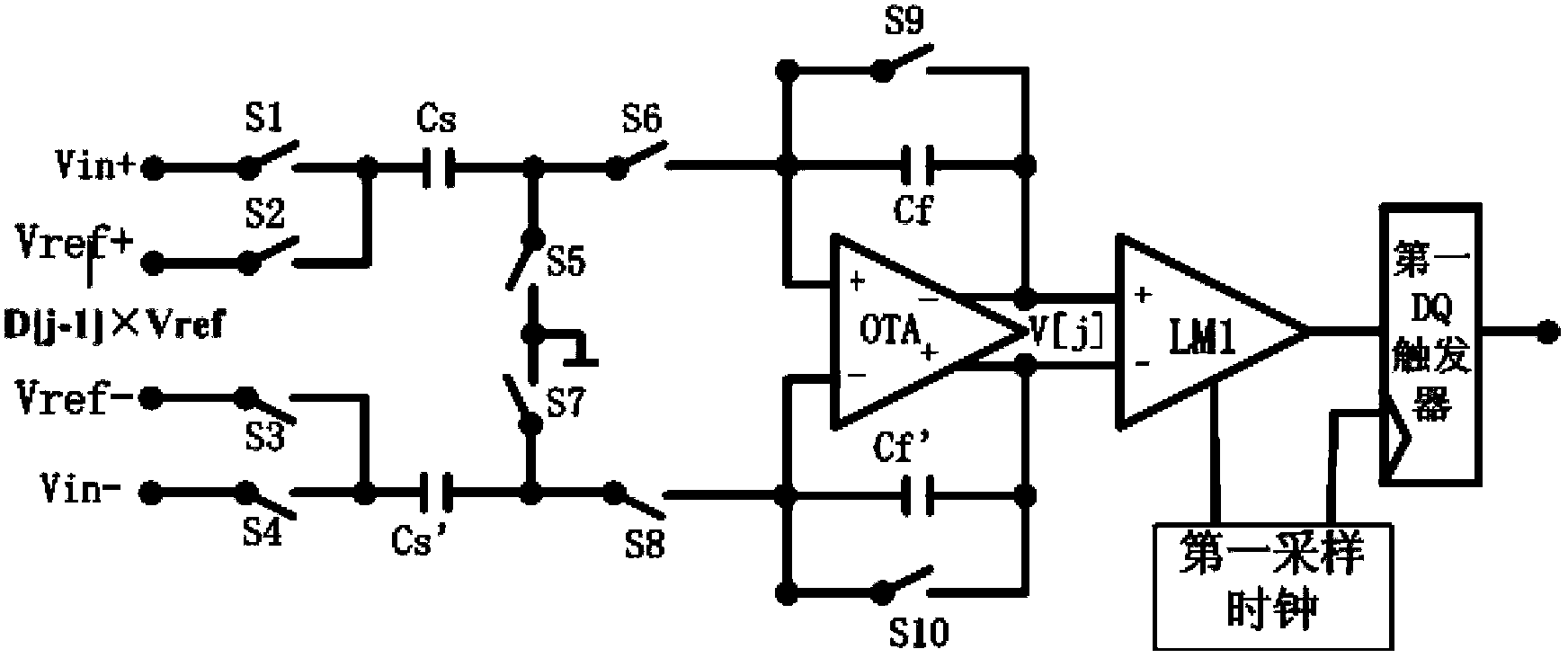

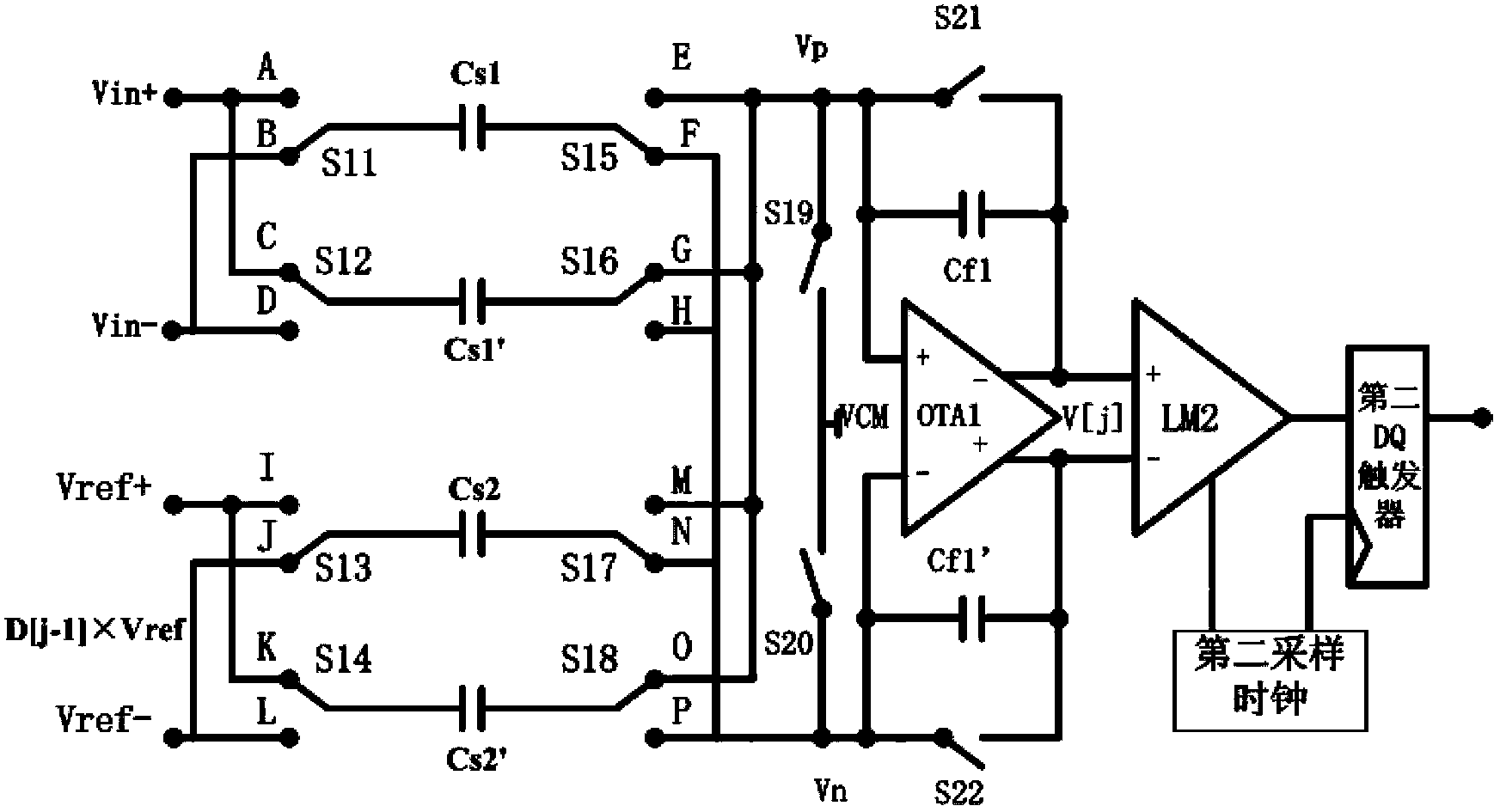

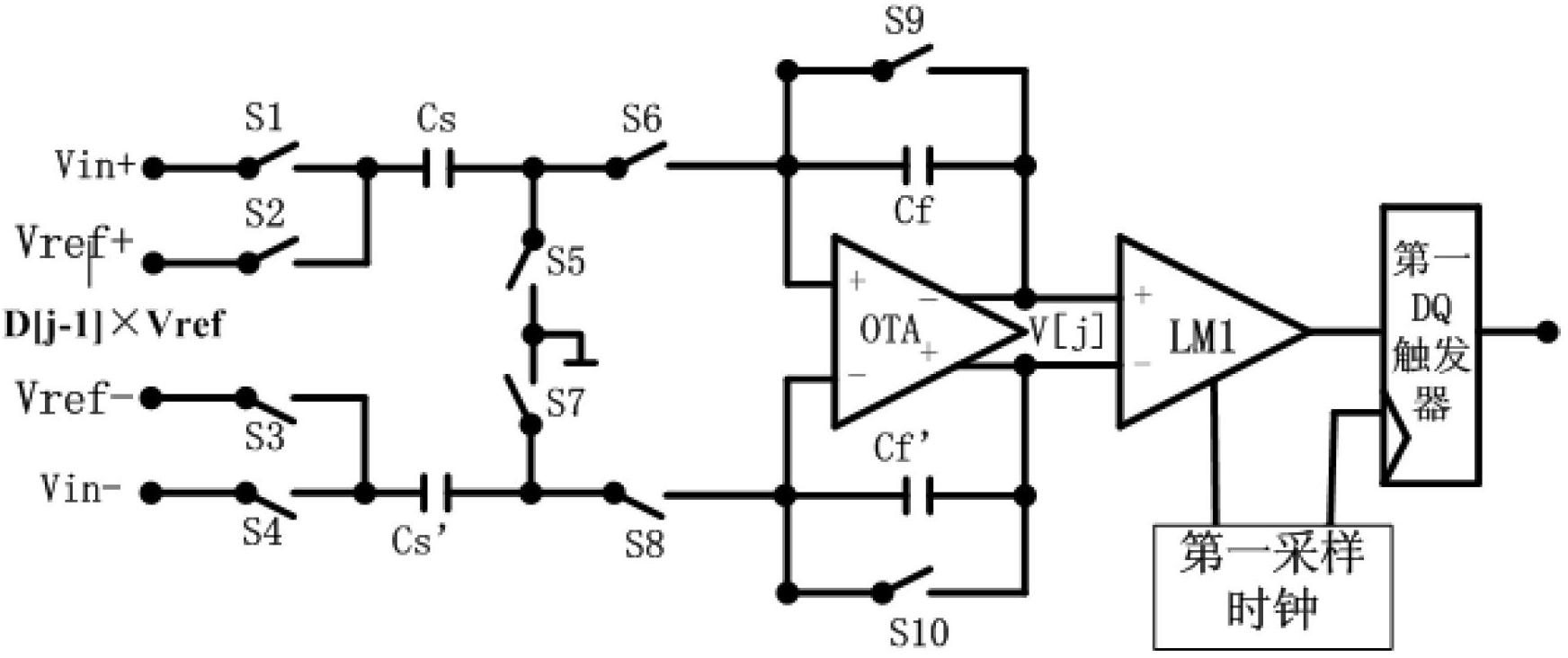

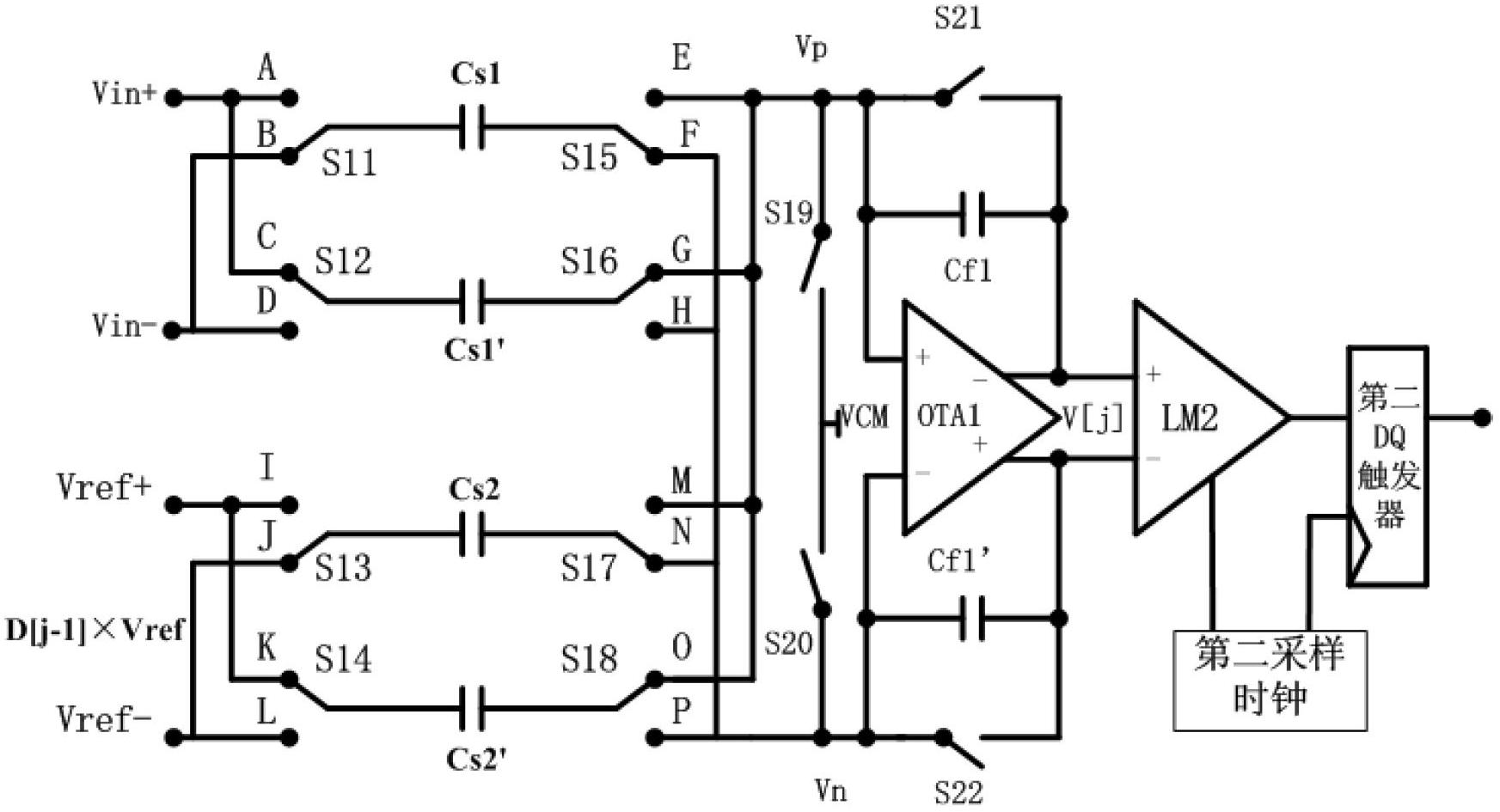

Double-sampling modulator applicable to incremental sigma delta ADC (analog to digital converter)

InactiveCN102694551BNo increase in areaImprove power efficiencyAnalogue-digital convertersCapacitanceIntegrator

The invention relates to a double-sampling modulator applicable to incremental sigma delta ADC (analog to digital converter) in the field of high precision analog to digital converters. A circuit structure of a complete floating double linear integrator is used, and two set of sampling capacitors and four reset switches are used. The double-sampling modulator has the advantages that power efficiency is enhanced, the problem of linearity deterioration caused by mismatch of the capacitors is solved, and chip area is not increased.

Owner:TSINGHUA UNIV

Double-sampling modulator applicable to incremental sigma delta ADC (analog to digital converter)

InactiveCN102694551ANo increase in areaImprove power efficiencyAnalogue-digital convertersCapacitanceIntegrator

The invention relates to a double-sampling modulator applicable to incremental sigma delta ADC (analog to digital converter) in the field of high precision analog to digital converters. A circuit structure of a complete floating double linear integrator is used, and two set of sampling capacitors and four reset switches are used. The double-sampling modulator has the advantages that power efficiency is enhanced, the problem of linearity deterioration caused by mismatch of the capacitors is solved, and chip area is not increased.

Owner:TSINGHUA UNIV

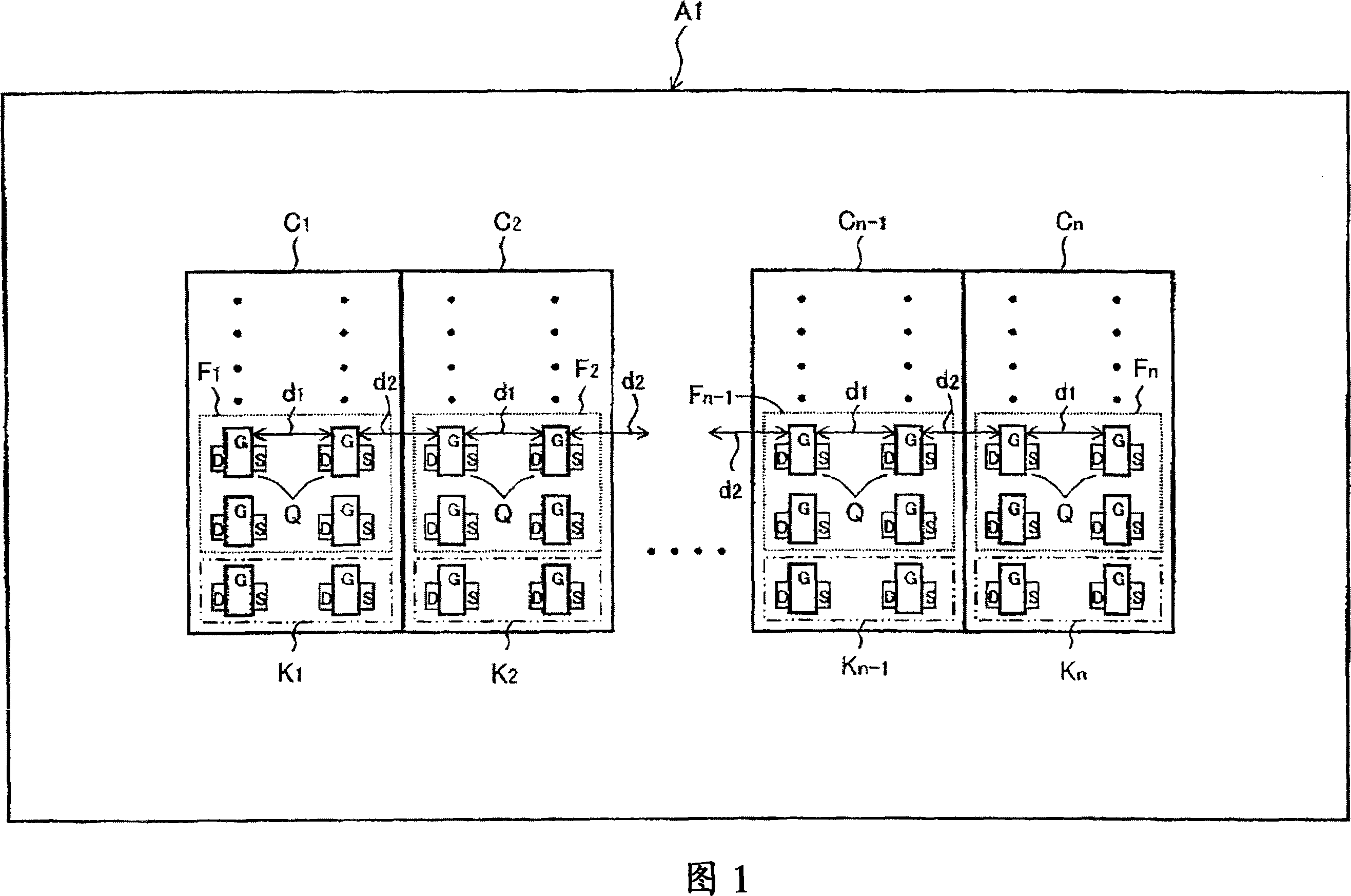

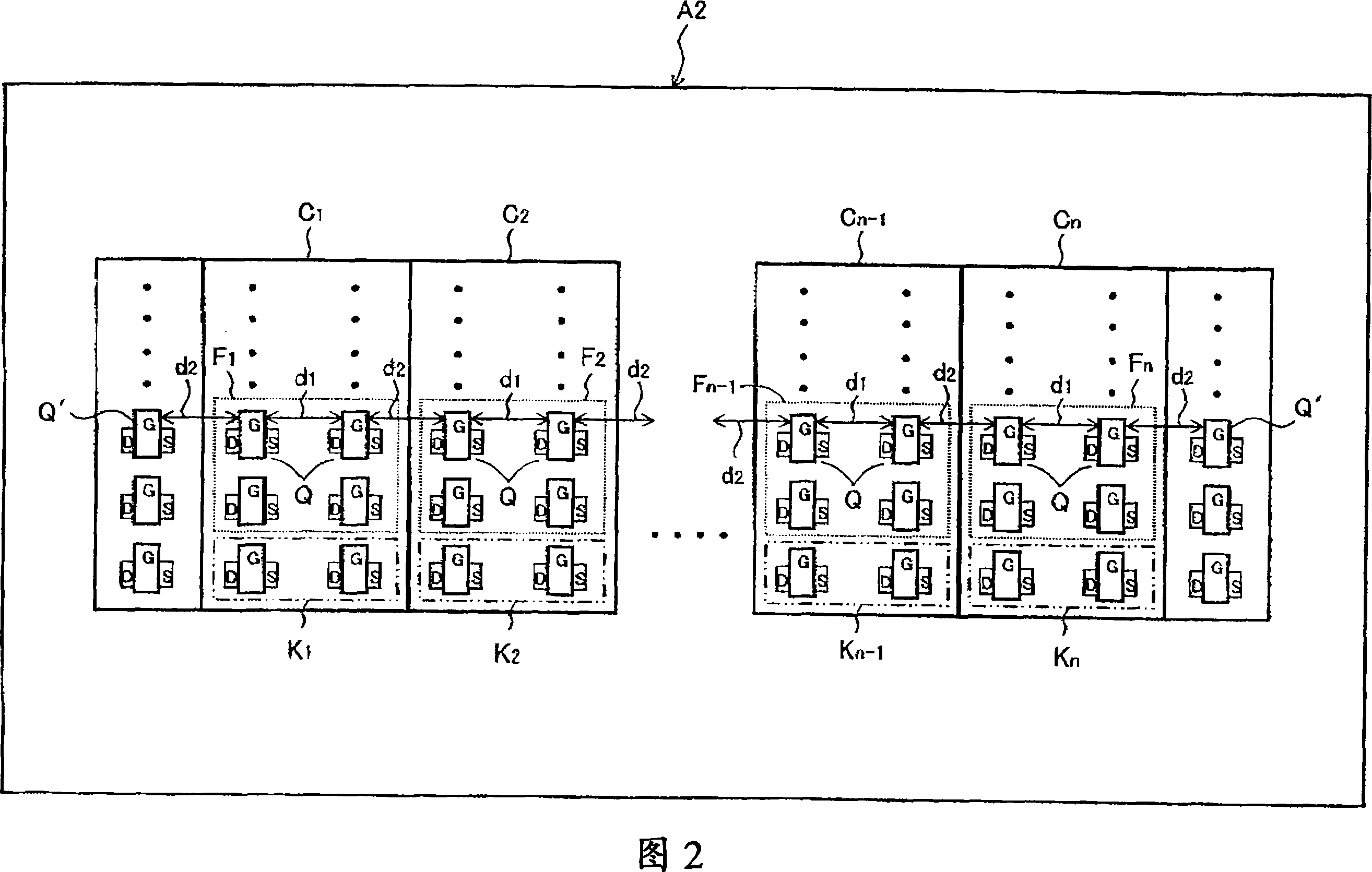

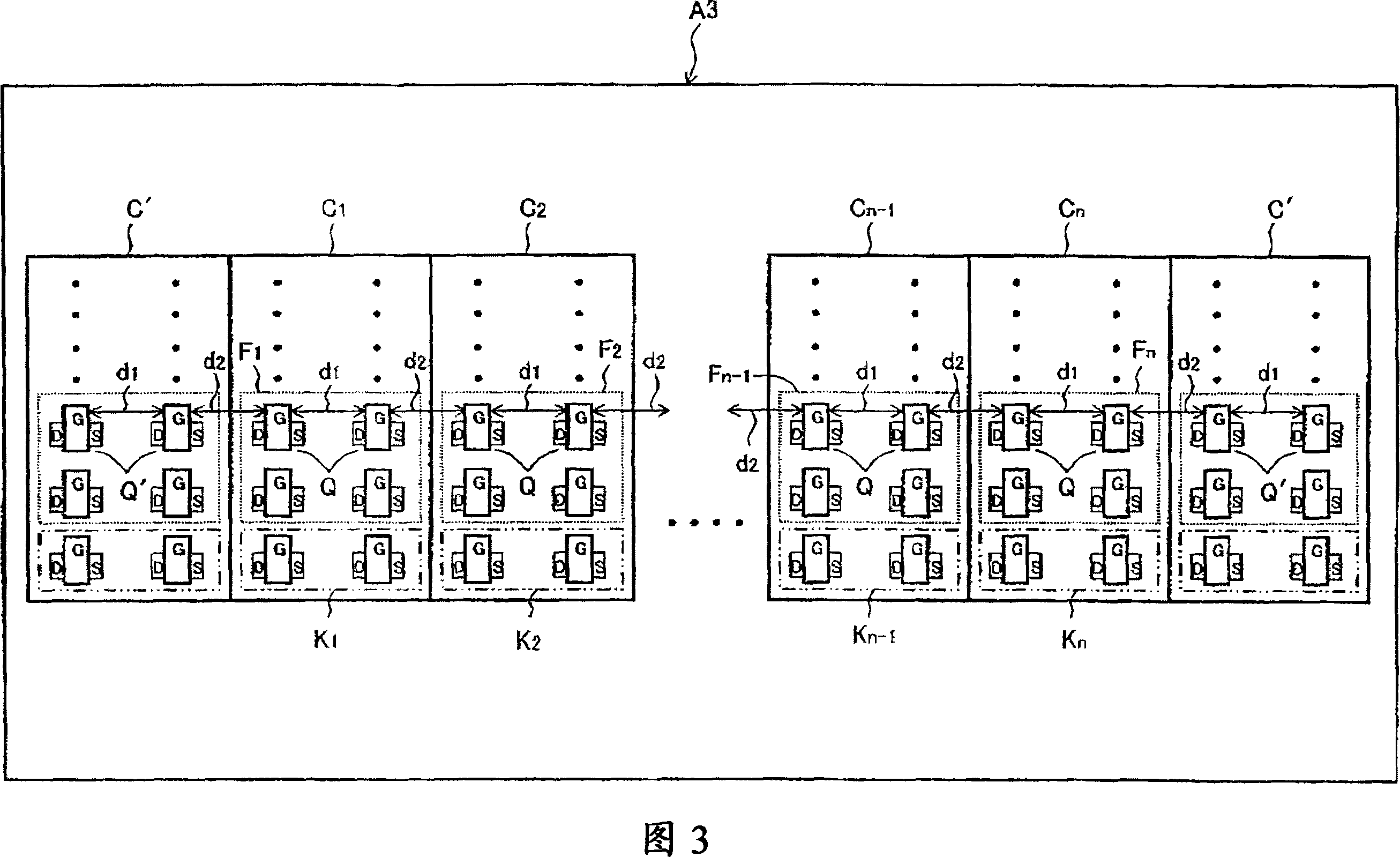

Layout method and semiconductor device

InactiveCN101093302AThe output characteristics are consistentWithout complexityStatic indicating devicesComputer aided designEngineeringTransistor

The present invention is provided with a plural cell including a transistor pair. The plural cells are arranged at equal intervals so as to configure a cell group. A inter-cell distance between a transistor in one of the cell and a transistor the other cell in each of adjacent cells in the cell group is equal to a intra-cell distance between one of the transistor and the other transistor in the transistor pair.

Owner:PANASONIC CORP

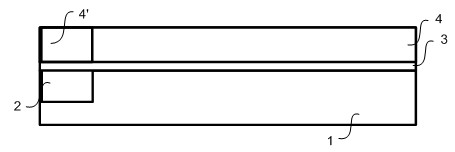

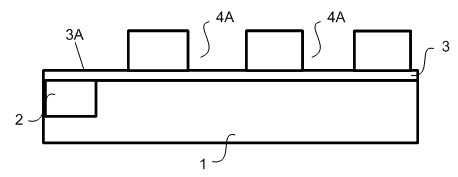

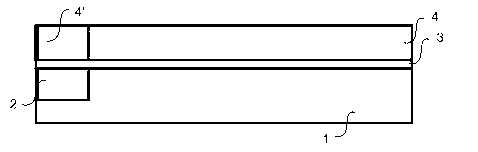

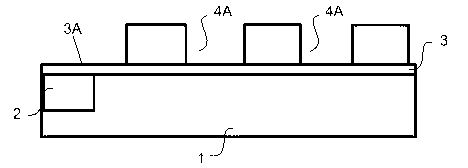

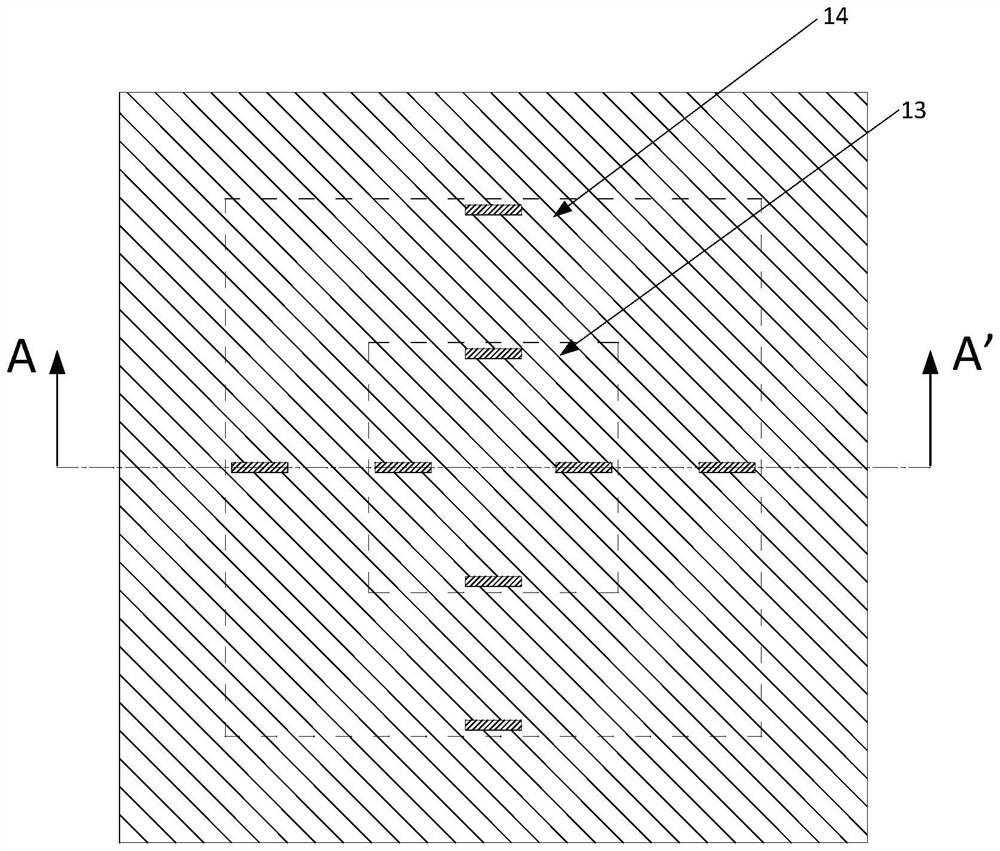

Method for improving metal-insulation-metal (MIM) capacitance density in semiconductor device and device

ActiveCN102420110AIncrease capacitance densityImprove compatibilitySolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceState of art

The invention discloses a method for improving metal-insulation-metal (MIM) capacitance density in a semiconductor device and a semiconductor device containing high-density MIM capacitance. The method comprises the following steps that: an appearance layer is arranged on a stop layer of a substrate, the appearance layer is etched, so the appearance layer is provided with a plurality of grooves, and a capacitance substrate covering the appearance layer is in a appearance shape to increase the area of the capacitance substrate and to further increase the capacitance density. Due to the adoption of the method, compared with the prior art, the area of a wafer is not increased, and a strong compatibility can be realized compared with the traditional technique.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

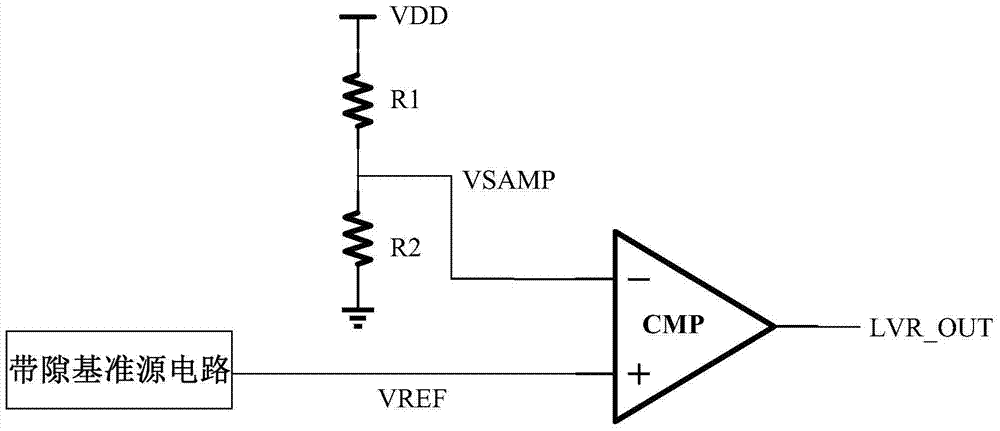

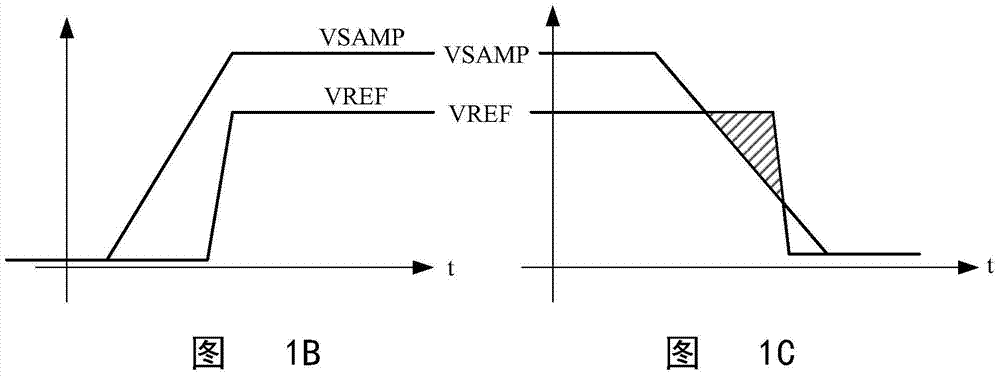

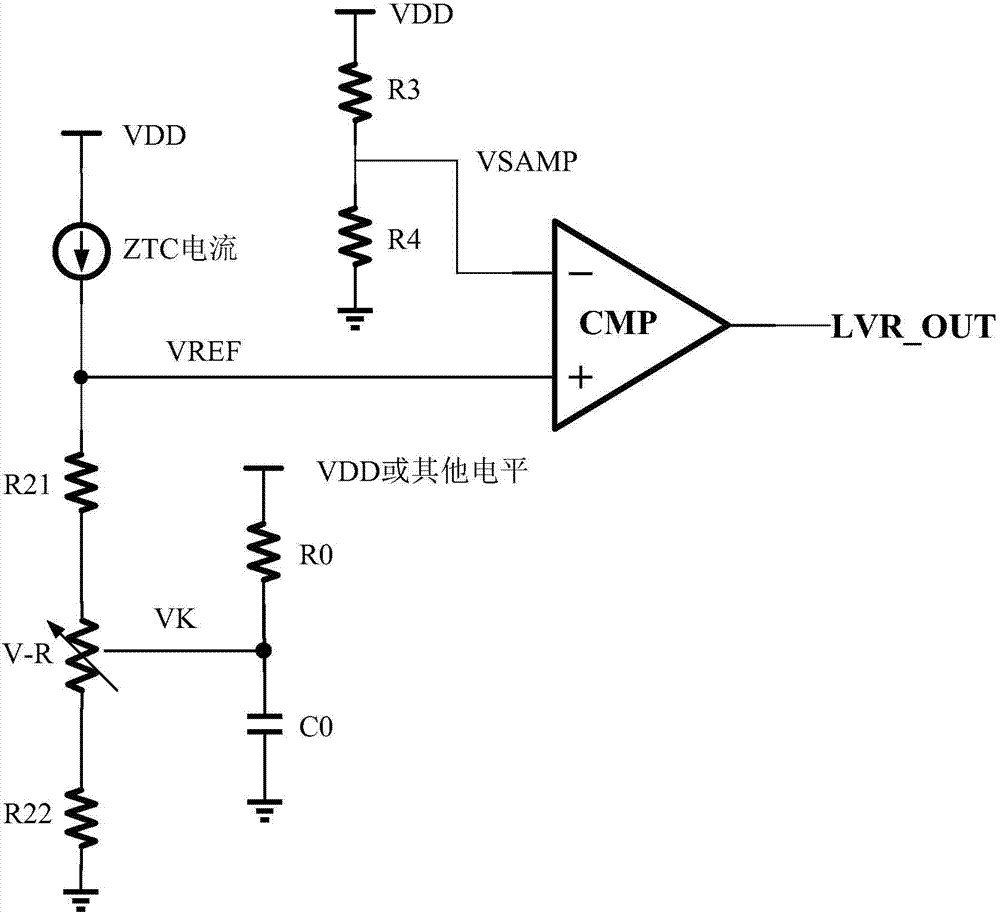

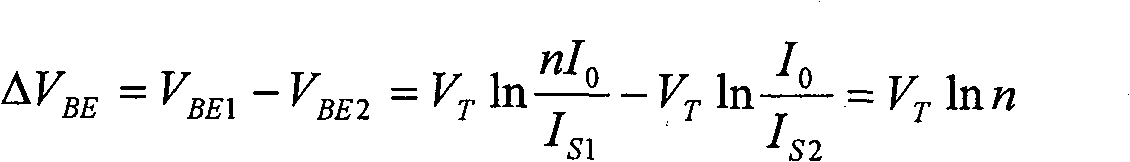

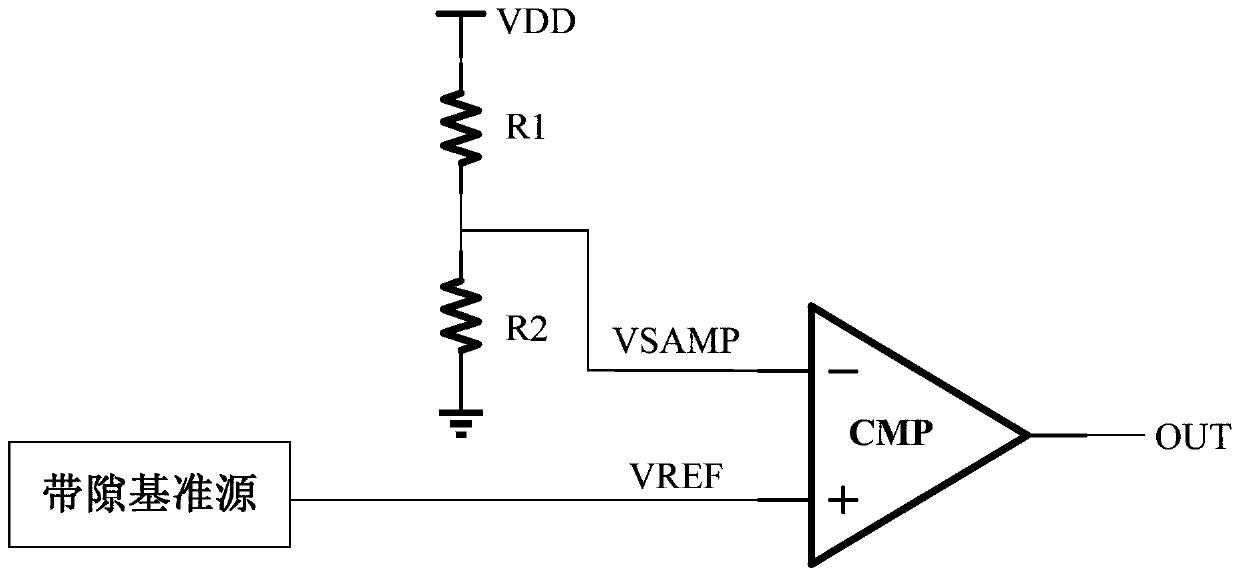

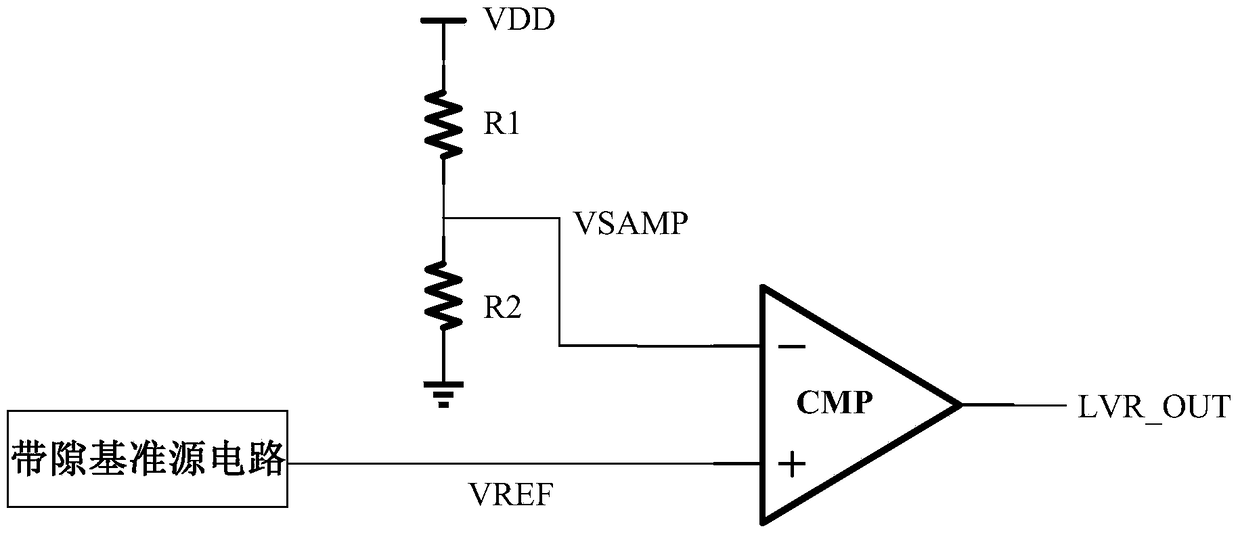

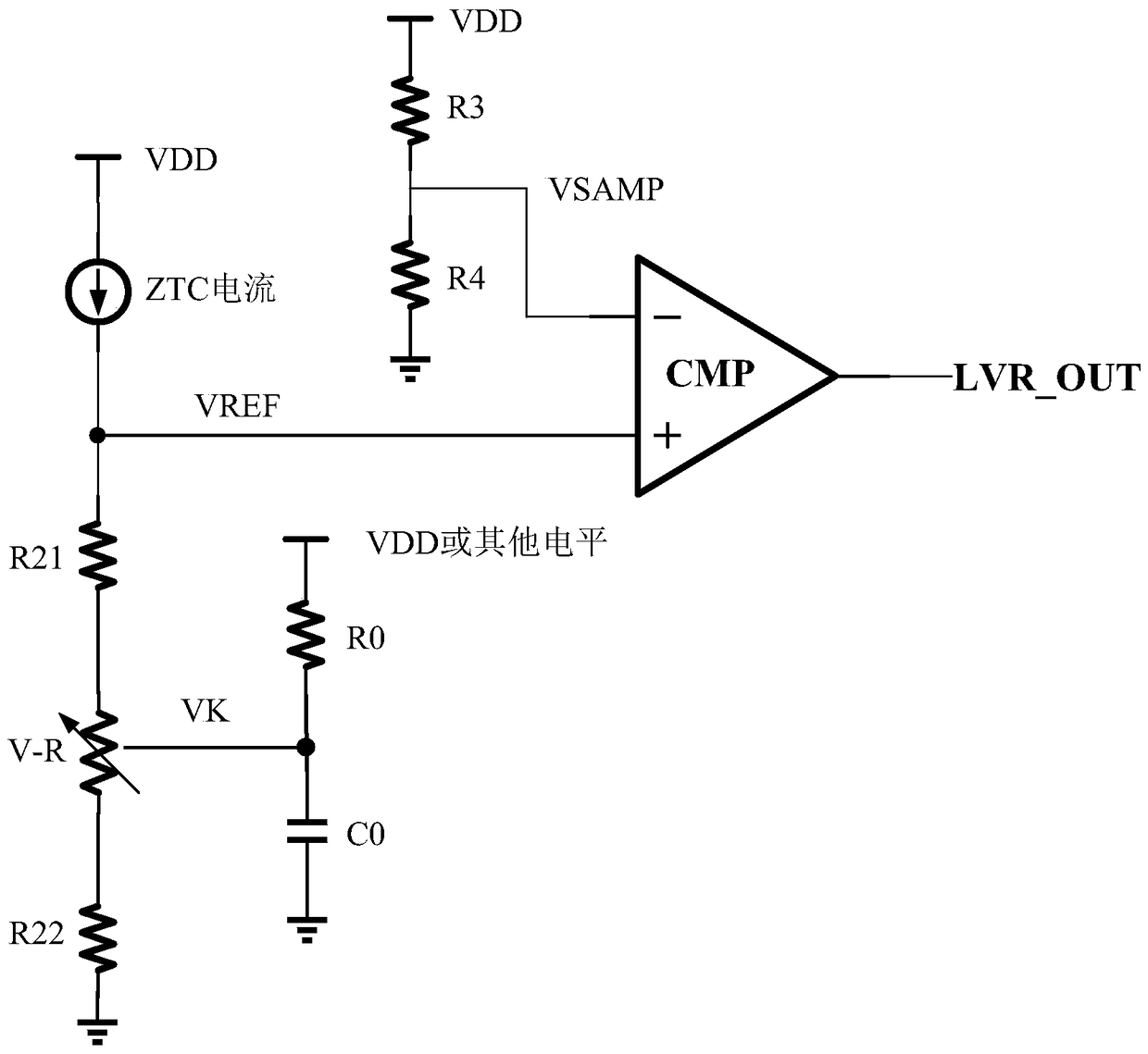

Low-voltage reset circuit

The invention provides a low-voltage reset circuit. The low-voltage reset circuit comprises a current source, a first resistor, a second resistor, a third resistor, a fourth resistor, a comparator and a voltage-controlled resistor; the current source, the first resistor, the voltage-controlled resistor and the second resistor are sequentially connected in series and are connected between a supply voltage and the ground; the third resistor and the fourth resistor are connected with each other in series and are connected between the current source and the ground; the negative input end of the comparator is connected with sampling voltages extracted from the third resistor and the fourth resistor; the positive input end of the comparator is connected with sampling voltages extracted from the current source and the first resistor, and the current source generates a current with a zero-temperature coefficient or a current with a positive-temperature coefficient and then is used for generating a stable reference voltage. According to the low-voltage reset circuit, a high-level pulse reset signal is generated correctly; in addition, when a system power source powers down to an ultra-low voltage, the reset signal cannot be released wrongly.

Owner:西安中颖电子有限公司

Output adjustable band-gap reference source circuit

An output adjustable band-gap reference source circuit is characterized by comprising: a high-gain operational amplification circuit; a voltage generation circuit independent of temperature and power source connected with the input end and output end of the high-gain operational amplification circuit by nodes, so as to implement output clamping effect; a start circuit, the output of which is connected to the node of the voltage generation circuit independent of temperature and power source to prevent the voltage generation circuit independent of temperature and power source entering a dead region; an output regulation circuit, the input of which is connected to the voltage generation circuit independent of temperature and power source, thereby to implement output clamping effect, and the output is the output of the whole band-gap reference source circuit.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Method for reducing stray capacitance in analogue circuit

InactiveCN101174583AImprove working bandwidthNo added costSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerParasitic capacitance

The invention relates to a method for reducing the parasitic capacitance in analog circuit, which comprises the following steps: an insulation layer is grown on the semiconductor substrate; then a signal line is prepared on the insulation layer, wherein, an N well layer is introduced before growing the insulation layer and is arranged between the insulation layer and the semiconductor substrate. The invention has the advantages that the parasitic capacitance is reduced without increasing the layout area simultaneously, that is, the parasitic capacitance of signal is reduced without increasing the circuit cost.

Owner:ZTE CORP

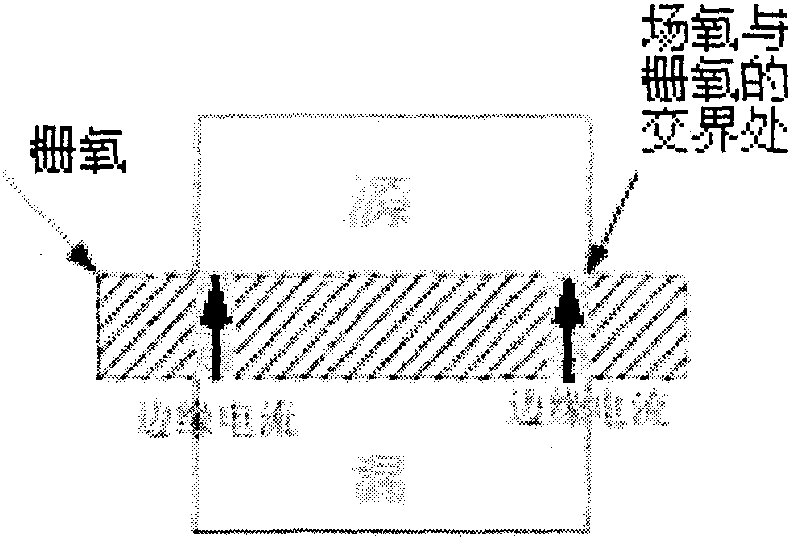

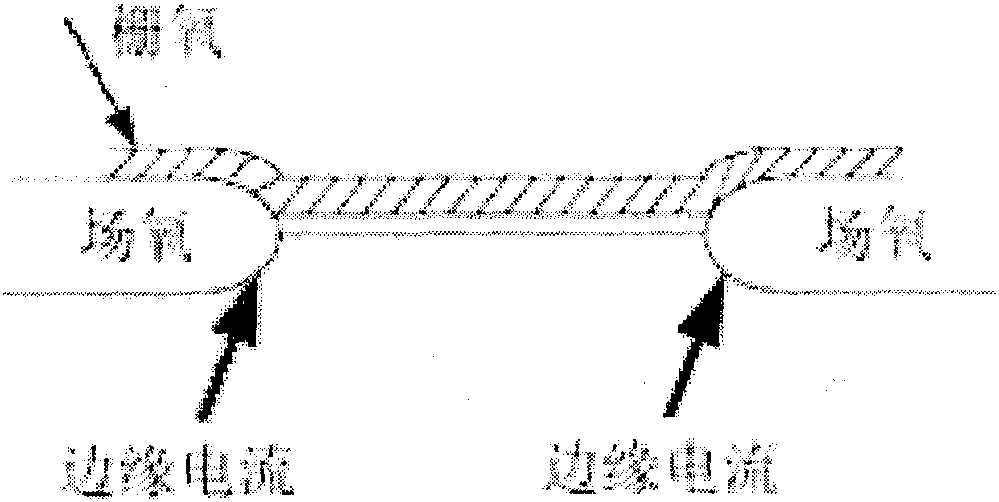

variable gate transistor

ActiveCN111630955BNo increase in areaEliminates edge leakage conditionsSemiconductor/solid-state device manufacturingGate leakage currentEngineering

The invention proposes a variable gate transistor that can be applied in the anti-radiation layout reinforcement technology. Including inserting gate oxide between the source terminal and the source terminal edge, between the drain terminal and the drain terminal edge, thereby cutting off the path from the source terminal to the source terminal edge and cutting off the current from the source terminal to the source terminal edge to the drain terminal edge to the drain terminal , while cutting off the current from drain to drain edge to source edge to source. Using this method, the basic structure of the transistor does not change, and the edge leakage current is well eliminated. Compared with ordinary gate transistors, for the same effective width-to-length ratio, the variable-gate transistor does not increase the area, and the effective width-to-length ratio is basically the same as that of ordinary gate transistors. The gate is consistent, and the source and drain regions are completely symmetrical.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP

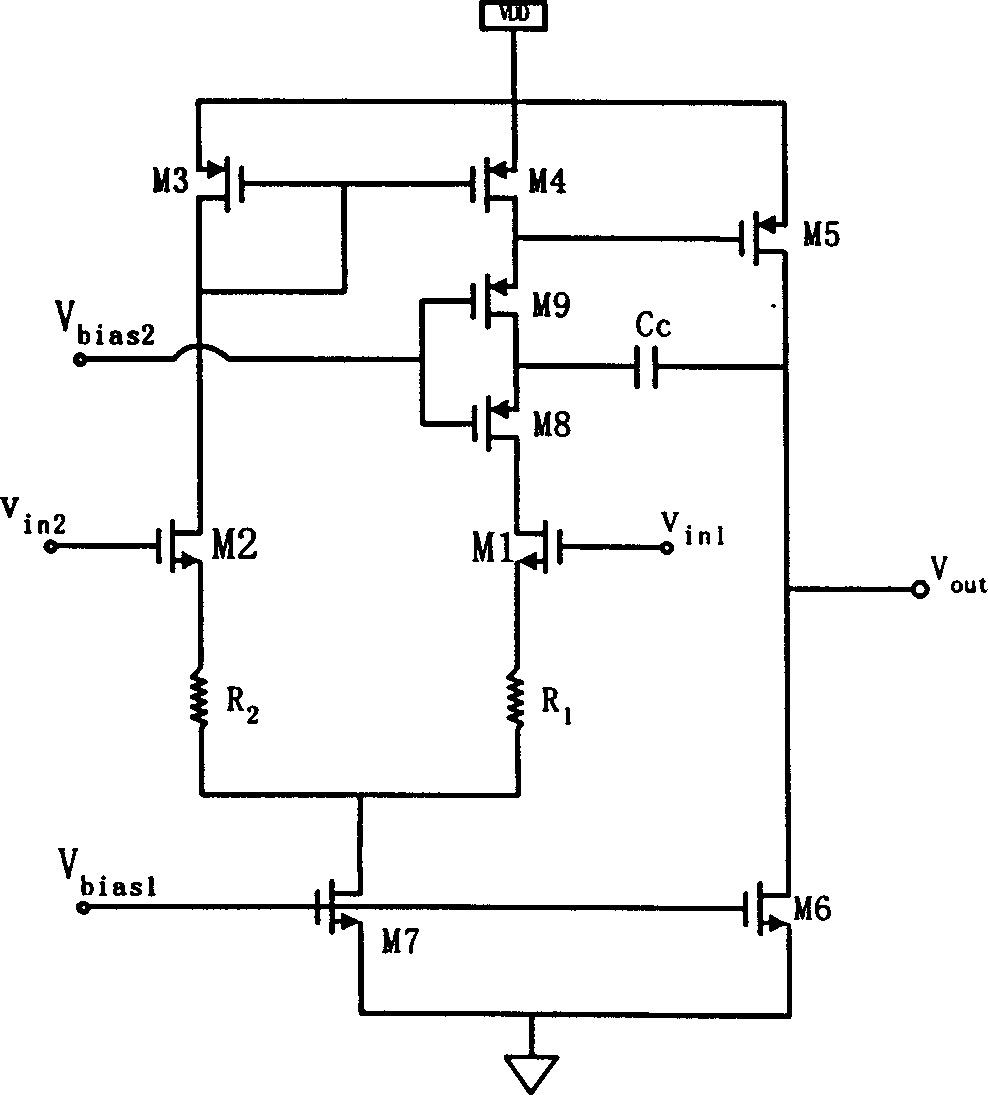

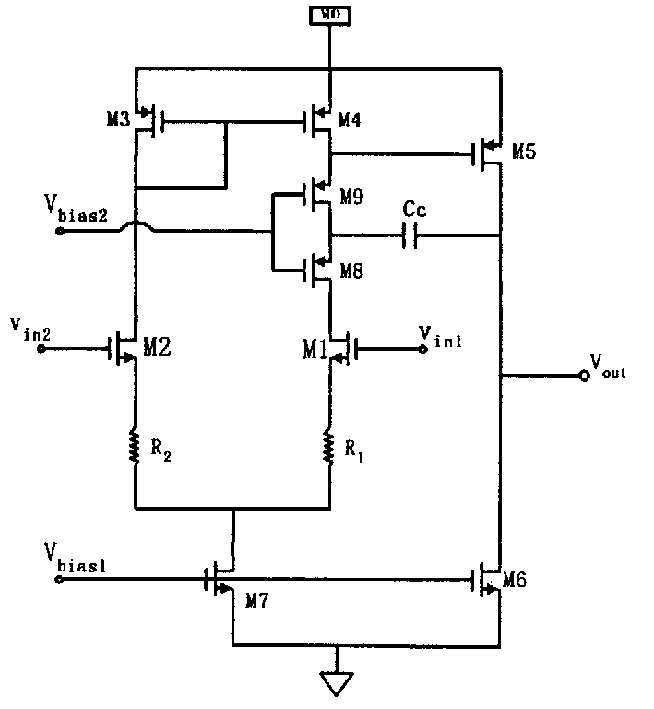

High-gain complementary metal oxide operation amplifier

InactiveCN1453931AHigh gainGood amplitude-frequency characteristicsSolid-state devicesDifferential amplifiersAudio power amplifierEngineering

The amplifier is composed of transistor and resistance which are prepared on the substrate. The source electrodes of amplifying tubes M1 and M2 are connected with earth separately through transistor M7 as two dissipative transistors M8 and M9 are connected with output electrode of amplifying tube M1 in series with M9 output end being connected to power source through constant-current source M4 and output end of amplifying tube M2 is connected with power source, bias voltage Mbias 1 and Vbias2 through constant-current source M3 as Vbias 2 being used to provide grid voltage for transistor M8 and M9 with its dynamic operative range of 3V and its gain up to 100 db within the entire operative range.

Owner:SOUTHEAST UNIV

High order Epsilon Delta noise shaping interpolator for direct digital frequency synthesis

InactiveCN100392976CNo increase in areaReduce areaPulse automatic controlDelta modulationLow noiseDigital analog converter

The invention relates to a high-order sigma delta noise rectification interpolator used in direct digital frequency synthesizer. The invention comprises a rectification accumulator (22), a delay circuit (23) and a phase accumulator (20). The external N bit frequency is input into the phase accumulator (20) whose output is connected to the rectification accumulator (22); the output of rectification accumulator (22) is used as the high p bits of the phase of sine or cosine and as the lower N-p bits of cut section, to connect the delay circuit (23) to process the transmission function as 1-(1-Z-1)n, to be output to the rectification accumulator (22); the output of rectified phase is connected to the sine or cosine look-up list (30) whose output via the digital / analogue converter (40) and the low-pass filter (50) is transformed to the sine or cosine wave with lower noise.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Method for increasing metal-insulating layer-metal (MIM) capacitor density in semiconductor device and structure thereof

ActiveCN102437015BImprove quality factor QIncrease the areaSemiconductor/solid-state device detailsSolid-state devicesCapacitancePower semiconductor device

The invention discloses a method for increasing the metal-insulating layer-metal (MIM) capacitor density in a semiconductor device and the semiconductor device comprising a high-density MIM capacitor. An appearance layer is arranged on a blocking layer of a base, the appearance layer is etched so that the appearance layer is provided with a plurality of grooves, and a capacitor base plate covered on the appearance layer is in an appearance shape for increasing the area of the capacitor base plate, so the capacitor density is increased, and simultaneously, the matching of a high capacitor and a copper metal electrode plate is realized through the appearance layer. Compared with the prior art, the method and the semiconductor device have the advantages that the wafer area is not increased, and simultaneously, the method has high compatibility with the traditional process.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

High order sigma delta noise shaping direct digital frequency synthesizer

InactiveCN1783701ANo increase in areaReduce areaPulse automatic controlOscillations generatorsDigital analog converterLow-pass filter

A high stage Sigma Delta noise shaping direct digital frequency synthesizer includes a phase accumulator, a high stage Sigma Delta noise shaping interpolator, a sine or a cosine inquiry list, a D / A converter and a low-pass filter, among which, the interpolator includes a shaping accumulator and a delay circuit, outside N bit frequency digits are input into a phase accumulator and the output of which is connected with the shaping accumulator, the output of which is divided into a high p bit as the sine or cosine phase value and an intercepted low N-p bit and its output is connected with the delay circuit, the operation output of which is returned to the shaping accumulator, the output of the shaped phased value is output to the enquiry list, the output of which is connected with the input of the D / A converter, finally the output of which is connected to the input of the filter.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

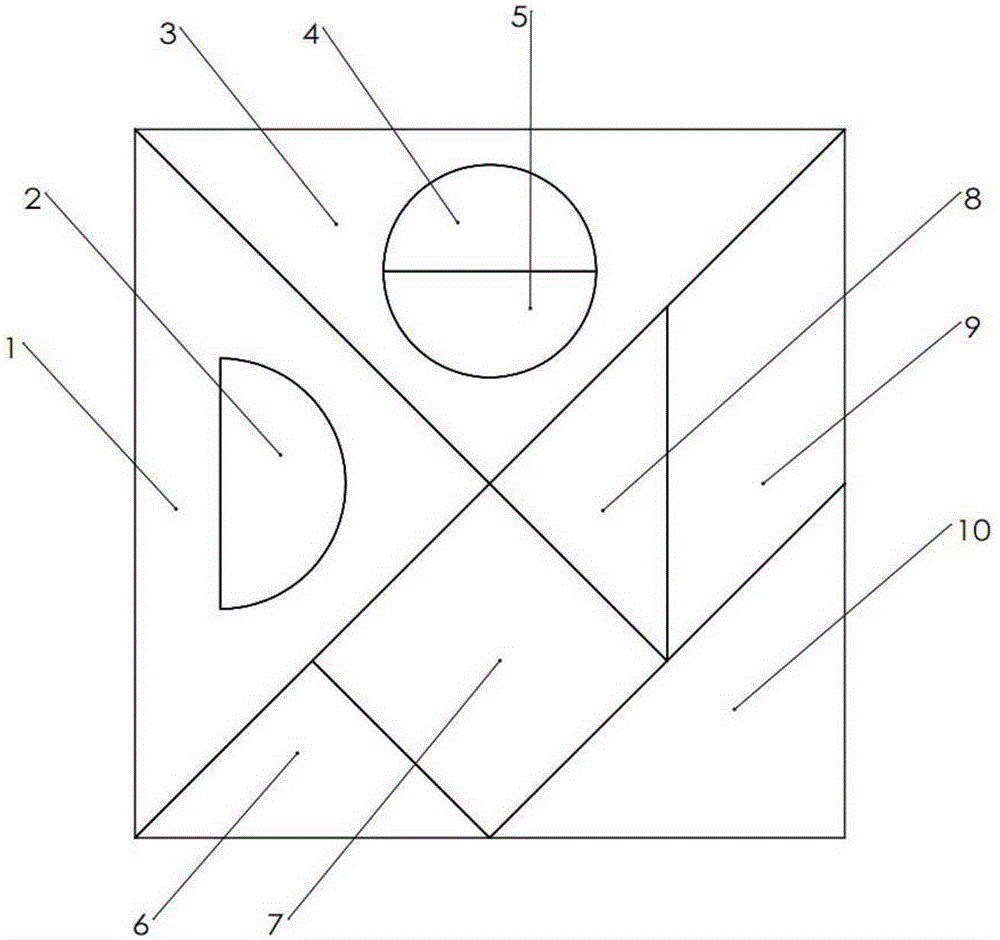

Ten-piece puzzle with round elements

InactiveCN105194869AImprove performanceInterestingIndoor gamesEducational modelsElectrical and Electronics engineeringEngineering

The invention relates to a jigsaw puzzle, and in particular relates to a ten-piece puzzle with round elements. The existing seven-piece puzzle has the defect of being lack of round elements. One semicircular die block (2) is cut down from the middle of a first big triangle (1) of the seven-piece puzzle, and two semicircular die blocks (4) and (5) are cut down from the middle of the second big triangle (3) to form the ten-piece puzzle. The cut-down semicircular die blocks can be embedded into a big triangular die block, or taken out to serve as independent die blocks, leaving round or semicircular gaps in the big triangular die block. According to the ten-piece puzzle, on the basis of the traditional seven-piece puzzle, 3 semicircular die blocks are added by cutting processing to form the ten-piece puzzle which greatly expands and enriches the expressiveness and interest of the traditional seven-piece puzzle and is beneficial for promoting the imagination and creativity of a user.

Owner:陈国经

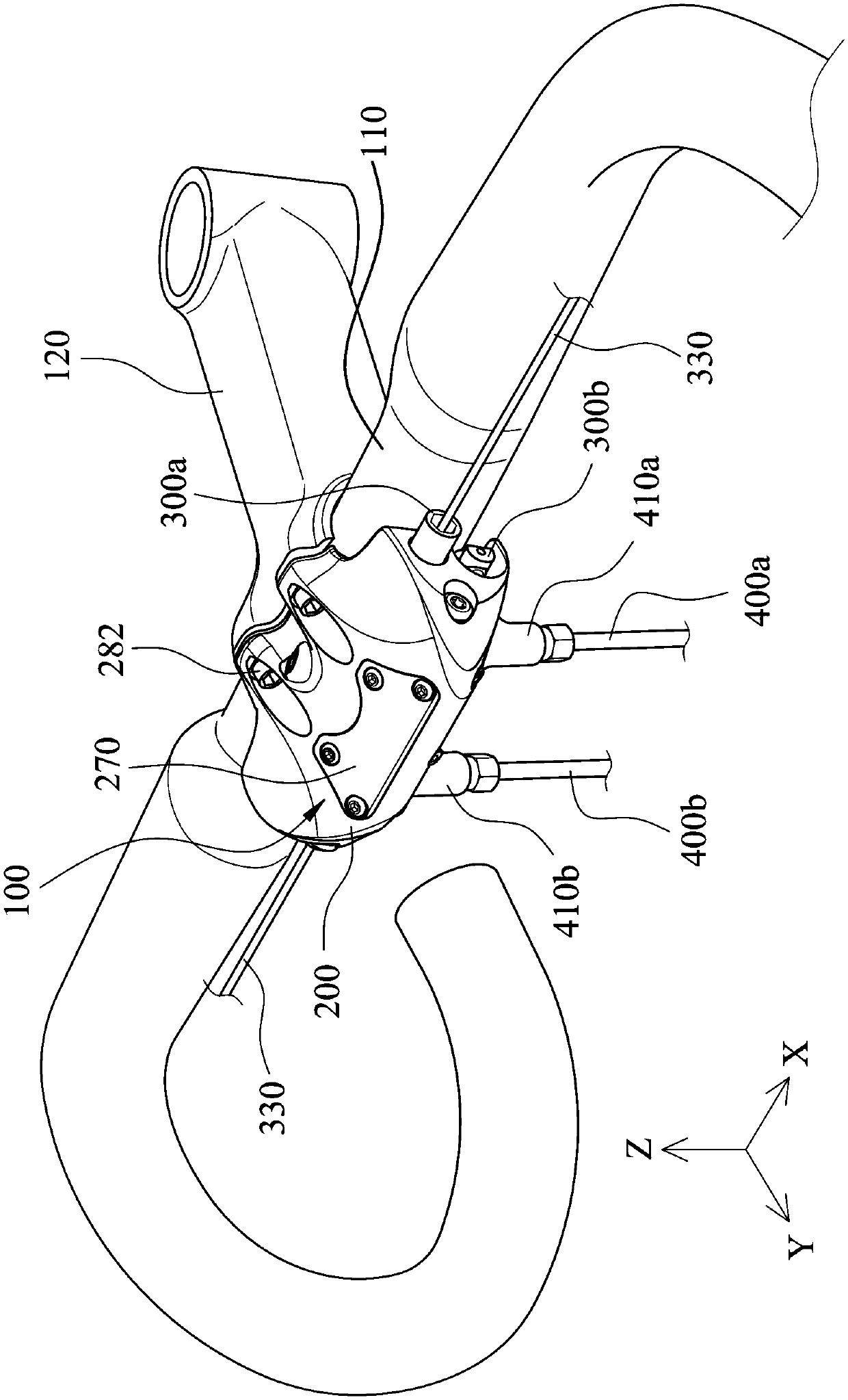

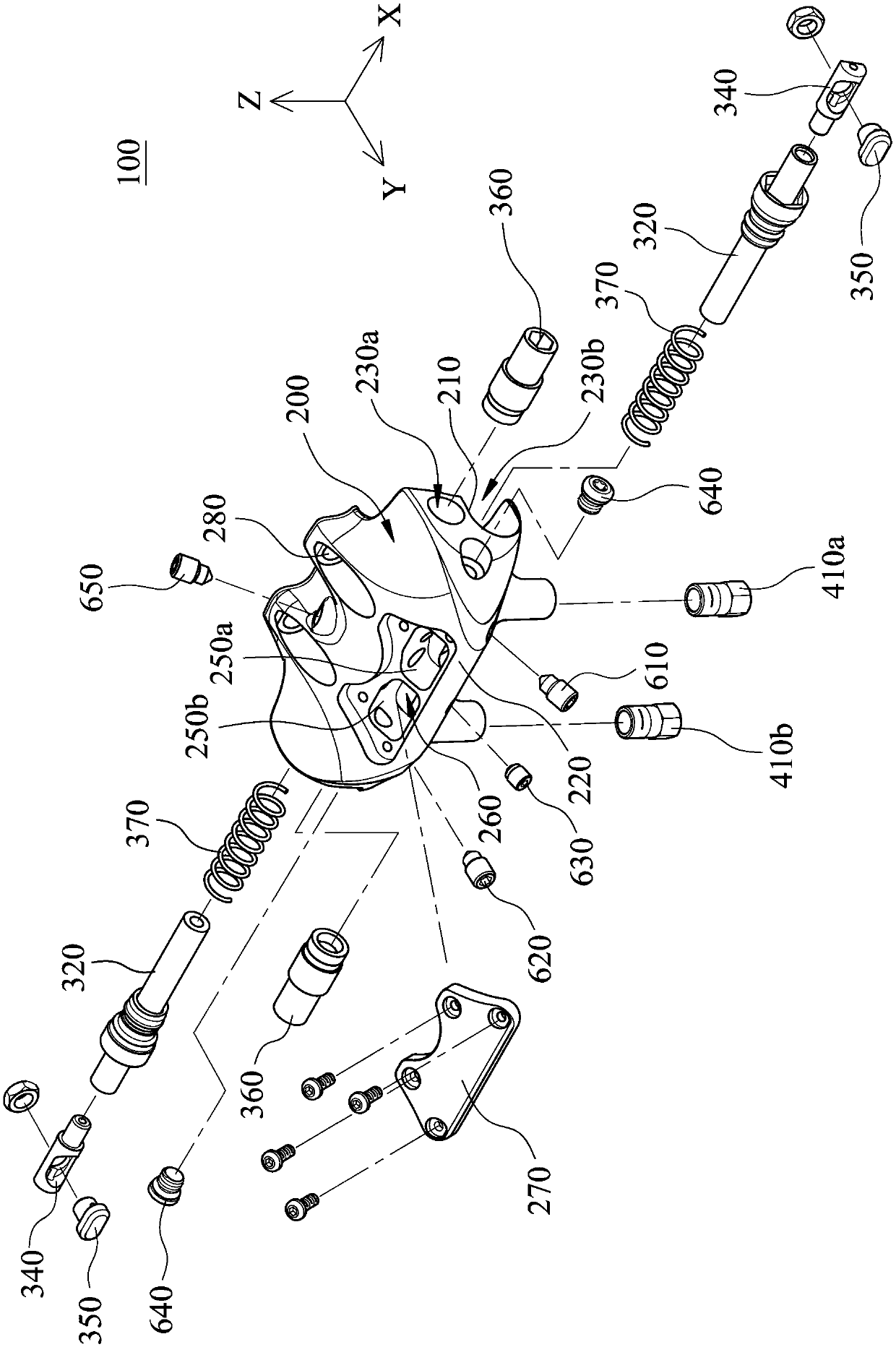

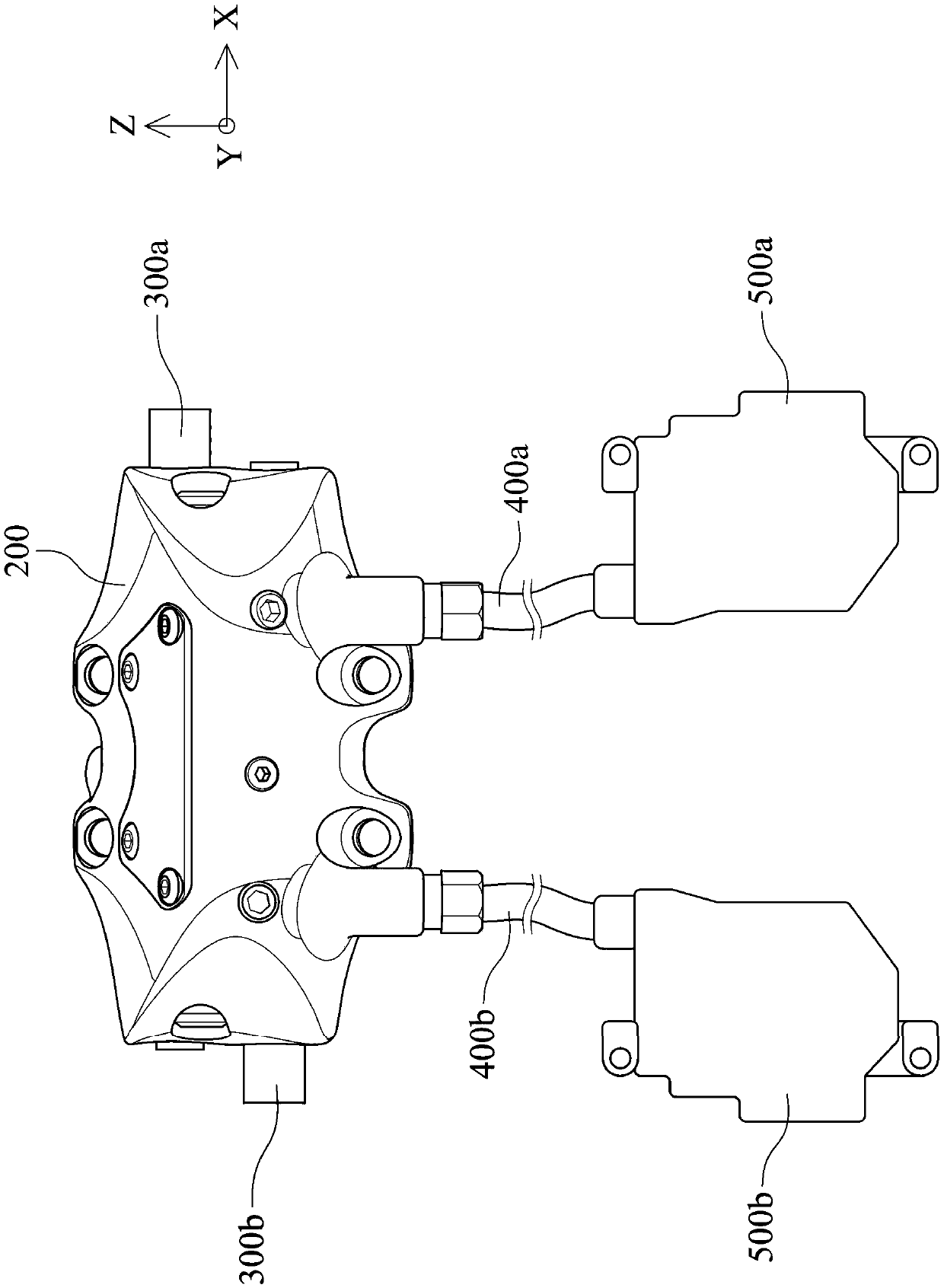

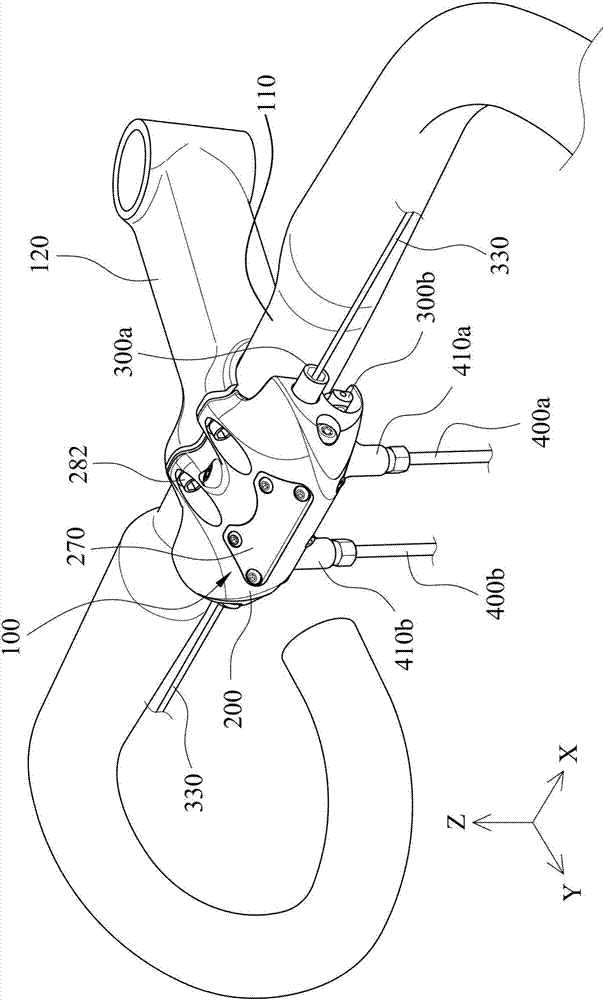

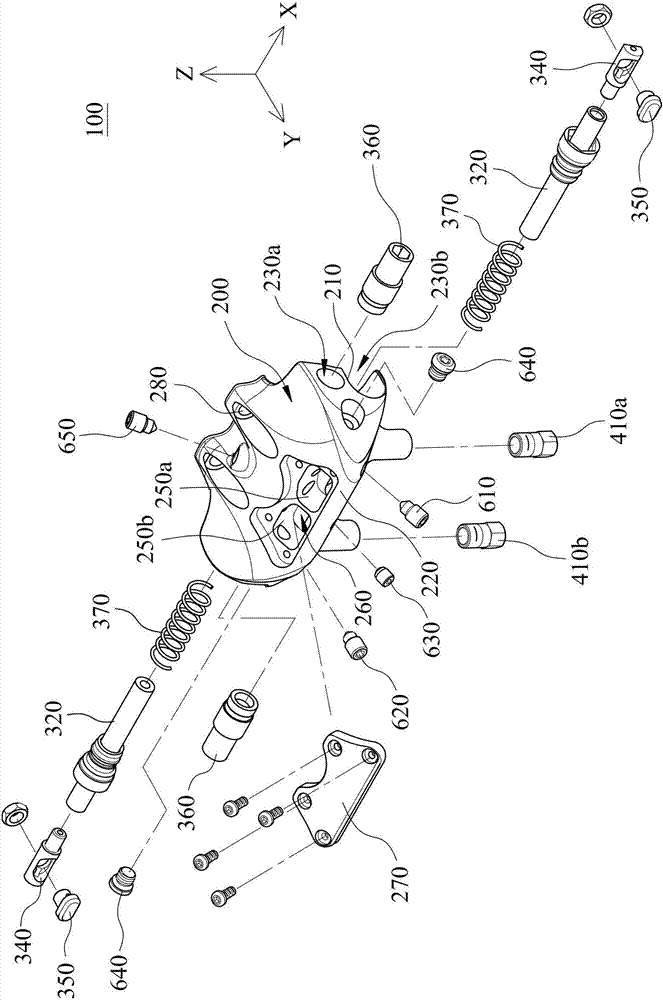

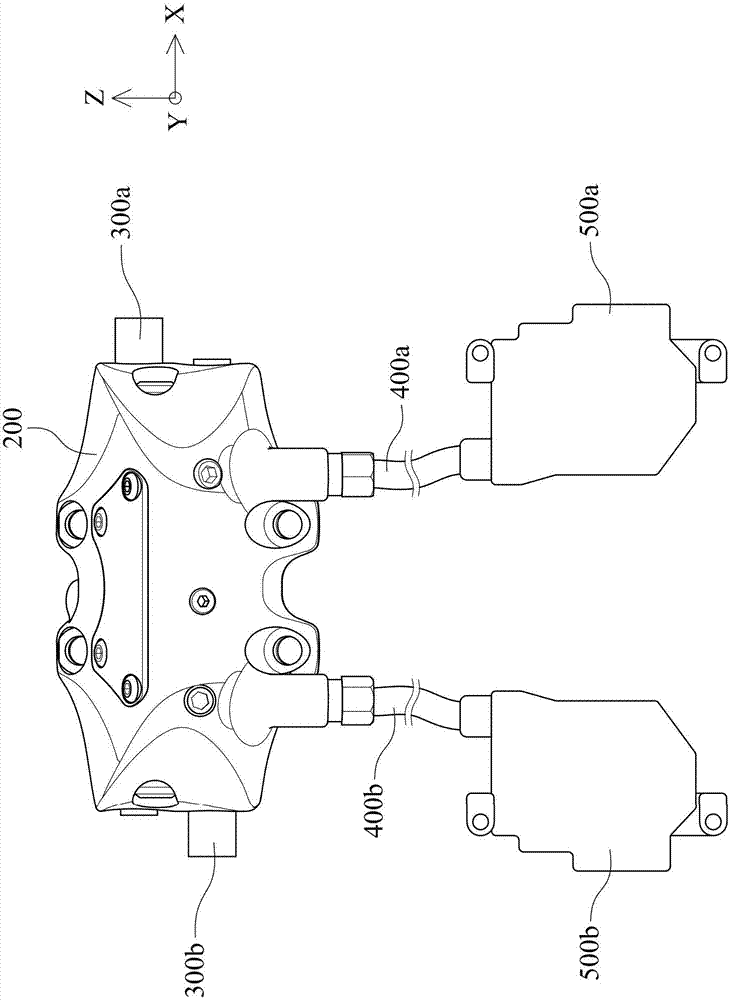

Bicycle hydraulic disc brake device

ActiveCN107010157BReduce wind resistanceNo increase in areaBrake actuating mechanismsCycle brakesHydraulic cylinderEngineering

A hydraulic disc brake device includes a cover, a hydraulic unit, an oil tube and a disc brake unit. The cover includes at least one accommodating space, at least one oil route, a proximal end and a distal end. The distal end towards a moving direction of the bicycle. The hydraulic unit includes a hydraulic cylinder and a piston. The hydraulic cylinder is assembled in the accommodating space. The piston is assembled in the hydraulic cylinder for controlling a pressure of the oil route. The disc brake unit is connected with the oil tube and controlled by a pressure of the oil tube.

Owner:GIANT BICYCLES

Hydraulic disc brake device for a bicycle

ActiveCN107010157AReduce wind resistanceNo increase in areaBrake actuating mechanismsCycle brakesHydraulic cylinderEngineering

A hydraulic disc brake device includes a cover, a hydraulic unit, an oil tube and a disc brake unit. The cover includes at least one accommodating space, at least one oil route, a proximal end and a distal end. The distal end towards a moving direction of the bicycle. The hydraulic unit includes a hydraulic cylinder and a piston. The hydraulic cylinder is assembled in the accommodating space. The piston is assembled in the hydraulic cylinder for controlling a pressure of the oil route. The disc brake unit is connected with the oil tube and controlled by a pressure of the oil tube.

Owner:GIANT BICYCLES

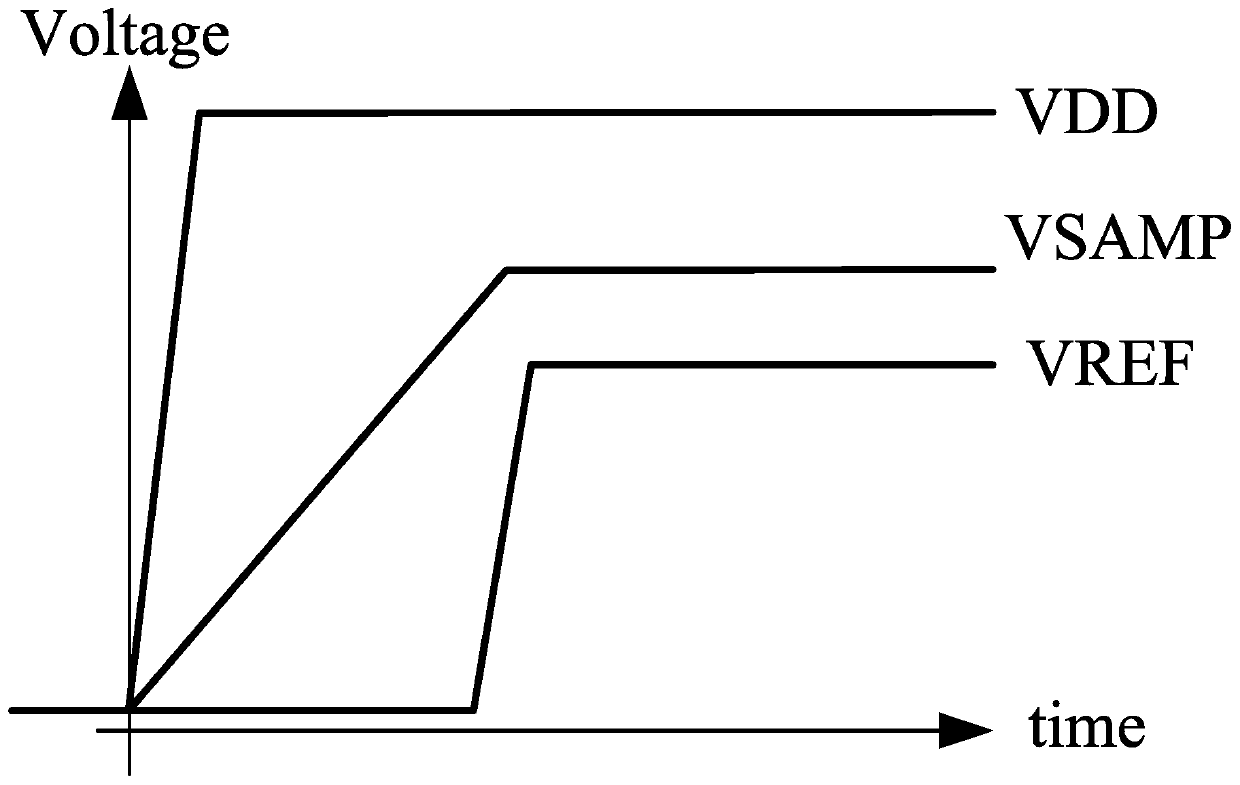

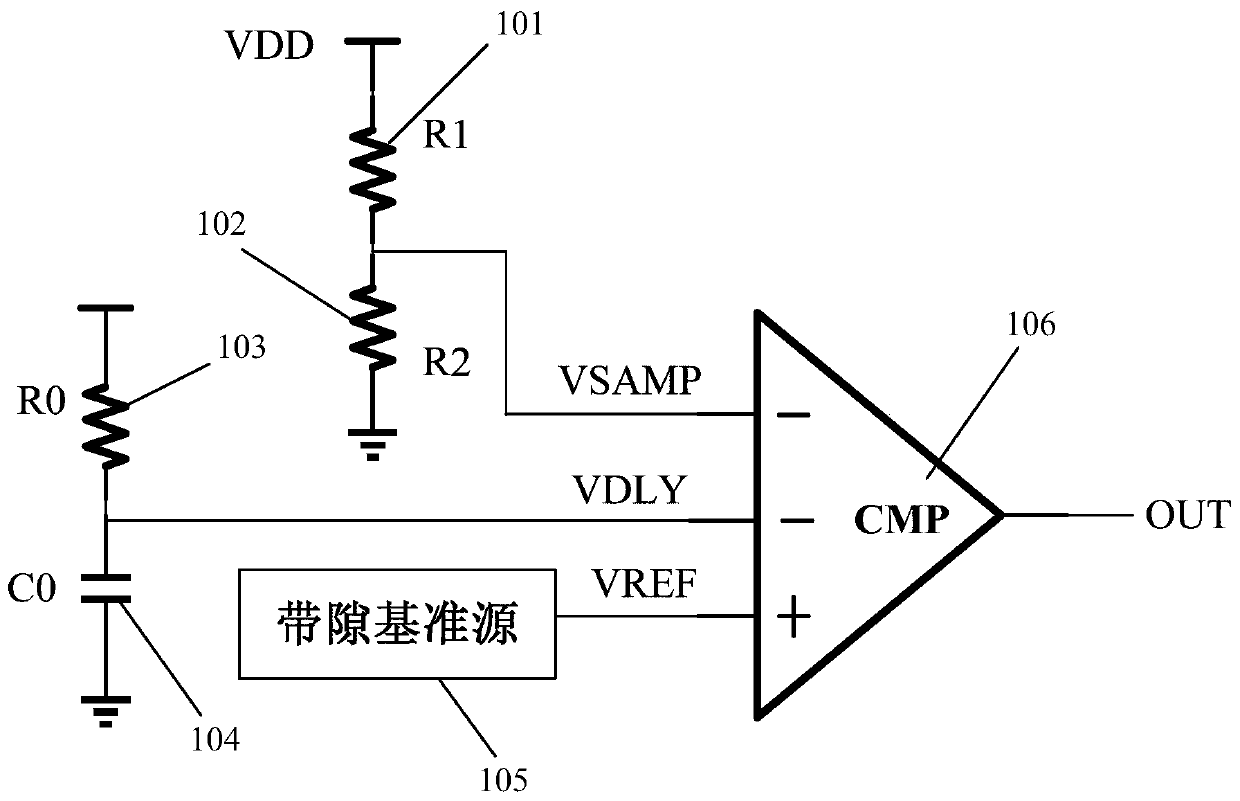

Low-voltage reset circuit

ActiveCN110739944AImprove circuit performanceImprove reliabilityElectronic switchingEnergy efficient computingPhysicsCapacitance

The invention provides a low-voltage reset circuit. The low-voltage reset circuit comprises a first resistor, a second resistor, a time-delay resistor, a time-delay capacitor, a band-gap reference source and a comparator. The first resistor and the second resistor are connected in series and are coupled between a power supply voltage and the ground. The time-delay resistor and the time-delay capacitor are connected in series and are coupled between the power supply voltage and the ground. The comparator is provided with a positive input end, a first negative input end, a second negative inputend and an output end, and the positive input end of the comparator is connected with reference voltage VREF generated by the band-gap reference source. A first negative input end of the comparator isconnected with a sampling voltage VSAMP extracted between the first resistor and the second resistor. A second negative input end of the comparator is connected with a delay voltage VDLY extracted between the delay resistor and the delay capacitor, and the output end of the comparator is used as an output result of the low-voltage reset circuit.

Owner:西安中颖电子有限公司

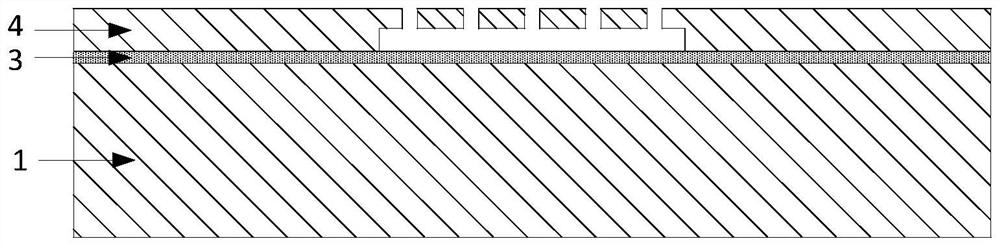

MEMS pressure sensor and preparation method thereof

PendingCN114235232AImprove linearityLarge rangeFluid pressure measurement using ohmic-resistance variationForce measurement using piezo-resistive materialsEngineeringStress sensors

The invention discloses an MEMS pressure sensor and a preparation method thereof. The MEMS pressure sensor comprises a bulk silicon layer, a substrate, a buried oxide layer, a top silicon layer, a piezoresistor, a stress film, an ohmic contact, a metal lead, an insulating dielectric layer, a small cavity, a large cavity, an inner Wheatstone bridge and an outer Wheatstone bridge. A small cavity is arranged in the top silicon layer, a large cavity is arranged in the bulk silicon layer, and the piezoresistor is arranged right above midpoints of four sides of the two cavities and in the top silicon layer. By arranging two Wheatstone bridges which are formed by two sets of piezoresistors and are located on stress films with different thicknesses, pressure in different measuring ranges is measured respectively, and the problems that a low-measuring-range pressure sensor loses linearity in a high-pressure environment and a high-measuring-range pressure sensor is low in sensitivity in a low-pressure environment are solved to a certain extent. The pressure sensor has a wide range and also has the sensitivity of a low-pressure environment; and meanwhile, the two cavities are stacked up and down in space, so that the chip area is saved, and the integration level is improved.

Owner:SOUTHEAST UNIV

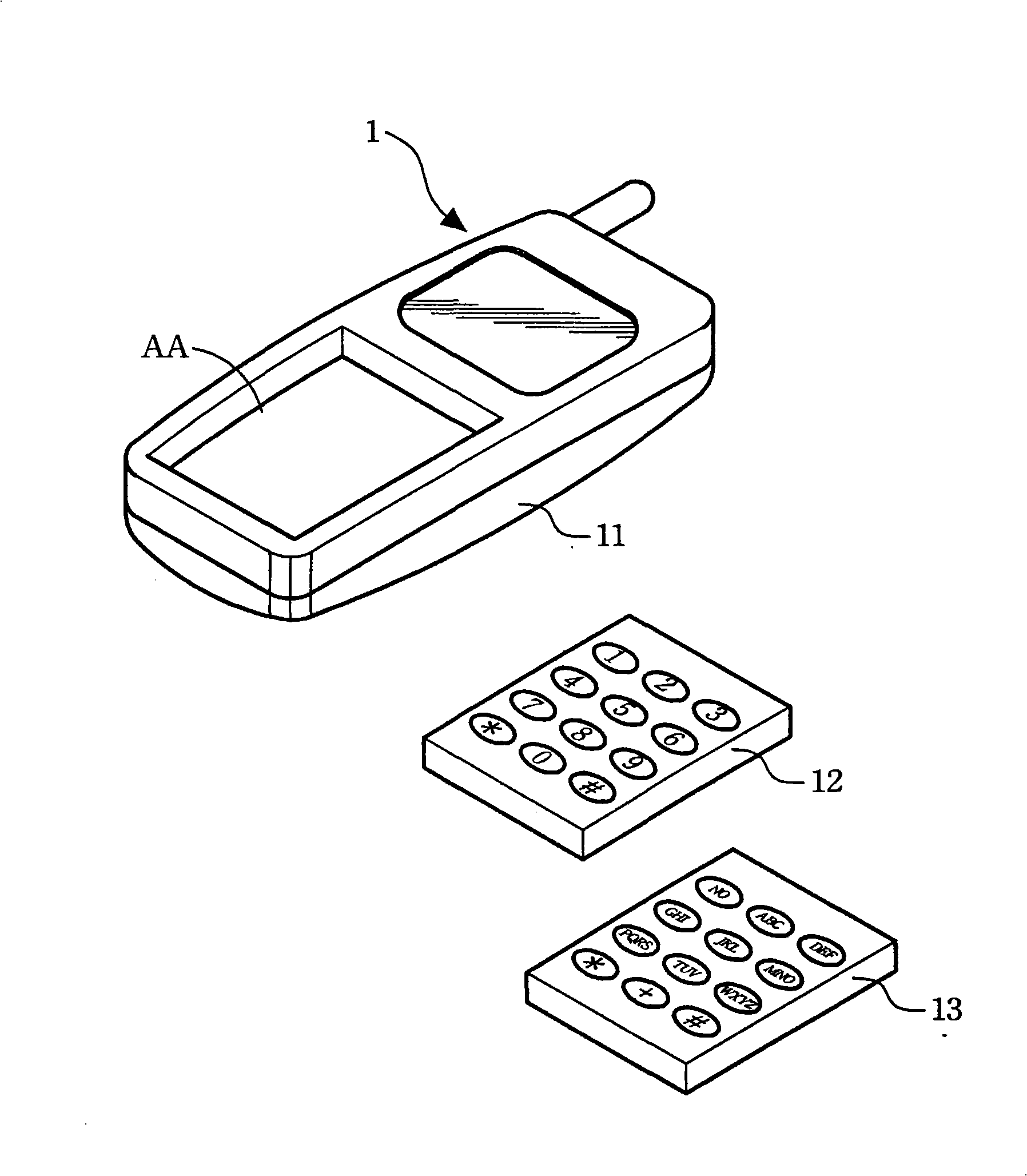

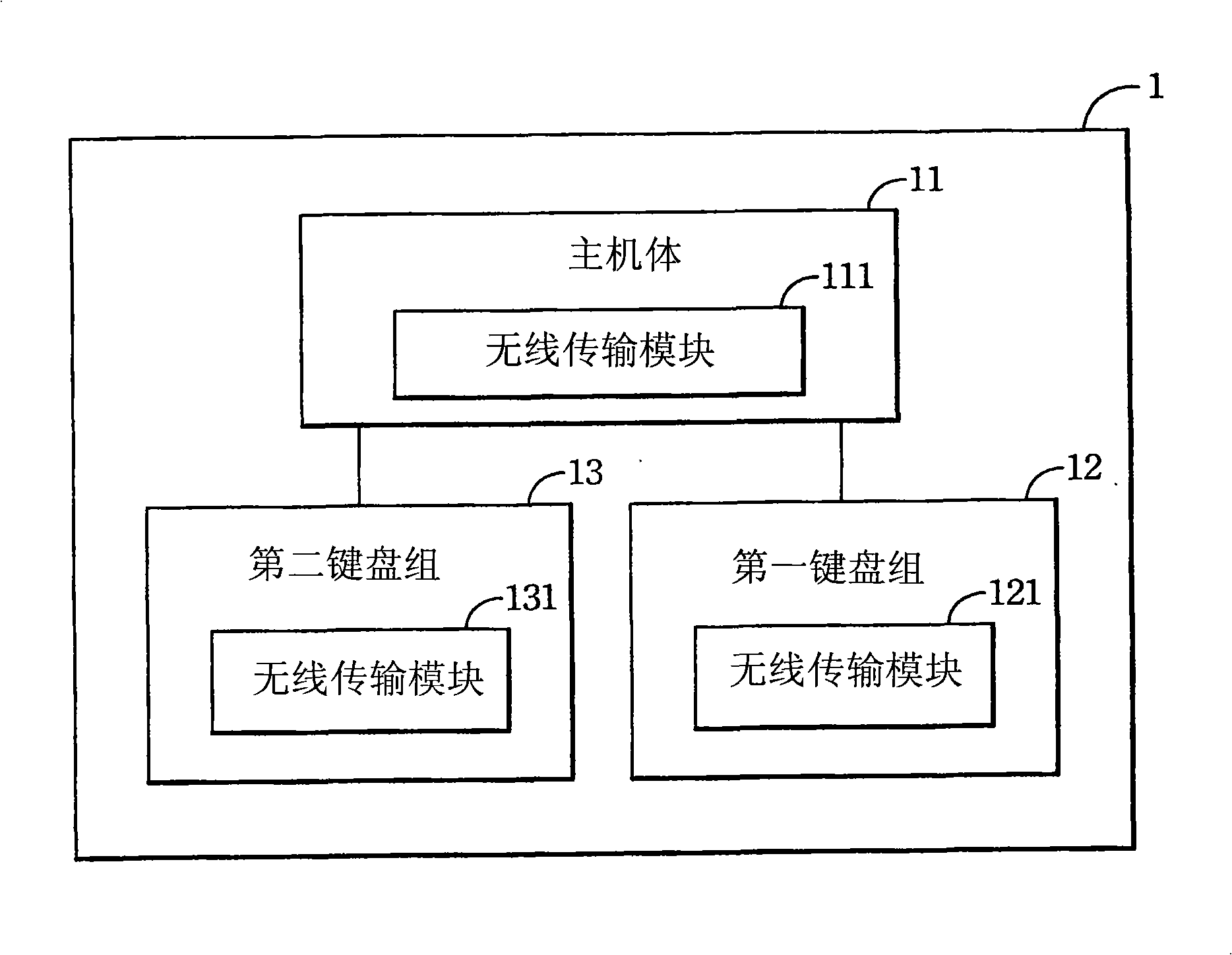

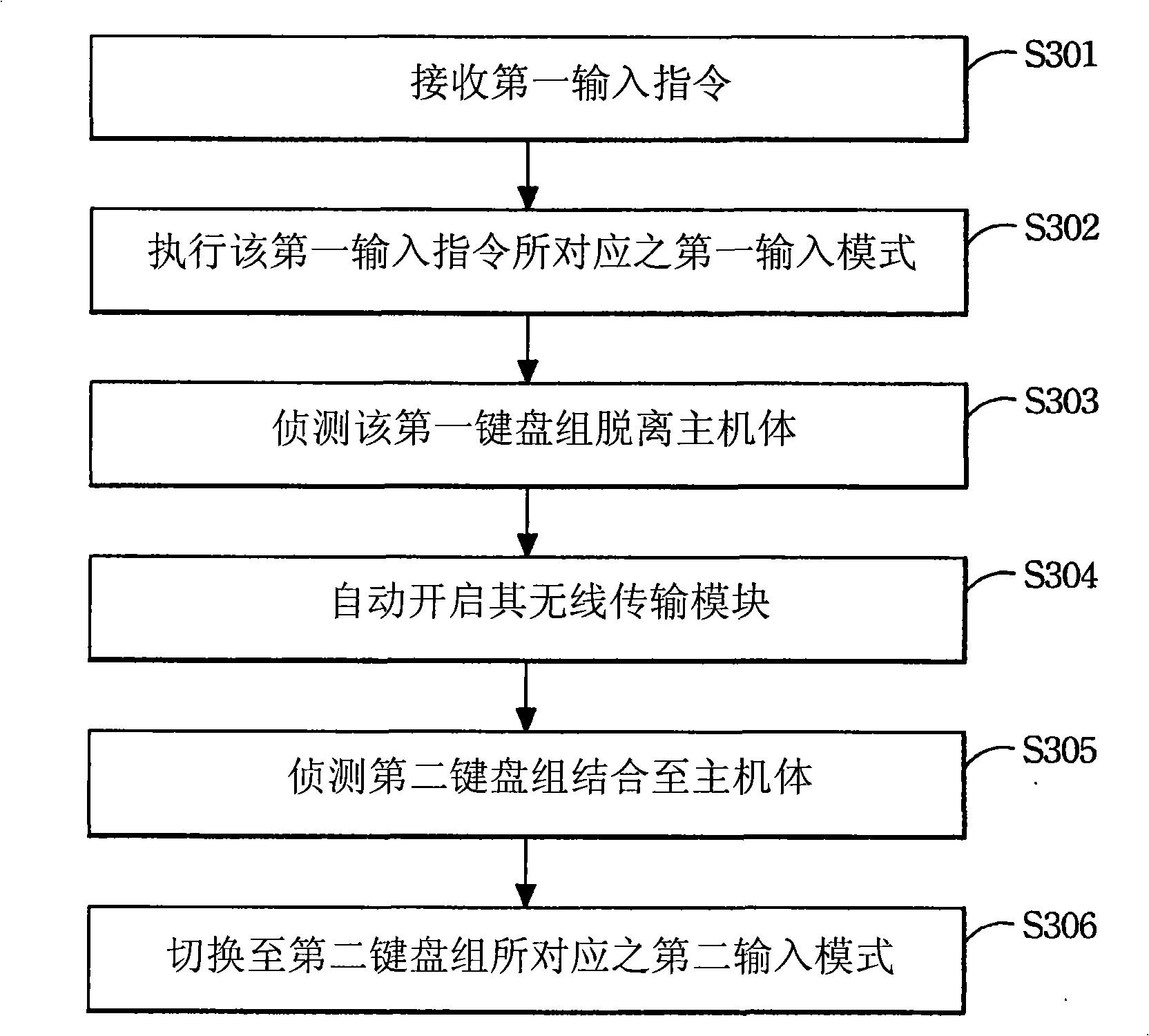

Mobile phone

InactiveCN101350851ANo added bulkNo increase in areaRadio/inductive link selection arrangementsTelephone set constructionsComputer scienceMobile phone

A cell phone is composed of a main body, a first keyboard group, a second keyboard group and a switching circuit. The main body is provided with an insertion slot in which the first keyboard group and the second keyboard group can be respectively arranged in a movable way and be electrically connected with the main body in to provide the operations of different input modes, for example, the dial-up input model and the essay editing model as well as other operations are available respectively. The switching circuit can be used for switching different input modes when different keyboard groups are provided within the insertion slot.

Owner:INVENTEC APPLIANCES CORP

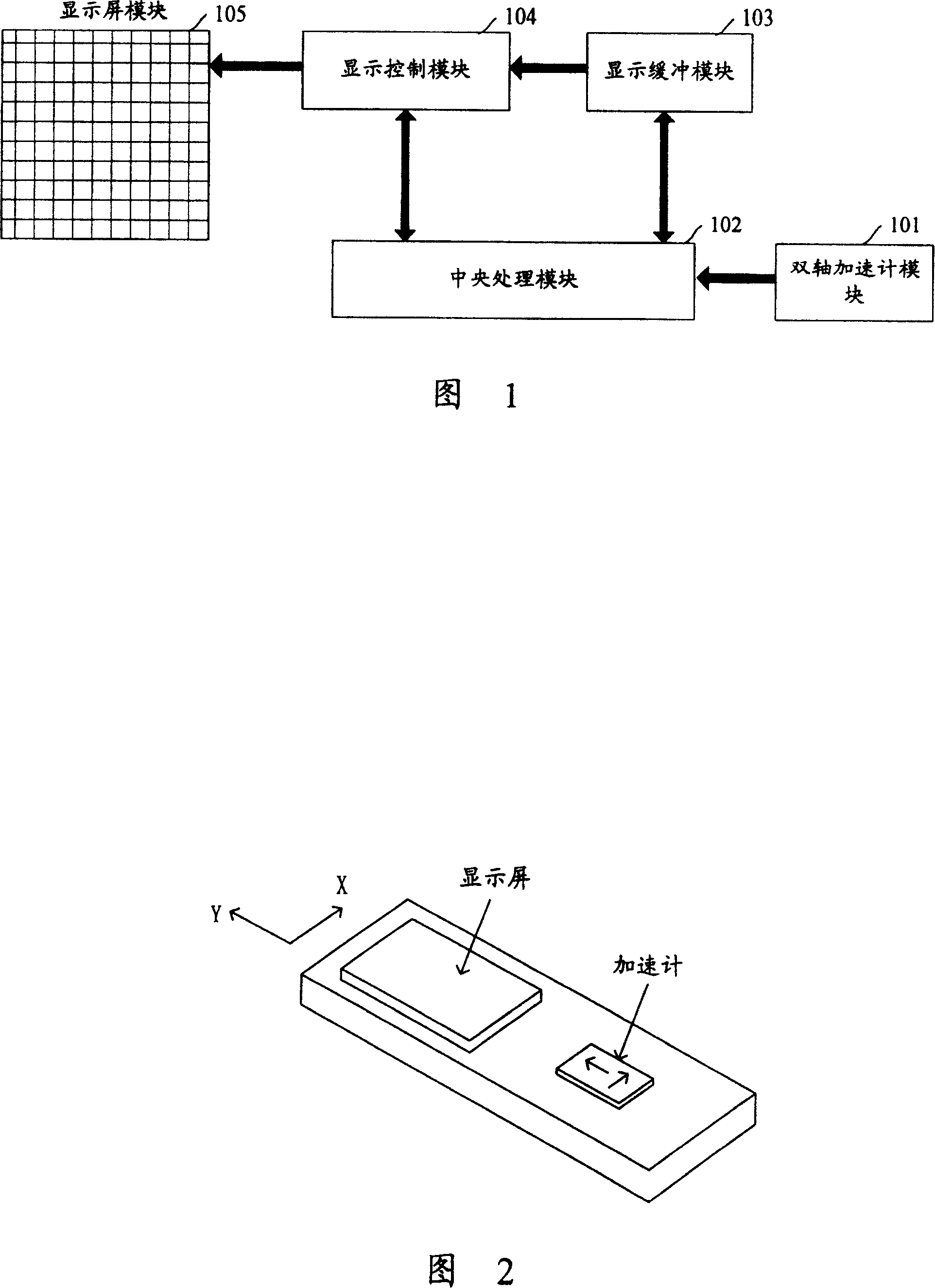

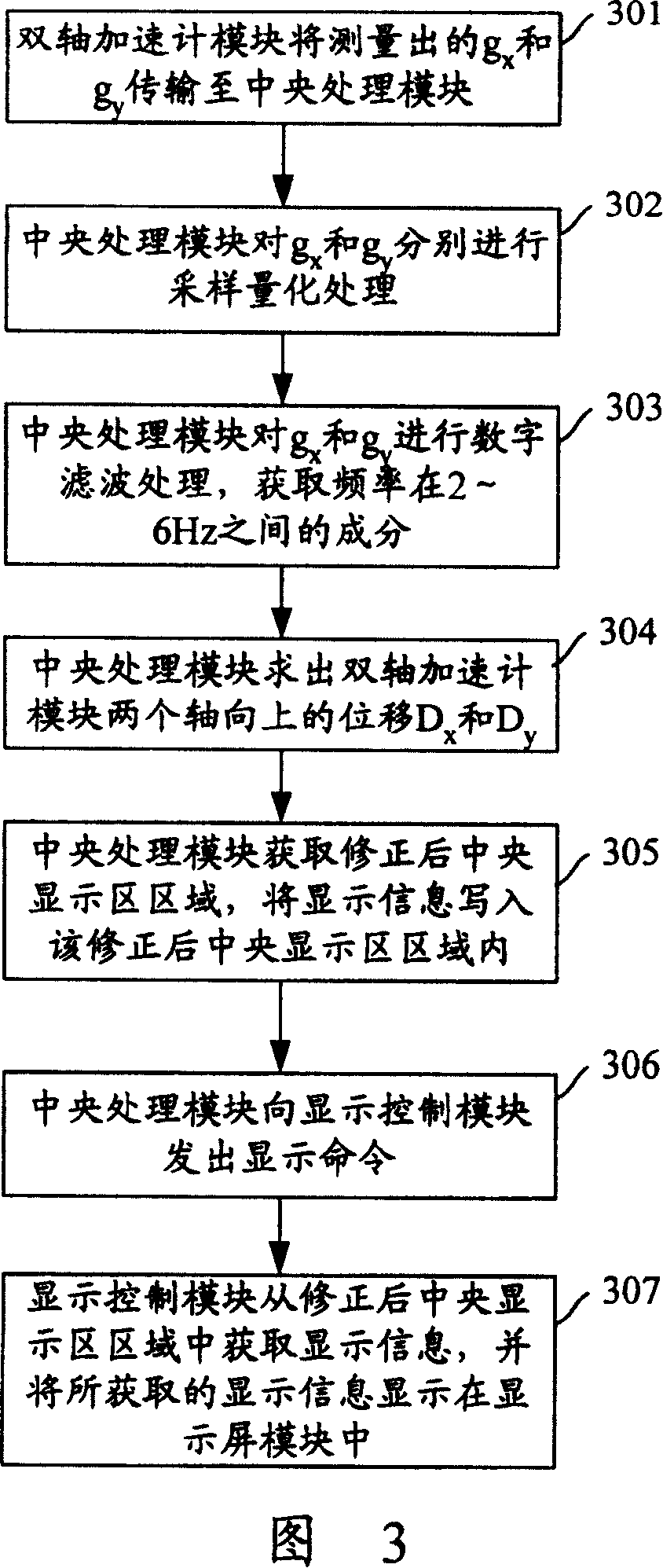

Method and apparatus for displaying information

InactiveCN100370512CStable positionImprove stabilityCathode-ray tube indicatorsAccelerometerDisplay device

This invention relates to a method and apparatus for displaying information. Wherein, setting dual-shaft accelerometer in the display device; obtaining the display screen displacement according to the upward acceleration vectors of two meter shafts determined by itself; correcting the current information area; displaying the corrected information. Besides, the device comprises a display buffer module, a display control module, a display screen module, an accelerometer module, and a central processing module. This invention keeps the display information stable to human eyes position in space, and improves the information display stability and distinguishability.

Owner:HUAWEI TECH CO LTD

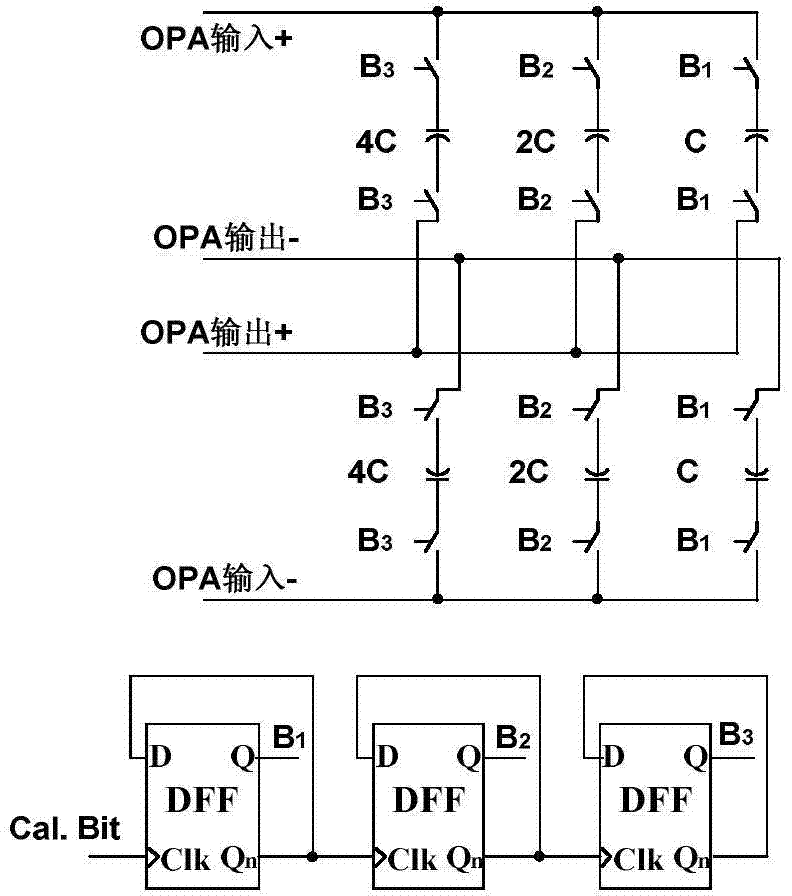

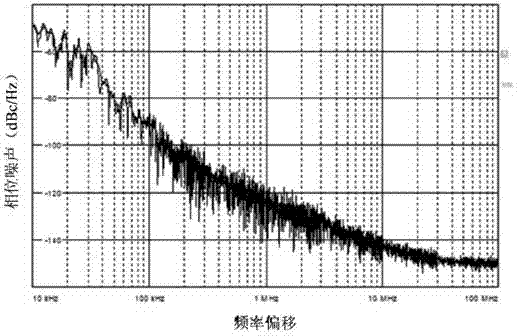

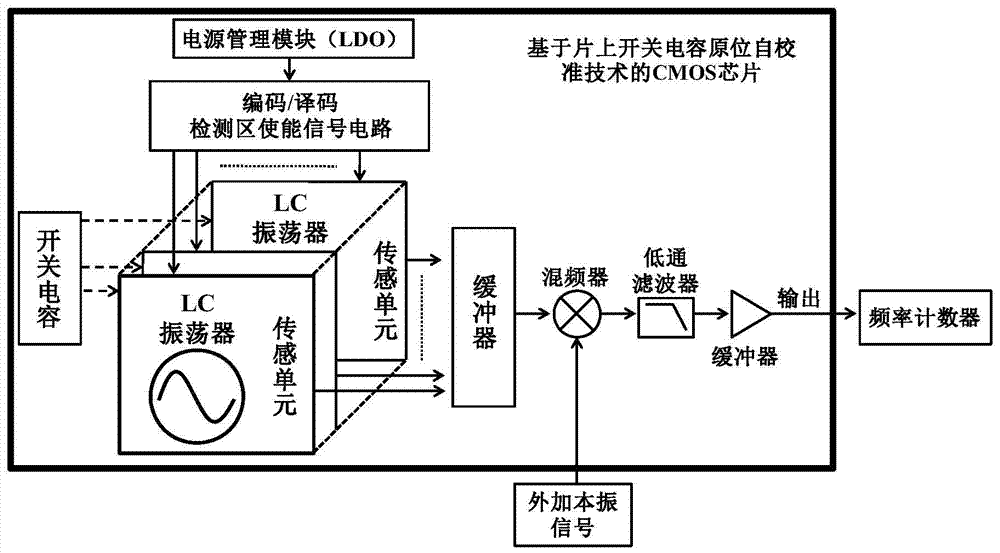

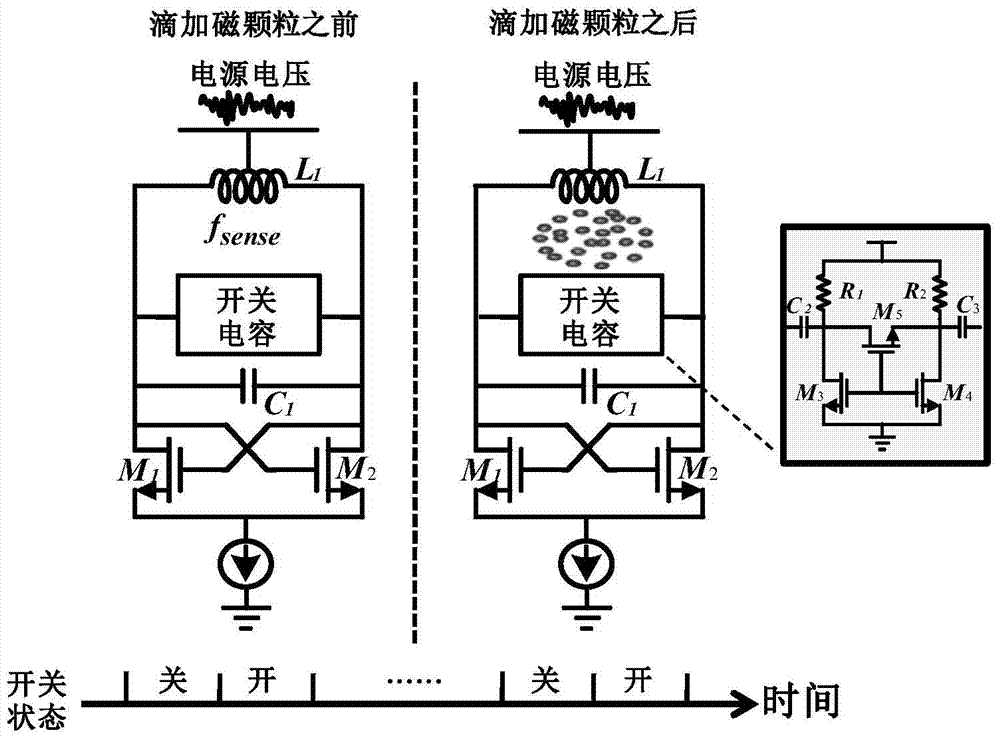

LC Oscillator Magnetic Sensitive Biosensor Based on Switched Capacitor In Situ Self-Calibration Technology

Owner:TSINGHUA UNIV

Low voltage reset circuit

ActiveCN104734679BNo error releaseImprove reliabilityElectronic switchingElectricityElectrical resistance and conductance

The present invention provides a low-voltage reset circuit, including: a current source, a first resistor, a second resistor, a third resistor, a fourth resistor, a comparator and a voltage-controlled resistor; a current source, a first resistor, a voltage-controlled resistor and a second The resistors are connected in series in sequence, connected between the power supply voltage and the ground; the third resistor and the fourth resistor are connected in series with each other, connected between the power supply voltage and the ground; the negative input terminal of the comparator is drawn between the third resistor and the fourth resistor The sampling voltage is connected; the positive input terminal of the comparator is connected to the reference voltage extracted between the current source and the first resistor; the current source generates a current with zero temperature coefficient or a current with positive temperature coefficient through the main circuit of the bandgap reference source , which in turn is used to generate a stable reference voltage. The present invention can correctly generate a high-level pulse reset signal in the process of fast power-on of the system; in addition, when the system power supply is powered down to ultra-low voltage, the reset signal will not be released by mistake.

Owner:西安中颖电子有限公司

Memory, and writing method and reading method of memory

The invention discloses a memory, and a writing method and a reading method of the memory. The memory comprises a spin orbit moment providing layer, two storage bits, two diodes, a first bit line, a second bit line, a word line, a source line and a transistor, one end of the spin orbit moment providing layer is connected with the first bit line, the other end of the spin orbit moment providing layer is connected with the transistor, and the transistor is connected with the word line and the source line. The two storage bits are arranged on the surface of the spin orbital moment providing layerat intervals, the ends, away from the spin orbital moment providing layer, of the storage bits are connected with the first ends of the diodes in series in a one-to-one correspondence mode, the electrodes corresponding to the first ends of the diodes connected with the two storage bits are different in positive and negative, and the second ends of the diodes are connected with the second bit lines respectively. According to the invention, the technical problems of large storage unit area, low integration level and incapability of realizing independent reading and writing of the memory in therelated art are solved.

Owner:CETHIK GRP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com