DRAM wafer level pin connectivity test circuit and method

A technology for testing circuits and testing methods, applied in static memory, instruments, etc., can solve problems such as high defect rate and inability to test chip pin connectivity, achieve short time consumption, increase product overall cost, and ensure product quality. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

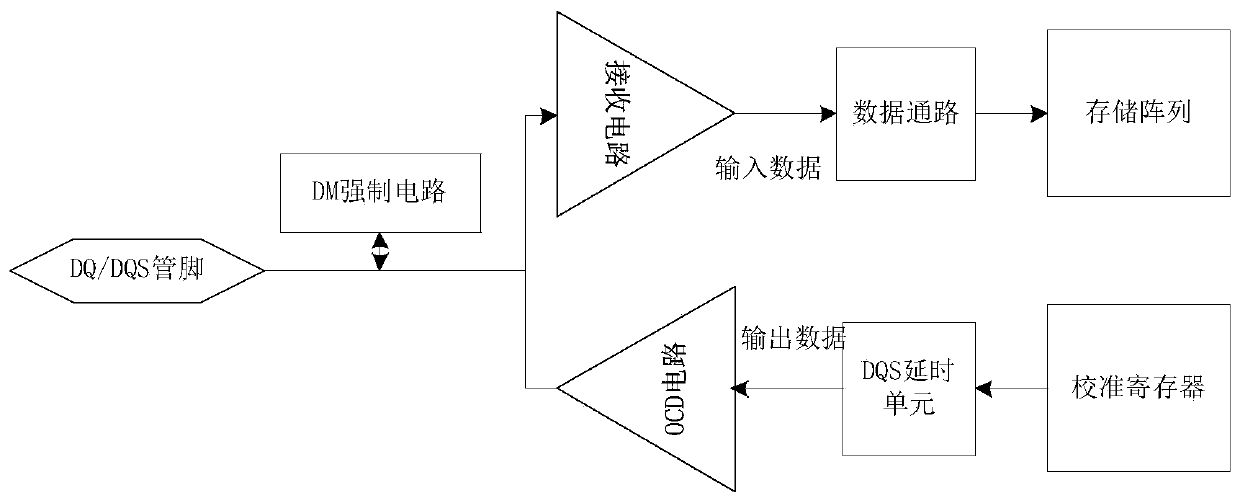

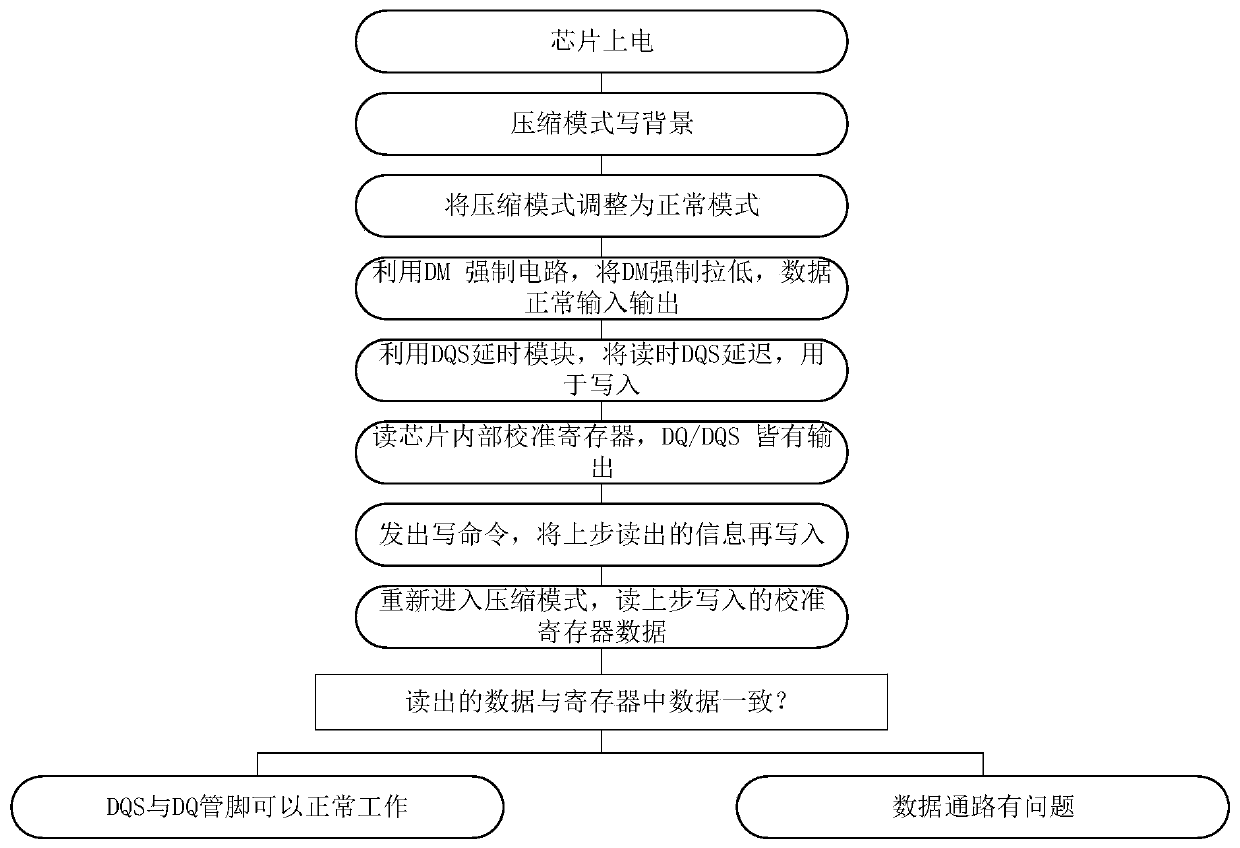

[0082] Specifically, such as image 3 As shown, the test process of DQ pins and DQS pins is as follows:

[0083] Step S11 power on the chip:

[0084] Specifically: enter the compression mode, and write the background data in the storage array;

[0085] Writing in compressed mode can save the number of pins that need to be connected in wafer testing, thereby greatly reducing the design and manufacturing cost of pin cards, increasing the number of simultaneous tests, and reducing the overall testing time.

[0086] Step S12 adjusts the compression mode to normal mode:

[0087] Specifically:

[0088] Use the DM forcing circuit to force the DM pin to be low, and the data is input and output normally; the purpose here is that the DM function of the DRAM does not work, and the data is read and written normally through the DQ / DQS pin.

[0089] Using the test mode, it is not necessary to connect the DM pins during wafer testing, which reduces the design and manufacturing costs of p...

Embodiment 2

[0099] Take the DM pin as an example for illustration: specifically, as Figure 4 As shown, the test flow of the DM pin is as follows:

[0100] Step S21 power on the chip:

[0101] Specifically: enter the compression mode, write the background data in the storage array; write in the compression mode, save the number of pins that need to be connected in the wafer test, thereby greatly reducing the design and manufacturing cost of the needle card, and increasing the same test number, reducing the overall test time;

[0102] Step S22 adjusts the compressed mode to the normal mode:

[0103] Specifically: use the DM forcing circuit to force the DM pin to be high, and the data will be shielded. The purpose here is that the DM function of DRAM works, and the data passing through the DQ / DQS pin will be masked.

[0104] In this way, the DM pin does not need to be connected during the test, which reduces the design and manufacturing cost of the needle card, increases the number of s...

Embodiment 3

[0127] In the following embodiments, the DQ / DQS pin and the DM pin are judged respectively.

[0128] refer to Figure 6 , which describes in detail an example of testing the connection performance of all datapath pins in the wafer-level mass production test of a product.

[0129] Step S31: Storage array writes background data

[0130] The chip is powered on, enters the compression mode, and writes background data in the storage array; this background data needs to be different from the data in the specified calibration register to identify whether the data rewriting is successful;

[0131] This step can reuse the writing steps in the normal wafer test, which simplifies the test complexity; there is no need to increase the number of connections of DQ pins, DQS pins and DM pins;

[0132] Step S32: Resetting the read and write timing

[0133] Change the chip's RL (read latency, read latency, product configurable application parameters defined by JEDEC), BL (burst length, burst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com