Method for reducing stray capacitance in analogue circuit

A parasitic capacitance and analog circuit technology, applied in the field of analog circuit layout design, can solve the problems of reducing current channel, increasing parasitic resistance, slowing down circuit speed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be further described below in conjunction with the specific implementation of the method of the present invention.

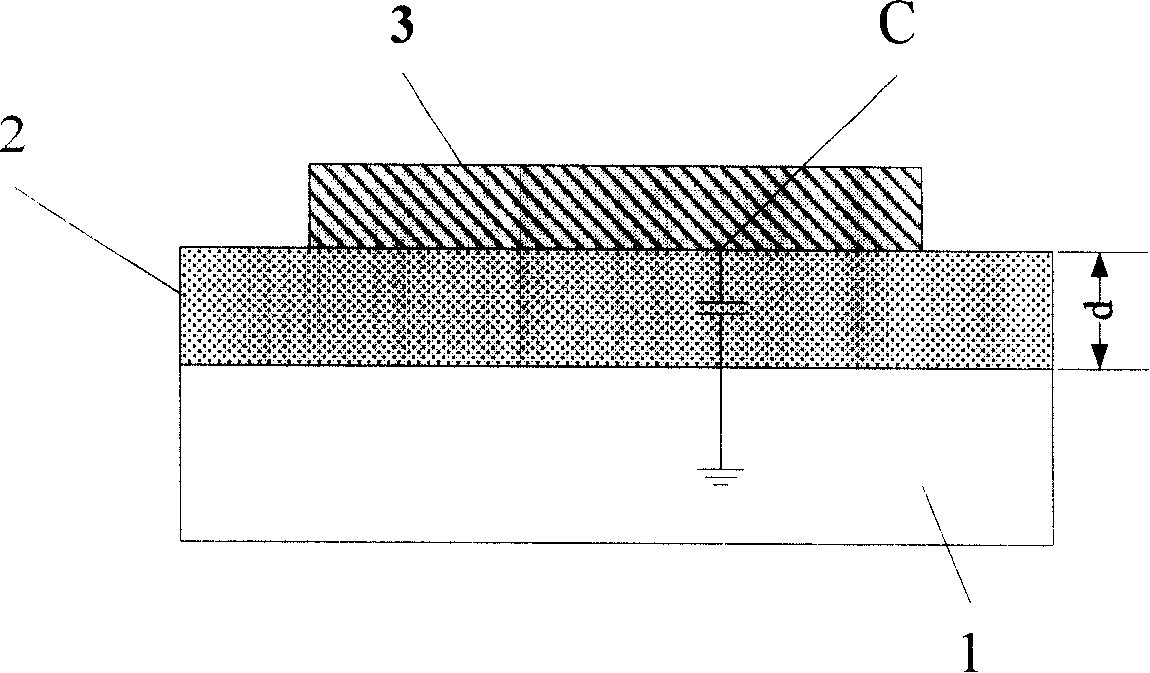

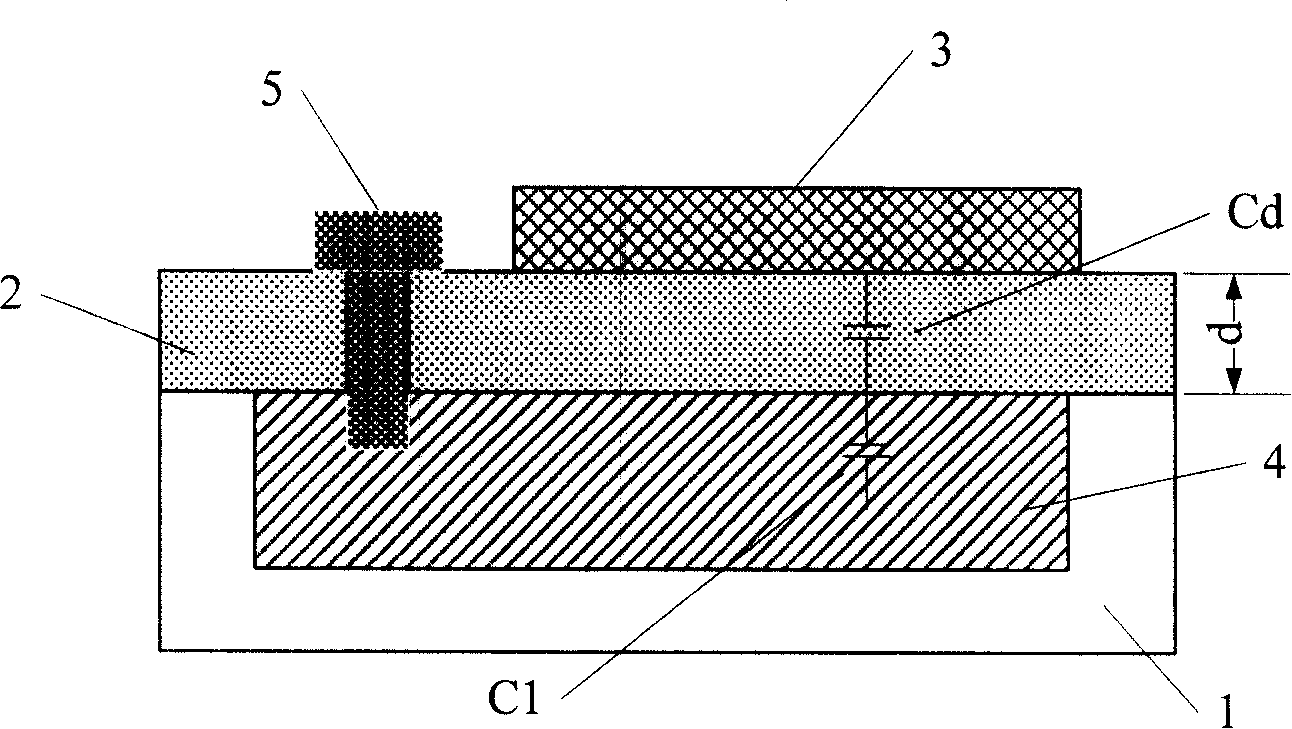

[0016] first refer to figure 2 , which is a cross-sectional view of a signal line and a substrate after adding an N well layer according to an embodiment of the present invention. Taking the semiconductor substrate as a P-type substrate 1 as an example, an N well layer 4 is introduced between the P-type substrate 1 and the insulating layer 2, and the above-mentioned N well layer 4 and the P-type substrate 1 form a capacitor C1, which is connected in series with the original capacitor Cd even. In order to effectively utilize C1 and reduce the original capacitance Cd between the signal line 3 and the substrate, the N well layer 4 must be AC floating (hereinafter referred to as AC floating). If the N well layer 4 is not AC floating, then in the case of alternating current (hereinafter referred to as AC), the potentials of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com