variable gate transistor

A transistor and variant technology, applied in the field of CMOS transistor layout, can solve the problems of edge leakage current and ring gate area consumption of common gate transistors, asymmetry of source and drain regions, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

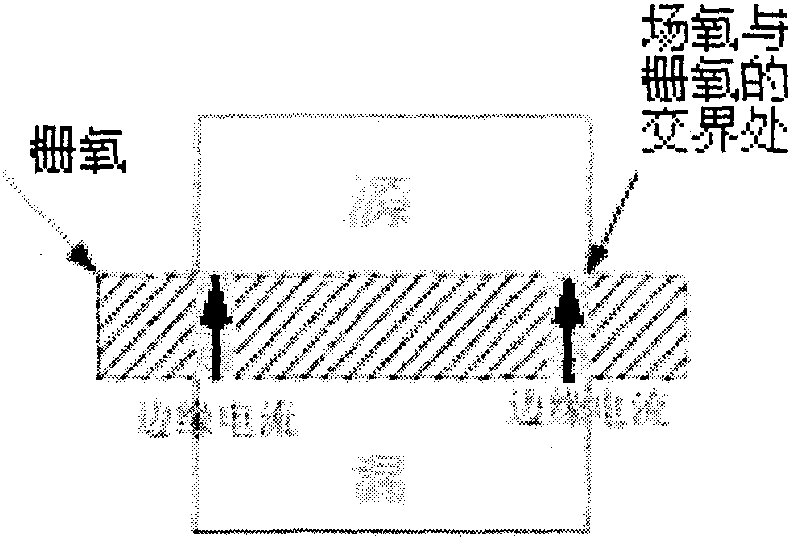

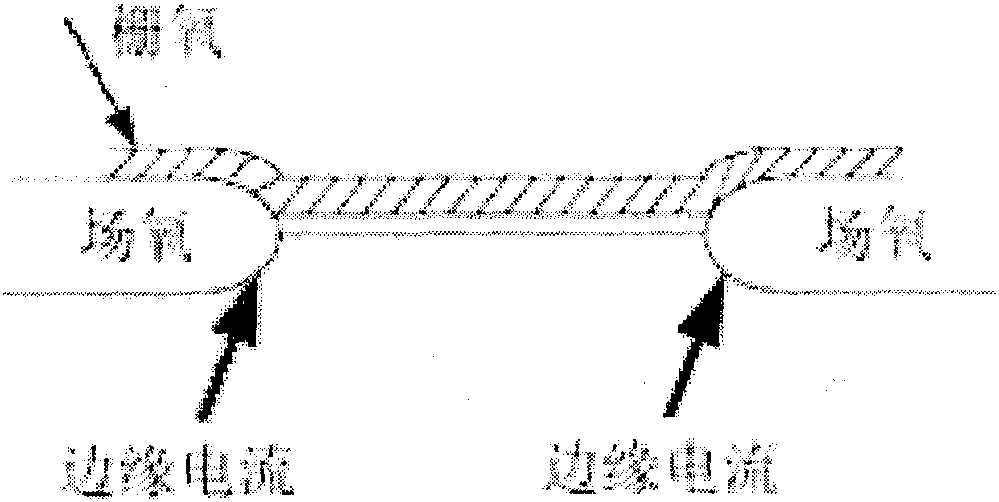

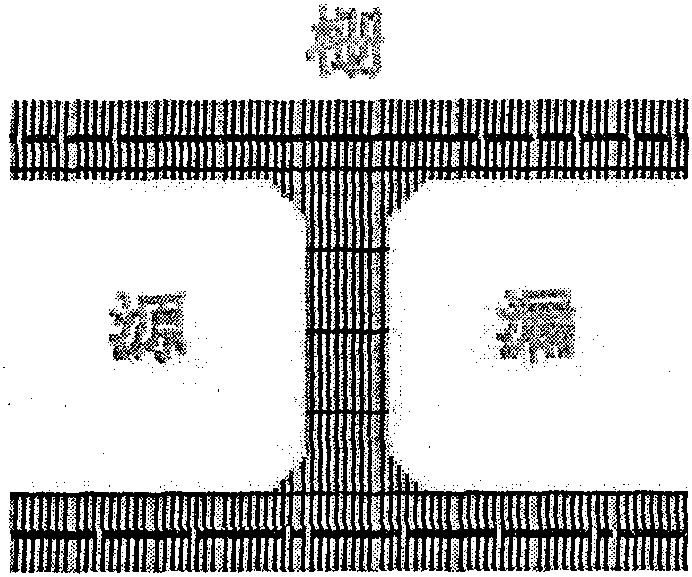

[0019] As shown in Figure 1 and Figure 2, this structure is a state-of-the-art structure diagram, the gate straddles the transistor channel, and overlaps with the field oxygen edge as field isolation at the edge of the transistor, and the source region and the drain are respectively on both sides Area. When no bias is applied to the gate, no inversion layer is formed under the gate oxide, and the transistor is turned off. Apply a bias voltage that is appropriately greater than the threshold voltage on the gate, an inversion layer is formed under the gate oxide, and there is a conductive channel. When an appropriate bias voltage is applied to both ends of the source and drain, current will flow, and the voltage and current characteristics exhibited are very good. Realize the transistor function. Such as image 3 As shown, the gate straddles the channel of the transistor, the two sides are the source region and the drain region, and the gate is used to cover the edge of the act...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com