Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

42results about How to "Lower turn-on resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

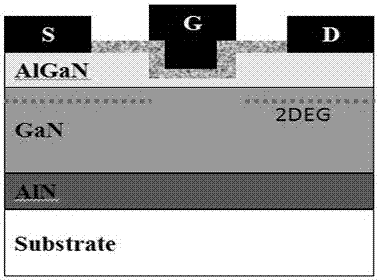

Field-effect semiconductor device

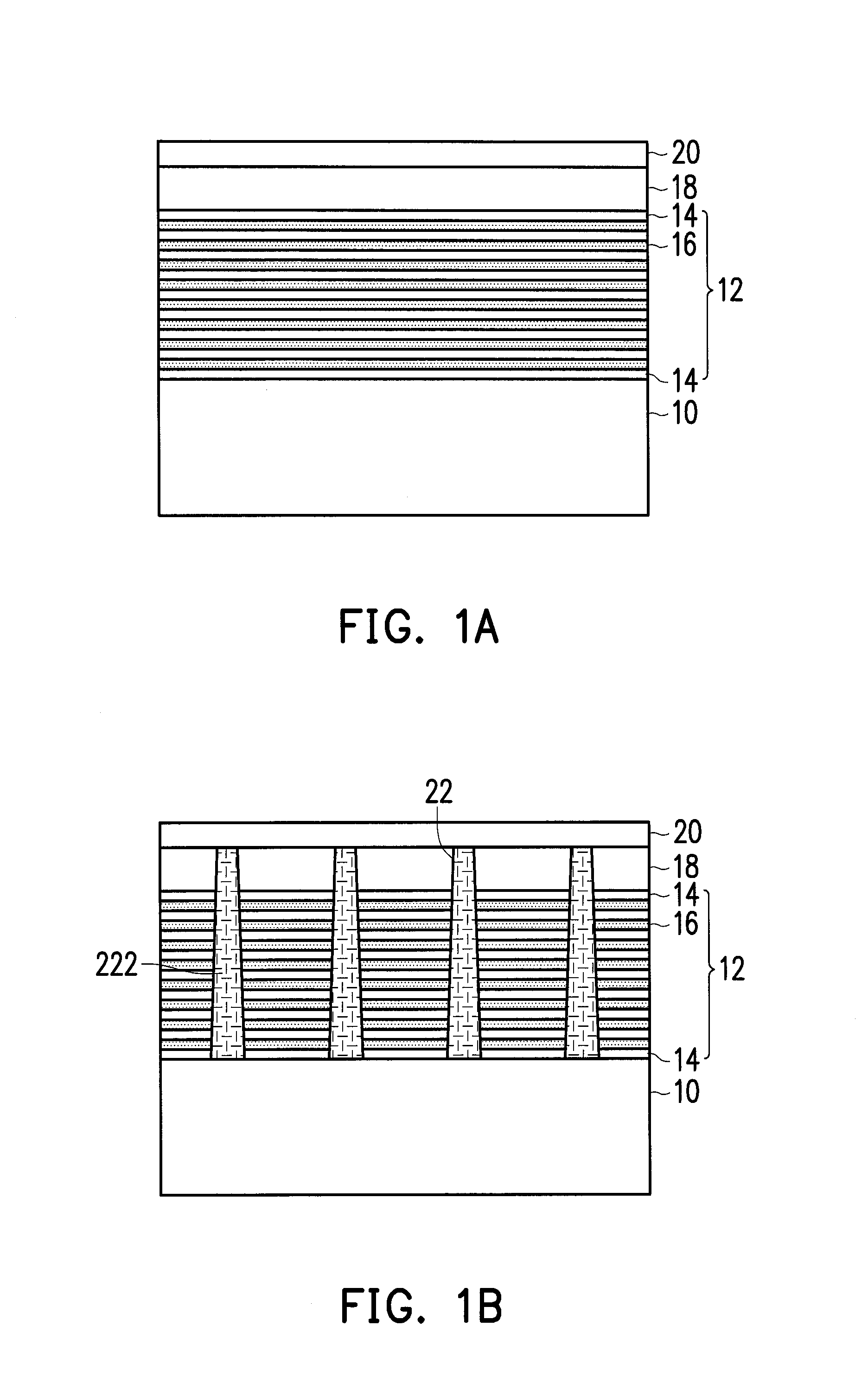

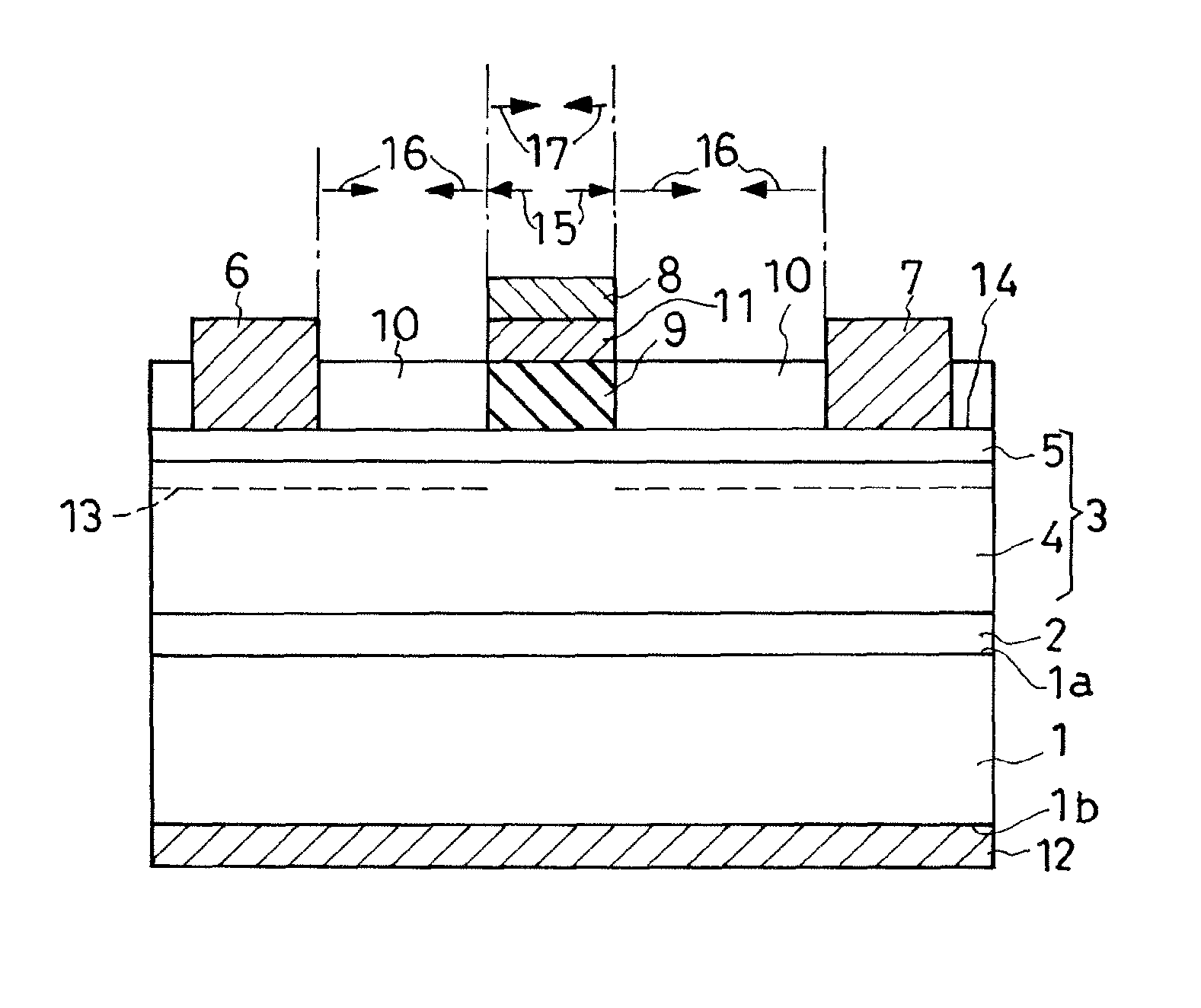

InactiveUS20080283870A1Reduce gate leakage currentLower turn-on resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceHeterojunction

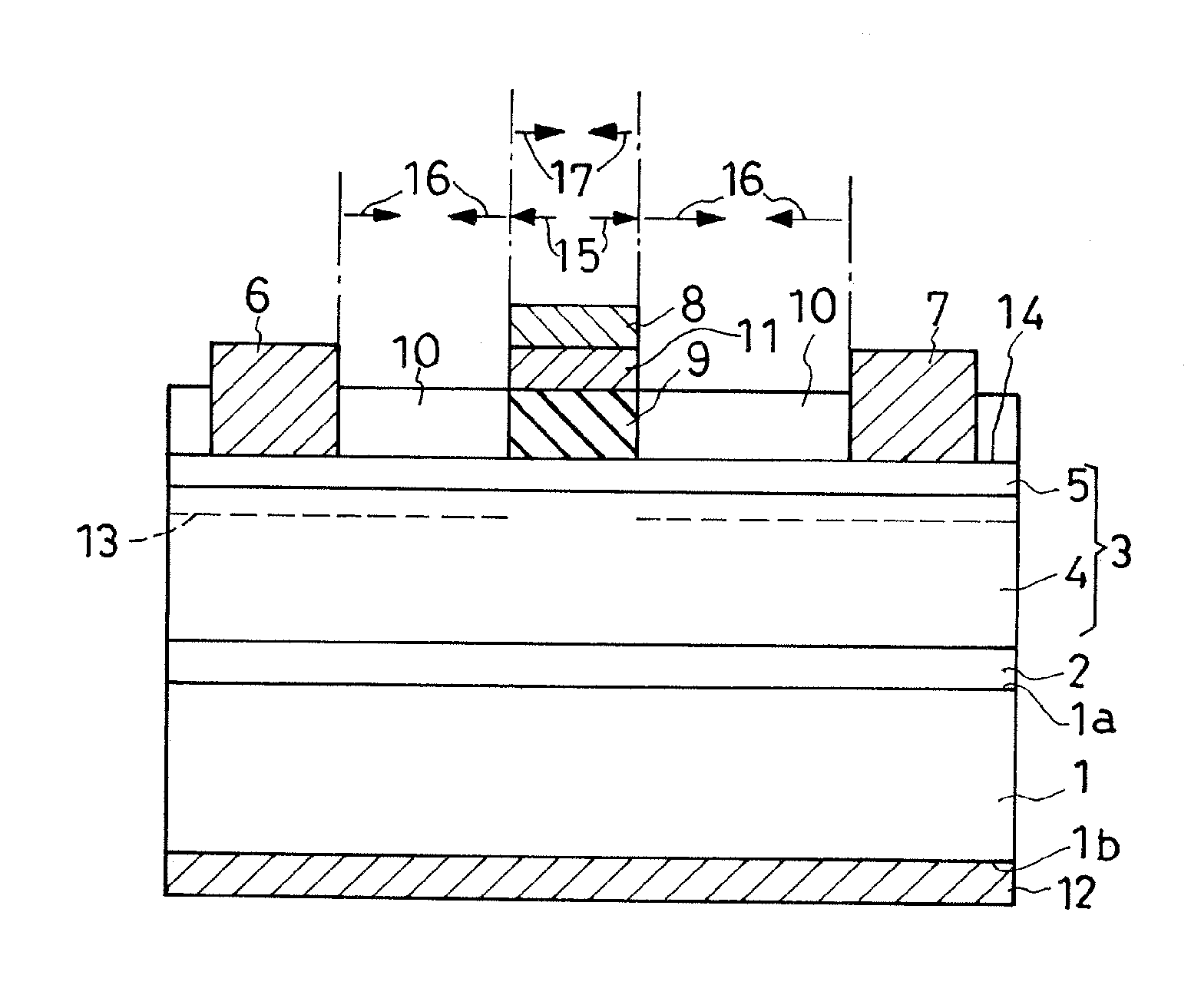

A HEMT-type field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on the main semiconductor region. Between these electrodes, with spacings therefrom, an insulator is provided with is made from a material capable of developing a stress to reduce carrier concentration in neighboring part of the two-dimensional electron gas layer, creating a discontinuity in this layer. A gate electrode overlies the insulator via a piezoelectric layer which is made from a material capable of developing, in response to a voltage applied to the gate electrode, a stress for canceling out the stress developed by the insulator. Thus the device is physically held off by the action of the insulator while no voltage is being impressed to the gate electrode and, upon voltage application thereto, piezoelectrically turns on by the action of the piezoelectric layer. The turn-on resistance of the device is relatively low as the insulator occupies only part of the source-drain spacing.

Owner:SANKEN ELECTRIC CO LTD

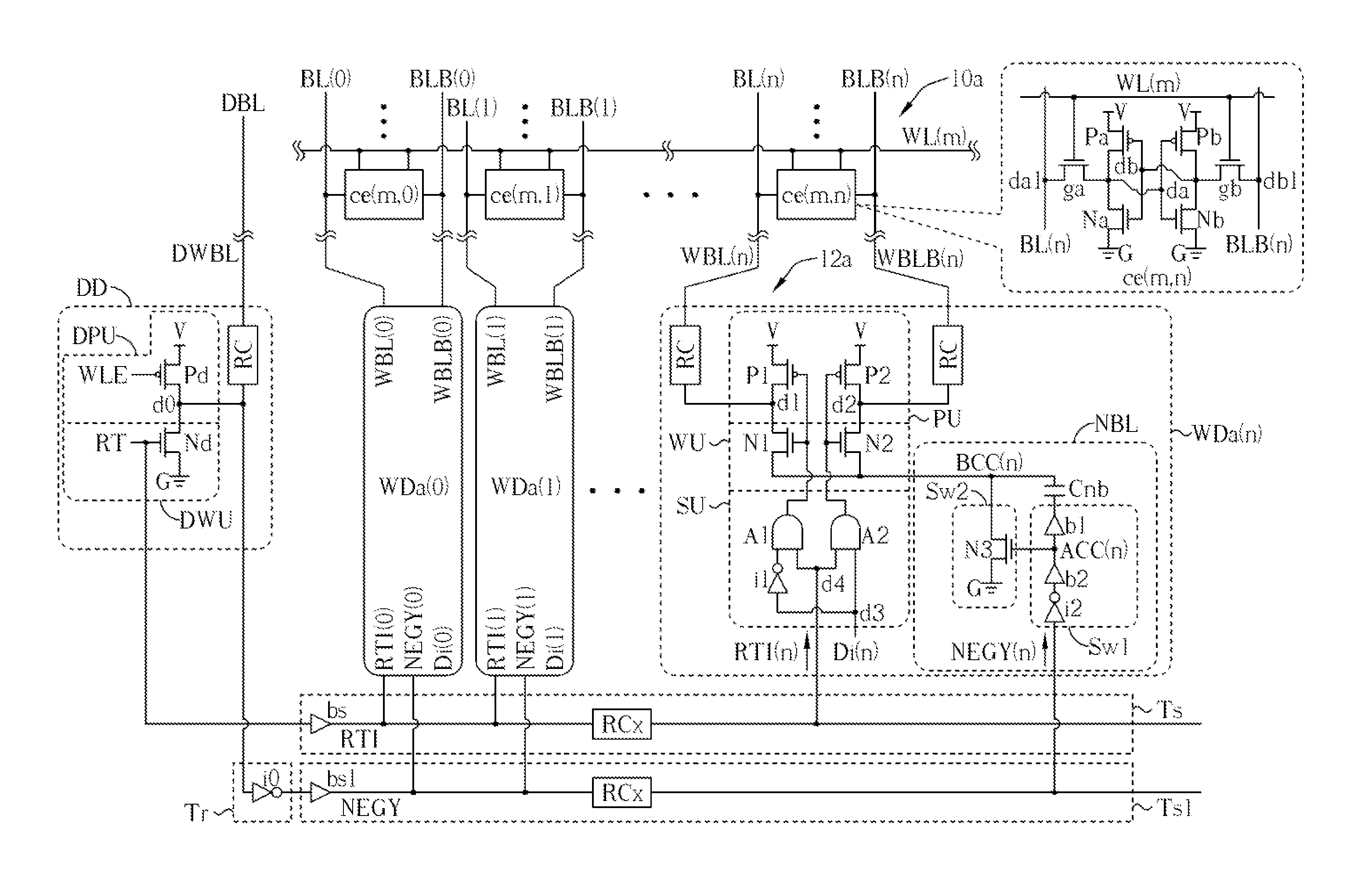

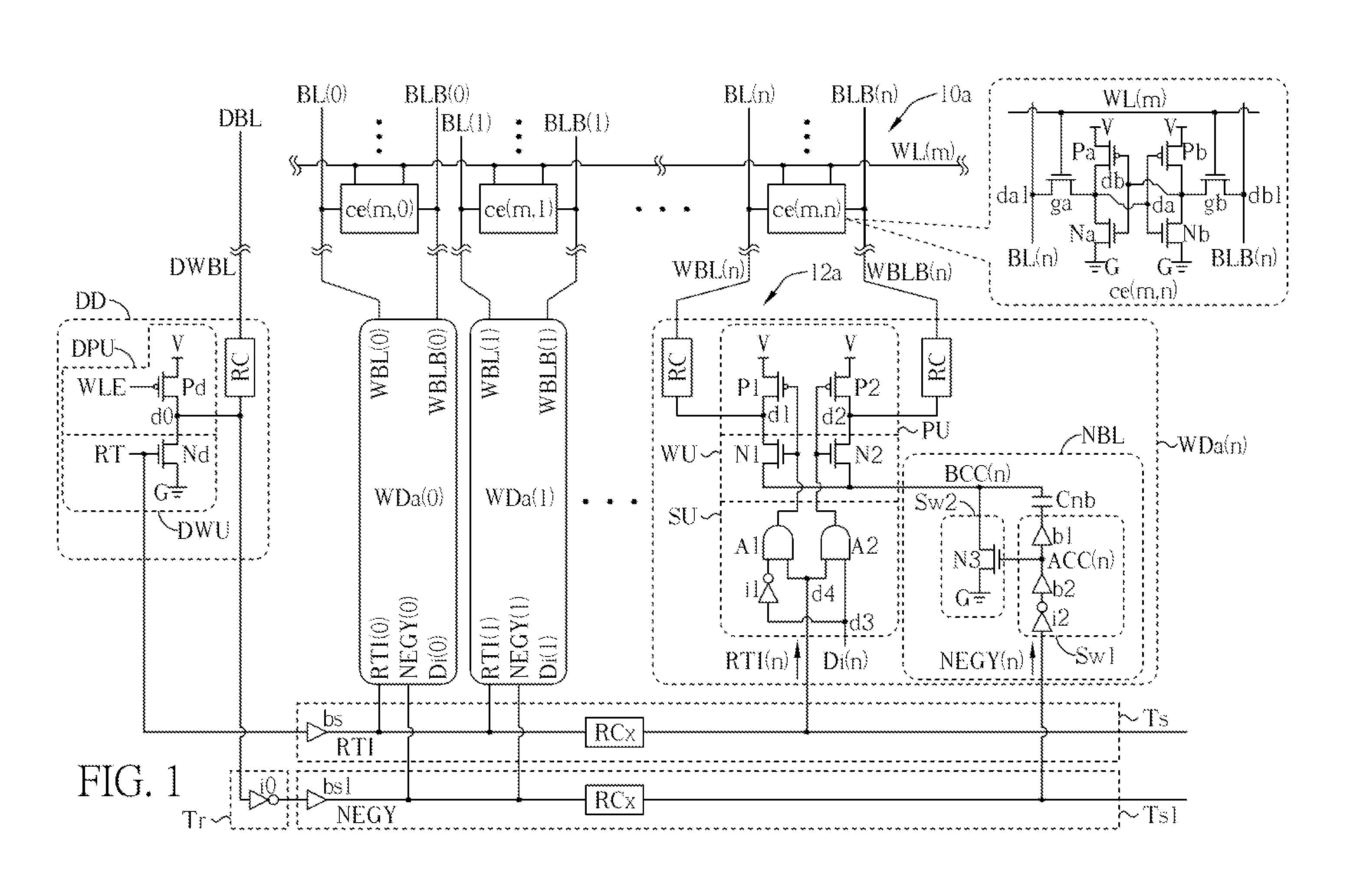

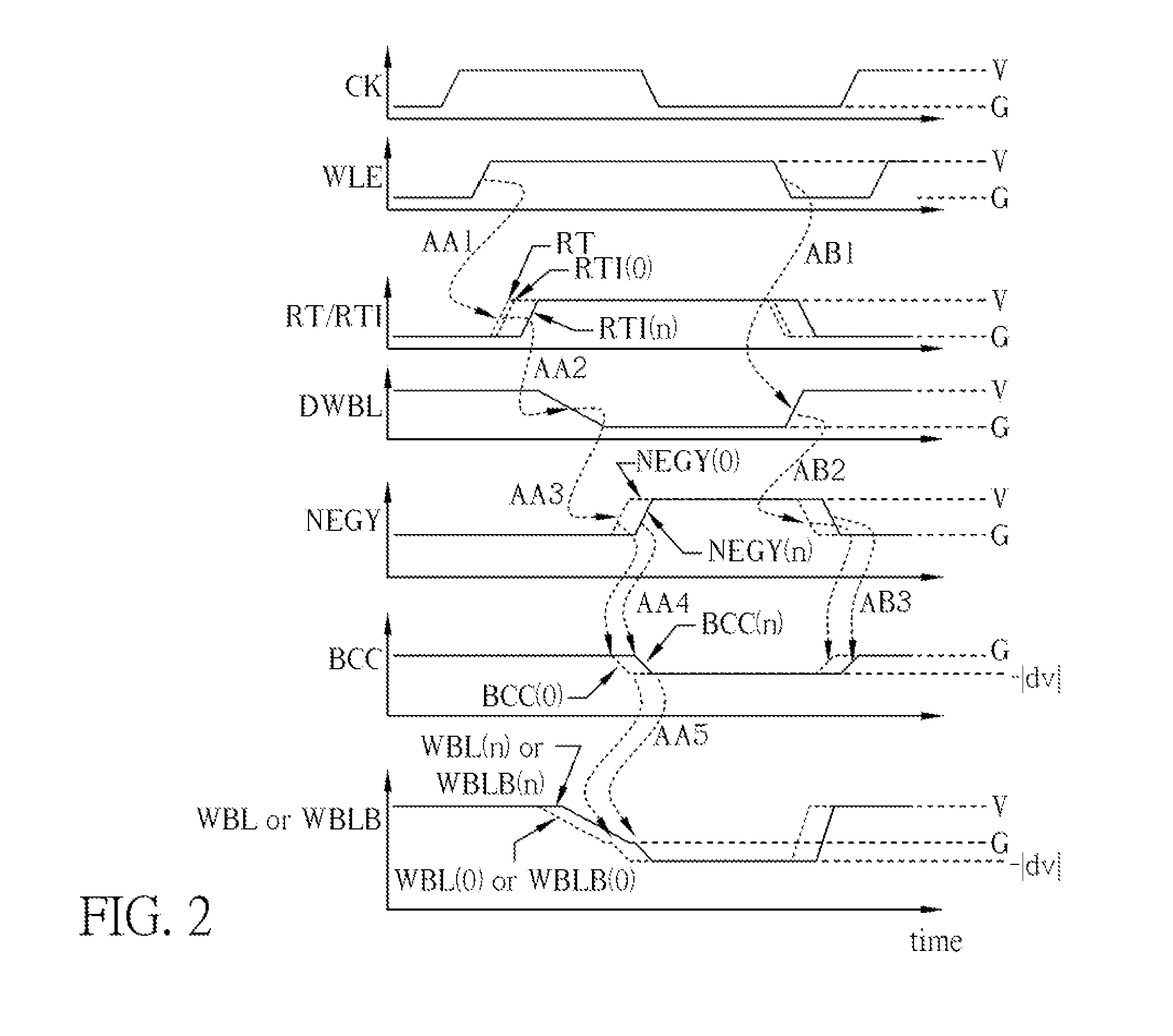

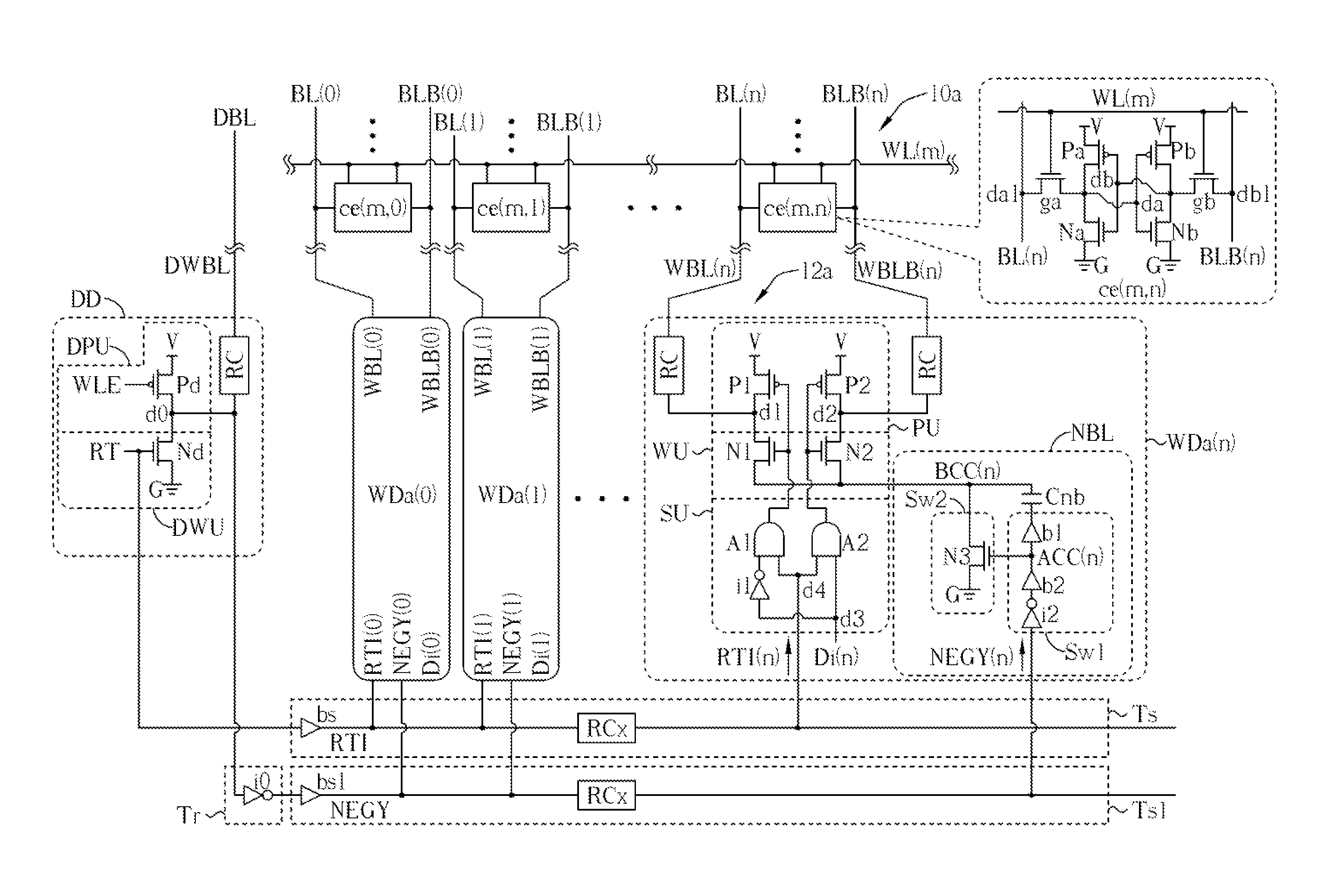

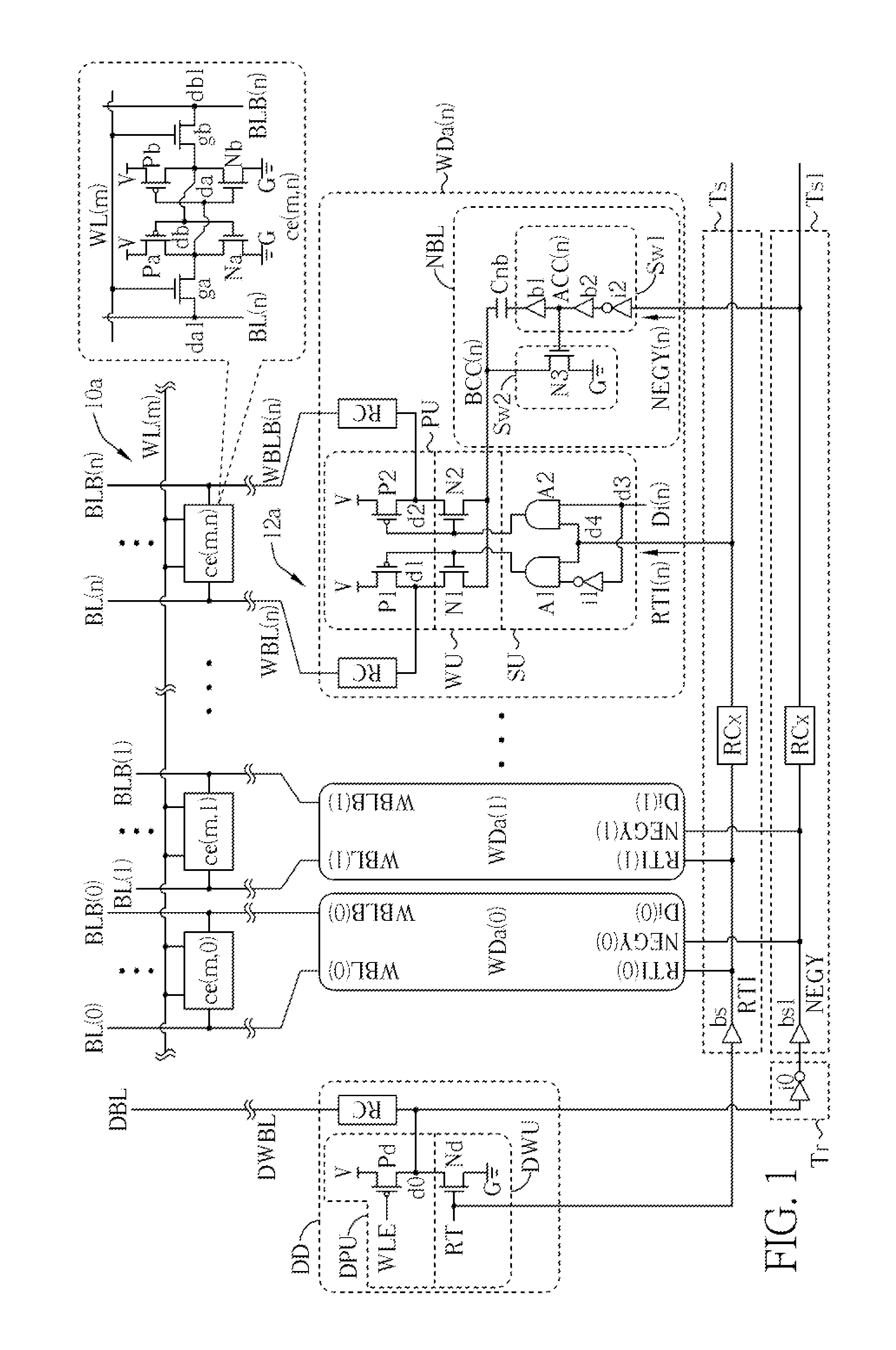

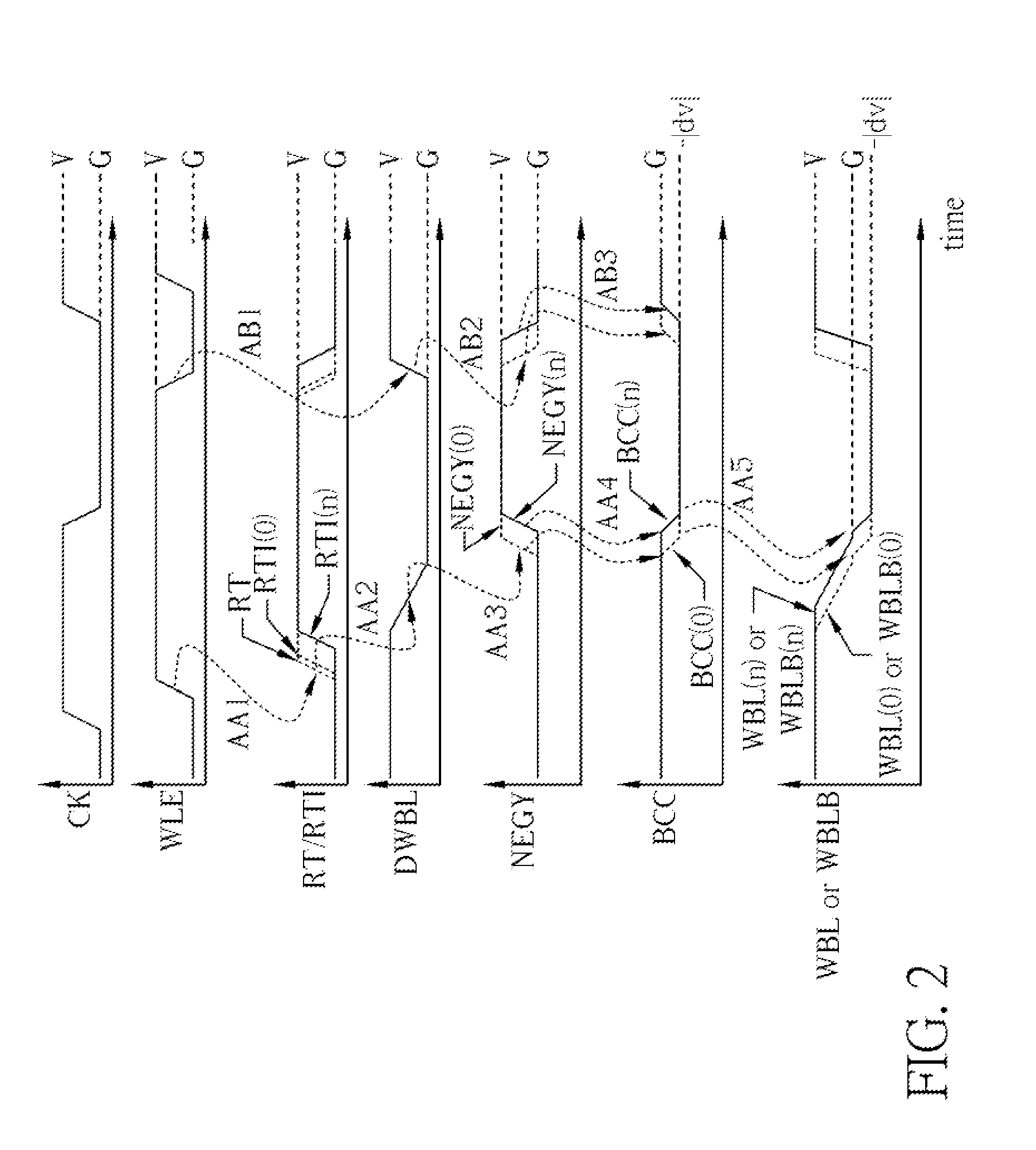

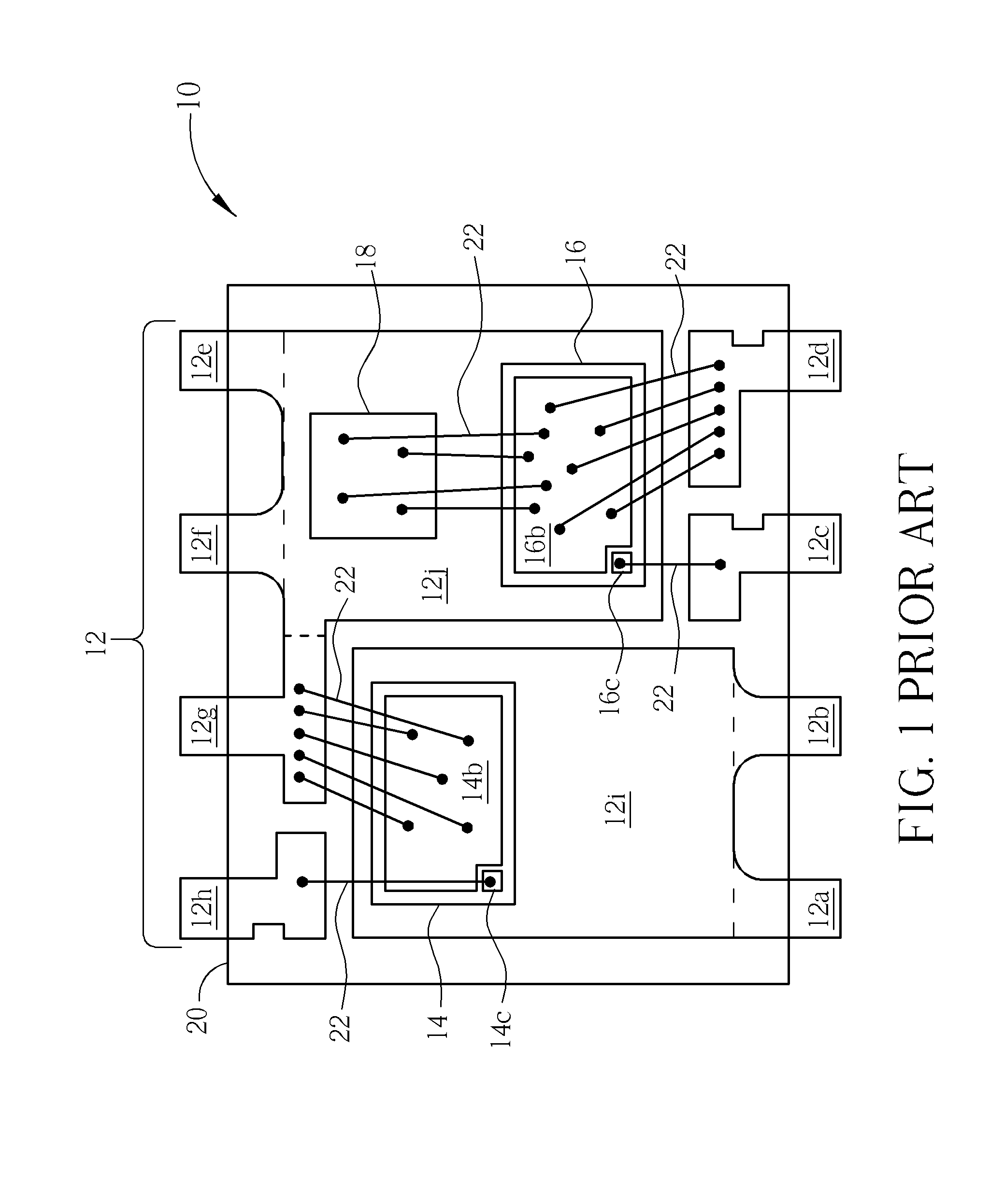

SRAM writing system and related apparatus

ActiveUS20110235444A1Lower on-resistanceLower turn-on resistanceDigital storageBit linePulse control

SRAM writing system and related apparatus are provided. The writing system of the invention has a dummy replica writing circuit, a negative pulse controller and at least a normal writing circuit; each normal writing circuit includes a write driver and a negative pulse supplier. While writing, the dummy replica writing circuit drives a dummy replica bit-line, such that the negative pulse controller generates a negative pulse control signal according to level of the dummy replica bit-line. In each writing circuit, when the write driver conducts to connect an associated bit-line to a bias end for driving a level transition, the negative pulse supplier switches the bias end from an operation voltage to a different negative pulse voltage according to the received negative pulse control signal.

Owner:FARADAY TECH CORP

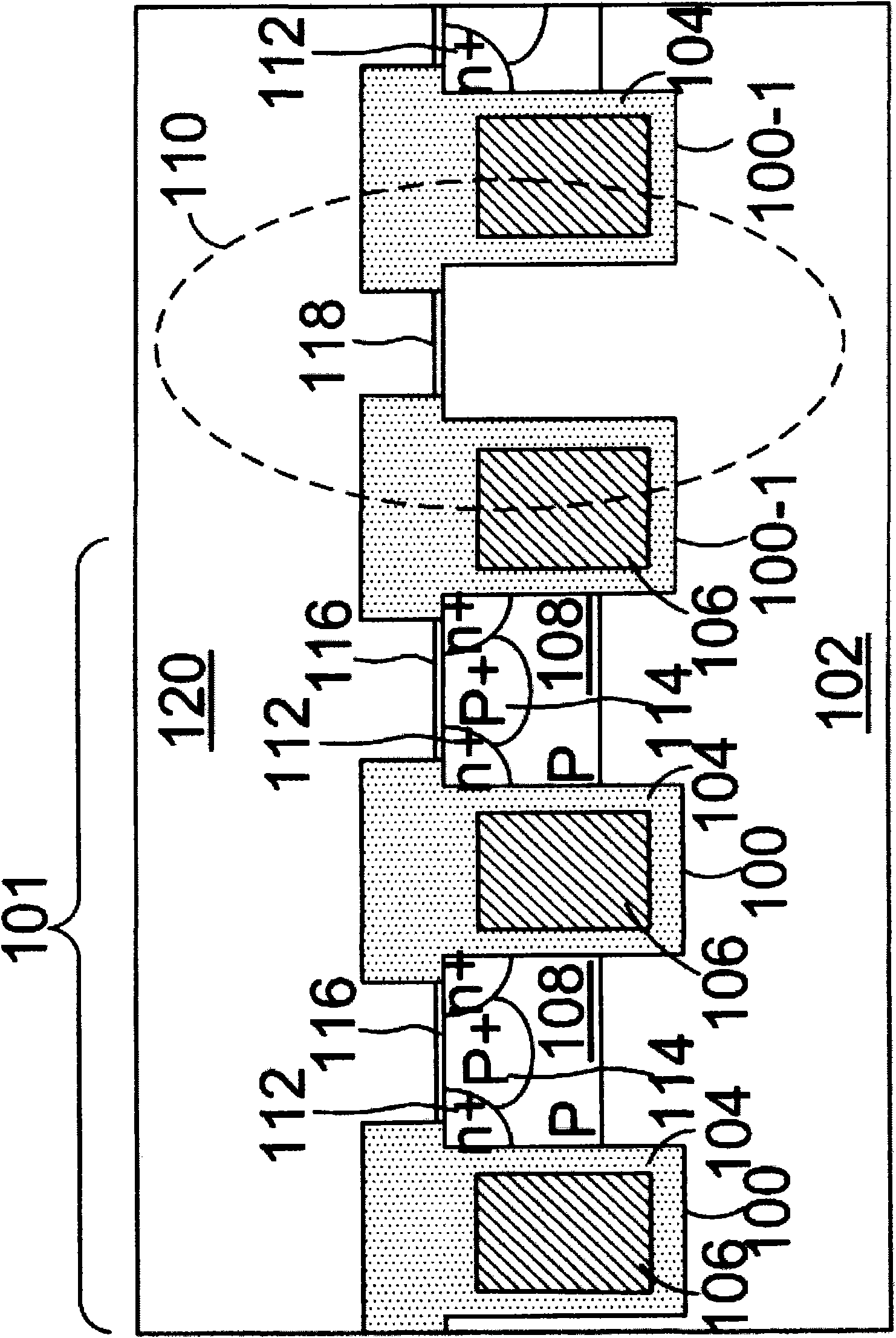

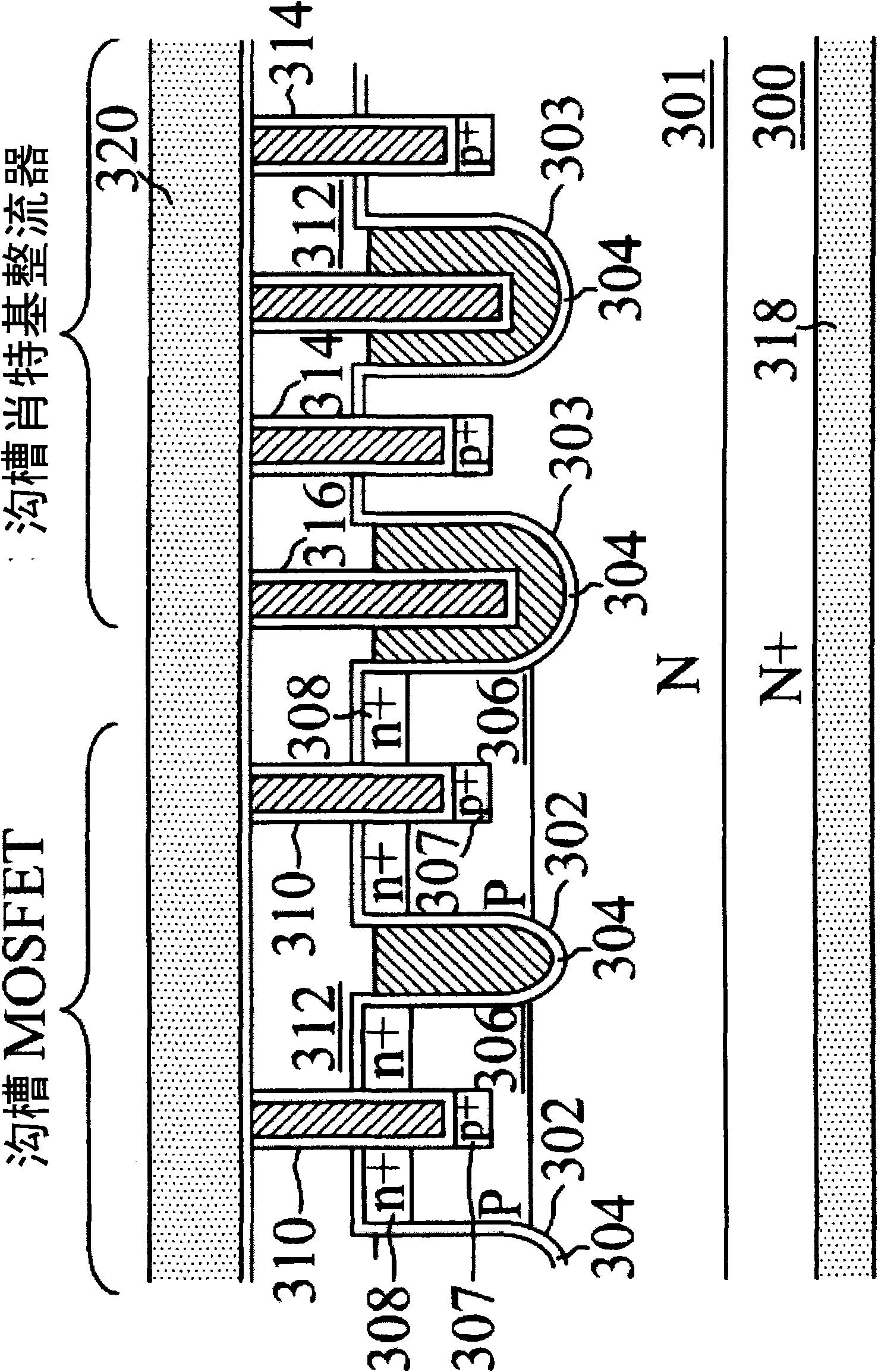

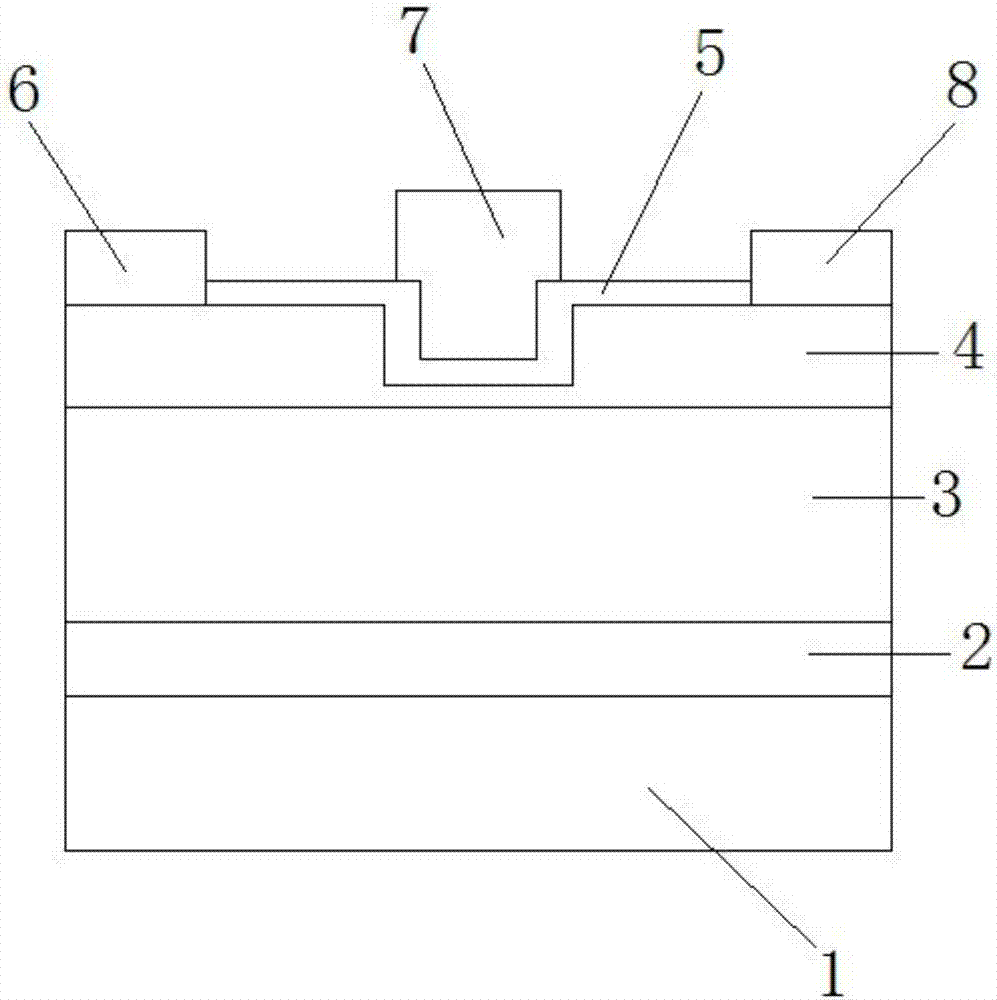

Semiconductor integrated circuit and manufacturing method thereof

InactiveCN102315220AReduce device sizeLower turn-on resistanceTransistorSemiconductor/solid-state device manufacturingMOSFETEngineering

The invention discloses a semiconductor integrated circuit and a manufacturing method thereof. The semiconductor integrated circuit comprises a plurality of grooved metal oxide semiconductor field effect transistors and a plurality of grooved Schottky rectifiers which are positioned on a same substrate, wherein the plurality of grooved metal oxide semiconductor field effect transistors are provided with grooved source contact regions; and the plurality of grooved Schottky rectifiers are provided with grooved anode contact regions. By the semiconductor integrated circuit with the structure, grooved metal oxide semiconductor field effect transistors have lower starting resistance and Schottky rectifiers have lower pre-position voltage and low reverse leakage current.

Owner:FORCE MOS TECH CO LTD

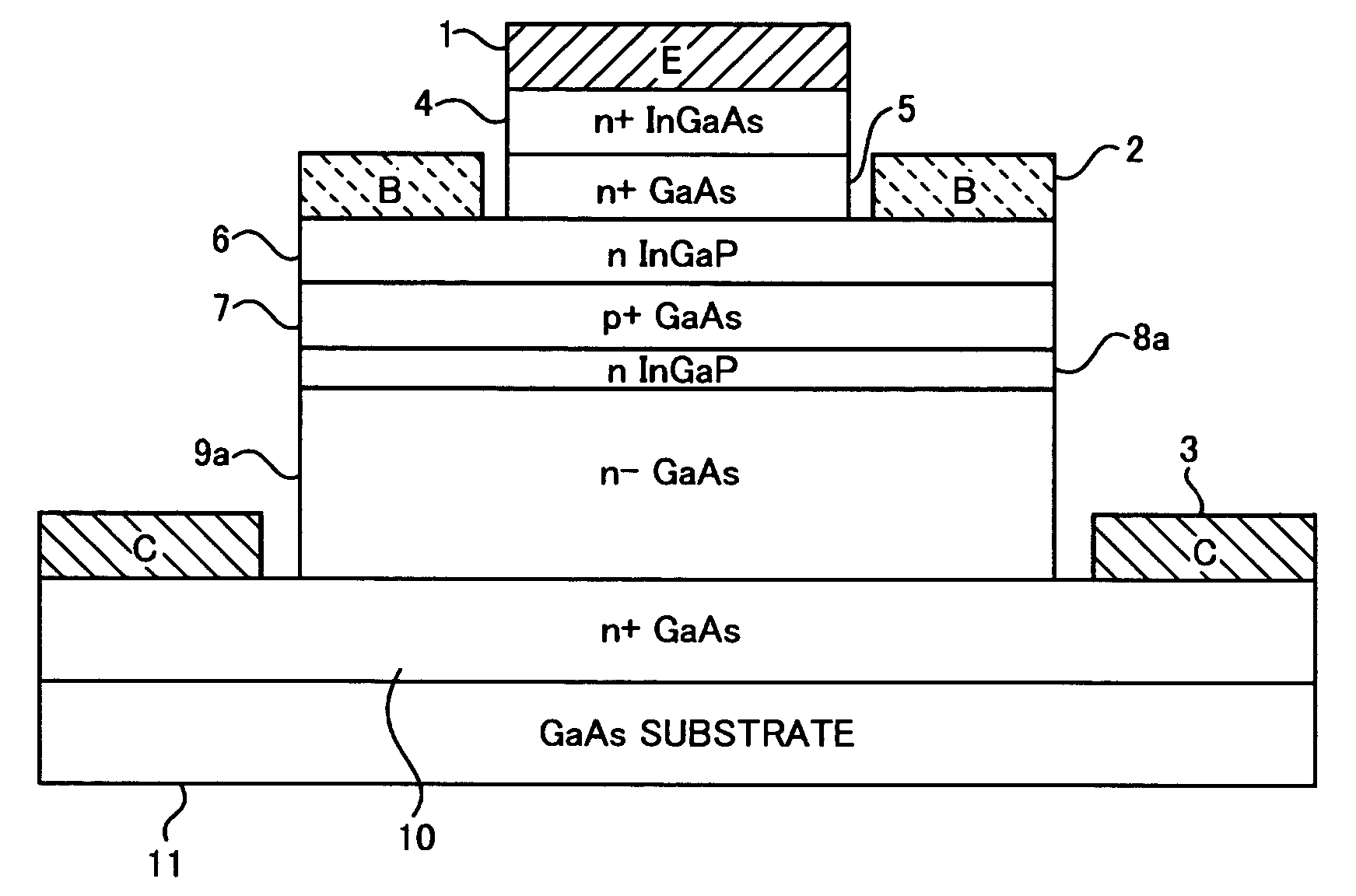

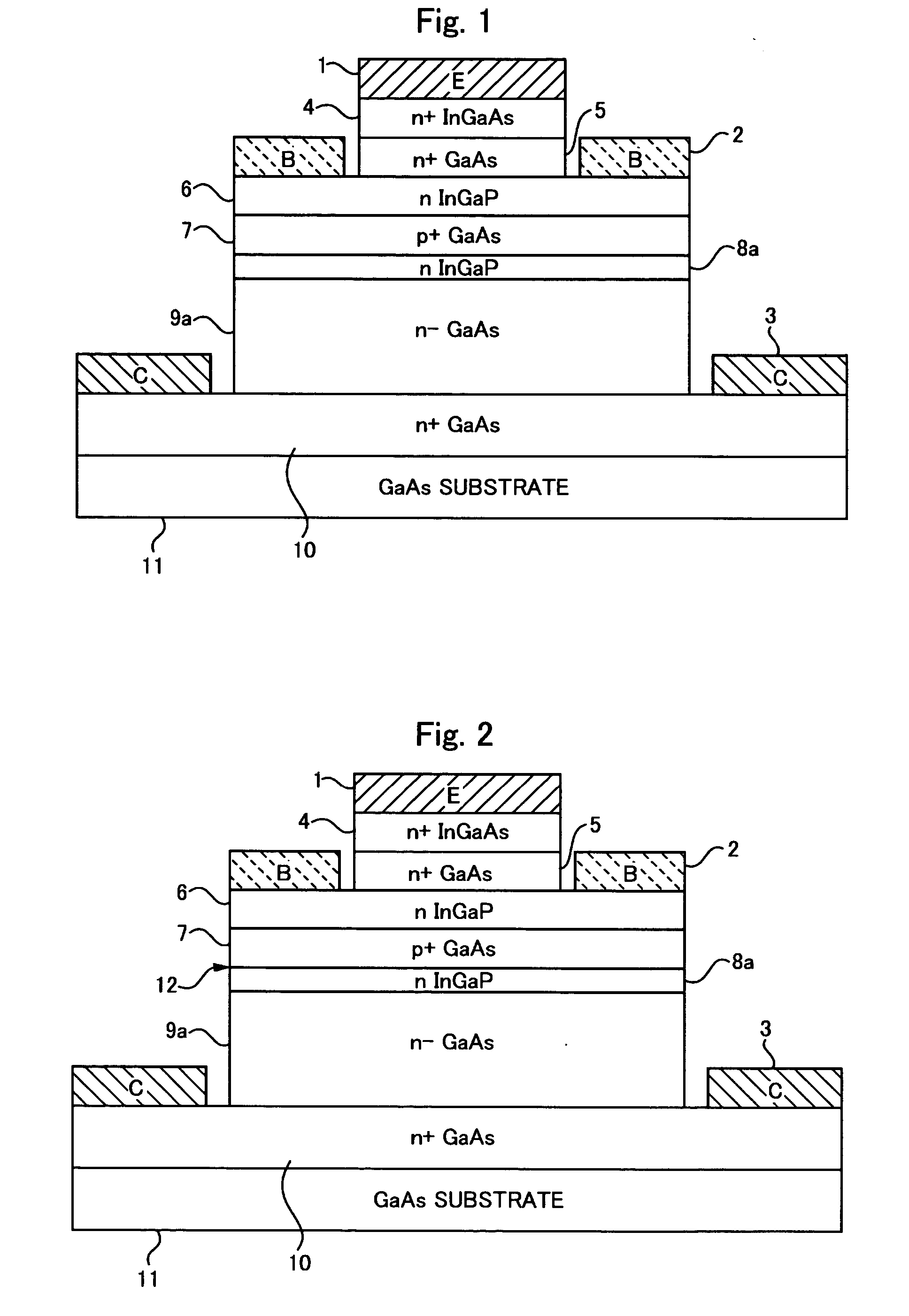

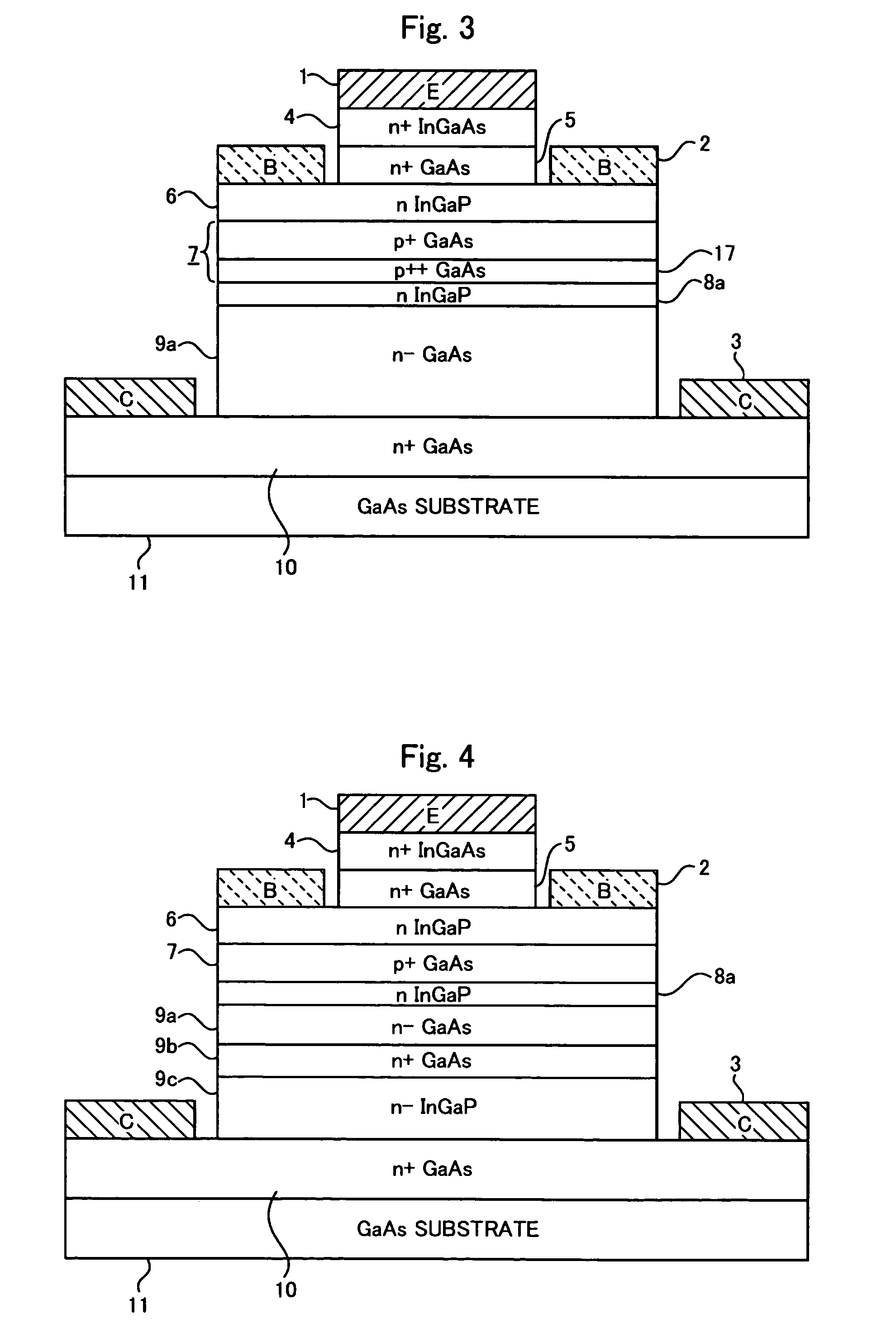

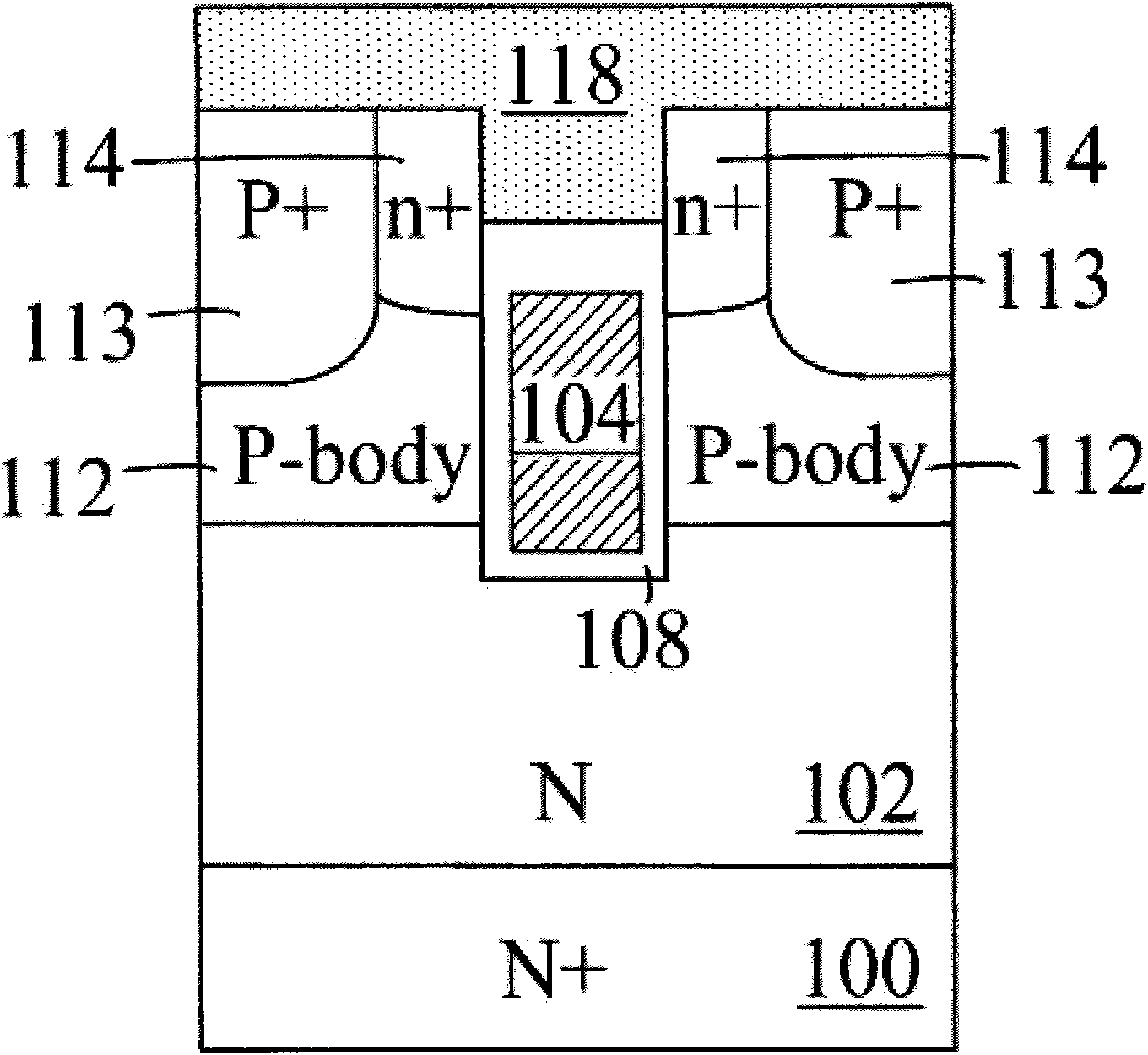

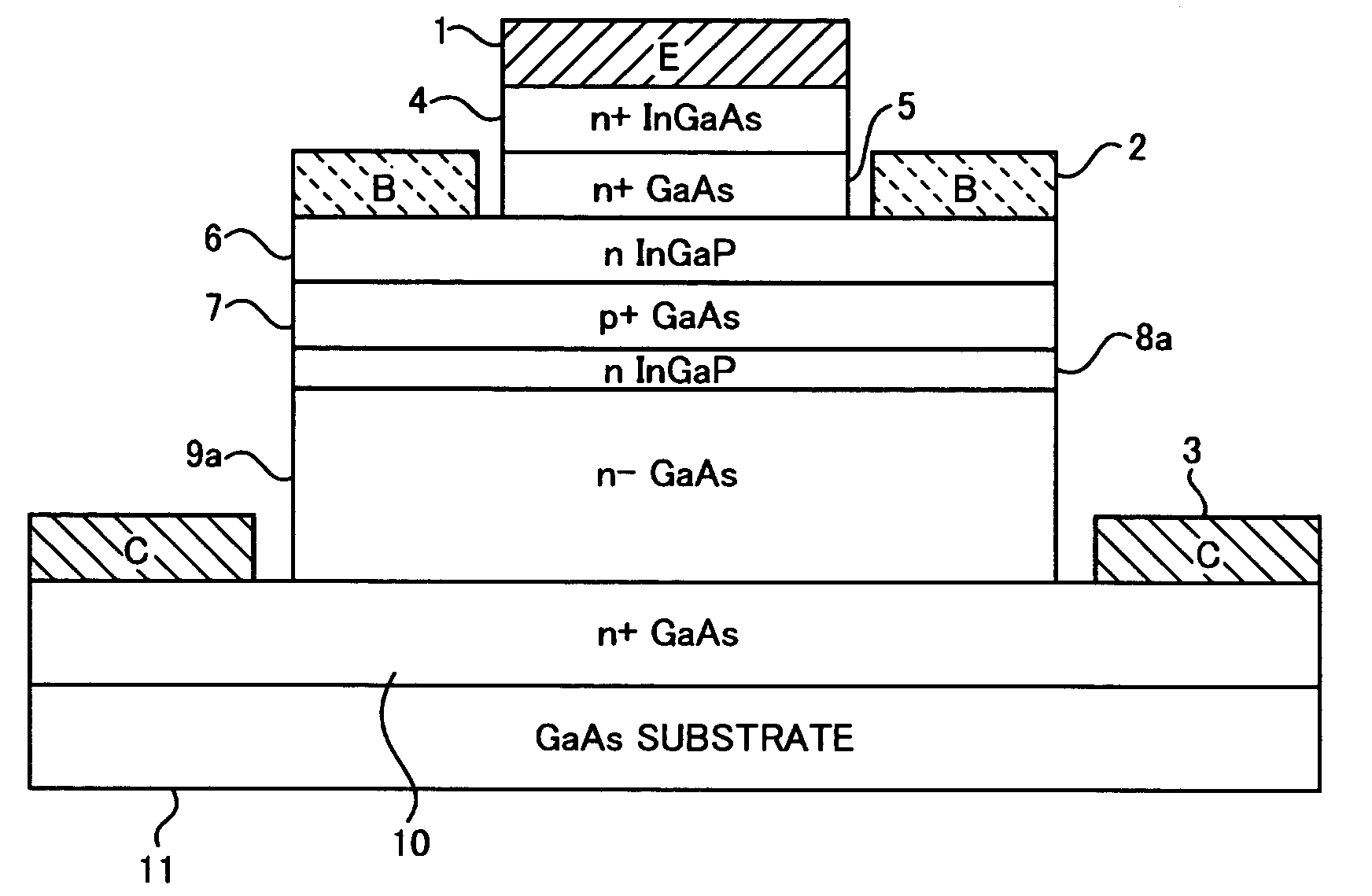

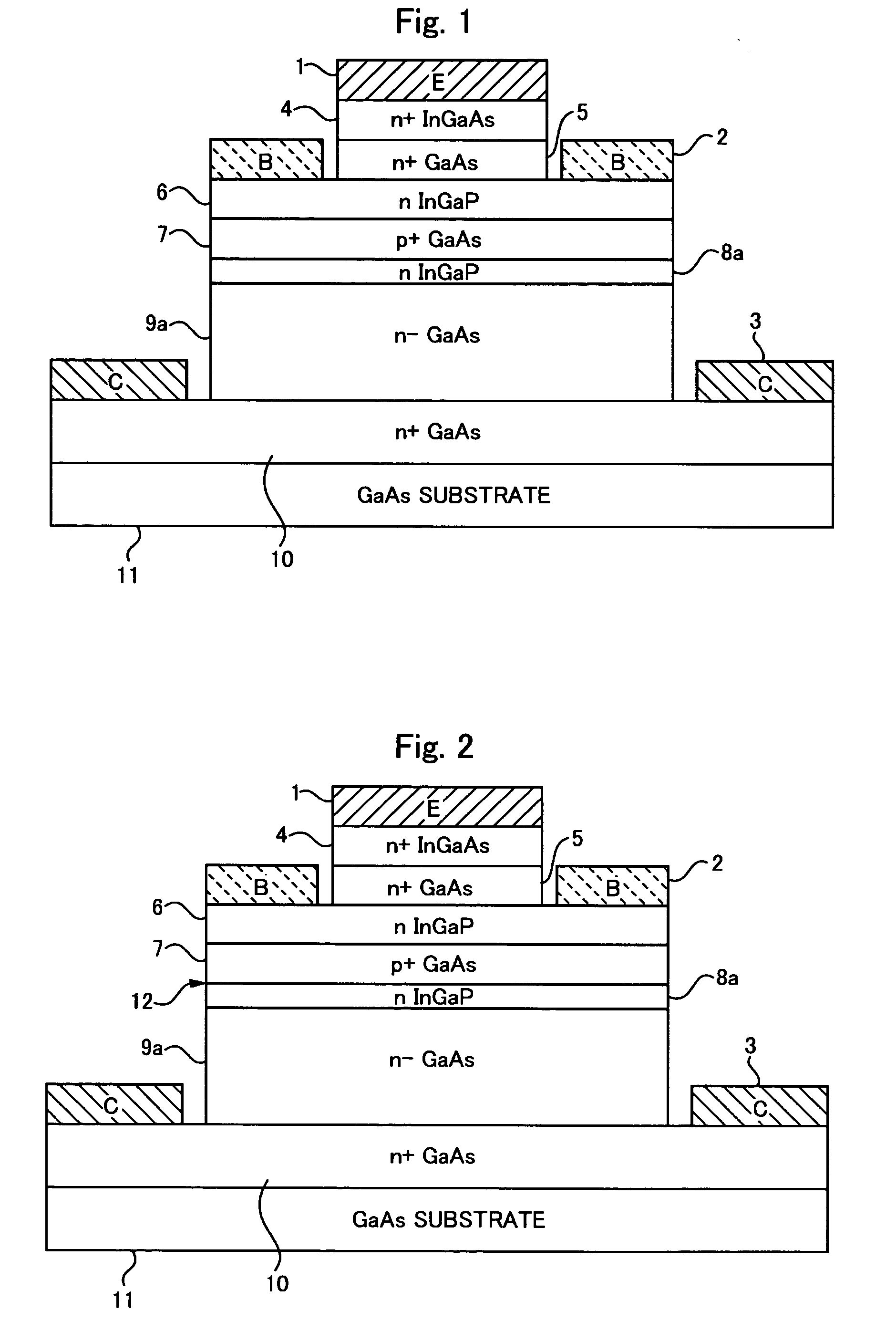

Semiconductor device

InactiveUS20050104088A1Lower turn-on resistanceImprove power added efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsDevice material

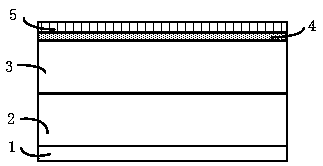

A heterojunction bipolar transistor, having a structure in which a subcollector layer of a first conductive type having a higher doping concentration than a collector layer, a collector layer of the first conductive type, a base layer of the second conductive type, and an emitter layer of the first conductive type are deposited, in order, on a semi-insulating semiconductor substrate, and in which a hole barrier layer of semiconductor material with a band gap wider than that of the base layer is inserted between the base layer and the collector layer, so as to be in direct contact with the base layer.

Owner:RENESAS ELECTRONICS CORP

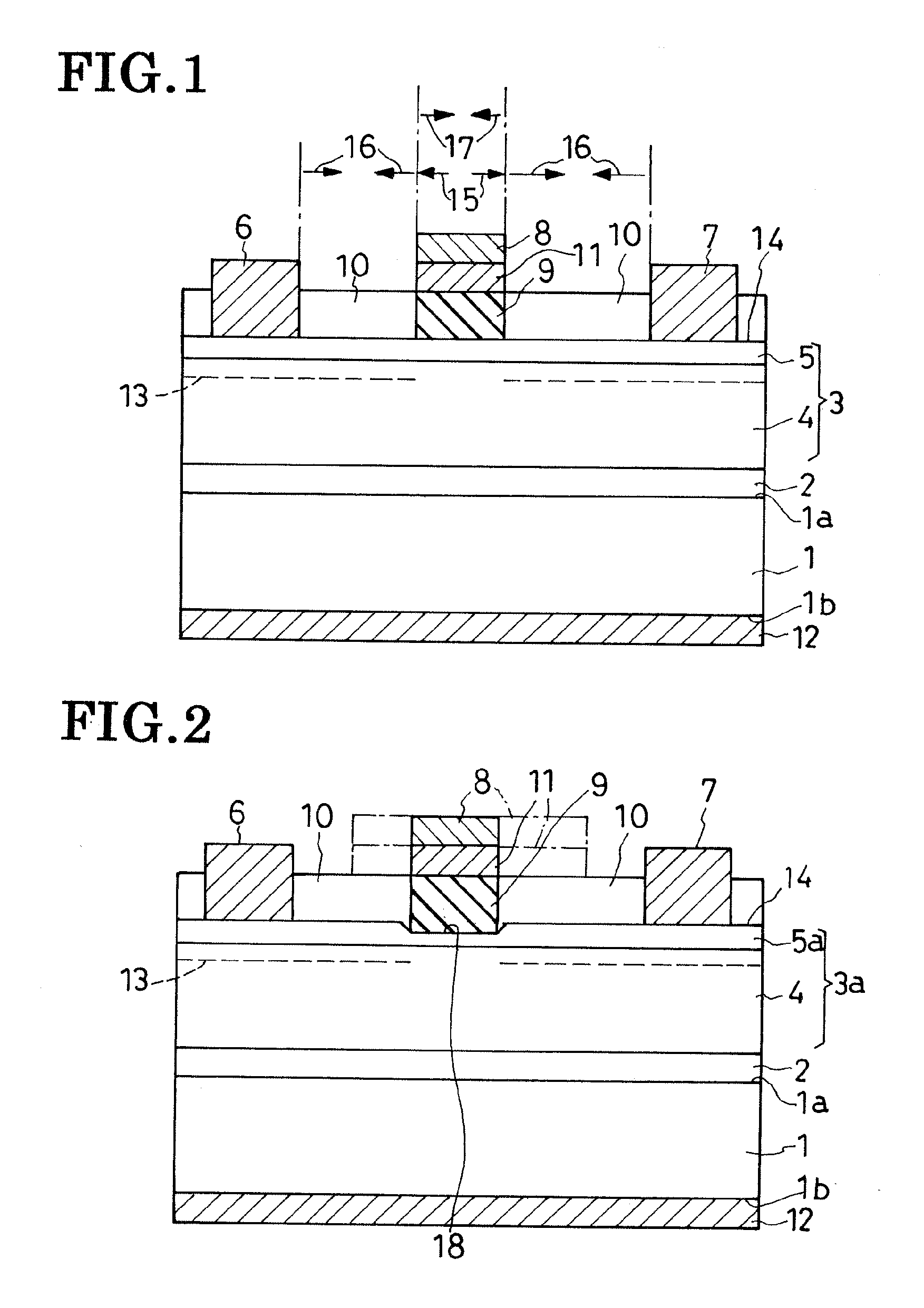

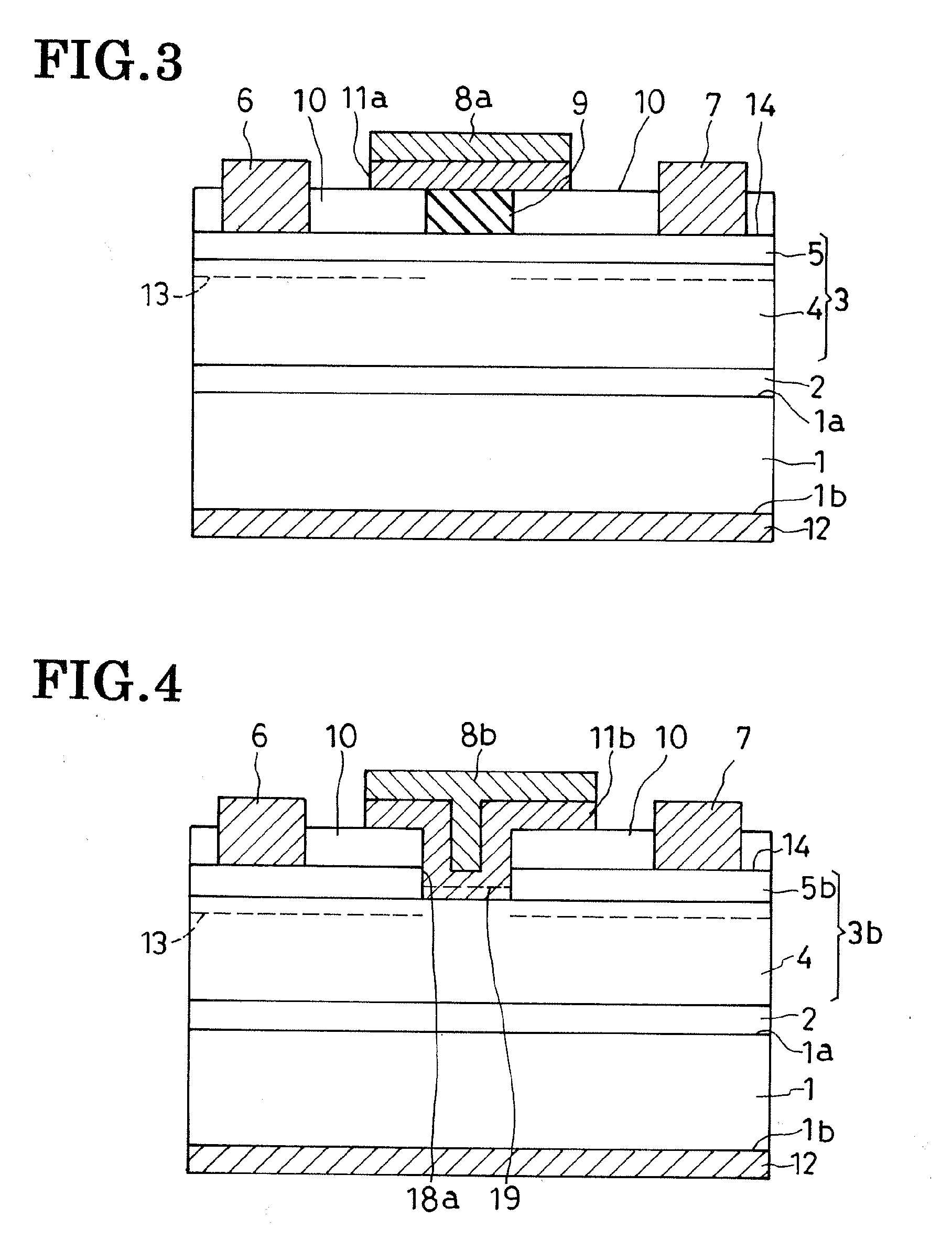

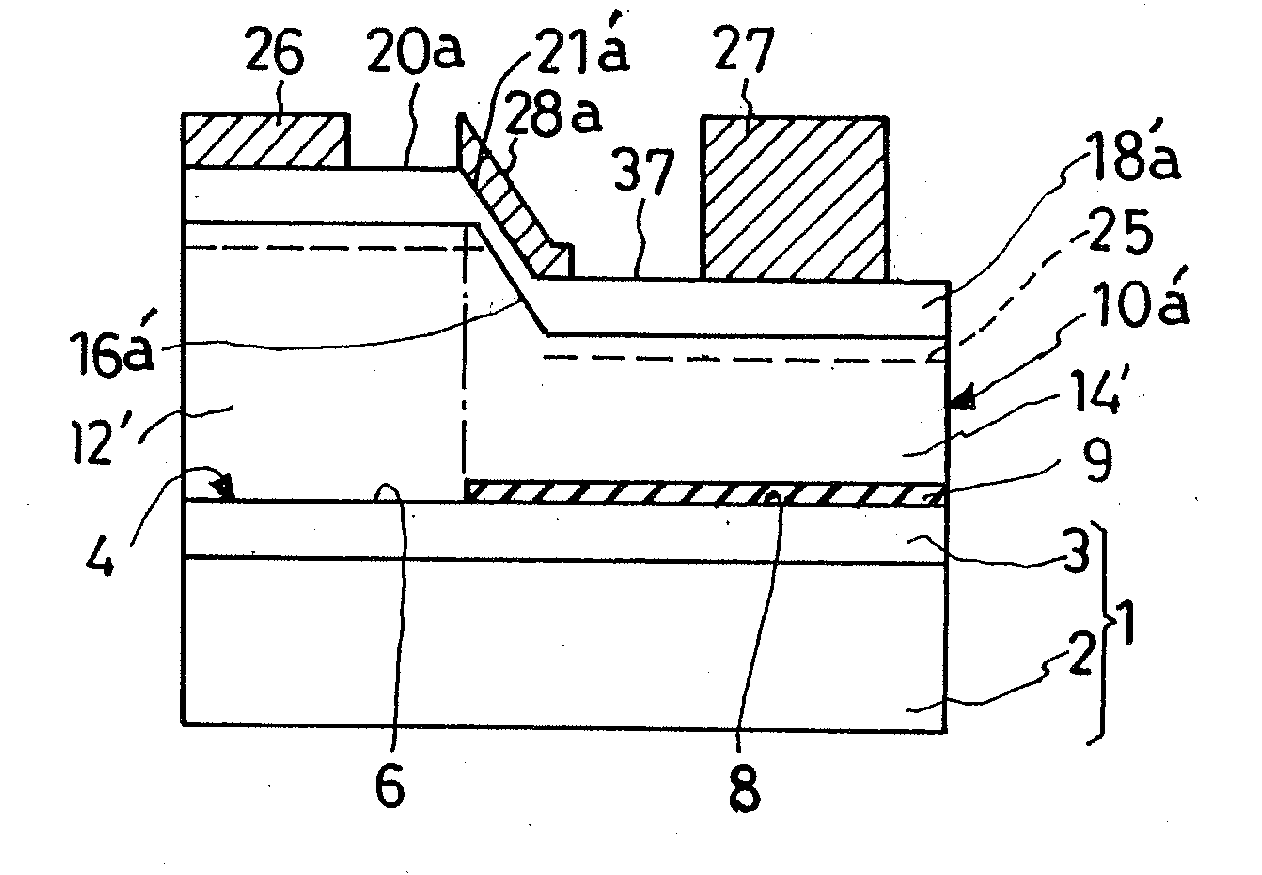

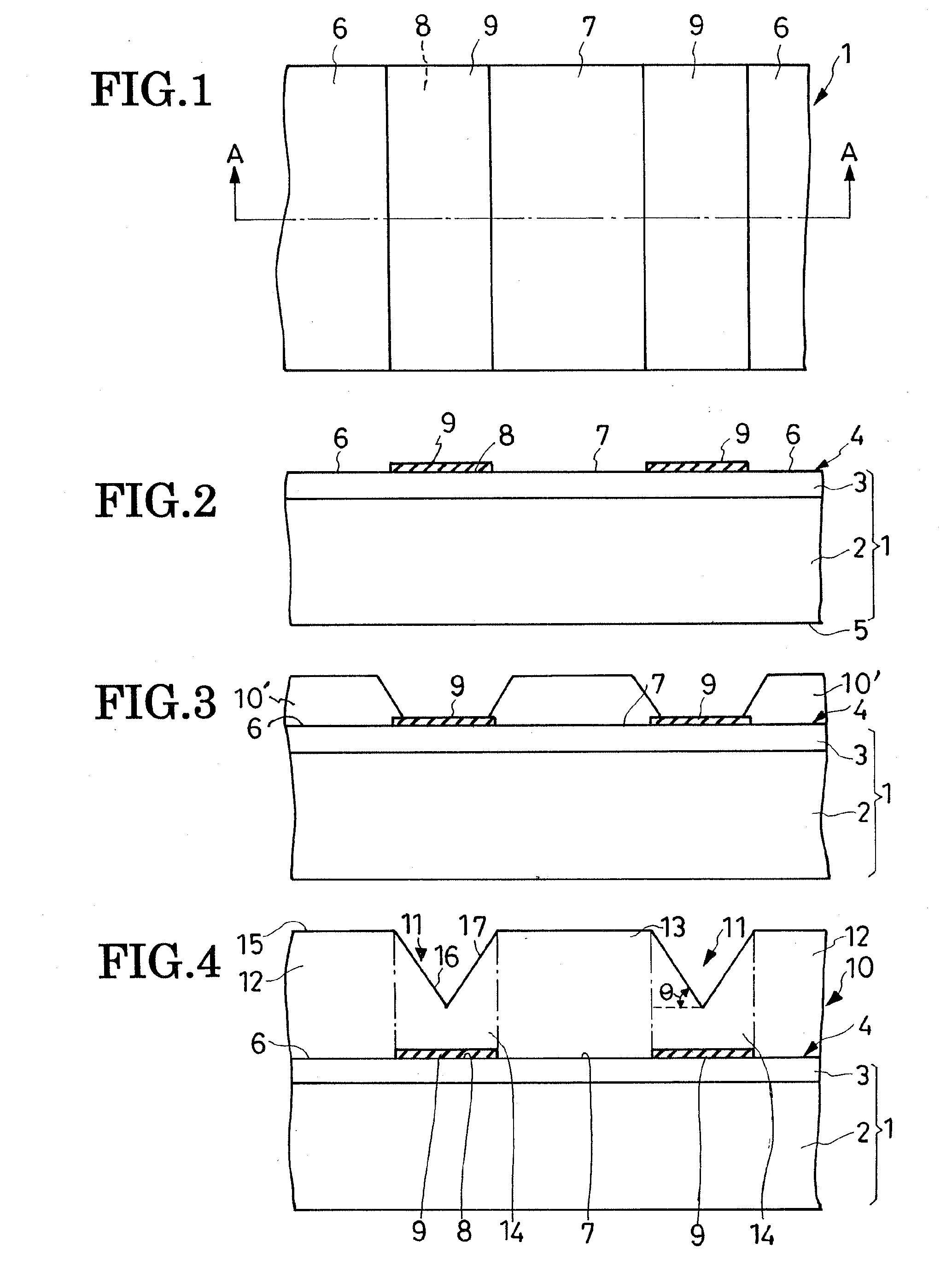

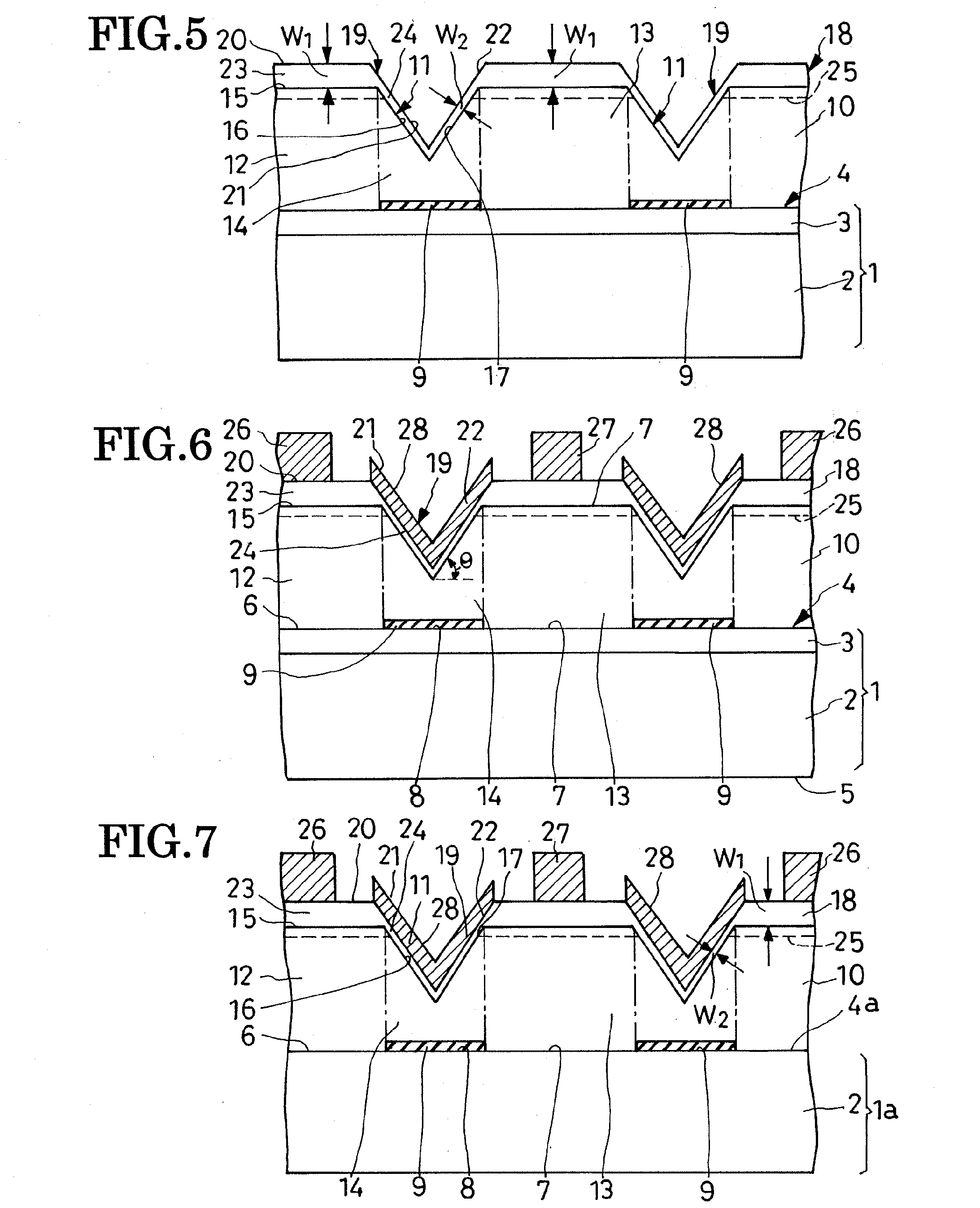

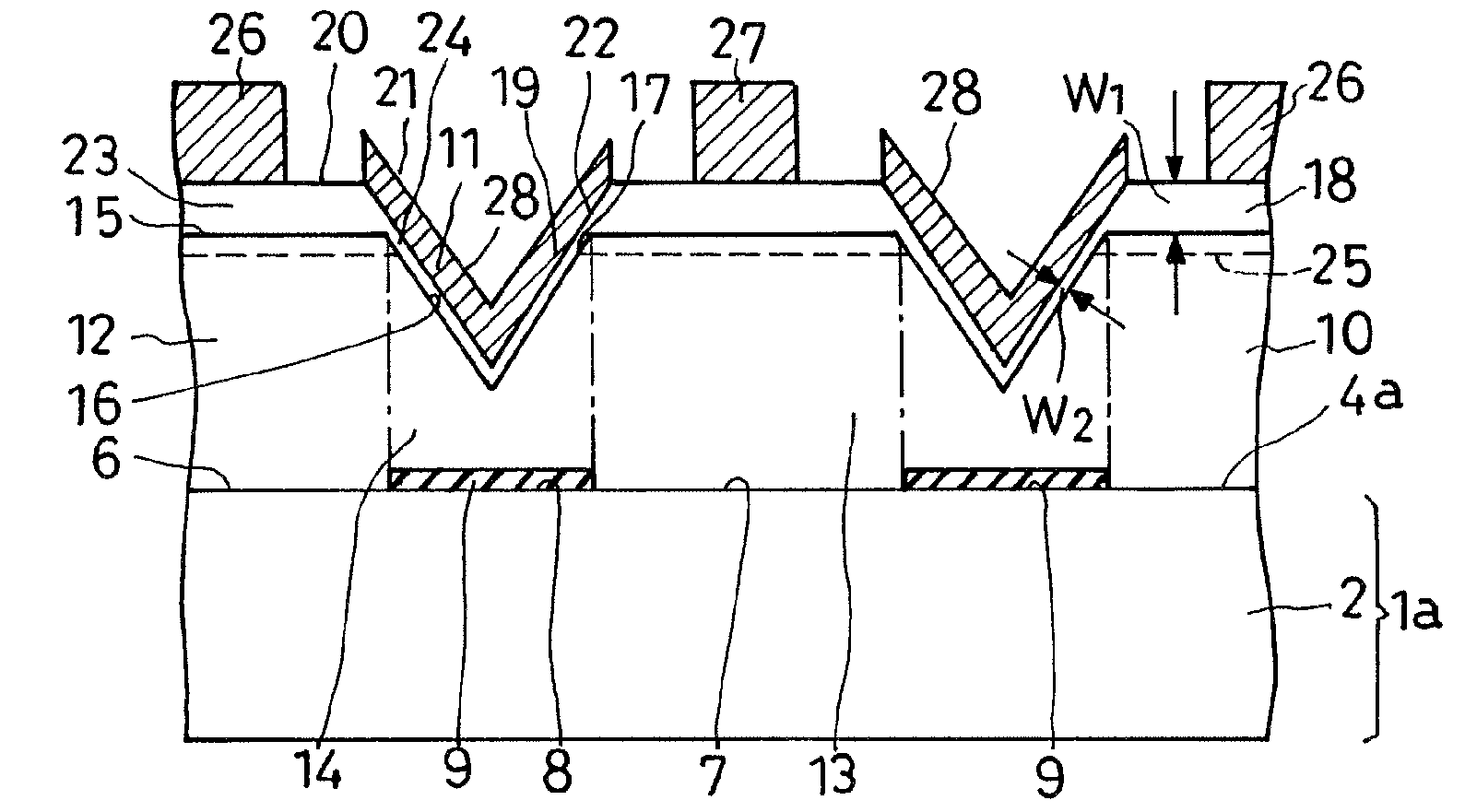

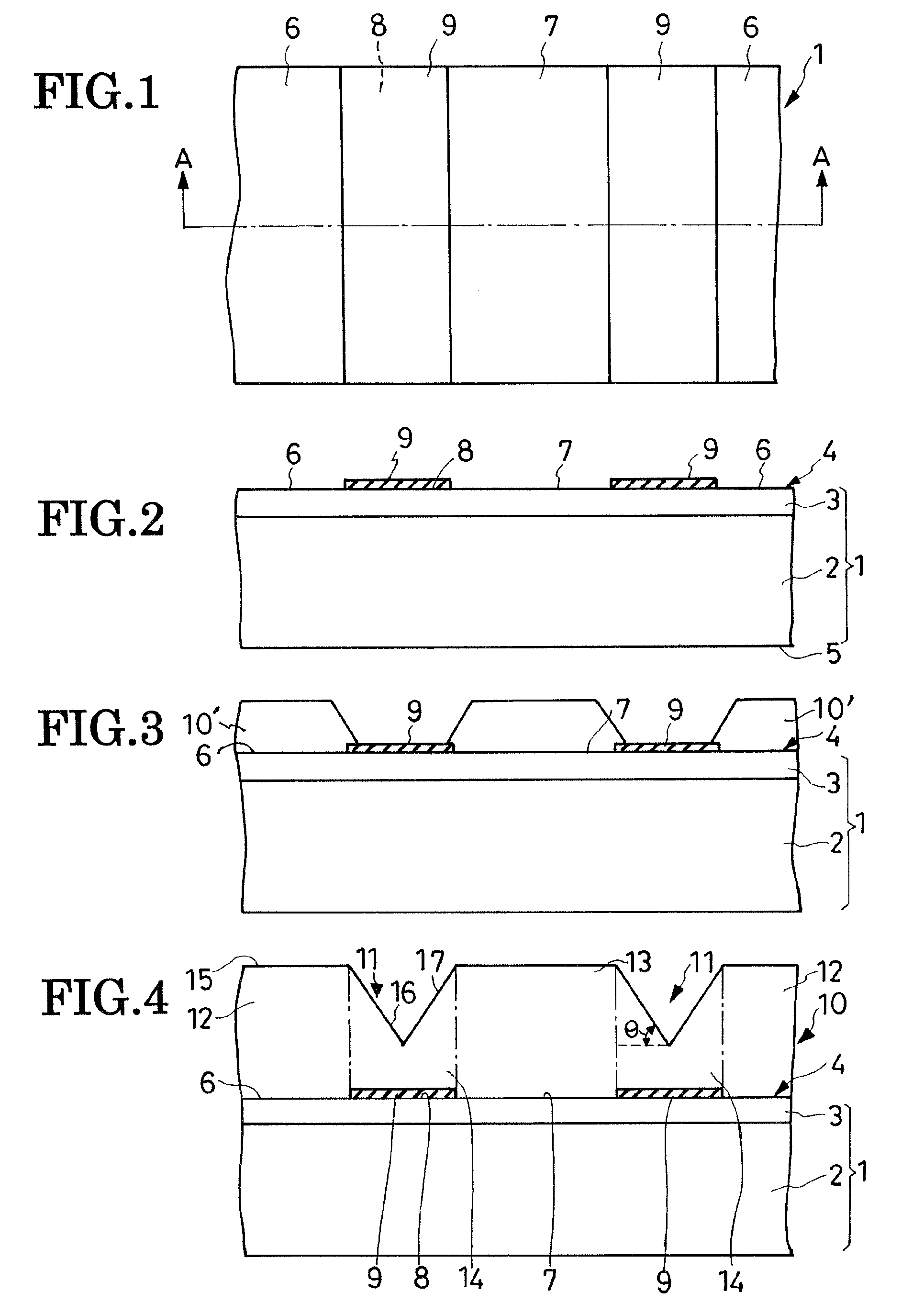

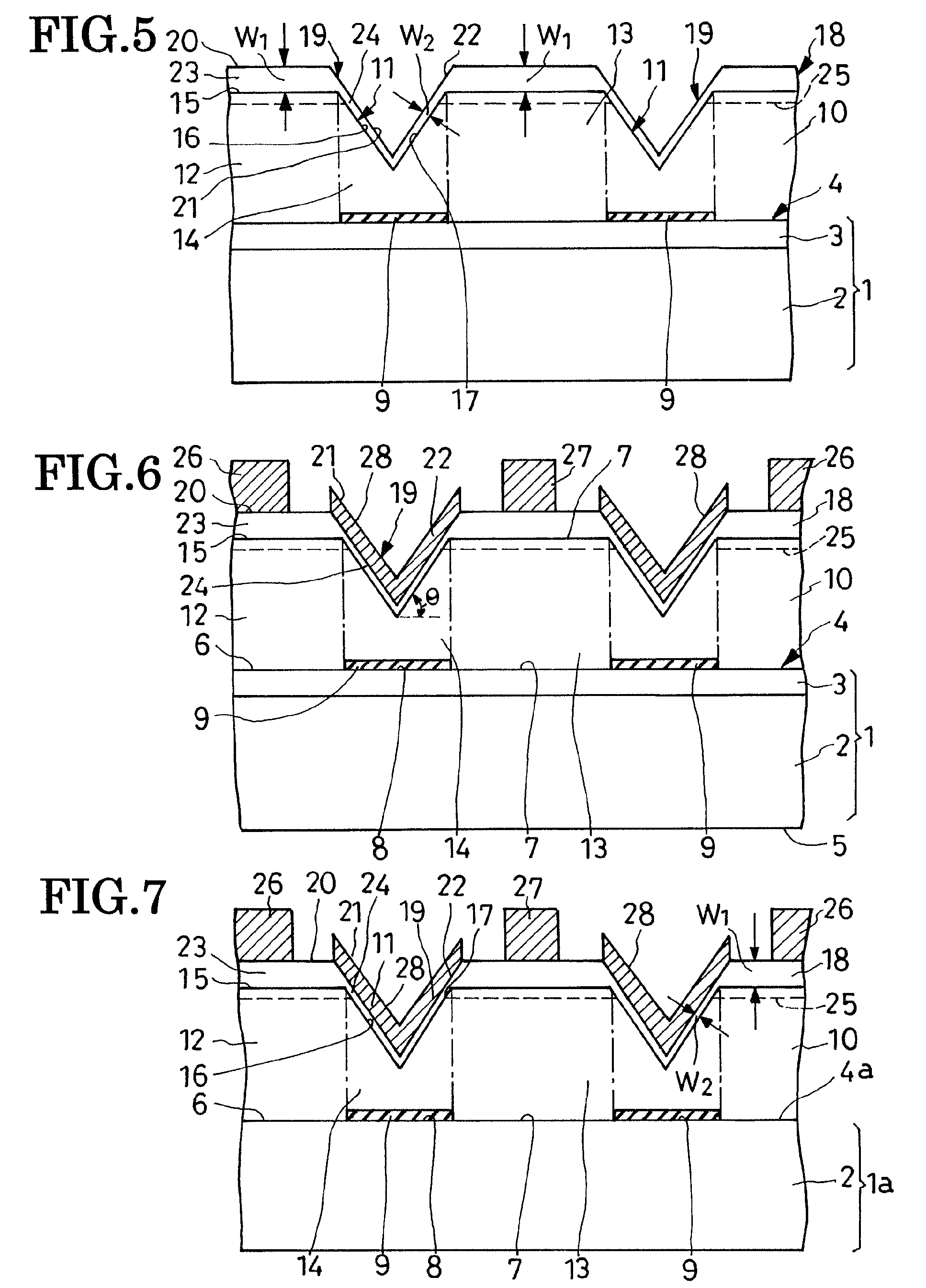

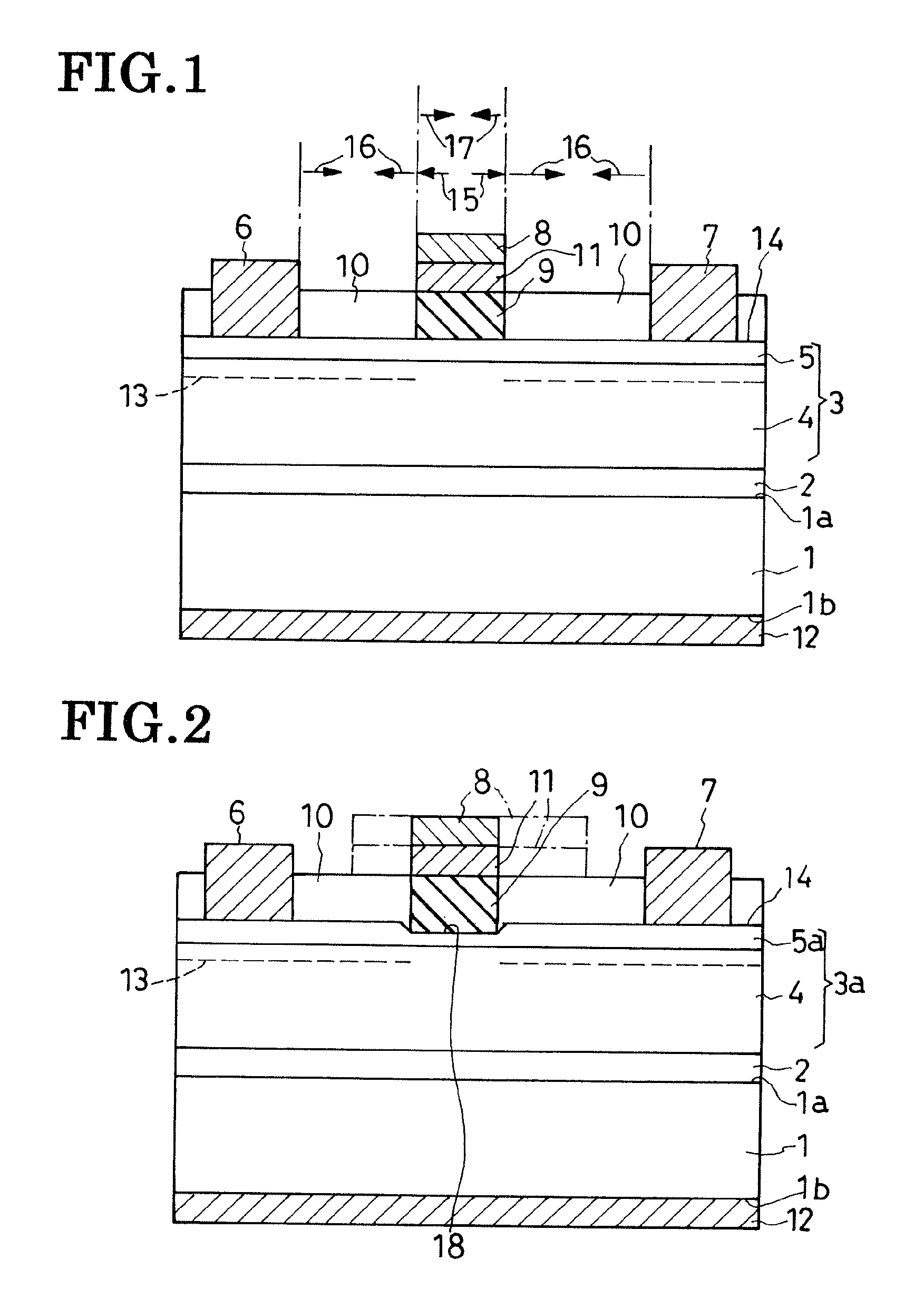

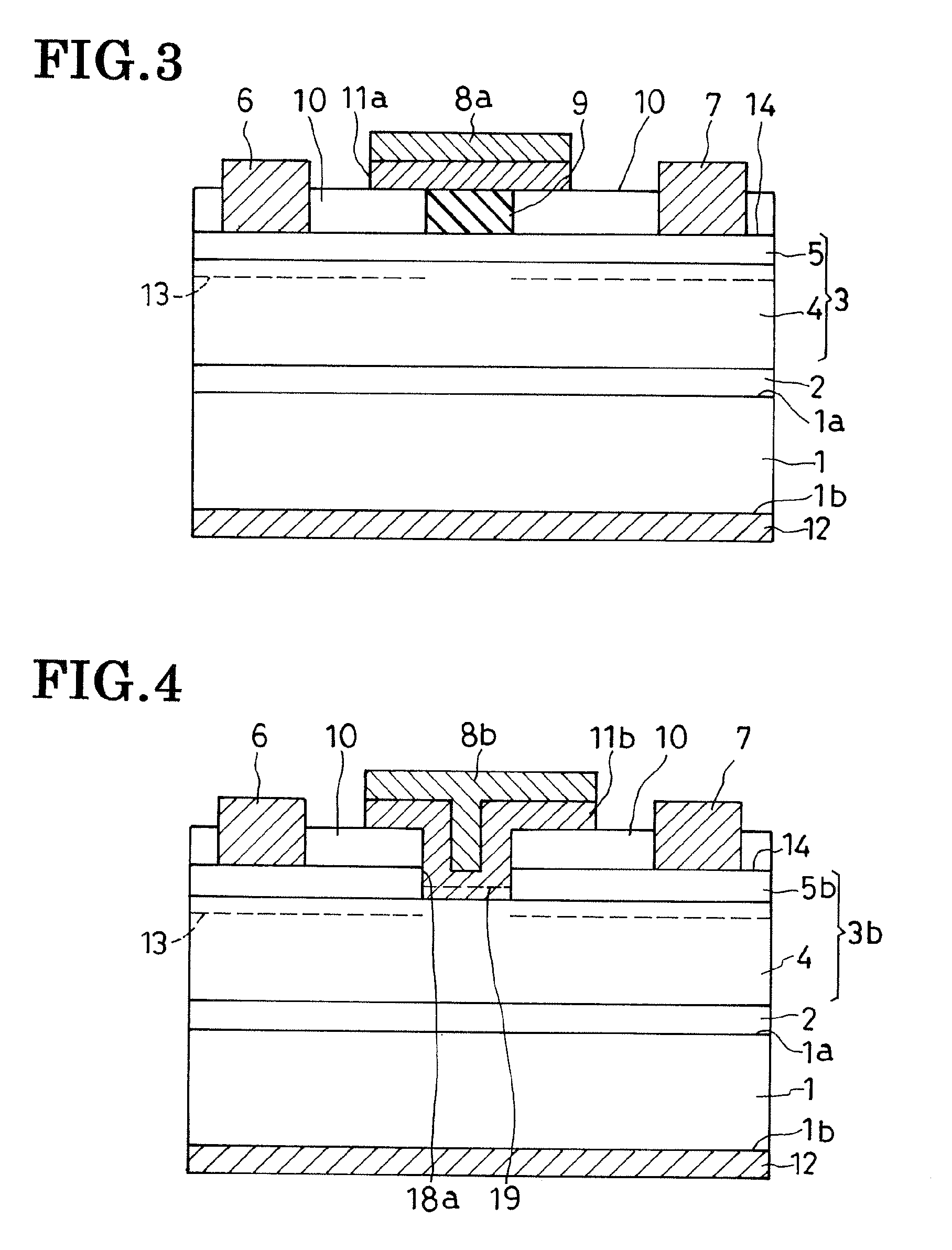

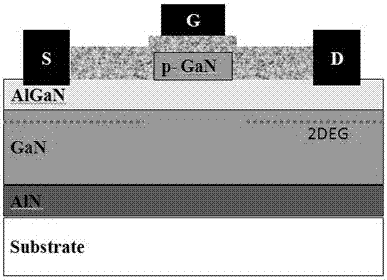

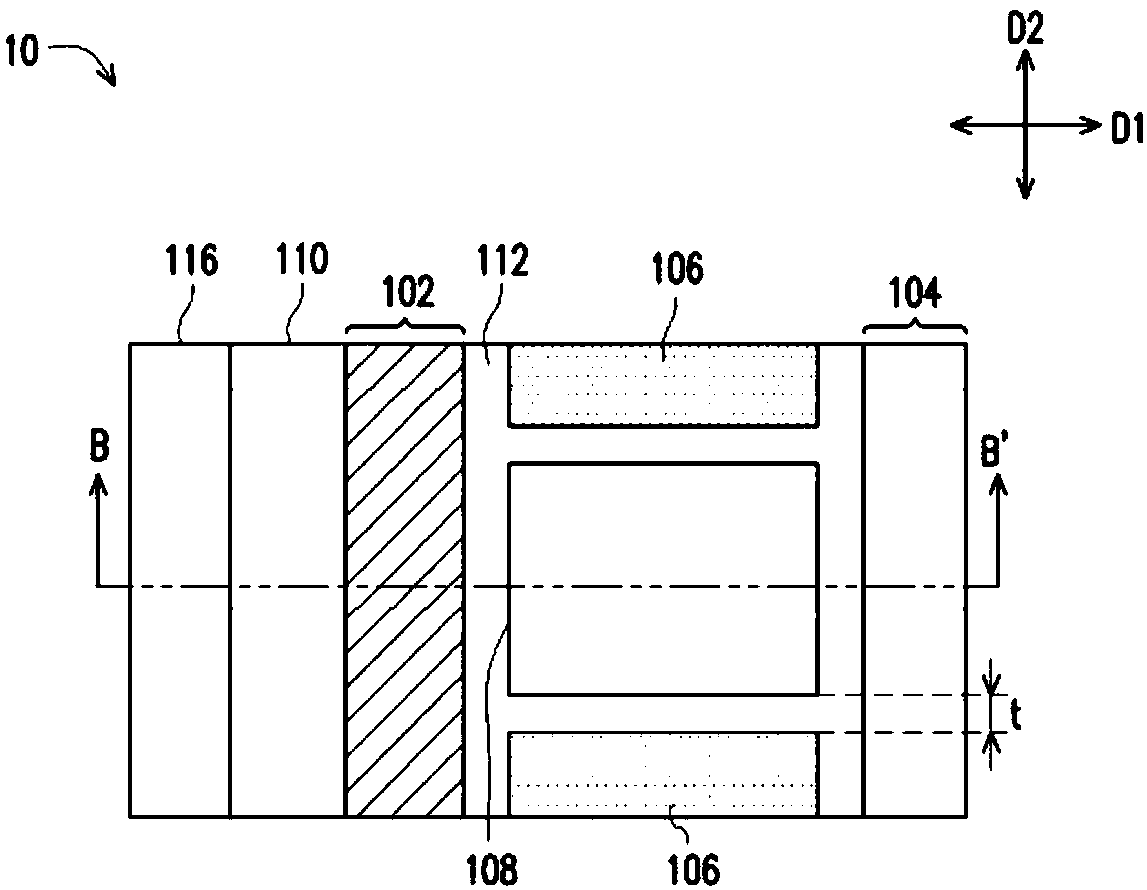

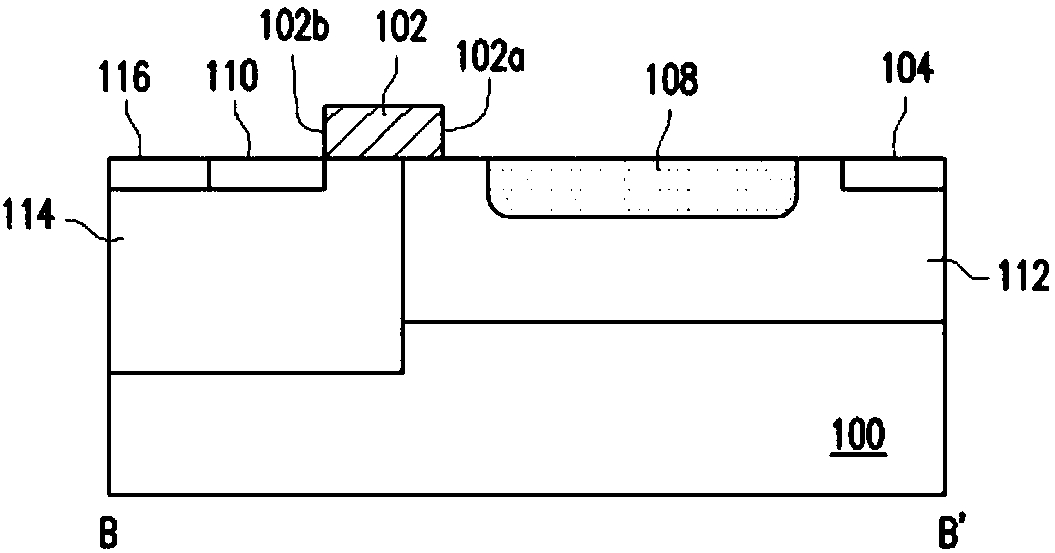

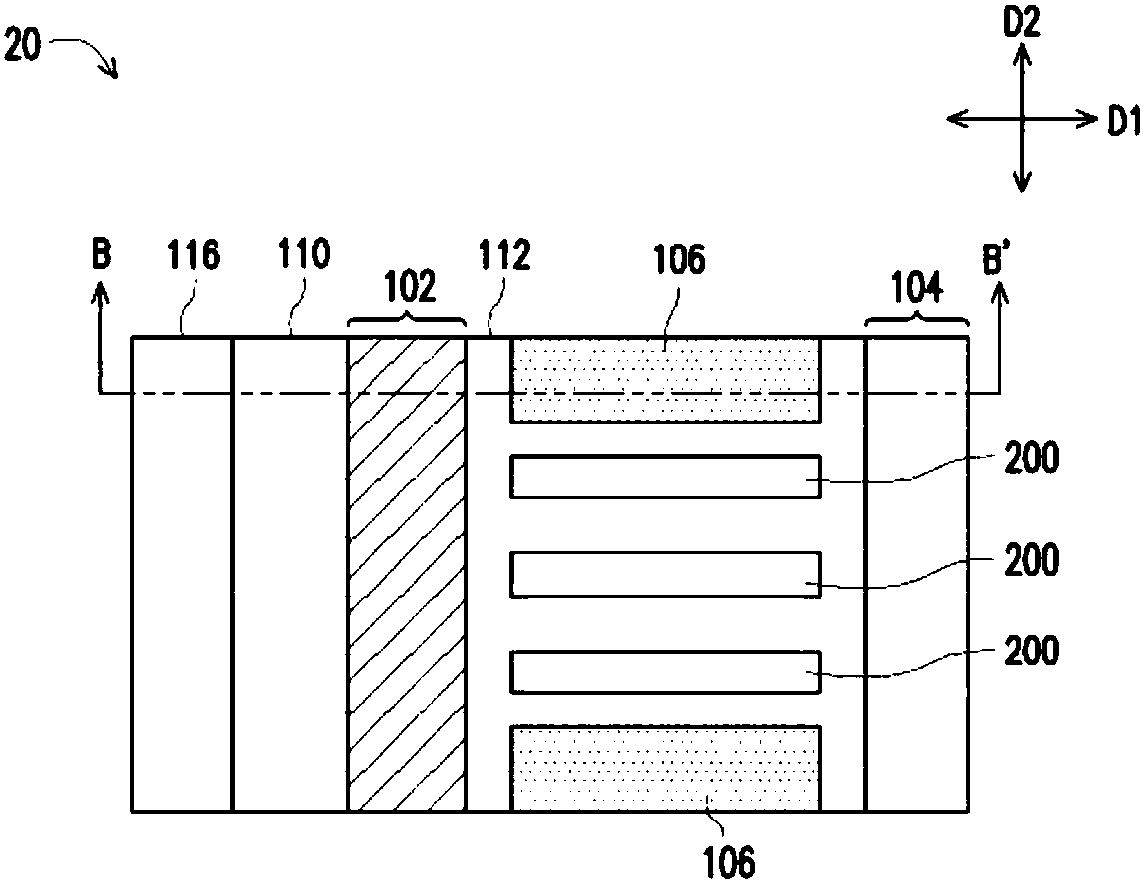

Normally-off field-effect semiconductor device, and method of fabrication

InactiveUS20090008676A1Easily and finely be adjustedLower turn-on resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionLateral overgrowth

A normally-off HEMT is made by first providing a substrate having its surface partly covered with an antigrowth mask. Gallium nitride is grown by epitaxy on the masked surface of the substrate to provide an electron transit layer comprised of two flat-surfaced sections and a V-notch-surfaced section therebetween. The flat-surfaced sections are formed on unmasked parts of the substrate surface whereas the V-notch-surfaced section, defining a V-sectioned notch, is created by lateral overgrowth onto the antigrowth mask. Aluminum gallium nitride is then deposited on the electron transit layer to provide an electron supply layer which is likewise comprised of two flat-surfaced sections and a V-notch-surfaced section therebetween. The flat-surfaced sections of the electron supply layer are sufficiently thick to normally generate two-dimensional electron gas layers due to heterojunctions thereof with the first and the second flat-surfaced section of the electron transit layer. The V-notch-surfaced section of the electron supply layer is not so thick, normally creating an interruption in the two-dimensional electron gas layer.

Owner:SANKEN ELECTRIC CO LTD

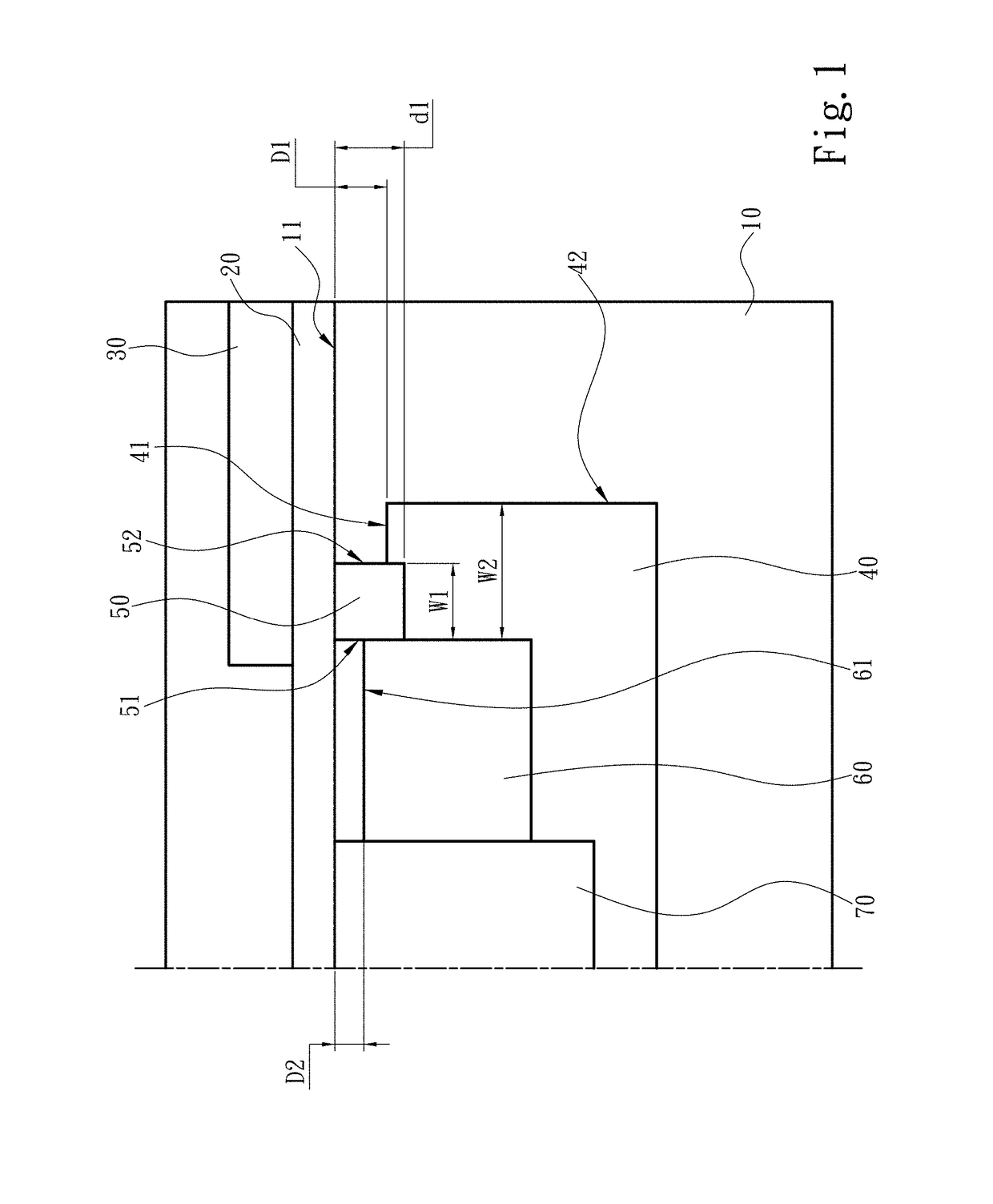

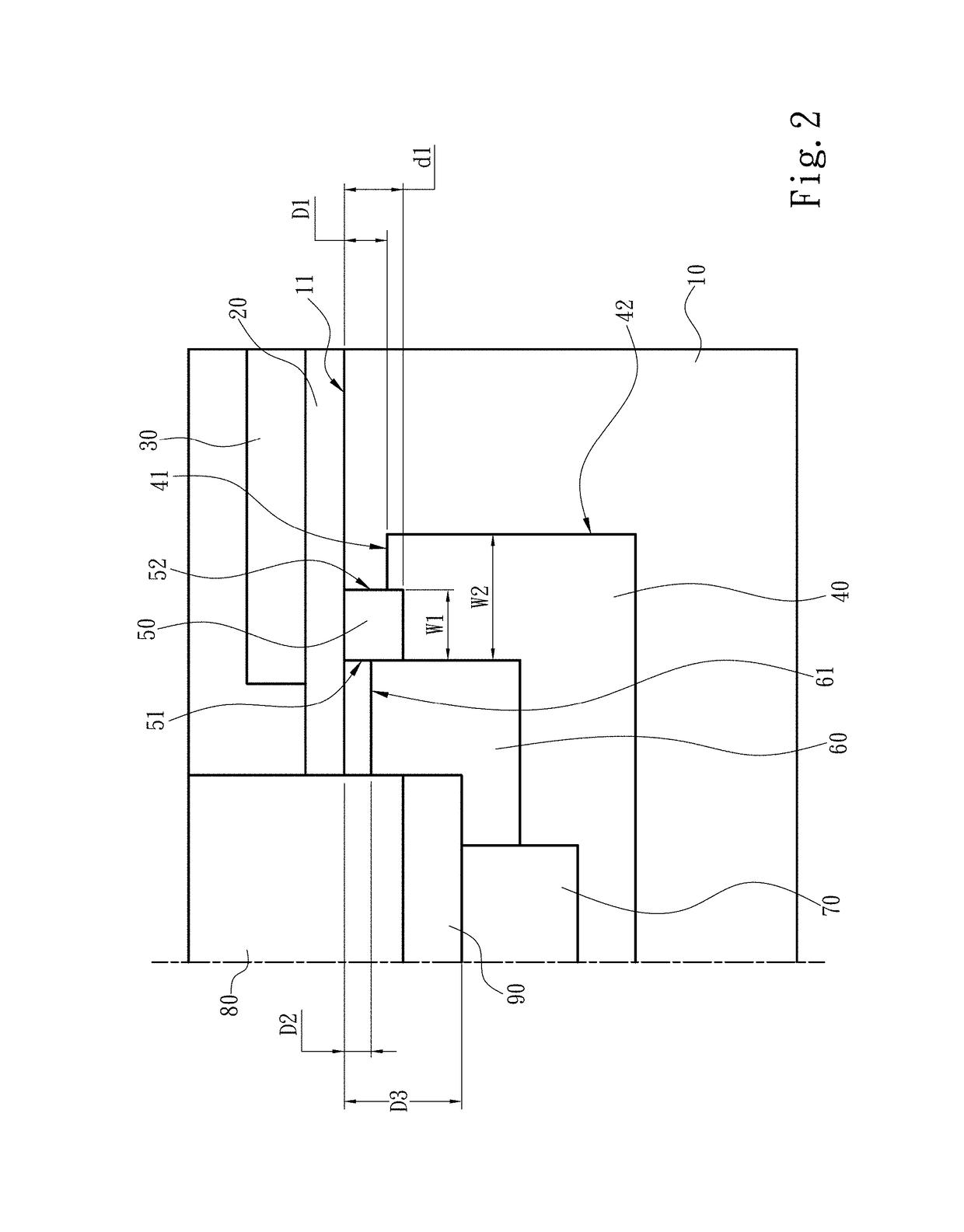

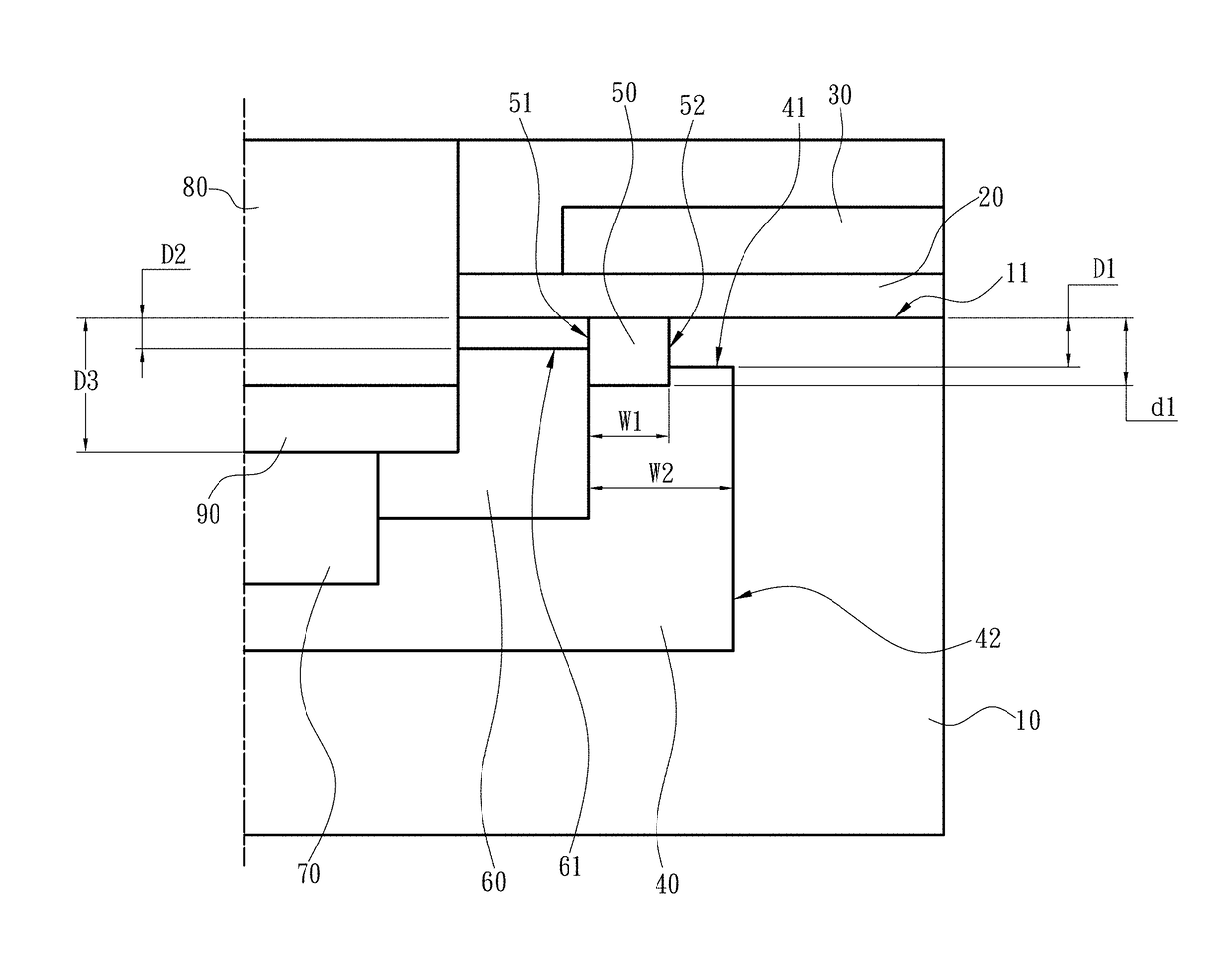

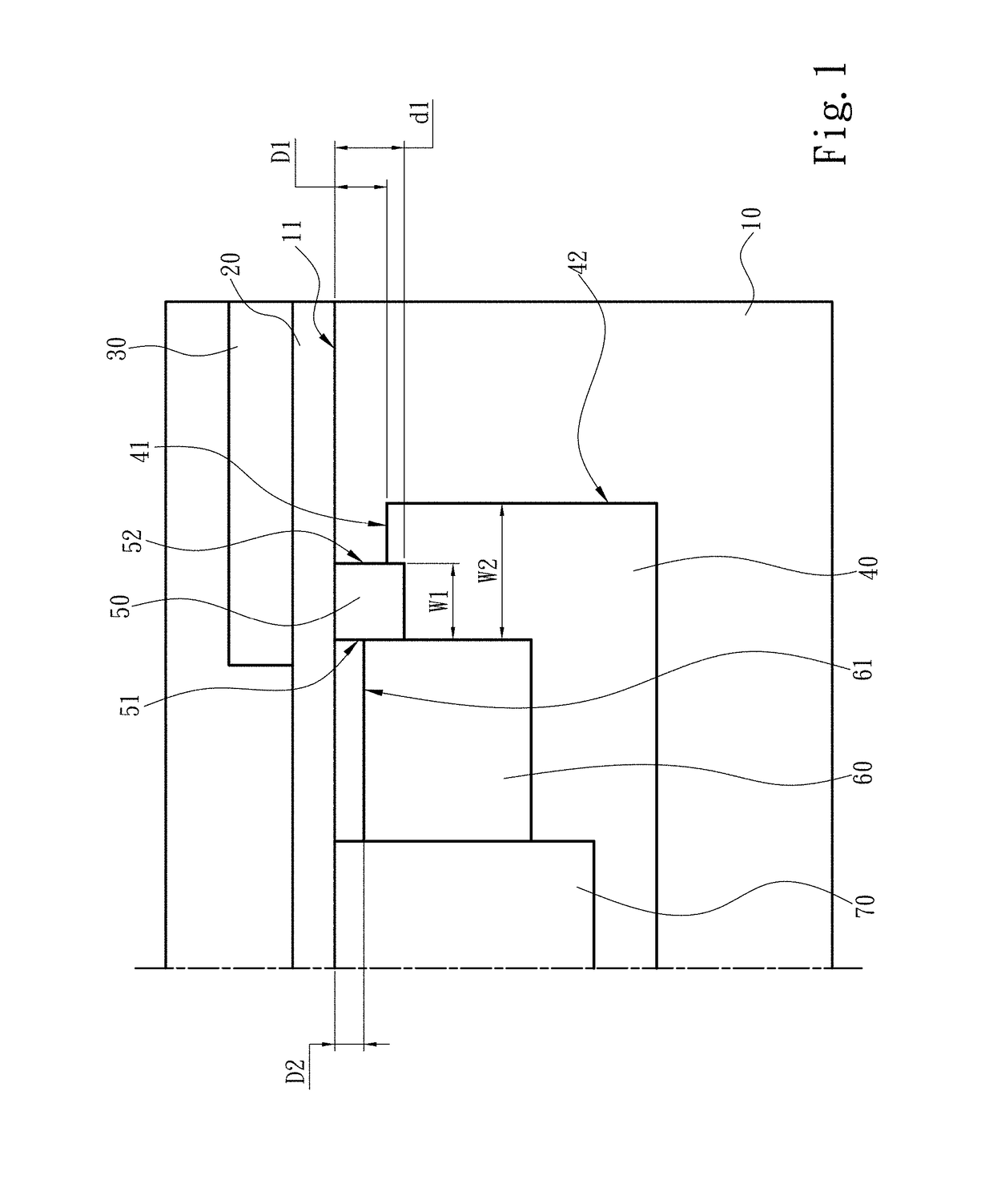

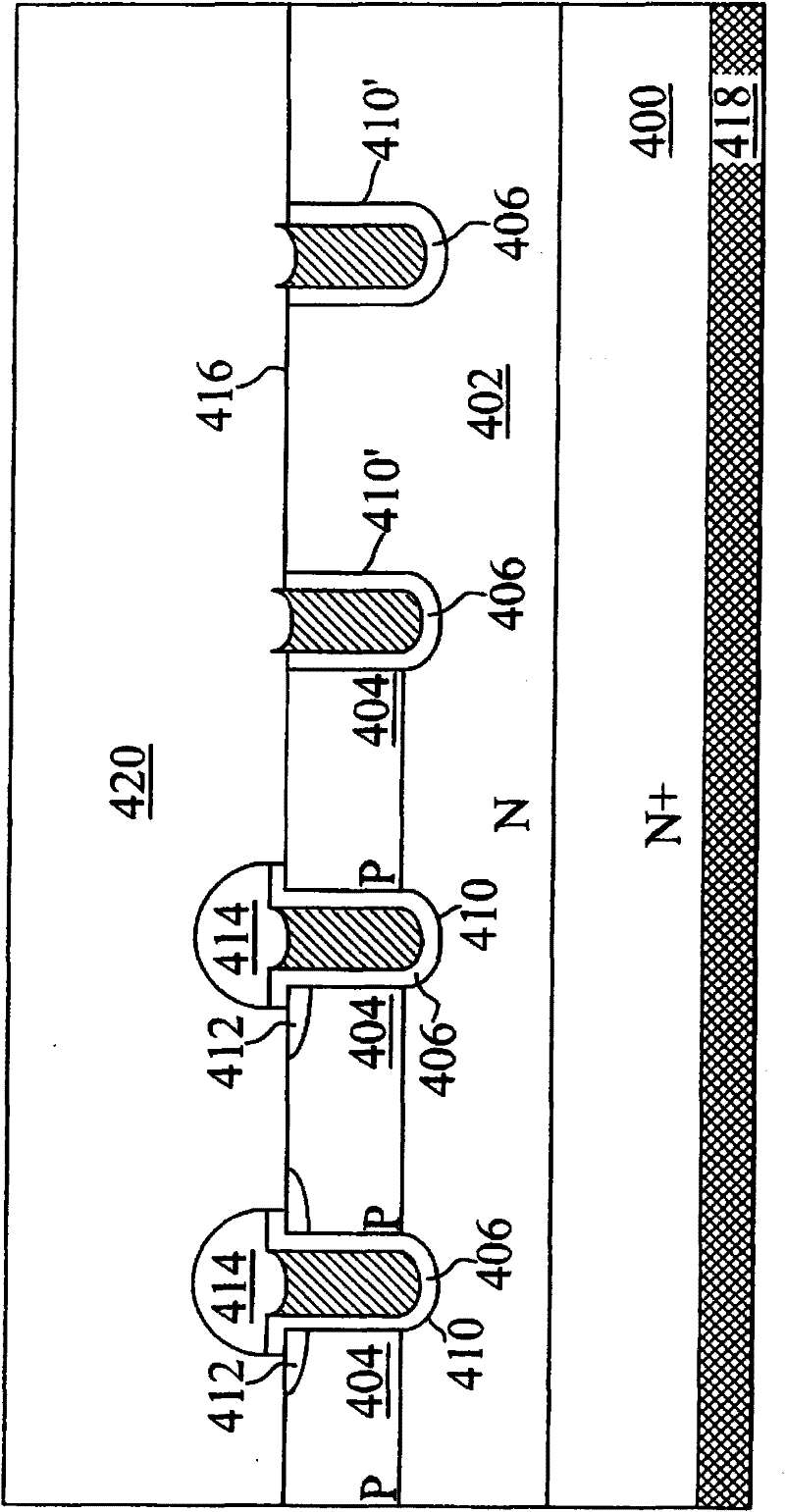

Trench metal oxide semiconductor field-effect transistor and manufacturing method for same

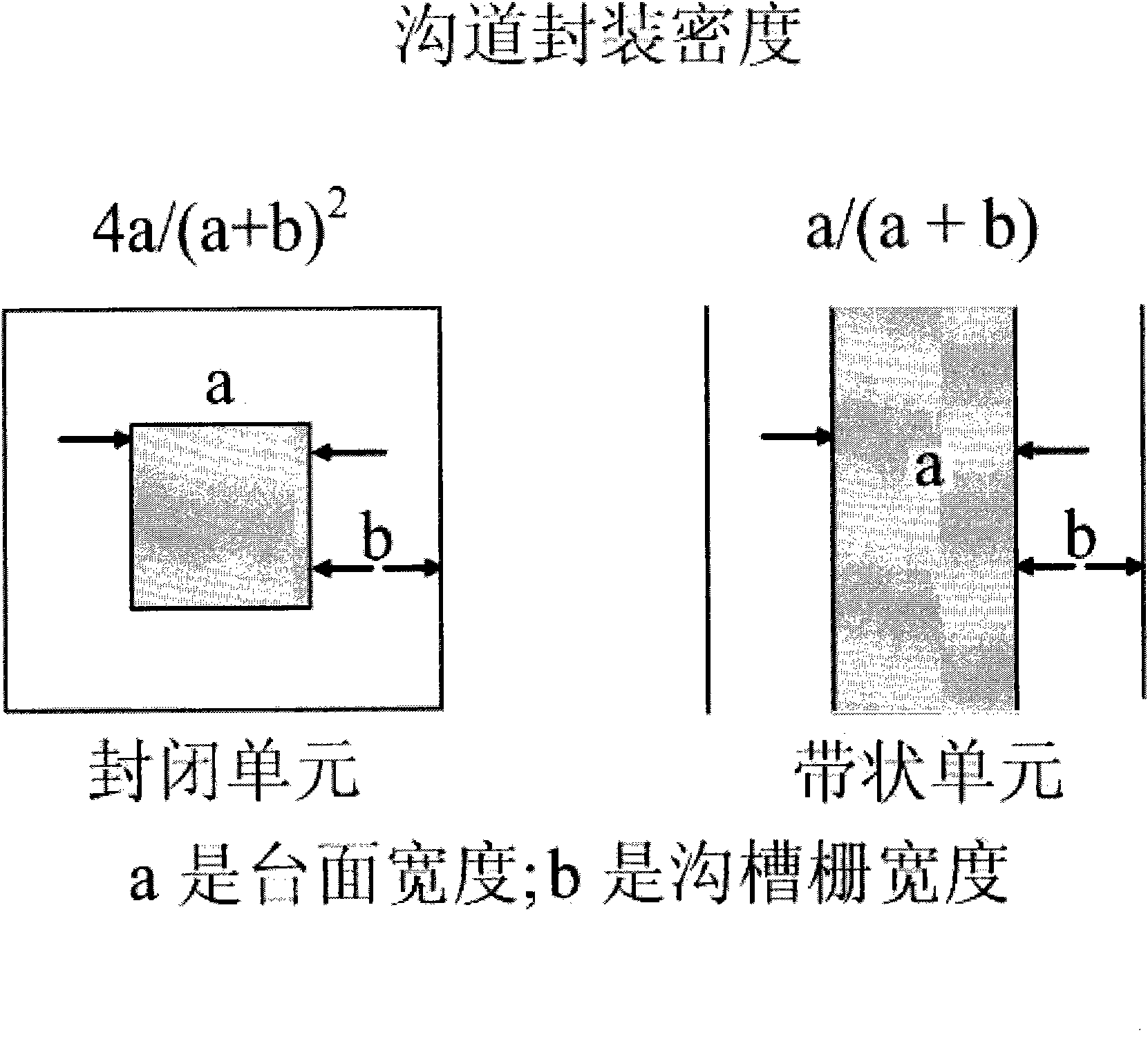

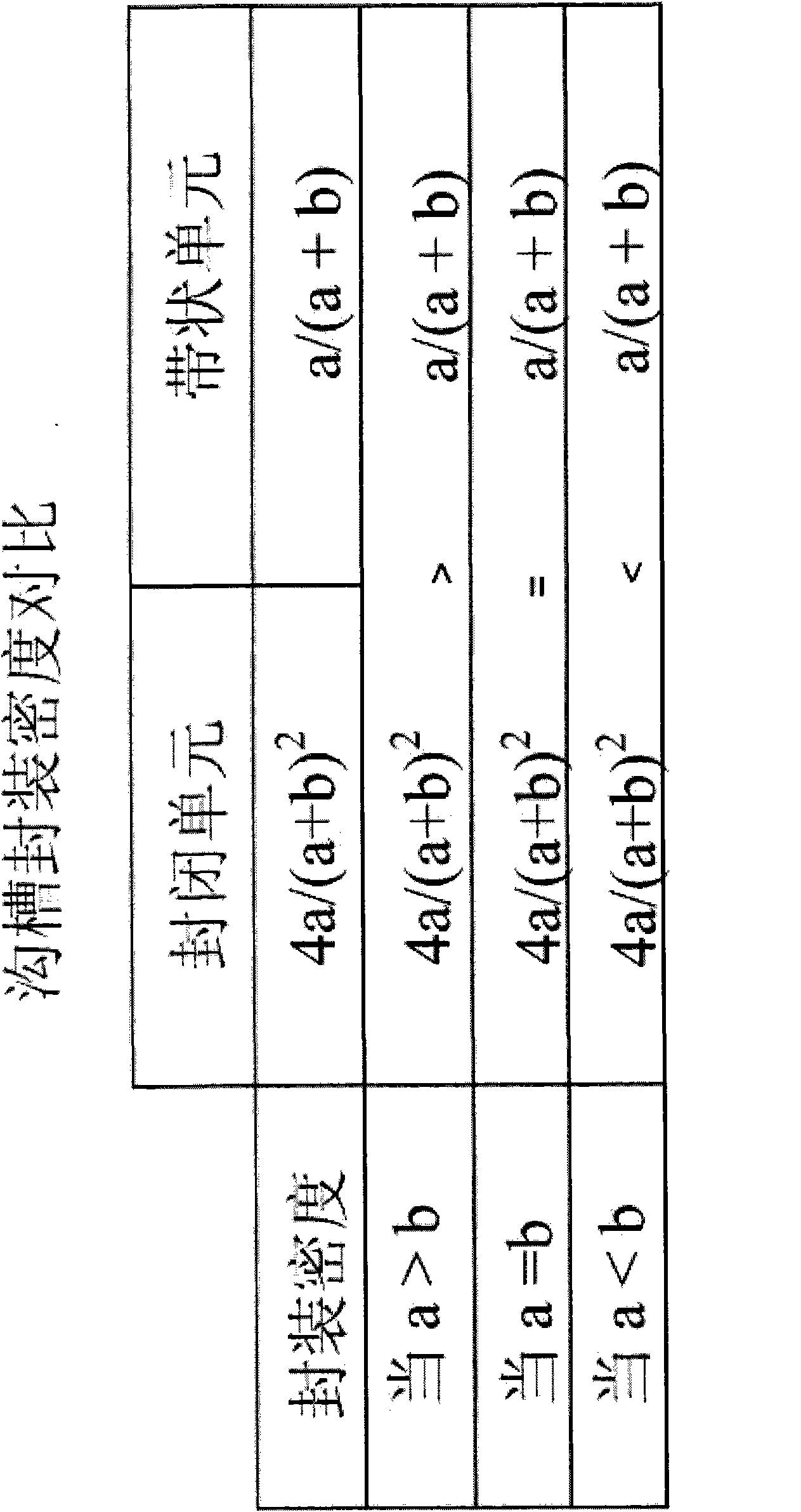

ActiveCN102403353ASmall footprintSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesUnit structureField-effect transistor

The invention discloses a trench metal oxide semiconductor field-effect transistor with ultrahigh cell density and a manufacturing method for the same. A source region and a body region are arranged in different areas of a device respectively so that the dimension of the device can be effectively decreased. Besides, trench metallic oxides of the trench metal oxide semiconductor field-effect transistor are in stripe cell structures, so that cell packing density is further increased, and starting resistance between a drain electrode and a source electrode is reduced.

Owner:FORCE MOS TECH CO LTD

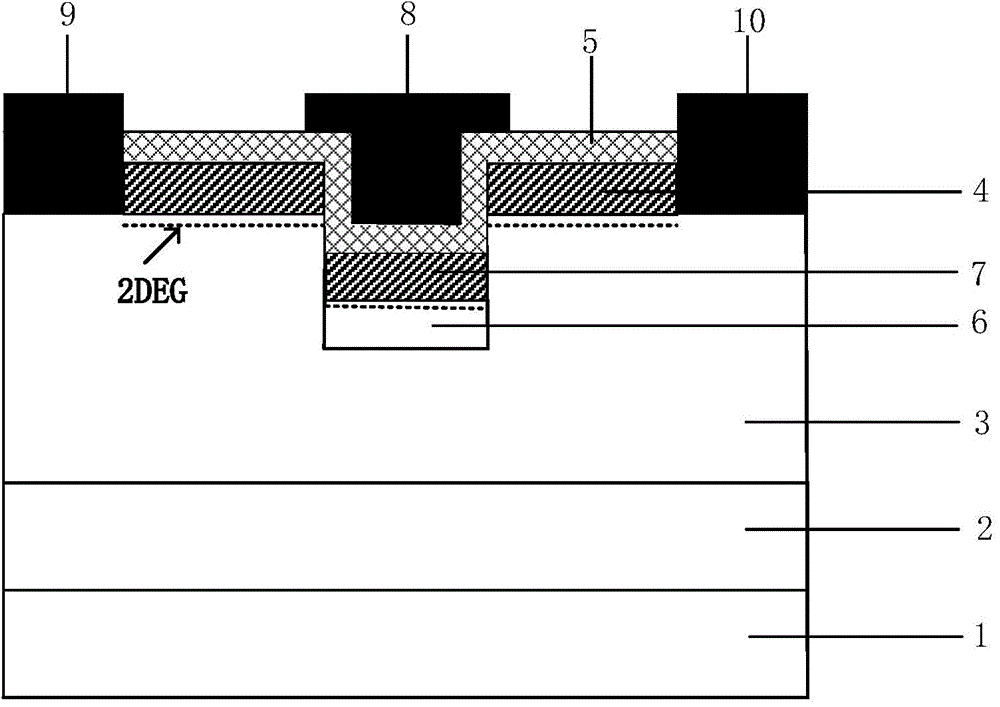

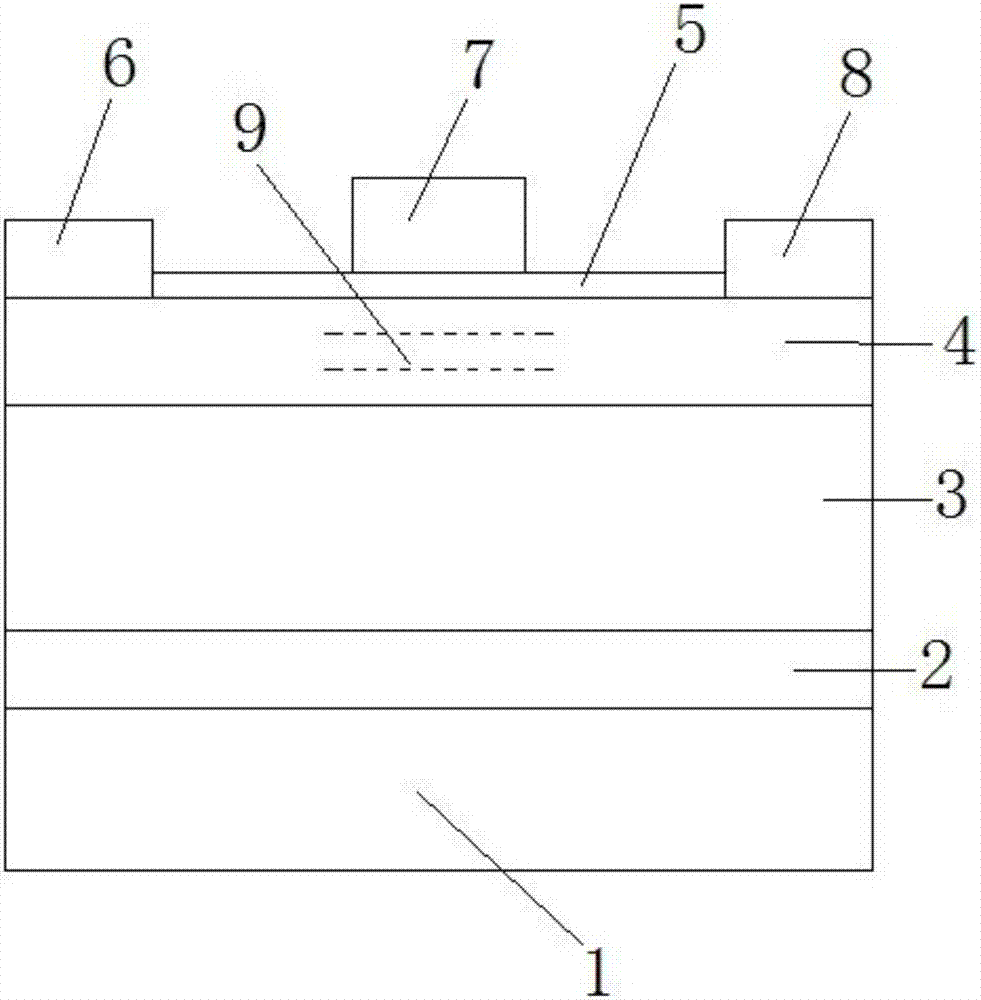

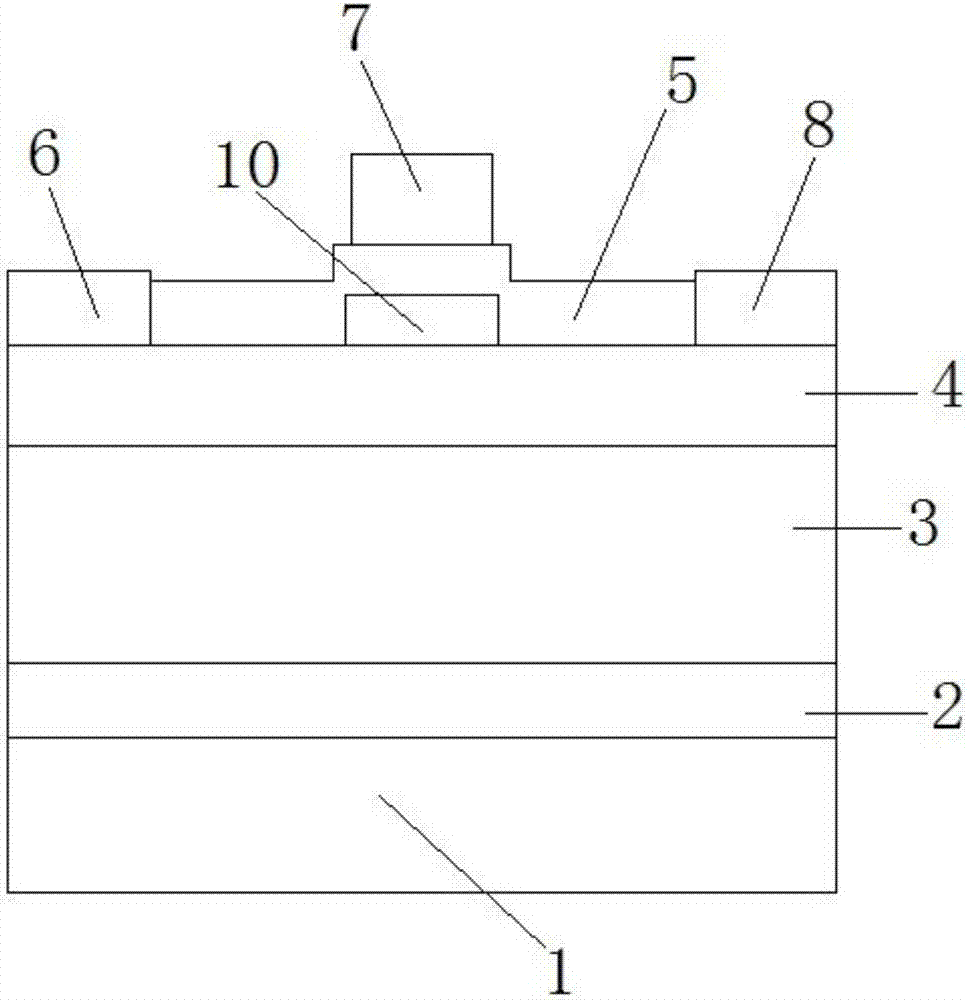

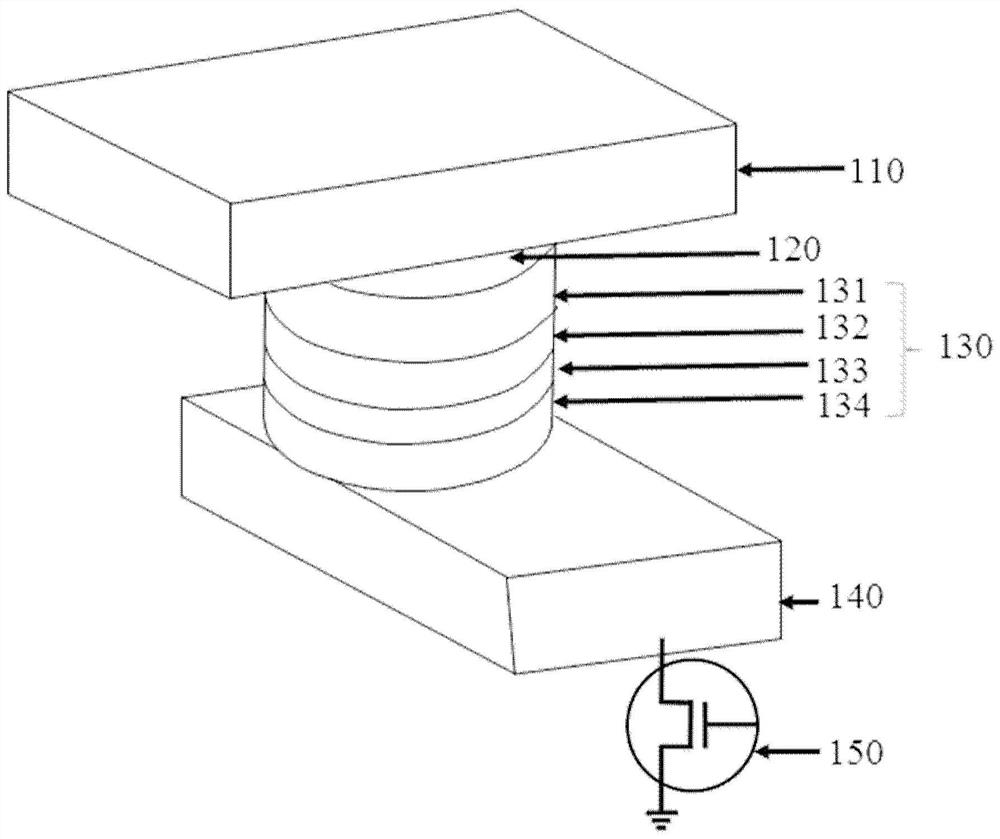

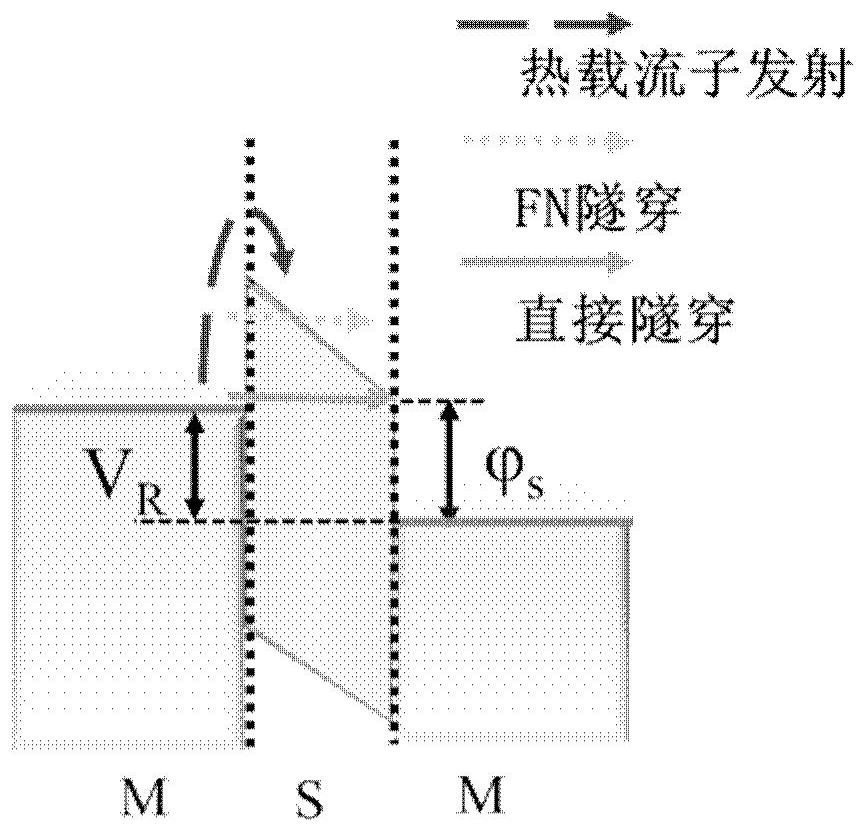

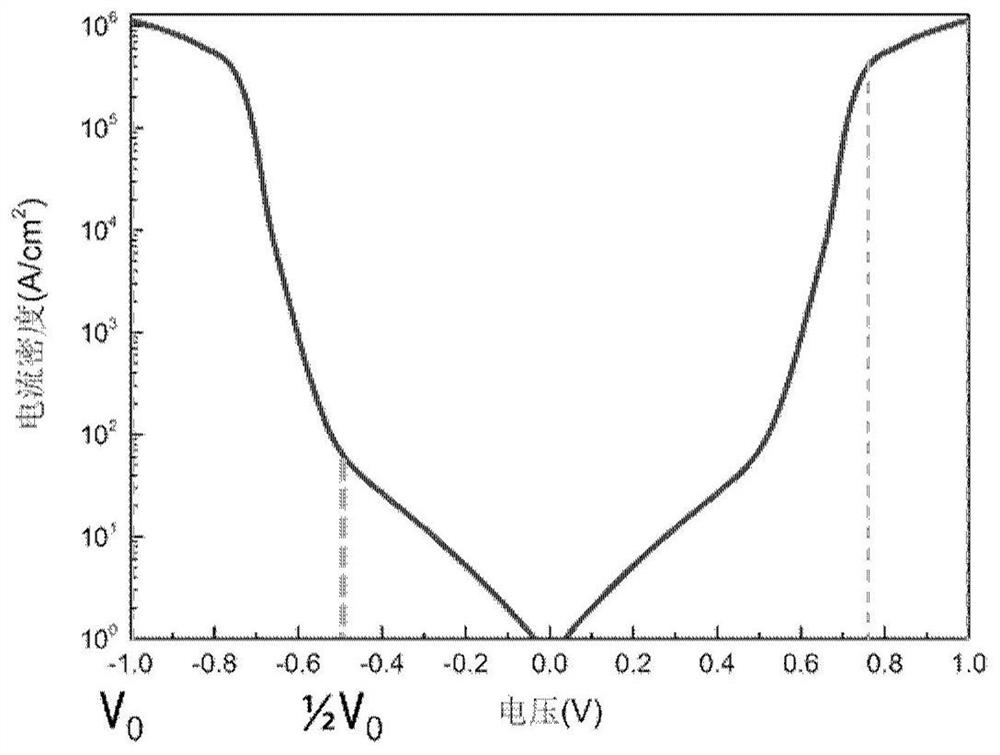

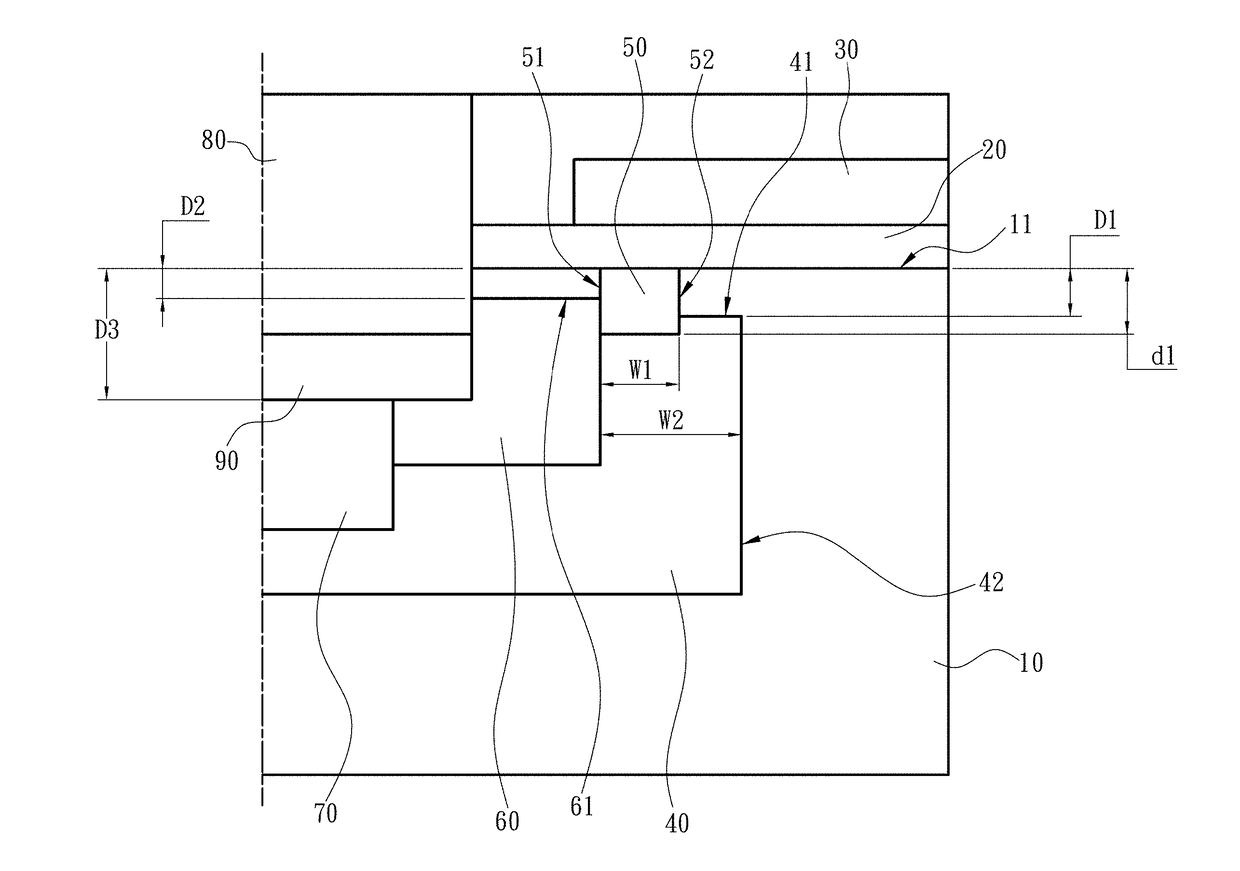

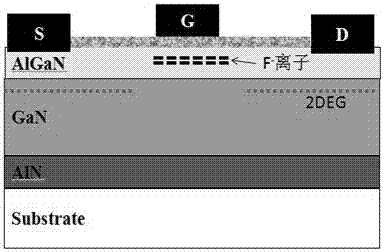

Longitudinal short-opening grid channel-type HEMT device and preparation method thereof

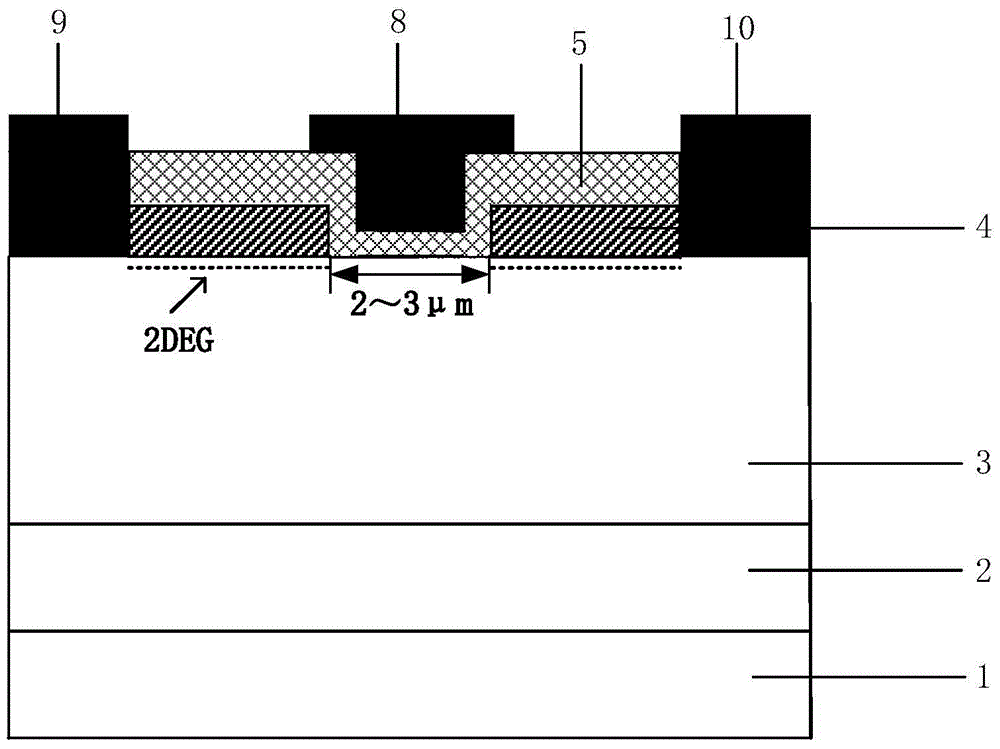

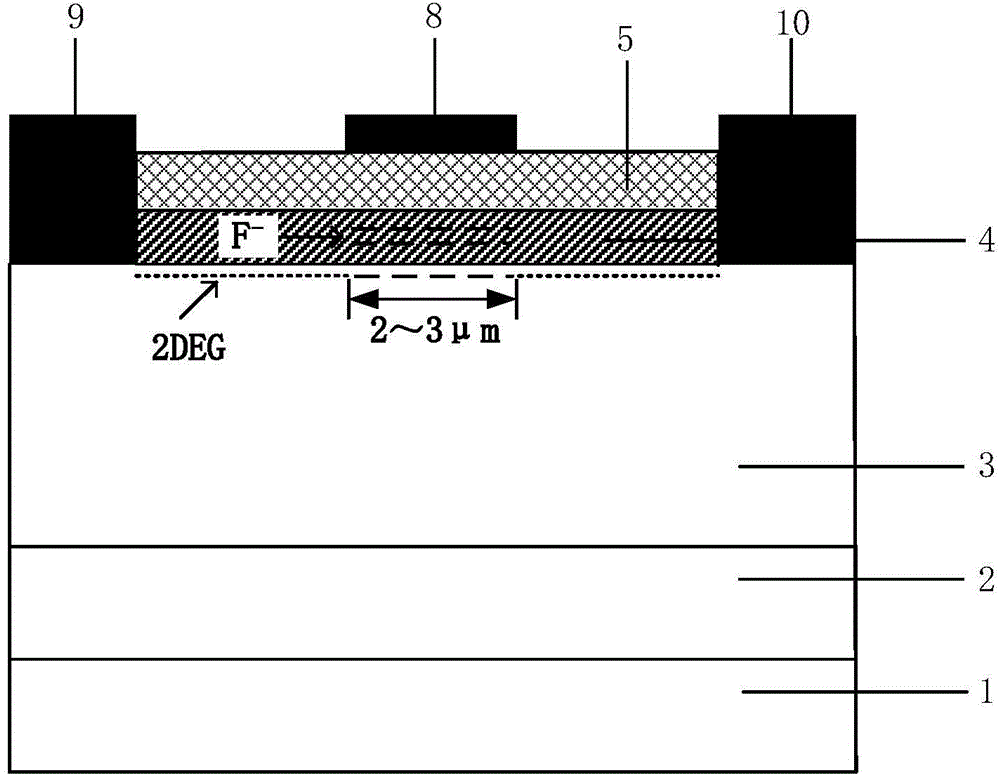

ActiveCN104916684AStable lengthLower turn-on resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceOperation mode

The present invention relates to the field of a semiconductor device and provides a longitudinal short-opening grid channel-type HEMT device and a preparation method thereof. The HEMT device comprises a substrate, a buffer layer, a first GaN layer, a second GaN layer, a second barrier layer, a first barrier layer, a dielectric layer, a source electrode, a drain electrode and a grid electrode, wherein the buffer layer is positioned on the substrate; the first GaN layer is positioned on the buffer layer; one side, whic is deviated from the buffer layer, of the first GaN layer is provided with a groove; the second GaN layer and the second barrier layer are sequentially embedded into the groove; the first barrier layer is positioned on the first GaN layer except for the groove; the dielectric layer is positioned on the first barrier layer and the second barrier layer; the source electrode and the drain electrode are in contact with the first GaN layer and the lateral surfaces of the source electrode and the drain electrode are sequentially in contact with the first barrier layer and the dielectric layer from bottom to top; and the grid electrode is in contact with the dielectric layer. According to the present invention, a normally-closed type operation mode of the HEMT device can be obtained; when a large threshold value voltage is realized, on resistance of the device is effectively reduced; and the grid electrode structure also has the characteristics of small capacitor, high switching speed of the device and the like.

Owner:DALIAN UNIV OF TECH

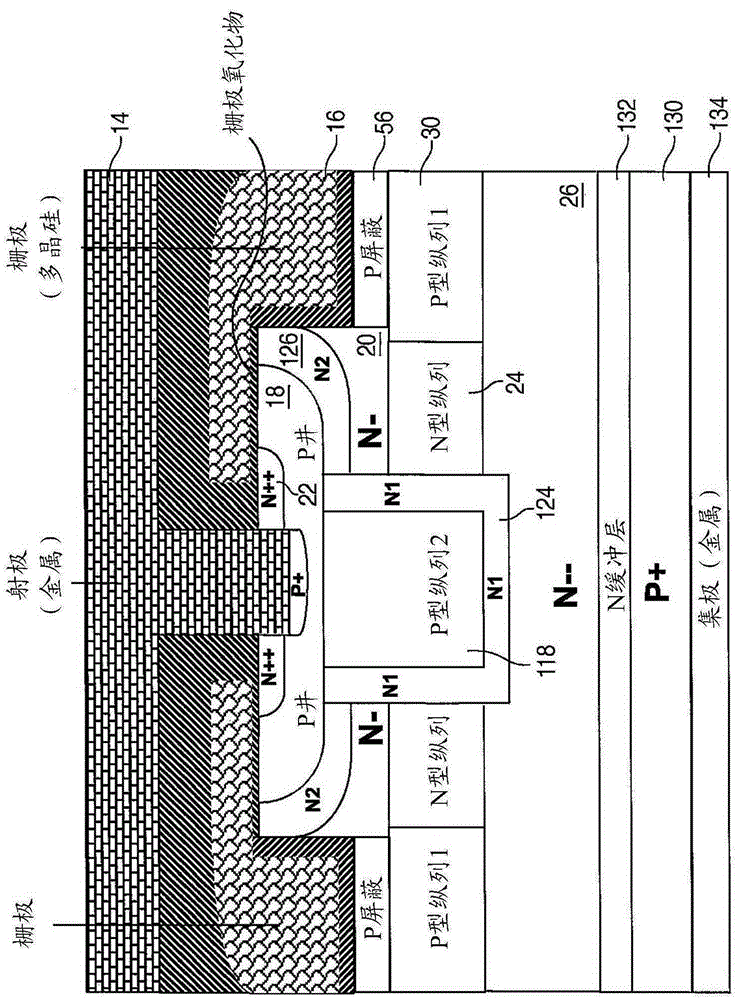

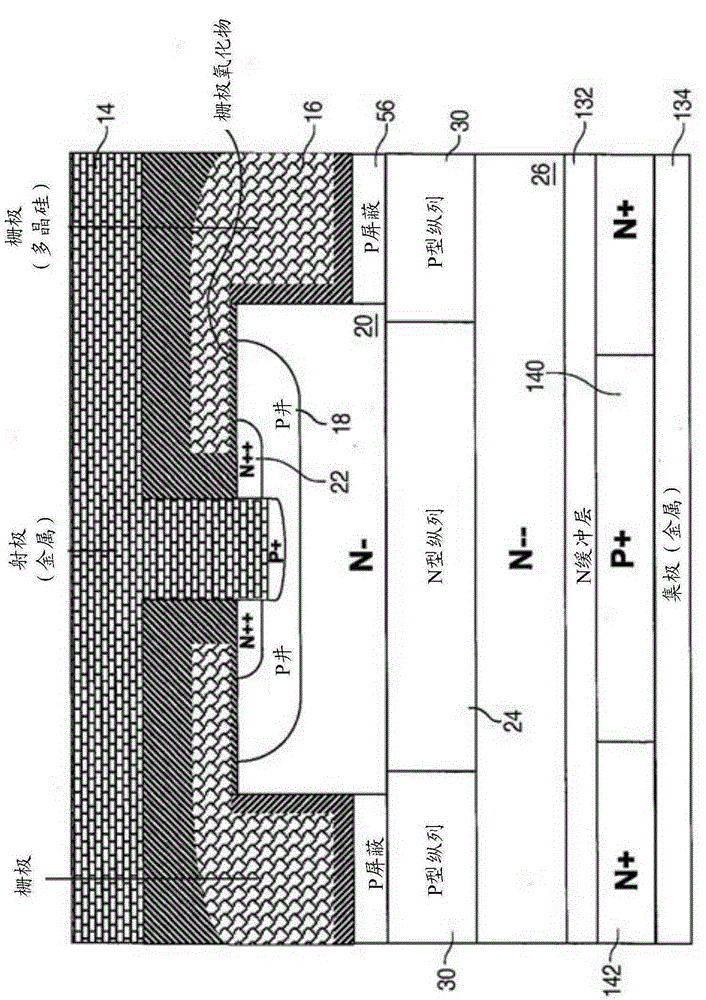

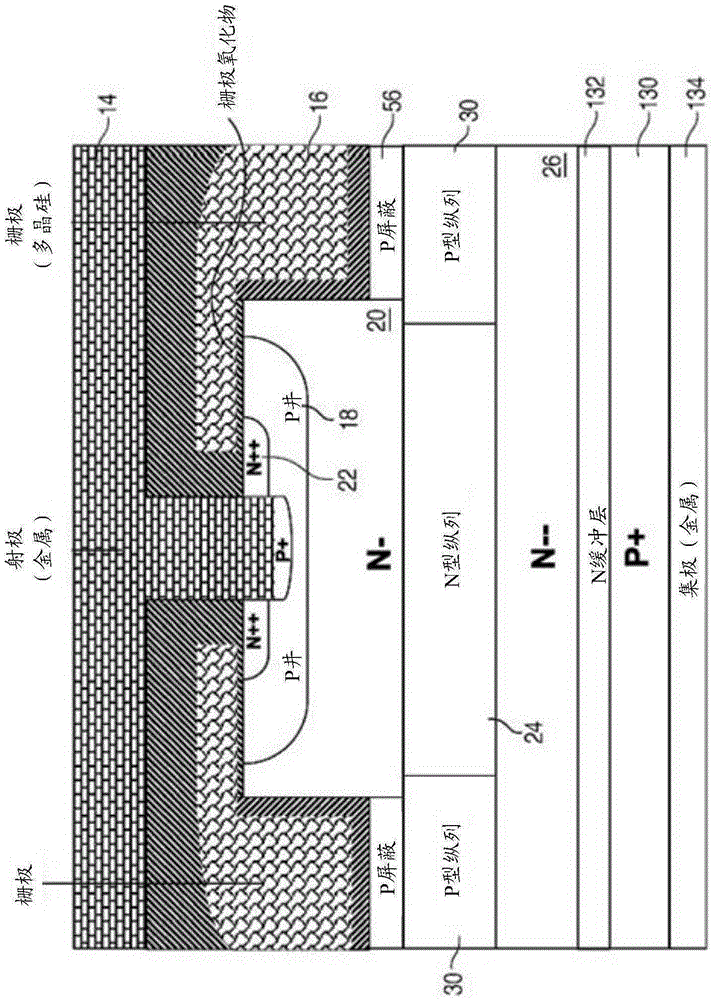

Vertical power mosfet including planar channel

ActiveCN105431946ALow costHigh dopingSemiconductor/solid-state device manufacturingSemiconductor devicesPlanar channelElectrode Contact

A power MOSFET cell includes an N+ silicon substrate having a drain electrode. A low dopant concentration N-type drift layer is grown over the substrate. Alternating N and P-type columns are formed over the drift layer with a higher dopant concentration. An N-type layer, having a higher dopant concentration than the drift region, is then formed and etched to have sidewalls. A P-well is formed in the N-type layer, and an N+ source region is formed in the P-well. A gate is formed over the P-well's lateral channel and next to the sidewalls as a vertical field plate. A source electrode contacts the P-well and source region. A positive gate voltage inverts the lateral channel and increases the conduction along the sidewalls. Current between the source and drain flows laterally and then vertically through the various N layers. On resistance is reduced and the breakdown voltage is increased.

Owner:无锡美偌科微电子有限公司

SRAM writing system and related apparatus

ActiveUS8325512B2Lower on-resistanceLower turn-on resistanceDigital storagePulse controlControl signal

SRAM writing system and related apparatus are provided. The writing system of the invention has a dummy replica writing circuit, a negative pulse controller and at least a normal writing circuit; each normal writing circuit includes a write driver and a negative pulse supplier. While writing, the dummy replica writing circuit drives a dummy replica bit-line, such that the negative pulse controller generates a negative pulse control signal according to level of the dummy replica bit-line. In each writing circuit, when the write driver conducts to connect an associated bit-line to a bias end for driving a level transition, the negative pulse supplier switches the bias end from an operation voltage to a different negative pulse voltage according to the received negative pulse control signal.

Owner:FARADAY TECH CORP

Graphene buried heat radiation layer and vertical channel GaN MISFET cellular structure and preparation method

PendingCN107393890ALower on-resistanceGood uniformity and repeatabilitySemiconductor/solid-state device detailsSolid-state devicesPhysicsVoltage

The invention discloses a graphene buried heat radiation layer and vertical channel GaN MISFET cellular structure and a preparation method; the cellular structure comprises a substrate, an AIN isolation layer, a graphene buried heat radiation layer, an AIN nucleating layer, a GaN buffer layer, a n type heavy doping GaN layer, a n type GaN layer, a P type GaN electronic stop layer, a non-doping GaN layer and an AlGaN barrier layer arranged from bottom to top; a cellular structure grating groove hole extends from the cellular structure top to the n type GaN layer; the gating groove hole side wall and bottom are respectively provided with a gate medium layer. An existing normally off GaN MISFET device cannot simultaneously have even and stable large threshold-voltage, low device conductive resistance and high switching rate; aiming at the normally off type GaN base III-V family material power device, the normally off GaN MISFET cellular structure with the vertical grid structure and the preparation method are provided so as to solve said problems, thus realizing GaN MISFET device stable large threshold-voltage normally off operations, and effectively reducing the device starting conduction resistance.

Owner:BEIJING HUAJINCHUANGWEI ELECTRONICS CO LTD

Method of fabrication of normally-off field-effect semiconductor device

InactiveUS7615452B2Less dislocationSacrificing performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionLateral overgrowth

A normally-off HEMT is made by first providing a substrate having its surface partly covered with an antigrowth mask. Gallium nitride is grown by epitaxy on the masked surface of the substrate to provide an electron transit layer comprised of two flat-surfaced sections and a V-notch-surfaced section therebetween. The flat-surfaced sections are formed on unmasked parts of the substrate surface whereas the V-notch-surfaced section, defining a V-sectioned notch, is created by lateral overgrowth onto the antigrowth mask. Aluminum gallium nitride is then deposited on the electron transit layer to provide an electron supply layer which is likewise comprised of two flat-surfaced sections and a V-notch-surfaced section therebetween. The flat-surfaced sections of the electron supply layer are sufficiently thick to normally generate two-dimensional electron gas layers due to heterojunctions thereof with the first and the second flat-surfaced section of the electron transit layer. The V-notch-surfaced section of the electron supply layer is not so thick, normally creating an interruption in the two-dimensional electron gas layer.

Owner:SANKEN ELECTRIC CO LTD

High power semiconductor device

ActiveUS20180033880A1Lower turn-on resistanceLower turn-on voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor

This application provides a high power semiconductor device, which is characterized by forming two diodes connected in parallel and a schottky contact on a channel layer to lower the turn-on voltage and turn-on resistance of the high power semiconductor device at the same time and to enhance the breakdown voltage.

Owner:EPISTAR CORP

Spin orbit torque magnetic random access memory unit, memory array and memory

PendingCN111740011AImprove reliabilitySmall sizeMagnetic-field-controlled resistorsSolid-state devicesMemory cellRandom access memory

The invention provides a spin orbit torque magnetic random access memory unit, a memory array and a memory. The spin orbit torque magnetic random access memory unit comprises a magnetic tunnel junction and a gating device; the gating device is a two-dimensional material-based gating device; the magnetic tunnel junction is arranged above the gating device; the magnetic tunnel junction comprises anantiferromagnetic layer and a free layer, and the free layer is adjacent to the antiferromagnetic layer; when the gating device is turned on, the memory unit is turned on, current generates spin current to be injected into the free layer, and the magnetization direction of the free layer is turned over under the action of the exchange bias effect of the free layer and the antiferromagnetic layer.An exchange bias effect is utilized without an external field, deterministic magnetization overturning of the SOT-MRAM memory cell under a room-temperature zero magnetic field can be achieved by applying a magnetic tunnel junction optimization bias voltage, the purpose of data writing is achieved, and the SOT-MRAM memory unit of a double-end structure is achieved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

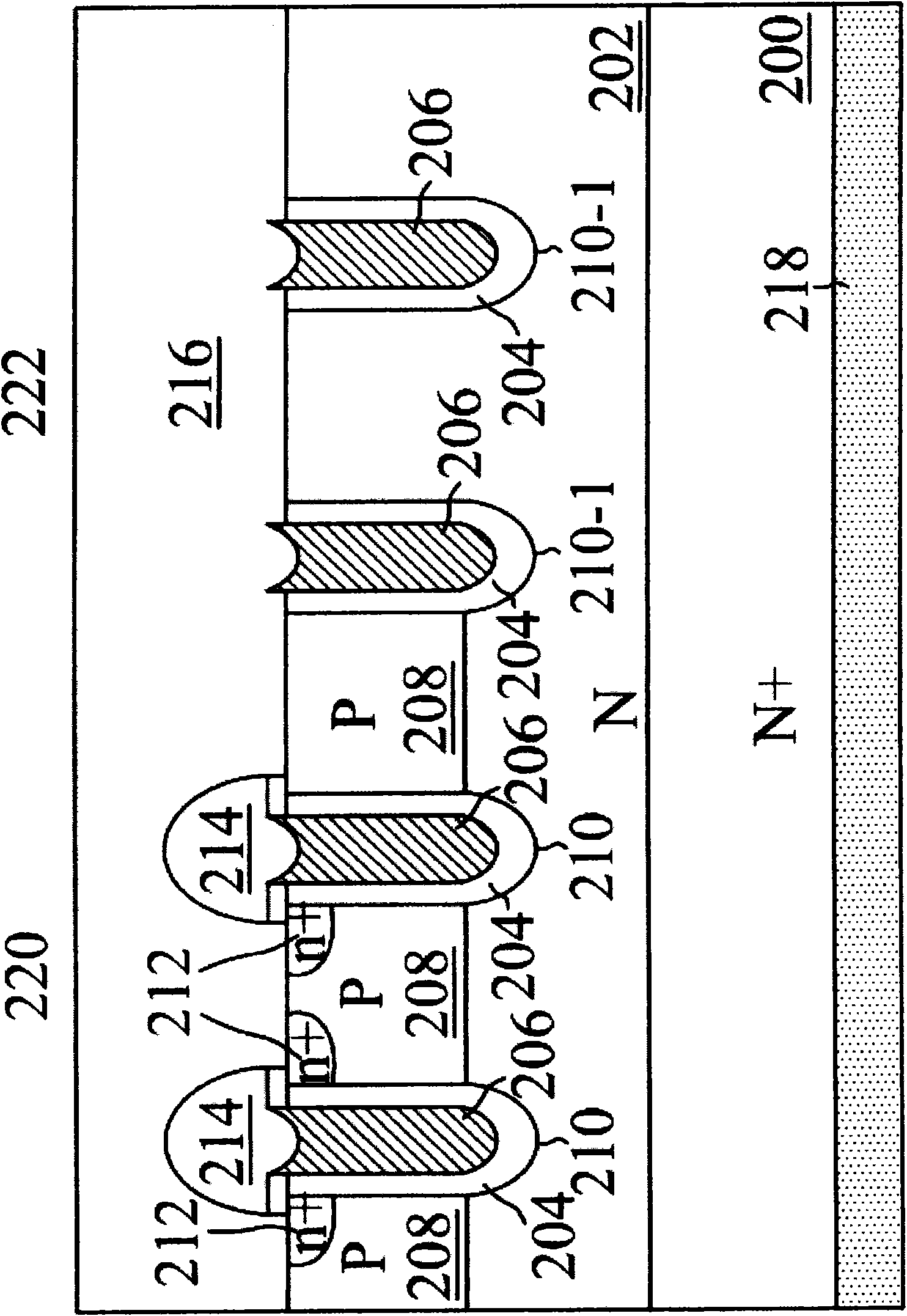

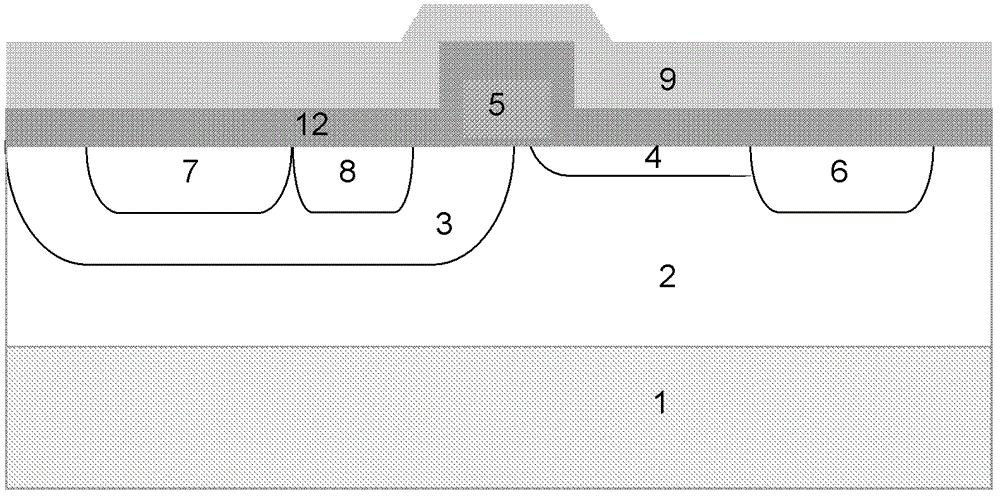

Silicon carbide semiconductor element and manufacturing method thereof

ActiveUS20170207305A1Lower turn-on resistanceImprove component reliabilitySemiconductor devicesSemiconductor/solid-state device manufacturingDielectric layerCondensed matter physics

A silicon carbide (SiC) semiconductor element includes a semiconductor layer, a dielectric layer on a surface of the semiconductor layer, a gate electrode layer on the dielectric layer, a first doped region, a second doped region, a shallow doped region and a third doped region. The semiconductor layer is of a first conductivity type. The first doped region is of a second conductivity type and includes an upper doping boundary spaced from the surface by a first depth. The shallow doped region is of the second conductivity type, and extends from the surface to a shallow doped depth. The second doped region is adjacent to the shallow doped region and is at least partially in the first doped region. The third doped region is of the second conductivity type and at least partially overlaps the first doped region.

Owner:SHANGHAI HESTIA POWER INC

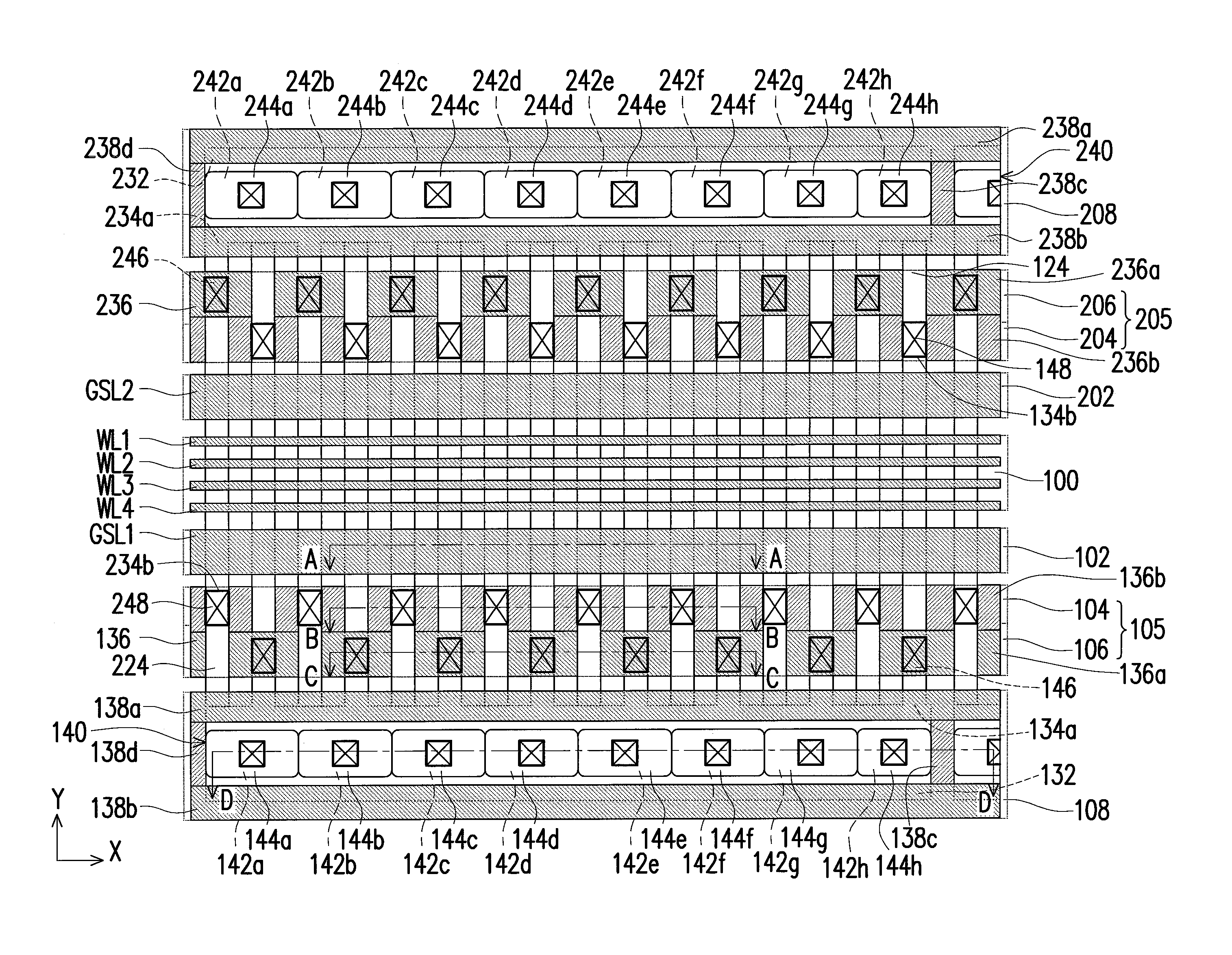

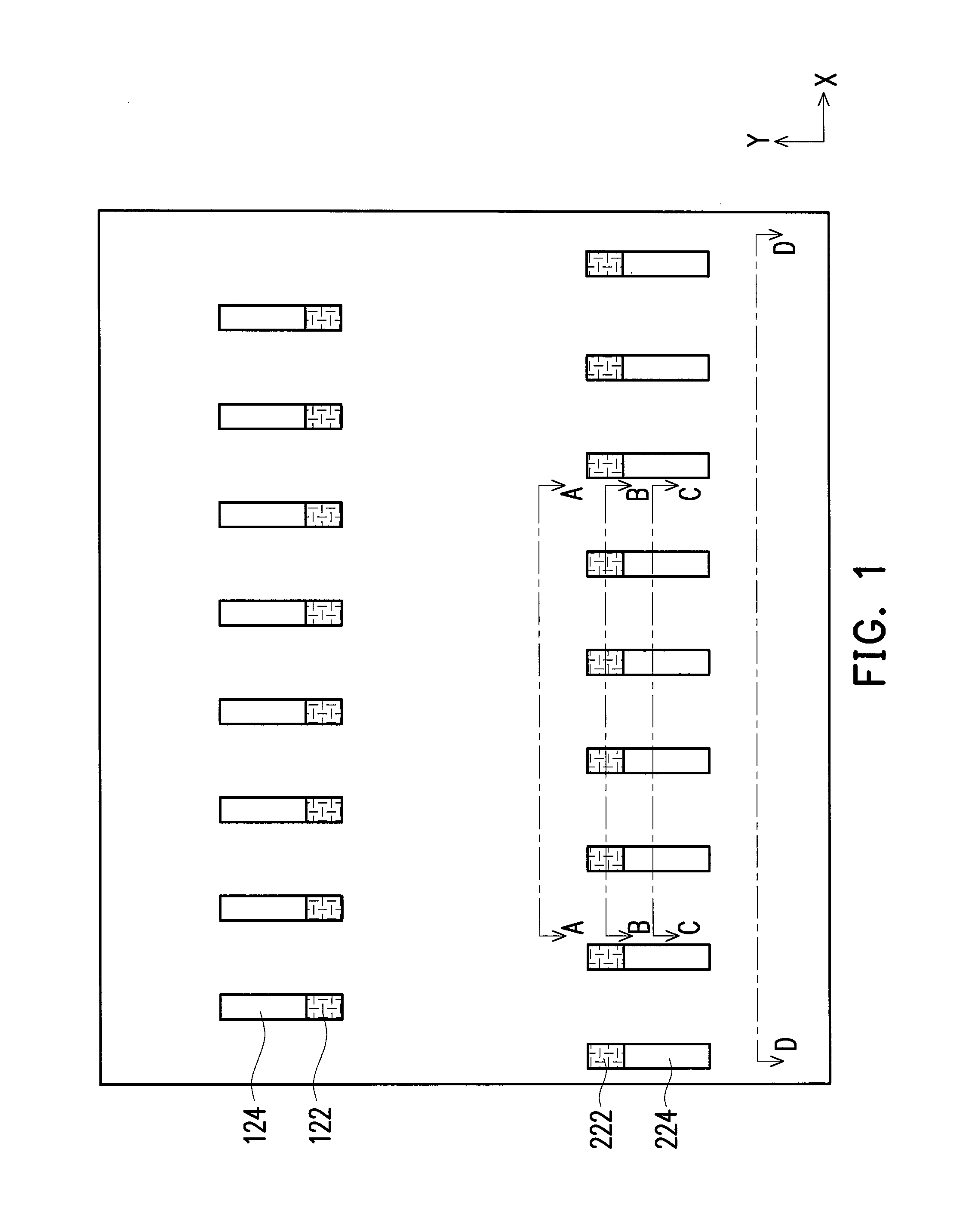

Three-dimensional memory and method of forming the same

ActiveUS9023701B1Improve reliabilityImprove uniformityTransistorSolid-state devicesBit lineEngineering

A method of forming a three-dimensional memory is provided. A stacked structure is patterned to form a comb structure including a bit line pad extending along a first direction and comb-teeth portions extending along a second direction. A charge storage layer is formed on top and sidewall of the comb structure. Bit lines and auxiliary gates are formed on the charge storage layer and extend along the first direction. Each bit line covers top and sidewall of partial comb-teeth portions. Auxiliary gates cover top and sidewall of edge regions of the bit line pad. The charge storage layer on top of the bit line pad is removed. The stacked structure of the bit line pad is patterned to form a stepped structure. An ion implantation is performed to the stepped structure, to form a doped region in the semiconductor layer below each step surface of the stepped structure.

Owner:MACRONIX INT CO LTD

Normally-closed GaN-based MOSFET structure with high threshold voltage and high conduction performance and fabrication method thereof

PendingCN107768252ARaise the threshold voltageImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

The invention relates to the technical field of semiconductor, in particular to a normally-closed GaN-based MOSFET structure with a high threshold voltage and high conduction performance and a fabrication method thereof. The fabrication method of the normally-closed GaN-based MOSFET structure with the high threshold voltage and high conduction performance comprises the following steps of firstly,providing a required substrate, sequentially and epitaxially growing a stress buffer layer, a GaN buffer layer, an AIN thin layer and an AlGaN thin layer on the substrate, and reserving the AlN thin layer and the AlGaN thin layer on a grid region by etching to obtain a substrate for epitaxy of a selection region; secondly, sequentially selecting a regional epitaxial GaN channel layer, a AIN insertion layer and a AIGaN barrier layer on the substrate to form a groove structure; and finally, depositing a grid dielectric layer, covering grid metal on a groove channel grid dielectric layer, and covering two ends of the grid with metal to form a source and a drain. By the fabrication method, the threshold voltage and the grid region mobility can be effectively improved, the channel resistance isreduced, and the conduction performance of the GaN MOSFET device is improved.

Owner:SUN YAT SEN UNIV

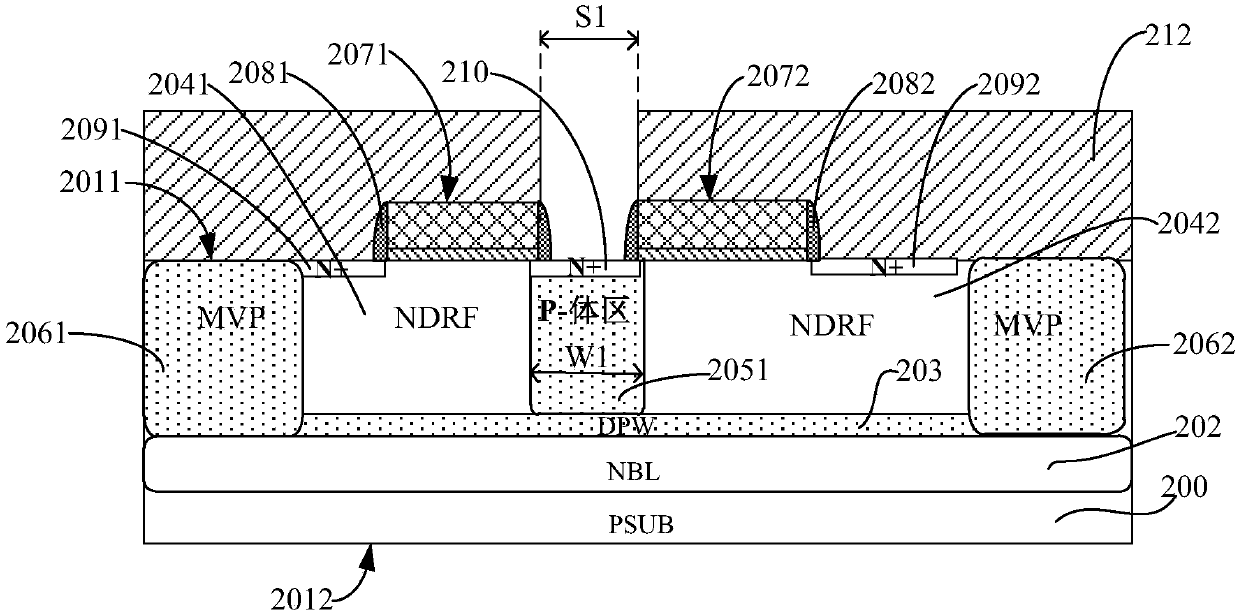

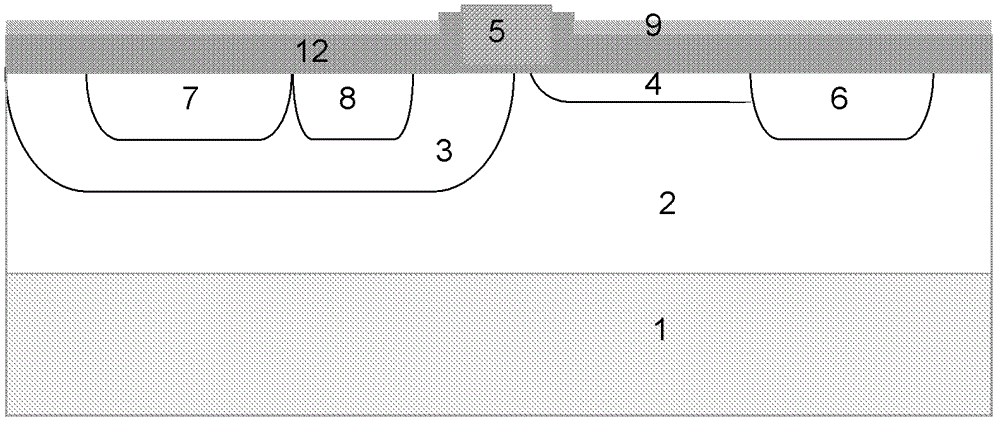

Radio frequency laterally diffused metal oxide semiconductor (LDMOS) device with thermometal silicide and manufacturing method

ActiveCN103137667ALower turn-on resistanceIncrease working voltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectricitySalicide

The invention discloses a radio frequency laterally diffused metal oxide semiconductor (LDMOS) device with thermometal silicide and a manufacturing method. A P-shaped silicon substrate is provided with P-shaped epitaxy. A N-shaped low doped drain region, a P trap and a N-shaped heavy doped drain region are arranged in the P-shaped epitaxy. A N-shaped heavy doped source region and a P-shaped heavy doped lead out region are arranged in the P trap. A drain electrode titanium silicide layer is arranged on the top of the N-shaped heavy doped source region. A source electrode titanium silicide layer is arranged on the top of the P-shaped heavy doped lead out region and the N-shaped heavy doped source region. A grid electrode titanium silicide layer is arranged on the top of a polycrystalline silicon grid electrode. Thickness of the grid electrode titanium silicide layer is larger than thickness of the drain electrode titanium silicide layer and the source electrode titanium silicide layer. Titanium silicide of a grid electrode is thicker, square resistance of the grid electrode is reduced, and normal thickness titanium silicide on a source electrode and a source electrode avoids electricity leakage to caused by junction penetration of source drain and the trap.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

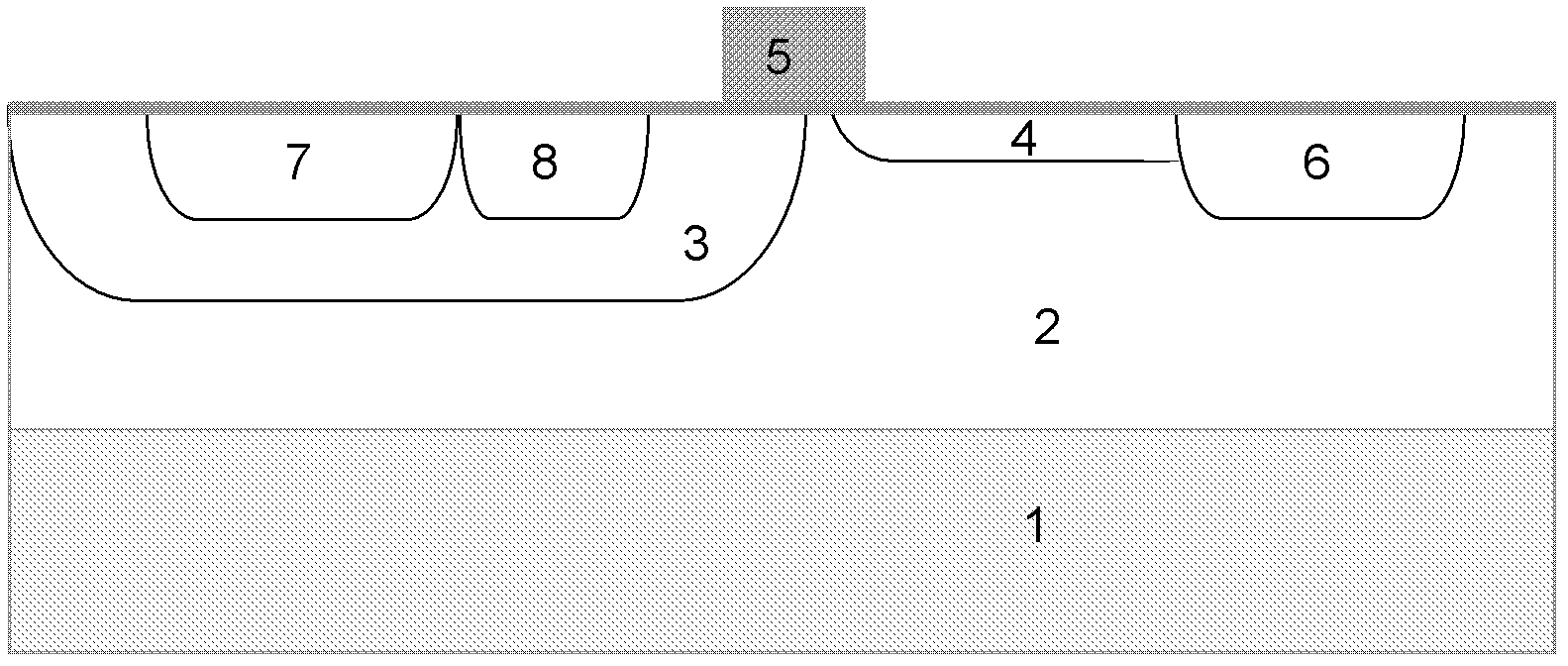

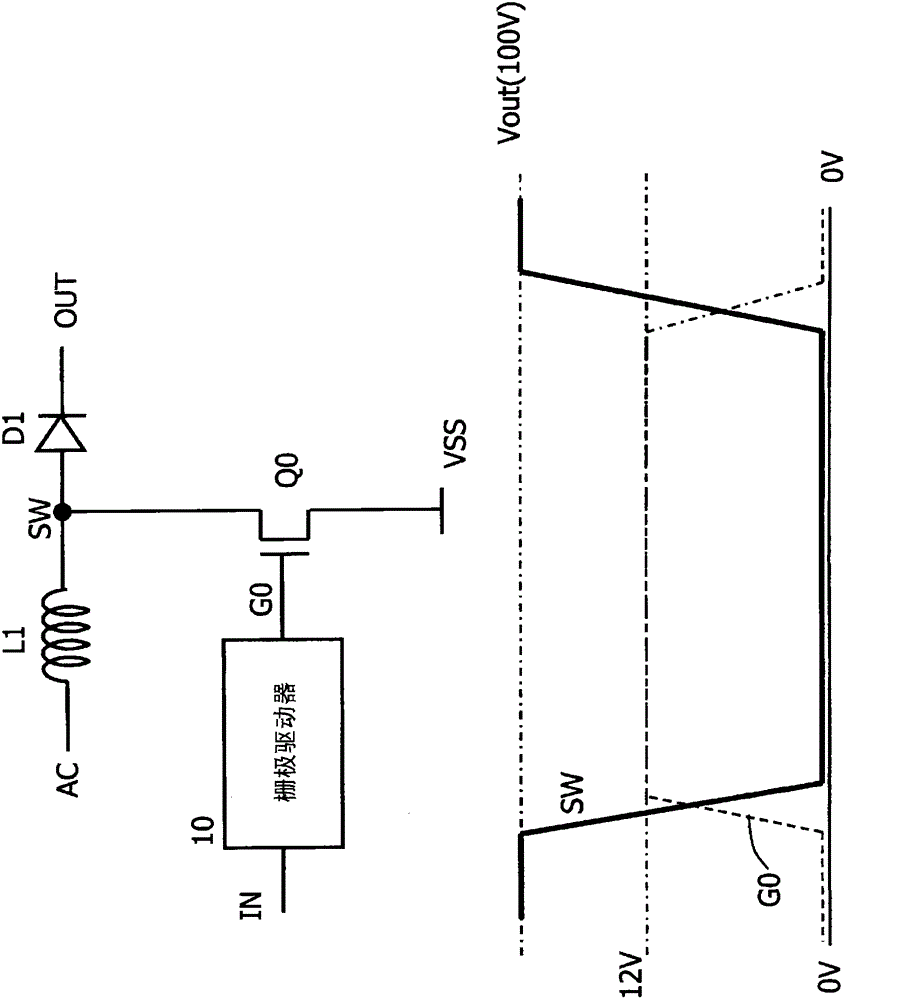

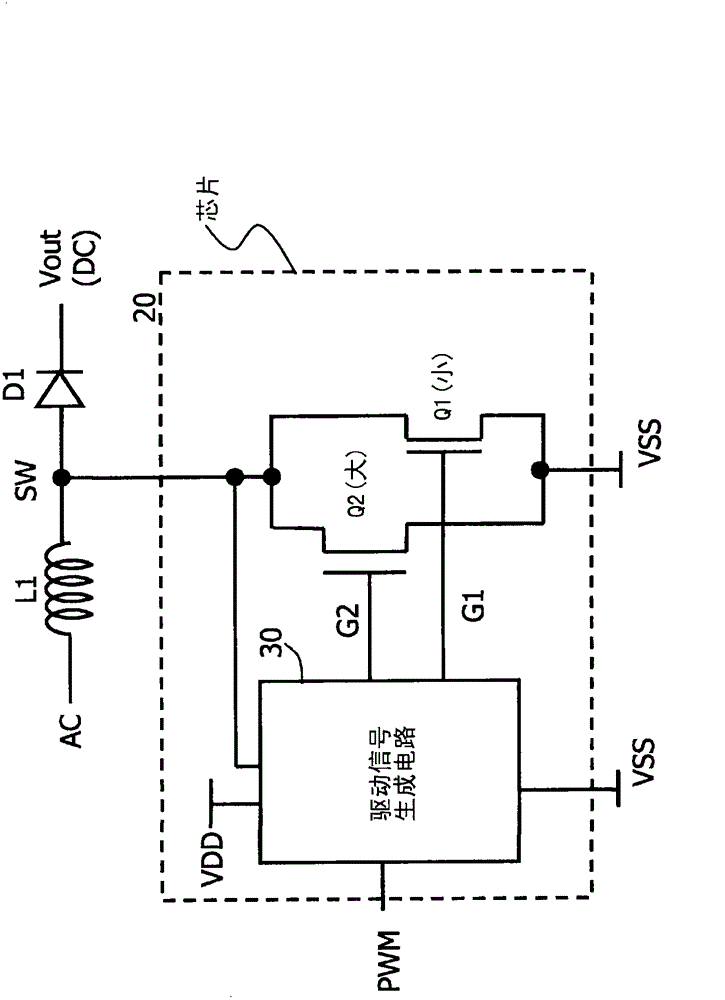

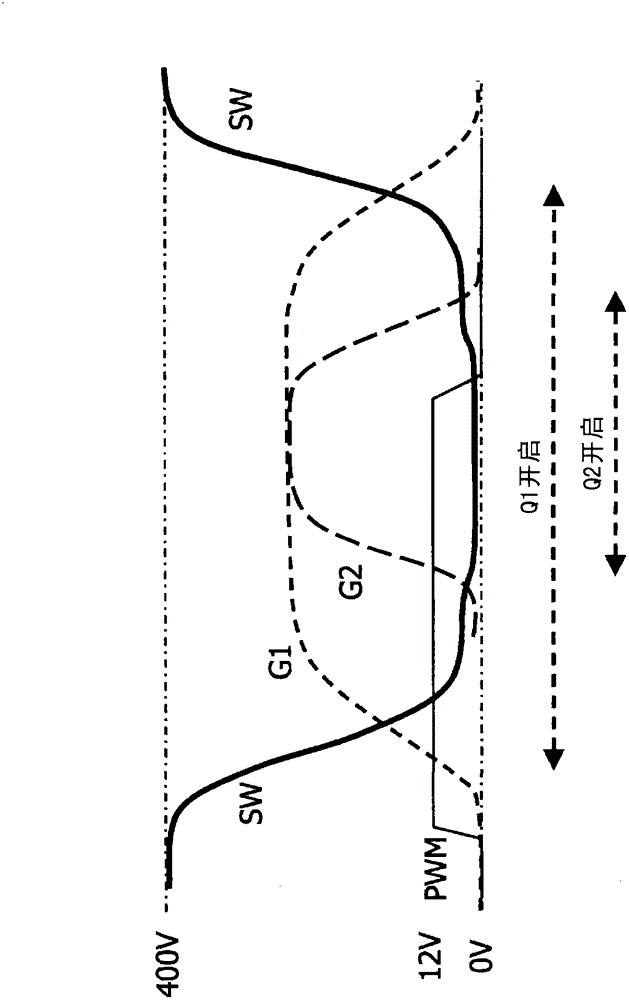

Switching circuit device and power supply device having same

InactiveCN102751852ASuppress rapid changesLower turn-on resistanceAc-dc conversionDc-dc conversionInductorEngineering

A switching circuit device provided between a first node and a second node within a power supply circuit, an inductor being coupled to the first or second node, the switching circuit device has: a first transistor that is provided between the first node and the second node and has a first gate width,a second transistor that is provided in parallel with the first transistor between the first node and the second node and has a second gate width larger than the first gate width,and a driving signal generation circuit, which, in response to a control signal generated according to an output voltage of the power supply circuit, outputs a first driving signal which drives the first transistor on and off, and a second driving signal which drives the second transistor on and off, with different timings between the first driving signal output and the second driving signal output.

Owner:TRANSPHORM JAPAN

Field-effect semiconductor device

InactiveUS7777253B2Lower turn-on resistanceTotal current dropSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceHeterojunction

A HEMT-type field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on the main semiconductor region. Between these electrodes, with spacings therefrom, an insulator is provided with is made from a material capable of developing a stress to reduce carrier concentration in neighboring part of the two-dimensional electron gas layer, creating a discontinuity in this layer. A gate electrode overlies the insulator via a piezoelectric layer which is made from a material capable of developing, in response to a voltage applied to the gate electrode, a stress for canceling out the stress developed by the insulator. Thus the device is physically held off by the action of the insulator while no voltage is being impressed to the gate electrode and, upon voltage application thereto, piezoelectrically turns on by the action of the piezoelectric layer. The turn-on resistance of the device is relatively low as the insulator occupies only part of the source-drain spacing.

Owner:SANKEN ELECTRIC CO LTD

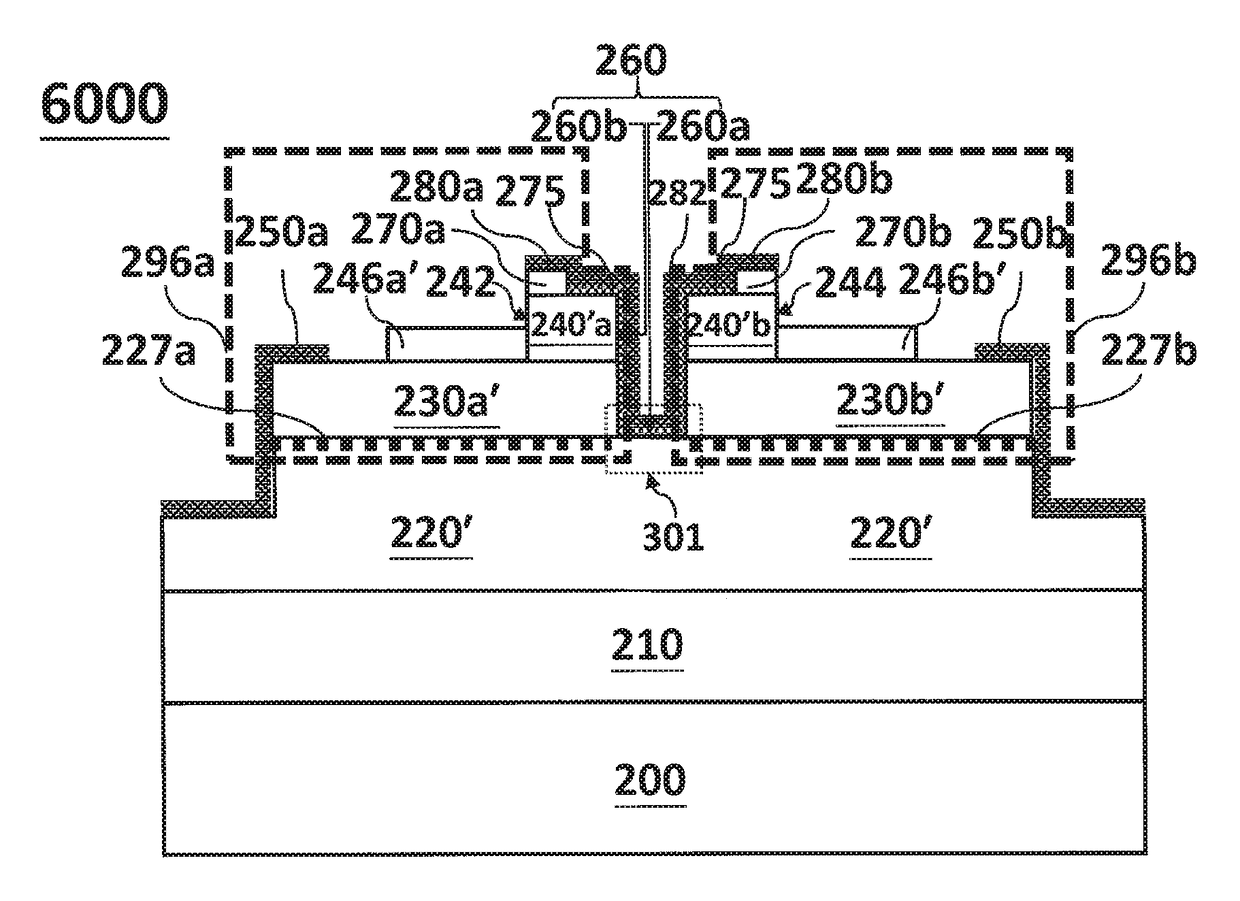

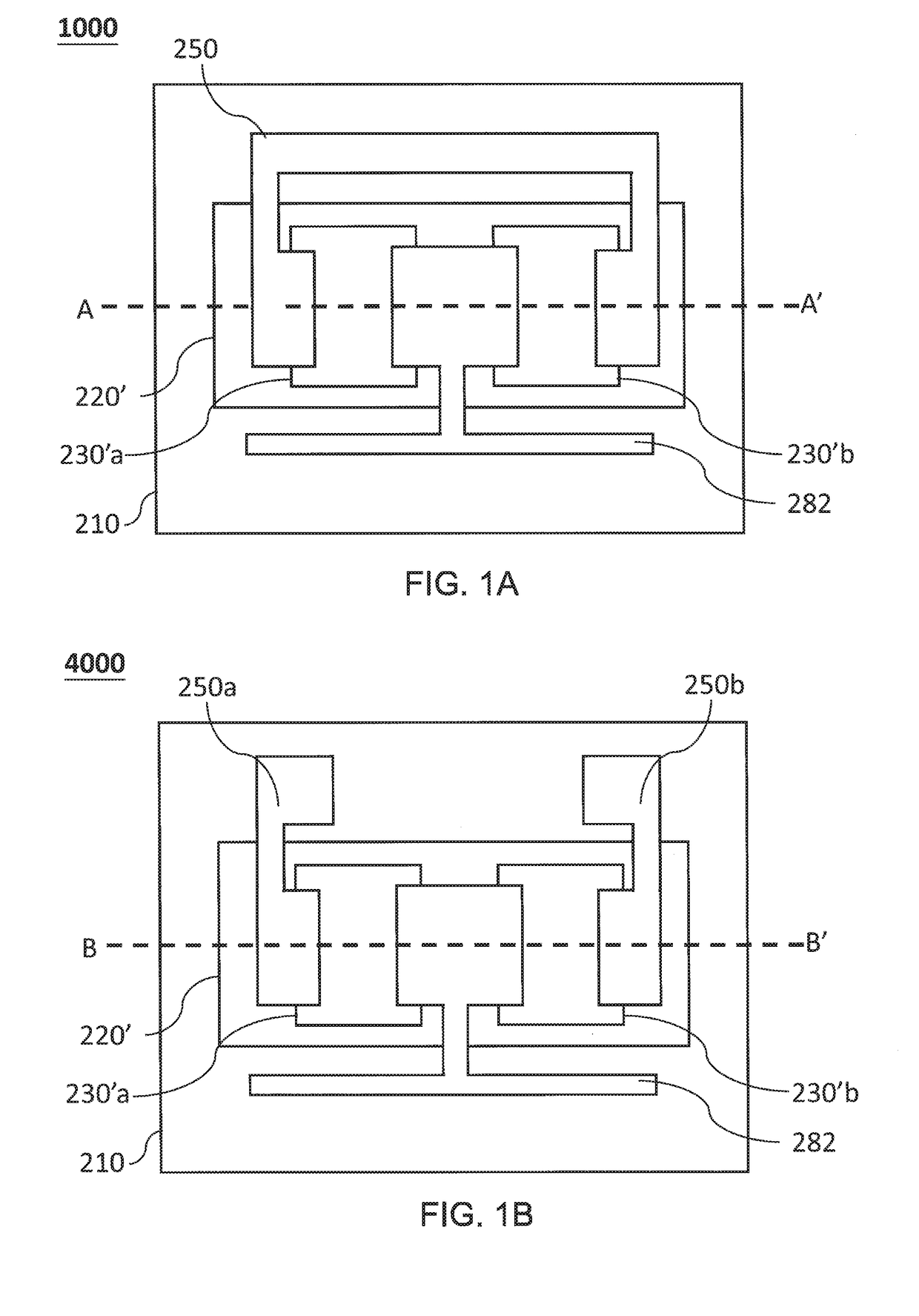

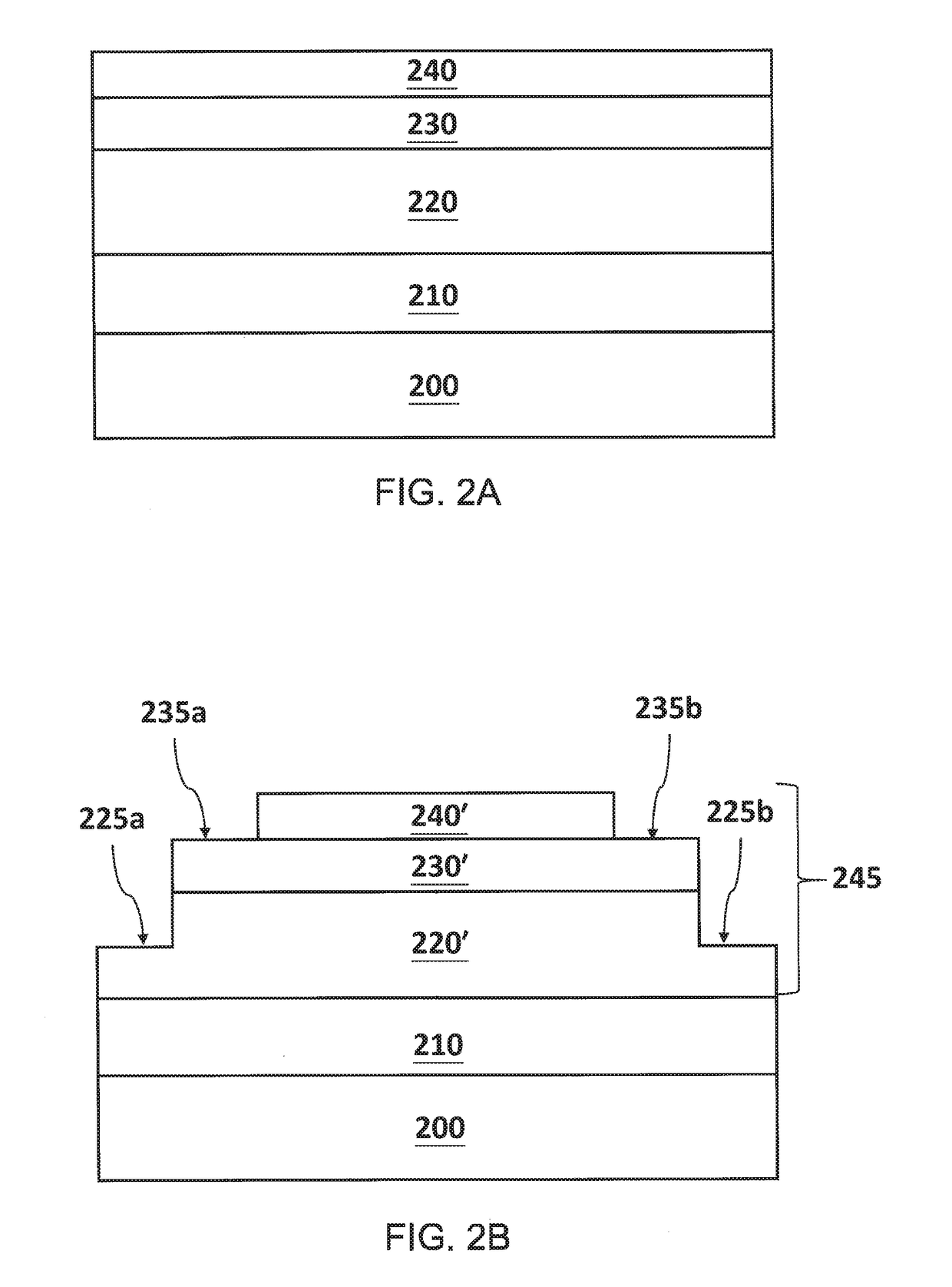

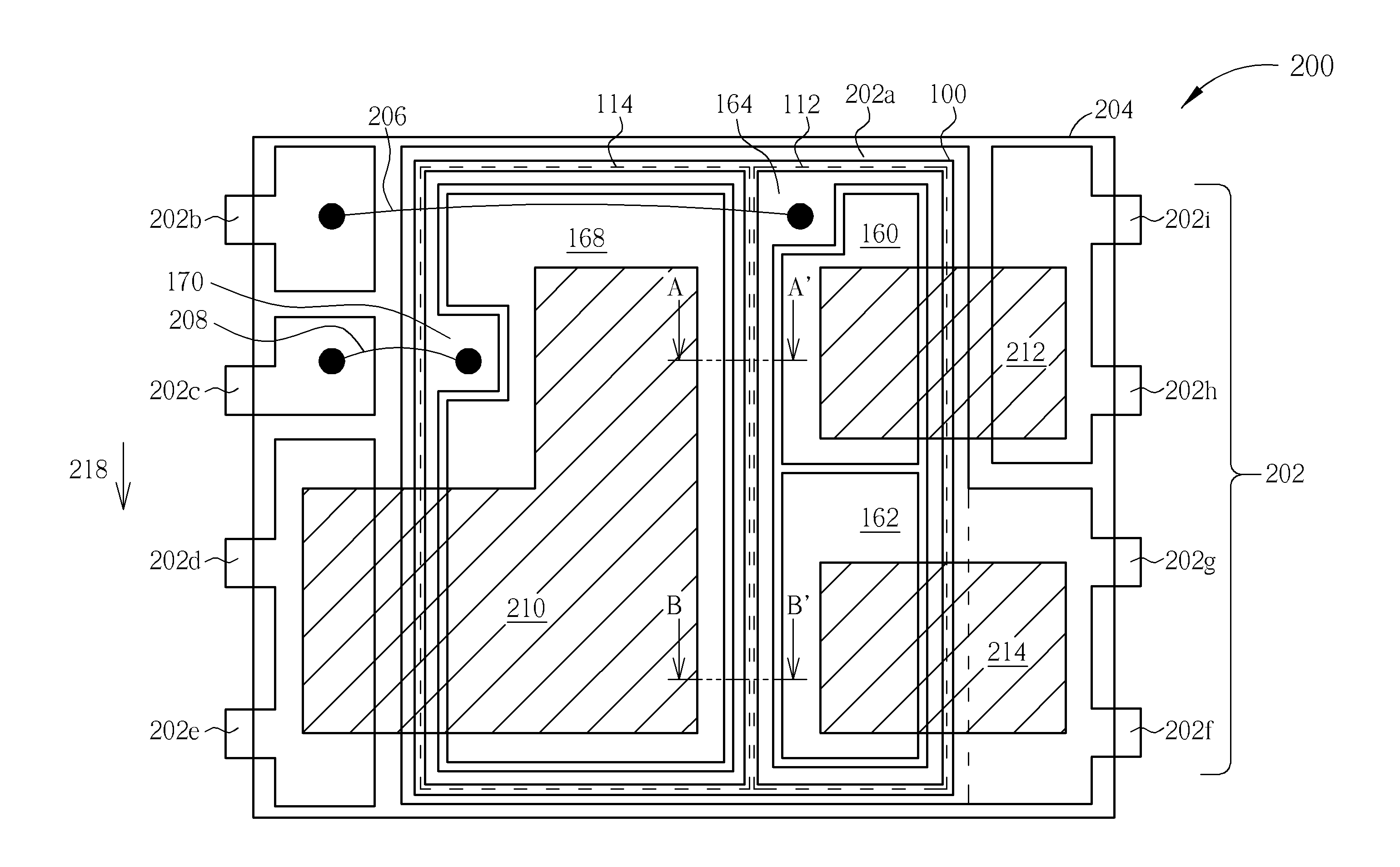

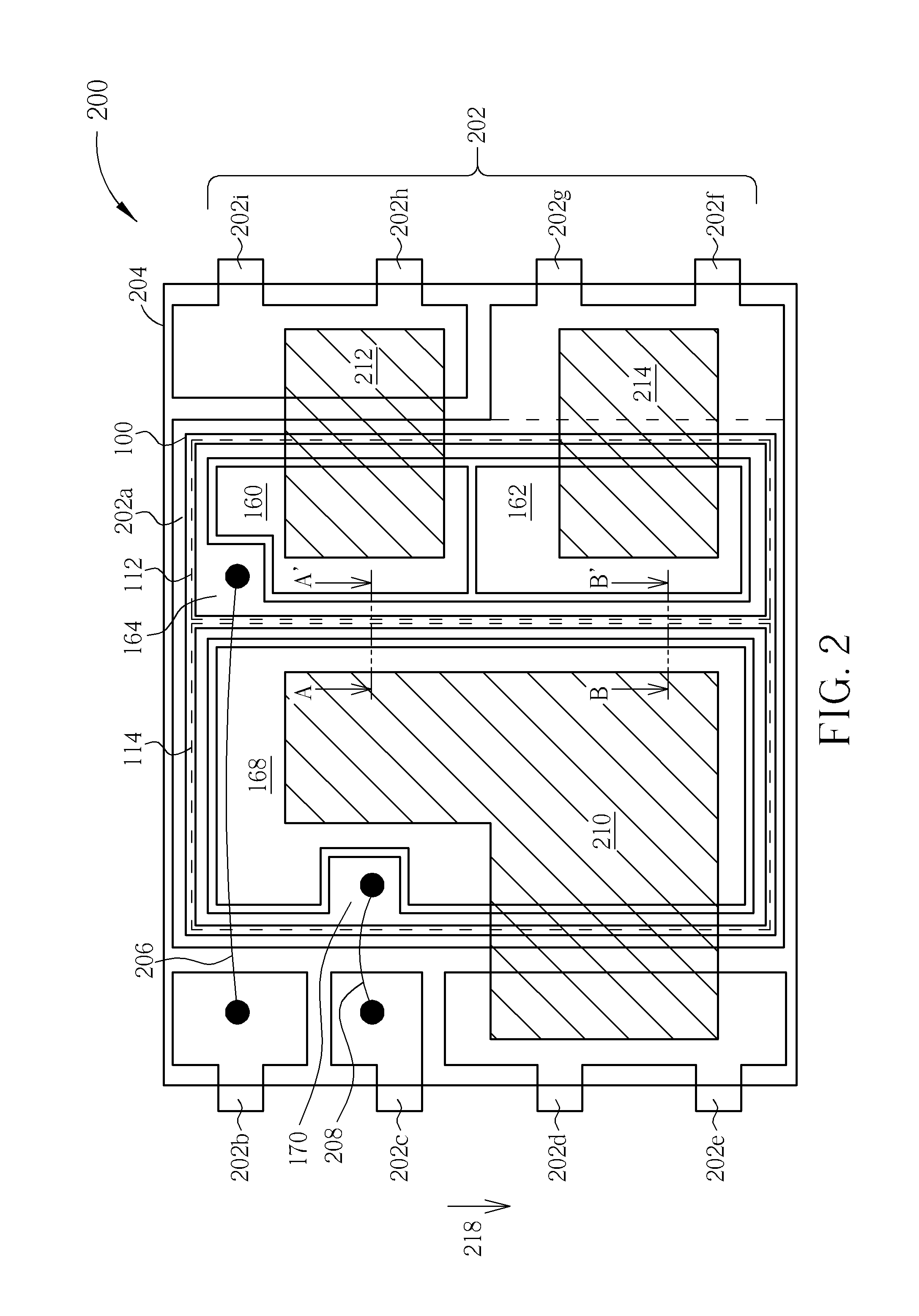

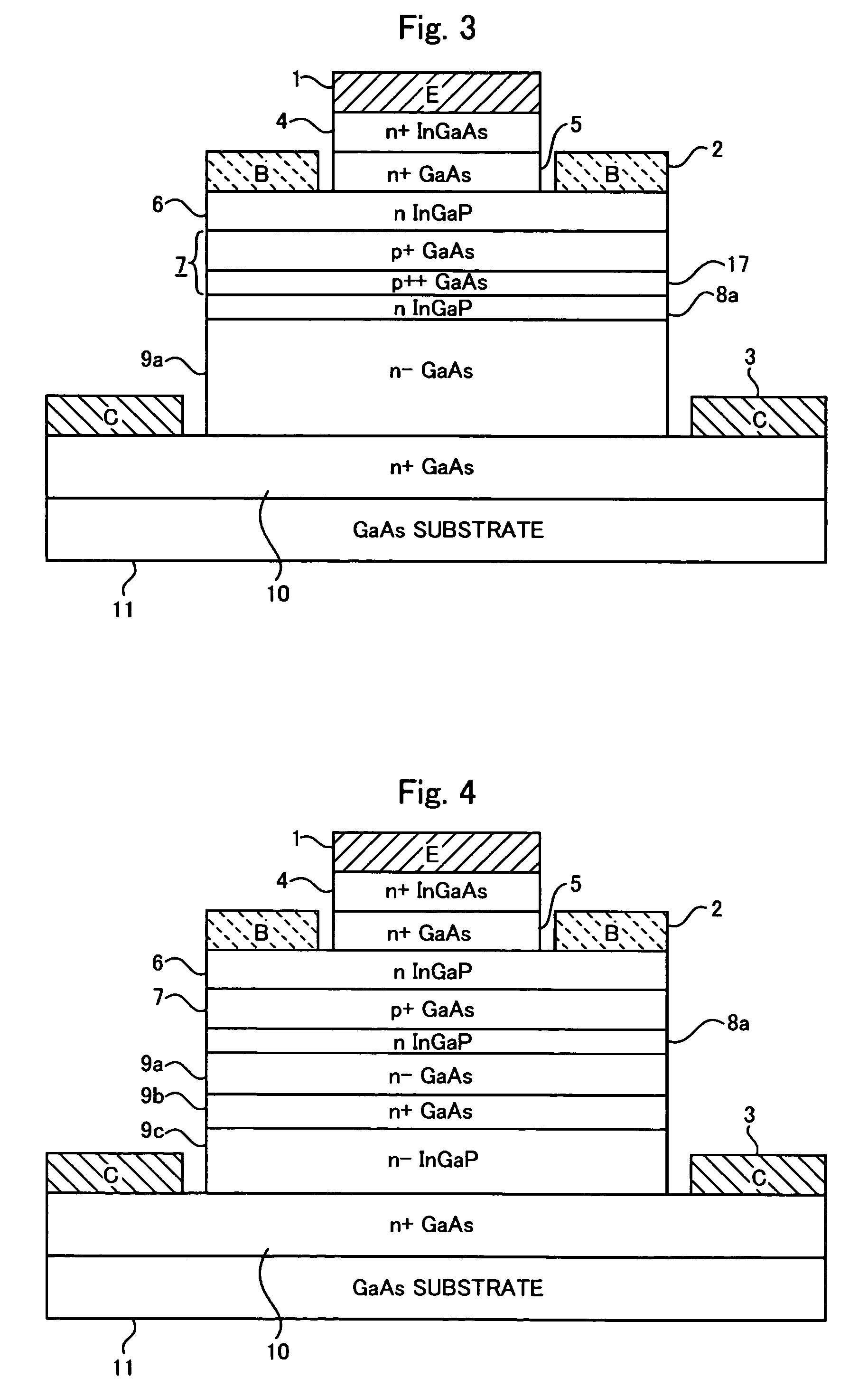

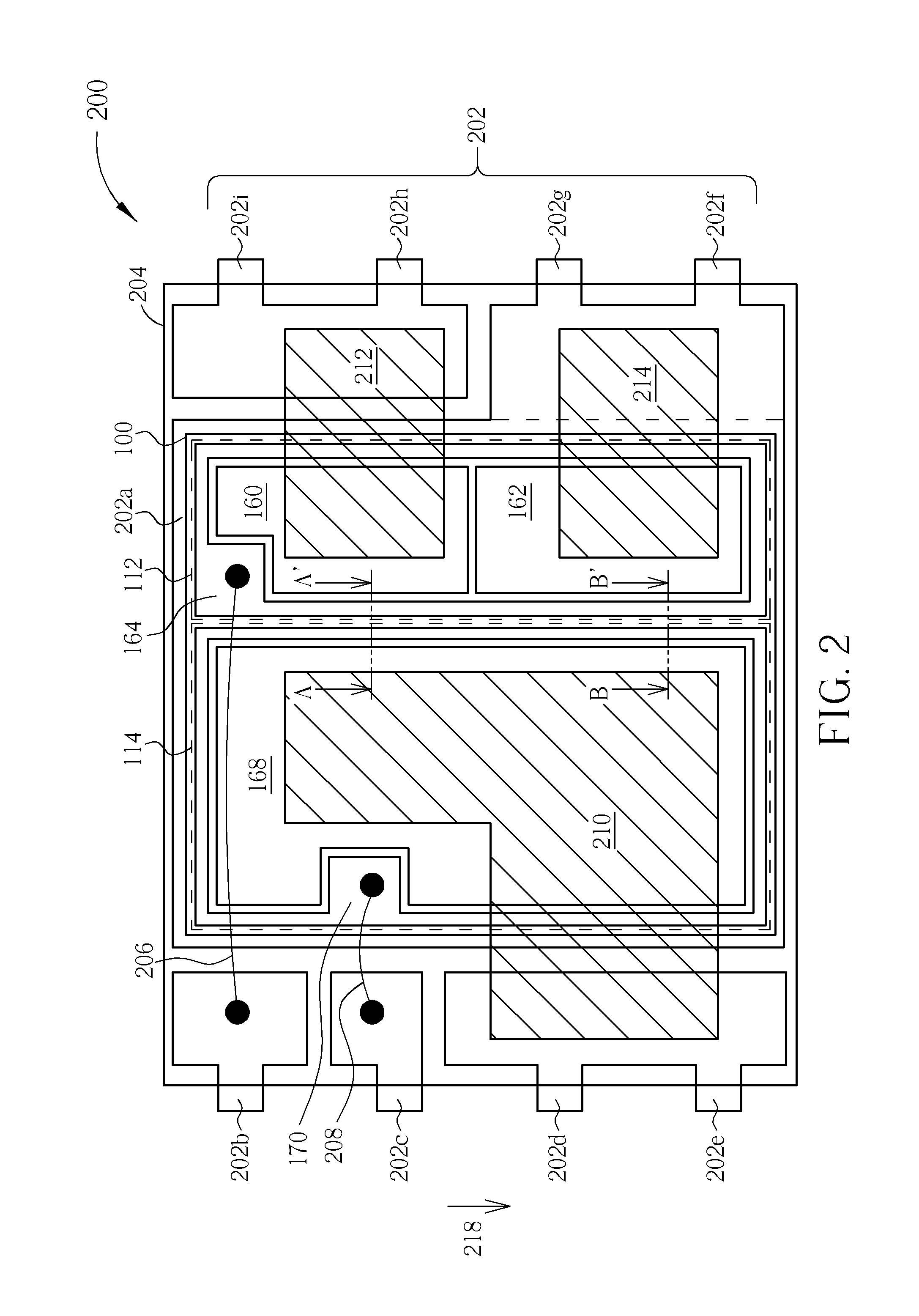

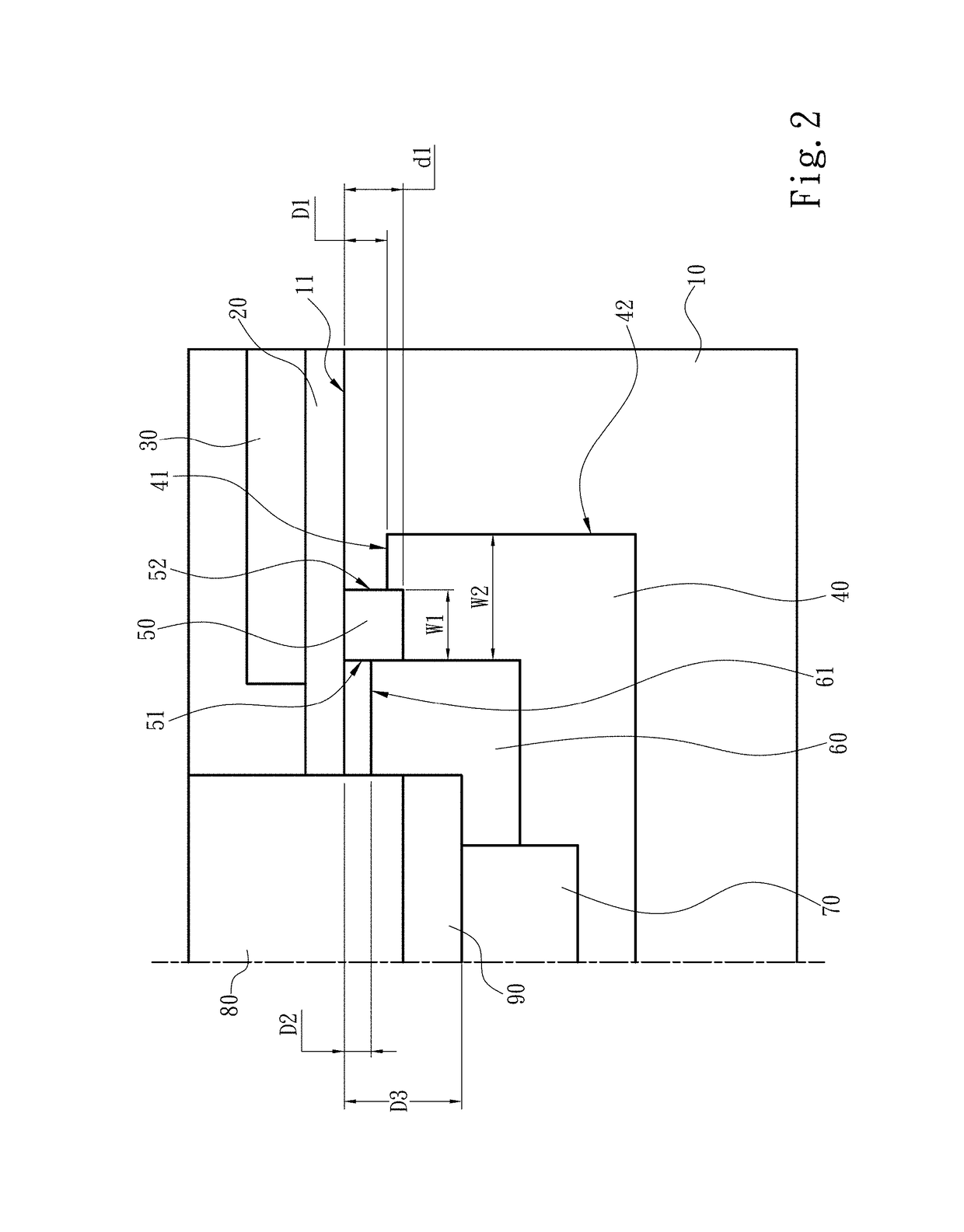

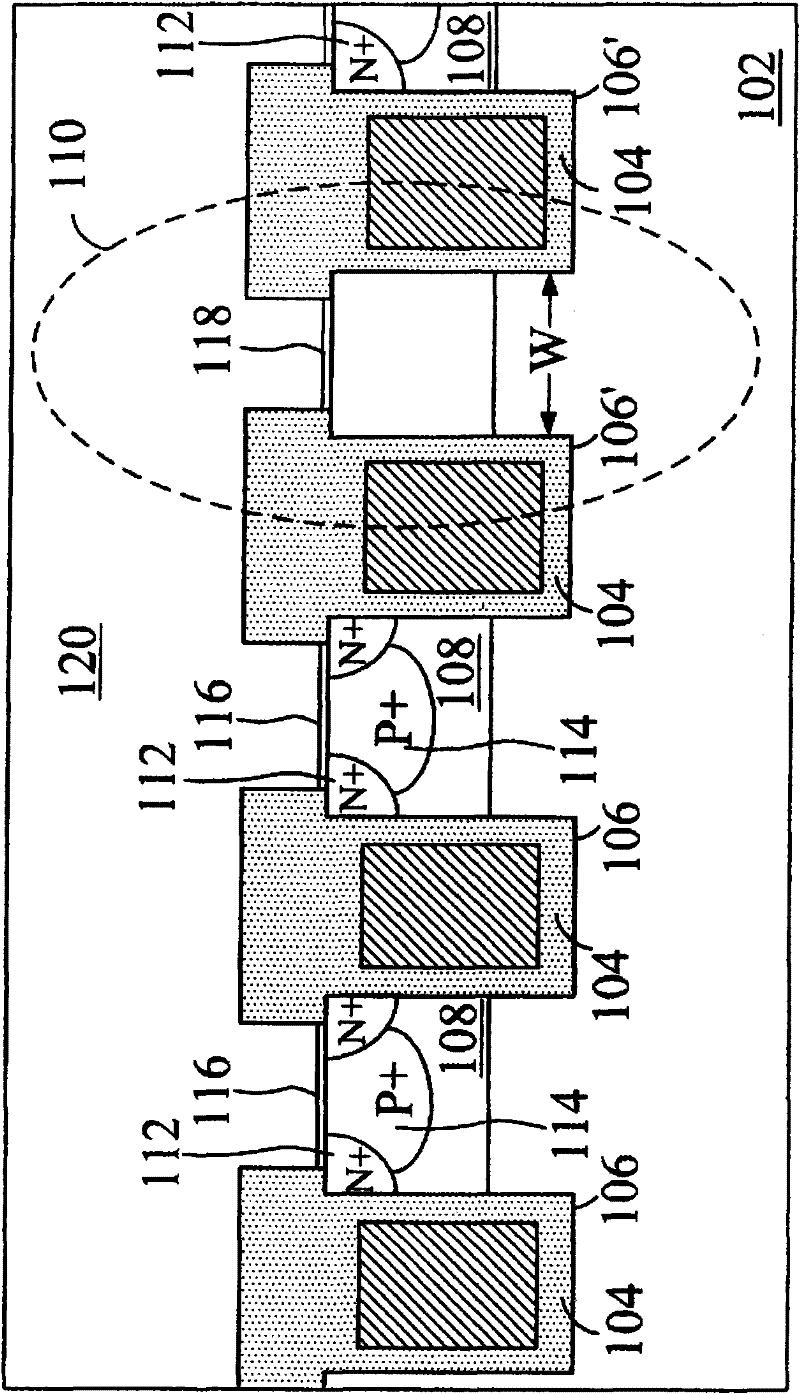

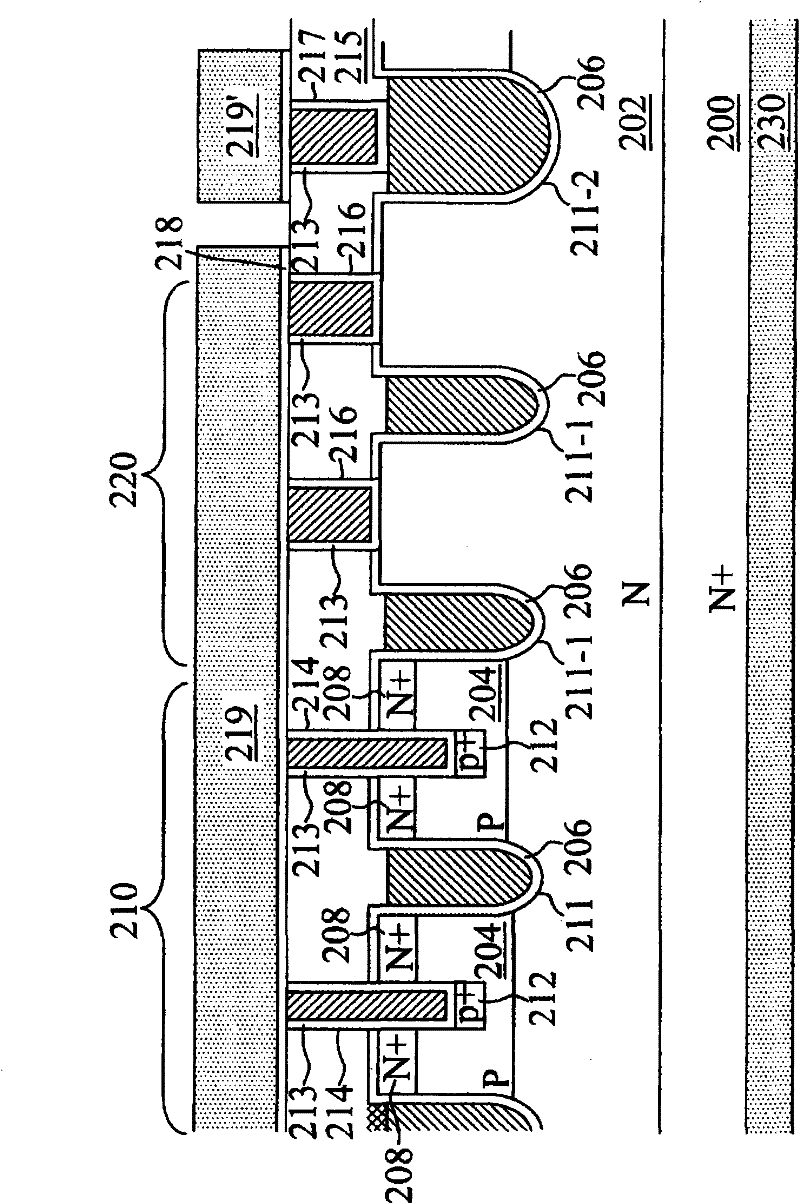

Semiconductor device integrated with converter and package structure thereof

ActiveUS20120056277A1Lower turn-on resistanceReduce supplyTransistorSemiconductor/solid-state device detailsPower semiconductor deviceSemiconductor

The present invention provides a semiconductor device including a semiconductor substrate having a first conductive type, at least one high-side transistor device and at least one low-side transistor device. The high-side transistor device includes a doped high-side base region having a second conductive type, a doped high-side source region having the first conductive type and a doped drain region having the first conductive type. The doped high-side base region is disposed within the semiconductor substrate, and the doped high-side source region and the doped drain region are disposed within the doped high-side base region. The doped high-side source region is electrically connected to the semiconductor substrate, and the semiconductor substrate is regarded as a drain of the low-side transistor device.

Owner:SINOPOWER SEMICON

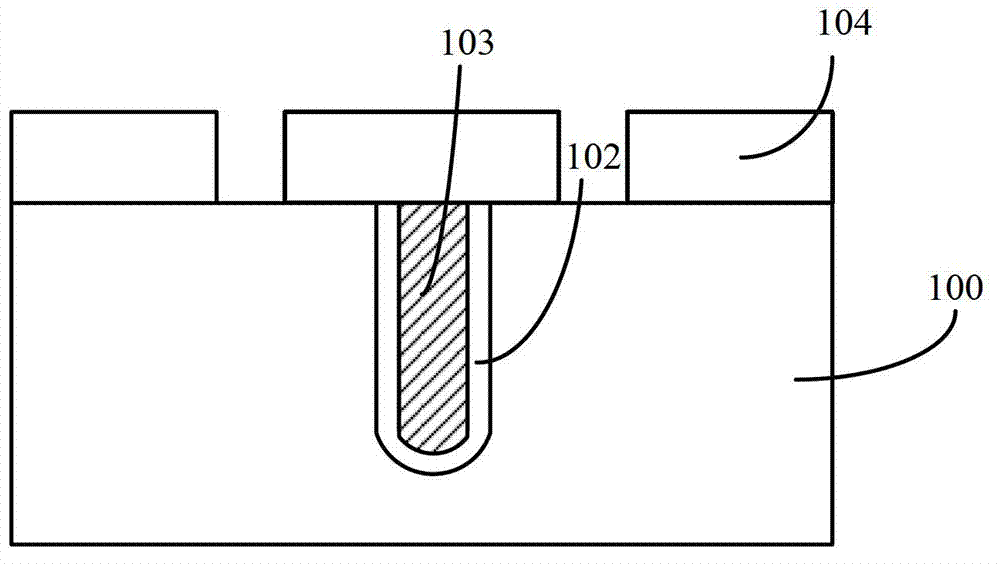

Transistor and forming method thereof

ActiveCN102779843AReduce contact resistanceThreshold Voltage StabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor

Provided are a transistor and a forming method thereof. The transistor comprises a semiconductor substrate, a groove located in the semiconductor substrate, a gate dielectric layer located on the lateral wall and the bottom surface of the groove, a gate electrode layer located on the surface of the gate dielectric layer, a source region and a drain region. The groove is formed by a first sub groove and a second sub groove located below the first sub groove, wherein the second sub groove is communicated with the first sub groove, an opening of the first sub groove is larger than that of the second sub groove, the lateral wall of the first sub groove is inclined relative to the surface of the semiconductor substrate, and the lateral wall of the second sub groove is perpendicular to the surface of the semiconductor substrate. The gate electrode layer fully fills the groove and the surface of the gate electrode layer is level to that of the semiconductor substrate. The source region is located in the semiconductor substrate on two sides of the groove. The drain region is located in the semiconductor substrate on one side opposite to the groove and is opposite to the second sub groove. The transistor is stable in threshold voltage and good in performance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Semiconductor device

InactiveUS7304333B2Lower turn-on resistanceImprove power added efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSemi insulating

A heterojunction bipolar transistor, having a structure in which a subcollector layer of a first conductive type having a higher doping concentration than a collector layer, a collector layer of the first conductive type, a base layer of the second conductive type, and an emitter layer of the first conductive type are deposited, in order, on a semi-insulating semiconductor substrate, and in which a hole barrier layer of semiconductor material with a band gap wider than that of the base layer is inserted between the base layer and the collector layer, so as to be in direct contact with the base layer.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device integrated with converter and package structure thereof

ActiveUS8426914B2Reduce power lossLower turn-on resistanceTransistorSemiconductor/solid-state device detailsPower semiconductor deviceSemiconductor

Owner:SINOPOWER SEMICON

GaNHEMT cell structure with graphene buried source and longitudinal gate and preparation method

PendingCN107195674ALower turn-on resistanceIncrease the areaSemiconductor/solid-state device manufacturingSemiconductor devicesHigh densityGraphite

The invention discloses a GaNHEMT cell structure with a graphene buried source and a longitudinal gate. The source is connected with a graphene buried cooling layer through a metal material; the device adopts a longitudinal gate structure, a long transverse channel opening mode in the traditional HEMT device is turned to a short longitudinal channel opening mode, a long transverse current control channel is turned to a short longitudinal current control channel for the gate, the device uses a short gate side wall channel to realize switch control, and the on resistance of the device can be effectively reduced. A high-density cell structure can be realized, and the effective using area and the unit area power density of the device are improved; and by using the excellent thermal conductivity of the graphene, heat generated in an active area of the device can be conducted rapidly, the high-power GaNHEMT device can be realized, and the high-temperature reliability of the device can be enhanced.

Owner:BEIJING HUAJINCHUANGWEI ELECTRONICS CO LTD

Silicon carbide semiconductor element and manufacturing method thereof

ActiveUS10020368B2Lower turn-on resistanceImprove component reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerCondensed matter physics

A silicon carbide (SiC) semiconductor element includes a semiconductor layer, a dielectric layer on a surface of the semiconductor layer, a gate electrode layer on the dielectric layer, a first doped region, a second doped region, a shallow doped region and a third doped region. The semiconductor layer is of a first conductivity type. The first doped region is of a second conductivity type and includes an upper doping boundary spaced from the surface by a first depth. The shallow doped region is of the second conductivity type, and extends from the surface to a shallow doped depth. The second doped region is adjacent to the shallow doped region and is at least partially in the first doped region. The third doped region is of the second conductivity type and at least partially overlaps the first doped region.

Owner:SHANGHAI HESTIA POWER INC

A kind of semiconductor integrated device and its manufacturing method

InactiveCN102270638ALower turn-on resistanceSmall sizeSemiconductor/solid-state device detailsSolid-state devicesOxide semiconductorOxide

The invention discloses a semiconductor integrated device comprising a plurality of trench metal oxide semiconductor field effect transistor units and a plurality of trench Schottky ballast units and a manufacturing method thereof. In the trench metal oxide semiconductor field effect transistor unit, the trench type contact area is adopted, which can reduce the turn-on resistance of the device while reducing the size of the device.

Owner:FORCE MOS TECH CO LTD

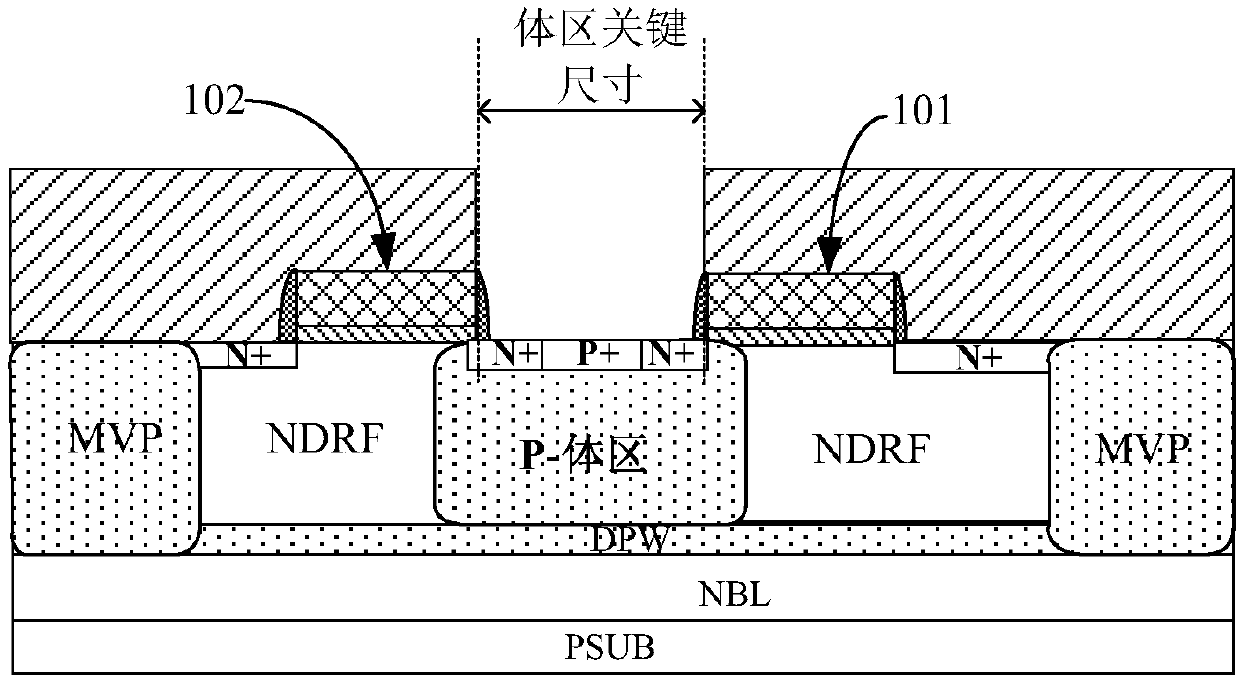

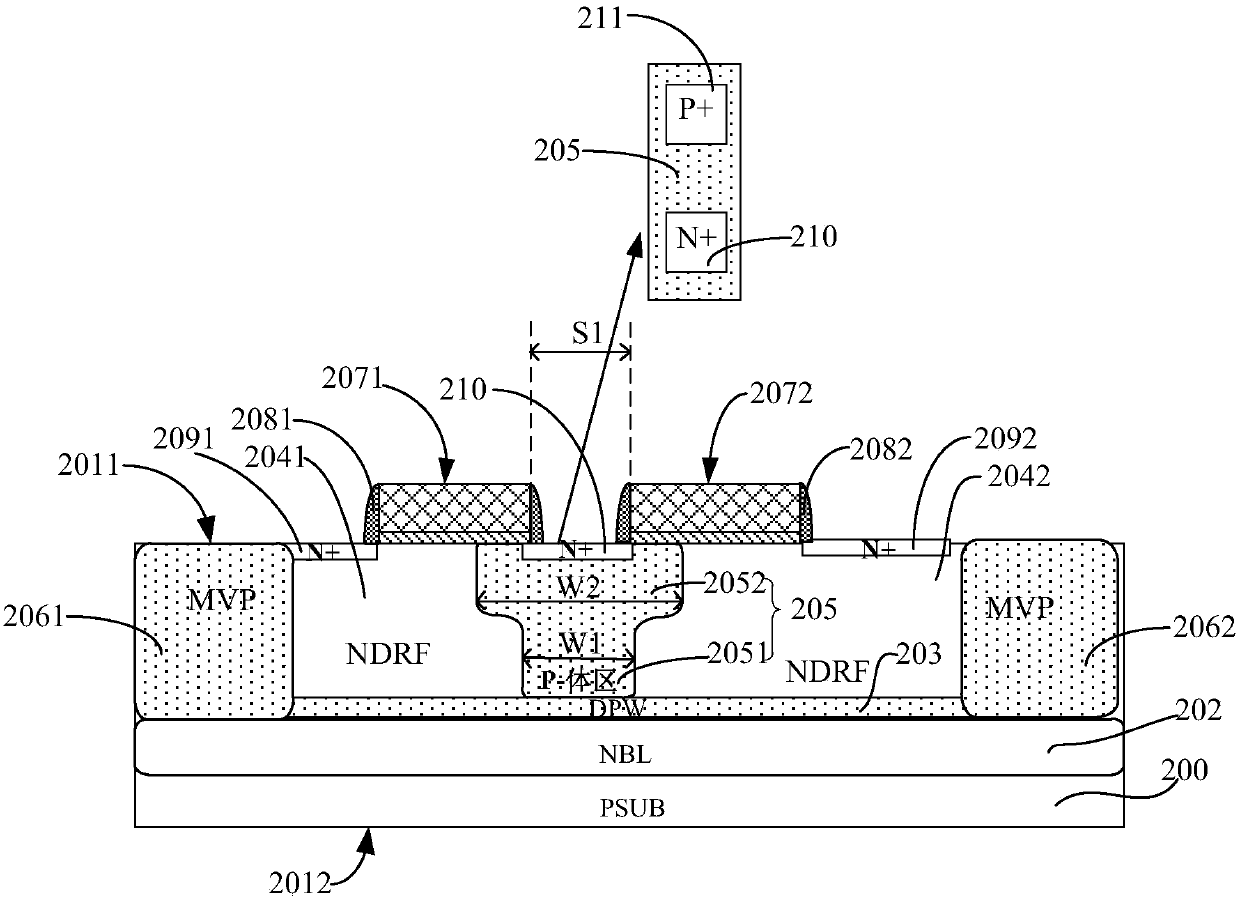

Semiconductor device and manufacturing method thereof, and electronic device

InactiveCN108122977ALower turn-on resistanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceBody region

The invention provides a semiconductor device, a manufacturing method thereof and an electronic device, which relate to the technical field of semiconductors. The semiconductor device comprises a semiconductor substrate having a first conduction type, a body region having a first conduction type, a first gate structure and a second gate structure, wherein the body region is formed in the semiconductor substrate, the body region comprises a first portion and a second portion which is positioned on and adjacent to the first portion, the second portion is close to the first surface of the semiconductor substrate, the first portion extends for a first width along a first direction, the second portion extends for a second width along the first direction, and the first width is less than the second width; the first gate structure is arranged on the first surface of the semiconductor substrate, and partially extends onto the body region; and the second gate structure is arranged on the firstsurface of the semiconductor substrate, partially extends onto the body region, and is arranged along the first direction in a manner of being spaced from the first gate structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

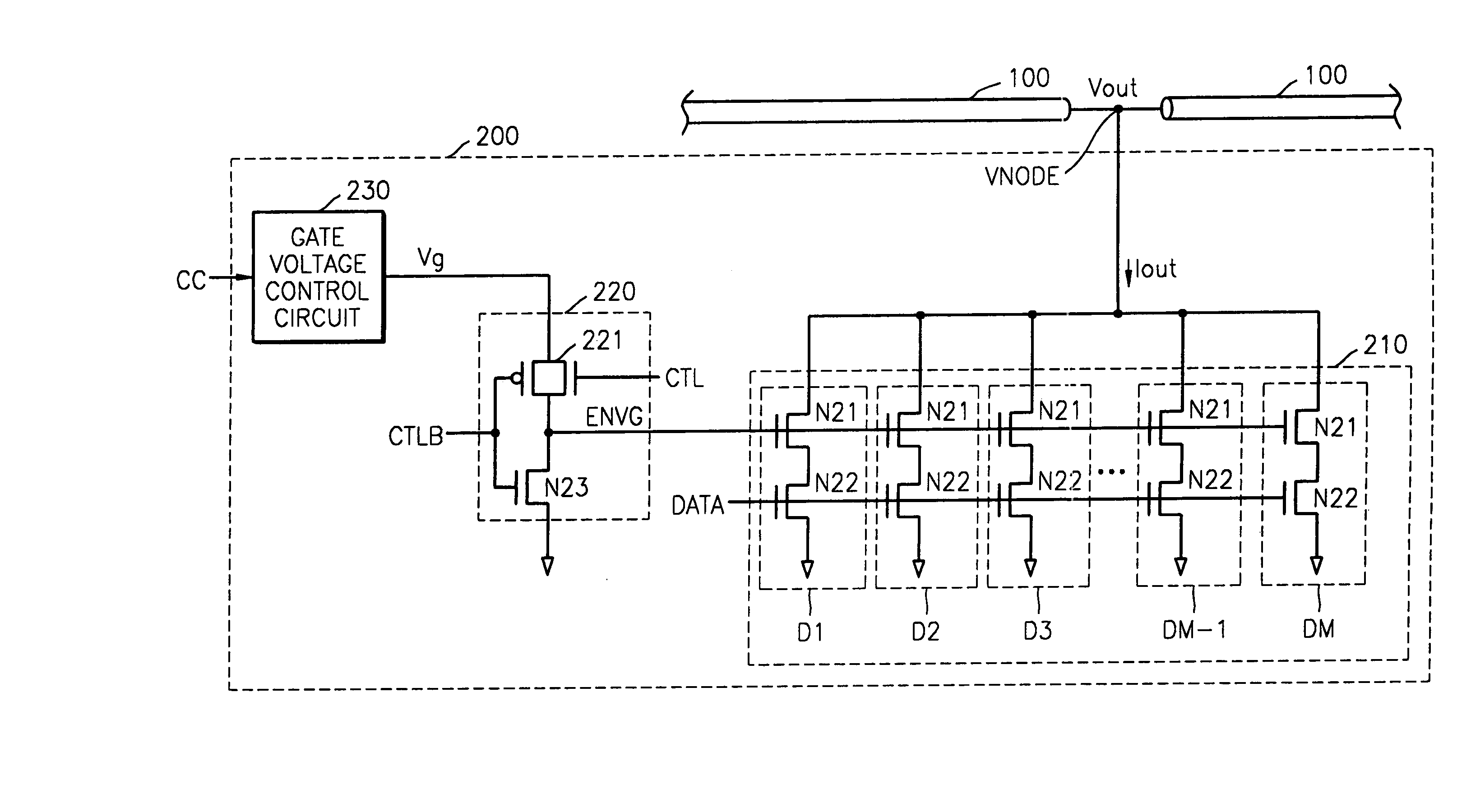

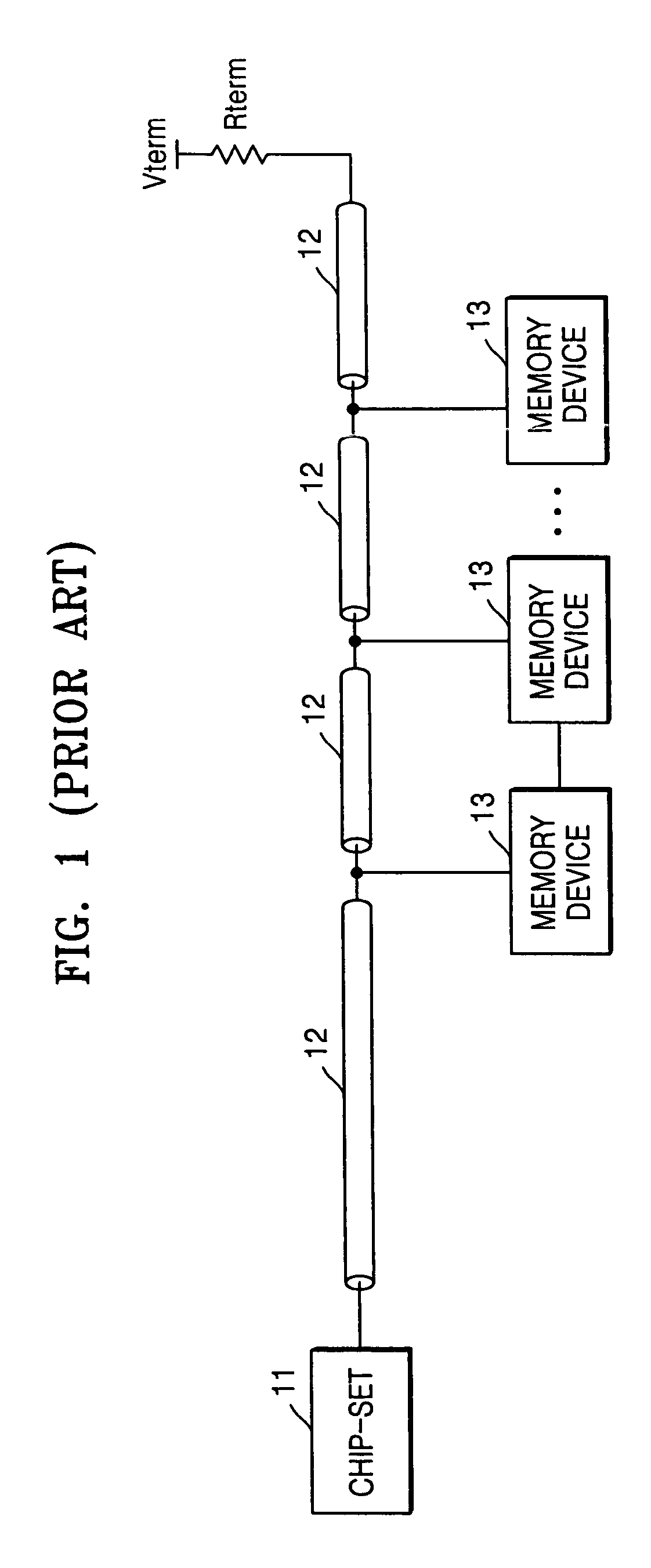

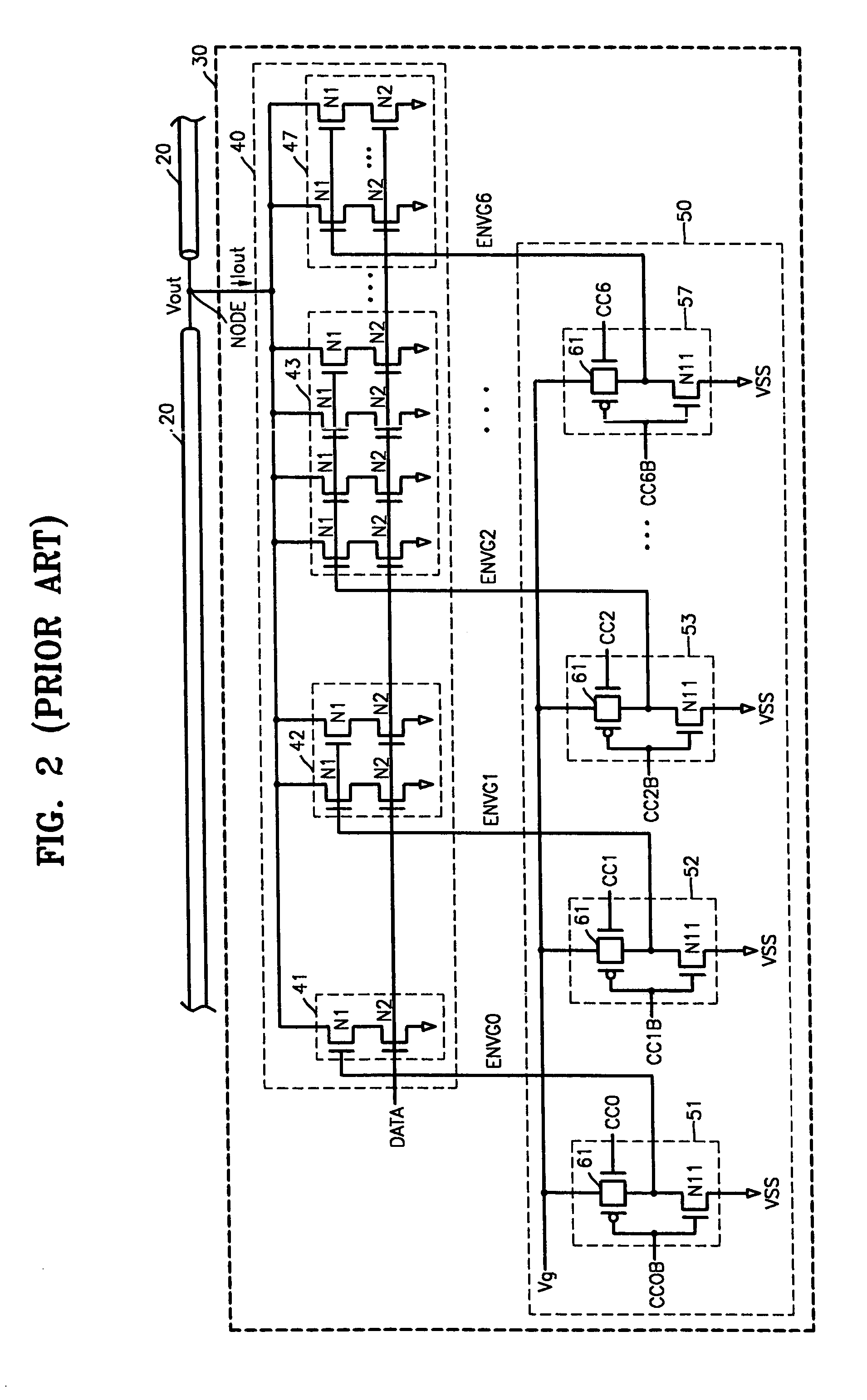

Current mode output driver

InactiveUS7072227B2Increase level of gate voltageDecrease turn-on resistance of MOSFETReliability increasing modificationsElectronic switchingTransmission lineGate voltage

A current mode output driver and output current control method of controlling an output current using a gate voltage are provided. The current mode output driver, which outputs data read from a memory core to a transmission line, includes a gate voltage control circuit, a bias circuit, and a driver circuit. The gate voltage control circuit generates a predetermined gate voltage in response to a current control signal. The bias circuit outputs the gate voltage as a first enable signal in an active mode, and outputs a ground voltage as a second enable signal in a standby mode. The driver circuit drives a predetermined output current in response to the first enable signal, outputs the predetermined output voltage to the transmission line according to the data, and stops its operation in response to the second enable signal. The gate voltage control circuit changes the level of the gate voltage according to a value of the current control signal and output the changed result. Therefore, it is possible to easily increase resolution of an output current and reduce the occupied area of the current mode output driver, thereby facilitating a circuit design.

Owner:SAMSUNG ELECTRONICS CO LTD

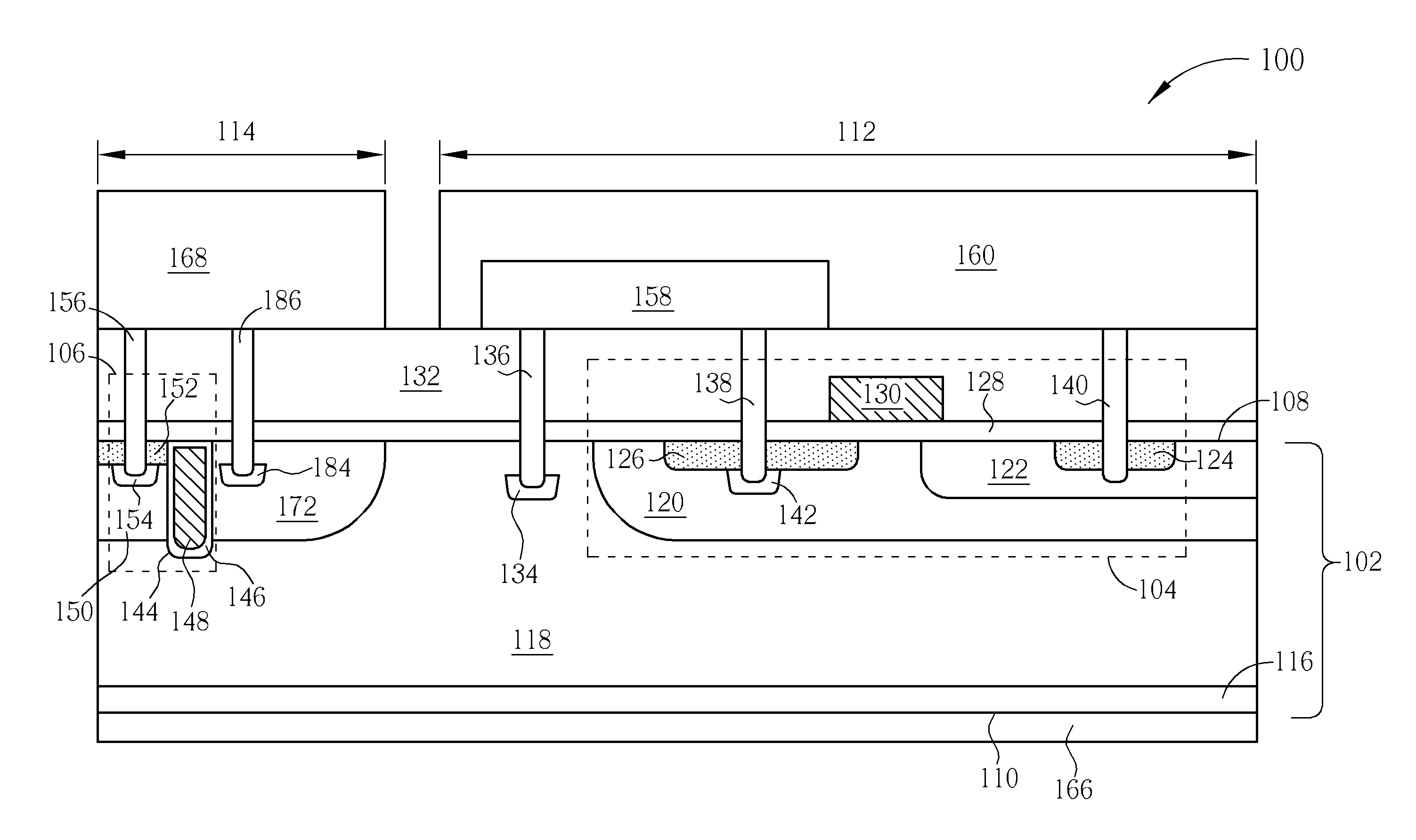

A lateral double diffused metal-oxide semiconductor device

ActiveCN107768421AReduce the length of the drift regionLower turn-on resistanceSemiconductor devicesEngineeringSemiconductor

A lateral double diffused metal-oxide semiconductor device includes a substrate, a gate structure, a drain region, a plurality of isolation structures, at least one doped region, and a source region.The gate structure is on the substrate. The drain region and the source region are respectively located in the substrate on the first side and the second side of the gate structure. The isolation structure and the doped region are located in the substrate between the gate structure and the drain region, wherein the extension direction of the isolation structure is different from the extension direction of the gate structure. The doped region may be located between two isolation structures or below the isolation structures. The doped region and the drain region have opposite conductive states,so that the turn-on resistance of the lateral double-diffused metal-oxide semiconductor device is reduced, the electric field between the gate structure and the drain region is reduced, and the breakdown voltage of the lateral double-diffused metal oxide semiconductor device is improved.

Owner:NUVOTON

Method for fabricating radio frequency ldmos devices with double metal silicides

ActiveCN103137667BLower turn-on resistanceIncrease working voltageSemiconductor/solid-state device manufacturingSemiconductor devicesRadio frequencyPolycrystalline silicon

The invention discloses a radio frequency laterally diffused metal oxide semiconductor (LDMOS) device with thermometal silicide and a manufacturing method. A P-shaped silicon substrate is provided with P-shaped epitaxy. A N-shaped low doped drain region, a P trap and a N-shaped heavy doped drain region are arranged in the P-shaped epitaxy. A N-shaped heavy doped source region and a P-shaped heavy doped lead out region are arranged in the P trap. A drain electrode titanium silicide layer is arranged on the top of the N-shaped heavy doped source region. A source electrode titanium silicide layer is arranged on the top of the P-shaped heavy doped lead out region and the N-shaped heavy doped source region. A grid electrode titanium silicide layer is arranged on the top of a polycrystalline silicon grid electrode. Thickness of the grid electrode titanium silicide layer is larger than thickness of the drain electrode titanium silicide layer and the source electrode titanium silicide layer. Titanium silicide of a grid electrode is thicker, square resistance of the grid electrode is reduced, and normal thickness titanium silicide on a source electrode and a source electrode avoids electricity leakage to caused by junction penetration of source drain and the trap.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com