Normally-closed GaN-based MOSFET structure with high threshold voltage and high conduction performance and fabrication method thereof

A high-threshold voltage, high conduction technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as the inability to achieve precise and controllable thin barrier layer thickness, small device threshold voltage, and high interface state density , to achieve the effects of reducing the concentration of two-dimensional electron gas, increasing the threshold voltage, and low on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

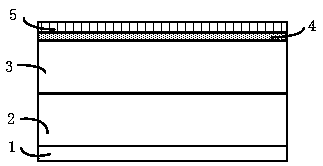

[0039] like Figure 11 Shown is a schematic diagram of the device structure of this embodiment, and its structure includes a substrate 1, a stress buffer layer 2, a GaN epitaxial layer 3, an AlN epitaxial layer 4, an AlGaN epitaxial layer 5, a secondary epitaxial layer 6, and a second epitaxial layer from bottom to top. A groove is formed by sub-epitaxy, a gate dielectric layer 7, a source 8 and a drain 9 are formed at both ends, and a gate 10 is covered on the dielectric layer 7 at the channel of the groove.

[0040] The preparation method of the above-mentioned normally-off GaN-based MOSFET with high threshold voltage and high conduction performance is as follows: Figure 1-Figure 11 shown, including the following steps:

[0041] S1, utilize metal-organic chemical vapor deposition method to grow a layer of stress buffer layer 2 on Si substrate 1, such as figure 1 shown;

[0042] S2. Using a metal organic chemical vapor deposition method to grow a GaN epitaxial layer 3 on t...

Embodiment 2

[0055] like Figure 13 Shown is a schematic diagram of the device structure of this embodiment, which differs from the structure of Embodiment 1 only in that in Embodiment 1, the AlN layer 4 and the AlGaN layer 5 above the gate region are retained by selective etching by photolithography, while In the embodiment 2, the AlN layer 4 and the AlGaN layer 5 are not etched, and the AlN layer 4 and the AlGaN layer 5 remain. On this substrate, a secondary epitaxial AlGaN layer 6 is grown in a selected region to form a recessed gate.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com