Vertical power mosfet including planar channel

A metal oxide half-field and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of reducing efficiency and breakdown voltage, MOSFET uneven current and temperature, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

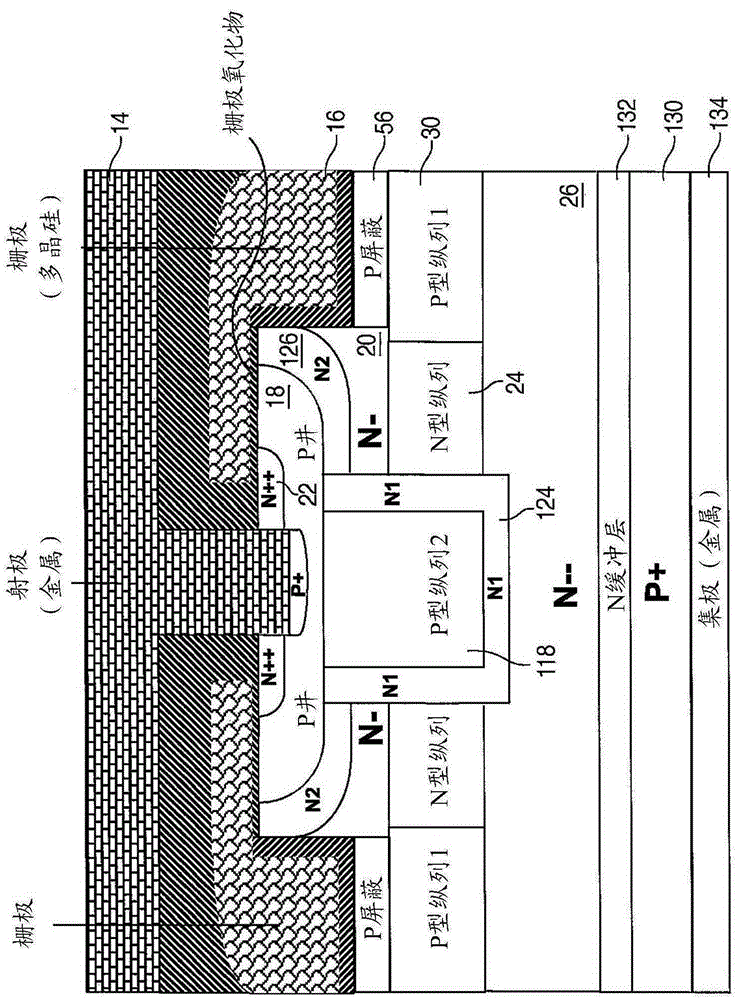

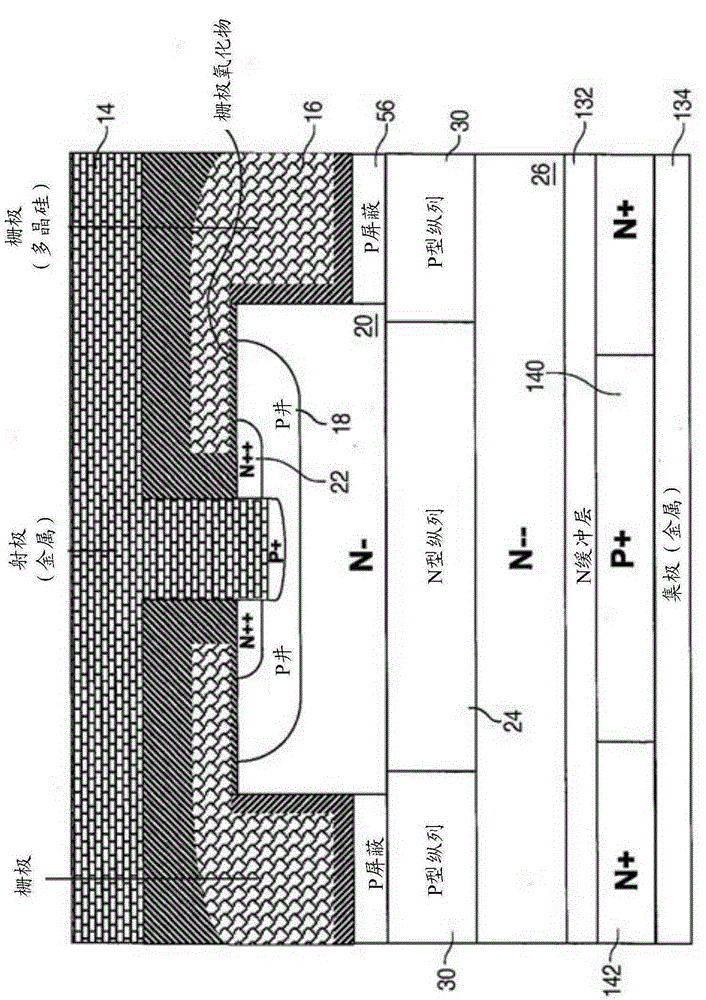

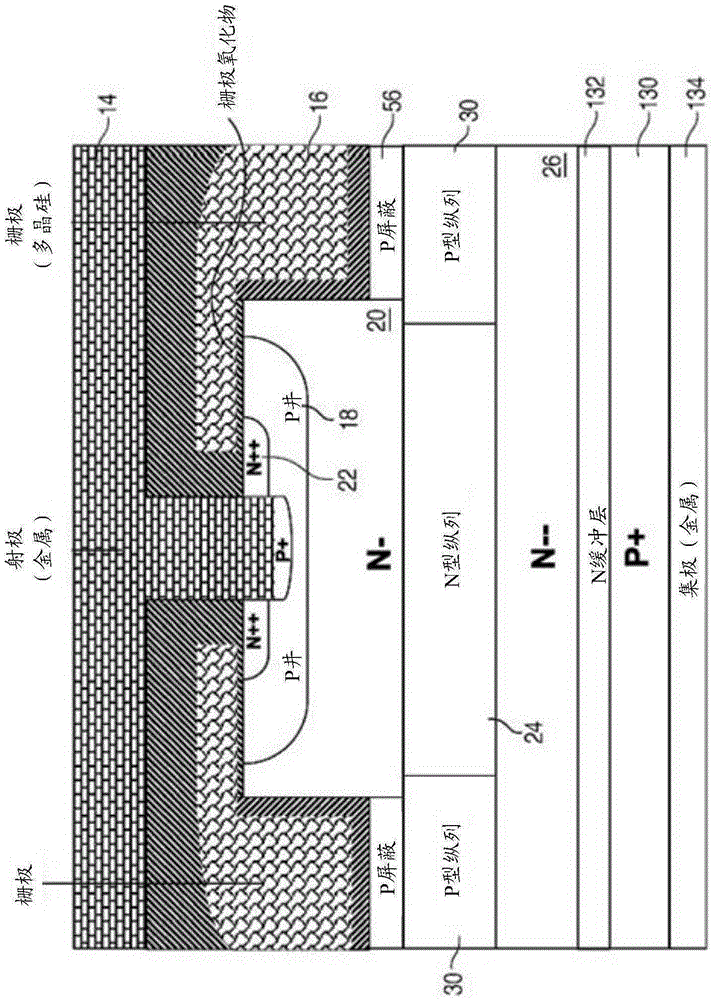

[0051] figure 1 is a cross-sectional view of a single vertical MOSFET cell 10 in a large array of identical contiguous MOSFET cells according to an embodiment of the invention. The cells shown are approximately 8-11 microns wide. The MOSFET cells 10 may have a breakdown voltage in excess of 600 volts, and the number of cells 10 in an array of the same cell determines the current handling capability, eg 20 amps. The cell array can be strip, quadrilateral, hexagonal or other existing shapes.

[0052] During normal operation, a positive voltage is applied to the bottom drain electrode 12 and a load connected between ground and the top source electrode 14 . When a positive voltage is applied to the conductive gate 16 and is greater than the threshold voltage, the top surface of the P-well 18 is inverted, and electrons accumulate along the vertical sidewalls of the N-layer 20 . The gate extends along the sidewall below the P-well 18 and creates a field plate to a lower electric ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com