Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Low state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

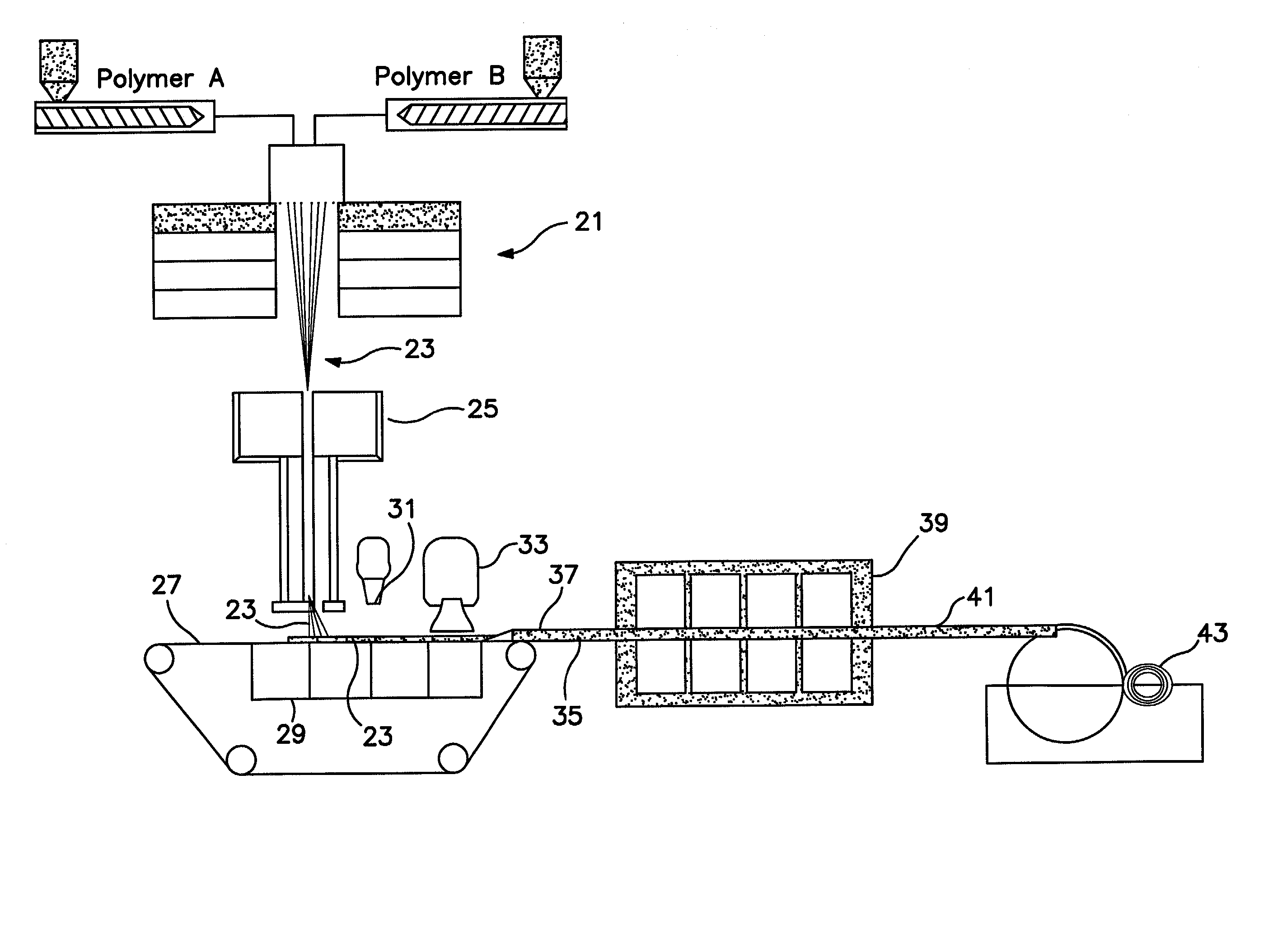

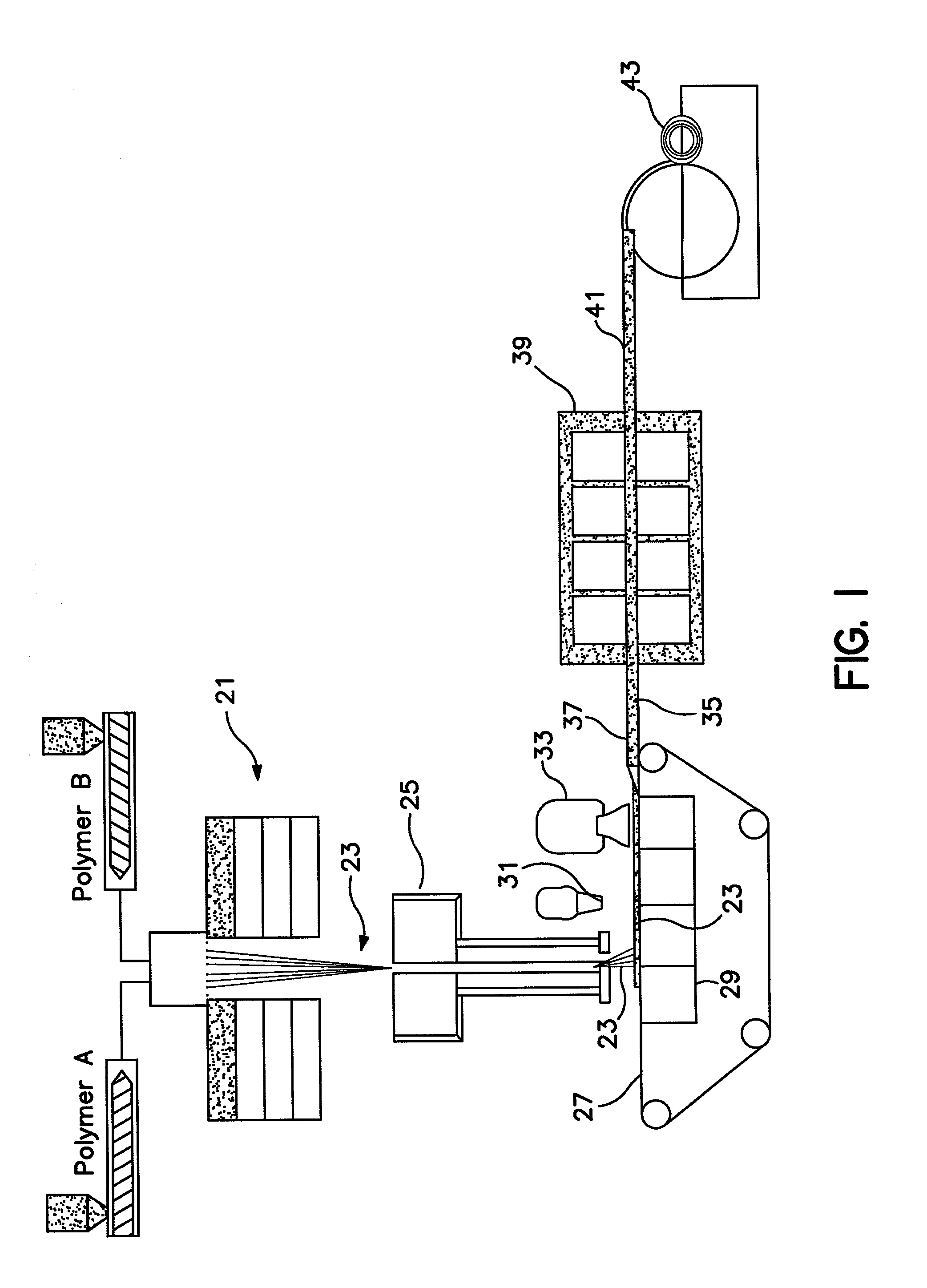

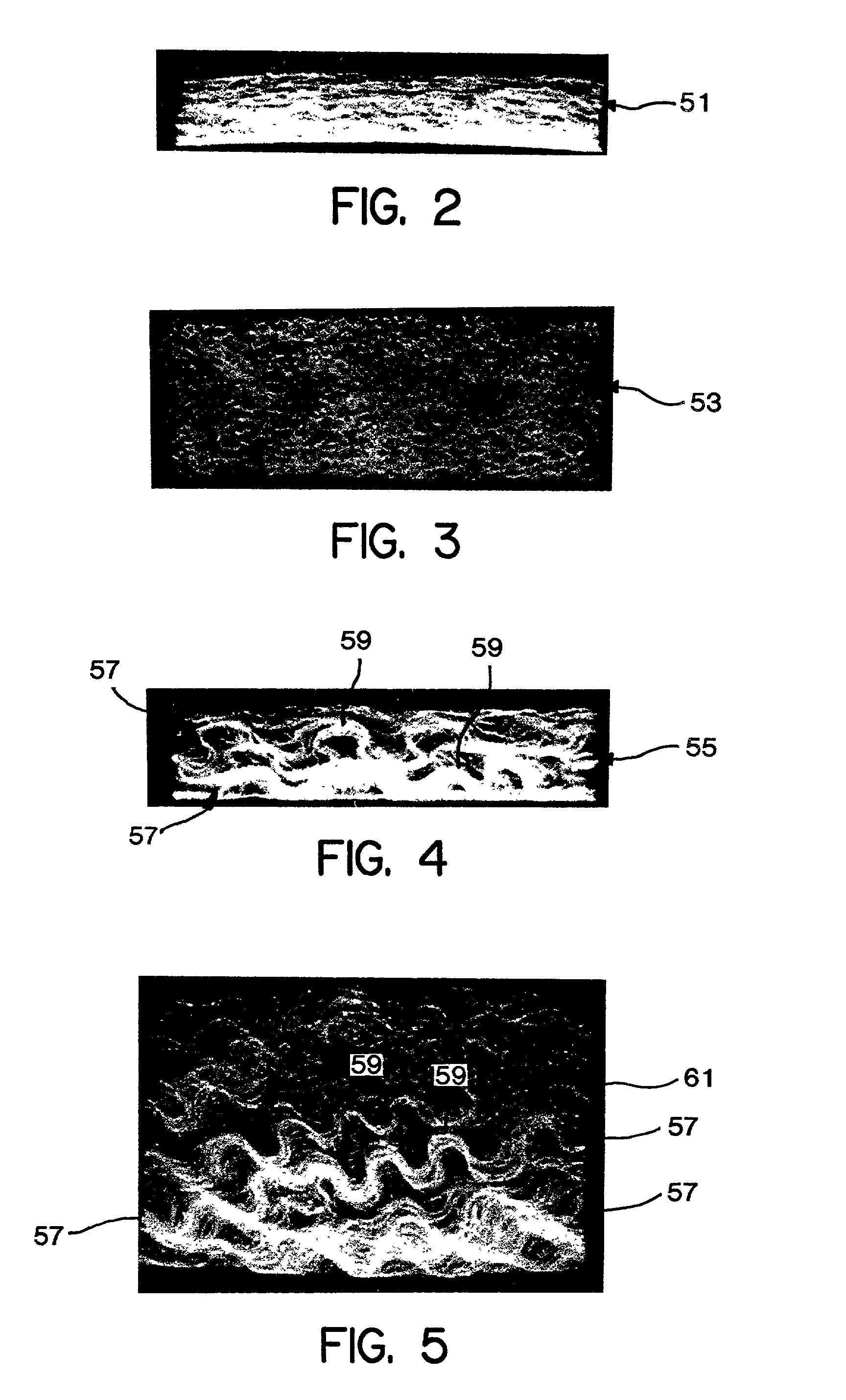

High loft low density nonwoven webs of crimped filaments and methods of making same

InactiveUS20030118816A1Maintain liquidityLow densityWoven fabricsNon-woven fabricsParticulatesPolymer science

High loft, low density nonwoven webs are produced by forming substantially continuous, spunbond, crimped, bicomponent fibers of A / B side by side morphology in an unheated fiber draw unit. The fibers are then heated and cooled in the absence of impeding forces to achieve maximum crimp in the z-direction and produce a web of lofted material. The resultant material is particularly suitable for use as an insulator. Particulates may be added to the webs if desired.

Owner:KIMBERLY-CLARK WORLDWIDE INC

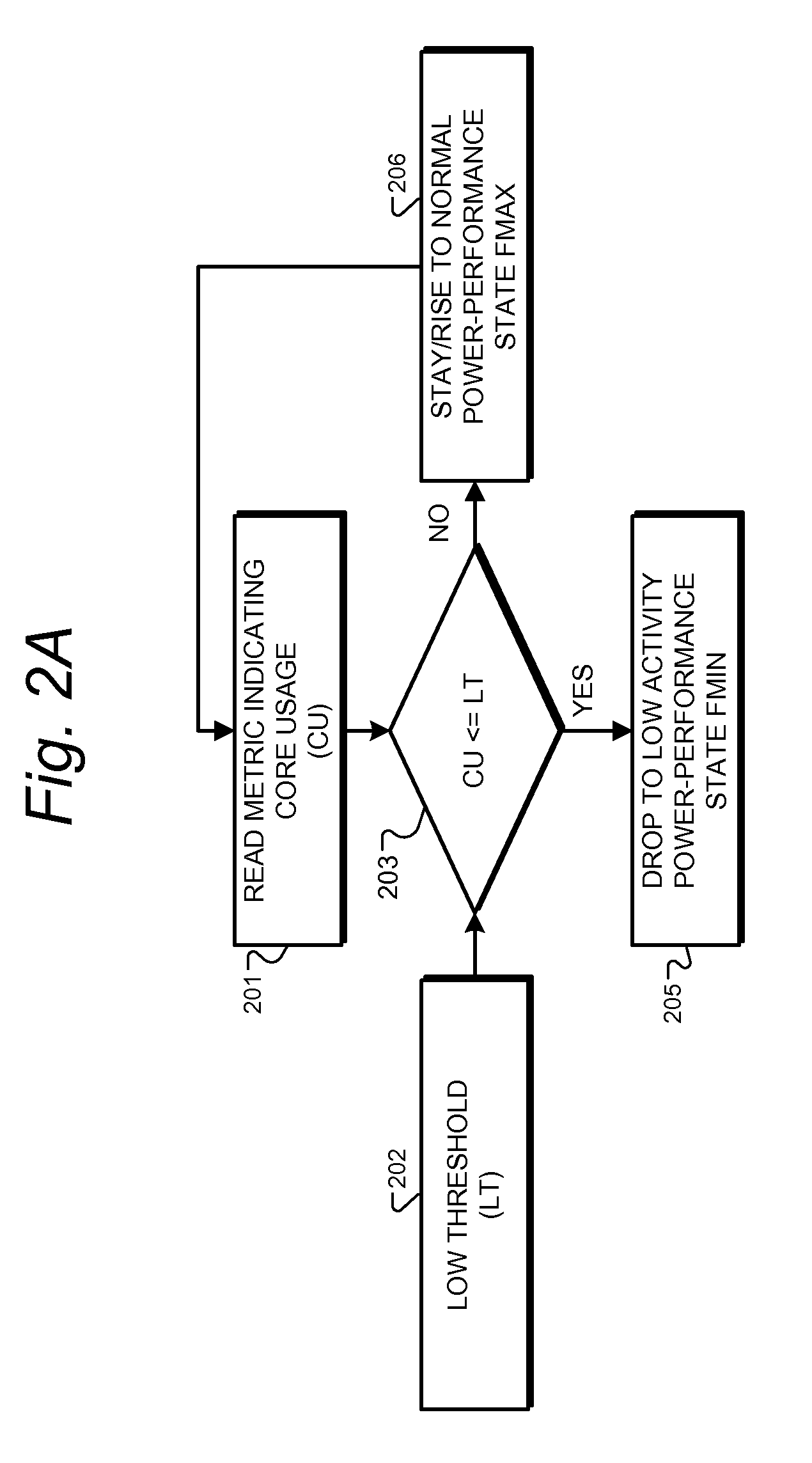

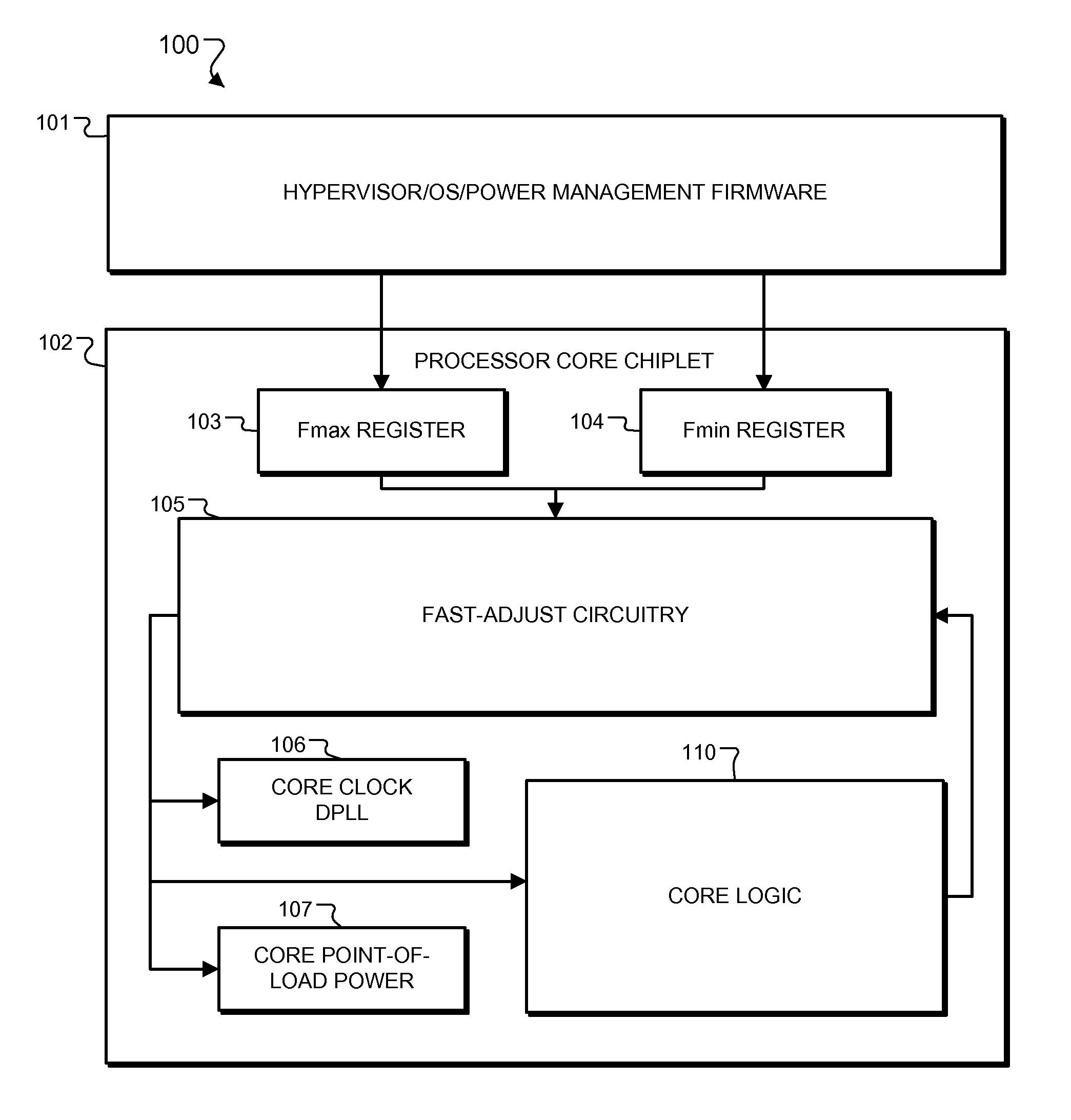

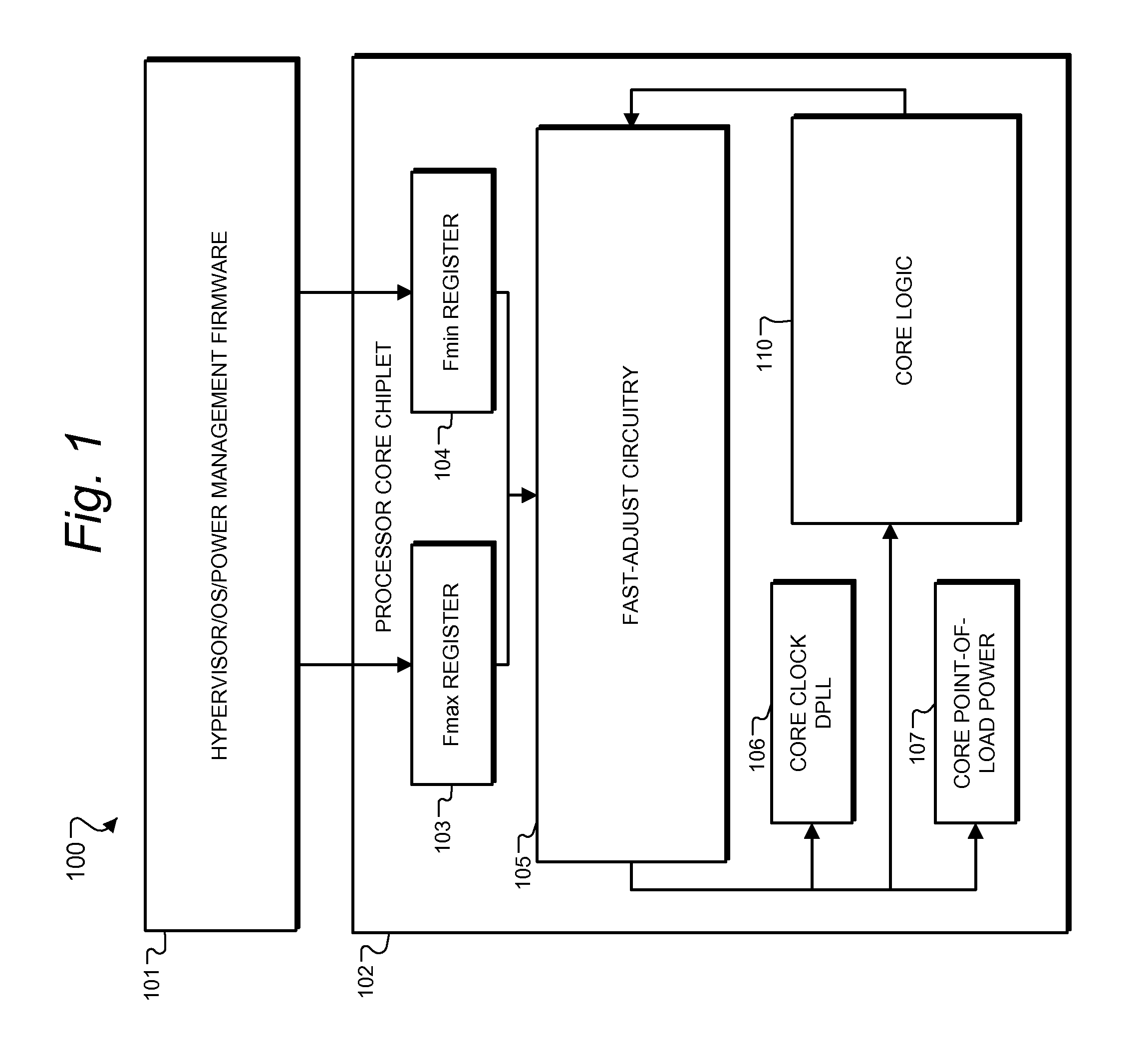

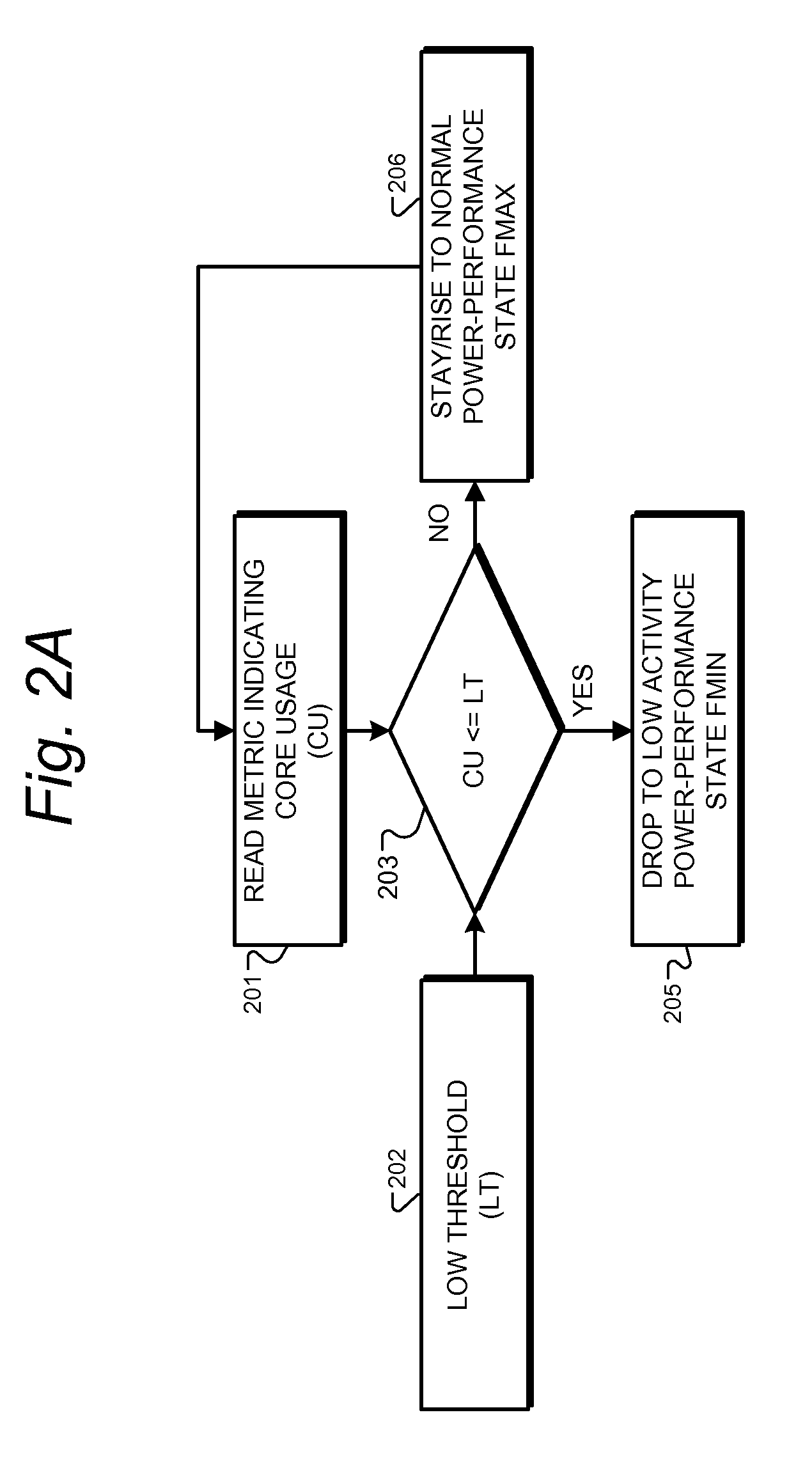

System and Method for Managing the Power-Performance Range of an Application

InactiveUS20100218029A1Improve power efficiencySacrificing performanceEnergy efficient ICTDigital computer detailsOperational systemProcessor register

Semiconductor device circuits and methods are provided for adjusting core processor performance based on usage metrics. Metric detection and adjustment are performed in digital logic hardware guided by registers providing maximum and minimum frequency settings, without intervening input from system software or firmware, thus greatly speeding the processor performance adjustment. Power-performance drivers provide applications or the operating system ability to specify maximum and minimum frequency requirements.

Owner:IBM CORP

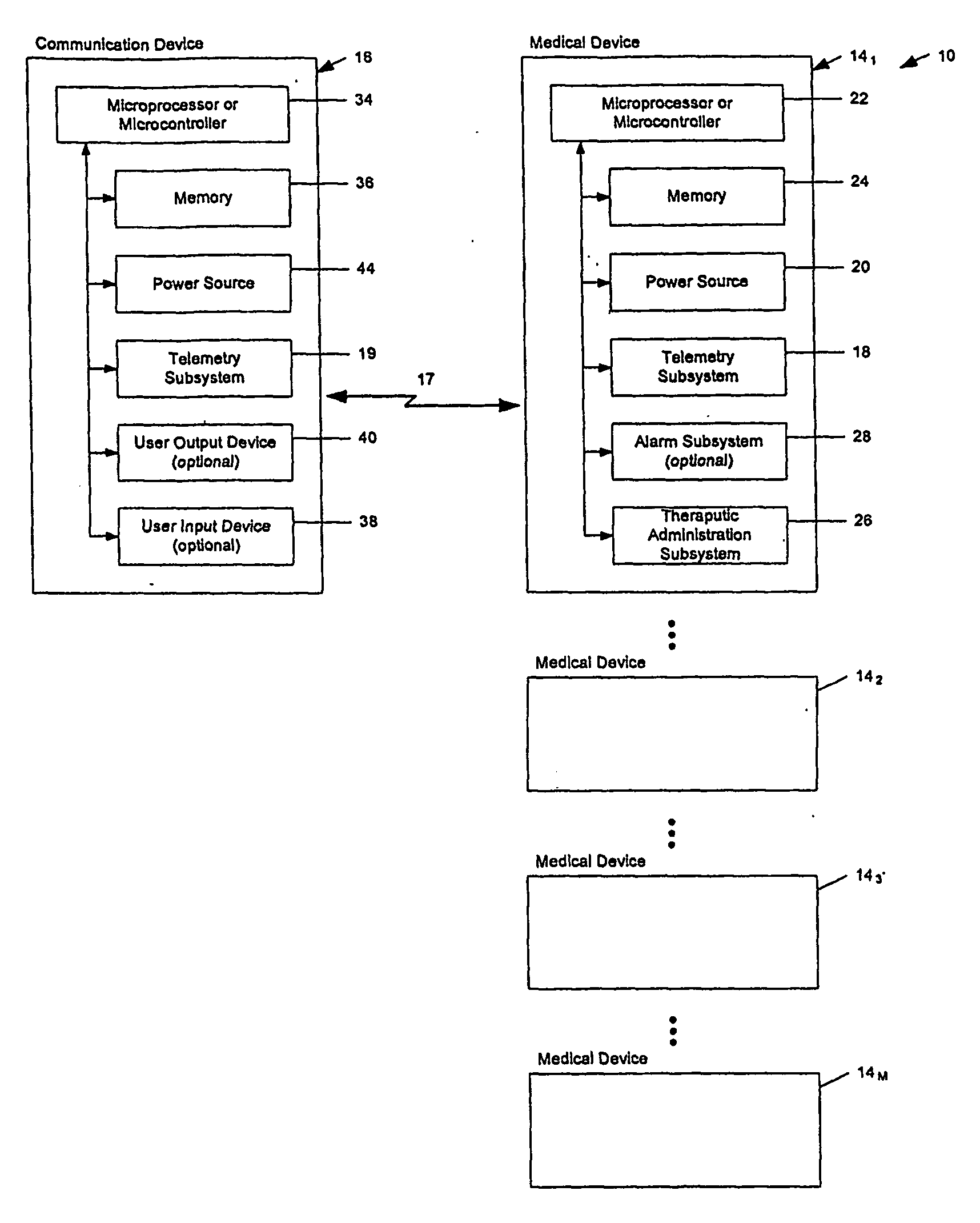

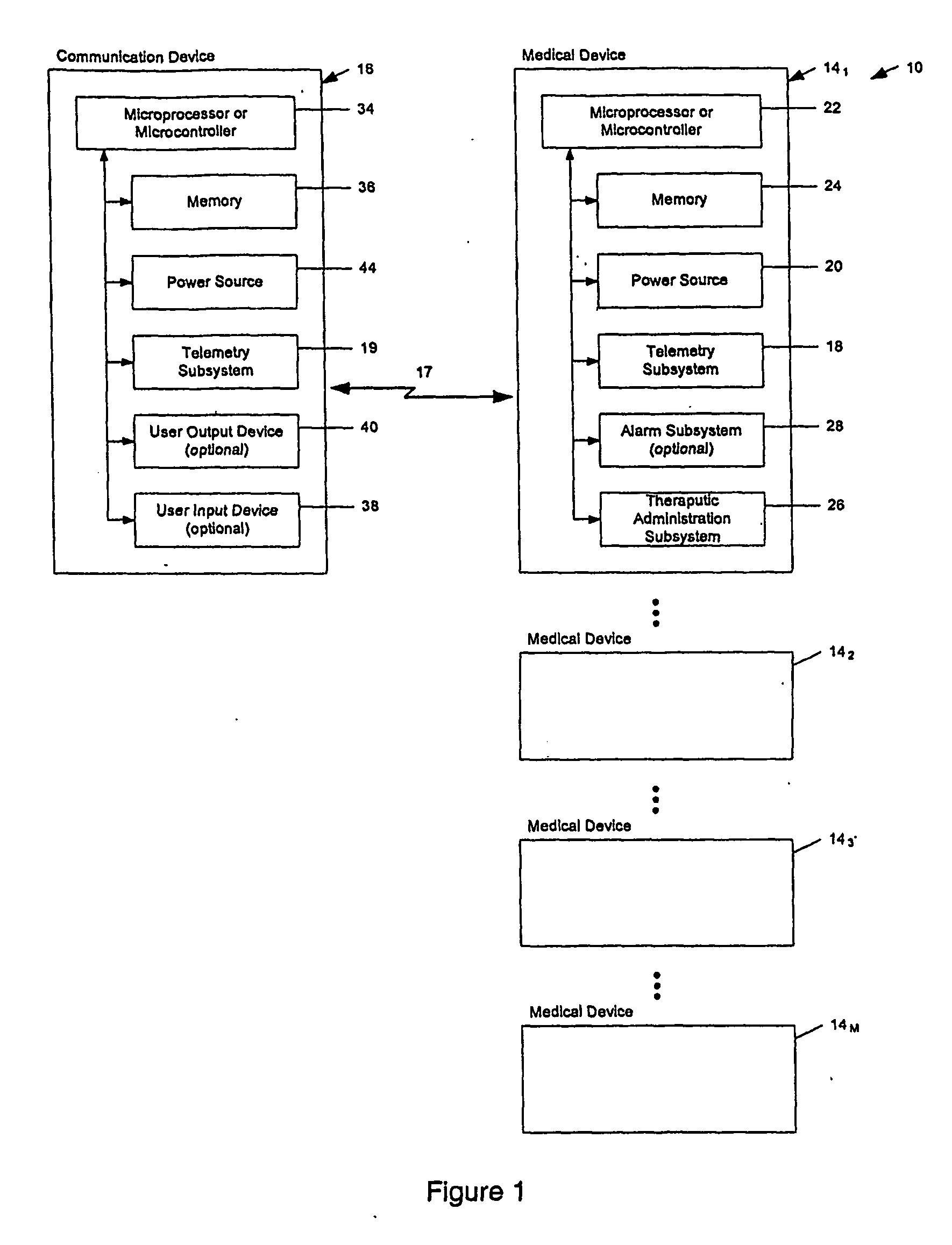

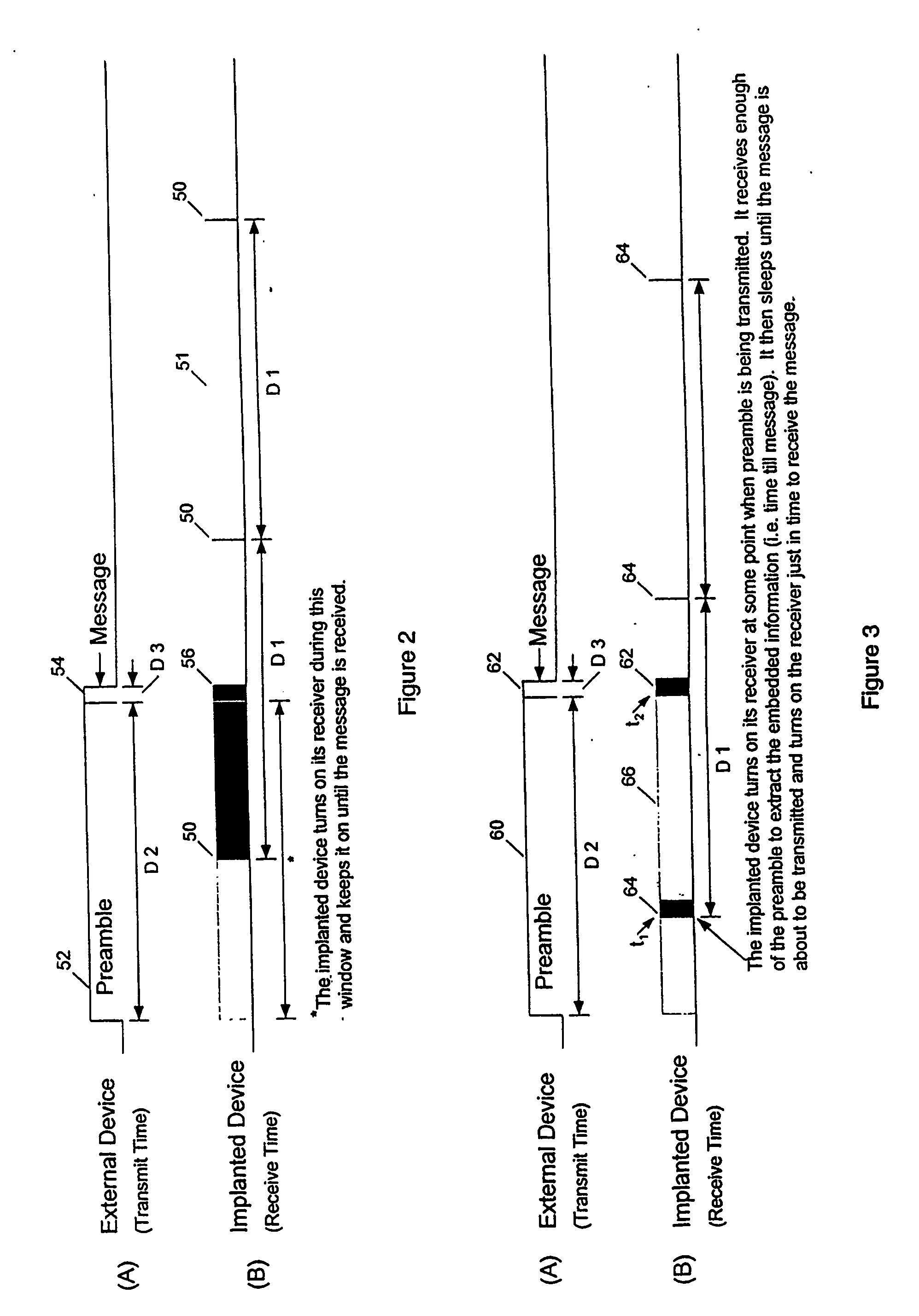

Telemetry method and apparatus for ambulatory medical device

InactiveUS20070167994A1Save energyReducing wake-up frequencyEnergy efficient ICTElectrotherapyTelemetry EquipmentSleep state

A medical system including an implantable battery operated therapy device and an external communication device configured for wireless communication in a manner to minimize energy consumption in the implanted device. The medical device is configured to wake periodically from a sleep state to look for a message preamble from the communication device. The preamble is formatted to include control information, e.g., information indicating the time of receipt of the forthcoming message.

Owner:MEDICAL RES PRODS A +1

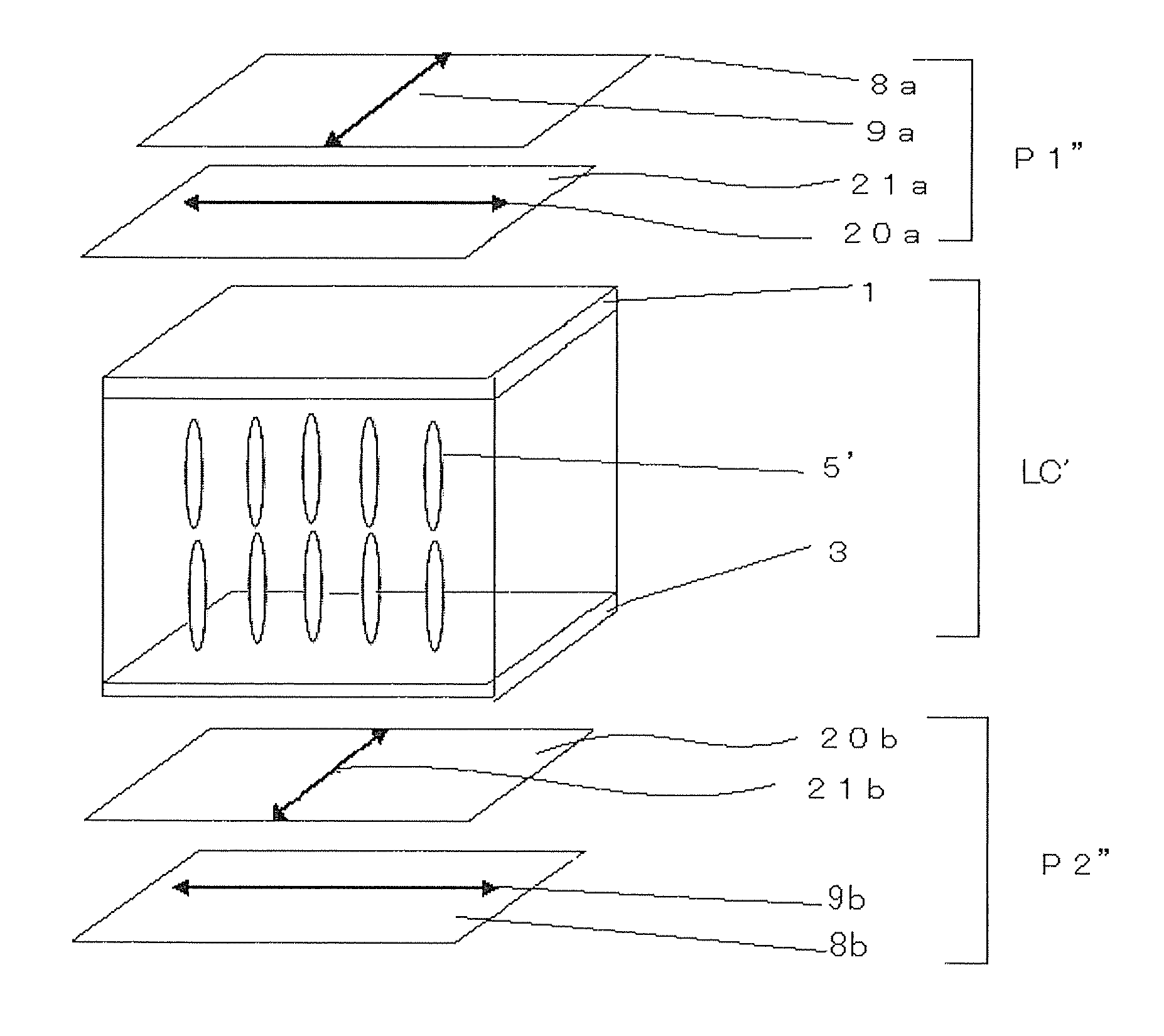

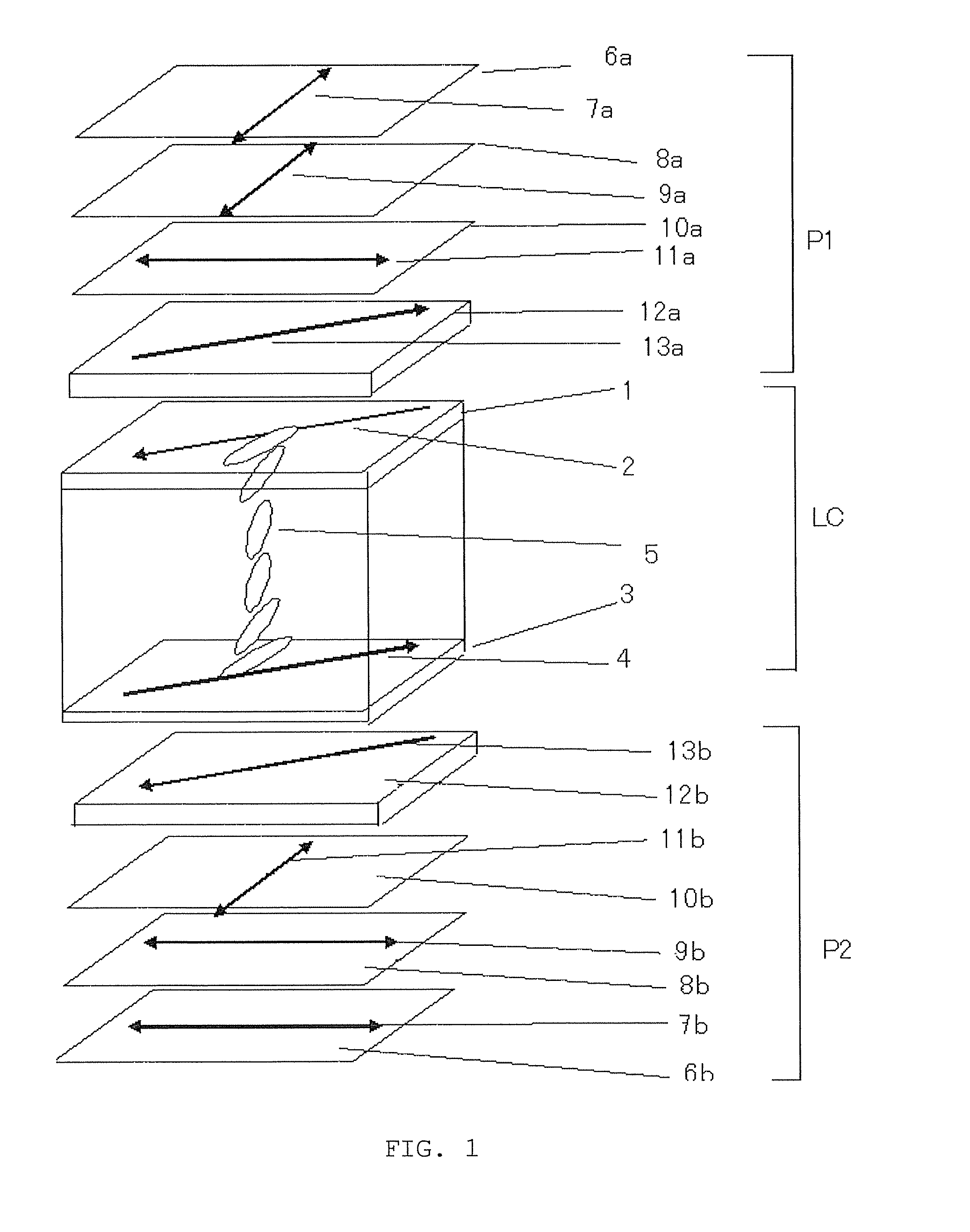

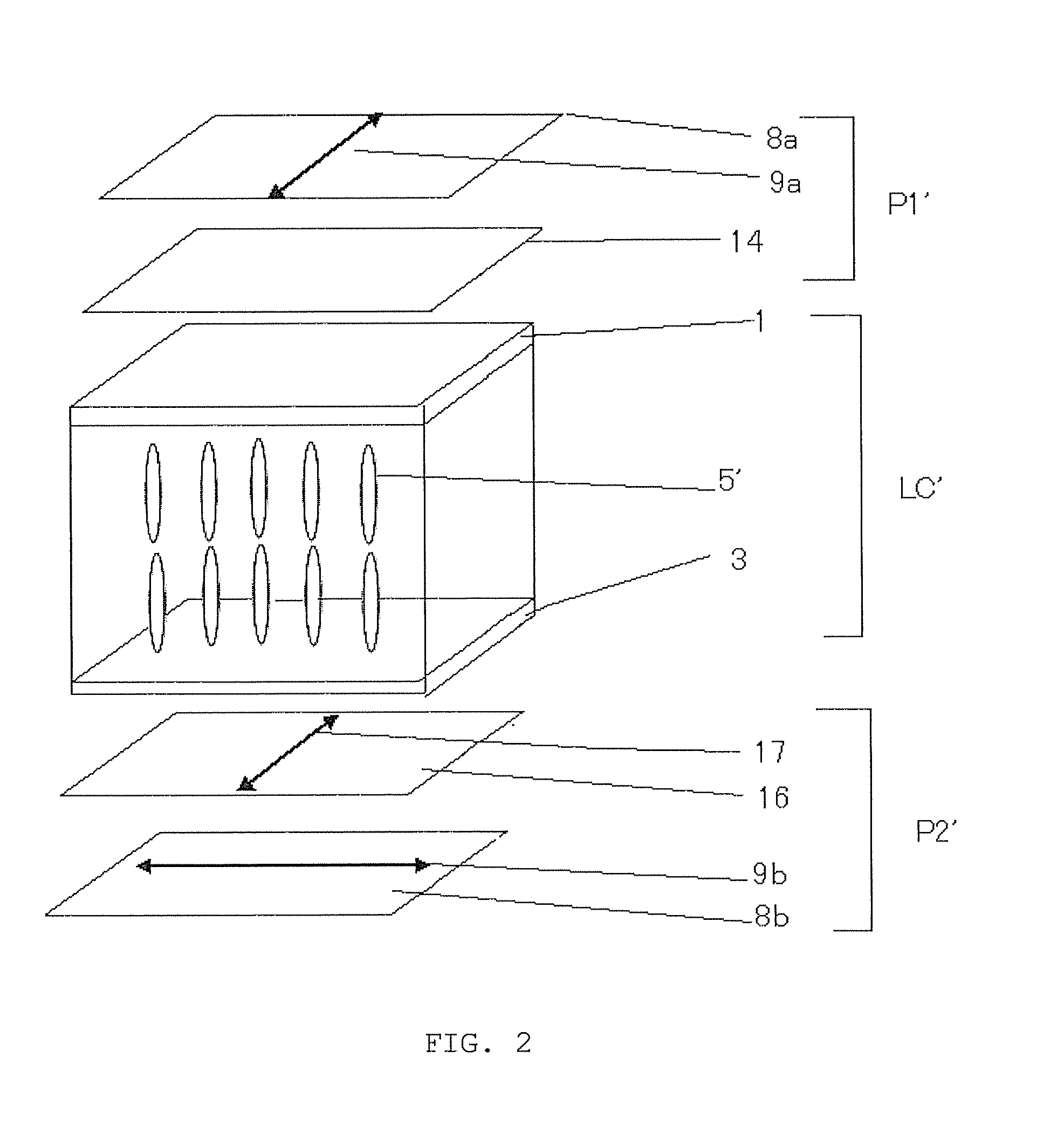

Liquid Crystal Display Device

InactiveUS20080158488A1Low transmissivity stateHigh color reproductionLiquid crystal compositionsNon-linear opticsPolarizerWavelength selectivity

A liquid crystal display device comprising at least a liquid crystal cell, and a polarizing plate (a first polarizing plate) disposed on at least one side of the outsides of the liquid crystal cell, wherein the liquid crystal cell comprises a pair of substrates which face each other, an electrode disposed on at least one of the pair of substrates, a liquid crystal layer sandwiched between the pair of substrates, and at least three pixel regions, a color filter showing wavelength selectivity in transmissivity is disposed on each of the at least three pixel regions is disclosed. In the liquid crystal display device, the thicknesses of the liquid crystal layers corresponding to a color filter showing a maximum transmissivity at a main wavelength λ1, a color filter showing a maximum transmissivity at a main wavelength λ2, and a color filter showing a maximum transmissivity at a main wavelength λ3, provided that λ1, λ2, and λ3 (unit: nm) are in an order from the smaller one, are d1, d2 and d3 (unit: nm) respectively, and Relation (1) is satisfied:d2<d3. : (1)

Owner:FUJIFILM CORP

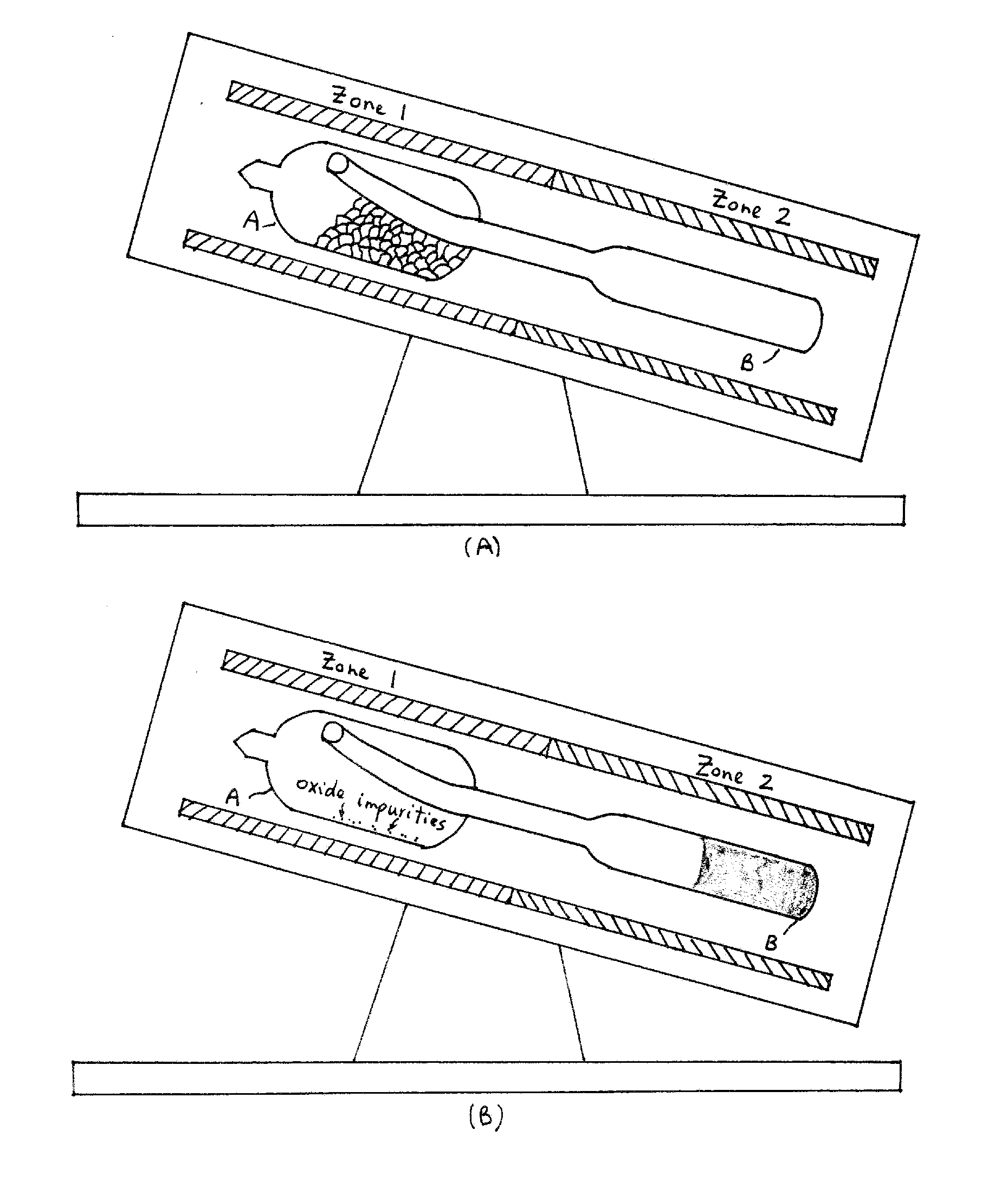

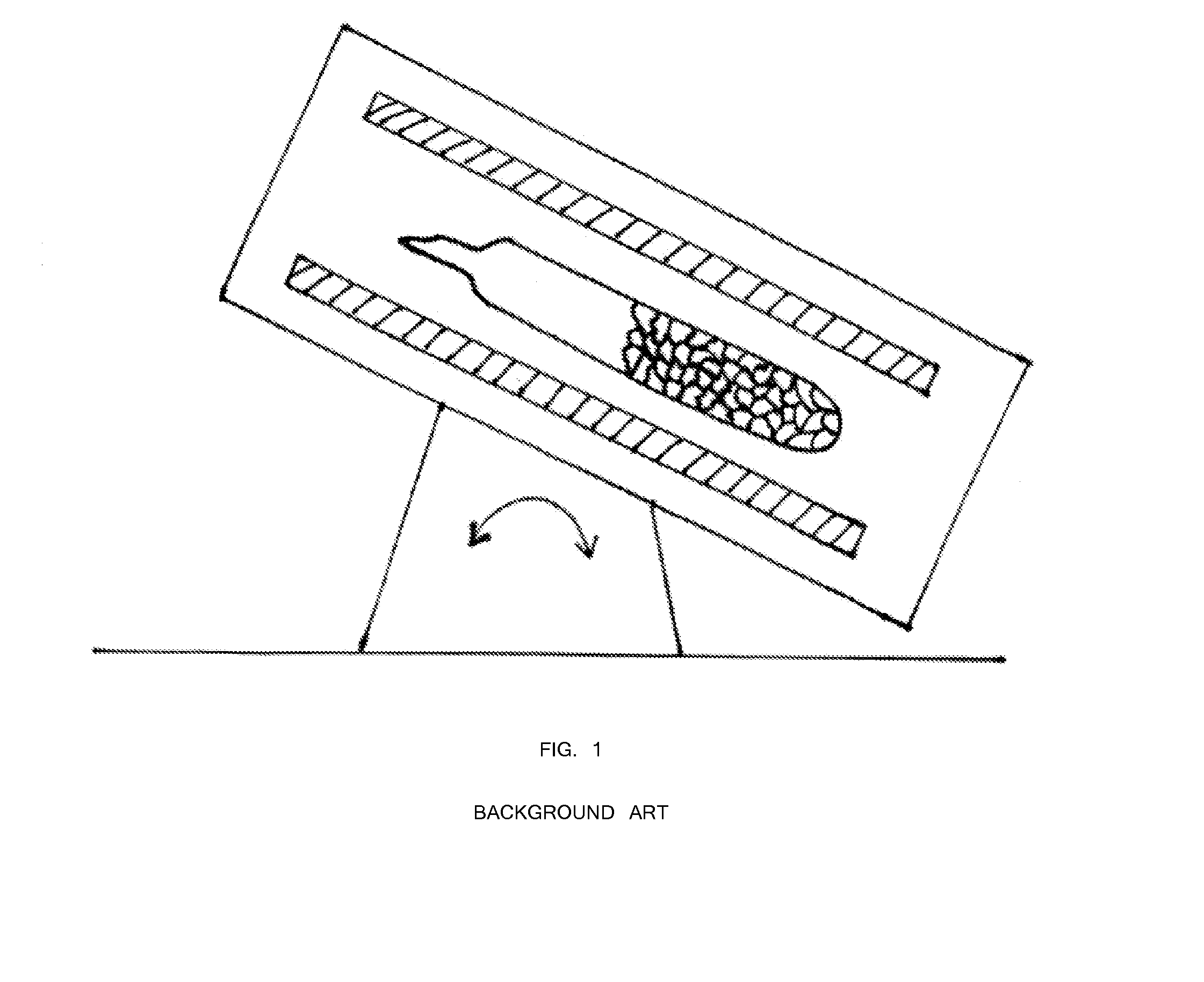

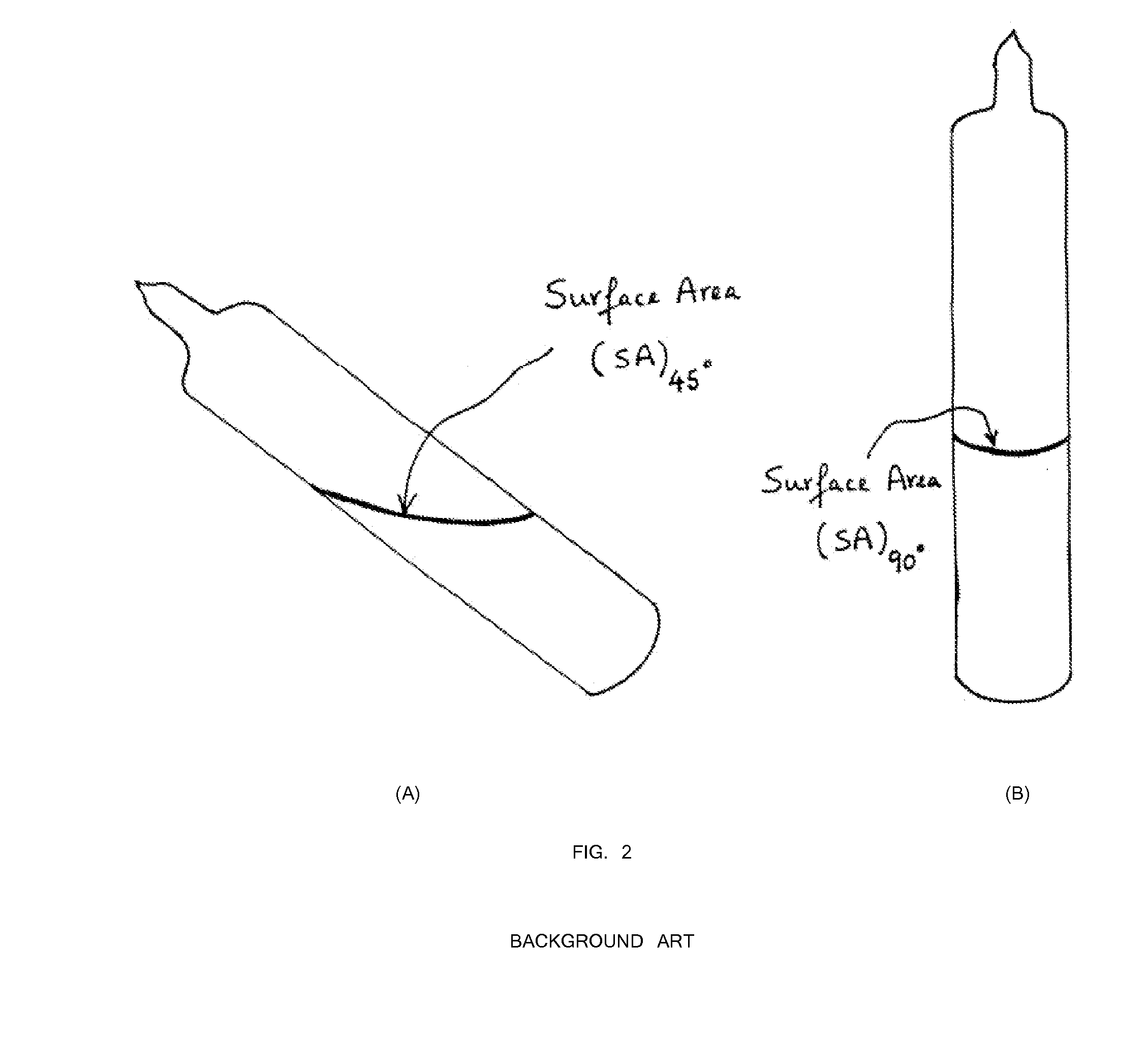

Manufacturing process for chalcogenide glasses

InactiveUS20100022378A1Minimize stressLow energy and stable statePot furnacesGlass furnace apparatusDistillationControl manner

The present invention is generally directed to a method of making chalcogenide glasses including holding the melt in a vertical furnace to promote homogenization and mixing; slow cooling the melt at less than 10° C. per minute; and sequentially quenching the melt from the top down in a controlled manner. Additionally, the present invention provides for the materials produced by such method. The present invention is also directed to a process for removing oxygen and hydrogen impurities from chalcogenide glass components using dynamic distillation.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

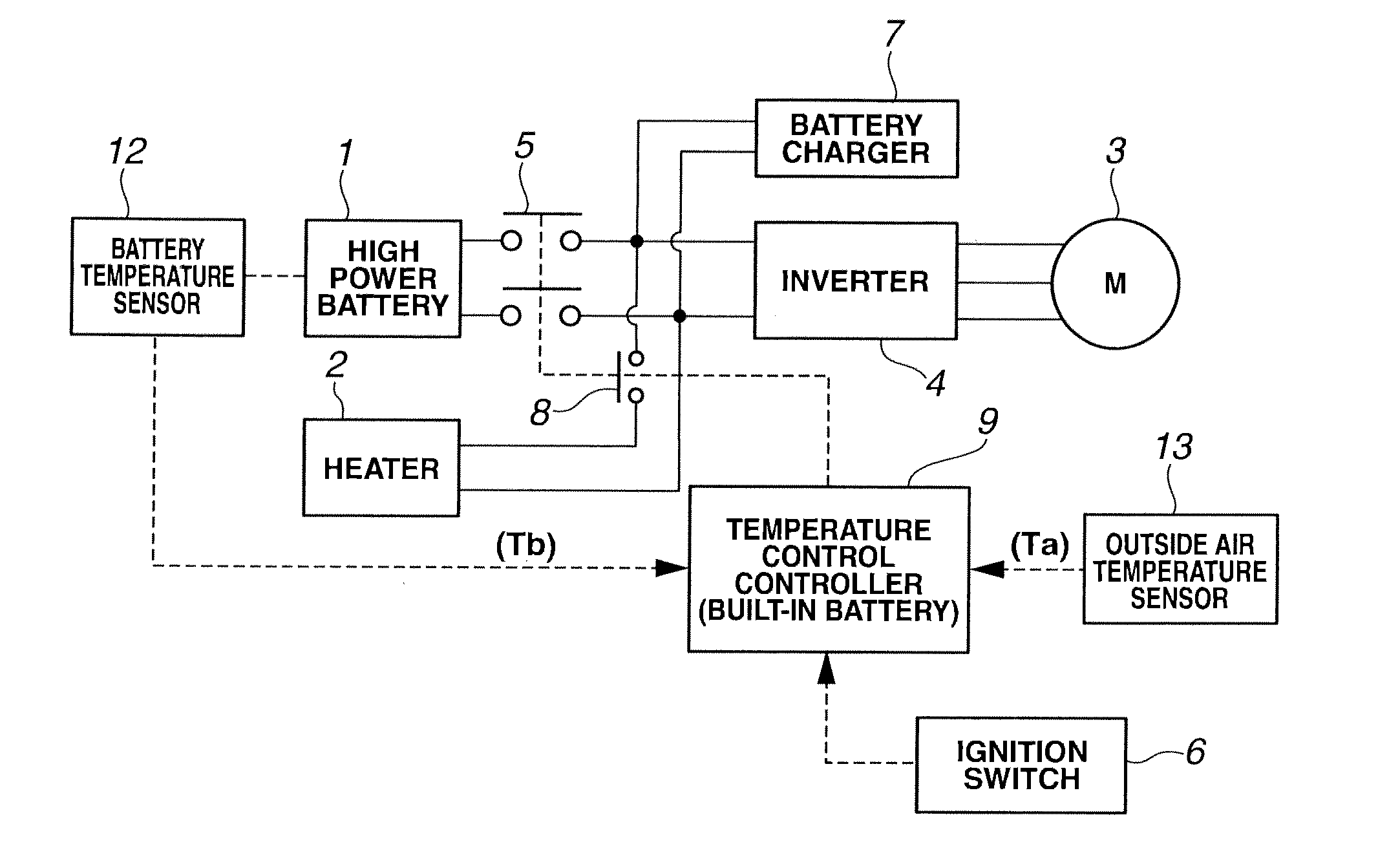

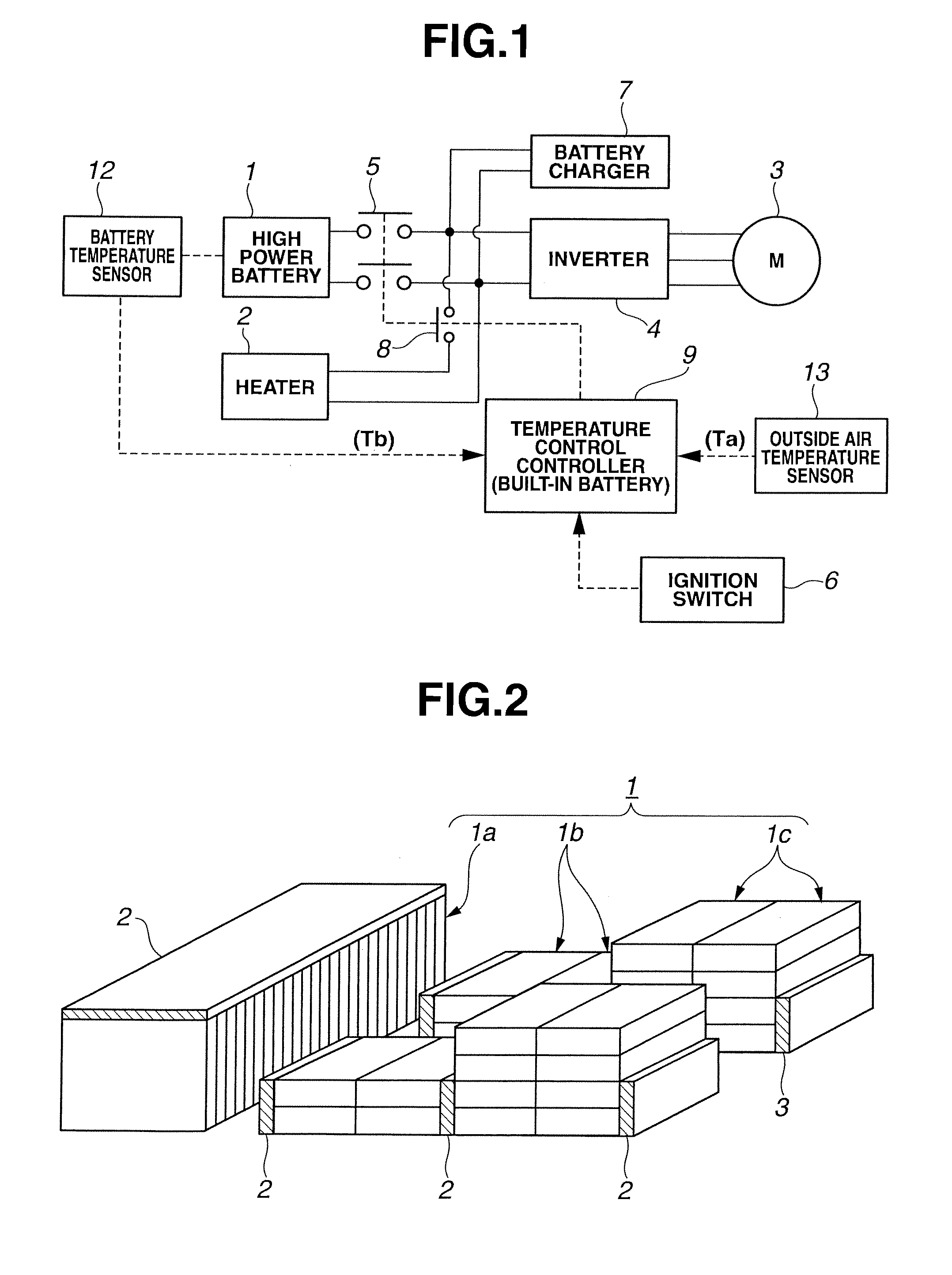

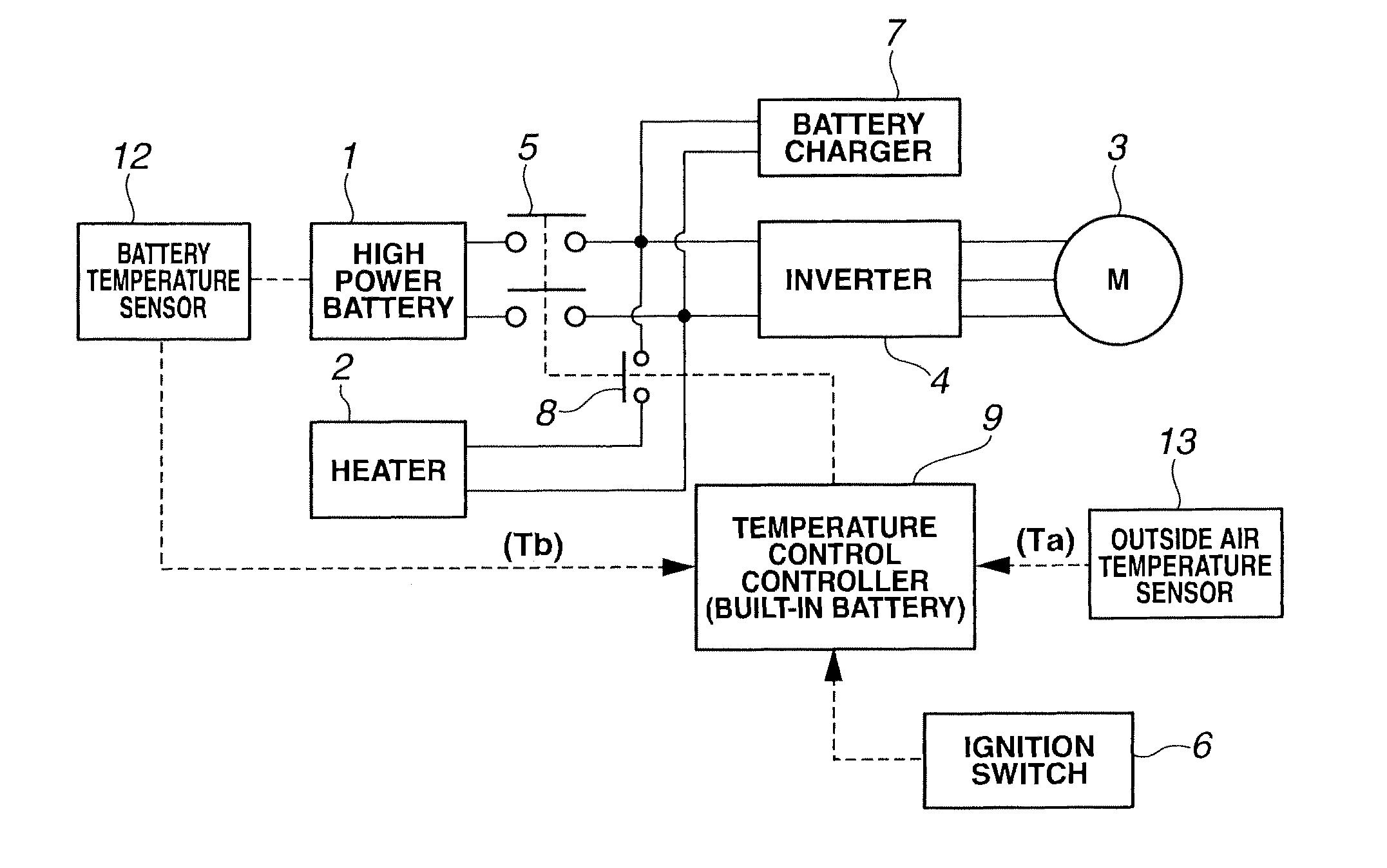

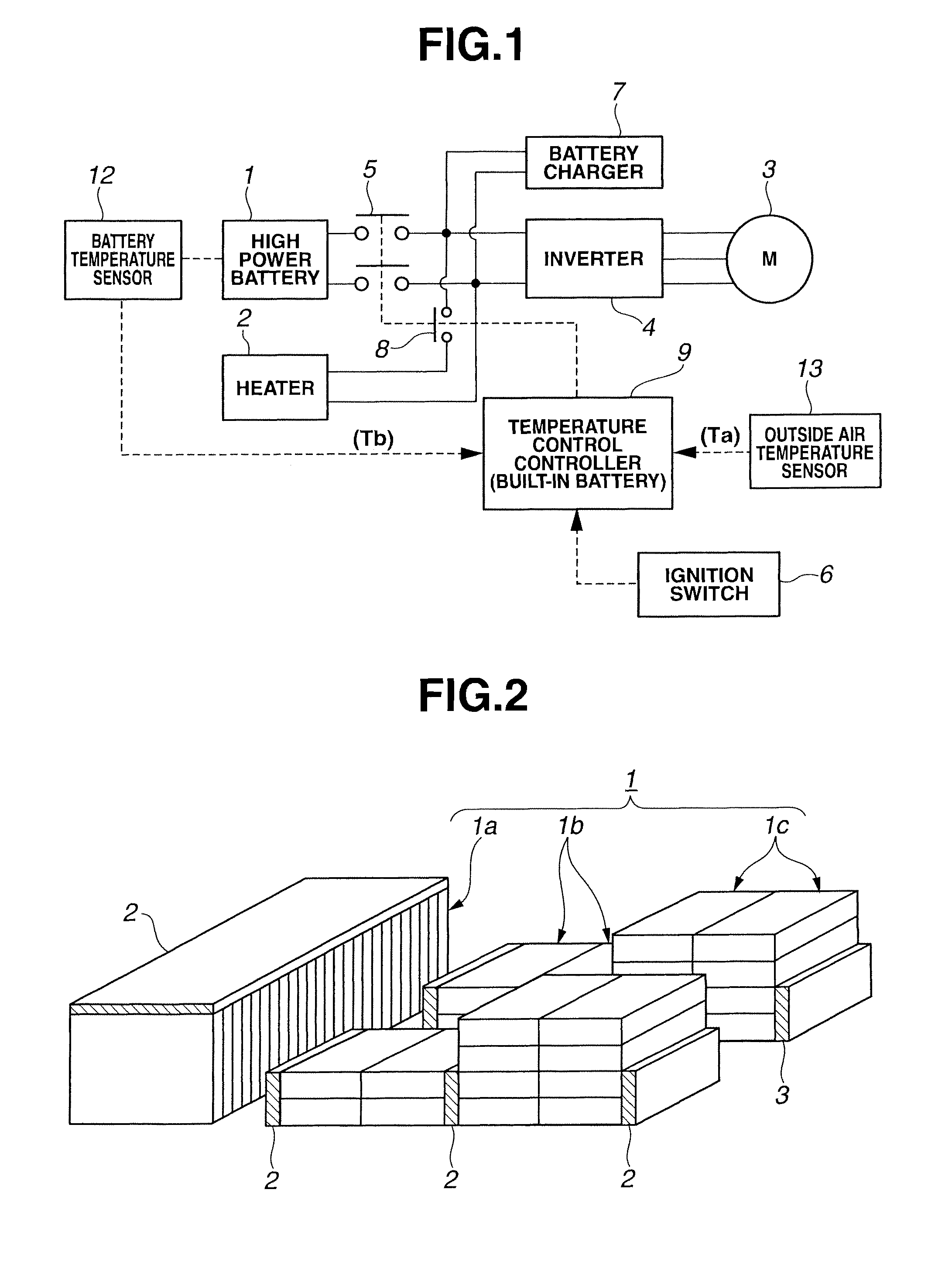

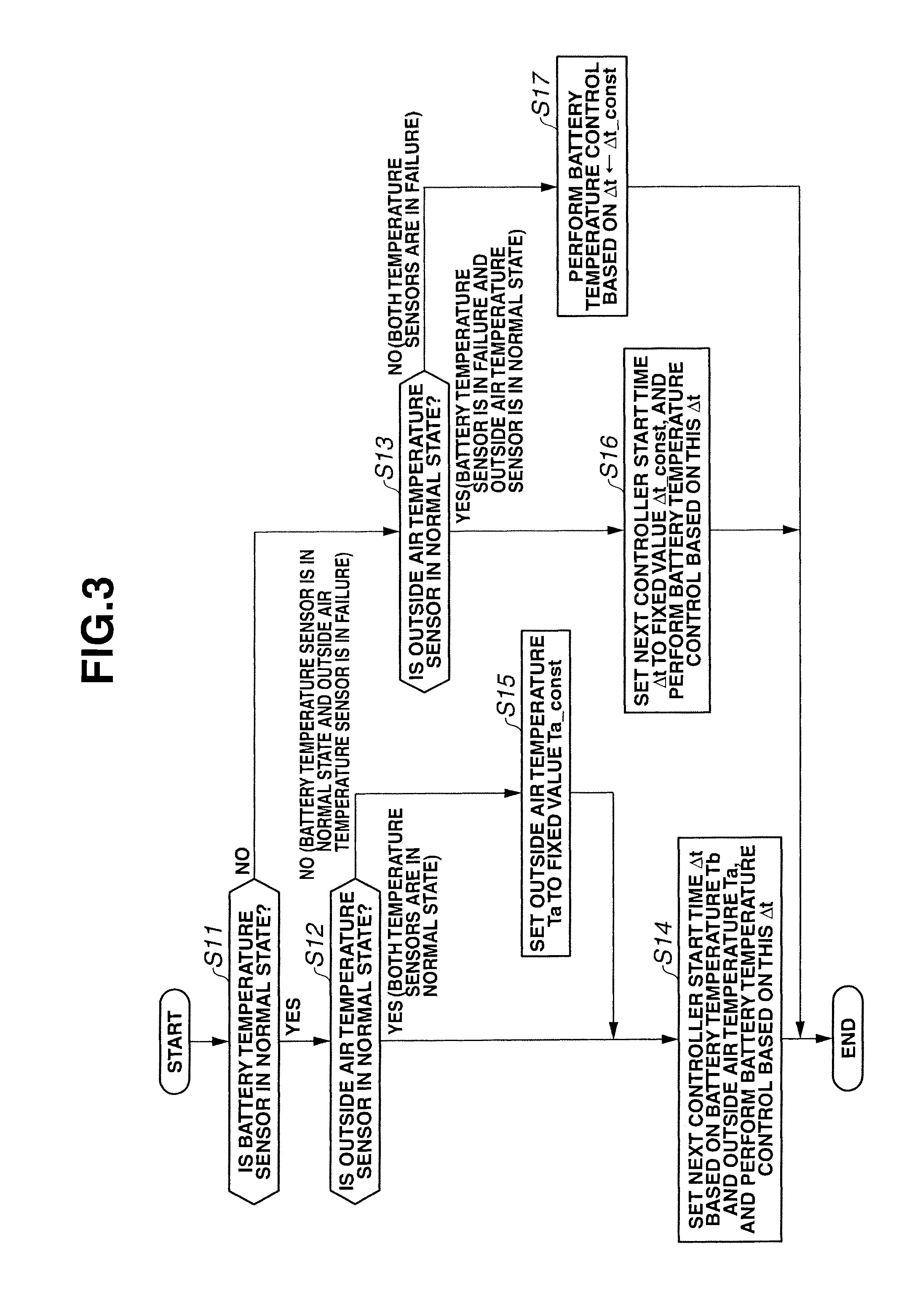

Battery temperature control device

ActiveUS20130183554A1Low stateCircuit monitoring/indicationIndicating/monitoring circuitsTemperature controlElectrical battery

Even when temperature sensors (12, 13) used in a device for warming a battery (1) being not in use by using a battery-driven heater (2) have failed, the battery (1) is prevented from freezing. Based on a battery temperature (Tb) and an outside air temperature (Ta), times (Δt1 to Δt8) during which Tb will decrease down to a warming start temperature (Tb_start) are each set to the next controller startup time (Δt). A controller (9) is started up every Δt, at t2, t3, and t4, and checks whether Tb<Tb_start is satisfied or not. At t4 when Tb<Tb_start is satisfied, a heater (2) is battery-driven to warm the battery (1). After t0 when the outside air temperature sensor (13) fails, the outside air temperature (Ta) is set to a fixed value (Ta_const) and based on this Ta=Ta_const and the battery temperature (Tb), the above control is repeated. Accordingly, it is unlikely that the temperature information (Ta) from the outside air temperature sensor (13) that is at fault causes Δt to become extremely long like ∞, so that it is avoided that the heater (2) cannot be operated because the controller (9) cannot be started up and the battery (1) freezes.

Owner:NISSAN MOTOR CO LTD

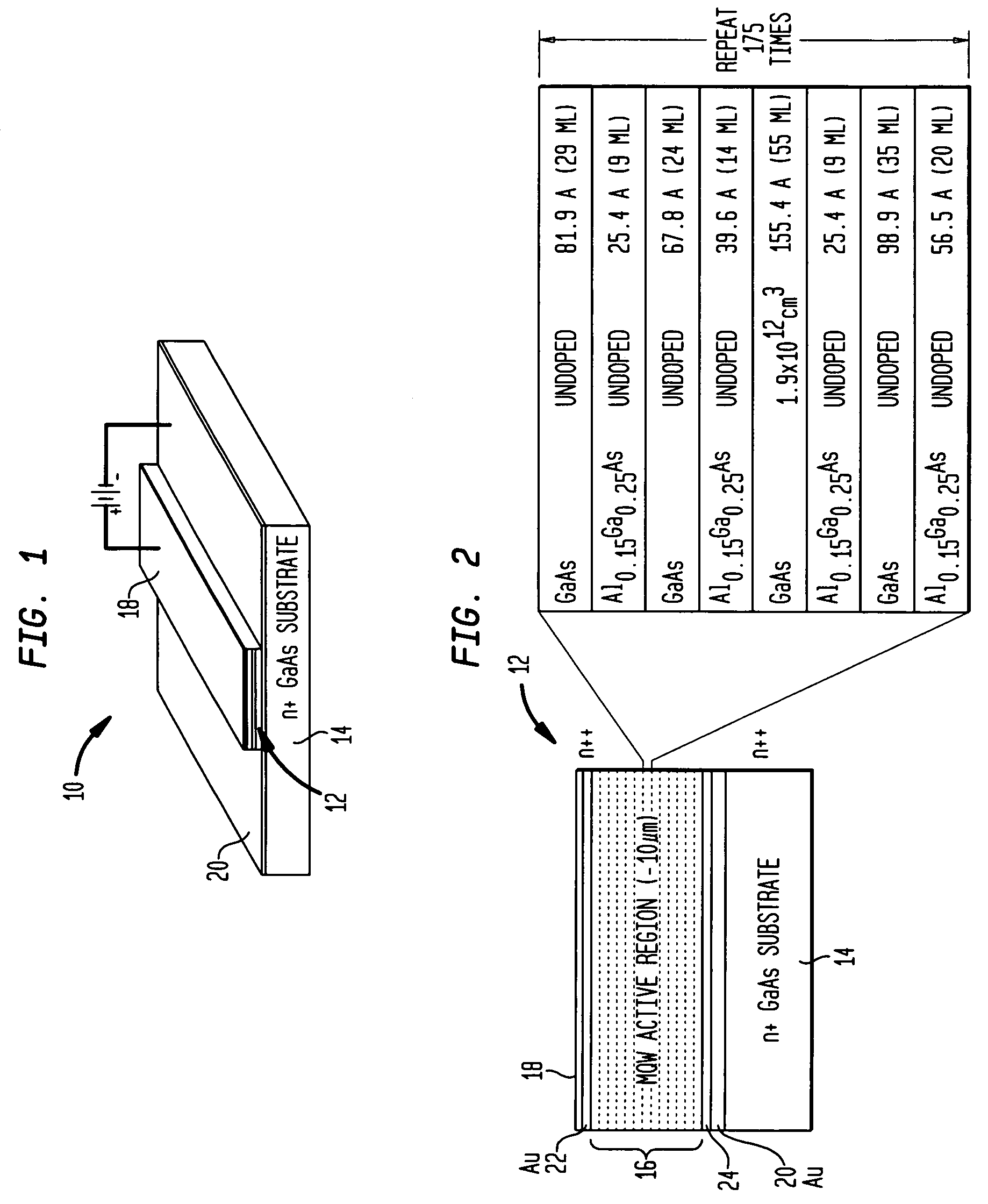

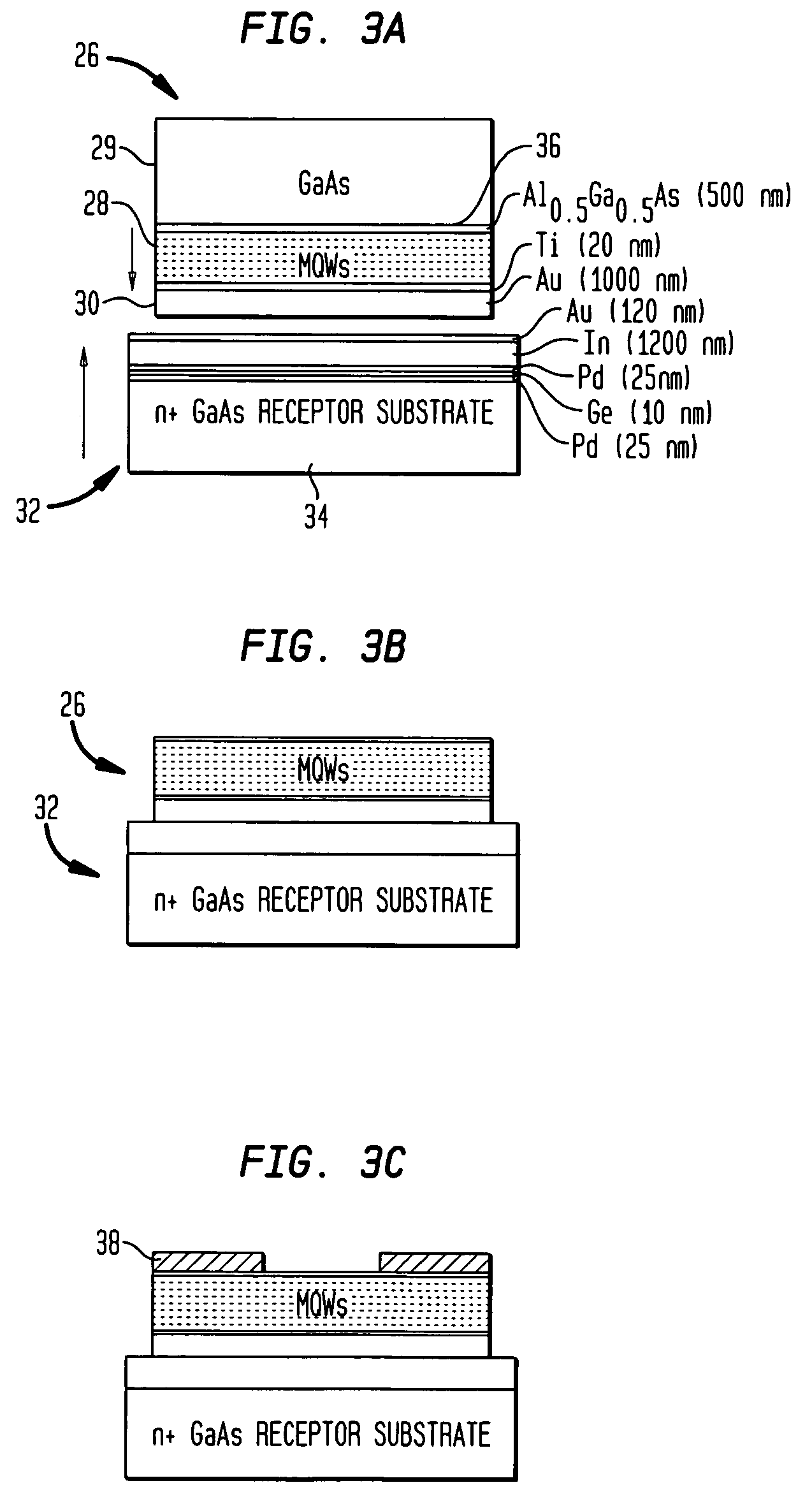

Terahertz lasers and amplifiers based on resonant optical phonon scattering to achieve population inversion

ActiveUS7158545B2Promote generationHigh selectivityOptical wave guidanceLaser using scattering effectsAudio power amplifierOptical frequencies

The present invention provides quantum cascade lasers and amplifier that operate in a frequency range of about 1 Terahertz to about 10 Terahertz. In one aspect, a quantum cascade laser of the invention includes a semiconductor heterostructure that provides a plurality of lasing modules connected in series. Each lasing module includes a plurality of quantum well structure that collectively generate at least an upper lasing state, a lower lasing state, and a relaxation state such that the upper and the lower lasing states are separated by an energy corresponding to an optical frequency in a range of about 1 to about 10 Terahertz. The lower lasing state is selectively depopulated via resonant LO-phonon scattering of electrons into the relaxation state.

Owner:MASSACHUSETTS INST OF TECH

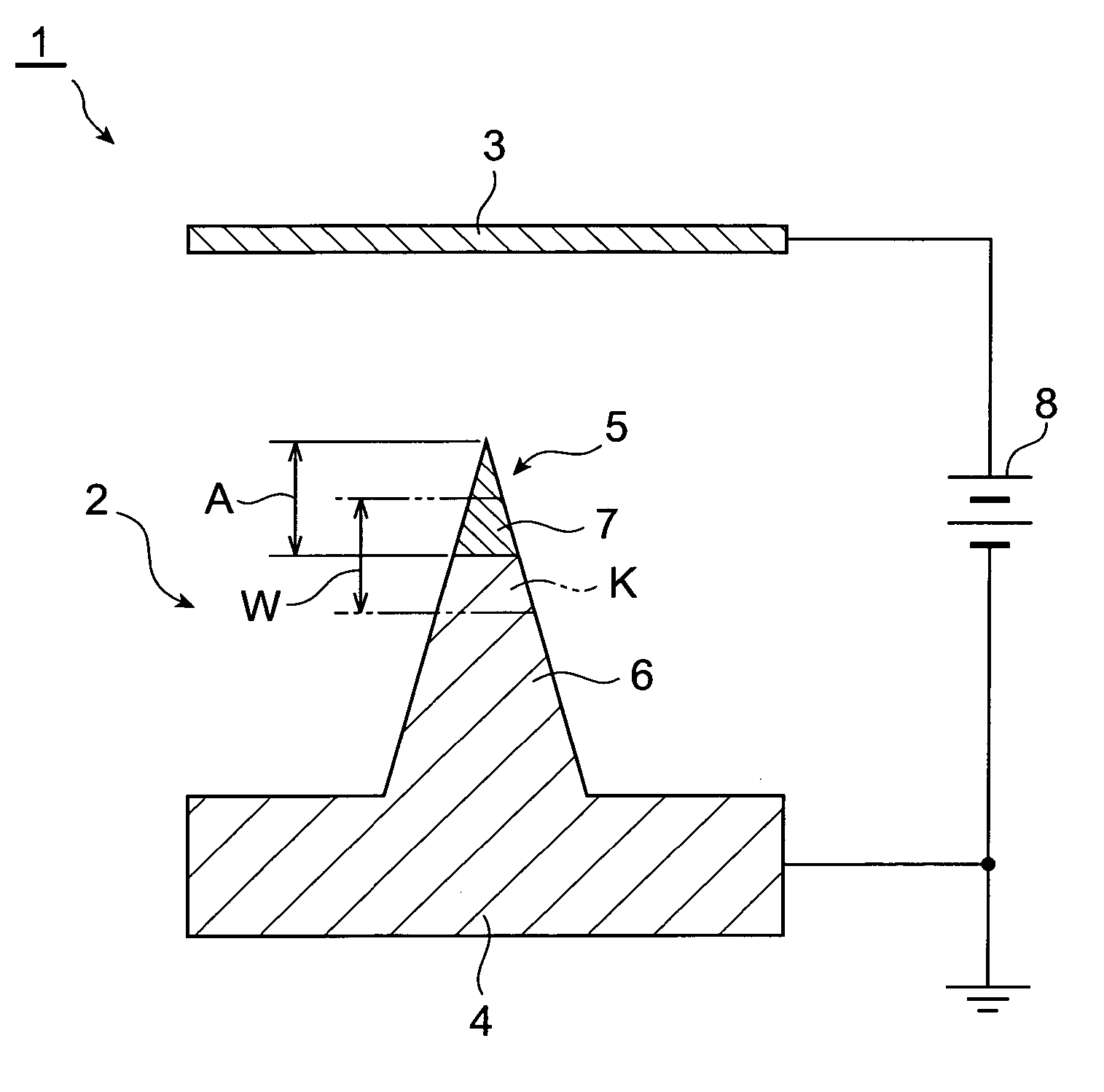

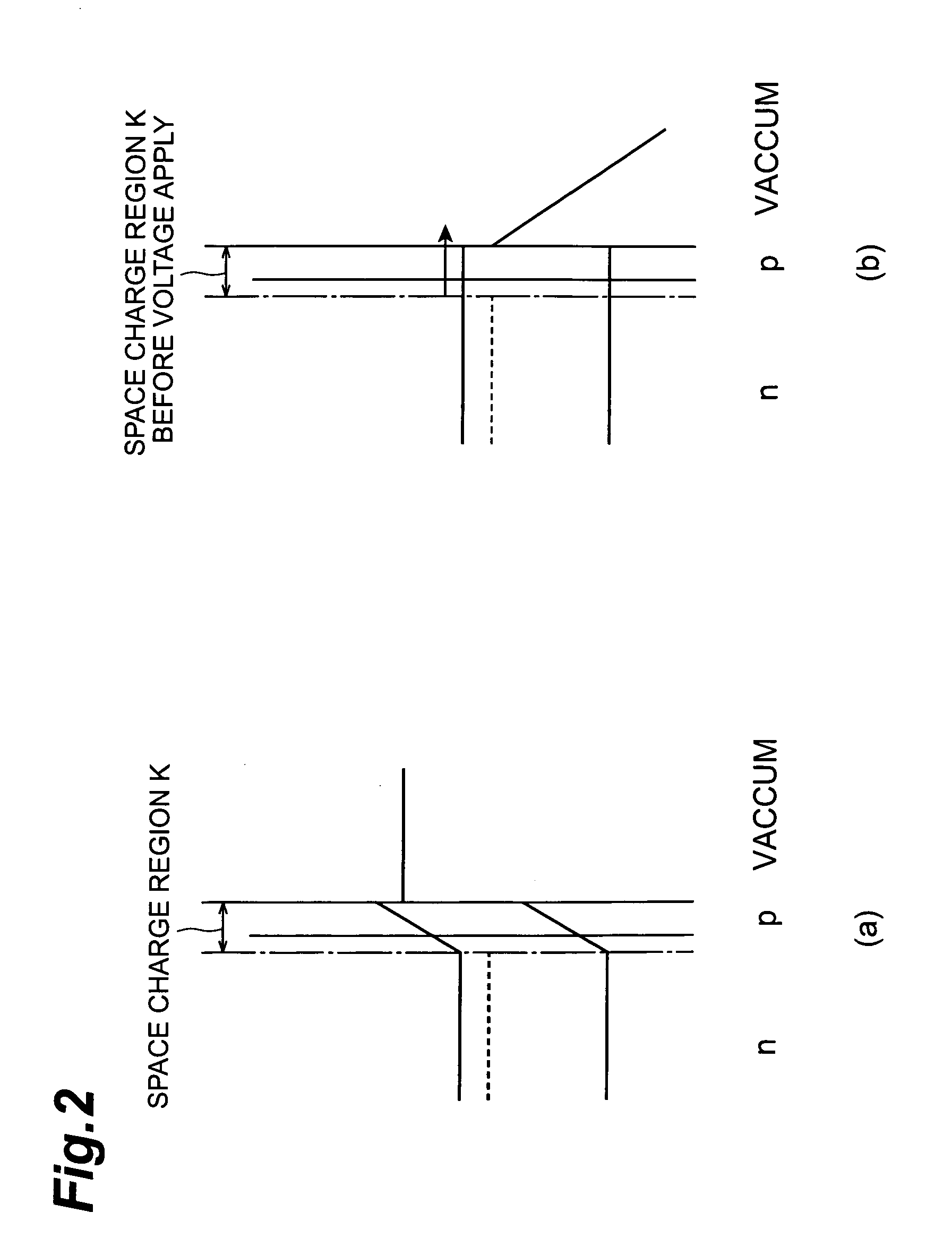

Electron emitting device

InactiveUS20050133735A1Low energy bandLow stateDischarge tube luminescnet screensLamp detailsElectronAtomic physics

The present invention relates to an electron emitting device having a structure for efficiently emitting electrons. The electron emitting device has a substrate comprised of an n-type diamond, and a pointed projection provided on the substrate. The projection comprises a base provided on the substrate side, and an electron emission portion provided on the base and emitting electrons from the tip thereof. The base is comprised of an n-type diamond. The electron emission portion is comprised of a p-type diamond. The length from the tip of the projection (electron emission portion) to the interface between the base and the electron emission portion is preferably 100 nm or less.

Owner:SUMITOMO ELECTRIC IND LTD

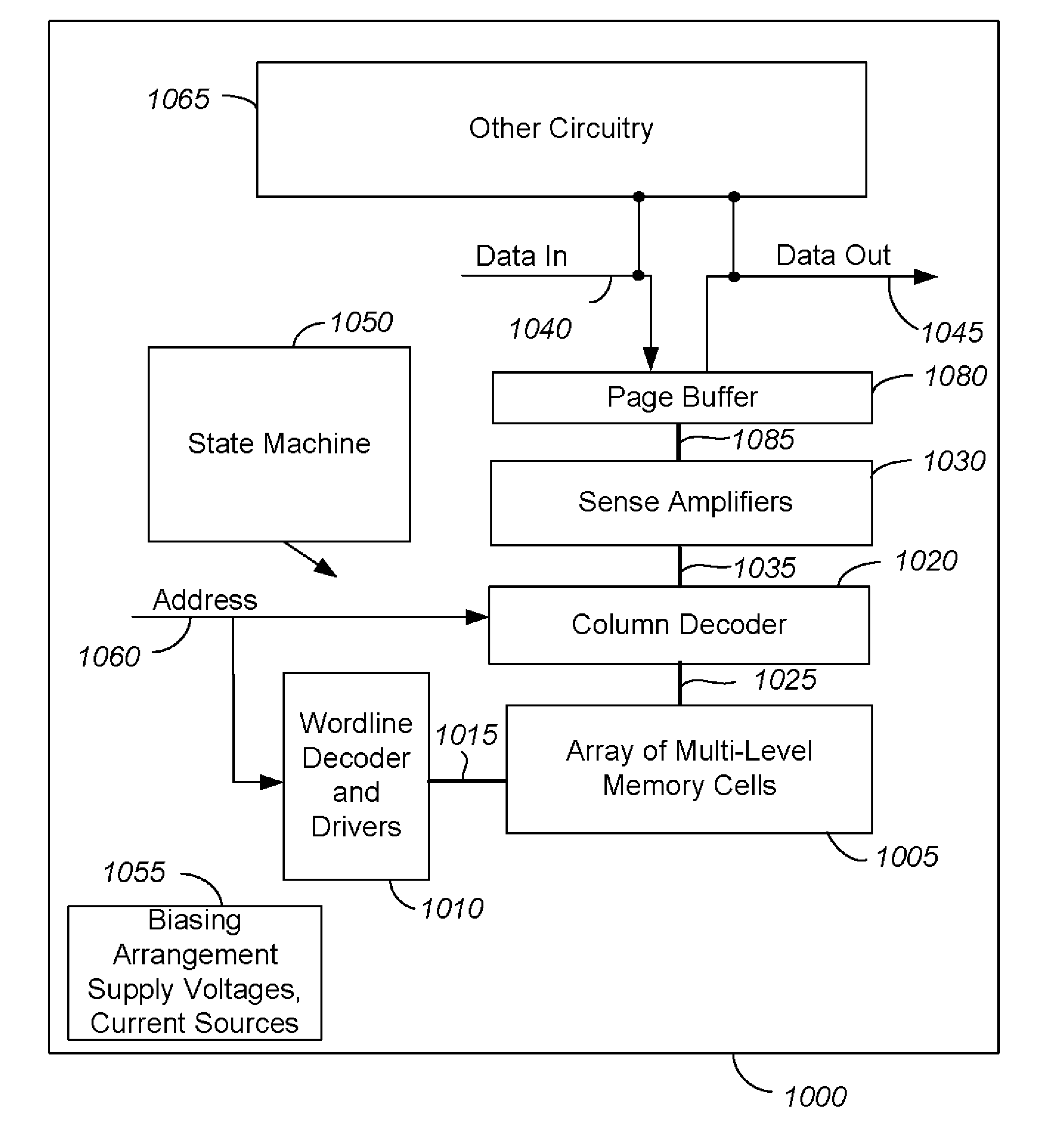

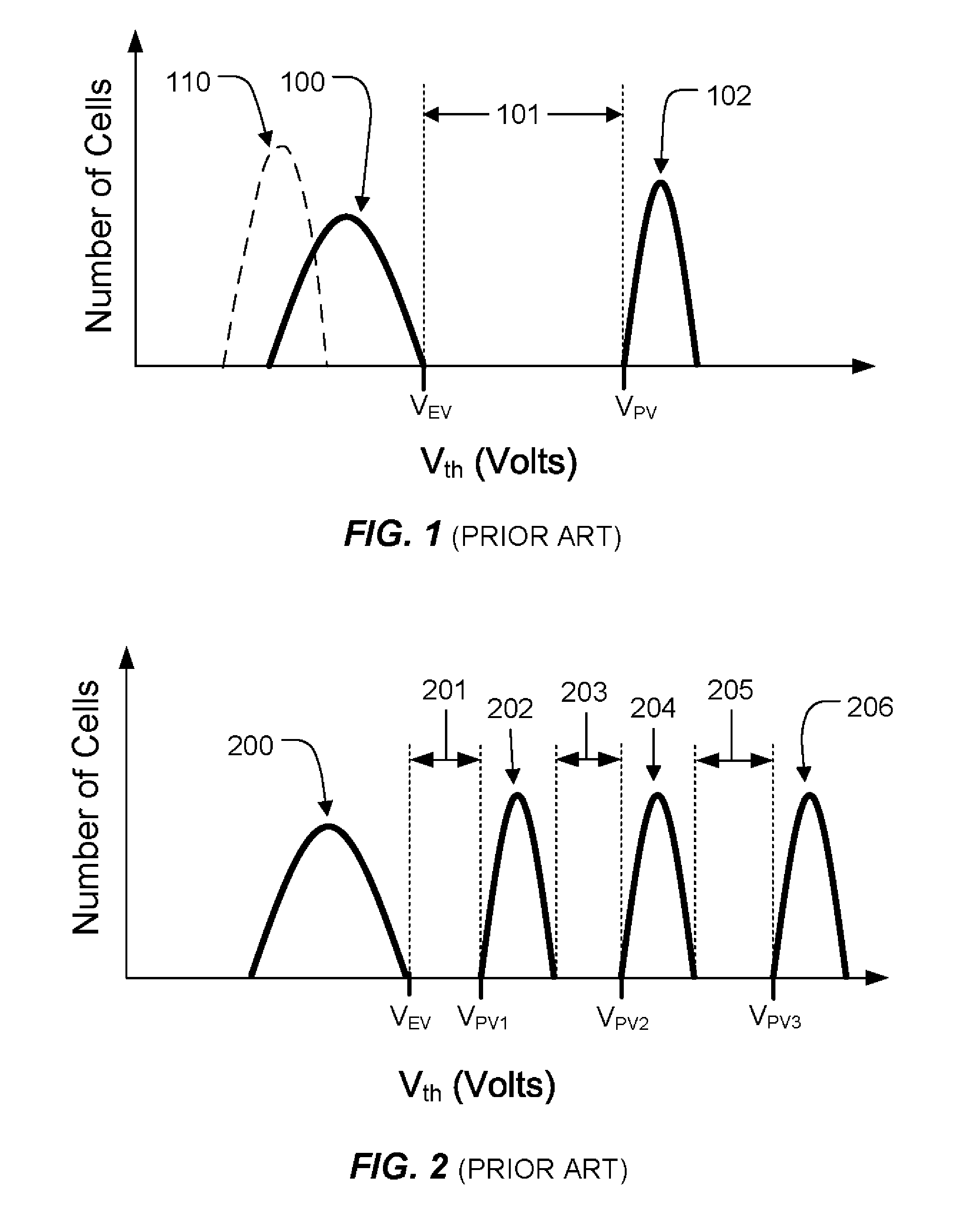

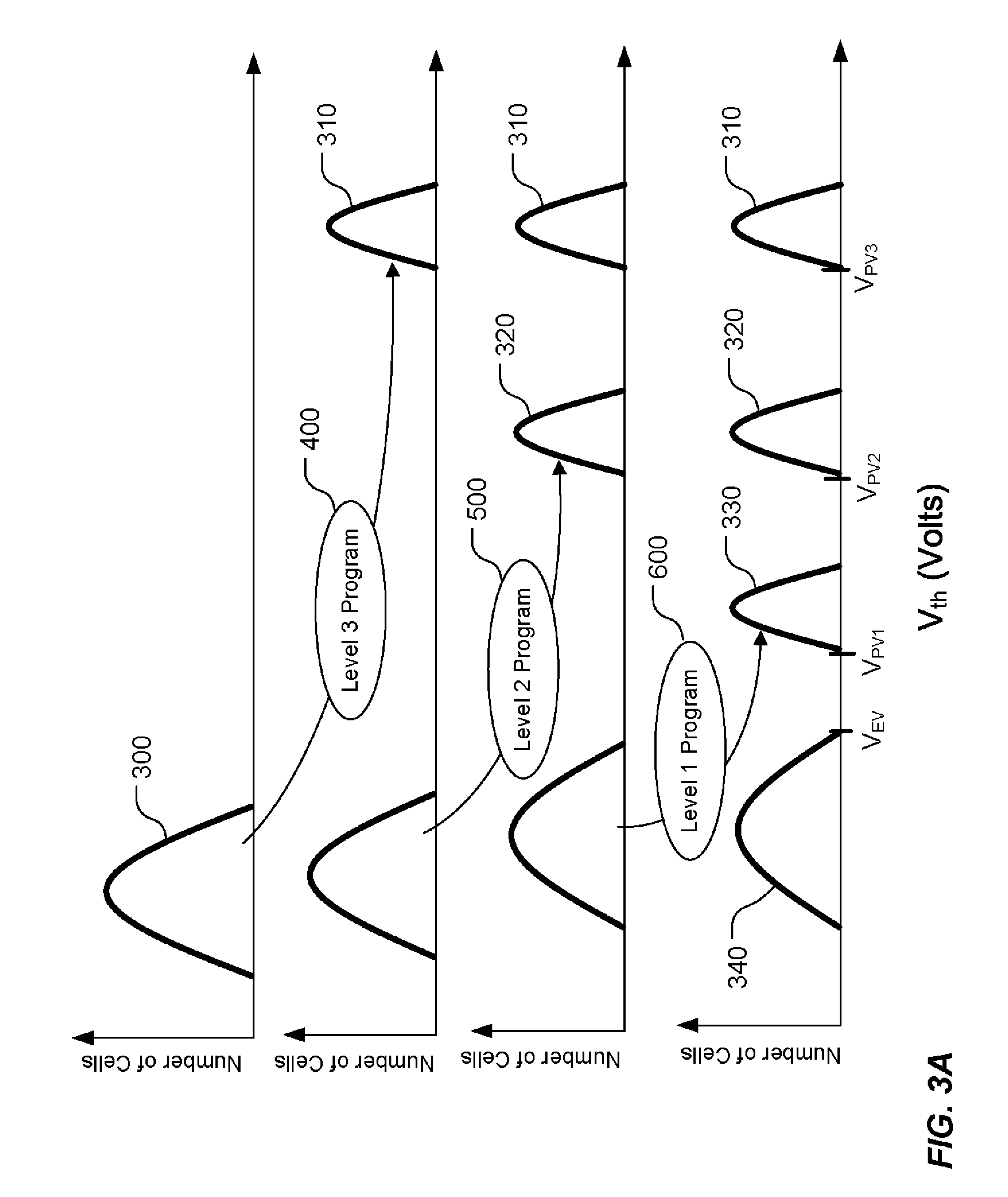

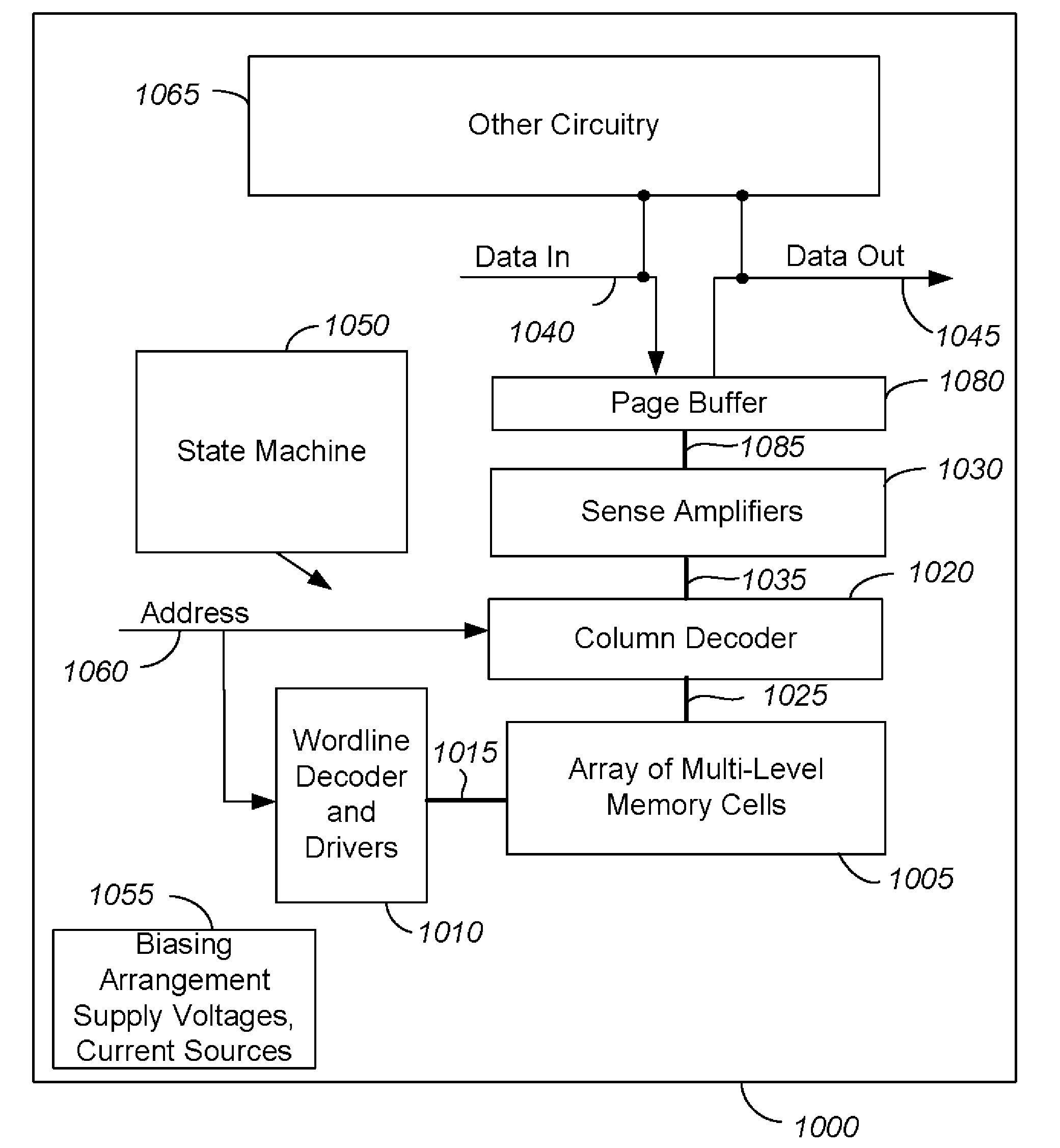

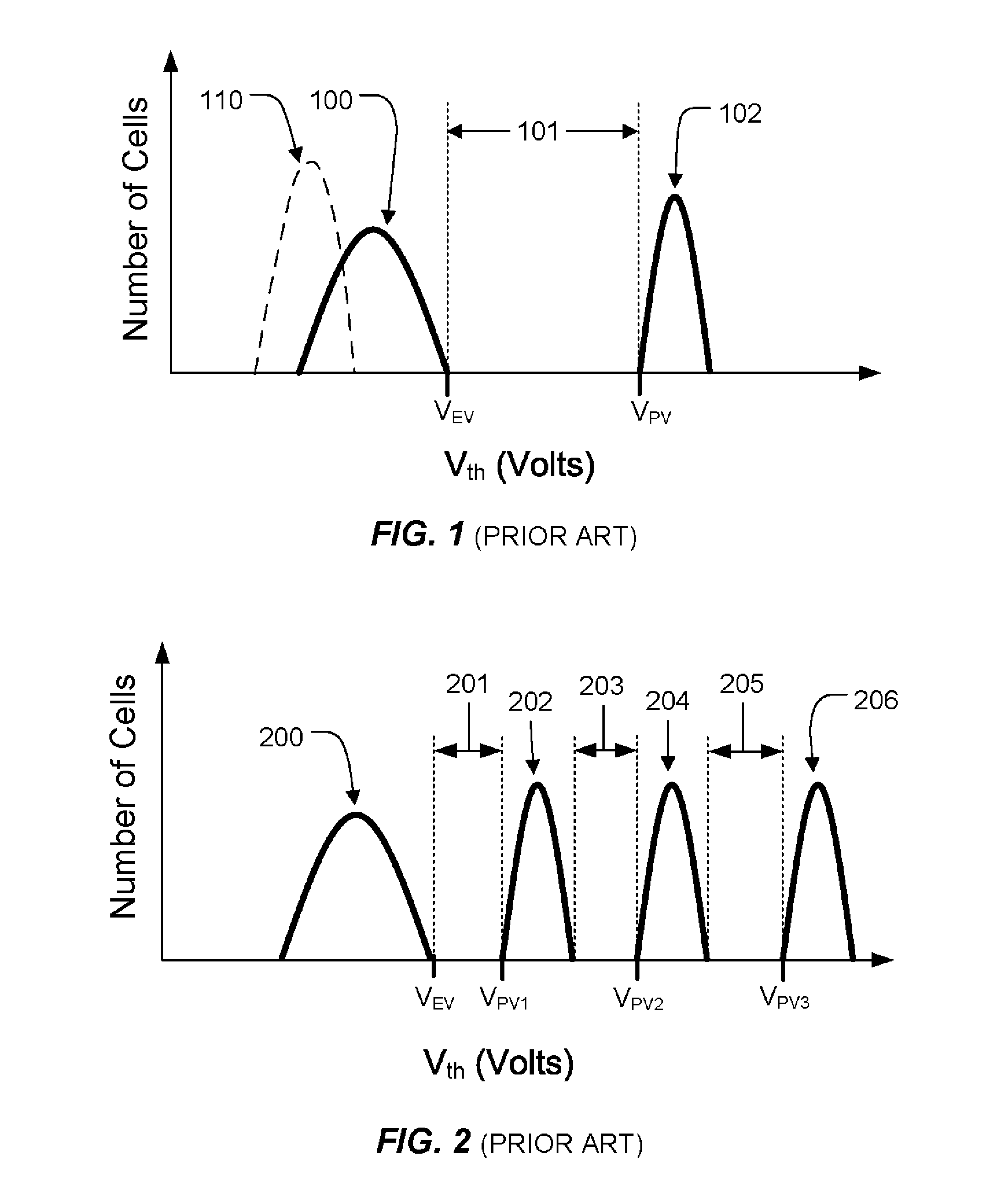

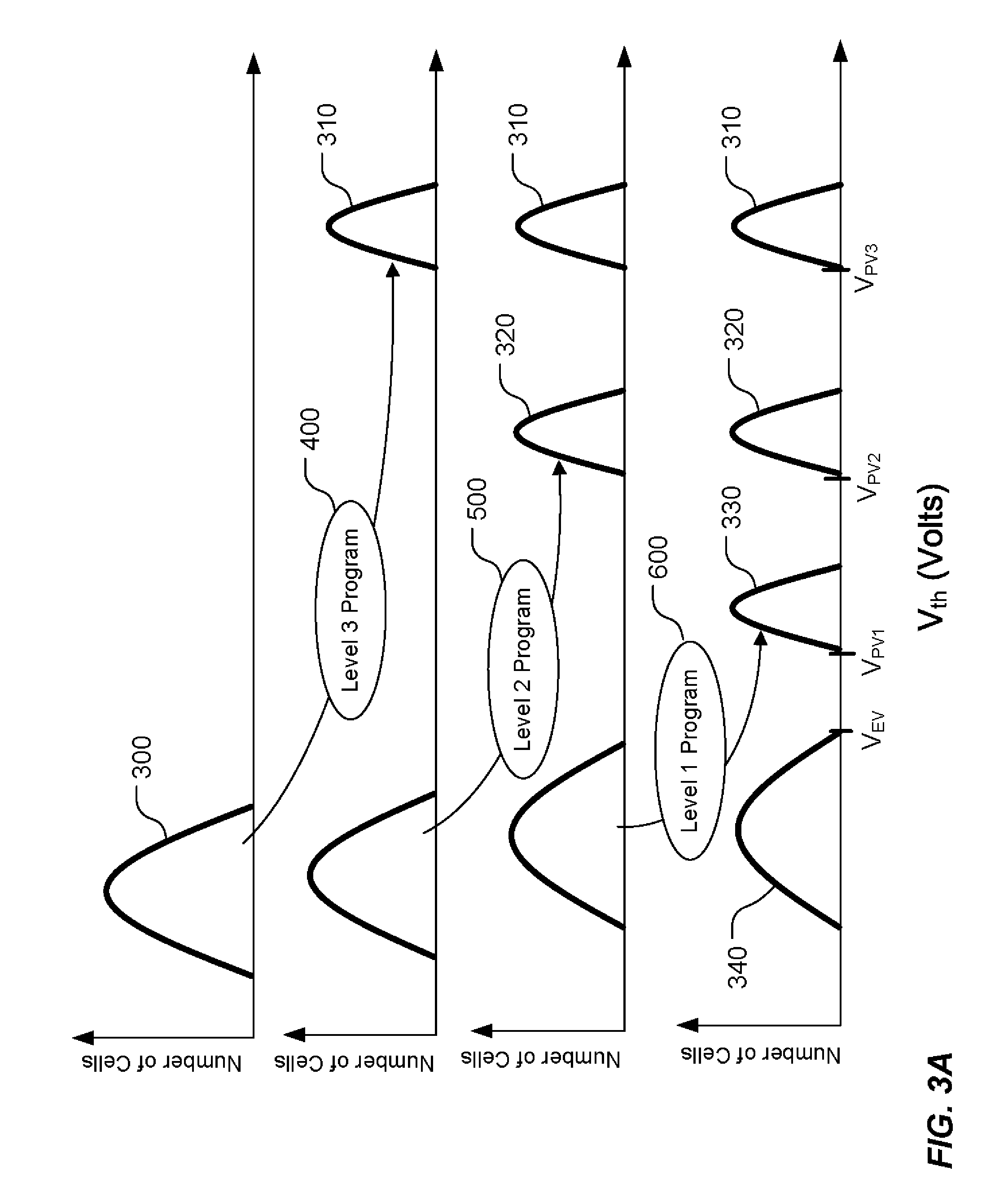

Multi-level memory cell programming methods

A method for programming a plurality of multi-level memory cells described herein includes iteratively changing a bias voltage applied to a first memory cell to program the first memory cell to a first threshold state and detecting when the first cell reaches a predetermined threshold voltage. The bias voltage applied to the first memory cell upon reaching the predetermined threshold voltage is recorded. A second memory cell is programmed to a second threshold state by applying an initial bias voltage to the second memory cell which is function of the recorded bias voltage.

Owner:MACRONIX INT CO LTD

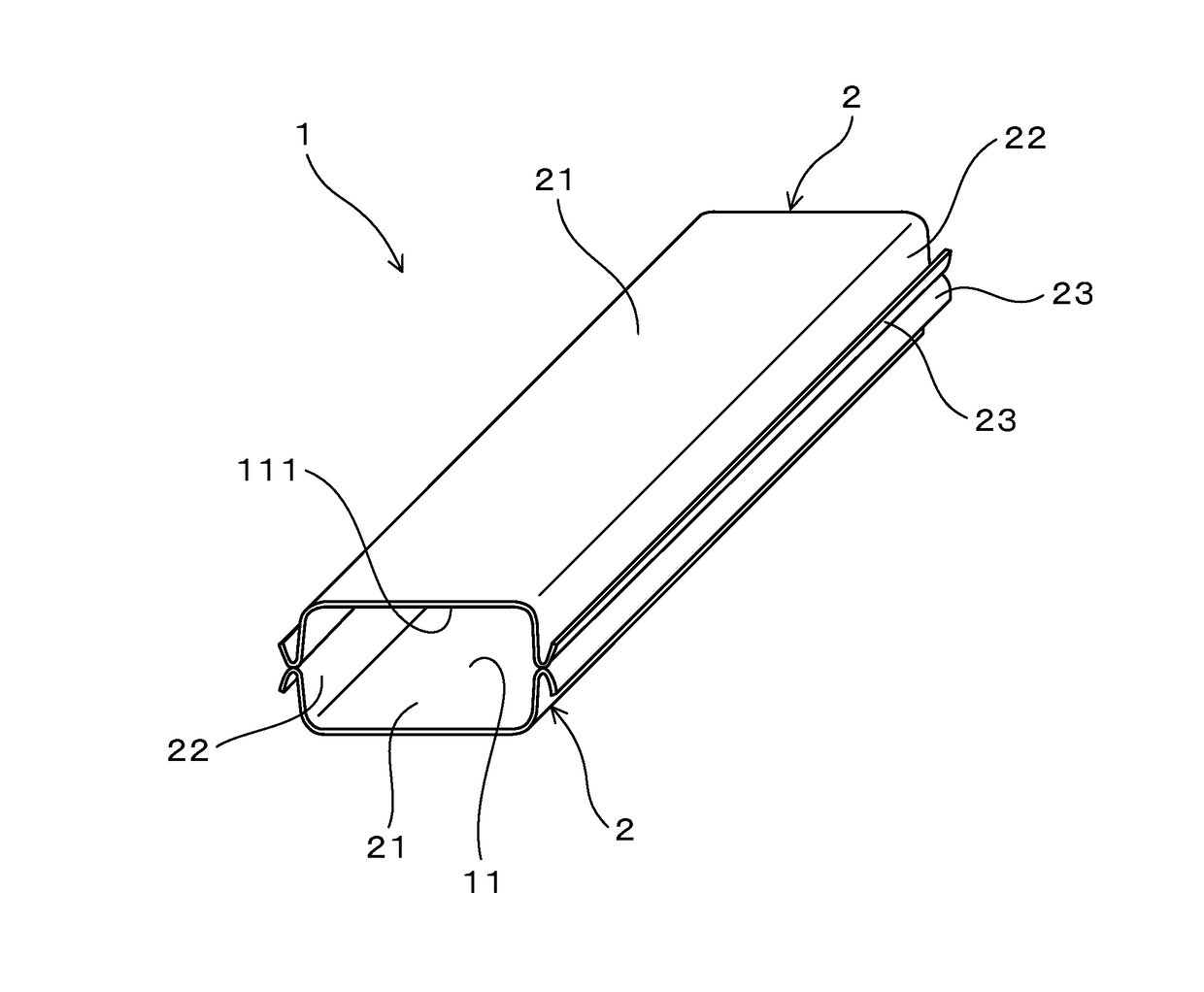

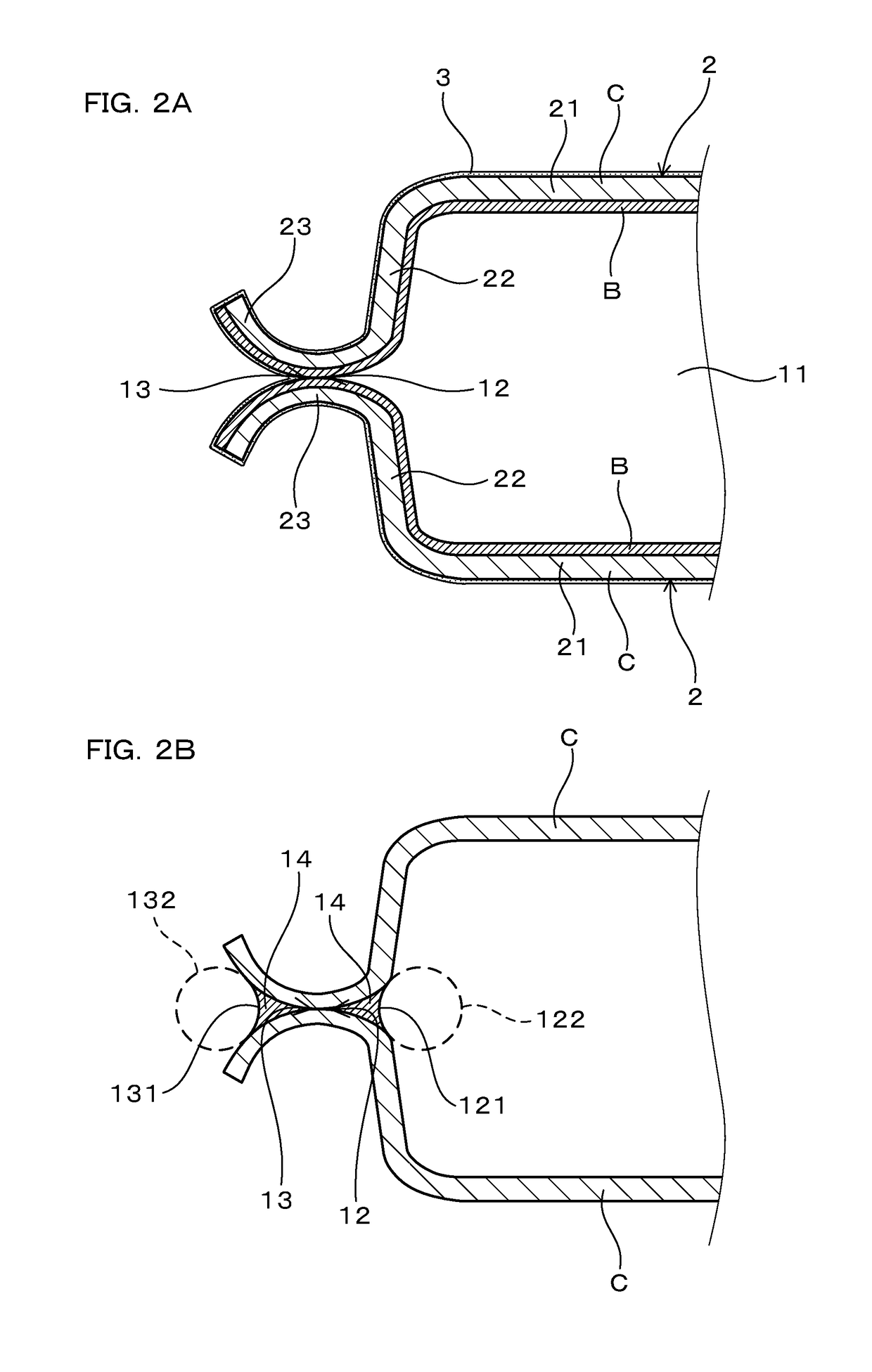

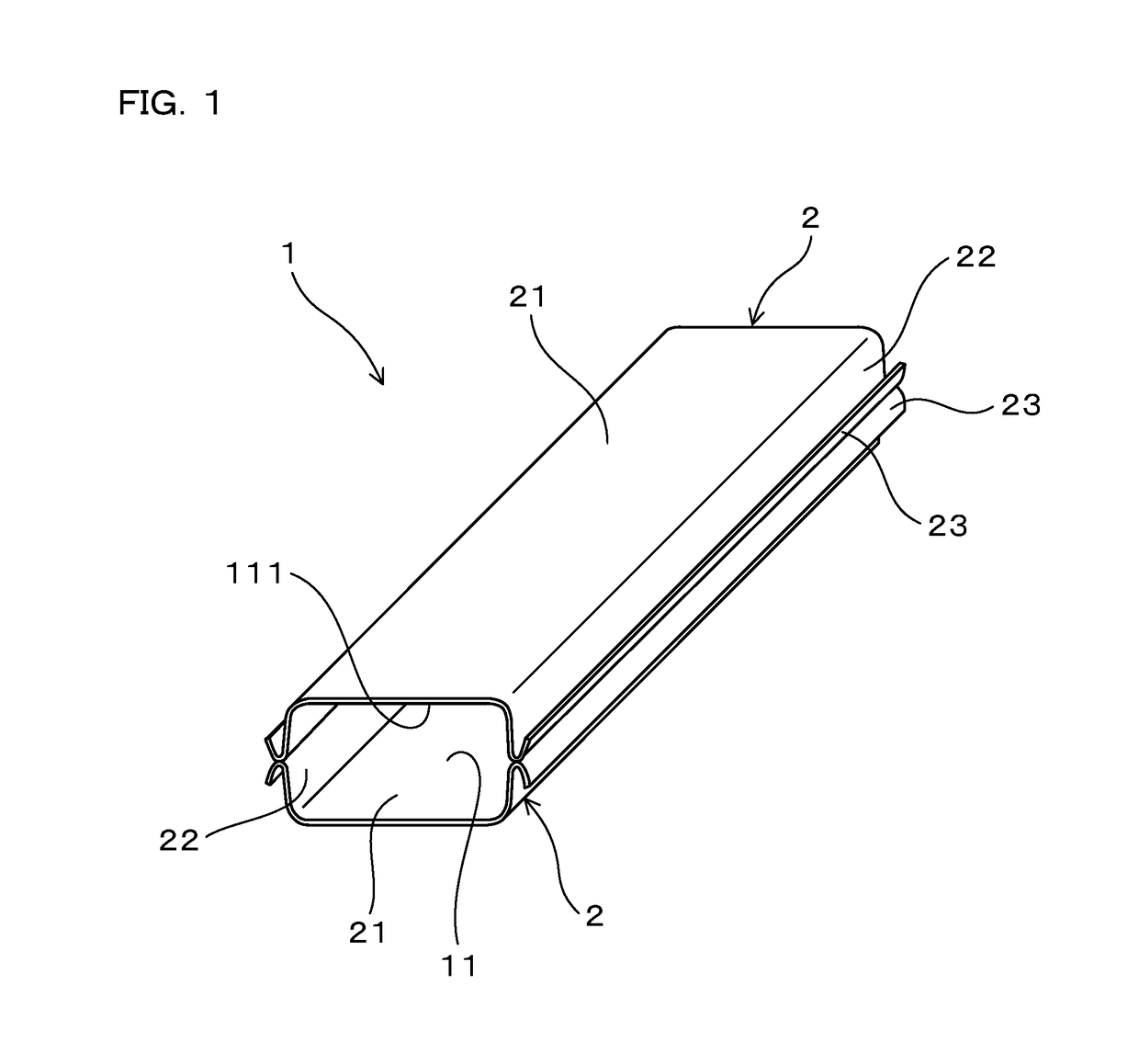

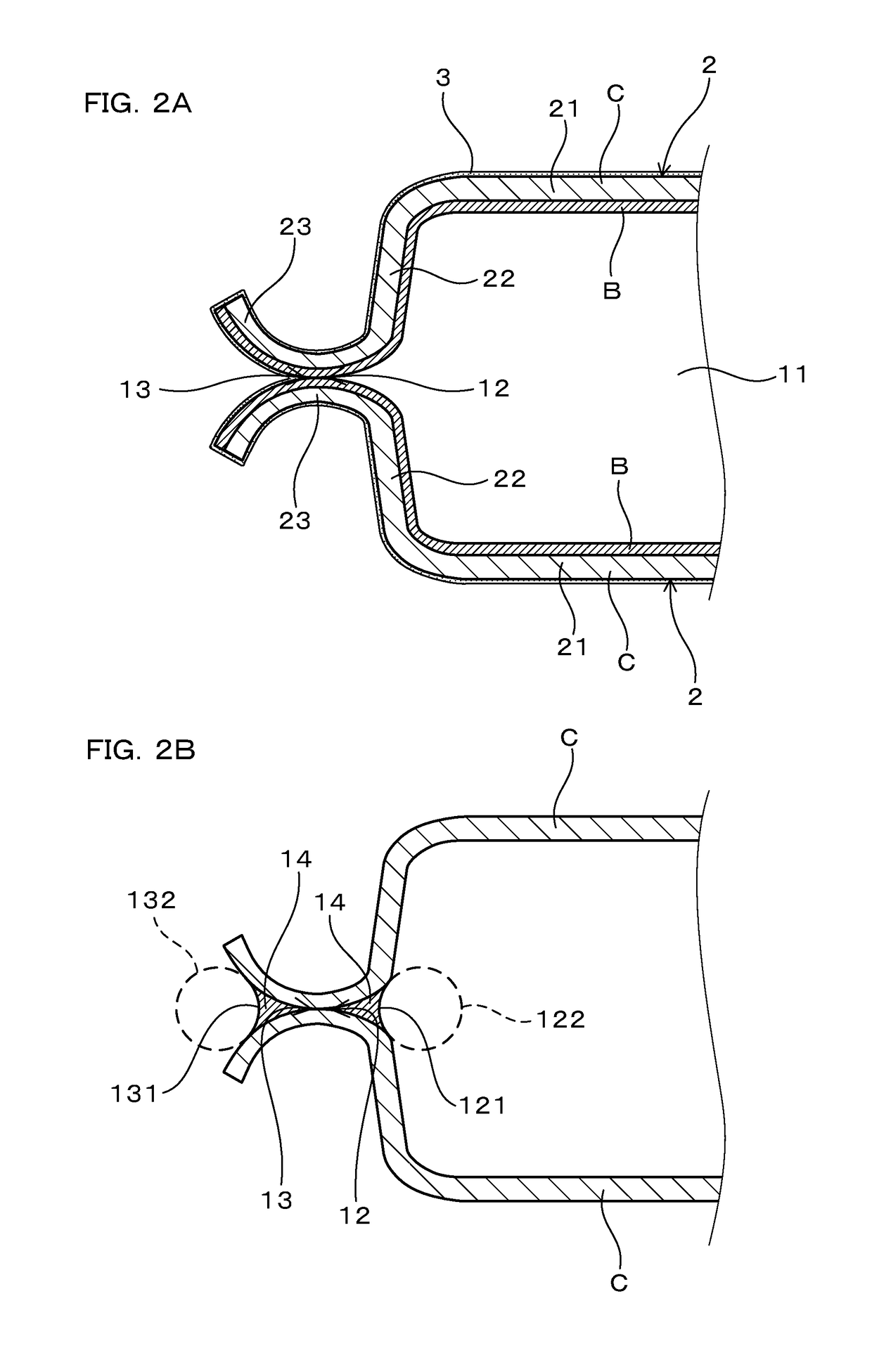

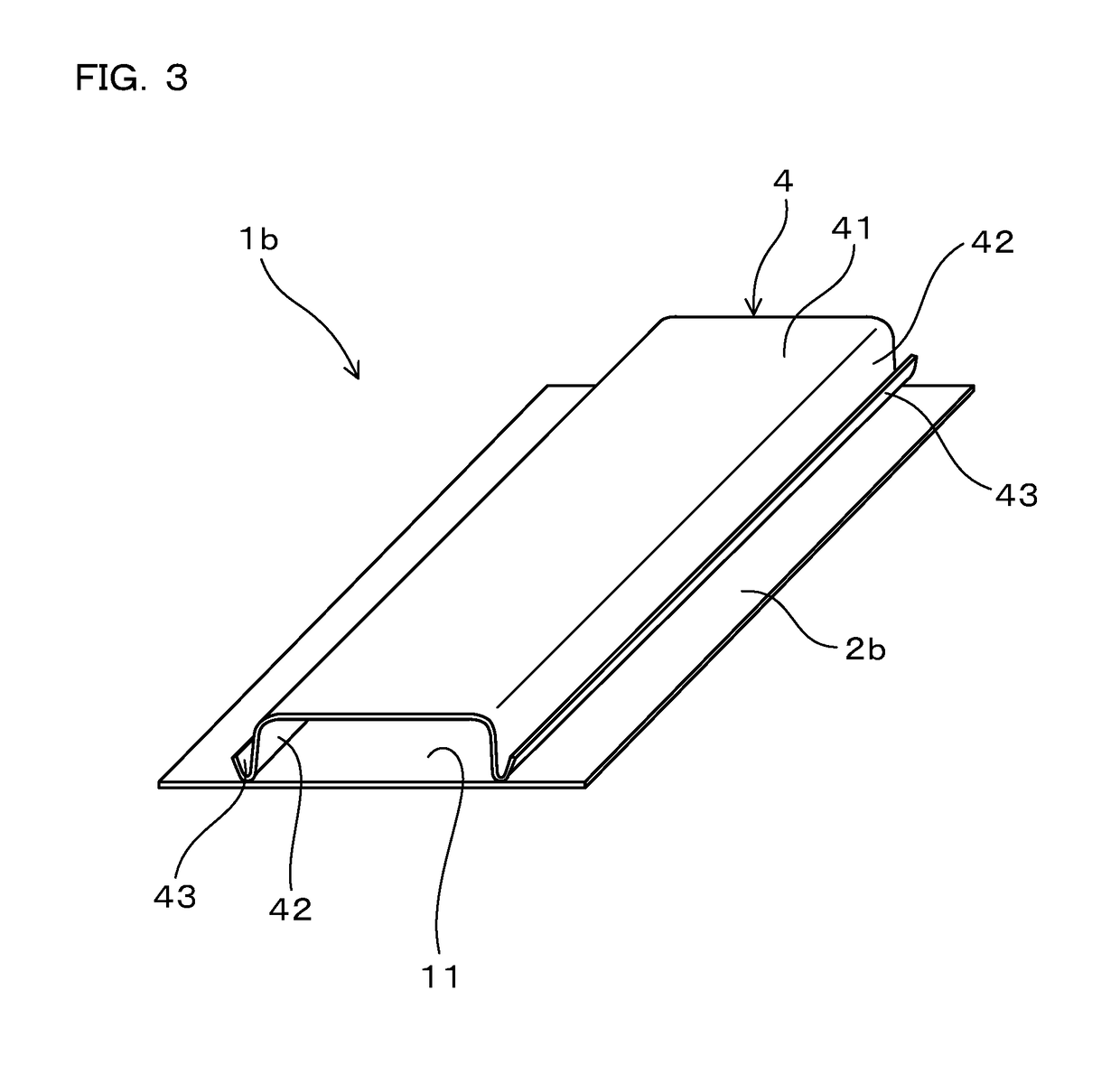

Brazing method

ActiveUS20170320170A1Low stateGood brazingWelding/cutting media/materialsMetal working apparatusFiller metalAtmosphere

A hollow aluminum structure that will be brazed includes at least one brazing sheet having a filler metal layer clad onto a core layer. The core layer is composed of aluminum or an aluminum alloy containing less than 0.2 mass % Mg. The filler metal layer is composed of an aluminum alloy that contains Si: 4.0-13.0 mass % and Bi: 0.01-0.3 mass %, and further contains Li: 0.004-0.08 mass % and / or Be: 0.006-0.12 mass %, the filler metal layer containing less than 0.1 mass % Mg. The hollow aluminum structure is assembled such that the filler metal layer is present at locations that will form both an interior-facing brazed joint and an exterior-facing brazed joint. Then, flux is applied onto the filler metal layer at the location that will form the exterior brazed joint, and the hollow aluminum structure heated in an inert gas atmosphere to form the interior brazed joint and the exterior brazed joint.

Owner:FURUKAWA SKY ALUMINUM CORP

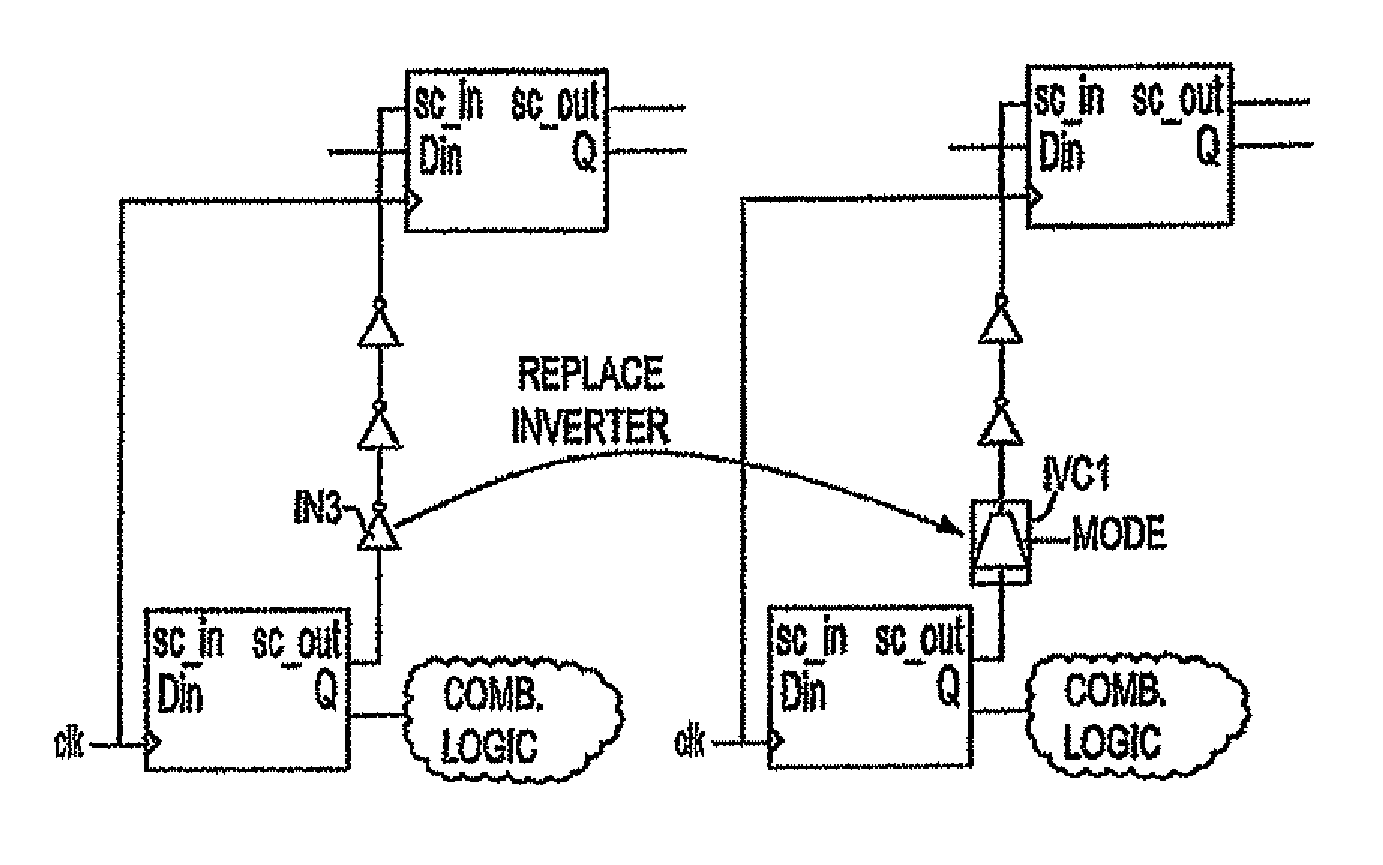

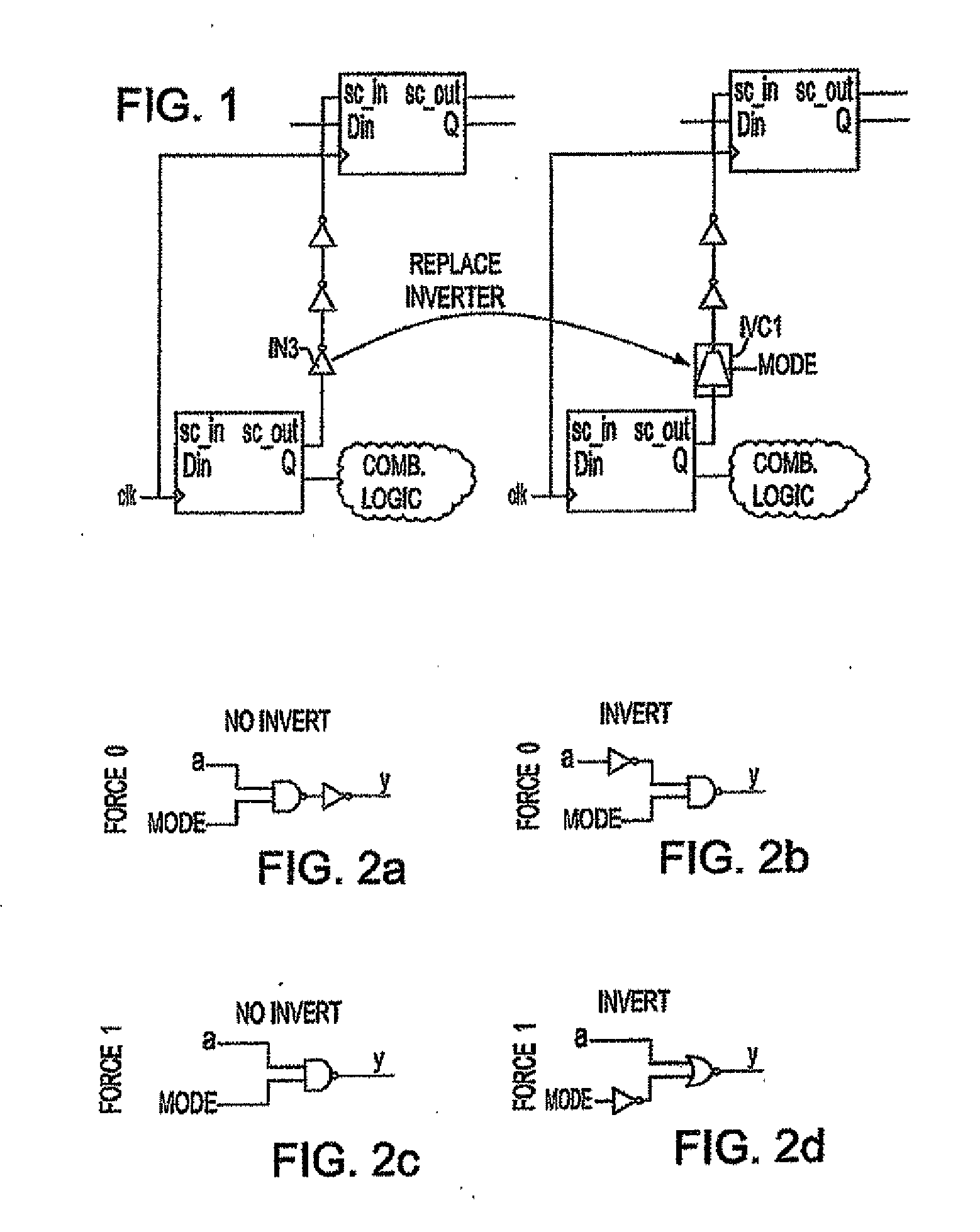

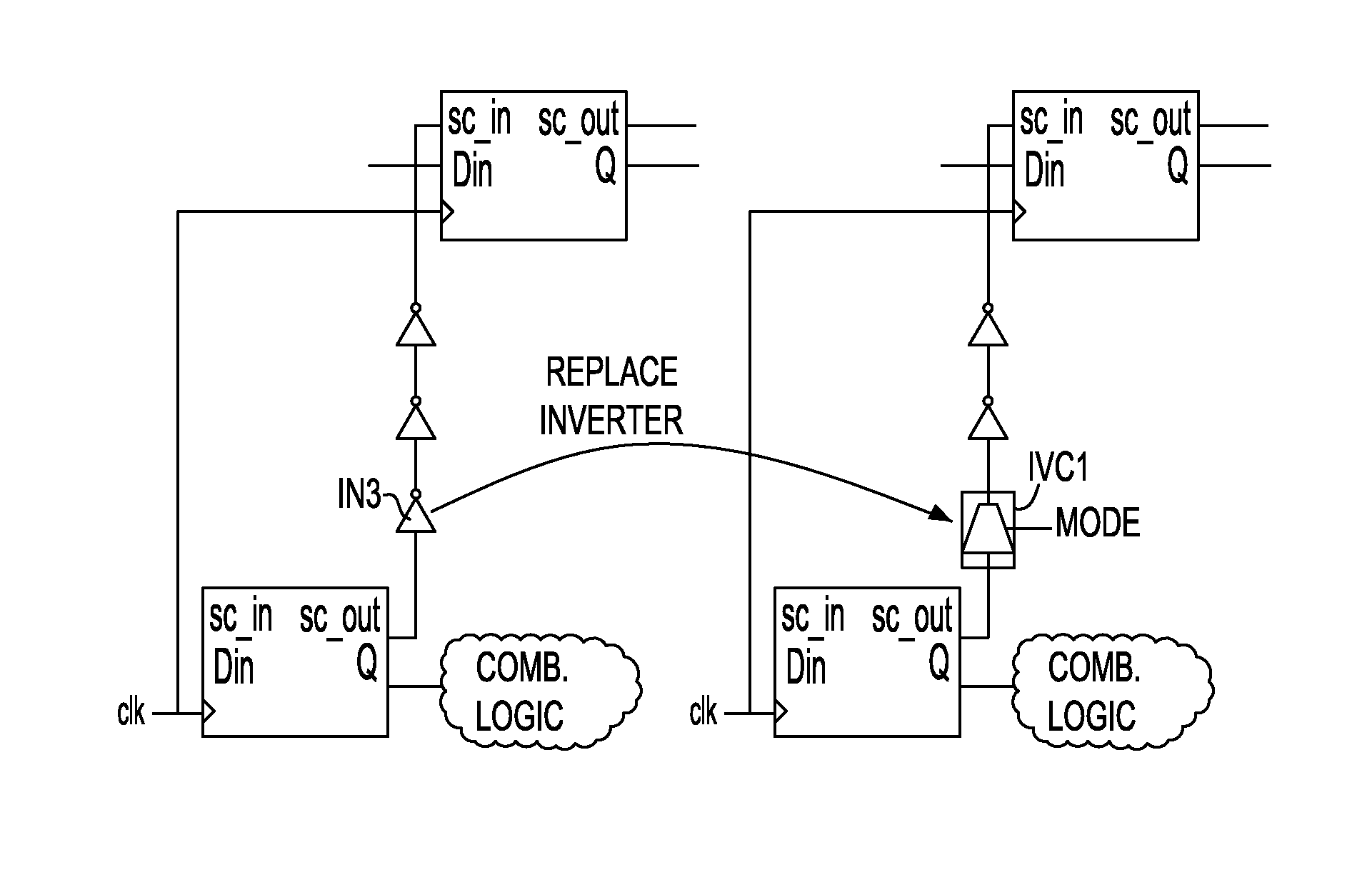

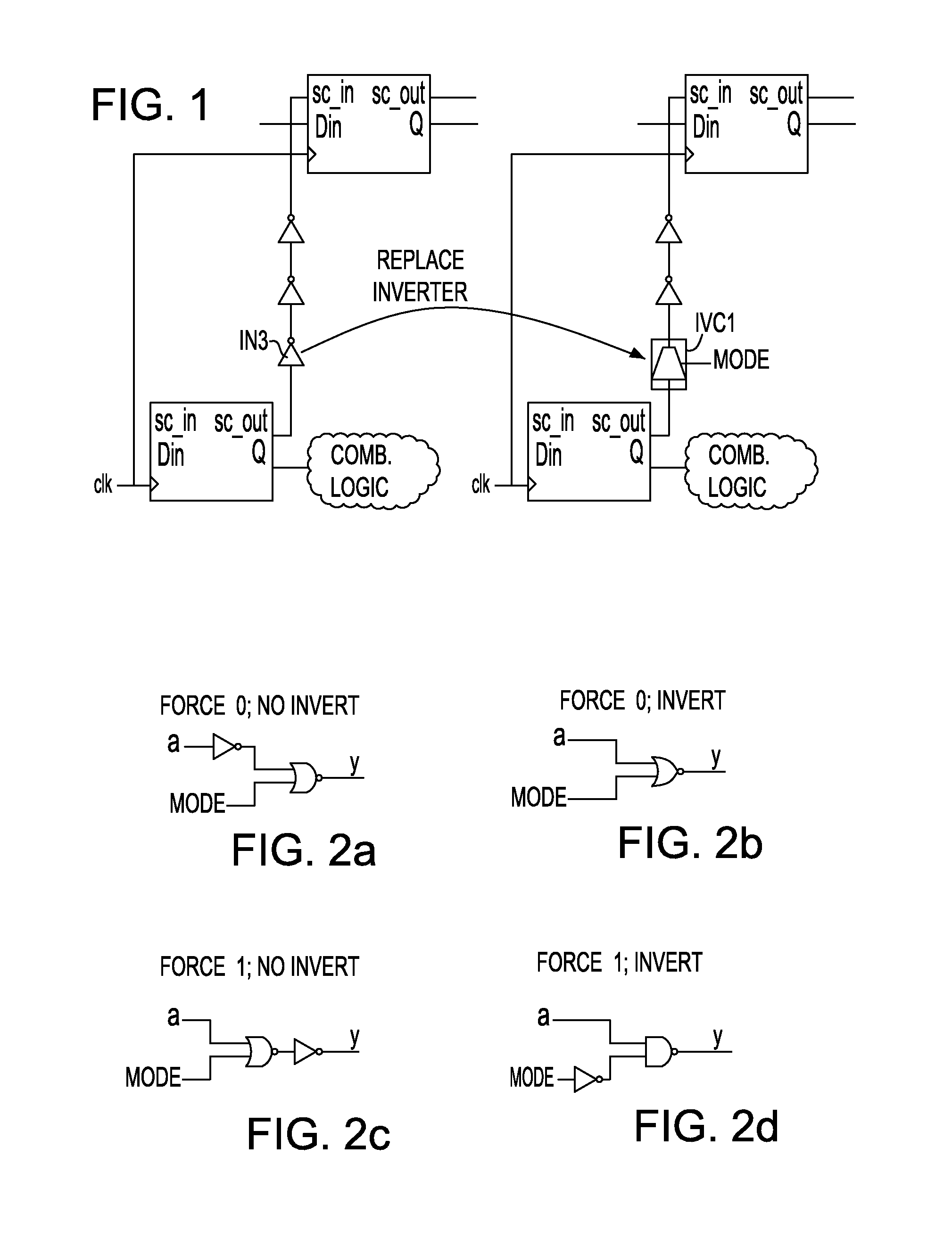

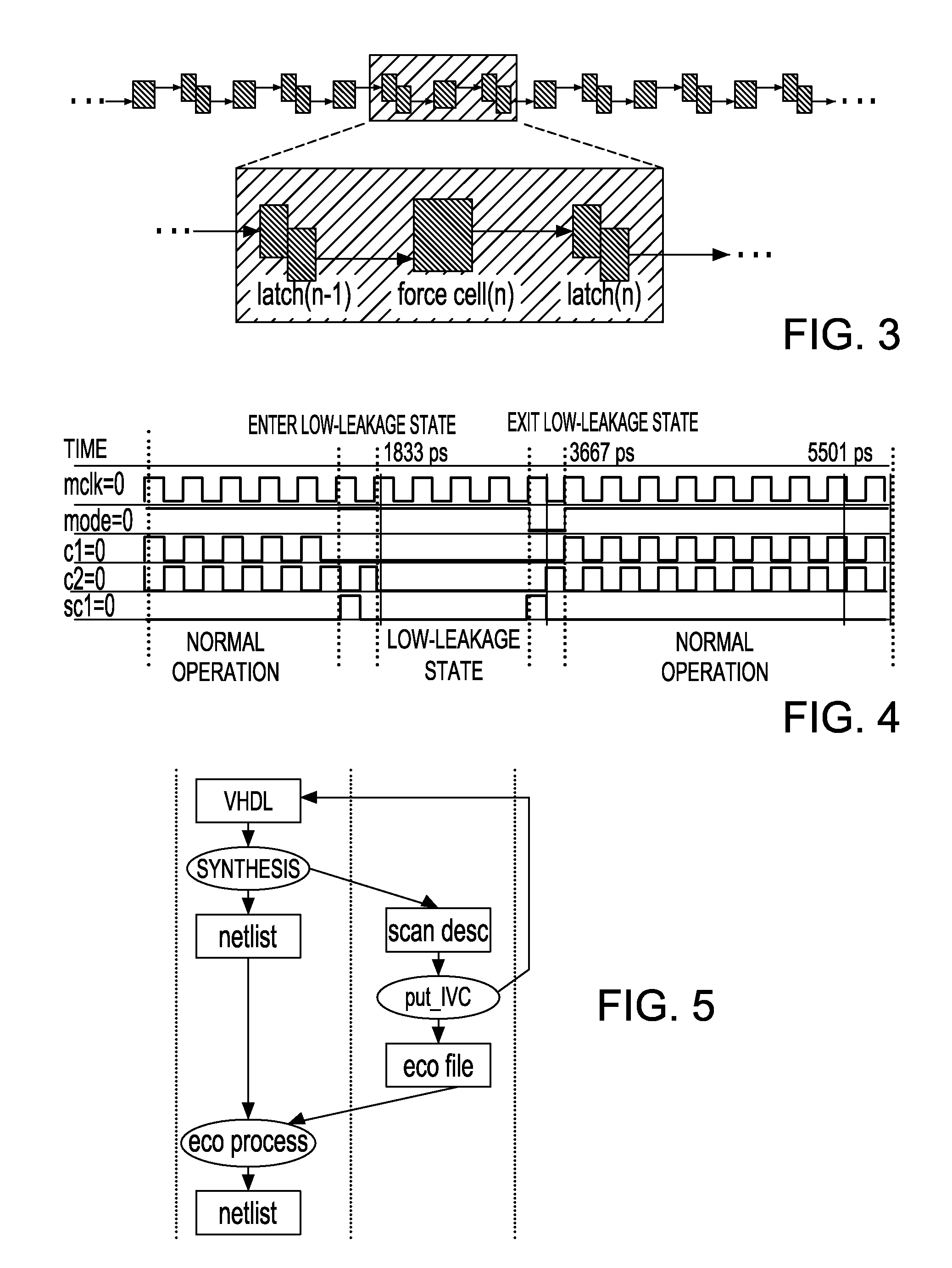

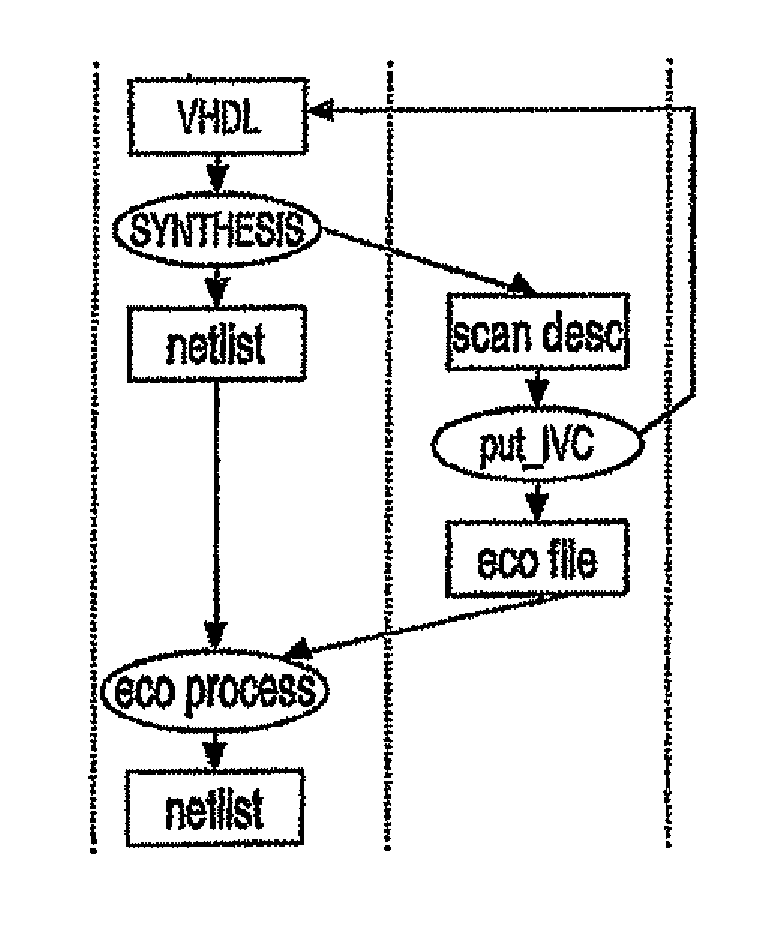

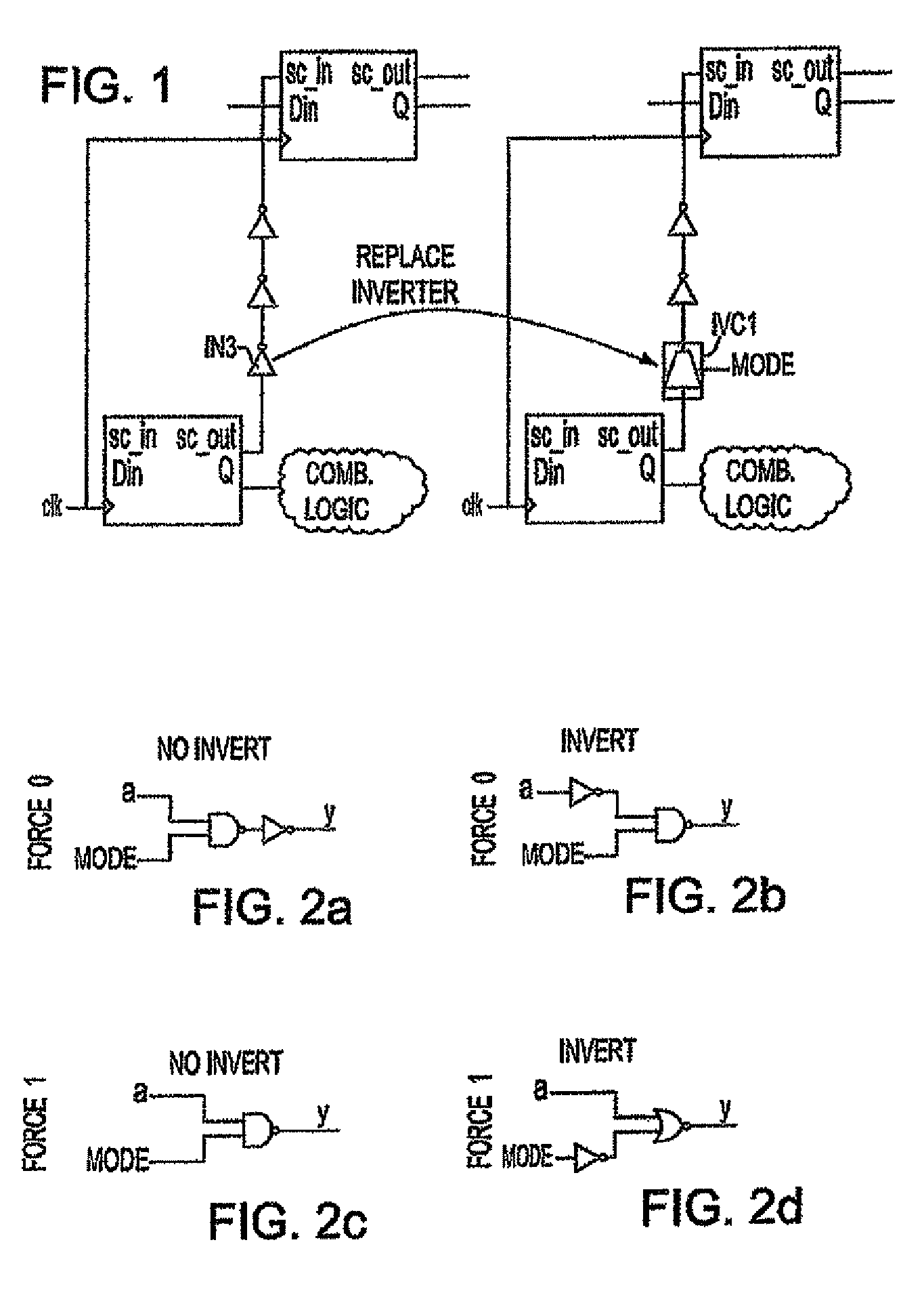

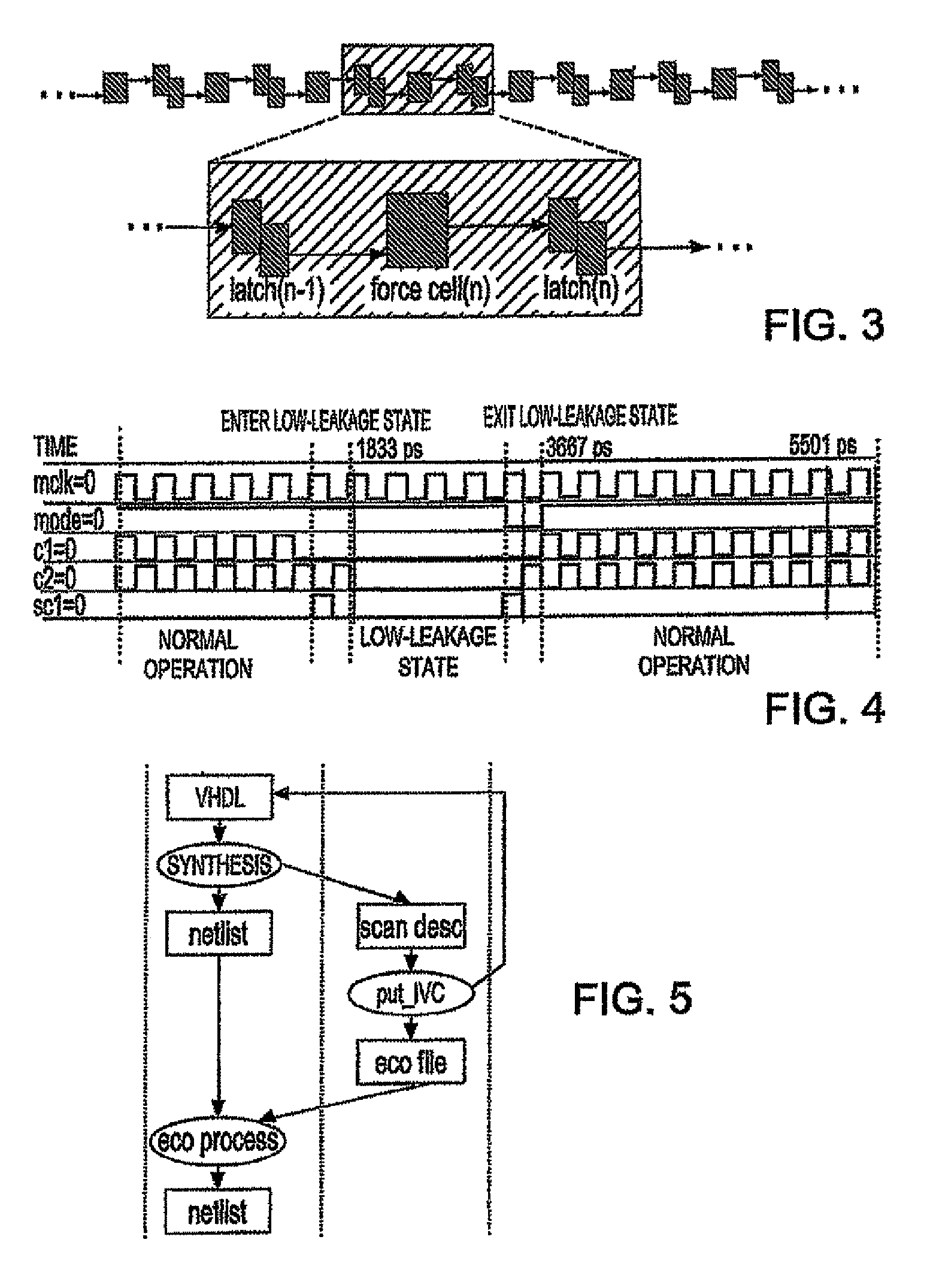

Method and apparatus for on-the-fly minimum power state transition

InactiveUS20090172615A1Reduce power consumptionMinimum area overheadSolid-state devicesElectrical testingData fileLow leakage

The invention includes a design structure embodied in a computer readable medium for performing a method for inserting a scan chain into a VLSI circuit design. The scan chain structure, or structures, are included in the design structure for the VLSI circuit design. The scan chain structure includes a first flip-flop (L1) and a second flip-flop (L2) configured to operate the first flip-flop (L1) in normal mode operation, in scan mode operation, in initialization mode and in low leakage power mode operation. A buffer circuit is electrically connected between the scan-out output of the second flip-flop (L2) and the scan-in input of the first flip-flop (L1) for the next latch in the scan chain. Buffer circuit control elements control the first flip-flop (L1) to switch between scan mode or low power leakage mode. The switching occurs in only one clock cycle. The design structure can include a netlist, which describes the VLSI circuit, reside on storage medium as a data format used for the exchange of layout data of integrated circuits, and preferably includes at least one of test data files, characterization data, verification data, or design specifications.

Owner:GLOBALFOUNDRIES INC

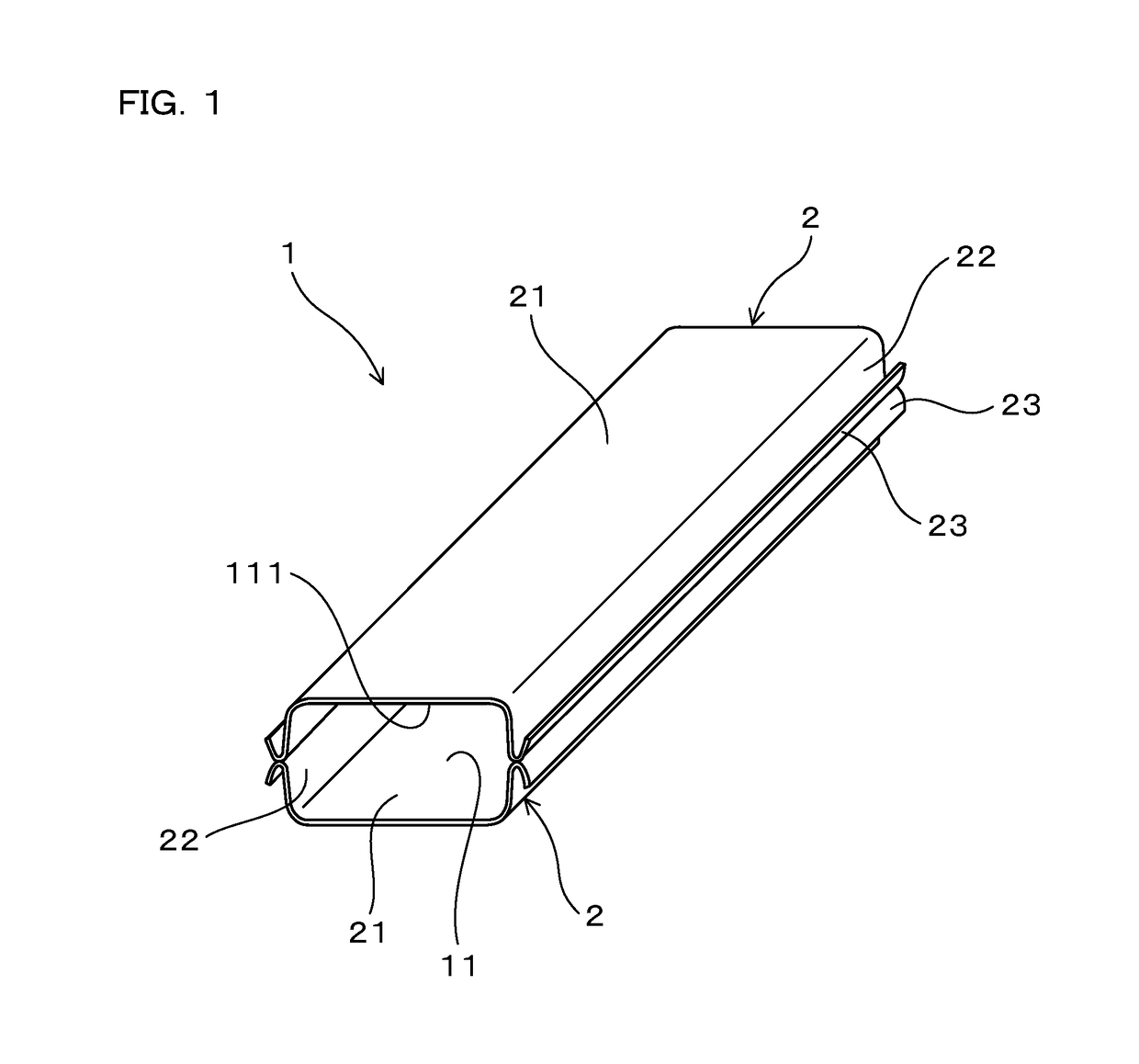

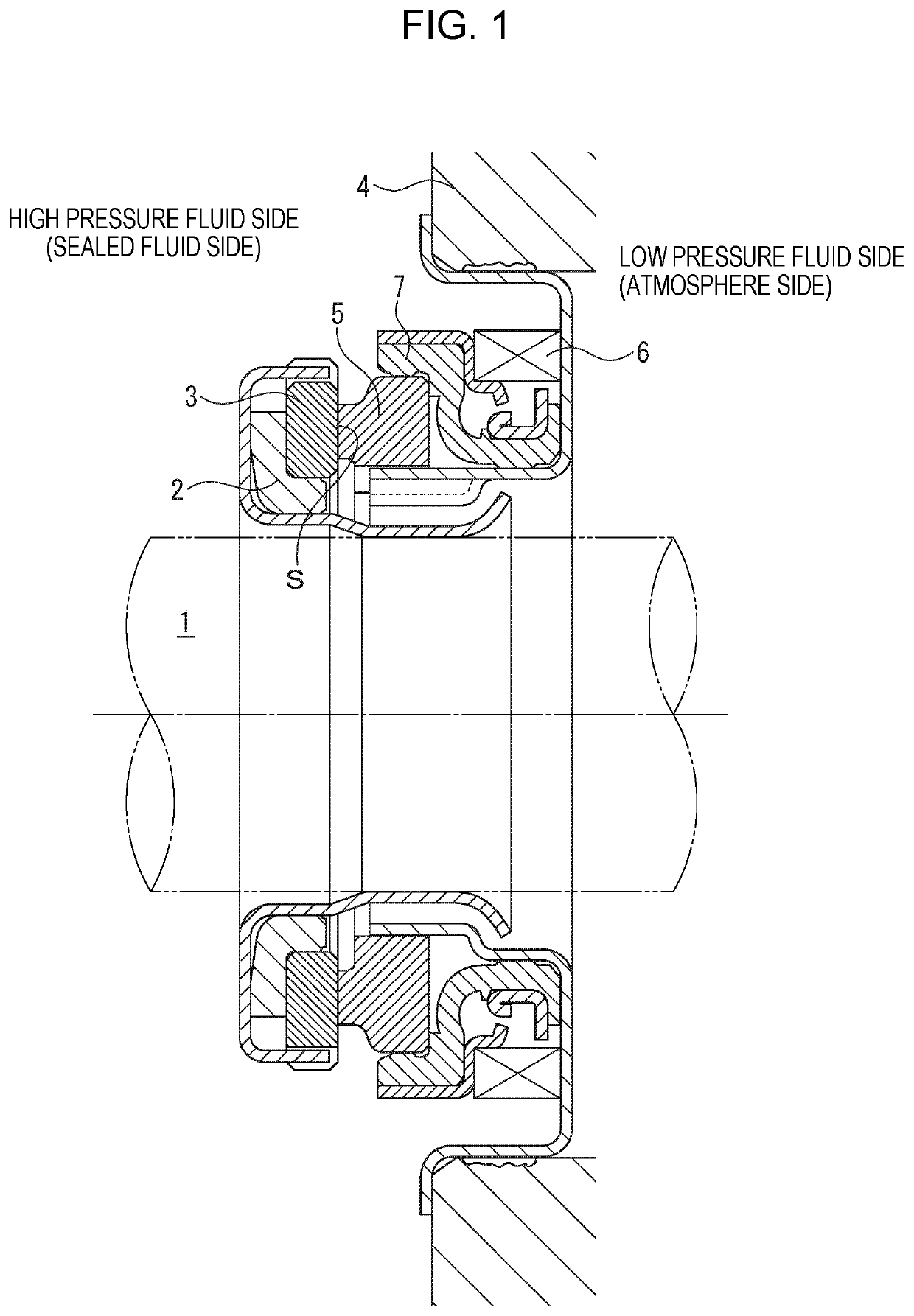

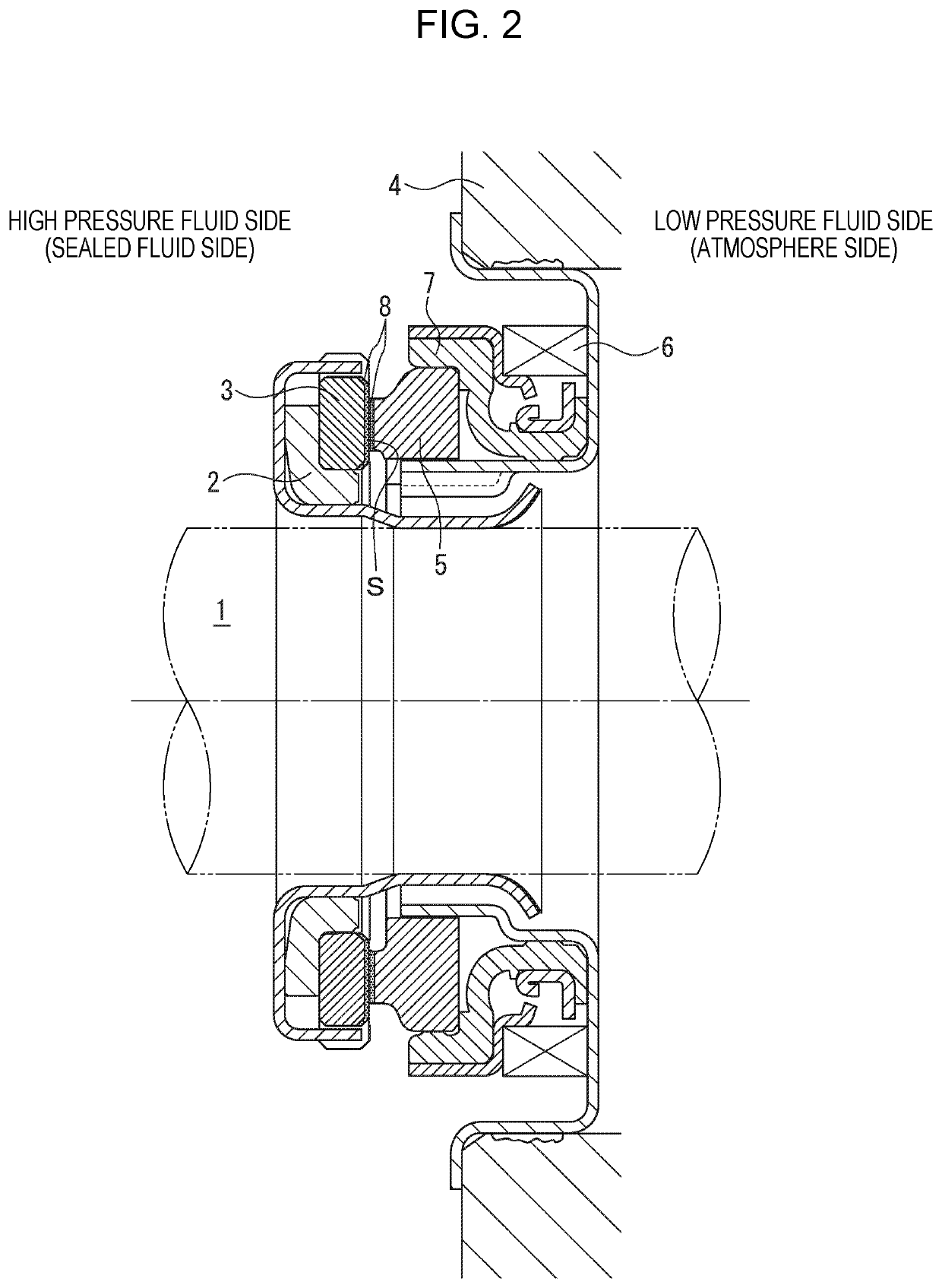

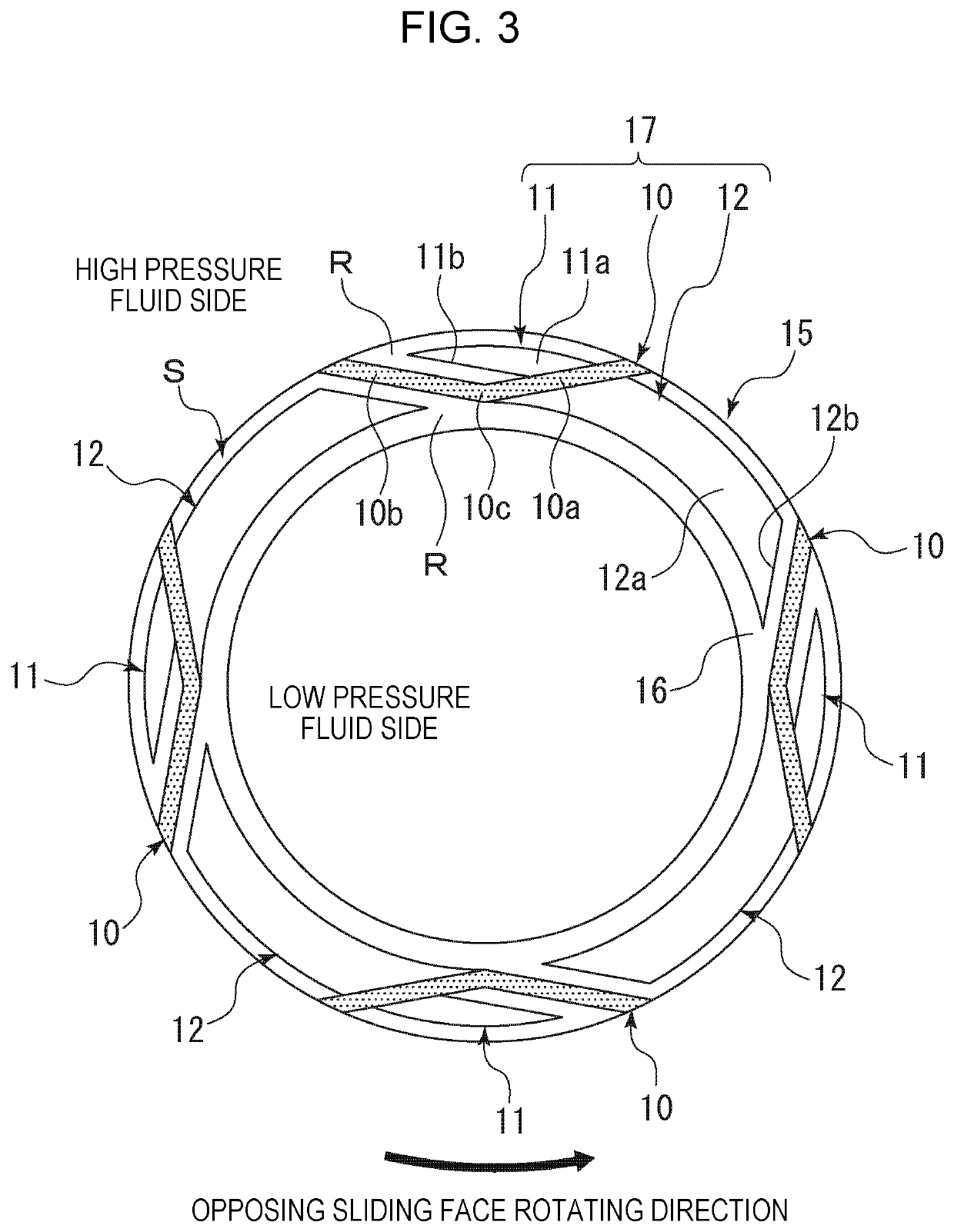

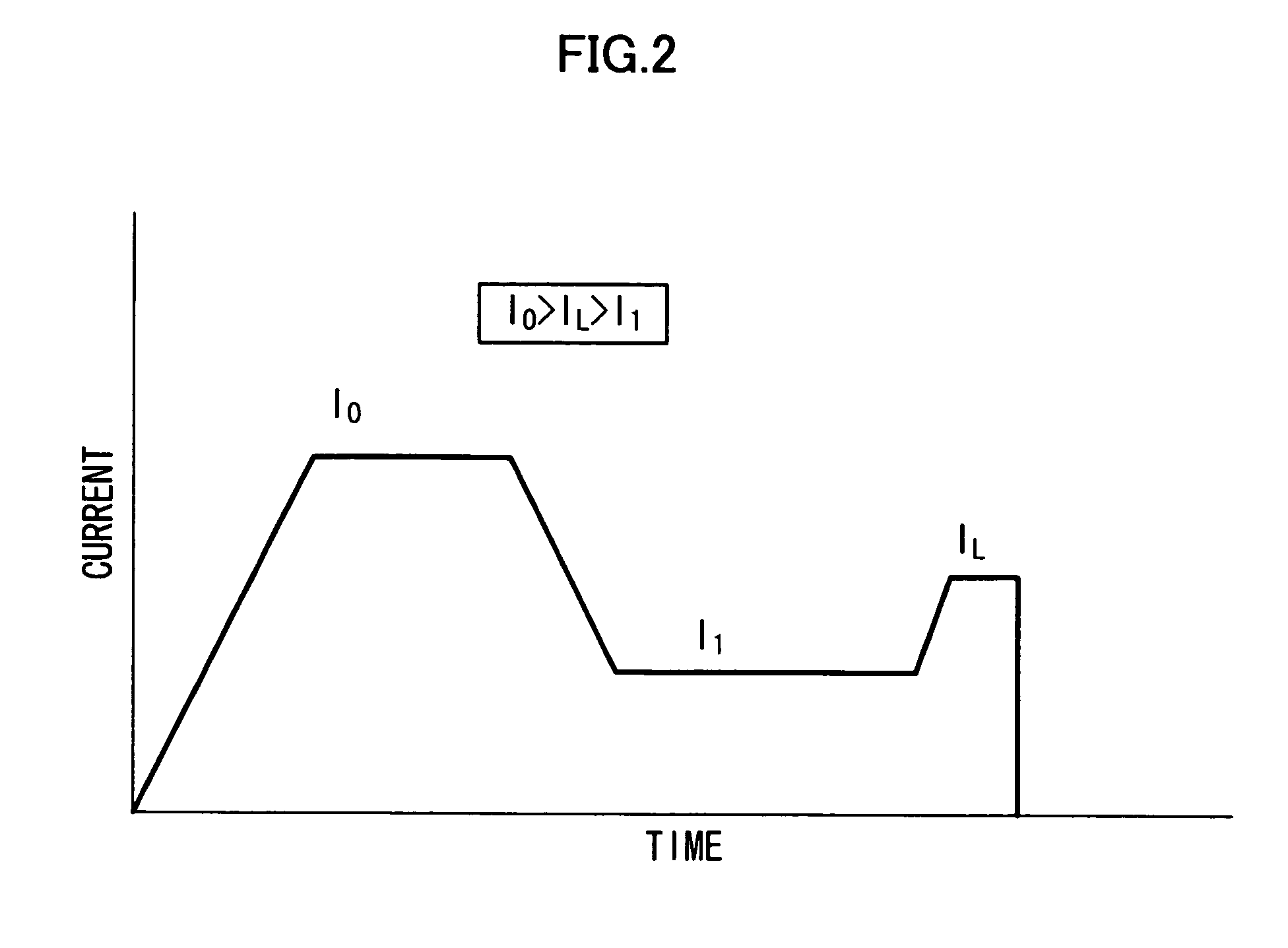

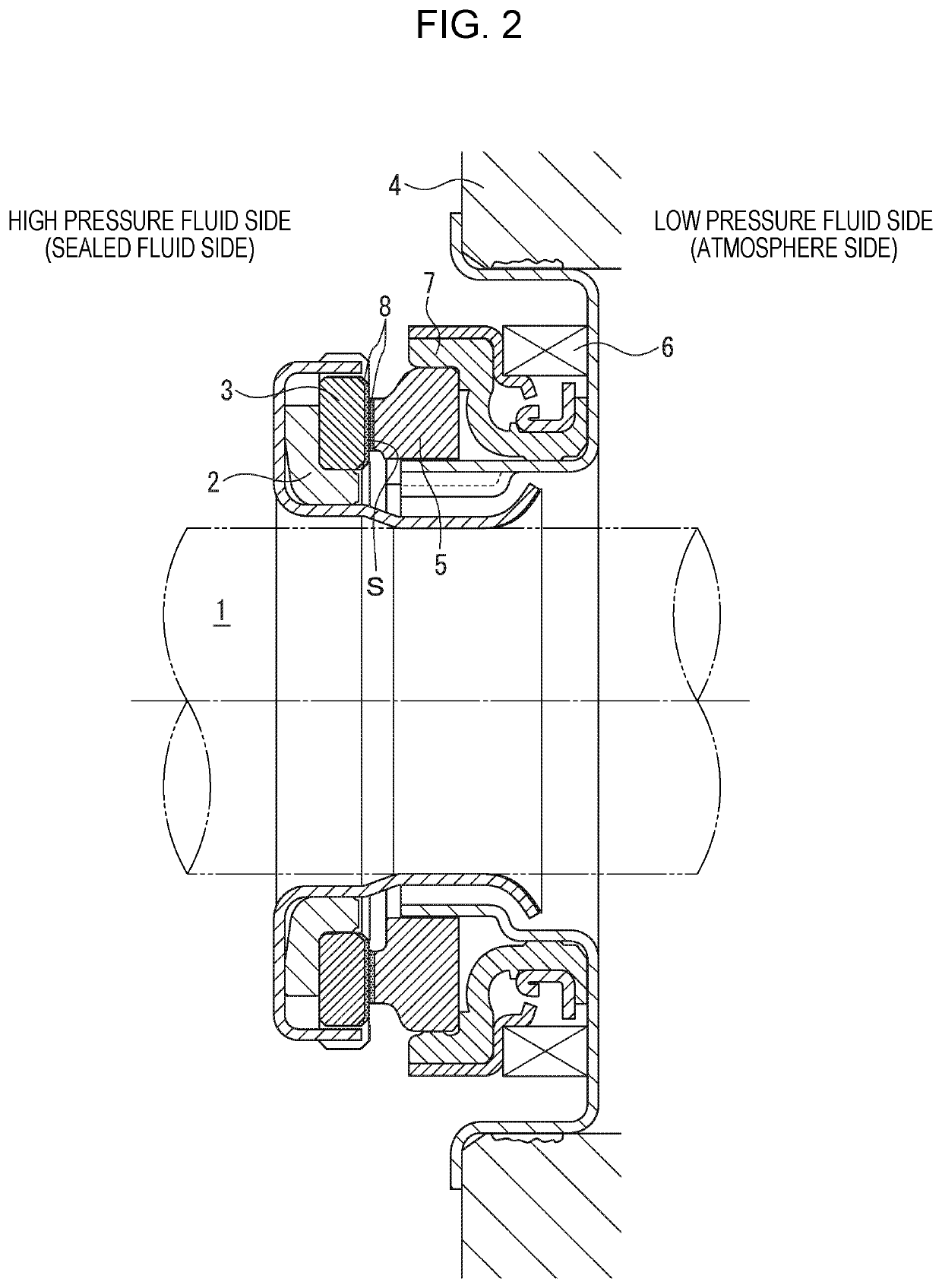

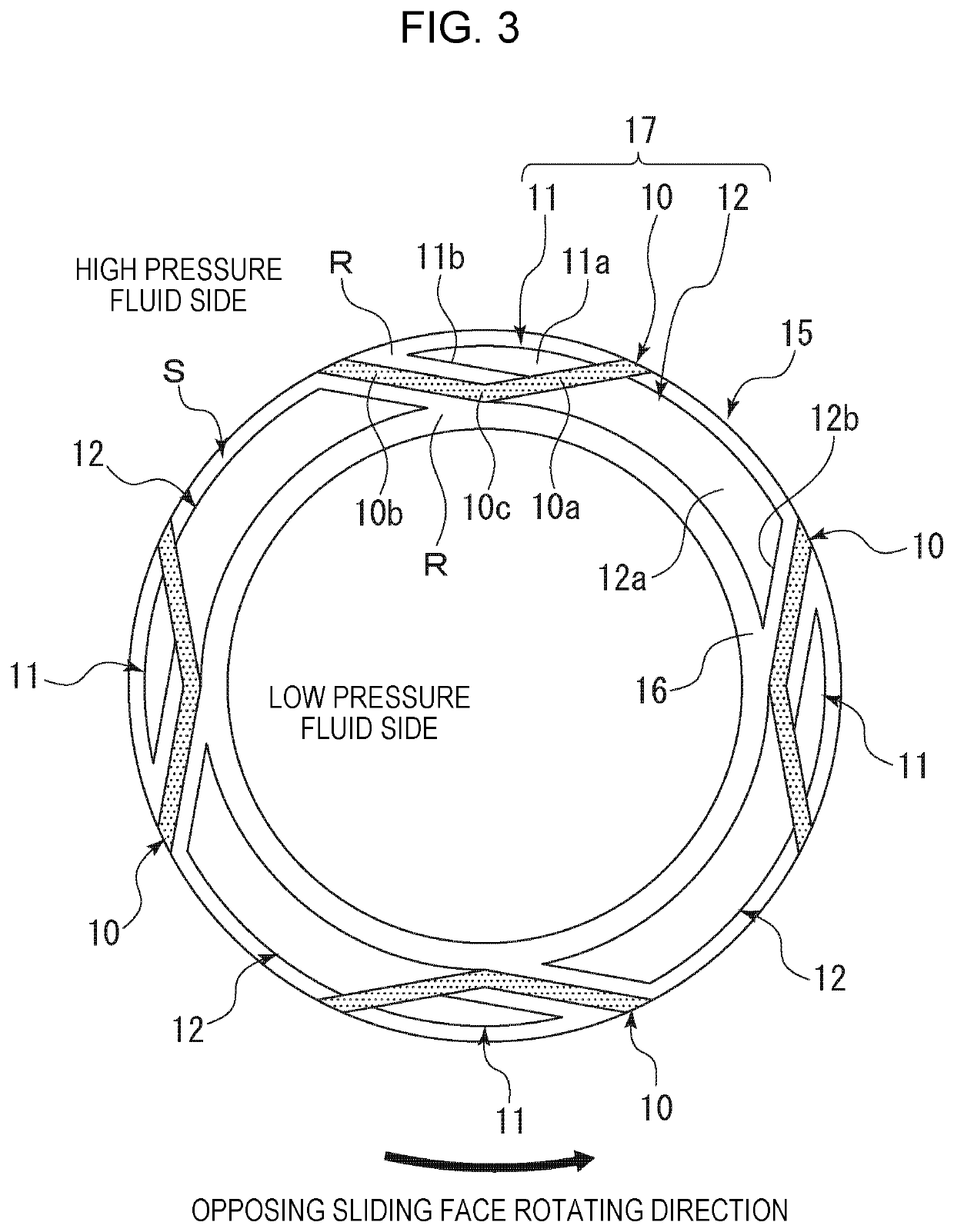

Sliding component

ActiveUS20200182356A1The effect is outstandingAvoid depositionEngine sealsBearing componentsCarbon filmRotational axis

In an exemplary embodiment, a sliding component includes an annular stationary side seal ring 5 fixed to the stationary side and an annular rotating side seal ring 3 to be rotated together with a rotating shaft, in which by relatively rotating opposing sealing faces S of the stationary side seal ring 5 and the rotating side seal ring 3, a silicate-containing sealed fluid present on one side in the radial direction of the relatively rotating sealing faces S is sealed, wherein an amorphous carbon film 8 formed by using a hydrocarbon gas containing no silicon compound is provided on at least any one of the sealing faces S of the stationary side seal ring 5 and the rotating side seal ring 3, and content of silicon of the amorphous carbon film 8 is 1.5 at % or less.

Owner:EAGLE INDS +1

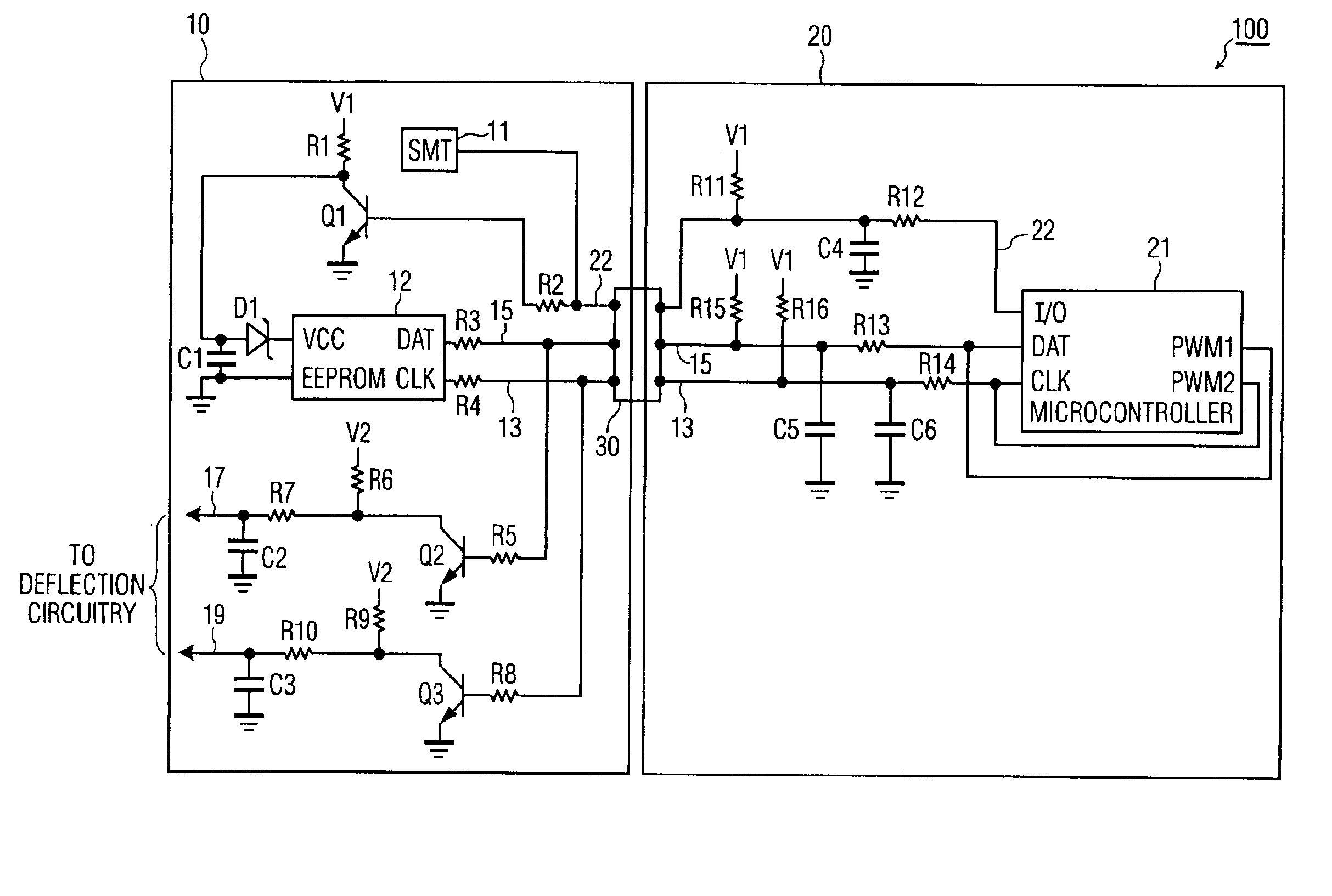

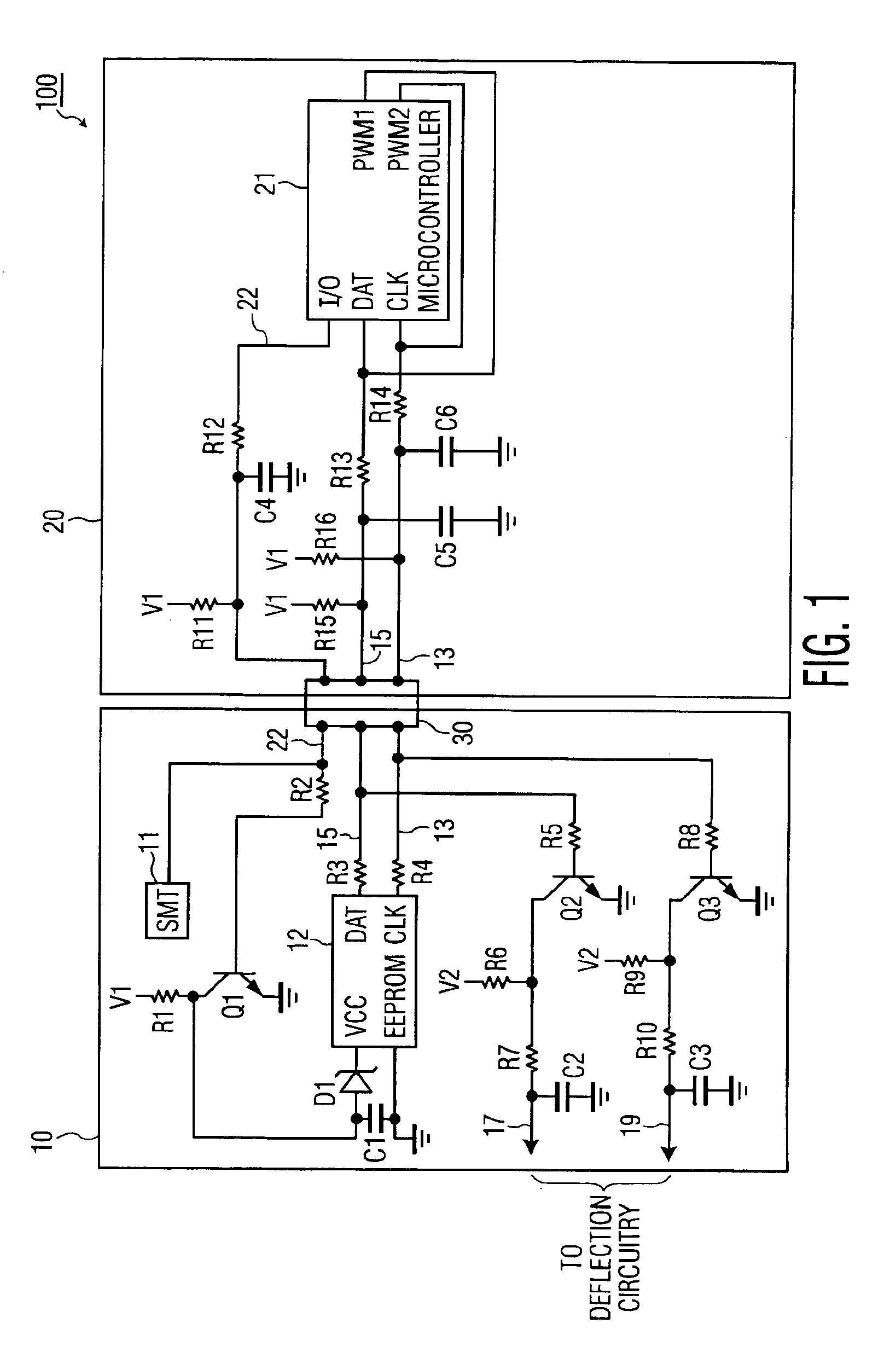

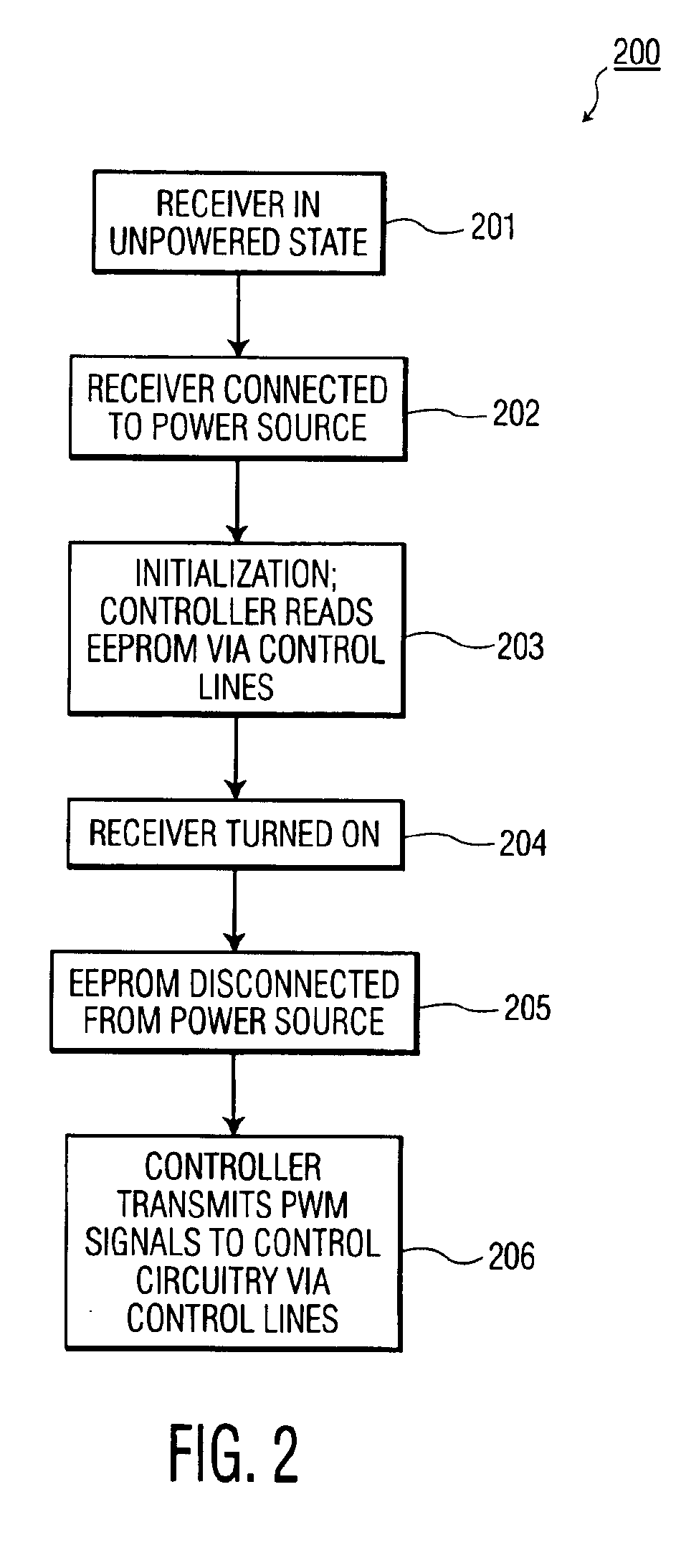

Apparatus and method for protecting a memory sharing signal control lines with other circuitry

InactiveUS6876400B2Low stateTelevision system detailsColor signal processing circuitsControl signalControl line

An apparatus such as a television signal receiver includes first and second circuit boards. The first circuit board includes a memory, and control circuitry for controlling at least one function of the apparatus. The second circuit board is operably coupled to the first circuit board via control lines. The second circuit board includes a controller for generating first and second control signals. The control lines transmit the first control signals from the controller to the memory when the apparatus is in a first operational state, and transmit the second control signals from the controller to the control circuitry when the apparatus is in a second operational state. To prevent inadvertent writes to the memory during the second operational state, the controller places the memory in an unpowered state when the controller transmits the second control signals to the control circuitry. Also, means are provided to prevent the memory from keeping the control lines in one state, for example, low level, during the unpowered state to allow communications to continue on the control lines.

Owner:INTERDIGITAL MADISON PATENT HLDG

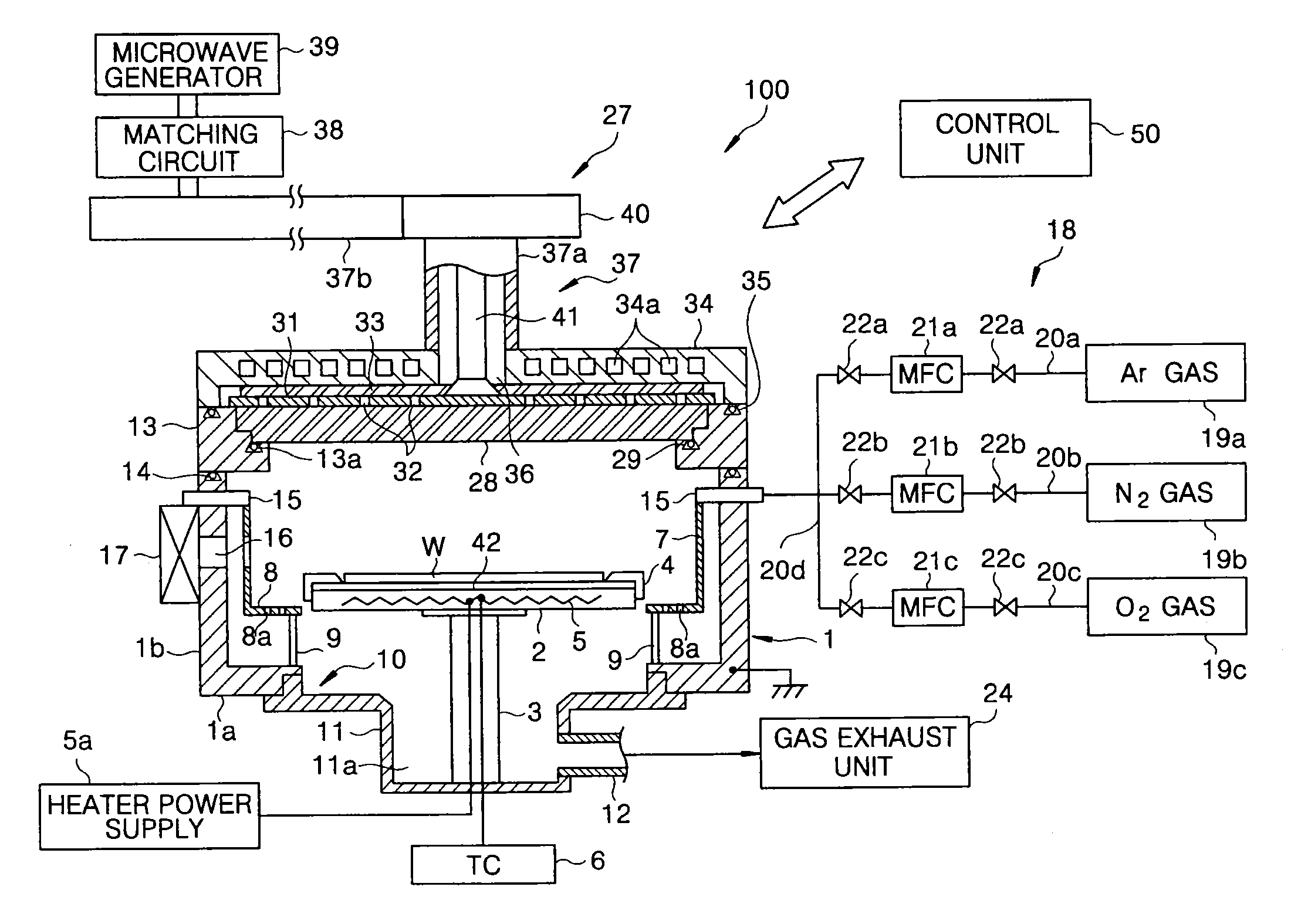

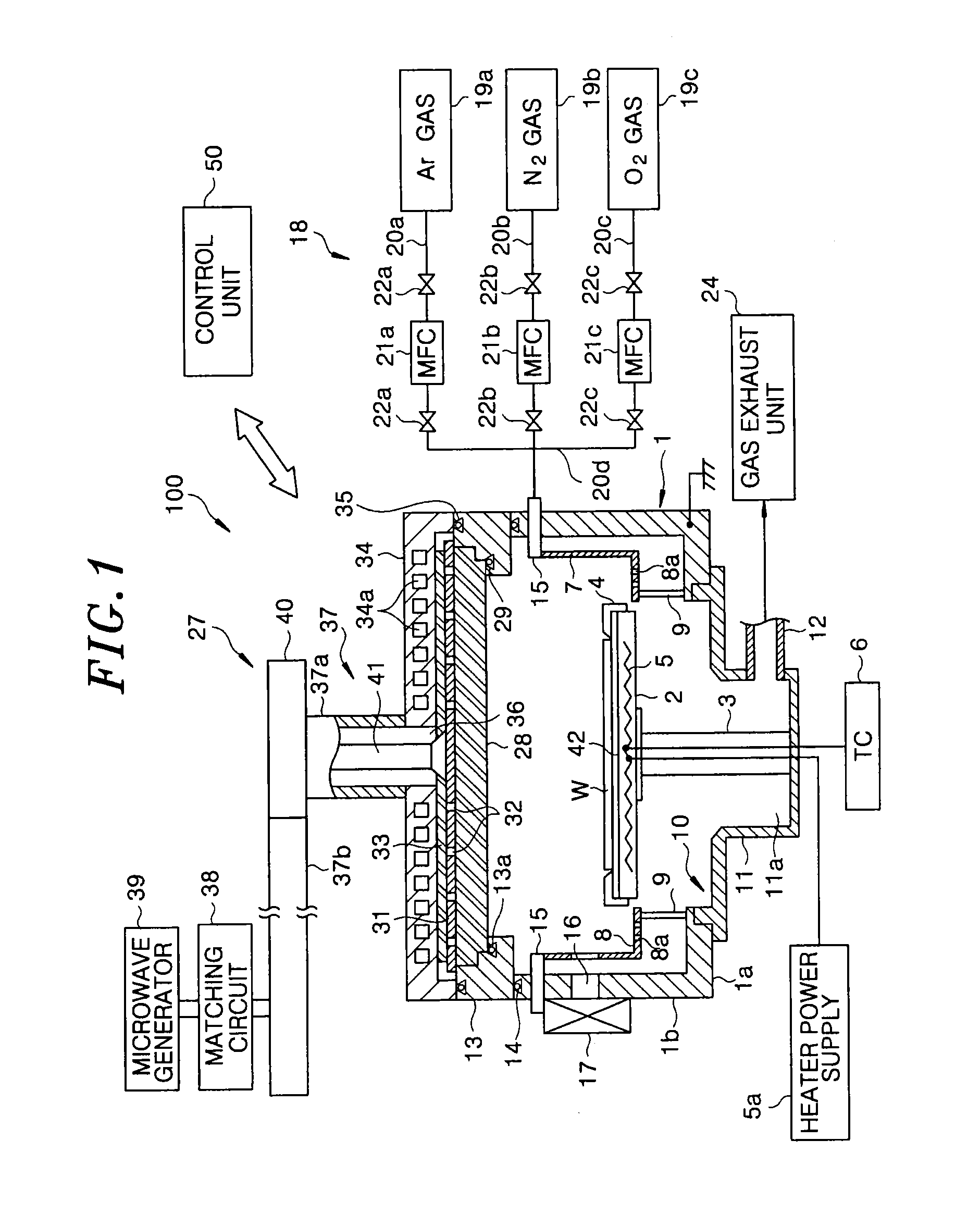

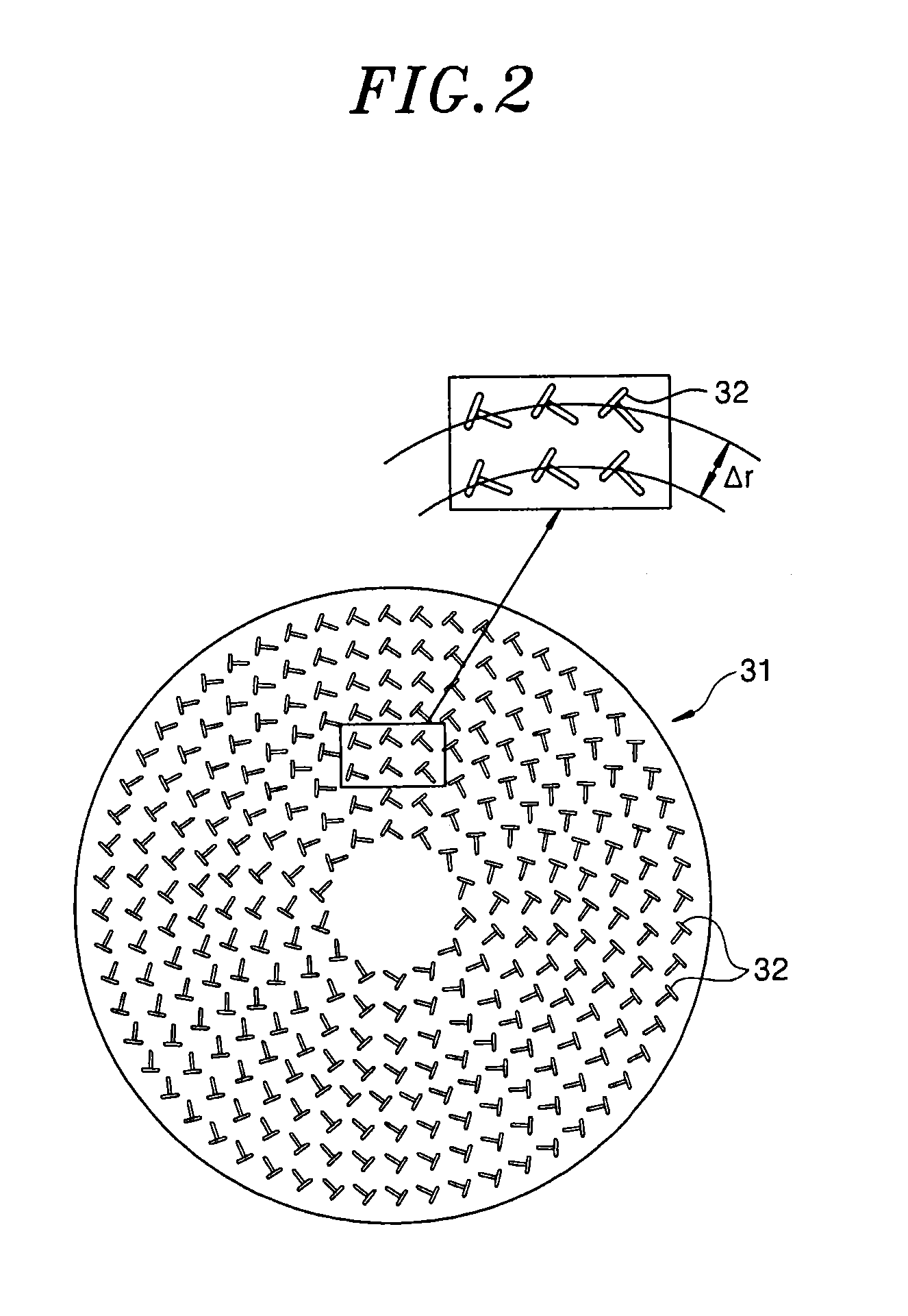

Plasma nitriding method

InactiveUS20130022760A1Stably carry-outReduce memory effectElectric discharge tubesSemiconductor/solid-state device manufacturingNitrogen plasmaNoble gas

A plasma nitriding method includes performing a high nitrogen-dose plasma nitriding process on an object having an oxide film by introducing a processing gas containing a nitrogen gas into a processing chamber of a plasma processing apparatus and generating a plasma containing a high nitrogen dose; and performing a low nitrogen-dose plasma nitriding process on the object by generating a plasma containing a low nitrogen dose. After the performing the high nitrogen-dose plasma nitriding process is completed, a plasma seasoning process is performed in the chamber by generating a nitrogen plasma containing a trace amount of oxygen by introducing a rare gas, a nitrogen gas and an oxygen gas into the chamber and setting a pressure in the chamber in a range from about 532 Pa to 833 Pa and a volume flow rate ratio of the oxygen gas in all the gases in a range from about 1.5% to 5%.

Owner:TOKYO ELECTRON LTD

Method and apparatus for on-the-fly minimum power state transition

InactiveUS7757137B2Reduce power consumptionMinimum area overheadElectronic circuit testingError detection/correctionPower modeElectricity

The invention includes a novel scan chain structure for LSSD or GSD IC operation. The scan chain structure includes a first flip-flop (L1) and a second flip-flop (L2) configured to operate the first flip-flop (L1) in normal mode operation, in scan mode operation, in initialization mode and in low leakage power mode operation, wherein each flip-flop within a long scan chain of latches includes a data input, data output, a clock input, a scan-in input and a scan-out output, arranged for normal mode operation. A buffer circuit is electrically connected between the scan-out output of the second flip-flop (L2) and the scan-in input of the first flip-flop (L1) for the next latch in the scan chain, the buffer circuit including a control element that controls the operation the first flip-flop (L1) to scan mode or low power leakage mode. The first flip-flop (L1) is set to a data output value upon exit from low power leakage mode that is the same value that it is set to at initialization during normal mode operation. The switching occurs in only one clock cycle.

Owner:GLOBALFOUNDRIES INC

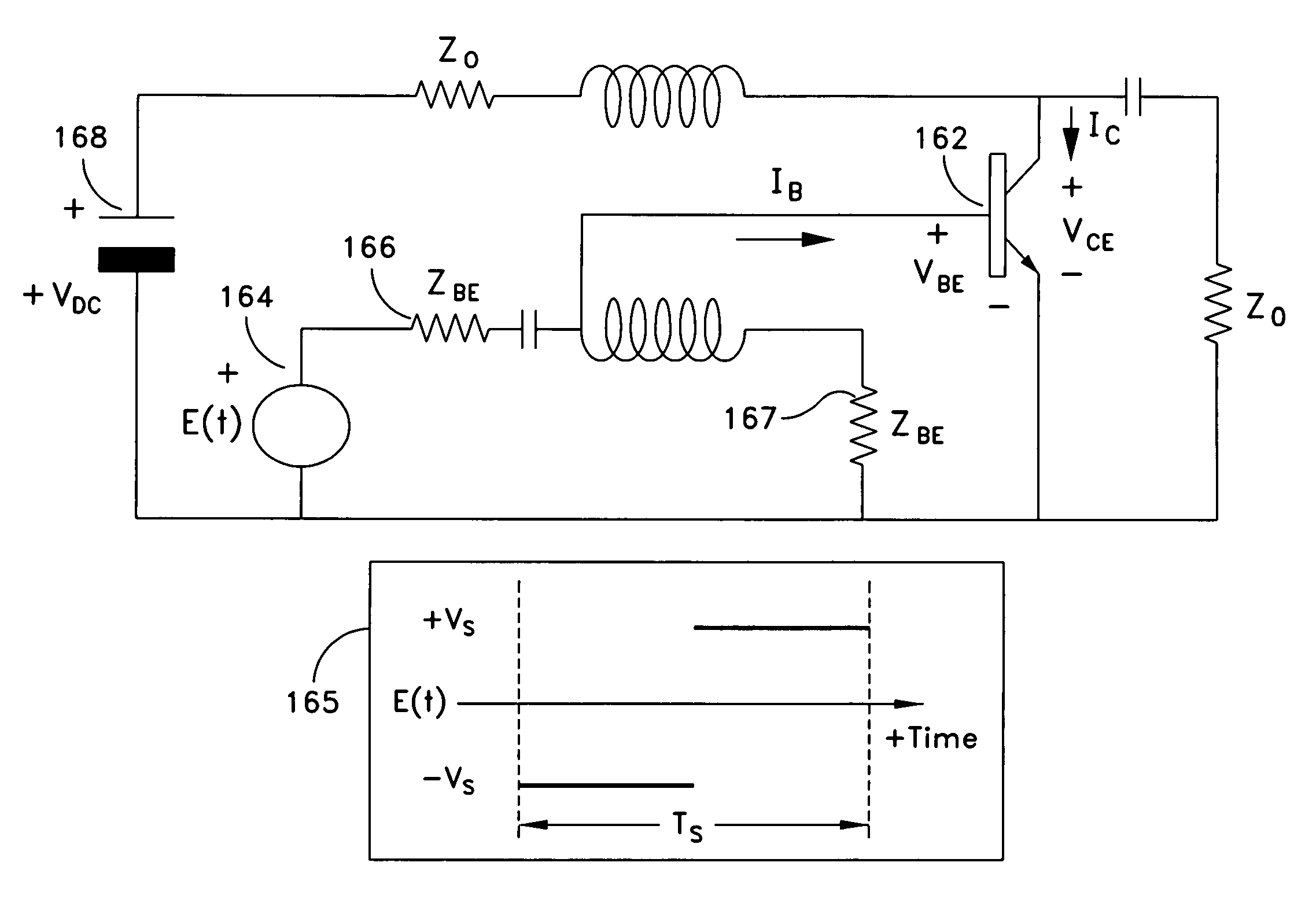

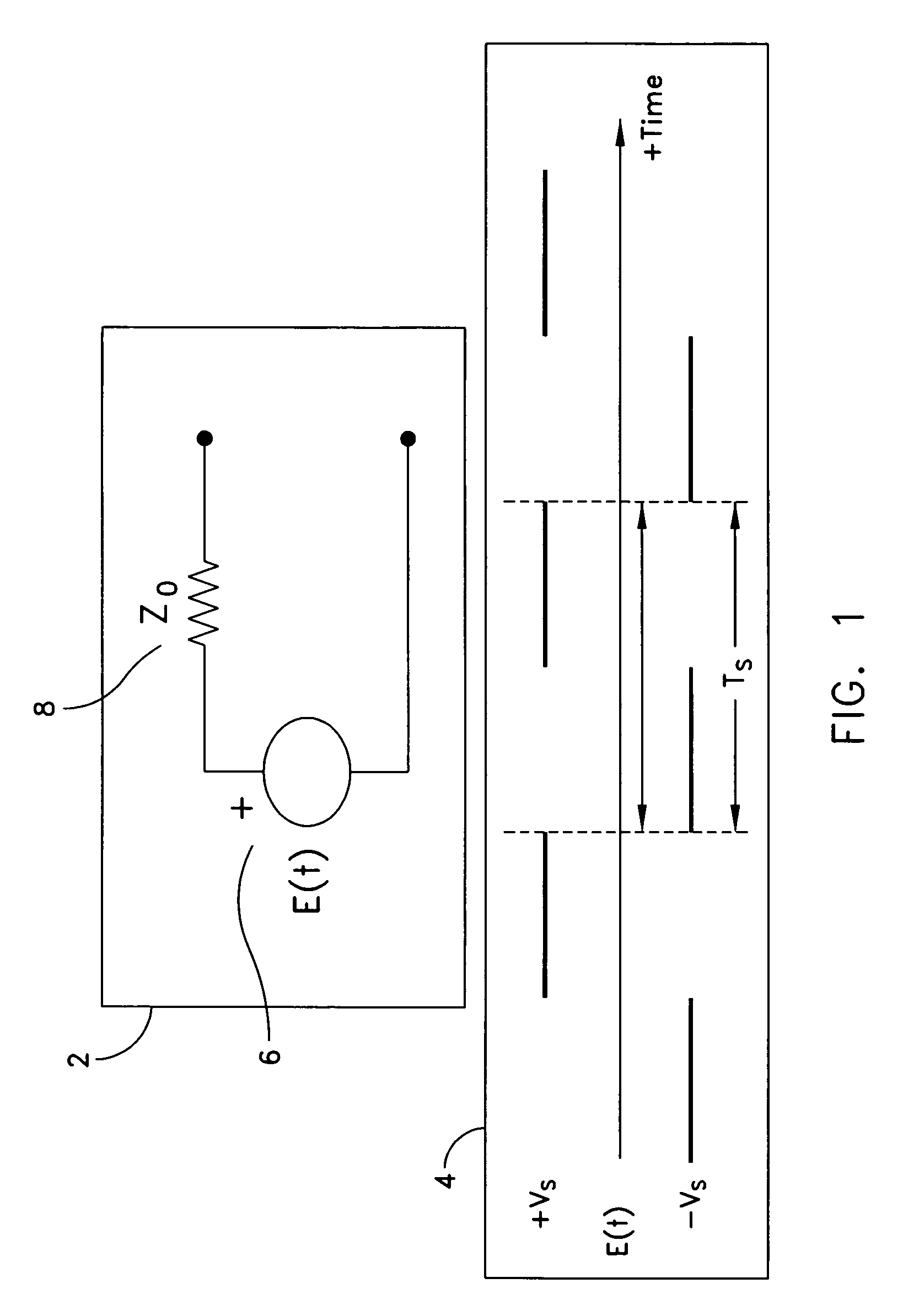

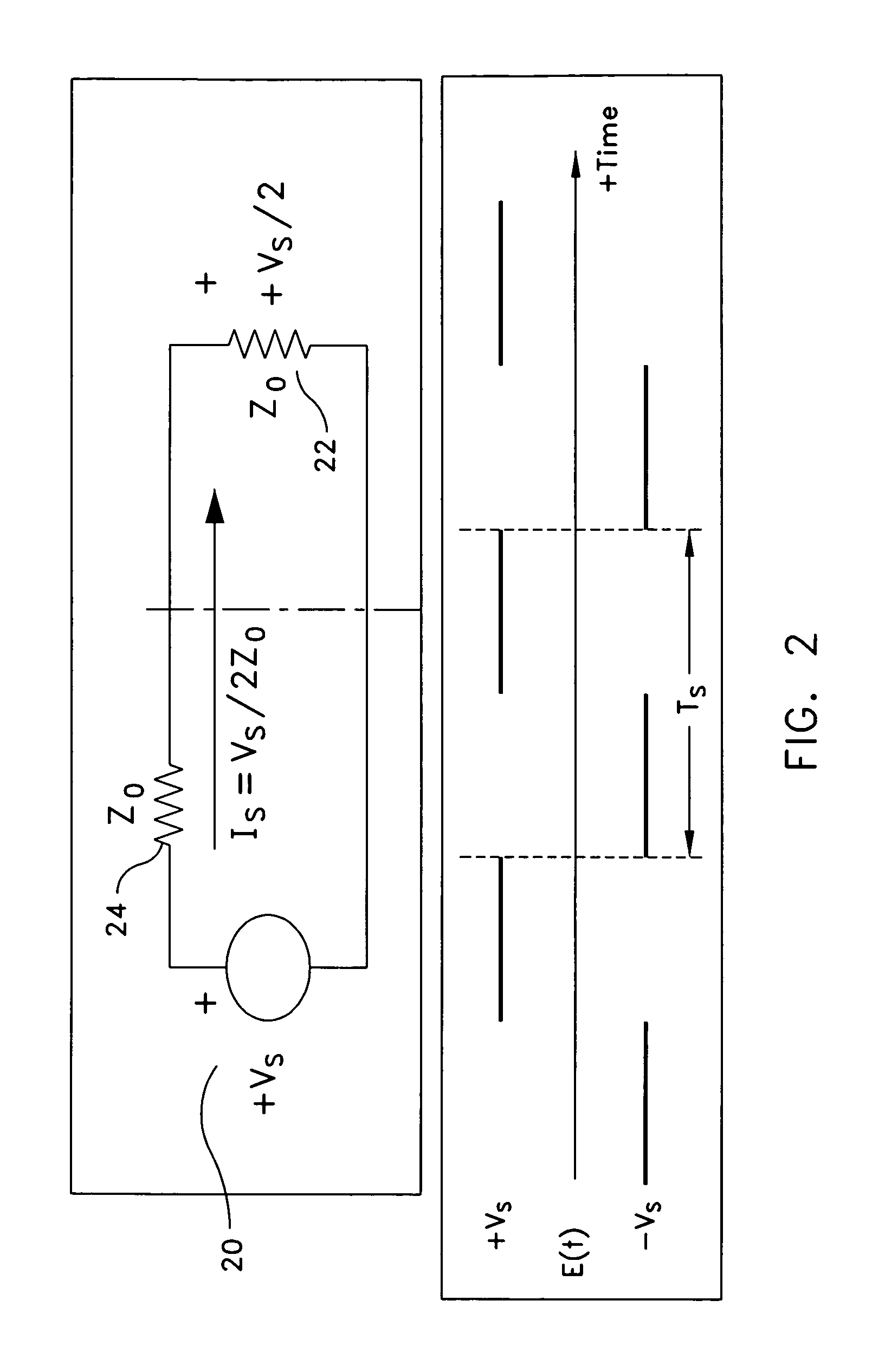

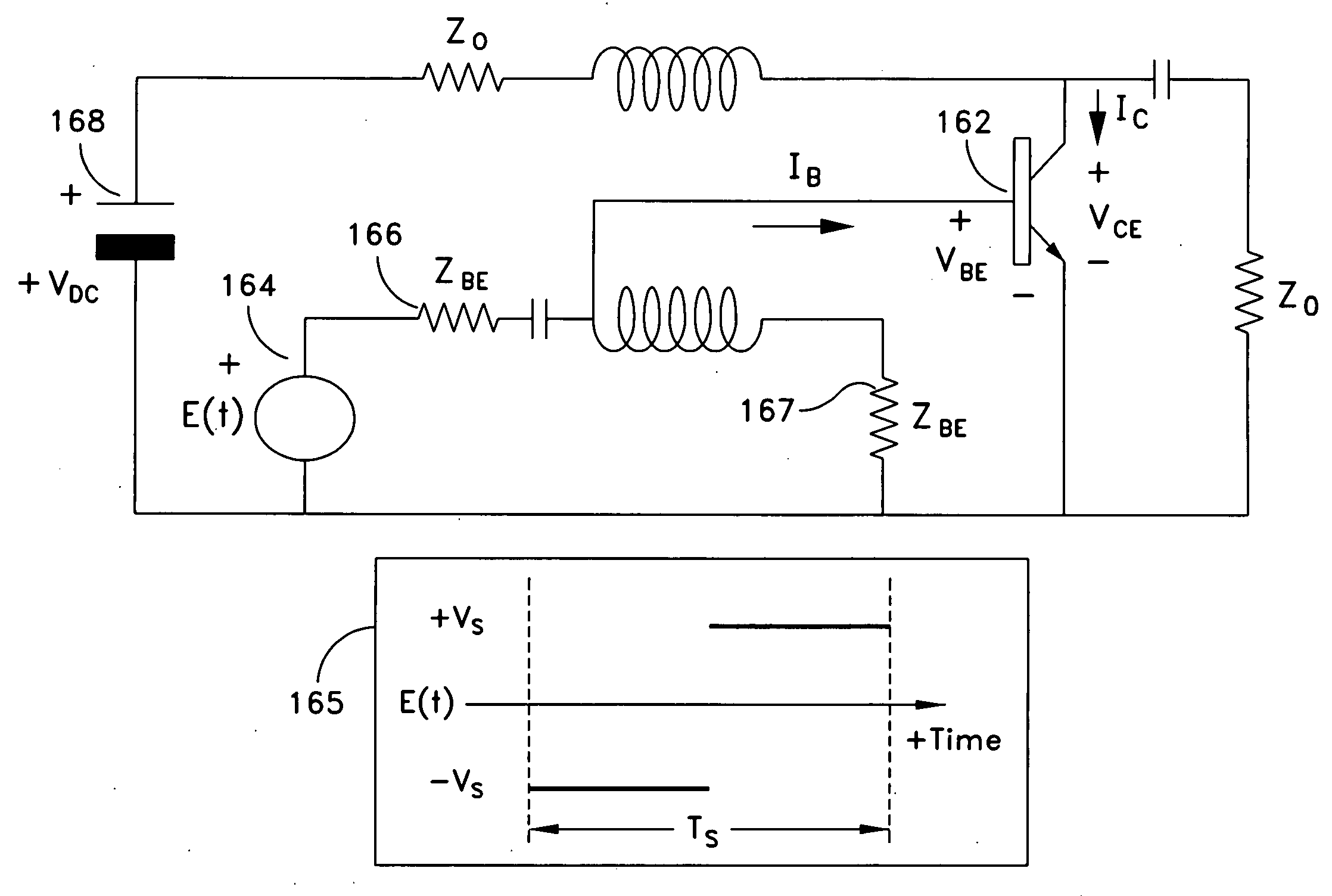

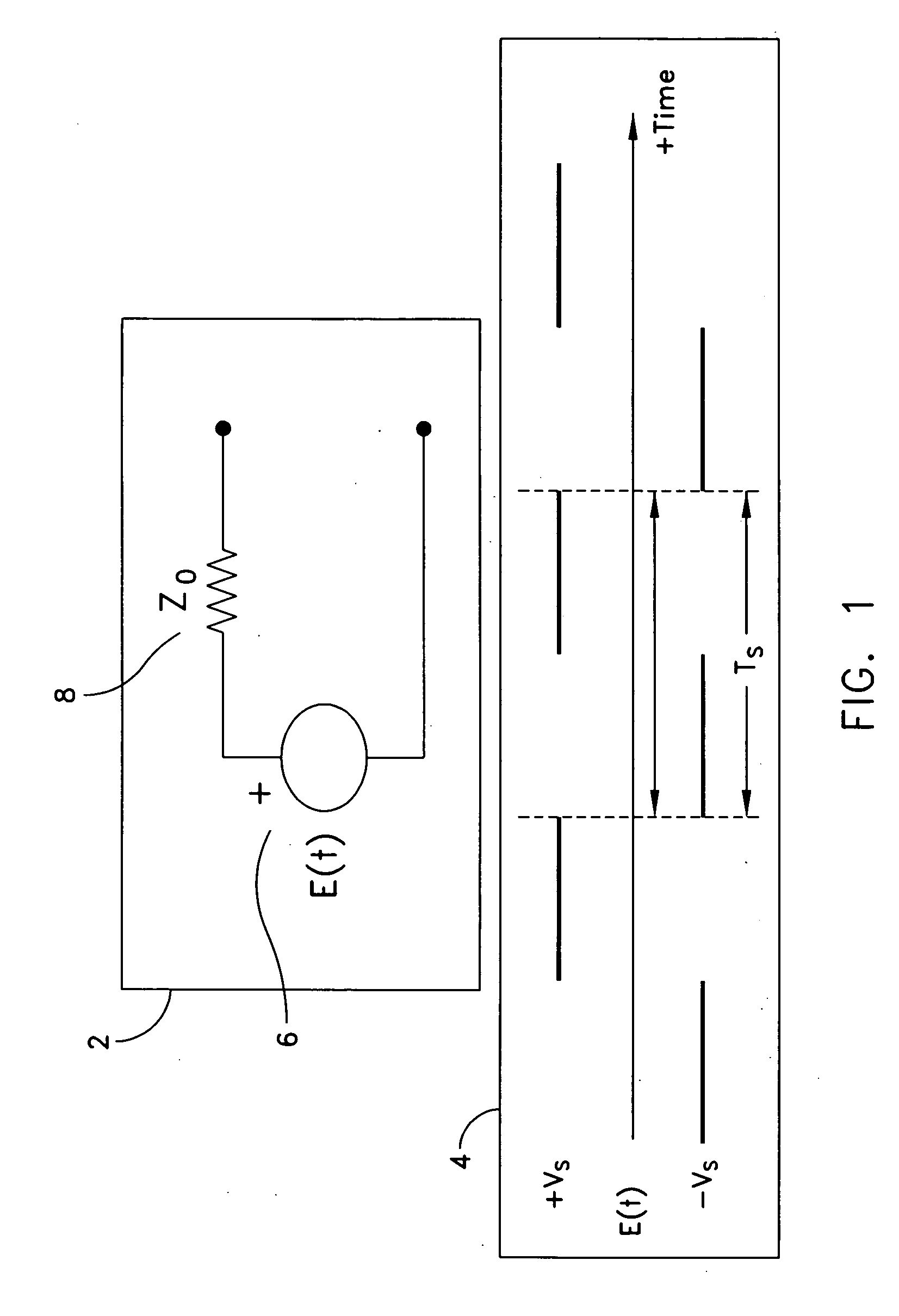

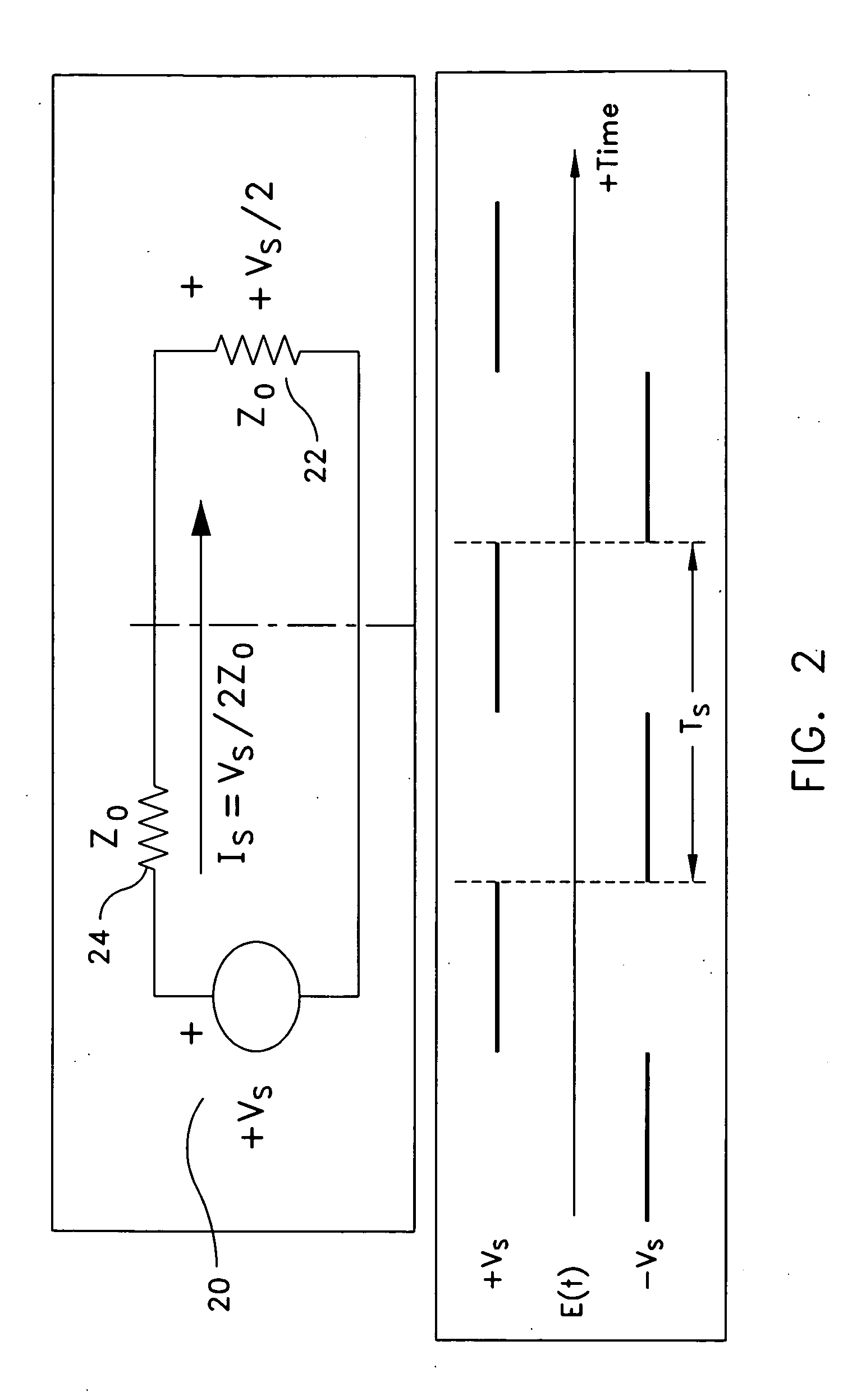

System and method for improving the efficiency and reliability of a broadband transistor switch for periodic switching applications

InactiveUS7679410B1Valid conversionImprove switching performanceTransistorElectronic switchingBroadbandEngineering

A driver circuit is provided for enabling a transistor collector-emitter path to be used as a broadband periodic switch. The broadband driver circuit controls the magnitude of the transistor base-emitter current in order to enable a CLOSED switch state and to simultaneously control the magnitude of the transistor base-emitter reverse-bias voltage in order to enable the OPEN-switch state. The precise control of these parameters minimizes base-charge storage and prevents reverse-breakdown failure.

Owner:UNITED STATES OF AMERICA

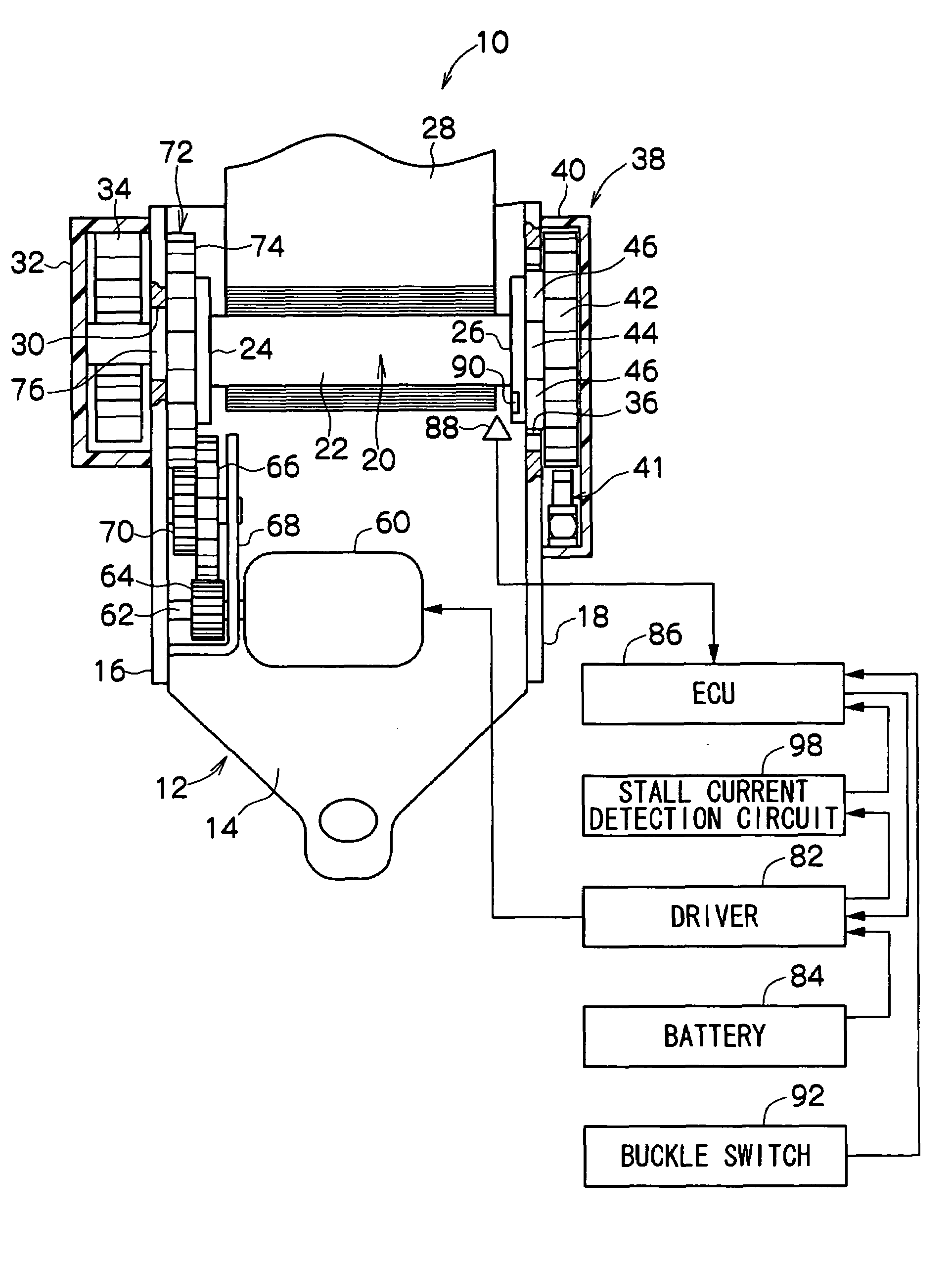

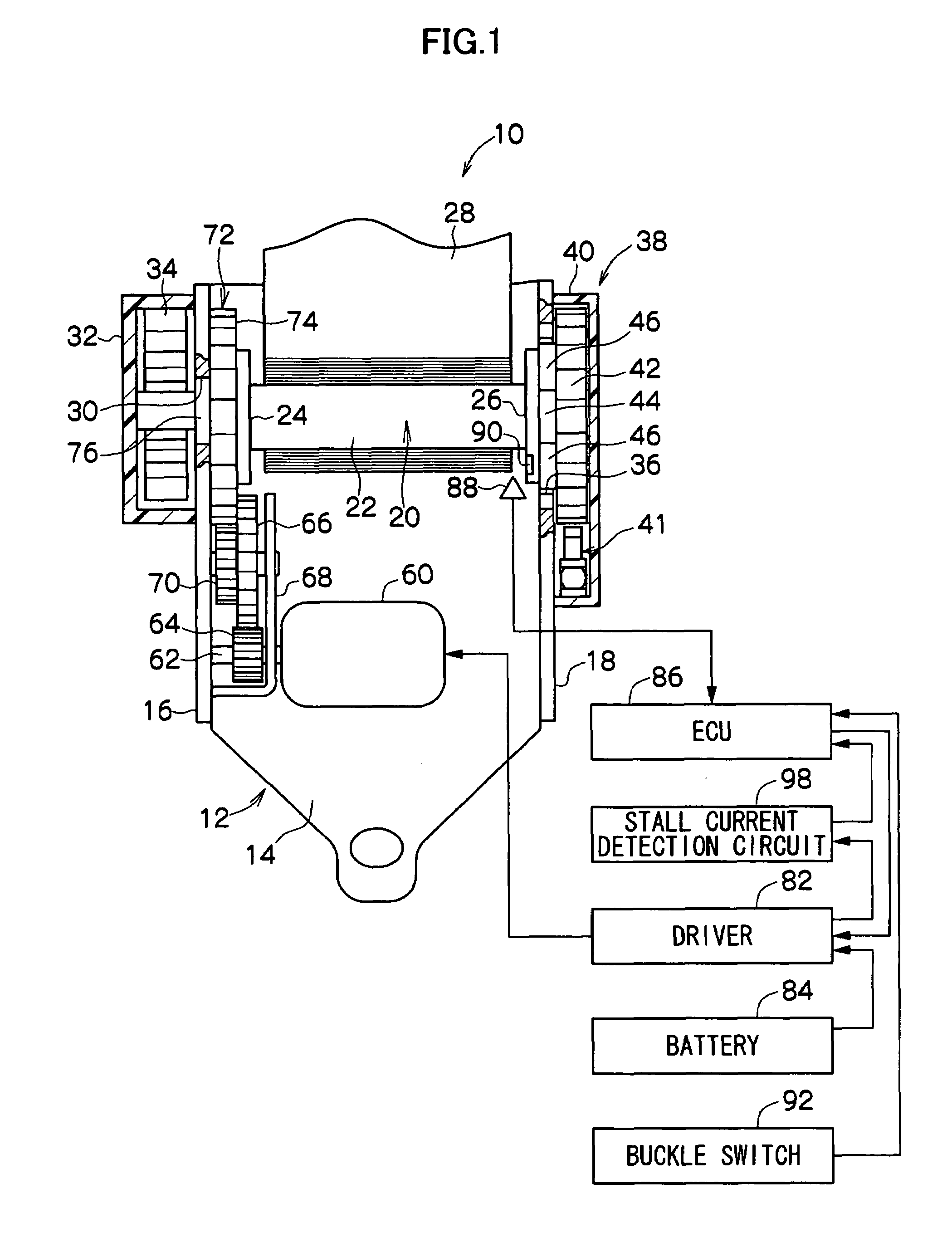

Motor retractor and drive control thereof

When the worn state of the webbing is lifted, current of a current value I0 corresponding to the appropriate storing speed of the webbing is supplied to the motor, whereby a take-up shaft rotates and the webbing is taken up. At a point in time when the webbing has been taken up to the extent that the webbing does not hinder the exiting of a vehicle by a passenger, the size of the supply current to the motor is reduced from the initial current value I1 to a current value I1. A reference current value IL of a stall current for determining whether to stop the motor when a foreign object or the like has become entangled between the webbing and an in-vehicle part can also be set to be small in correspondence to the reduced current value I1.

Owner:KK TOKAI RIKA DENKI SEISAKUSHO

Sliding component

ActiveUS11009130B2Keep it smoothPrevent leakageEngine sealsBearing componentsCarbon filmRotational axis

In an exemplary embodiment, a sliding component includes an annular stationary side seal ring 5 fixed to the stationary side and an annular rotating side seal ring 3 to be rotated together with a rotating shaft, in which by relatively rotating opposing sealing faces S of the stationary side seal ring 5 and the rotating side seal ring 3, a silicate-containing sealed fluid present on one side in the radial direction of the relatively rotating sealing faces S is sealed, wherein an amorphous carbon film 8 formed by using a hydrocarbon gas containing no silicon compound is provided on at least any one of the sealing faces S of the stationary side seal ring 5 and the rotating side seal ring 3, and content of silicon of the amorphous carbon film 8 is 1.5 at % or less.

Owner:EAGLE INDS +1

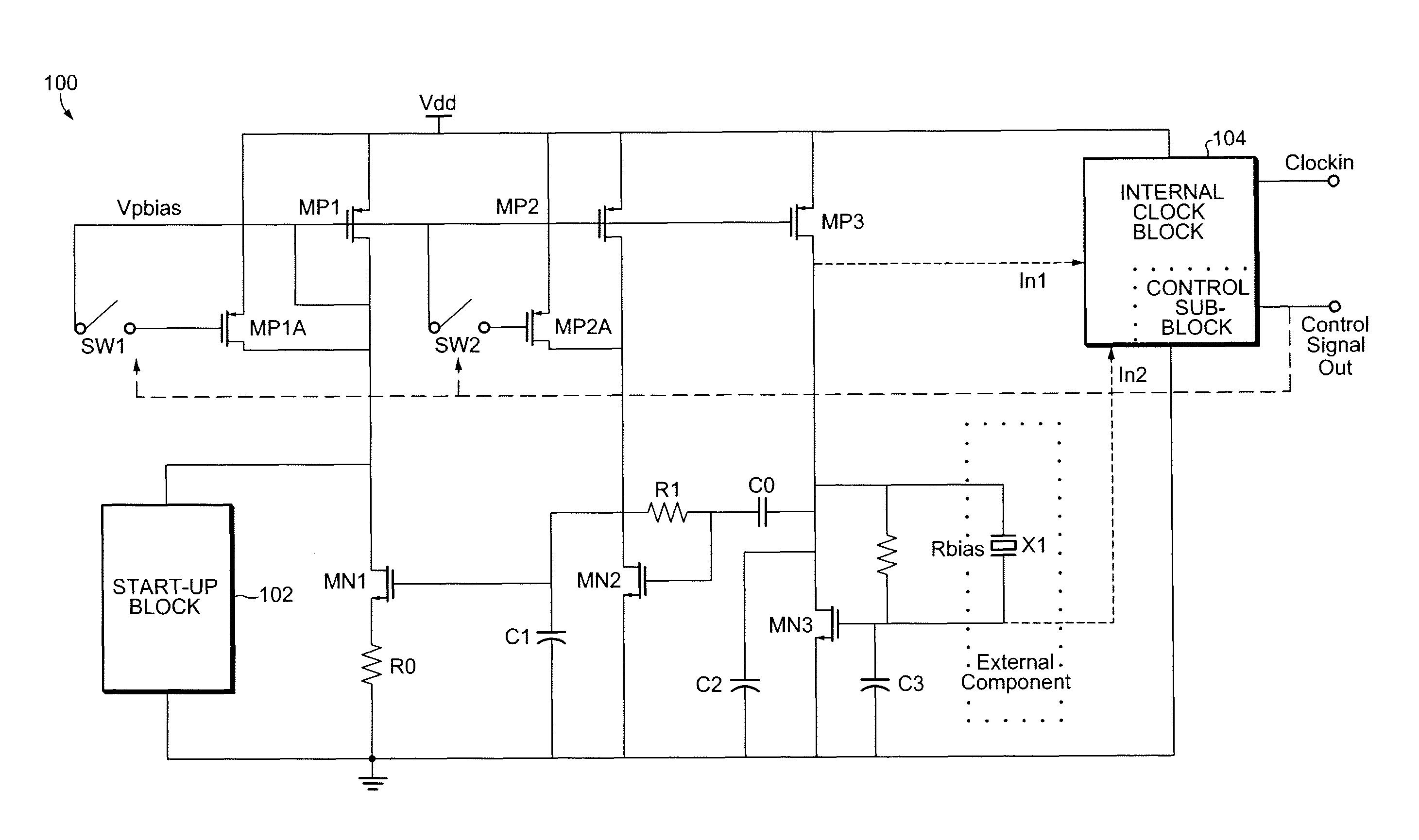

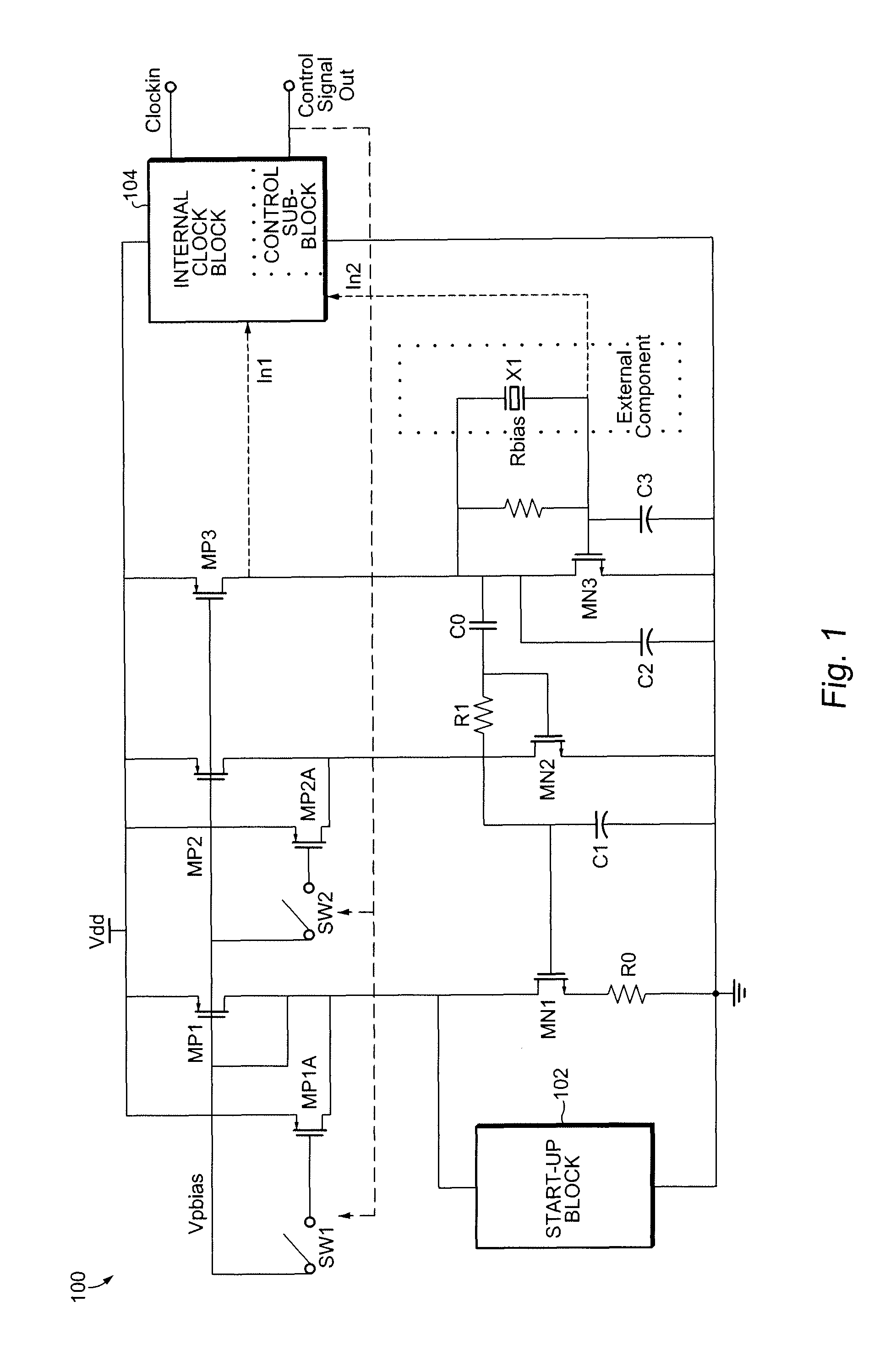

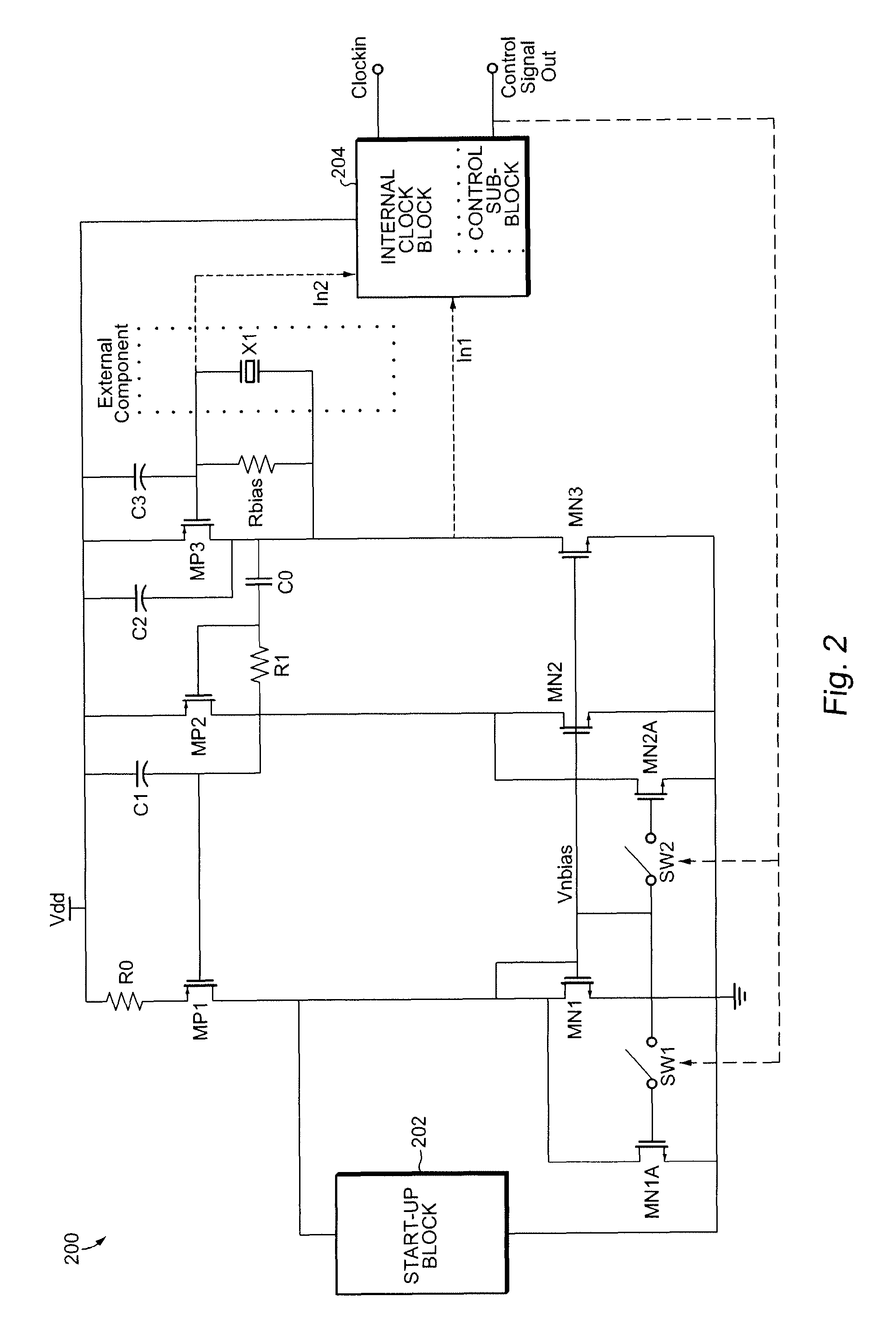

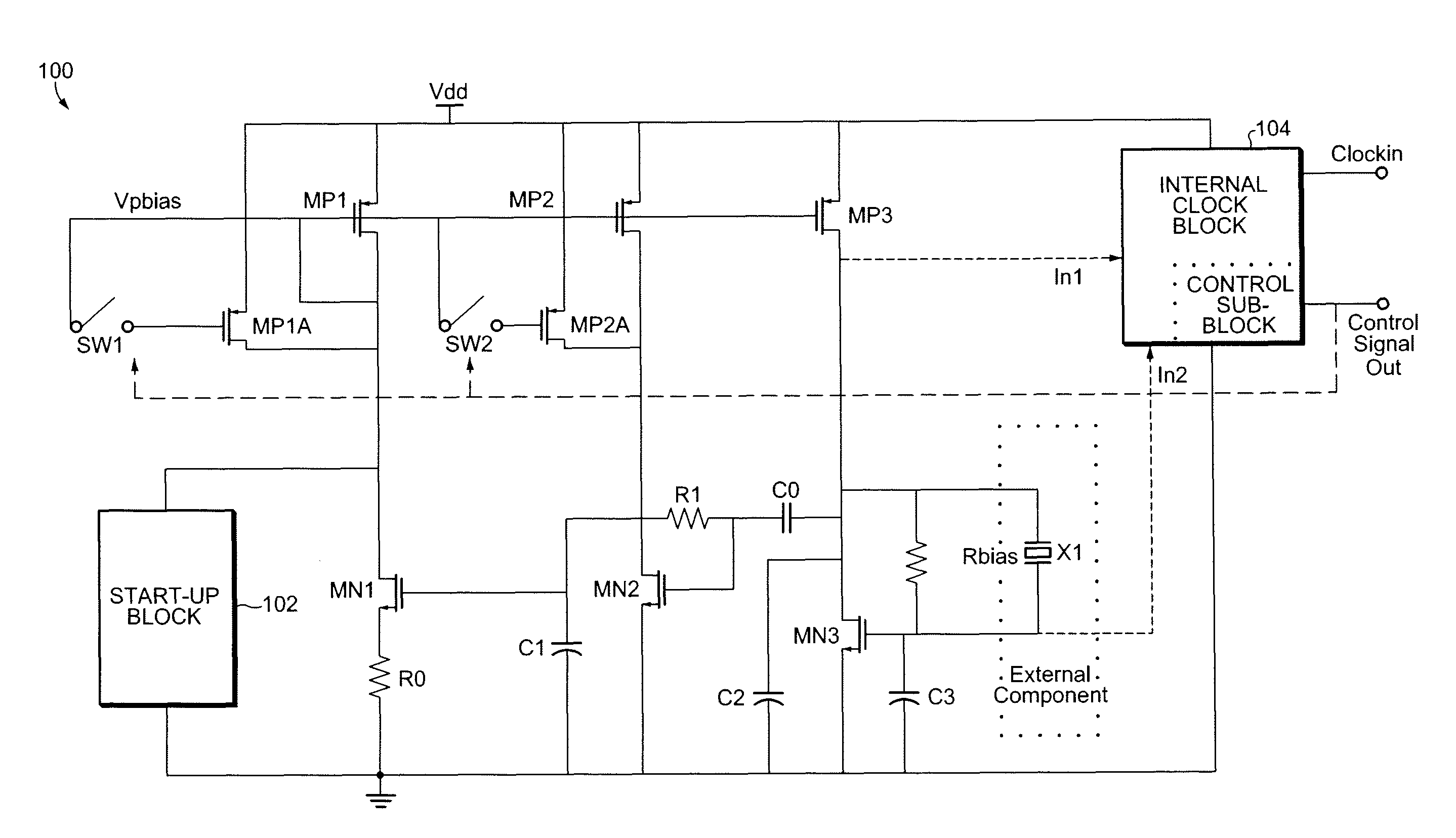

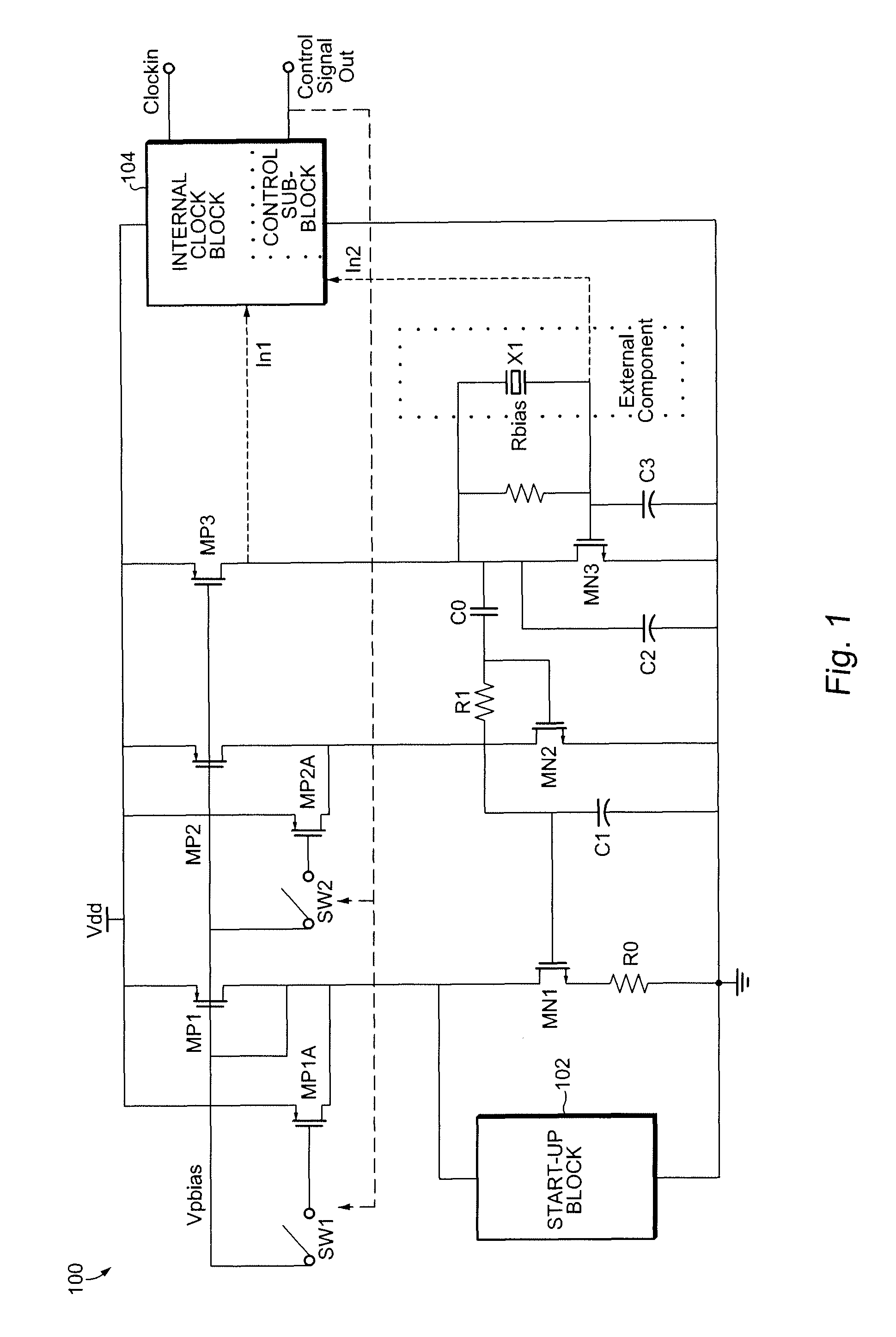

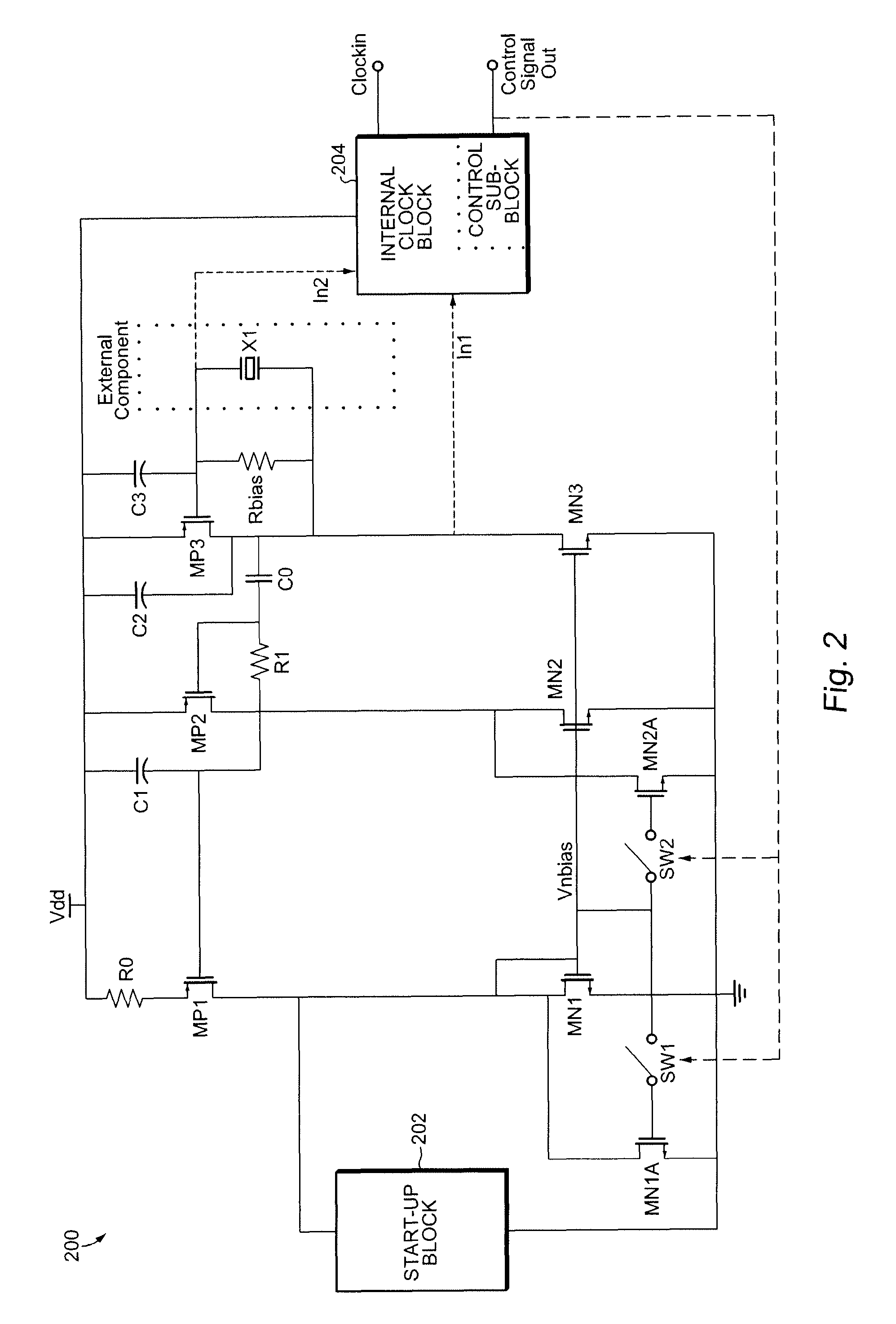

Method to Shorten Crystal Oscillator's Startup Time

ActiveUS20130141171A1Reduce startup timeImprove performancePulse automatic controlGenerator starterAudio power amplifierControl signal

An oscillator circuit includes an amplifier including at least two terminals for receiving a crystal and an automatic amplitude control loop coupled to the amplifier including biasing circuitry switched between a first operational mode and a second operational mode. The first operational mode occurs during an initial time period and the second operational mode occurs after the initial time period is expired. The biasing circuitry includes first and second PMOS transistor circuits, each transistor circuit including an unswitched PMOS transistor and a switched PMOS transistor. Alternatively, the biasing circuitry can include first and second NMOS transistor circuits, each transistor circuit including an unswitched NMOS transistor and a switched NMOS transistor. The biasing circuitry is under control of an internally generated control signal.

Owner:TELEFON AB LM ERICSSON (PUBL)

System and method for improving the efficiency and reliability of a broadband transistor switch for periodic switching applications

InactiveUS20100079196A1Valid conversionEasy to processTransistorElectronic switchingDriver circuitEngineering

Owner:UNITED STATES OF AMERICA

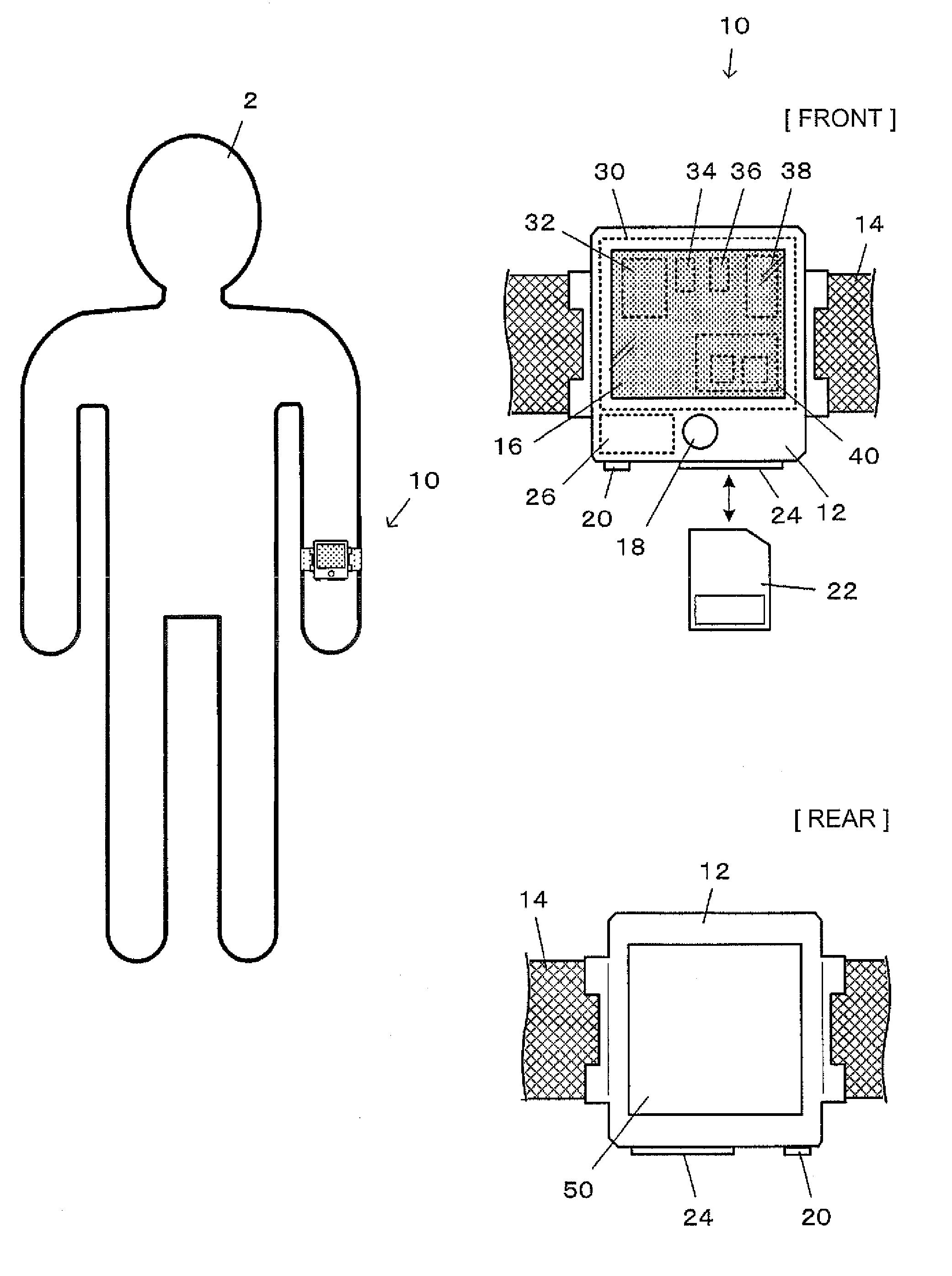

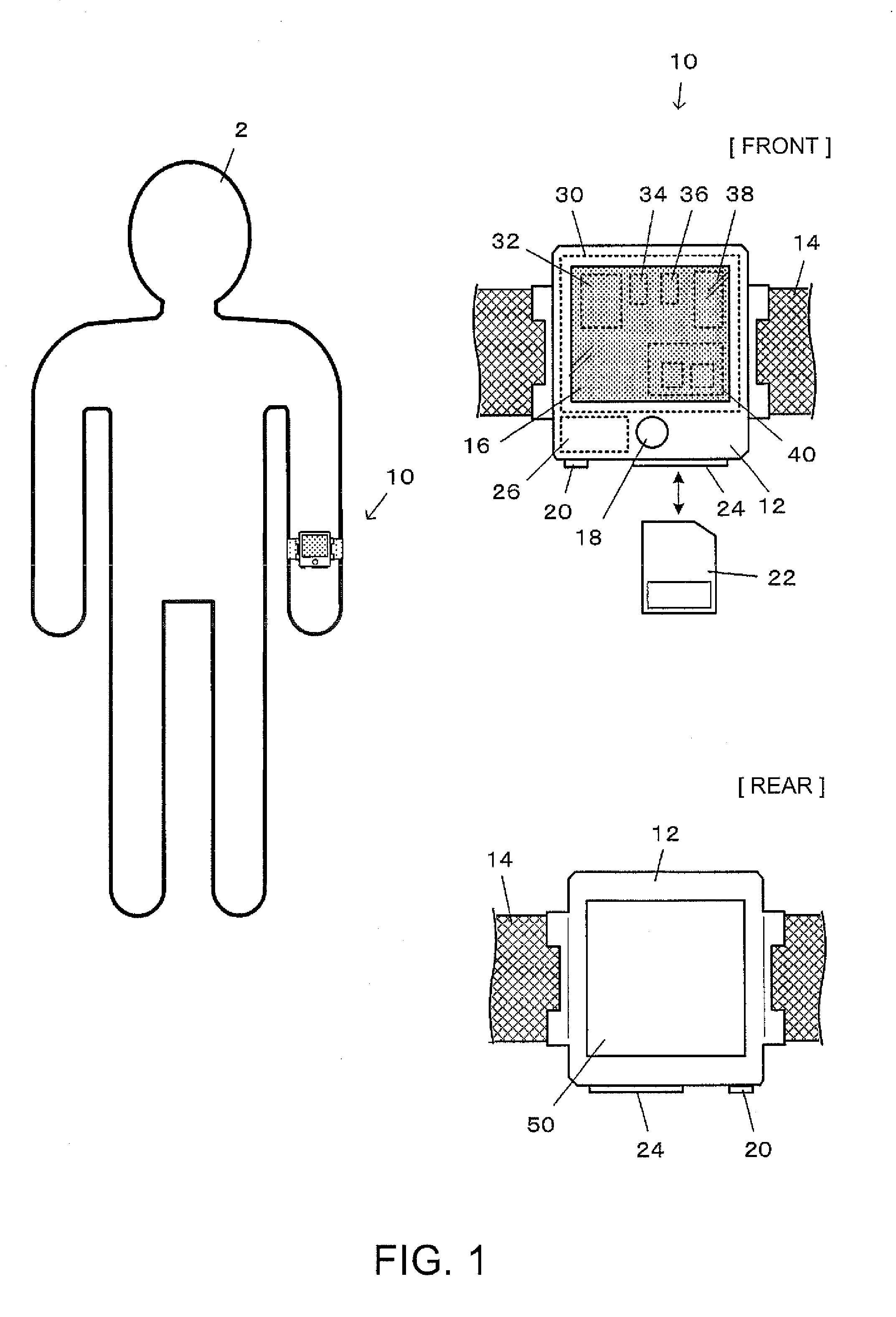

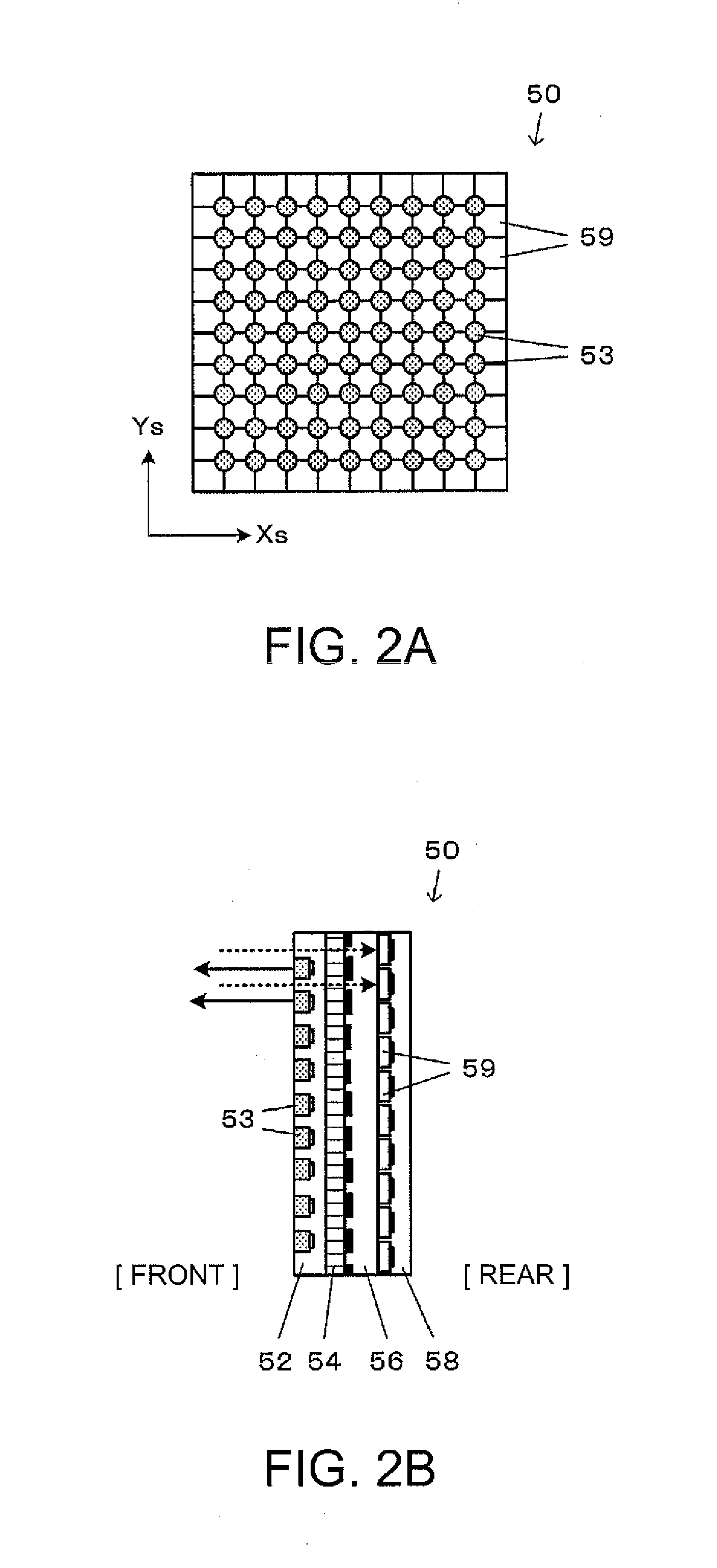

Blood glucose level measurement apparatus and blood glucose level measurement method

InactiveUS20150216457A1Quick checkReduce power consumptionOptical sensorsBlood characterising devicesGlucose polymersLevel measurement

A blood glucose level measurement apparatus is a non-invasive measurement apparatus mounted on a wrist or the like of a user and using light, and intermittently measures a blood glucose level of the user. A measurement interval is set according to a measured blood glucose level. For example, in a case where the measured blood glucose level is low, the measurement interval is set to be short.

Owner:SEIKO EPSON CORP

Method and apparatus for on-the-fly minimum power state transition

InactiveUS7949971B2Reduce power consumptionMinimum area overheadSolid-state devicesElectrical testingData fileEngineering

The invention includes a design structure embodied in a computer readable medium for performing a method for inserting a scan chain into a VLSI circuit design. The scan chain structure, or structures, are included in the design structure for the VLSI circuit design. The scan chain structure includes a first flip-flop (L1) and a second flip-flop (L2) configured to operate the first flip-flop (L1) in normal mode operation, in scan mode operation, in initialization mode and in low leakage power mode operation. A buffer circuit is electrically connected between the scan-out output of the second flip-flop (L2) and the scan-in input of the first flip-flop (L1) for the next latch in the scan chain. Buffer circuit control elements control the first flip-flop (L1) to switch between scan mode or low power leakage mode. The switching occurs in only one clock cycle. The design structure can include a netlist, which describes the VLSI circuit, reside on storage medium as a data format used for the exchange of layout data of integrated circuits, and preferably includes at least one of test data files, characterization data, verification data, or design specifications.

Owner:GLOBALFOUNDRIES INC

Multi-level memory cell programming methods

ActiveUS20090201725A1Quick and efficientLow stateRead-only memoriesDigital storageEngineeringThreshold voltage

A method for programming a plurality of multi-level memory cells described herein includes iteratively changing a bias voltage applied to a first memory cell to program the first memory cell to a first threshold state and detecting when the first cell reaches a predetermined threshold voltage. The bias voltage applied to the first memory cell upon reaching the predetermined threshold voltage is recorded. A second memory cell is programmed to a second threshold state by applying an initial bias voltage to the second memory cell which is function of the recorded bias voltage.

Owner:MACRONIX INT CO LTD

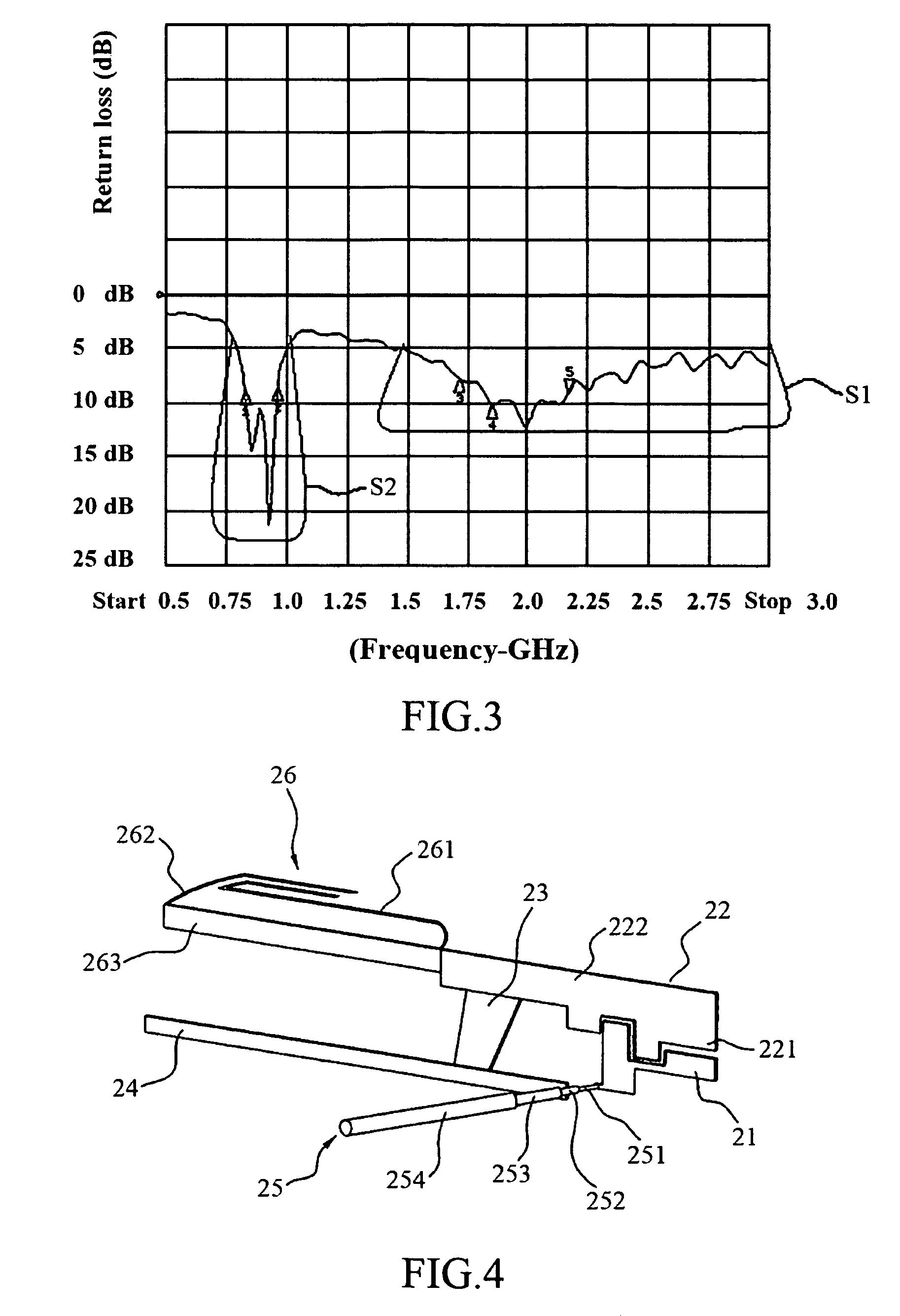

Antenna module

InactiveUS7786941B2Enhanced radiationImprove transmission bandwidthSimultaneous aerial operationsAntenna supports/mountingsElectrical conductorGround plane

An antenna module is provided. The antenna module comprises a first radiation conductor, a second radiation conductor, a short-circuit element (s / c element), a ground plane, a feed-in cable and a spurious radiation conductor. One terminal of the second radiation conductor is near the first radiation conductor with a gap. One terminal of the s / c element is connected to the second radiation conductor and the other side of the s / c element is connected to the ground plane. The feed-in cable comprises a centre conductor and an external conductor, wherein the centre conductor is connected to the first radiation conductor and the external conductor is connected to the ground plane. The spurious radiation conductor is connected to the second radiation conductor. The second radiation conductor comprises a spurious radiation plate, a first radiation piece and a second radiation piece within the two sides of the second radiation conductor. The first radiation piece and a second radiation piece are in parallel and a gap is conducted between the first radiation piece and the second radiation piece.

Owner:ADVANCED CONNECTEK INC

Managing the power-performance range of an application

InactiveUS8276015B2Adjustable performanceLow stateEnergy efficient ICTDigital computer detailsProcessor registerPerformance tuning

Semiconductor device circuits and methods are provided for adjusting core processor performance based on usage metrics. Metric detection and adjustment are performed in digital logic hardware guided by registers providing maximum and minimum frequency settings, without intervening input from system software or firmware, thus greatly speeding the processor performance adjustment. Power-performance drivers provide applications or the operating system ability to specify maximum and minimum frequency requirements.

Owner:INT BUSINESS MASCH CORP

Method to shorten crystal oscillator's startup time

ActiveUS8736391B2Reduce startup timeImprove performancePulse automatic controlGenerator starterAudio power amplifierControl signal

An oscillator circuit includes an amplifier including at least two terminals for receiving a crystal and an automatic amplitude control loop coupled to the amplifier including biasing circuitry switched between a first operational mode and a second operational mode. The first operational mode occurs during an initial time period and the second operational mode occurs after the initial time period is expired. The biasing circuitry includes first and second PMOS transistor circuits, each transistor circuit including an unswitched PMOS transistor and a switched PMOS transistor. Alternatively, the biasing circuitry can include first and second NMOS transistor circuits, each transistor circuit including an unswitched NMOS transistor and a switched NMOS transistor. The biasing circuitry is under control of an internally generated control signal.

Owner:TELEFON AB LM ERICSSON (PUBL)

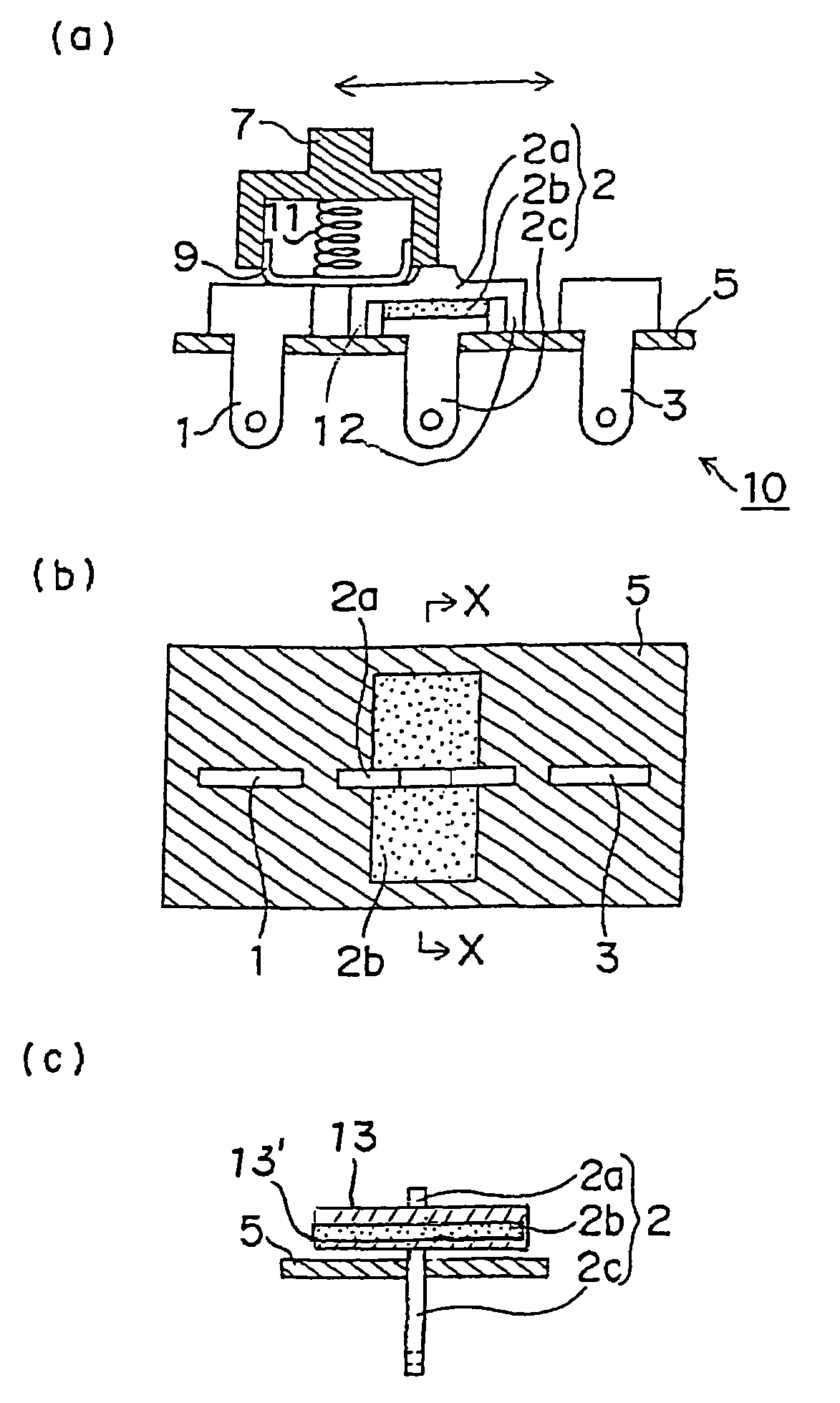

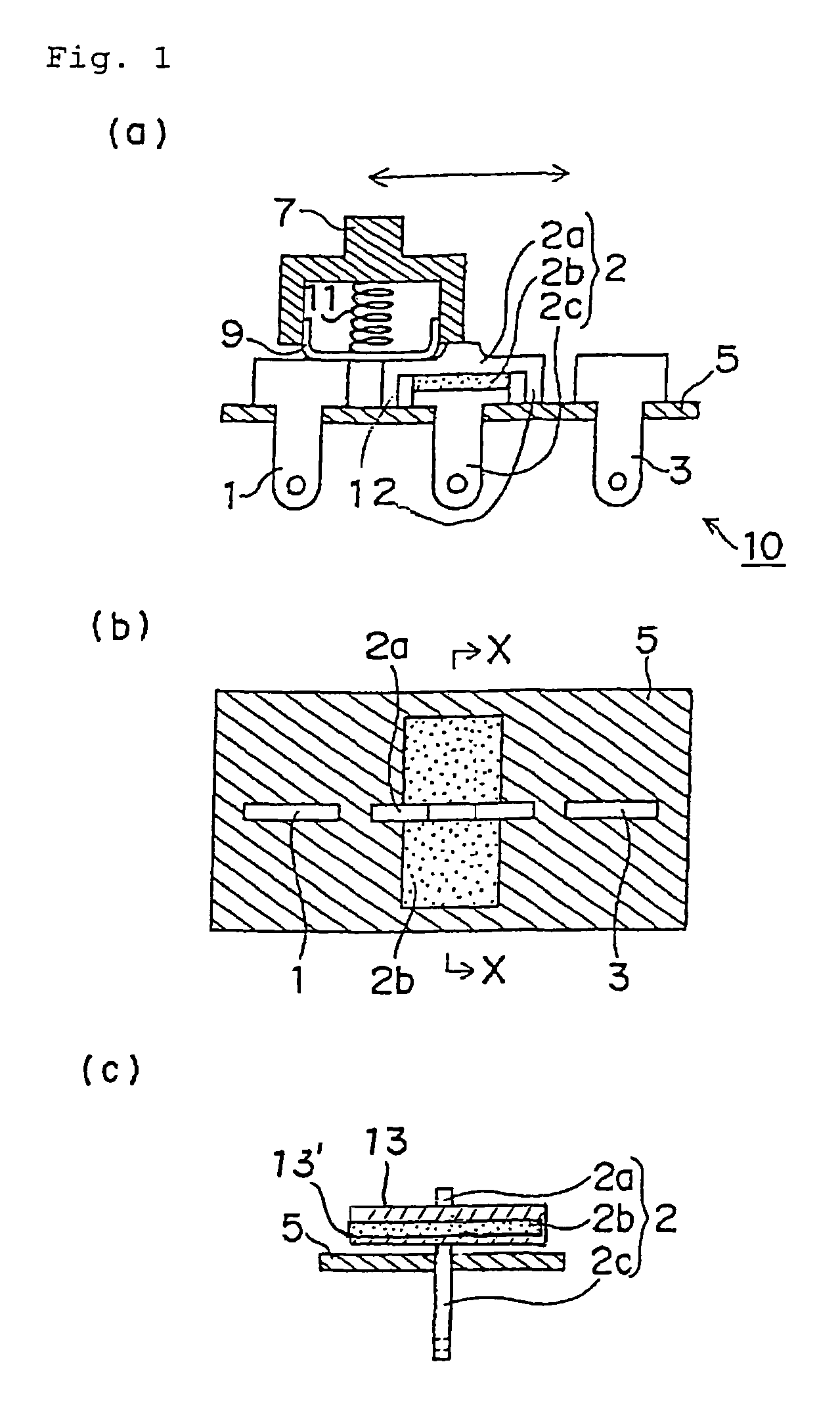

Switch and device using the switch

ActiveUS8395062B2Space minimizationLow number of componentsHigh-tension/heavy-dress switchesElectrothermally operated protective switchesEngineeringOver current protection

There is provided a novel switch having a function of overcurrent protection. In a switch comprising a conductive movable member (9) and at least two terminals (1, 2, 3) and being switchable by mechanically moving the movable member (9) between a state in which the movable member (9) contacts with the two terminals (1, 2) simultaneously and a state in which the movable member (9) is apart from either one (1) of the two terminals (1, 2), at least one (2) of the two terminals (1, 2) is separated into a conductive contact part (2a) for contacting with the movable member (9) and a conductive connect part (2b) for being electrically connected with an external element (not shown), and a PTC member (2b) is located between the contact part (2a) and the connect part (2c). The PTC member (2b) may be a PTC element having a PTC material layer and a pair of conductive material layers each located on opposed surfaces of the PTC material layer.

Owner:TYCO ELECTRONICS RAYCHEM KK

Brazing method

ActiveUS10150186B2Efficient use ofConducive to simplificationWelding/cutting media/materialsMetal working apparatusFiller metalMetal

A hollow aluminum structure that will be brazed includes at least one brazing sheet having a filler metal layer clad onto a core layer. The core layer is composed of aluminum or an aluminum alloy containing less than 0.2 mass % Mg. The filler metal layer is composed of an aluminum alloy that contains Si: 4.0-13.0 mass % and Bi: 0.01-0.3 mass %, and further contains Li: 0.004-0.08 mass % and / or Be: 0.006-0.12 mass %, the filler metal layer containing less than 0.1 mass % Mg. The hollow aluminum structure is assembled such that the filler metal layer is present at locations that will form both an interior-facing brazed joint and an exterior-facing brazed joint. Then, flux is applied onto the filler metal layer at the location that will form the exterior brazed joint, and the hollow aluminum structure heated in an inert gas atmosphere to form the interior brazed joint and the exterior brazed joint.

Owner:FURUKAWA SKY ALUMINUM CORP

Battery temperature control device

ActiveUS9246201B2Low stateCircuit monitoring/indicationIndicating/monitoring circuitsTemperature controlEngineering

Even when temperature sensors (12, 13) used in a device for warming a battery (1) being not in use by using a battery-driven heater (2) have failed, the battery (1) is prevented from freezing. Based on a battery temperature (Tb) and an outside air temperature (Ta), times (&Dgr;t1 to &Dgr;t8) during which Tb will decrease down to a warming start temperature (Tb_start) are each set to the next controller startup time (&Dgr;t). A controller (9) is started up every &Dgr;t, at t2, t3, and t4, and checks whether Tb<Tb_start is satisfied or not. At t4 when Tb<Tb_start is satisfied, a heater (2) is battery-driven to warm the battery (1). After t0 when the outside air temperature sensor (13) fails, the outside air temperature (Ta) is set to a fixed value (Ta_const) and based on this Ta=Ta_const and the battery temperature (Tb), the above control is repeated. Accordingly, it is unlikely that the temperature information (Ta) from the outside air temperature sensor (13) that is at fault causes &Dgr;t to become extremely long like ∞, so that it is avoided that the heater (2) cannot be operated because the controller (9) cannot be started up and the battery (1) freezes.

Owner:NISSAN MOTOR CO LTD

Manufacturing process for chalcogenide glasses

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com