Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

67results about How to "Increase decoding rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for guaranteeing secure transmission of wireless data based on fountain codes

ActiveCN105306168AImprove transmission efficiencyIncrease decoding rateError preventionFountain codePacket loss

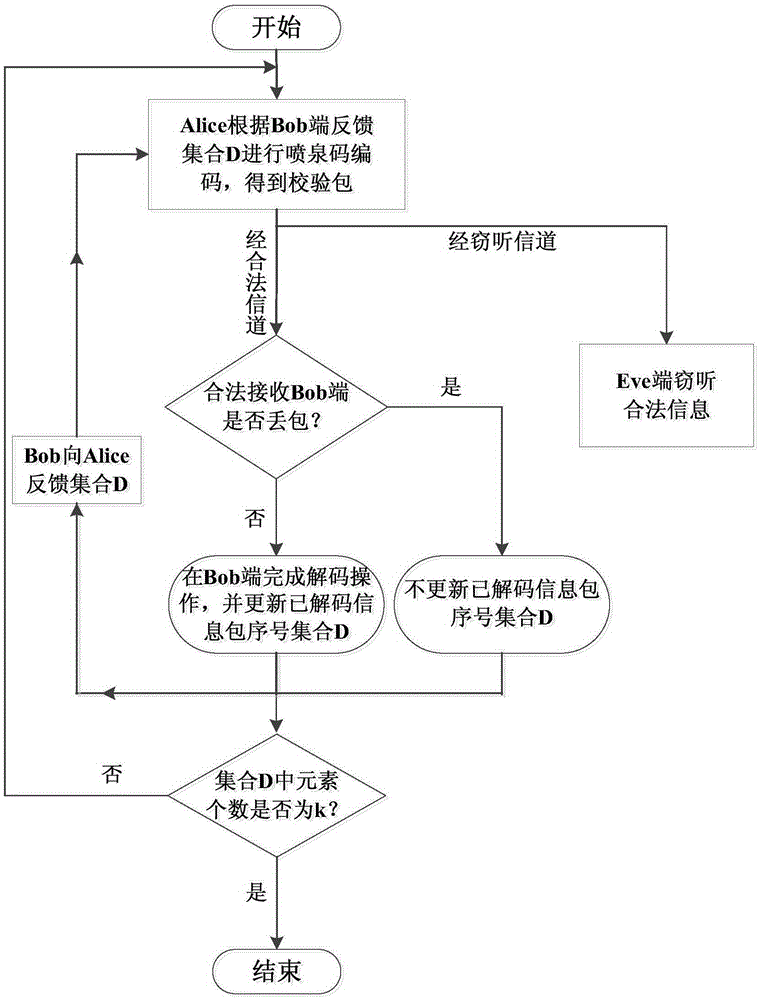

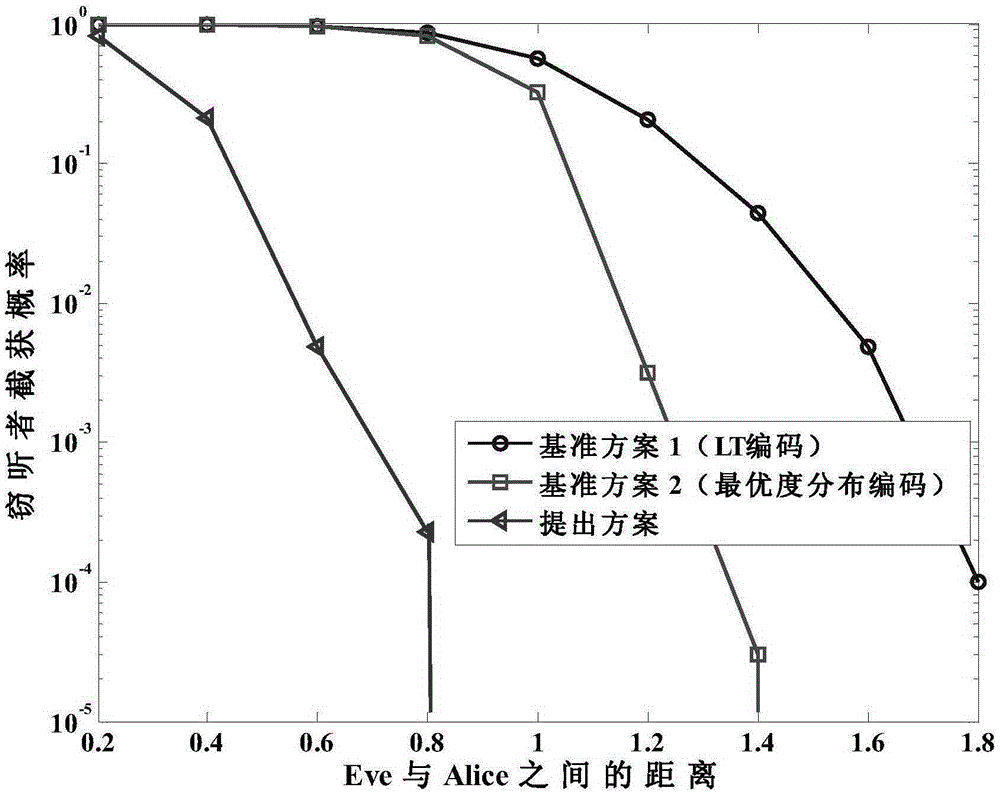

The invention discloses a method for guaranteeing secure transmission of wireless data based on fountain codes. The method comprises the following steps that each time slot sending end adopts a fountain code method to complete a check package encoding process; after the check package generated at the sending end is subjected to CRC (Cyclic Redundancy Check) coding of a data link layer and channel coding of a physical layer, the check package is sent to a legal user, and a tapping user taps current time slot transmission check package information; when packet loss does not occur in the channel, a legal receiving end completes a decoded operation of the received check package, and updates a set of serial numbers of decoded information packets and feeds the set back to the sending end after correct decoding, otherwise the set of the serial numbers of the decoded information packets is not updated; and the legal receiving end judges whether the number of the successfully decoded information packets is equal to the number of source information packets and decides whether to inform the sending end to stop sending the check package according to the information. According to the method, real-time adjustment of an encoding scheme for the sending end is carried out according to the decoding speed of the legal user, so that the intercept probability for the tapping user in a wireless data transmission process is remarkably reduced and the transmission efficiency of the sending end is improved.

Owner:博纳信远能源科技有限公司

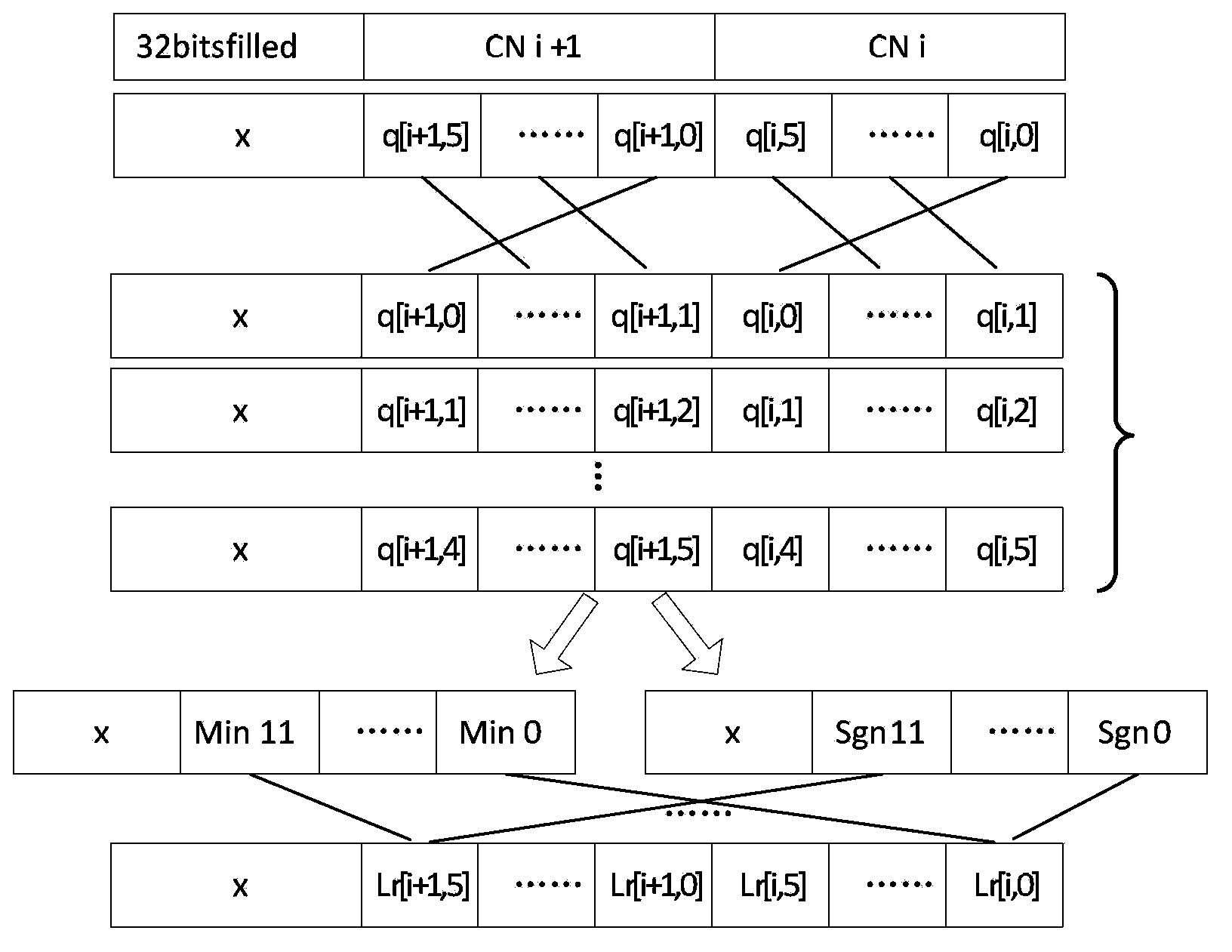

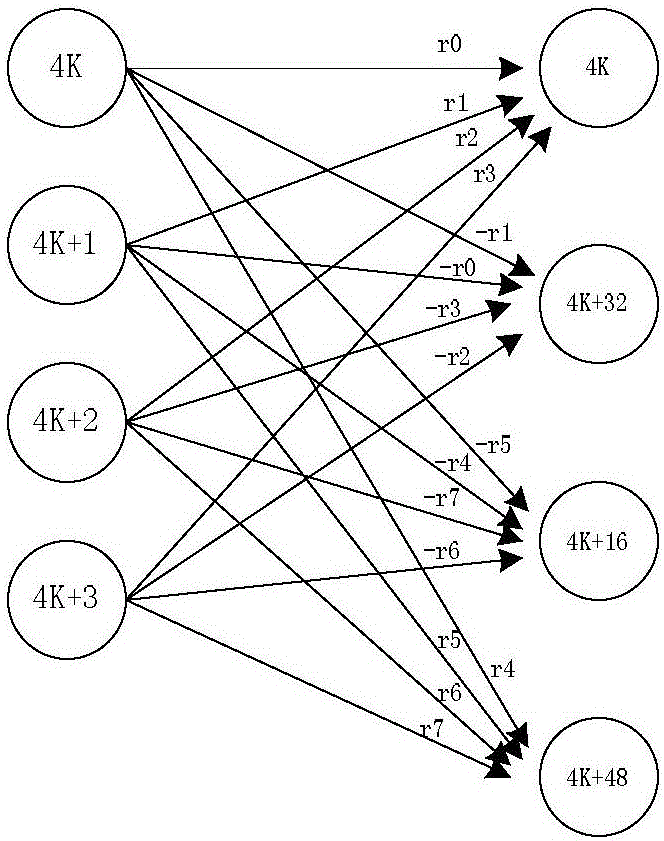

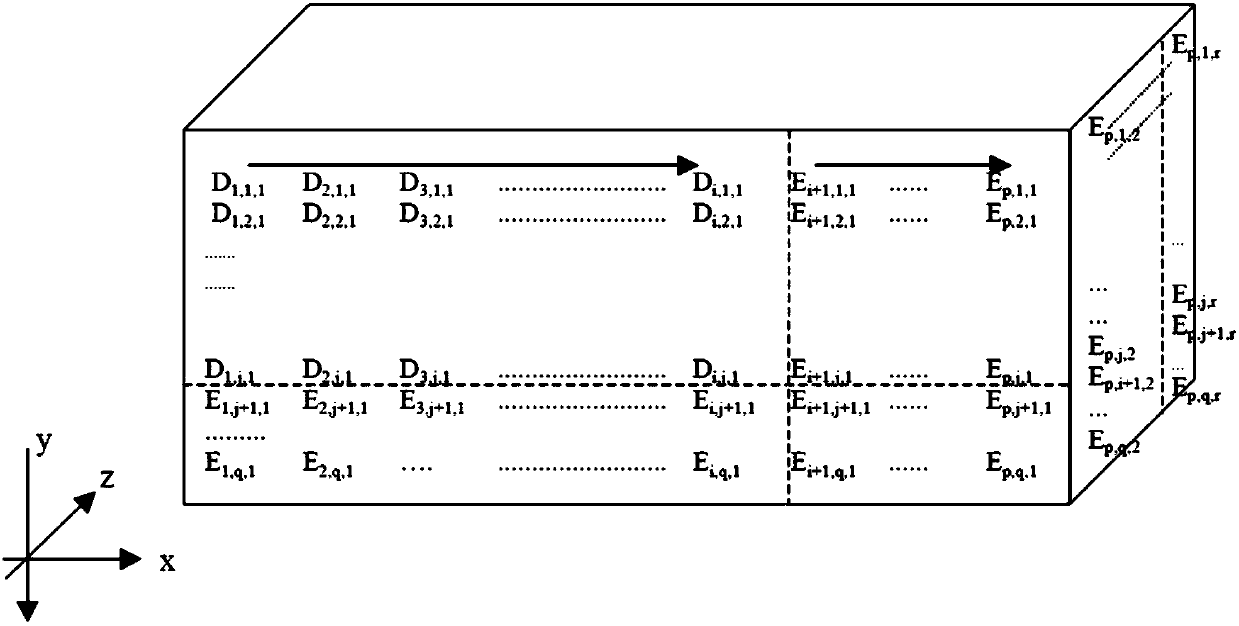

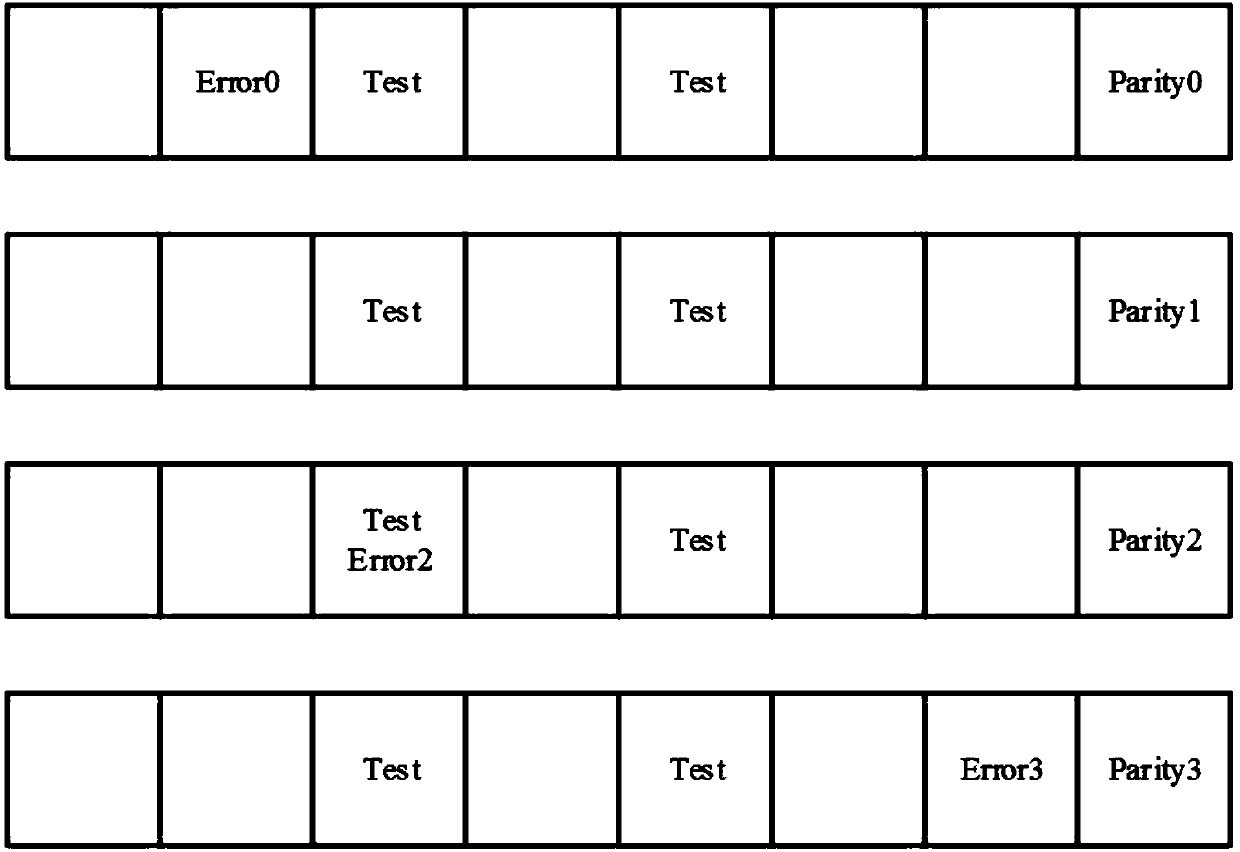

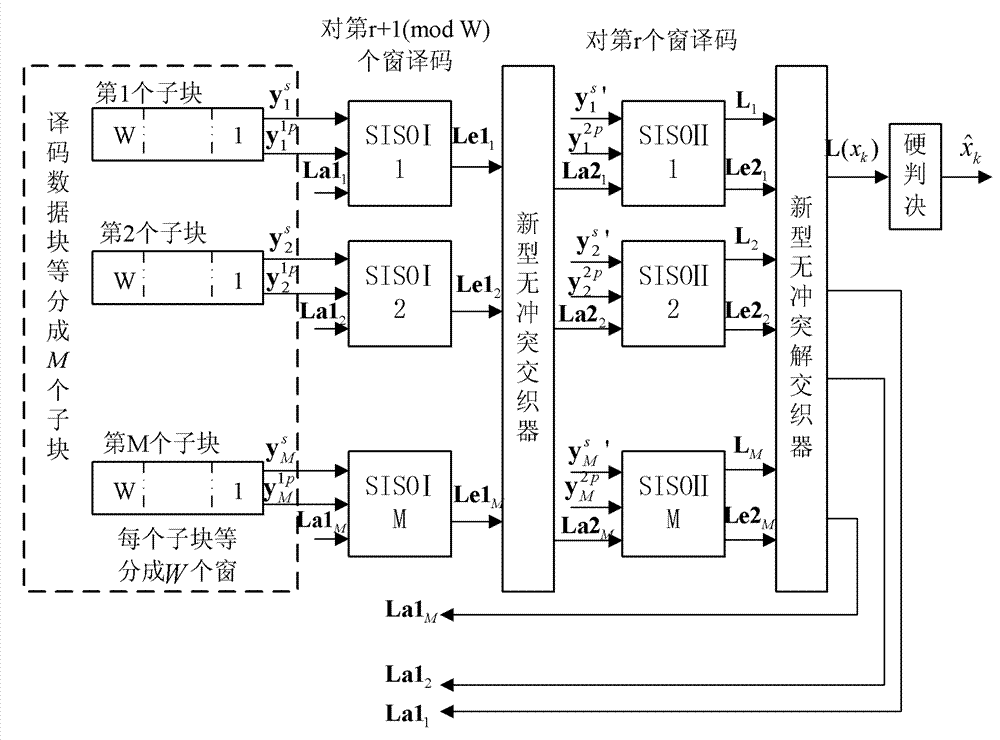

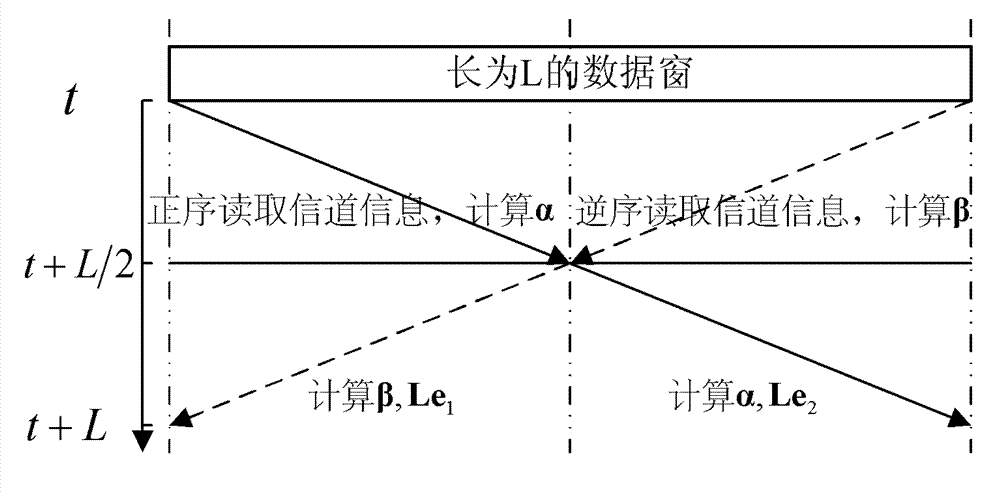

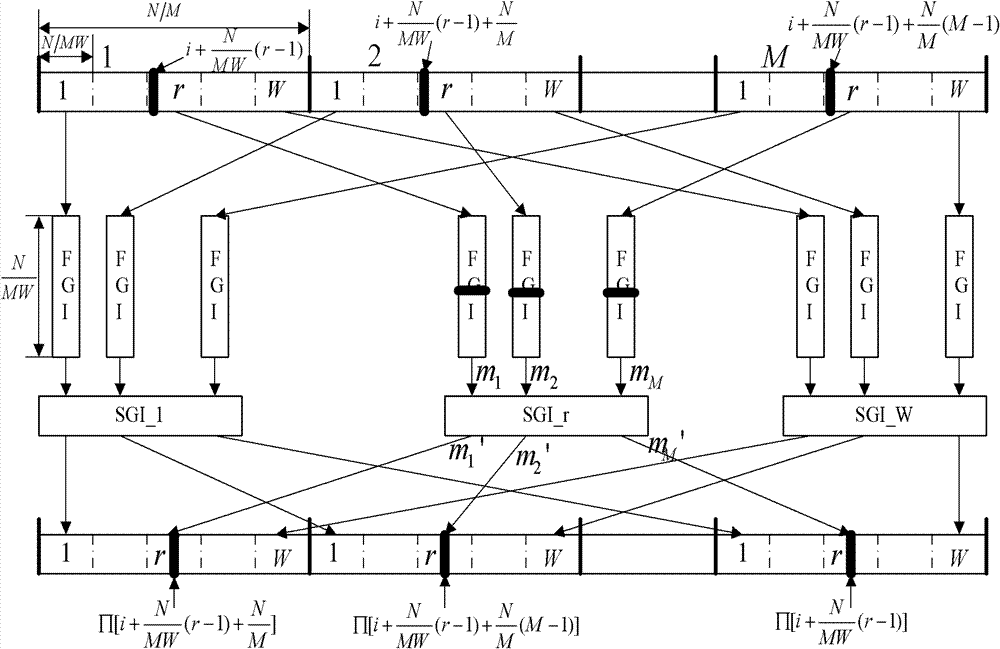

Novel conflict-free interleaver-based low delay parallel Turbo decoding method

InactiveCN102064838ADecoding reductionIncrease decoding rateError preventionError correction/detection using interleaving techniquesPrior informationLow delay

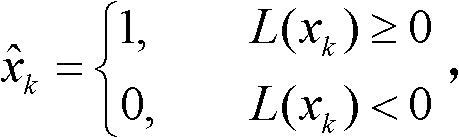

The invention discloses a novel conflict-free interleaver-based low delay parallel Turbo decoding method, which mainly solves the problem of high decoding delay in MAP algorithms due to iteration and recursive calculation. The method comprises the following steps of: blocking and windowing the received channel information; initializing prior information and state measurement initial values; making a primary soft input and soft output processor (SISO I) and a secondary soft input and soft output processor (SISO II) to synchronously slide forwards to decode; interleaving and de-interleaving the external information generated by the SISO I and the SISO II by using a novel conflict-free interleaver respectively; and when the iteration reaches the maximum iteration times, comparing the obtained likelihood ratio L (xk) with the threshold 0, and performing hard decision to obtain an estimation value of decoding bit. The method has the advantages of low decoding delay, high throughput rate, low performance loss and the like, and can be used for a Turbo decoder of a long term evolution (LTE) receiver.

Owner:XIDIAN UNIV

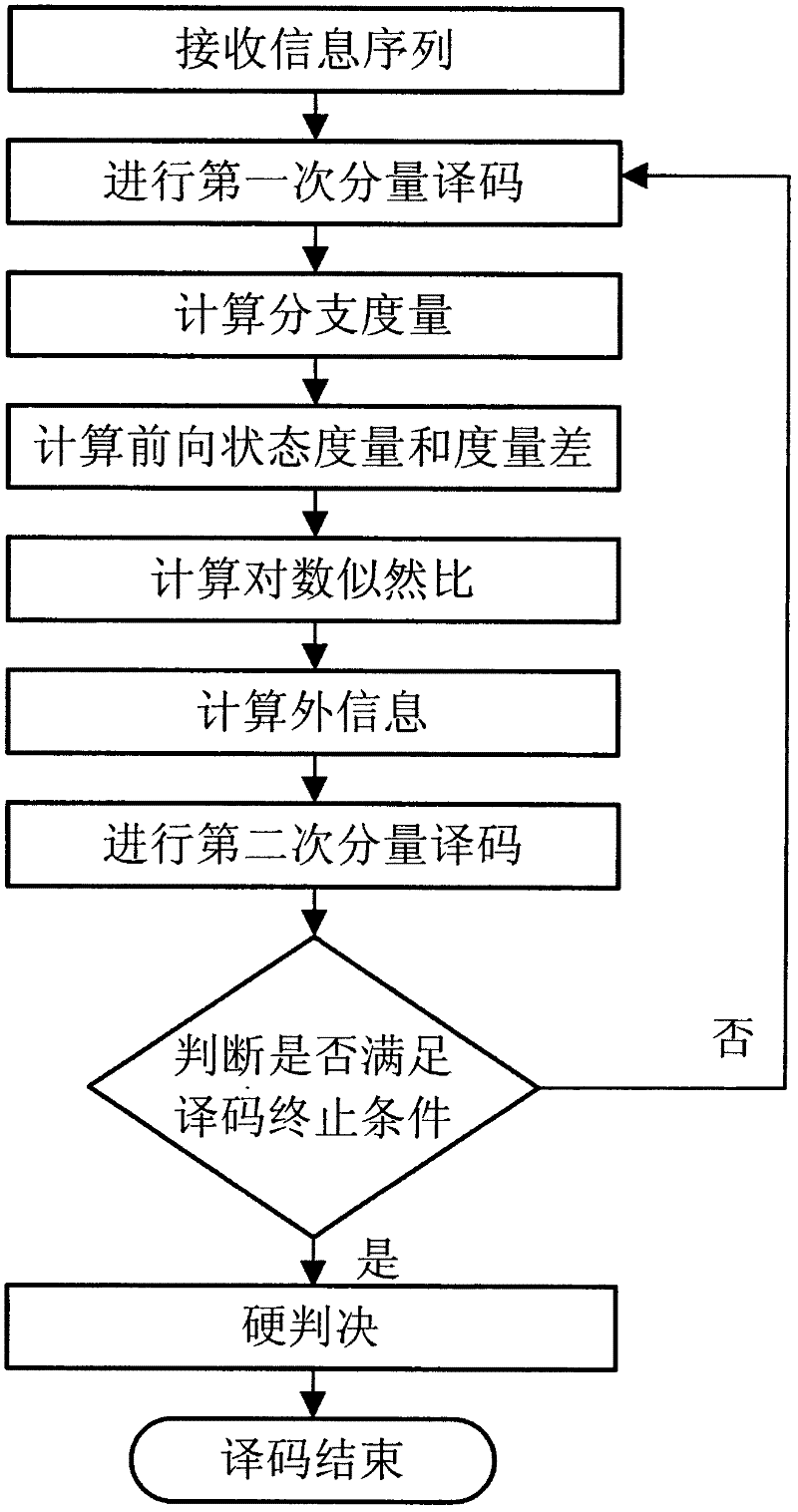

Universal and configurable high-speed Turbo code decoding system and method thereof

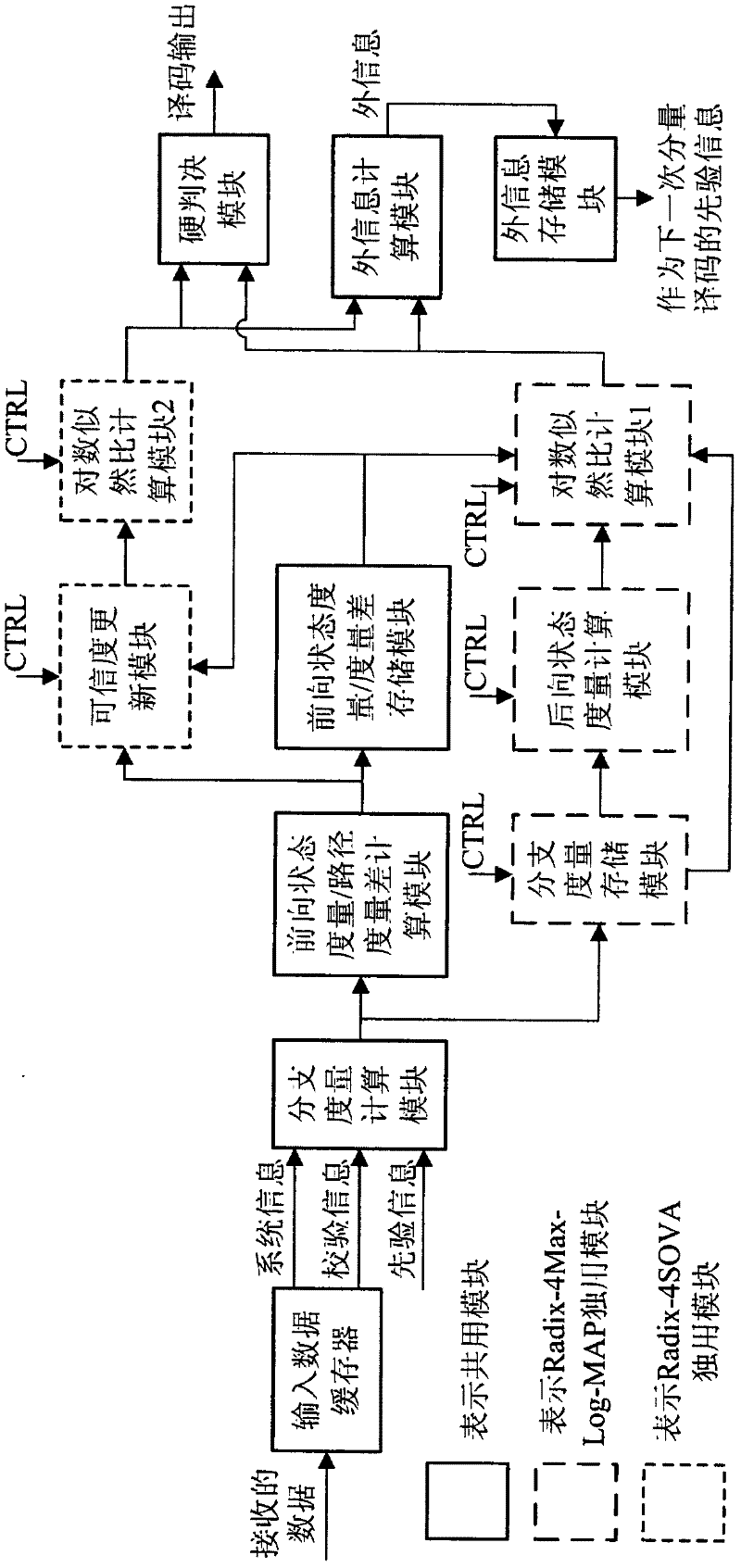

InactiveCN102523076AReduce consumptionOvercome the disadvantage of low decoding rateError preventionCommunications systemParallel computing

The invention discloses a universal and configurable high-speed Turbo code decoding system and a method thereof, solving the problem that the consumption of hardware resources is overlarge due to simultaneous configuration of independent Radix-4Max-Log-Map algorithm and Radix-4SOVA algorithm implementation modules in a Turbo code decoder in the prior art. The implementation method comprises the following steps of: receiving information; reading information in sequence, and carrying out first-time component decoding; calculating branch measurement; calculating forward state measurement and measurement difference; calculating logarithmic likelihood ratio; calculating extrinsic information; reading the information according to interweaved addresses, and carrying out second-time component decoding; carrying out decoding stopping decision; and carrying out hard decision. According to the invention, the common characters of the two Radix-4 algorithms are utilized to finish universal and configurable high-speed Turbo code decoding with simultaneous implementation of the two Radix-4 algorithms in one decoding system, the consumption of the hardware resources is reduced and the universal and configurable high-speed Turbo code decoding system and the method thereof can be used for a Turbo code decoder in a next-generation wideband wireless communication system.

Owner:XIDIAN UNIV

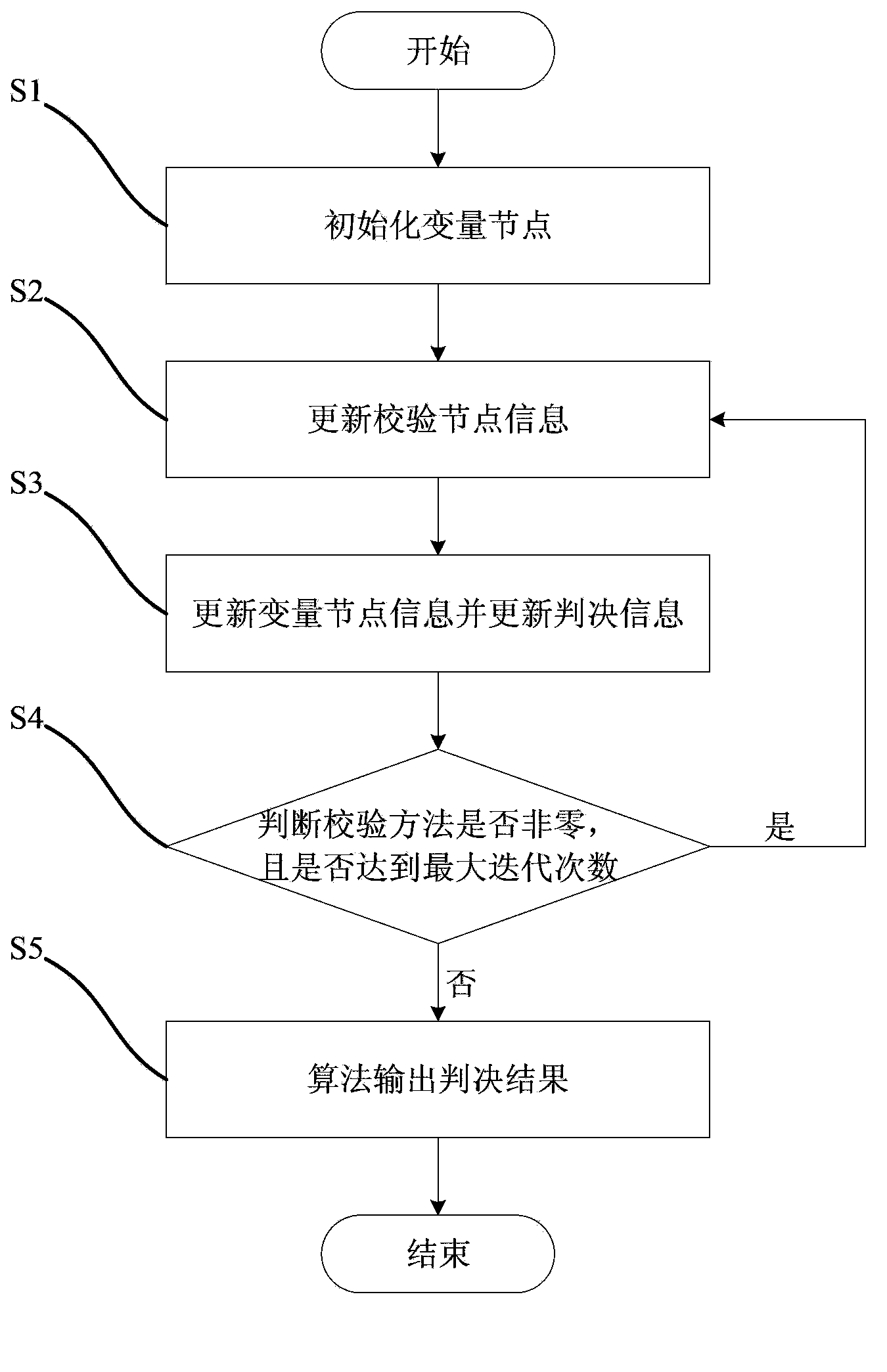

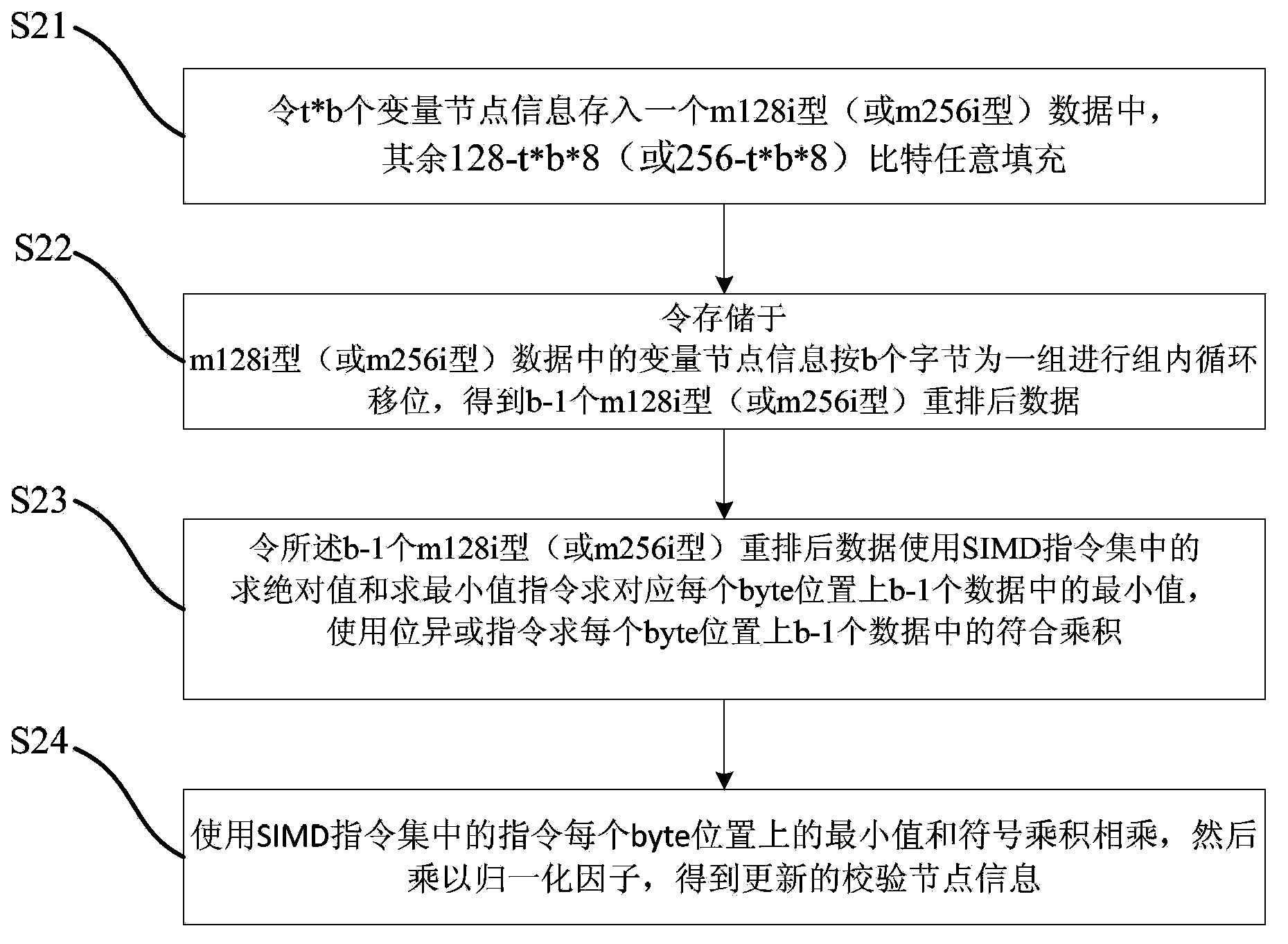

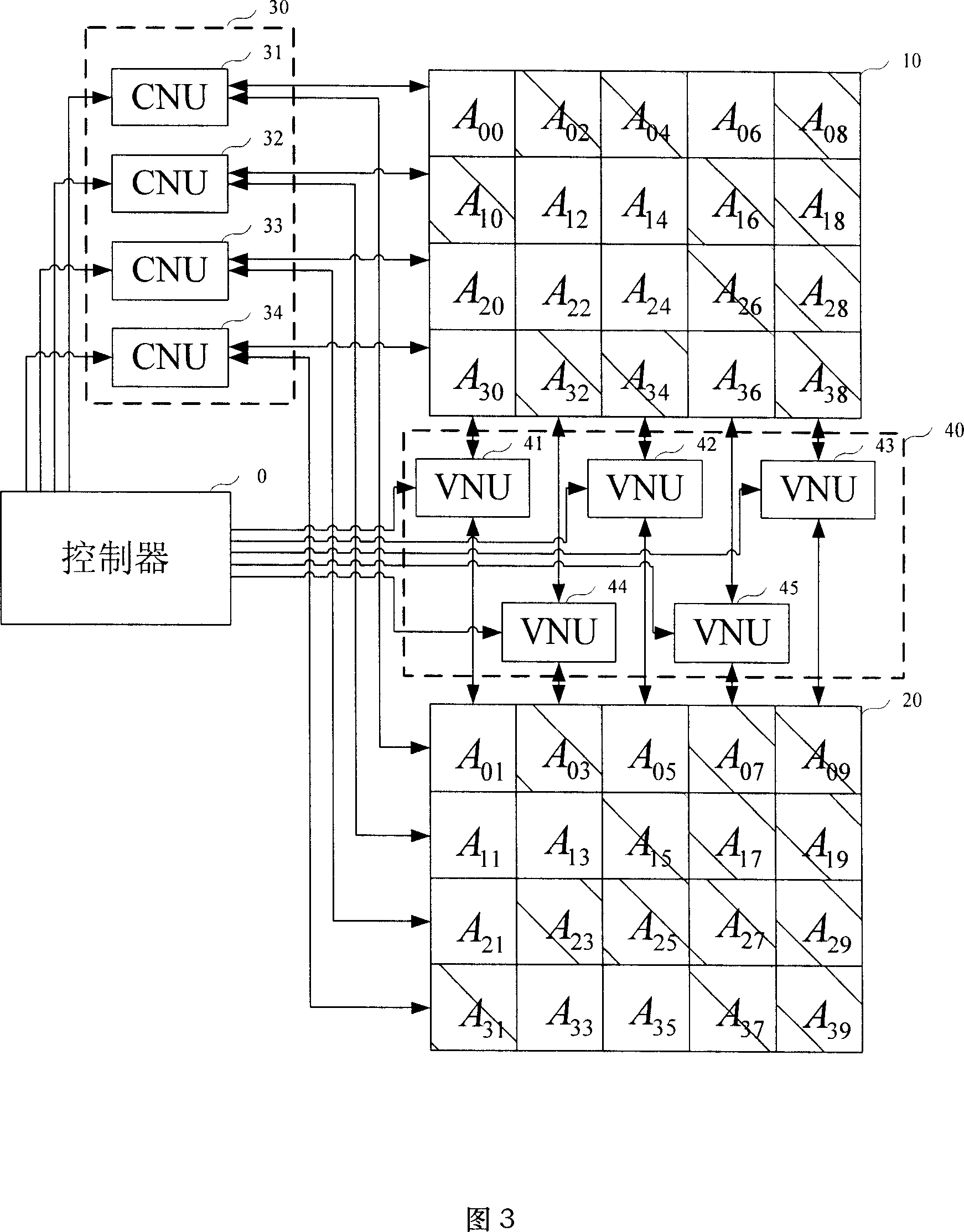

Realization method of high-speed low density parity code (LDPC) decoder

ActiveCN103684474AIncrease decoding rateSolve the problem of low throughputError correction/detection using multiple parity bitsDesign cycleTheoretical computer science

The invention provides a realization method of a high-speed low density parity code (LDPC) decoder. The method comprises the following steps that checking node information and variable node information are updated in a decoding process, numbers and filling formats of the checking node information and the variable node information which can be processed simultaneously are selected according to a row weight and a column weight satisfied according to a coding check matrix; the obtained checking node information and the variable node information are circularly shifted and rearranged, and rearranged data are processed by using a single instruction multiple data (SIMD)instruction, finally the updated checking node information and the variable node information are obtained. The realization method of the high-speed low density parity code (LDPC) decoder disclosed by the invention is short in design cycle, low in cost, easy to modify and extend, and further solves the problem of small throughput for realizing LDPC decoding and speeds up the decoding speed.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

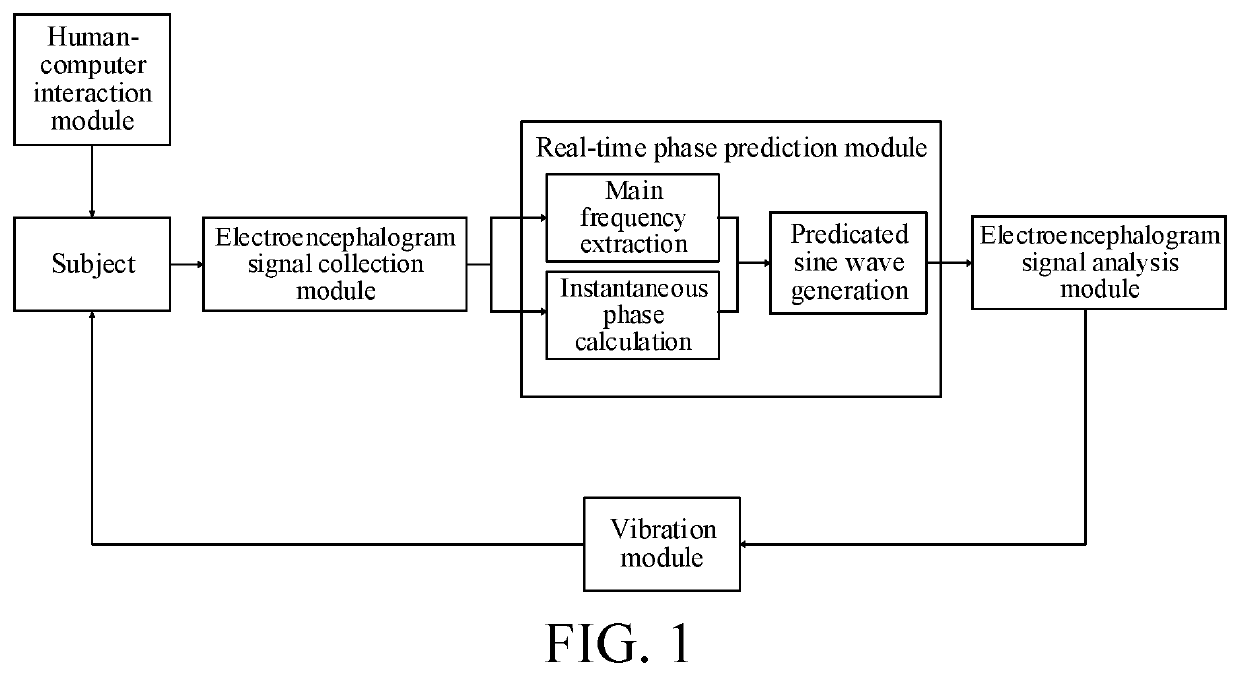

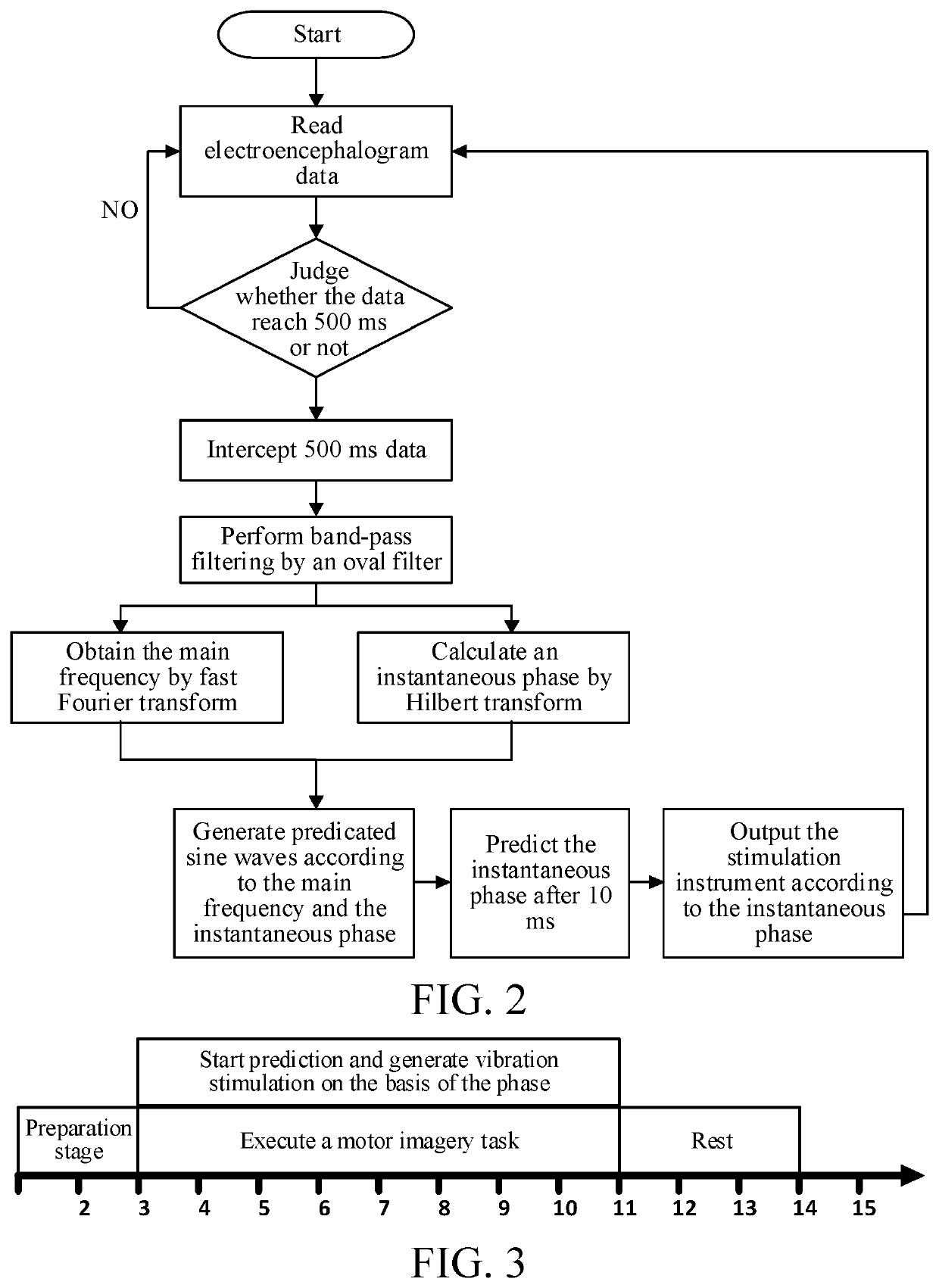

Brain-computer interface method and system based on real-time closed loop vibration stimulation enhancement

ActiveUS20200401226A1Improve signal-to-noise ratioImprove decoding rateInput/output for user-computer interactionElectroencephalographyBci brain computer interfaceMotor vibration

The present invention discloses a brain-computer interface method and system based on real-time closed loop vibration stimulation enhancement. The method includes: displaying and providing a motor imagery task to a subject, and collecting a generated digital electroencephalogram signal; reading the digital electroencephalogram signal, judging whether a preset time period is exceeded or not, performing interception if YES, and performing continuous reading if NO; performing band-pass filtering, obtaining time-frequency characteristics of the digital electroencephalogram signal through calculation by fast Fourier transform, and extracting a frequency value with highest frequency energy as a main frequency; obtaining an instantaneous phase of the digital electroencephalogram signal through calculation by Hilbert transform; generating predicted sine waves by respectively using the main frequency and the instantaneous phase as a frequency and an initial phase of sine waves, and predicting and obtaining real-time phase information; and judging whether the real-time phase is in a vibration stimulation application phase interval or not, generating and outputting a control instruction, and controlling a vibration motor to vibrate and to stimulate a sensory channel of the subject according to the control instruction. The present invention improves a signal-to-noise ratio of a brain-computer interface system, and enhances a recognition rate of a motor imagery signal.

Owner:SOUTHEAST UNIV

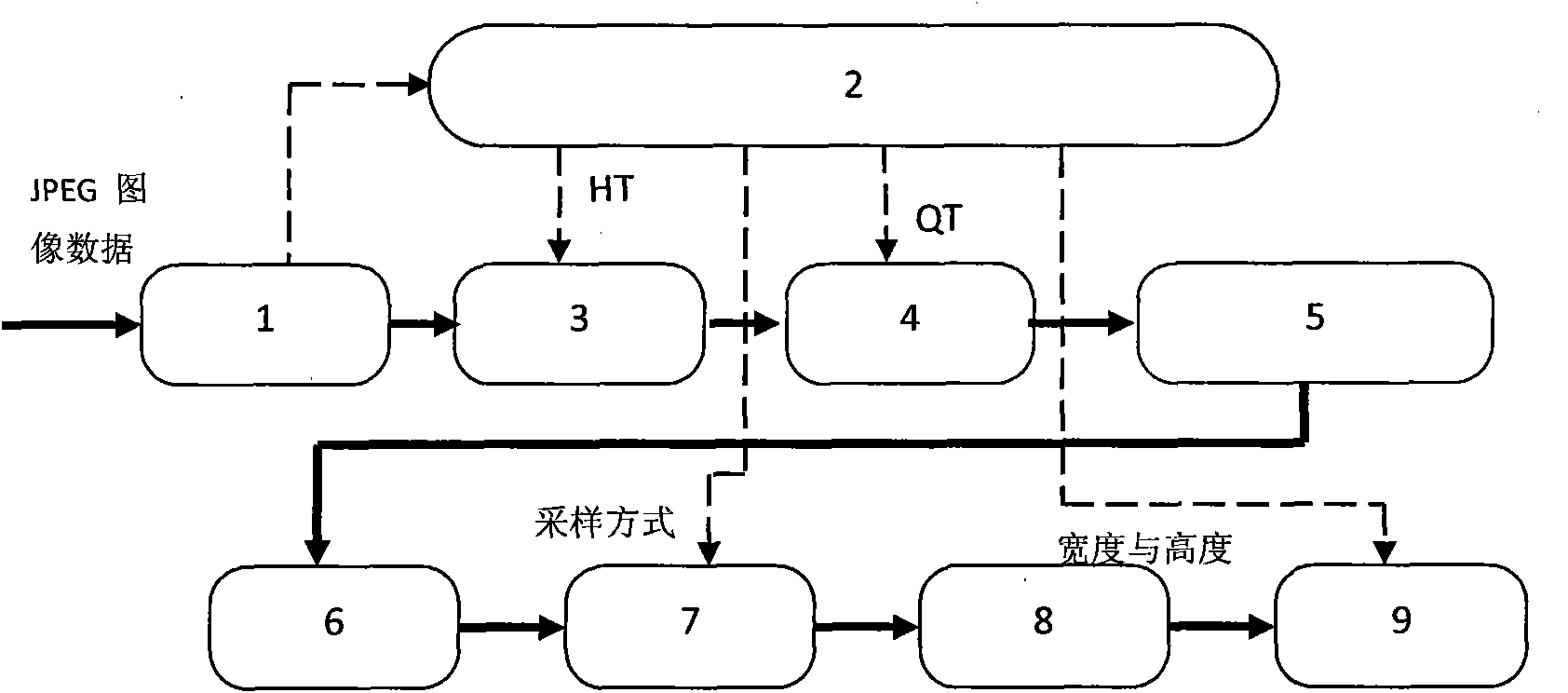

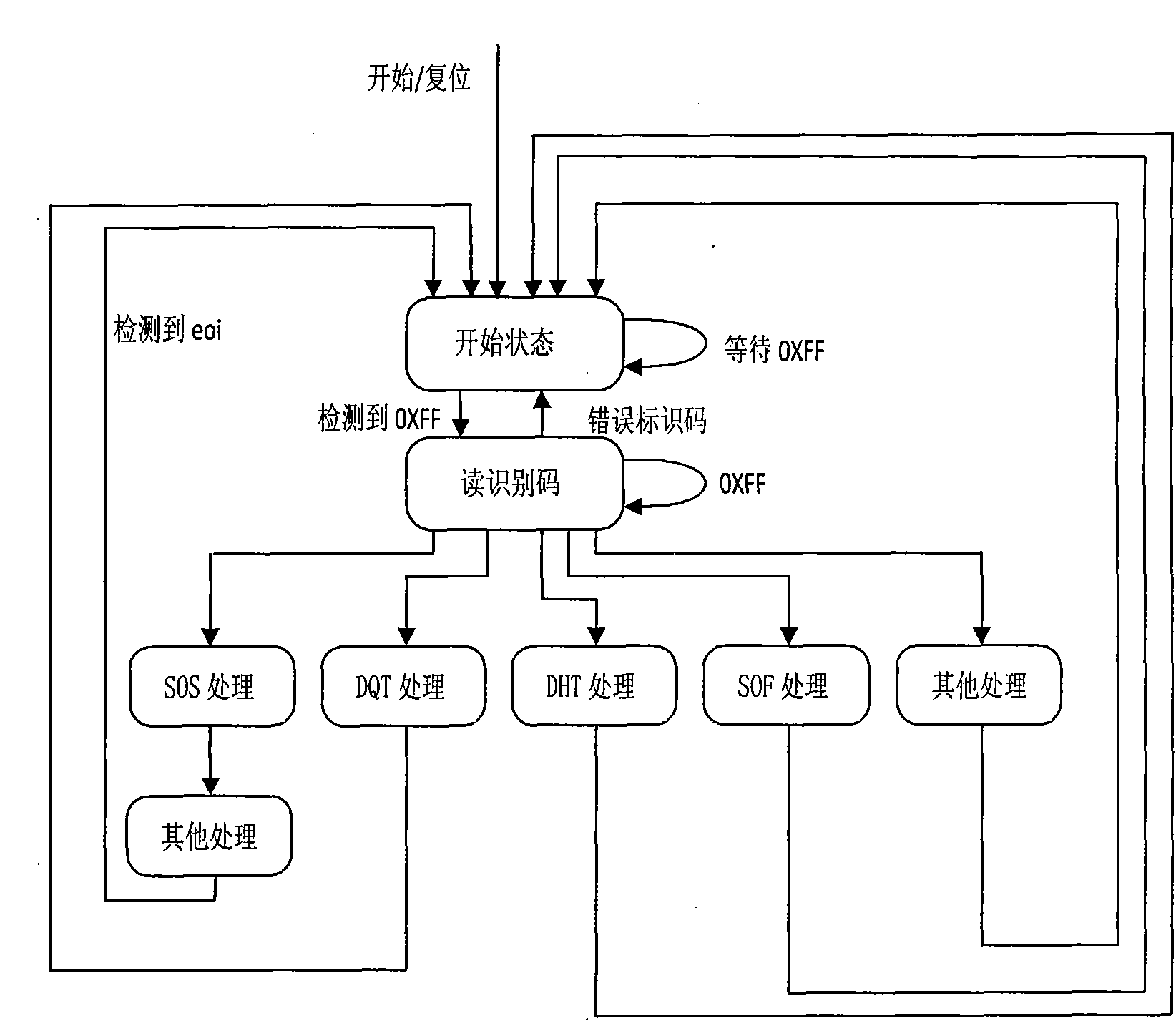

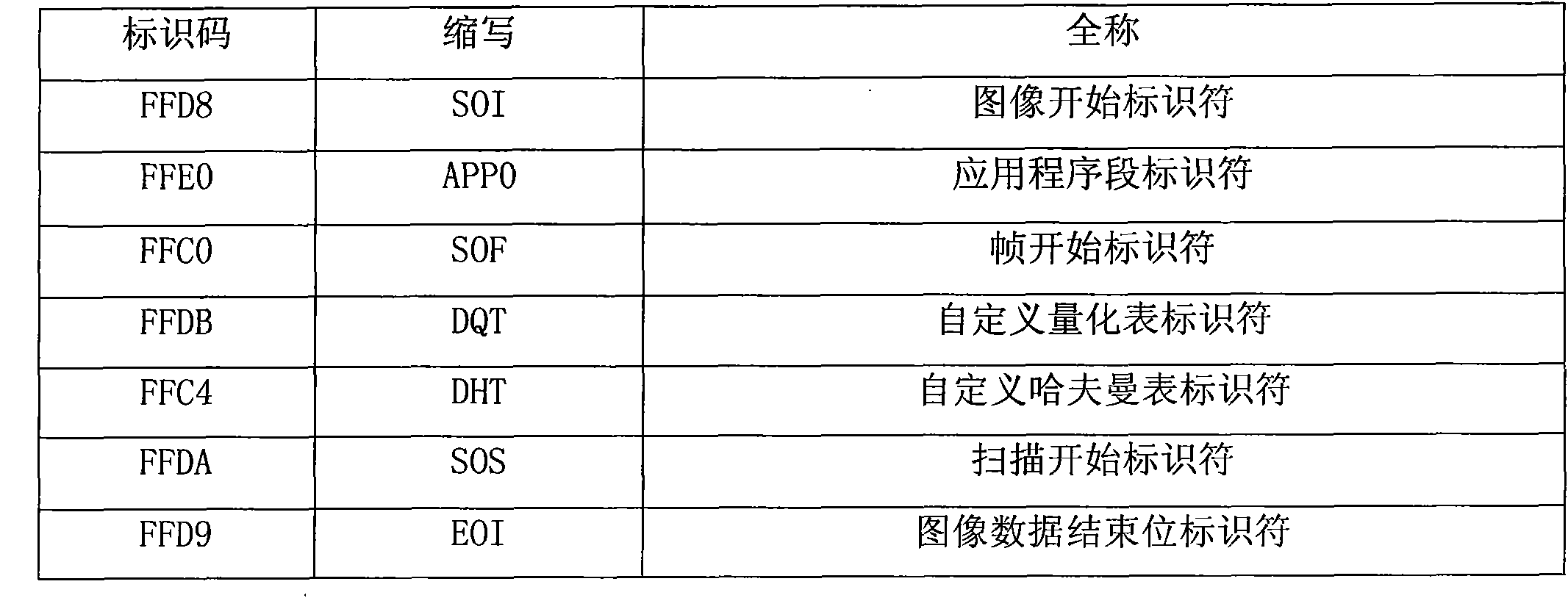

VLSI system structure of JPEG image decoder and realization method thereof

InactiveCN101790094AProcessing speedReduce areaTelevision systemsDigital video signal modificationComputer architectureHuffman decoding

The invention discloses a VLSI system structure of a JPEG image decoder and a realization method thereof. The VLSI system structure mainly comprises an input FIFO module, a header code stream analytic module, an entropy decoding module, a dequaztization module, an anti-zigzag conversion module, a inverse discrete cosine transform module, a de-sampling module, a color gamut conversion module and a display module. The entire design of the VLSI system structure adopts the assembly line design which can process multiple images simultaneously and continuously; the huffman decoding in the entropy decoding module adopts the modes of multibyte buffer and decoding word length feedback, thus increasing the operational speed of a huffman decoding module; to-be-decoded coefficient for counting and indicating is added in the inverse discrete cosine transform module which combines module data end mark method so that only nonzero coefficient data can be inputted, the data input cycle of single decoding module is greatly reduced, the decoding velocity is effectively increased, and the whole decoding speed is well improved. Simulation tests show that by using the VLSI system structure of the invention, 60fps of decoding effect can be realized under 800*600 resolution and 100MHz clock frequency.

Owner:SHANDONG UNIV

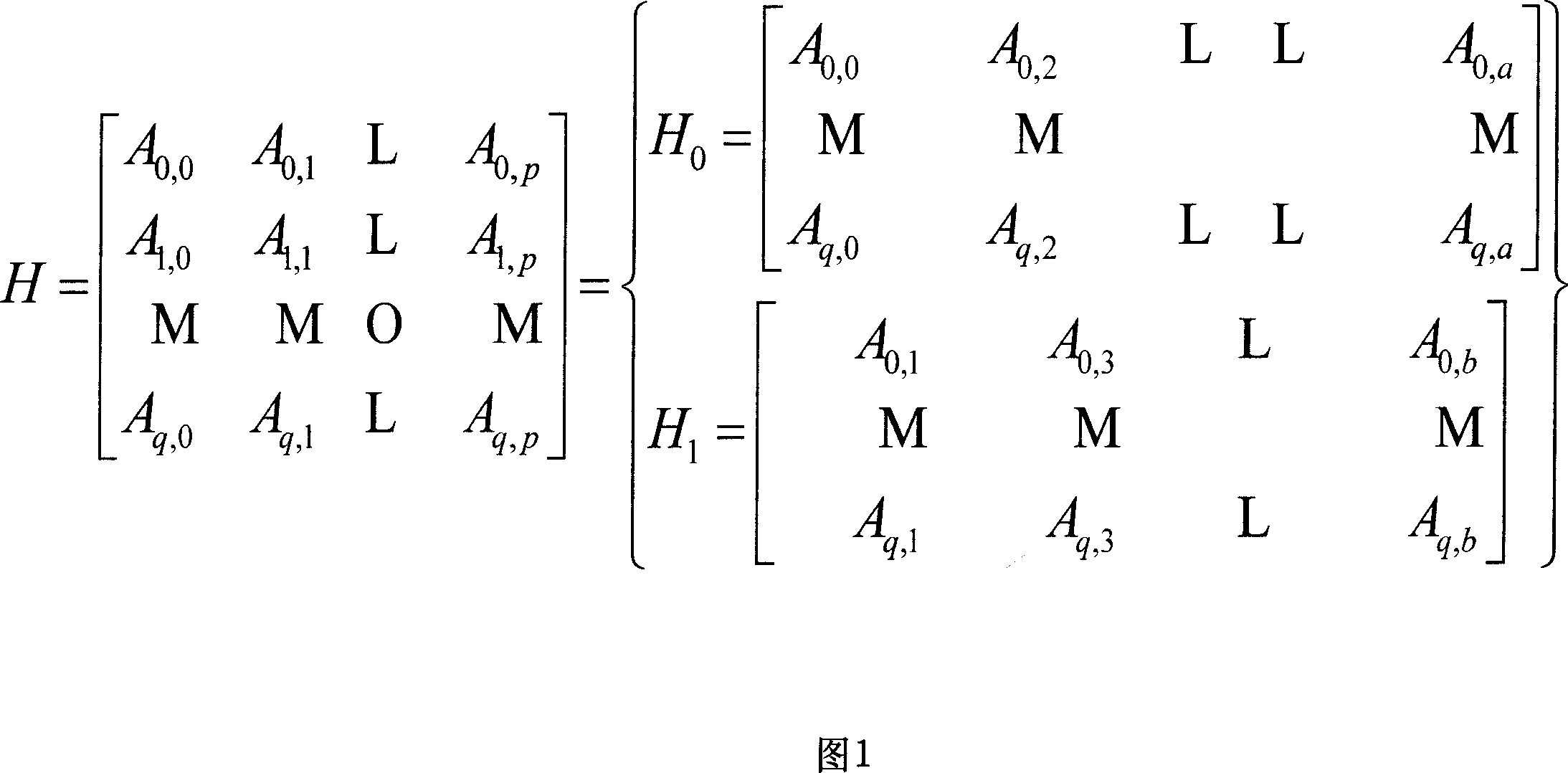

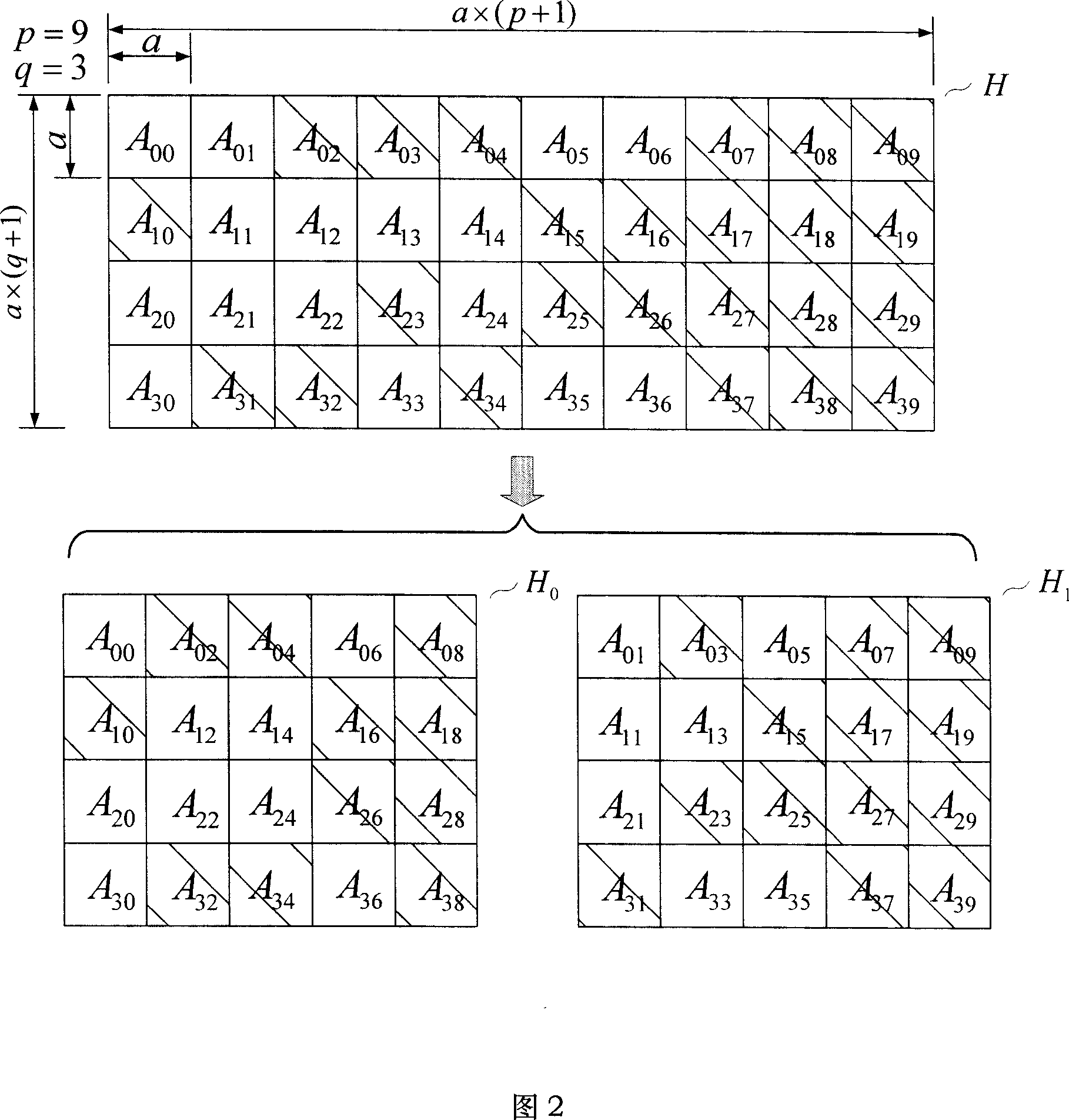

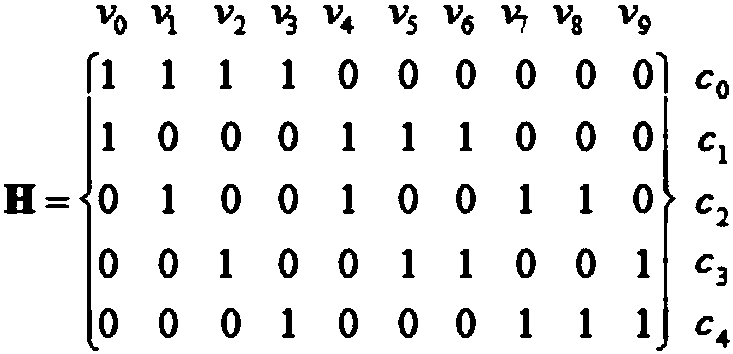

Parity verification matrix based decoding method and decoder of the LDPC code

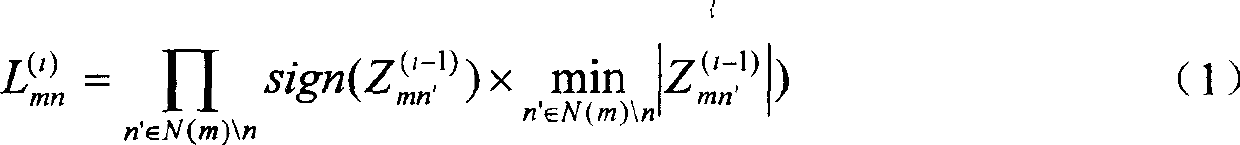

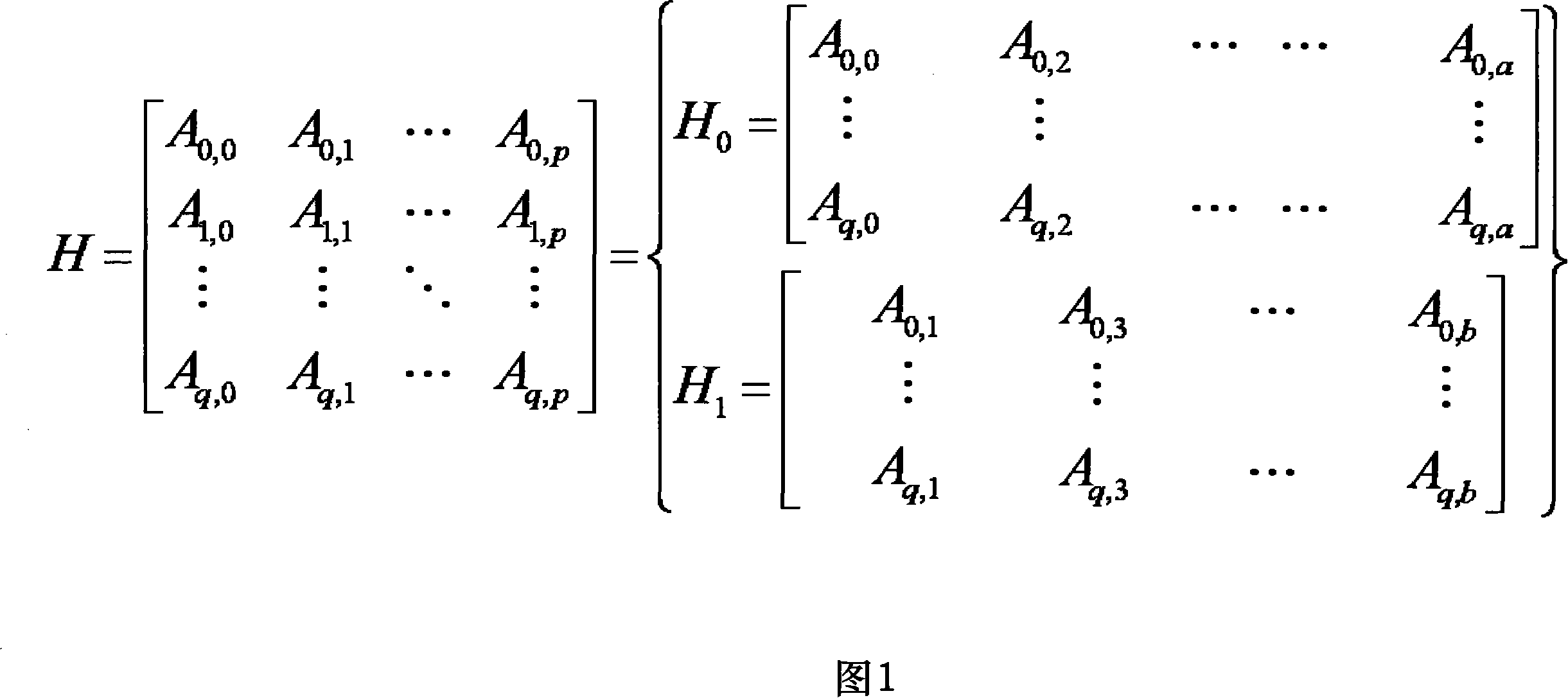

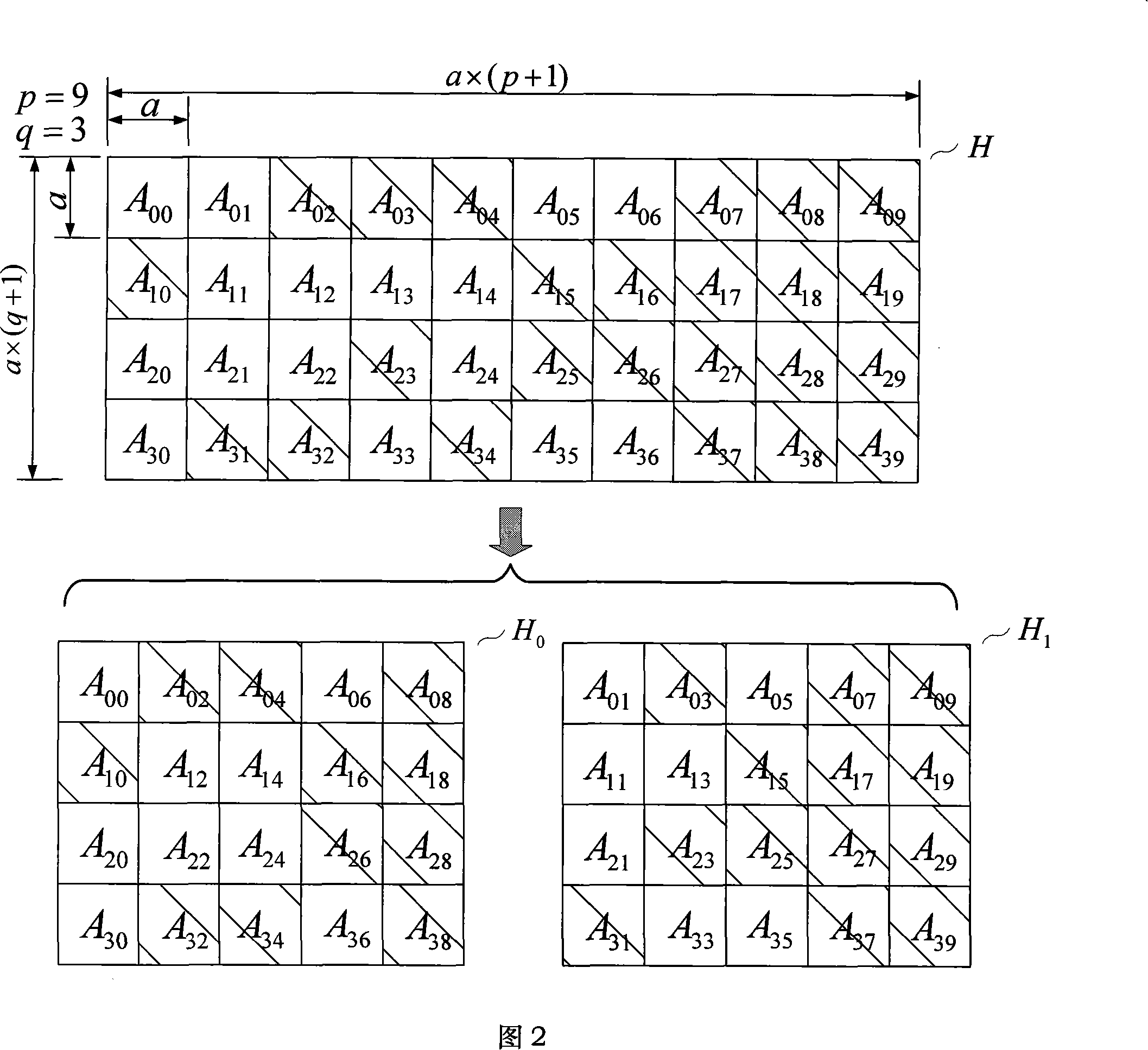

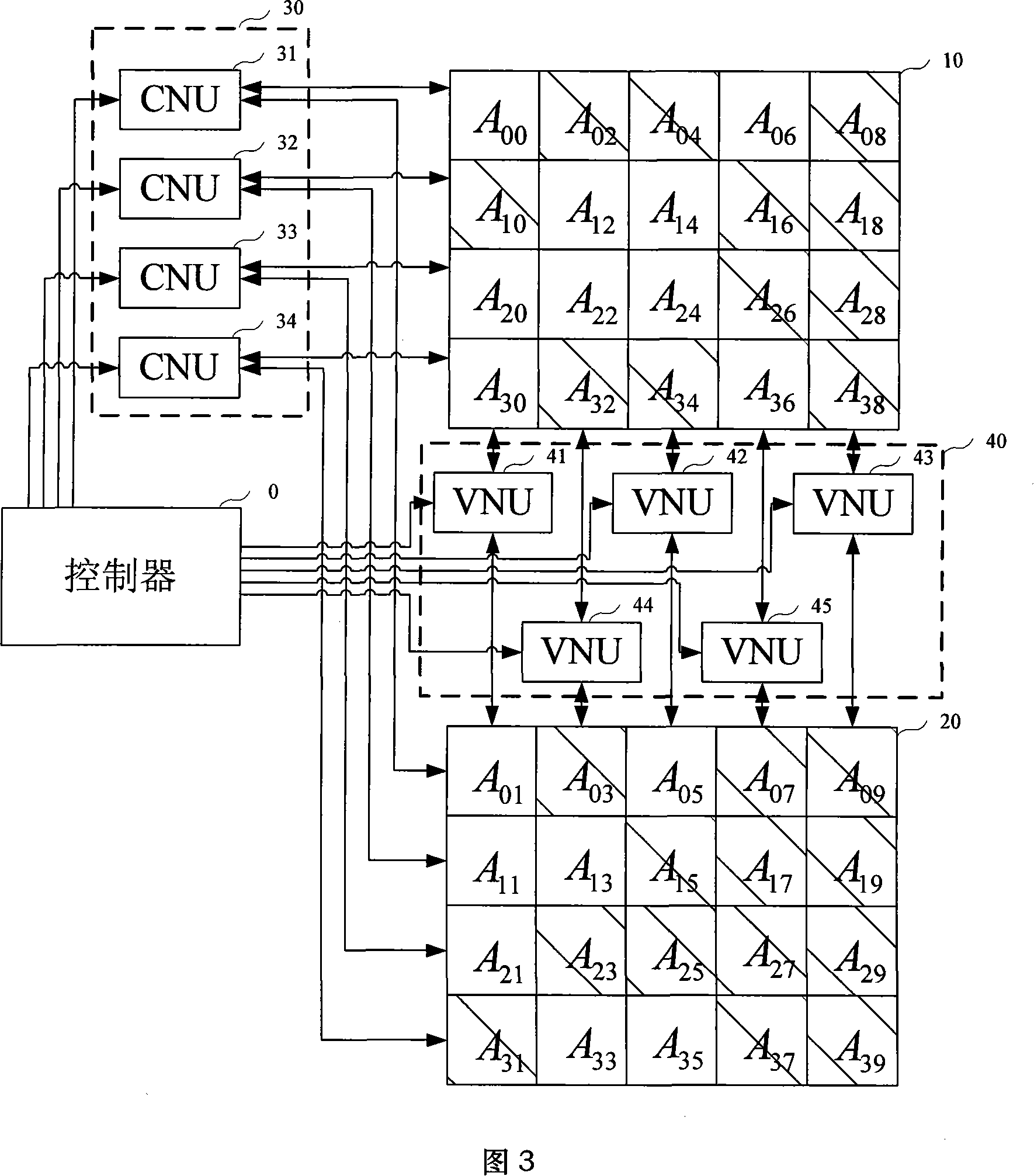

InactiveCN1996764ASmall scaleIncrease decoding rateError preventionError correction/detection using multiple parity bitsDecoding methodsParity-check matrix

This invention provides one LDPC code method and coder based on odd and even metric, which comprises the following steps: firstly cracking the metric; the single new matrix sets the correction point update unit and variable point update unit and planning correction points and variable update computation to process each new matrix for middle information computation to update original whole odd and even matrix point information to repeat above computation steps till the end of codes.

Owner:BEIHANG UNIV

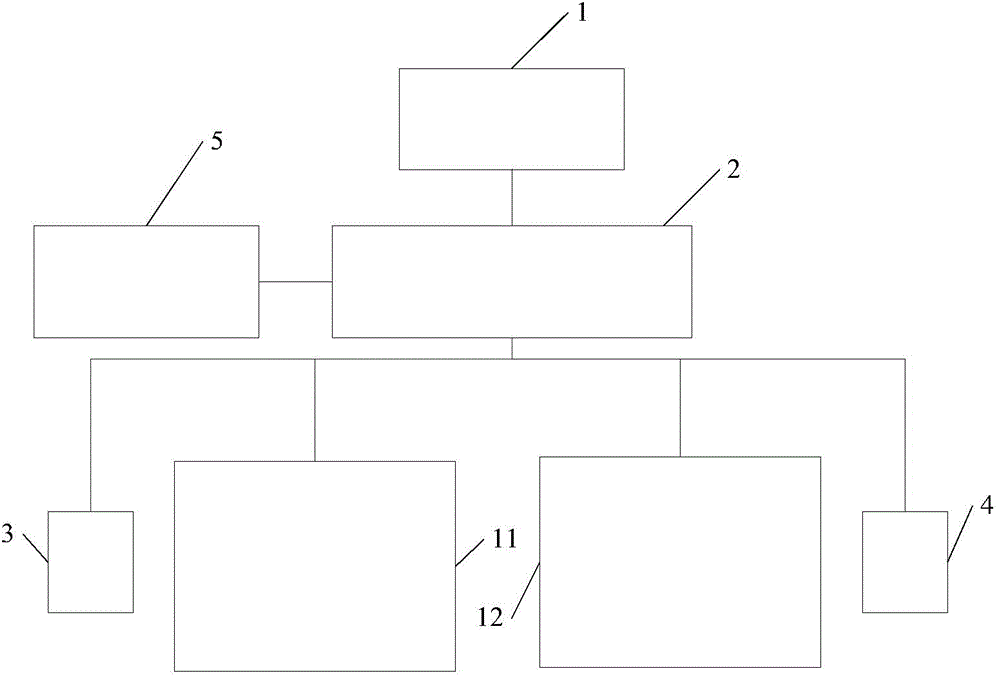

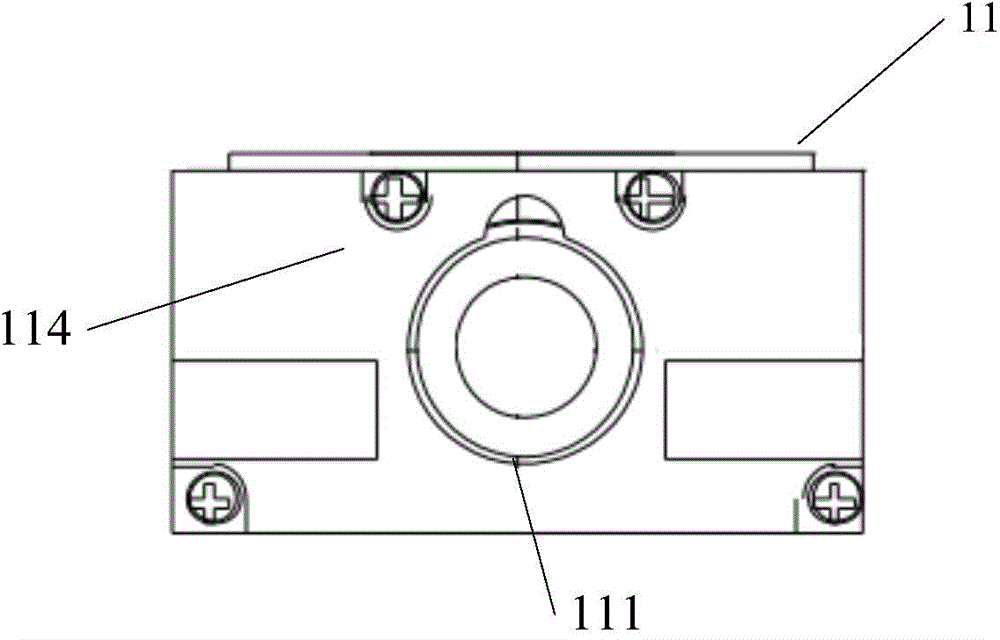

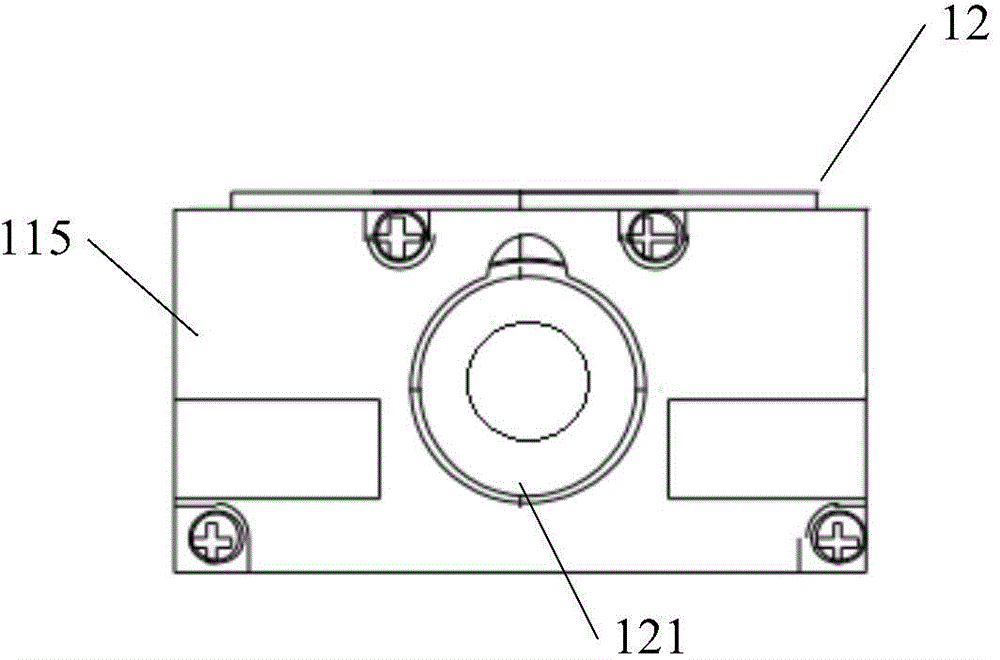

Bar code reading device

InactiveCN104537331AIncrease decoding rateIncreased field of viewSensing by electromagnetic radiationCode readingDepth of field

The invention provides a bar code reading device which comprises at least two bar code decoding engines. The at least two bar code decoding engines have two depths of focus to be suitable for bar codes of different sizes. Under the triggering of a decoding triggering mode, bar code images are collected according to the set sequence, and reading and decoding are conducted. After one bar code decoding engine successfully decodes the bar codes and is the first to successfully read and decode the bar codes, the decoding processing of other bar code decoding engines is automatically stopped, and the bar code reading and decoding speed is increased.

Owner:FUJIAN NEWLAND AUTO ID TECH CO LTD

High speed storage demand reducing low density correction code decoder

InactiveCN1822510AReduce occupancyTakes up less logicError correction/detection using multiple parity bitsCode conversionHigh speed memoryParallel computing

Present invention discloses a high-speed memory requirement reduced low density check code decoder. It contains parameter calculating unit VPU module, verification node computing element CPU module and control logic module, wherein VPU module receiving decode sequence, memory said original information and starting iteration decode, in iterate decode process, CPU module and VPU module mutually transferring information each to proceed line and row operation, CPU storing verification operation result, controlling logical module to VPU module and CPU module cycle operation control, and outputting decode to obtain legal code word. Said invention fully utilizes minimal and decode algorithm to reduce memory requirement and height parallel to raise decode rate to shift LDPC code, saving message storage requirement and reaching faster decode speed and higher throughput rate.

Owner:NANJING UNIV

Decoding method of LDPC code based on parity check matrix and decoder thereof

InactiveCN101232288ASmall scaleIncrease decoding rateError preventionError correction/detection using multiple parity bitsDecoding methodsParity-check matrix

Owner:BEIHANG UNIV

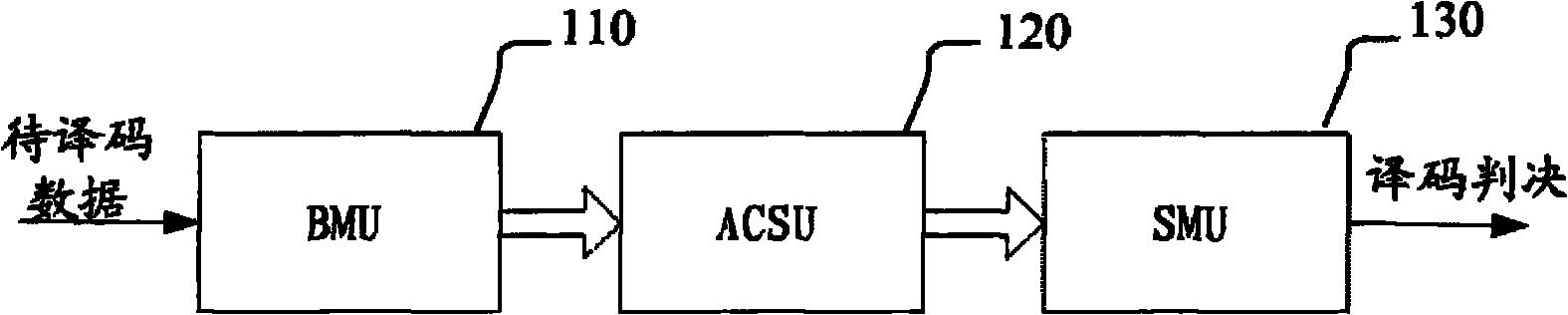

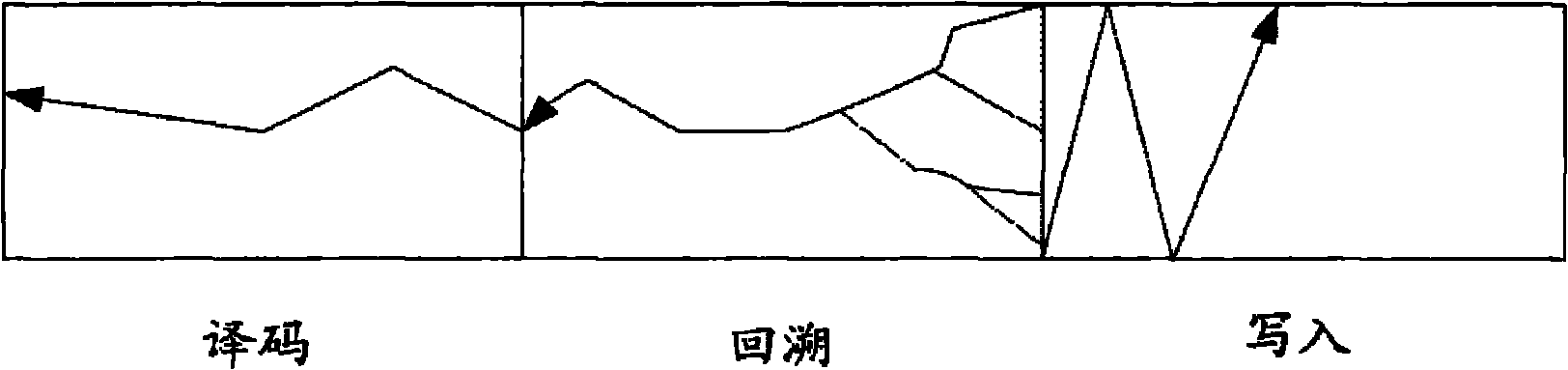

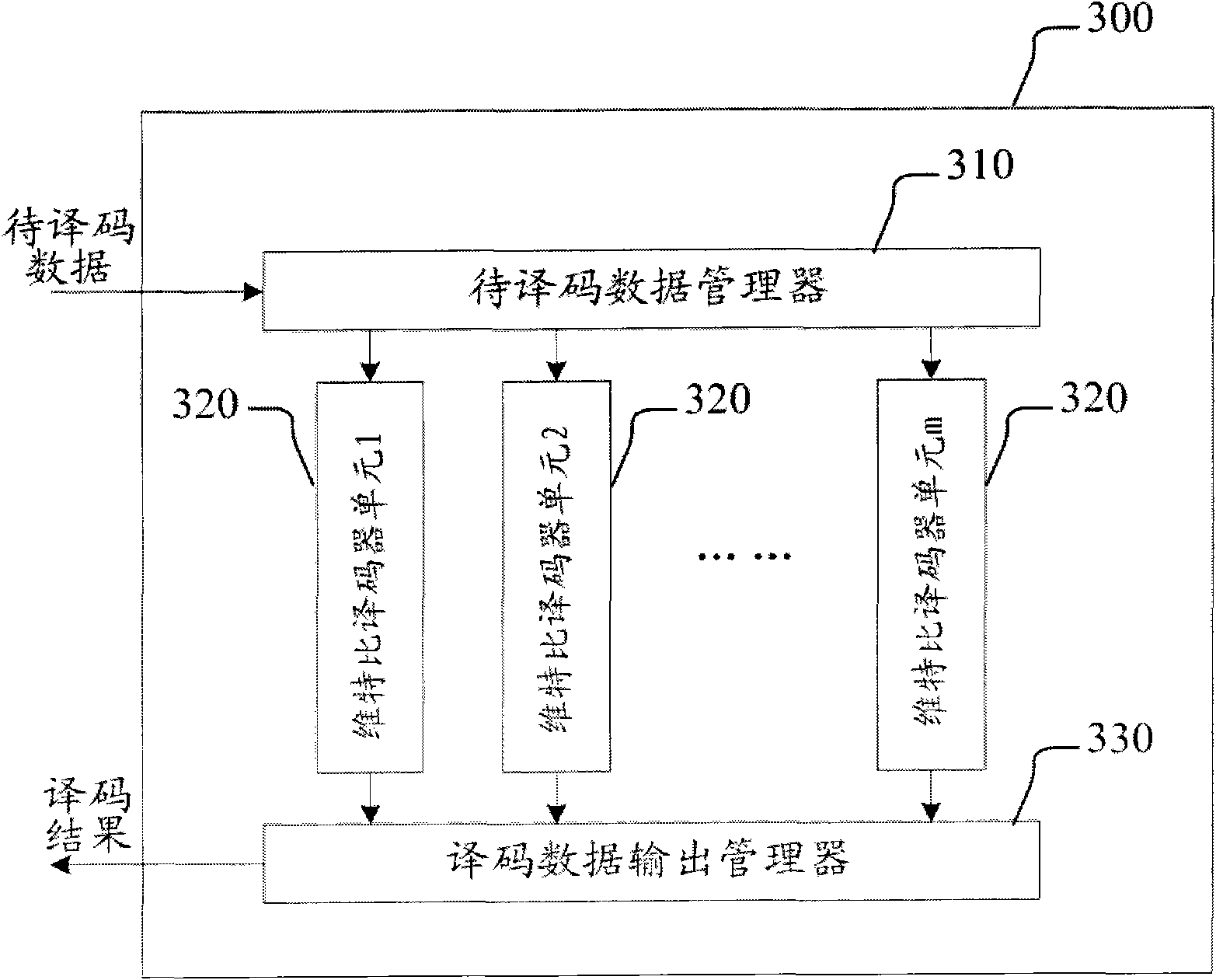

Viterbi decoder and Viterbi decoding method

InactiveCN102761342AImprove resource utilizationIncrease decoding rateOther decoding techniquesViterbi decoderComputer hardware

The invention discloses a Viterbi decoder and a Viterbi decoding method. The Viterbi decoder comprises a manager of data to be decoded, a plurality of Viterbi decoder units and a decoding data output manager, wherein the manager of the data to be decoded is used for distributing input data to be decoded to the plurality of Viterbi decoder units; each Viterbi decoder unit is used for independently carrying out Viterbi decoding based on a forward slide block mode on the distributed data to be decoded to obtain decoding data of the data to be decoded, wherein the data to be decoded, corresponding to each Viterbi decoder unit, comprises a synchronization block, a decoding block and a backtracking block which are successive; and the decoding data output manager is used for receiving corresponding decoding data from the plurality of Viterbi decoder units and combining and outputting the decoding data. According to the Viterbi decoder and the Viterbi decoding method, a higher decoding rate and a higher hardware resource utilization ration can be provided.

Owner:SONY CORP +1

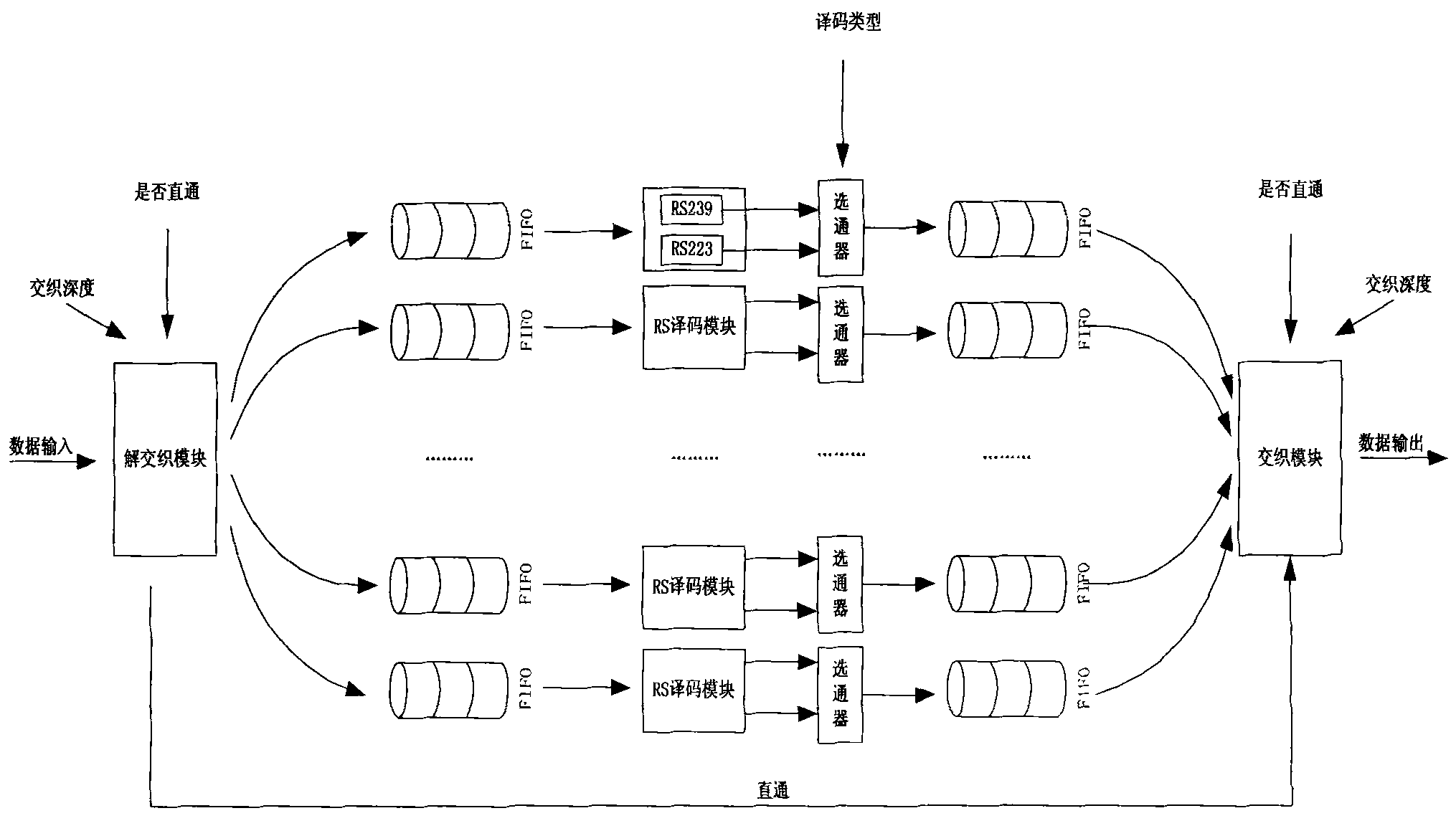

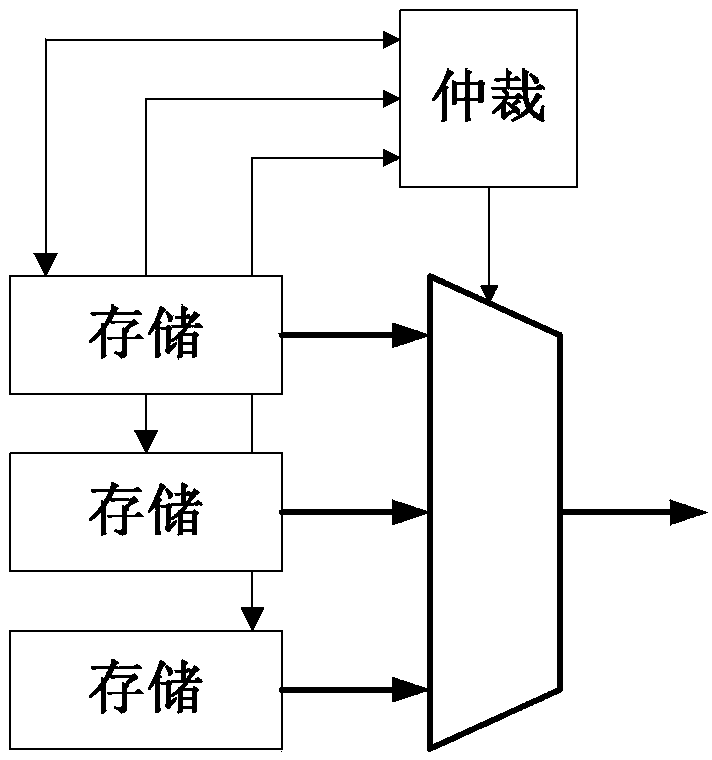

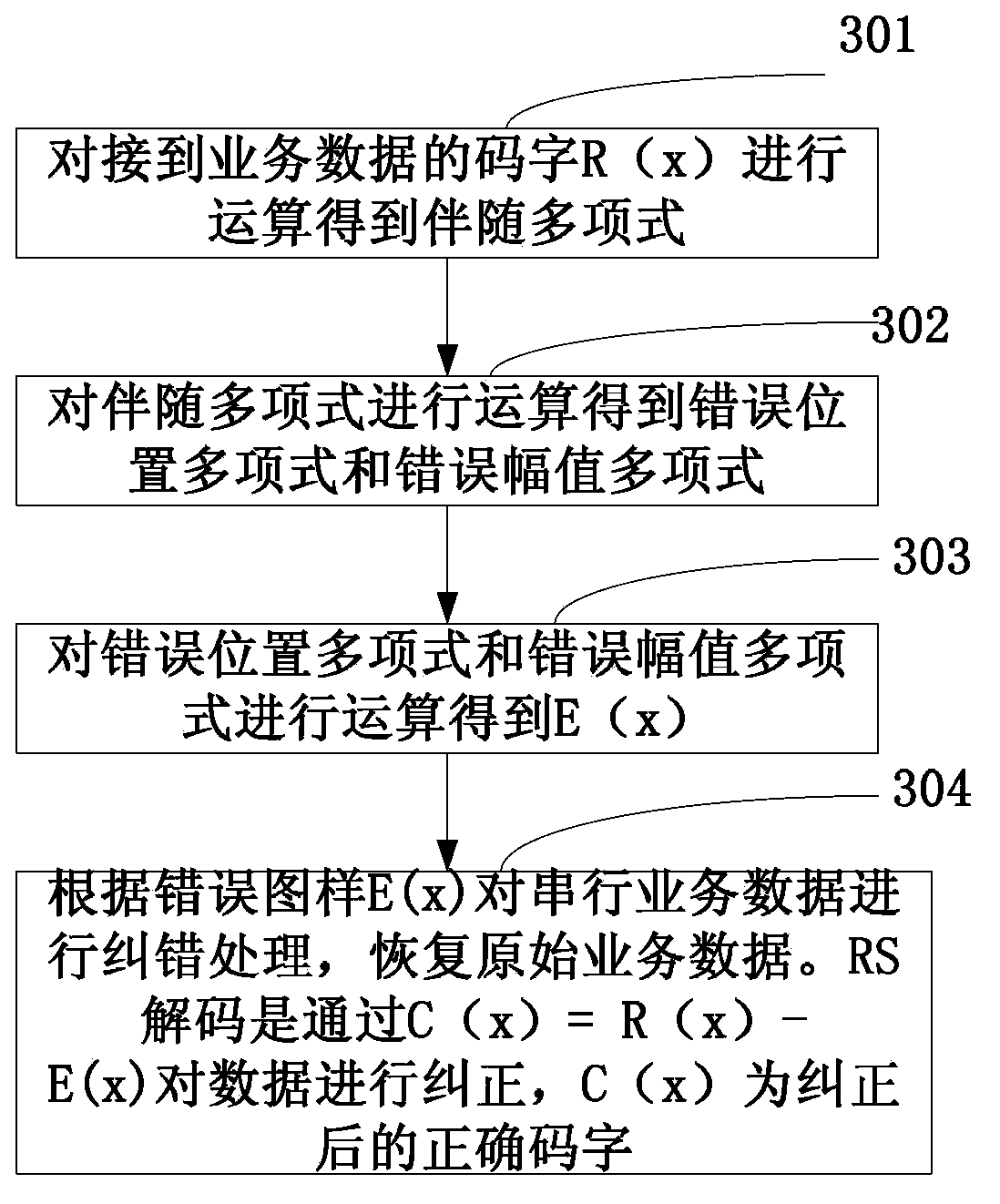

High-speed parallel RS decoding method for space communication

ActiveCN101969358AFlexibility to adapt to encoding formatsMinimizeError preventionData systemDegree of parallelism

The invention relates to a high-speed parallel Reed-Solomon (RS) decoding method for space communication. In the method, two decoding modules RS (255, 223) and RS (255, 239) are configured simultaneously, so that a decoder can configure decoding types on line according to coding parameters to flexibly adapt to two coding formats specified by the consultative committee for space data system (CCSDS) standard; input data is filled and acquired in first in first out (FIFO) by ping-pong operation during deinterlacing and interlacing, a multi-channel parallel pipeline mode is adopted during decoding, and a composite structure ensures the maximization of system performance and realizes the minimization of resources and is suitable for 1 to 8 arbitrary interlacing depths; and measures such as multi-channel parallel RS decoding, the optimization of realization logic of a finite field multiplier, and the like are adopted, so that decoding rate is greatly improved. The method can be directly applied to a high-code-rate remote sensing satellite ground receiving system and can further increase parallelism degree and improve performance when necessary by modular design.

Owner:SPACE STAR TECH CO LTD

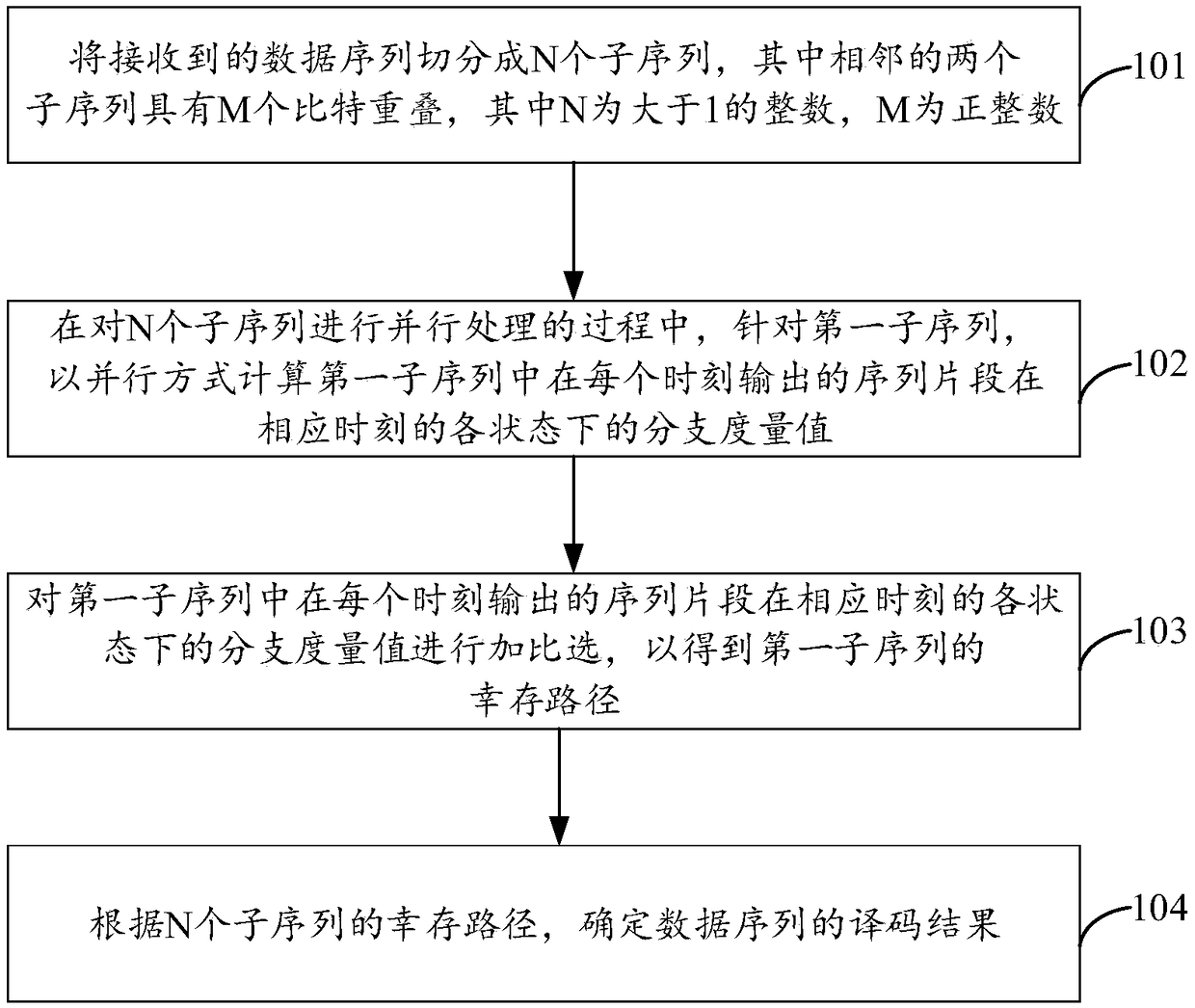

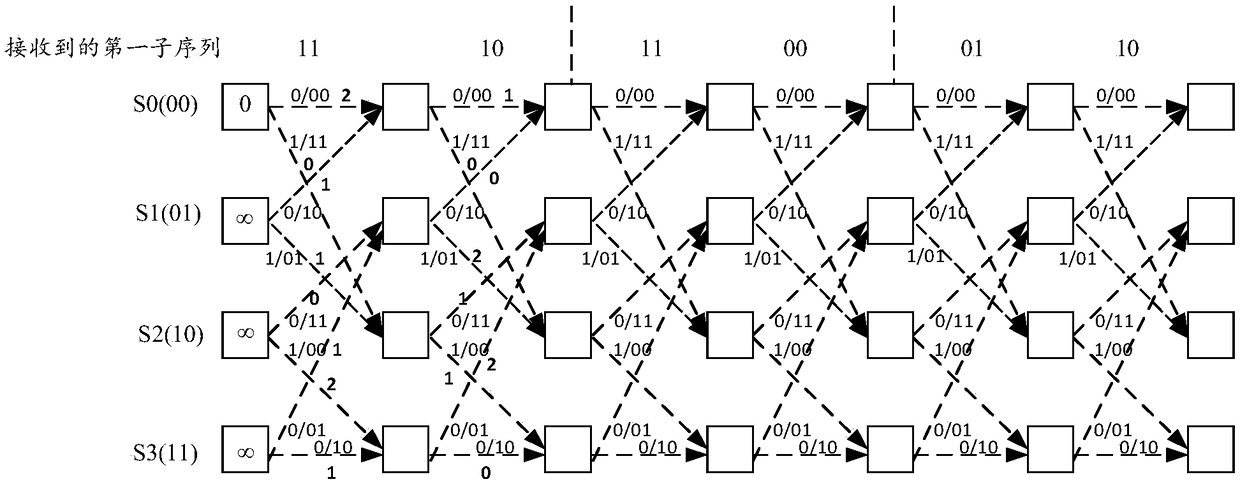

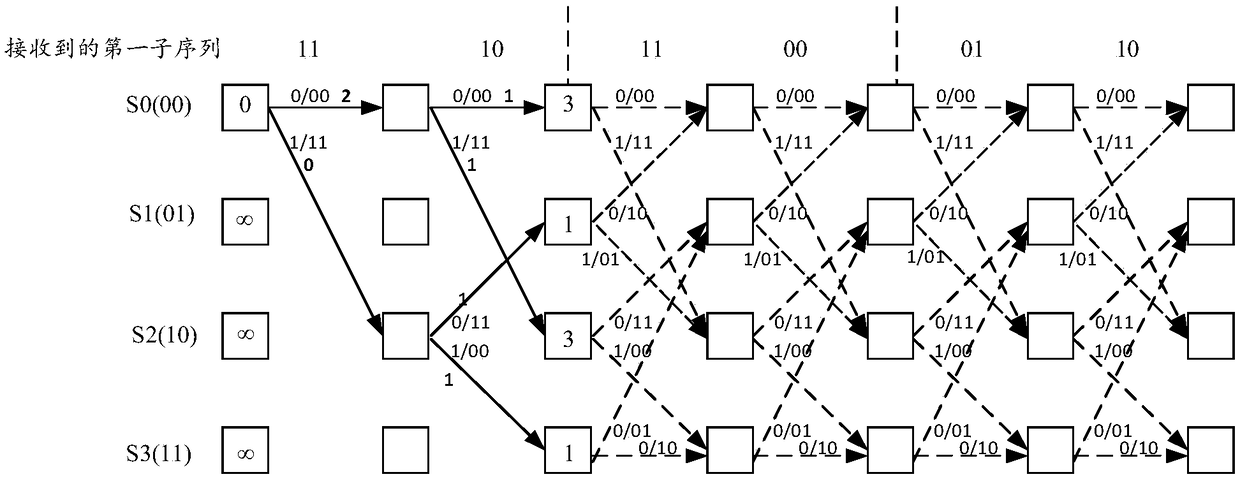

Viterbi decoding method, equipment and storage medium

ActiveCN109462407AIncrease decoding rateOther decoding techniquesHigh level techniquesDecoding methodsData sequences

The embodiment of the invention provides a Viterbi decoding method, equipment and a storage medium. The Viterbi decoding method comprises the following steps: on the basis of segmented parallel decoding of received data sequences, further, for subsequences formed by each segment, calculating branch metrics of sequence segments output at each moment at the moment state for all states within each moment in parallel, and performing parallel add-compare-select on the branch metrics of the sequence segments output at each moment at the moment state in each subsequence, thereby determining a surviving path of each subsequence; and after that, determining a decoding result of the received data sequences according to the surviving path of each subsequence. According to the Viterbi decoding methodprovided by the embodiment of the invention, in the Viterbi decoding process of the received data sequences, twice parallel calculations are introduced, which can improve the decoding rate.

Owner:RUIJIE NETWORKS CO LTD

Decoding method and device for video data compressed code stream and encoding method and device for video data

PendingCN107483942ATroubleshoot technical inefficienciesIncrease decoding rateDigital video signal modificationData compressionComputer engineering

The invention provides a decoding method and device for video data compressed code stream and an encoding method and device for video data. The decoding method for the video data compressed code stream comprises the steps of: parsing the video data compressed code stream, and acquiring sampling format information and / or decoding mode information; according to the sampling format information and / or the decoding mode information, selecting a first sampling format and a decoding mode corresponding to the first sampling format from various preset sampling formats and decoding modes; and carrying out decoding on decoding blocks in the first sampling format and in the decoding mode corresponding to the first sampling format. By the decoding method and device and the encoding method and device, which are provided by the invention, the technical problem of excessively low efficiency when a single sampling format and a single decoding mode are adopted to carry out decoding in the related art is solved.

Owner:TONGJI UNIV +1

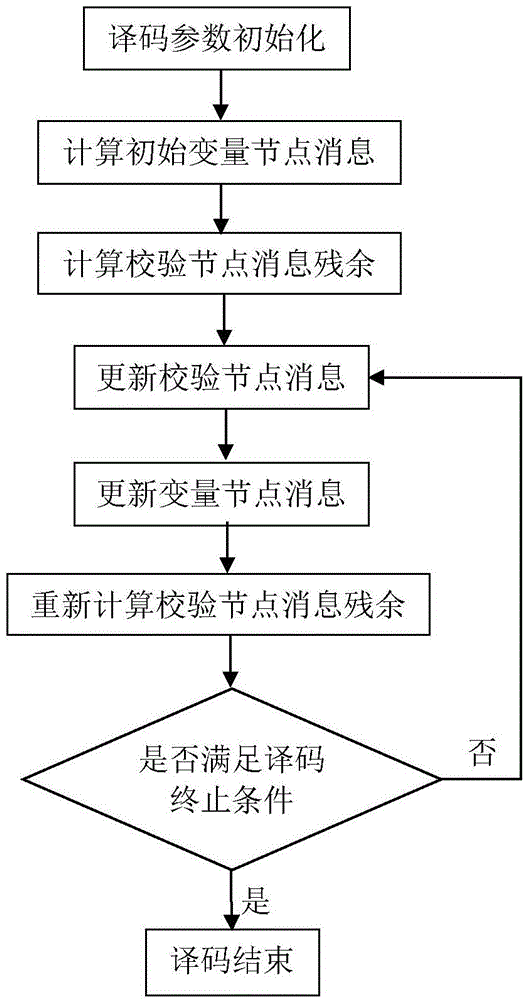

Linear programming decoding method for high-rate low-density parity check code

InactiveCN104682968AIncrease decoding rateDecoding Convergence AccelerationError correction/detection using multiple parity bitsLdpc decodingHigh rate

The invention discloses a linear programming decoding method for a high-rate low-density parity check (LDPC) code, and solves a problem of low decoding rate of an LDPC decoding method in the prior art. The method comprises the following steps: initializing a decoding parameter; calculating an initial variable node message; calculating a residual check node message; updating a check node message; updating a variable node message; re-calculating the residual check node message; judging decoding termination; outputting a decoding result. The check node message of one check node with the best decoding convergence effect and the variable node message of a variable node adjacent to the check node are only updated in decoding iteration each time, so that the decoding rate is greatly increased.

Owner:XIDIAN UNIV

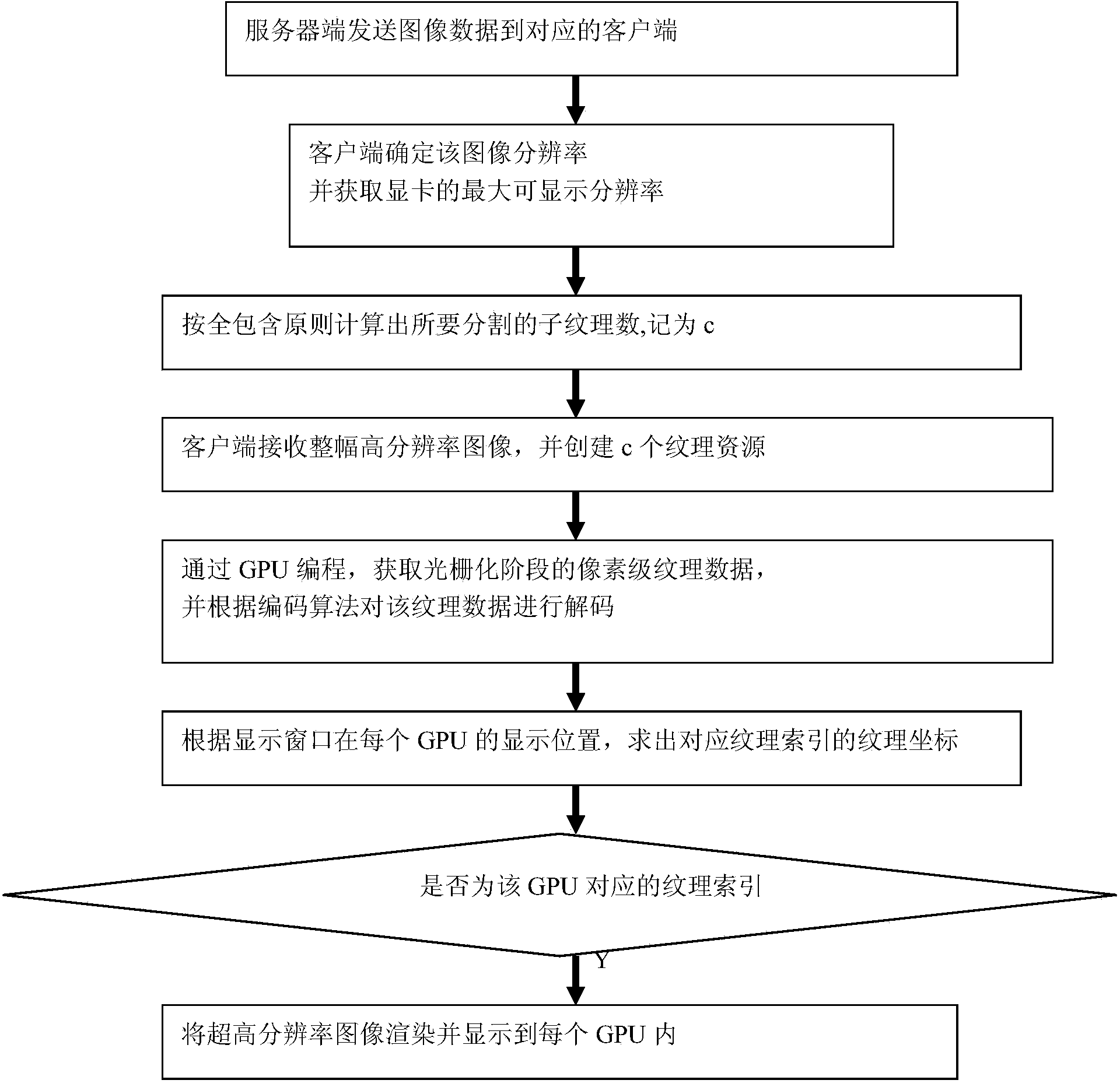

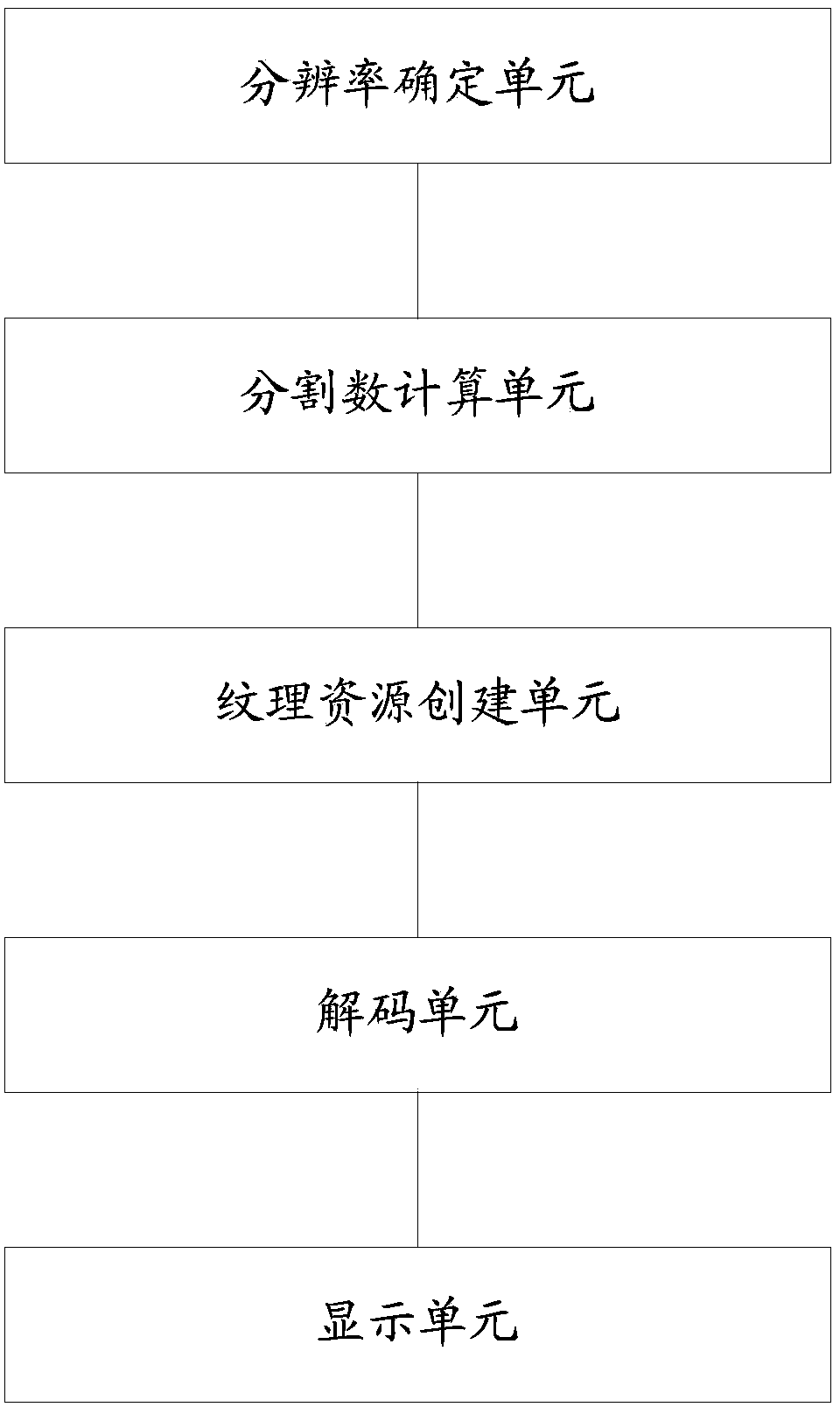

Method and system for displaying ultrahigh resolution images

InactiveCN103730097AMeeting urgent needsIncrease decoding rateCathode-ray tube indicatorsGraphicsImage resolution

The invention discloses a method and system for displaying ultrahigh resolution images. After the ultrahigh resolution images are received, image data are stored into texture data by using a Direct3d display technology rather than carrying out CPU decoding directly, the color value of each pixel is obtained in a rasterizer stage of a graphic plotting pipeline, and the decoding process of the texture data is completed according to the guidance of an encryption algorithm. The advantage that GPU floating-point calculation capacity is strong is fully utilized in the decoding process, the decoding speed is improved greatly, the display frame rate can be improved obviously, and the ultrahigh resolution images greatly meet the urgent needs of people for searching huge amounts of image data under high-definition display media.

Owner:GUANGDONG VTRON TECH CO LTD

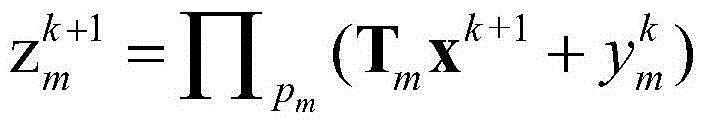

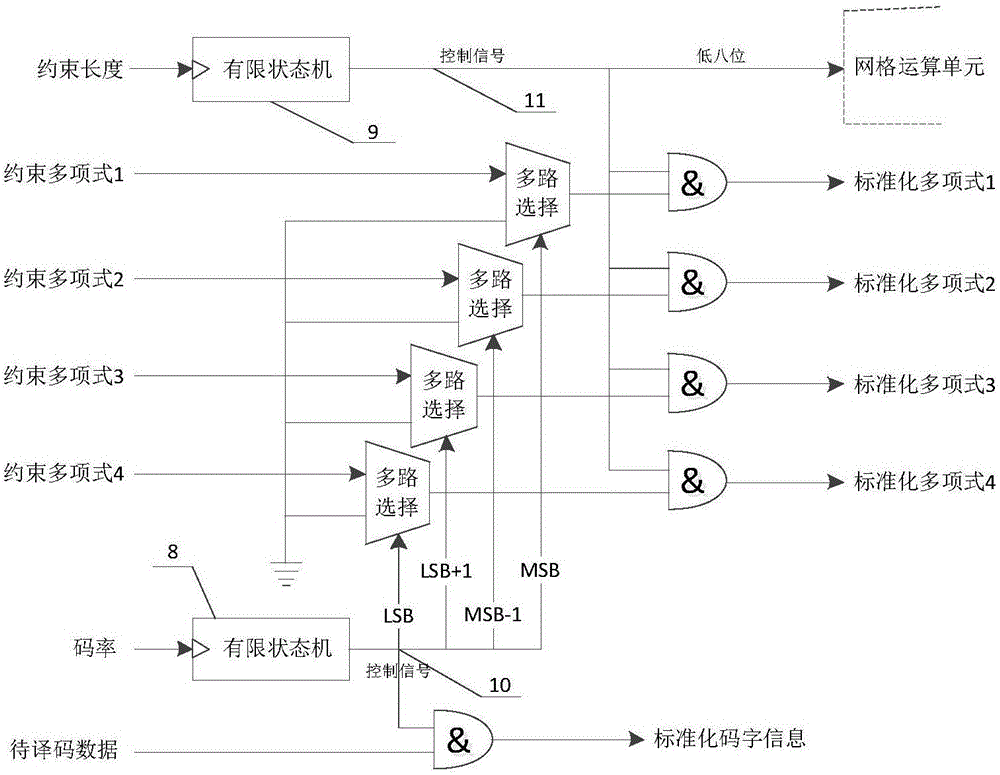

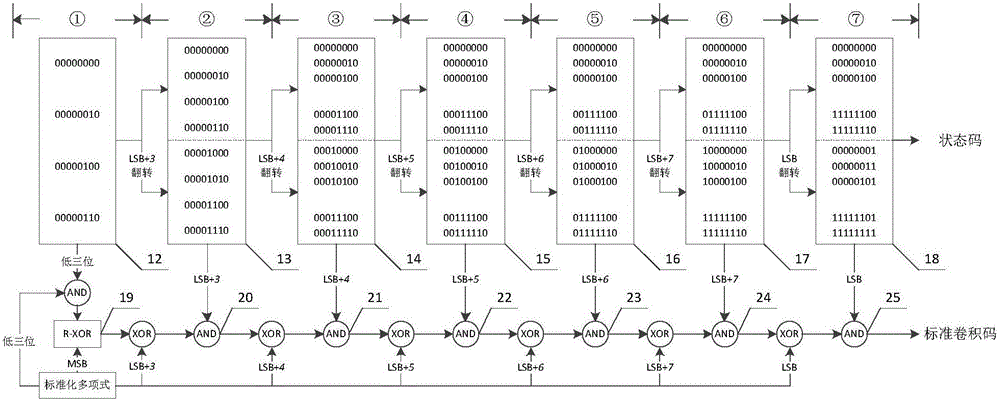

Multi-parameter configurable Viterbi decoder with low resource consumption

PendingCN106209117AImprove throughputReduce areaError correction/detection using convolutional codesCode conversionConvolutional codeBranch Metrics

The invention relates to a multi-parameter configurable Viterbi decoder with low resource consumption. The multi-parameter configurable Viterbi decoder comprises an input configuration unit used for standardizing decoding inputs, a standard code calculation unit used for calculating standard recurrent codes, a branch metric calculation unit used for calculating branch metric values, a grid computation unit used for reconstructing a grid chart and calculating survival paths, a status metric storage and comparison unit, a survival path storage unit, and a backtracking unit used for reconstructing a decoding sequence according to the survival paths and the grid chart. The invention provides a recursive reuse method for the standard code calculation unit. The method comprises the following steps: enumerating four groups of status codes as standard code elements, calculating the standard recurrent codes of the standard code elements, sequentially overturning the highest five digits and the lowest digit of each standard code element, carrying out iterative computation of the standard recurrent codes of the standard code elements and the overturned bits, and obtaining the standard recurrent codes of all the status codes after the iterative computation has been carried out for six times. The method has the advantages that the standard code elements are reused for calculation, so that resource consumption is reduced.

Owner:JIANGNAN UNIV

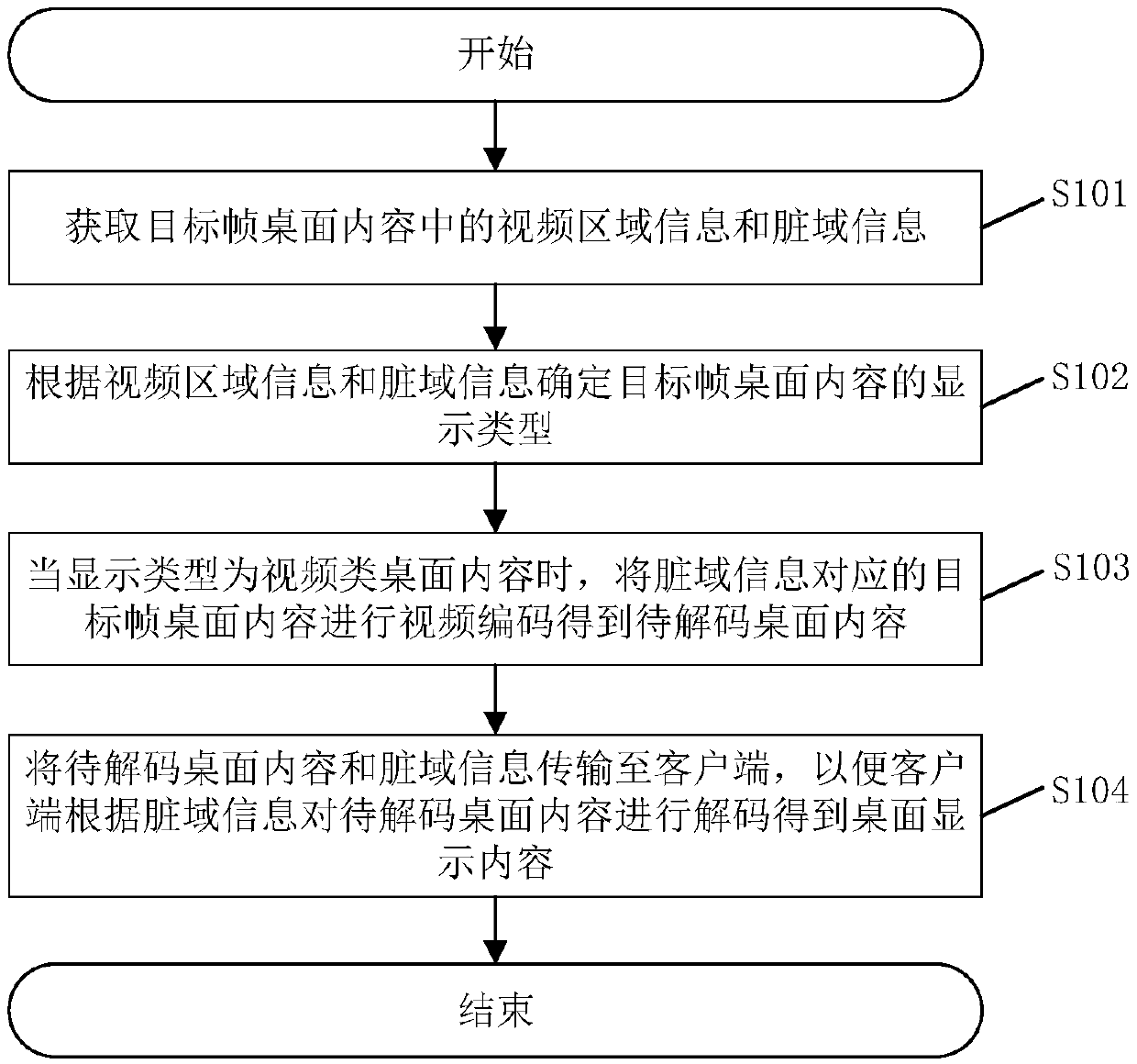

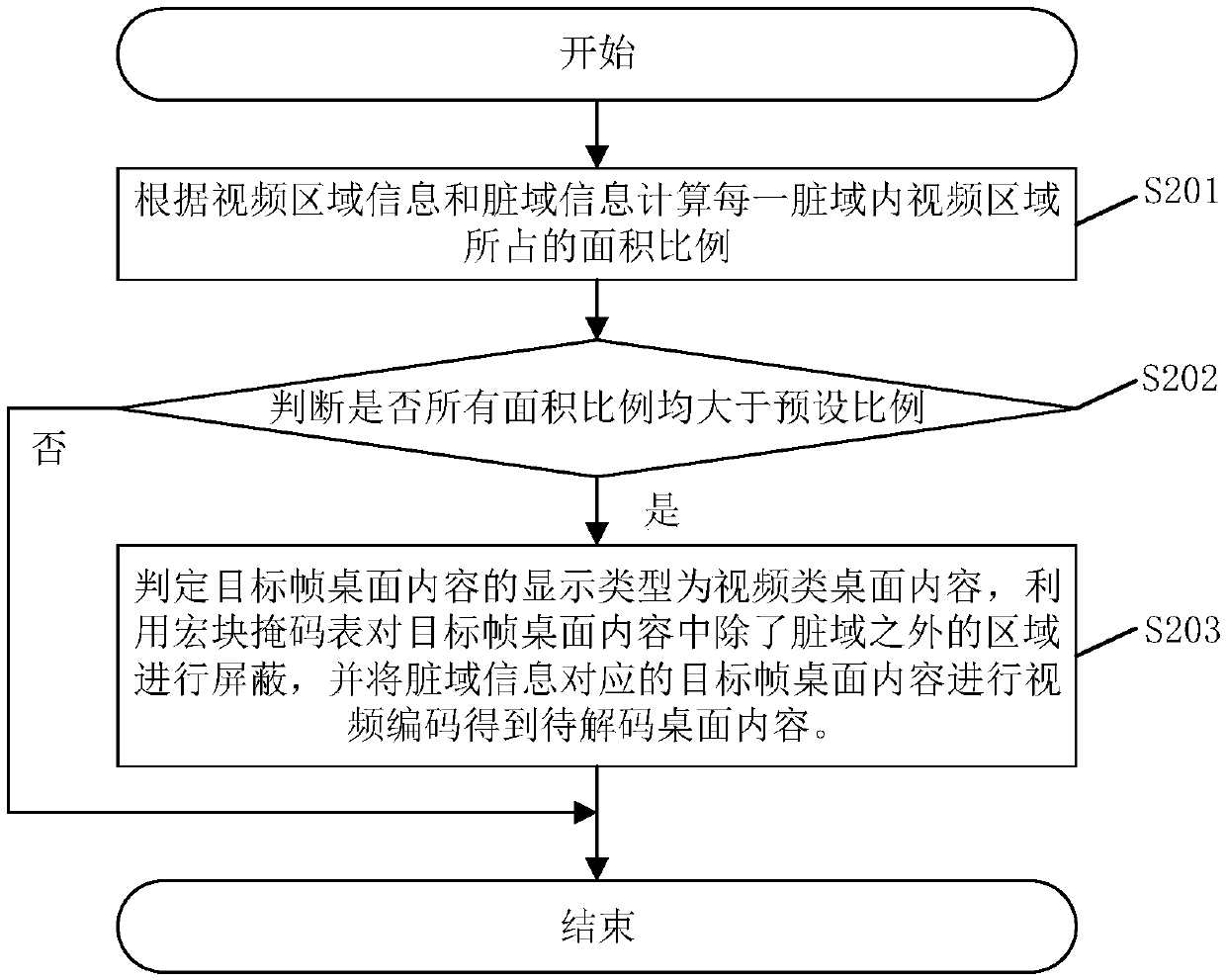

Desktop content transmission method and system of virtual desktop and related components

PendingCN111245879AReduce resource usageIncrease decoding rateDigital video signal modificationTransmissionComputer hardwareVideo encoding

The invention discloses a desktop content transmission method of a virtual desktop. The desktop content transmission method comprises the steps of obtaining video region information and dirty region information in target frame desktop content; when determining that the display type of the target frame desktop content is video desktop content according to the video area information and the dirty domain information, performing video coding on the content corresponding to the dirty domain information to obtain desktop content to be decoded; and transmitting the desktop content to be decoded and the dirty domain information to a client. According to the method, the resource occupation of the client by the desktop content transmitted by the server can be reduced, and the decoding rate of the client is improved. The invention also discloses a desktop content transmission system of the virtual desktop, a desktop content display method and system of the virtual desktop, a virtual desktop server, a virtual desktop client, a computer readable storage medium and a virtual desktop system, which have the above beneficial effects.

Owner:SANGFOR TECH INC

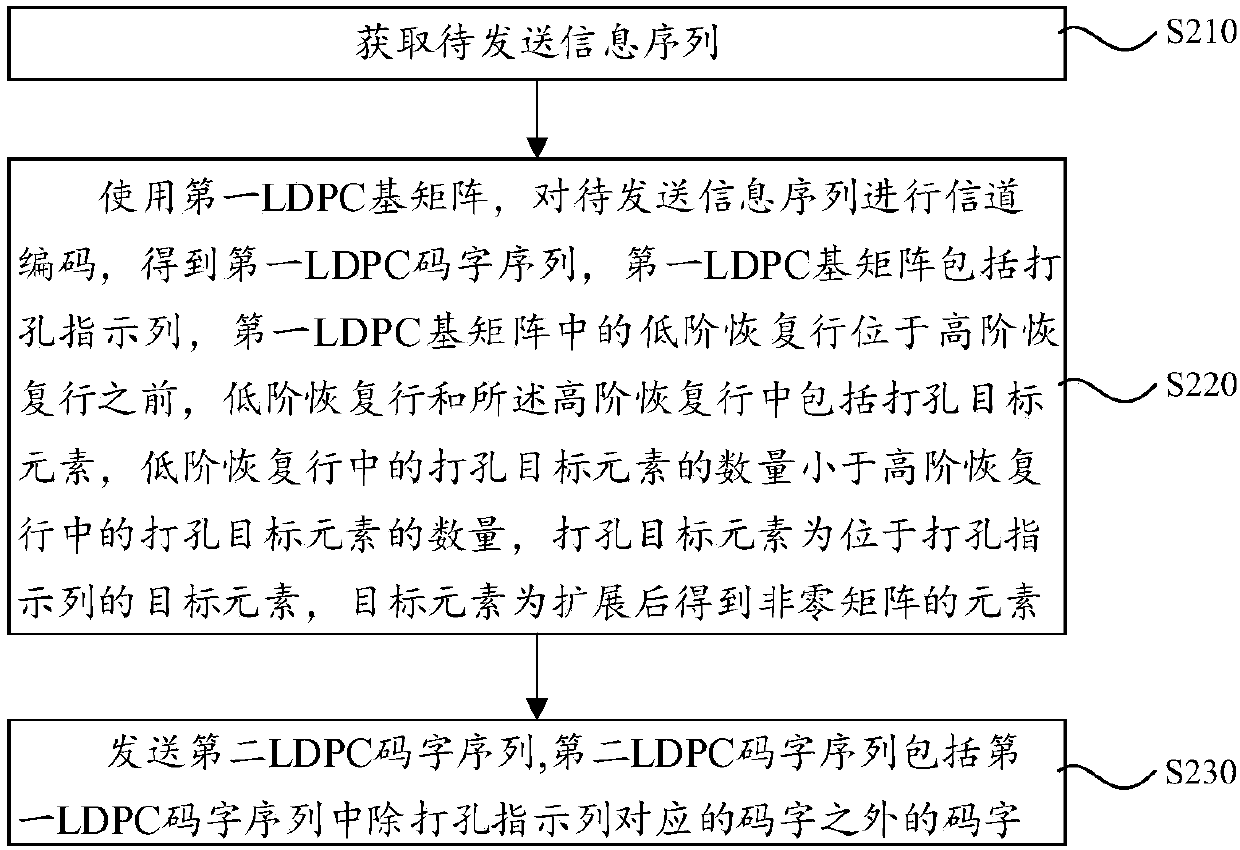

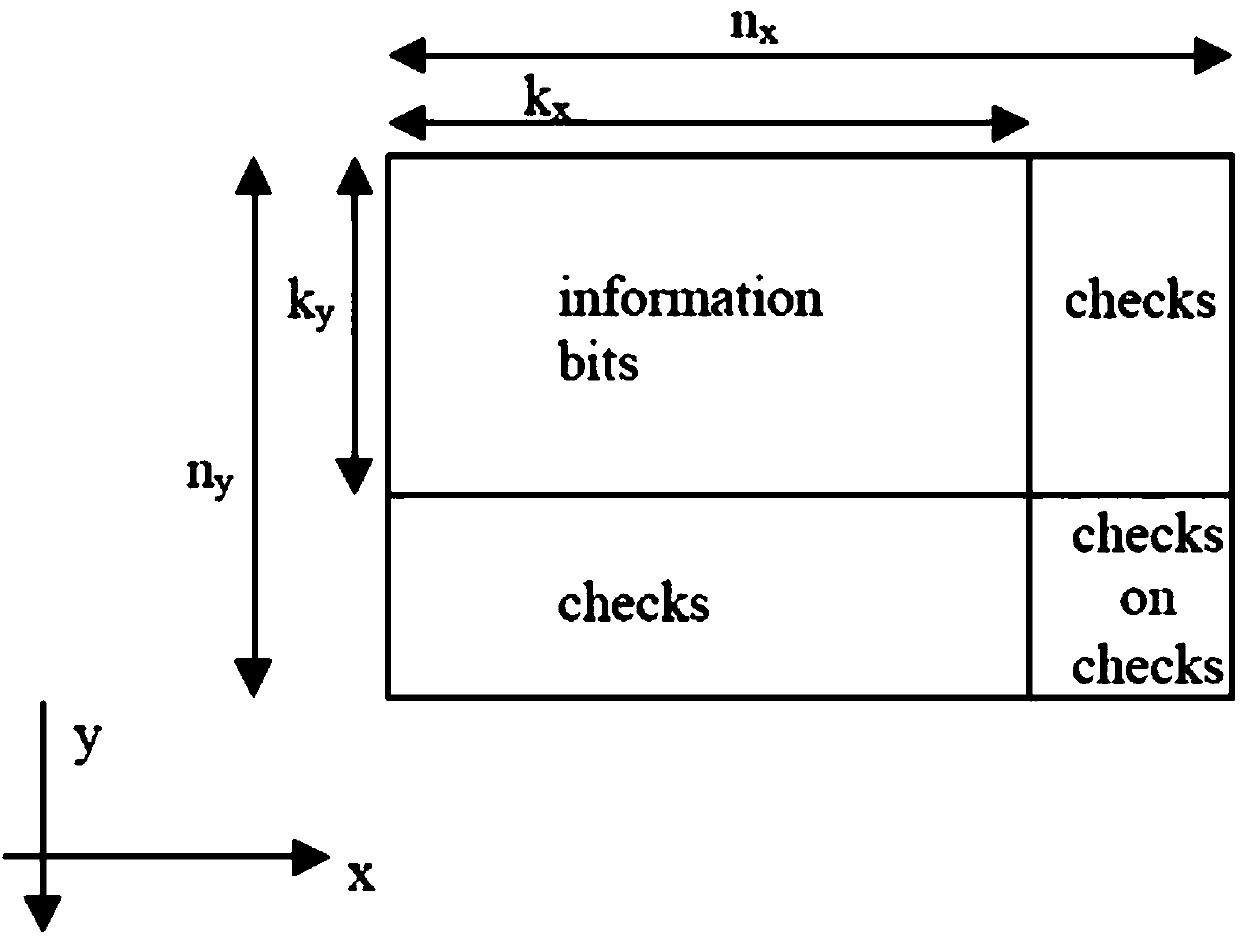

Communication method based on LDPC code and communication equipment

ActiveCN108270510AIncrease decoding rateImprove communication efficiencyError preventionPunchingZero matrix

The embodiment of the invention provides a communication method based on the LDPC code and communication equipment. The communication method comprises the steps that an information sequence to be transmitted is acquired; a first LDPC basis matrix is applied to perform channel coding on the information sequence to be transmitted so as to obtain a first LDPC code word sequence, wherein the first LDPC basis matrix includes a punching instruction column, the low order recovery row of the first LDPC basis matrix is before the high order recovery row, the number of the punching target elements in the low order recovery row is less than that of the punching target elements in the high order recovery row, and the punching target elements are the target elements arranged in the punching instructioncolumn; and a second LDPC code word sequence is transmitted, wherein the second LDPC code word sequence includes the cord words apart from the code words corresponding to the punching instruction column in the first LDPC code word sequence, and the target elements are the extended elements of the non-zero matrix. According to the communication method based on the LDPC code and the communication equipment, the decoding speed of the communication equipment is enhanced so that the communication efficiency is enhanced.

Owner:HUAWEI TECH CO LTD

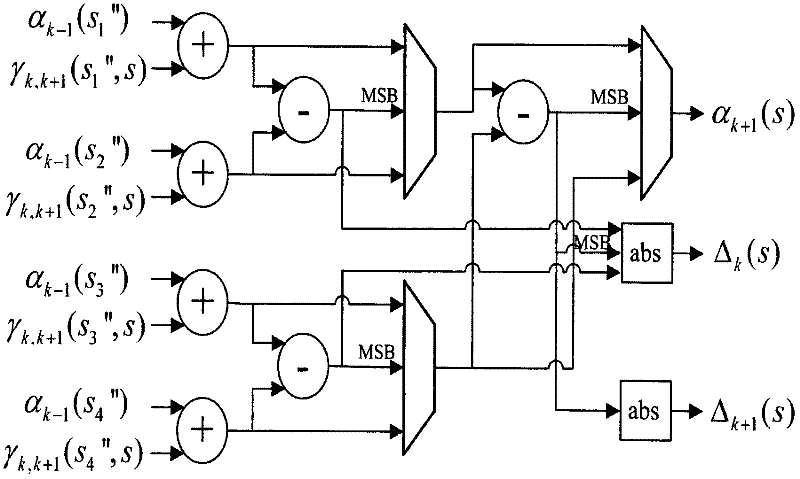

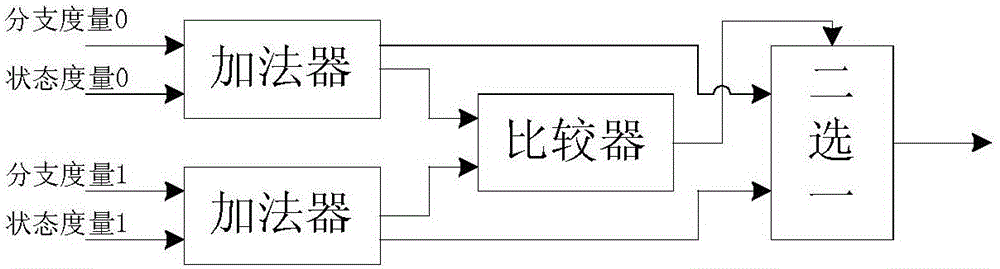

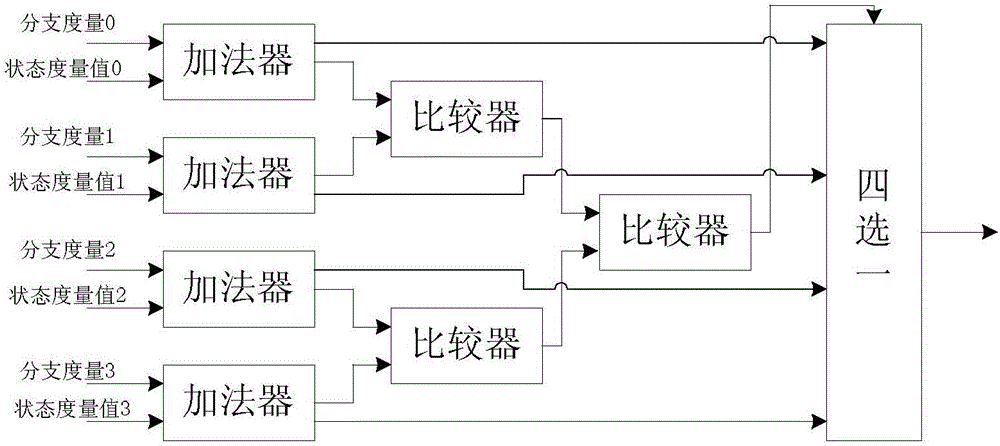

Addition comparison selection calculation method and addition comparison selection calculation device in radix-4 algorithm

ActiveCN105162474ALower latencyIncrease decoding rateError correction/detection using convolutional codesOther decoding techniquesComputer scienceCalculation methods

The invention discloses an addition comparison selection calculation method in a radix-4 algorithm. The addition comparison selection calculation method comprises the following steps: adding a branch measurement value to a corresponding state measurement value to obtain four temporary state measurement values; pairwise comparing the four temporary state measurement values, and simultaneously, respectively subtracting a certain state measurement value at a previous time from the four temporary state measurement values so as to obtain statute operated state measurement values; and selecting the maximal / minimal value in the four statute operated state measurement values as new state measurement values according to a comparison result. The invention further discloses an addition comparison selection calculation device in the radix-4 algorithm. According to the invention, the critical path delay of a decoding unit can be reduced; the decoding rate can be increased; and thus, the decoding performance of the whole system can be improved.

Owner:BEIJING SMART LOGIC TECH CO LTD

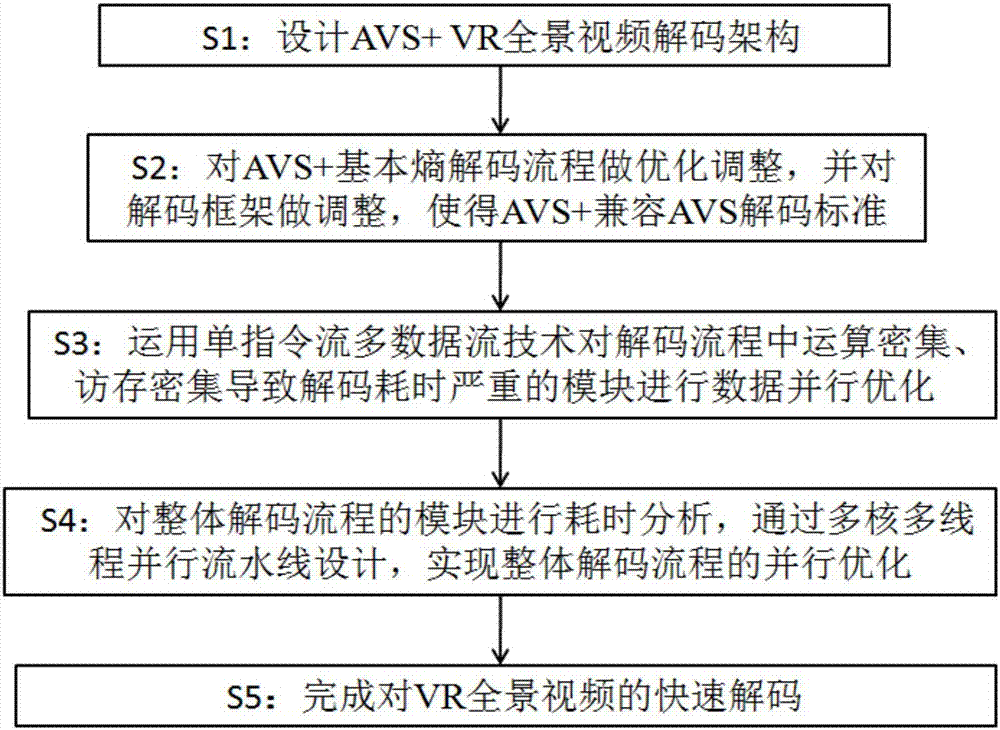

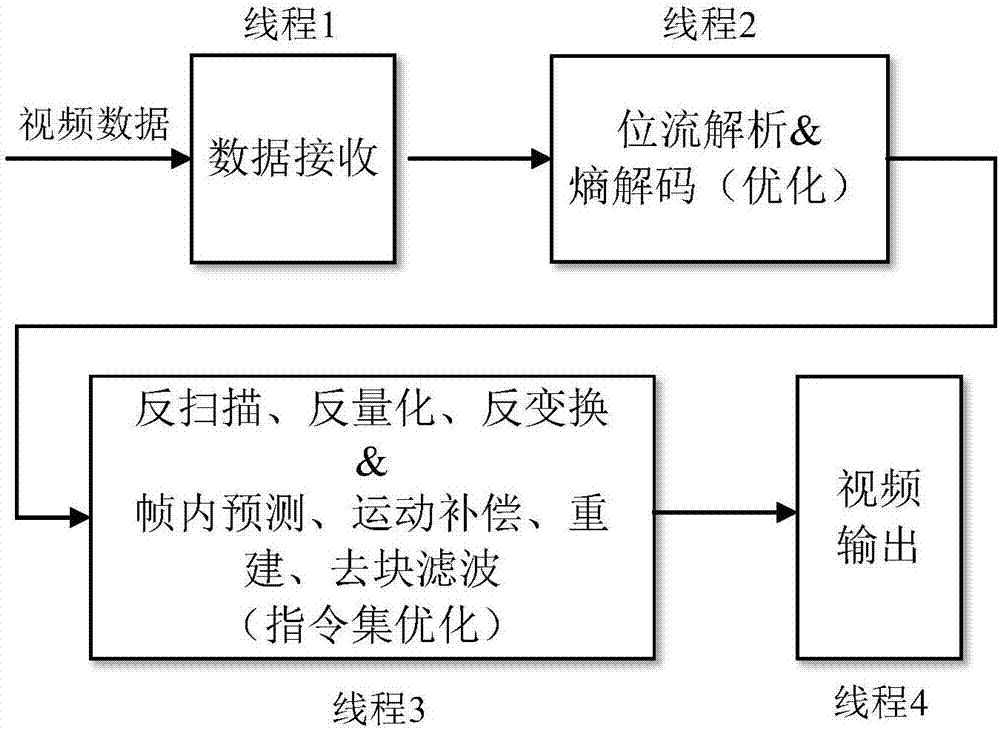

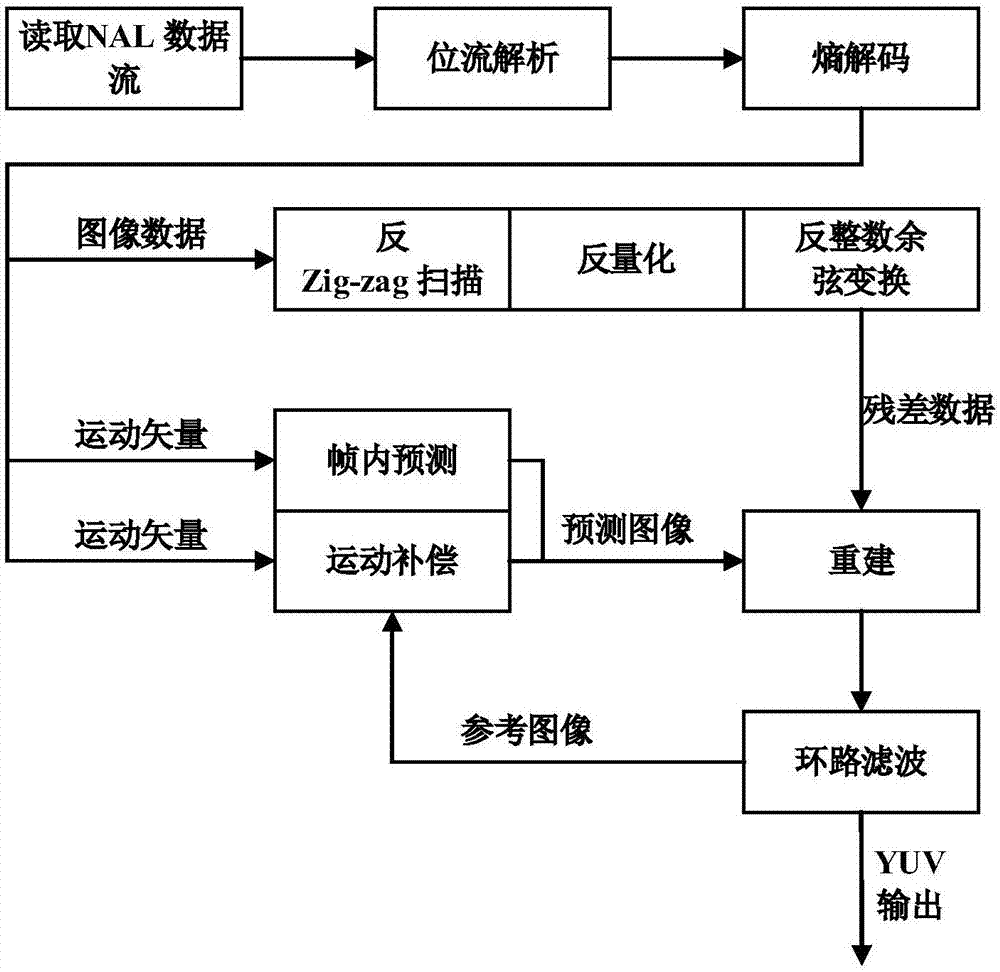

AVS+-based VR panoramic video live broadcast high-speed decoding method and system

InactiveCN107454406AReduce decoding timeIncrease decoding rateDigital video signal modificationData streamProcess module

The invention provides an AVS+-based VR panoramic video live broadcast high-speed decoding method comprising the steps of: S1: designing an AVS+VR panoramic video decoding architecture; S2: optimizing and adjusting a AVS+ basic entropy decoding process so as to make the AVS+ compatible with a AVS decoding standard; S3: performing data parallel optimization by using single-instruction-flow multi-data-stream technology; S4: performing time-consuming analysis on a overall decoding process module, and achieving parallel optimization of the overall decoding process through multi-core and multi-threaded parallel pipeline design; and S5: completing the fast decoding of a VR panoramic video. The decoding method and system of the present invention, from the perspective of task-level parallel optimization, achieve the parallel optimization of the overall decoding process by using effective multi-core multi-threaded parallel pipeline design according to the module time-consuming analysis of the overall decoding process after the data-level parallel optimization, and shorten the decoding time of a single frame of image to achieve an increase in the overall video sequence decoding rate.

Owner:AVIT

Video analyzing method and video analyzing device

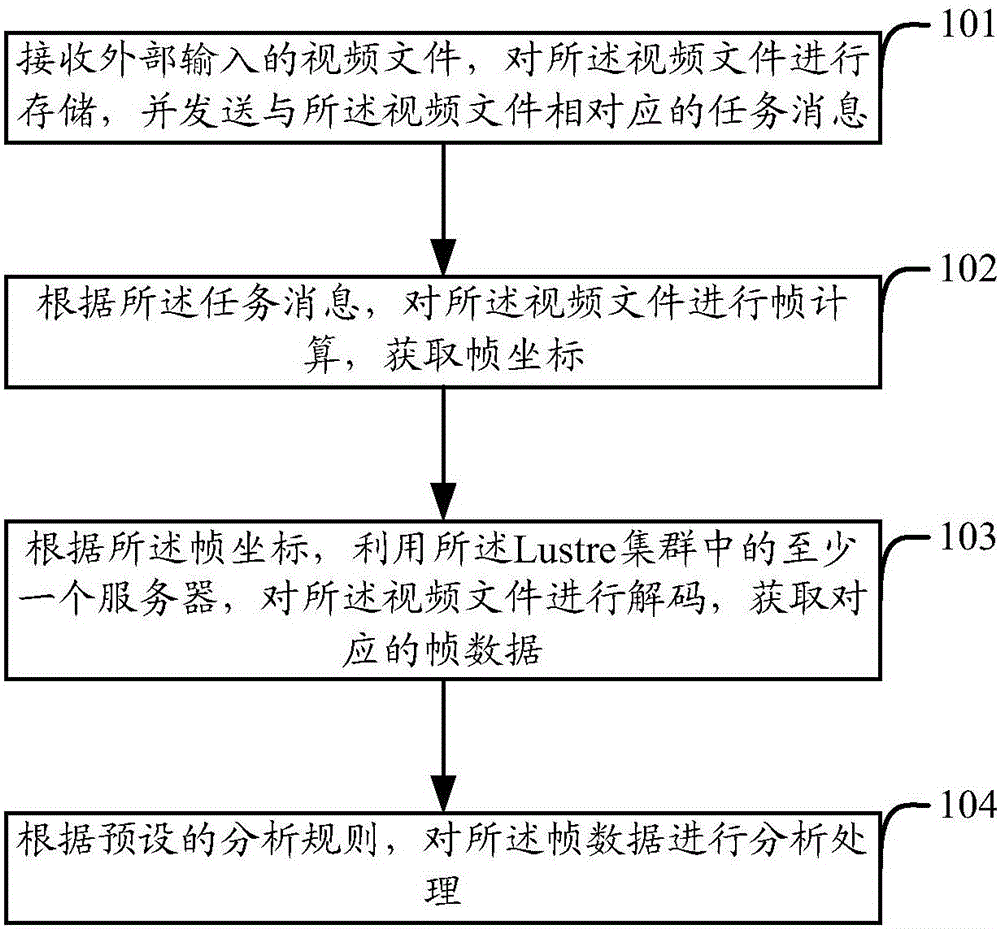

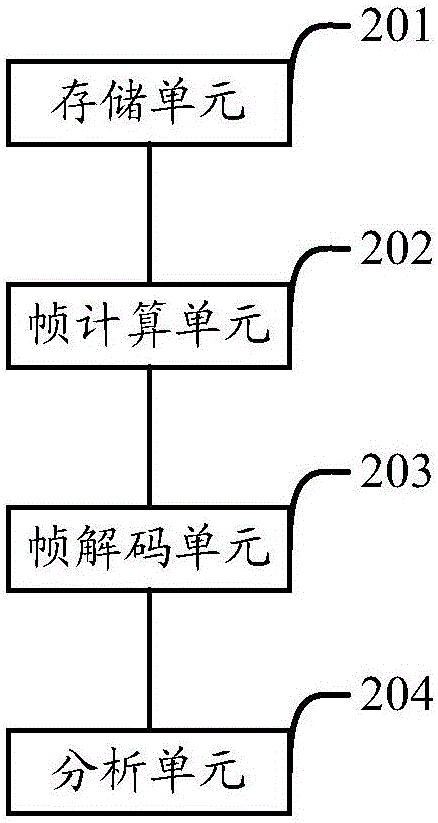

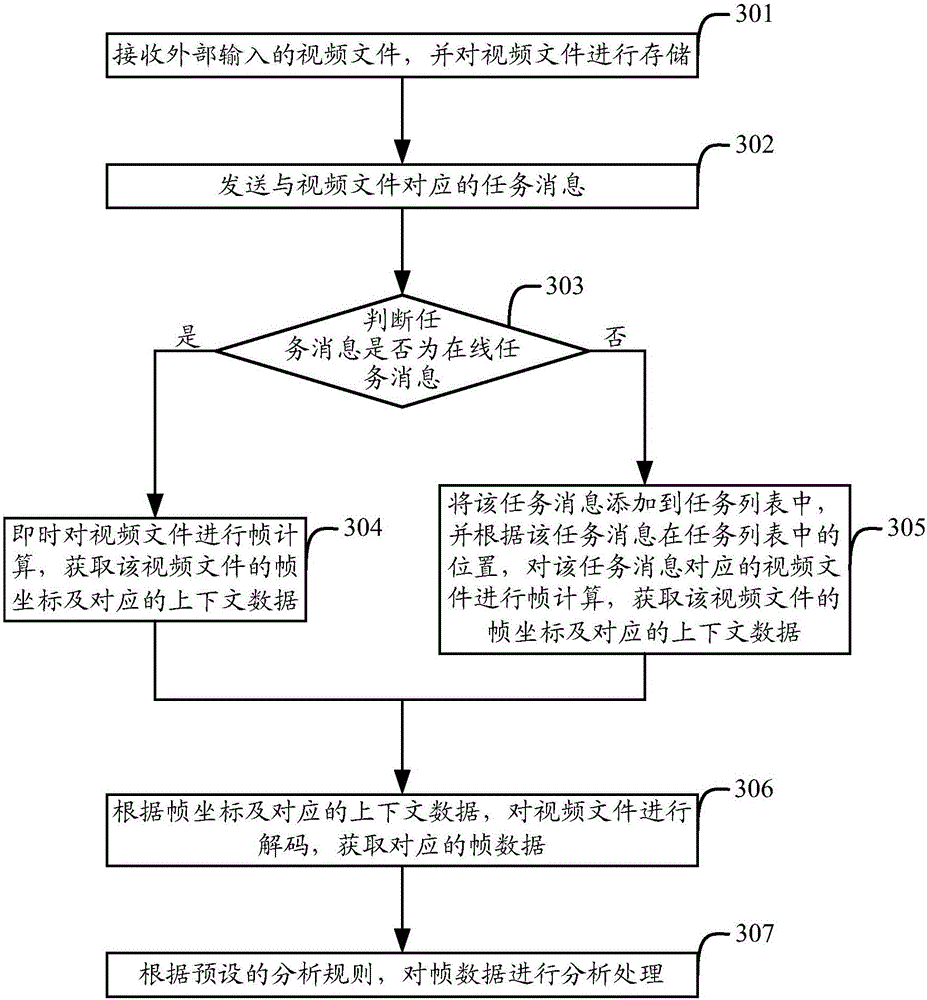

InactiveCN105791888AImprove analysis efficiencyIncrease decoding rateSelective content distributionComputer graphics (images)

The invention provides a video analyzing method and a video analyzing device. The video analyzing method and the video analyzing device are applied on a Lustre cluster. The video analyzing method comprises the steps of receiving a video file which is input from outside, storing the video file, and transmitting task information which corresponds with the video file; performing frame calculation on the video file according to the task information, thereby obtaining a frame coordinate; decoding the video file according to the frame coordinate through utilizing at least one server in the Lustre cluster, and obtaining corresponding frame data; and analyzing the frame data according to a preset analysis rule. The video analyzing device comprises a storage unit, a frame calculation unit, a frame decoding unit and an analyzing unit. The video analyzing method and the video analyzing device can improve video analyzing efficiency.

Owner:INSPUR SOFTWARE CO LTD

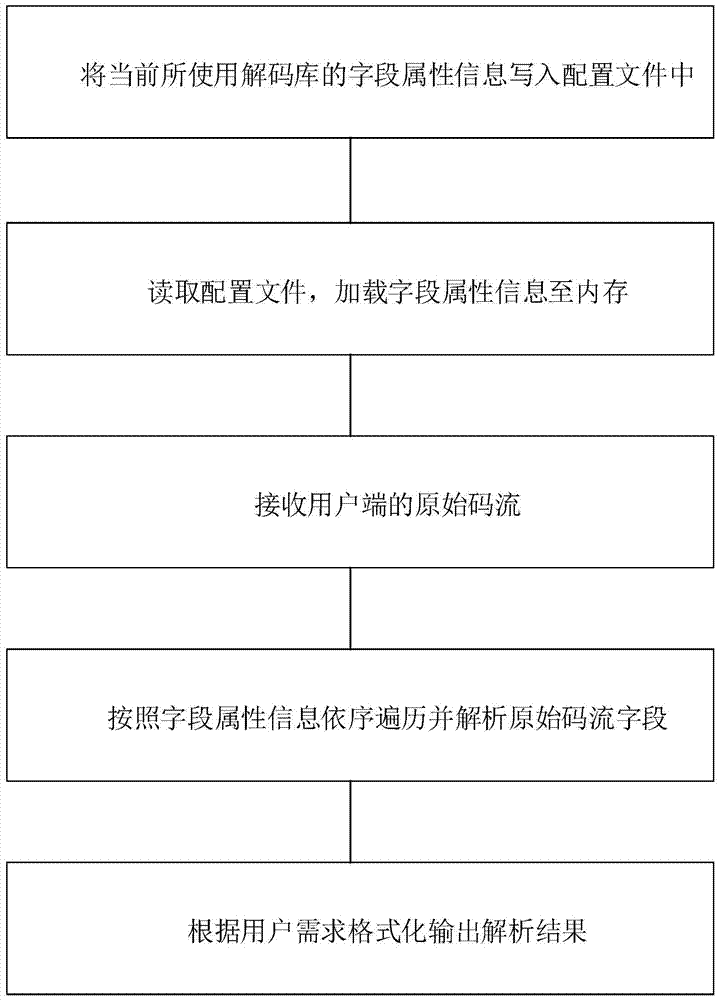

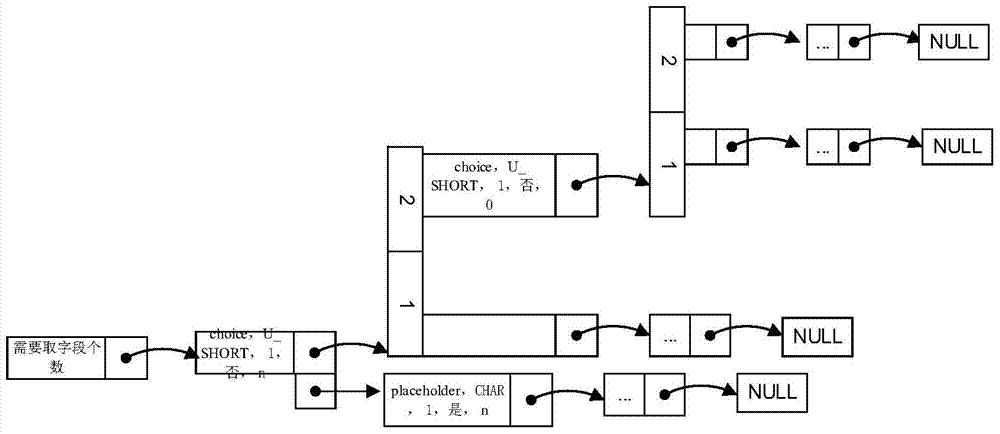

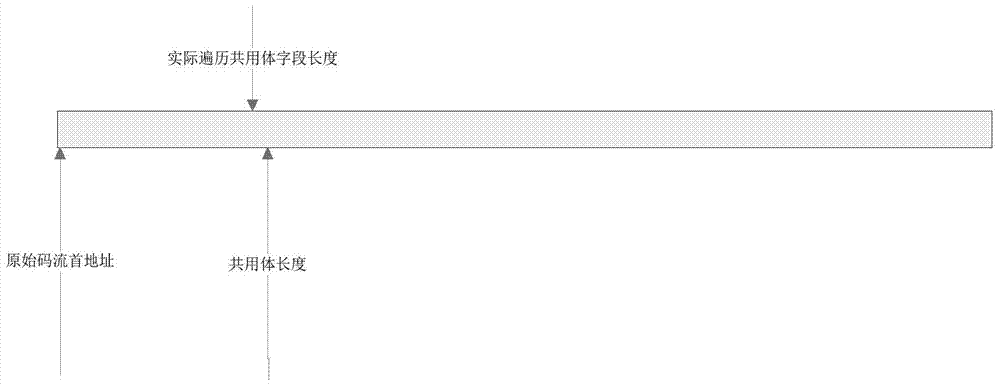

Method and system for decoding of original code flow

ActiveCN107025125AImprove linearityIncrease decoding rateProgram controlMemory systemsByteData structure

The invention relates to a method and system for decoding of an original code flow. The method comprises the steps that field attribute information which uses a decoding base at present is written into a configuration document; the configuration document is read, and the field attribute information is loaded to memory; an original code flow of a user side is received; fields of the original code flow are traversed and analyzed successively according to the field attribute information; and analysis results are output in a formatted manner according to user demands. According to the invention, code flow data structure information is completely decoupled with a program; when a field value needs to be acquired, only simple modification of the configuration document is necessary, so that a freshman can rapidly join a project, and code rows will not linearly increase with the quantity of fields. Forcible data structure conversion is not needed; the original code flow is accessed by a pointer according to bytes (unit) and accessed successively according to offset amounts; during frequent decoding, the decoding can be accelerated effectively; and the code rows are stable, and will not be modified or changed obviously according to demands.

Owner:SHANGHAI DATANG MOBILE COMM EQUIP +1

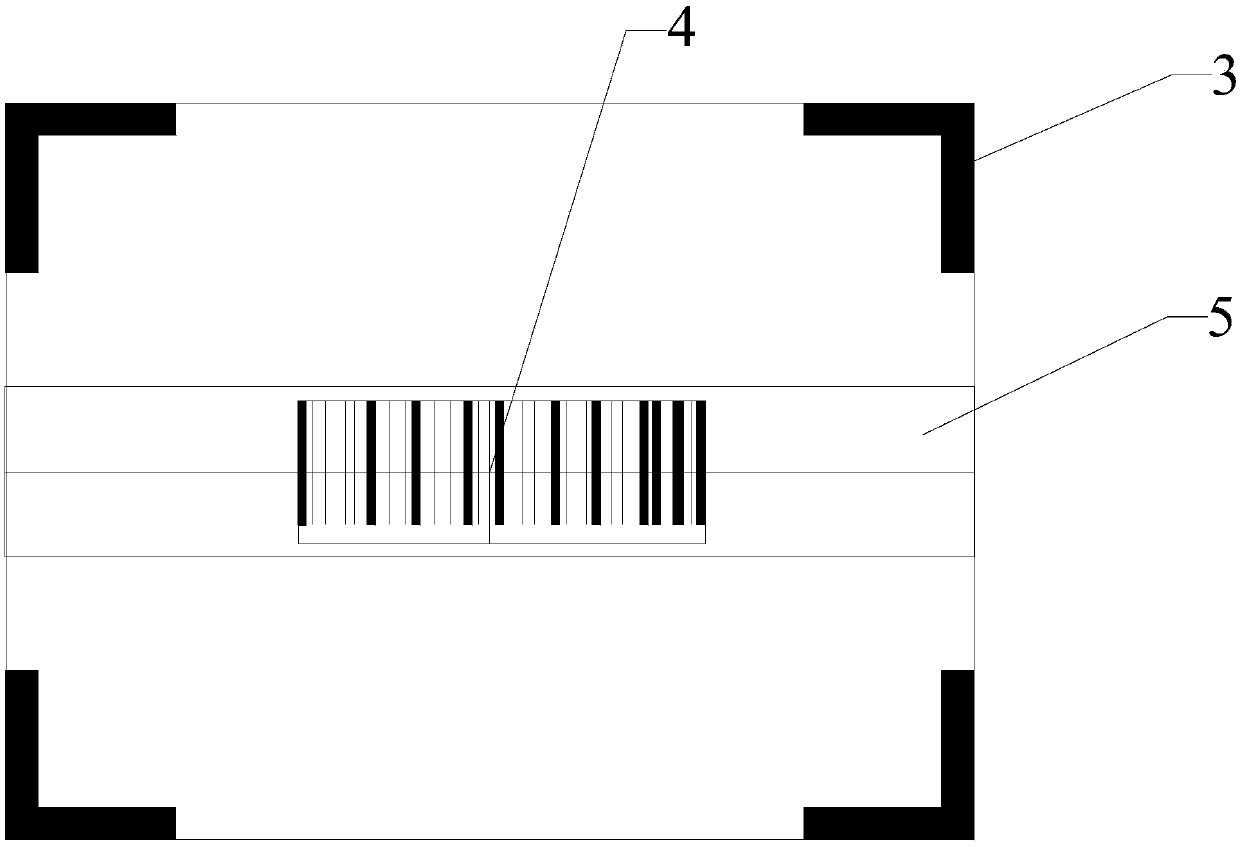

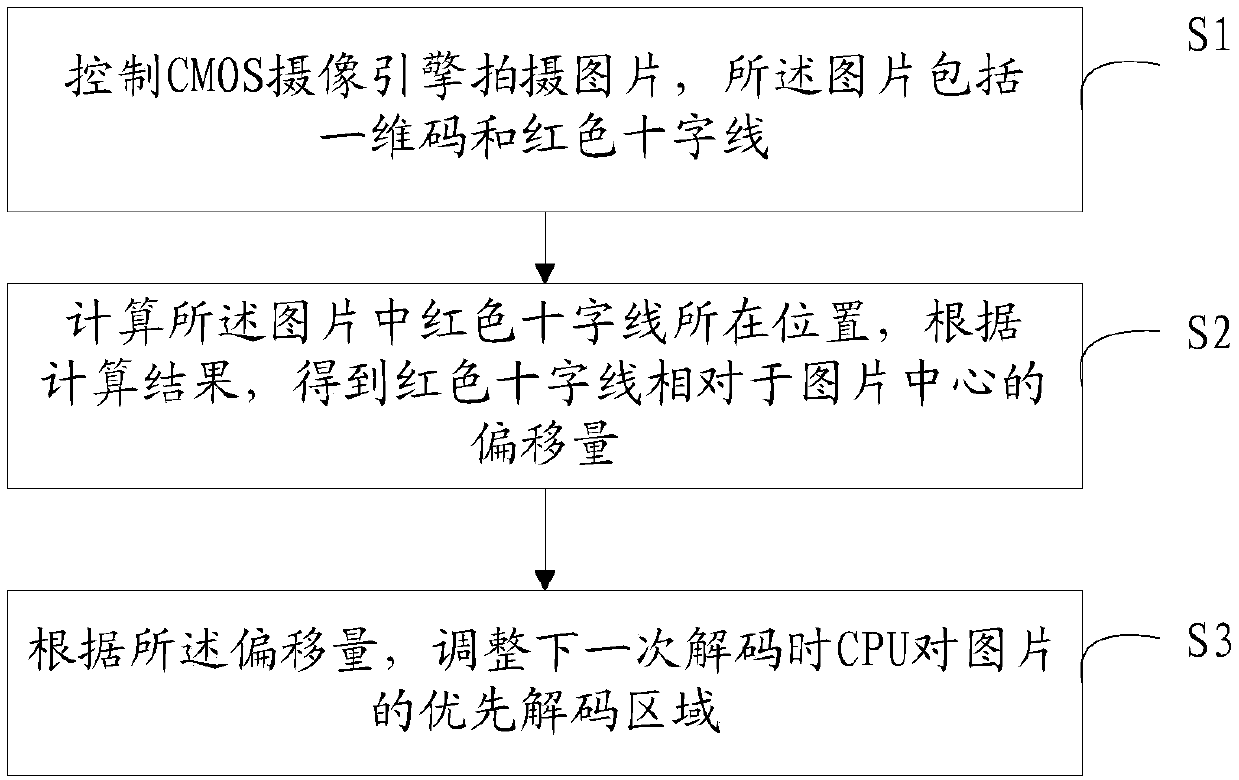

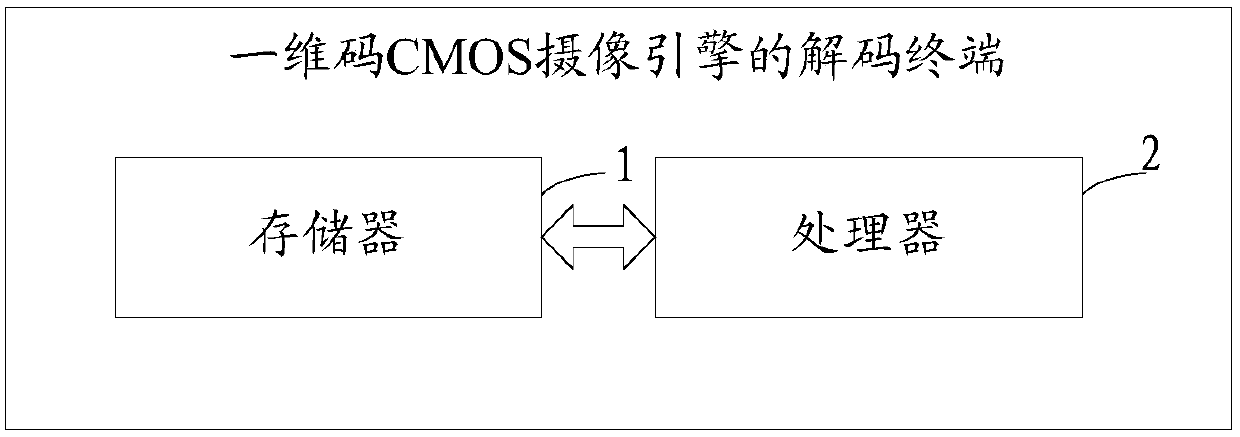

Decoding method and terminal for one-dimensional code CMOS camera engine

ActiveCN107644183AGuaranteed yieldIncrease decoding rateSensing by electromagnetic radiationCMOSInstallation Error

The invention relates to the technical field of codes and in particular to a decoding method and terminal for a one-dimensional code CMOS camera engine. The method includes: controlling a CMOS cameraengine to take a picture including a one-dimensional code and a red cross line; calculating the position of the red cross line in the picture and obtaining the offset of the red cross line relative toa picture center according to a calculation result; and adjusting the preferential decoding area of the picture by a CPU during the decoding next time. The method adjusts the preferential decoding area during the decoding next time by calculating the offset of the red cross line relative to the picture center, so as to increase a decoding rate and to solve a problem that installation errors in the manufacturing process of the CMOS camera engine module may cause that a barcode in not located in the center of a positioning frame so as to lead to an over slow decoding rate or a decoding incapability, thereby ensuring a CMOS camera engine product yield.

Owner:FUJIAN LANDI COMML EQUIP CO LTD

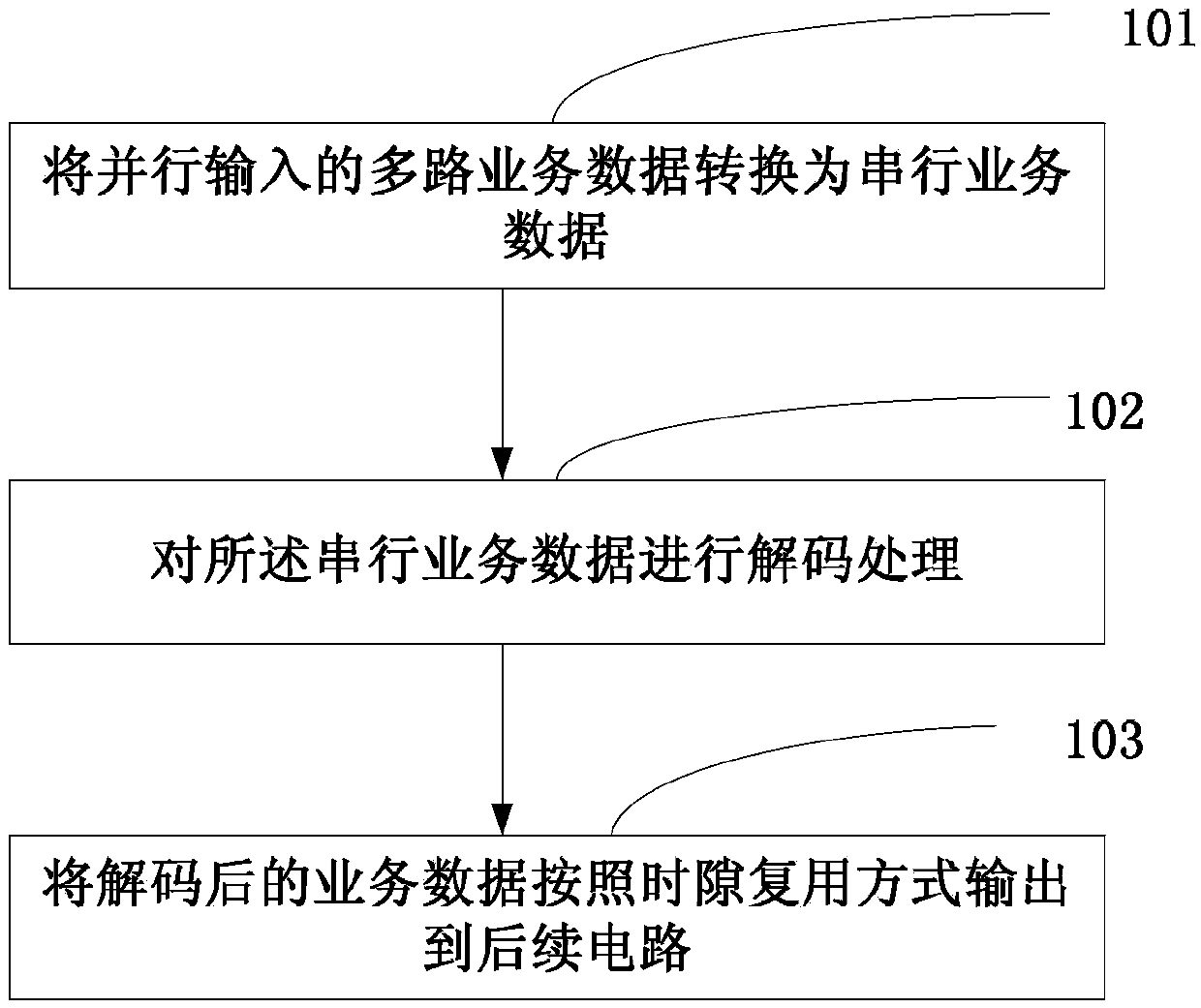

Decoding method and device

ActiveCN104184544AImprove decoding efficiencyIncrease decoding rateError preventionTime-division multiplexComputer hardwareMultiplexing

Embodiments of the present invention provide a decoding method and apparatus. The decoding method of the embodiments of the present invention comprises: converting parallelly input multi-way service data into a serial service data; decoding the serial service data; and outputting the decoded service data to a following circuit by using a timeslot multiplexing mode. By using the method, the decoding efficiency can be improved, and the resource consumption can be reduced.

Owner:SANECHIPS TECH CO LTD

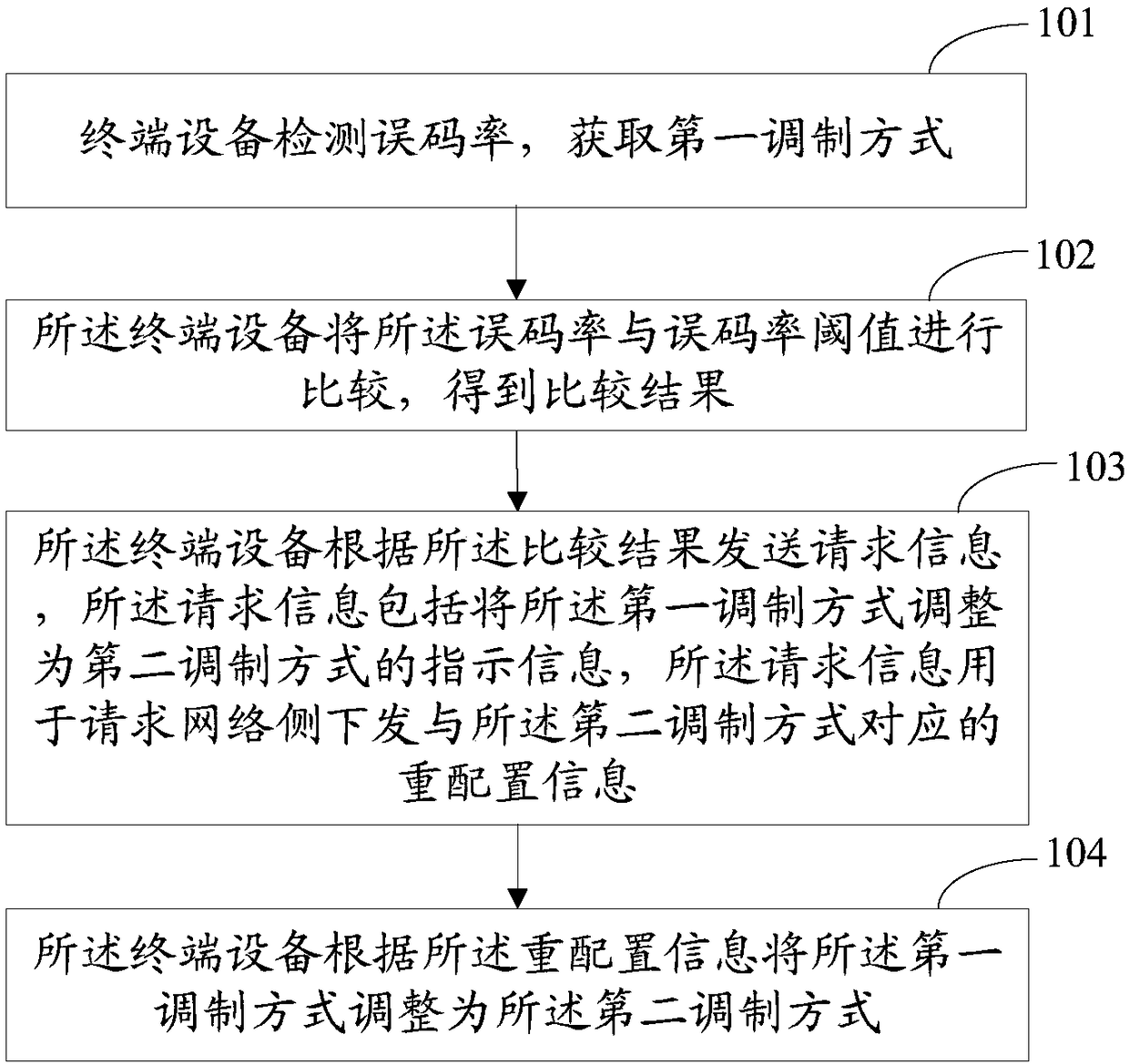

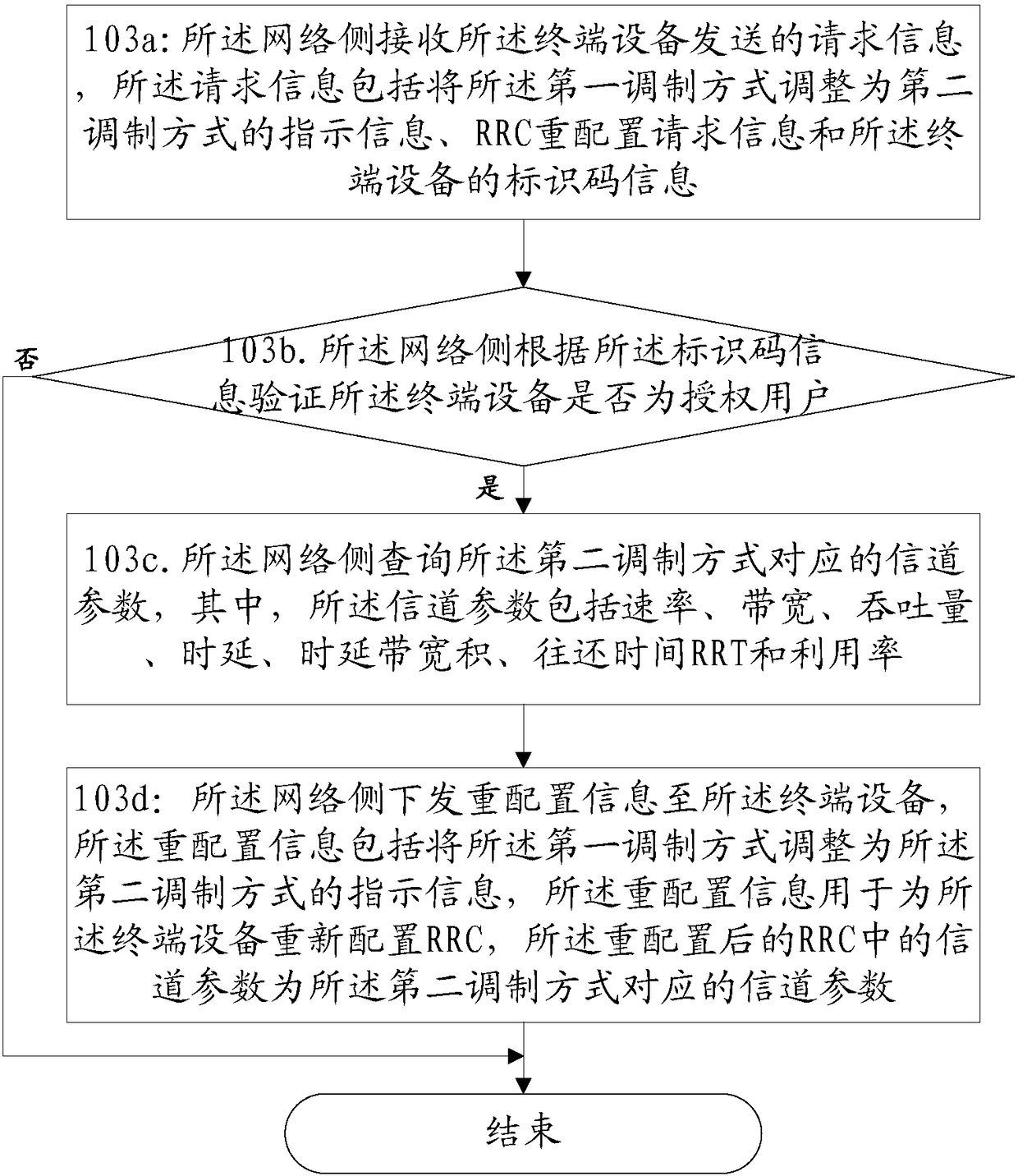

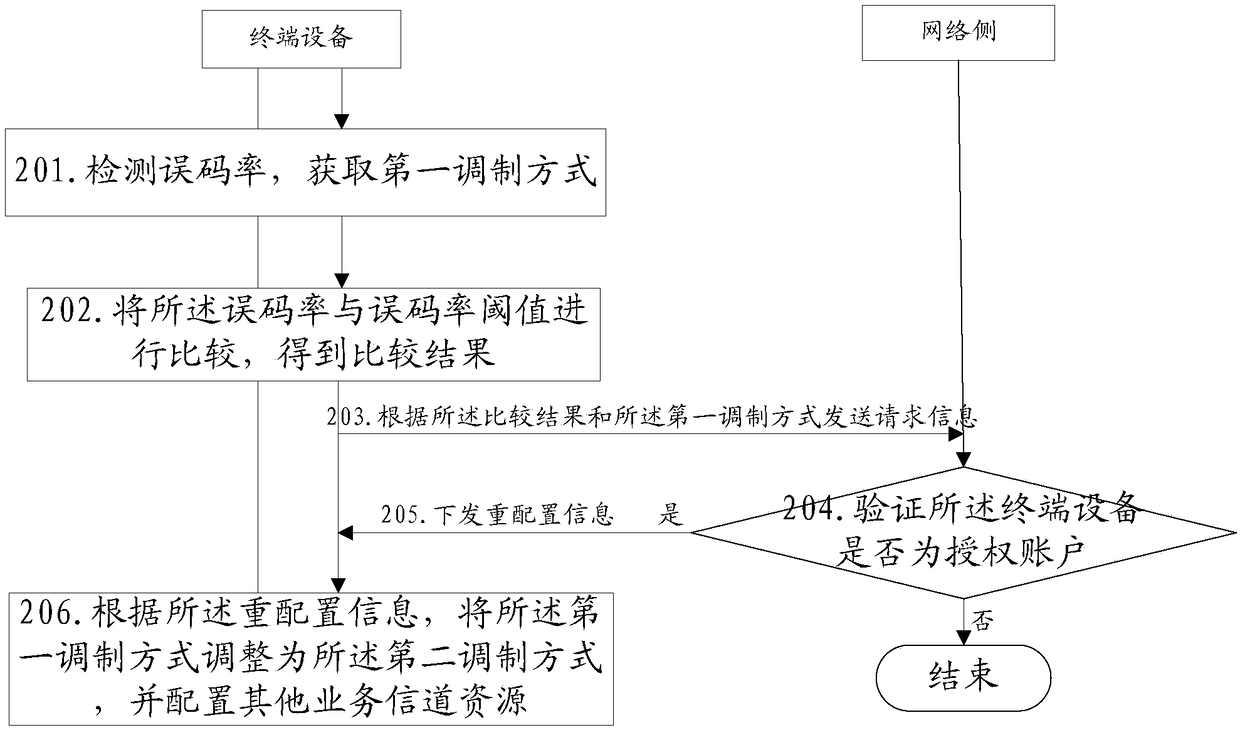

Data communication method, and related product

ActiveCN108337068AIncrease decoding rateImprove decoding rateTransmission rate adaptationTerminal equipmentComputer terminal

The embodiment of the invention discloses a data communication method, and a related product. The method comprises the following steps: a terminal device detects a bit error rate, and obtains a firstmodulation mode; the terminal device compares the bit error rate with a bit error rate threshold to obtain a comparison result; the terminal device sends request information according to the comparison result and the first modulation mode, wherein the request information comprises indication information for adjusting the first modulation mode to a second modulation mode, and the request information is used for requesting a network side to deliver reconfiguration information corresponding to the second modulation mode; and the terminal device adjusts the first modulation mode to the second modulation mode according to the reconfiguration information. By adoption of the embodiment of the invention, the modulation mode can be dynamically adjusted according to the bit error rate, and the network delay and the jamming problems are solved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

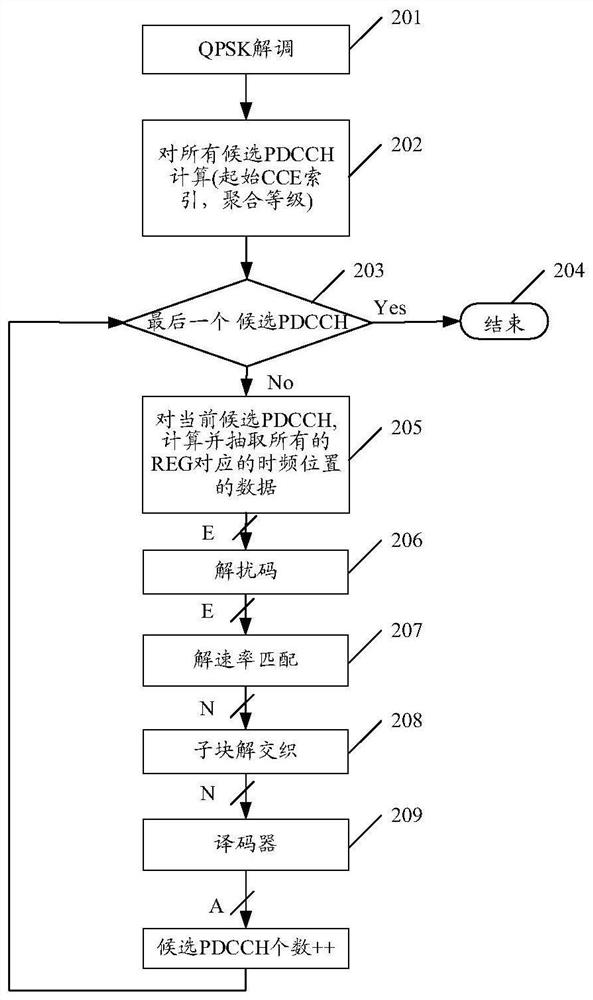

Information processing method, device, terminal, chip and storage medium

PendingCN113572572AReduce stepsIncrease decoding rateReceiver specific arrangementsSignalling characterisationComputer hardwareMultiplexing

The embodiment of the invention discloses an information processing method, a device, a terminal, a chip and a storage medium. The information processing method comprises the following steps: determining a candidate physical downlink control channel (PDCCH), and a data length and a rate matching mode corresponding to the candidate PDCCH according to a preset configuration parameter; when the current candidate PDCCH is subjected to decoding processing, determining a target candidate PDCCH from the candidate PDCCHs which are subjected to decoding processing; wherein the target candidate PDCCH and the current candidate PDCCH have overlapped data; according to a first data length and a first rate matching mode corresponding to the target candidate PDCCH, and a second data length and a second rate matching mode corresponding to the current candidate PDCCH, judging whether a preset multiplexing condition is satisfied; if it is judged that the preset multiplexing condition is met, determining a data multiplexing mode corresponding to the current candidate PDCCH; and decoding the current candidate PDCCH according to the data multiplexing mode.

Owner:ZEKU TECH (BEIJING) CORP LTD

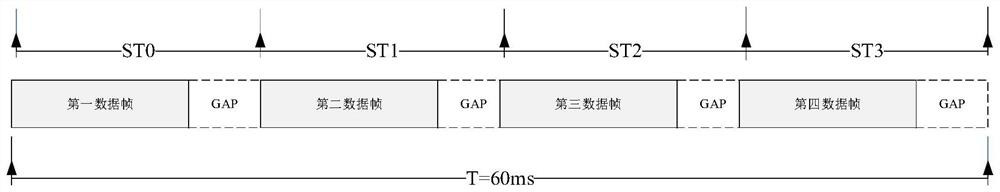

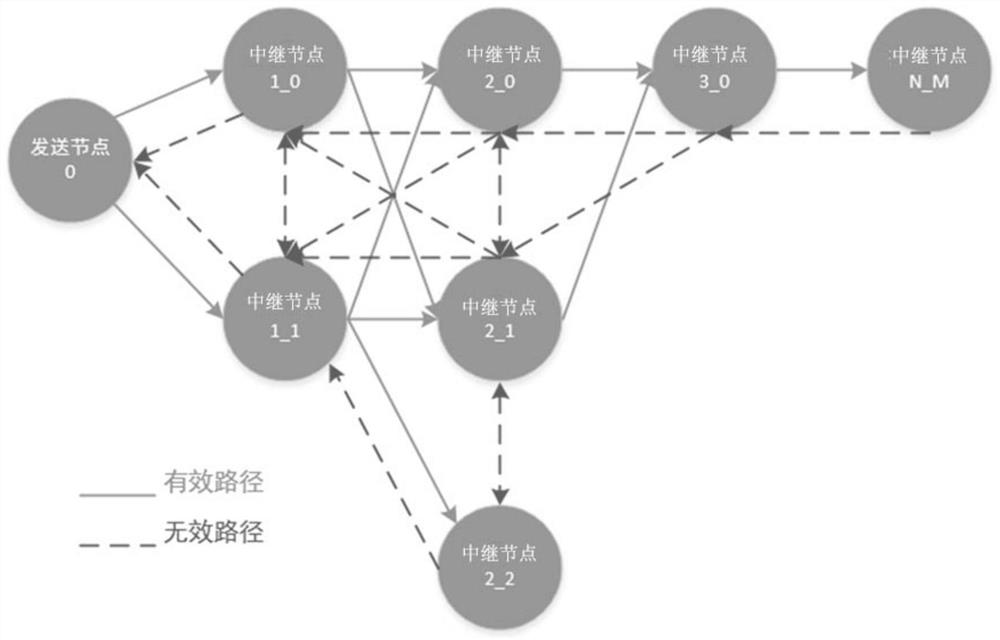

Superframe-based wireless relay method, node and network

InactiveCN111935776APrevent reverse transmissionImprove usabilityNetwork traffic/resource managementAdaptation strategy characterisationPhysical layerTrunking

The invention discloses a superframe-based wireless relay method, node and network, and the method comprises the steps: decoding a received wireless signal in a physical layer, and detecting or correcting the decoding according to the channel coding information obtained through decoding, thereby obtaining a data frame; judging whether the current node is matched with a target node of the data frame or not; if so, processing the data frame; if not, judging whether the data frame meets a forwarding condition, wherein the forwarding condition comprises that the forwarded hop count is smaller thanthe total hop count; if yes, modifying the forwarded hop count, forwarding the data frame after encoding, and enabling the current node to enter a sleep mode within the remaining time of the superframe. After forwarding or sending the data frame, the node enters a sleep mode, so that energy is saved on one hand, and reverse transmission of the data frame is prevented on the other hand, wherein the total hop count is used for controlling the life cycle of the data frame; the data frame is detected or corrected through the channel coding information, so that the high availability and the receiving sensitivity of the data frame are improved, and the influence of data frame retransmission on channel capacity production is avoided.

Owner:北京融讯信通科技有限公司

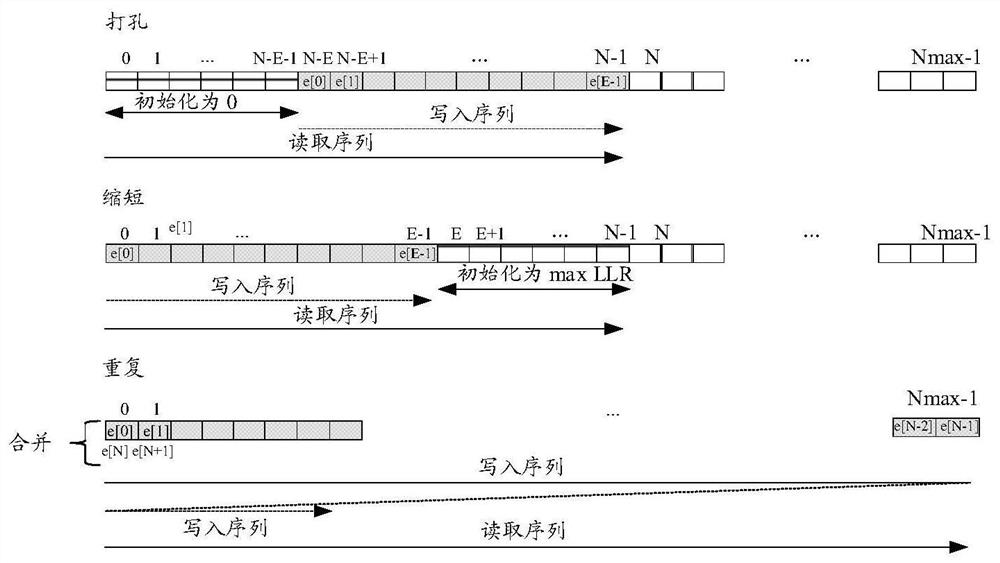

TPC high-speed decoding method

ActiveCN107682019AIncrease decoding rateMinimize computing resourcesCode conversionError correction/detection by combining multiple code structuresDecoding methodsIntermediate variable

The invention relates to a TPC high-speed decoding method. The number of operations and intermediate variables can be minimized by only processing the active bits are processed between twice iteration, thereby minimizing the computation and storage resources, and greatly improving the TPC decoding rate.

Owner:CHENGDU FOURIER ELECTRONICS TECH +1

Novel conflict-free interleaver-based low delay parallel Turbo decoding method

InactiveCN102064838BDecoding reductionIncrease decoding rateError preventionError correction/detection using interleaving techniquesPrior informationLow delay

The invention discloses a novel conflict-free interleaver-based low delay parallel Turbo decoding method, which mainly solves the problem of high decoding delay in MAP algorithms due to iteration and recursive calculation. The method comprises the following steps of: blocking and windowing the received channel information; initializing prior information and state measurement initial values; making a primary soft input and soft output processor (SISO I) and a secondary soft input and soft output processor (SISO II) to synchronously slide forwards to decode; interleaving and de-interleaving the external information generated by the SISO I and the SISO II by using a novel conflict-free interleaver respectively; and when the iteration reaches the maximum iteration times, comparing the obtained likelihood ratio L (xk) with the threshold 0, and performing hard decision to obtain an estimation value of decoding bit. The method has the advantages of low decoding delay, high throughput rate, low performance loss and the like, and can be used for a Turbo decoder of a long term evolution (LTE) receiver.

Owner:XIDIAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com