High speed storage demand reducing low density correction code decoder

A technology of low-density check code and storage requirements, applied in the field of forward error correction devices, which can solve the problems of increased decoder area and reduced decoding rate, and achieve the goals of reducing storage requirements, increasing decoding rate, and saving message storage requirements Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] A high-speed low-density check code decoder for reducing memory requirements of the present invention, it includes a parameter node calculation unit VPU module, a check node calculation unit CPU module and a control logic module; a parameter node calculation unit ( VPU) receives the sequence to be decoded, stores the original information and starts iterative decoding. During the iterative decoding process, the CPU module and the VPU module transmit information to each other, perform row operations and column operations respectively, and store the verification operation results by the CPU; control logic The module controls the cyclic operation of the VPU module and the CPU module, and outputs legal codewords obtained by decoding.

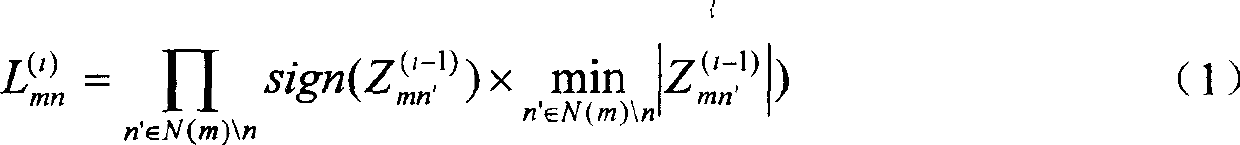

[0062] Principle of the present invention and the algorithm adopted are described as follows:

[0063] It is assumed that the check matrix H is composed of c×t sub-matrices, and each sub-matrix is a P×P square matrix. Then the decoder inclu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com