Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

53results about How to "Reduce logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

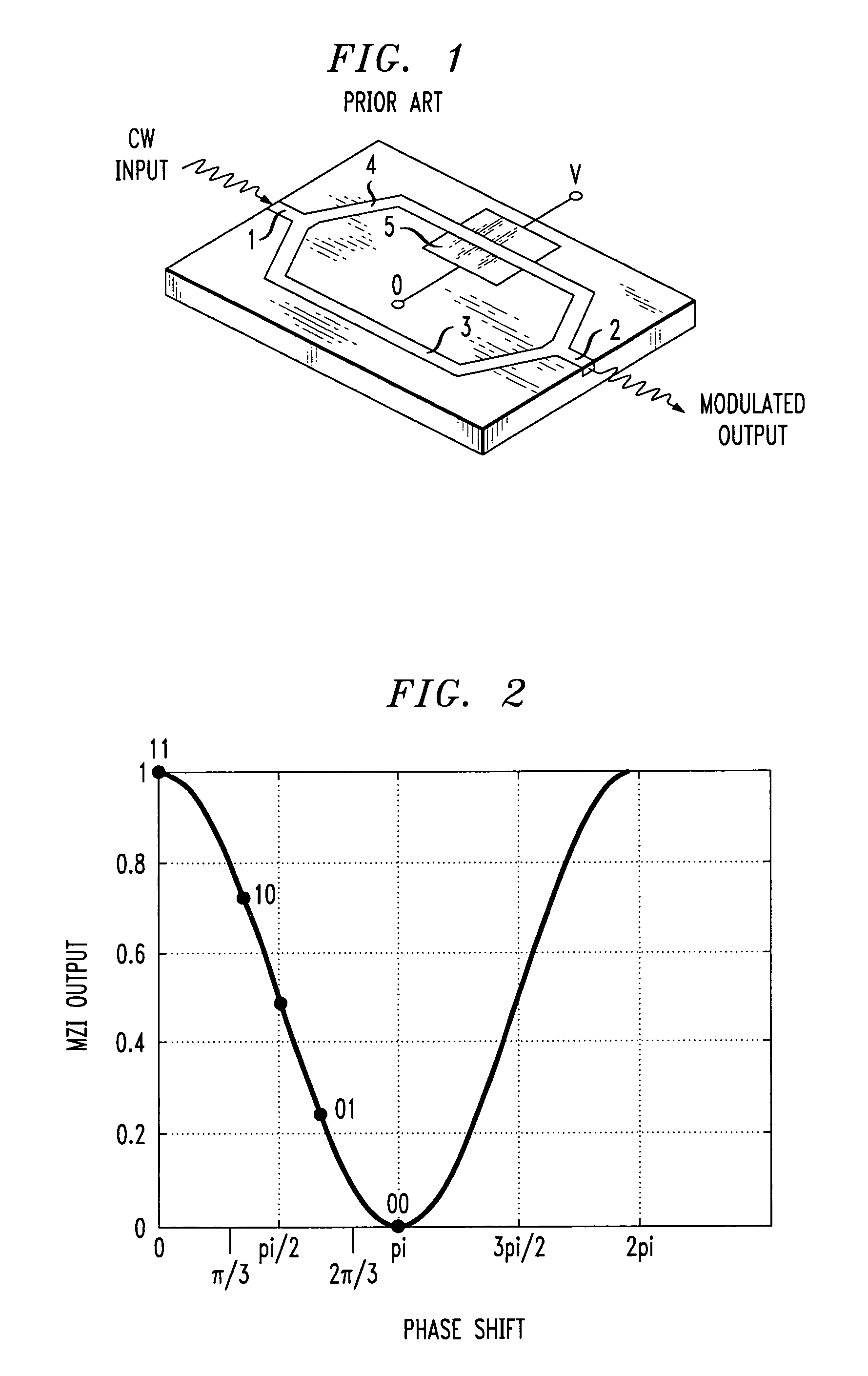

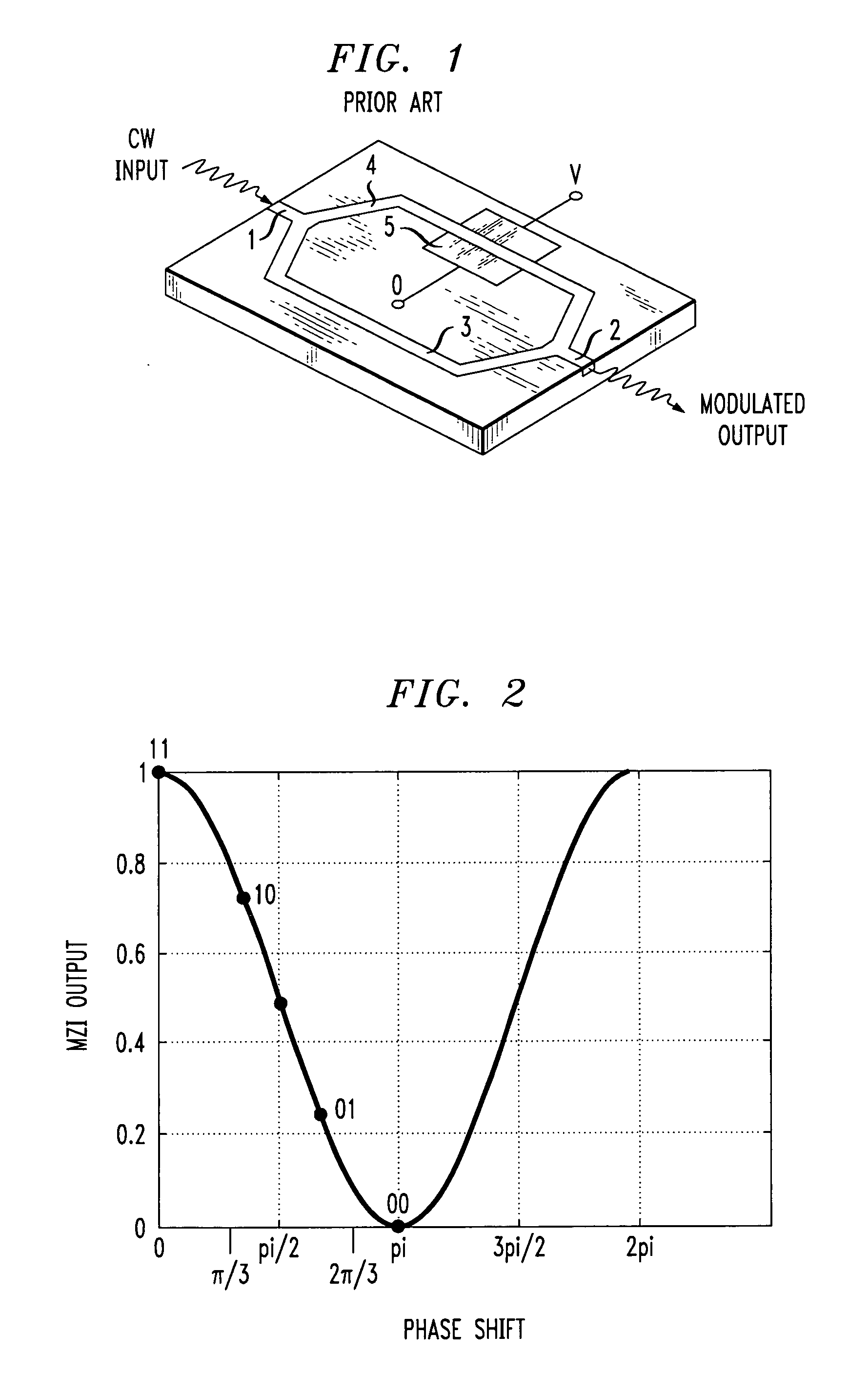

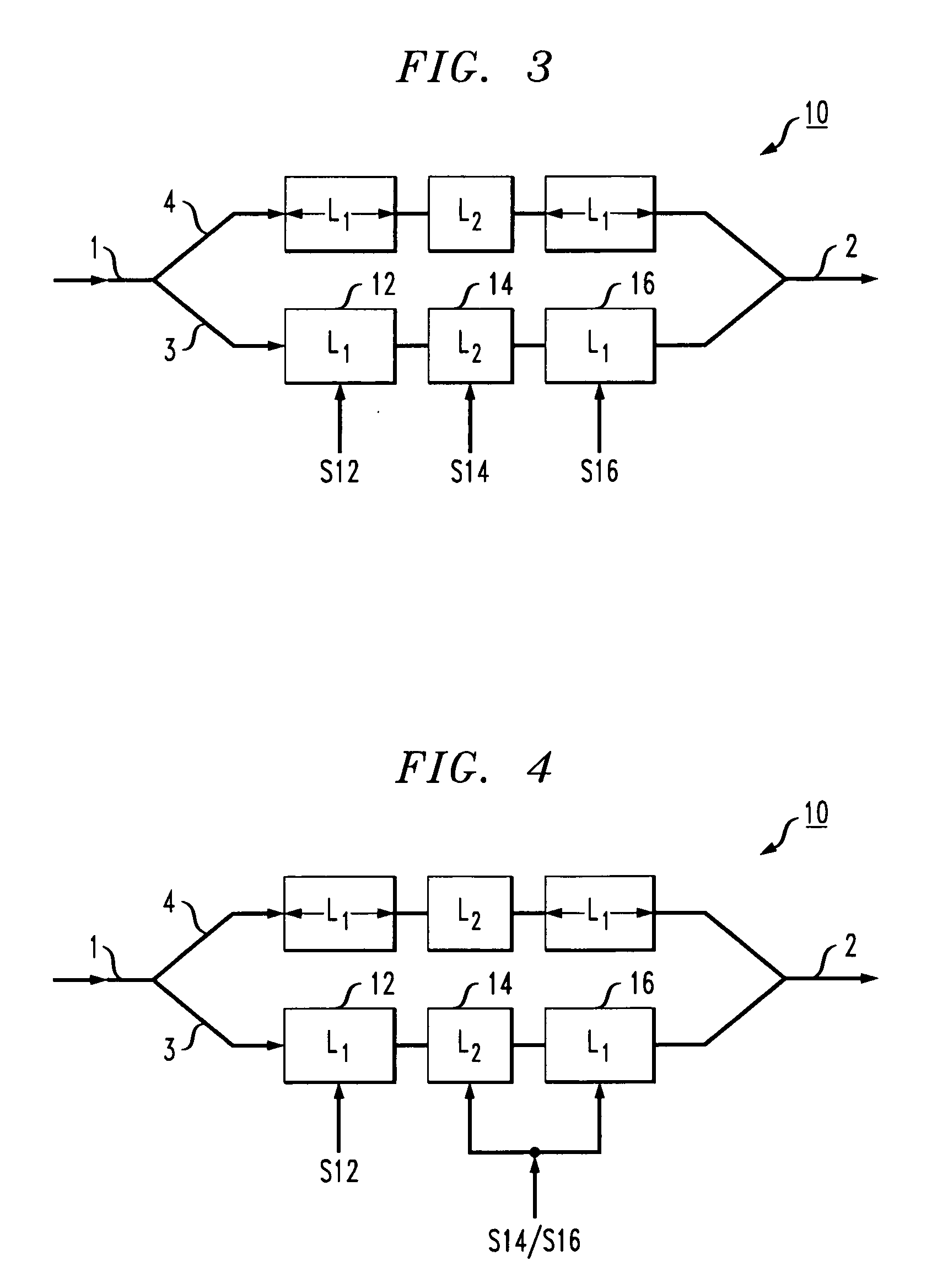

Optical modulator utilizing multi-level signaling

InactiveUS7483597B2Reduce rateReduce logicElectromagnetic transmissionNon-linear opticsPhase shiftedOptical modulator

Owner:CISCO TECH INC

Serial communication method and apparatus

InactiveCN101399654AEasy to implementReduce logicSynchronising arrangementBus networksData signalEmbedded system

The invention discloses a method of serial communication, wherein, master equipment is connected with at least one slave equipment; the master equipment provides a communication clock signal (CLK) to the slave equipment by a clock signal wire, notifies the slave equipment to start reading / writing operation by a synchronous signal (SYN), and transmits a slave equipment address or a register address to the slave equipment by a downstream data signal (CMD); and the master equipment transmits downstream data to the slave equipment by the downstream data signal (CMD), or the slave equipmen transmits upstream data to the master equipment by an upstream data signal (DAT). The method of serial communication comprises a serial communication method of the master equipment, a serial communication method of the slave equipment and a serial communication method for interaction of the master equipment and the slave equipment. The invention also discloses the master equipment and the slave equipment. The proposal of the invention has the advantages of easy realization, pin resource conservation and cost reduction.

Owner:HUAWEI TECH CO LTD

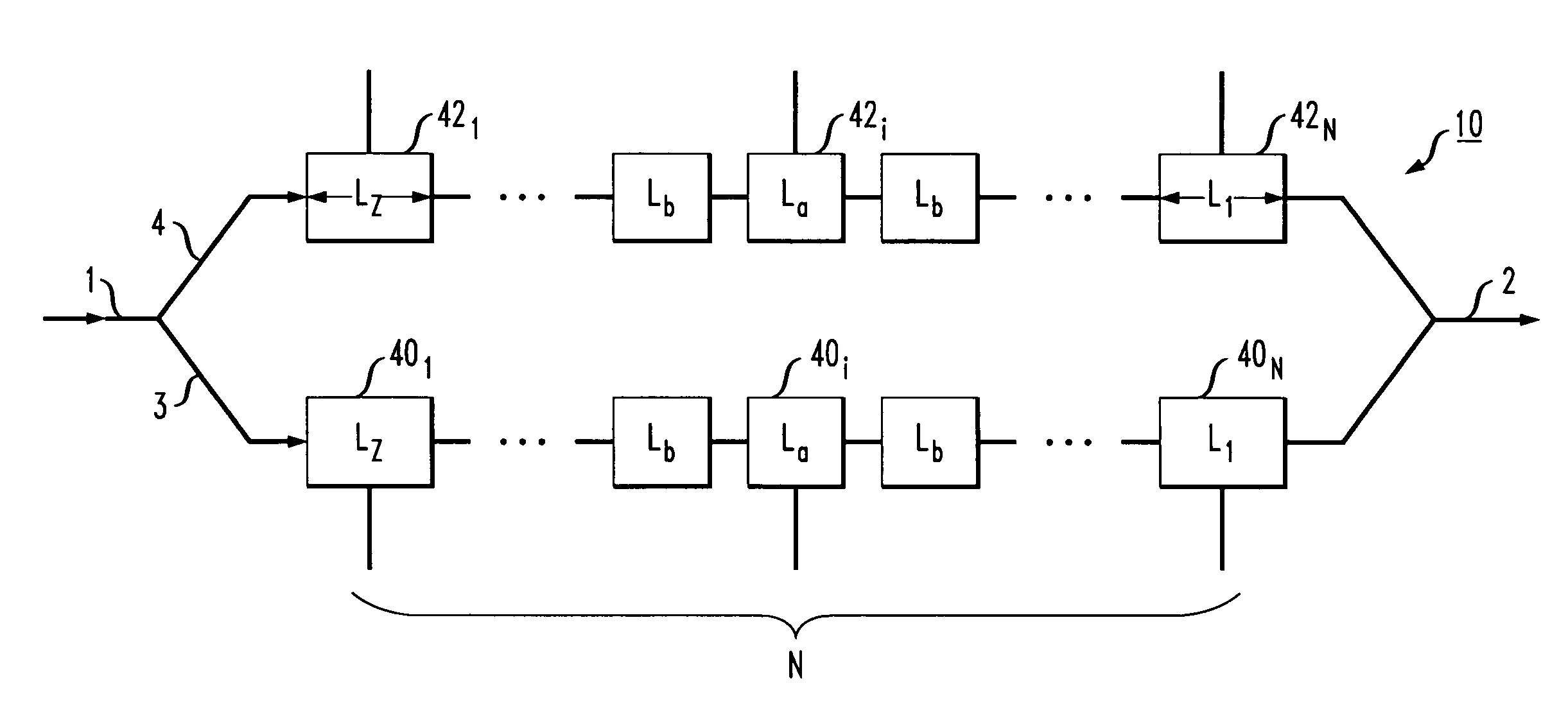

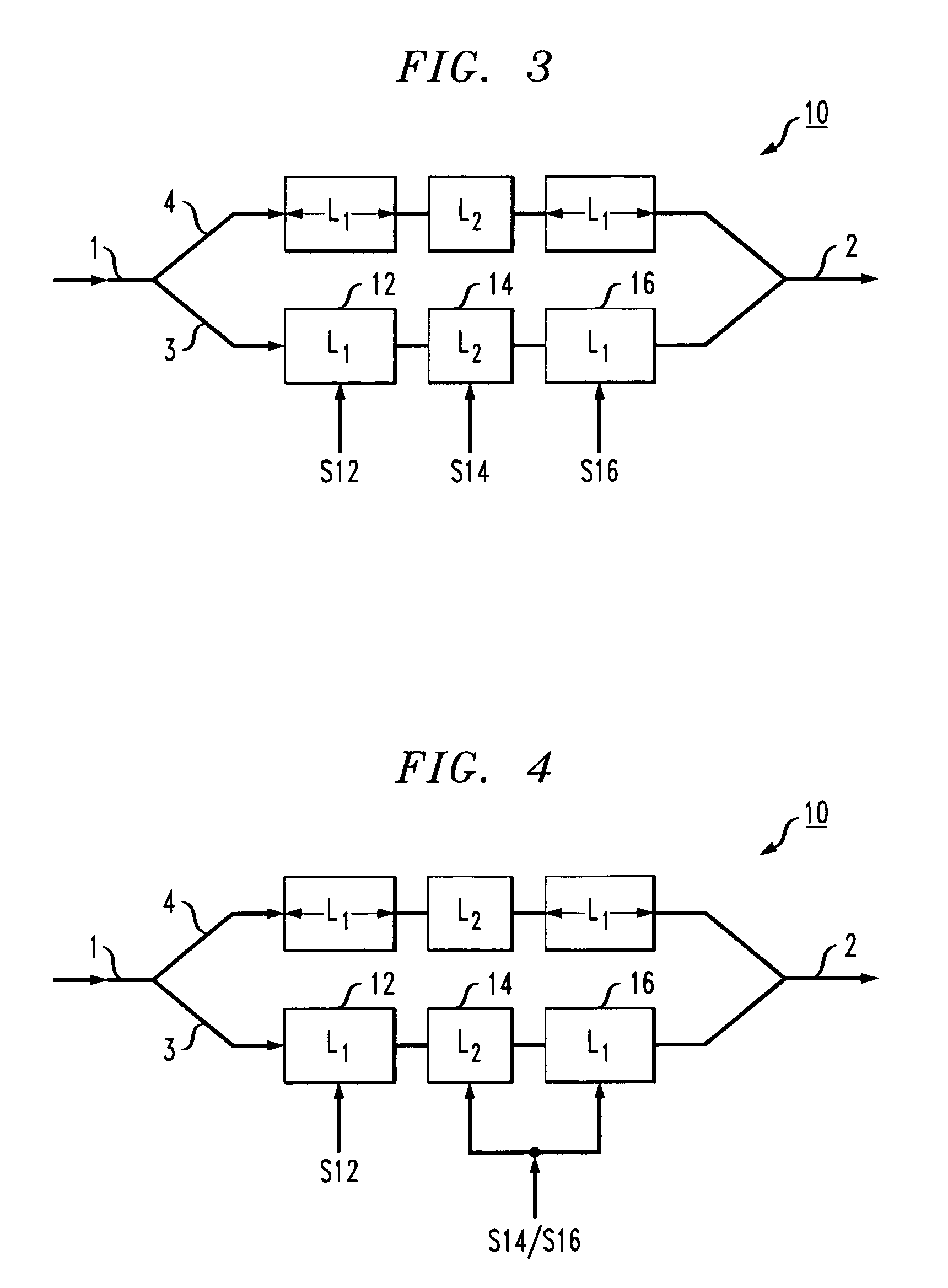

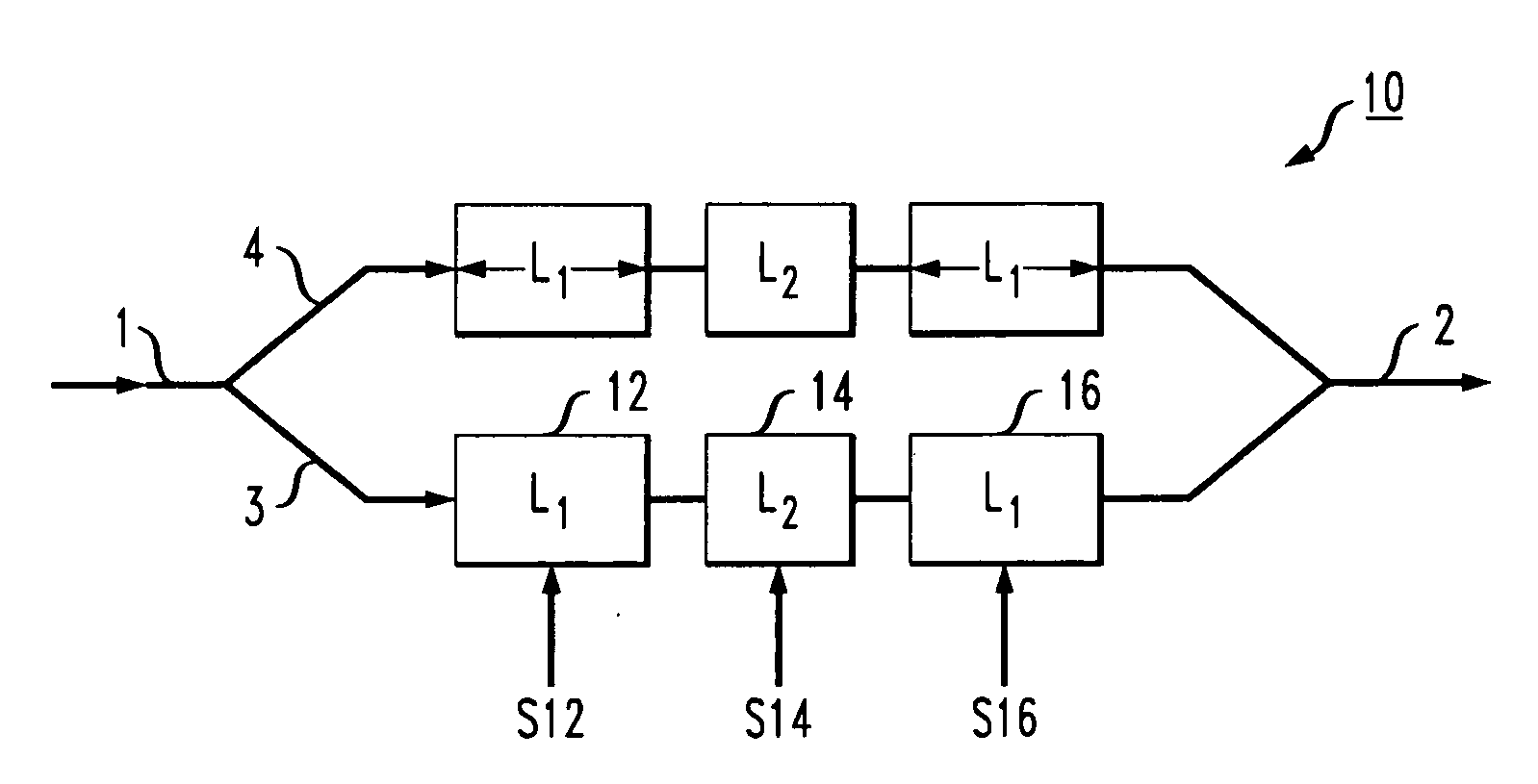

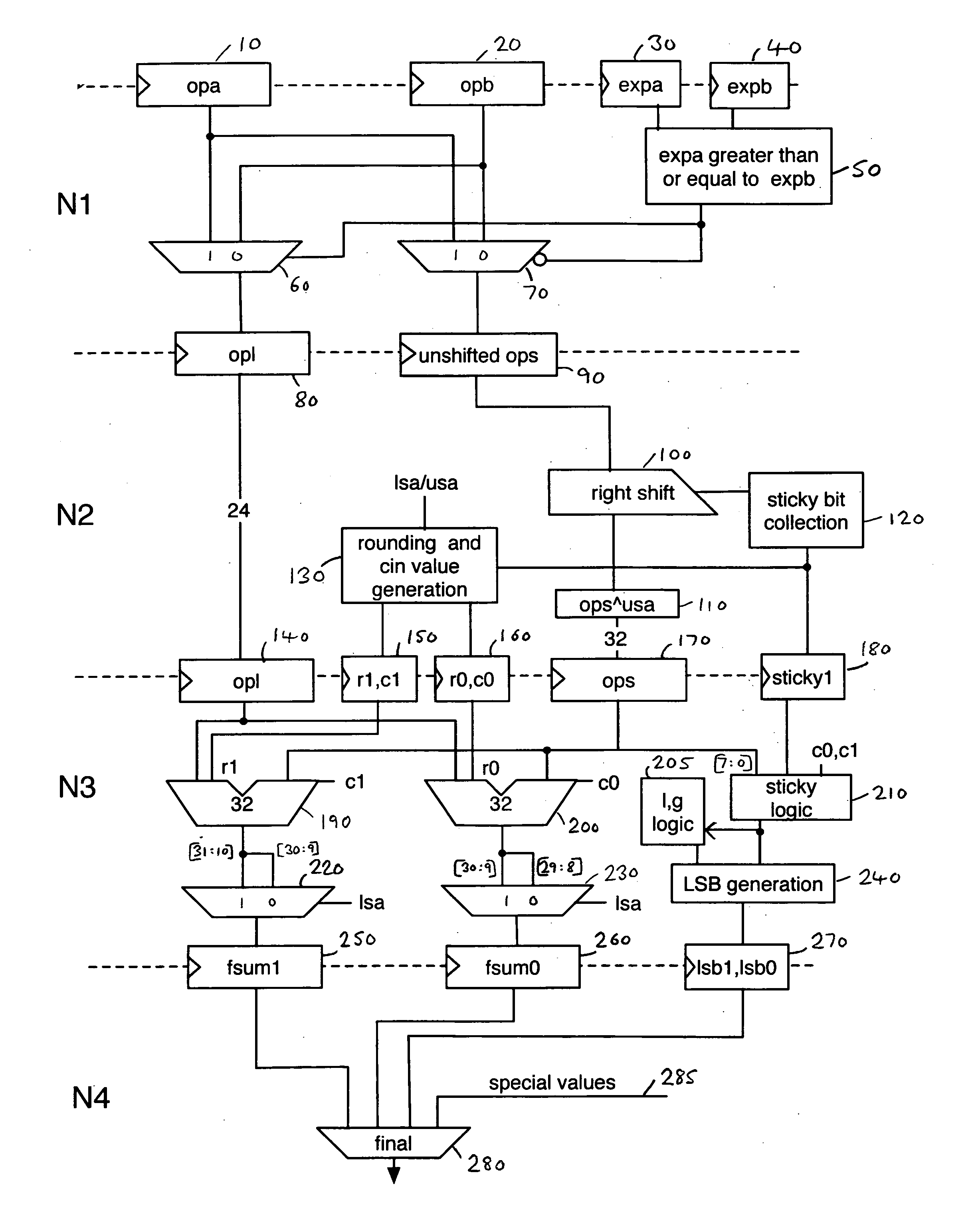

Optical modulator utilizing multi-level signaling

InactiveUS20080095486A1Reduce rateReduce logicElectromagnetic transmittersNon-linear opticsPhase shiftedOptical modulator

An optical modulator is formed to include a plurality of separate electrodes disposed along one arm, the electrodes having different lengths and driven with different signals to provide for multi-level signaling (e.g., PAM-4 signaling). By using separate drivers to energize the different sections, the number of sections energized at a given point in time will define the net phase shift introduced to the optical signal. The total length of the combined modulator sections is associated with a π phase shift (180°). Each section is driven by either a digital “one” or “zero”, so as to create the multi-level modulation. An essentially equal change in power between adjacent transmitted symbols is accomplished by properly adjusting the lengths of each individual section.

Owner:CISCO TECH INC

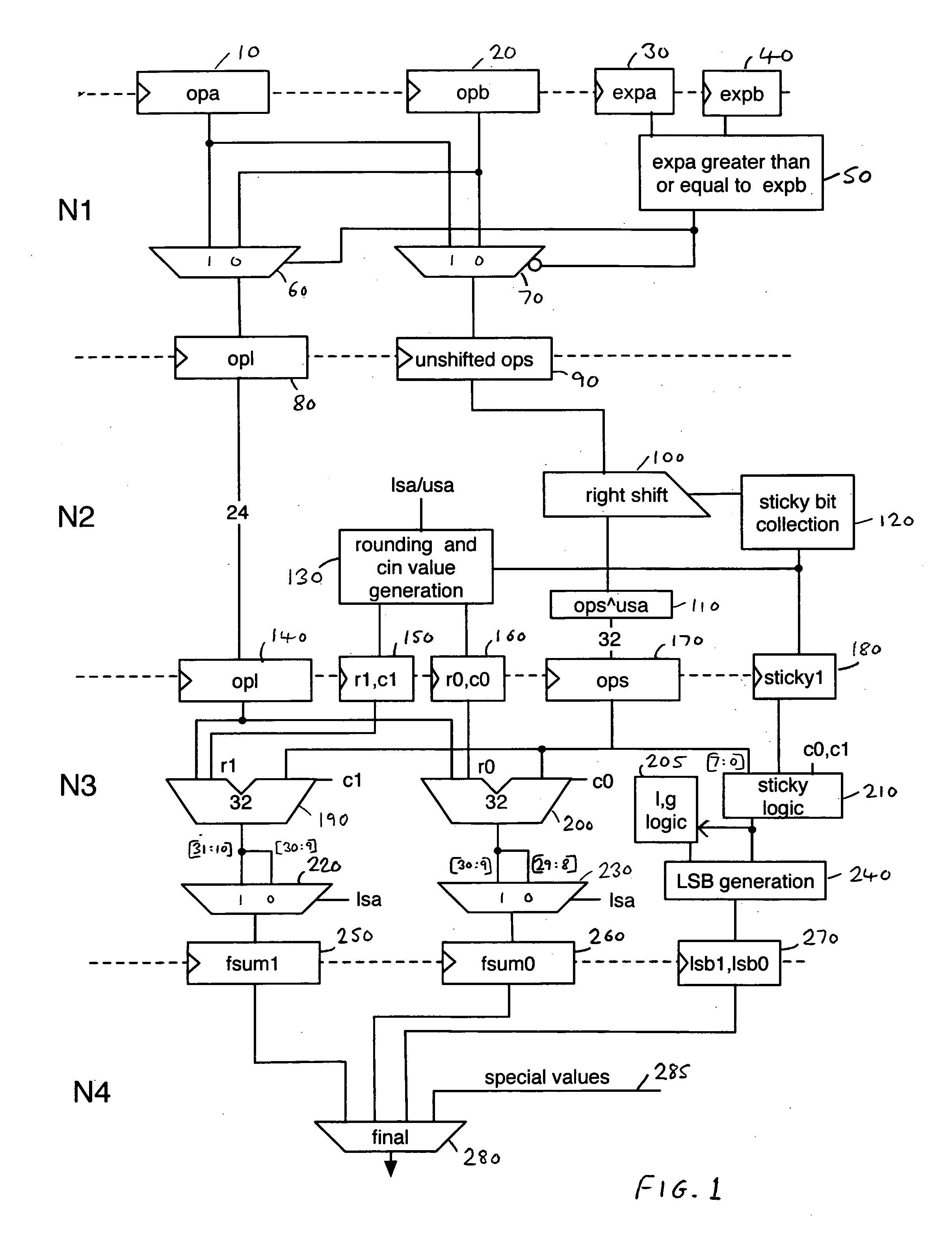

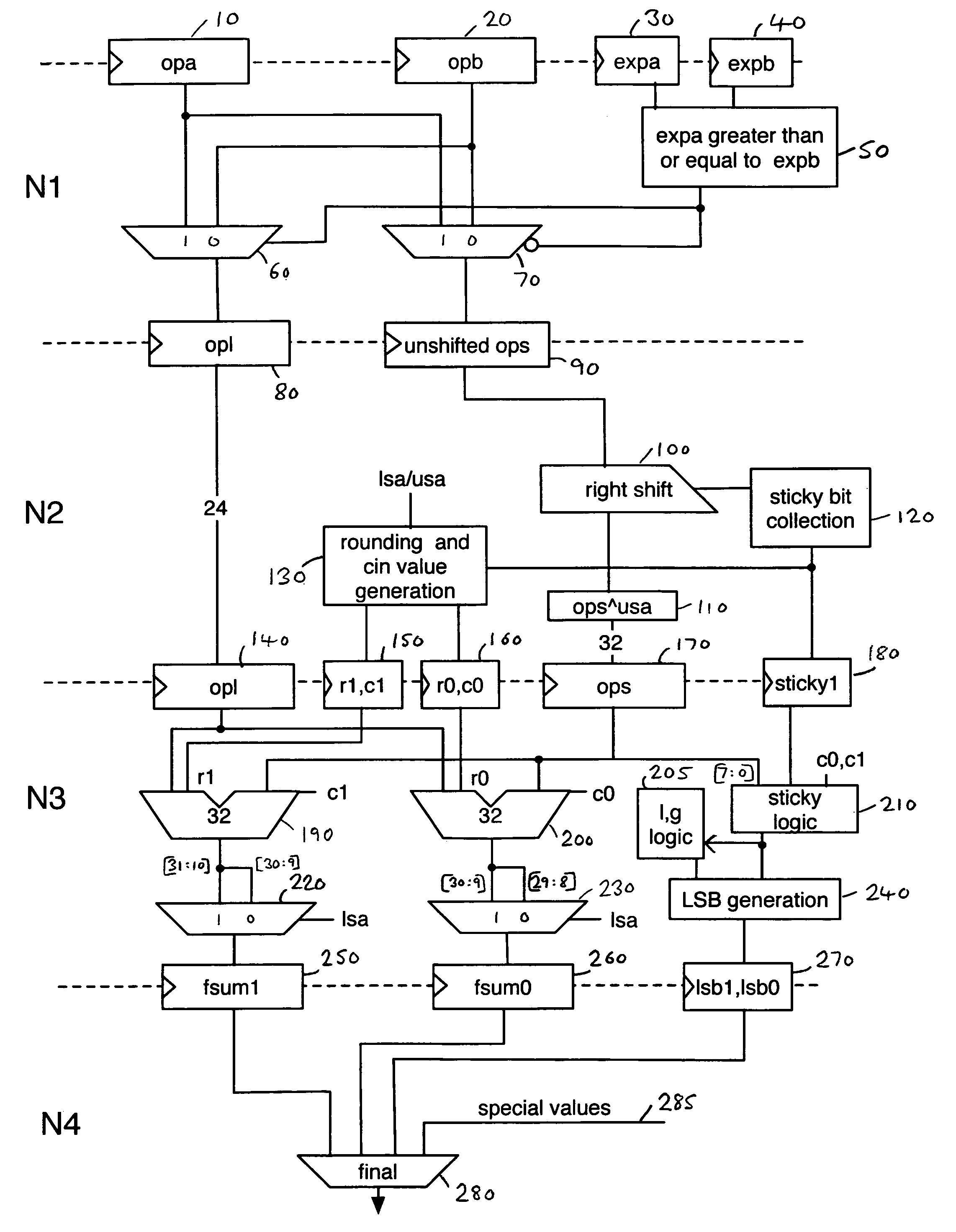

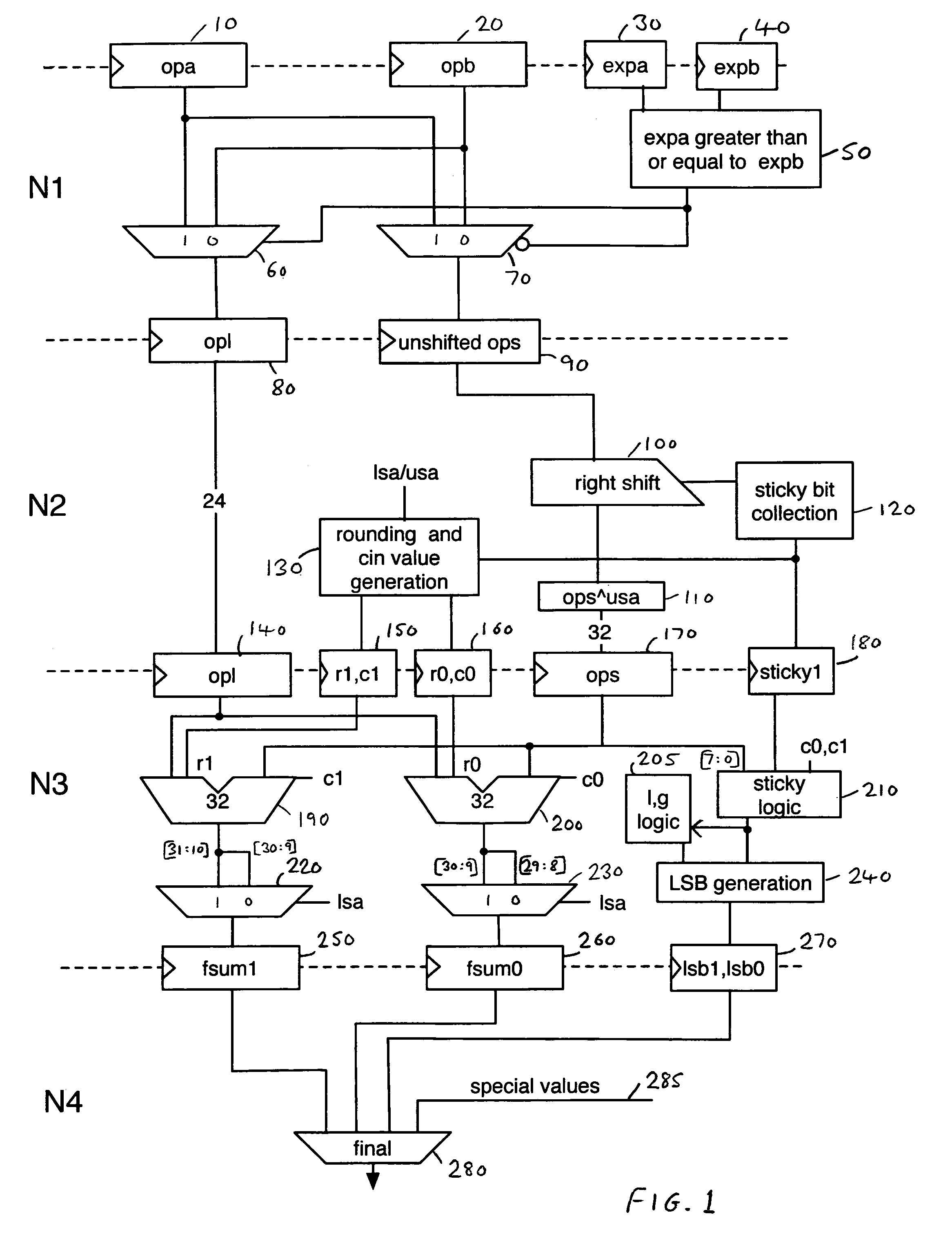

Data processing apparatus and method for performing floating point addition

ActiveUS20060136543A1Reduce logicLow costComputations using contact-making devicesComputation using non-contact making devicesSingle levelOperand

A data processing apparatus and method are provided for adding n-bit significands of first and second floating point operands to produce an n-bit result. The data processing apparatus comprises determination logic operable to determine the larger operand of the first and second operands, and alignment logic operable to align the n-bit significand of the smaller operand with the n-bit significand of the larger operand. First adder logic is then operable to perform a first sum operation in order to generate a first rounded result in non-redundant form equivalent to the addition of the aligned significands with a rounding increment injected at a first predetermined rounding position appropriate for a non-overflow condition, the first adder logic comprising a single level of adder logic. Further, second adder logic is provided to perform a second sum operation in order to generate a second rounded result in non-redundant form equivalent to the addition of the aligned significands with a rounding increment injected at a second predetermined rounding position appropriate for an overflow condition, the second adder logic also comprising a single level of adder logic. Selector logic is then used to derive the n-bit result from either the first rounded result or the second rounded result.

Owner:ARM LTD

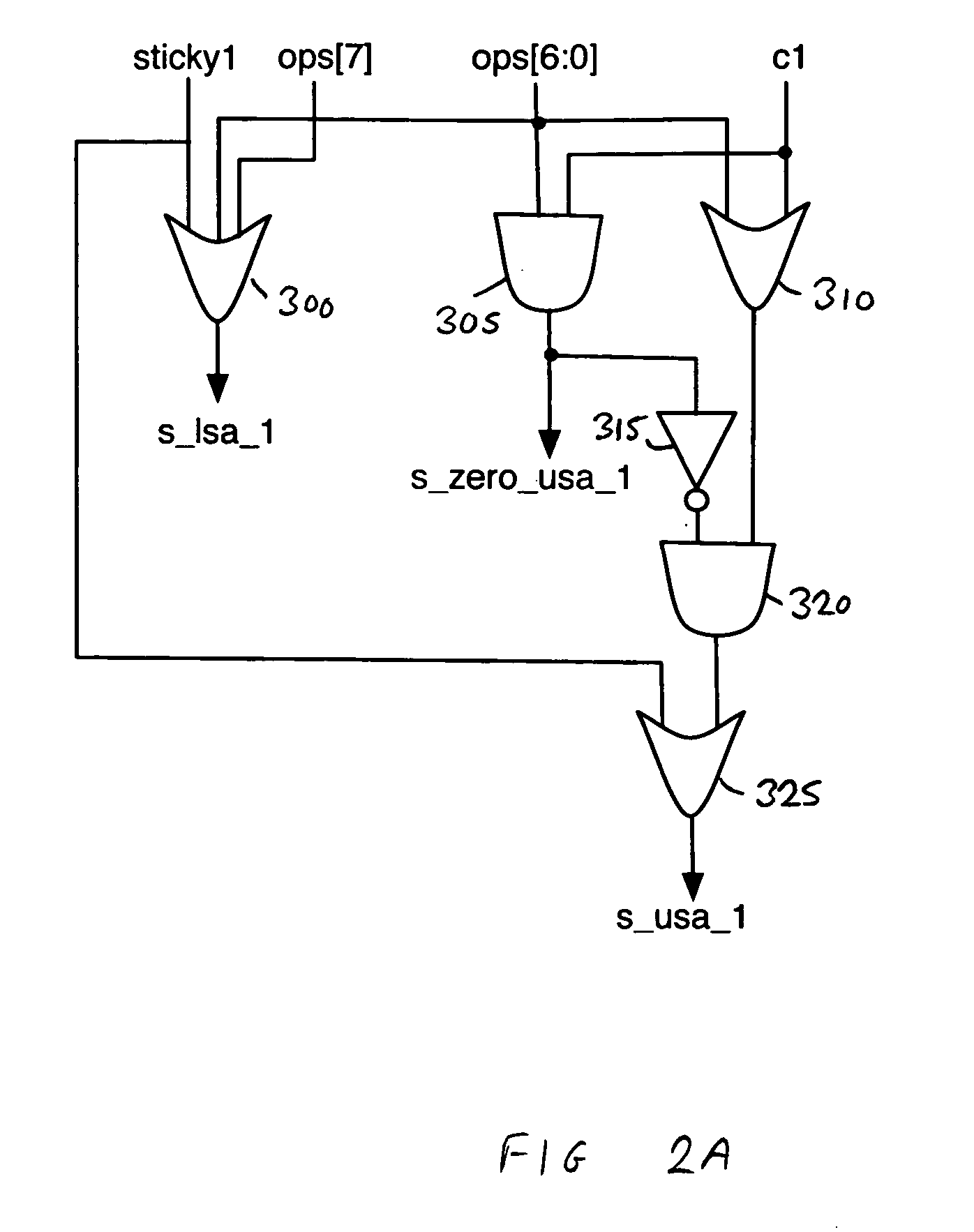

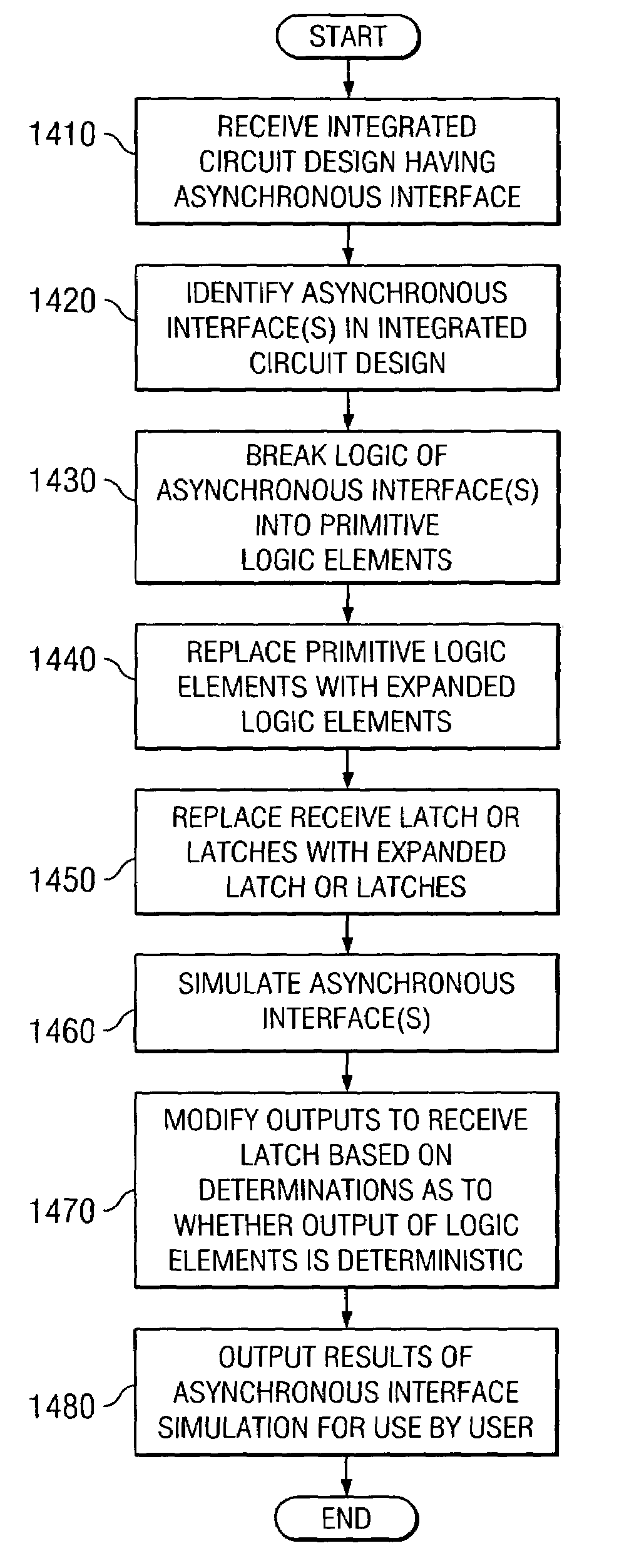

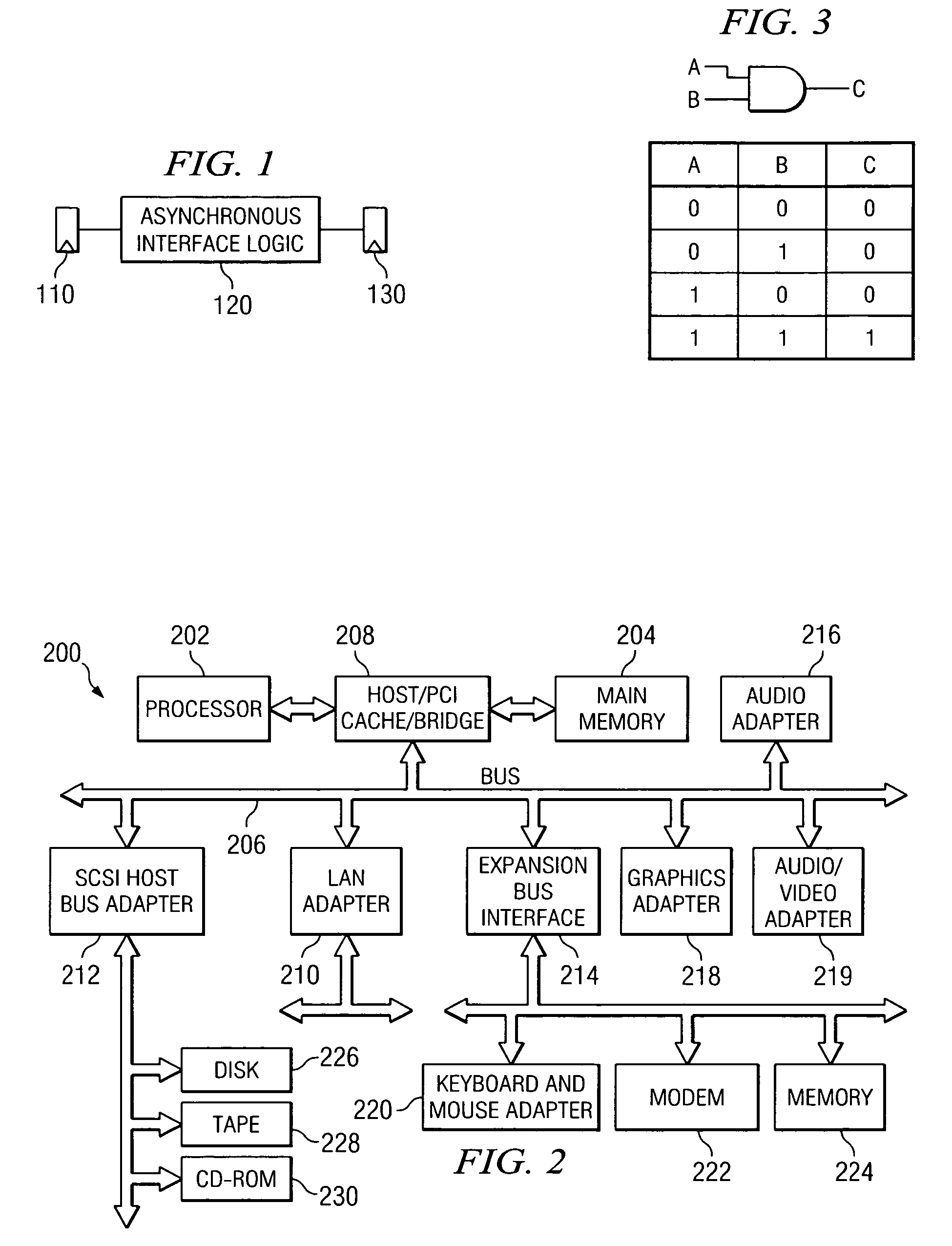

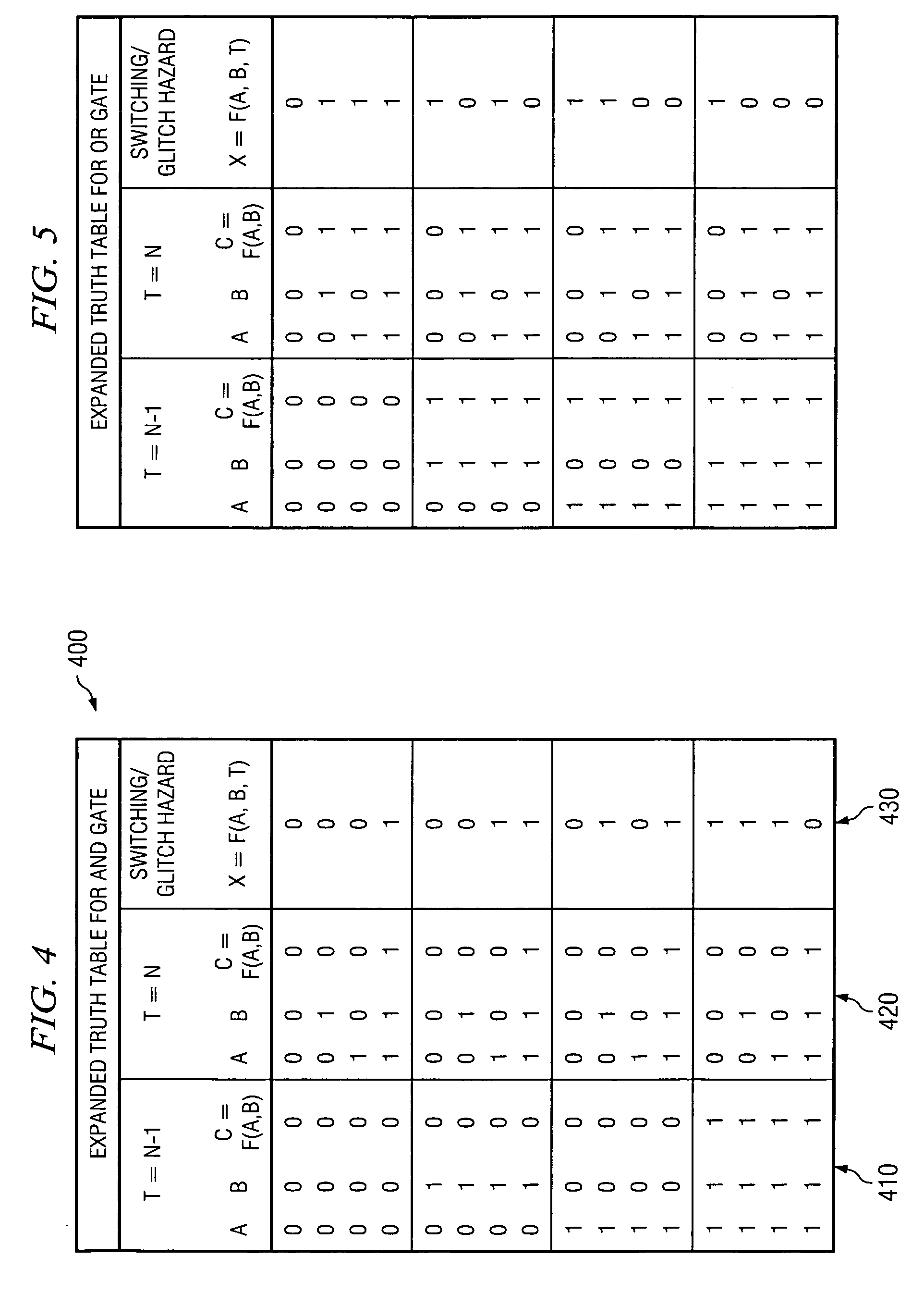

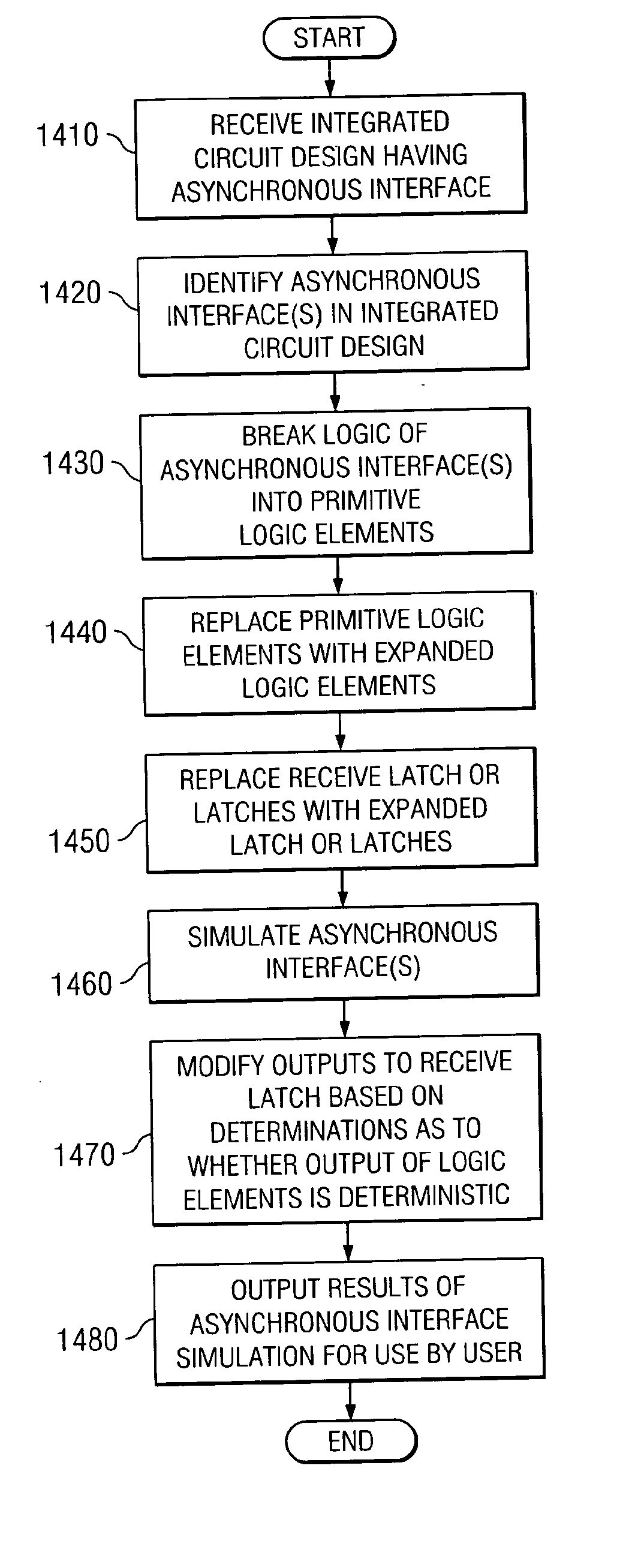

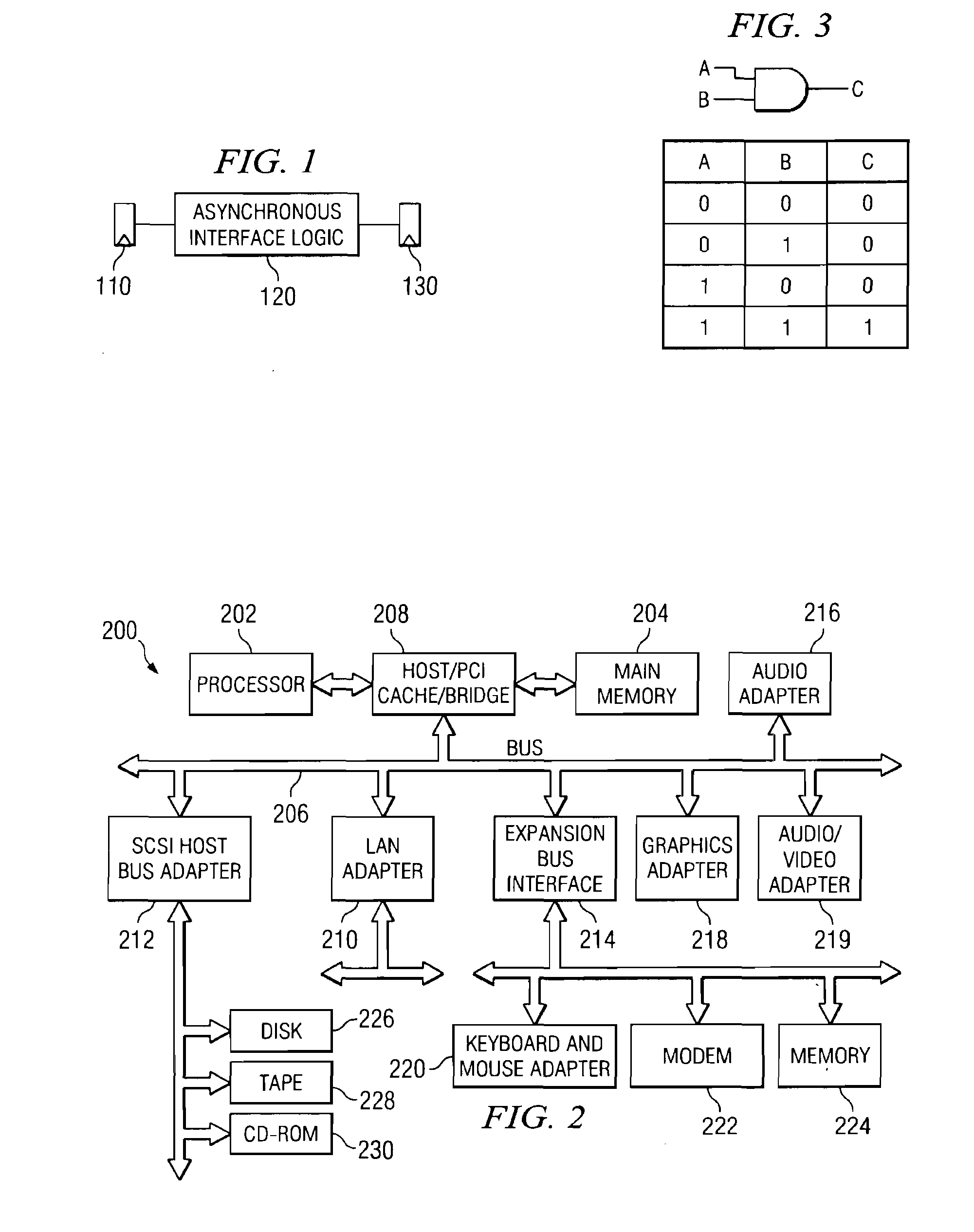

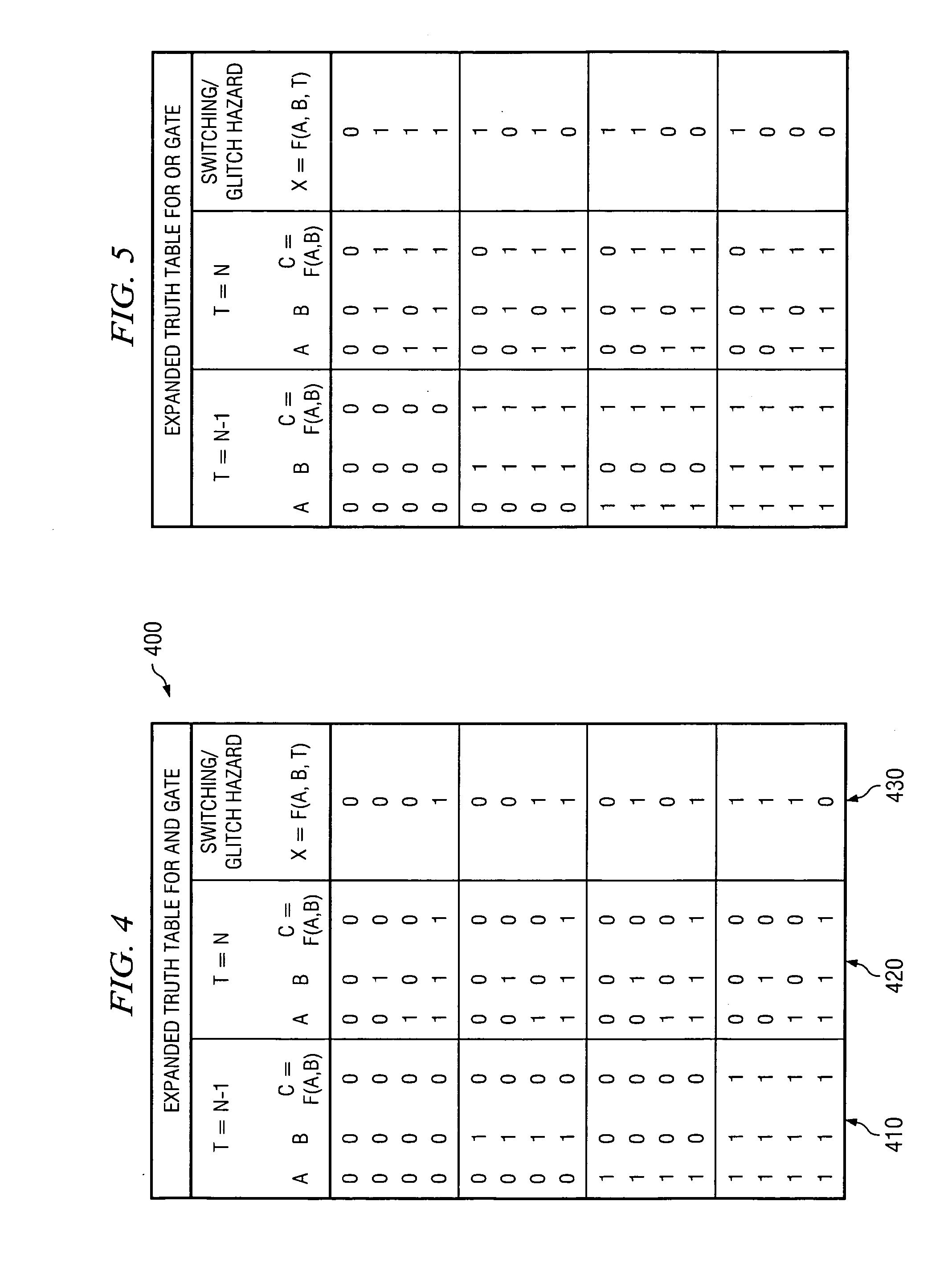

System and method for accurately modeling an asynchronous interface using expanded logic elements

InactiveUS7299436B2Accurate modelingReduce logicCAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceLogic element

A system and method for accurately modeling an asynchronous interface using expanded logic elements are provided. With the apparatus and method, the logic of an asynchronous interface is reduced to primitive logic elements. These primitive logic elements are expanded by the mechanisms of the present invention to take into consideration whether or not the primitive logic elements themselves may be experiencing a switching or glitch hazard and whether or not the inputs to the primitive logic elements may be based on a switching or glitch hazard from another primitive logic element in the asynchronous interface logic. These expanded logic elements are used in an integrated circuit design to replace the original primitive logic elements in the design. The asynchronous interface may then be simulated with the expanded logic elements providing outputs indicative of whether the actual data output of the expanded logic elements is deterministic or not.

Owner:GLOBALFOUNDRIES INC

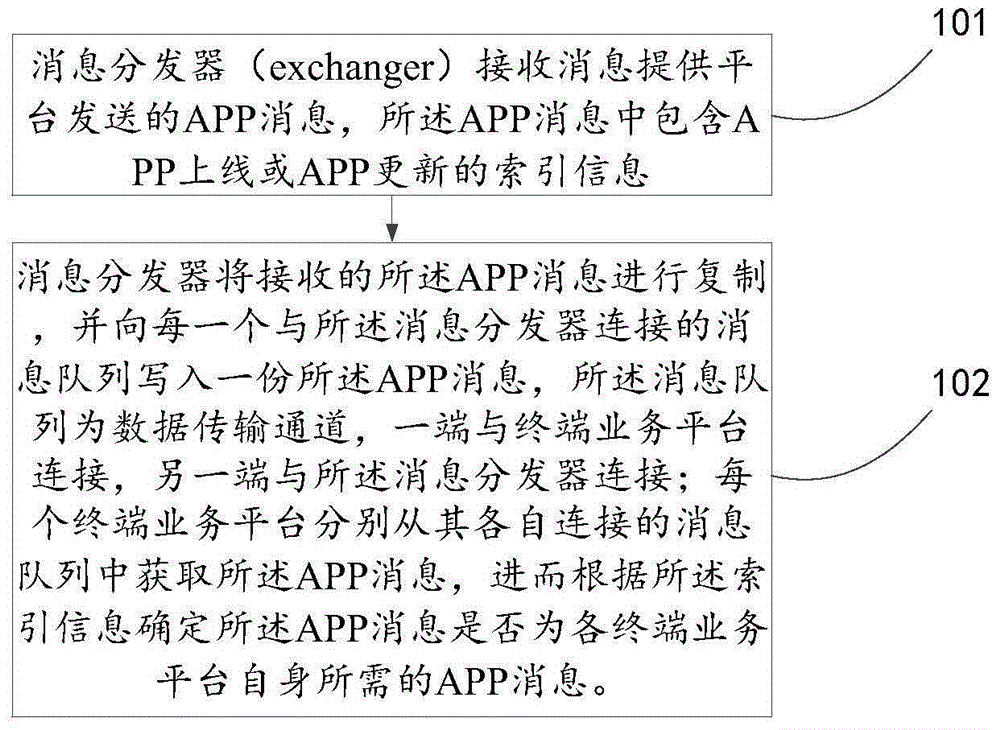

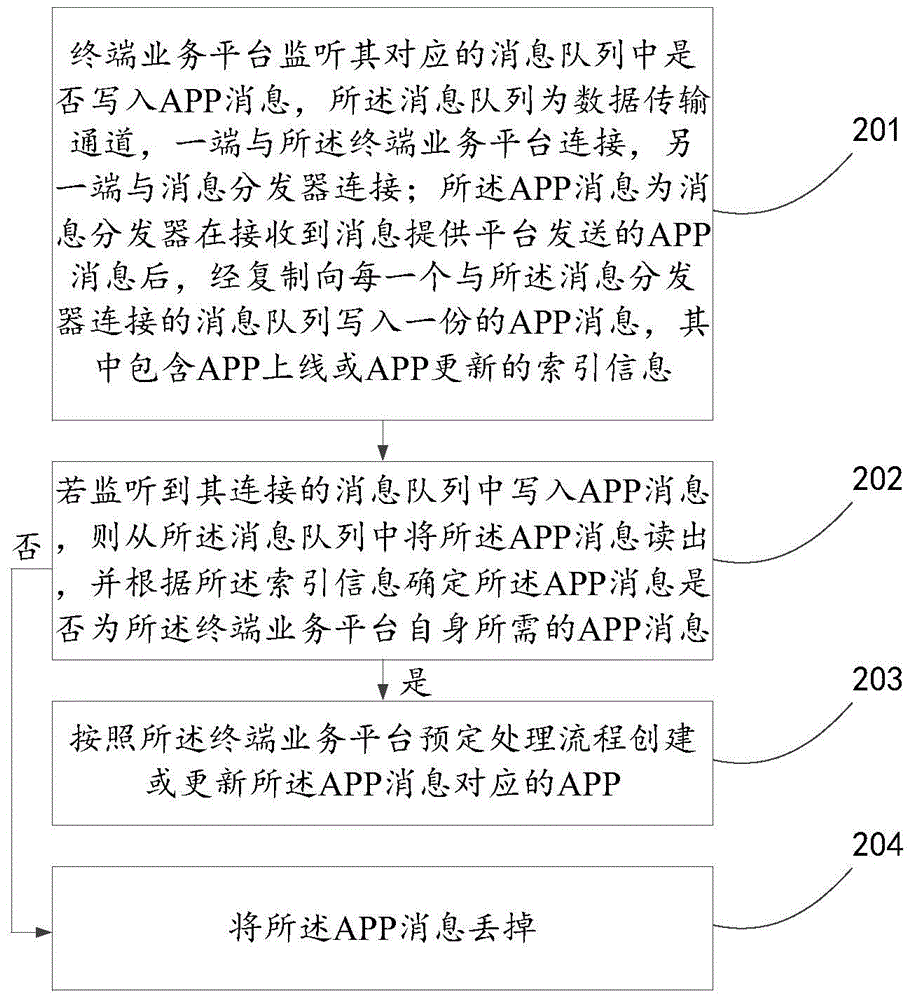

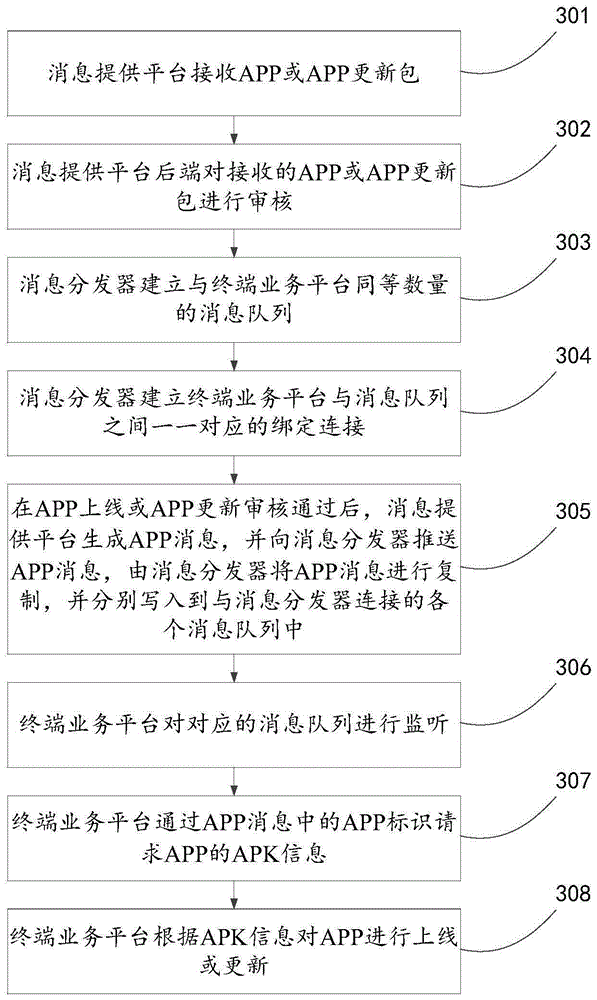

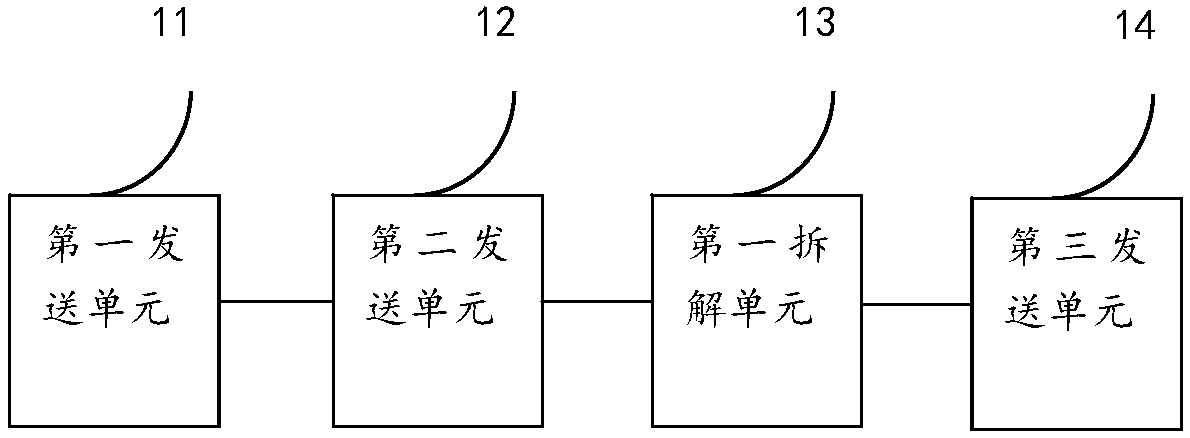

Message distribution method, device and system

InactiveCN105871966AAvoid complex logicReduce logicTransmissionMessage queueInformation transmission

The present invention discloses a message distribution method, device and system, and relates to the field of the digital information transmission. The objective of the invention is to solve the problem that the distribution logic of a distribution platform is complex. The method comprises: the message distribution device receives the application program APP message sent by the platform, wherein the APP message includes the index information of APP online or APP update; the received APP message is copied, APP messages are written in each message queue connected with the message distribution device; the message queue is a data transmission channel, one end of the data transmission channel is connected with a terminal business platform, and the other end thereof is connected with the message distribution device; and each terminal business platform obtains the APP message from the message queues respectively connected with each terminal business platform, and it is determined whether the APP message is required by each terminal business platform according to the index information. The message distribution method, device and system are mainly applicable to the process of the APP online distribution or APP update information.

Owner:LETV INFORMATION TECH BEIJING

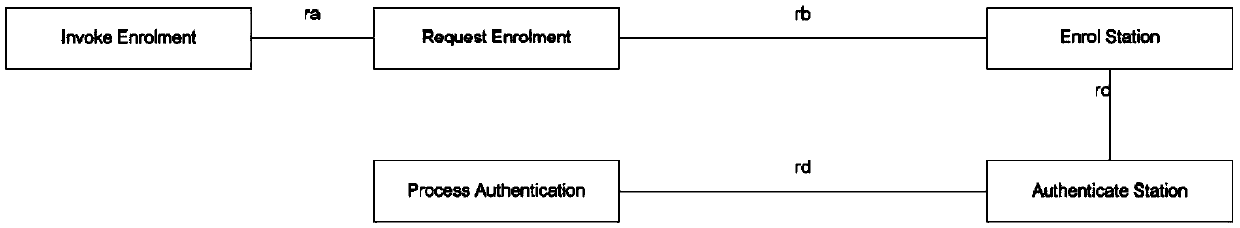

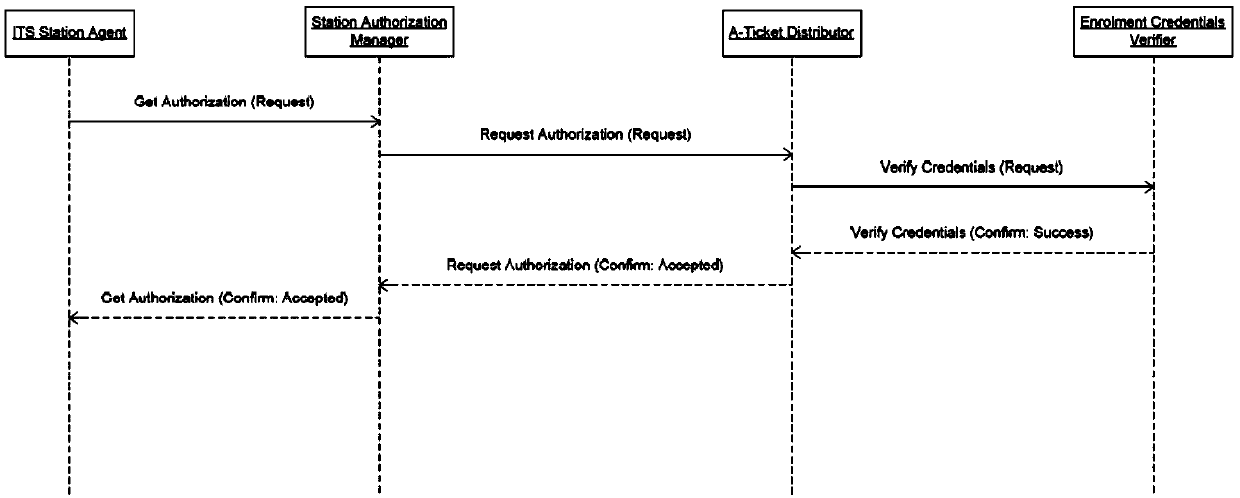

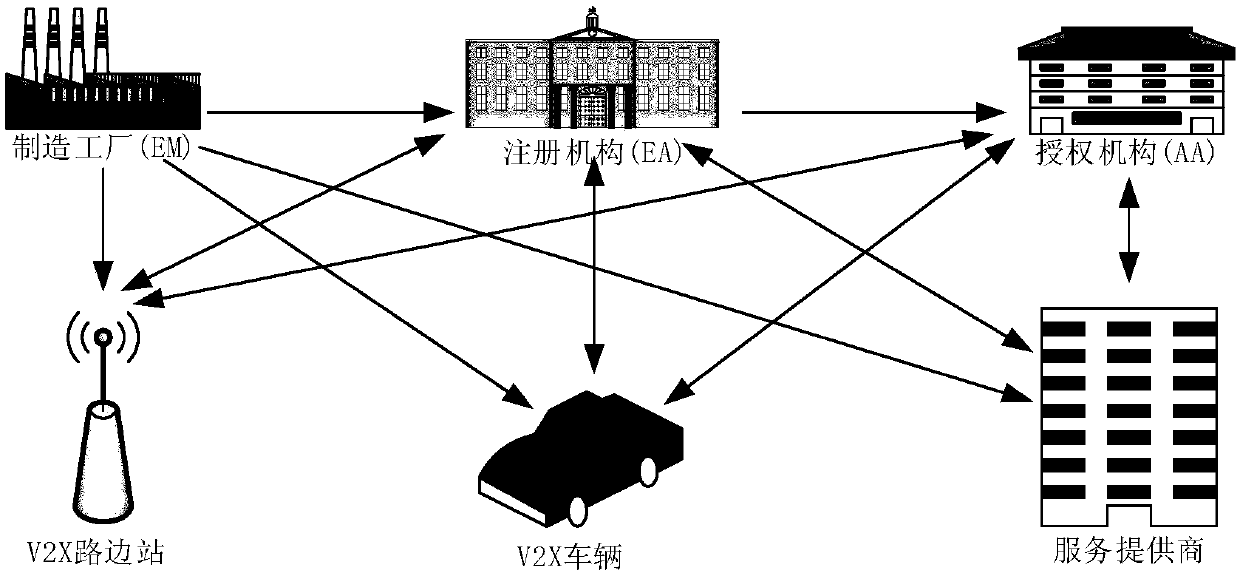

Vehicle identity authentication system and method adapting to V2X communication

InactiveCN109688111AImprove dynamic performanceIncrease randomnessParticular environment based servicesVehicle-to-vehicle communicationCommunications securityPrivacy protection

The invention relates to a vehicle identity authentication system and method adapting to V2X communication. One specific embodiment of the system comprises an IC server side and a CC server side, wherein the IC server side sends an identity authentication request of a vehicle to a first CA server side, and the first CA server side verifies the identity authentication request and returns a verification result to the IC server side; if the verification is passed, an IC server side cluster sends a request instruction for generating a communication credential to the CC server side; and the CC server side generates the communication credential based on the request instruction, and returns the generated communication credential to the vehicle through the IC server side to realize the identity authentication of the vehicle. Through adoption of the vehicle identity authentication system and method, the authentication and privacy protection can be fully balanced; the characteristics of high dynamics, high randomness and low delay in V2X communication can be met; the whole V2X communication security system can efficiently and reliably serve V2X communication; and a car factory can be guidedto form safety module of a V2X communication vehicle end easily and clearly.

Owner:CHINA INTELLIGENT & CONNECTED VEHICLES (BEIJING) RES INST CO LTD

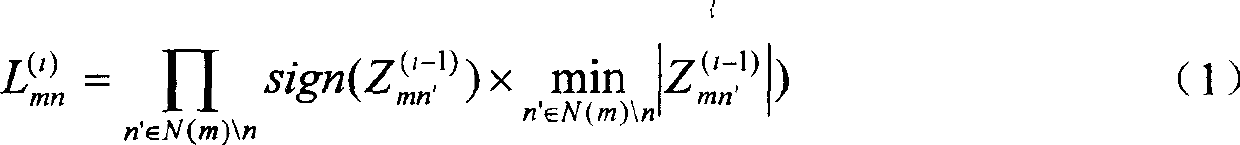

High speed storage demand reducing low density correction code decoder

InactiveCN1822510AReduce occupancyTakes up less logicError correction/detection using multiple parity bitsCode conversionHigh speed memoryParallel computing

Present invention discloses a high-speed memory requirement reduced low density check code decoder. It contains parameter calculating unit VPU module, verification node computing element CPU module and control logic module, wherein VPU module receiving decode sequence, memory said original information and starting iteration decode, in iterate decode process, CPU module and VPU module mutually transferring information each to proceed line and row operation, CPU storing verification operation result, controlling logical module to VPU module and CPU module cycle operation control, and outputting decode to obtain legal code word. Said invention fully utilizes minimal and decode algorithm to reduce memory requirement and height parallel to raise decode rate to shift LDPC code, saving message storage requirement and reaching faster decode speed and higher throughput rate.

Owner:NANJING UNIV

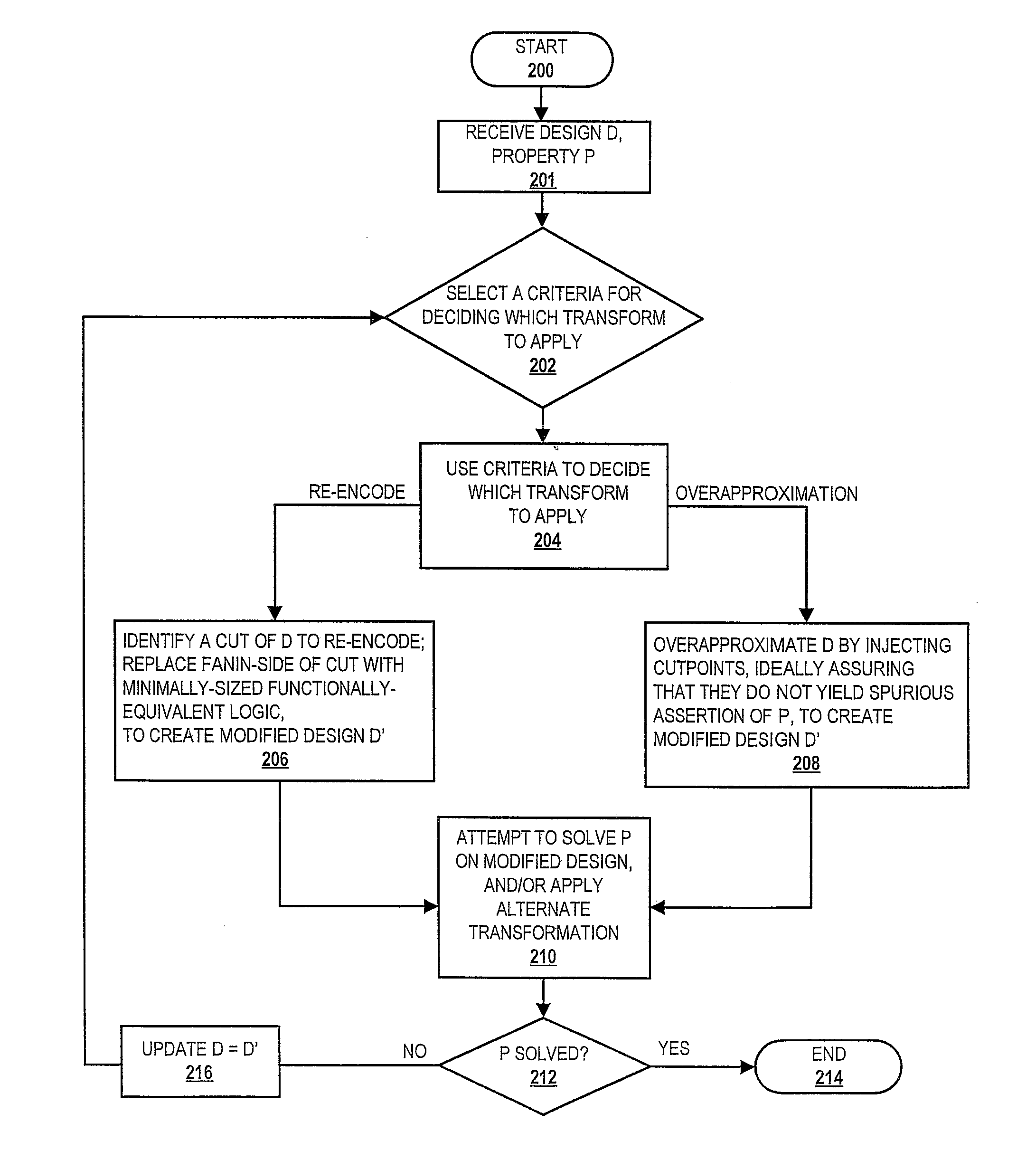

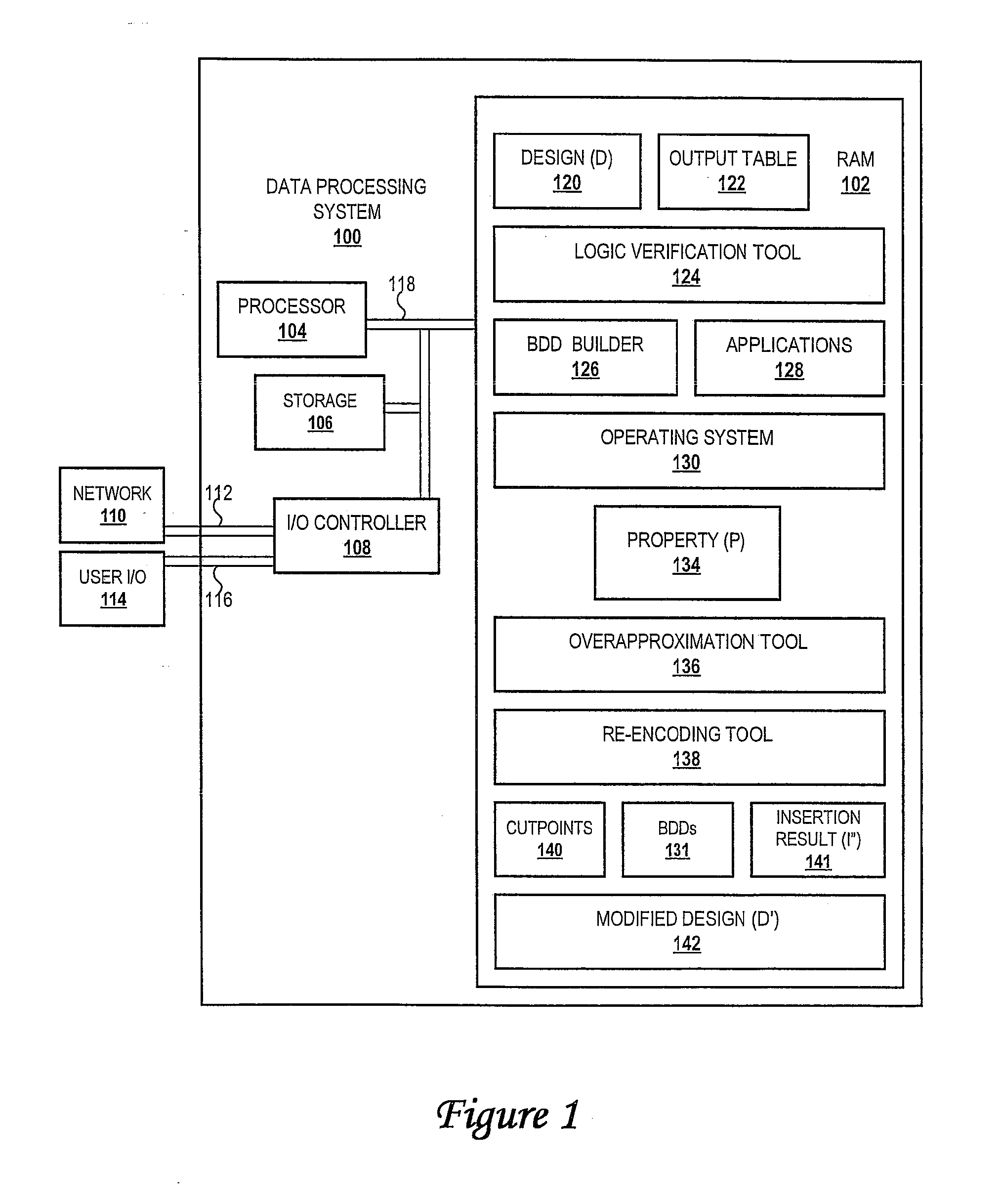

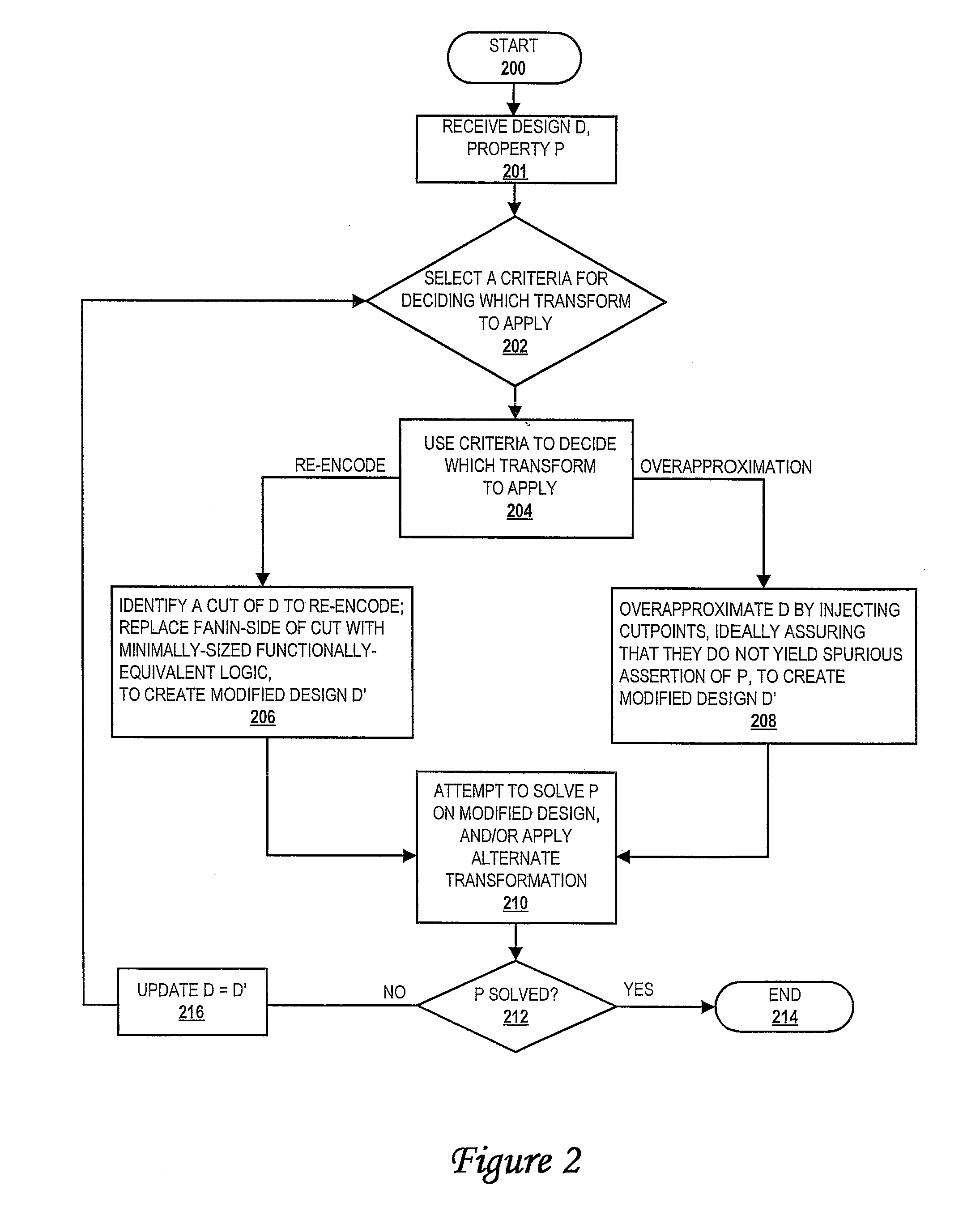

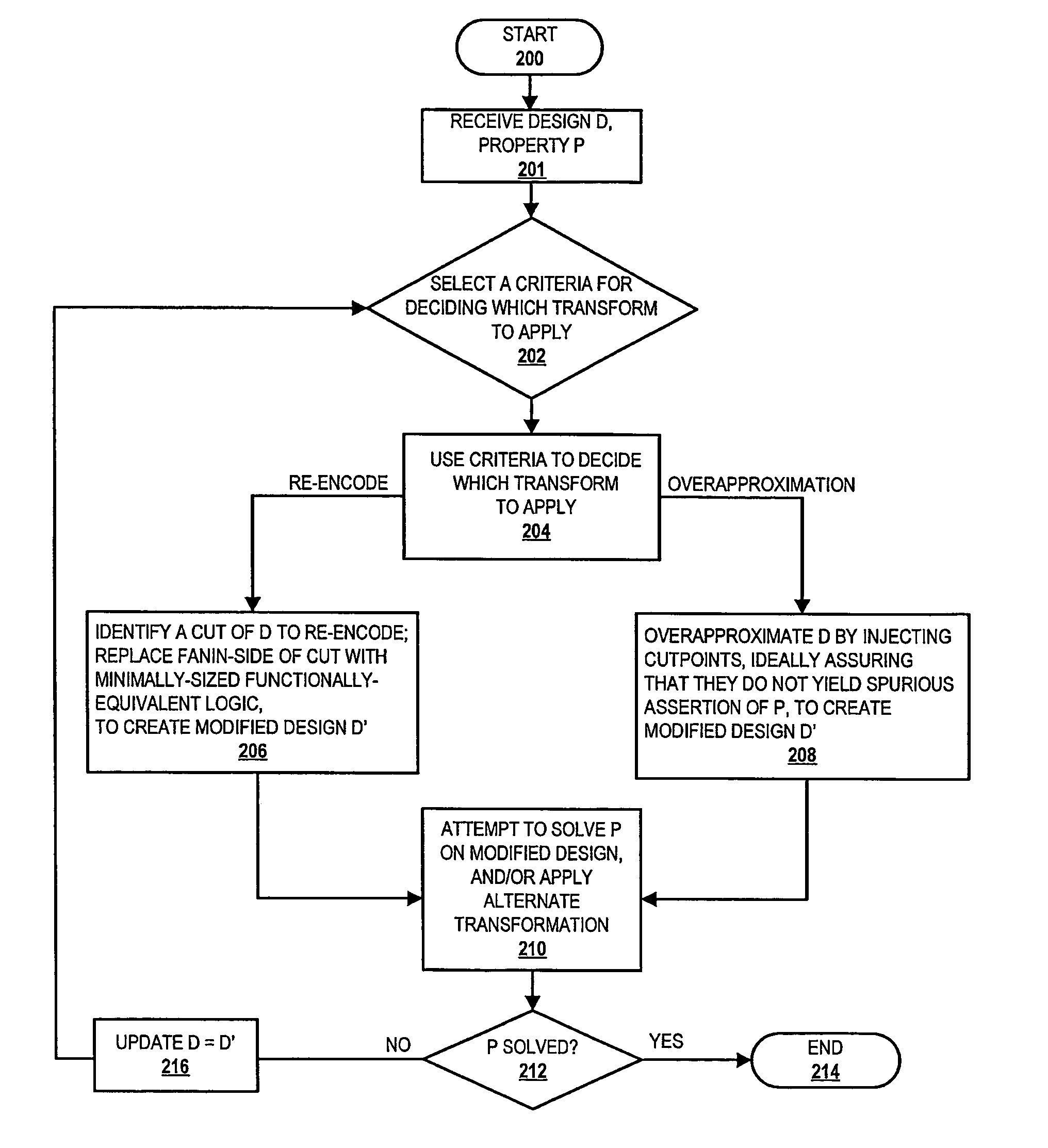

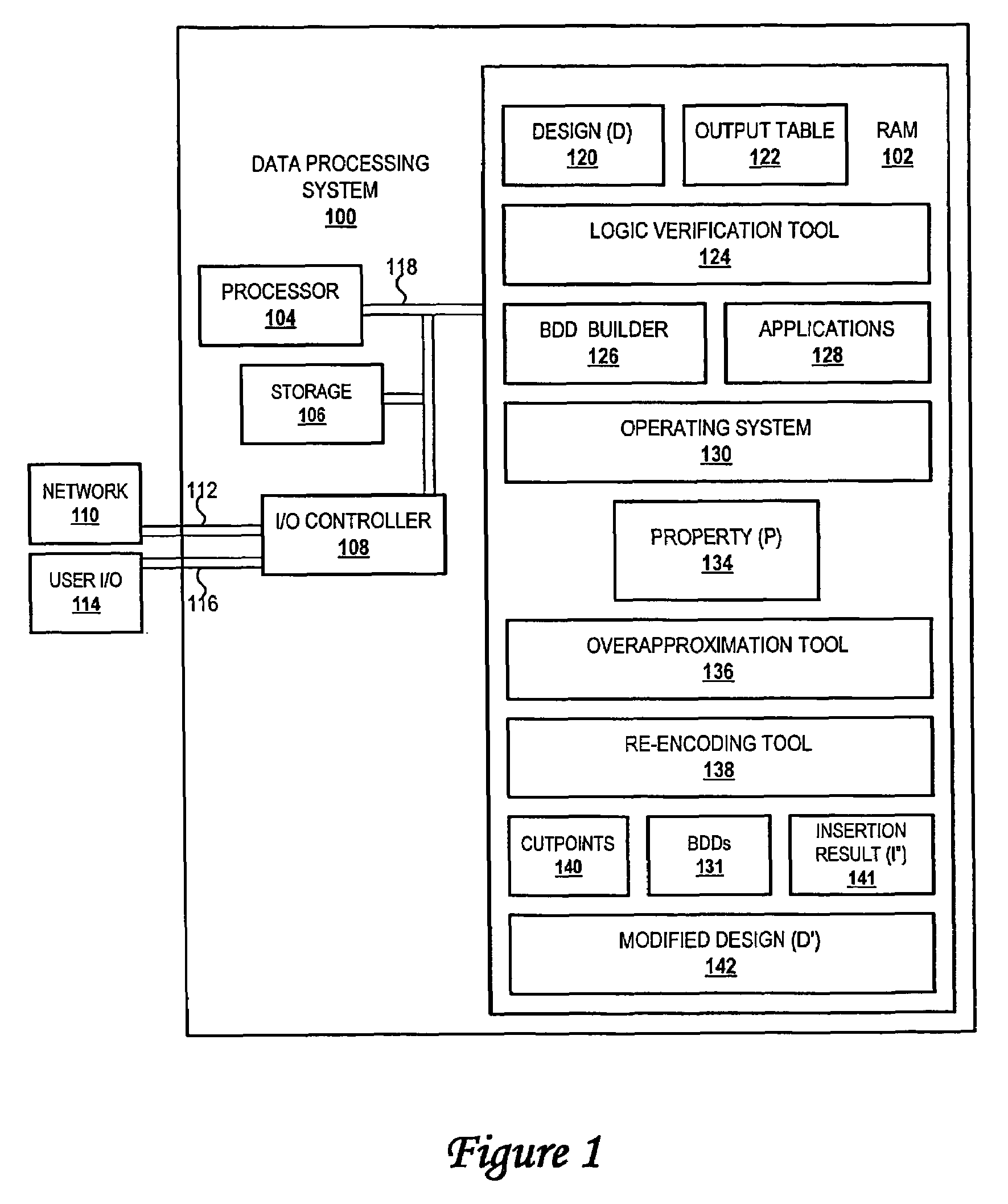

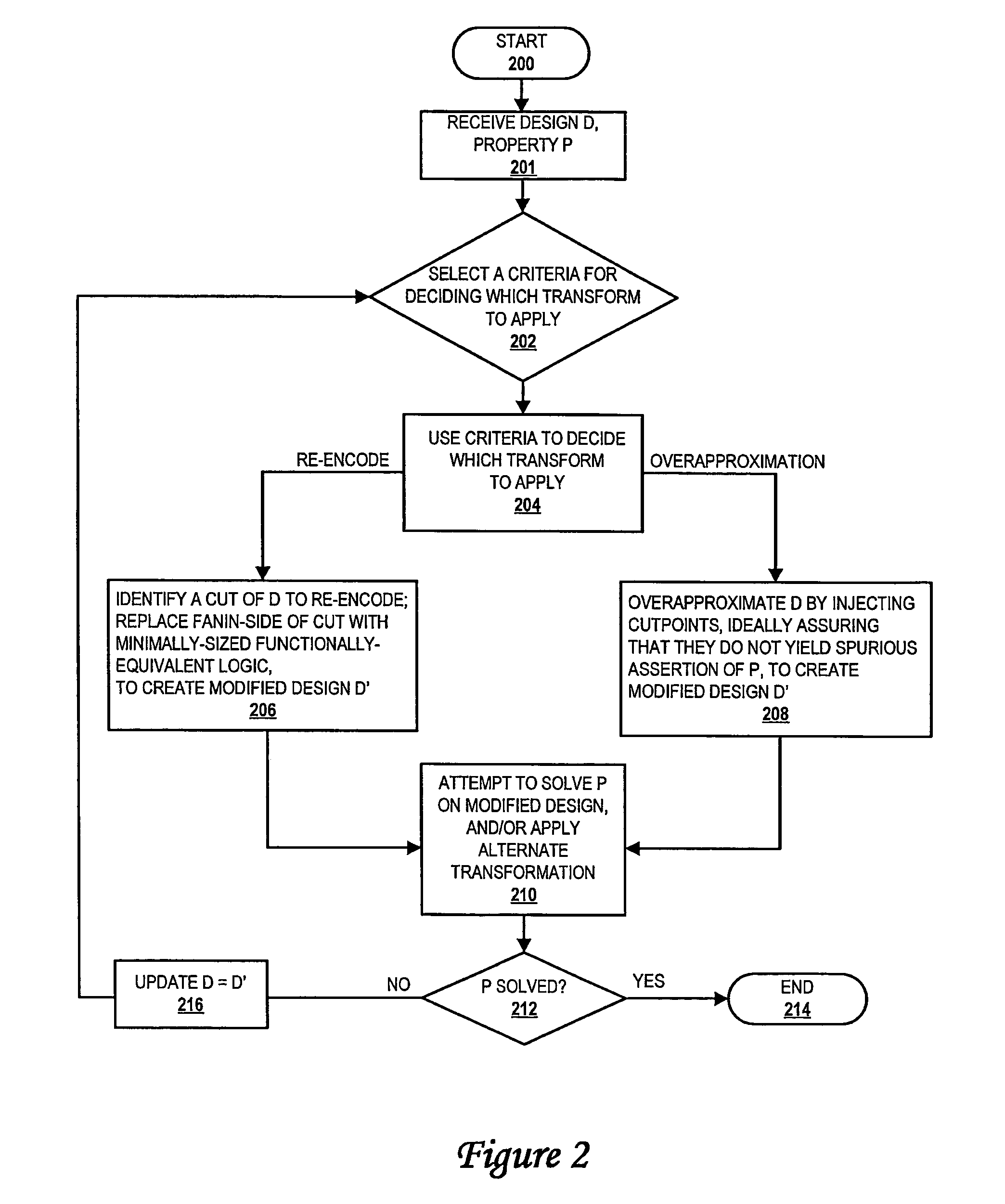

System and Program Product for Incremental Design Reduction via Iterative Overapproximation and Re-Encoding Strategies

InactiveUS20080127002A1Reduce logicCAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceIncremental design

A method of incrementally reducing a design is disclosed. A logic verification tool receives a design and a property for verification with respect to the design, and then selects one or more of a plurality of diverse techniques for reducing the design. The logic verification tool then reduces the design to create a reduced design using the one or more techniques and attempts to generate a valid solution for the property on the reduced design. The logic verification tool determines whether a valid solution is generated, and, if not, replaces the design with the reduced design. Until a valid solution is generated, the logic verification tool iteratively performs the selecting, reducing, determining and replacing steps.

Owner:GLOBALFOUNDRIES INC

Method for incremental design reduction via iterative overapproximation and re-encoding strategies

InactiveUS7370292B2Reduce logicCAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceIncremental design

Owner:GLOBALFOUNDRIES INC

Configuration method of gigabit passive optical network terminal device

ActiveCN103369417AClear handlingAny porting and reuseMultiplex system selection arrangementsTerminal equipmentGigabit

The invention relates to the field of gigabit passive optical network, and especially relates to a configuration method of a gigabit passive optical network terminal device. The method comprises the following steps that: an OLT (Optical Line Terminal) issues configuration, and a business parsing layer parses out the configuration issued by the OLT according to a received OMCI (Ont Management And Control Interface) message; according to whether a MDU (Multi Dwelling Unit) or a SFU (Single Family Unit) works currently, if the SFU works currently, the business parsing layer directly issues the configuration to a chip bottom layer and a PON (Passive Optical Network) chip software processing module; if the MDU works, the business parsing layer adds the internal VLAN (Virtual Local Area Network) processing mechanism, and issues the configuration to corresponding SWITCH and the PON chip software processing module. The method is completely irrelevant to a hardware scheme, and has good portability and reusability. The configuration method can guarantee that development of MDU basic service can be finished around the same time when the SFU is developed.

Owner:TAICANG T&W ELECTRONICS CO LTD

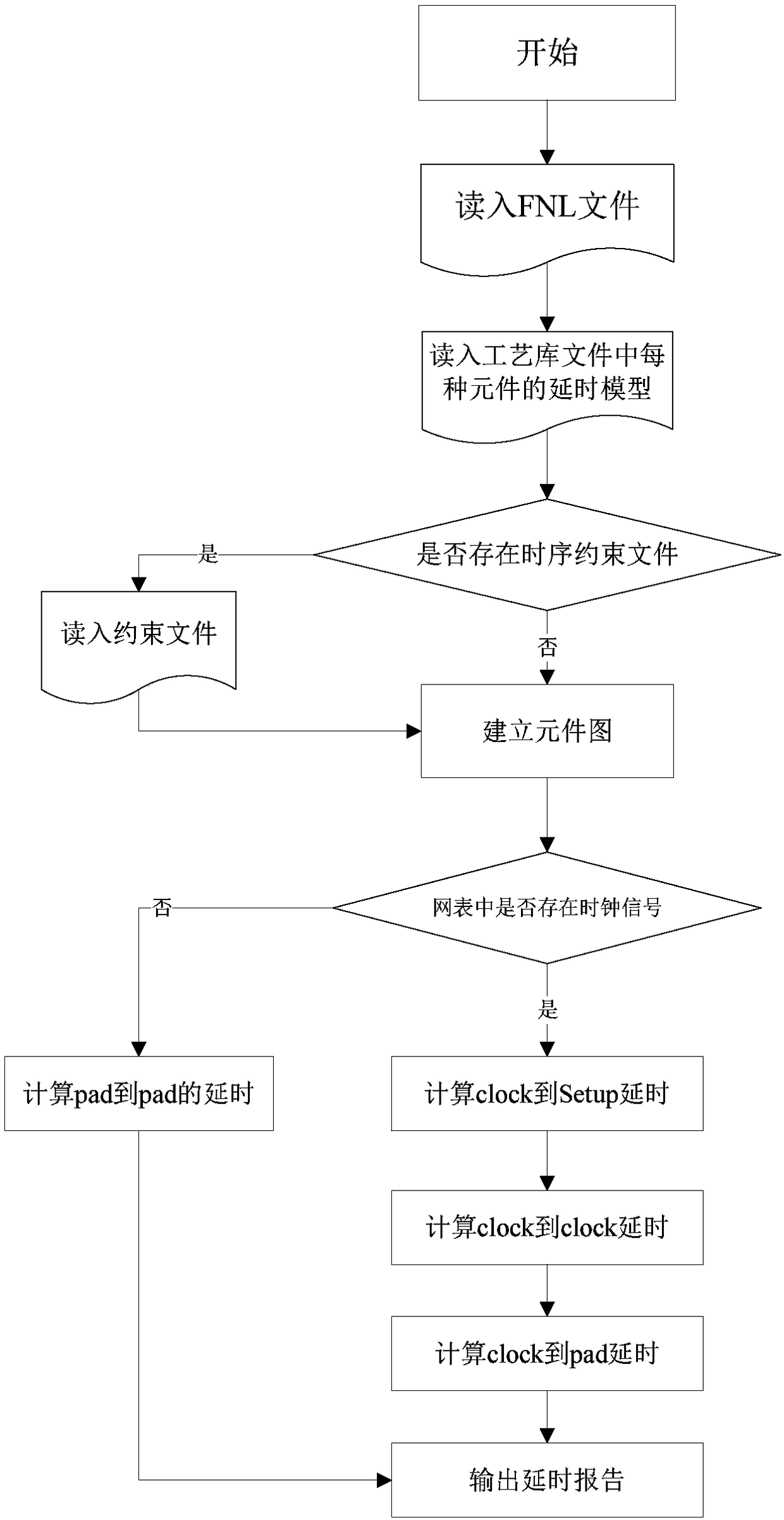

FPGA static timing analysis algorithm

ActiveCN108073771AReduce logicReduce routing delayCAD circuit designSpecial data processing applicationsStatic timing analysisCritical path method

The invention relates to an FPGA static timing analysis algorithm which specifically comprises the steps of extracting all timing paths existing in an entire circuit, checking whether signals meet therequirements of timing constraints when passing through the paths, and finding errors violating the timing constraints by analyzing a maximum path delay and a minimum path delay. According to the method, a critical path that makes the chip timing fail and has a decisive effect on the chip performance can be found more quickly.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

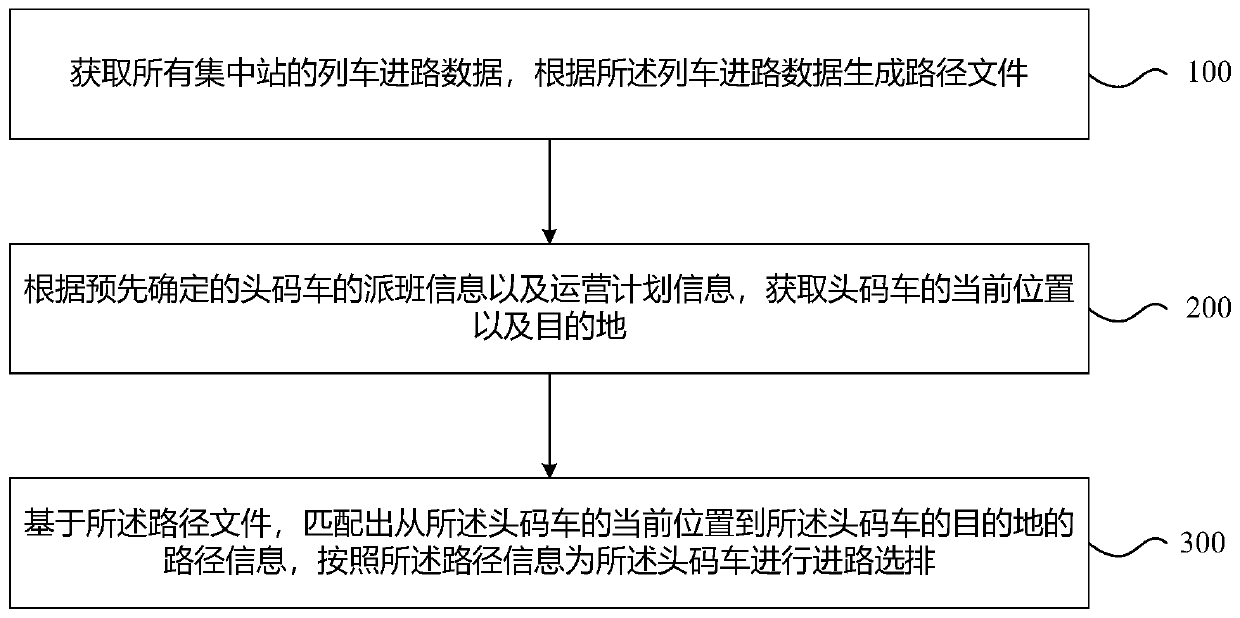

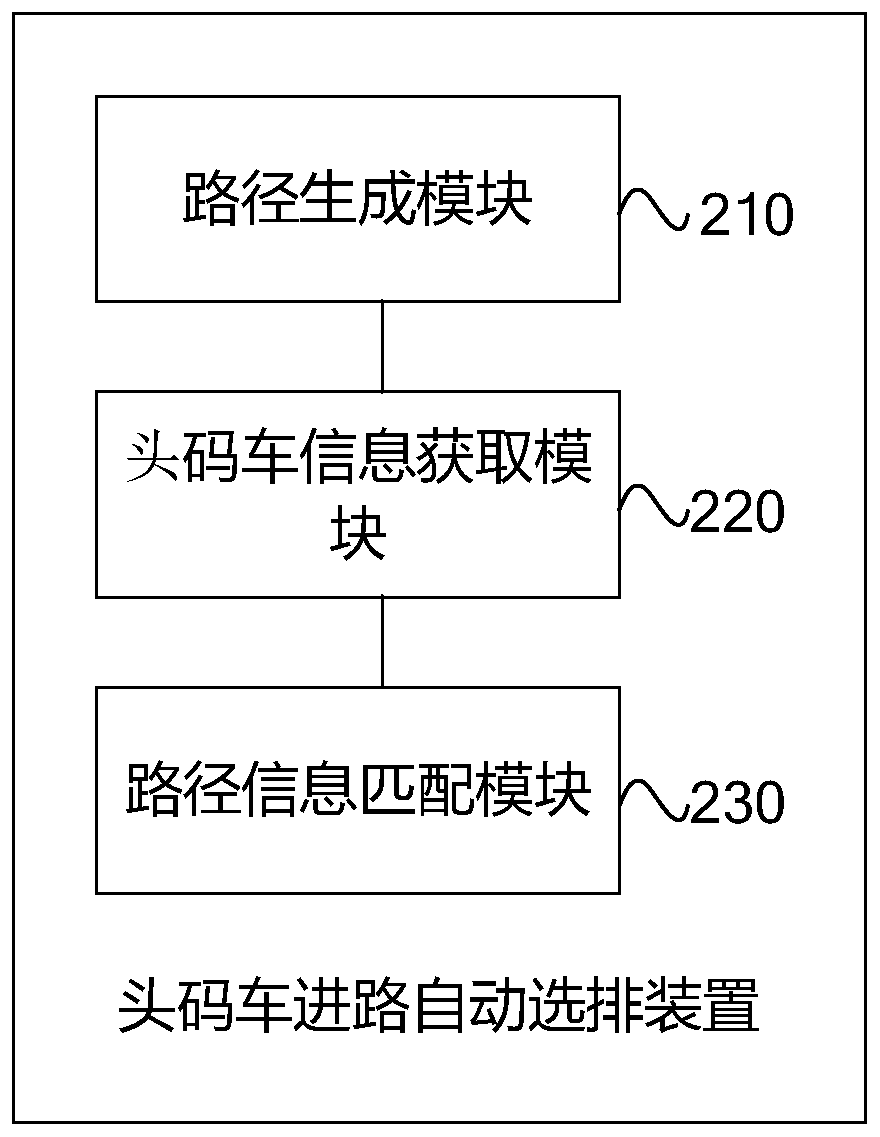

Automatic route selection method and device for unplanned targeting train

ActiveCN110962889AAddressing the need for flexible operationsImprove reliabilityAutomatic systemsSimulationEngineering

The embodiment of the invention provides an automatic route selection method and device for a unplanned targeting train, and the method comprises the following steps: acquiring train route data of allcentralized stations, and generating a route file according to the train route data; obtaining a current position and a destination of a unplanned targeting train according to pre-determined dispatching information and operation plan information of the unplanned targeting train; and based on the route file, matching route information from the current position of the head code vehicle to the destination of the head code vehicle, and performing route selection for the head code vehicle according to the route information. According to the embodiment of the invention, the route file is automatically generated based on the train route data, so that configuration errors caused by manual misoperation are reduced; relevant verification of route connection and route trigger rails is carried out through an automatic route generation process, so that the data reliability is improved; the route is matched according to the destination of the head code vehicle, so that the use scenes of the head code vehicle are increased, and the requirement of flexible operation is met; and the operation efficiency of the pull-in prediction software algorithm is improved.

Owner:通号城市轨道交通技术有限公司

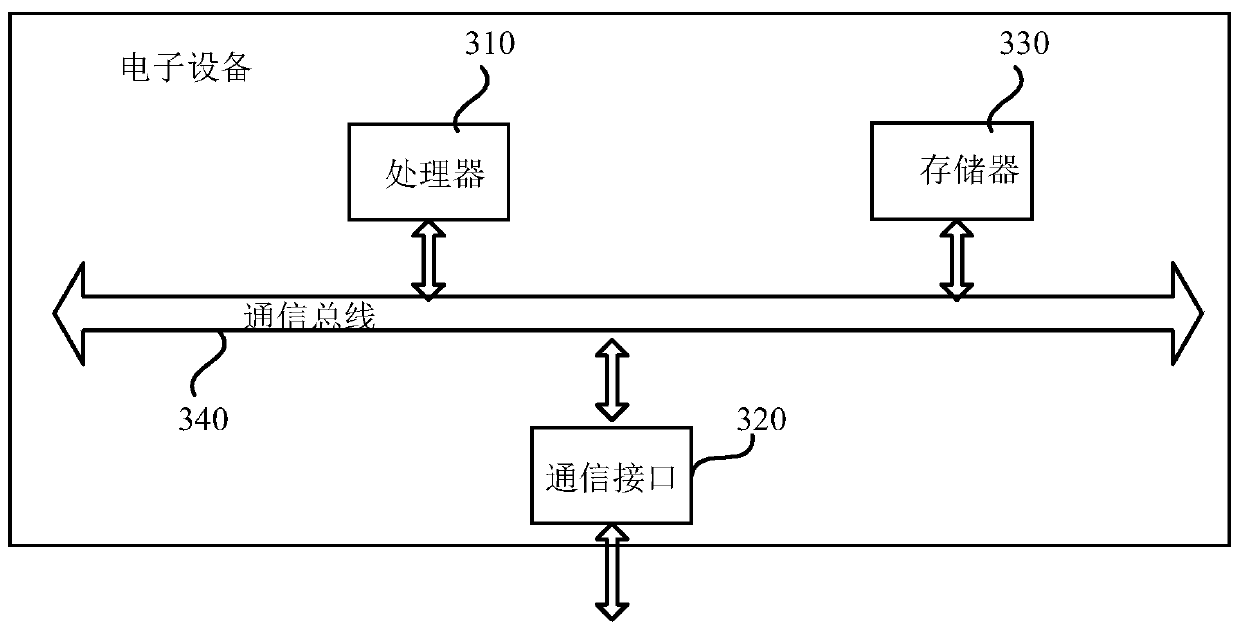

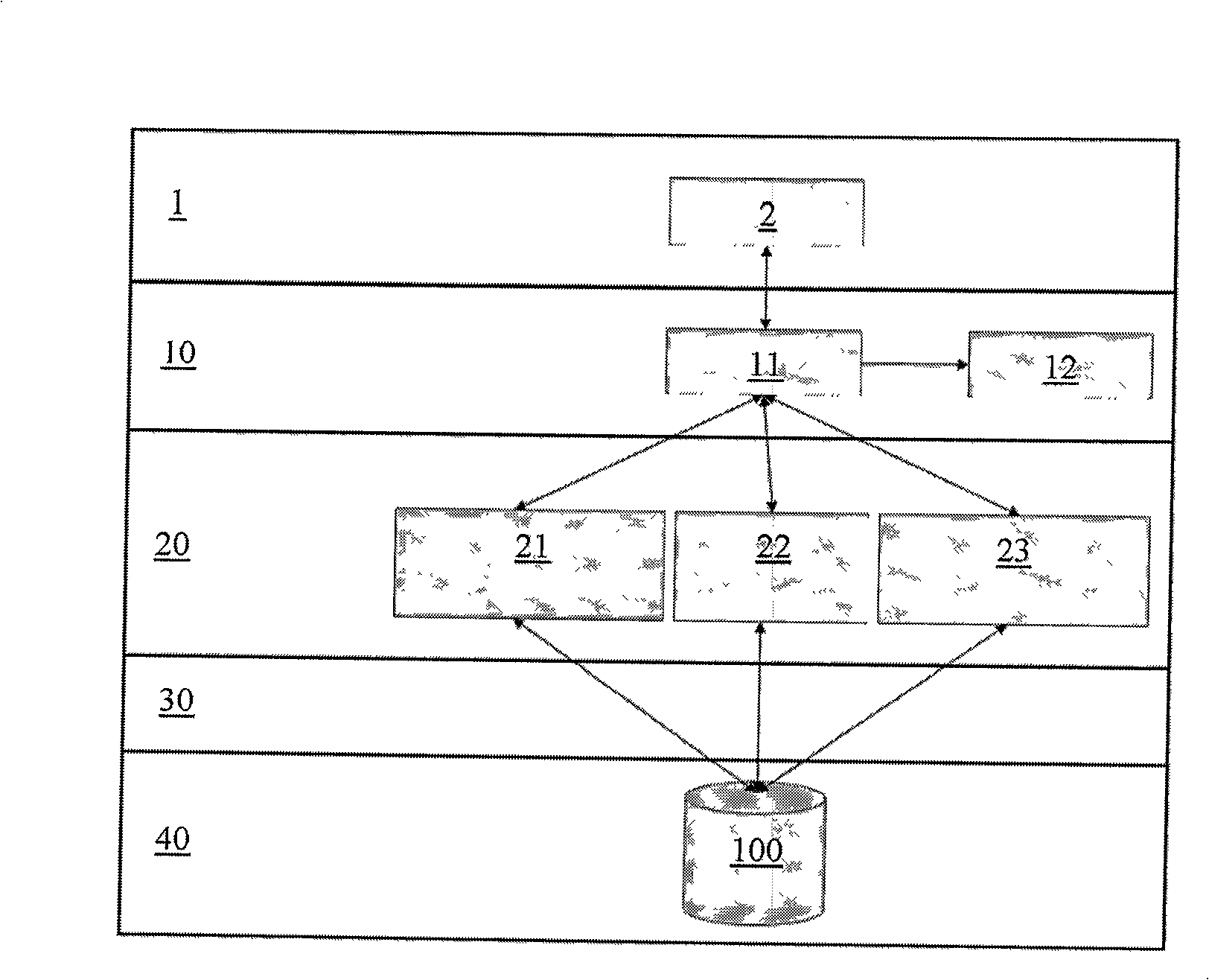

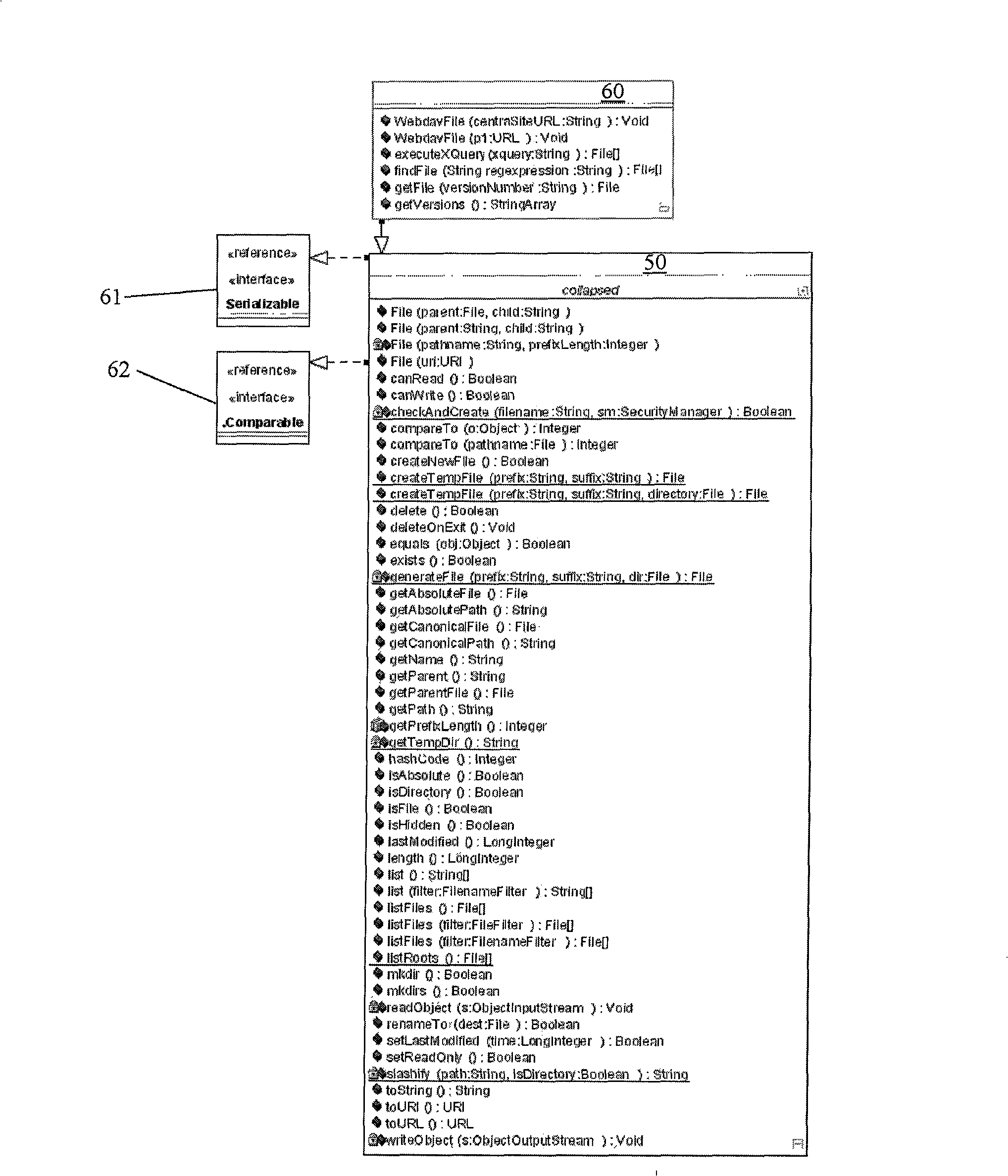

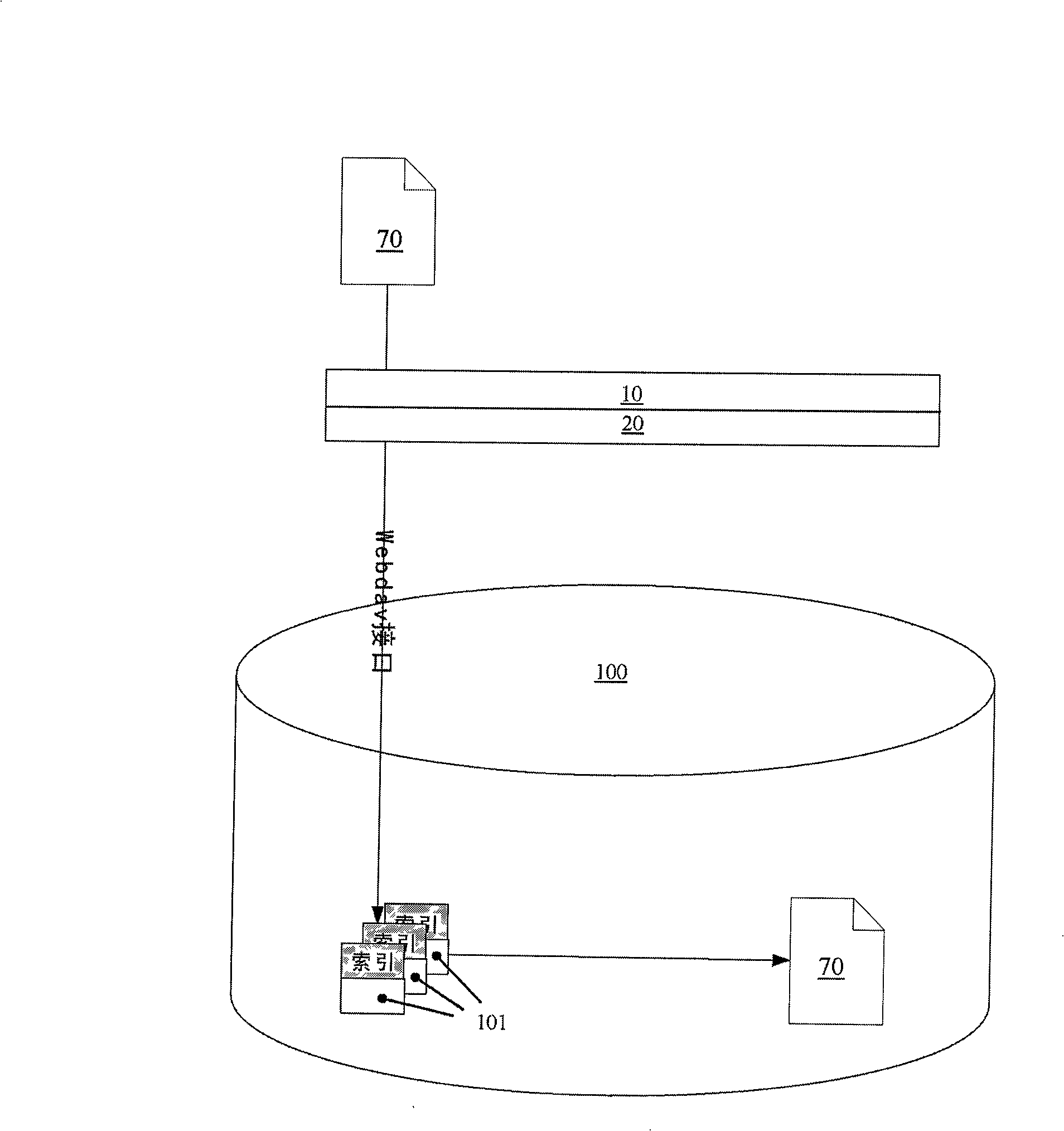

System and method for accessing files in a physical data storage

InactiveCN101286167AWin programming efficiencyReduce logicSemi-structured data queryingSpecial data processing applicationsApplication programming interfaceJava

Owner:SOFTWARE AG

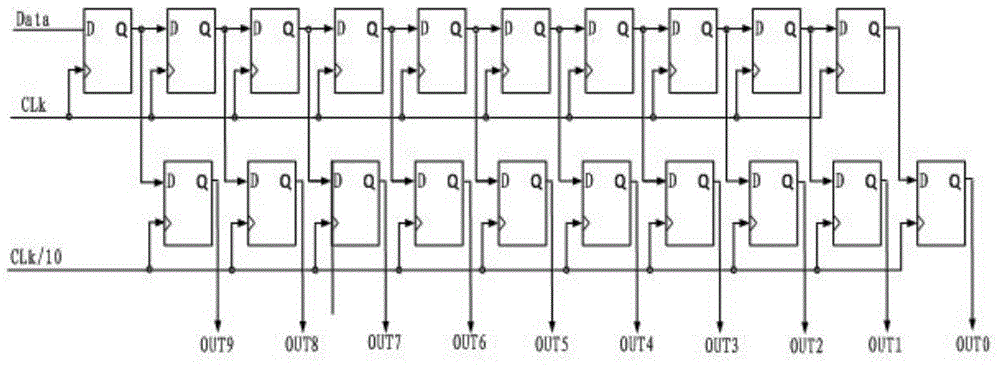

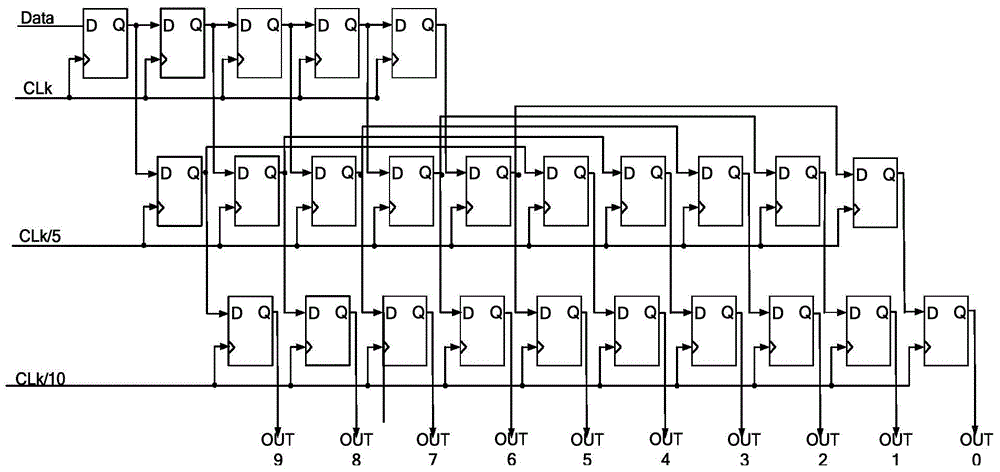

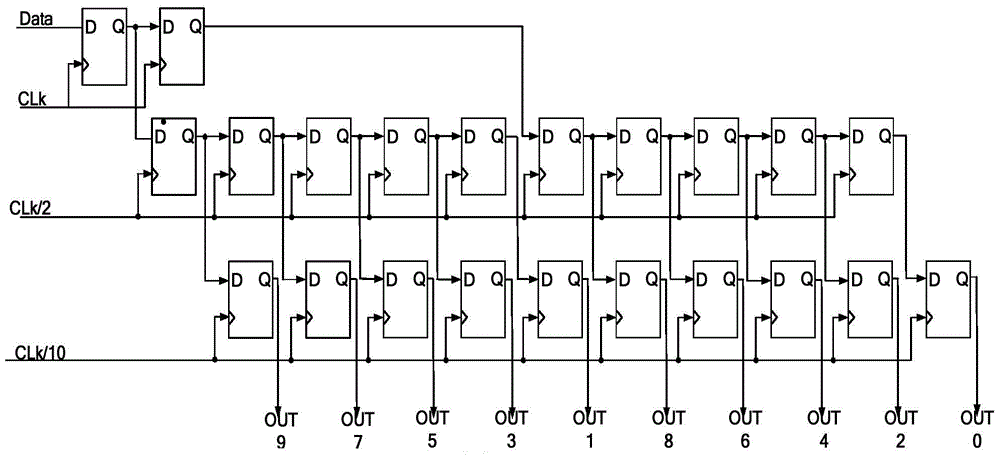

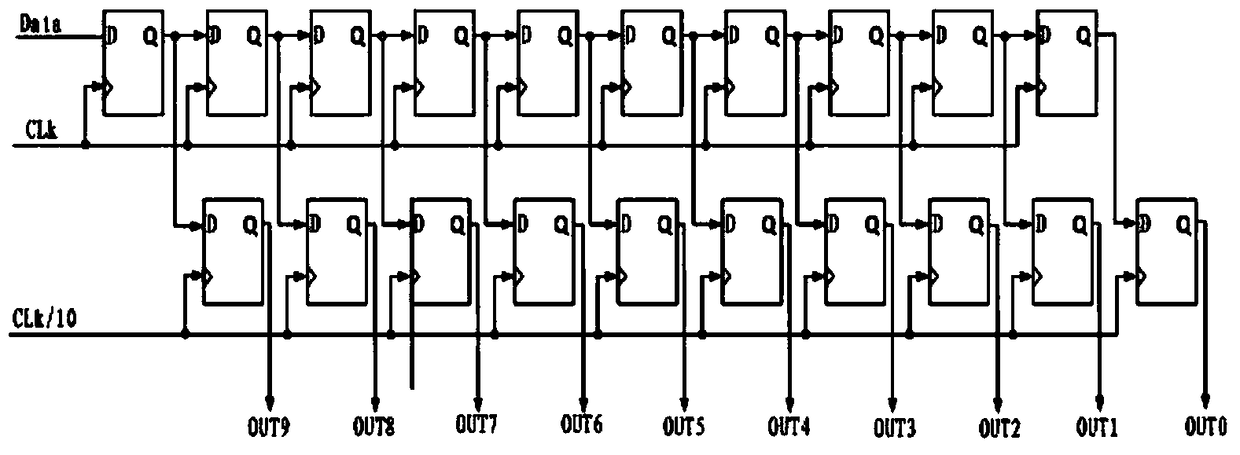

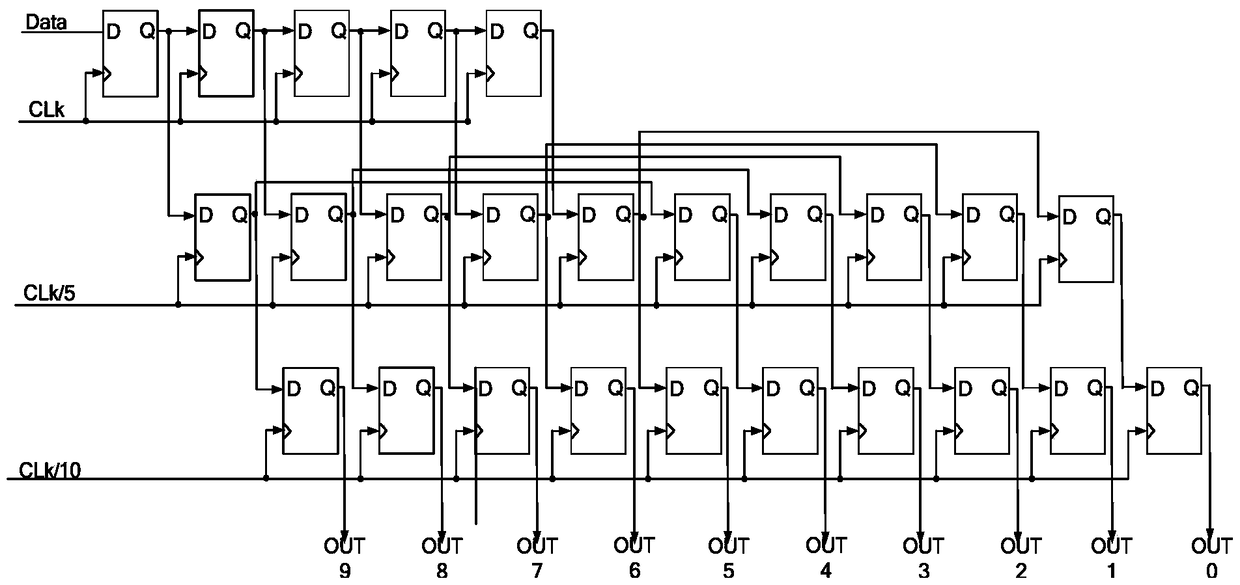

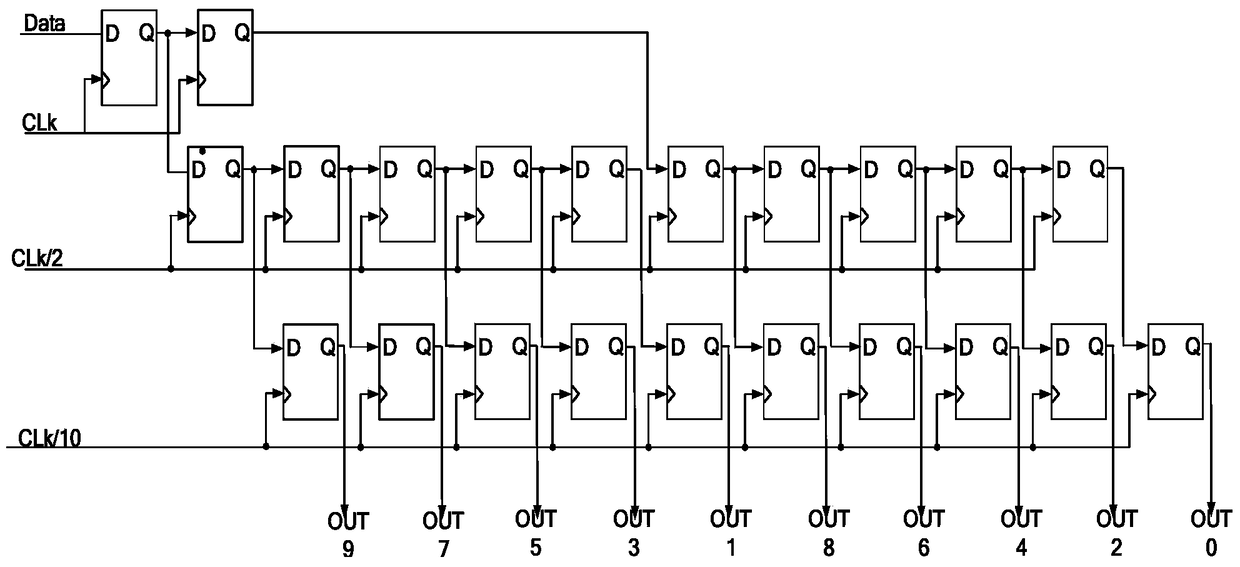

Multistage serial-parallel conversion circuit

ActiveCN105591645AReduce the number of triggersReduce logicLogic circuits coupling/interface using field-effect transistorsEngineeringClock signal

The invention discloses a multistage serial-parallel conversion circuit, which is characterized by comprising at least three stages of D trigger groups. The first stage of D trigger groups comprises n cascaded D triggers with the same first clock signals; the second stage of D trigger groups comprises n*m cascaded D triggers with the same second clock signals; the third stage of D trigger groups comprises n*m cascaded D triggers with the same third clock signals; in the first stage of D trigger groups, the output end of the ath D trigger is connected with the input end of the ath D trigger in the second stage of D trigger groups; the output end of the ((m-1)*n+a)th D trigger in the second stage of D trigger groups is connected with the input end of the (m*n+a)th D trigger in the second stage of D trigger groups and is also connected with the input end of the ((m-1)*n+a)th D trigger in the third stage of D trigger groups; and n, m and a are all natural numbers, and a< / =n.

Owner:CAPITAL MICROELECTRONICS

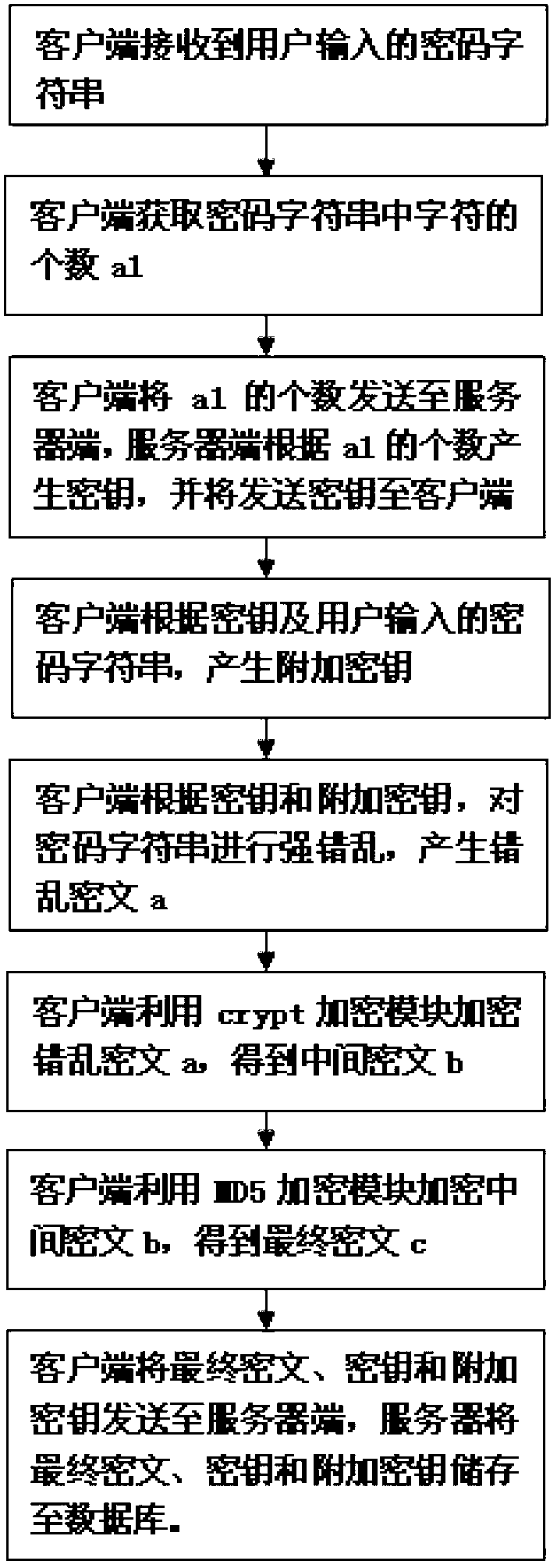

Password encryption method for social website

InactiveCN102710416AReduce logicIncrease the difficultyKey distribution for secure communicationClient-sideMD5

The invention discloses a password encryption method for a social website. A password character string is subjected to strong disturbance before the conventional message-digest algorithm 5 (MD5) encryption is performed, so that the logicality of the encrypted character string is greatly reduced. Crypt encryption processing is performed before MD5 encryption is performed, so that the original text subjected to MD5 encryption is a character string without logical relationship. Hacker needs brand new original text / ciphertext control database which does not exist at present and has huge data to decipher the ciphertext, so the difficulty of ciphertext decipher by the hacker is greatly increased and the safety of the password is improved. The encryption flow is completely performed on the client side and the password character string input by a user does not pass through a server completely, therefore, even if the hacker breaks the firewall of the server, the hacker can only find the secret key and the ciphertext and cannot find the trace of the password character string, and the safety of the password is improved.

Owner:SHANGHAI PORT BUSINESS CONSULTING

Data processing apparatus and method for performing floating point addition

ActiveUS7433911B2Reduce logicLow costComputations using contact-making devicesComputation using non-contact making devicesSingle levelOperand

A data processing apparatus and method are provided for adding n-bit significands of first and second floating point operands to produce an n-bit result. The data processing apparatus comprises determination logic operable to determine the larger operand of the first and second operands, and alignment logic operable to align the n-bit significand of the smaller operand with the n-bit significand of the larger operand. First adder logic is then operable to perform a first sum operation in order to generate a first rounded result in non-redundant form equivalent to the addition of the aligned significands with a rounding increment injected at a first predetermined rounding position appropriate for a non-overflow condition, the first adder logic comprising a single level of adder logic. Further, second adder logic is provided to perform a second sum operation in order to generate a second rounded result in non-redundant form equivalent to the addition of the aligned significands with a rounding increment injected at a second predetermined rounding position appropriate for an overflow condition, the second adder logic also comprising a single level of adder logic. Selector logic is then used to derive the n-bit result from either the first rounded result or the second rounded result.

Owner:ARM LTD

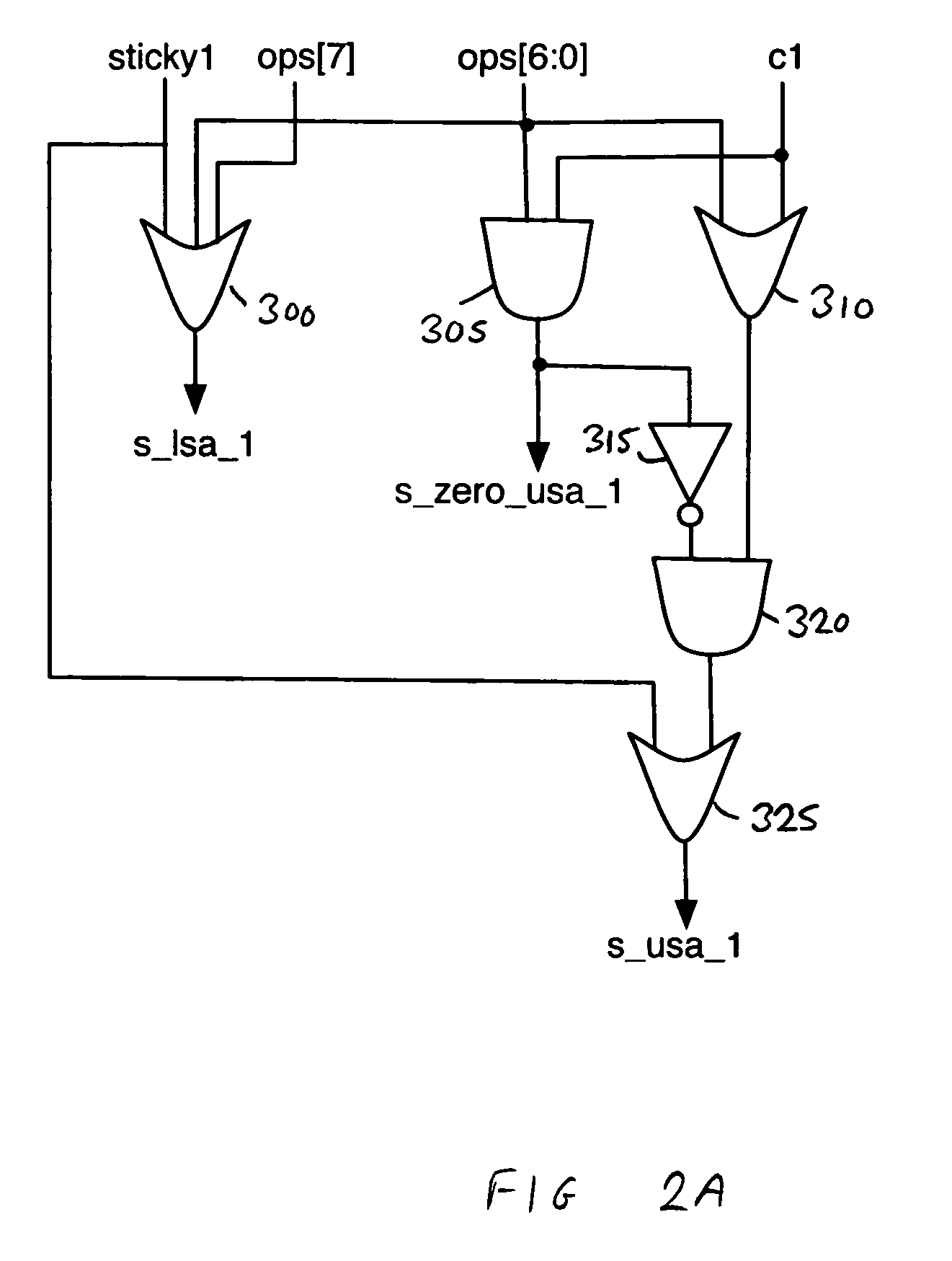

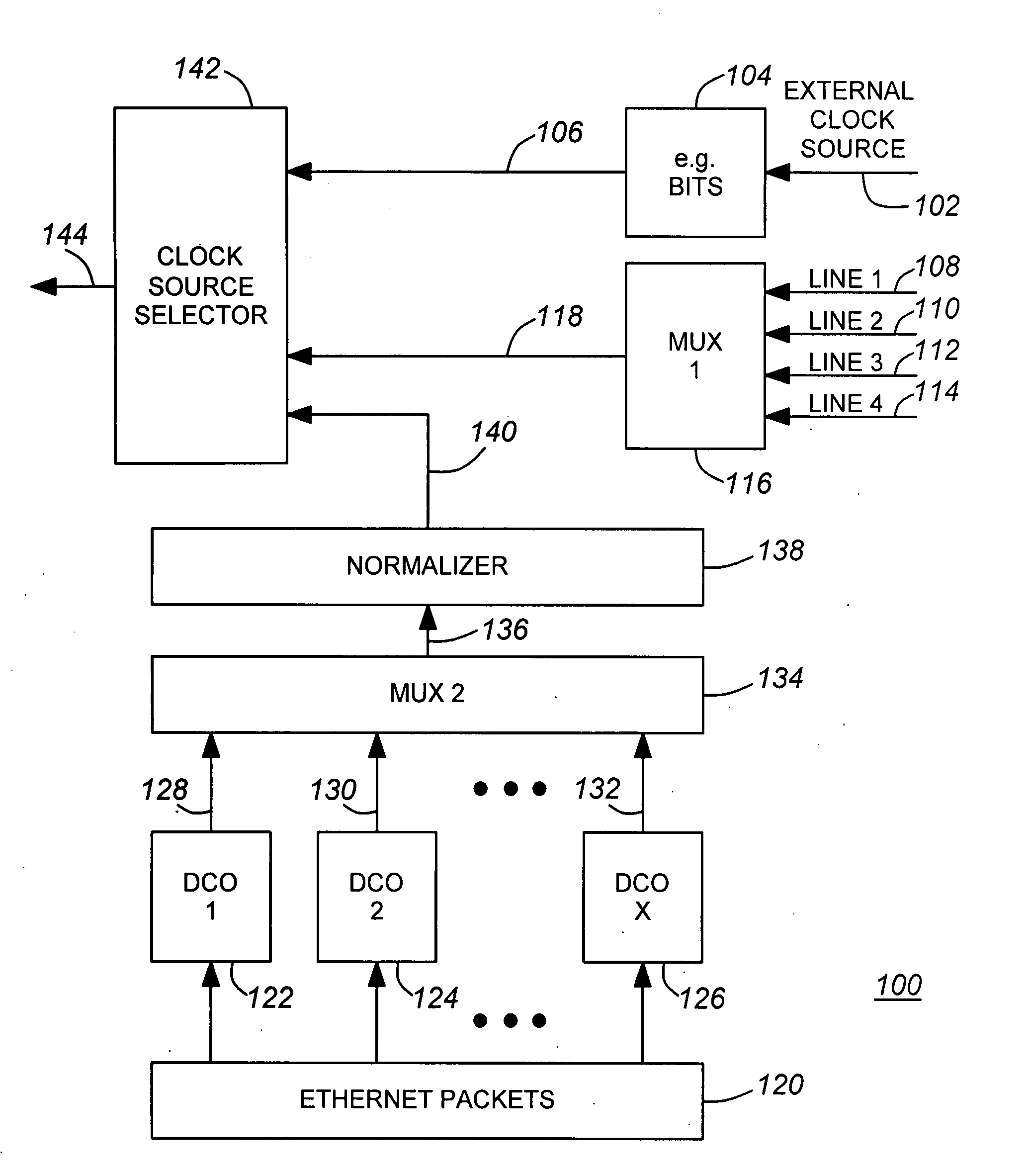

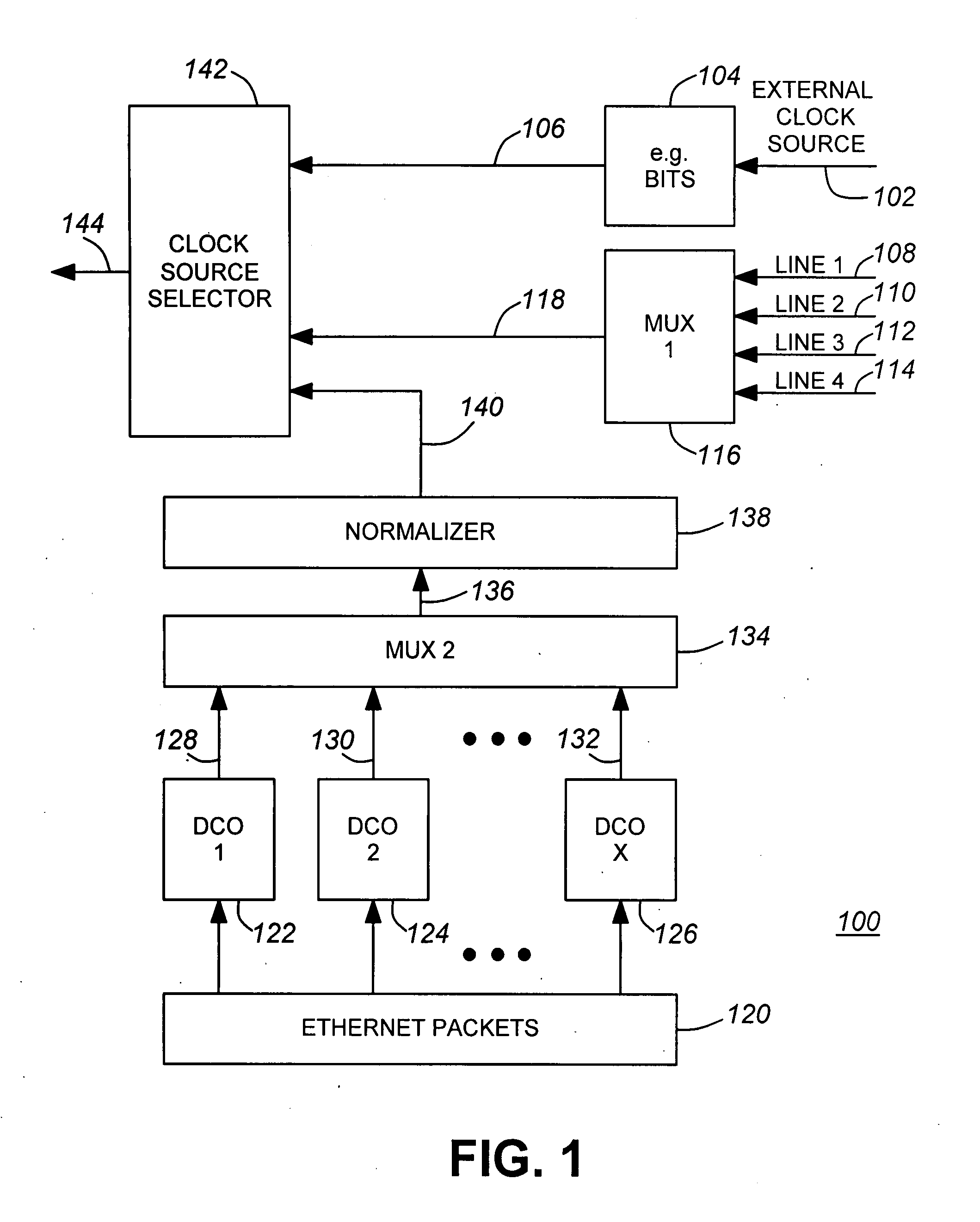

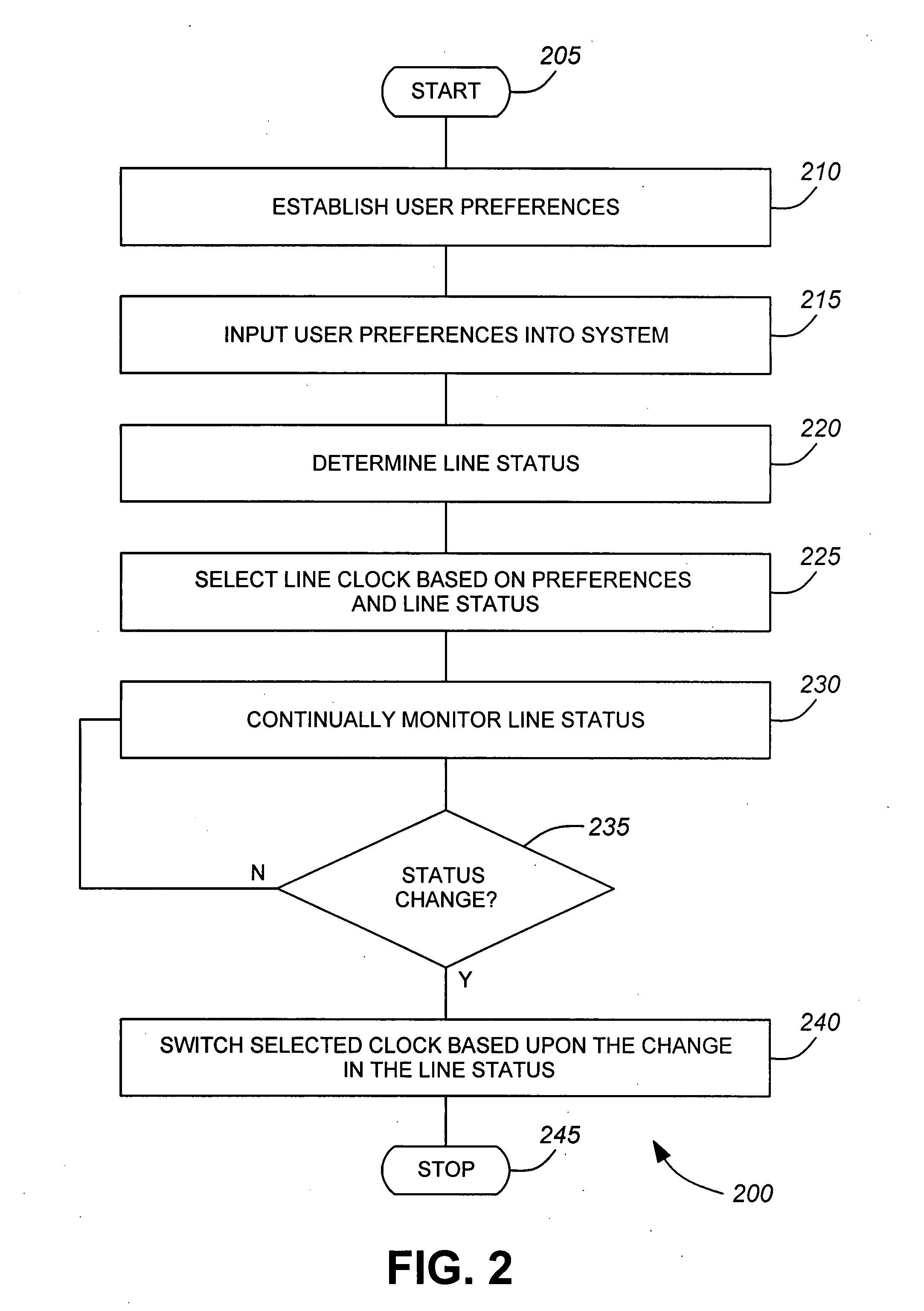

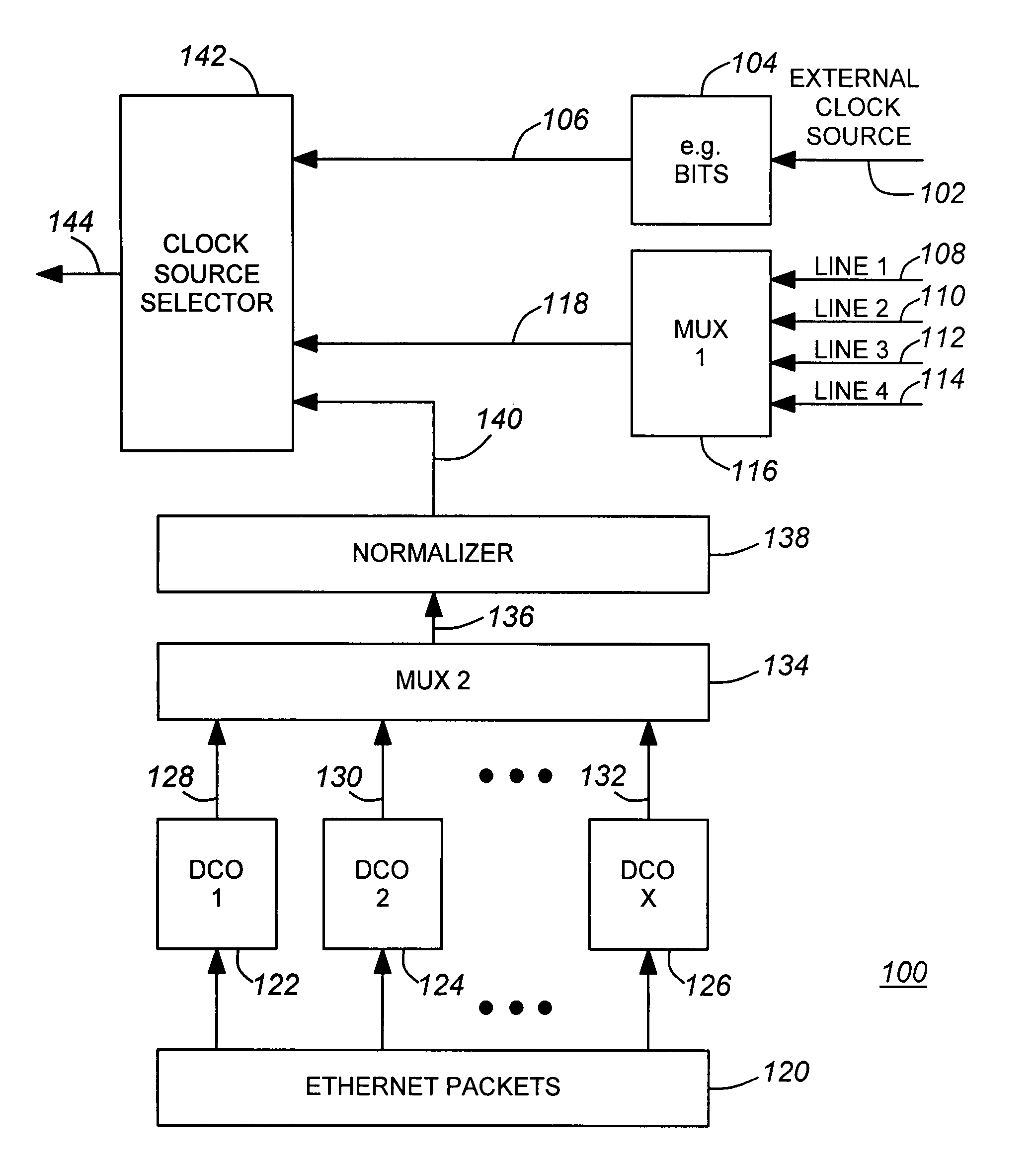

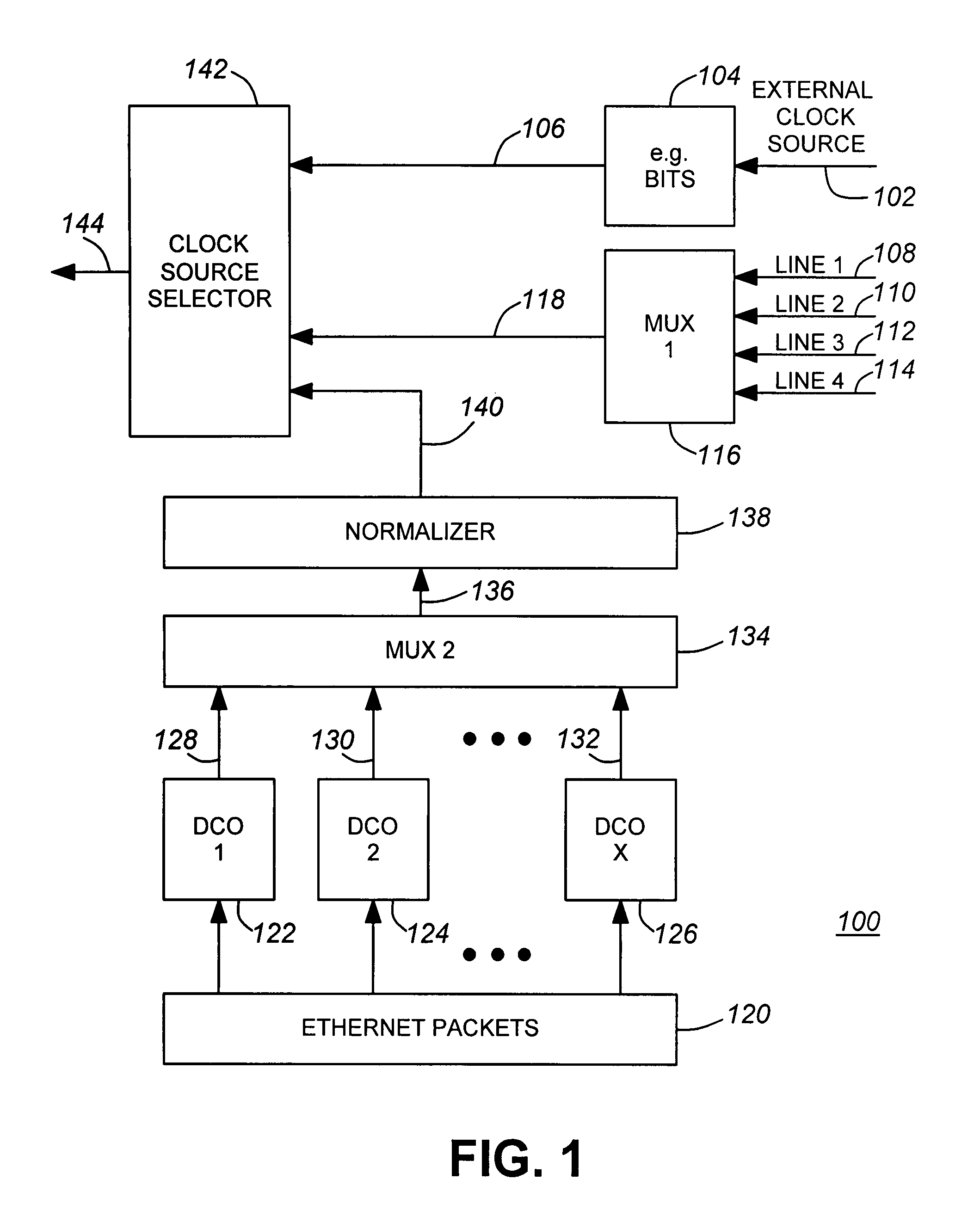

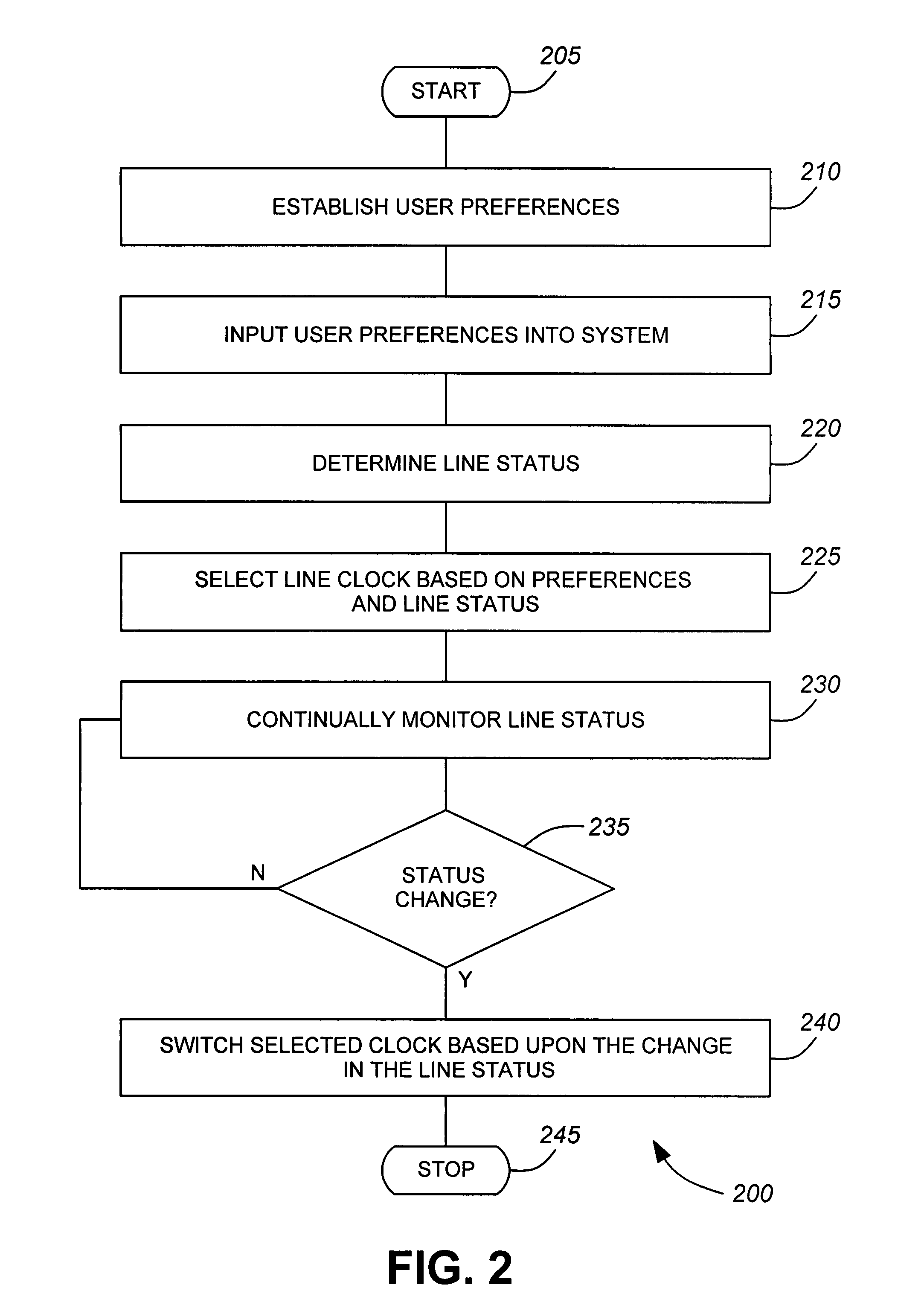

Advanced clock distribution mechanism for circuit emulation applications

ActiveUS20090141743A1Reducing amount of bufferingTight synchronizationDigital data processing detailsTime-division multiplexMultiplexerNetwork packet

A clock distribution mechanism for circuit emulation applications, and related method, including one or more of the following: a plurality of digitally controlled oscillators, each of the plurality of digitally controlled oscillators receiving one or more Ethernet packets and generating a recovered clock from the one or more Ethernet packets; a multiplexer for receiving the recovered clocks generated by the plurality of digitally controlled oscillators, selecting a one of the recovered clocks generated by the plurality of digitally controlled oscillators, and outputting the selected one of the recovered clocks; a normalizer that receives a frequency of the selected one of the recovered clocks and generates a normalized frequency output based on the received frequency of the selected one of the recovered clocks and outputs the normalized frequency output; a clock source selector for receiving a plurality of input clock sources, one of the input clock sources being the normalized frequency output of the normalizer, the clock source selector selecting the normalized frequency output from among the plurality of input clock sources and transmitting the selected normalized frequency to a node; and one or more nodes for receiving the selected normalized frequency.

Owner:META PLATFORMS INC

System and Method for Accurately Modeling an Asynchronous Interface using Expanded Logic Elements

InactiveUS20080040695A1Accurate modelingReduce logicCAD circuit designSoftware simulation/interpretation/emulationLogical elementTheoretical computer science

Owner:GLOBALFOUNDRIES INC

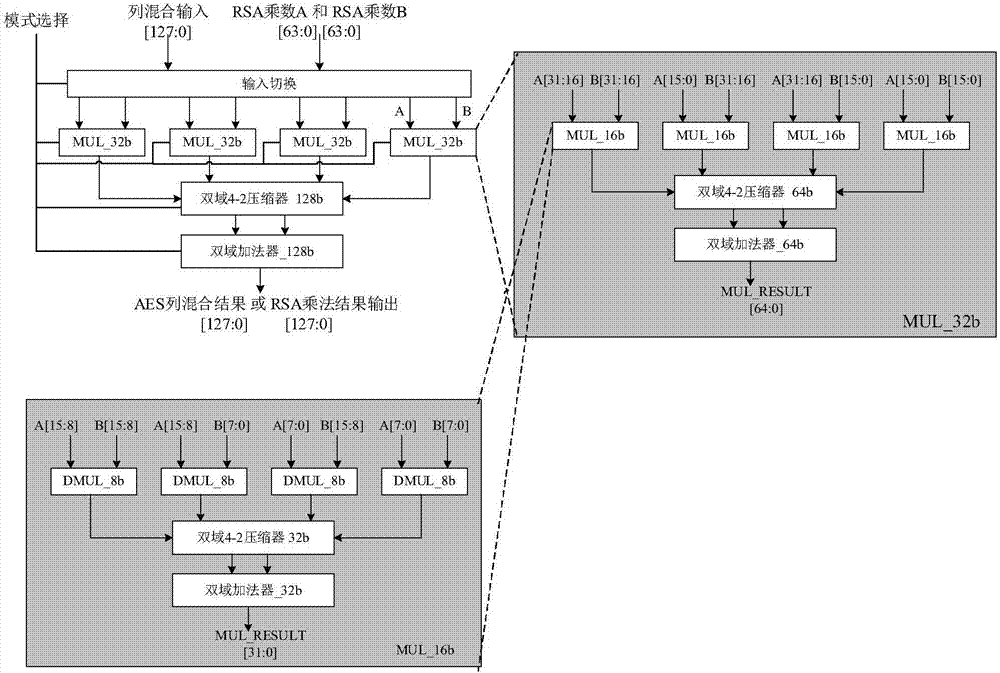

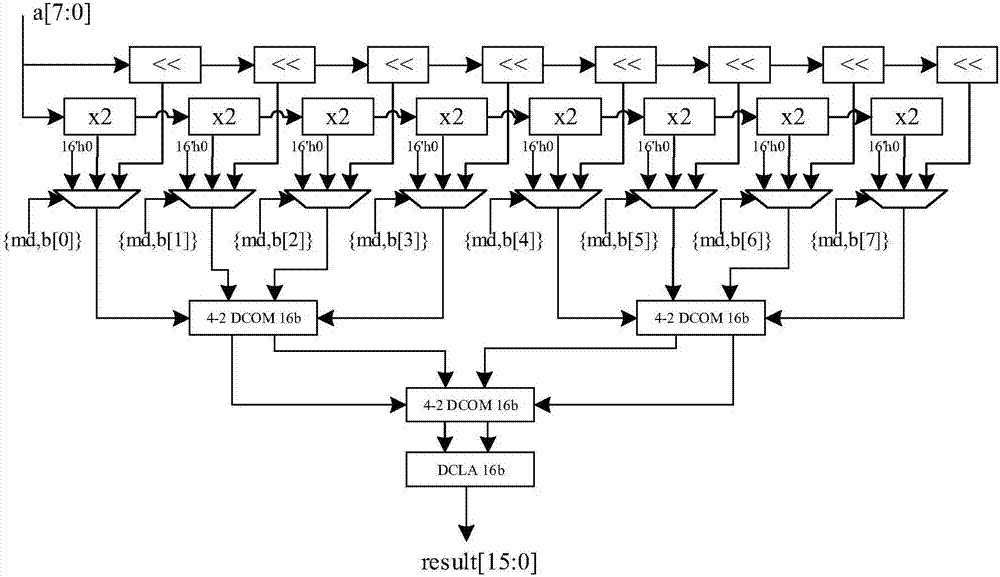

Configurable multiplication device applied to AES and RSA mixed algorithm hardware circuit

ActiveCN107241183AReduce logicEncryption apparatus with shift registers/memoriesPublic key for secure communicationComputer hardwareBinary multiplier

The invention discloses a configurable multiplication device of which hardware implementation can be applied to an AES and RSA mixed algorithm hardware circuit, and belongs to the field of cryptographic algorithm hardware implementation. Compared with an implementation scheme based on an ordinary multiplier in the past, the device has the advantages that a large number of configurable circuits are adopted by designing a special circuit structure, large-area multipliers and adders are reused, an AES MixColumn function and an RSA multiplication function are achieved in one operational circuit on the basis of additionally consuming a small number of selectors, and compared with the method of implementing the two kinds of operation singly, less circuit area is consumed, and less logic is used.

Owner:SOUTHEAST UNIV

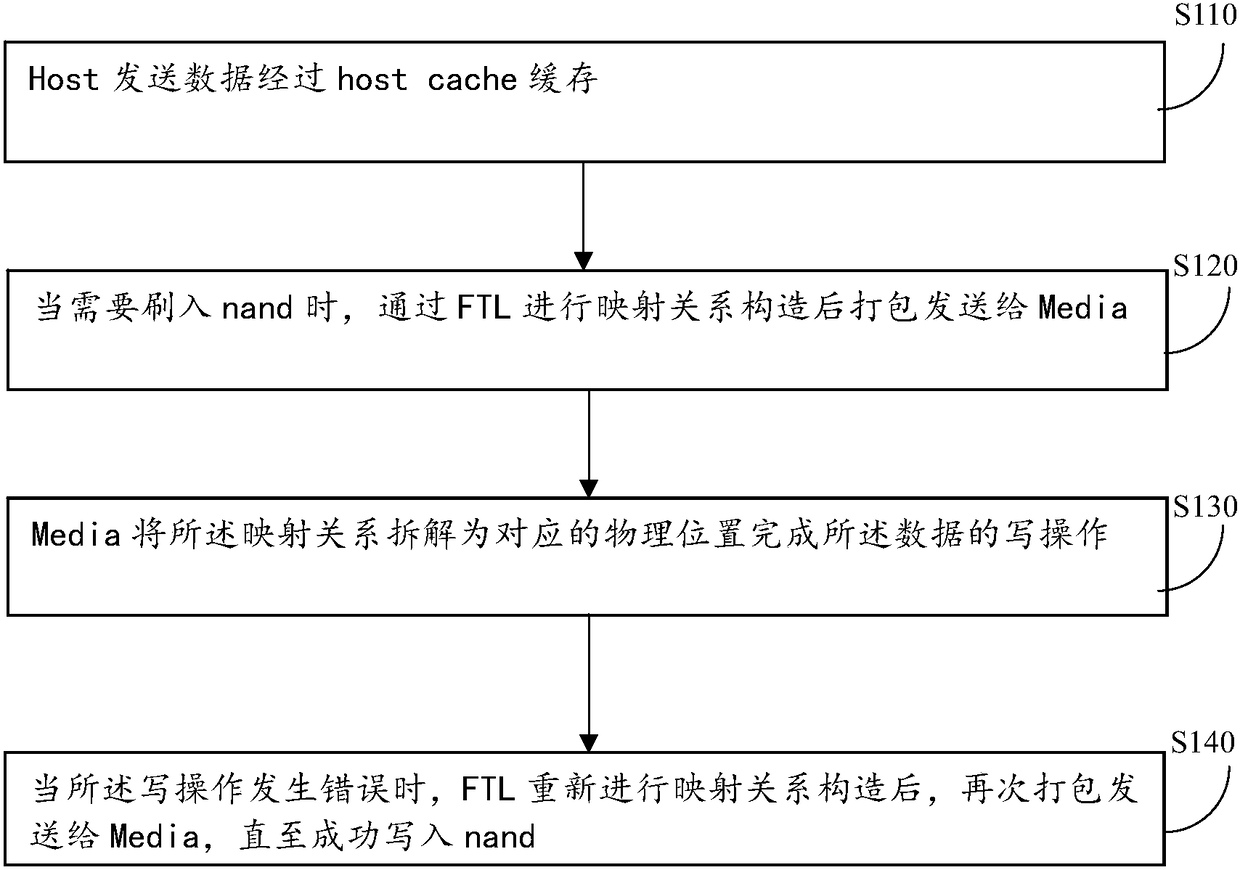

Data processing method and device for SSD

ActiveCN108255426ASimple logicReduce flash operationsInput/output to record carriersData processingInformation processing

The invention provides a data processing method and device for an SSD and relates to the technical field of information processing. The method includes the steps that data is sent through a host and cached through a host cache; when nand needs to be written in, a mapping relationship is constructed through an FTL and then packed and sent to Media; Media disassembles the mapping relationship into acorresponding physical location to complete a write operation of the data; when the write operation goes wrong, the FTL re-constructs the mapping relationship and then packs and sends the mapping relationship to Media again till nand is successfully written in. The technical effects of simplifying logic and reducing flash memory operations are achieved.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

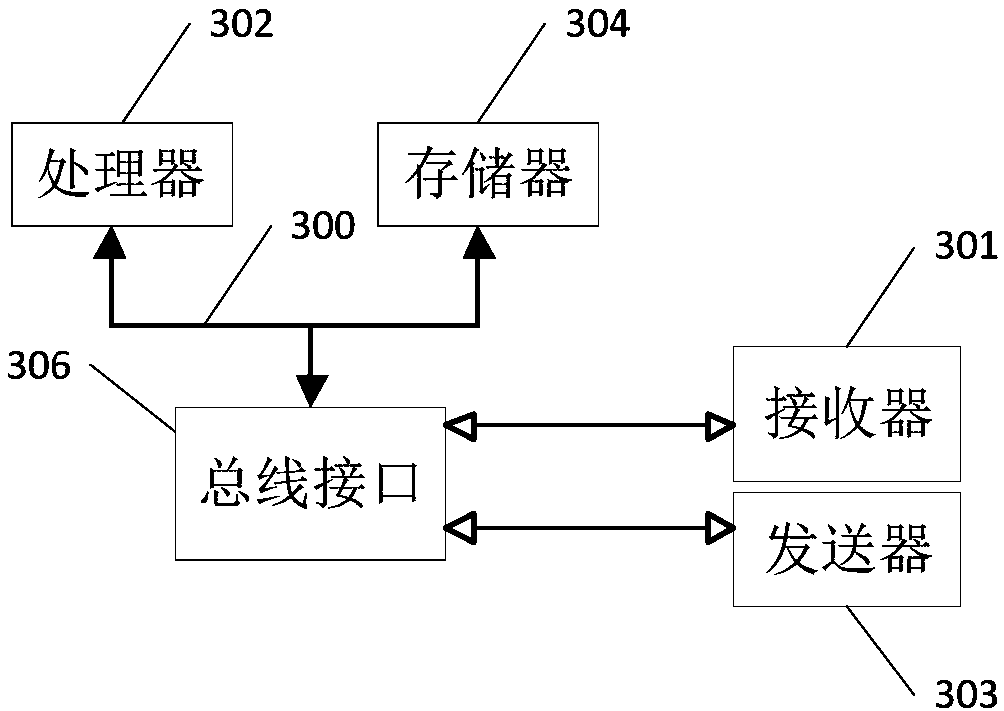

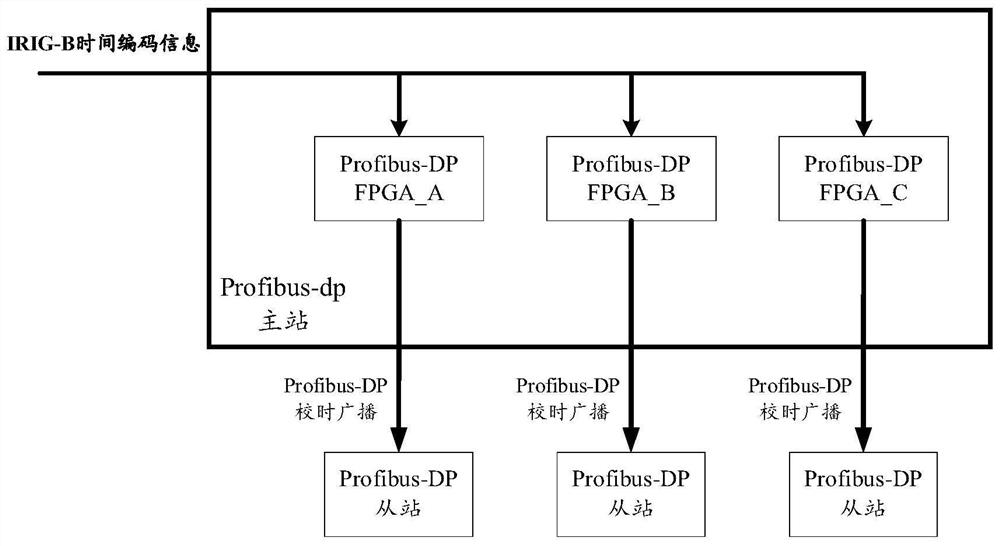

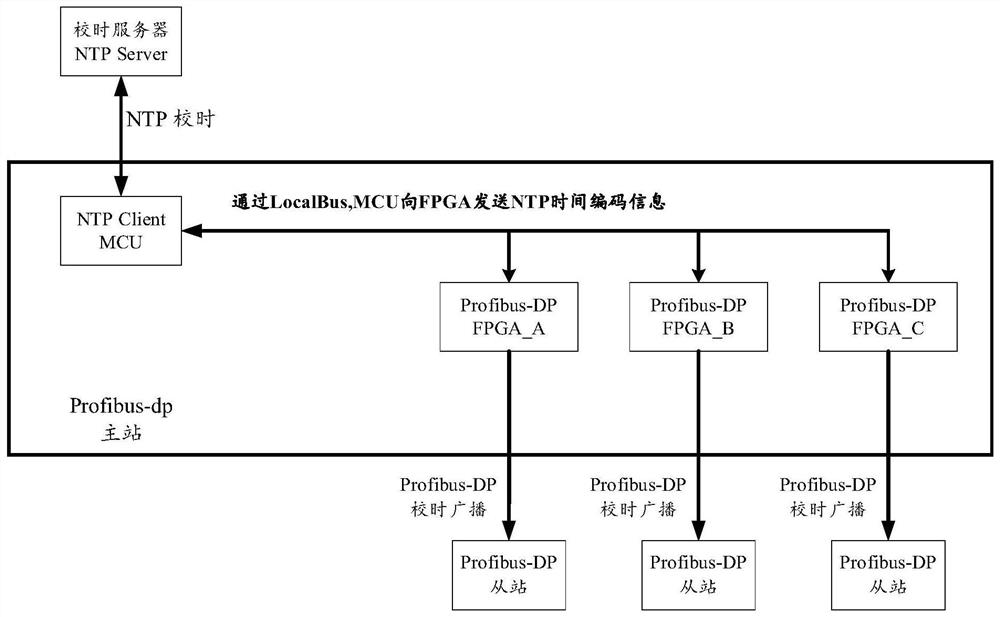

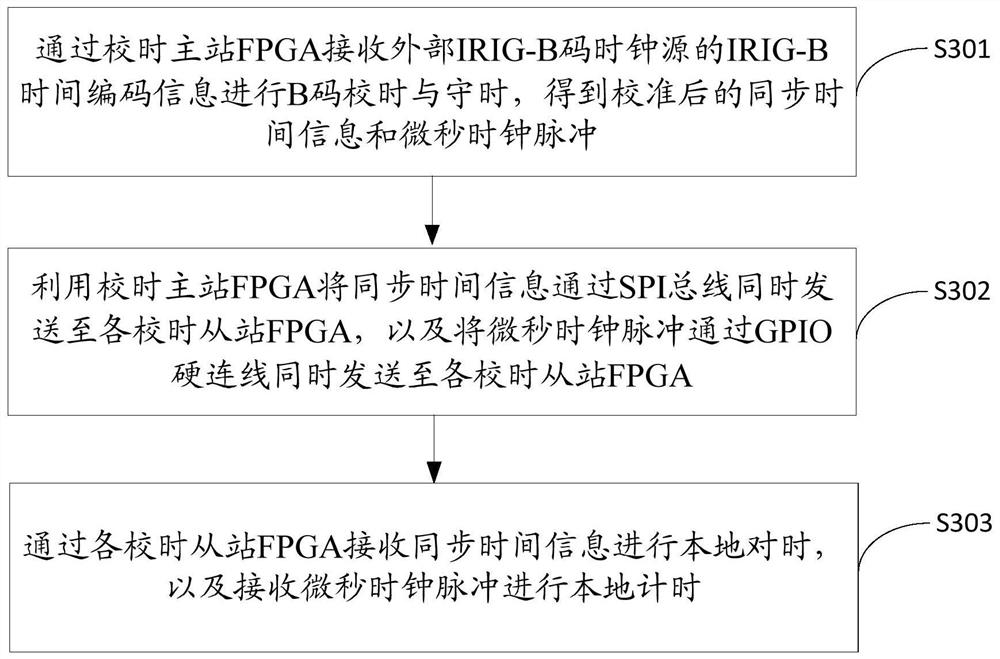

Time synchronization method and device among multiple FPGAs, equipment and storage medium

ActiveCN112506268AReduce logicAvoid wastingGenerating/distributing signalsTotal factory controlComputer hardwareTime information

The invention discloses a time synchronization method and device among multiple FPGAs, equipment and storage medium, and the method comprises the steps of receiving IRIGB time coding information of anexternal IRIGB code clock source through a timing main station FPGA, carrying out the B code timing and punctuality, and obtaining the calibrated synchronization time information and microsecond clock pulse; using the timing master station FPGA to send the synchronization time information to each timing slave station FPGA through an SPI bus at the same time, and sending the microsecond clock pulse to each timing slave station FPGA through a GPIO hard connection line at the same time; and receiving the synchronous time information by the FPGA of each timing slave station to perform local timing, and receiving the microsecond clock pulse to perform local timing. Therefore, precious logic of the FPGA is effectively saved, meanwhile, the timing precision and the synchronism among a pluralityof board-level devices can be guaranteed, and resource waste caused by independent timing in each FPGA is avoided.

Owner:HANGZHOU HOLLYSYS AUTOMATION

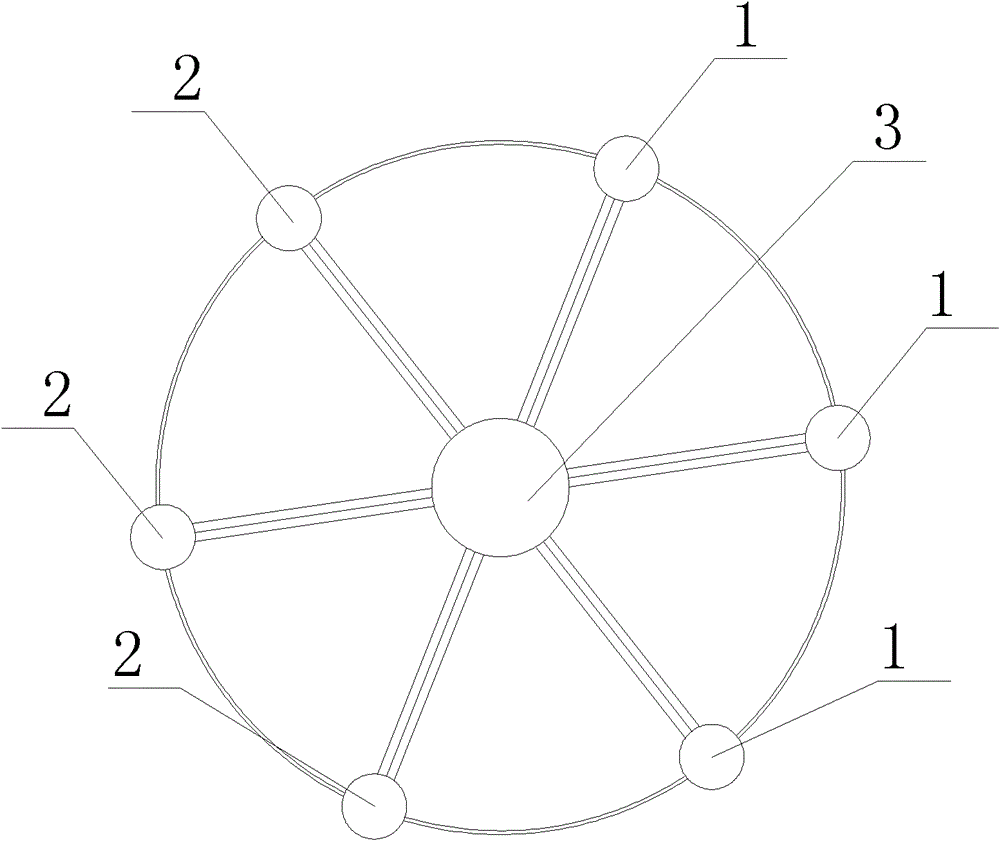

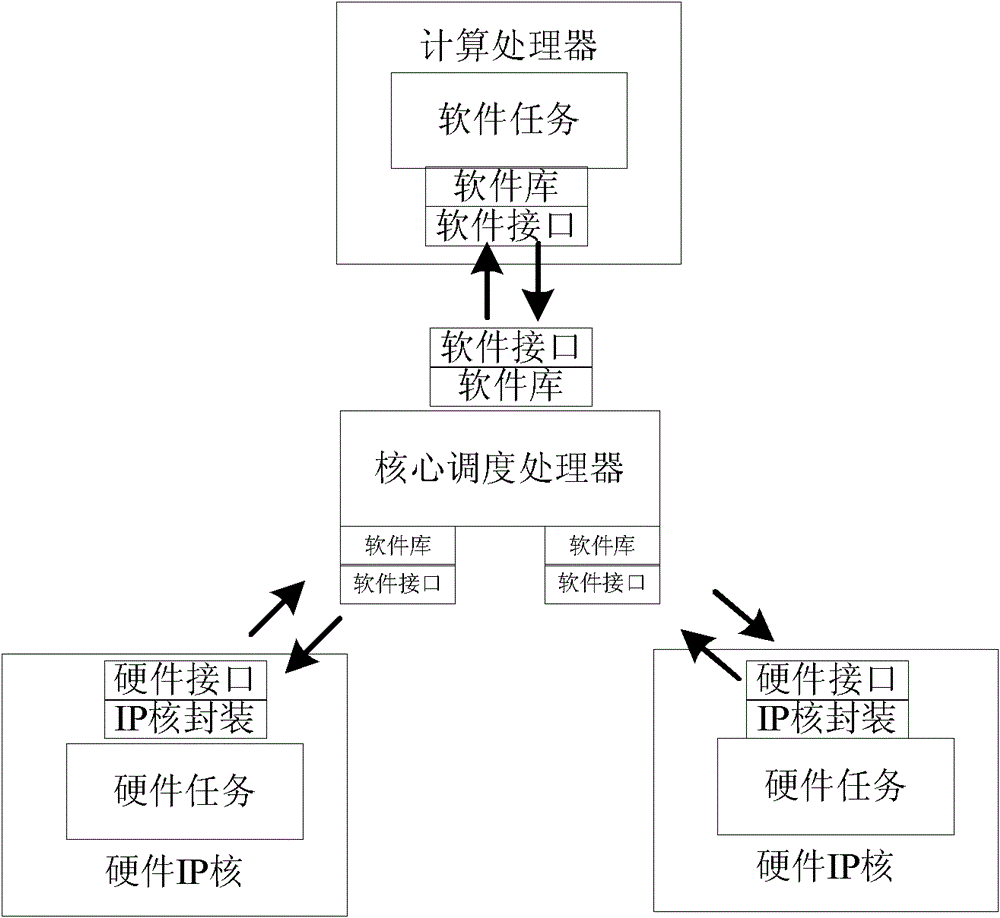

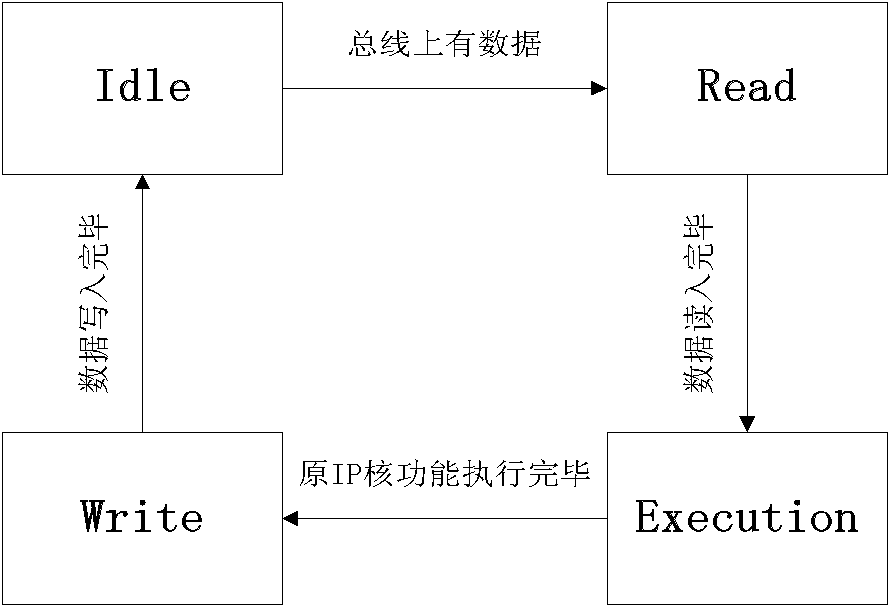

On-chip heterogeneous multi-core system based on star type interconnection structure, and communication method thereof

ActiveCN102135950BReduce logicMask internal programming timeDigital computer detailsElectric digital data processingExtensibilityInterconnection

The invention discloses an on-chip heterogeneous multi-core system based on a star type interconnection structure, and a communication method thereof. The system comprises a core scheduling processor, at least one calculation processor and at least one hardware IP core, and is characterized in that a chip network based on a point-to-point bus is respectively used between the core scheduling processor and the calculation processor and between the core scheduling processor and the hardware IP core for interconnection so as to form a star type interconnection structure; message transmission is carried out on a communication model based on the star type interconnection structure between the core scheduling processor and the calculation processor; and the communication module is realized by using a non-blocking interface. The system improves the throughput rate and the expandability of the access.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

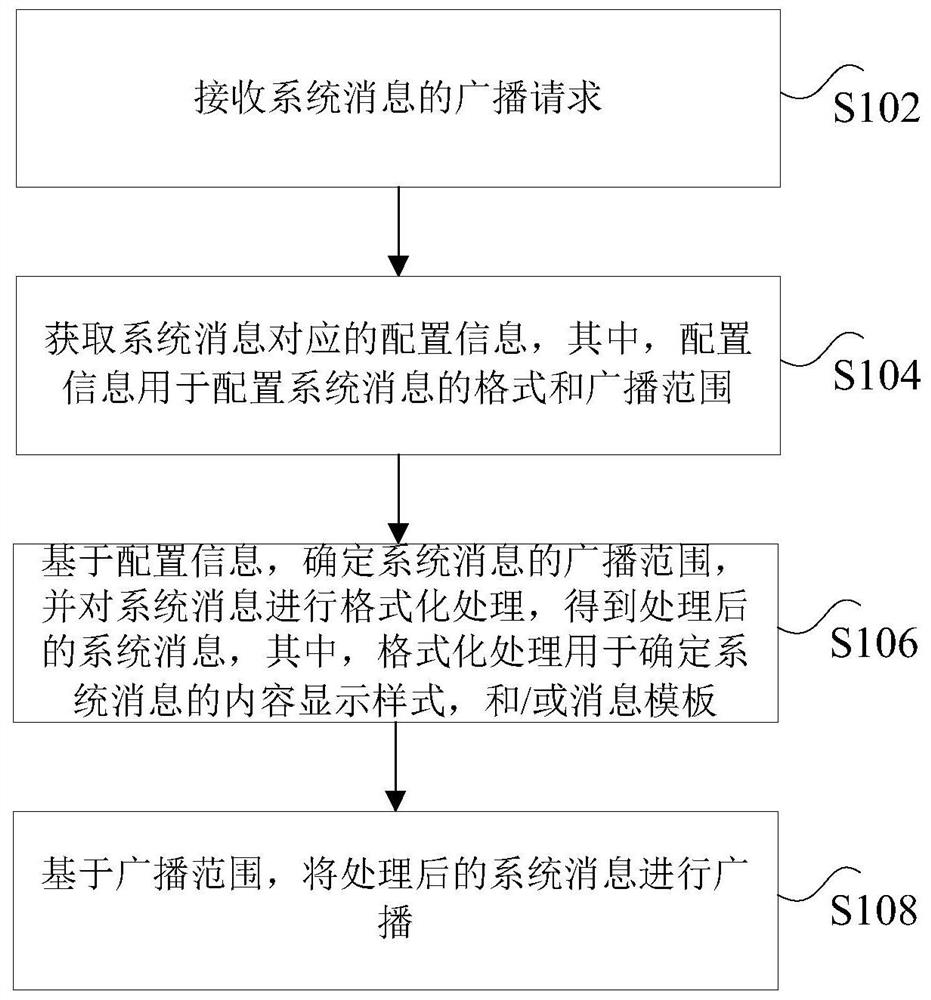

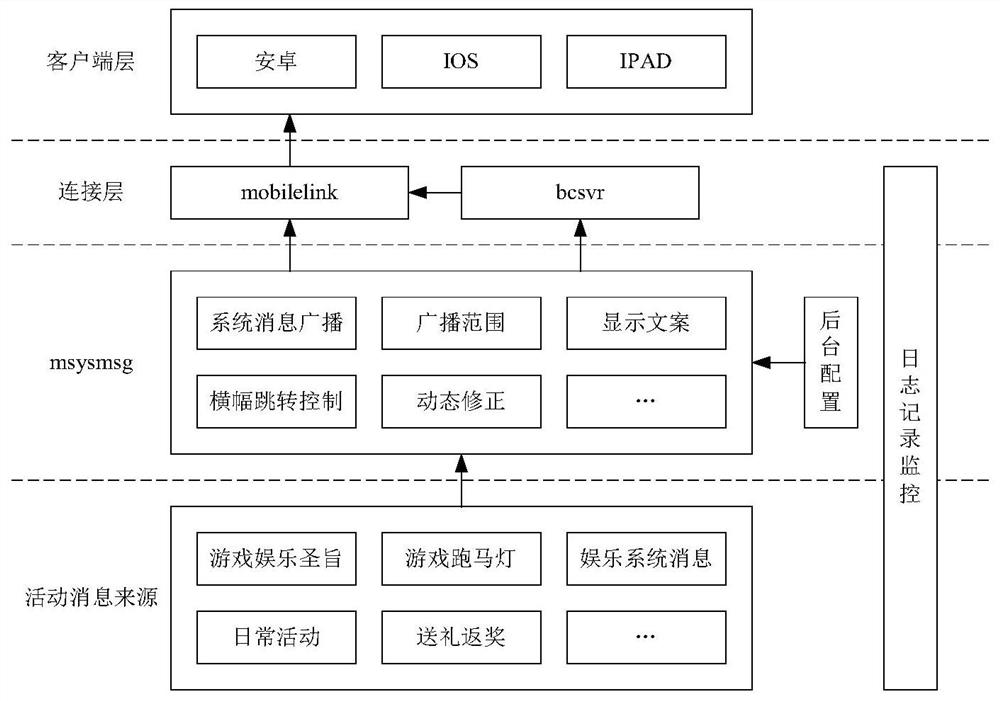

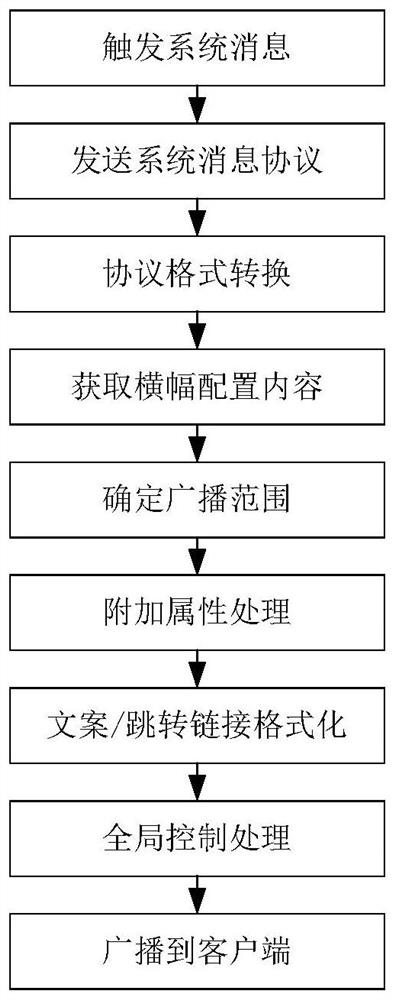

System message processing method and device for live broadcast application

InactiveCN111614972AImprove processing efficiencyIncreased processing flexibilitySelective content distributionTelecommunicationsMessage processing

The invention discloses a system message processing method and device for a live broadcast application. The method comprises the following steps: receiving a broadcast request of a system message; acquiring configuration information corresponding to the system message, the configuration information being used for configuring a format and a broadcast range of the system message; determining a broadcast range of the system message based on the configuration information, and formatting the system message to obtain a processed system message, the formatting being used for determining a content display style of the system message and / or a message template; and broadcasting the processed system message based on the broadcast range. According to the invention, the technical problems of poor flexibility and low efficiency of the implementation mode of the system message in related technologies are solved.

Owner:NETEASE (HANGZHOU) NETWORK CO LTD

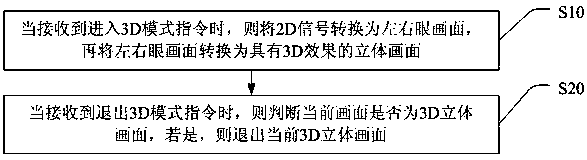

Method for automatically switching 3D mode, storage medium and smart television

InactiveCN109936736AReduce logicGuarantee the development progressSelective content distributionSteroscopic systemsSimulationMode switch

The invention discloses a method for automatically switching a 3D mode, a storage medium and an intelligent television, and the method comprises the steps: when receiving an instruction of entering the 3D mode, converting a 2D signal into left and right eye images, and converting the left and right eye images into a 3D image with a 3D effect; and when an instruction of exiting the 3D mode is received, judging whether the current picture is a 3D picture, and if yes, exiting the current 3D picture. According to the invention, a unified 3D mode switching standard process is formulated from the perspective of application; in this way, automatic switching can be achieved in the switching process of all the applications, switching of all the applications is not needed, the logic problem of 3D switching in a project is reduced, the project development progress is guaranteed, automatic 3D switching is achieved to a certain degree, and great convenience is brought to a user.

Owner:SHENZHEN TCL NEW-TECH CO LTD

Method for accessing shared volume by centralized gateway

PendingCN112929298AReduce logicReduce errorsDigital data information retrievalData switching networksAccess methodEngineering

The invention provides a method for accessing a shared volume by a centralized gateway, which comprises the following steps of: S1, configuring a gateway on a gateway switch, and uploading messages of all storage switches to the gateway switch; S2, managing the sent messages by the gateway switch in a bucket classification mode; and S3, querying a required message, and performing matching to complete access. According to the shared volume access method provided by the invention, the centralized gateway is adopted to store the routing information, the logic on the service is reduced, the storage switch is dynamically added and deleted without modifying the service logic, the quick delivery of the service is realized, the routing of each sub-switch is kept independent, the error caused by the service logic is reduced, and the robustness of the service is improved.

Owner:紫光云技术有限公司

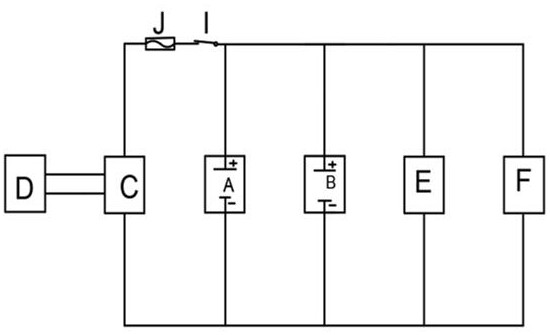

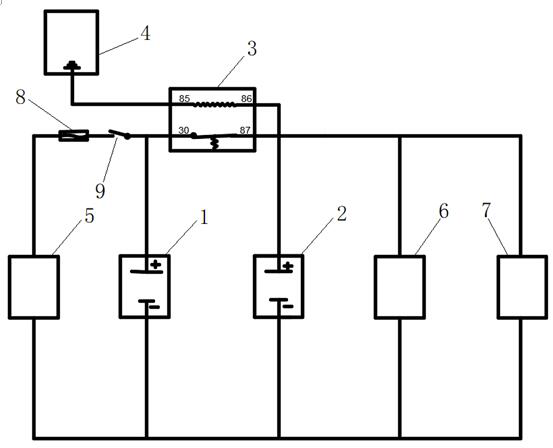

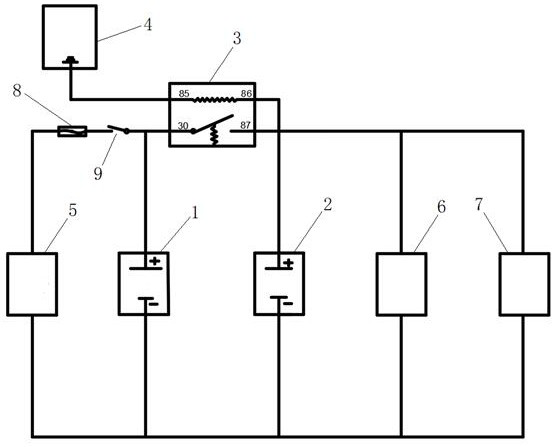

Dual-power isolation circuit, system and method for intelligent driving

PendingCN114552750ASimple structureClear logicElectric powerVehicular energy storageMotor homeControl signal

The invention discloses a dual-power isolation circuit, system and method for intelligent driving, a normally-closed relay is connected in series in a dual-power system circuit, and the opening and closing of the normally-closed relay are controlled under the opening and closing of an engine starting control signal so as to control the isolation of a main power supply and an auxiliary power supply. The circuit is simple in structure, clear in logic, few in related components, free of interference and influence of other components, convenient to maintain and capable of being modified in a short time. The relay is low in cost, can be widely applied to circuits with dual-power systems, such as the field of intelligent automobiles, large-scale equipment mounting and refitting markets, motor homes and the like, and can effectively reduce the cost. And the cost can be effectively controlled in the modification of the intelligent automobile. The circuit design has no space limitation, can be arranged together with an automobile circuit, can effectively isolate intelligent equipment, a main power supply and an automobile auxiliary power supply when the starter works, does not consume electric energy, improves the utilization rate of the electric energy, and has a stable safety characteristic.

Owner:CHONGQING CHANGAN AUTOMOBILE CO LTD

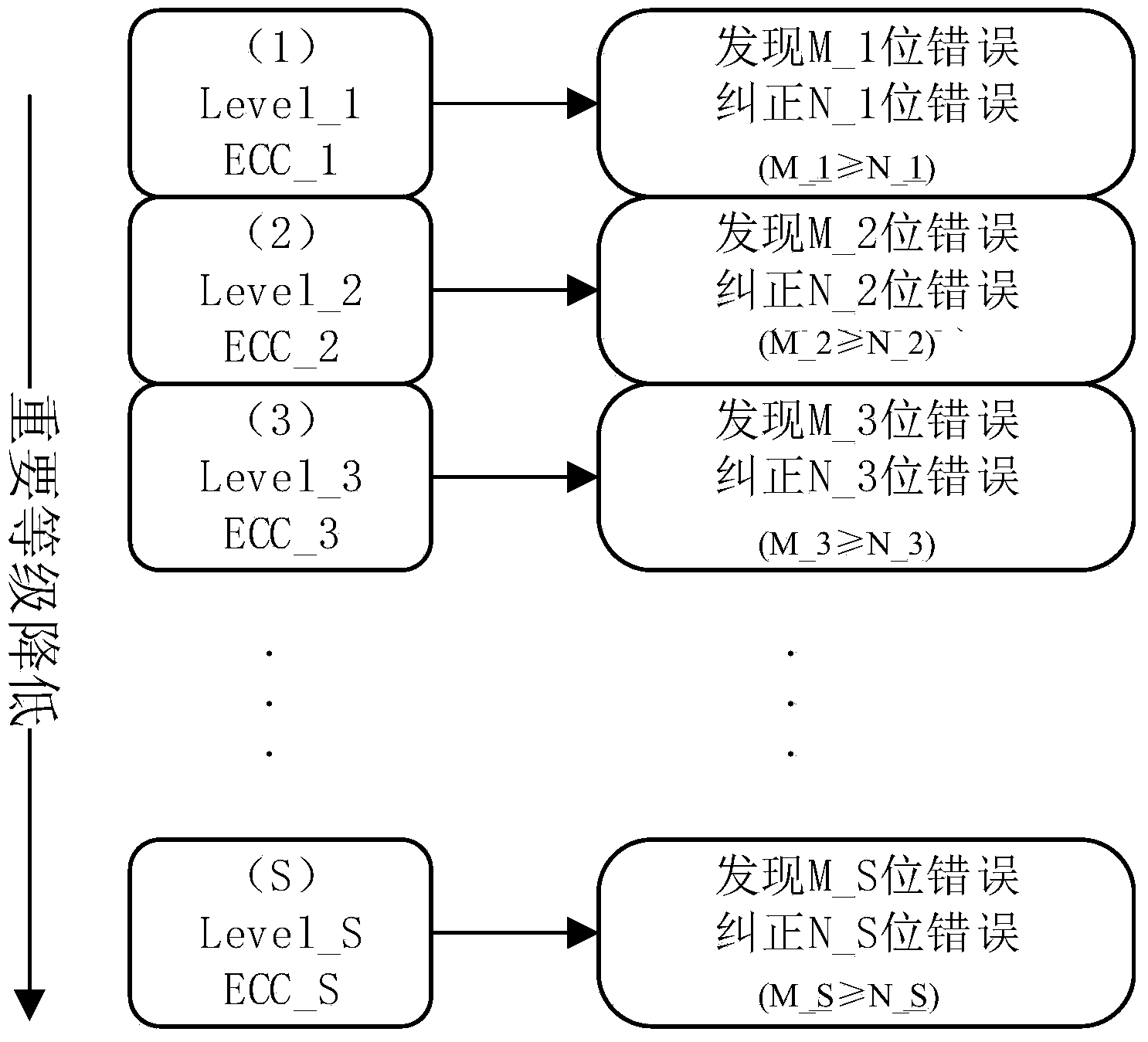

Method for selecting error correction circuit in memory

The invention provides a method for selecting an error correction circuit in a memory. ECC circuits with different performances are used for correcting data contents with different importance in the memory, so that the ECC circuits with the relatively high performances are used for correcting the data contents with the relatively high importance, and the ECC circuits with the relatively low performances are used for correcting the data contents with the relatively low importance, so as to avoid the power consumption waste caused by application of the same ECC circuits with the strong performances, and meanwhile, the logics of the ECC circuits, truly used at the any moment, are effectively reduced to reduce the soft error probability of the ECC circuit.

Owner:SHANGHAI XINCHU INTEGRATED CIRCUIT

Advanced clock distribution mechanism for circuit emulation applications

ActiveUS7929574B2Reduce the amount requiredTight synchronizationDigital data processing detailsTime-division multiplexMultiplexerNetwork packet

A clock distribution mechanism for circuit emulation applications, and related method, including one or more of the following: a plurality of digitally controlled oscillators, each of the plurality of digitally controlled oscillators receiving one or more Ethernet packets and generating a recovered clock from the one or more Ethernet packets; a multiplexer for receiving the recovered clocks generated by the plurality of digitally controlled oscillators, selecting a one of the recovered clocks generated by the plurality of digitally controlled oscillators, and outputting the selected one of the recovered clocks; a normalizer that receives a frequency of the selected one of the recovered clocks and generates a normalized frequency output based on the received frequency of the selected one of the recovered clocks and outputs the normalized frequency output; a clock source selector for receiving a plurality of input clock sources, one of the input clock sources being the normalized frequency output of the normalizer, the clock source selector selecting the normalized frequency output from among the plurality of input clock sources and transmitting the selected normalized frequency to a node; and one or more nodes for receiving the selected normalized frequency.

Owner:META PLATFORMS INC

A kind of multi-stage serial-to-parallel conversion circuit

ActiveCN105591645BReduce logicIncrease the maximum speedLogic circuits coupling/interface using field-effect transistorsThree stageEngineering

The invention discloses a multistage serial-parallel conversion circuit, which is characterized by comprising at least three stages of D trigger groups. The first stage of D trigger groups comprises n cascaded D triggers with the same first clock signals; the second stage of D trigger groups comprises n*m cascaded D triggers with the same second clock signals; the third stage of D trigger groups comprises n*m cascaded D triggers with the same third clock signals; in the first stage of D trigger groups, the output end of the ath D trigger is connected with the input end of the ath D trigger in the second stage of D trigger groups; the output end of the ((m-1)*n+a)th D trigger in the second stage of D trigger groups is connected with the input end of the (m*n+a)th D trigger in the second stage of D trigger groups and is also connected with the input end of the ((m-1)*n+a)th D trigger in the third stage of D trigger groups; and n, m and a are all natural numbers, and a< / =n.

Owner:CAPITAL MICROELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com