Method for selecting error correction circuit in memory

An error correction circuit and memory technology, applied in static memory, instruments, etc., can solve the problems of increasing ECC logic circuit area soft errors, wasting power consumption, etc., achieve logic reduction, avoid power consumption waste, and reduce soft errors The effect of chance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

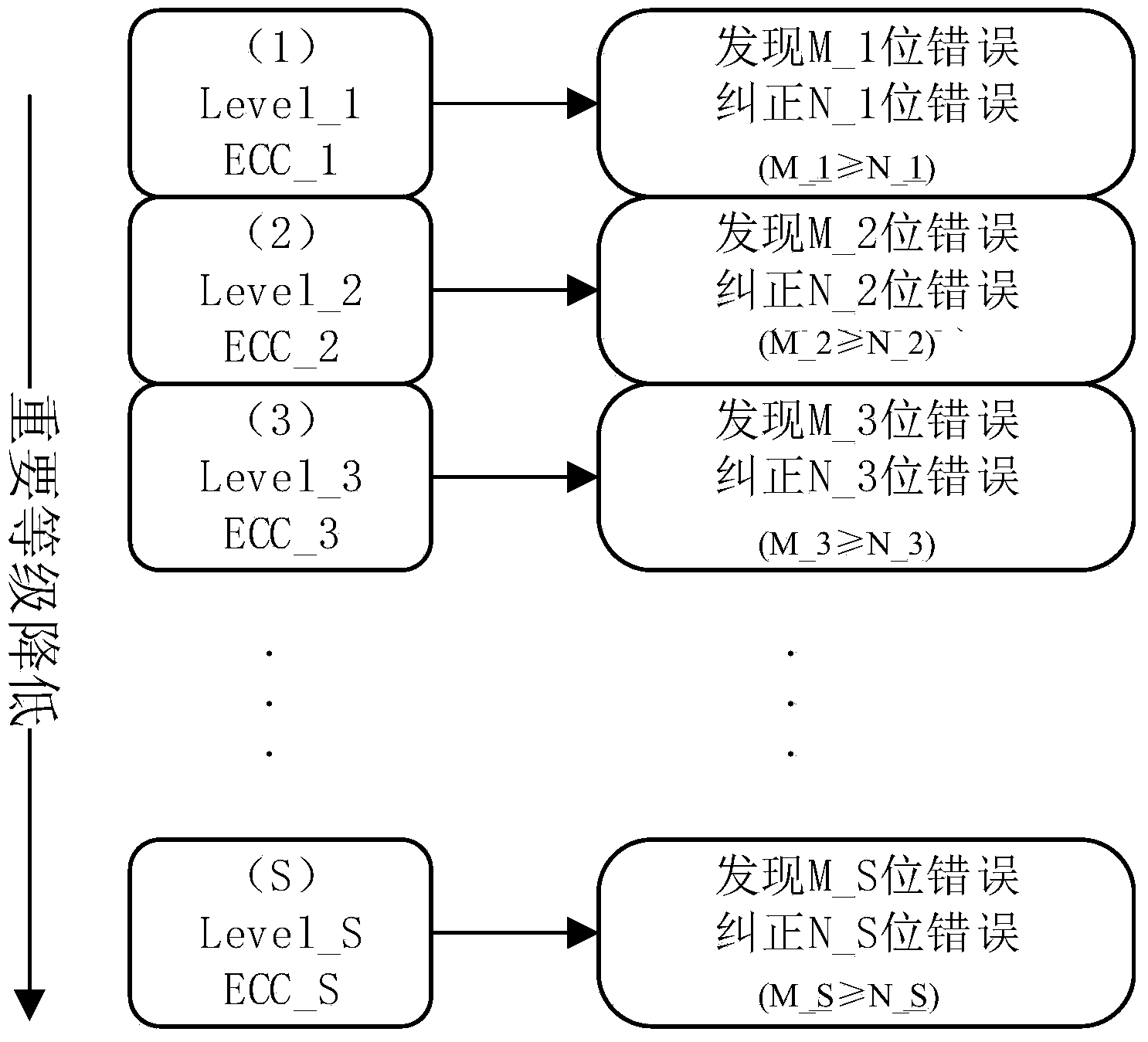

[0029] The invention proposes a method for selecting an error correction circuit in a memory, mainly by dividing the data content in the memory into several parts, and using different error correction circuits for different parts to correct errors, so as to optimize the power consumption of the memory and appropriately reduce The size of the effective error correction circuitry in memory.

[0030] The method of the present invention mainly includes: step S1: providing a memory containing a plurality of error correction circuits with different performances; step S2: dividing the stored content in the memory into several grades according to the importance; All error correction circuits and levels are paired in such a way that higher error correction circuits protect more important content.

[0031] A method for selecting an error correction circuit in a memory proposed by the present invention will be described in detail below in conjunction with the accompanying drawings and sp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com