A kind of multi-stage serial-to-parallel conversion circuit

A technology for converting circuits and circuits, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc. problem, to achieve the effect of reducing logic, reducing the number of flip-flops, and increasing the maximum speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The technical solutions of the present invention will be further described in detail below through the accompanying drawings and embodiments.

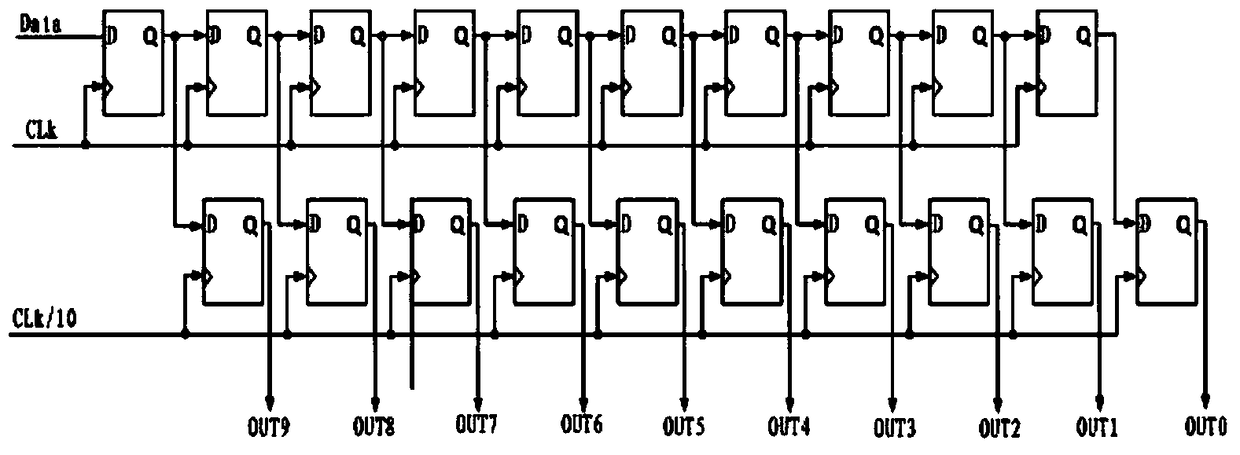

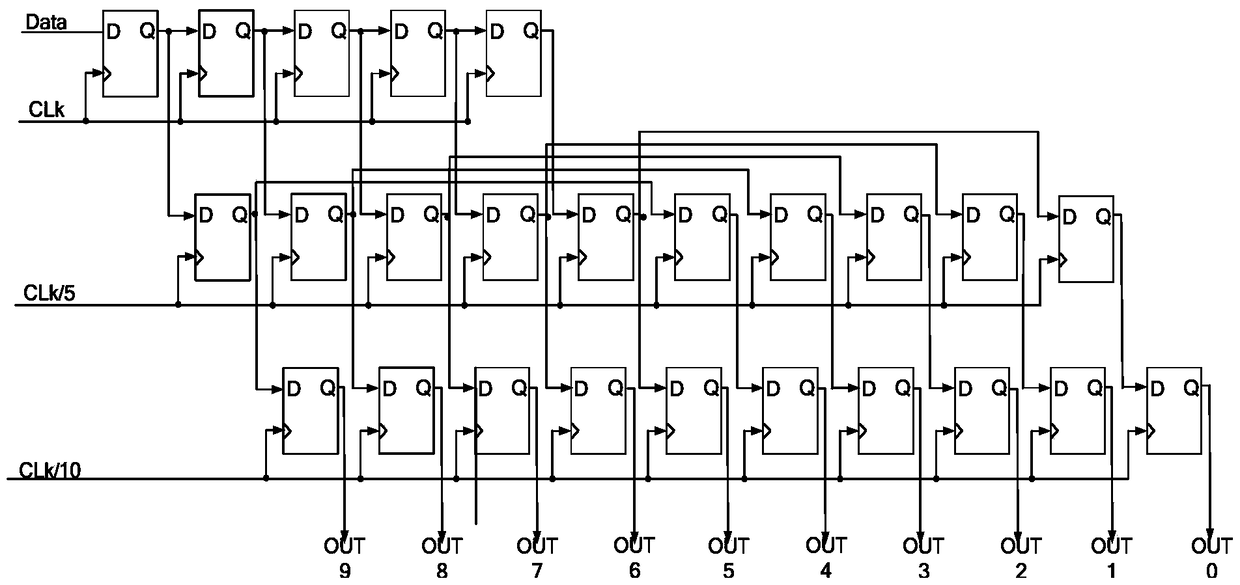

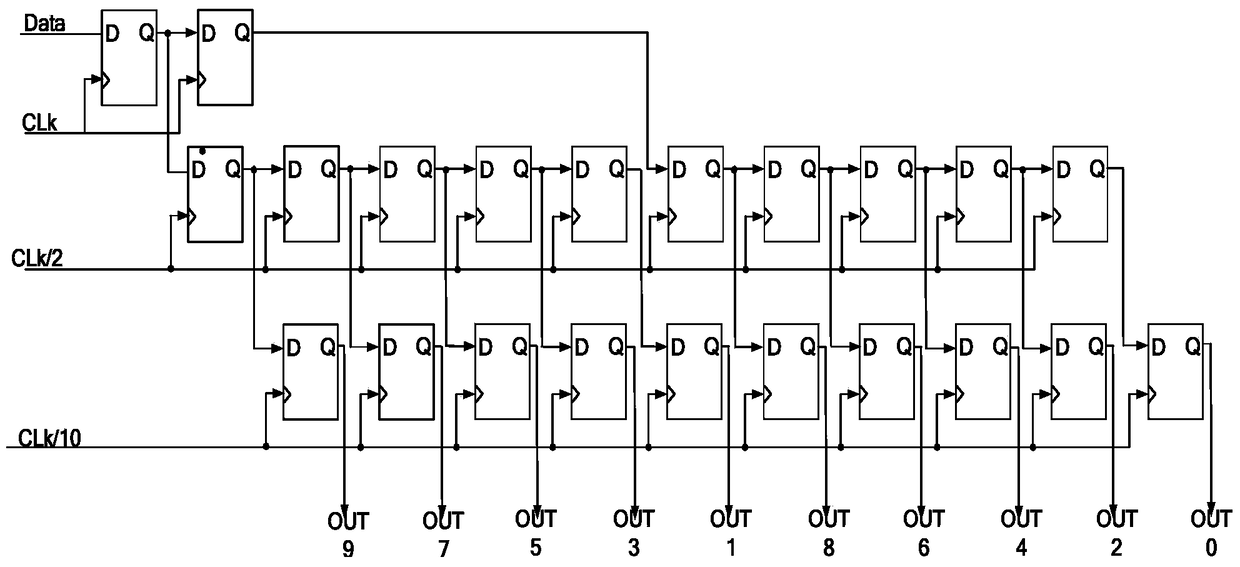

[0035] figure 2 This is a circuit diagram of a multi-stage serial-to-parallel converter in Embodiment 1 of the present invention, and the multi-stage serial-to-parallel converter circuit can be applied to a serializer / paralleler interface.

[0036] Such as figure 2 As shown, the circuit of the multi-stage serial-parallel converter includes: at least three-stage D flip-flop groups;

[0037] The first-level D flip-flop group includes n cascaded D flip-flops (5 cascaded D flip-flops are taken as an example for illustration in this embodiment, that is, n=5), and n cascaded D flip-flops Have the same first clock signal CLK 1 , When the first clock signal CLK 1 When it arrives, all D flip-flops in the first-level D flip-flop group are triggered; the second-level D flip-flop group includes n×m cascaded D flip-flops (in this embodiment, 10 c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com