VLSI system structure of JPEG image decoder and realization method thereof

A technology for system implementation and implementation method, which is applied in image communication, television, electrical components, etc., can solve problems such as chip area expansion and chip cost increase, and achieve the effect of reducing chip area, reducing chip cost, and speeding up processing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

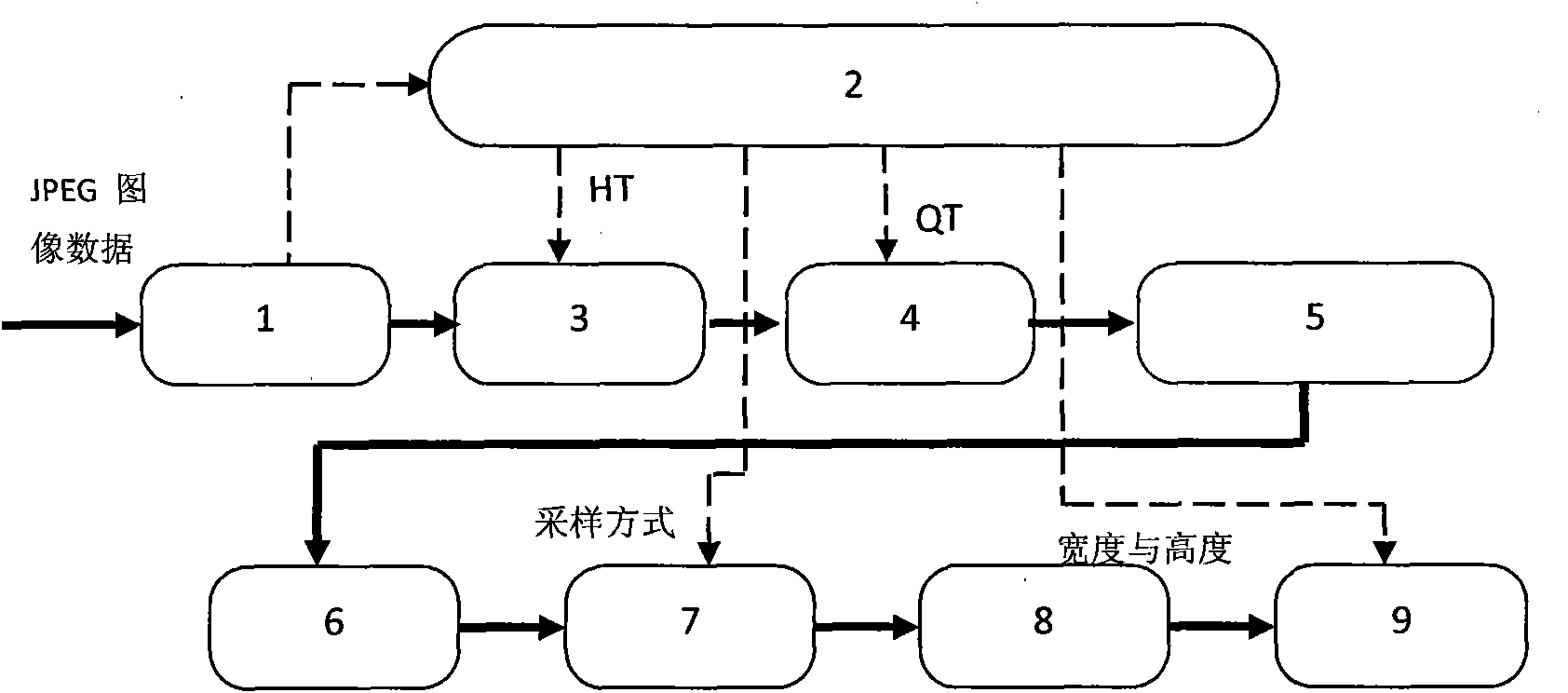

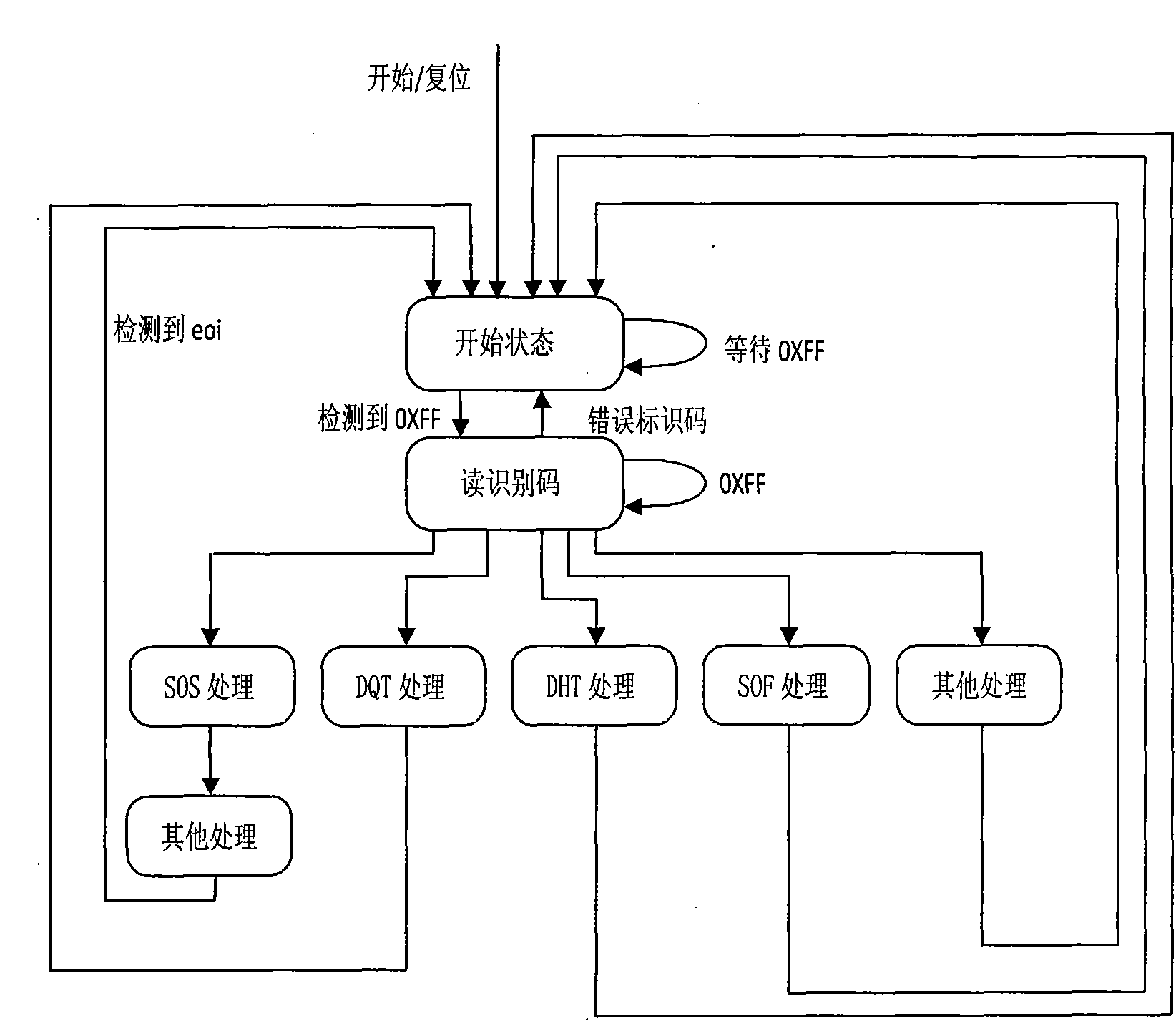

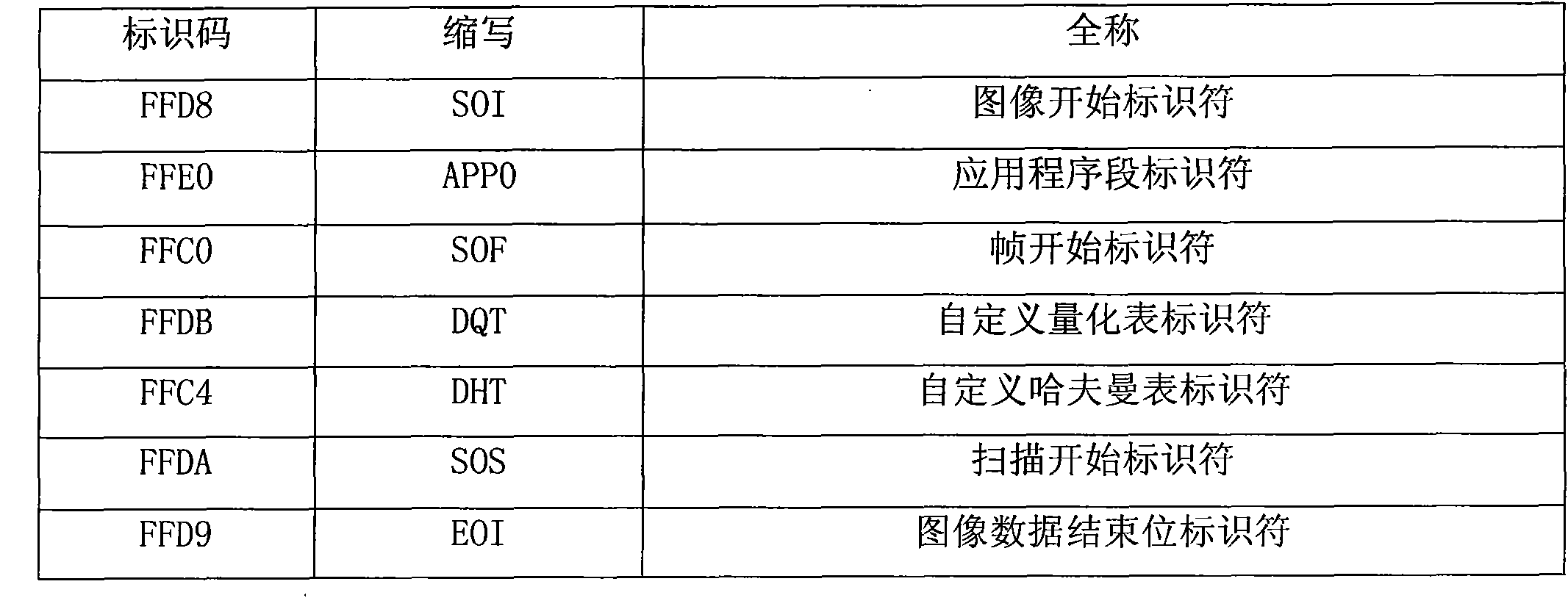

[0037] combine first figure 1 The overall process of this embodiment is briefly described. figure 1 Among them, HT represents the huffman table, and QT represents the quantization table. The 8-bit data stream input from the outside first enters the input FIFO module 1, and then the header stream analysis module 2 analyzes the output data of the input FIFO module 1 according to the JFIF file format. In this process, the transition diagram of the state machine used is as follows figure 2 shown. The header stream of a JPEG file in JFIF format is divided into segments to store (but not all of them are segments), and each segment has a two-byte long identifier at the beginning. The first byte of each identifier is hexadecimal 0xFF. The second byte corresponds to its own value according to the data in the current segment. First of all, the state machin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com