Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

47results about "Resist coating" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Patterning process

ActiveUS20090081595A1Increase contrastFunction increaseResist coatingPhotosensitive materialsSolubilityResist

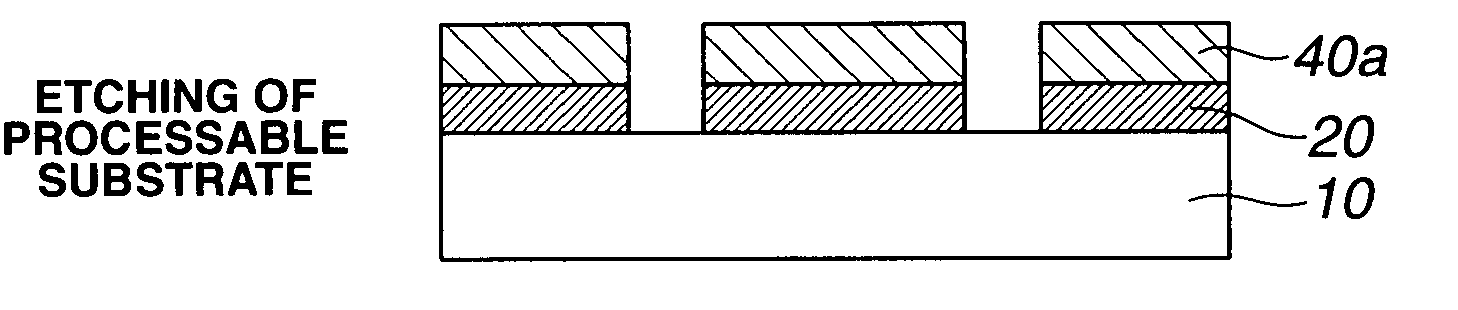

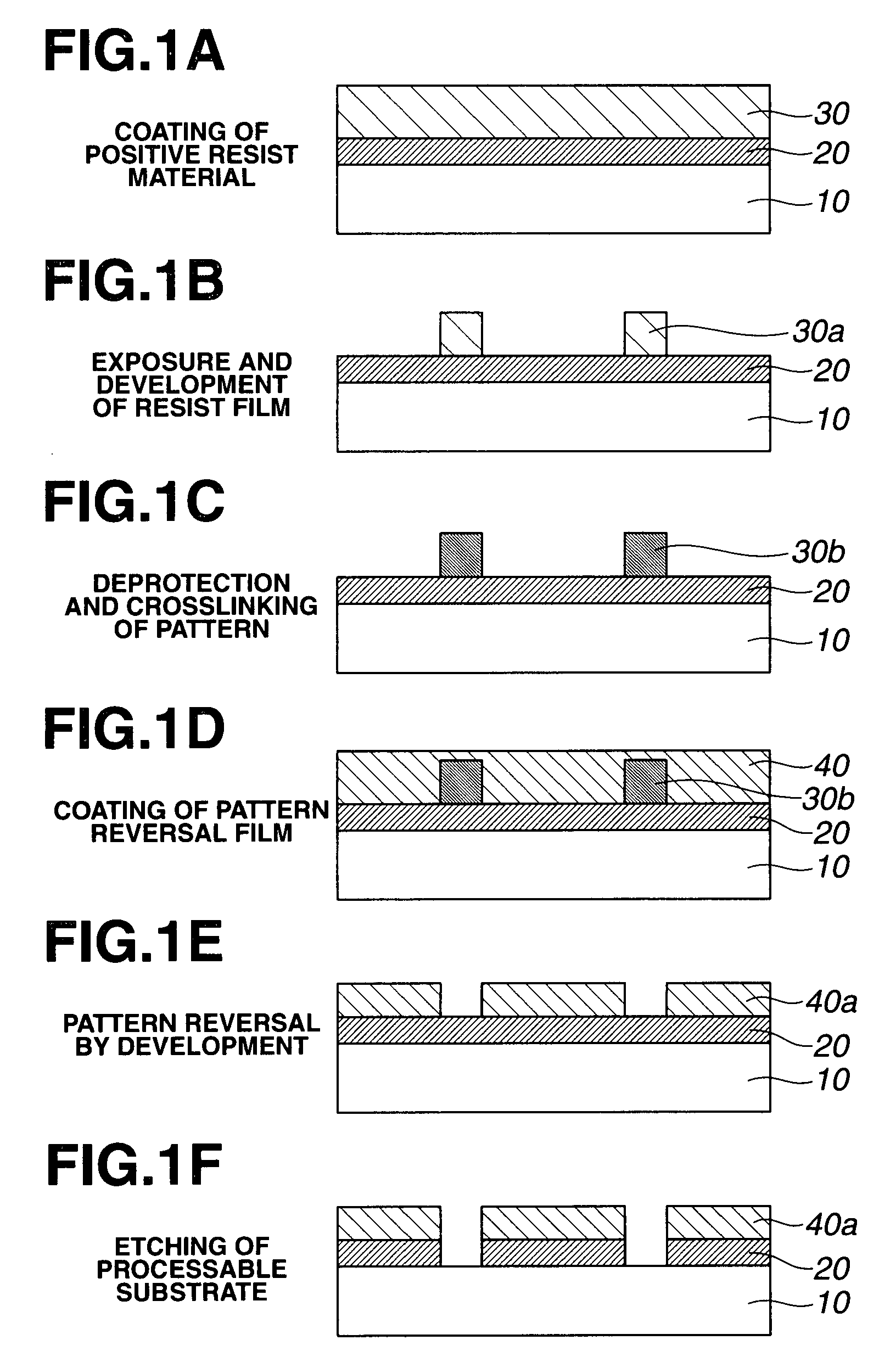

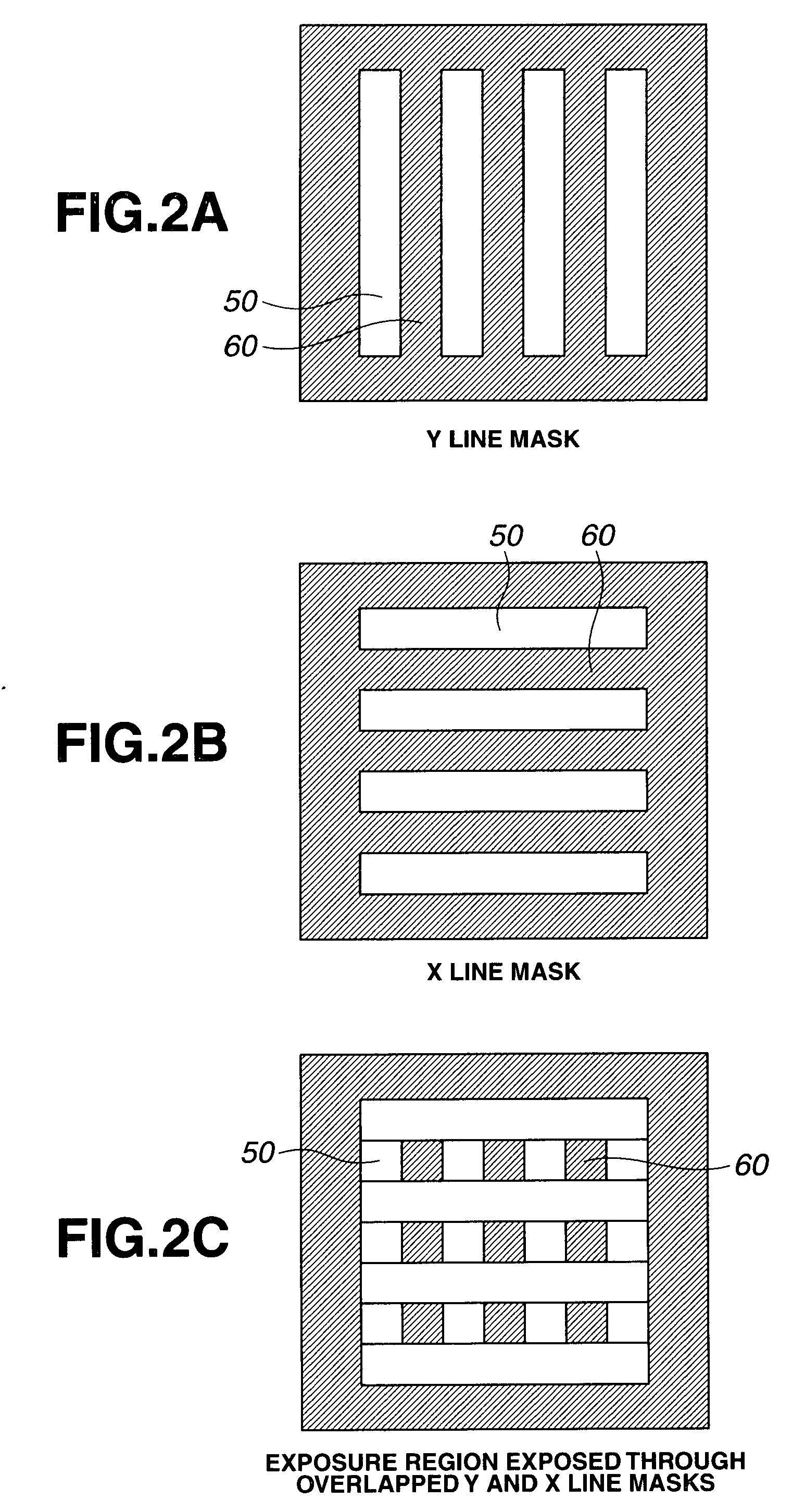

A pattern is formed through positive / negative reversal by coating a chemically amplified positive resist composition comprising an acid labile group-bearing resin, a photoacid generator, and an organic solvent onto a substrate, prebaking the resist composition, exposing the resist film to high-energy radiation, post-exposure heating, and developing the exposed resist film with an alkaline developer to form a positive pattern; irradiating or heating the positive pattern to facilitate elimination of acid labile groups and crosslinking for improving alkali solubility and imparting solvent resistance; coating a reversal film-forming composition thereon to form a reversal film; and applying an alkaline wet etchant thereto for dissolving away the positive pattern.

Owner:SHIN ETSU CHEM IND CO LTD

Fabricating method for printed circuit board

InactiveUS20080052905A1No peelingFabrication can be reducedPrinted circuit assemblingResist coatingFine lineProduction rate

A method of fabricating a printed circuit board is disclosed. A method of fabricating a printed circuit board that includes: stacking an insulation layer on at least one surface of a core layer, on which an inner circuit is formed, and forming an outer circuit pattern; burying the outer circuit pattern in the insulation layer; removing the outer circuit pattern to form minute grooves and curing the insulation layer; and forming an outer circuit by filling metal in the minute grooves, makes it possible to readily form high-resolution fine-line circuits, as well as to reduce fabrication costs and increase productivity.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

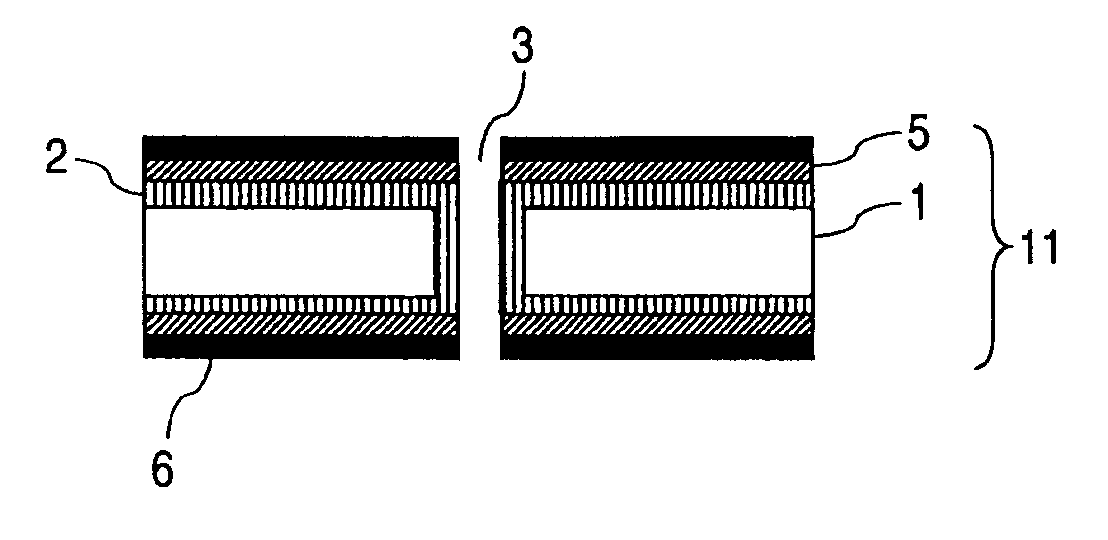

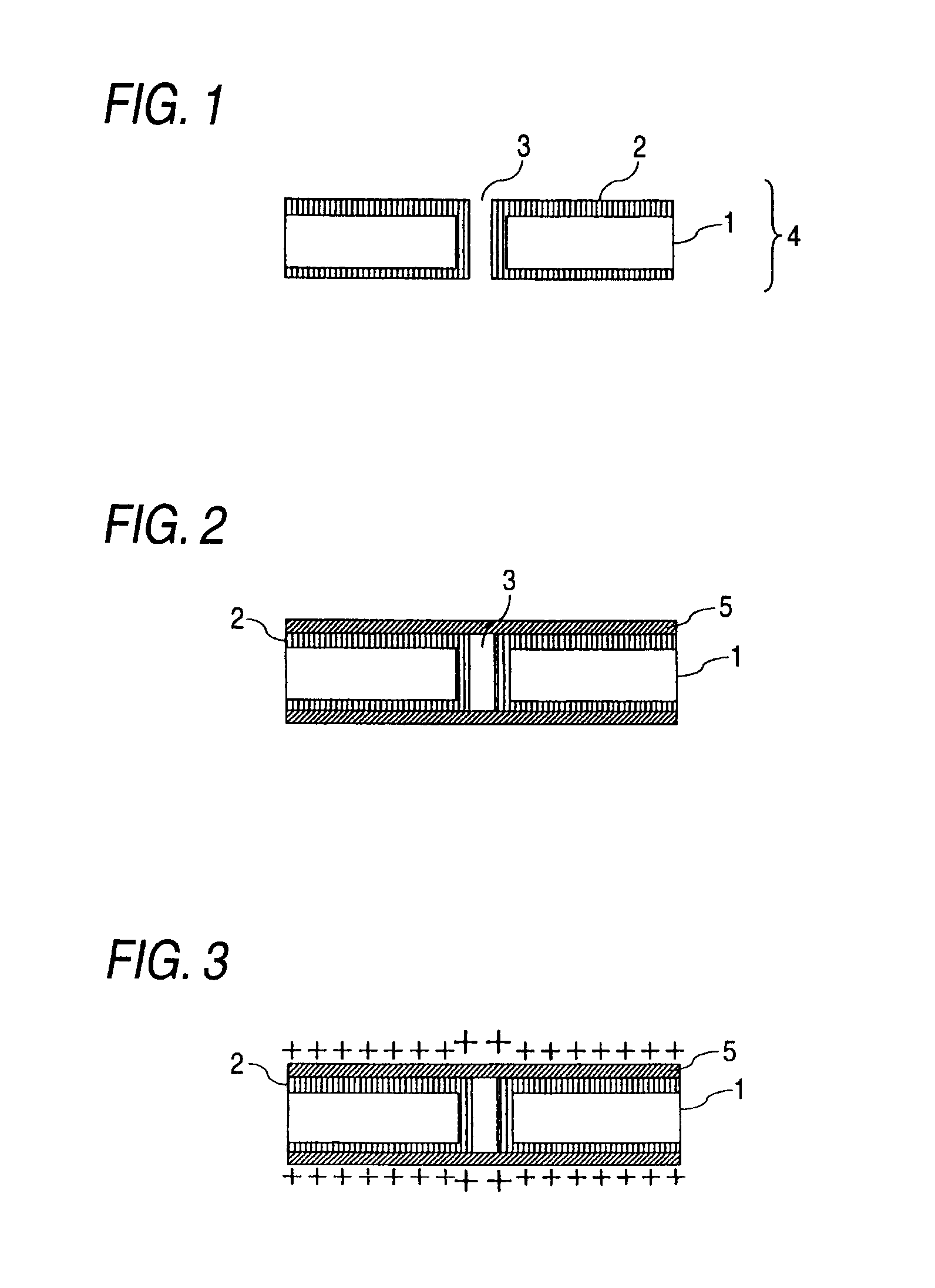

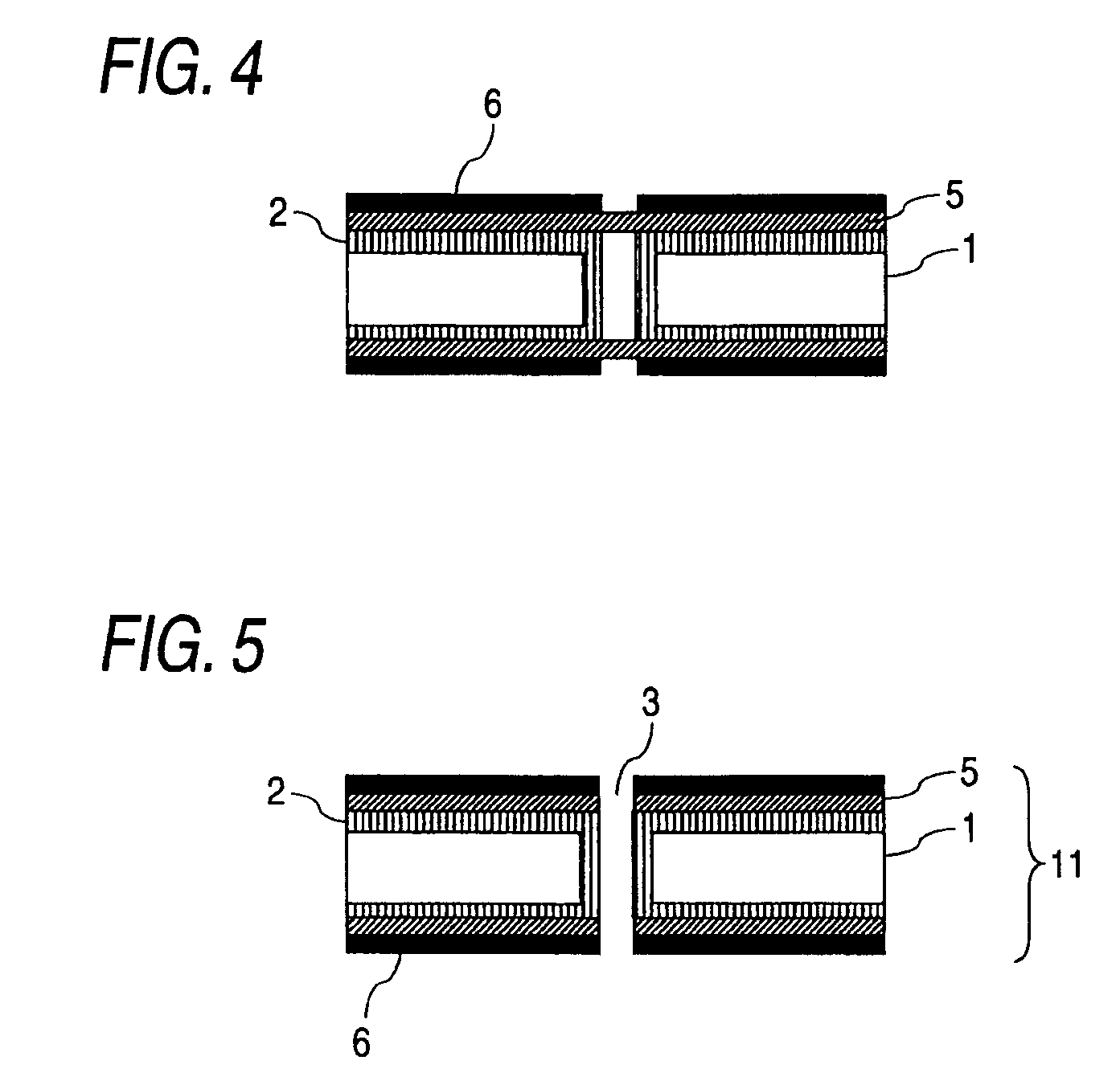

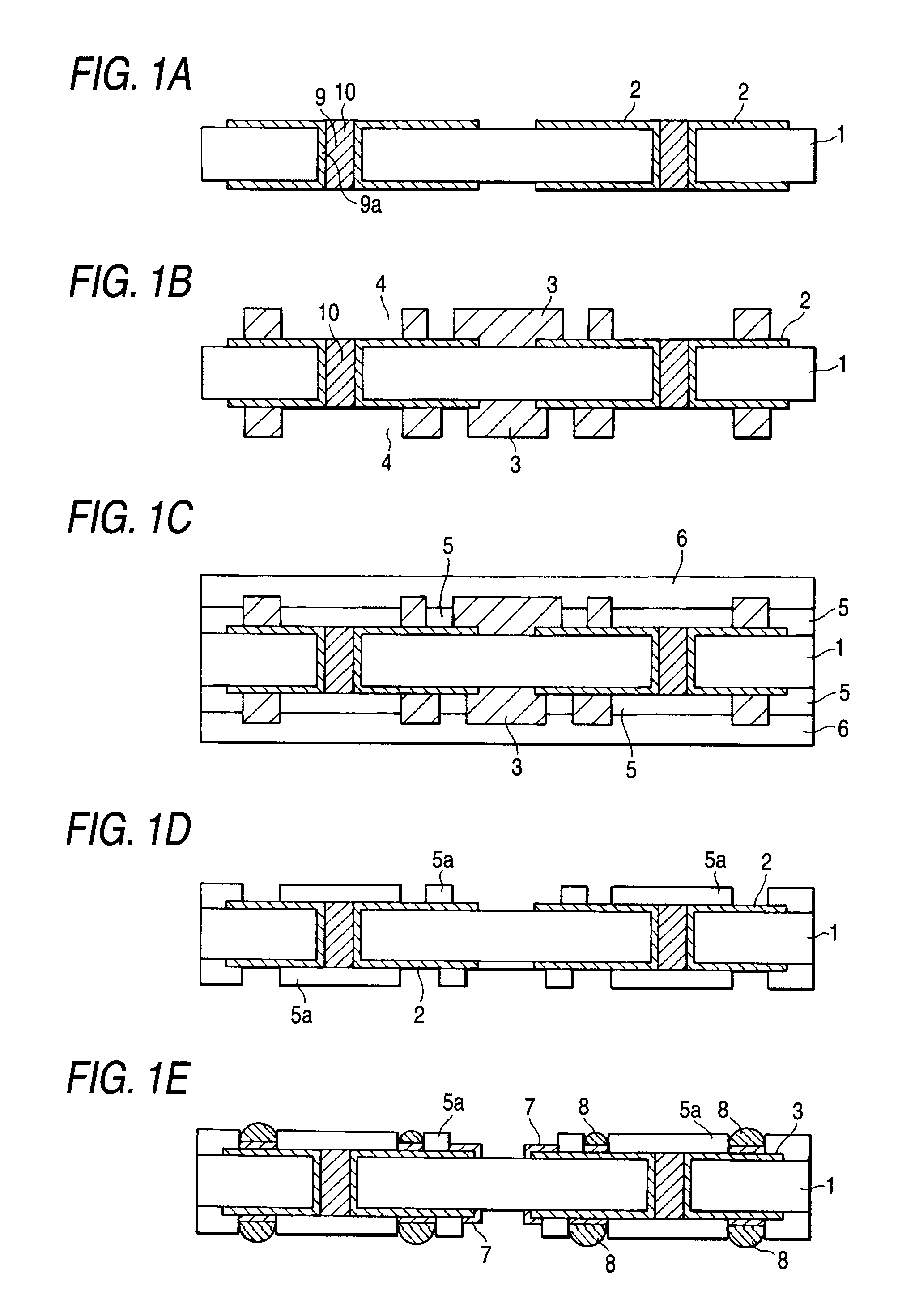

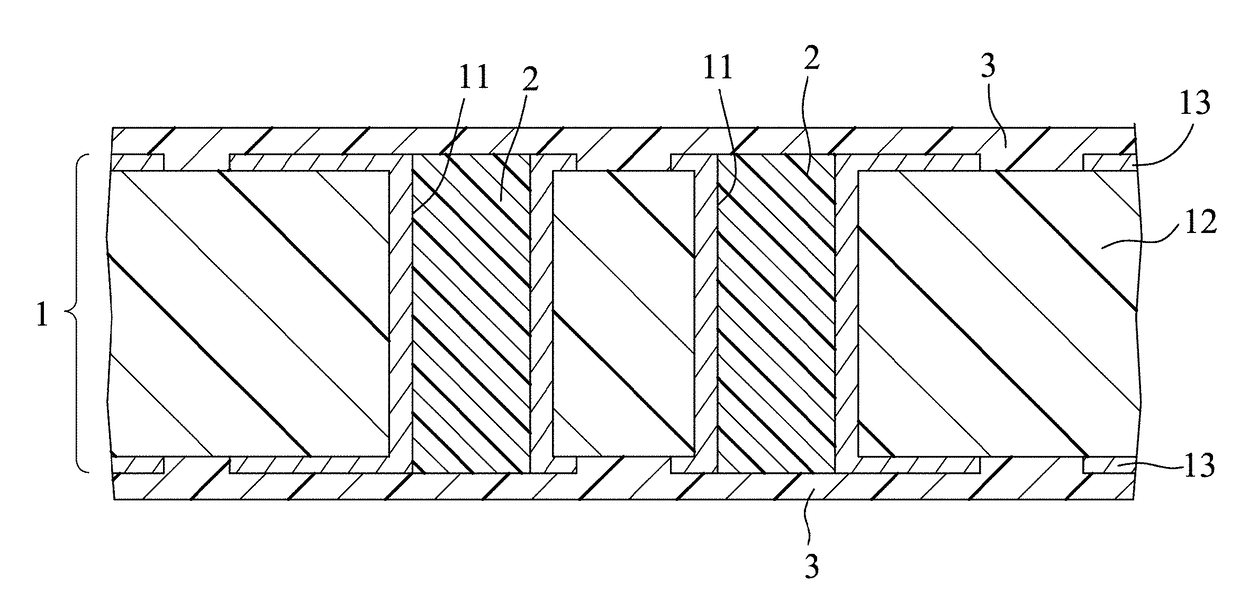

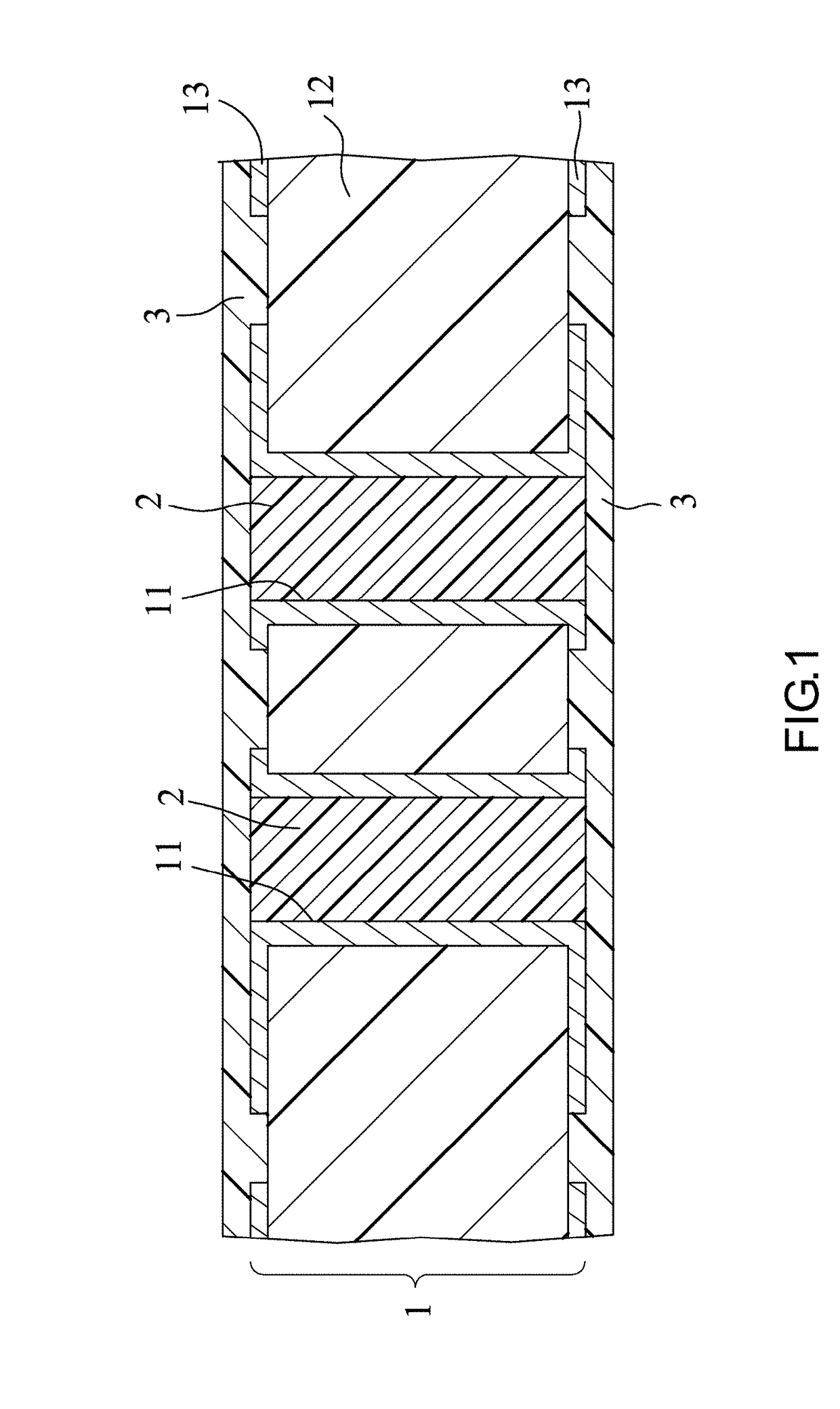

Circuit board manufacturing method and circuit board

InactiveUS20070181994A1Easy to manufactureSemiconductor/solid-state device detailsSolid-state devicesResistPotential difference

As means for solving a problem of a positional shift of a land and a hole which is caused by an alignment in the formation of an etching resist layer and a plated resist layer in a method of manufacturing a circuit board, there are provided a method of manufacturing a circuit board including the steps of forming a first resin layer on a surface of an insulating substrate having a conductive layer on the surface and an internal wall of a through hole or / and a non-through hole, forming a second resin layer which is insoluble or slightly soluble in a developing solution for the first resin layer on the first resin layer provided on the surface conductive layer, and removing the first resin layer provided over the hole with the developing solution for the first resin layer, and a method of manufacturing a circuit board including the step of uniformly charging a surface of the first resin layer to induce a potential difference to the first resin layer provided over the hole and the first resin layer provided on the surface conductive layer before forming the second resin layer. Moreover, there is provided a circuit board having a hole with a small positional shift and high precision.

Owner:SHINKO ELECTRIC IND CO LTD +1

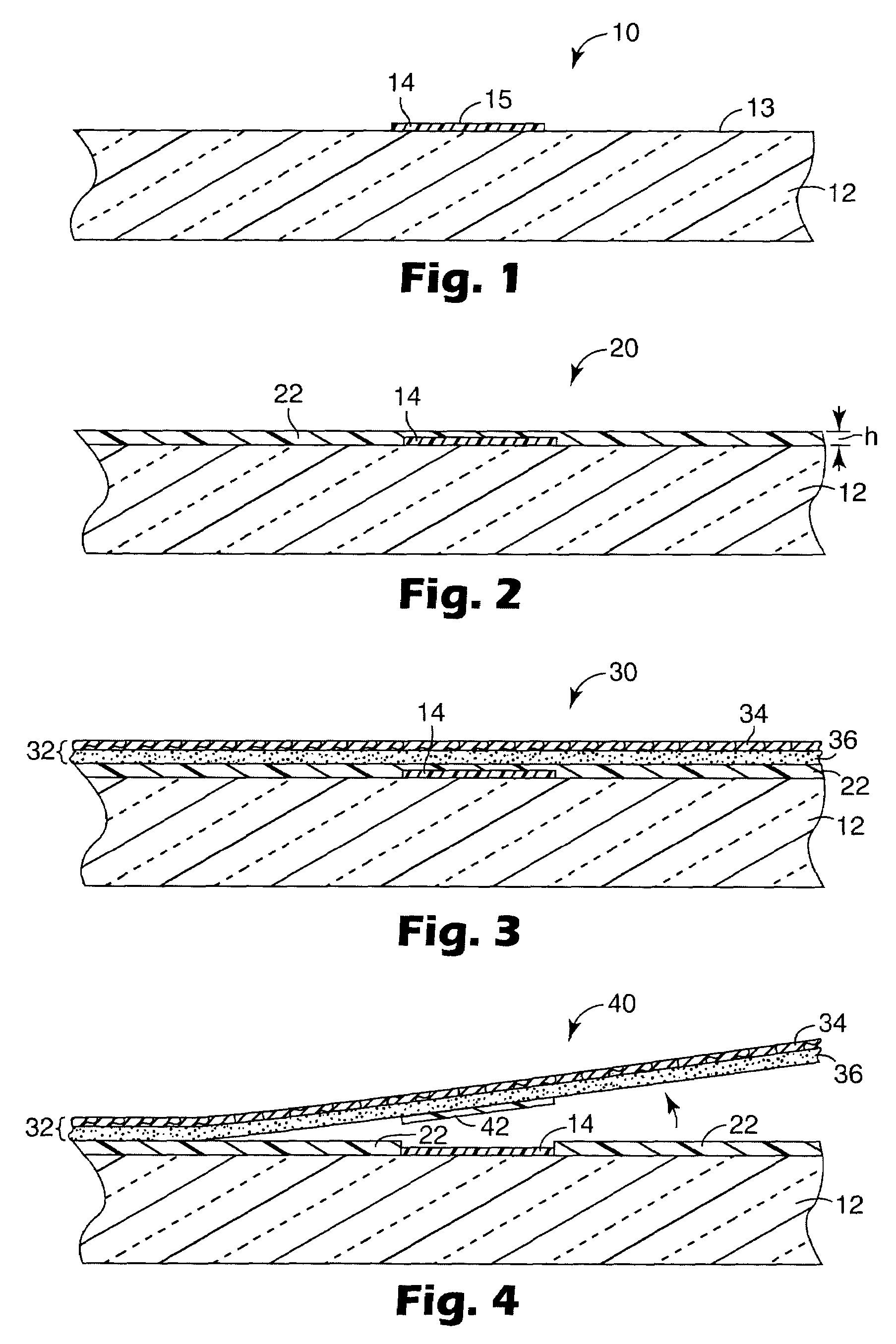

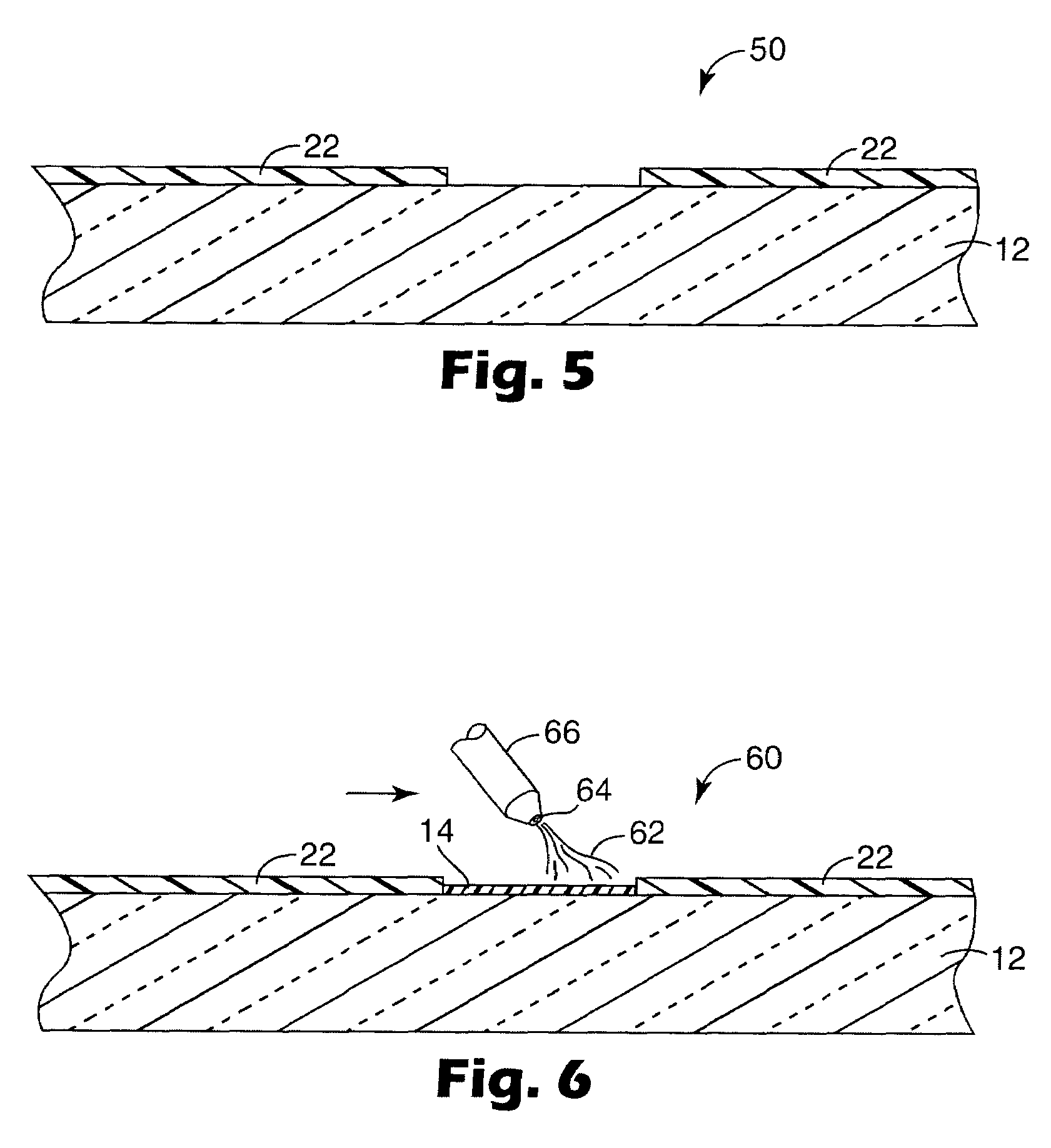

Patterned coating method employing polymeric coatings

Patterned articles can be prepared by applying a release polymer to a substrate in a desired pattern, applying a substrate-adherent polymer over the pattern and substrate, and mechanically removing the substrate-adherent polymer from the pattern without requiring solvent. Suitable mechanical removal methods include applying adhesive tape to the substrate-adherent polymer and peeling the tape and substrate-adherent polymer away from the pattern, and abrading the substrate-adherent polymer from the pattern using impact media.

Owner:3M INNOVATIVE PROPERTIES CO

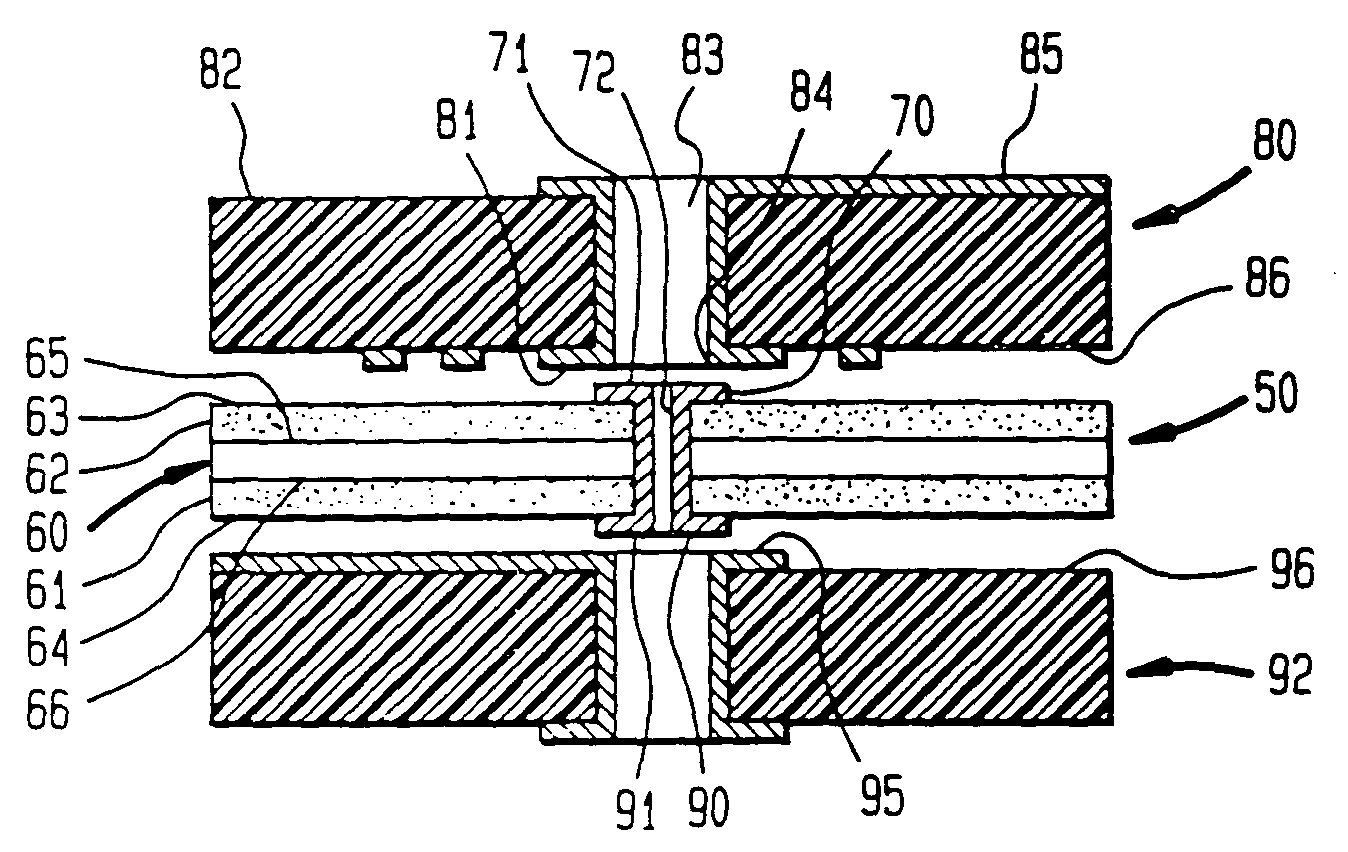

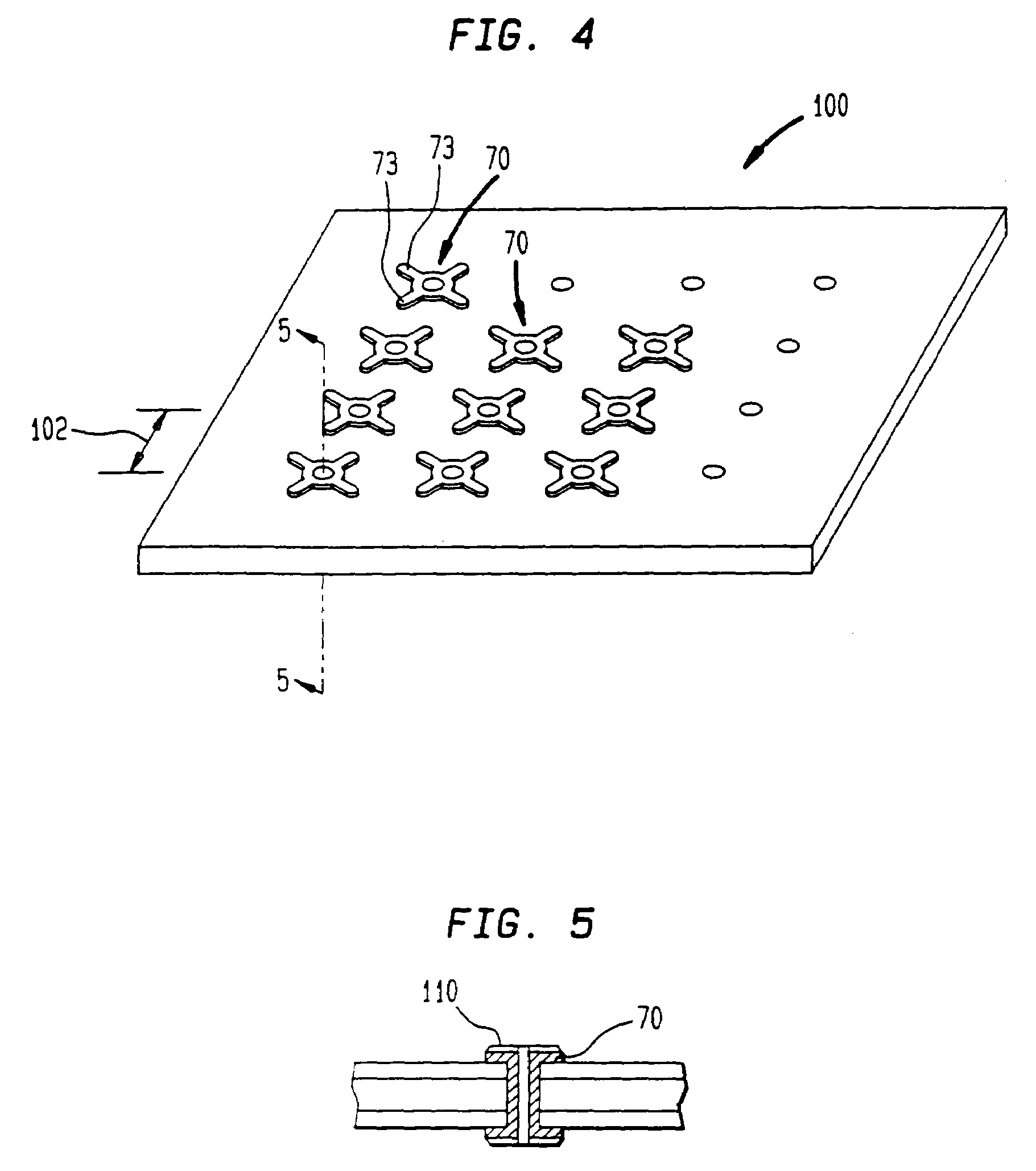

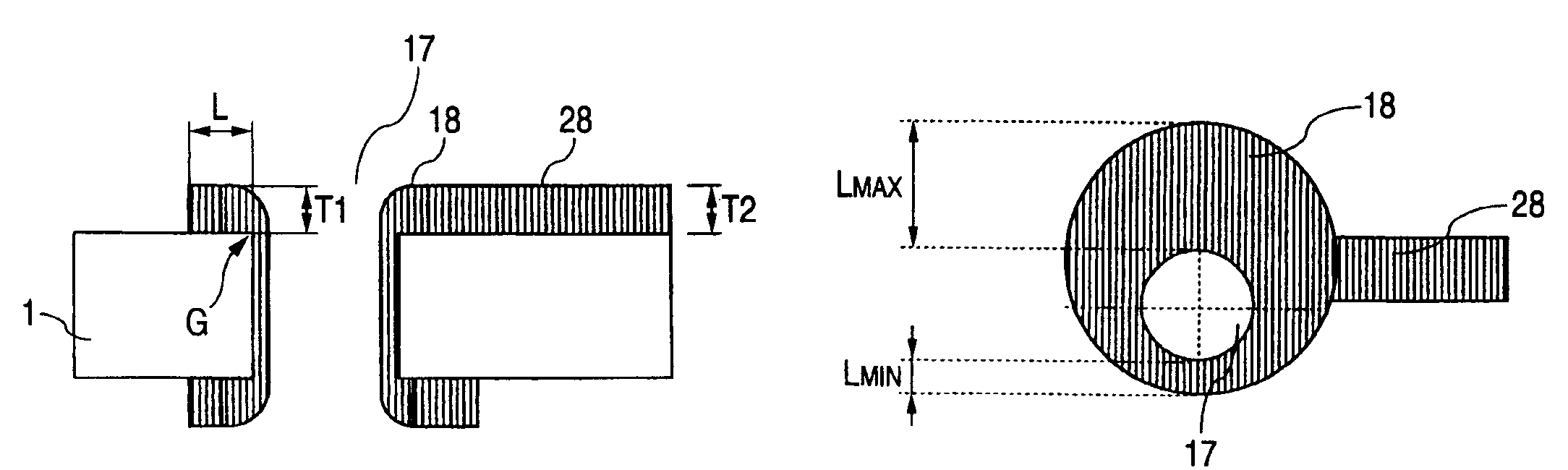

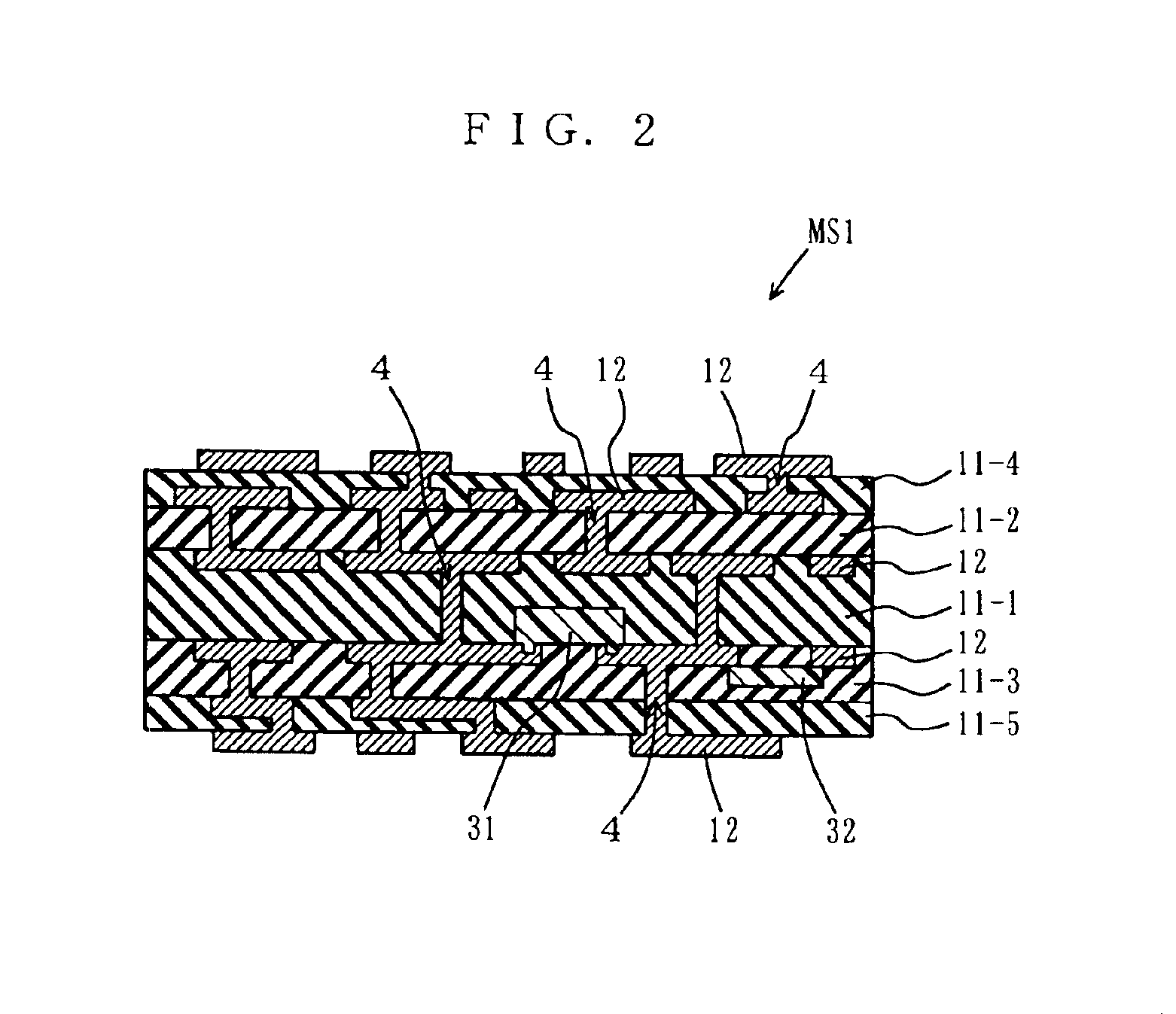

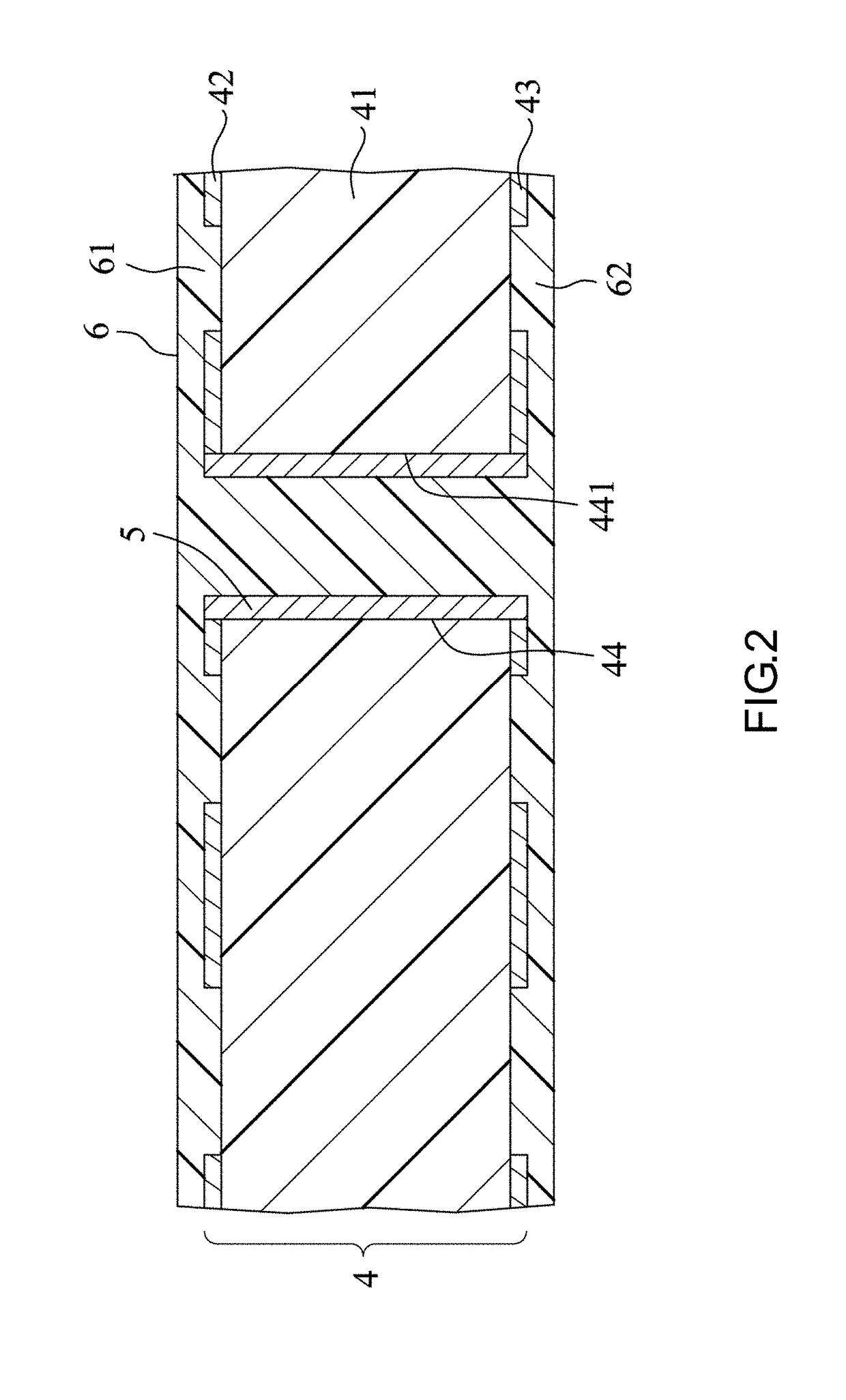

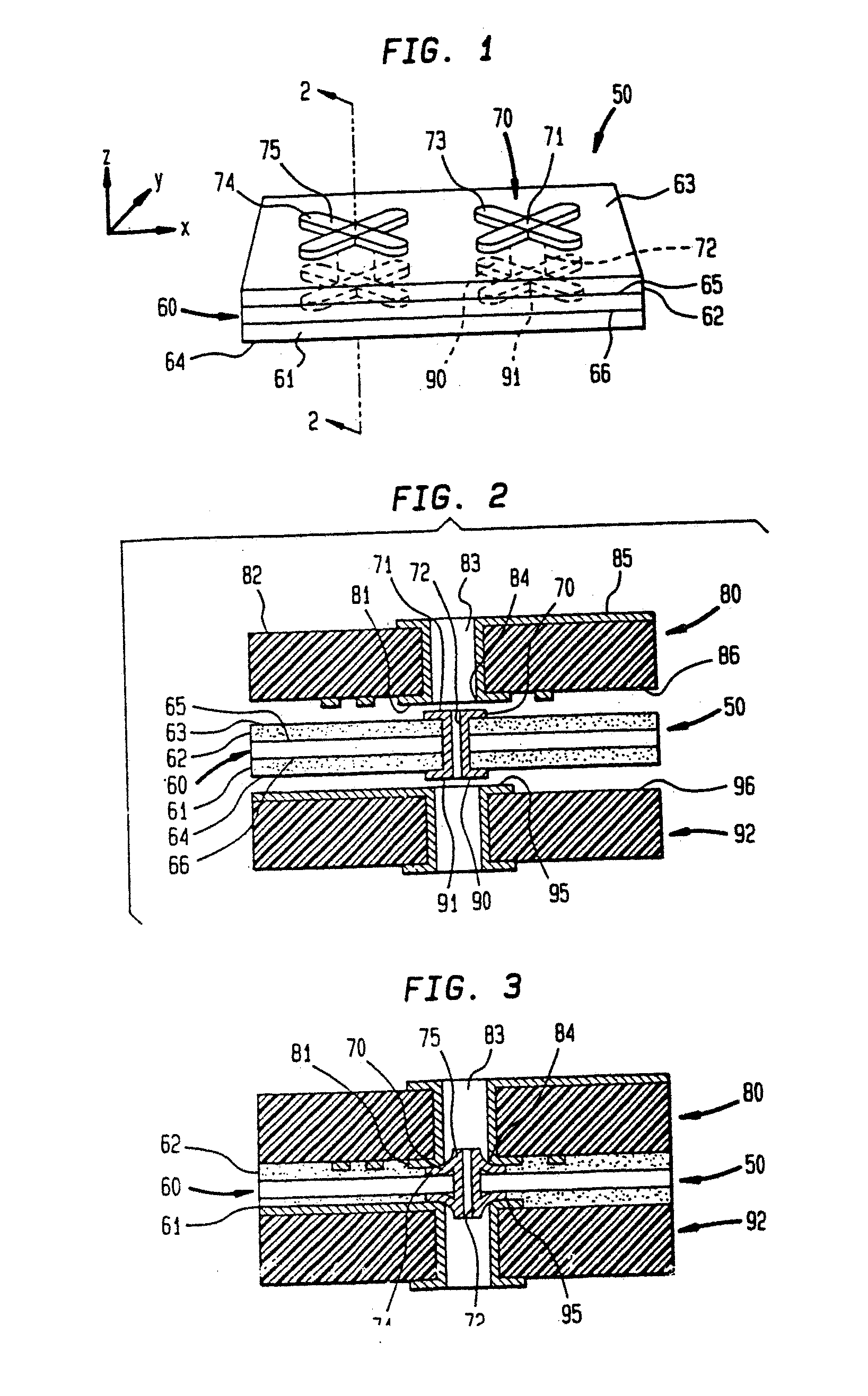

Method for making a microelectronic interposer

InactiveUS6978538B2Easy vertical movementEffective and low resistance electrical connectionSemiconductor/solid-state device detailsSolid-state devicesInterposerStructural material

A microelectronic interposer is made by providing a sacrificial layer over the surface of a planar body. Apertures are formed passing through the body and the sacrificial layer. A layer of an electrically conductive structural material is deposited in each of the apertures and over the sacrificial layer, proximate to each aperture to thereby form contacts. The sacrificial layer is removed leaving the contacts with outwardly flaring peripheral portions spaced vertically above the surface of the planar body.

Owner:TESSERA INC

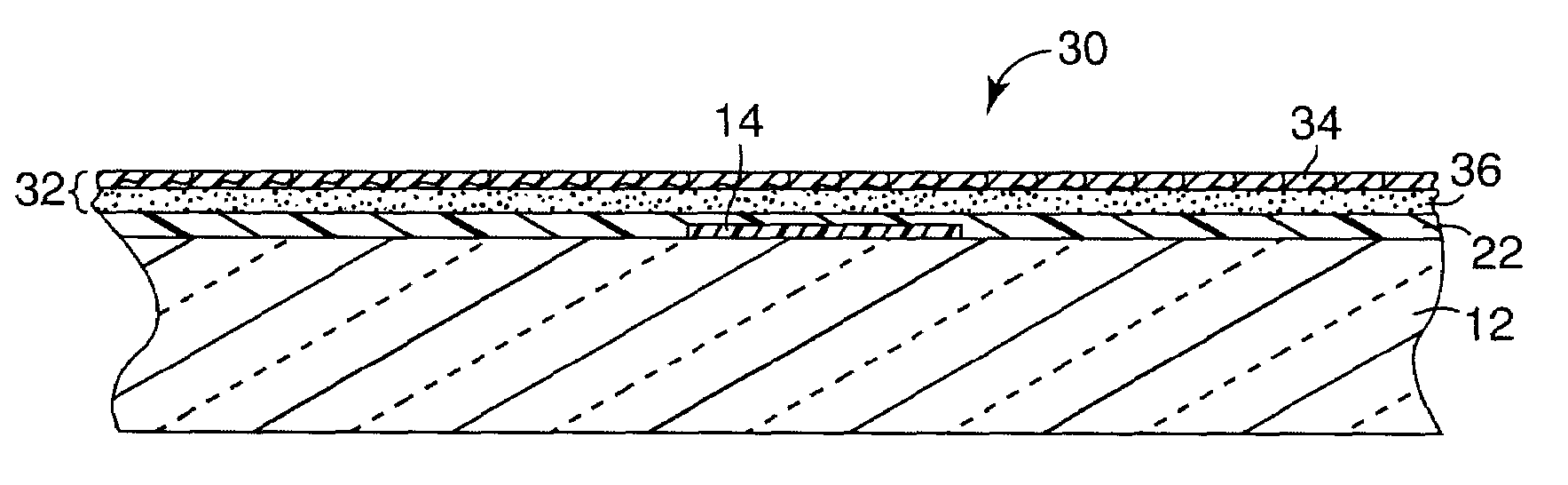

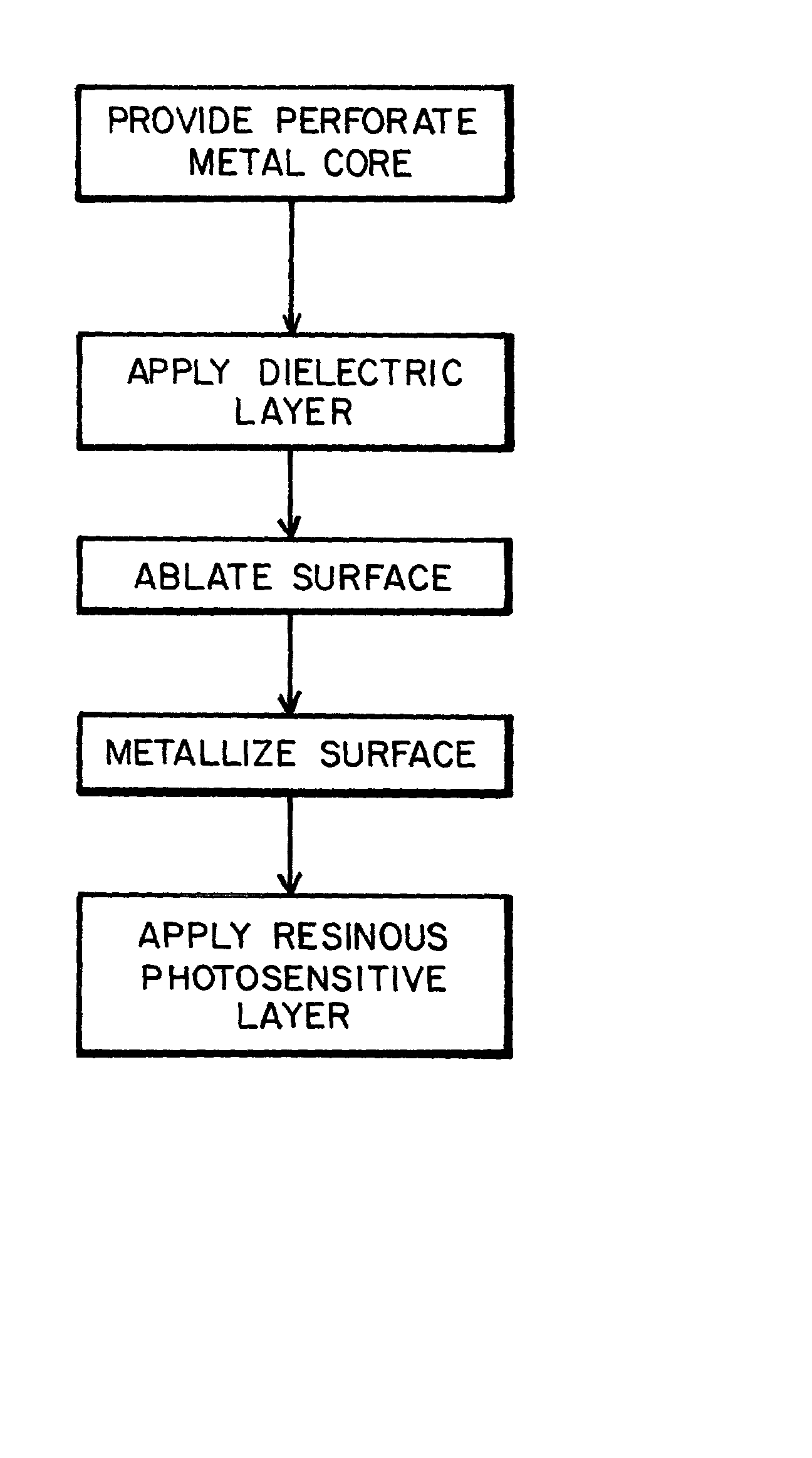

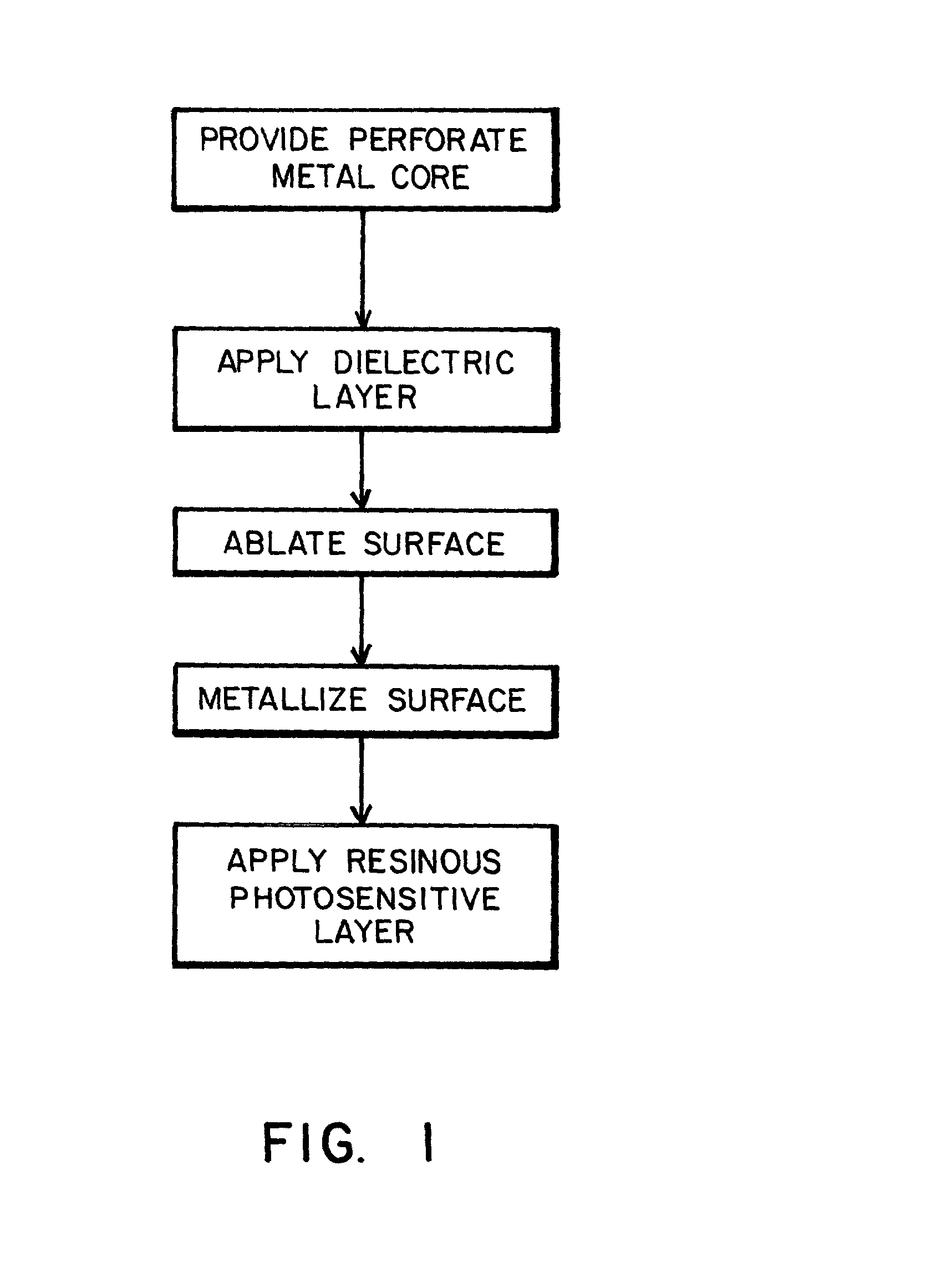

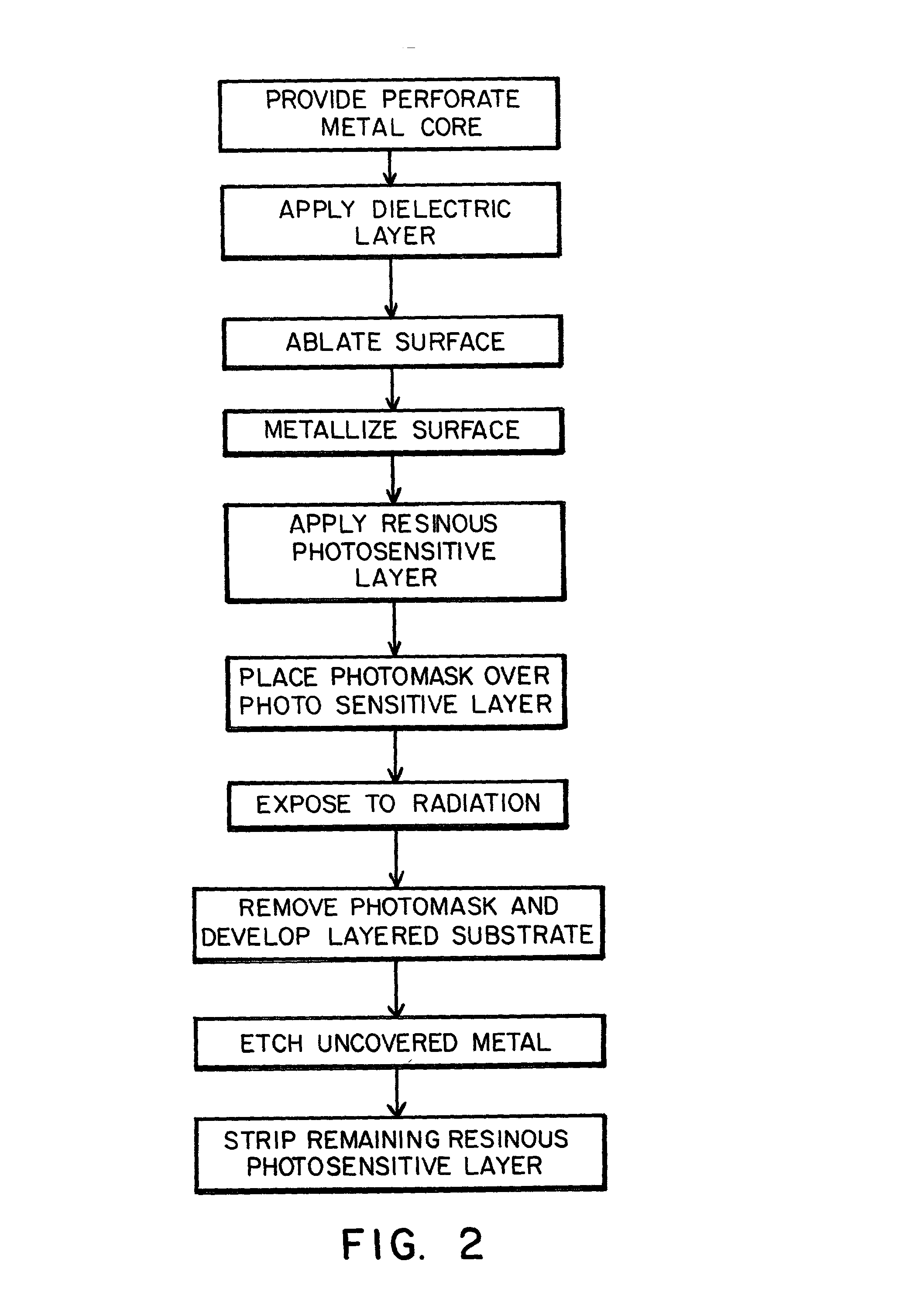

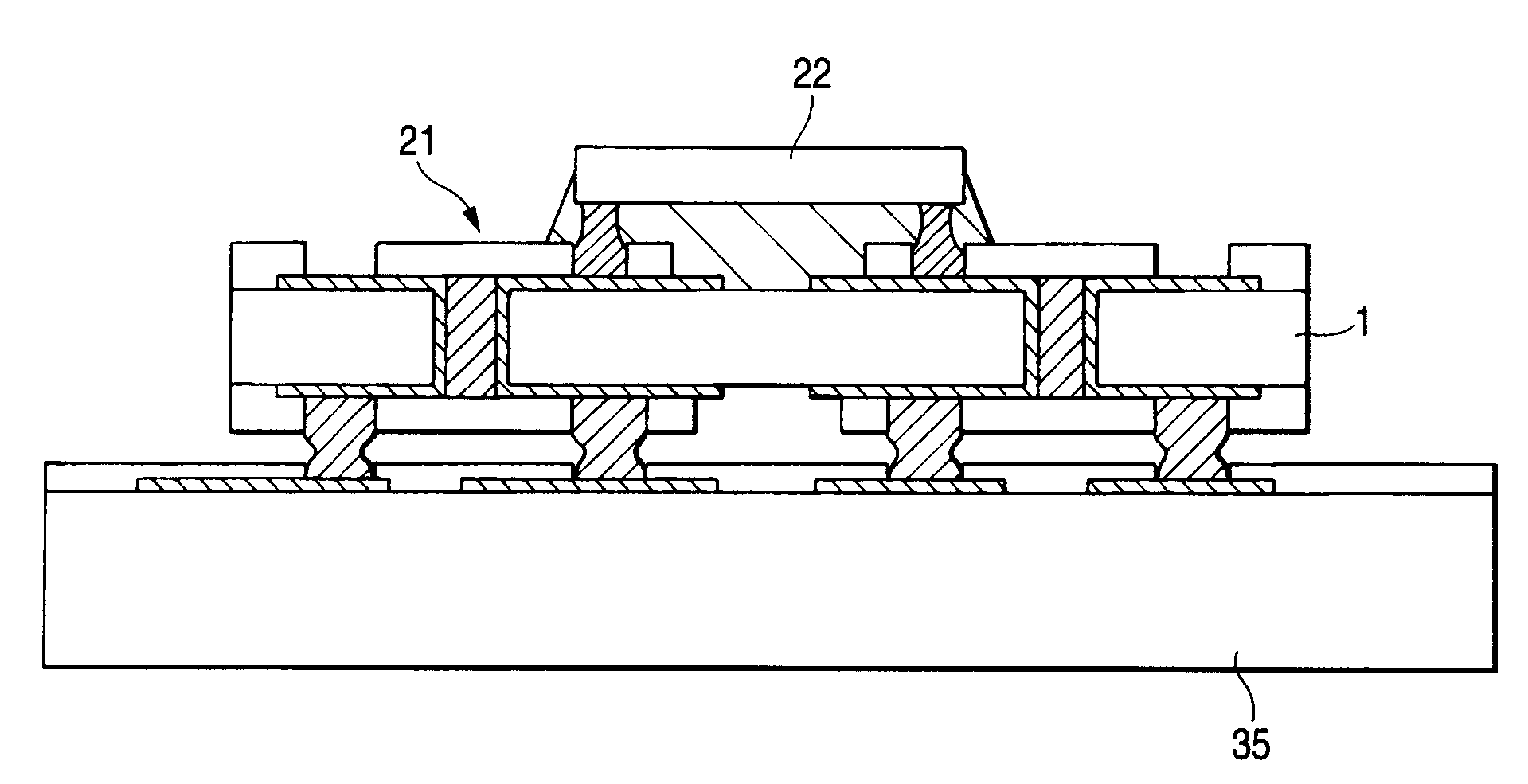

Process for preparing a multi-layer circuit assembly

InactiveUS20020127494A1Increased via densityMoreSemiconductor/solid-state device detailsSolid-state devicesDielectricThermal coefficient

A process for fabricating a multi-layer circuit assembly is provided comprising the following steps: (a) providing a perforate metal core; (b) applying a dielectric polymer onto all exposed surfaces of the metal core to form a conformal coating of substantially uniform thickness on all exposed surfaces of the metal core; (c) ablating the surface of the dielectric polymer in a predetermined pattern to expose sections of the metal core; (d) applying a layer of metal to all surfaces to form metallized vias through the metal core; and (e) applying a resinous photosensitive layer to the metal layer. Additional processing steps such as circuitization may be included. Circuit assemblies produced by the process of the present invention comprise component layers having high via density and thermal coefficients of expansion that are compatible with those of semiconductor chips and rigid wiring boards which may be attached as components of the circuit assembly.

Owner:PPG IND OHIO INC

Process for fabricating circuit assemblies using electrodepositable dielectric coating compositions

Provided is a process for forming metallized vias in a substrate including the steps of (I) applying to an electroconductive substrate an electrodepositable coating composition onto all exposed surfaces of the substrate to form a conformal dielectric coating; (II) ablating a surface of the dielectric coating to expose a section of the substrate; (III) applying a layer of metal to all surfaces to form metallized vias in the substrate. Also disclosed are processes for fabricating a circuit assembly which include the application of an electrodoepositable coating composition onto exposed surfaces of the substrate / core to form a conformal dielectric coating thereon. The electrodepositable coating composition includes a resinous phase dispersed in an aqueous phase, where the resinous phase has a covalently bonded halogen content of at least 1 percent by weight. The dielectric coating derived therefrom has a low dielectric constant and low dielectric loss factor.

Owner:PPG IND OHIO INC

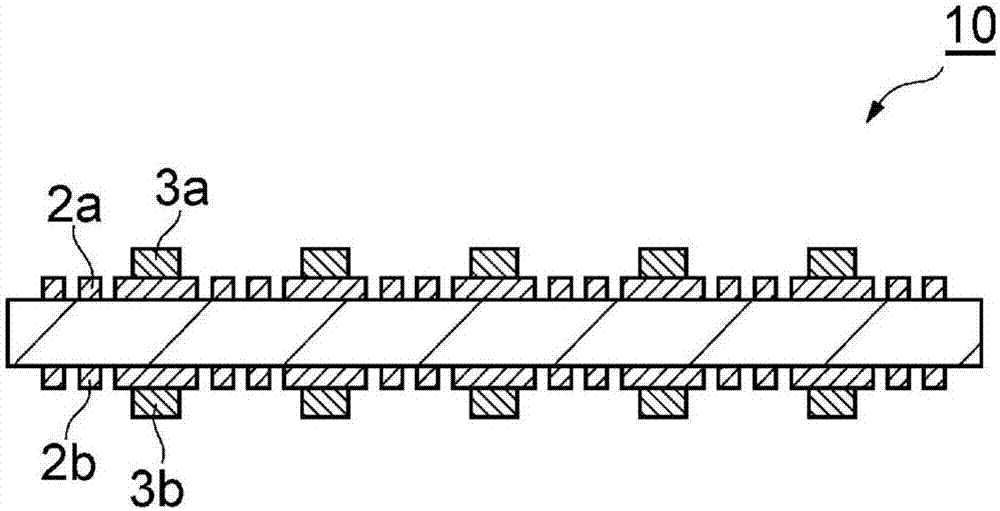

Component for semiconductor package and manufacturing method of component for semiconductor package

InactiveUS20090121341A1Lower Reliability RequirementsResist coatingSemiconductor/solid-state device detailsSemiconductor packageConductive materials

A component for semiconductor package which has a protective insulating layer on at least one surface of a component body and exposes a conductive material of the component body to an opening part of the protective insulating layer is manufactured by a method including the steps of (a) forming a mask on at least one surface of the component body, (b) forming the protective insulating layer by filling an opening part of the mask with a protective insulating material by a molding method using a metal mold comprising a mold release film, and (c) removing the metal mold and removing the mask. A typical component is a lead frame or a substrate for semiconductor package.

Owner:SHINKO ELECTRIC IND CO LTD

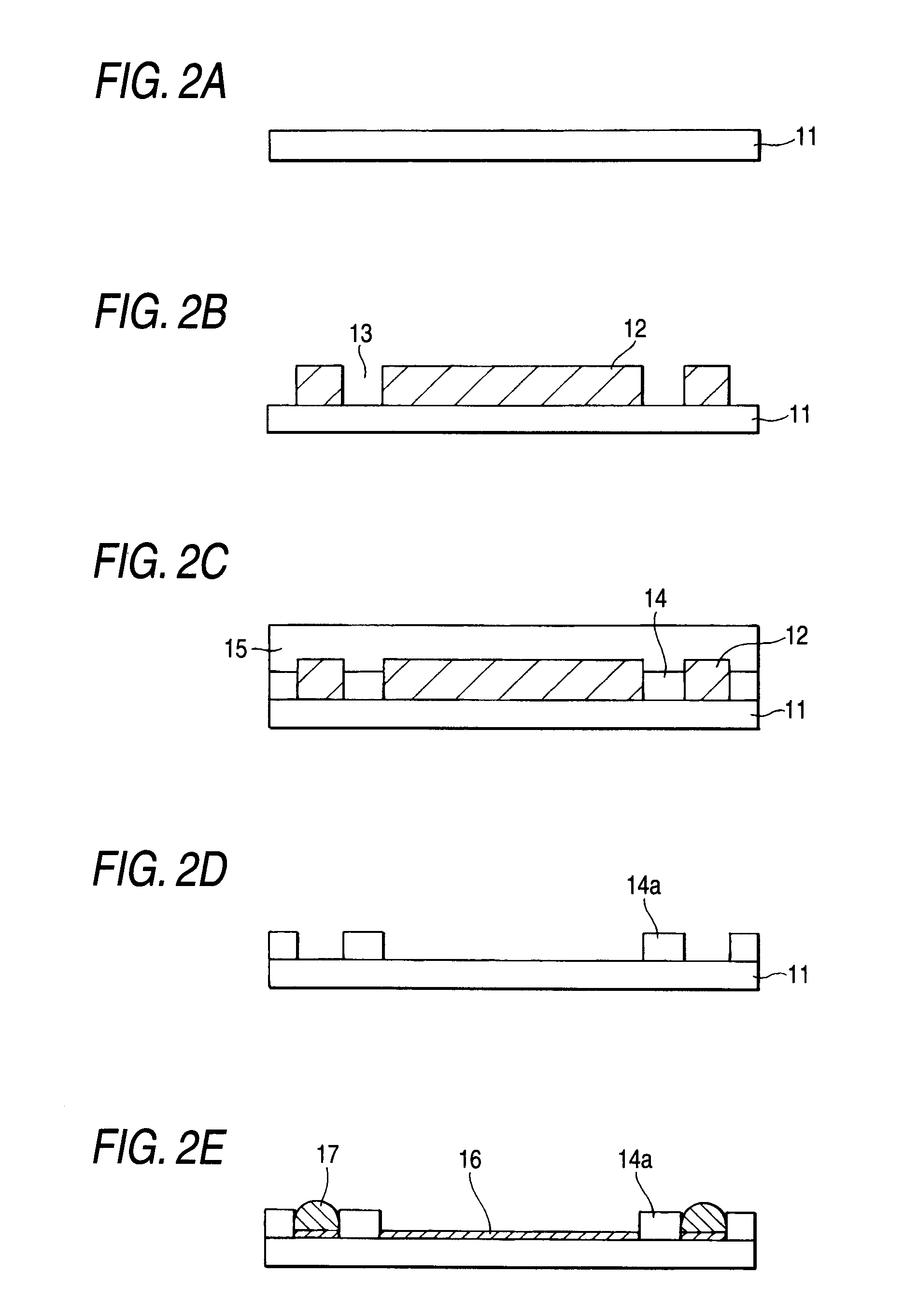

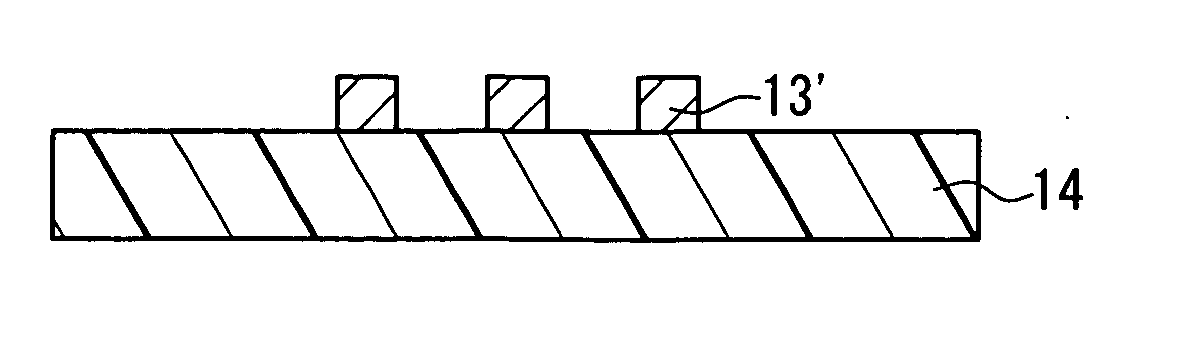

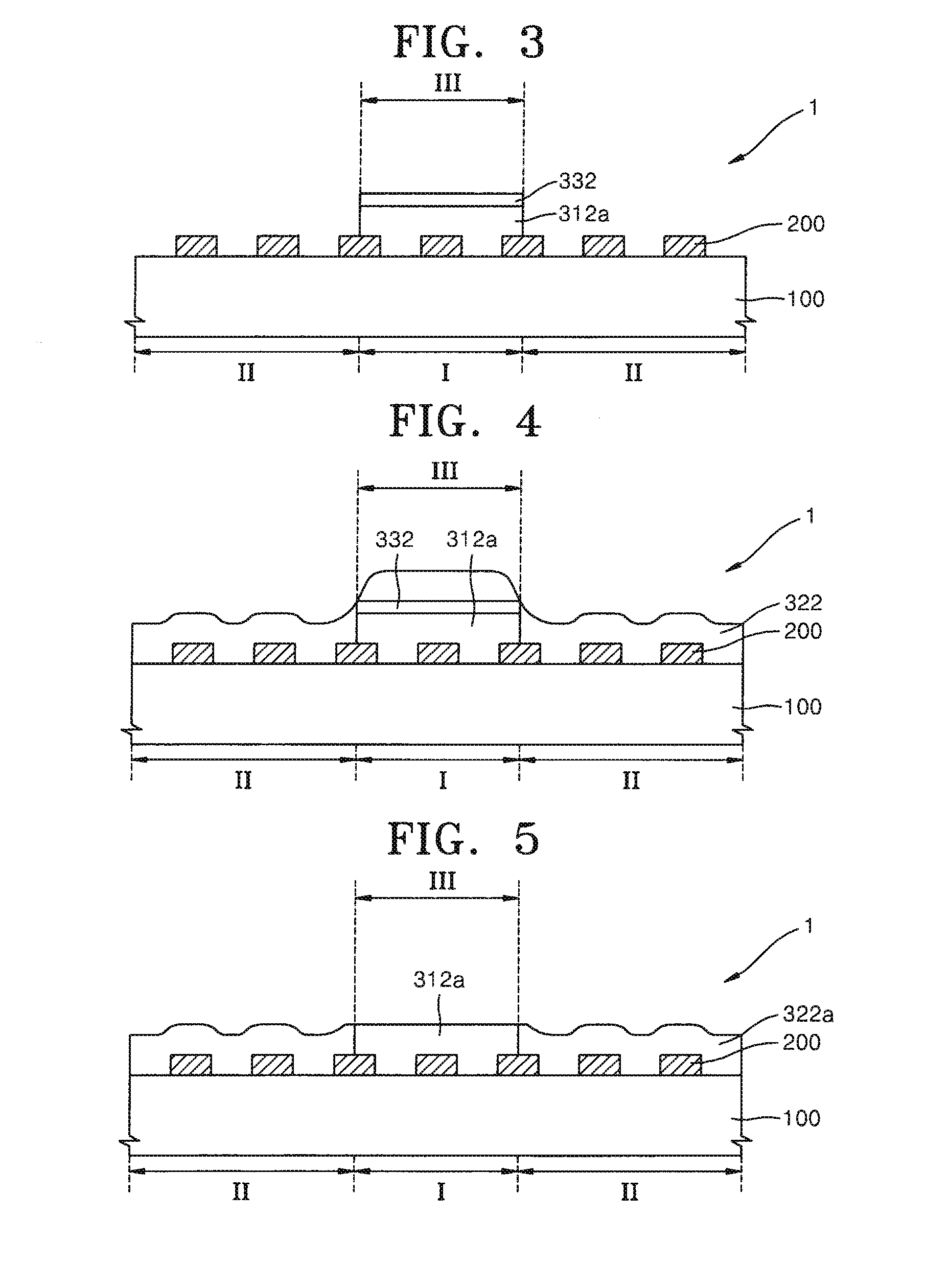

Metal pattern and process for producing the same

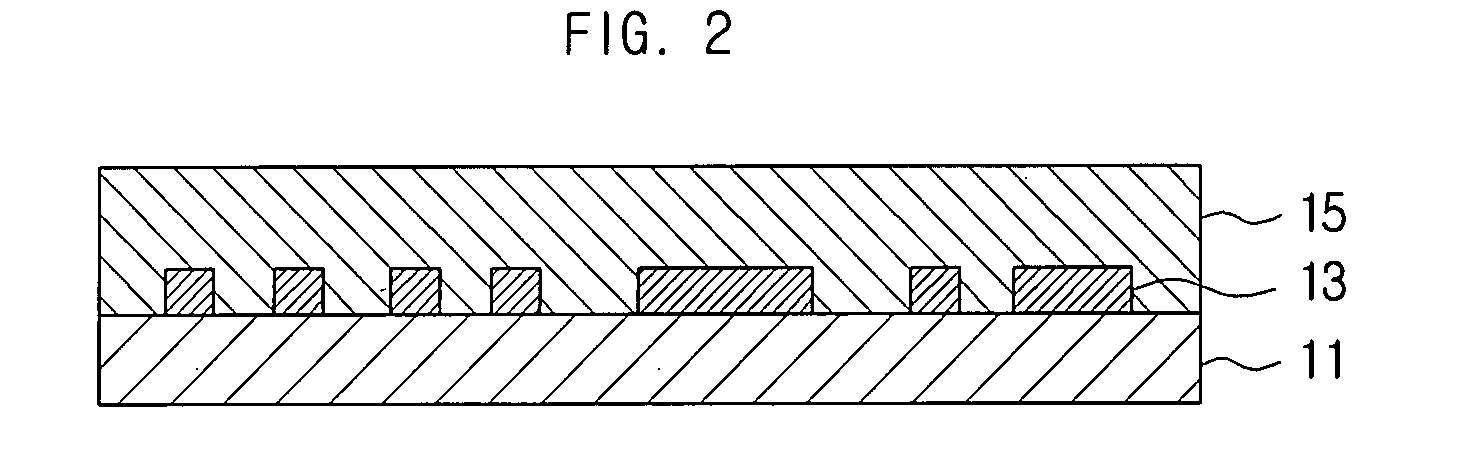

A metal pattern of the present invention is a metal pattern (13′) formed on a surface of a substrate by etching, and a monomolecular film containing fluorinated alkyl chains (CF3(CF2)n—, where n represents an integer) is formed on a surface of a metal film composing the metal pattern (13′), and a masking film (18) is formed by penetration of a molecule having a mercapto group (—SH) or a disulfide (—SS—) group into interstices between molecules composing the monomolecular film. The metal pattern is produced by: forming a monomolecular film containing fluorinated alkyl chains (CF3(CF2)n—, where n represents an integer) on a surface of a metal film; forming a masking film by applying a solution in which a molecule having a mercapto group (—SH) or a disulfide (—SS—) group is dissolved over a surface of the monomolecular film so that the molecule having a mercapto group (—SH) or a disulfide (—SS—) group penetrates in interstices between molecules composing the monomolecular film; and etching the metal film by exposing the surface of the metal film to an etching solution so that a portion of the metal film in a region not covered with the masking film is removed.

Owner:PANASONIC CORP

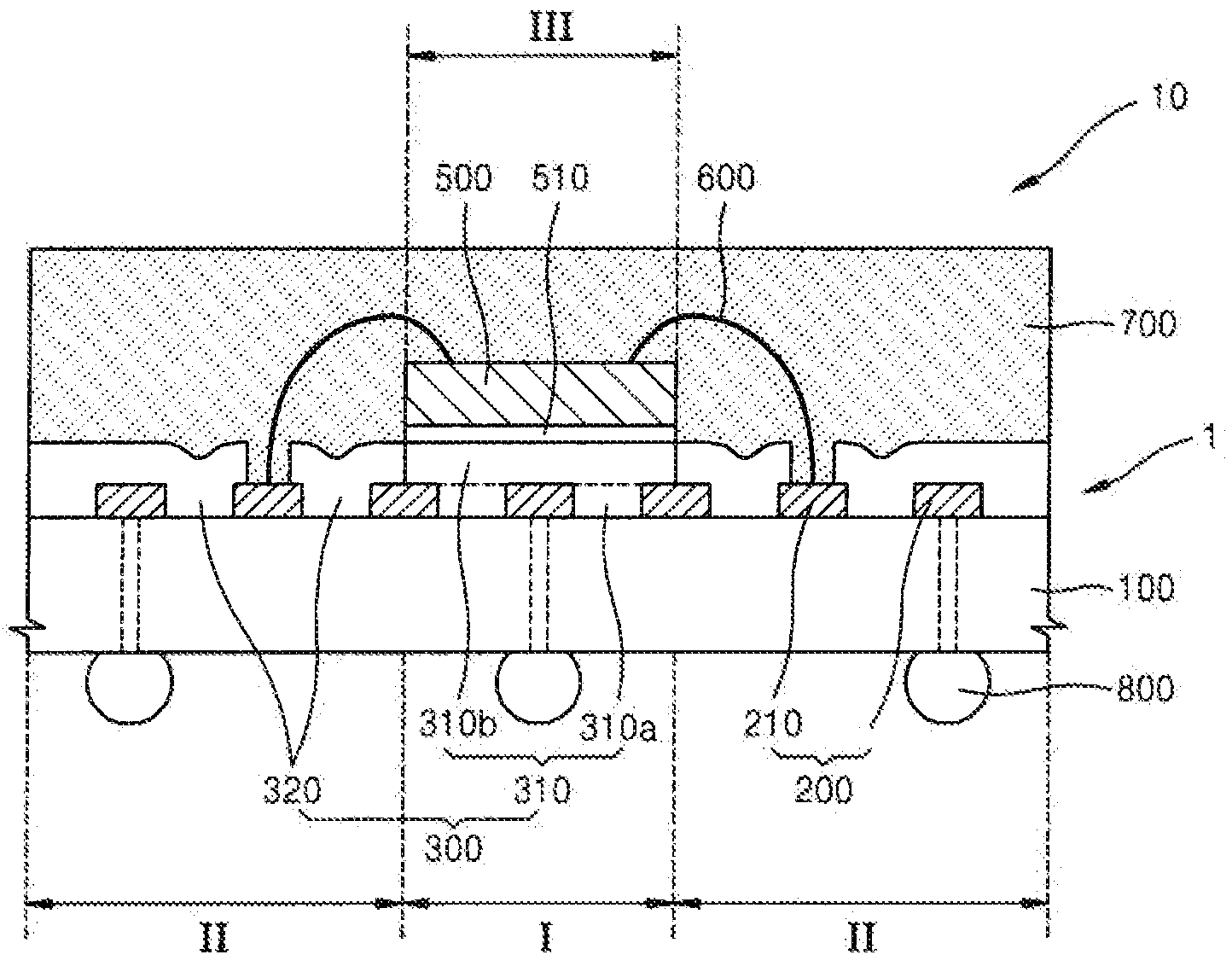

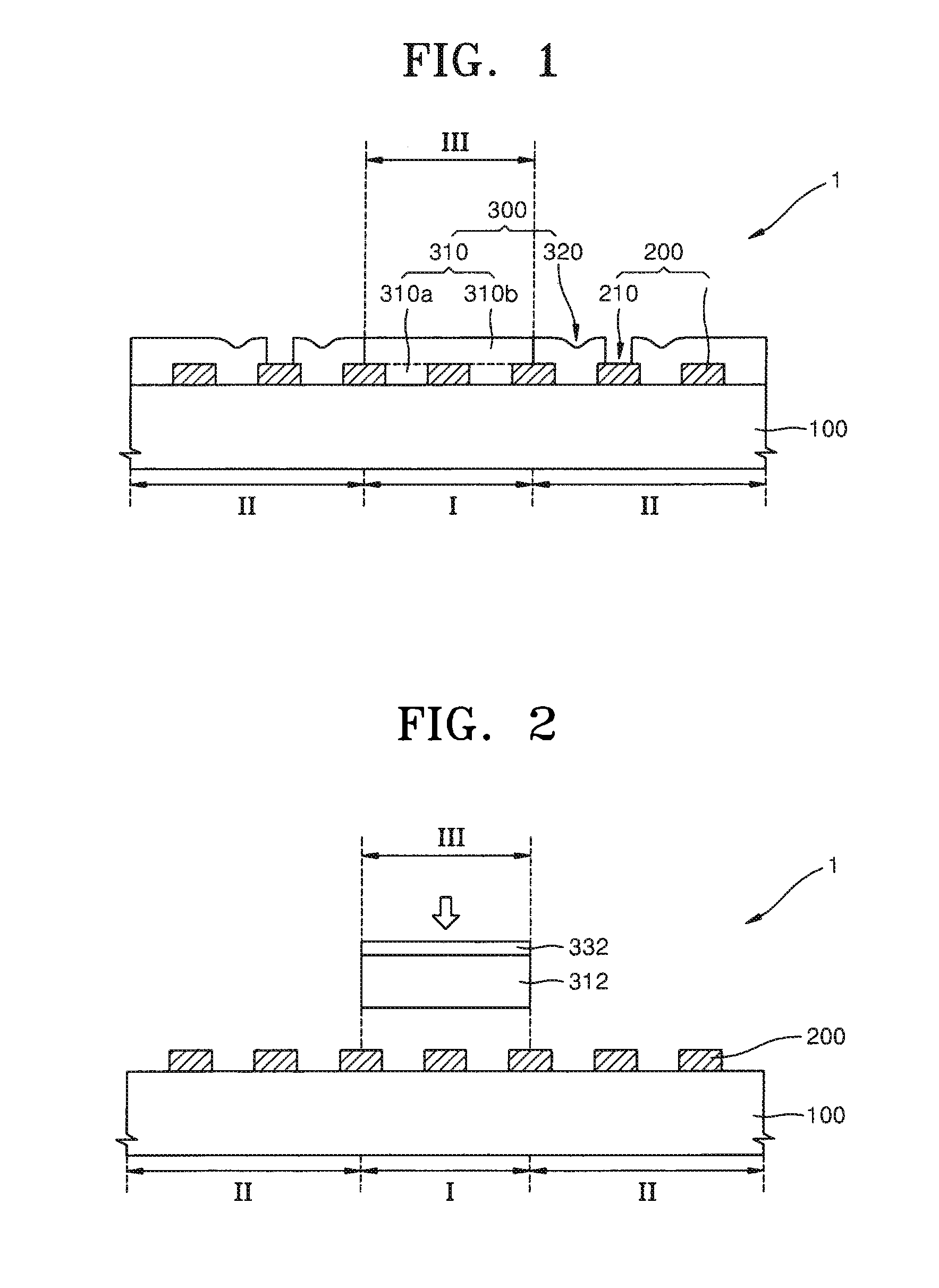

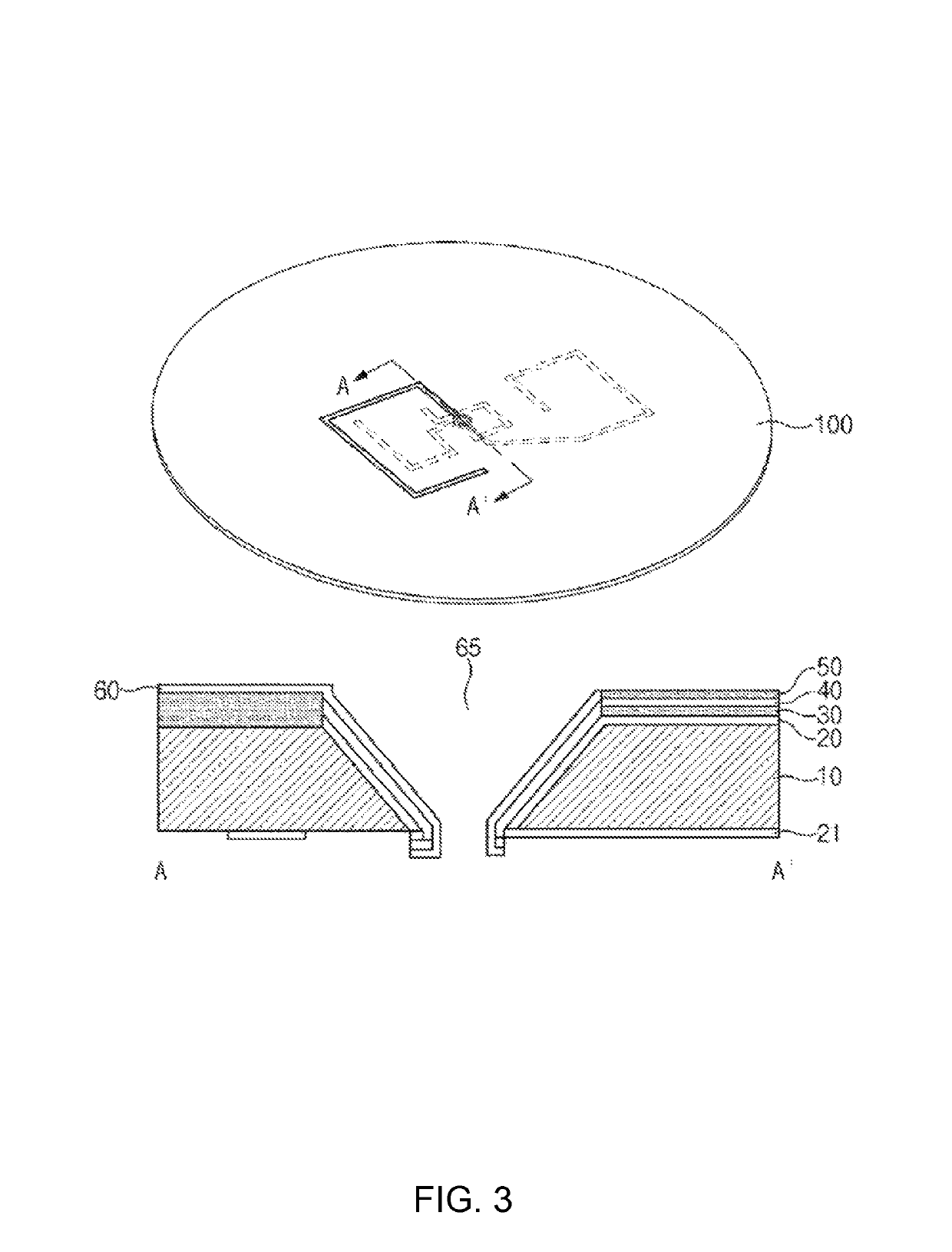

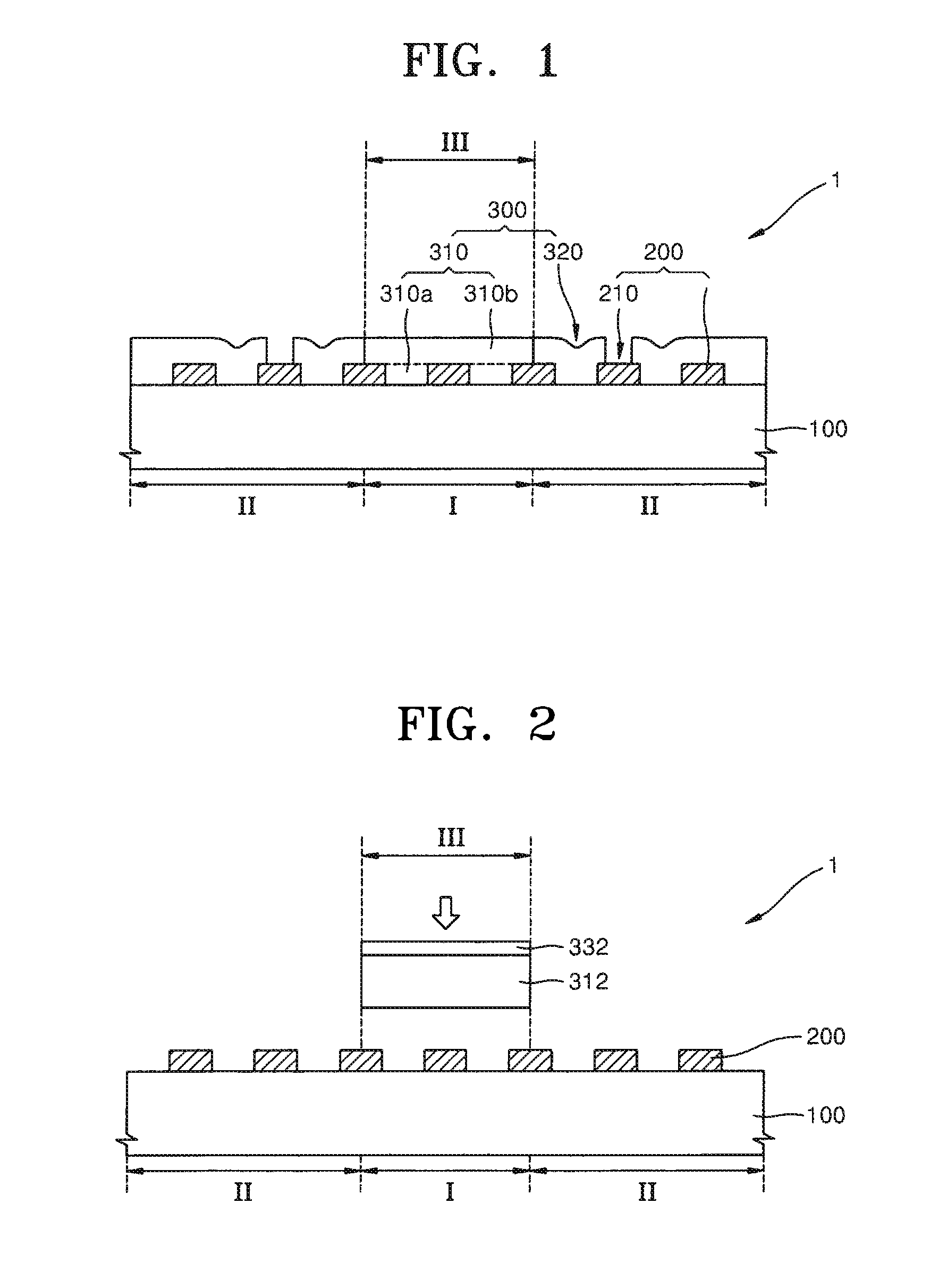

Printed circuit board and semiconductor package including the same

InactiveUS20090179335A1Avoid voidsAvoid delaminationSemiconductor/solid-state device detailsSolid-state devicesResistSurface roughness

A printed circuit board (PCB) and a semiconductor package that are configured to prevent delamination and voids. In one example embodiment, the semiconductor package includes a PCB having a base substrate on which conductive patterns are formed and which includes an interior region having a die paddle for receiving a semiconductor chip and an exterior region disposed outside the interior region. The PCB also includes a first solder resist formed on a portion of the base substrate corresponding to the interior region and a second solder resist formed on a portion of the base substrate corresponding to the exterior region. The second solder resist may also have a greater surface roughness than the surface roughness of the first solder resist.

Owner:SAMSUNG ELECTRONICS CO LTD

Fabricating method for printed circuit board

InactiveUS8065797B2Fabrication can be reducedImprove efficiencyPrinted circuit assemblingResist coatingProduction rateFine line

A method of fabricating a printed circuit board is disclosed. A method of fabricating a printed circuit board that includes: stacking an insulation layer on at least one surface of a core layer, on which an inner circuit is formed, and forming an outer circuit pattern; burying the outer circuit pattern in the insulation layer; removing the outer circuit pattern to form minute grooves and curing the insulation layer; and forming an outer circuit by filling metal in the minute grooves, makes it possible to readily form high-resolution fine-line circuits, as well as to reduce fabrication costs and increase productivity.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

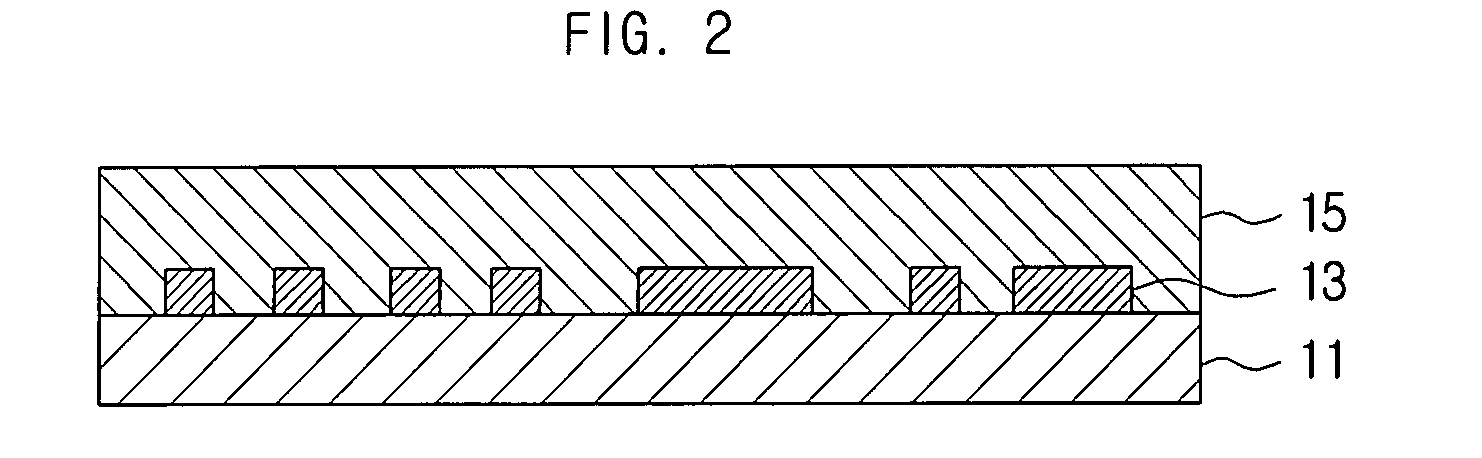

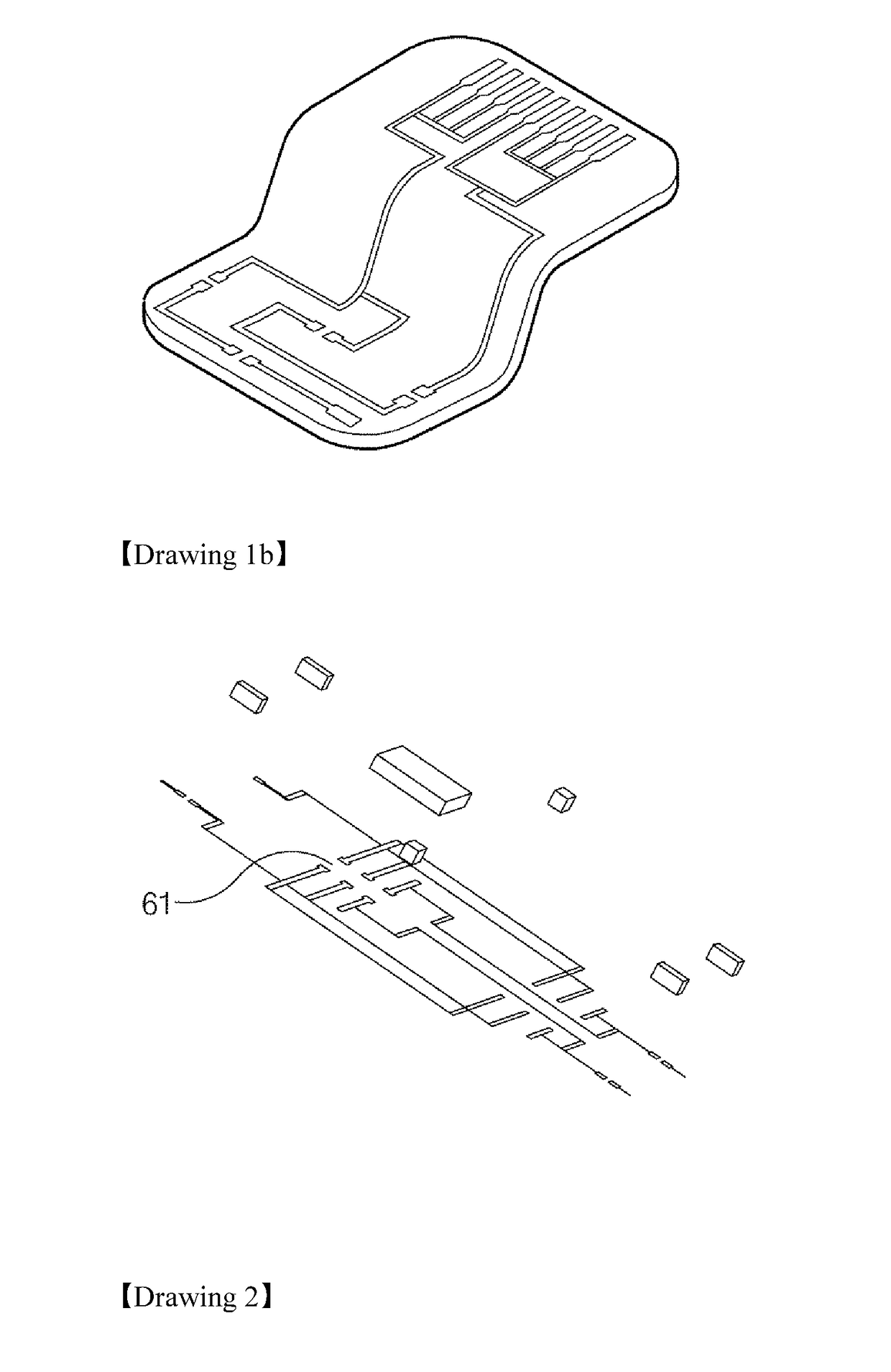

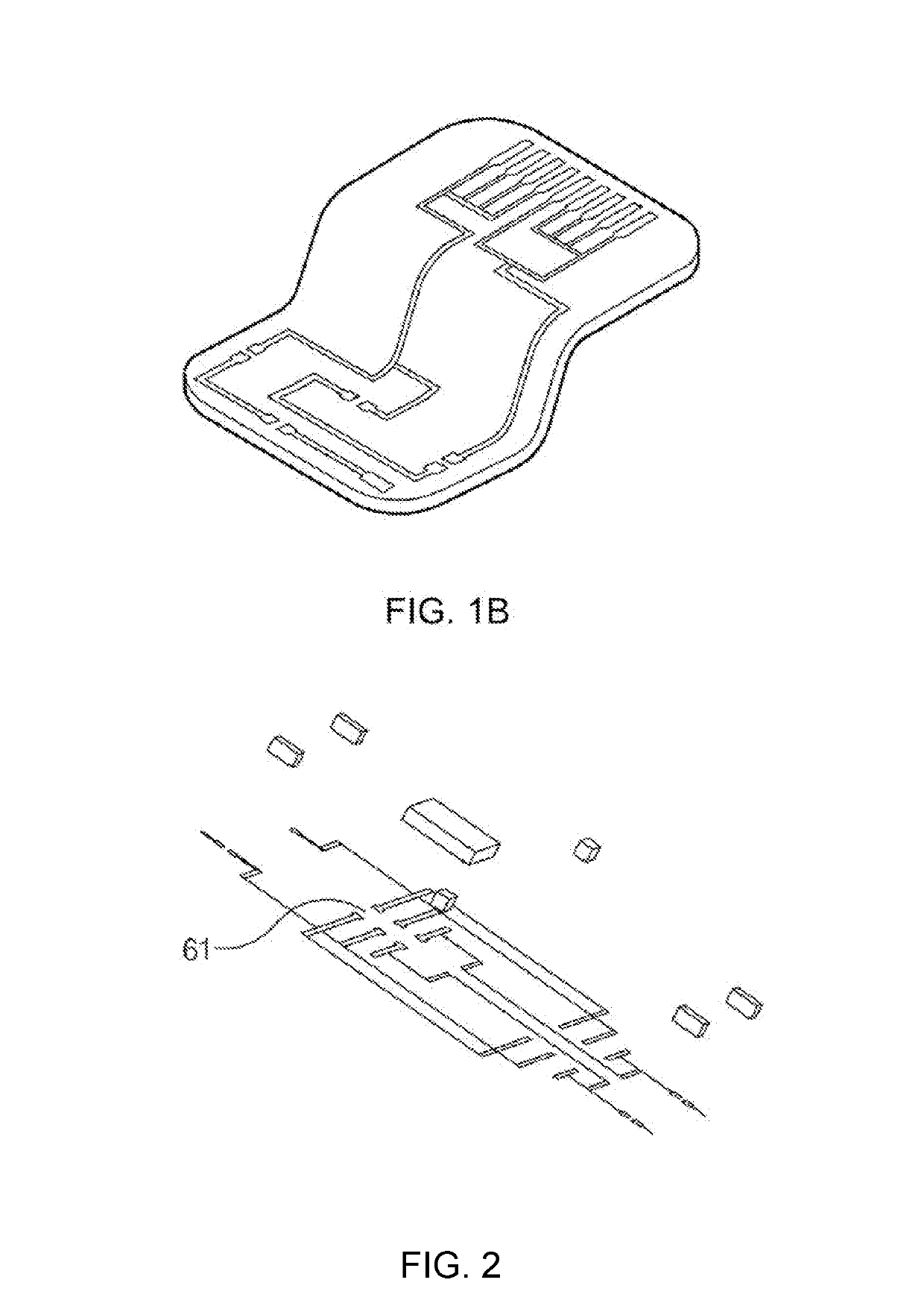

Method for manufacturing a circuit having a lamination layer using laser direct structuring process

ActiveUS20170094801A1Delay manufacturing processEfficient use ofResist coatingSecond resist patternEngineeringInjection moulding

The present disclosure relates to the method of manufacturing circuit having lamination layer using LDS (Laser Direct Structuring) to ease the application on surface structure for applied product of various electronic circuit and particularly, in which can form circuit structure of single-layer to multiple-layer on the surface of injection-molded substrate in the shape of plane or curved surface, metal product, glasses, ceramic, rubber or other material.

Owner:KYOCERA AVX COMPONENTS (SAN DIEGO) INC

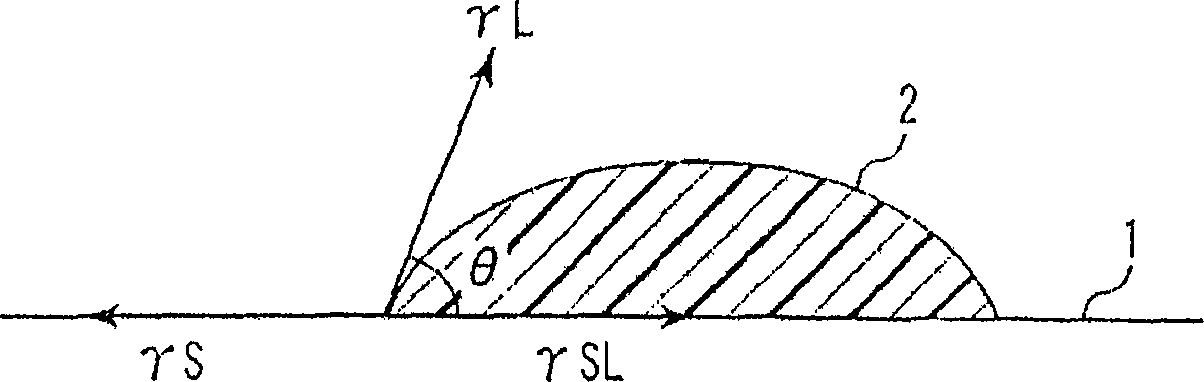

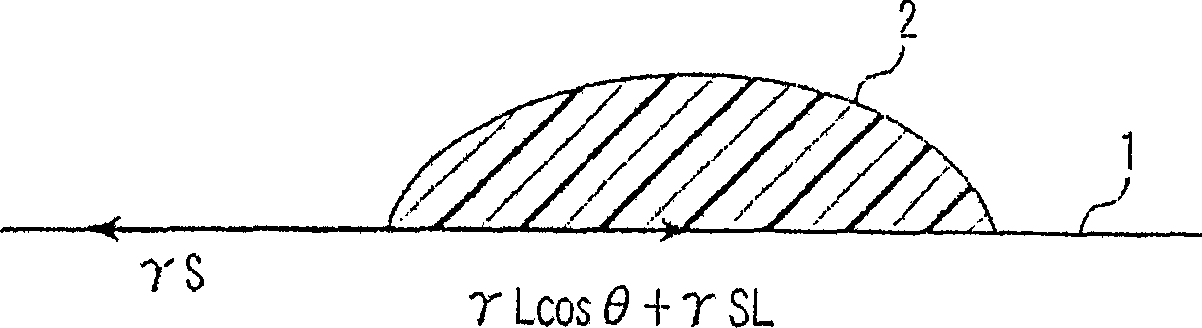

Insulating pattern and method of forming the same

InactiveCN1849854AImprove productivityExcellent film propertiesResist coatingNon-metallic protective coating applicationEngineeringCoating

The present invention provides a method for forming an insulating pattern, which is characterized in that: (1) on a substrate on which a circuit is formed, a repellent (A) is applied and fixed on a pattern that is in a complementary relationship with the insulating layer pattern; process; (2) a process of applying a liquid insulating resin composition (B) having a surface tension higher than that of the fixed repellant (A) but lower than that of the substrate on the entire surface of the substrate obtained in the process (1); and ( 3) A step of fixing the coating film of the liquid insulating resin composition (B) obtained in step (2) on the substrate by curing by active energy ray irradiation and / or heating, or by heating and drying to form an insulating layer. In the steps (2) to (3) above, the liquid insulating resin composition (B) is repelled by the fixed matter of the repelling agent (A) to obtain an insulating pattern.

Owner:TAIYO INK MFG

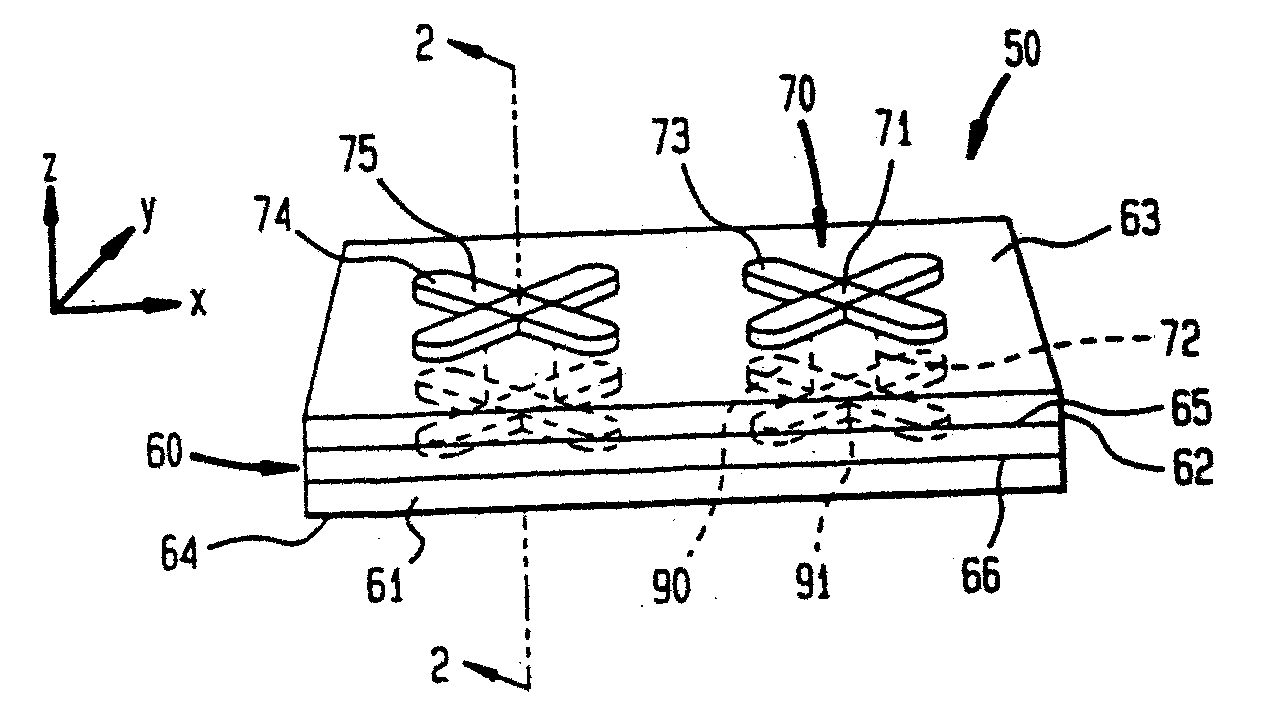

Method of forming multilayer interconnection structure, and manufacturing method for multilayer wiring boards

Method of forming a multilayer interconnection structure that includes a contact hole for reliably connecting between layers, without damaging a substrate. A column shaped mask material is formed in a position for forming a contact hole using a resist, and an interlayer insulating film is applied to the whole surface of the substrate excluding the mask material. Then, the mask material is removed by a method such as peeling. As a result, a hole generated thereby is used as a contact hole.

Owner:SEIKO EPSON CORP

Process for fabricating circuit assemblies using electrodepositable dielectric coating compositions

Provided is a process for forming metallized vias in a substrate including the steps of (I) applying to an electroconductive substrate an electrodepositable coating composition onto all exposed surfaces of the substrate to form a conformal dielectric coating; (II) ablating a surface of the dielectric coating to expose a section of the substrate; (III) applying a layer of metal to all surfaces to form metallized vias in the substrate. Also disclosed are processes for fabricating a circuit assembly which include the application of an electrodoepositable coating composition onto exposed surfaces of the substrate / core to form a conformal dielectric coating thereon. The electrodepositable coating composition includes a resinous phase dispersed in an aqueous phase, where the resinous phase has a covalently bonded halogen content of at least 1 percent by weight. The dielectric coating derived therefrom has a low dielectric constant and low dielectric loss factor.

Owner:PPG IND OHIO INC

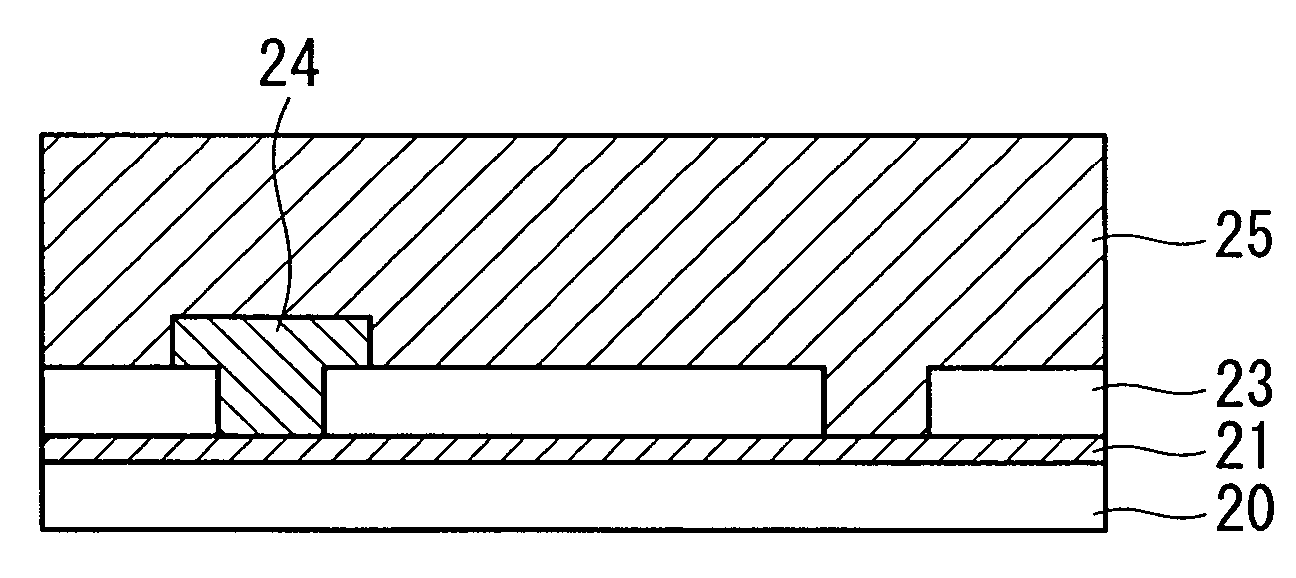

Structure containing conductor circuit, method for manufacturing same, and heat-curable resin composition

InactiveCN106922088AFull and efficient manufacturingImprove reliabilityResist coatingSemiconductor/solid-state device detailsElectrical conductorEngineering

A method for manufacturing a structure containing a conductor circuit according to the present invention can provide openings in various shapes by patterning a first photosensitive resin layer in a first patterning process according to shapes of openings formed in a heat-curable resin layer. Further, in the method for manufacturing a structure containing a conductor circuit, a plurality of openings can be formed at the same time and a residue of the resin around the opening can be reduced, unlike a case in which openings are formed with a laser. Therefore, it is possible to sufficiently efficiently manufacture the structure having excellent reliability even when the number of pins of a semiconductor element increases and it is necessary to provide a great number of fine openings.

Owner:HITACHI CHEM CO LTD

Method for manufacturing a circuit having a lamination layer using laser direct structuring process

ActiveUS10448518B2Easy to processEfficient use ofResist coatingSecond resist patternSubject matterEngineering

The present subject matter relates to the method of manufacturing circuit having lamination layer using LDS (Laser Direct Structuring) to ease the application on surface structure for applied product of various electronic circuit and particularly, in which can form circuit structure of single-layer to multiple-layer on the surface of injection-molded substrate in the shape of plane or curved surface, metal product, glasses, ceramic, rubber or other material.

Owner:KYOCERA AVX COMPONENTS (SAN DIEGO) INC

PCB solder masking process

InactiveUS20060226202A1Low production costQuality improvementResist coatingNon-printed masksSolder maskHardness

A PCB solder masking process allowing easier process, reduced production cost and improved PCB quality involves dispensing low hardness resin on contacts to be exposed on the PCB, resin being solidified, non-solidified area covered with mask, UV exposed, non-solidified area removed, PCB sprayed insulation varnish, solidified, varnish and resin on surface of contact removed, either sanded or sandblasted, and finally cleaned and rinsed.

Owner:YANG HO CHING

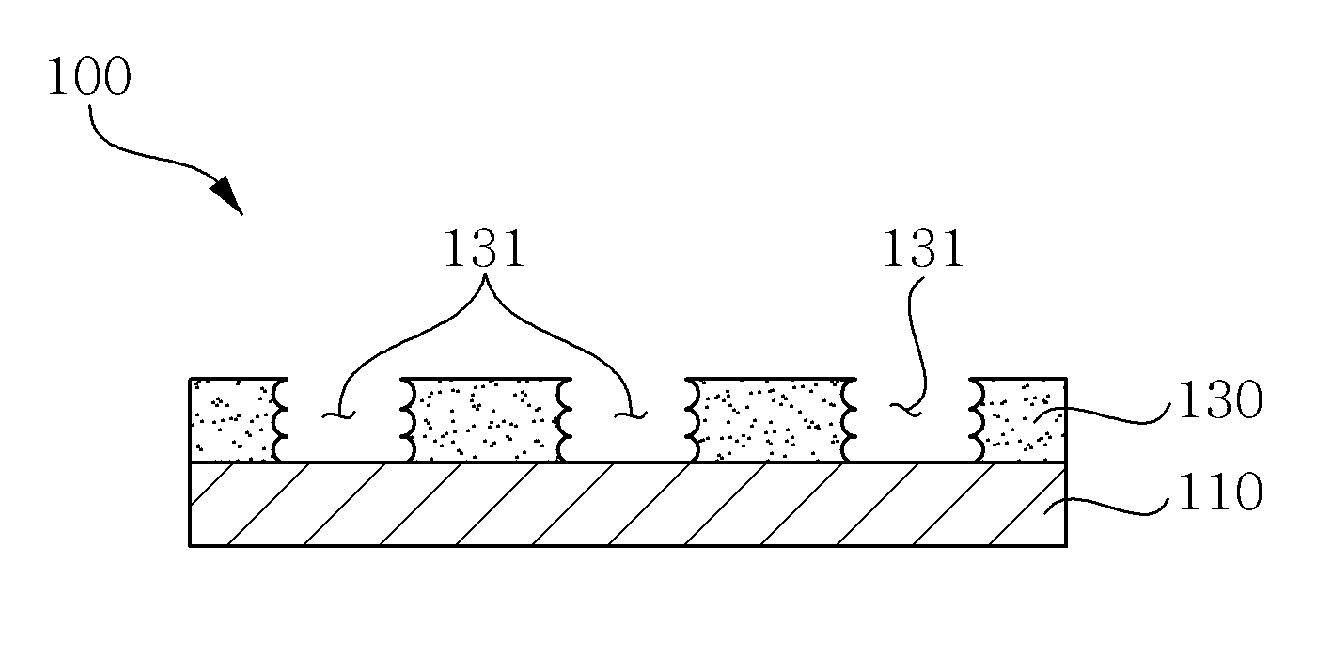

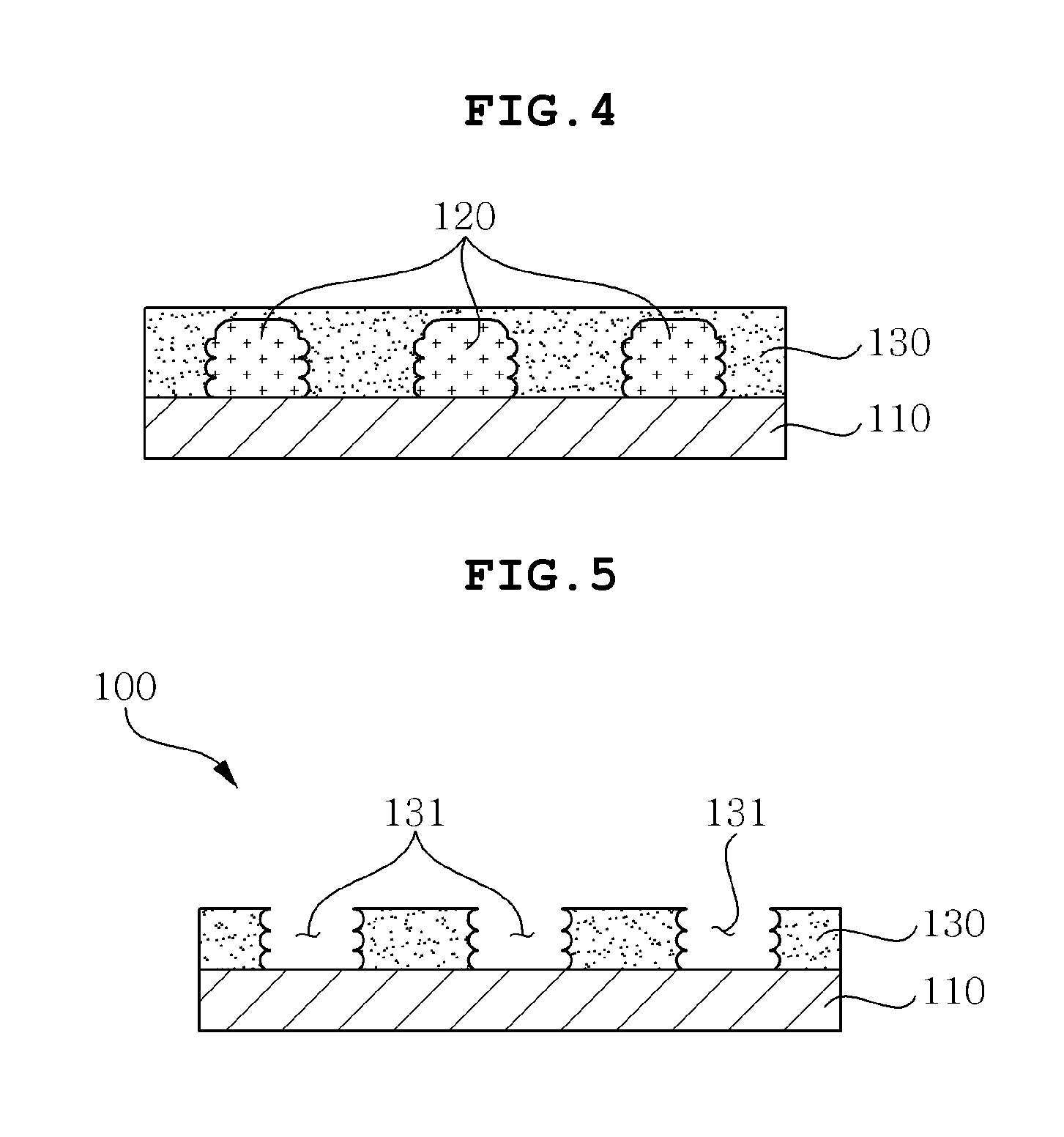

Printed circuit board and method of manufacturing the same

InactiveUS20130112471A1Low costReduce processing proceduresRadiation applicationsPretreated surfacesPrinting inkEngineering

Disclosed herein is a printed circuit board and a method of manufacturing the same. The printed circuit board includes preparing a base substrate; forming a pattern layer for forming via holes on the base substrate by printing ink for forming via holes; forming an insulating layer on the base substrate including the pattern layer for forming via holes; and removing the pattern layer for forming via holes.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Manufacturing method of rigid-flex PCB

ActiveCN104968164AIncrease productivityImprove versatilityResist coatingMultilayer circuit manufactureCooking & bakingScreen printing

The invention discloses a manufacturing method of a rigid-flex PCB. The method includes the steps: A, manufacturing a screen print film, the lower oil level area of the screen print film being 1mm smaller than a windowing duct single side; B, performing acid and alkali resistance glue peelable printing, and filling and covering a windowing duct; C, carrying out a baking step, and solidifying acid and alkali resistance peelable glue; and D, performing electroless copper electroplating, and tearing off the acid and alkali resistance peelable glue after electroplating. A screen printing technology is adopted to fill peelable glue in windowing places to replace conventional gluing by hands, so the production efficiency is greatly improved and the labor intensity is reduced. For different dimensions, people can perform printing filling on flexible areas with different shapes without considering whether glue paper matches the flexible areas in shape and dimension. Therefore, the manufacturing method is improved in universality.

Owner:SHENZHEN KINWONG ELECTRONICS

Fabrication method of circuit board

InactiveUS6968613B2Increased process complexitySimplify the manufacturing processPrinted circuit assemblingLine/current collector detailsResistSolder ball

A fabrication method of a circuit board is proposed, wherein a core layer is formed with a plurality of conductive traces, and photo resist is respectively applied on terminals of the conductive traces. Then, a non-solderable material is applied over the core layer as to cover the conductive traces except for the insulating material, and the non-solderable material is adapted to be surface-flush with the insulating material, allowing the insulating material to be exposed from the non-solderable material. Finally, the insulating material is removed from the core layer to expose the terminals of the conductive traces, wherein the exposed terminals are used as bond pads or bond fingers where solder balls, solder bumps or bonding wires can be bonded. This circuit board is cost-effectively fabricated by simplified processes, and beneficial in precisely exposing bond pads or bond fingers, thereby significantly improving yield of fabricated circuit boards.

Owner:UTAC HEADQUARTERS PTE LTD

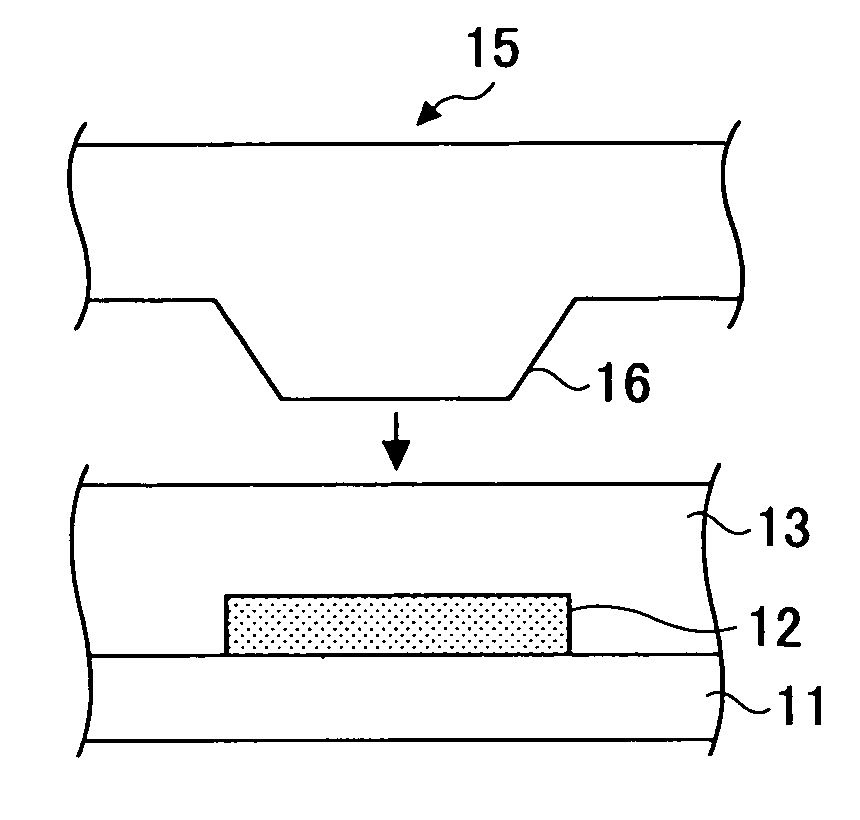

Method of producing multilayer interconnection board

InactiveUS7438945B2Avoid elevationReduce residual resinResist coatingPretreated surfacesInterconnectionEngineering

A method of producing a multilayer interconnection board is disclosed that includes the steps of processing a resin member on an interconnection layer by imprinting press, and removing residue of the resin member at the bottom of a via hole after forming the via hole. In the method of producing a multilayer interconnection board, a thermal setting resin, which has a setting temperature higher than that of the resin member, is applied on a via-connecting portion of the interconnection layer, the resin member is formed on the interconnection layer, an interconnection groove and a via hole are formed by imprinting press on the resin member by using a tool, and an un-cured portion of the high temperature setting resin is dissolved and removed by using a resin solvent. Thereby, residue of the resin member on the thermal setting resin is removed.

Owner:SHINKO ELECTRIC IND CO LTD

Circuit board manufacturing method and circuit board

InactiveUS7679004B2Easy to manufactureSemiconductor/solid-state device detailsSolid-state devicesResistPotential difference

As means for solving a problem of a positional shift of a land and a hole which is caused by an alignment in the formation of an etching resist layer and a plated resist layer in a method of manufacturing a circuit board, there are provided a method of manufacturing a circuit board including the steps of forming a first resin layer on a surface of an insulating substrate having a conductive layer on the surface and an internal wall of a through hole or / and a non-through hole, forming a second resin layer which is insoluble or slightly soluble in a developing solution for the first resin layer on the first resin layer provided on the surface conductive layer, and removing the first resin layer provided over the hole with the developing solution for the first resin layer, and a method of manufacturing a circuit board including the step of uniformly charging a surface of the first resin layer to induce a potential difference to the first resin layer provided over the hole and the first resin layer provided on the surface conductive layer before forming the second resin layer. Moreover, there is provided a circuit board having a hole with a small positional shift and high precision.

Owner:SHINKO ELECTRIC IND CO LTD +1

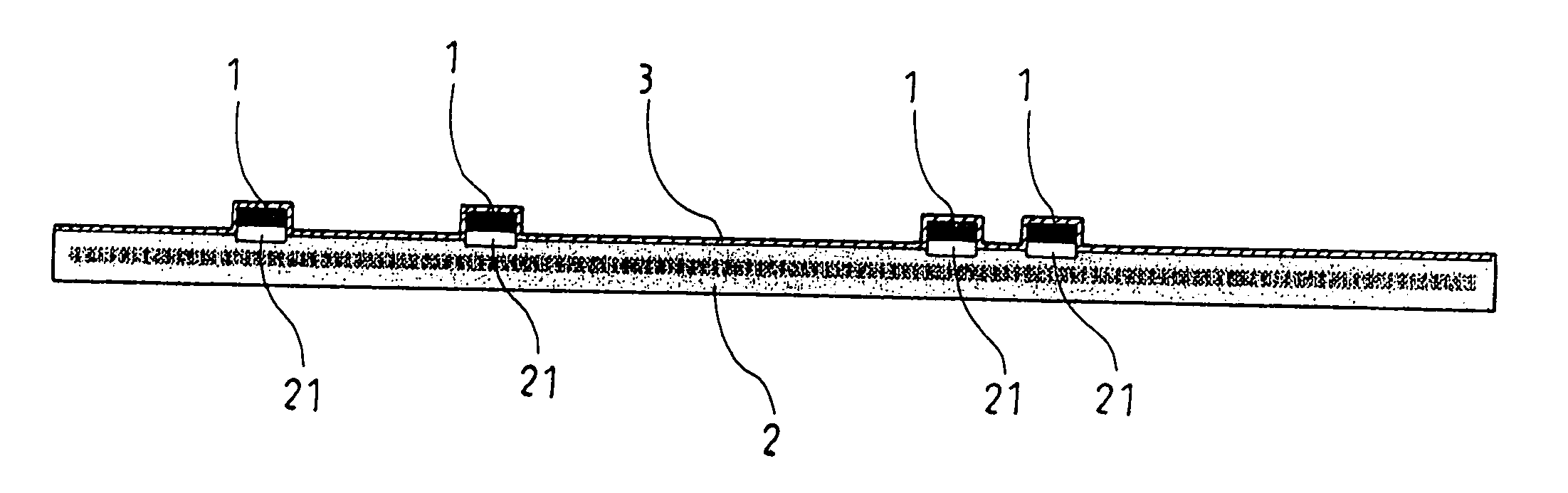

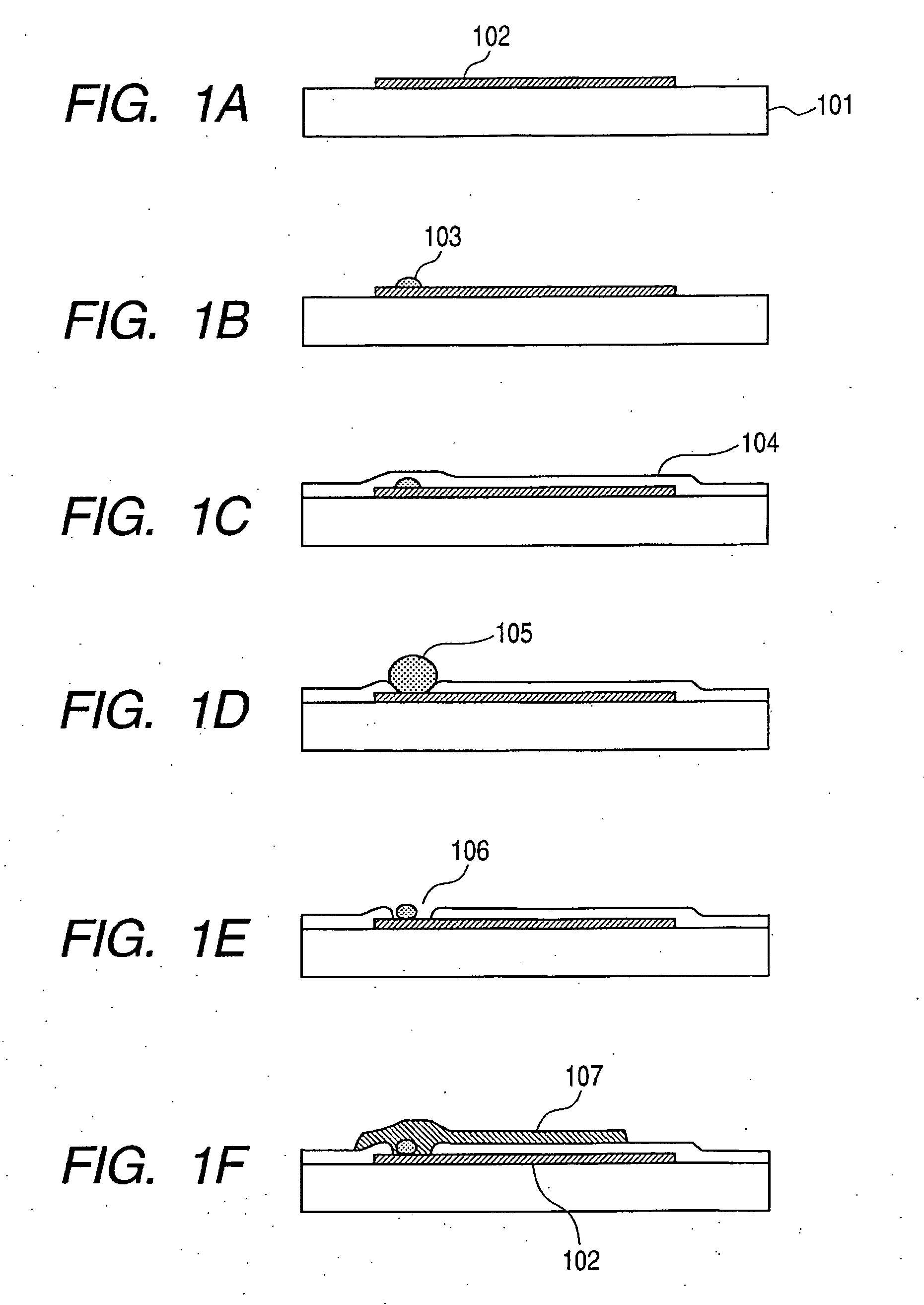

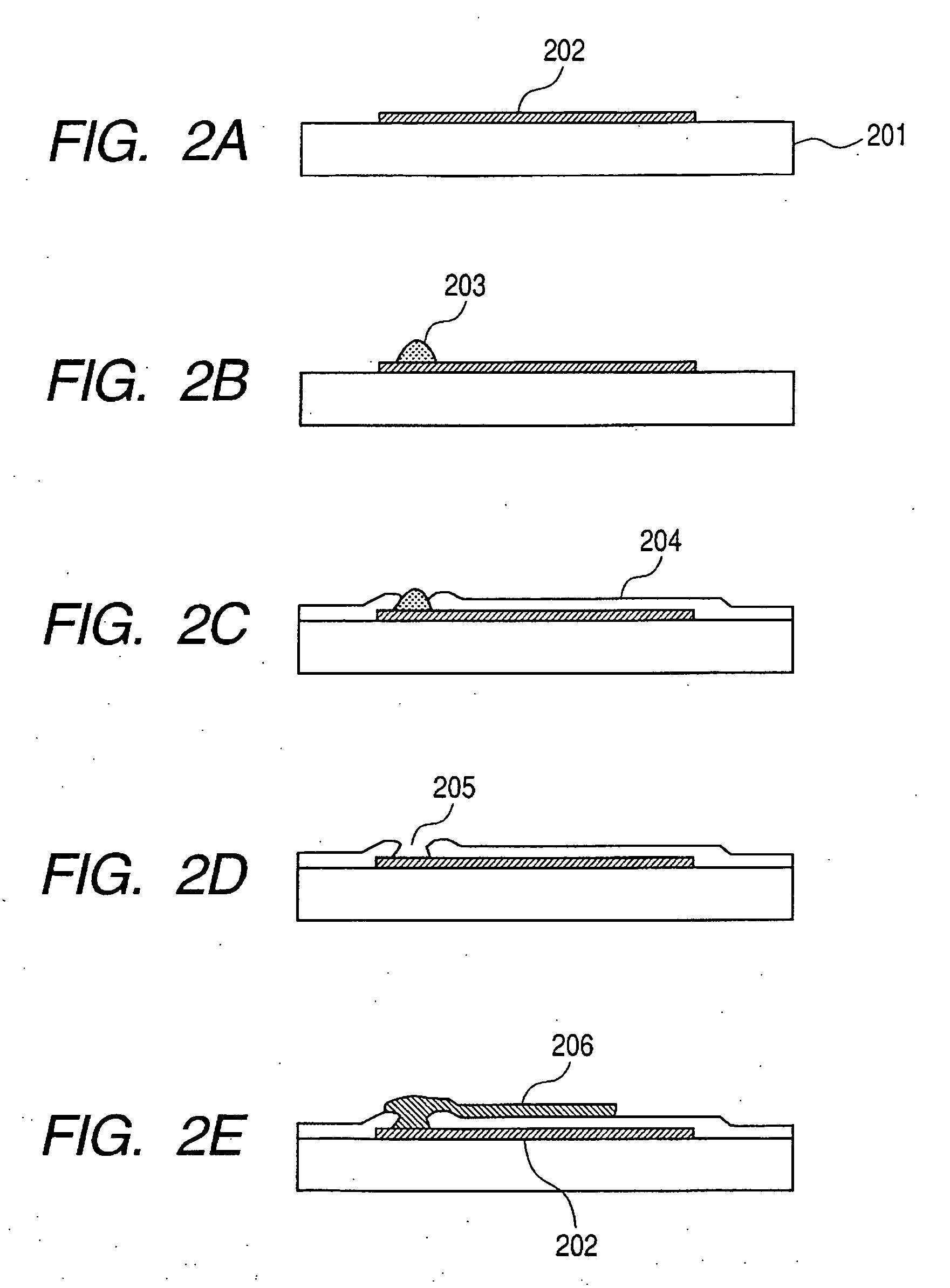

Method of forming through hole and method of manufacturing electronic circuit

Provided is a method of manufacturing an electronic circuit. The method includes the steps of: forming a nucleus comprising thermo-expandable particles on a conductive layer provided on an insulating substrate; forming an insulating film on the conductive layer having the nucleus-formed thereon; forming an opening by heating the substrate to expand the thermo-expandable particles and form a cleavage in the insulating film; and forming another conductive layer comprising a conductive material on the opening and the insulating film such that the upper and lower conductive layers are electrically connected to each other via the conductive material through the insulating film. This allows formation of a through hole in an electric circuit with ease without photolithographic processes such as exposure, development, and etching.

Owner:CANON KK

Printed circuit board and semiconductor package including the same

InactiveUS8063313B2Avoid voidsAvoid delaminationSecond resist masksPrinted circuit assemblingResistSemiconductor chip

Owner:SAMSUNG ELECTRONICS CO LTD

Method for manufacturing outer layer graph of thick copper plate

InactiveCN105873368AImprove qualityMeet thickness requirementsInsulating substrate metal adhesion improvementResist coatingSingle exposureCopper

The invention discloses a method for making an outer layer pattern of a thick copper plate, comprising the following steps: a. sticking a dry film on the copper surface of the thick copper plate according to the copper thickness of the outer layer; b. first exposure and first development; c. , coating wet film; d, second exposure, second development, making outer layer circuit graphics; e, laser window opening, will need to make thick copper layer by laser window opening at the position where the hole is sealed by dry film; f , Pattern electroplating, to meet the requirements for the thickness of the copper layer in the hole and on the surface of the copper plate. For the thick copper core board with uneven surface, apply the dry film first, seal the hole with the dry film after making the circuit pattern, and then apply the wet film to fill the gap, which improves the dry film and copper surface only. Combined with the problem of being weak and easy to fall off, the quality of the thick copper plate is improved, the production yield is improved, and the production cost is reduced.

Owner:SHENZHEN SUNTAK MULTILAYER PCB

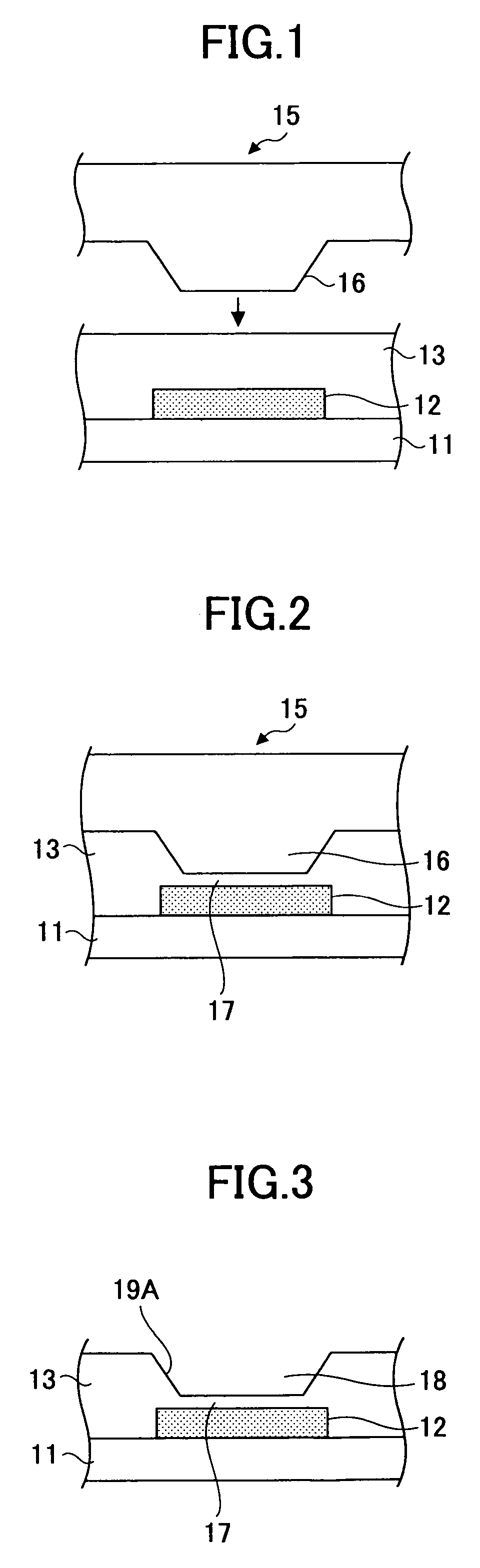

Multilayered circuit board forming method and multilayered circuit board

InactiveUS6971167B2Improve accuracyQuality improvementPrinted circuit assemblingLine/current collector detailsPilot holeElectrical conductor

A multilayered circuit board and a method of forming the multilayered circuit board are provided. In a first circuit forming process, a first circuit is formed on an insulating board with a conductor; in a circuit embedding process, the first circuit is embedded in the insulating board so as to have a predetermined surface flatness and a predetermined parallelism; in a masking process, a pilot hole for a via hole is masked at a part of a surface of the circuit; in an insulating layer forming process P5p, an insulating material is applied as a layer to the surface except that portion thereof covered by the mask; in an insulating material layer flattening process, the surface of the insulating material layer is flattened so as to have the predetermined surface flatness and the predetermined parallelism; and in a pilot hole forming process, the mask is removed.

Owner:PANASONIC CORP

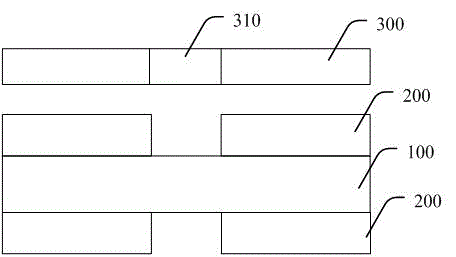

Photosensitive and via-forming circuit board

ActiveUS20180263122A1Increase flexibilityImprove heat resistanceResist coatingPrinted circuit aspectsEpoxyElectrical conductor

A photosensitive and via-forming circuit board comprising a laminate unit, a conductor unit, and a cover layer unit is provided. The laminate unit includes an insulating layer, a first conductive wiring layer and a second conductive wiring layer formed at two opposite sides of the insulating layer, respectively, and at least one through-hole surface defining a through hole extending from the upper surface of the first conductive wiring layer through the insulating layer to the lower surface of the second conductive wiring layer. The conductor unit is formed on the at least one through-hole surface. The cover layer unit is formed from a photosensitive composition comprising an epoxy group-containing compound and a photosensitive polyimide capable of reacting with the epoxy group of the epoxy group-containing compound, and includes a first cover layer formed on the first conductive wiring layer and extending into and filling the through hole.

Owner:MICROCOSM TECH

Method for making a microelectronic interposer

InactiveUS20060040522A1Effective and low resistance electrical connectionImprove bindingSemiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A microelectronic interposer is made by providing a sacrificial layer over the surface of a planar body. Apertures are formed passing through the body and the sacrificial layer. A layer of an electrically conductive structural material is deposited in each of the apertures and over the sacrificial layer, proximate to each aperture to thereby form contacts. The sacrificial layer is removed leaving the contacts with outwardly flaring peripheral portions spaced vertically above the surface of the planar body.

Owner:TESSERA INC

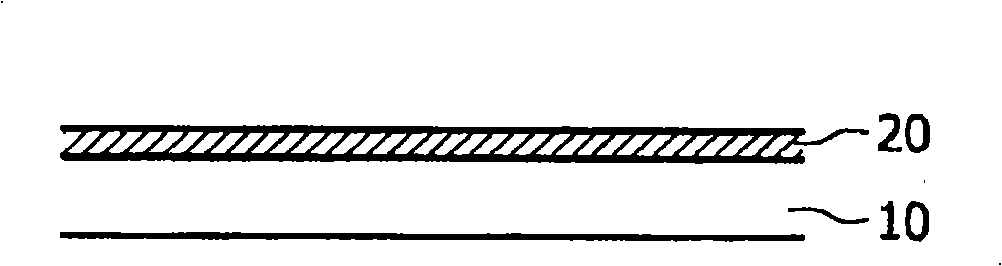

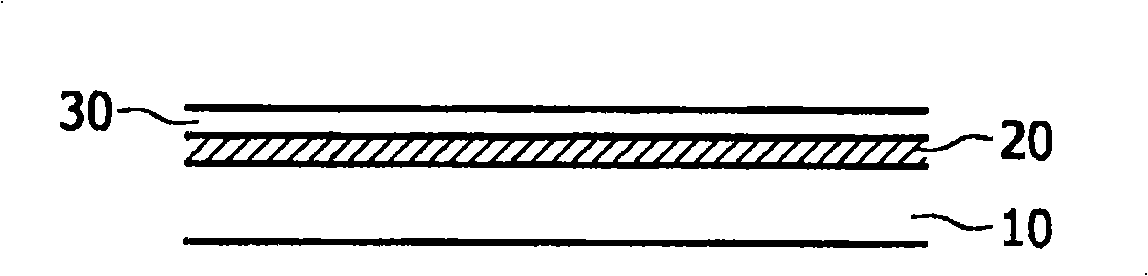

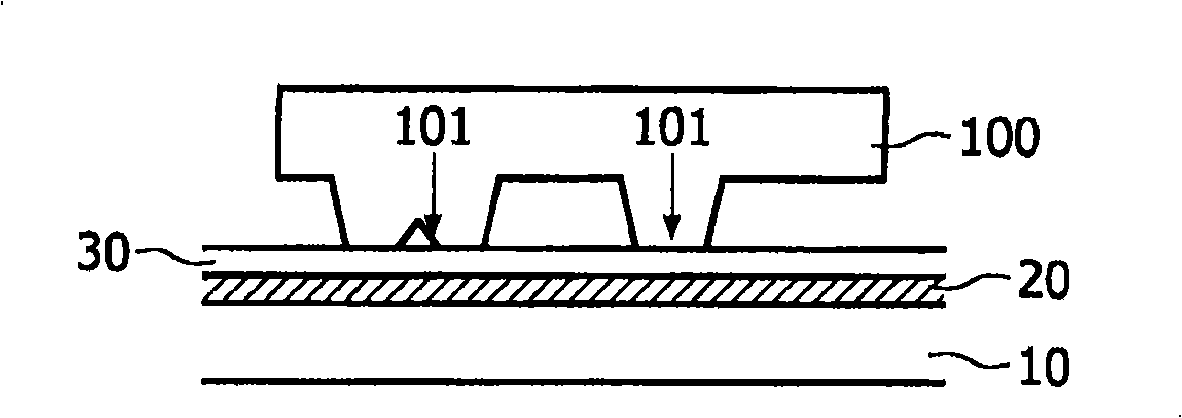

A method of manufacturing a structure

InactiveCN101297398AEasily exposedMaterial nanotechnologyResist coatingMicrocontact printingGold layer

A gold layer (20) is patterned with a gold oxide mask (30), which mask is patterned with an acid, preferably with microcontactprinting. The gold oxide mask (30) is stable in alkalic etch solutions for the gold layer (20). The gold oxide mask (30) may be maintained to create a reexposable gold pad (20).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Popular searches

Semiconductor/solid-state device manufacturing Photomechanical exposure apparatus Photosensitive material processing Microlithography exposure apparatus Originals for photomechanical treatment Photosensitive materials for photomechanical apparatus Photographic processes Conductive pattern formation Conductive material chemical/electrolytical removal Printed element electric connection formation

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com