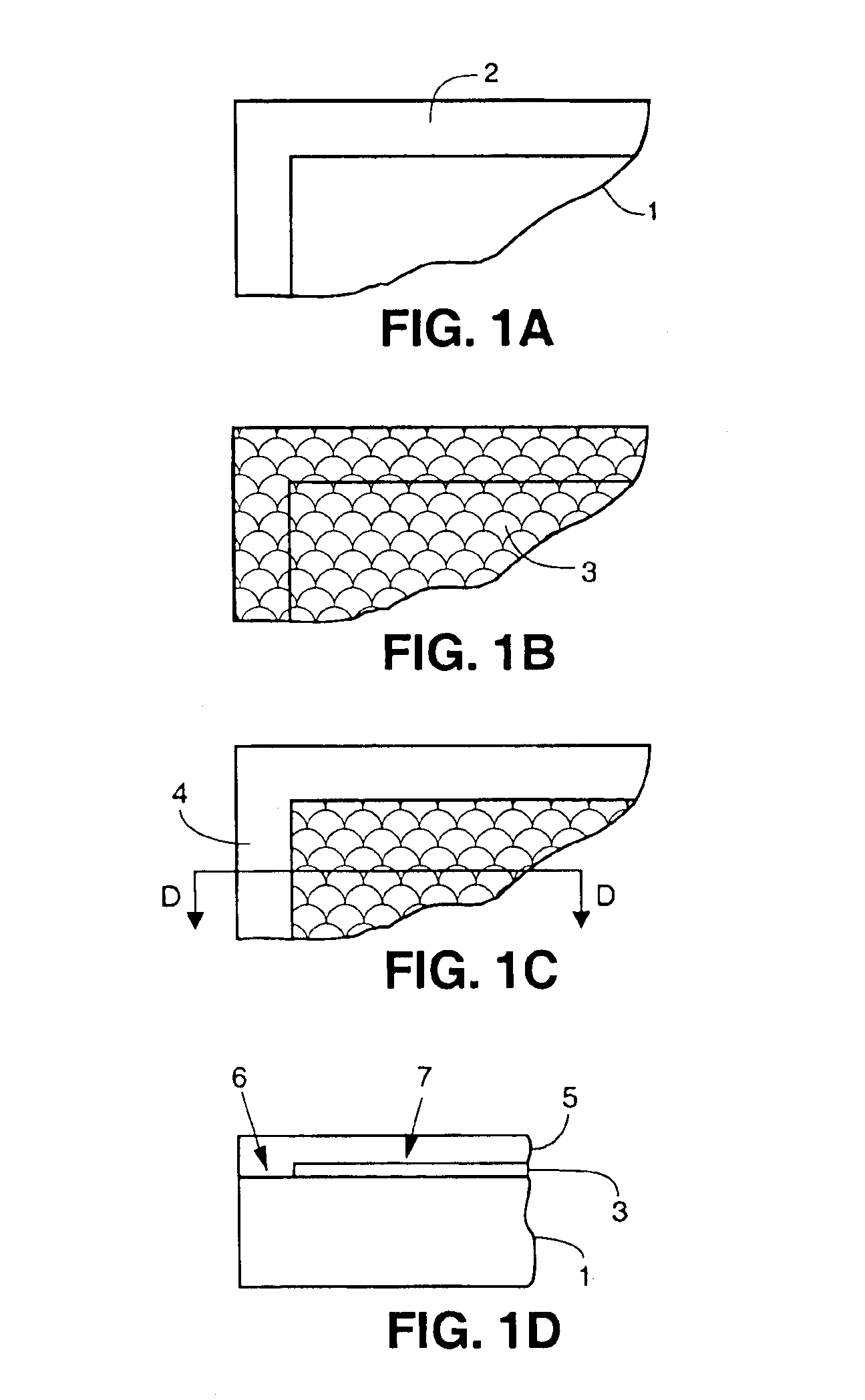

Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

977results about "Programmable/customizable/modifiable circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

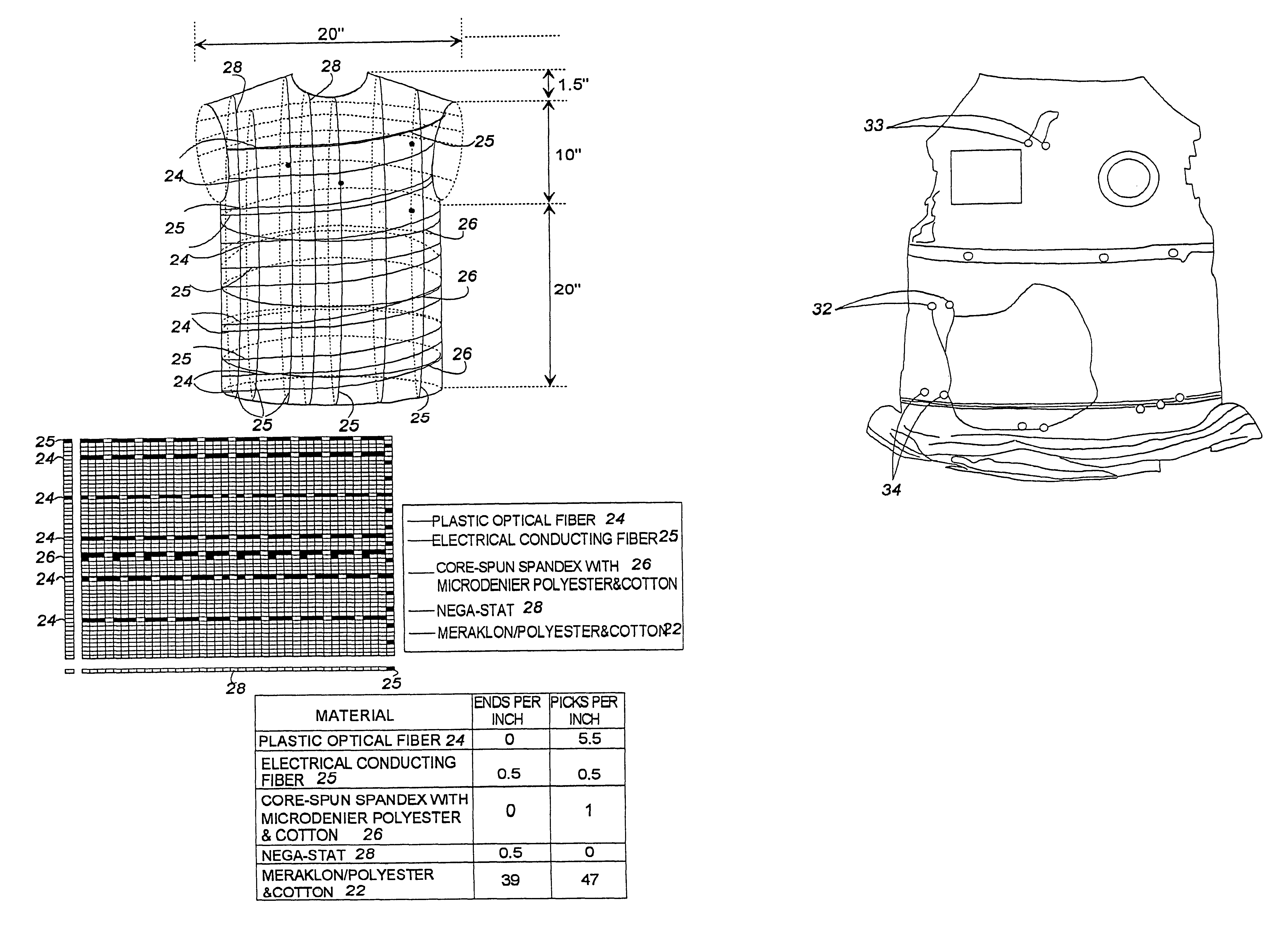

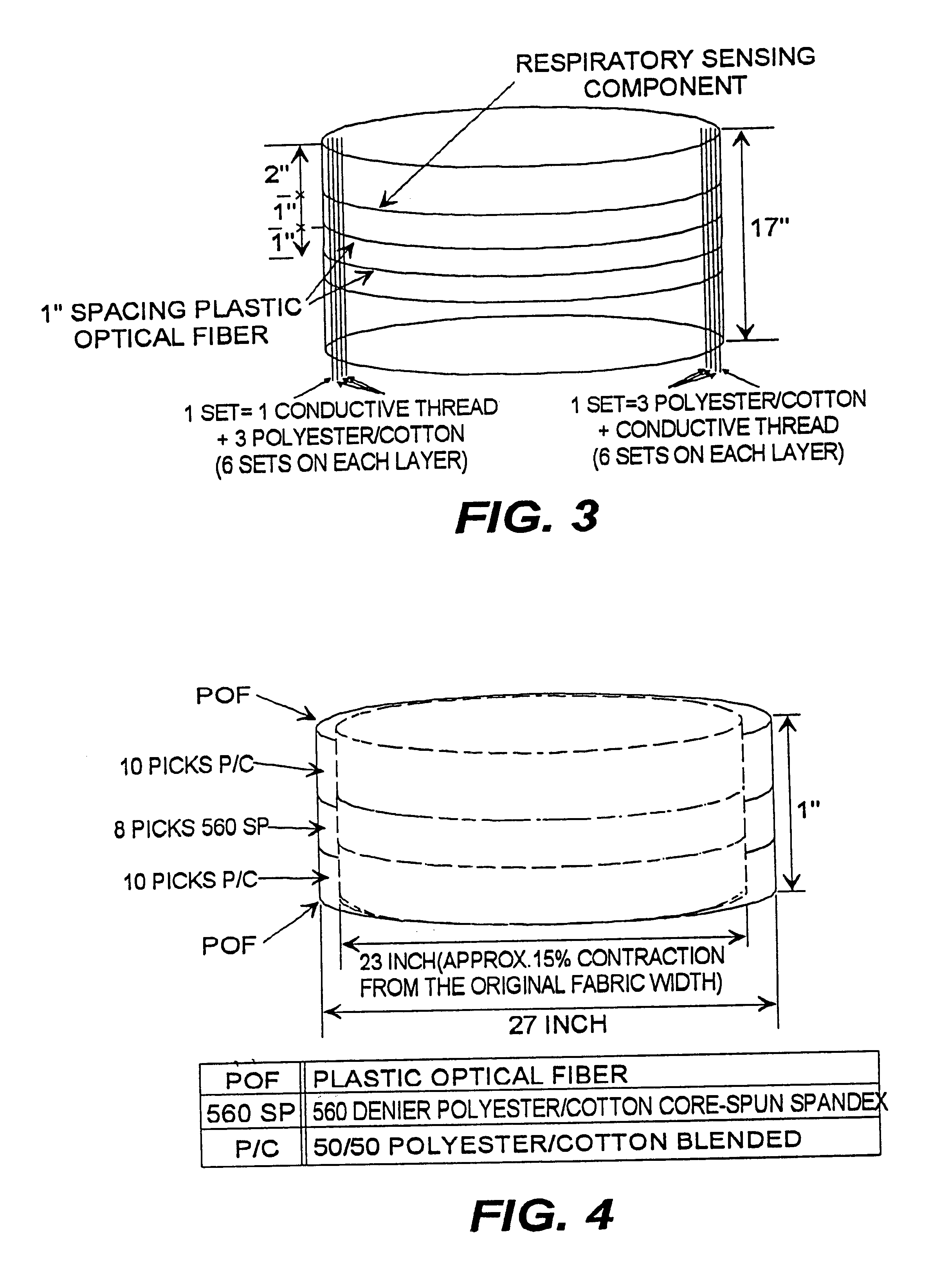

Fabric or garment with integrated flexible information infrastructure

InactiveUS6381482B1Raise the ratioImprove high temperature stabilityWeft knittingOrnamental textile articlesInformation processingEngineering

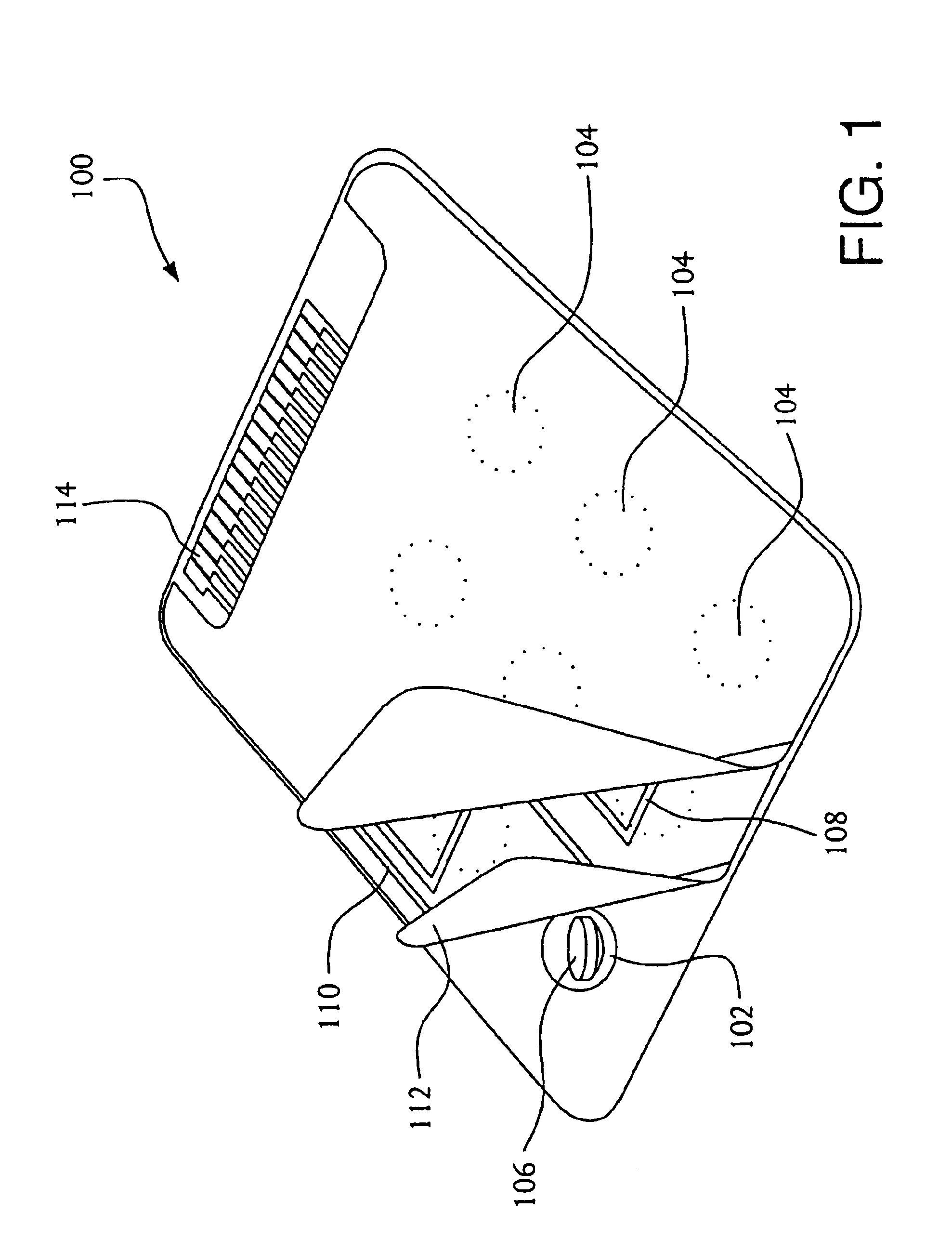

A fabric, in the form of a woven or knitted fabric or garment, including a flexible information infrastructure integrated within the fabric for collecting, processing, transmitting and receiving information concerning-but not limited to-a wearer of the fabric. The fabric allows a new way to customize information processing devices to "fit" the wearer by selecting and plugging in (or removing) chips / sensors from the fabric thus creating a wearable, mobile information infrastructure that can operate in a stand-alone or networked mode. The fabric can be provided with sensors for monitoring physical aspects of the wearer, for example body vital signs, such as heart rate, EKG, pulse, respiration rate, temperature, voice, and allergic reaction, as well as penetration of the fabric. The fabric consists of a base fabric ("comfort component"), and an information infrastructure component which can consist of a penetration detection component, or an electrical conductive component, or both. The preferred penetration detection component is a sheathed optical fiber. The information infrastructure component can include, in addition to an electrically conductive textile yarn, a sensor or a connector for a sensor. A process is provided for making an electrical interconnection between intersecting electrically conductive yarns. Furthermore, a process is established for sheathing the plastic optical fiber and protecting it.

Owner:GEORGIA TECH RES CORP

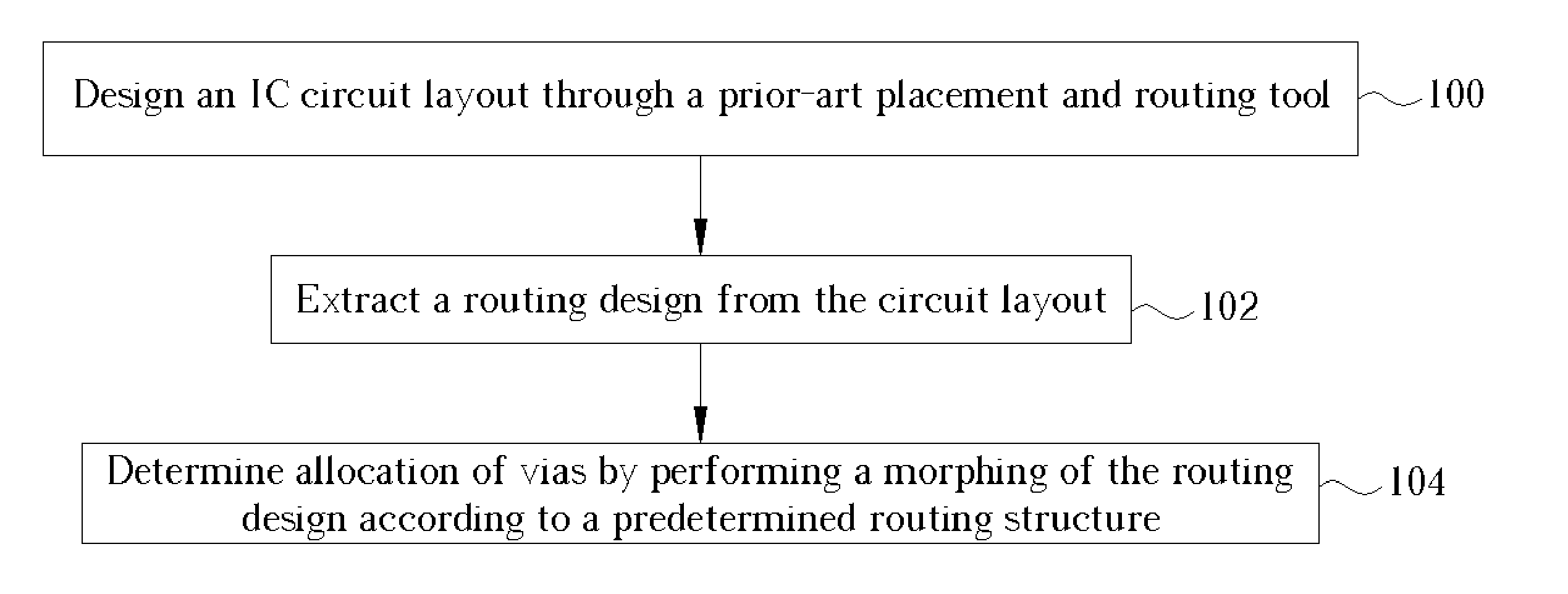

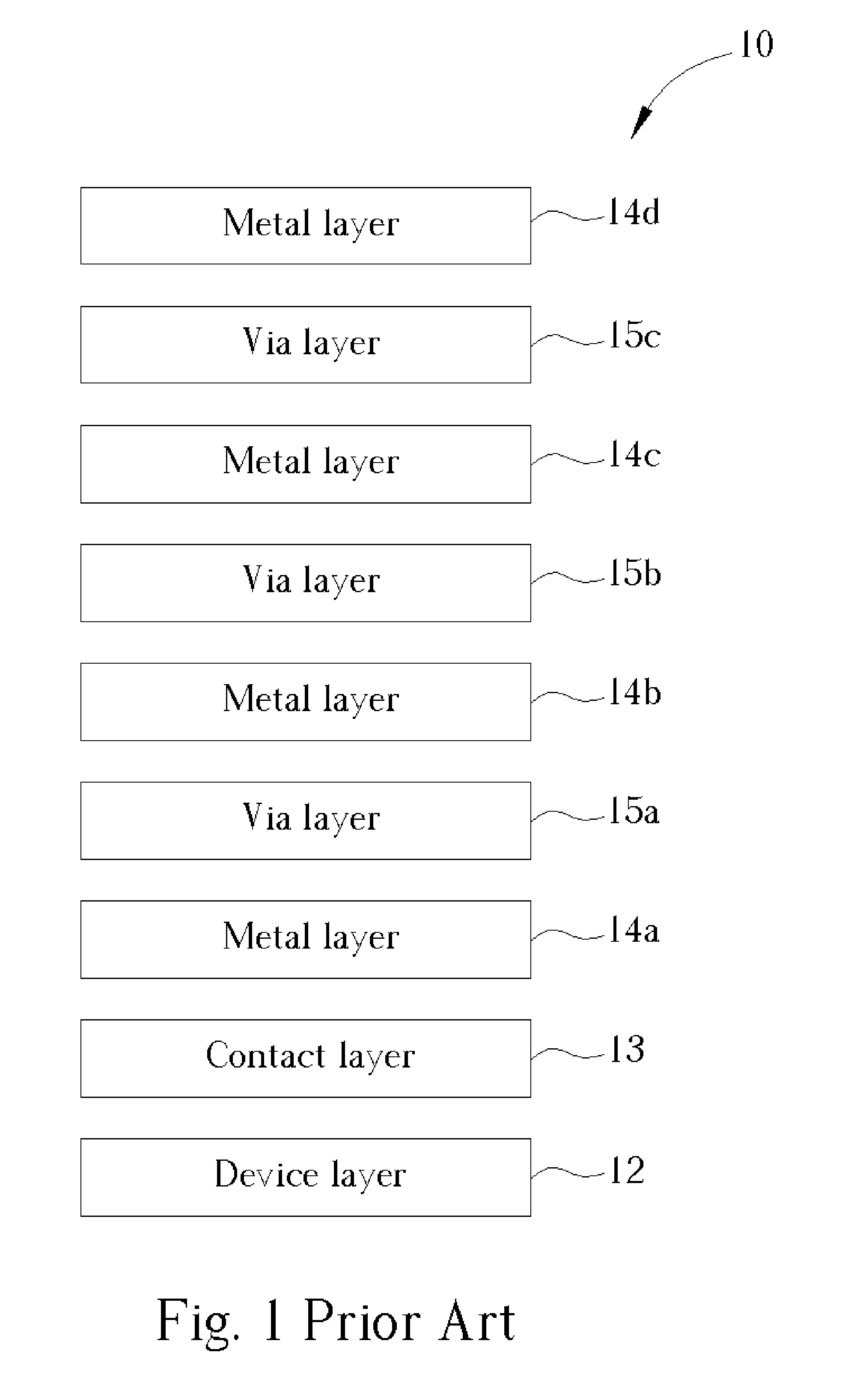

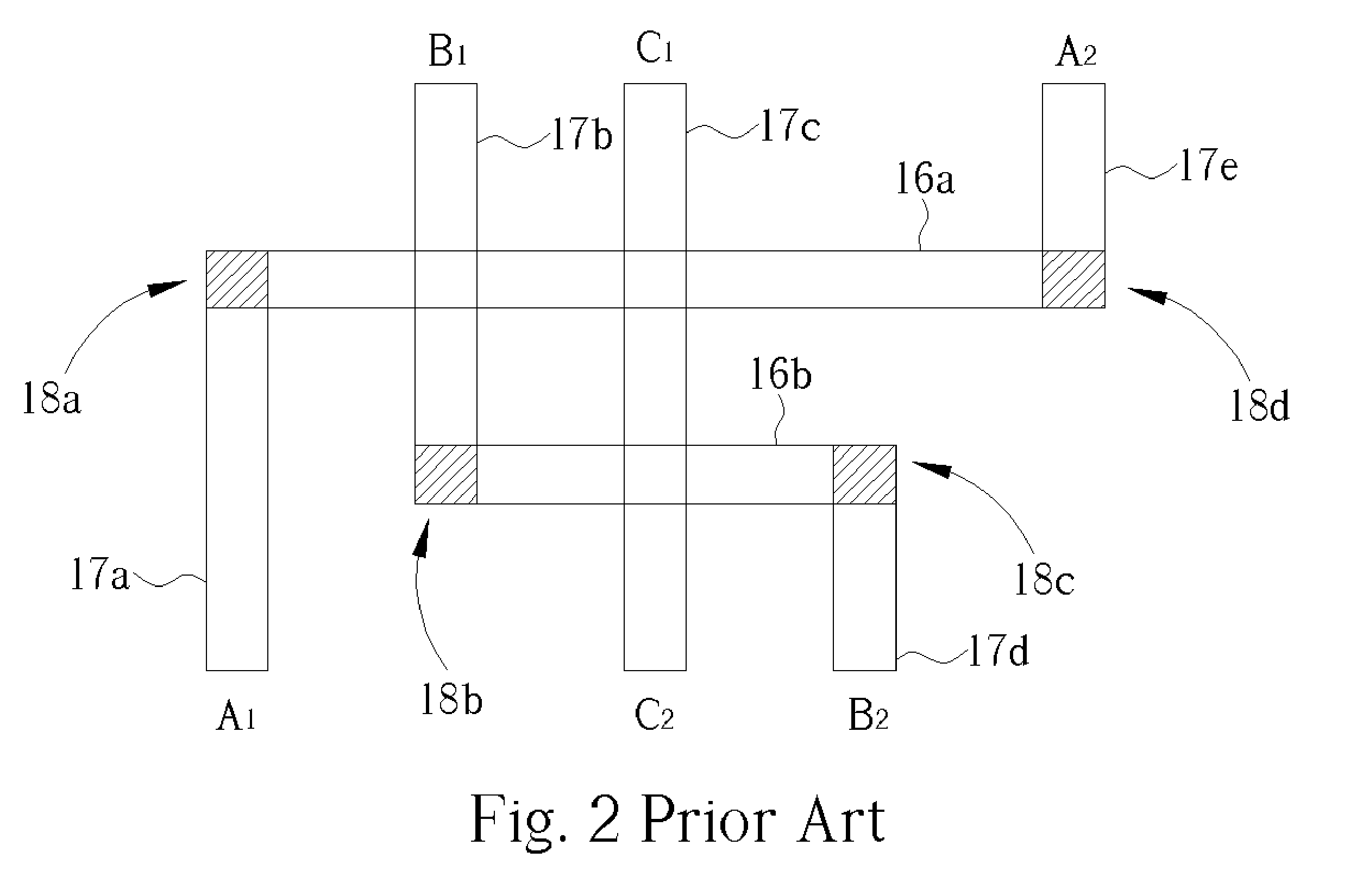

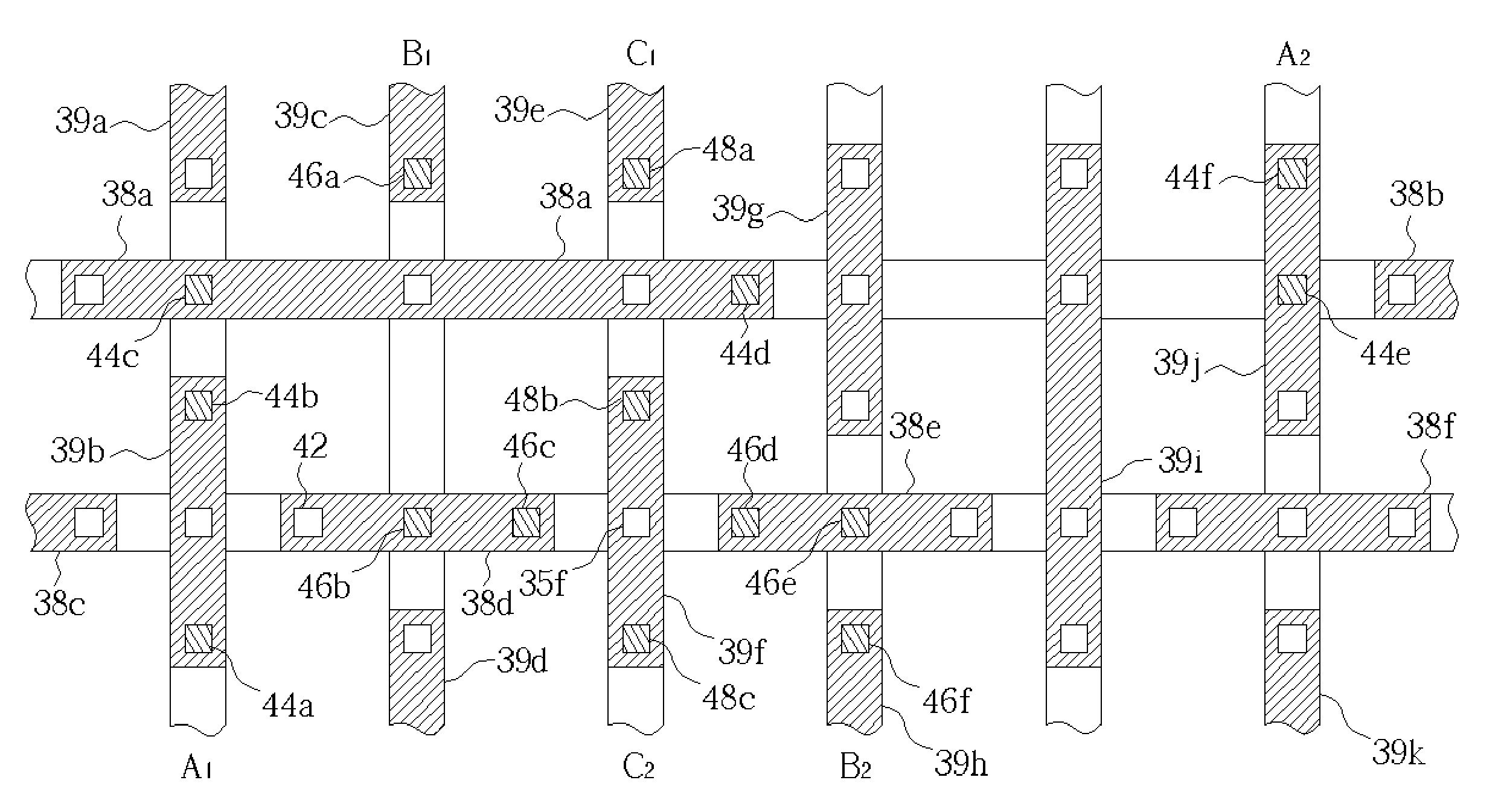

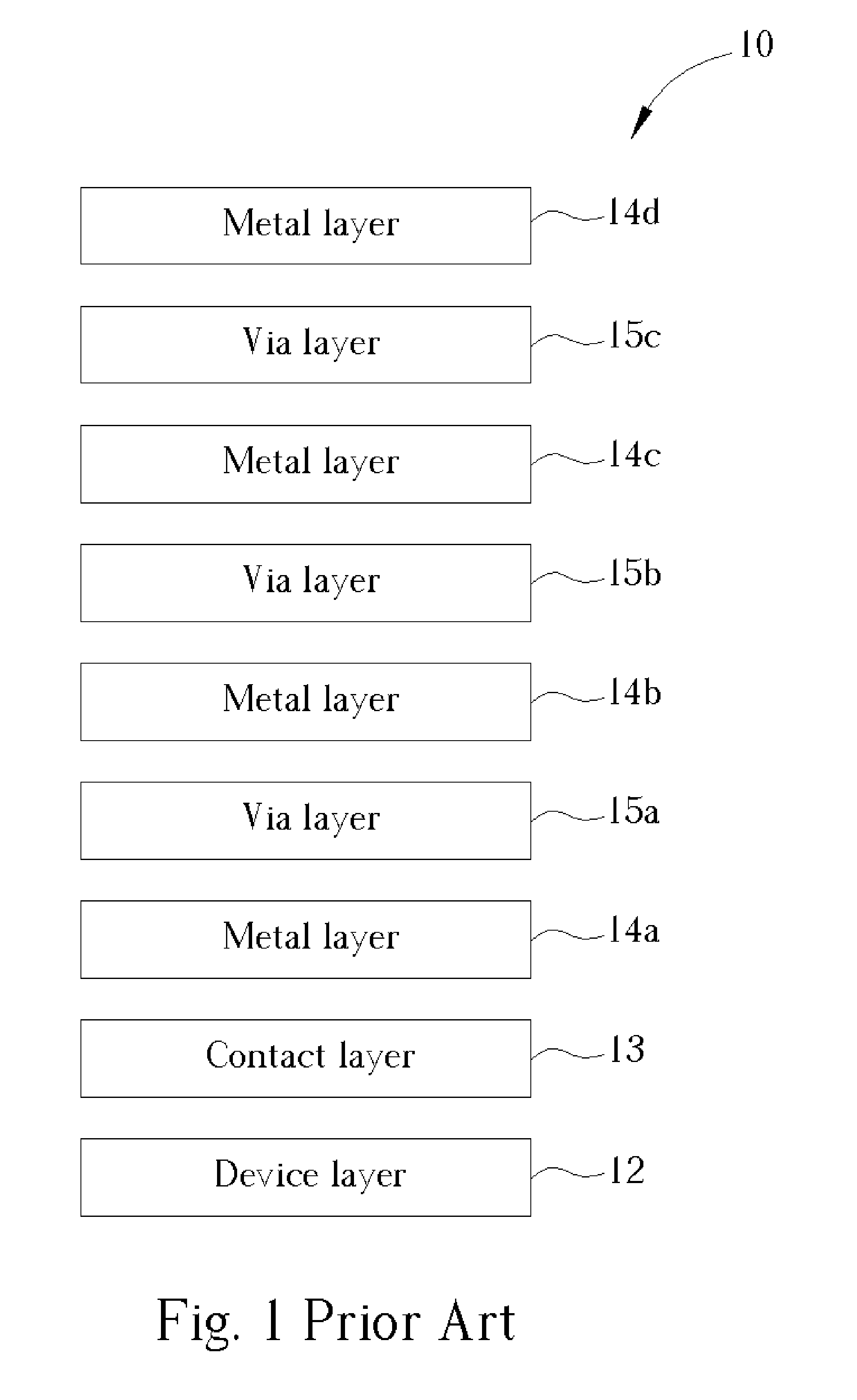

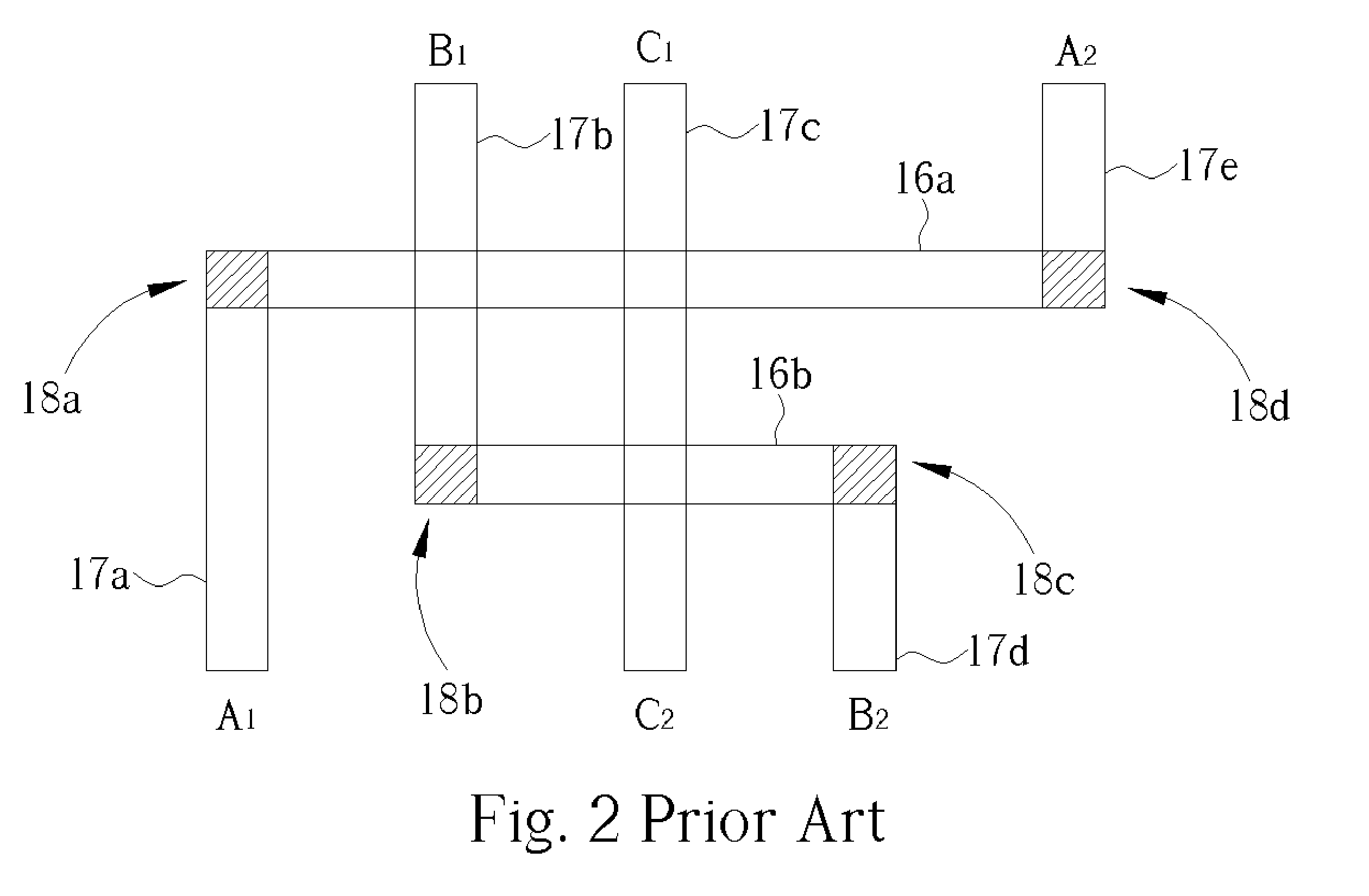

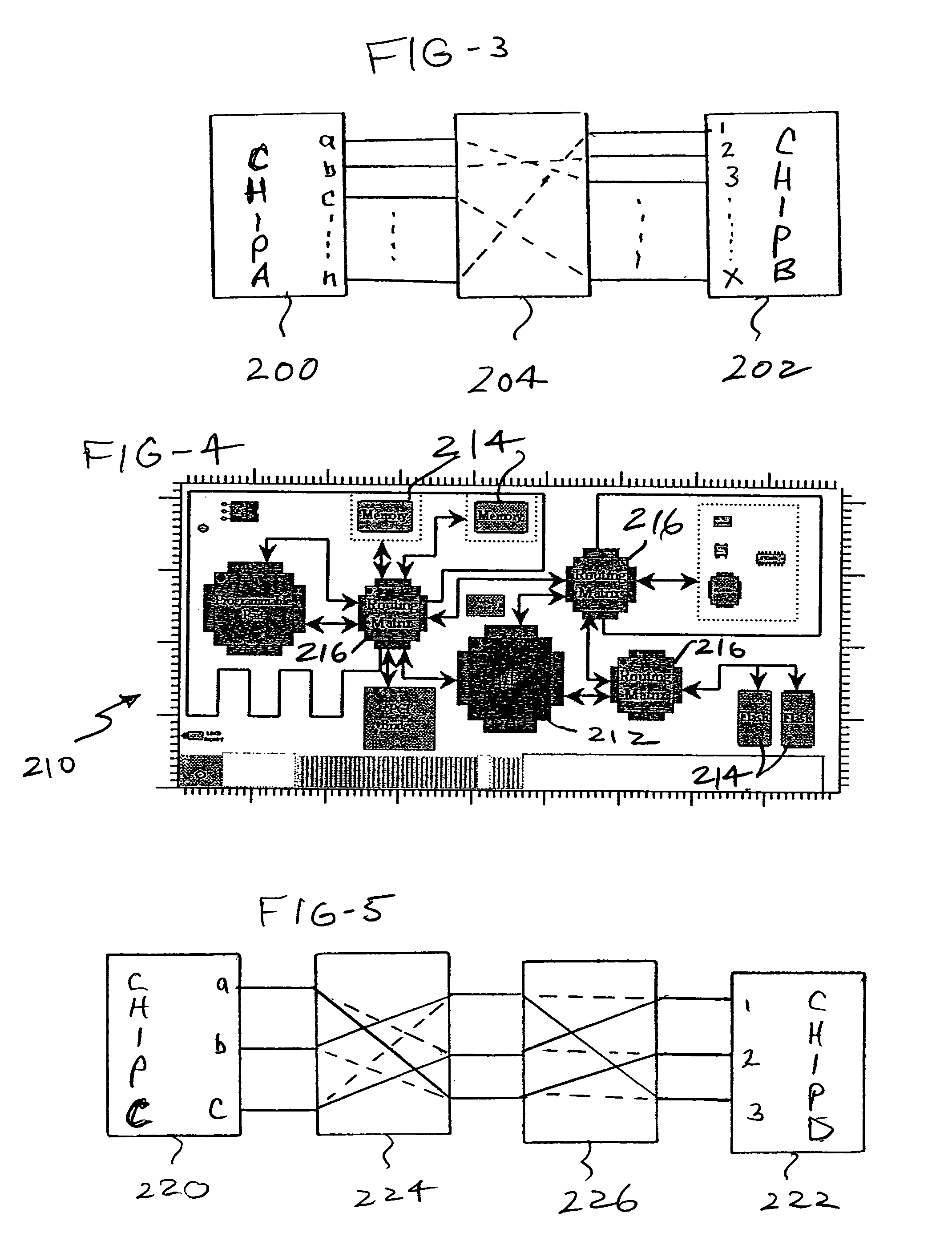

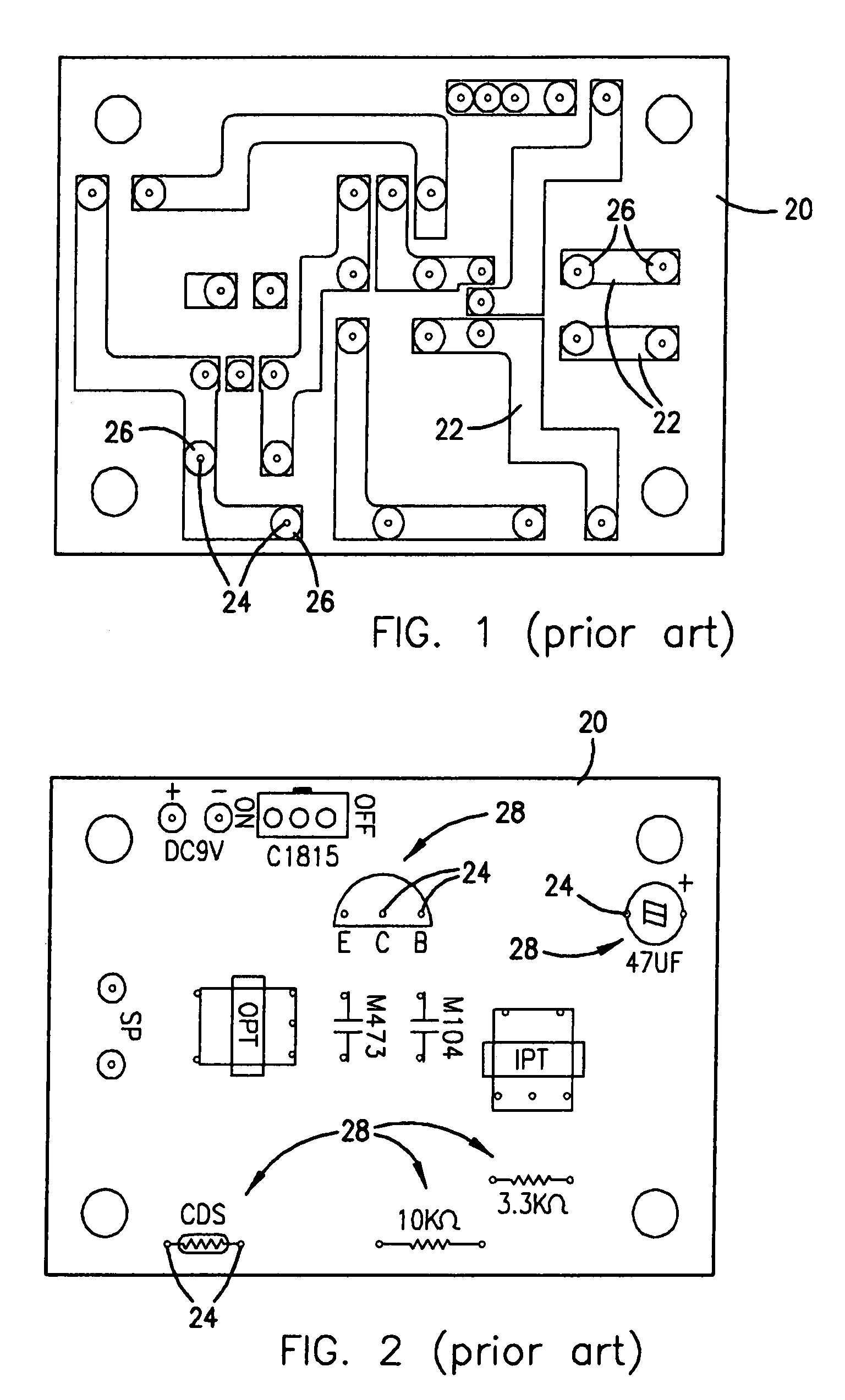

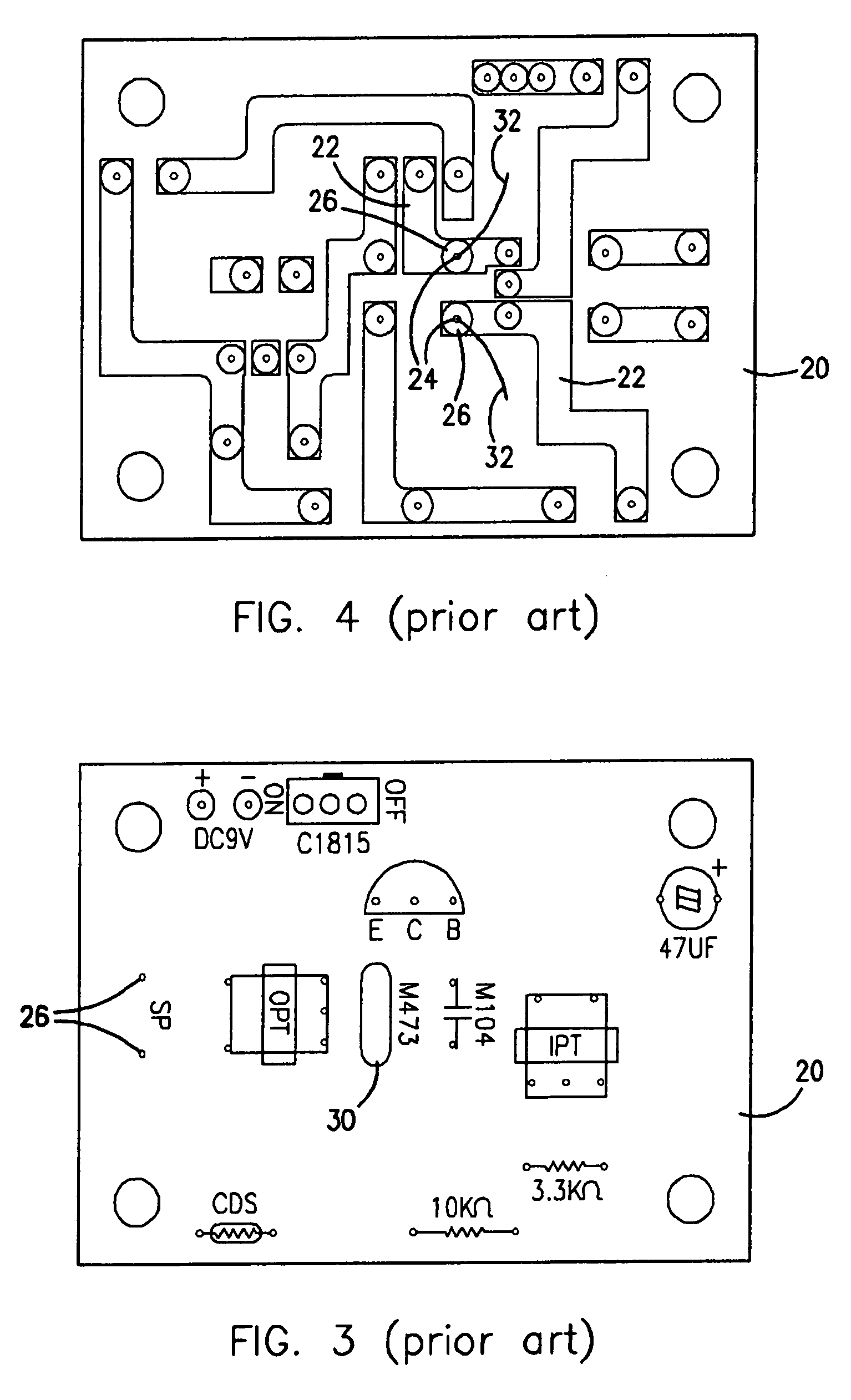

Method for programming a routing layout design through one via layer

ActiveUS20050055828A1Avoid feesPrinted circuit assemblingLine/current collector detailsComputer science

A method for programming a routing layout design through one via layer includes forming a plurality of metal traces on a first routing layer and a second routing layer, and positioning a plurality of vias within a via layer disposed between the first and second routing layers for connecting the metal traces on the first and second routing layers according to a first current route defined by a predetermined circuit layout design to connect a first node and a second node so as to establish a second current route equivalent to the first current route.

Owner:FARADAY TECH CORP

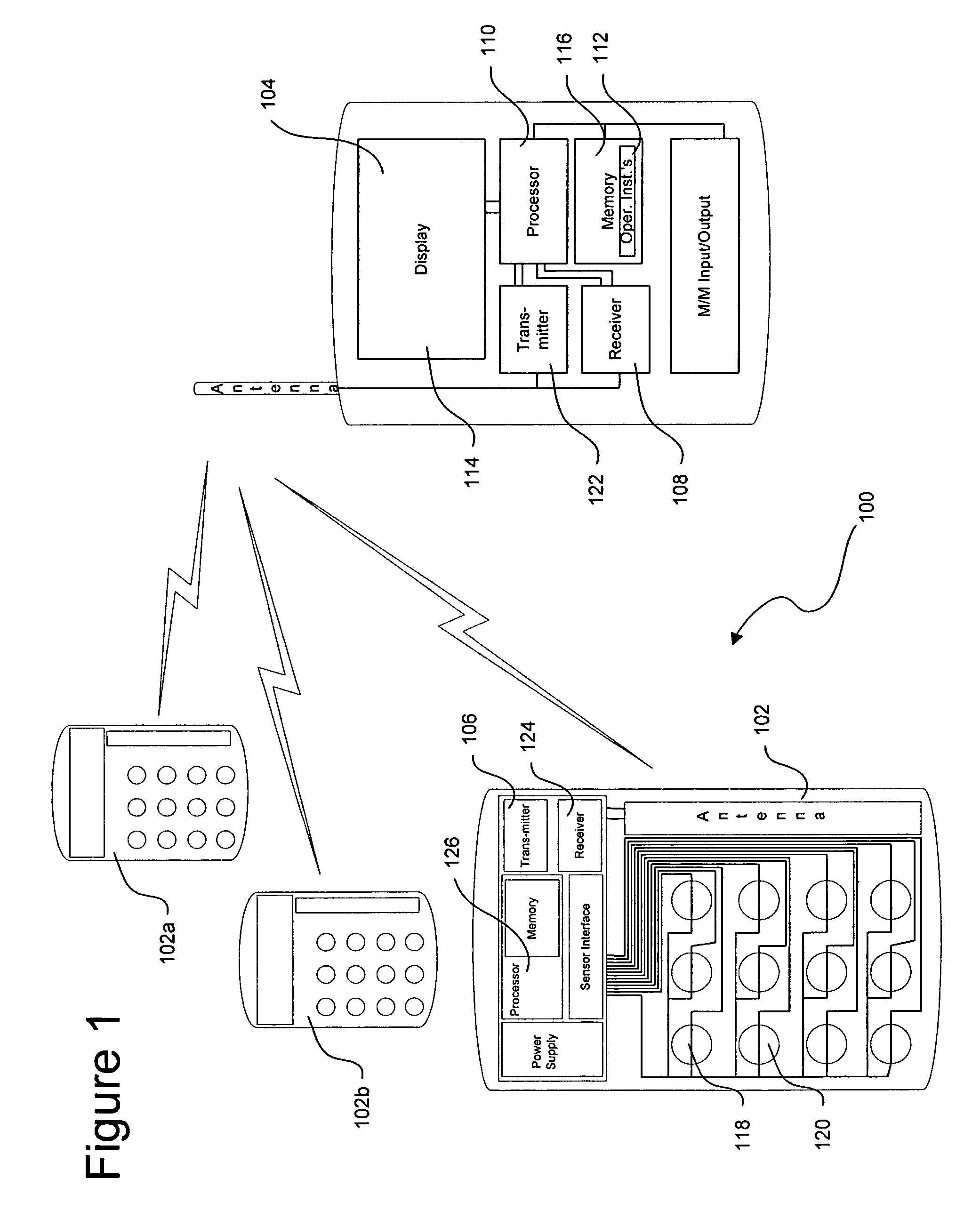

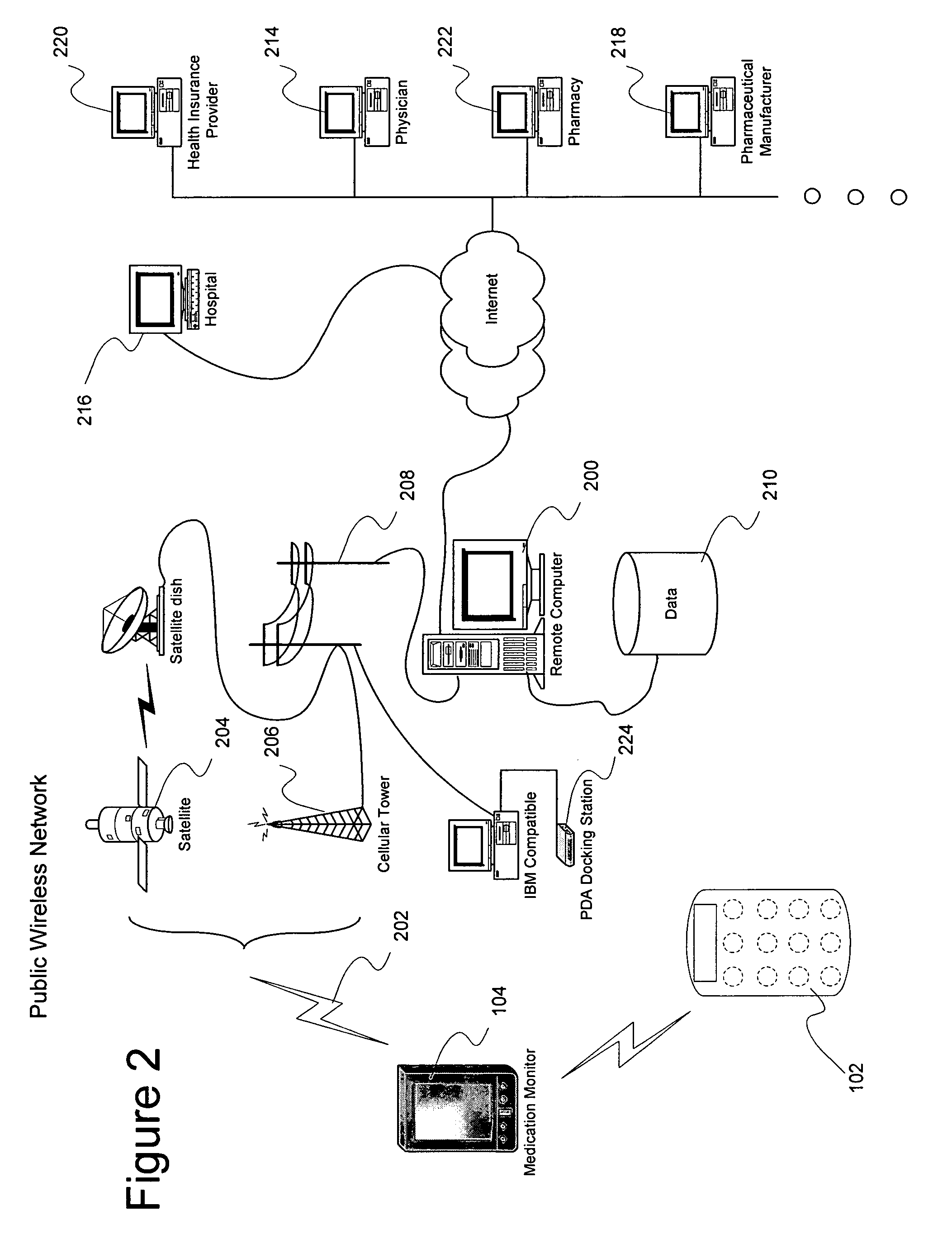

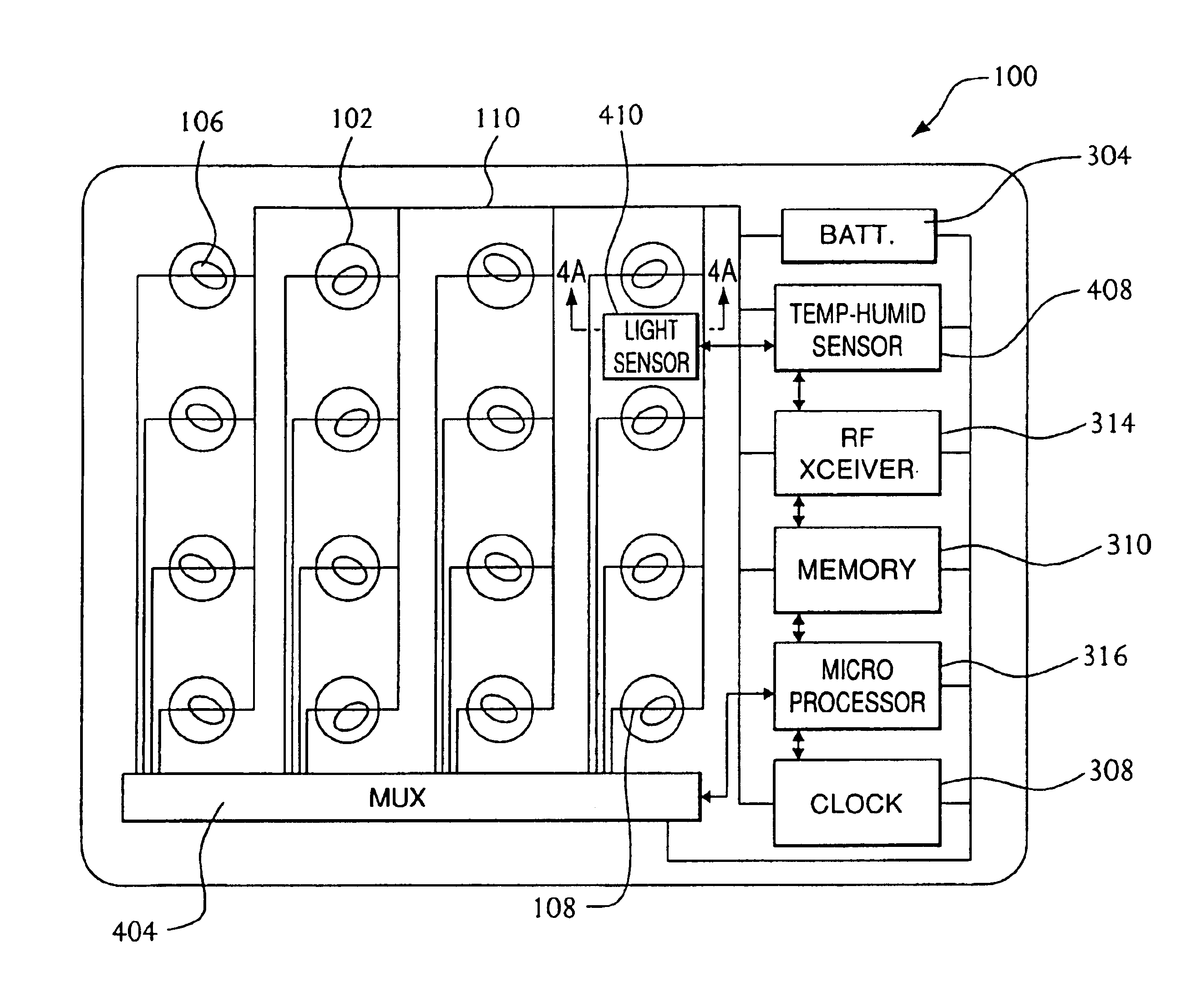

Drug delivery management system

The present invention relates to assisting patients in the taking of medication, and to assisting third parties in accumulating information regarding patient medication intake. The invention may be embodied a system including a portable medication monitor used in association with an instrumented medication package to provide intake data acquisition and patient support functions. The system may further be connected to a computer or computer network allowing information distribution between the medication monitor and third parties, such as physicians or pharmacists.

Owner:DDMS HLDG

Method for programming a routing layout design through one via layer

A method for programming a routing layout design through one via layer includes forming a plurality of metal traces on a first routing layer and a second routing layer, and positioning a plurality of vias within a via layer disposed between the first and second routing layers for connecting the metal traces on the first and second routing layers according to a first current route defined by a predetermined circuit layout design to connect a first node and a second node so as to establish a second current route equivalent to the first current route.

Owner:FARADAY TECH CORP

Drug delivery management system

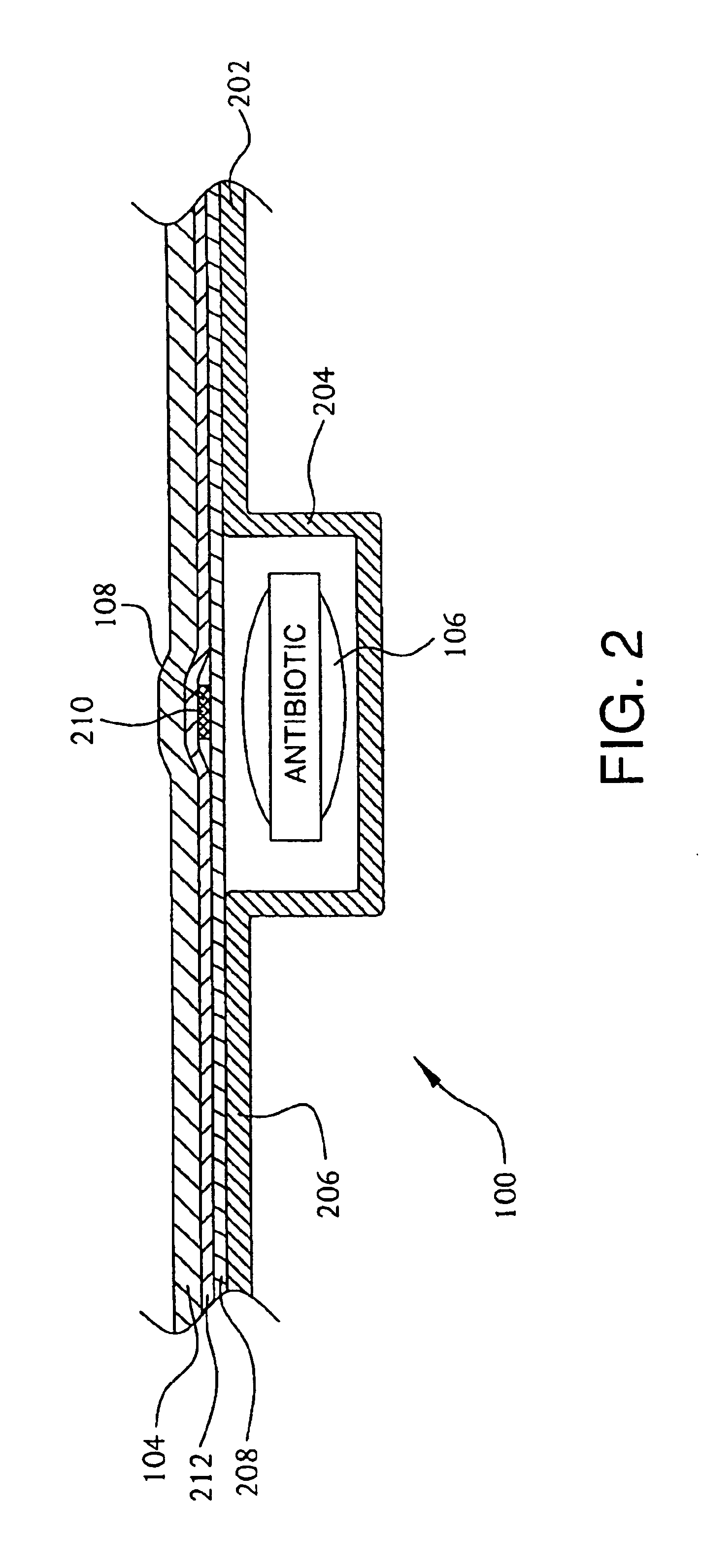

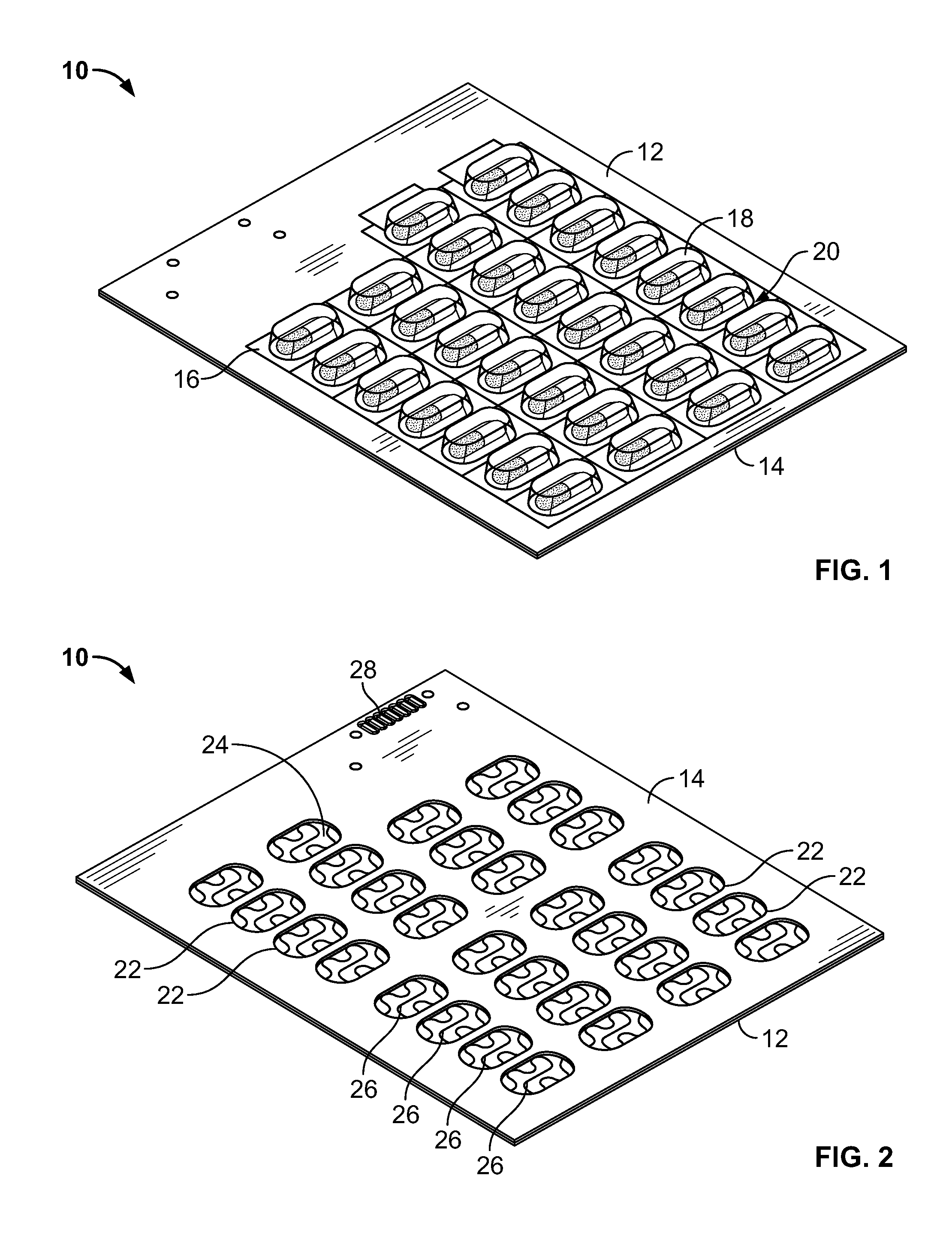

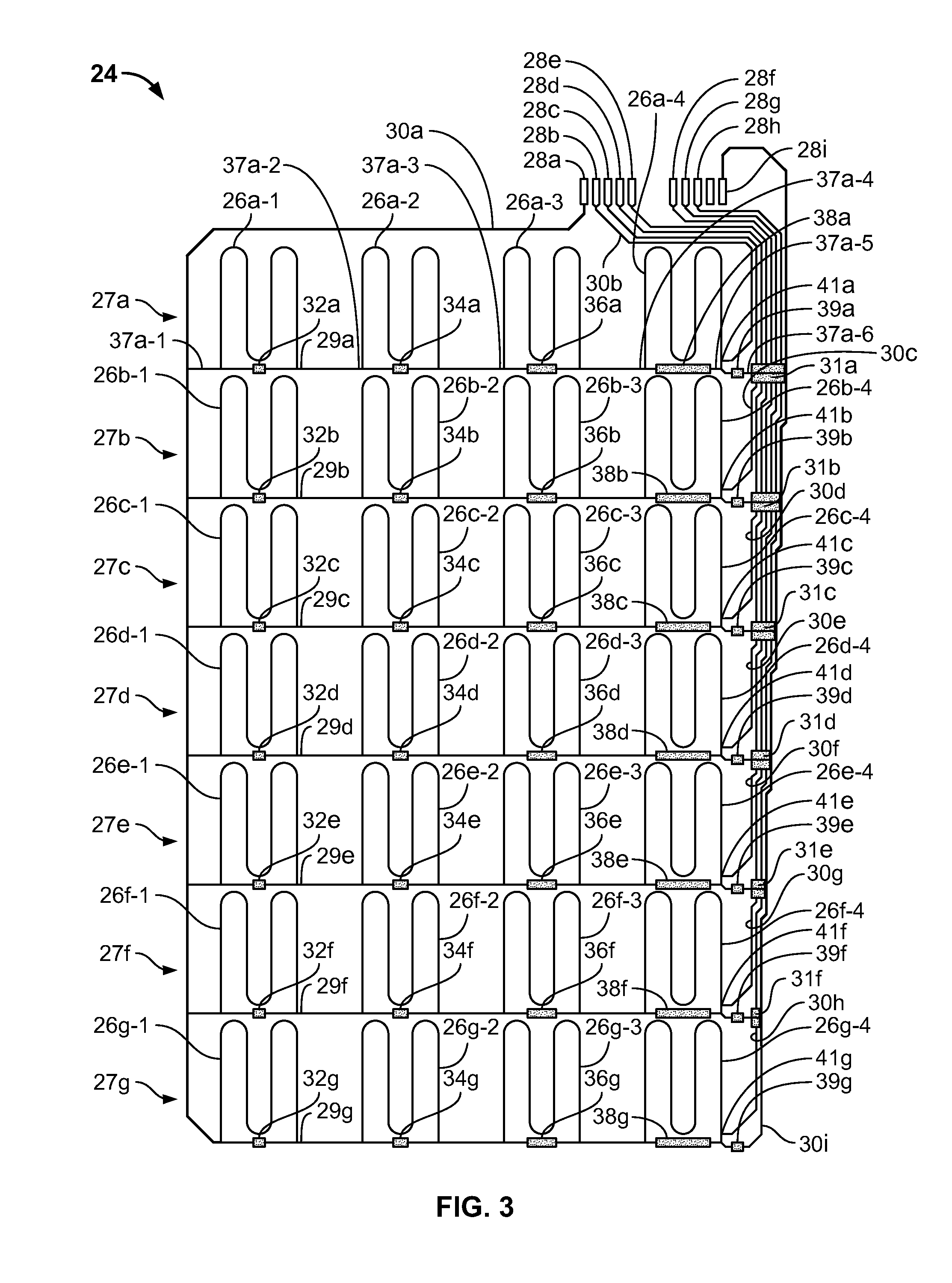

A system for managing delivery of pharmaceutical drugs is formed of a blister package that includes a plurality of cells arranged in a grid. Each of the cells is sealed by a breakable wall and holds a unit-dose of medication. A user gains access to the medication in a given cell by puncturing the breakable wall associated with the given cell. A severable conductor is positioned proximate to each breakable wall. The severable conductor associated with a given cell ruptures upon puncturing of the breakable wall associated with the given cell. A computer chip is electrically connected to the severable conductors. The computer chip senses the puncturing of each cell in the grid by monitoring the rupturing of each of the severable conductors. An RF transmitter is coupled to the computer chip. The RF transmitter sends information corresponding to usage of each of medications stored in the blister package to a remote information transceiver.

Owner:DDMS HLDG

Tamper resistant circuit boards

InactiveUS7015823B1Circuit security detailsPrinted circuit aspectsProgrammable logic devicePhysical Barrier

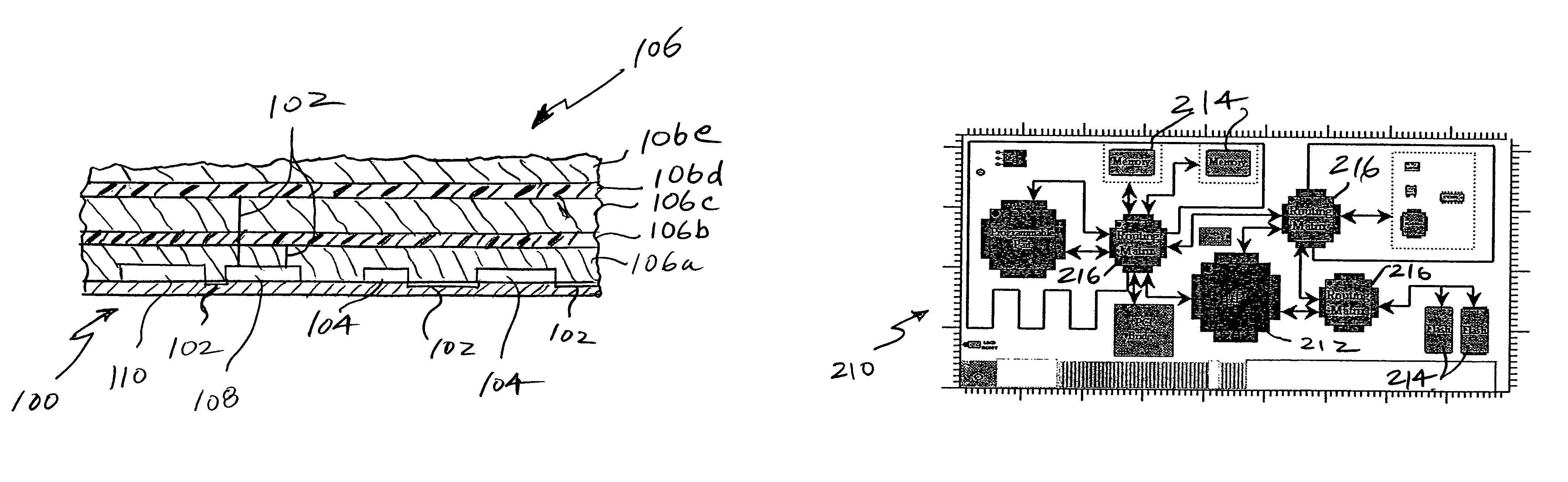

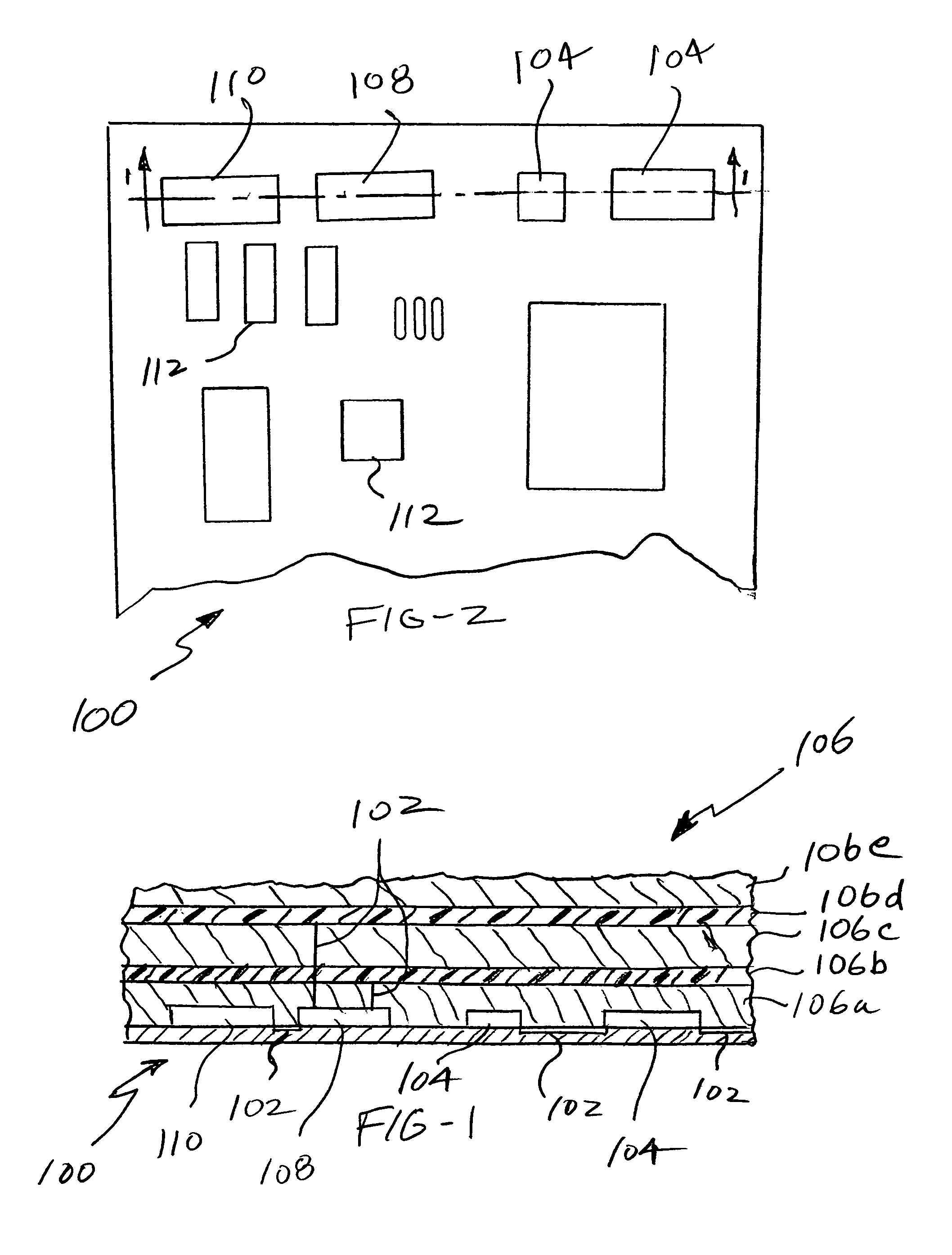

A physical barrier for a circuit board also functions as a tampering sensor or sensors monitored by electrical circuitry that generates a tamper signal for erasing information critical for the operation of the circuit board in the event of sensed tampering. One or more routing matrices configured in at least one programmable device is programmed to interconnect operating as well as optional dummy components on the board so that routing information is erased in the event of sensed tampering.

Owner:INFOSCITEX

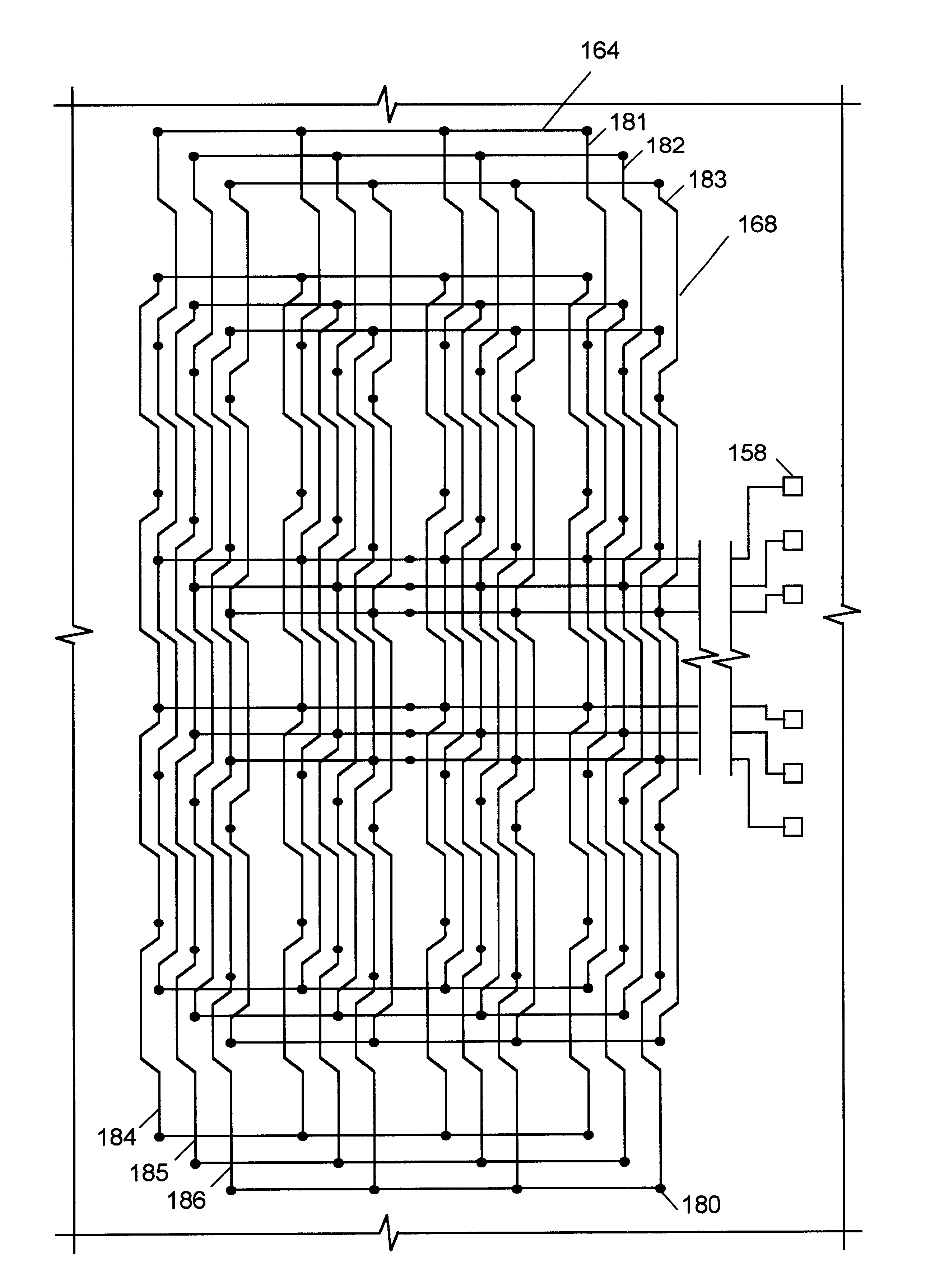

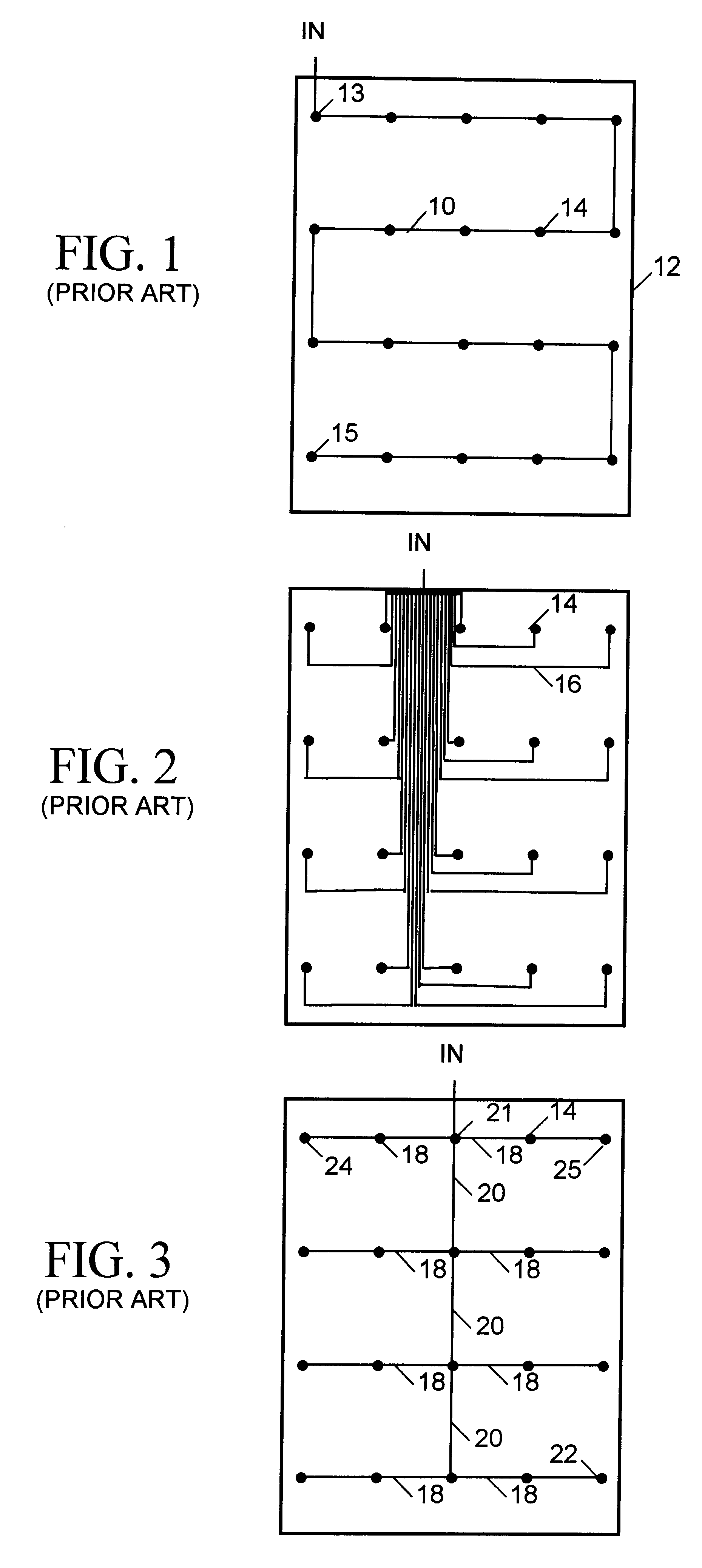

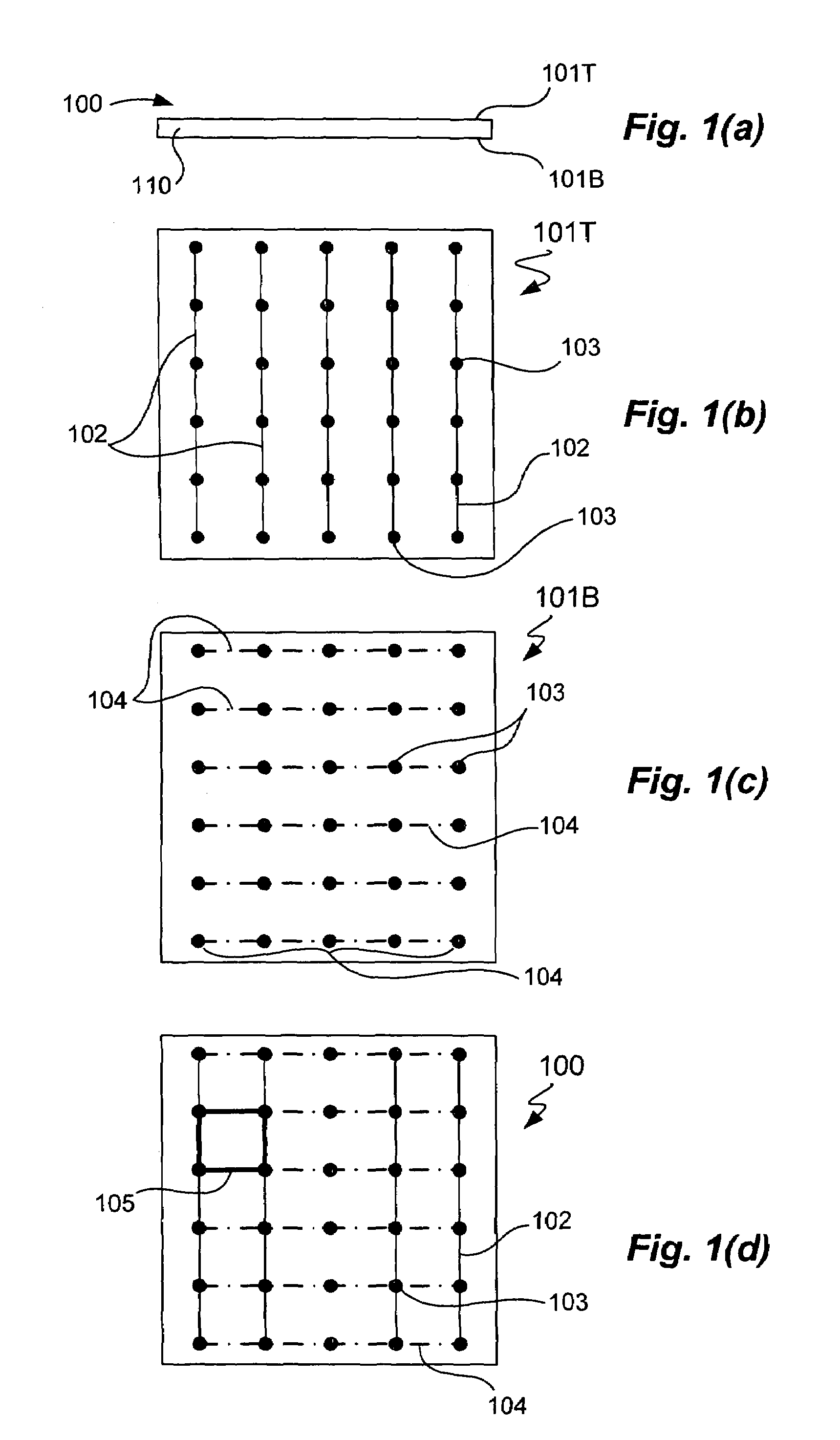

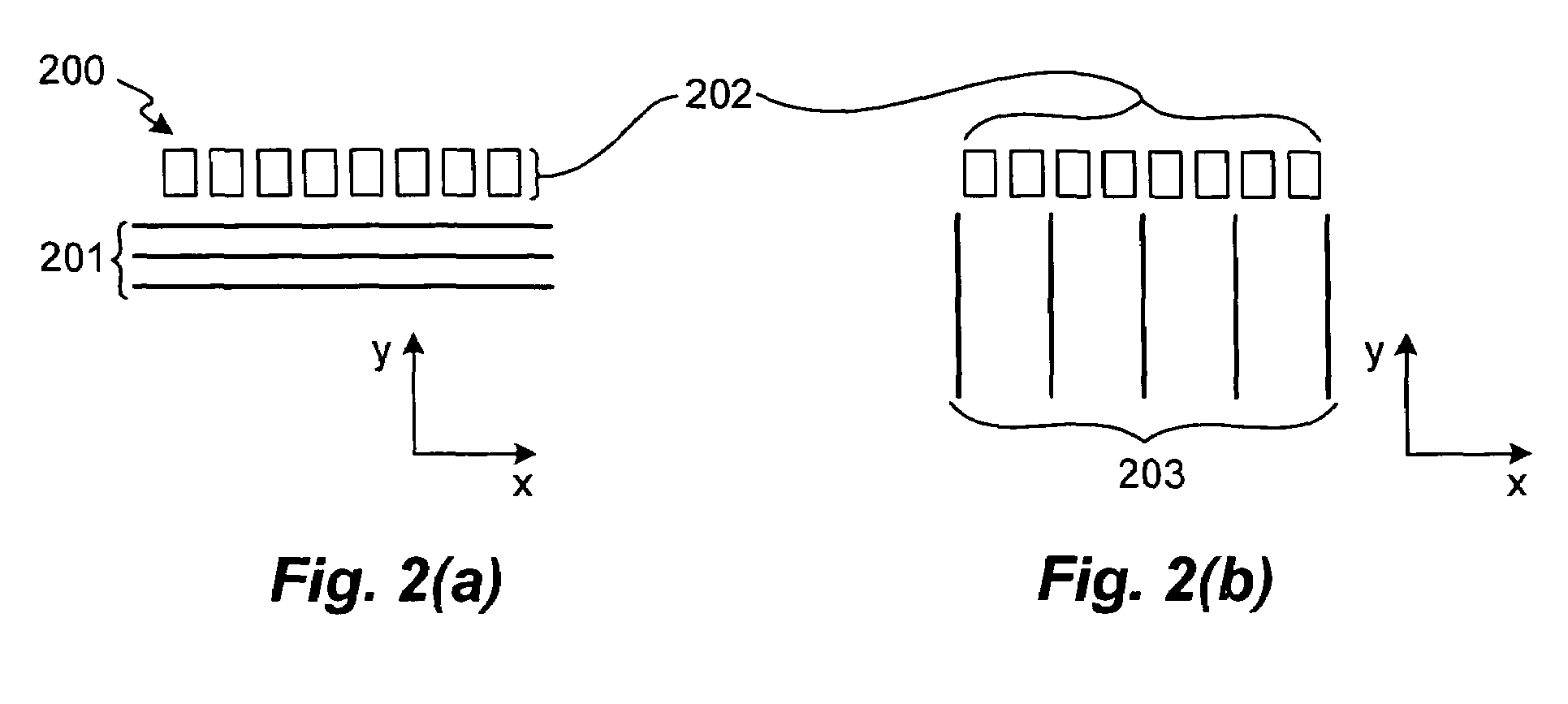

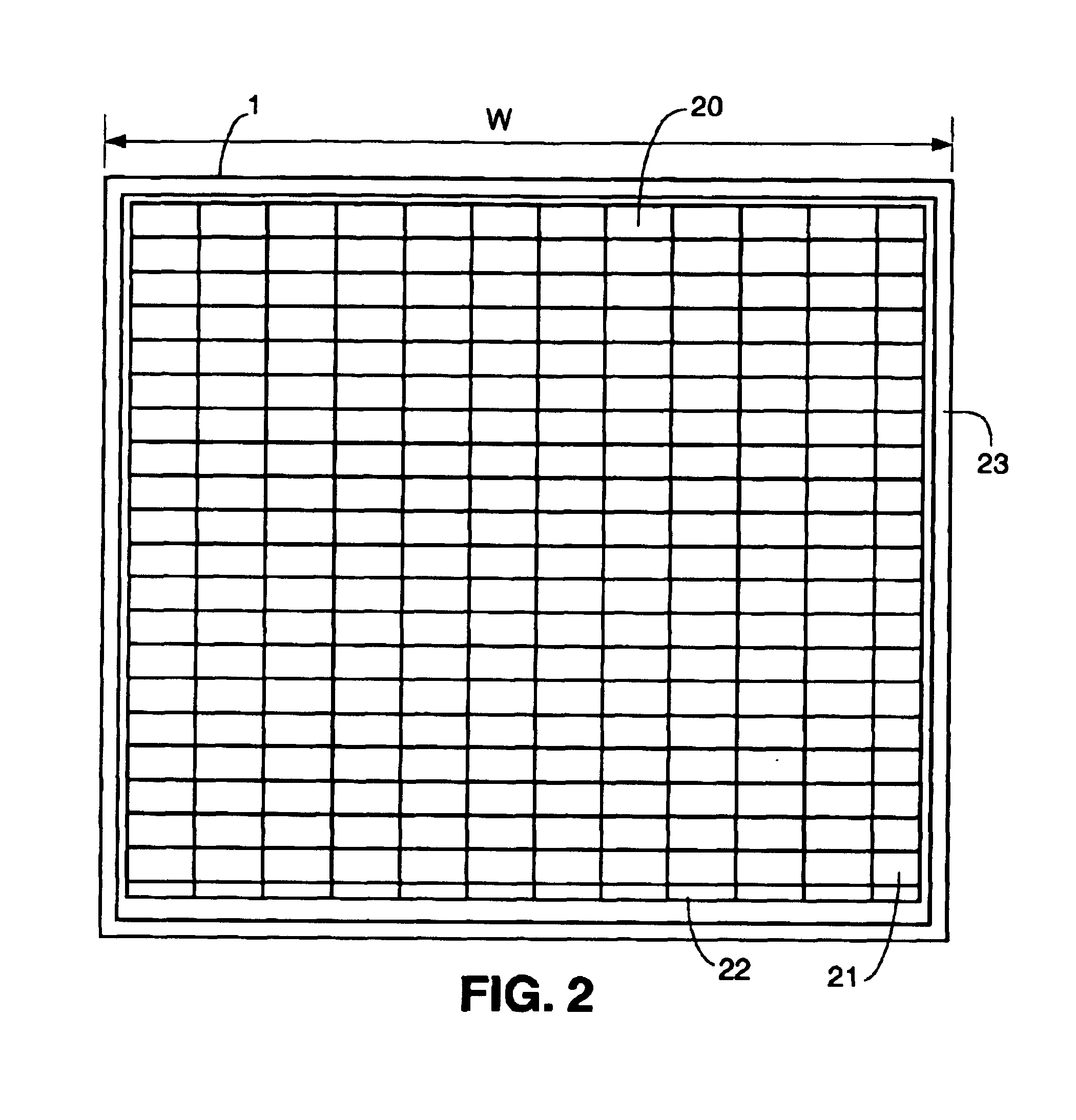

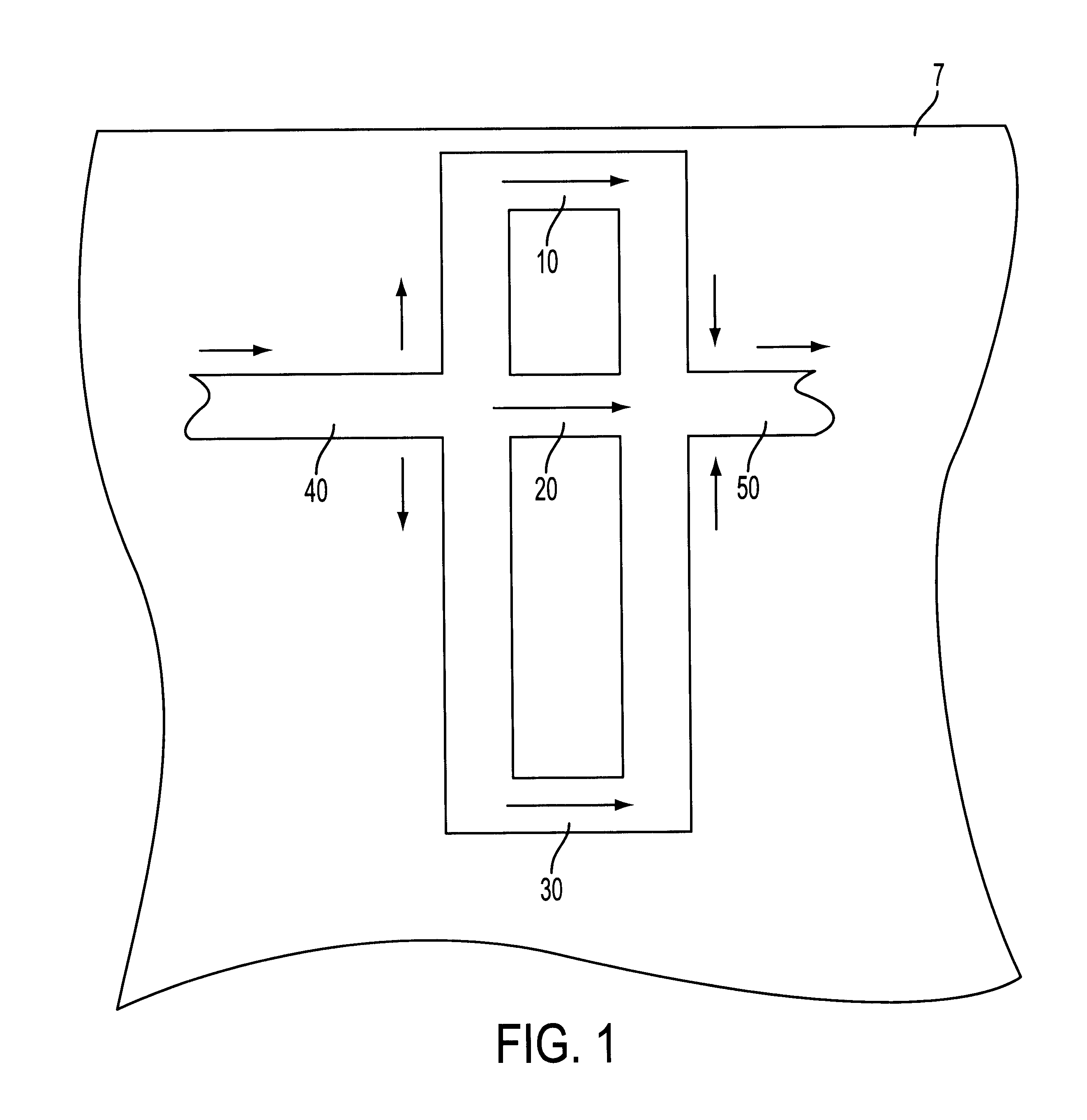

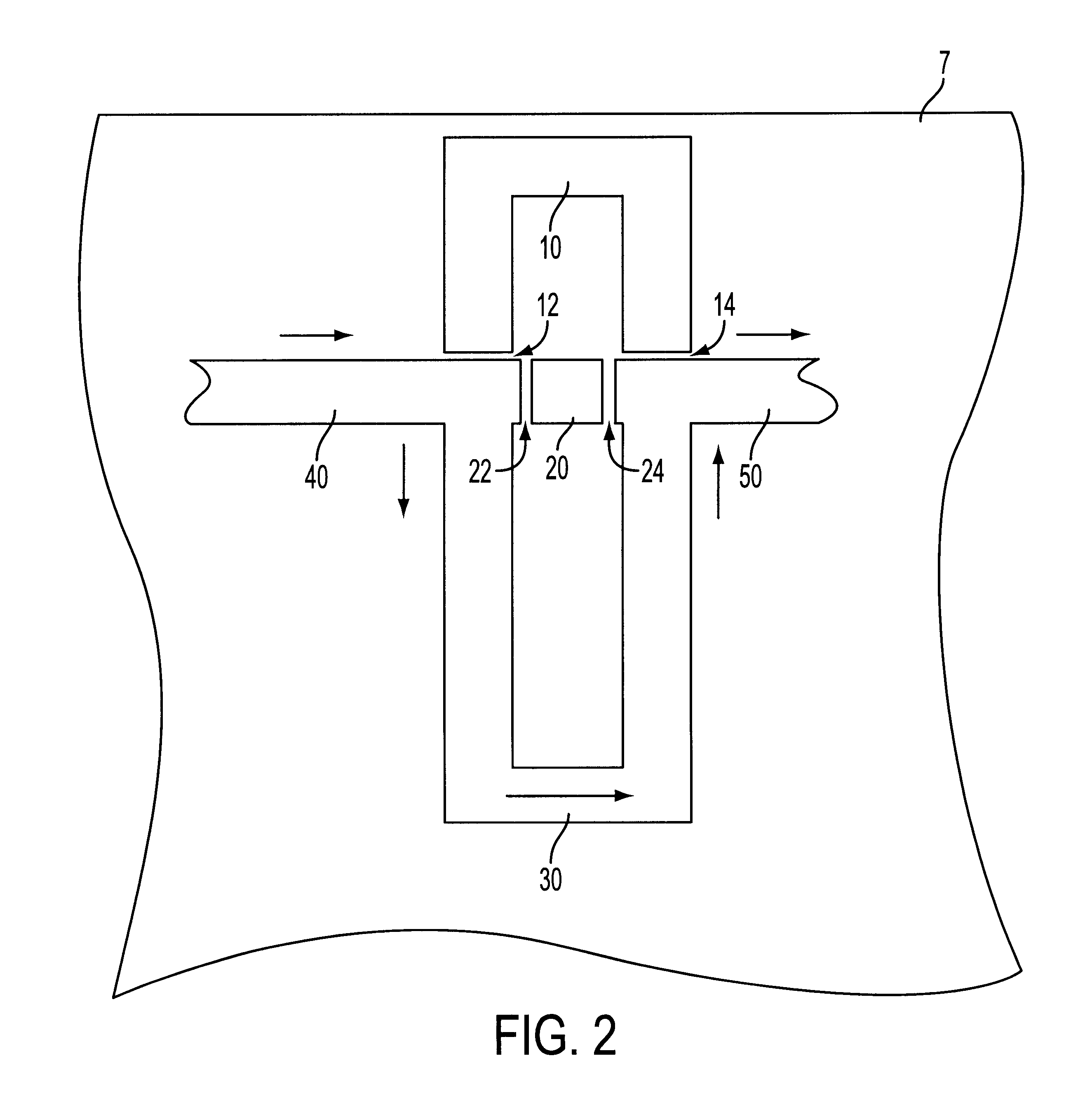

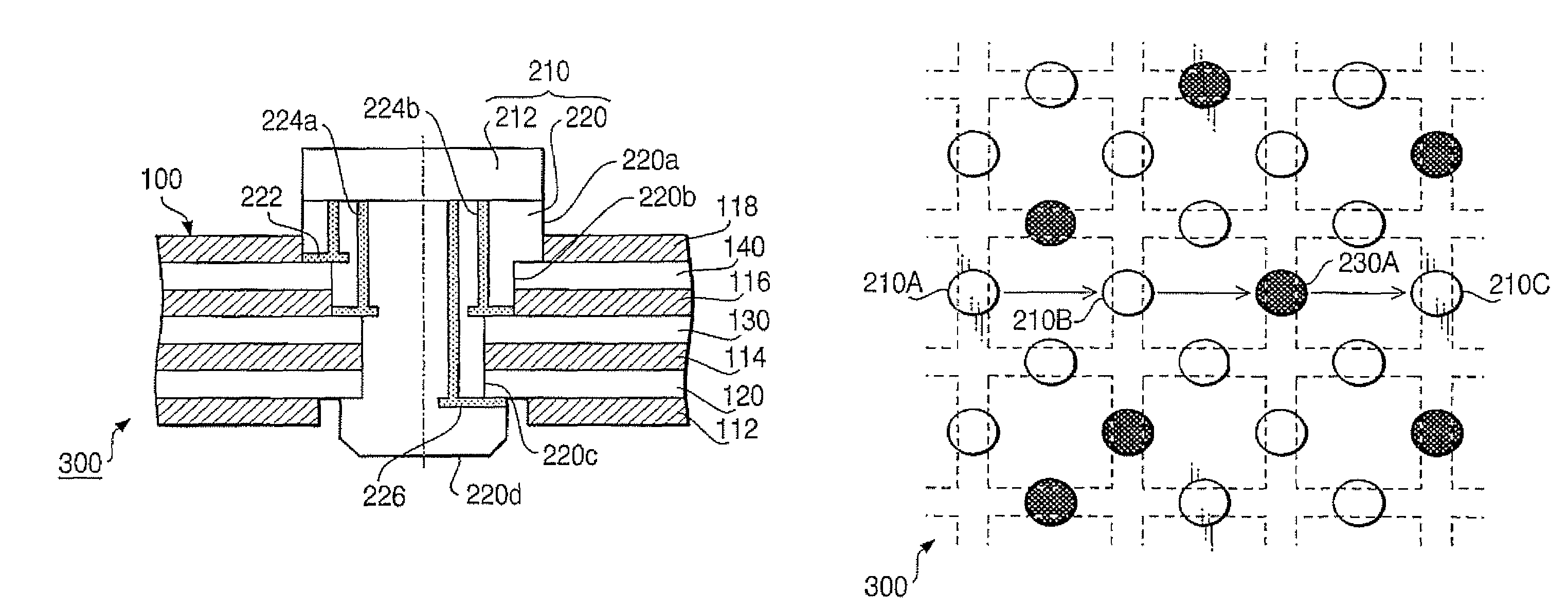

Closed-grid bus architecture for wafer interconnect structure

InactiveUS6603323B1Electrical measurement instrument detailsCross-talk/noise/interference reductionContact padSemiconductor

An interconnect structure employs a closed-grid bus to link an integrated circuit tester channel to an array of input / output (I / O) pads on a semiconductor wafer so that the tester channel can concurrently communicate with all of the I / O pads. The interconnect structure includes a circuit board implementing an array of bus nodes, each corresponding to a separate one of the I / O pads. The circuit board includes at least two layers. Traces mounted on a first layer form a set of first daisy-chain buses, each linking all bus nodes of a separate row of the bus node array. Traces mounted on a second circuit board layer form a set of second daisy-chain buses, each linking all bus nodes of a separate column of the bus node array. Vias and other circuit board interconnect ends of the first and second daisy-chain buses so that they form the closed-grid bus. Each bus node is connected though a separate isolation resistor to a separate contact pad mounted on a surface of the circuit board. A set of spring contacts or probes link each contact pad to a separate one of the I / O pads on the wafer.

Owner:FORMFACTOR INC

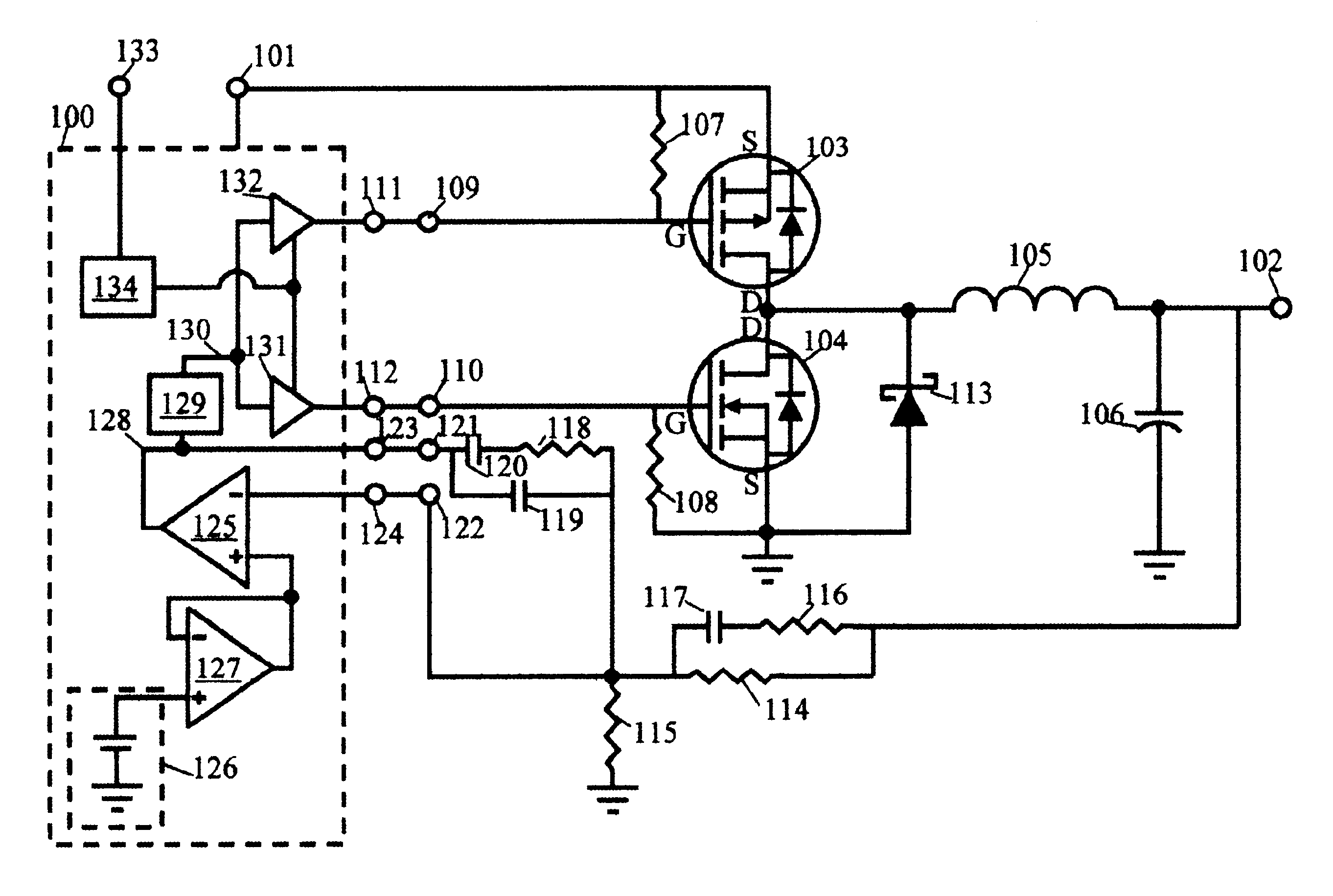

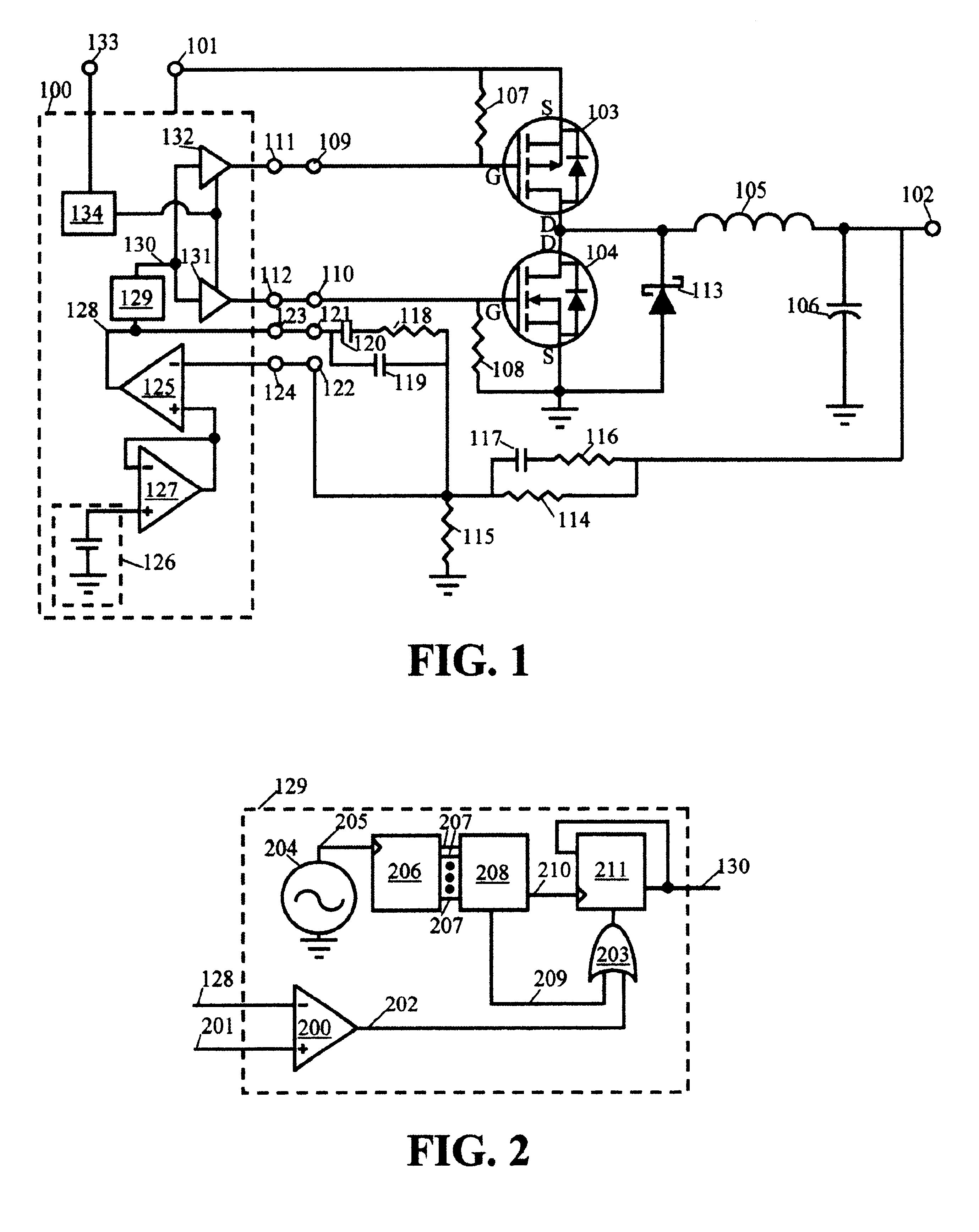

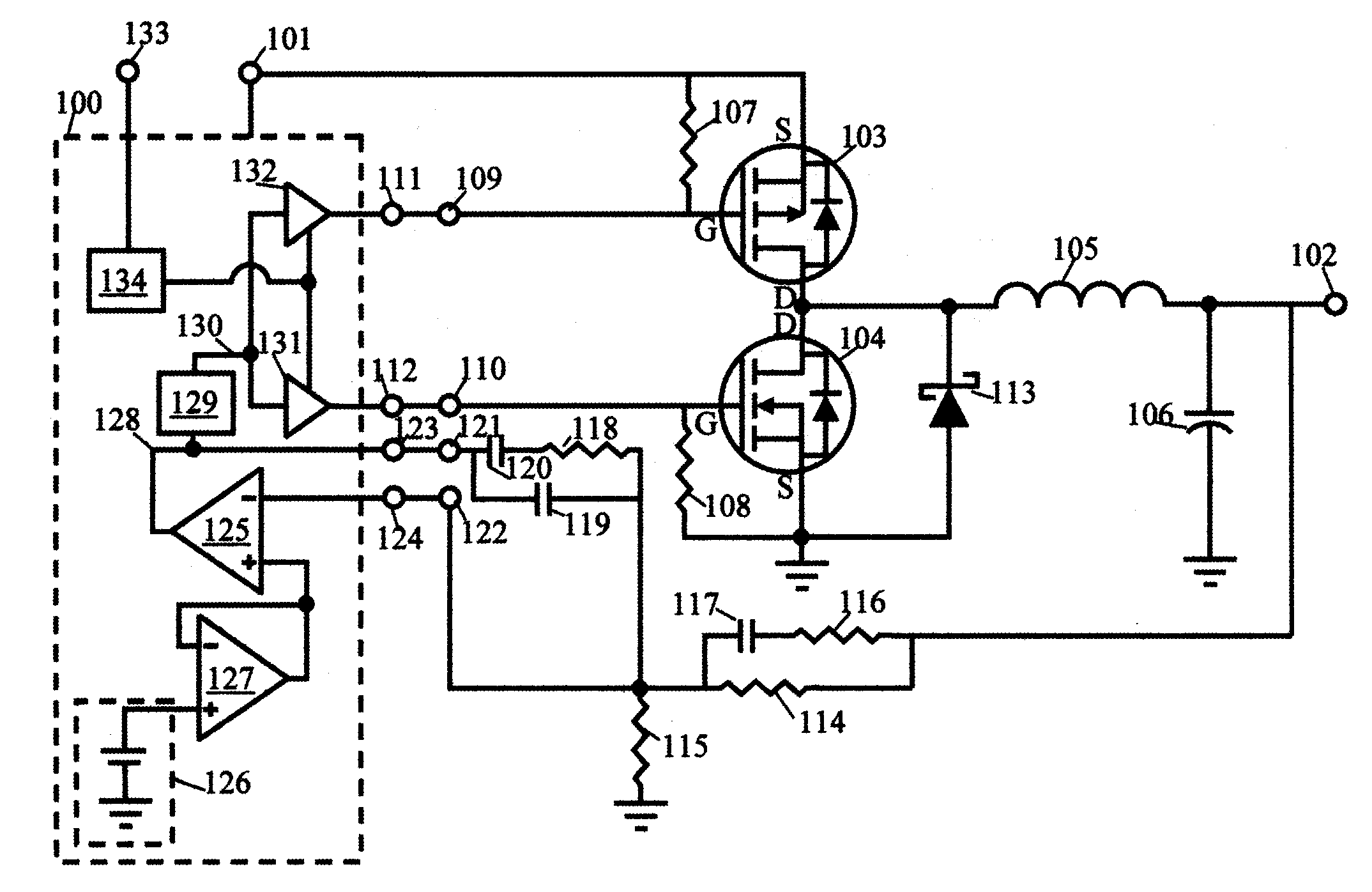

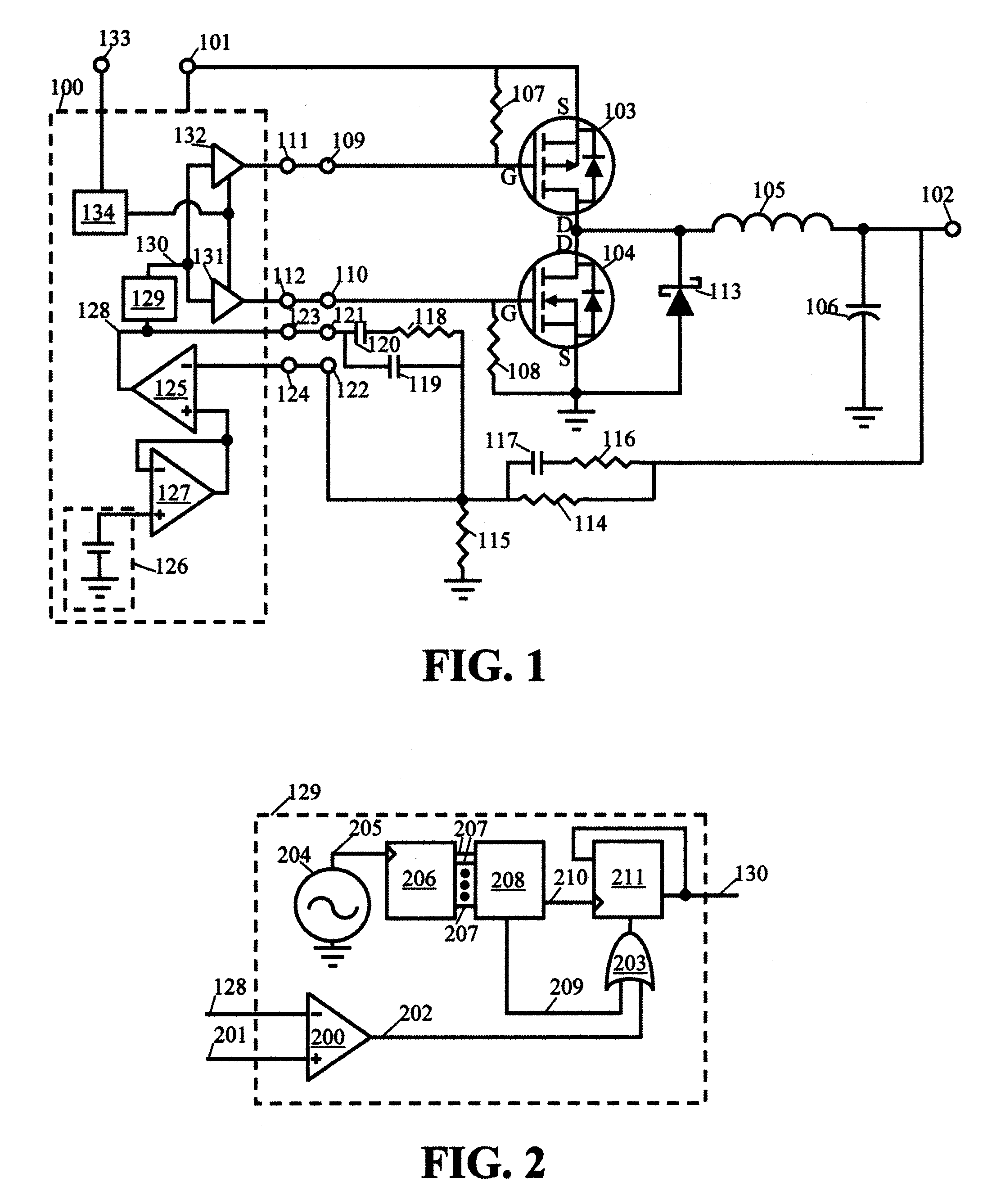

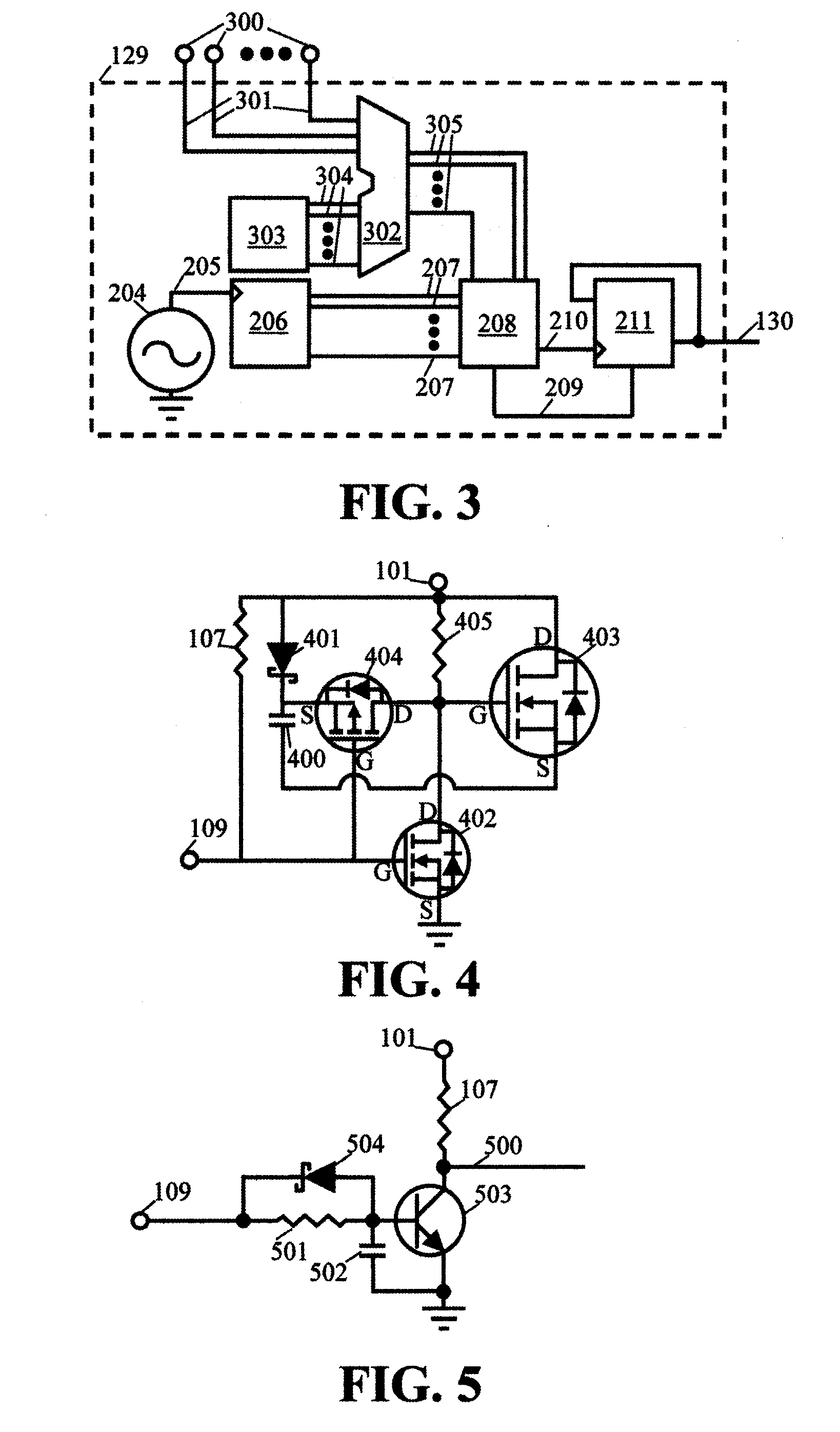

System and method for integrating a digital core with a switch mode power supply

InactiveUS6940189B2Improve powerMinimal costVolume/mass flow measurementSolid-state devicesVoltage converterPower switching

A digital core embodied within a semiconductor die that requires plural separate power supply voltage domains is situated within any of a variety of integrated circuit packaging technologies. Within the integrated circuit package including this semiconductor die also exists a switch mode DC-to-DC voltage converter, preferably a synchronous step-down regulator powering the entire integrated circuit from one supply voltage. The components contained within the integrated circuit package along with the semiconductor die include the switch mode power supply's power switching transistors, inductor core and windings, digital open-loop output voltage fixing circuitry, output capacitors and substrate for mounting said components when integrated within a packaging technology that does not already include a substrate.

Owner:CUFER ASSET LTD LLC

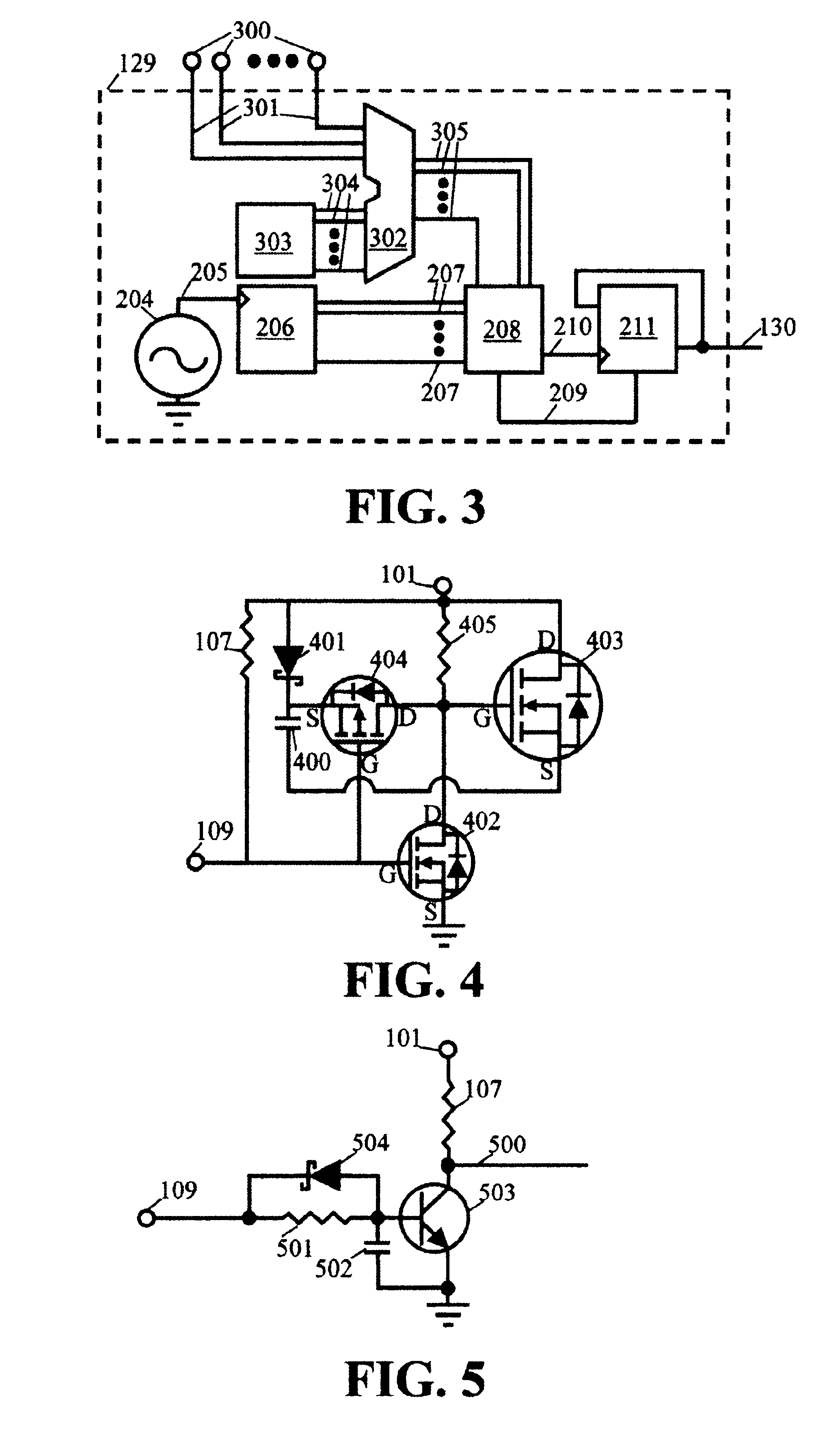

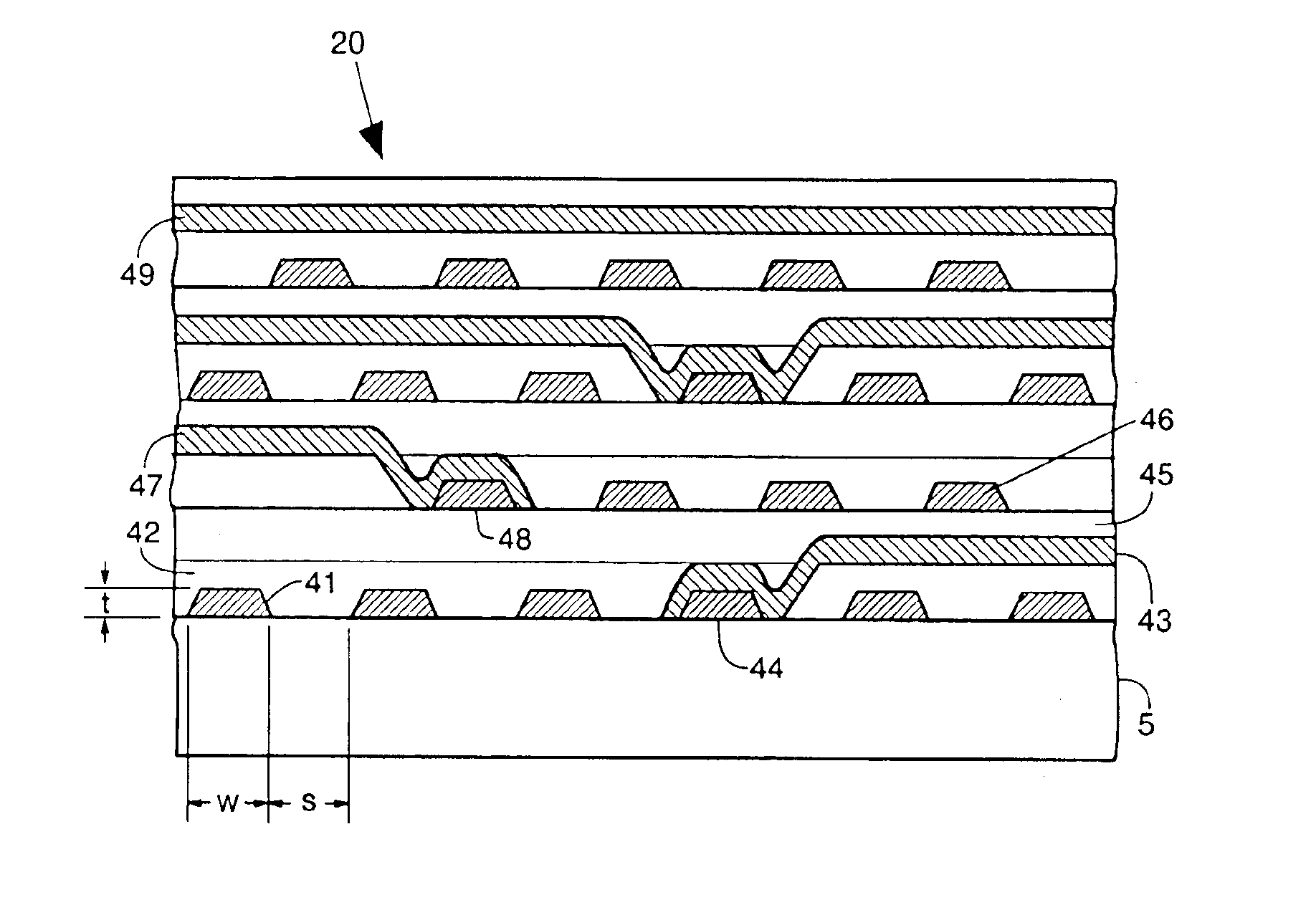

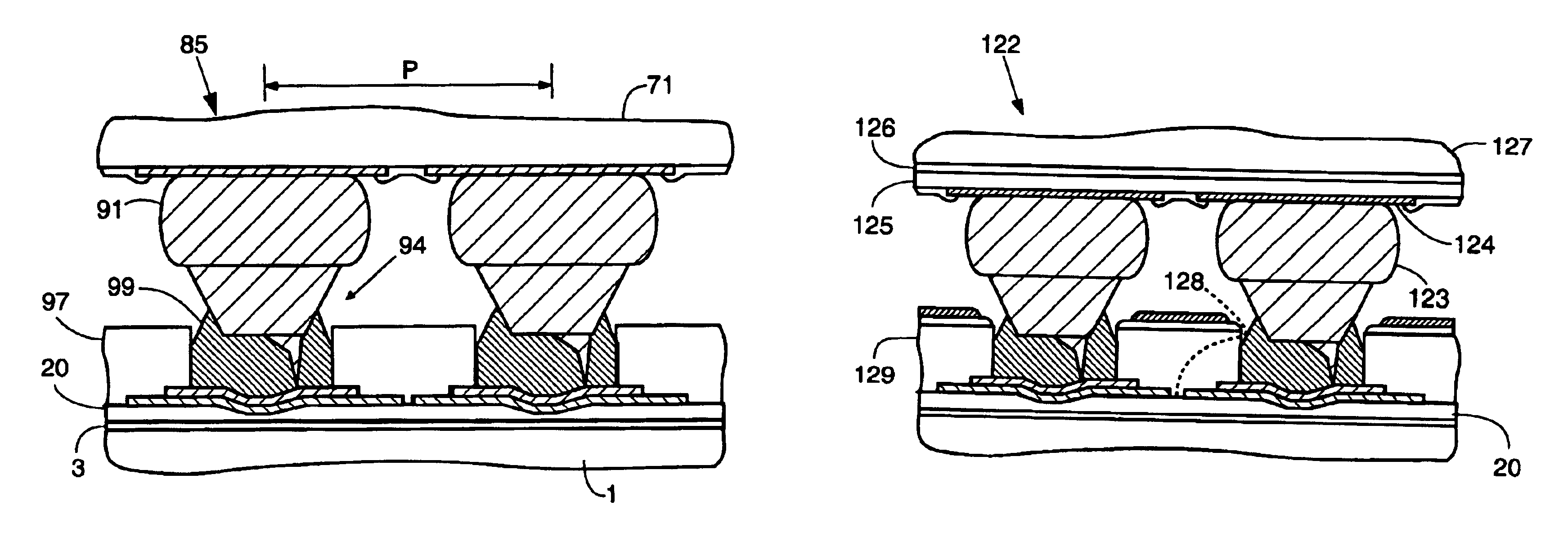

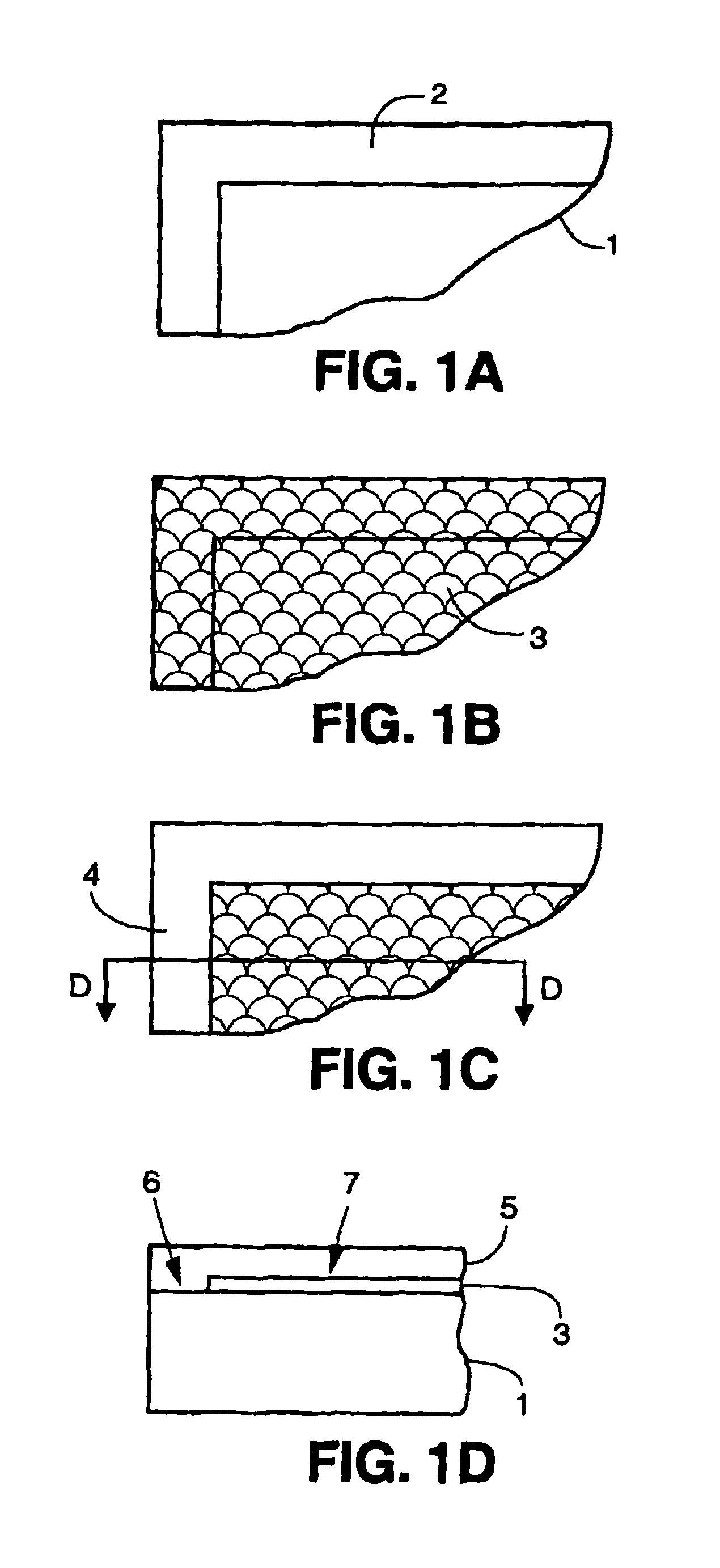

Component connections using bumps and wells

InactiveUS6881609B2Conveniently formedAccurate locationPrinted circuit assemblingFinal product manufactureHigh densityInterconnection

This specification describes techniques for fabricating connections between pairs of components. Each connection includes an array of bumps on a male component, and a matching array of wells filled with bonding material on a female component. The bump / well connections can be spaced with a pitch of less than 100 microns. One application of the invention is the attachment of electronic components to interconnection circuits or circuit assemblies to form electronic modules. The electronic components may be IC chips or high-density interconnect cables. Another application is alignment of optical components. The direct chip attachment techniques are described in the context of fabrication, assembly, test, rework, and cooling of electronic modules employing flip chip components. The preferred method is to fabricate the module on a glass carrier using a release layer so that the carrier can be removed after most of the processing is done.

Owner:SK HYNIX INC

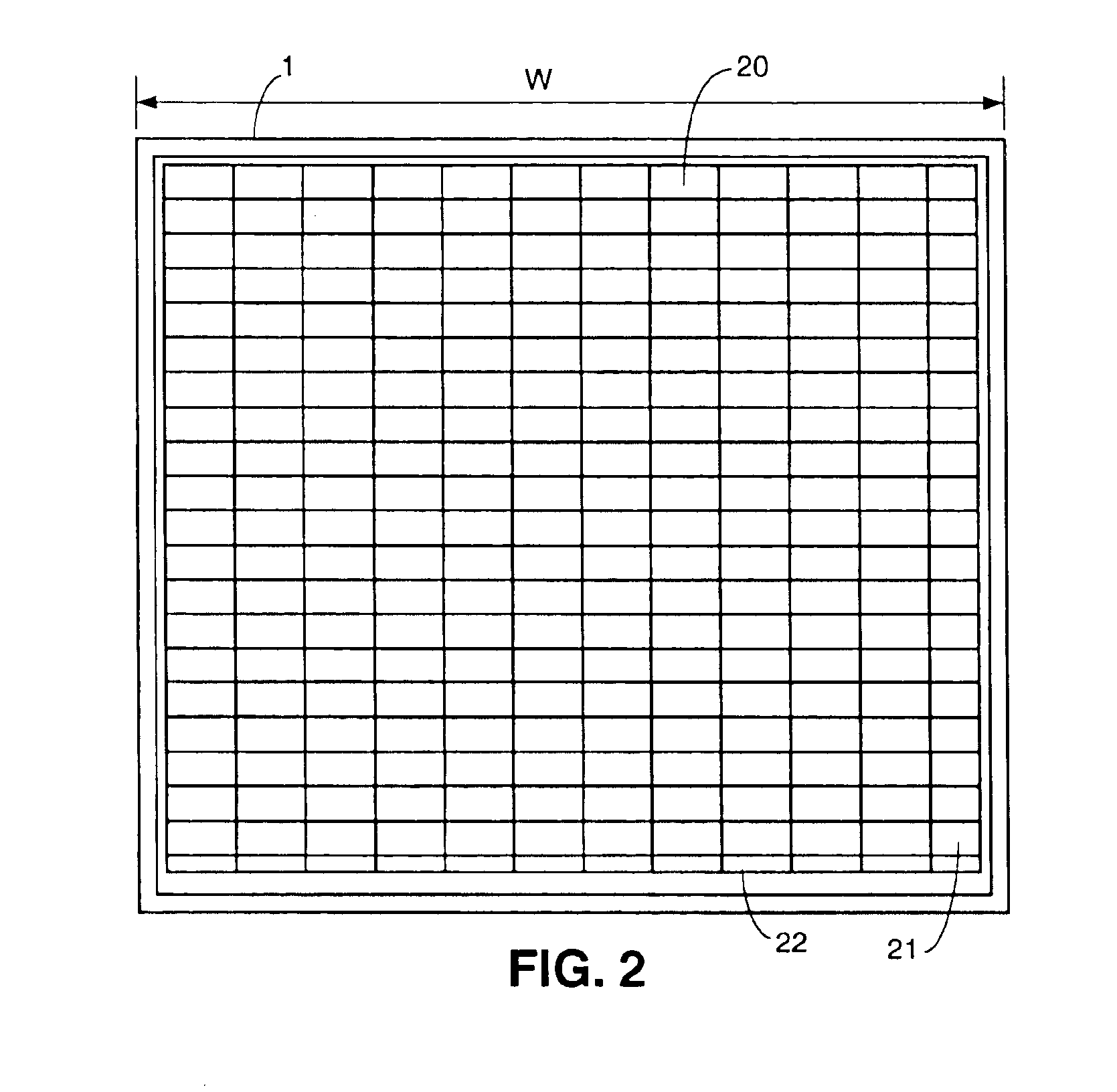

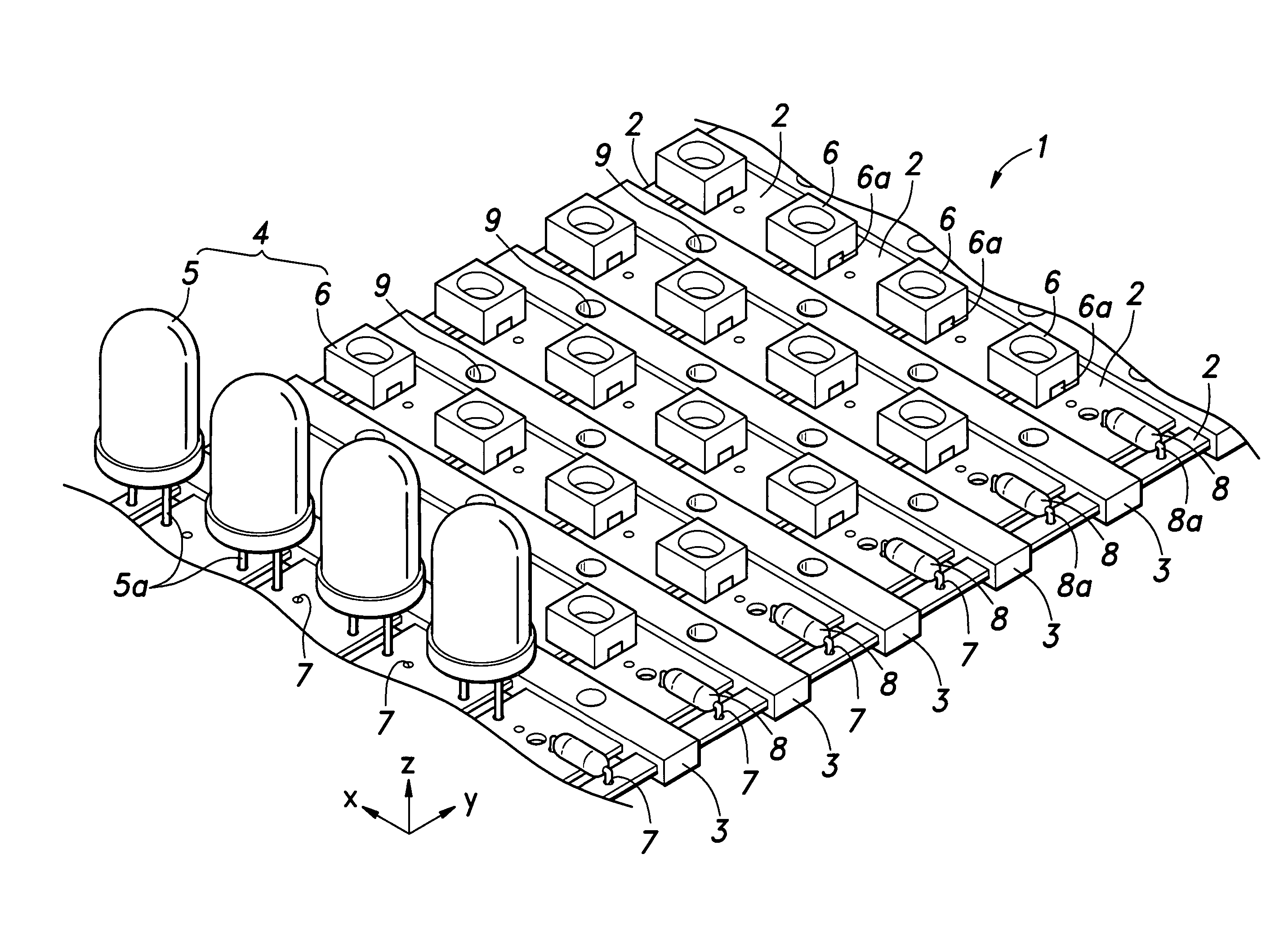

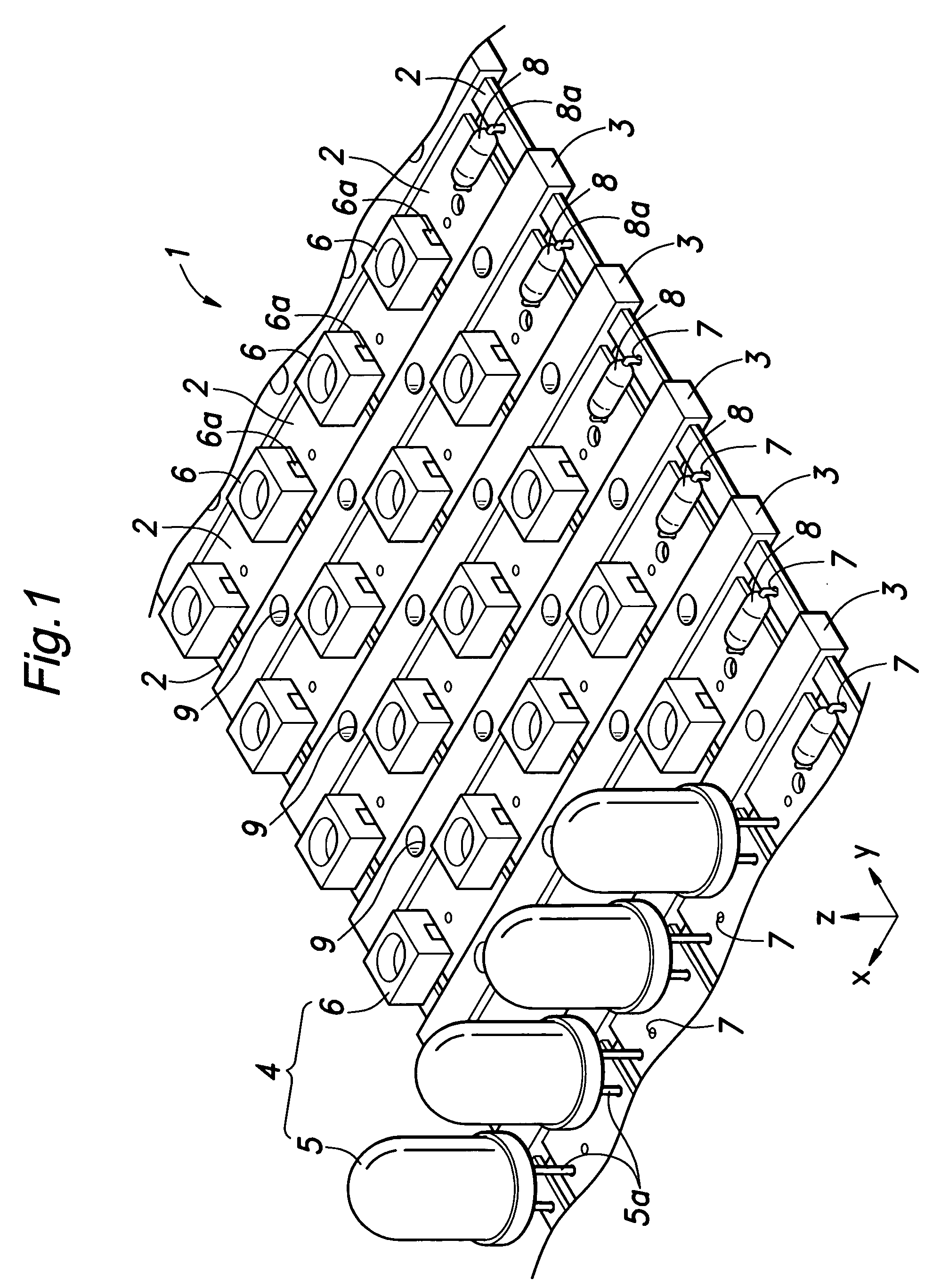

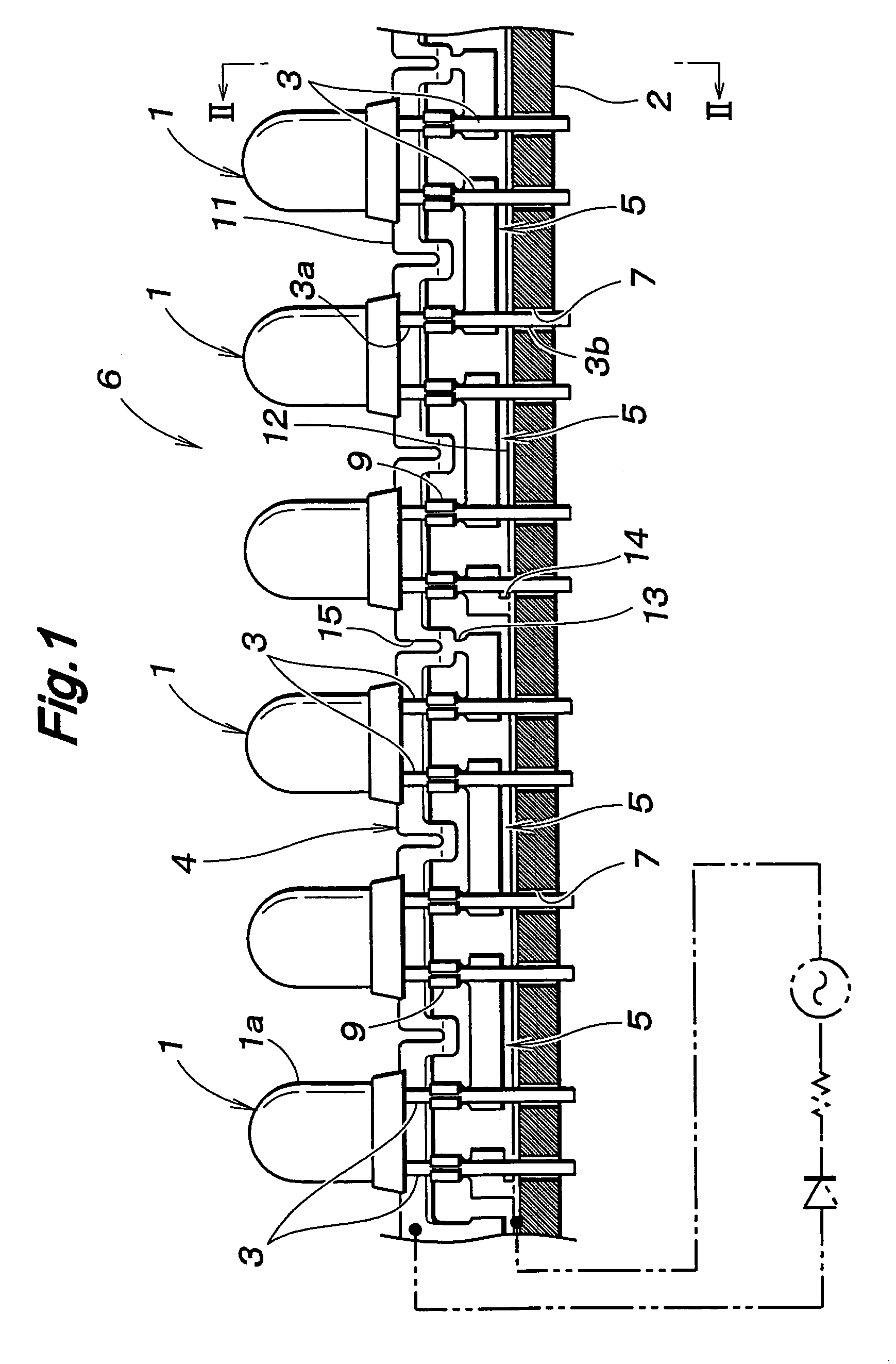

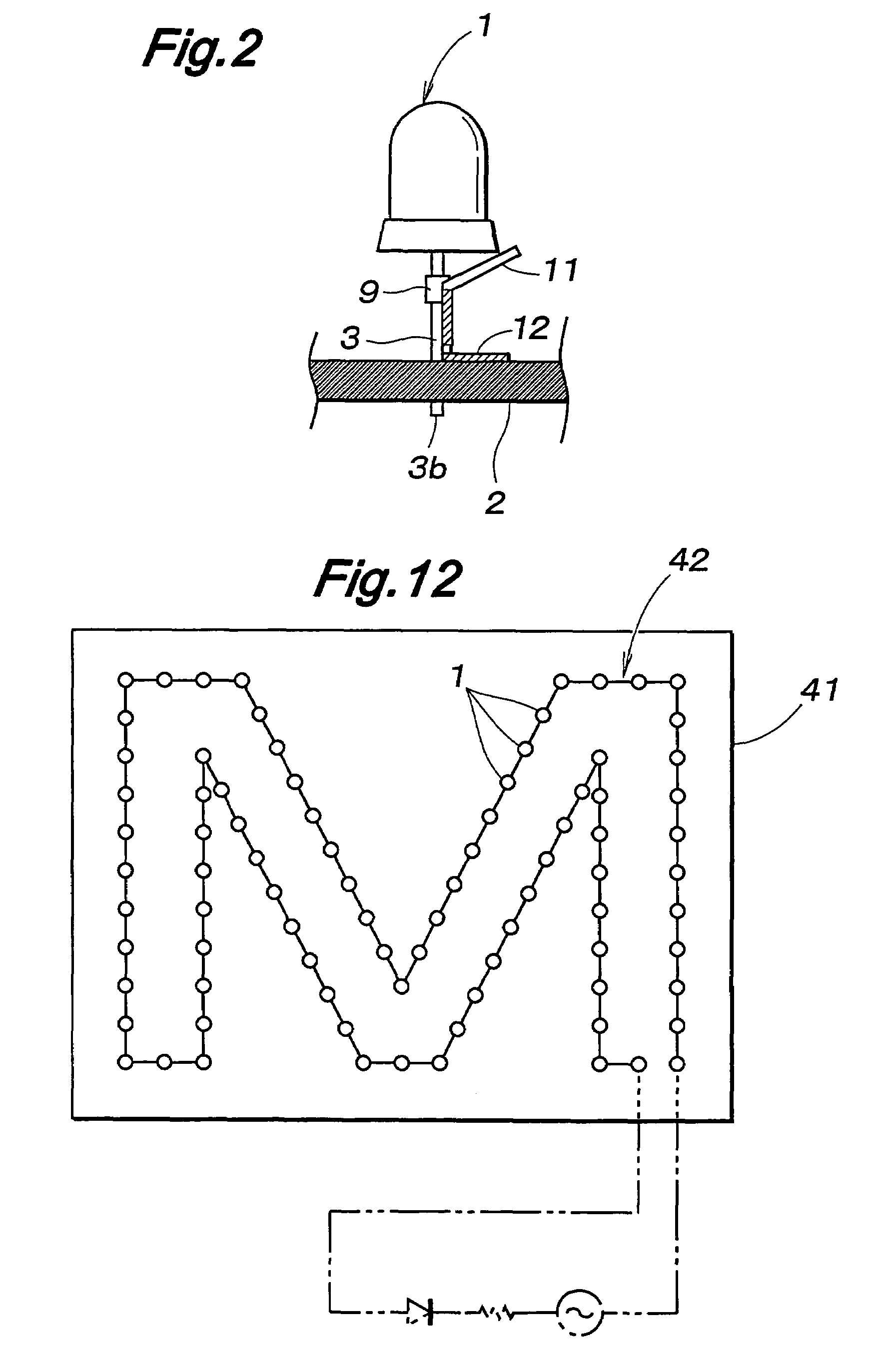

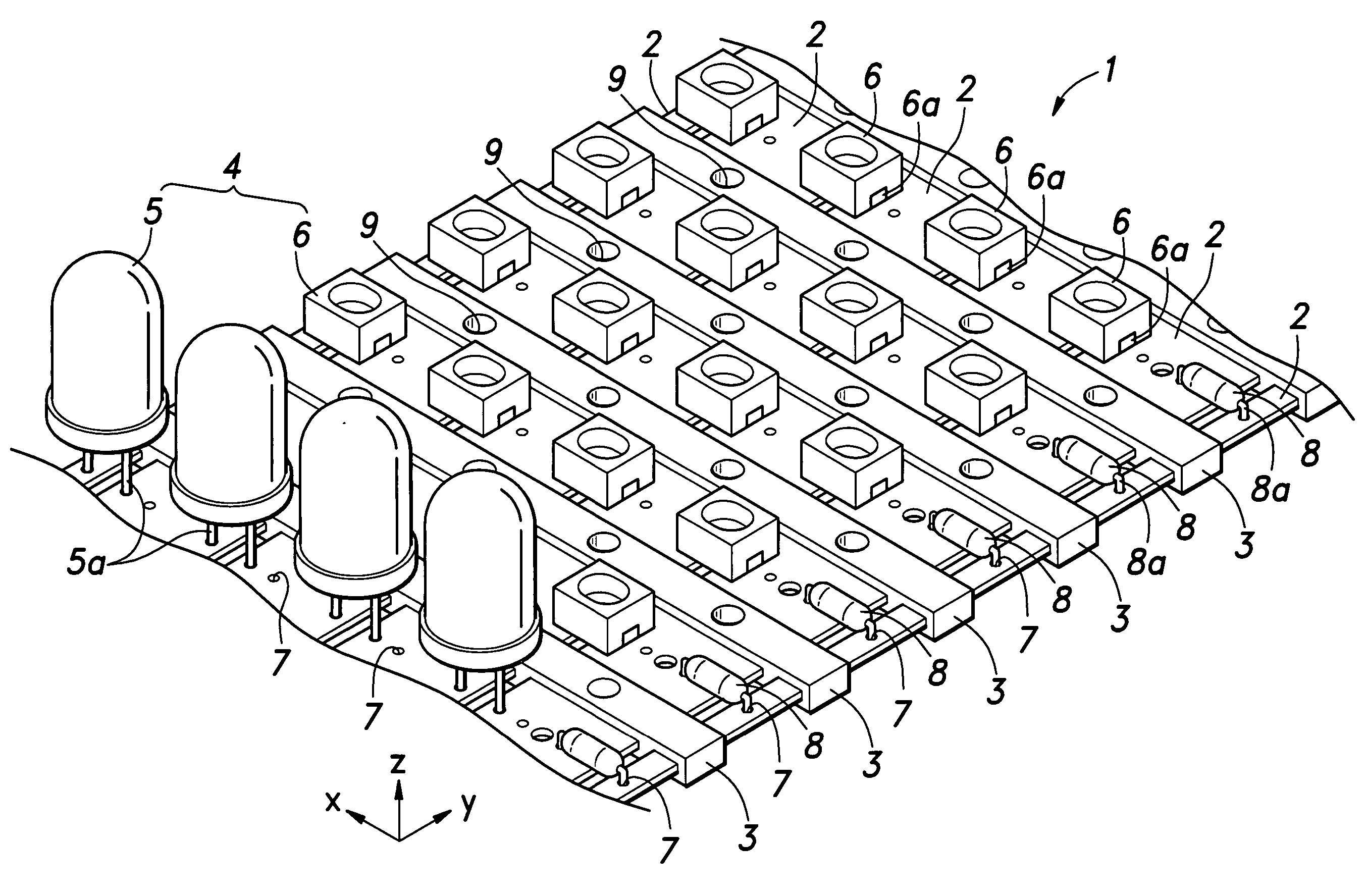

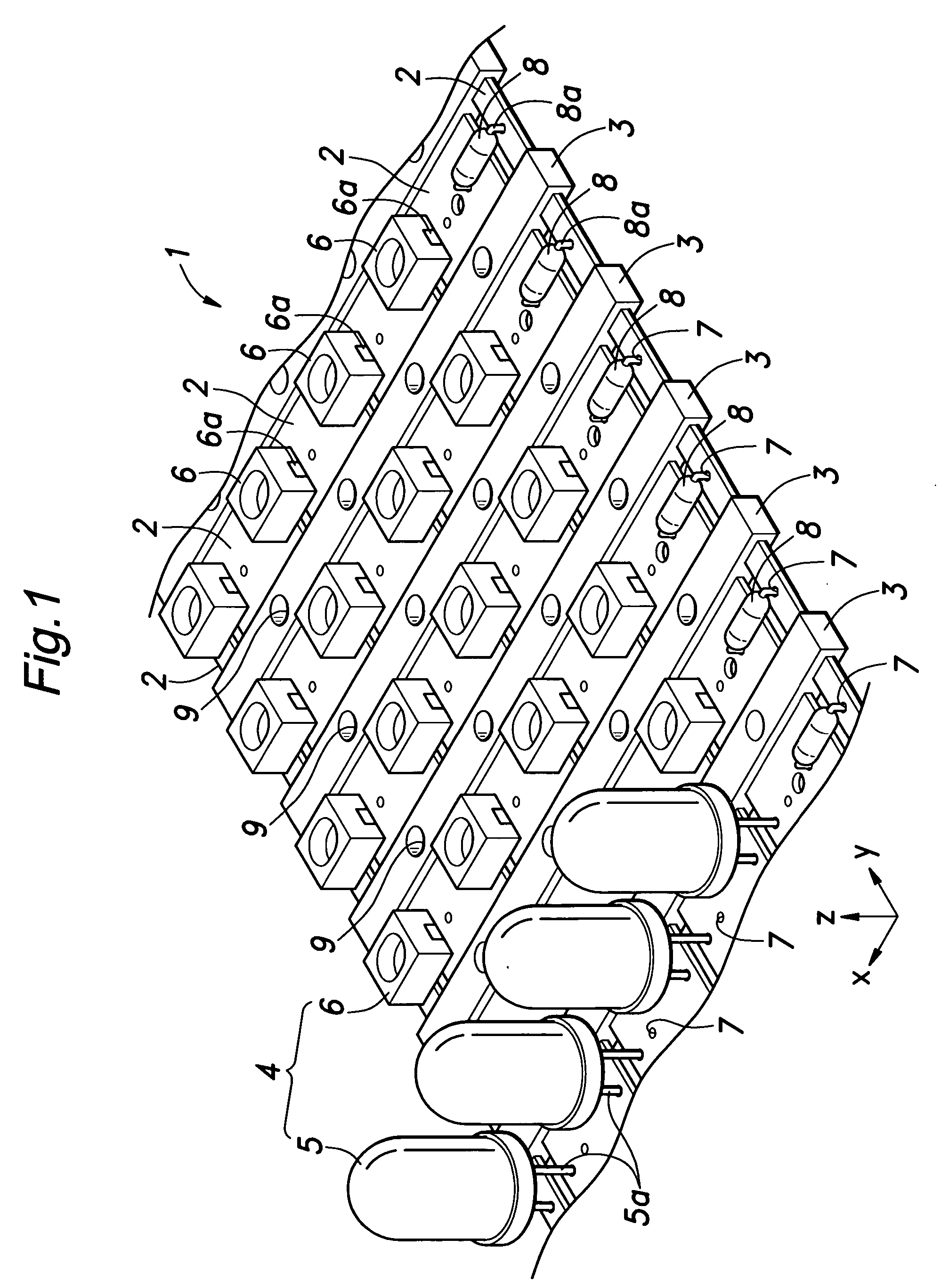

Light emitting module

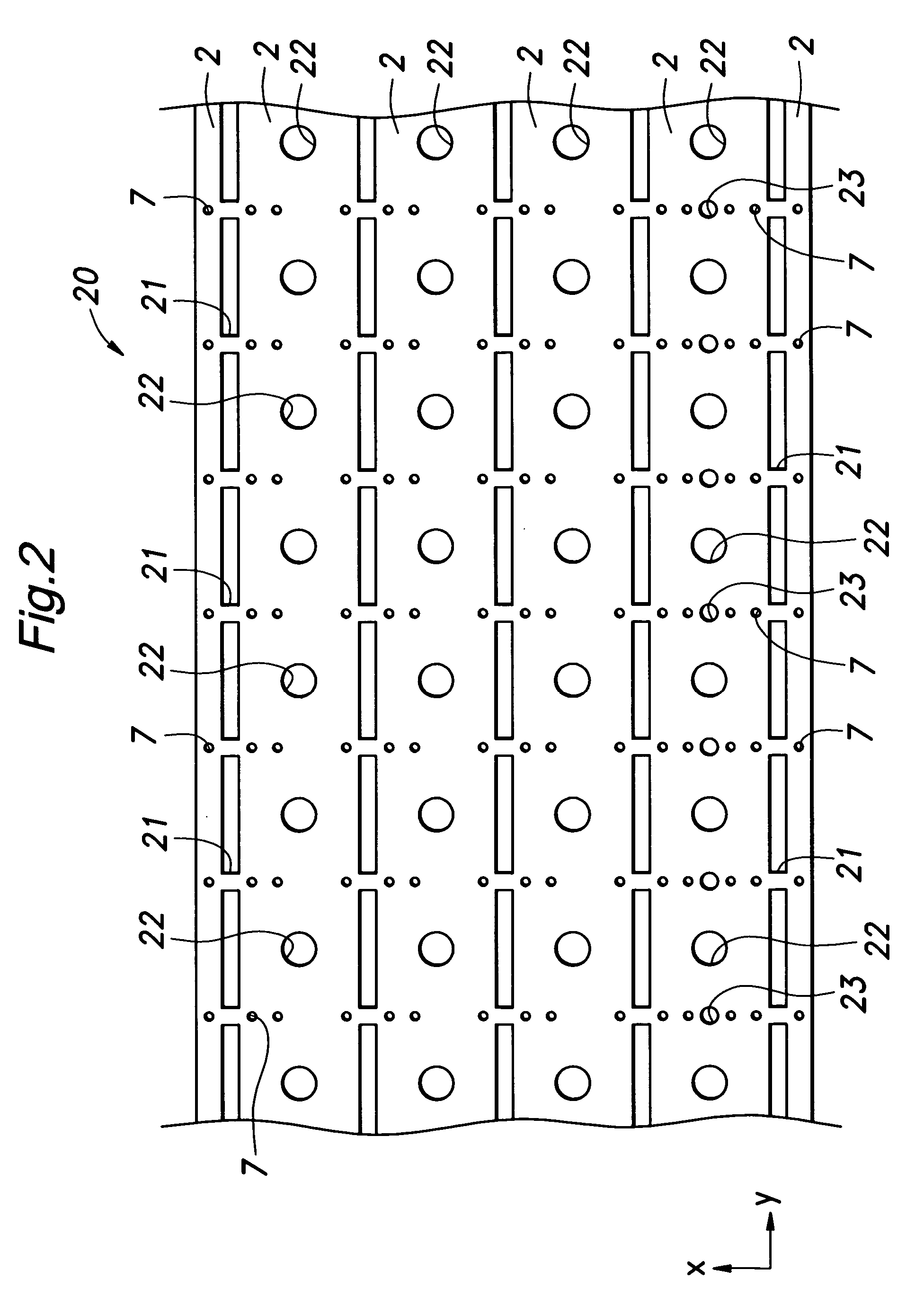

InactiveUS7201511B2Improve cooling effectDifficult to handlePlanar light sourcesLighting support devicesJoint componentElectrical conductor

The present invention provides a light emitting module, comprising: a plurality of thin plate-shaped conductors (2) spaced apart from each other in a first direction; at least one light source (4) connected between at least one pair of adjoining ones of said conductors; and at least one insulating joint member (4) for mechanically joining said plurality of conductors, wherein said at least one insulating joint member exposes both sides of at least a portion of said conductors where said light source is mounted.

Owner:MORIYAMA SANGYO

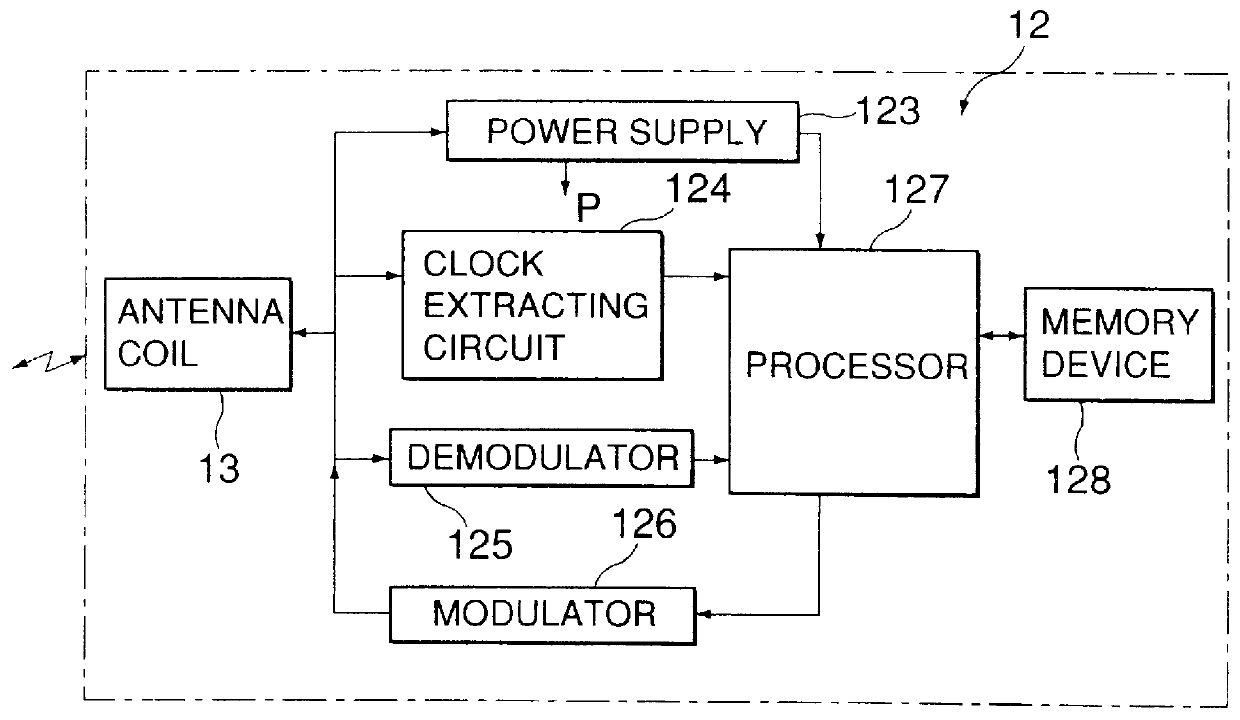

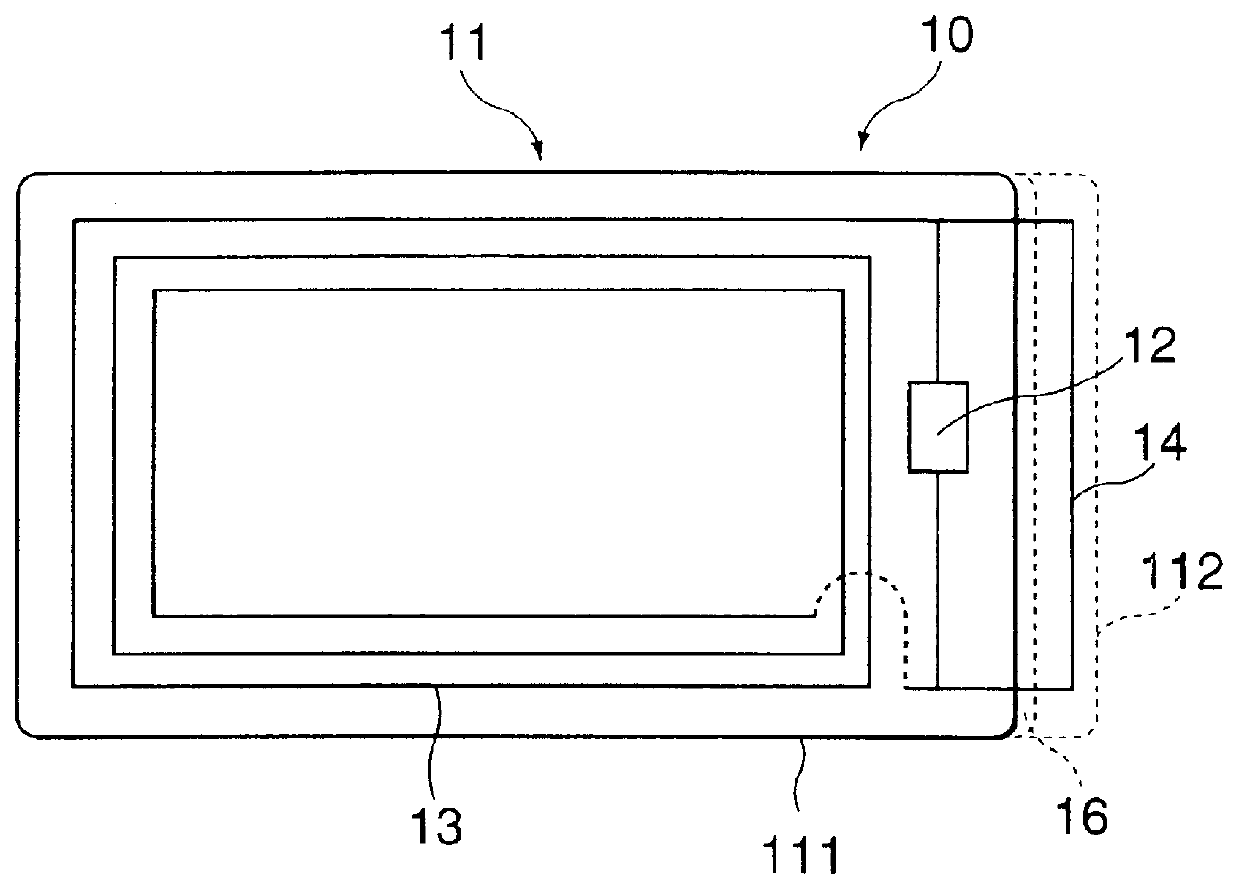

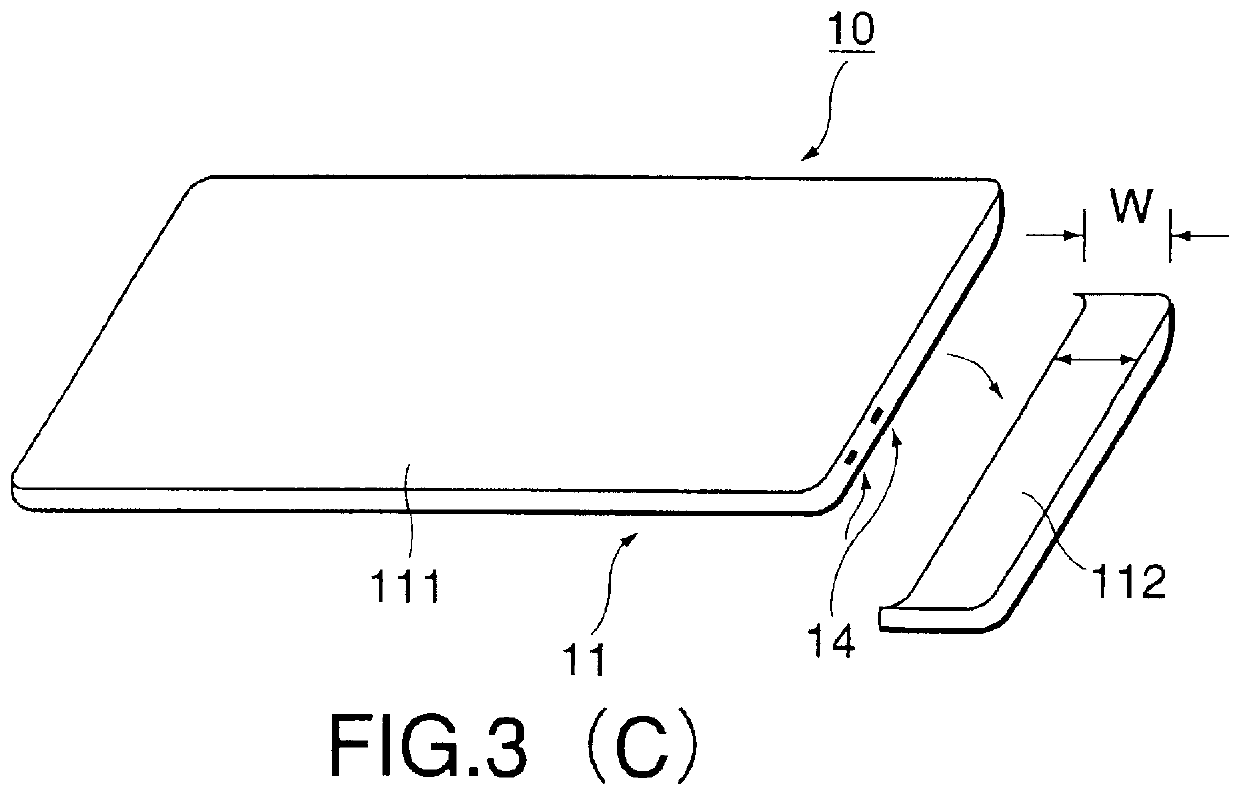

Noncontact IC device

InactiveUS6073856ACircuit security detailsPrinted circuit aspectsEngineeringElectrical and Electronics engineering

A noncontact IC card is provided with an antenna coil, an IC chip and a short-circuiting circuit formed on a base card. The noncontact IC card is kept inoperative unless the short-circuiting circuit is opened and the noncontact IC card is rendered operative when the short-circuiting circuit is opened. The short-circuiting circuit is formed to extend across a main part and a removable identification part included in the base card. The short-circuiting circuit can be opened by removing the identification part from the base card.

Owner:DAI NIPPON PRINTING CO LTD

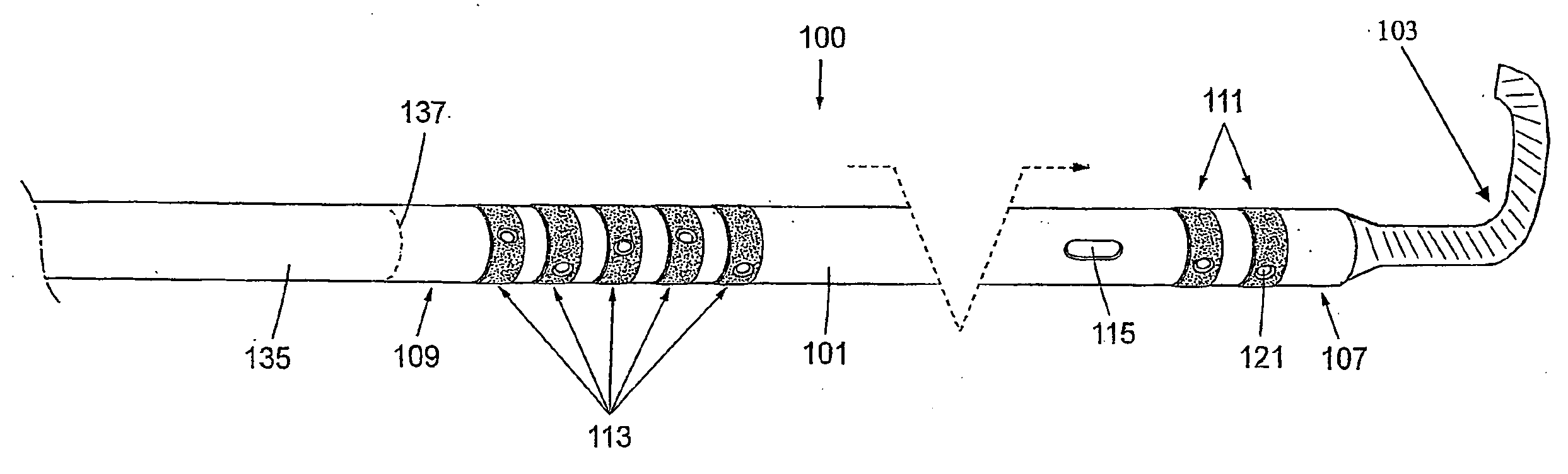

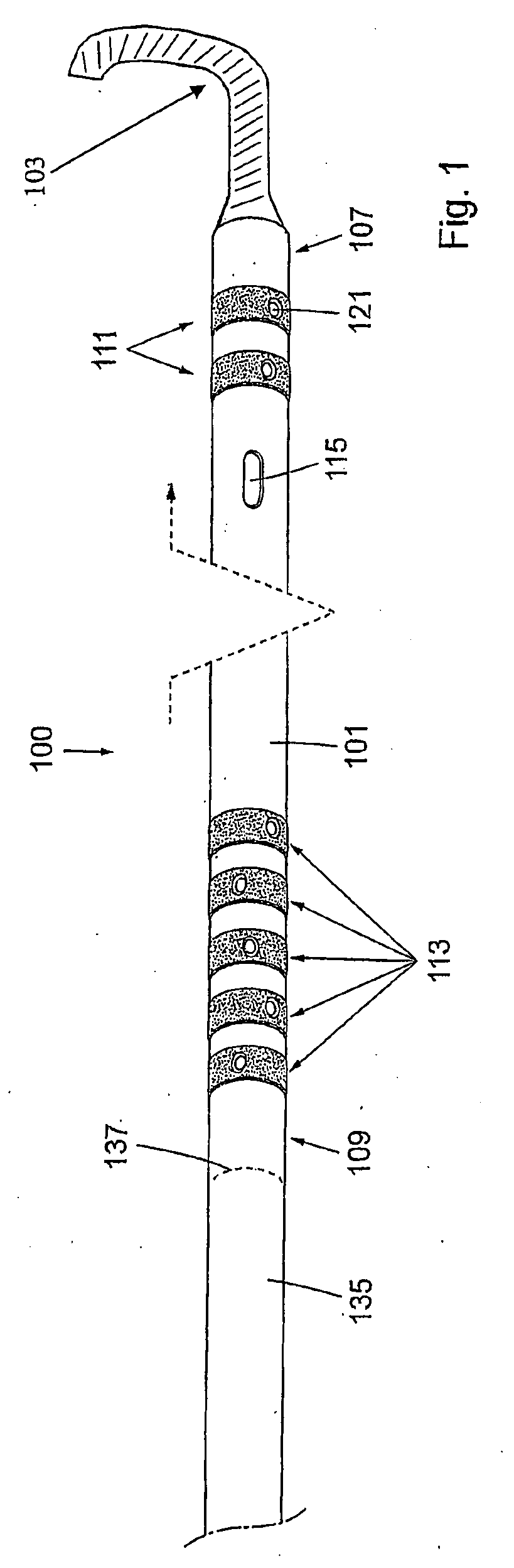

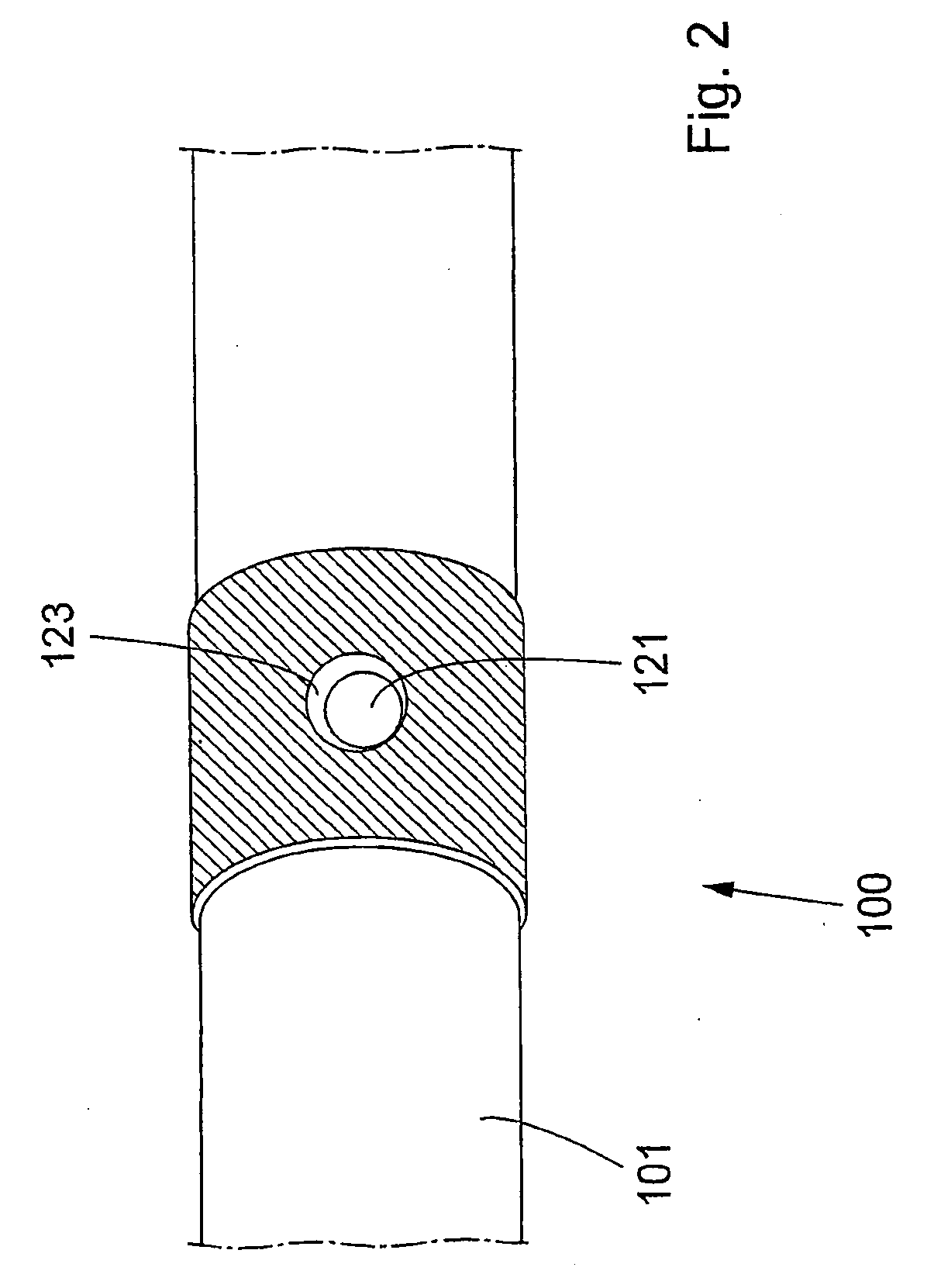

Device for Invasive Use

A device for invasive use, comprising a support member comprising a flexible material. The support member comprises a layer of a conductive line or pattern thereon. The support member is formed into an elongated tube shape, and the inside of the support member can be sealed from the outside of the support member. An electrically conductive line or pattern extends on the inside of the tube shaped support member, and the support member may comprise a sensing, stimulating and / or processing element. Furthermore, there is described a manufacturing method for the device, a system where the device is a part of the system and the use of the device for invasive use.

Owner:CATHPRINT

Hybrid ground grid for printed circuit board

InactiveUS7129416B1Efficient routingCross-talk/noise/interference reductionPrinted circuit aspectsGrounding gridPrinted circuit board

Electrical mounting boards and methods for their fabrication and use are disclosed herein. In particular, such mounting boards embodiments utilize hybrid ground lines interconnected through a substrate core to form multilayer ground grids. Such hybrid ground lines include groups of substantially parallel ground lines configured such that the groups of ground lines are positioned in transverse arrangement with other groups of ground lines formed on the same level. Such implementations have many uses, including, but not limited to, the ability to more efficiently route signal lines and connect electrical components on a circuit board.

Owner:APPLE INC

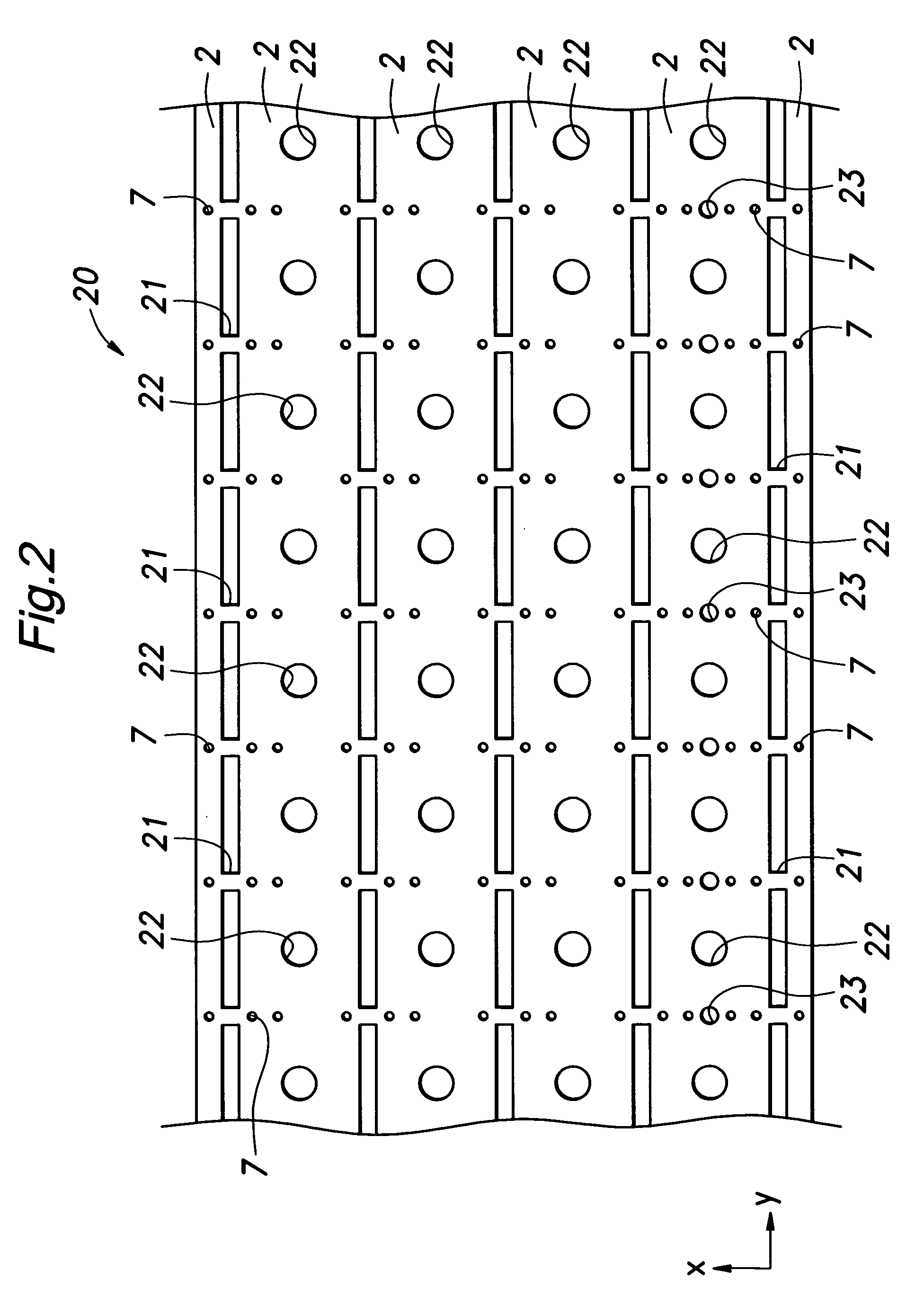

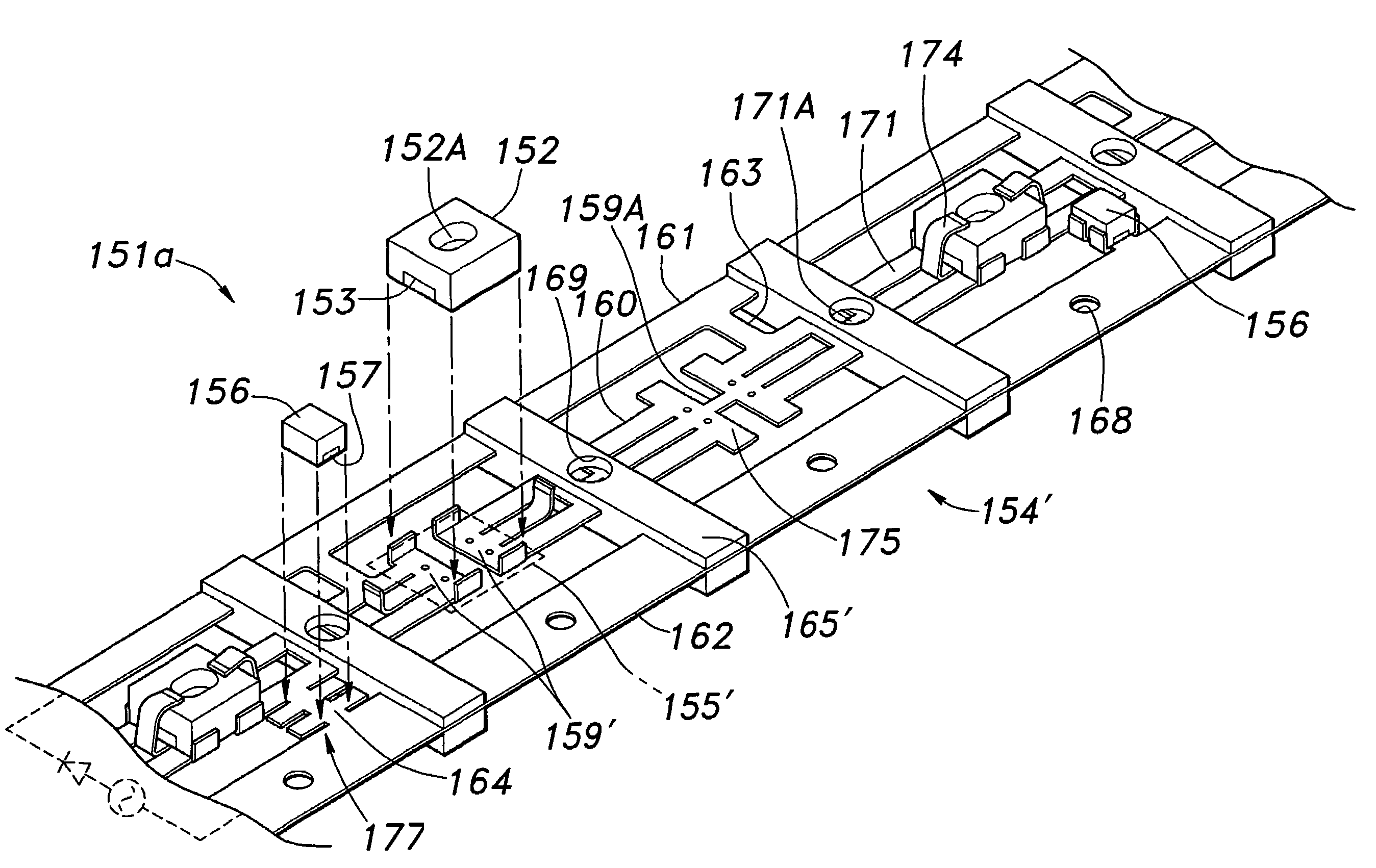

Light source coupler, illuminant device, patterned conductor, and method for manufacturing light source coupler

InactiveUS7380961B2Efficient preparationLow costCoupling device connectionsLighting support devicesElectrical conductorEngineering

To provide a light source assembly that does not use a printed circuit board and can be manufactured at a low cost even when produced in small quantities, a light source assembly according to the present invention comprises a plurality of light sources and a connective conductor structure extending in a direction of arrangement of the light sources to join the light sources, wherein the connective conductor structure is formed by cutting off parts of a substantially plate-like patterned conductor as required, the patterned conductor being provided with a prescribed pattern. Thus, by changing the parts to be cut off in the patterned conductor, it is possible to manufacture light source assemblies having various light source connection patterns in a single manufacturing line, allowing efficient and low cost manufacture of the light source assemblies to be achieved even when the light sources are manufactured in small quantities.

Owner:MORIYAMA SANGYO

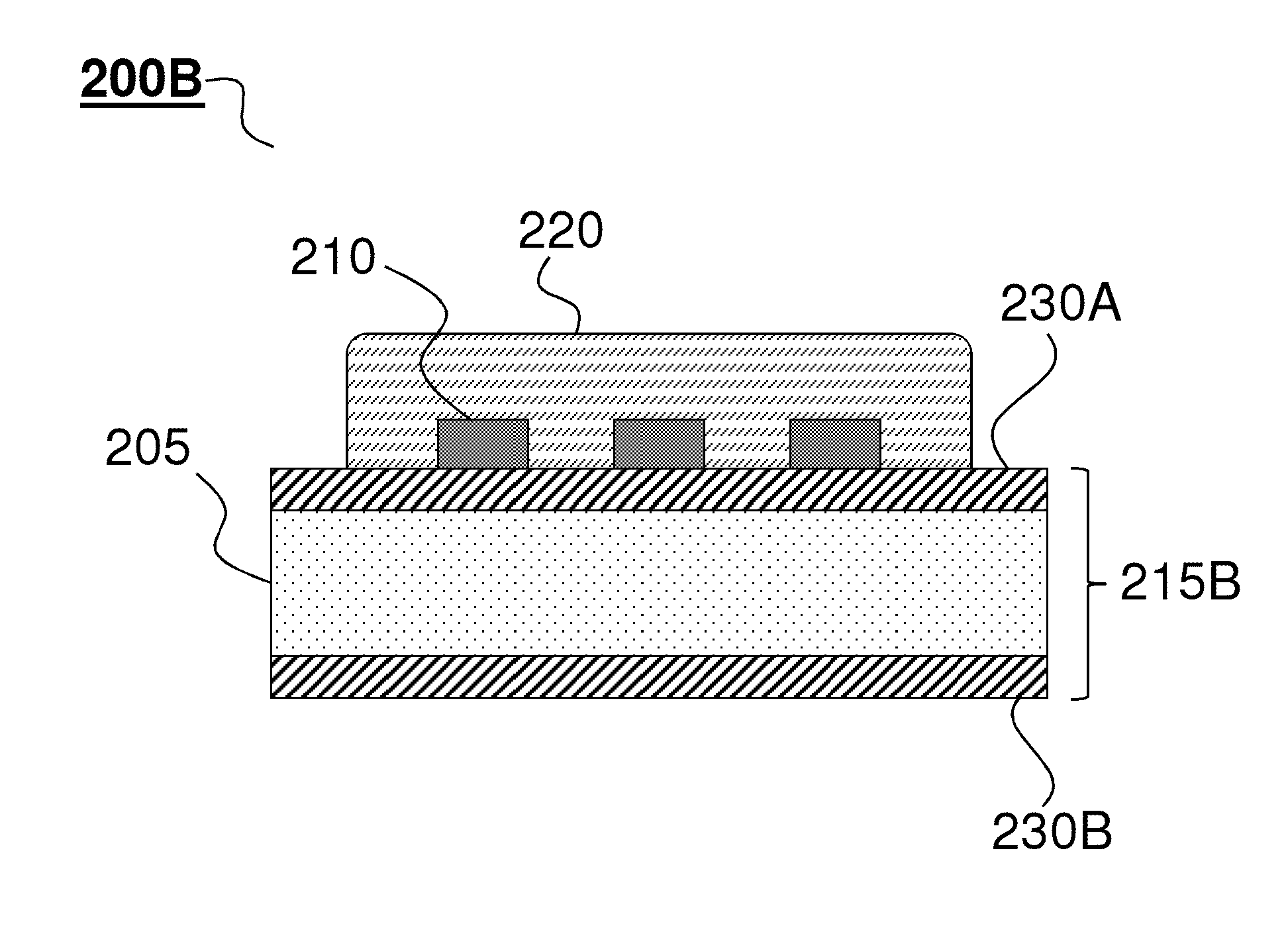

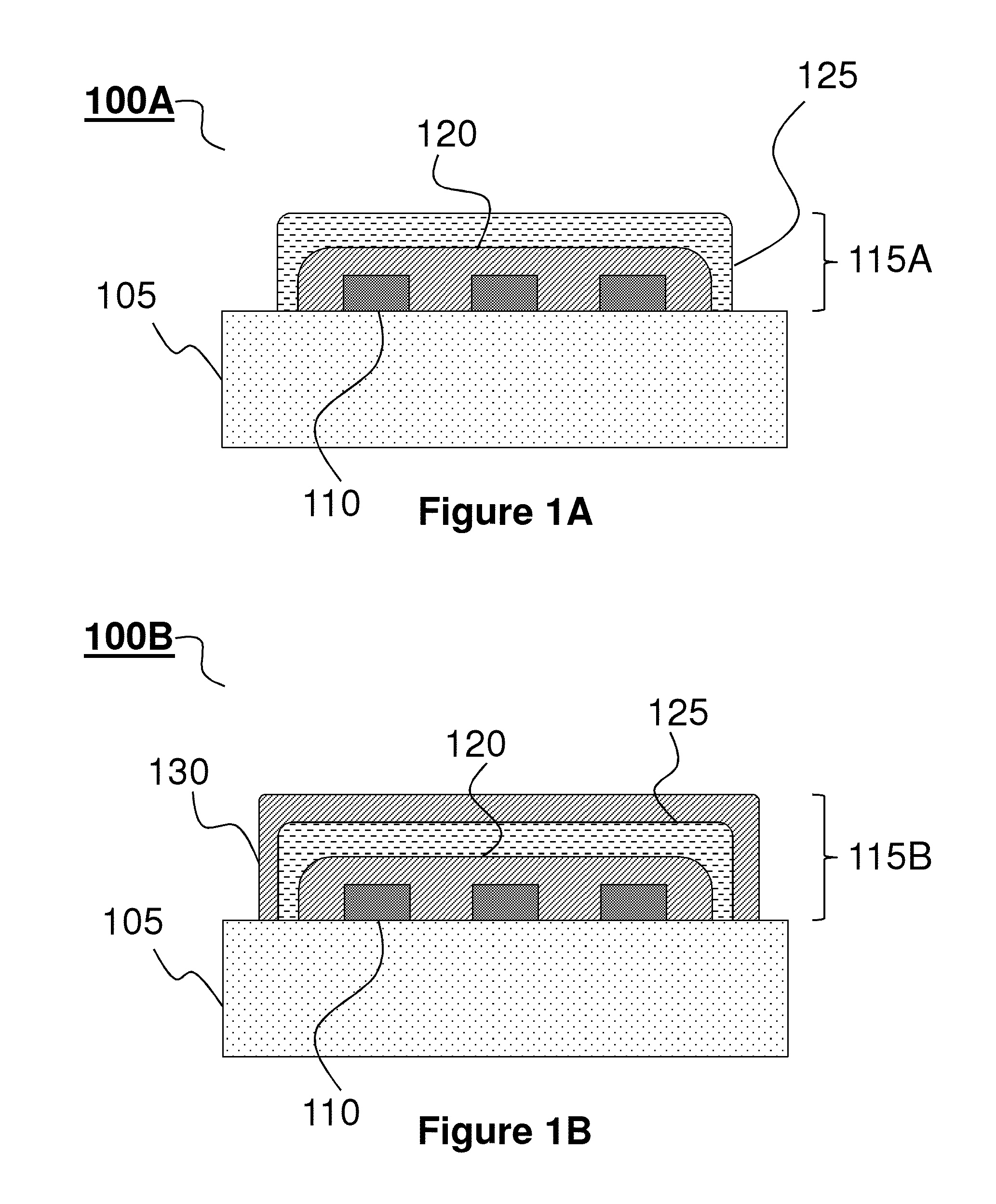

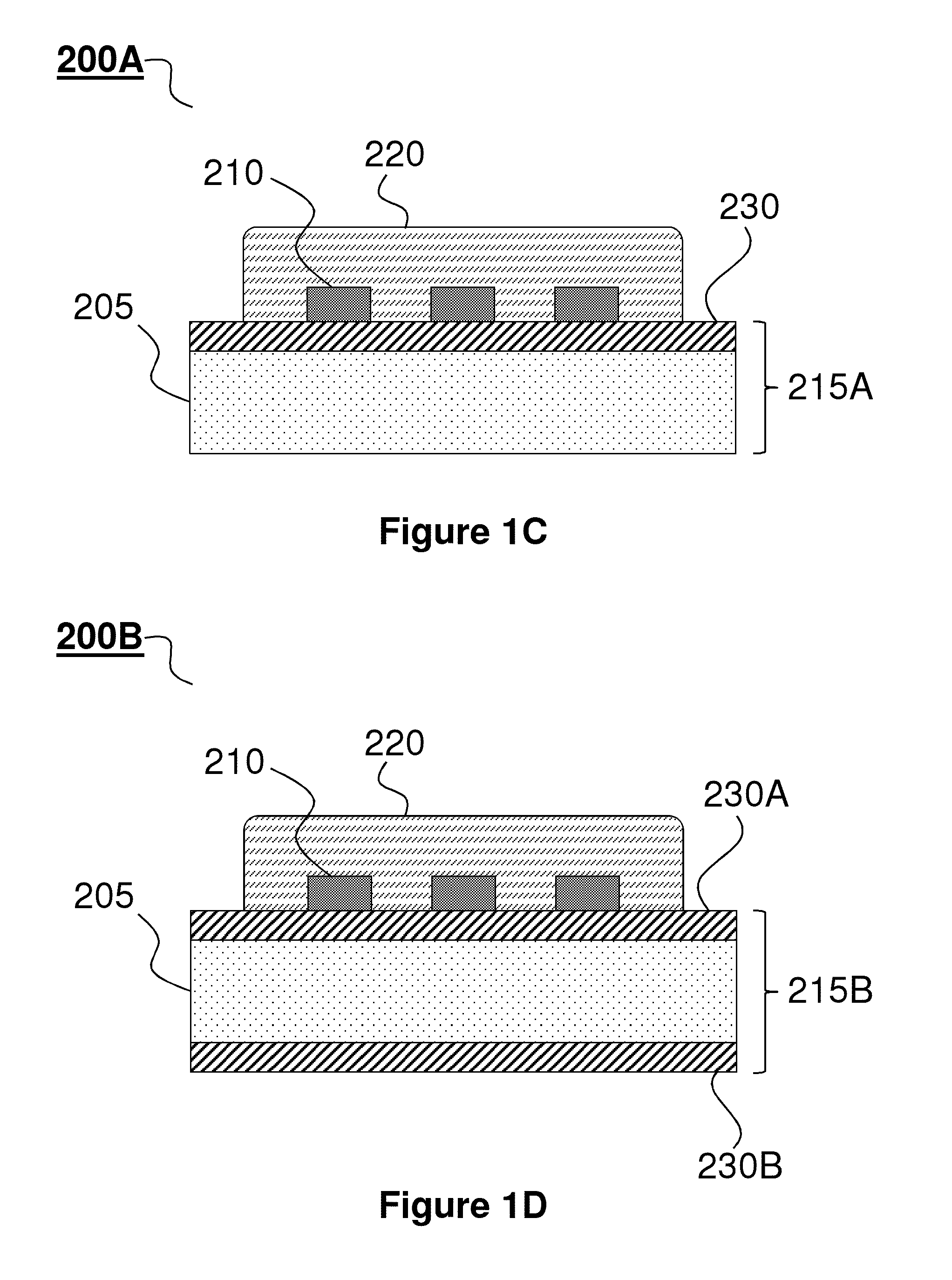

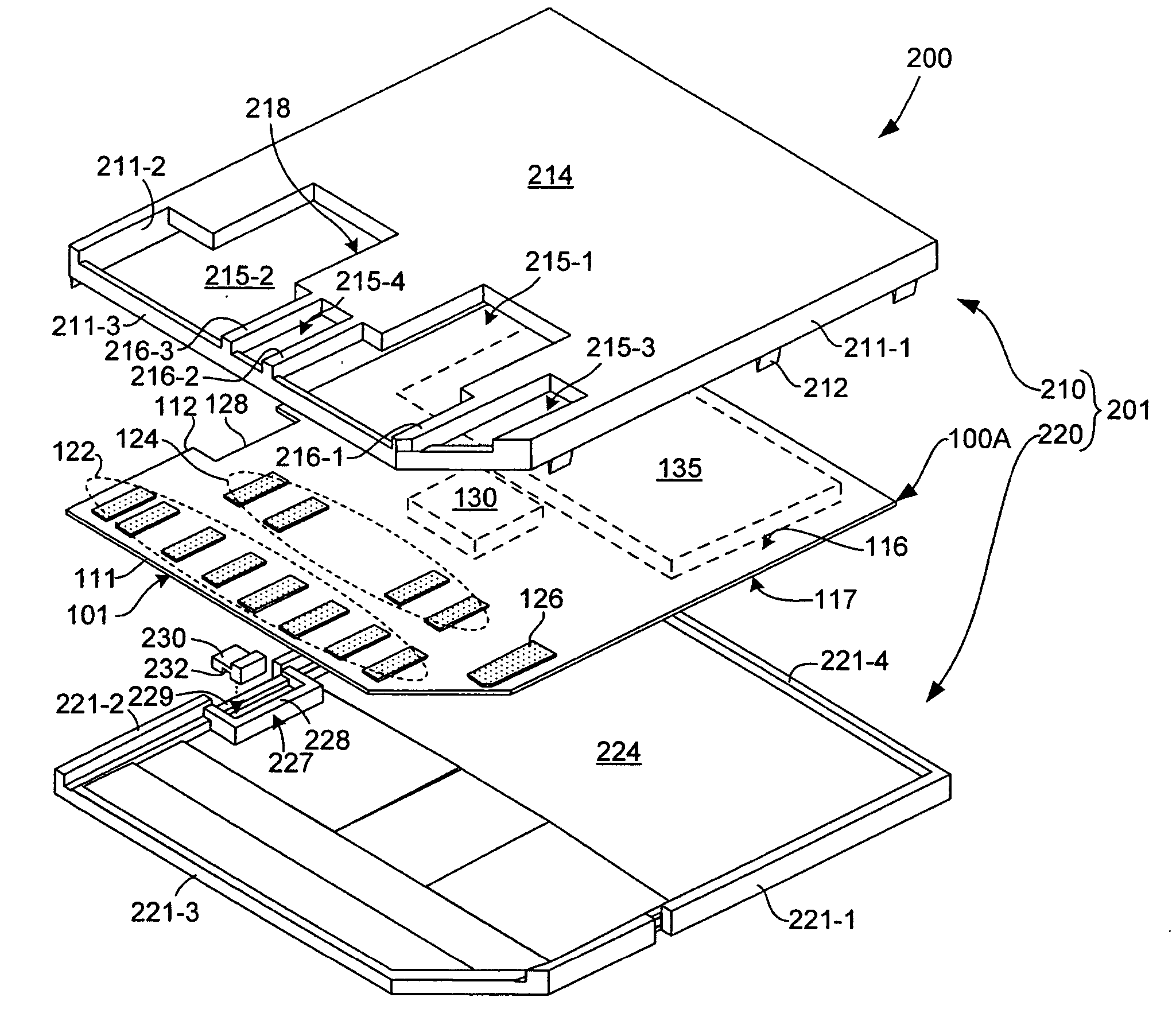

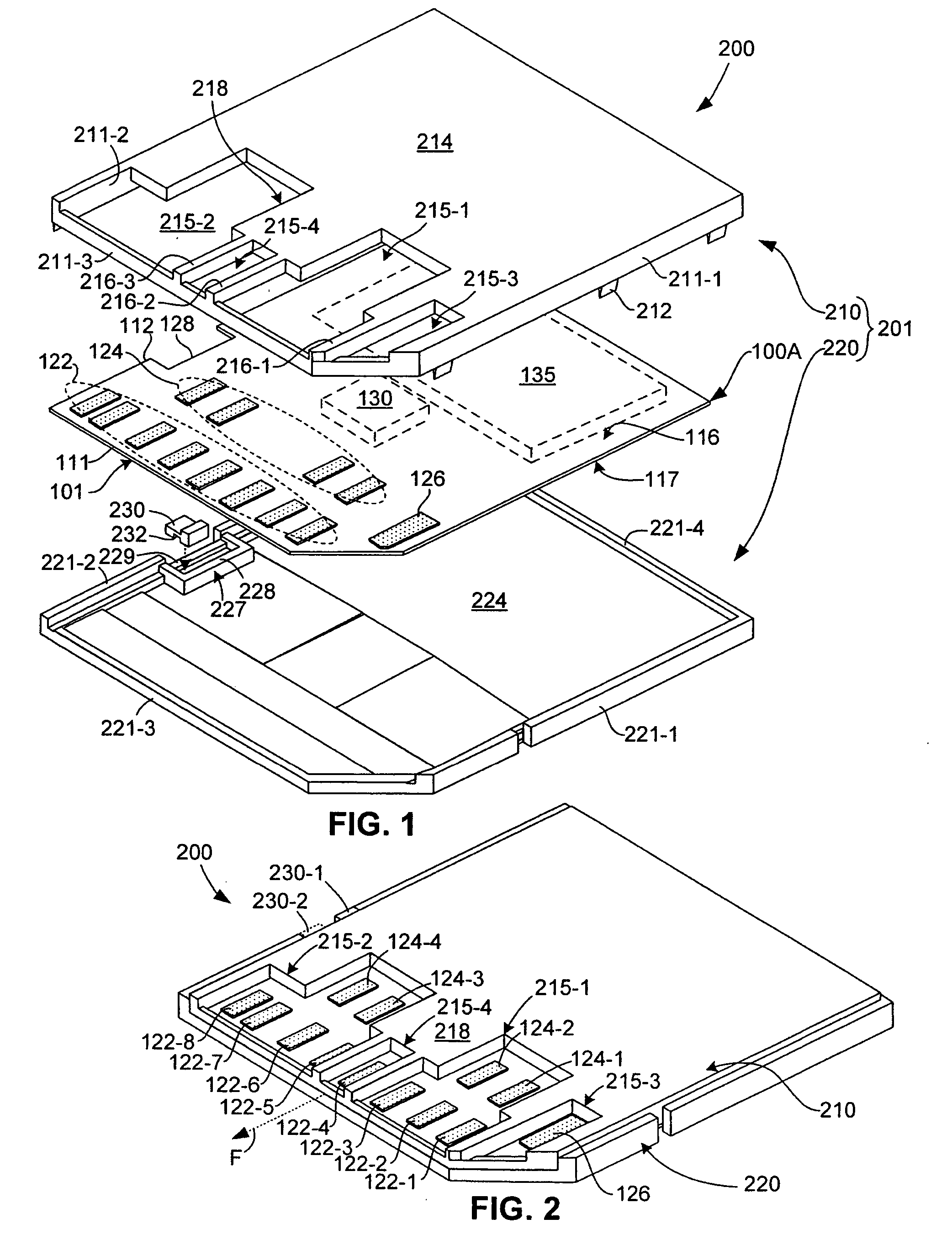

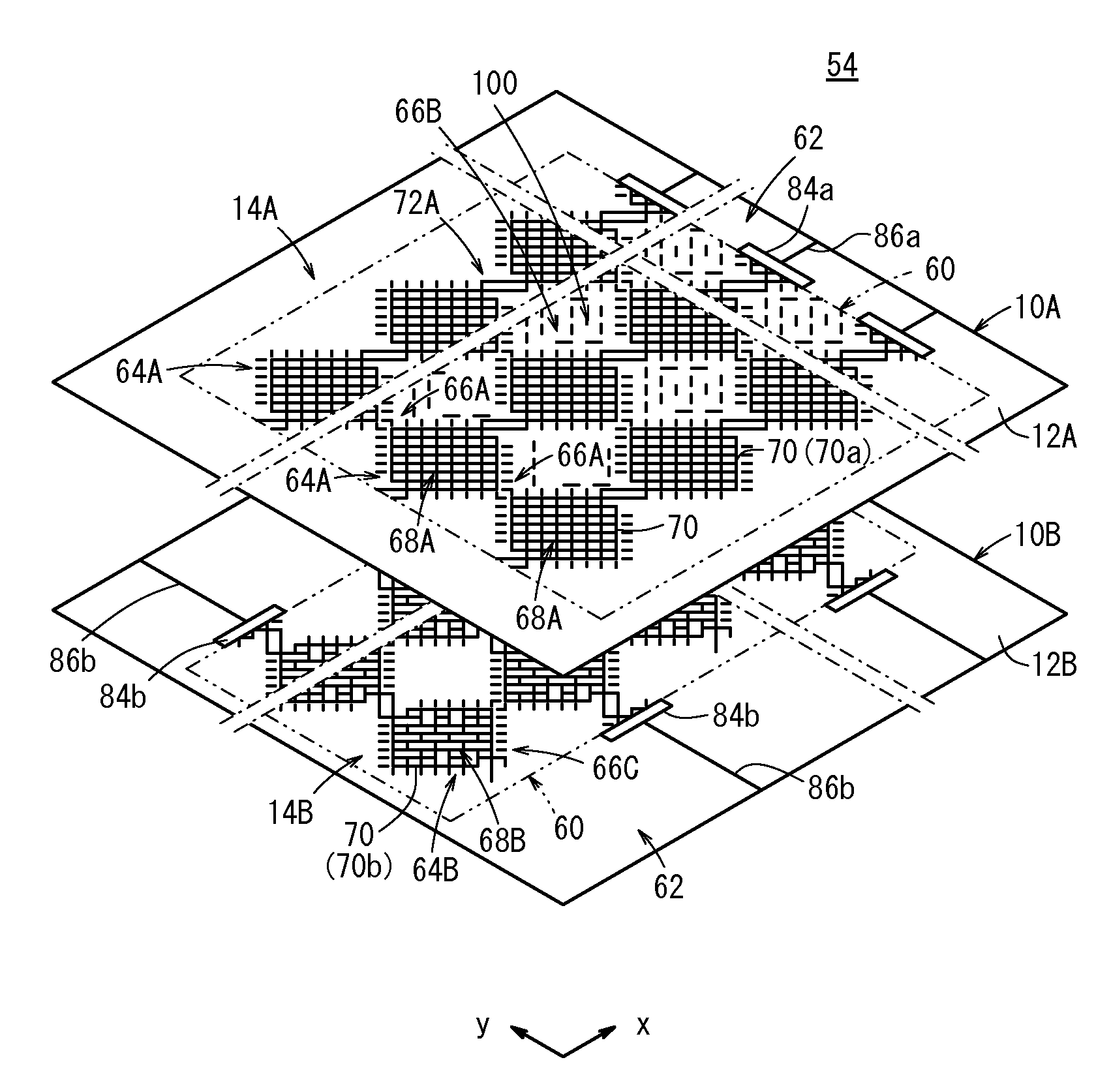

Electronic system modules and method of fabrication

InactiveUS6927471B2Good dimensional stabilityLow costPrinted circuit assemblingFinal product manufactureDielectricEngineering

This specification describes techniques for manufacturing an electronic system module. The module includes flexible multi-layer interconnection circuits with trace widths of 5 microns or less. A glass panel manufacturing facility, similar to those employed for making liquid crystal display, LCD, panels is used to fabricate the interconnection circuits. A polymer base layer is formed on a glass carrier with an intermediate release layer. Alternate layers of metal and dielectric are formed on the base layer, and patterned to create an array of multi-layer interconnection circuits on the glass panel. A thick layer of polymer is deposited on the interconnection circuit, and openings formed at input / output (I / O) pad locations. Solder paste is deposited in the openings to form wells filled with solder. After dicing the glass carrier to form separated interconnection circuits, IC chips are stud bumped and assembled using flip chip bonding, wherein the stud bumps on the components are inserted into corresponding wells on the interconnection circuits. The IC chips are tested and reworked to form tested circuit assemblies. Methods for connecting to testers and to other modules and electronic systems are described. Module packaging layers are provided for hermetic sealing and for electromagnetic shielding. A blade server embodiment is also described.

Owner:SK HYNIX INC

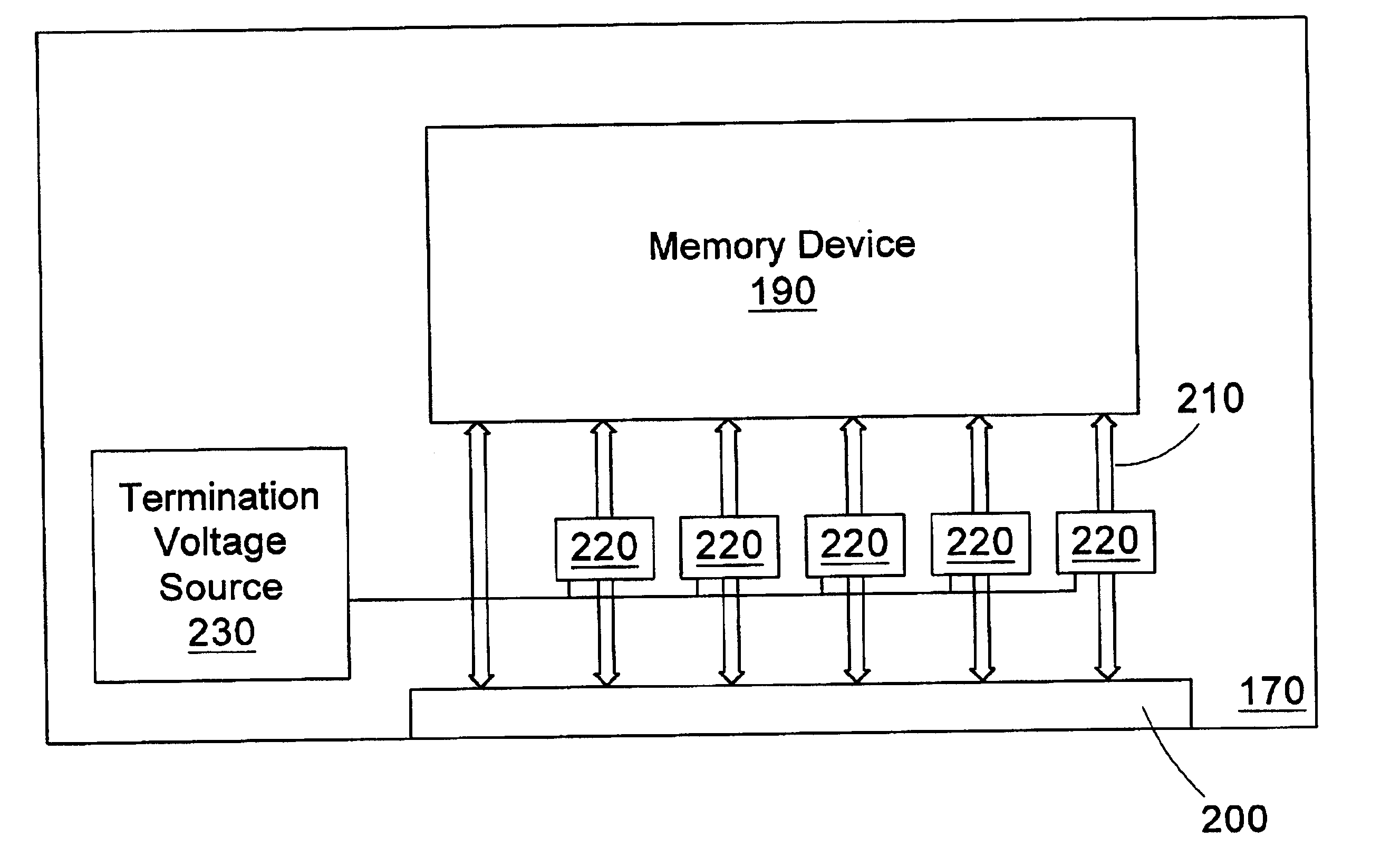

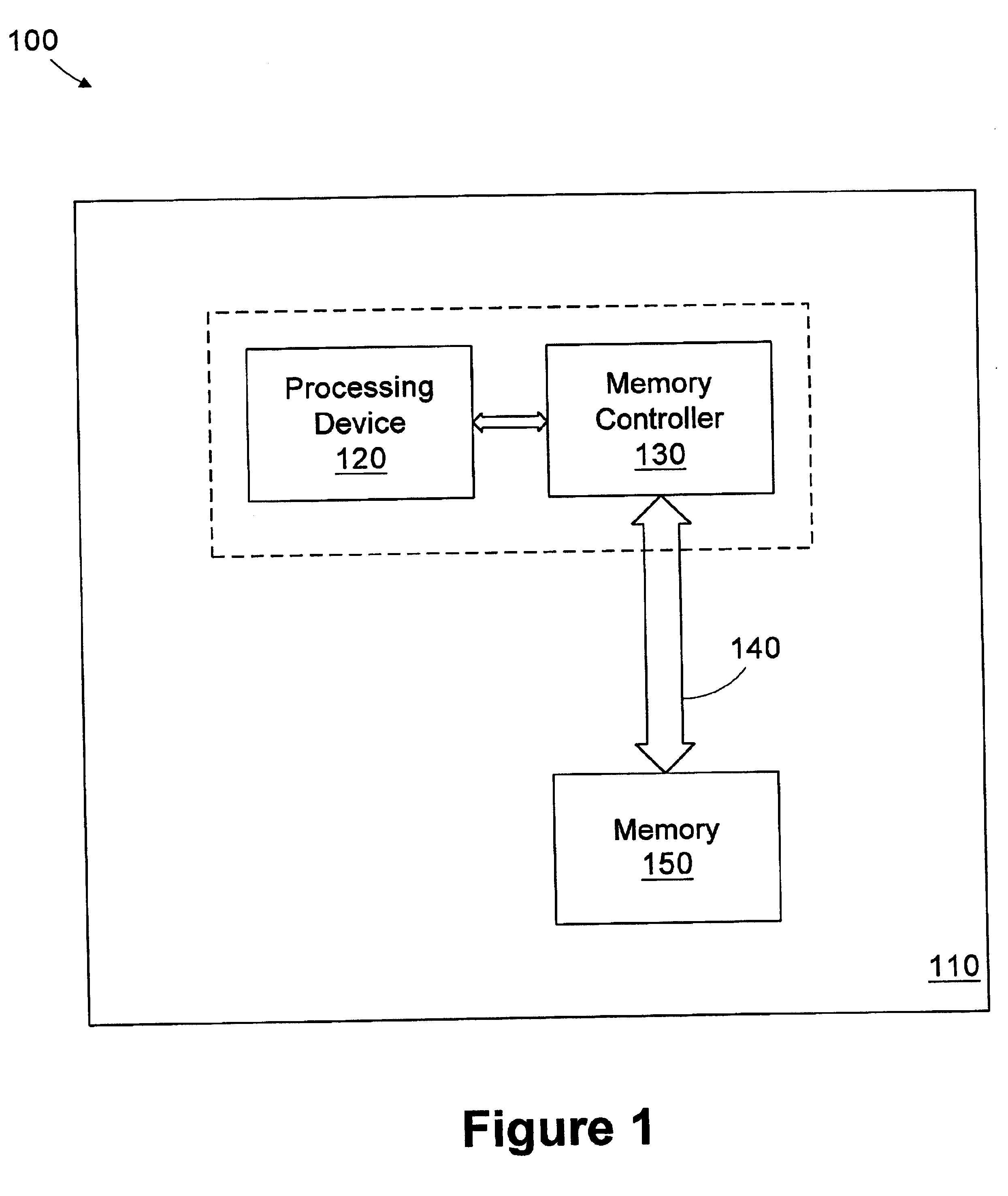

Memory module with integrated bus termination

A memory module includes a memory device, a connector, a plurality of lines coupling the memory device and the connector, and termination circuitry coupled to at least a subset of the lines. A method for terminating a memory bus includes providing at least two expansion sockets coupled to the memory bus; interfacing two expansion memory modules including termination circuitry with the expansion sockets; and disabling the termination circuitry for one of the expansion memory modules.

Owner:ROUND ROCK RES LLC

Transient electronic devices comprising inorganic or hybrid inorganic and organic substrates and encapsulates

ActiveUS20140305900A1Effective fabrication of deviceUseful overall permeabilityLayered productsFinal product manufactureSingle crystalInorganic materials

The invention provides transient devices, including active and passive devices that physically, chemically and / or electrically transform upon application of at least one internal and / or external stimulus. Incorporation of degradable device components, degradable substrates and / or degradable encapsulating materials each having a programmable, controllable and / or selectable degradation rate provides a means of transforming the device. In some embodiments, for example, transient devices of the invention combine degradable high performance single crystalline inorganic materials with selectively removable substrates and / or encapsulants.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Combination SD/MMC flash memory card with thirteen contact pads

InactiveUS20050279838A1Improve efficiencyCheap productionPrinted circuit aspectsSensing record carriersContact padEngineering

A memory card including a PCB assembly that is consistent with existing 13-pad MMC mechanical form factors, and a housing that is consistent with the SD mechanical form factor, thereby providing a single PCBA and housing arrangement that can be used to produce both MMC and SD memory cards. The thirteen contact pads support all MMC and SD contact pad patterns, but are modified to facilitate a write protect switch. The housing includes an enlarged window (or windows) that exposes two or more contact pads in each of the multiple rows, thereby facilitating slidable insertion of the memory card into a socket of a host system. Alignment notches are formed in the side edges of the PCB, and / or alignment pins are utilized for properly aligning the PCBA within the housing.

Owner:SUPER TALENT ELECTRONICS

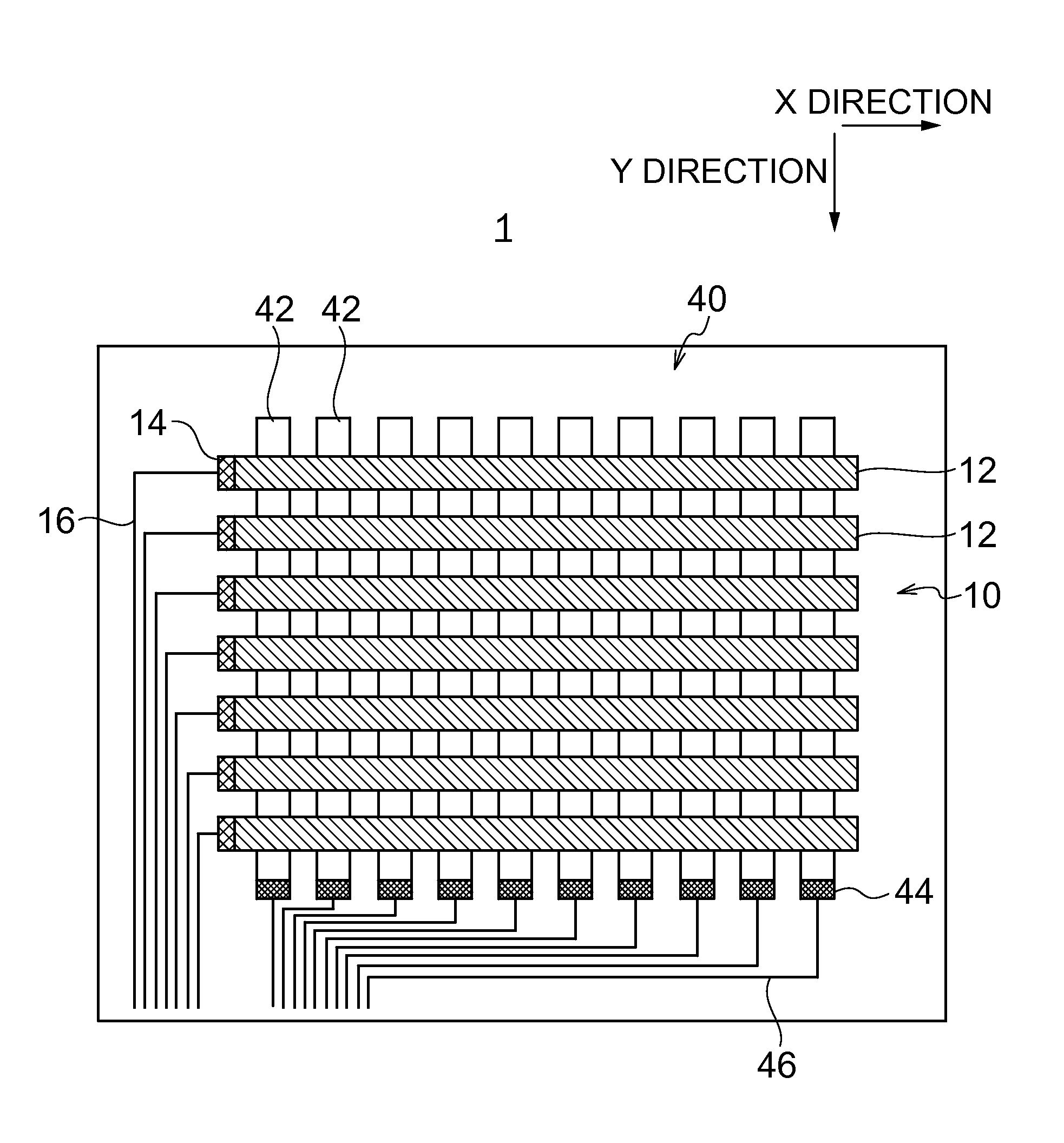

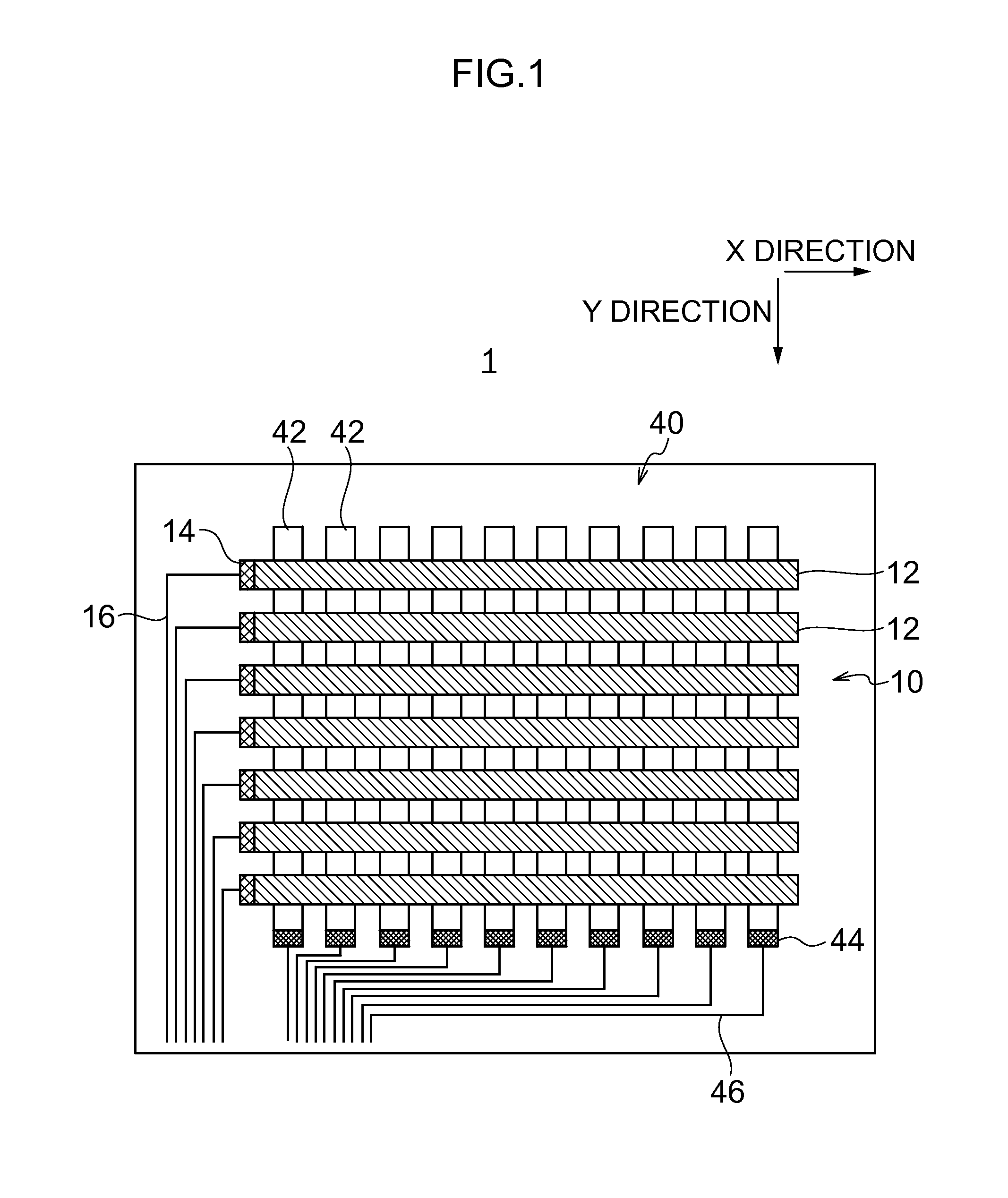

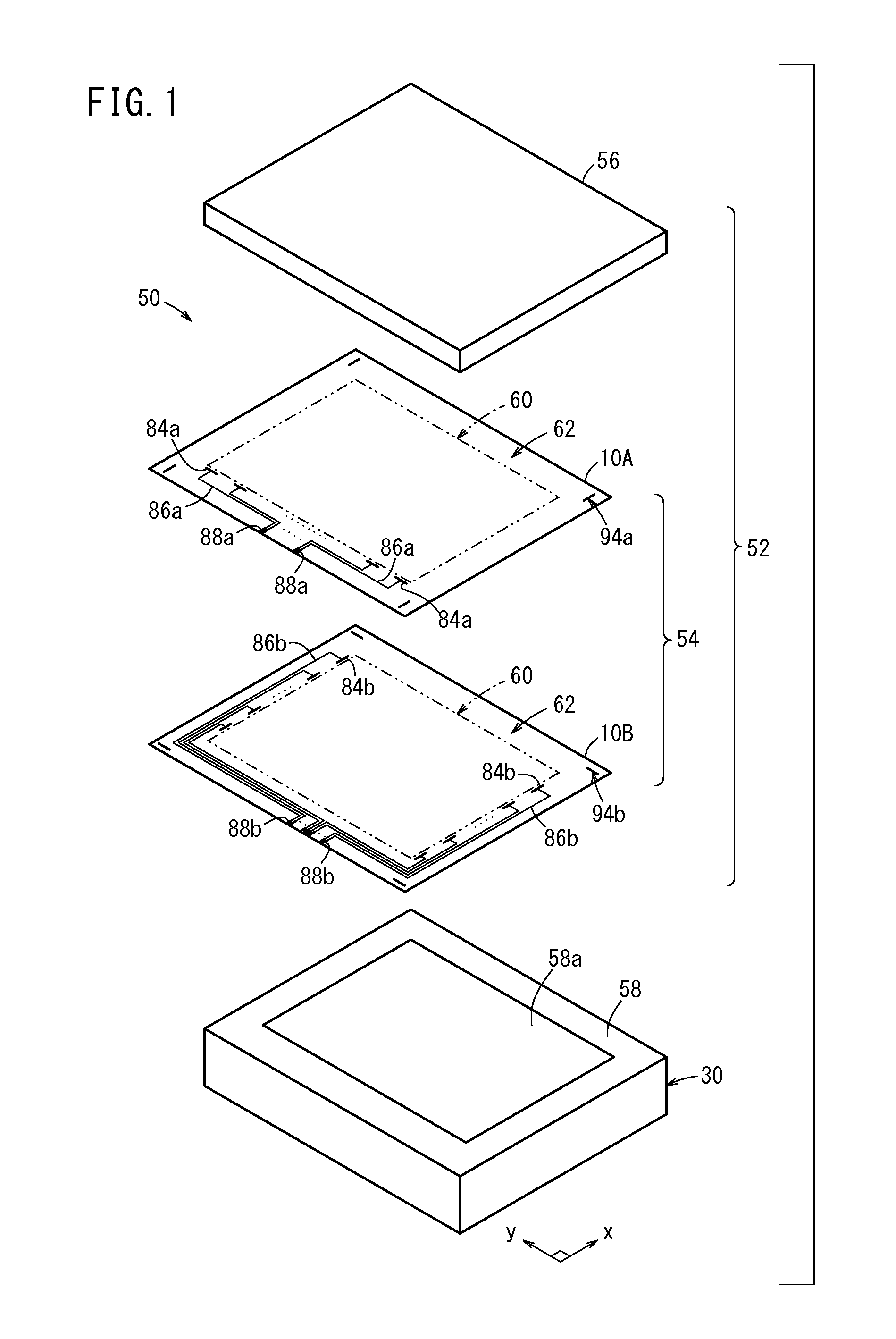

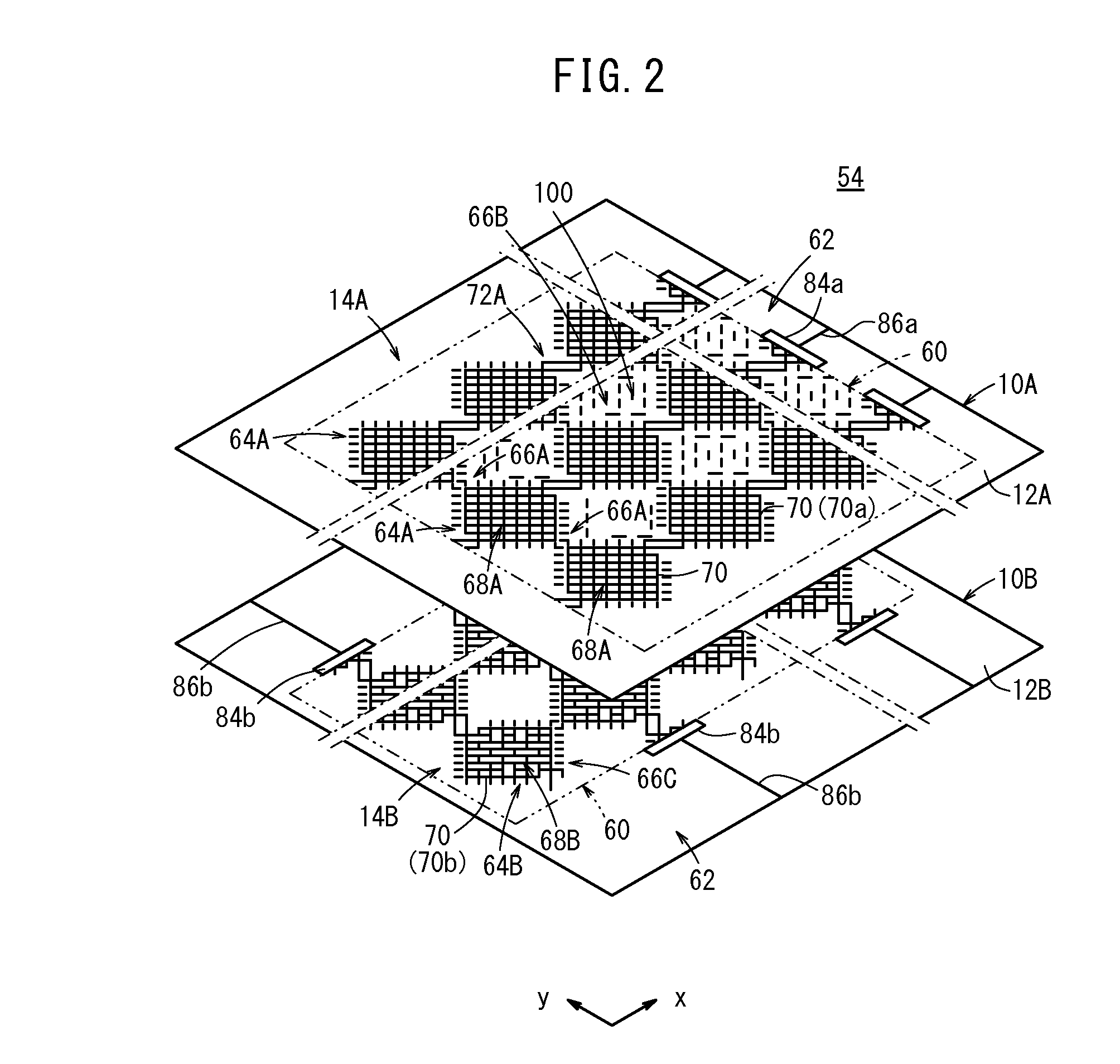

Conductive sheet and touch panel

ActiveUS20140299361A1Improve visibilityImprove detection accuracyCircuit optical detailsTransparent dielectricsEngineeringTouch panel

A conductive sheet includes: a substrate having a first main surface and a second main surface; and a first electrode pattern placed on the first main surface of the substrate. The first electrode pattern is made of metal thin wires, and includes a plurality of first conductive patterns that extend in a first direction. Each first conductive pattern includes, at least, inside thereof, a sub-nonconduction pattern that is electrically separated from the first conductive pattern. An area A of each first conductive pattern and an area B of each sub-nonconduction patterns satisfy a relation of 5%<B / (A+B)<97%. Accordingly, a conductive sheet and a touch panel having a high detection accuracy can be provided.

Owner:FUJIFILM CORP

Magnetic component connector, circuit boards for use therewith, and kits for building and designing circuits

InactiveUS7611357B2Firmly connectedEasy to removePrinted circuit aspectsCoupling contact membersMagnetic tension forceContact pad

Printed circuit boards and breadboard devices have contact pads and magnetic component connectors where connection between the contact pads and the magnetic component connectors are made by magnetic force. Either the contact pad or the magnetic component connector will be magnetic and the other will be made of a material to which a magnet will be attracted. For example, printed circuit boards, which usually have copper traces, include contact pads made of a material to which a magnet will be attracted. Circuit components are connected to magnetic component connectors having magnetic legs which then connect the components to the contact pads of the circuit board or breadboard device. This makes the connection of components to a printed circuit board or breadboard device fast and easy and provides for easy removal and replacement of components. Magnetic component connectors can also be configured to connect magnetically to one another.

Owner:MR BOARD

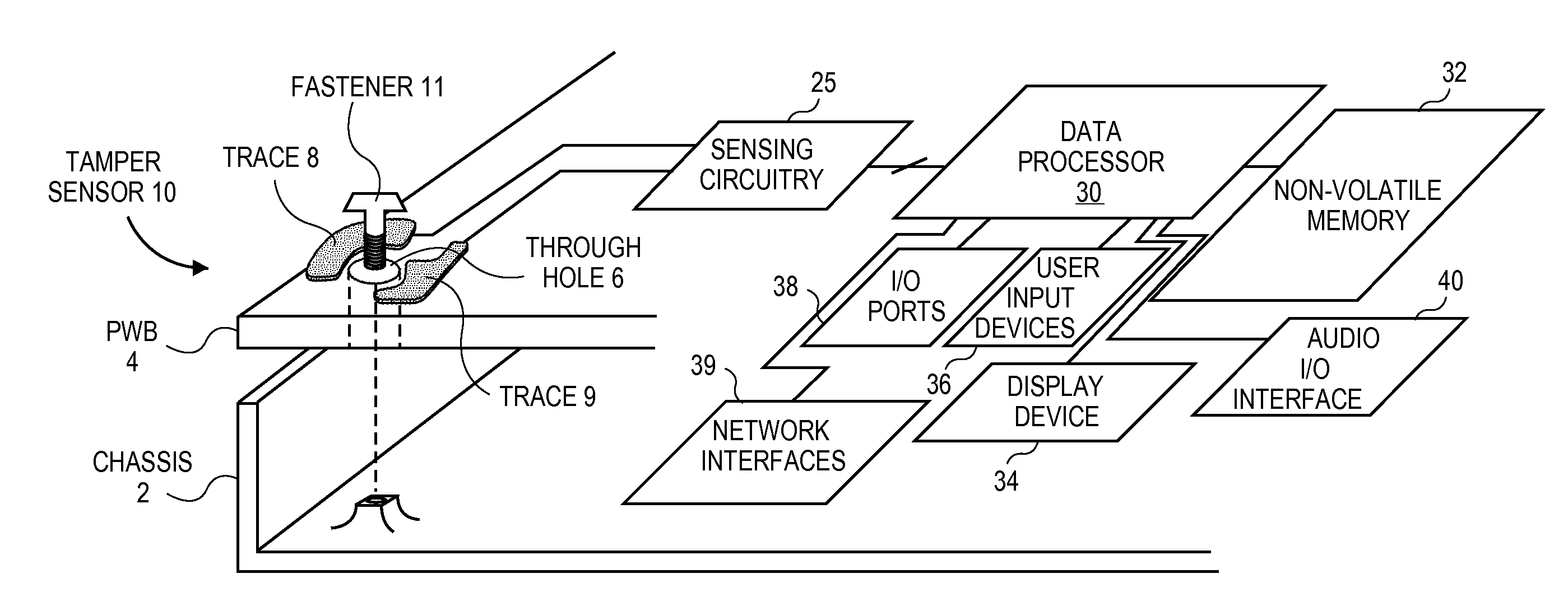

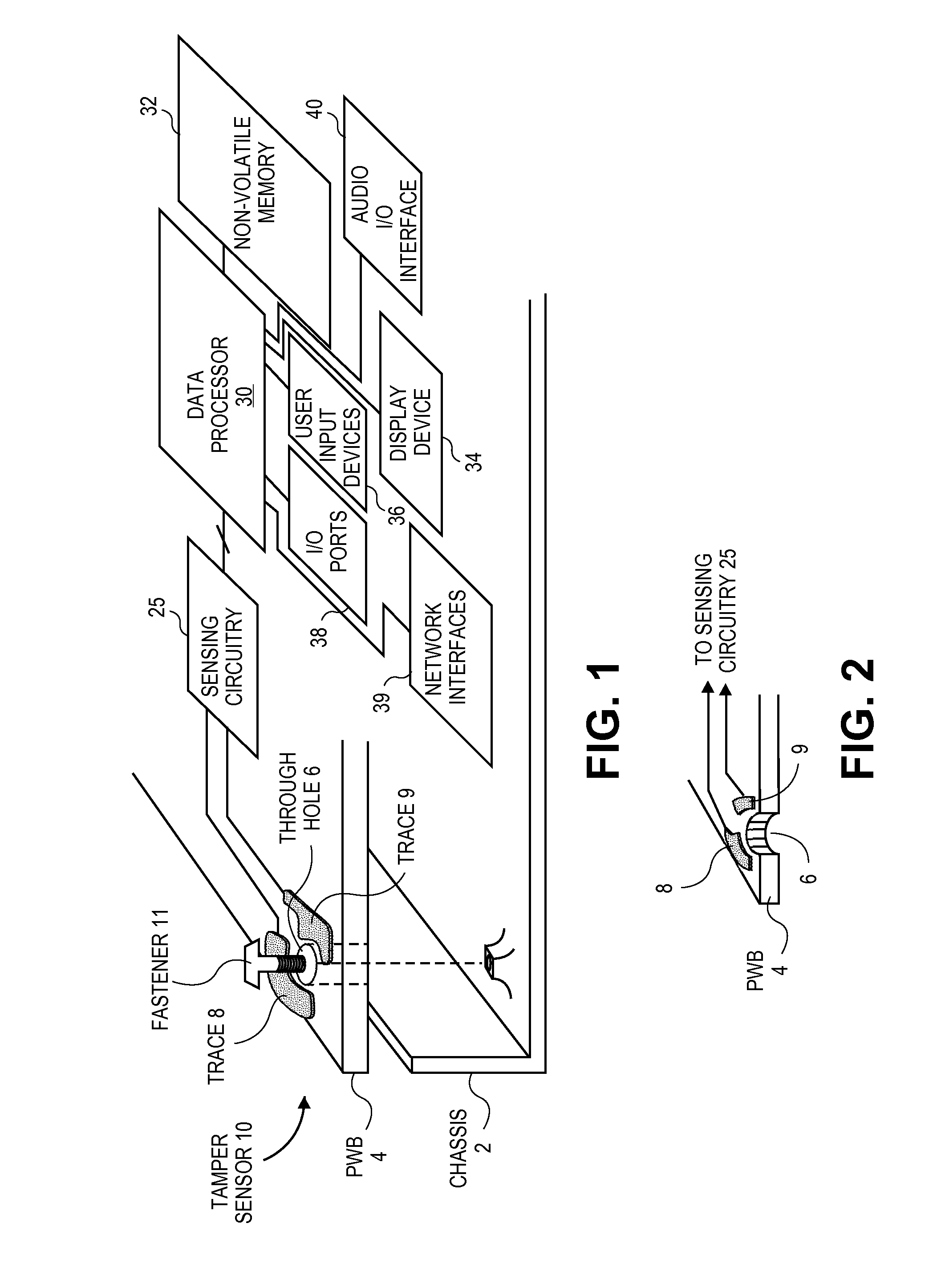

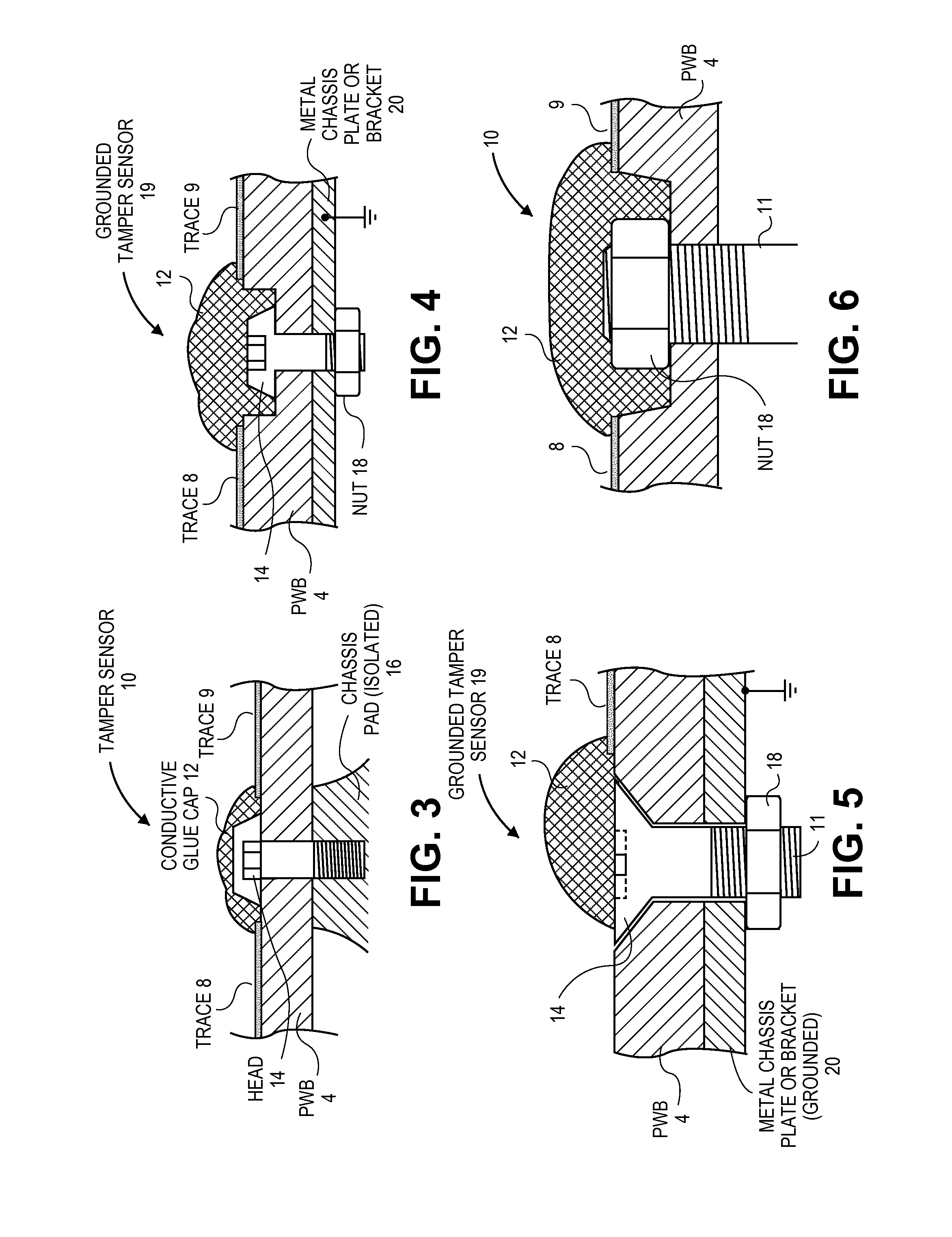

Mechanisms for detecting tampering of an electronic device

ActiveUS20110031985A1Electrical testingInternal/peripheral component protectionElectronic equipmentFastener

An electronic device has a chassis, and a printed wiring board (PWB) having a hole. A fastener is installed in the hole thereby securing the PWB to the chassis. A pair of conductive traces is formed in the PWB. A cap, being an amount of conductive glue, covers a part of the fastener and fills an electrically insulating gap between the two traces, to thereby form a conductive path that connects the two traces. A sensing circuit is coupled to the traces, to detect a change in impedance of the path and signal a tamper event alert. Other embodiments are also described and claimed.

Owner:APPLE INC

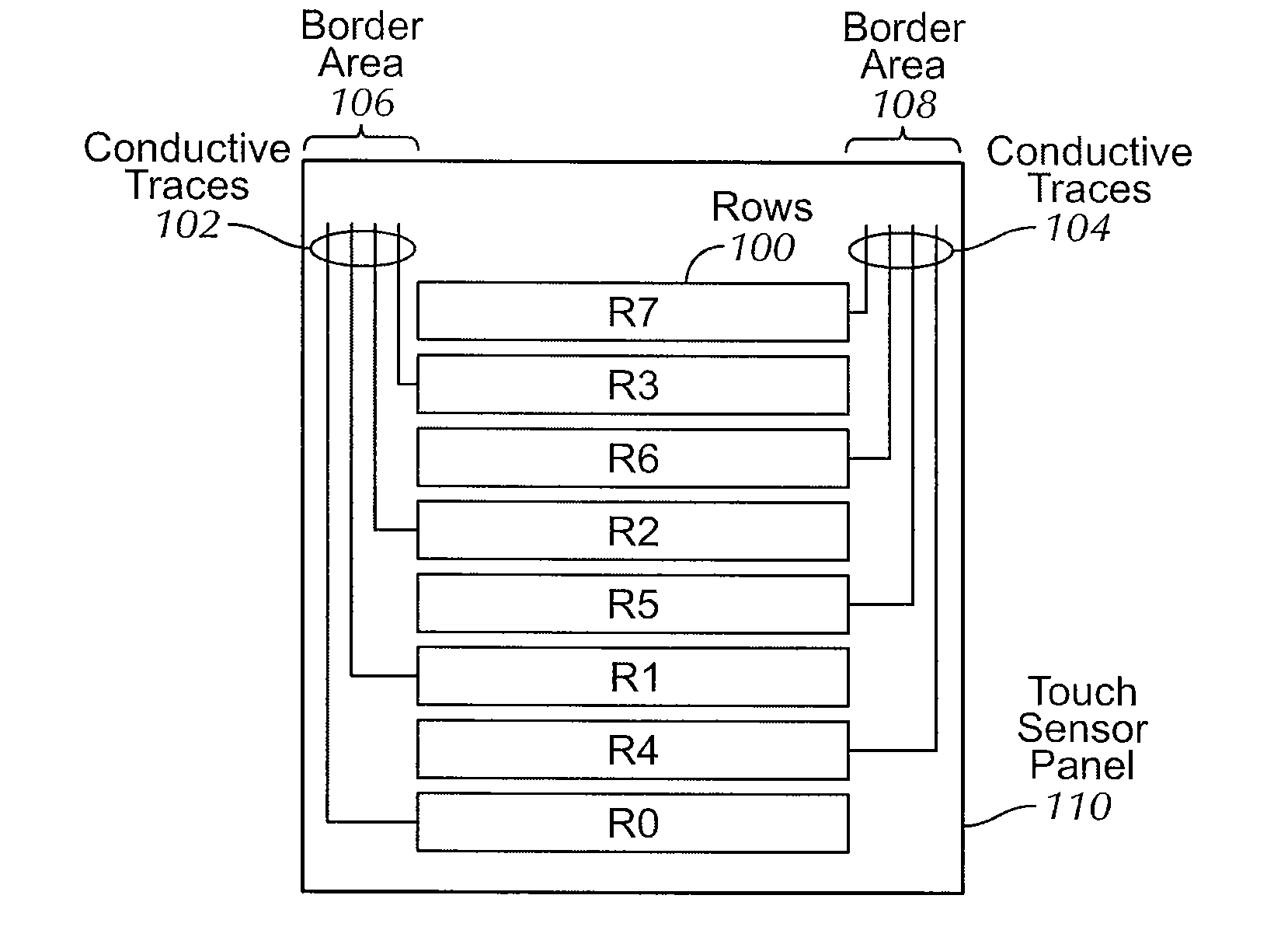

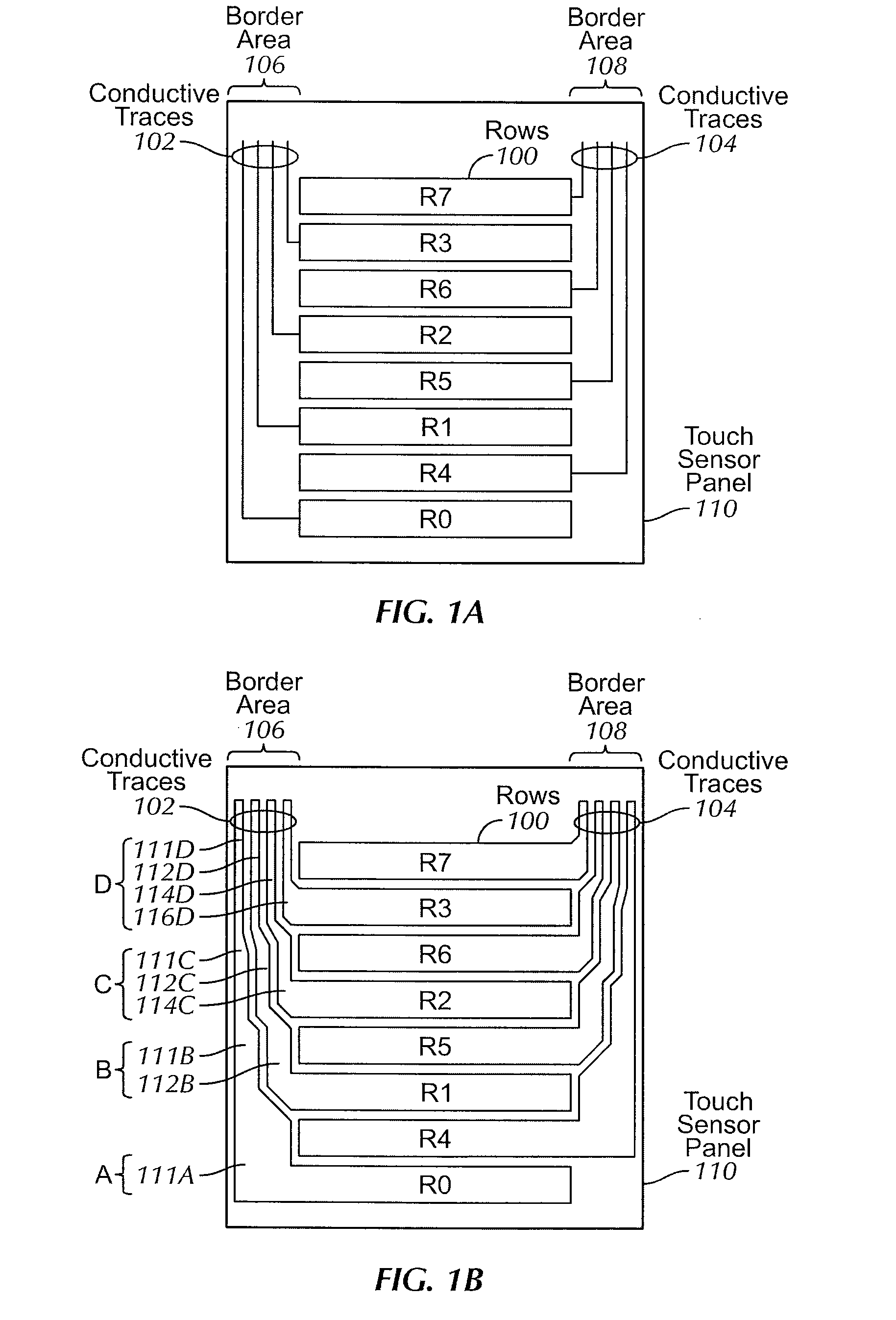

High Resistivity Metal Fan Out

ActiveUS20090303189A1Improve reliabilityGood rejectionTransparent dielectricsConductive pattern reinforcementManufacturing cost reductionHigh resistivity

The formation of metal traces in the border areas of a touch sensor panel to provide improved reliability, better noise rejection, and lower manufacturing costs is disclosed. The metal traces can be coupled to rows on the touch sensor panel in an interleaved manner, so that any two successive rows can be coupled to metal traces in border areas on opposite sides of the touch sensor panel. In addition, by utilizing the full width available in the border areas in some embodiments, the metal traces can be formed from higher resistivity metal, which can reduce manufacturing costs and improve trace reliability. The wider traces can also provide better noise immunity from noise sources such as an LCD by providing a larger fixed-potential surface area and by more effectively coupling the drive lines to the fixed potential.

Owner:APPLE INC

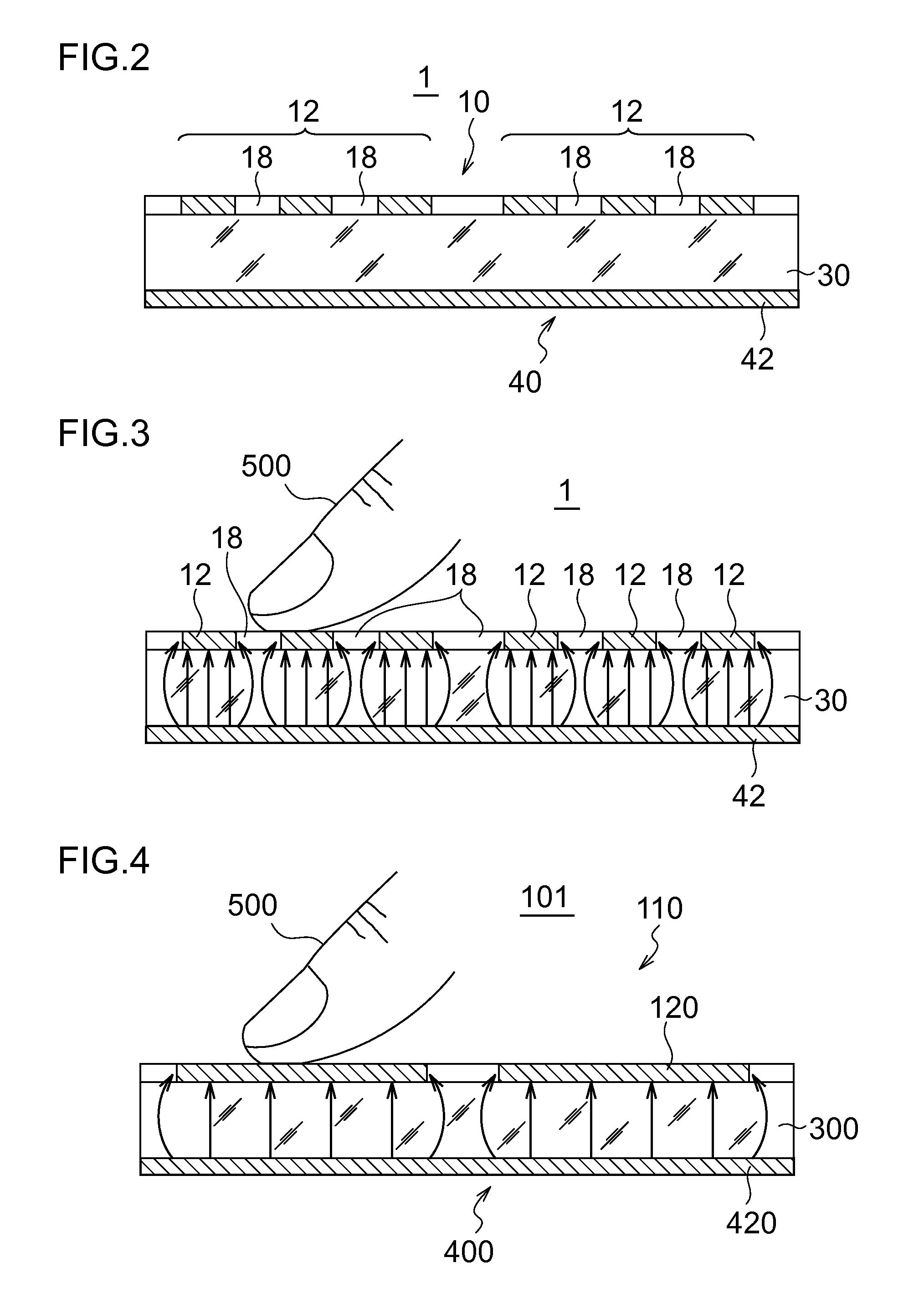

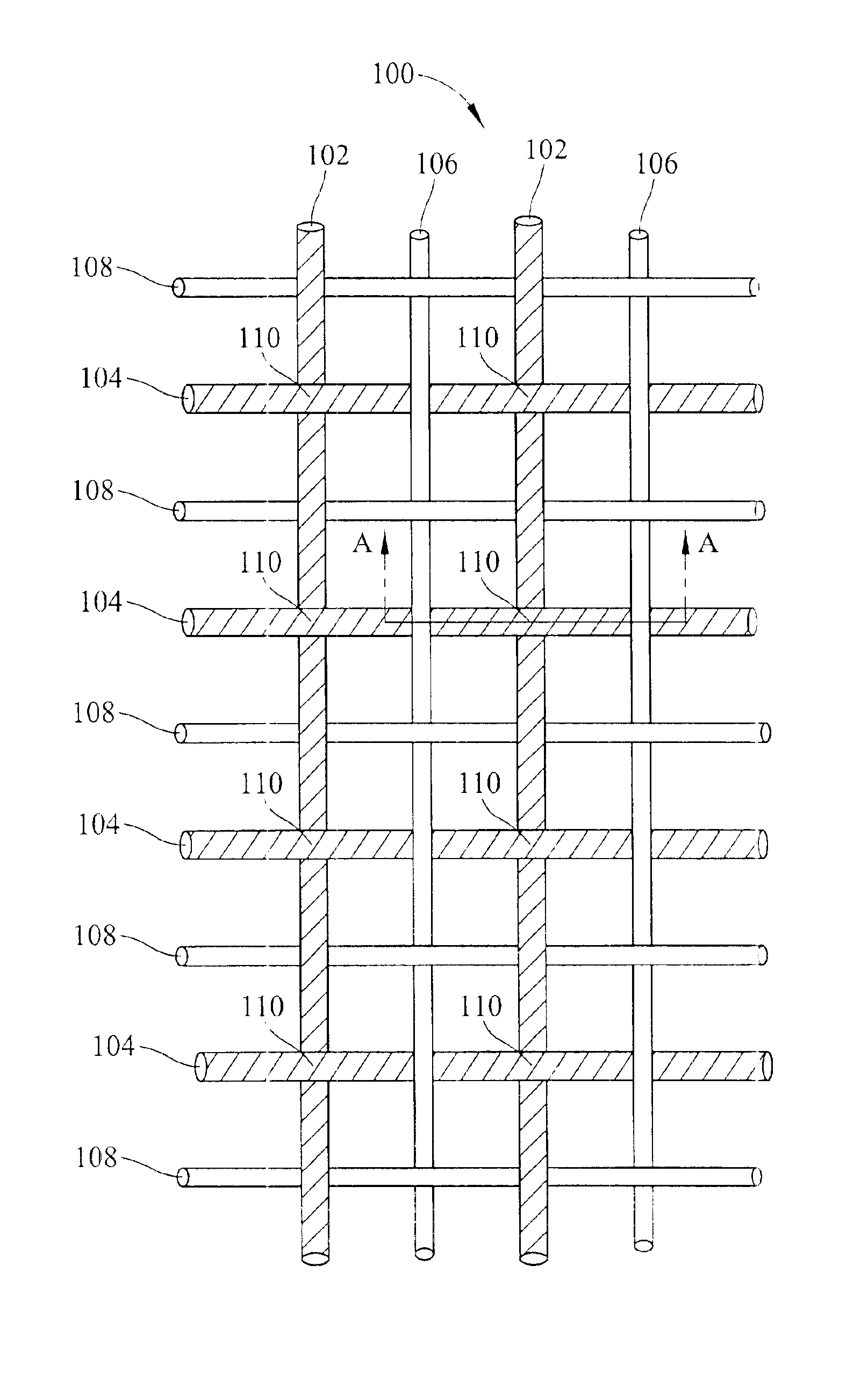

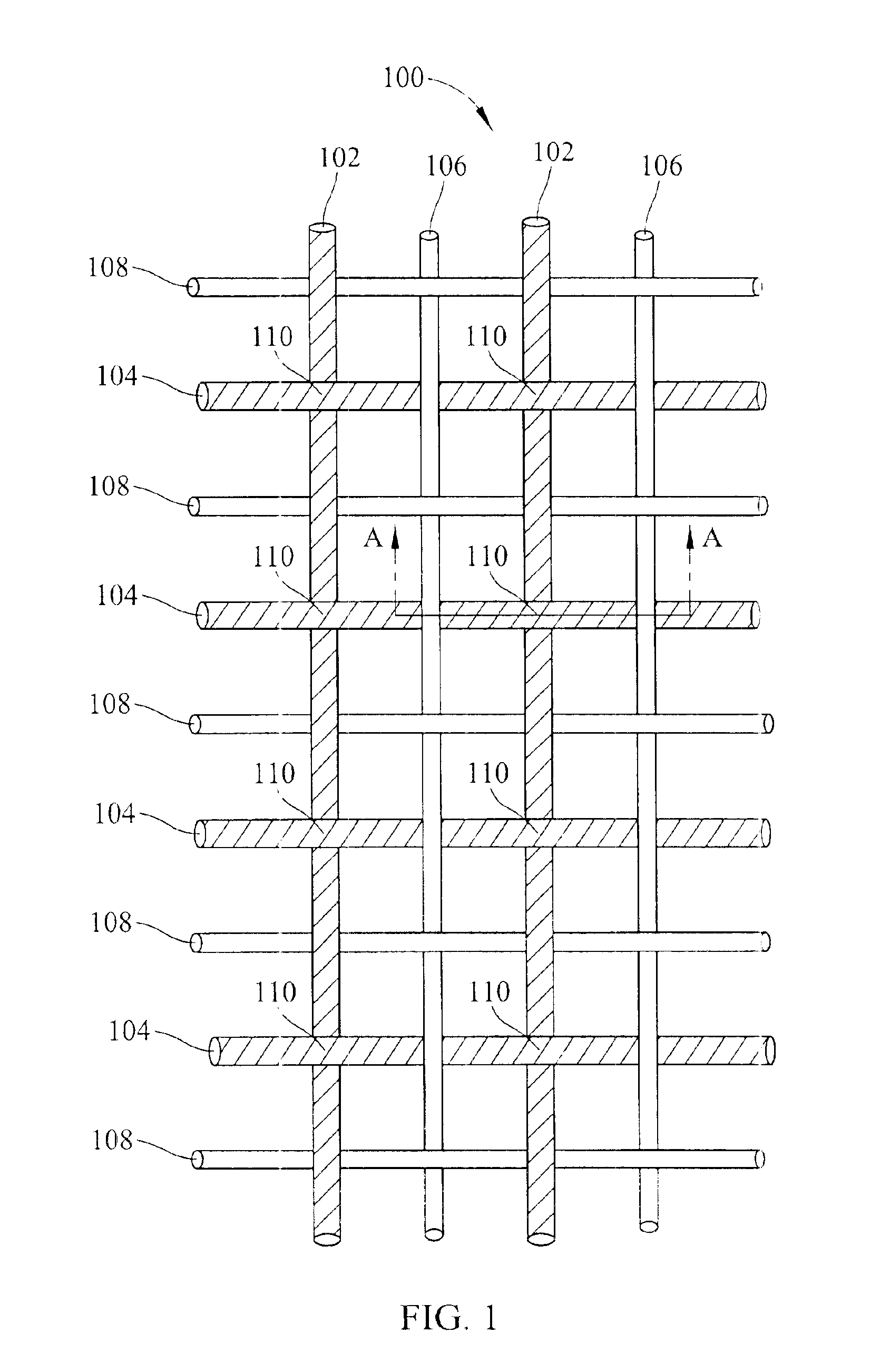

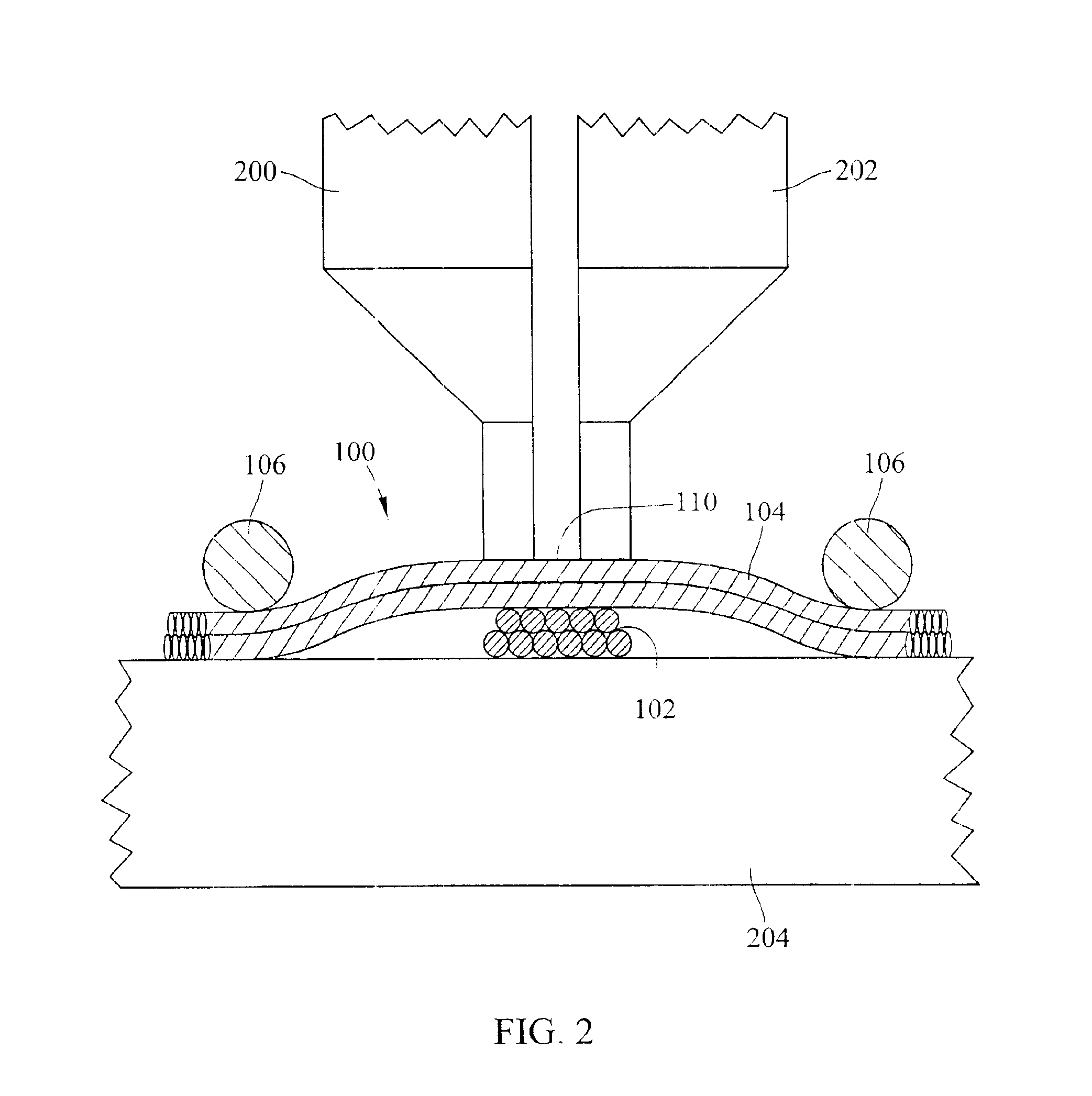

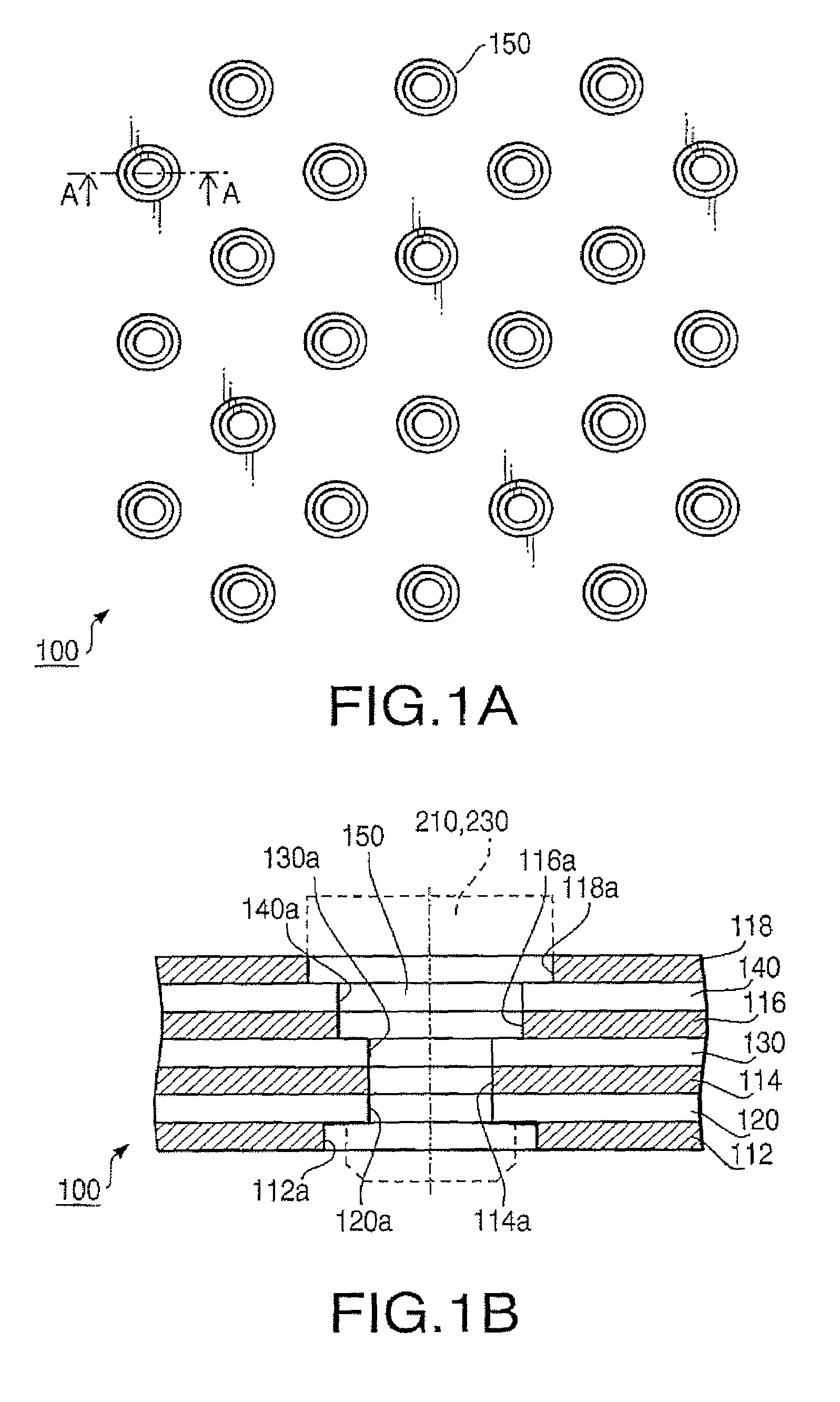

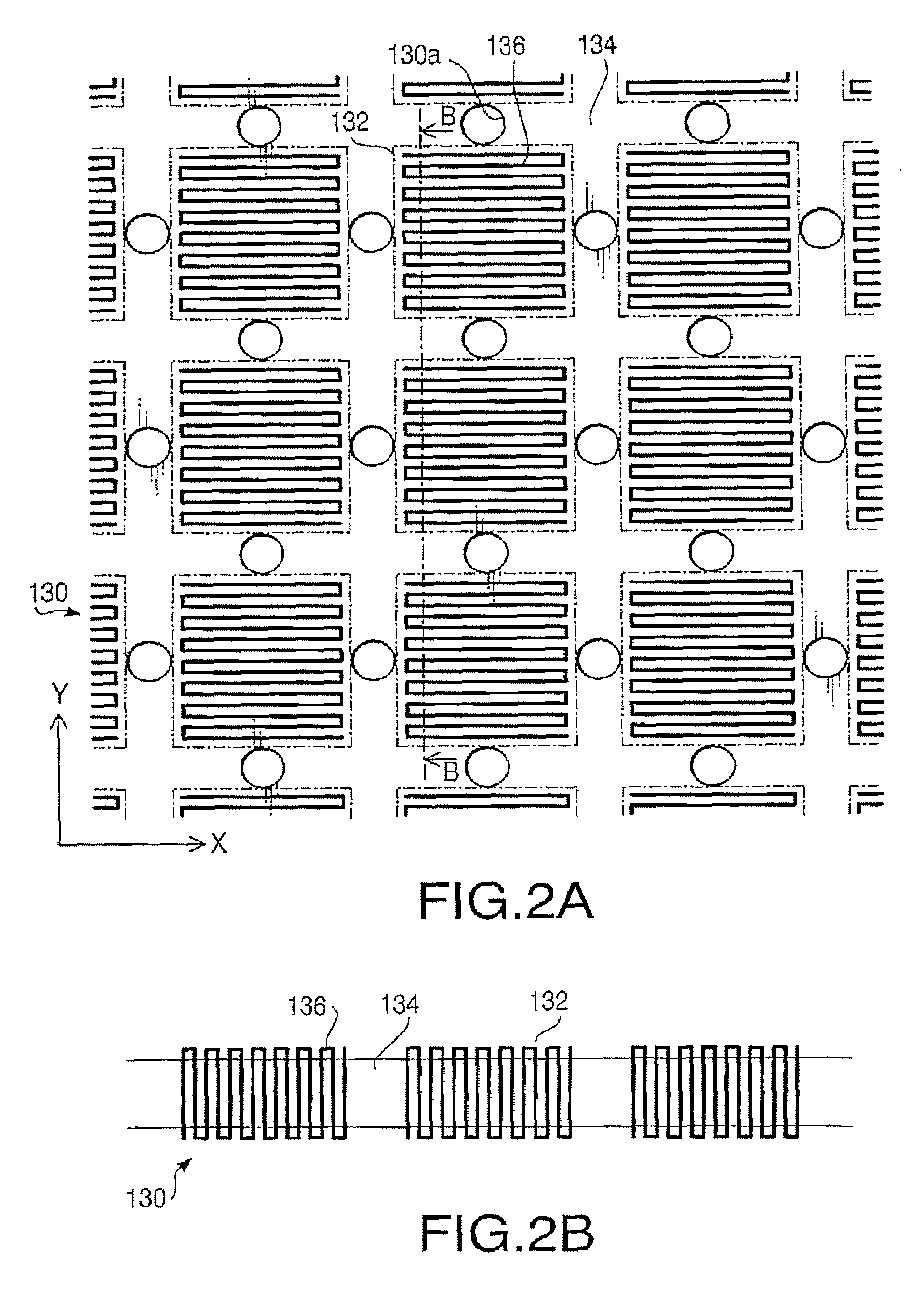

Methods and systems for selectively connecting and disconnecting conductors in a fabric

InactiveUS6852395B2Improve featuresReduced footprintThin material handlingMetal layered productsElectrical conductorEngineering

Methods and systems for selectively connecting and disconnecting conductors in a fabric are disclosed. First and second conductors are integrated into a fabric such that the conductors intersect at a crossover point. The conductors are bonded to each other at the crossover point to improve AC and DC characteristics. Disconnect areas may be provided near the crossover point to allow selective disconnection of the conductors from the crossover point.

Owner:NORTH CAROLINA STATE UNIV

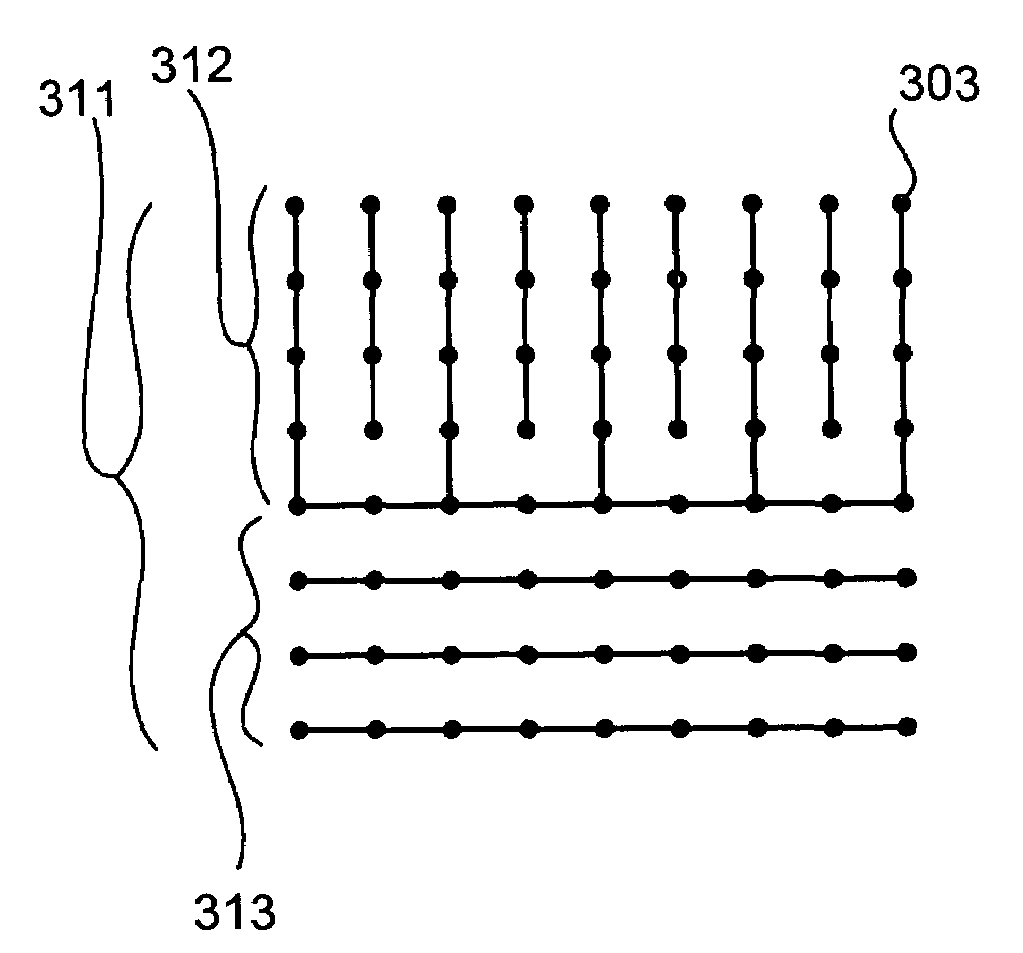

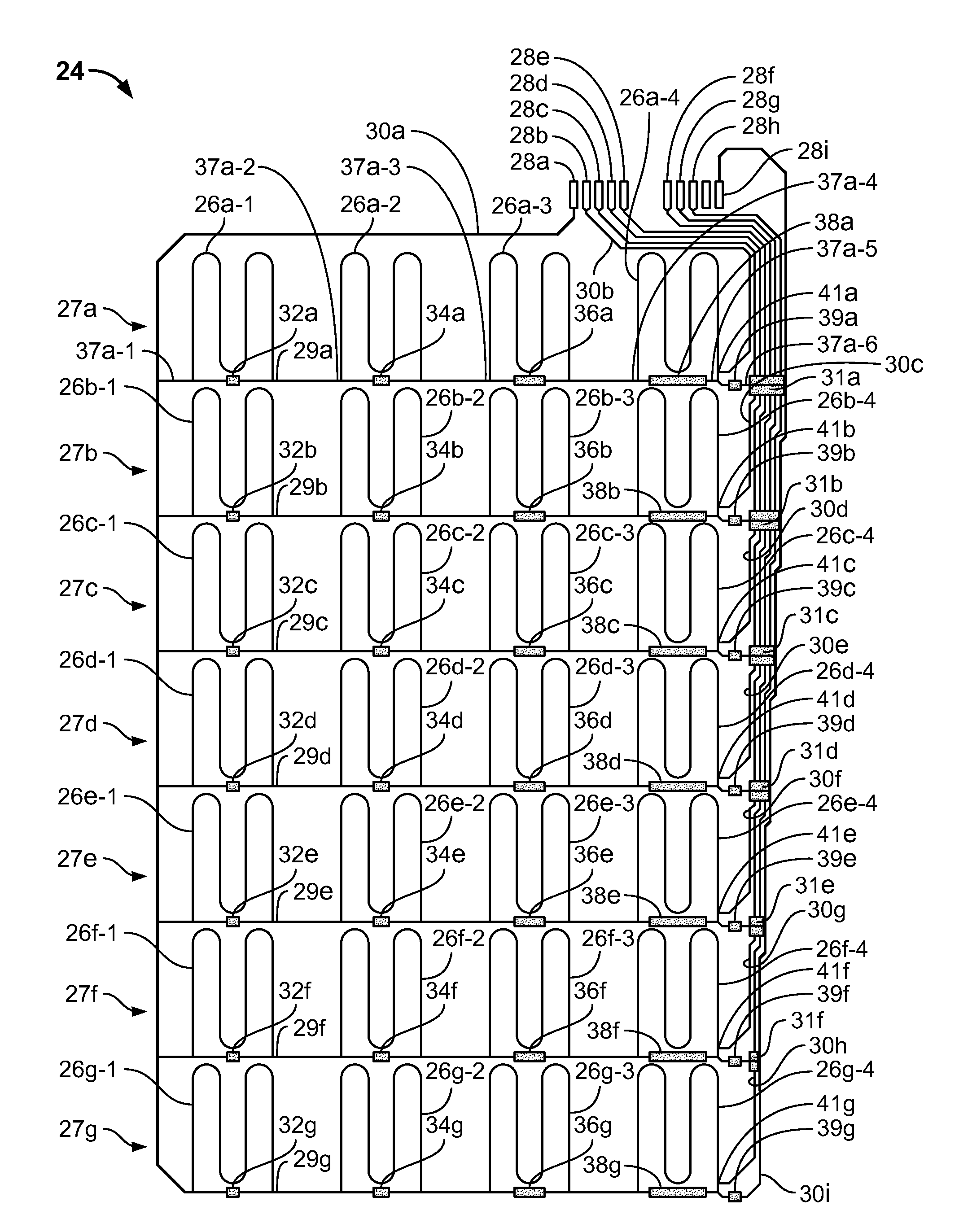

Dosage form package and a frangible electrical circuit sheet therefor

A frangible electrical circuit sheet for a dosage form package includes a first plurality of electrically conductive trace subnetworks interconnected with one another to form a network of electrically conductive traces and disposed on the sheet. The sheet further includes a second plurality of circuit elements connected to the network of electrically conductive traces such that each circuit element is associated with one of the subnetworks. At least some of the circuit elements have element values that differ from one another.

Owner:MTS MEDICATION TECH

Method and apparatus for reducing signal timing skew on a printed circuit board

An apparatus and method are described for reducing the timing skew on a printed circuit board including a plurality of conductive traces interconnecting a first node and a second node. At least one section is removed from at least one printed circuit board trace to thereby sever a trace and prevent signals passing from the first node to the second node from following the severed trace. In this manner, signal path length can be adjusted to reduce timing skews in the circuit. Sections are removed from the traces by using a laser, CVD, a router, a plasma or by passing sufficient current through weakened areas of the traces.

Owner:MICRON TECH INC

Conductive layer, manufacturing method of the same, and signal transmission substrate

InactiveUS7670144B2Improve accuracyEasy alignmentCoupling device connectionsElectric discharge tubesElectrical resistance and conductanceHigh resistance

Owner:HOYA CORP

Electroconductive sheet and touch panel

InactiveUS20140054070A1Increase awarenessThin line widthCircuit optical detailsPrinted circuit aspectsTouch panelElectrical and Electronics engineering

An electroconductive sheet and a touch panel, wherein the electroconductive sheet has a first electroconductive section and a second electroconductive section; the first electroconductive section has a plurality of first electroconductive patterns arrayed in one direction and to which a plurality of first electrodes, respectively, are connected; the second electroconductive section has a plurality of second electroconductive patterns arrayed in a direction orthogonal to the arrayed direction of the first electroconductive patterns and to which a plurality of second electrodes, respectively, are connected; and the electroconductive sheet has dummy electrodes disposed between the first electrodes and the second electrodes, and other dummy electrodes disposed in portions corresponding to the second electrodes.

Owner:FUJIFILM CORP

Light emitting module

InactiveUS20050239342A1Improve cooling effectEasy to handlePlanar light sourcesSemiconductor/solid-state device detailsElectrical conductorEngineering

The present invention provides a light emitting module, comprising: a plurality of thin plate-shaped conductors (2) spaced apart from each other in a first direction; at least one light source (4) connected between at least one pair of adjoining ones of said conductors; and at least one insulating joint member (4) for mechanically joining said plurality of conductors, wherein said at least one insulating joint member exposes both sides of at least a portion of said conductors where said light source is mounted.

Owner:MORIYAMA SANGYO

Semiconductor memory module and module system

InactiveUS6388886B1Shorten the transmission pathReduce signal distortionCircuit arrangements on support structuresSemiconductor/solid-state device detailsComputer moduleParasitic capacitance

Provided is a semiconductor memory module capable of decreasing a parasitic capacitance and a parasitic inductance which are incidental to a signal transmission path, thereby reducing a distortion of a signal waveform. In a memory module, four DRAMs are provided on a muttilayer printed circuit board in one line corresponding to a direction of arrangement of external terminals thereof and board terminal groups of the module are provided to make a pair along two long sides of the multilayer printed circuit board. The DRAM has external terminals extended from one of the long sides and external terminals extended from the other long side. Board terminals and board terminals in the board terminal group of the module are connected to the DRAM, and board terminals and board terminals in the board terminal group TGB of the module are connected to the DRAM.

Owner:MITSUBISHI ELECTRIC CORP

System and method for integrating a digital core with a switch mode power supply

InactiveUS20050024908A1Good power savingMinimal costDigital data processing detailsDc-dc conversionCapacitanceEngineering

A digital core embodied within a semiconductor die is situated within any of a variety of integrated circuit packaging technologies including but not limited to Ball Grid Array or Quad Flat Pack surface mount technology. Said semiconductor die is of the variety that requires plural separate power supply voltage domains such as a digital core supply of differing voltage than the input / output pad ring supply voltage. Within the integrated circuit package including said semiconductor die also exists a high efficiency DC-to-DC voltage converter of type commonly known as a chopper or a switch mode power supply. In the preferred embodiment this switch mode power supply would be of the highest efficiency, a synchronous step-down regulator, thus to enable powering the entire integrated circuit from one supply voltage. The components contained within the integrated circuit package along with the semiconductor die include the majority if not the totality of the components comprising the switch mode power supply, which could include the power switching transistors; an inductor core and windings; the output voltage fixing circuitry; the output capacitor; and the substrate for mounting said components when integrated within a packaging technology that does not already include a substrate such as within the periphery of a lead frame for leaded devices.

Owner:CUFER ASSET LTD LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com