Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38 results about "Charged-device model" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The charged-device model (CDM) is a model for characterizing the susceptibility of an electronic device to damage from electrostatic discharge (ESD). The model is an alternative to the human-body model (HBM).

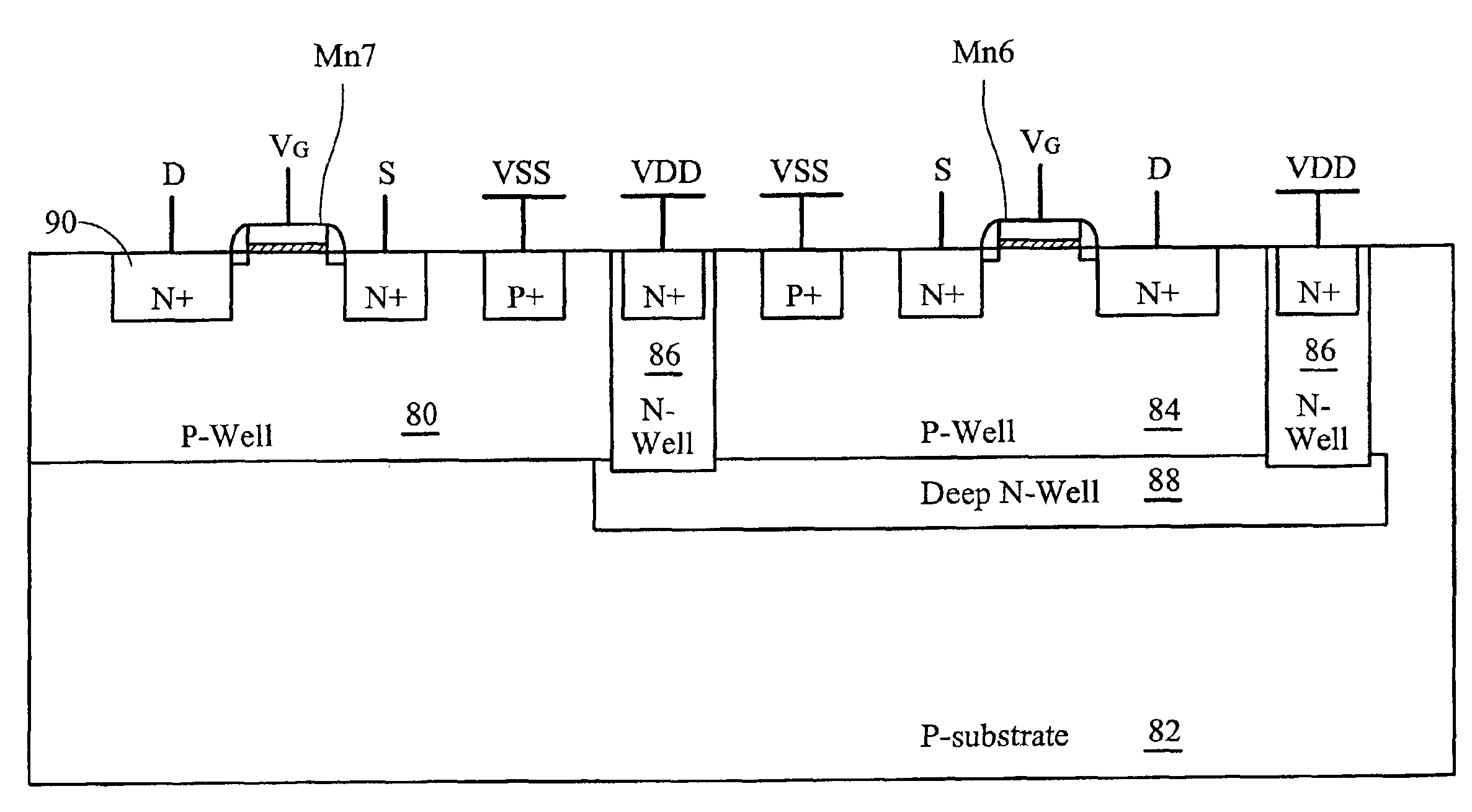

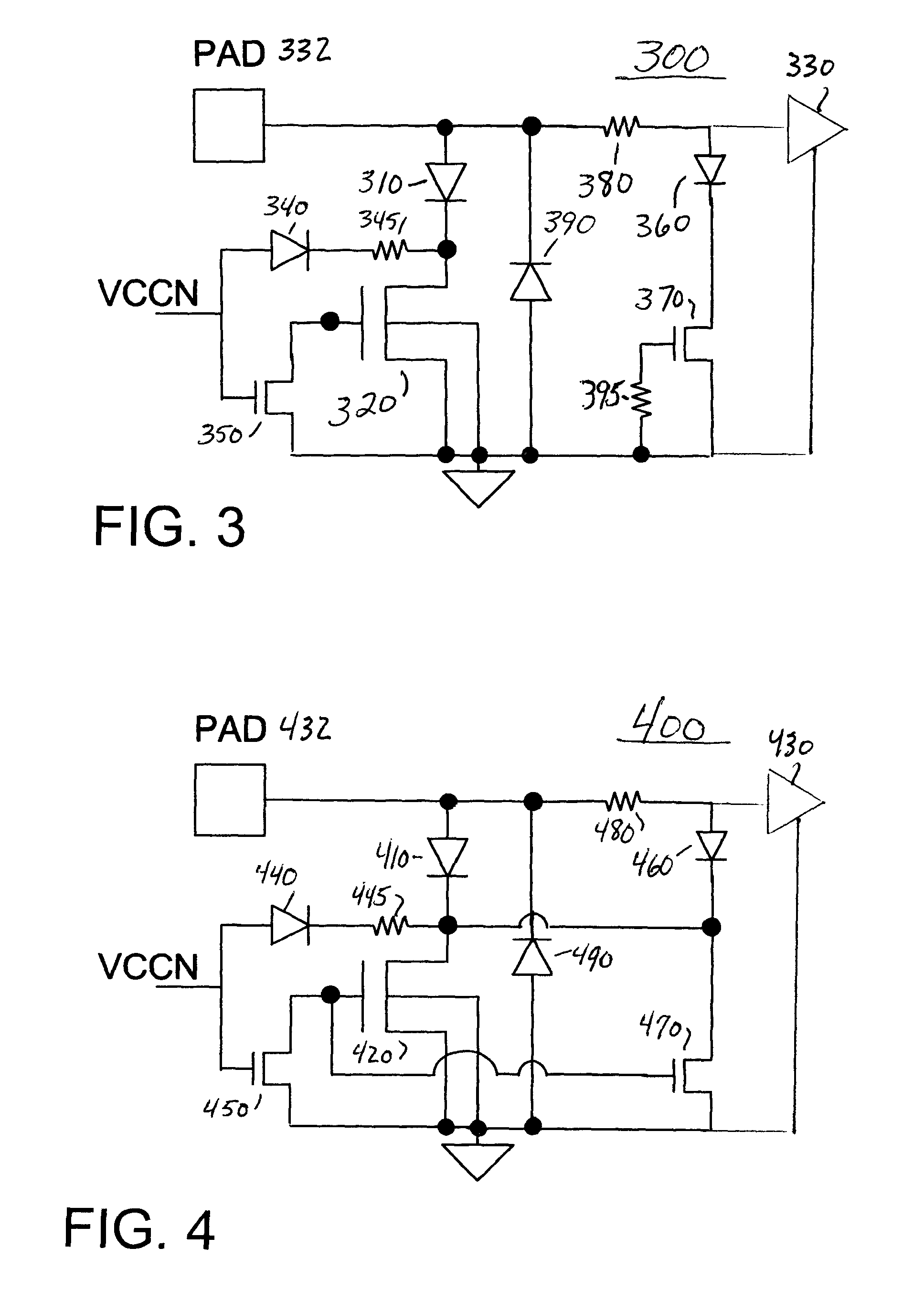

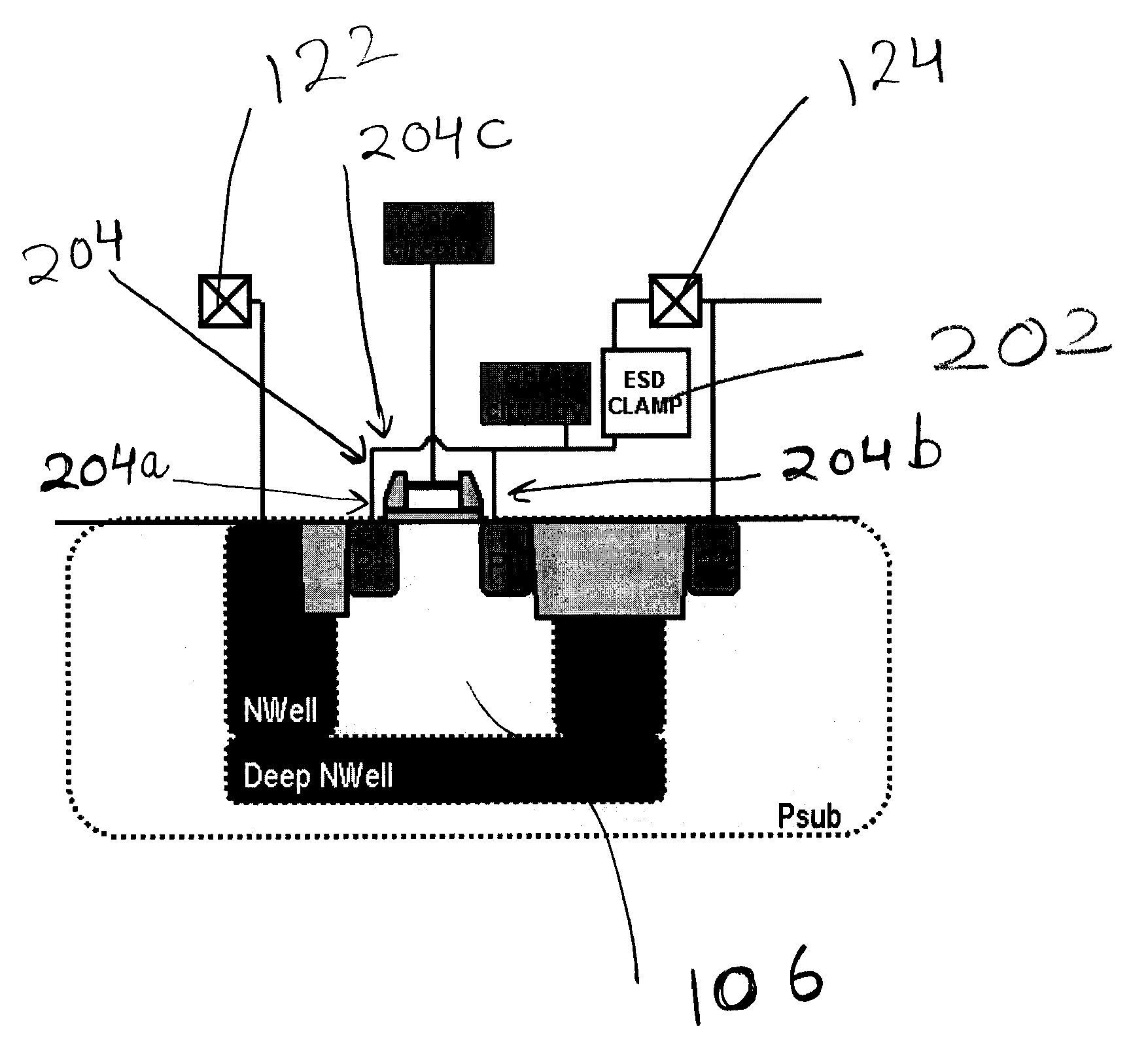

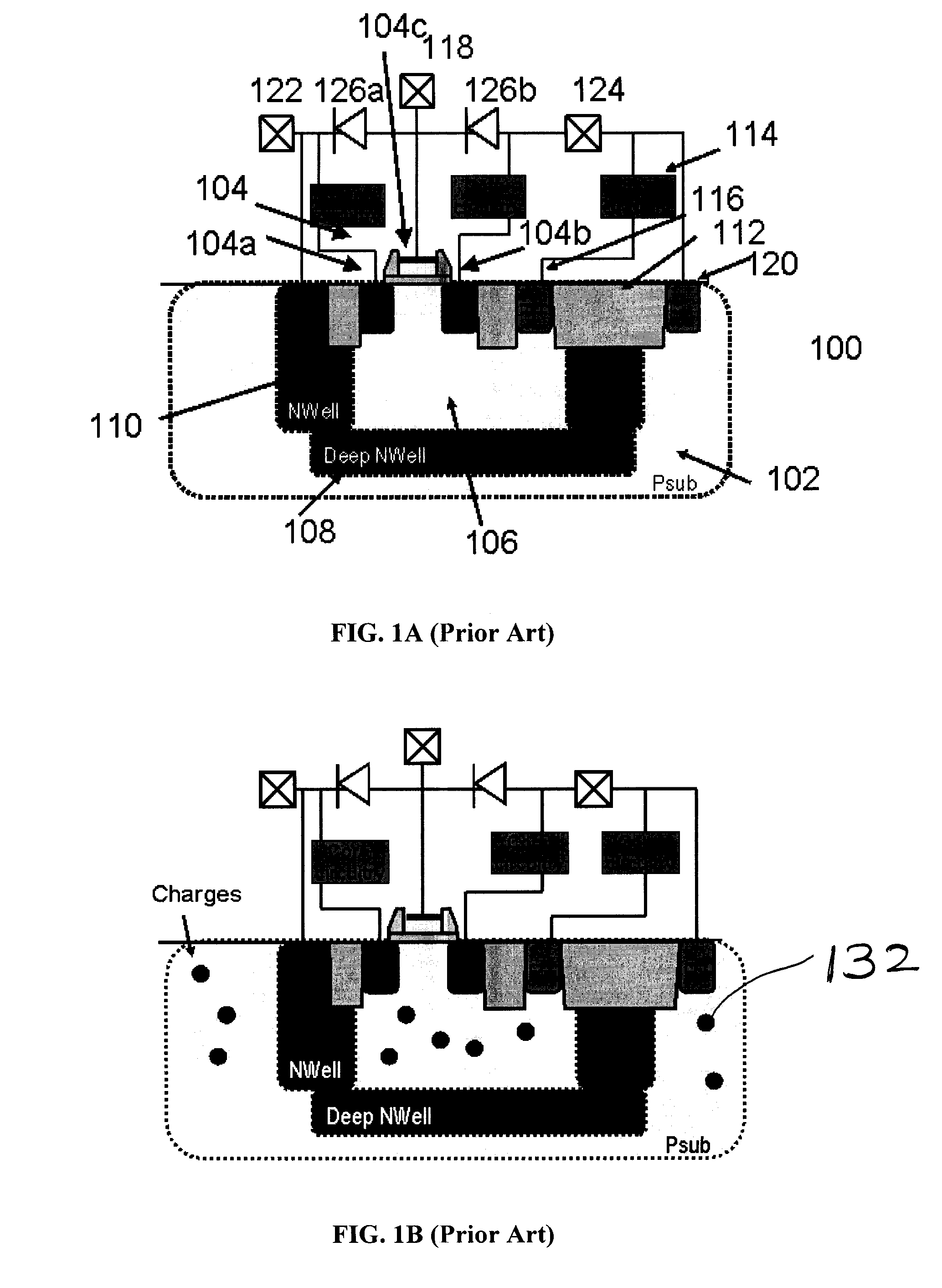

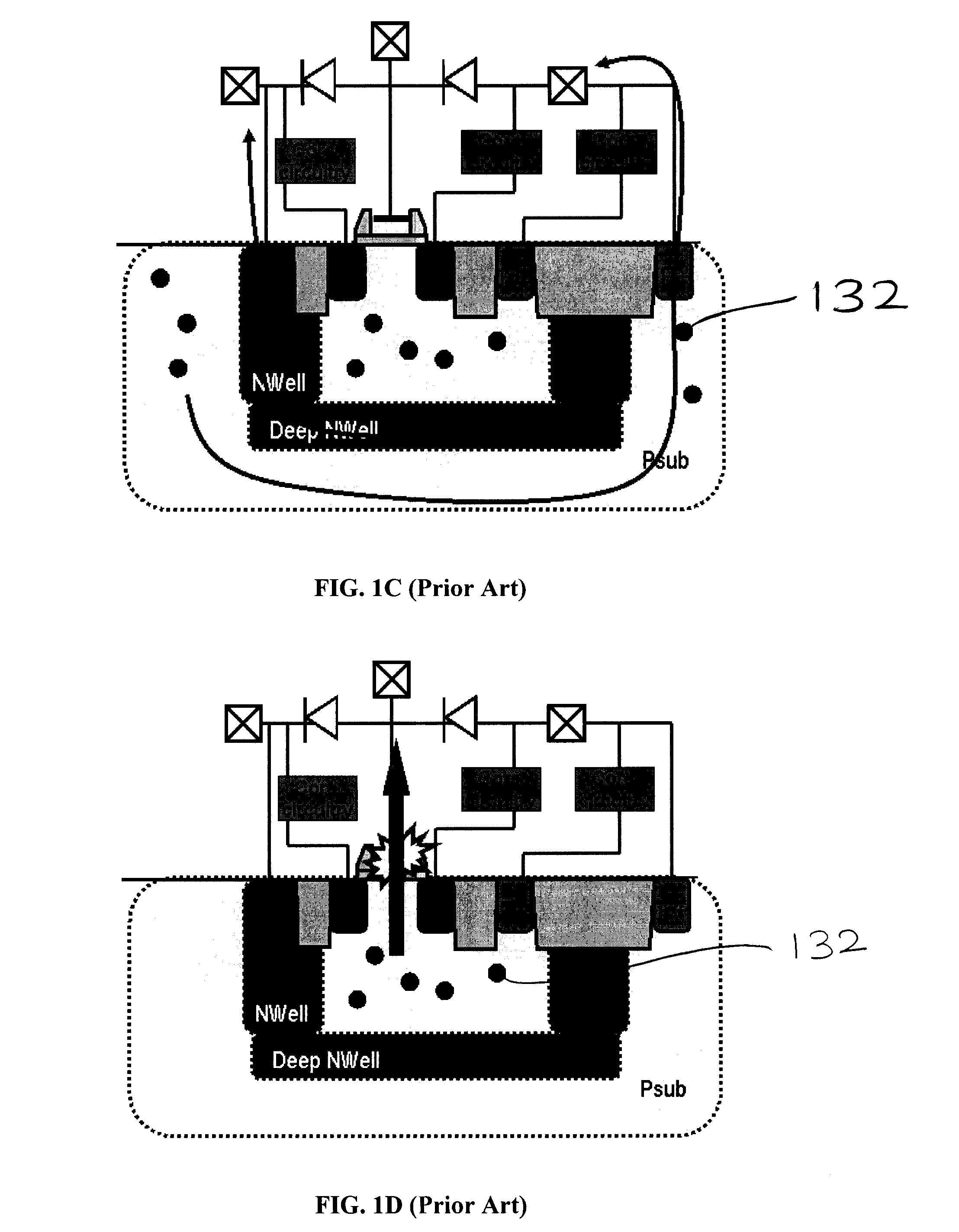

CDM ESD protection design using deep N-well structure

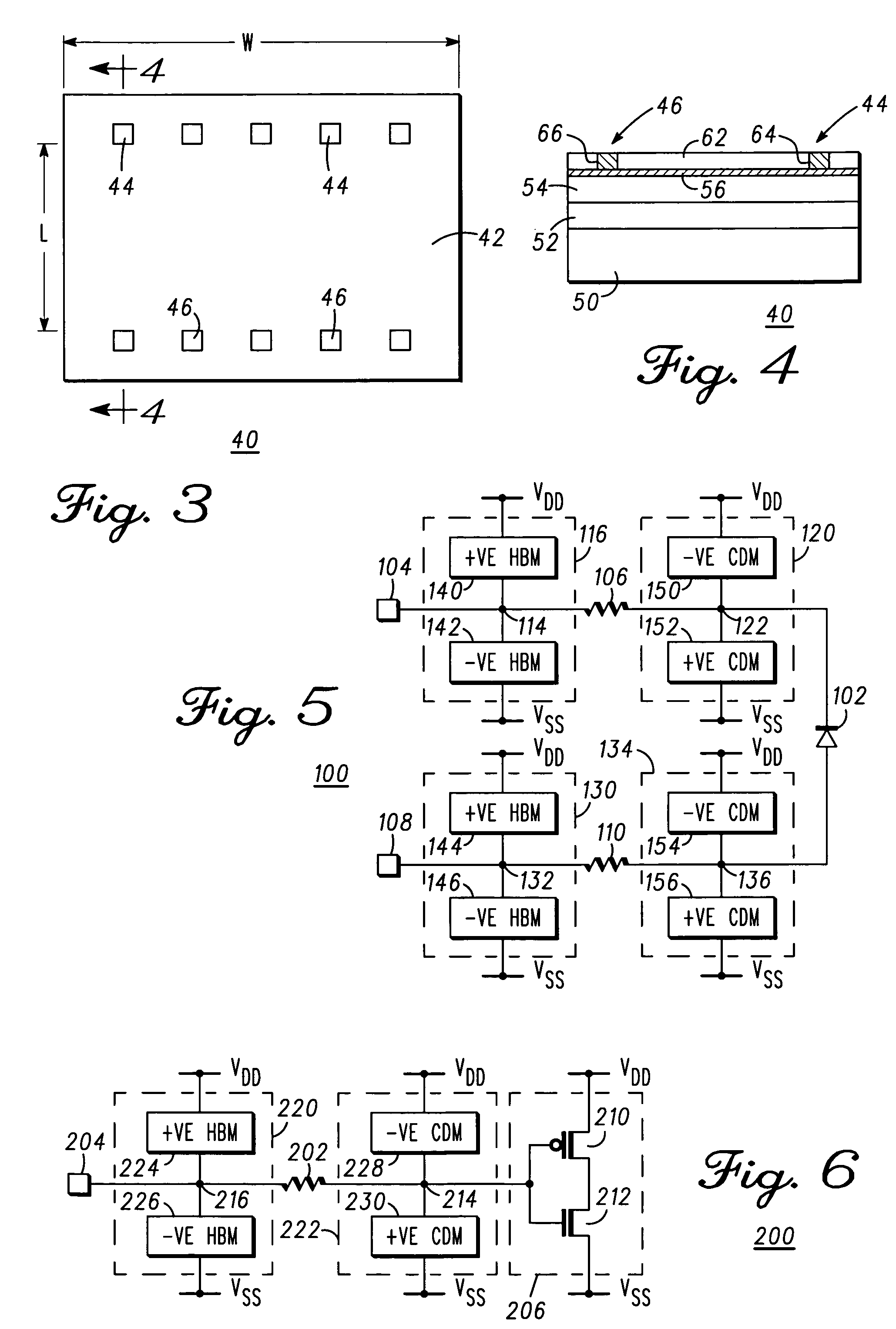

InactiveUS6885529B2Maintain circuit performanceReduce noise couplingSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitCharged-device model

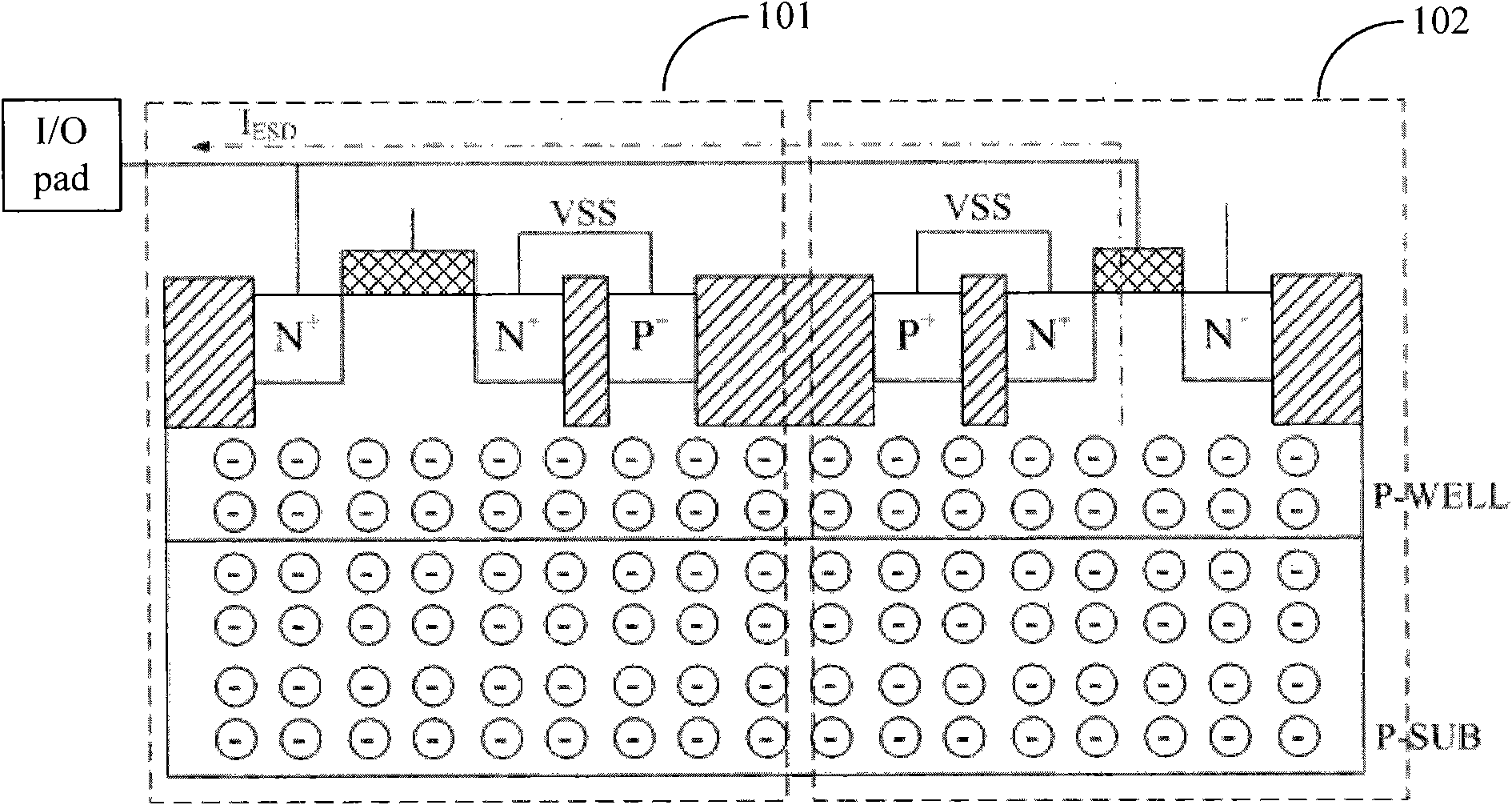

An object of the present invention is to provide a charged-device model (CDM) electrostatic discharge (ESD) protection circuit for an integrated circuit (IC). The ESD protection circuit comprises an ESD clamp device and a functional component. The ESD clamp device is coupled to a pad and a substrate having a first conductivity type. Under normal power operation, the ESD clamp device is closed. The functional component is formed on the substrate and coupled to the pad. The functional component has a first well having the first conductivity type and an isolating region having a second conductivity type for isolating the first well from the substrate. Under normal power operation, the functional component transmits signals between the IC and an external linkage. During an CDM ESD event, the CDM charges accumulated in the substrate are discharged via the ESD clamp circuit. Hence, the functional component is protected.

Owner:TAIWAN SEMICON MFG CO LTD

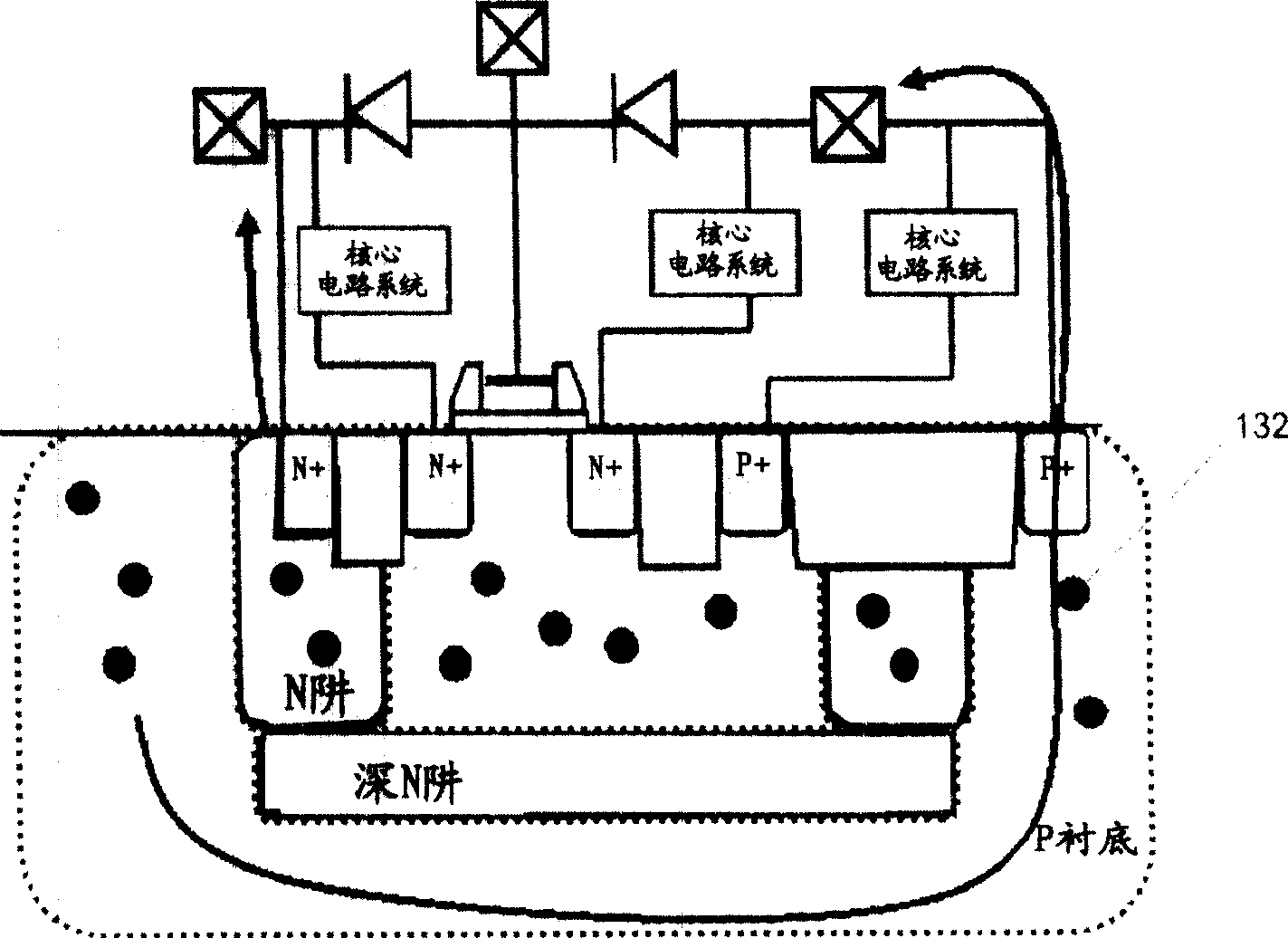

CDM (Charged Device Model) ESD (Electro-Static Discharge) protection circuit

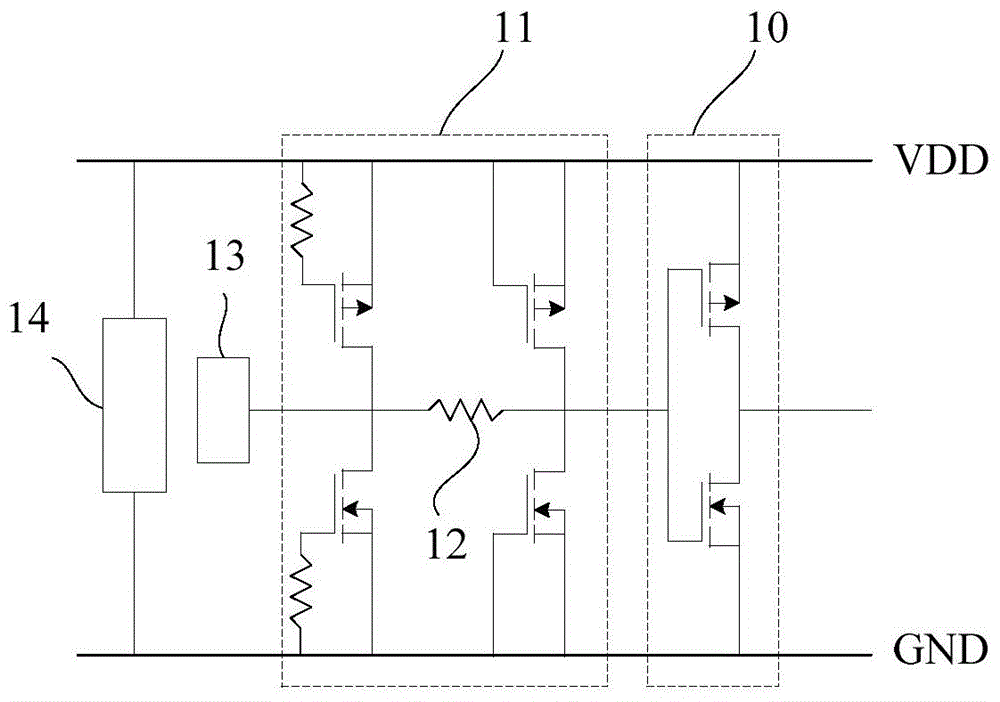

ActiveCN102148499AImprove performanceAvoid failureSemiconductor/solid-state device detailsSolid-state devicesLow voltageEngineering

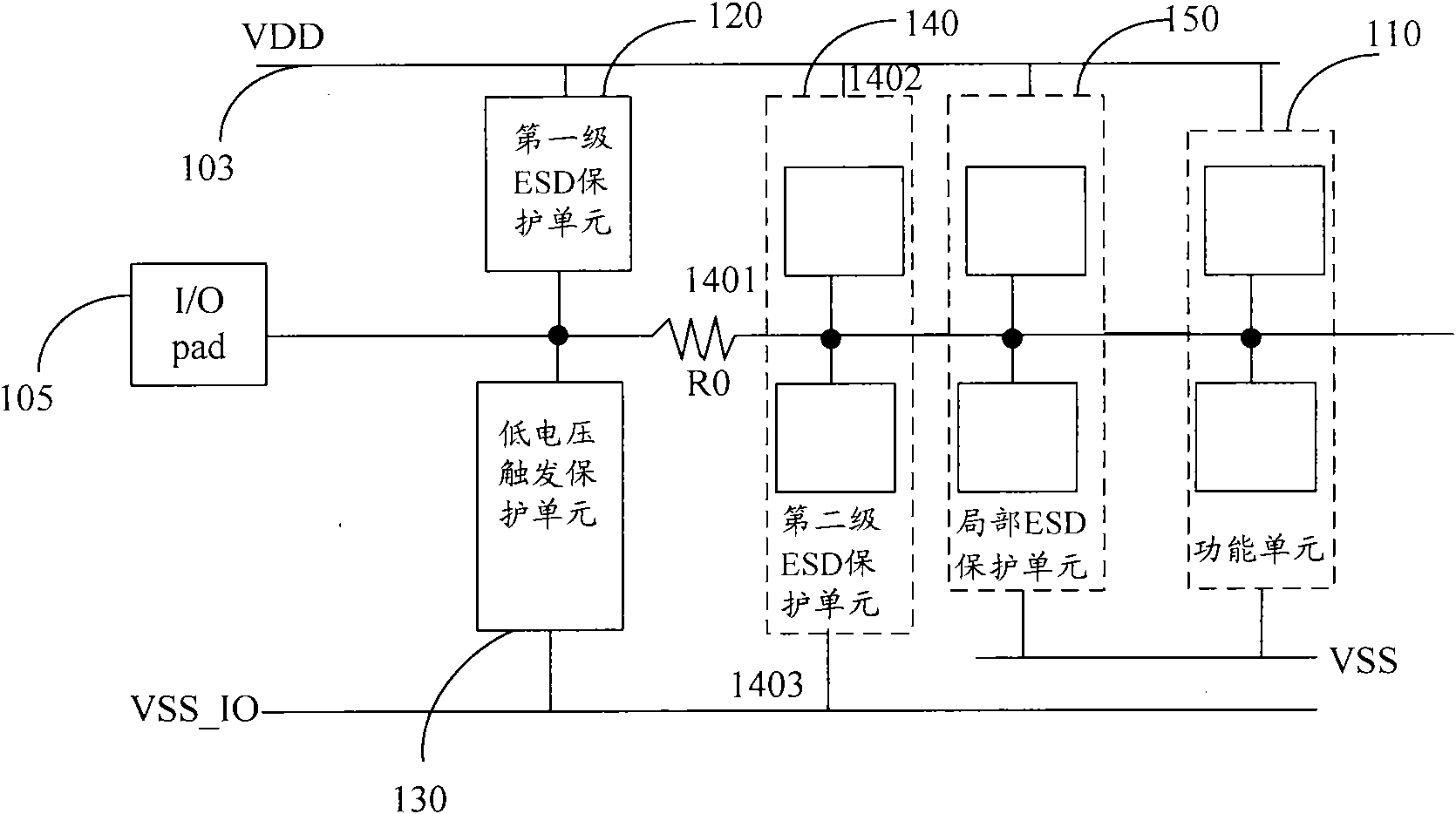

The invention provides a CDM (Charged Device Model) ESD (Electro-Static Discharge) protection circuit which is used for protecting a functional unit. The CDM ESD protection circuit comprises a first stage of ESD protection unit, a low voltage trigger protection unit, a second stage of ESD protection unit and a local ESD protection unit, wherein the first end of the low voltage trigger protection unit is coupled to the input / output pin, and the second end of the low voltage trigger protection unit is coupled to the substrate. When the electric potential of the substrate is smaller than that of the input / output pin and exceeds a second specific voltage, the low voltage trigger protection unit operates. Therefore, the performance of the CDM ESD protection circuit is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

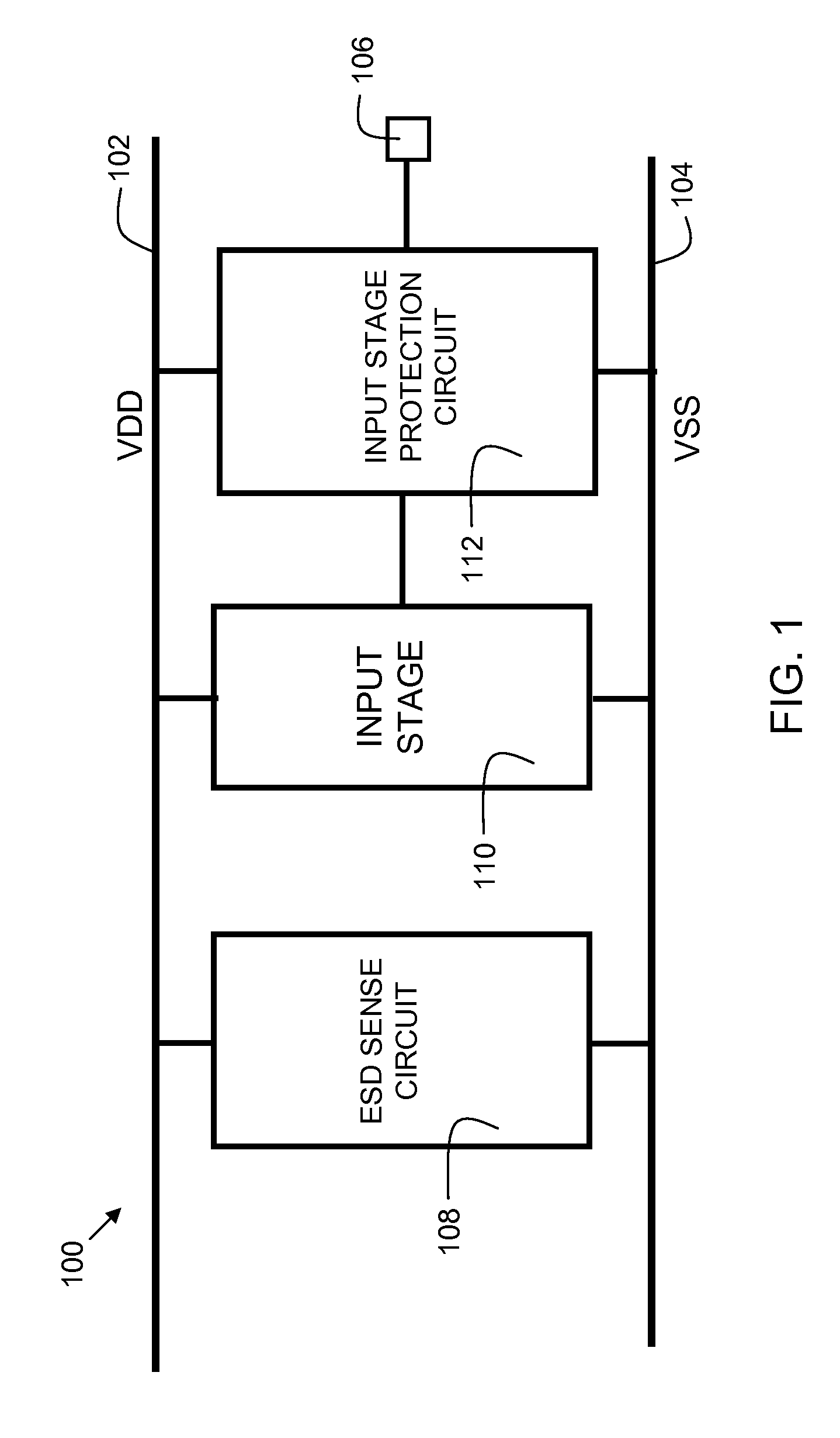

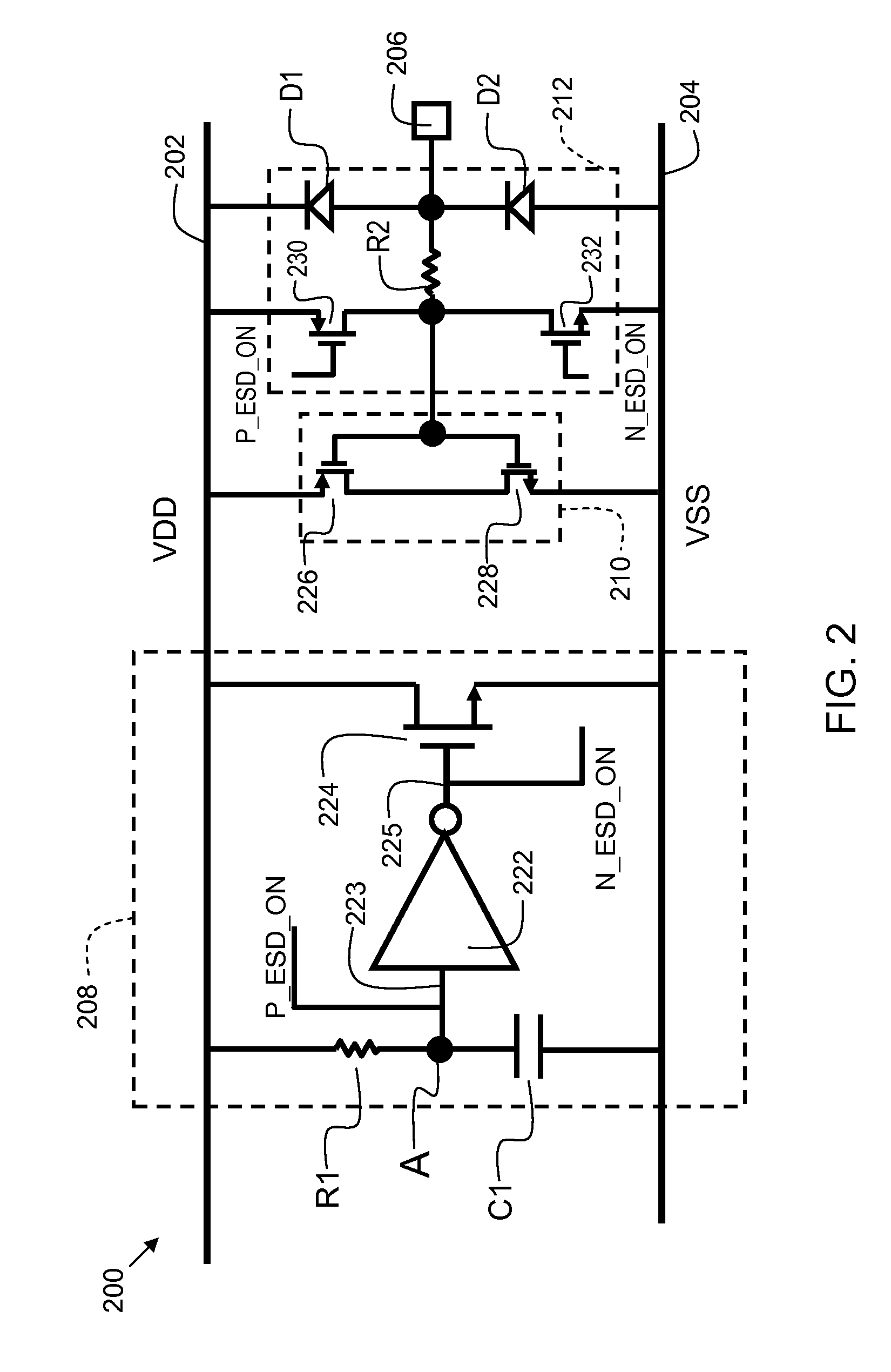

Enhanced charge device model clamp

InactiveUS20140362481A1Emergency protective arrangements for limiting excess voltage/currentPower flowTransistor

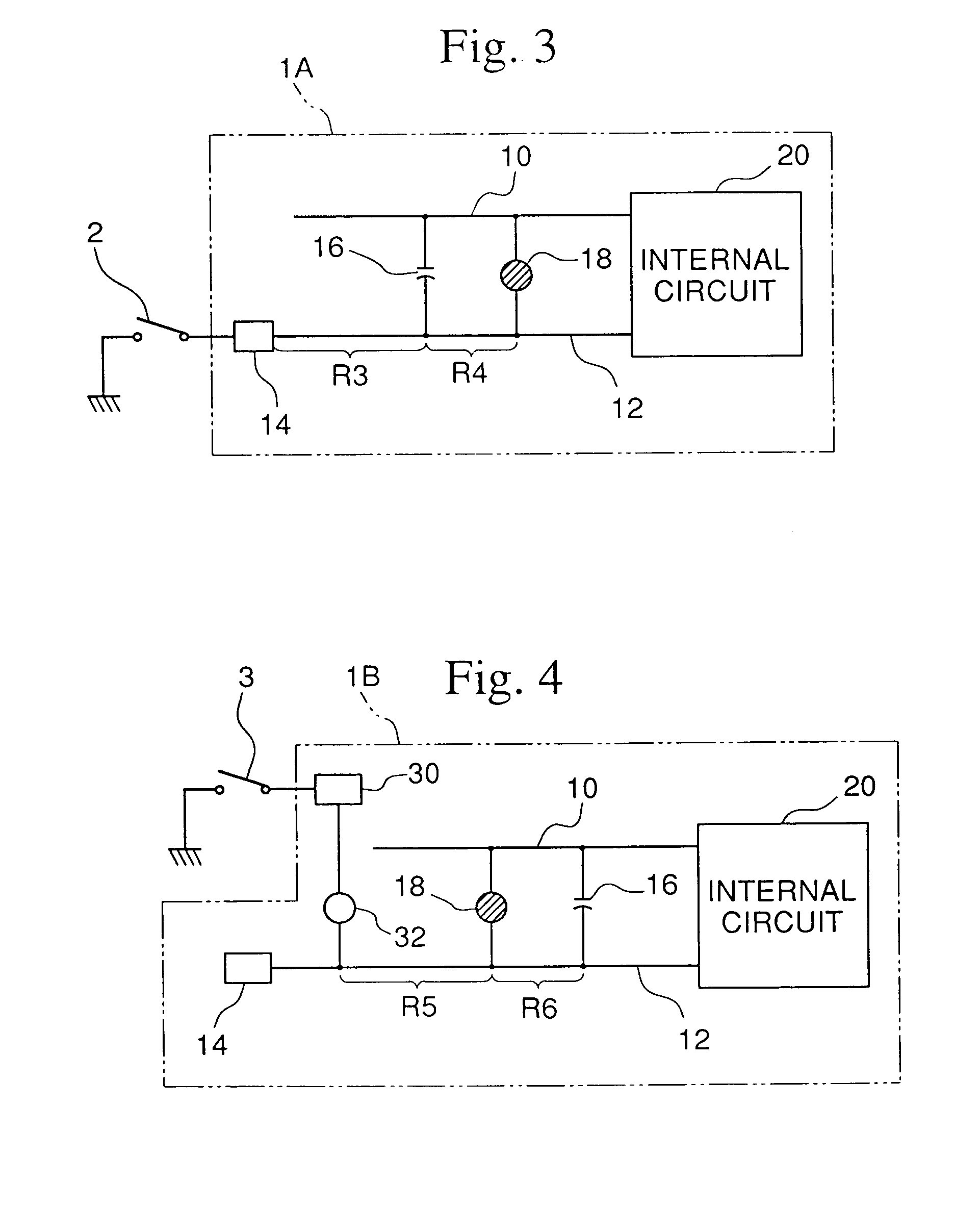

A circuit for electrostatic discharge (ESD) protection is disclosed. The circuit includes multiple transistors that are selectively turned on during an ESD event. An ESD sense circuit detects an ESD event and asserts signals to activate an ESD protection circuit which closes multiple protection transistors to dissipate current during the ESD event. During normal operation of the circuit, the signals are de-asserted, disabling the ESD protection circuit.

Owner:GLOBALFOUNDRIES INC

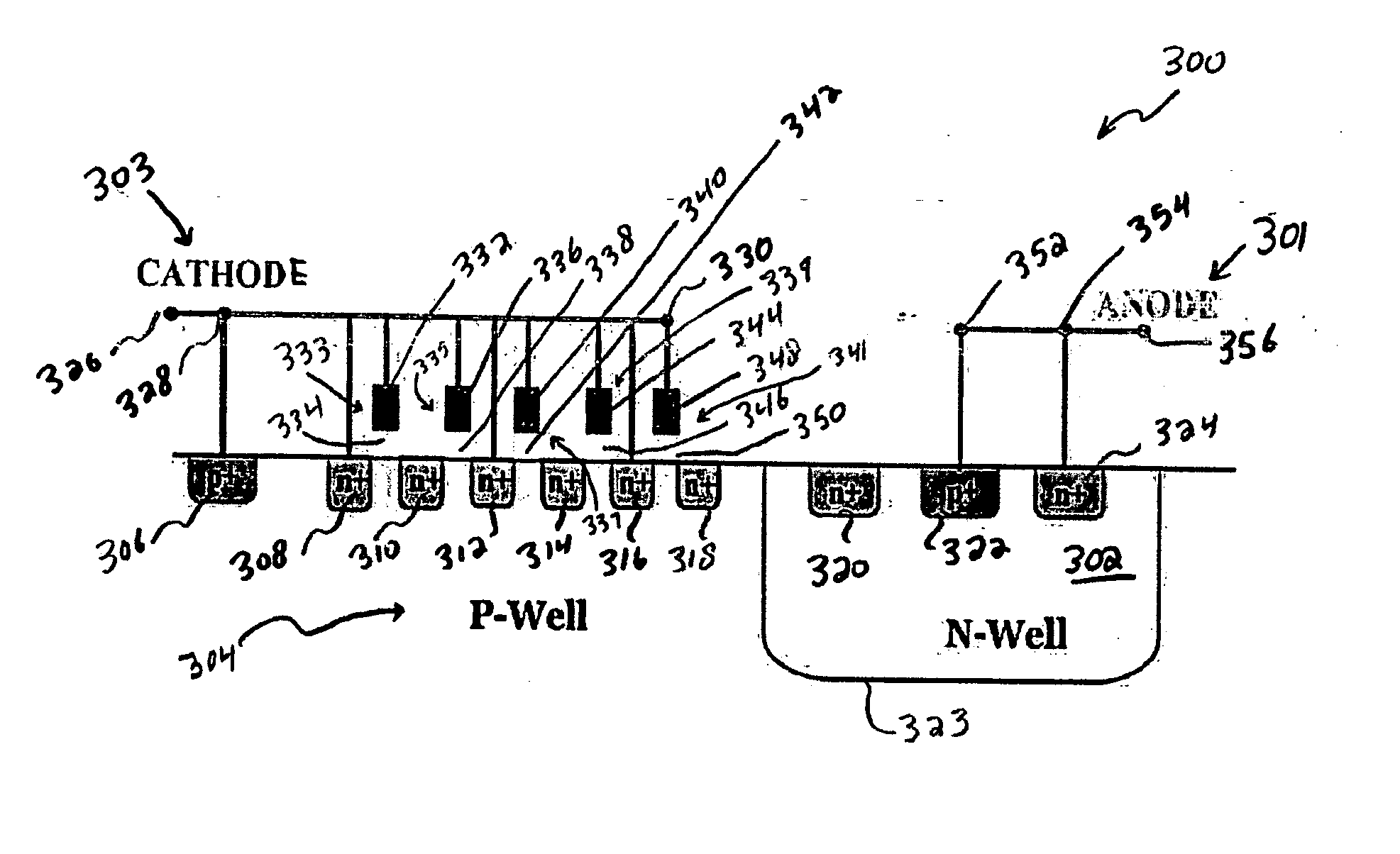

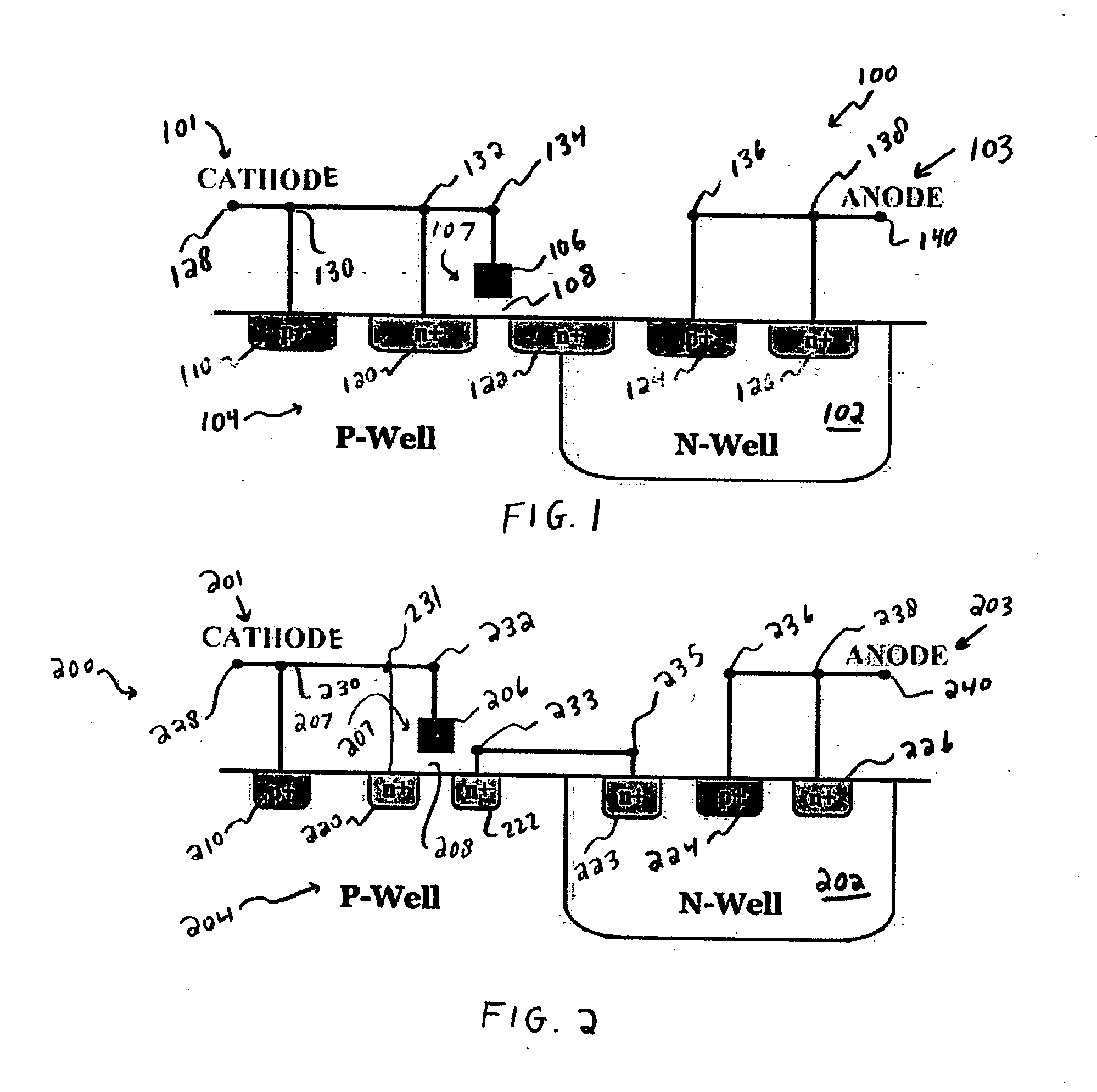

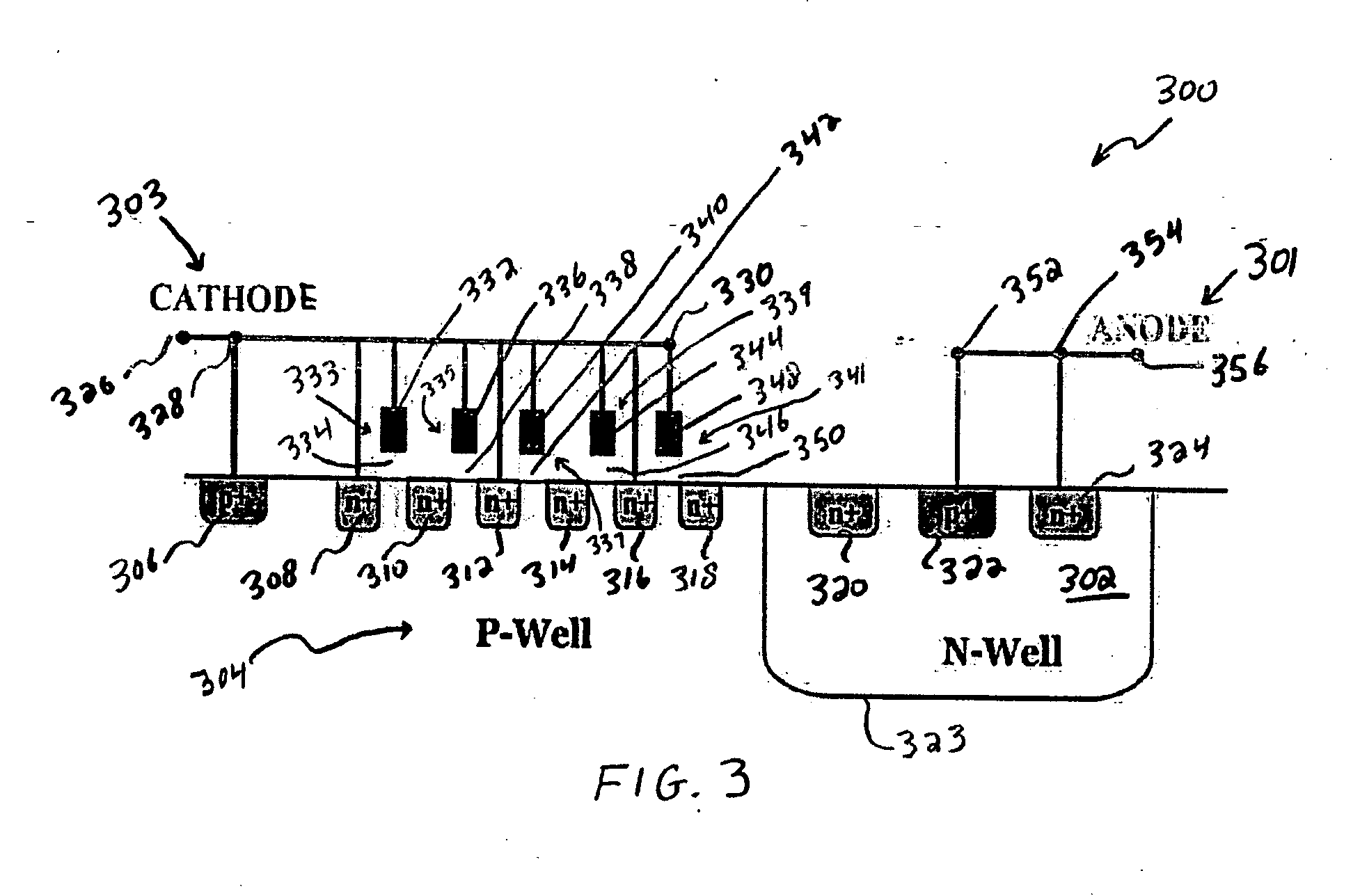

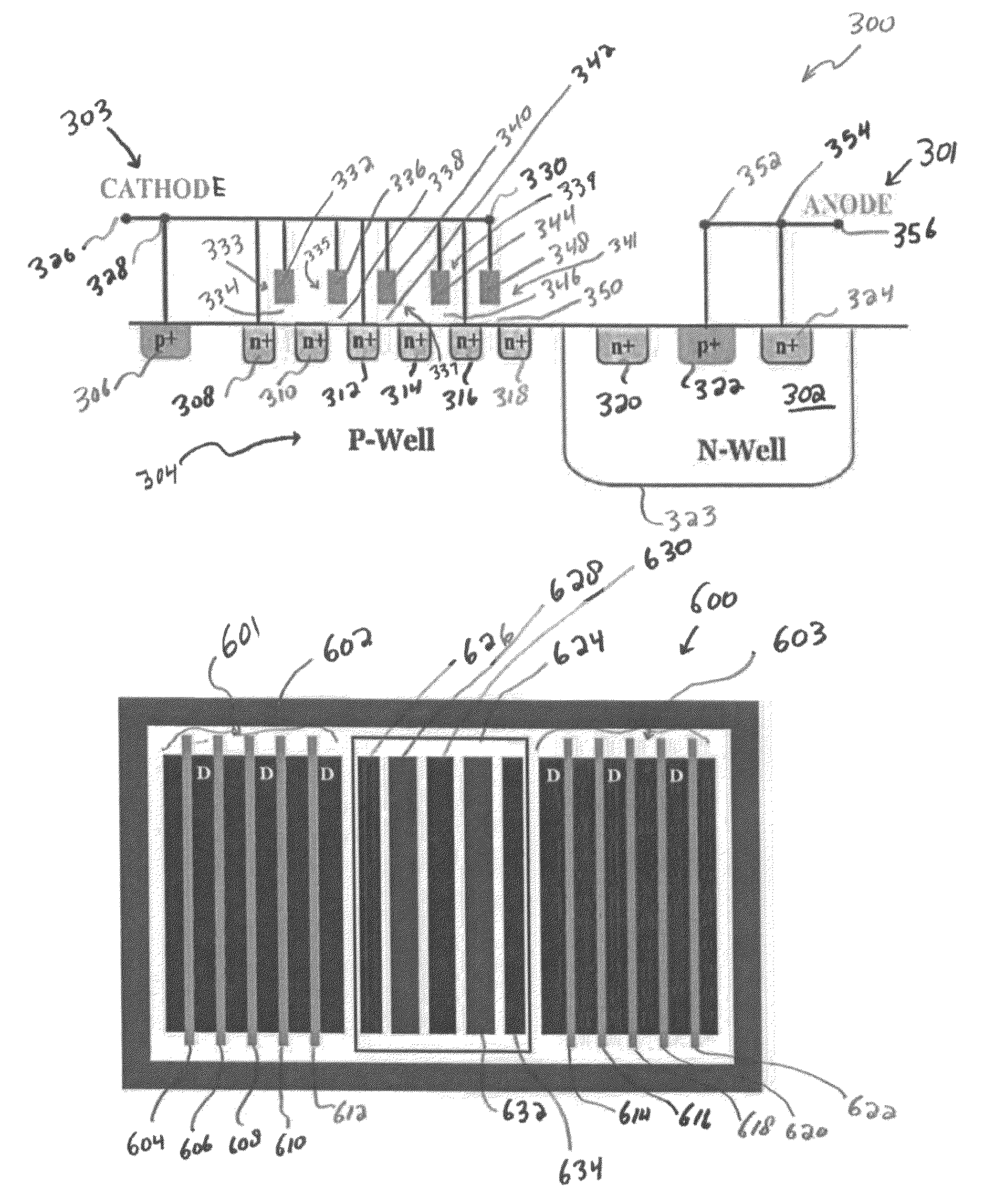

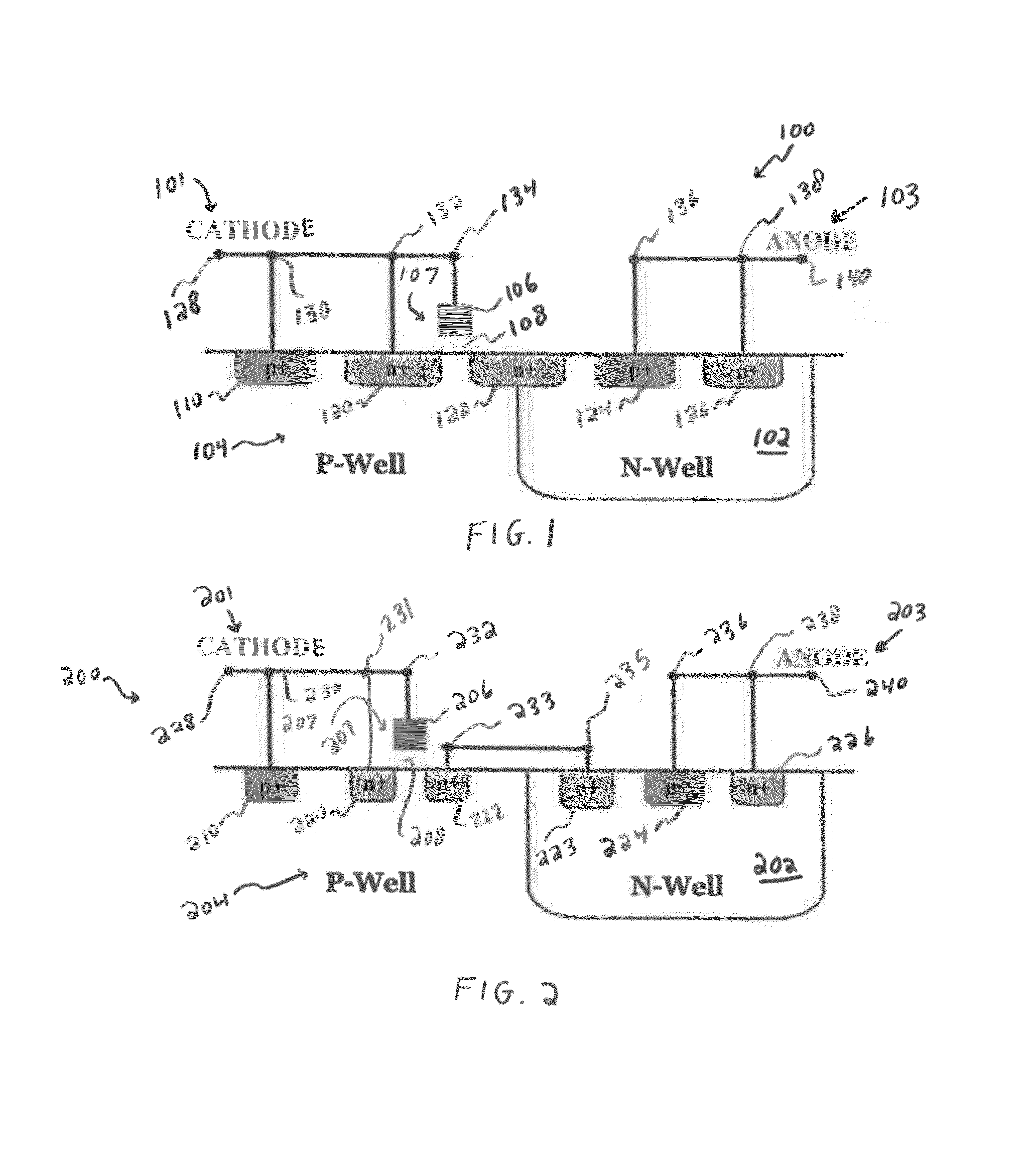

Design of silicon-controlled rectifier by considering electrostatic discharge robustness in human-body model and charged-device model devices

InactiveUS20070045656A1Easy to understandImprove ESD protection capabilityTransistorThyristorSilicon-controlled rectifierLow voltage

A silicon-controlled rectifier apparatus, comprising a substrate upon which a low-voltage triggered silicon-controlled rectifier is configured. A plurality of triggering components (e.g., NMOS fingers) are formed upon the substrate and integrated with the low-voltage triggered silicon-controlled rectifier, wherein the plurality of triggering components are inserted into the low-voltage triggered silicon-controlled rectifier in order to permit the low-voltage triggered silicon-controlled rectifier to protect against electrostatic discharge during human-body model and charged-device model stress events.

Owner:ORTIZ & LOPEZ PLLC +1

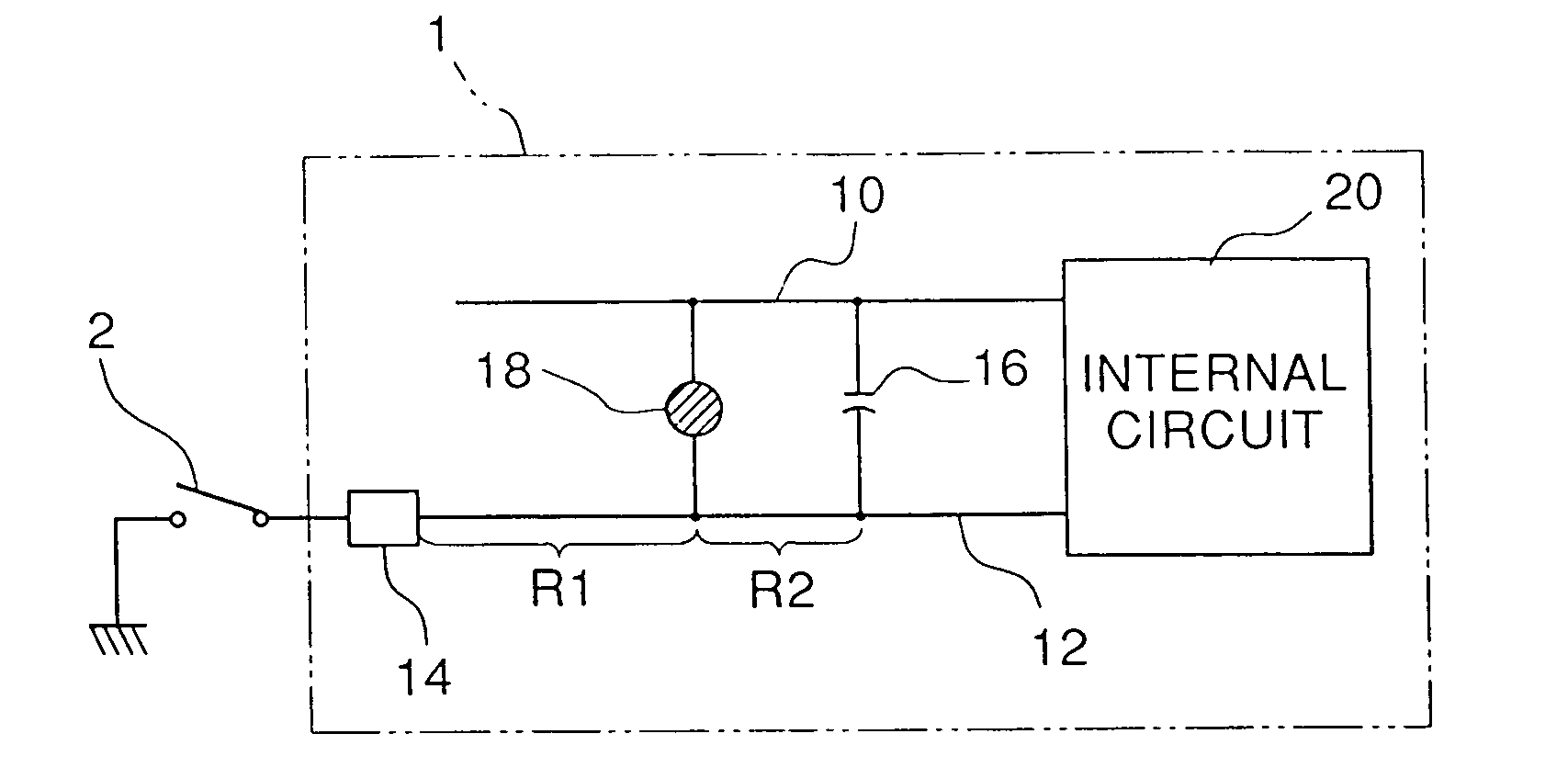

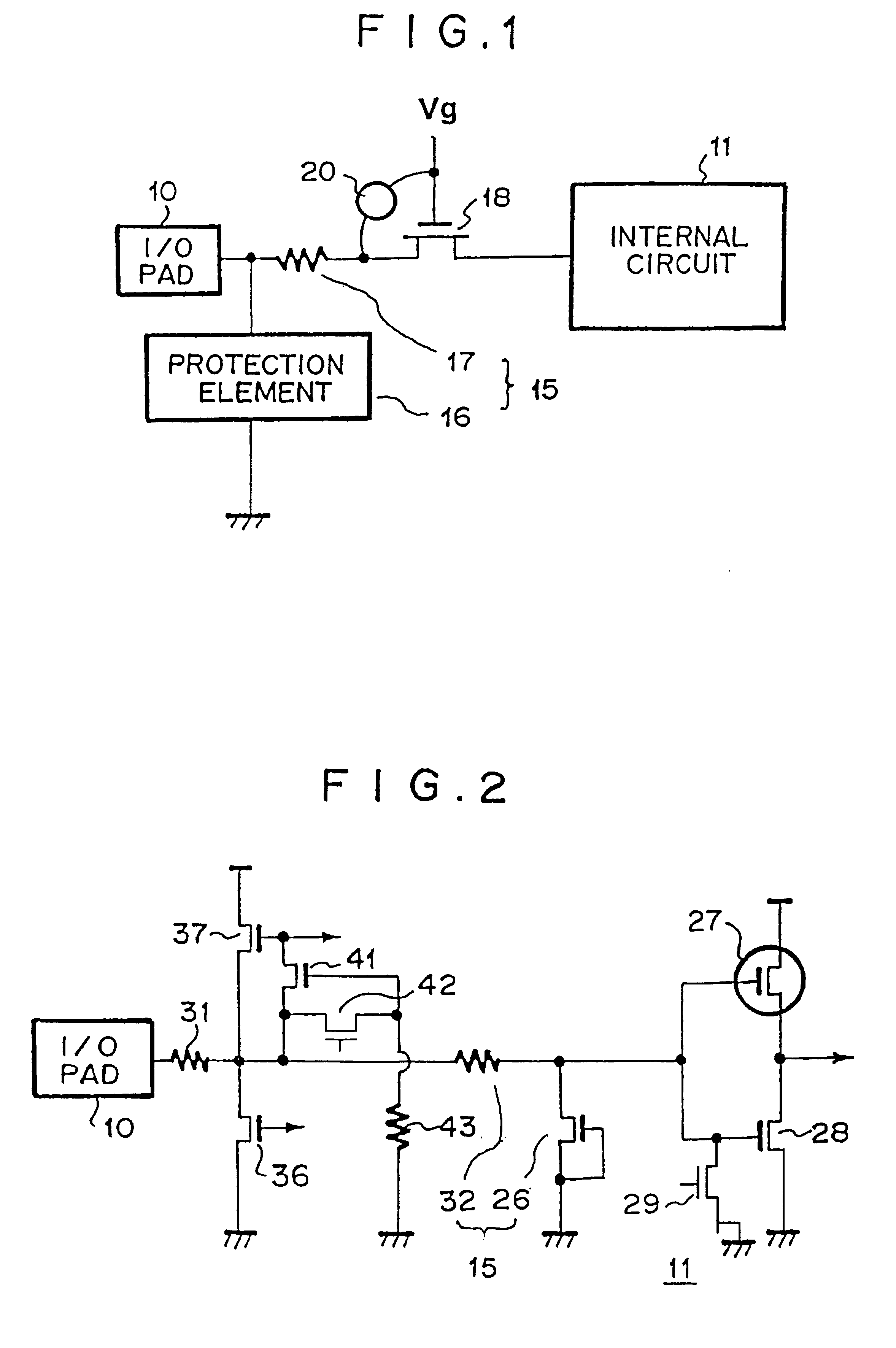

Semiconductor integrated circuit

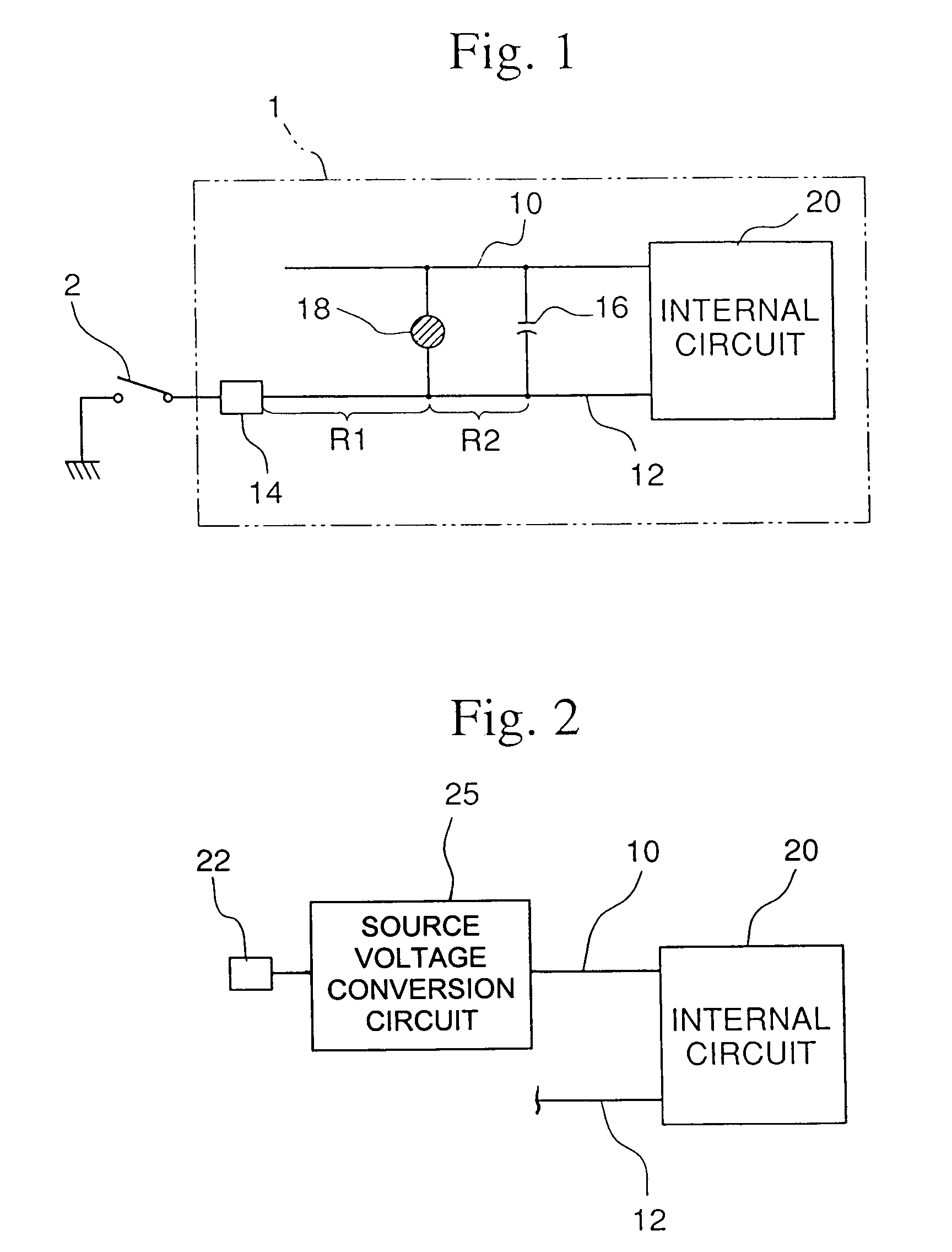

InactiveUS6943412B1Improve pressure resistanceTransistorSemiconductor/solid-state device detailsCapacitanceElectrical resistance and conductance

A semiconductor integrated circuit is provided, which has an improved withstanding voltage for electrostatic breakdown at the time of electrostatic discharge by the charged device model, in the case of protecting a MOS capacitor provided at the input side of the internal circuit. The semiconductor integrated circuit comprises an internal circuit 20 for inputting an external signal, an internal circuit MOS capacitor 16, one end of which is connected to a power source wire 10 for supplying the source voltage and the other end of which is connected to a ground potential wire 12 for supplying the ground potential; a ground terminal 14 to which one end of the ground potential wire is connected; an electrostatic protection element 18 connected in parallel with the MOS capacitor 16 between the ground terminal 14 and the MOS capacitor, wherein the MOS capacitor and the electrostatic protection element are connected between the power source wire and the ground potential wire such that the wire resistance R1 of the ground potential wire between the ground terminal and the connection point with one end of the electrostatic protection element is larger than the wire resistance R2 of the ground potential wire between the connection point with one end of the electrostatic protection element and the connection point with one end of the MOS capacitor.

Owner:LONGITUDE SEMICON S A R L

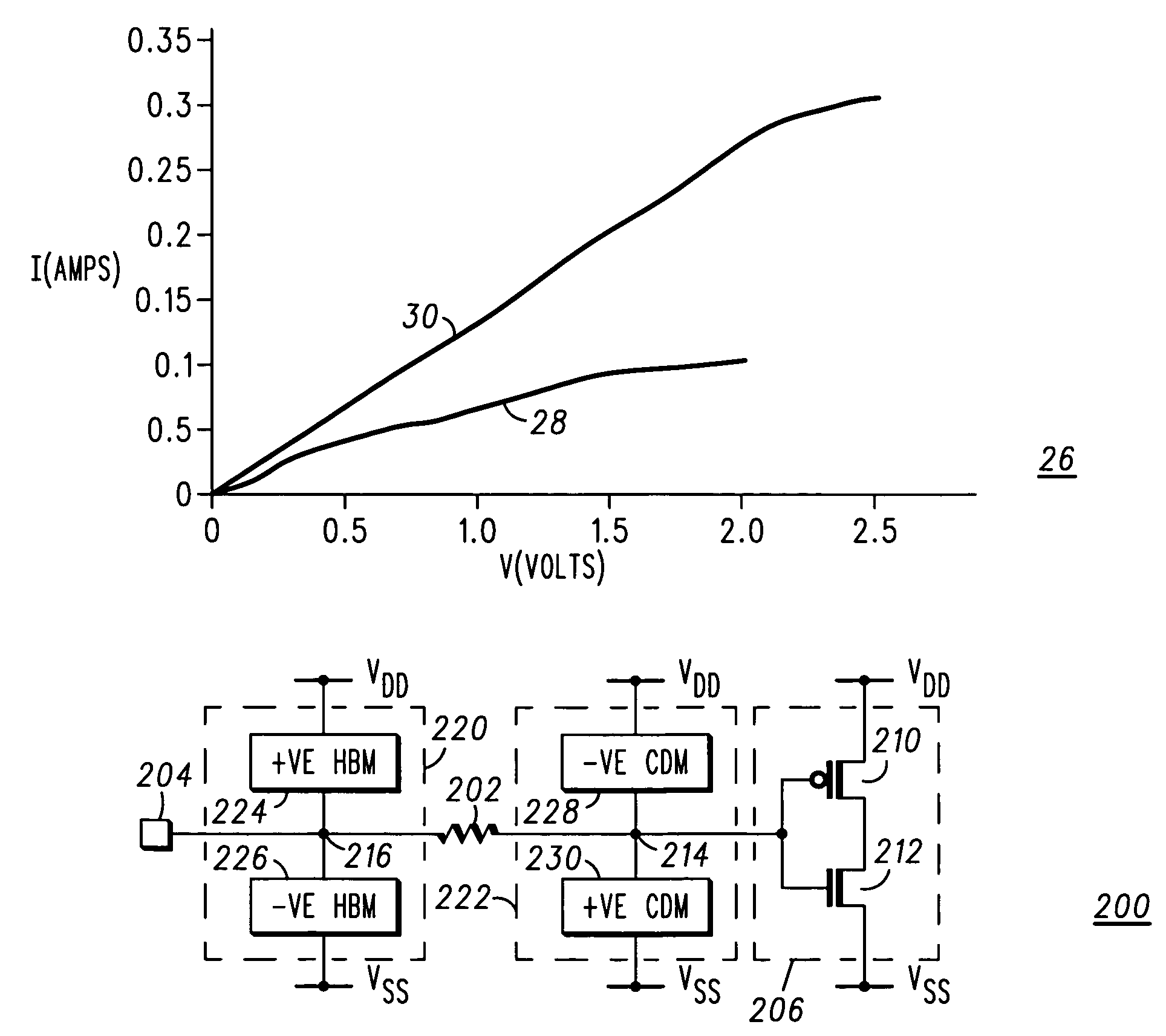

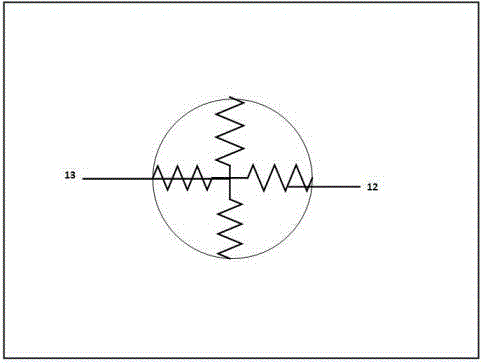

Semiconductor component and method of manufacture

A semiconductor component having a tuned variable resistance resistor and a method for manufacturing the tuned variable resistance resistor. A semiconductor process for manufacturing a semiconductor component is selected. For the selected process, the tuned variable resistance resistor is characterized to determine the maximum stress current as a function of the width of the tuned variable resistance resistor. Then, for a given width and maximum stress current, the voltages across the resistors are characterized as a function of length. A tuned variable resistance resistor having a length and width capable of sustaining a predetermined maximum stress current is integrated into a semiconductor component. The semiconductor component may include protection circuitry designed in accordance with the Human Body Model, the Charge Device Model, or both.

Owner:GLOBALFOUNDRIES INC

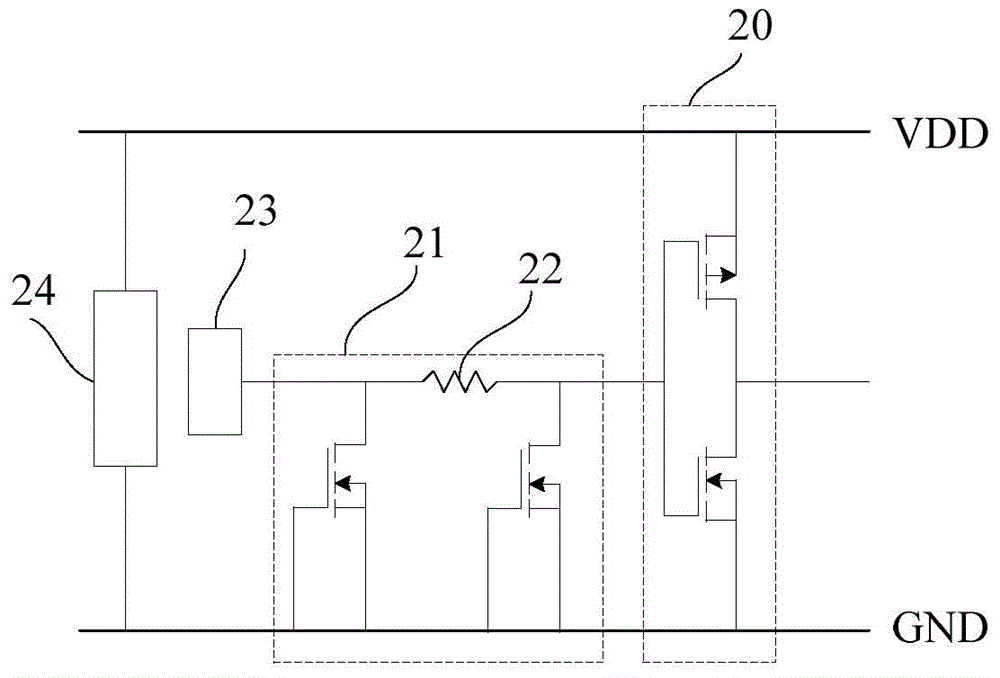

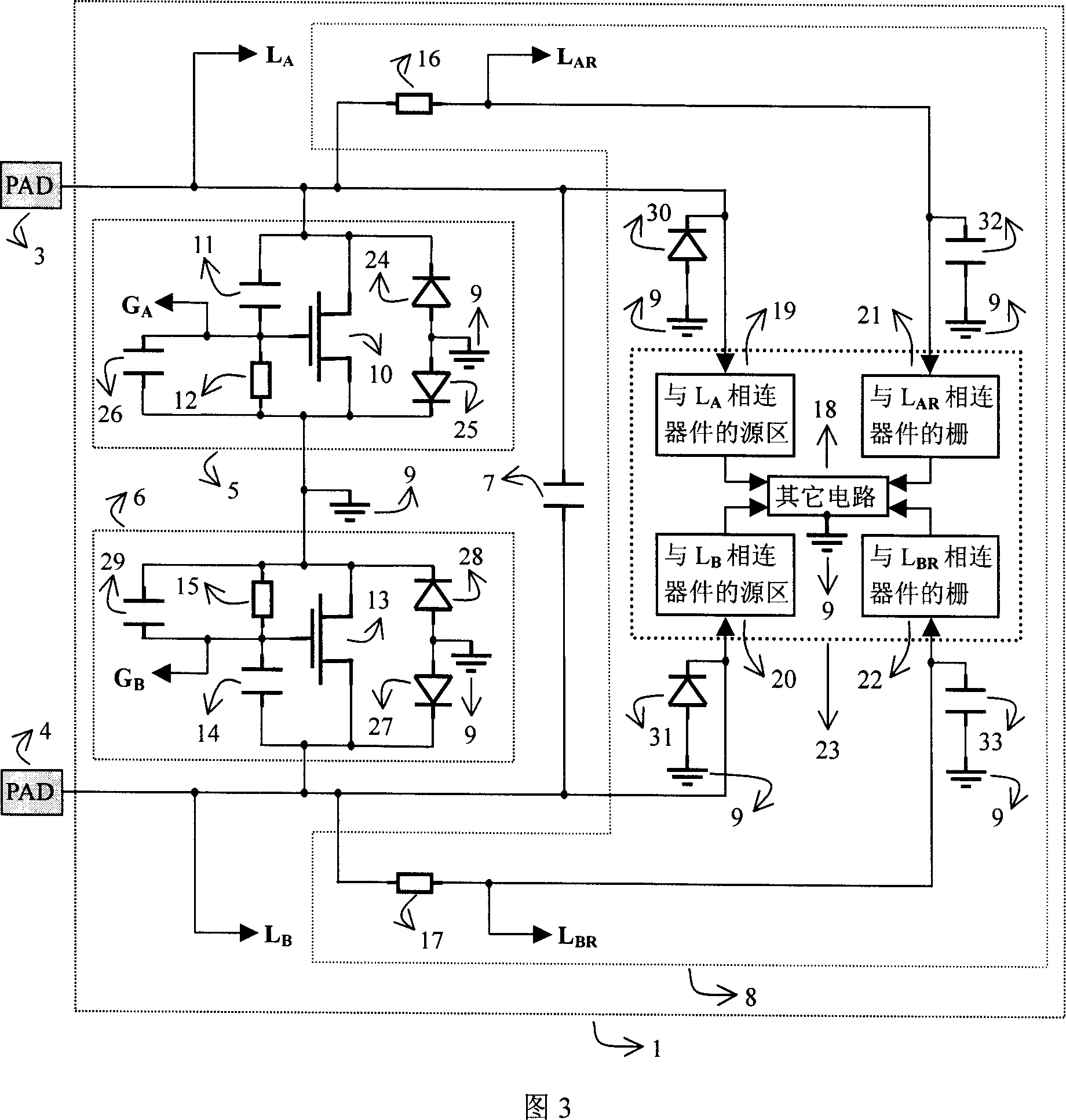

CDM (Charged-Device-Model) electrostatic protection circuit

InactiveCN104319271AAchieve protectionSemiconductor/solid-state device detailsSolid-state devicesEngineeringPulse voltage

The invention provides a CDM (Charged-Device-Model) electrostatic protection circuit. The CDM electrostatic protection circuit comprises an input and output pin, a power supply output terminal, a grounding terminal, a functional unit, a first level protection unit and a second level protection unit; the functional unit is connected with the input and output pin, the power supply output terminal and the grounding terminal; the first level protection unit is connected with the power supply output terminal and the grounding terminal; the second level protection unit is connected with the power supply output terminal and the grounding terminal; an inductance coil and a clamping circuit are connected in series between the first level protection unit and the second level protection unit; the clamping circuit is connected with the power supply output terminal and the grounding terminal. According to the CDM electrostatic protection circuit, the pulse voltage is mainly applied to two ends of the inductance coil when electrostatic pulses are produced and accordingly the voltage at two ends of each protection unit does not rapidly rise along with the electrostatic pulses and meanwhile the electrostatic pulses are released through the first level protection unit and the second level protection unit to implement the protection on the functional unit.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

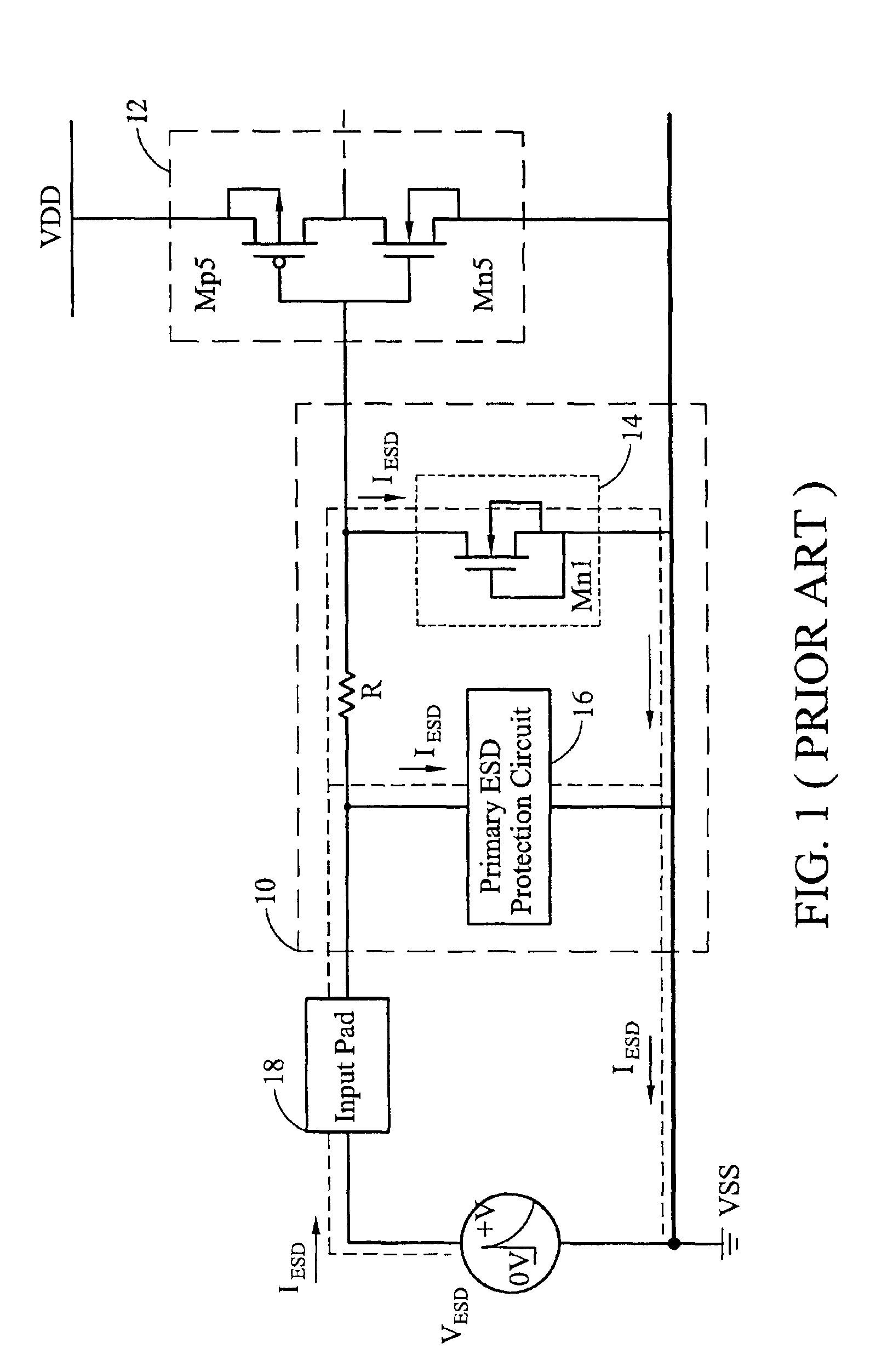

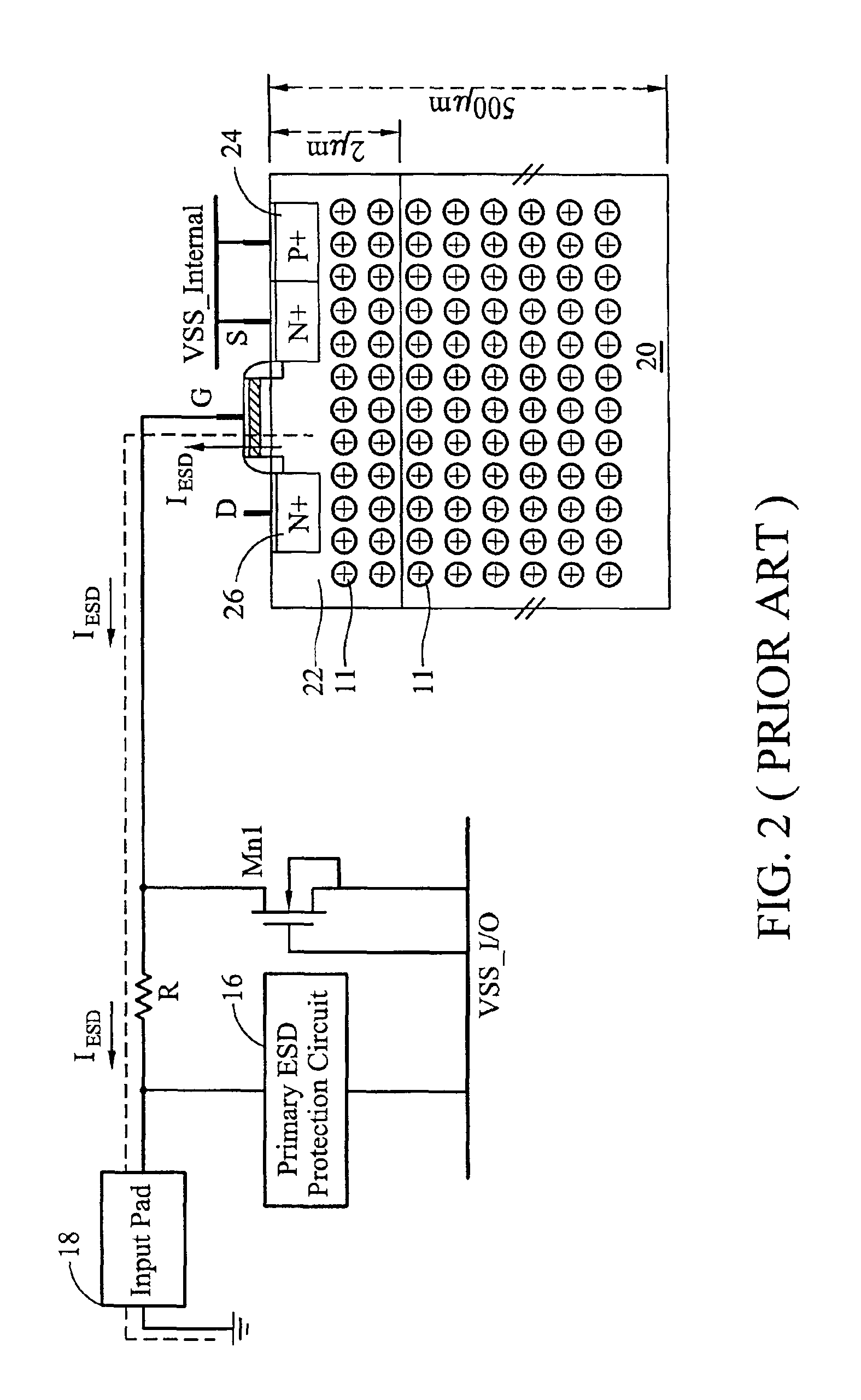

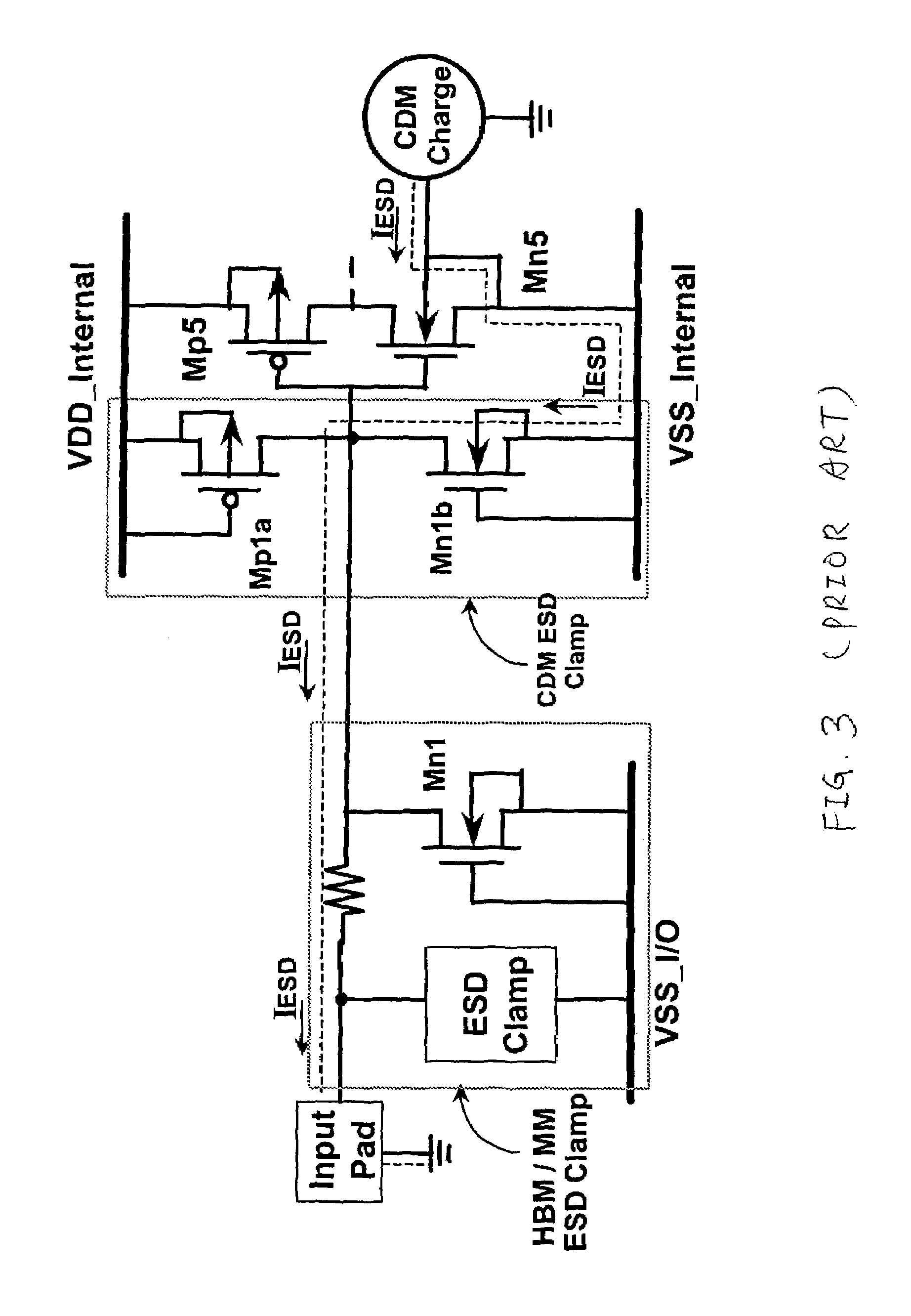

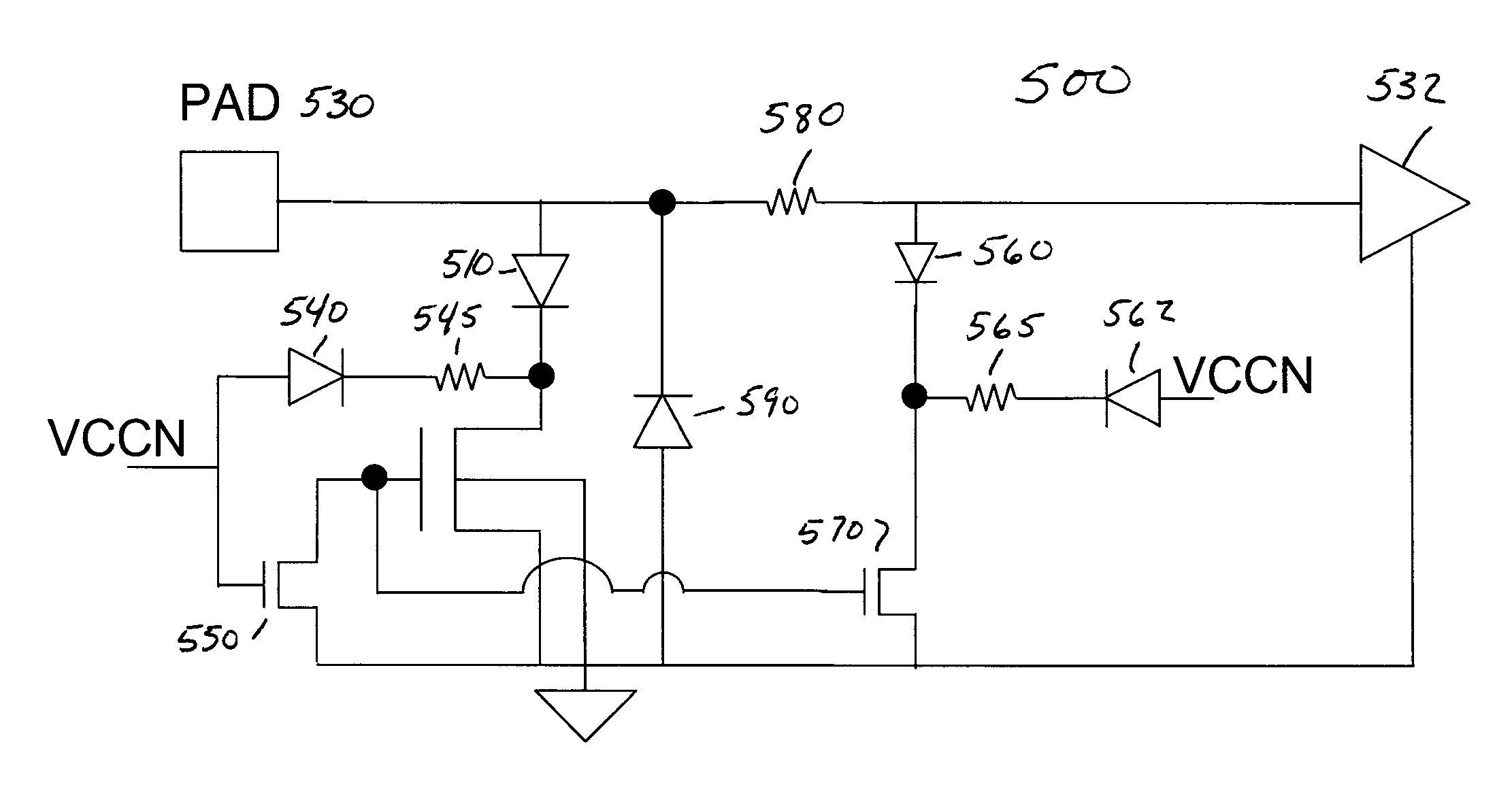

Charge-device model electrostatic discharge protection using active device for CMOS circuits

An integrated circuit for providing electrostatic discharge protection that includes a contact pad, a CMOS device including a transistor having a substrate, and a CDM clamp for providing electrostatic discharge protection coupled between the contact pad and the CMOS device, the CDM clamp including at least one active device, wherein the CDM clamp conducts electrostatic charges accumulated in the substrate of the transistor to the contact pad and wherein the CMOS device is coupled between a high voltage line and a low voltage line.

Owner:IND TECH RES INST

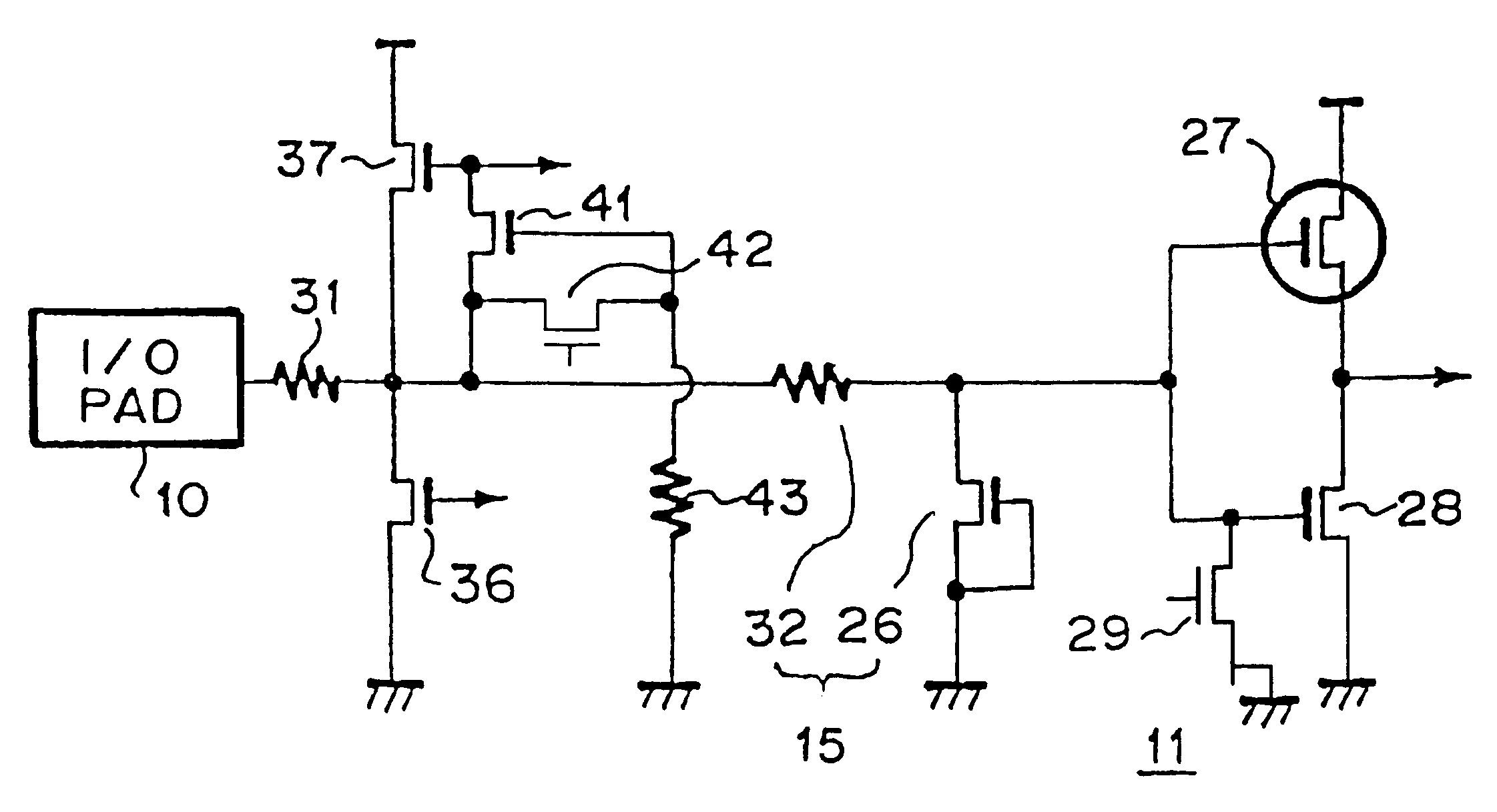

Semiconductor integrated circuit with protection circuit against electrostatic discharge

InactiveUS6191633B1Avoid failurePulse automatic controlSemiconductor/solid-state device detailsParasitic bipolar transistorEngineering

A Semiconductor integrated circuit with a protection circuit against electrostatic discharge. A clamping element is connected with MIS transistor to prevent the breakdown under the charged device model. A parasitic bipolar transistor, a MOS transistor or MIS transistor whose gate is composed of an insulating film thicker than that of the transfer gate, can be used as the clamping element.

Owner:LONGITUDE LICENSING LTD

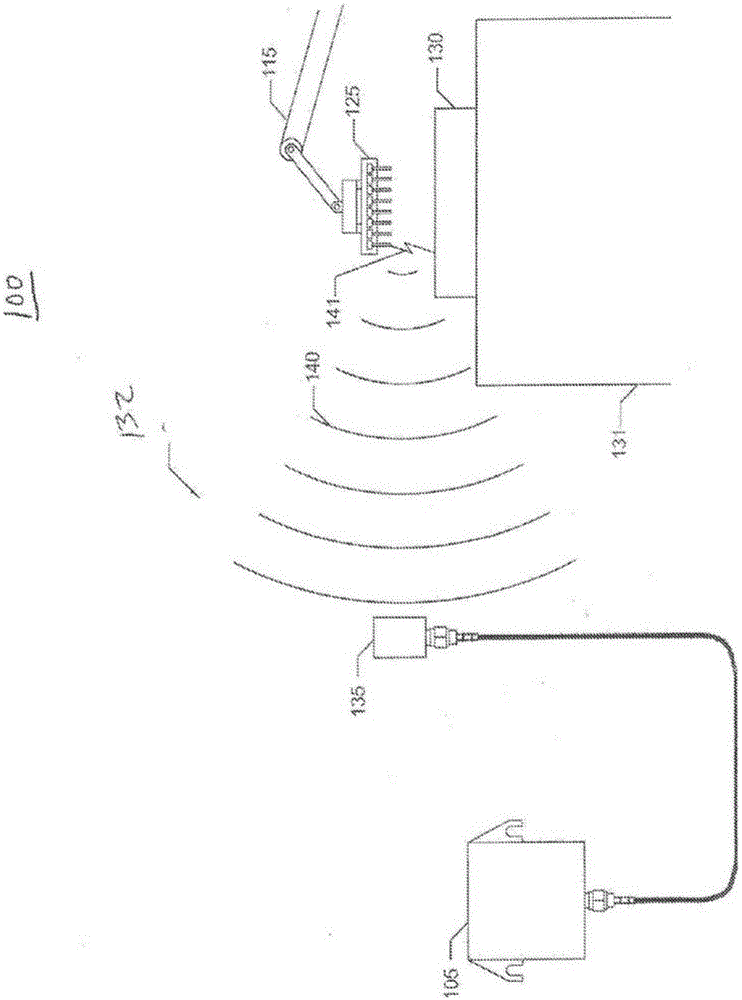

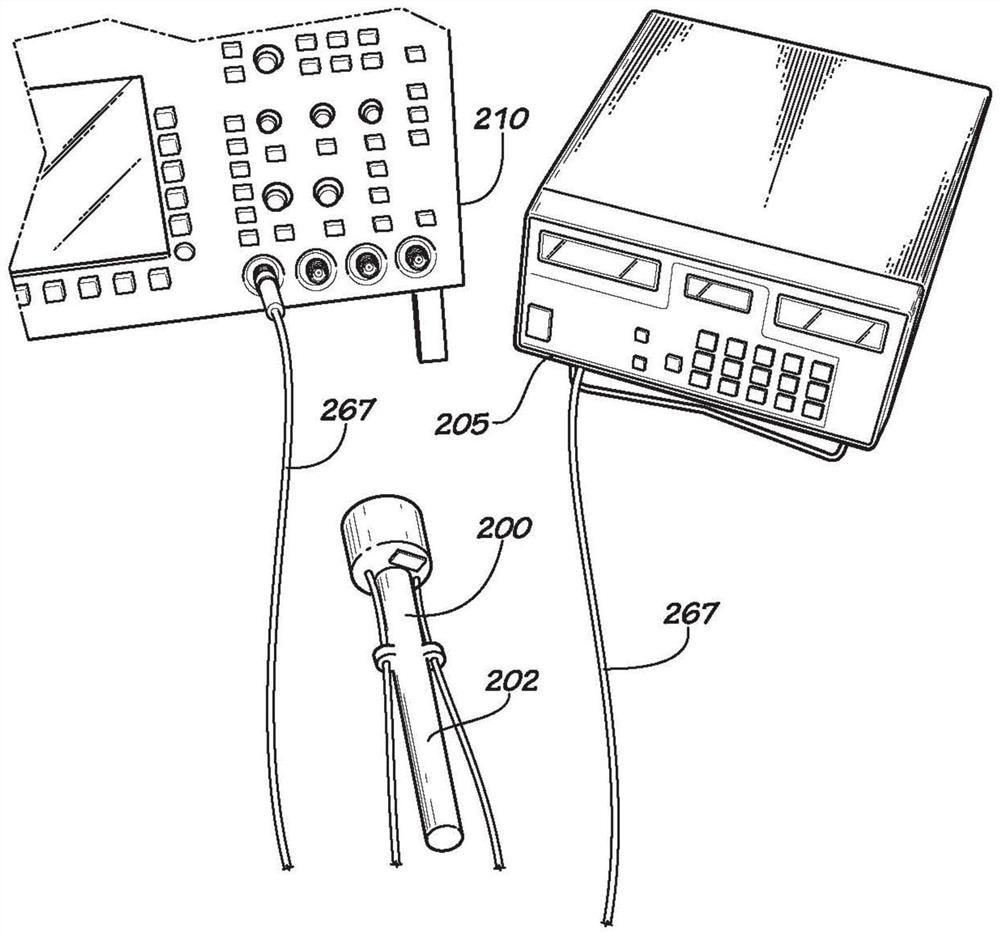

In-tool ESD events monitoring method and apparatus

In one embodiment of the invention, an apparatus for electrostatic discharges (ESD) events monitoring incorporating a charged device model event simulator (CDMES) unit comprises: at least one antenna positioned in a process area; an ESD detector coupled to said at least one antenna; said ESD detector wirelessly coupled to said CDMES unit; and said ESD detector calibrated for different discharge energies generated by said CDMES unit.

Owner:ILLINOIS TOOL WORKS INC

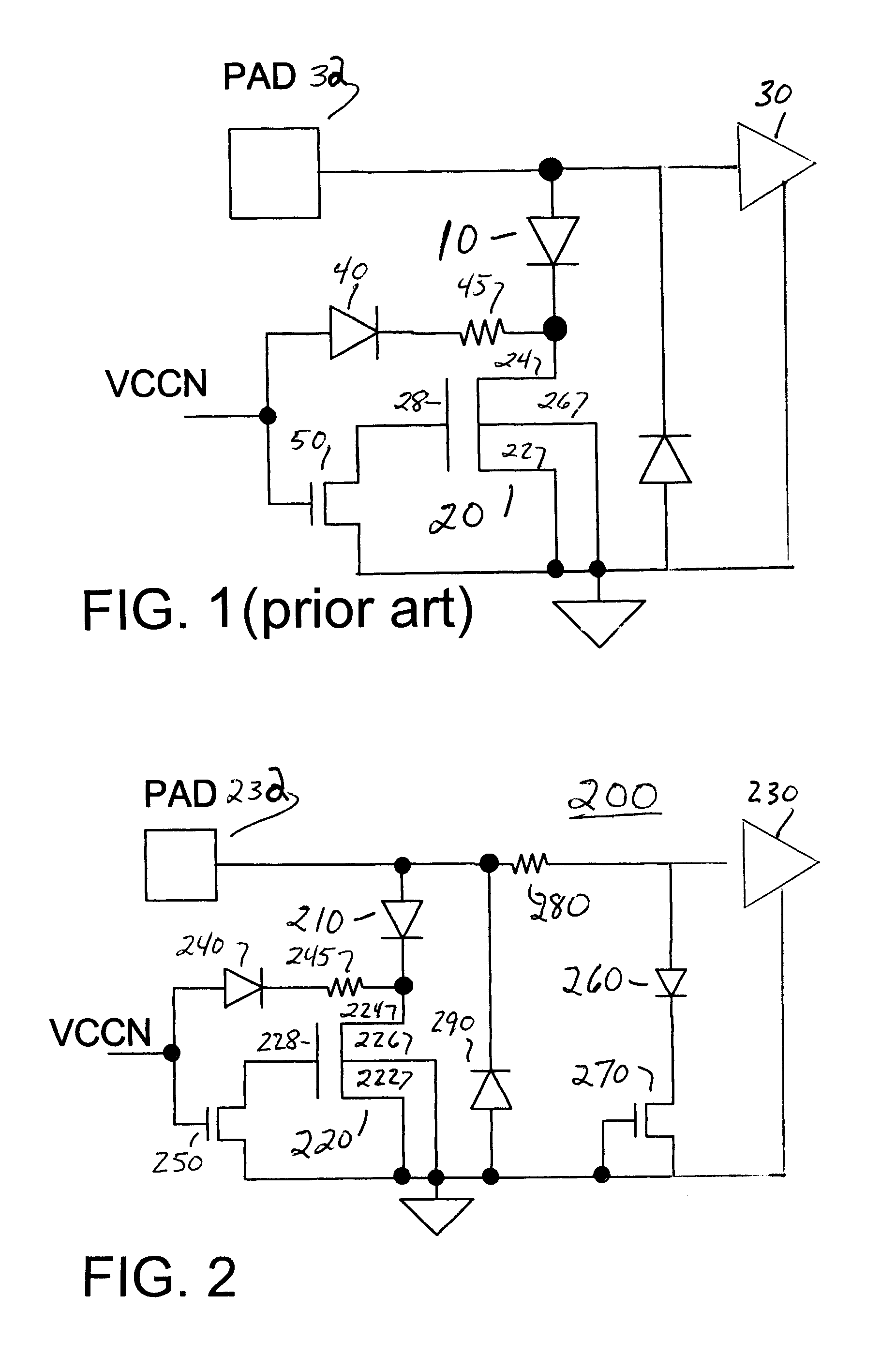

CDM performance of high speed CLK inputs

InactiveUS7760477B1Emergency protective arrangement detailsEmergency protective arrangements for limiting excess voltage/currentElectrical resistance and conductanceCapacitance

A conventional ESD protection circuit connects a diode and main clamp between a pad or node to be protected and ground. To preserve high speed operation while improving charge device model (CDM) performance, the invention also connects between pad and ground a small diode in series with a secondary clamp and a small isolation resistance. The isolation resistance is approximately 20 ohms. The secondary clamp can be as small as 30 nm wide. Parallel diodes on the main clamp can be replaced with an N+ / p-substrate (native) diode 290 to further reduce capacitance.

Owner:ALTERA CORP

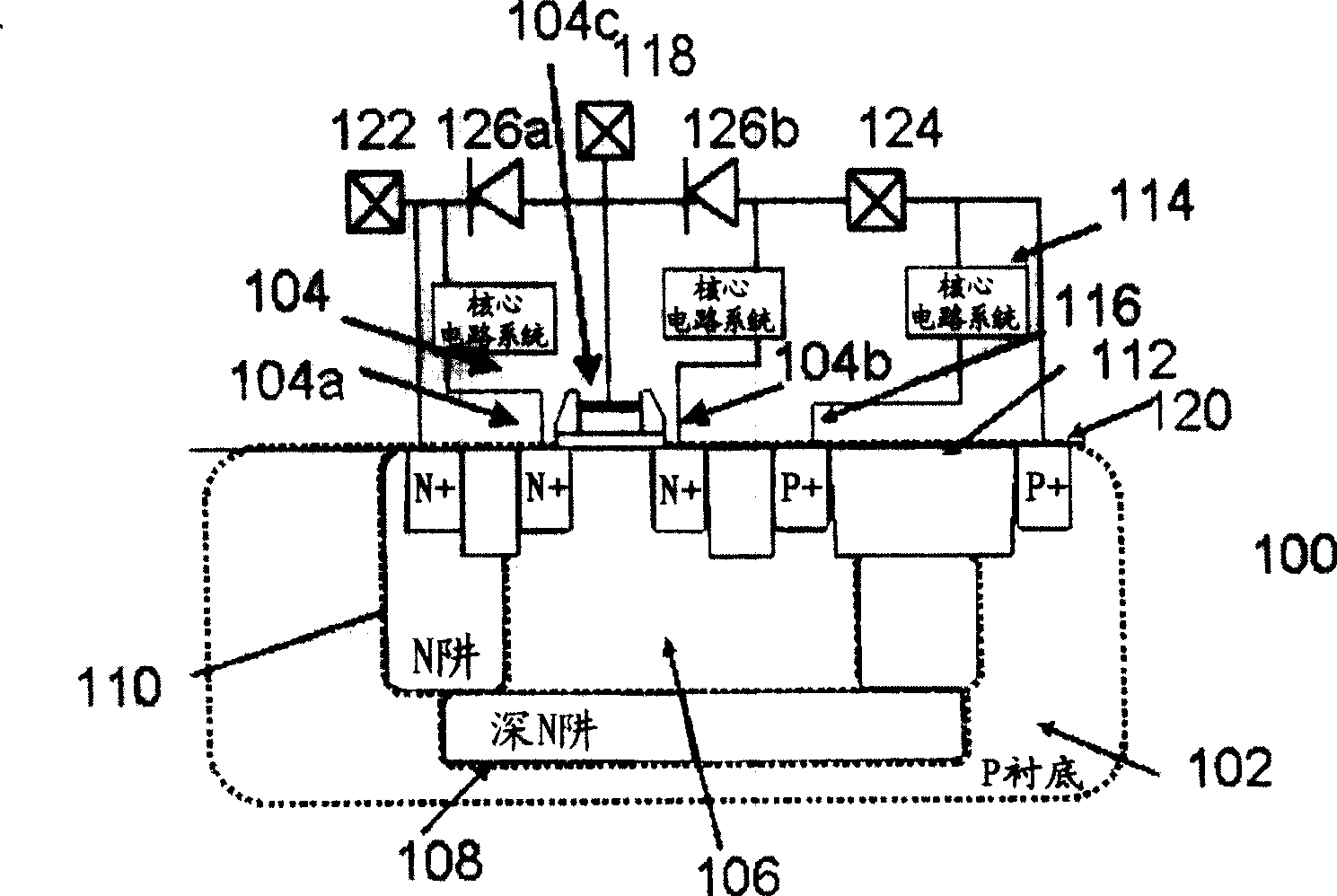

Cdm ESD protection for integrated circuits

InactiveCN101399264ASolid-state devicesEmergency protective arrangements for limiting excess voltage/currentEngineeringPhotonic integrated circuit

The present invention provides a charged-device model (CDM) electrostatic discharge (ESD) protection circuit for an integrated circuit (IC). The ESD protection circuit comprises a substrate of first conductivity type; a MOS component of second conductivity type formed on a first well on the substrate, and coupled to a pad; an isolating well / region having the second conductivity type being formed between the first well and the substrate to separate the first well and the substrate. Additionally, the circuit comprises an ESD clamp coupled to the isolated well / region. Under normal power operation, the ESD clamp is open. During a CDM ESD event, the CDM charges accumulated in the substrate and the MOS component are removed by the ESD clamp to prevent damage to the IC.

Owner:SARNOFF CORP +1

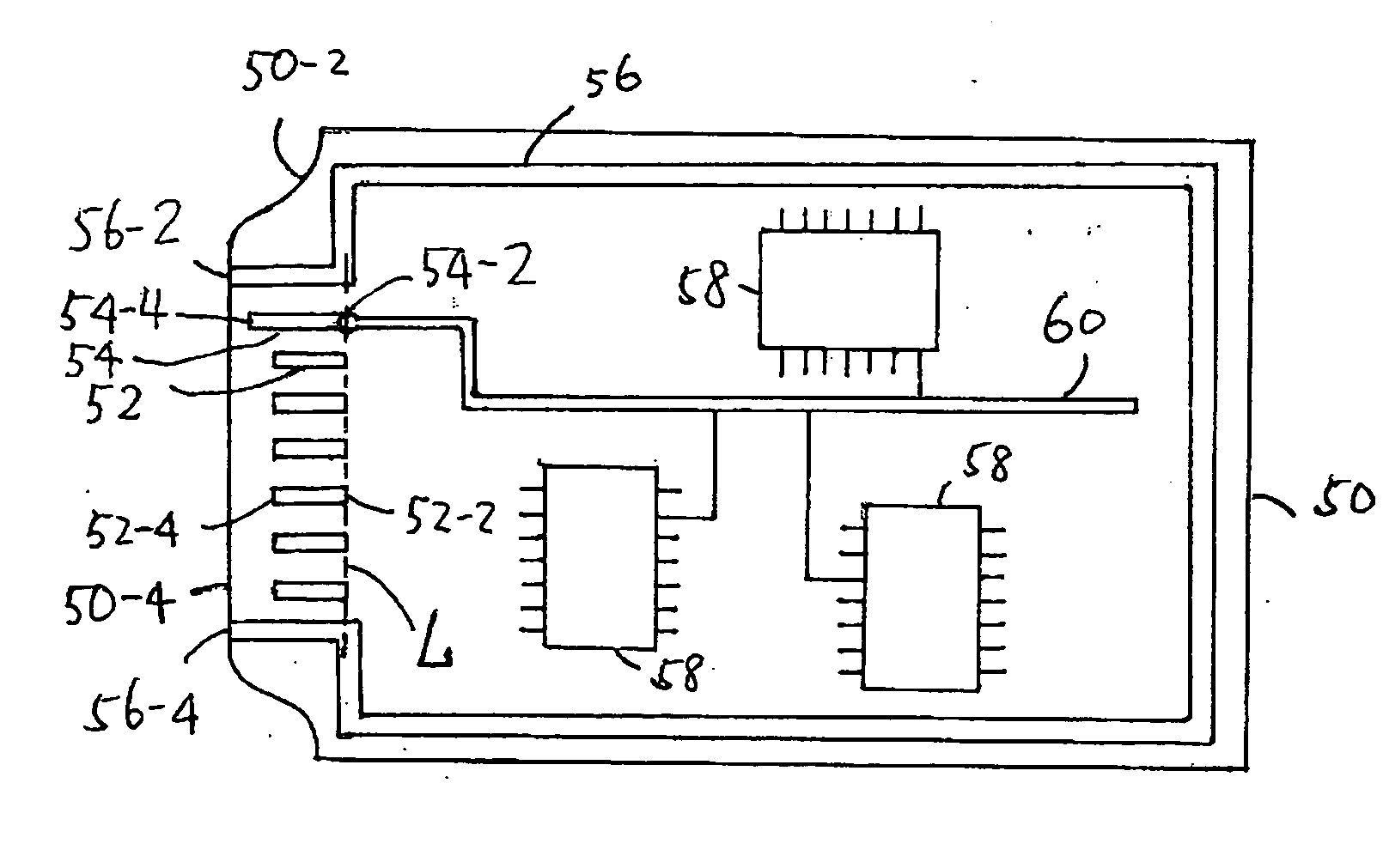

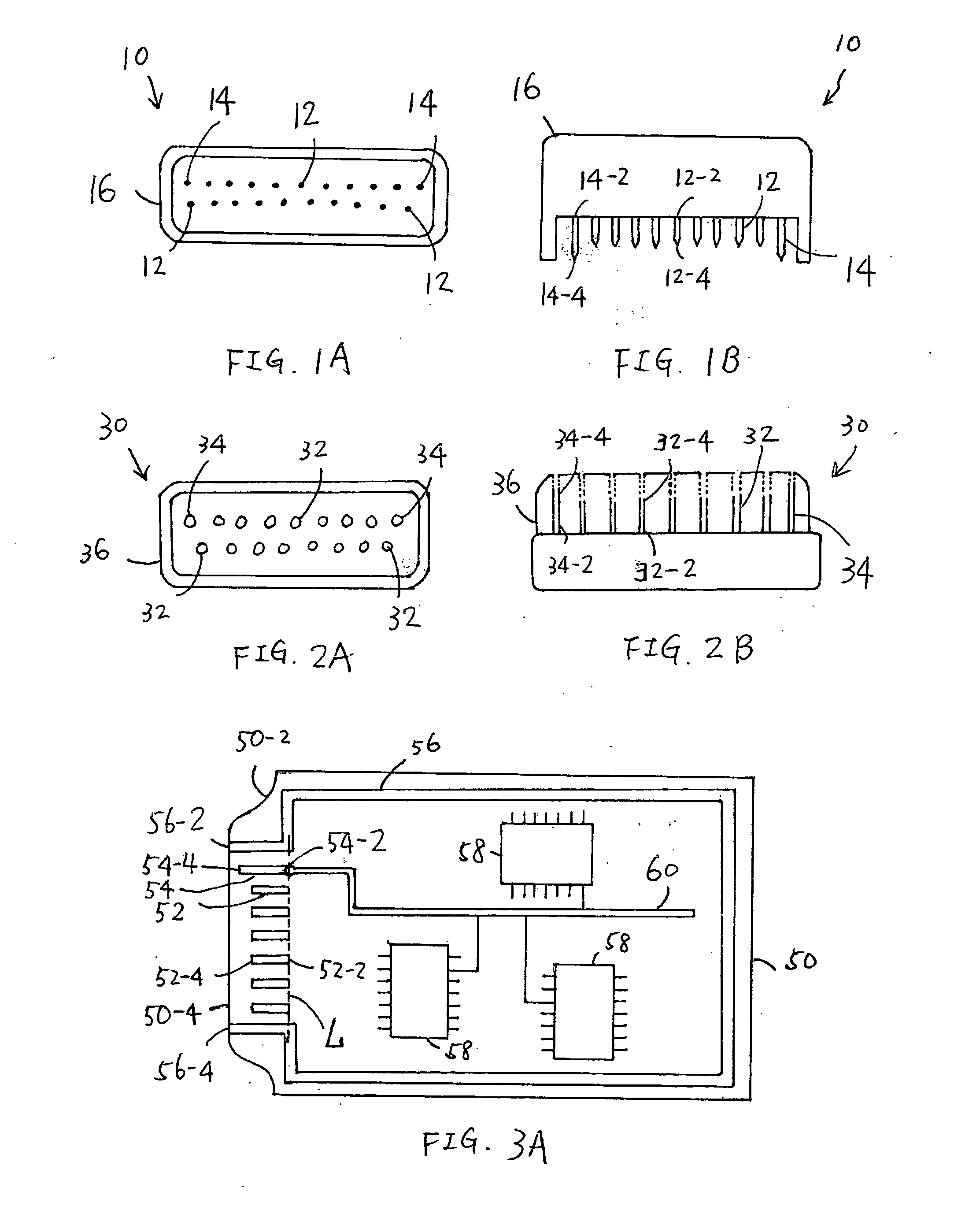

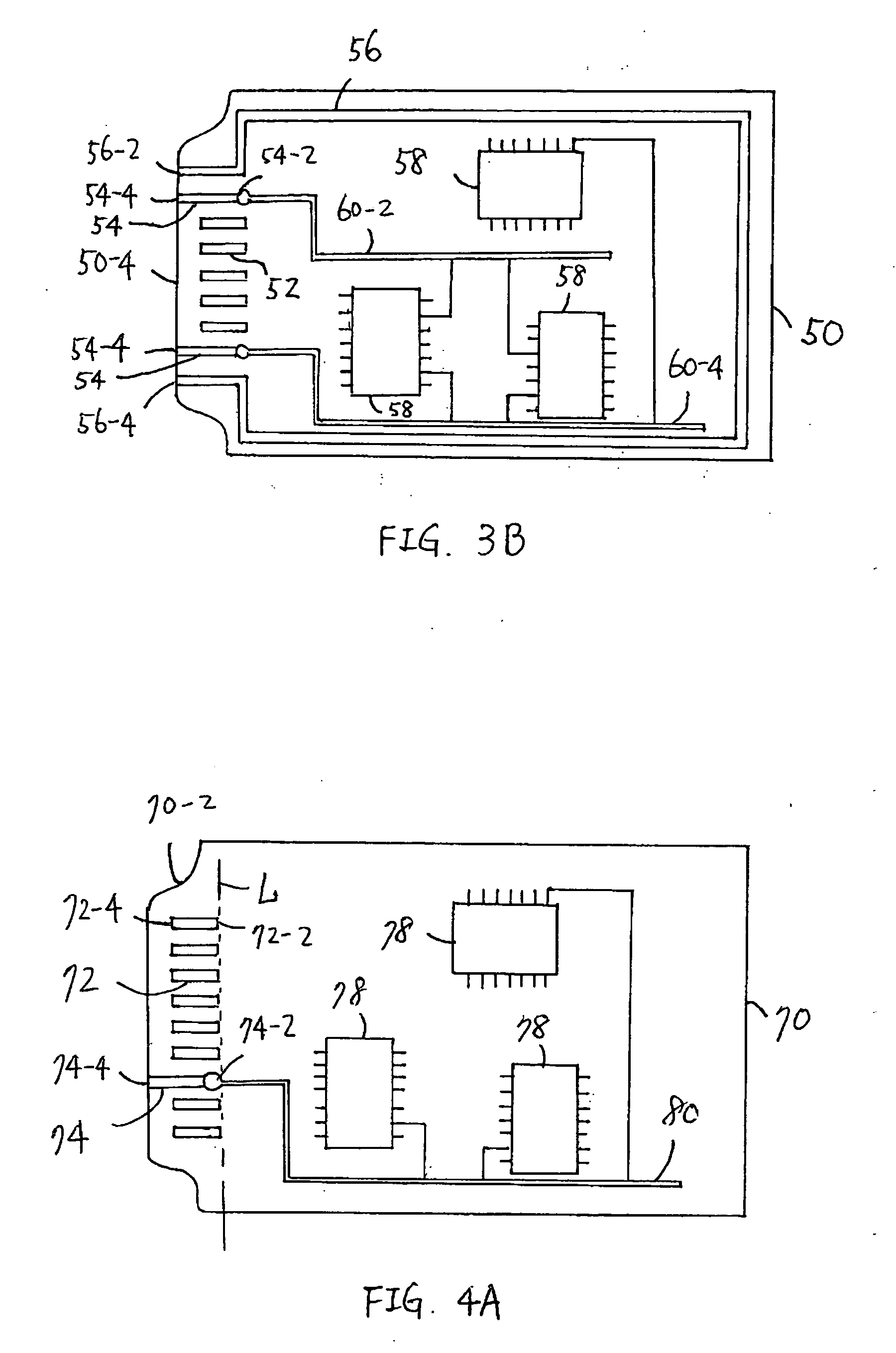

ESD protection design against charge-device model ESD events

InactiveUS20050122645A1Eliminate the problemElectrostatic discharge protectionPrinted circuit aspectsEngineeringElectrostatic discharge protection

An interface device coupled to a board on which integrated circuits are mounted for providing electrostatic discharge protection for the integrated circuits that comprises a plurality of first contact members, each of the first contact members including one end connected to the board and the other end to connect to an external device, and at least one second contact member connected to a voltage line of a voltage level, wherein the at least one second contact member includes a length greater than that of each of the first contact members.

Owner:TRANSPACIFIC IP LTD

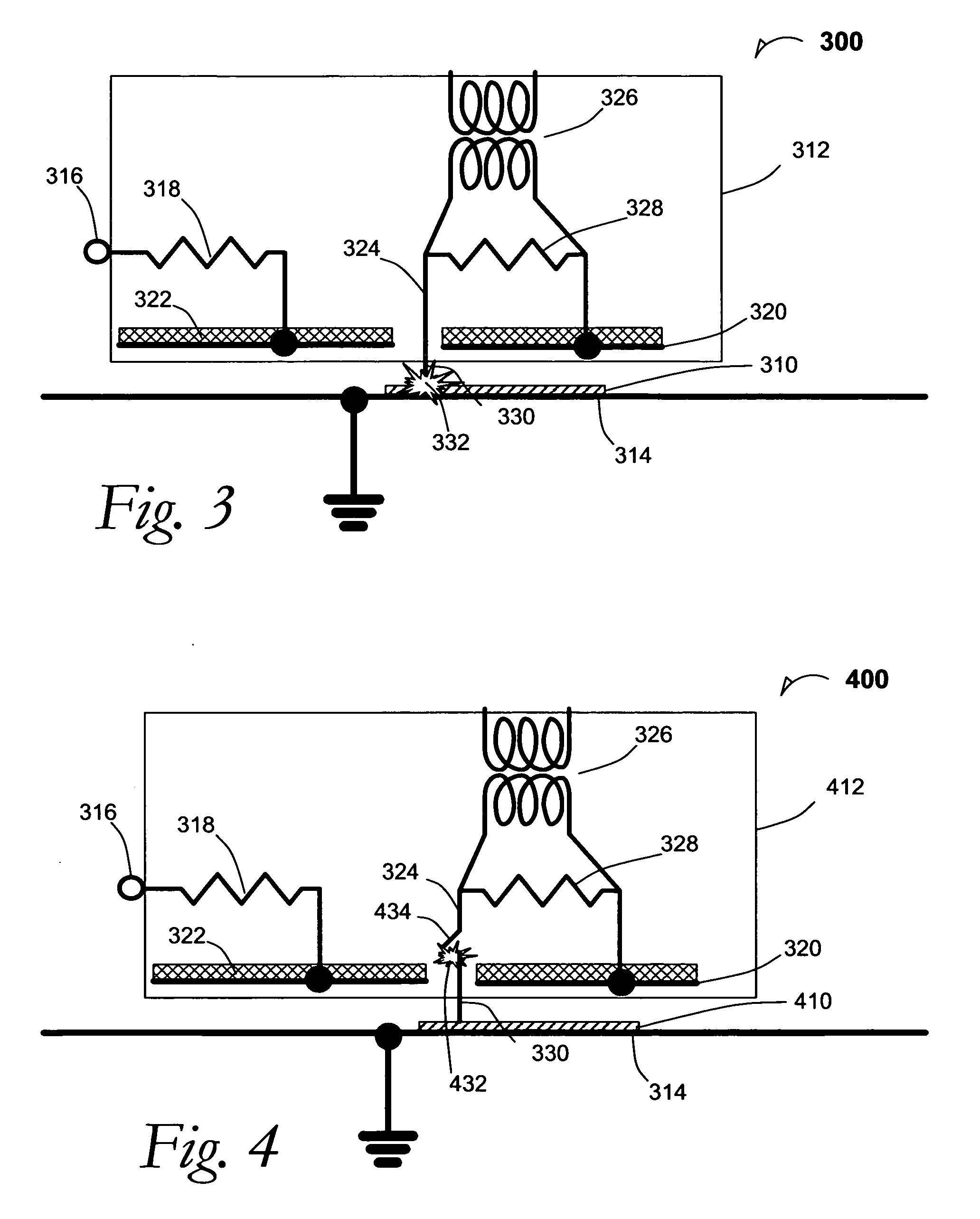

Charged device model contact plate

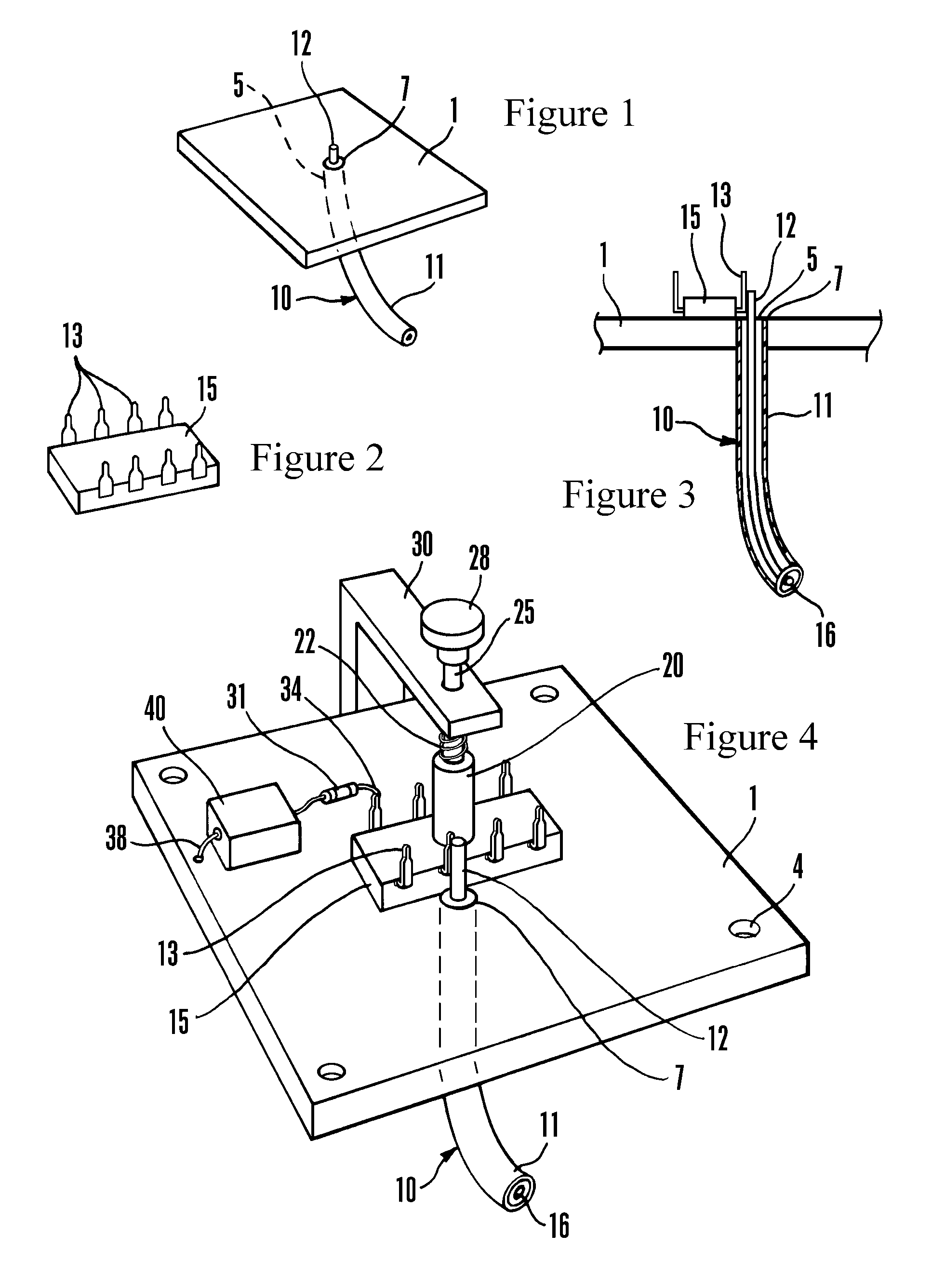

ActiveUS7733107B1Easy to measureMinimal effectElectrical measurement instrument detailsShort-circuit testingMeasurement testingElectrical conductor

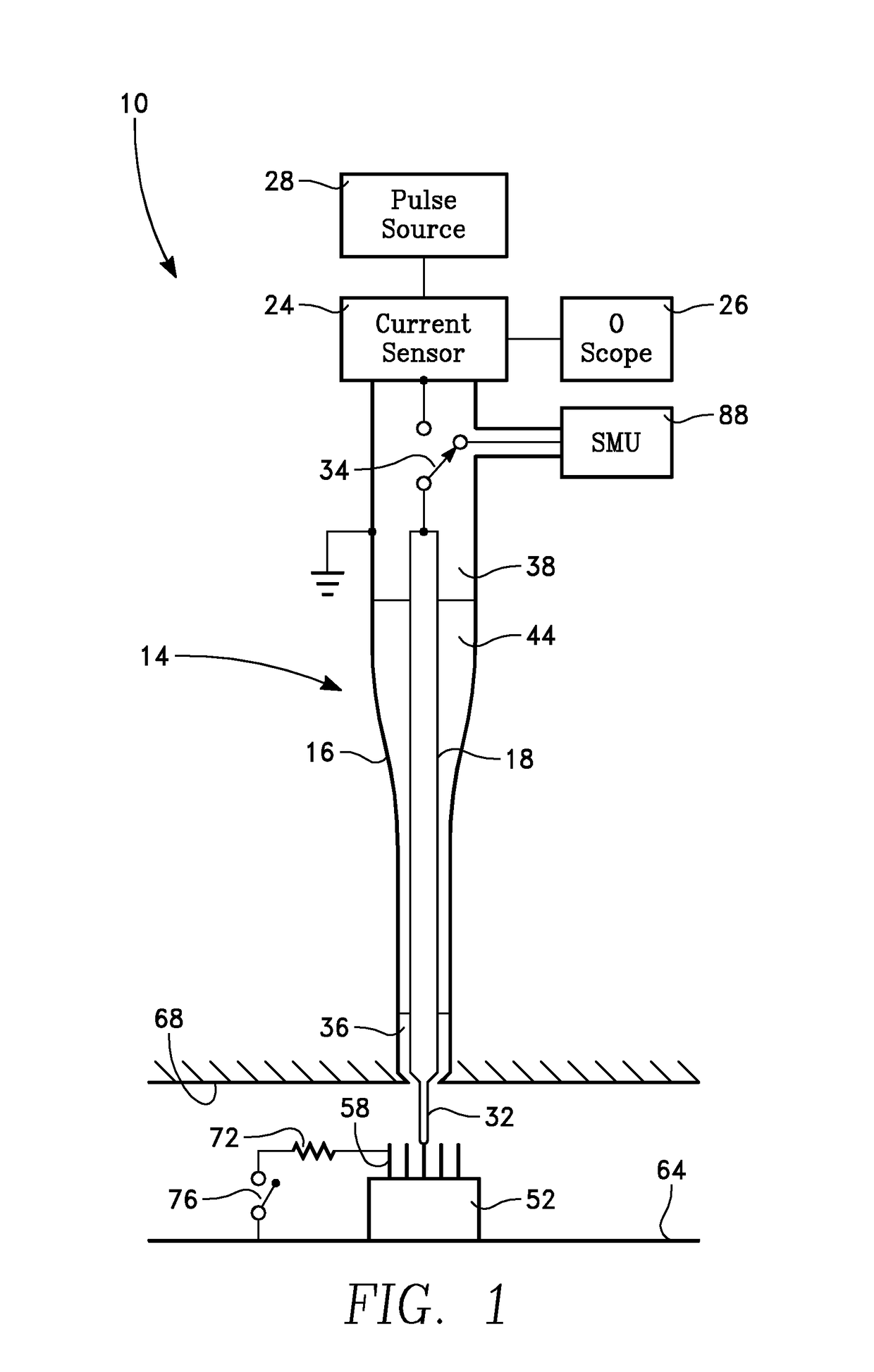

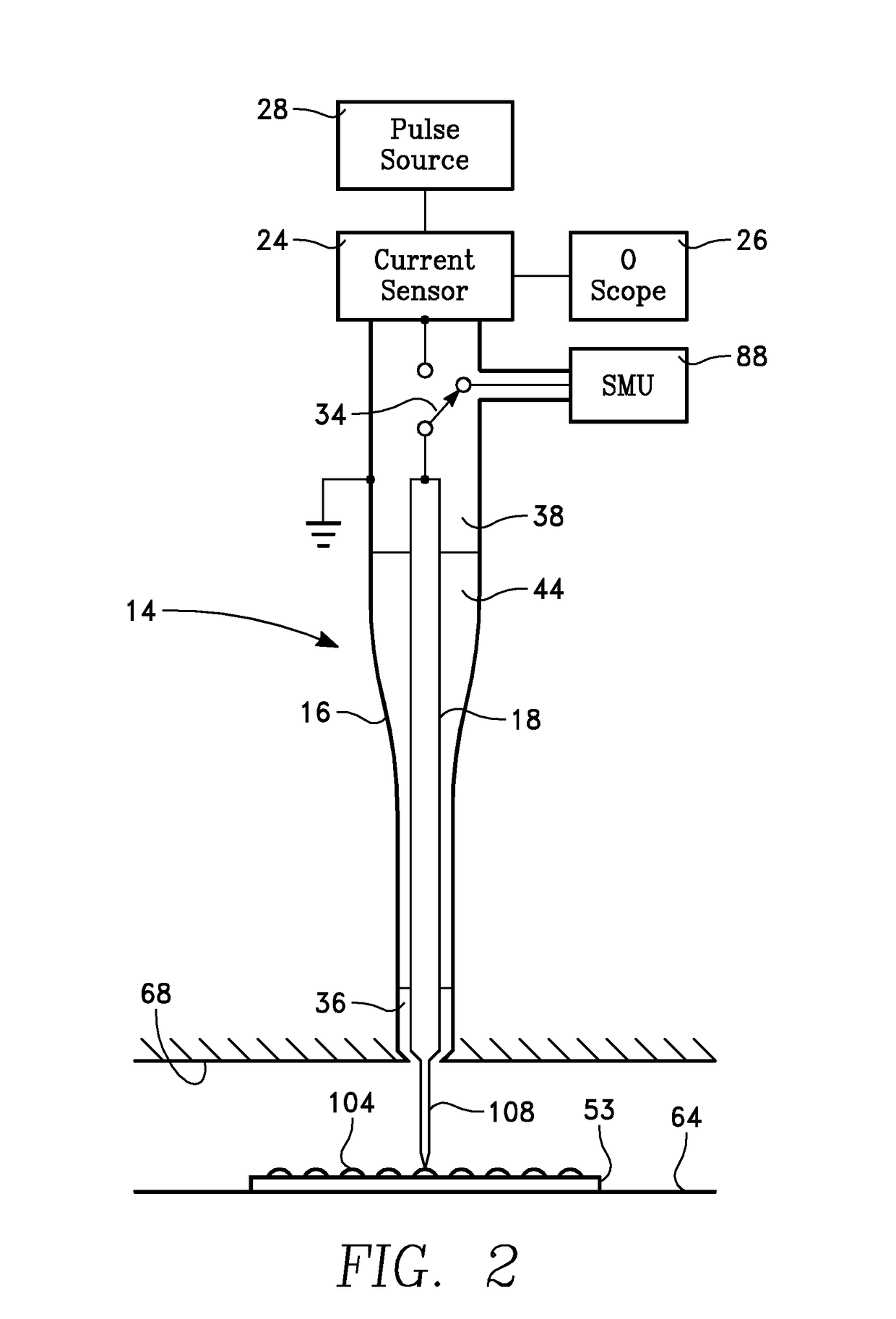

A tester for applying very fast transmission line pulses (“VFTLP”) to select pins of a device under test (“DUT”), for example, an integrated circuit. The tester also provides for leakage measurement testing of the DUT after VFTLP testing. An end of a coaxial cable is received within an aperture formed in a metal ground plane. The outer conductor of the coaxial cable is attached to the metal ground plane and the inner conductor of the coaxial cable projects above an upper surface of the metal ground plane. A grip attached to the metal ground plane selectively retains the DUT upon the upper surface of the metal ground plane in a position placing a select pin in physical contact with the projecting inner conductor of the coaxial cable, completing the VFTLP circuit.

Owner:BARTH JON E +1

Cdm ESD protection for integrated circuits

InactiveUS20080285187A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringPhotonic integrated circuit

The present invention provides a charged-device model (CDM) electrostatic discharge (ESD) protection circuit for an integrated circuit (IC). The ESD protection circuit comprises a substrate of first conductivity type; a MOS component of second conductivity type formed on a first well on the substrate, and coupled to a pad; an isolating well / region having the second conductivity type being formed between the first well and the substrate to separate the first well and the substrate. Additionally, the circuit comprises an ESD clamp coupled to the isolated well / region. Under normal power operation, the ESD clamp is open. During a CDM ESD event, the CDM charges accumulated in the substrate and the MOS component are removed by the ESD clamp to prevent damage to the IC.

Owner:SOFICS BVBA

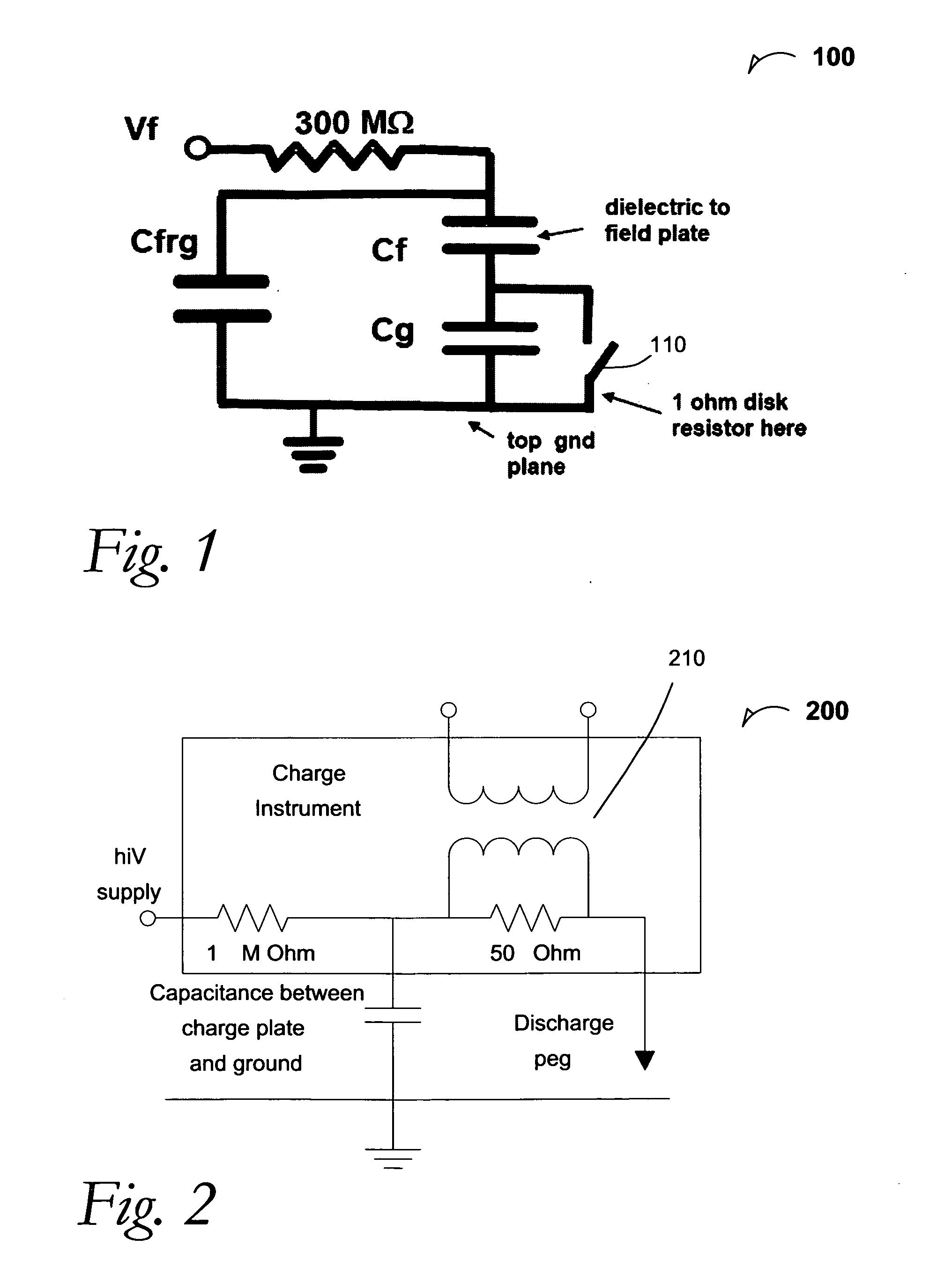

Water-level charged device model for electrostatic discharge test methods, and apparatus using same

ActiveUS20100165537A1Electrographic process apparatusMeasuring interference from external sourcesTime domainTransformer

A charged device model (CDM) electrostatic discharge (ESD) testing is carried out at wafer level. Wafer CDM pulses are repeatedly applied and monitored. The wafer CDM (WCDM) pulses are accomplished with a probe-mounted printed-circuit board and a high-frequency transformer that captures fast CDM pulses. Modeling of CDM and WCDM in the time and frequency domain illustrates the dominant effects, and shows that WCDM can reproduce all the major phenomena of package-level CDM testing.

Owner:INTEL CORP

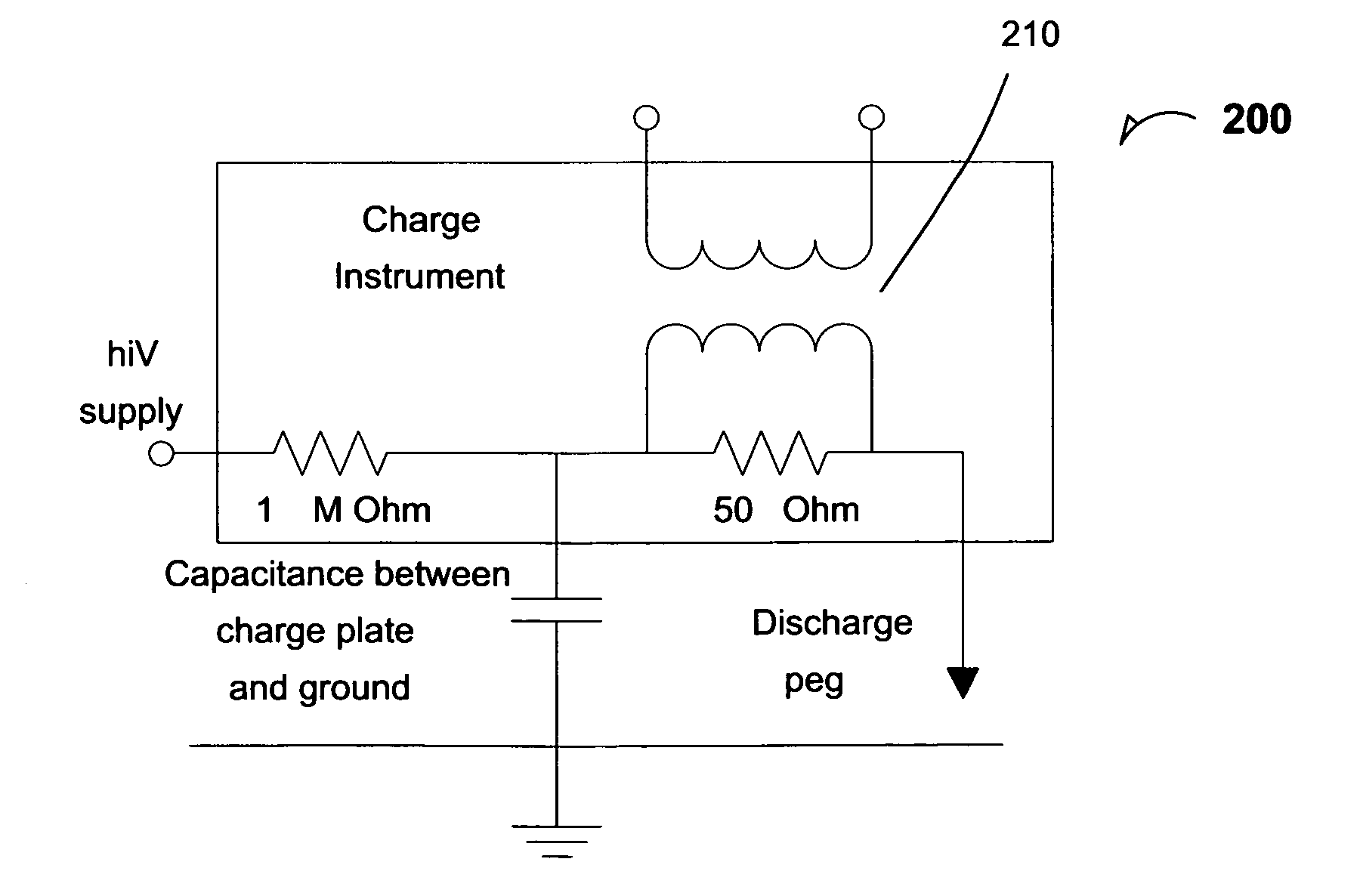

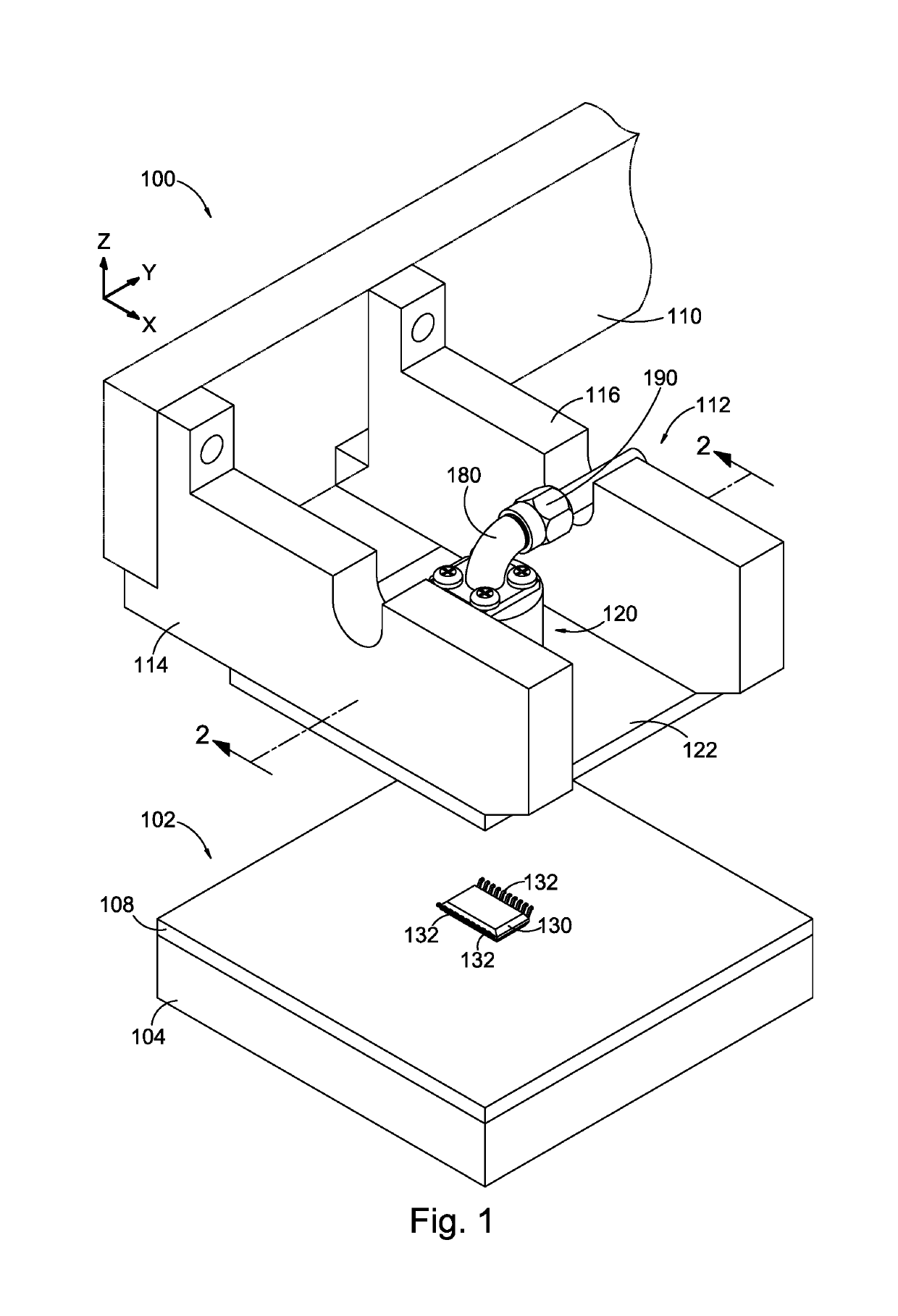

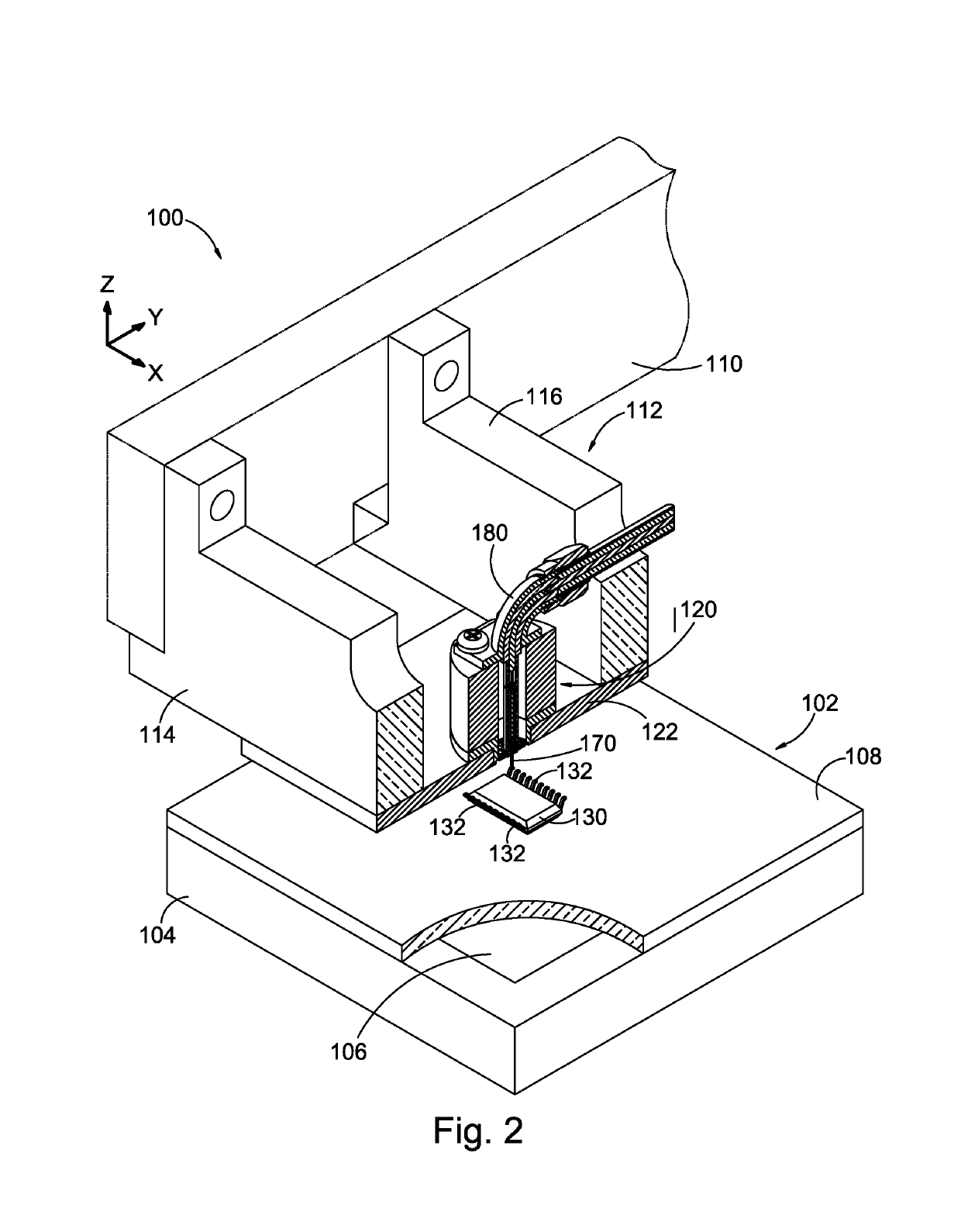

Controlled impedance charged device tester

ActiveUS9726707B1Minimize reflectionEasy constructionTesting dielectric strengthElectronic circuit testingElectrical resistance and conductanceTester device

An ESD tester transforms high speed pulses from s 50-ohm impedance to the optimum lower impedance necessary to simulate the Charged Device Model (“CDM”) test impedance. Direct connections to the device under test eliminates the variations in spark or contact resistance of the present test while transforming the test pulse impedances to the appropriate level. Direct device connections with controlled impedance current paths provide either internal device discharge or external test pulse testing to simulate the original test. The sparkless direct connection controlled impedance transformation is identified by its ability to simulate similar device failures at similar test voltage failure levels.

Owner:BARTH JON E

Electrostatic discharge protection circuit for RF identification chip

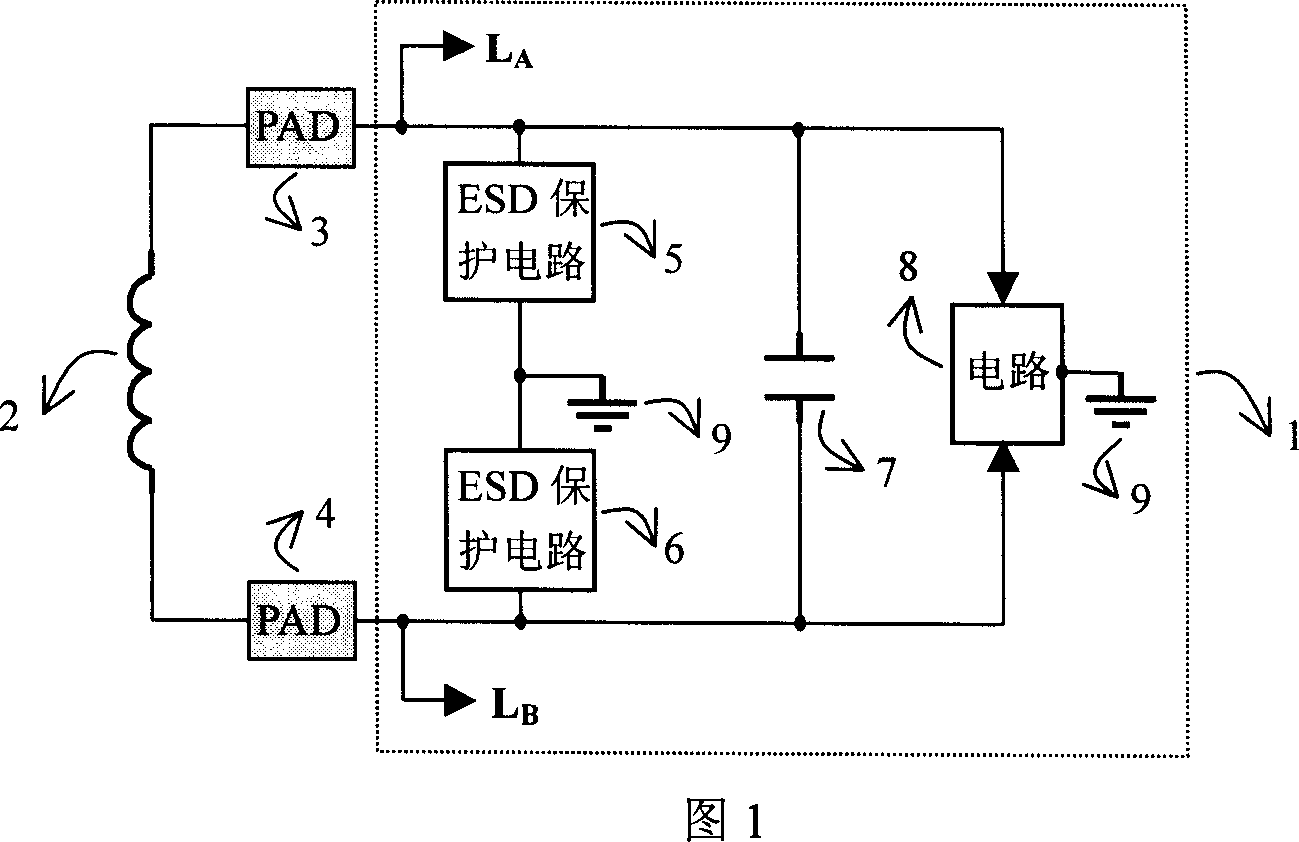

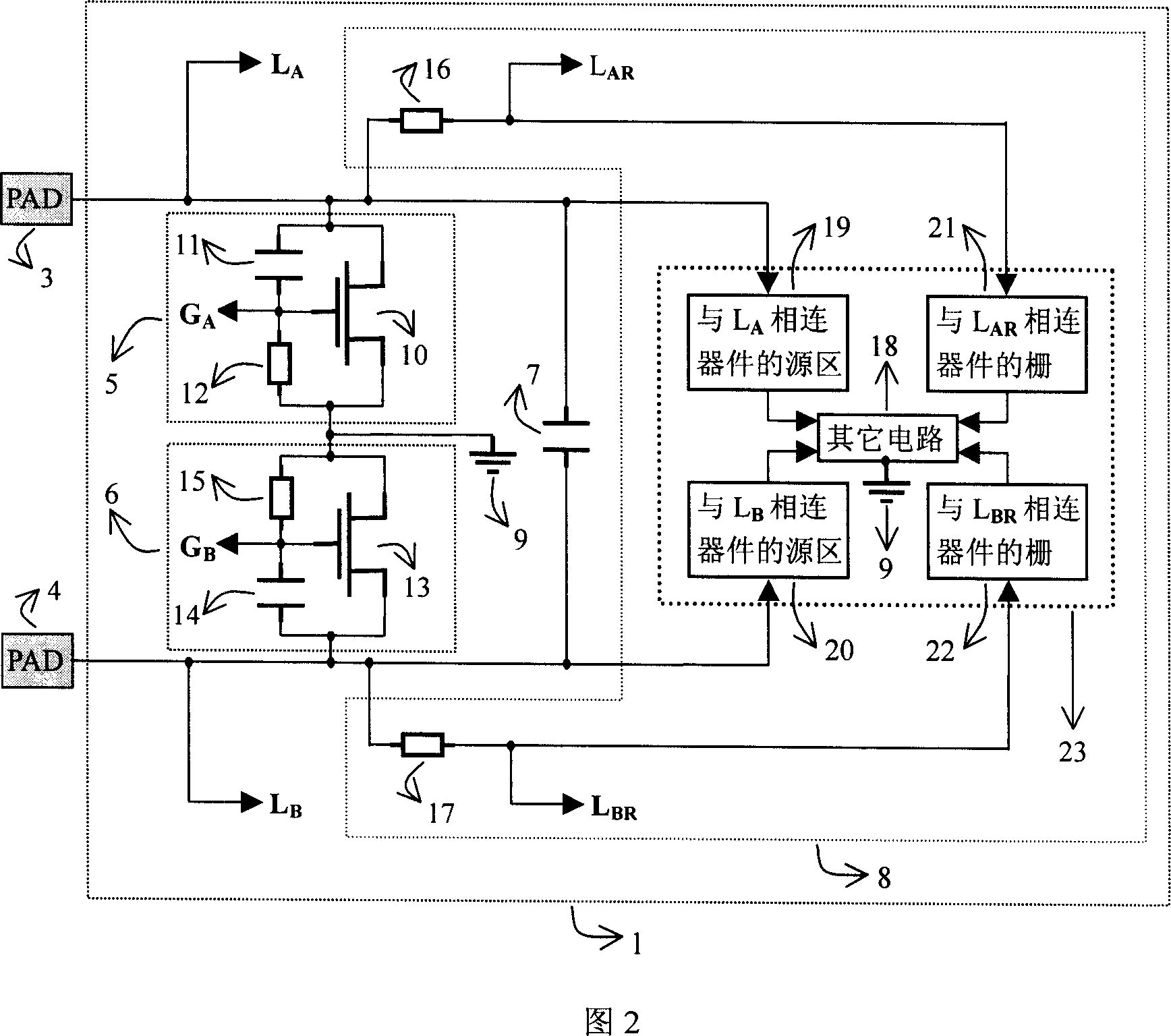

InactiveCN1949509AStrong anti-ESD performanceSufficient discharge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringRadio frequency

The invention advances a CMOS process-based on-chip electrostatic discharge (ESD) protection circuit applied to radio frequency identification (RFID) chips, composed of chip ground on-chip ESD protection circuit used to connect two pressure points of an outside-chip antenna, and inside-chip circuit directly or indirectly connected with pressure points, and giving circuit structure and design method, where the on-chip ESD protection circuit for the RFID chip is an important solution to assure the chip avoids ESD failure. And it considers three discharging models of human body model (HBM), machine model (MM) and charging device model (CDM) and simultaneously considers validity of ESD protection circuit and insensibility to process, and it is an ESD protection circuit with strong robustness, applied to RFID chip.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

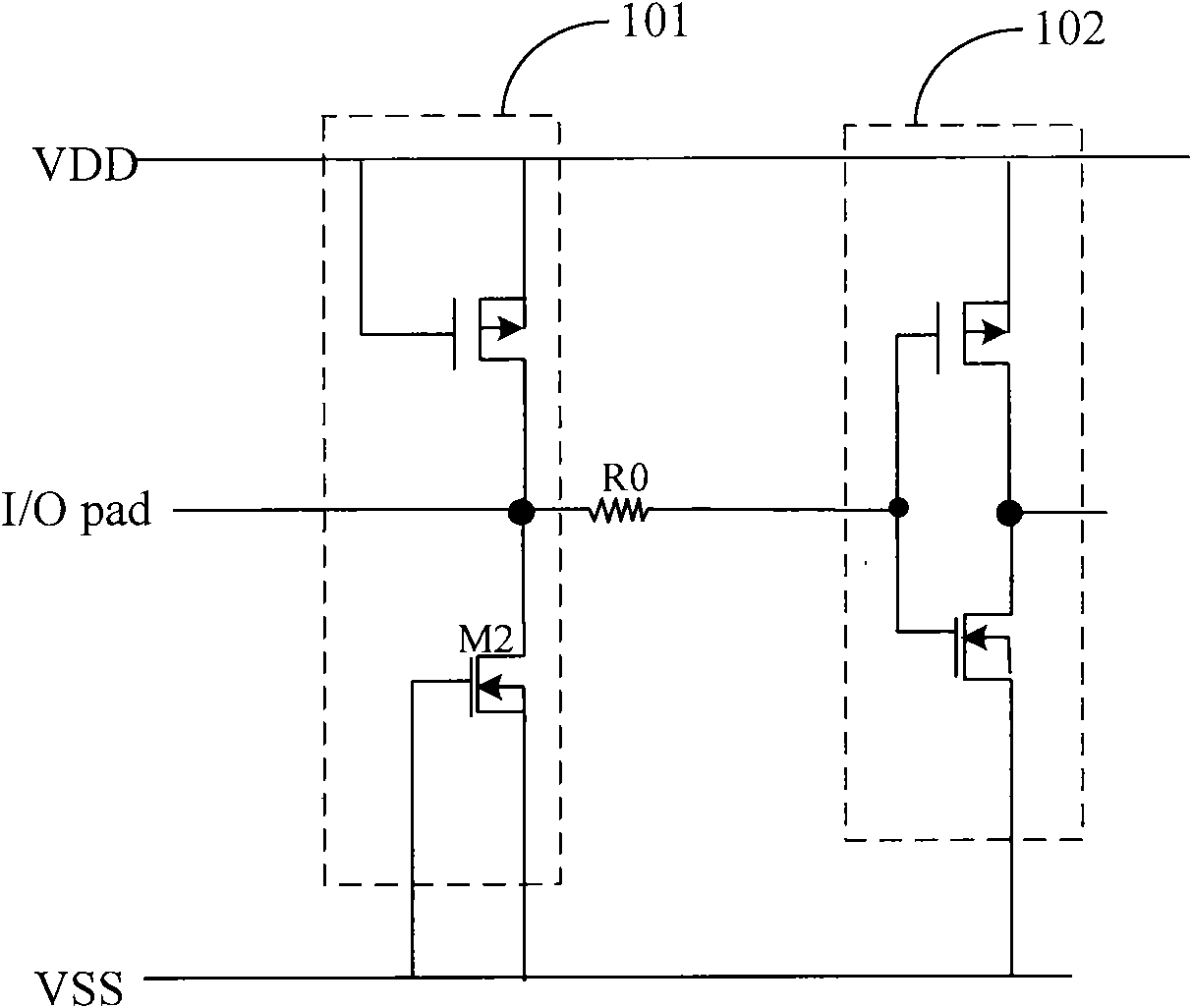

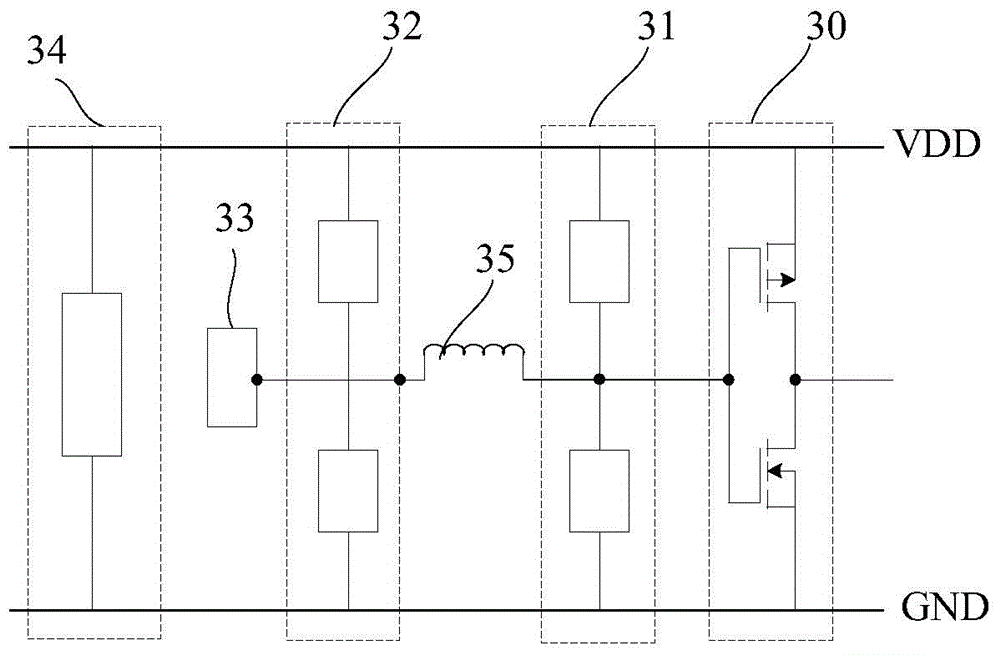

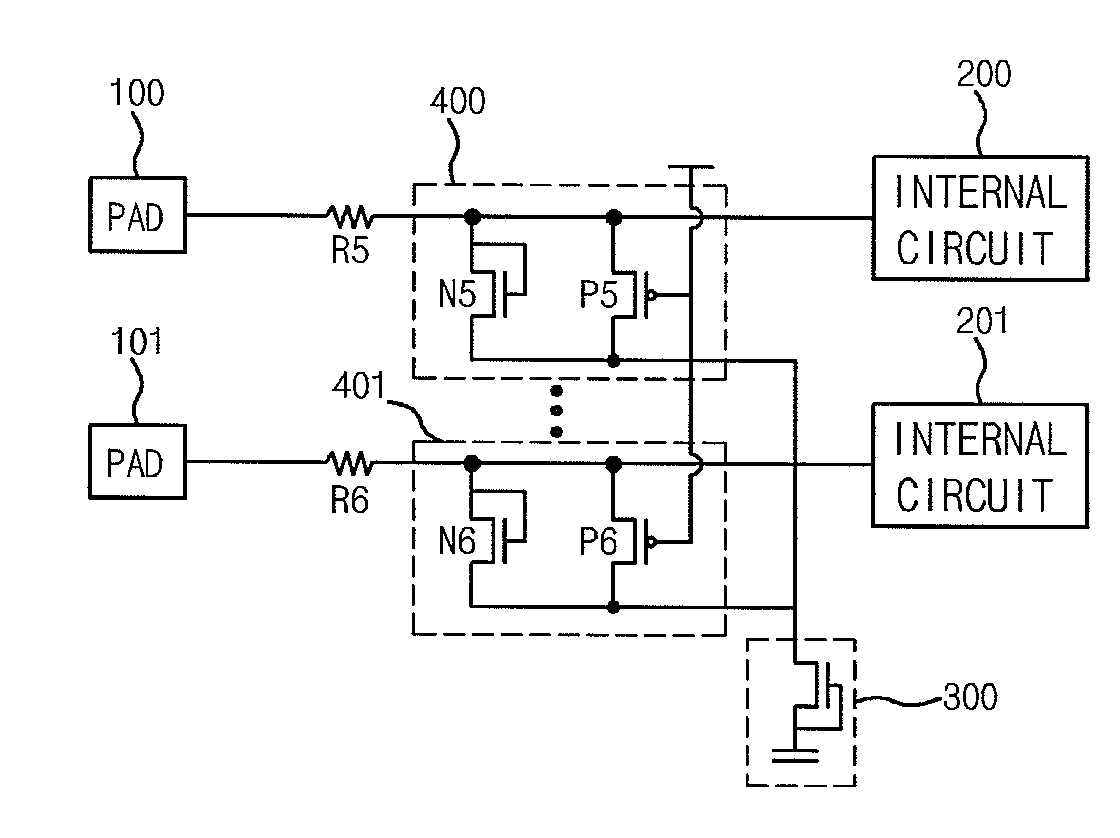

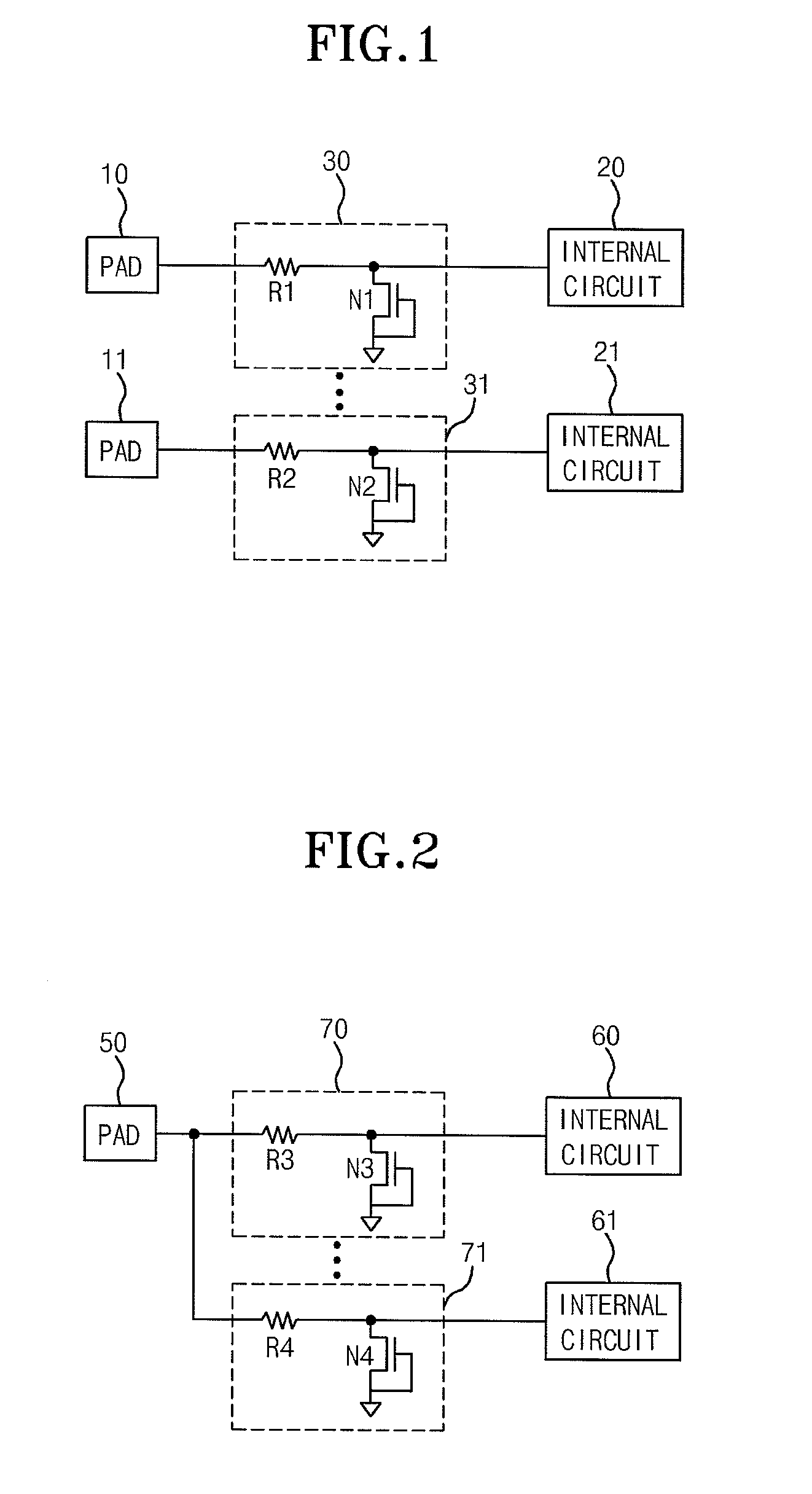

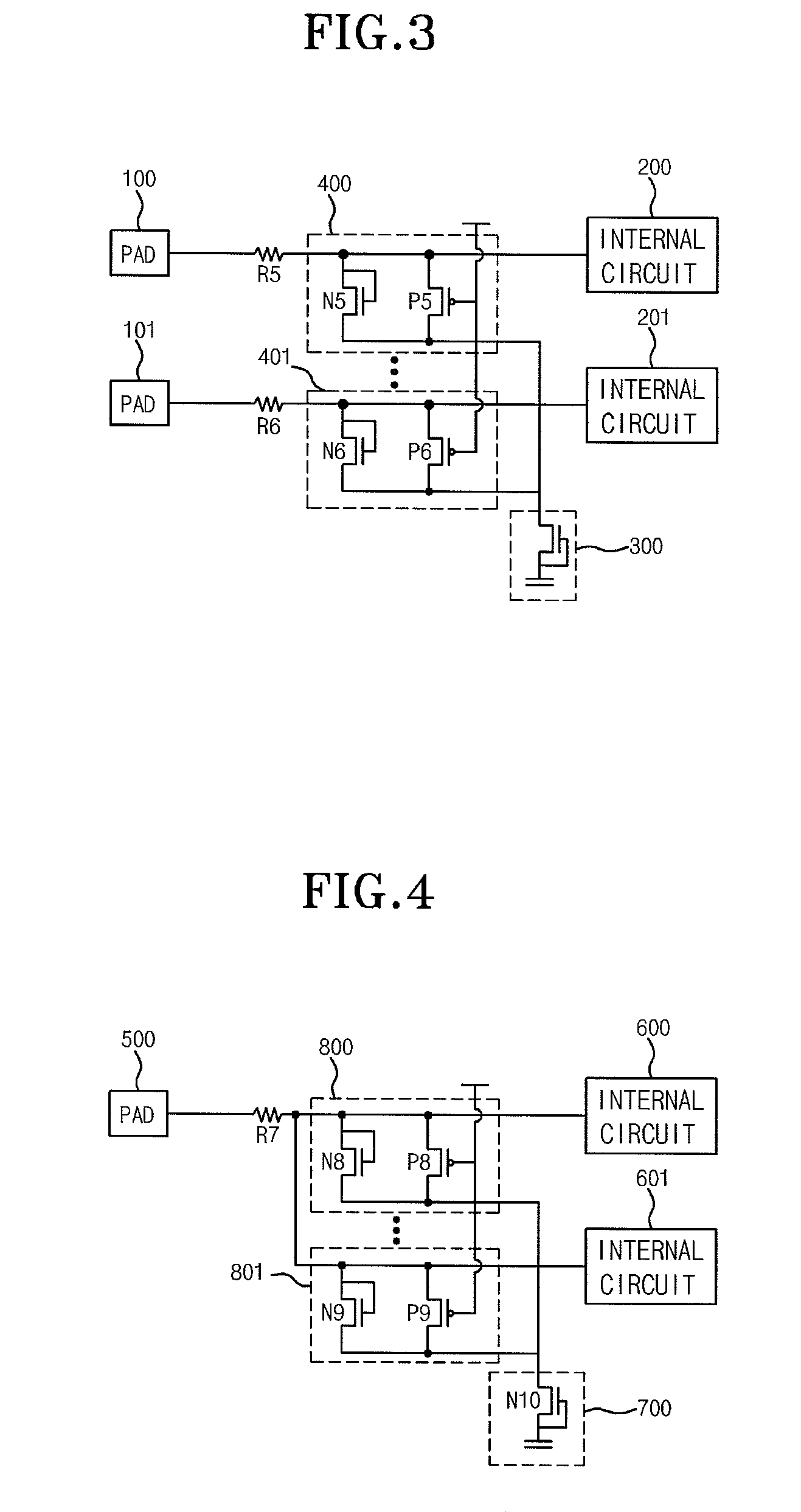

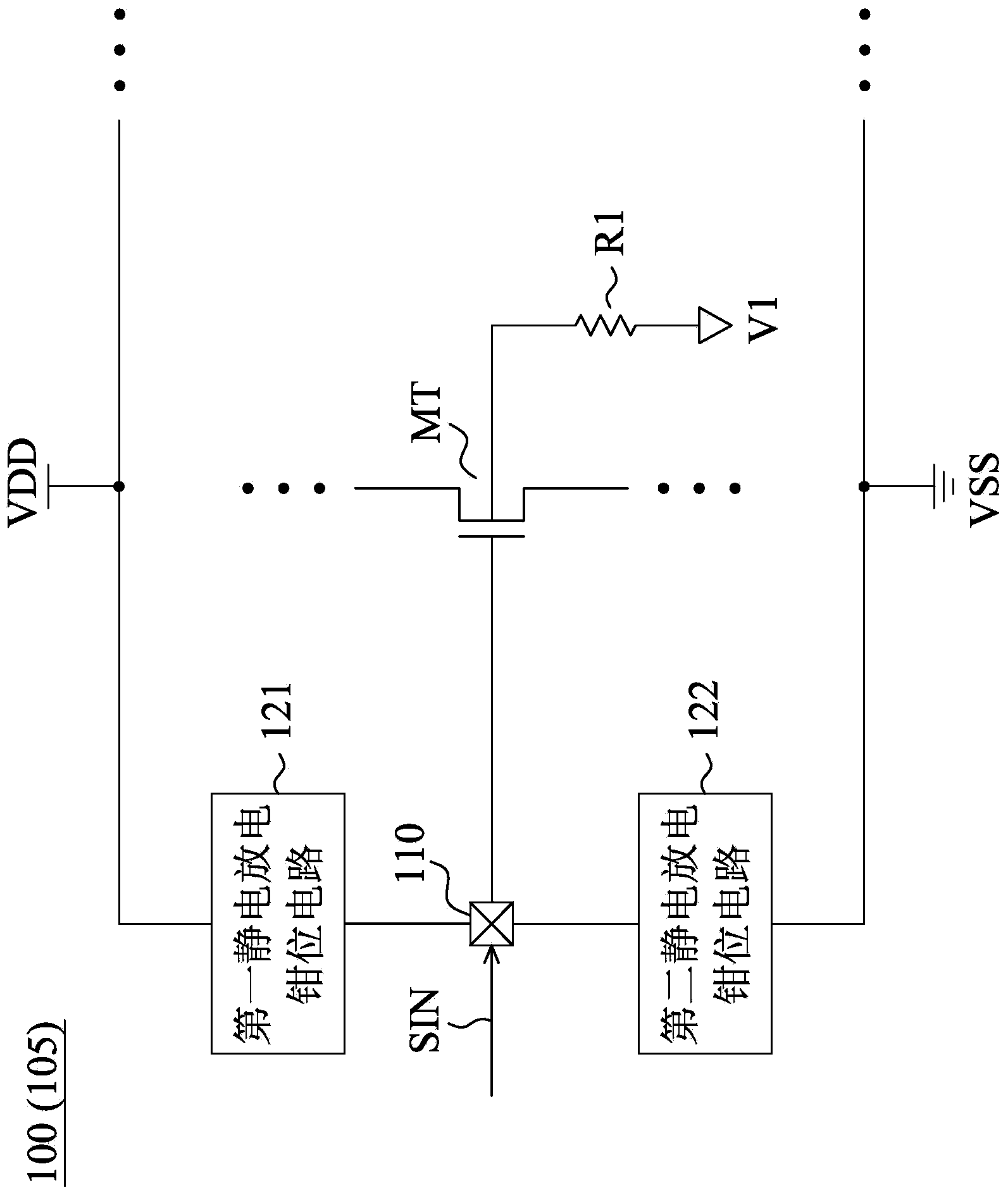

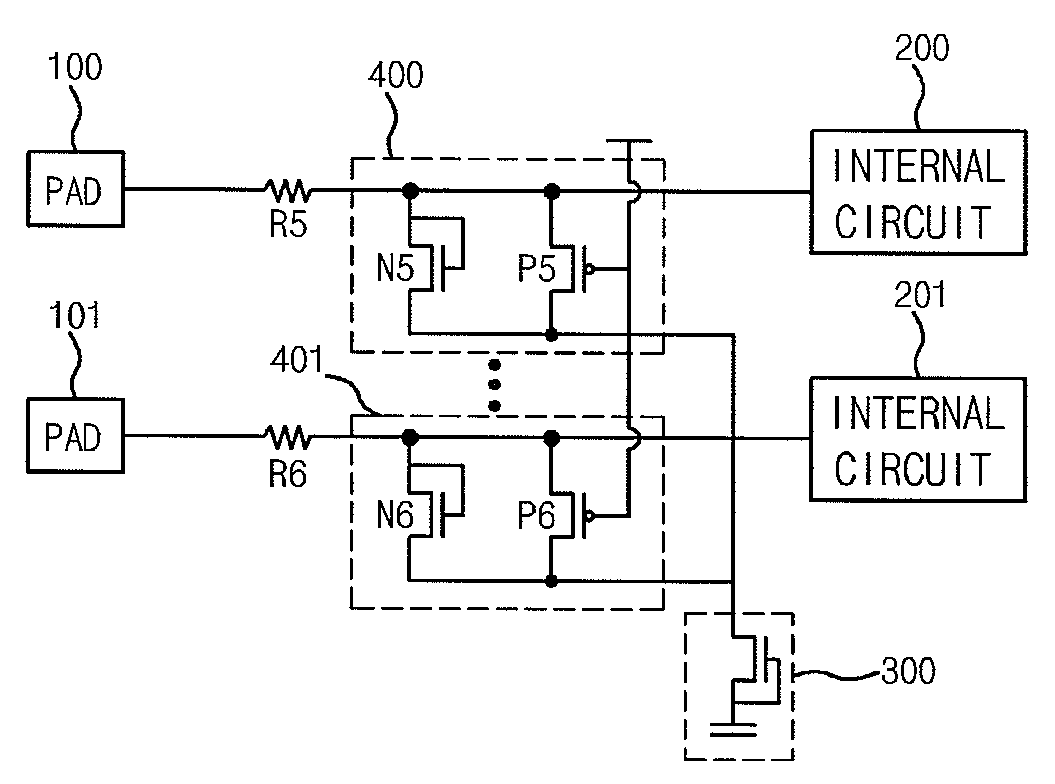

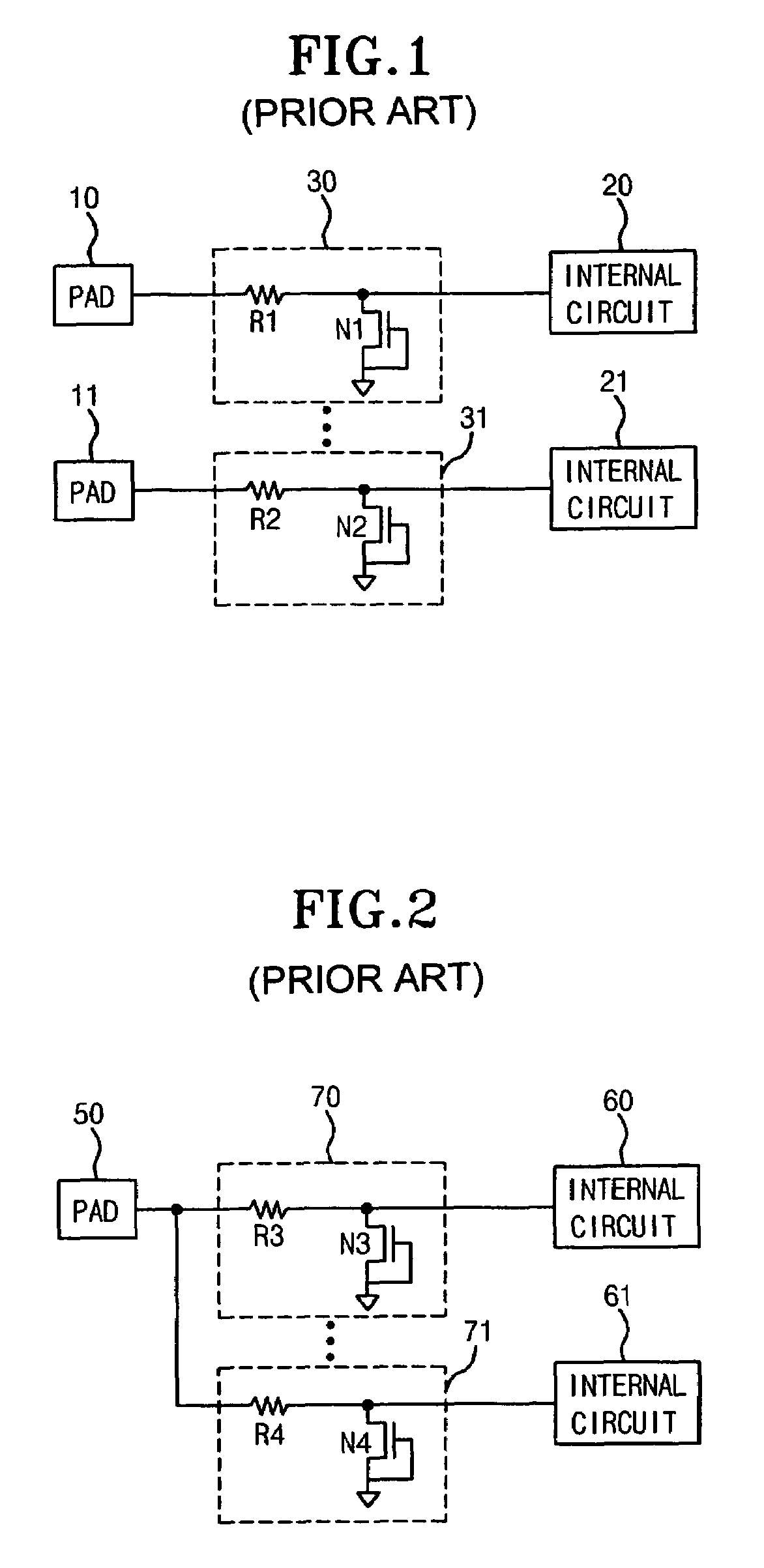

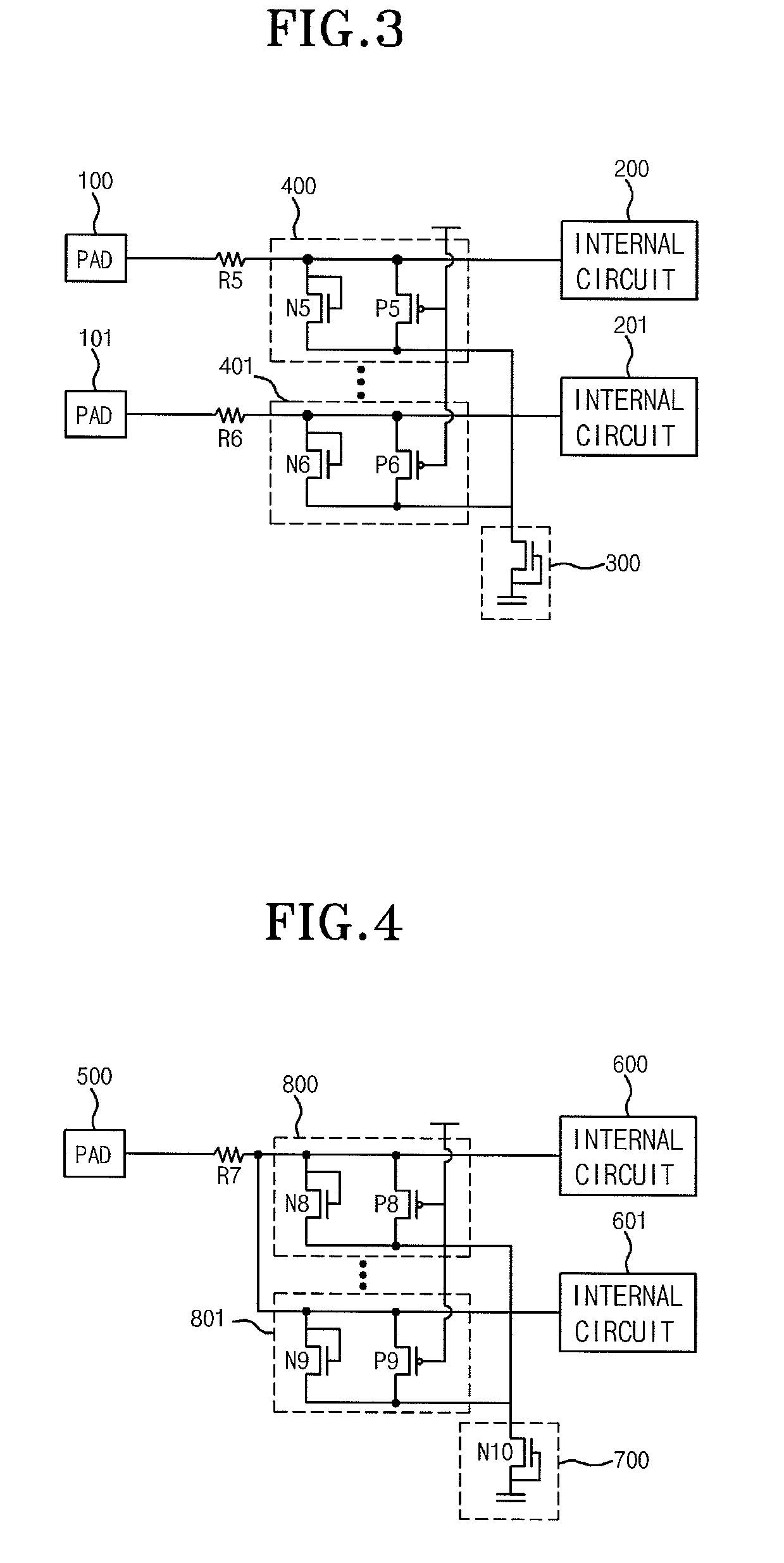

Circuit for discharging static electricity

ActiveUS20080123231A1Reduce areaReduce capacitanceSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentLow voltageEngineering

The present invention relates to a semiconductor circuit, and more particularly, to a circuit for discharging static electricity, which is connected between an internal circuit and an input / output pad to provide a charge device model (CDM) discharging path. The circuit includes a plurality of input / output pads; a plurality of switching units corresponding one-to-one to the input / output pads and turned on in a low voltage state; resistors connected between the input / output pads and the switching units so as to correspond one-to-one to the input / output pads and the switching units; and a CDM discharge unit shared in serial by the plurality of the switching units and providing a ground path.

Owner:SK HYNIX INC

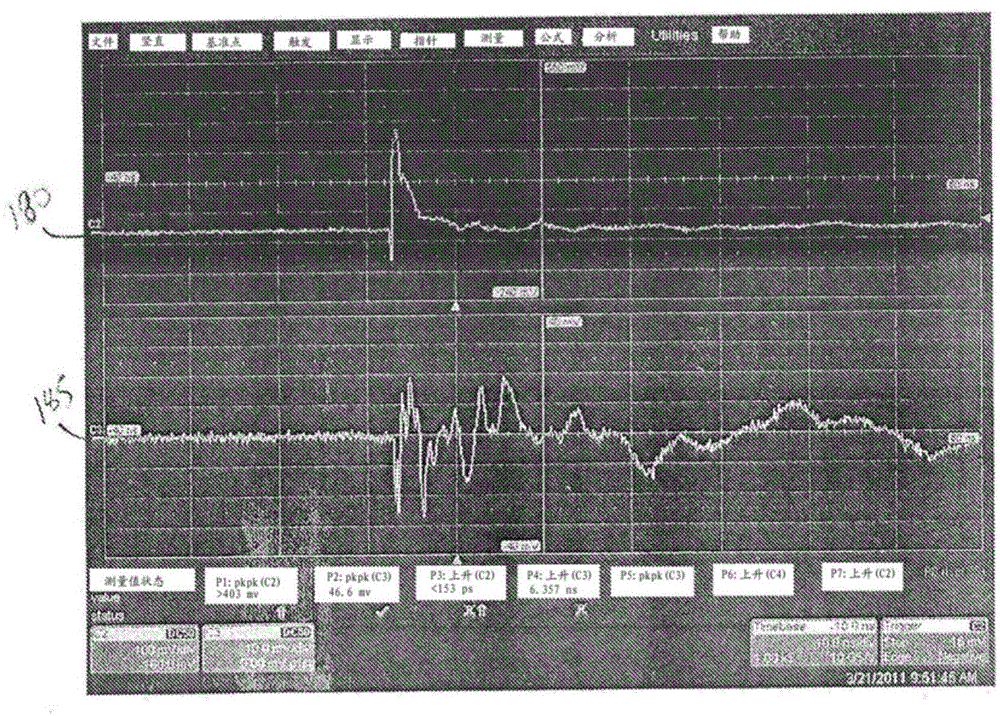

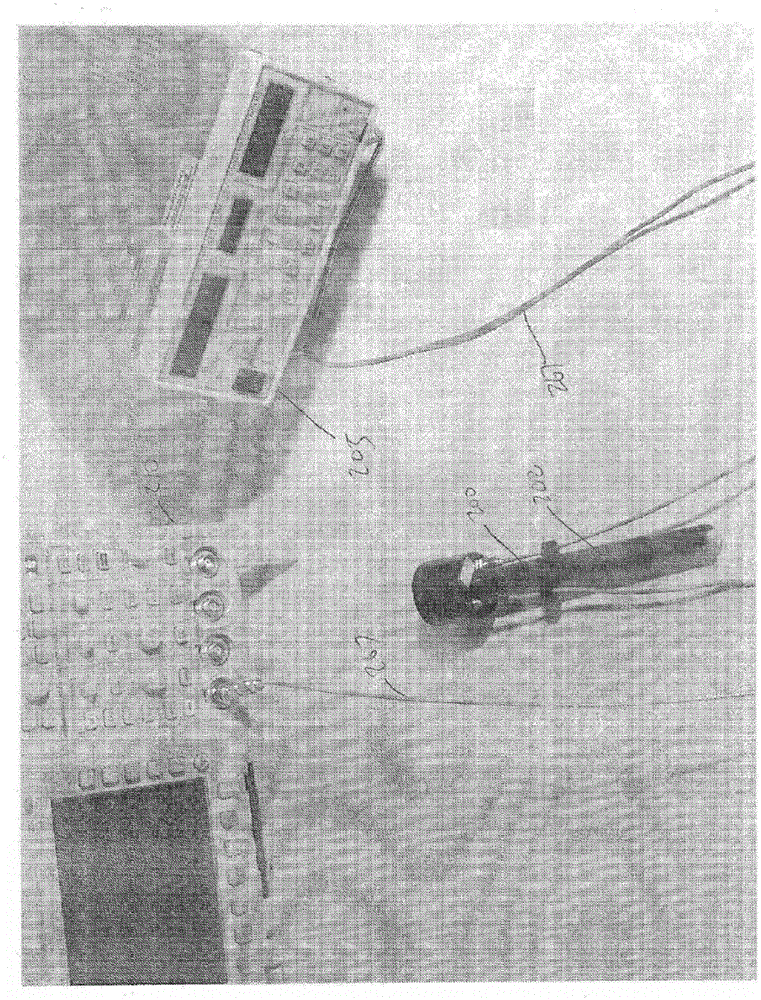

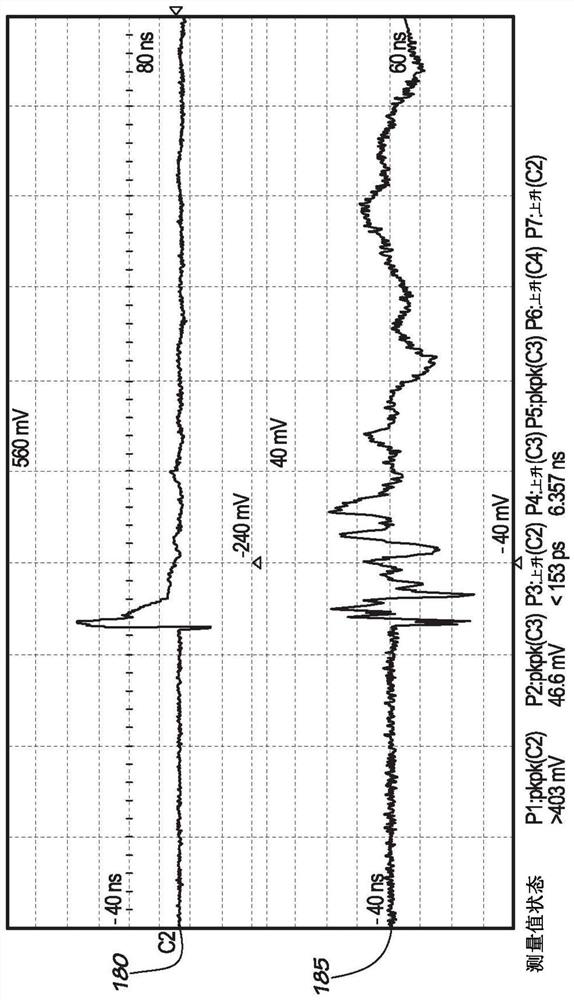

Electro-static discharge circuit waveform detection system and test method

InactiveCN107436382AEasy to buildLow costSpectral/fourier analysisDigital variable/waveform displayCapacitanceCoaxial cable

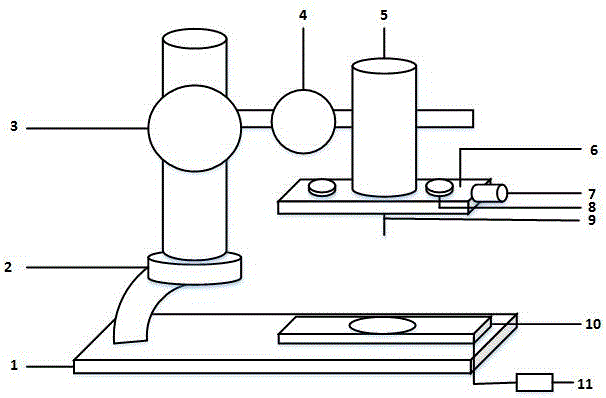

The present invention provides a CDM (Charged Device Model) current detection system and test method in an ESD (Electro-Static Discharge) electro-static protection. The objective of the invention is to complete the capture of the ESD current waveform of the CDM model so as to facilitate provide data support for ESD electro-static protection taking the CDM as a basis. The system structure comprises a testing machine configured for support, and the pedestal of the machine is provided with a test device DUT (DeviceUnder Test); a machine support is configured to fix the detection module of the system, and the detection module comprises a pogo (pogo stick) probe, a test plate and the like; the testing machine is made of aluminum alloy materials, has a lifting spiral regulation function and is provided with a fixing device capable of fixing the test plate of the device, and the test plate is a dual-layer FR-4 plate; and the pogo probe is a mobile phone antenna special probe capable of satisfying the signal test in the condition of the 18GHz and being less than 18GHz; and the characteristic impedance of a coaxial cable is 50 [Omega], the used calibration module (namely a calibration capacitor) is FR-4 materials, and a capacitance value is 4pF.

Owner:SHANGHAI RES INST OF MICROELECTRONICS SHRIME PEKING UNIV

Design of silicon-controlled rectifier by considering electrostatic discharge robustness in human-body model and charged-device model devices

Owner:ORTIZ & LOPEZ PLLC +1

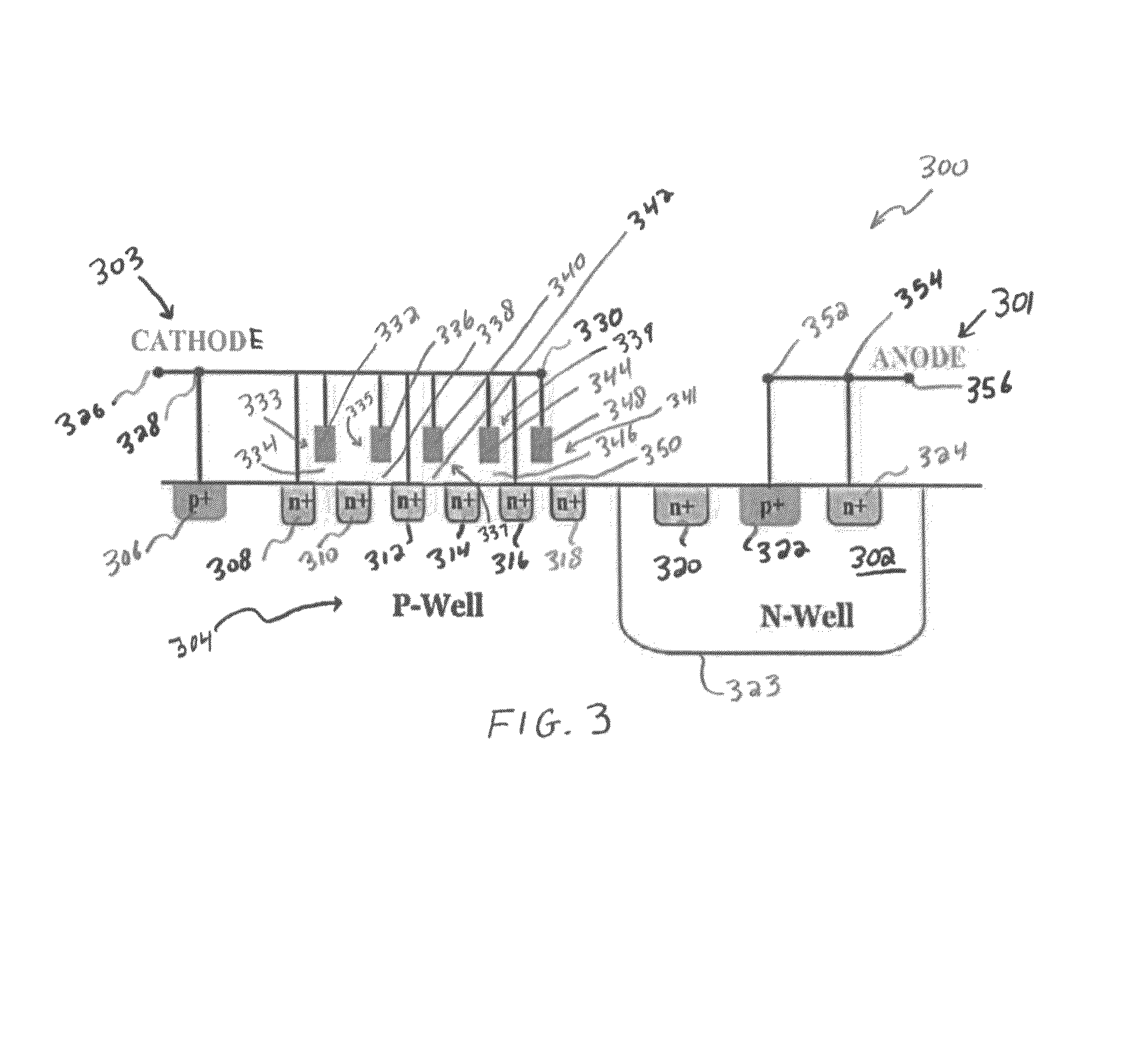

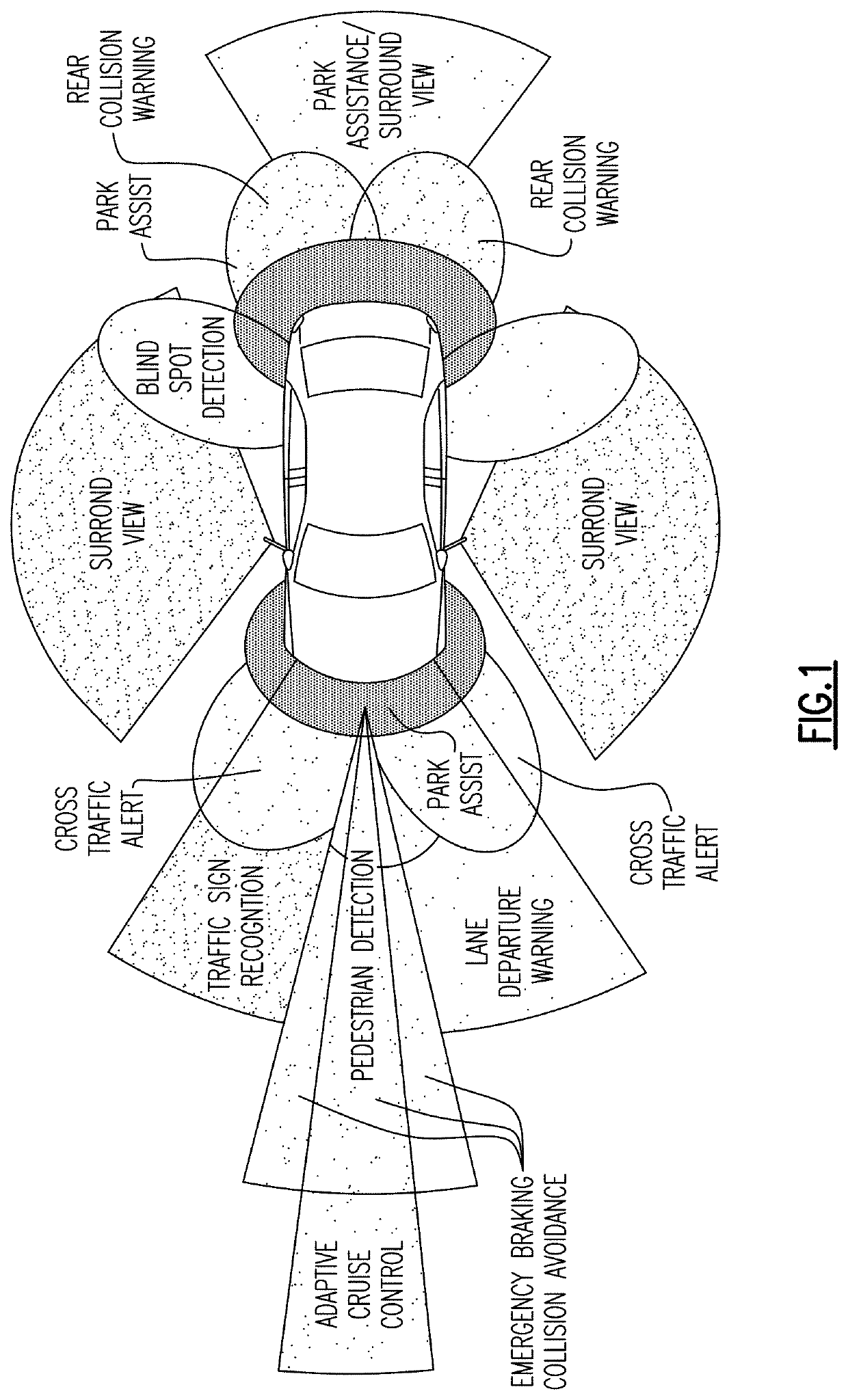

Microwave amplifiers tolerant to electrical overstress

ActiveUS20200350875A1Relieve stressTransistorAmplifier modifications to raise efficiencyElectrical connectionRadio frequency signal

Microwave amplifiers tolerant to electrical overstress are provided. In certain embodiments, a monolithic microwave integrated circuit (MMIC) includes a signal pad that receives a radio frequency (RF) signal, a ground pad, a balun including a primary section that receives the RF signal and a secondary section that outputs a differential RF signal, an amplifier that amplifies the differential RF signal, and a plurality of decoupling elements, some of them electrically connected between the primary section and the ground pad, others electrically connected in the secondary section to a plurality of the amplifier's nodes, and operable to protect the amplifier from electrical overstress. Such electrical overstress events can include electrostatic discharge (ESD) events, such as field-induced charged-device model (FICDM) events, as well as other types of overstress conditions.

Owner:ANALOG DEVICES INT UNLTD

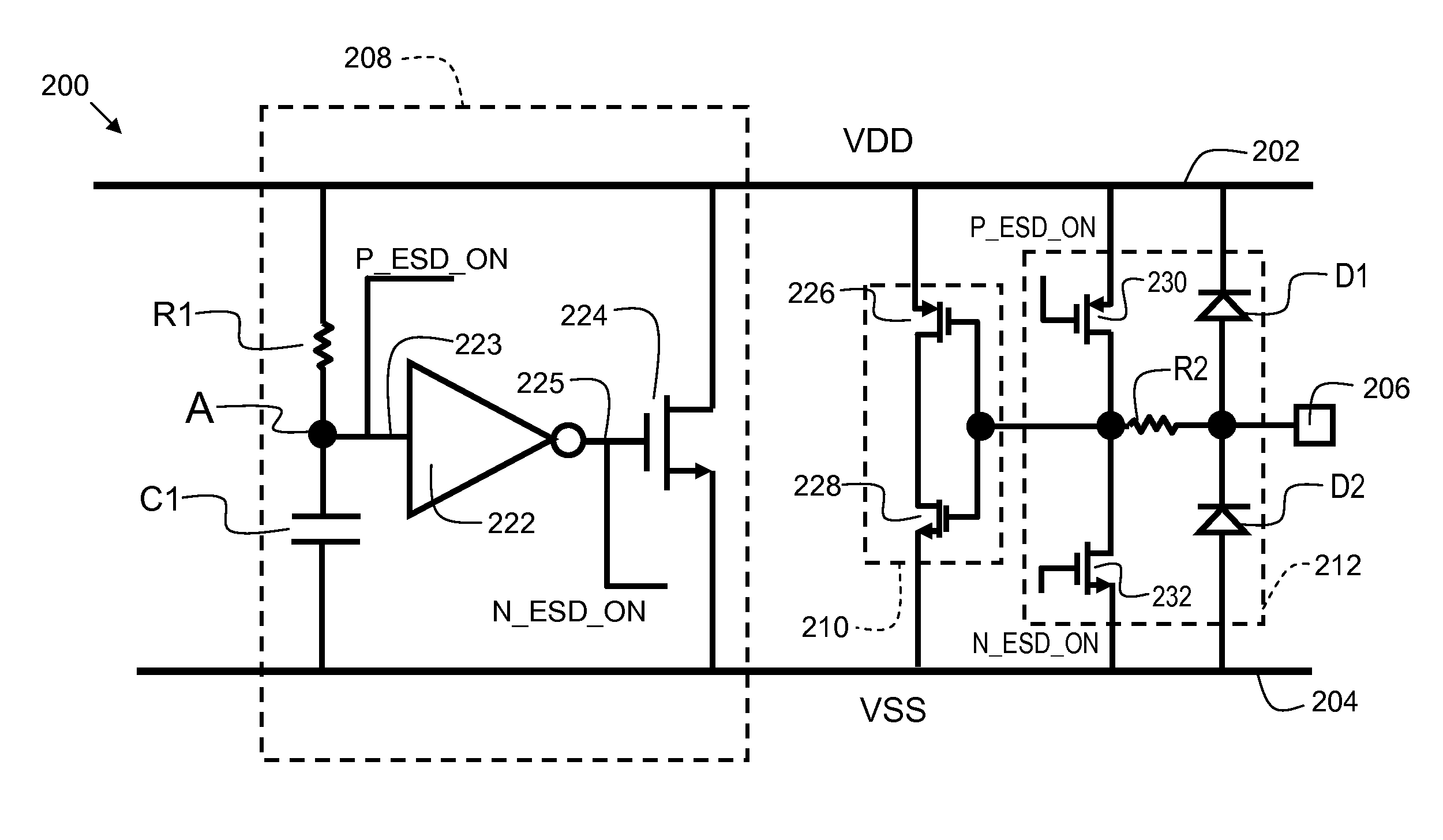

Enhanced charge device model clamp

InactiveUS9030791B2Emergency protective arrangement detailsOvervoltage protection resistorsPower flowEngineering

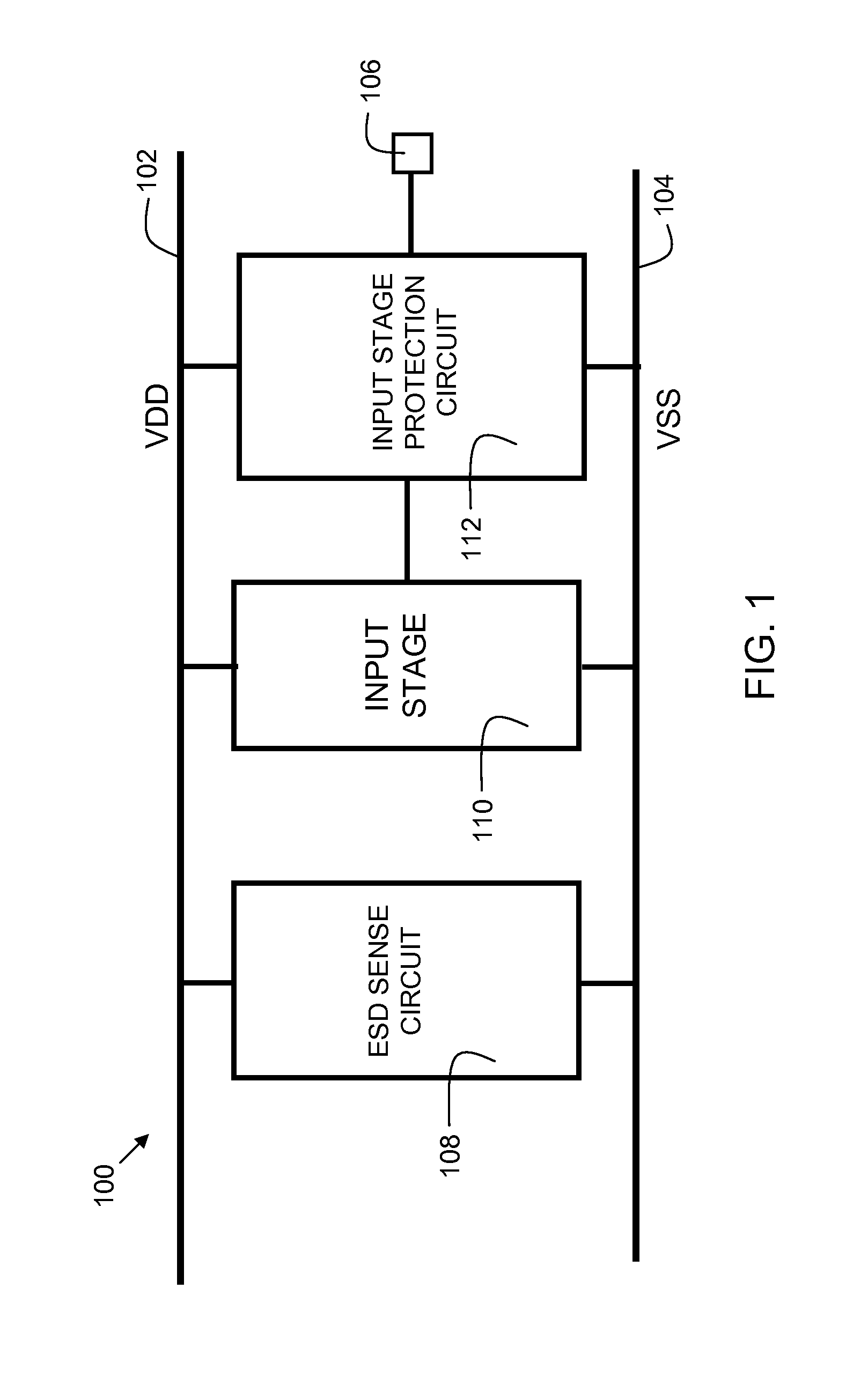

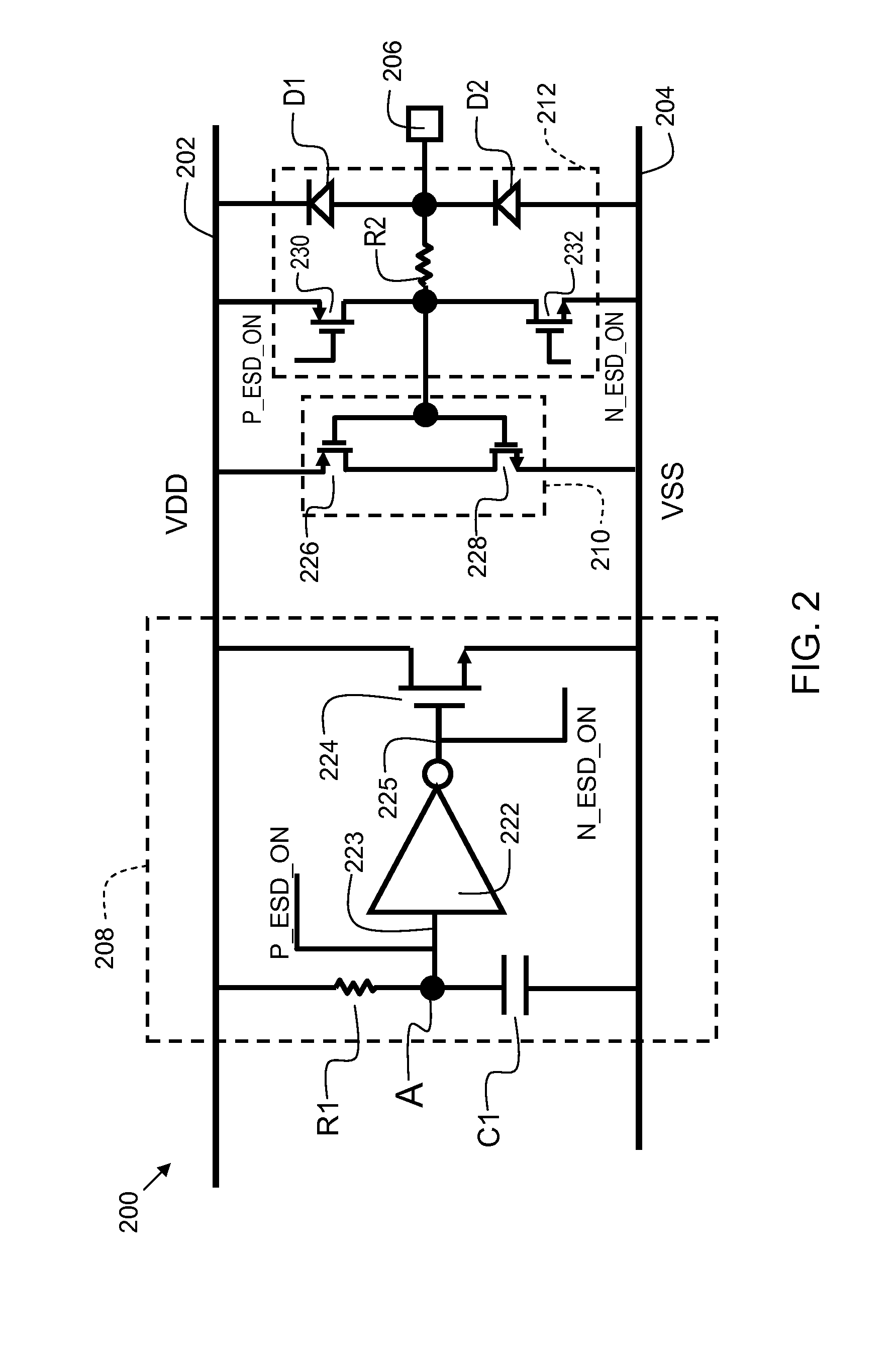

A circuit for electrostatic discharge (ESD) protection is disclosed. The circuit includes multiple transistors that are selectively turned on during an ESD event. An ESD sense circuit detects an ESD event and asserts signals to activate an ESD protection circuit which closes multiple protection transistors to dissipate current during the ESD event. During normal operation of the circuit, the signals are de-asserted, disabling the ESD protection circuit.

Owner:GLOBALFOUNDRIES INC

Electrostatic discharge structure and chip with the same

InactiveCN104241253AImprove robustnessLow costSemiconductor/solid-state device detailsSolid-state devicesResistorOperating voltage

An ESD (Electrostatic discharge) structure for enhancing robustness of CDM (Charge Device Model) at least includes an input stage. The input stage includes an input pad, a first ESD clamp circuit, a second ESD clamp circuit, a resistor, and a transistor. The input pad is configured to receive an input signal. The first ESD clamp circuit is coupled between the input pad and a work voltage. The second ESD clamp circuit is coupled between the input pad and a ground voltage. The first clamp circuit and the second clamp circuit are capable of bypassing an electrostatic current. The transistor has a first source / drain, a second source / drain, a gate coupled to the input pad, and a bulk coupled through the resistor to the work voltage or the ground voltage.

Owner:MEDIATEK INC

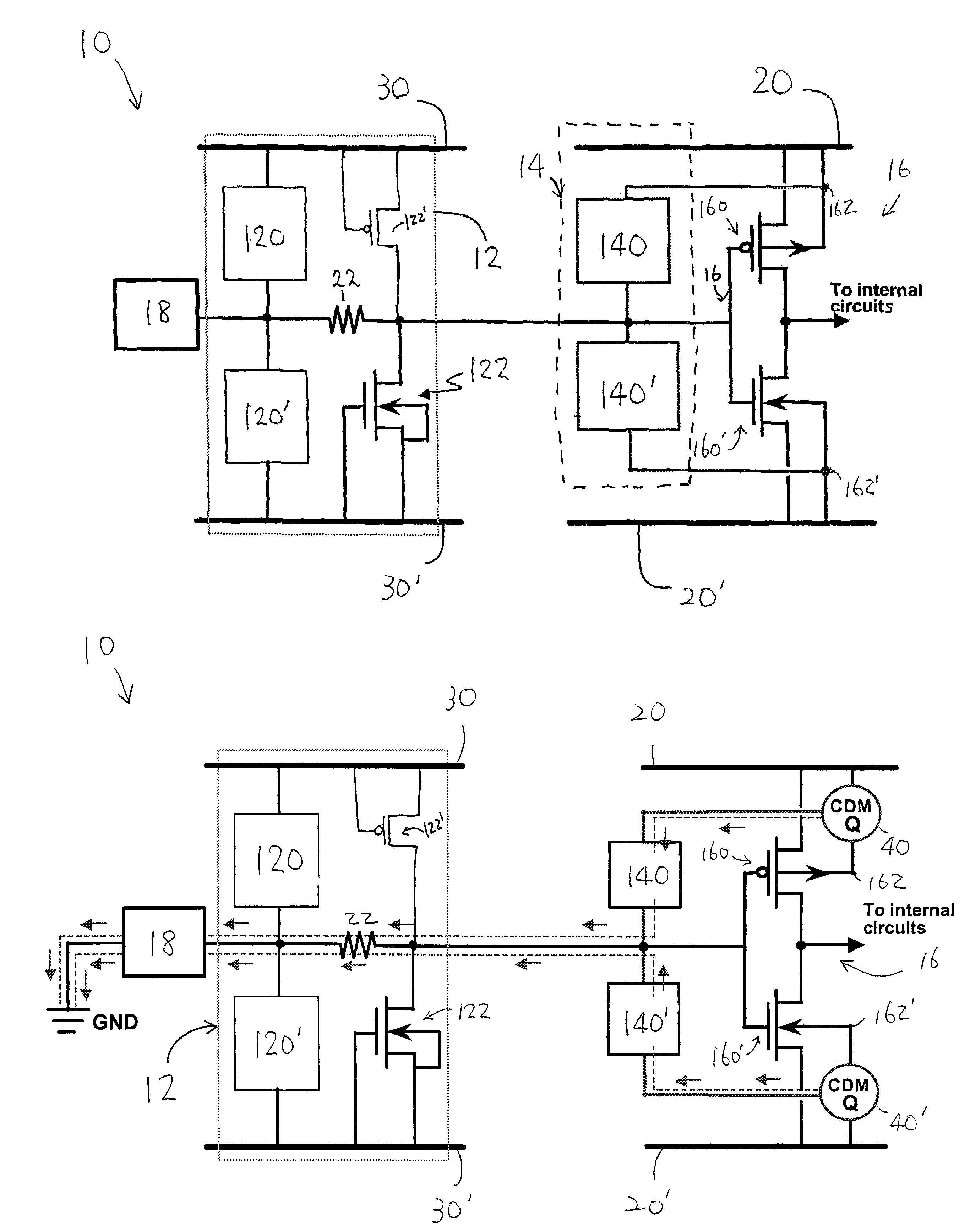

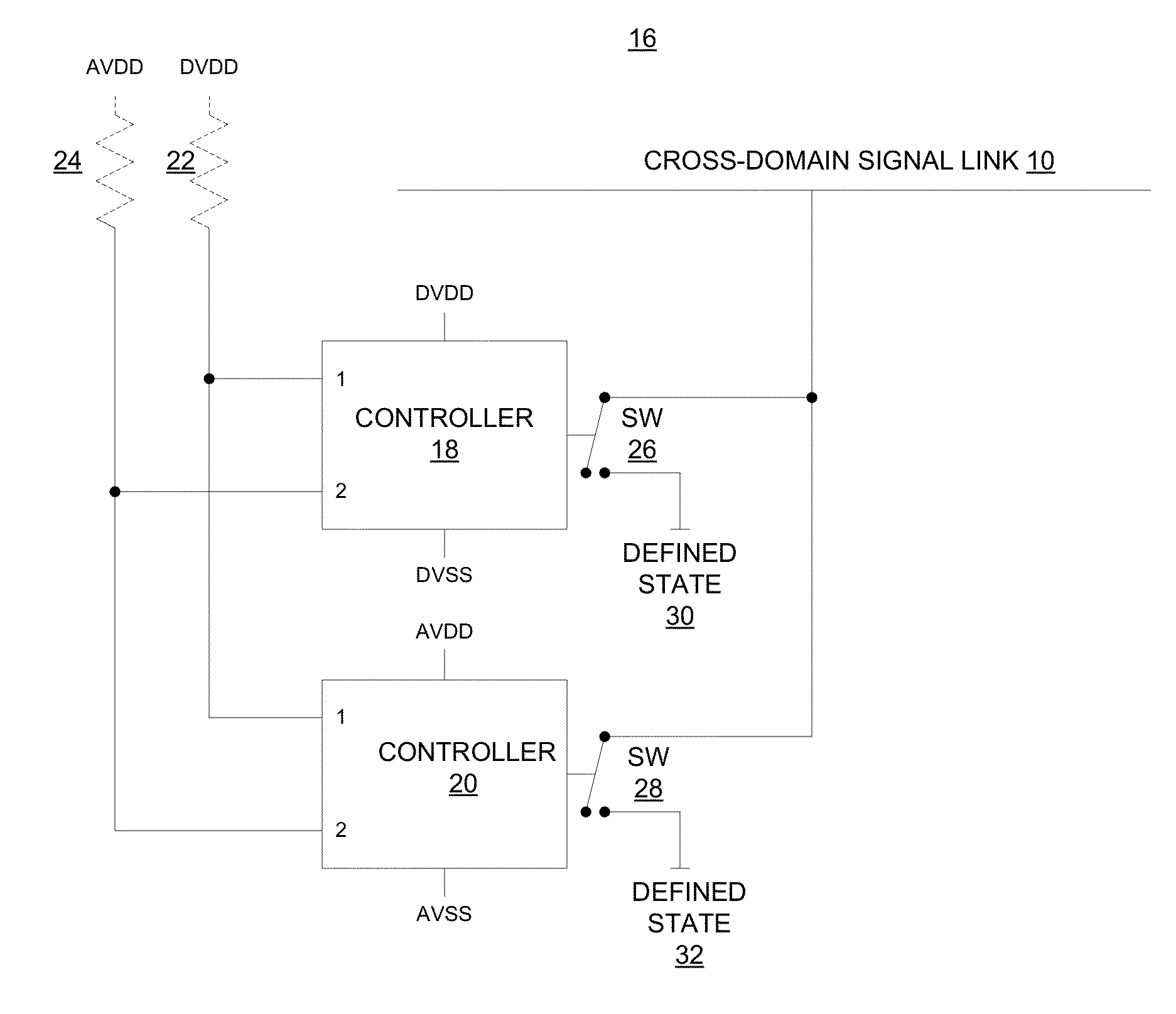

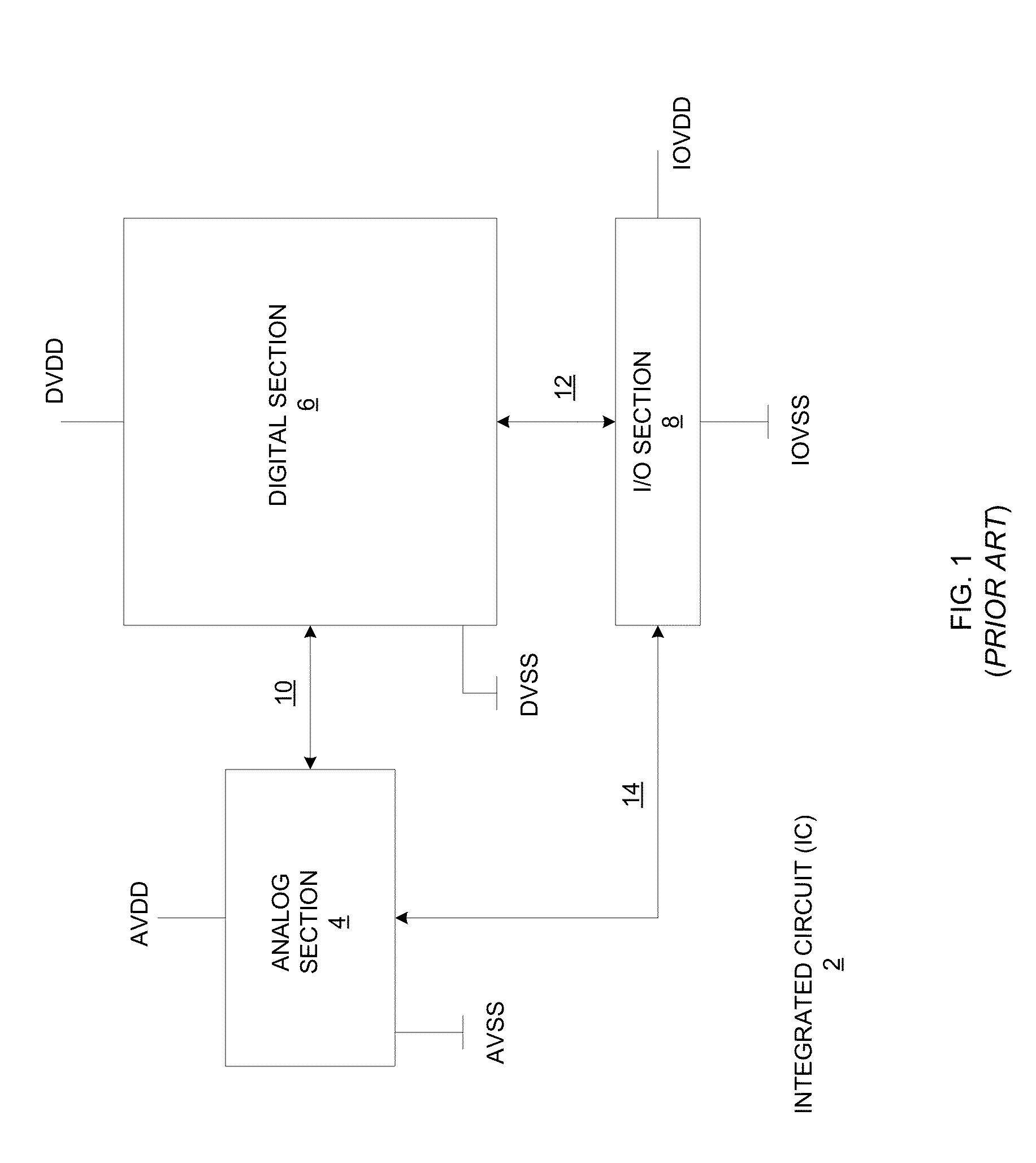

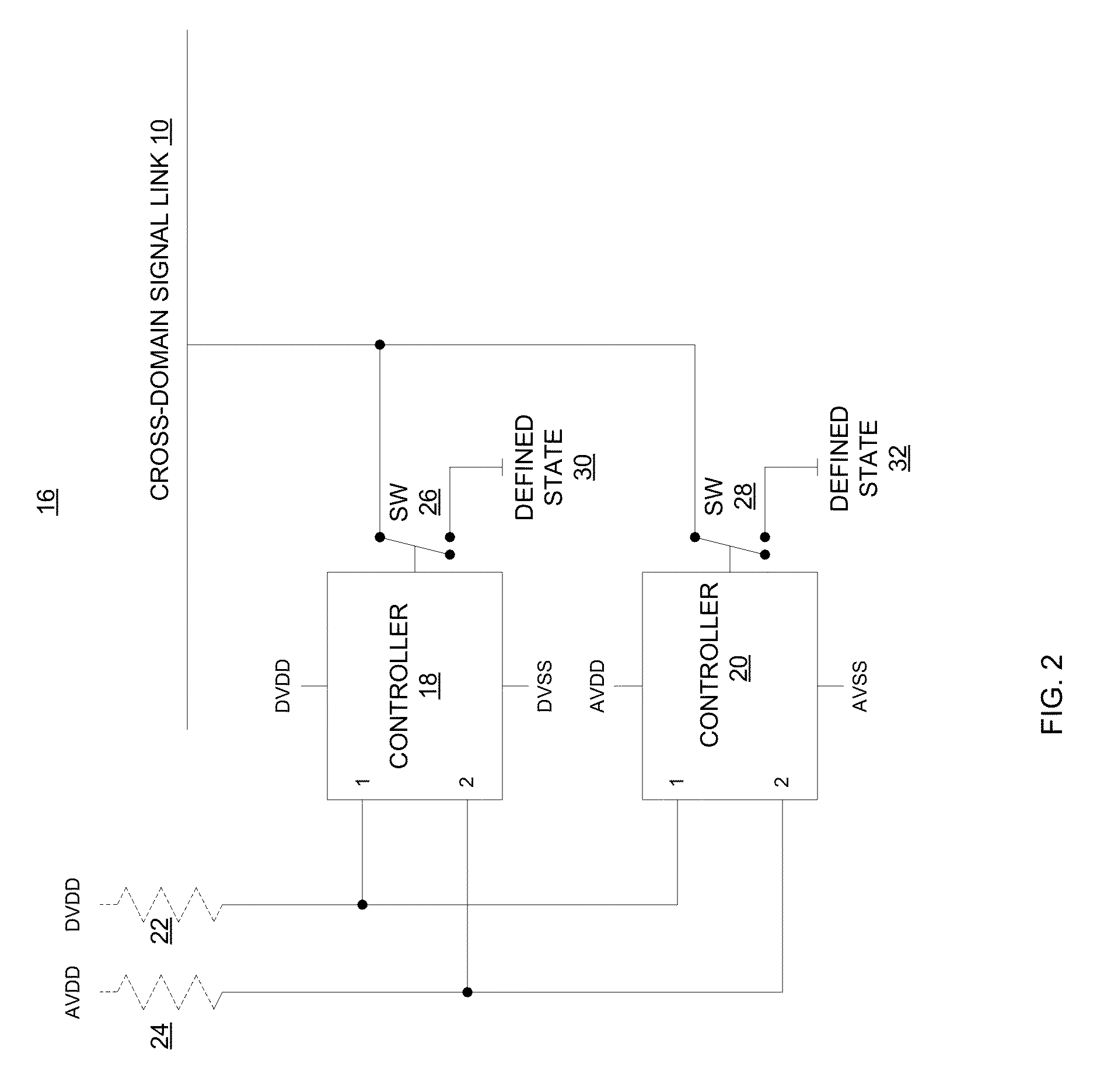

Apparatus for interfacing circuit domains

An interface circuit for controlling a cross-domain signal link between a first circuit domain and a second circuit domain in a circuit may include first and second controllers, each of the first and second controllers including a first input coupled to a first voltage source of the first circuit domain and a second input coupled to a second voltage source of the second circuit domain. The interface circuit may further include a first switch controlled by an output of the first controller, the first switch including a first end coupled to the cross-domain signal link and a second end coupled to a first defined voltage state, and a second switch controlled by an output of the second controller, the second switch including a first end coupled to the cross-domain signal link and a second end coupled to a second defined voltage state, in which during a power-up of the circuit, if one of the first and second voltage sources is unavailable, at least one of the first and second controllers generates a control signal to engage at least one of the first and second switches and pull the cross-domain signal link to one of the first and second defined voltage states, while providing cross-domain protection against field-induced charge device model (FICDM) stress conditions at small drivers and receiver inputs connected to the signal interface link.

Owner:ANALOG DEVICES INC

Circuit for discharging static electricity

ActiveUS7545616B2Reduce areaReduce capacitanceSolid-state devicesEmergency protective arrangement detailsLow voltageEngineering

The present invention relates to a semiconductor circuit, and more particularly, to a circuit for discharging static electricity, which is connected between an internal circuit and an input / output pad to provide a charge device model (CDM) discharging path. The circuit includes a plurality of input / output pads; a plurality of switching units corresponding one-to-one to the input / output pads and turned on in a low voltage state; resistors connected between the input / output pads and the switching units so as to correspond one-to-one to the input / output pads and the switching units; and a CDM discharge unit shared in serial by the plurality of the switching units and providing a ground path.

Owner:SK HYNIX INC

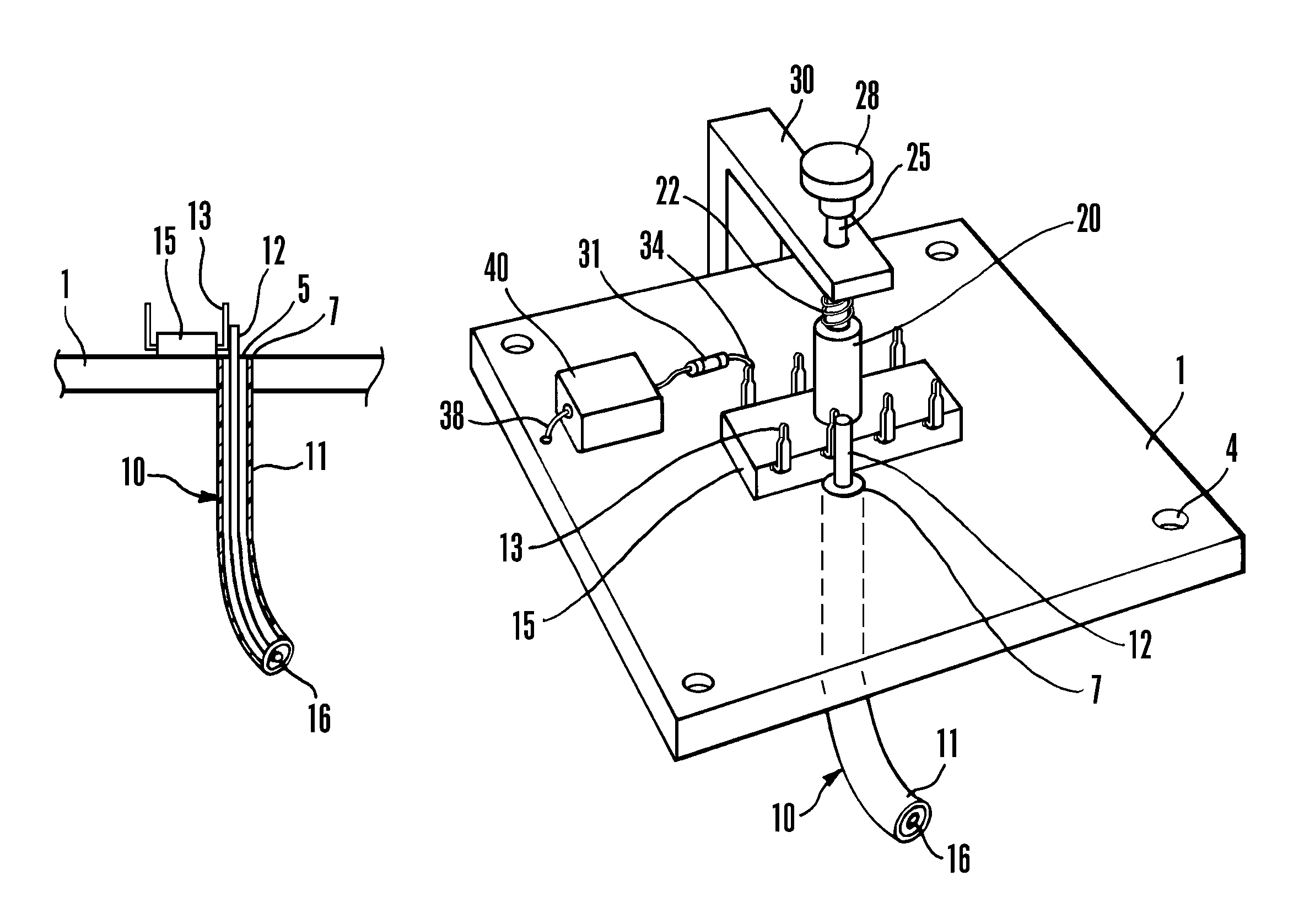

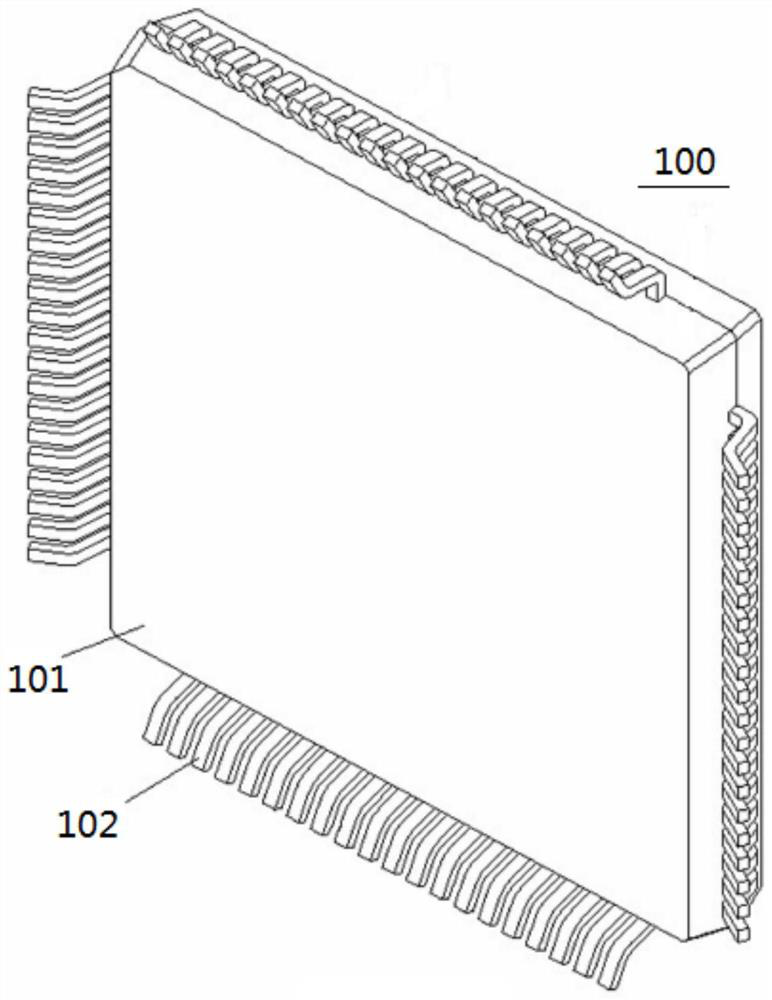

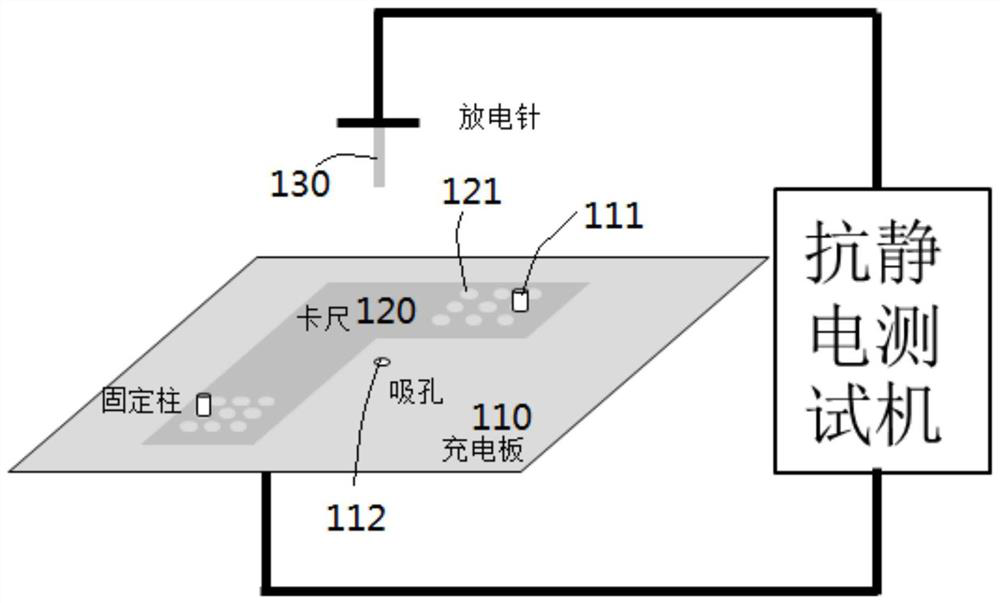

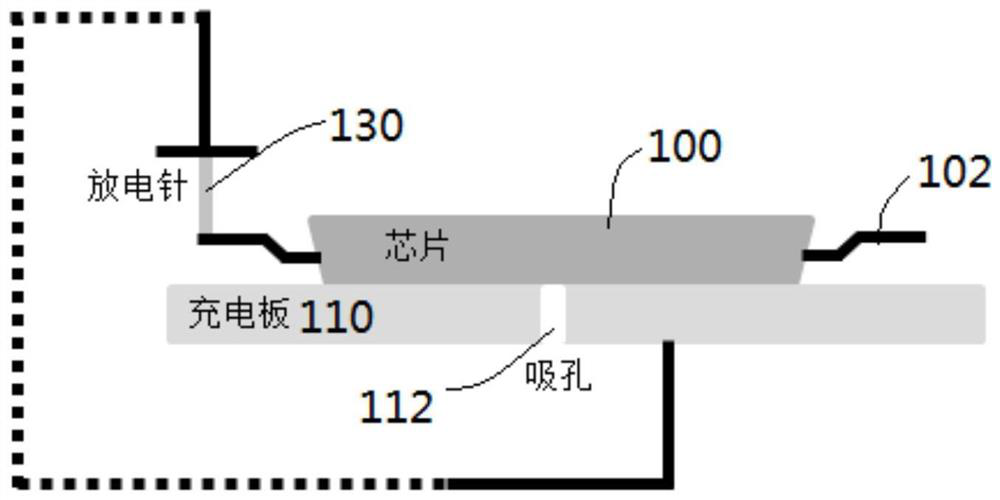

Antistatic test machine for charging device model and test board applied to antistatic test machine

ActiveCN112782548AIndividual semiconductor device testingIntegrated circuit manufacturingManufacturing technology

The invention relates to an antistatic test machine for a charging device model of an LQFP packaging chip, and relates to a semiconductor integrated circuit manufacturing technology, a plurality of LQFP packaging chip sockets are simultaneously arranged on a test board, and one LQFP packaging chip socket is arranged in a slot of each socket, so that the plurality of LQFP packaging chip sockets can be simultaneously carried on one test board; test time is saved in the antistatic test of the charging device model; and in addition, each LQFP packaging chip socket comprises a chip slot and a slot side wall which is formed by surrounding the slot, so that when the LQFP packaging chip is arranged in the chip slot, the pins of the chip extend out of the body of the chip and are borne on the first surface of the side wall of the slot to support the pins of the chip, and the pins of the chip are supported in the testing process, namely, the pins of the LQFP packaging chip are not suspended any more, so that accurate and lossless antistatic performance testing and subsequent functionality and parameter testing are ensured in the testing process, and the accuracy and the test efficiency of the chip-level test are improved.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

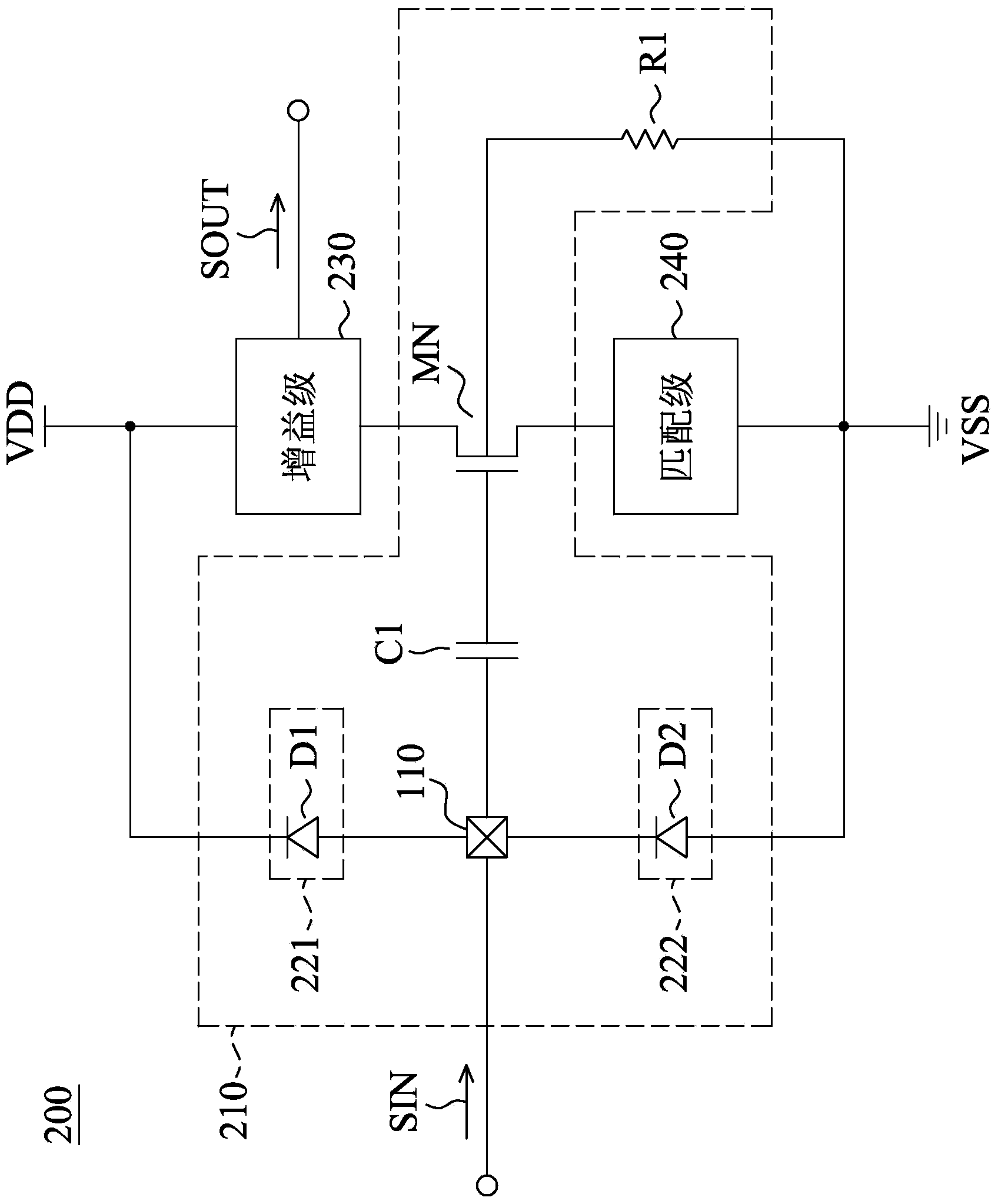

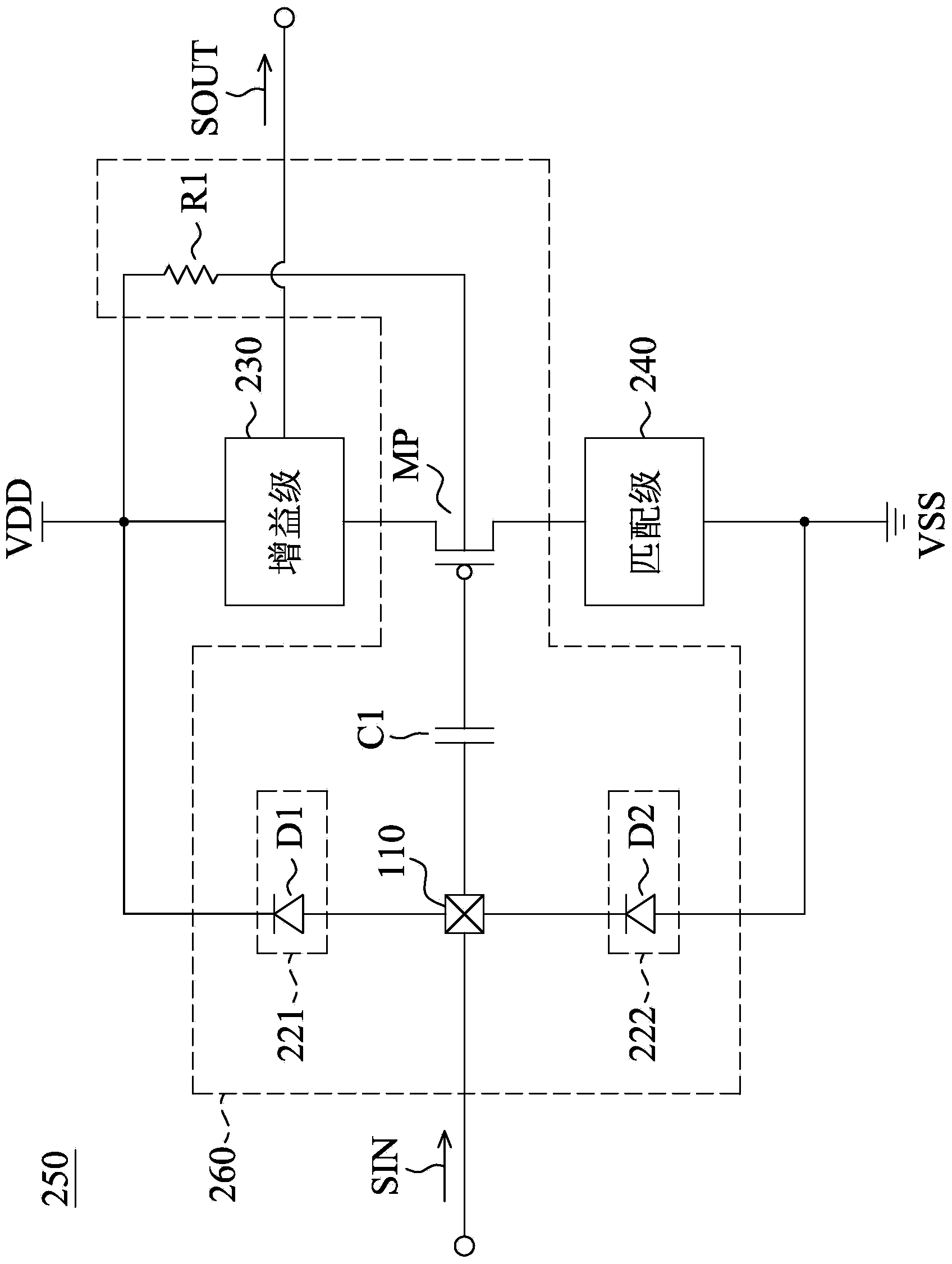

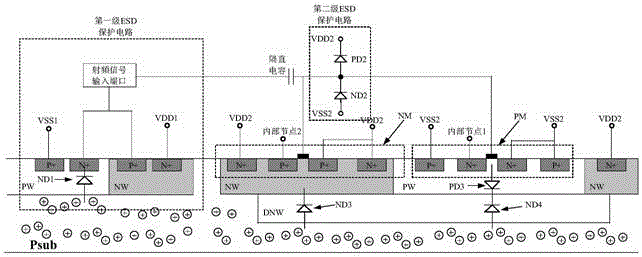

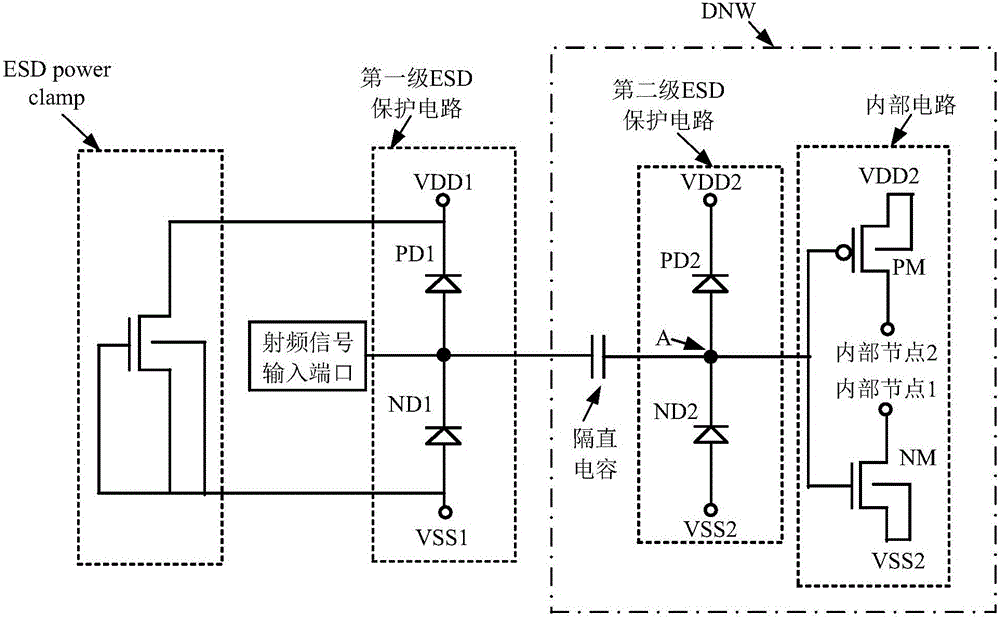

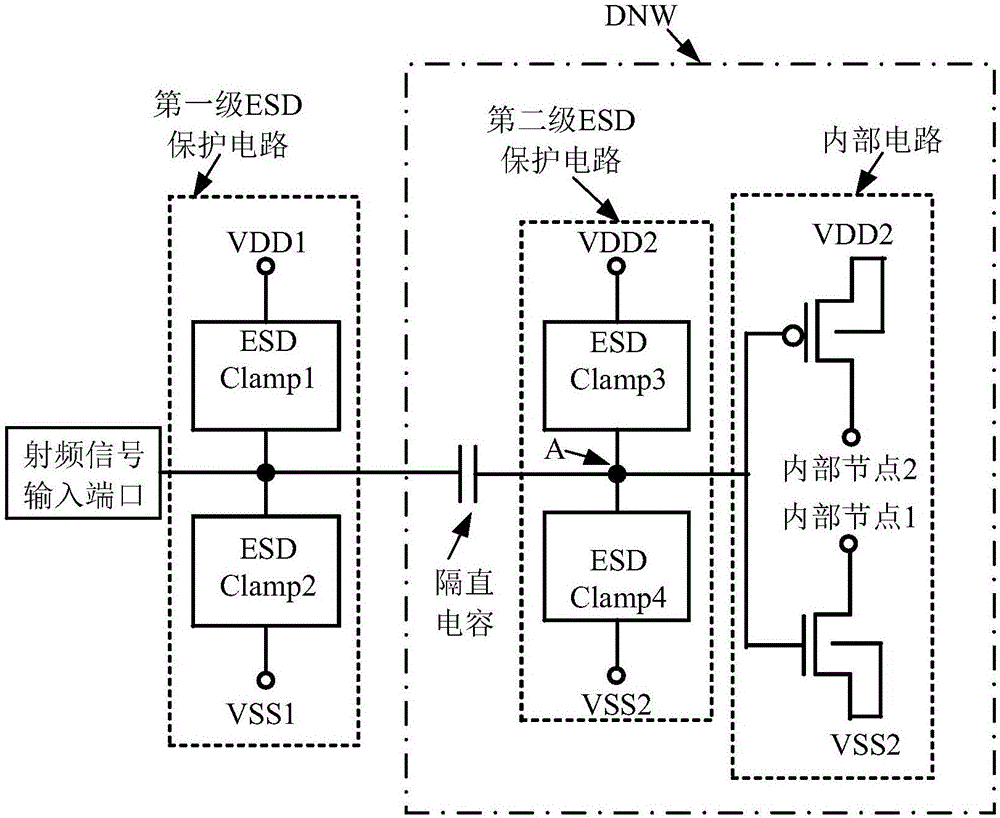

CDM protection circuit structure

InactiveCN106783806AImprove protectionSemiconductor/solid-state device detailsSolid-state devicesCharged-device modelIntegrated circuit

The present invention discloses a CDM (Charged Device Model) protection circuit structure, and is suitable for the design of an ESD (Electro-Static Discharge) protection circuit. The CDM protection circuit structure is characterized in that: the CDM protection circuit structure can improve the CDM protection capacity of a radiofrequency signal input port in a radio frequency circuit, and mainly employs the ESD protection circuit performing dual-way low triggering for a power supply in a first-level ESD protection circuit and employs an ESD protection circuit performing dual-way low triggering for the ground at the same time. The CDM protection circuit structure employs the ESD protection circuit performing dual-way low triggering for the power supply and employs the ESD protection circuit performing dual-way low triggering at the same time in a second-level ESD protection circuit, and in the CDM event, when the radio-frequency signal input port is earthed, the circuit can effectively release the electrostatic charge in the substrate and play the CDM protection effect.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

In-tool ESD events monitoring method and apparatus

The invention discloses an in-tool ESD events monitoring method and apparatus. In one embodiment of the invention, an apparatus for electrostatic discharges (ESD) events monitoring incorporating a charged device model event simulator (CDMES) unit comprises: at least one antenna positioned in a process area; an ESD detector coupled to said at least one antenna; said ESD detector wirelessly coupledto said CDMES unit; and said ESD detector calibrated for different discharge energies generated by said CDMES unit.

Owner:ILLINOIS TOOL WORKS INC

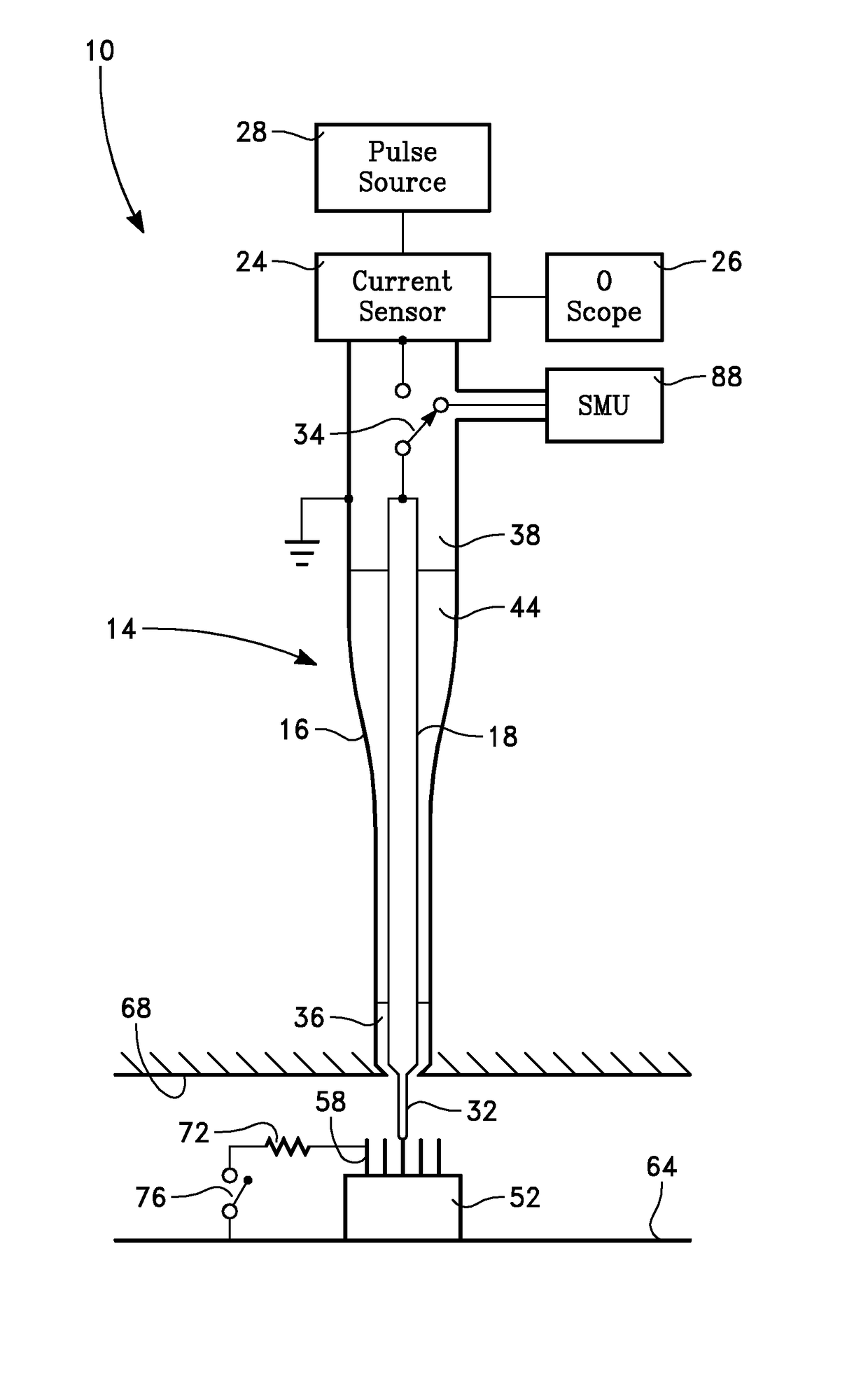

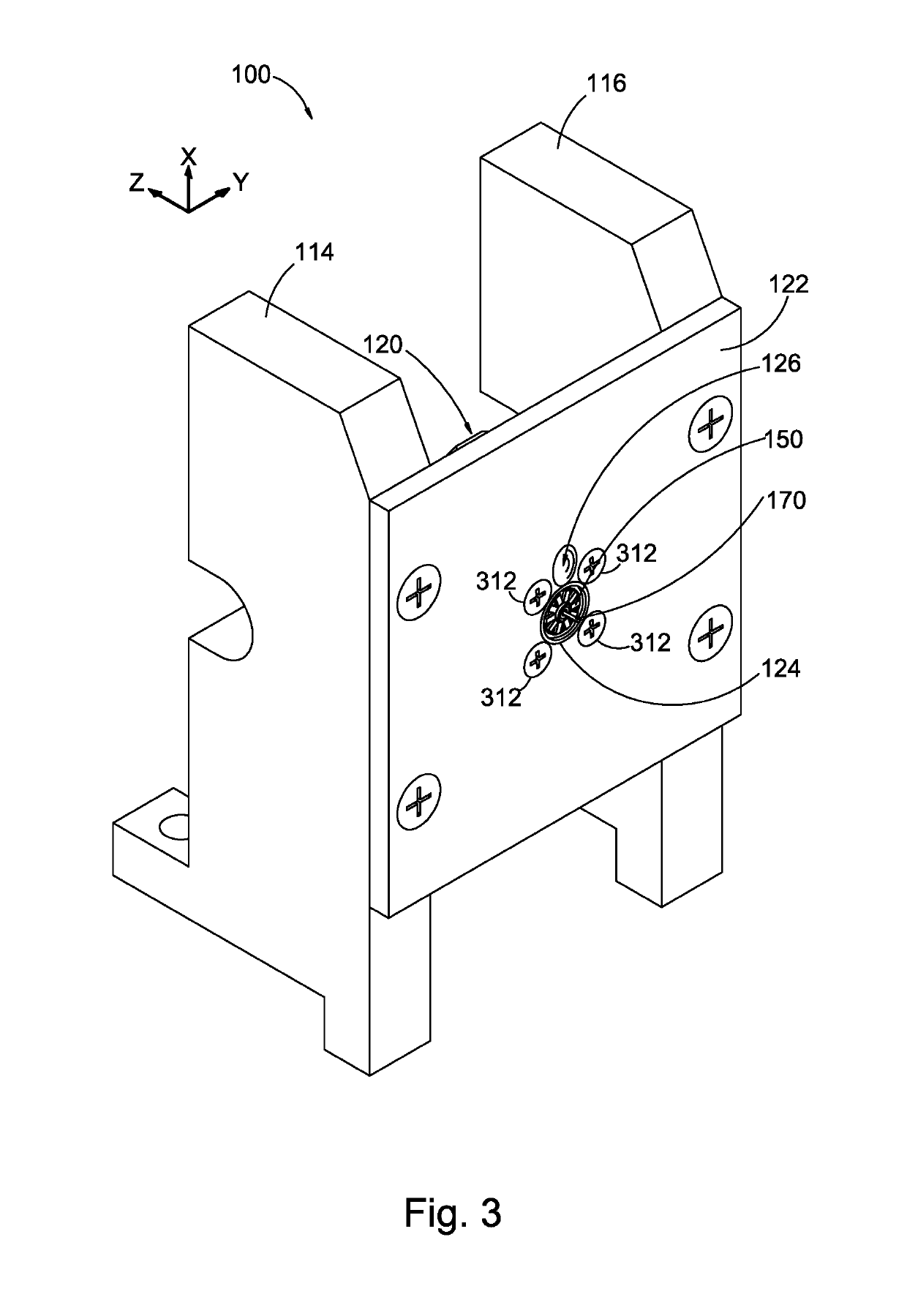

Current sensor having microwave chip resistors in parallel radial arrangement

ActiveUS10267838B1Improve the immunityMaterial removalTesting dielectric strengthElectrical measurement instrument detailsElectrical conductorCurrent sensor

A current sensor for use with a charged device model (CDM) tester includes an outer conductor and a cylindrical inner conductor. The inner conductor is positioned within a central cylindrical bore of the outer conductor to provide a characteristic transmission line impedance of approximately 50 ohms. A test probe conductor extends from the distal end of the inner conductor and is electrically connected to the inner conductor. An array of self-supporting ceramic chip resistors is radially positioned between the distal ends of the inner conductor and the outer conductor to provide a uniformly distributed resistance between the inner conductor and the outer conductor. When the test probe conductor is applied to a pin of a charged device under test (DUT), a discharge current passes through the resistors and produces a voltage on the inner conductor that is provided as a signal voltage proportional to the discharge current.

Owner:BARTH JON E +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com