Electrostatic discharge protection circuit for RF identification chip

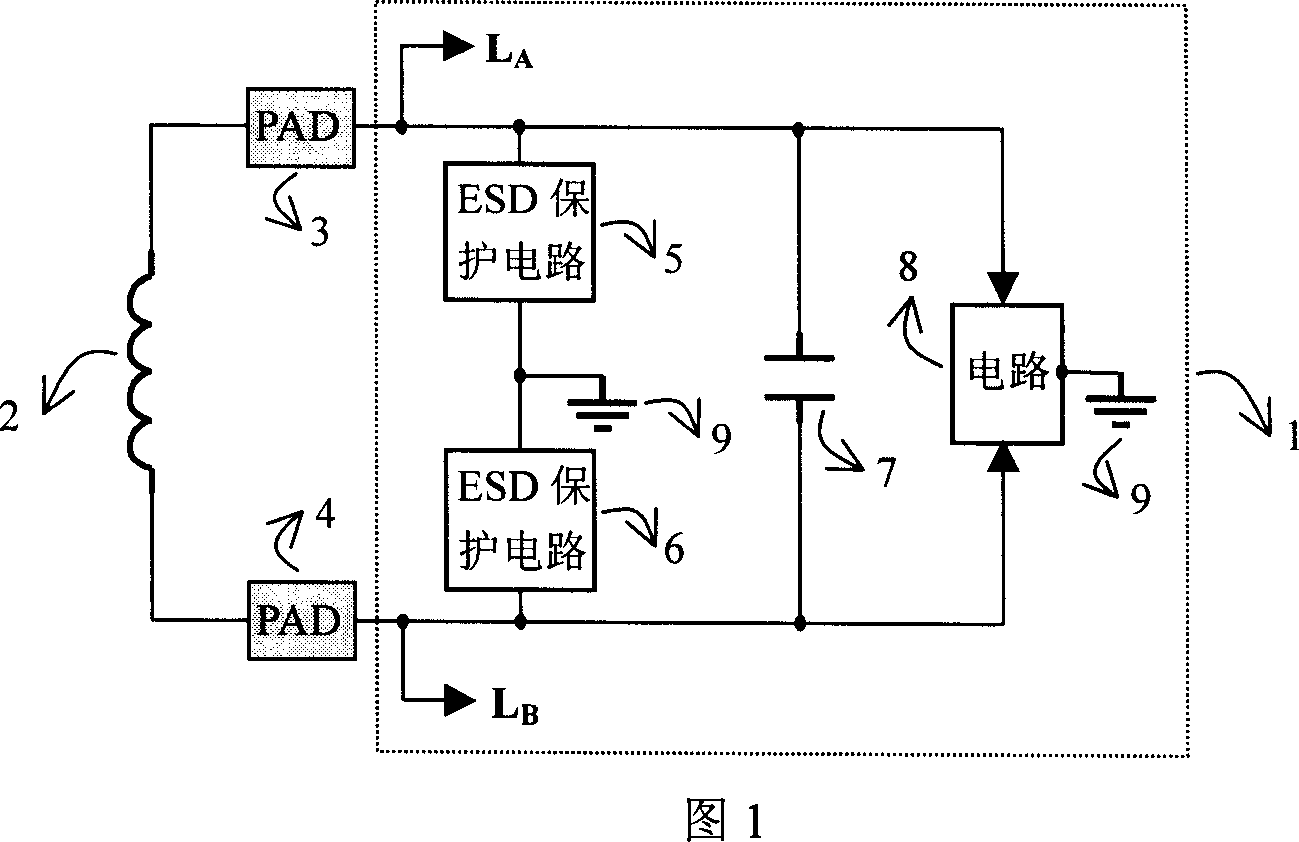

A technology of electrostatic discharge protection and radio frequency identification, applied in circuits, electrical components, electric solid devices, etc., can solve problems such as performance degradation, failure to work, passivation layer cracks, etc., and achieve strong ESD resistance and fast turn-on time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] 5.1 Circuit structure

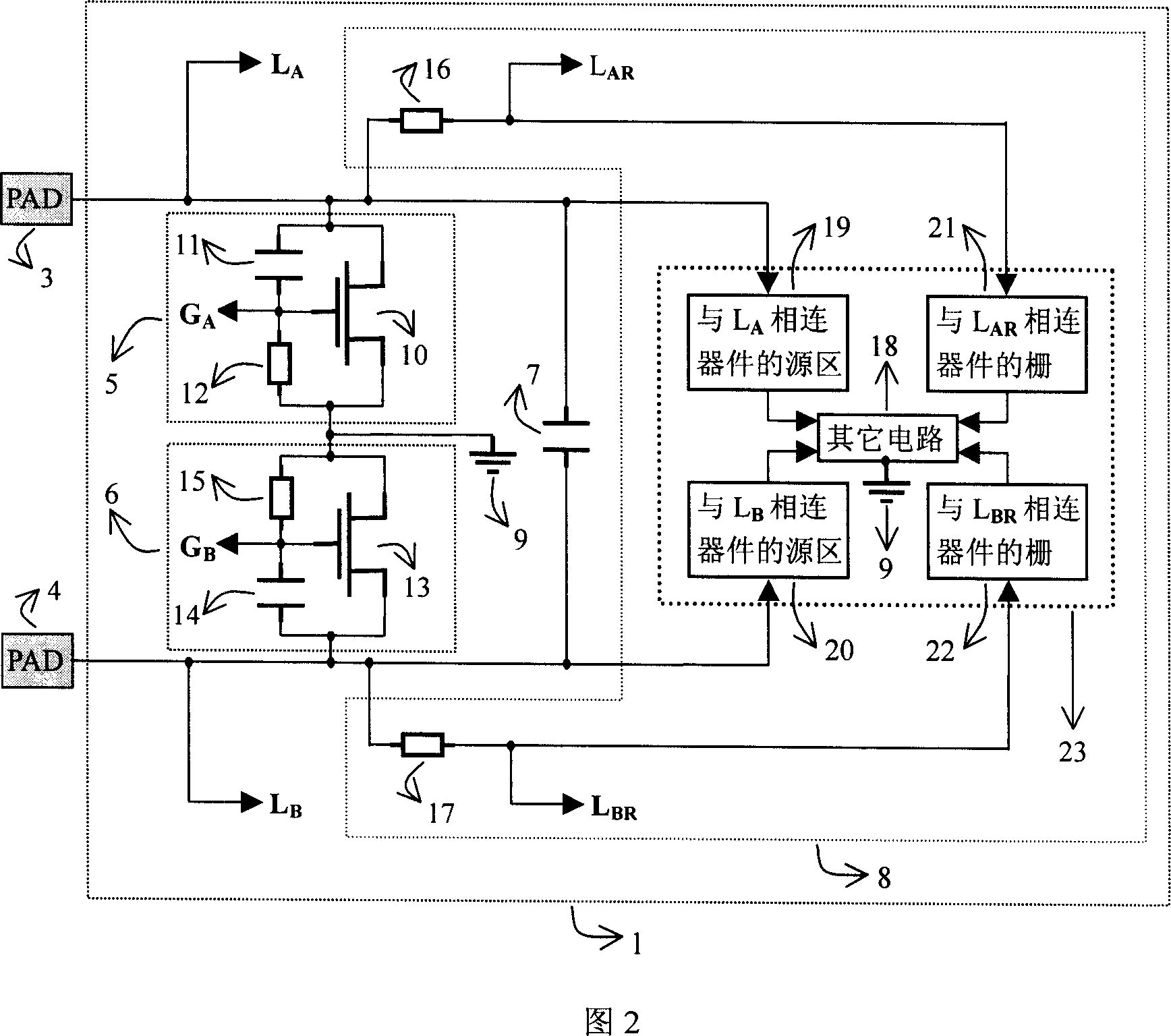

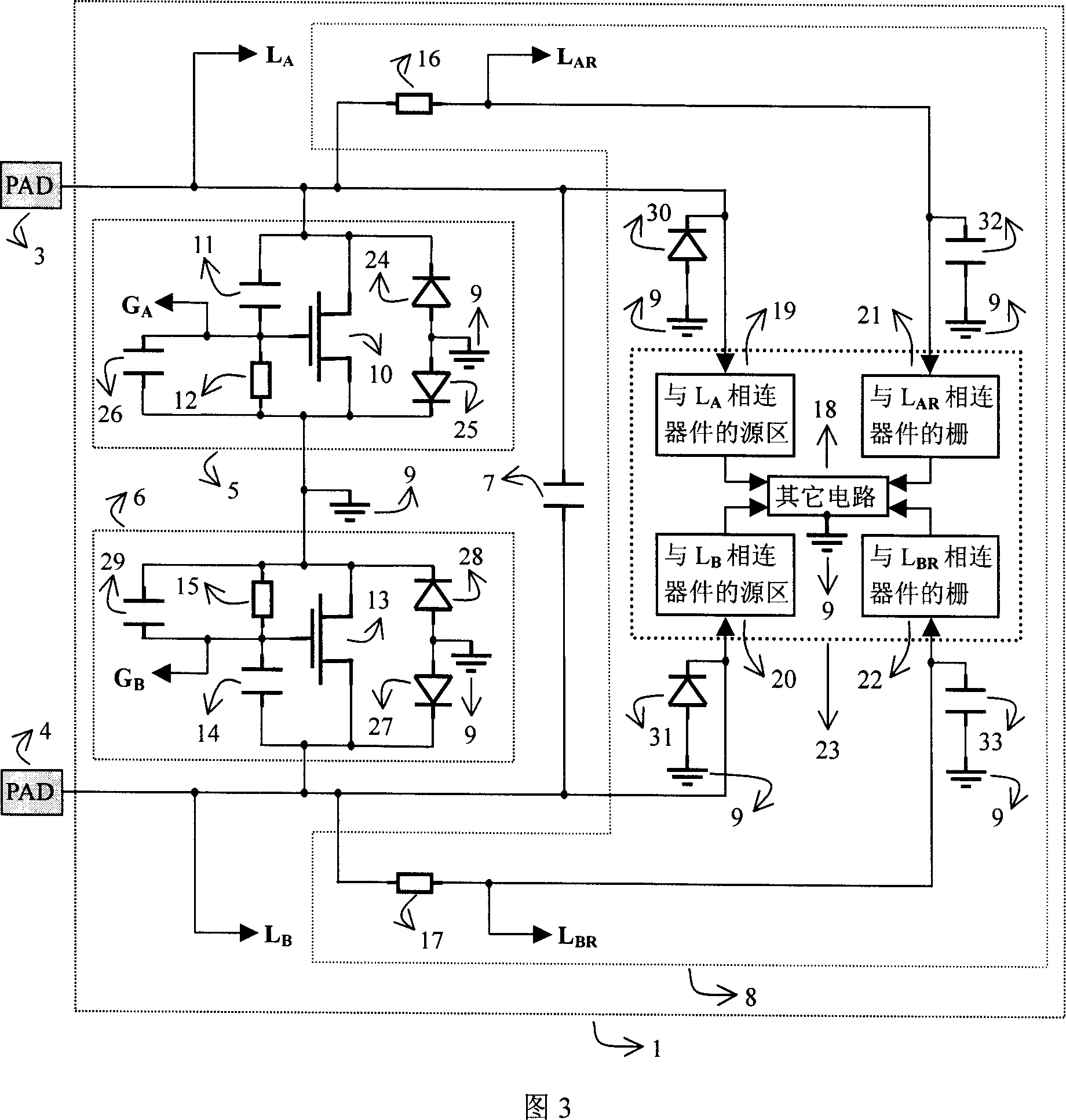

[0019] The ESD protection circuit structure is shown in Figure 2.

[0020] Among them, the discharge capacity, turn-on time and process insensitivity can be achieved by designing ESD protection circuits 5 and 6. Under the discharge phenomenon that the ESD protection circuit cannot be turned on, the ESD protection circuit and related circuits have certain resistance capabilities by selecting appropriate devices (Including 7, 10-17, 19-22 in the figure) to achieve; ESD protection circuit can not affect the normal operation of the chip to achieve through the overall design of circuit parameters.

[0021] 5.2 Parameter design

[0022] Since L A End and L B End has symmetry, so we only use L A Take the circuit parameter design of the terminal as an example.

[0023] A). Discharge capacity design

[0024] This can be achieved by designing the aspect ratio of the NMOS tube 10 in the ESD protection circuit 5, and the specific layout requires comprehensive co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com