Cdm ESD protection for integrated circuits

A technology of circuit and clamping circuit, applied in the field of electrostatic discharge protection circuit system, can solve problems such as threats

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

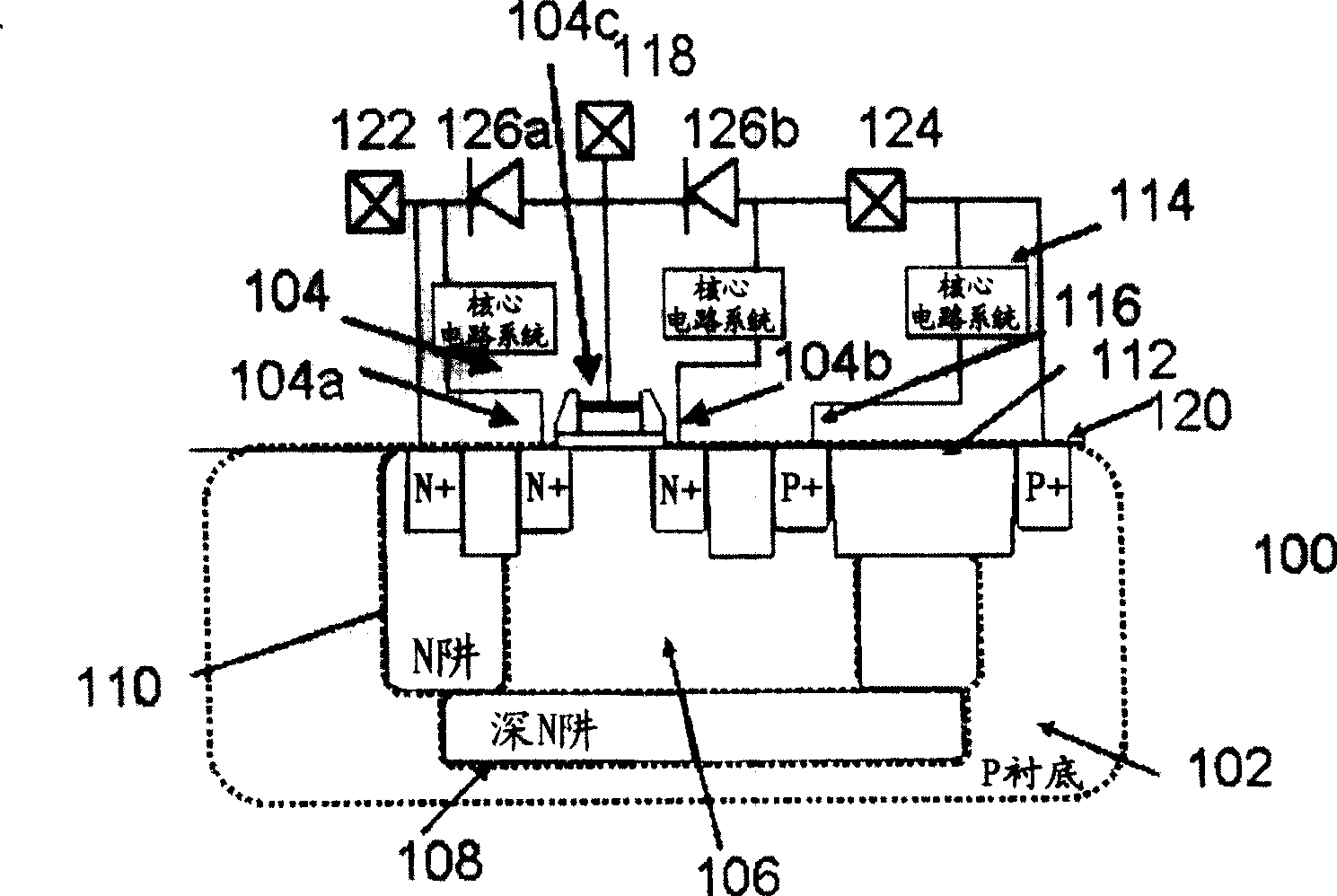

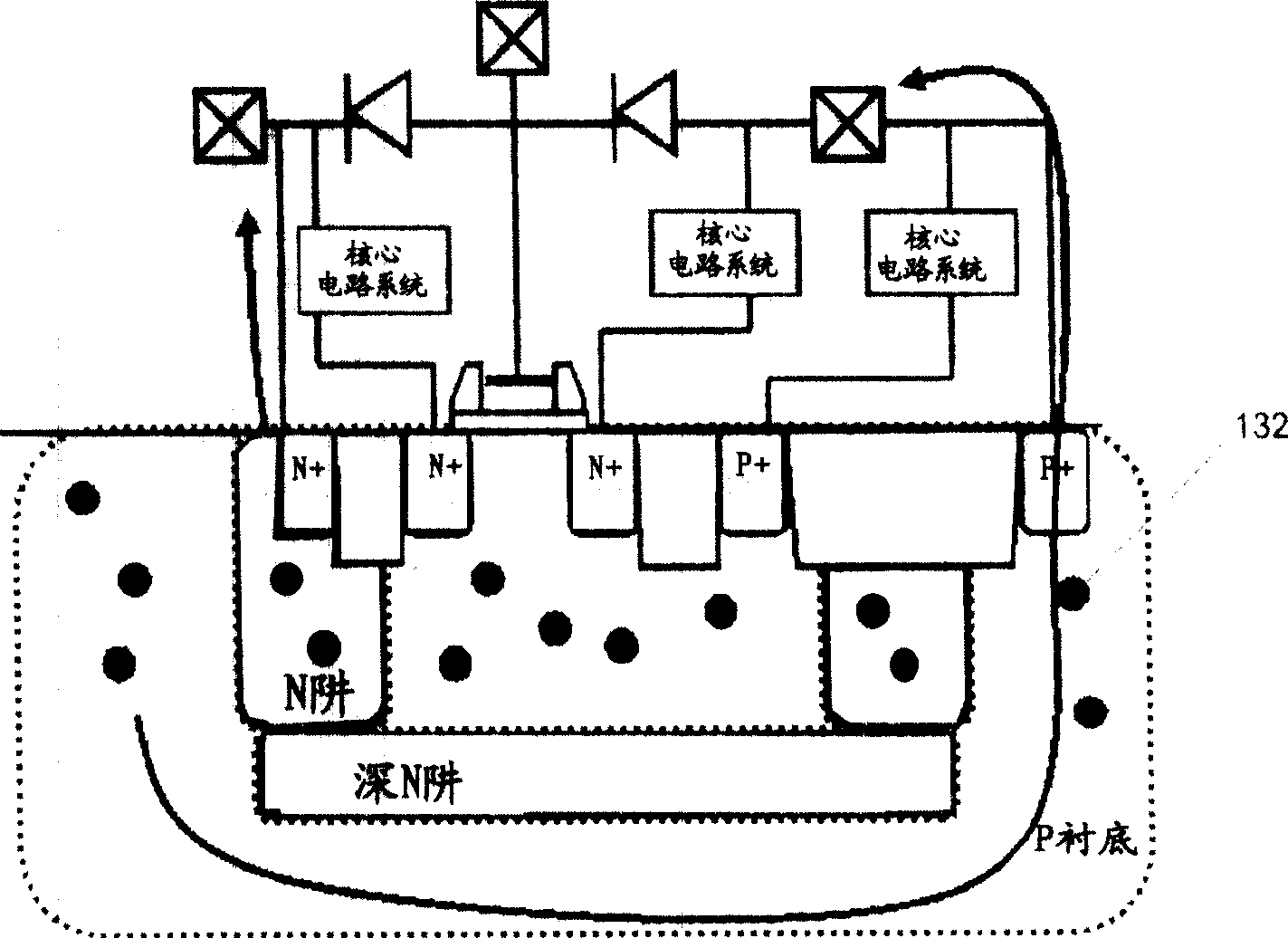

[0023] The present invention relates to a technique to increase the CDM performance of an IC by connecting an additional ESD clamp circuit to the isolation well (or junction). Figure 2A shows a cross-sectional view of an integrated circuit IC 200 for CDM ESD protection according to one embodiment of the present invention. IC 200 shows a cross-sectional view of transistor 104 formed in isolated P-well region 106 , deep N-well 108 and N-well 110 form a ring structure around the isolation region to isolate / separate P-well region 106 from P-substrate 104 . Additionally, an additional ESD clamp circuit 202 is coupled to the isolated P-well 106, as shown in FIG. 2A. Specifically, ESD clamp circuit 202 is placed between isolated P-well 106 and the reference node. Selection of the reference node depends on normal operating requirements such as noise, cross-coupling, and other ESD factors. Preferably for ESD and in this example of FIG. 2A , the terminal to the isolated well 106 is co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com