Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

64results about How to "Improve ESD protection capability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

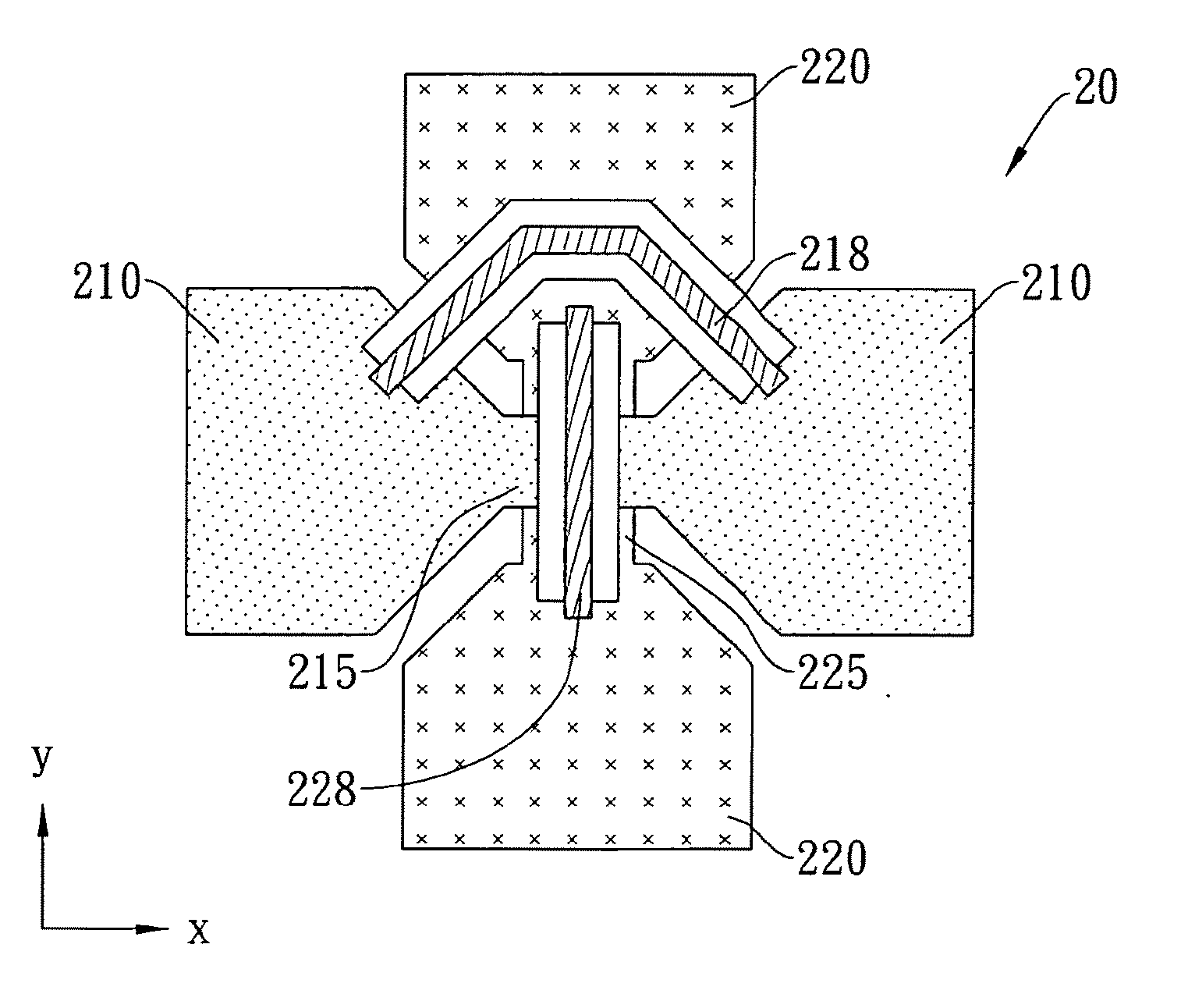

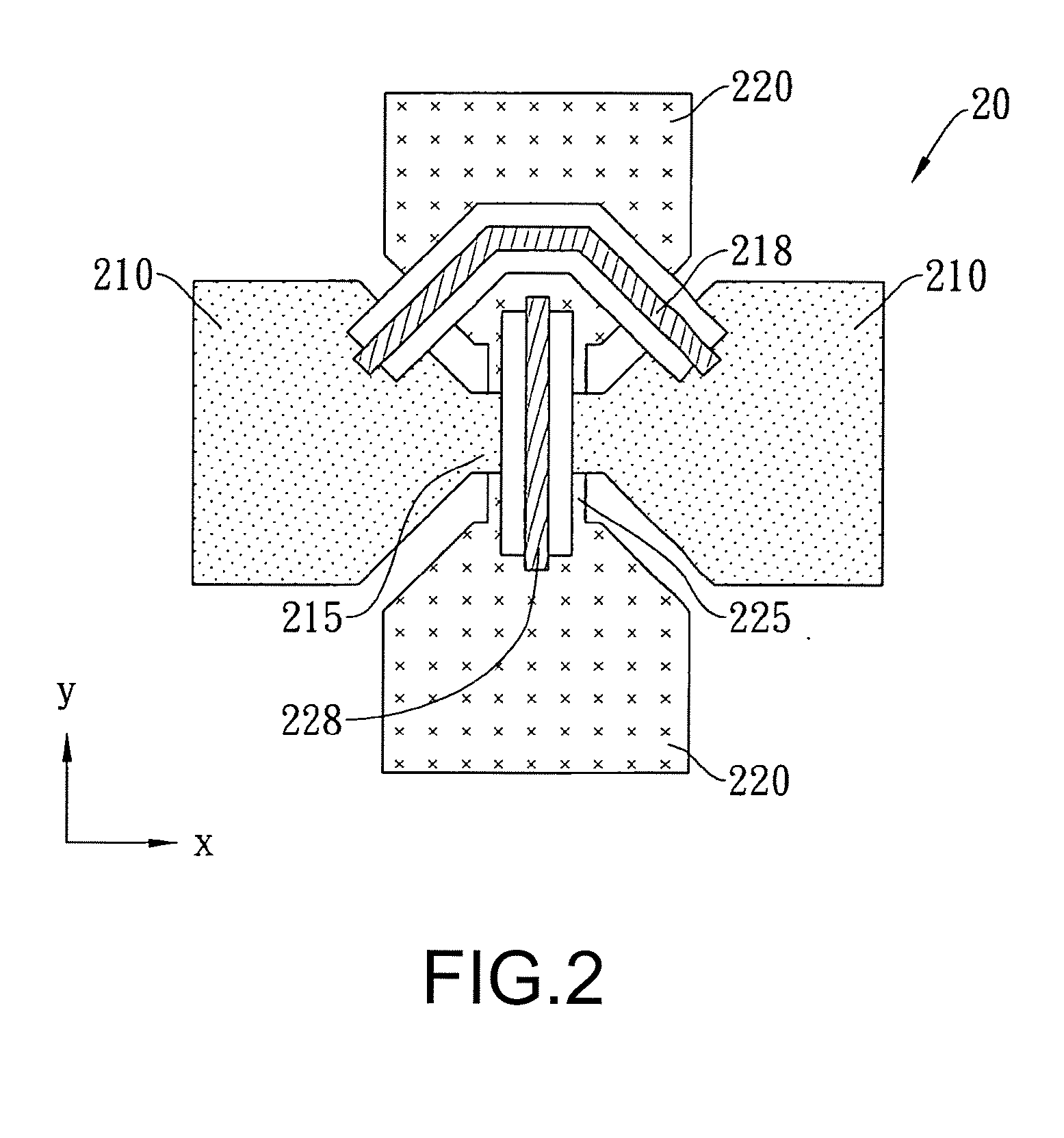

Touch panel

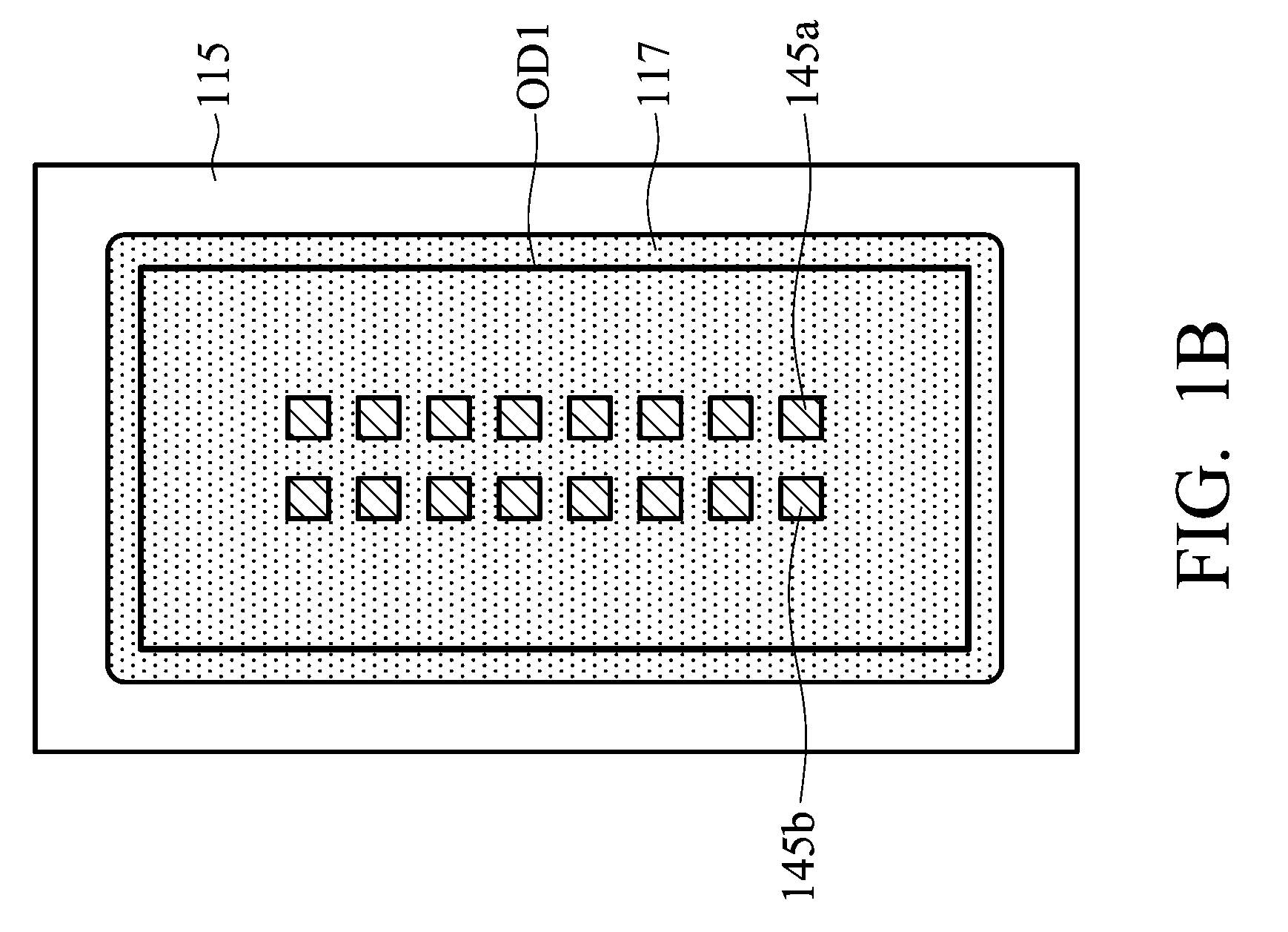

InactiveUS20150060125A1Enhance electrostatic discharge protection abilityImprove ESD protection capabilityHigh voltage circuit adaptationsOvervoltage circuit protectionInsulation layerEngineering

A touch panel includes a substrate, a plurality of first axis electrodes, a plurality of second axis electrodes and a first insulation layer. Each first axis electrode includes a plurality of first sub-electrodes and a plurality of first connection parts disposed between two adjacent first sub-electrodes. The first sub-electrodes and the first connection parts are monolithically formed. Each second axis electrode includes a plurality of second sub-electrodes and a plurality of second connection parts disposed between two adjacent second sub-electrodes. The second sub-electrodes and the second connection parts are monolithically formed. The first sub-electrodes and the second sub-electrodes are disposed on an identical surface. The first insulation layer is disposed on and completely covers the first axis electrodes. The first insulation layer is partially disposed between the first connection part and the second connection part. The first axis electrodes are disposed between the first insulation layer and the substrate.

Owner:WINTEK CORP

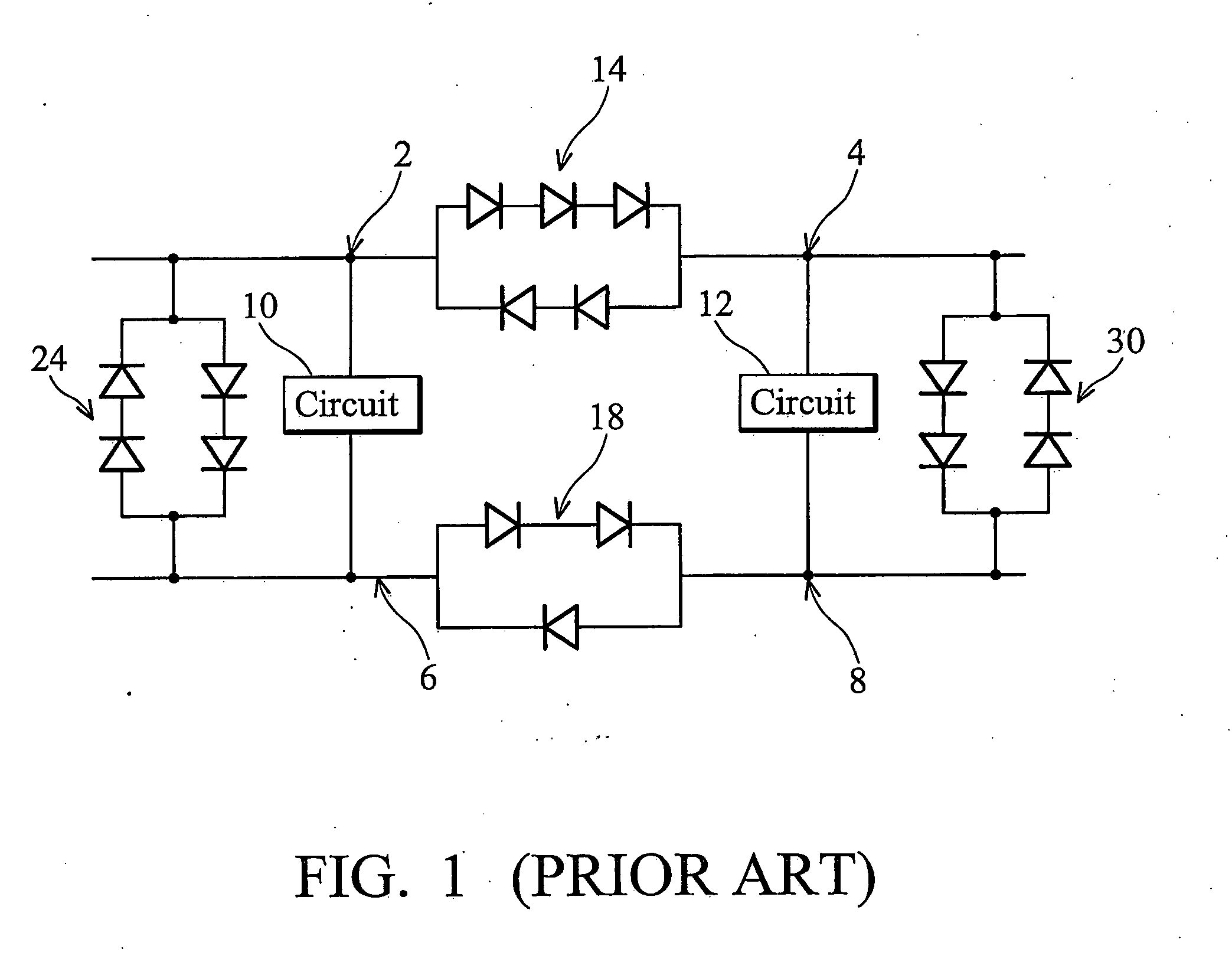

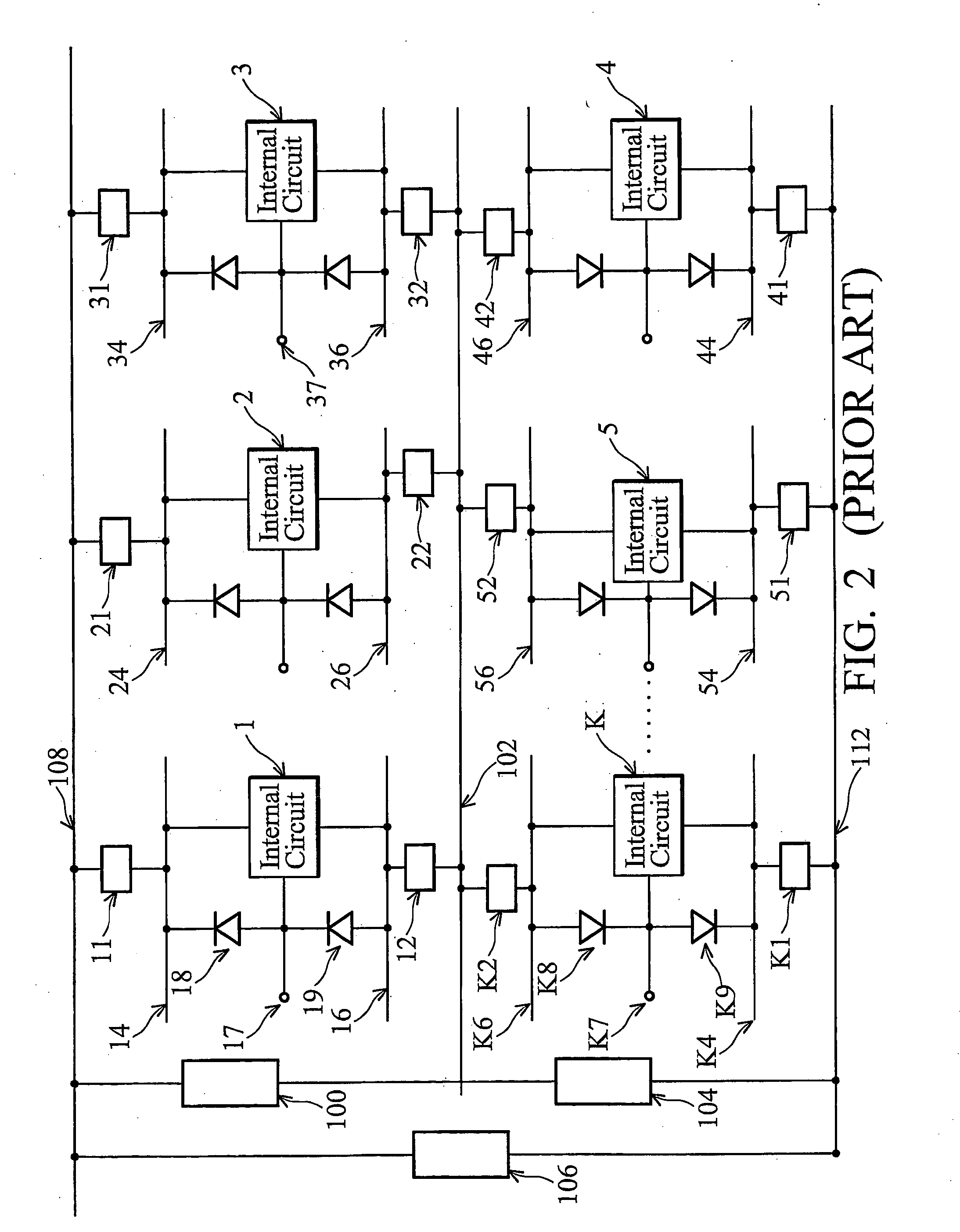

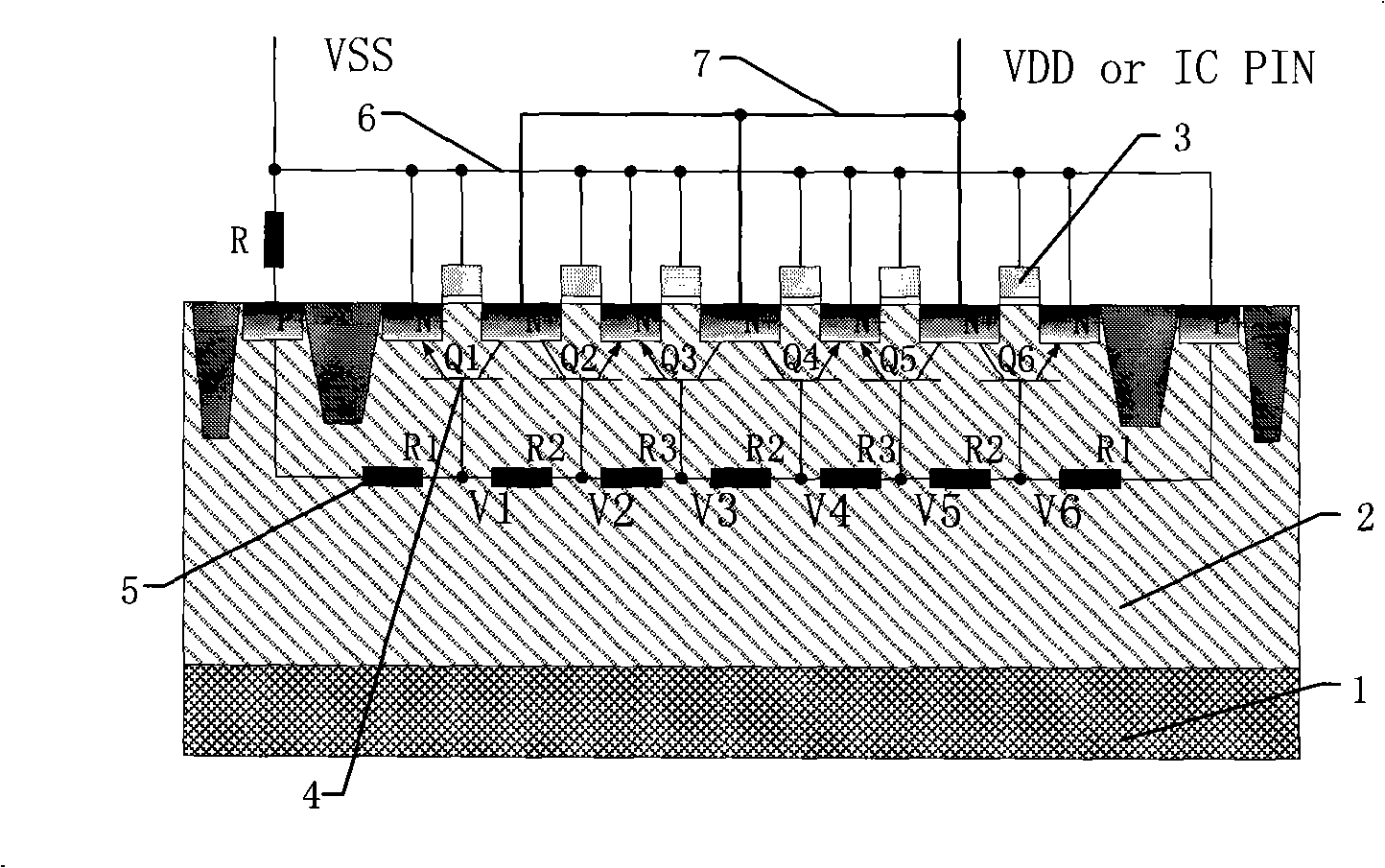

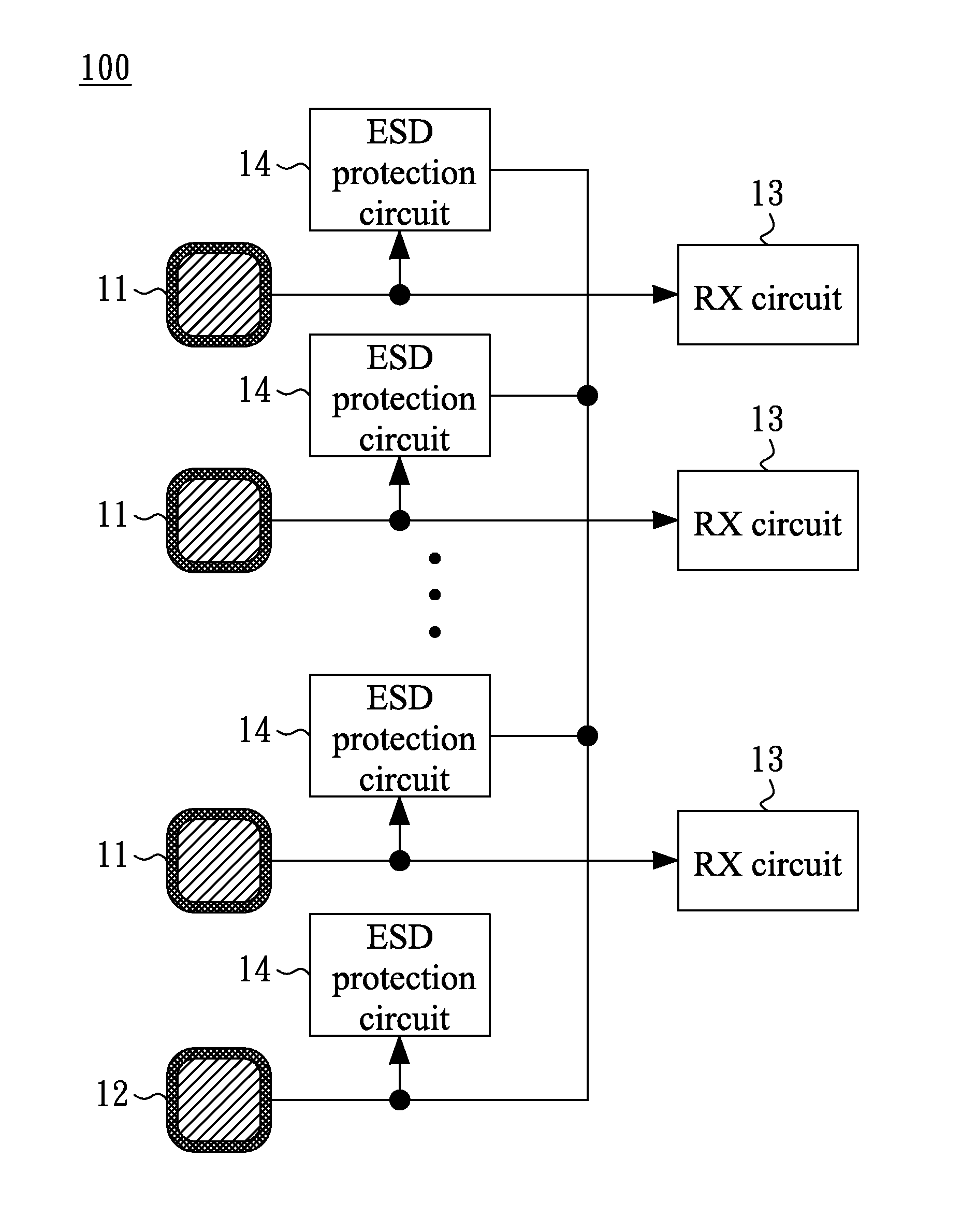

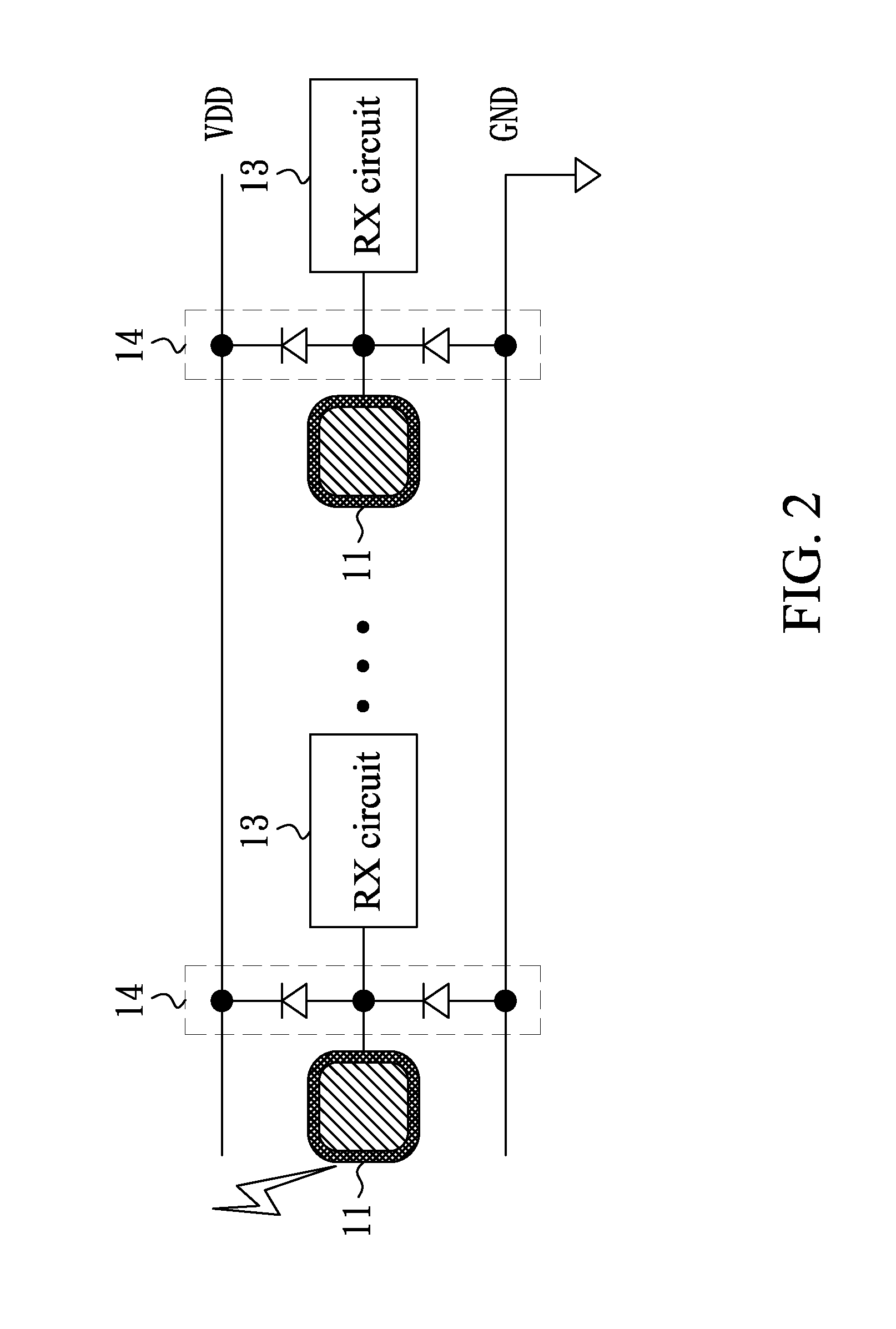

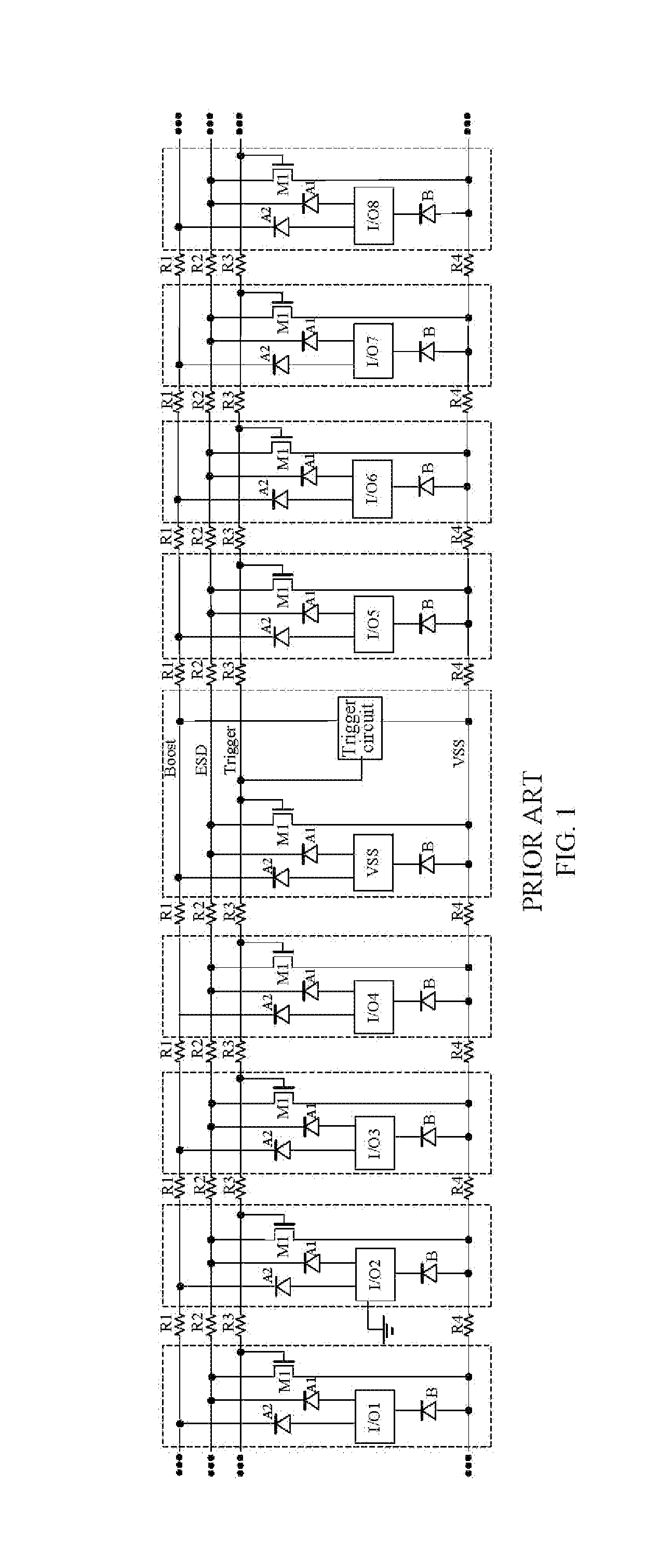

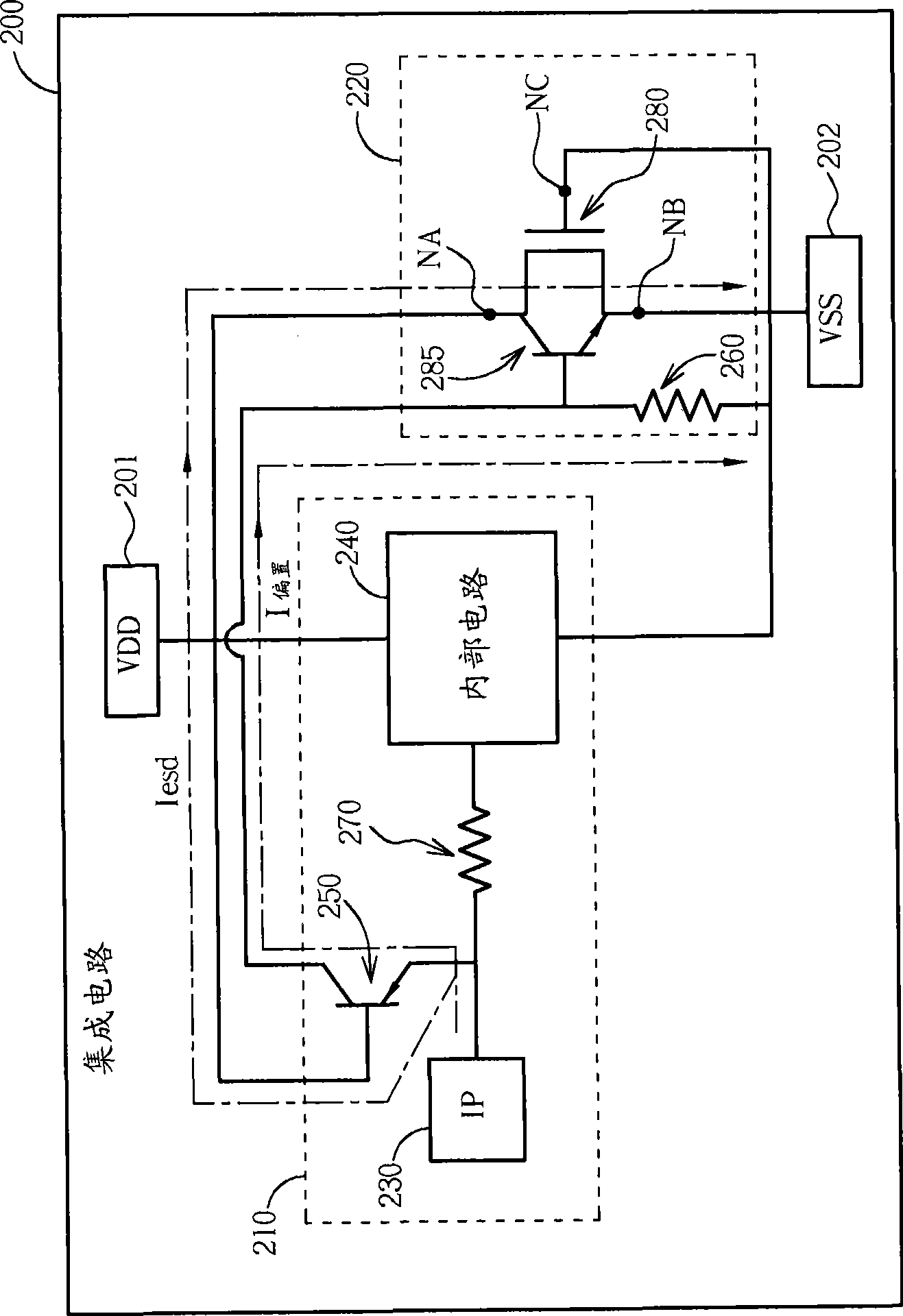

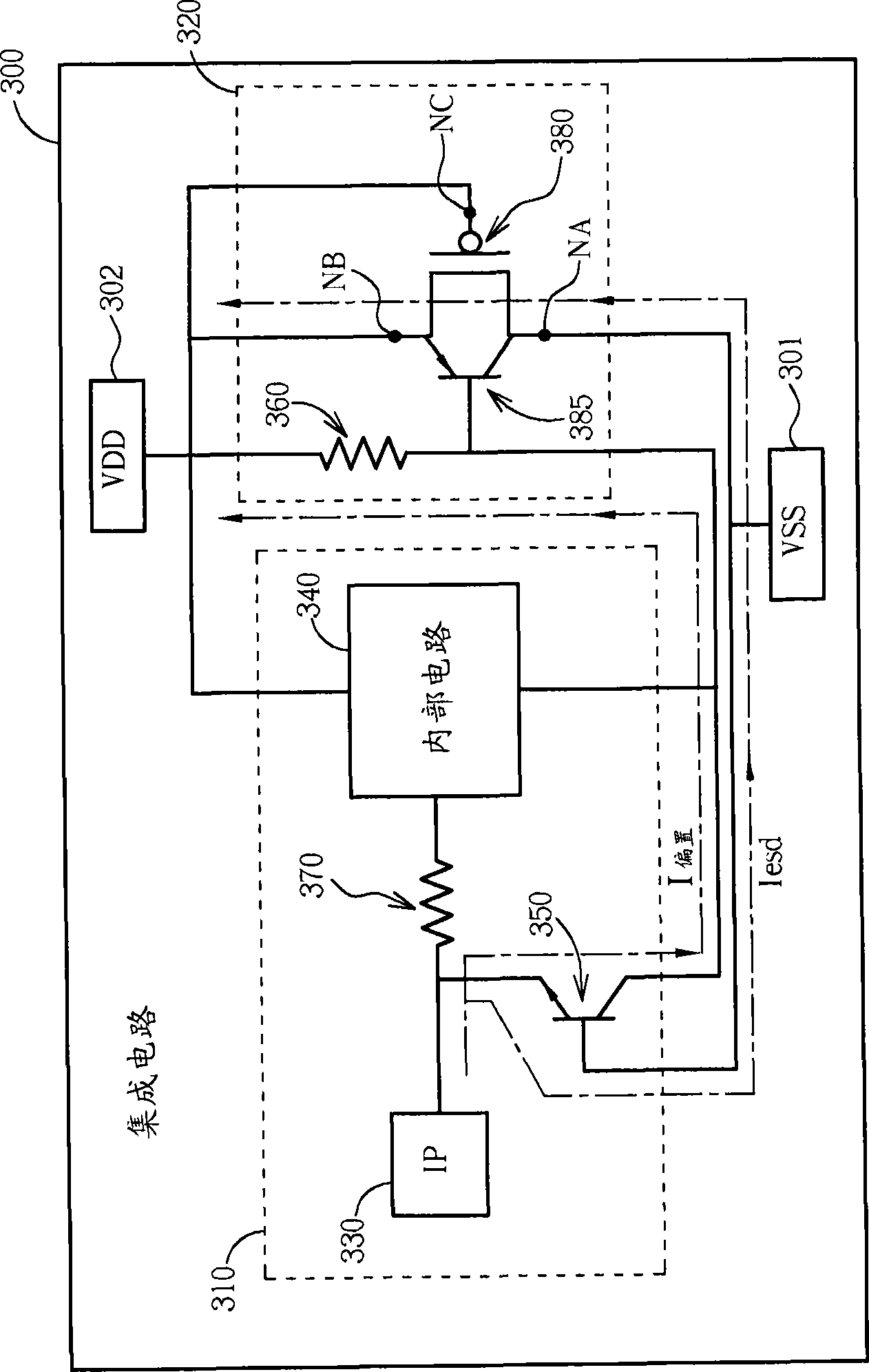

Multi-domain ESD protection circuit structure

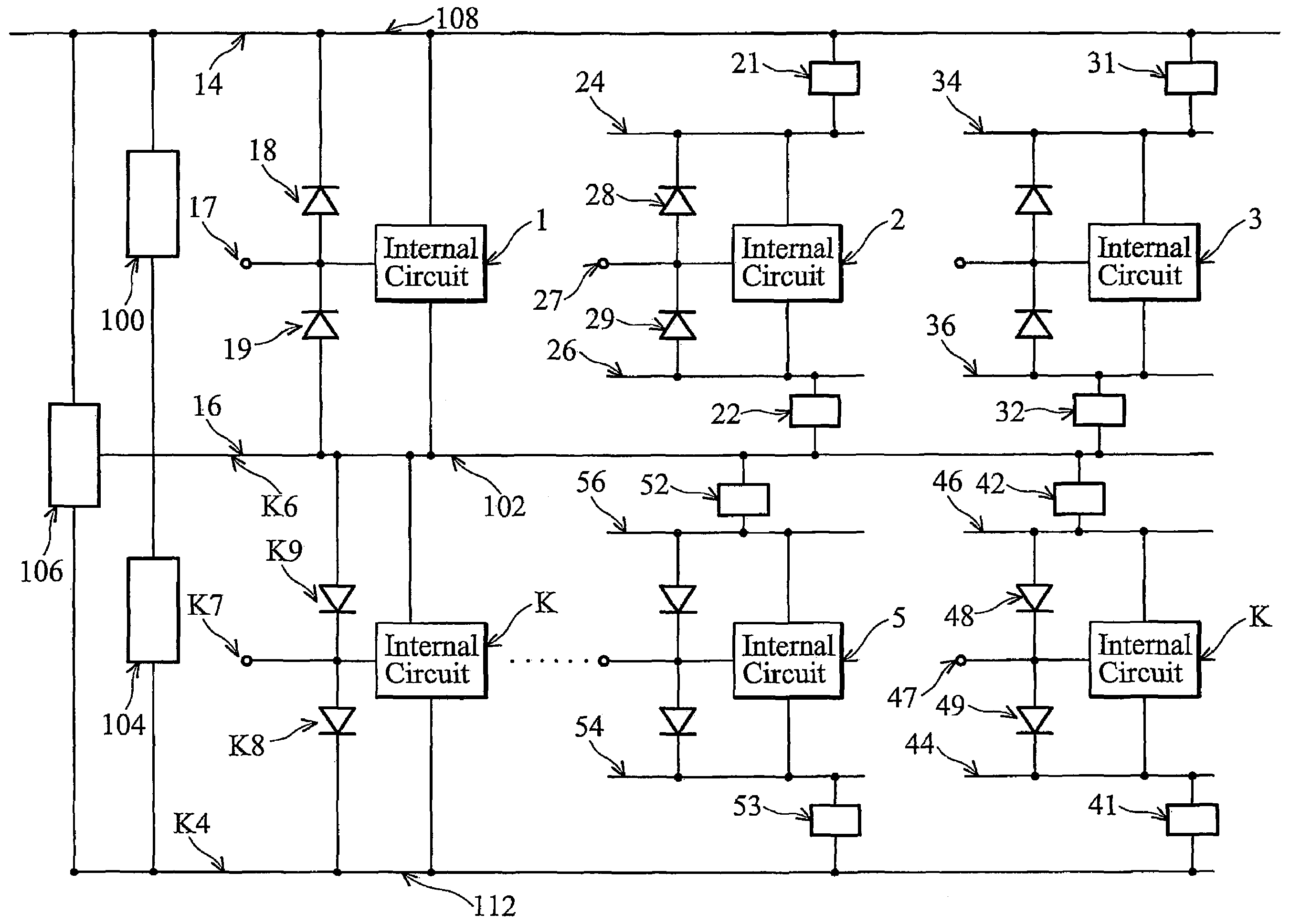

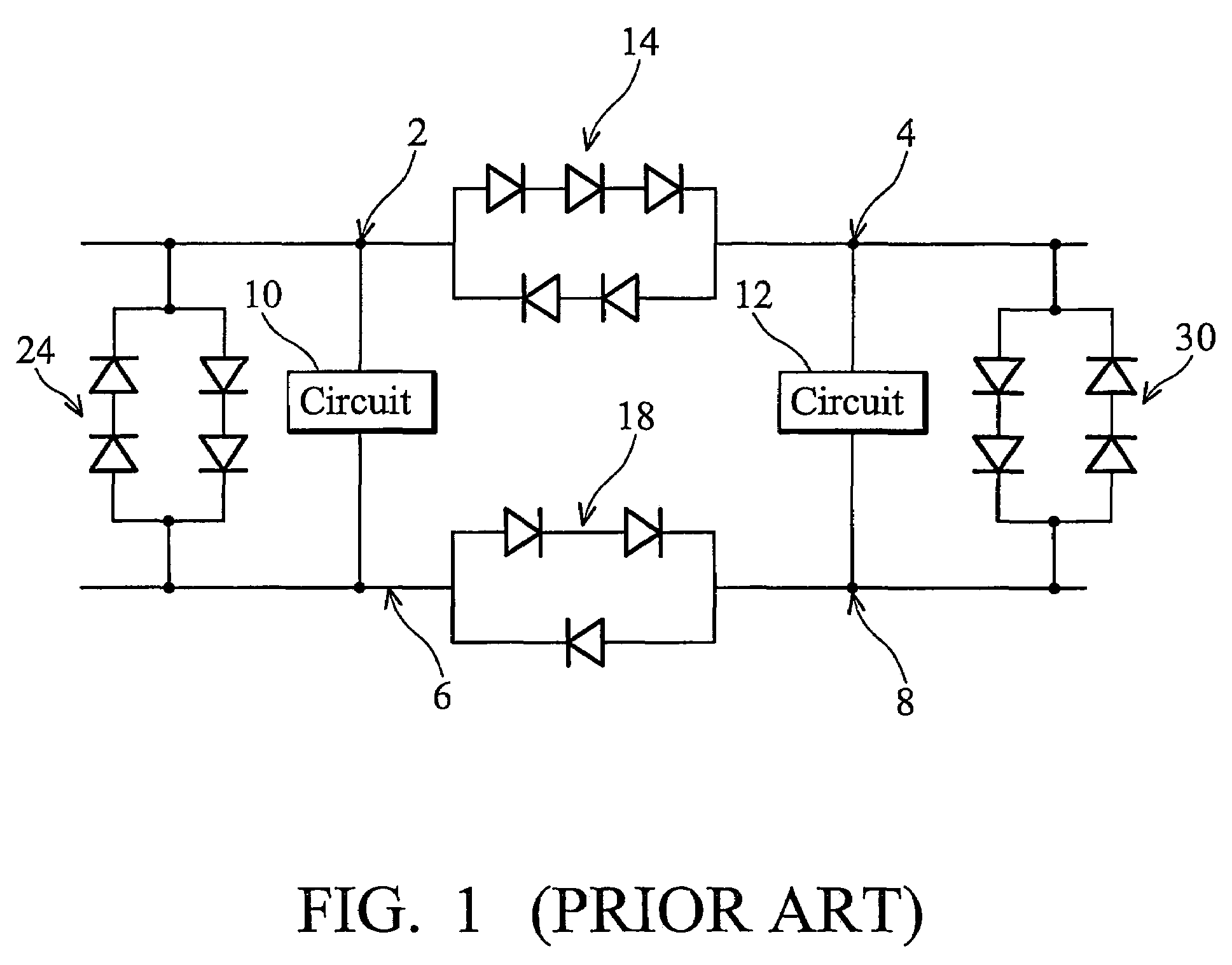

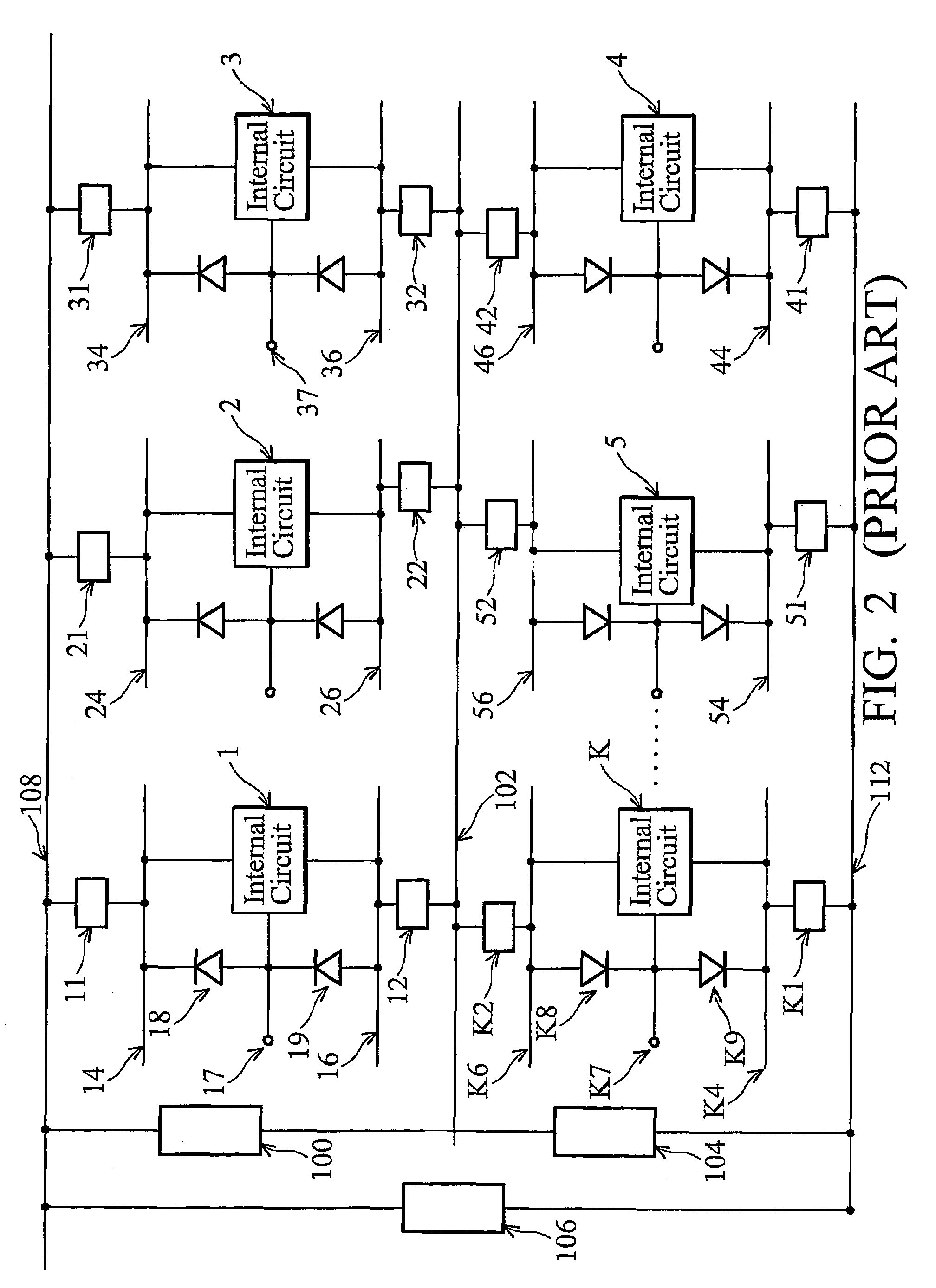

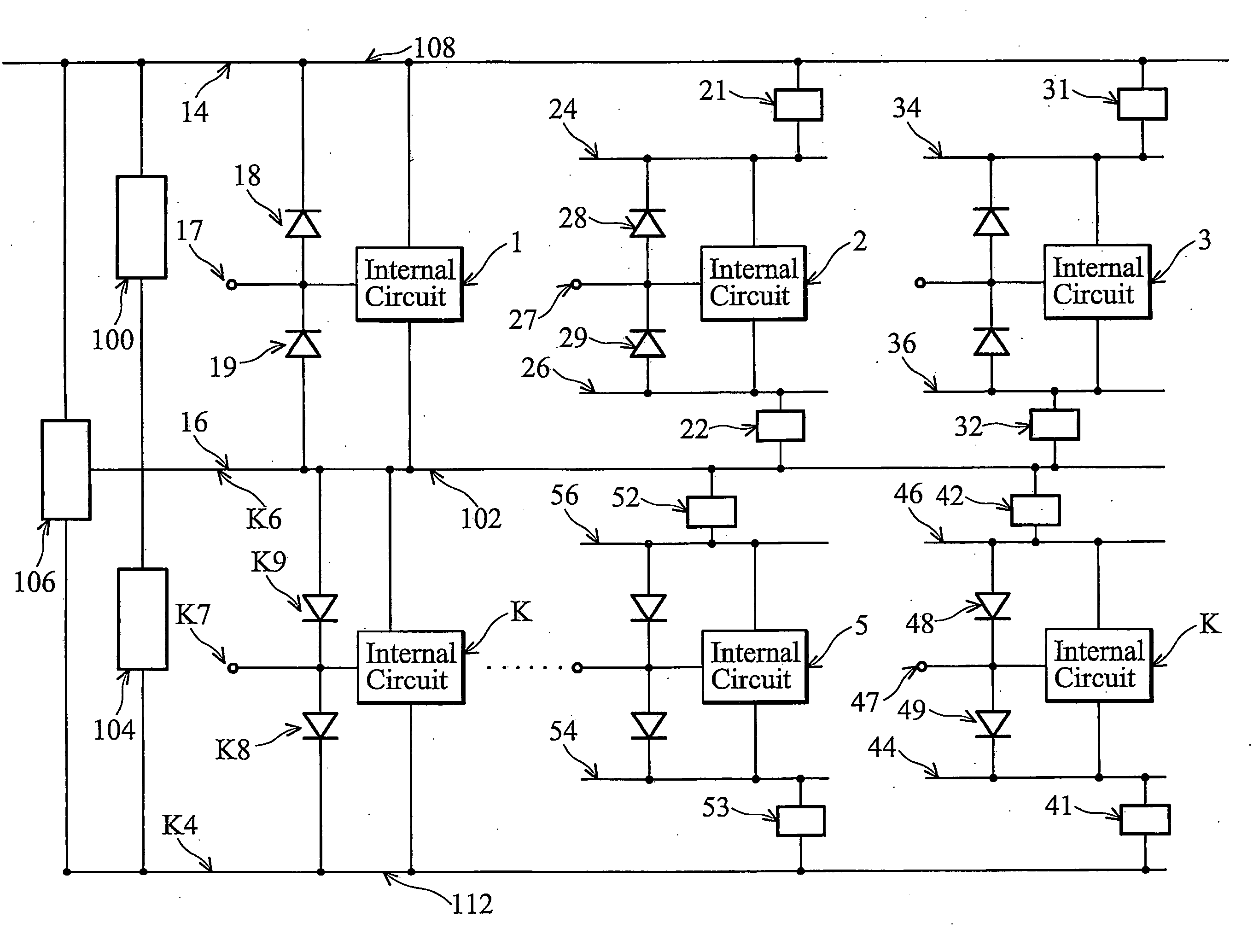

InactiveUS7411767B2Improve ESD protection capabilitySave layout area andSemiconductor/solid-state device detailsSolid-state devicesEngineeringMulti domain

A multi-domain ESD protection circuit structure is described. The preferred embodiment of the present invention selects power lines of an internal circuit as ESD buses. The power lines of the remaining internal circuits are coupled with the ESD buses through the ESD connection cells. In another embodiment of the preferred invention, the VDD power line from one internal circuit and the VSS power line from another circuit are selected as ESD buses. In yet another embodiment, either a VDD power line or a VSS power line of an internal circuit is selected as an ESD bus.

Owner:TAIWAN SEMICON MFG CO LTD

Multi-domain ESD protection circuit structure

InactiveUS20050270712A1Improve ESD protection performanceSave layout area andSemiconductor/solid-state device detailsSolid-state devicesEngineeringMulti domain

A multi-domain ESD protection circuit structure is described. The preferred embodiment of the present invention selects power lines of an internal circuit as ESD buses. The power lines of the remaining internal circuits are coupled with the ESD buses through the ESD connection cells. In another embodiments of the preferred invention, the VDD power line from one internal circuit and the VSS power line from another circuit are selected as ESD buses. In yet another embodiment, either a VDD power line or a VSS power line of an internal circuit is selected as an ESD bus.

Owner:TAIWAN SEMICON MFG CO LTD

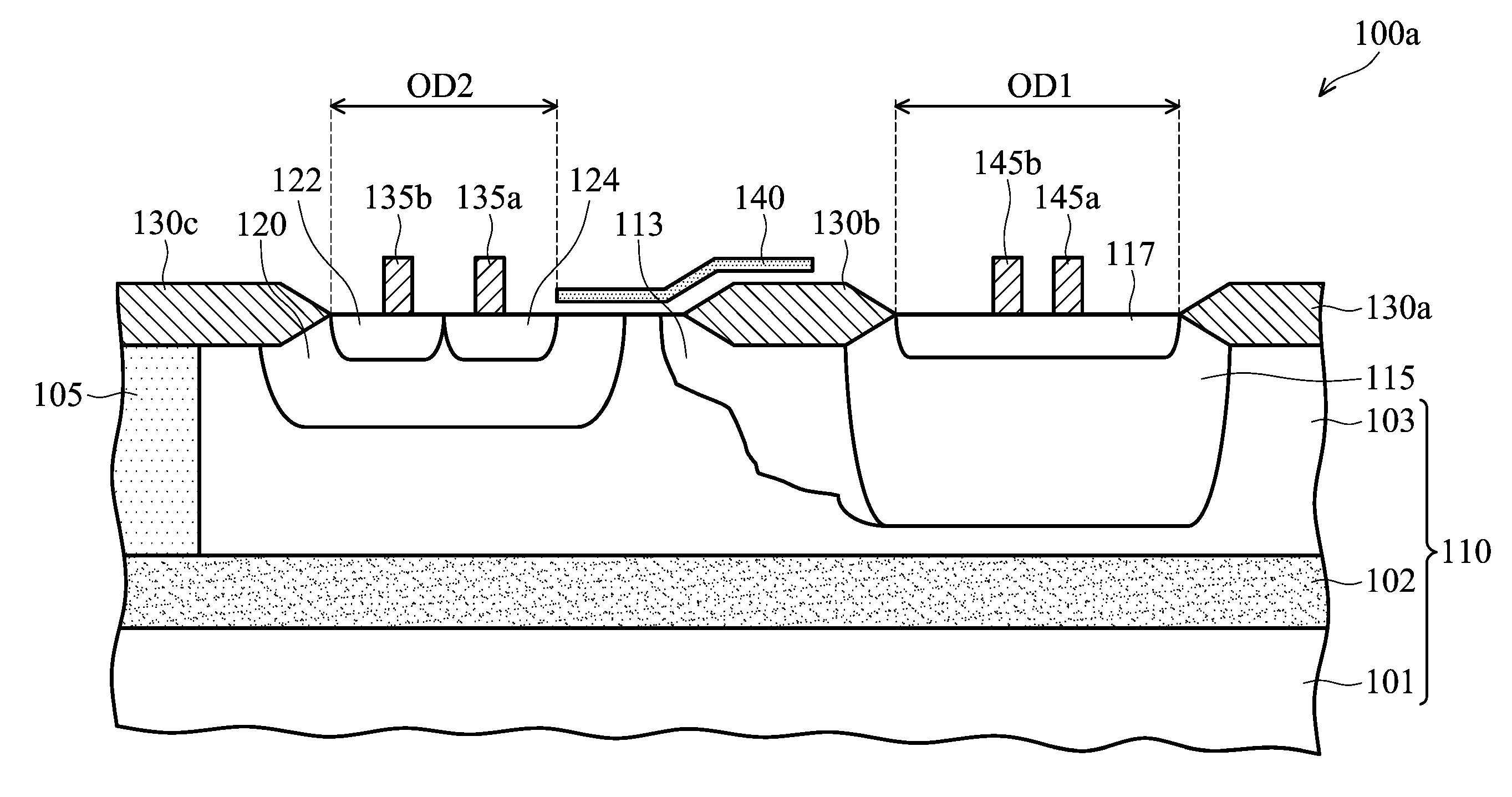

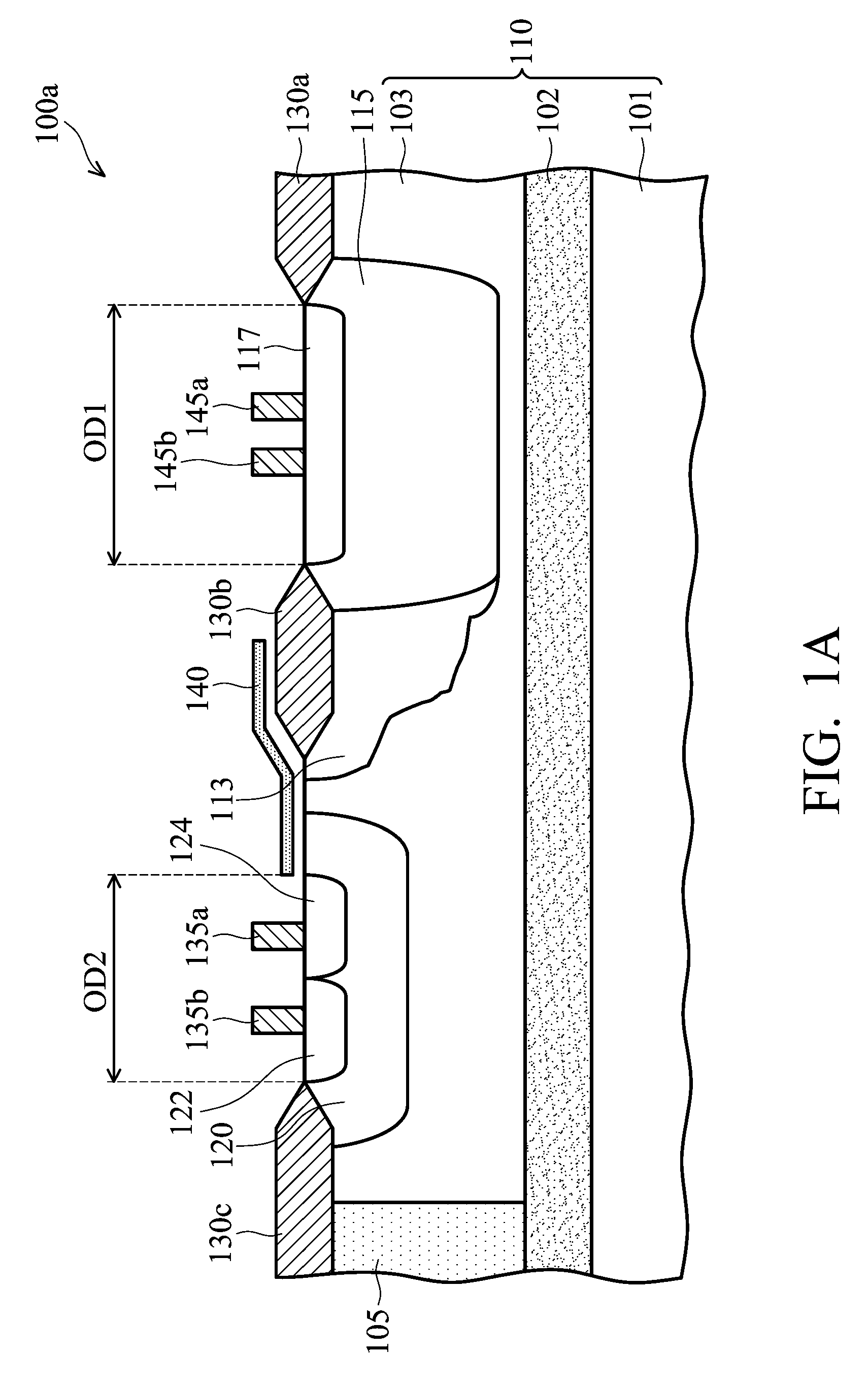

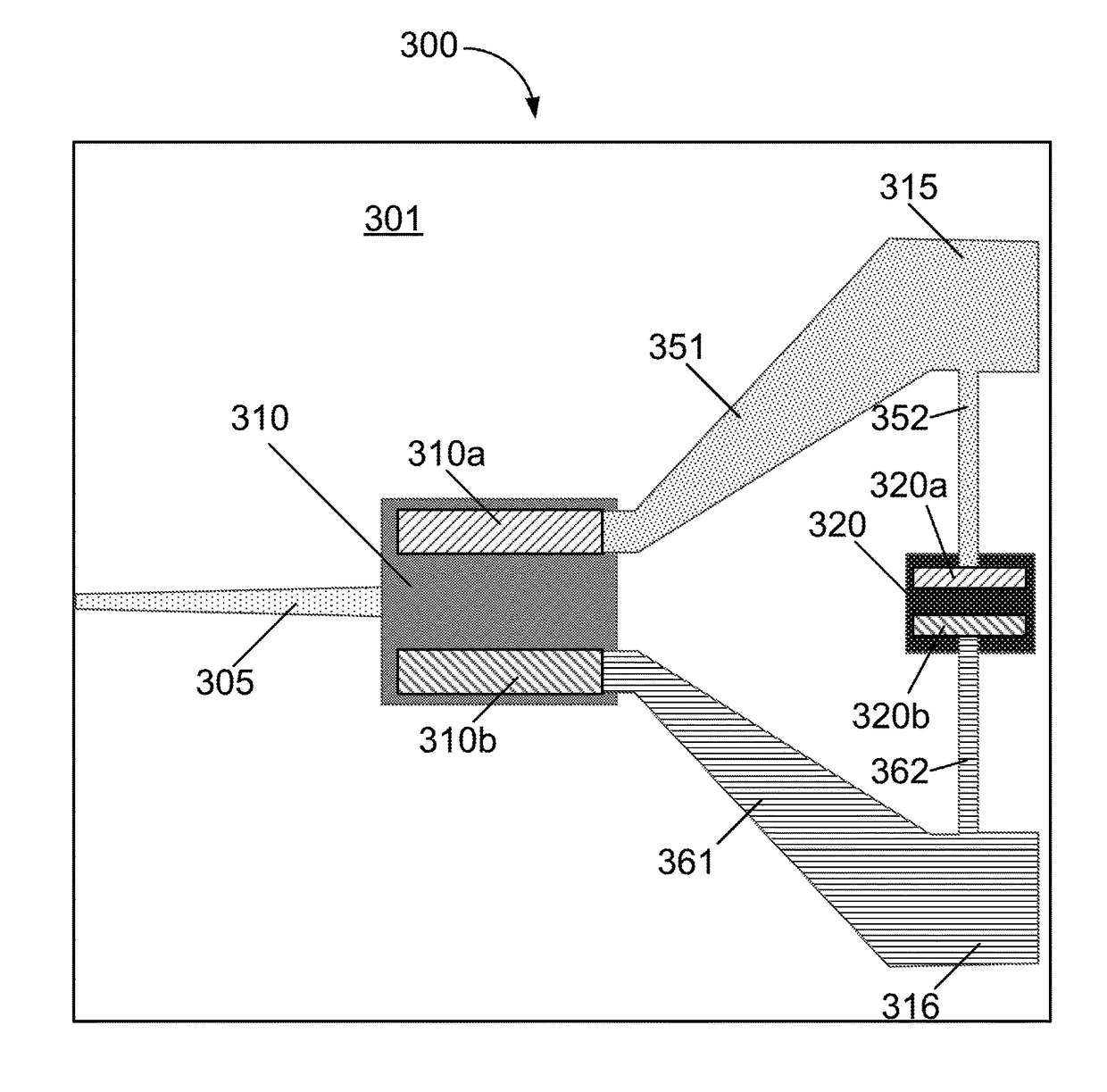

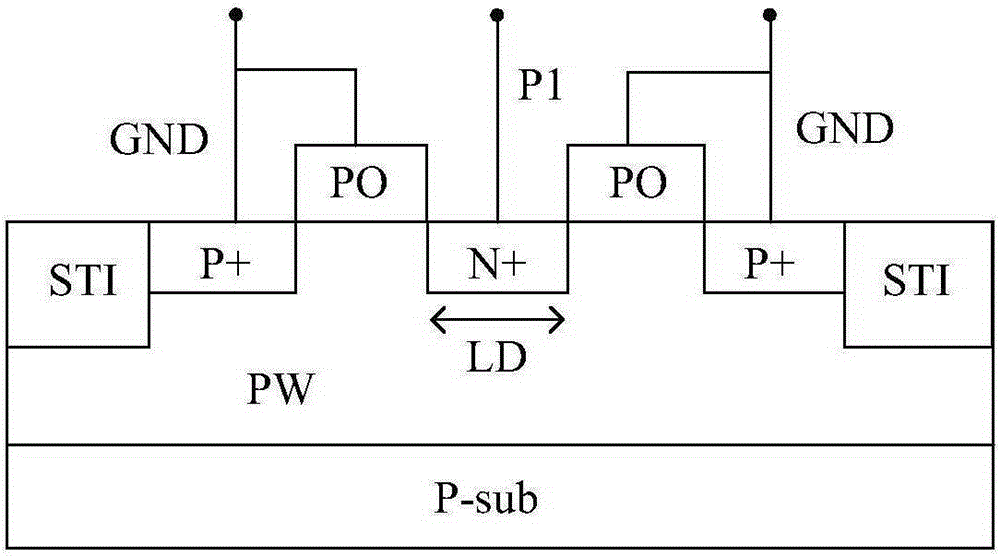

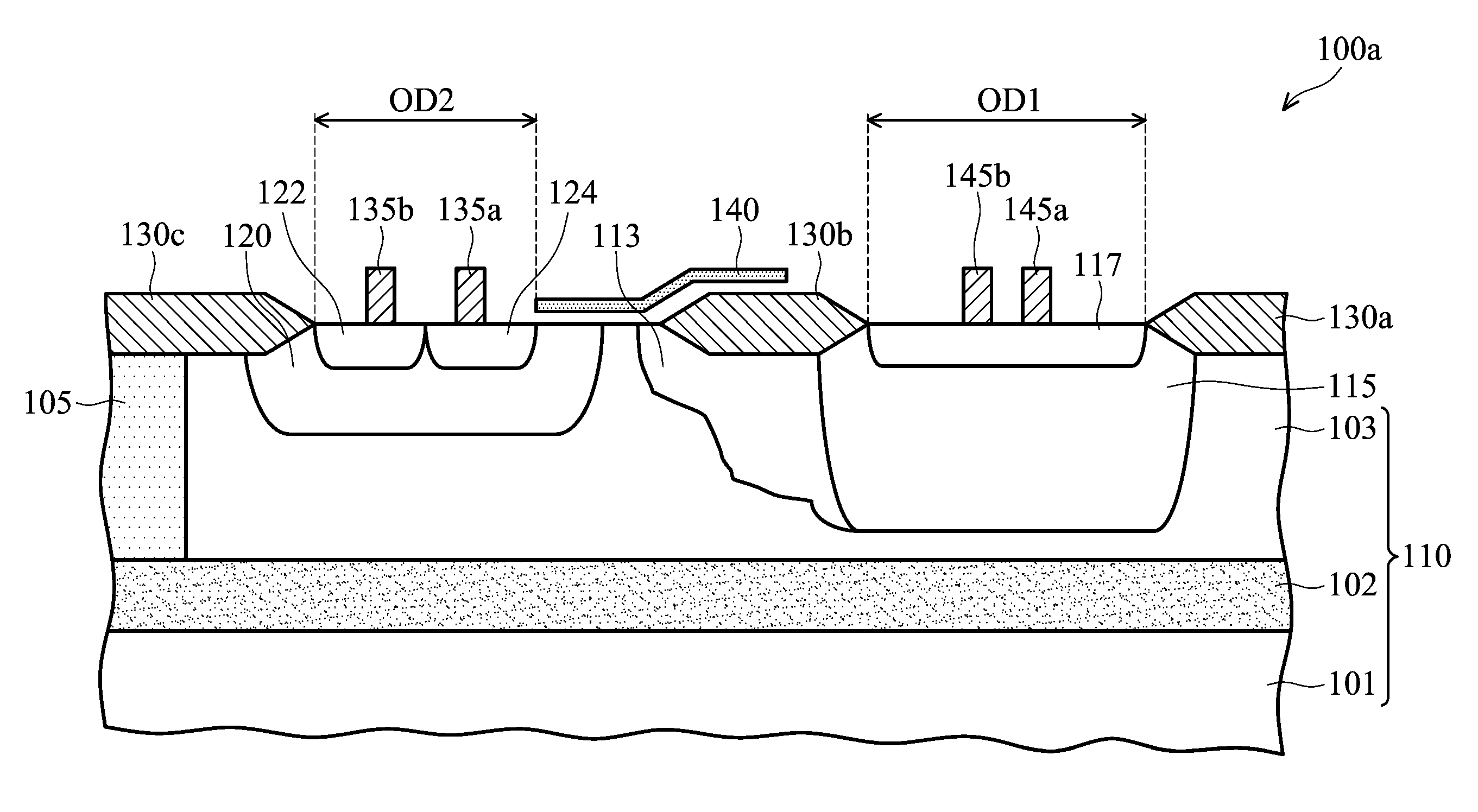

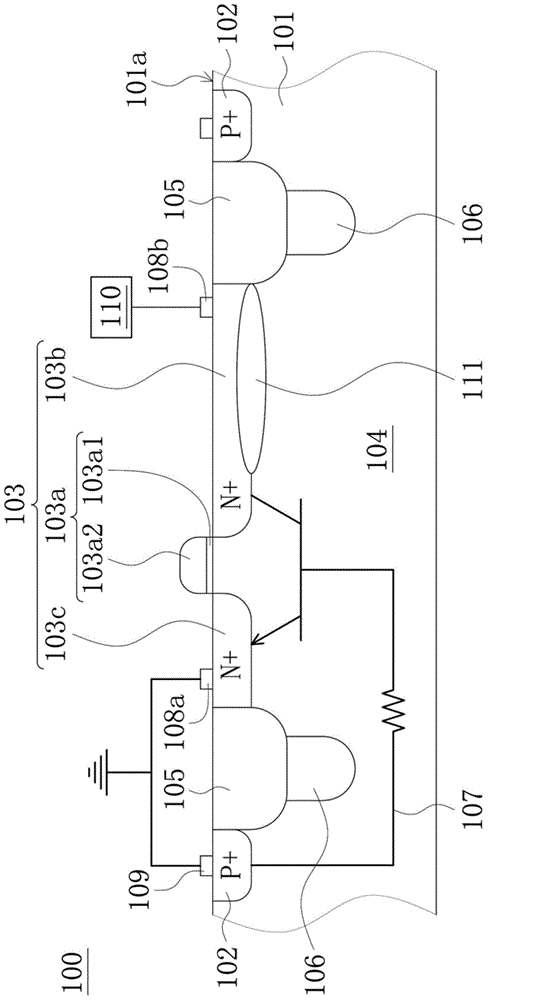

Insulated gate bipolar transistor (IGBT) electrostatic discharge (ESD) protection devices

ActiveUS20100187566A1Improve esd protection capabilityEnlarge regionTransistorSolid-state devicesElectrostatic dischargeInsulated-gate bipolar transistor

Insulated gate bipolar transistor (IGBT) electrostatic discharge (ESD) protection devices are presented. An IGBT-ESD device includes a semiconductor substrate and patterned insulation regions disposed on the semiconductor substrate defining a first active region and a second active region. A high-V N-well is formed in the first active region of the semiconductor substrate. A P-body doped region is formed in the second active region of the semiconductor substrate, wherein the high-V N-well and the P-body doped region are separated with a predetermined distance exposing the semiconductor substrate. A P+ doped drain region is disposed in the high-V N-well. A P+ diffused region and an N+ doped source region are disposed in the P-body doped region. A gate structure is disposed on the semiconductor substrate with one end adjacent to the N+ doped source region and the other end extending over the insulation region.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

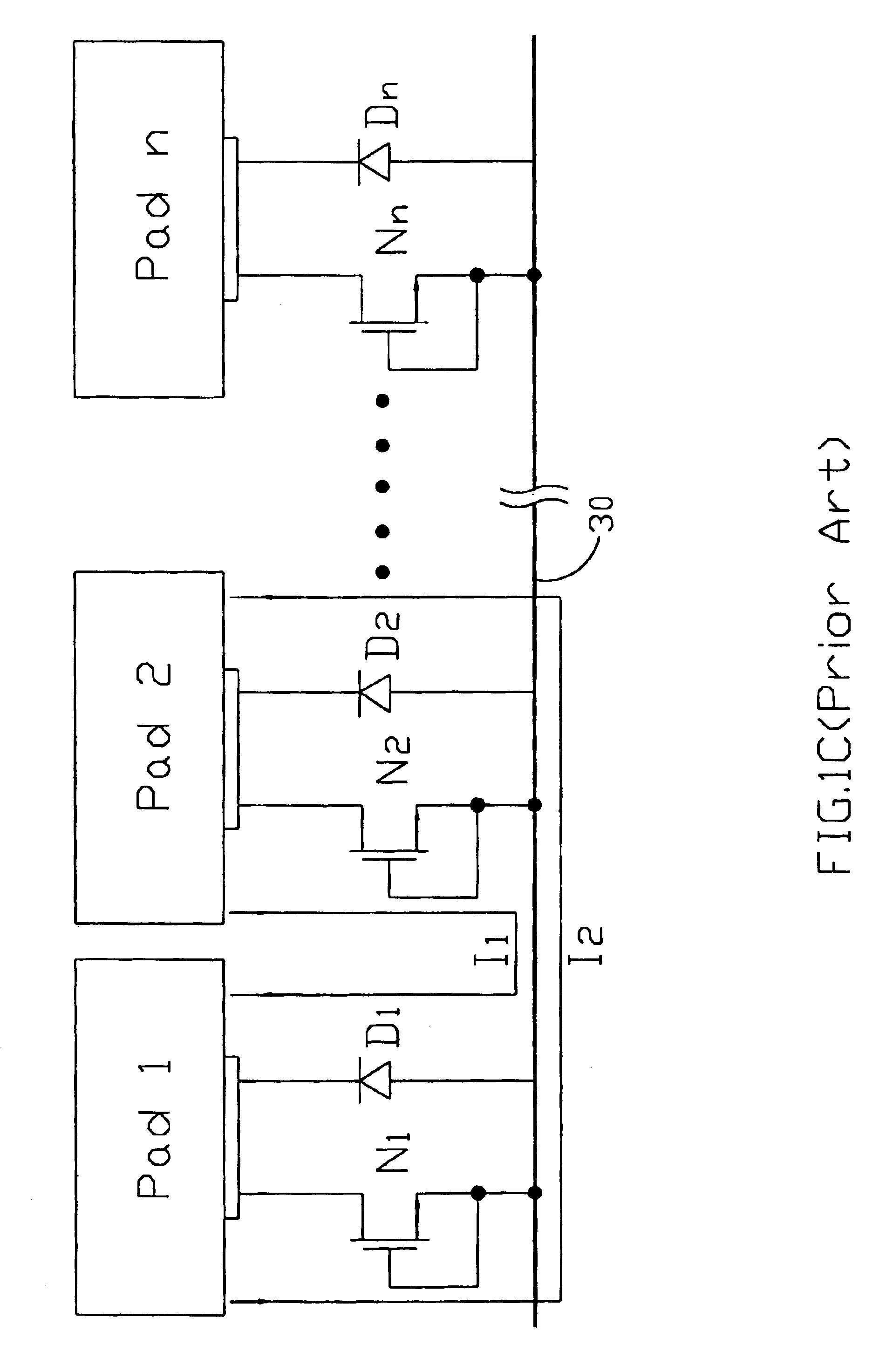

Electrostatic discharge protective circuitry equipped with a common discharge line

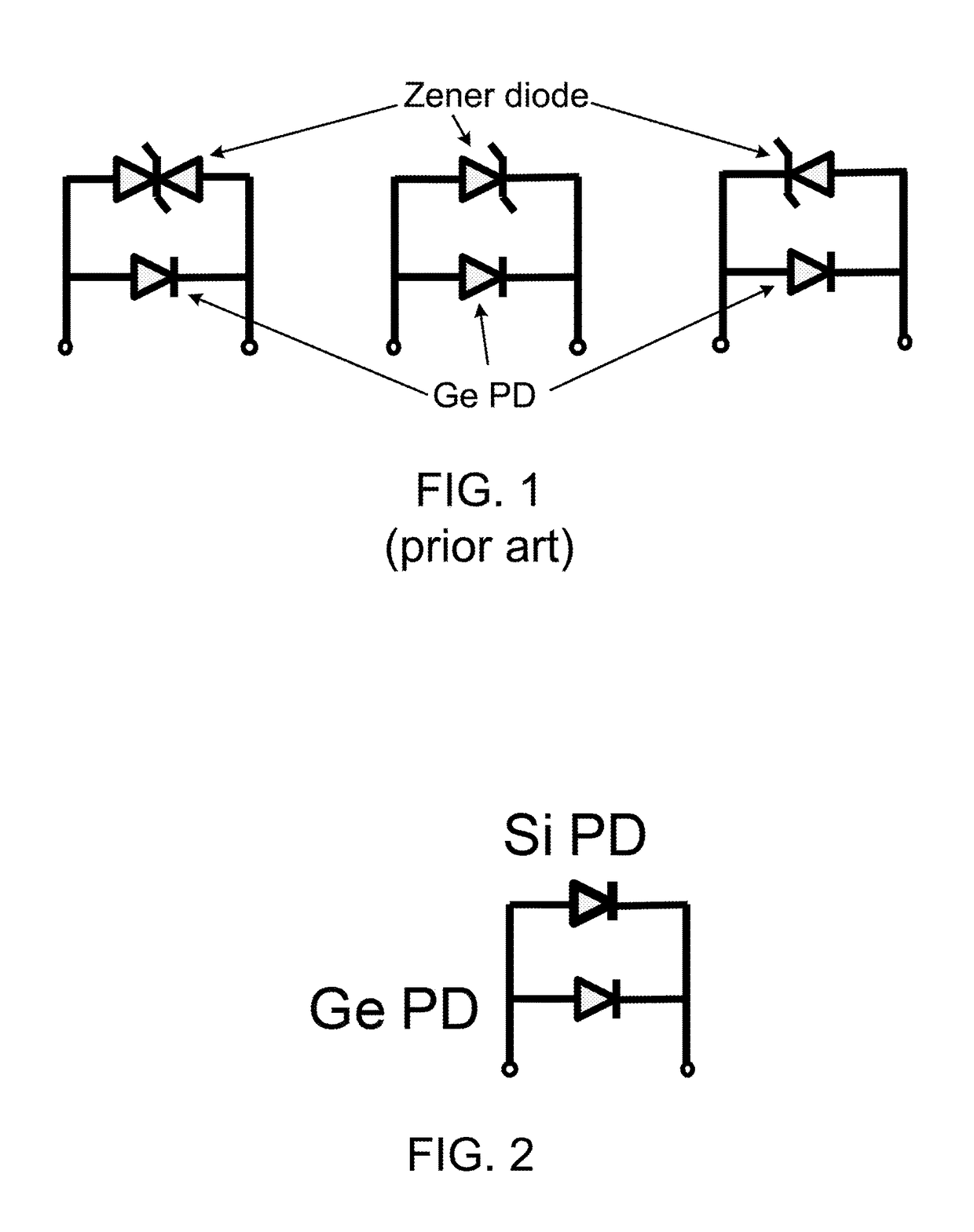

InactiveUS6873505B2Efficient preparationIncrease heightTransistorSolid-state devicesSilicon-controlled rectifierZener diode

A semiconductor device having an electrostatic discharge protective circuitry adapted to a common discharge line (CDL) is disclosed. In the embodiments of the present invention, semiconductor device includes a plurality of bonding pads, each having at least one connecting terminal, a common discharge line, and a protective device connected between the connecting terminal and the common discharge line. Moreover, the protective device is composed of a silicon-control-rectifier that is used for electrostatic discharge protection and a zener diode for lowering a trigger voltage of the silicon-control-rectifier.

Owner:UNITED MICROELECTRONICS CORP

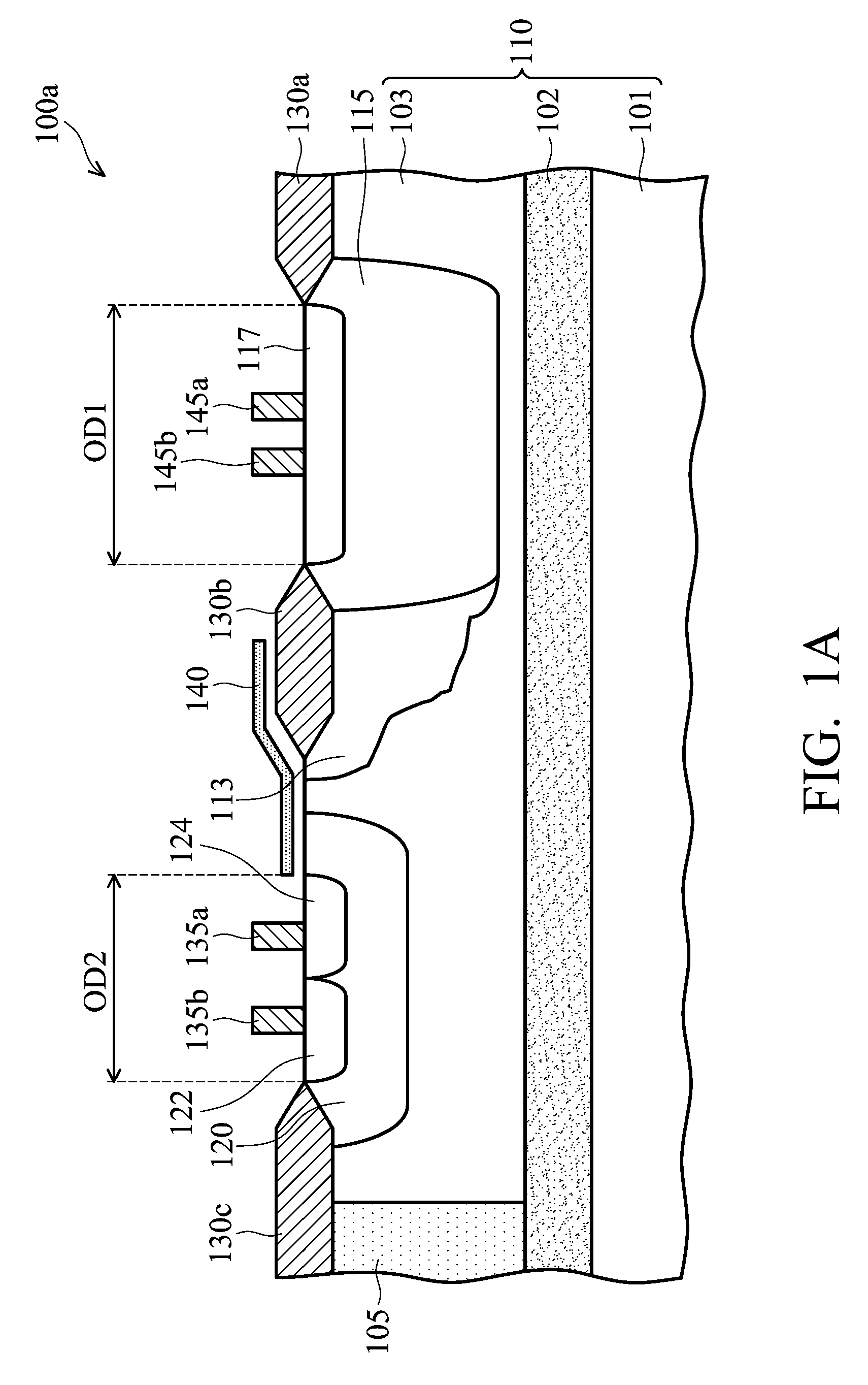

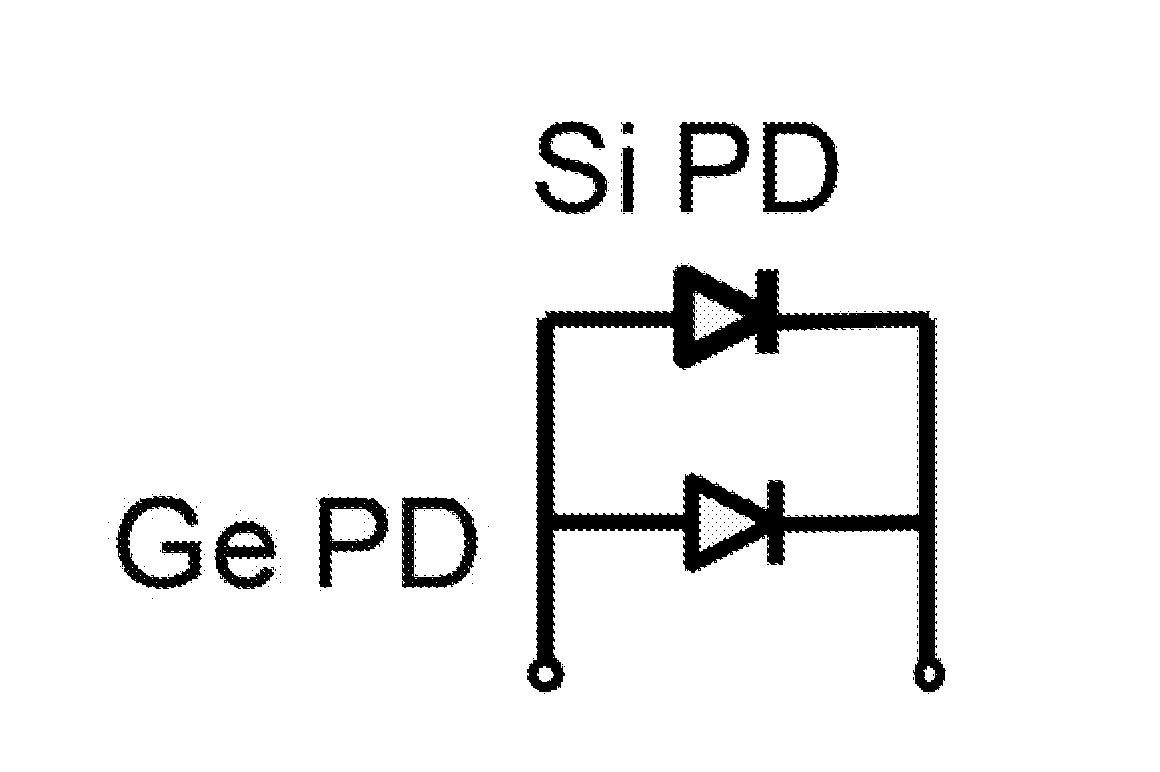

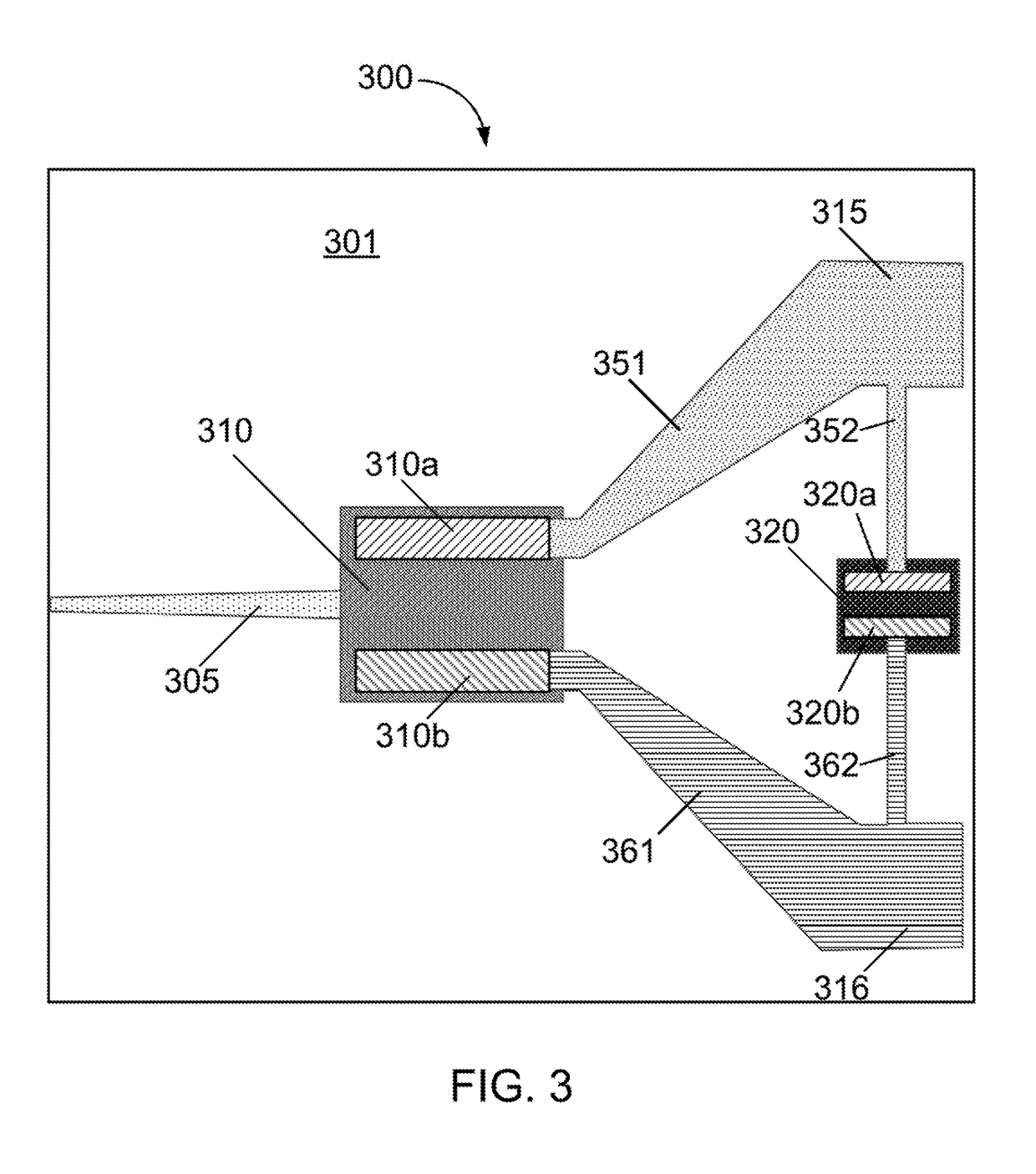

Integrated photo detector, method of making the same

ActiveUS9726841B1Enhanced electrostatic discharge damage (ESD) protectionReduce widthSolid-state devicesCoupling light guidesCapacitancePhotovoltaic detectors

An integrated photo detector with enhanced electrostatic discharge damage (ESD) protection. The integrated photo detector includes a first photodiode formed in the SOI substrate and associated with a first p-electrode and a first n-electrode. Additionally, the integrated photo detector includes a second photodiode formed in the SOI substrate associated with a second p-electrode and a second n-electrode forming a capacitance no larger than a few femto Faradays. Moreover, the integrated photo detector includes a first electrode and a second electrode disposed respectively on the SOI substrate. The first / second electrode is respectively connected to the first p / n-electrode via a first / second metallic layer patterned with a reduced width from the first / second electrode to the first p / n-electrode and connected to the second p / n-electrode via a first / second metallic wire to make a parallel coupling between the first photodiode and the second photodiode with an ESD threshold of about 100V.

Owner:MARVELL ASIA PTE LTD

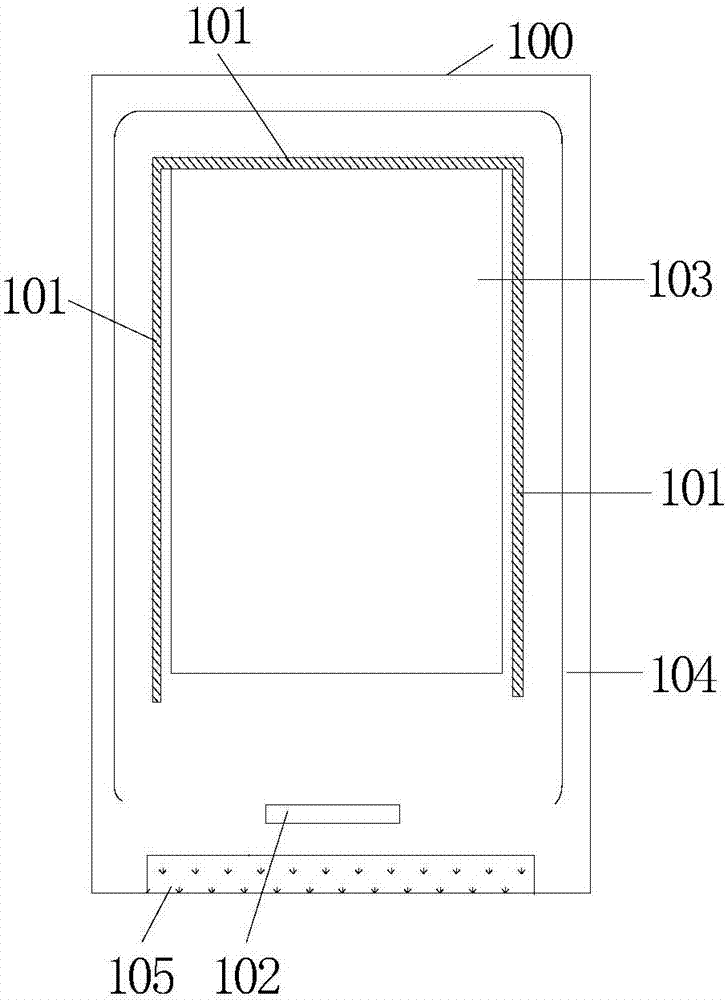

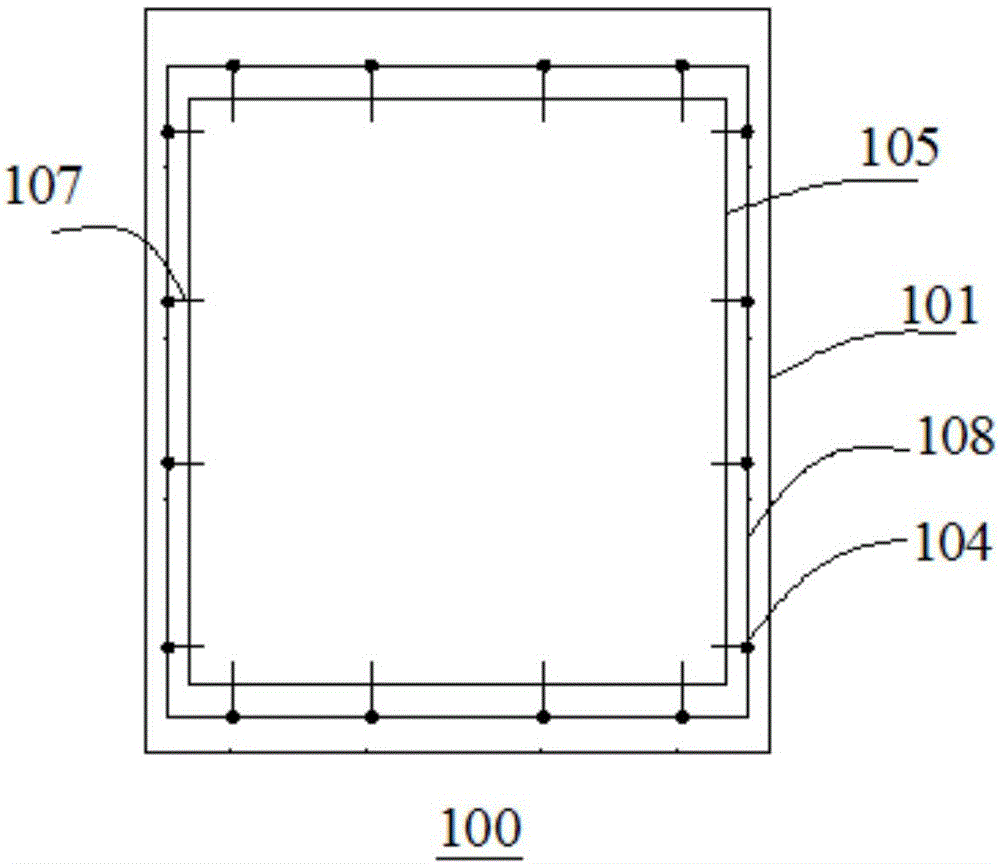

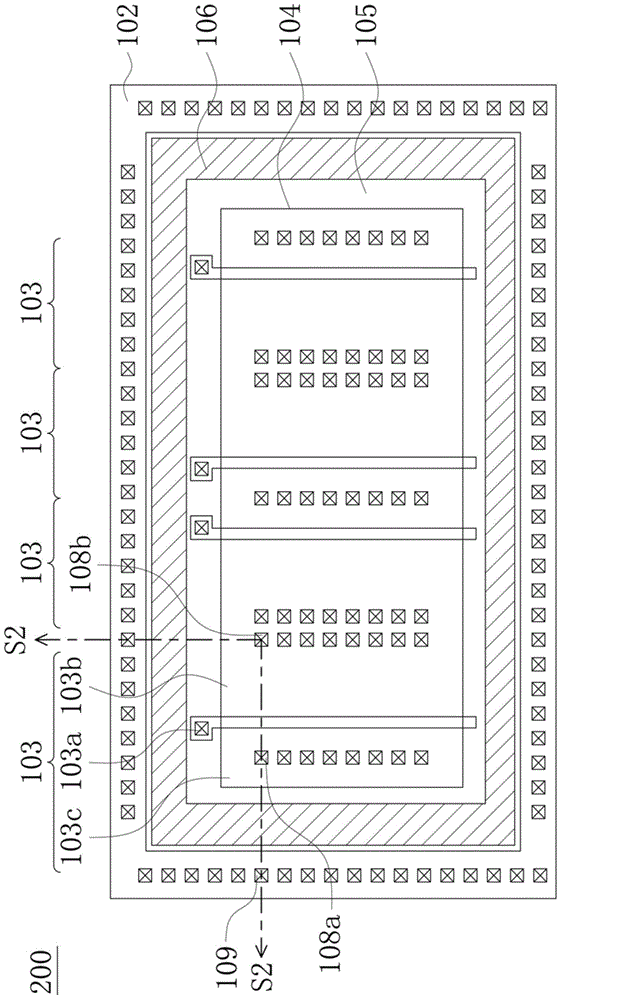

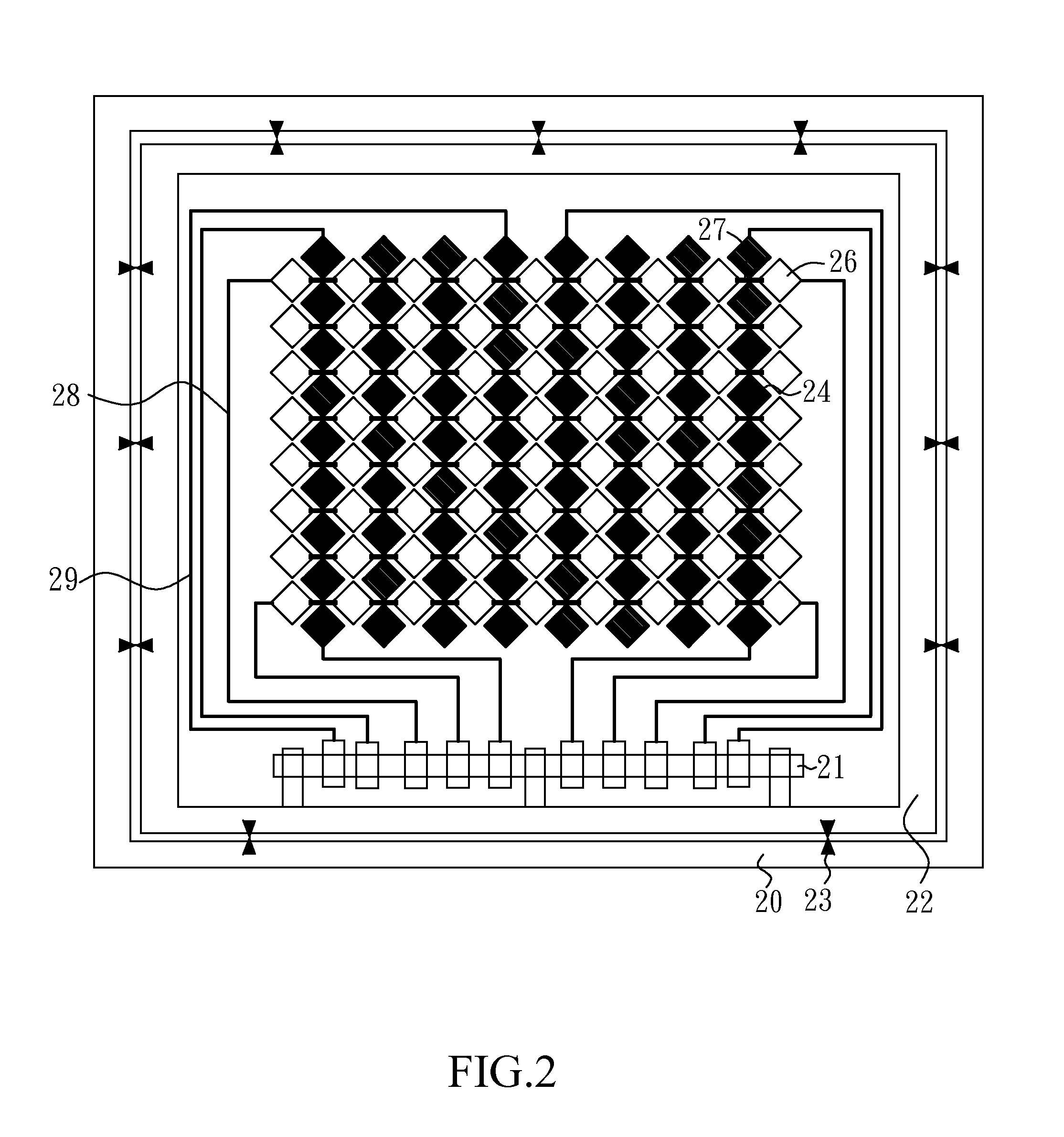

Touch panel

InactiveUS20150077649A1Improve ESD protection capabilityNon-linear opticsInput/output processes for data processingEngineeringUltimate tensile strength

A touch panel includes a transparent substrate, electrodes, traces and at least two ground rings on the transparent substrate. The traces connect the electrodes to transmit signals. At least two ground rings connect to each other through a plurality of bridges and surround the electrodes and the traces. Each bridge has at least one ESD tip or peak to enhance local electric field strength and electrostatic discharge.

Owner:HENGHAO TECH CO LTD

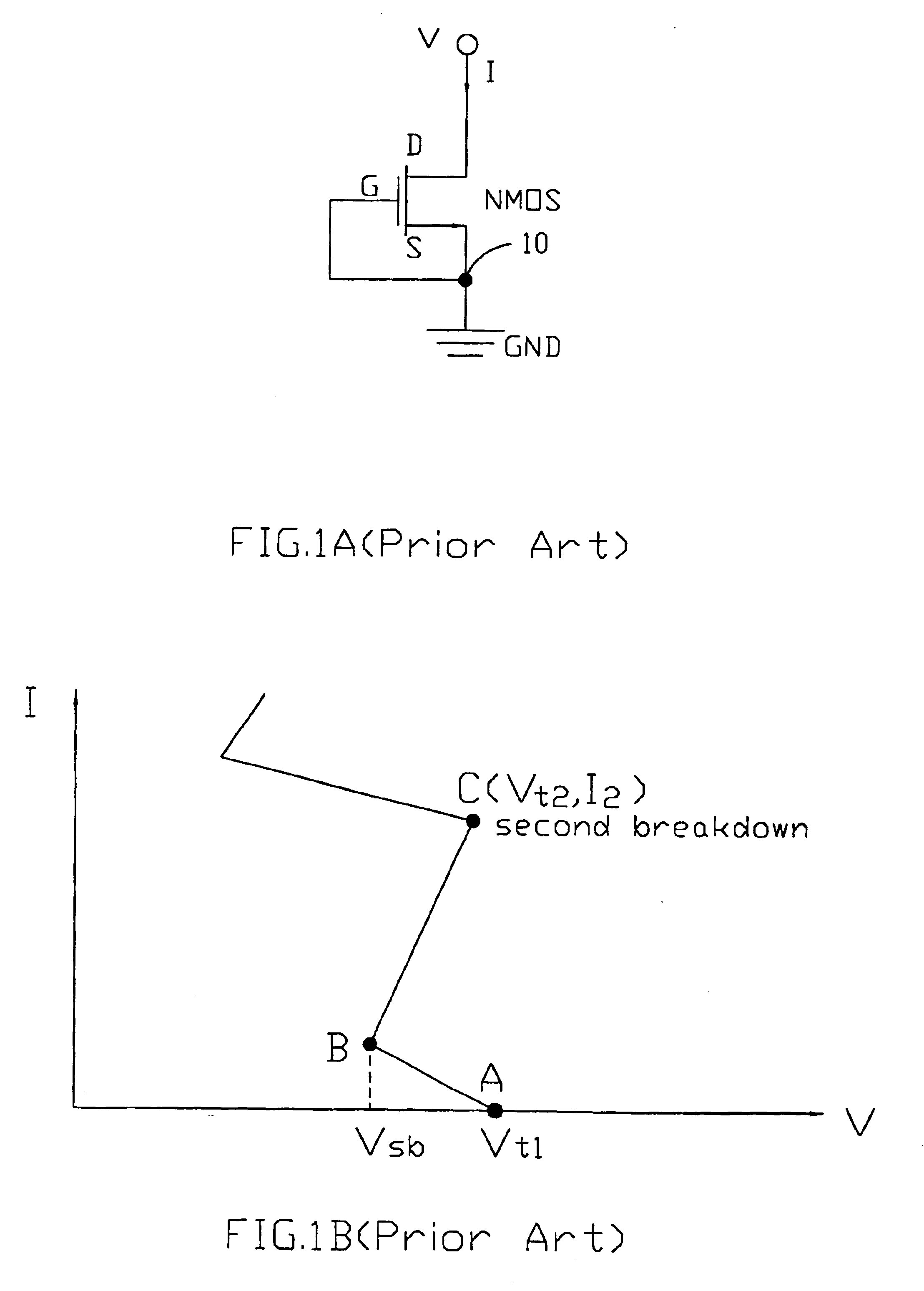

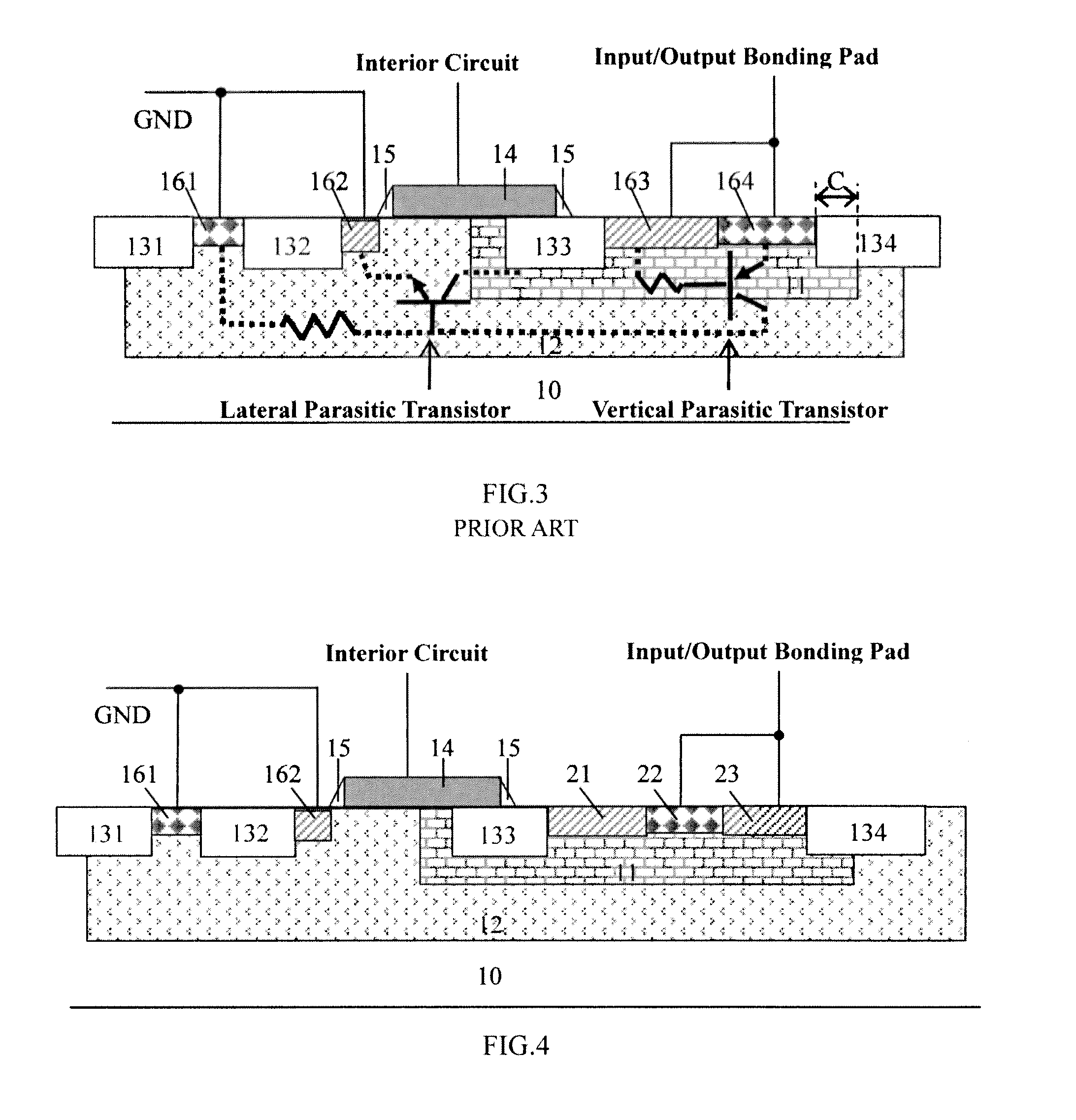

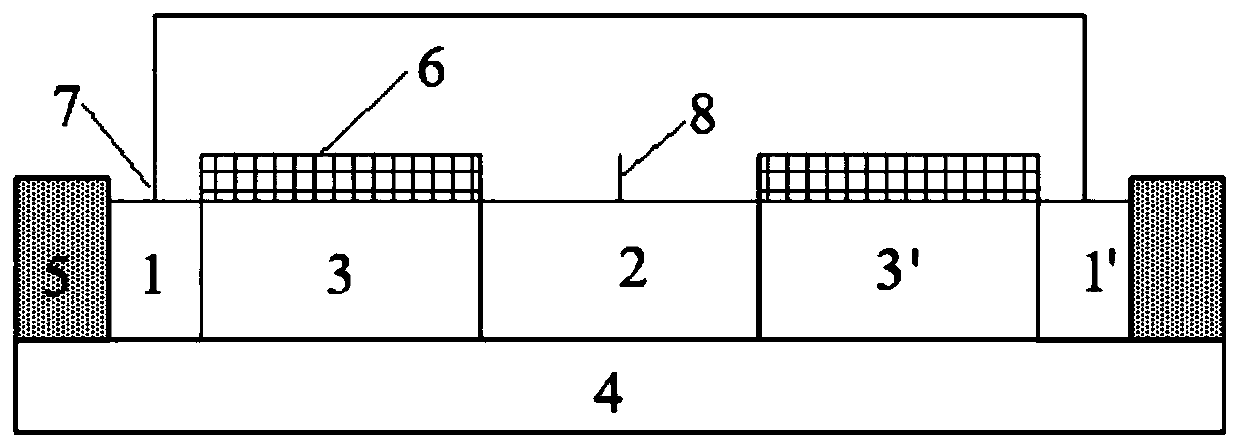

ESD protection structure

A device used as an ESD protection structure, which is a modified N-type LDMOS device is disclosed. A conventional LDMOS includes only one N-type heavily doped region as a drain in an N-type lightly doped region (11), while the device of the invention includes a P-type heavily doped region (22) in an N-type lightly doped region (11), dividing the N-type heavily doped region into two N-type heavily doped regions (21, 23) unconnected and independent to each other. The N-type heavily doped region (21) close to the gate (14) has no picking-up terminal. The N-type heavily doped region (23) away from the gate (14) together with the P-type heavily doped region (22) is picked up and connected to an input / output bonding pad.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

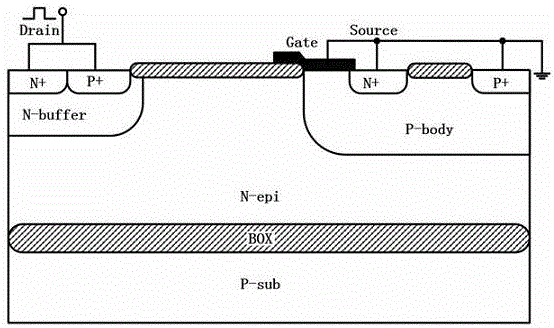

High-voltage electronic static discharge (ESD) protection device with positive-negative (PN) junction auxiliary trigger silicon controlled rectifier-laterally diffused metal oxide semiconductor (SCR-LDMOS) structure

ActiveCN105742281AImprove ESD protection capabilityEnhanced ESD robustnessSolid-state devicesDiodeNegative feedbackLDMOS

The invention discloses a high-voltage electronic static discharge (ESD) protection device with a positive-negative (PN) junction auxiliary trigger silicon controlled rectifier-laterally diffused metal oxide semiconductor (SCR-LDMOS) structure. The high-voltage ESD protection device comprises a P-type substrate, wherein a buried oxygen layer is arranged on the P-type substrate, a shift region is arranged on the buried oxygen layer, an N-buffer region, a P region and a P-body region are sequentially arranged on the shift region from left to right, a first drain heavily-doping N+ region and a first drain heavily-doping P+ region are sequentially arranged in the N-buffer region from left to right, a second source heavily-doping N+ region, a second source heavily-doping P+ region and a third source heavily-doping P+ region are sequentially arranged in the P-body region from left to right, and the P region and the second source heavily-doping P+ region are connected through a wire. When a drain of the ESD protection device encounters a positive ESD pulse, a reverse bias PN junction is used for helping improving the hole carrier concentration before trigger starting, and a trigger voltage V<t1> is reduced; and moreover, with the introduction of the reverse bias PN junction into the device, the positive and negative feedback effect of a parasitic SCR can be effectively prevented, thus, the maintaining voltage V<h> of the device can be effectively increased, and the latch-up effect of the device is prevented.

Owner:ANHUI LONGXINWEI TECH CO LTD

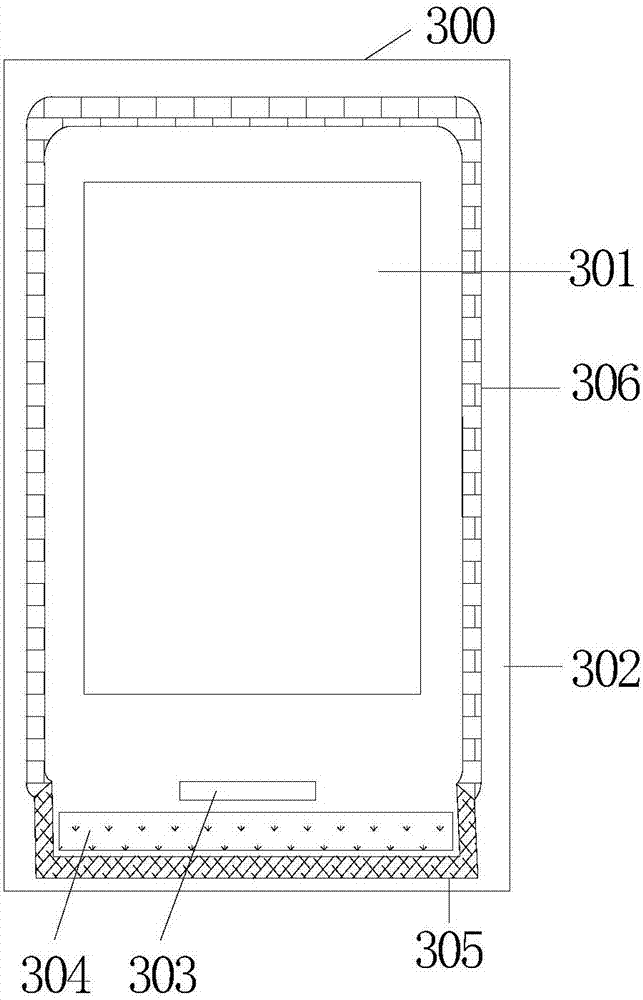

Organic light-emitting display panel and display device

ActiveCN106887525AImprove ESD protection capabilityFacilitates narrow bezel designSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSurface plate

The invention presents an organic light-emitting display panel and a display device. The organic light-emitting display panel comprises a substrate, a display function layer and a package layer, which are arranged in sequence. The display function layer comprises a thin film transistor layer which consists of a gate metal layer and a source-drain metal layer. The organic light-emitting display panel comprises a display area and a surrounding area around the display area. The surrounding area comprises a flexible printed circuit binding area. The surrounding area comprises a metal ring which is arranged around the display area and connected with a ground potential. The metal ring comprises cushion metal and a metal wire. The U-shaped cushion metal half-surrounds the display area, and the opening of the U shape faces the flexible printed circuit binding area. The metal wire is at least partially disposed on a side, away from the display area, of the flexible printed circuit binding area, and the two ends of the metal wire are electrically connected with the two ends of the cushion metal. The metal ring provides overall electrostatic protection for the display panel.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

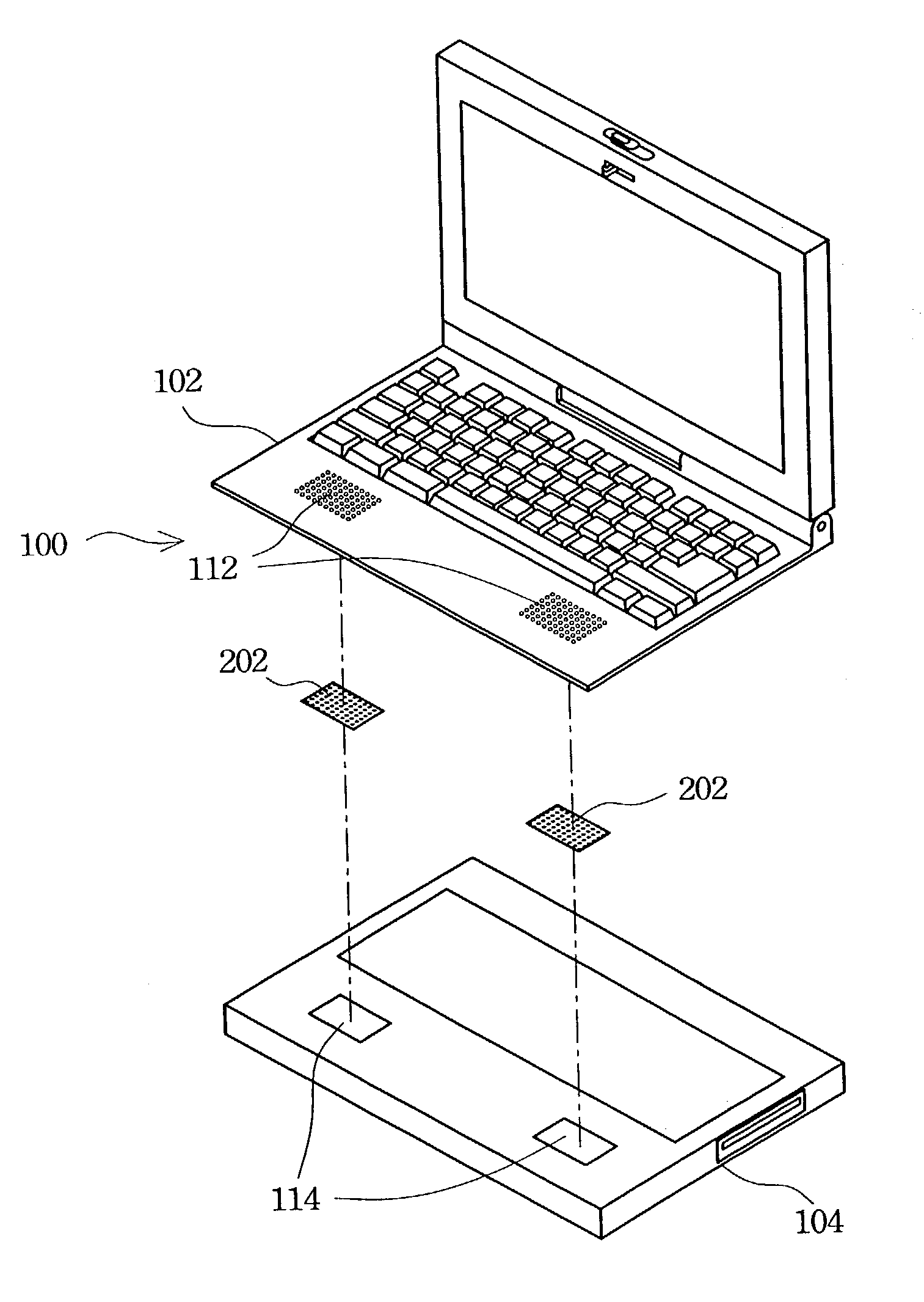

Electrostatic discharge protection apparatus

InactiveUS7012796B2Improve ESD protection capabilityEasy to chargeMagnetic/electric field screeningDigital processing power distributionEngineeringElectronic component

An electrostatic discharge protection apparatus is described. A multi-hole conductive layer is placed between a multi-hole structure and an electronic element of an electronic device. The multi-hole electric conductive layer contacts a conductive layer on the inside surface of a case of the electronic device. It dissipates the electric charges accumulated on the multi-hole structure because of a lack of the conductive layer, and thus prevents the accumulated electric charges from discharging to damage the electronic element.

Owner:ARIMA COMP

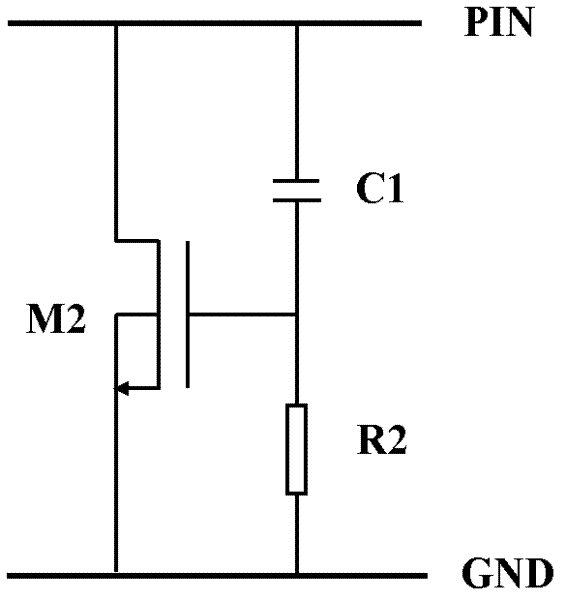

Electrostatic protection circuit of submicron integrated circuit

ActiveCN102339825AImprove ESD protection capabilityUniform conductionSolid-state devicesSemiconductor devicesCapacitanceHemt circuits

The invention discloses an electrostatic protection circuit of a submicron integrated circuit, comprising a first NMOS (N-metal-oxide-semiconductor) tube, a second capacitor, a second NMOS tube, a second resistor, a third capacitor and a first diode. The electrostatic protection circuit is used for solving the problems that the conduction is uneven and the coupling capacitance influences input and output signals in a GCNMOS (grounded-gate negative-channel metal oxide semiconductor) structure and provides preferable ESD (electrostatic discharge) protection for the submicron integrated circuit as well as is in no need of additional processing steps, thus reaching the purposes of improving the ESD electrostatic protection capacity of the integrated circuit and simplifying the technology, avoiding the cost increment and improving the product competitiveness.

Owner:WUXI CRYSTAL SOURCE MICROELECTRONICS CO LTD

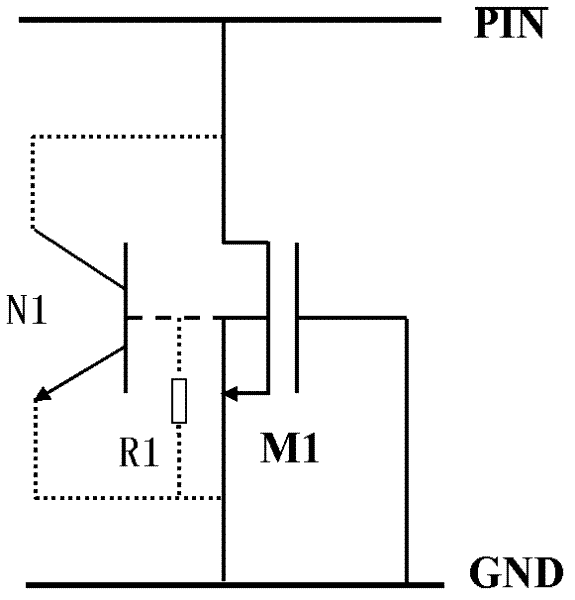

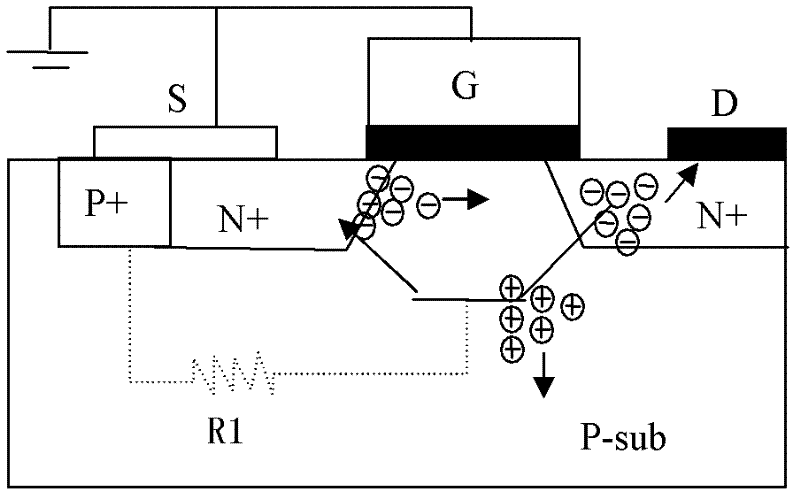

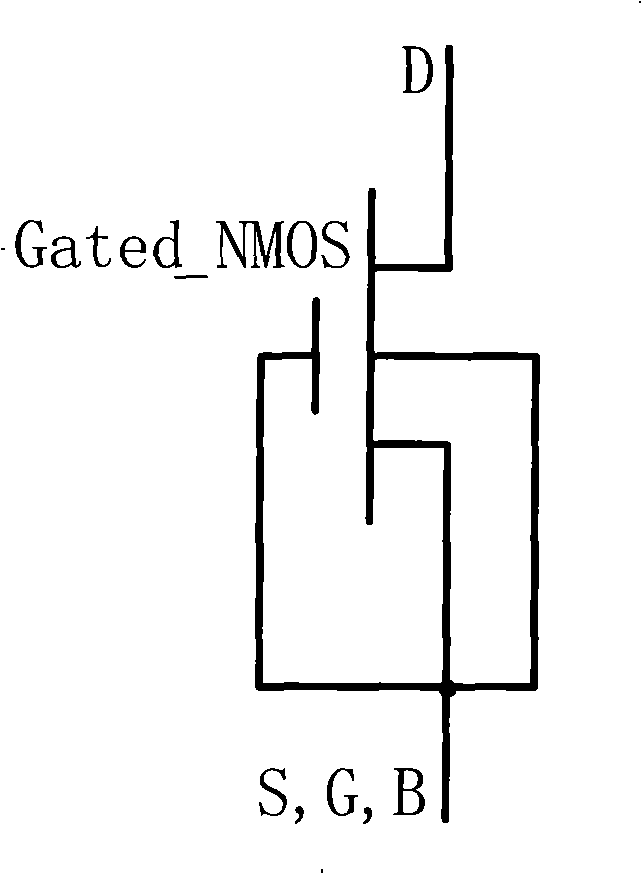

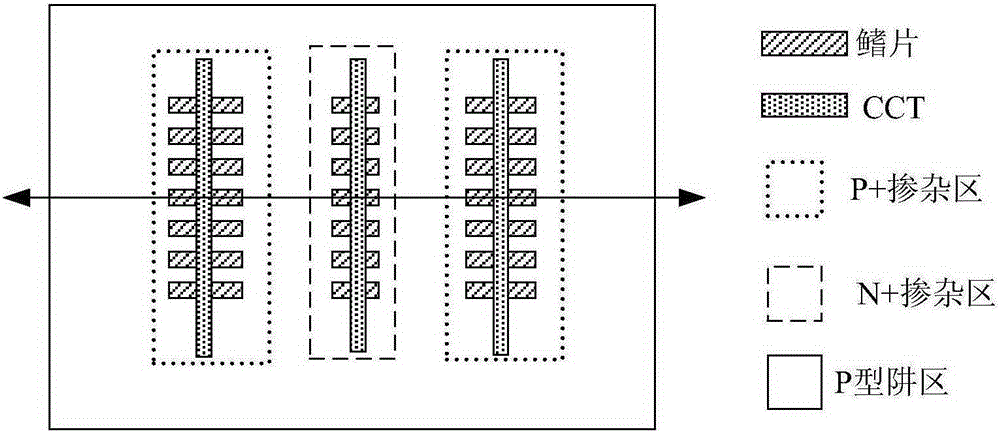

Method for improving ESD protection device uniform conduction

InactiveCN101409444AImprove uniform conductionLower the trigger voltageSemiconductor/solid-state device detailsSolid-state devicesHigh resistanceCommon drain

The invention discloses a method for improving even conduction of an ESD protection device. The method is suitable for characteristic improvement of an electrostatic discharge (ESD) protection device in an integrated circuit, wherein, an MOS transistor is provided with a plurality of finger-shaped components which are connected with each other in parallel, and each of the finger-shaped component is respectively connected with a parasitic triode in parallel, and a collector electrode (i.e., a drain electrode of the MOS transistor) of each parasitic triode is coupled with an operating potential terminal or an I / O terminal of the integrated circuit by a common drain line; an emitter electrode (i.e., a source electrode of the MOS transistor) of the parasitic triode is connected with a common ground potential terminal together with a gate electrode and a substrate of the MOS transistor. The method is characterized in that: the substrate terminal of the MOS transistor is also serially connected with a high-resistance apparatus in the ESD protection device, and the substrate terminal of the MOS transistor is further coupled to the common ground potential terminal together with the source electrode and the gate electrode, which can reduce trigger voltage of Gated_MOSFET, causes a large-sized protection device to be more evenly conducted, improves the ESD protection capability of the device, and further reduces the circuit design area and lower the development cost.

Owner:HEJIAN TECH SUZHOU

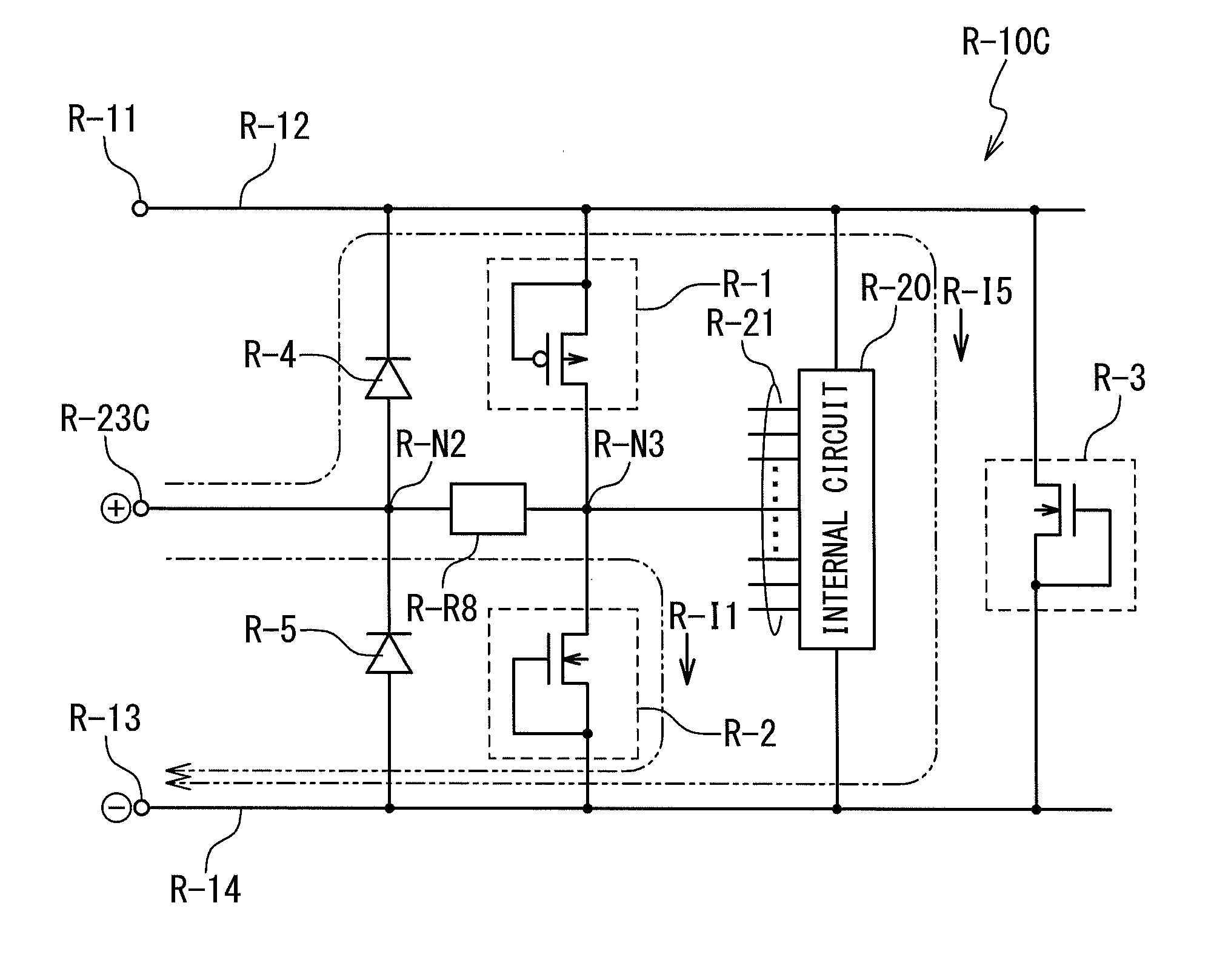

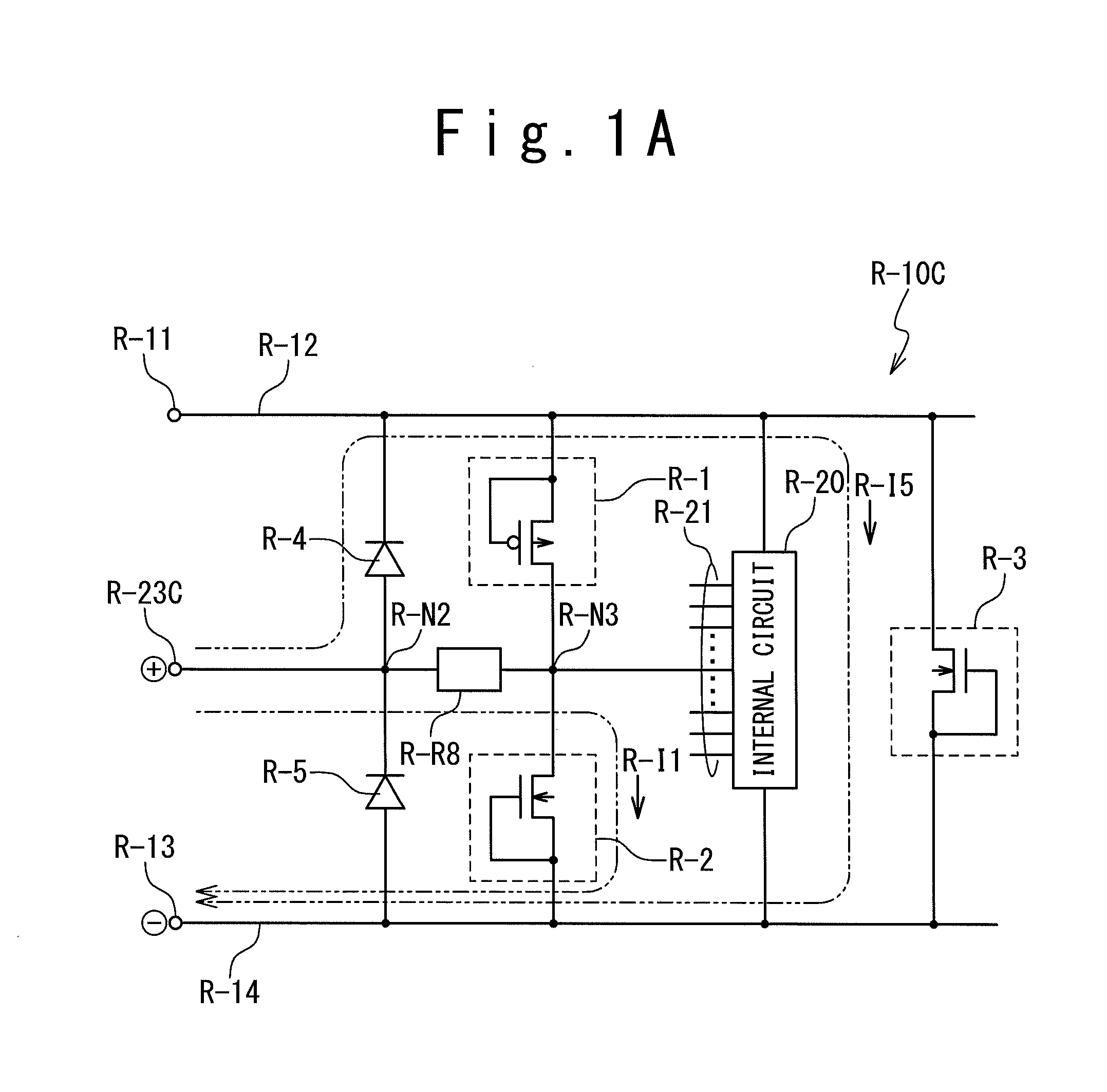

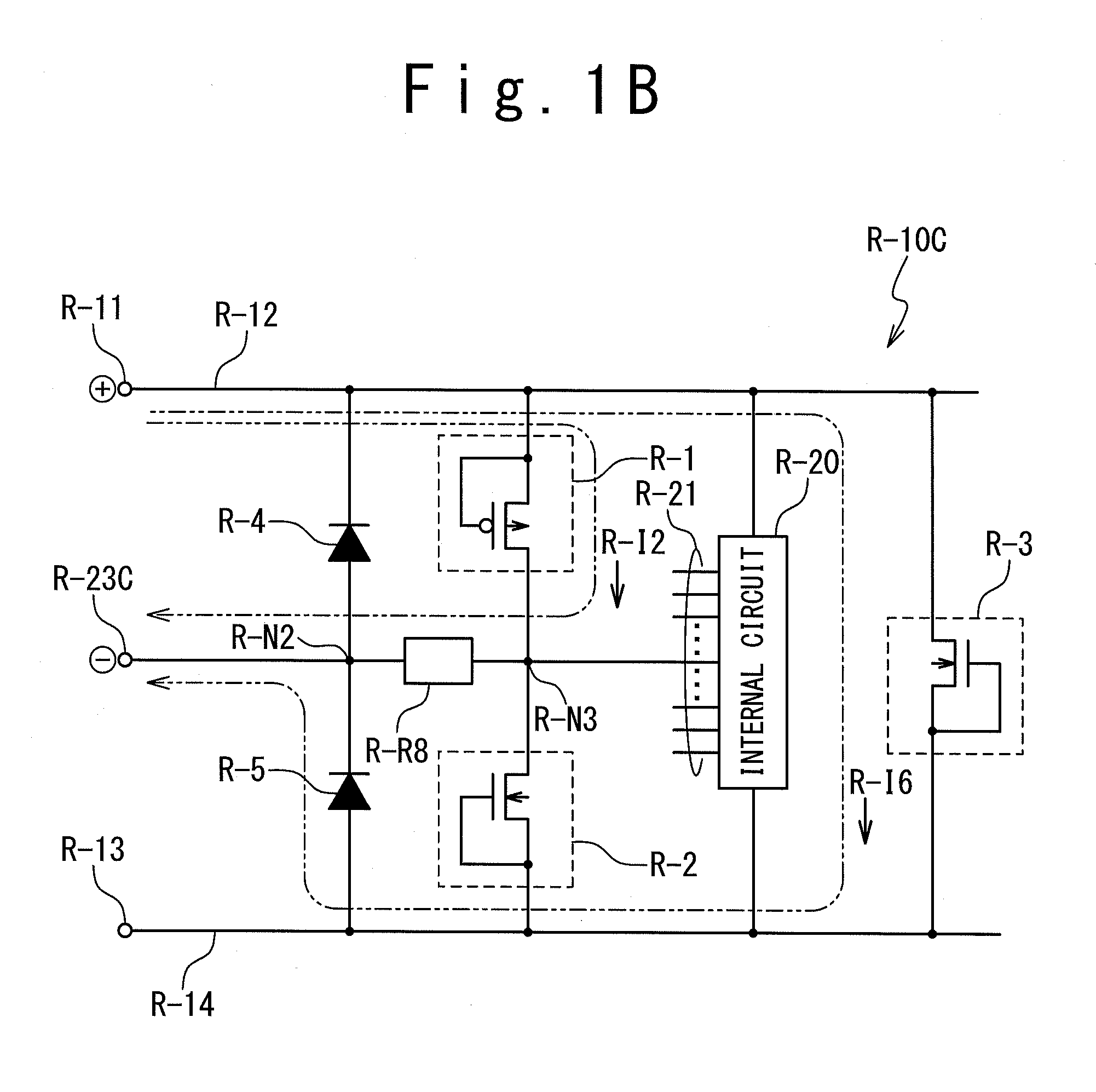

Semiconductor device and electrostatic discharge protection method for the semiconductor device

InactiveUS20100309593A1Improve ESD protection capabilitySuppress surge voltageEmergency protective arrangements for limiting excess voltage/currentPower semiconductor deviceEngineering

For enhancing performance of the electrostatic discharge protection for a semiconductor IC (integrated circuit), the electrostatic discharge protection circuit includes: a power source system for supplying a current to a semiconductor IC in the semiconductor device through a power source potential line and a reference potential line; a primary protection circuit for releasing a surge current to the power source system through a first node connected to a signal terminal when the surge current is generated at the signal terminal; a trigger circuit for generating a trigger signal in response to a surge voltage generated at the power source system; and a secondary protection circuit. The secondary protection circuit releases the surge current to the power source system through a second node connected between the first node and the semiconductor IC in response to the trigger signal, so that the surge voltage can be rapidly suppressed near the semiconductor IC.

Owner:RENESAS ELECTRONICS CORP

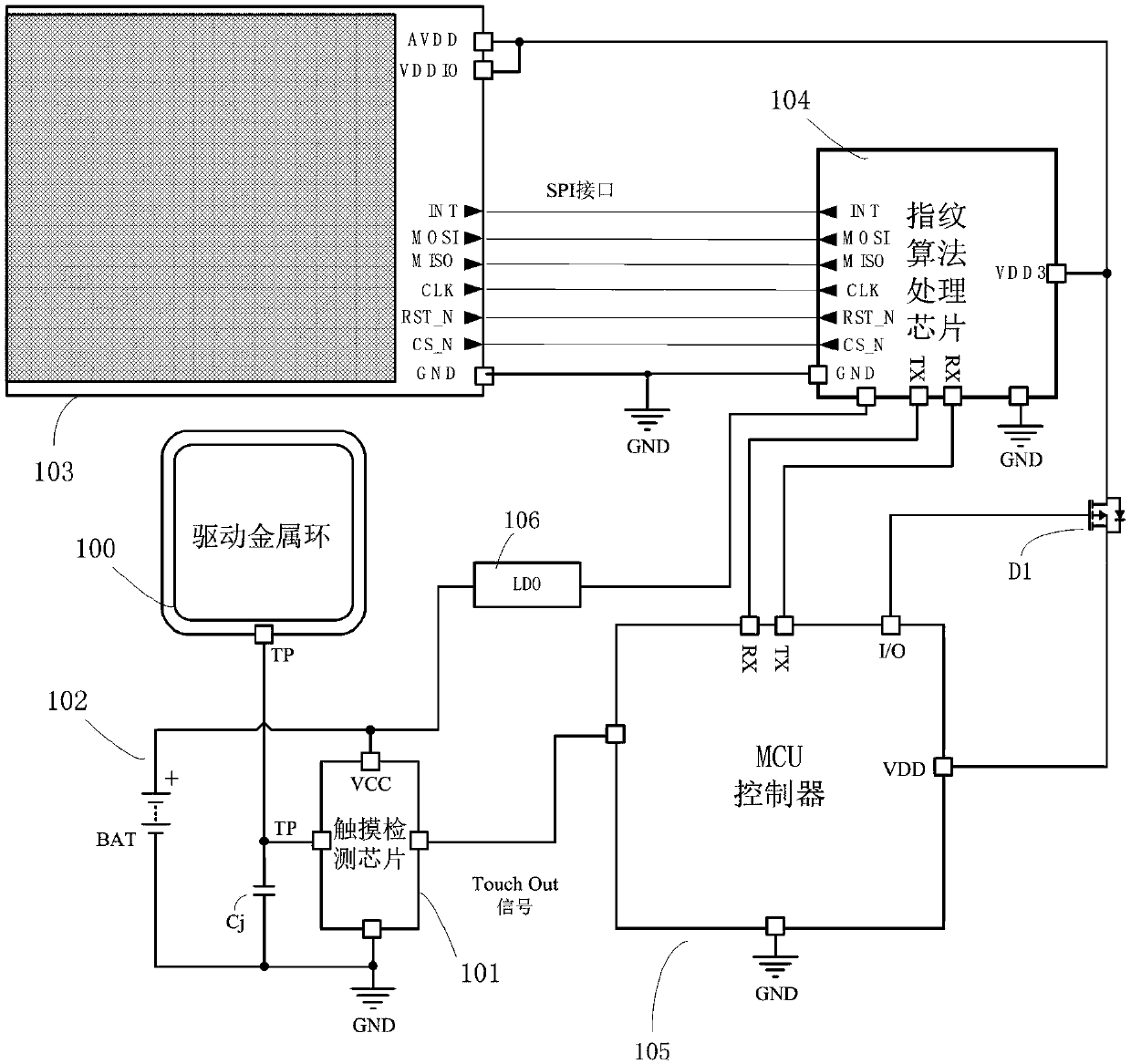

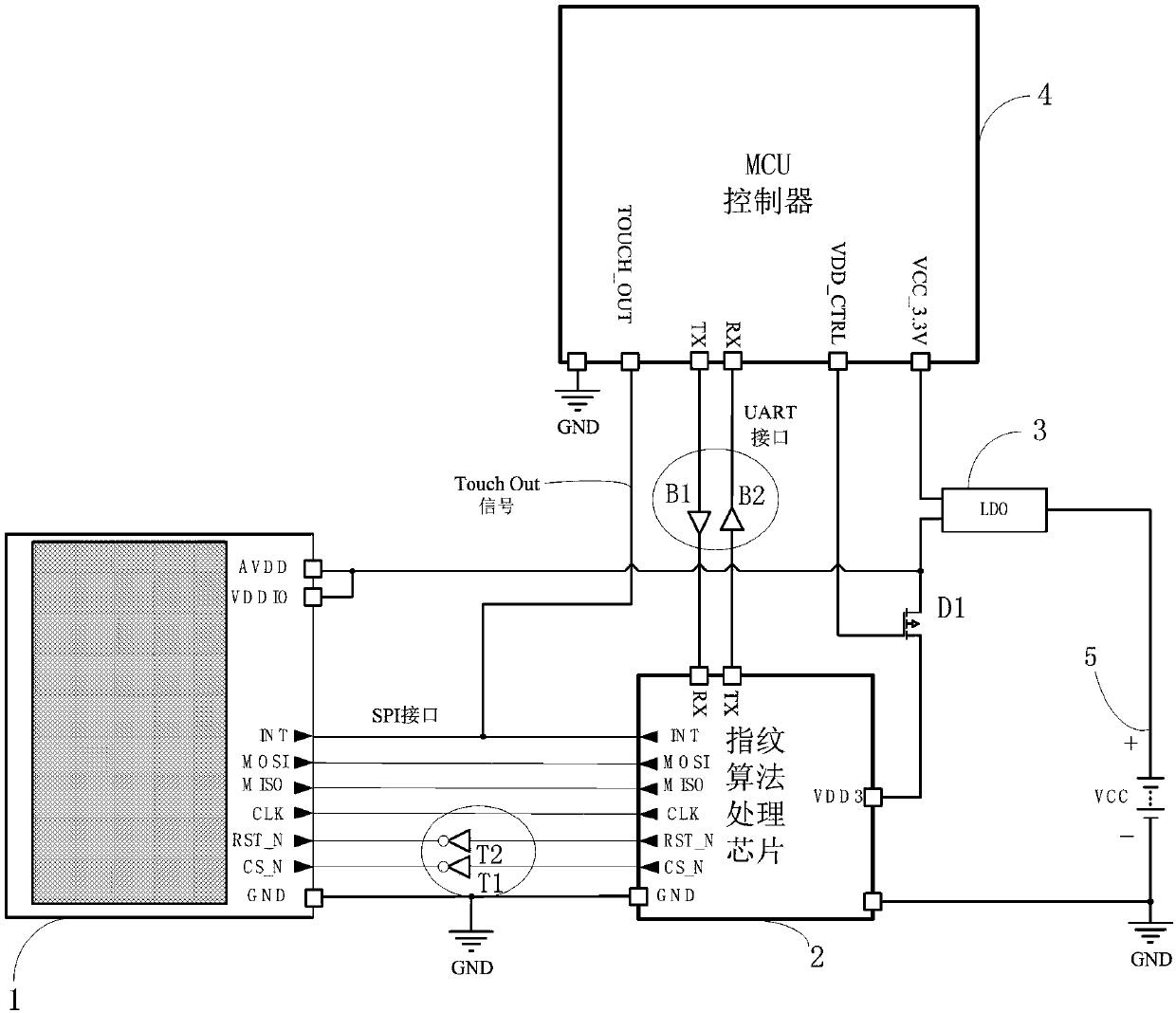

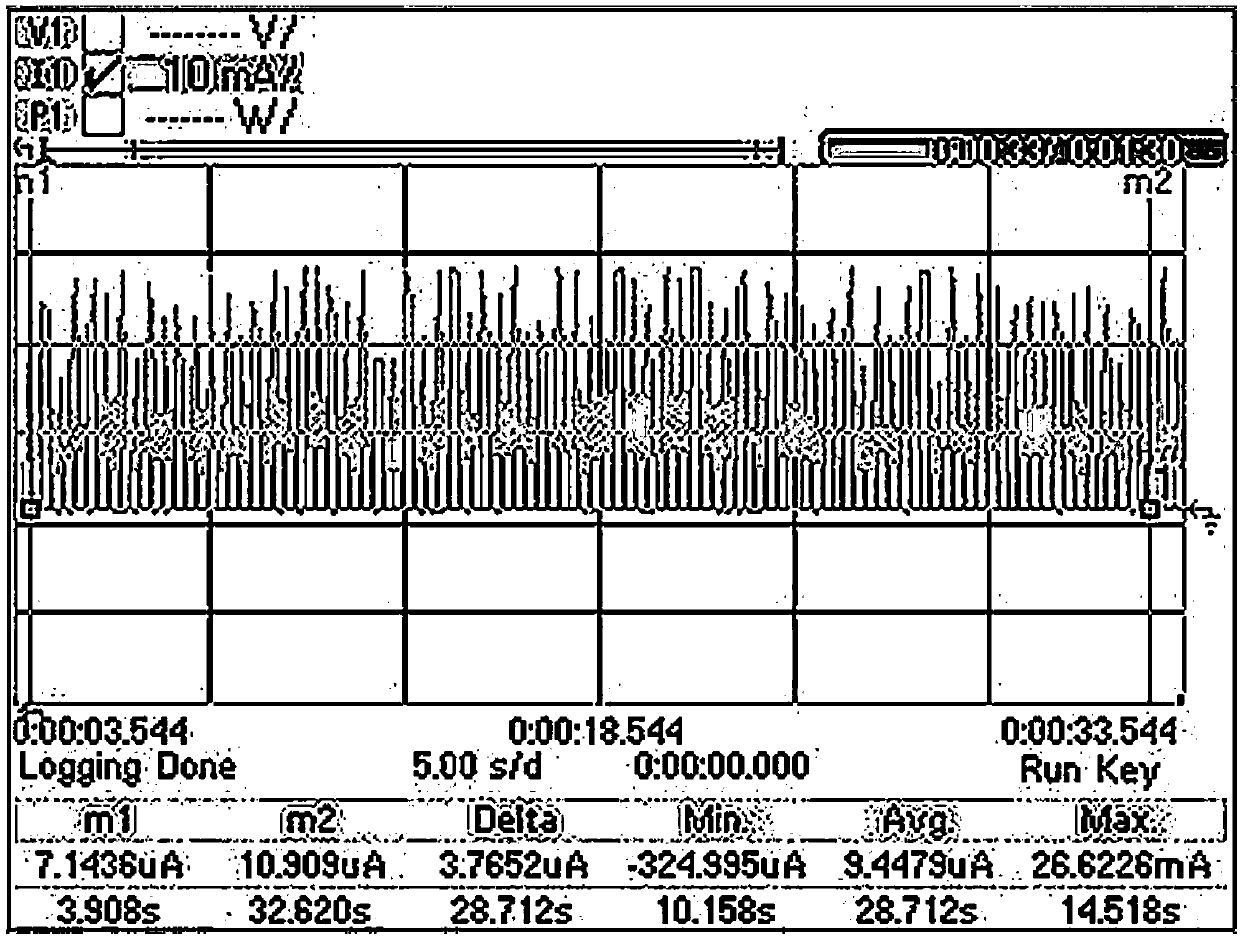

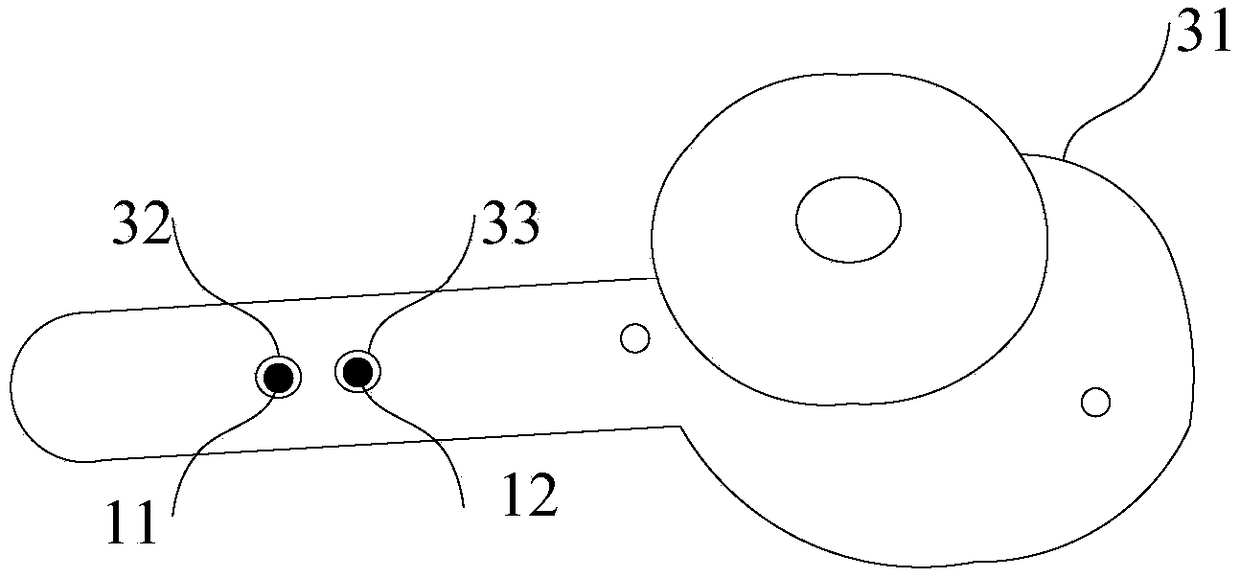

A fingerprint identification device and method without a metal ring and a touch detection chip

InactiveCN109684975AMeet the detection functionMeet the testing requirementsCharacter and pattern recognitionElectricityIdentification device

The invention discloses a fingerprint identification device without a metal ring and a touch detection chip, and the device comprises a fingerprint sensor which supports a low-power-consumption fingerdetection mode, and is used for collecting fingerprint data; The fingerprint algorithm chip is connected to the fingerprint sensor; The power supply unit is used for providing power; MCU controller:the Fingerprint sensor, The fingerprint algorithm chip and the power supply unit are electrically connected to the MCU controller. The MCU controller is used for controlling the MCU controller to be used for controlling the MCU controller. when the fingerprint sensor detects that a finger touches the fingerprint sensor in a finger detection mode, the output end of the power supply unit is connected with the power supply end of the fingerprint algorithm chip, so that the fingerprint algorithm chip is powered on, and fingerprint data collected by the fingerprint sensor are processed. A metal ring and a touch detection chip are not needed, and the finger detection function and the low-power-consumption standby requirement can be met.

Owner:SHENZHEN BETTERLIFE ELECTRONICS SCI & TECH

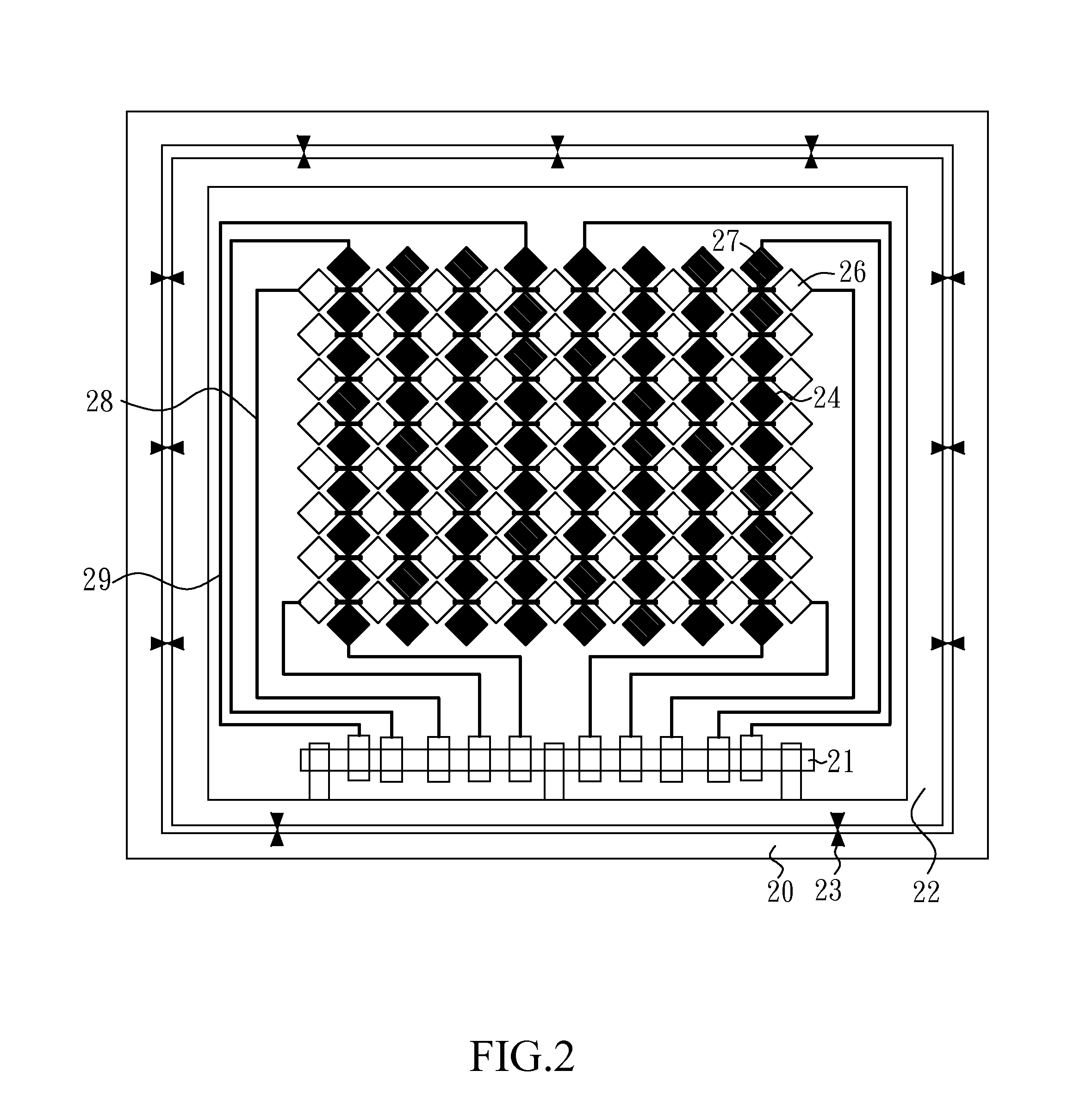

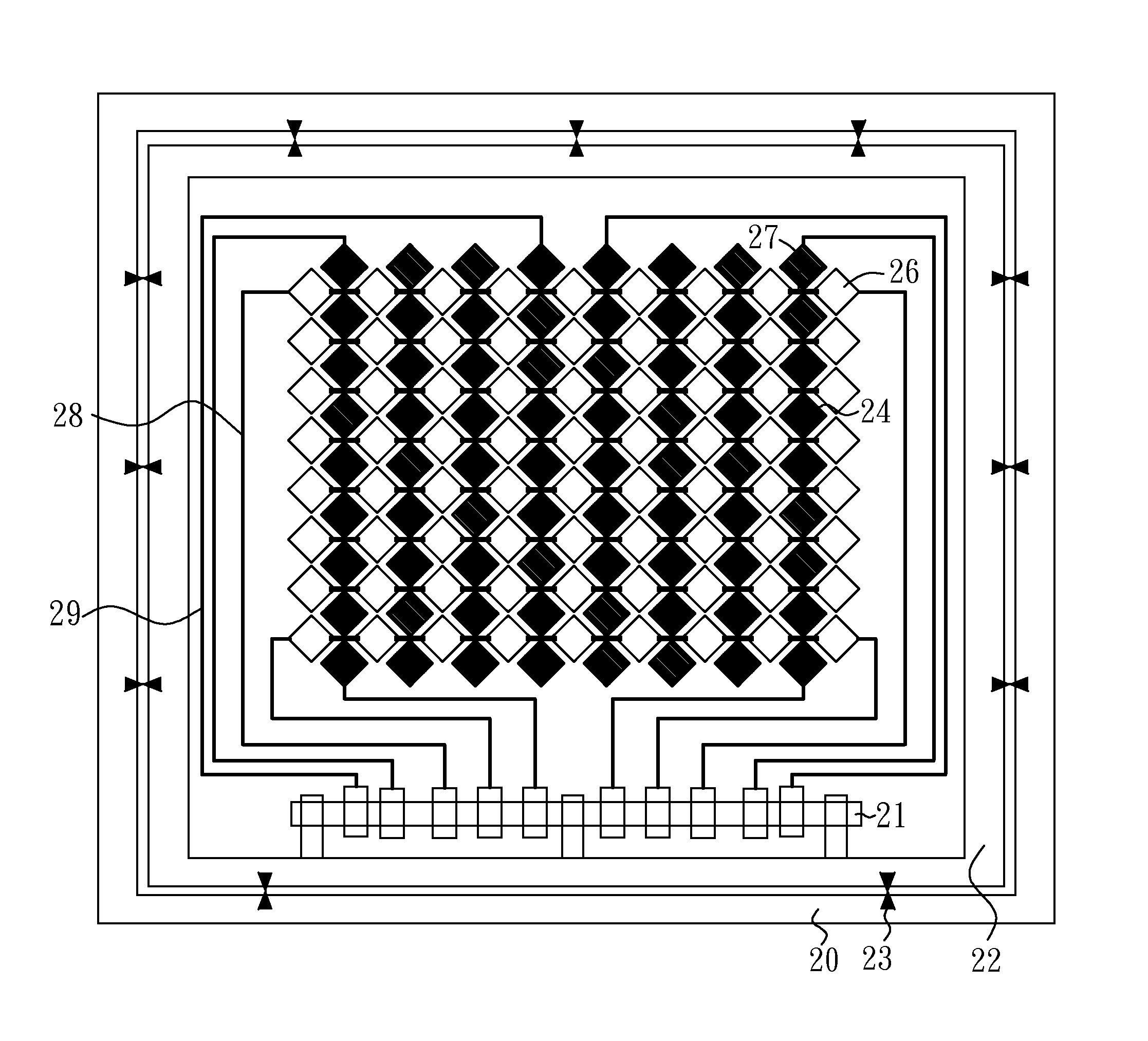

Fingerprint identification chip with enhanced ESD protection

ActiveUS20160154989A1Improve ESD protection capabilityCharacter and pattern recognitionCable/conductor manufactureEngineeringFingerprint

A fingerprint identification chip with enhanced ESD protection includes receiving pads disposed on a surface of a chip and arranged in a matrix format. The receiving pad has a central region and a peripheral region which surrounds at least an edge of the central region. The peripheral region of the receiving pad is higher than the central region.

Owner:EGALAX EMPIA TECH INC

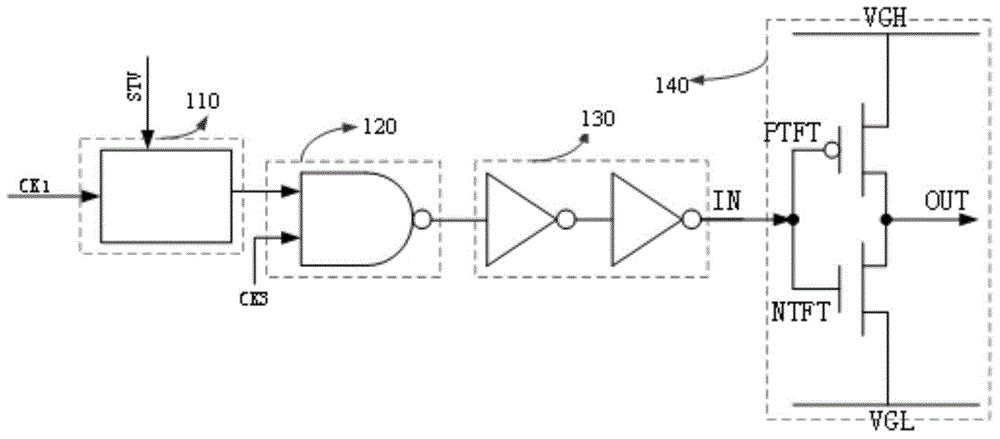

Low-power-consumption phase inverter, low-powder-consumption GOA circuit and liquid crystal display panel

ActiveCN104952413AAvoid short-circuit power dissipationShorten recovery timeStatic indicating devicesLiquid-crystal displayCoupling

The invention discloses a low-power-consumption phase inverter, a low-powder-consumption GOA circuit and a liquid crystal display panel, wherein the low-power-consumption phase inverter comprises a phase inverter body which is formed by connecting a P-type transistor and an N-type transistor in series; a voltage coupling element is arranged between the input end and the output end of the phase inverter body, so as to enable the amplitude of voltage jump occurring at the output end to be greater than that occurring at the input end when voltage jump occurs at the input end. According to the low-power-consumption phase inverter, the low-powder-consumption GOA circuit and the liquid crystal display panel, provided by the invention, the short circuit power consumption of the phase inverter is avoided, the switching recovery time of the phase inverter is shortened, the response speed of the circuit is increased, and the ESD protection capability of the entire circuit is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

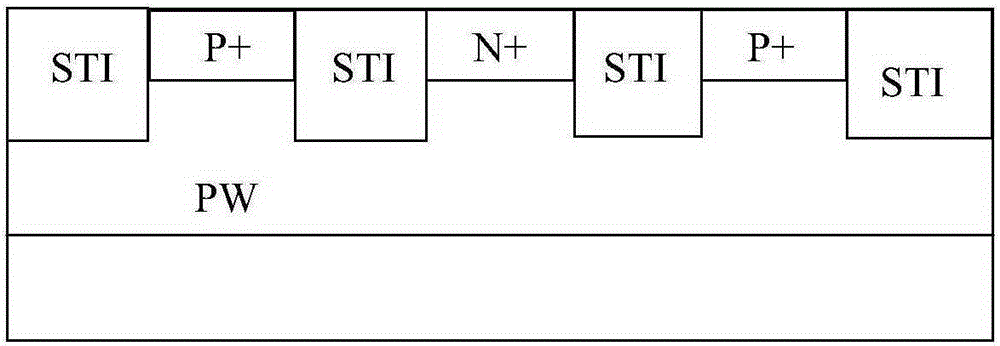

STI diode for ESD protection

ActiveCN106558622AIncrease the secondary breakdown currentLower on-resistanceSolid-state devicesDiodeSalicidePower flow

The invention provides an STI diode for ESD protection, and relates to the technical field of semiconductors. The diode comprises a semiconductor substrate, wherein the interior of the semiconductor substrate is provided with a well region of a first conductive type; a plurality of first fins which are located on the semiconductor substrate and extend in a first direction, wherein the interior of each first fin is provided with a first doped region of a first conductive type, which extends in the first direction; a plurality of second fins which are located among the first fins and extend in the first direction, wherein the interior of each second fin is provided with a second doped region of a second conductive type, which extend in the first direction; and an isolation structure which is formed on the semiconductor substrate between the first fins and the second fins. The diode provided by the invention improves the area efficiency of a device, enables the uniformity of metal silicide to be better, and enables an ESD device to be higher in secondary breakdown current and smaller in on resistance (Ron).

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

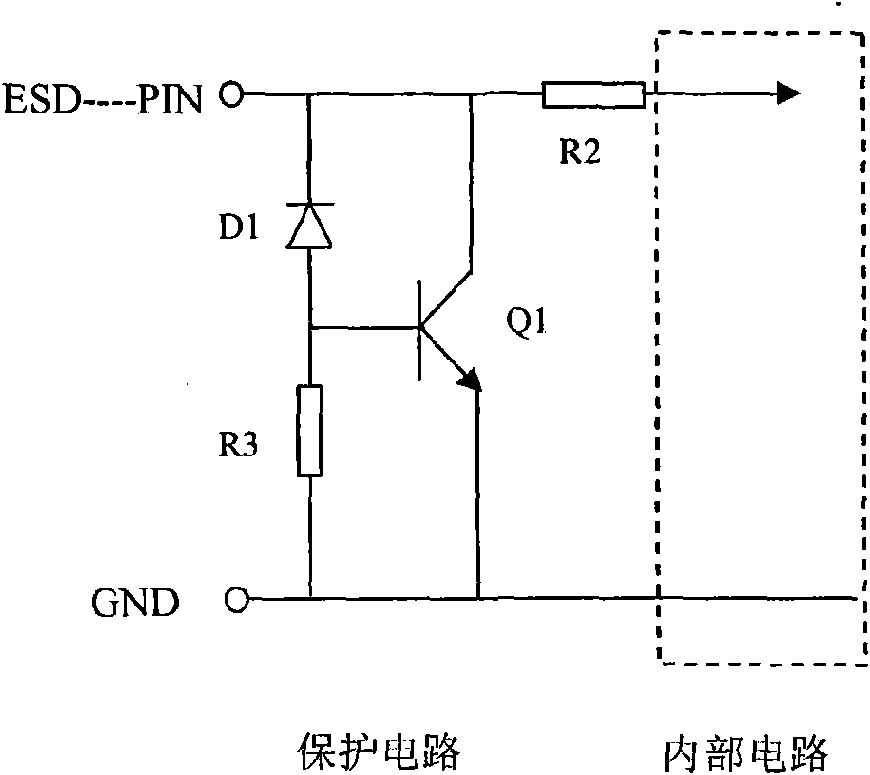

Effective electrostatic discharge protection circuit

ActiveCN101621198AEffective protectionImprove reliabilityEmergency protective arrangements for limiting excess voltage/currentManufacturing technologyBicmos process

The invention relates to an effective electrostatic discharge protection circuit; electrostatic discharge (ESD) is the most important reliability problem in the current integrated circuits. Along with the development of manufacturing technology of the integrated circuits, characteristic dimension is reduced continuously, the anti-static electricity capacity is weaker, however, under the micro-electronic manufacturing and using environment, the chance that devices suffer from ESD is more, and the effect of the ESD on the integrated circuits is greater, and ESD damage is an attention focus on the new process. The invention starts from the basic starting point, the limit of the traditional simple ESD protective circuit is broken through, and the ESD protective circuit is improved on the structure with the consideration of domain layout and design rules, but the process flows are basically consistent with the regular BICMOS processes, thereby ensuring good ESD protecting capacity of the integrated circuits and being capable of not leading the process to be complicated, improving the reliability of the circuit without increasing cost and improving the competitiveness of the circuit.

Owner:WUXI CRYSTAL SOURCE MICROELECTRONICS CO LTD

Insulated gate bipolar transistor (IGBT) electrostatic discharge (ESD) protection devices

ActiveUS8049307B2Improve ESD protection capabilityEnlarge regionTransistorSolid-state devicesParasitic bipolar transistorEngineering

Insulated gate bipolar transistor (IGBT) electrostatic discharge (ESD) protection devices are presented. An IGBT-ESD device includes a semiconductor substrate and patterned insulation regions disposed on the semiconductor substrate defining a first active region and a second active region. A high-V N-well is formed in the first active region of the semiconductor substrate. A P-body doped region is formed in the second active region of the semiconductor substrate, wherein the high-V N-well and the P-body doped region are separated with a predetermined distance exposing the semiconductor substrate. A P+ doped drain region is disposed in the high-V N-well. A P+ diffused region and an N+ doped source region are disposed in the P-body doped region. A gate structure is disposed on the semiconductor substrate with one end adjacent to the N+ doped source region and the other end extending over the insulation region.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

Integrated photo detector, method of making the same

ActiveUS20180019239A1Enhanced electrostatic discharge damage (ESD) protectionReduce widthSolid-state devicesRadiation controlled devicesCapacitancePhotovoltaic detectors

An integrated photo detector with enhanced electrostatic discharge damage (ESD) protection. The integrated photo detector includes a first photodiode formed in the SOI substrate and associated with a first p-electrode and a first n-electrode. Additionally, the integrated photo detector includes a second photodiode formed in the SOI substrate associated with a second p-electrode and a second n-electrode forming a capacitance no larger than a few femto Faradays. Moreover, the integrated photo detector includes a first electrode and a second electrode disposed respectively on the SOI substrate. The first / second electrode is respectively connected to the first p / n-electrode via a first / second metallic layer patterned with a reduced width from the first / second electrode to the first p / n-electrode and connected to the second p / n-electrode via a first / second metallic wire to make a parallel coupling between the first photodiode and the second photodiode with an ESD threshold of about 100V.

Owner:MARVELL ASIA PTE LTD

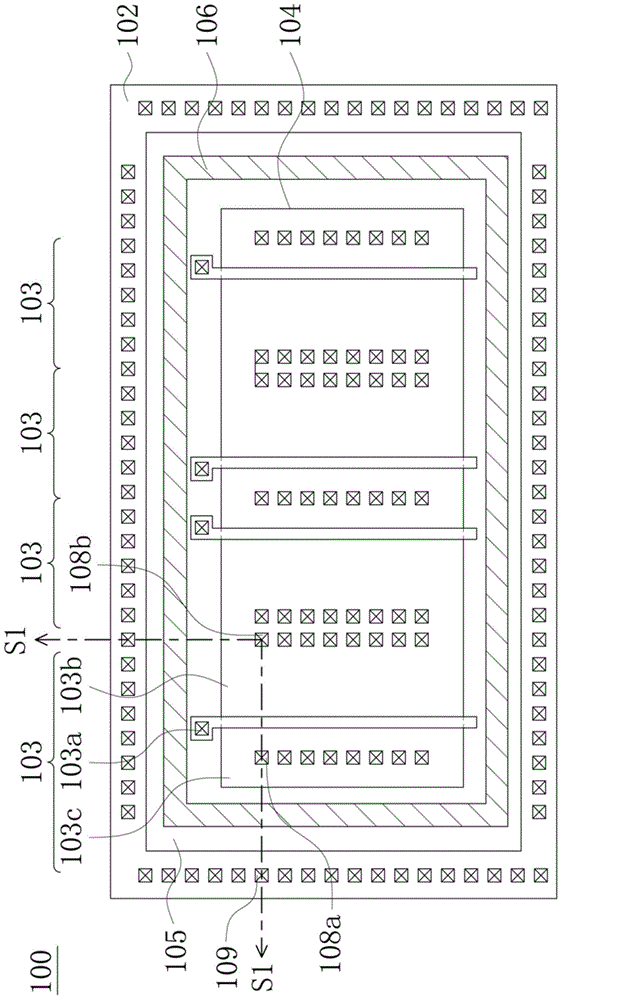

Array substrate and liquid crystal display

InactiveCN106773399AImprove ESD protection capabilityStrong ESD protection abilityNon-linear opticsLiquid-crystal displayElectrode

The embodiment of the invention provides an array substrate. The array substrate comprises a substrate and a metal layer, a flat layer, an insulation layer and a common electrode layer which are sequentially formed on the substrate, wherein the public electrode layer is grounded. By enabling the public electrode layer to be grounded, the ESD protection capacity of the public electrode layer is improved, the public electrode layer is prevented from being damaged by explosion, and then the stability of the array substrate is improved. In addition, the debugging process of a liquid crystal display can be simplified. The liquid crystal display is high in ESD protection capacity and stability.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

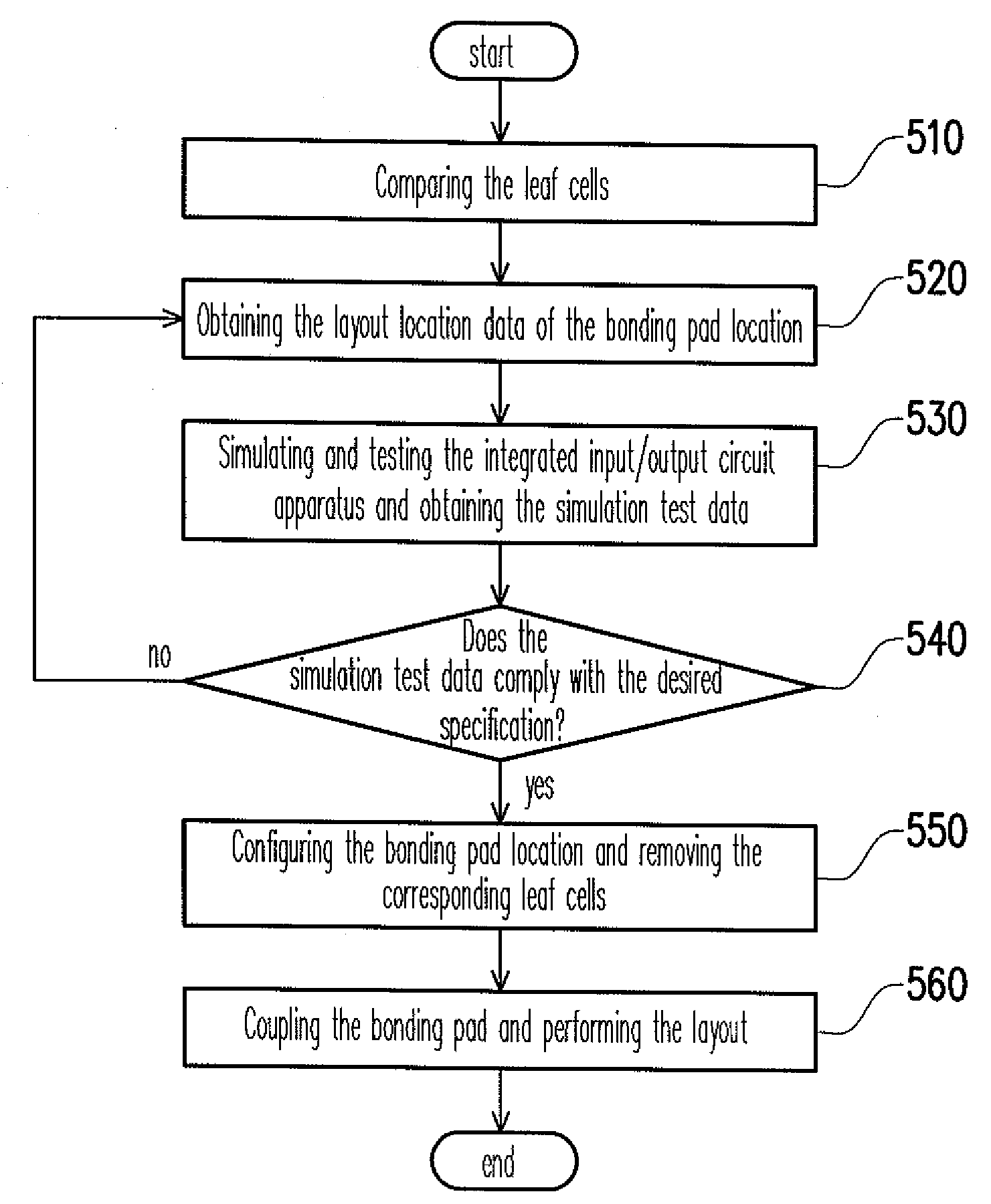

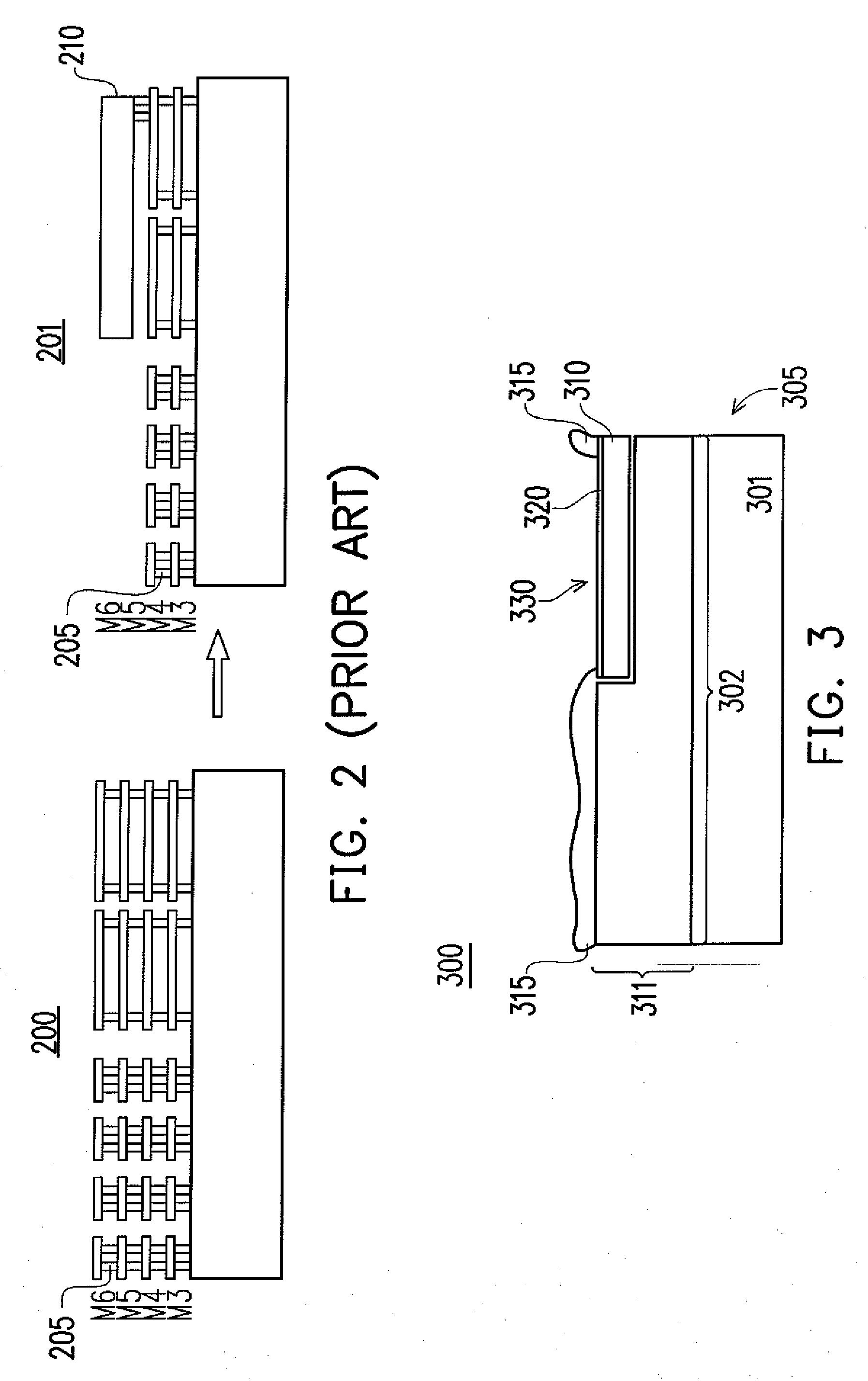

Apparatus for integrated input/output circuit and verification method thereof

InactiveUS20080163146A1Reduce occupancyReduce resistanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical resistance and conductanceElectricity

An apparatus for integrated input / output circuit and a verification method thereof are provided. The apparatus effectively reduces the chip area occupation and cost, and decreases the resistance on an electrical transmission path of the integrated input / output circuit to improve the circuit efficiency. The apparatus comprises a metal structure and a plurality of integrated circuit components. Wherein, the integrated circuit comprises the integrated circuit components and the metal structure that has a bonding pad. In addition, the integrated circuit components are disposed directly under the metal structure and coupled to the metal structure. In which, the metal structure provides an electrical transmission path for the integrated circuit.

Owner:WU CHIH HUNG +1

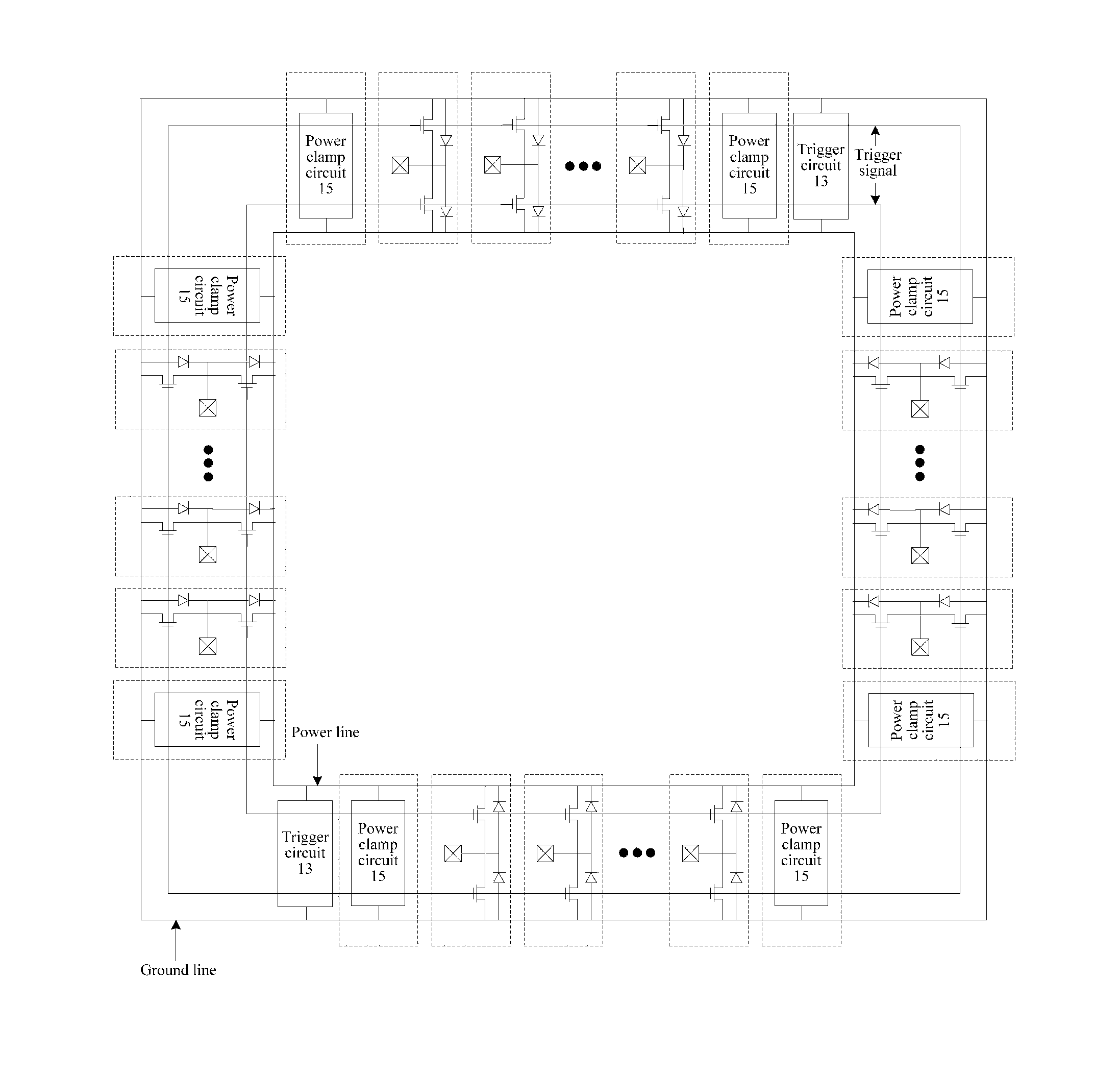

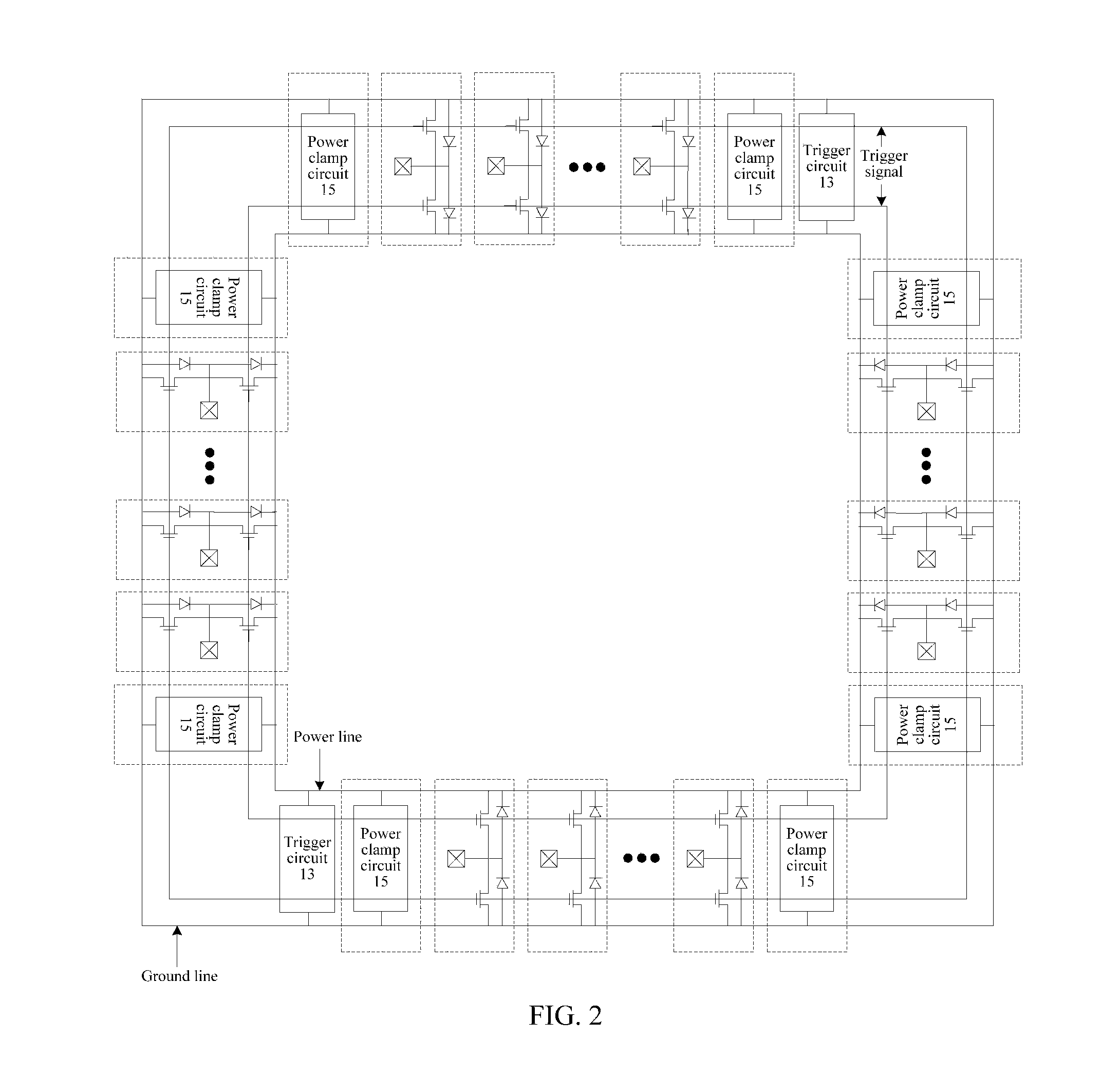

Whole-Chip Esd Protection Circuit and Esd Protection Method

InactiveUS20150055259A1Improve esd protection capabilityChip size be reduceSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentElectrostatic dischargeInput/output

A whole-chip Electrostatic Discharge (ESD) protection circuit and protection method are provided. The whole-chip ESD protection circuit comprises: input / output (I / O) units located between a power line and a grounding wire; a power clamp circuit located between the power line and the grounding wire and connected to the I / O units, any power clamp circuit being shared by multiple I / O units; and an ESD trigger circuit located between the power line and the grounding wire. The ESD trigger circuit generates an ESD trigger signal when an ESD events occurs and transmits the ESD trigger signal to the power clamp circuit and each I / O unit so that the power clamp circuit and each I / O unit form a current discharge path from the power line to the grounding wire respectively. Compared with the prior art, the present invention fully utilizes an existing driving transistor in the I / O unit to realize efficient whole-chip ESD protection and avoids adding too many power clamp circuits in the whole chip with regard to ESD, thereby reducing the overall size of the chip and lowering the cost.

Owner:MONTAGE TECHNOLOGY CO LTD

An ESD protection circuit and an electronic device

InactiveCN109149540AImprove the protective effectAvoid interferenceEmergency protective arrangements for limiting excess voltage/currentEngineeringElectron

The embodiment of the invention provides an ESD protection circuit and an electronic device. The circuit comprises an input terminal, a ground terminal, an ESD protection device, a secondary protection circuit and an output terminal. The input terminal is used for receiving an ESD current signal when an ESD event occurs. The ESD protection device is respectively connected with the input terminal and the ground terminal, and is used for providing a discharge path for the ESD current signal, and guiding the ESD current signal from the input terminal to the ground terminal; The secondary protection circuit is connected in parallel with the ESD protection device and used for suppressing the ESD current signal; The output terminal is connected with the secondary protection circuit, and is usedfor connecting with the protected circuit. Thus, the ESD protection device and the secondary protection circuit can perform ESD protection on the protect circuit and reduce the influence of ESD on theelectronic components in the circuit.

Owner:MOBVOI INFORMATION TECH CO LTD

Semiconductor electrostatic discharge protection device

InactiveCN104681542AImprove ESD protection capabilityLarge resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringProtection ring

The invention discloses a semiconductor electrostatic discharge protection device, which comprises a first electric transistor, a second electric trap region, a second electric protection ring and a semiconductor separation region, wherein the first electric transistor is formed in the second electric trap region, the second electric protection ring surrounds the first electric transistor, the semiconductor separation region is positioned between the first electric transistor and the second electric protection ring, and surrounds the first electric transistor, and in addition, the semiconductor separation region is a non-doping region, a first electric doping region or a second electric doping region with the doping concentration being smaller than that of the second electric trap region.

Owner:UNITED MICROELECTRONICS CORP

Touch panel

InactiveUS9086772B2Improve ESD protection capabilityInput/output processes for data processingEngineeringUltimate tensile strength

A touch panel includes a transparent substrate, electrodes, traces and at least two ground rings on the transparent substrate. The traces connect the electrodes to transmit signals. At least two ground rings connect to each other through a plurality of bridges and surround the electrodes and the traces. Each bridge has at least one ESD tip or peak to enhance local electric field strength and electrostatic discharge.

Owner:HENGHAO TECH CO LTD

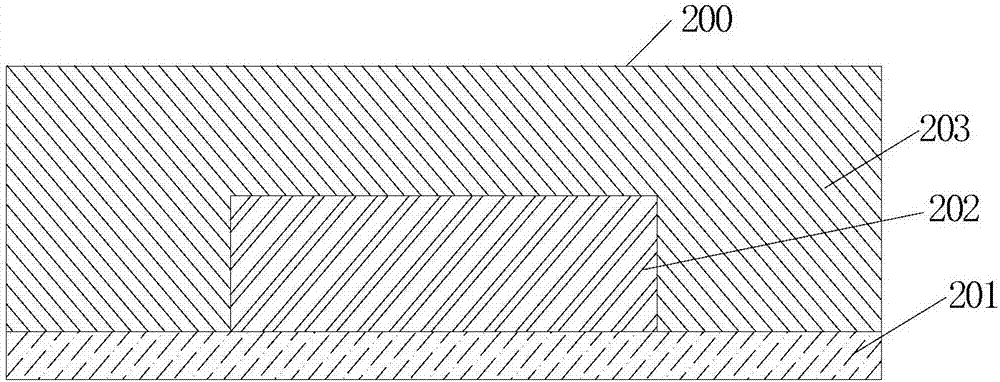

Sensing structure of one-glass solution (OGS) touch panel

InactiveUS20150370394A1Improve ESD protection capabilityLow costDigital data processing detailsInput/output processes for data processingProcess complexityTouch panel

A sensing structure of a one-glass solution (OGS) touch panel is provided, which has a designed diversion structure, such that an electrostatic discharge (ESD) protection capability of the sensing structure is improved. According to such design, the ESD protection capability of the sensing structure is improved without increasing a process complexity, so as to avoid energy release of electrostatic charges to cause a damage of the sensing structure.

Owner:CANDO

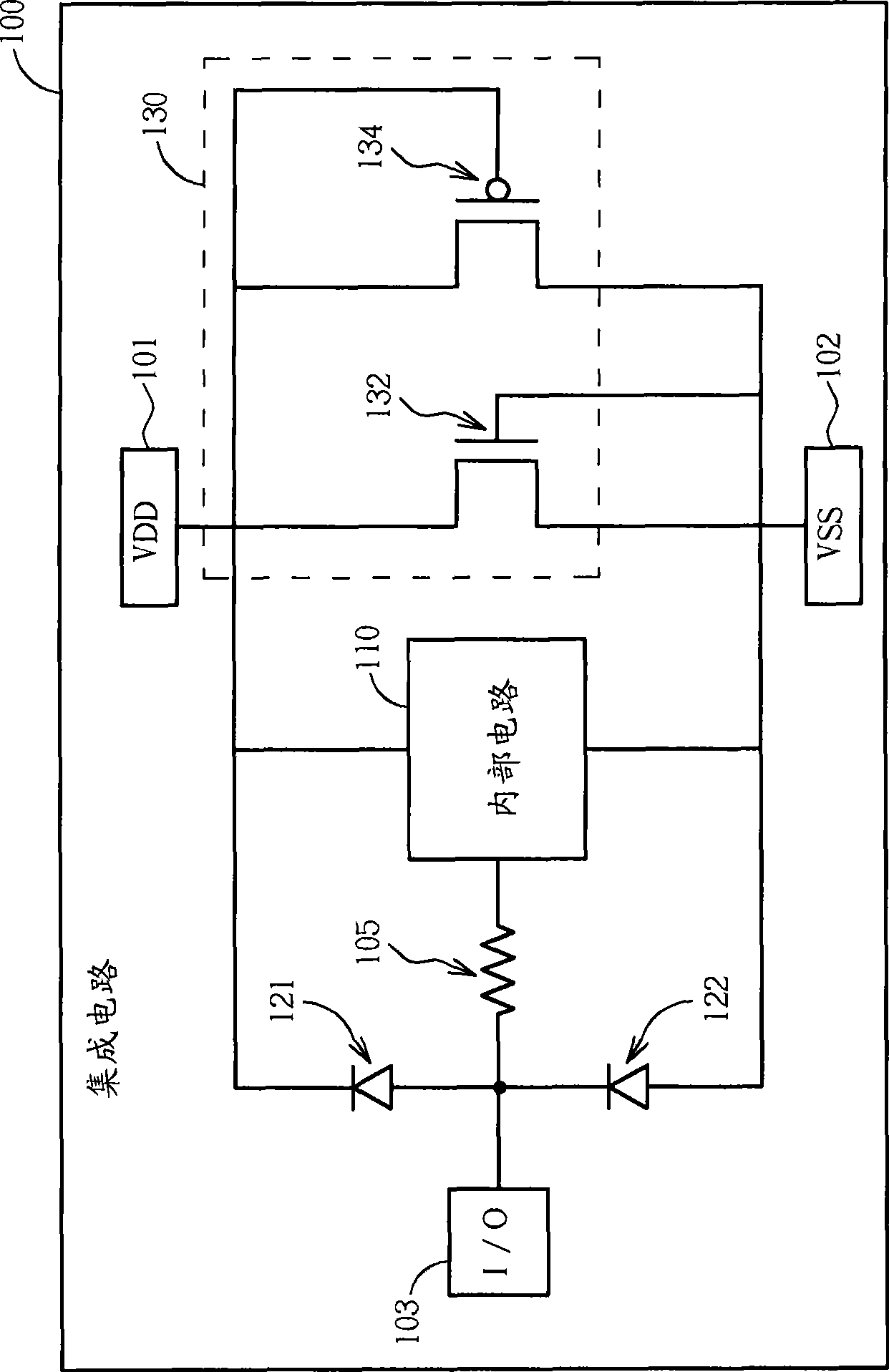

Integrated circuit with electrostatic discharge protecting circuit

ActiveCN101521372AFeatures to Reduce Conduction InconsistencyImprove ESD protection capabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

The invention discloses an integrated circuit with an electrostatic discharge protecting circuit. The integrated circuit comprises a first power source connecting pad, a second power source connecting pad, at least one circuit module and a power source clamping circuit. The circuit module comprises a signal connecting pad, an internal circuit and a first bipolar junction transistor. A first parasitic resistance is arranged between the collector of the first bipolar junction transistor and the second power source connecting pad. The power source clamping circuit comprises at least one first metal-oxide-semiconductor transistor and at least one first parasitic bipolar junction transistor.

Owner:RAYDIUM SEMICON

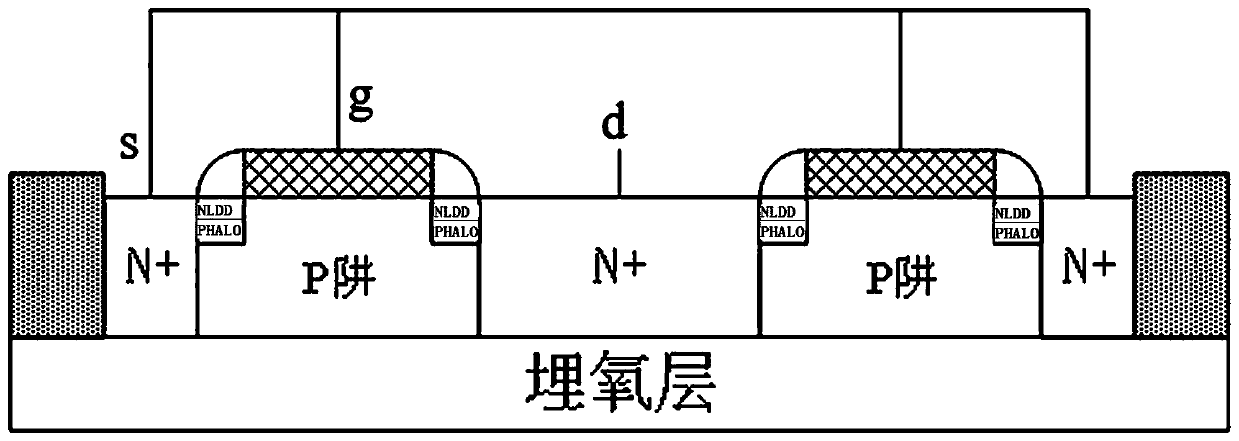

Electrostatic discharge protection structure based on SOI process

ActiveCN111403379AAvoid concentrationEliminate breakdown and burnoutTransistorSolid-state devicesSalicidePower flow

The invention discloses an electrostatic discharge protection structure based on an SOI process. The electrostatic discharge protection structure comprises an SOI substrate and an ESD protection device located on the SOI substrate. The ESD protection device comprises a first conductive area, a second conductive area and a third conductive area, wherein the first conductive area, the second conductive area and the third conductive area are located on the same plane, and the third conductive area makes contact with the first conductive area and the second conductive area respectively. A first electrode is formed on the first conductive area, a second electrode is formed on the second conductive area, a silicide barrier layer is arranged above the third conductive area, and the first electrode and the second electrode are isolated by the silicide barrier layer. According to the invention, the first electrode and the second electrode are isolated through the silicide barrier layer, and when ESD impact occurs, the parasitic triode is conducted to discharge ESD current, so a protected circuit is protected. According to the electrostatic discharge protection structure, an ESD current canbe enabled to flowto a deeper region, and the electrostatic discharge protection capability of the device can be effectively improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com