Method for improving ESD protection device uniform conduction

A device and uniform technology, which is applied in the field of improving the uniform conduction of ESD protection devices, can solve the problems such as the lack of obvious improvement in ESD protection tolerance and the realization of burdens due to high circuit integration, so as to improve ESD protection ability and large ESD Protection capability and the effect of reducing development costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

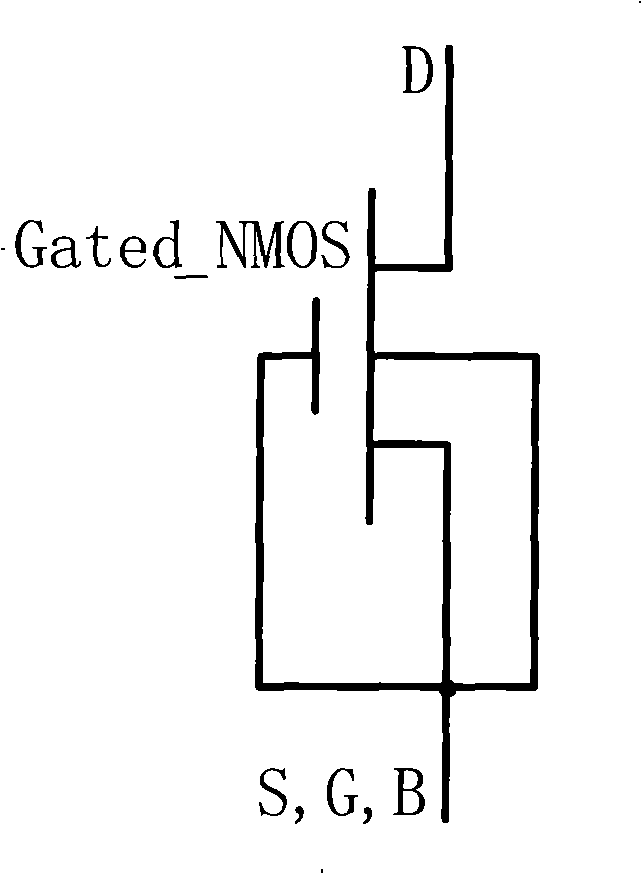

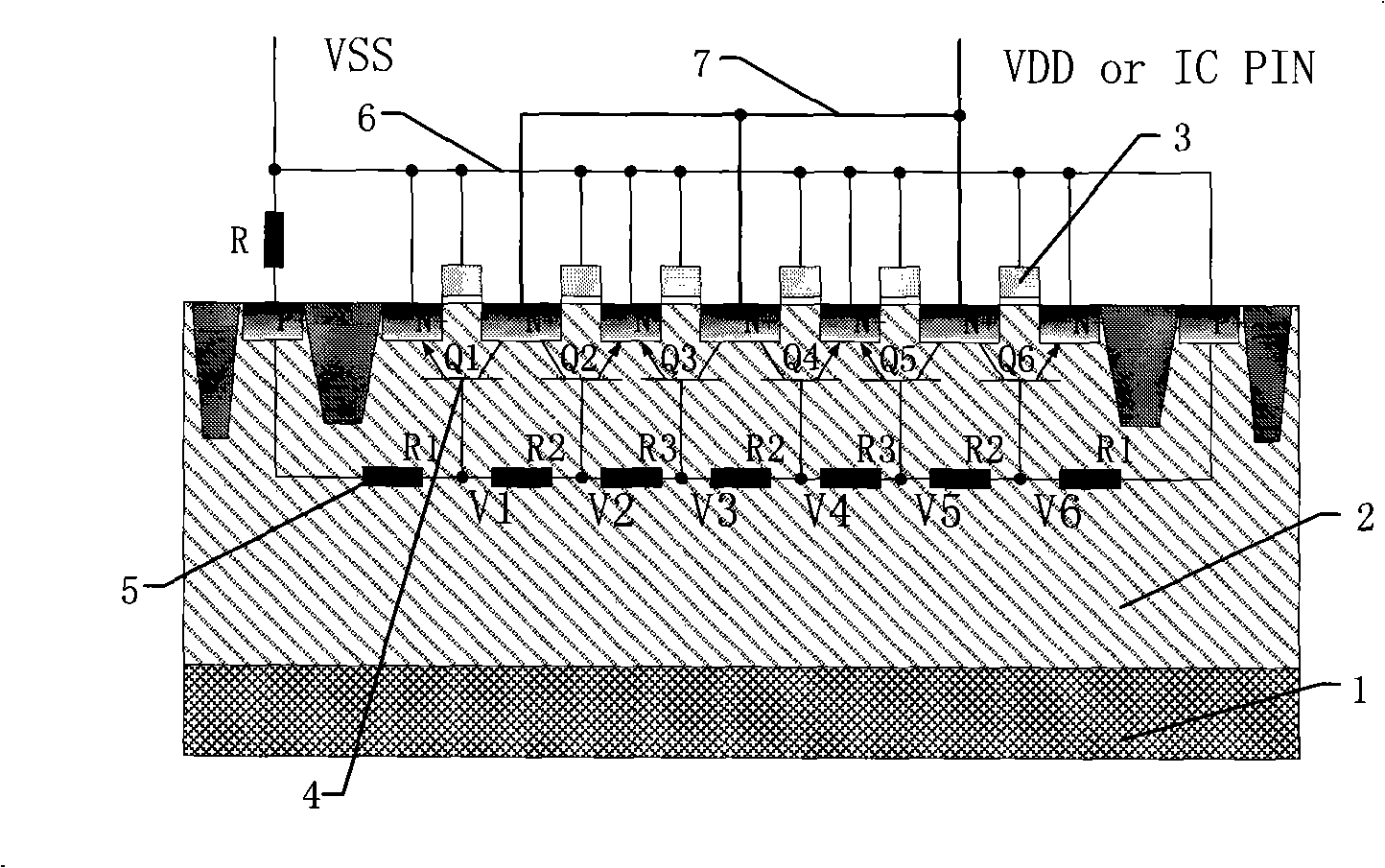

[0035] like image 3 The layout cross-sectional view of the ESD protection device under the implementation of high resistance for the method of the present invention to improve uniform conduction; as Figure 4 for image 3 Schematic diagram of the equivalent circuit of the device. image 3 In the same example, an NMOS transistor containing six finger elements is taken as an example, wherein the bottom end of the NMOS transistor is a P-type or N-type substrate 1, and there are multiple finger elements connected in parallel, which are respectively connected in parallel to the P well 2. The fingers are each associated with a parasitic triode 4 . As shown in the figure, it can be seen that the collectors of these parallel parasitic transistors (that is, the drain D of the NMOS transistor) are coupled to the working potential terminal VDD or the I / O terminal of the integrated circuit through the common drain line 7, and its The source S, the gate G and the substrate terminal B a...

no. 2 example

[0039] like Figure 5 The layout sectional view of the ESD protection device under the implementation of the diode for the method of the present invention to improve uniform conduction; as Figure 6 for Figure 5 Schematic diagram of the equivalent circuit of the device. The parts in the figure that are the same as those in the first embodiment will not be described here again, but different from the above-mentioned embodiments, the special feature of this embodiment is that a diode is used to replace the above-mentioned high resistance resistor R, and the anode of the diode is connected to the common ground The potential terminal VSS is coupled, and the cathode is coupled to the substrate terminal of the ESD protection device. When the drain of the NMOSFET transistor is forward-biased, the diode is in a reverse cut-off state. Due to its relatively high breakdown voltage, this high-resistance device can also make the base of the parasitic transistor in different positions T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com