Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

55results about How to "Save layout area and" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

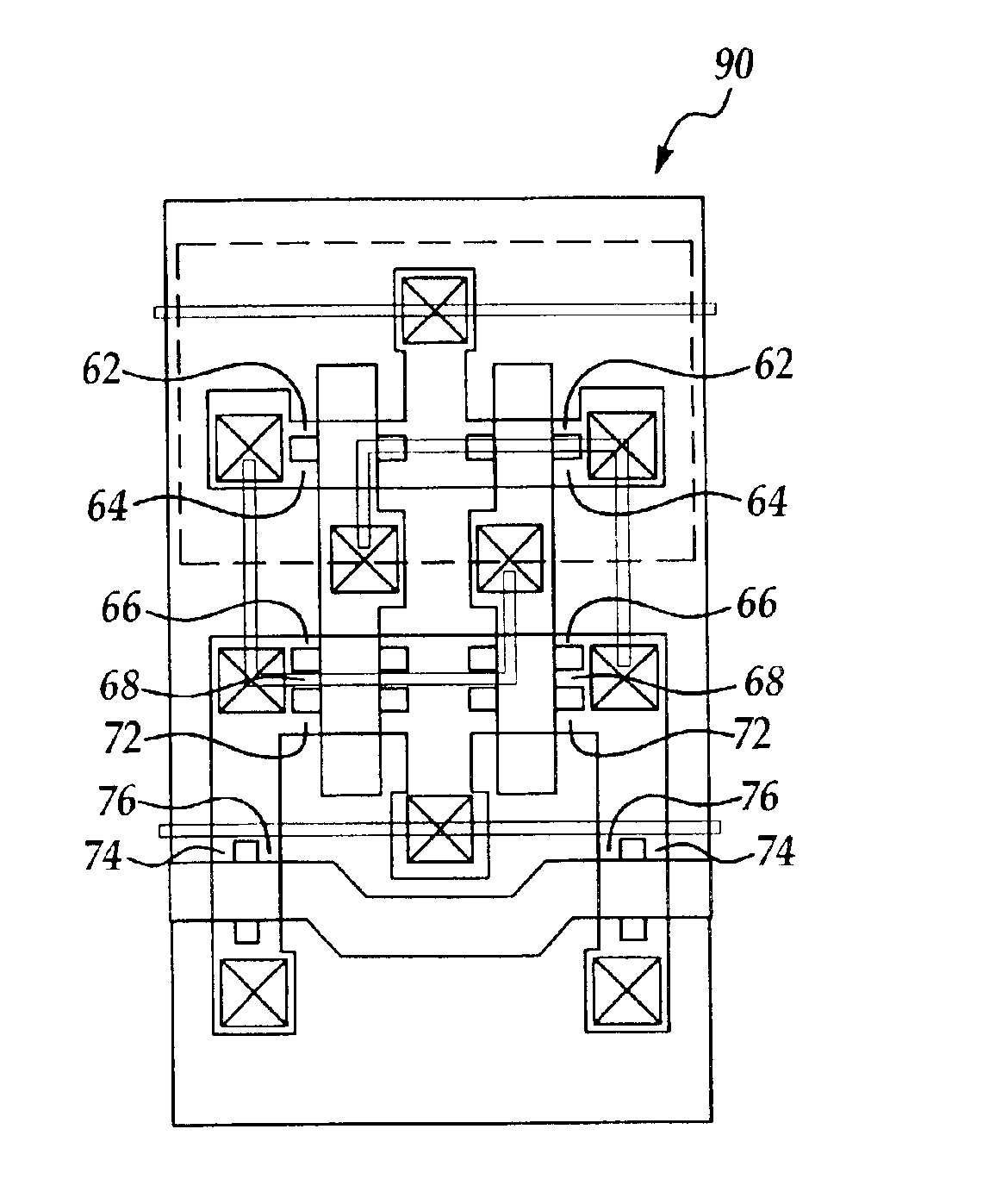

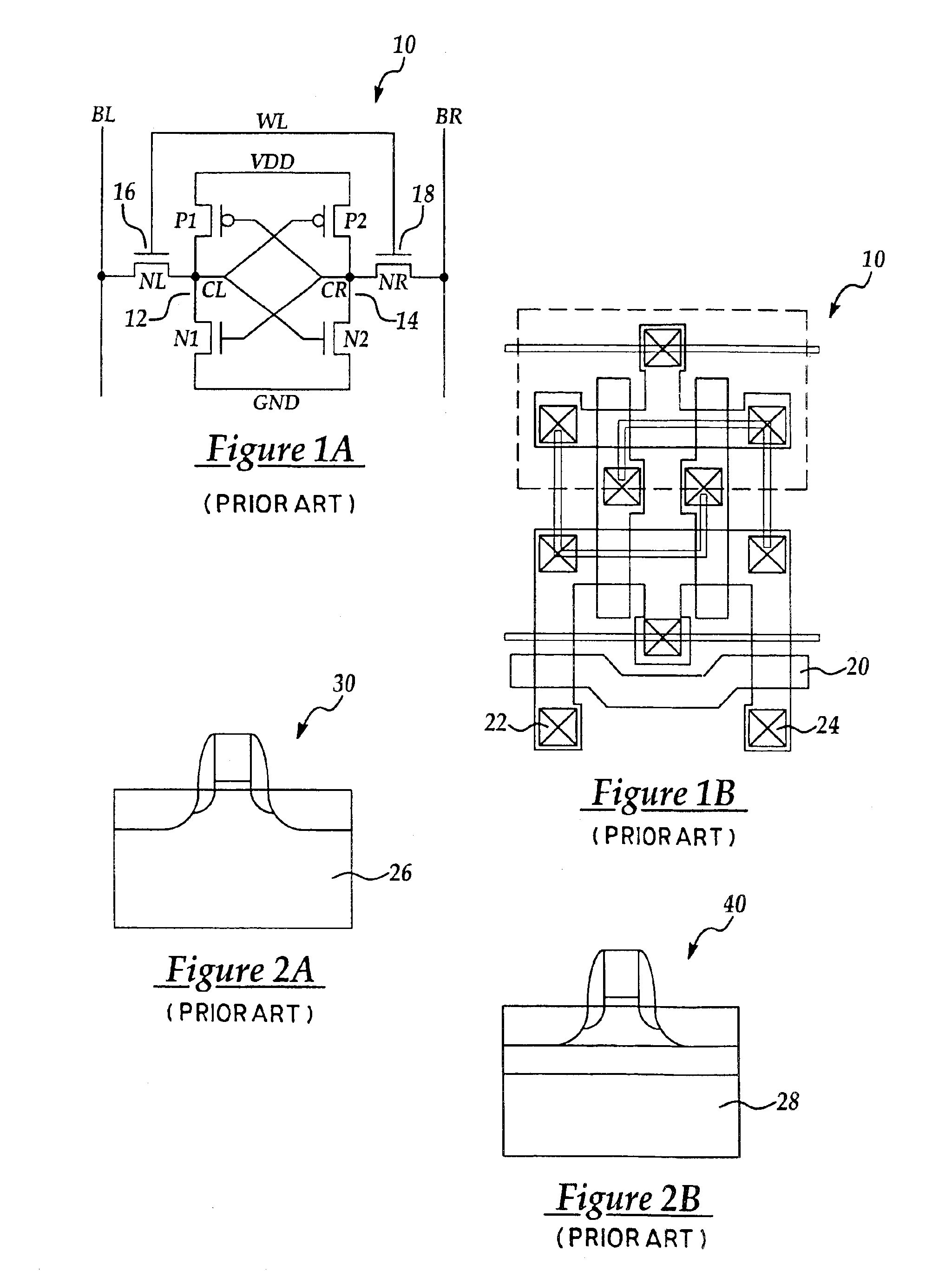

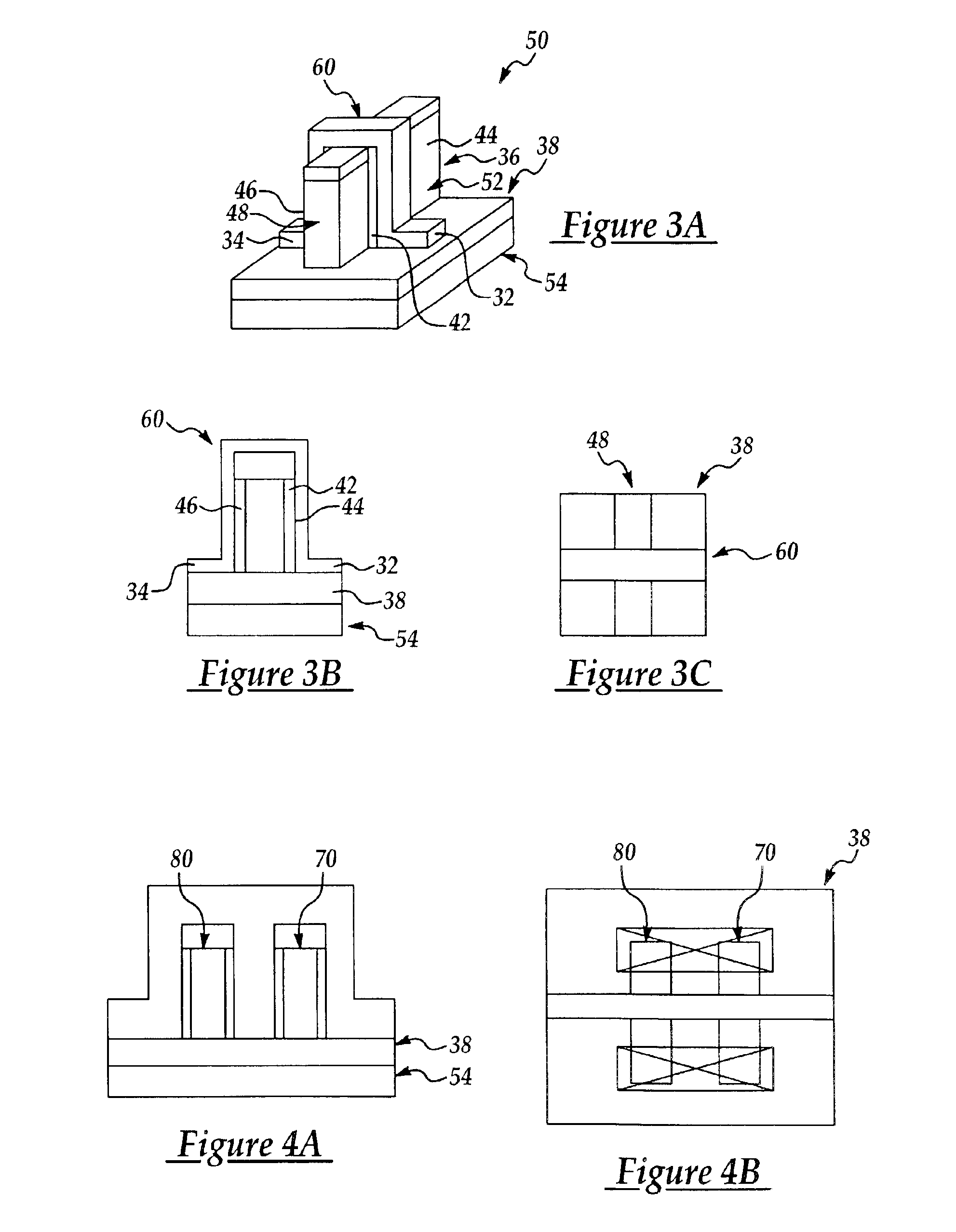

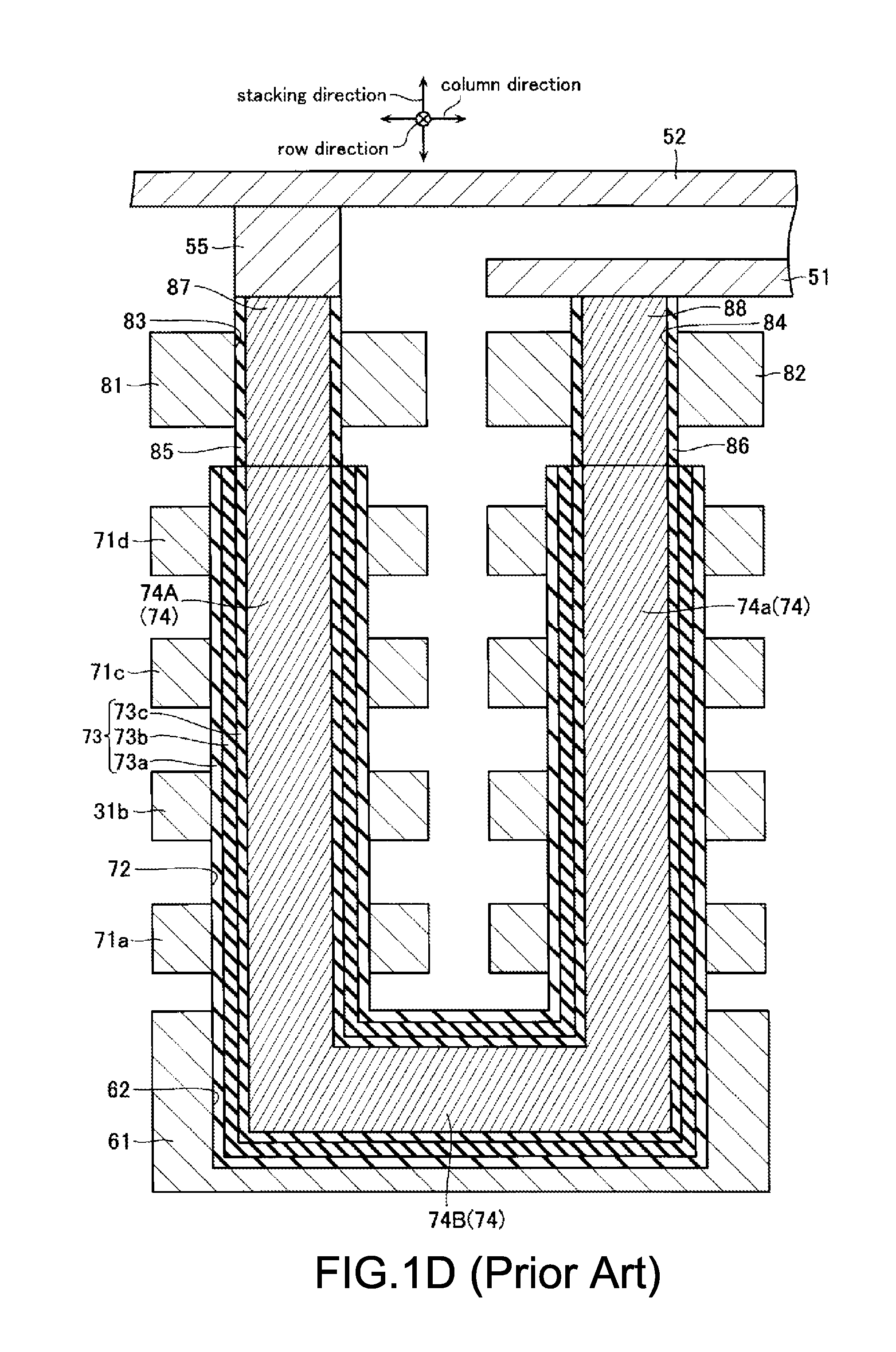

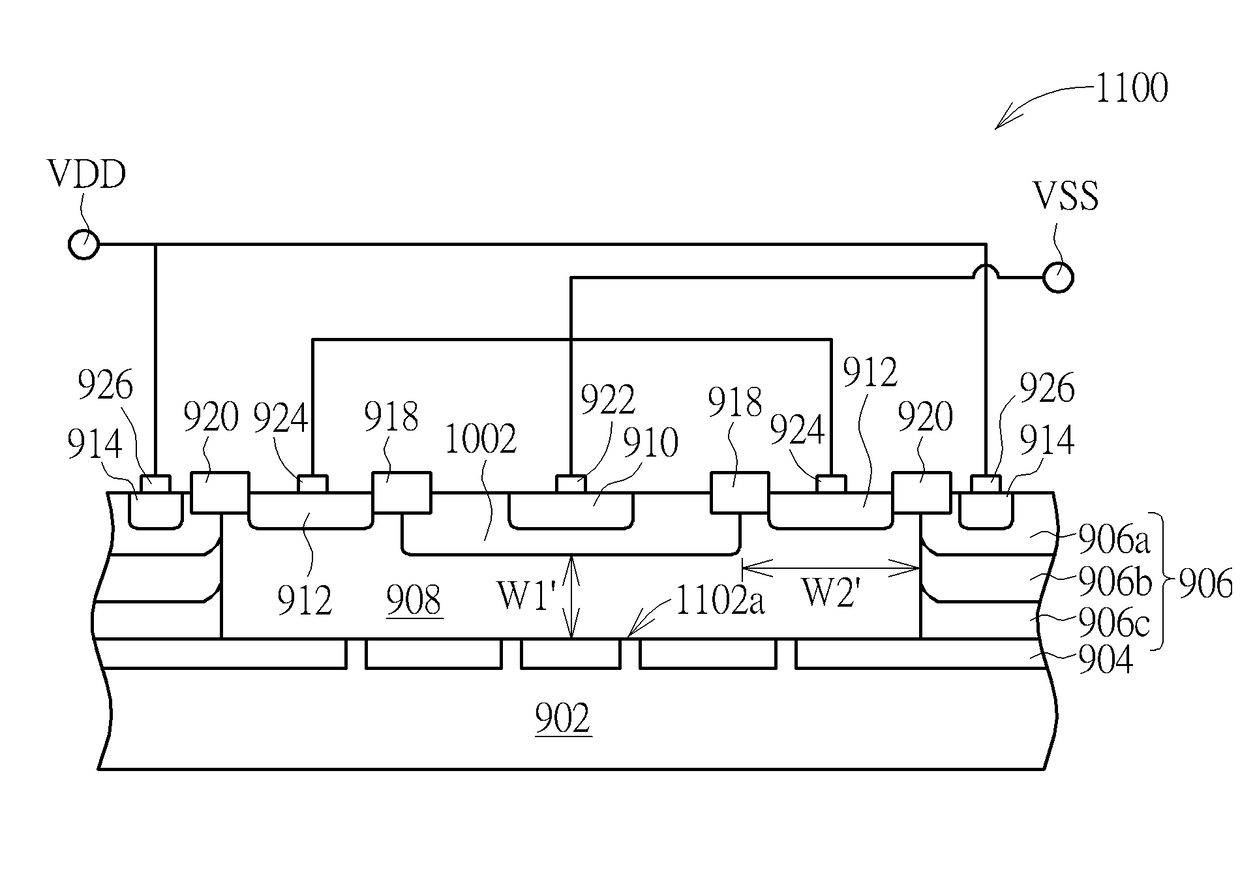

CMOS SRAM cell configured using multiple-gate transistors

InactiveUS6864519B2High dielectric constantSave layout area andTransistorSemiconductor/solid-state device detailsCMOSBit line

A complementary metal-oxide-semiconductor static random access memory cell that is formed by a pair of P-channel multiple-gate field-effect transistors (P-MGFETs), a pair of N-channel multiple-gate field-effect transistors (N-MGFETs), a second pair of N-MGFETs that has a drain respectively connected to a connection linking the respective drain of the N-MGFET of the first pair of N-MGFET to the drain of the P-MGFET of the pair of P-MGFETs; a pair of complementary bit lines, each respectively connected to the source of the N-MGFET of the second pair of N-MGFETS; and a word line connected to the gates of the N-MGFETs of the second pair of N-MGFETs.

Owner:TAIWAN SEMICON MFG CO LTD

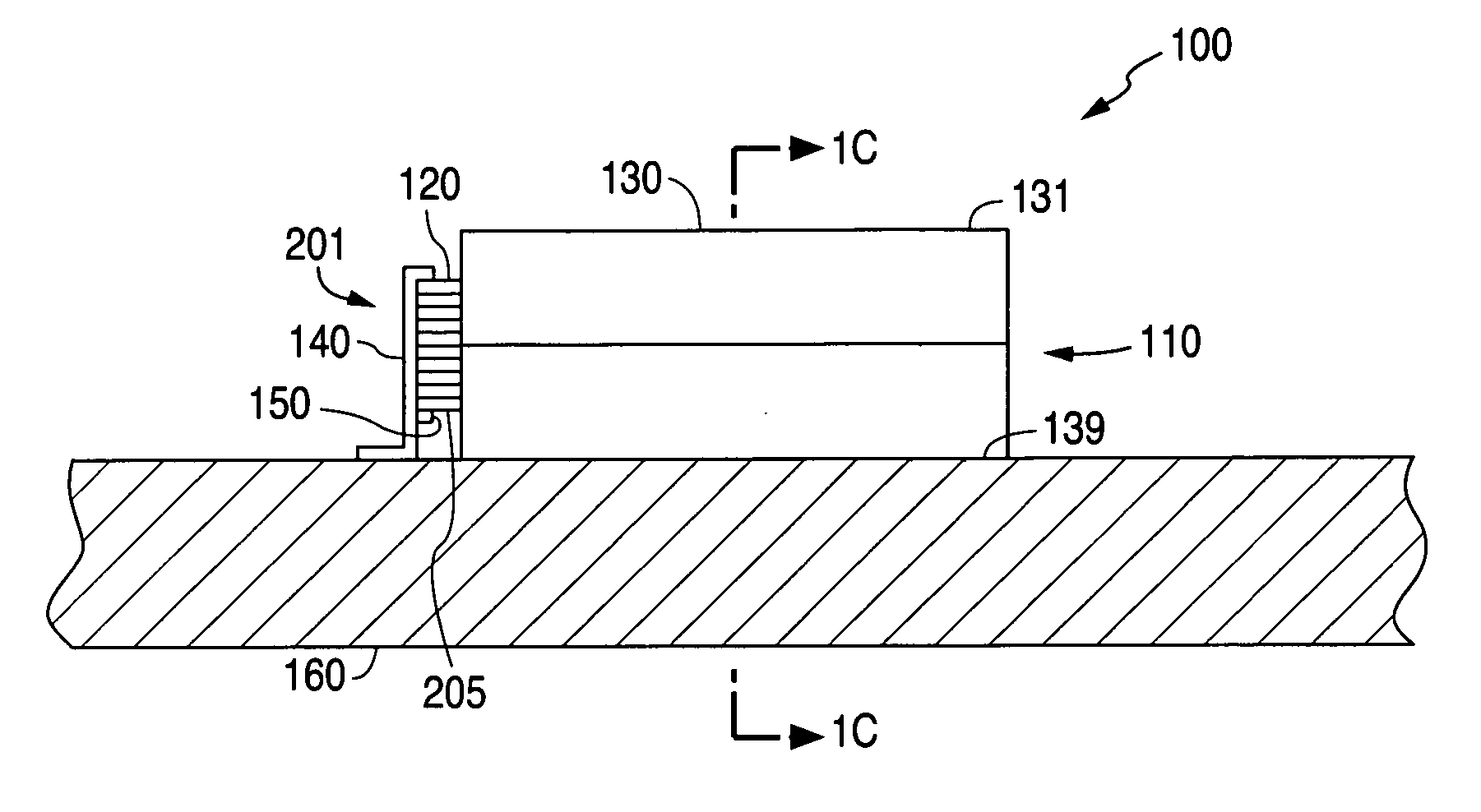

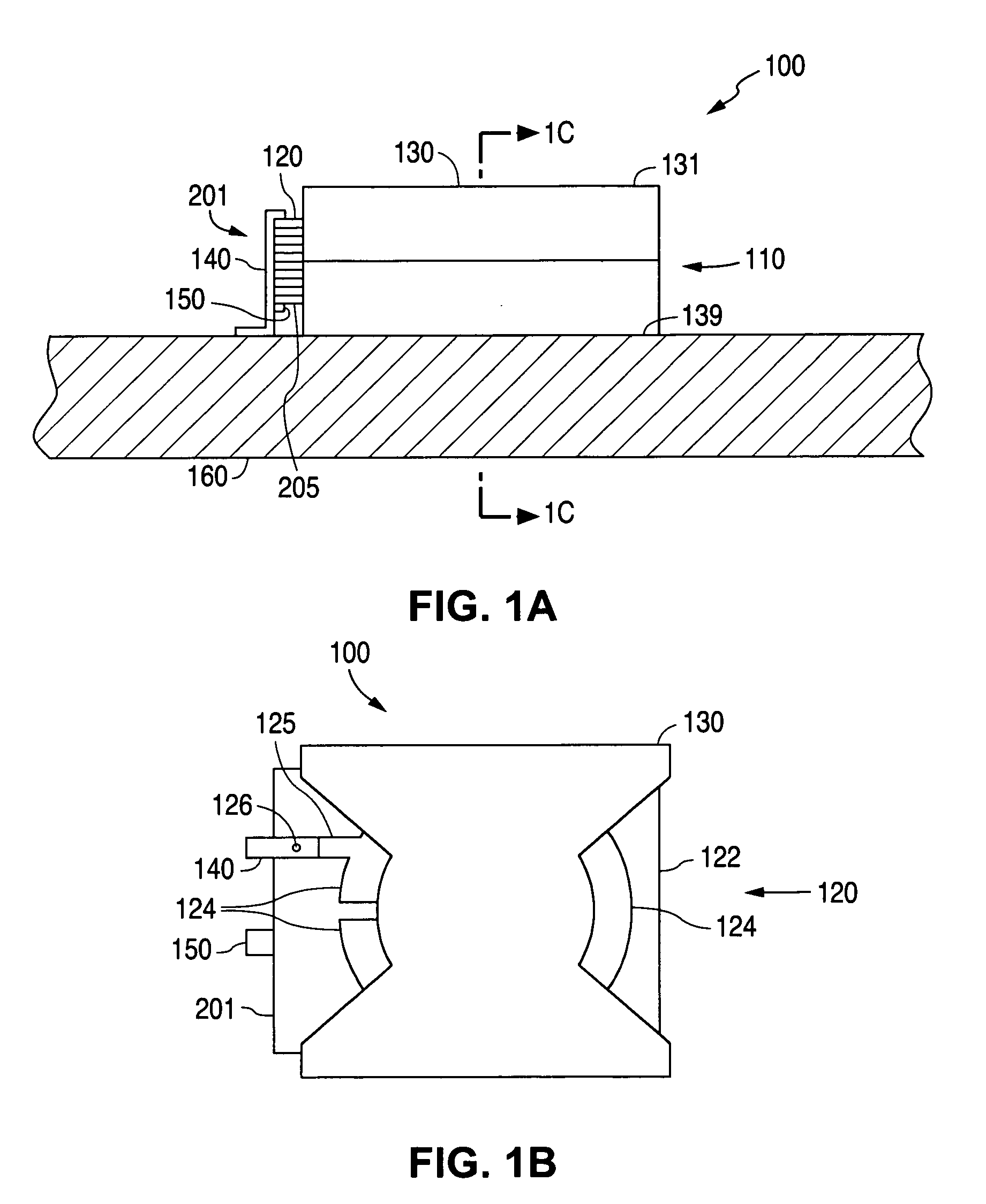

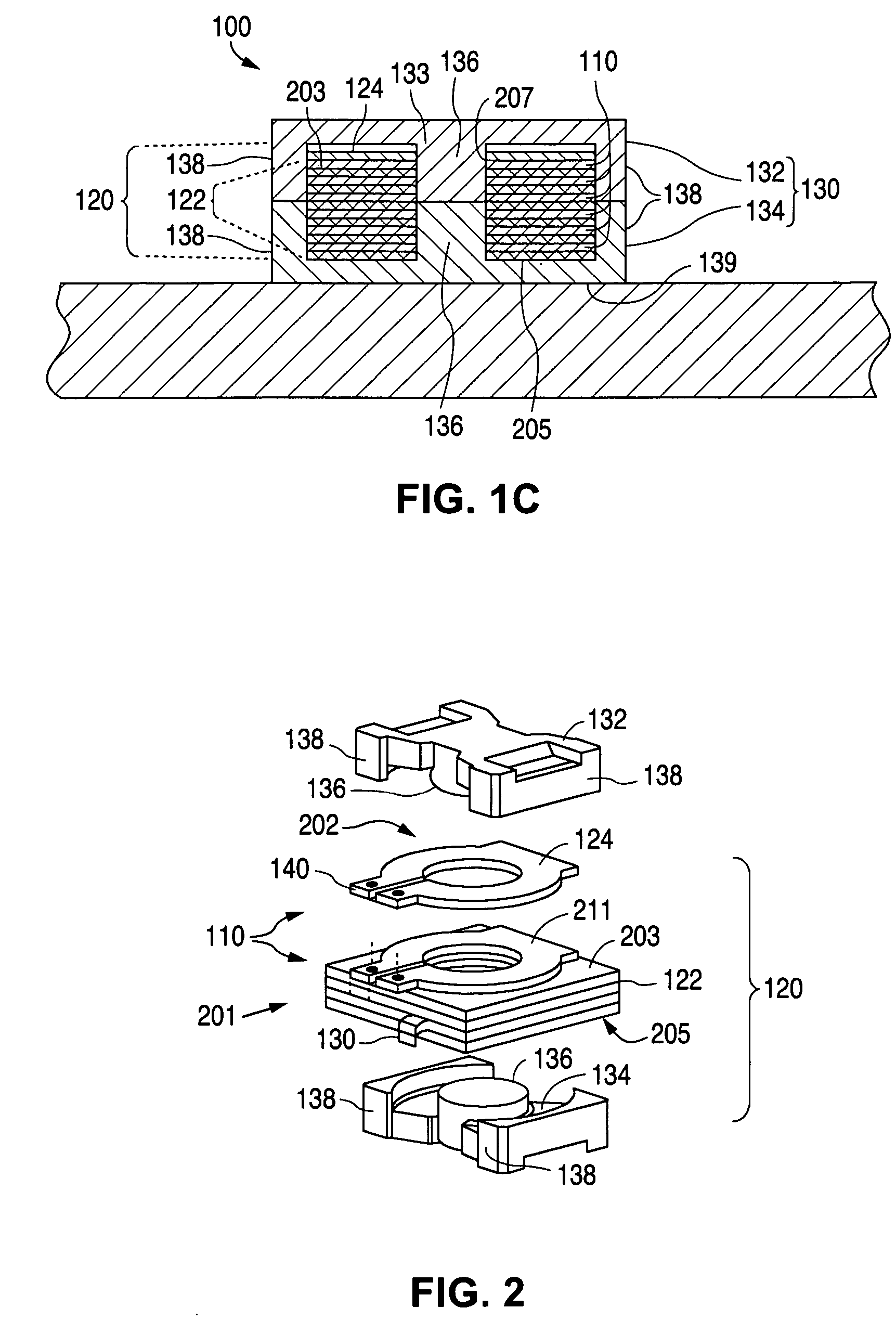

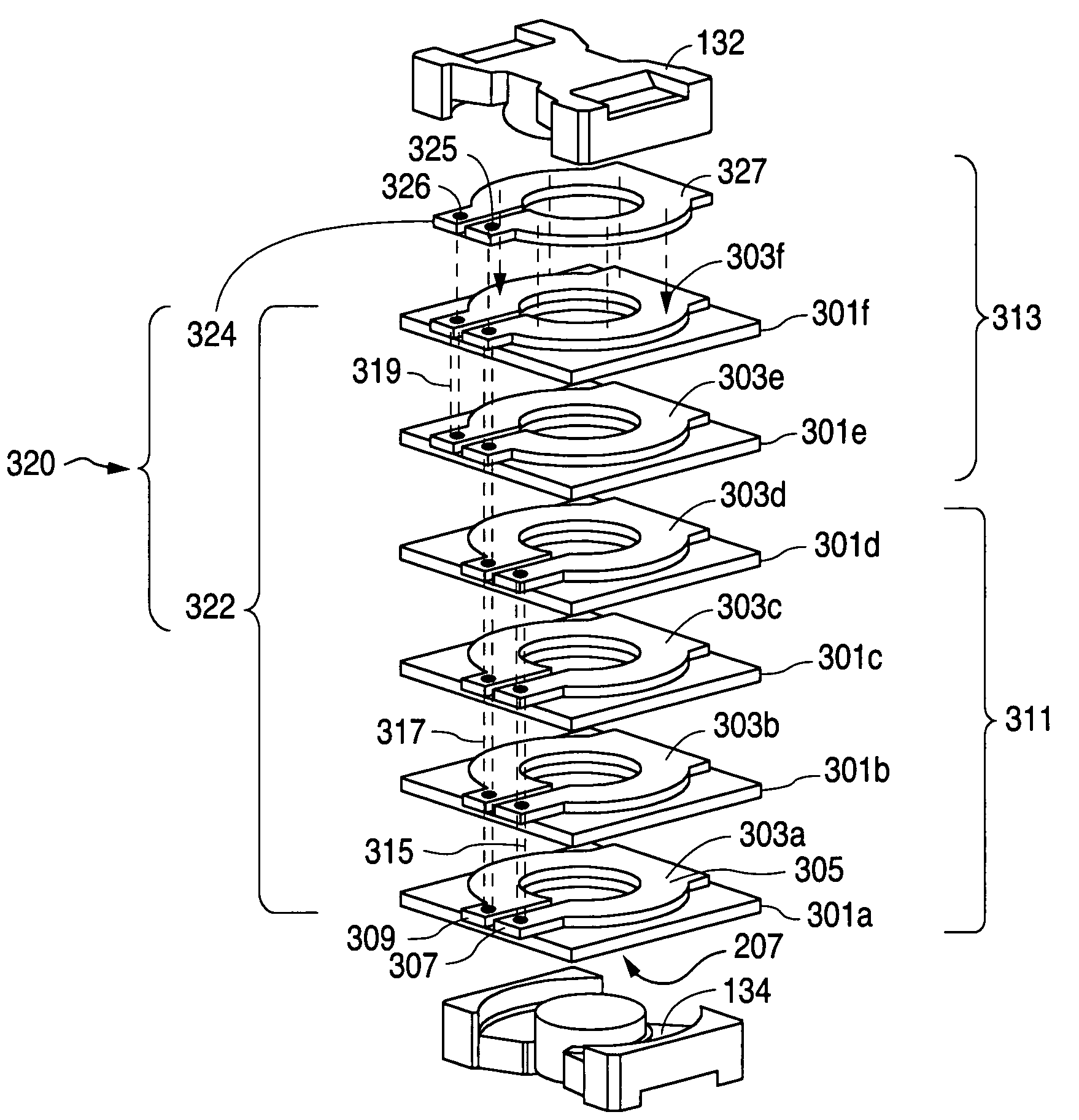

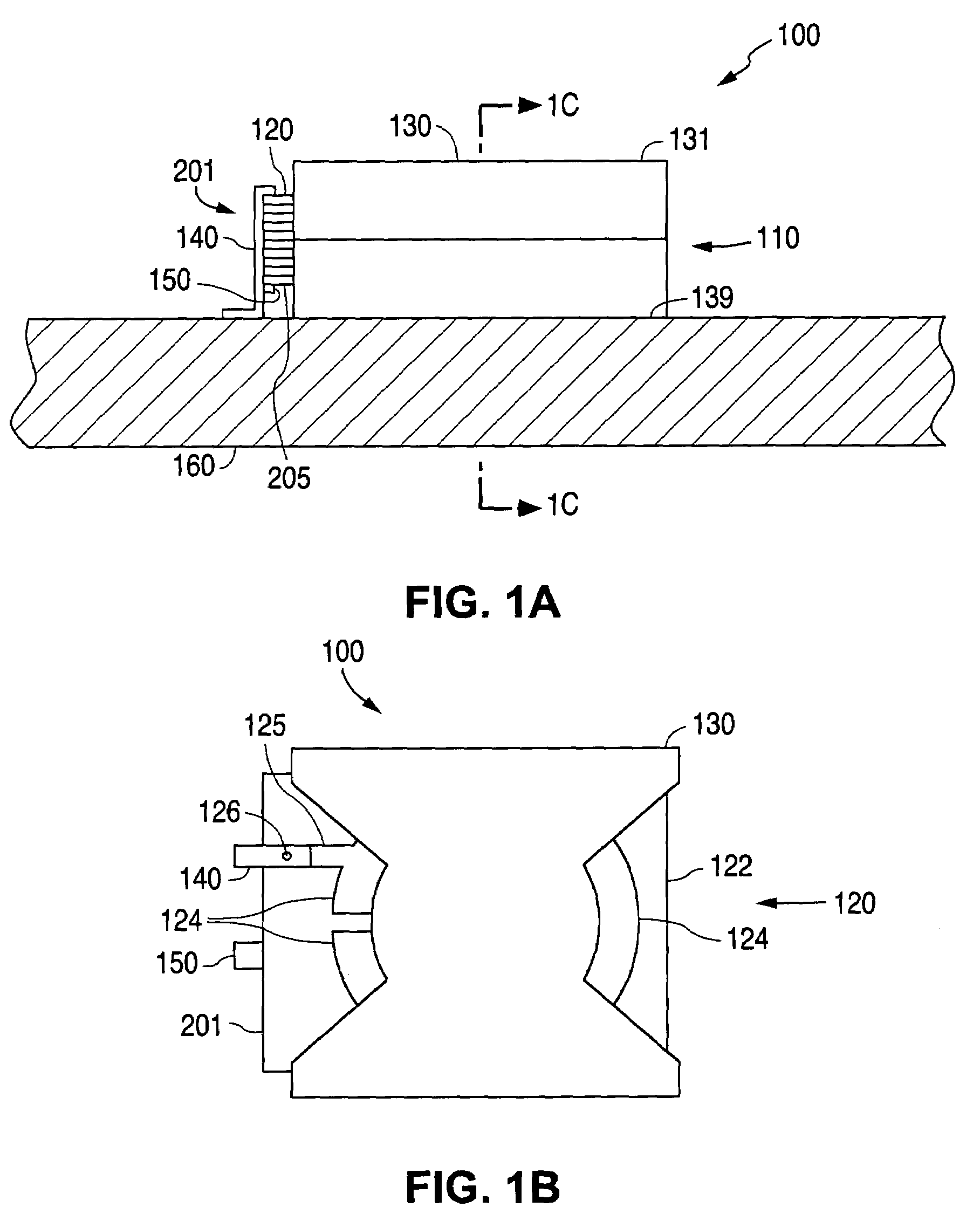

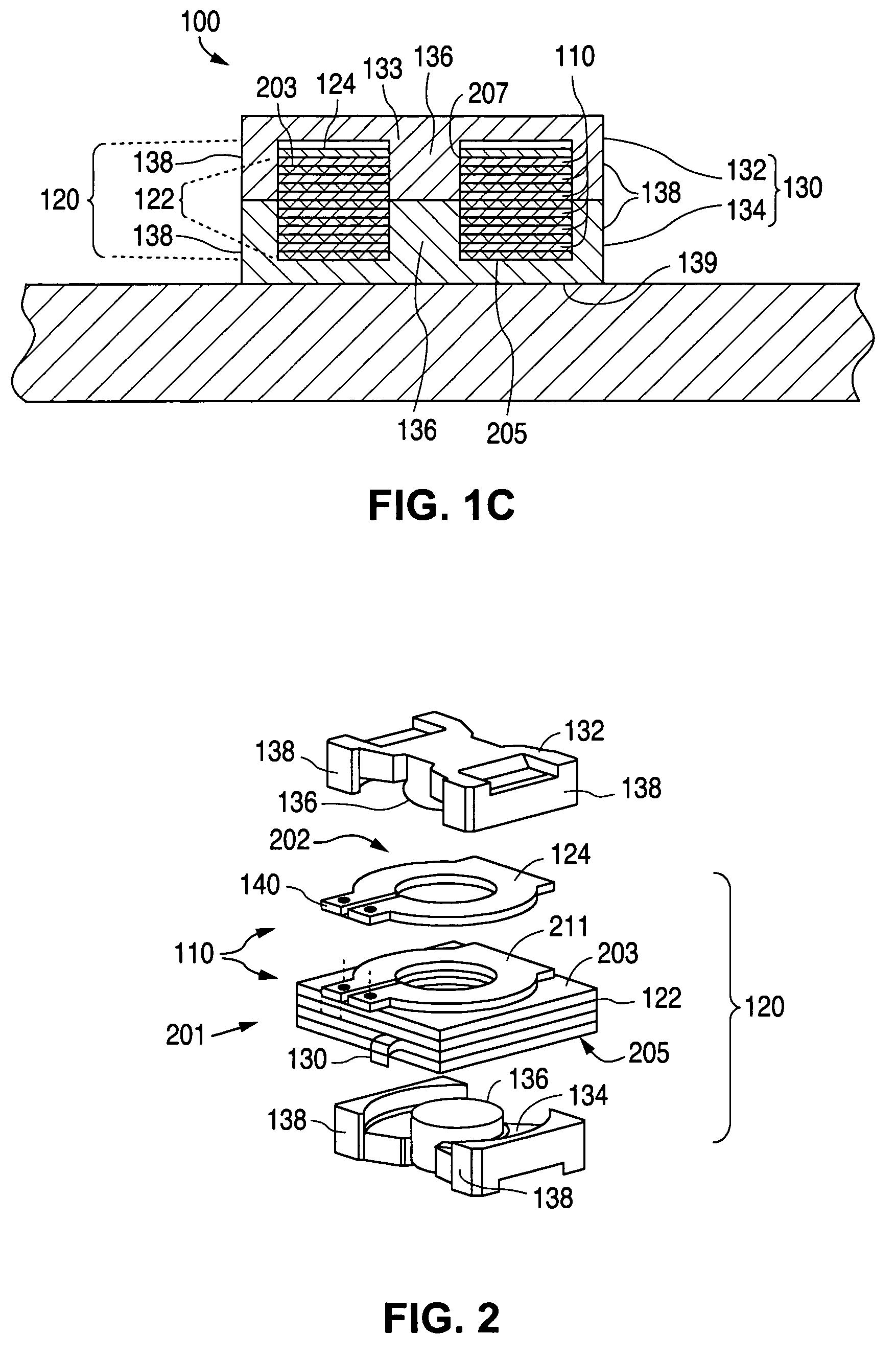

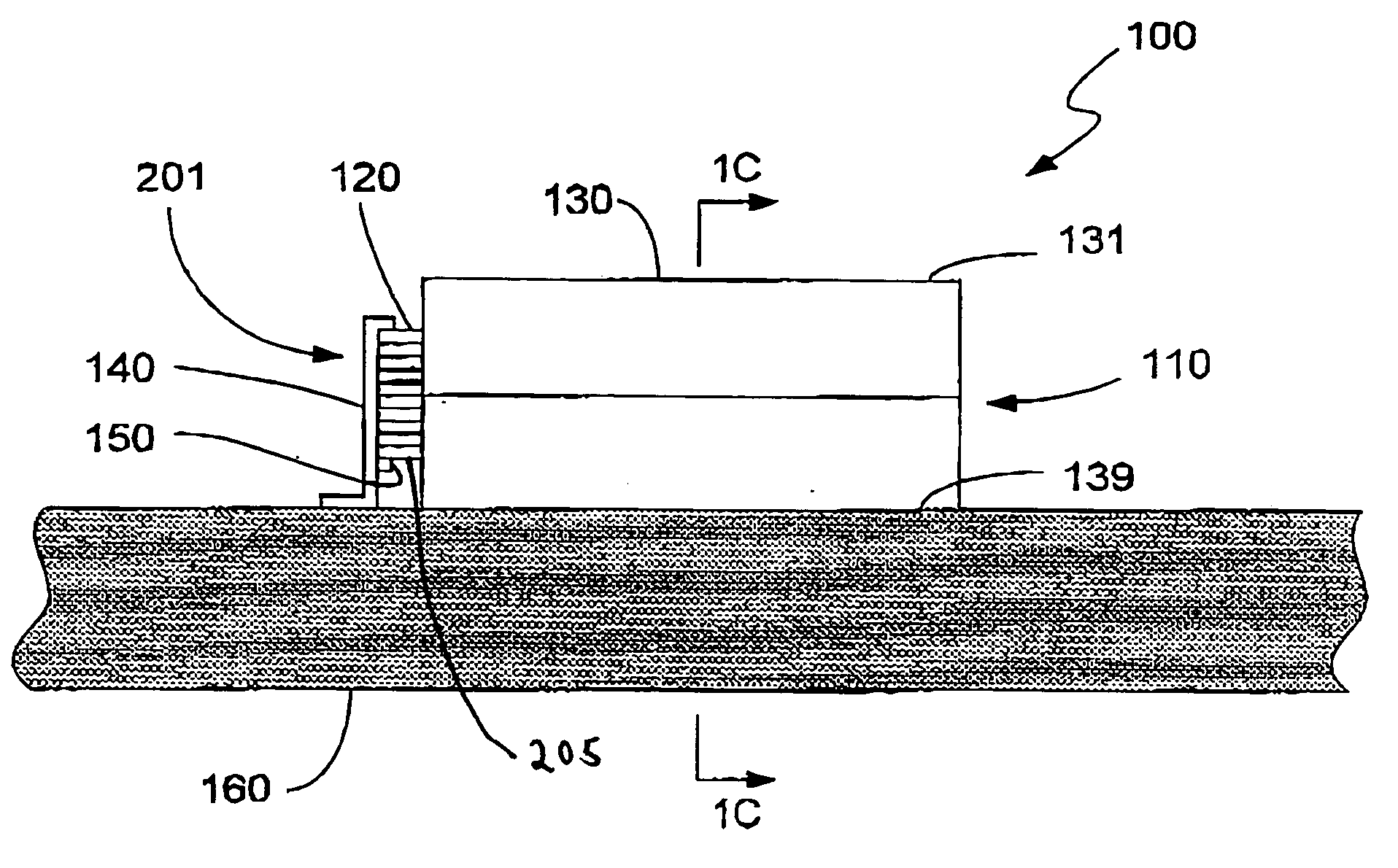

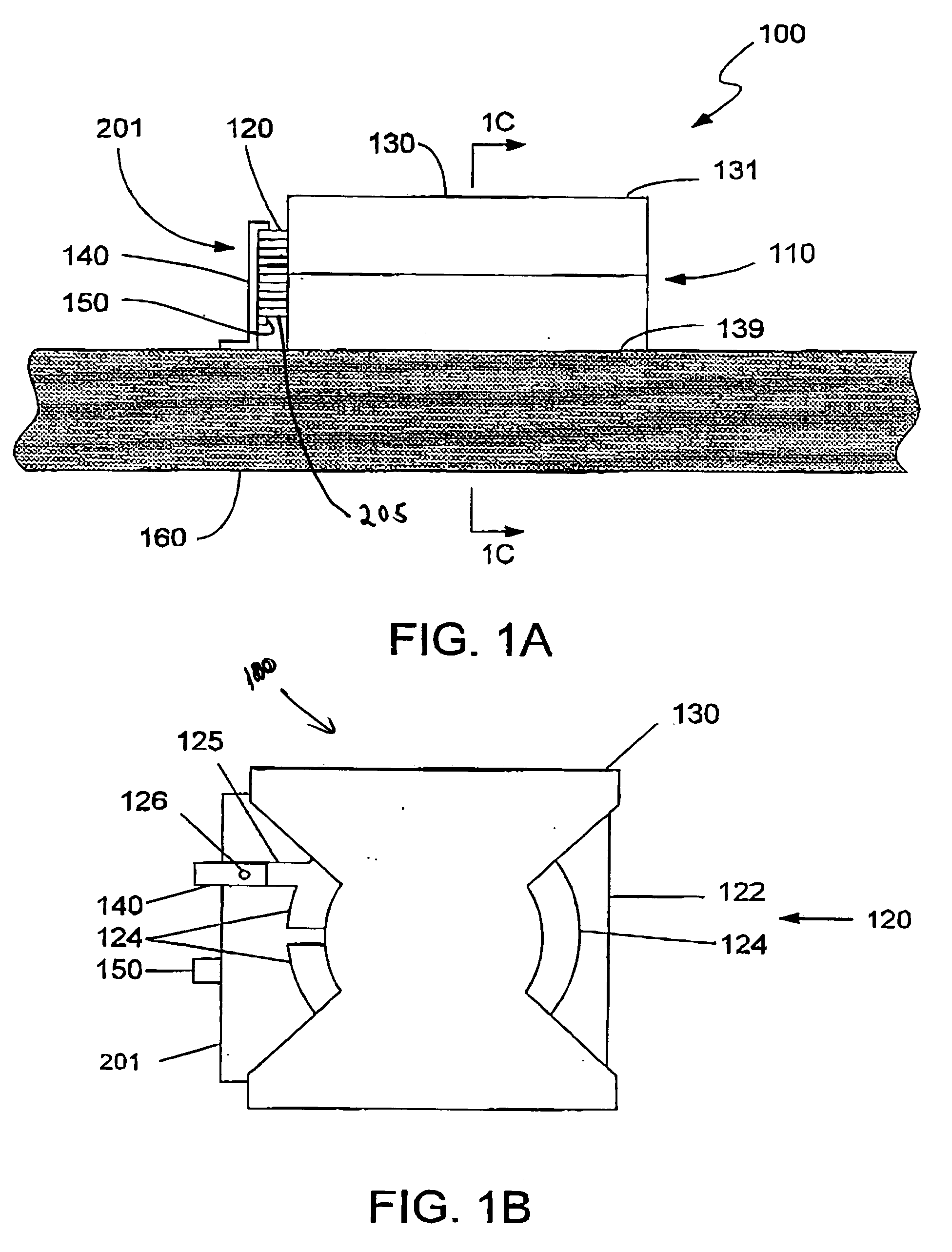

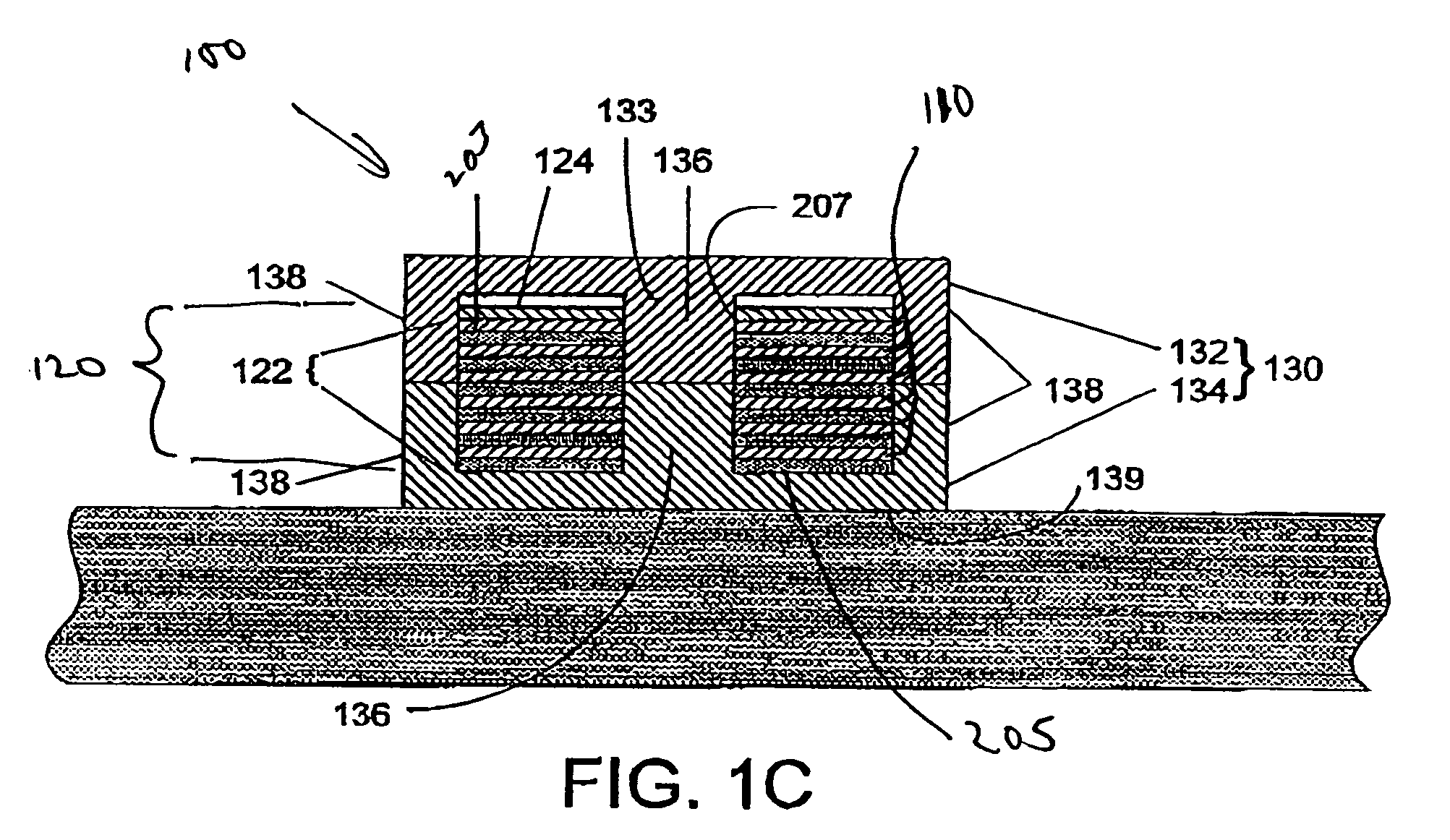

Multi-layer printed circuit board transformer winding

InactiveUS20050212640A1High currentImprove efficiencyTransformers/reacts mounting/support/suspensionTransformers/inductances coils/windings/connectionsSurface mountingEngineering

The present invention provides a transformer formed from adjacent conducting layers of a multi-layer PCB and at least one additional conducting layer in contact with the PCB. The inventive transformer includes one or more winding turns of a first winding formed by connecting the multiple layers of the multi-layer PCB with conductive vias and one or more winding turns of a second winding formed by connecting one or more other layers of the multi-layer PCB. The additional conducting layer or layers is connected to respective selected one or more of said conducting layers of said PCB. In one embodiment, an additional conducting layer is soldered to a top conducting layer of the PCB, effectively increasing the cross-sectional area of the top winding layer. In another embodiment, an additional conducting layer is separated from a conducting PCB layer formed on the surface thereof by a layer of insulation, permitting the additional conducting layer to form a separate winding turn. The inventive transformer can be surface mounted to a PCB, and can be used in other electromagnetic devices. The windings thus constructed are capable of accepting larger currents with lower resulting temperature increases than windings formed only from PCBs, and are less expensive to manufacture than PCB-only windings.

Owner:ASTEC INT LTD

Multi-layer printed circuit board inductor winding with added metal foil layers

ActiveUS7248138B2High currentImprove efficiencyTransformers/inductances casingsPrinted electric component incorporationInductor windingsSurface mounting

The present invention provides an electromagnetic component formed from adjacent conducting layers of a multi-layer PCB and two additional conducting layers in contact with the PCB. The inventive component includes one or more winding turns formed by connecting the multiple layers of the multi-layer PCB with conductive vias and by connecting the additional conducting layers to respective top and bottom surfaces of the PCB. In one embodiment, one of the conducting layers is soldered to a top conducting layer of the PCB and the other of the conductive layers is soldered to a bottom conducting layer of the PCB, effectively increasing the cross-sectional area of the top and bottom winding layers. In another embodiment, the additional conducting layers are separated from the adjacent conducting PCB layers by a layer of insulation, permitting the additional conducting layers to form separate winding turns. The inventive winding stack can be surface mounted to a PCB, and can be used as an inductor, or in other electromagnetic devices. The winding thus constructed is capable of accepting larger currents with lower resulting temperature increases than windings formed only from PCBs, and are less expensive to manufacture than PCB-only windings.

Owner:ASTEC INT LTD

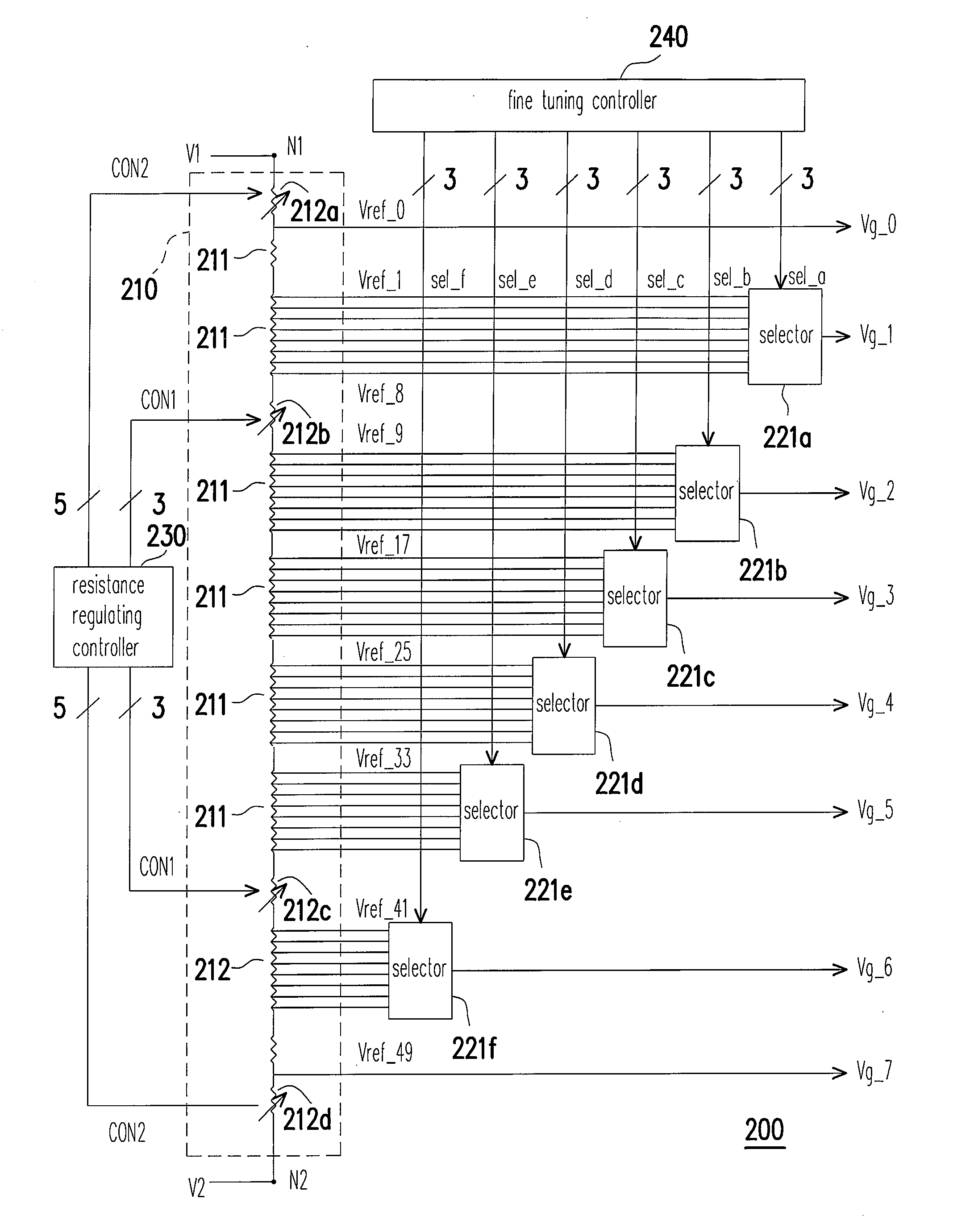

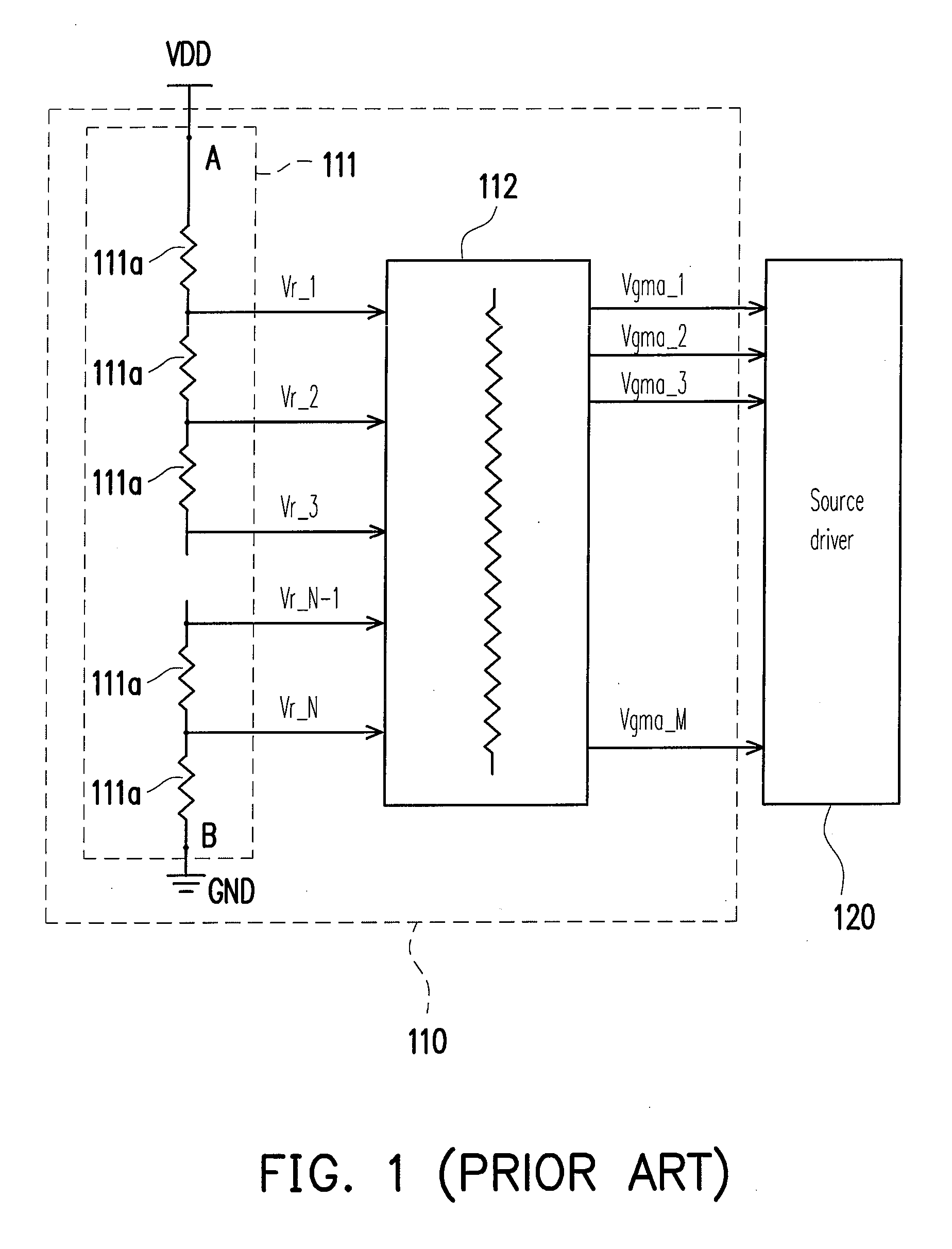

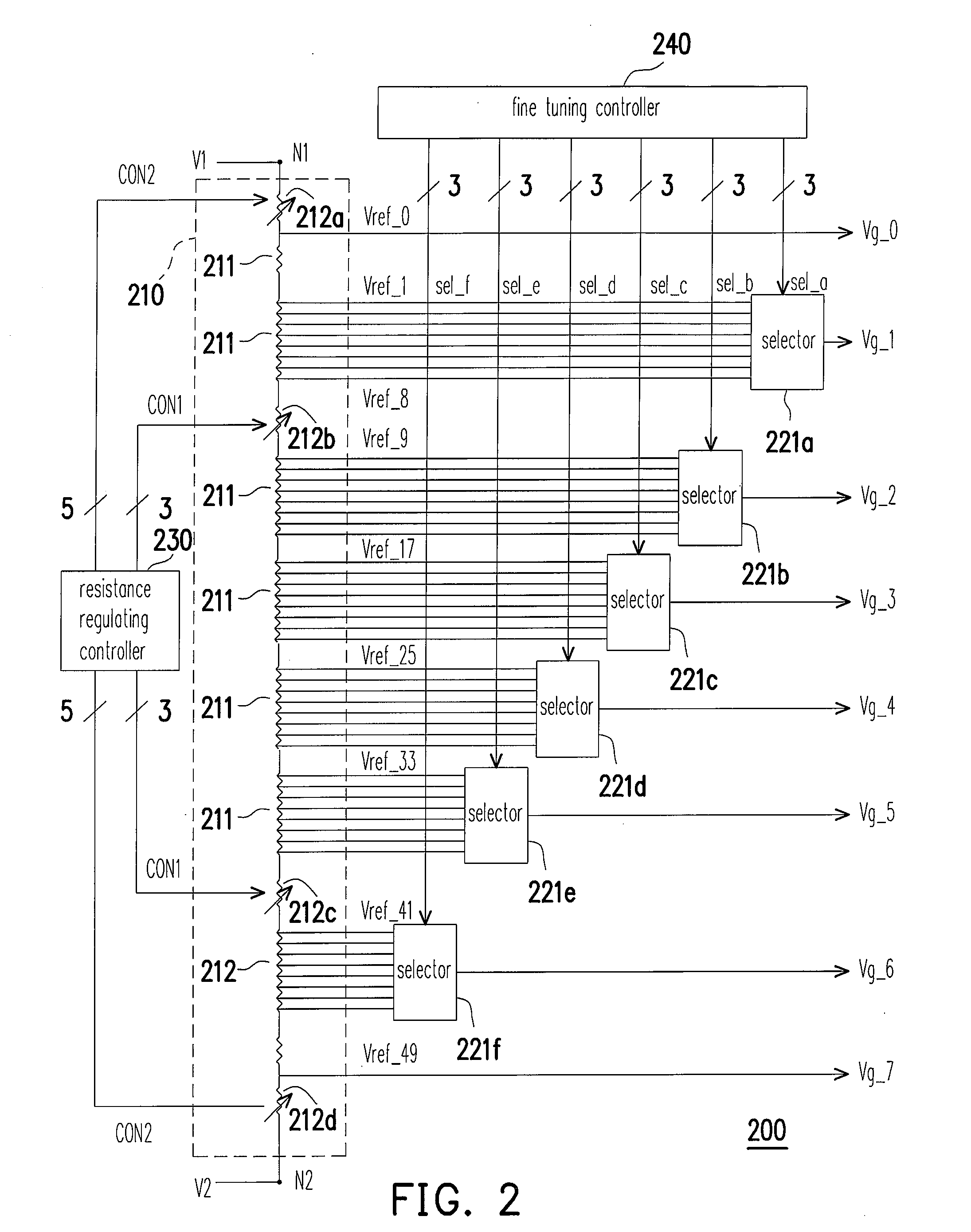

Gamma reference voltage generating device and gamma voltage generating device

InactiveUS20090135116A1Improve panel feed through problemAvoid flickeringStatic indicating devicesImage resolutionVoltage reference

A gamma reference voltage generating device and a gamma voltage generating device are provided herein. The gamma reference voltage generating device includes a reference voltage source and a selector. The reference voltage source has a first terminal and a second terminal respectively coupled to a first adjustable voltage and a second adjustable voltage for providing a plurality of reference voltages. The selector selectively outputs one of the reference voltages as a gamma reference voltage according to a selecting signal. By regulating the first and the second adjustable voltage, the range of the reference voltages provided by the reference voltage source can be adjusted so as to adjust the gamma reference voltage and the outputted voltage resolution.

Owner:HIMAX TECH LTD

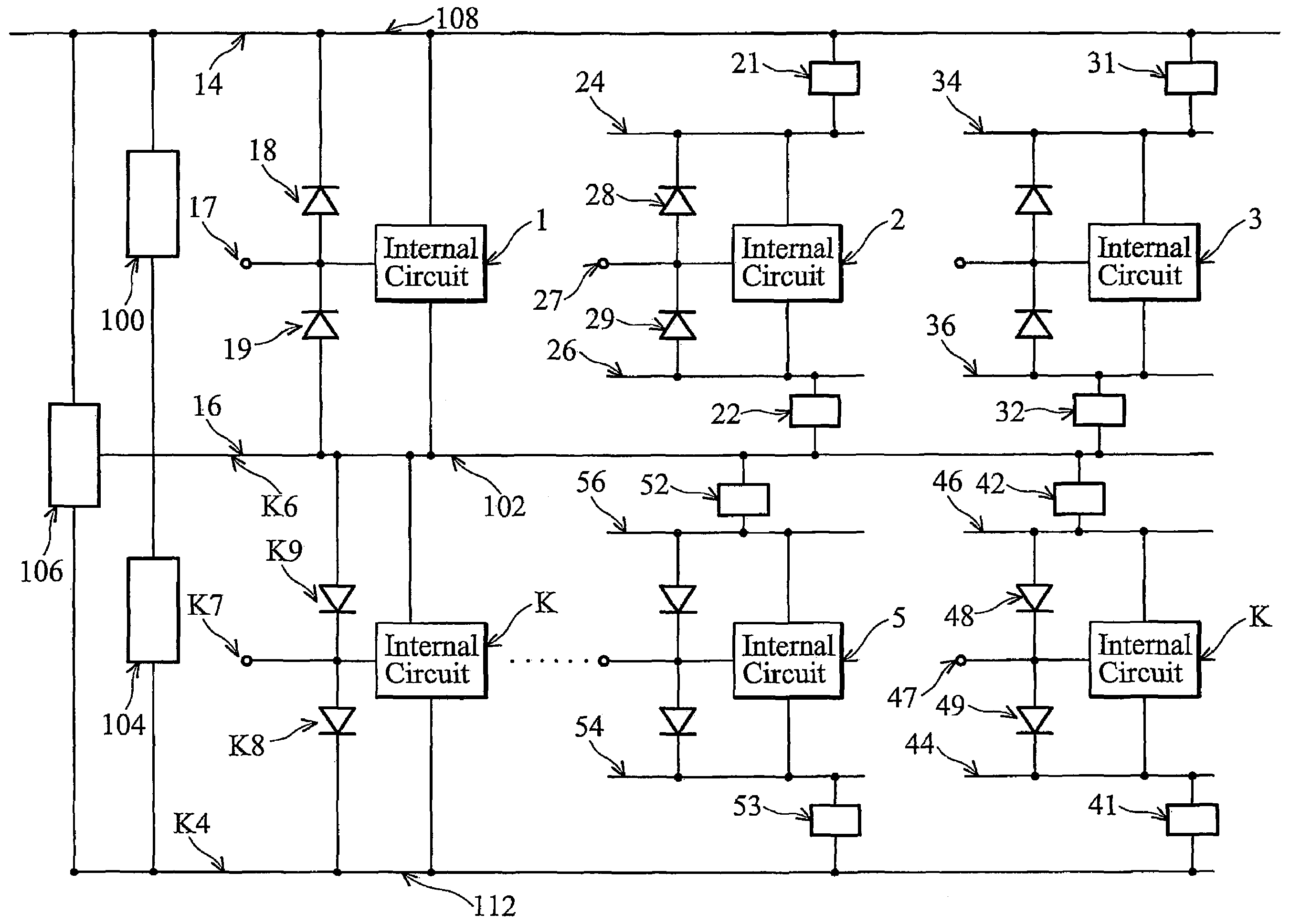

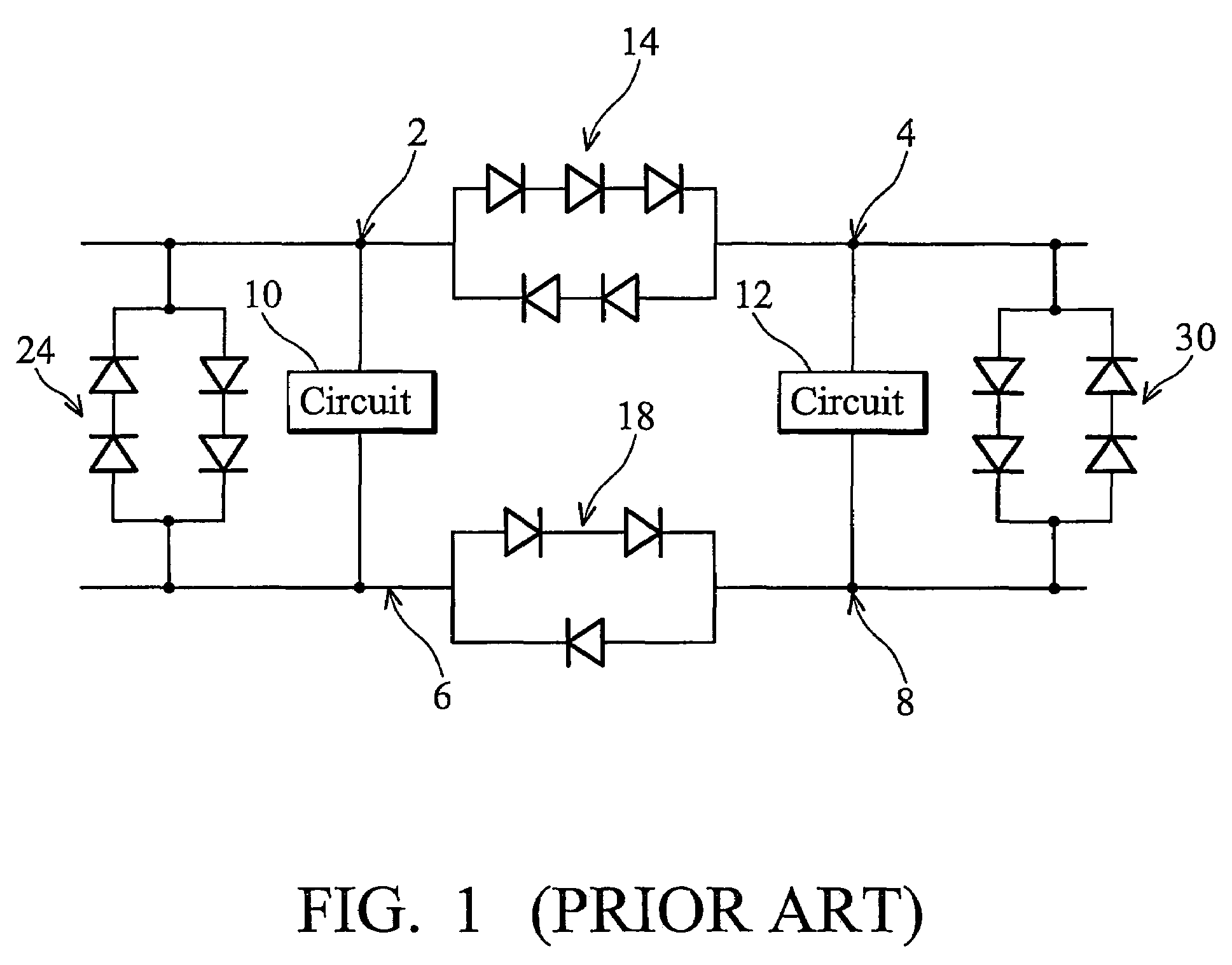

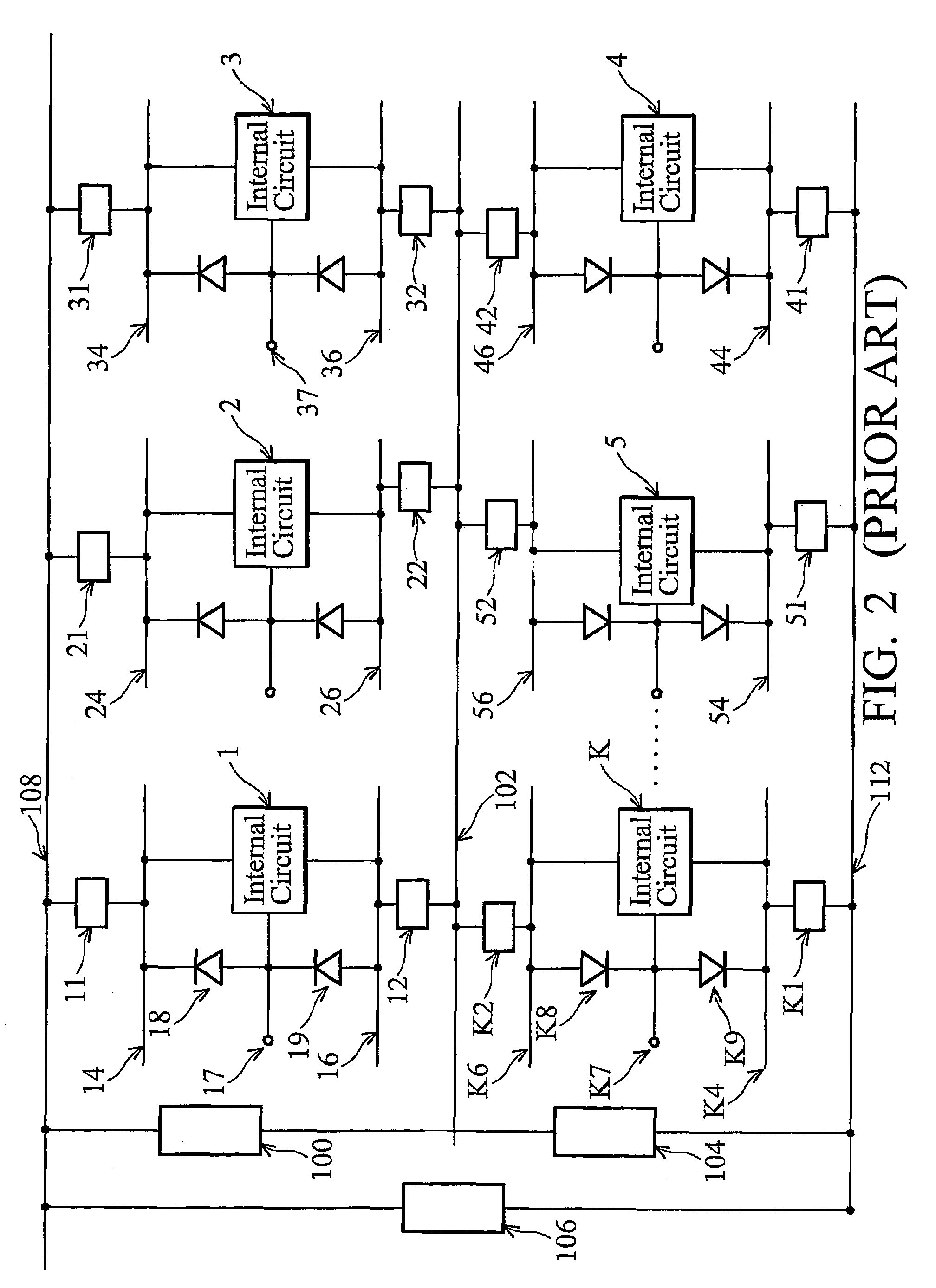

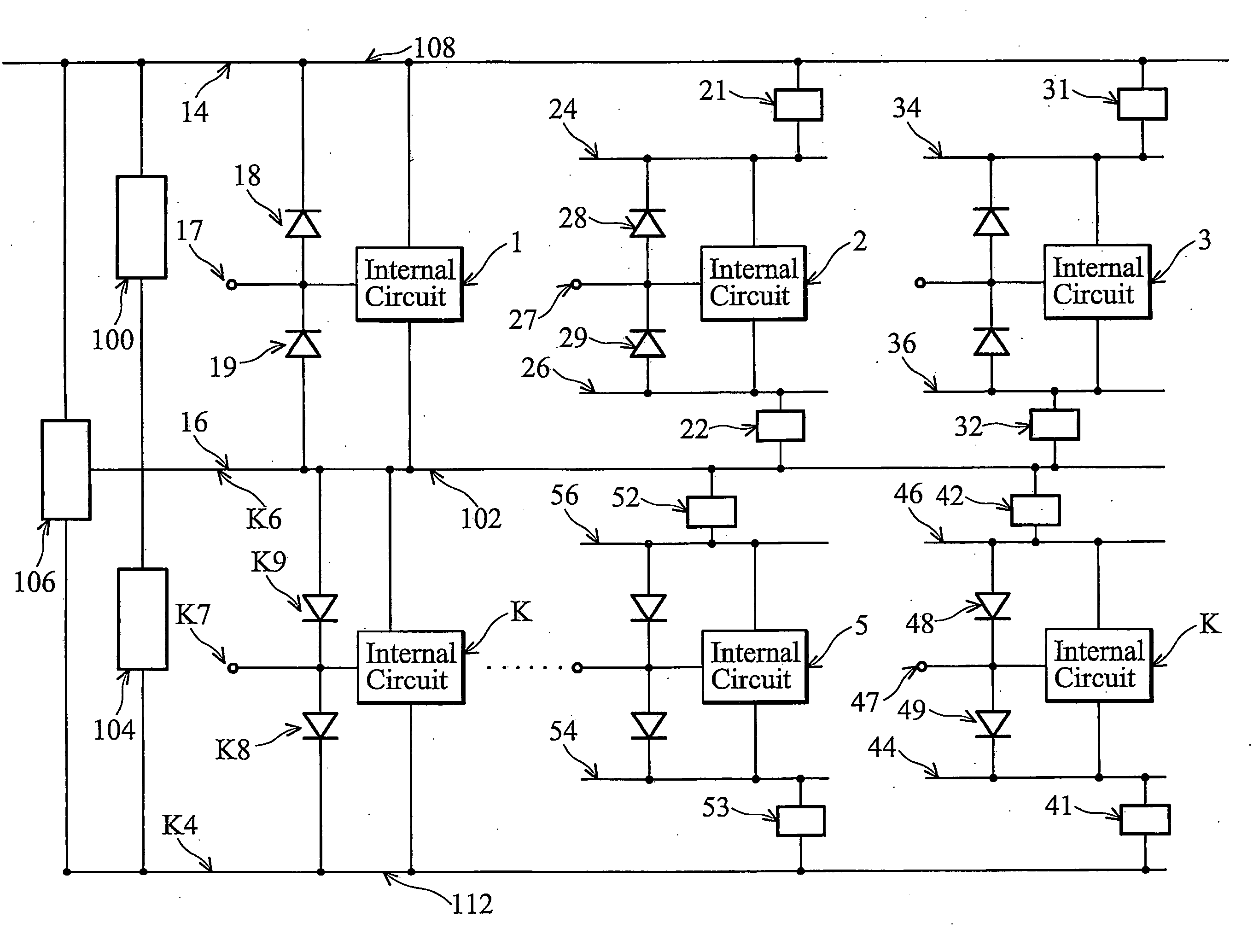

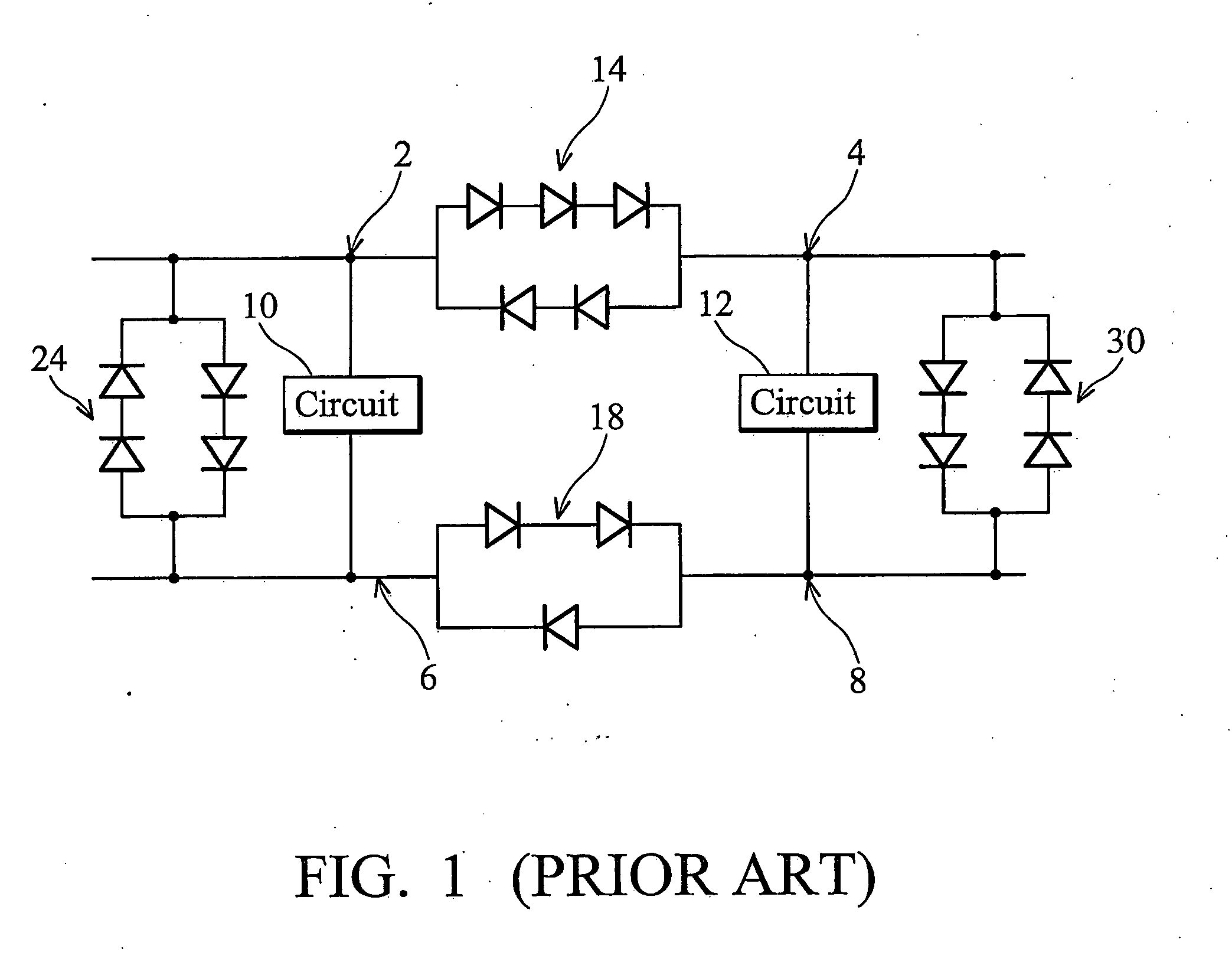

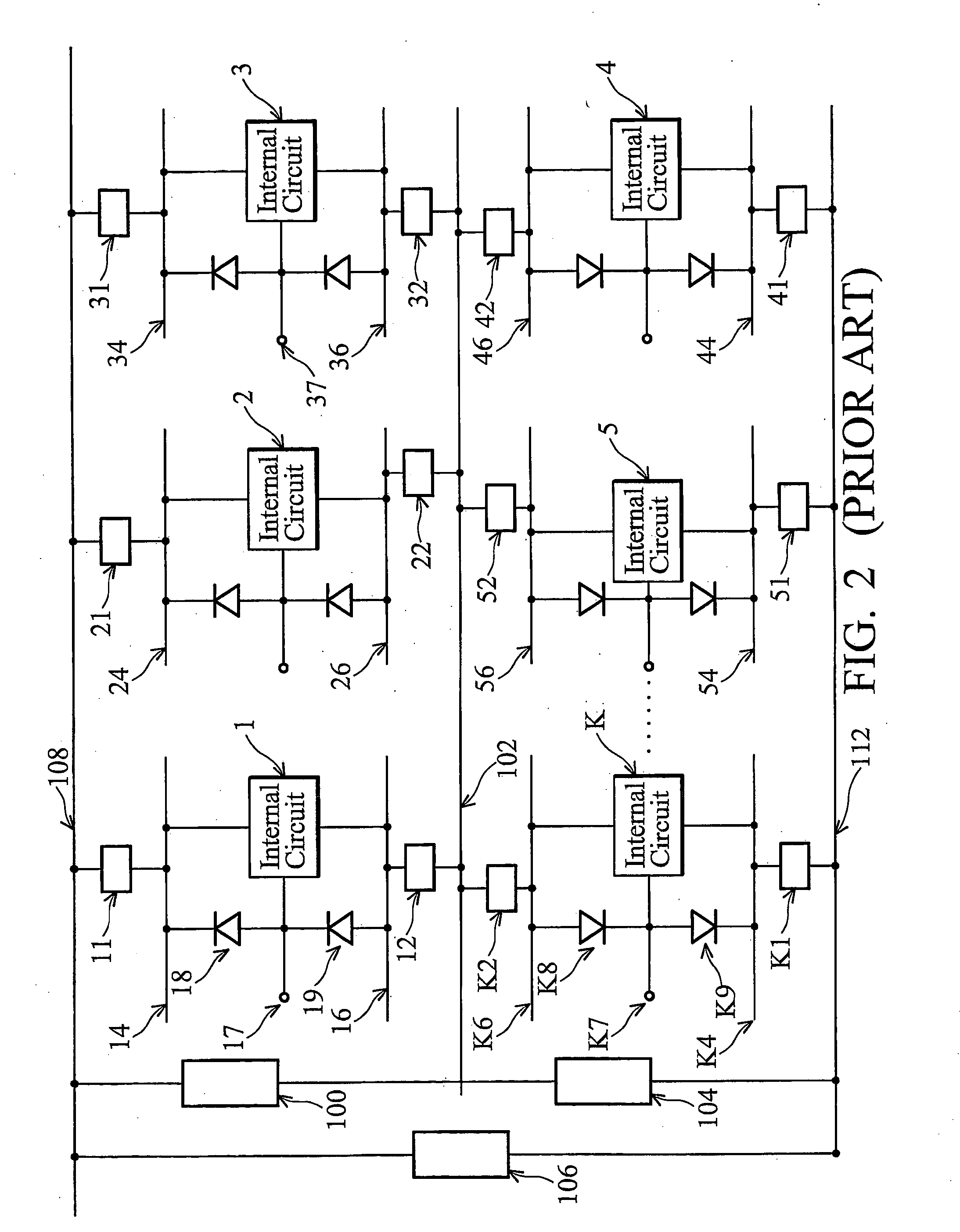

Multi-domain ESD protection circuit structure

InactiveUS7411767B2Improve ESD protection capabilitySave layout area andSemiconductor/solid-state device detailsSolid-state devicesEngineeringMulti domain

A multi-domain ESD protection circuit structure is described. The preferred embodiment of the present invention selects power lines of an internal circuit as ESD buses. The power lines of the remaining internal circuits are coupled with the ESD buses through the ESD connection cells. In another embodiment of the preferred invention, the VDD power line from one internal circuit and the VSS power line from another circuit are selected as ESD buses. In yet another embodiment, either a VDD power line or a VSS power line of an internal circuit is selected as an ESD bus.

Owner:TAIWAN SEMICON MFG CO LTD

Multi-domain ESD protection circuit structure

InactiveUS20050270712A1Improve ESD protection performanceSave layout area andSemiconductor/solid-state device detailsSolid-state devicesEngineeringMulti domain

A multi-domain ESD protection circuit structure is described. The preferred embodiment of the present invention selects power lines of an internal circuit as ESD buses. The power lines of the remaining internal circuits are coupled with the ESD buses through the ESD connection cells. In another embodiments of the preferred invention, the VDD power line from one internal circuit and the VSS power line from another circuit are selected as ESD buses. In yet another embodiment, either a VDD power line or a VSS power line of an internal circuit is selected as an ESD bus.

Owner:TAIWAN SEMICON MFG CO LTD

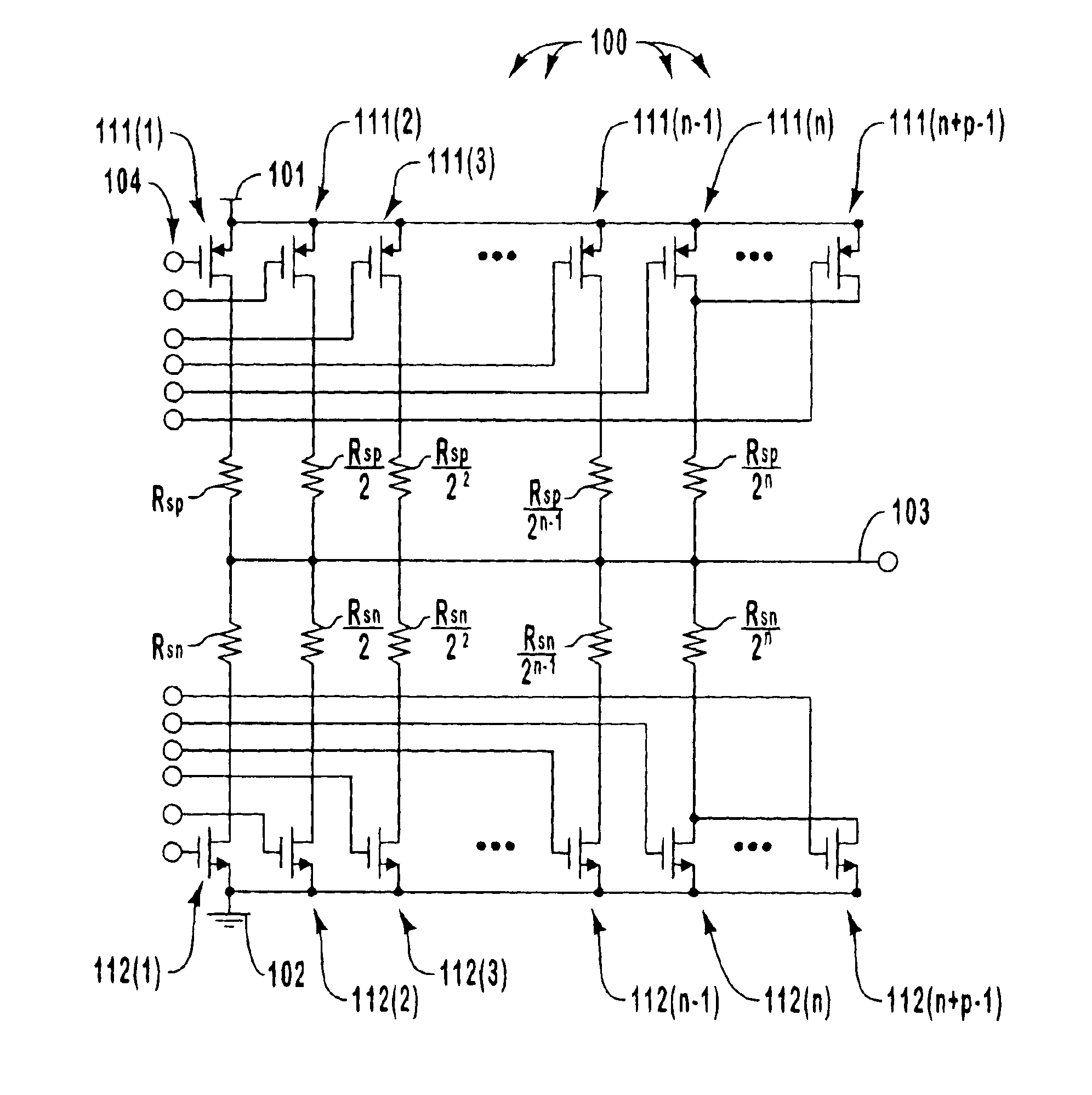

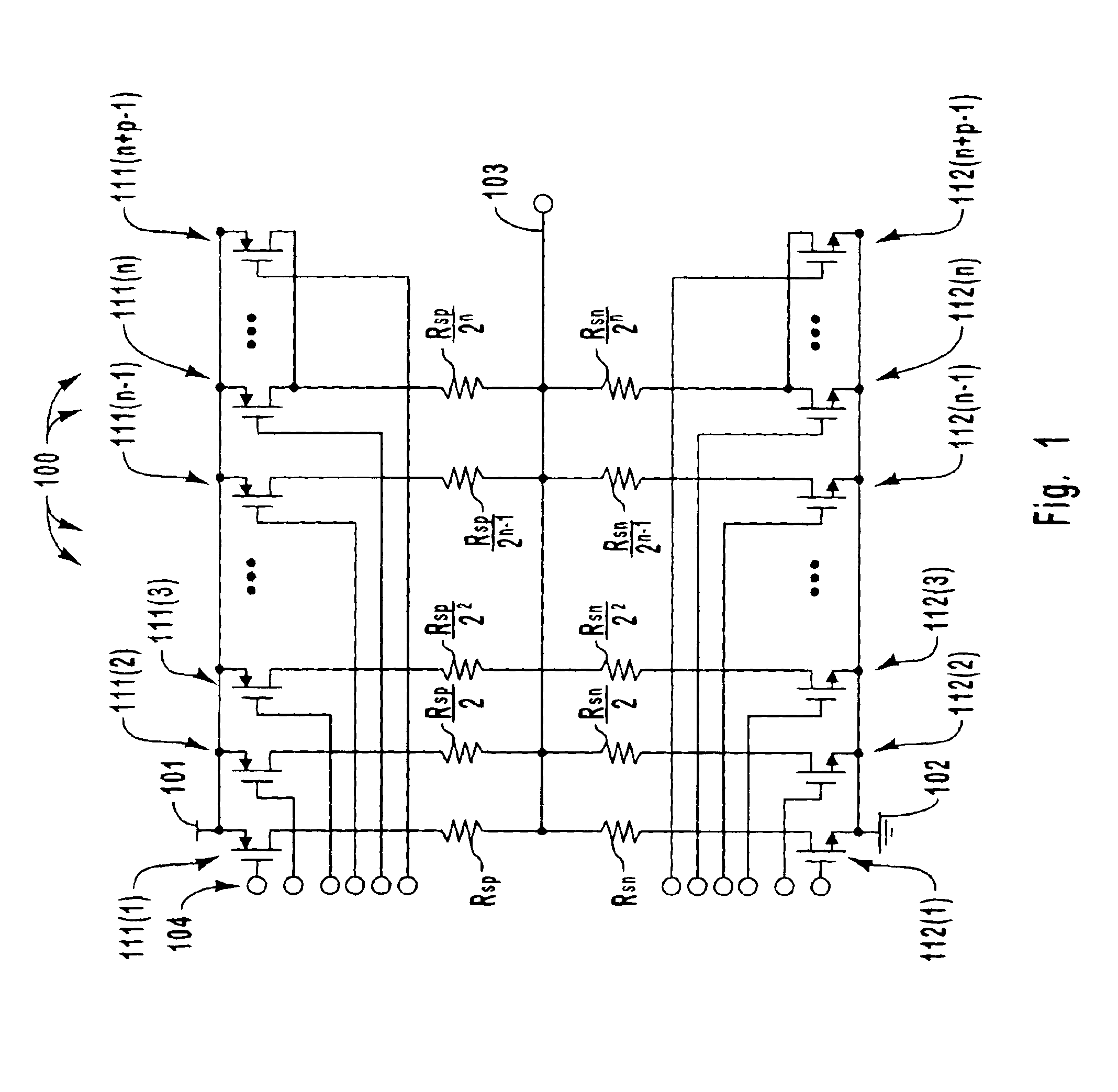

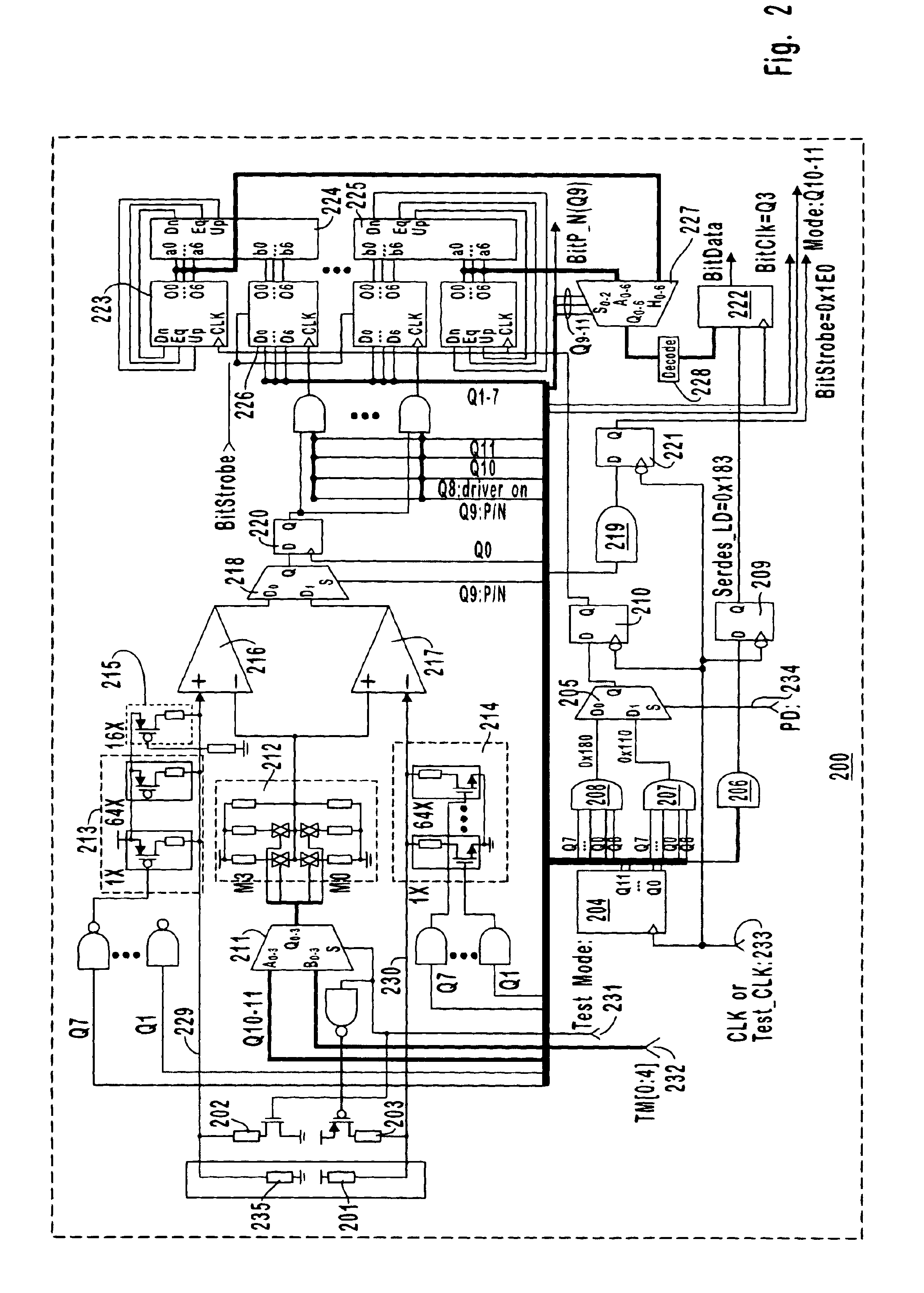

Digitally controlled impedance driver matching for wide voltage swings at input/output node and having programmable step size

InactiveUS6909305B1Save layout area andSmall sizeInput/output impedence modificationReliability increasing modificationsDriver circuitEngineering

A digitally controlled impedance driver circuit including a number of fingers, some of which having FETs and series resistors sized in binary or other differential ratios, and some of the higher power FETs being sized in equal ratio and perhaps sharing a series resistor. A DCI controller circuit periodically determines a configuration of the DCI driver circuit that would result in the DCI driver circuit approximating a target impedance. Each time the DCI controller circuit does this, a comparator determines if the impedance of the DCI driver circuit should be increased or decreased. A noise attenuation circuit turns off (or on) only one of the high power fingers if the controller circuit determines that more (or less) impedance is needed even if turning off (or on) only one of the fingers would not result in the configuration of the DCI driver circuit determined by the controller circuit.

Owner:SEMICON COMPONENTS IND LLC

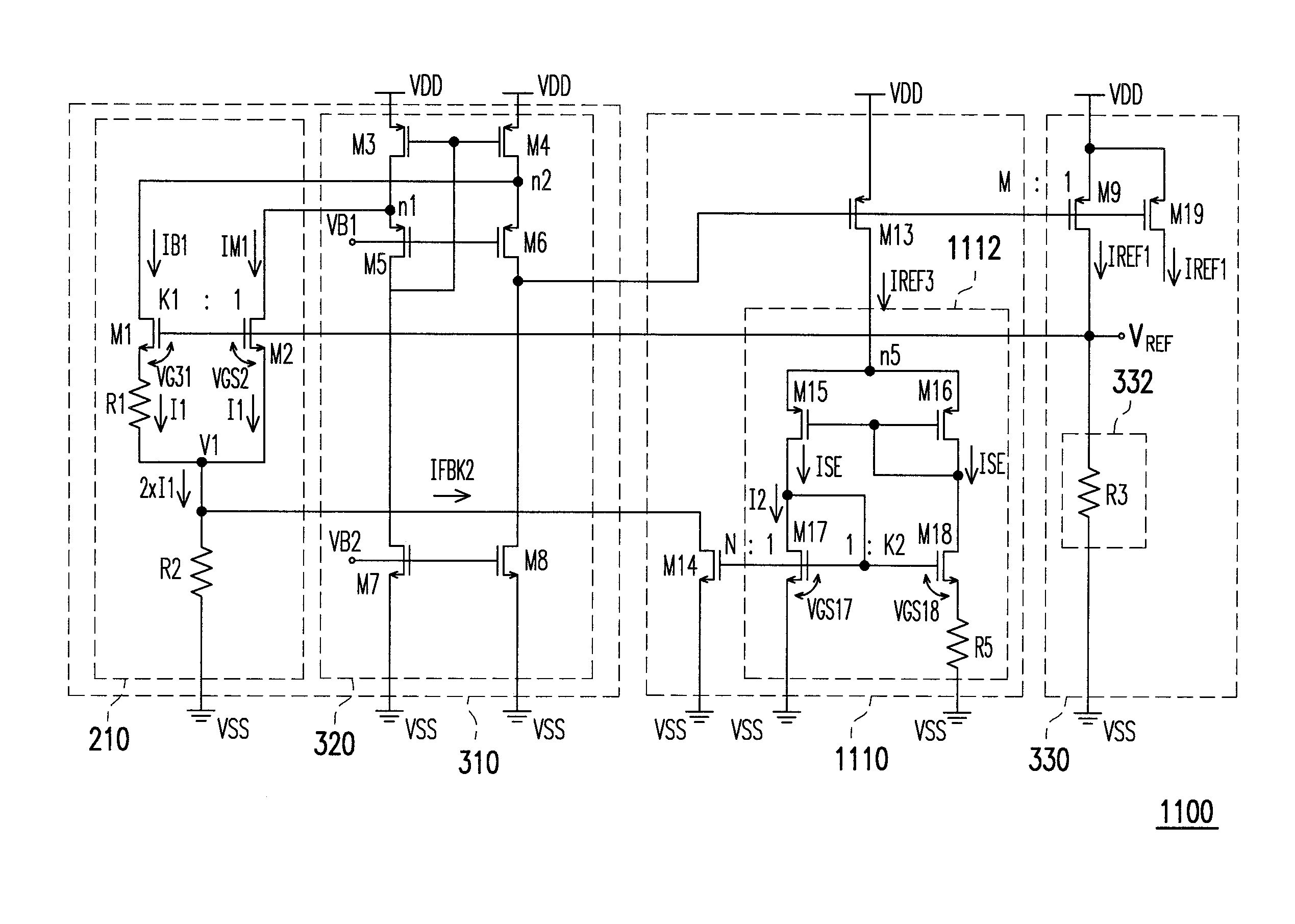

Reference voltage generator

InactiveUS20140091780A1Improve power supply rejection ratioReduce voltageElectric variable regulationVoltage generatorEngineering

A reference voltage generator including a reference voltage generating unit is provided. The reference voltage generating unit receives a first bias voltage current and a first mirror current and generates a reference voltage. The reference voltage generating unit includes a first metal-oxide-semiconductor (MOS) transistor, a second MOS transistor, a first impedance providing element and a second impedance providing element. The first and the second MOS transistors operate in a sub-threshold region so as to generate a first gate-source voltage and a second gate-source voltage having a negative temperature coefficient. The first impedance providing element is configured to generate a first current having a positive temperature coefficient. The second impedance providing element is configured to generate a first voltage having a negative temperature coefficient at its first terminal. The reference voltage is equal to a sum of the second gate-source voltage and the first voltage.

Owner:NOVATEK MICROELECTRONICS CORP

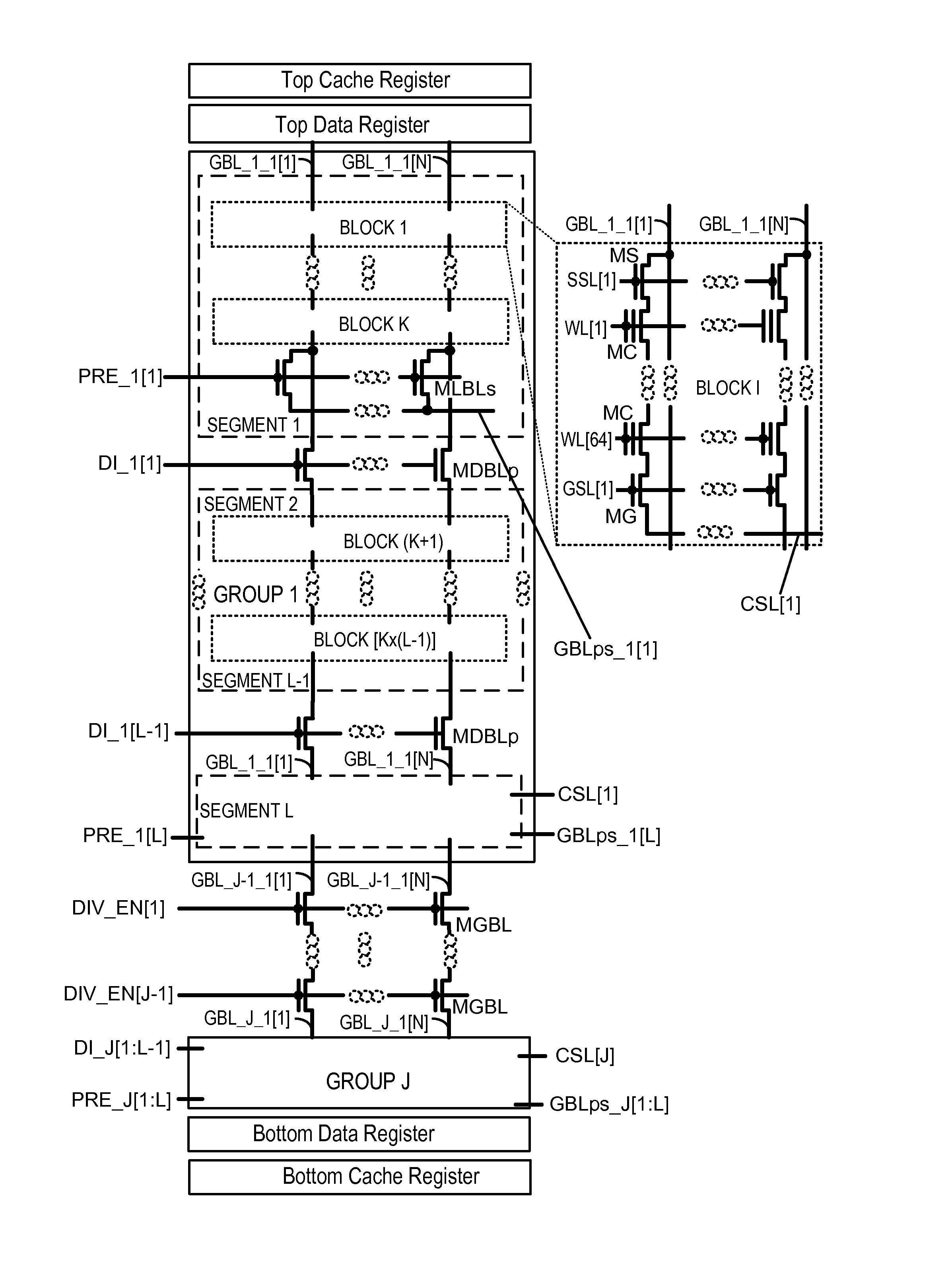

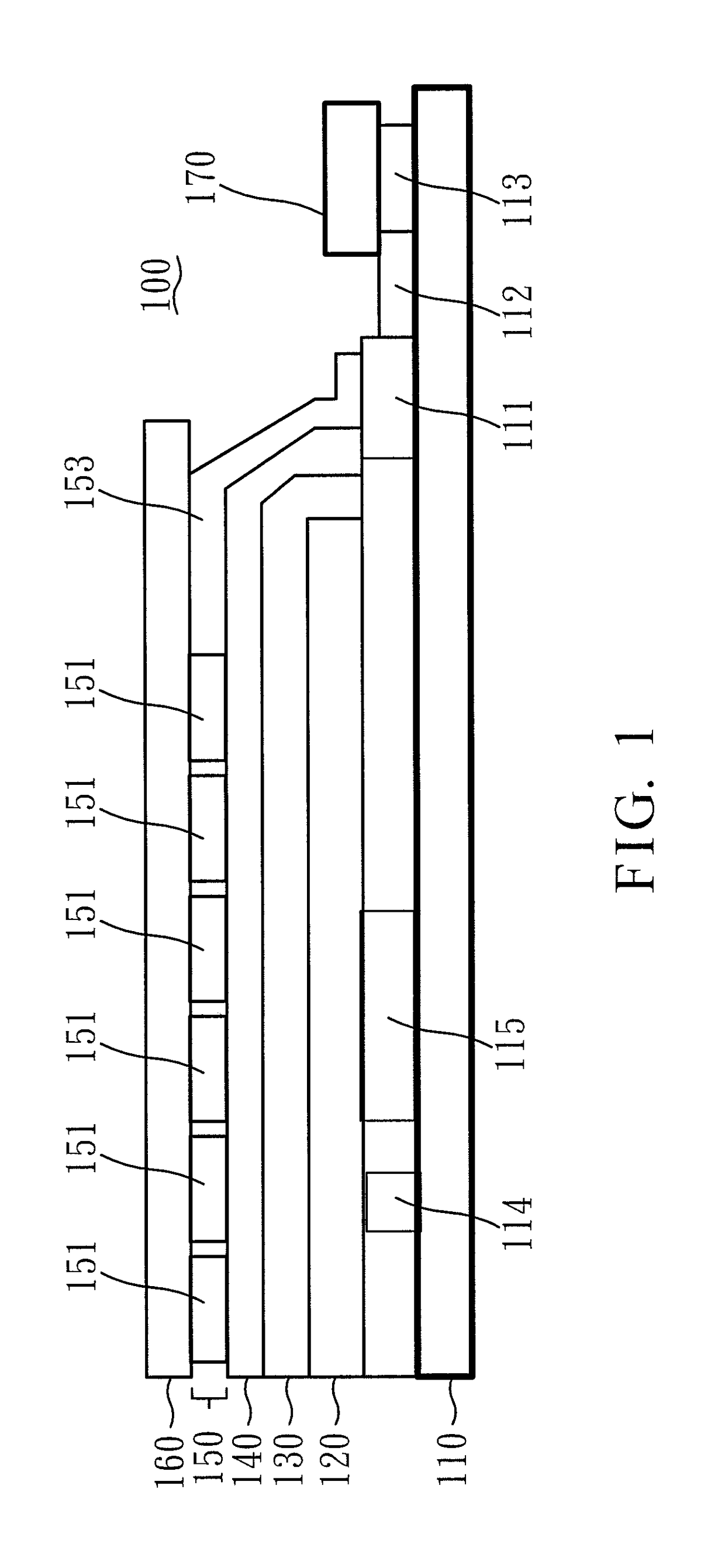

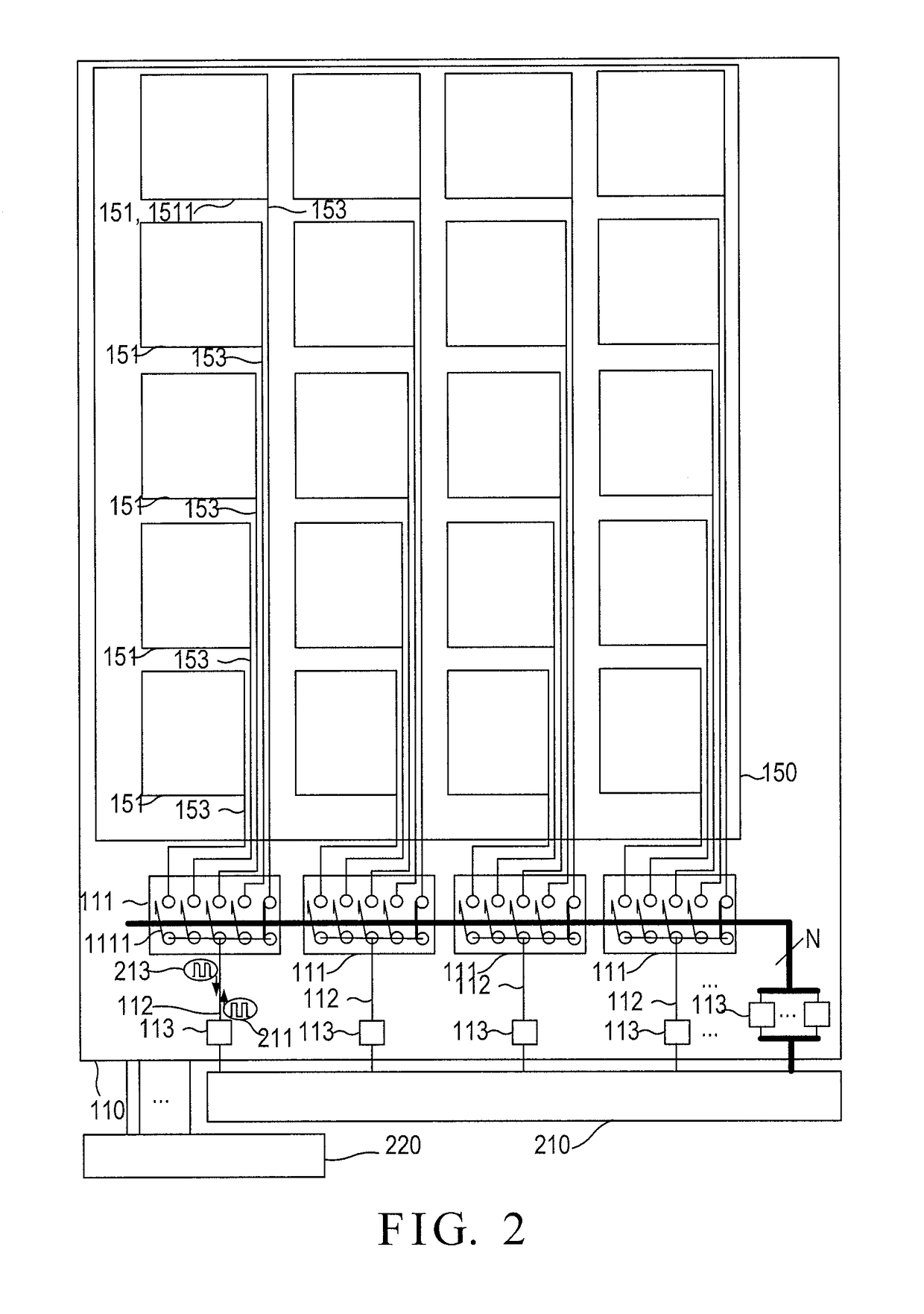

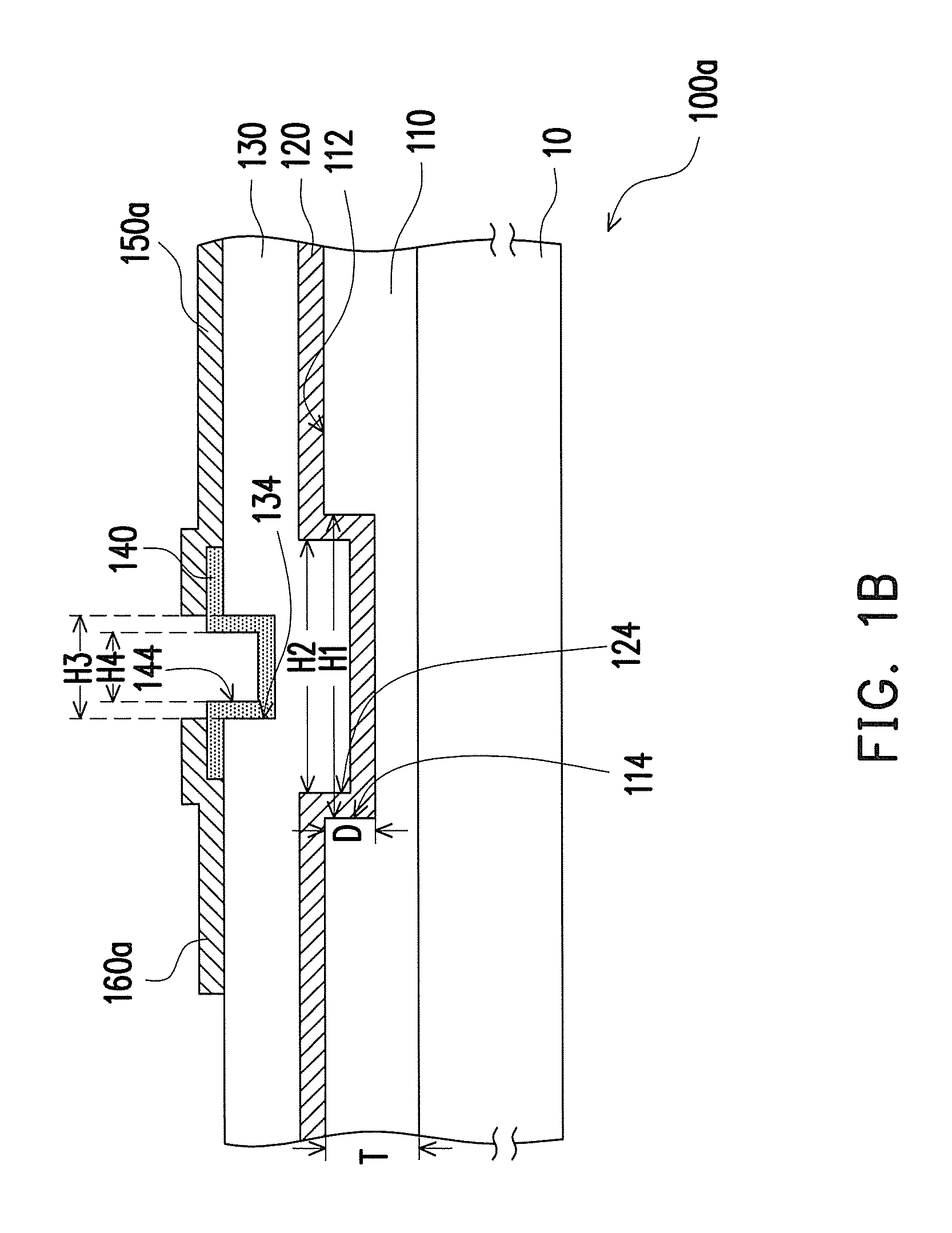

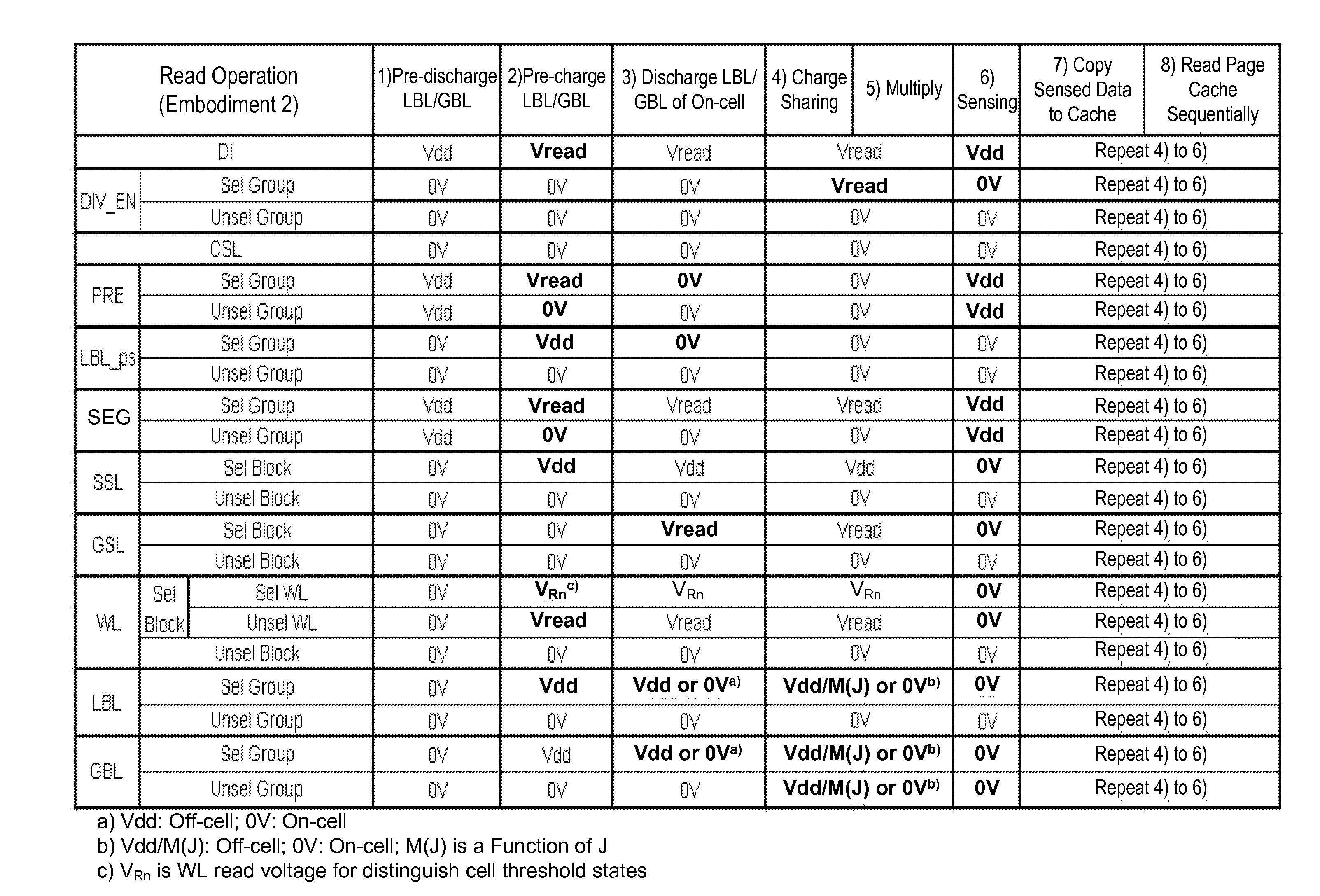

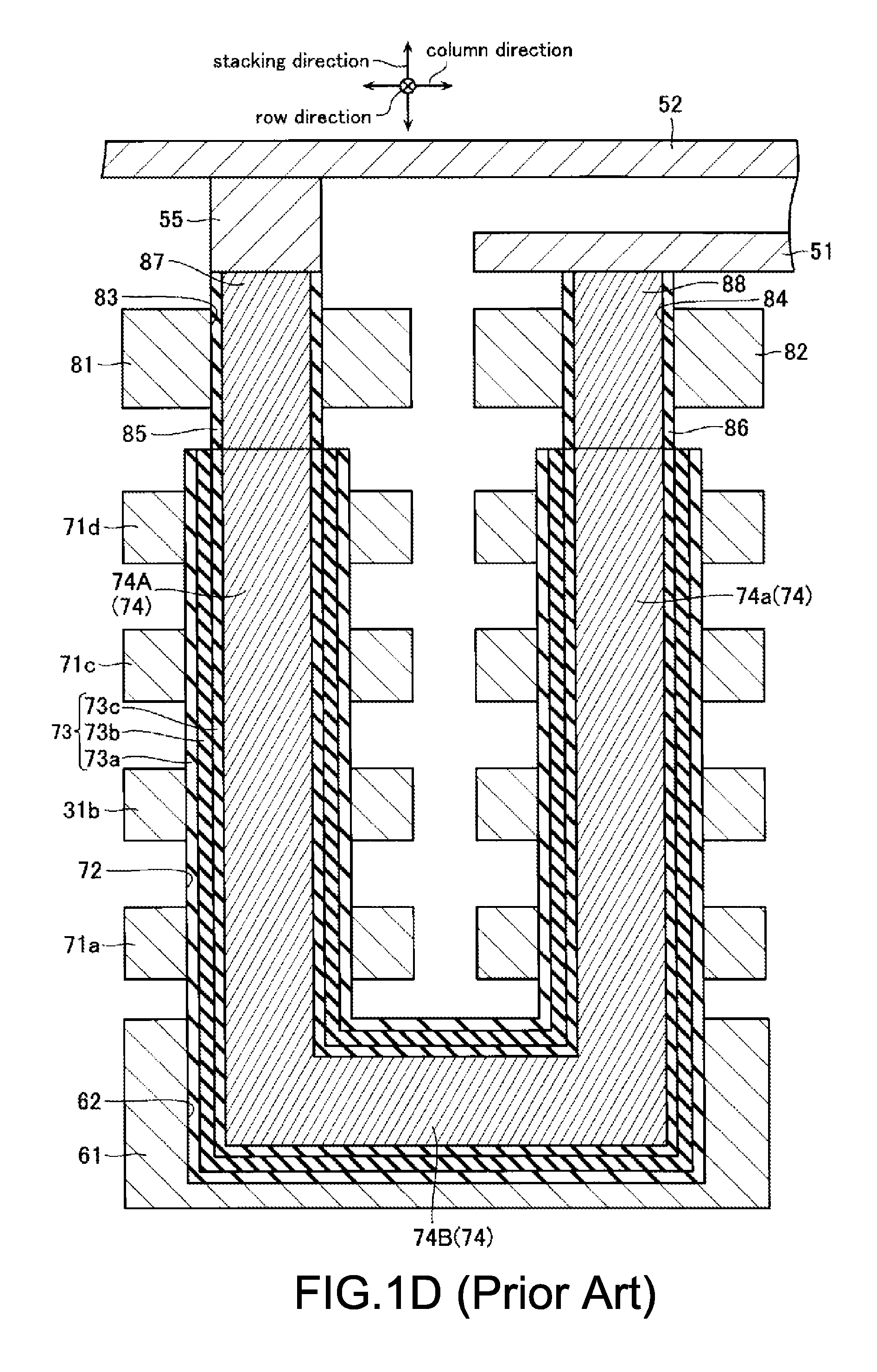

NAND array hiarchical bl structures for multiple-wl and all-bl simultaneous erase, erase-verify, program, program-verify, and read operations

ActiveUS20150078080A1Fast readingImprove reading speedRead-only memoriesDigital storageBit lineComputer architecture

Several 2D and 3D HiNAND flash memory arrays with 1-level or 2-level broken BL-hierarchical structures are provided for Multiple Whole-WL and All-BL simultaneous operations in Dispersed Blocks. The global bit line (GBL) is divided to multiple 1(top)-level broken metal2 GBLs plus optional lower-level broken metal1 local bit lines (LBLs). A preferred Vinhibit supply higher than Vdd can be selectively supplied via horizontal metal0 power line LBLps to charge selected broken GBLs / LBLs which can also be selectively discharged via a String source line. Charge-sharing technique for precharging and discharging of broken GBL / LBL capacitors for NAND cell data sensing is used in Read and Verify operations with reduced power consumption and latency. Recall technique to restore the desired Program Data stored in the broken GBL / LBL capacitors is used for Multiple-WL and All-BL Program and Program-Verify operation with reduced program current for highest program yield superior P / E cycles.

Owner:APLUS FLASH TECH

Multi-layer printed circuit board inductor winding with added metal foil layers

ActiveUS20050195060A1High currentImprove efficiencyTransformers/inductances casingsPrinted electric component incorporationInductor windingsSurface mounting

The present invention provides an electromagnetic component formed from adjacent conducting layers of a multi-layer PCB and two additional conducting layers in contact with the PCB. The inventive component includes one or more winding turns formed by connecting the multiple layers of the multi-layer PCB with conductive vias and by connecting the additional conducting layers to respective top and bottom surfaces of the PCB. In one embodiment, one of the conducting layers is soldered to a top conducting layer of the PCB and the other of the conductive layers is soldered to a bottom conducting layer of the PCB, effectively increasing the cross-sectional area of the top and bottom winding layers. In another embodiment, the additional conducting layers are separated from the adjacent conducting PCB layers by a layer of insulation, permitting the additional conducting layers to form separate winding turns. The inventive winding stack can be surface mounted to a PCB, and can be used as an inductor, or in other electromagnetic devices. The winding thus constructed is capable of accepting larger currents with lower resulting temperature increases than windings formed only from PCBs, and are less expensive to manufacture than PCB-only windings.

Owner:ASTEC INT LTD

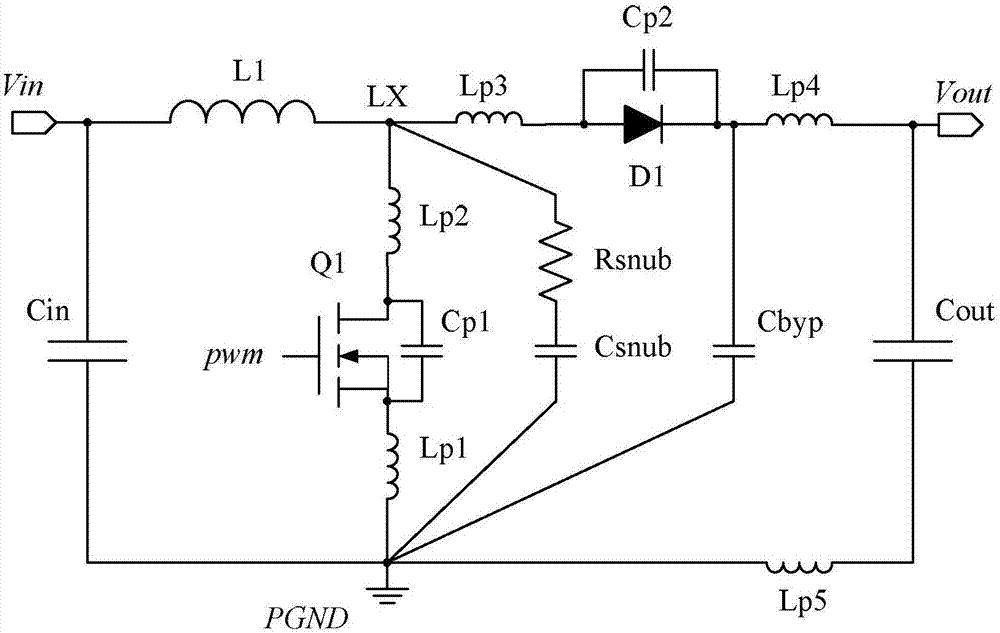

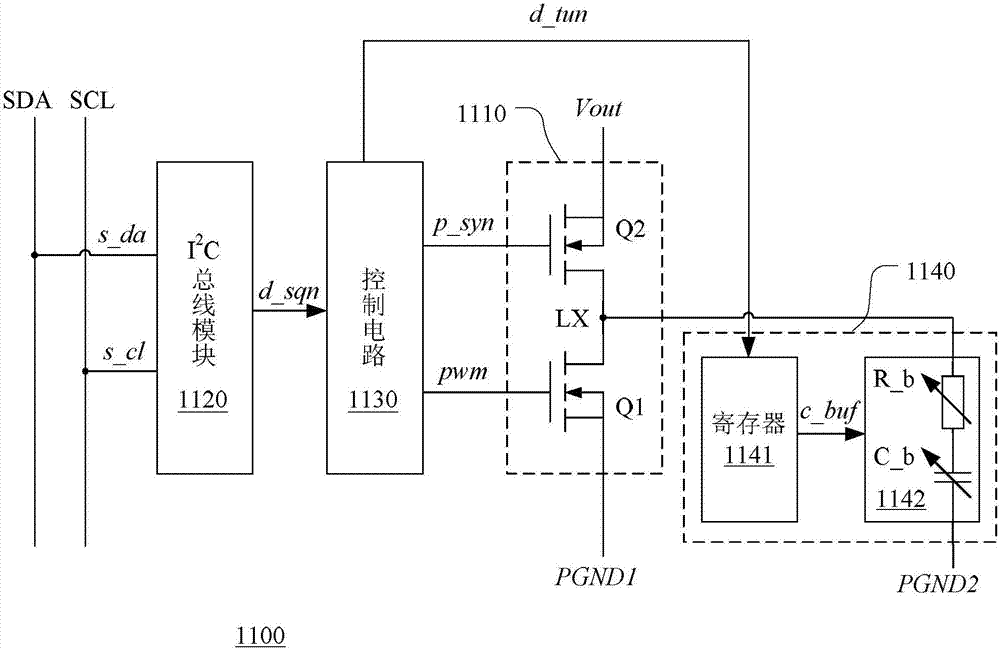

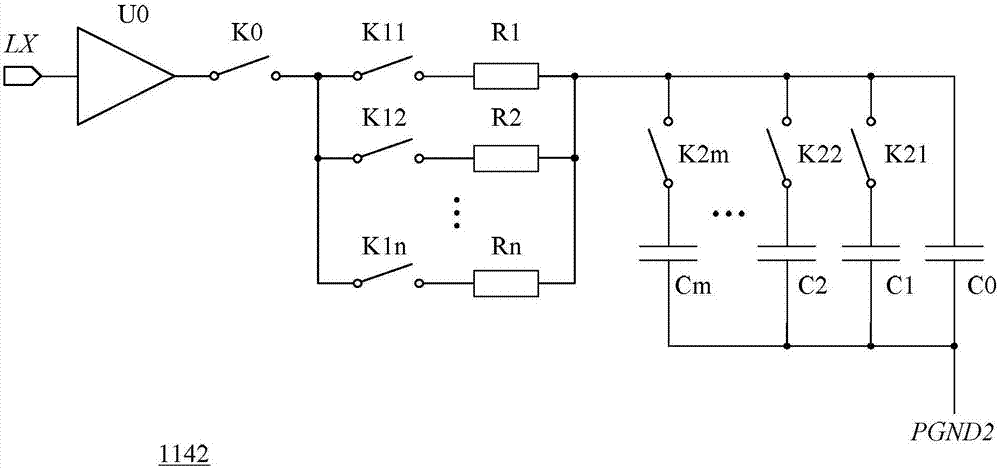

Switch power supply circuit and adjusting method thereof

ActiveCN106953511AImprove signal waveform integrityImprove debugging efficiencyPower conversion systemsCapacitanceComputer module

The invention discloses a switch power supply circuit and an adjusting method thereof. The switch power supply circuit comprises a main circuit, an I<2>C bus module, a control circuit, and a buffer circuit; the main circuit comprises a switch node and a main switch tube controlled by a switch signal, and the main circuit comprises a first grounding end, an input end for receiving an input DC signal, and an output end for providing an output DC signal; the I<2>C bus module generates control data; the control circuit generates the switch signal according to the control data and / or the output DC signal, and generates an adjustment data signal according to the control data; and the buffer circuit is connected between a second grounding end and the switch node of the main circuit, and resistance and capacitance values of the buffer circuit are controlled by the adjustment data signal, so repeated welding and removal do not need to be performed on the buffer circuit, a buffer grounding path matching the main circuit of the switch power supply circuit is provided at a position of the switch node then, and signal waveform integrity and debugging efficiency at the position of the switch node are improved.

Owner:KUSN INFOVISION OPTOELECTRONICS

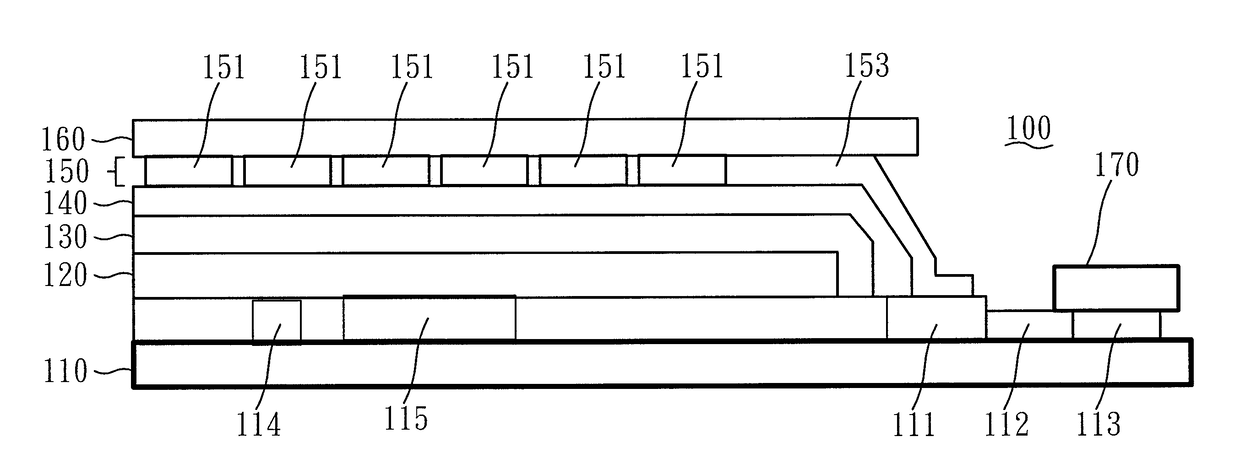

OLED touch display device

InactiveUS20180308902A1Reduce in quantitySave layout area andSolid-state devicesInput/output processes for data processingTouch SensesDisplay device

An OLED touch display device includes a TFT substrate and a touch electrode layer. The TFT substrate has a surface formed thereon plural switch devices, plural second touch traces and plural conductive pads. Each switch device has plural touch TFT switches. The touch electrode layer includes plural first touch traces and plural touch sense electrodes divided into plural groups each having at least one touch sense electrode, and each group is corresponding to one of the conductive pads. The touch sense electrodes are corresponding to the first touch traces one by on. Each touch sense electrode is connected to the corresponding first touch trace. Each first touch trace is connected to one touch TFT switch of the corresponding switch device, and each switch device is connected to one second touch trace and the corresponding conductive pad.

Owner:SUPERC TOUCH CORP

NAND array hiarchical BL structures for multiple-WL and all-BL simultaneous erase, erase-verify, program, program-verify, and read operations

ActiveUS9230677B2Addressing slow performanceSave layout area andRead-only memoriesDigital storagePower flowData storing

Several 2D and 3D HiNAND flash memory arrays with 1-level or 2-level broken BL-hierarchical structures are provided for Multiple Whole-WL and All-BL simultaneous operations in Dispersed Blocks. The global bit line (GBL) is divided to multiple 1(top)-level broken metal2 GBLs plus optional lower-level broken metal1 local bit lines (LBLs). A preferred Vinhibit supply higher than Vdd can be selectively supplied via horizontal metal0 power line LBLps to charge selected broken GBLs / LBLs which can also be selectively discharged via a String source line. Charge-sharing technique for precharging and discharging of broken GBL / LBL capacitors for NAND cell data sensing is used in Read and Verify operations with reduced power consumption and latency. Recall technique to restore the desired Program Data stored in the broken GBL / LBL capacitors is used for Multiple-WL and All-BL Program and Program-Verify operation with reduced program current for highest program yield superior P / E cycles.

Owner:APLUS FLASH TECH

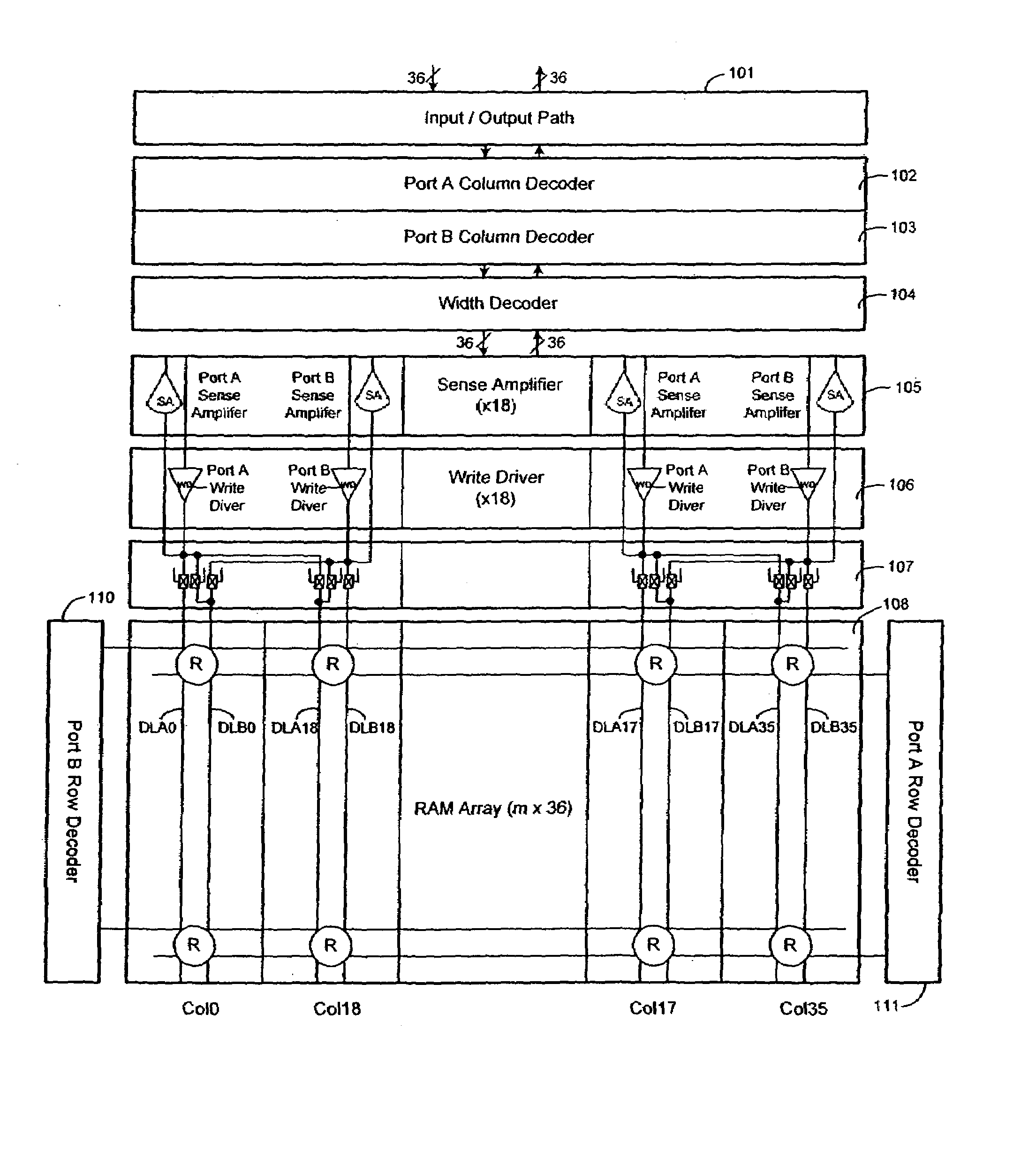

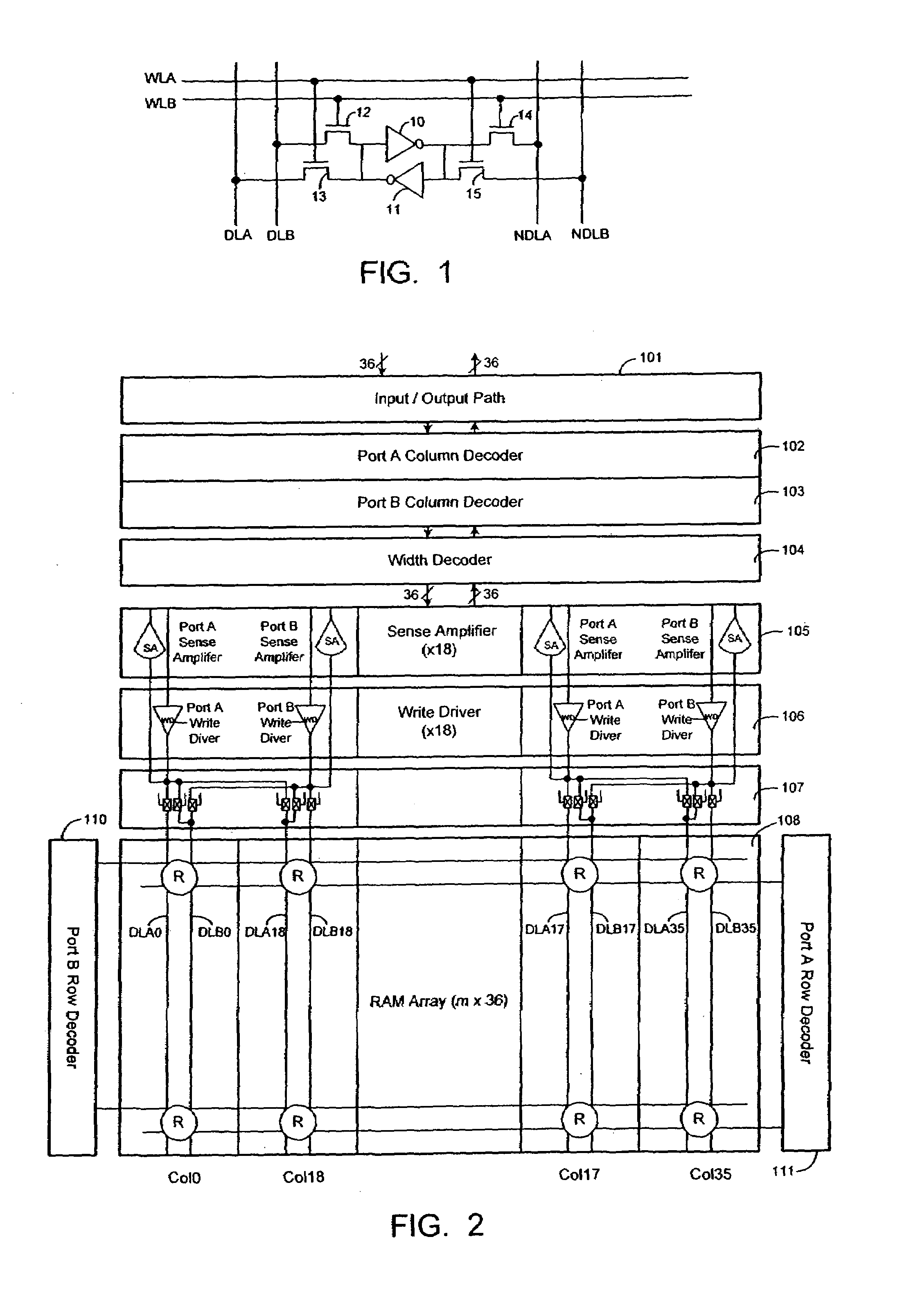

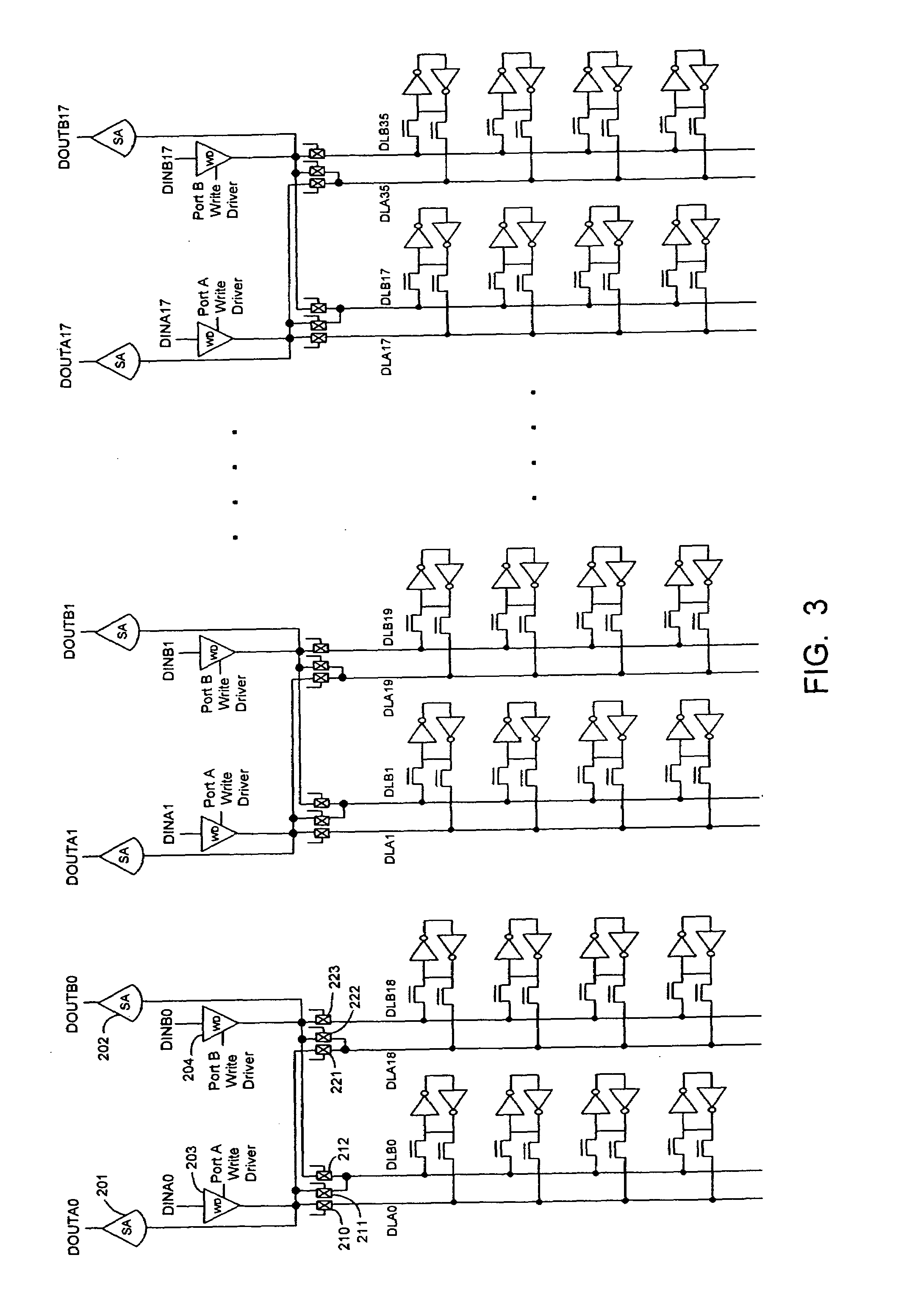

Dual-port memory array using shared write drivers and read sense amplifiers

Dual port memory blocks that have a reduced layout area are provided. The write drivers and sense amplifiers are shared between the dual ports to reduce the number of write drivers and sense amplifiers to save layout area. The write drivers for the two ports are used to write into all of the first port's bitlines. The sense amplifiers for the two ports are used to read from all of the second port's bitlines. A memory block can to support true dual port (TDP) and simple dual port (SDP) operation using substantially less write drivers and sense amplifiers.

Owner:ALTERA CORP

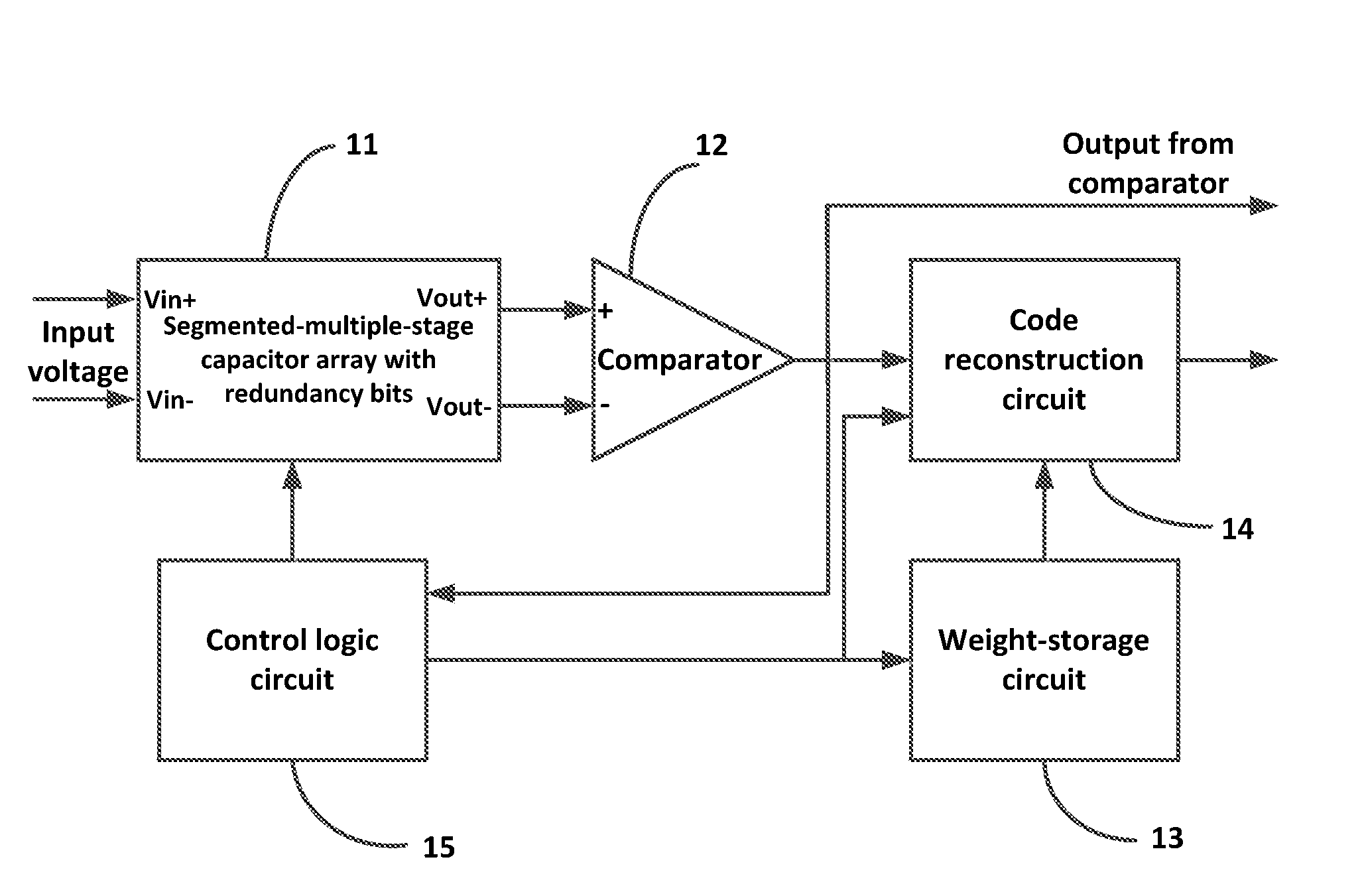

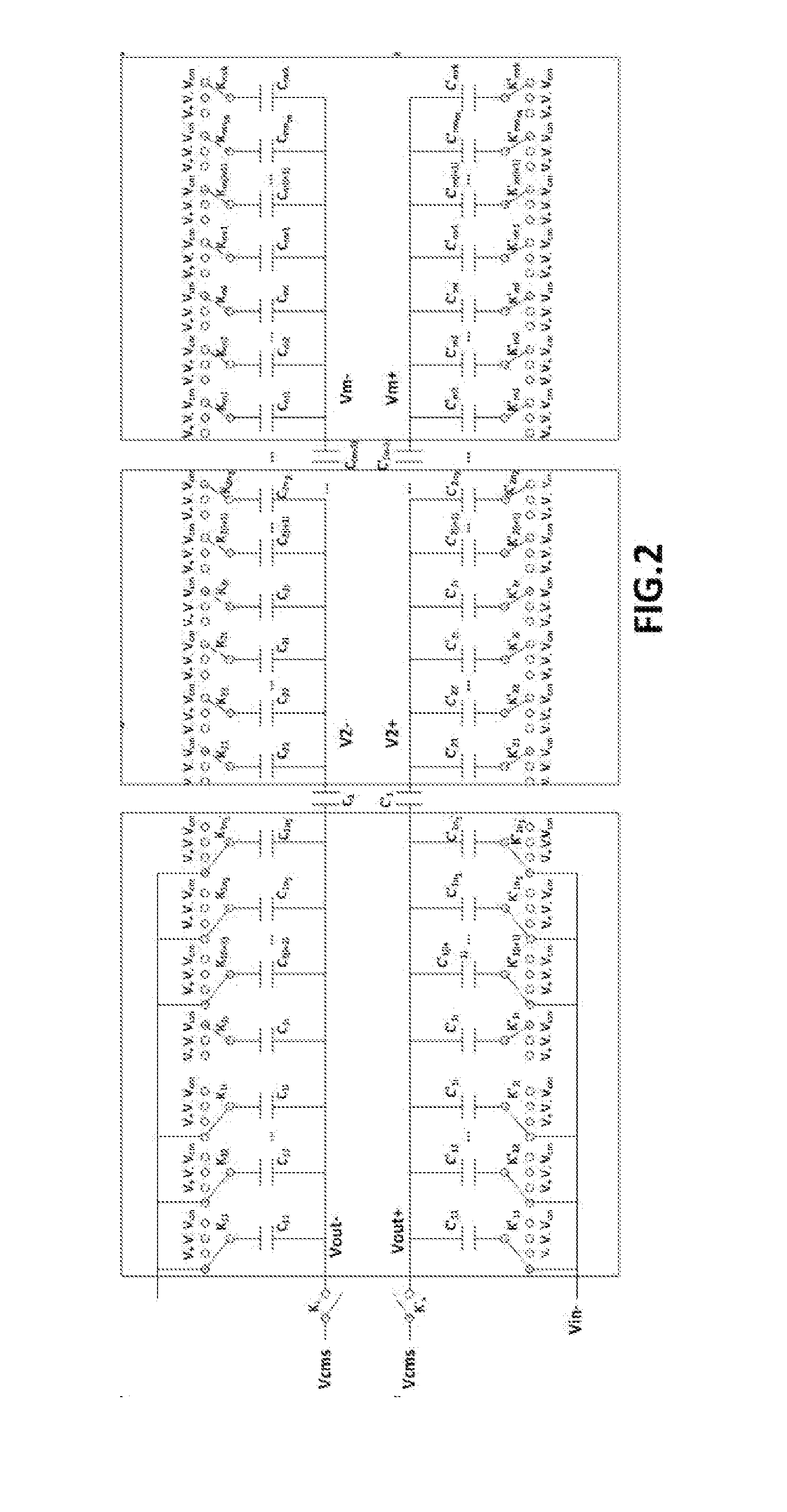

Successive approximation analog-to-digital converter and conversion method thereof

ActiveUS20160112059A1Reduce complexityHigh resolutionElectric signal transmission systemsAnalogue-digital convertersCapacitanceA d converter

A successive approximation analog-to-digital converter and conversion method thereof are provided, the successive approximation analog-to-digital converter includes a segmented-multiple-stage capacitor array with redundancy bits, a comparator, a weight-storage circuit, a code reconstruction circuit and a control logic circuit. The successive approximation analog-to-digital converter helps to decrease the complexity of circuit design, featuring small size and low power. Without auxiliary capacitor array, switches and control logic, the circuit can work to precisely measure and correct capacitor mismatch errors.

Owner:CHONGQING GIGACHIP TECH CO LTD

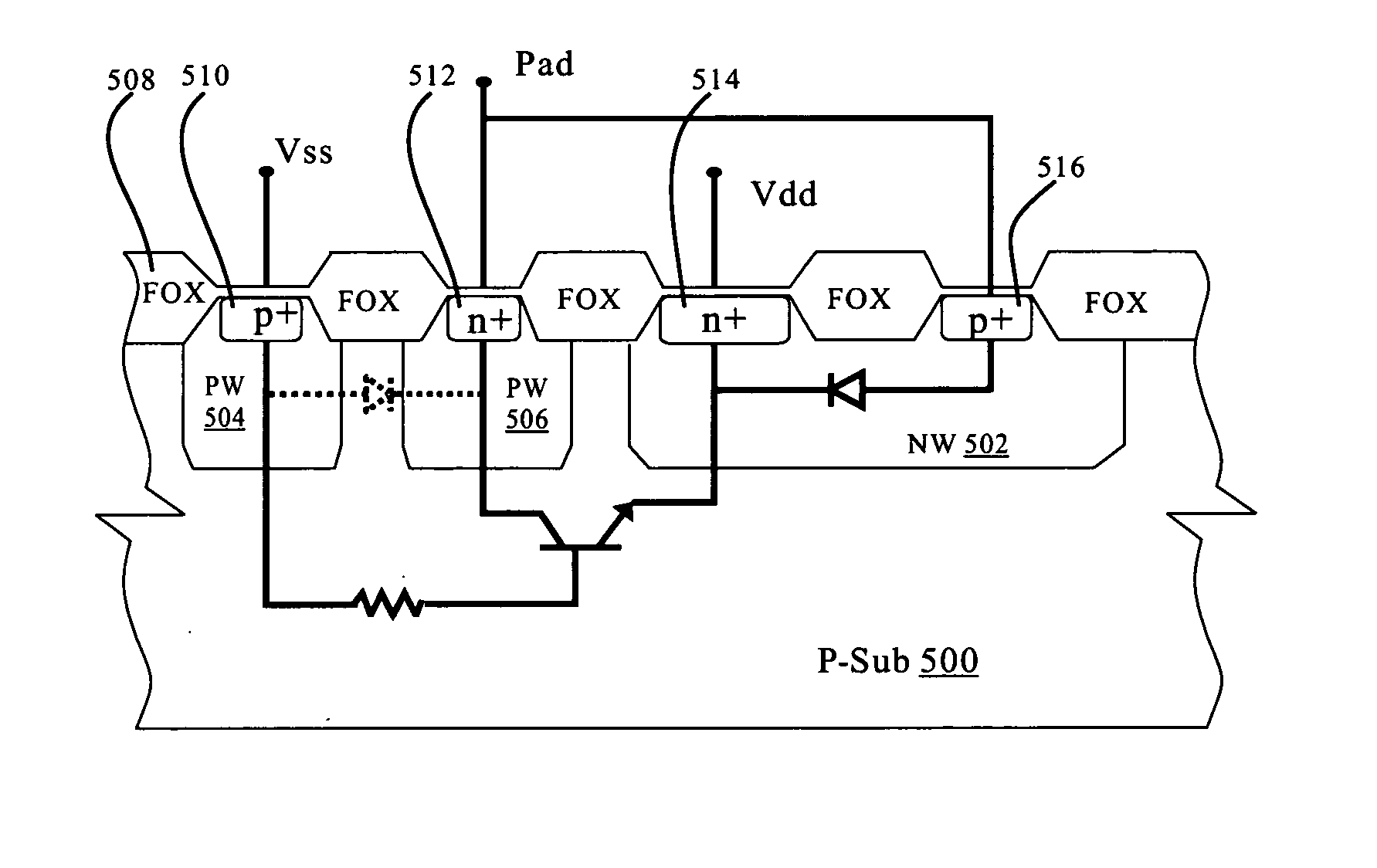

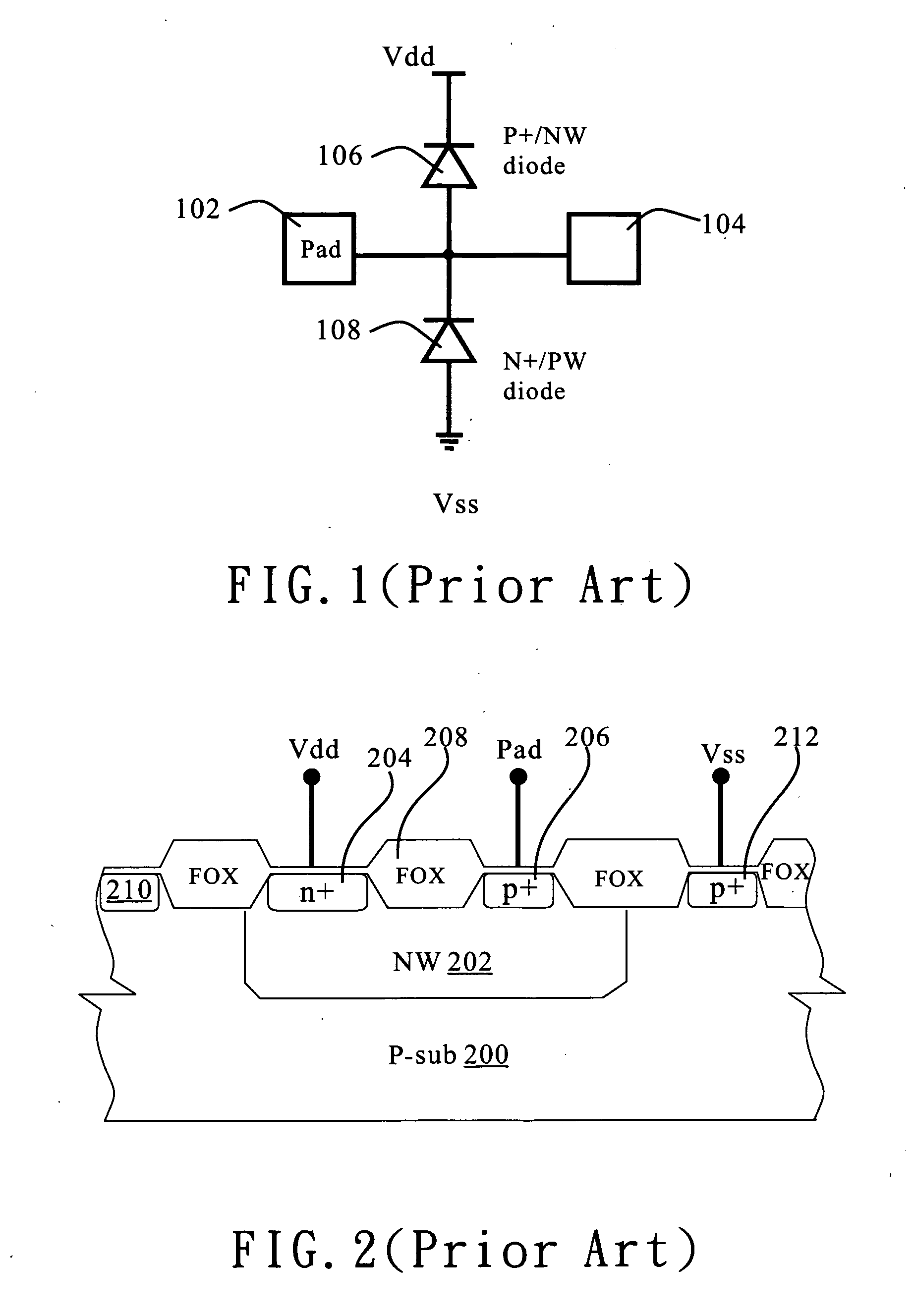

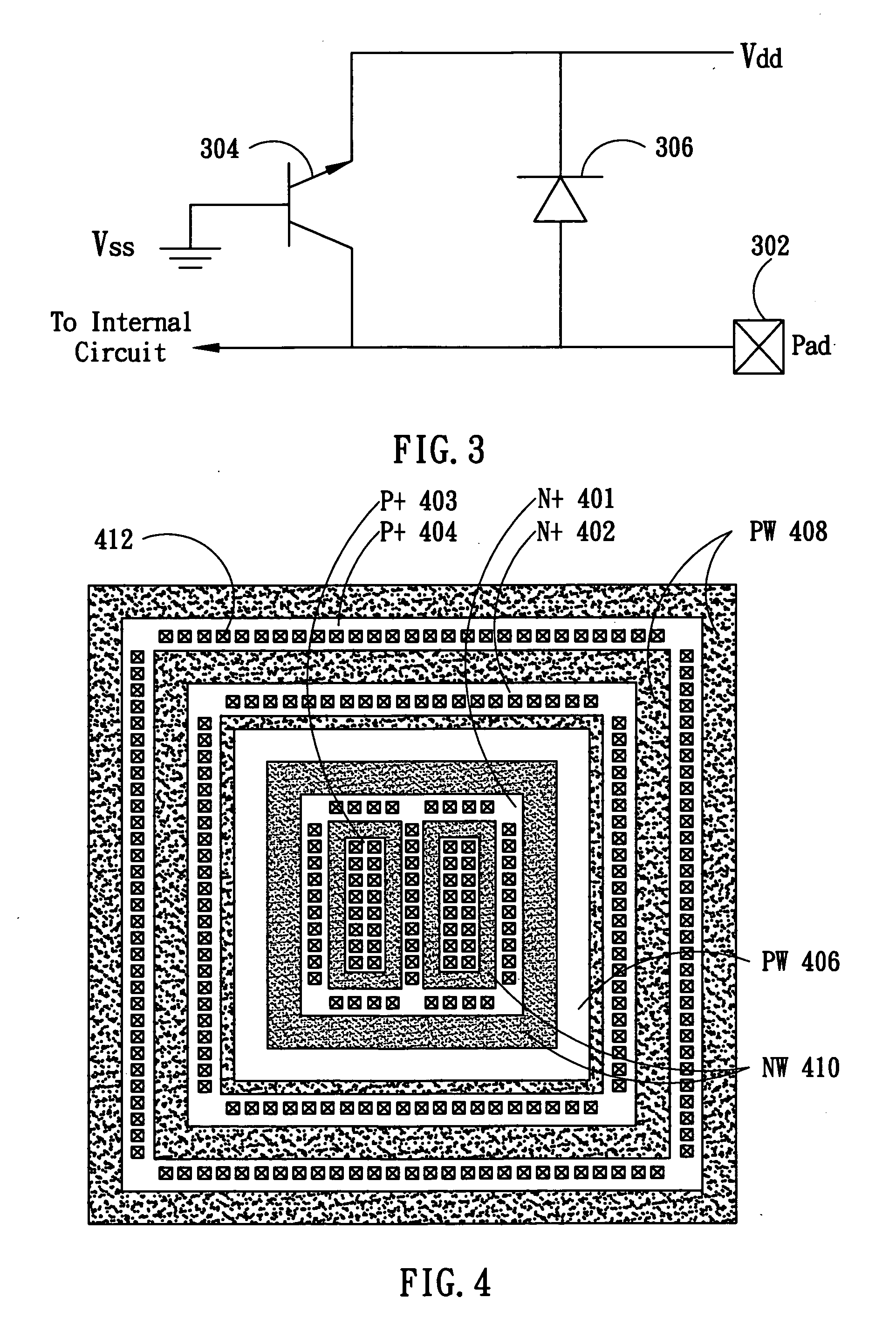

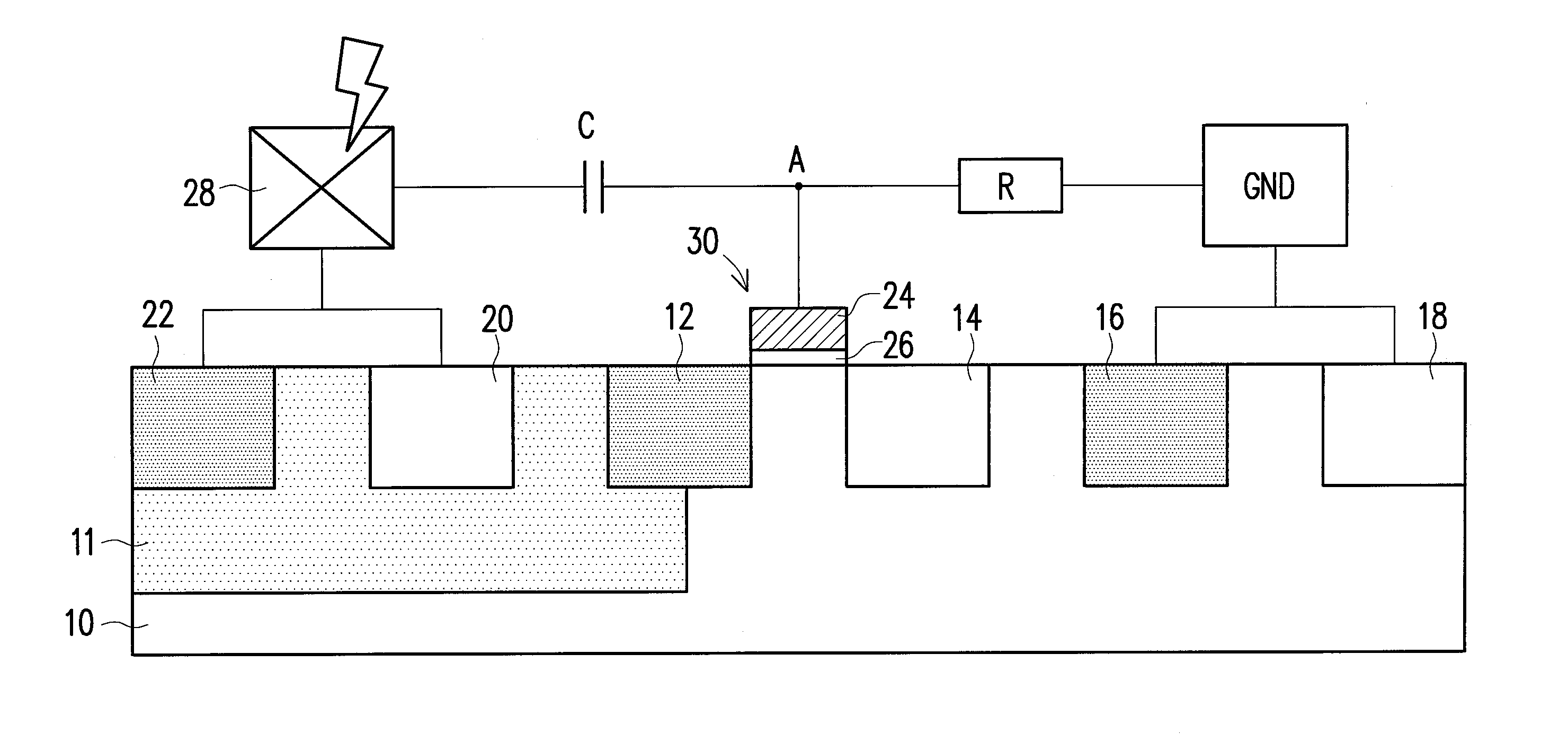

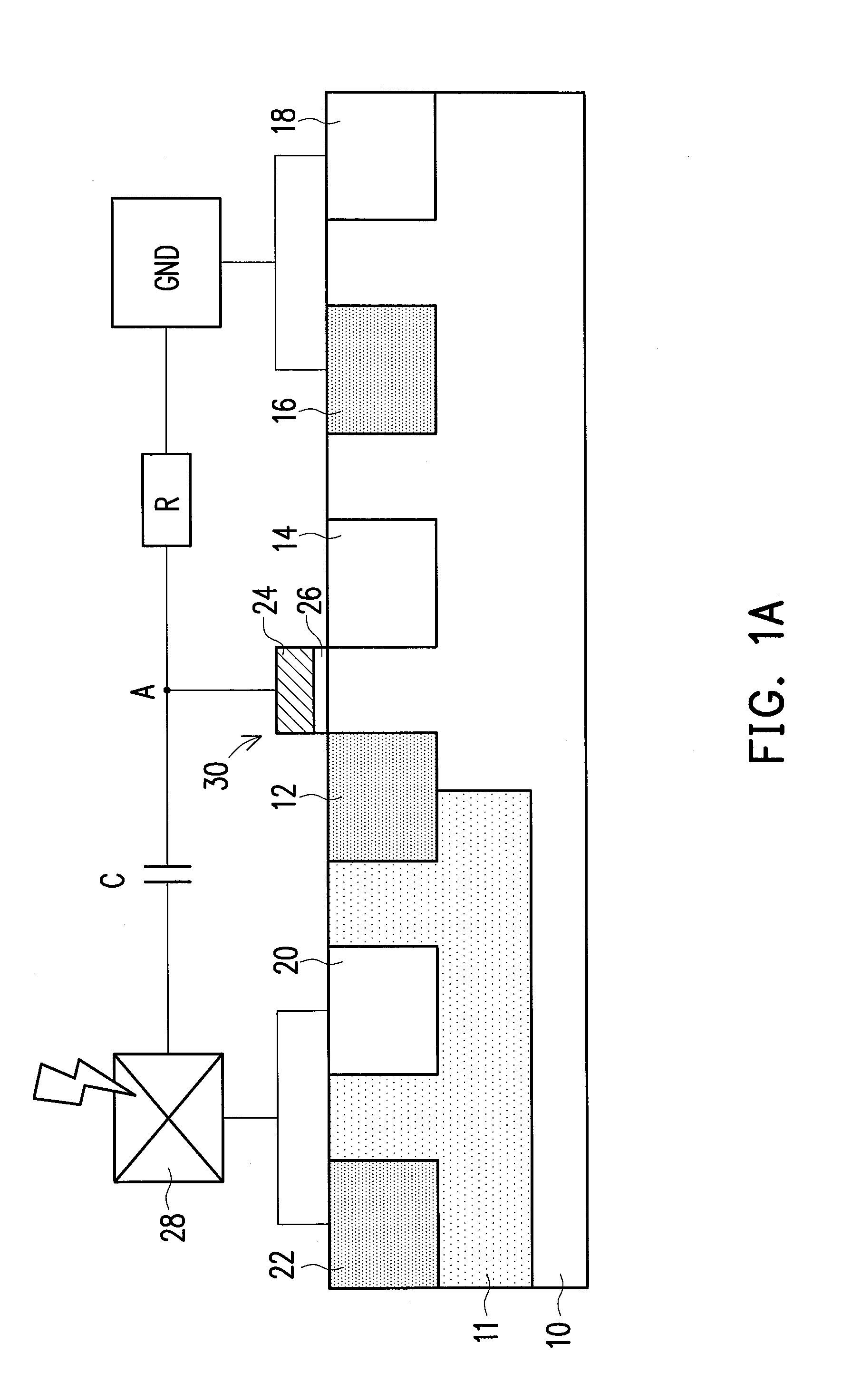

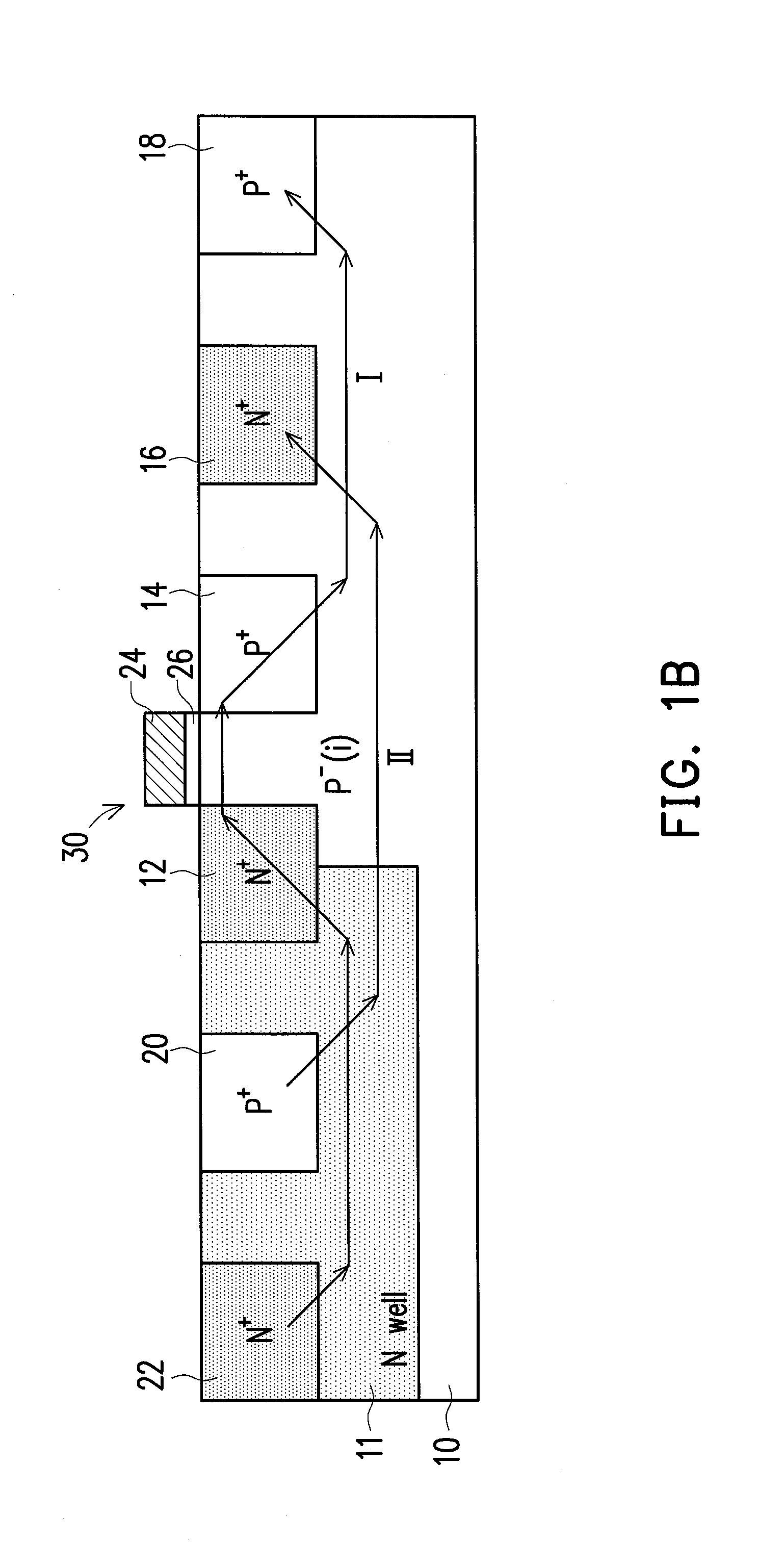

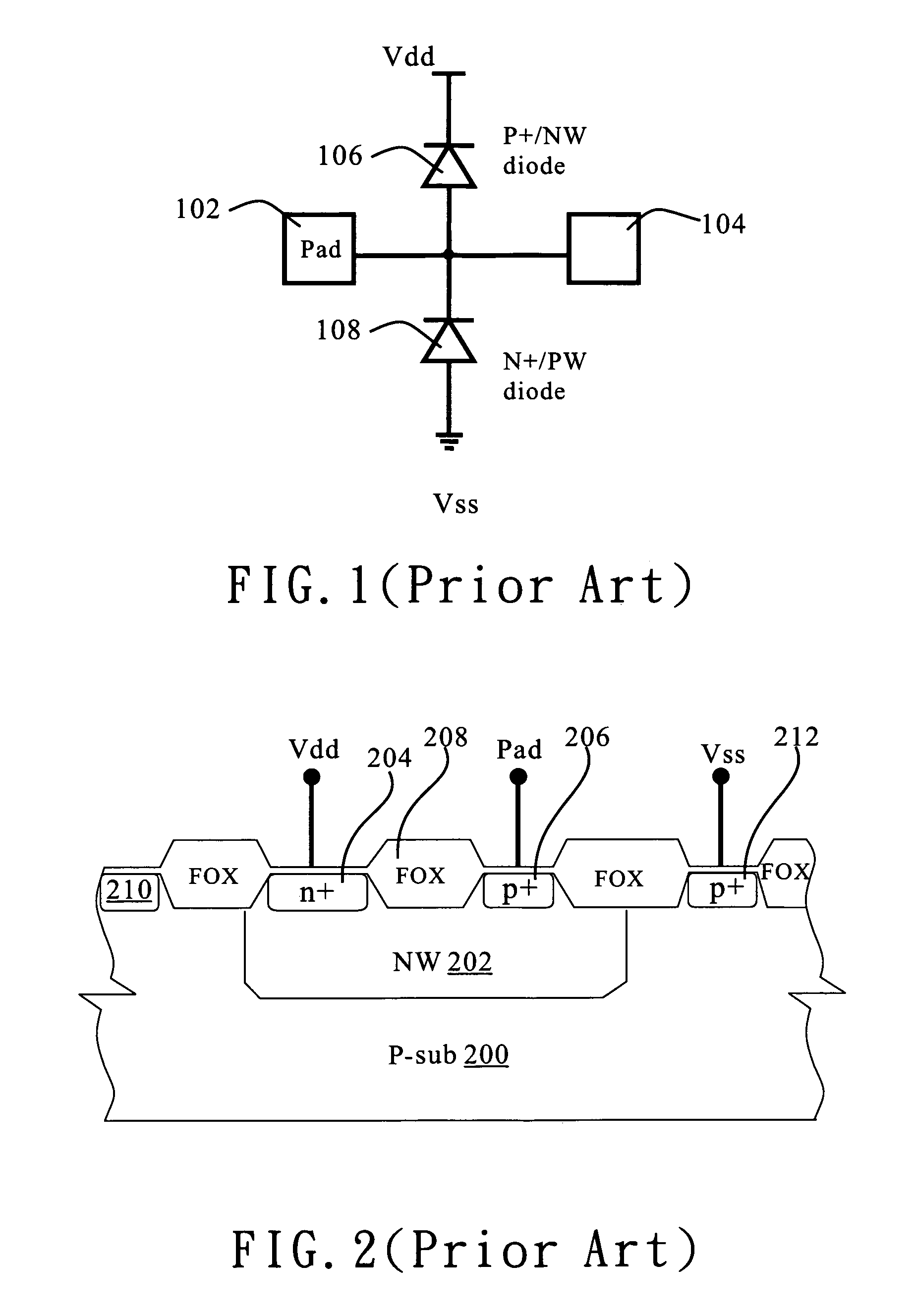

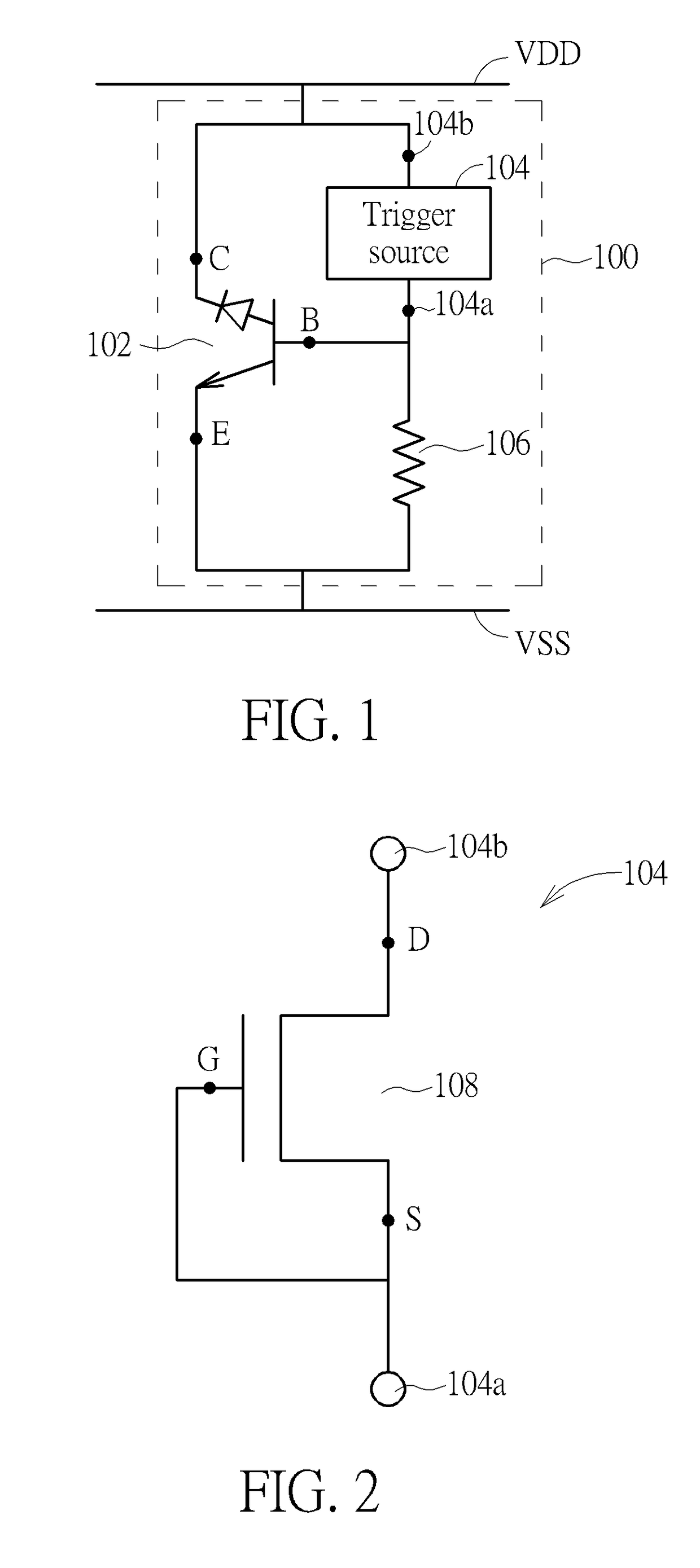

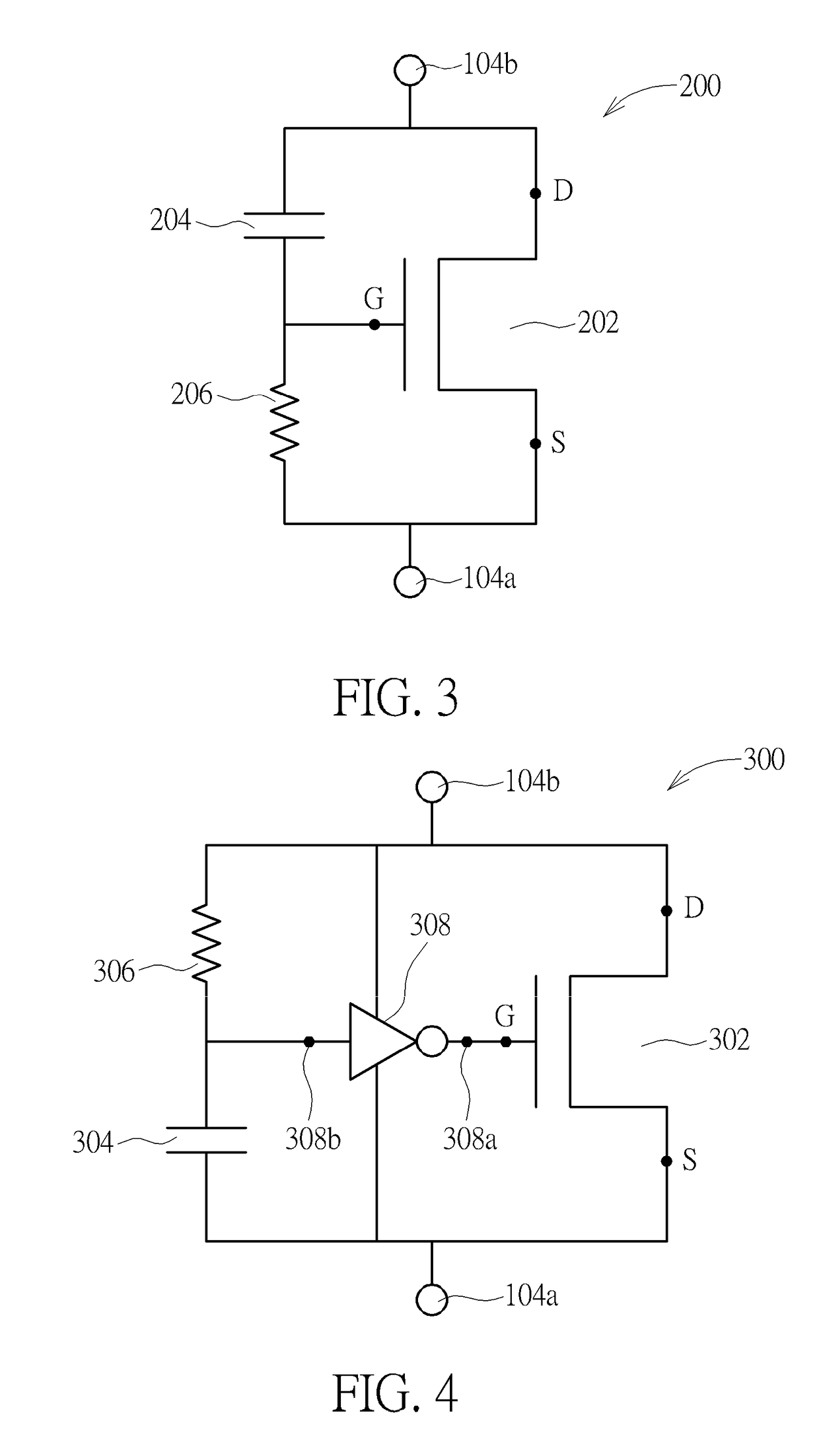

Device for electrostatic discharge protection

InactiveUS20070045743A1Maintain performanceSave layout area andTransistorSemiconductor/solid-state device detailsElectrostatic discharge protectionIntegrated circuit

A device for electrostatic discharge (ESD) protection is disclosed. The device for electrostatic discharge protection comprises a lateral bipolar transistor and a diode. The semiconductor transistor has an emitter, a base and a collector electrically connected to a first power line (such as Vdd), a second power line (such as Vss) and a bond pad of an integrated circuit respectively, wherein the lateral bipolar transistor comprises a lateral bipolar transistor. The diode has an n electrode and a p electrode electrically connected to the first power line and the bond pad respectively.

Owner:WINBOND ELECTRONICS CORP

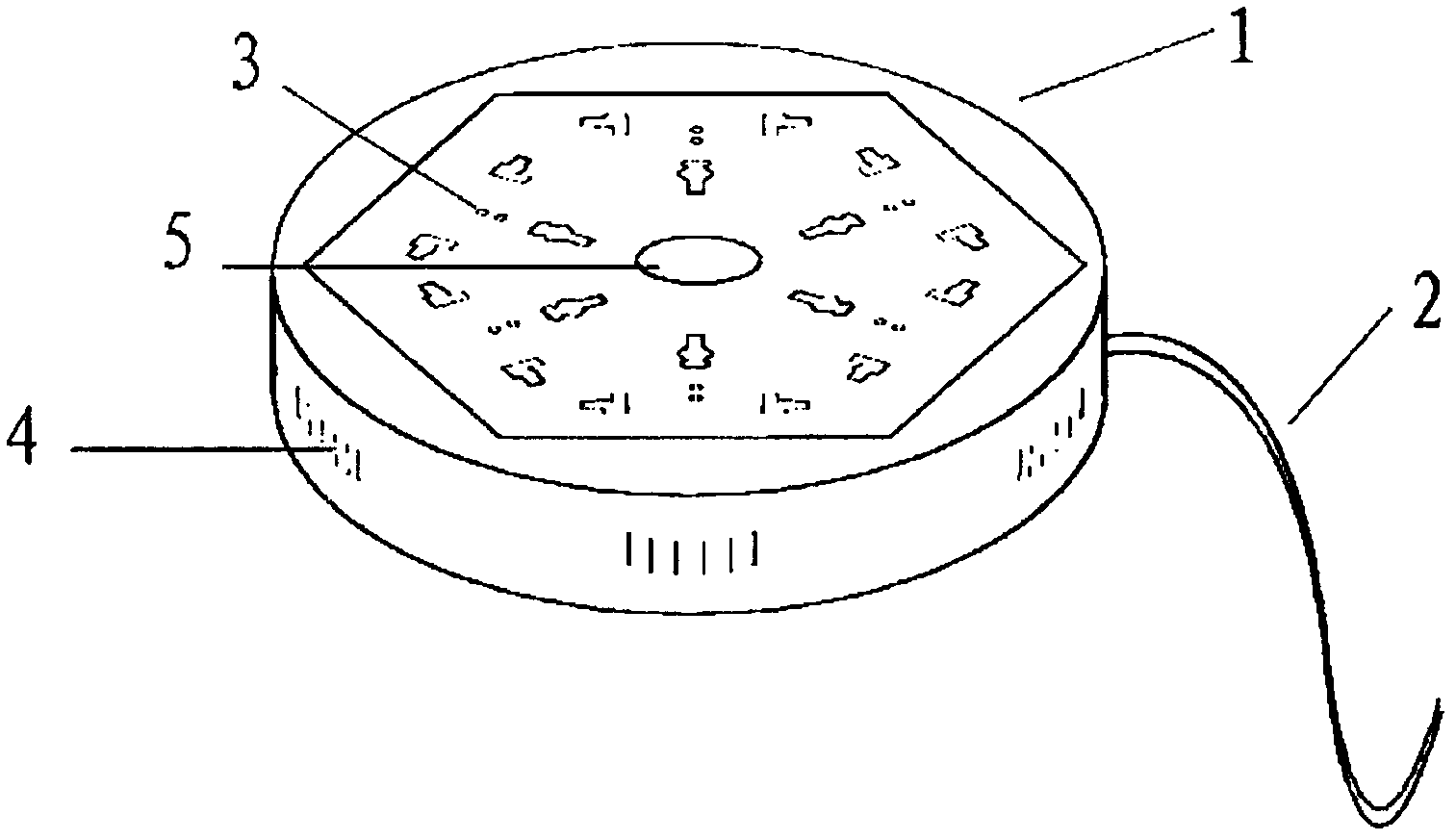

Area-saving type socket with ring-shaped arrangement of jacks

The invention discloses an area-saving type socket with ring-shaped arrangement of jacks. The area-saving type socket is characterized by being provided with a socket body and a power line electrically connected onto the socket body, wherein the socket body has a disc-shaped structure and is circularly provided with a plurality of three-hole power jacks; a ground line jack of each three-hole power jack is positioned at the inner side of the socket body; and on the round edge wall of the socket body, branch switches for controlling the three-hole power jacks are arranged at the corresponding positions of all the three-hole power jacks. In the area-saving type socket disclosed by the invention, due to the disc-shaped structure, the ground line jacks are suitable for being distributed inwards, so that the distribution area is saved; and simultaneously, each power jack is controlled by the branch switch, so that the switching on and the switching off of electric appliances are more convenient.

Owner:NANTONG XINYING DESIGN SERVICE

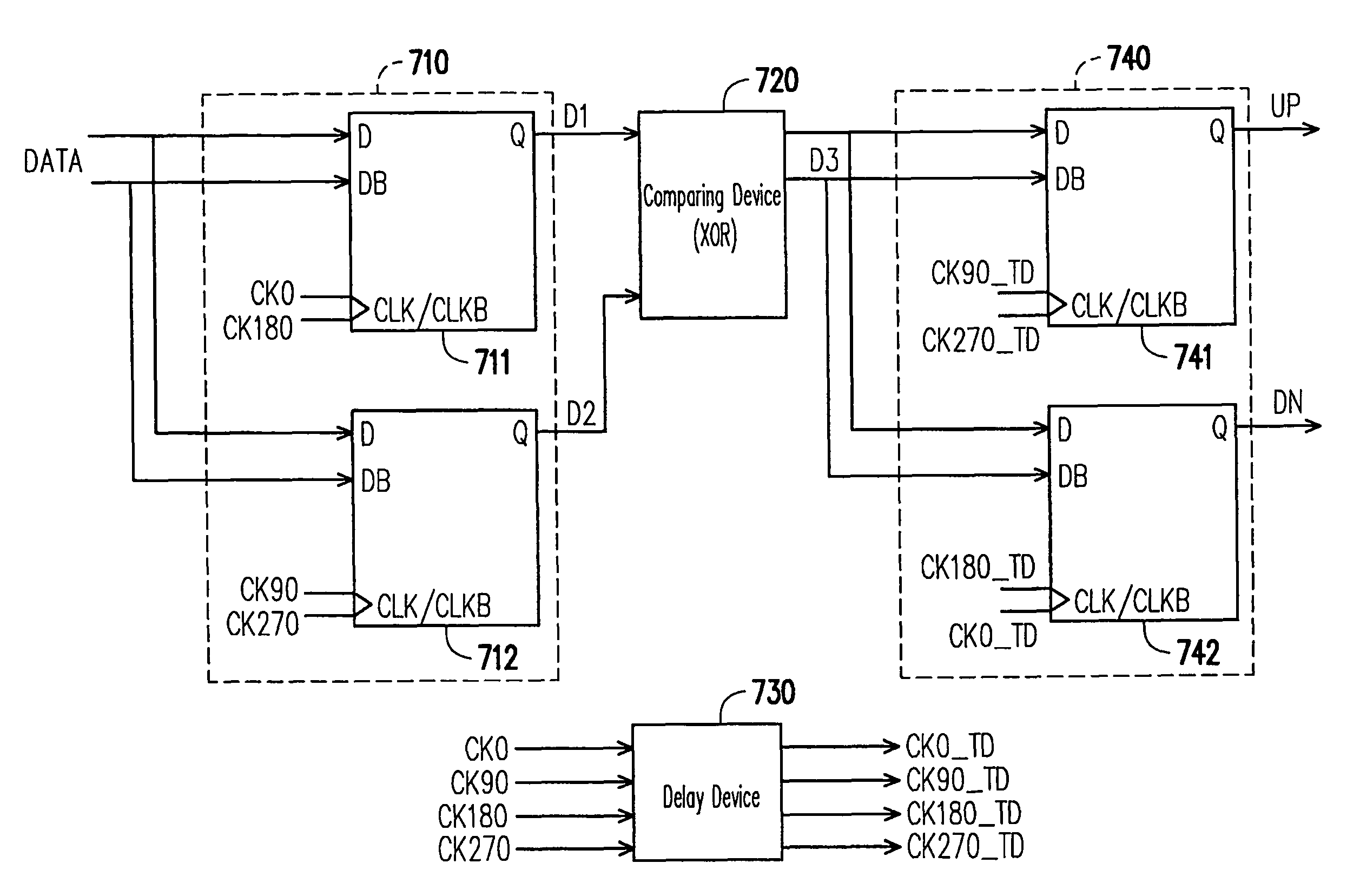

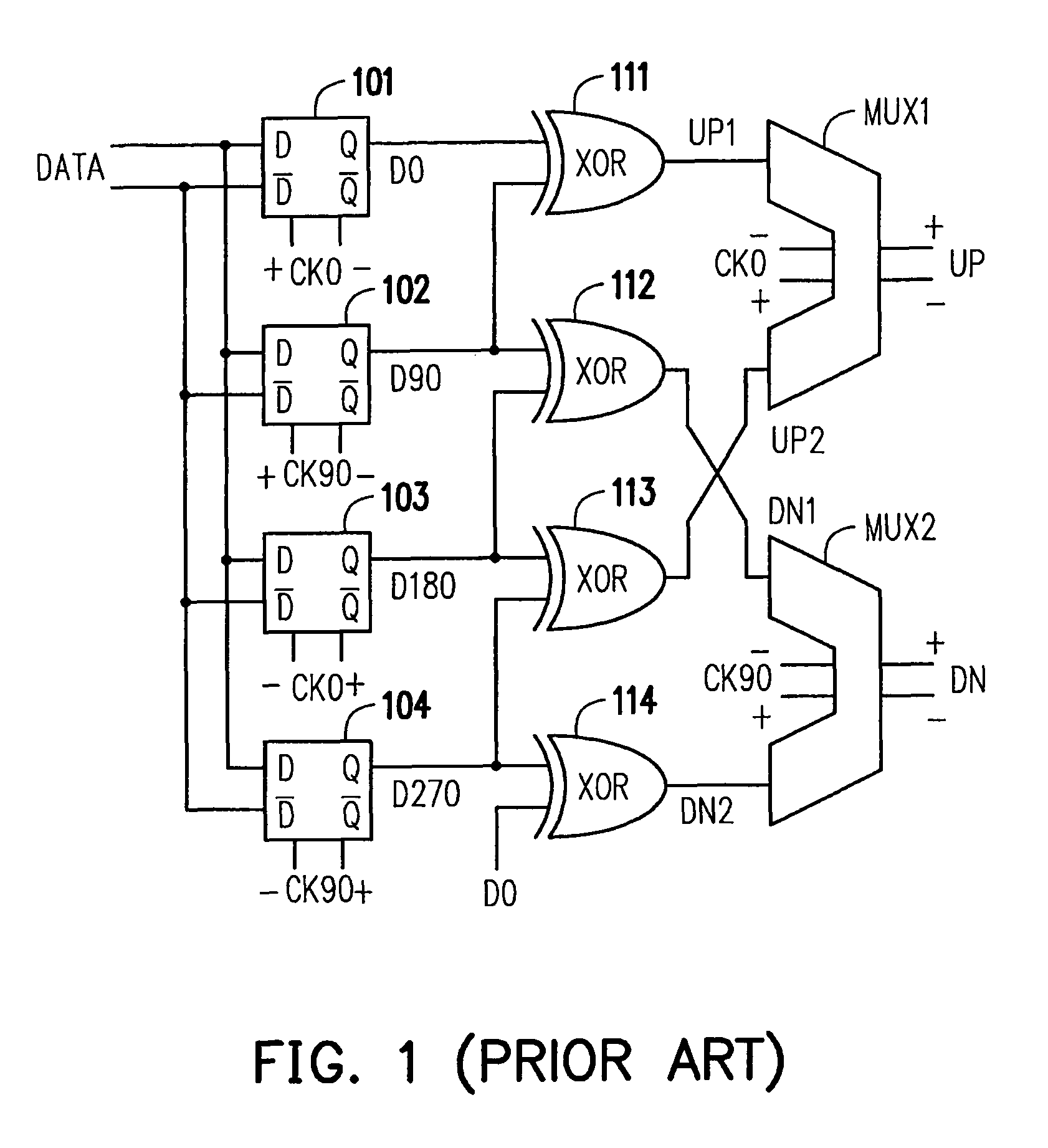

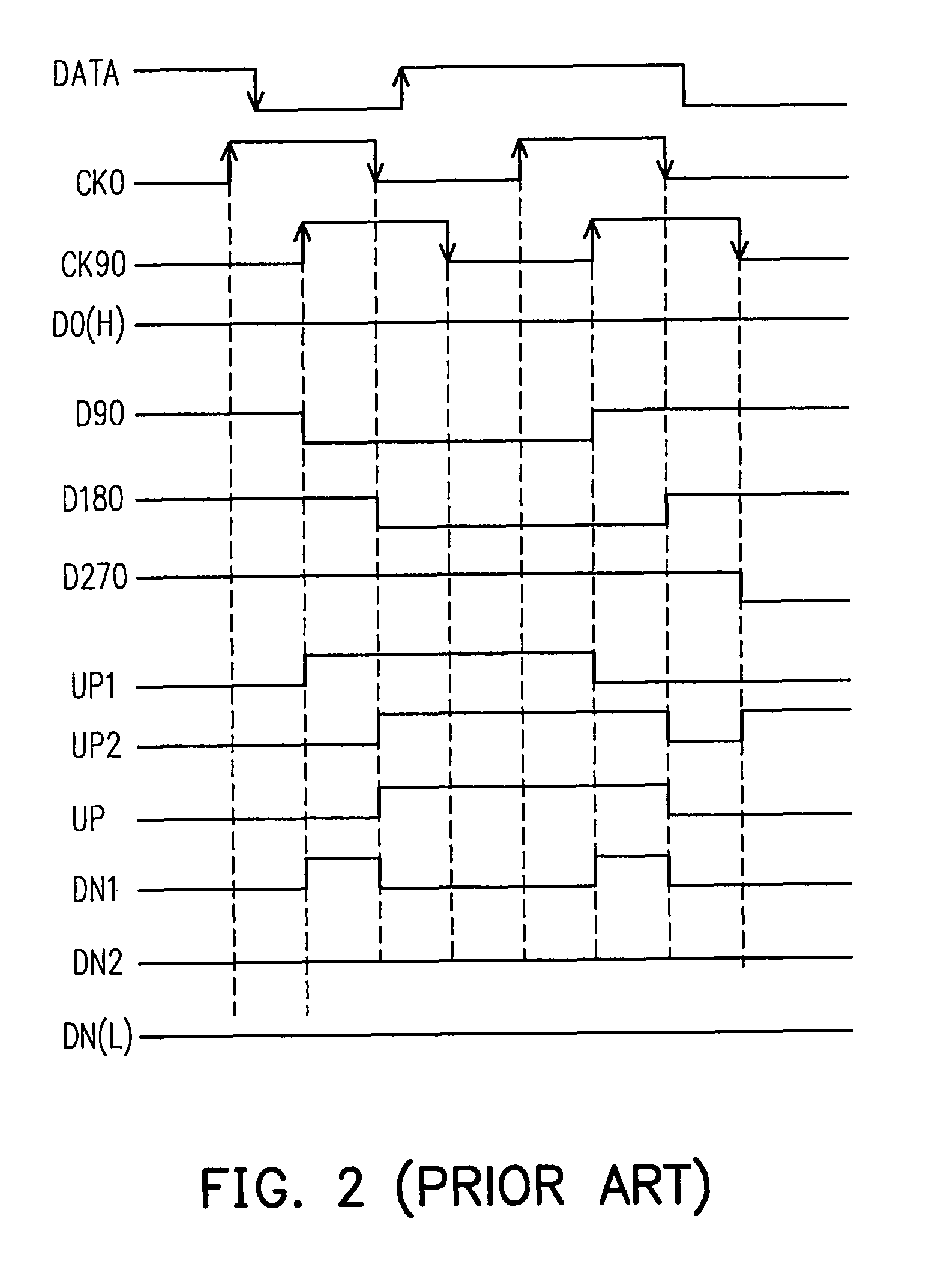

Phase detector for half-rate bang-bang CDR circuit

InactiveUS7795926B2Effectively eliminating generationAvoid flashPulse automatic controlVoltage-current phase anglePhase detectorBang bang

A phase detector, including a sampling device, a comparing device, and an output device, is provided. The sampling device samples a data signal according to a plurality of clock signals, so as to provide a plurality of corresponding sampling values. The clock signals have the same frequency and different phases. The comparing device is coupled to the sampling device, and provides a plurality of corresponding comparison values according to comparison results of each of the sampling values comparing with the next sampling value. The output device is coupled to the comparing device, and outputs two of the comparison values in response to edges of the clock signals. The two outputted comparison values serve as a first instruction signal and a second instruction signal respectively. The first and the second instruction signals are referred to in controlling the frequency and the phase of the foregoing clock signals.

Owner:FARADAY TECH CORP

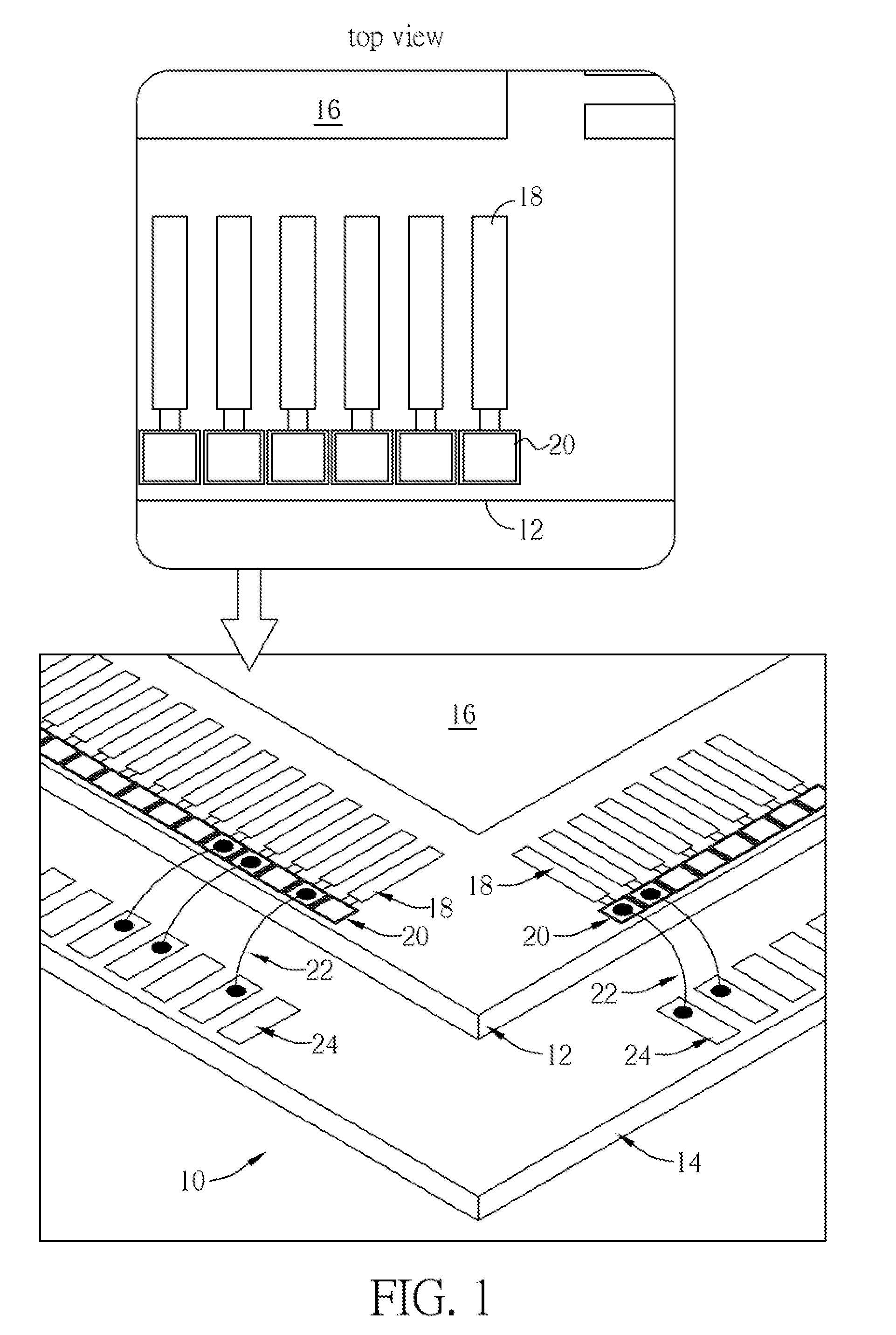

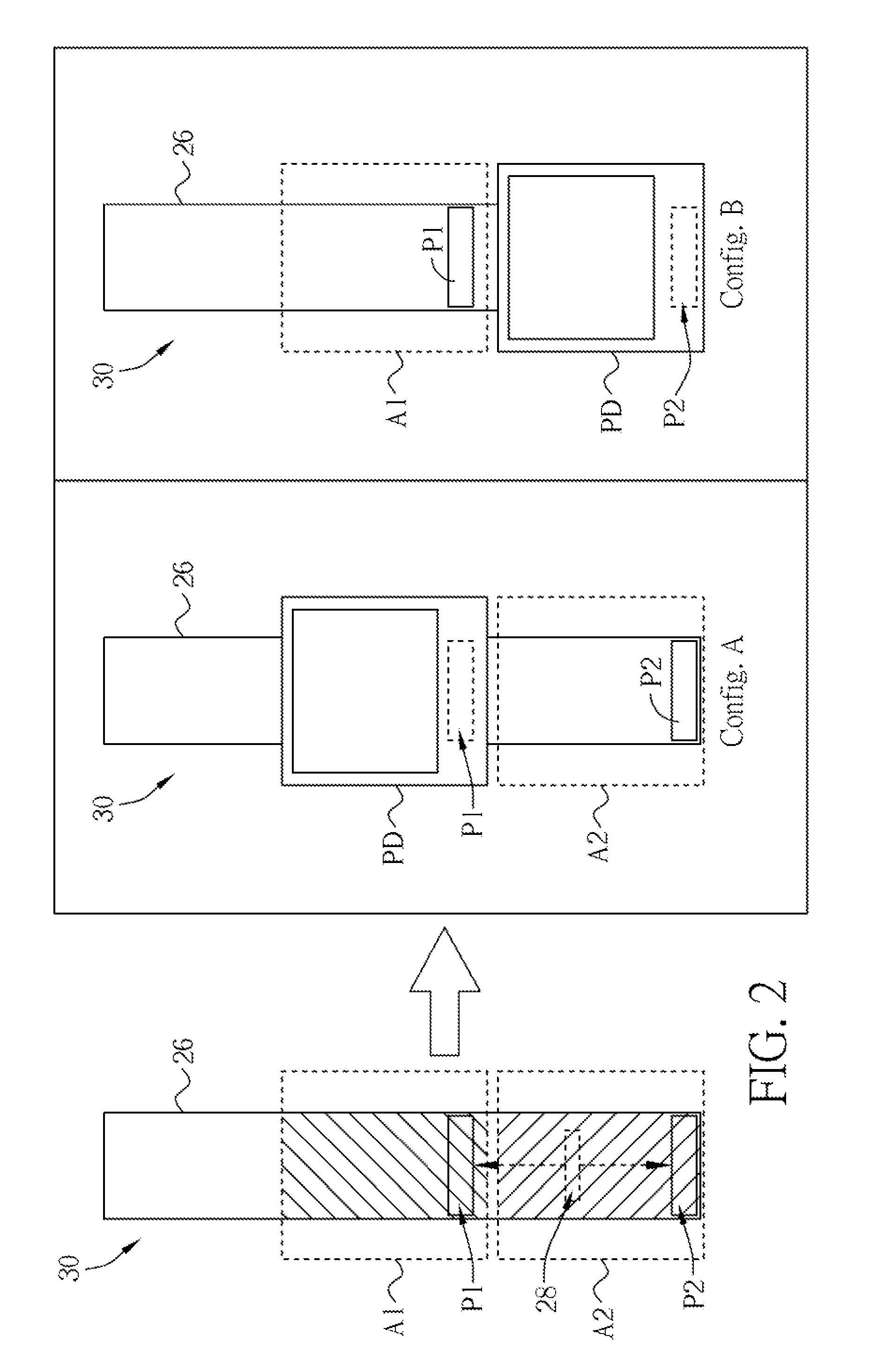

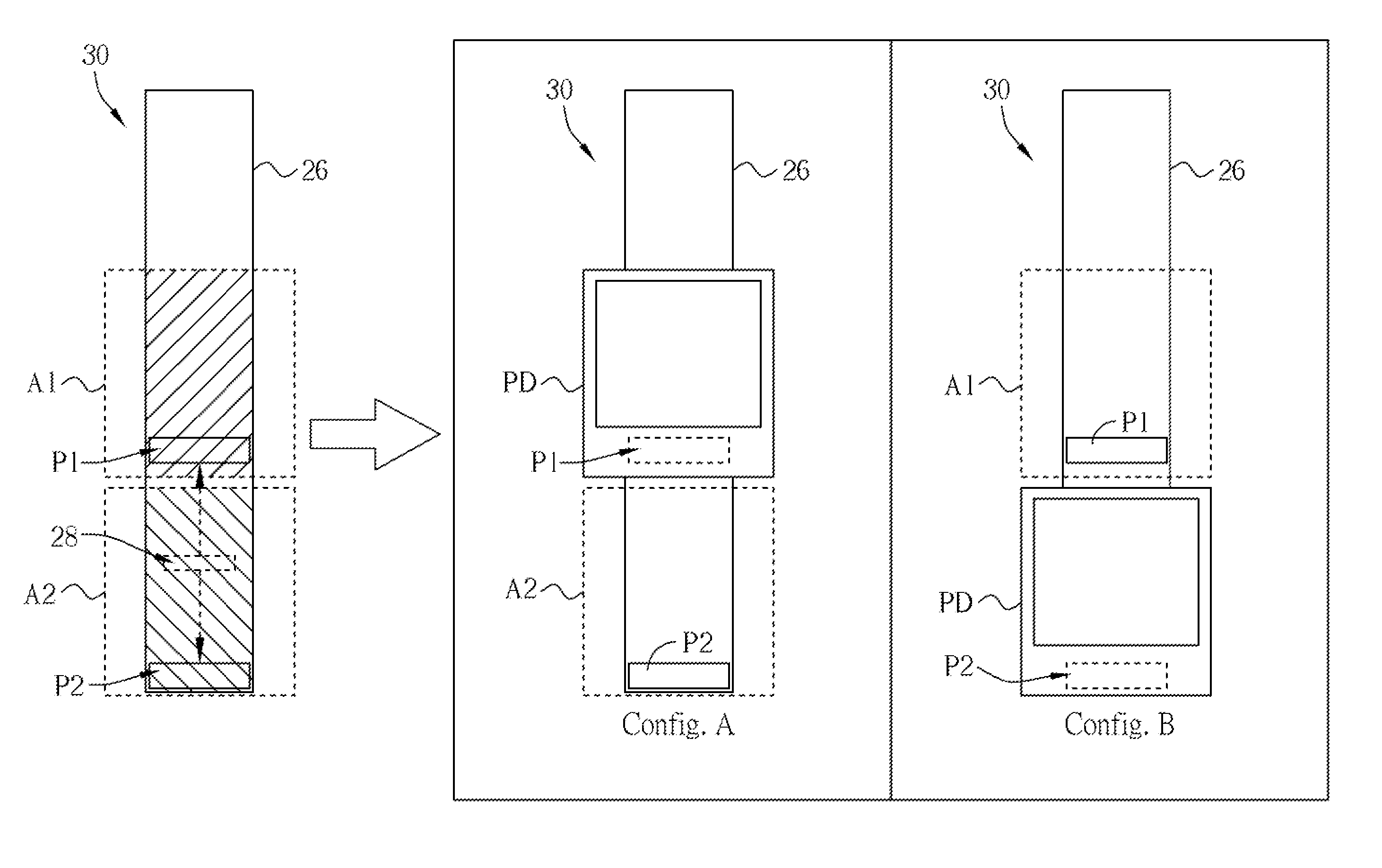

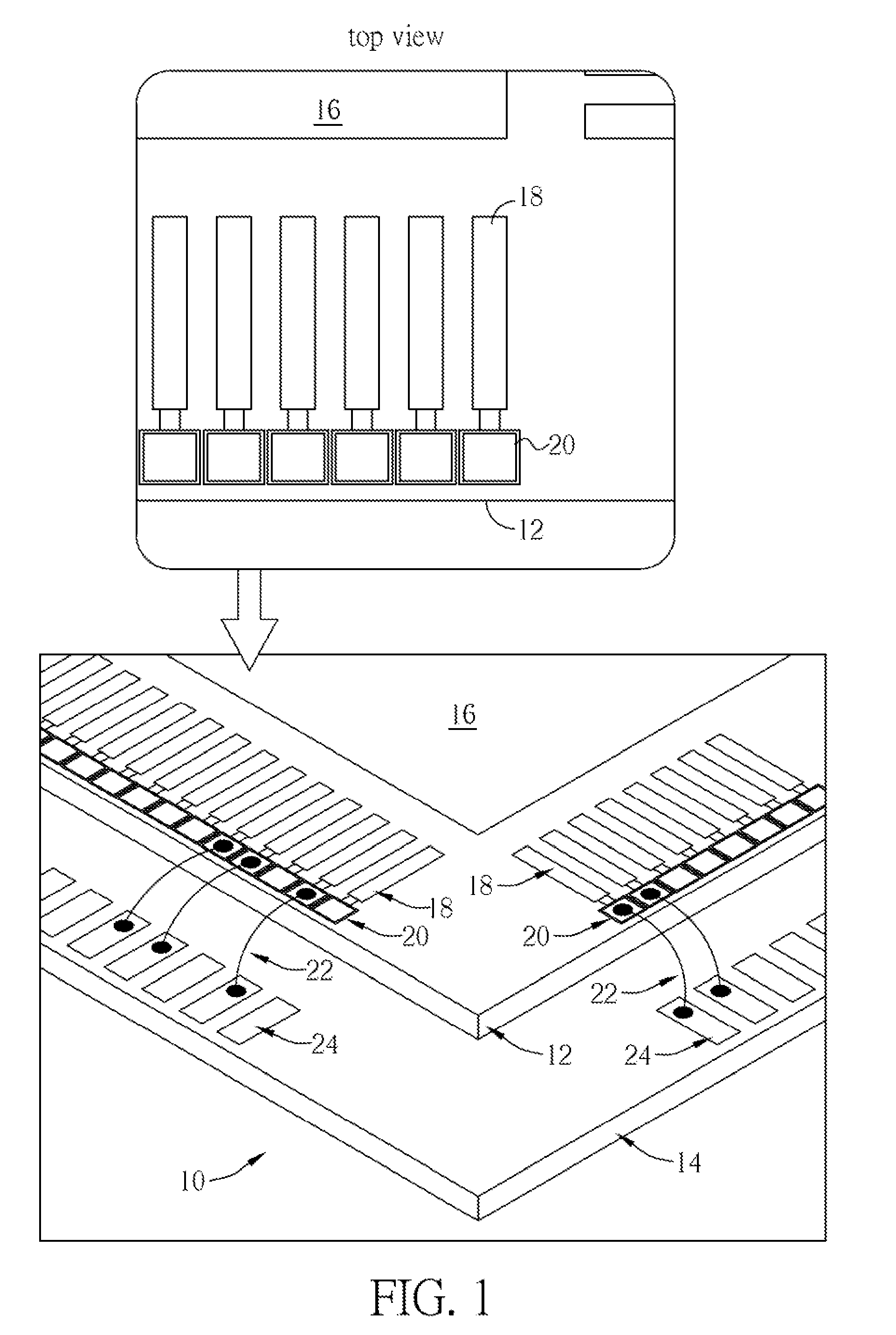

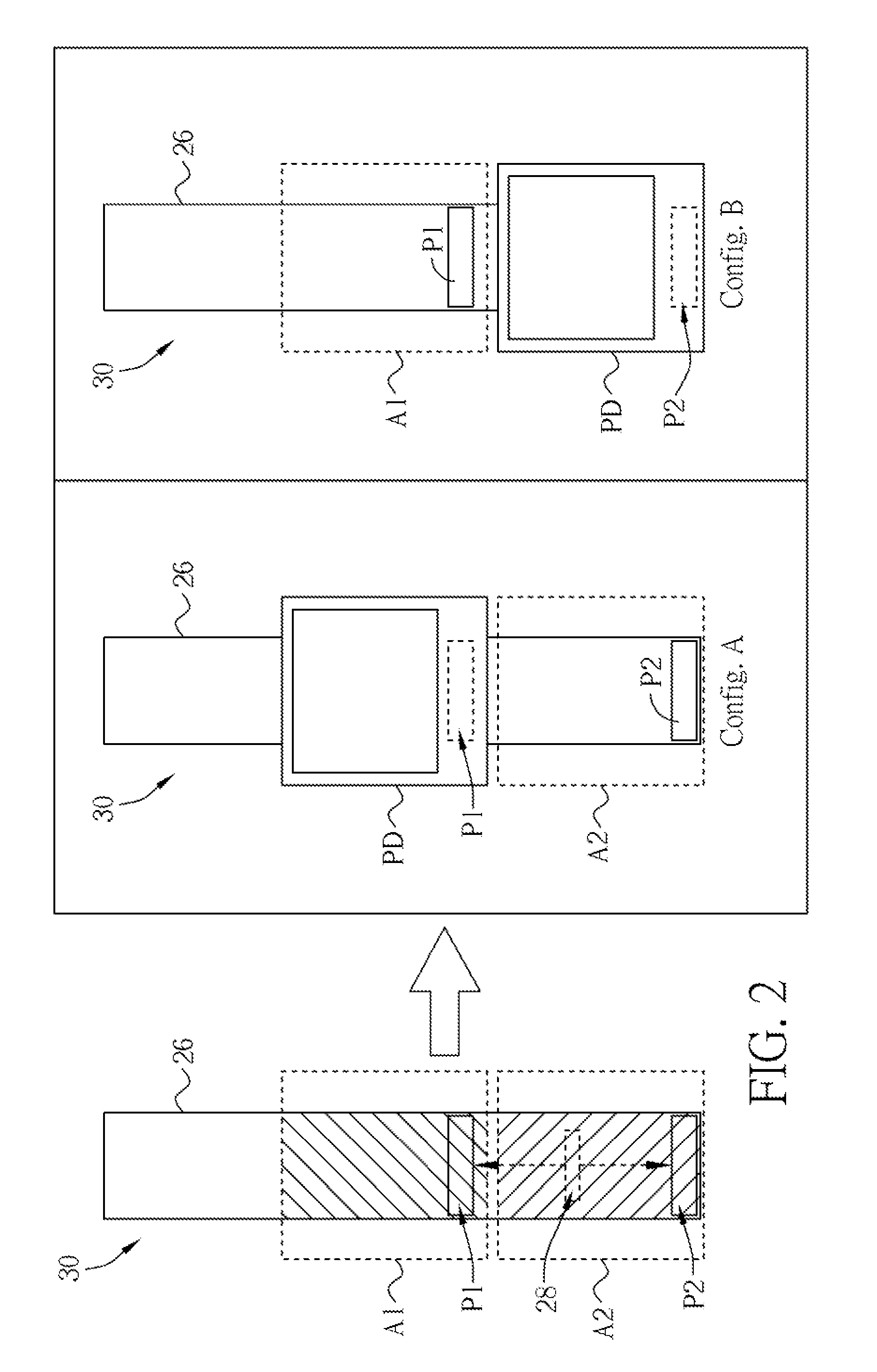

Io cell with multiple io ports and related techniques for layout area saving

ActiveUS20100237509A1Compact chip layout area savingSave layout area andSemiconductor/solid-state device detailsSolid-state devicesComputer science

An IO cell with multiple IO ports and related techniques are provided. The IO cell has a plurality of IO ports for transmitting signal of a same IO pin, and each IO port corresponds to a predetermined region for containing an IO pad, wherein at least one of the plural predetermined regions of the plural IO ports partially overlaps with active circuit layout region of the IO cell. In a chip, if a given IO cell has a predetermined region of an IO port overlapping an IO pad location of another adjacent IO cell, then a predetermined region of another IO port is selected for implementing an IO pad of the given IO cell, such that the IO cells can be arranged more compactly for chip layout area saving.

Owner:FARADAY TECH CORP

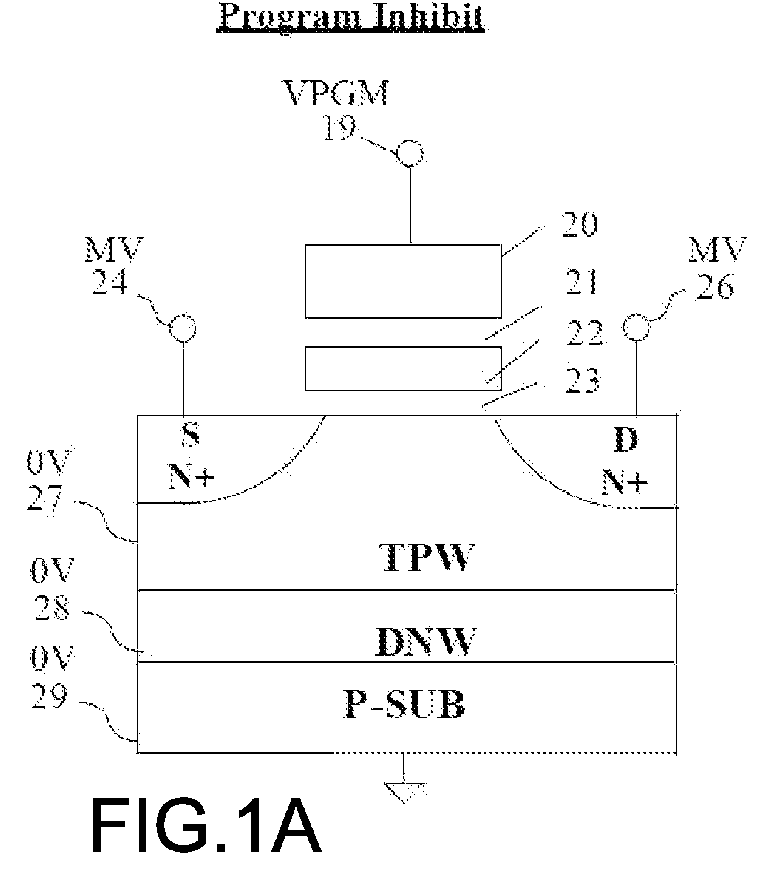

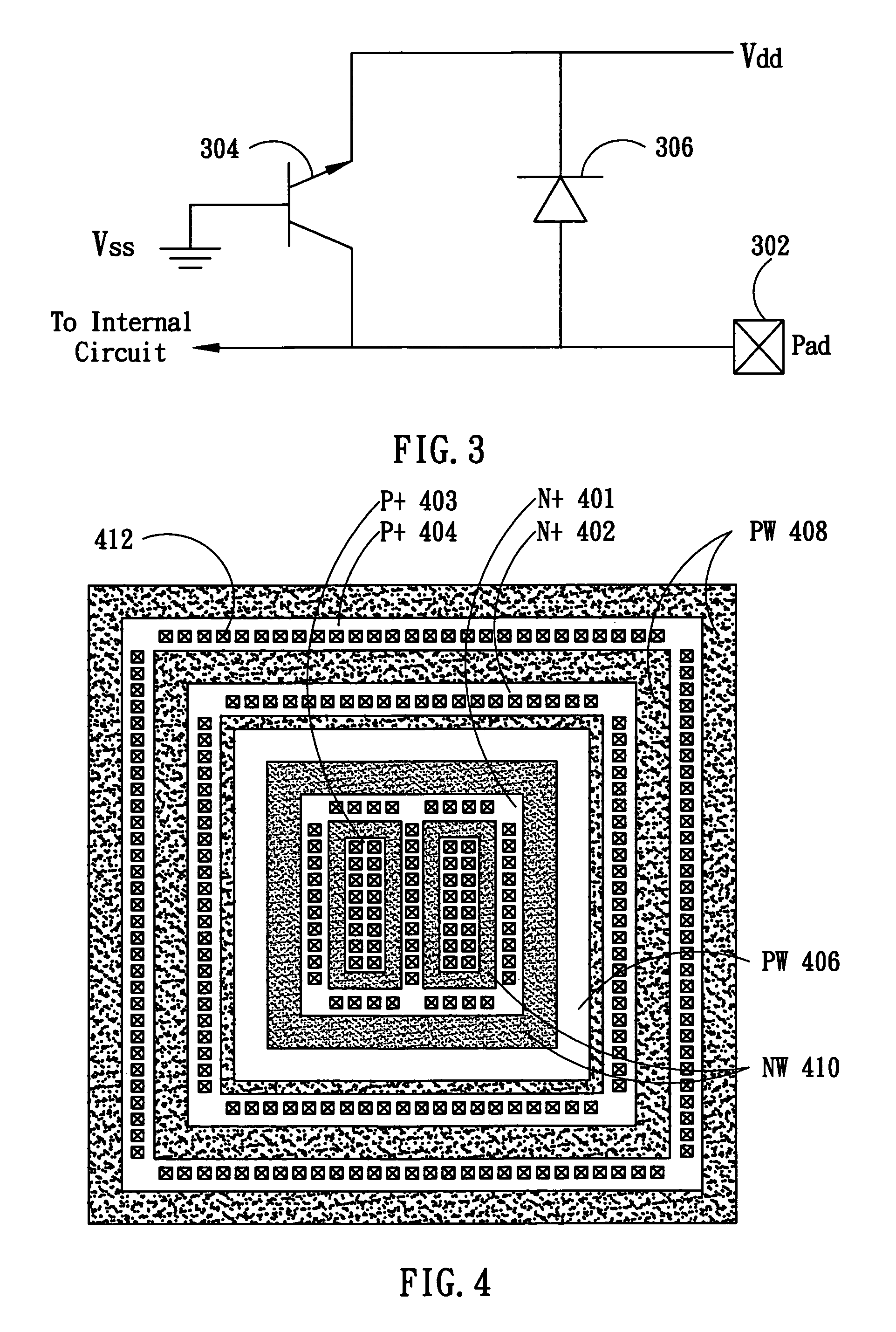

Electrostatic discharge protection device

ActiveUS20140061740A1Reduce distanceSave layout area andTransistorSemiconductor/solid-state device detailsElectrostatic discharge protectionPhysics

An ESD protection device is described, including a substrate of a first conductivity, a well of a second conductivity, a transistor including a first doped region of the second conductivity located in the substrate and extending into the well, a second doped region of the first conductivity and a gate over the substrate between the two doped regions, a third doped region of the second conductivity and a fourth doped region of the first conductivity disposed in the substrate in sequence from an outer side of the second doped region and coupled to ground, and a fifth doped region of the first conductivity and a sixth doped region of the second conductivity disposed in the well in sequence from an outer side of the first doped region and coupled to a bonding pad. When an ESD voltage is applied to the bonding pad, it is coupled to the gate.

Owner:MACRONIX INT CO LTD

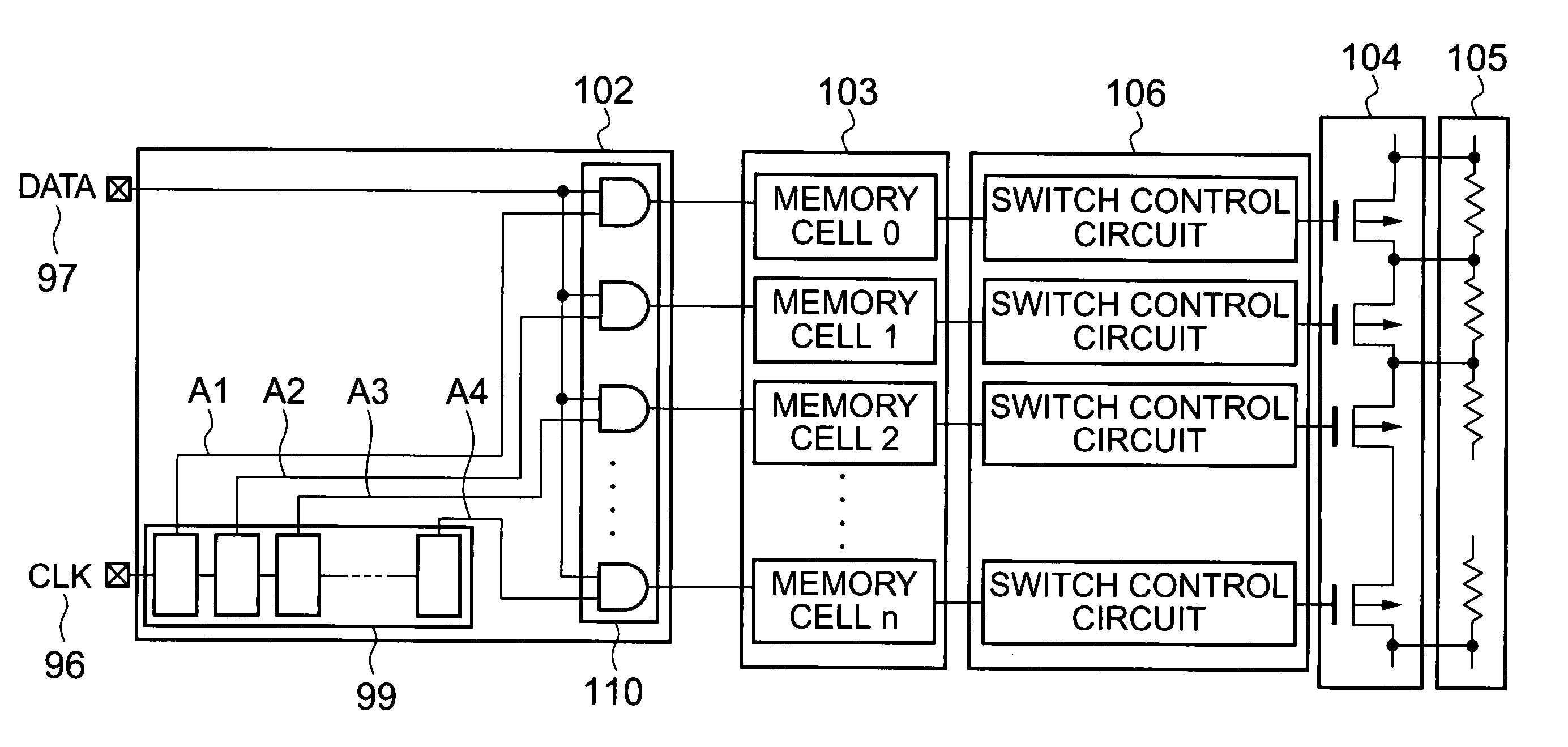

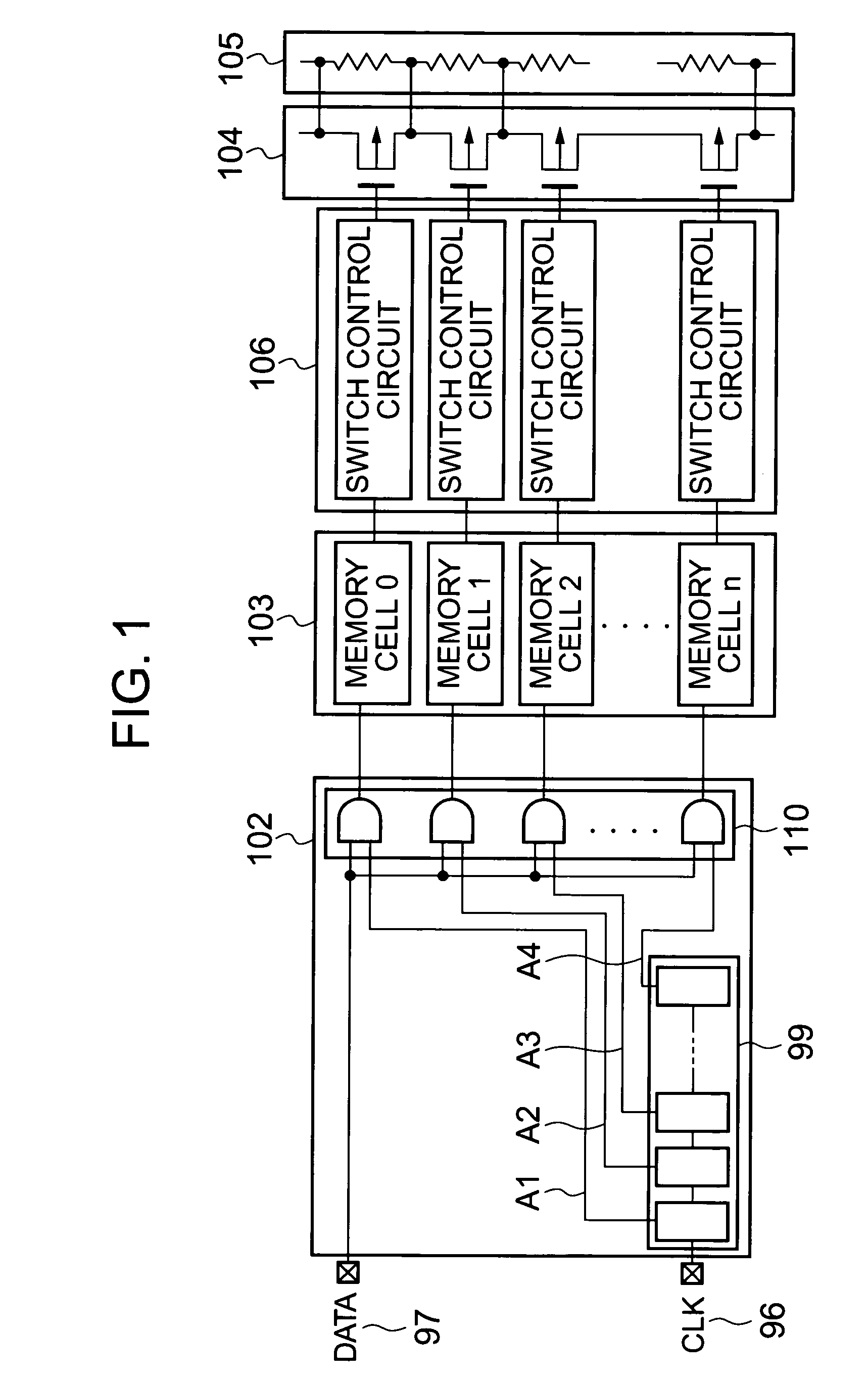

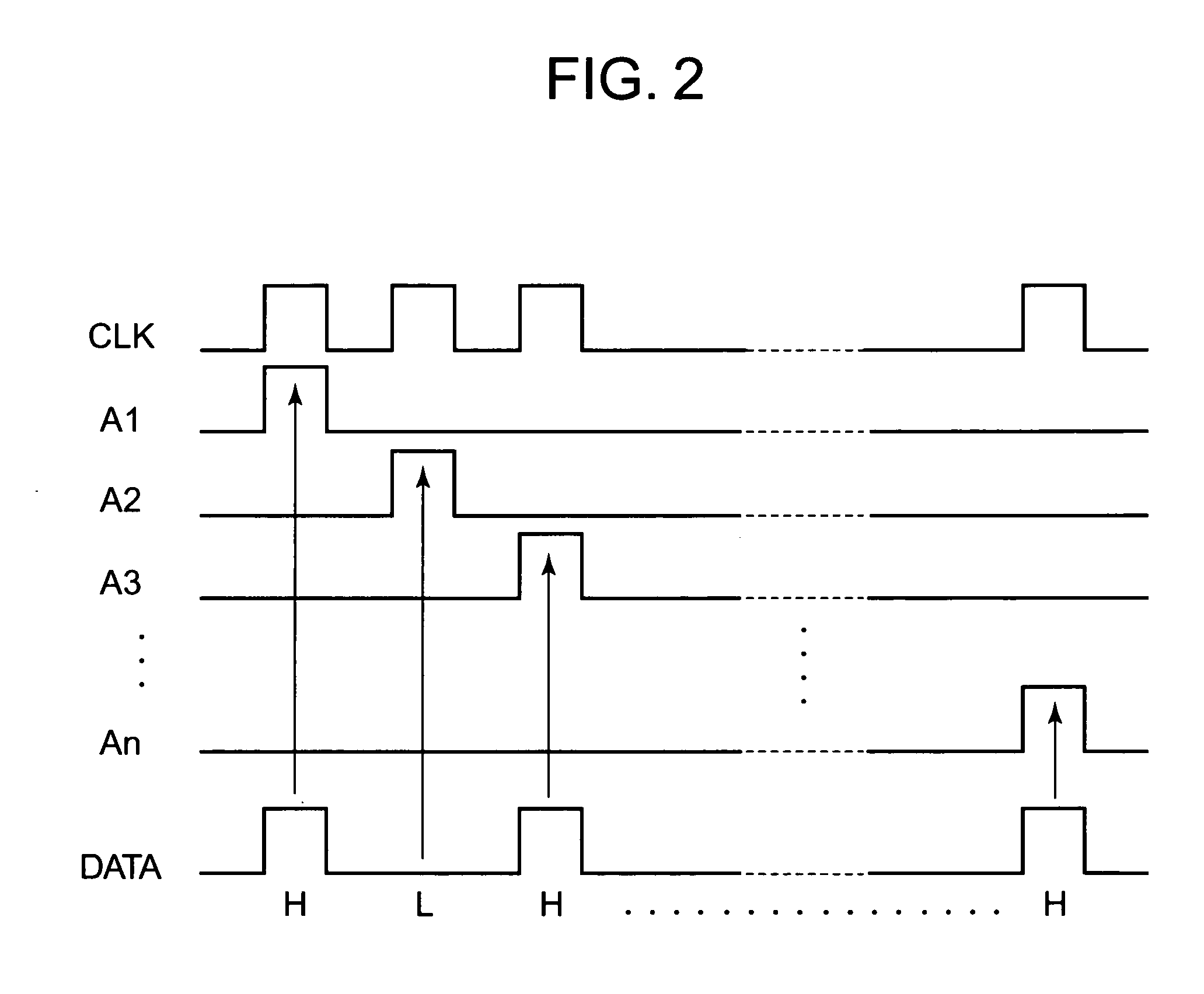

Semiconductor integrated circuit

ActiveUS20050231405A1Save layout area andLow costElectric signal transmission systemsSolid-state devicesEngineeringBleeder resistor

To provide a semiconductor integrated circuit including a trimmable bleeder resistor circuit, where a layout area of a trimming circuit is saved. In a semiconductor integrated circuit of the present invention, serially inputted trimming data are sequentially written to plural memory cells in accordance with selection signals for trimming a bleeder resistor, making it possible to dispense with a data resistor for storing the trimming data.

Owner:ABLIC INC

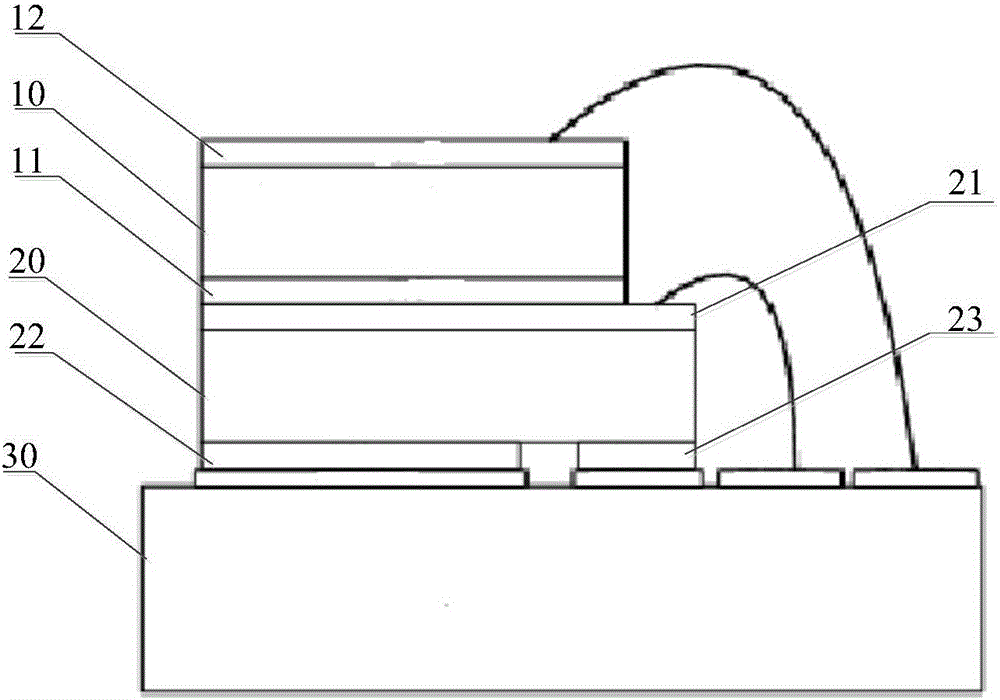

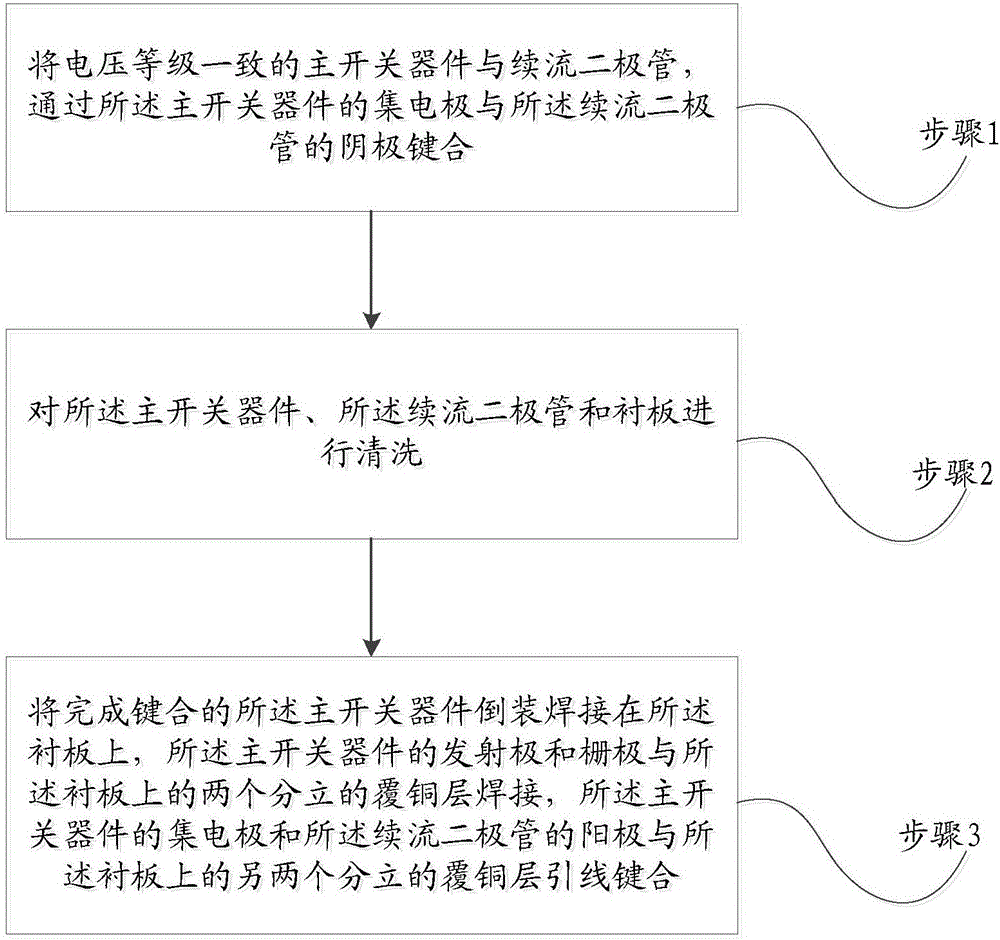

Power module structure and manufacture method thereof

InactiveCN105914205AImprove power densityAchieve compactnessSemiconductor/solid-state device detailsSolid-state devicesPower flowMiniaturization

The present invention discloses a power module structure and a manufacture method thereof. The power module structure comprises: a main switch device has the same voltage grade with a freewheeling diode, and has the same size of the current with the freewheeling diode; the collector of the main switch device is bonded with the cathode of the freewheeling diode, and the main switch device is welded on a liner plate in an inverted mode; the liner plate is provided with a plurality of discrete copper-cladding layer; the emitting electrode of the main switch device is welded with the first copper-cladding layer of the liner plate, and a grid is welded with the second copper-cladding layer on the liner plate; and the collector outgoing line of the main switch device is bonded with the third copper-cladding layer of the liner plate, and the anode outgoing line of the freewheeling diode is bonded with the fourth copper-cladding layer on the liner plate. The power module structure and manufacture method thereof realize the compaction and the miniaturization and improve the power density of the power module through welding the bonded main switch device and the freewheeling diode on the liner plate.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

Device for electrostatic discharge protection

InactiveUS7329925B2Maintain performanceSave layout area andTransistorThyristorElectricitySemiconductor

A device for electrostatic discharge (ESD) protection is disclosed. The device for electrostatic discharge protection includes a lateral bipolar transistor and a diode. The semiconductor transistor has an emitter, a base and a collector electrically connected to a first power line (such as Vdd), a second power line (such as Vss) and a bond pad of an integrated circuit respectively. The diode has an n electrode and a p electrode electrically connected to the first power line and the bond pad respectively.

Owner:WINBOND ELECTRONICS CORP

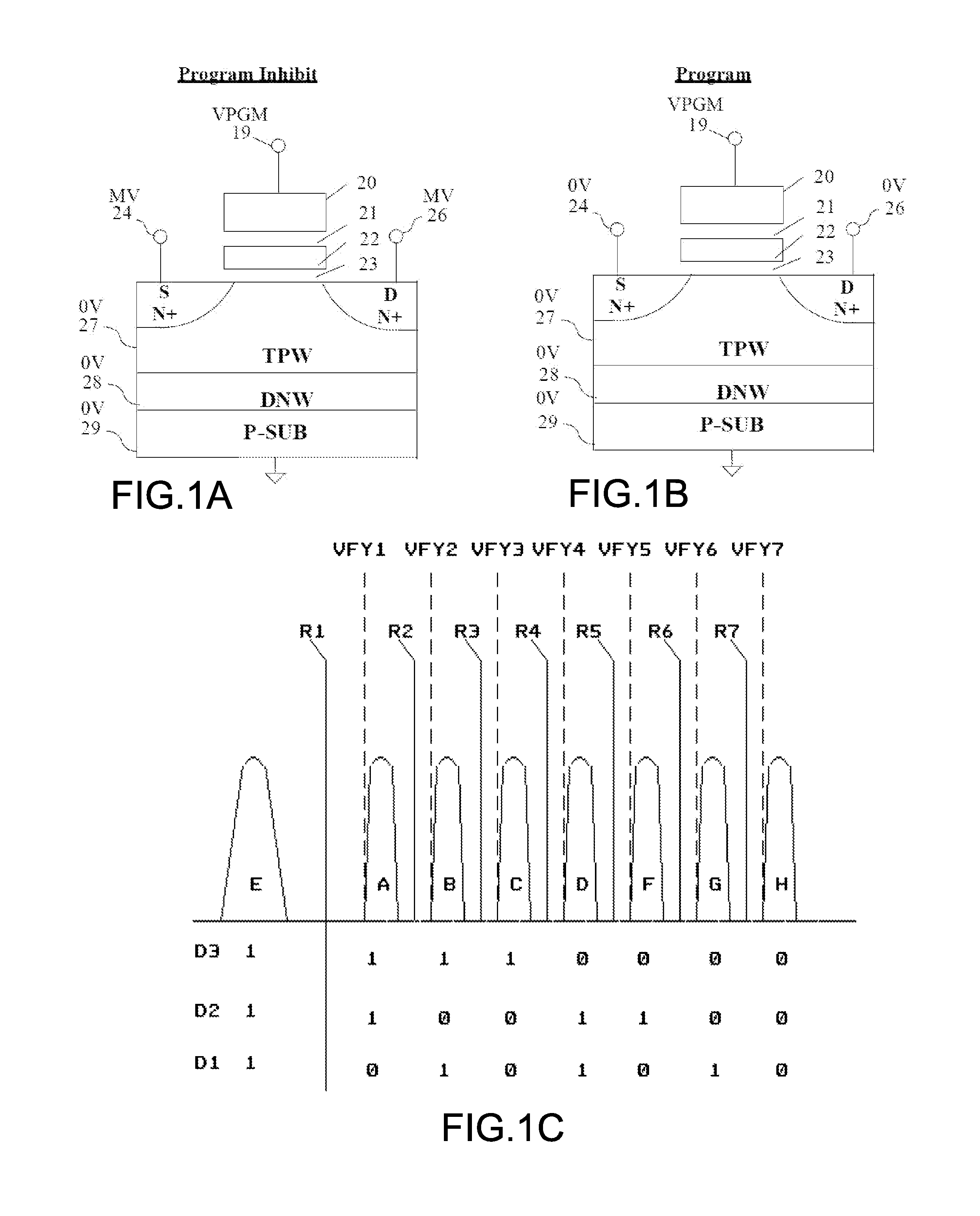

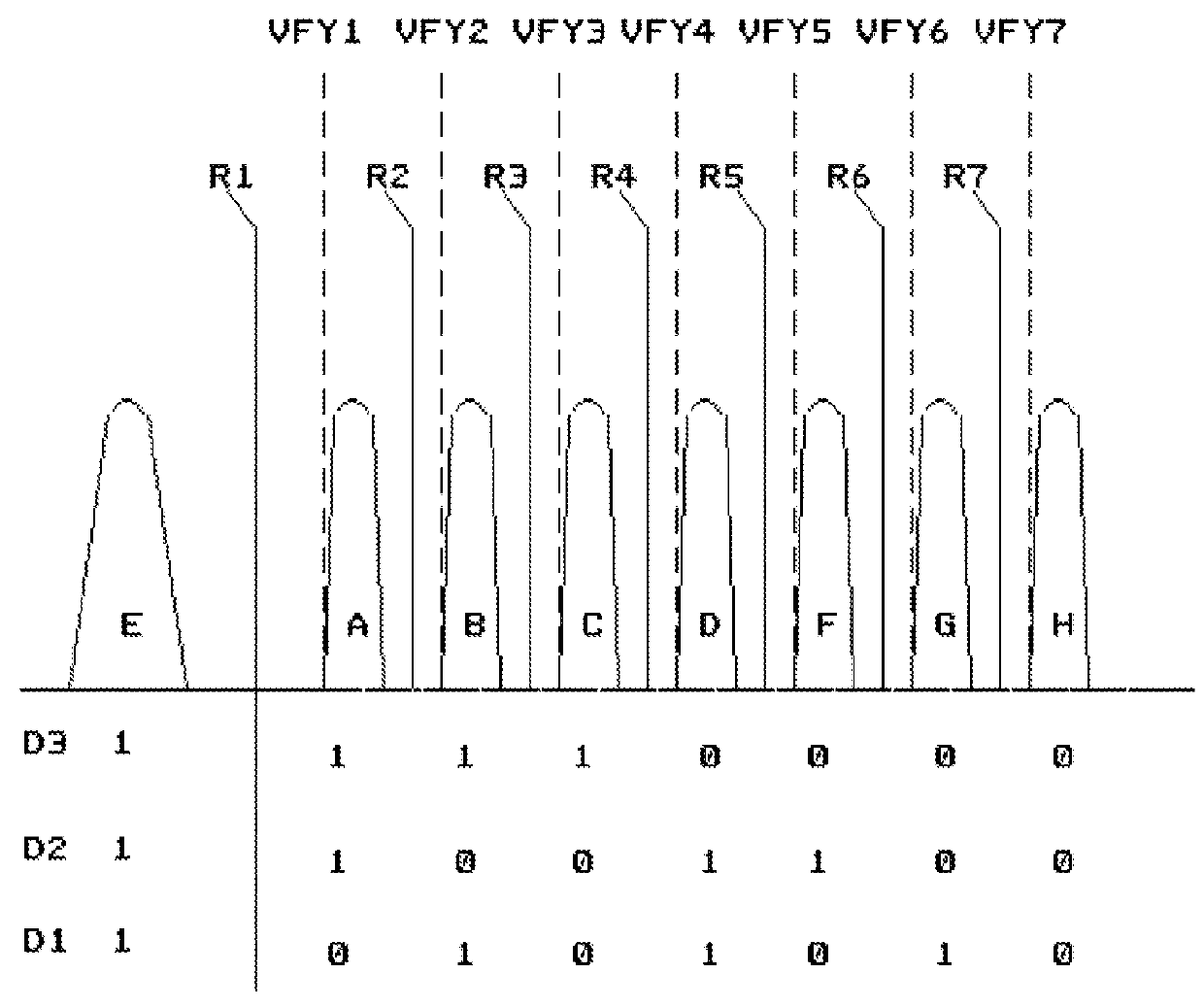

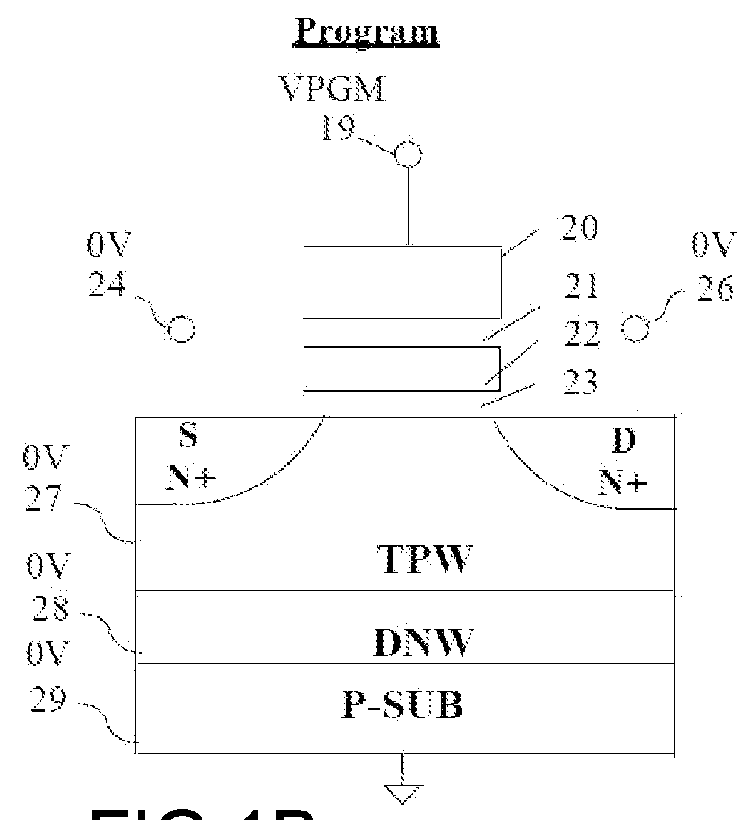

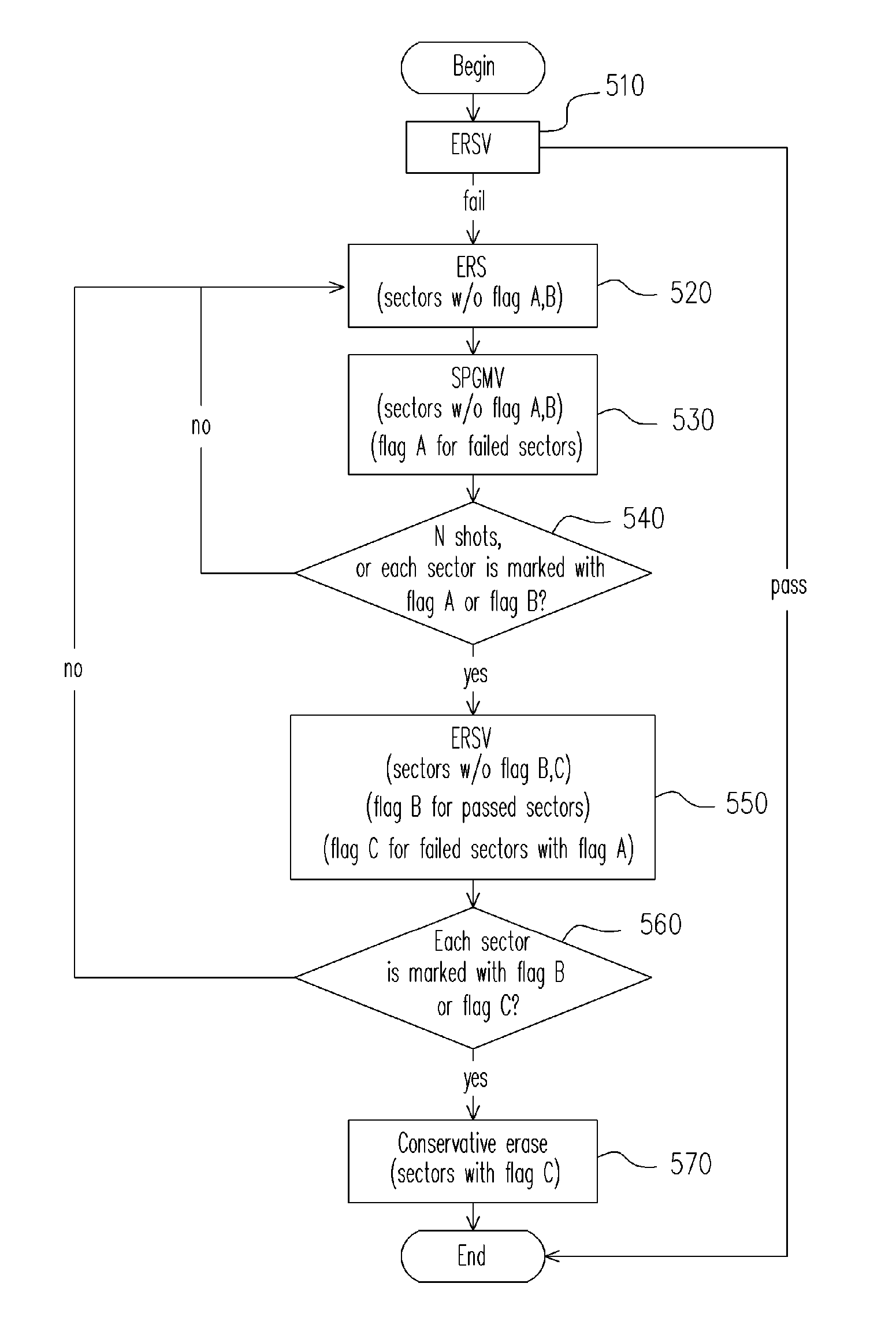

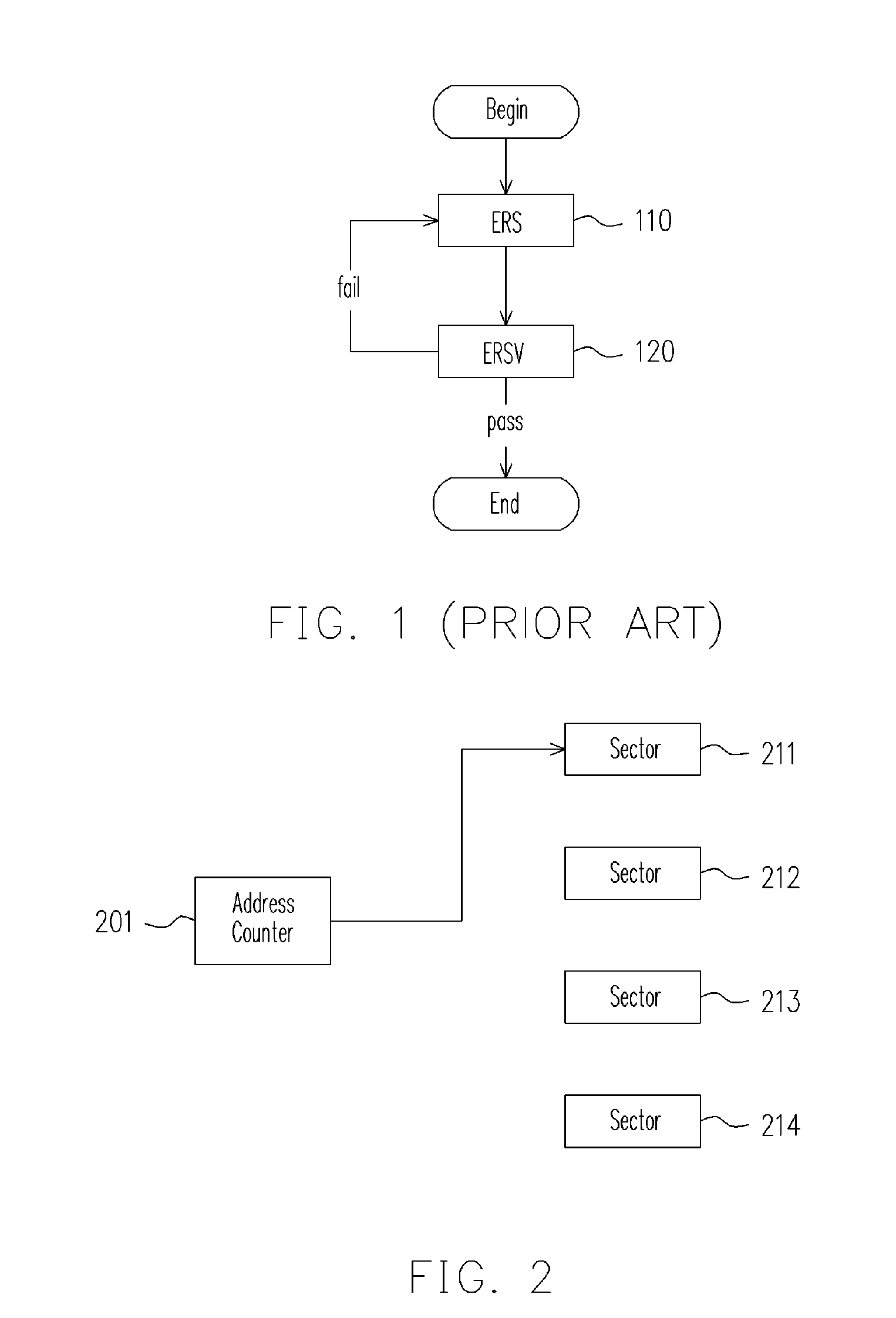

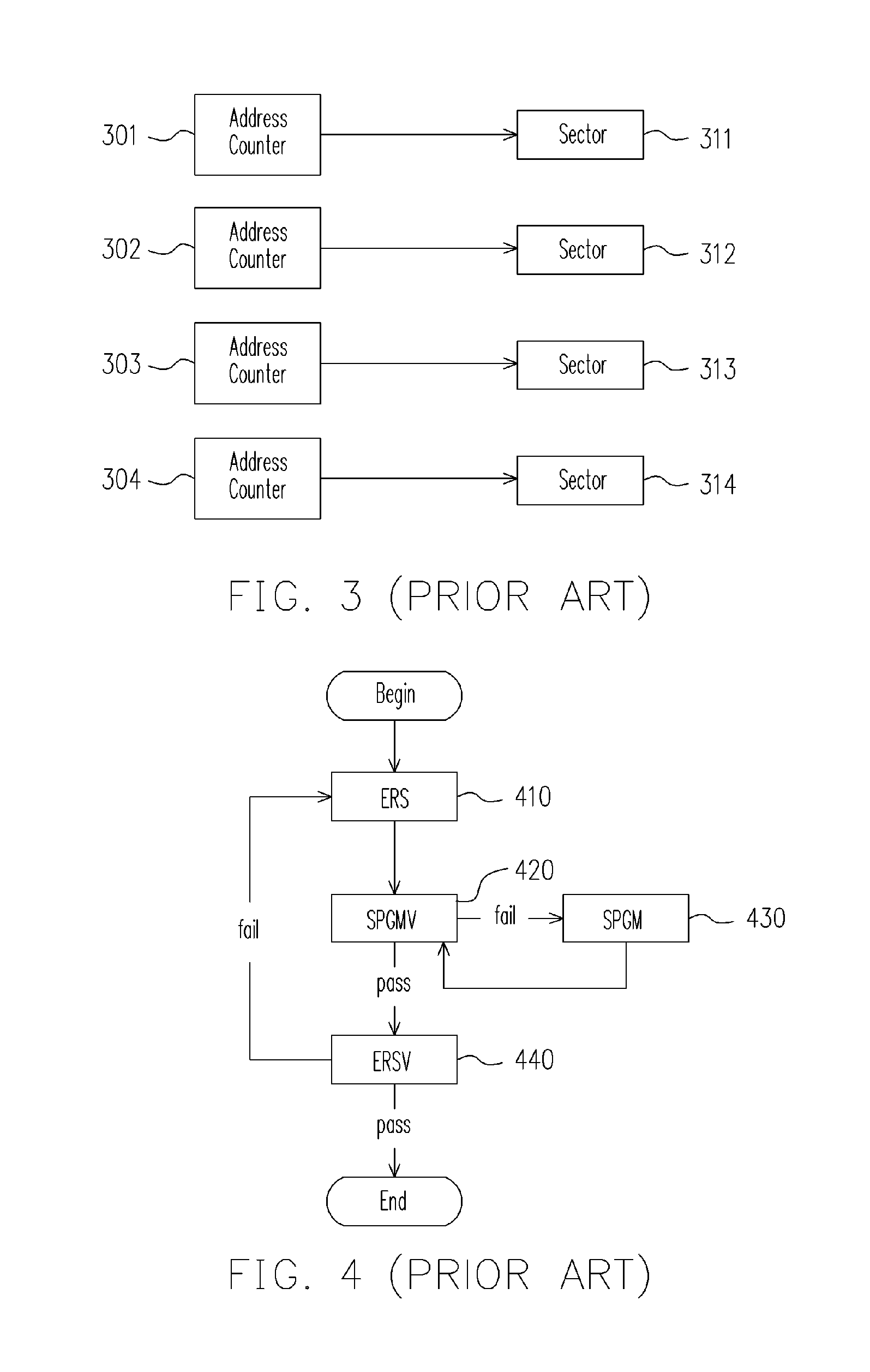

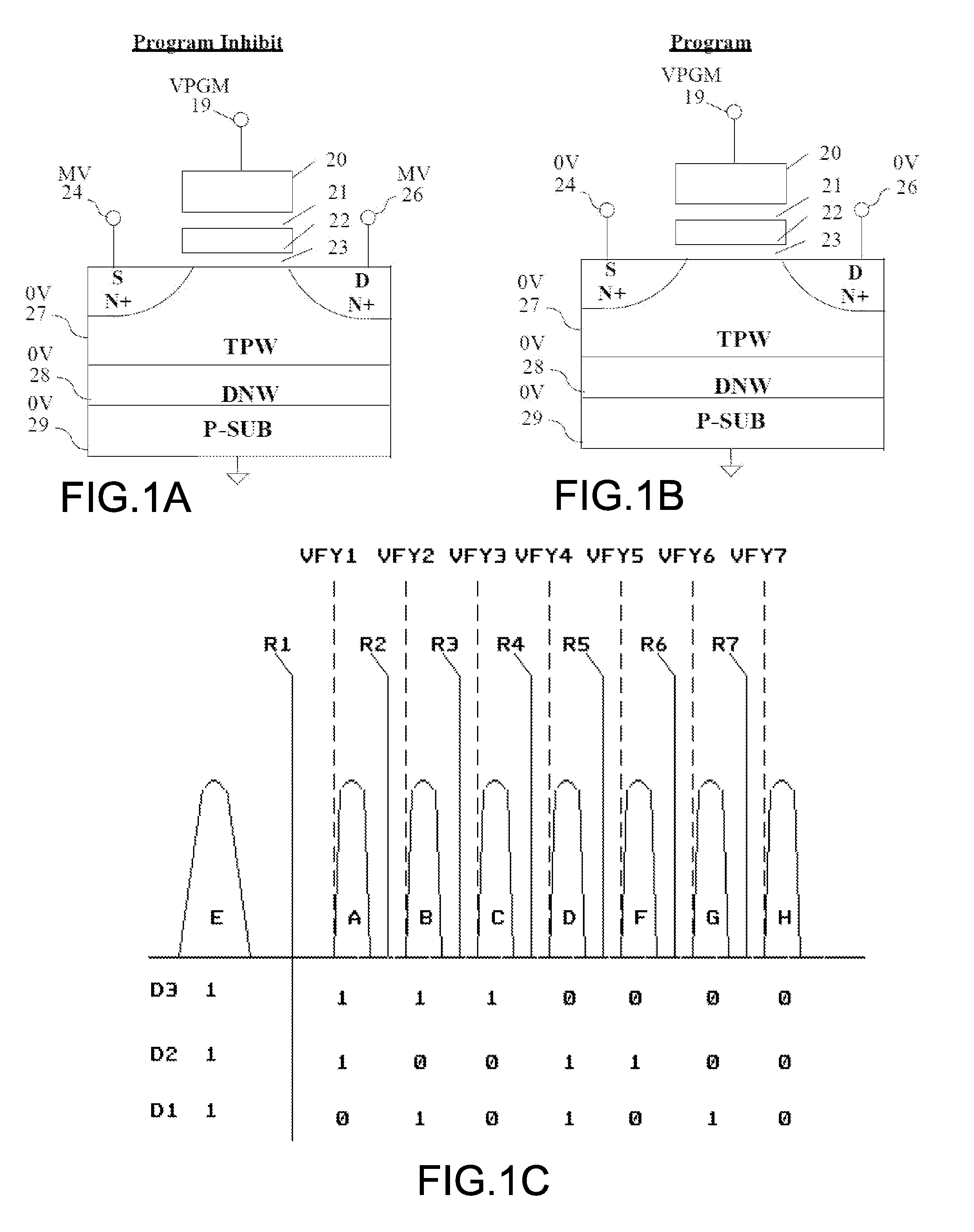

A reliable method for erasing a flash memory

ActiveUS20070247922A1Preventing deep over-eraseEfficient methodRead-only memoriesDigital storageBit lineTheoretical computer science

A method for erasing a flash memory group is provided, which comprises the following steps. (a) Apply a erase (ERS) pulse to a first subset of the group. (b) Perform one of a soft program verification (SPGMV) and a tight soft program verification (TSPGMV) on the first subset of the group. (c) Repeat steps (a) and (b) until a first predetermined condition is true. (d) Perform an erase verification (ERSV) on a second subset of the group. (e) Repeat steps (a) to (d) until a second predetermined condition is true. And (f) fix bit line leakage in a third subset of the group with a slow program (SLPGM) and apply an ERS pulse to the third subset.

Owner:ELITE SEMICON MEMORY TECH INC

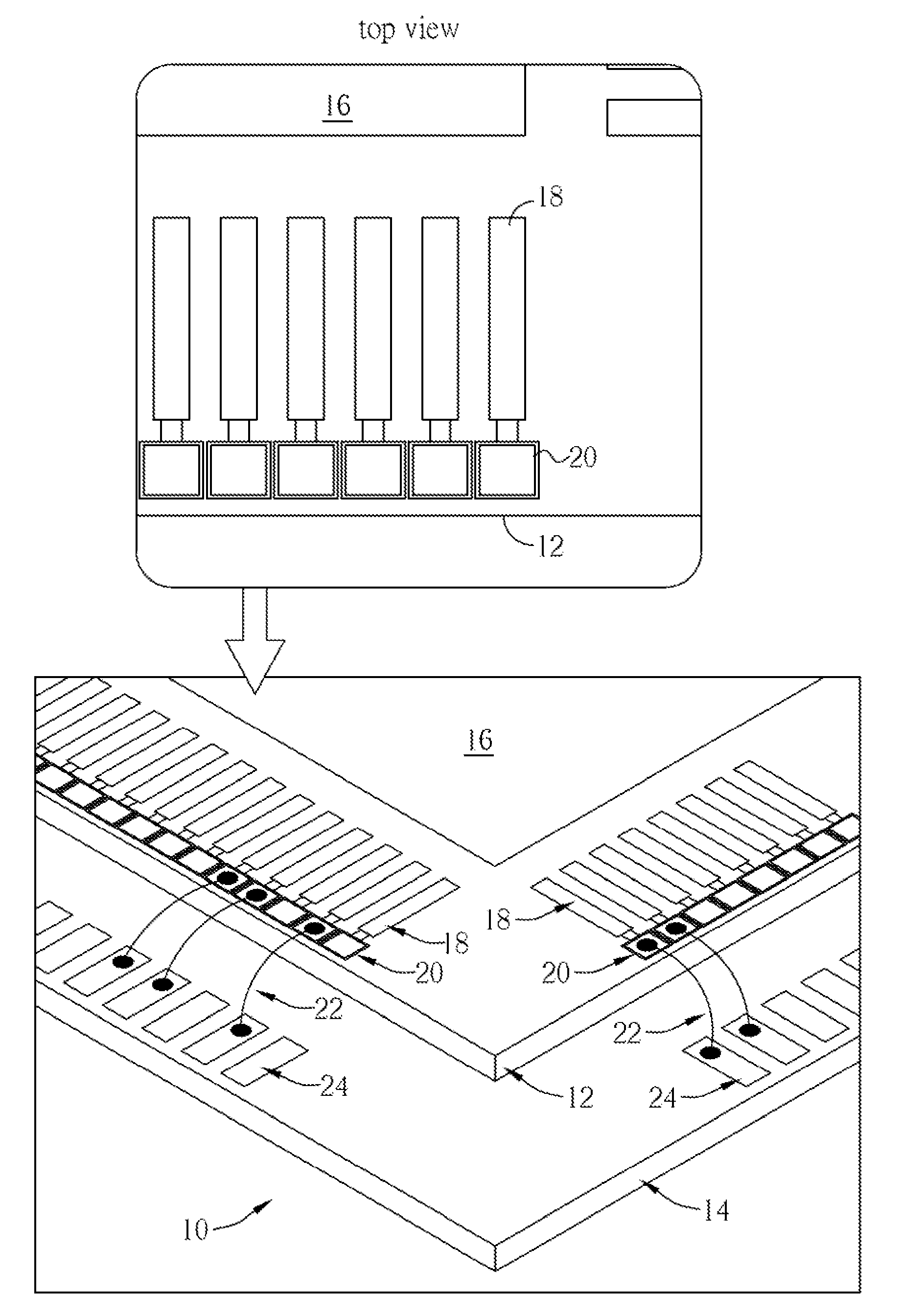

IO cell with multiple IO ports and related techniques for layout area saving

ActiveUS8169068B2Effective areaSave layout area andSemiconductor/solid-state device detailsSolid-state devicesComputer science

An IO cell with multiple IO ports and related techniques are provided. The IO cell has a plurality of IO ports for transmitting signal of a same IO pin, and each IO port corresponds to a predetermined region for containing an IO pad, wherein at least one of the plural predetermined regions of the plural IO ports partially overlaps with active circuit layout region of the IO cell. In a chip, if a given IO cell has a predetermined region of an IO port overlapping an IO pad location of another adjacent IO cell, then a predetermined region of another IO port is selected for implementing an IO pad of the given IO cell, such that the IO cells can be arranged more compactly for chip layout area saving.

Owner:FARADAY TECH CORP

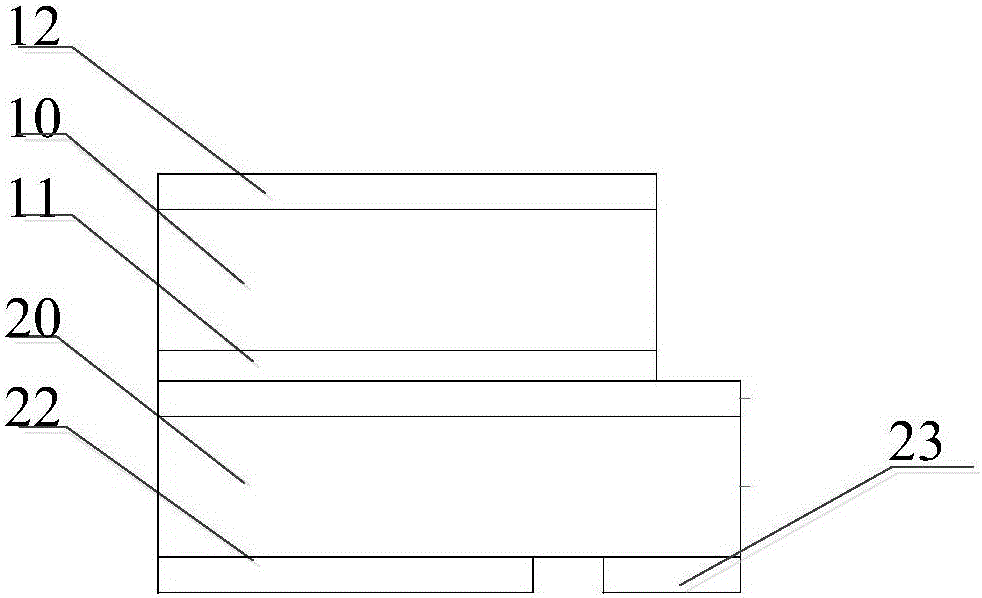

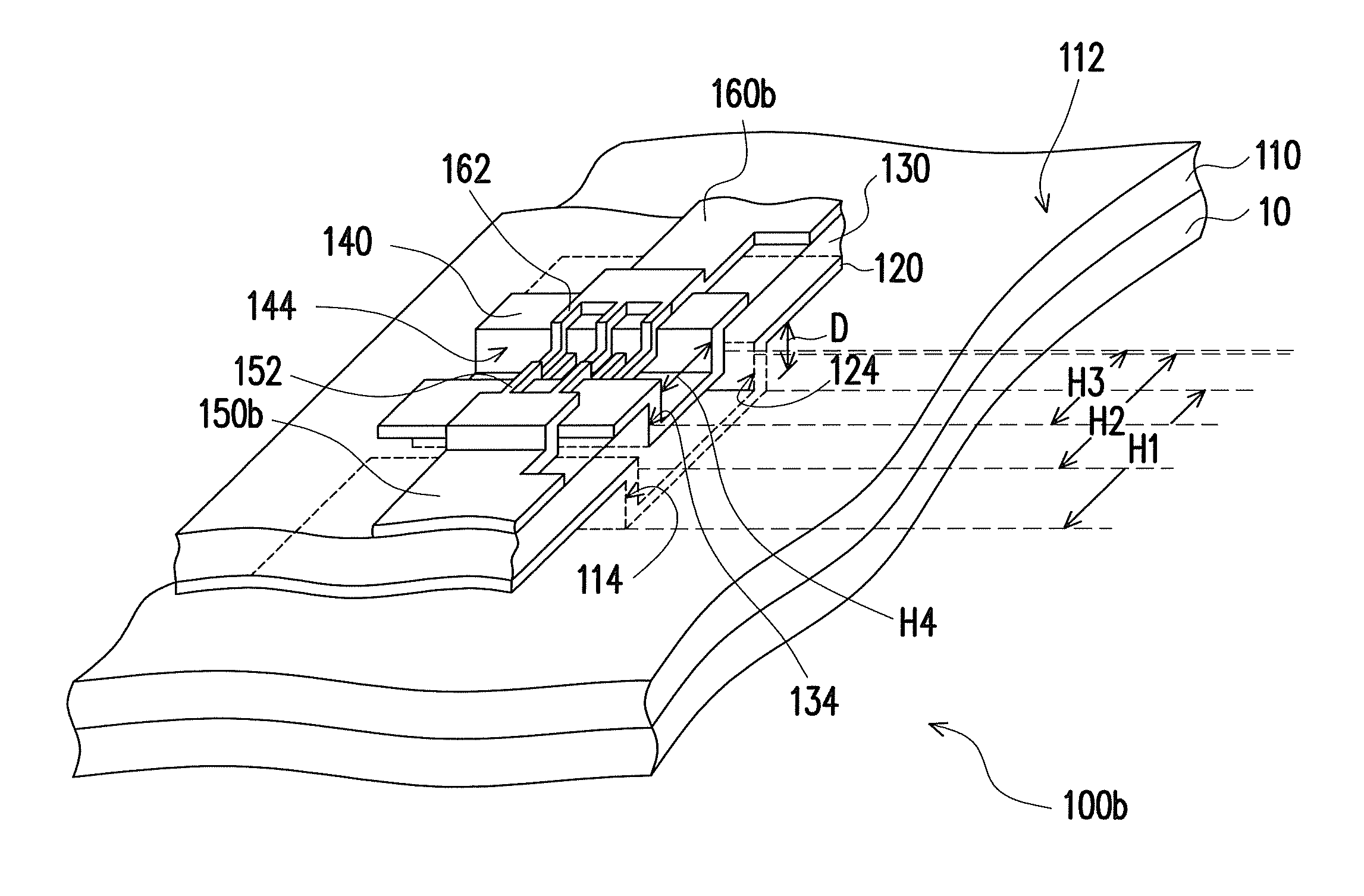

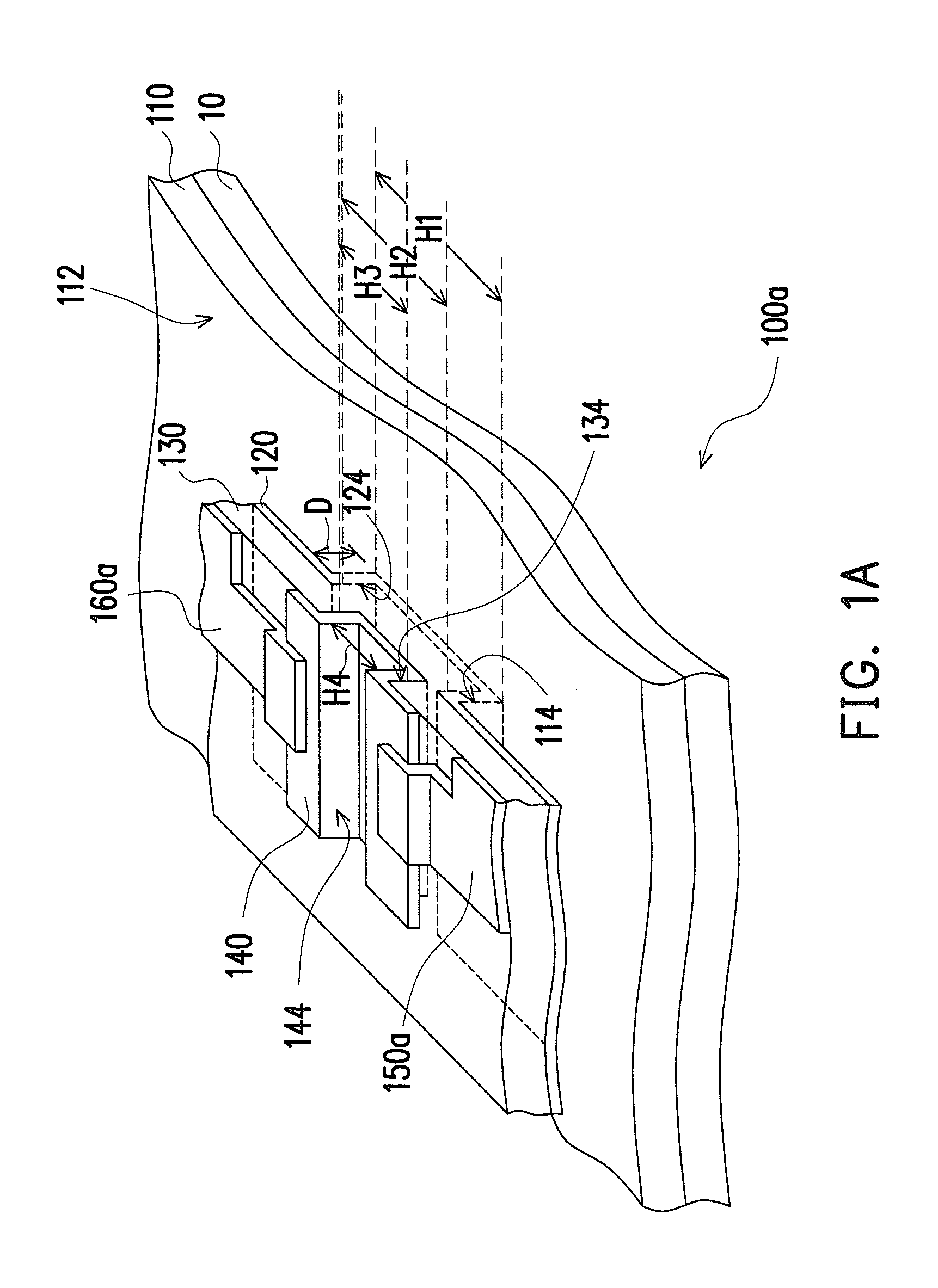

Semiconductor device

ActiveUS20130228779A1Increase layout areaReduce layout areaTransistorSolid-state devicesDevice materialEngineering physics

A semiconductor device including a substrate, a metal layer, an insulating layer, a semiconductor layer, a drain and a source is provided. The substrate has a surface and a first cavity. The metal layer is disposed on the substrate and covers the surface and inner-wall of the first cavity to define a second cavity corresponding to the first cavity. The insulating layer covers the metal layer and inner-wall of the second cavity to define a third cavity corresponding to the second cavity. The semiconductor layer exposes out a portion of the insulating layer and covers the inner-wall of the third cavity to define a fourth cavity corresponding to the third cavity. The drain and source are disposed on the semiconductor layer and covers a portion of the semiconductor layer and a portion of the insulating layer, in which the drain and source expose out the fourth cavity.

Owner:E INK HLDG INC

NAND array hiarchical bl structures for multiple-wl and all-bl simultaneous erase, erase-verify, program, program-verify, and read operations

ActiveUS20160078928A1Addressing slow performanceSave layout area andRead-only memoriesDigital storageBit lineComputer architecture

Owner:LEE PETER WUNG

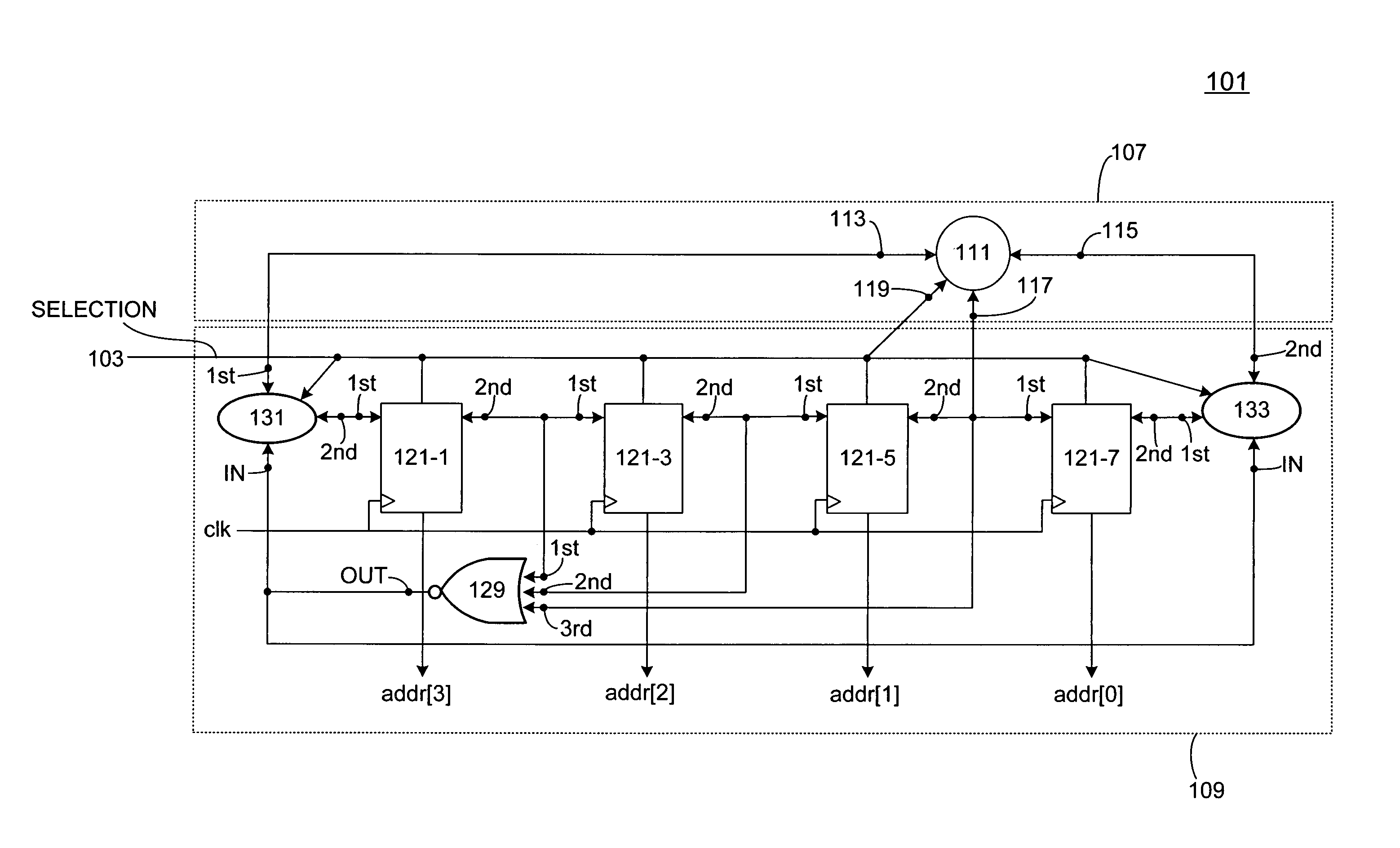

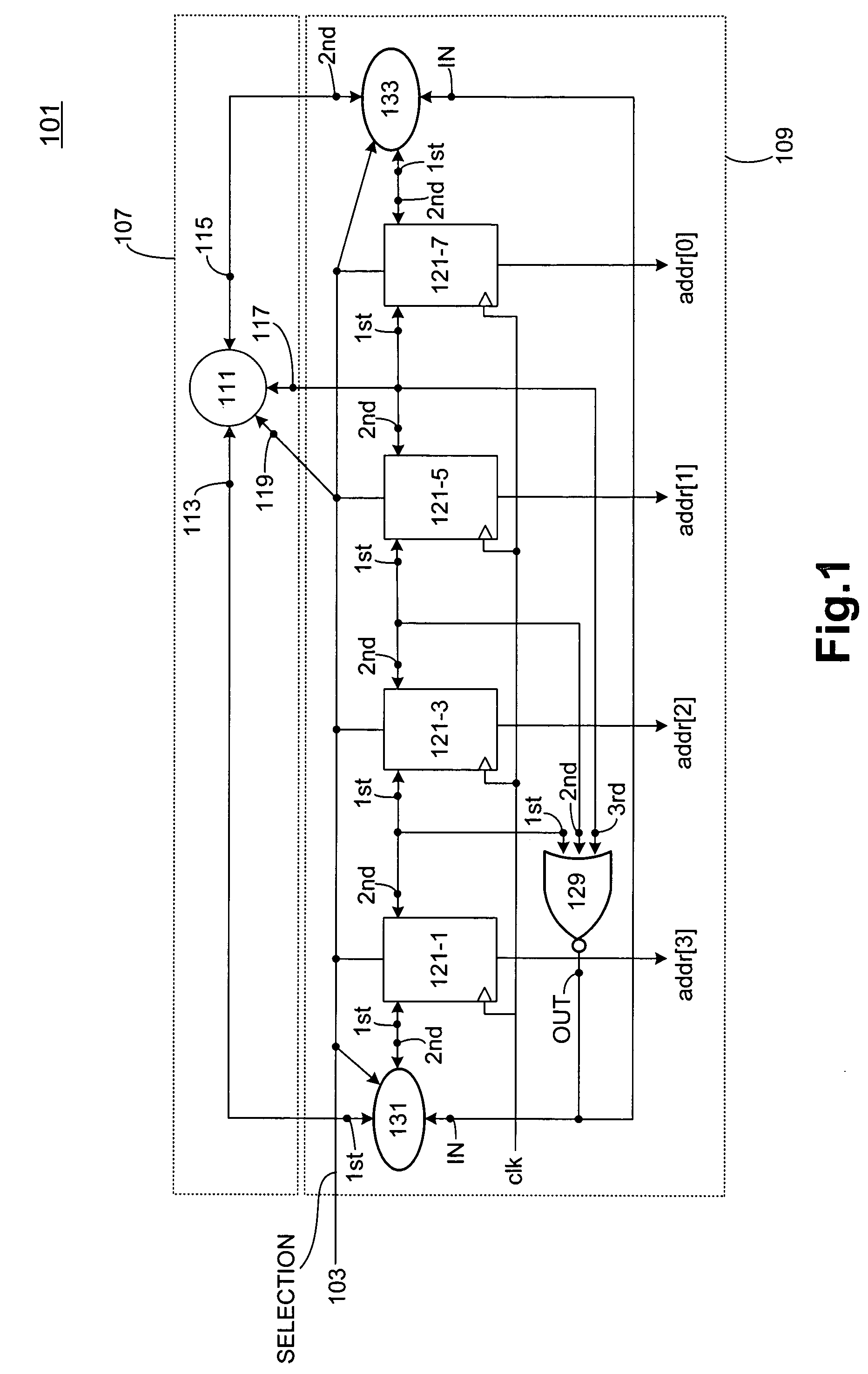

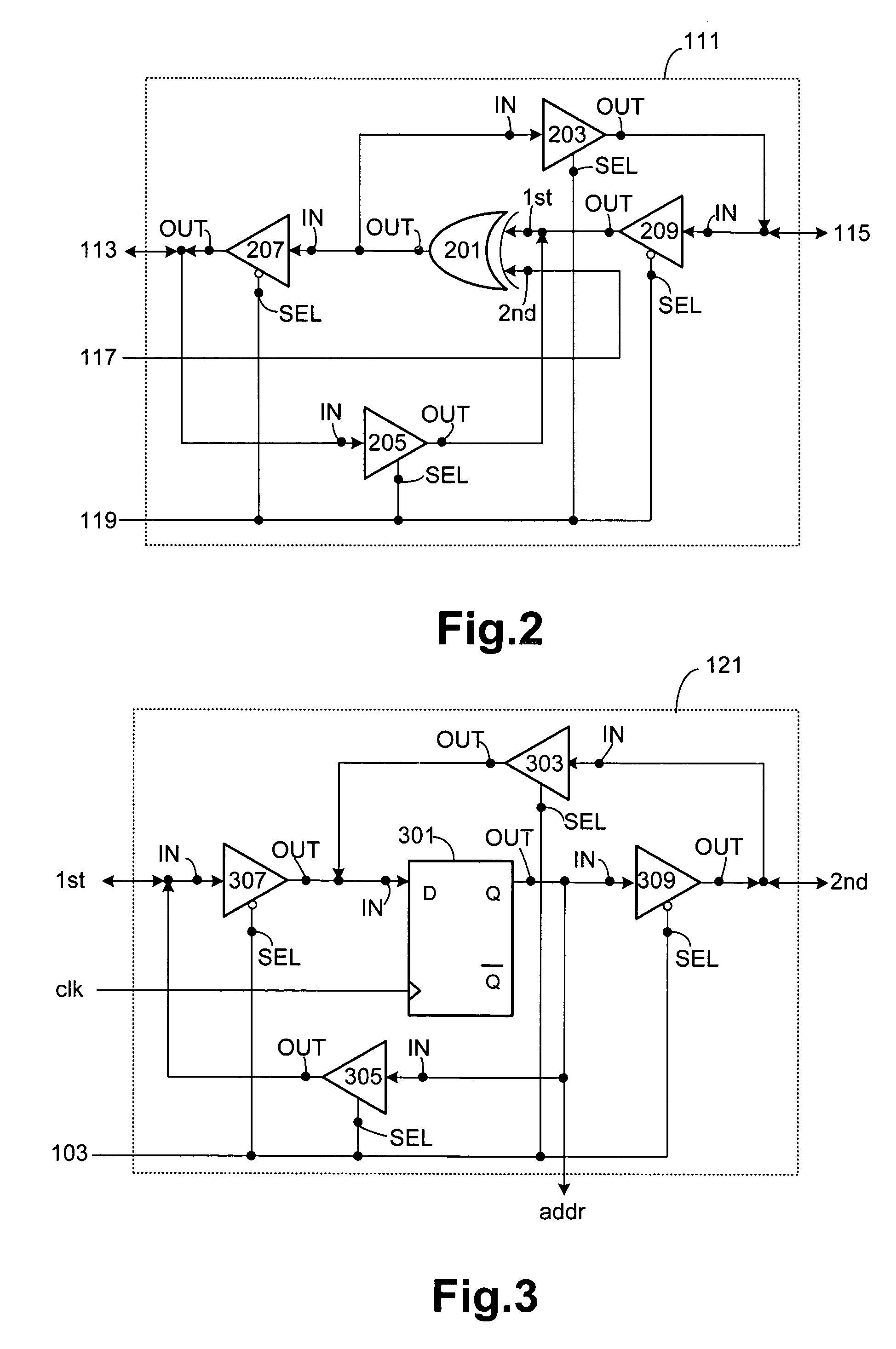

Pointer generator for stack

InactiveUS7038965B2Save layout areaIncrease operating frequencyHandling data according to predetermined rulesDigital storageCharacteristic polynomialComputer science

The present invention discloses a pointer generator which generates pointer values for a stack (LIFO memory). The pointer generator includes a selection input terminal and a bi-direction linear feedback shift register. The selection input terminal transmits a selection signal to the bi-direction linear feedback shift register in response to a command to read / write the stack. The fundamental structure of the bi-direction linear feedback shift register is a linear feedback shift register. After receiving the selection signal from the selection input terminal, the bi-direction linear feedback shift register performs calculation of a specific primitive characteristic polynomial, and then creates a number sequence. When the selection signal changes, the bi-direction linear feedback shift register creates another number sequence by performing calculation of another specific primitive characteristic polynomial. The two number sequences are exactly opposite to each other in order. Therefore, one sequence can be used as up-counting stack pointer values for the “write” command, and the other sequence can be used as down-counting stack pointer values for “read” command.

Owner:BENQ CORP

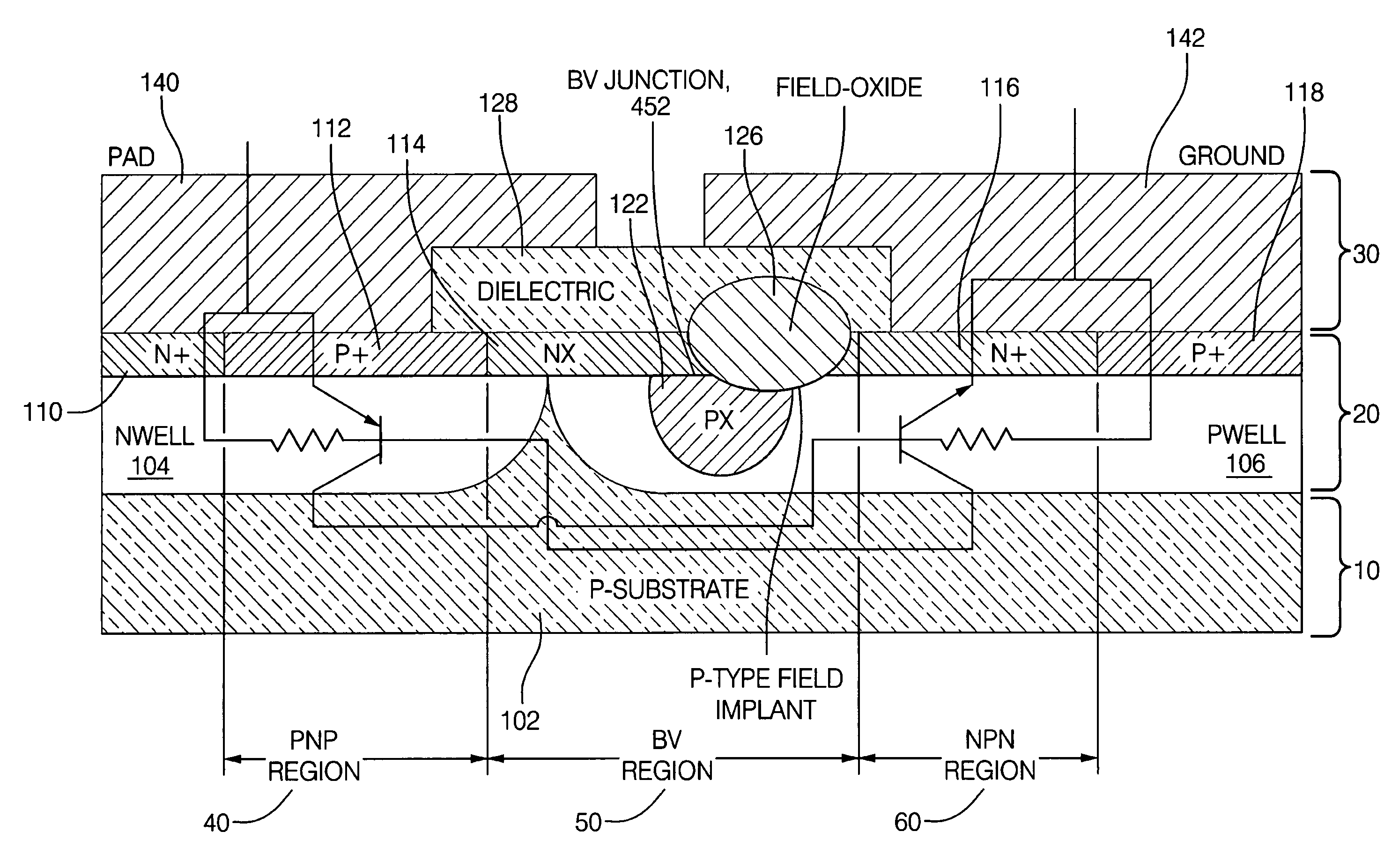

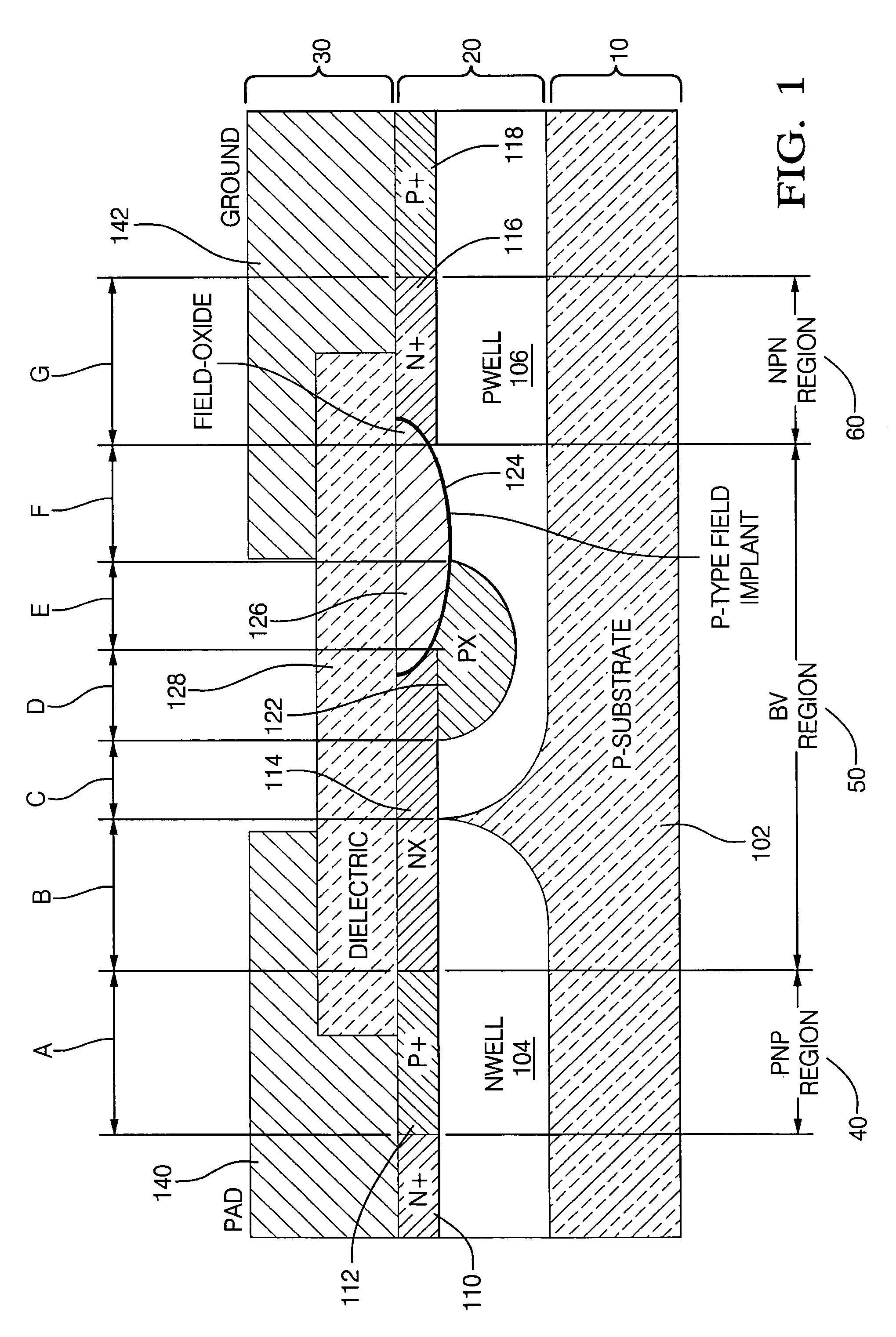

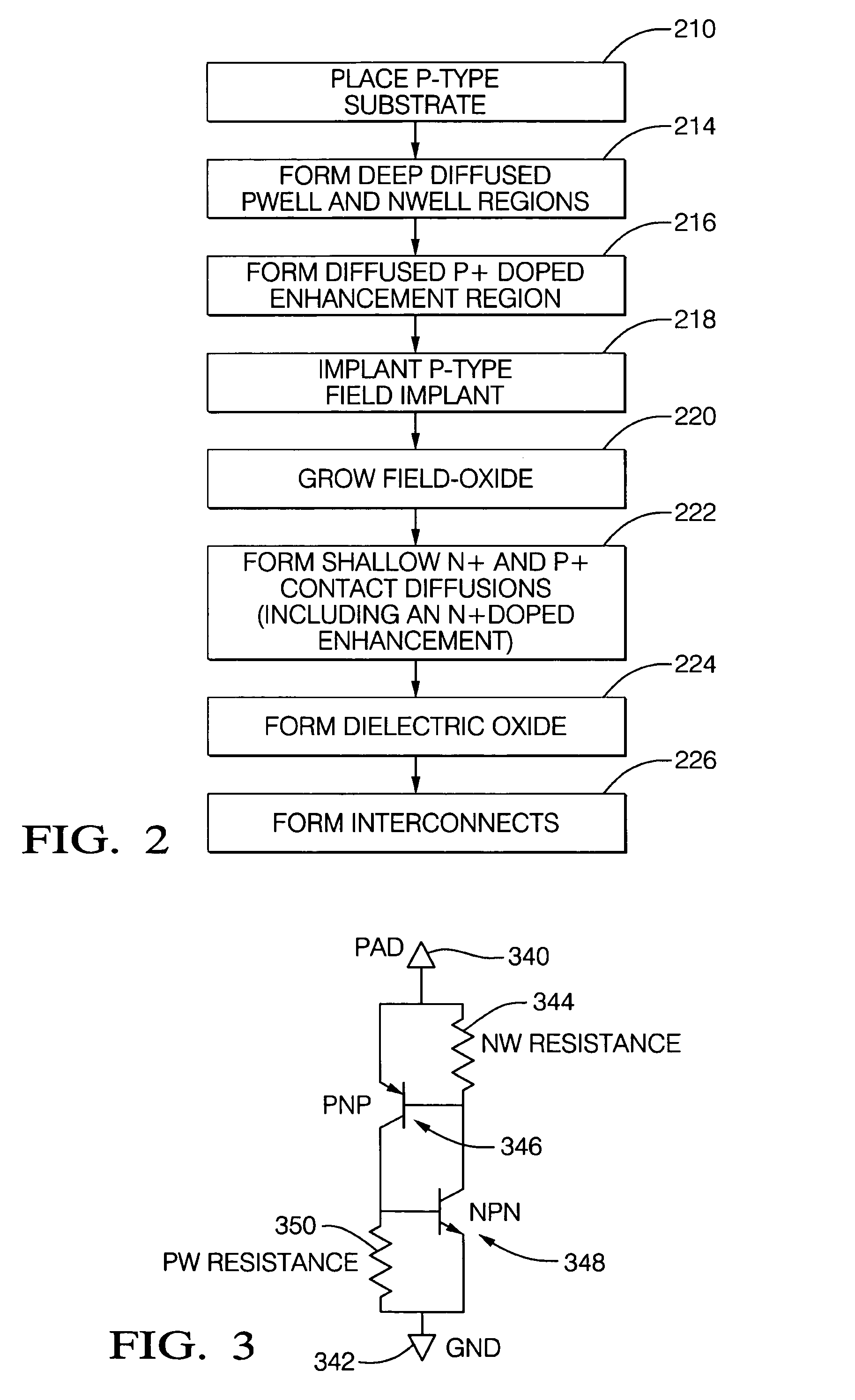

Method and apparatus for electrostatic discharge protection having a stable breakdown voltage and low snapback voltage

ActiveUS7601990B2Time stableLower average currentTransistorSemiconductor/solid-state device detailsEngineeringElectrostatic discharge protection

Electrostatic discharge (ESD) protection is provided for an integrated circuit. Snap back from a lower initial critical voltage and critical current is provided, as compared to contemporary designs. A dynamic region having doped regions is formed on a substrate, interconnects contacting the dynamic region. The dynamic region includes an Nwell region, a Pwell region and shallow diffusions, defining a PNP region, an NPN region and a voltage Breakdown region. In an aspect, the Nwell region includes a first N+ contact, a first P+ contact and an N+ doped enhancement, while the Pwell region includes a second N+ contact, a second P+ contact and a P+ doped enhancement. The N+ doped enhancement contacts the P+ doped enhancement forming the breakdown voltage region therebetween, in one case forming a buried breakdown voltage junction. Independent control is provided over breakdown voltage, NPN critical voltage, NPN critical current and PNP critical current, by varying doping levels, widths and positioning of various doping regions.

Owner:DELPHI TECH IP LTD

Electrostatic discharge protection circuit

ActiveUS20170213818A1Increase holding voltageSave layout area andTransistorSolid-state devicesLow voltageEngineering

Owner:UNITED MICROELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com