Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

54 results about "Bang bang" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Bang-Bang Controller and Control Method For Variable Speed Wind Turbines During Abnormal Frequency Conditions

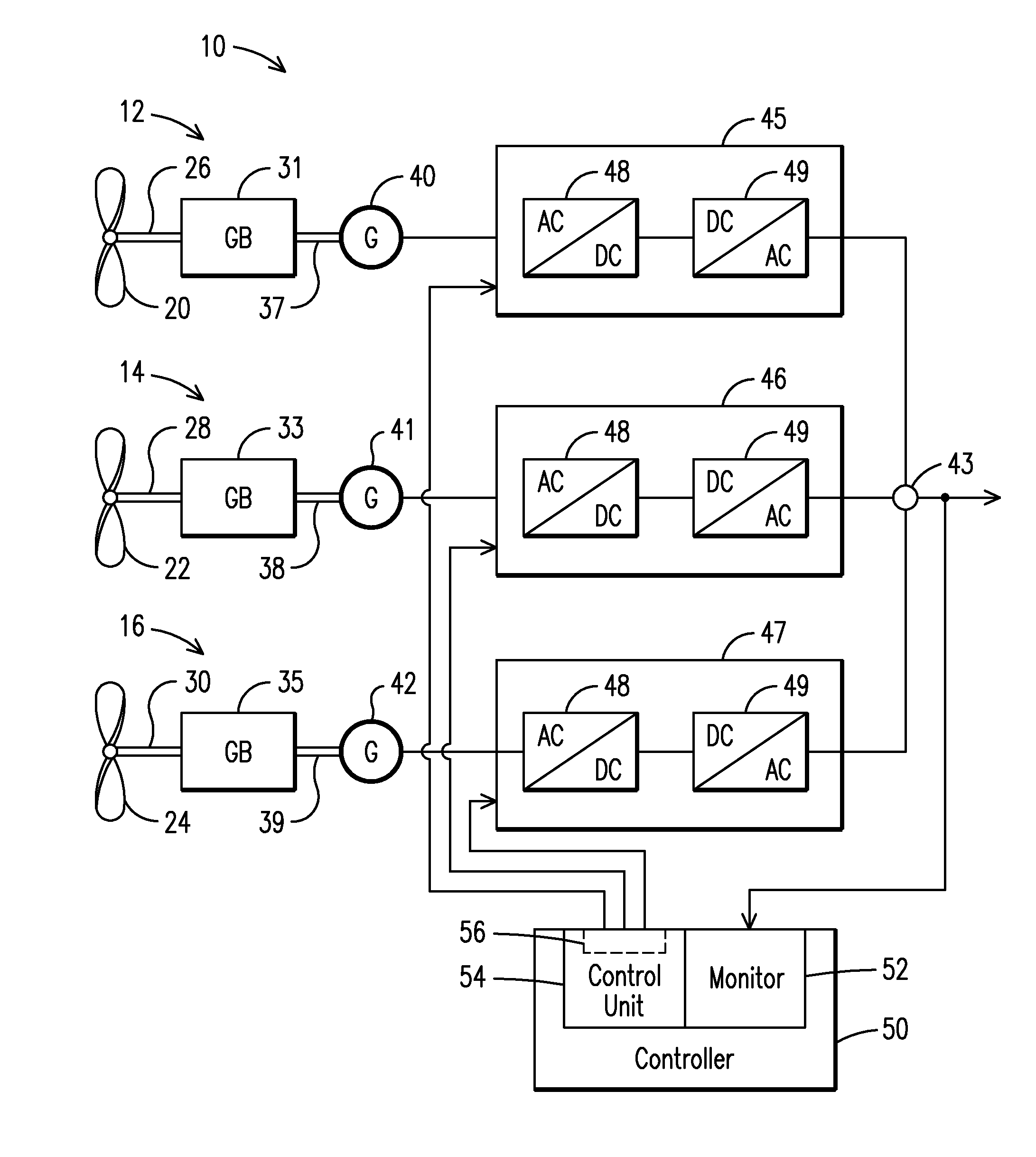

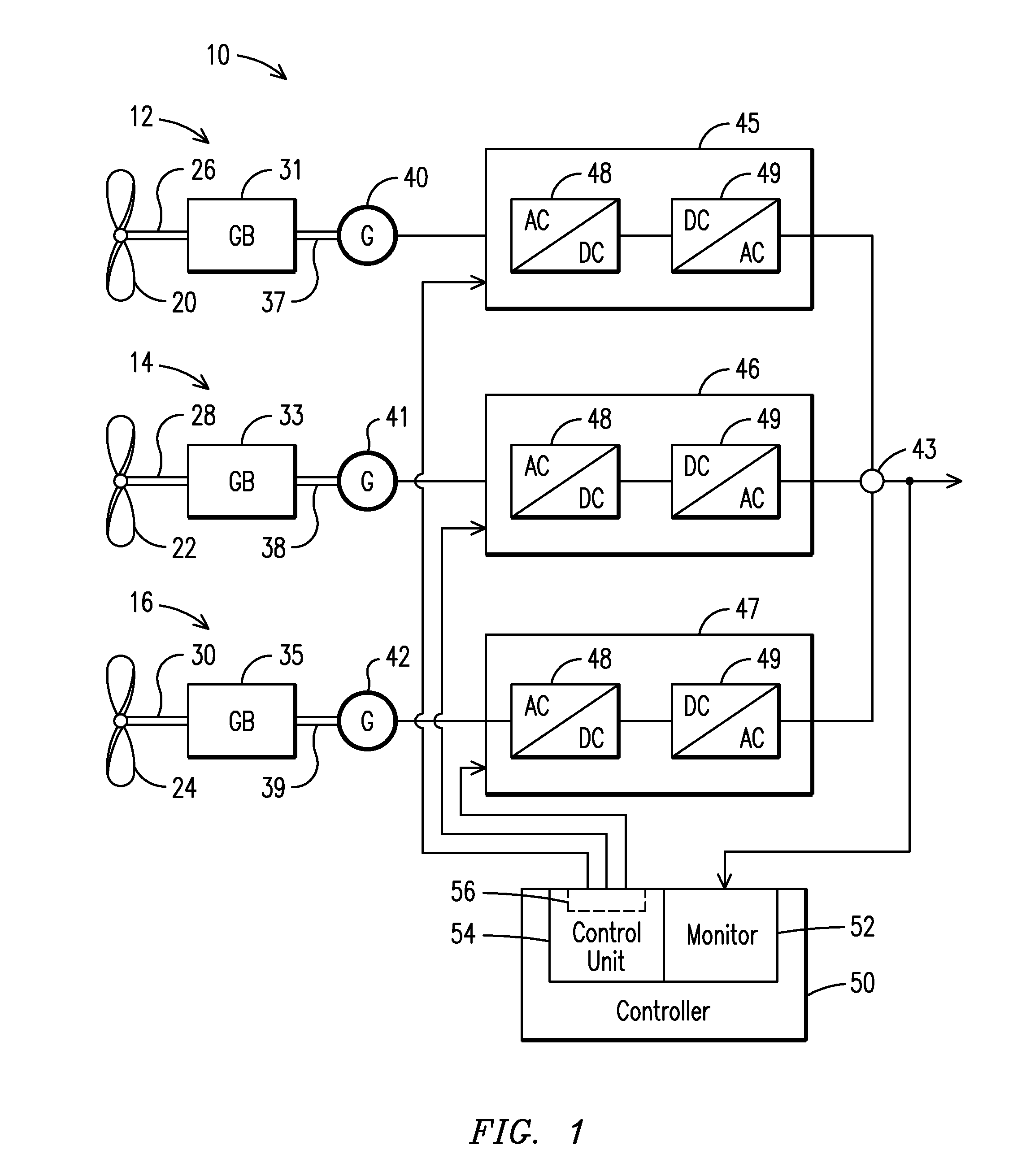

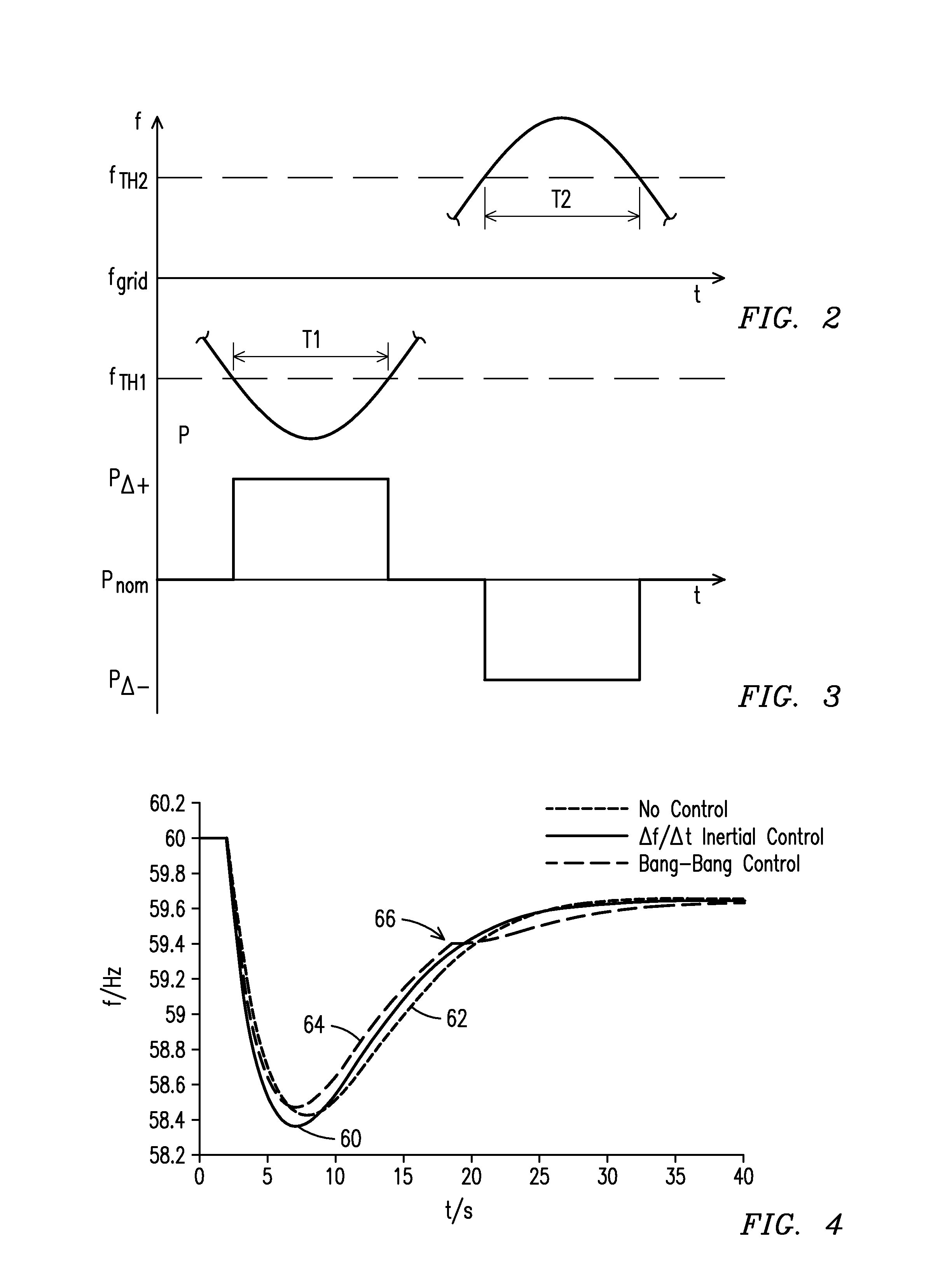

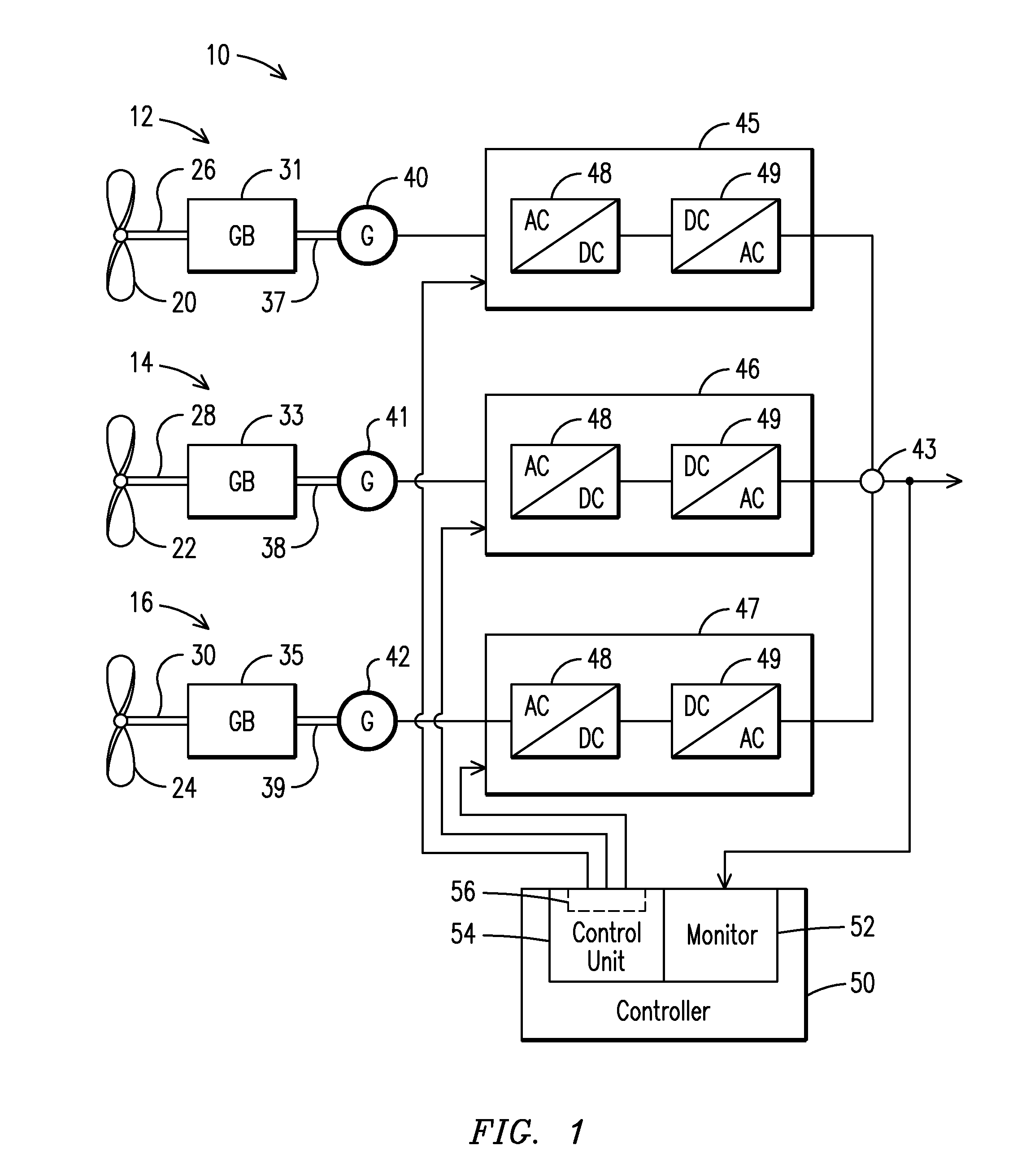

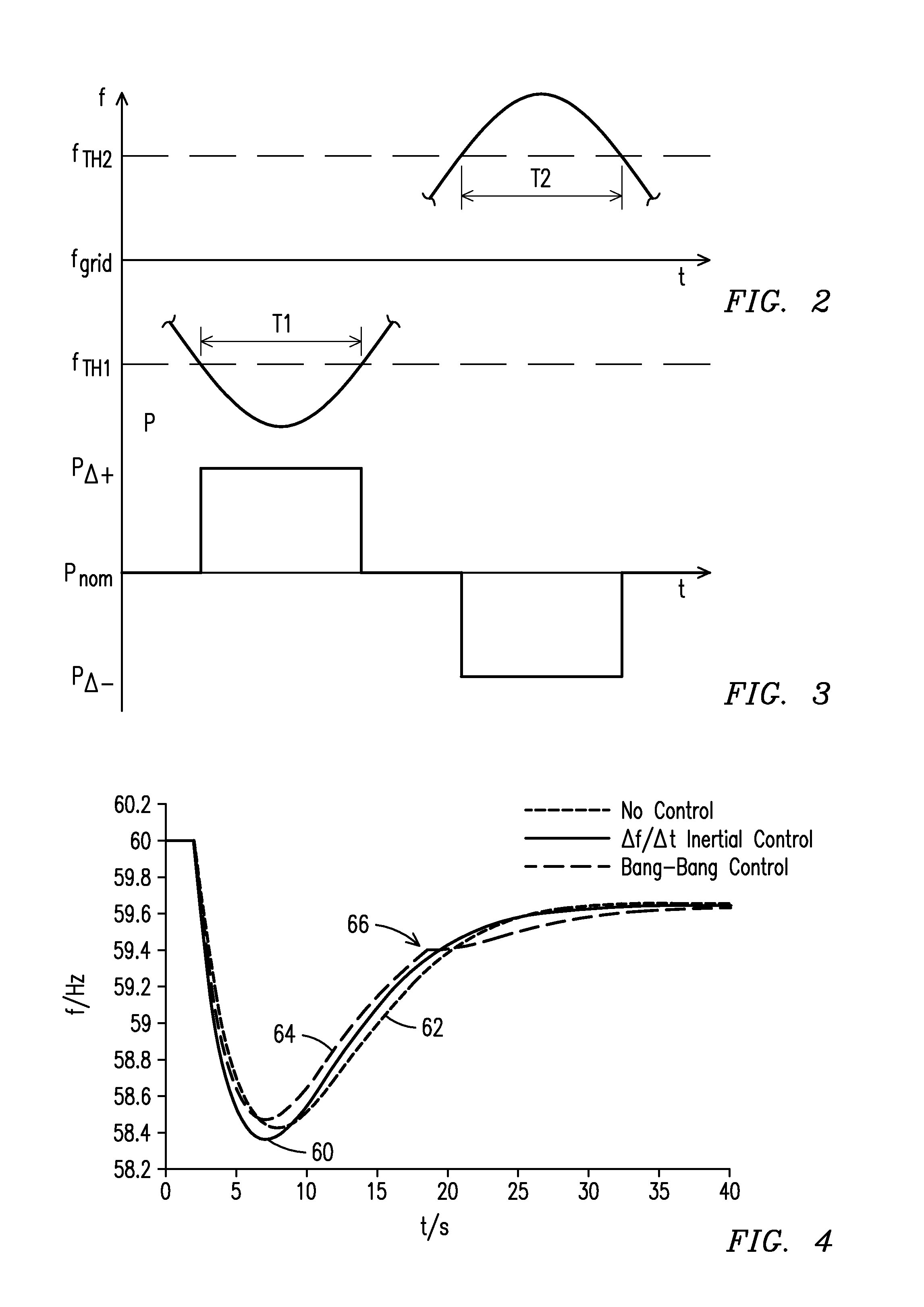

A wind farm (10) may include a plurality of variable speed wind turbines (12, 14,16). A centralized controller (50) may be configured to selectively adjust a respective electrical output power from each of the wind turbines at least during an underfrequency condition. The controller may include a monitor (52) configured to monitor a grid frequency value relative to at least a first threshold value. A deviation of the grid frequency value beyond the first threshold value is indicative of the underfrequency condition. The controller further includes a control unit (54) configured to effect a step response to the electrical output power of the wind turbine in a direction selected to counteract the underfrequency condition.

Owner:SIEMENS GAMESA RENEWABLE ENERGY AS

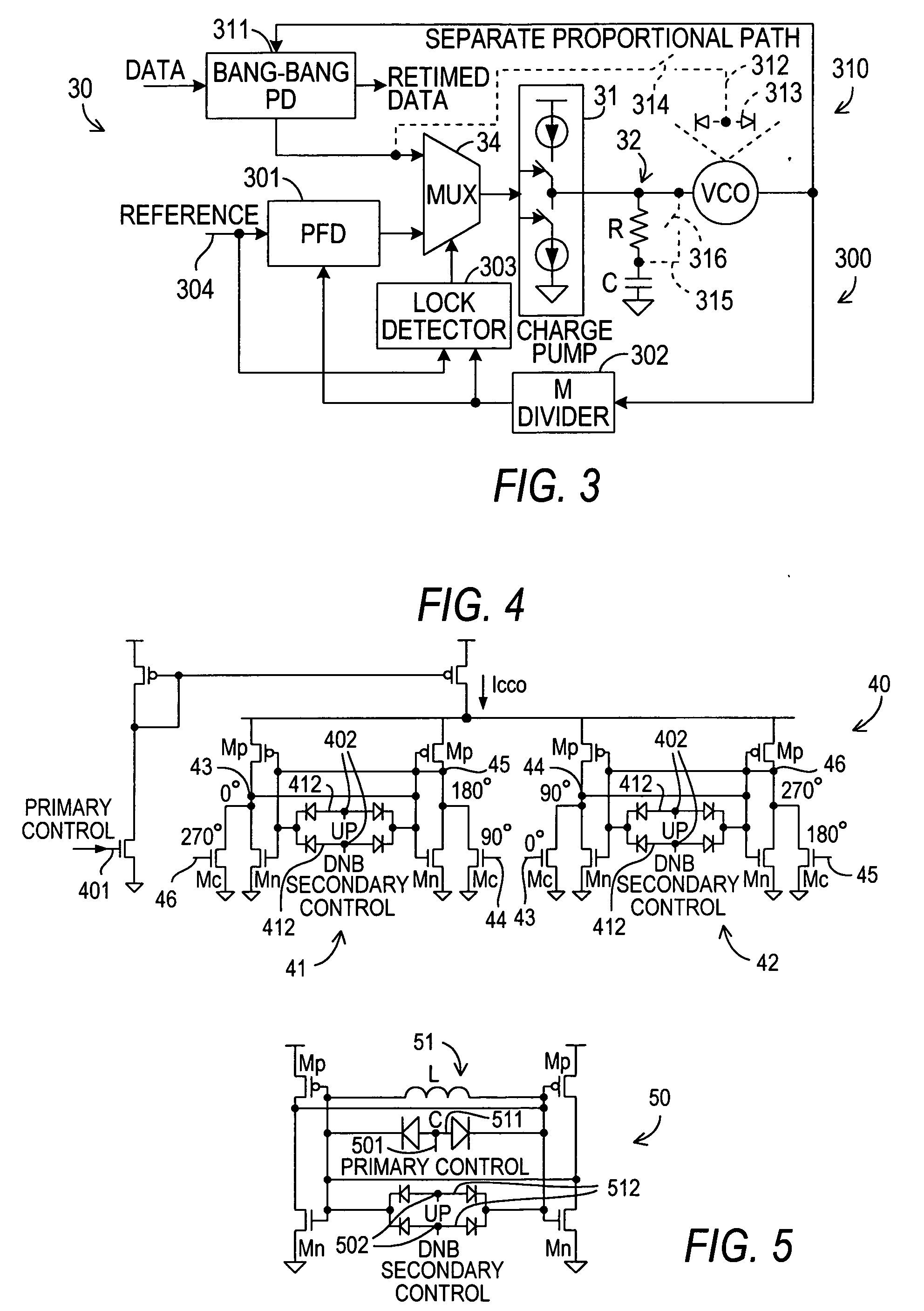

Clock data recovery loop with separate proportional path

InactiveUS7580497B2Improve stabilityLittle effectReceiver initialisationModulated-carrier systemsPhase detectorLoop filter

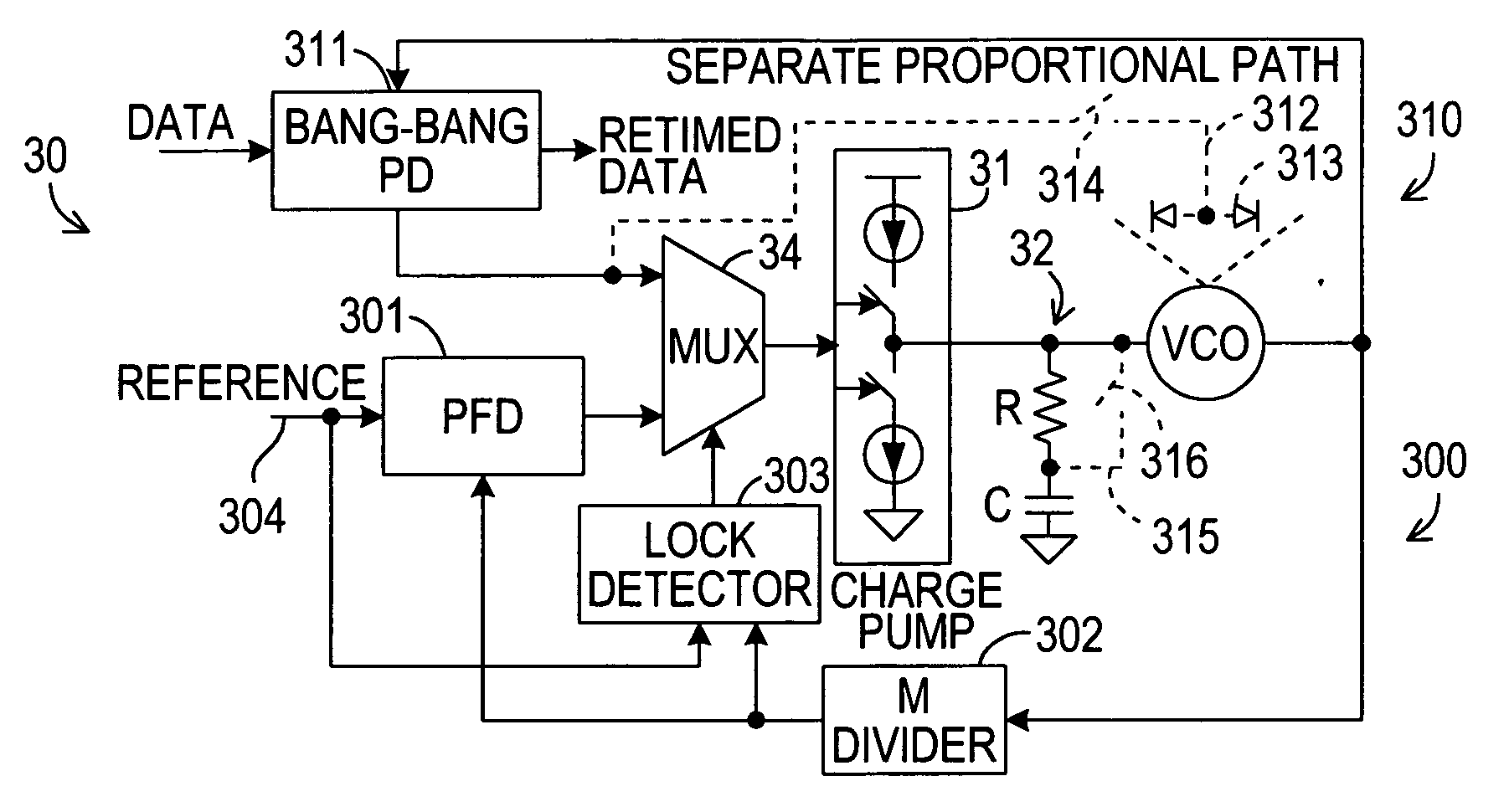

A clock data recovery loop that can be used over a wide range of data rates and maintain second-order behavior includes a nonlinear (e.g., Bang-Bang) phase detector, a charge pump, an RC loop filter, and signal generator (e.g., a voltage controlled oscillator (VCO)). At low data rates, the loop may be operated with the charge pump and loop filter with stable second-order behavior, with the resistor R of the loop filter serving as a proportional path. A separate proportional path is also provided that provides phase detector output directly to a control input of the VCO, while the resistor R of the loop filter is also bypassed. As increasing data rates give rise to third-order effects, the separate proportional path may be activated to maintain second-order behavior.

Owner:ALTERA CORP

Clock data recovery loop with separate proportional path

InactiveUS20070002993A1Improve stabilityLittle effectReceiver initialisationPulse automatic controlPhase detectorLoop filter

A clock data recovery loop that can be used over a wide range of data rates and maintain second-order behavior includes a nonlinear (e.g., Bang-Bang) phase detector, a charge pump, an RC loop filter, and signal generator (e.g., a voltage controlled oscillator (VCO)). At low data rates, the loop may be operated with the charge pump and loop filter with stable second-order behavior, with the resistor R of the loop filter serving as a proportional path. A separate proportional path is also provided that provides phase detector output directly to a control input of the VCO, while the resistor R of the loop filter is also bypassed. As increasing data rates give rise to third-order effects, the separate proportional path may be activated to maintain second-order behavior.

Owner:ALTERA CORP

Current mode bang-bang controller in a switching voltage regulator

ActiveUS6906499B2Apparatus without intermediate ac conversionElectric variable regulationBang bangVoltage regulation

A regulator provides a load voltage. The regulator includes a power driver having a feedback input and a power driver voltage. The regulator includes a comparator having a comparator output related to a combination of the load voltage and a power driver current. The regulator includes a pulse generator controlled by the comparator output and having output pulses with fixed pulse widths. The regulator includes a time limit circuit controlled by the output pulses. The time limit circuit provides the output pulses to the feedback input subject to a time limit between the output pulses.

Owner:SEAGATE TECH LLC

Turbine speed control system and method

ActiveUS7194863B2Improve performanceMinimizing system weightWind motor controlGas turbine plantsBang bangTurbine blade

One embodiment of the invention provides a turbine control system that adjusts the control thresholds of two-position valves, which provide propellant to the turbine, based on turbine load so as to compensate for increased turbine speed overshoot at low load and the increased turbine speed undershoot at high load. These two-position on-off modulated valves are used in a bang-bang (fully open or fully closed) regulation scheme to eliminate or minimize speed droop by using variable speed bounds implemented as a function of load.

Owner:HONEYWELL INT INC

Method and apparatus for jitter reduction

A low bandwidth phase lock loop (PLL) arranged in a dual-loop configuration is disclosed. The first loop is a standard loop configuration using a crystal oscillator as a reference clock. The loop parameters for this first PLL can be optimized to work over a wide range of output frequencies, and with a minimum amount of jitter. The first loop outputs a reference signal, which is a VCO output. The second loop comprises a bang-bang detector configured to drive a digital loop filter, which then drives a phase interpolator. The phase interpolator manipulates the output phase. Since phase and frequency are related, where frequency is the derivative of phase, small frequency offsets can be made using a phase control signal, generated within the second loop based on the relation between the reference signal and the clock input signal. The second loop sets the jitter transfer bandwidth of the system.

Owner:MACOM TECH SOLUTIONS HLDG INC

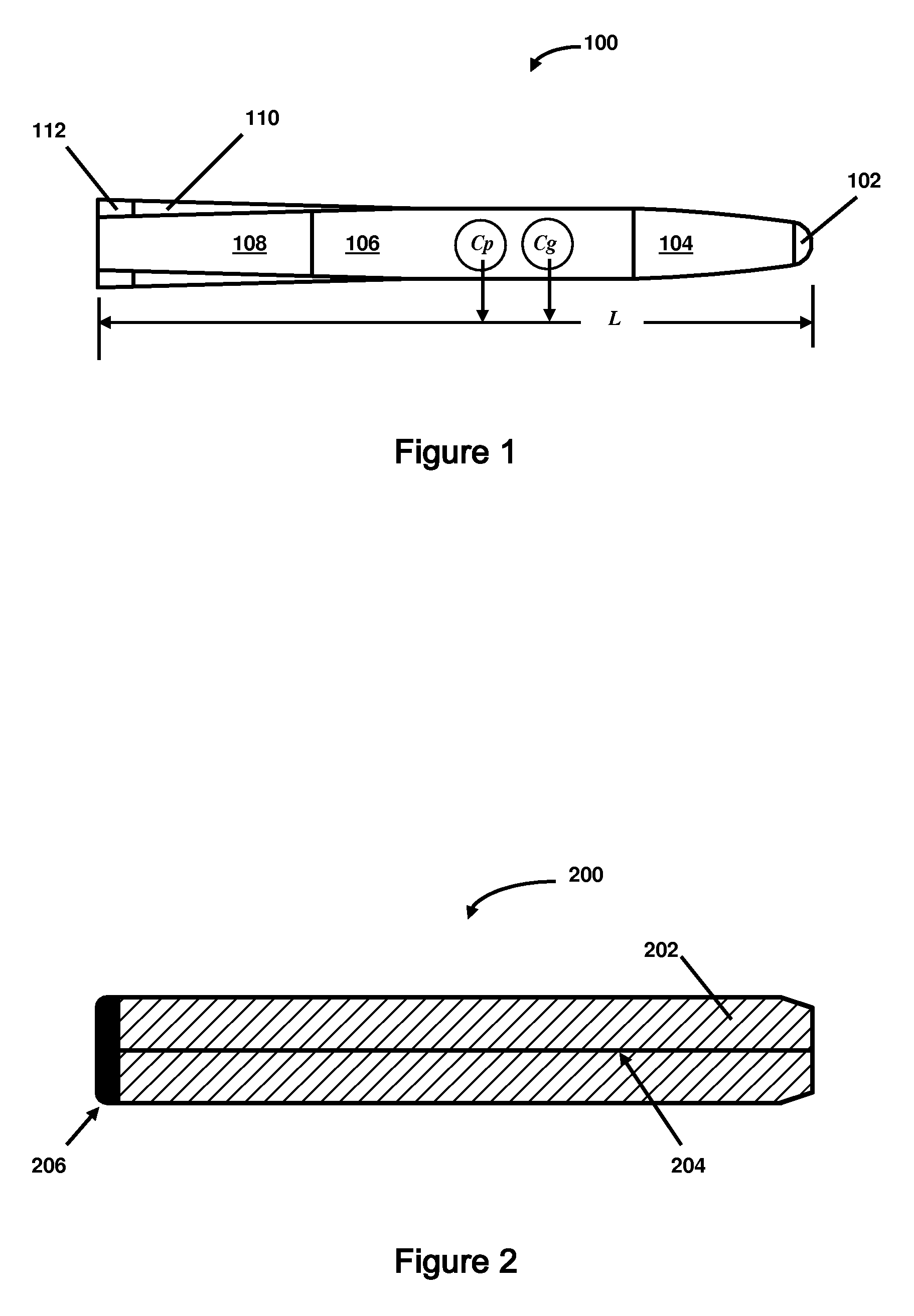

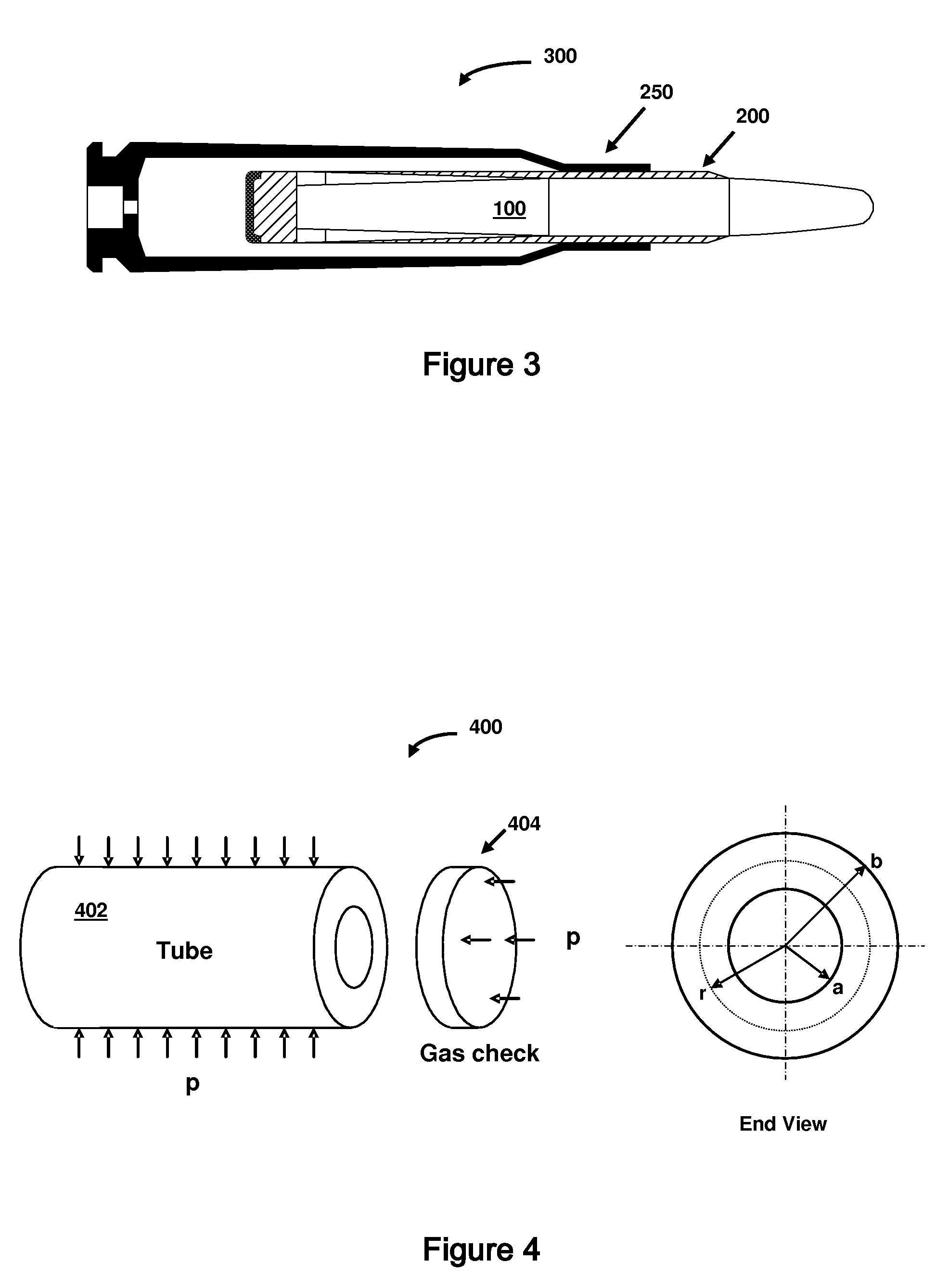

Small caliber guided projectile

A non-spinning projectile that is self-guided to a laser designated target and is configured to be fired from a small caliber smooth bore gun barrel has an optical sensor mounted in the nose of the projectile, a counterbalancing mass portion near the fore end of the projectile and a hollow tapered body mounted aft of the counterbalancing mass. Stabilizing strakes are mounted to and extend outward from the tapered body with control fins located at the aft end of the strakes. Guidance and control electronics and electromagnetic actuators for operating the control fins are located within the tapered body section. Output from the optical sensor is processed by the guidance and control electronics to produce command signals for the electromagnetic actuators. A guidance control algorithm incorporating non-proportional, “bang-bang” control is used to steer the projectile to the target.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

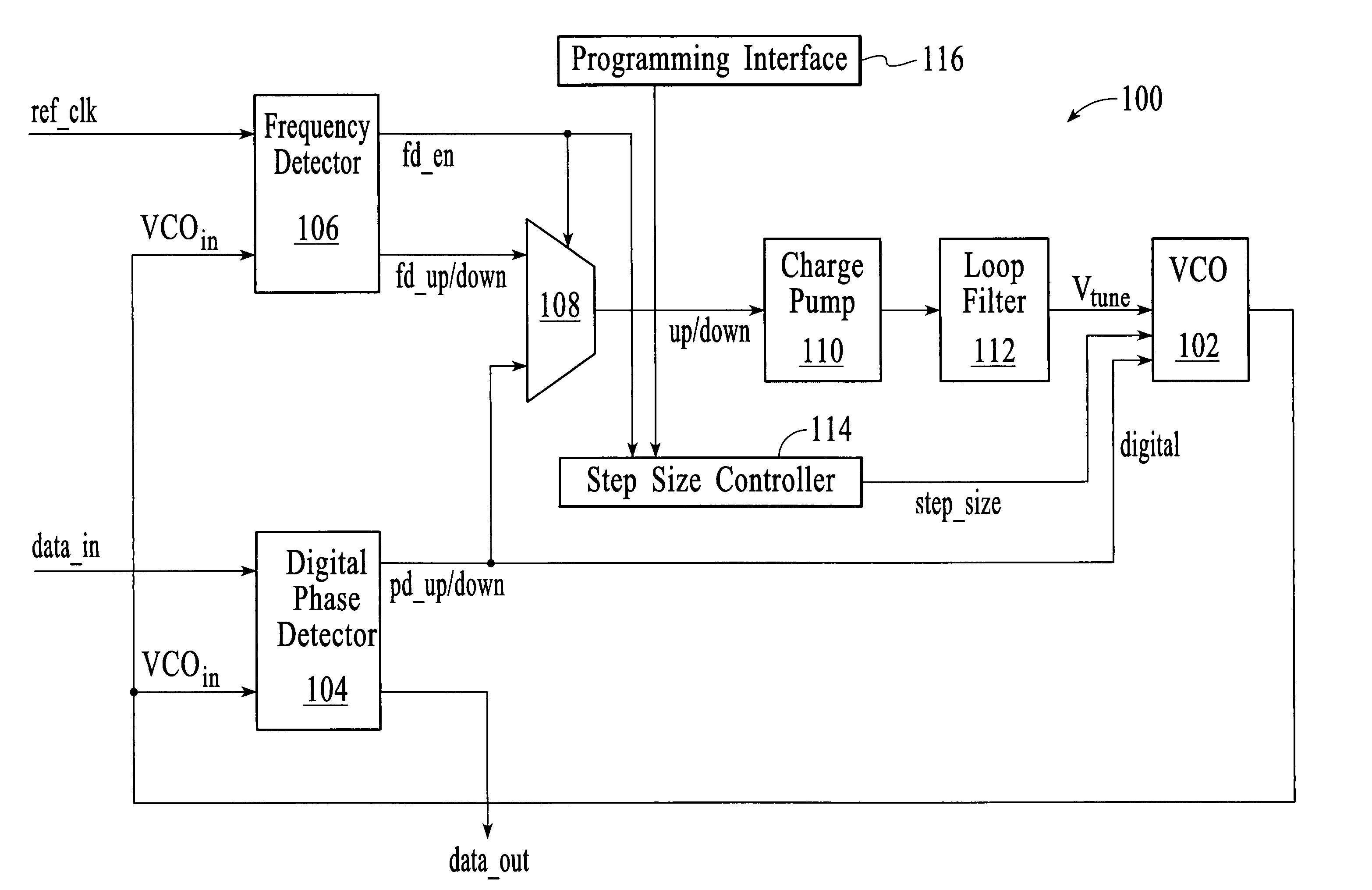

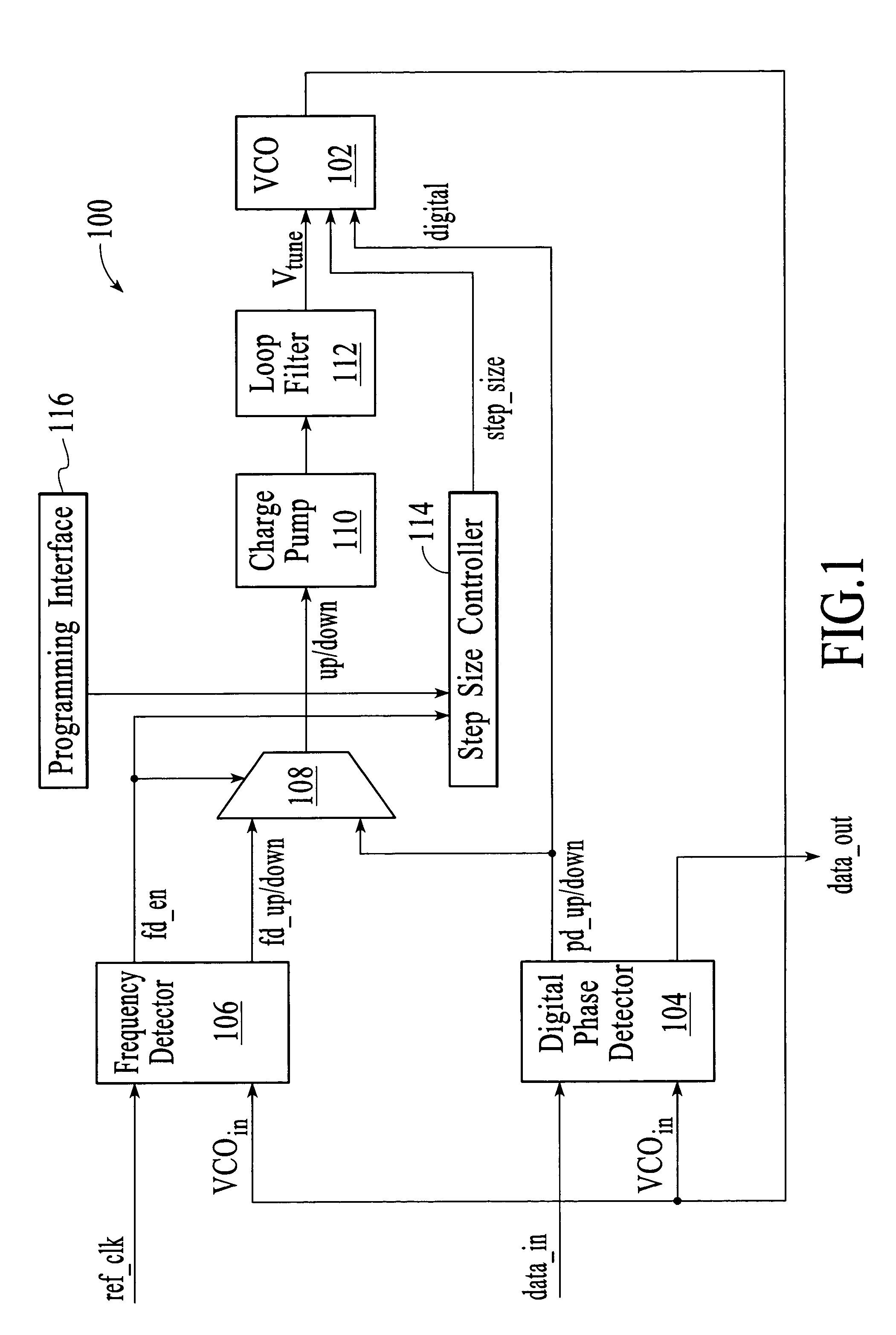

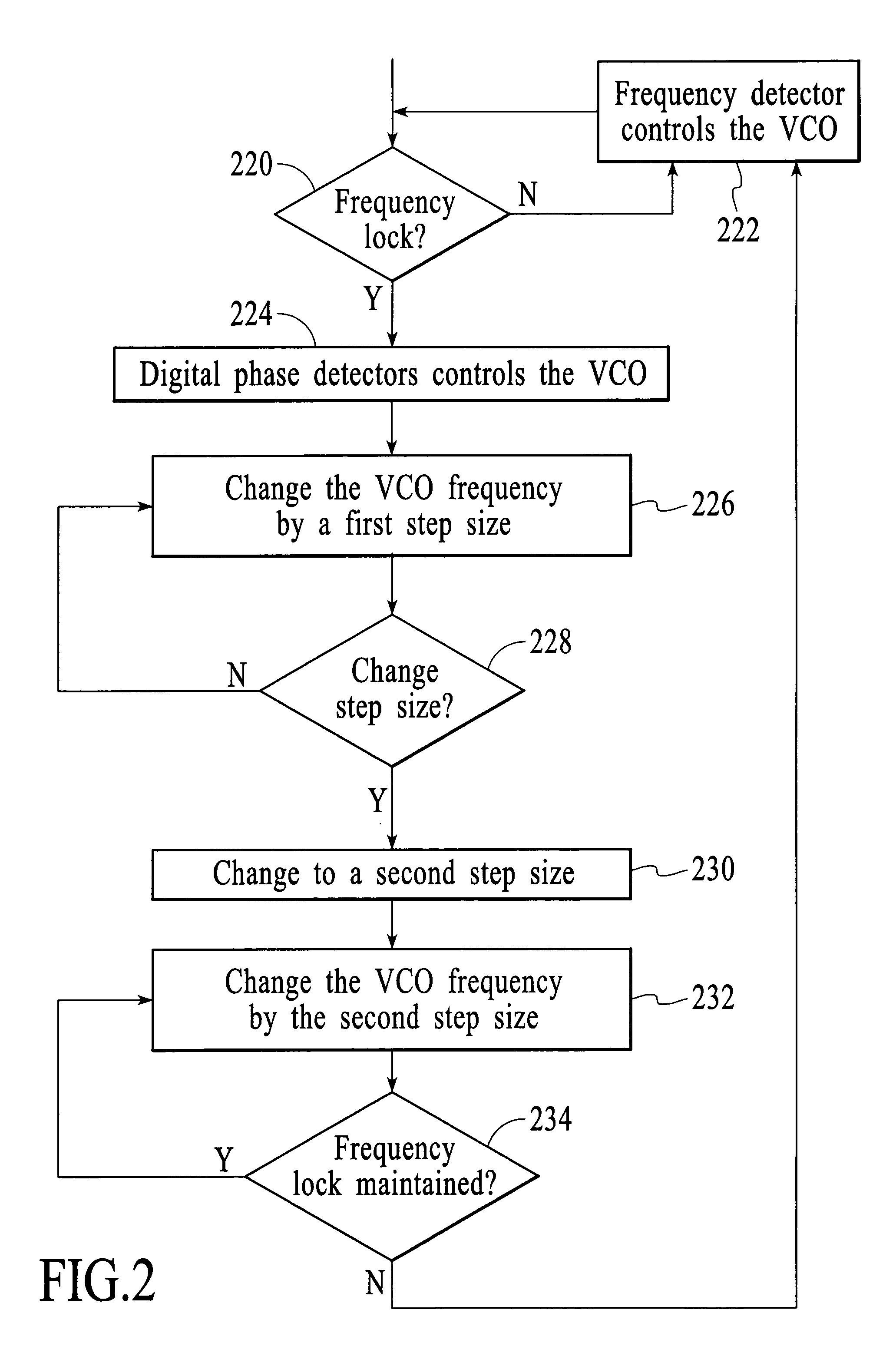

Controlling a voltage controlled oscillator in a bang-bang phase locked loop

InactiveUS7053719B2Reduce negative impactFaster ratePulse automatic controlOscillations generatorsPhase detectorBang bang

The frequency changes in a bang-bang PLL that are generated using a digital phase detector's up / down signal are initially set to produce a faster pull-in rate and then reduced to produce a slower pull-in rate. The faster pull-in involves relatively large frequency changes and the slower pull-in rate involves smaller frequency changes. The changes in frequency of a bang-bang PLL can be implemented using a step size controller that includes timing control logic and step size logic. The function of the timing control logic is to control the timing of step size changes. The function of the step size logic is to set the step size of the frequency changes that are made by the VCO in response to the pd_up / down signal that is delivered directly to the VCO from the digital phase detector.

Owner:AGILENT TECH INC

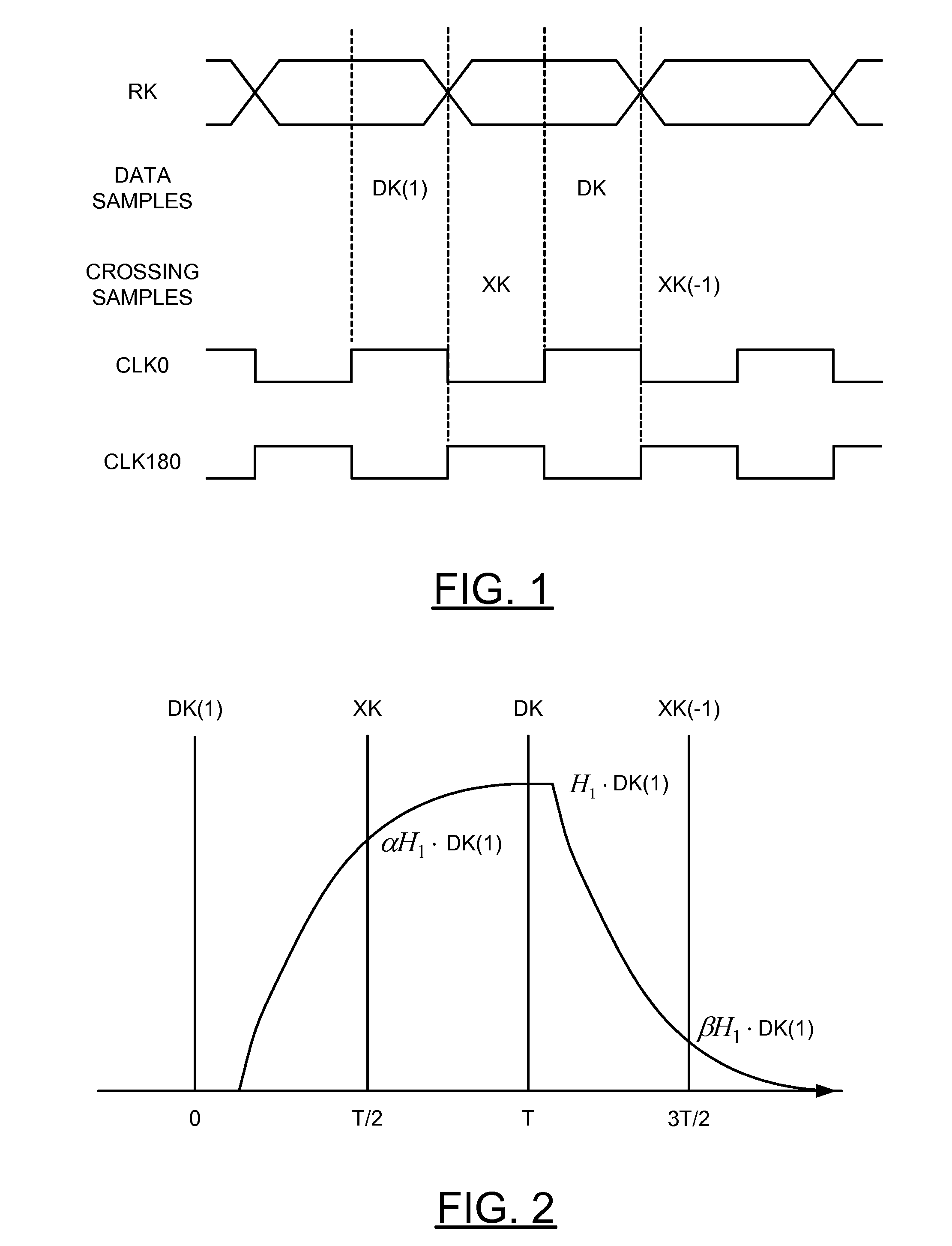

Decoupling bang-bang cdr and dfe

InactiveUS20120155530A1Improves jitter toleranceError propagationMultiple-port networksDelay line applicationsPhase detectorBang bang

An apparatus including a bang-bang clock data recovery module and a decision feedback equalizer. A phase detector of the bang-bang clock and data recovery module may be configured to eliminate coupling between the bang-bang clock and data recovery module and the decision feedback equalizer based upon an error signal of the decision feedback equalizer and a predetermined coefficient.

Owner:AVAGO TECH INT SALES PTE LTD

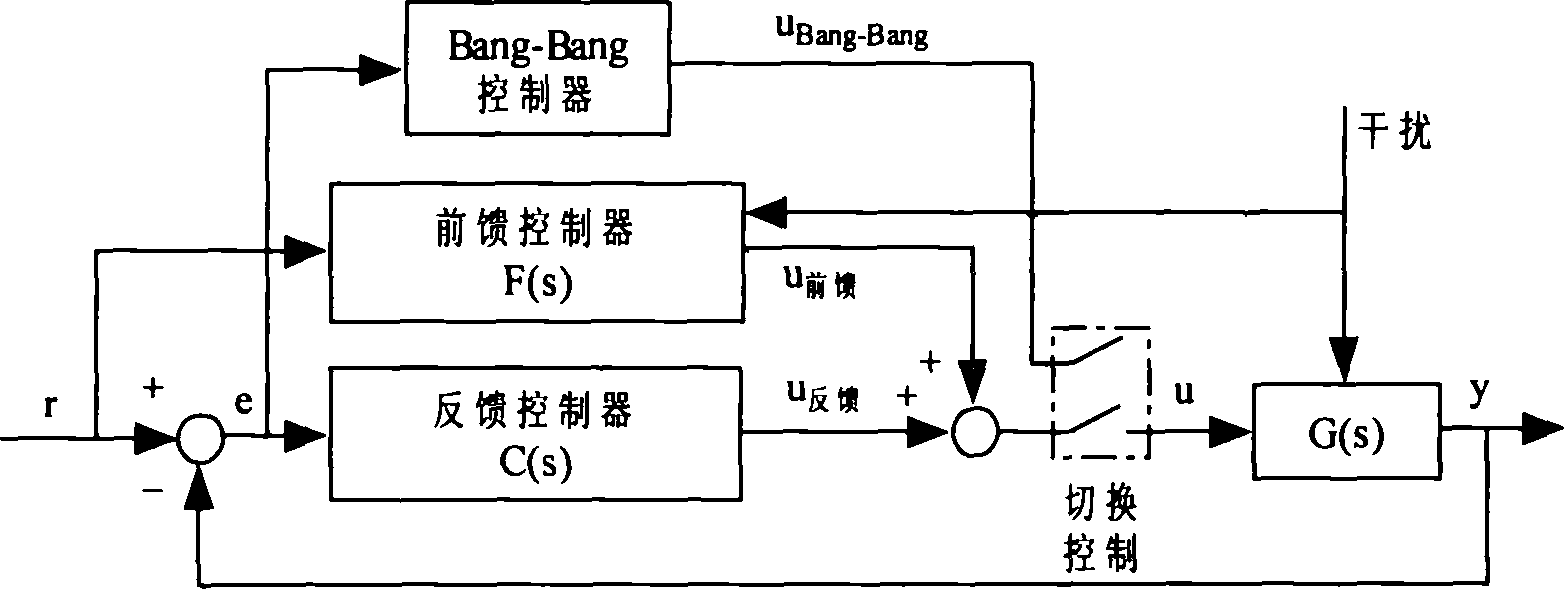

Compound controlling method for semiconductor refrigerator fast heating/refrigerating system

InactiveCN1888998AQuick responseFast heating and cooling rateSpeed/accelaration controlTemperature control using electric meansTemperature controlBang bang

A compound temperature control method for the quick heating / cooling system of the semiconductor refrigerator. The invention leads the feed forward, the feedback and the Bang-Bang controlling method in the temperature control system according the module of the controlling object. It uses the Bang-Bang controlling method firstly and changes to the 'feed forward with the PID'mode when the deviation is less than the threshold quantity. They are all done by the controller. The feed forward and the Bang-Bang control reach the tracking quickly and the feedback control is the PID control with the changing structure which match to the feed forward to celebrate the speed of the rising or dropping the temperature and decrease the tracking error. It can decreases the 36% of the rising time with the 80% overshoot at the same time.

Owner:SHANGHAI JIAO TONG UNIV

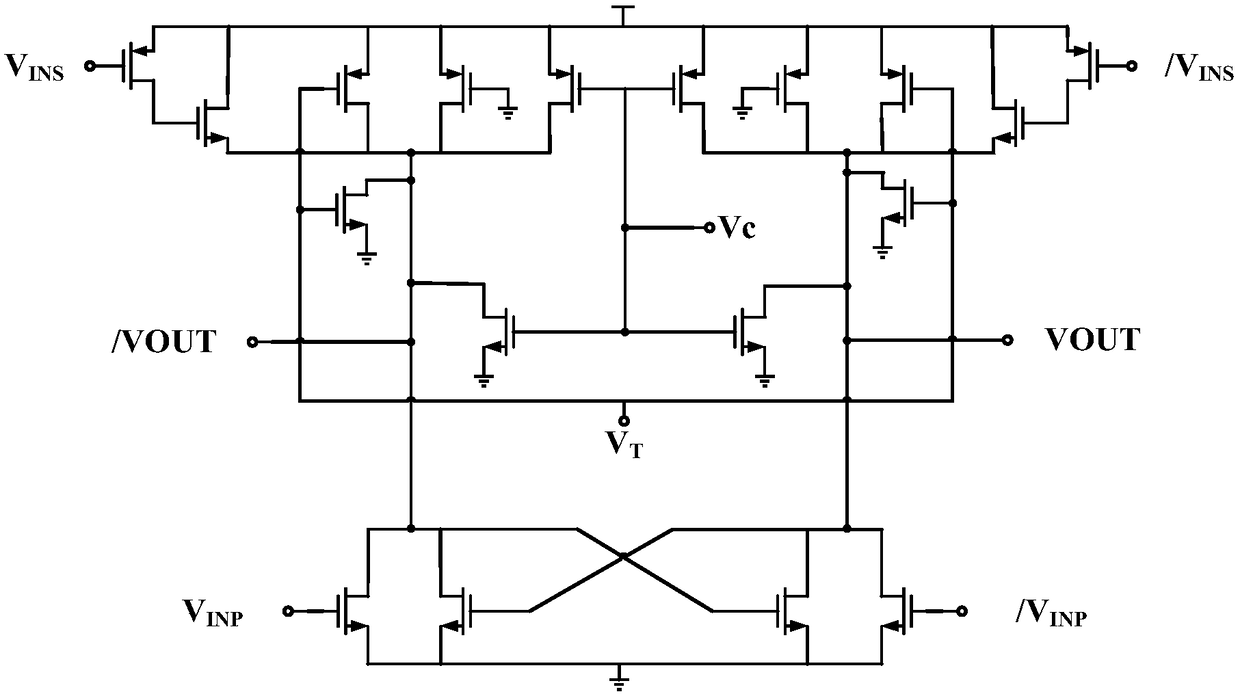

Differential bang-bang phase detector (BBPD) with latency reduction

InactiveUS7482841B1Improve performancePulse automatic controlVoltage-current phase angleBang bangDifferential phase

Bang-bang phase detection (BBPD) methods and circuits are presented for providing low latency, low jitter phase detection for use in high data-rate applications. A shortened data-path implementation of BBPD methods and circuits provides low-latency production of two output signals including alternating samples of the input signal. Combinational logic circuitry is also provided to produce a clock-data recovery (CDR) signal indicative of the phase of the input signal with respect to a clock signal. The use of differential signals throughout the BBPD timing circuitry provides for the production of a low jitter CDR signal.

Owner:ALTERA CORP

Bang-bang controller and control method for variable speed wind turbines during abnormal frequency conditions

A wind farm (10) may include a plurality of variable speed wind turbines (12, 14, 16). A centralized controller (50) may be configured to selectively adjust a respective electrical output power from each of the wind turbines at least during an underfrequency condition. The controller may include a monitor (52) configured to monitor a grid frequency value relative to at least a first threshold value. A deviation of the grid frequency value beyond the first threshold value is indicative of the underfrequency condition. The controller further includes a control unit (54) configured to effect a step response to the electrical output power of the wind turbine in a direction selected to counteract the underfrequency condition.

Owner:SIEMENS GAMESA RENEWABLE ENERGY AS

Adaptation of crossing latch threshold

ActiveUS20120057626A1Reduce the impactReduce impactMultiple-port networksDelay line applicationsBang bangComputer science

An apparatus including a bang-bang clock data recovery module and a decision feedback equalizer. The decision feedback equalizer is coupled with the bang-bang clock data recovery module. The apparatus is configured to reduce an effect on a settling point of the bang-bang clock and data recovery module due to coupling between the bang-bang clock and data recovery module and the decision feedback equalizer.

Owner:AVAGO TECH INT SALES PTE LTD

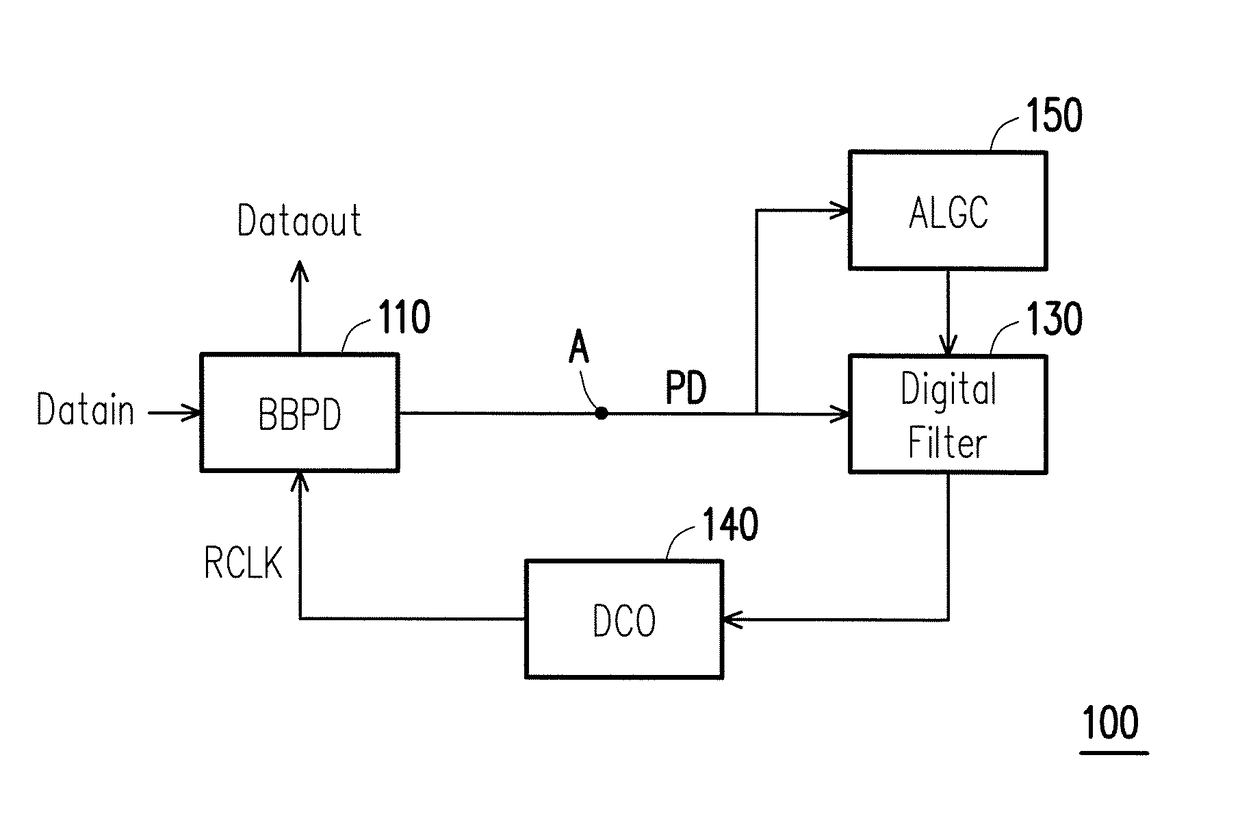

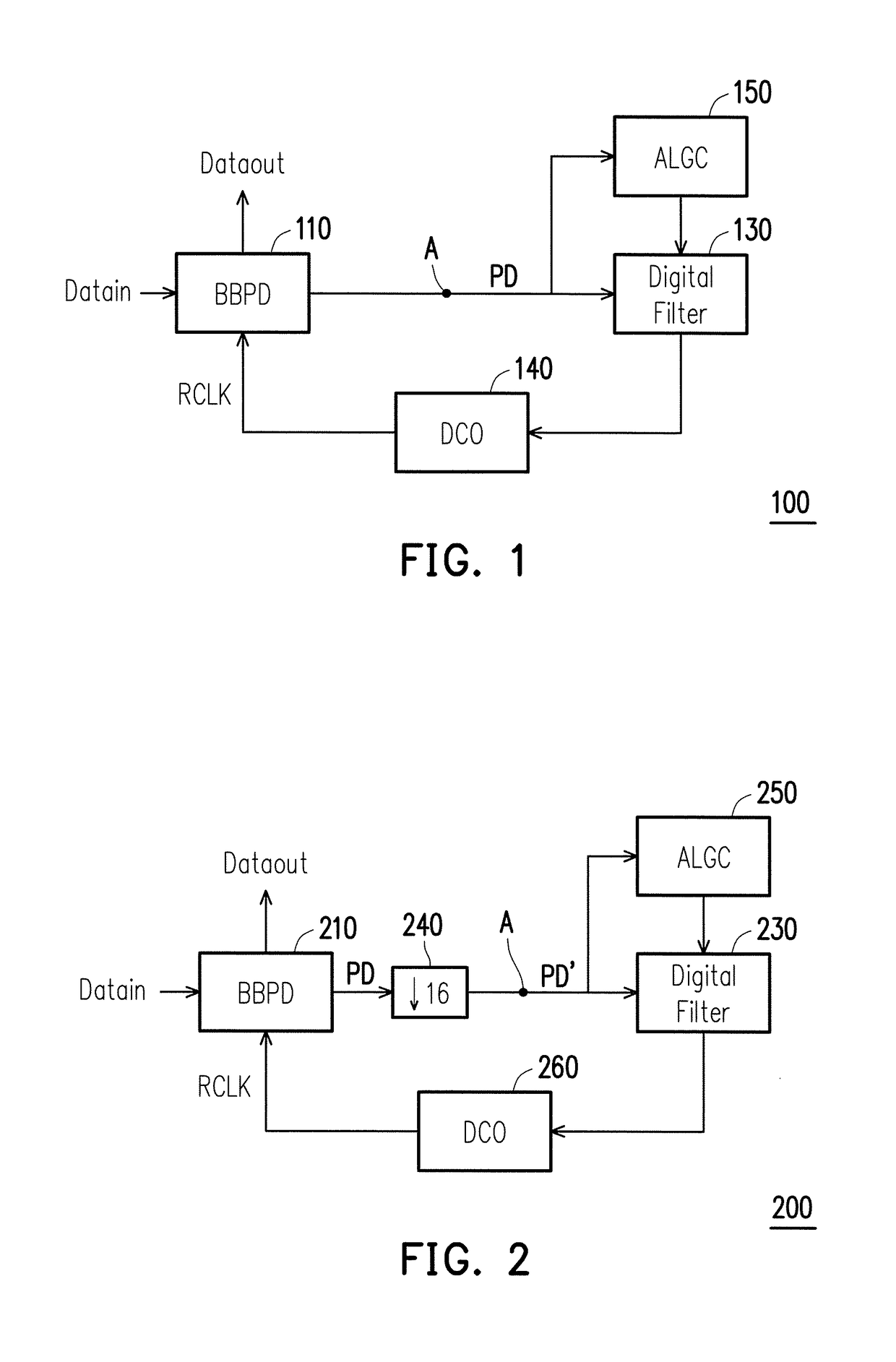

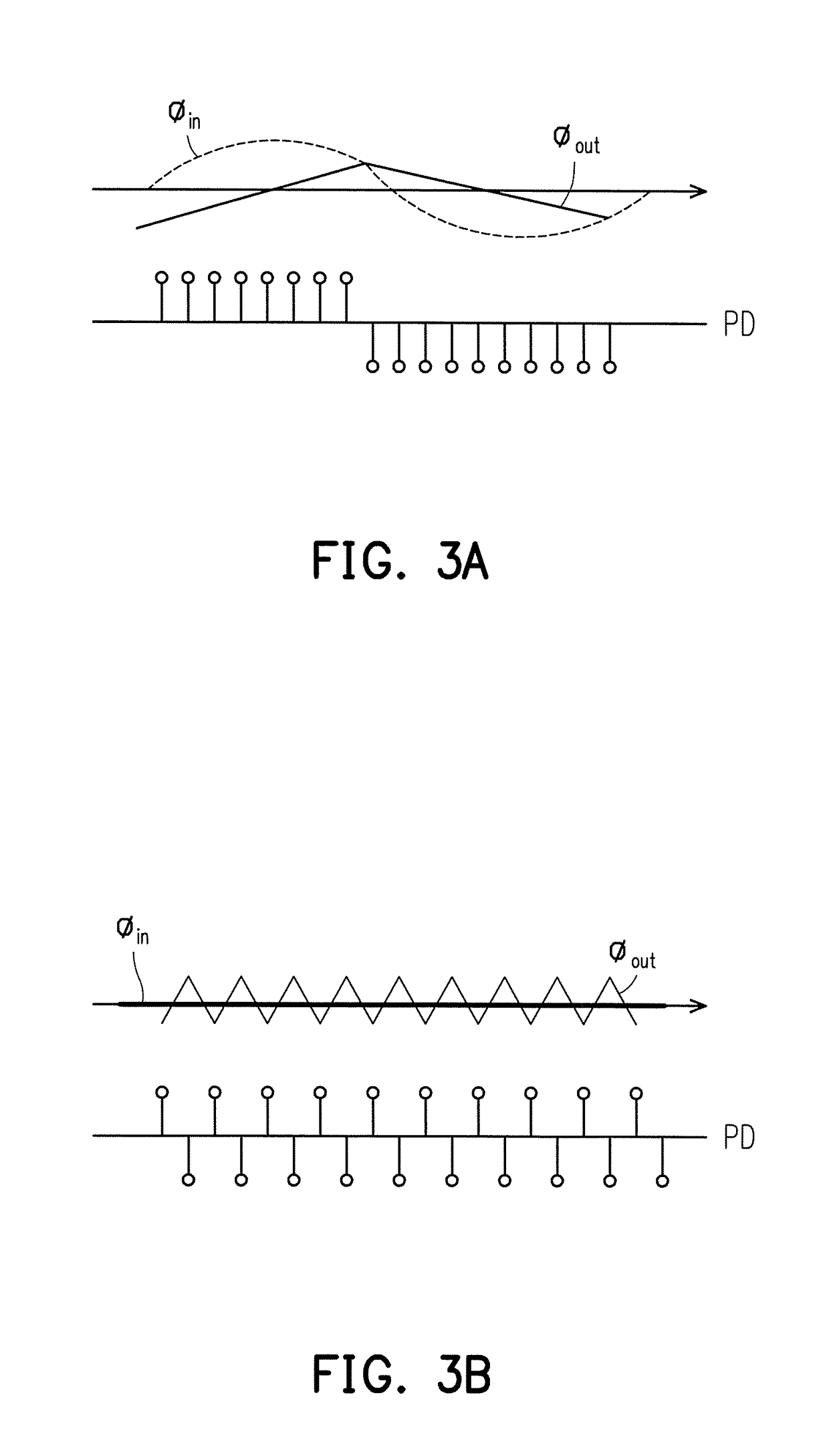

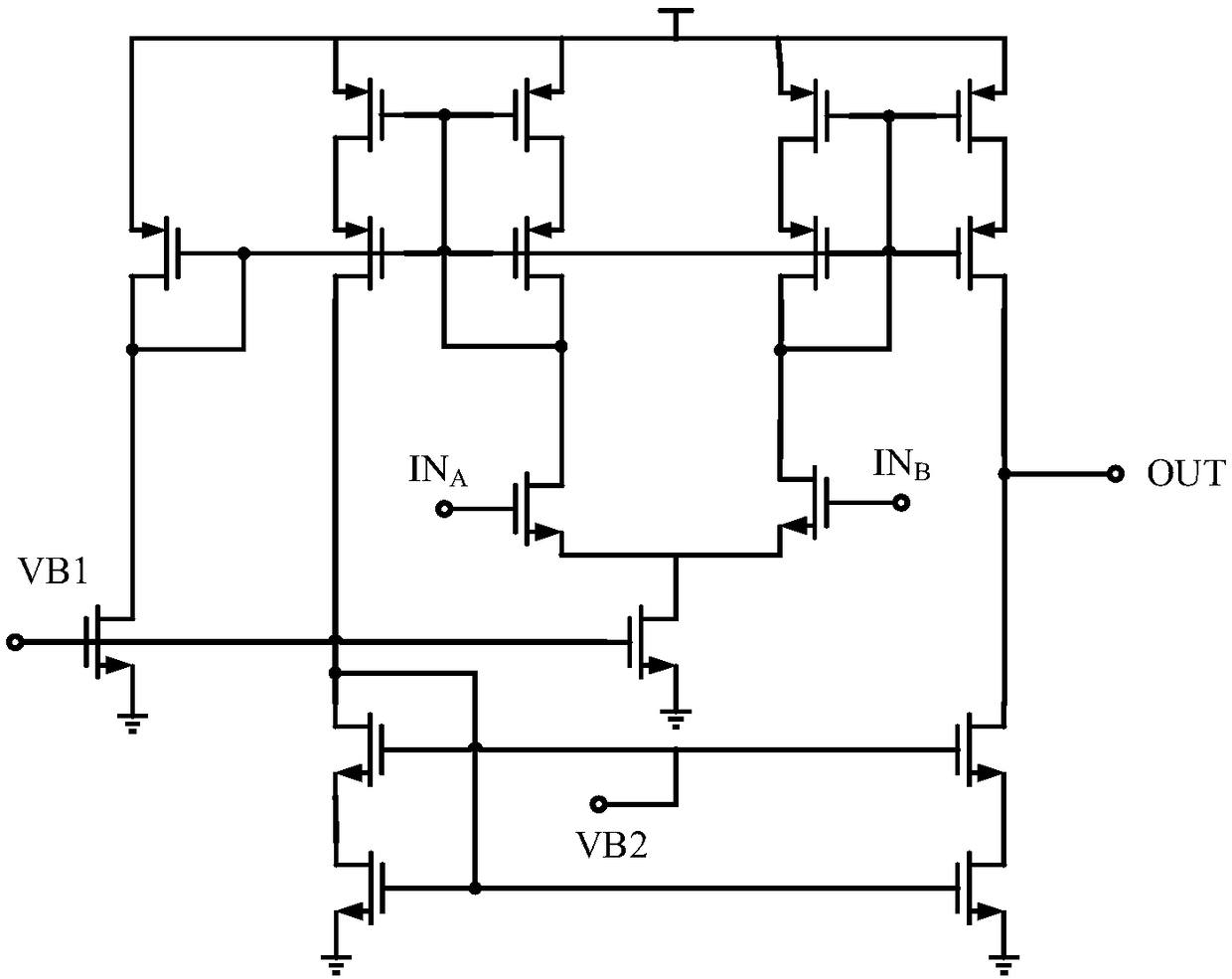

Clock and data recovery circuit with jitter tolerance enhancement

ActiveUS20180198597A1Improve toleranceSynchronisation error correctionPulse automatic controlBang bangLoop bandwidth

A clock and data recovery circuit with jitter tolerance enhancement is provided. The CDR circuit includes: a bang-bang phase detector, a digital filter, a digitally controlled oscillator, and an adaptive loop gain control circuit. The CDR circuit detects a loop bandwidth variation and adjusts the loop bandwidth of CDR circuit by adjusting proportional path and integral path gain factors of the digital filter of the CDR circuit. The loop gain controller uses two methods to adjust the loop gain in CDR circuit: bang-bang adjusting method and linear adjusting method.

Owner:NOVATEK MICROELECTRONICS CORP

Turbine speed control system and method

ActiveUS20060042262A1Improve system performanceMinimizing system weightWind motor controlEfficient propulsion technologiesBang bangControl system

One embodiment of the invention provides a turbine control system that adjusts the control thresholds of two-position valves, which provide propellant to the turbine, based on turbine load so as to compensate for increased turbine speed overshoot at low load and the increased turbine speed undershoot at high load. These two-position on-off modulated valves are used in a bang-bang (fully open or fully closed) regulation scheme to eliminate or minimize speed droop by using variable speed bounds implemented as a function of load.

Owner:HONEYWELL INT INC

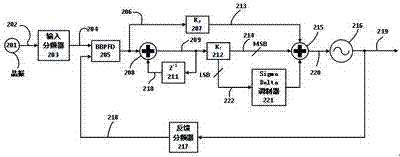

Method for quick locking of Bang-Bang digital phase-locked loop

ActiveCN104753525AAdjust the step size to decreaseHigh locking precisionPulse automatic controlBang bangPhase frequency detector

The present invention relates to a method for quick locking of a Bang-Bang digital phase-locked loop. The digital phase-locked loop comprises a quick locking controller, a proportion passageway, an integration passageway and an optional Sigma-Delta modulator for enhancing locking precision. Through the adoption of the method of the patent, the contradiction between high locking precision and long locking time of the Bang-Bang digital phase-locked loop is eliminated. Under the condition of not sacrificing the locking precision, the locking speed is greatly increased and the locking time is decreased. The quick locking of the Bang-Bang digital phase-locked loop is achieved in the frequency locking mode of multistage variable step length of automatically regulating step length, the factor of the proportion passageway and the factor of the integration passageway through the adoption of information, outputted by a BBPFD (Bang-Bang Phase Frequency Detector), for reflecting phase lead or lag between a reference clock and a feedback clock. The method of the patent can be realized through the adoption of software or hardware.

Owner:成都华大九天科技有限公司

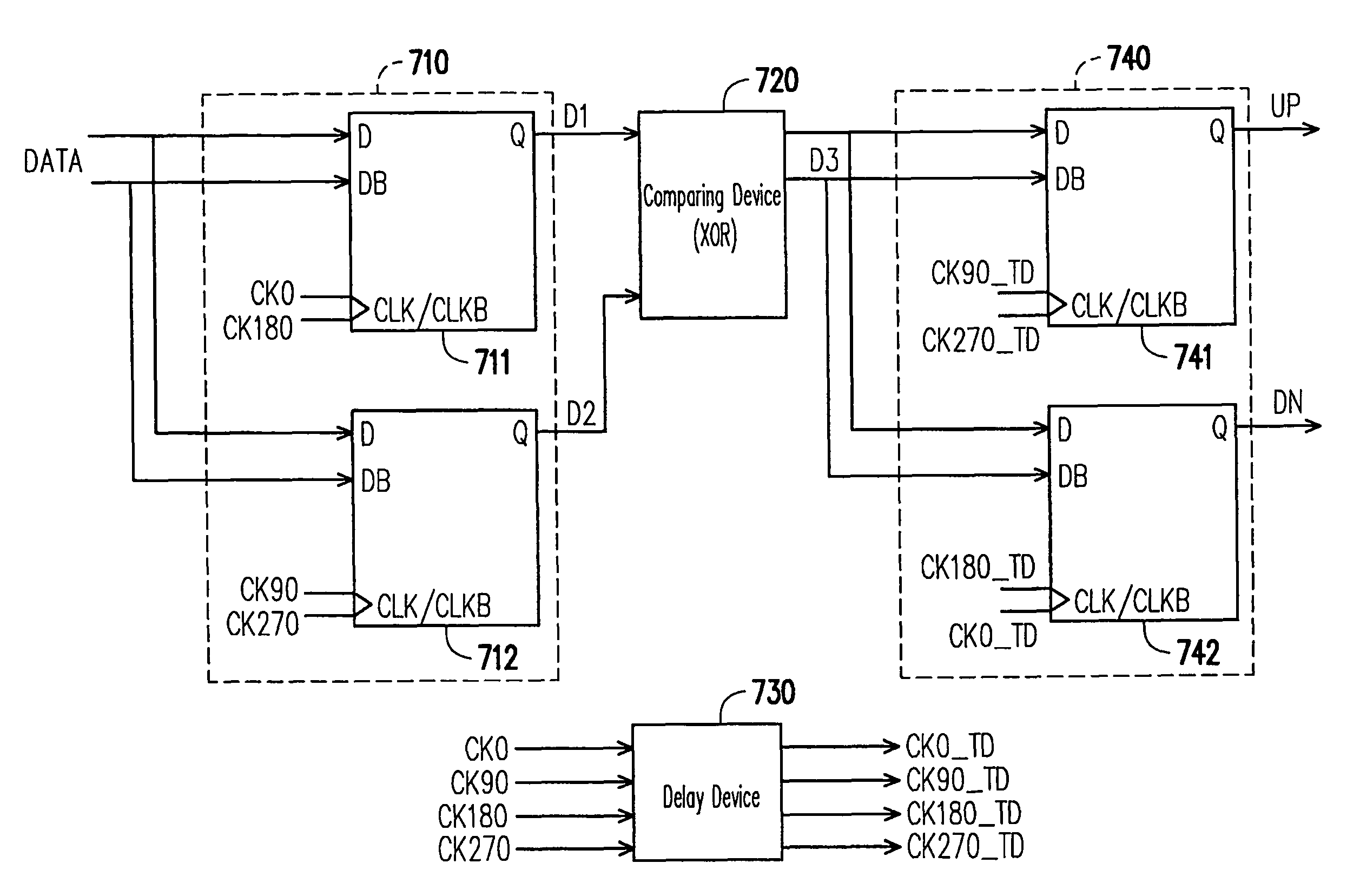

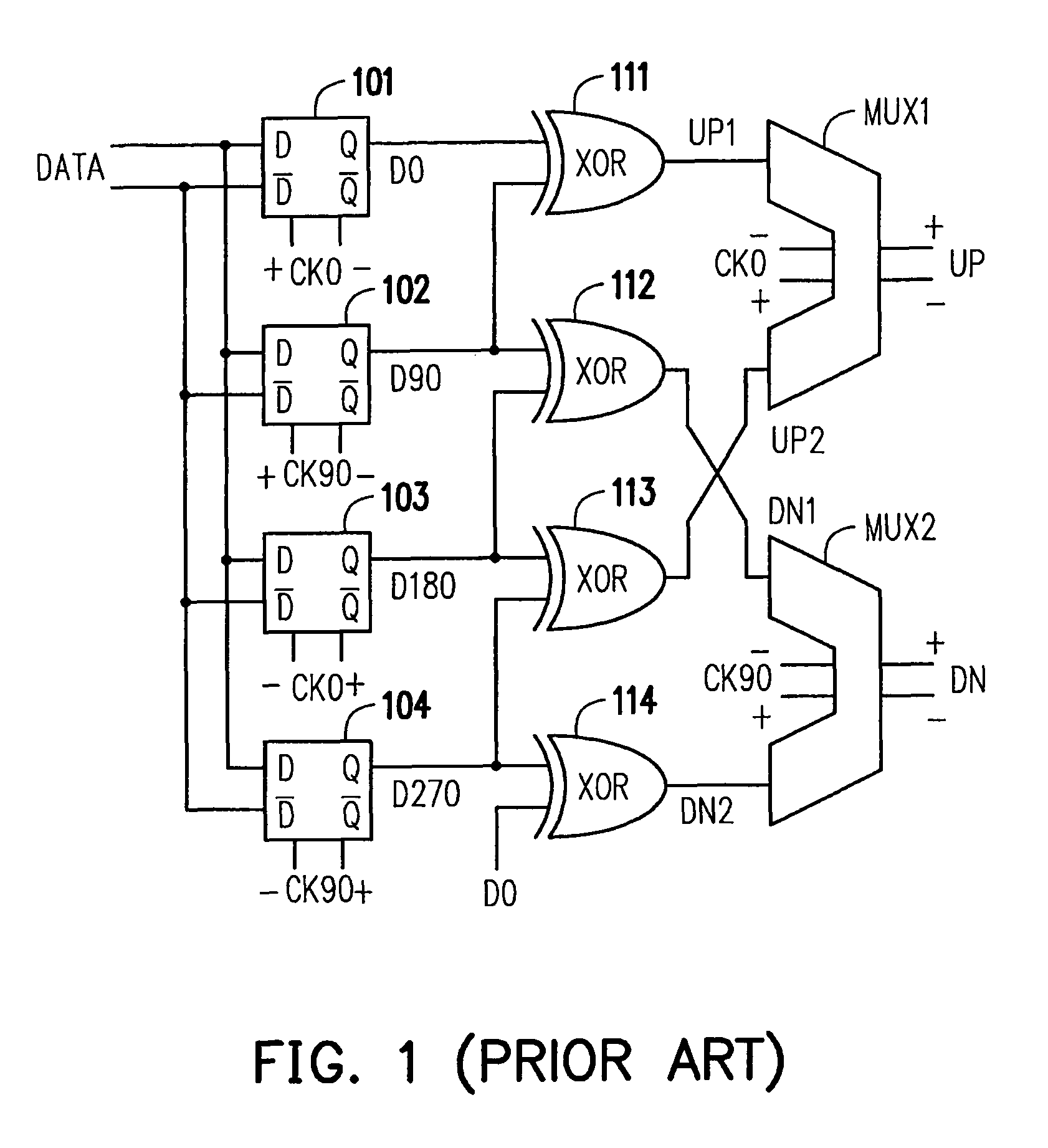

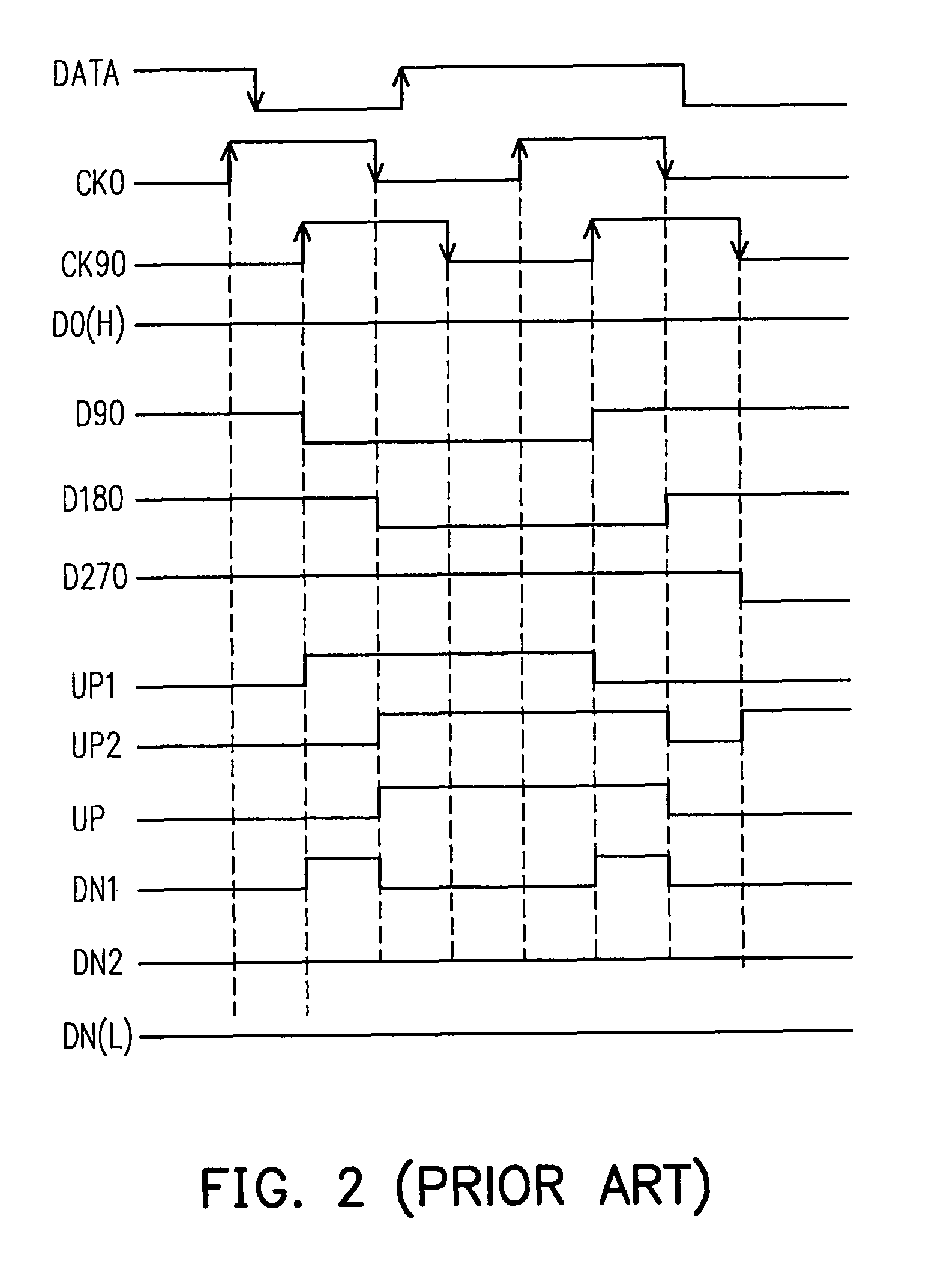

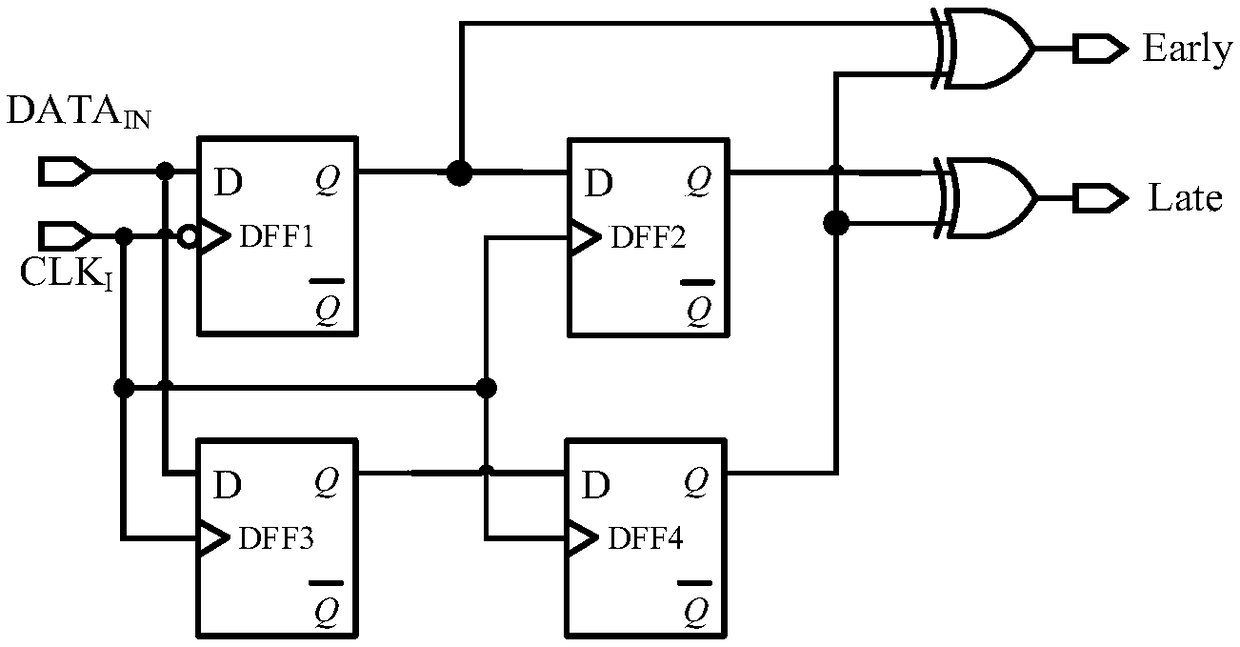

Phase detector for half-rate bang-bang cdr circuit

InactiveUS20090256629A1Avoid jitterAvoid failurePulse automatic controlVoltage-current phase anglePhase detectorBang bang

A phase detector, including a sampling device, a comparing device, and an output device, is provided. The sampling device samples a data signal according to a plurality of clock signals, so as to provide a plurality of corresponding sampling values. The clock signals have the same frequency and different phases. The comparing device is coupled to the sampling device, and provides a plurality of corresponding comparison values according to comparison results of each of the sampling values comparing with the next sampling value. The output device is coupled to the comparing device, and outputs two of the comparison values in response to edges of the clock signals. The two outputted comparison values serve as a first instruction signal and a second instruction signal respectively. The first and the second instruction signals are referred to in controlling the frequency and the phase of the foregoing clock signals.

Owner:FARADAY TECH CORP

Fast-locking bang-bang PLL with low ouput jitter

ActiveUS8203369B2Reduce output jitterFast locking timePulse automatic controlPhase correctionBang bang

The present invention relates to a gigitaol phaselocked loop DPLL (300, 400) having a phase-to-digital P2D (60) with an enhanced bang-bang phase detector BBPD. Such a P2D (60) comprises a BBPD (62), an additional digital circuit (200) including a sign detector (210), a counter (220) and a mapping function (230), and a summer block (64). During the locking process, the BBPD (62) may-output a repeating value, namely a string of data bits of same polarity value either “+1” or “−1”. The polarity sign is detected by the sign detector (210), and the data string length is determined by the counter (220) that is reset to zero whenever the BBPD output changes sign. The mapping function (230) is configured for mapping the data string length in input to the phase correction level in output Its output is added to that of the BBPD (62) through the summer block (64), such that the phase correction level is increased to enhance the locking process whenever a data string is detected.

Owner:NXP BV

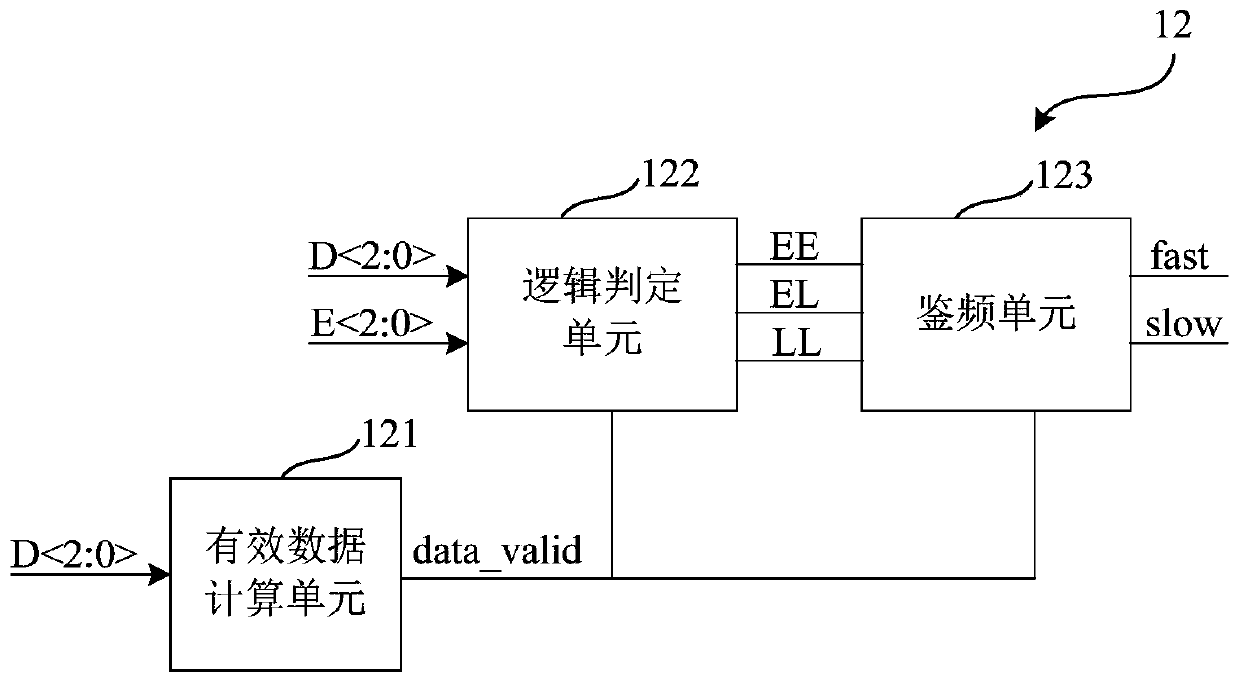

Frequency discriminator, PAM4 clock data frequency locking method, recovery method and circuit

ActiveCN109787615AReduce frequencyLower requirementPulse automatic controlDiscriminatorRecovery method

The invention provides a frequency discriminator, a PAM4 clock data frequency locking method, a PAM4 clock data frequency recovery method and a PAM4 clock data frequency locking circuit. The method comprises the following steps: respectively sampling data and edges of an input signal by adopting a data and edge sampling clock; Obtaining a logic result of the speed of the sampling clock according to the sampling data of at least two adjacent clock periods and the sampling edge between the two sampling data; Determining the frequency of the sampling clock relative to the input signal based on the logic results of at least three adjacent clock periods, and enabling the frequency of the sampling clock to be equal to that of the input signal; based on the Bang-Bang logics, adjusting the phase of the sampling clock, so that the sampling edge of the sampling clock is respectively positioned in the data of the input signal and the middle area of the edge. The non-reference clock frequency locking and phase locking technology is adopted, so that the frequency and the phase can be accurately locked; The requirement for the frequency difference between the starting frequency of the voltage-controlled oscillator and an input signal is low, the clock data recovery function of the large-range input data rate can be supported, the application range is wide, and the stability is high.

Owner:PHOTONIC TECH SHANGHAI CO LTD

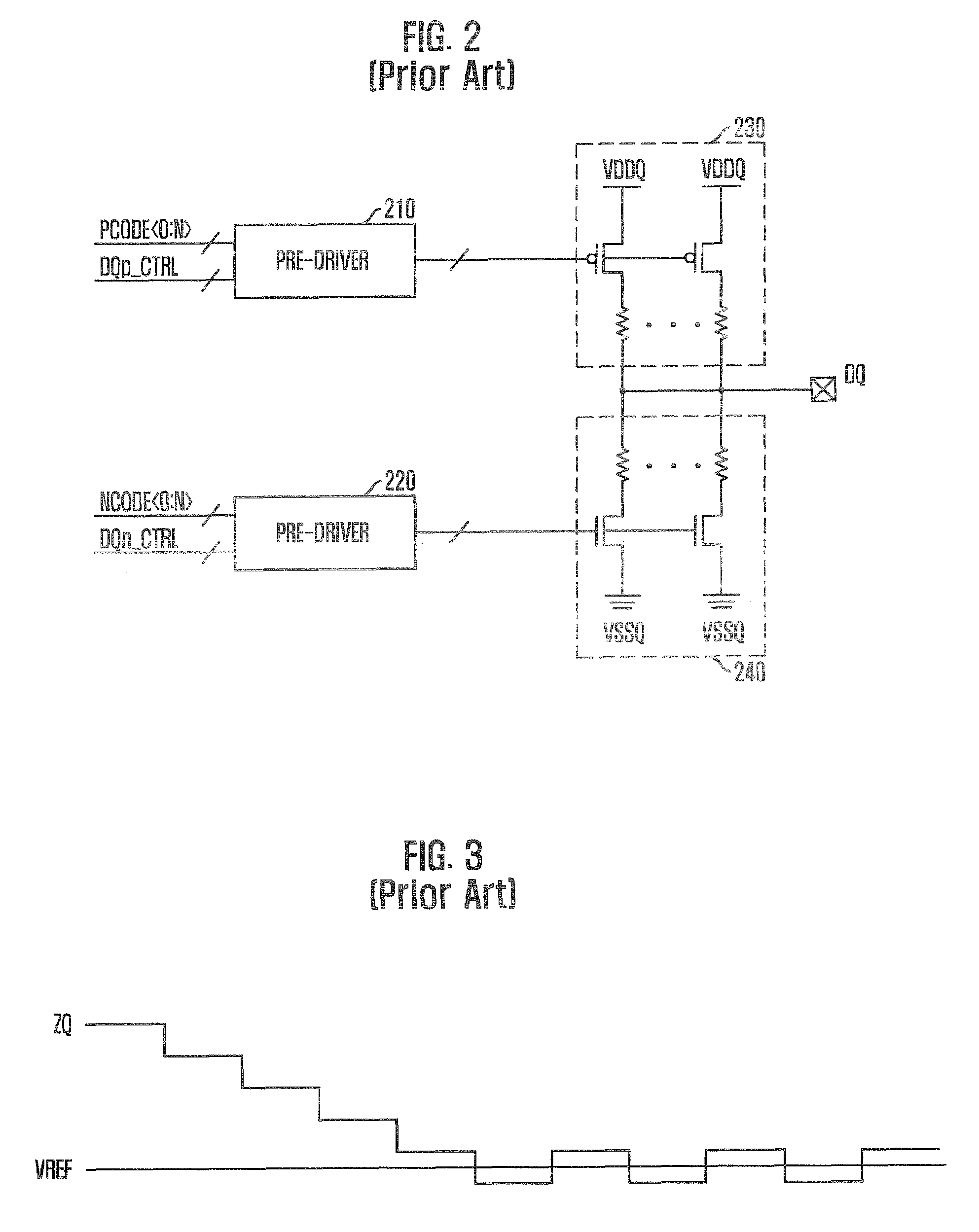

Circuit and method for preventing bang-bang error, calibration circuit including the circuit, and analog-to-digital converter including the circuit

ActiveUS20090146694A1Avoid mistakesInput/output impedence modificationElectric signal transmission systemsBang bangControl signal

A circuit including a comparing unit for comparing a target voltage with a stepwise-varying tracking voltage, a counting unit for counting a code according to the comparison result of the comparing unit and a control signal generating unit for generating a signal for controlling a counting operation of the counting unit.

Owner:SK HYNIX INC

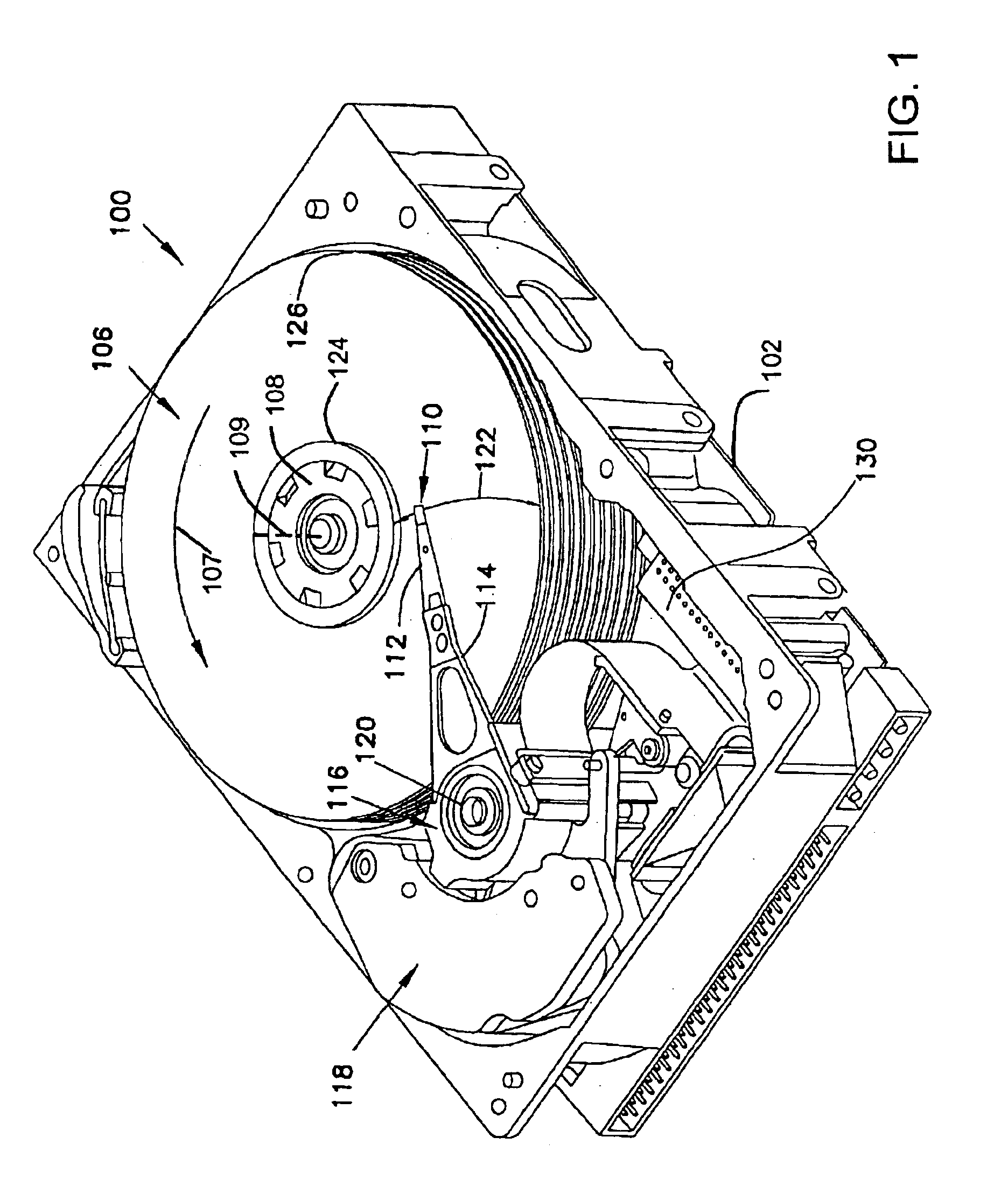

Cosine bang-bang seek control for a voice coil of a disc drive

InactiveUS6870342B2Extension of timeMinimizing affectionDC motor speed/torque controlDynamo-electric converter controlController architectureBang bang

A method and apparatus for improving the timing of a seek operation through the removal of the coast phase of conventional model reference waveform type control systems are provided. With the apparatus and method, the coast phase is removed such that an acceleration phase is immediately followed by a deceleration phase in the waveform of the control system. A (1-Cos) / 2 shaping is applied to the resulting square waveform so that the affects of high frequency harmonics are minimized. The resulting “cosine bang-bang” waveform provides a reduction in seek time when compared to conventional model reference waveform based control. In addition to the above, the present invention provides a controller architecture in which the cosine bang-bang waveform may be applied to a voice coil motor to control the actuation of the read / write heads of a disc drive. With this controller architecture, the low-pass filters required in a model reference waveform approach are eliminated in favor of (1-Cos) / 2 shaping of the square waveform of the present invention. As a result, the increased time requirement due to low pass filtering is eliminated in the controller of the present invention.

Owner:SEAGATE TECH LLC

Phase detector for half-rate bang-bang CDR circuit

InactiveUS7795926B2Effectively eliminating generationAvoid flashPulse automatic controlVoltage-current phase anglePhase detectorBang bang

A phase detector, including a sampling device, a comparing device, and an output device, is provided. The sampling device samples a data signal according to a plurality of clock signals, so as to provide a plurality of corresponding sampling values. The clock signals have the same frequency and different phases. The comparing device is coupled to the sampling device, and provides a plurality of corresponding comparison values according to comparison results of each of the sampling values comparing with the next sampling value. The output device is coupled to the comparing device, and outputs two of the comparison values in response to edges of the clock signals. The two outputted comparison values serve as a first instruction signal and a second instruction signal respectively. The first and the second instruction signals are referred to in controlling the frequency and the phase of the foregoing clock signals.

Owner:FARADAY TECH CORP

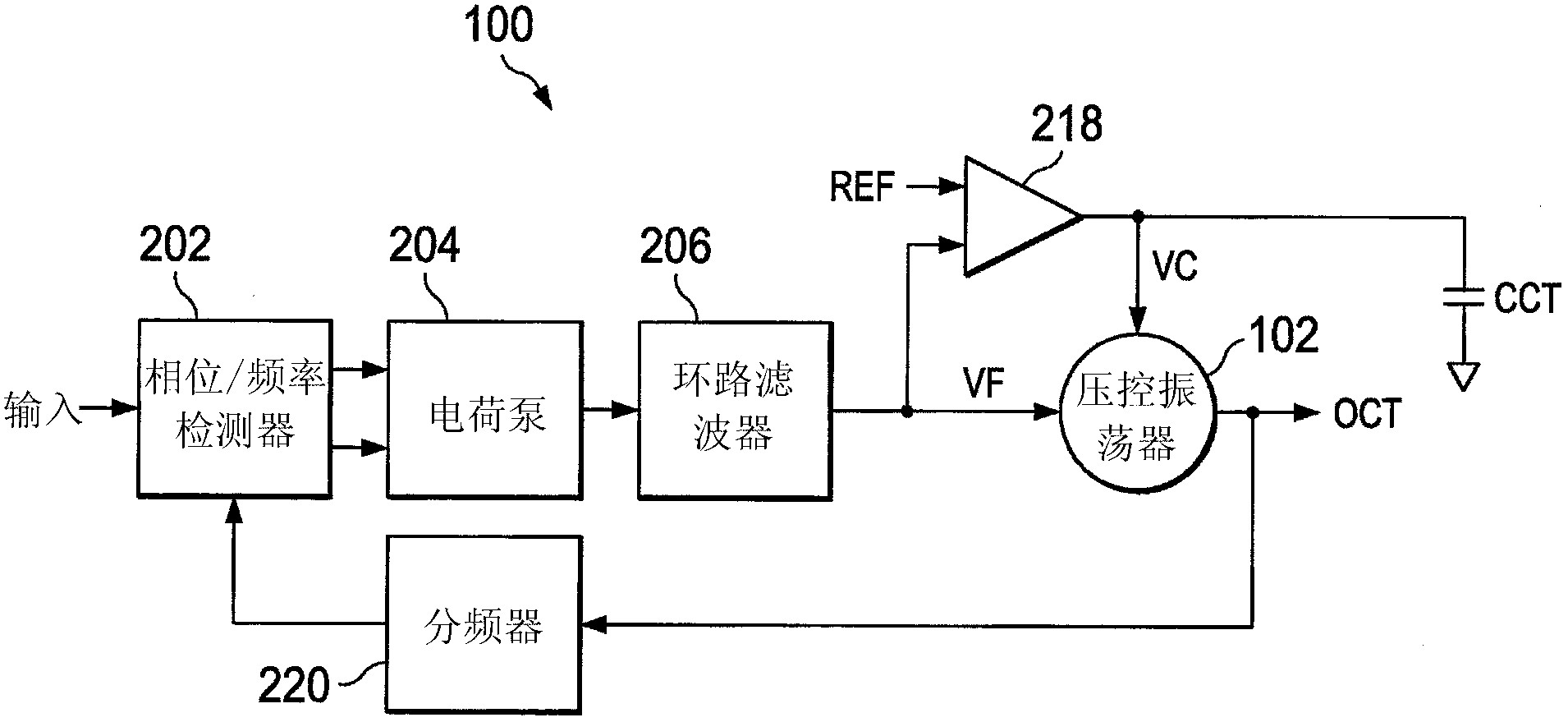

Phase Locked Loop (PLL) With Analog And Digital Feedback Controls

A phase locked loop (PLL 200), such as employed in a synthesizer, has two continuous (analog) control loops and one digital on-off ('bang-bang') control loop. The control loop of PLL 200 provides additional discrete time controls for a voltage controlled oscillator (VCO 208). The control loop measures the coarse voltage (VC) and input signal (IN) to adjust the switched capacitor array (214) to help decrease settling time. Precision lock detector (222) monitors input phase error, while narrow window circuit (226) and wide window circuit (228) specify a voltage window. Based on lock detection from the precision lock detector (222) and a voltage window from the narrow and wide window circuits (226, 228), a window adjust circuit 224 sets threshold voltages VH, VL for the on-off (bang-bang) controller 230.

Owner:TEXAS INSTR INC

Intelligent water temperature control system and method

InactiveCN105138040AReduce consumptionQuick responseAuxillary controllers with auxillary heating devicesTemperature controlBang bang

The invention discloses an intelligent water temperature control system, which comprises a temperature measurement module, an infrared remote control module, a sound production module, a display module and a single chip microcomputer, wherein the temperature measurement module is used for monitoring water temperature in real time and acquiring real-time water temperature Tg; the infrared remote control module is used for setting target water temperature Tw which needs to arrive at in a remote control mode; the sound production module is used for producing a sound for prompting when the target water temperature Tw is set successfully; the display module is used for displaying the real-time water temperature Tg and the target water temperature Tw; and the single chip microcomputer is used for acquiring a water temperature difference value e=Tw-Tg and a difference value change rate ec=de / dt according to the real-time water temperature Tg and the target water temperature Tw, comparing an absolute value |e| for the water temperature difference value and a preset threshold e0, adopting a Bang-Bang variable structure control method to carry out control heating on a heating module via a temperature control module when |e|> / =e0, and adopting an adaptive PID control-based PWM control method to carry out control heating on the heating module via the temperature control module when |e|<e0 to enable the water temperature to reach the target water temperature Tw finally. The invention also discloses an intelligent water temperature control method. Accuracy and stability are improved.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

Circuit and method for preventing bang-bang error, calibration circuit including the circuit, and analog-to-digital converter including the circuit

ActiveUS7714763B2Input/output impedence modificationElectric signal transmission systemsBang bangControl signal

A circuit including a comparing unit for comparing a target voltage with a stepwise-varying tracking voltage, a counting unit for counting a code according to the comparison result of the comparing unit and a control signal generating unit for generating a signal for controlling a counting operation of the counting unit.

Owner:SK HYNIX INC

Device for adjusting an operating variable of an engine

InactiveUS20100121552A1Avoid putting excessive demand on the electric motorAvoid developmentAnalogue computers for vehiclesEngine controlBang bangActuator

This device serves to adjust at least one operating variable of an engine as a function of a setpoint. It comprises:calculation means for calculating an error obtained from the difference between a measurement of the variable and the setpoint;a command generator unit for responding to said error to generate a bang-bang type command for application to a slow actuator;an inhibit unit placed upstream from the command generator unit, suitable for inhibiting the error when it lies within a determined range;a quantizing unit for quantizing the duration of the bang-bang command; anda sender unit for sending the command to the slow actuator.

Owner:ARIANEGRP SAS

High-speed low-jitter frequency discrimination phase discriminator and clock data recovery circuit

ActiveCN109150171ALarge frequency assist capture rangeReduce jitterPulse automatic controlDiscriminatorPhase detector

The invention discloses a high-speed low-jitter frequency discrimination phase discriminator and a clock data recovery circuit. The frequency discrimination phase discriminator comprises a Q-channel Bang-Bang-type PD generating a Q-channel signal, an Alexander PD generating an I-channel signal and a tri-state Output FD; the Q-channel Bang-Bang-type PD includes DFF6, DFF7, and DFF8; the Alexander PD includes DFF1, DFF2, DFF3, DFF4, DFF5, XOR1, and XOR2, where DFF1, DFF3, and DFF5 constitute an I-channel Bang-Bang type PD; the three-state output FD includes Latch1, Latch2, and a three-state selector. The Alexander PD in the present invention is additionally provided with two DFFs and two XORs based on the Bang-Bang type PD. The FD consists of the two latches and the three-state selector. ThePFD of the present invention can perform the frequency acquisition function quickly in the frequency discrimination process, and the phase tracking process of the Alexander PD after the frequency lock.

Owner:NANJING UNIV OF POSTS & TELECOMM

Auxiliary supply for a switched-mode power supply controller using bang-bang regulation

A method in a switched-mode power supply (SMPS) and SMPS circuits are provided. The method and circuits use bang-bang regulation to provide for an auxiliary power supply that can be used to power a controller of the SMPS. The additional circuitry required to achieve the method and circuits is minimal and represents advantages over techniques that require an additional power supply or require an auxiliary winding in a transformer. The bang-bang regulation controls switch devices within the SMPS such that a normally-on switch device is enabled while a normally-off switch device is disabled for some period of time. During this period, current is supplied to the SMPS controller and an associated energy-storage device.

Owner:INFINEON TECH AUSTRIA AG

Fast-locking bang-bang pll with low ouput jitter

ActiveUS20110084741A1Improve performanceFast locking timePulse automatic controlPhase correctionBang bang

The present invention relates to a gigitaol phaselocked loop DPLL (300, 400) having a phase-to-digital P2D (60) with an enhanced bang-bang phase detector BBPD. Such a P2D (60) comprises a BBPD (62), an additional digital circuit (200) including a sign detector (210), a counter (220) and a mapping function (230), and a summer block (64). During the locking process, the BBPD (62) may-output a repeating value, namely a string of data bits of same polarity value either “+1” or “−1”. The polarity sign is detected by the sign detector (210), and the data string length is determined by the counter (220) that is reset to zero whenever the BBPD output changes sign. The mapping function (230) is configured for mapping the data string length in input to the phase correction level in output Its output is added to that of the BBPD (62) through the summer block (64), such that the phase correction level is increased to enhance the locking process whenever a data string is detected.

Owner:NXP BV

System And Method For Hybrid Control Of Reduced Pressures Delivered To A Tissue Site

Owner:3M INNOVATIVE PROPERTIES CO

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com