Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

167results about How to "Suppression offset" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

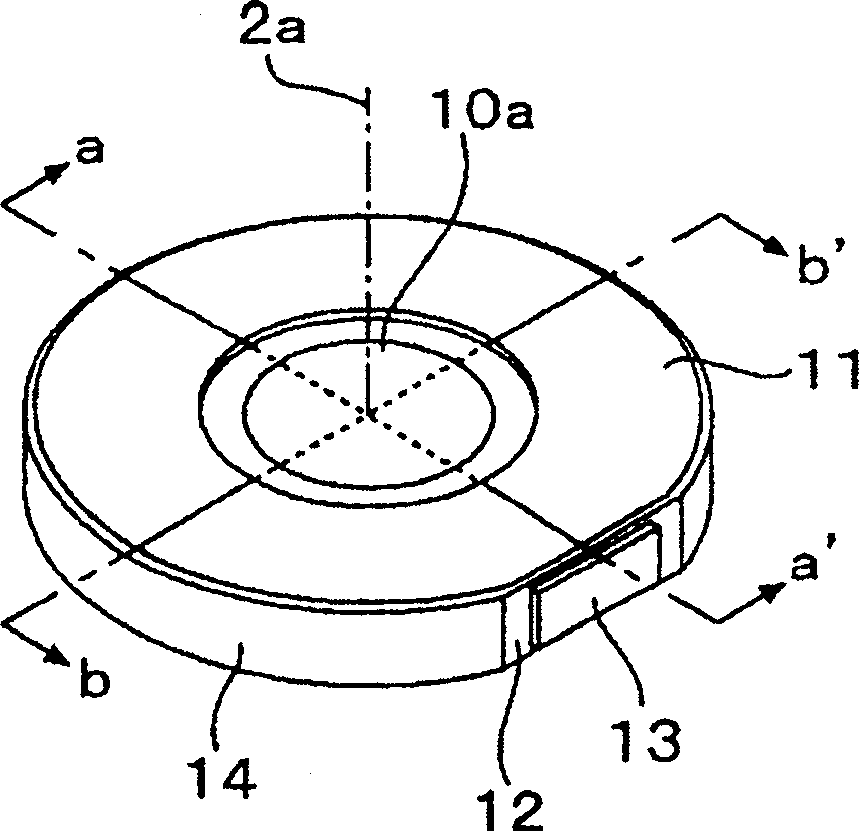

Lens device

ActiveCN1808201AEasily and reliably provideSuppression of optical axis deviationMountingsOptical axisEngineering

Owner:MAXELL HLDG LTD

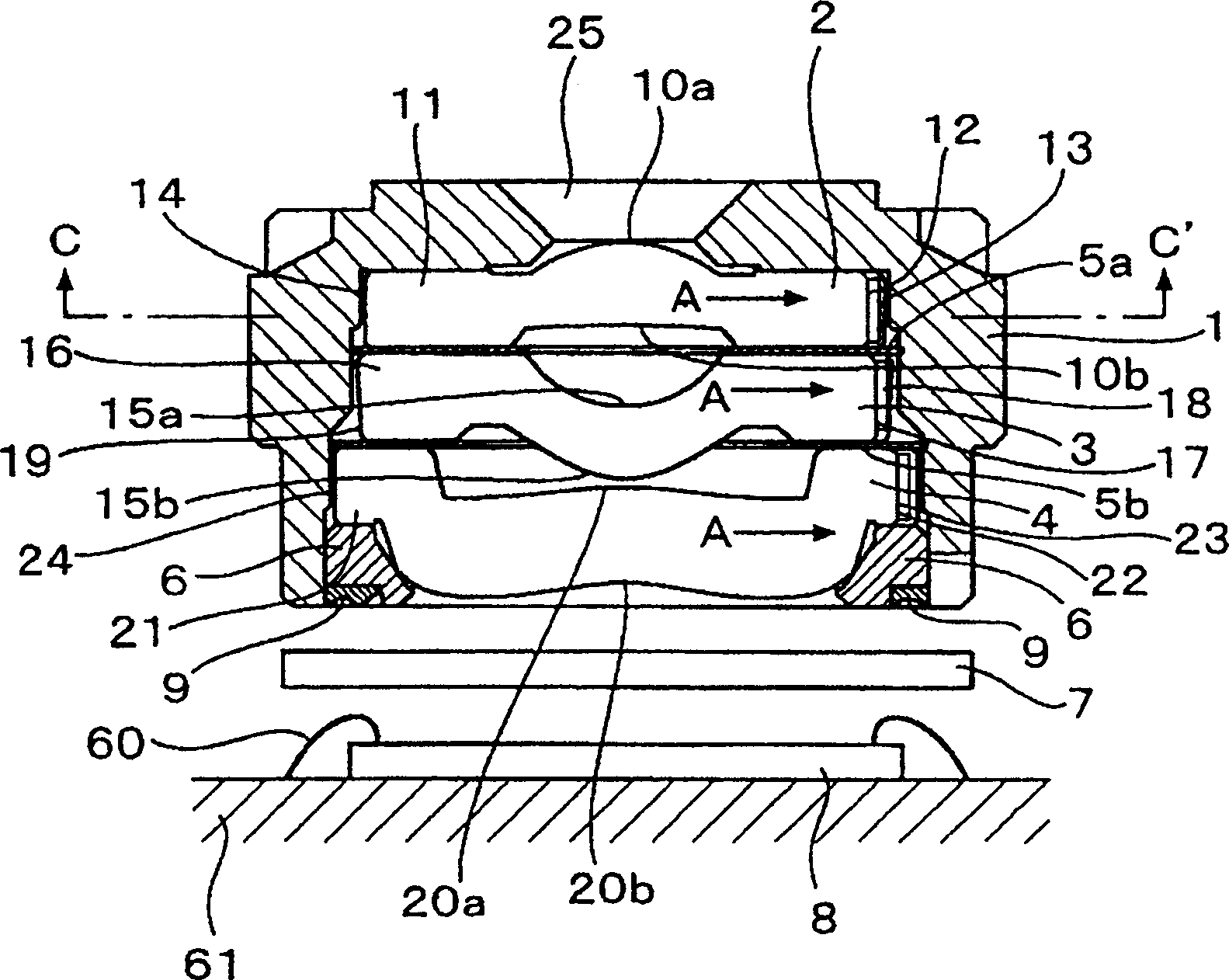

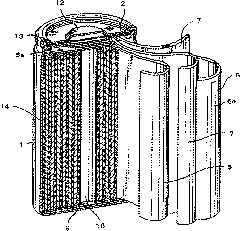

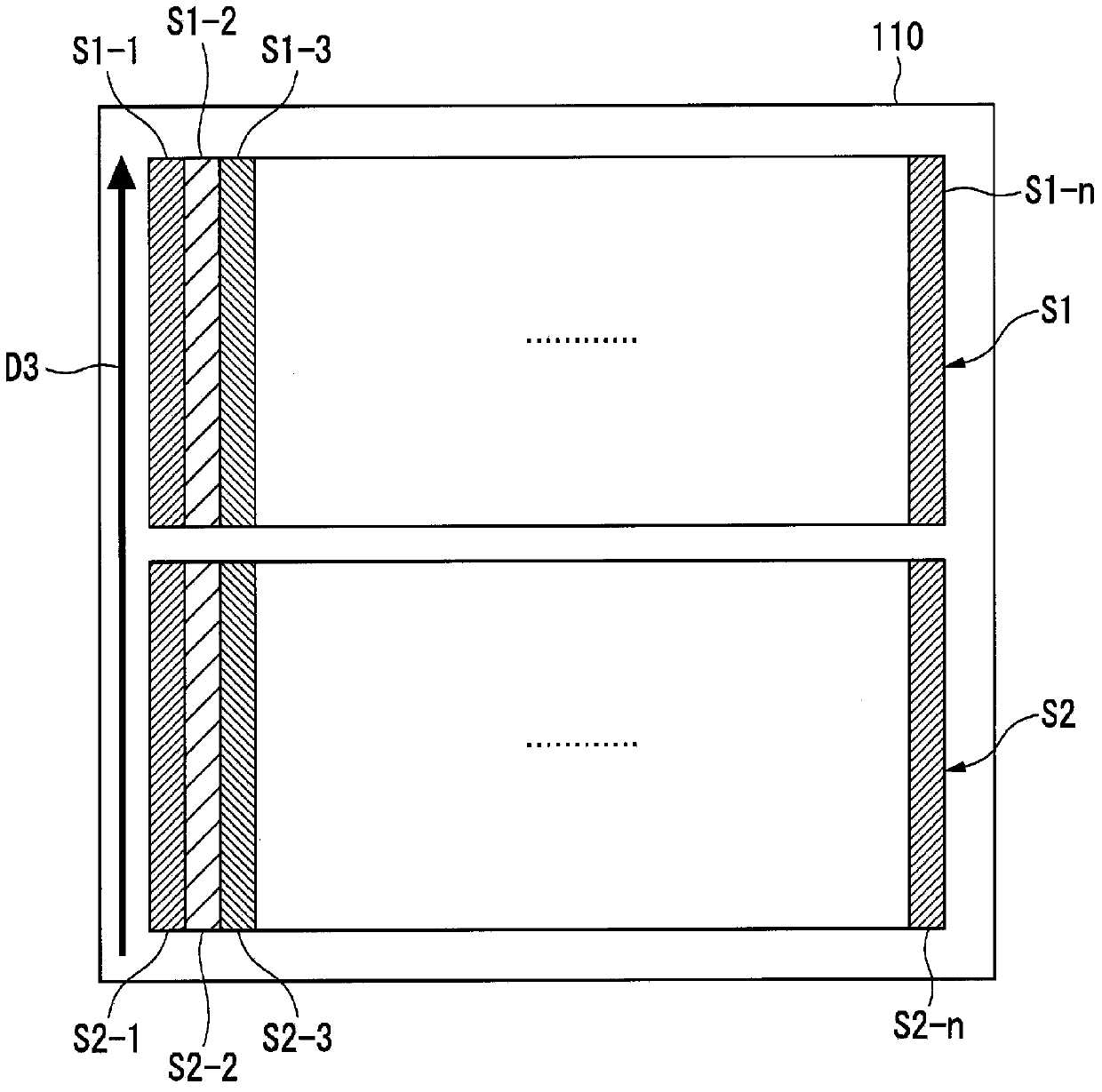

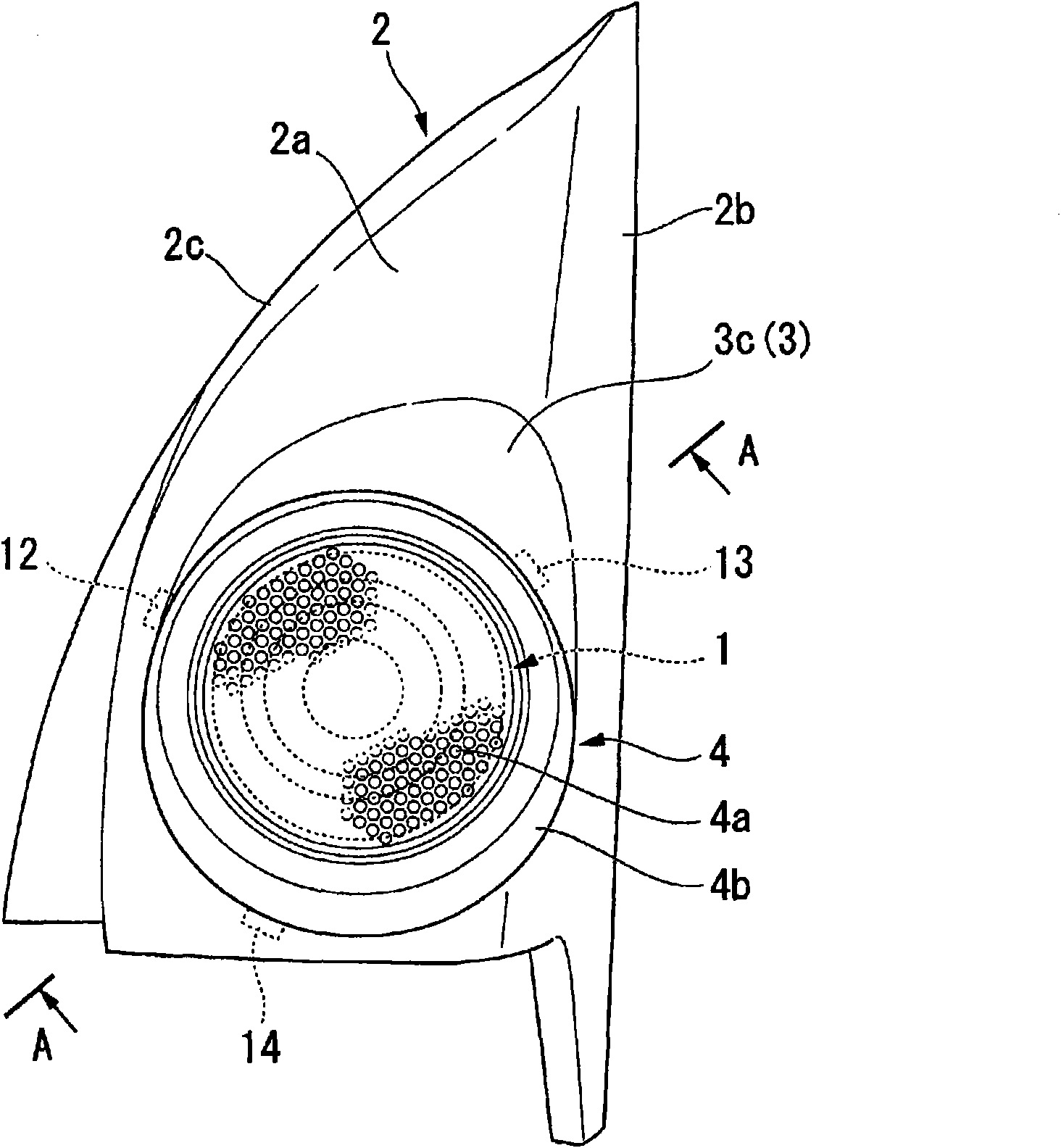

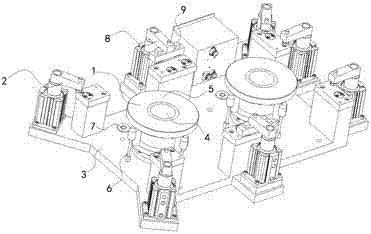

Battery module and its manufacturing method

InactiveCN101180749AImprove stabilityPromote exchangeCell component detailsElectrical and Electronics engineeringEngineering

In a battery module of the invention, a first battery row and a second battery row have the same number of cylindrical batteries (2) arranged side by side, and both ends in the battery axis direction of each of the battery rows are held by holding frames (3). Each holding frame (3) is formed in a rectangular solid where an inner frame (4) and two outer frames (7, 8) are separably connected to each other. In each holding frame (3), semicircular arc-shaped cutout-like holding receiving sections (4a, 7b, 8b) of the same number as the number of the batteries in the battery rows are formed in bothsides of the inner frame (4) and in those sides of the two outer frames (7, 8) which face the inner frame (4), and half sections of the cylindrical batteries (2) are fitted in the holding receiving sections (4a, 7b, 8b). Two adjacent cylindrical batteries (2) are electrically connected via an inter-battery connection plate (9).

Owner:PANASONIC CORP

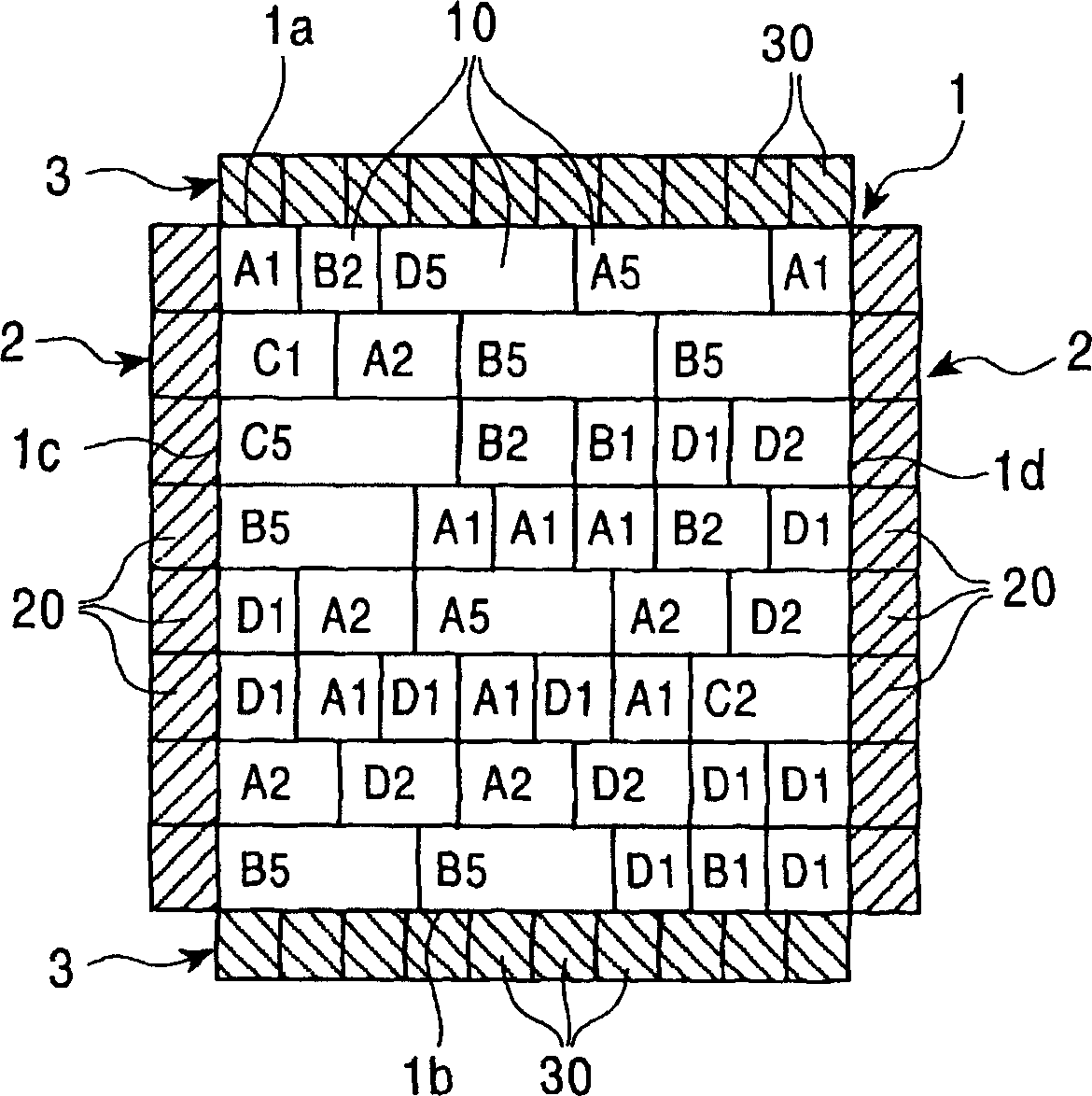

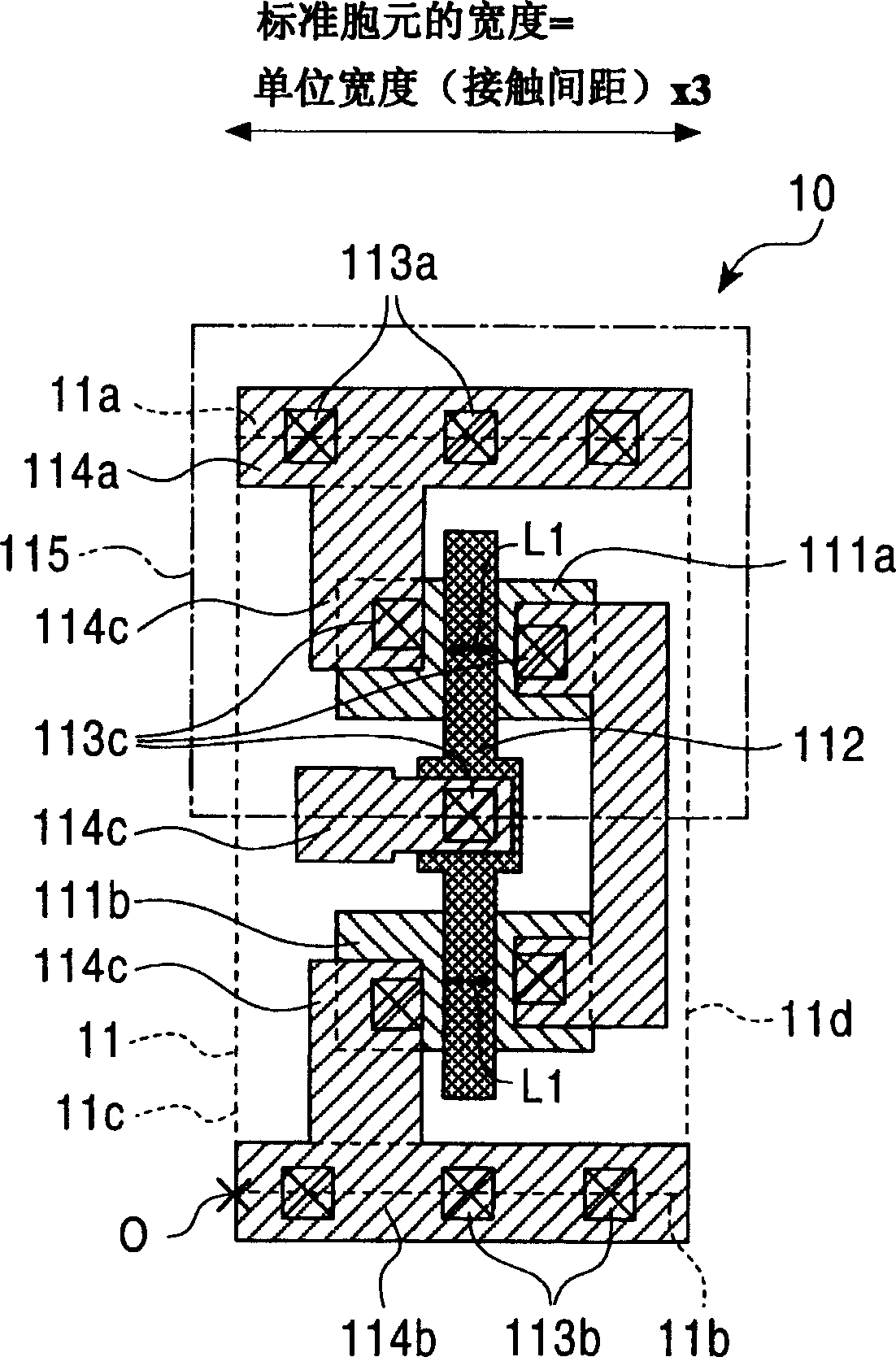

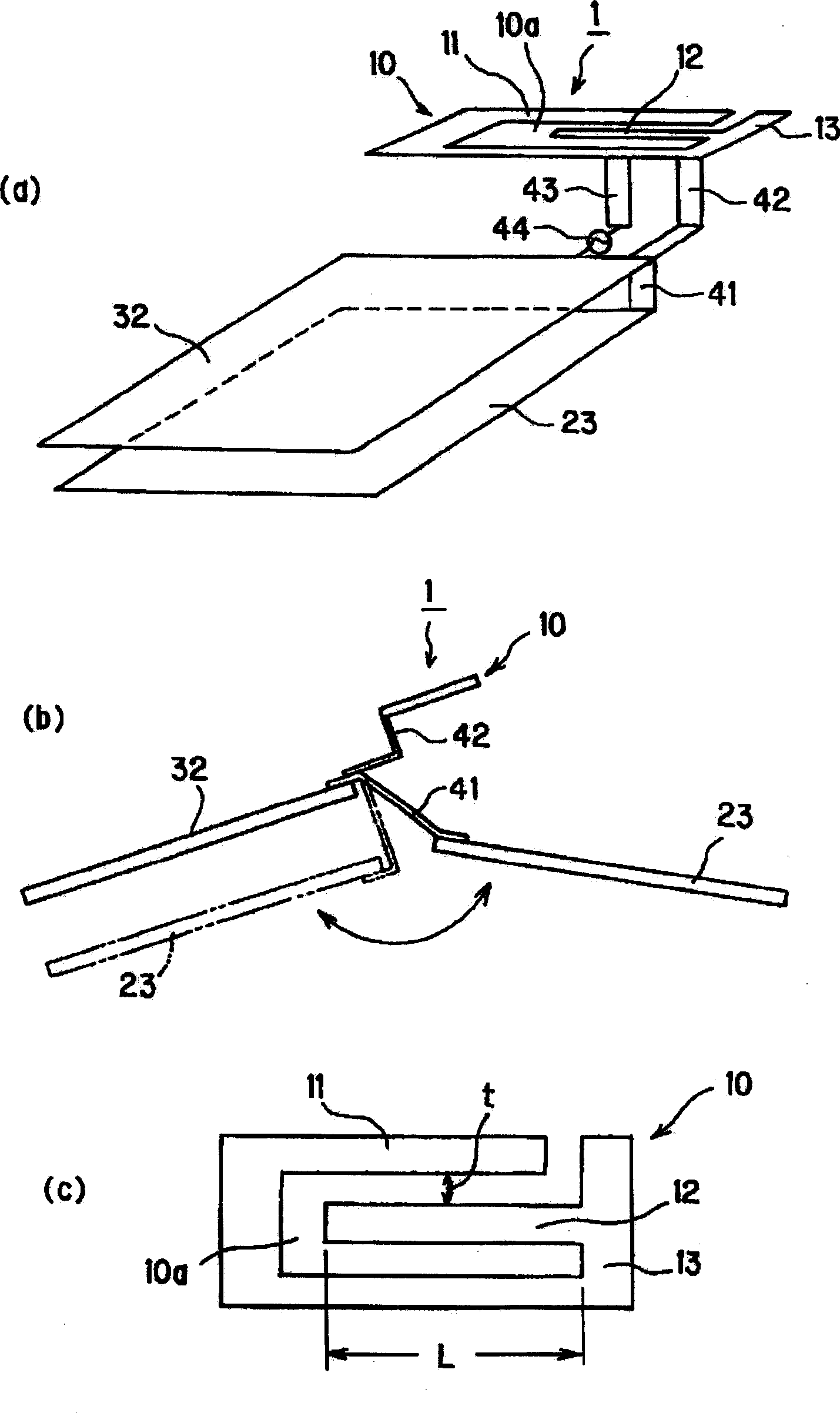

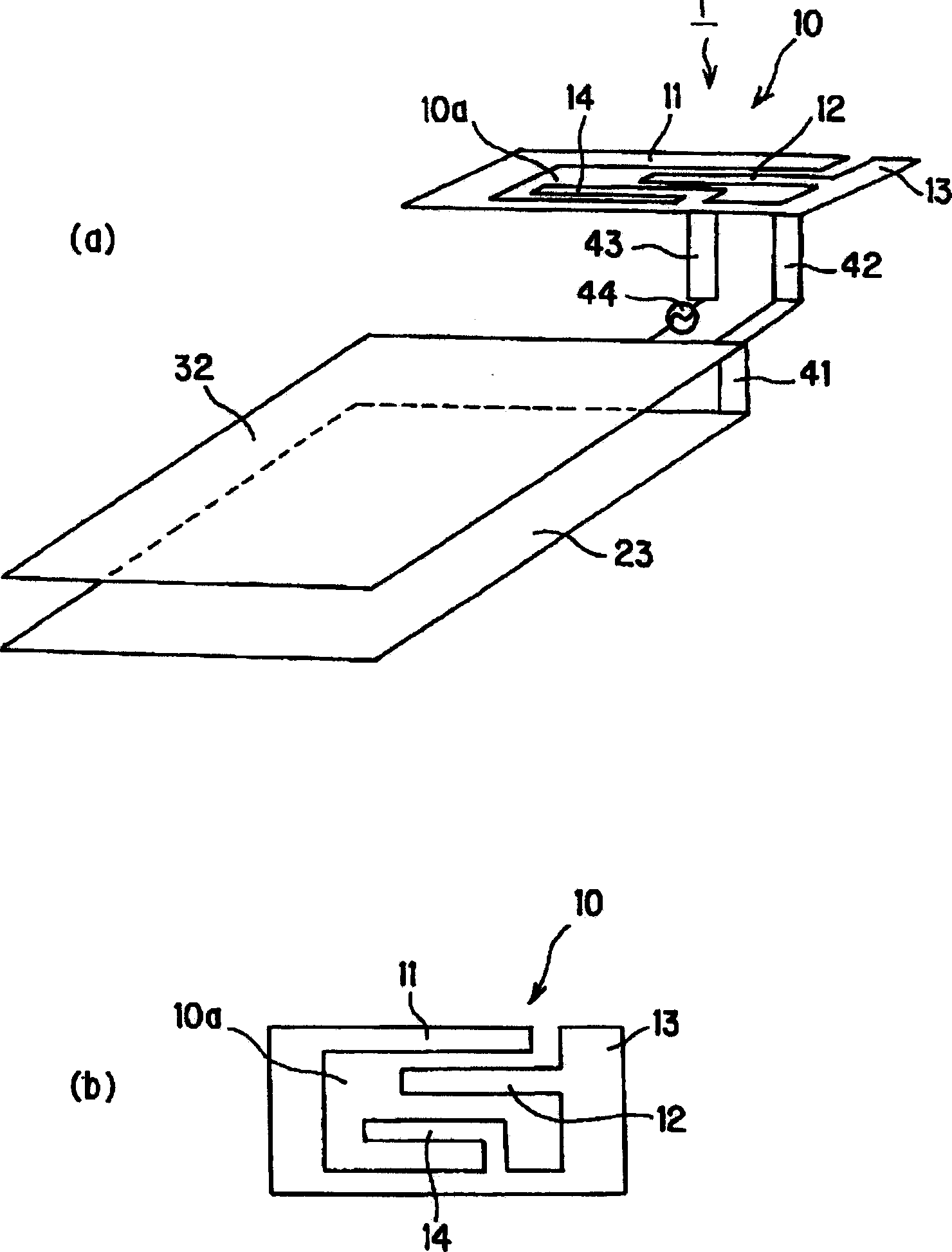

Layout method of semiconductor integrated circuit, layout structure thereof, and photomask for forming the layout structure

InactiveCN1585110AReduce size offsetSize shift improvementSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A plurality of standard cells 10 are arranged to form a channel-less standard cell array 1 , which has vertical and horizontal sides. A plurality of first proximity dummy cells 20 are arranged along each of the vertical sides of the standard cell array to form a first proximity dummy bands 20 such that the upper and lower sides of the first proximity dummy cells are in contact with each other and such that the left or right side of each of the first proximity dummy cells is in contact with the vertical side of the standard cell array 1 . Furthermore, a plurality of second proximity dummy bands are arranged along each of the horizontal sides of the standard cell array to form a second proximity dummy bands such that the upper or lower side of each of the second proximity dummy cells is in contact with the horizontal side of the standard cell 1.

Owner:KAWASAKI MICROELECTRONICS

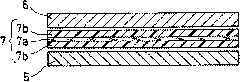

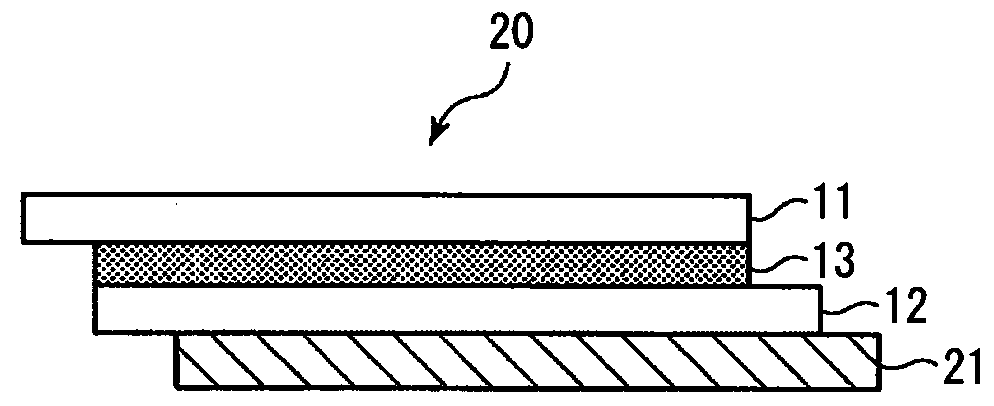

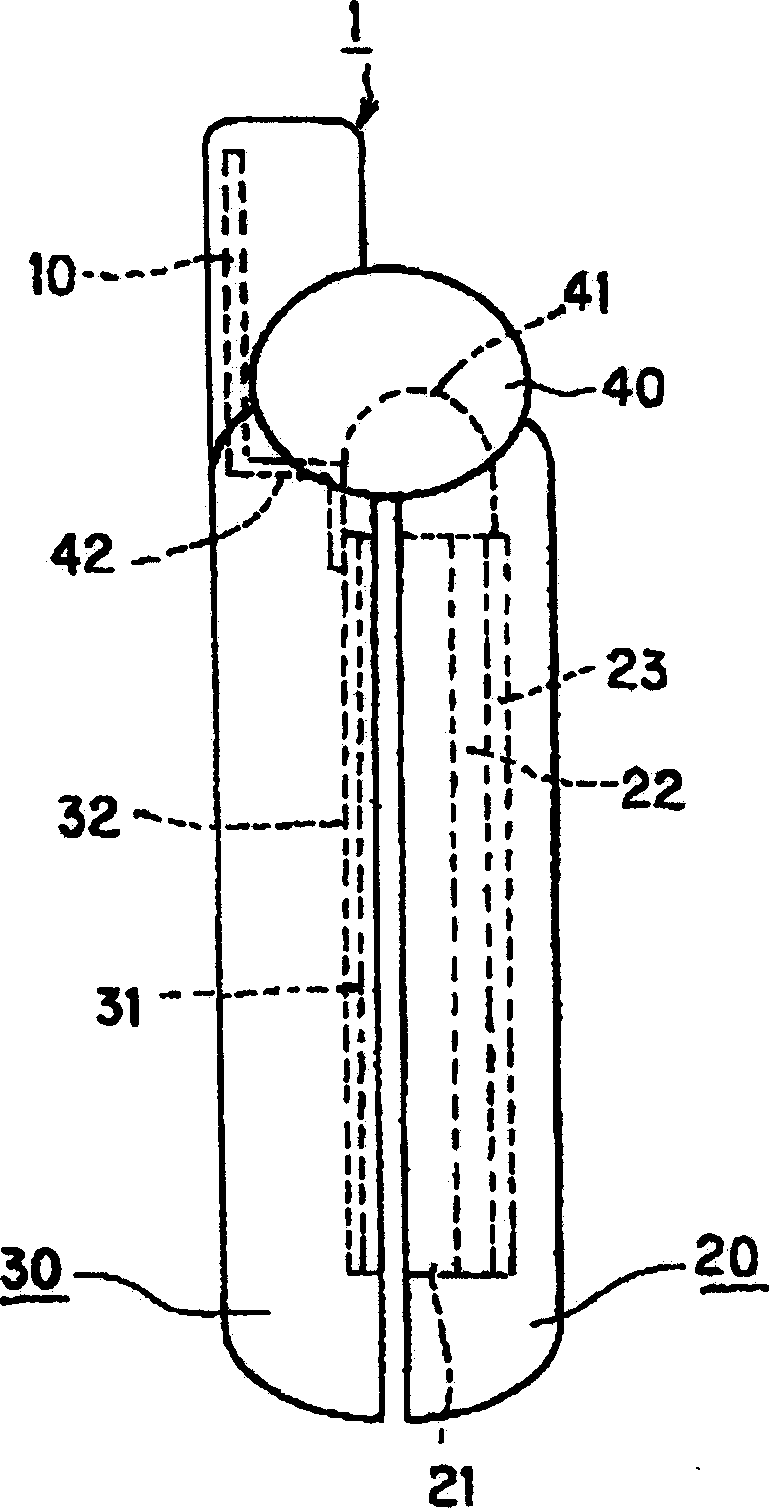

Nonaqueous electrolyte secondary battery and method for manufacturing same

InactiveCN102197511ASuppression offsetAvoid damageFinal product manufactureSecondary cellsHeat deflection temperaturePolyolefin

Disclosed is a nonaqueous electrolyte secondary battery which comprises: an electrode group in which a positive electrode that contains a long positive electrode collector and a positive electrode active material layer attached to the surface of the positive electrode collector, a negative electrode that contains a long negative electrode collector and a negative electrode active material layer attached to the surface of the negative electrode collector, and a separator for separating the positive electrode and the negative electrode from each other are wound up in a spiral form; and a nonaqueous electrolyte. The separator comprises a heat-resistant porous membrane that contains a heat-resistant resin, a first porous polyolefin membrane that covers the entire positive electrode-side surface of the heat-resistant porous membrane, and a second porous polyolefin membrane that covers the entire negative electrode-side surface of the heat-resistant porous membrane. The melting point or heat distortion temperature of the heat-resistant resin is higher than the melting point or heat distortion temperature of the polyolefin that is contained in the first and second porous polyolefin membranes. The heat-resistant porous membrane has a thickness of 1-16 [mu]m, the first porous polyolefin membrane has a thickness of 2-17 [mu]m, the second porous polyolefin membrane has a thickness of 2-17 [mu]m, and the separator has a thickness of 5-35 [mu]m.

Owner:PANASONIC CORP

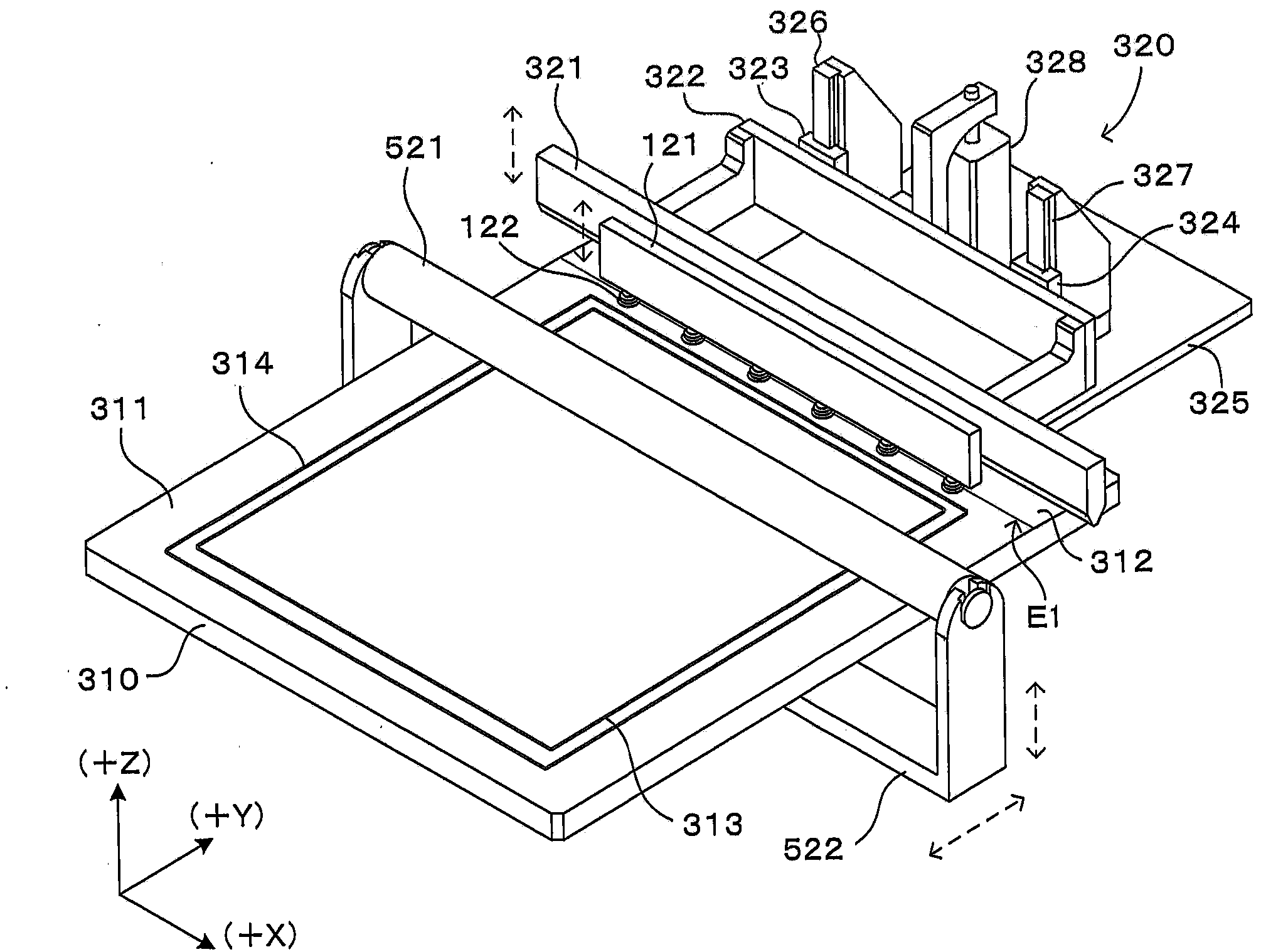

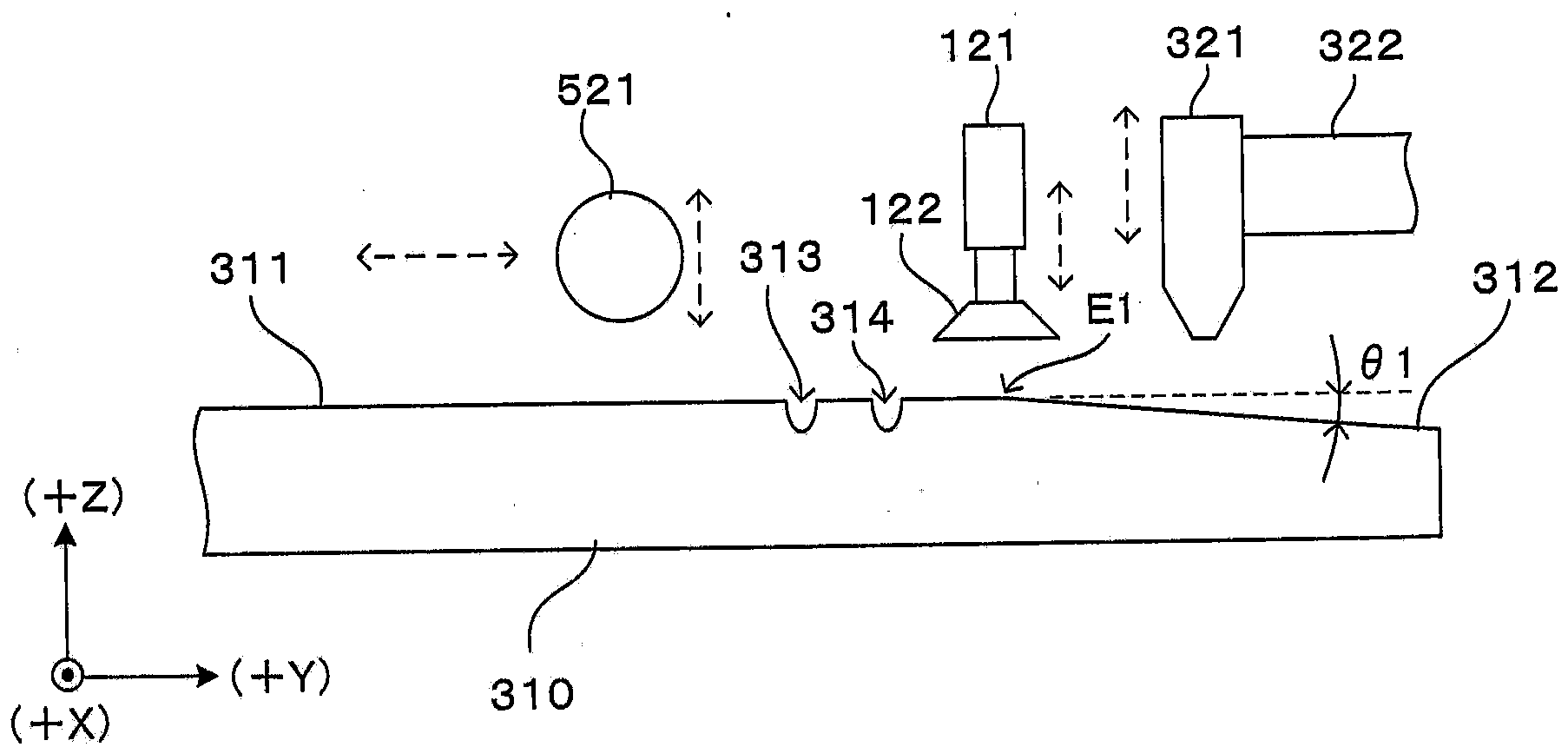

Detaching apparatus and detaching method

ActiveCN103963421ASuppression offsetEfficient strippingLamination ancillary operationsLaminationEngineeringMechanical engineering

Owner:DAINIPPON SCREEN MTG CO LTD

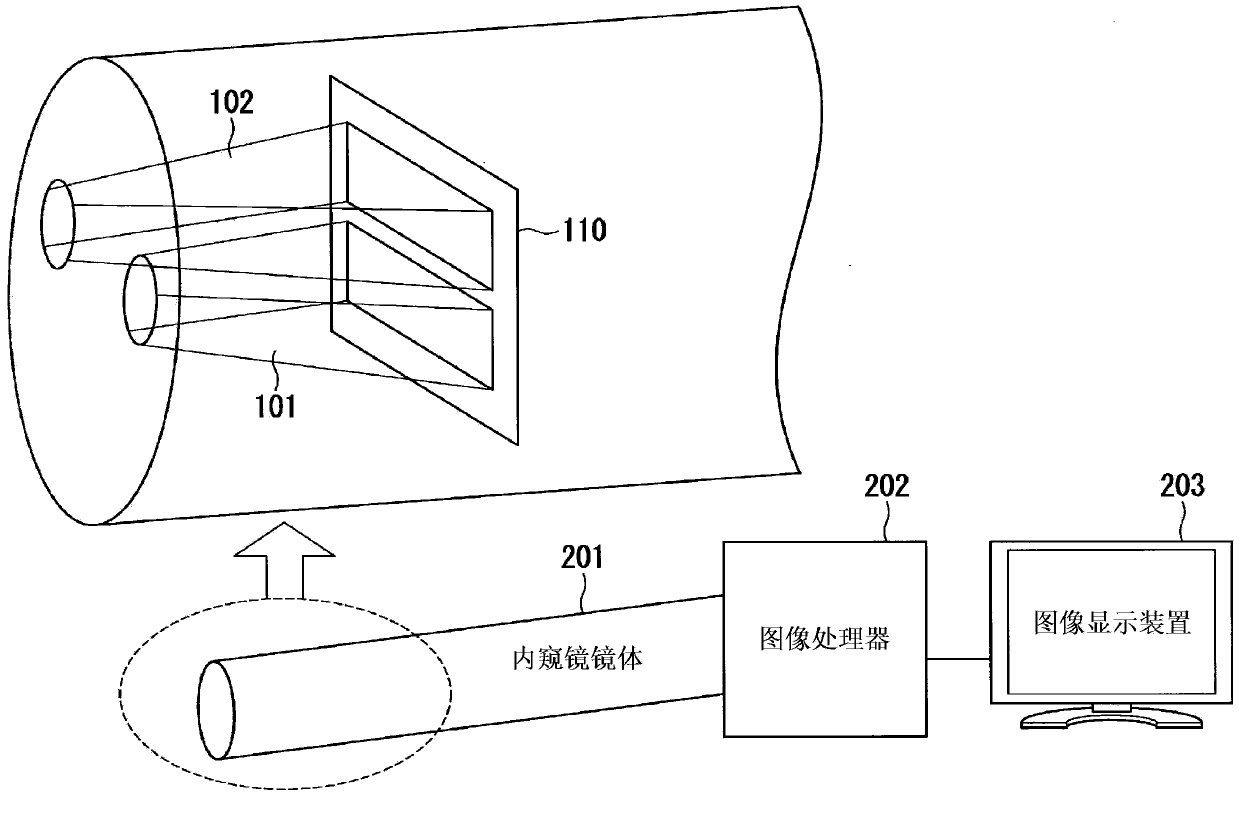

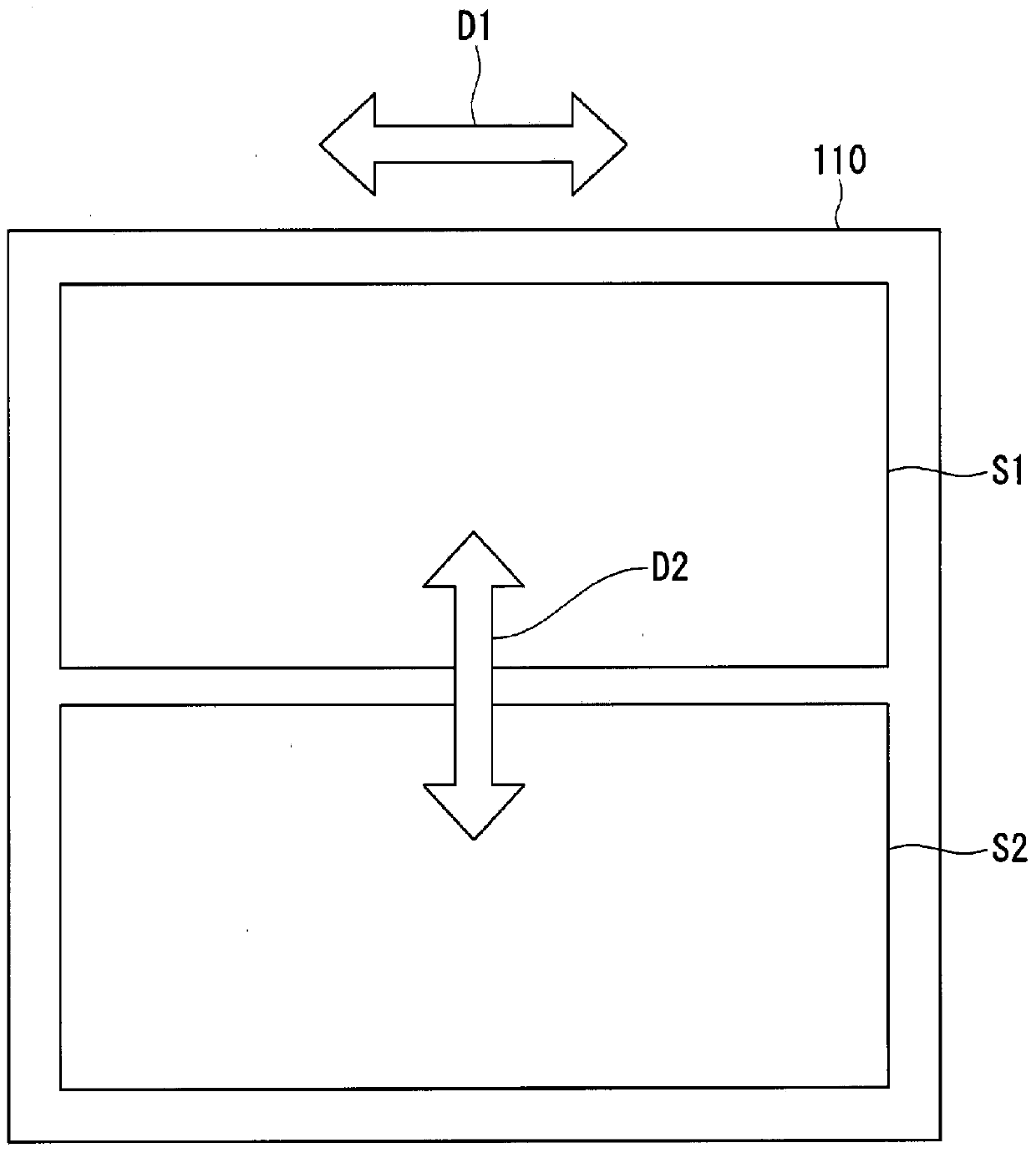

3d endoscope device

In the present invention, an endoscope scope is provided with a left-eye optical system and a right-eye optical system that form an image with light corresponding to a left-eye image and a right-eye image, and is provided with a CMOS sensor on which first light and second light obtained through the left-eye optical system and the right-eye optical system are formed into separate images on a single light receiving surface. A straight line that connects the center of a first image and the center of a second image formed on the light receiving surface of the CMOS sensor is orthogonal to the parallax direction. On the light receiving surface of the CMOS sensor, a first region in which the center of the first image and the second image are formed is divided into a plurality of first divided regions, and a second region is divided into a plurality of second divided regions. When the CMOS sensor reads data constituting image signals from the first region and the second region, the CMOS sensor reads data by alternating scanning a first divided region at a position corresponding to the left-eye image and a second divided region at a position corresponding to the right-eye image.

Owner:OLYMPUS CORP

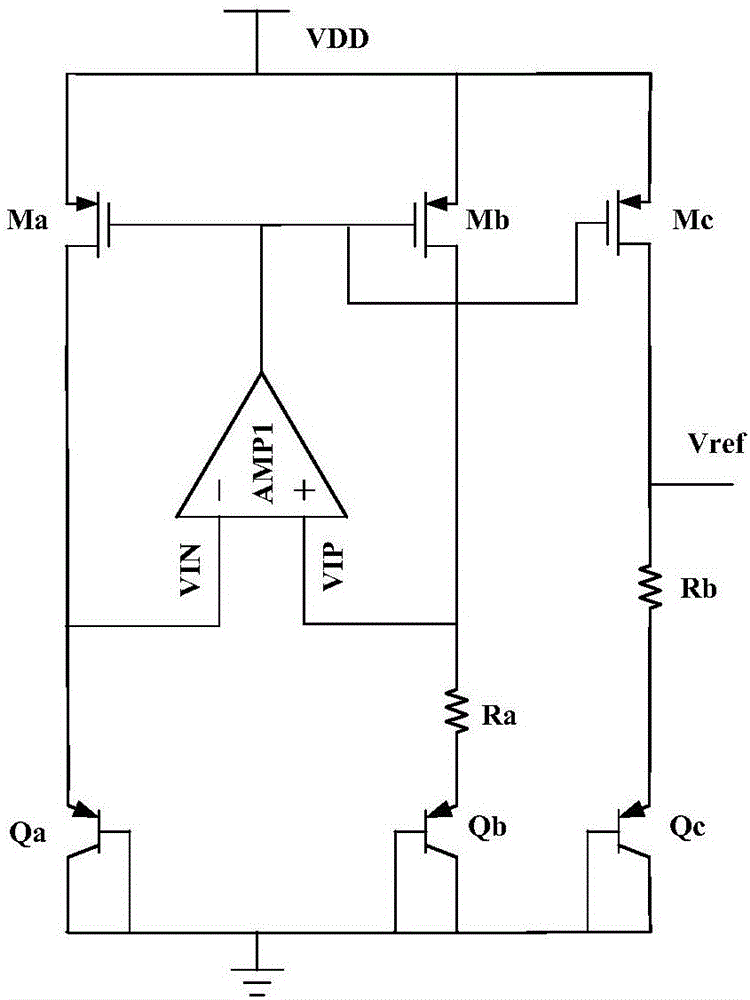

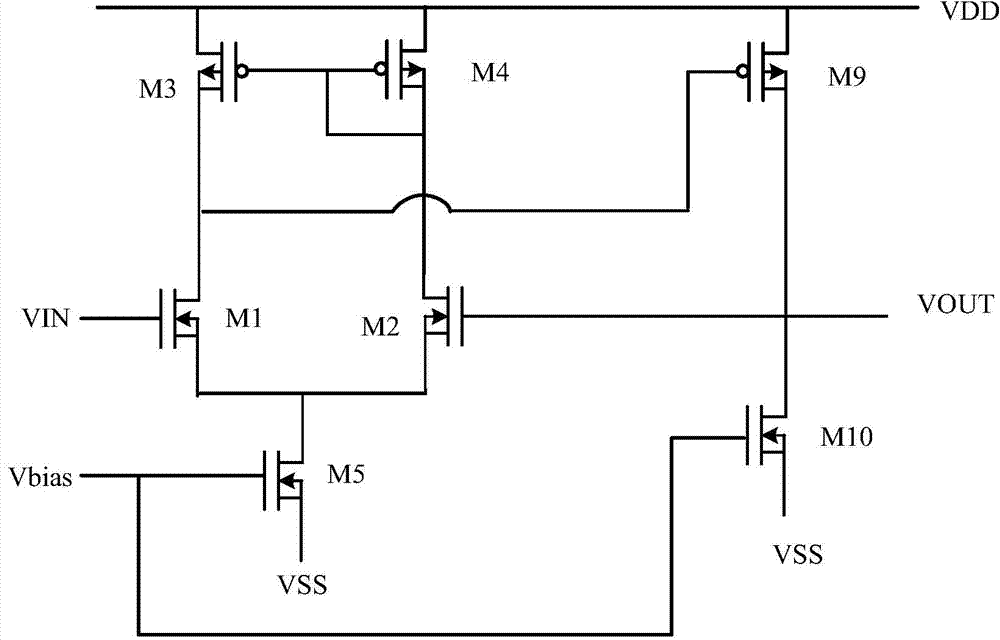

Sectional multi-order compensation high-precision voltage and current reference circuit

ActiveCN106708150ASmall output voltage offsetSuppression offsetElectric variable regulationProcess deviationsNegative temperature

The invention relates to a sectional multi-order compensation high-precision voltage and current reference circuit which is used for generating stable reference voltage and current to provide voltage and current bias for other modules inside. The reference circuit is an on-chip circuit and comprises a basic band gap circuit, a low-temperature first-order negative temperature coefficient compensation circuit, a high-temperature high-order positive temperature coefficient compensation circuit, a voltage stabilization trimming circuit and a trimming logic circuit. Through sectional multi-order compensation of basic band gap voltage, the reference circuit has high temperature stability and is small in output deviation in a wide temperature range. By designing the trimming circuit, output bias caused by process deviation can be adjusted, so that precision of output voltage is further guaranteed. The reference circuit is simple in structure, high in precision and suitable for various analog integrated circuits.

Owner:BEIJING MXTRONICS CORP +1

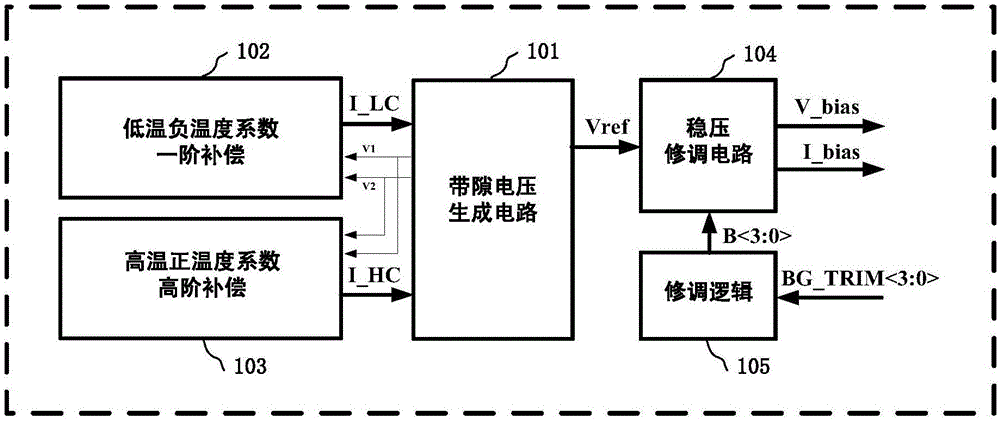

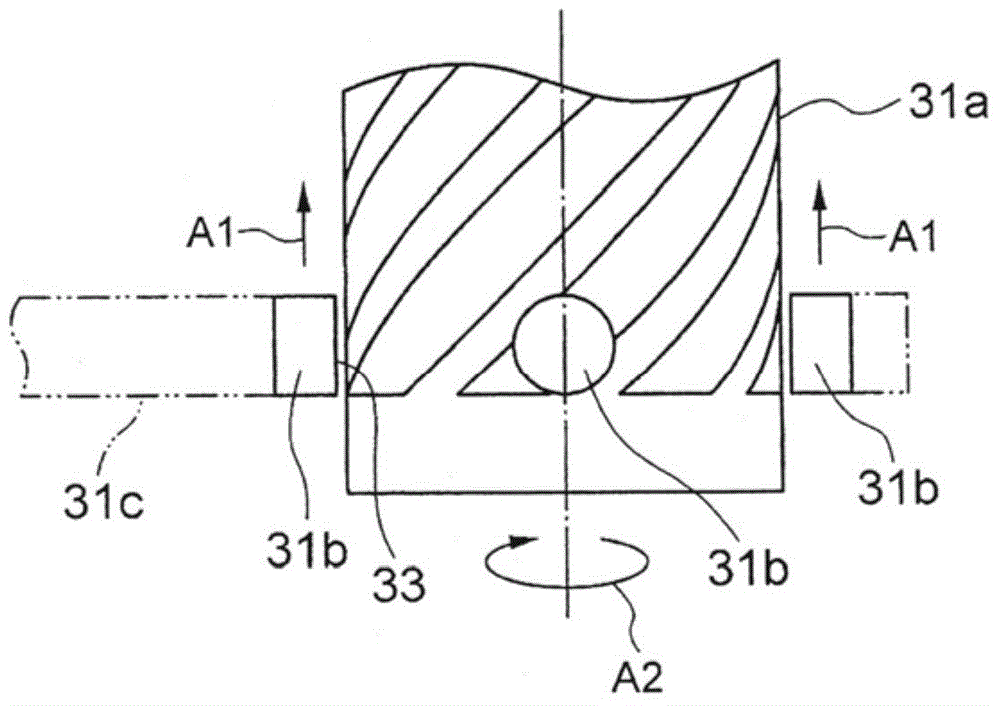

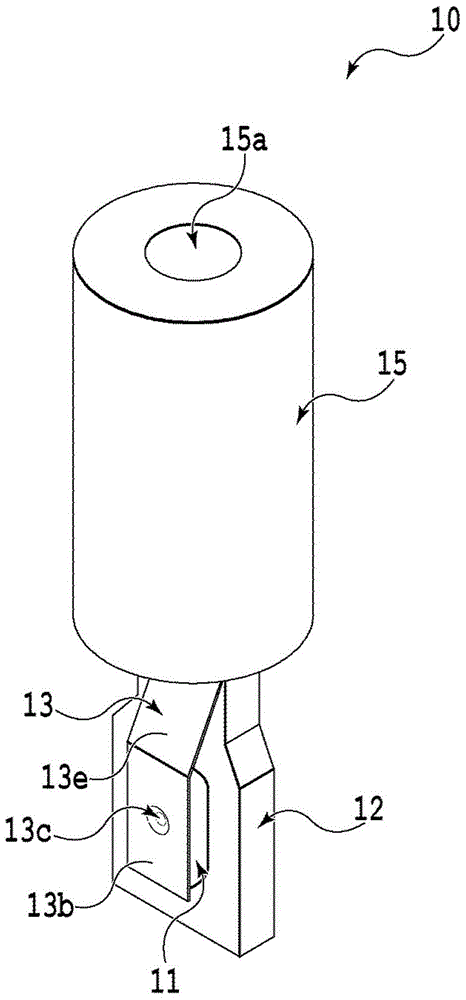

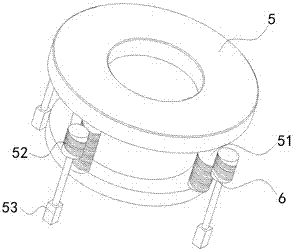

Spin treatment apparatus

InactiveCN104465359AInhibitionSuppression offsetLiquid surface applicatorsSemiconductor/solid-state device manufacturingMagnetic polesEngineering

A spin treatment apparatus according to an embodiment can suppress generation of dust and displacement of a substrate when clamped, performs a treatment while rotating a substrate and includes: at least three clamp pins configured to contact an outer peripheral surface of the substrate and clamp the substrate; rotatable pin rotators provided for the respective clamp pins and each configured to retain the corresponding clamp pin at a position offset from a rotation axis of the pin rotator parallel with a rotation axis of the substrate; magnet gears provided for the respective pin rotators around outer peripheral surfaces thereof and each having a magnetic-pole part formed spirally about the rotation axis of the pin rotator; rotation magnets provided for the respective magnet gears and positioned to attract and be attracted by the magnetic-pole part of the corresponding magnet gear; and a movement mechanism configured to move the rotation magnets along the rotation axes of the pin rotators.

Owner:SHIBAURA MECHATRONICS CORP

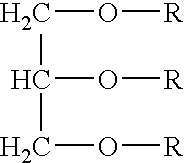

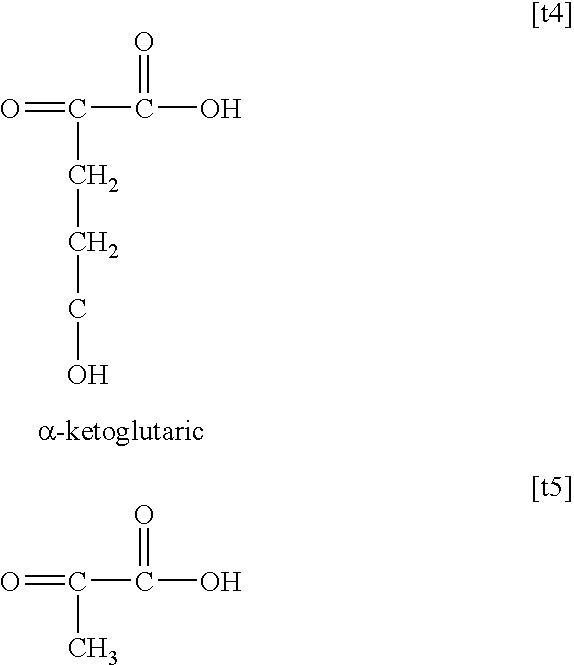

Antioxidant triacylglycerols and lipid compositions

InactiveUS20050165101A1High degreeSuppression offsetBiocideOrganic active ingredientsLipid formationAntioxidant

A lipid composition includes triacylglycerols that include unsaturated fatty acids such as alpha linolenic acid and antioxidant moeities such as pyruvic acid.

Owner:ALBERTA INNOVATES TECH FUTURES

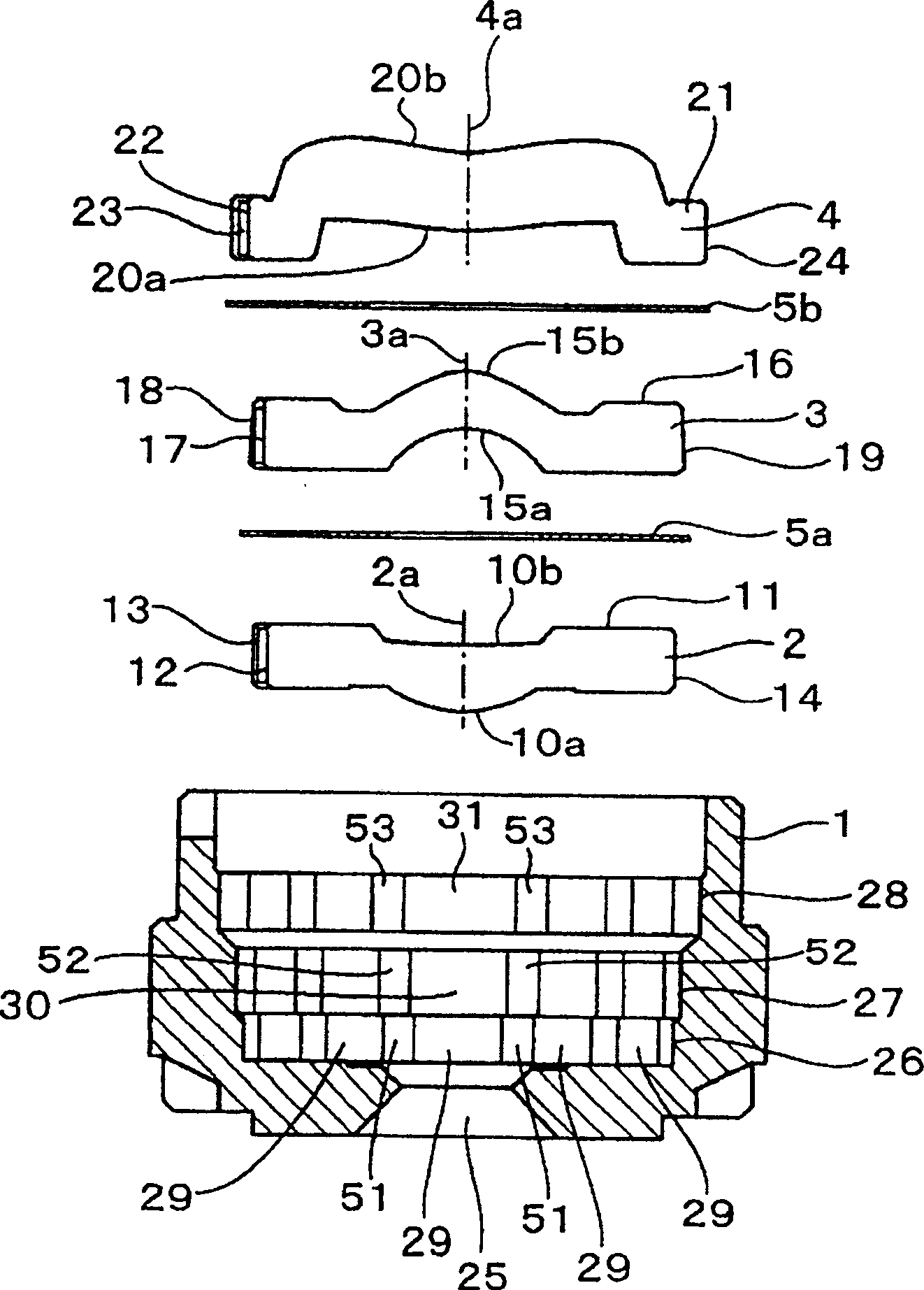

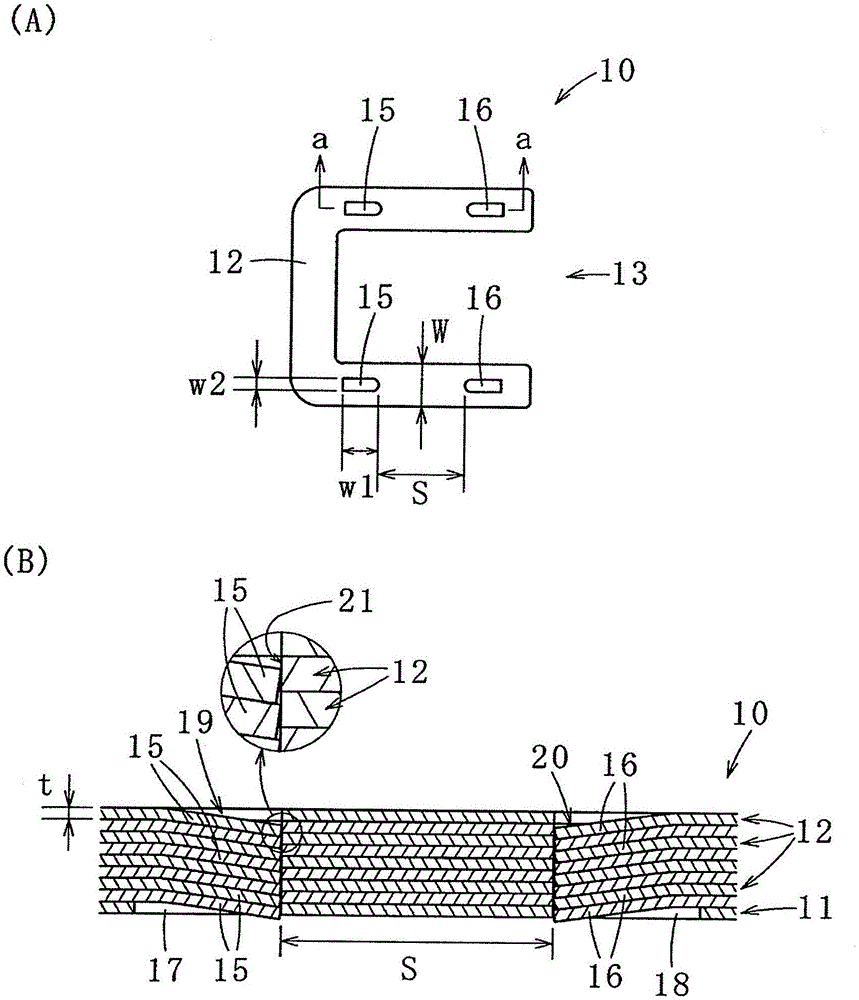

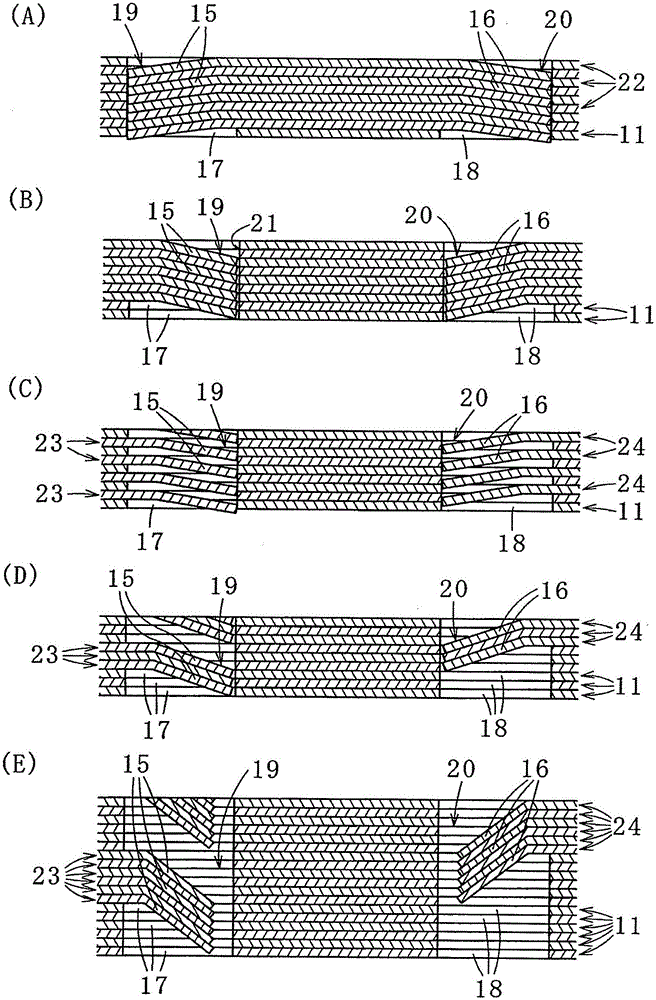

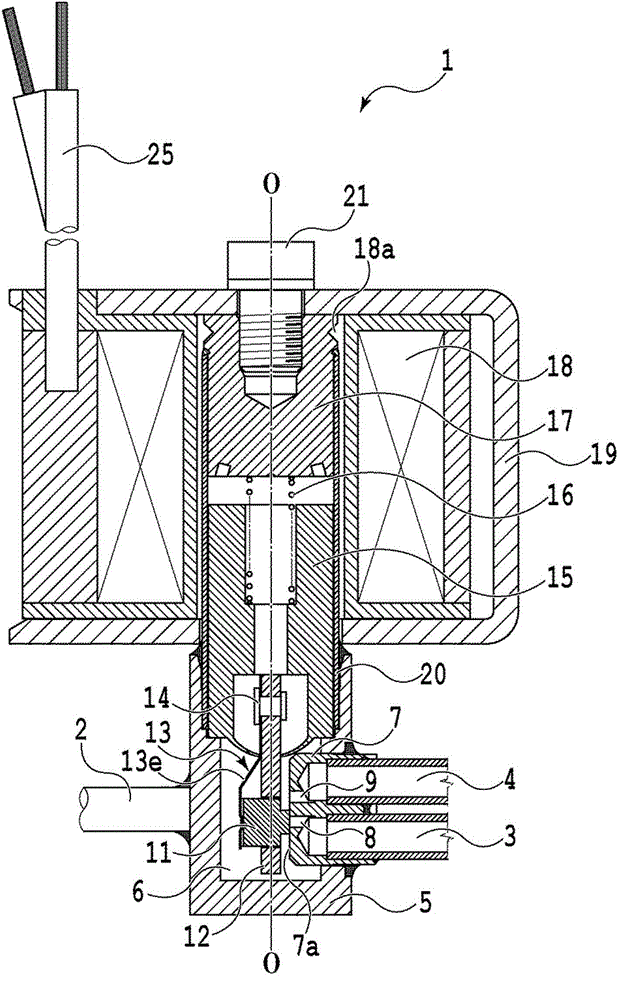

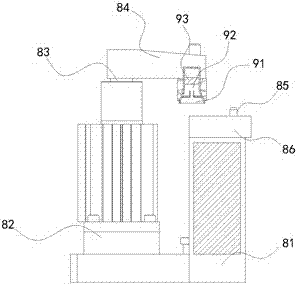

Laminated iron core, method for manufacturing laminated iron core, and punch for caulking formation used in the method

InactiveCN106451827AStrong connectionExcellent magnetic propertiesInductances/transformers/magnets manufactureManufacturing stator/rotor bodiesPunchingMaterials science

The invention provides a laminated iron core, a method for manufacturing the laminated iron core, and a punch for caulking formation used in the method. Solid stack riveting stack can also be carried out by means of thin plates of thickness of 0.2mm or less. The laminated core (10) is formed with a plurality of iron chips (12) punched out from a sheet (14) having a thickness of 0.2 mm or less; one end portion is continuous, the other parts are separated and tilted; the overlapping pieces (15,16) of the adjacent iron chips(12) are fitted into the opening portions (19, 20) to connect the plurality of iron chips (11,12); the overlapping rivet protrusions (15,16)are arranged at intervals (S), and the other end portions of the pair of overlapping rivet protrusions (15, 16) are formed in the direction or phase away from each other. The manufacturing method includes a stack riveting protrusions forming step, a punching step, and a laminating step, and the overlapping rivet protrusions (15, 16) are formed in the stack riveting process. And a punch portion (15, 16) for forming the above-mentioned stacking protrusions(15,16) is provided symmetrically with respect to the punch (30).

Owner:MITSUI HIGH TEC INC

Antioxidant triacylglycerols and lipid compositions

InactiveUS7041840B2High degreeSuppression offsetBiocideOrganic active ingredientsLipid formationColnelenic acid

A lipid composition includes triacylglycerols that include unsaturated fatty acids such as alpha linolenic acid and antioxidant moeities such as pyruvic acid.

Owner:ALBERTA RES COUNCIL INC

Antioxidant triacylglycerols and lipid compositions

InactiveUS20040122093A1High degreeSuppression offsetMilk preparationBiocideAntioxidantColnelenic acid

A lipid composition includes triacylglycerols that include unsaturated fatty acids such as alpha linolenic acid and antioxidant moeities such as pyruvic acid.

Owner:ALBERTA RES COUNCIL INC

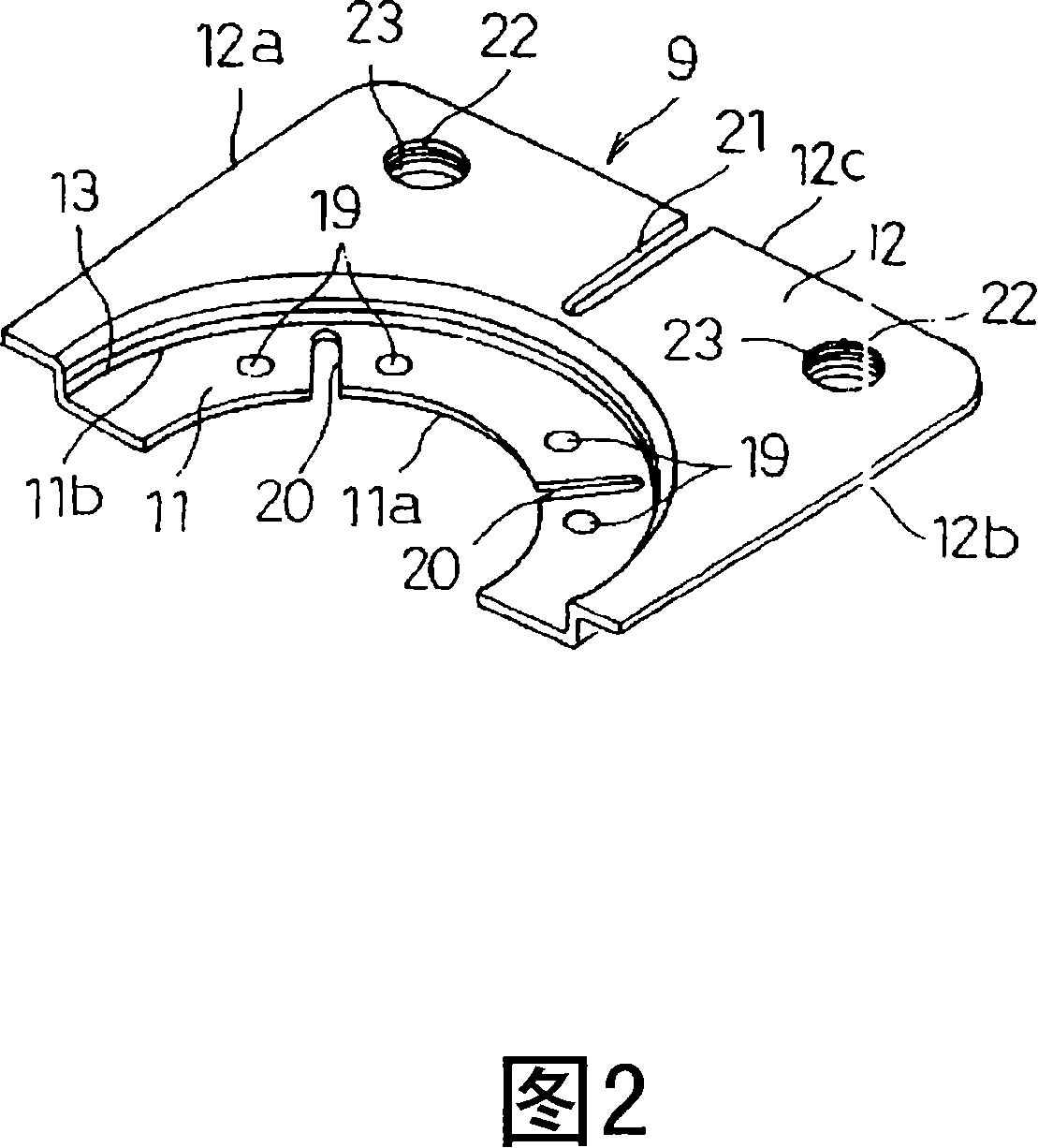

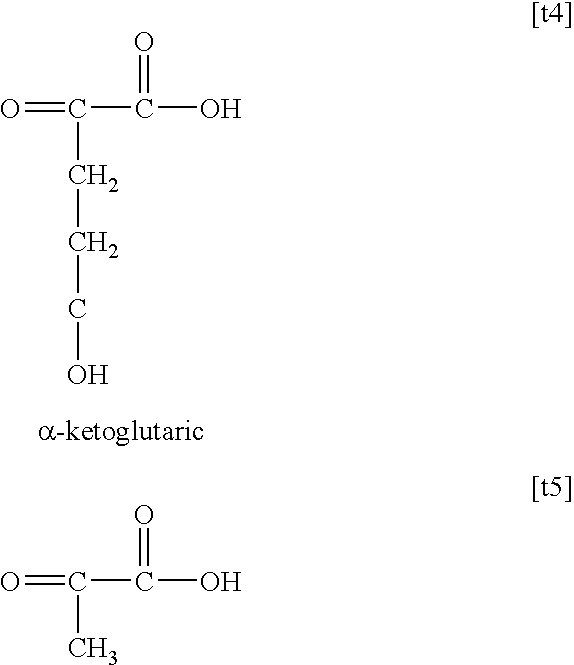

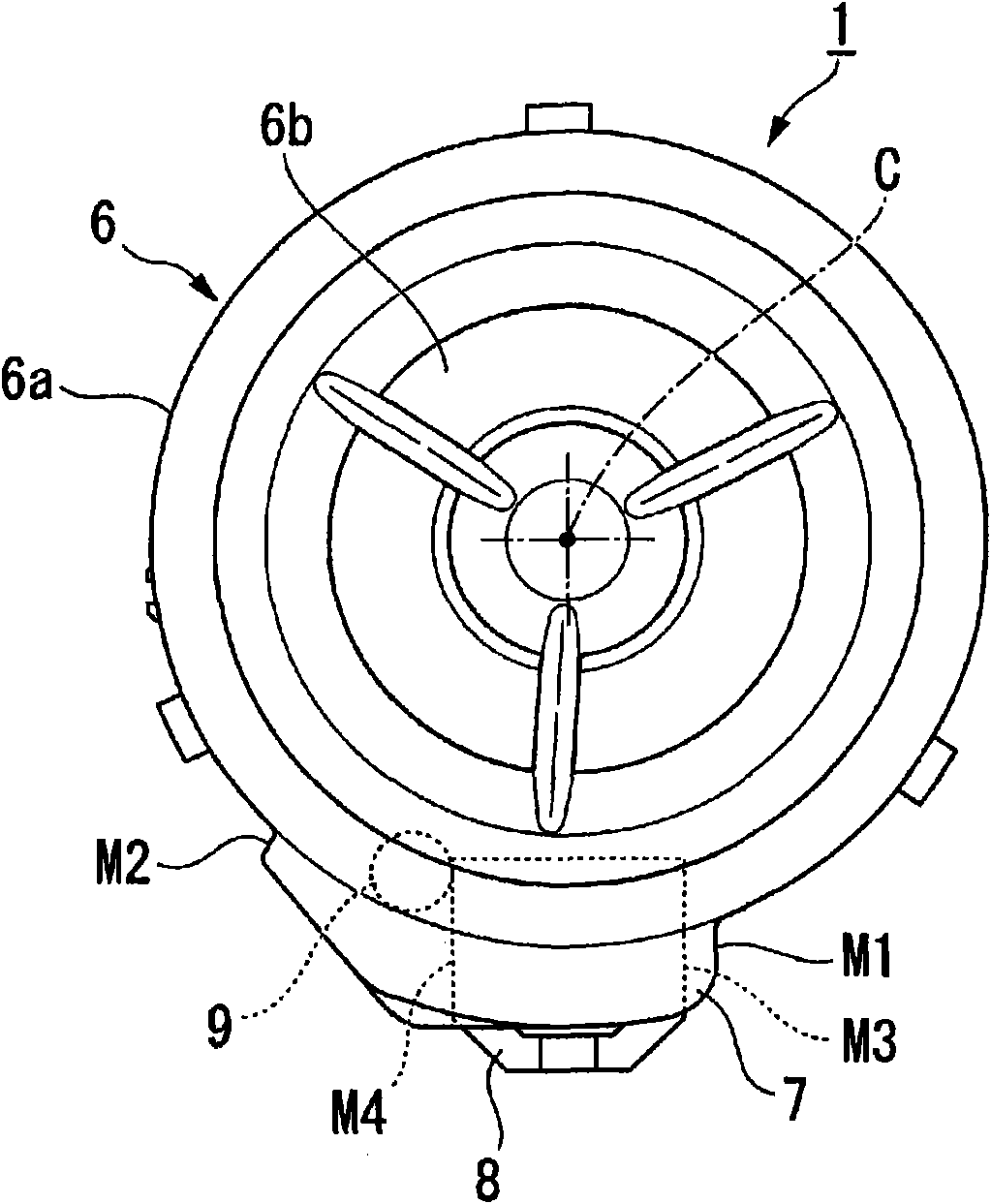

Loudspeaker mounting structure

ActiveCN101646111APrevent rotationAvoid breakingLoudspeaker screensLoudspeaker casing supportsEngineeringLoudspeaker

The present invention provides a structure clamping with a loudspeaker between a vehicle body side mounting member and a grizzly screen and being suitable when pushing and keeping a loudspeaker mounting structure for vehicle. The grizzly screen (4) is provided with short ribs (23, 24), and the loudspeaker (1) is provided with a first and second end surfaces (M1, M2) corresponding to the short ribs(23, 24); under the state of pushing and keeping the loudspeaker (1) between the vehicle body side mounting member and the grizzly screen, the short ribs (23, 24) and the first and second end surfaces (M1, M2) are mutually blocked on the circumferential direction of the loudspeaker (1) .

Owner:HONDA MOTOR CO LTD

Slide valve

The invention provides a slide valve preventing inclination in back pressure in a simple construction. The slide valve at least has a valve main body drawing out a valve body having an inlet side port in an opening; a valve seat configured to be in the valve body and having at least one outlet side port, relative to a valve body opening, in a valve body surface; and a valve core assembly at least comprising a plunger driven by a solenoid and a connection rod, a valve core and a leaf spring assembled on the plunger in an integrated mode. The slide valve opens and closes the outlet side port. The valve core is maintained to be at the connection rod, opens and closes at least one outlet side port and slides on a valve seat surface of a valve seat. The valve core also has a sealing surface opening and closing the outlet side portion and a back surface opposite to the sealing surface. The leaf spring is abutted against the back surface of valve core and presses the valve core on the valve seat surface of the valve seat. A protrusion forms on the leaf spring. A step portion comprising a bottom surface abutted against the protrusion forming on the leaf spring forms on the back surface of the valve core.

Owner:SAGINOMIYA SEISAKUSHO INC

Output buffering circuit, array substrate and display device

InactiveCN103794188ASimple structureGuaranteed stabilityStatic indicating devicesAmplifier with semiconductor-devices/discharge-tubesPower flowAudio power amplifier

The invention discloses an output buffering circuit which comprises a first-stage operational amplifying circuit, a second-stage operational amplifying circuit and a feedback circuit arranged between the first-stage operational amplifying circuit and the second-stage operational amplifying circuit. The first-stage operational amplifying circuit is used as a differential input circuit, the second-stage operational amplifying circuit is used as a common-source cascade amplifying circuit with an active load, and the feedback circuit is used for providing a bias voltage and having the driving capacity of alternatively providing a source current and a sink current. The first-stage operational amplifying circuit and the second-stage operational amplifying circuit form a unit gain amplifier through the feedback circuit, so that the whole circuit can have the driving capacity of alternatively providing the source current and the sink current. A special voltage stabilizing circuit is not required any more, the circuit structure is simple, the chip area can be reduced, power consumption can be further lowered due to the fact that the special voltage stabilizing circuit is not required any more, meanwhile, fluctuations of the output voltage can be restrained, the stability of the circuit during working is guaranteed, shifting is restrained to the maximum degree, an output signal is accurate, and a displayed image is good in quality.

Owner:BEIJING BOE DISPLAY TECH CO LTD +1

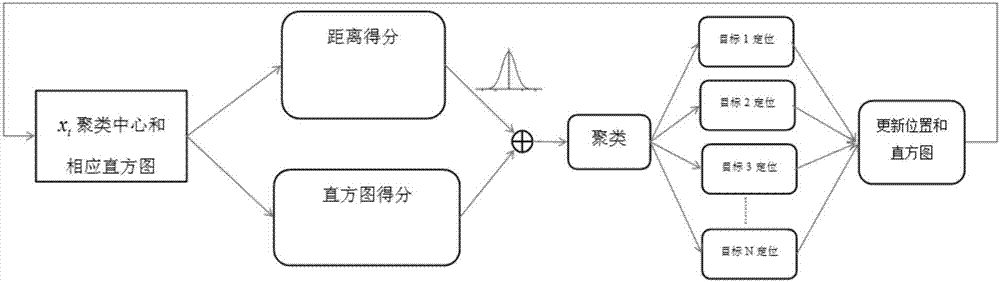

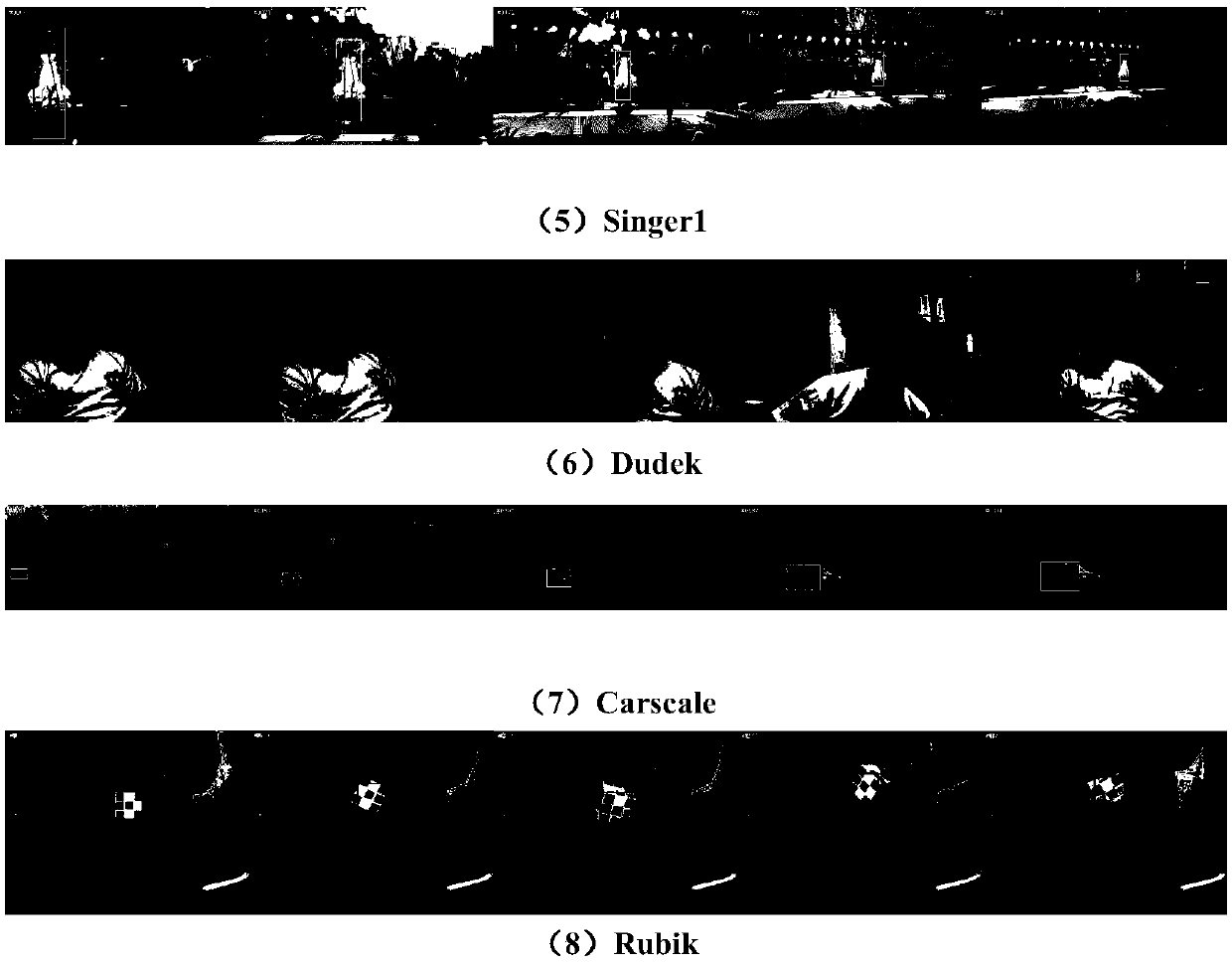

Multi-target tracking method based on color and distance clustering

ActiveCN106951841AReduce dependenceSuppression offsetImage analysisCharacter and pattern recognitionMulti target trackingHistogram

The invention provides a multi-target tracking method based on color and distance clustering. According to the method, the influence caused by tracking target deformation can be reduced, the degree of distinction between the targets can be increased and the degree of dependence on the detector can be reduced. According to the method, position information of successive frames and histogram information of the targets are combined, foreground points are clustered and the score of the foreground points is calculated and finally the target position is located, and the histogram characteristics and the position information of the targets are continuously updated.

Owner:SYSU CMU SHUNDE INT JOINT RES INST +1

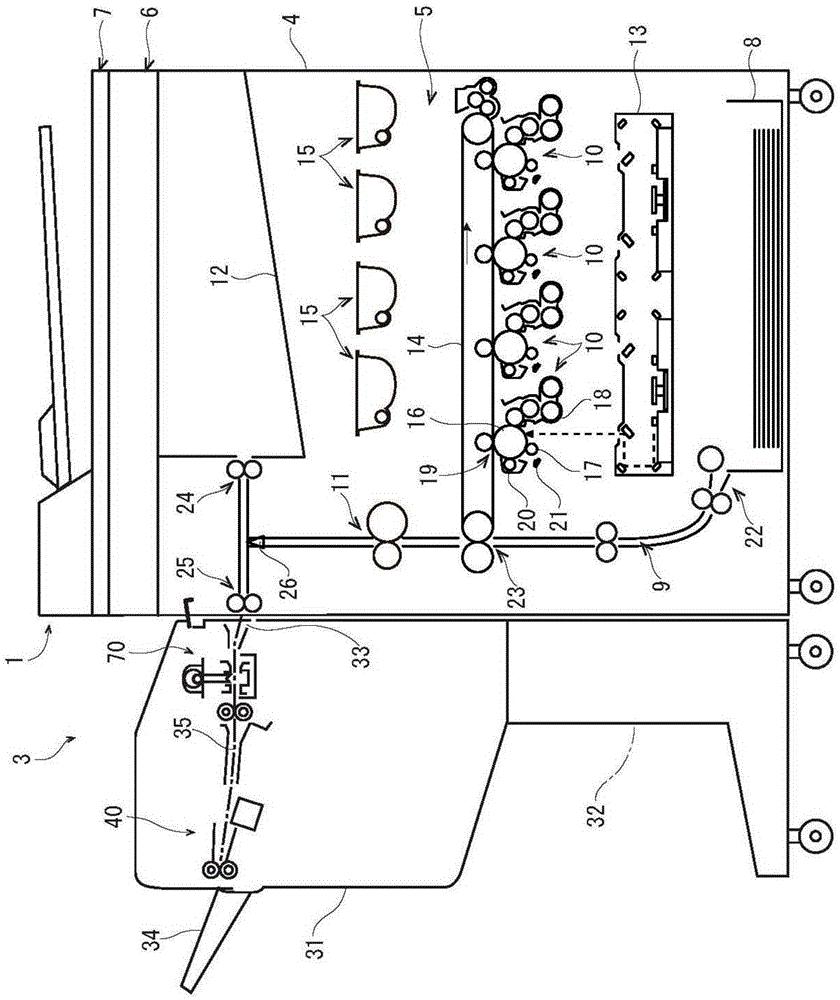

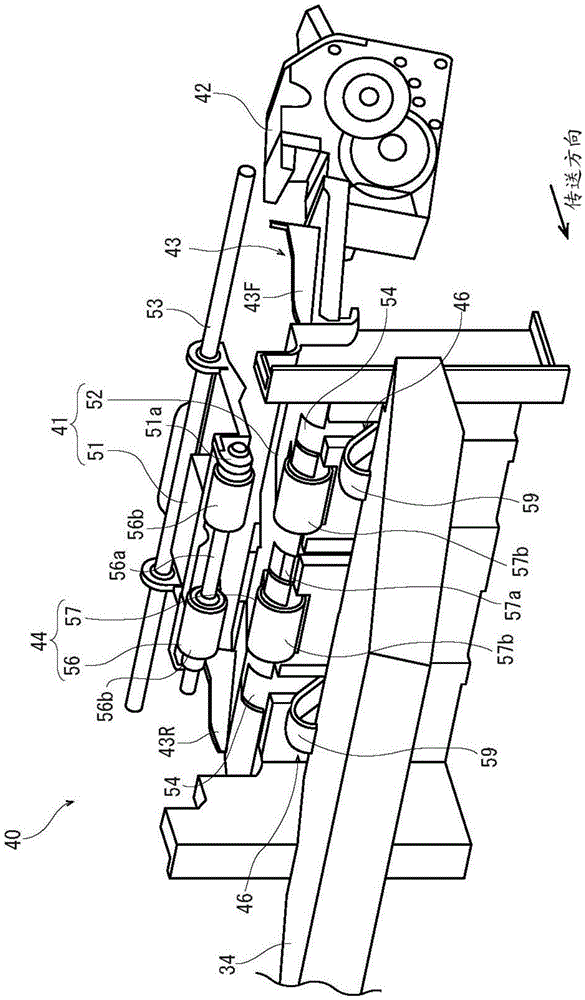

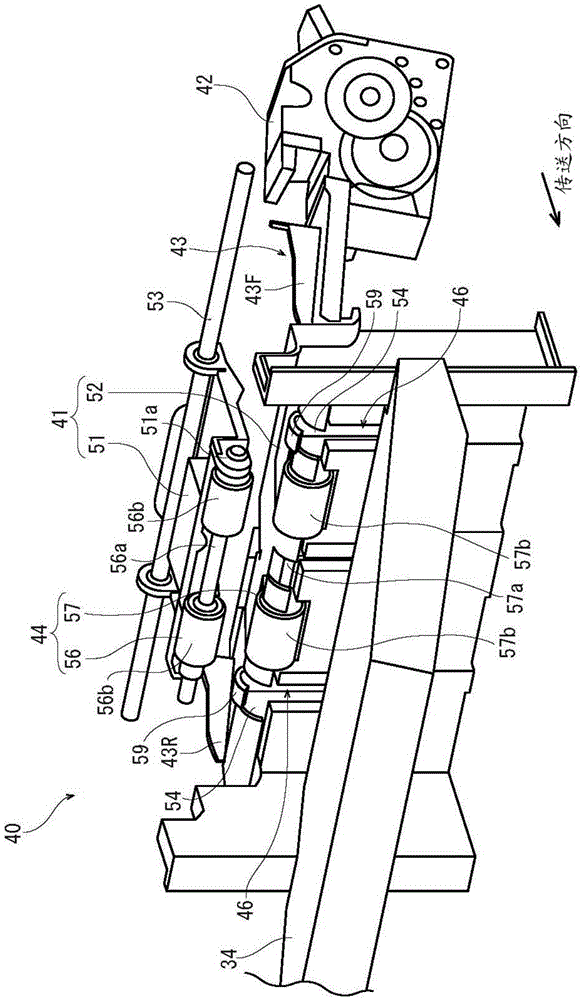

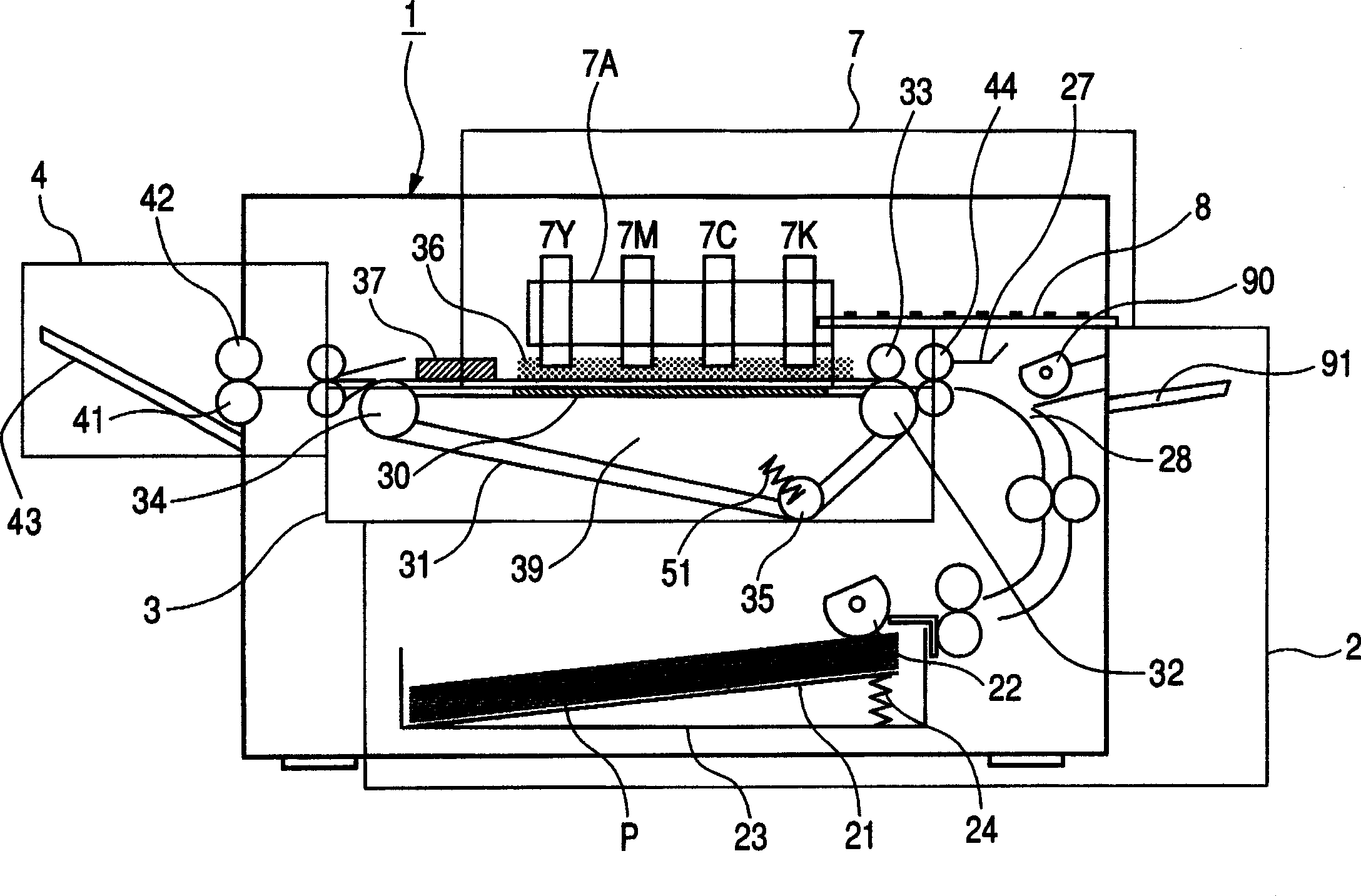

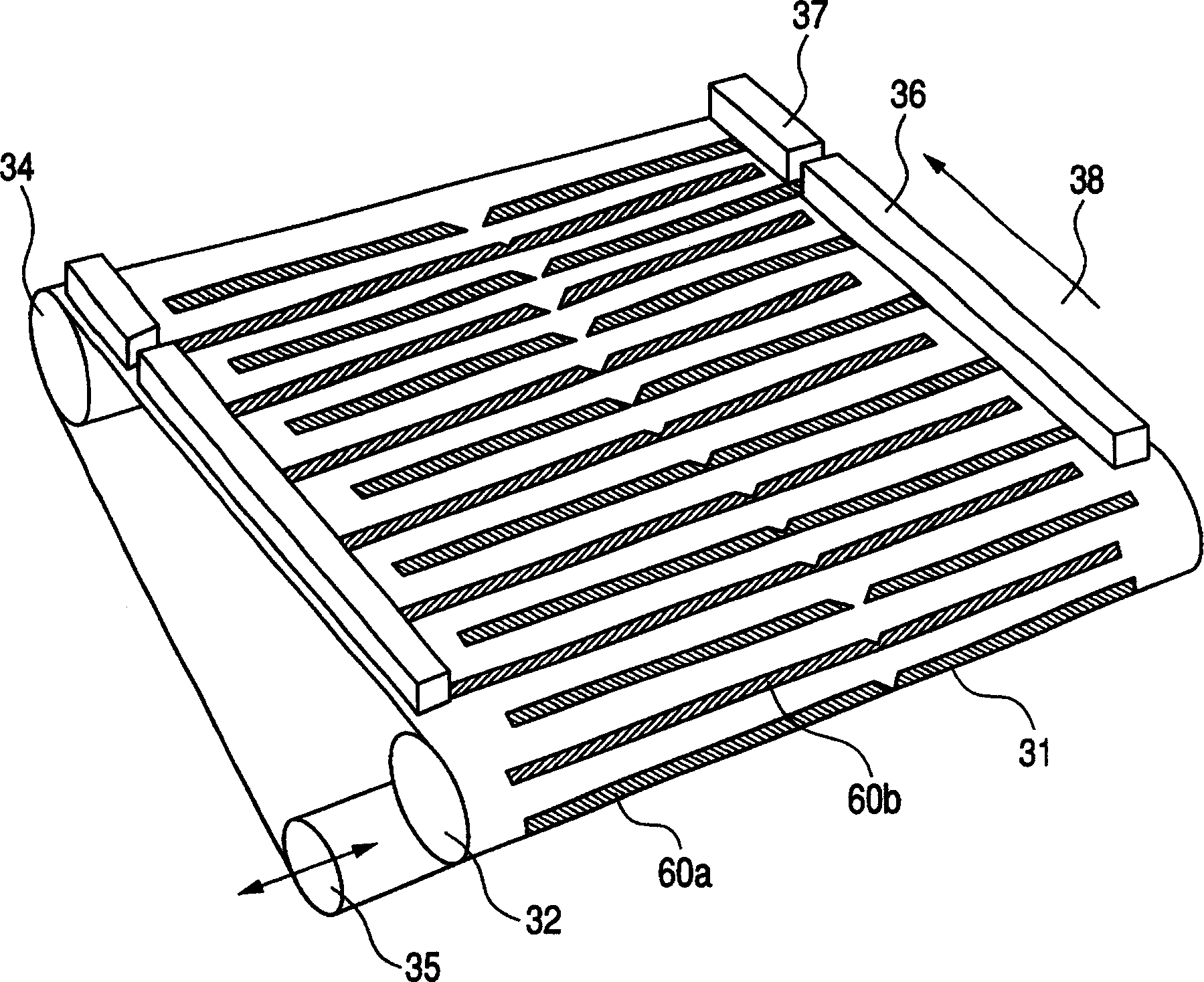

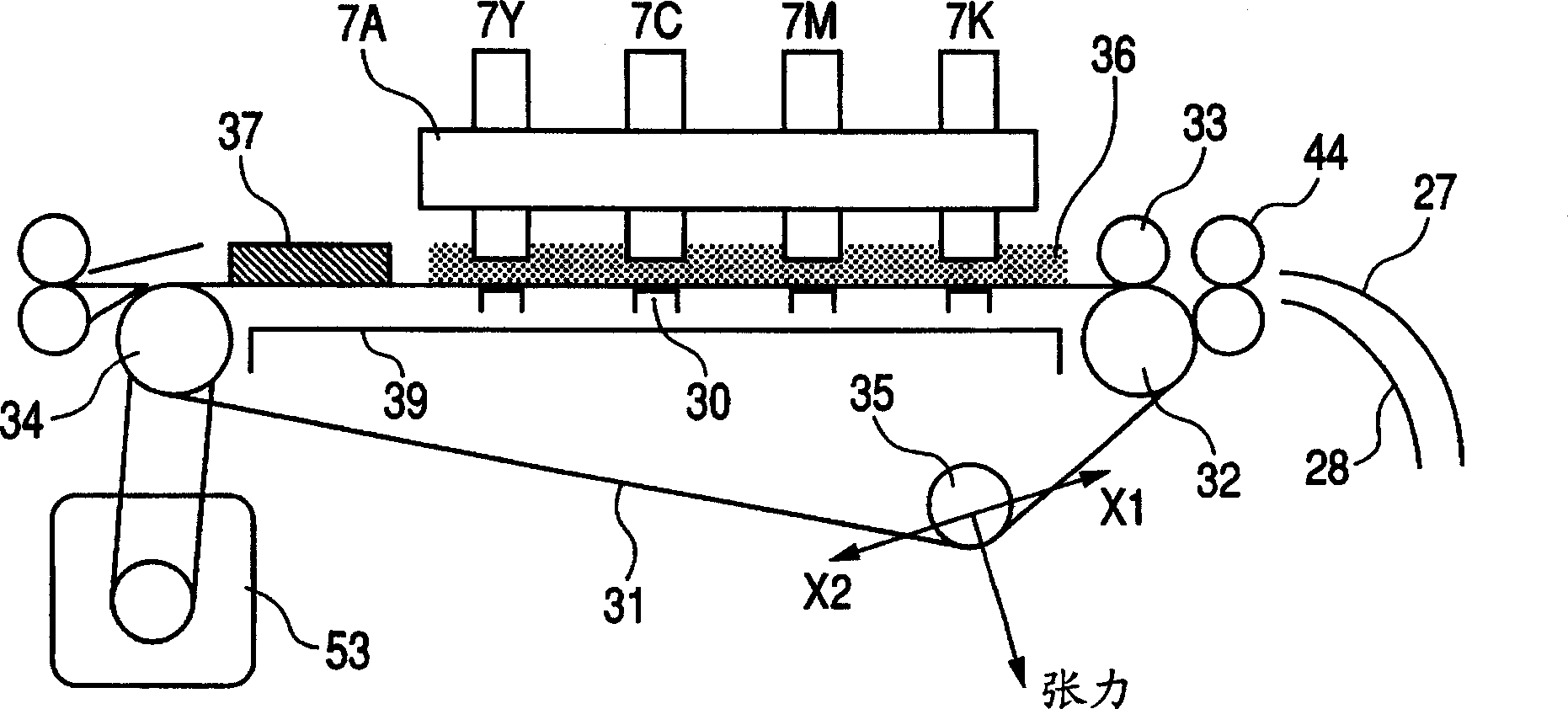

Sheet processing device and image forming device

ActiveCN105636888AReduce exposureSuppression offsetPile receiversArticle deliveryEngineeringMechanical engineering

A sheet processing device (2) is provided with: a shift device (43) that shifts a stack of sheets in the width direction on a processing tray (41); a discharge portion (44) that discharges the stack of sheets from the processing tray (41); a holding tray (34) on which the discharged stack of sheets are held; and a pressing lever (46) that can turn between a first position with the pressing lever (46) abutting on the stack of sheets on the holding tray (34) and a second position where the pressure lever (46) is moved from the first position to the discharge portion (44) side. The discharge portion (44) comprises an upper roller (56) and a lower roller (57). The lower roller (57) abuts the lowermost sheet of the stack of sheets. The upper roller (56) separates upwardly from the lower roller (57) during shifting, while the upper roller (56) approaches the lower roller (57) during discharging. The pressing lever (46) is provided so as to protrude upward of the top of the lower roller (57) at the second position and turns to the second position during shifting.

Owner:KYOCERA DOCUMENT SOLUTIONS INC

Microelectonic device and microelectonic device manufacturing method

ActiveCN110379807ASuppression offsetPrevent degradationTransistorSemiconductor/solid-state device detailsElectron injectionEngineering

The invention provides a microelectonic device and a microelectonic device manufacturing method. The microelectonic device includes at least two mutually spaced doping wells which are opposite to a substrate in doping type and are formed based on the substrate, and an epitaxial structure which is formed based on one side of the substrate and is in contact with each doping well, one side of the epitaxial structure away from the substrate is provided with at least two cascaded power devices, each of the power devices is disposed corresponding to the doping well, and a low potential end of each power device is connected with the corresponding doping well. The microelectonic device is advantaged in that by forming the mutually spaced doping wells in the substrate, a low potential end of each power device is connected with the corresponding doping well, a substrate voltage and the low potential end of each power device are made to have the same potential, performance offset or degradation of the power devices due to electron injection into the epitaxial structure is inhibited.

Owner:湖南三安半导体有限责任公司

Sheet conveying apparatus and image forming apparatus

InactiveCN1877458AAvoid wear and tearSuppression offsetConveyorsControl devices for conveyorsMechanical engineering

Owner:CANON KK

Upper table board

PendingCN107020527AAct as a stabilizing supportImprove structural strengthPositioning apparatusMetal-working holdersElectric machineStructural engineering

Owner:ZHEJIANG YIFAN AUTOMATION EQUIP CO LTD

Method for manufacturing electro-optical device and electro-optical device

InactiveCN101086591ASuppression offsetStatic indicating devicesNon-linear opticsElectricityLength wave

A method of the invention comprises the following steps: a partition wall forming step for forming the partition wall (41) that divides the pixel area on the opposite substrate (12); and an opposite electrode forming step for respectively coating the opposite electrode forming material liquid (51) respectively in the areas divided by the partition wall (41) to form the opposite electrode (43); in the opposite electrode forming procedure the layer thickness of the opposite electrode (43) is set according to the wavelength strip of the light transmitting the corresponding arranged color filter layers (42R, 42G and 42B). Each color according to the displaying is provided, and the invention provides a method for manufacturing the electro-optical device which can be formed with transparent electrodes with different layer thickness and the electro-optical device.

Owner:SEIKO EPSON CORP

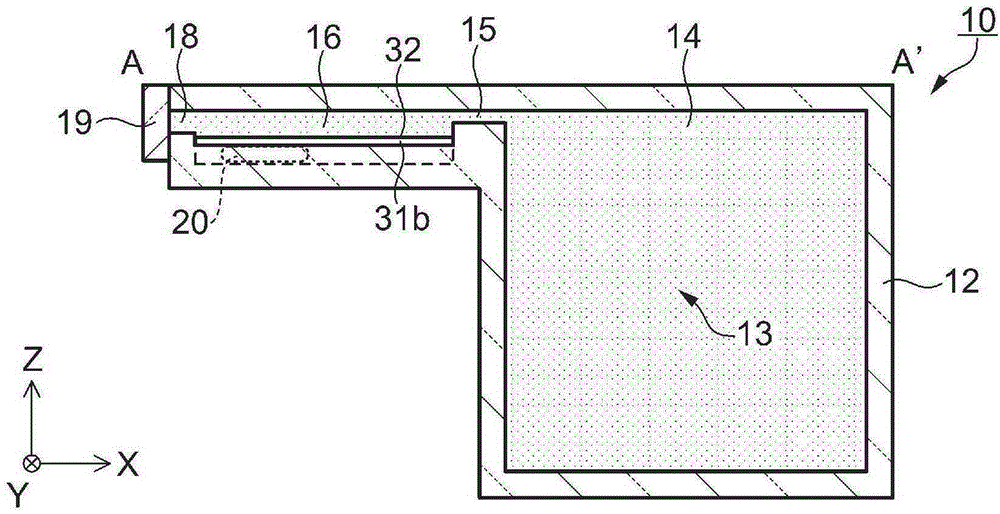

Magnetism measuring device, manufacturing method of magnetism measuring device, and manufacturing method of gas cell

InactiveCN105607014ASituations that inhibit movementPrevent prolapseNon-pressured vesselsSingle device manufacturingEngineeringMechanical engineering

The invention provides a magnetism measuring device which can stably and preciously performing metering, a manufacturing method of the magnetism measuring device, and a manufacturing method of a gas cell. The magnetism measuring device (100) includes: a gas cell (10) which includes a cell portion (12) that has a main chamber (14), a reservoir (16), a communication hole (15) which allows the main chamber and the reservoir to communicate with each other, and an opening (18) provided in the reservoir, a sealing portion (19) which seals the opening, an ampoule (20) disposed in the reservoir, and an alkali metal gas (13) which fills the main chamber and the reservoir (16). The ampoule is disposed at a predetermined position in the reservoir, and the opening is provided at a position that is distant from the predetermined position.

Owner:SEIKO EPSON CORP

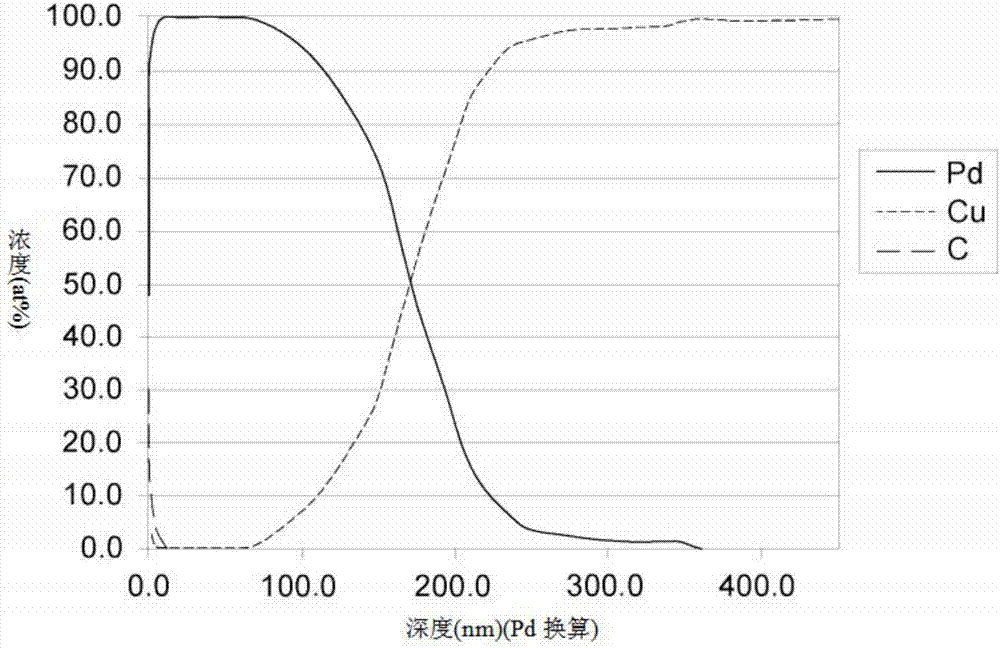

Noble metal-coated copper wire for ball bonding

ActiveCN107039295AThe first joint is stableSuppression offsetConductive materialSolid-state devicesCopper wireCopper-wiring

The invention discloses a noble metal-coated copper wire for ball bonding, with a wire diameter between 10 [mu]m or more, and 25 [mu]m or less, the noble metal-coated copper wire including a core material having a copper alloy having a copper purity of 98 mass % or higher, and a noble metal-coating layer formed on the core material. The noble metal-coating layer includes a palladium cavitating layer containing palladium; at least one element selected from the group consisting of Group 13 to 16 elements or an oxygen element, finely dispersed in the palladium; and a diffusion layer formed of copper diffused into the palladium. According to the invention, the noble metal-coated copper wire for ball bonding can enable a palladium enriching layer to be evenly dispersed on the entire surface of the fusion copper ball of the core material and the palladium does not flow into a solidified copper ball, such that cavities do not form. The noble metal-coated copper wire here is suitable for mass production.

Owner:TANAKA DENSHI KOGYO KK

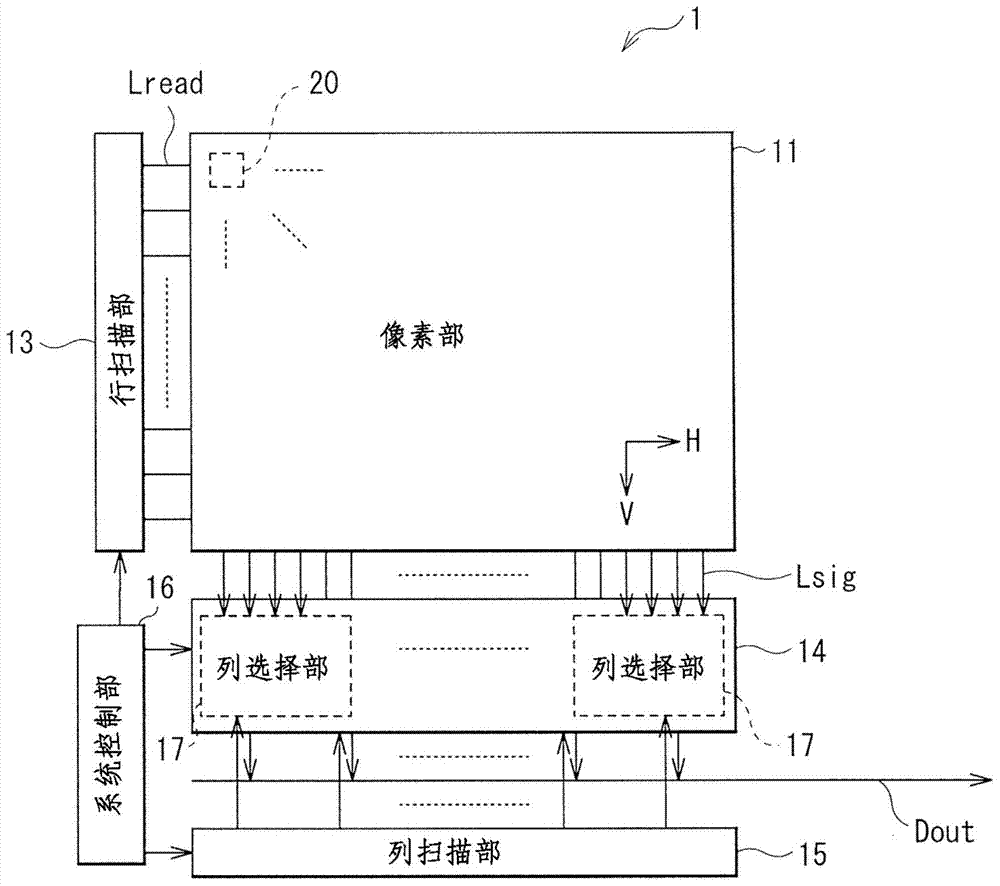

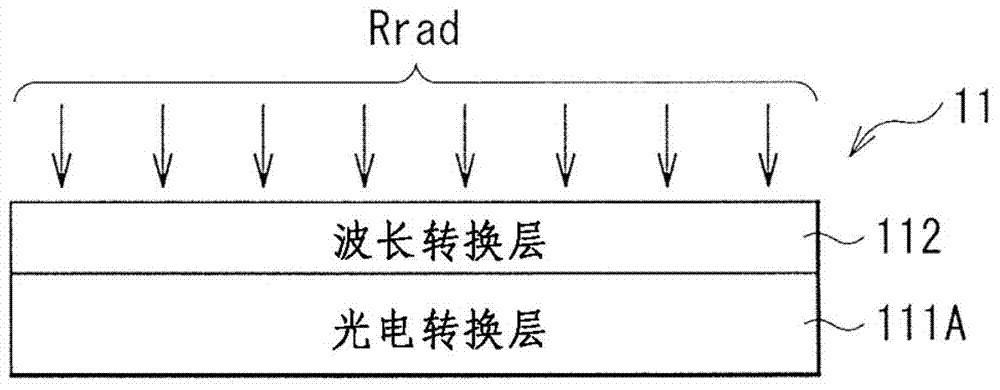

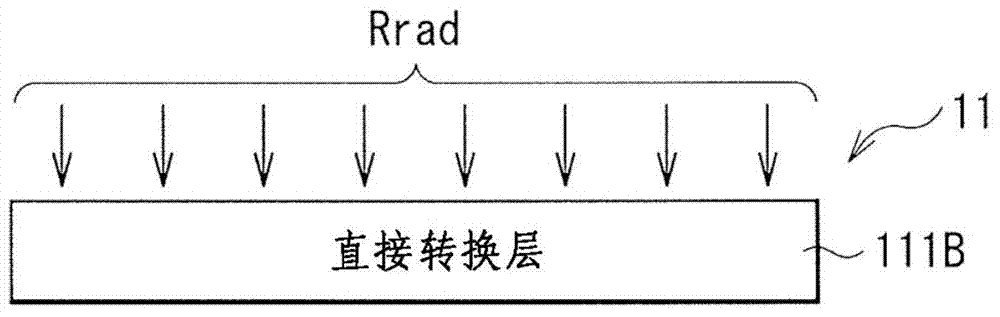

Radiation image pickup unit and radiation image pickup display system

InactiveCN104299977ASuppresses characteristic deteriorationSuppression offsetTelevision system detailsSolid-state devicesSilicon oxideField-effect transistor

A radiation image pickup unit includes: a plurality of pixels each configured to generate a signal charge based on a radiation; and a field effect transistor to readout the signal charges from the plurality of pixels. The transistor includes a semiconductor layer including an active layer, a first gate electrode disposed to face the semiconductor layer, a first gate insulating film provided between the semiconductor layer and the first gate electrode, and including a first silicon oxide film, a source electrode and a drain electrode that are electrically connected to the semiconductor layer, and a second silicon oxide film provided in a layer different from the first gate insulating film. The first silicon oxide film of the first gate insulating film is a porous film lower in film density than the second silicon oxide film.

Owner:SONY SEMICON SOLUTIONS CORP

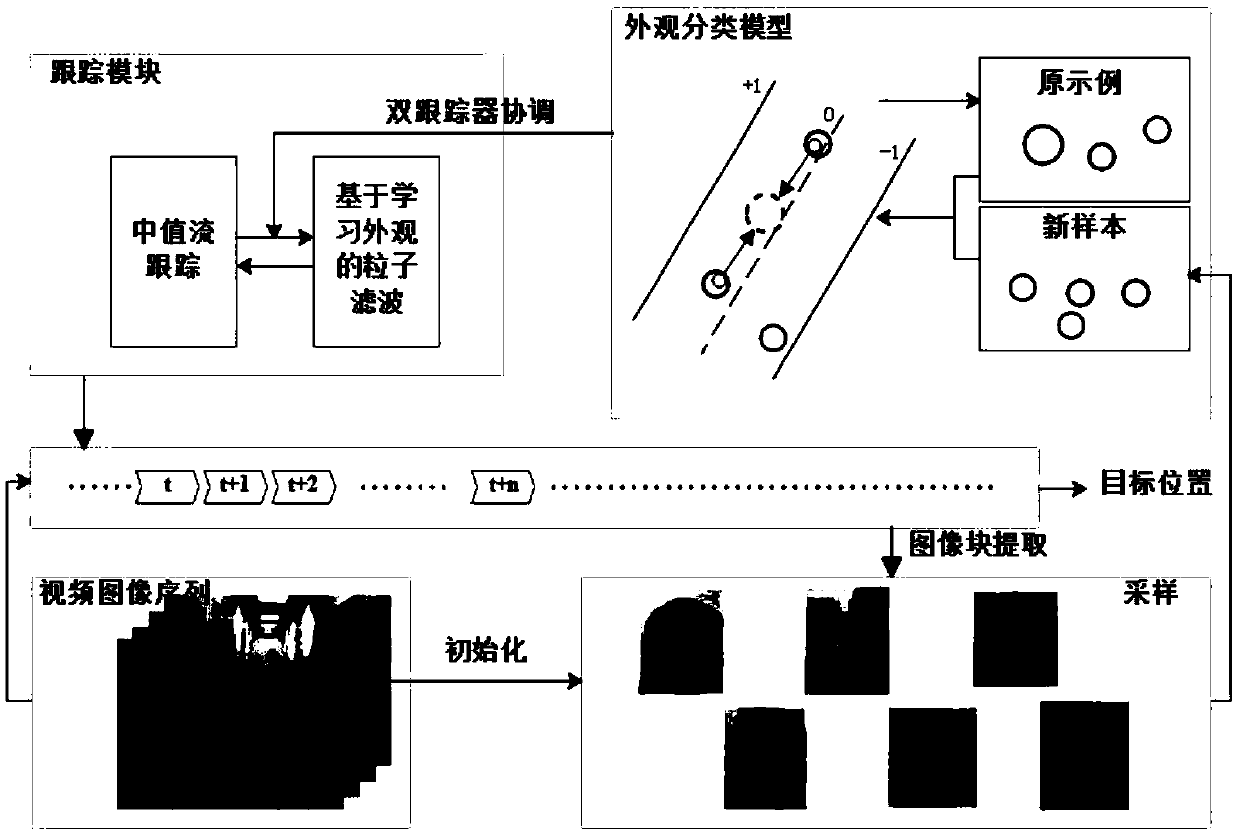

Robust visual target tracking method suitable for long-range tracking

ActiveCN108921872ASuppression offsetSolve the problem of spatial redundancyImage enhancementImage analysisRobustificationSupport vector machine

The invention discloses a robust visual target tracking method suitable for long-range tracking. The method includes: extracting positive and negative samples according to an initial frame image of avideo sequence and position information of a target in an initial frame, performing feature extraction on sample image blocks to obtain low-dimensional eigenvectors, using the linear support vector machine technique to initialize a target appearance model; performing logistic regression on the obtained support vector machine model, and estimating a target position for the target appearance model under a particle filtering framework; combining the median flow tracking algorithm and the current particle filtering algorithm to perform collaborative tracking, using the incremental reduction technique to update the appearance model online in the tracking process, and combining the original appearance model and new samples to update the appearance model online till the last frame is updated. Inthis way, the visual target tracking of the robust is achieved. The parallel complementation of the two-way tracking method with different mechanisms is achieved, and the problem of spatial redundancycaused by continuously generating new information in the tracking process can be solved.

Owner:NANJING UNIV OF SCI & TECH

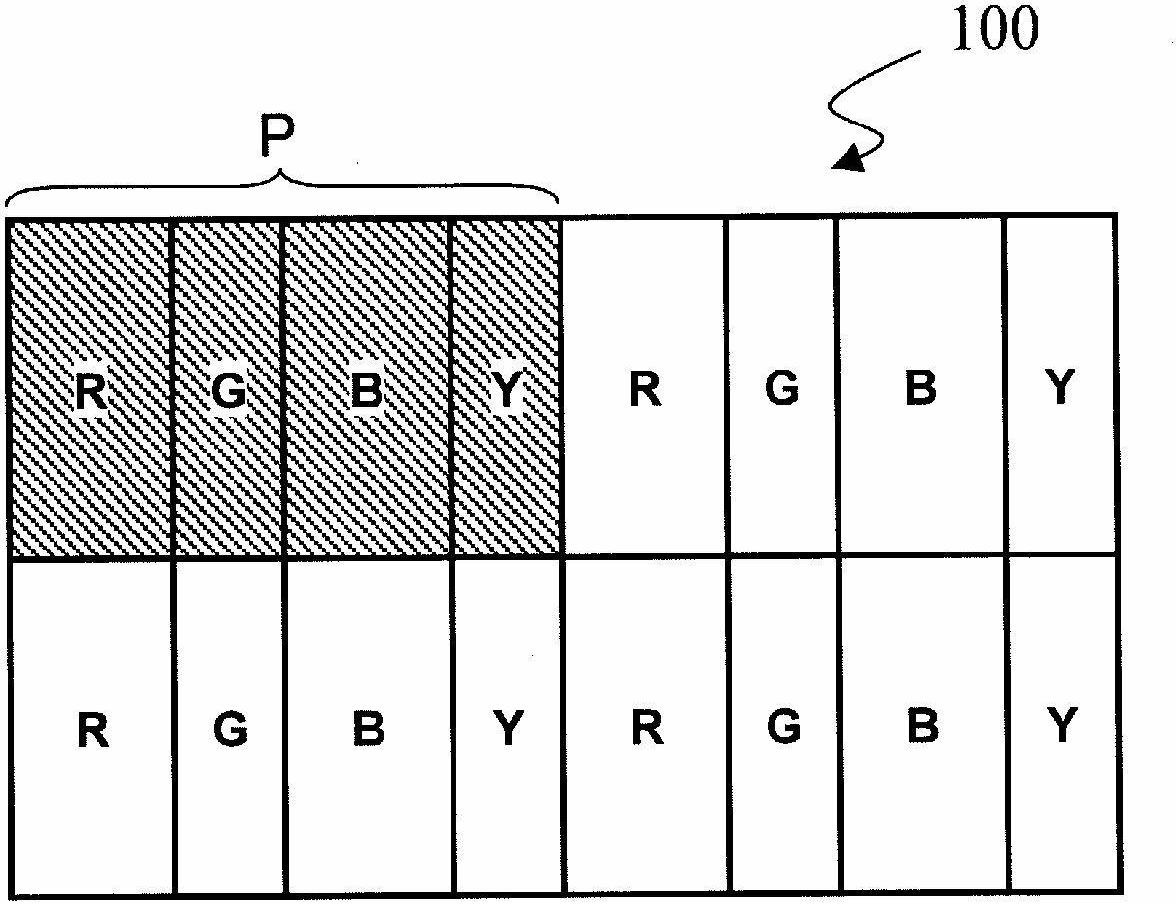

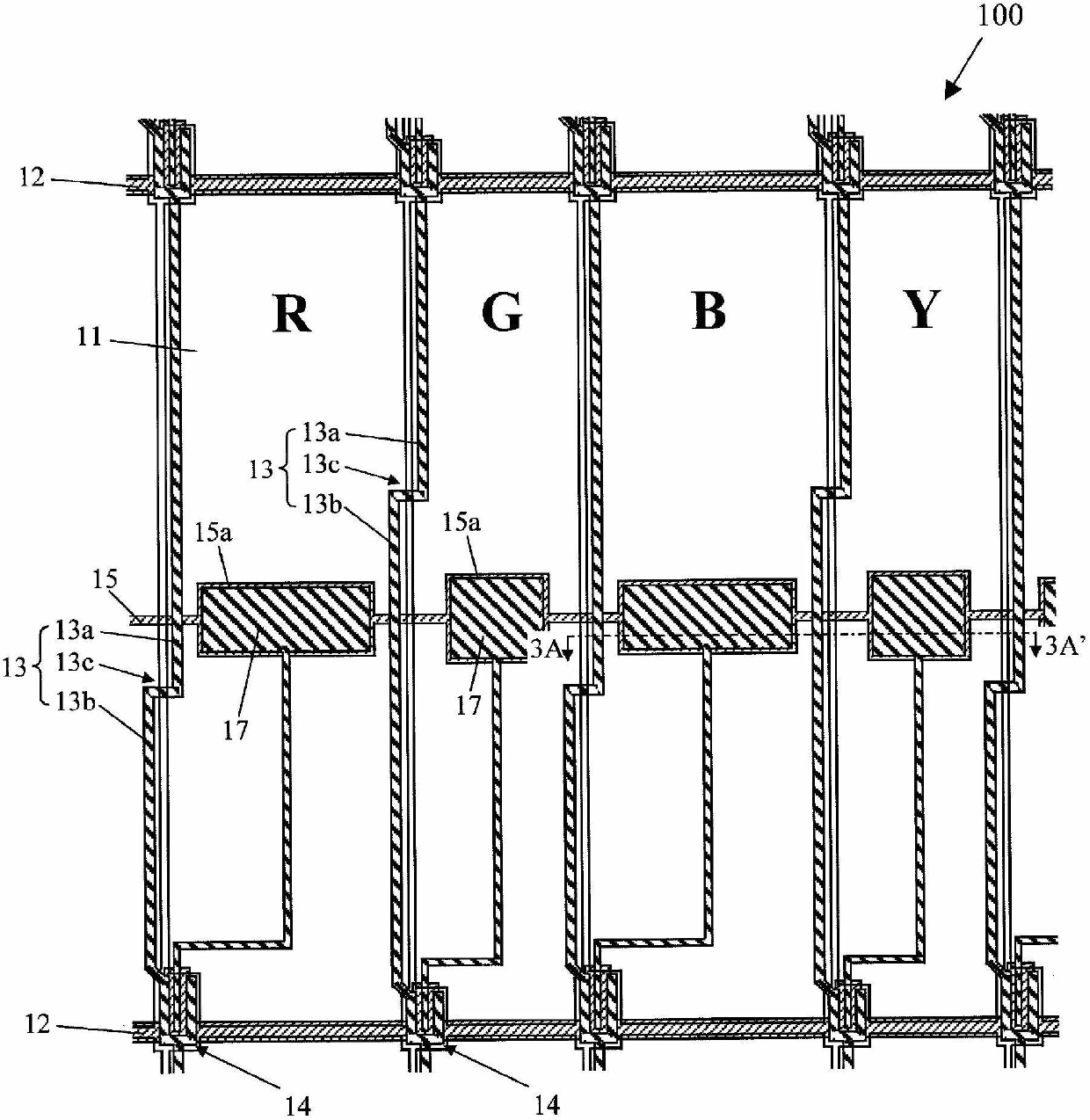

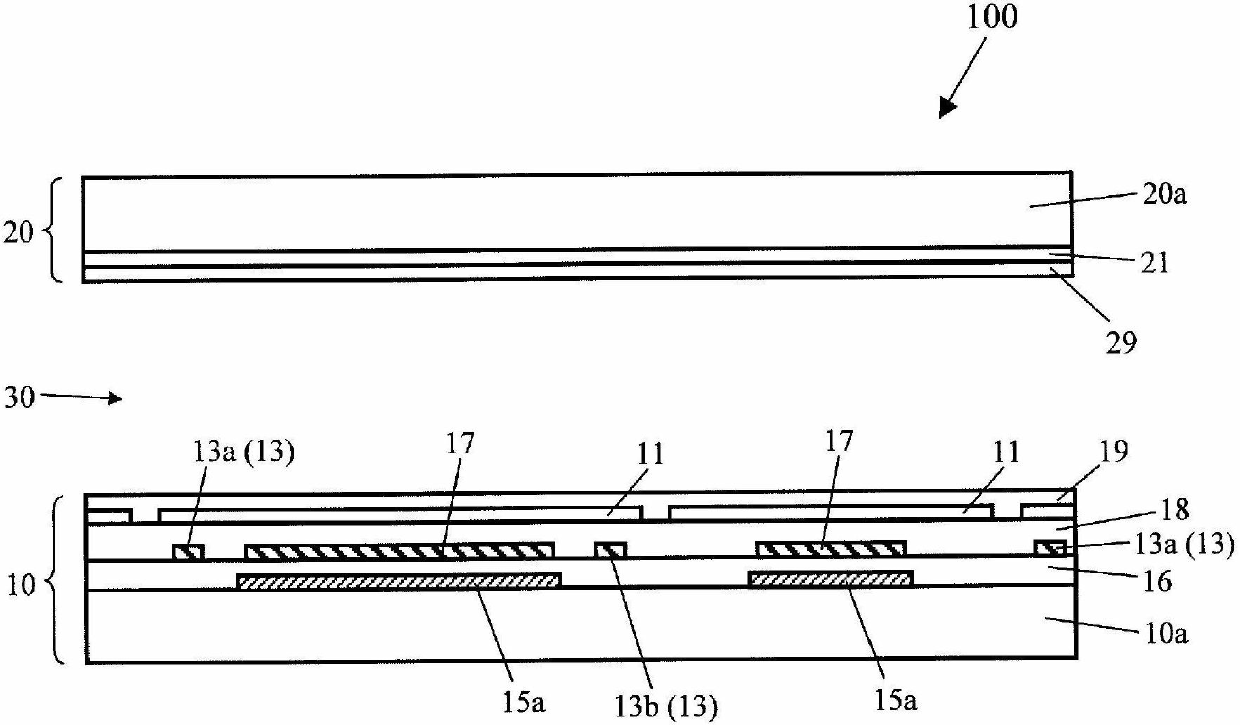

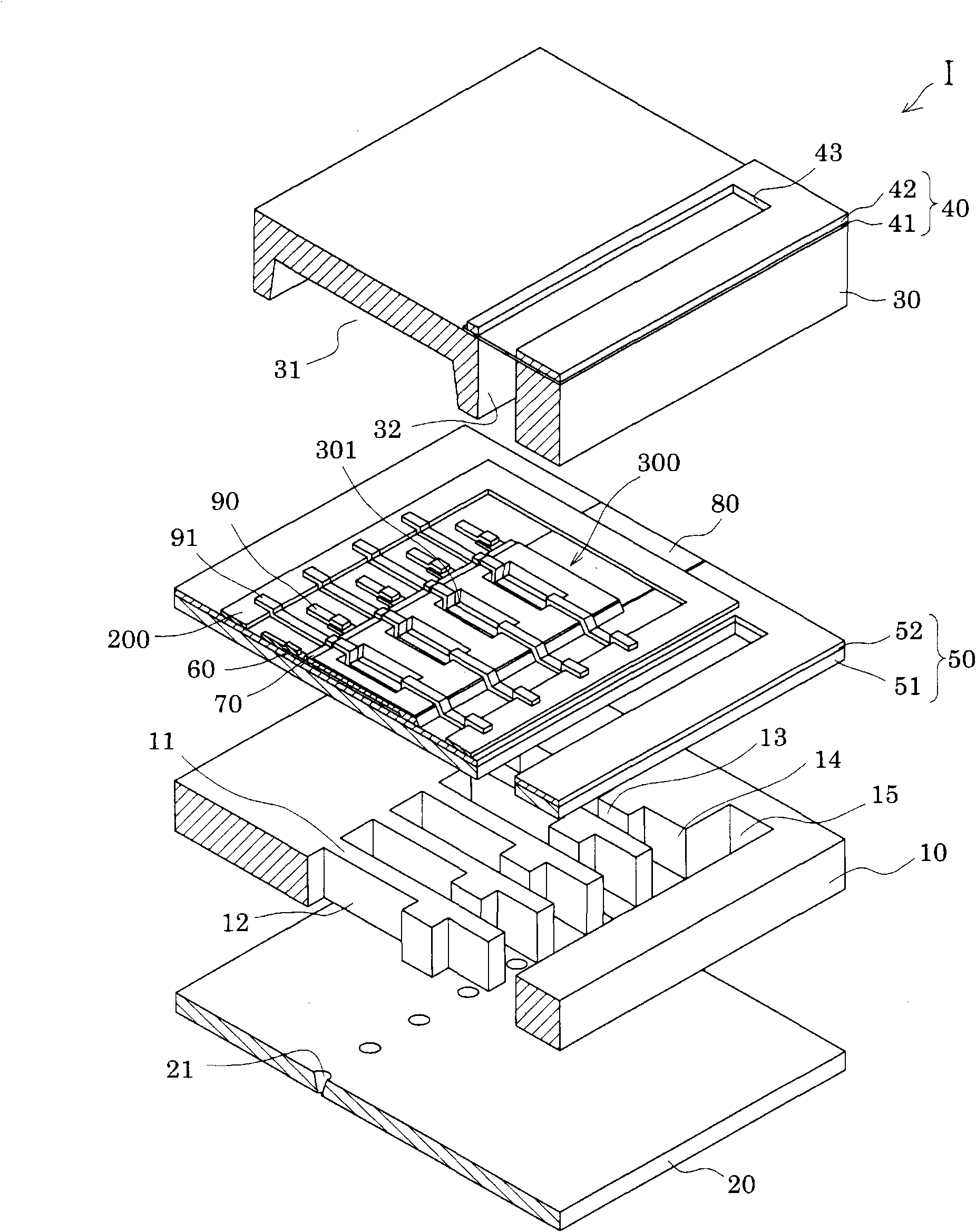

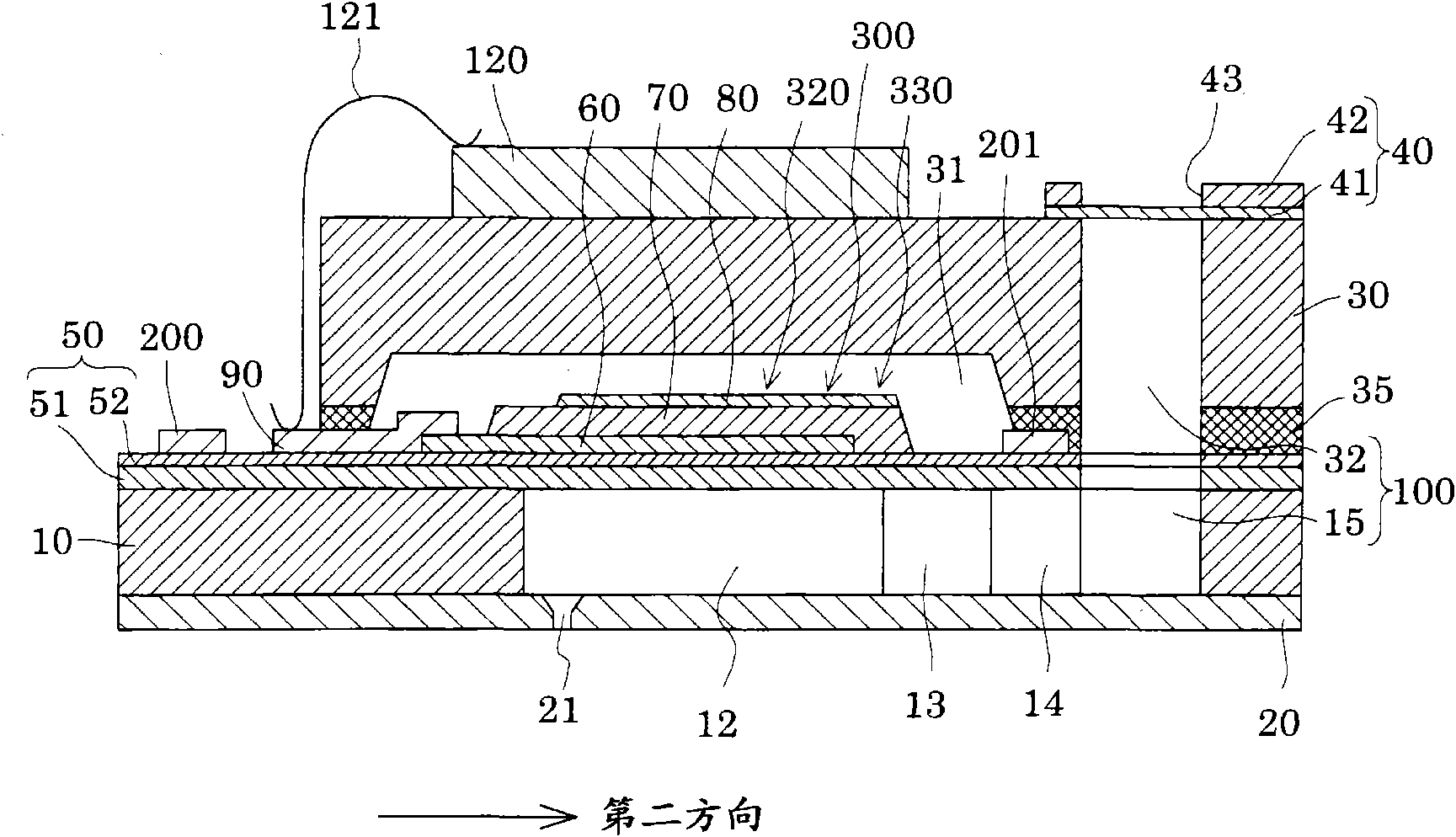

Liquid crystal display device

Provided is a liquid crystal display device, wherein each of a plurality of signal lines (13) comprises, in a region corresponding to each of a plurality of pixel rows, a first straight line section (13a) that overlaps with only one pixel electrode (11) of two pixel electrodes (11) adjacent to the signal line (13), a second straight line section (13b) that overlaps with only the other pixel electrode (11), and a bent section (13c) that connects the first straight line section (13a) and the second straight line section (13b) to each other, and the positions in the column direction of the bent sections (13c) of arbitrarily defined two signal lines (13) that are adjacent along the row direction among the plurality of signal lines (13) are different from each other. Consequently, the source-to-drain capacitance (Csd) can be easily adjusted pixel by pixel.

Owner:SHARP KK

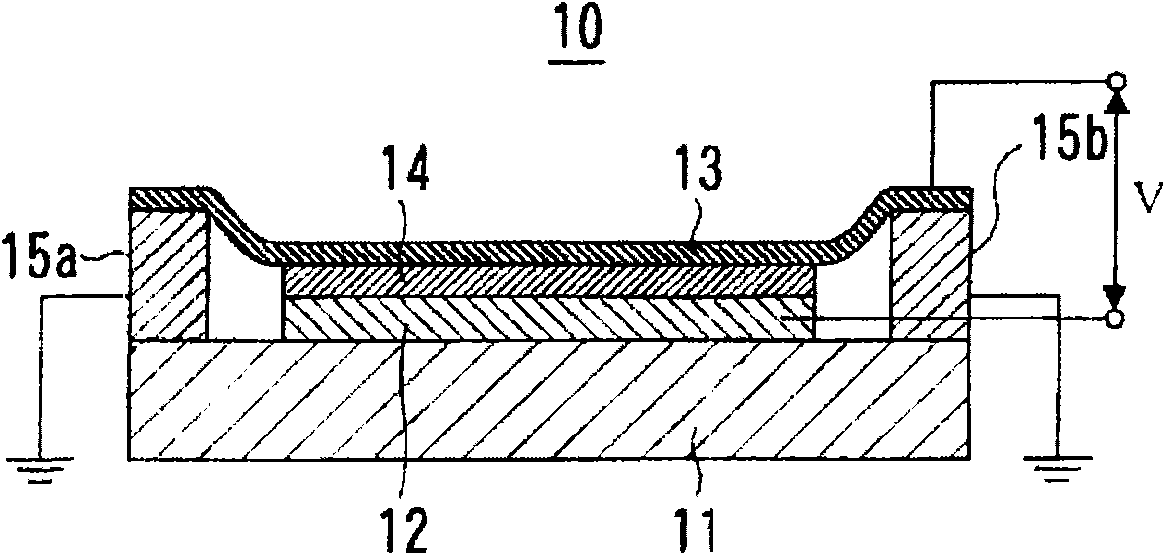

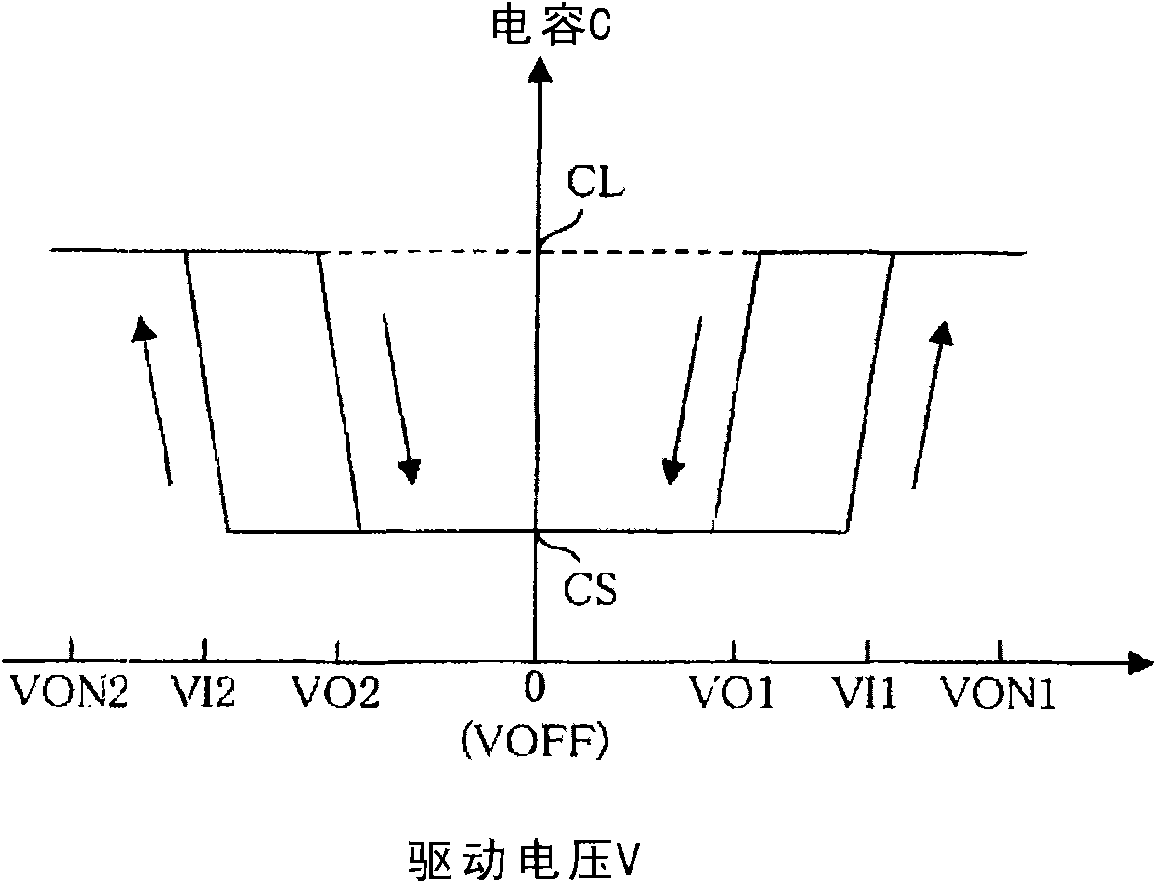

Variable capacitive element, variable capacitive device, and method for driving the variable capacitive element

InactiveCN102054587ASuppression offsetCapacitor with electrode distance variationCapacitanceEngineering

A variable capacitive element includes a first fixed electrode and a second fixed electrode that are insulated from each other, a movable electrode arranged to face the first fixed electrode and the second fixed electrode, a dielectric layer provided between the movable electrode and the first fixed electrode as well as the second fixed electrode, a first wiring part for applying a first driving voltage to the first fixed electrode with reference to a potential of the movable electrode, and a second wiring part for applying a second driving voltage to the second fixed electrode with reference to the potential of the movable electrode, the second driving voltage having a polarity different from a polarity of the first driving voltage.

Owner:FUJITSU LTD

Liquid ejecting head, liquid ejecting head unit, and liquid ejecting apparatus

ActiveCN102211454AUniform spray characteristicsSuppress crosstalkInking apparatusLiquid jetVoltage drop

The invention provides a liquid ejecting head, a liquid ejecting head unit, and a liquid ejecting apparatus, which can suppress a crosstalk between piezoelectric elements and through a partition wall, as well as a voltage drop, thereby suppressing deviation of ink droplet landing position and stabilizing liquid ejection characteristic, thus contributing to improving printing quality. The piezoelectric element includes a first electrode serving as an individual electrode, a piezoelectric layer, and a second electrode serving as a common electrode is attached on a face of a flow path substrate via a vibrating plate. A piezoelectric active portion defined by the first electrode and the second electrode serving as a substantial driver of the piezoelectric element is provided in a region opposing the pressure chamber. An opening formed by removing the second electrode and the piezoelectric layer is provided in a region of the piezoelectric element opposing the partition wall. A wiring electrode and the second electrode provided on the flow path substrate are connected via a common lead electrode provided on the piezoelectric active portion, and the common lead electrode is provided at least on the partition wall inside the opening.

Owner:SEIKO EPSON CORP

Polyvinyl acetal resin film for laminated glass

ActiveCN110494404ASuppression offsetAvoid deformationSynthetic resin layered productsVehicle componentsPolymer sciencePolyvinyl alcohol

The present invention relates to a polyvinyl acetal resin film for laminated glass, the polyvinyl acetal resin film having a thickness of 10-350 [mu]m, wherein the viscosity of a solution, in which toluene / ethanol=1 / 1 (mass ratio) and the concentration of a polyvinyl acetal resin in a resin composition constituting the polyvinyl acetal resin film is 10 mass%, is 100-1000 mPa*s as measured at 20 DEG C and 30 rpm using a Brookfield-type (B-type) viscometer, the amount of a plasticizer in the polyvinyl acetal resin film is 0-20 mass% on the basis of the total mass of the resin composition constituting the polyvinyl acetal resin film, the average spacing Sm value of recesses and protrusions on at least one surface is at least 500 [mu]m, and the ratio Sm / Rz of the average spacing Sm value of the recesses and protrusions on at least one surface with respect to the ten-point average roughness Rz value is at least 200.

Owner:KURARAY EURO GMBH

Matkapuhelimen antenni antenn f?r mobiltetefon

InactiveCN1485949ARealize widebandSuppression offsetCollapsable antennas meansSimultaneous aerial operationsResonanceMetal

A mobile phone antenna has: a first conductive radiation element that is formed in a sheet metal conductor and resonates at a predetermined resonance frequency; a second conductive radiation element that is formed in the sheet metal conductor and resonates at the predetermined resonance frequency; and a ground that is connected through a conductive ground connector with the second conductive radiation element. The ground is placed such that the ground is not opposed to the first and second conductive radiation elements.

Owner:HITACHI CABLE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com