Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38results about How to "Increase deposition thickness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

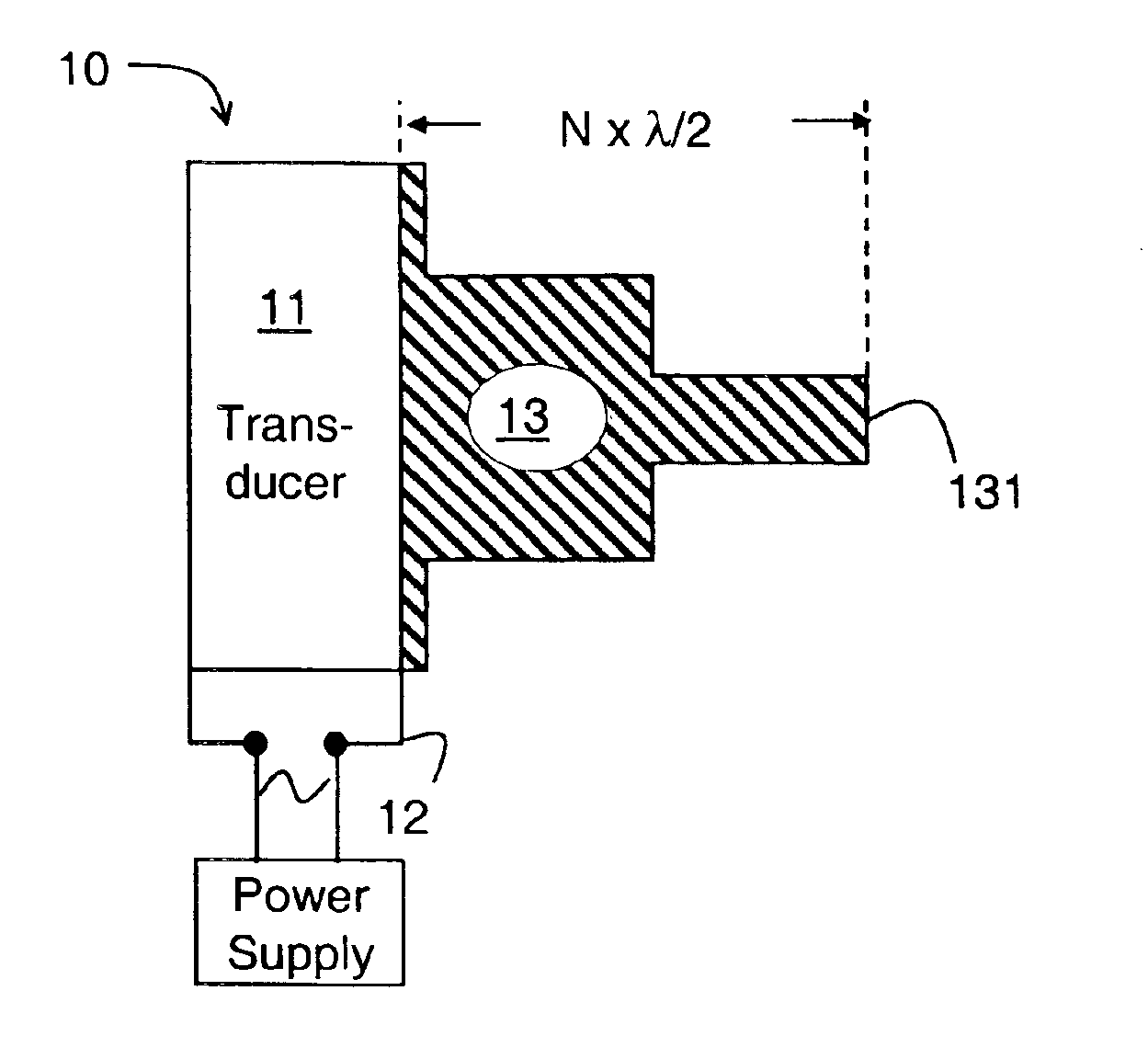

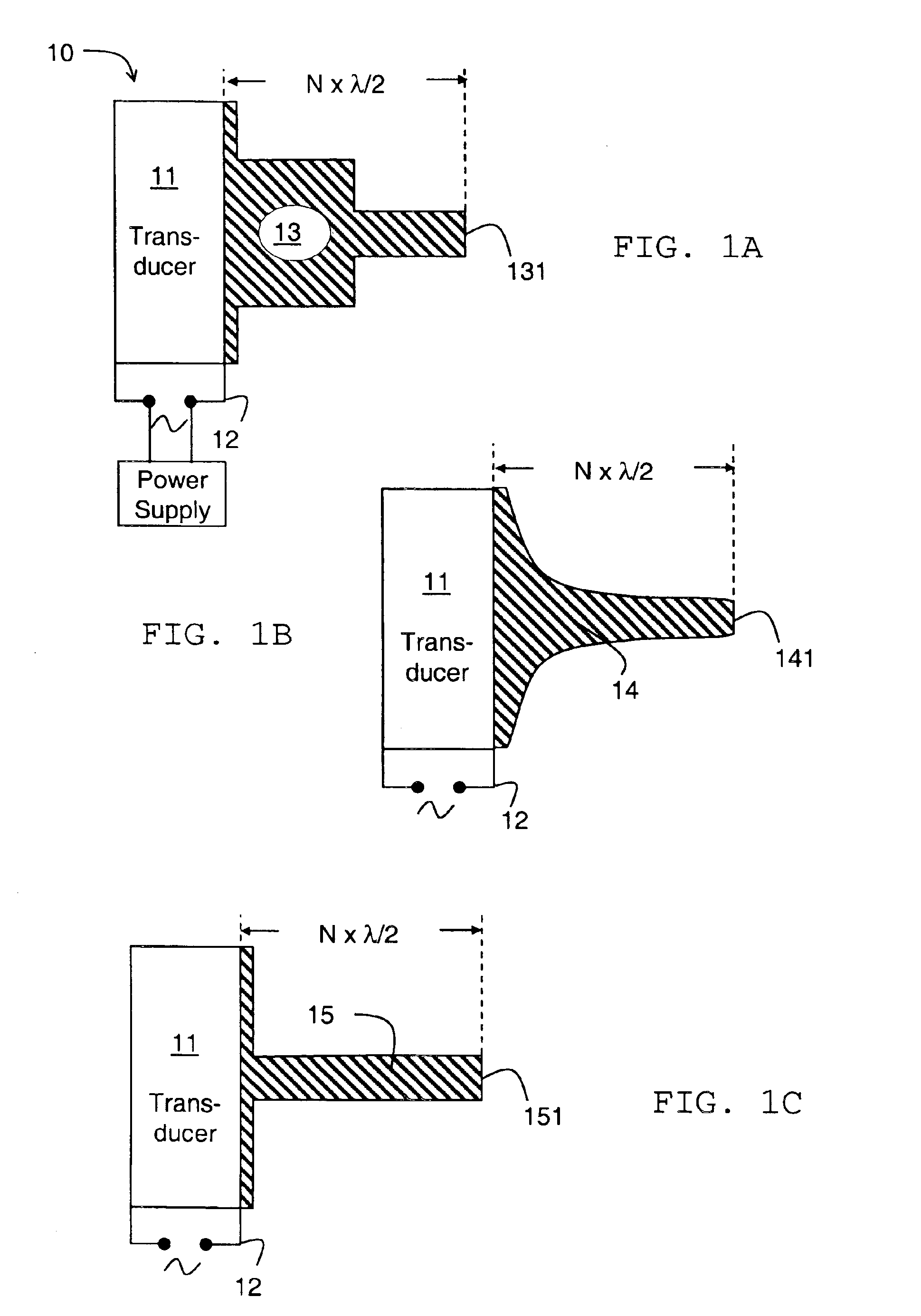

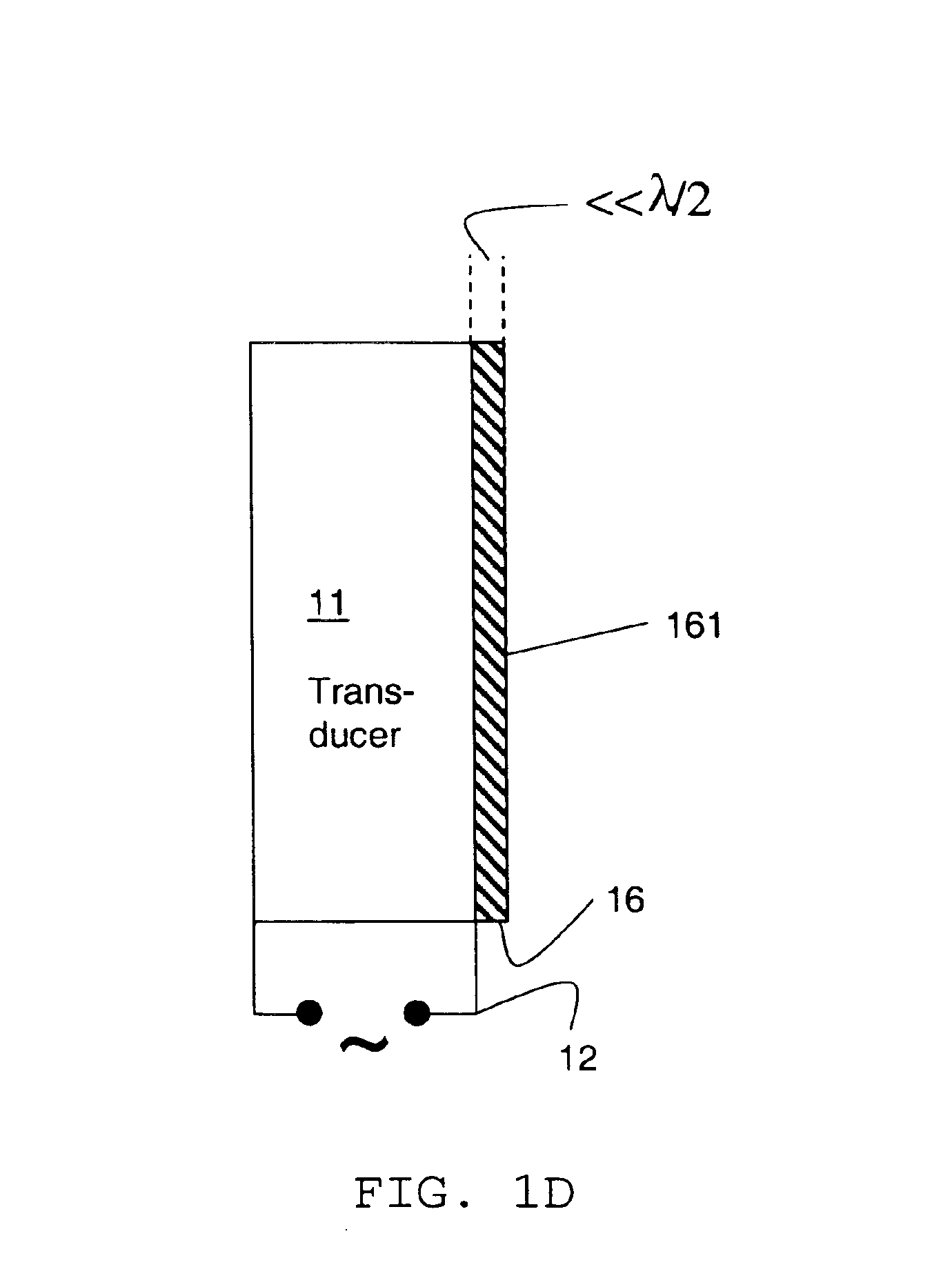

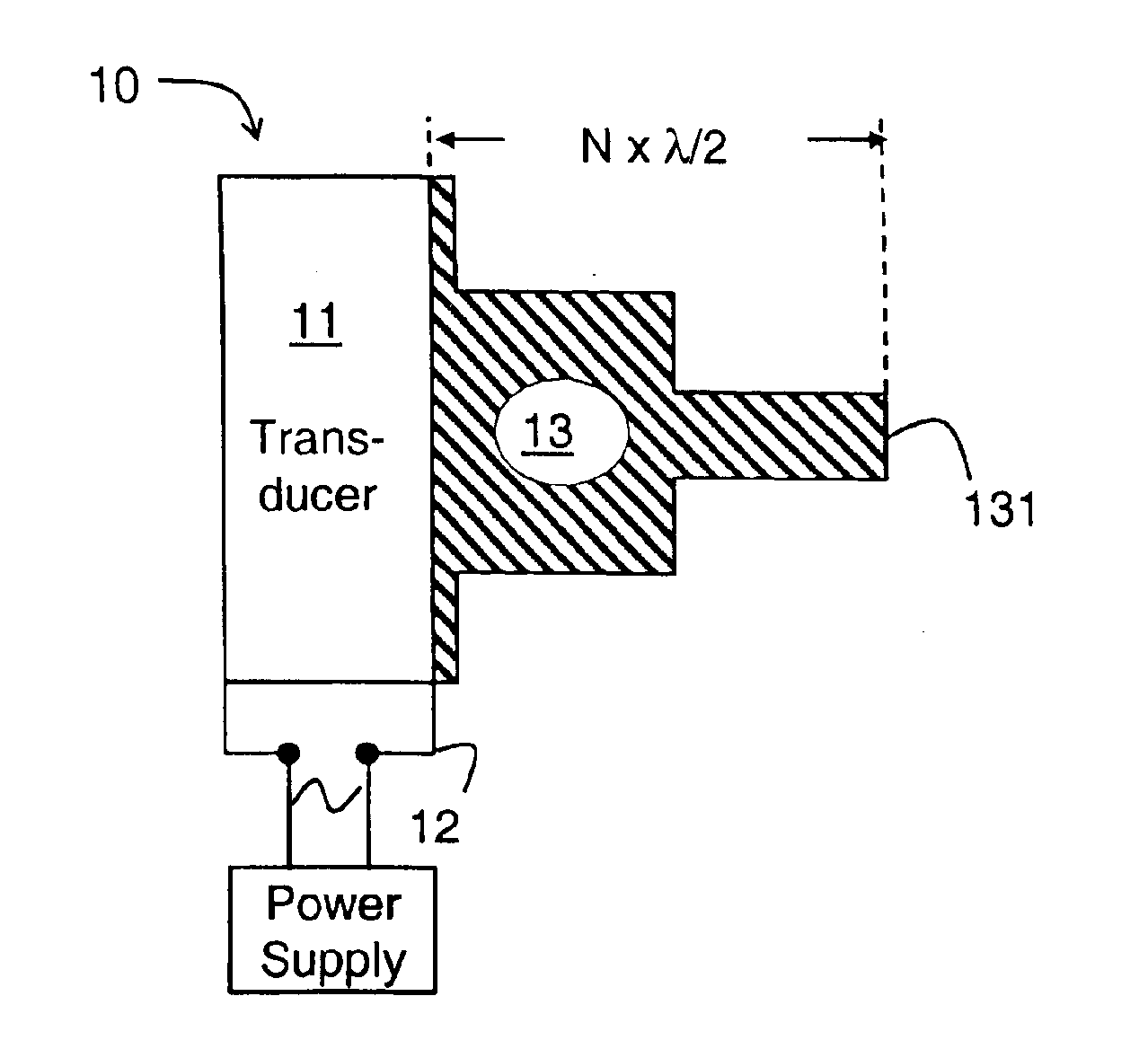

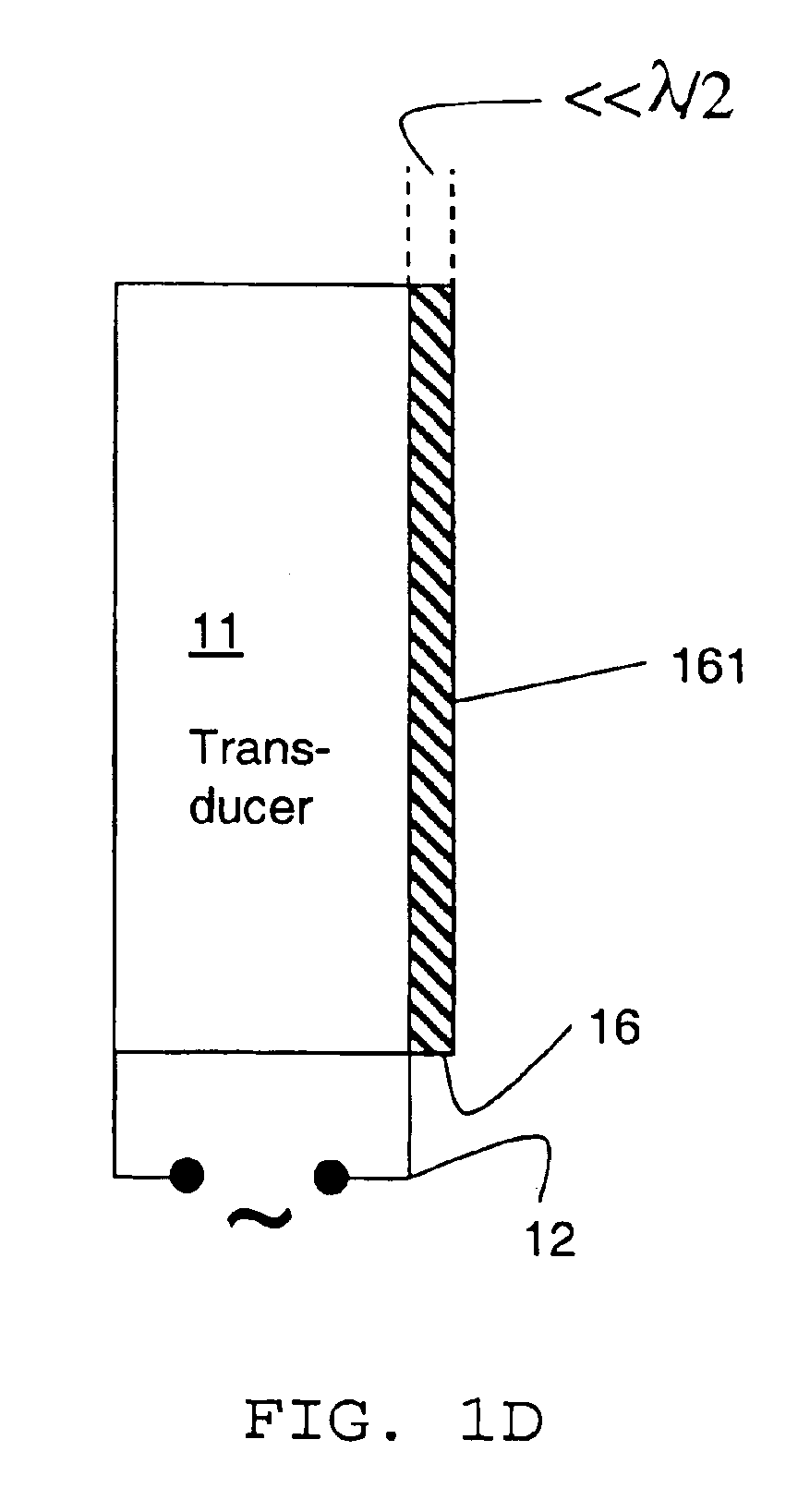

Deposition monitoring system

InactiveUS6880402B1Increase deposition thicknessConveniently determinedVibration measurement in solidsAnalysing fluids using sonic/ultrasonic/infrasonic wavesMonitoring systemOperation mode

Described is an apparatus for detecting and removing deposits from a surface exposed to wellbore fluids. The apparatus can monitor the rate of deposition and subsequently remove the deposited material. The combination of detection apparatus and removal apparatus provides an instrument with self-cleaning operation mode.

Owner:SCHLUMBERGER TECH CORP

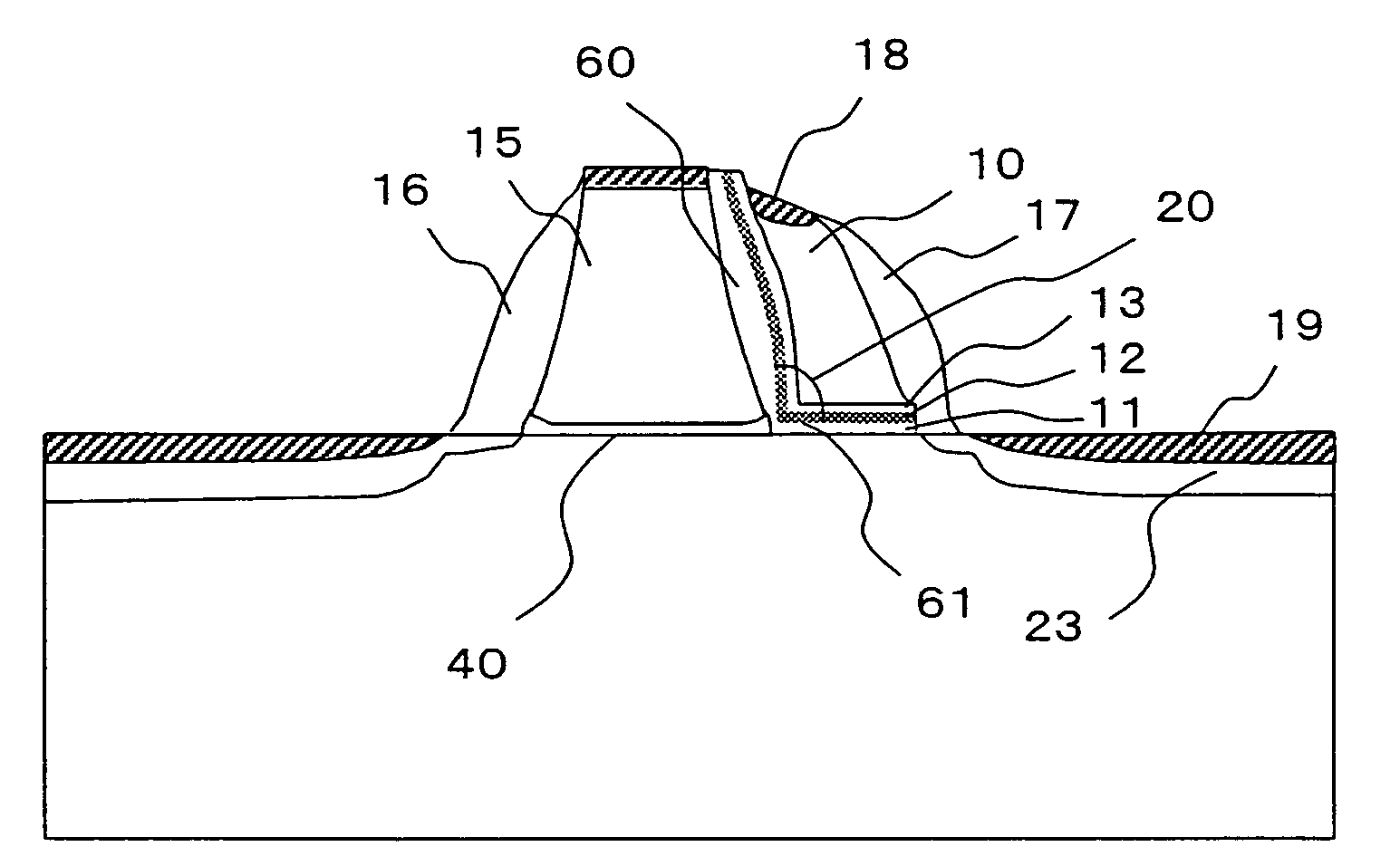

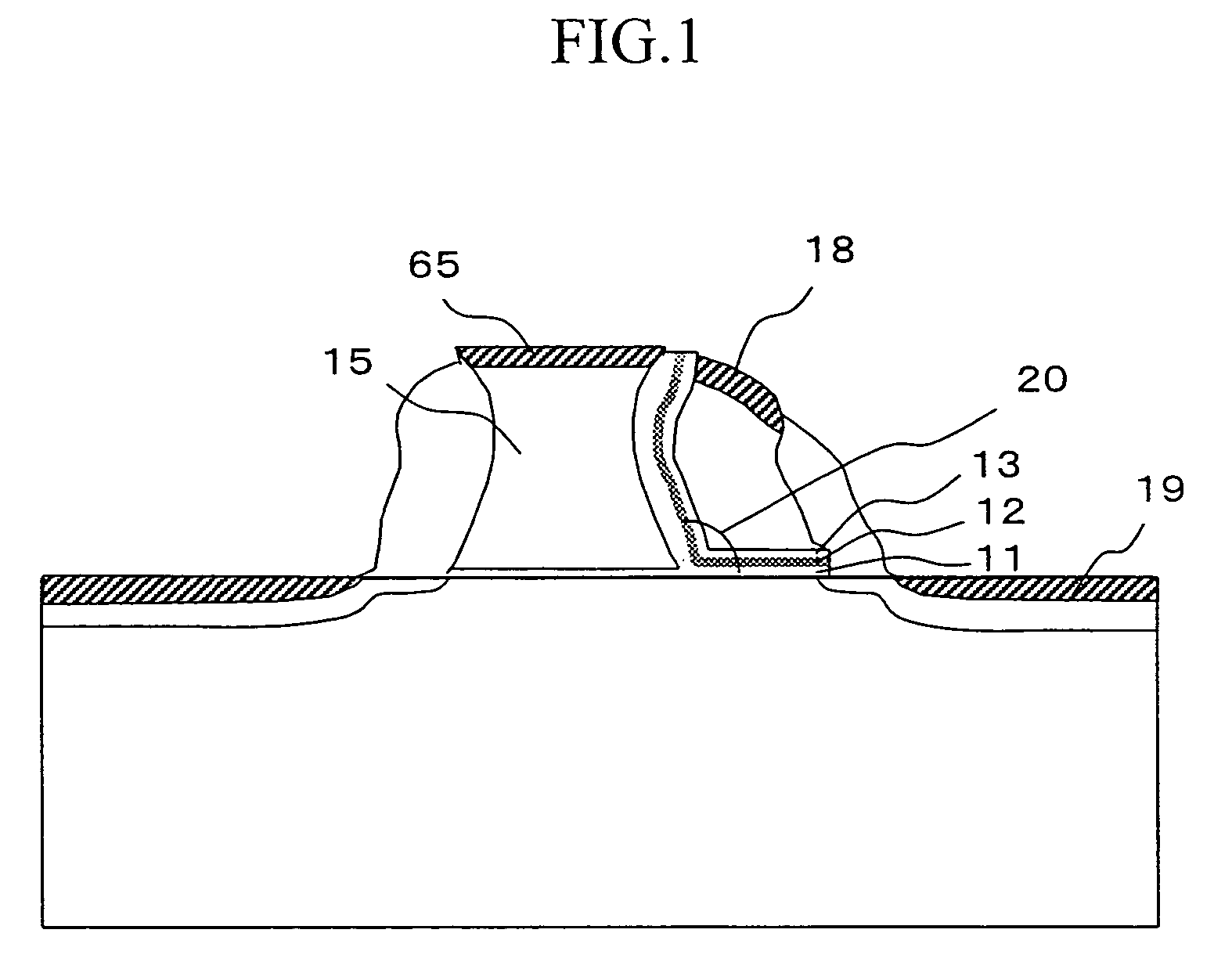

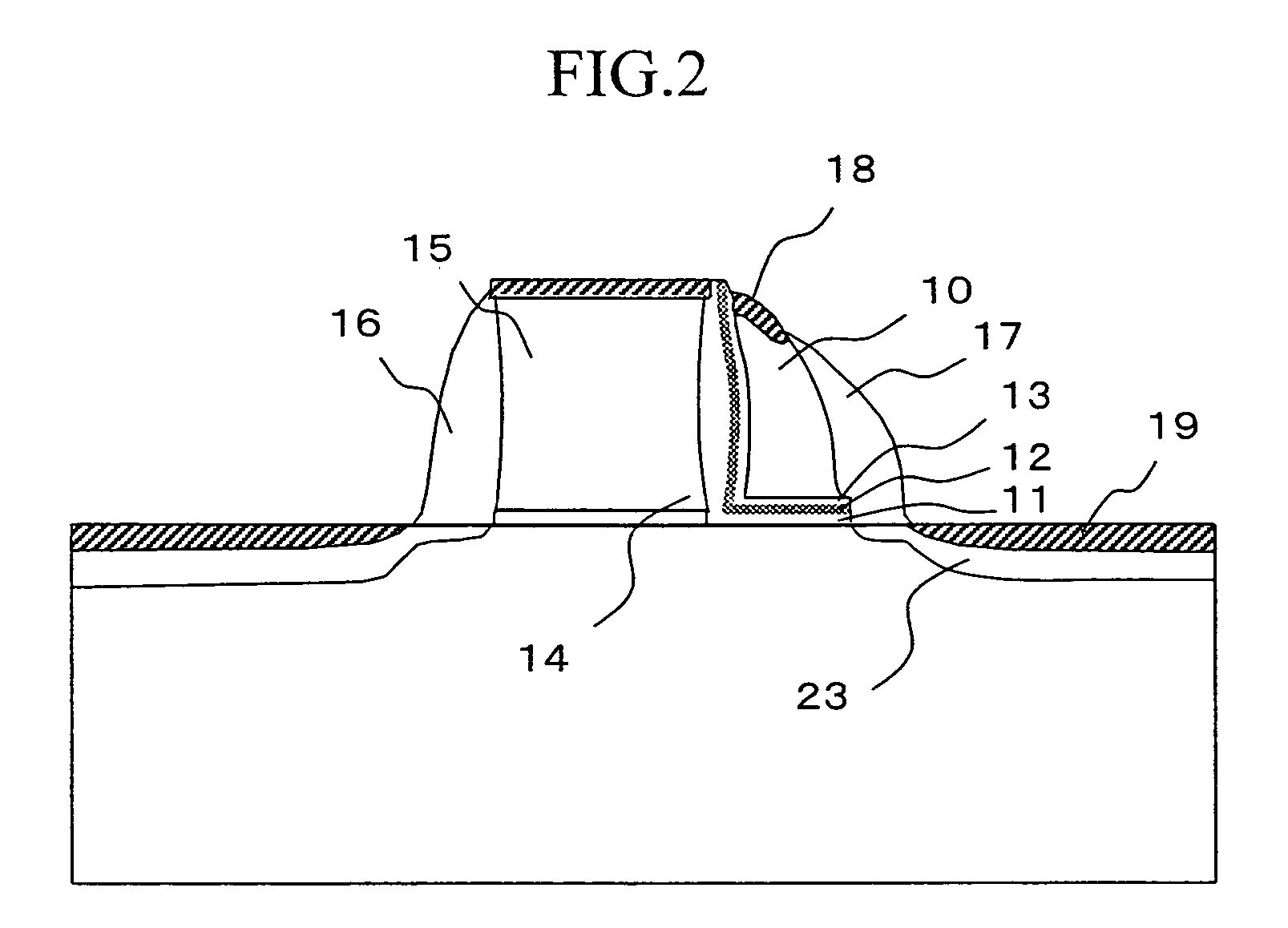

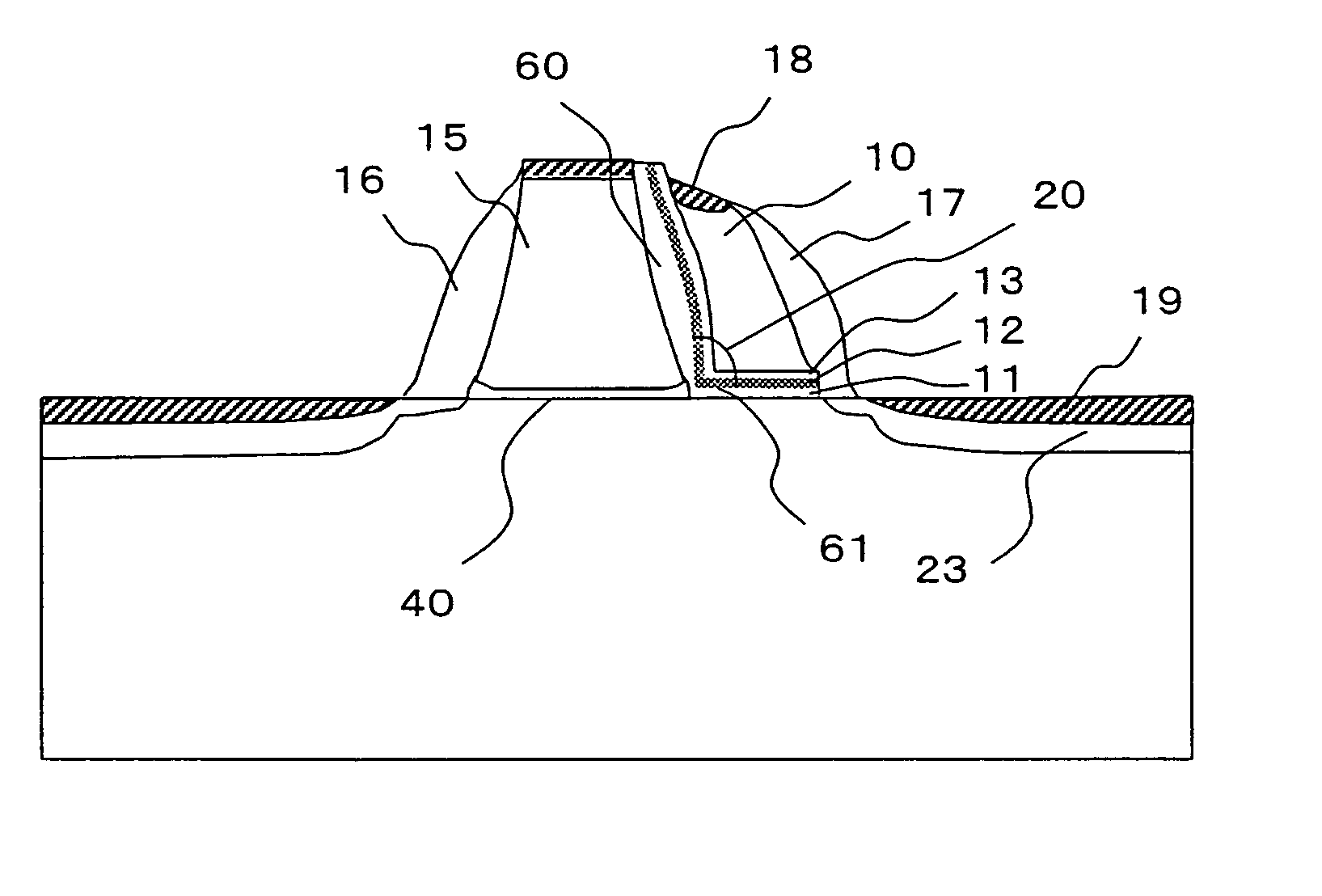

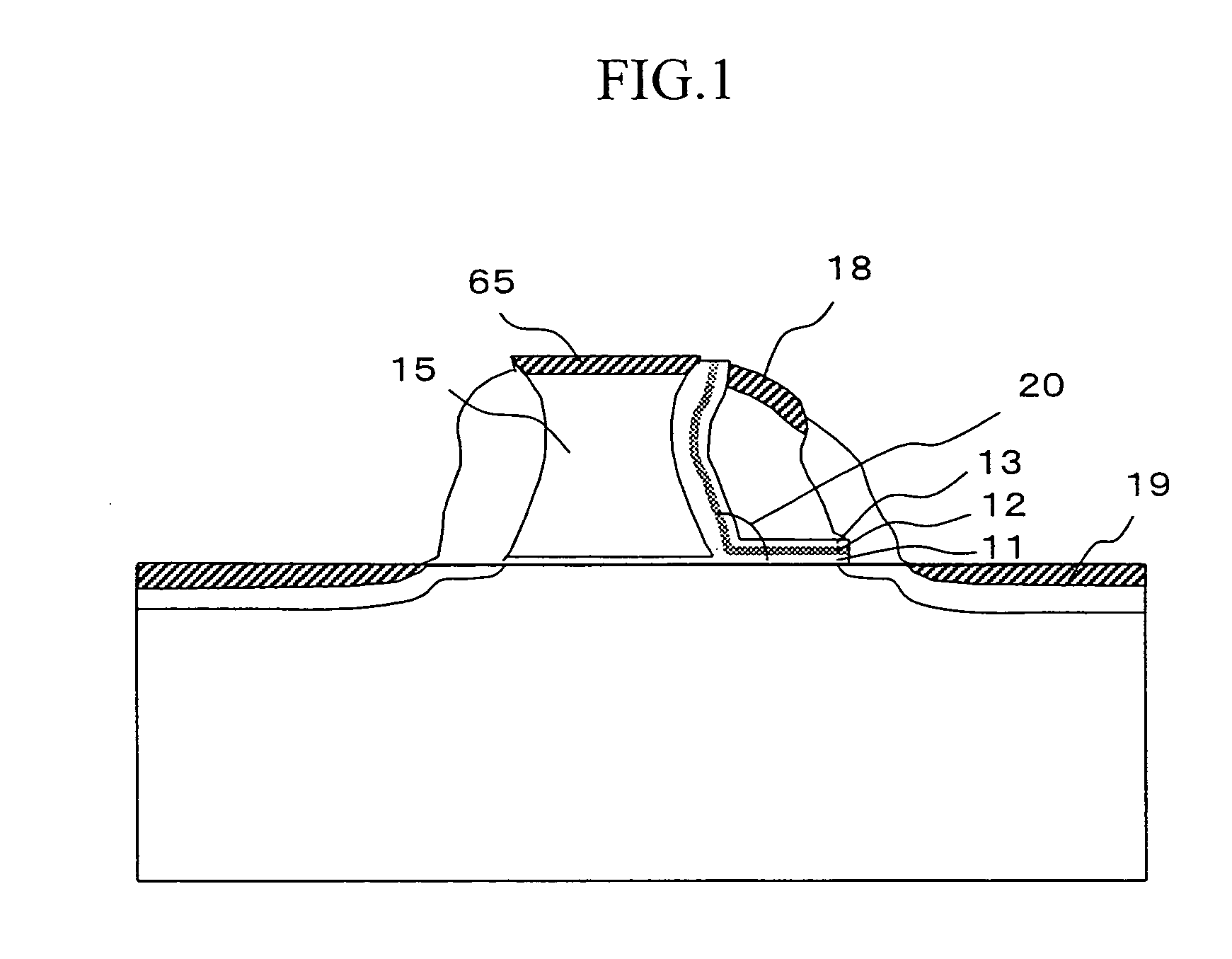

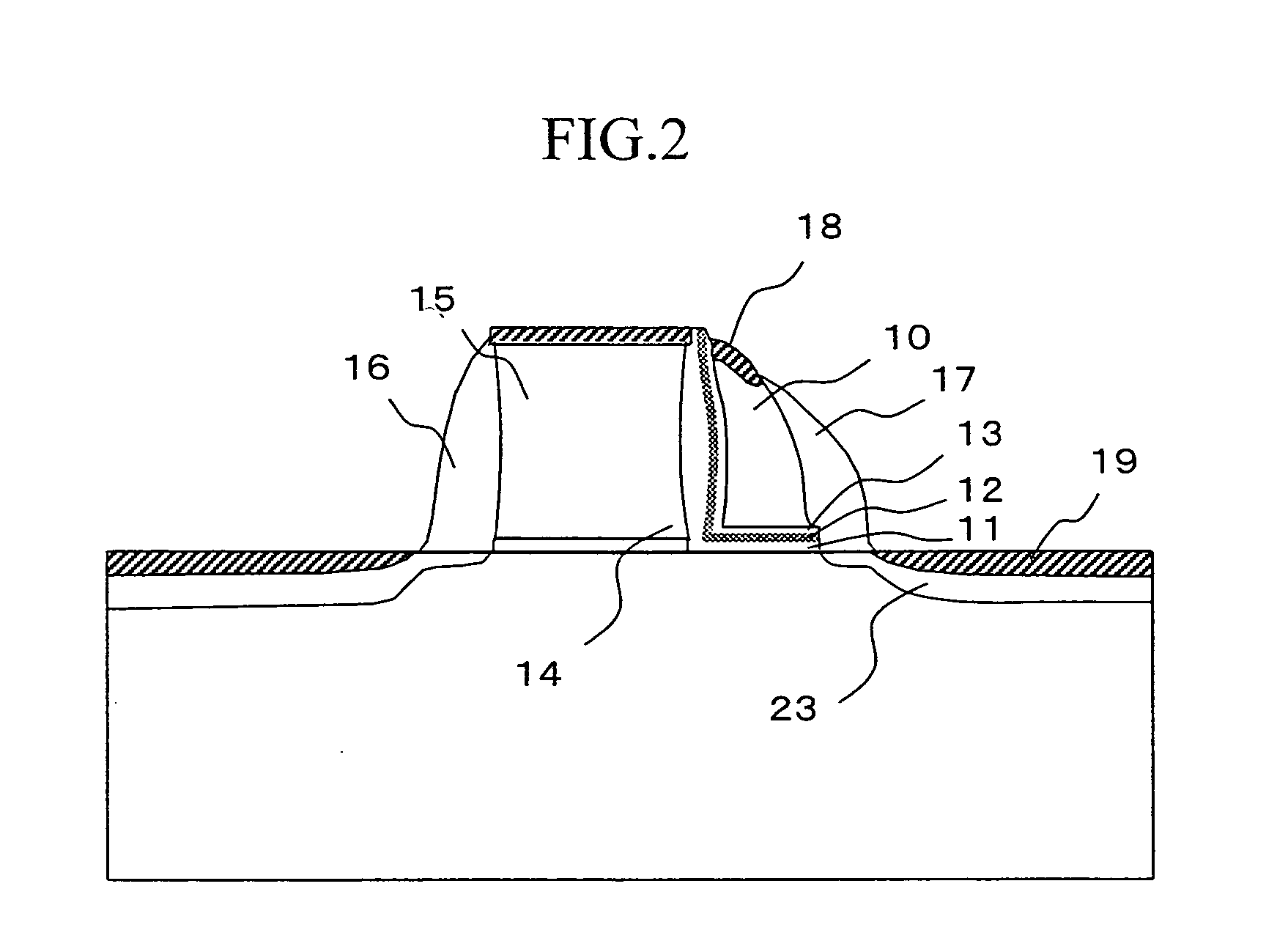

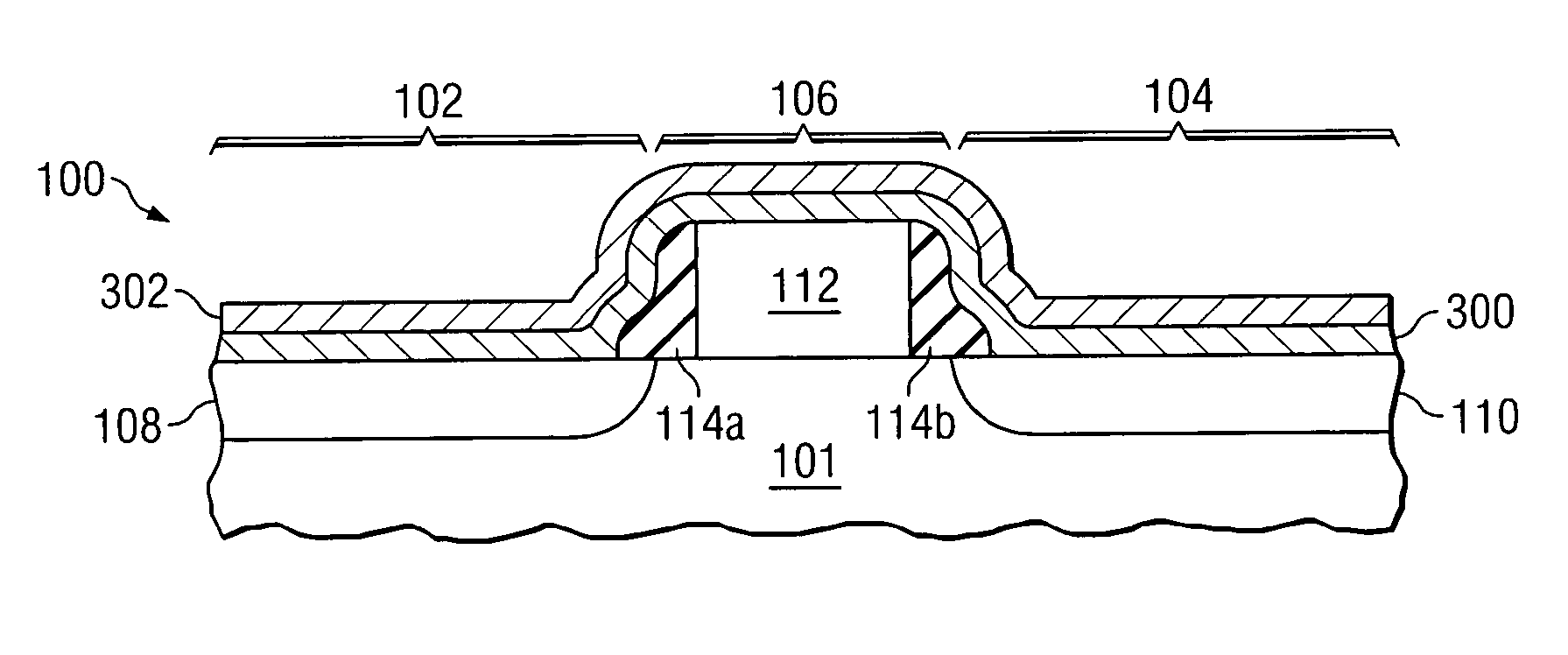

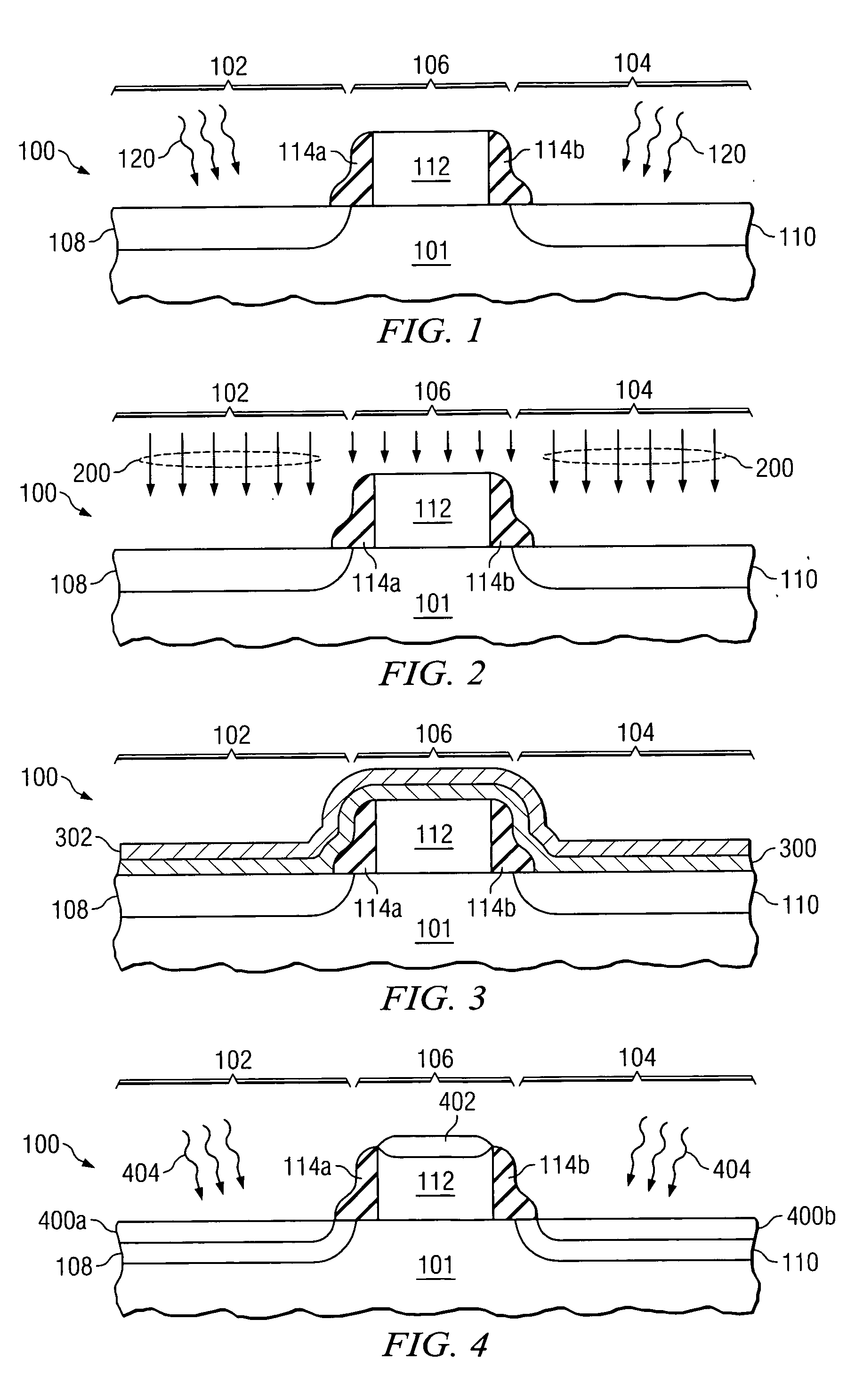

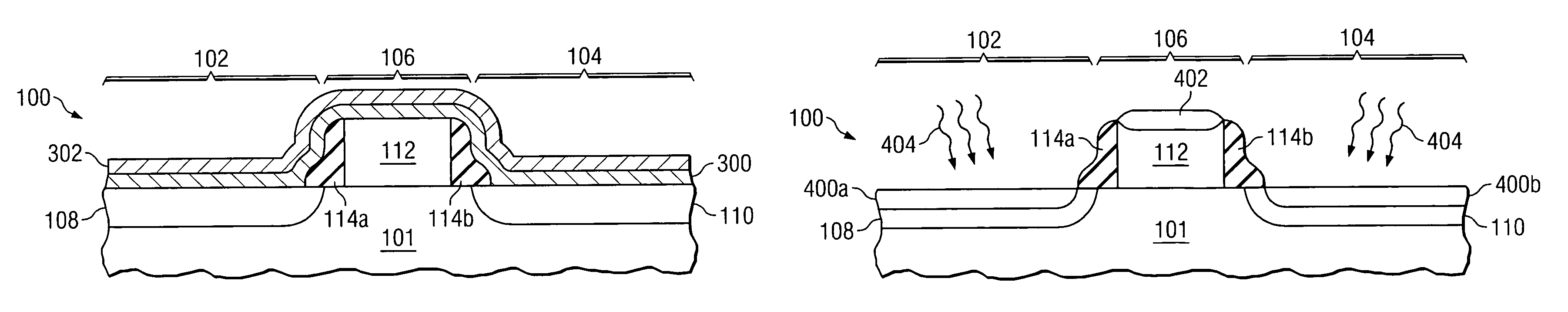

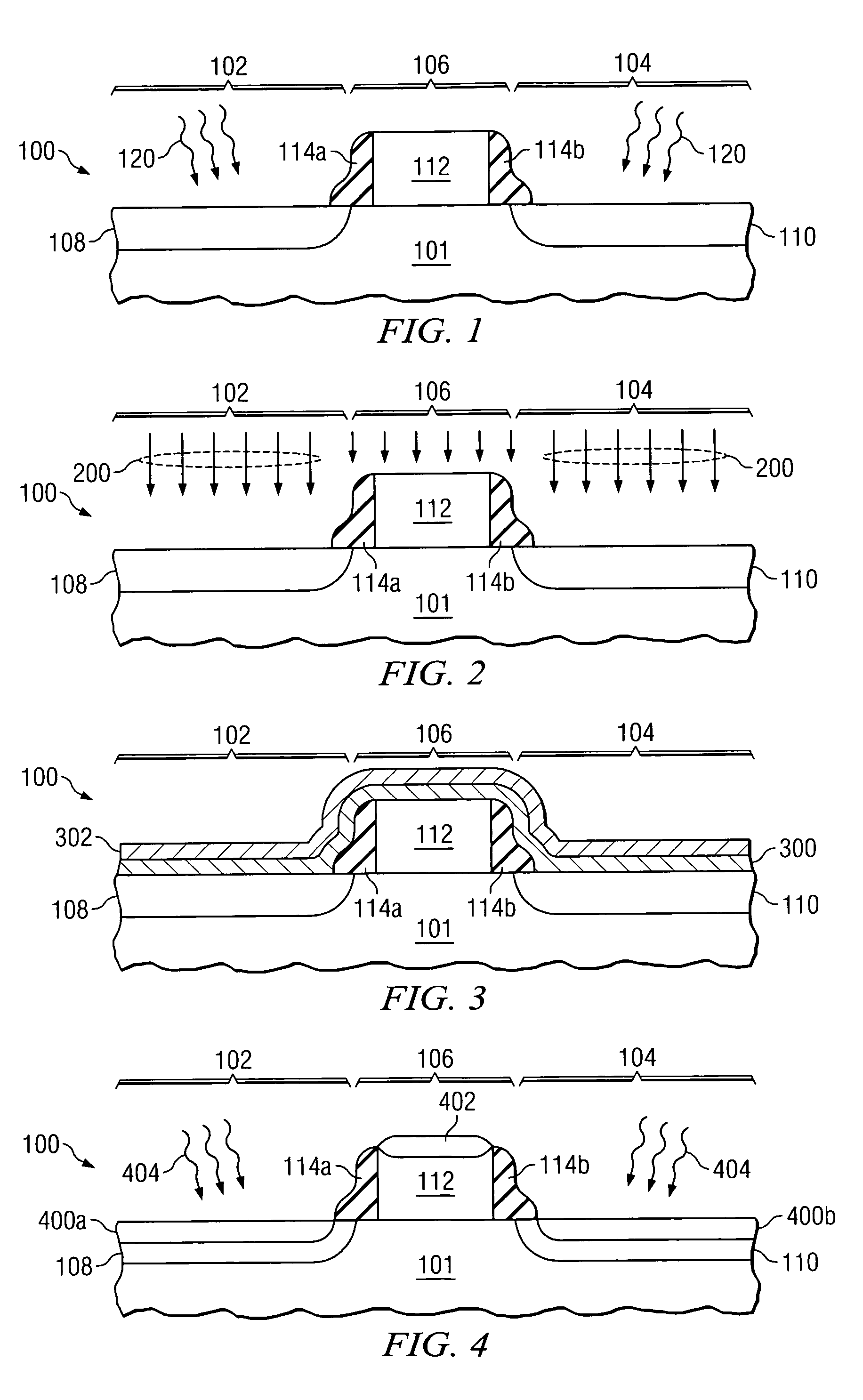

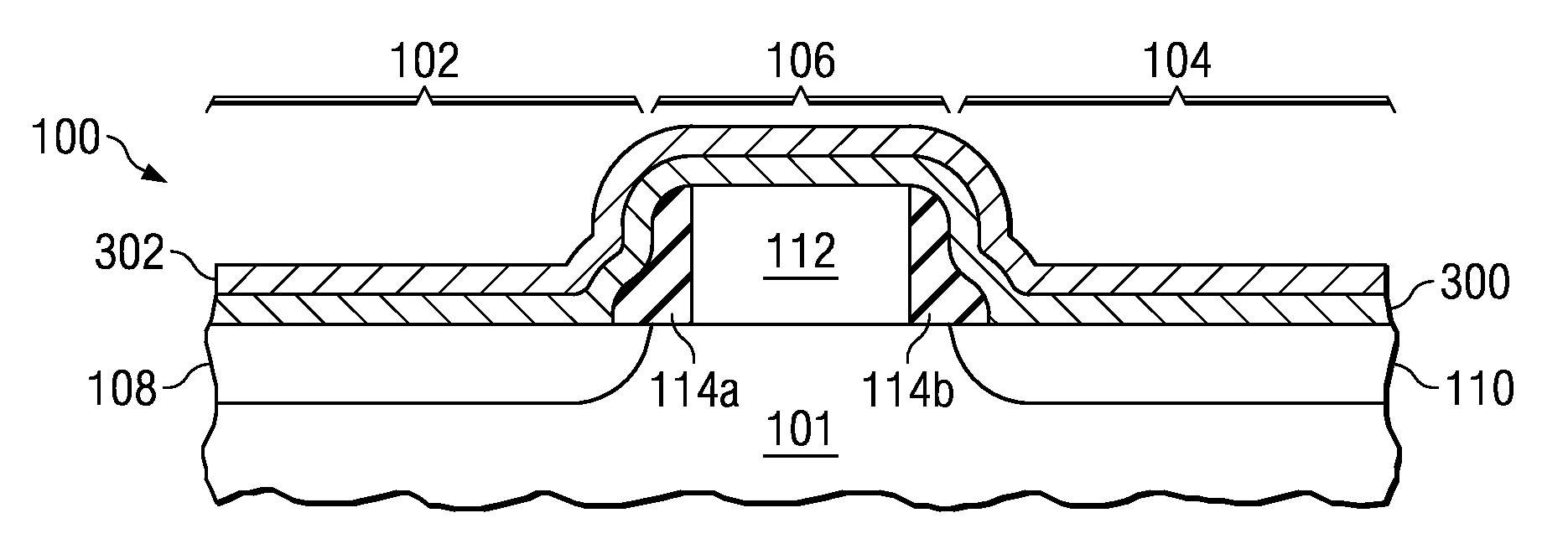

Nonvolatile semiconductor memory device with tapered sidewall gate and method of manufacturing the same

ActiveUS7235441B2Increase deposition thicknessReduce thicknessTransistorSolid-state devicesSalicideEngineering

In a split gate type nonvolatile memory cell in which a MOS transistor for a nonvolatile memory using a charge storing film and a MOS transistor for selecting it are adjacently formed, the charge storing characteristic is improved and the resistance of the gate electrode is reduced. In order to prevent the thickness reduction at the corner portion of the charge storing film and improve the charge storing characteristic, a taper is formed on the sidewall of the select gate electrode. Also, in order to stably perform a silicide process for reducing the resistance of the self-aligned gate electrode, the sidewall of the select gate electrode is recessed. Alternatively, a discontinuity is formed between the upper portion of the self-aligned gate electrode and the upper portion of the select gate electrode.

Owner:RENESAS ELECTRONICS CORP

Downhole deposition monitoring system

InactiveUS6886406B1Increase deposition thicknessConveniently determinedVibration measurement in solidsAnalysing fluids using sonic/ultrasonic/infrasonic wavesMonitoring systemEngineering

Described is a downhole apparatus for detecting and removing deposits from a surface exposed to wellbore fluids. The apparatus can monitor the rate of deposition and subsequently remove the deposited material. The combination of detection apparatus and removal apparatus provides a downhole instrument with self-cleaning operation mode.

Owner:SCHLUMBERGER TECH CORP

Nonvolatile semiconductor memory device with tapered sidewall gate and method of manufacturing the same

ActiveUS20050085039A1Increase currentRun at high speedTransistorSolid-state devicesSalicideEngineering

In a split gate type nonvolatile memory cell in which a MOS transistor for a nonvolatile memory using a charge storing film and a MOS transistor for selecting it are adjacently formed, the charge storing characteristic is improved and the resistance of the gate electrode is reduced. In order to prevent the thickness reduction at the corner portion of the charge storing film and improve the charge storing characteristic, a taper is formed on the sidewall of the select gate electrode. Also, in order to stably perform a silicide process for reducing the resistance of the self-aligned gate electrode, the sidewall of the select gate electrode is recessed. Alternatively, a discontinuity is formed between the upper portion of the self-aligned gate electrode and the upper portion of the select gate electrode.

Owner:RENESAS ELECTRONICS CORP

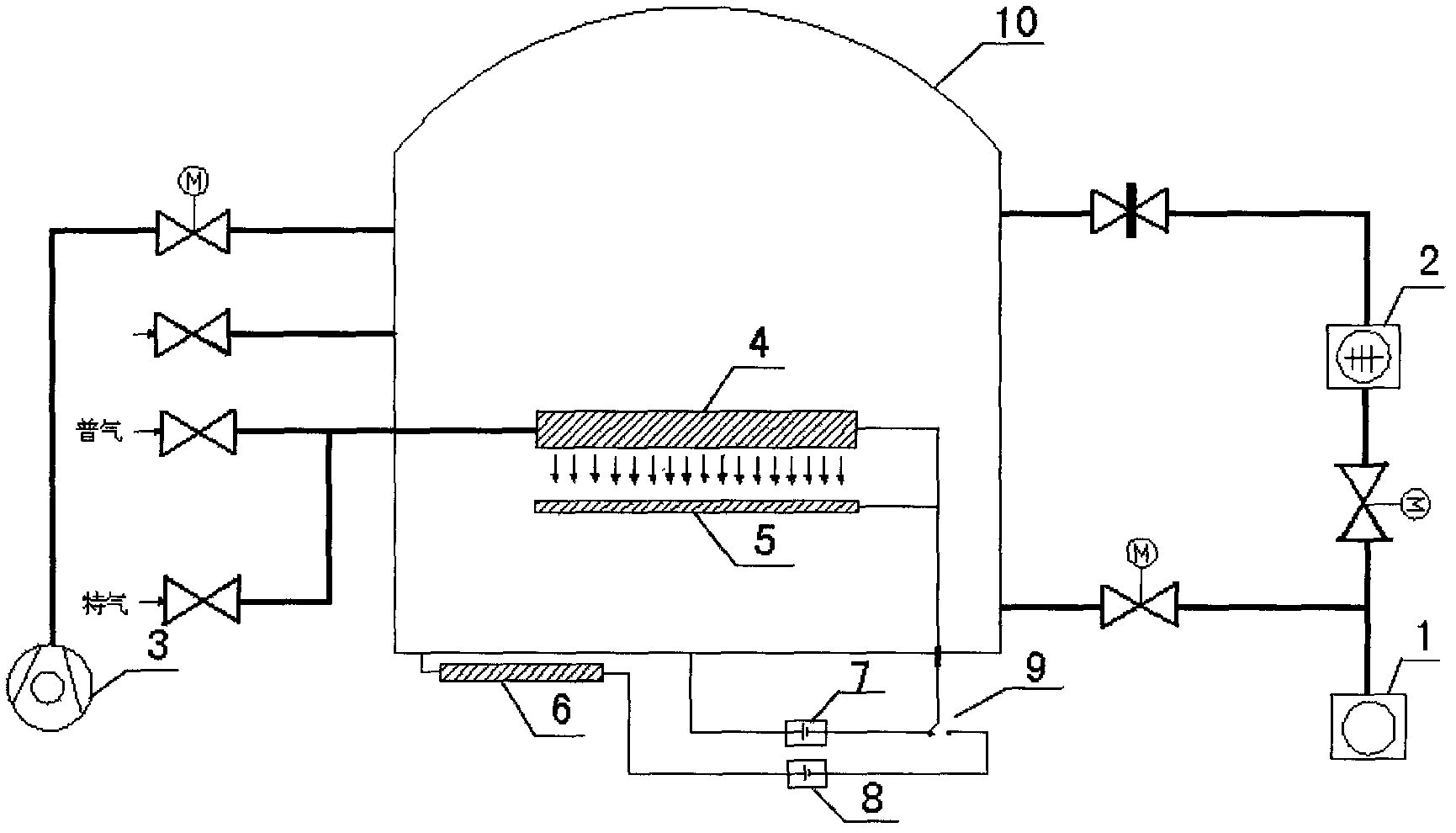

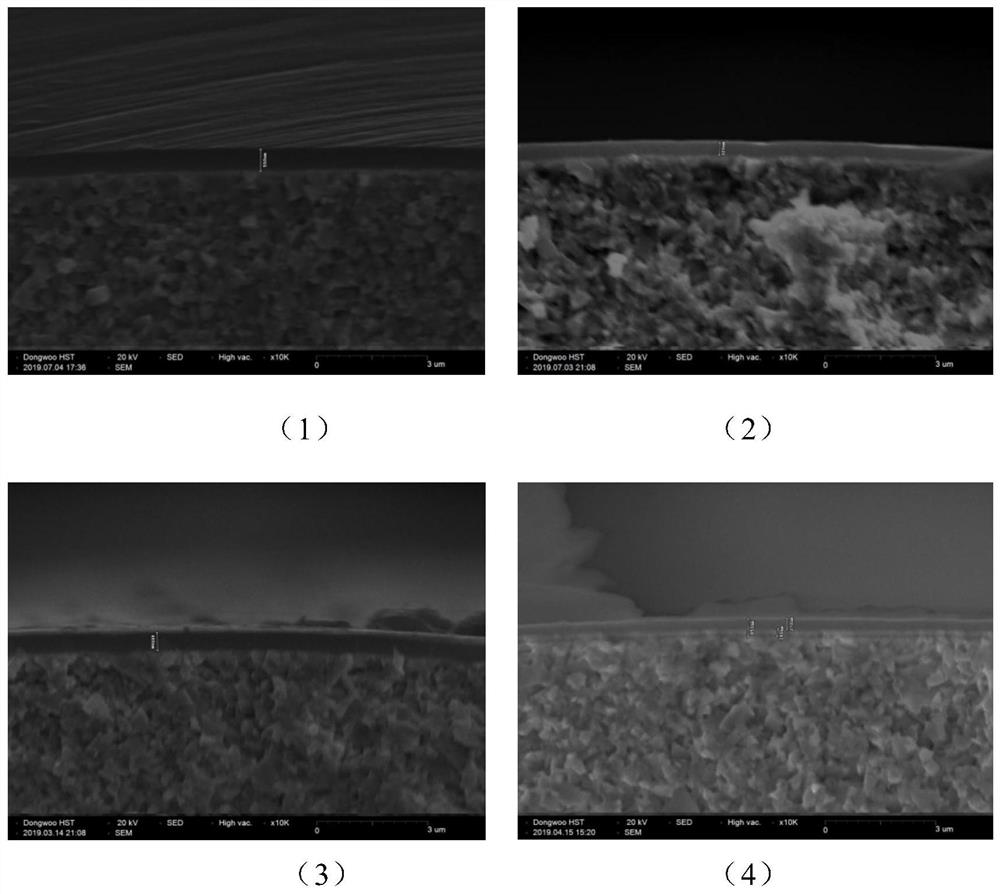

Ultra high speed preparation method for ultra thick diamond-like coating

ActiveCN102994967ASimple processGood thickness controllabilityVacuum evaporation coatingSputtering coatingSilanesPlasma effect

The present invention relates to an ultra high speed preparation method for an ultra thick diamond-like coating. According to the method, a plasma immersion ion injection and high density plasma chemical vapor deposition integration technology is adopted to achieve ultra high speed deposition of an ultra thick diamond-like coating on various sample substrates such as stainless steel, aluminum alloy, titanium alloy, copper, ceramics and the like, wherein a deposition rate is 80-140 nm / min. The method comprises: firstly performing silicon or nitrogen immersion ion injection on a sample substrate, and adopting high density plasma effect alternating deposition to periodically change silicon content in a diamond-like coating in mixing atmosphere of silane, acetylene and argon to finally obtain the ultra thick diamond-like coating with a thickness of 8-30 mum on the sample substrate. The obtained ultra thick diamond-like coating has characteristics of high film substrate binding strength, low friction coefficient and long service life.

Owner:LANZHOU INST OF CHEM PHYSICS CHINESE ACAD OF SCI

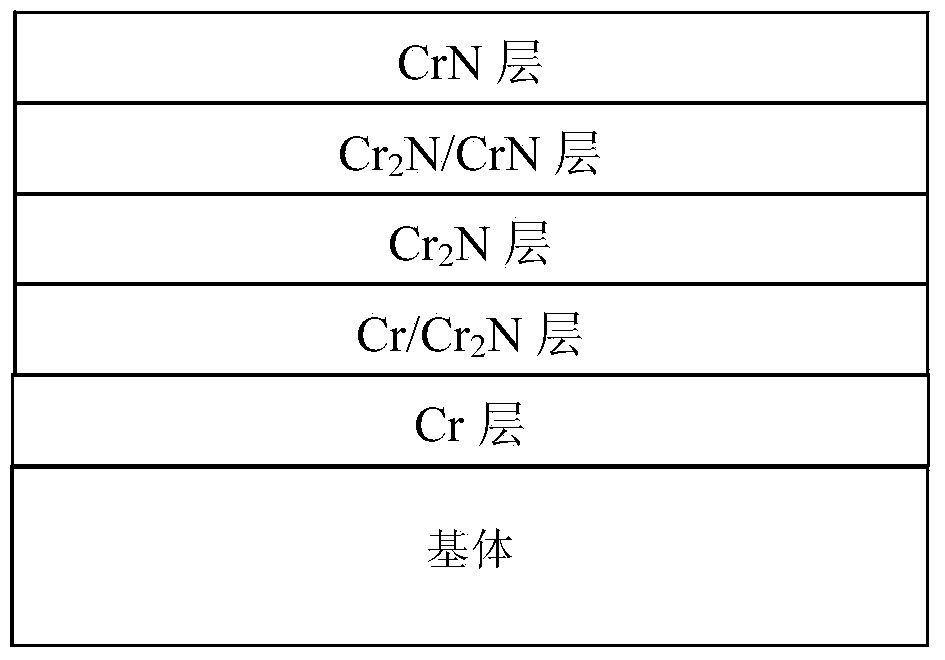

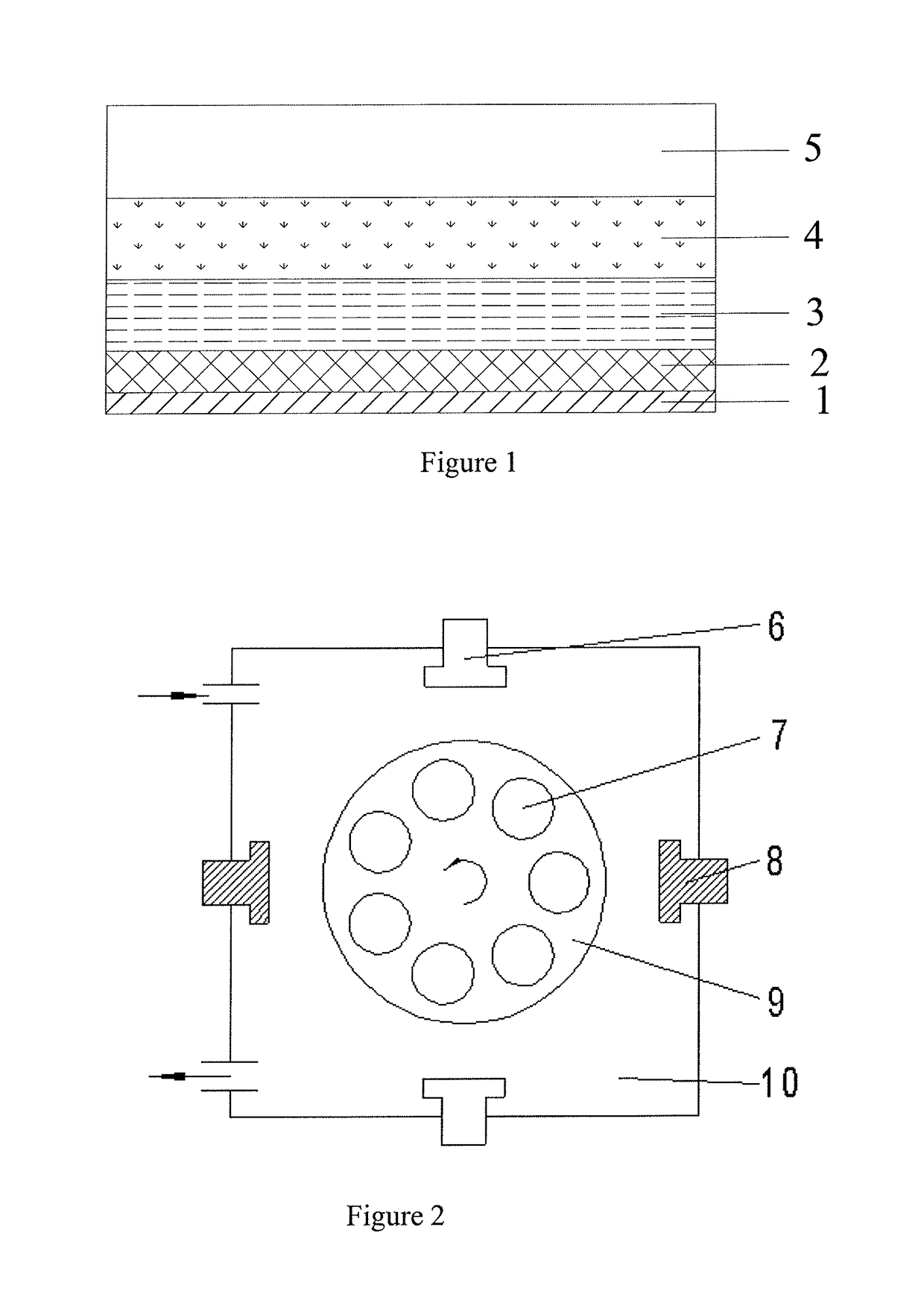

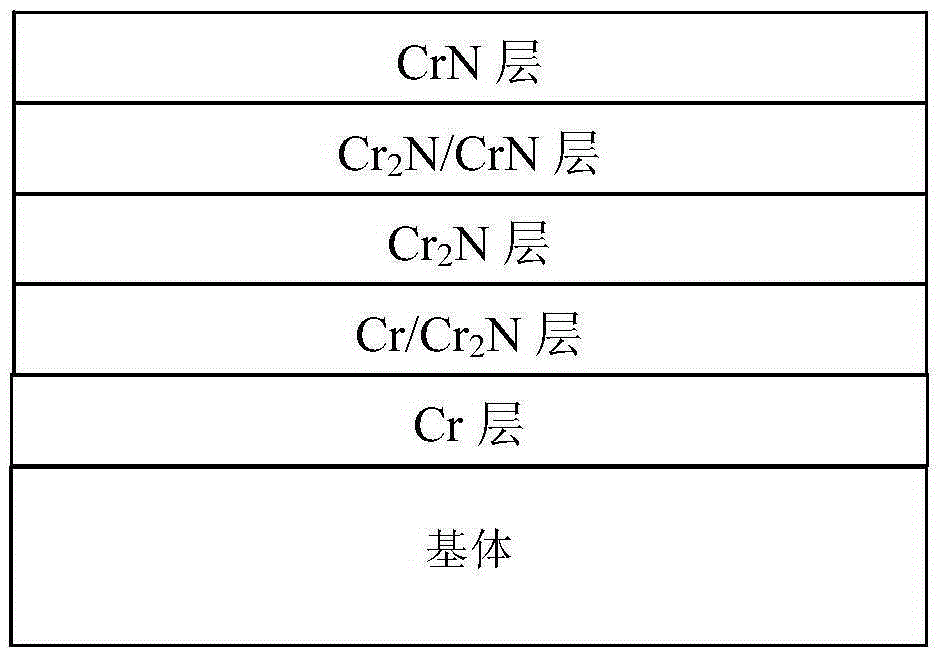

Composite coating on surface of valve sealing piece and preparation method for composite coating

ActiveCN103522627AImprove load bearing and wear resistanceAvoid failureVacuum evaporation coatingSputtering coatingNitrogen gasIon plating

The invention provides a composite coating on the surface of a valve sealing piece. The coating takes the valve sealing piece as a base body and consists of a Cr layer, a Cr / Cr2N layer formed by mixing Cr and Cr2N, a Cr2N layer, a Cr2N / CrN layer formed by mixing the Cr2N and CrN, and a CrN layer. Compared with an existing CrN coating with a single structure, the composite coating with multiple layers of gradients has the advantages that the bearing and anti-abrasion capability and the corrosion resistance are improved. Furthermore, the composite coating is prepared by a multi-arc ion plating technology, and the respective layers are obtained by sequentially performing deposition on the surface of the base body by controlling the argon flow, the nitrogen flow and the deposition time; the preparation method is simple and feasible; batch production can be realized; the composite coating has a good application prospect.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

Device and method for realizing three-dimensional printing micro-nano structure by utilizing alternating-current electrospining

InactiveCN106182785AIncreasing the thicknessAvoid changes in the electric field distributionAdditive manufacturing apparatusThree dimensional modelNanofiber

The invention provides a device and a method for realizing a three-dimensional printing micro-nano structure by utilizing alternating-current electrospining. The method comprises the following steps of: putting printing raw materials into an injecting system, and forming spherical liquid drops of the printing raw materials at a needle head; applying alternating-current high-voltage electricity to the needle head and a receiving plate, and forming alternating high-voltage electric fields between the needle head and the receiving plate, enabling the printing raw materials to form single jet flow under the action of the alternating high-voltage electric fields, and depositing the single jet flow on the receiving plate to form micro-nano fibers; enabling the temperature of the receiving plate to be stabilized to be lower than a smelting point of the printing raw materials, and curing micro-nano fibers; controlling the receiving plate to move, thereby obtaining layered sections of a three-dimensional model; and sequentially scanning each layer of the three-dimensional model to complete printing of the three-dimensional model. The method can effectively improve three-dimensional printing precision.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

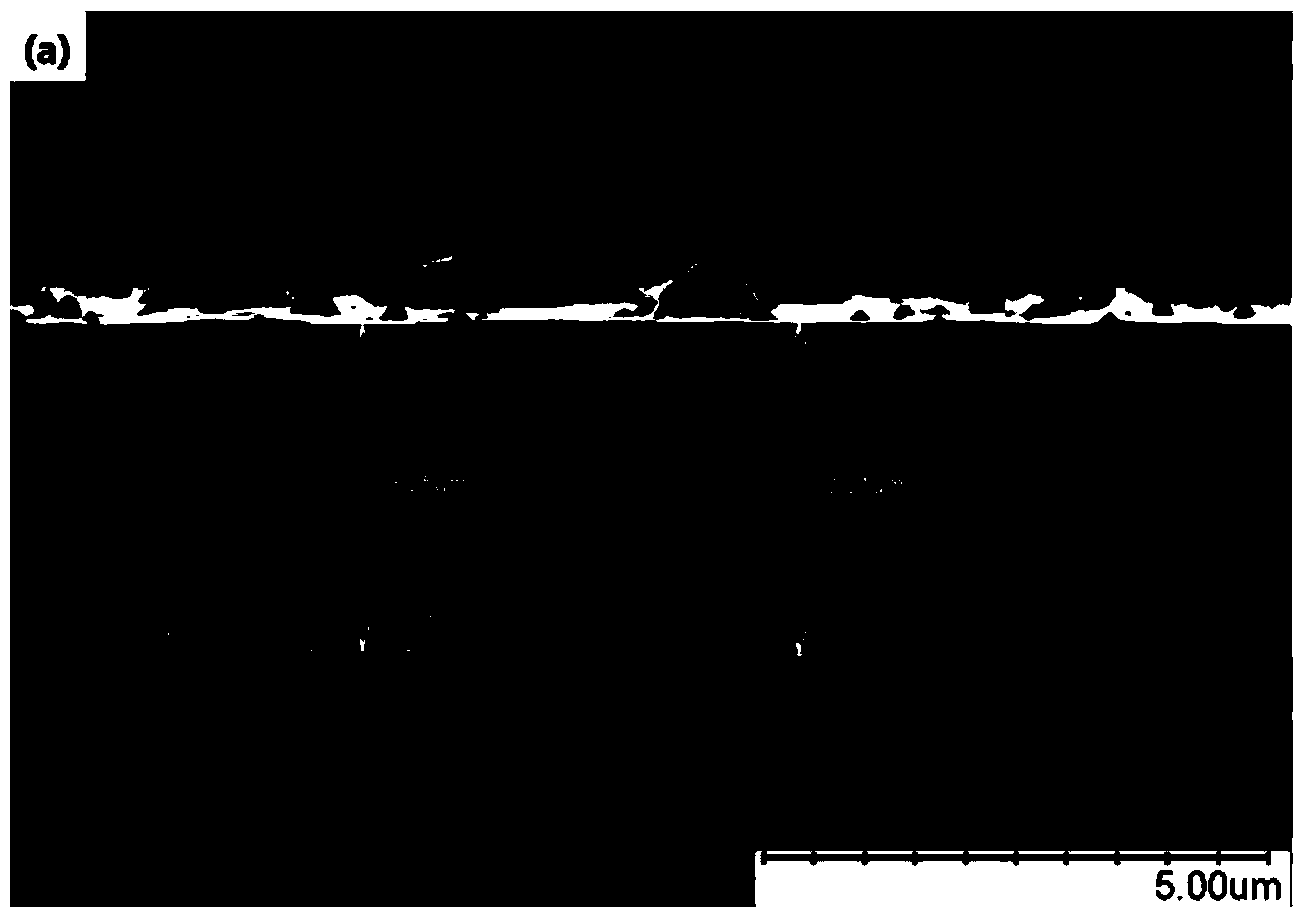

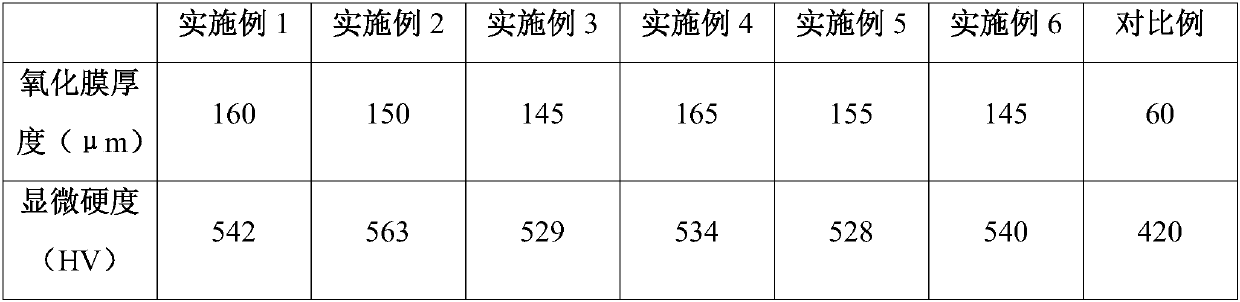

Aluminum alloy anode oxidation technology

The invention belongs to the technical field of metal surface treatment, and relates to an aluminum alloy anode oxidation technology. According to the technology, an aluminum alloy section is arrangedin an electrolytic bath loaded with oxidation electrolyte, so as to be electrolyzed; the electrolysis temperature is 10 to 30 DEG C; the aluminum alloy section is taken as an anode; a lead plate is taken as a cathode; an electrolysis mode is a direct current-alternating current overlapped method, so that an oxidation film is formed on the surface of the aluminum alloy section subjected to anode oxidation, the electrolysis speed is further improved through strict controlling of direct current-alternating current ratio, the deposition rate of the oxidation film is improved, an oxidation film with the thickness greater than 100 micrometers can be formed within 5min, the micro hardness of the obtained aluminum alloy section oxidation film is greatly improved, defects on the surface of the oxidation film are reduced, and the surface texture is denser.

Owner:CHINA ZHONGWANG

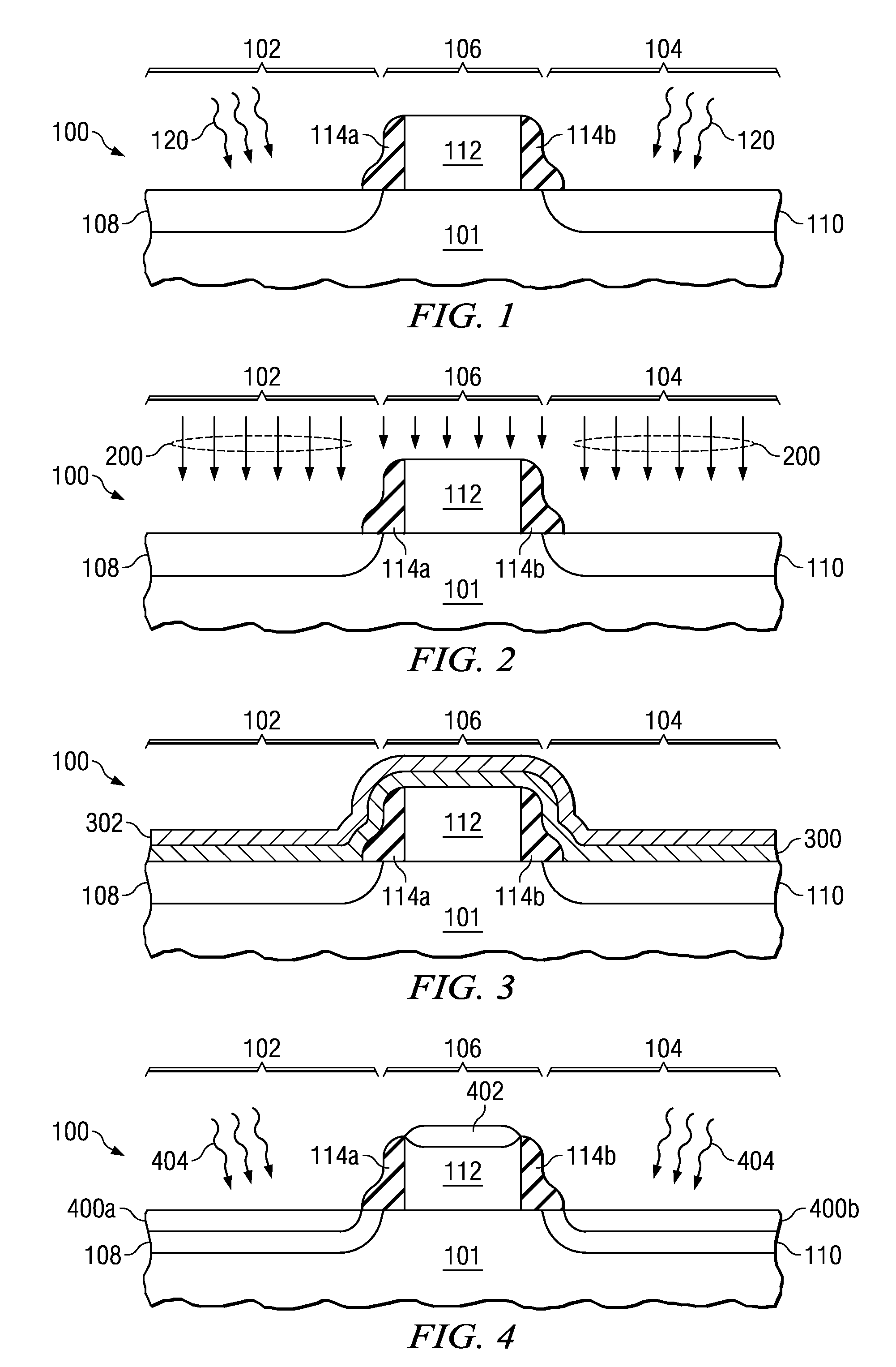

Method and system for improved nickel silicide

ActiveUS20060073656A1Improve performanceReduce sheet resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMaterials scienceNickel silicide

According to one embodiment of the invention, a method for nickel silicidation includes providing a substrate having a source region, a gate region, and a drain region, forming a source in the source region and a drain in the drain region, annealing the source and the drain, implanting, after the annealing the source and the drain, a heavy ion in the source region and the drain region, depositing a nickel layer in each of the source and drain regions, and heating the substrate to form a nickel silicide region in each of the source and drain regions by heating the substrate.

Owner:TEXAS INSTR INC

Preparation method of super-hydrophobic electromagnetic shielding fabric

InactiveCN110344241AImprove electromagnetic shielding performanceElectromagnetic shielding effectiveness has no significant changeLight resistant fibresLiquid repellent fibresCarnuba waxElectromagnetic shielding

The invention discloses a preparation method of a super-hydrophobic electromagnetic shielding fabric. The preparation method comprises the steps of firstly constructing graphene oxide on the surface of a cationized fabric, then adsorbing aniline monomer molecules on the surface of the fabric, then polymerizing the aniline monomer into polyaniline through an oxidant to form a fabric constructed bygraphene / polyaniline, and finally finishing emulsified carnauba wax on the fabric through an impregnation method. Compared with the prior art, the preparation method of the super-hydrophobic electromagnetic shielding fabric has the advantages that super-hydrophobization finishing is carried out on a coated fabric, so that the durability of the shielding performance of the fabric is improved. Special equipment is not needed in the whole assembly process, the requirement on experimental conditions is not high, and the production process is simple and easy to operate.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

Method and system for improved nickel silicide

ActiveUS7825025B2Improve performanceReduce sheet resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMaterials scienceHeavy ion

According to one embodiment of the invention, a method for nickel silicidation includes providing a substrate having a source region, a gate region, and a drain region, forming a source in the source region and a drain in the drain region, annealing the source and the drain, implanting, after the annealing the source and the drain, a heavy ion in the source region and the drain region, depositing a nickel layer in each of the source and drain regions, and heating the substrate to form a nickel silicide region in each of the source and drain regions by heating the substrate.

Owner:TEXAS INSTR INC

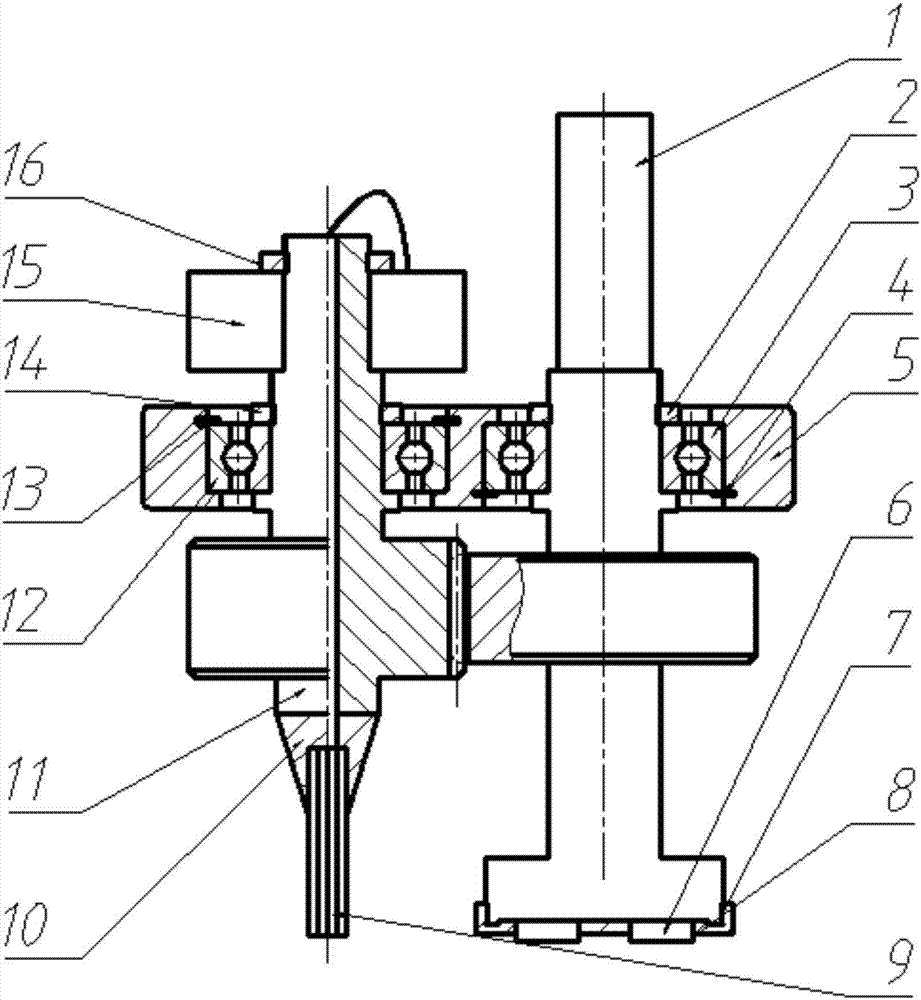

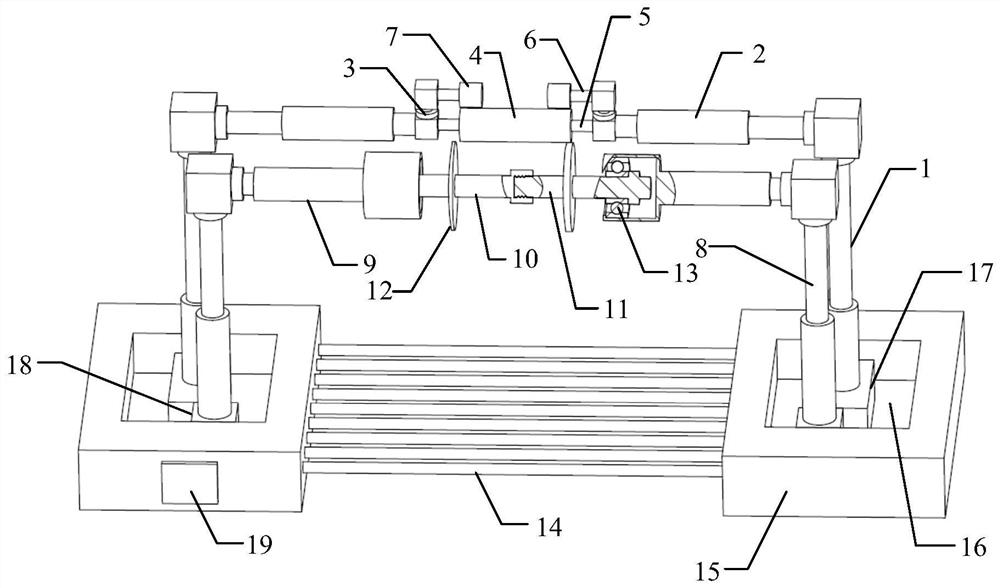

Flexible electrode electrospark deposition composite rolling machining tool

A flexible electrode electrospark deposition composite rolling machining tool includes a bearing plate, a rolling knife spindle, a rotating disk, pin rollers, an electrode spindle, a rotating joint, and a flexible electrode; the rolling knife spindle is rotatably mounted on the right side of the bearing plate, the pin rollers are rotatably mounted on the rotating disk, and the rotating disk is rotatably mounted on the lower end of the rolling knife spindle through an annular cover; the electrode spindle is rotatably mounted on the left side of the bearing plate, and the flexible electrode is mounted on an electrode clamp in a retractable mode; and the electrode clamp is installed on the lower end of the electrode spindle, and the inner ring of the rotating joint is fixed to the upper end of the electrode spindle. The invention provides the flexible electrode electrospark deposition composite rolling machining tool. The flexible electrode electrospark deposition composite rolling machining tool can be used to prepare a layer of nanocrystal on metal materials and perform flexible electrode electrospark deposition machining at the same time, so that the quality of the material surfaceis greatly improved.

Owner:ZHEJIANG UNIV OF TECH

Method of applying a varnish to a component, in-particular to a vehicle headlight reflector

InactiveUS6773761B2Good application effectLimit tendencyPretreated surfacesInductances/transformers/magnets manufactureEngineeringSolvent

A method of applying a varnish, whether or not it includes a solvent, on a component, in particular a vehicle headlight reflector, comprises the following steps: (i) selecting a varnish having a viscosity at ambient temperature of about 500 to 2000 mPa.s, and a viscosity at the application temperature which is lower than about 200 mPa.s, with a viscosity which is substantially independent of variation in the temperature within the range of application; (ii) heating the surface of the component before the step of moistening the varnish at a selected temperature thetap1; (iii) heating the varnish at the moment of application to a selected temperature thetav; and (iv) during the spreading step, maintaining the component at a selected temperature thetap2 for a selected time tp2.

Owner:VALEO VISION SA

Preparation method of anode film linear ion source assisted cBN (cubic boron nitride) coated cutting tool

InactiveCN106119798AIncrease ionization rateExtended service lifeVacuum evaporation coatingSputtering coatingRadio frequency magnetron sputteringBack bias

The invention provides a preparation method of an anode film linear ion source assisted cBN (cubic boron nitride) coated cutting tool. The preparation method is characterized by mainly comprising steps as follows: a substrate of the cutting tool is pretreated; the substrate is placed in an anode film linear ion source assisted radio frequency magnetron sputtering deposition system for deposition of a cBN coating, specific parameters of the deposition are as follows: flow of N2 is 5-10 sccm, flow of Ar is 25-40 sccm, the substrate is arranged above a target material about 90 mm, back bias voltage of the substrate is 100-220 V, substrate temperature is 600-900 DEG C, radio-frequency power is 300 W, anode film linear ion source power is 100-300 W, base pressure is 5*10<-4>Pa, deposition pressure is 0.5 Pa, and deposition time is 4-5 h. The preparation method has the advantages that the process is simple, the operation is easier, bonding performance of the coating and the substrate is improved remarkably, and toughness of the cutting tool is improved greatly.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

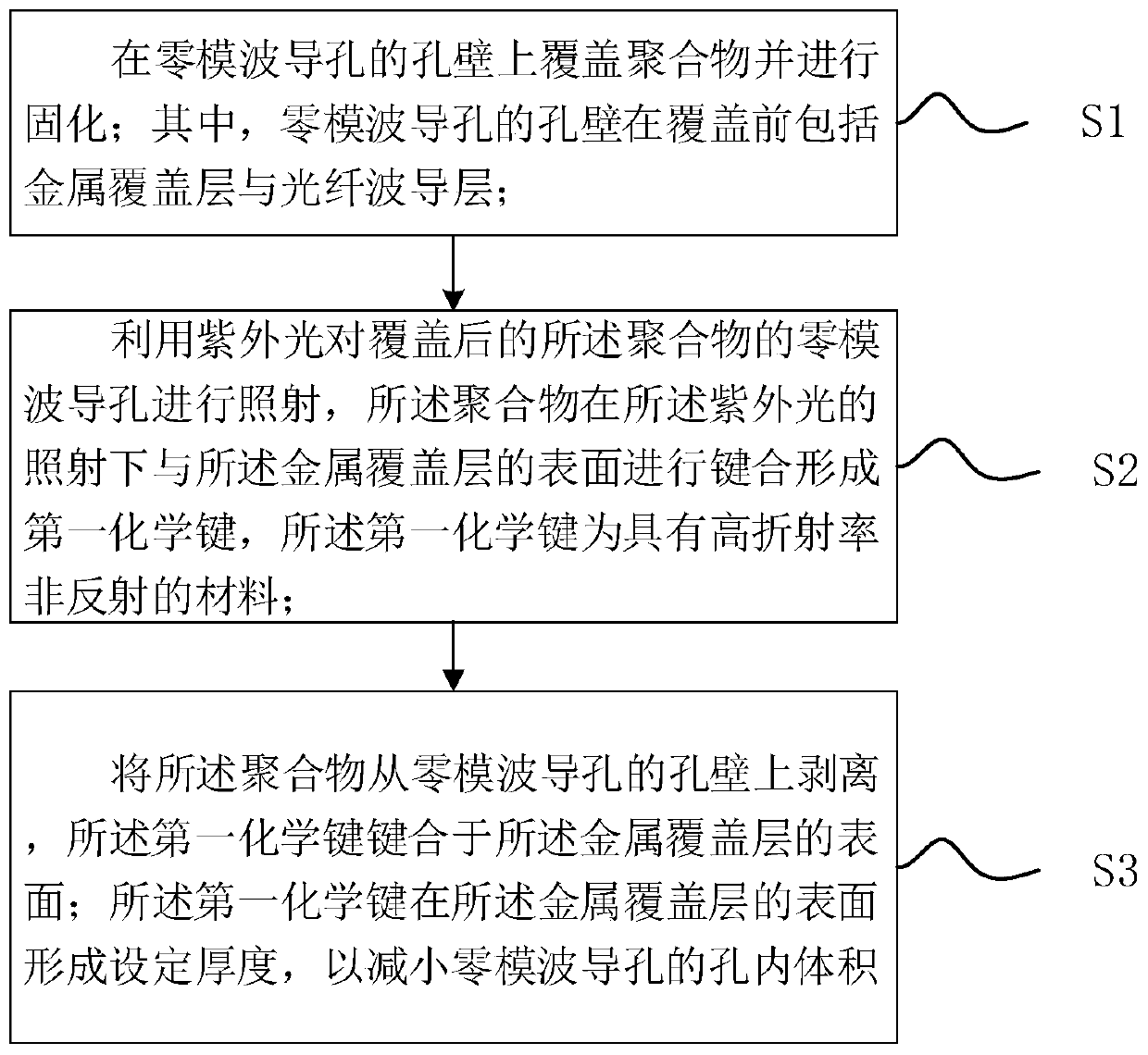

Zero-mode waveguide hole wall modification method and zero-mode waveguide hole structure

ActiveCN111123428AReduced pore volumeIncrease deposition thicknessBioreactor/fermenter combinationsBiological substance pretreatmentsPhoto irradiationFluorescence

The invention provides a zero-mode waveguide hole wall modification method. The method comprises the following steps: covering a polymer; irradiating ultraviolet light on the surface of a metal covering layer to form a first chemical bond; and stripping the polymer. The invention also relates to a zero-mode waveguide hole structure. The hole wall of the zero-mode waveguide hole is covered with thepolymer, and ultraviolet light irradiates the surface of the metal covering layer for bonding to form a high-refractive-index non-reflective first chemical bond; the in-hole volume of the zero-mode waveguide hole can be reduced by increasing the deposition thickness of the first chemical bond of the high-refractive-index non-reflective material, so that free nucleotides in the hole can be significantly reduced, and the signal-to-noise ratio can be improved. Besides, the position of excited fluorescence can be far away from the metal wall of the zero-mode waveguide hole by depositing the firstchemical bond of a high-refractive-index non-reflective material in the hole, so that the fluorescence cannot be weakened or even quenched, and the detection is more sensitive while the fluorescenceeffect is enhanced.

Owner:SUZHOU INST OF BIOMEDICAL ENG & TECH CHINESE ACADEMY OF SCI

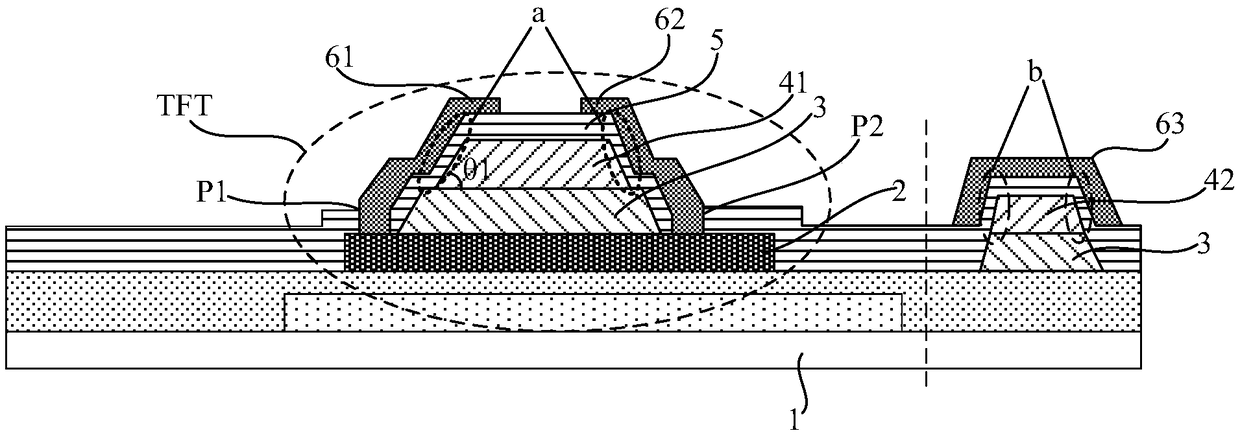

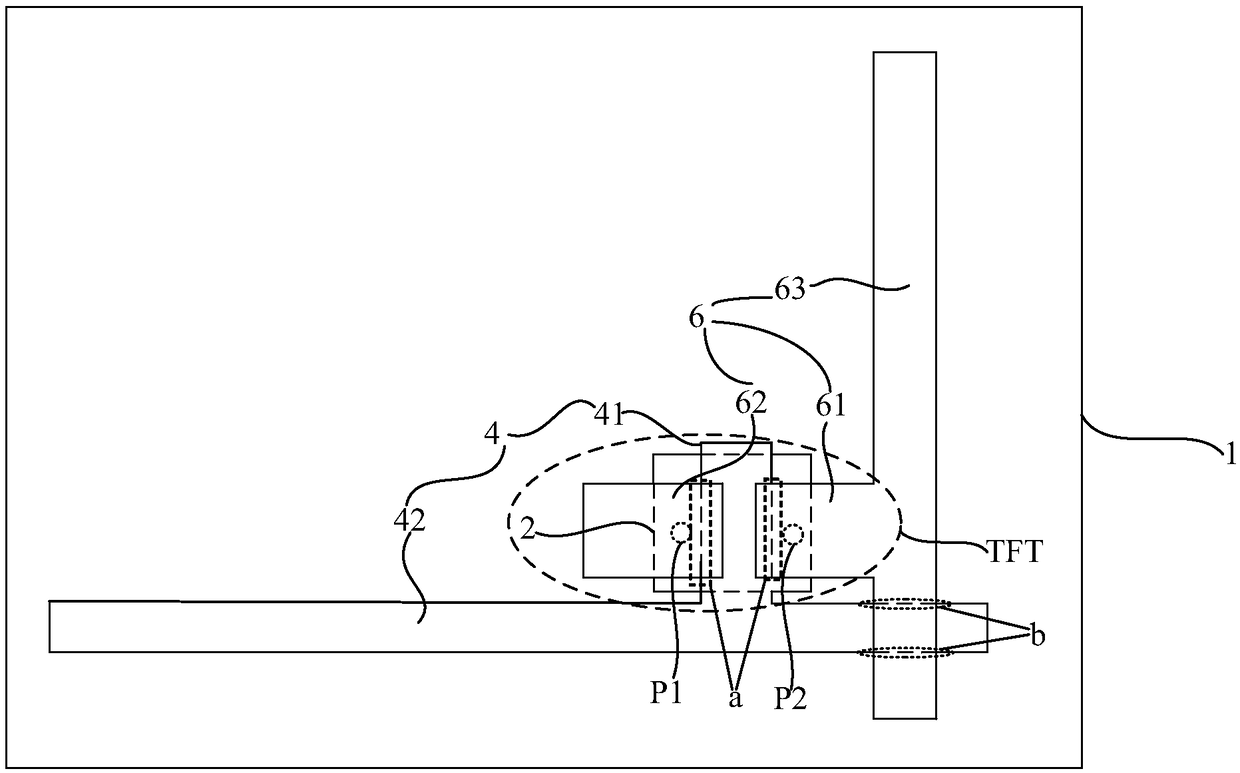

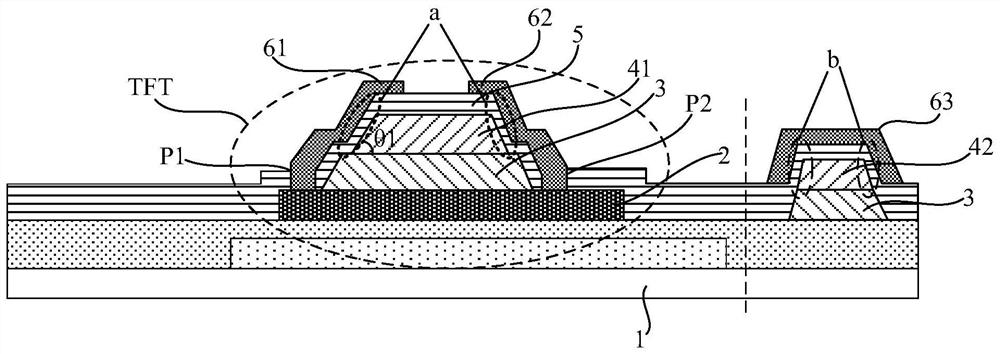

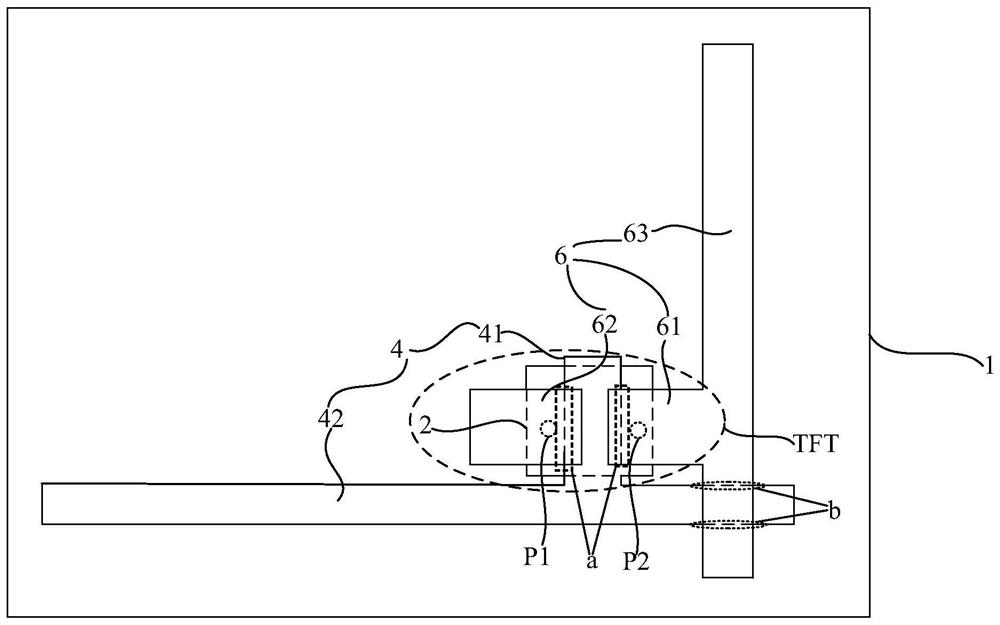

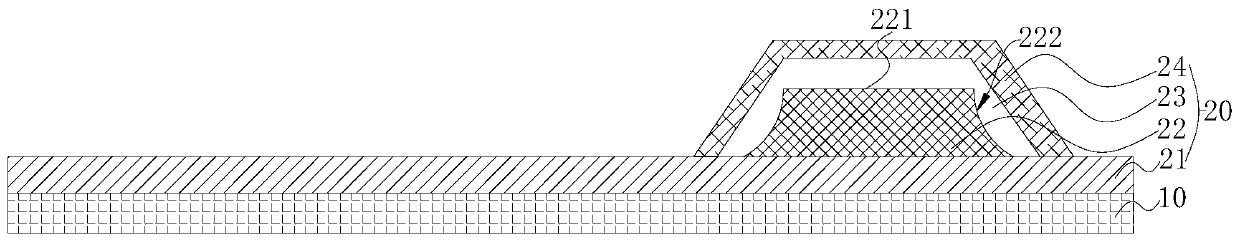

Array substrate and preparation method thereof

ActiveCN109378320ASolve the problem of yield dropIncrease deposition thicknessTransistorSolid-state devicesEngineeringActive layer

The invention relates to the technical field of display, especially to an array substrate and a preparation method thereof. The array substrate and the preparation method thereof are used to solve theproblem that overlap regions between a gate and a source and a drain are prone to short circuit in the related art, which causes the decrease of panel yield. The embodiments of the invention providesthe array substrate. Multiple TFTs are arranged on the array substrate. Each TFT includes an active layer, a gate insulating layer, a gate, a first interlayer insulating layer, a second interlayer insulating layer, a source and a drain which are arranged on the substrate in order. Each source and drain are in contact with the corresponding active layer at least passing through a hole through thecorresponding first interlayer insulating layer. Each second interlayer insulating layer includes a first insulation pattern. Each first insulation pattern is located between the corresponding first interlayer insulating layer and the corresponding source and the corresponding drain and is located in the area where the corresponding TFT is located. Each first insulation pattern at least covers anoverlap region between the corresponding source and the corresponding drain and the side surface of the corresponding gate in the area where the corresponding TFT is located. The array substrate and the preparation method thereof are used for production and manufacturing of display panels.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

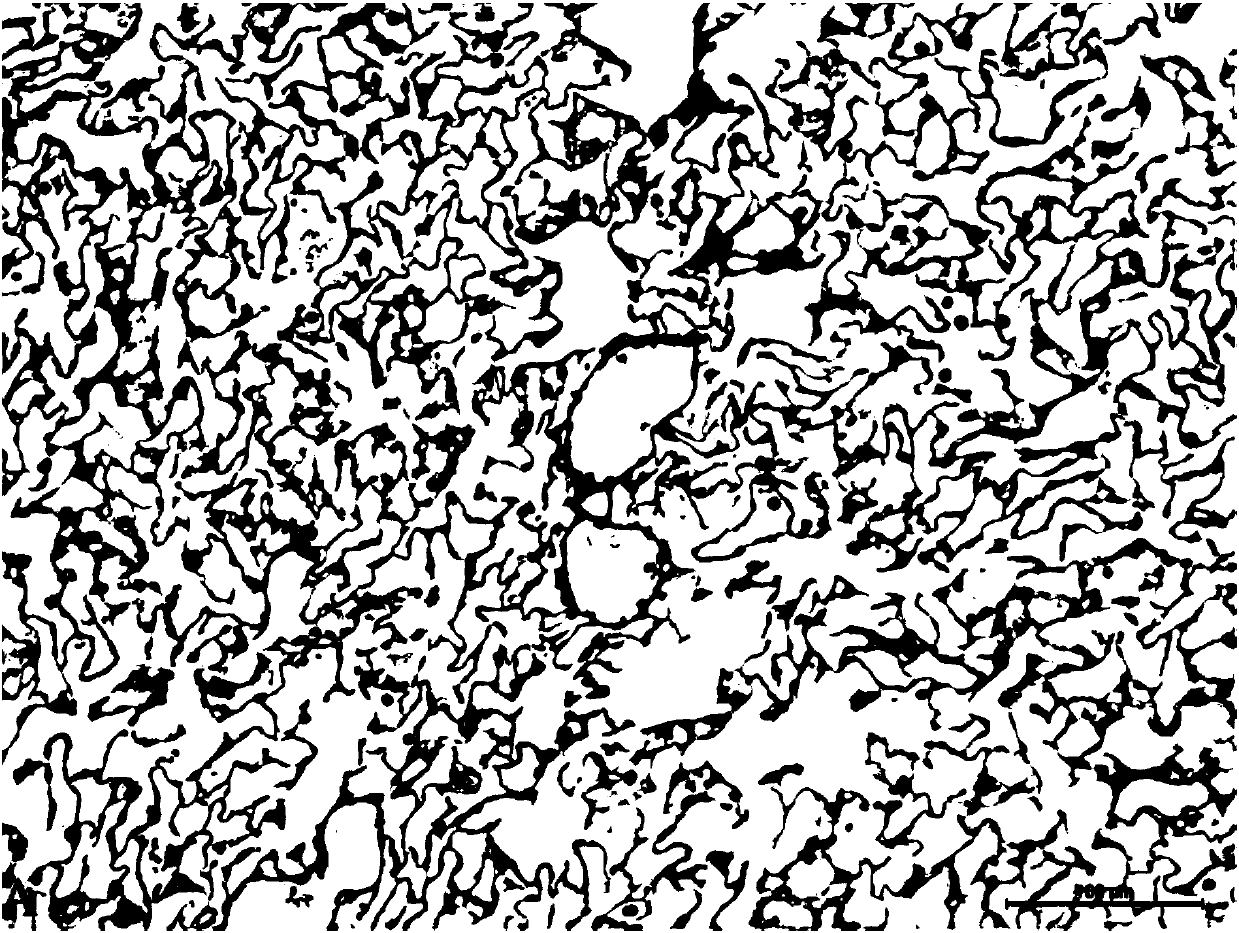

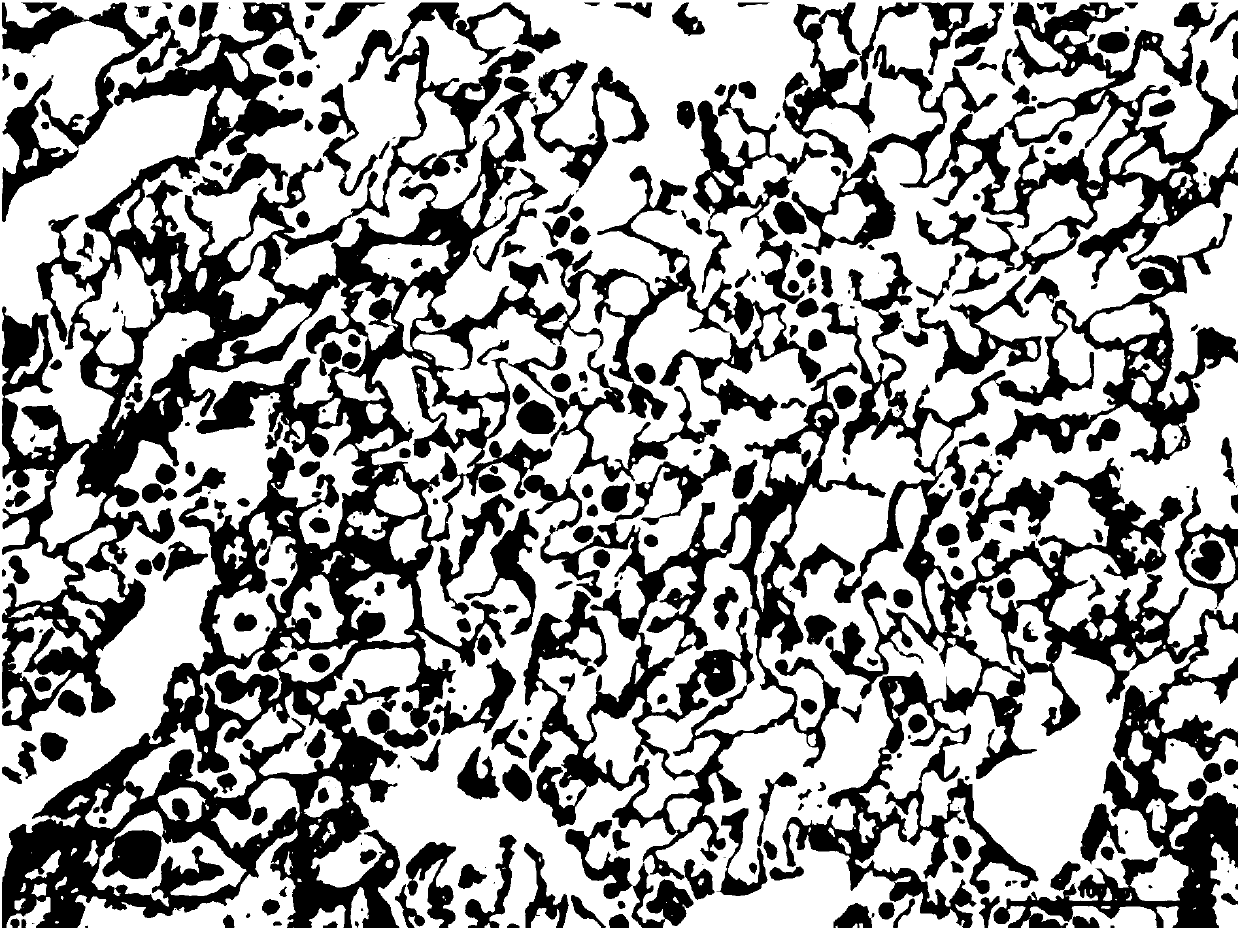

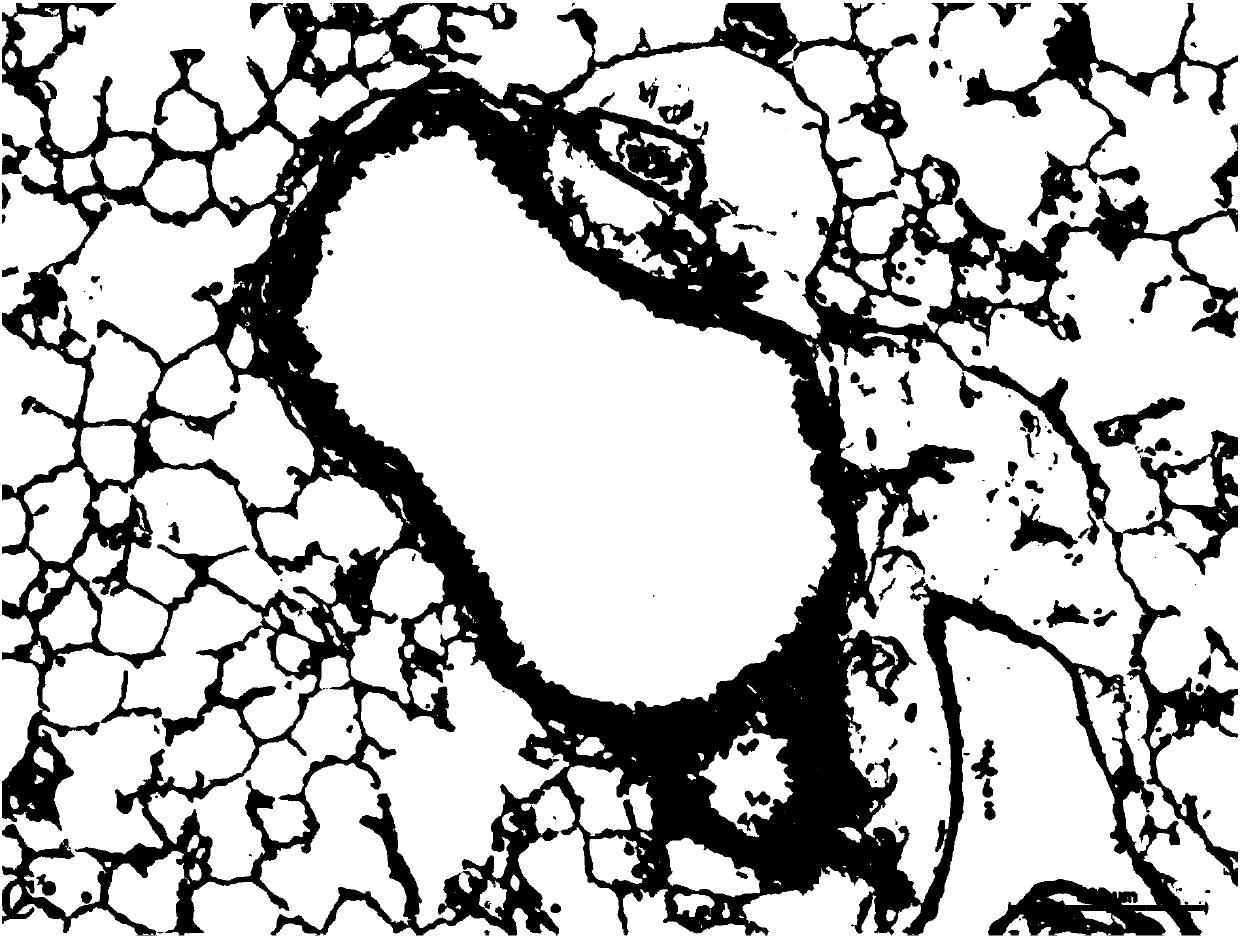

Noninvasive pulmonary fibrosis model building method

InactiveCN108042239AReduce inspiratory volumeIncrease Inflammation ScorePreparing sample for investigationUsing optical meansNasal cavityIntensive care medicine

The invention relates to a pulmonary fibrosis animal model building method. The method comprises the step that a pulmonary fibrosis animal model is prepared by dripping a PM2.5 suspension into a nasalcavity. The method has the advantages that a mouse pulmonary fibrosis model is built through PM2.5 nasal cavity dripping for the first time, the feasibility is verified through experiments, and by means of PM2.5 nasal cavity dripping for eight consecutive weeks, mouse pulmonary fibrosis can be induced. According to the pulmonary fibrosis animal model building method, bleomycin is not used, an airpipe is not used for dripping, operation is easy and convenient, and the trauma is small.

Owner:SHANGHAI CHEST HOSPITAL

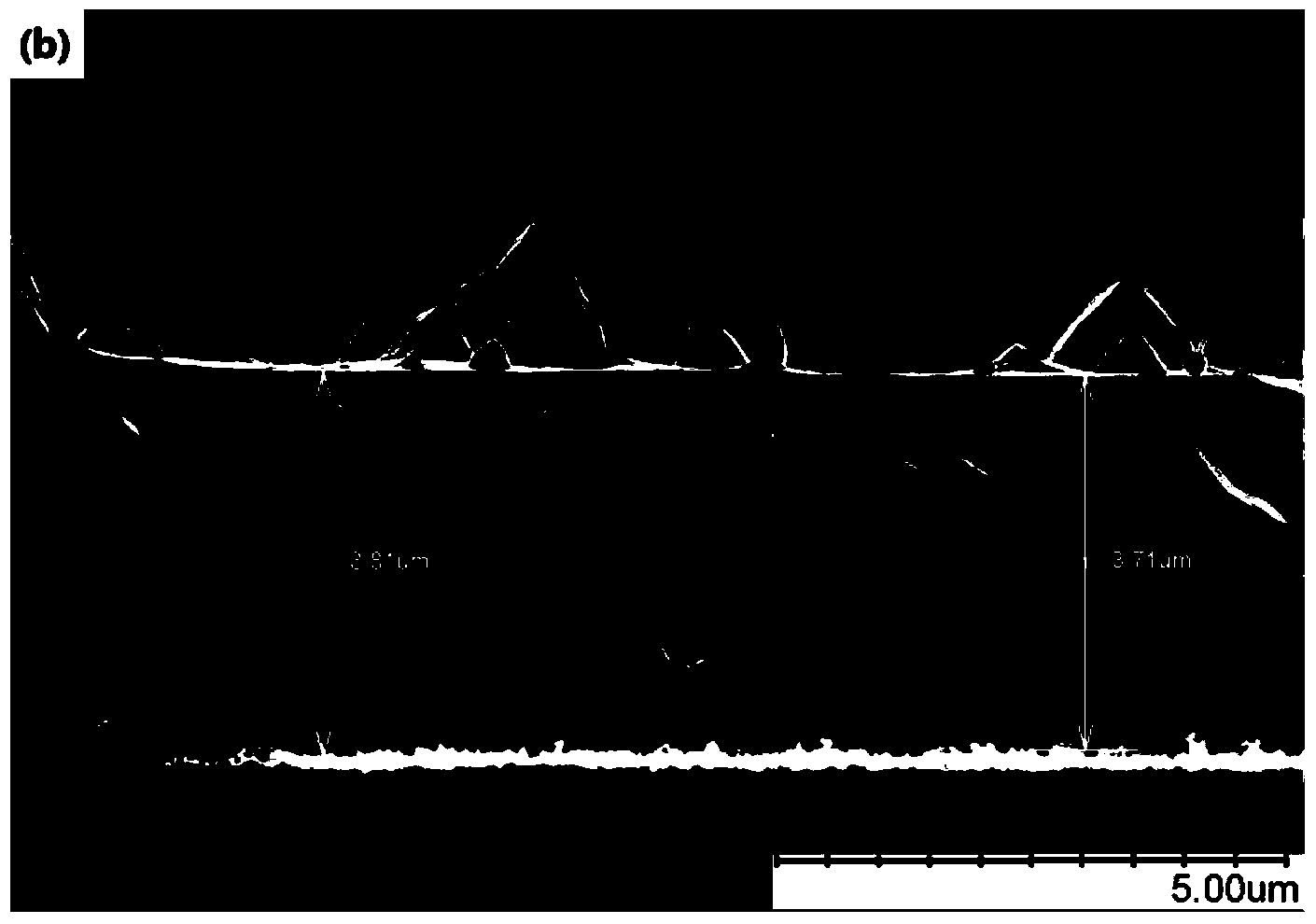

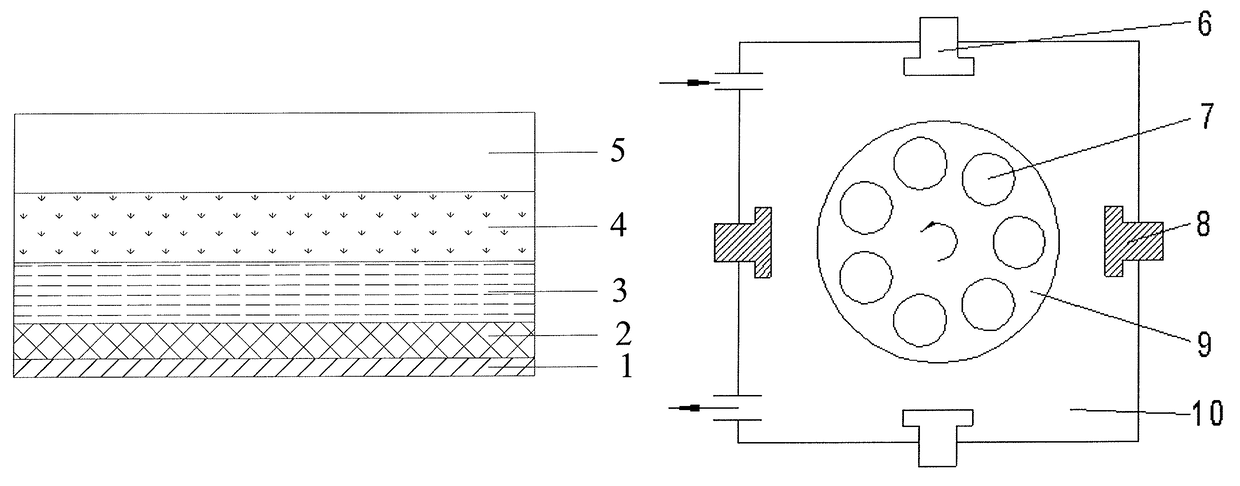

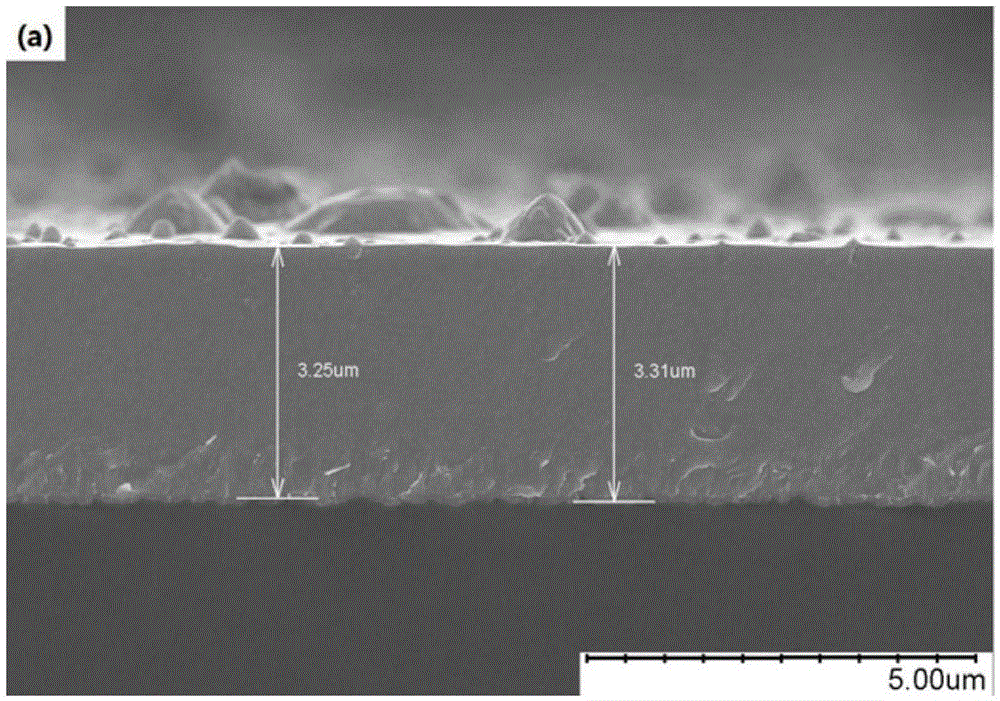

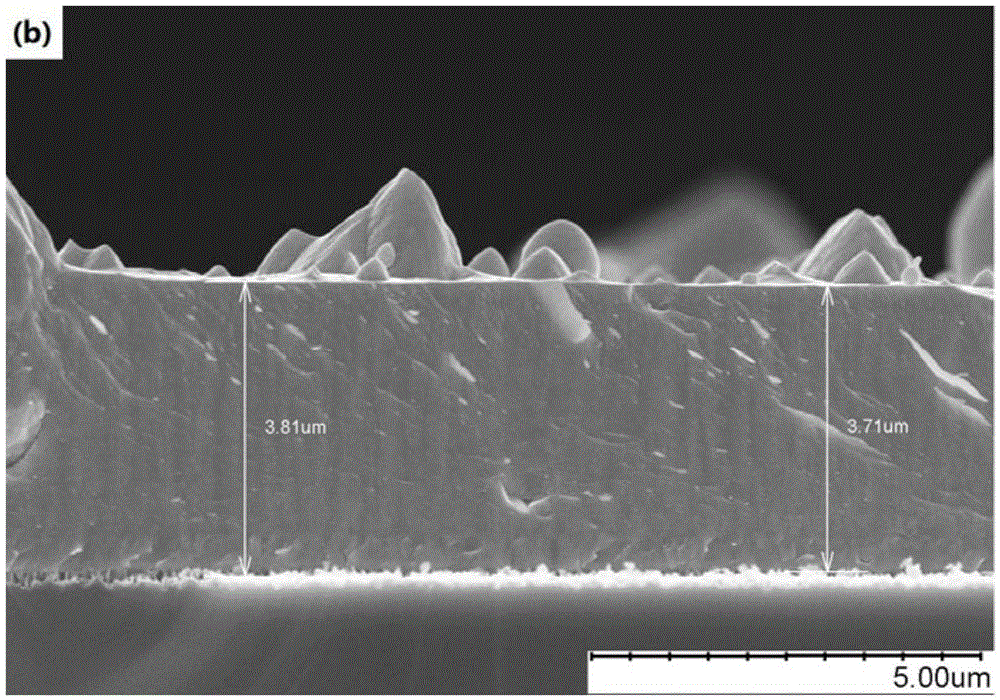

Multilayer multi-element composite hard pvd coating on the surface of a piston ring, a piston ring and a preparation process

ActiveUS9927029B2Reduce coefficient of frictionIncrease deposition thicknessPiston ringsVacuum evaporation coatingMaterials scienceHigh adhesion

The invention relates to a multilayer multi-element composite hard PVD coating with low friction coefficient on the surface of a piston ring, a piston ring and a preparation process. The present invention employs vacuum multi-arc ion plating vapor deposition process, which uses multiple multi-arc ion sources, in the combination of equipping with different single metal target material and multi-element target material to deposit multilayer multi-element composite hard PVD coating with low friction coefficient on the surface of a steel or cast iron piston ring. The coating consists of five layers with the total thickness of up to 60 μm. The coating has high adhesion with the surface of piston ring, high hardness, low friction coefficient and good abrasion resistance. By controlling the adding amount of additive elements Al, Mo, W, B, Si and Ti, the friction coefficient of the coating can be further reduced 5 to 20% compared with that of a single TiN or CrN deposited layer.

Owner:ASIMCO SHUANGHUAN PISTON RING YIZHENG

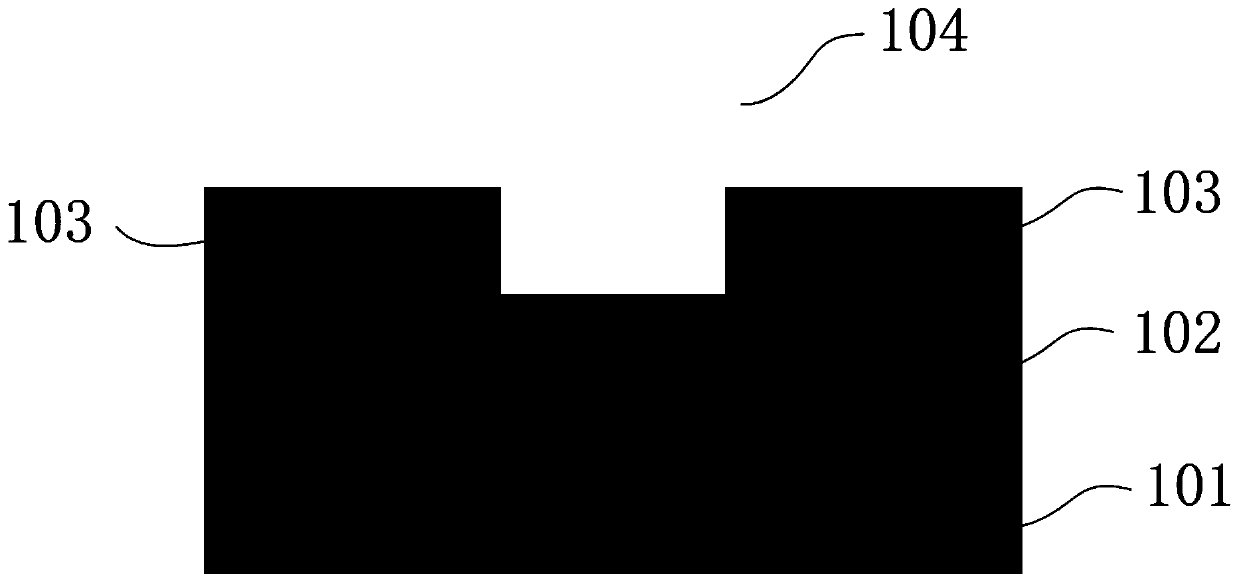

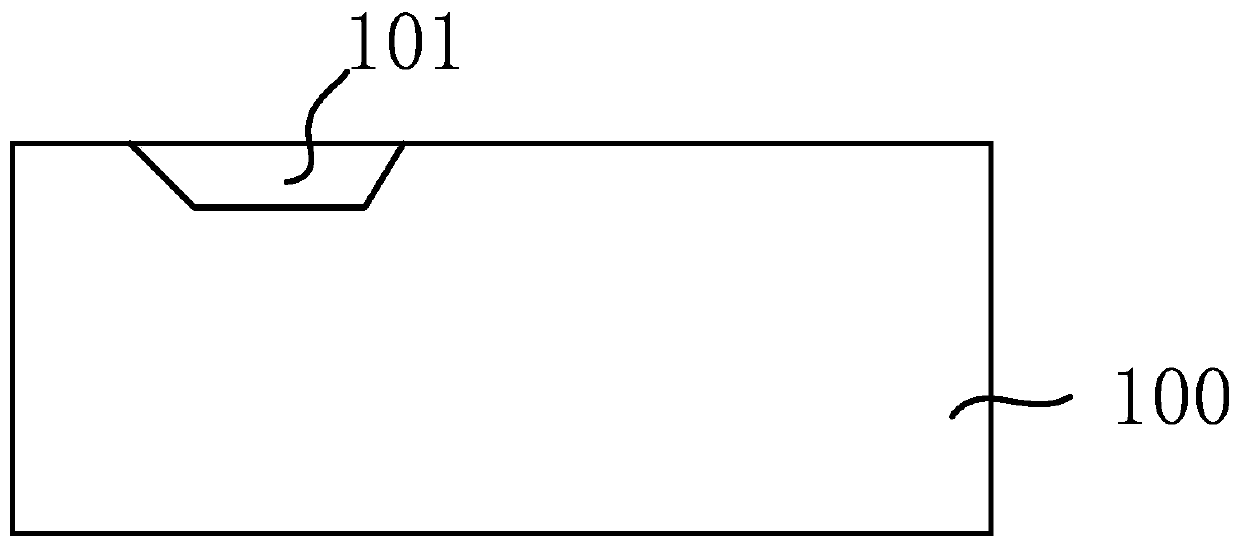

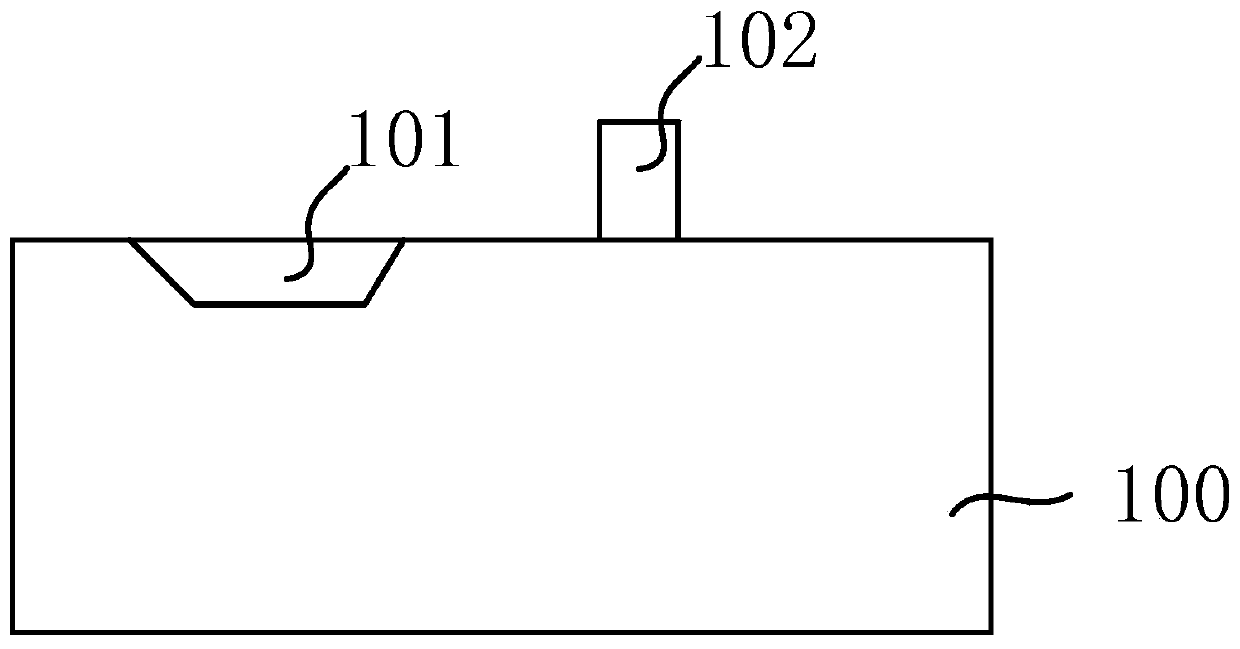

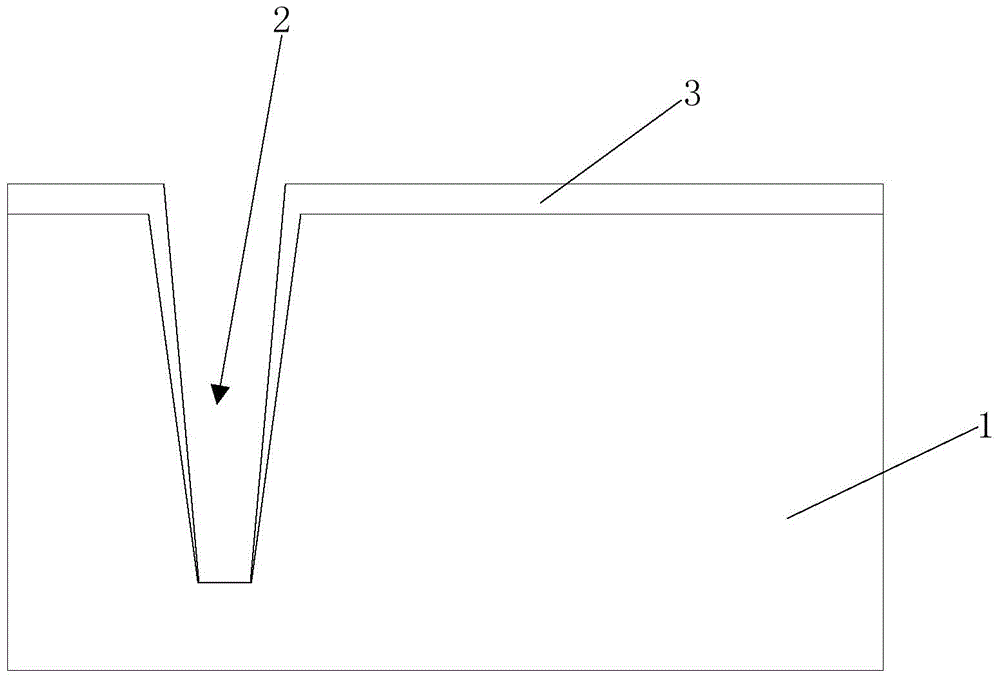

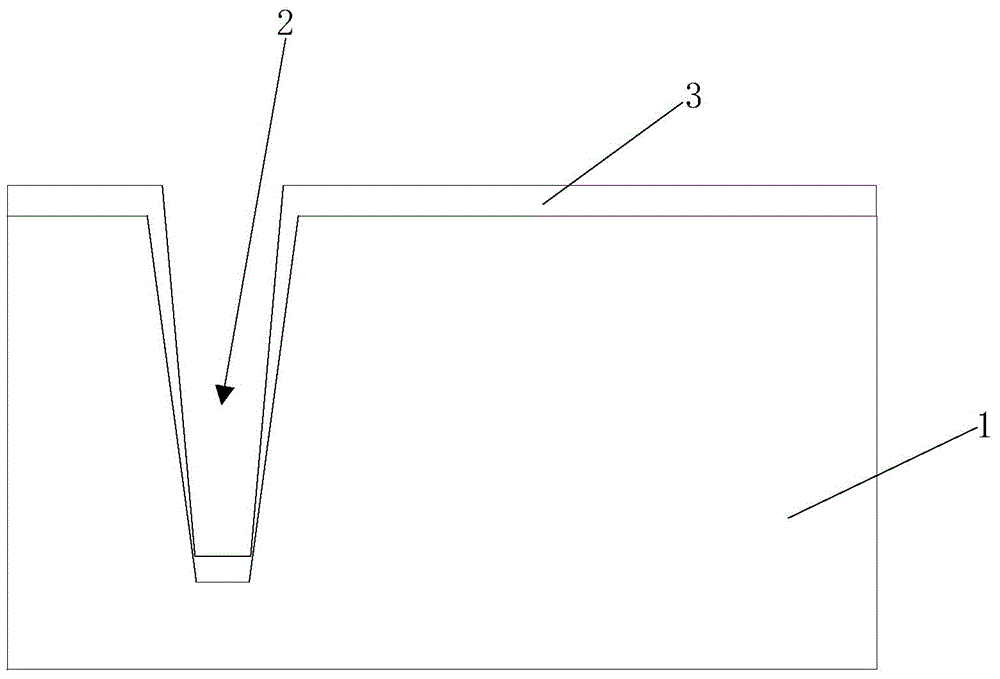

Manufacturing method for deep trough isolation structure

InactiveCN109994420AIncrease deposition thicknessReduce removal processSemiconductor/solid-state device manufacturingDielectric layerSemiconductor

The invention provides a manufacturing method for a deep trough isolation structure. The manufacturing method is characterized in that a semiconductor substrate is provided, a shallow trough isolationstructure and a grid are formed in the semiconductor substrate; a first dielectric layer is formed, the first dielectric layer covers the semiconductor substrate, the shallow trough isolation structure and the grid, and thickness of the first dielectric layer is greater than thickness of a target side; an opening is formed, the opening penetrates through the first dielectric layer and the shallowtrough isolation structure, and the semiconductor substrate is exposed; the first dielectric layer is taken as a mask, and the semiconductor substrate is etched in the opening to form a deep trough;the first dielectric layer on the surface of the semiconductor substrate, the surface of the shallow trough isolation structure and a top surface of the grid is removed, the first dielectric layer ona side wall of the grid is reserved to form a side wall structure, and thickness of the side wall structure is thickness of the target side wall; a second dielectric layer is formed, and the deep trough is filled by the second dielectric layer to form the deep trough isolation structure.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method and system for improved nickel silicide

ActiveUS20110014768A1Improve performanceReduce sheet resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMaterials scienceNickel silicide

According to one embodiment of the invention, a method for nickel silicidation includes providing a substrate having a source region, a gate region, and a drain region, forming a source in the source region and a drain in the drain region, annealing the source and the drain, implanting, after the annealing the source and the drain, a heavy ion in the source region and the drain region, depositing a nickel layer in each of the source and drain regions, and heating the substrate to form a nickel silicide region in each of the source and drain regions by heating the substrate.

Owner:TEXAS INSTR INC

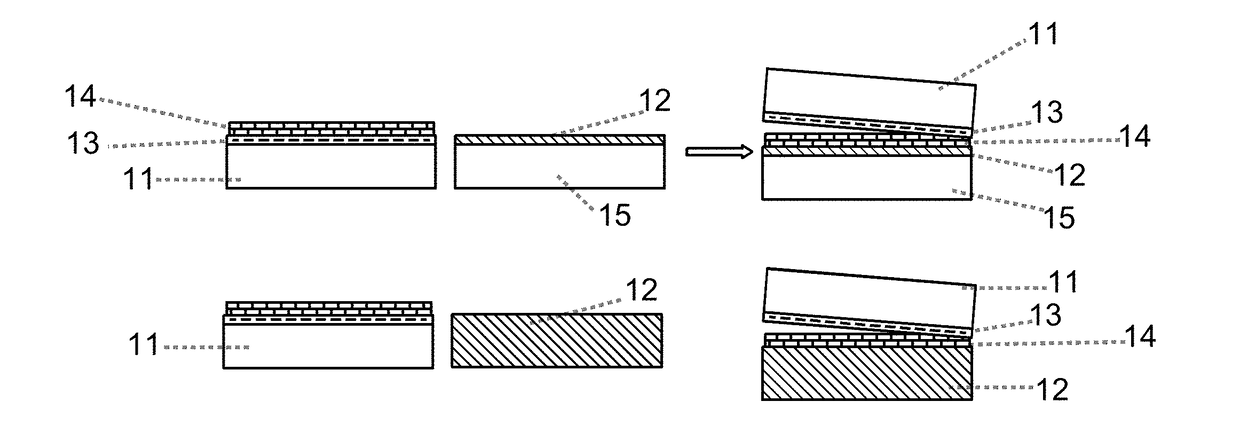

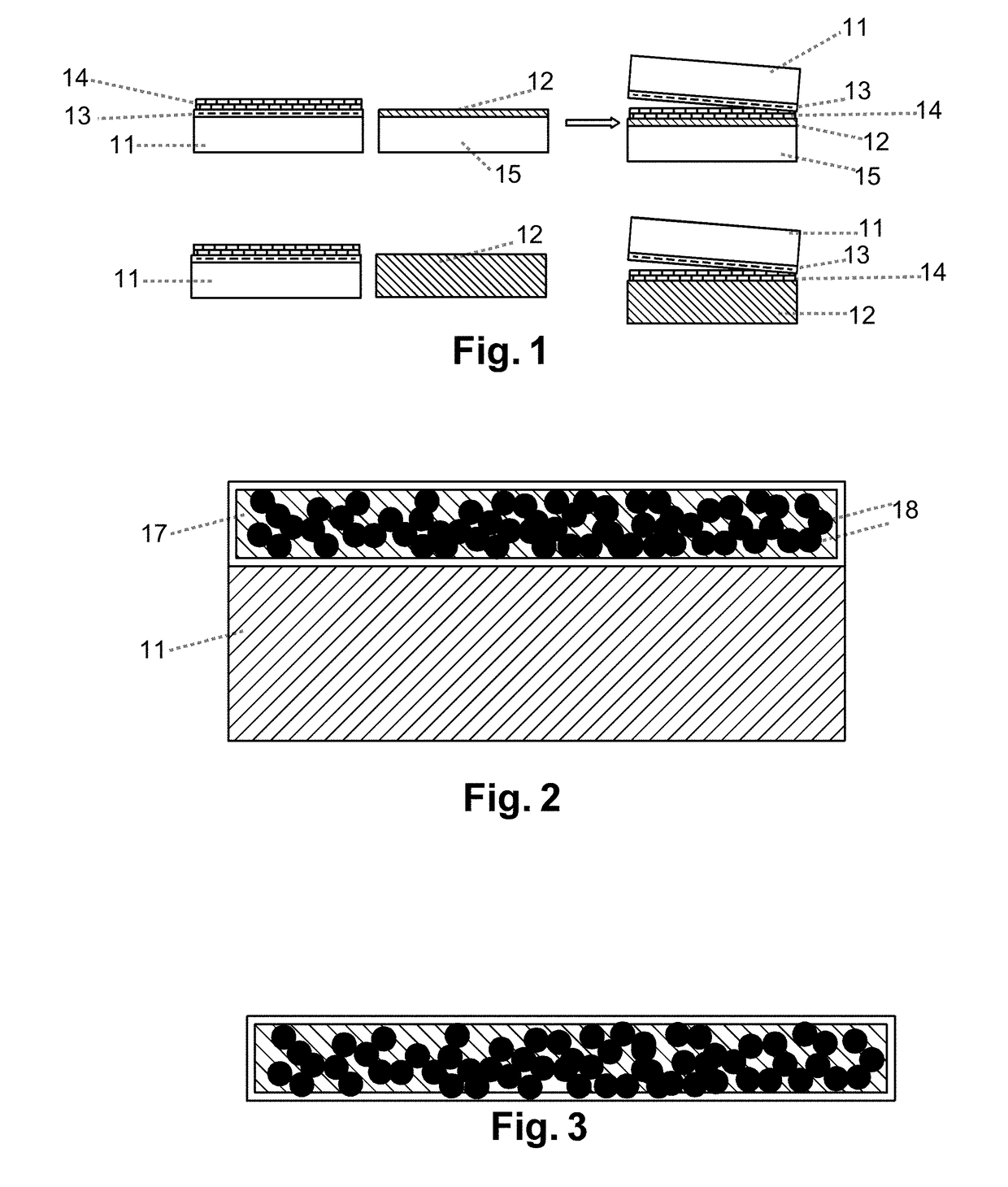

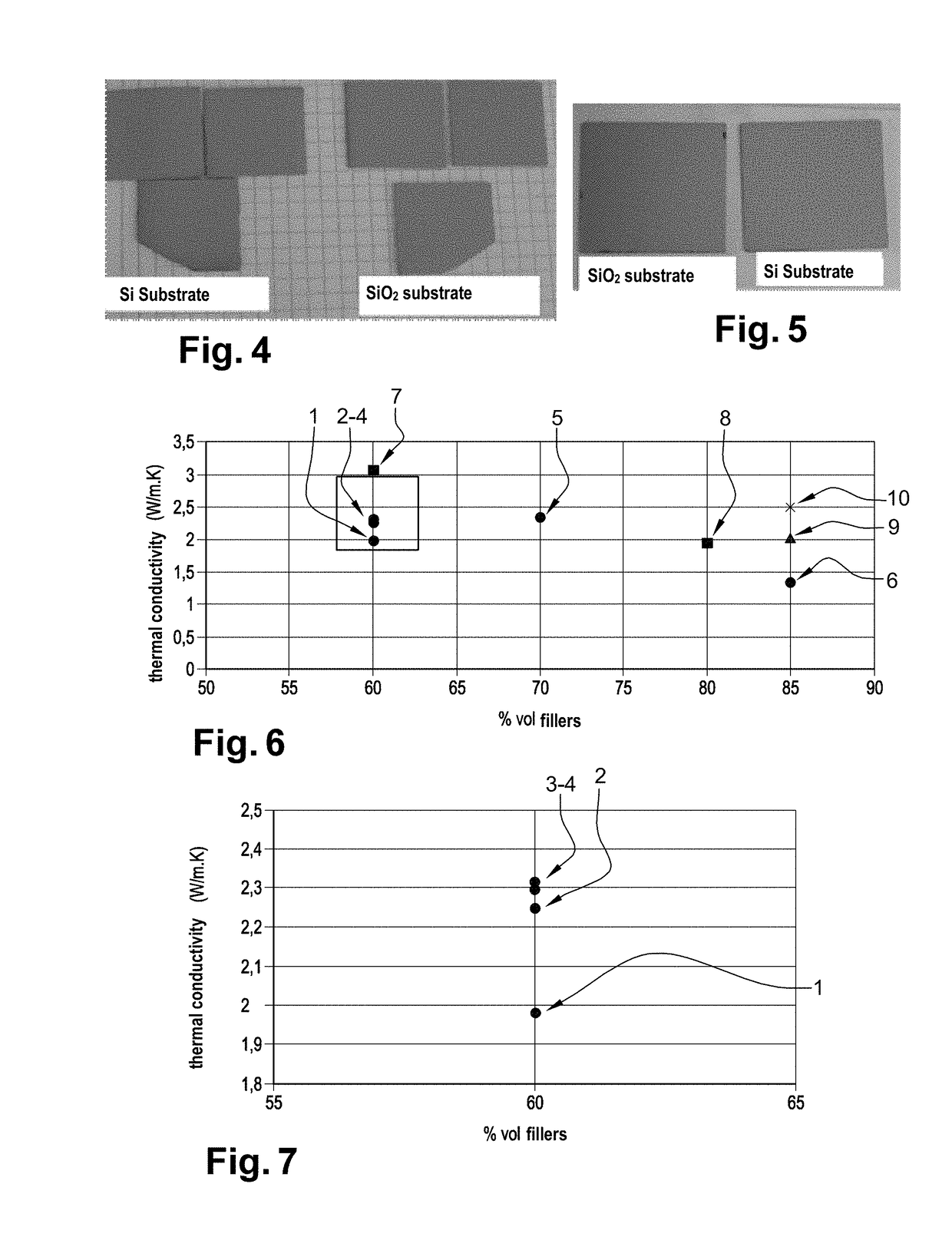

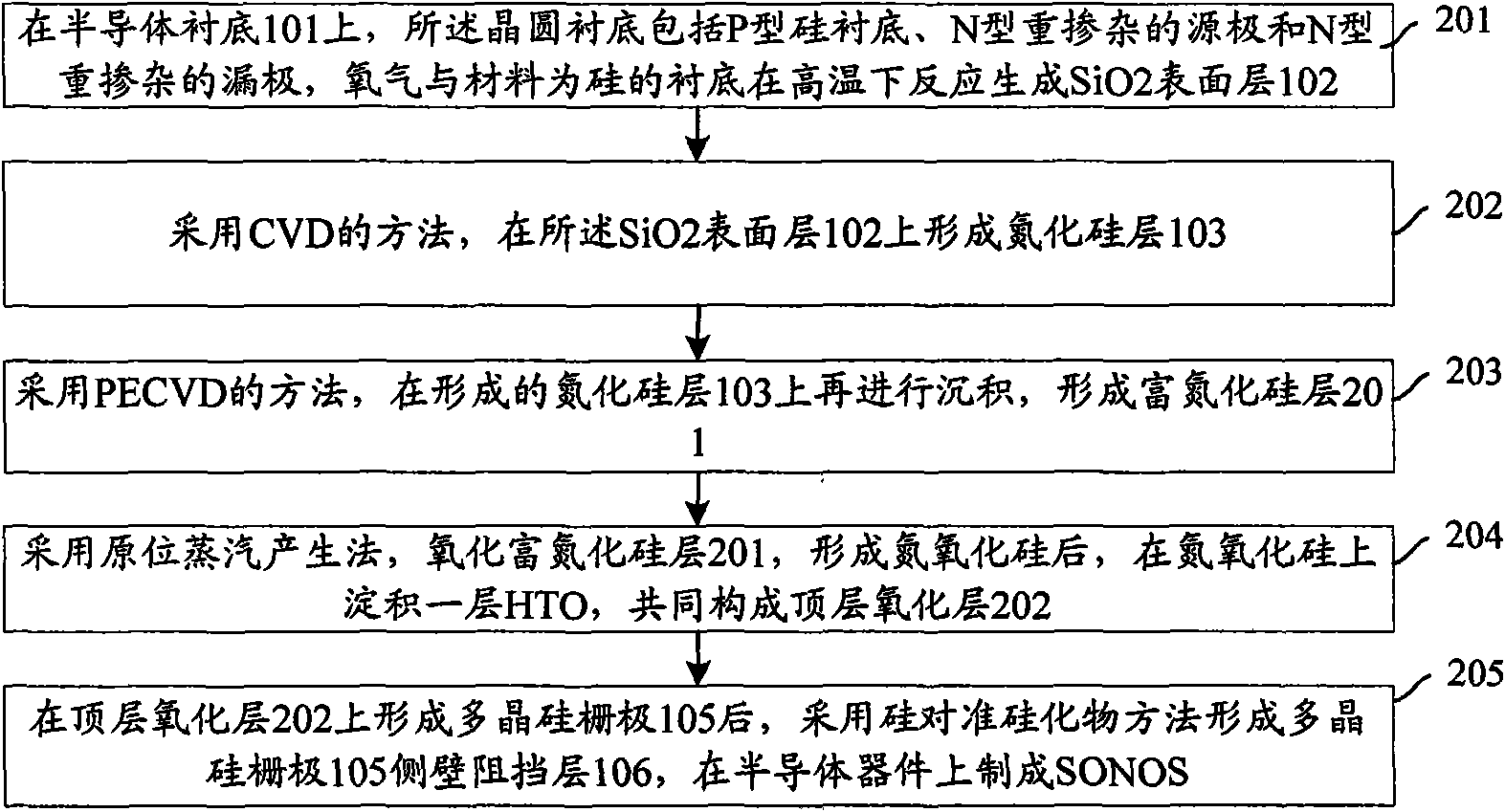

Adhesive Composition And Use Thereof In Electronics

InactiveUS20180171185A1Easy to shapeIncrease deposition thicknessNon-macromolecular adhesive additivesSolid-state devicesOrganic solventPolymer chemistry

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

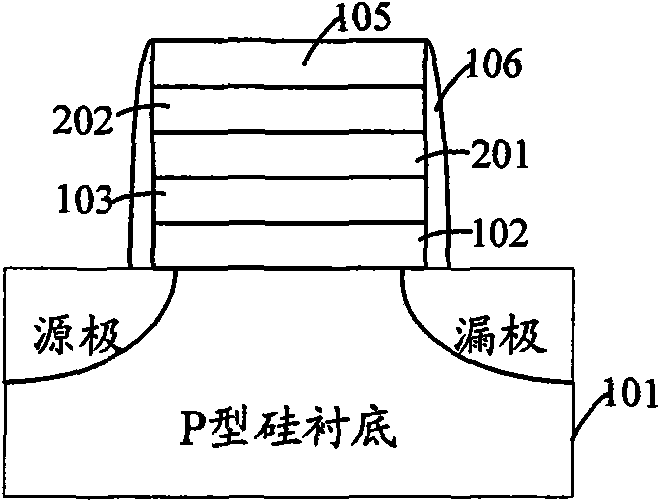

Method for improving performance of non-volatile memory

InactiveCN101944510AImproved leakage current characteristicsImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSurface layerOxygen ions

The invention discloses a method for improving the performance of a non-volatile memory. In the process of producing an oxygen-nitrogen-oxygen structure in the non-volatile memory, the method comprises the following steps of: performing deposition on a wafer substrate to obtain a silicon dioxide surface layer; performing the deposition on the silicon dioxide surface layer to form a silicon nitride layer; and generating positive oxygen ions by an in-situ steam generating method, and after the generated positive oxygen ions is reacted with the silicon nitride layer to form silicon oxynitride, performing the deposition to obtain a high-temperature oxide layer. The method provided by the invention improves the performance of the non-volatile memory.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

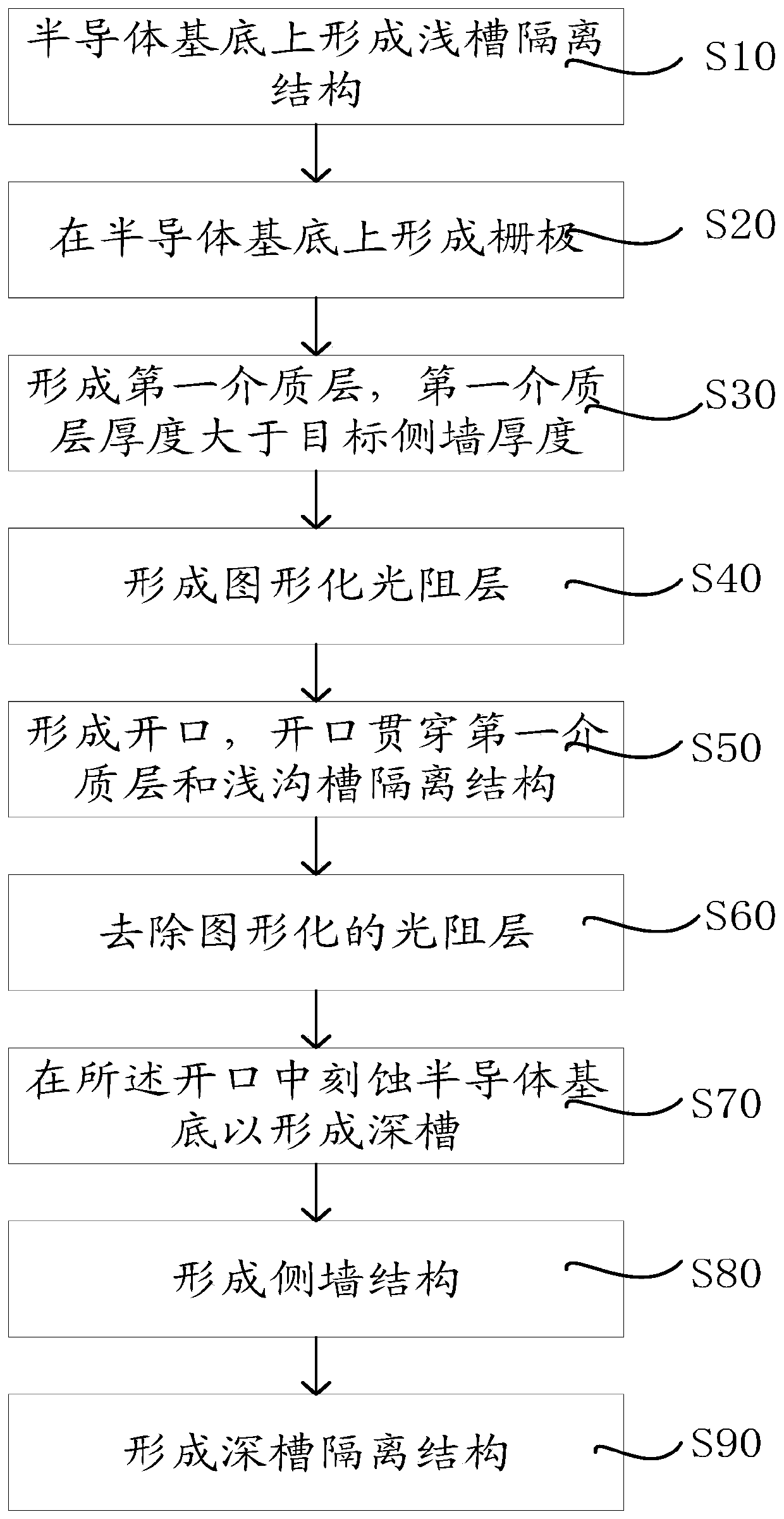

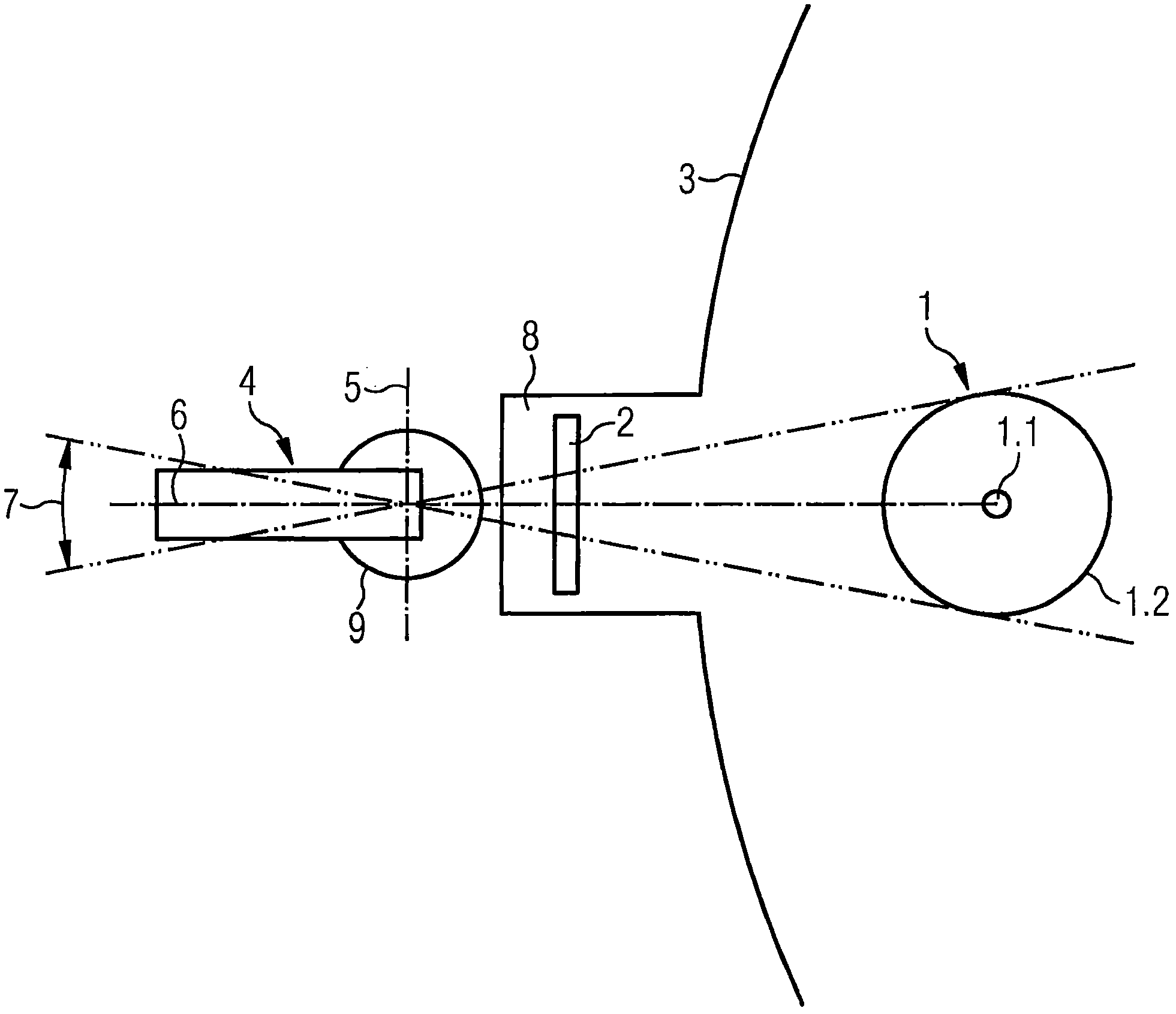

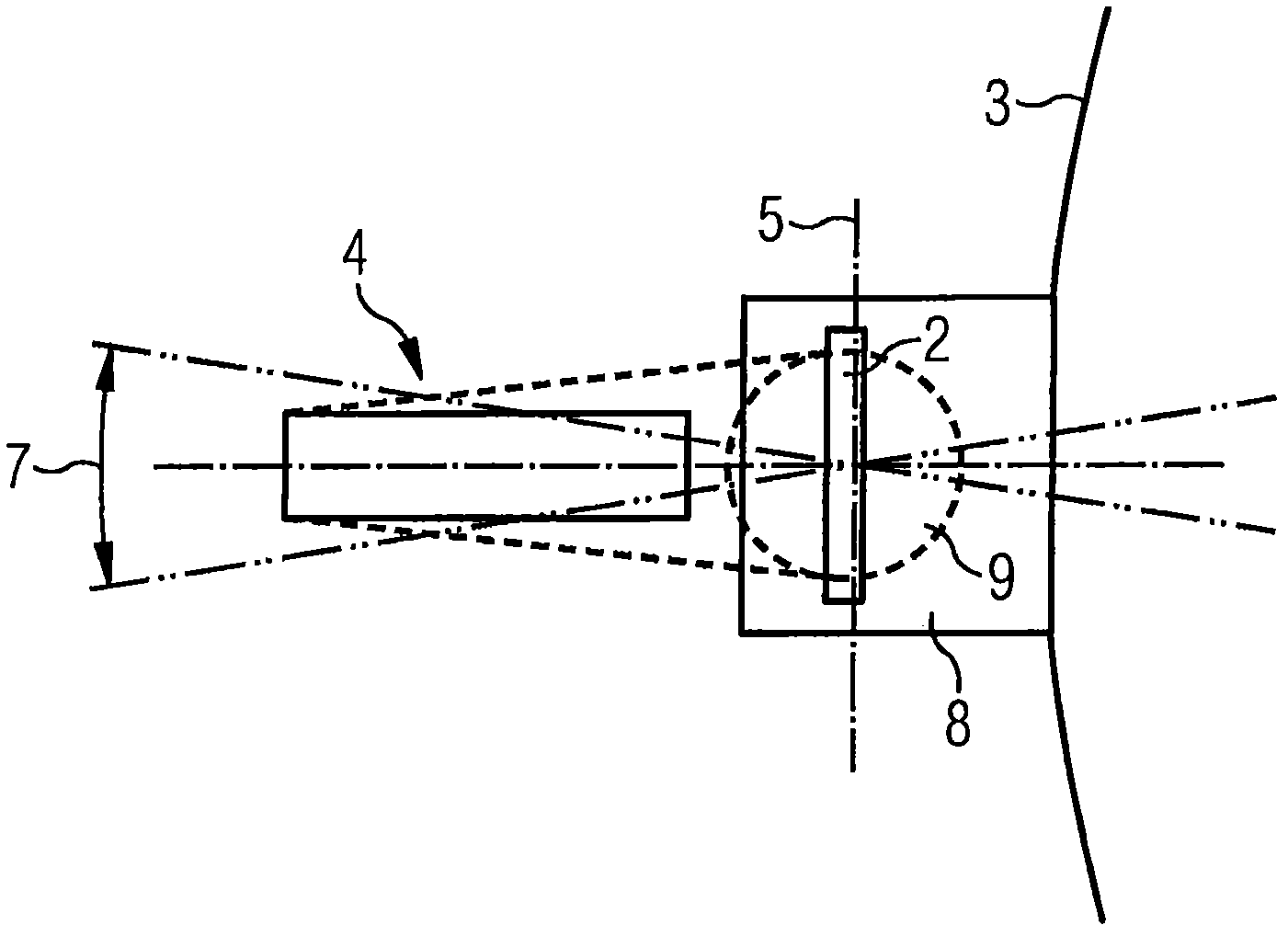

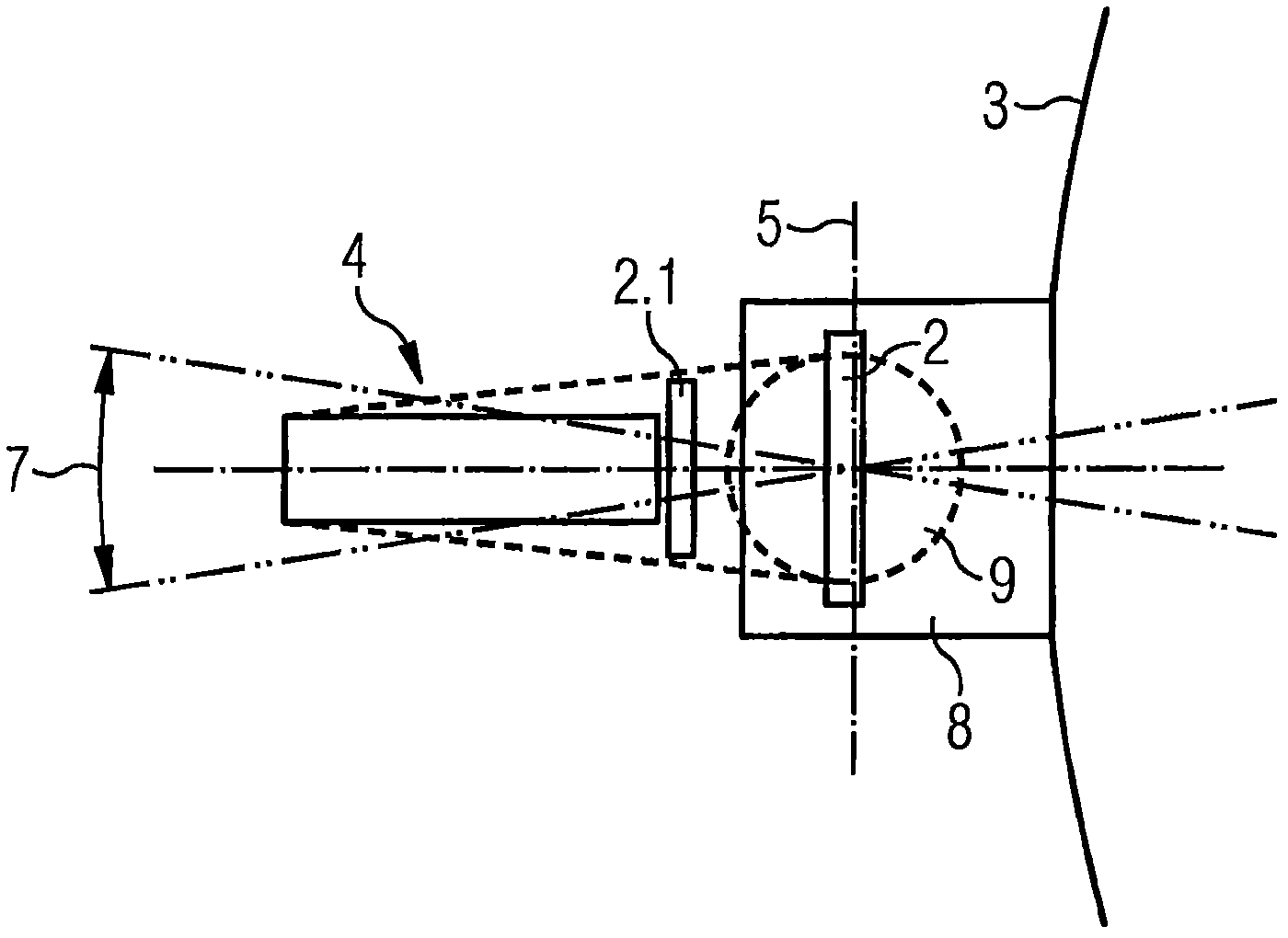

Arrangement and method for measurement of temperature and of thickness growth of silicon rods in silicon deposition reactor

InactiveCN102300809BAvoid excessive temperatureConstant growth thicknessSemiconductor/solid-state device testing/measurementUsing optical meansMeasurement deviceDeposition process

An arrangement for measurement of temperature and thickness growth of silicon rods in a silicon deposition reactor employs a temperature measurement device located outside the reactor. Continuous temperature measurement and measurement of the thickness growth throughout the entire deposition process is achieved with a contactlessly operating temperature measurement device arranged outside the silicon deposition reactor in front of a viewing window. The temperature measurement device can be pivoted horizontally about a rotation axis by a rotating drive. The pivoting axis runs parallel to a longitudinal axis of the silicon rod, and the central axis of the temperature measurement device runs through the pivoting axis.

Owner:硅科技有限责任公司

Method for manufacturing electroplating seed layer

InactiveCN105112972AIncrease deposition thicknessPrevent disconnectionVacuum evaporation coatingSputtering coatingCompound (substance)Engineering

The invention provides a method for manufacturing an electroplating seed layer. The function of the electroplating seed layer lies in that a good conducting layer is provided for the subsequent metal electroplating technology. The manufacturing method is used for a semiconductor device. At least one contact hole is formed in the surface of the semiconductor device, and the hole bottoms of the contact holes are made of metal. The manufacturing method includes the steps that the electroplating seed layer is deposited on the surface of the semiconductor device through the chemical metal coating technology, and covers the surface of the semiconductor device and the hole walls and the hole bottoms of the contact holes; the deposition thickness of the positions, located on the hole bottoms of the contact holes, of the electroplating seed layer is increased through the metal vacuum evaporation process, so that the electroplating seed layer completely covers the hole bottoms of the contact holes. In this way, the phenomenon that the hole bottoms of the contact holes of the electroplating seed layer are disconnected can be prevented.

Owner:CHENGDU HIWAFER SEMICON CO LTD

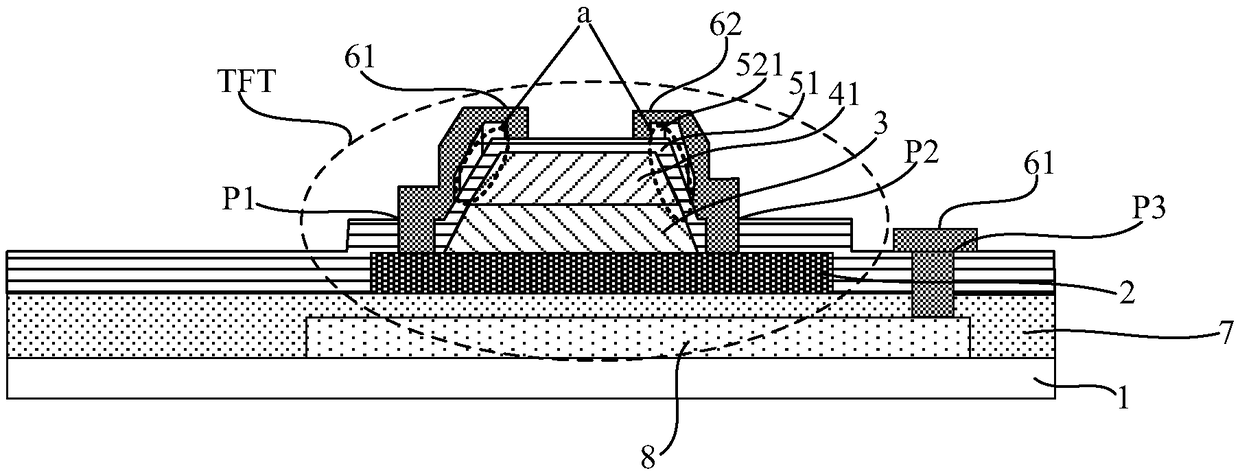

A kind of array substrate and preparation method thereof

ActiveCN109378320BSolve the problem of yield dropIncrease deposition thicknessTransistorSolid-state devicesEngineeringActive layer

The present invention relates to the field of display technology, in particular to an array substrate and a preparation method thereof. The method is used to solve the problem in the related art that the overlapping area between the gate, the source and the drain is prone to short circuit, which causes the yield rate of the panel to decrease. An embodiment of the present invention provides an array substrate, on which a plurality of TFTs are arranged, and each TFT includes an active layer, a gate insulating layer, a gate, a first interlayer insulating layer, The second interlayer insulating layer, the source electrode and the drain electrode; the source electrode and the drain electrode are in contact with the active layer at least through the via holes penetrating the first interlayer insulating layer; the second interlayer insulating layer includes a first insulating pattern, the first The insulating pattern is located between the first interlayer insulating layer and the source and drain, and is located in the area where the TFT is located. The first insulating pattern at least covers the overlapping area of the side of the source, the drain and the gate in the area where the TFT is located. The embodiments of the present invention are used in the production and manufacture of display panels.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

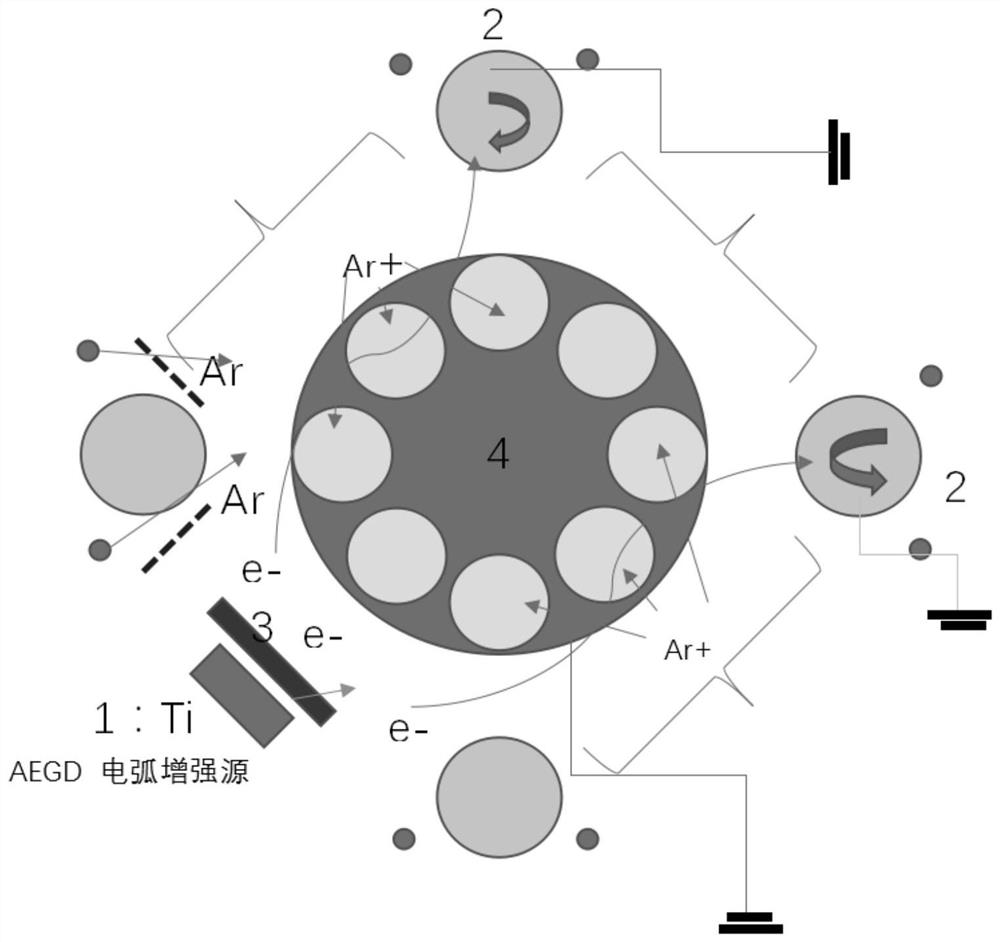

Novel ion cleaning technology based on plating of hard alloy surface with ta-C film

ActiveCN113151797AGood deposition thicknessHigh hardnessVacuum evaporation coatingSputtering coatingElectron flowMaterials science

The invention discloses a novel ion cleaning technology based on plating of a hard alloy surface with ta-C film. The technology comprises the following steps that 1, impurities on the surface of a plasma substrate are ultrasonically cleaned, and charging is performed; 2, arc light enhanced argon ion bombardment is carried out in vacuum coating equipment to remove the impurities on the surface of the substrate, arc ion plating is adopted as an ionization source, the density of provided electron flow can reach 10+19 / m<3>, meanwhile, a columnar coating cathode opposite to the ionization source is converted into an anode in the process, the high-density electron flow is guided to pass through a cleaned workpiece area, Ar atoms are ionized, and the Ar<+> flow is used as an ion cleaning source for the workpiece; and 3, a vacuum plating technology step is started. According to the technology, the high-density ion flow can be provided for cleaning the workpiece, and it is guaranteed that all angles of the workpiece are fully cleaned; and under the condition that low bias voltage is used, excessive bombardment action of overhigh metal ion current on the precise workpiece can be prevented, and the workpiece is prevented from being damaged.

Owner:NORTHEASTERN UNIV +1

Method for modifying hole wall of zero-mode waveguide hole and structure of zero-mode waveguide hole

ActiveCN111123428BReduced pore volumeIncrease deposition thicknessBioreactor/fermenter combinationsBiological substance pretreatmentsPhoto irradiationFluorescence

The invention provides a method for modifying the wall of a zero-mode waveguide hole, which includes covering polymer, irradiating ultraviolet light to form a first chemical bond on the surface of the metal covering layer, and peeling off the polymer. The invention also relates to a zero-mode waveguide hole structure. In the present invention, the polymer is covered on the hole wall of the zero-mode waveguide hole, and the surface of the metal coating layer is irradiated by ultraviolet light to bond to form a first chemical bond with a high refractive index non-reflection; increase the high refractive index non-reflective material The deposition thickness of the first chemical bond can reduce the volume in the hole of the zero-mode waveguide hole, significantly reduce the free nucleotides in the hole, and improve the signal-to-noise ratio. In addition, by depositing the first chemical bond of a high-refractive index non-reflective material inside the hole, the position of the excited fluorescence can be kept away from the metal wall of the zero-mode waveguide hole, so that the fluorescence will not be weakened or even quenched. more sensitive.

Owner:SUZHOU INST OF BIOMEDICAL ENG & TECH CHINESE ACADEMY OF SCI

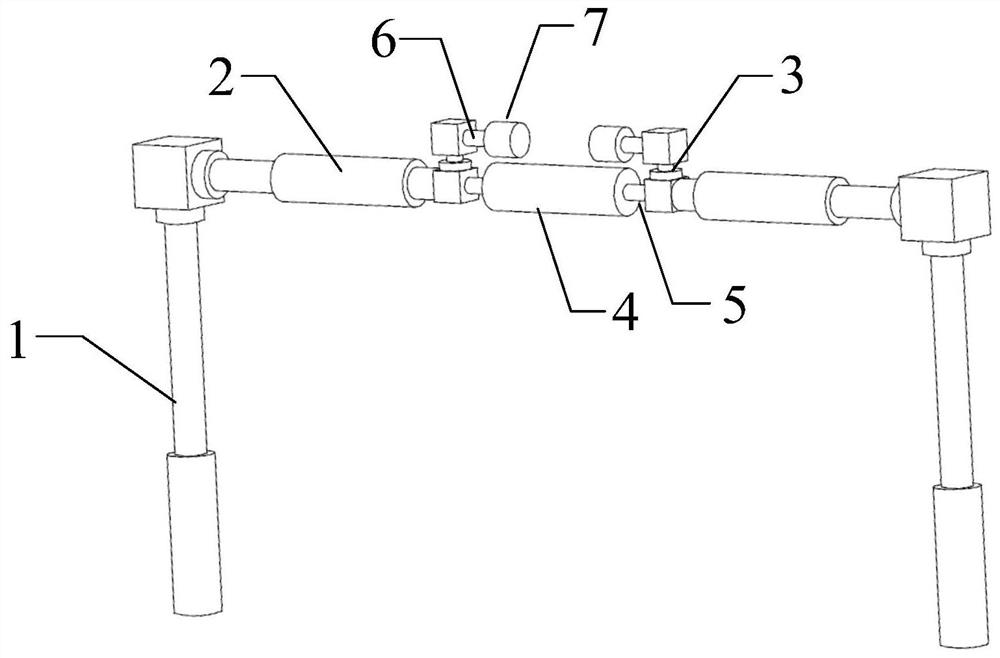

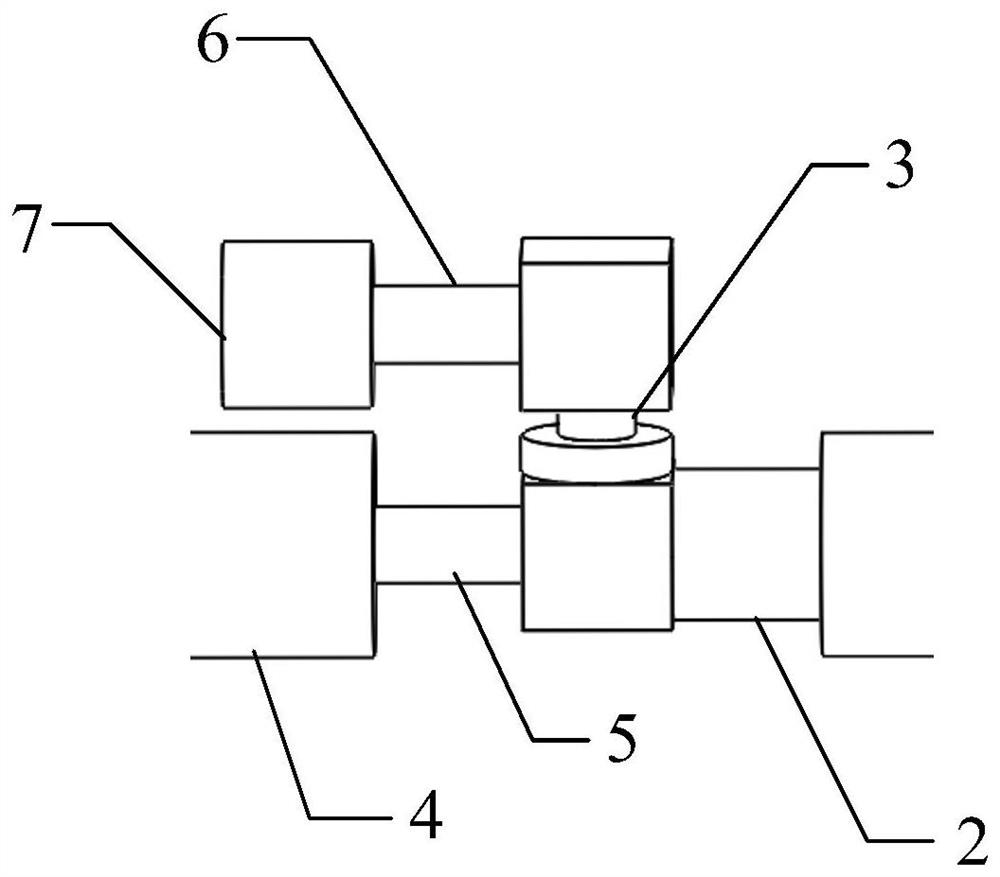

Clamping device for electrical contact of isolating switch

ActiveCN112547355BAchieve surface restorationImprove performanceSpraying apparatusSpray coatingEngineering

The invention discloses a clamping device for an electrical contact of an isolating switch, comprising: a base, a first clamping part and a second clamping part; the first clamping part comprises: two first telescopic rods, two second Two telescopic rods, two third telescopic rods, rollers, two first rotating shafts, two second rotating shafts and two rollers, the second clamping part includes: two fourth telescopic rods, two fifth Telescoping rod, third hinge, fourth hinge and two clips. The present invention adapts to electrical contacts of different sizes and radians by adjusting the components of the first clamping part and the second clamping part before and during spraying. Adjust the parts of the first clamping part and the second clamping part to move the electrical contacts, adjust the spraying position, angle and distance, and maintain the plane spraying of the electrical contacts, so as to improve the deposition efficiency of spraying, the quality of the deposited layer and the deposition thickness, no need to move the spraying device, greatly reducing the workload, and the operation is simple and convenient.

Owner:国网宁夏电力有限公司超高压公司 +1

Composite coating on the surface of a valve seal and its preparation method

ActiveCN103522627BImprove load bearing and wear resistanceAvoid failureVacuum evaporation coatingSputtering coatingNitrogen gasIon plating

The invention provides a composite coating on the surface of a valve sealing piece. The coating takes the valve sealing piece as a base body and consists of a Cr layer, a Cr / Cr2N layer formed by mixing Cr and Cr2N, a Cr2N layer, a Cr2N / CrN layer formed by mixing the Cr2N and CrN, and a CrN layer. Compared with an existing CrN coating with a single structure, the composite coating with multiple layers of gradients has the advantages that the bearing and anti-abrasion capability and the corrosion resistance are improved. Furthermore, the composite coating is prepared by a multi-arc ion plating technology, and the respective layers are obtained by sequentially performing deposition on the surface of the base body by controlling the argon flow, the nitrogen flow and the deposition time; the preparation method is simple and feasible; batch production can be realized; the composite coating has a good application prospect.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

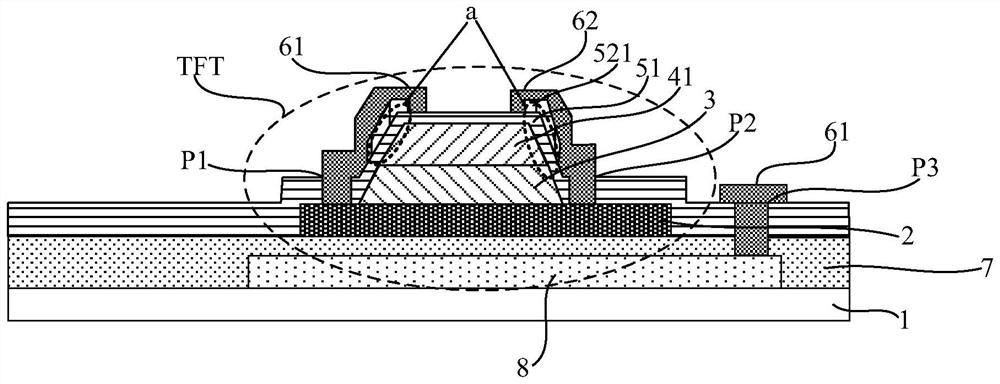

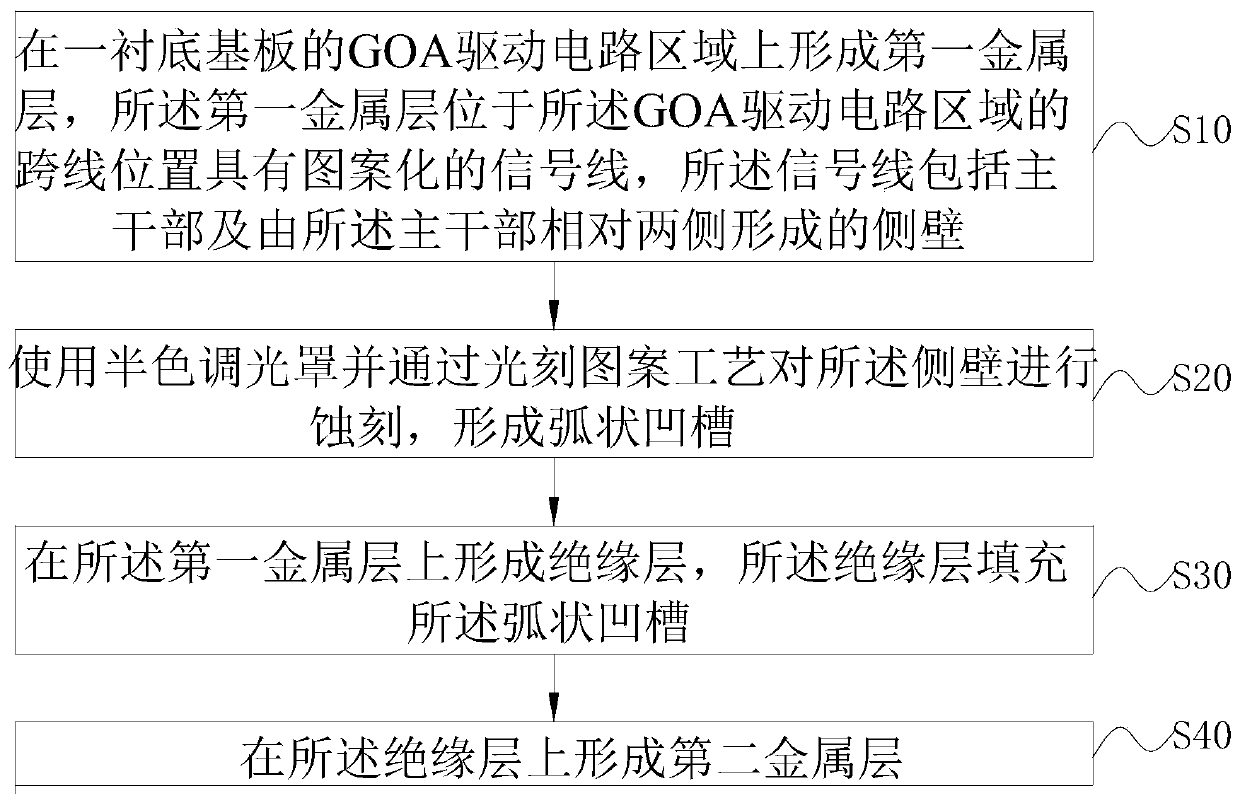

GOA array substrate and preparation method thereof

ActiveCN111524903AIncrease deposition thicknessAvoid short circuitSemiconductor/solid-state device detailsSolid-state devicesHemt circuitsEngineering

The invention discloses a GOA array substrate and a preparation method thereof. The GOA array substrate comprises a substrate body and a GOA drive circuit arranged on the substrate body. The GOA drivecircuit comprises a plurality of connected GOA units, and each GOA unit comprises a thin film transistor array layer, a first metal layer formed on the thin film transistor array layer, an insulatinglayer arranged on the first metal layer and a second metal layer arranged on the insulating layer; the first metal layer is provided with a patterned signal line at a position crossing the second metal layer, the signal line comprises a trunk part and side walls formed by two opposite sides of the trunk part, and each side wall is provided with an arc-shaped groove. According to the embodiment ofthe invention, the short circuit of the signal line formed by the first metal layer and the signal line formed by the second metal layer at the overline position can be prevented, and the stability of the GOA drive circuit in the GOA array substrate is further improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com