Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

207results about How to "High bonding reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

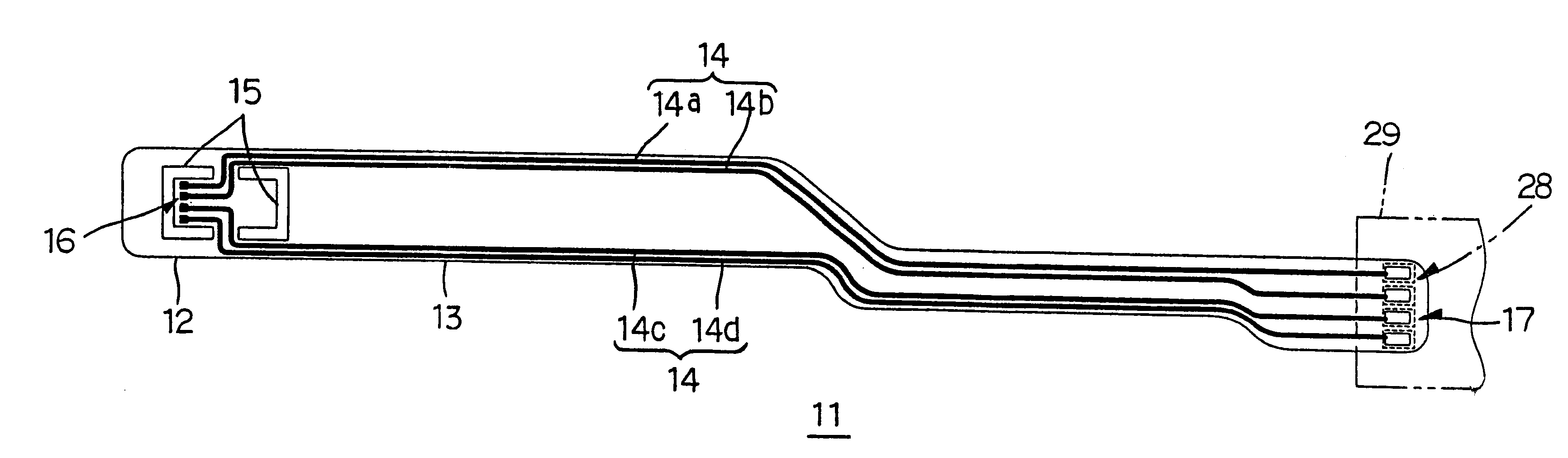

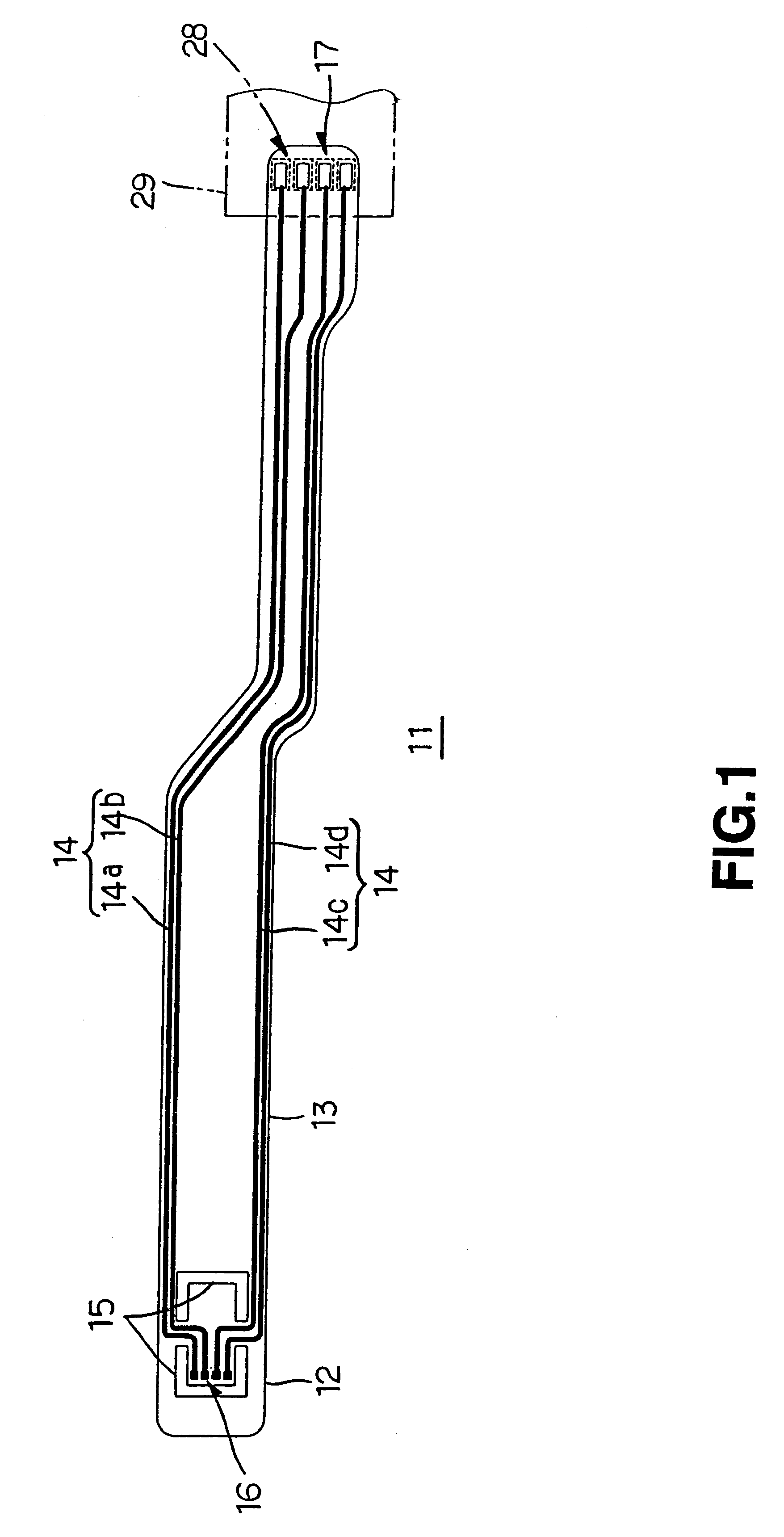

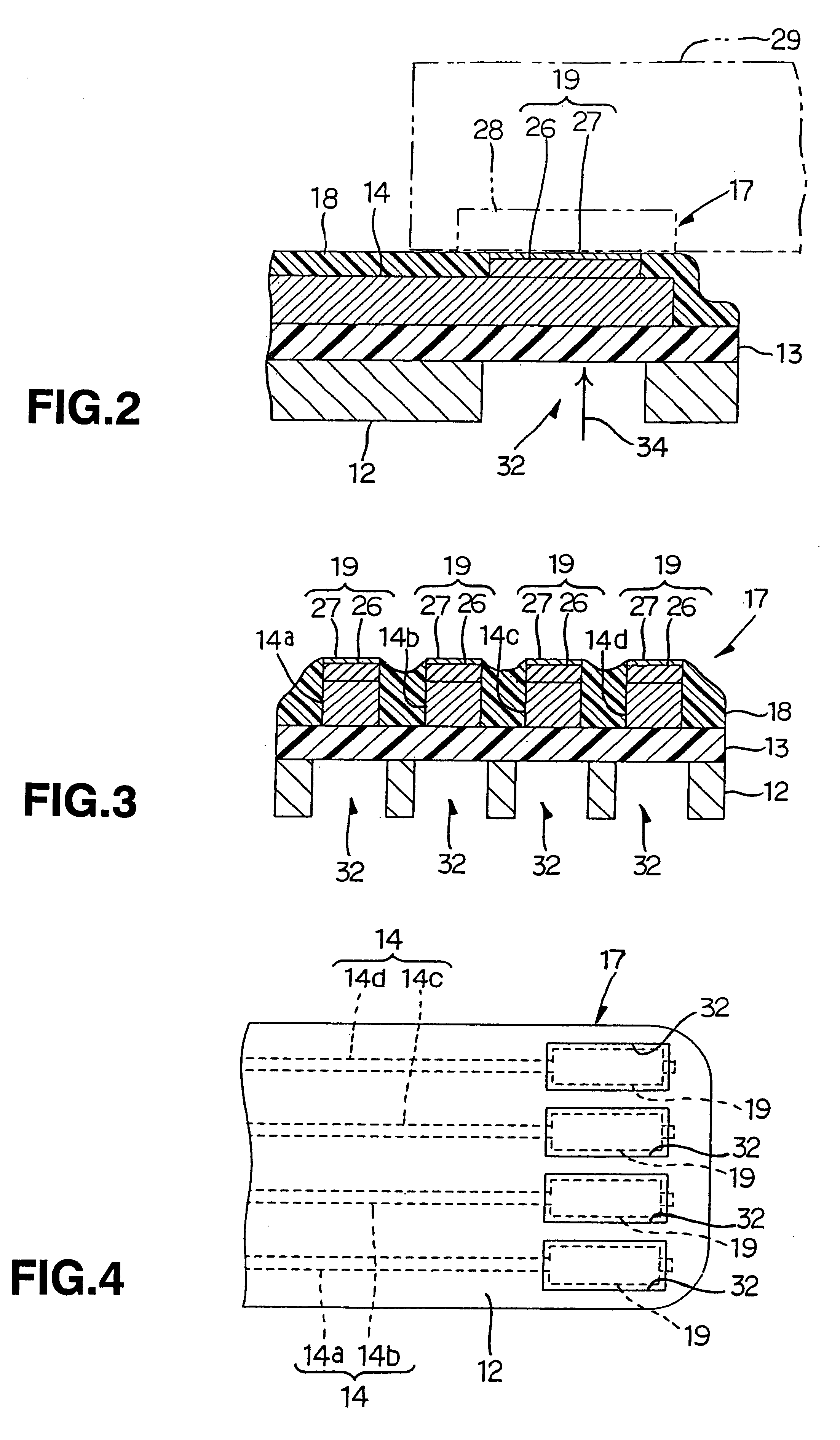

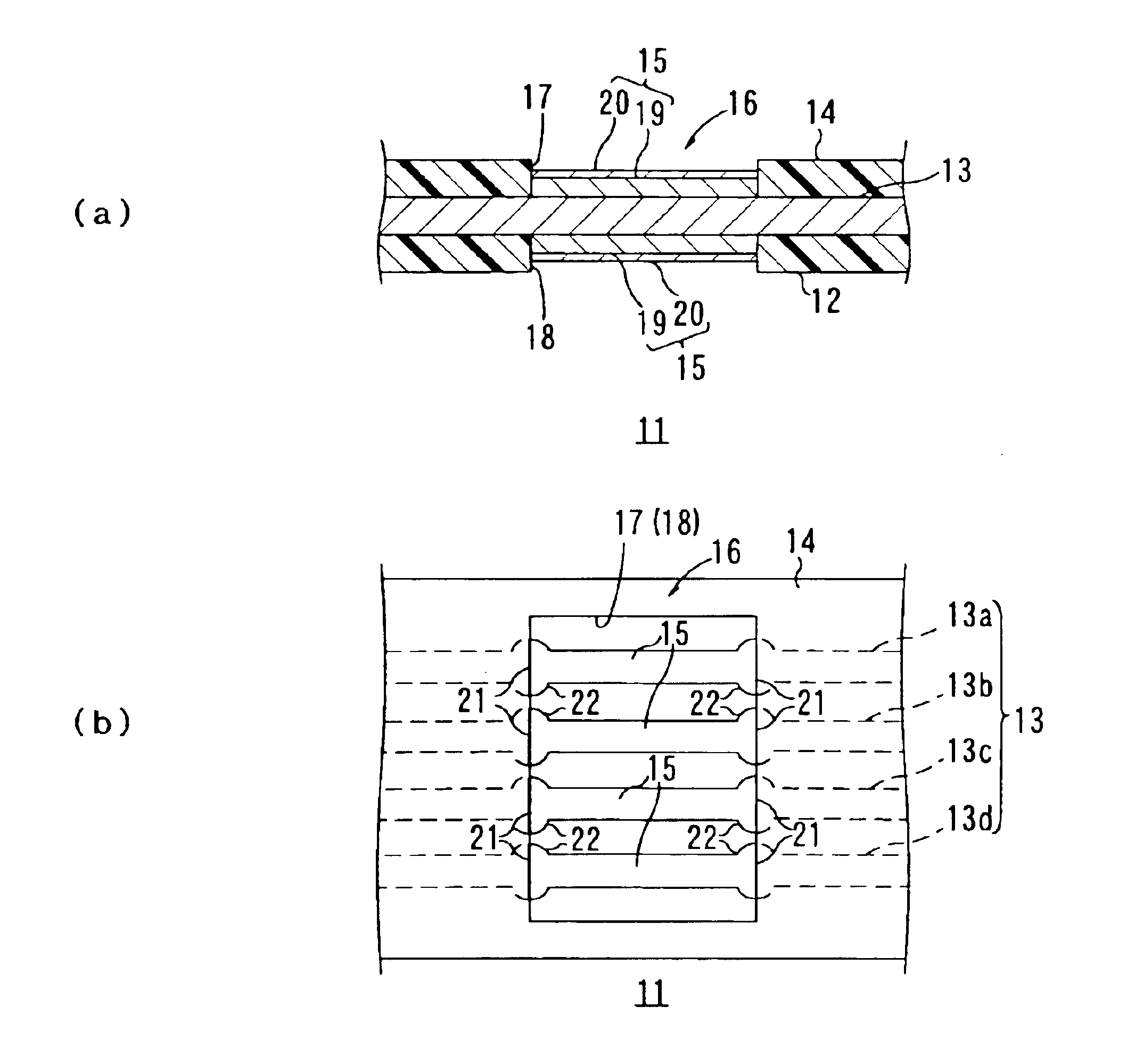

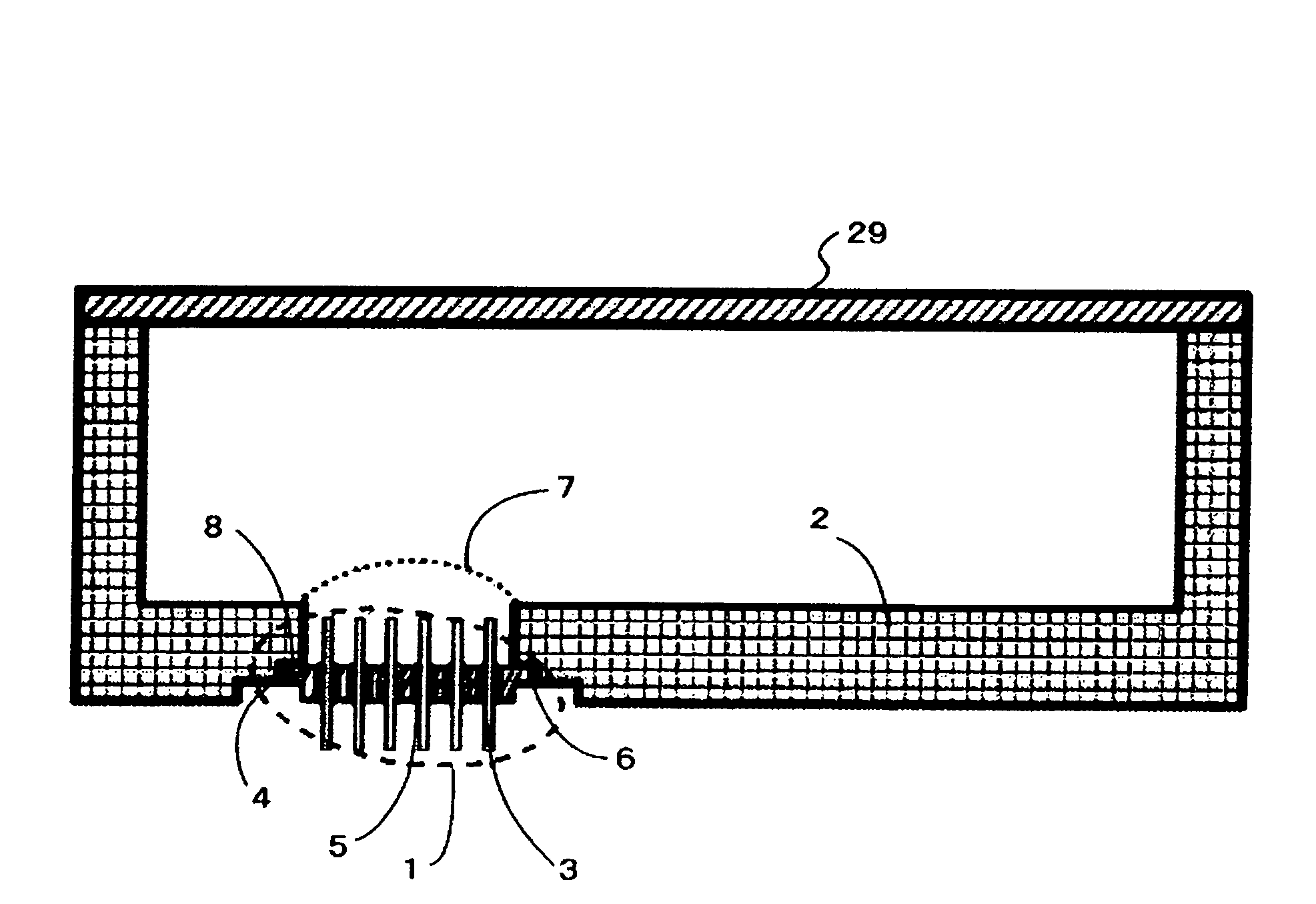

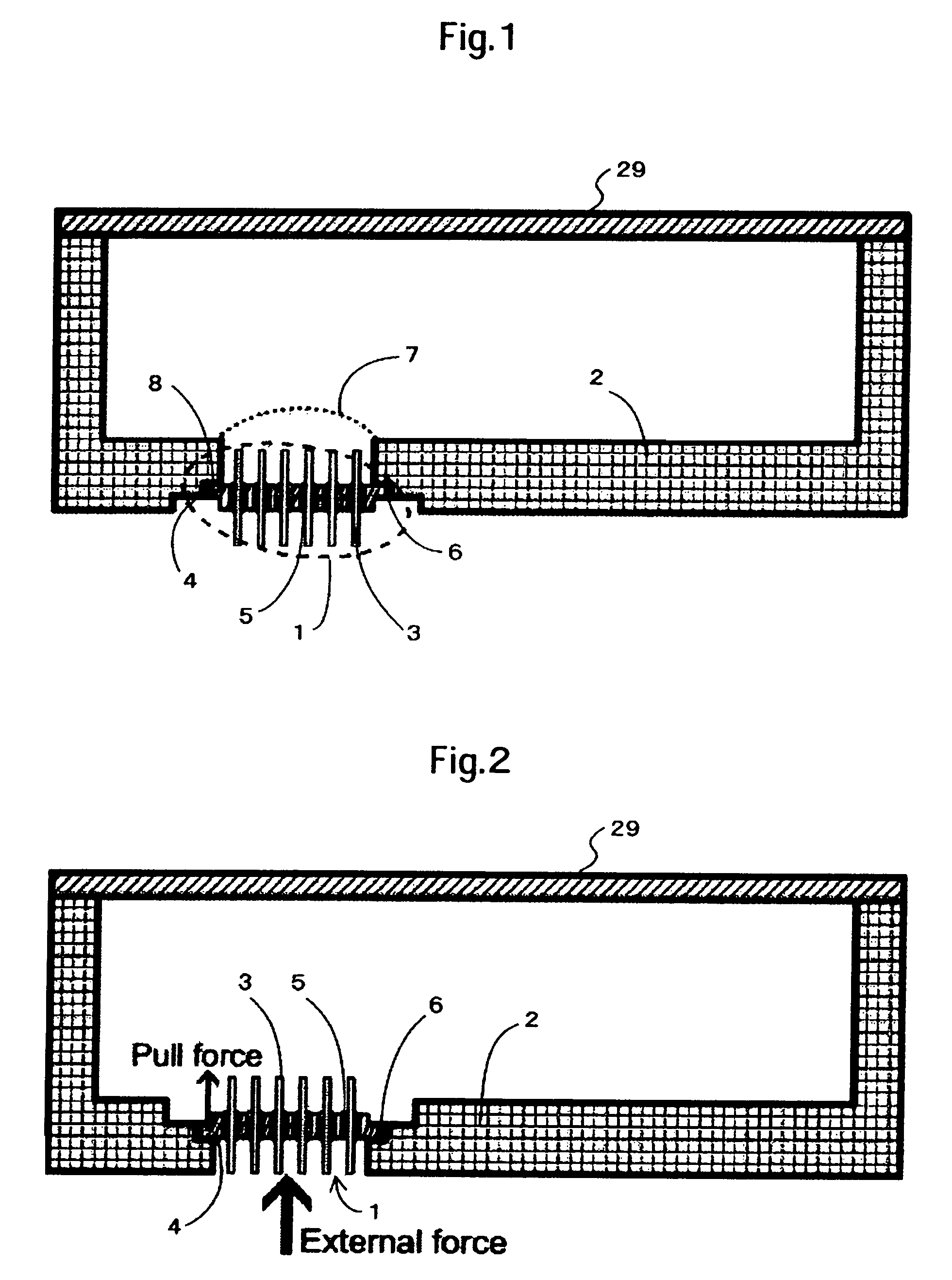

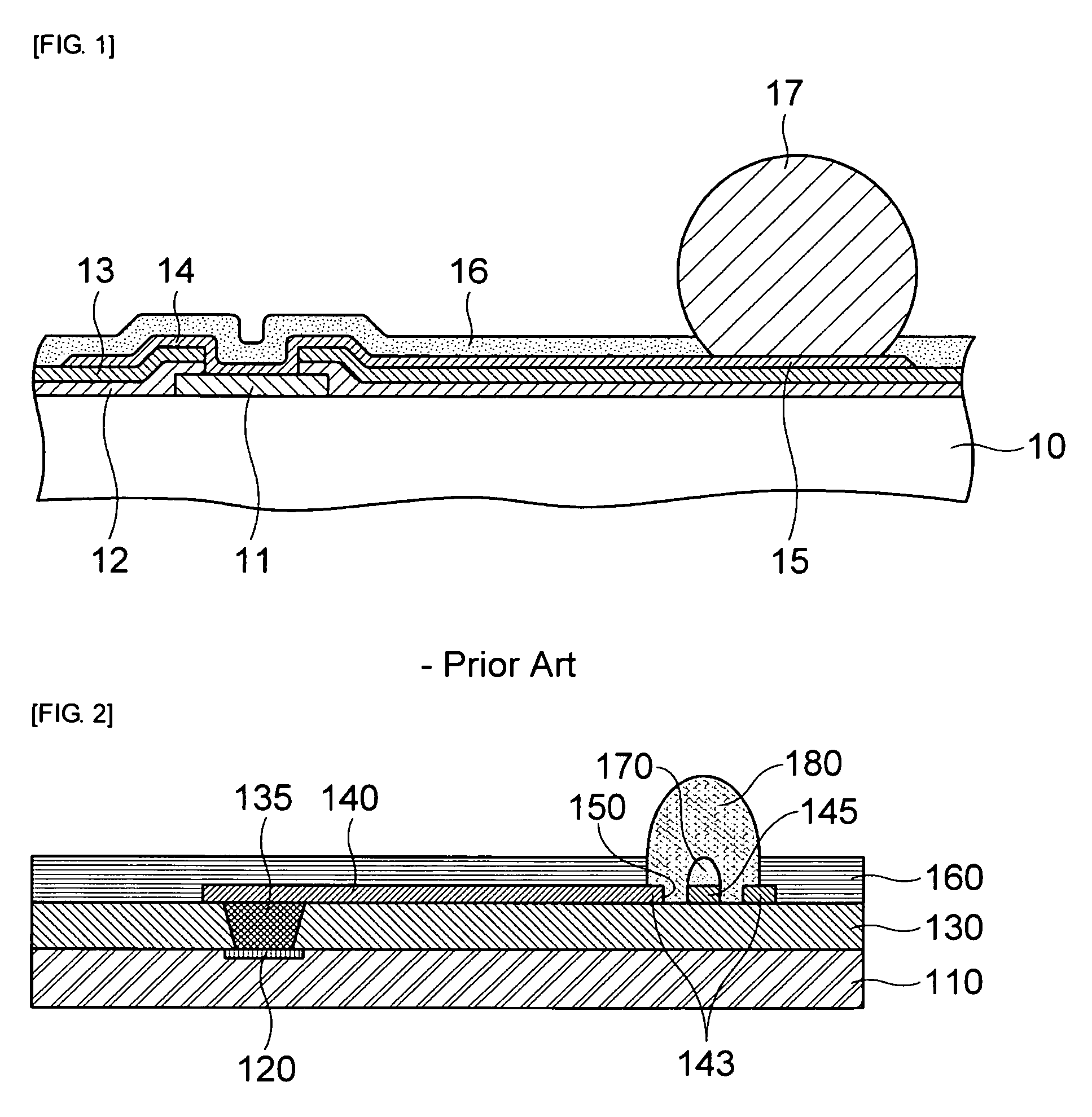

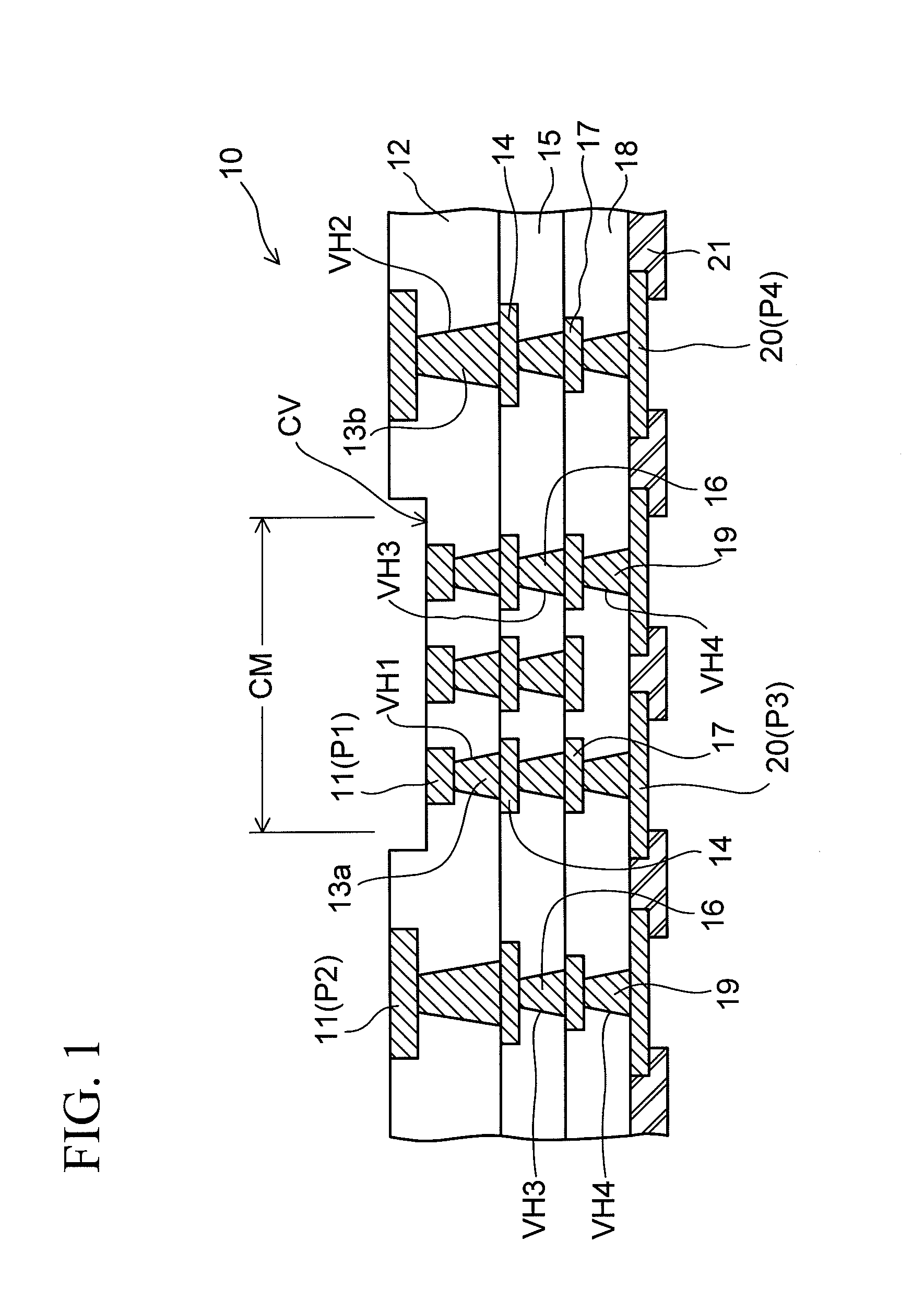

Suspension board with circuit

InactiveUS6399899B1High strengthSimple structureRelieving strain on wire connectionRecord information storageExternal connectionEngineering

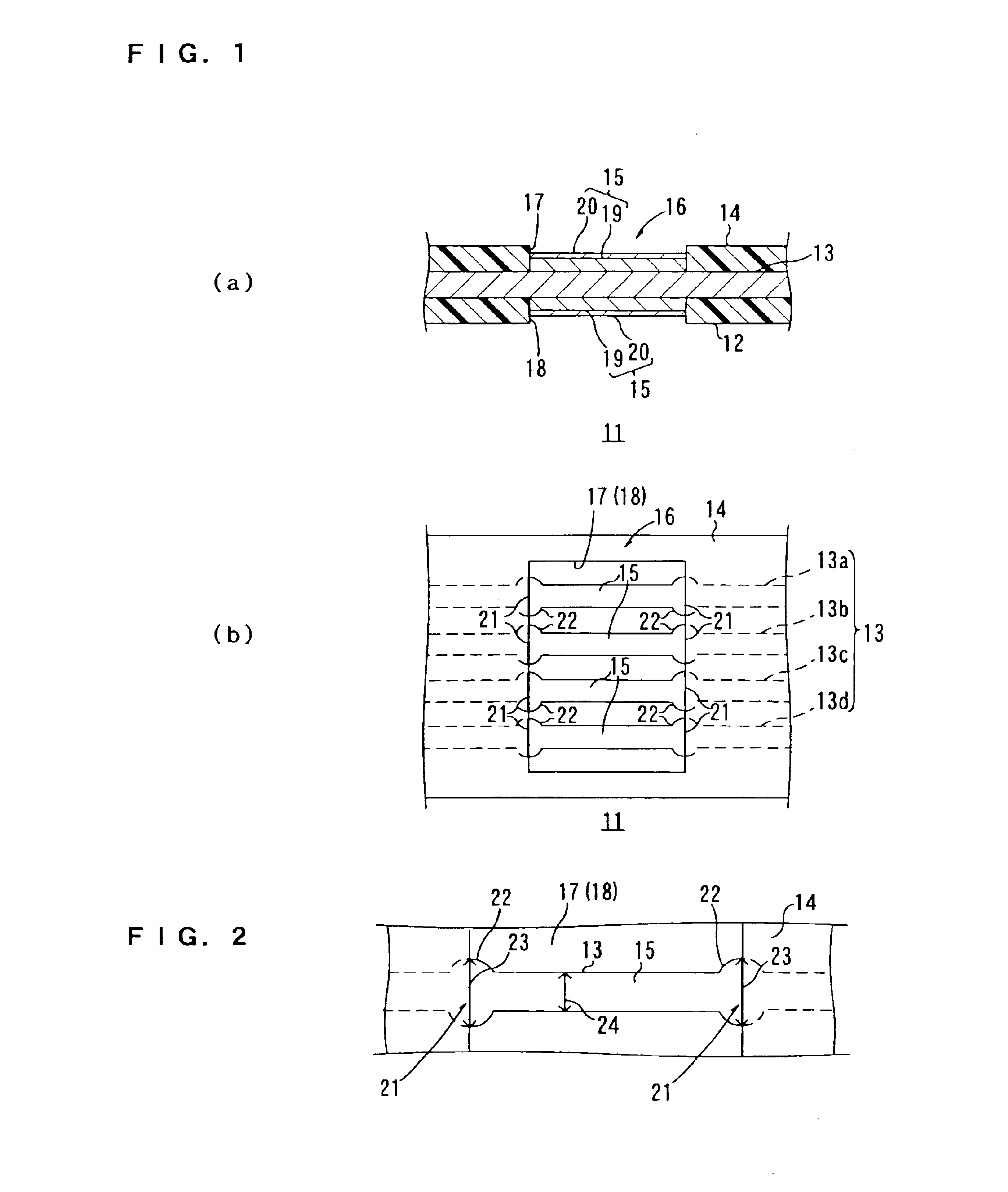

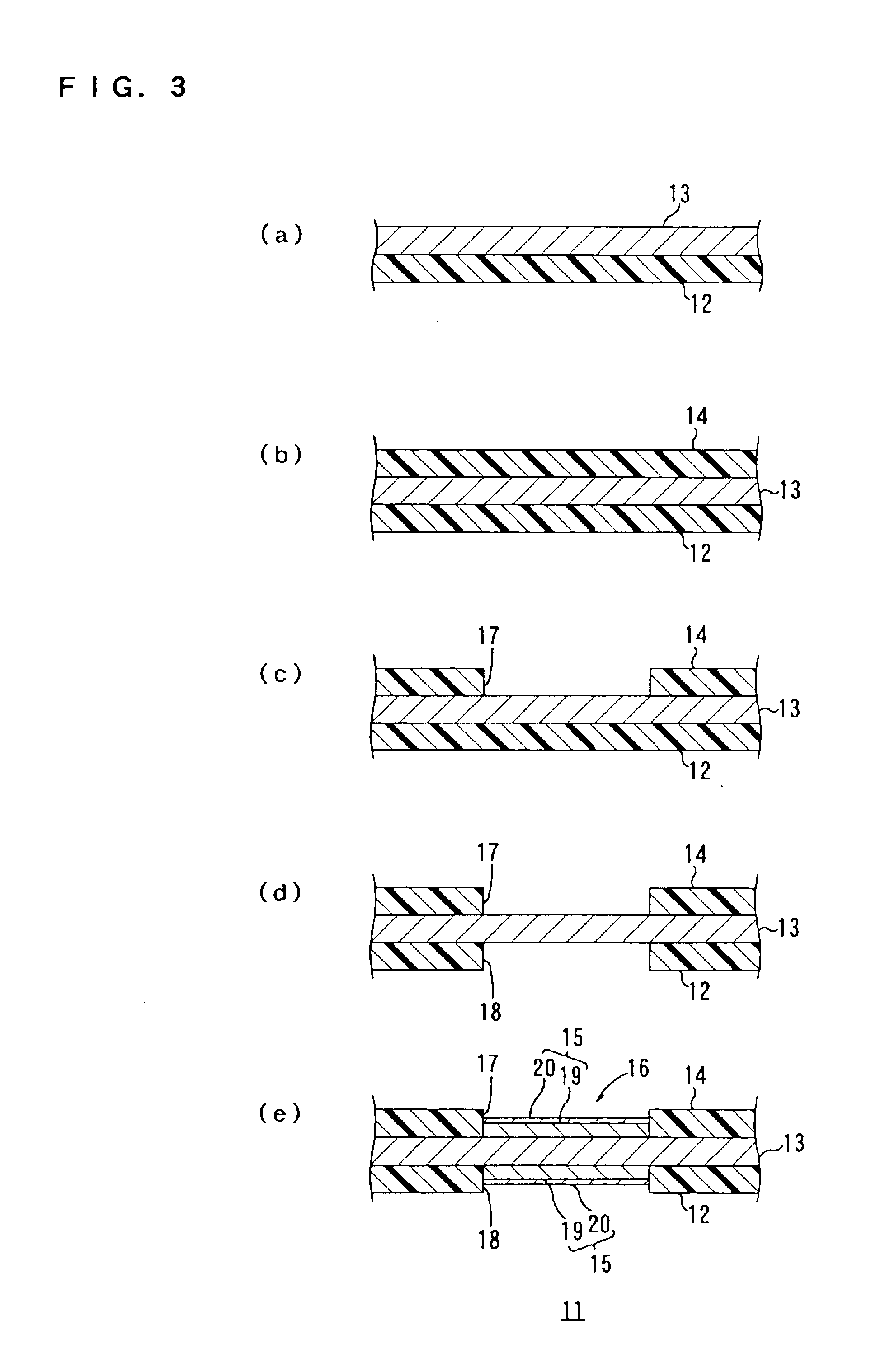

To provide a suspension board with circuit that enables its terminals to be bonded to the other terminals with sufficient strength with simple structure, to ensure sufficient bonding reliability, the suspension board with circuit 11 includes a suspension board 12, a base layer 13 formed on the suspension board 12, and a conductive layer 14 formed on the base layer 13 and a cover layer 18 with which the conductive layer 14 is covered, wherein external connection terminals 17 to be bonded to terminals 28 of a read / write board 29 are formed without the suspension board 12 and / or the base layer 13 being formed.

Owner:NITTO DENKO CORP

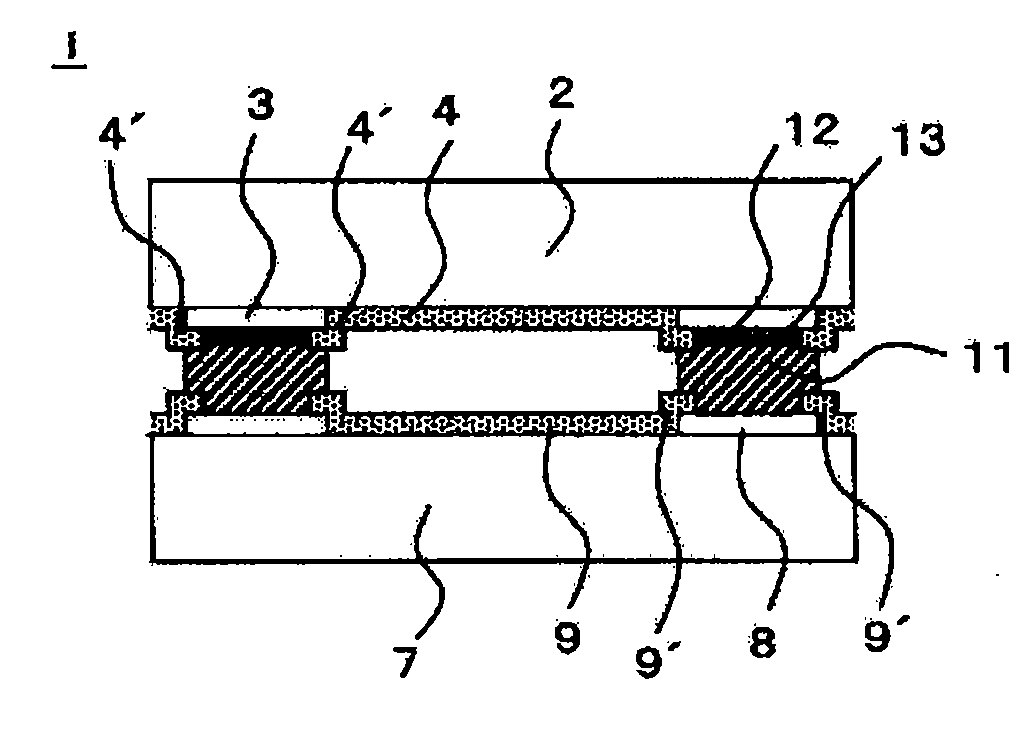

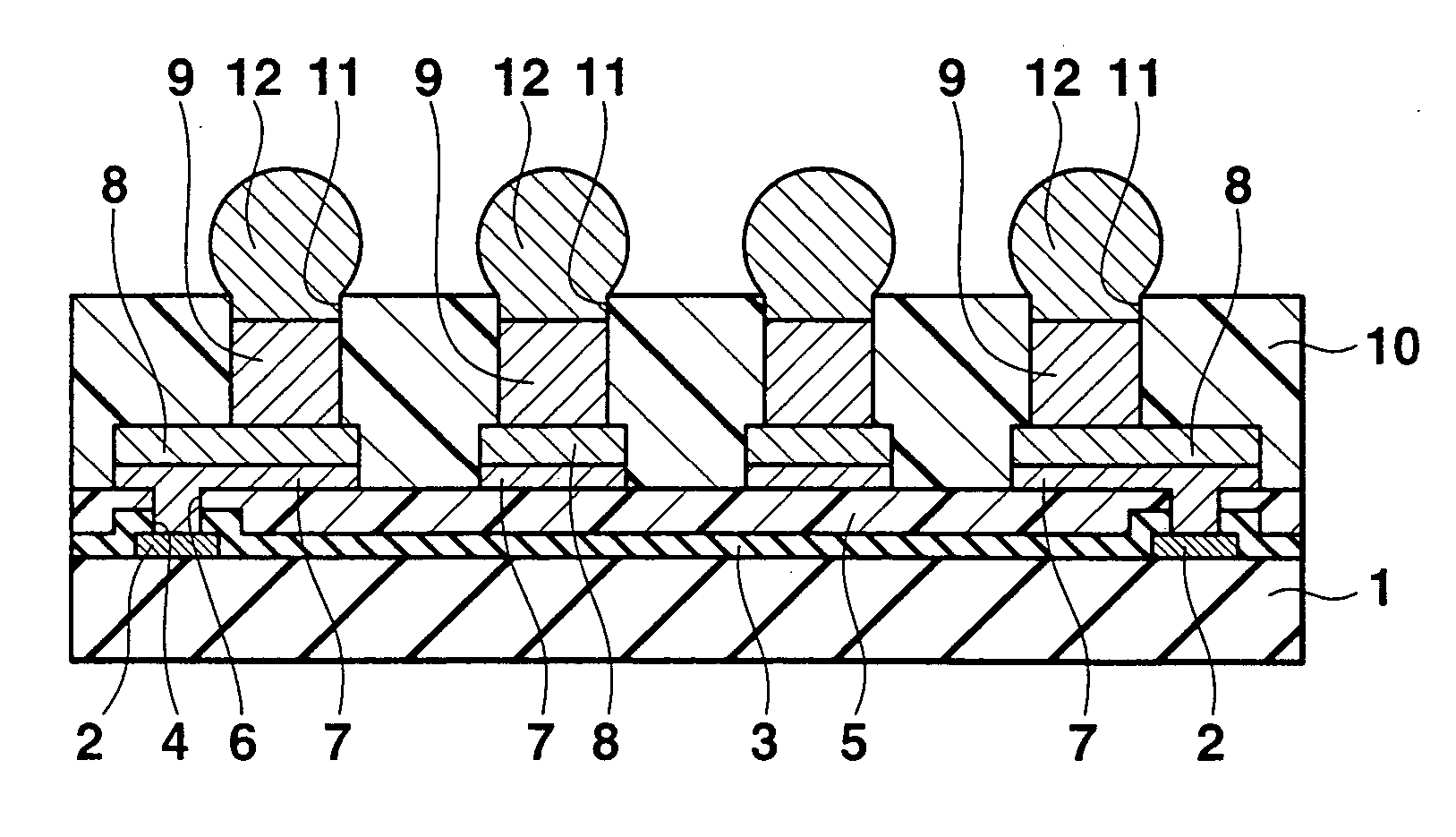

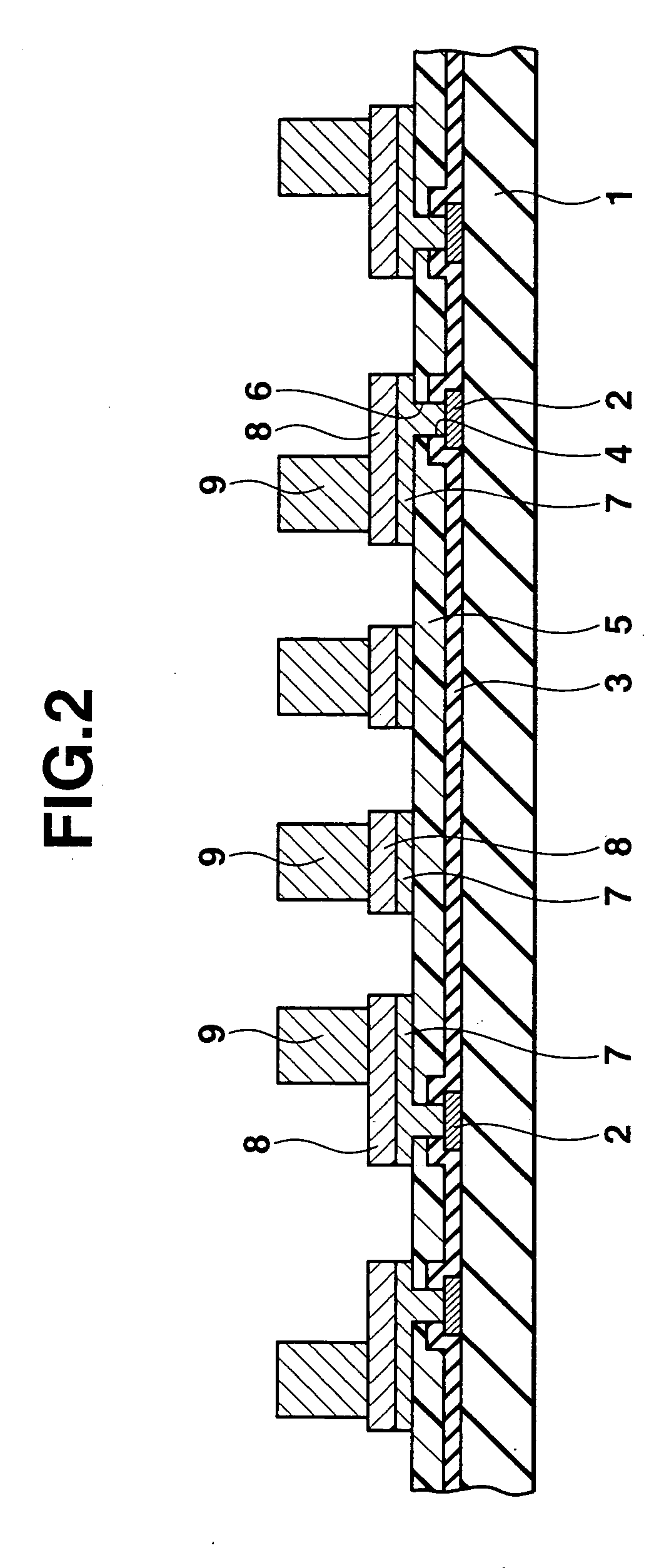

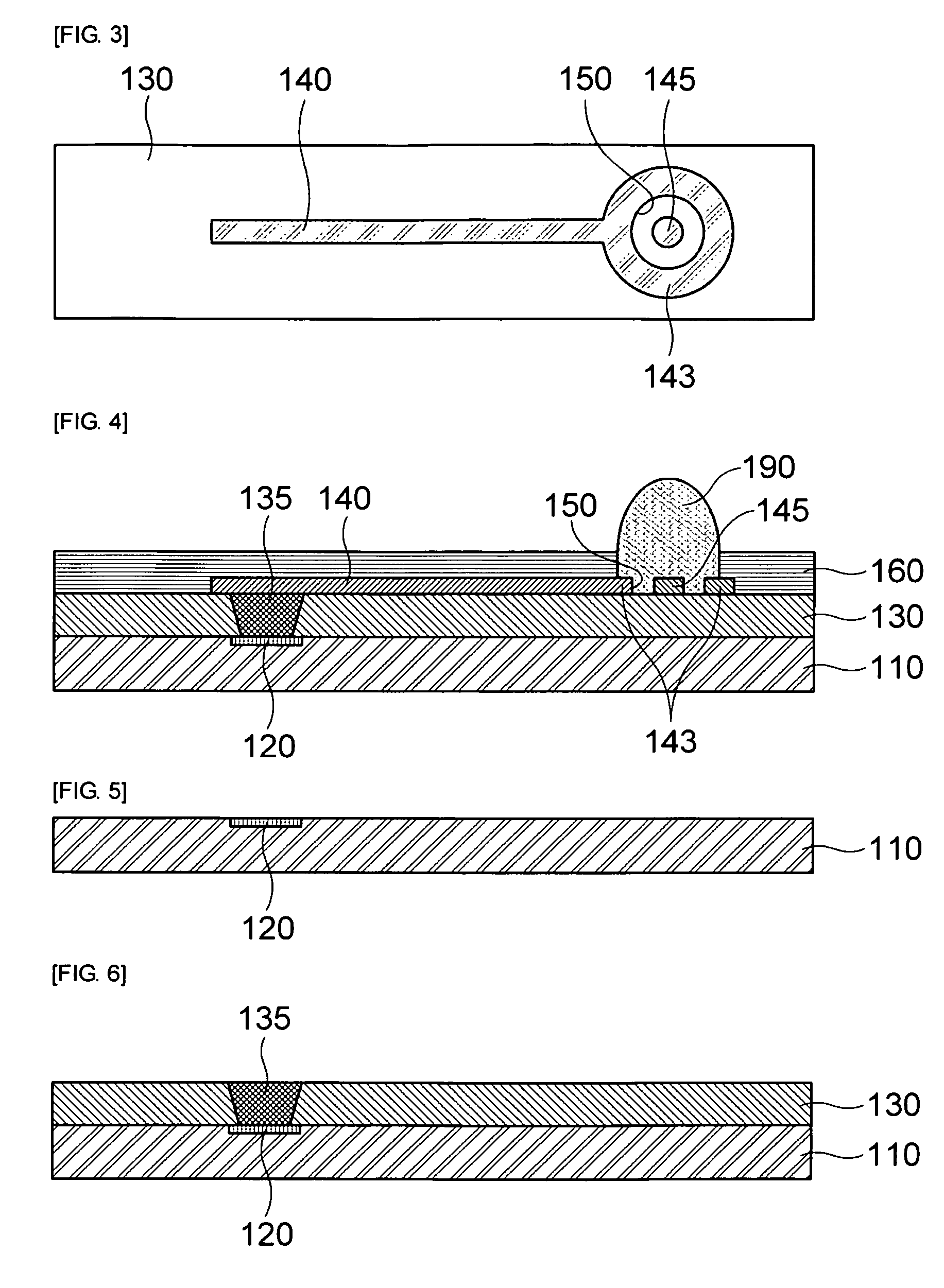

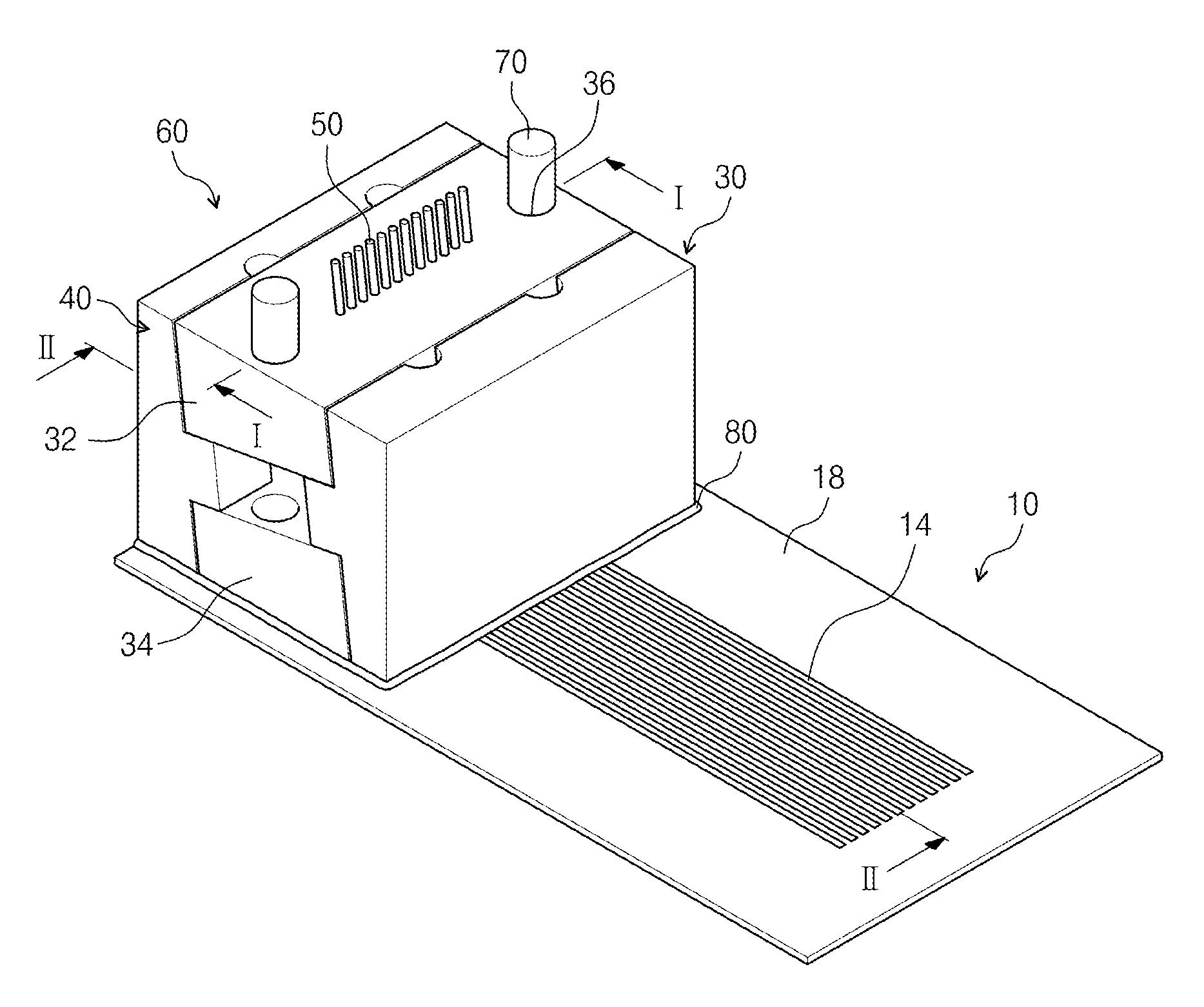

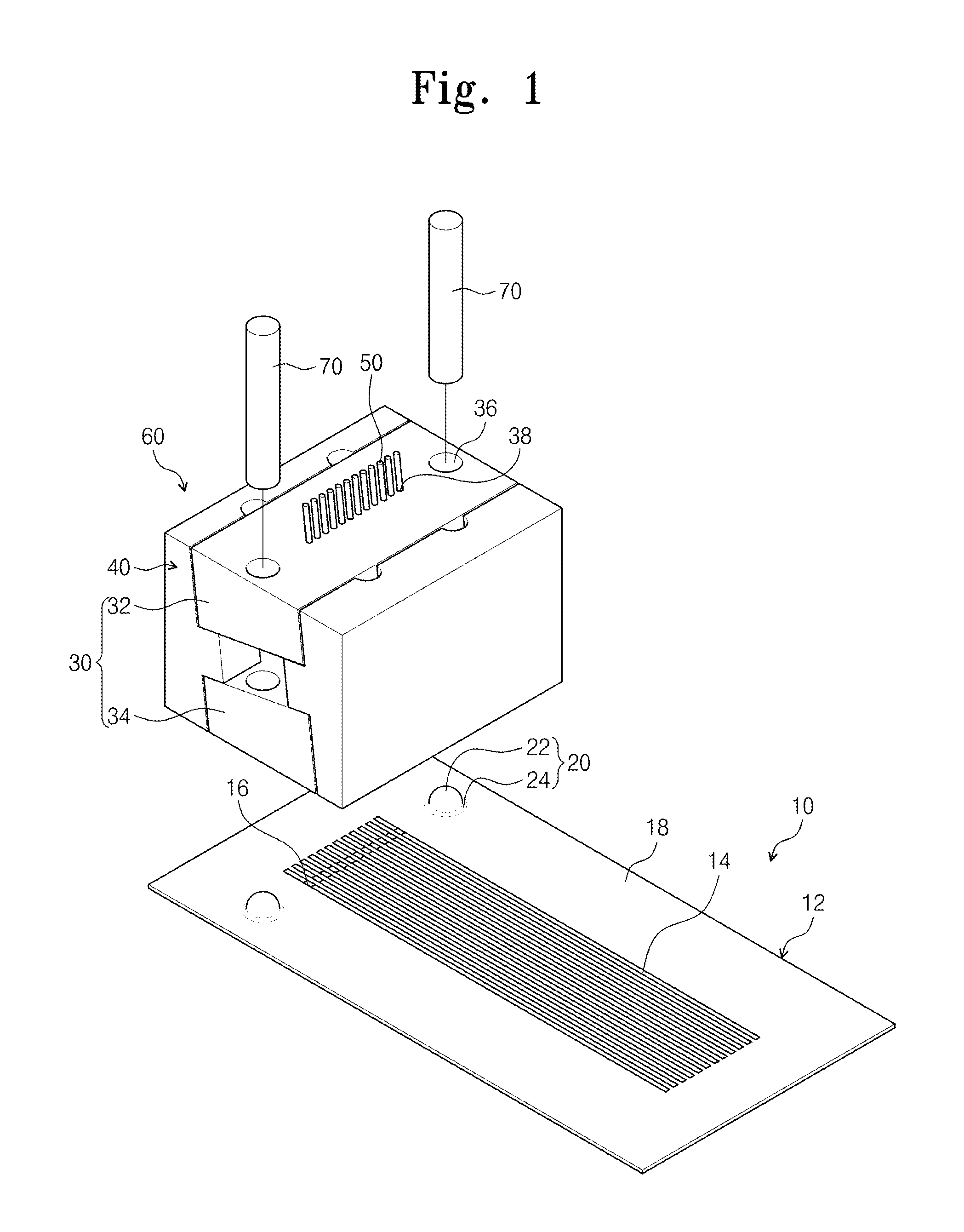

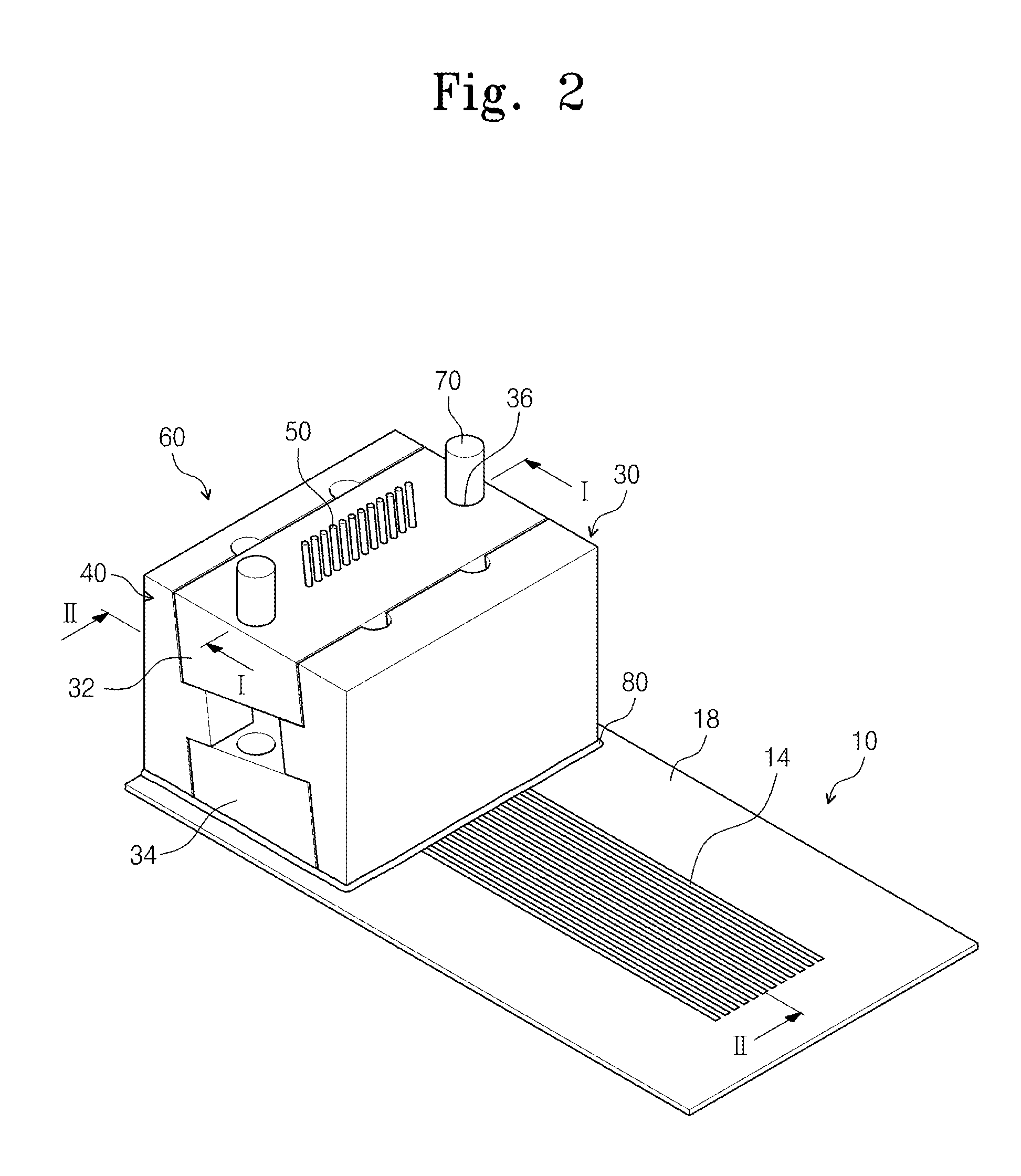

Wired circuit board

InactiveUS6841737B2High bonding reliabilityIncrease physical strengthPrinted circuit assemblingElectrical connection between head and armPrinted circuit boardEngineering

Owner:NITTO DENKO CORP

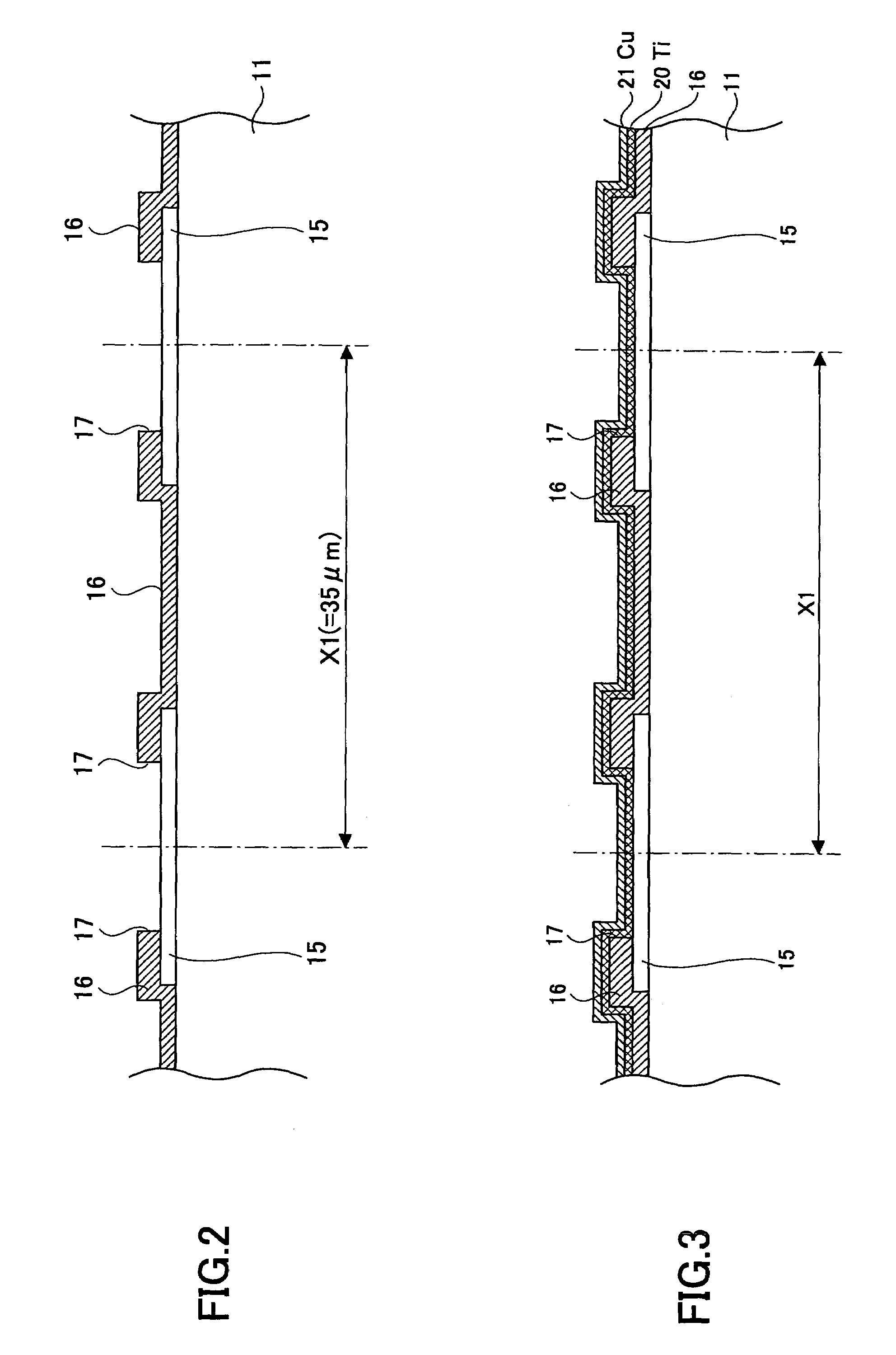

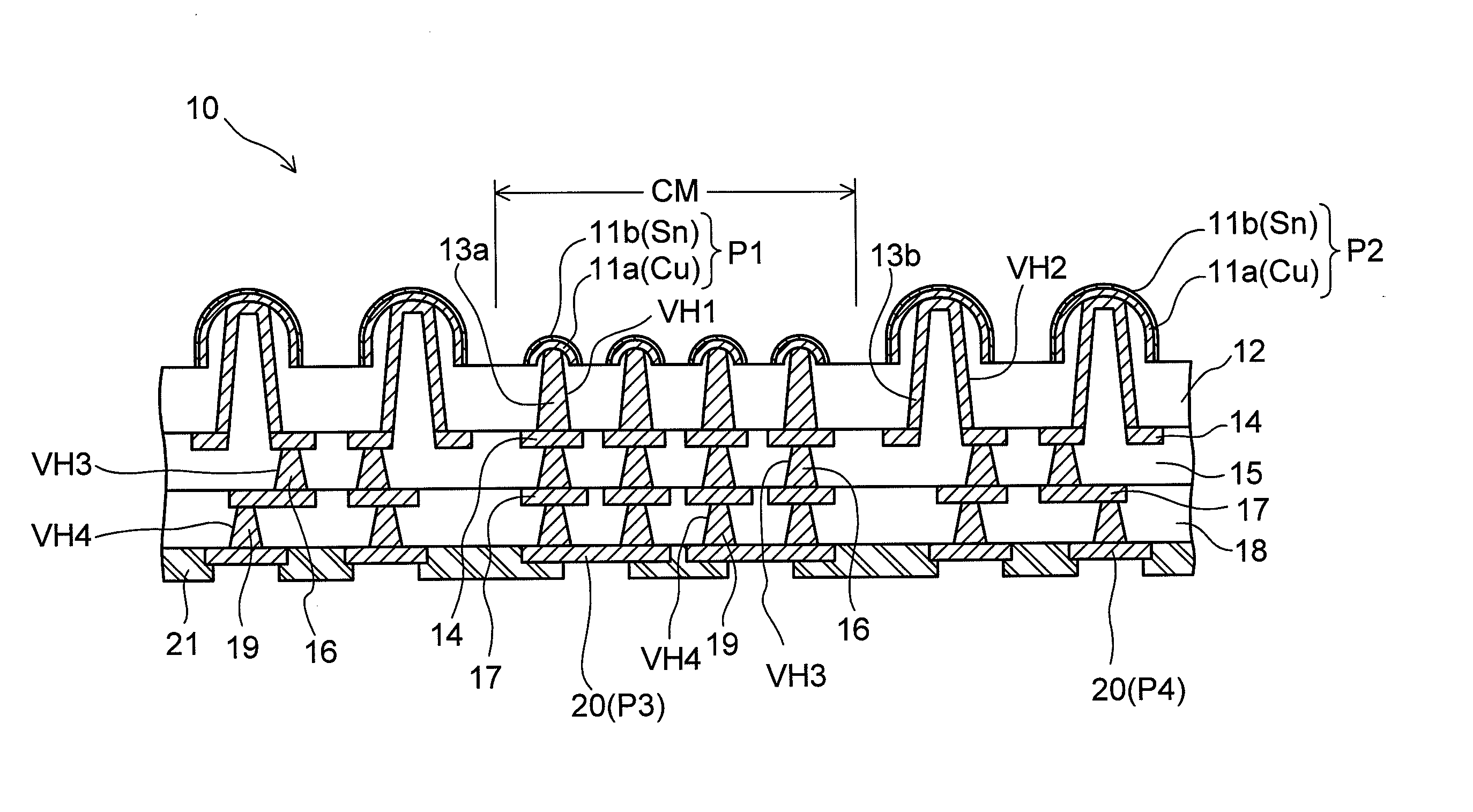

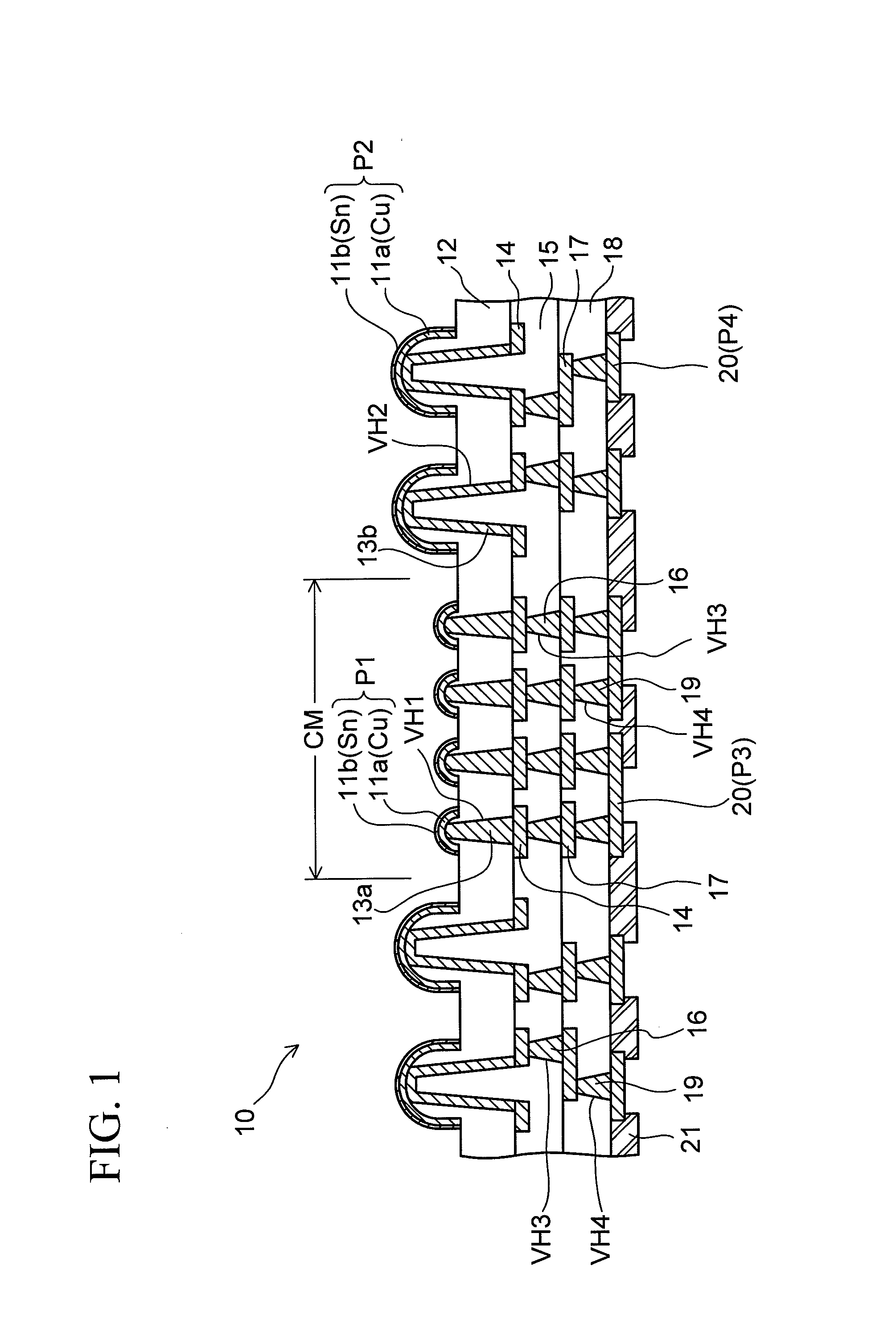

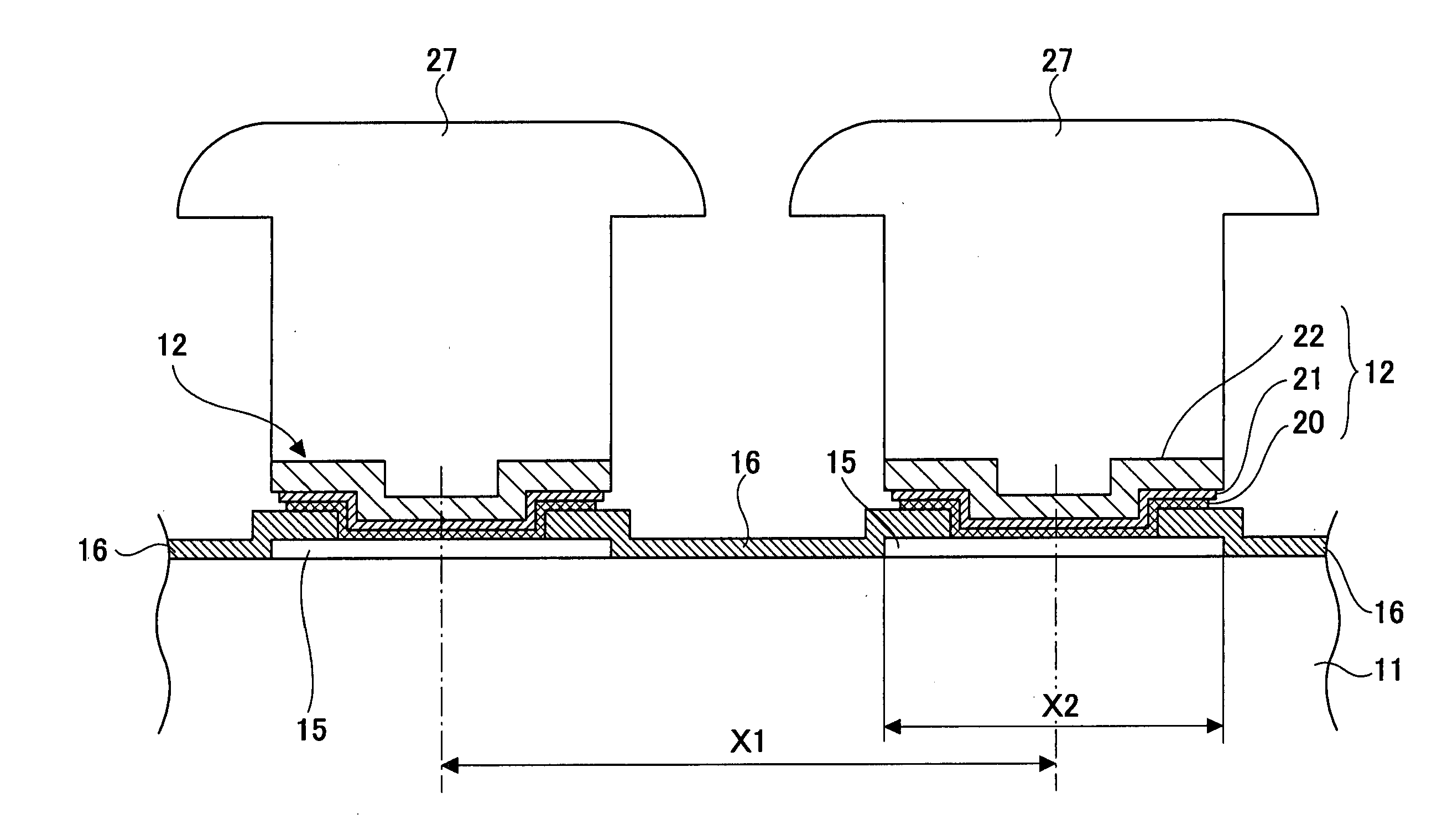

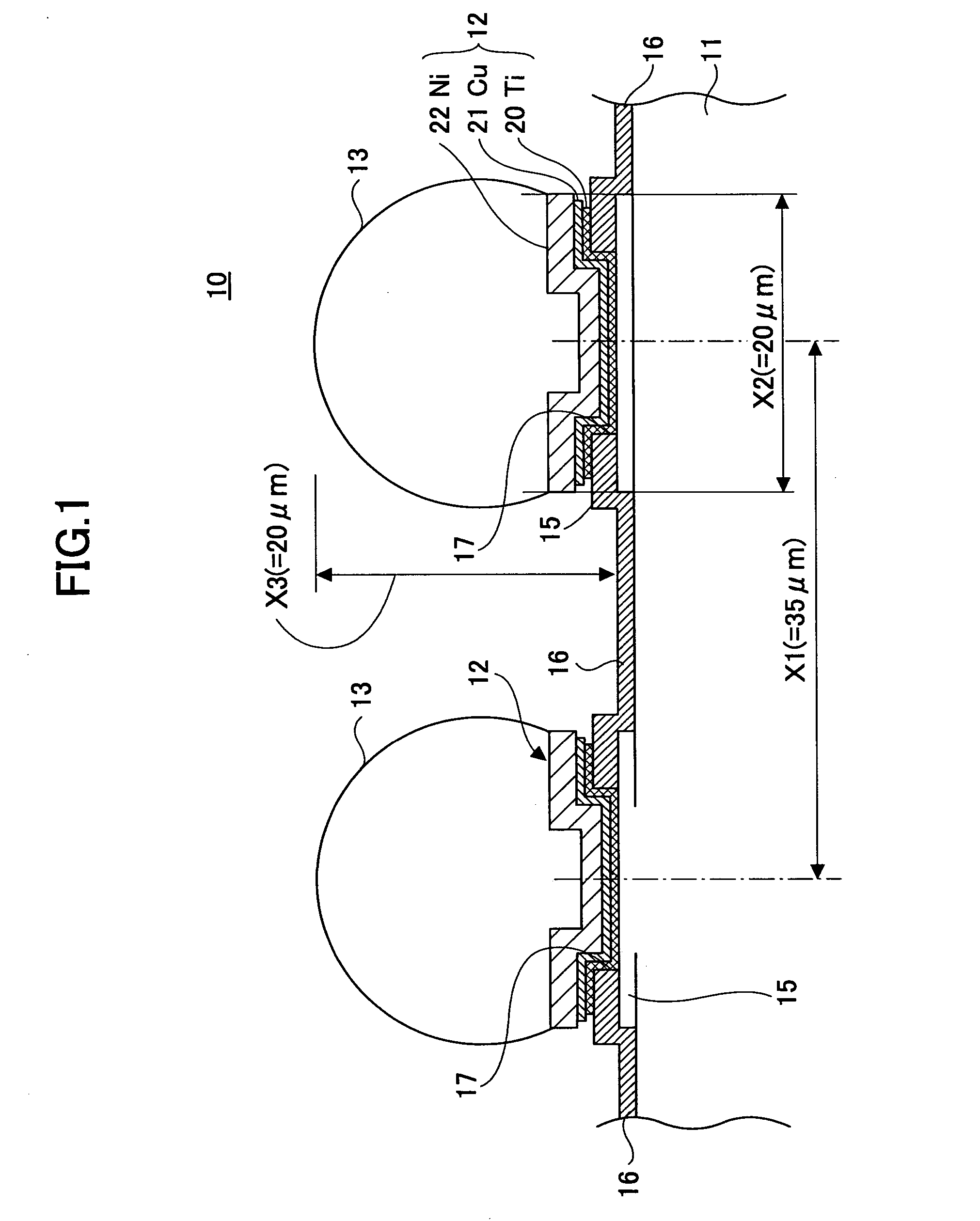

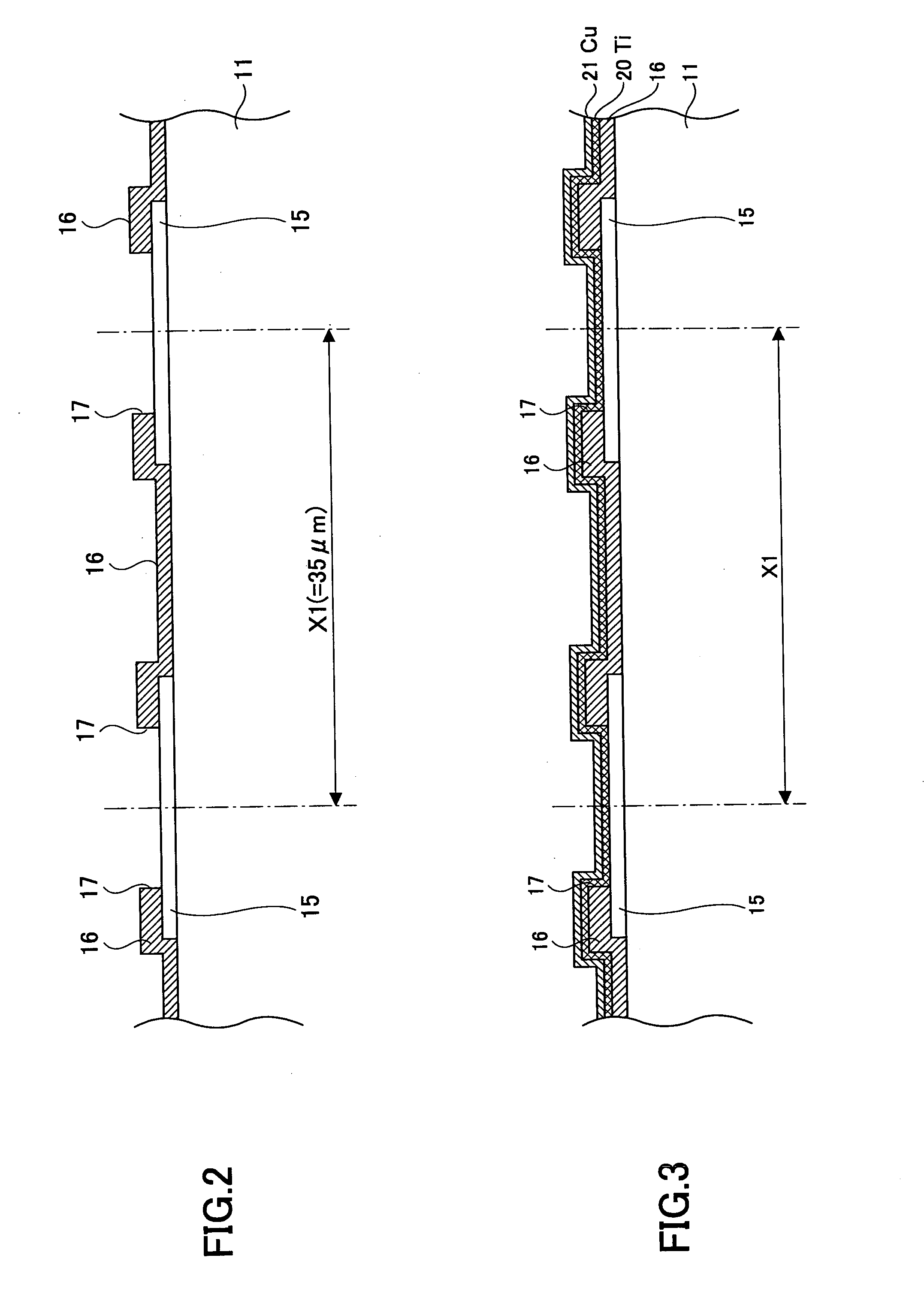

Semiconductor device and method of fabricating the same

InactiveUS7064436B2High aspect ratioHigh bonding reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrode arraySemiconductor

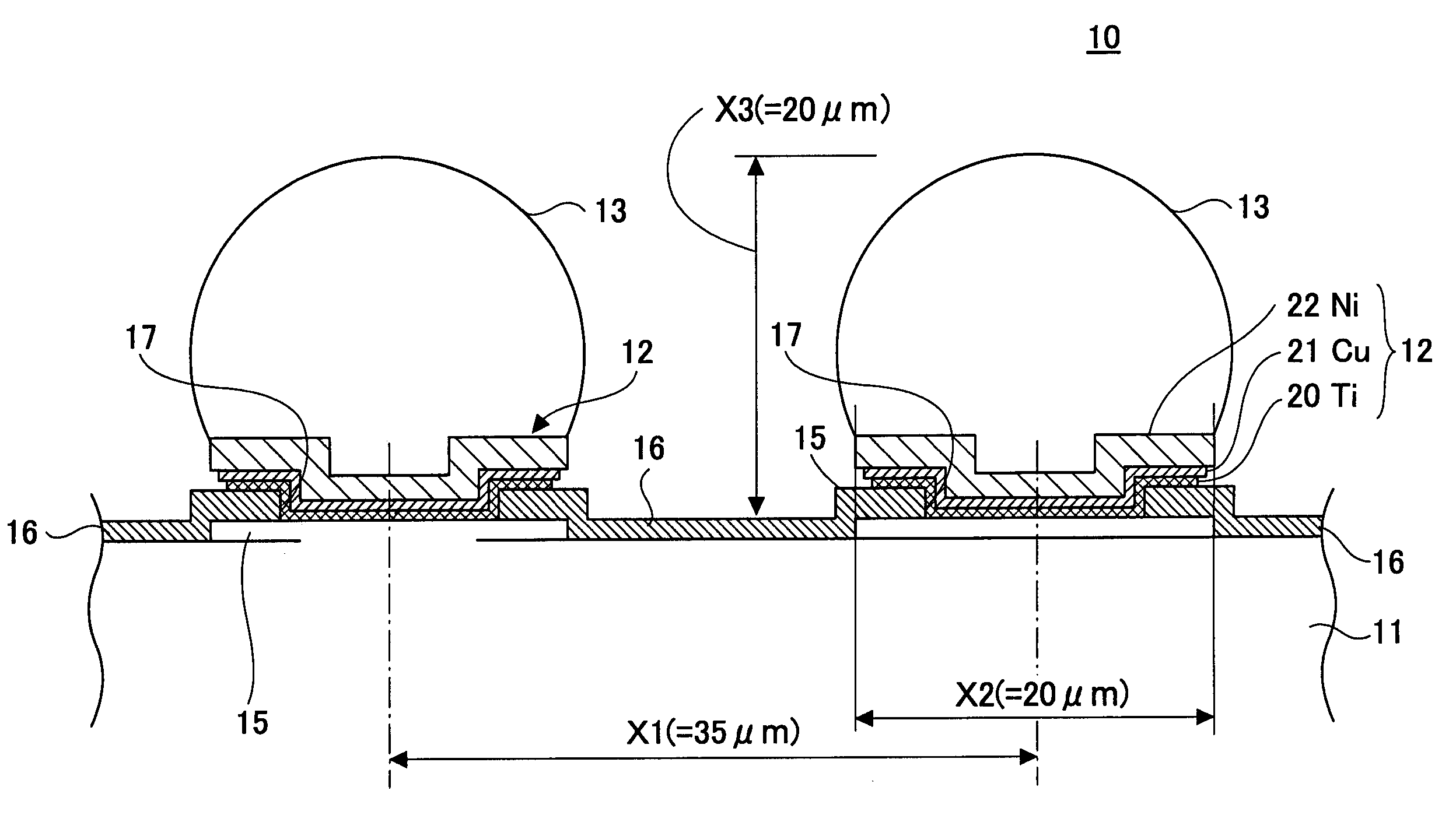

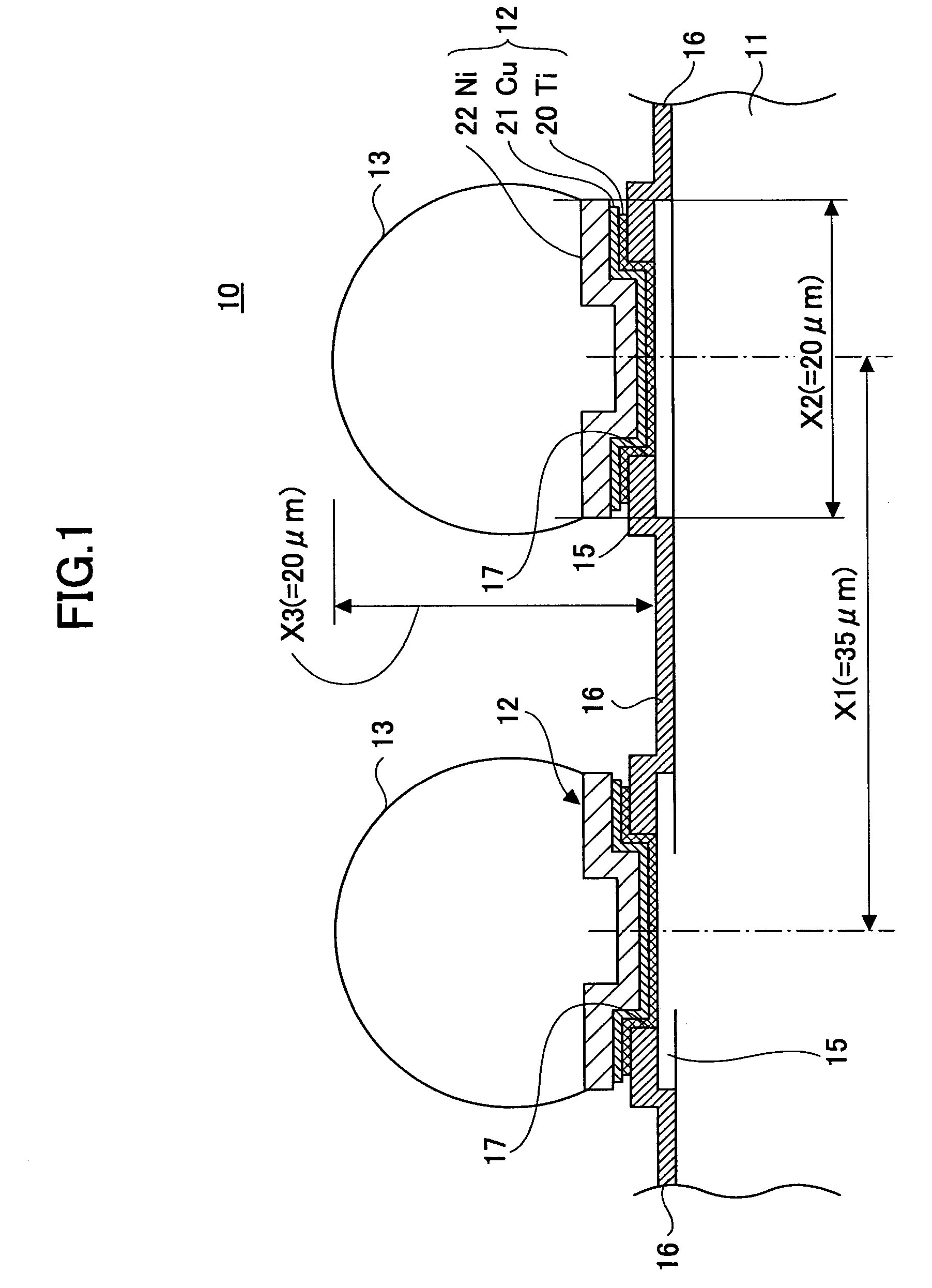

A semiconductor device includes a semiconductor substrate and an array of protruding electrodes arranged at a pitch X1. Each of the protruding electrodes has a height X3 and is formed on a barrier metal base of diameter X2 coupled to an electrode arranged on the semiconductor substrate so as to satisfy the relations (X1 / 2)≦X2≦(3*X1 / 4) and (X1 / 2)≦X3≦(3*X1 / 4).

Owner:FUJITSU LTD

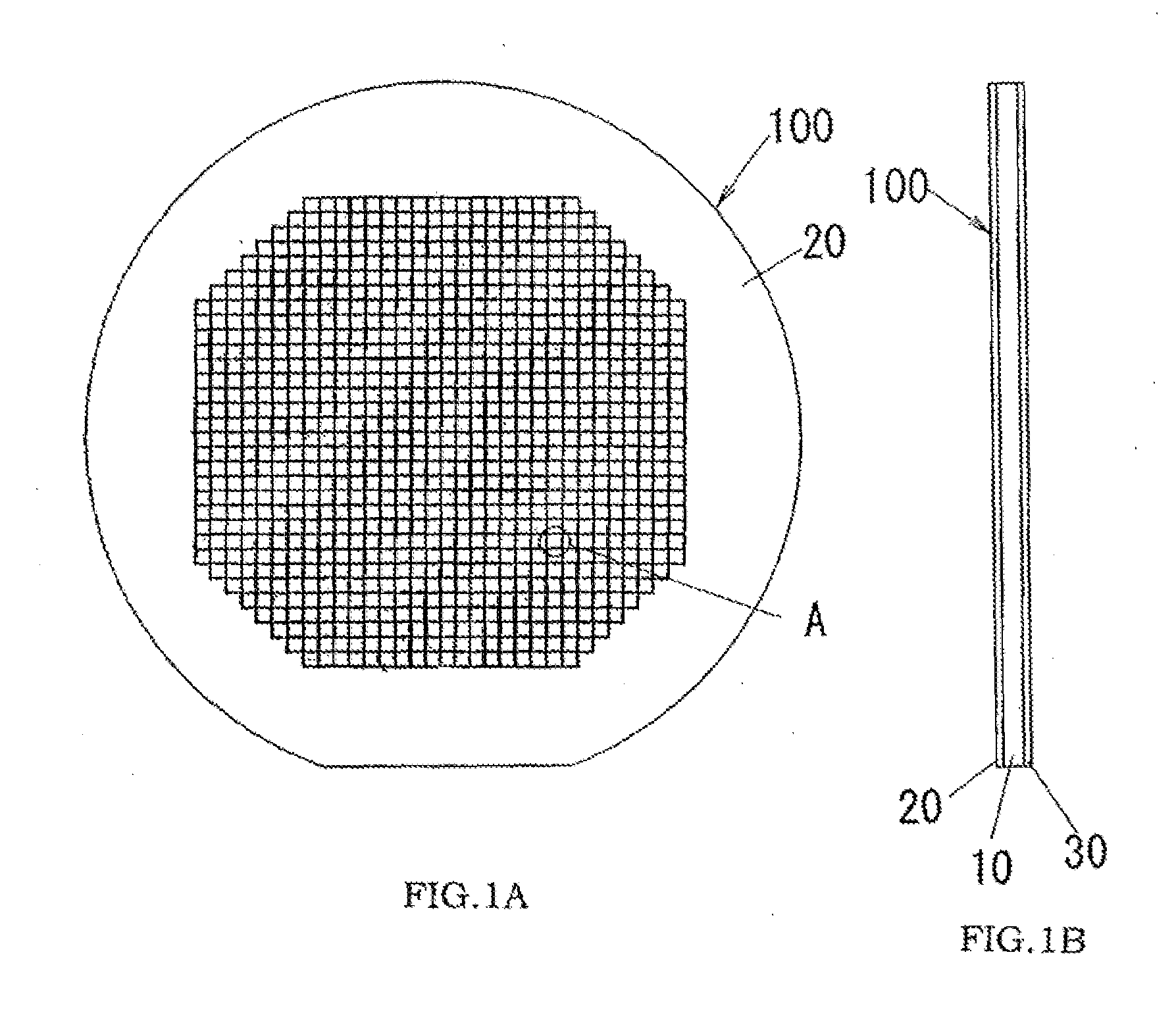

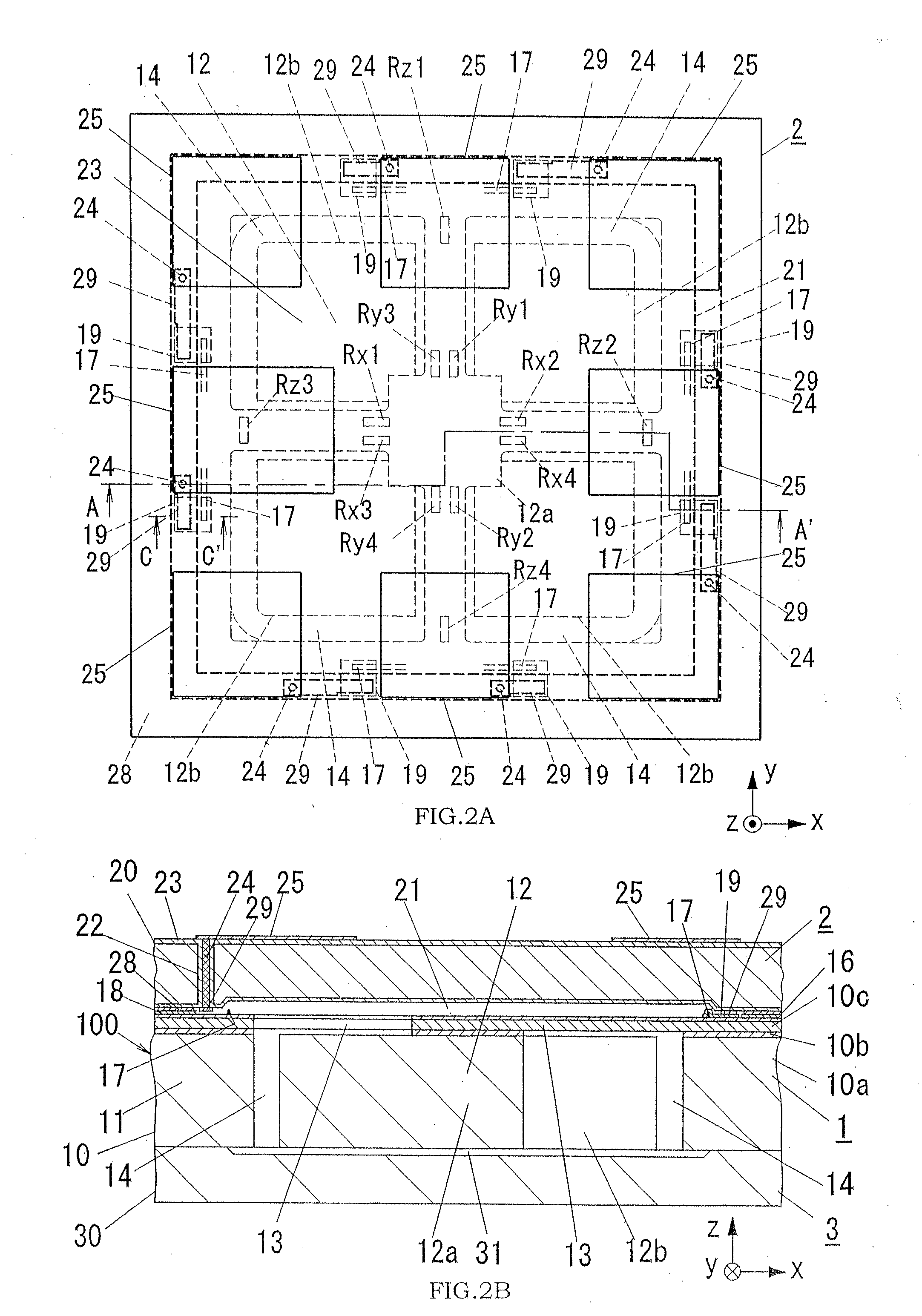

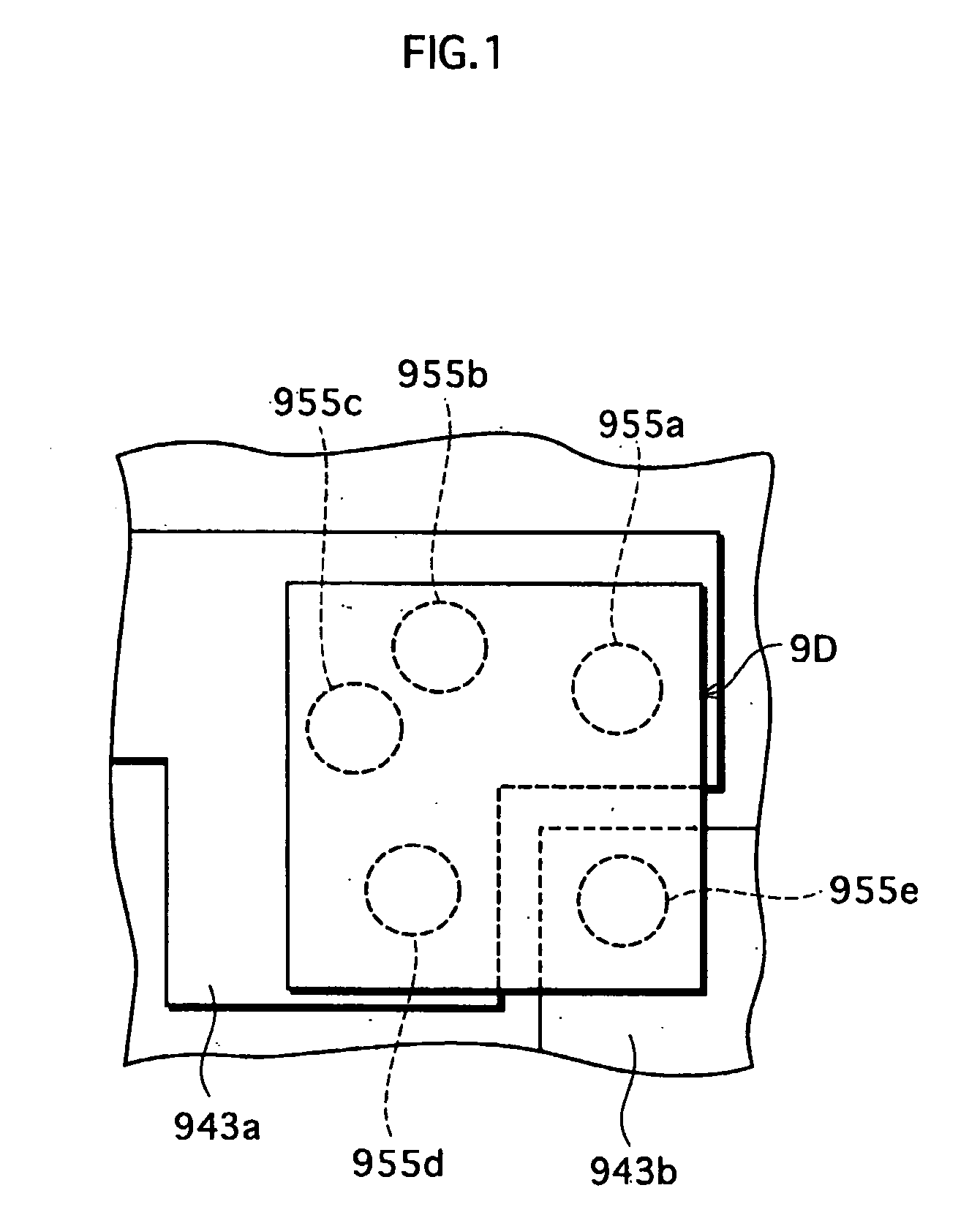

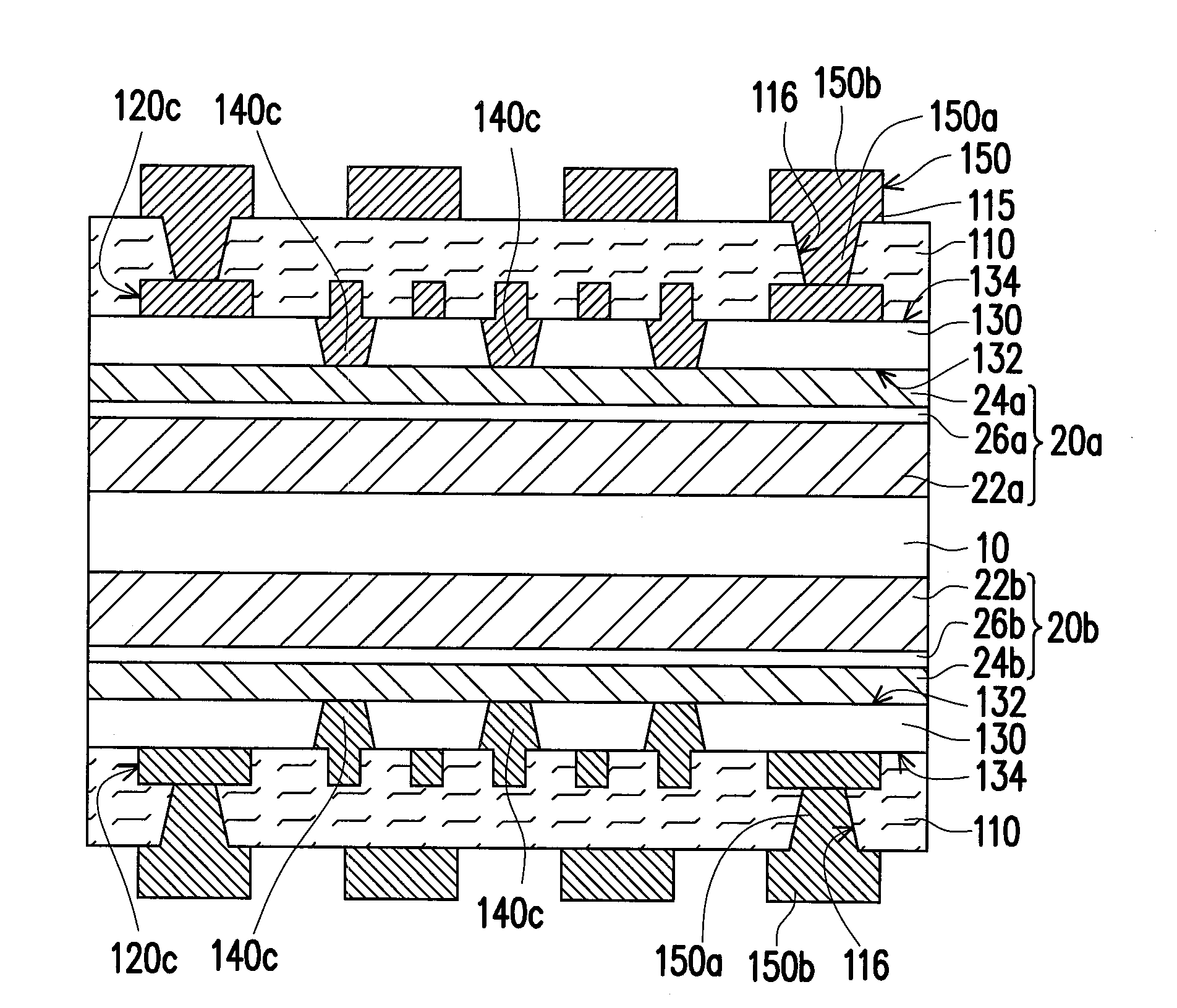

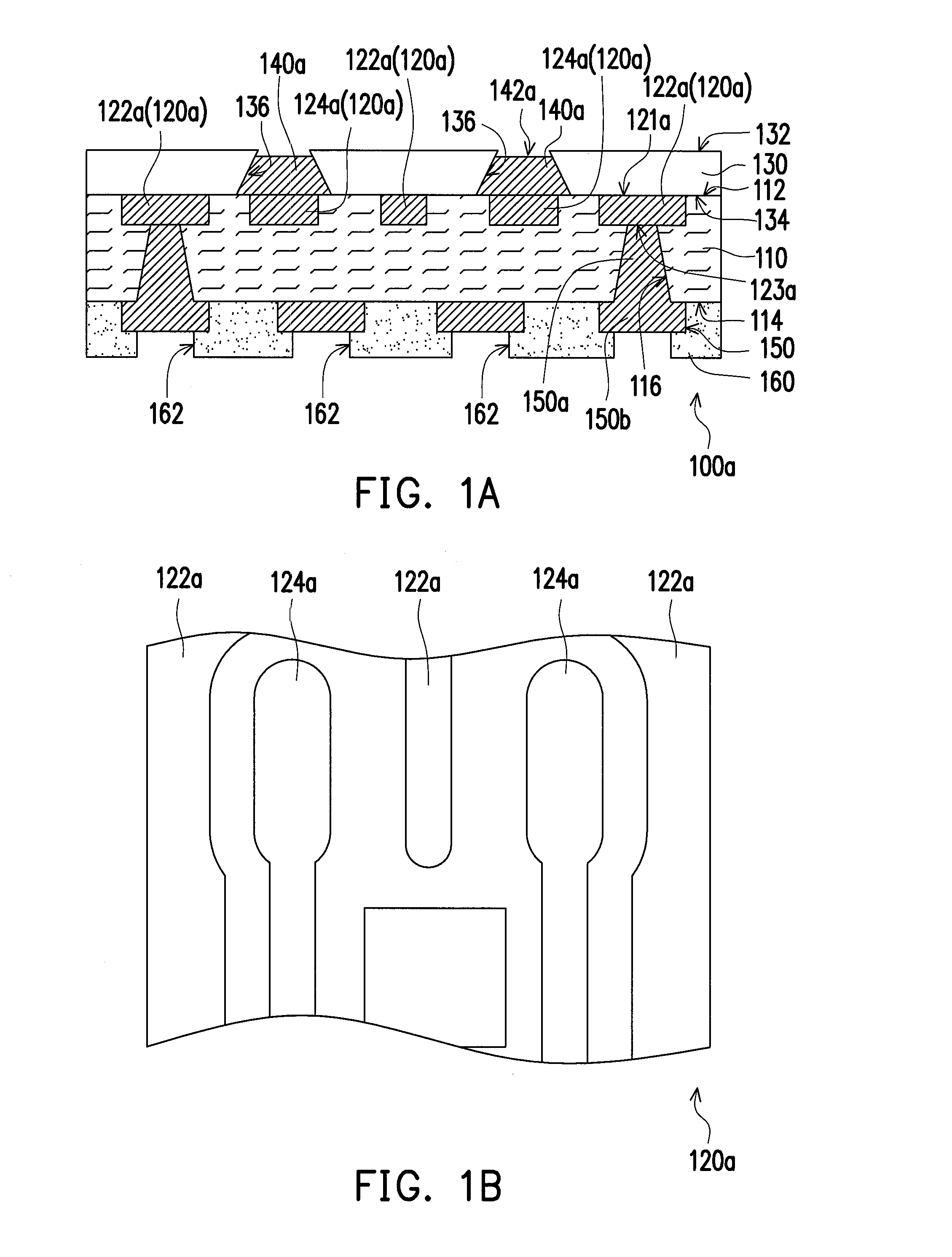

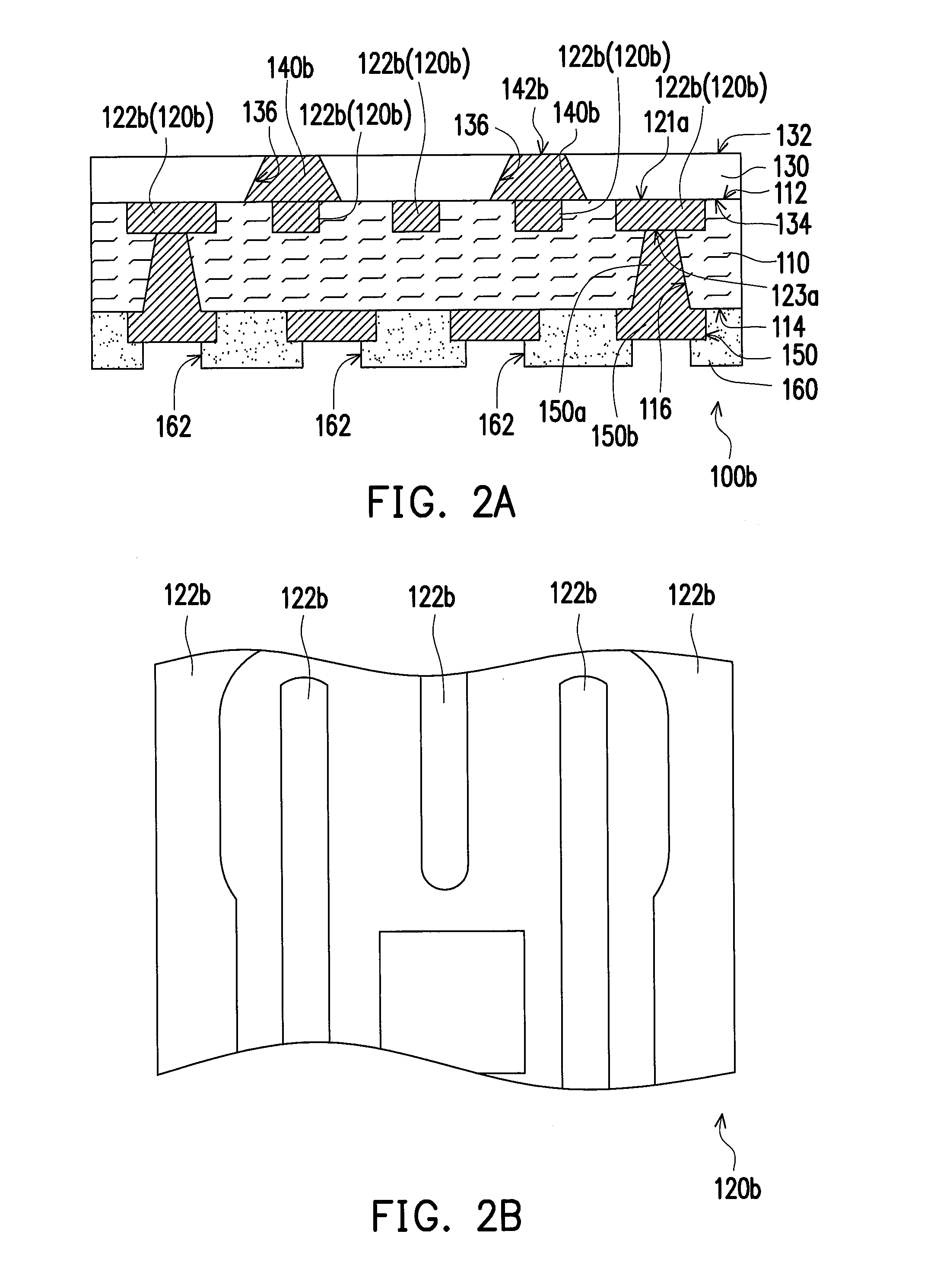

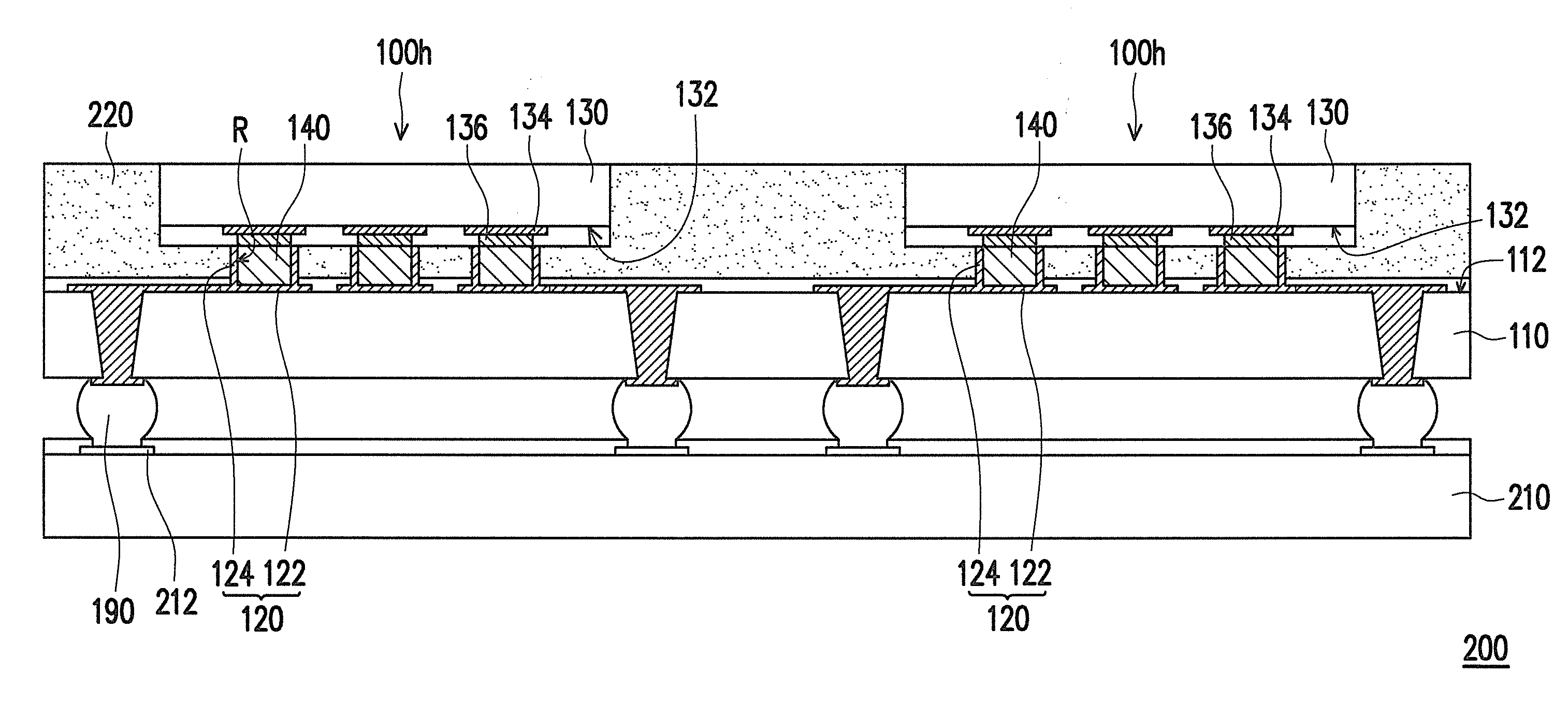

Wafer level package structure, and sensor device obtained from the same package structure

InactiveUS20090267165A1Little changeReducing atmosphereAcceleration measurement using interia forcesSemiconductor/solid-state device testing/measurementDiffusionGyroscope

A wafer level package structure with a plurality of compact sensors such as acceleration sensors and gyro sensors is provided. This package structure is composed of a semiconductor wafer with plural sensor units, and a pair of package wafers bonded to both surfaces of the semiconductor wafer. Each of the sensor units has a frame having an opening, a movable portion held in the opening to be movable relative to the frame, and a detecting portion for outputting an electric signal according to a positional displacement of the movable portion. Since the semiconductor wafer is bonded to each of the package wafers by a solid-phase direct bonding without diffusion between a surface-activated region formed on the frame and a surface-activated region formed on the package wafer, it is possible to prevent that variations in sensor characteristics occur due to residual stress at the bonding interface.

Owner:MATSUSHITA ELECTRIC WORKS LTD

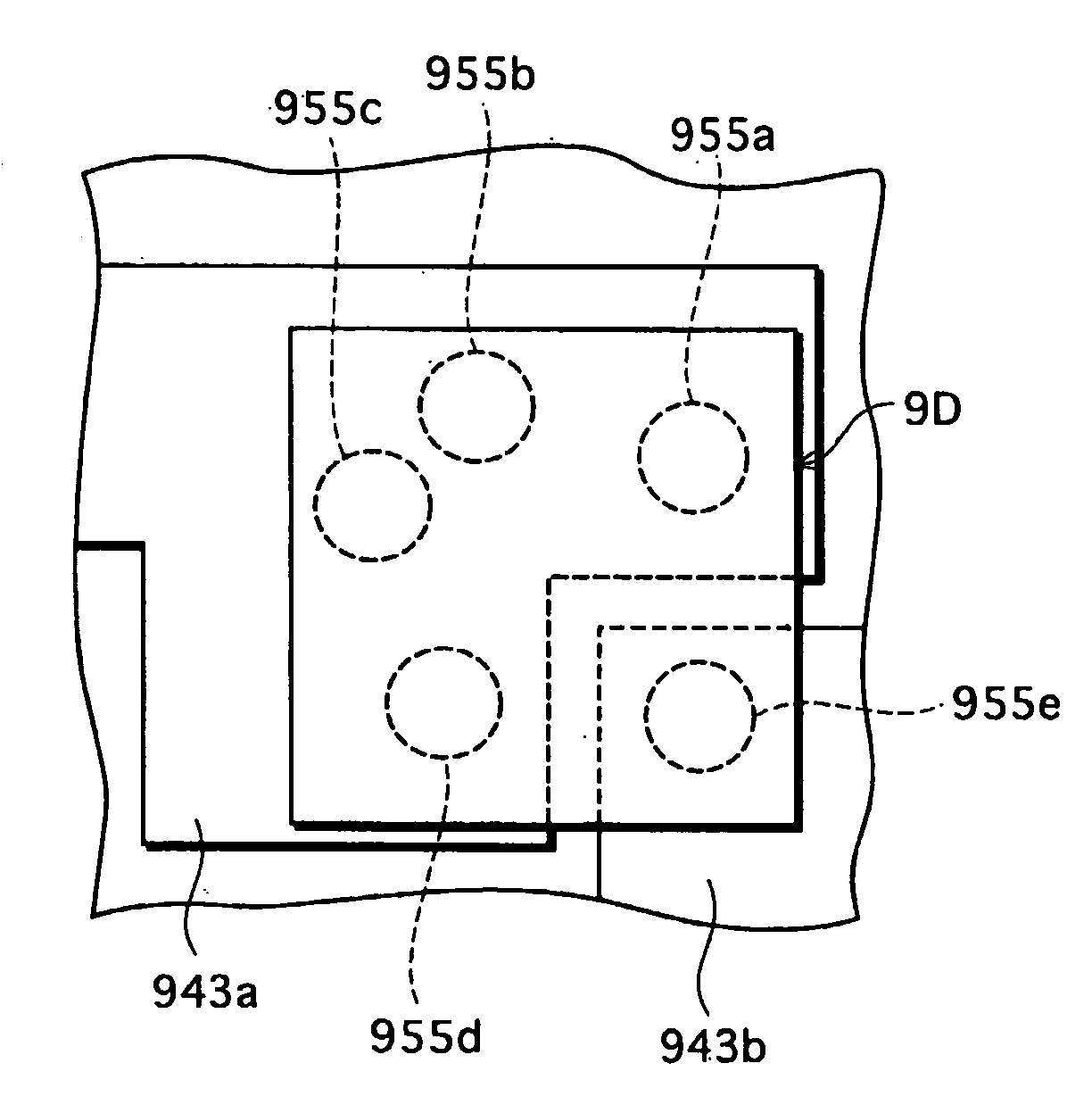

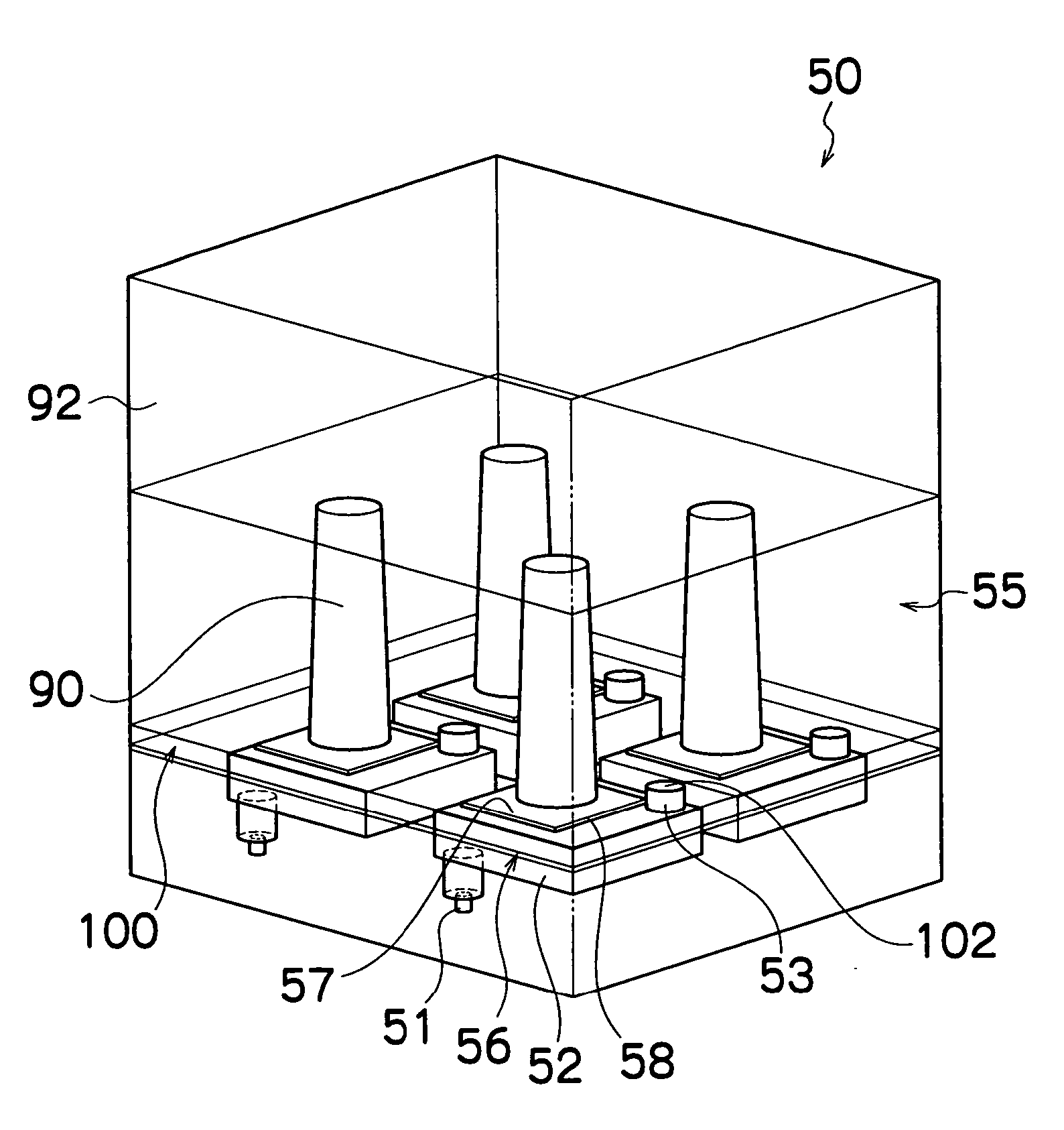

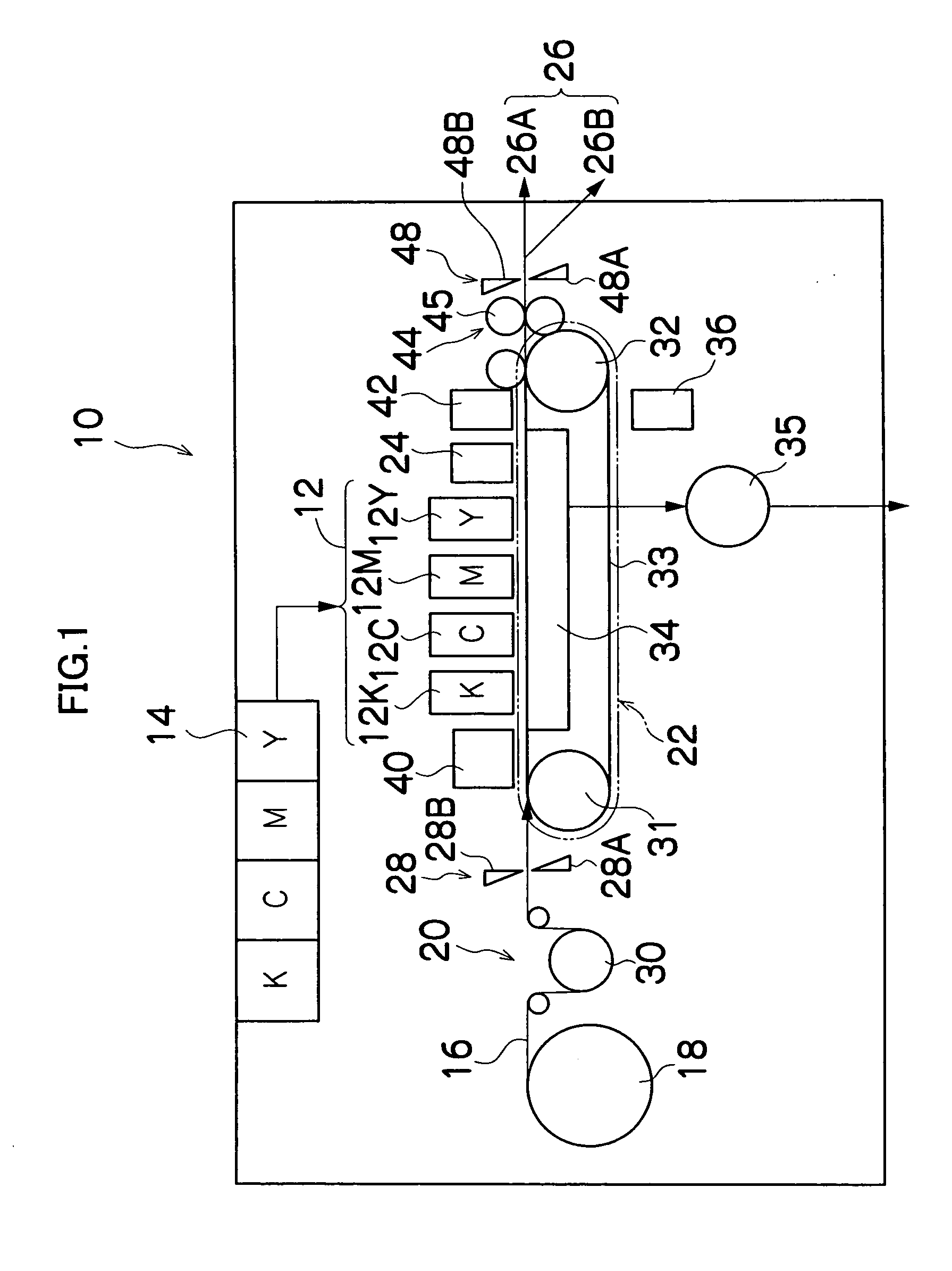

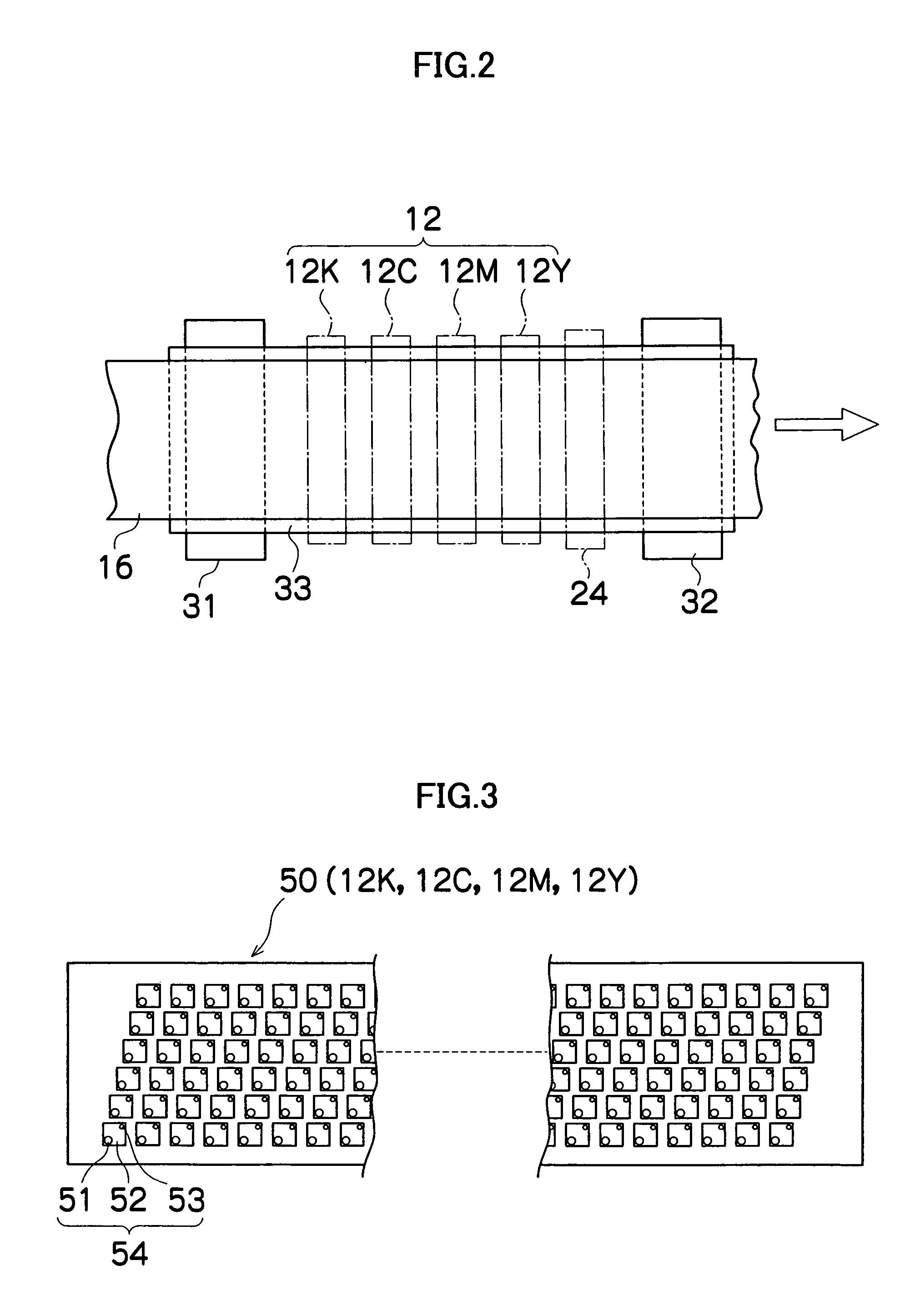

Light source, manufacturing method of light source, lighting apparatus, and display apparatus

ActiveUS20090039376A1Improve bindingReduce the possibilityPlanar light sourcesPoint-like light sourceLight emitting deviceLight source

Provided is a light source that has high reliability and hardly causes conductivity failure between a light emitting device and a conductive land. In an LED light source of the present invention, an LED bare chip is mounted to conductive lands of a substrate, using bumps (55a, 55b). The LED bare chip (D65) is provided with a p-electrode (Lp) and an n-electrode (Ln) on a rear surface. The p-electrode (Lp) is larger in area than the n-electrode (Ln). The p-electrode (Lp) is bonded to a corresponding conductive land via four bumps (55a), whereas the n-electrode (Ln) is bonded to a corresponding conductive land via one bump (55b). A bonded area (Sn) between the n-electrode (Ln) and the bump (55b) is larger than a bonded area (Sp) between the p-electrode (Lp) and one of the bumps (55a).

Owner:PANASONIC CORP

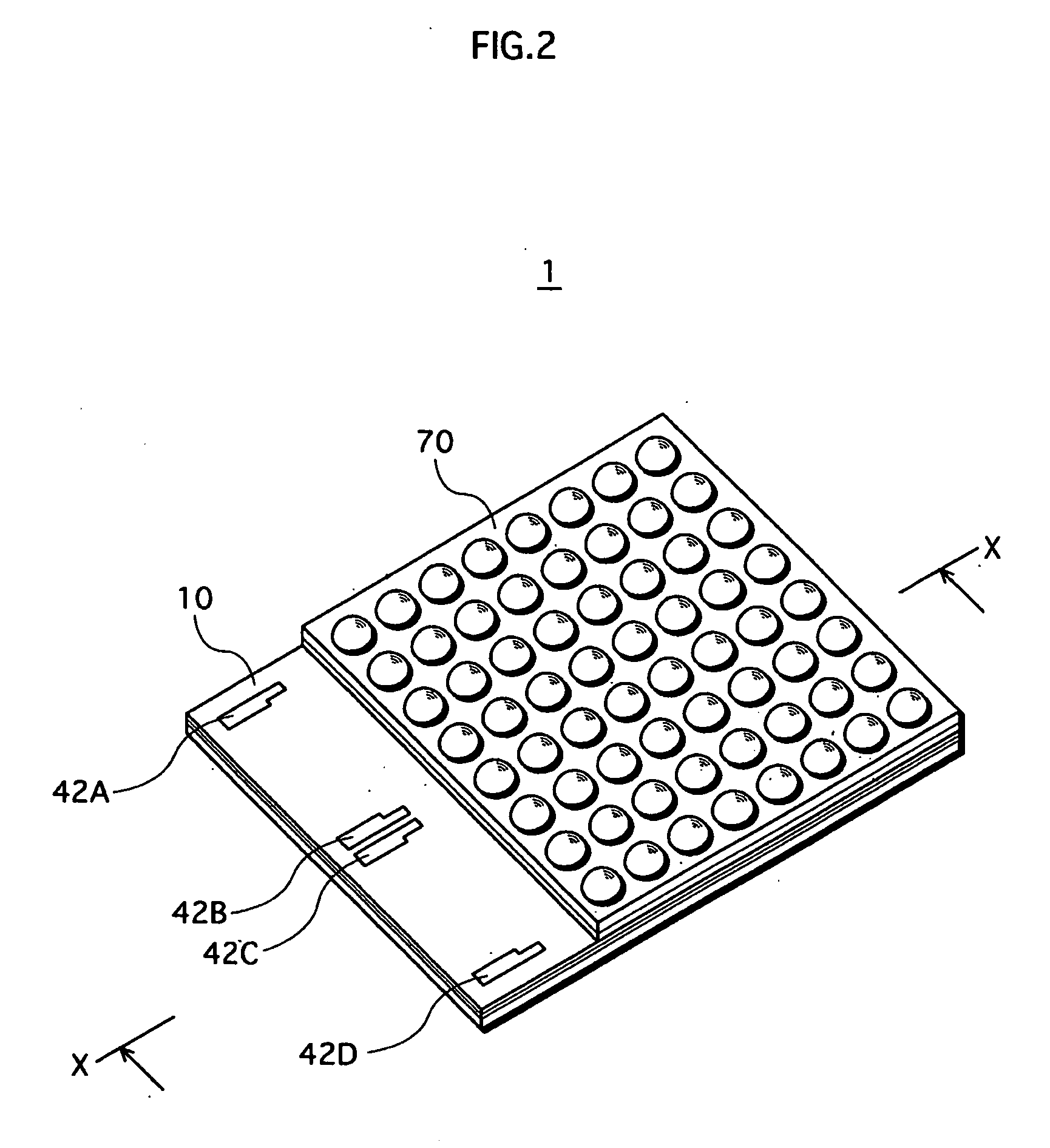

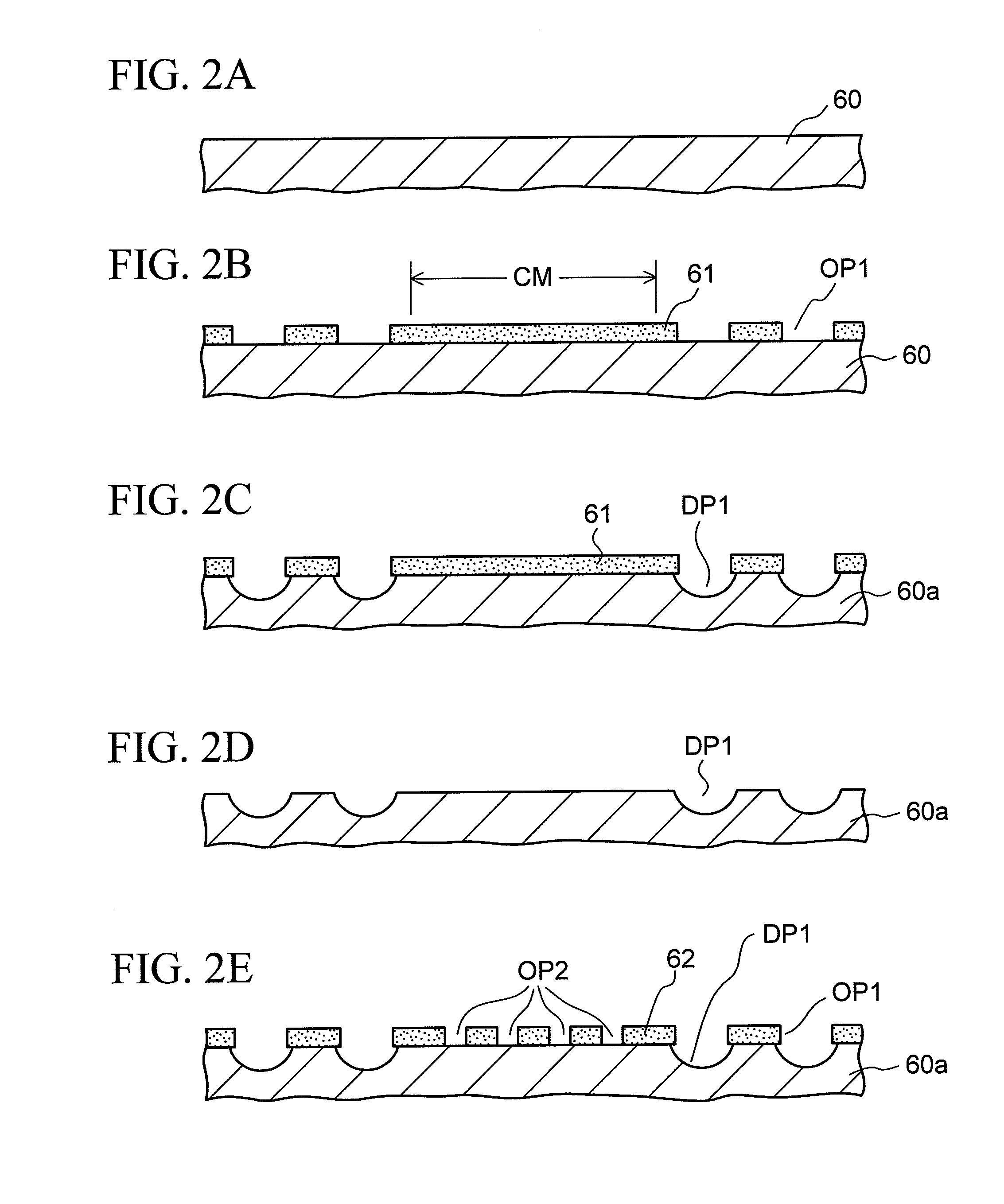

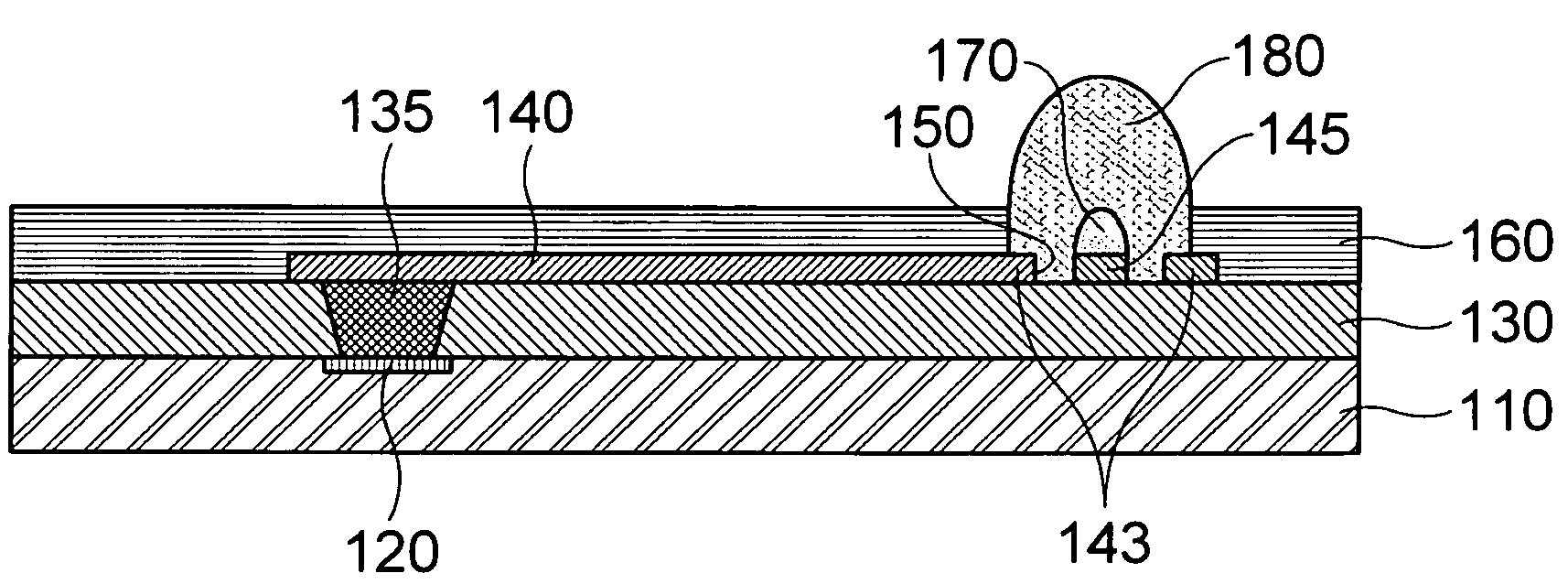

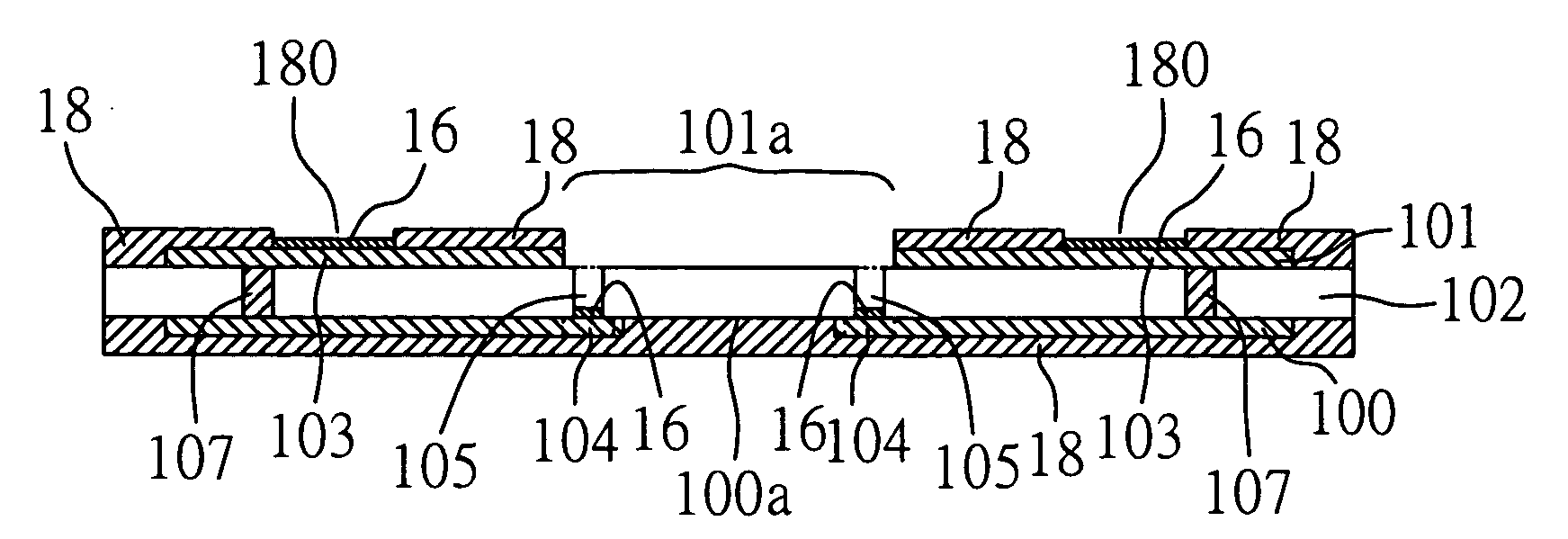

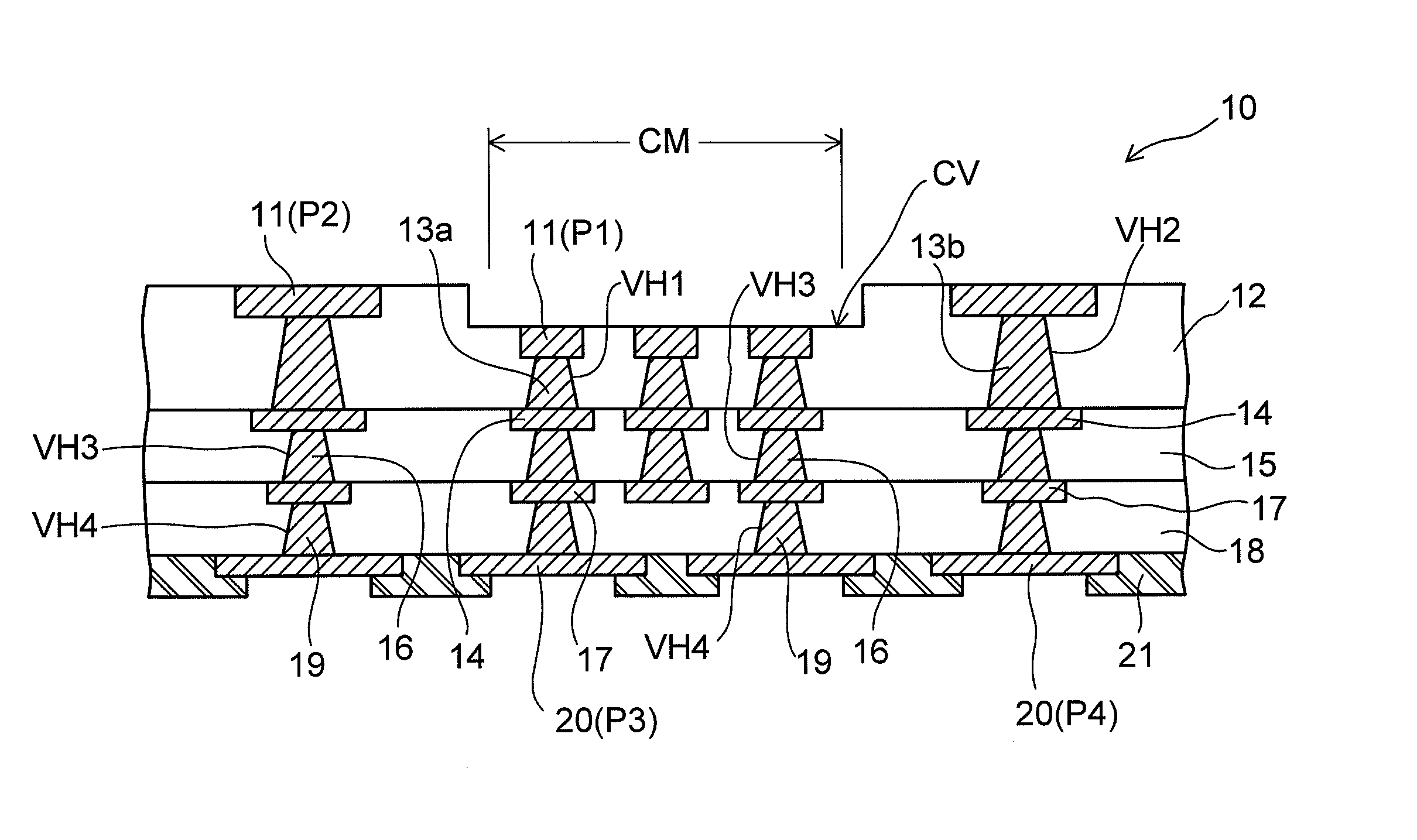

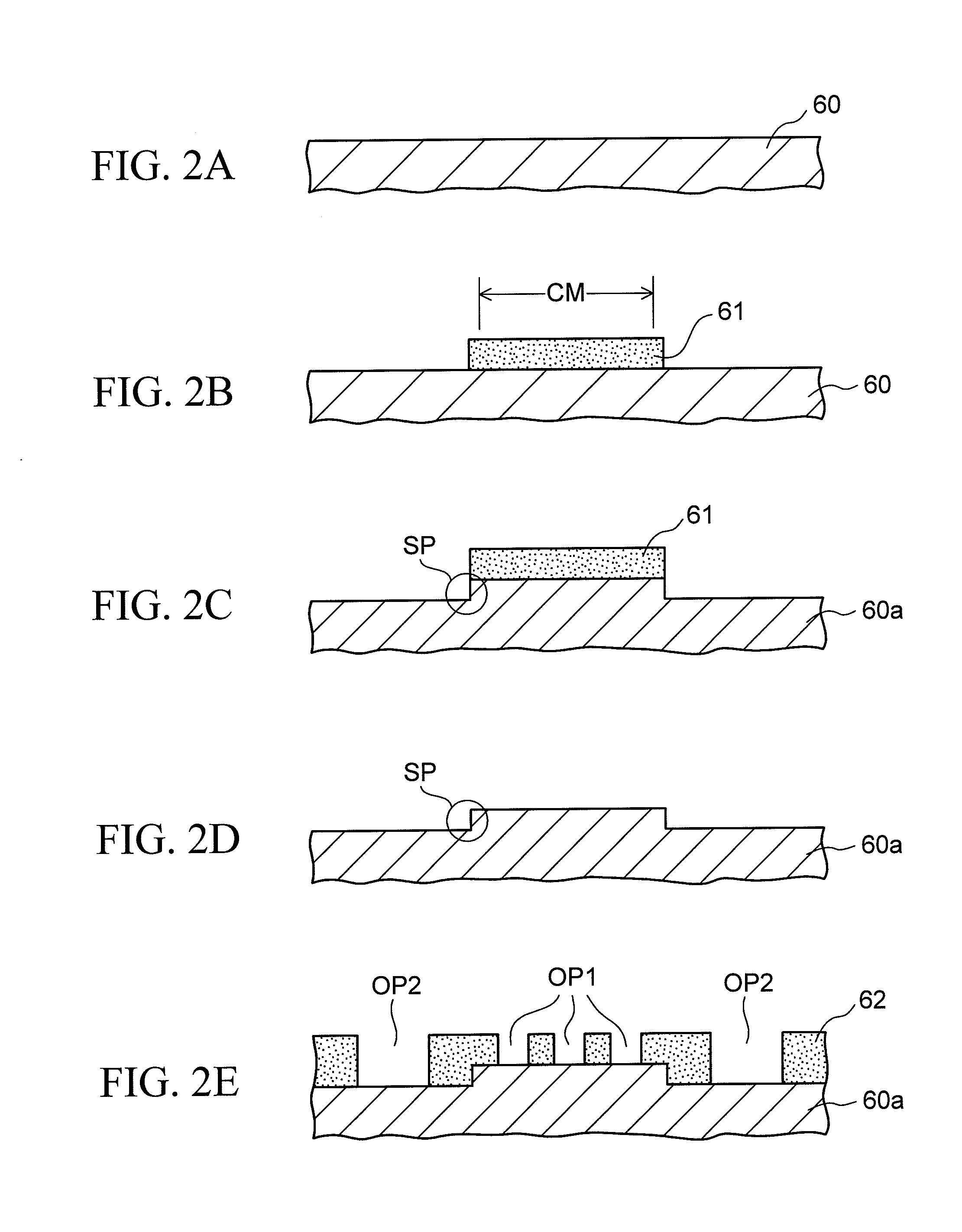

Wiring board and method of manufacturing the same

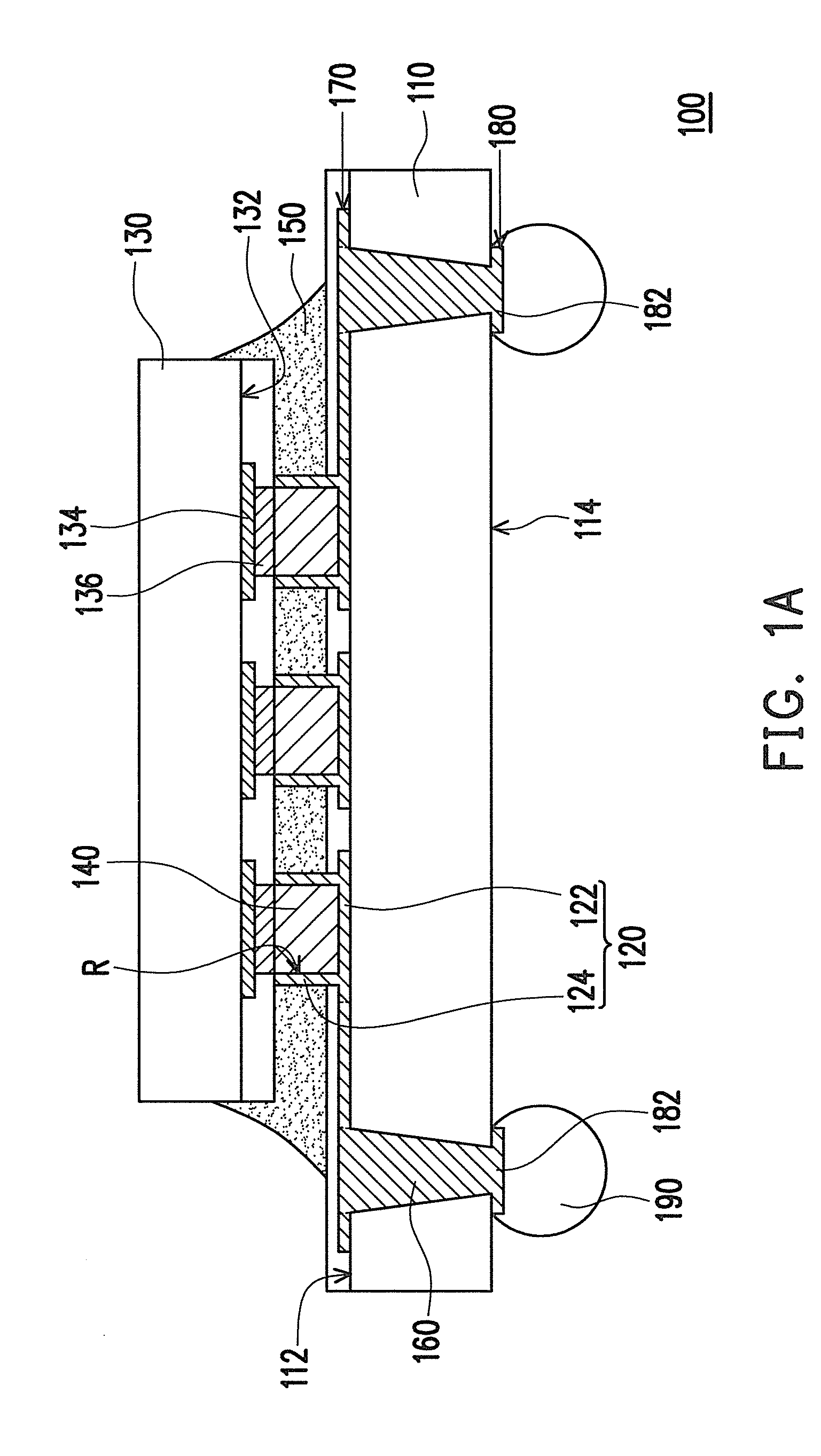

ActiveUS20100147574A1Low costImprove reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsElectrical and Electronics engineeringPackage on package

A wiring board (package) has a structure in which multiple wiring layers are stacked one on top of another with insulating layers each interposed between corresponding two of the wiring layers, and the wiring layers are connected to each other through vias formed in the insulating layers. In the peripheral region around the chip mounting area of the outermost insulating layer on one of both surfaces of the board, a pad is formed in a bump shape to cover a surface of a portion of the outermost insulating layer, the portion being formed to protrude, and a pad whose surface is exposed from the insulating layer is arranged in the chip mounting area. A chip is flip-chip bonded to the pad of the package, and another package is bonded to the bump shaped pad in a peripheral region around the chip (package-on-package bonding).

Owner:SHINKO ELECTRIC IND CO LTD

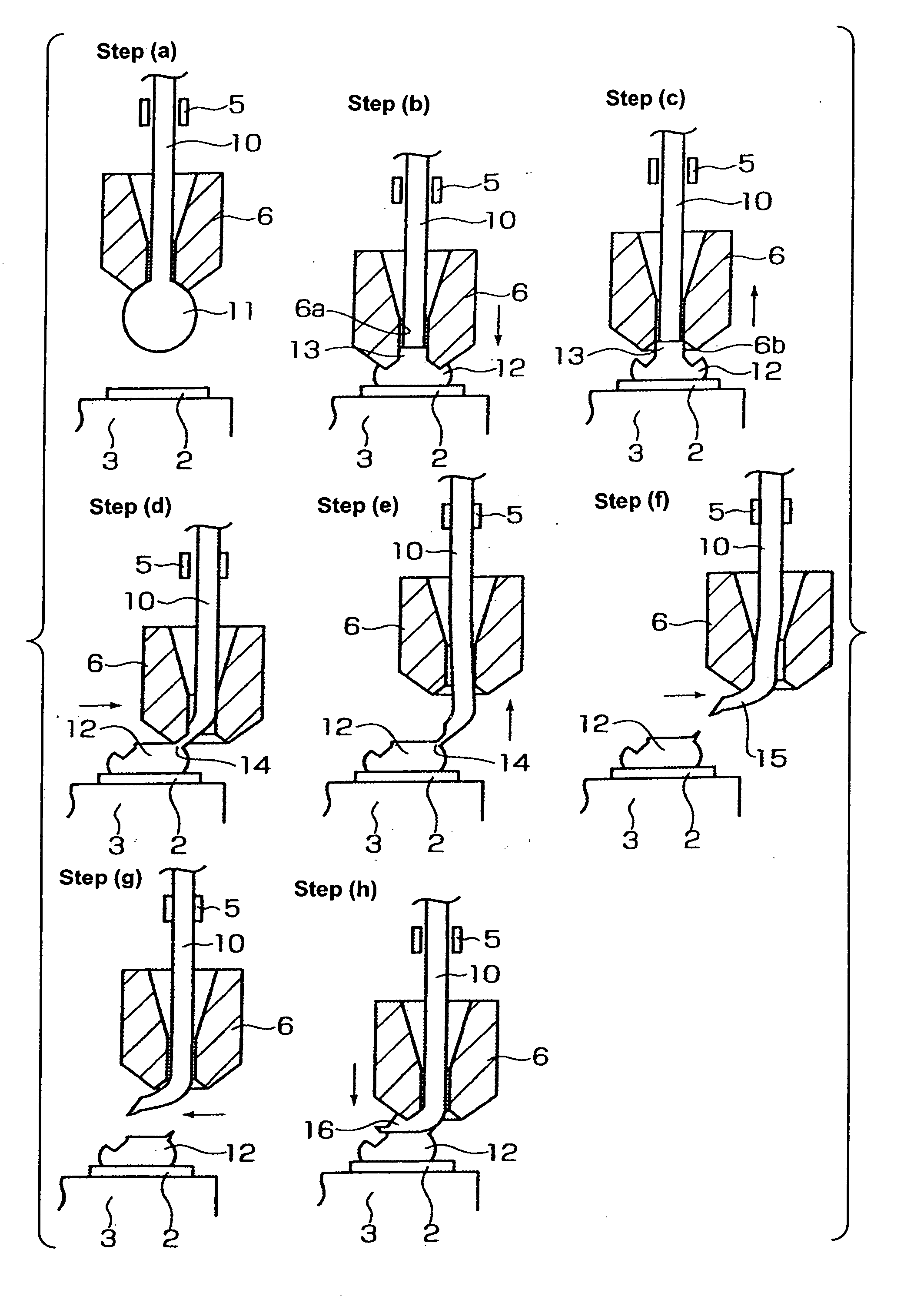

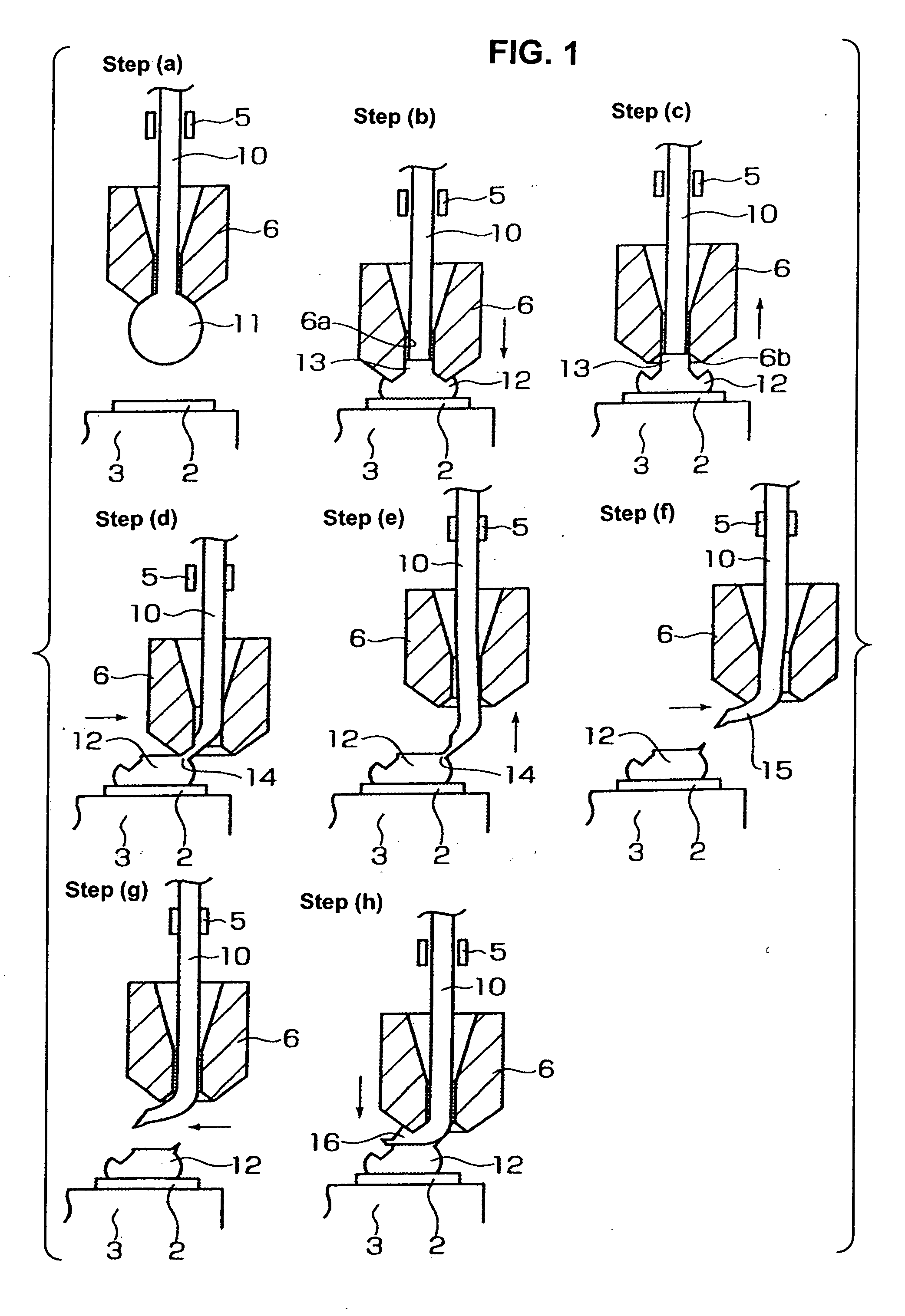

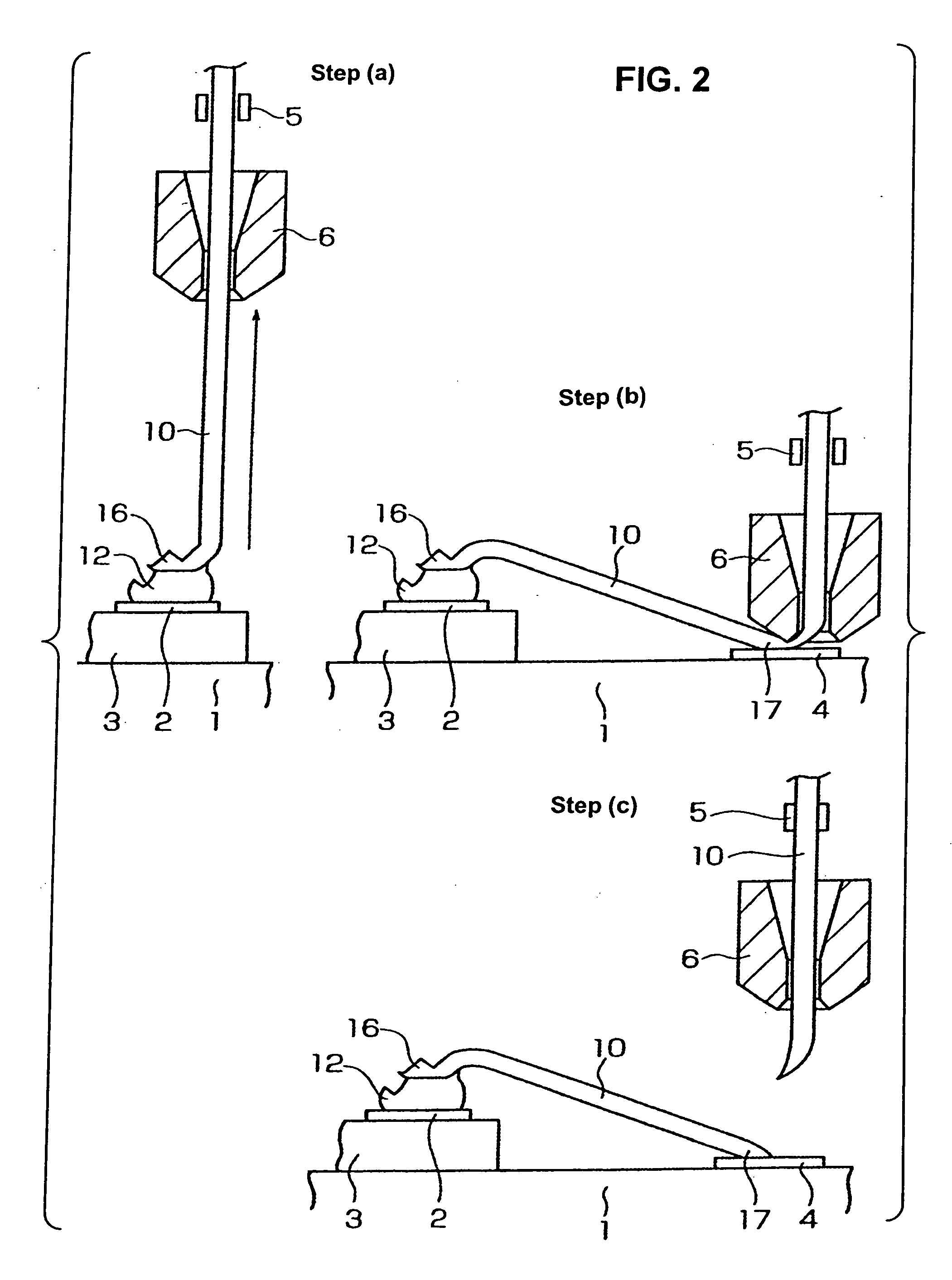

Wire bonding method

InactiveUS20060175383A1Improve implementationReduce decreaseSemiconductor/solid-state device detailsSolid-state devicesWire cuttingEngineering

A wire bonding method with the process of performing a first bonding to a pad of a die that is a first bond point, and the process of performing a second bonding to an interconnect wiring (or a lead) that is a second bond point, thus connecting the pad and the interconnect wiring with a wire. A bump is first formed on a pad, and, in a wire cutting step performed during the step of forming the bump, the wire protruding from the tip end of a capillary is bent in the lateral direction to form a bent part, and then the bent part is bonded to the bump, thus completing the first bonding process; after which the wire is bonded to the interconnect wiring, thus completing the second bonding process.

Owner:SHINKAWA CO LTD

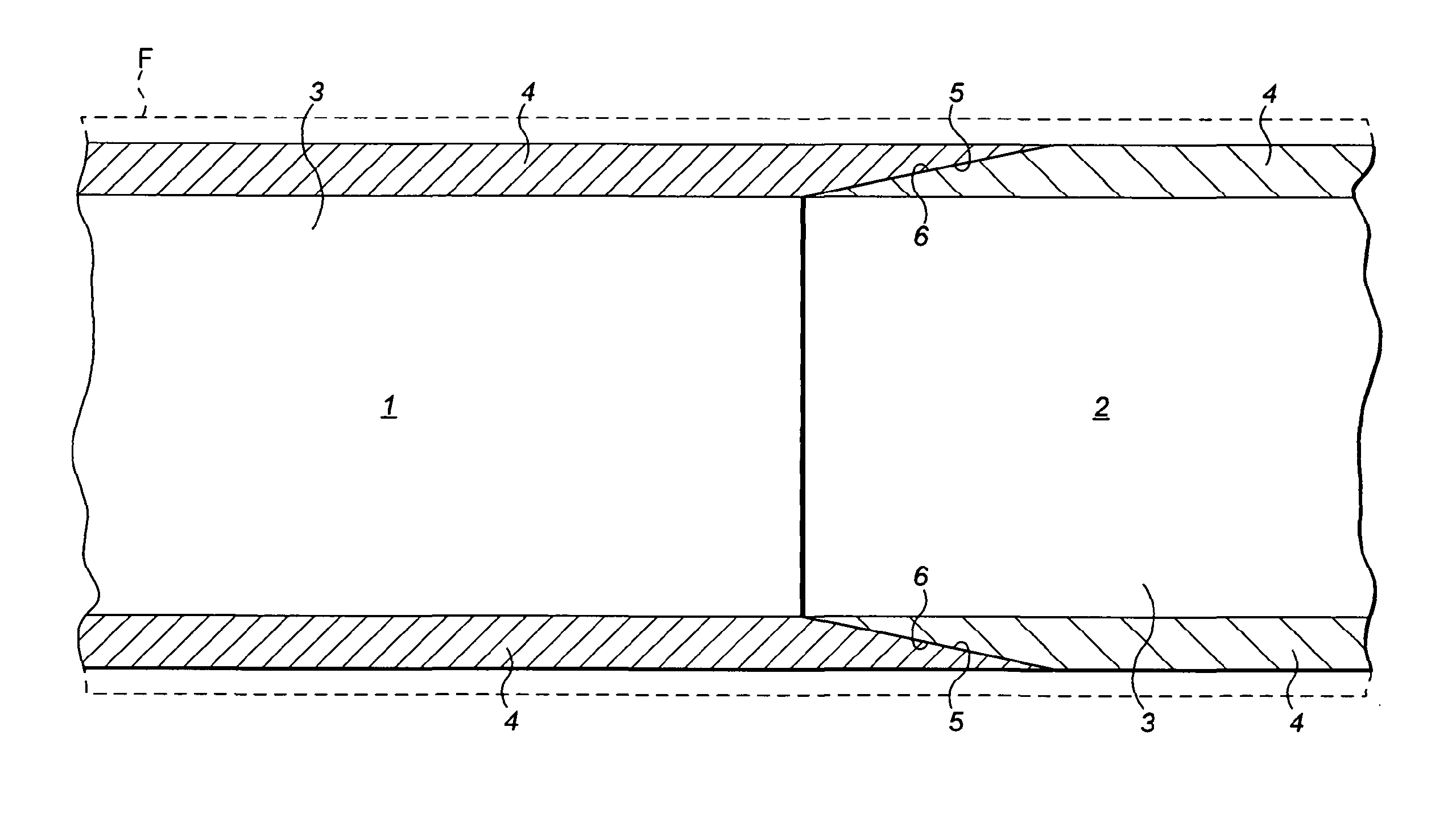

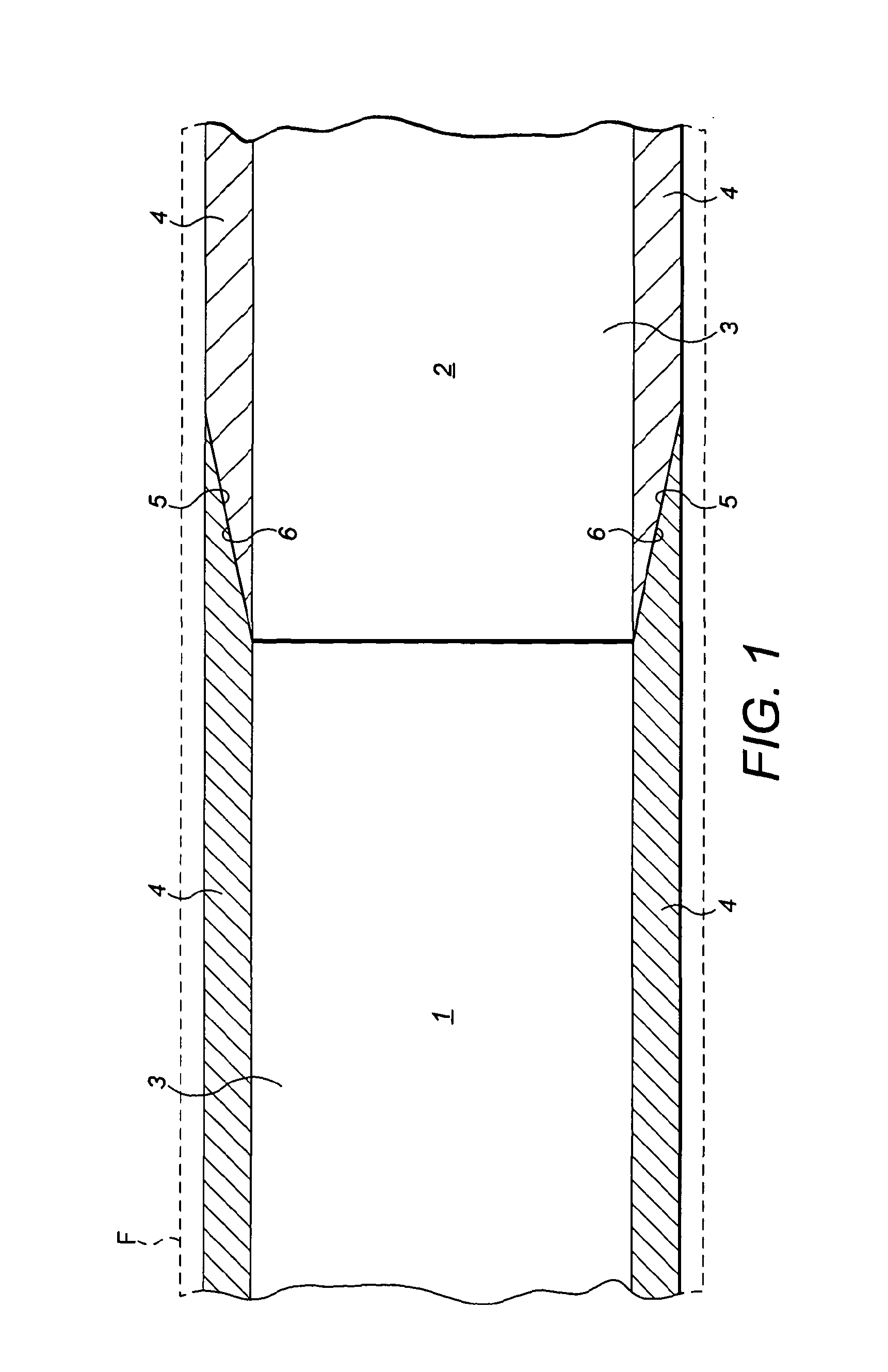

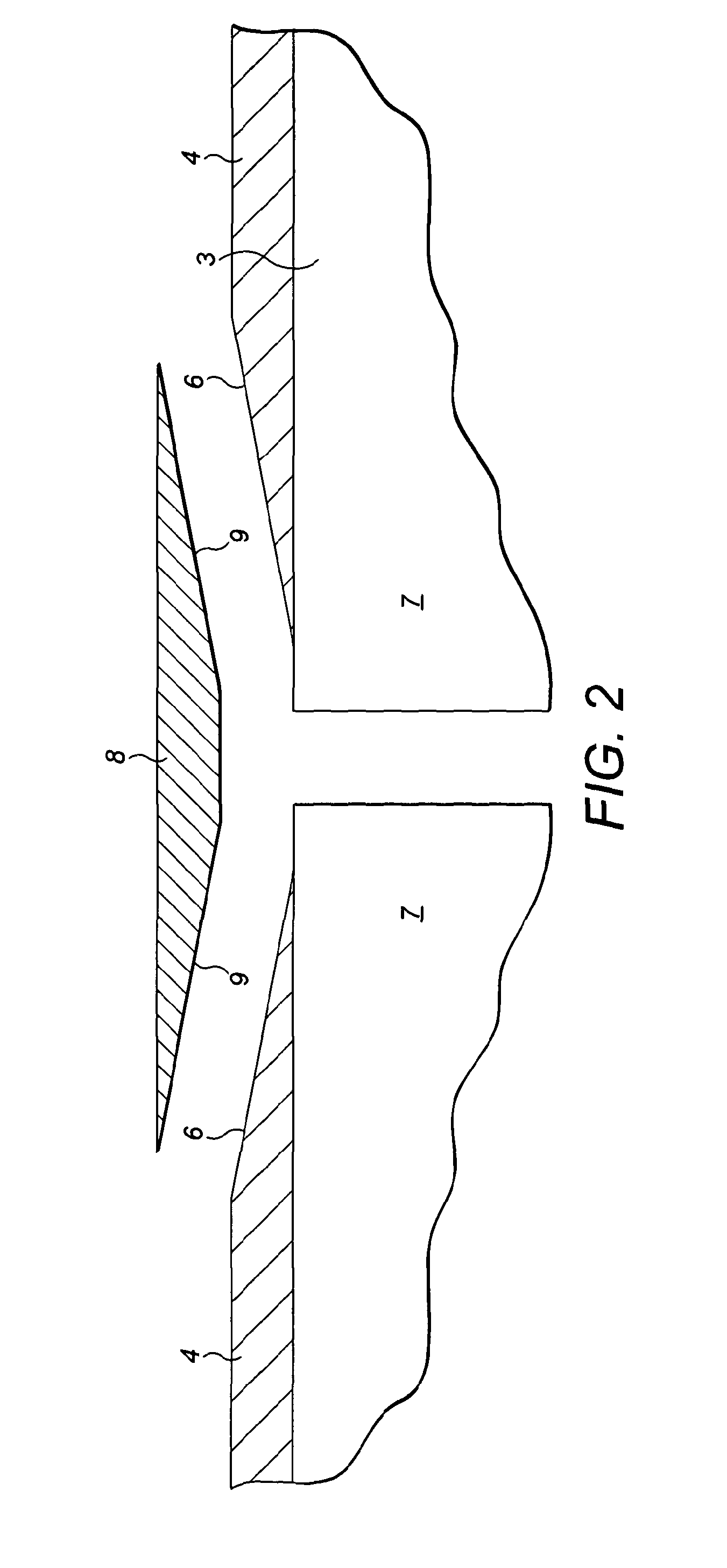

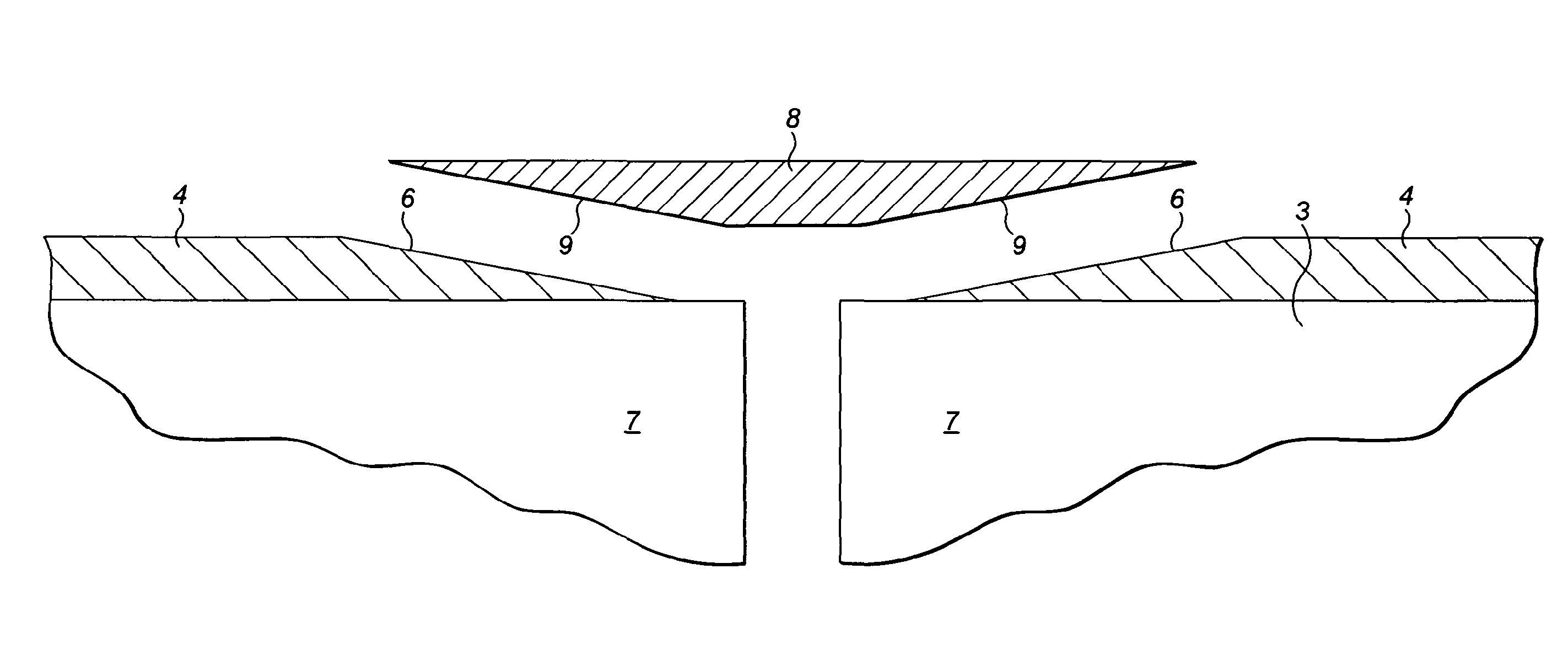

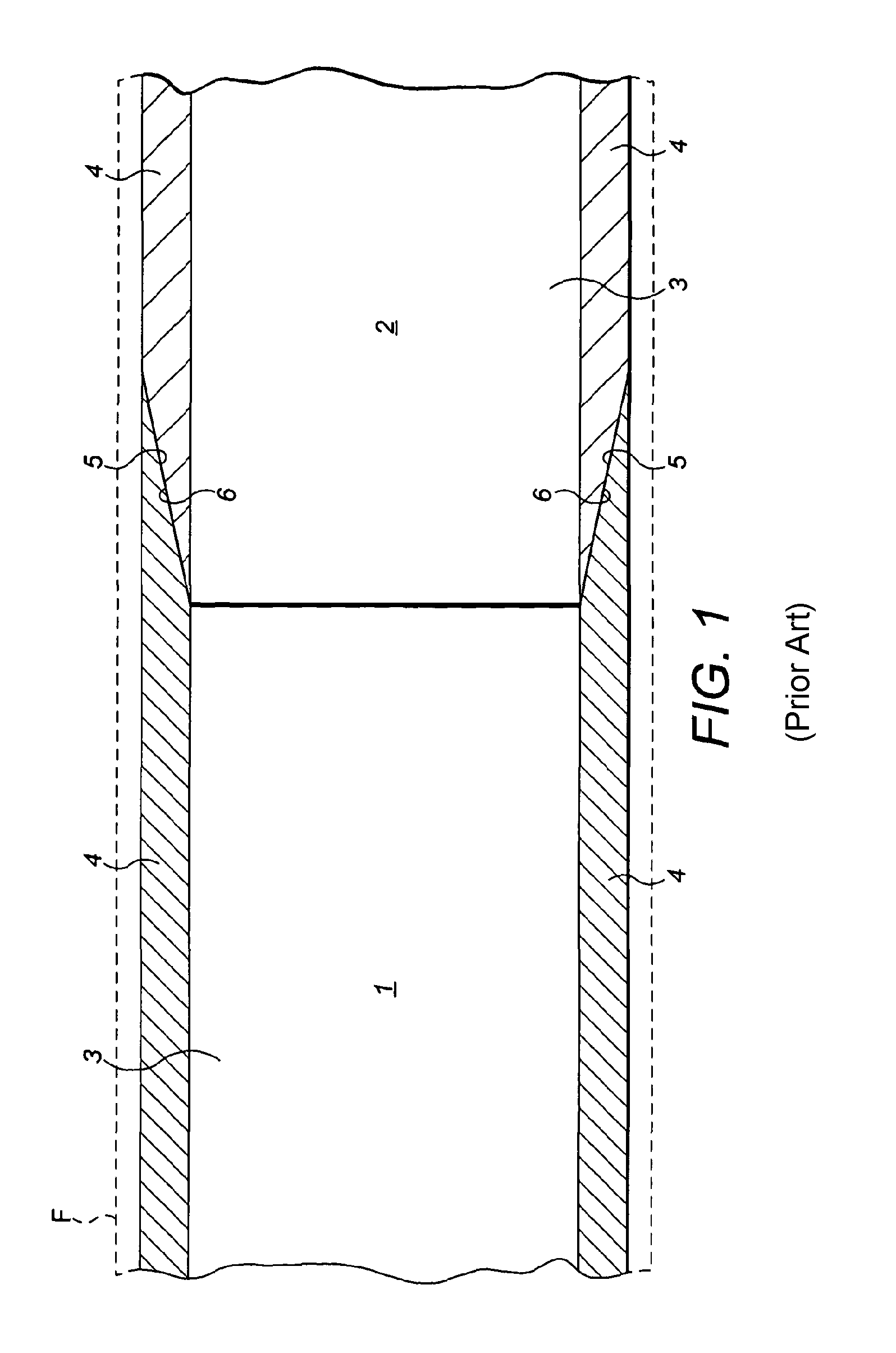

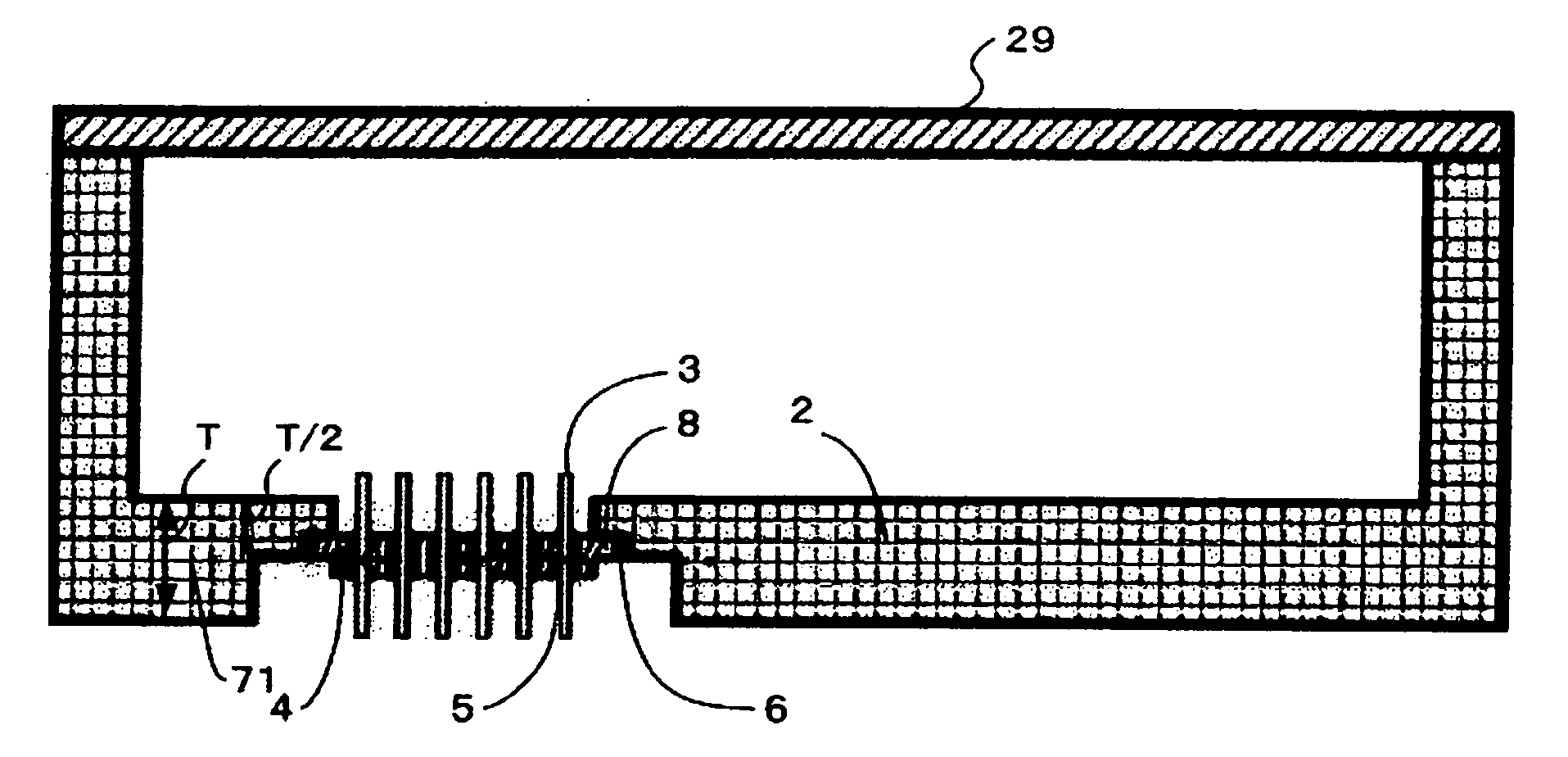

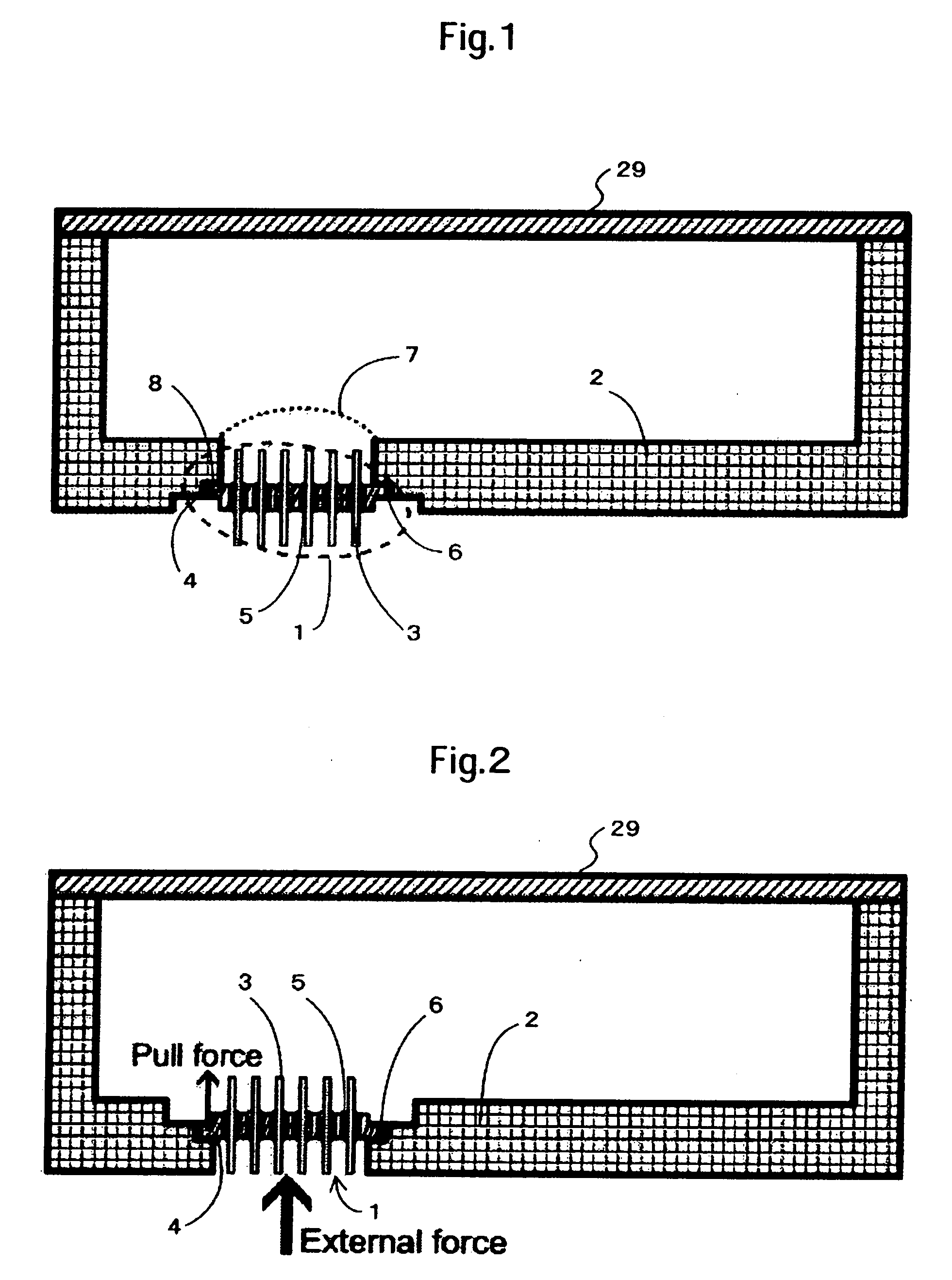

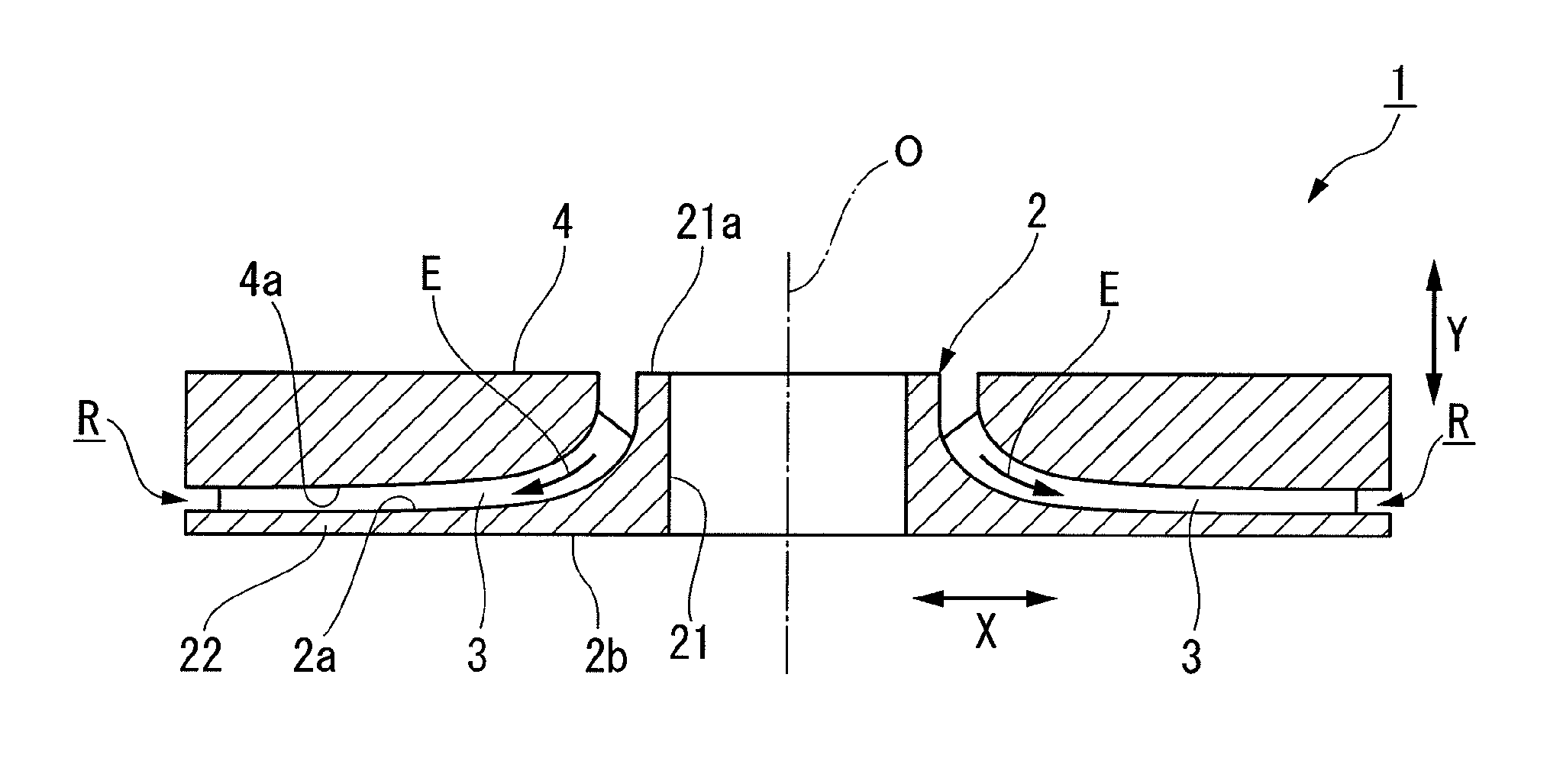

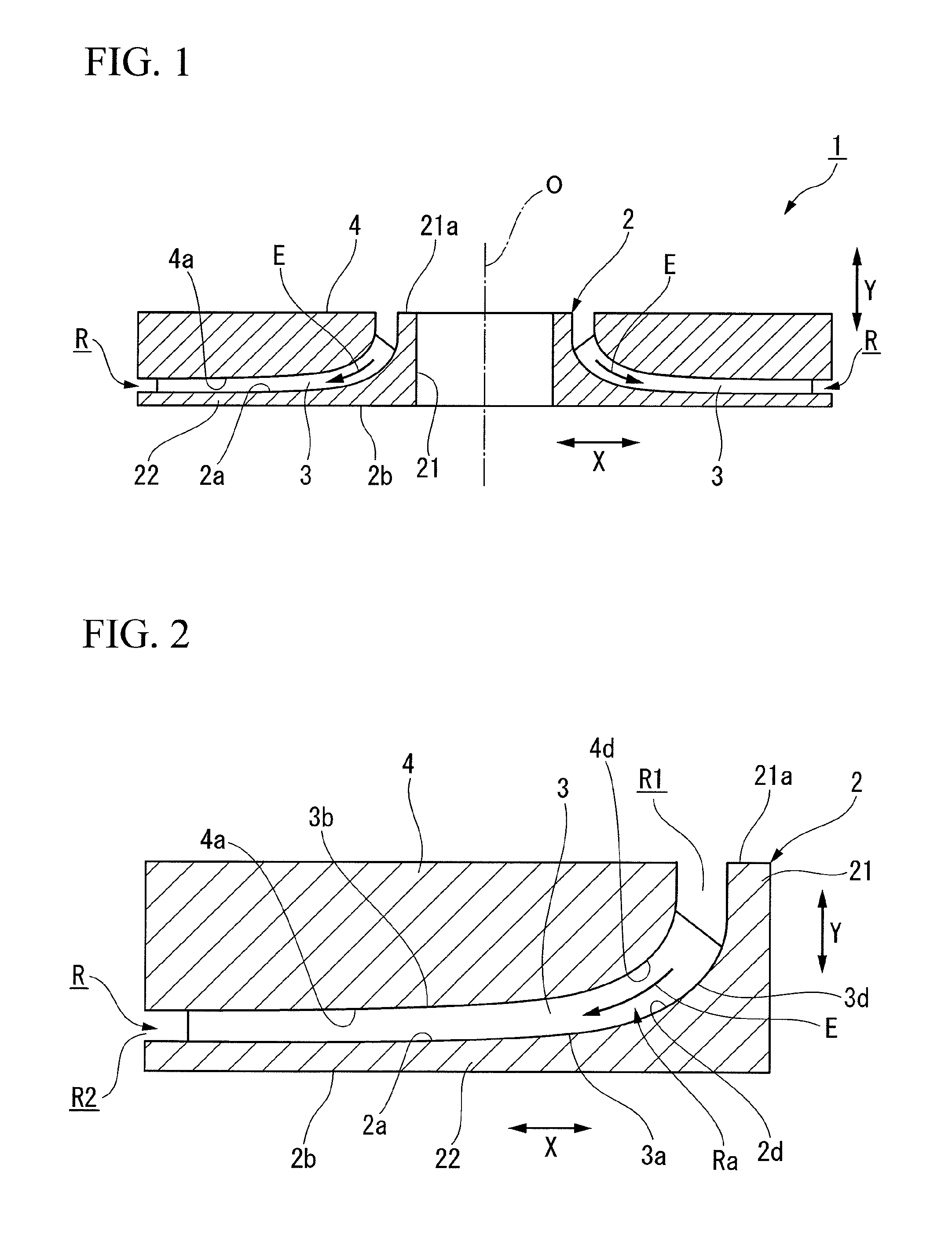

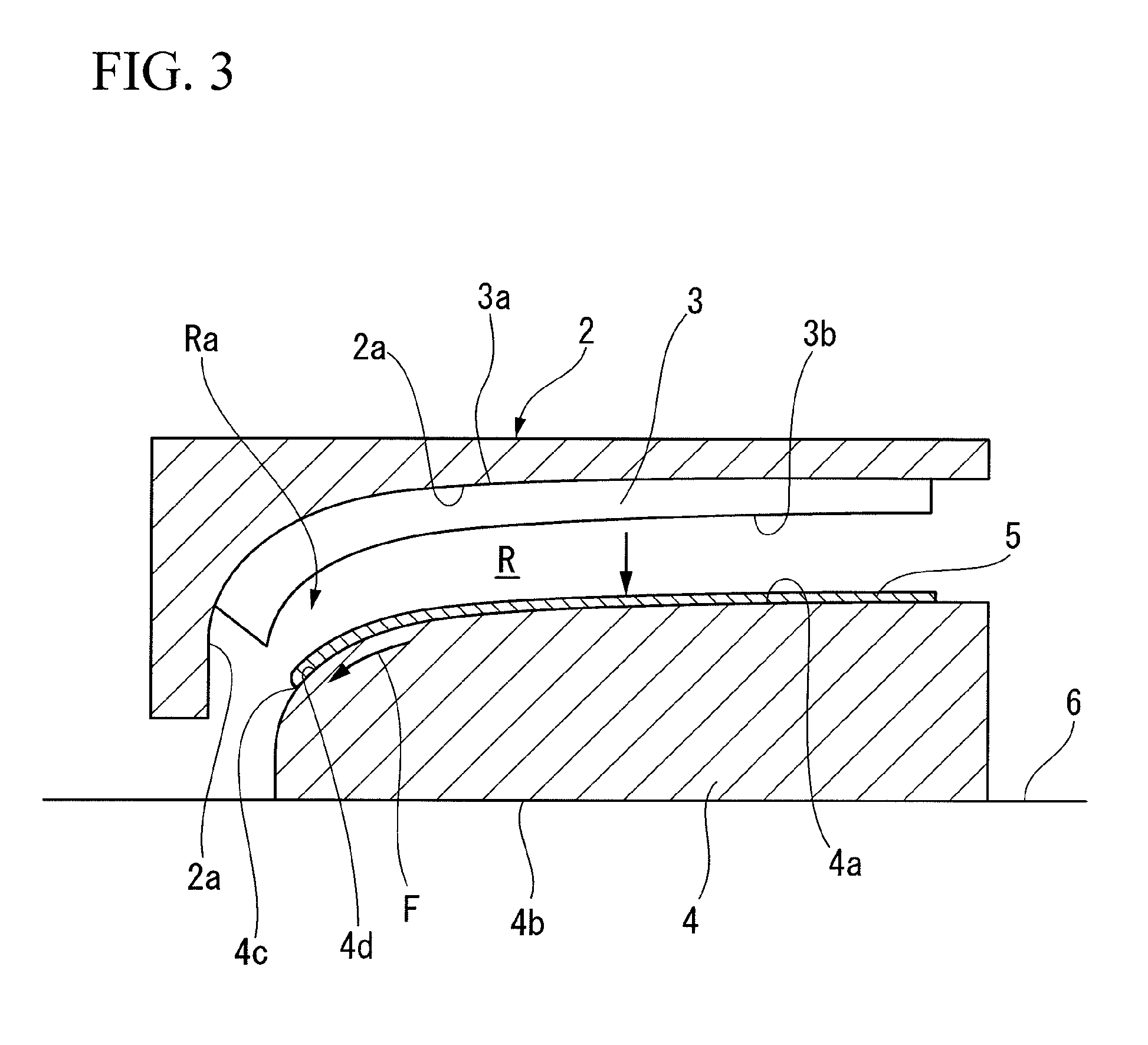

Wind turbine blade

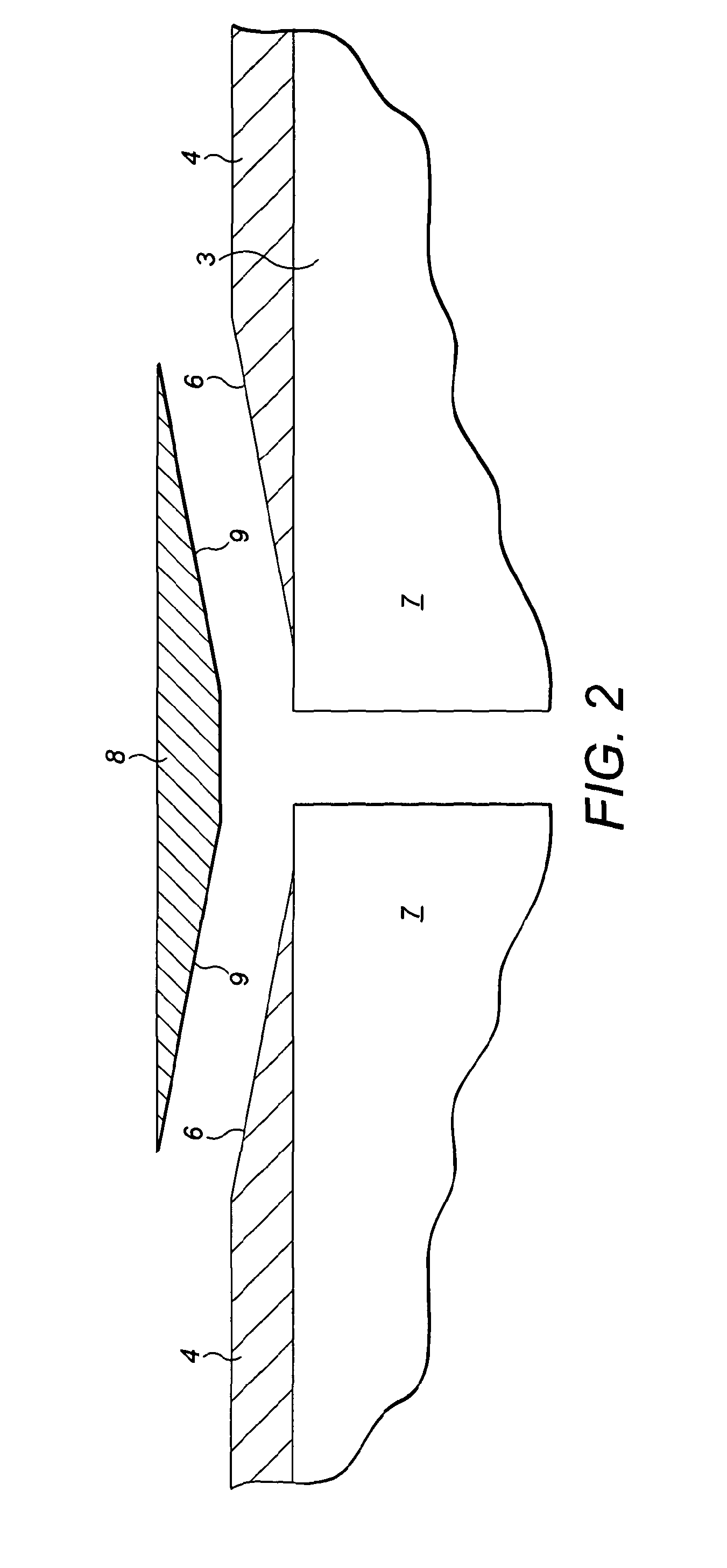

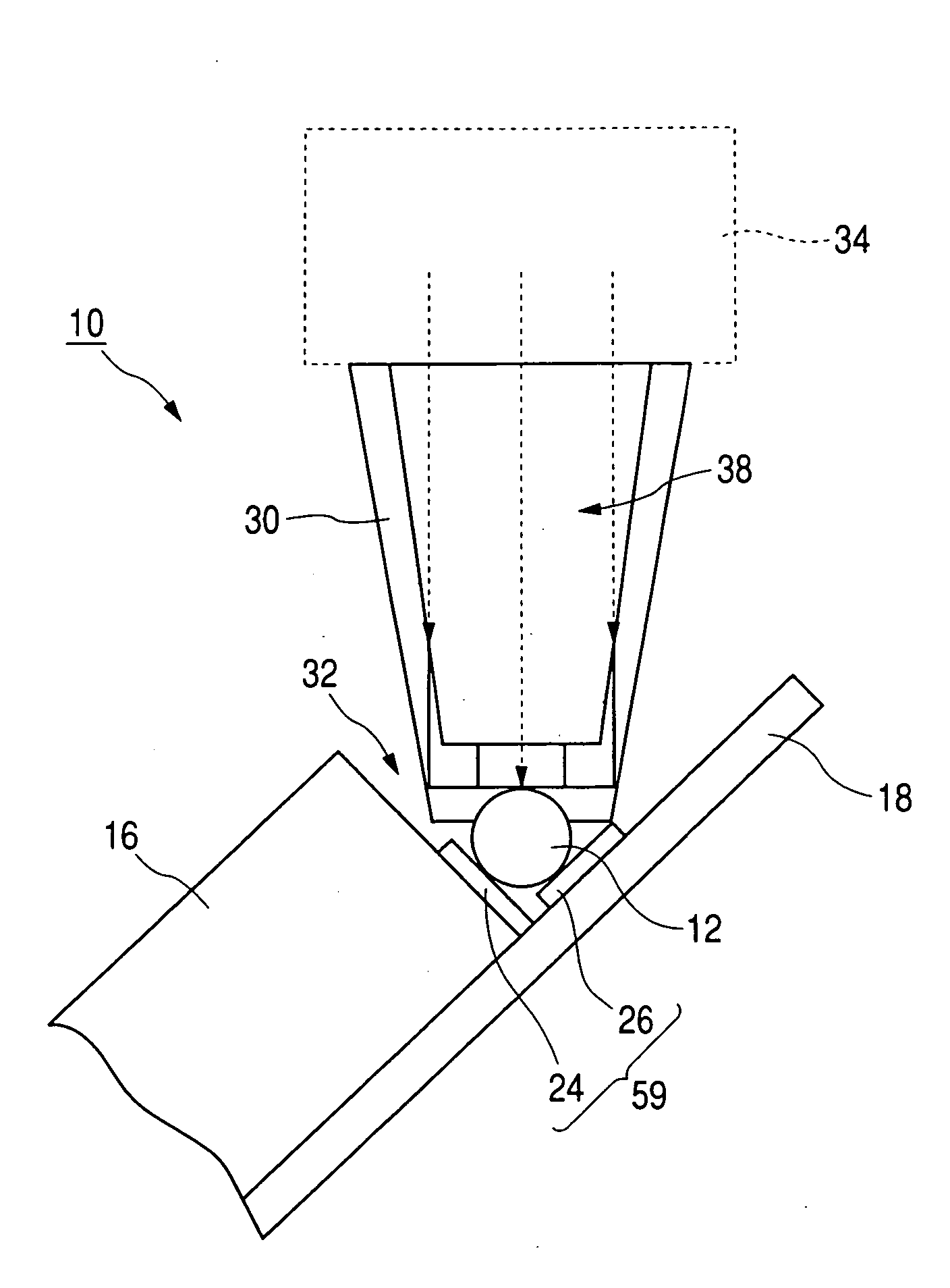

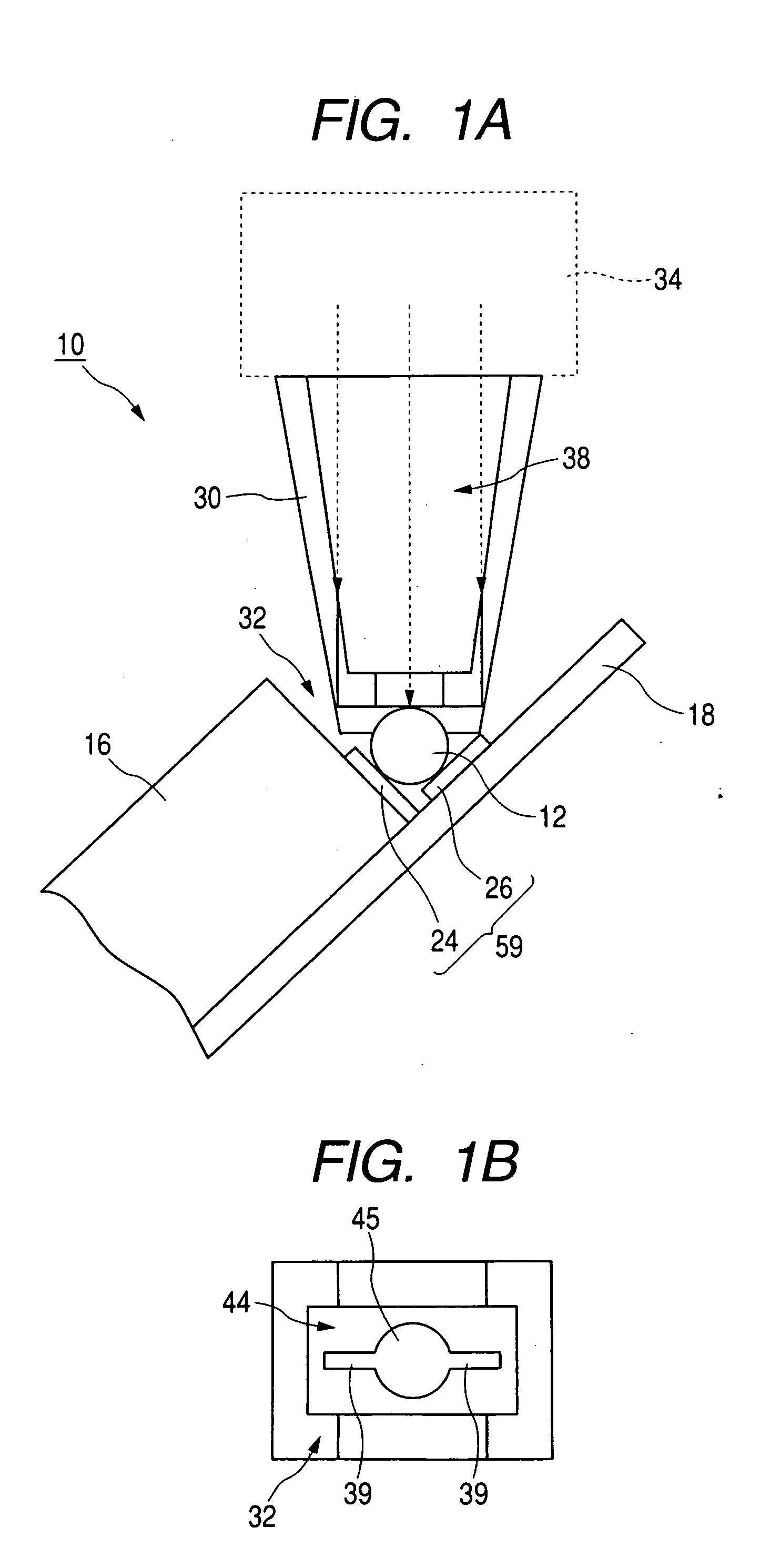

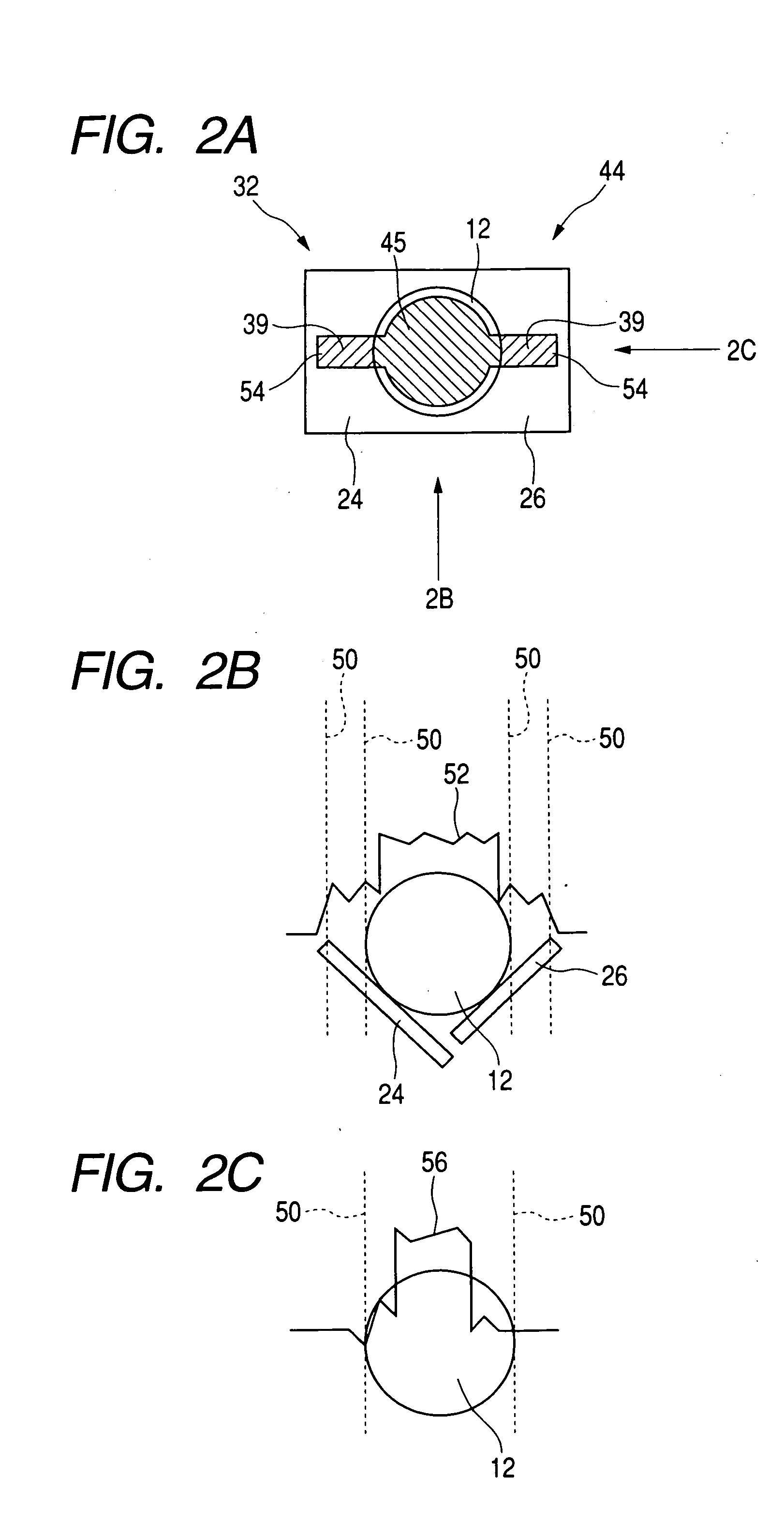

ActiveUS20130129518A1Simplify constructionQuality of laminate be highReaction enginesEngine componentsWind forceTurbine blade

A wind turbine blade comprising an aerodynamic fairing supported along at least a portion of its axial length by a spar (12). The spar comprises at least two spar segments (12) joined end-to-end at an interface (9), each spar segment comprising a shear web (3) with a spar cap (4) on each side. The outer face (6) of each spar cap tapers inwardly towards the interface such that its depth is reduced towards the interface creating a recess on each side of the interface formed by the tapered faces of adjacent spar caps. A respective connection piece (8) is sized to fit into each recess. Each connection piece (8) is sized to fit into each recess. Each connection piece (8) being fixed to the tapered faces of adjacent spar caps to form a double scarf joint.

Owner:BLADE DYNAMICS LTD

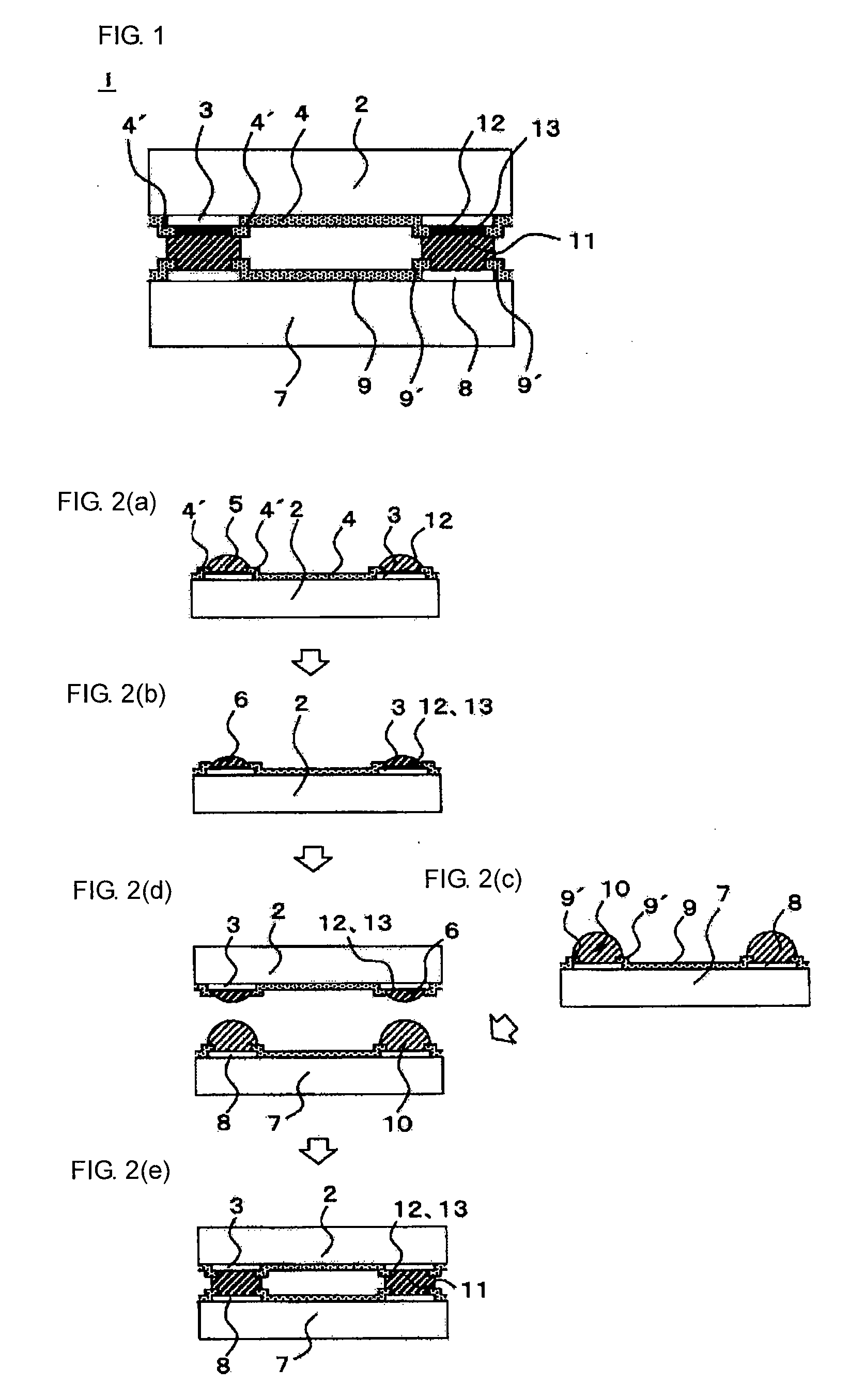

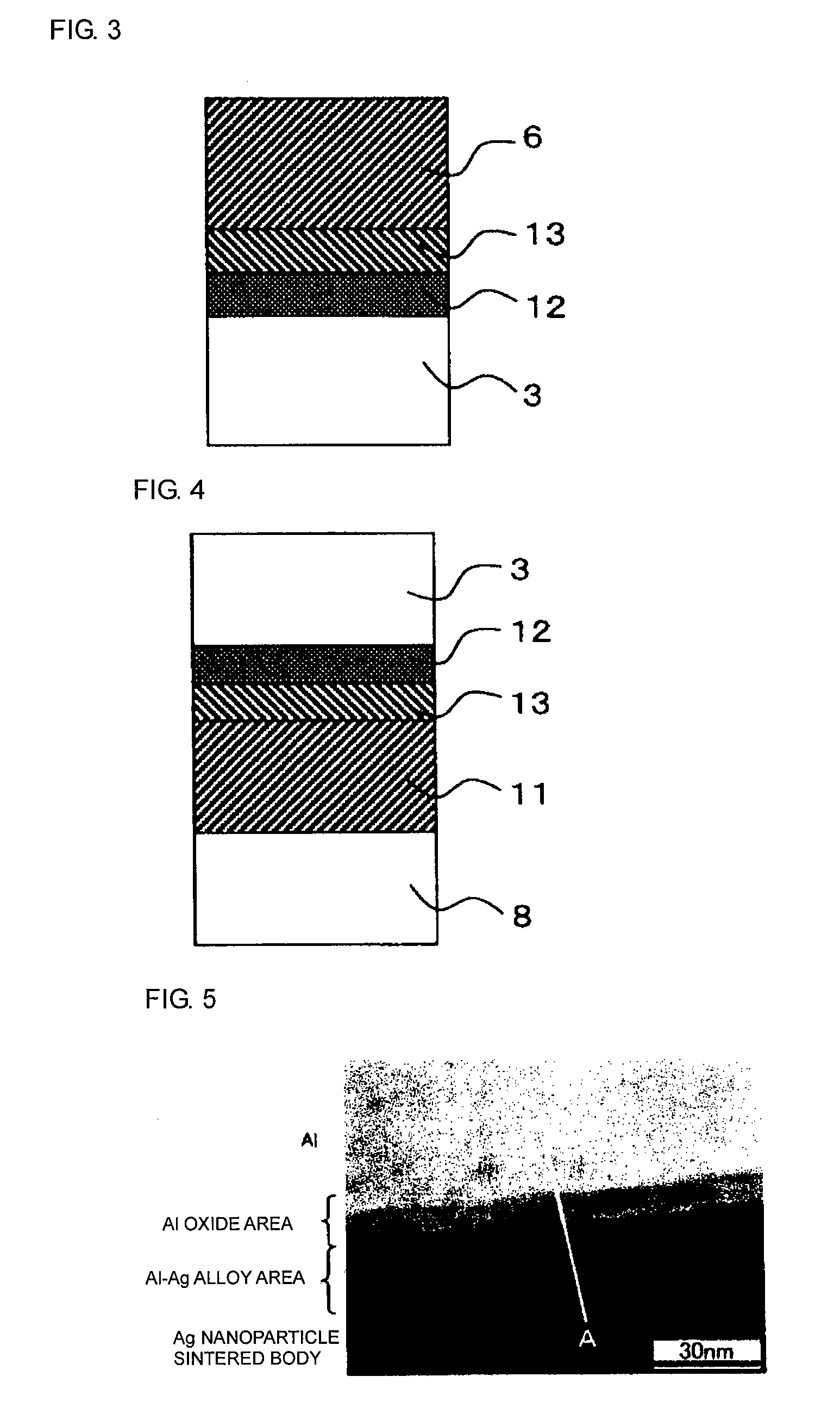

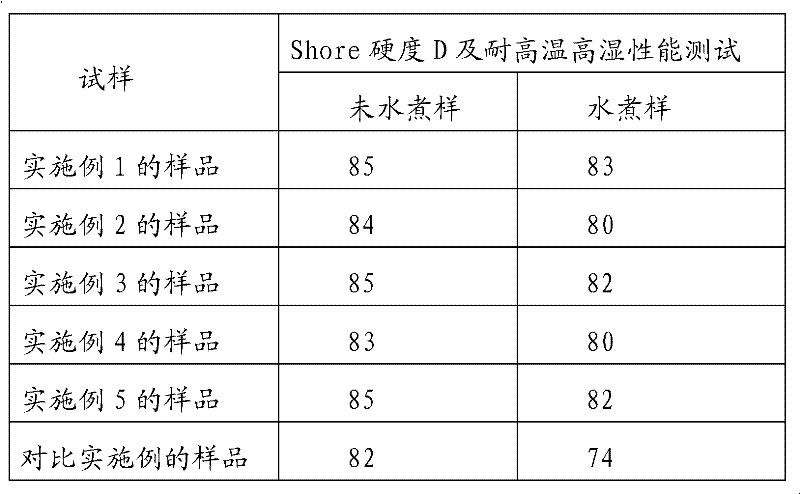

Electronic Element, Electronic Element Device Using the Same, and Manufacturing Method Thereof

ActiveUS20090039507A1Bonding reliability can be stablyAvoid insufficient thicknessNanotechSemiconductor/solid-state device detailsBond interfaceElement composition

An electronic element including an electronic element base and electrodes each of which has a first electrode having a surface composed of at least Al or an Al alloy and a second electrode composed of a metal nanoparticle sintered body and bonded to the first electrode. A bonding interface between the first electrode and the second electrode has a multilayer structure including, from the side of the first electrode to the side of the second electrode, (a) a first layer primarily composed of Al, (b) a second layer primarily composed of an Al oxide, (c) a third layer primarily composed of an alloy of Al and a constituent element of metal nanoparticles, and (d) a fourth layer primarily composed of the constituent element of the metal nanoparticles.

Owner:MURATA MFG CO LTD

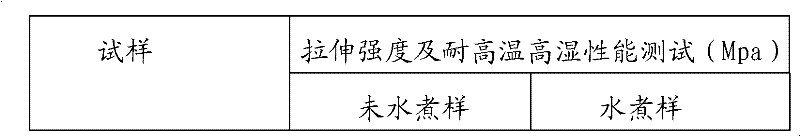

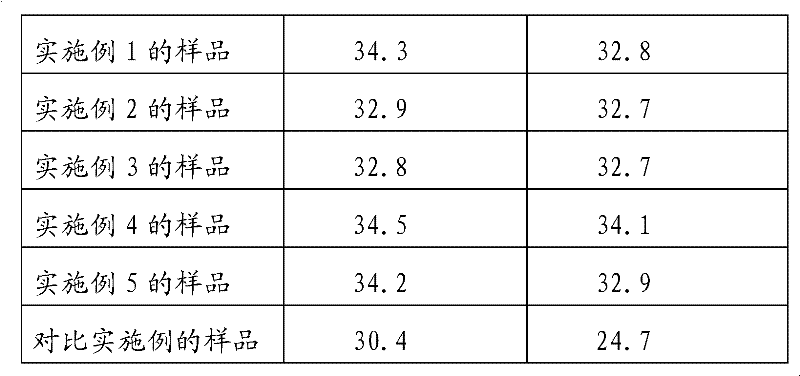

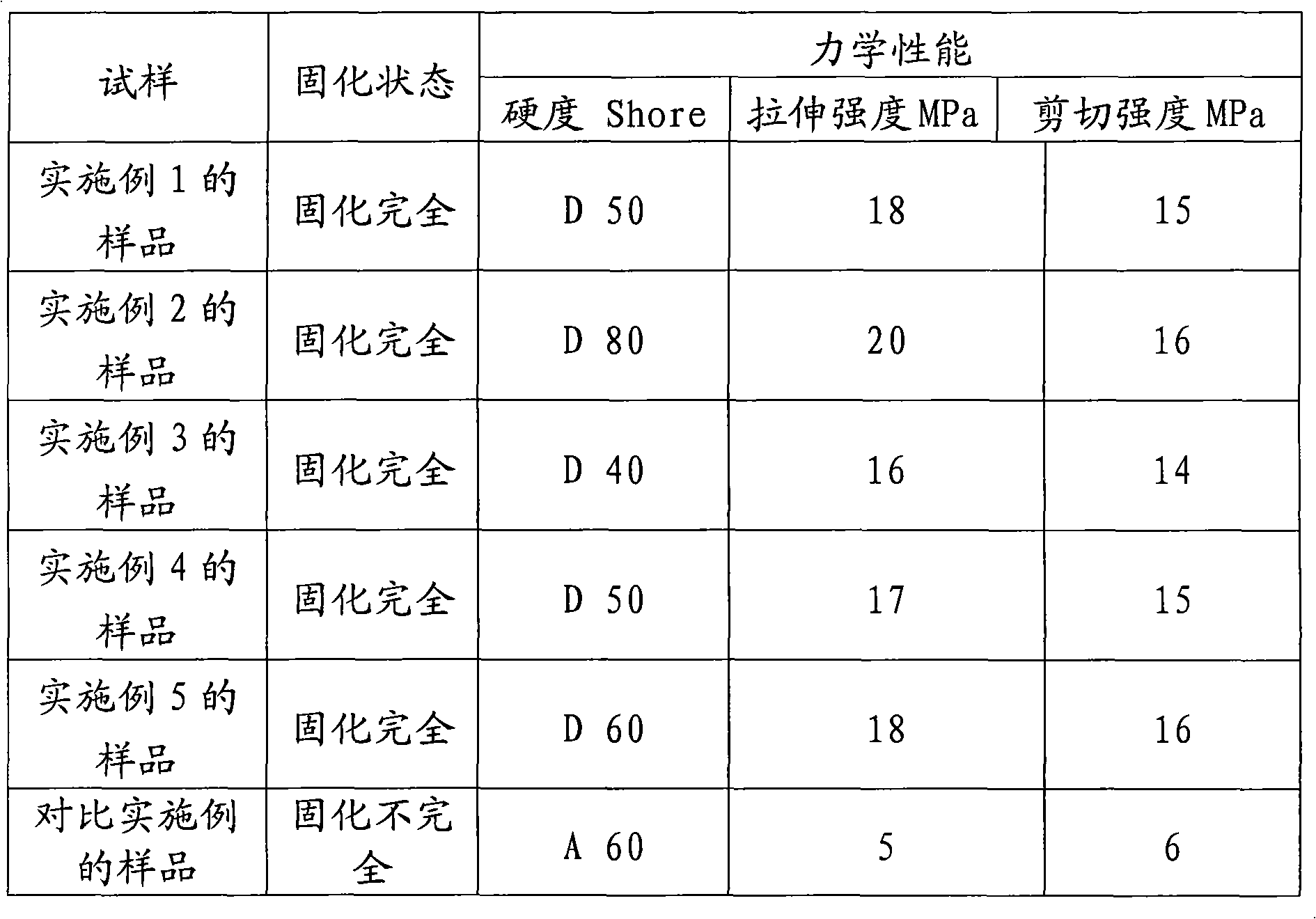

High-humidity and high-temperature resisting single component epoxy adhesive and its preparation method

InactiveCN102191002ASolve the high temperature and high humidity performance requirementsHigh bonding reliabilitySemiconductor/solid-state device detailsSolid-state devicesHigh humidityFilling materials

The invention relates to a high-humidity and high-temperature resisting single component epoxy adhesive and its preparation method. The epoxy adhesive comprises the following raw materials by weight: 40% to 60% of epoxy resin, 1% to 5% of reactive diluent, 30% to 50% of filling material, 0.5% to 1% of coupling agent, 0 to 1% of cross-linking agent, 1% to 10% of flexibilizer, 3% to 8% of latent curing agent and 3% to 5% of curing accelerator. According to the invention, the requirement of high temperature and high humidity resisting performance after the electronic packaging can be satisfied by the high-humidity and high-temperature resisting single component epoxy adhesive, the application scope of the electronic and electric appliances can be greatly extended, and the solidified system has the advantages of high adhesion reliability and wide application range.

Owner:YANTAI DARBOND TECH

Silver layer formed by electrosilvering substrate material

InactiveUS20080006911A1Effective reflectionInhibited DiffusionSemiconductor/solid-state device detailsSolid-state devicesSilver plateSilver coating

Owner:MATSUSHITA ELECTRIC WORKS LTD

Semiconductor device manufacturing method

InactiveUS20050084989A1High bonding reliabilityReliable executionSemiconductor/solid-state device testing/measurementElectronic circuit testingDevice materialSolder ball

After columnar electrodes and a sealing film are formed above a semiconductor substrate in a wafer state, probe pins are brought into contact with the upper surfaces of the columnar electrodes, and burn-in is executed. Next, solder balls are formed on the columnar electrodes, and the semiconductor substrate in a wafer state is diced. As a result, any unwanted deformation of the solder balls by contact of the probe pins can be prevented. In addition, even when the heights of the solder balls vary, burn-in can be performed.

Owner:CASIO COMPUTER CO LTD

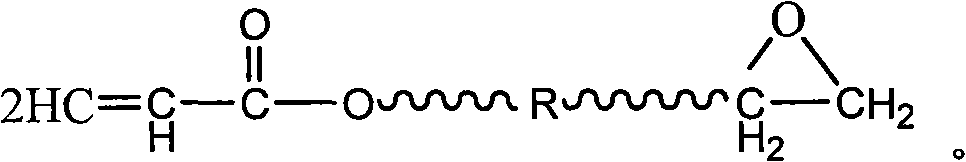

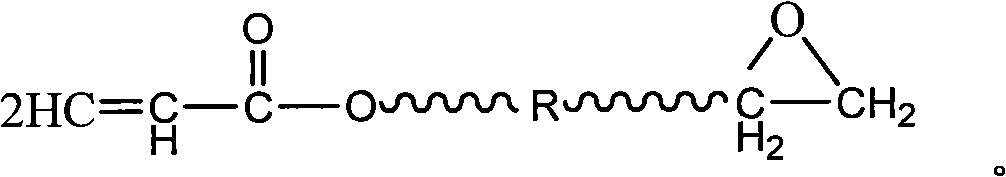

Single-component photo-curable and thermal-curable adhesive and preparation method thereof

InactiveCN102337099ASolve problems that cannot be fully curedImprove bindingModified epoxy resin adhesivesEpoxyAdhesive

The invention relates to a single-component photo-curable and thermal-curable adhesive and a preparation method thereof. The single-component photo-curable and thermal-curable adhesive consists of the following components in percentage by weight: 1 to 10 percent of epoxy resin, 1 to 10 percent of vinyl epoxy resin, 15 to 60 percent of acrylate oligomer, 20 to 50 percent of acrylate active diluent, 2 to 7 percent of photoinitiator and 0.5 to 7 percent of latent curing agent. The preparation method for the single-component photo-curable and thermal-curable adhesive comprises the following stepsof: weighing a proper amount of epoxy resin, vinyl epoxy resin, acrylate oligomer, acrylate active diluent, photoinitiator and latent curing agent in percentage by weight, adding into a stirrer in turn, uniformly stirring in vacuum, naturally cooling to room temperature, and performing sealing packaging.

Owner:YANTAI DARBOND TECH

Liquid ejection head and method of manufacturing liquid ejection head

Owner:FUJIFILM CORP

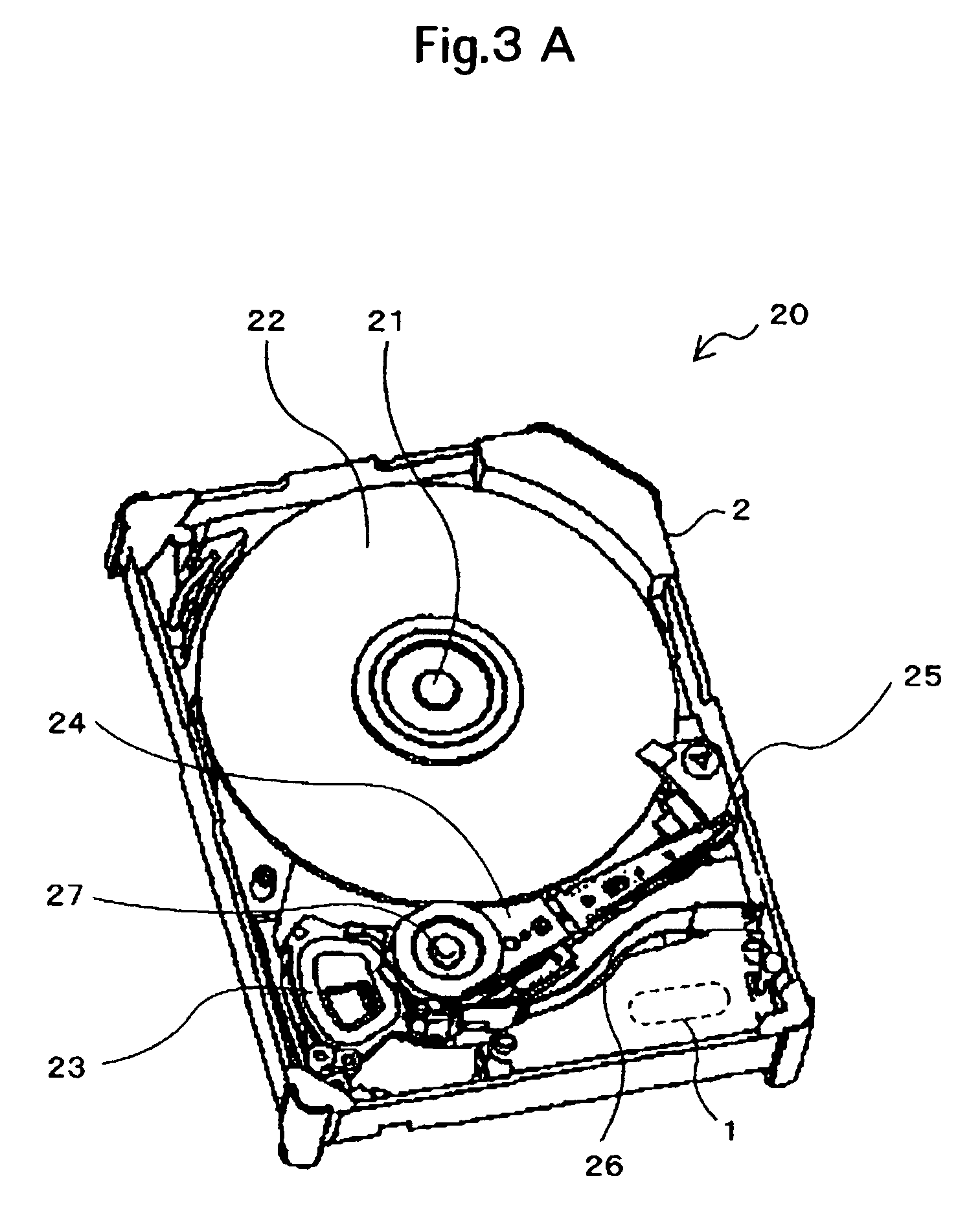

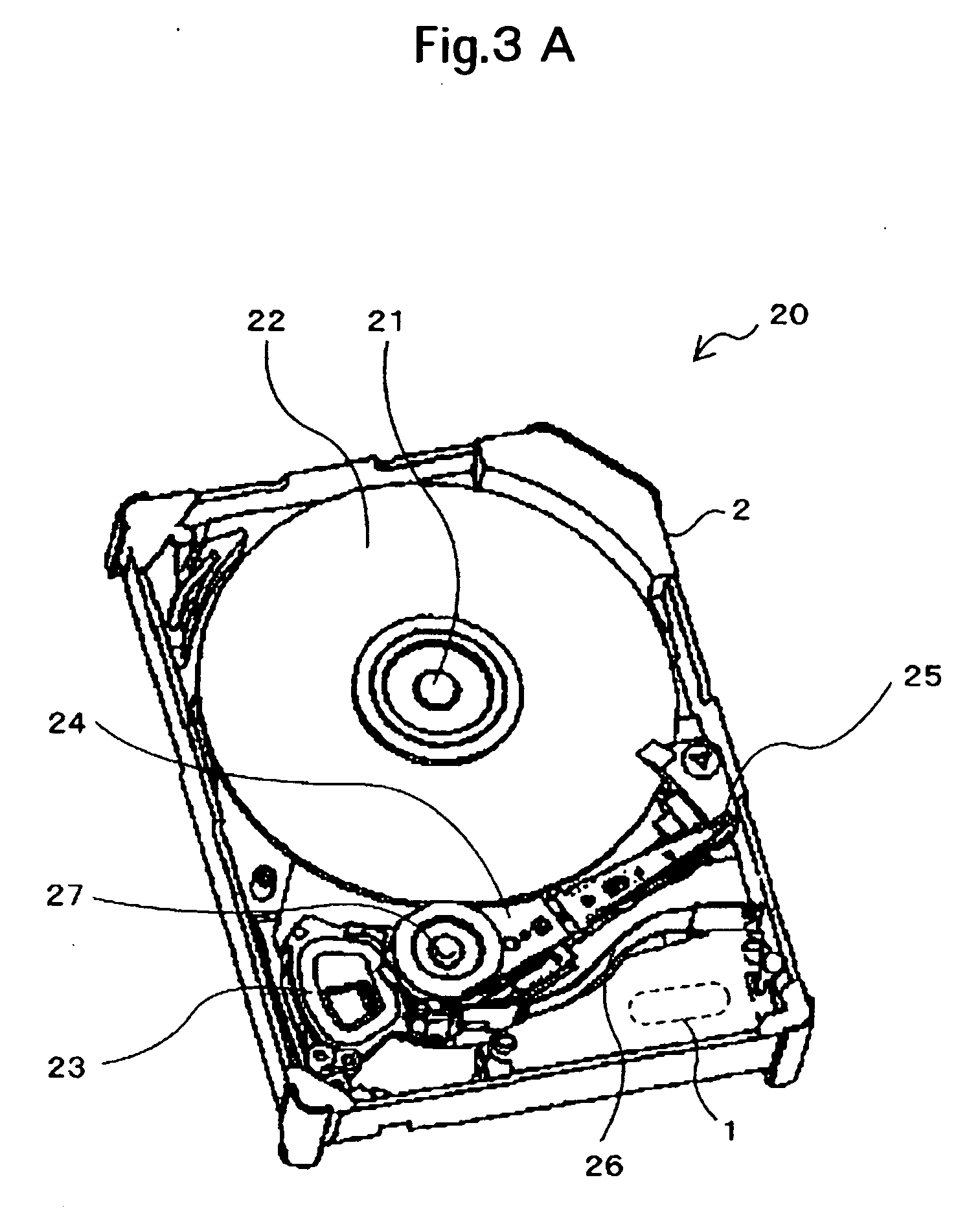

Magnetic disk device

ActiveUS7876527B2High bonding reliabilityOuter shape becomes largeUndesired vibrations/sounds insulation/absorptionRecord information storageElectric signalFlange

Owner:WESTERN DIGITAL TECH INC

Wafer level package and manufacturing method thereof

InactiveUS7663250B2High bonding reliabilitySemiconductor/solid-state device detailsSolid-state devicesMetalElectrical and Electronics engineering

A wafer level package and a manufacturing method thereof capable of reducing stress between an under bump metal and a bump. The wafer level package includes a substrate provided with a plurality of chip pads on a top surface; a first passivation layer to expose the chip pads; vias connected to the chip pads by passing through the first passivation layer; a metal wiring layer formed on the first passivation layer and connected to the vias; an under bump metal formed on the first passivation layer to be connected to the metal wiring layer and having a buffer pattern separated through a trench on a center; a second passivation layer formed on the first passivation layer to expose the under bump metal; a first bump formed on the buffer pattern; and a second bump filling the trench and formed on the first bump and the under bump metal.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Wind turbine blade

ActiveUS8764401B2Simplifies assembly process and reliabilityEasy to handlePropellersPump componentsScarf jointTurbine blade

A wind turbine blade comprising an aerodynamic fairing supported along at least a portion of its axial length by a spar (12). The spar comprises at least two spar segments (12) joined end-to-end at an interface (9), each spar segment comprising a shear web (3) with a spar cap (4) on each side. The outer face (6) of each spar cap tapers inwardly towards the interface such that its depth is reduced towards the interface creating a recess on each side of the interface formed by the tapered faces of adjacent spar caps. A respective connection piece (8) is sized to fit into each recess. Each connection piece (8) is sized to fit into each recess. Each connection piece (8) being fixed to the tapered faces of adjacent spar caps to form a double scarf joint.

Owner:BLADE DYNAMICS LTD

Photonics chip and optical apparatus including the same

InactiveUS20120121218A1Increase optical alignment efficiencyImprove alignment efficiencyOptical waveguide light guidePhotonic ChipOptical coupler

Provided are a photonics chip and an optical apparatus including the same. The chip may include a substrate, an optical waveguide, an optical coupler, and a plurality of alignment units. The optical waveguide is formed on the substrate. The optical coupler is formed at the optical waveguide. The alignment units align an optical connector which fixes at least one optical fiber coupled to the optical coupler, on the substrate.

Owner:ELECTRONICS & TELECOMM RES INST

Solder bonding method and solder bonding device

ActiveUS20050067395A1Reduce temperature differenceHigh bonding reliabilityPrinted circuit assemblingSoldering apparatusMetallurgyElectrical connection

A solder bonding method and a solder bonding device are provided, in which solder is melted, and heating of electrode portions is performed by irradiating laser light to an inner side of a region where electrodes portions are provided, making the temperature difference between the electrode portions and the melted solder smaller to improve the wettability of the solder and increase bonding reliability. The solder bonding method and the solder bonding device perform bonding of the electrode portions that are formed on an object to be bonded by melting the solder. After supplying the solder onto the electrode portions before melting, a laser is irradiated to the solder and to the electrode portions in the periphery of the solder. The solder melts, and the electrode portions are heated. The wettability of the solder with respect to the electrode portions thus improves, and the reliability of an electrical connection between the electrode portions can be increased.

Owner:SAE MAGNETICS H K LTD 50

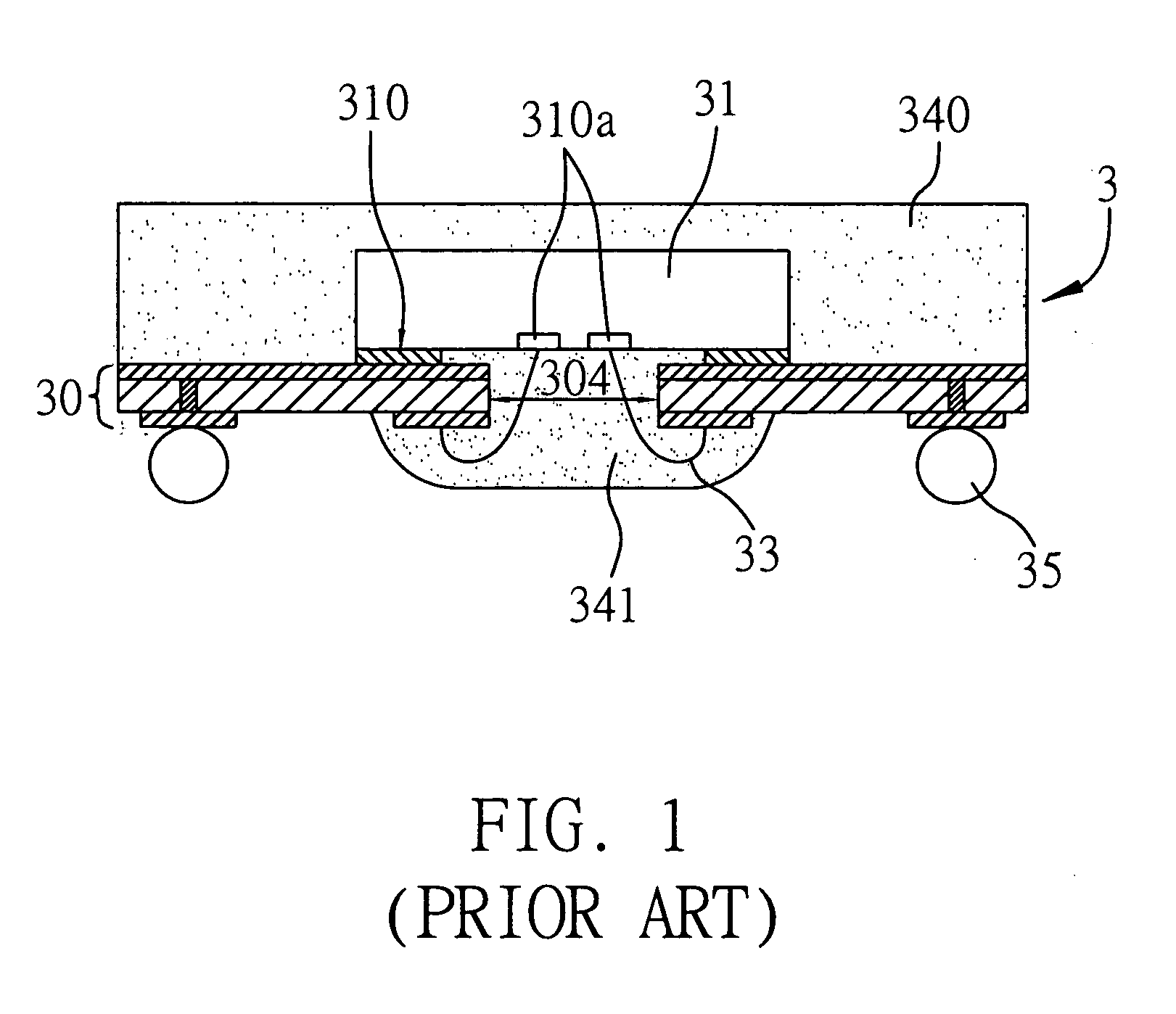

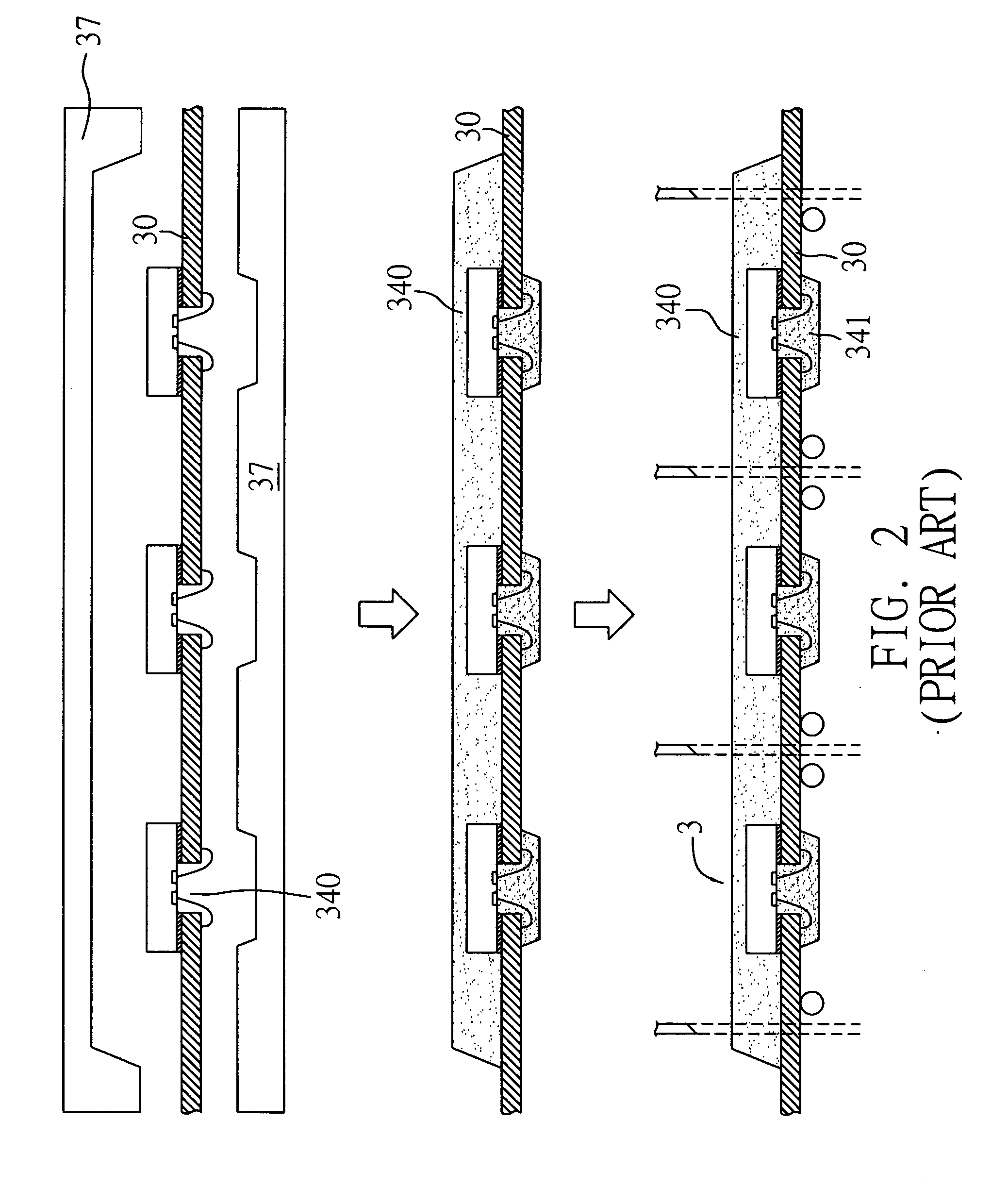

Semiconductor package and method for fabricating the same

InactiveUS20050253284A1Avoid damageHigh bonding reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package and a method for fabricating the same are proposed. A substrate having a first circuit layer, a second circuit layer, and a core layer formed between the first and second circuit layers is provided. At least one second opening is formed on the second circuit layer. At least one first opening is formed on the first circuit layer corresponding to the second opening. A plurality of finger holes corresponding to bond fingers on the first circuit layer are formed in the core layer. A through opening is formed in the core layer and communicates with the first and second openings. At least one chip is mounted on the first circuit layer and covers the first opening, with its active surface being exposed to the first opening. An encapsulant is formed to fill the first and second openings and the through opening and encapsulate the chip.

Owner:SILICONWARE PRECISION IND CO LTD

Solder ball

InactiveUS20100127044A1Increase productionHigh bonding reliabilityPrinted circuit manufactureWelding/cutting media/materialsSolder ballAliphatic hydrocarbon

An object of the present invention is to improve a yield of electronic devices in a ball mounting process by preventing a micro-bonding and change in color of the solder balls, and to improve a bonding reliability of the solder balls by reducing an oxide film on a surface of the solder ball.The solder ball has a surface thereof coated with an organic compound containing a cyclic structure and an aliphatic hydrocarbon group.

Owner:HITACHI METALS LTD

Carrier substrate and manufacturing method thereof

ActiveUS20140332253A1Easy to distinguishPrevent oxidationLamination ancillary operationsPrinted circuit aspectsInsulation layerDielectric layer

A carrier substrate includes a dielectric layer, a first circuit layer, an insulation layer, conductive blocks, and a first conductive structure. The dielectric layer has a first surface, a second surface, and blind vias. The first circuit layer is embedded in the first surface and the blind vias extend from the second surface to the first circuit layer. The insulation layer is disposed on the first surface and has a third surface, a fourth surface, and first openings. The first openings expose the first circuit layer and an aperture of each first opening is increased gradually from the third surface to the fourth surface. The conductive blocks fill the first openings and connect with the first circuit layer. The first conductive structure includes conductive vias filling the blind vias and a second circuit layer disposed on a portion of the second surface.

Owner:UNIMICRON TECH CORP

Semiconductor device and method of fabricating the same

InactiveUS20050140004A1High aspect ratioHigh bonding reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialElectrode array

A semiconductor device includes a semiconductor substrate and an array of protruding electrodes arranged at a pitch X1. Each of the protruding electrodes has a height X3 and is formed on a barrier metal base of diameter X2 coupled to an electrode arranged on the semiconductor substrate so as to satisfy the relations (X1 / 2)≦X2≦(3*X1 / 4) and (X1 / 2)≦X3≦(3*X1 / 4).

Owner:FUJITSU LTD

Chip package structure

InactiveUS20100207266A1Improve bonding reliabilityHigh bonding reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A chip package structure including a substrate, a plurality of electrodes, a chip, and a plurality of bumps is provided. Each of the electrodes has a bottom portion and an annular element, wherein the bottom portion is disposed on the substrate, the annular element is disposed on the bottom portion, and the bottom portion and the annular element define a containing recess. The chip is disposed above the substrate and has an active surface facing the substrate and a plurality of pads disposed on the active surface. The bumps are respectively disposed on the pads and respectively inserted into the containing recesses. The melting point of the electrodes is higher than that of the bumps. A chip package method is also provided.

Owner:IND TECH RES INST

Magnetic disk device

ActiveUS20080024908A1High bonding reliabilityOuter shape becomes largeUndesired vibrations/sounds insulation/absorptionRecord information storageEngineeringElectric signal

Embodiments in accordance with the present invention improve bonding reliability in a feedthrough sealing portion. According to one embodiment of the present invention, an opening of a through hole is provided on the bottom of the base of the magnetic disk device and a feedthrough mounting plane which is one of the steps formed toward the outside of the device is provided around the opening. The feedthrough includes a flange and pins which are fixed to the flange by a glass material and pass an electric signal. The flange is larger in outer shape than the opening of the base. The periphery of the flange of the feedthrough is mounted on the feedthrough mounting plane of the base from the outside and bonded thereto by solder.

Owner:WESTERN DIGITAL TECH INC

Manufacturing method of impeller

ActiveUS20100189568A1Bonded firmlyEliminate the problemBlade accessoriesSoldering apparatusImpellerEngineering

A manufacturing method of an impeller includes: forming a plurality of blades integrally on a blade attachment surface of one of a disc and a cover; placing the cover on a floor so as to face up the blade attachment surface of the cover; disposing the disc on the cover so as to face down the blade attachment surface of the disc; and bonding the plurality of blades to the blade attachment surface of the other of the disc and the cover which is not formed integrally with the plurality of blades by using a bonding material.

Owner:MITSUBISHI HEAVY IND LTD

Wiring board and method of manufacturing the same

ActiveUS8067695B2Easy POP bondingLow costSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductorPower strip

Owner:SHINKO ELECTRIC IND CO LTD

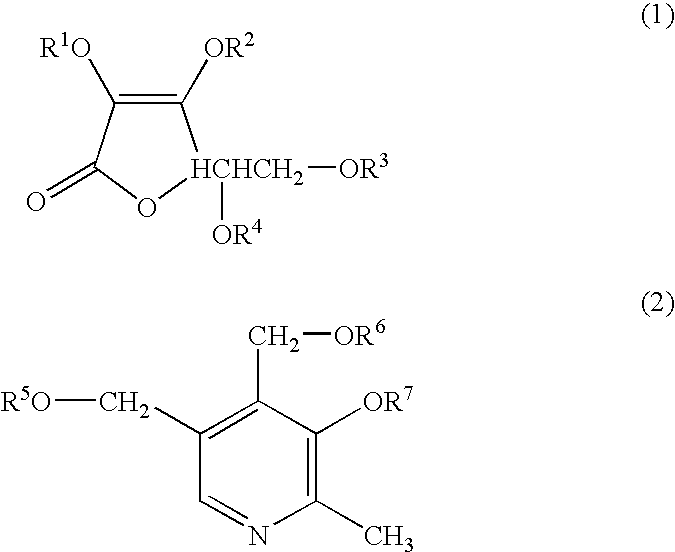

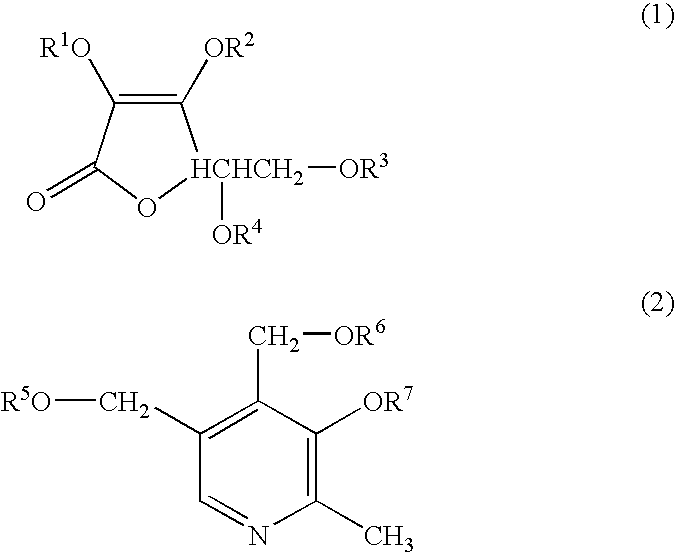

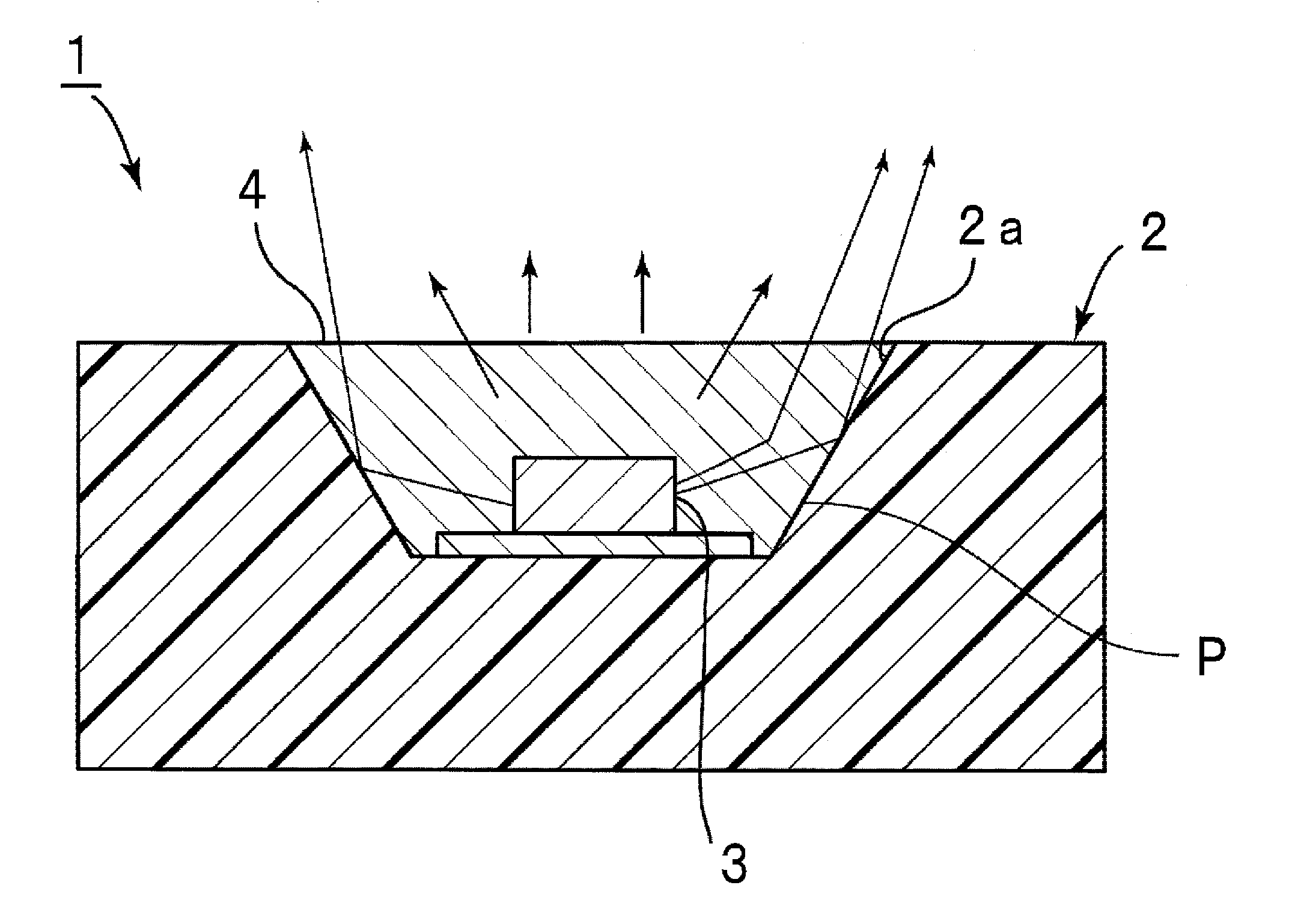

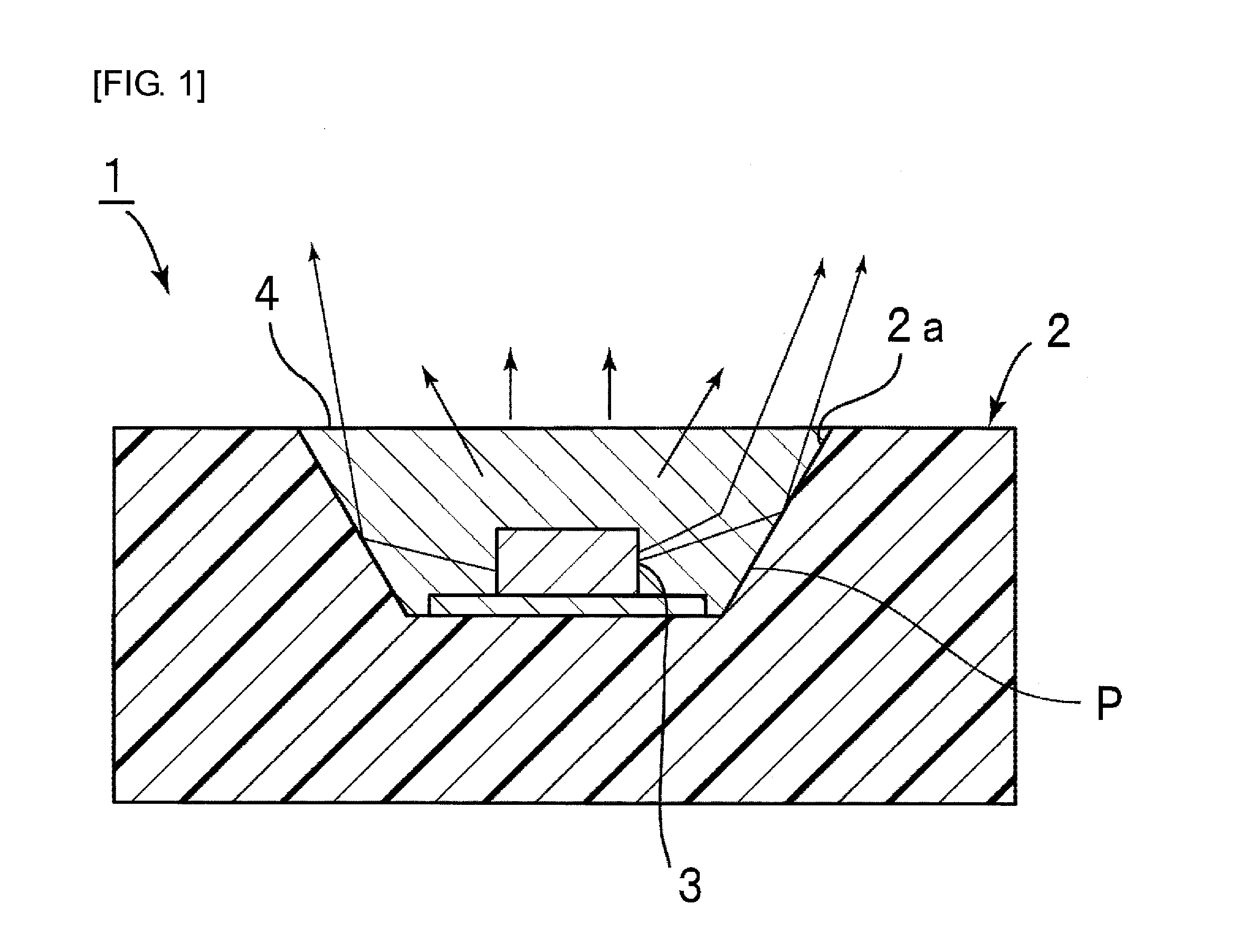

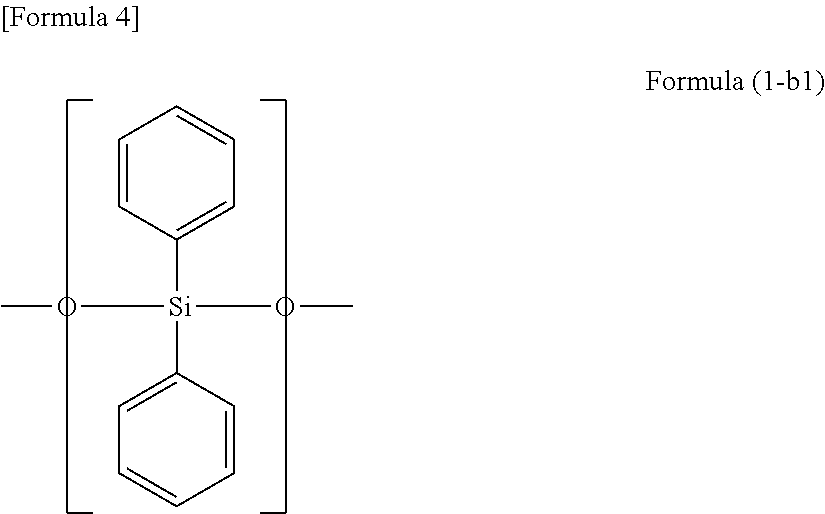

Encapsulating agent for optical semiconductor devices, and optical semiconductor device using same

InactiveUS20130221400A1Improve adhesionHigh bonding reliabilityOther chemical processesSemiconductor/solid-state device detailsSimple Organic CompoundsPower semiconductor device

Provided is an encapsulant for optical semiconductor devices, which is capable of enhancing the adhesion between a housing and the encapsulant when an optical semiconductor device is encapsulated in the housing, and which is also capable of enhancing the bonding reliability with respect to humidity. The encapsulant for optical semiconductor devices includes: a first organopolysiloxane having an alkenyl group bonded to a silicon atom and an aryl group bonded to a silicon atom, but not having a hydrogen atom bonded to a silicon atom; a second organopolysiloxane having a hydrogen atom bonded to a silicon atom and an aryl group bonded to a silicon atom; a catalyst for hydrosilylation reaction; and an organic compound having a titanium atom.

Owner:SEKISUI CHEM CO LTD

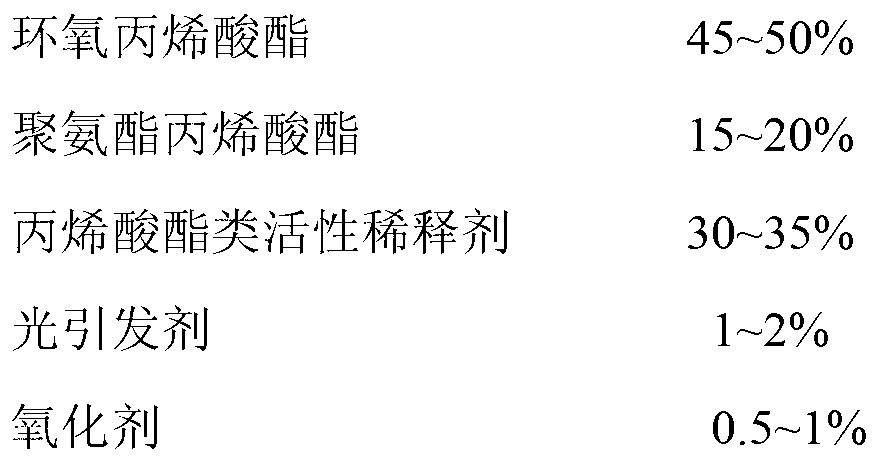

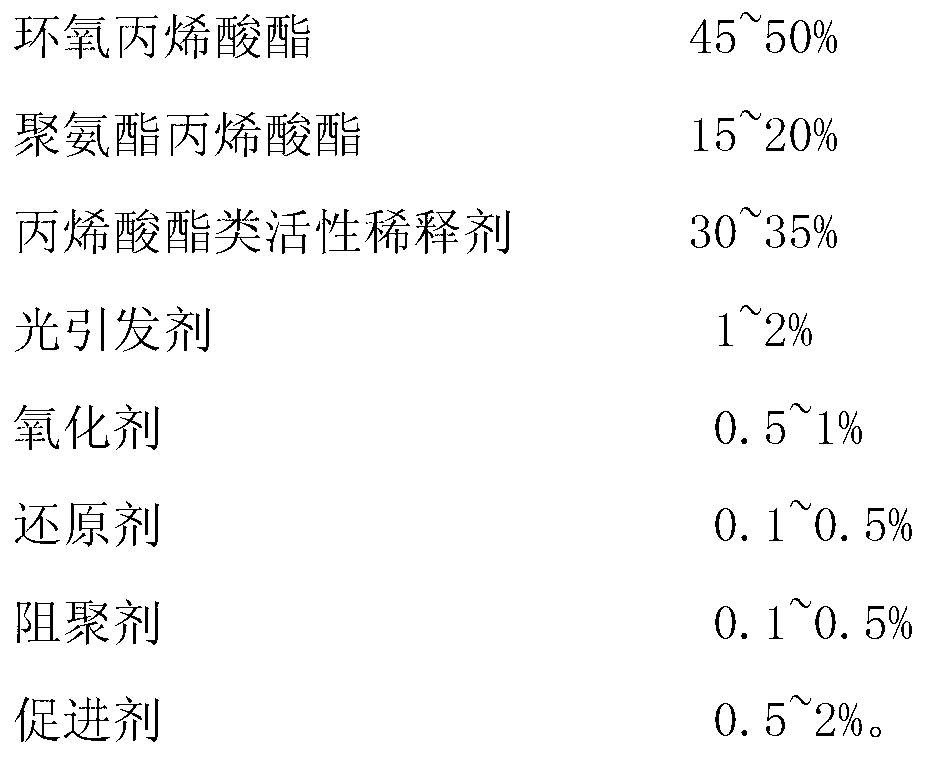

One-component ultraviolet-light-anaerobic dual-curing adhesive

ActiveCN103320075AImprove bindingSolve problems that cannot be fully curedNon-macromolecular adhesive additivesPolyureas/polyurethane adhesivesAdhesiveUltraviolet lights

The invention discloses a one-component ultraviolet-light-anaerobic dual-curing adhesive. The adhesive comprises the following active ingredients in percentage by weight: 40-50% of epoxy acrylate, 15-20% of polyurethane acrylate, 30-35% of acrylics reactive diluents, 1-2% of photoinitiator, 0.5-1% of oxidizing agent, 0.1-0.5% of reducing agent, 0.1-0.5% of polymerization inhibitor, and 0.5-2% of accelerator. The one-component ultraviolet-light-anaerobic dual-curing adhesive has the advantage of entirely solving the difficulty that the photocuring adhesive cannot be entirely cured at the shading parts. In addition, the adopted resin contains acrylate and double bonds. Through the one-component ultraviolet-light-anaerobic dual-curing adhesive, the photocuring reaction and anaerobic curing reaction are well combined, the reaction system is uniform, the curing property is excellent, the binding reliability is high, the energy resource can be saved, and the application range is wide.

Owner:天津市合成材料工业研究所有限公司

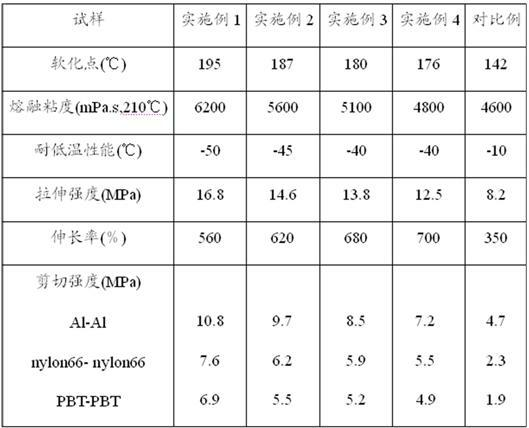

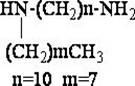

Dimer acid type polyamide hot melt adhesive and preparation method thereof

InactiveCN102220105AHigh elongationImprove low temperature resistanceAdhesivesPolymer scienceLow pressure molding

The invention relates to a dimer acid type polyamide hot melt adhesive and a preparation method thereof. The polyamide hot melt adhesive contains an N alkyl substitution diamine structure and consists of 50 percent of component A and 50 percent of component B according to mole percent, wherein the component A consists of 60-90 percent of unsaturated aliphatic dimer acid and 10-40 percent of aliphatic dicarboxylic acid according to the mole percent; the component B comprises 60-90 percent of N alkyl substituted aliphatic diamine, 10-30 percent of aliphatic diamine and 0-10 percent of heterocyclic diamine according to the mole percent. The dimer acid type polyamide hot melt adhesive has high softening point, good low-temperature resistance, high elongation, low high-temperature melting viscosity, high tensile strength and shearing intensity, and is suitable for low-pressure molding-injection forming process; and the dimer acid type polyamide hot melt adhesive has high bonding reliability and is particularly suitable for bonding of polar high polymer materials.

Owner:YANTAI DARBOND TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com